## サイプレスはインフィニオンテクノロジーズになりました

この表紙に続く文書には「サイプレス」と表記されていますが、これは同社が最初にこの製品を開発したからです。新規および既存のお客様いずれに対しても、引き続きインフィニオンがラインアップの一部として当該製品をご提供いたします。

### 文書の内容の継続性

下記製品がインフィニオンの製品ラインアップの一部として提供されたとしても、それを理由としてこの文書に変更が加わることはありません。今後も適宜改訂は行いますが、変更があった場合は文書の履歴ページでお知らせします。

### 注文時の部品番号の継続性

インフィニオンは既存の部品番号を引き続きサポートします。ご注文の際は、データシート記載の注文部品番号をこれまで通りご利用下さい。

## enCoRe™ V フルスピード USB コントローラ

### 特長

- 強力なハーバード アーキテクチャ プロセッサ

- 最大 24 MHz で動作する M8C プロセッサ

- 高速動作でも低消費電力

- 割り込みコントローラ

- USB を使用しない場合の動作電圧は 3.0 V ~ 5.5 V

- USB イネーブル時の動作電圧 :

- ・ 3.3 V を中心とした電源電圧は 3.15 V ~ 3.45 V

- ・ 5.0 V を中心とした電源電圧は 4.35 V ~ 5.25 V

- 民生用温度範囲 : 0 °C ~ +70 °C

- 工業用温度範囲 : -40 °C ~ +85 °C

- 柔軟性のあるオンチップ メモリ

- 最大 32 KB のフラッシュ プログラム領域 :

- ・ 5 万回の消去と書き込みが可能

- ・ 柔軟性のある保護モード

- 最大 2,048 バイトの SRAM データ領域

- システム内シリアル プログラミング (ISSP) 対応

- すべてを備えた開発ツール

- 無償の開発ツール (PSoC Designer™)

- 必要な機能を網羅したインサーキット エミュレータおよび インサーキット プログラマ

- フルスピードのエミュレーション

- 複雑なブレークポイント構造に対応

- 128 KB のトレース メモリ

- プログラム可能な高精度クロック供給

- 水晶振動子または発振子を外付けとした発振回路

- 6 MHz、12 MHz、または 24 MHz の内部メイン発振器（精度 ±5.0%）

- ・ 外部部品を必要とせずに、USB データに発振器をロックすることで 0.25% の精度を実現

- ・ ウオッチドッグおよびスリープ タイマ用の 32 kHz 内部低速発振器。周波数範囲は 19 ~ 50 kHz (標準値 32 kHz)

- プログラム可能なピン構成

- 最大 36 個の GPIO (個数はパッケージ依存)

- すべての GPIO で 25 mA のシンク電流に対応

- ・ 偶数ポートピンで 60mA の総合シンク電流に対応、奇数ポートピンで 60mA の総合シンク電流に対応

- ・ すべての GPIO で 120 mA の総合シンク電流に対応

- すべての GPIO でプルアップ、High-Z、オープン ドライン、CMOS の各駆動モードが可能

- CMOS 駆動モード A – ソース電流 5 mA (ポート 0 とポート 1)、1 mA (ポート 2、ポート 3、ポート 4)

- ・ すべての GPIO で 20 mA の合計ソース電流に対応

- ポート 1 ピンの低ドロップアウト電圧レギュレータ

- ・ 出力を 3.0V、2.5V、または 1.8V にプログラム可能

- ポート 1 の選択可能な安定化デジタル I/O

- ポート 1 のコンフィグレーション可能な入力閾値

- ポート 1 のホットスワップ機能

- フルスピード USB (12 Mbps)

- 8 個の単方向エンドポイント

- 1 個の双方向制御エンドポイント

- USB 2.0 準拠 : TID# 40000893

- 512 バイトの専用バッファ

- 外部水晶振動子は不要

- その他のシステム リソース

- コンフィグレーション可能な通信速度

- I<sup>2</sup>C スレーブ :

- ・ 50 kHz、100 kHz、または 400 kHz を選択可能

- ・ 実装でのクロック ストレッチは不要

- ・ 消費電力 100mA 未満のスリープモード中の実装が可能

- ・ ハードウェア アドレスの検出

- SPI マスターおよび SPI スレーブ :

- ・ 46.9 kHz ~ 12 MHz の範囲でコンフィグレーション可能

- 3 個の 16 ビット タイマ

- 外部部品を追加することでバッテリ電圧などの各種信号を監視できる 10 ビット ADC

- ウオッチドッグ タイマおよびスリープ タイマ

- 内蔵の監視回路

## enCoRe V のブロック図

エラッタ：シリコンエラッタの詳細については、37 ページのエラッタを参照してください。詳細は、トリガー条件、影響を受けるデバイス、および提案された回避策が含まれます。

## 目次

|                                |    |                            |    |

|--------------------------------|----|----------------------------|----|

| <b>機能の概要</b>                   | 4  | <b>レジスタ リファレンス</b>         | 14 |

| enCoRe V コア                    | 4  | <b>レジスタの表記法</b>            | 14 |

| フルスピード USB                     | 4  | <b>レジスタ マッピング テーブル</b>     | 14 |

| 10 ビット ADC                     | 5  | <b>電気的仕様</b>               | 17 |

| SPI                            | 5  | 絶対最大定格                     | 18 |

| I2C スレーブ                       | 6  | 動作温度                       | 18 |

| その他のシステム リソース                  | 7  | DC 特性                      | 19 |

| <b>はじめに</b>                    | 7  | AC 電気的特性                   | 23 |

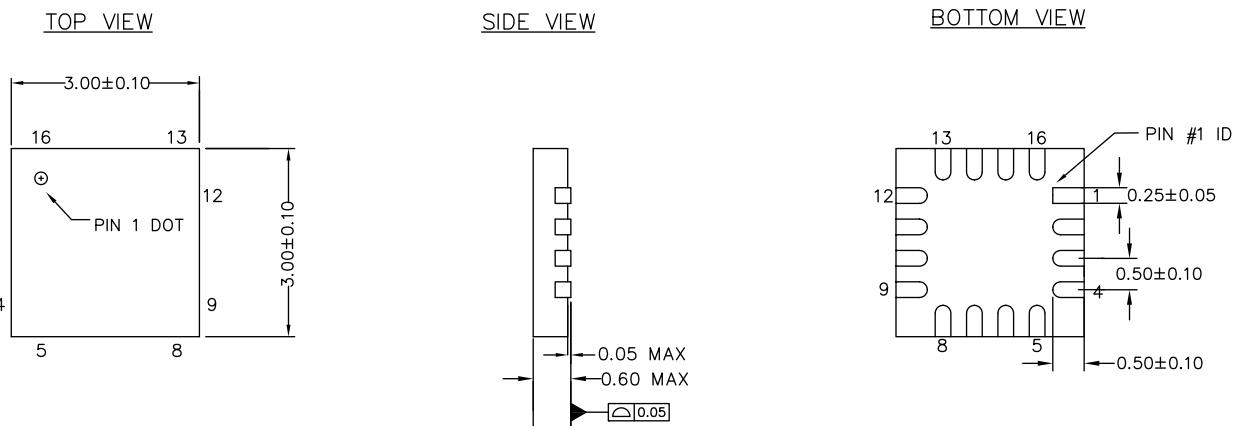

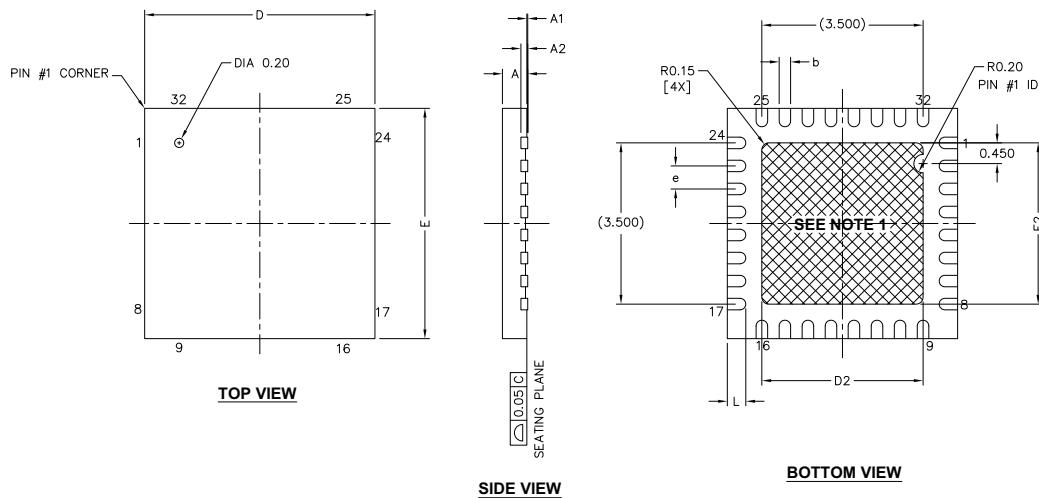

| アプリケーション ノート                   | 7  | <b>パッケージ図</b>              | 30 |

| 開発キット                          | 7  | パッケージの寸法                   | 30 |

| トレーニング                         | 7  | パッケージの取り扱い                 | 33 |

| CYPros コンサルタント                 | 7  | 熱インピーダンス                   | 33 |

| ソリューションズ ライブラリ                 | 7  | 水晶振動子ピンの静電容量               | 33 |

| 技術サポート                         | 7  | はんだリフローのピーク温度              | 33 |

| <b>開発ツール</b>                   | 8  | <b>オーダ情報</b>               | 34 |

| PSoC Designer ソフトウェア サブシステム    | 8  | 注文コードの定義                   | 35 |

| <b>PSoC Designer を使用したデザイン</b> | 9  | <b>略語</b>                  | 36 |

| ユーザ モジュールの選択                   | 9  | <b>本書の表記法</b>              | 36 |

| ユーザ モジュールの設定                   | 9  | 測定単位                       | 36 |

| 構成と接続                          | 9  | 数値の表記法                     | 36 |

| 生成、検証、およびデバッグ                  | 9  | <b>エラッタ</b>                | 37 |

| <b>ピン情報</b>                    | 10 | <b>改訂履歴</b>                | 39 |

| 16 ピン製品のピン配置                   | 10 | <b>セールス、ソリューションおよび法律情報</b> | 40 |

| ピンの定義                          | 10 | ワールドワイド販売と設計サポート           | 40 |

| 32 ピン製品のピン配置                   | 11 | 製品                         | 40 |

| ピンの定義                          | 11 | PSoC® ソリューション              | 40 |

| 48 ピン製品のピン配置                   | 12 | サイプレス開発者コミュニティ             | 40 |

| ピンの定義                          | 12 | テクニカル サポート                 | 40 |

## 機能の概要

enCoRe V デバイス ファミリは、フルスピード USB マイクロコントローラのシステム コンポーネントを複数使用した従来の構成を、低コストでプログラマブルな 1 個のシングルチップデバイスに置き換えることを目的とします。周辺通信回路 ( $\text{I}^2\text{C}/\text{SPI}$ )、高速 CPU、フラッシュ プログラム メモリ、SRAM データ メモリ、およびコンフィグレーション可能な I/O が、使いやすいピン配列でまとめられています。

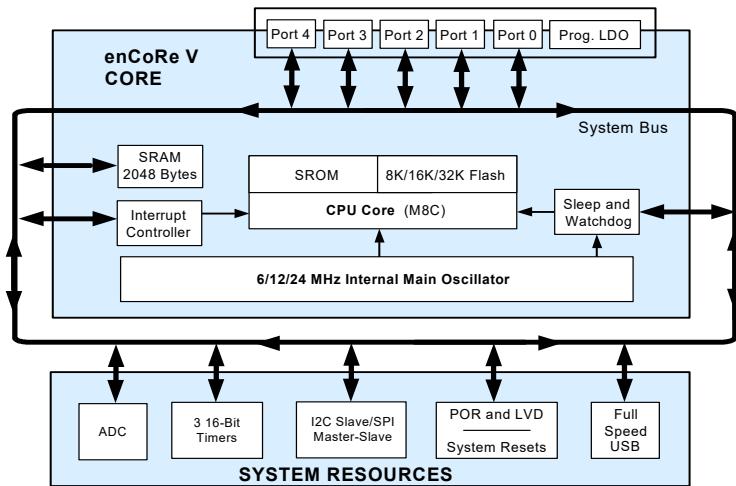

このデバイス ファミリのアーキテクチャは、2 ページの [enCoRe V のブロック図](#) に示すように、CPU コアとシステムリソースの 2 つの主要領域で構成されます。また、enCoRe V パッケージによっては、最大 36 個の汎用 I/O (GPIO) を持つものがあります。

この製品は、サイプレスの実績あるフルスピード USB 周辺コントローラを拡張した製品です。この拡張の内容として、低電圧動作での CPU 速度の向上、消費電流の削減、RAM およびフラッシュの容量倍増、ホットスワップ可能な I/O、 $\text{I}^2\text{C}$  によるハードウェア アドレス認識、新しい超低消費電流スリープモード、新しいパッケージオプションなどがあります。

### enCoRe V コア

enCoRe V コアは、豊富な命令セットをサポートする高性能エンジンです。このコアは、データ記憶用の SRAM、割り込みコントローラ、スリープ タイマとウォッチドッグ タイマ、および内部メイン発振器 (IMO) と内部低速発振器 (ILO) で構成されます。CPU コアには、最大 24 MHz で動作する高性能プロセッサ M8C を使用しています。M8C は、4 MIPS の 8 ビット ハード アーキテクチャマイクロプロセッサです。

USB 動作中は、CPU 速度を任意の設定に設定できます。USB スループットは、CPU 速度の低下とともに低下することに注意してください。最大スループットを得るには、CPU クロックをシステムクロックと等しくする必要があります。USB 操作を行うには、システムクロックが 24MHz である必要があります。

システムリソースは、コンフィグレーション可能な  $\text{I}^2\text{C}$  スレーブおよび SPI マスター スレーブの通信インターフェース、M8C がサポートするさまざまなシステム リセットなどの追加機能を提供します。

### フルスピード USB

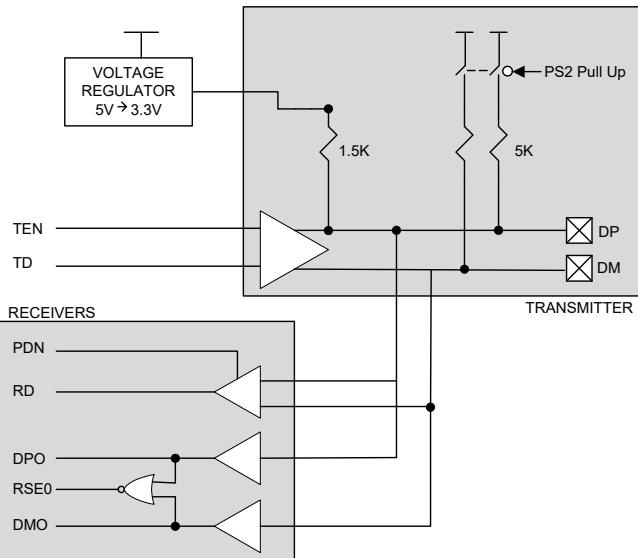

enCoRe V の USB システム リソースは、1 個のアップストリーム ポートと 1 個の USB アドレスによって 12 Mb/s で動作するフルスピード デバイスの USB 2.0 仕様に準拠しています。enCoRe V の USB は以下のコンポーネントで構成されます。

- シリアル インタフェース エンジン (SIE) ブロック

- PSoC メモリ アービタ (PMA) ブロック

- 512 バイトの専用 SRAM

- 内部レギュレータおよび 2 個の専用 USB ピンを備えるフルスピード USB トランシーバ

図 1. USB トランシーバのレギュレータ

enCoRe V のシステム レベルで、このフルスピード USB システム リソースは、M8C のレジスタ アクセス命令を使用して enCoRe V のシステム リソース以外の部分とインタフェースし、2 個の USB ピンを使用して外部環境とインタフェースします。SIE では、1 個の双方向制御エンドポイント (エンドポイント 0) と 8 個の单方向データエンドポイント (エンドポイント 1 ~ 8) の合計 9 個のエンドポイントをサポートします。この单方向データエンドポイントのそれぞれは、IN または OUT として個別にコンフィグレーションできます。

フルスピード USB の駆動インピーダンス要件を満たすためには、値の小さい直列抵抗  $R_{EXT}$  ( $22\Omega$ ) を D+ および D- ラインの外部に追加する必要があります。

USB シリアル インタフェース エンジン (SIE) を使用すると、enCoRe V デバイスはフルスピードのデータ転送速度 (12 Mb/s) で USB ホストと通信できます。SIE によって、ファームウェアの介入なしに以下の USB 処理タスクを自動的に実行することで USB トラフィックへのインターフェースが簡単になります。

- エンコードされた受信データを変換し、バス上に送信するデータにフォーマットする。

- 巡回冗長検査 (CRC) を生成し、チェックする。チェックサム検証に不合格となった着信パケットは無視されます。

- アドレスをチェックする。そのデバイスに対しアドレス指定されていないすべてのトランザクションを無視します。

- ACK、NAK、およびストールのうち、適切なハンドシェークを送信する。

- トークンの種類 (SETUP、IN、OUT) を識別し、有効なトークンを受信すると該当のトークン ビットを送信する。

- フレームの開始 (SOF) を識別し、フレーム カウントを保存する。

- PSoC メモリ アービタ (PMA) を使用し、USB SRAM との間でデータを送受信する。

ファームウェアは、USB インタフェースのさまざまな部分の処理を要求されます。SIE は、重要な USB イベントの後、割込みを発行し、以下の適切なタスクの実行をファームウェアに指示します。

- USB SRAM の USB データ バッファを満たす、または空にする。

- PMA チャネルを適切にイネーブルにする。

- USB デバイス要求をデコードすることにより、エニュメレーションの整合性を確保する。

- 整合処理を一時停止または再開する。

- データトグル値を検証し、選択する。

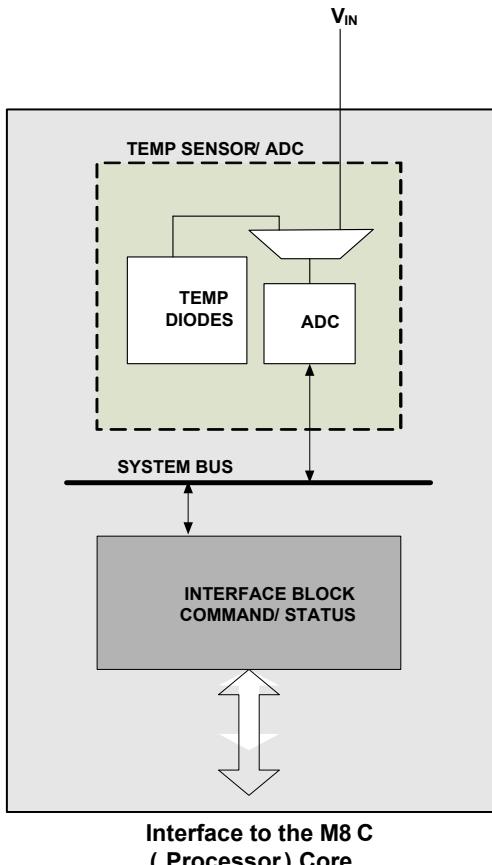

## 10 ビット ADC

enCoRe V デバイスの ADC は独立したブロックであり、このブロックへのアクセスを制御するステート マシン インタフェースを備えます。ADC は温度センサ コアとともにパッケージ化されていて、温度センサ コアまたはアナログ多重化バスに接続できます。デフォルトの動作では、ADC は温度センサ ダイオードに接続され、その温度のデジタル値を提供します。

図 2. ADC システム パフォーマンスのブロック図

ADC ユーザ モジュールには、積分器ブロックと、マルチプレクサで設定された正と負の電圧を入力とする 1 個のコンパレータがあります。積分器段への入力は、 $0V \sim V_{REFADC}$  の入力電

圧範囲で、アナログ グローバル入力マルチプレクサまたは温度センサから得られます。

ADC のみのコンフィグレーション（デフォルトの温度センサではなく、アナログ多重化バスとの接続を ADC マルチプレクサで選択したコンフィグレーション）では、外部電圧を変調器入力に接続して電圧を変換できます。ADC は、ADC で必要とする分解能に応じ、タイマで設定された回数で実行されます。カウンタによって、コンパレータで発生したトリップ数がカウントされます。この値は入力電圧に比例します。温度センサ ブロックのクロック速度は 36 MHz ですが、ADC 処理では 1 ~ 12 MHz に分周されます。

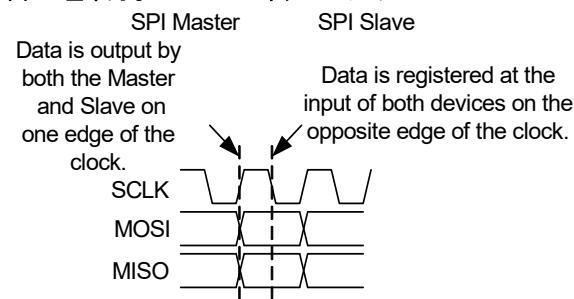

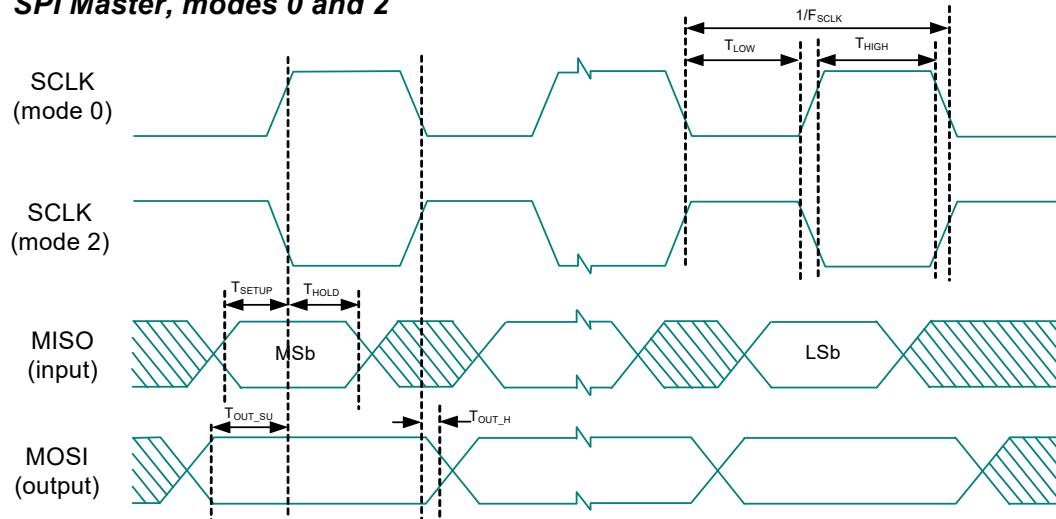

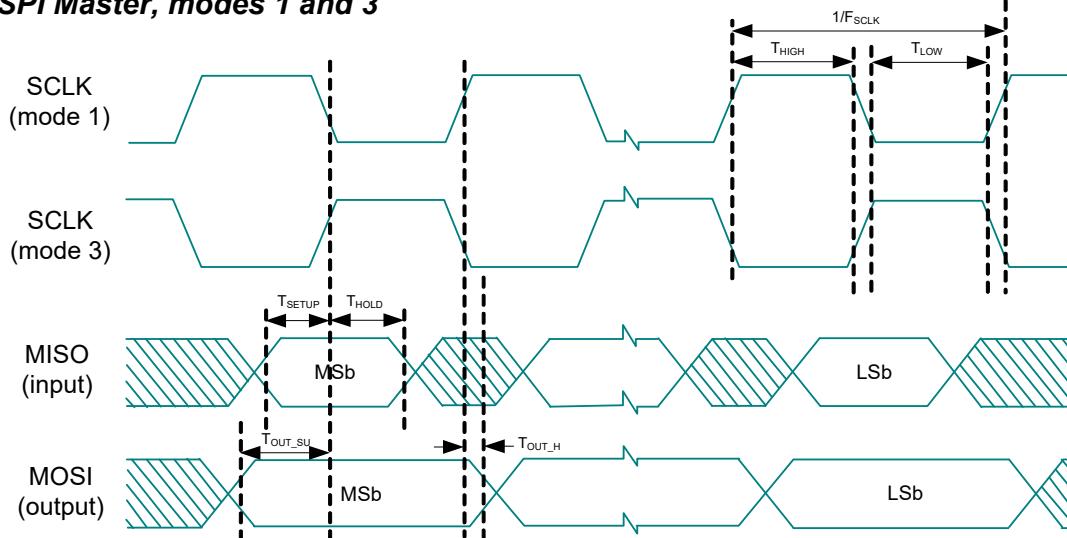

## SPI

SPI (シリアル周辺装置相互接続) の 3 線式プロトコルでは、クロックの両方のエッジを使用することで、厳密なセットアップ アンド ホールドを必要とせずに同期通信を実現できます。

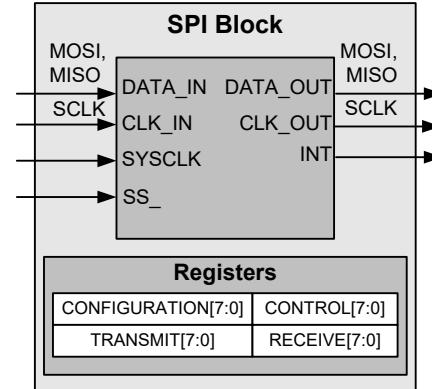

図 3. 基本的な SPI コンフィグレーション

デバイスはマスタまたはスレーブにできます。マスタは、クロックとデータをスレーブ デバイスに出力し、スレーブからのデータを入力します。スレーブ デバイスは、マスタ デバイスからのクロックとデータを入力とし、マスタへの入力となるデータを出力します。マスタとスレーブの組合せは基本的に巡回シフトレジスタであり、マスタがクロックを生成し、データ転送を開始します。

8 回のクロックに同期して 8 ビットのデータをマスタから送信することで基本的なデータ転送となります。どの転送でも、マスタとスレーブの両方で送受信が同時に発生します。マスタがデータの送信のみ行う場合は、スレーブからの受信データは無視されます。スレーブからマスタにデータを渡す場合は、マスタからスレーブにダミー バイトを送信してクロックを生成し、それに同期してスレーブからデータを送信できるようにする必要があります。

図 4. SPI ブロック図

SPI コンフィグレーション レジスタ (SPI\_CFG) は、マスター／スレーブ機能、クロック速度、および割り込み選択を設定します。SPI 制御レジスタ (SPI\_CR) には、デバイスとのインターフェースと同期に使用する 4 個の制御ビットと 4 個のステータス ビットがあります。

SPIM ハードウェアは Slave Select (SS\_) 信号の駆動をサポートしていません。この信号の動作と使用はアプリケーションと enCoRe V デバイスに依存しているので、必要な場合はファームウェアで実装する必要があります。

SPIS には追加のデータ入力として Slave Select (SS\_) があります。これはアクティブ LOW 信号です。SPIS で送受信を可能にするには、SS\_ をアサートする必要があります。SS\_ は次の 2 つの高レベル機能を備えます。

- マルチスレーブ環境で特定のスレーブを選択できるようにする。

- SPI モード 0 およびモード 1 で送信データのキュー処理に使用する追加クロックを提供する。

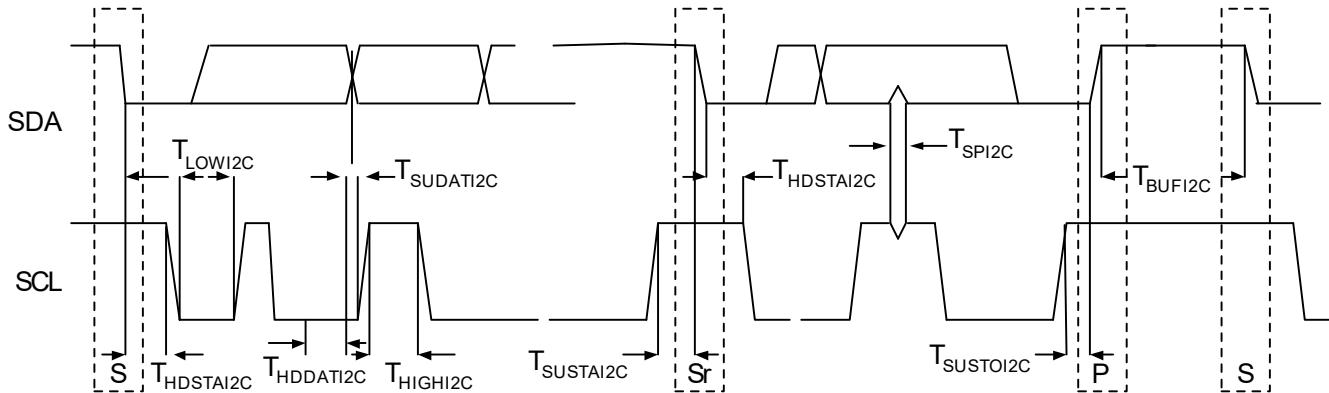

## I<sup>2</sup>C スレーブ

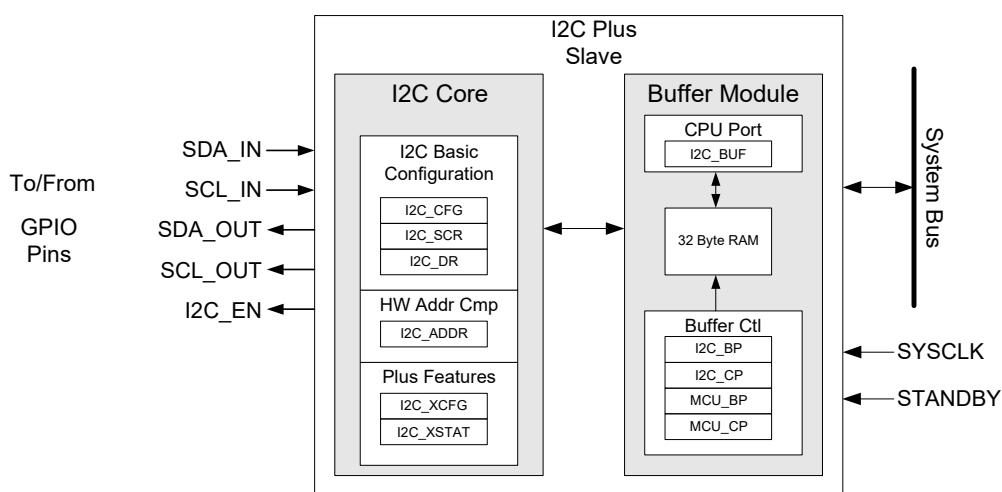

I<sup>2</sup>C スレーブ拡張通信ブロックは、enCoRe V デバイスと 2 線式 I<sup>2</sup>C シリアル通信バスとのインターフェースを実現するシリアル・パラレル・プロセッサです。CPU の過剰な介入とオーバーヘッドを不要するために、このブロックはステータス検出およびフレーミング ビット生成のための I<sup>2</sup>C 固有のサポートを提供します。I<sup>2</sup>C スレーブ拡張モジュールは、前世代の I<sup>2</sup>C スレーブ機能との間でファームウェアの互換性をデフォルトで維持します。同時に、このモジュールは、内部および外部両方のインターフェース処理で大きな柔軟性を実現する、コンフィグレーション可能な新しい機能も備えます。I<sup>2</sup>C の基本的な機能は以下のとおりです。

- スレーブ、トランスマッタ、およびレシーバの各動作

- CPU オーバーヘッド低減のためのバイト処理

- 割り込みまたはポーリングによる CPU インタフェース

- 最大 400 kHz のクロック速度のサポート

- フームウェアのサポートによる 7 ビットまたは 10 ビットのアドレス指定

- フームウェアのサポートによる SMBus 動作

- I<sup>2</sup>C スレーブ拡張モジュールの拡張機能は以下のとおりです。

- 7 ビット ハードウェア アドレス比較のサポート

- 柔軟なデータ バッファ方式

- 「バス ストールなし」の動作モード

- 低消費電力のバス監視モード

I<sup>2</sup>C ブロックは、2 つの専用 GPIO ピンへの直接接続を通じて、外部の I<sup>2</sup>C インタフェースとの間でデータ (SDA) とクロック (SCL) を制御します。I<sup>2</sup>C がインエーブルになっているときには、これらの GPIO ピンを汎用用途には使用できません。enCoRe V CPU フームウェアは、I/O レジスタの読み取りおよび書き込みを通じてこのブロックと対話し、ポーリングまたは割り込み、あるいはその両方を使用してファームウェアの同期を実現します。

旧バージョンの I<sup>2</sup>C スレーブ モジュールとの間でファームウェアの互換性を維持するデフォルトの動作モードでは、アドレスまたはバイトを受信するたびに I<sup>2</sup>C バスがストールします。I<sup>2</sup>C バスでの処理を続行するには、必要なデータの読み出しまたはデータの供給を CPU 側で実行する必要があります。一方、この I<sup>2</sup>C スレーブ拡張モジュールは、拡張機能として新しいデータ バッファリング機能を備えます。この EZI<sup>2</sup>C バッファリング モードでは、外部の I<sup>2</sup>C マスターに対して I<sup>2</sup>C スレーブ インタフェースが 32 バイトの RAM バッファとして機能します。この外部マスターは、事前定義済みの単純なプロトコルを使用して、この RAM の読み出しポインタと書き込みポインタを制御します。この方法をインエーブルにすると、スレーブによってバスがストールしなくなります。このプロトコルでは、この RAM に存在するデータ (CPU で管理) が有効になります。

図 5. I<sup>2</sup>C ブロック図

## その他のシステム リソース

システム リソースは、システムの構築に効果的な追加機能を提供します。一部のシステム リソースについてはすでに説明しました。この他の追加リソースとして、低電圧検出やパワーオンリセットなどがあります。これらのシステム リソースの利点は次のとおりです。

- 低電圧検出 (LVD) 割込みは、電圧レベルの低下を通知する信号をアプリケーションに送信します。同時に、高度な POR (パワーオン リセット) 回路を使用することでシステム監視が不要になります。

- 最大入力 5V で、出力電圧を 1.8V、2.5V、または 3V から選択可能な LDO レギュレータは、I/O の安定化を実現します。レジスタ制御バイパス モードを使用すると、LDO をディスエーブル状態にすることができます。

- enCoRe V 部品ファミリのデバッグには、標準のサイプレス PSoC IDE ツール群を利用できます。

## はじめに

enCoRe V の半導体デバイスを効率的に理解するには、このデータ シートの内容を把握して、PSoC Designer による統合開発環境 (IDE) を使用してみることを推奨します。このデータ シートは PSoC 集積回路の概要を紹介するもので、特定のピンおよびレジスタの仕様と電気的仕様を示します。詳細情報やプログラミングの詳細情報については、この PSoC デバイスの [enCoRe™ V CY7C643xx, enCoRe™ V LV CY604xx Technical Reference Manual \(TRM\)](#) を参照してください。

オーダ、パッケージ、および電気的仕様の最新情報については、Web 上で [PSoC デバイスの最新データ シート \(<http://www.cypress.com>\)](#) を参照してください。

## アプリケーション ノート

アプリケーション ノートは、PSoC を使用したさまざまなデザインを行ううえで優れたガイドになります。アプリケーション ノートは <http://www.cypress.com> で入手できます。

## 開発キット

PSoC 開発キットはサイプレス (<http://www.cypress.com>) からオンラインで入手できます。また、各地域や世界規模で広がる Arrow、Avnet、Digi-Key、Farnell、Future Electronics、および Newark などの販売代理店からも入手できます。

## トレーニング

<http://www.cypress.com> では、無料の PSoC テクニカルトレーニング (オン デマンド、Web セミナー、ワークショップ) をオンラインで利用できます。さまざまなトピックとスキル レベルのトレーニングがお客様の設計を支援します。

## CYPros コンサルタント

認定された PSoC コンサルタントが、技術支援から完成した PSoC 設計までのあらゆるニーズに対応します。CYPros 認定コンサルタントの検索、または PSoC コンサルタントとしての認定申請については、<http://www.cypress.com> を参照してください。

## ソリューションズ ライブ ライ

ソリューションに特化した設計についてライブラリを拡充しています。<http://www.cypress.com> を参照してください。ライブラリには、設計を素早く完成するうえで役立つ、ファームウェアおよびハードウェア設計ファイルを含むさまざまなアプリケーション設計が用意されています。

## 技術サポート

技術的な問題について支援が必要な場合は、(<http://www.cypress.com>) の KnowledgeBase 記事およびフォームで検索できます。解決策が見つからない場合は、テクニカルサポート (1-800-541-4736) まで連絡してください。

## 開発ツール

画期的な統合設計環境 (IDE) である PSoC Designer™ を使うと、ユーザが必要とするアプリケーション要件を満たすよう PSoC をカスタマイズすることが可能になります。PSoC Designer ソフトウェアは、システム設計や製品化までの時間をスピードアップするお手伝いをいたします。ユーザモジュールと呼ばれる予め特徴付けされたデジタル周辺回路とアナログ周辺回路のライブラリを使って、ドラッグ & ドロップの設計環境で独自のアプリケーションを開発できます。また、動的に生成されるアプリケーション プログラミング インタフェース (API) のコードライブラリを活用しながら、設計をカスタマイズすることも可能です。そして設計のデバッグおよびテストは、回路内エミュレーションや一般的なソフトウェア デバッグ機能などを備えた、統合デバッグ環境で行います。PSoC Designer には以下が含まれます。

- デバイス、ユーザ モジュール コンフィグレーションおよびダイナミック再コンフィグレーション向けのアプリケーション エディタ グラフィカル ユーザ インタフェース (GUI)

- 広範なユーザ モジュール カタログ

- 統合ソース コード エディタ (C およびアセンブリ)

- サイズや使用時間の制限がない C コンパイラを無料で添付

- ビルトイン デバッガ

- インサーキット エミュレータ

- 通信インターフェースの組込みサポート機能は以下のとおりです。

- ハードウェアおよびソフトウェアの I<sup>2</sup>C スレーブおよびマスター

- フルスピード USB 2.0

- 最大 4 個の全二重汎用非同期レシーバ / トランスマッタ (UART)、SPI マスターおよび SPI スレーブ、ワイヤレス

PSoC Designer は、PSoC 1 デバイスの全ライブラリをサポートします。また、Windows XP、Windows Vista、Windows 7 上で動作します。

## PSoC Designer ソフトウェア サブシステム

### デザインエントリ

チップレベルビューでは、まず目的の基本デバイスを選択します。次に、PSoC ブロックを使用するアナログおよびデジタルの各種オンボード コンポーネント (ユーザ モジュール) を選択します。ユーザ モジュールの例として、アナログ - デジタル変換器 (ADC)、デジタル - アナログ変換器 (DAC)、アンプ、フィルタがあります。選択したアプリケーションに適したユーザ モジュールをコンフィグレーションし、他のユーザ モジュールや適切な各ピンに接続します。その後、プロジェクトを生成します。それにより、アプリケーションのプログラミングに使用できる API とライブラリがプロジェクトに事前設定されます。

またこのツールを使用すると、マルチ コンフィグレーションやダイナミック再コンフィグレーションにより容易に開発できます。ダイナミック再コンフィグレーションにより、ランタイム中にコンフィグレーションを変更できます。基本的に、既存のアプリケーションの 100 パーセント以上の PSoC's リソースを利用できます。

### コード生成ツール

コード生成ツールは、PSoC Designer のインターフェースでシステムレスに動作し、さまざまなデバッグツールでテスト済みです。C、アセンブリ、または両方の組合せで設計を開発できます。

アセンブリ アセンブリでは、アセンブリ コードを C コードとシステムレスにマージできます。リンク ライブラリでは、自動的に絶対アドレス指定を使用できるほか、相対モードでコンパイルしたうえで他のソフトウェア モジュールとリンクし、絶対アドレス指定も取得できます。

C 言語コンパイラ PSoC ファミリのデバイスをサポートする C 言語コンパイラを利用できます。これらの製品を使用することで、PSoC ファミリ デバイス向けに完成した C プログラムを作成できます。これらの最適化 C コンパイラは、PSoC のアーキテクチャに合わせて設定した C 言語のすべての機能を提供します。これらのコンパイラには、ポートとバスの操作、標準のキーパッドとディスプレイのサポート、および拡張計算機能を提供する組込みライブラリが付属します。

### デバッガ

PSoC Designer はハードウェアによるインサーキット エミュレーション機能を提供するデバッグ環境を備えているため、物理システムでプログラムをテストでき、同時に PSoC デバイスの内部ビューを参照できます。デバッガ コマンドを使用して、読み取りとプログラム、データ メモリの読み出しと書き込み、I/O レジスタの読み出しと書き込みができます。また、CPU レジスタの読み出しと書き込み、ブレークポイントの設定と消去、プログラムの実行、停止、およびステップ制御が可能です。また、調査対象のレジスタとメモリ位置のトレース バッファをデバッガでも作成できます。

### オンライン ヘルプ システム

ユーザは、オンライン ヘルプ システムを使用して、コンテキスト依存型のオンライン ヘルプを表示できます。機能のサブシステムごとに固有のコンテキスト依存ヘルプがあり、手順のヘルプとクイック リファレンスとして使用できます。また、このヘルプ システムは設計者を支援するためのチュートリアル、FAQ とオンライン サポート フォーラムへのリンクを提供しています。

### インサーキット エミュレータ

システムへの負担が少なく、機能性の高いインサーキット エミュレータが用意されており、開発作業の効率化に効果的です。このハードウェアは単独のデバイスをプログラムできます。

このエミュレータは、USB ポートを介して PC に接続する 1 つの基本ユニットで構成されています。この基本ユニットは汎用型で、すべての PSoC デバイスで動作します。各デバイス ファミリのエミュレーション ポッドは、それぞれ独立して利用できます。エミュレーション ポッドは、作業対象のボード上で PSoC デバイスに代わり、フルスピード (24 MHz) で動作します。

## PSoC Designer を使用したデザイン

PSoC デバイスの開発プロセスは、従来の固定機能マイクロプロセッサの開発プロセスとは異なります。コンフィグレーション可能なアナログおよびデジタル ハードウェア ブロックにより、PSoC アーキテクチャに独自の柔軟性がもたらされ、開発時の仕様変更の管理や在庫費用の低減に役立ちます。これらのコンフィグレーション可能なリソースは PSoC ブロックと呼ばれ、ユーザが選択可能なさまざまな機能を実装できます。PSoC 開発プロセスは次のとおりです。

1. ユーザ モジュールの選択

2. ユーザ モジュールの設定

3. 構成と接続

4. 生成、検証、およびデバッグ

### ユーザ モジュールの選択

PSoC Designer は、あらかじめ構築され、テスト済みのハードウェア周辺コンポーネント群のライブラリを備えます。ユーザ モジュールと呼ばれるこれらのコンポーネントにより、アナログとデジタル両方の周辺デバイスの選択と実装を簡素化できます。

### ユーザ モジュールの設定

選択した各ユーザ モジュールによって、選択した機能を実装する基本的なレジスタ設定が確立されます。また、特定のアプリケーションに合わせて、コンポーネントの適格なコンフィグレーションを設定できるパラメータおよびプロパティも各種提供されます。たとえば、パルス幅変調器 (PWM) ユーザ モジュールでは、8 ビットの分解能ごとにデジタル PSoC ブロックを 1つ使用し、分解能を 8 ビット増すごとにより多くのデジタル PSoC ブロックがコンフィグレーションされます。これらのパラメータを使って、パルス幅とデューティ比を設定できます。選択したアプリケーションに対応するように、パラメータとプロパティをコンフィグレーションします。値は直接入力することも、ドロップダウンメニューから選択することもできます。すべてのユーザ モジュールはデータシートに文書化され、PSoC Designer またはサイプレスのウェブサイトで直接確認できます。これらのユーザ モジュール データシートには、ユーザ モジュールの内部動作に関する説明と性能仕様が記載されています。また、各データシートにはユーザ モジュールの各パラメータの使用方法や、設計を適切に実装するために必要なその他の情報もまとめられています。

### 構成と接続

ユーザ モジュールを他のモジュールおよび I/O ピンに相互接続することによって、チップ レベルでシグナル チェーンを構築できます。すべてのオンチップ リソースを完全に制御できるように、選択、コンフィグレーション、およびルーティングを行います。

### 生成、検証、およびデバッグ

ハードウェアのコンフィグレーションのテスト、またはプロジェクトのコード開発への移行の準備ができたら、「コンフィグレーション ファイルを生成する」手順を実行します。この手順で PSoC Designer によって生成されるソース コードは、仕様に合わせてデバイスを自動的にコンフィグレーションし、システム用のソフトウェアを提供します。生成されたコードは、ランタイムで発生するハードウェア イベントの制御とそれに対する応答を実現する API、および必要に応じて修正して使用できる割り込みサービス ルーチンを提供します。

高い完成度のコード開発環境により、C、アセンブリ言語、またはその両方を使用したアプリケーションの開発とカスタマイズが可能です。

開発プロセスの最後のステップは、PSoC Designer のデバッガ内で進めます（接続のアイコンをクリックしてアクセスします）。PSoC Designer によって HEX イメージが ICE にダウンロードされ、フルスピードで実行されます。PSoC Designer のデバッガ機能は、PSoC Designer よりもはるかに高価なシステムの機能に匹敵します。デバッガ インタフェースは、シングルステップ実行、ブレークポイントまでの実行、変数値の追跡などの従来からの機能のほか、大容量のトレース バッファを備えており、アドレスとデータ バス値の監視、メモリ位置の監視、外部信号の監視などの複雑なブレークポイント イベントを定義できます。

## ピン情報

enCoRe V USB デバイスは、以下の図に示すさまざまなパッケージで提供されます。

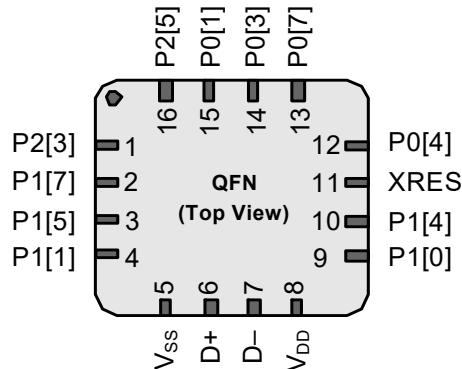

### 16 ピン製品のピン配置

図 6. CY7C64315/CY7C64316 16 ピン enCoRe V USB デバイス

## ピンの定義

16 ピン製品 (QFN パッケージ) のピン配置

| ピン番号 | 種類      | ピン名                     | 説明                                              |

|------|---------|-------------------------|-------------------------------------------------|

| 1    | I/O     | P2[3]                   | デジタル I/O、水晶振動子入力 (Xin)                          |

| 2    | I/OHR   | P1[7]                   | デジタル I/O、SPI SS、I <sup>2</sup> C SCL            |

| 3    | I/OHR   | P1[5]                   | デジタル I/O、SPI MISO、I <sup>2</sup> C SDA          |

| 4    | I/OHR   | P1[1] <sup>[1, 2]</sup> | デジタル I/O、ISSP CLK、I <sup>2</sup> C SCL、SPI MOSI |

| 5    | 電源      | V <sub>SS</sub>         | グラウンド接続                                         |

| 6    | USB ライン | D+                      | USB PHY                                         |

| 7    | USB ライン | D-                      | USB PHY                                         |

| 8    | 電源      | V <sub>DD</sub>         | 電源                                              |

| 9    | I/OHR   | P1[0] <sup>[1, 2]</sup> | デジタル I/O、ISSP DATA、I <sup>2</sup> C SDA、SPI CLK |

| 10   | I/OHR   | P1[4]                   | デジタル I/O、オプションの外部クロック入力 (EXTCLK)                |

| 11   | 入力      | XRES                    | チップ内部でプルダウンされているアクティブ HIGH の外部リセット ピン           |

| 12   | I/OH    | P0[4]                   | デジタル I/O                                        |

| 13   | I/OH    | P0[7]                   | デジタル I/O                                        |

| 14   | I/OH    | P0[3]                   | デジタル I/O                                        |

| 15   | I/OH    | P0[1]                   | デジタル I/O                                        |

| 16   | I/O     | P2[5]                   | デジタル I/O、水晶振動子出力 (Xout)                         |

凡例 I = 入力、O = 出力、OH = 5 mA 高出力駆動、R = 安定化出力

### 注

- 電源オンイベントまたはリセットイベント中、デバイスの P1[0] および P1[1] が I<sup>2</sup>C バスに干渉する場合があります。問題が発生する場合は別のピンを使用してください。

- これらはシステム内シリアル プログラミング (ISSP) のピンであり、パワーオン リセット (POR) では High-Z なりません。

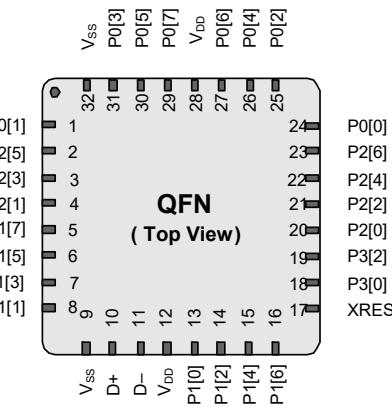

## 32 ピン製品のピン配置

図 7. CY7C64343/CY7C64345/CY7C64346 32 ピン enCoRe V USB デバイス

## ピンの定義

32 ピン製品 (QFN パッケージ) のピン配置

| ピン番号 | 種類    | ピン名                     | 説明                                              |

|------|-------|-------------------------|-------------------------------------------------|

| 1    | I/OH  | P0[1]                   | デジタル I/O                                        |

| 2    | I/O   | P2[5]                   | デジタル I/O、水晶振動子出力 (Xout)                         |

| 3    | I/O   | P2[3]                   | デジタル I/O、水晶振動子入力 (Xin)                          |

| 4    | I/O   | P2[1]                   | デジタル I/O                                        |

| 5    | I/OHR | P1[7]                   | デジタル I/O、I <sup>2</sup> C SCL、SPI SS            |

| 6    | I/OHR | P1[5]                   | デジタル I/O、I <sup>2</sup> C SDA、SPI MISO          |

| 7    | I/OHR | P1[3]                   | デジタル I/O、SPI CLK                                |

| 8    | I/OHR | P1[1] <sup>[3, 4]</sup> | デジタル I/O、ISSP CLK、I <sup>2</sup> C SCL、SPI MOSI |

| 9    | 電源    | VSS                     | グラウンド                                           |

| 10   | I/O   | D+                      | USB PHY                                         |

| 11   | I/O   | D-                      | USB PHY                                         |

| 12   | 電源    | VDD                     | 電源電圧                                            |

| 13   | I/OHR | P1[0] <sup>[3, 4]</sup> | デジタル I/O、ISSP DATA、I <sup>2</sup> C SDA、SPI CLK |

| 14   | I/OHR | P1[2]                   | デジタル I/O                                        |

| 15   | I/OHR | P1[4]                   | デジタル I/O、オプションの外部クロック入力 (EXTCLK)                |

| 16   | I/OHR | P1[6]                   | デジタル I/O                                        |

| 17   | リセット  | XRES                    | チップ内部でプルダウンされているアクティブ HIGH の外部リセットピン            |

| 18   | I/O   | P3[0]                   | デジタル I/O                                        |

| 19   | I/O   | P3[2]                   | デジタル I/O                                        |

| 20   | I/O   | P2[0]                   | デジタル I/O                                        |

| 21   | I/O   | P2[2]                   | デジタル I/O                                        |

| 22   | I/O   | P2[4]                   | デジタル I/O                                        |

| 23   | I/O   | P2[6]                   | デジタル I/O                                        |

| 24   | I/OH  | P0[0]                   | デジタル I/O                                        |

| 25   | I/OH  | P0[2]                   | デジタル I/O                                        |

| 26   | I/OH  | P0[4]                   | デジタル I/O                                        |

| 27   | I/OH  | P0[6]                   | デジタル I/O                                        |

| 28   | 電源    | VDD                     | 電源電圧                                            |

| 29   | I/OH  | P0[7]                   | デジタル I/O                                        |

| 30   | I/OH  | P0[5]                   | デジタル I/O                                        |

| 31   | I/OH  | P0[3]                   | デジタル I/O                                        |

| 32   | 電源    | VSS                     | グラウンド                                           |

| CP   | 電源    | VSS                     | パッケージ中央のパッドは必ずグラウンドに接続してください。                   |

凡例 I = 入力、O = 出力、OH = 5 mA 高出力駆動、R = 安定化出力

注

3. 電源オンイベントまたはリセットイベント中、デバイスの P1[0] および P1[1] が I<sup>2</sup>C バスに干渉する場合があります。問題が発生する場合は別のピンを使用してください。

4. これらはシステム内シリアル プログラミング (ISSP) のピンであり、パワーオン リセット (POR) では High-Z なりません。

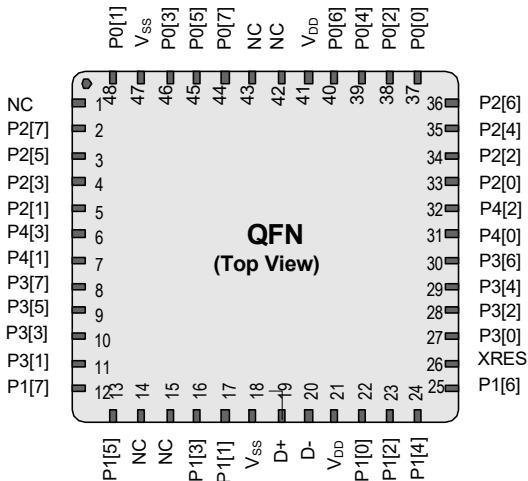

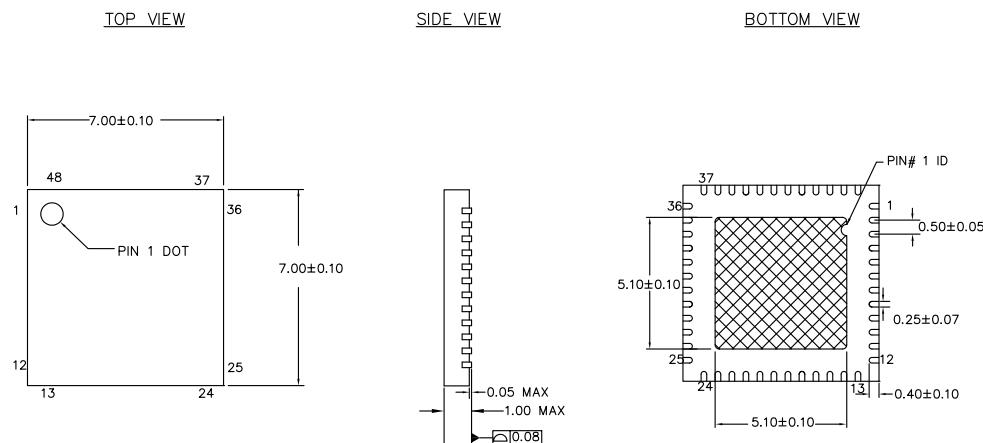

## 48 ピン製品のピン配置

図 8. CY7C64355/CY7C64356 48 ピン enCoRe V USB デバイス

## ピンの定義

48 ピン製品 (QFN パッケージ) のピン配置

| ピン番号 | 種類    | ピン名                     | 説明                                              |

|------|-------|-------------------------|-------------------------------------------------|

| 1    | NC    | NC                      | 接続なし                                            |

| 2    | I/O   | P2[7]                   | デジタル I/O                                        |

| 3    | I/O   | P2[5]                   | デジタル I/O、水晶振動子出力 (Xout)                         |

| 4    | I/O   | P2[3]                   | デジタル I/O、水晶振動子入力 (Xin)                          |

| 5    | I/O   | P2[1]                   | デジタル I/O                                        |

| 6    | I/O   | P4[3]                   | デジタル I/O                                        |

| 7    | I/O   | P4[1]                   | デジタル I/O                                        |

| 8    | I/O   | P3[7]                   | デジタル I/O                                        |

| 9    | I/O   | P3[5]                   | デジタル I/O                                        |

| 10   | I/O   | P3[3]                   | デジタル I/O                                        |

| 11   | I/O   | P3[1]                   | デジタル I/O                                        |

| 12   | I/OHR | P1[7]                   | デジタル I/O、I <sup>2</sup> C SCL、SPI SS            |

| 13   | I/OHR | P1[5]                   | デジタル I/O、I <sup>2</sup> C SDA、SPI MISO          |

| 14   | NC    | NC                      | 接続なし                                            |

| 15   | NC    | NC                      | 接続なし                                            |

| 16   | I/OHR | P1[3]                   | デジタル I/O、SPI CLK                                |

| 17   | I/OHR | P1[1] <sup>[5, 6]</sup> | デジタル I/O、ISSP CLK、I <sup>2</sup> C SCL、SPI MOSI |

| 18   | 電源    | V <sub>SS</sub>         | 電源グラウンド                                         |

| 19   | I/O   | D+                      | USB                                             |

| 20   | I/O   | D-                      | USB                                             |

| 21   | 電源    | V <sub>DD</sub>         | 電源電圧                                            |

| 22   | I/OHR | P1[0] <sup>[5, 6]</sup> | デジタル I/O、ISSP DATA、I <sup>2</sup> C SDA、SPI CLK |

| 23   | I/OHR | P1[2]                   | デジタル I/O                                        |

| 24   | I/OHR | P1[4]                   | デジタル I/O、オプションの外部クロック入力 (EXTCLK)                |

注

5. 電源オンイベントまたはリセットイベント中、デバイスの P1[0] および P1[1] が I<sup>2</sup>C バスに干渉する場合があります。問題が発生する場合は別のピンを使用してください。

6. これらはシステム内シリアル プログラミング (ISSP) のピンであり、パワーオン リセット (POR) では High-Z なりません。

## 48 ピン製品 (QFN パッケージ ) のピン配置

| ピン番号 | 種類    | ピン名             | 説明                                    |

|------|-------|-----------------|---------------------------------------|

| 25   | I/OHR | P1[6]           | デジタル I/O                              |

| 26   | XRES  | 外部リセット          | チップ内部でプルダウンされているアクティブ HIGH の外部リセット ピン |

| 27   | I/O   | P3[0]           | デジタル I/O                              |

| 28   | I/O   | P3[2]           | デジタル I/O                              |

| 29   | I/O   | P3[4]           | デジタル I/O                              |

| 30   | I/O   | P3[6]           | デジタル I/O                              |

| 31   | I/O   | P4[0]           | デジタル I/O                              |

| 32   | I/O   | P4[2]           | デジタル I/O                              |

| 33   | I/O   | P2[0]           | デジタル I/O                              |

| 34   | I/O   | P2[2]           | デジタル I/O                              |

| 35   | I/O   | P2[4]           | デジタル I/O                              |

| 36   | I/O   | P2[6]           | デジタル I/O                              |

| 37   | I/OH  | P0[0]           | デジタル I/O                              |

| 38   | I/OH  | P0[2]           | デジタル I/O                              |

| 39   | I/OH  | P0[4]           | デジタル I/O                              |

| 40   | I/OH  | P0[6]           | デジタル I/O                              |

| 41   | 電源    | V <sub>DD</sub> | 電源電圧                                  |

| 42   | NC    | NC              | 接続なし                                  |

| 43   | NC    | NC              | 接続なし                                  |

| 44   | I/OH  | P0[7]           | デジタル I/O                              |

| 45   | I/OH  | P0[5]           | デジタル I/O                              |

| 46   | I/OH  | P0[3]           | デジタル I/O                              |

| 47   | 電源    | V <sub>SS</sub> | 電源グラウンド                               |

| 48   | I/OH  | P0[1]           | デジタル I/O                              |

| CP   | 電源    | V <sub>SS</sub> | パッケージ中央のパッドは必ずグラウンドに接続してください。         |

凡例 I = 入力、O = 出力、OH = 5 mA 高出力駆動、R = 安定化出力

## レジスタ リファレンス

ここでは、enCoRe V デバイスのレジスタについて説明します。すべてのレジスタをアドレス順にマッピング テーブルに示します。

### レジスタの表記法

次の表に、このセクションで使用しているレジスタの表記法を示します。

表 1. レジスタの表記法

| 表記 | 説明                 |

|----|--------------------|

| R  | 読み出しレジスタまたは読み出しビット |

| W  | 書き込みレジスタまたは書き込みビット |

| L  | 論理レジスタまたは論理ビット     |

| C  | 消去可能なレジスタまたはビット    |

| #  | アクセスはビット固有です。      |

### レジスタ マッピング テーブル

enCoRe V デバイスには、合計 512 バイトのレジスタ アドレス空間があります。このレジスタ空間は I/O 空間とも呼ばれ、バンク 0 (ユーザ空間) とバンク 1 (コンフィグレーション空間) の 2 つの部分で構成されています。フラグ レジスタ (CPU\_F) 内の XIO ビットは、ユーザが現在どのバンクに存在しているかを示します。XIO ビットが設定されている場合は、ユーザが「拡張」アドレス空間または「コンフィグレーション」レジスタに存在するとみなされます。

**表 2. レジスタ マップ バンク 0 テーブル : ユーザ空間**

| 名前        | アドレス<br>(0,16 進) | アクセス | 名前       | アドレス<br>(0,16 進) | アクセス | 名前        | アドレス<br>(0,16 進) | アクセス | 名前        | アドレス<br>(0,16 進) | アクセス |

|-----------|------------------|------|----------|------------------|------|-----------|------------------|------|-----------|------------------|------|

| PRT0DR    | 00               | RW   | EP1_CNT0 | 40               | #    |           | 80               |      |           | C0               |      |

| PRT0IE    | 01               | RW   | EP1_CNT1 | 41               | RW   |           | 81               |      |           | C1               |      |

|           | 02               |      | EP2_CNT0 | 42               | #    |           | 82               |      |           | C2               |      |

|           | 03               |      | EP2_CNT1 | 43               | RW   |           | 83               |      |           | C3               |      |

| PRT1DR    | 04               | RW   | EP3_CNT0 | 44               | #    |           | 84               |      |           | C4               |      |

| PRT1IE    | 05               | RW   | EP3_CNT1 | 45               | RW   |           | 85               |      |           | C5               |      |

|           | 06               |      | EP4_CNT0 | 46               | #    |           | 86               |      |           | C6               |      |

|           | 07               |      | EP4_CNT1 | 47               | RW   |           | 87               |      |           | C7               |      |

| PRT2DR    | 08               | RW   | EP5_CNT0 | 48               | #    |           | 88               |      | I2C_XCFG  | C8               | RW   |

| PRT2IE    | 09               | RW   | EP5_CNT1 | 49               | RW   |           | 89               |      | I2C_XSTAT | C9               | R    |

|           | 0A               |      | EP6_CNT0 | 4A               | #    |           | 8A               |      | I2C_ADDR  | CA               | RW   |

|           | 0B               |      | EP6_CNT1 | 4B               | RW   |           | 8B               |      | I2C_BP    | CB               | R    |

| PRT3DR    | 0C               | RW   | EP7_CNT0 | 4C               | #    |           | 8C               |      | I2C_CP    | CC               | R    |

| PRT3IE    | 0D               | RW   | EP7_CNT1 | 4D               | RW   |           | 8D               |      | CPU_BP    | CD               | RW   |

|           | 0E               |      | EP8_CNT0 | 4E               | #    |           | 8E               |      | CPU_CP    | CE               | R    |

|           | 0F               |      | EP8_CNT1 | 4F               | RW   |           | 8F               |      | I2C_BUFS  | CF               | RW   |

| PRT4DR    | 10               | RW   |          | 50               |      |           | 90               |      | CUR_PP    | D0               | RW   |

| PRT4IE    | 11               | RW   |          | 51               |      |           | 91               |      | STK_PP    | D1               | RW   |

|           | 12               |      |          | 52               |      |           | 92               |      |           | D2               |      |

|           | 13               |      |          | 53               |      |           | 93               |      | IDX_PP    | D3               | RW   |

|           | 14               |      |          | 54               |      |           | 94               |      | MVR_PP    | D4               | RW   |

|           | 15               |      |          | 55               |      |           | 95               |      | MVW_PP    | D5               | RW   |

|           | 16               |      |          | 56               |      |           | 96               |      | I2C_CFG   | D6               | RW   |

|           | 17               |      |          | 57               |      |           | 97               |      | I2C_SCR   | D7               | #    |

|           | 18               |      | PMA0_DR  | 58               | RW   |           | 98               |      | I2C_DR    | D8               | RW   |

|           | 19               |      | PMA1_DR  | 59               | RW   |           | 99               |      |           | D9               |      |

|           | 1A               |      | PMA2_DR  | 5A               | RW   |           | 9A               |      | INT_CLR0  | DA               | RW   |

|           | 1B               |      | PMA3_DR  | 5B               | RW   |           | 9B               |      | INT_CLR1  | dB               | RW   |

|           | 1C               |      | PMA4_DR  | 5C               | RW   |           | 9C               |      | INT_CLR2  | DC               | RW   |

|           | 1D               |      | PMA5_DR  | 5D               | RW   |           | 9D               |      |           | DD               |      |

|           | 1E               |      | PMA6_DR  | 5E               | RW   |           | 9E               |      | INT_MSK2  | de               | RW   |

|           | 1F               |      | PMA7_DR  | 5F               | RW   |           | 9F               |      | INT_MSK1  | DF               | RW   |

|           | 20               |      |          | 60               |      |           | A0               |      | INT_MSK0  | E0               | RW   |

|           | 21               |      |          | 61               |      |           | A1               |      | INT_SW_EN | E1               | RW   |

|           | 22               |      |          | 62               |      |           | A2               |      | INT_VC    | E2               | RC   |

|           | 23               |      |          | 63               |      |           | A3               |      | RES_WDT   | E3               | W    |

|           | 24               |      | PMA8_DR  | 64               | RW   |           | A4               |      |           | E4               |      |

|           | 25               |      | PMA9_DR  | 65               | RW   |           | A5               |      |           | E5               |      |

|           | 26               |      | PMA10_DR | 66               | RW   |           | A6               |      |           | E6               |      |

|           | 27               |      | PMA11_DR | 67               | RW   |           | A7               |      |           | E7               |      |

|           | 28               |      | PMA12_DR | 68               | RW   |           | A8               |      |           | E8               |      |

| SPI_TXR   | 29               | W    | PMA13_DR | 69               | RW   |           | A9               |      |           | E9               |      |

| SPI_RXR   | 2A               | R    | PMA14_DR | 6A               | RW   |           | AA               |      |           | EA               |      |

| SPI_CR    | 2B               | #    | PMA15_DR | 6B               | RW   |           | AB               |      |           | EB               |      |

|           | 2C               |      | TMP_DR0  | 6C               | RW   |           | AC               |      |           | EC               |      |

|           | 2D               |      | TMP_DR1  | 6D               | RW   |           | AD               |      |           | ED               |      |

|           | 2E               |      | TMP_DR2  | 6E               | RW   |           | AE               |      |           | EE               |      |

|           | 2F               |      | TMP_DR3  | 6F               | RW   |           | AF               |      |           | EF               |      |

|           | 30               |      |          | 70               |      | PT0_CFG   | B0               | RW   |           | F0               |      |

| USB_SOF0  | 31               | R    |          | 71               |      | PT0_DATA1 | B1               | RW   |           | F1               |      |

| USB_SOF1  | 32               | R    |          | 72               |      | PT0_DATA0 | B2               | RW   |           | F2               |      |

| USB_CR0   | 33               | RW   |          | 73               |      | PT1_CFG   | B3               | RW   |           | F3               |      |

| USBIO_CR0 | 34               | #    |          | 74               |      | PT1_DATA1 | B4               | RW   |           | F4               |      |

| USBIO_CR1 | 35               | #    |          | 75               |      | PT1_DATA0 | B5               | RW   |           | F5               |      |

| EP0_CR    | 36               | #    |          | 76               |      | PT2_CFG   | B6               | RW   |           | F6               |      |

| EP0_CNT0  | 37               | #    |          | 77               |      | PT2_DATA1 | B7               | RW   | CPU_F     | F7               | RL   |

| EP0_DR0   | 38               | RW   |          | 78               |      | PT2_DATA0 | B8               | RW   |           | F8               |      |

| EP0_DR1   | 39               | RW   |          | 79               |      |           | B9               |      |           | F9               |      |

| EP0_DR2   | 3A               | RW   |          | 7A               |      |           | BA               |      |           | FA               |      |

| EP0_DR3   | 3B               | RW   |          | 7B               |      |           | BB               |      |           | FB               |      |

| EP0_DR4   | 3C               | RW   |          | 7C               |      |           | BC               |      |           | FC               |      |

| EP0_DR5   | 3D               | RW   |          | 7D               |      |           | BD               |      |           | FD               |      |

| EP0_DR6   | 3E               | RW   |          | 7E               |      |           | BE               |      | CPU_SCR1  | FE               | #    |

| EP0_DR7   | 3F               | RW   |          | 7F               |      |           | BF               |      | CPU_SCR0  | FF               | #    |

灰色のフィールドは予約されています。これらのフィールドにはアクセスしないでください。# アクセスはビット固有です。

**表 3. レジスタマップ バンク 1 テーブル：コンフィグレーション空間**

| 名前      | アドレス<br>(1,16 進) | アクセス | 名前       | アドレス<br>(1,16 進) | アクセス | 名前          | アドレス<br>(1,16 進) | アクセス | 名前        | アドレス<br>(1,16 進) | アクセス |

|---------|------------------|------|----------|------------------|------|-------------|------------------|------|-----------|------------------|------|

| PRT0DM0 | 00               | RW   | PMA4_RA  | 40               | RW   |             | 80               |      |           | C0               |      |

| PRT0DM1 | 01               | RW   | PMA5_RA  | 41               | RW   |             | 81               |      |           | C1               |      |

|         | 02               |      | PMA6_RA  | 42               | RW   |             | 82               |      |           | C2               |      |

|         | 03               |      | PMA7_RA  | 43               | RW   |             | 83               |      |           | C3               |      |

| PRT1DM0 | 04               | RW   | PMA8_WA  | 44               | RW   |             | 84               |      |           | C4               |      |

| PRT1DM1 | 05               | RW   | PMA9_WA  | 45               | RW   |             | 85               |      |           | C5               |      |

|         | 06               |      | PMA10_WA | 46               | RW   |             | 86               |      |           | C6               |      |

|         | 07               |      | PMA11_WA | 47               | RW   |             | 87               |      |           | C7               |      |

| PRT2DM0 | 08               | RW   | PMA12_WA | 48               | RW   |             | 88               |      |           | C8               |      |

| PRT2DM1 | 09               | RW   | PMA13_WA | 49               | RW   |             | 89               |      |           | C9               |      |

|         | 0A               |      | PMA14_WA | 4A               | RW   |             | 8A               |      |           | CA               |      |

|         | 0B               |      | PMA15_WA | 4B               | RW   |             | 8B               |      |           | CB               |      |

| PRT3DM0 | 0C               | RW   | PMA8_RA  | 4C               | RW   |             | 8C               |      |           | CC               |      |

| PRT3DM1 | 0D               | RW   | PMA9_RA  | 4D               | RW   |             | 8D               |      |           | CD               |      |

|         | 0E               |      | PMA10_RA | 4E               | RW   |             | 8E               |      |           | CE               |      |

|         | 0F               |      | PMA11_RA | 4F               | RW   |             | 8F               |      |           | CF               |      |

| PRT4DM0 | 10               | RW   | PMA12_RA | 50               | RW   |             | 90               |      |           | D0               |      |

| PRT4DM1 | 11               | RW   | PMA13_RA | 51               | RW   |             | 91               |      |           | D1               |      |

|         | 12               |      | PMA14_RA | 52               | RW   |             | 92               |      | ECO_ENBUS | D2               | RW   |

|         | 13               |      | PMA15_RA | 53               | RW   |             | 93               |      | ECO_TRIM  | D3               | RW   |

|         | 14               |      | EP1_CR0  | 54               | #    |             | 94               |      |           | D4               |      |

|         | 15               |      | EP2_CR0  | 55               | #    |             | 95               |      |           | D5               |      |

|         | 16               |      | EP3_CR0  | 56               | #    |             | 96               |      |           | D6               |      |

|         | 17               |      | EP4_CR0  | 57               | #    |             | 97               |      |           | D7               |      |

|         | 18               |      | EP5_CR0  | 58               | #    |             | 98               |      | MUX_CR0   | D8               | RW   |

|         | 19               |      | EP6_CRO  | 59               | #    |             | 99               |      | MUX_CR1   | D9               | RW   |

|         | 1A               |      | EP7_CR0  | 5A               | #    |             | 9A               |      | MUX_CR2   | DA               | RW   |

|         | 1B               |      | EP8_CR0  | 5B               | #    |             | 9B               |      | MUX_CR3   | dB               | RW   |

|         | 1C               |      |          | 5C               |      |             | 9C               |      | IO_CFG1   | DC               | RW   |

|         | 1D               |      |          | 5D               |      |             | 9D               |      | OUT_P1    | DD               | RW   |

|         | 1E               |      |          | 5E               |      |             | 9E               |      | IO_CFG2   | DE               | RW   |

|         | 1F               |      |          | 5F               |      |             | 9F               |      | MUX_CR4   | DF               | RW   |

|         | 20               |      |          | 60               |      |             | A0               |      | OSC_CR0   | E0               | RW   |

|         | 21               |      |          | 61               |      |             | A1               |      | ECO_CFG   | E1               | #    |

|         | 22               |      |          | 62               |      |             | A2               |      | OSC_CR2   | E2               | RW   |

|         | 23               |      |          | 63               |      |             | A3               |      | VLT_CR    | E3               | RW   |

|         | 24               |      |          | 64               |      |             | A4               |      | VLT_CMP   | E4               | R    |

|         | 25               |      |          | 65               |      |             | A5               |      |           | E5               |      |

|         | 26               |      |          | 66               |      |             | A6               |      |           | E6               |      |

|         | 27               |      |          | 67               |      |             | A7               |      |           | E7               |      |

|         | 28               |      |          | 68               |      |             | A8               |      | IMO_TR    | E8               | W    |

| SPI_CFG | 29               | RW   |          | 69               |      |             | A9               |      | ILO_TR    | E9               | W    |

|         | 2A               |      |          | 6A               |      |             | AA               |      |           | EA               |      |

|         | 2B               |      |          | 6B               |      |             | AB               |      | SLP_CFG   | EB               | RW   |

|         | 2C               |      | TMP_DR0  | 6C               | RW   |             | AC               |      | SLP_CFG2  | EC               | RW   |

|         | 2D               |      | TMP_DR1  | 6D               | RW   |             | AD               |      | SLP_CFG3  | ED               | RW   |

|         | 2E               |      | TMP_DR2  | 6E               | RW   |             | AE               |      |           | EE               |      |

|         | 2F               |      | TMP_DR3  | 6F               | RW   |             | AF               |      |           | EF               |      |

| USB_CR1 | 30               | #    |          | 70               |      |             | B0               |      |           | F0               |      |

|         | 31               |      |          | 71               |      |             | B1               |      |           | F1               |      |

|         | 32               |      |          | 72               |      |             | B2               |      |           | F2               |      |

|         | 33               |      |          | 73               |      |             | B3               |      |           | F3               |      |

| PMA0_WA | 34               | RW   |          | 74               |      |             | B4               |      |           | F4               |      |

| PMA1_WA | 35               | RW   |          | 75               |      |             | B5               |      |           | F5               |      |

| PMA2_WA | 36               | RW   |          | 76               |      |             | B6               |      |           | F6               |      |

| PMA3_WA | 37               | RW   |          | 77               |      |             | B7               |      | CPU_F     | F7               | RL   |

| PMA4_WA | 38               | RW   |          | 78               |      |             | B8               |      |           | F8               |      |

| PMA5_WA | 39               | RW   |          | 79               |      |             | B9               |      |           | F9               |      |

| PMA6_WA | 3A               | RW   |          | 7A               |      |             | BA               |      | IMO_TR1   | FA               | RW   |

| PMA7_WA | 3B               | RW   |          | 7B               |      |             | BB               |      |           | FB               |      |

| PMA0_RA | 3C               | RW   |          | 7C               |      |             | BC               |      |           | FC               |      |

| PMA1_RA | 3D               | RW   |          | 7D               |      | USB_MISC_CR | BD               | RW   |           | FD               |      |

| PMA2_RA | 3E               | RW   |          | 7E               |      |             | BE               |      |           | FE               |      |

| PMA3_RA | 3F               | RW   |          | 7F               |      |             | BF               |      |           | FF               |      |

灰色のフィールドは予約されています。これらのフィールドにはアクセスしないでください。# アクセスはビット固有です。

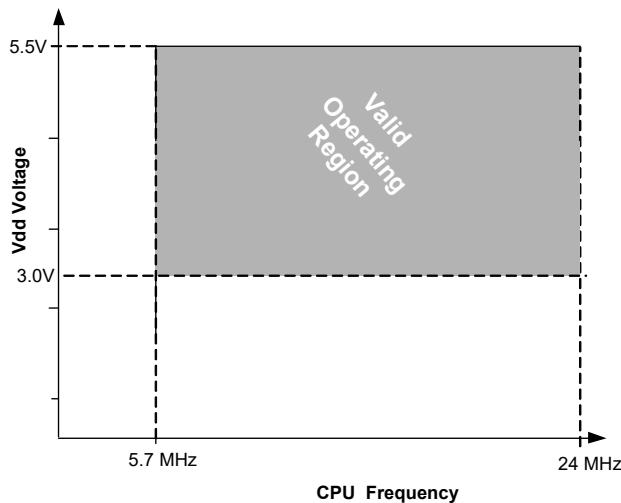

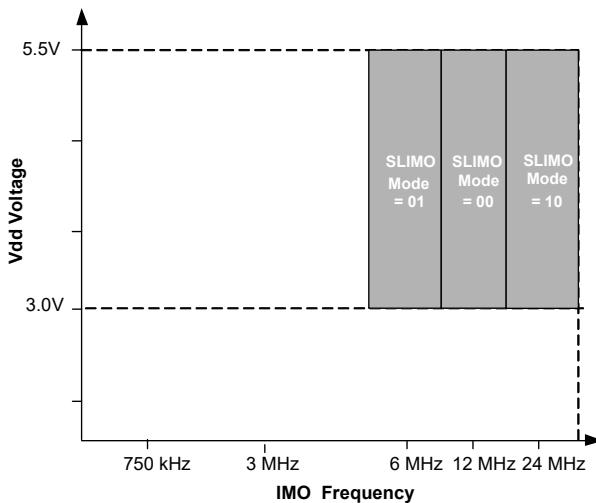

## 電気的仕様

ここでは、enCoRe V USB デバイスの電気的仕様 (DC および AC) について説明します。弊社の Web サイト (<http://www.cypress.com>) にアクセスして、お持ちのデータシートが最新のものかどうかを確認し、常に最新の電気的仕様を参照するようにしてください。

図 9. 電圧と CPU のクロック周波数の関係

図 10. IMO 周波数のトリムオプション

## 絶対最大定格

最大定格を超えると、デバイスの耐用寿命が短くなる可能性があります。ユーザ ガイドラインは未テストです。

表 4. 絶対最大定格

| 記号                 | 説明                         | 条件                                                                                    | 最小値                   | 標準値 | 最大値                   | 単位 |

|--------------------|----------------------------|---------------------------------------------------------------------------------------|-----------------------|-----|-----------------------|----|

| T <sub>STG</sub>   | 保存温度 [10]                  | 保存温度が高いと、データ保存期間が短くなります。推奨保存温度は +25 °C ± 25 °C です。<br>85°C を超える温度で長期間保管すると、信頼性が低下します。 | -55                   | +25 | +125                  | °C |

| V <sub>DD</sub>    | V <sub>SS</sub> を基準にした電源電圧 |                                                                                       | -0.5                  | -   | +6.0                  | V  |

| V <sub>IO</sub>    | DC 入力電圧                    |                                                                                       | V <sub>SS</sub> - 0.5 | -   | V <sub>DD</sub> + 0.5 | V  |

| V <sub>IOZ</sub>   | トライステート DC 電圧              |                                                                                       | V <sub>SS</sub> - 0.5 | -   | V <sub>DD</sub> + 0.5 | V  |

| I <sub>MIO</sub>   | ポートピン最大電流                  |                                                                                       | -25                   | -   | +50                   | mA |

| ESD                | 静電放電電圧                     | 人体モデルでの ESD                                                                           | 2000                  | -   | -                     | V  |

| L <sub>U</sub> [8] | ラッチアップ電流                   | JESD78 標準による                                                                          | -                     | -   | 200                   | mA |

## 動作温度

表 5. 動作温度

| 記号              | 説明              | 条件                                                                                             | 最小値 | 標準値 | 最大値  | 単位 |

|-----------------|-----------------|------------------------------------------------------------------------------------------------|-----|-----|------|----|

| T <sub>AI</sub> | 工業用周囲温度         |                                                                                                | -40 | -   | +85  | °C |

| T <sub>AC</sub> | 民生用周囲温度         |                                                                                                | 0   | -   | +70  | °C |

| T <sub>JI</sub> | ダイの工業用動作温度 [11] | 周囲温度に対する接合部の温度上昇はパッケージにより異なります。33 ページのパッケージ別の熱インピーダンスの表を参照してください。この要件を満たすように、消費電力を制限する必要があります。 | -40 | -   | +100 | °C |

| T <sub>JC</sub> | ダイの民生用動作温度      | 周囲温度に対する接合部の温度上昇はパッケージにより異なります。33 ページのパッケージ別の熱インピーダンスの表を参照してください。この要件を満たすように、消費電力を制限する必要があります。 | 0   | -   | +85  | °C |

注

7. V<sub>DD</sub> が 1.71 V ~ 1.9 V の範囲にある時間が 50  $\mu$ sec を超えている場合、1.71 V ~ 1.9 V の範囲から 2 V を超える電圧まで VDD が上昇するときに POR をトリガされないようにするには、スルーレートを 1 V/500  $\mu$ sec 未満にする必要があります。これ以外の電圧範囲や電圧の移行の際のスルーレートについては、SRPOWER\_UP パラメータが唯一の制限です。

8. エラッタ : ポート 1 のピン P1[1], P1[4], および P1[5] の場合、この仕様を満たすには 300 オームの外部抵抗が必要です。詳細については、37 ページのエラッタを参照してください。

9. スタンバイスリープモードで電源を遮断する場合、V<sub>DD</sub> の電圧低下状態を適切に検出し、この状態から回復できるようにするには、次のいずれかの措置をとる必要があります。

- ・電源を遮断する前にデバイスをスリープ状態から復帰させる。

- ・電源を再びオンにする前に、V<sub>DD</sub> が 100 mV を下回っているようにする。

- ・OSC\_CRO レジスタで No Buzz (ブザーなし) ビットを設定して、スリープ中でも電圧監視回路への電源供給を維持する。

- ・ブザーレートを上げて、V<sub>DD</sub> の立ち下りエッジを確実にキャプチャできるようにする。このレートは SLP\_CFG レジスタで PSSDC ビットを使用してコンフィグレーションします。

関連するレジスタについては、「enCoRe V Technical Reference Manual」を参照してください。ディープスリープモードでは、追加の低電圧監視回路によって、1V/ms より早いエッジレートでの V<sub>DD</sub> 電力低下状態を検出できます。

## DC 特性

### チップ レベルの DC 仕様

表 6 に、すべての電圧範囲および温度範囲で保証されている最大値と最小値の仕様を示します。

表 6. チップ レベルの DC 仕様

| 記号           | 説明                                 | 条件                                                                                                                       | 最小値  | 標準値 | 最大値  | 単位 |

|--------------|------------------------------------|--------------------------------------------------------------------------------------------------------------------------|------|-----|------|----|

| $V_{DD}$     | 動作電圧 [7, 9]                        | USB アクティビティなし                                                                                                            | 3.0  | —   | 5.5  | V  |

| $I_{DD24,3}$ | 供給電流、CPU = 24 MHz                  | 条件 : $V_{DD} = 3.0 \text{ V}$ , $T_A = 25^\circ\text{C}$ , CPU = 24 MHz, USB/I <sup>2</sup> C/SPI なし                     | —    | 2.9 | 4.0  | mA |

| $I_{DD12,3}$ | 供給電流、CPU = 12 MHz                  | 条件 : $V_{DD} = 3.0 \text{ V}$ , $T_A = 25^\circ\text{C}$ , CPU = 12 MHz, USB/I <sup>2</sup> C/SPI なし                     | —    | 1.7 | 2.6  | mA |

| $I_{DD6+3}$  | 供給電流、CPU = 6 MHz                   | 条件 : $V_{DD} = 3.0 \text{ V}$ , $T_A = 25^\circ\text{C}$ , CPU = 6 MHz, USB/I <sup>2</sup> C/SPI なし                      | —    | 1.2 | 1.8  | mA |

| $I_{SB1,3}$  | POR、LVD、およびスリープ タイマを使用した場合のスタンバイ電流 | $V_{DD} = 3.0 \text{ V}$ , $T_A = 25^\circ\text{C}$ , I/O レギュレータはオフ                                                      | —    | 1.1 | 1.5  | μA |

| $I_{SB0,3}$  | ディープ スリープ電流                        | $V_{DD} = 3.0 \text{ V}$ , $T_A = 25^\circ\text{C}$ , I/O レギュレータはオフ                                                      | —    | 0.1 | —    | μA |

| $V_{DDUSB}$  | 動作電圧                               | USB アクティビティあり、USB レギュレータはイネーブル                                                                                           | 4.35 | —   | 5.25 | V  |

| $I_{DD24,5}$ | 供給電流、CPU = 24 MHz                  | 条件 : $V_{DD} = 5.0 \text{ V}$ , $T_A = 25^\circ\text{C}$ , CPU = 24 MHz, IMO = 24 MHz, USB アクティブ、I <sup>2</sup> C/SPI なし | —    | 7.1 | —    | mA |

| $I_{DD12,5}$ | 供給電流、CPU = 12 MHz                  | 条件 : $V_{DD} = 5.0 \text{ V}$ , $T_A = 25^\circ\text{C}$ , CPU = 12 MHz, IMO = 24 MHz, USB アクティブ、I <sup>2</sup> C/SPI なし | —    | 6.2 | —    | mA |

| $I_{DD6,5}$  | 供給電流、CPU = 6 MHz                   | 条件 : $V_{DD} = 5.0 \text{ V}$ , $T_A = 25^\circ\text{C}$ , CPU = 6 MHz, IMO = 24 MHz, USB アクティブ、I <sup>2</sup> C/SPI なし  | —    | 5.8 | —    | mA |

| $I_{SB1,5}$  | POR、LVD、およびスリープ タイマを使用した場合のスタンバイ電流 | $V_{DD} = 5.0 \text{ V}$ , $T_A = 25^\circ\text{C}$ , I/O レギュレータはオフ                                                      | —    | 1.1 | —    | μA |

| $I_{SB0,5}$  | ディープ スリープ電流                        | $V_{DD} = 5.0 \text{ V}$ , $T_A = 25^\circ\text{C}$ , I/O レギュレータはオフ                                                      | —    | 0.1 | —    | μA |

| $V_{DDUSB}$  | 動作電圧                               | USB アクティビティあり、USB レギュレータはバイパス                                                                                            | 3.15 | 3.3 | 3.60 | V  |

注

10. 保管温度が高いと、データ保存期間が短くなります。推奨保管温度は  $+25^\circ\text{C} \pm 25^\circ\text{C}$  です。85 °C を超える温度で長期間保管すると、信頼性が低下します。

11. 周囲温度に対する接合部の温度上昇はパッケージにより異なります。33 ページの [パッケージの取り扱い](#) を参照してください。この要件を満たすように、消費電力を制限する必要があります。

表 7. DC の特性 - USB インタフェース

| 記号     | 説明                     | 条件               | 最小値   | 標準値  | 最大値   | 単位 |

|--------|------------------------|------------------|-------|------|-------|----|

| Rusbi  | USB D+ プルアップ抵抗         | アイドル バスあり        | 0.900 | —    | 1.575 | kΩ |

| Rusba  | USB D+ プルアップ抵抗         | トラフィック受信中        | 1.425 | —    | 3.090 | kΩ |

| Vohusb | スタティック出力 High          |                  | 2.8   | —    | 3.6   | V  |

| Volusb | スタティック出力 Low           |                  | —     | —    | 0.3   | V  |

| Vdi    | 差動入力感度                 |                  | 0.2   | —    | —     | V  |

| Vcm    | 差動入力同相モード範囲            |                  | 0.8   | —    | 2.5   | V  |

| VSE    | シングルエンドのレーザーバー値        |                  | 0.8   | —    | 2.0   | V  |

| Cin    | トランシーバ静電容量             |                  | —     | —    | 50    | pF |

| Iio    | High-Z 状態でのデータ ライン漏れ電流 | D+ ラインまたは D- ライン | -10   | —    | +10   | μA |

| Rps2   | PS/2 プルアップ抵抗           |                  | 3     | 5    | 7     | kΩ |

| Rext   | 外部 USB 直列抵抗            | 各 USB ピンと直列      | 21.78 | 22.0 | 22.22 | Ω  |

## ADC の電気的仕様

表 8. ADC ユーザ モジュールの電気的仕様

| 記号                  | 説明             | 条件                                                                       | 最小値                 | 標準値                 | 最大値                 | 単位   |

|---------------------|----------------|--------------------------------------------------------------------------|---------------------|---------------------|---------------------|------|

| <b>入力</b>           |                |                                                                          |                     |                     |                     |      |

| V <sub>IN</sub>     | 入力電圧範囲         |                                                                          | 0                   | —                   | V <sub>REFADC</sub> | V    |

| C <sub>IIN</sub>    | 入力容量           |                                                                          | —                   | —                   | 5                   | pF   |

| R <sub>IIN</sub>    | 入力抵抗           | 8 ビット、9 ビット、または 10 ビットの分解能に相当するスイッチド キャッシュ入力抵抗                           | 1/(500fF* データ クロック) | 1/(400fF* データ クロック) | 1/(300fF* データ クロック) | Ω    |

| <b>リファレンス</b>       |                |                                                                          |                     |                     |                     |      |

| V <sub>REFADC</sub> | ADC リファレンス電圧   |                                                                          | 1.14                | —                   | 1.26                | V    |

| <b>変換速度</b>         |                |                                                                          |                     |                     |                     |      |

| F <sub>CLK</sub>    | データ クロック       | ソースはチップの内部メイン発振器です。精度については、チップレベルの AC 仕様を参照してください。                       | 2.25                | —                   | 6                   | MHz  |

| S8                  | 8 ビットサンプリング速度  | データ クロックを 6 MHz に設定。<br>サンプリング速度 = 0.001/(2 <sup>n</sup> 分解能 / データ クロック) | —                   | 23.4375             | —                   | ksps |

| S10                 | 10 ビットサンプリング速度 | データ クロックを 6 MHz に設定。<br>サンプリング速度 = 0.001/(2 <sup>n</sup> 分解能 / データ クロック) | —                   | 5.859               | —                   | ksps |

| <b>DC 精度</b>        |                |                                                                          |                     |                     |                     |      |

| RES                 | 分解能            | 8 ビット、9 ビット、または 10 ビットに設定可能                                              | 8                   | —                   | 10                  | ビット  |

| DNL                 | 微分非直線性         |                                                                          | -1                  | —                   | +2                  | LSB  |

| INL                 | 積分非直線性         |                                                                          | -2                  | —                   | +2                  | LSB  |

| E <sub>Offset</sub> | オフセット誤差        | 8 ビット分解能<br>10 ビット分解能                                                    | 0<br>0              | 3.2<br>12.8         | 19.2<br>76.8        | LSB  |

| E <sub>gain</sub>   | ゲイン誤差          | 任意の分解能                                                                   | -5                  | —                   | +5                  | %FSR |

| <b>電源</b>           |                |                                                                          |                     |                     |                     |      |

| I <sub>ADC</sub>    | 動作電流           |                                                                          | —                   | 2.1                 | 2.6                 | mA   |

| PSRR                | 電源電圧変動除去比      | PSRR (V <sub>DD</sub> > 3.0 V)                                           | —                   | 24                  | —                   | dB   |

|                     |                | PSRR (V <sub>DD</sub> < 3.0 V)                                           | —                   | 30                  | —                   | dB   |

**汎用 I/O の DC 仕様**

表 9 に、3.0V ~ 5.5V の電圧範囲と パッケージごとの温度範囲で保証されている最大値と最小値の仕様を示します。標準のパラメータは、温度 25°C、電圧 5V および 3.3V の場合の値です。これはデザインの参考データにすぎません。

**表 9. 3.0V および 5.5V での GPIO の DC 仕様**

| 記号                | 説明                                                    | 条件                                                                                                                               | 最小値                   | 標準値   | 最大値  | 単位 |

|-------------------|-------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-----------------------|-------|------|----|

| R <sub>PU</sub>   | プルアップ抵抗                                               |                                                                                                                                  | 4                     | 5.6   | 8    | kΩ |

| V <sub>OH1</sub>  | HIGH 出力電圧<br>ポート 2 またはポート 3 の各ピン                      | I <sub>OH</sub> ≤ 10 μA、すべての I/O でソース電流が最大 10 mA                                                                                 | V <sub>DD</sub> - 0.2 | -     | -    | V  |

| V <sub>OH2</sub>  | HIGH 出力電圧<br>ポート 2 またはポート 3 の各ピン                      | I <sub>OH</sub> = 1 mA、すべての I/O でソース電流が最大 20 mA                                                                                  | V <sub>DD</sub> - 0.9 | -     | -    | V  |

| V <sub>OH3</sub>  | HIGH 出力電圧<br>ポート 0 またはポート 1 の各ピン (LDO レギュレータはディスエーブル) | I <sub>OH</sub> < 10 μA、すべての I/O でソース電流が最大 10 mA                                                                                 | V <sub>DD</sub> - 0.2 | -     | -    | V  |

| V <sub>OH4</sub>  | HIGH 出力電圧<br>ポート 0 またはポート 1 の各ピン (LDO レギュレータはディスエーブル) | I <sub>OH</sub> = 5 mA、すべての I/O でソース電流が最大 20 mA                                                                                  | V <sub>DD</sub> - 0.9 | -     | -    | V  |

| V <sub>OH5</sub>  | HIGH 出力電圧<br>ポート 1 の各ピン (出力 3V で LDO レギュレータはイネーブル)    | I <sub>OH</sub> < 10 μA、V <sub>DD</sub> > 3.1 V、最大 4 個の I/O すべてのソース電流が 5 mA                                                      | 2.85                  | 3.00  | 3.3  | V  |

| V <sub>OH6</sub>  | HIGH 出力電圧<br>ポート 1 の各ピン (出力 3V で LDO レギュレータはイネーブル)    | I <sub>OH</sub> = 5 mA、V <sub>DD</sub> > 3.1 V、すべての I/O でソース電流が最大 20 mA                                                          | 2.20                  | -     | -    | V  |

| V <sub>OH7</sub>  | HIGH 出力電圧<br>ポート 1 の各ピン (出力 2.5V で LDO はイネーブル)        | I <sub>OH</sub> < 10 μA、V <sub>DD</sub> > 3.0 V、すべての I/O でソース電流が最大 20 mA                                                         | 2.35                  | 2.50  | 2.75 | V  |

| V <sub>OH8</sub>  | HIGH 出力電圧<br>ポート 1 の各ピン (出力 2.5V で LDO はイネーブル)        | I <sub>OH</sub> = 2 mA、V <sub>DD</sub> > 3.0 V、すべての I/O でソース電流が最大 20 mA                                                          | 1.90                  | -     | -    | V  |

| V <sub>OH9</sub>  | HIGH 出力電圧<br>ポート 1 の各ピン (出力 1.8V で LDO はイネーブル)        | I <sub>OH</sub> < 10 μA、V <sub>DD</sub> > 3.0 V、すべての I/O でソース電流が最大 20 mA                                                         | 1.60                  | 1.80  | 2.1  | V  |

| V <sub>OH10</sub> | HIGH 出力電圧<br>ポート 1 の各ピン (出力 1.8V で LDO はイネーブル)        | I <sub>OH</sub> = 1 mA、V <sub>DD</sub> > 3.0 V、すべての I/O でソース電流が最大 20 mA                                                          | 1.20                  | -     | -    | V  |

| V <sub>OL</sub>   | LOW 出力電圧                                              | I <sub>OL</sub> = 25 mA、V <sub>DD</sub> > 3.3 V、偶数ポートピン (P0[2]、P1[4]など) の最大シンク電流 60 mA および奇数ポートピン (P0[3]、P1[5]など) の最大シンク電流 60 mA | -                     | -     | 0.75 | V  |

| V <sub>IL</sub>   | 入力 LOW 電圧                                             |                                                                                                                                  | -                     | -     | 0.8  | V  |

| V <sub>IH</sub>   | 入力 HIGH 電圧                                            |                                                                                                                                  | 2.0                   | -     | -    | V  |

| V <sub>H</sub>    | 入力ヒステリシス電圧                                            |                                                                                                                                  | -                     | 80    | -    | mV |

| I <sub>IL</sub>   | 入力漏れ電流 (絶対値)                                          |                                                                                                                                  | -                     | 0.001 | 1    | μA |

| C <sub>PIN</sub>  | ピン静電容量                                                | パッケージとピンによって異なります。<br>温度 = 25 °C                                                                                                 | 0.5                   | 1.7   | 5    | pF |

### POR および LVD の DC 仕様

表 10 に、すべての電圧範囲および温度範囲で保証されている最大値と最小値の仕様を示します。

表 10. POR および LVD の DC 仕様

| 記号         | 説明                                                              | 条件 | 最小値  | 標準値  | 最大値  | 単位 |

|------------|-----------------------------------------------------------------|----|------|------|------|----|

| $V_{PPOR}$ | PPOR がトリップするための $V_{DD}$ 値 <sup>[12]</sup><br>PORLEV[1:0] = 10b |    | –    | 2.82 | 2.95 | V  |

| $V_{LVD0}$ | LVD がトリップするための $V_{DD}$ 値<br>$VM[2:0] = 000b$                   |    | –    | –    | –    | V  |

| $V_{LVD1}$ | $VM[2:0] = 001b$                                                |    | –    | –    | –    | V  |

| $V_{LVD2}$ | $VM[2:0] = 010b$                                                |    | 2.85 | 2.92 | 2.99 | V  |

| $V_{LVD3}$ | $VM[2:0] = 011b$                                                |    | 2.95 | 3.02 | 3.09 | V  |

| $V_{LVD4}$ | $VM[2:0] = 100b$                                                |    | 3.06 | 3.13 | 3.20 | V  |

| $V_{LVD5}$ | $VM[2:0] = 101b$                                                |    | –    | –    | –    | V  |

| $V_{LVD6}$ | $VM[2:0] = 110b$                                                |    | –    | –    | –    | V  |

| $V_{LVD7}$ | $VM[2:0] = 111b$                                                |    | 4.62 | 4.73 | 4.83 | V  |

### プログラミングの DC 仕様

表 11 に、すべての電圧範囲および温度範囲で保証されている最大値と最小値の仕様を示します。

表 11. プログラミングの DC 仕様

| 記号             | 説明                                                                 | 条件                                               | 最小値                  | 標準値 | 最大値                  | 単位   |

|----------------|--------------------------------------------------------------------|--------------------------------------------------|----------------------|-----|----------------------|------|

| $V_{DDIWRITE}$ | フラッシュ書き込み動作の電源電圧                                                   |                                                  | 1.71                 | –   | 5.25                 | V    |

| $I_{DDP}$      | プログラミングまたは検証時の電源電流                                                 |                                                  | –                    | 5   | 25                   | mA   |

| $V_{ILP}$      | プログラミングまたは検証時の入力 LOW 電圧                                            | 該当する <a href="#">汎用 I/O の DC 仕様</a> の表を参照してください。 | –                    | –   | $V_{IL}$             | V    |

| $V_{IHP}$      | プログラミングまたは検証時の入力 HIGH 電圧                                           |                                                  | 1.71                 | –   | $V_{DDIWRITE} + 0.3$ | V    |

| $I_{ILP}$      | プログラミングまたは検証時に P1[0] または P1[1] に Vilp を入力したときの入力電流 <sup>[13]</sup> |                                                  | –                    | –   | 0.2                  | mA   |

| $I_{IHP}$      | プログラミングまたは検証時に P1[0] または P1[1] に Vihp を入力したときの入力電流 <sup>[13]</sup> |                                                  | –                    | –   | 1.5                  | mA   |

| $V_{OLP}$      | プログラミングまたは検証時の出力 LOW 電圧                                            |                                                  | –                    | –   | $V_{SS} + 0.75$      | V    |

| $V_{OHP}$      | プログラミングまたは検証時の出力 HIGH 電圧                                           |                                                  | $V_{DDIWRITE} - 0.9$ | –   | $V_{DDIWRITE}$       | V    |

| $Flash_{ENPB}$ | フラッシュ書き込み耐久性 <sup>[14]</sup>                                       |                                                  | 50,000               | –   | –                    | サイクル |

| $Flash_{DR}$   | フラッシュのデータ保存期間 <sup>[15]</sup>                                      |                                                  | 10                   | 20  | –                    | 年    |

### 注

12. 電源電圧低下に備え、必ず  $V_{PPOR}$  (PORLEV = 10) +50 mV を上回る値とします。

13. 内部プルダウン抵抗を駆動する電流。

14. ブロックあたりの消去／書き込みの回数。

15. Tamb = 55 °C および Tj = 70 °C でのフラッシュ書き込み最大回数に従います。

## AC 電気的特性

### チップ レベルの AC 仕様

以下の表に、電圧範囲および温度範囲全体で保証されている最大値と最小値の仕様を示します。

表 12. チップ レベルの AC 仕様

| 記号                     | 説明                                               | 条件                    | 最小値  | 標準値 | 最大値  | 単位   |

|------------------------|--------------------------------------------------|-----------------------|------|-----|------|------|

| F <sub>CPU</sub>       | 処理周波数 <sup>[16]</sup>                            |                       | 5.7  | —   | 25.2 | MHz  |

| F <sub>32K1</sub>      | 内部低速発振器 (ILO) 周波数                                | トリムあり <sup>[17]</sup> | 19   | 32  | 50   | kHz  |

| F <sub>32K_U</sub>     | 内部低速発振器 (ILO) のトリムなし周波数                          |                       | 13   | 32  | 82   | kHz  |

| F <sub>32K2</sub>      | 内部低速発振器 (ILO) 周波数                                | トリムなし                 | 13   | 32  | 82   | kHz  |

| F <sub>IMO24</sub>     | 24 MHz ± 5% での内部メイン発振器 (IMO) 安定性 <sup>(12)</sup> |                       | 22.8 | 24  | 25.2 | MHz  |

| F <sub>IMO12</sub>     | 12 MHz での内部メイン発振器 (IMO) 安定性 <sup>[17]</sup>      |                       | 11.4 | 12  | 12.6 | MHz  |

| F <sub>IMO6</sub>      | 6 MHz での内部メイン発振器 (IMO) 安定性 <sup>[17]</sup>       |                       | 5.7  | 6.0 | 6.3  | MHz  |

| DC <sub>IMO</sub>      | IMO のデューティ比                                      |                       | 40   | 50  | 60   | %    |

| DC <sub>ILO</sub>      | ILO のデューティ比                                      |                       | 40   | 50  | 60   | %    |

| SR <sub>POWER_UP</sub> | 電源電圧スルーレート                                       |                       | —    | —   | 250  | V/ms |

| T <sub>XRST</sub>      | 電源オン時の外部リセットパルス幅                                 | 電源電圧が有効になった後          | 1    | —   | —    | ms   |

| T <sub>XRST2</sub>     | 電源オン後の外部リセットパルス幅 <sup>[18]</sup>                 | 製品のブート後               | 10   | —   | —    | μs   |

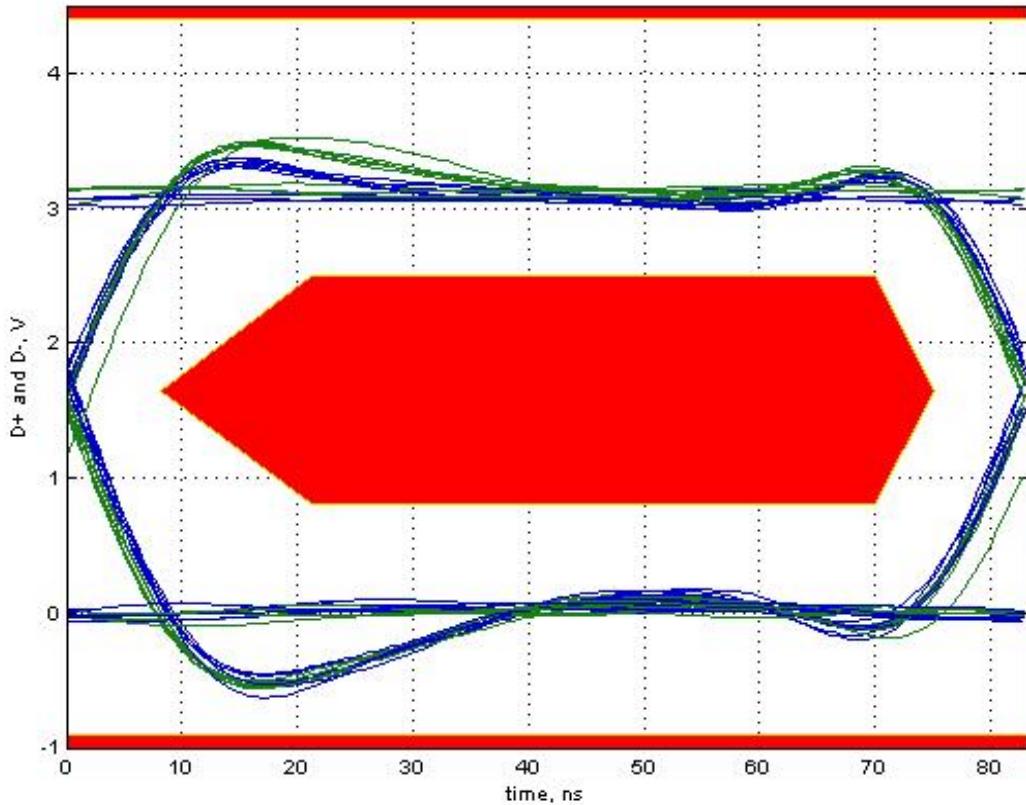

表 13. AC 特性 - USB データ タイミング

| 記号                 | 説明               | 条件        | 最小値   | 標準値 | 最大値   | 単位  |

|--------------------|------------------|-----------|-------|-----|-------|-----|

| Td <sub>rate</sub> | フルスピード データ転送速度   | 平均ビット レート | 11.97 | 12  | 12.03 | MHz |

| Tdjr1              | レシーバ データジッタ許容範囲  | 次の遷移まで    | -18.5 | —   | 18.5  | ns  |

| Tdjr2              | レシーバ データジッタ許容範囲  | ペアの遷移まで   | -9    | —   | 9     | ns  |

| Tudj1              | ドライバ差分ジッタ        | 次の遷移まで    | -3.5  | —   | 3.5   | ns  |

| Tudj2              | ドライバ差分ジッタ        | ペアの遷移まで   | -4.0  | —   | 4.0   | ns  |

| Tfdeop             | 差分遷移のソース ジッタ     | SE0 遷移まで  | -2    | —   | 5     | ns  |

| Tfeopt             | EOP のソース SE0 間隔  |           | 160   | —   | 175   | ns  |

| Tfeopr             | EOP のレシーバ SE0 間隔 |           | 82    | —   | —     | ns  |

| Tfst               | 差分遷移中の SE0 間隔の幅  |           | —     | —   | 14    | ns  |

表 14. AC 特性 - USB ドライバ

| 記号                 | 説明              | 条件    | 最小値   | 標準値 | 最大値   | 単位 |

|--------------------|-----------------|-------|-------|-----|-------|----|

| Tr                 | 立ち上り遷移時間        | 50 pF | 4     | —   | 20    | ns |

| Tf                 | 立ち下り遷移時間        | 50 pF | 4     | —   | 20    | ns |

| TR <sup>[19]</sup> | 立ち上り／立ち下り時間の一一致 |       | 90.00 | —   | 111.1 | %  |

| Vcrs               | 出力信号交差電圧        |       | 1.3   | —   | 2.0   | V  |

注

16. V<sub>DD</sub> = 3.0V および T<sub>j</sub> = 85°C での CPU 速度。

17. 工場出荷時のトリム値を使用して、3.3V 動作向けにトリム。

18. デバイスのプログラミングで必要な最小 XRES パルス長は、この値より長くなります (表 17 を参照)。

19. エラッタ : ポート 1 のピン P1[1], P1[4], および P1[5] の場合、この仕様を満たすには 300 オームの外部抵抗が必要です。詳細については、37 ページのエラッタを参照してください。

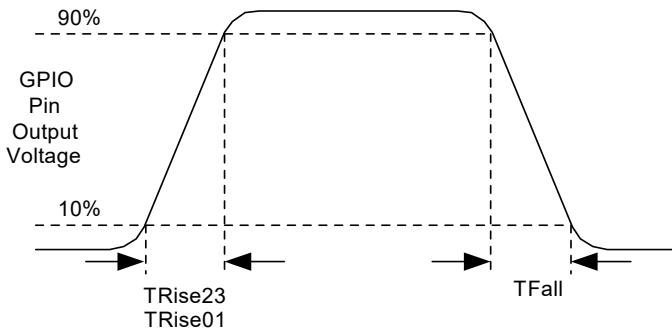

**汎用 I/O の AC 仕様**

表 15 に、すべての電圧範囲および温度範囲で保証されている最大値と最小値の仕様を示します。

**表 15. GPIO の AC 仕様**

| 記号         | 説明                                       | 条件                                              | 最小値 | 標準値 | 最大値 | 単位  |

|------------|------------------------------------------|-------------------------------------------------|-----|-----|-----|-----|

| $F_{GPIO}$ | GPIO 動作周波数                               | 通常の Strong (ストロング) モード、ポート 0、ポート 1              | –   | –   | 12  | MHz |

| TRise23    | 立ち上り時間、Strong (ストロング) モード<br>ポート 2、ポート 3 | $V_{DD} = 3.0 \sim 3.6 \text{ V},$<br>10% ~ 90% | 15  | –   | 80  | ns  |

| TRise01    | 立ち上り時間、Strong (ストロング) モード<br>ポート 0、ポート 1 | $V_{DD} = 3.0 \sim 3.6 \text{ V},$<br>10% ~ 90% | 10  | –   | 50  | ns  |

| TFall      | 立ち下り時間、Strong (ストロング) モード<br>全ポート        | $V_{DD} = 3.0 \sim 3.6 \text{ V},$<br>10% ~ 90% | 10  | –   | 50  | ns  |

**図 11. GPIO タイミング図**

**外部クロックの AC 仕様**

表 16 に、すべての電圧範囲および温度範囲で保証されている最大値と最小値の仕様を示します。

**表 16. 外部クロックの AC 仕様**

| 記号           | 説明           | 条件 | 最小値   | 標準値 | 最大値  | 単位            |

|--------------|--------------|----|-------|-----|------|---------------|

| $F_{OSCEXT}$ | 周波数          |    | 0.750 | –   | 25.2 | MHz           |

| –            | HIGH 期間      |    | 20.6  | –   | 5300 | ns            |

| –            | LOW 期間       |    | 20.6  | –   | –    | ns            |

| –            | IMO への切り替え時間 |    | 150   | –   | –    | $\mu\text{s}$ |

### プログラミングの AC 仕様

表 17 に、すべての電圧範囲および温度範囲で保証されている最大値と最小値の仕様を示します。

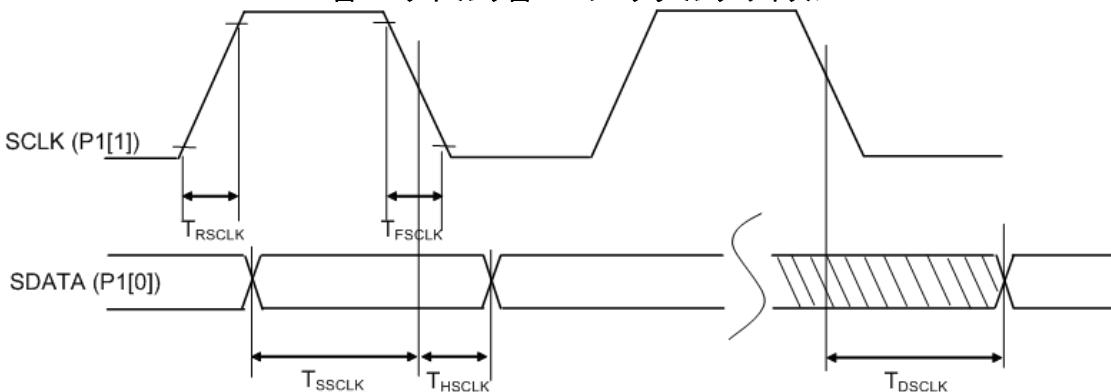

表 17. プログラミングの AC 仕様

| 記号           | 説明                          | 条件                                       | 最小値 | 標準値 | 最大値 | 単位            |

|--------------|-----------------------------|------------------------------------------|-----|-----|-----|---------------|

| $T_{RSCLK}$  | SCLK の立ち上り時間                |                                          | 1   | –   | 20  | ns            |

| $T_{FSCLK}$  | SCLK の立ち下り時間                |                                          | 1   | –   | 20  | ns            |

| $T_{SSCLK}$  | SCLK の立ち下りエッジまでのデータセットアップ時間 |                                          | 40  | –   | –   | ns            |

| $T_{HSCLK}$  | SCLK の立ち下りエッジからのデータホールド時間   |                                          | 40  | –   | –   | ns            |

| $F_{SCLK}$   | SCLK の周波数                   |                                          | 0   | –   | 8   | MHz           |

| $T_{ERASEB}$ | フラッシュ消去時間 ( ブロック )          |                                          | –   | –   | 18  | ms            |

| $T_{WRITE}$  | フラッシュブロック書き込み時間             |                                          | –   | –   | 25  | ms            |

| $T_{DSCLK1}$ | SCLK の立ち下りエッジからのデータ出力遅延     | $V_{DD} > 3.6 \text{ V}$                 | –   | –   | 60  | ns            |

| $T_{DSCLK2}$ | SCLK の立ち下りエッジからのデータ出力遅延     | $3.0 \text{ V} < V_{DD} < 3.6 \text{ V}$ | –   | –   | 85  | ns            |

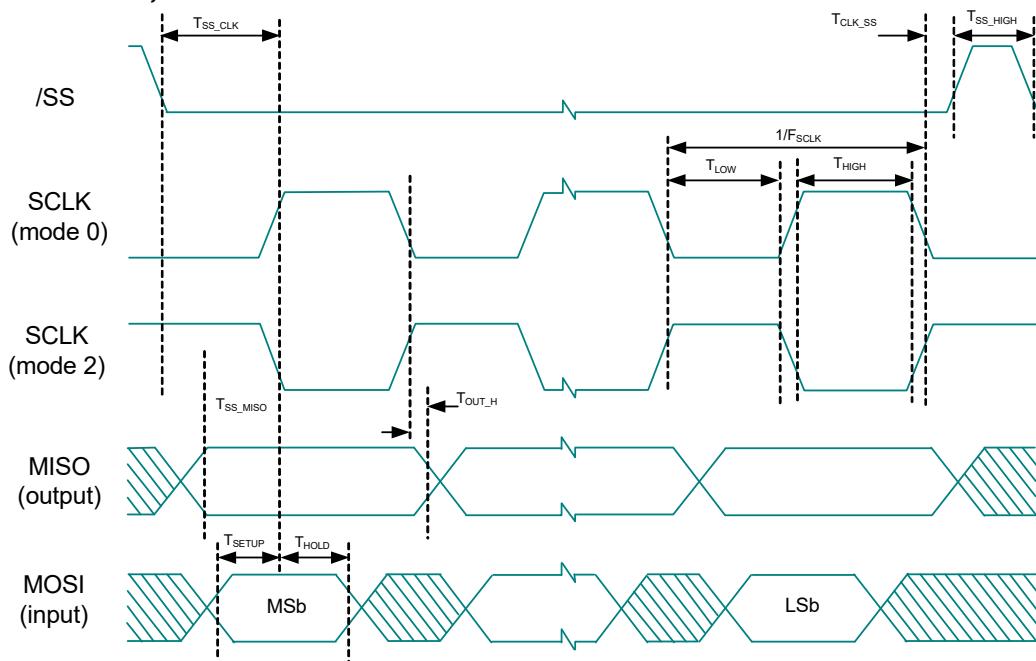

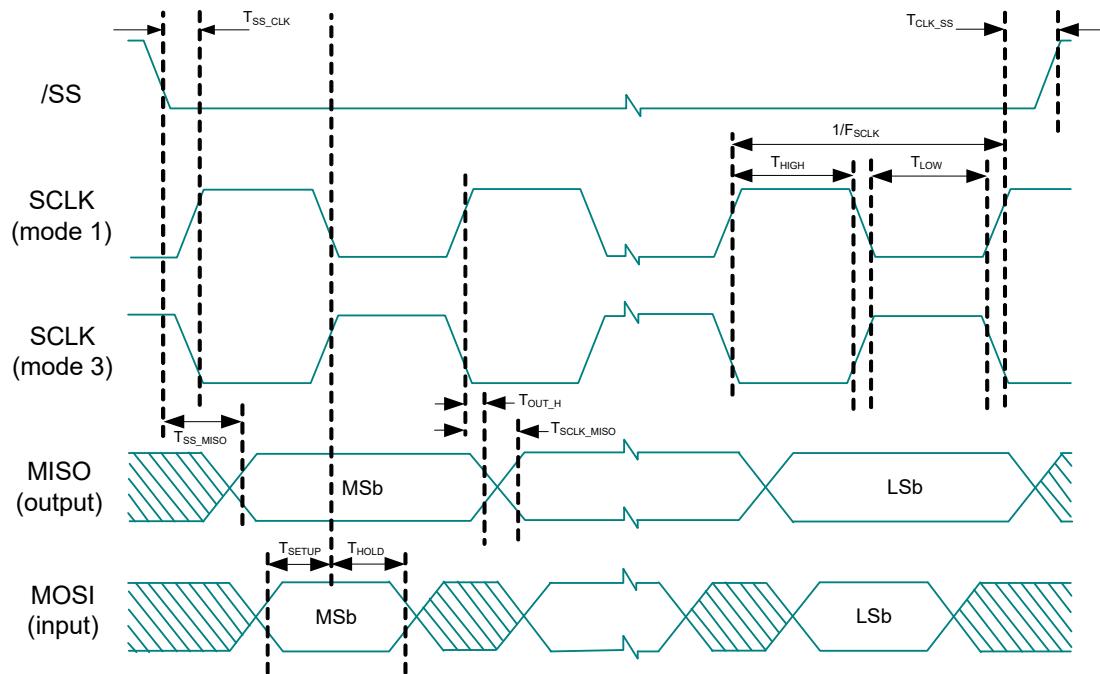

| $T_{XRST3}$  | 電源オン後の外部リセットパルス幅            | スリープから復帰してプログラミングモードに入るために必要             | 263 | –   | –   | $\mu\text{s}$ |