#### **Features**

- Integrated state machine for low-power and real time operation

- · Flexible frame definition enabled by hardware sequencer

- 60 GHz radar with 7 GHz bandwidth and ramp speed up to 700 MHz/μs

- Embedded SAR ADCs with 20 MSps

- Antenna in Package (AiP) with ±60° FoV

## **Potential Applications**

- Presence detection, segmentation and tracking for smart home devices such as TV's, monitors, smart speakers, air conditioners and doorbell applications

- Vital sign tracking for health care devices, such as sleep trackers and baby monitors

- Gesture sensing for smart appliances such as kitchen machines or thermostats

#### **Product Validation**

Qualified for applications listed above based on the test conditions in the relevant tests of JEDEC JESD47.

#### **Description**

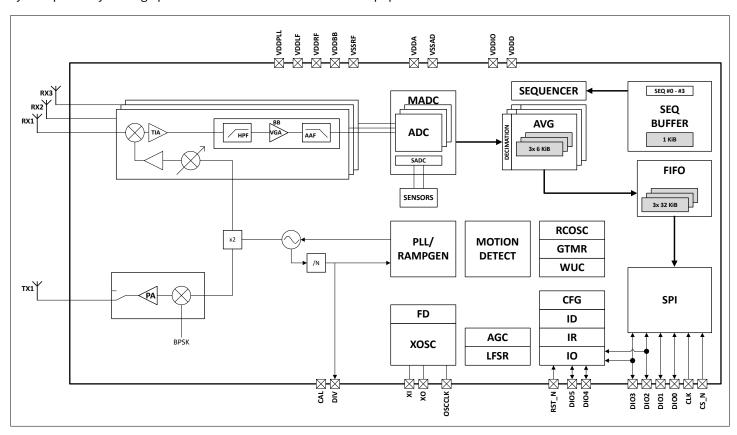

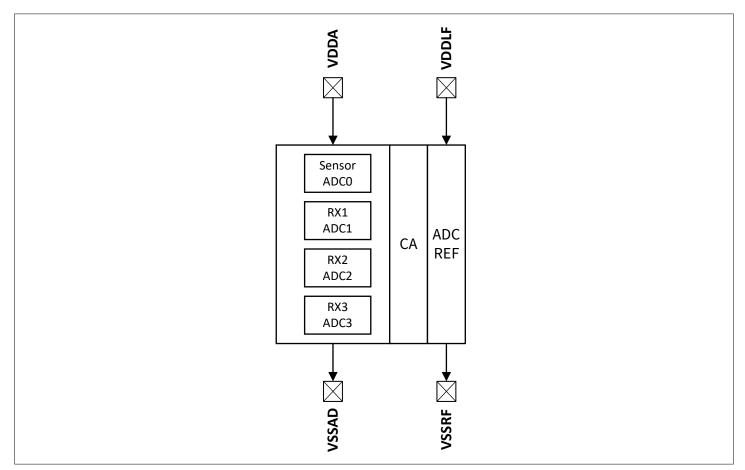

The CMOS radar, a 60 GHz radar sensor with antenna in package, provides ultra-wide bandwidth FMCW operation with a single chip solution inside a small package. Sensor configuration, data acquisition trigger and data transfer are enabled by a digital interface so called Serial Peripheral Interface (SPI). An integrated hardware sequencer together with a finite state machine (FSM) offers full flexibility to the user defining configurable chirps and timings while ensuring cycle accurate data acquisition with lowest power consumption. The embedded motion/presence detection block with low false alarm rate reduces further the system power by waking up external hosts via a dedicated interrupt pin.

**BGT60CUTR13AIP simplified block diagram**

## **Preliminary Target Datasheet**

Table of contents

## **Table of contents**

|       | Table of contents                        |

|-------|------------------------------------------|

| 1     | Pin Configuration                        |

| 1.1   | Pin Assignment                           |

| 1.2   | Pin Definitions and Functions            |

| 2     | General Product Characteristics          |

| 2.1   | Absolute Maximum Ratings                 |

| 2.2   | Functional Range                         |

| 2.3   | Thermal Resistance                       |

| 2.4   | Current Consumption                      |

| 2.4.1 | Current Consumption Overall 1.2 V Domain |

| 2.4.2 | Current Consumption Overall 1.8 V Domain |

| 2.4.3 | Current Consumption IO Domain            |

| 2.4.4 | Current Consumption D Domain             |

| 2.4.5 | Current Consumption A Domain             |

| 2.4.6 | Current Consumption PLL Domain           |

| 2.4.7 | Current Consumption RF Domain            |

| 2.4.8 | Current Consumption BB Domain            |

| 2.4.9 | Current Consumption LF Domain            |

| 2.5   | ESD Integrity                            |

| 2.6   | Extended Temperature Range               |

| 3     | IO                                       |

| 3.1   | DIO                                      |

| 3.1.1 | Electrical Characteristics DIO           |

| 3.2   | Reset                                    |

| 3.2.1 | Electrical Characteristics RESET         |

| 3.3   | SPI                                      |

| 3.3.1 | Standard Timing                          |

| 3.3.2 | High Speed Timing                        |

| 3.3.3 | Electrical Characteristics               |

| 3.3.4 | SPI Operation Modes                      |

| 4     | <b>XOSC</b>                              |

| 4.1   | Overview                                 |

| 4.2   | XOSC Parameters                          |

| 5     | RCOSC                                    |

| 5.1   | RCOSC Parameters                         |

| 6     | PLL                                      |

| 6.1   | PLL Parameters                           |

| 6.1.1 | Settling Time                            |

| 0.1.1 | Section 5 mile                           |

V0.50

## **Preliminary Target Datasheet**

## Table of contents

|        | Disclaimer                          | 30 |

|--------|-------------------------------------|----|

| 12     | Revision History                    | 38 |

| 11     | Terms and Abbreviations             | 35 |

| 10.2.1 | Built-in Antenna Parameters         | 33 |

| 10.2   | Built-in Antenna Specification      | 33 |

| 10.1   | Package                             | 31 |

| 10     | Package Information                 | 31 |

| 9.2    | ADC Parameters                      | 29 |

| 9.1    | Overview                            | 29 |

| 9      | ADC                                 | 29 |

| 8.4    | Analog Baseband AAF Parameters      | 27 |

| 8.3    | Analog Baseband Gain Parameters     | 27 |

| 8.2    | Analog Baseband HPF Parameters      | 27 |

| 8.1    | Analog Baseband Current Consumption | 26 |

| 8      | Analog Baseband                     | 26 |

| 7.2    | On-chip Sensor Parameters           | 25 |

| 7.1    | RF FE Parameters                    | 24 |

| 7      | RF Frontend                         | 24 |

| 6.1.2  | Ramp Linearity                      | 23 |

V0.50

1 Pin Configuration

## **1** Pin Configuration

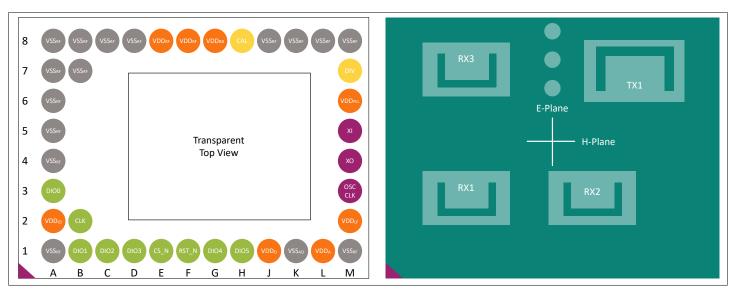

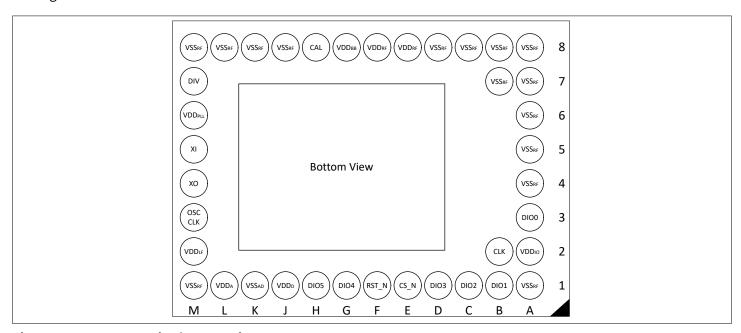

The following Figure 1 shows the transparent top view of laminate package with the pin and antenna number assignment.

## 1.1 Pin Assignment

Figure 1 BGT60CUTR13AIP pin out in bottom view (left) and antenna numbers assignment in top view (right)

| Ball | Symbol            |

|------|-------------------|

| A1   | VSS <sub>RF</sub> |

| A2   | VDD <sub>IO</sub> |

| A3   | DIO0              |

| A4   | VSS <sub>RF</sub> |

| A5   | VSS <sub>RF</sub> |

| A6   | VSS <sub>RF</sub> |

| A7   | VSS <sub>RF</sub> |

| A8   | VSS <sub>RF</sub> |

| B1   | DIO1              |

| B2   | CLK               |

| B7   | VSS <sub>RF</sub> |

| B8   | VSS <sub>RF</sub> |

| C1   | DIO2              |

| C8   | VSS <sub>RF</sub> |

| D1   | DIO3              |

| D8   | VSS <sub>RF</sub> |

| E1   | CS_N              |

| E8   | VDD <sub>RF</sub> |

## **Preliminary Target Datasheet**

1 Pin Configuration

| F1 | RST_N              |

|----|--------------------|

| F8 | VDD <sub>RF</sub>  |

| G1 | DIO4               |

| G8 | VDD <sub>BB</sub>  |

| H1 | DIO5               |

| H8 | CAL                |

| J1 | VDD <sub>D</sub>   |

| J8 | VSS <sub>RF</sub>  |

| K1 | VSS <sub>AD</sub>  |

| K8 | VSS <sub>RF</sub>  |

| L1 | VDD <sub>A</sub>   |

| L8 | VSS <sub>RF</sub>  |

| M1 | VSS <sub>RF</sub>  |

| M2 | $VDD_LF$           |

| M3 | OSCCLK             |

| M4 | ХО                 |

| M5 | XI                 |

| M6 | VDD <sub>PLL</sub> |

| M7 | DIV                |

| M8 | VSS <sub>RF</sub>  |

|    | I                  |

## 1.2 Pin Definitions and Functions

| Symbol             | Package | Direction | Туре   | Domain | Description                |

|--------------------|---------|-----------|--------|--------|----------------------------|

| Supply pins        |         |           |        |        |                            |

| VDD <sub>D</sub>   | Yes     | Input     | Power  | Supply | Supply for digital LDO     |

| VDD <sub>PLL</sub> | Yes     | Input     | Power  | Supply | Supply for PLL             |

| VDD <sub>LF</sub>  | Yes     | Input     | Power  | Supply | Supply for PLL loop filter |

| VDD <sub>A</sub>   | Yes     | Input     | Power  | Supply | Supply for ADC             |

| VDD <sub>BB</sub>  | Yes     | Input     | Power  | Supply | Supply for BB              |

| VDD <sub>RF</sub>  | Yes     | Input     | Power  | Supply | Supply for RF              |

| VDD <sub>IO</sub>  | Yes     | Input     | Power  | Supply | Supply for IO pads         |

| VSS <sub>RF</sub>  | Yes     | Input     | Ground | Supply | Ground for PLL and RF      |

| VSS <sub>AD</sub>  | Yes     | Input     | Ground | Supply | Ground for ADC and digital |

## **Preliminary Target Datasheet**

1 Pin Configuration

| Antenna pins | i    |                 |         |    |                                                                |

|--------------|------|-----------------|---------|----|----------------------------------------------------------------|

| Test pins    |      |                 |         |    |                                                                |

| DIV          | Yes  | Output          | Analog  | RF | Divided VCO output                                             |

| CAL          | Yes  | Input           | Analog  | ВВ | PD calibration                                                 |

| Input output | pins |                 |         |    |                                                                |

| XI           | Yes  | Input           | Analog  | LF | XOSC input (XTAL)<br>or clock input for<br>external oscillator |

| XO           | Yes  | Output          | Analog  | LF | XOSC output (XTAL)                                             |

| OSCCLK       | Yes  | Output          | Analog  | LF | XOSC output clock                                              |

| RST_N        | Yes  | Input           | Digital | Ю  | Chip reset (active low)                                        |

| CS_N         | Yes  | Input           | Digital | Ю  | SPI chip select (active low)                                   |

| CLK          | Yes  | Input           | Digital | Ю  | SPI clock                                                      |

| DIO0         | Yes  | Input<br>Output | Digital | Ю  | SPI MOSI or SPI<br>IO0                                         |

| DIO1         | Yes  | Input<br>Output | Digital | Ю  | SPI MISO or SPI<br>IO1                                         |

| DIO2         | Yes  | Input<br>Output | Digital | Ю  | DIO or SPI IO2                                                 |

| DIO3         | Yes  | Input<br>Output | Digital | Ю  | DIO or SPI IO3                                                 |

| DIO4         | Yes  | Input<br>Output | Digital | 10 | DIO                                                            |

| DIO5         | Yes  | Input<br>Output | Digital | Ю  | DIO                                                            |

#### **Preliminary Target Datasheet**

2 General Product Characteristics

## **2** General Product Characteristics

## 2.1 Absolute Maximum Ratings

#### Table 1 Absolute maximum ratings

All voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter              | Symbol                   | Values |      |      | Unit | Note or condition |

|------------------------|--------------------------|--------|------|------|------|-------------------|

|                        |                          | Min.   | Тур. | Max. |      |                   |

| RF input power level   | $P_{RF}$                 | -      | -    | 7    | dBm  | At RX input port  |

| Storage<br>temperature | $T_{\rm stg}$            | -40    | -    | 150  | °C   | -                 |

| Supply                 |                          |        |      |      |      | ·                 |

| Supply Digital         | <i>VDD</i> <sub>D</sub>  | -0.3   | -    | 1.32 | V    | -                 |

| Supply PLL             | VDD <sub>PLL</sub>       | -0.3   | -    | 1.32 | V    | -                 |

| Supply Loop<br>Filter  | VDD <sub>LF</sub>        | -0.3   | -    | 2    | V    | -                 |

| Supply ADC             | <i>VDD</i> <sub>A</sub>  | -0.3   | -    | 2    | V    | -                 |

| Supply Base<br>Band    | <i>VDD</i> <sub>BB</sub> | -0.3   | -    | 2    | V    | -                 |

| Supply RF              | <i>VDD</i> <sub>RF</sub> | -0.3   | -    | 1.32 | V    | -                 |

| Supply IO              | VDD <sub>IO</sub>        | -0.3   | -    | 2    | V    | -                 |

| Functional             |                          | ·      |      |      |      |                   |

| Chip Reset             | RST_N                    | -0.3   | -    | 2    | V    | -                 |

| SPI Chip Select        | CS_N                     | -0.3   | -    | 2    | V    | -                 |

| SPI Clock              | CLK                      | -0.3   | -    | 2    | V    | -                 |

| Digital IO             | DIO                      | -0.3   | -    | 2    | V    | -                 |

| XTAL input             | XI                       | -0.2   | -    | 1.89 | V    | DC                |

| XTAL output            | ХО                       | -0.2   | -    | 1.89 | V    | DC                |

| Oscillator clock out   | OSCCLK                   | -0.2   | -    | 1.15 | V    | AC                |

| Test                   |                          | '      | •    |      |      |                   |

| RF Divider             | DIV                      | -0.4   | -    | 1.15 | V    | AC                |

| Calibration            | CAL                      | -0.3   | -    | 2    | V    | -                 |

Attention:

Stresses above the maximum values listed here may cause permanent damage to the device. Maximum ratings are absolute ratings; exceeding only one of these values may cause irreversible damage to the integrated circuit. Exposure to conditions at or below absolute maximum rating but above the specified maximum operation conditions may affect device reliability and lifetime. Functionality of the device might not be given under these conditions.

## **Preliminary Target Datasheet**

2 General Product Characteristics

#### **Functional Range** 2.2

Table 2 **Functional range**

| Parameter                    | Symbol                   |      | Values |       |     | Note or condition                                                                           |  |  |

|------------------------------|--------------------------|------|--------|-------|-----|---------------------------------------------------------------------------------------------|--|--|

|                              |                          | Min. | Тур.   | Max.  |     |                                                                                             |  |  |

| Backside<br>temperature      | T <sub>b</sub>           | -20  | -      | 85    | °C  | Measured with the on-chip temperature sensor                                                |  |  |

| Frequency range              | $f_{RF}$                 | 57   | -      | 63.36 | GHz | MASH3 3rd order (SDMALGO_SEL=2 <sub>D</sub> ) Phase noise and chirp linearity optimized     |  |  |

| Frequency<br>range           | $f_{RF}$                 | 57   | -      | 64    | GHz | Rhee/DeMuer 3rd order (SDMALGO_SEL=0 <sub>D</sub> ) Bandwidth and best resolution optimized |  |  |

| System clock<br>frequency    | $f_{SYSCLK}$             | 75   | 80     | 85    | MHz |                                                                                             |  |  |

| Low power<br>clock frequency | $f_{RCOSC}$              | 71   | 80     | 84    | kHz |                                                                                             |  |  |

| Supply                       |                          |      |        |       |     |                                                                                             |  |  |

| Supply Digital               | $VDD_{D}$                | 1.14 | 1.2    | 1.26  | V   | ± 5 %                                                                                       |  |  |

| Supply PLL                   | VDD <sub>PLL</sub>       | 1.14 | 1.2    | 1.26  | V   | ± 5 %                                                                                       |  |  |

| Supply Loop<br>Filter        | <i>VDD</i> <sub>LF</sub> | 1.71 | 1.8    | 1.89  | V   | ± 5 %                                                                                       |  |  |

| Supply ADC                   | <i>VDD</i> <sub>A</sub>  | 1.71 | 1.8    | 1.89  | V   | ± 5 %                                                                                       |  |  |

| Supply Base<br>Band          | <i>VDD</i> <sub>BB</sub> | 1.71 | 1.8    | 1.89  | V   | ± 5 %                                                                                       |  |  |

| Supply RF                    | <i>VDD</i> <sub>RF</sub> | 1.14 | 1.2    | 1.26  | V   | ± 5 %                                                                                       |  |  |

| Supply IO 1V2                | VDD <sub>IO</sub>        | 1.14 | 1.2    | 1.26  | V   | ± 5 %                                                                                       |  |  |

| Supply IO 1V8                | VDD <sub>IO</sub>        | 1.71 | 1.8    | 1.89  | V   | ± 5 %                                                                                       |  |  |

| Ground Digital               | VSS <sub>D</sub>         | -    | 0      | -     | V   | -                                                                                           |  |  |

| Ground ADC                   | VSS <sub>A</sub>         | -    | 0      | -     | V   | -                                                                                           |  |  |

| Ground RF                    | VSS <sub>RF</sub>        | -    | 0      | -     | V   | -                                                                                           |  |  |

| Functional                   |                          |      |        |       |     |                                                                                             |  |  |

| Chip Reset                   | RST_N                    | 0    | 1.2    | 1.26  | V   | VDDIO = 1.2 V                                                                               |  |  |

| SPI Chip Select              | CS_N                     | 0    | 1.2    | 1.26  | V   | VDDIO = 1.2 V                                                                               |  |  |

| SPI Clock                    | CLK                      | 0    | 1.2    | 1.26  | V   | VDDIO = 1.2 V                                                                               |  |  |

| Digital IO                   | DIO                      | 0    | 1.2    | 1.26  | V   | VDDIO = 1.2 V                                                                               |  |  |

| XTAL input                   | XI                       | 0    | 0.9    | 0.99  | V   | -                                                                                           |  |  |

| XTAL output                  | ХО                       | 0    | 0.9    | 0.99  | V   | -                                                                                           |  |  |

| Oscillator clock out         | OSCCLK                   | 0    | 0.9    | 0.99  | V   | -                                                                                           |  |  |

(table continues...)

#### **Preliminary Target Datasheet**

**2 General Product Characteristics**

Table 2 (continued) Functional range

| Parameter   | Symbol | Values |      | /alues Unit |   | Note or condition |  |  |

|-------------|--------|--------|------|-------------|---|-------------------|--|--|

|             |        | Min.   | Тур. | Max.        |   |                   |  |  |

| Test        |        |        |      |             |   |                   |  |  |

| Calibration | CAL    | 0      | 1.8  | 1.98        | V | -                 |  |  |

Note:

Within the functional or operating range, the IC operates as described in the circuit description. The electrical characteristics are specified within the conditions given in the electrical characteristics table.

### 2.3 Thermal Resistance

#### Table 3 Thermal resistance

| Parameter                        | Symbol          | Values |      |      | Unit | Note or condition                    |

|----------------------------------|-----------------|--------|------|------|------|--------------------------------------|

|                                  |                 | Min.   | Тур. | Мах. |      |                                      |

| Package<br>thermal<br>resistance | R <sub>th</sub> | -      | 35   | -    | K/W  | Chip backside to ambient temperature |

## 2.4 Current Consumption

## 2.4.1 Current Consumption Overall 1.2 V Domain

#### Table 4 Current consumption overall 1.2 V domain

$VDD_D = VDD_{PLL} = VDD_{RF} = 1.26V$ , Tb = -20°C to +85°C

| Parameter      | Symbol                |      | Values |      | Unit | Note or condition                                    |

|----------------|-----------------------|------|--------|------|------|------------------------------------------------------|

|                |                       | Min. | Тур.   | Max. |      |                                                      |

| Idd Deep Sleep | Idd <sub>DS</sub>     | 0.02 | 0.1    | 1.8  | mA   | All off                                              |

| Idd Active     | Idd <sub>ACTIVE</sub> | 200  | 345    | 500  | mA   | XOSC active, analog modules powered up and PA active |

## 2.4.2 Current Consumption Overall 1.8 V Domain

## Table 5 Current consumption overall 1.8 V domain

$VDD_{1O} = VDD_{LF} = VDD_{A} = VDD_{BB} = 1.89V$ , Tb = -20°C to +85°C

| Parameter      | Symbol                       | Values |       |       | Unit | Note or condition                                    |

|----------------|------------------------------|--------|-------|-------|------|------------------------------------------------------|

|                |                              | Min.   | Тур.  | Max.  |      |                                                      |

| Idd Deep Sleep | Idd <sub>DS</sub>            | 0      | 0.000 | 0.004 | mA   | All off                                              |

| Idd Active     | <i>Idd</i> <sub>ACTIVE</sub> | 20     | 100   | 150   | mA   | XOSC active, analog modules powered up and PA active |

V0.50

**2 General Product Characteristics**

## 2.4.3 Current Consumption IO Domain

#### Table 6 Current consumption supply domain VDDIO

$VDD_D = VDD_{PLL} = VDD_{RF} = 1.26V$ ,  $VDD_{IO} = VDD_{LF} = VDD_A = VDD_{BB} = 1.89V$ ,  $Tb = -20^{\circ}C$  to  $+85^{\circ}C$

| Parameter      | Symbol Values                |      | Unit  | Note or condition |    |   |

|----------------|------------------------------|------|-------|-------------------|----|---|

|                |                              | Min. | Тур.  | Мах.              |    |   |

| Idd Deep Sleep | Idd <sub>DS</sub>            | 0    | 0.5   | 2.5               | μΑ | - |

| Idd Active     | <i>Idd</i> <sub>ACTIVE</sub> | 0    | 0.001 | 0.002<br>5        | mA | - |

## 2.4.4 Current Consumption D Domain

#### Table 7 Current consumption supply domain VDDD

$VDD_{D} = VDD_{PLL} = VDD_{RF} = 1.26V$ ,  $VDD_{IO} = VDD_{LF} = VDD_{A} = VDD_{BB} = 1.89V$ ,  $Tb = -20^{\circ}C$  to  $+85^{\circ}C$

| Parameter      | Symbol                       | Values |      |      | Unit | Note or condition                     |

|----------------|------------------------------|--------|------|------|------|---------------------------------------|

|                |                              | Min.   | Тур. | Max. |      |                                       |

| Idd Deep Sleep | Idd <sub>DS</sub>            | 0.02   | 0.1  | 1.45 | mA   | All off                               |

| Idd Active     | <i>Idd</i> <sub>ACTIVE</sub> | 2      | 4.2  | 9    | mA   | XOSC active, sequencer and FSM active |

## 2.4.5 Current Consumption A Domain

## Table 8 Current consumption supply domain VDDA

$VDD_{D} = VDD_{PLL} = VDD_{RF} = 1.26V$ ,  $VDD_{IO} = VDD_{LF} = VDD_{A} = VDD_{BB} = 1.89V$ ,  $Tb = -20^{\circ}C$  to  $+85^{\circ}C$

| Parameter             | Symbol                     |      | Values |      |    | Note or condition                                                                   |

|-----------------------|----------------------------|------|--------|------|----|-------------------------------------------------------------------------------------|

|                       |                            | Min. | Тур.   | Max. |    |                                                                                     |

| Idd Deep Sleep        | <i>Idd</i> <sub>DS</sub>   | 0    | 0.013  | 1.5  | μΑ | All off                                                                             |

| Idd Idle              | <i>Idd</i> <sub>IDLE</sub> | 13.3 | 14.6   | 15.6 | mA | MADC (4 ADC) powered up, no conversion, inactive.<br>Values verified by CV over DoE |

| Idd Active 4<br>ADC's | Idd <sub>ACTIVE</sub>      | 13.9 | 15.2   | 16.2 | mA | ADC active and converting (20 MSps)                                                 |

## 2.4.6 Current Consumption PLL Domain

#### Table 9 Current consumption supply domain VDDPLL

$VDD_{\rm D} = VDD_{\rm PLL} = VDD_{\rm RF} = 1.26 \text{V}, VDD_{\rm IO} = VDD_{\rm LF} = VDD_{\rm A} = VDD_{\rm BB} = 1.89 \text{V}, Tb = -20 ^{\circ}\text{C} \text{ to } +85 ^{\circ}\text{C}$

| Parameter      | Symbol                       | Values |      |       | Unit | Note or condition |

|----------------|------------------------------|--------|------|-------|------|-------------------|

|                |                              | Min.   | Тур. | Max.  |      |                   |

| Idd Deep Sleep | <i>Idd</i> <sub>DS</sub>     | 0.015  | 0.20 | 75.50 | μΑ   | -                 |

| Idd Active     | <i>Idd</i> <sub>Active</sub> | 50     | 86   | 108   | mA   | -                 |

V0.50

#### **Preliminary Target Datasheet**

**2 General Product Characteristics**

## 2.4.7 Current Consumption RF Domain

#### Table 10 Current consumption supply domain VDDRF

$VDD_{D} = VDD_{PLL} = VDD_{RF} = 1.26V$ ,  $VDD_{IO} = VDD_{LF} = VDD_{A} = VDD_{BB} = 1.89V$ ,  $Tb = -20^{\circ}C$  to  $+85^{\circ}C$

| Parameter       | Symbol                       |      | Values |      | Unit | Note or condition                                       |

|-----------------|------------------------------|------|--------|------|------|---------------------------------------------------------|

|                 |                              | Min. | Тур.   | Мах. |      |                                                         |

| Idd Deep Sleep  | <i>Idd</i> <sub>DS</sub>     | 0    | 0.40   | 62   | μΑ   | -                                                       |

| Idd Idle        | <i>Idd</i> <sub>IDLE</sub>   | 0.9  | 1.2    | 1.5  | mA   | Powered up, PA inactive. Values verified by CV over DoE |

| Idd Active 3 RX | <i>Idd</i> <sub>ACTIVE</sub> | 150  | 255    | 303  | mA   | PA active                                               |

## 2.4.8 Current Consumption BB Domain

## Table 11 Current consumption supply domain VDDBB

$VDD_{\rm D} = VDD_{\rm PLL} = VDD_{\rm RF} = 1.26 \text{V}, VDD_{\rm IO} = VDD_{\rm LF} = VDD_{\rm A} = VDD_{\rm BB} = 1.89 \text{V}, Tb = -20 ^{\circ}\text{C} \text{ to } +85 ^{\circ}\text{C}$

| Parameter            | Symbol                       |      | Values |      | Unit | Note or condition                                               |

|----------------------|------------------------------|------|--------|------|------|-----------------------------------------------------------------|

|                      |                              | Min. | Тур.   | Max. |      |                                                                 |

| Idd Deep Sleep       | <i>Idd</i> <sub>DS</sub>     | 0    | 0.20   | 22   | μΑ   | -                                                               |

| Idd Idle             | Idd <sub>IDLE</sub>          | 0.5  | 0.8    | 1.1  | mA   | Power up, RF/BB blocks inactive. Values verified by CV over DoE |

| Idd Active 2<br>BB's | <i>Idd</i> <sub>ACTIVE</sub> | 36   | 44     | 54   | mA   | BB blocks active. Values verified by CV over DoE                |

| Idd Active 3<br>BB's | <i>Idd</i> <sub>ACTIVE</sub> | 35   | 59     | 77   | mA   | BB blocks active                                                |

## 2.4.9 Current Consumption LF Domain

### Table 12 Current consumption supply domain VDDLF

$VDD_{\rm D} = VDD_{\rm PLL} = VDD_{\rm RF} = 1.26 \text{V}, VDD_{\rm IO} = VDD_{\rm LF} = VDD_{\rm A} = VDD_{\rm BB} = 1.89 \text{V}, Tb = -20 ^{\circ} \text{C} \text{ to } +85 ^{\circ} \text{C}$

| Parameter      | Symbol                       | Values |      |      | Unit | Note or condition   |

|----------------|------------------------------|--------|------|------|------|---------------------|

|                |                              | Min.   | Тур. | Max. |      |                     |

| Idd Deep Sleep | <i>Idd</i> <sub>DS</sub>     | 0      | 0.04 | 6    | μΑ   |                     |

| Idd Active     | <i>Idd</i> <sub>ACTIVE</sub> | 4.5    | 9    | 14.4 | mA   | OSCCLK pad disabled |

#### **Preliminary Target Datasheet**

2 General Product Characteristics

## 2.5 ESD Integrity

Table 13 ESD integrity

| Parameter Symbol       |                      |       | Values |      |   | Note or condition   |

|------------------------|----------------------|-------|--------|------|---|---------------------|

|                        |                      | Min.  | Тур.   | Max. |   |                     |

| ESD robustness,<br>HBM | V <sub>ESD-HBM</sub> | -2000 | -      | 2000 | V | According to JS-001 |

| ESD robustness,        | V <sub>ESD-CDM</sub> | -500  | -      | 500  | V | According to JS-002 |

Note:

CDM: Field-Induced Charged-Device Model ANSI/ESDA/JEDEC JS-002. Simulates charging/discharging events that occur in production equipment and processes. Potential for CDM ESD events occurs whenever there is metal-to-metal contact in manufacturing.

HBM: Human Body Model ANSI/ESDA/JEDEC JS-001 (R = 1.5 k $\Omega$ , C = 100 pF).

## 2.6 Extended Temperature Range

The device is stressed during qualification up to 125°C junction temperature. The stress due to higher temperature range does not damage the functionality of the device. It has been characterized up to +105°C backside temperature (which implies a junction temperature of ~125°C, ~20K higher). The effect of the extended temperature range leads to a degradation of several parameters, including transmitter output power, receiver conversion gain, PLL locking range, etc. Thus, a drop of the performance has to be expected. An overview is reported in the table below for the most important parameters (deviation vs typ values at room temperature).

Table 14 Extended temperature range parameters

| Parameter                                       | Symbol                    |      | Values |      | Unit | Note or condition      |

|-------------------------------------------------|---------------------------|------|--------|------|------|------------------------|

|                                                 |                           | Min. | Тур.   | Мах. |      |                        |

| Drop of transmit output power                   | $P_{TX}$                  | TBD  | 2      | TBD  | dB   | T <sub>b</sub> = 105°C |

| Increase of receiver NFssb @1 MHz               | NFSSB <sub>RX_1MH</sub> z | TBD  | 2      | TBD  | dB   | T <sub>b</sub> = 105°C |

| Increase of PLL<br>phase noise @<br>1MHz offset | PN <sub>PLL_1MHz</sub>    | TBD  | 3      | TBD  | dB   | T <sub>b</sub> = 105°C |

| Reduction of PLL locking range                  | PLL_BW                    | TBD  | +/-0.5 | TBD  | GHz  | T <sub>b</sub> = 105°C |

| Increase of<br>VDDD domain<br>Idd Deep Sleep    | VDDD_Idd <sub>DS</sub>    | TBD  | TBD    | TBD  | μΑ   | T <sub>b</sub> = 105°C |

| Drop of conversion gain                         | CG <sub>RX</sub>          | TBD  | 1.5    | TBD  | dB   | T <sub>b</sub> = 105°C |

## 3 10

#### 3.1 DIO

For control and communication purposes, the device comes with several digital input output (DIO) pins. Some of them are fixed to a certain functionality while others could be flexible mapped to the specific functionality required by the application.

### 3.1.1 Electrical Characteristics DIO

Table 15 Electrical characteristics DIO

| Parameter                              | Symbol               |                            | Values                                                      |                            |    | Note or condition                                               |

|----------------------------------------|----------------------|----------------------------|-------------------------------------------------------------|----------------------------|----|-----------------------------------------------------------------|

|                                        |                      | Min.                       | Тур.                                                        | Max.                       |    |                                                                 |

| Input                                  |                      |                            |                                                             |                            | •  |                                                                 |

| Low level                              | V <sub>IL</sub>      | 0                          | _                                                           | 0.3 *<br>VDD <sub>IO</sub> | V  | -                                                               |

| High level                             | V <sub>IH</sub>      | 0.7 *<br>VDD <sub>IO</sub> | -                                                           | VDD <sub>IO</sub>          | V  | -                                                               |

| Minimum<br>hysteresis<br>voltage range | V <sub>HYST</sub>    | 0.1                        | -                                                           | -                          | V  | V <sub>HSYST_H</sub> - V <sub>HYST_L</sub> , Verified by design |

| Lower<br>hysteresis level              | V <sub>HYST_L</sub>  | 0.3 *<br>VDD <sub>IO</sub> | 0.5 *<br>VDD <sub>IO</sub><br>-<br>V <sub>HYST</sub> /<br>2 | -                          | V  | Verified by design                                              |

| Upper<br>hysteresis level              | V <sub>HYST_H</sub>  | -                          | 0.5 *<br>VDD <sub>IO</sub><br>+<br>V <sub>HYST</sub> /<br>2 | 0.7 *<br>VDD <sub>IO</sub> | V  | Verified by design                                              |

| Output                                 |                      |                            |                                                             |                            |    |                                                                 |

| Maximum load                           | $C_{LOAD}$           | -                          | -                                                           | 15                         | pF | -                                                               |

| Current                                |                      |                            |                                                             |                            |    |                                                                 |

| Pull-up current                        | I <sub>PU</sub>      | 0                          | -                                                           | 15                         | uA | VDD <sub>IO</sub> = 1.8 V, Verified by design                   |

| Pull-down<br>current                   | I <sub>PD</sub>      | 0                          | -                                                           | 30                         | uA | VDD <sub>IO</sub> = 1.8 V, Verified by design                   |

| Leakage                                | I <sub>LEAKAGE</sub> | 0                          | -                                                           | 1                          | uA | No pin activity                                                 |

## 3.2 Reset

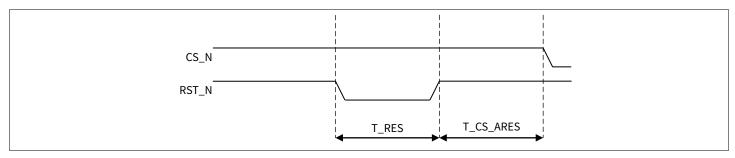

For a proper operation the device must be set to a defined state. This is done by applying an asynchronous hardware reset to the complete circuitry.

2025-10-09

After all supply voltages are settled and stable at the device input, the RST\_N pin must be driven to a low level for at least the minimum T RES time. Figure 2 illustrates the hardware reset sequence.

Figure 2 Hardware reset sequence

#### 3.2.1 Electrical Characteristics RESET

Table 16 Electrical characteristics RESET

| Parameter             | Symbol               |                   | Values |                   | Unit | Note or condition  |  |

|-----------------------|----------------------|-------------------|--------|-------------------|------|--------------------|--|

|                       |                      | Min.              | Тур.   | Мах.              |      |                    |  |

| Low level             | V <sub>IL</sub>      | 0                 | -      |                   | V    | -                  |  |

|                       |                      |                   |        | 0.3 *             |      |                    |  |

|                       |                      |                   |        | VDD <sub>IO</sub> |      |                    |  |

| High level            | $V_{IH}$             | 0.7 *             | -      | $VDD_{IO}$        | V    | -                  |  |

|                       |                      | VDD <sub>IO</sub> |        |                   |      |                    |  |

| Time for active reset | $T_{RES}$            | 300               | -      | -                 | ns   | Verified by design |  |

| Time CS after reset   | T <sub>CS_ARES</sub> | 5                 | -      | -                 | μs   | Verified by design |  |

#### 3.3 SPI

For communication with the device, a serial peripheral interface (SPI) with mode 0 is provided. It is used to configure the chip in order to operate in the targeted mode and read out the captured sensor data.

The device features up to six DIO pins for SPI communication whereby four of them are fixed in terms of functionality and two of them flexible programmable based on the application needs.

- CS N to be connected to SS of the SPI master

- CLK to be connected to the CLK of the SPI master

- DIO0 to be connected to the MOSI/IO0 of the SPI master

- DIO1 to be connected to the MISO/IO1 of the SPI master

- DIO2 to be connected to the IO2 of the SPI master (optional, required by Quad SPI)

- DIO3 to be connected to the IO3 of the SPI master (optional, required by Quad SPI)

The device operates in mode 0 with clock polarity (CPOL) and clock phase (CPH) zero.

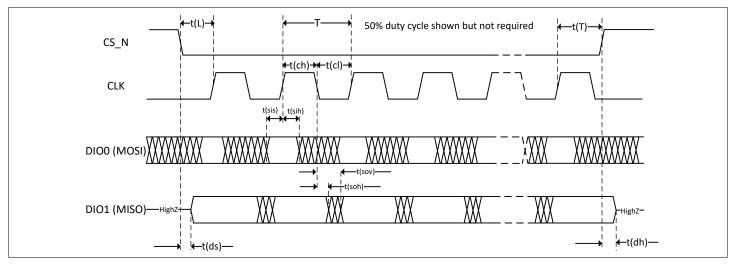

## 3.3.1 Standard Timing

The timing diagram for standard SPI timing is presented in the following Figure 3. A SPI transfer is started with a falling edge of chip select signal CS\_N generated by the SPI master. At the same time the SPI master shall drive the level of the data input signal DIO0 (MOSI) according to the first bit. Also, with the falling edge of the chip select signal CS\_N the SPI slave applies the level of the data on the output signal DIO1 (MISO) according to the first bit which shall

be transferred to the SPI master, the level becomes stable after the period  $t_{ds}$ . The SPI master has to wait for the time  $t_L$  before the clock signal CLK can be generated. With the rising edge of CLK the SPI slave captures the level of DIO0. The SPI master must keep the DIO0 level stable for  $t_{sis}$  before and for  $t_{sih}$  after the rising edge of CLK to ensure valid setup and hold time of the SPI slave. With the falling edge of CLK the SPI master shall set the level of DIO0 according to the next bit the master wants to send. The SPI master is supposed to read the level of DIO1 with the rising edge of CLK. The SPI slave keeps the DIO1 level stable for  $t_{soh}$  after the falling edge of CLK. With the falling edge of CLK the SPI slave drives the level of DIO1 according to the next bit, DIO1 becomes stable after latest  $t_{sov}$ . After the last bit has been transferred and CLK has gone to low level, the SPI master must set CSN to high level to stop the transfer. The master must take care that the period between the last rising edge of CLK and the rising edge of CS\_N is not shorter than  $t_T$ . Within the period  $t_{dh}$  after the rising edge of CS\_N the SPI slave drives DIO1 to high impedance state again.

Figure 3 SPI standard timing

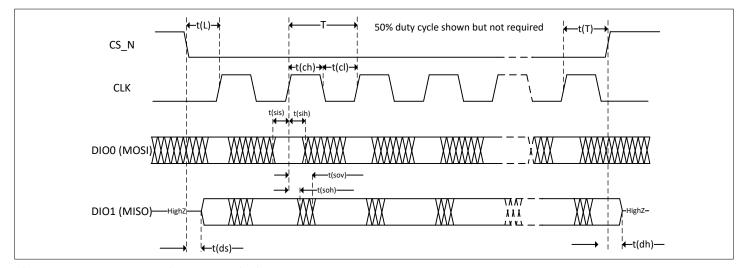

## 3.3.2 High Speed Timing

The device can operate at SPI clock frequencies up to 50 MHz, but the maximum achievable SPI clock frequency is limited by input related setup and hold times of SPI master and SPI slave. In case the SPI master requires a longer setup time than T/2 -  $t_{sov}$ , the SPI clock speed in the standard SPI must be reduced. However, this device offers a mode that sends out the data earlier to still allow higher speed. The timing diagram for this SPI mode is presented in the following Figure 4. The SPI master is still supposed to capture the level of DIO1 with the rising edge of CLK. The SPI slave keeps the level of DIO1 stable for  $t_{soh}$  after the rising edge of CLK, and then sets the level of DIO1 according to the next bit which is send out. This alternative SPI mode enables frequencies higher than 25 MHz.

Figure 4 SPI high speed timing

3 10

## 3.3.3 Electrical Characteristics

Table 17 Electrical characteristics

| Parameter                                                | Symbol                |      | Values | i    | Unit | Note or condition                                                        |

|----------------------------------------------------------|-----------------------|------|--------|------|------|--------------------------------------------------------------------------|

|                                                          |                       | Min. | Тур.   | Max. |      |                                                                          |

| Clock frequency                                          | $f_{SPI}$             | -    | 25     | 50   | MHz  | -                                                                        |

| Clock period                                             | $T_{SPI}$             | 20   | 40     | -    | ns   | -                                                                        |

| Clock duty cycle                                         | DC <sub>SPI_CLK</sub> | 45   | 50     | 55   | %    | -                                                                        |

| Clock high phase                                         | t <sub>ch</sub>       | 9.0  | -      | -    | ns   | At maximum f <sub>SPI</sub>                                              |

| Clock low phase                                          | t <sub>cl</sub>       | 9.0  | -      | -    | ns   | At maximum f <sub>SPI</sub>                                              |

| Slave input<br>setup                                     | t <sub>sis</sub>      | 5.0  | -      | -    | ns   | -                                                                        |

| Slave input hold                                         | t <sub>sih</sub>      | 5.0  | -      | -    | ns   | -                                                                        |

| Slave output                                             | $t_{\sf sov}$         | -    | -      | 12.0 | ns   | @ 15 pF load <sup>1)</sup> ,                                             |

| valid                                                    |                       |      |        |      |      | $f_{SPI}$ > 25 MHz output driving edge is rising edge.                   |

|                                                          |                       |      |        |      |      | Pad driver strength set to strong.                                       |

| Slave output<br>hold                                     | $t_{soh}$             | 1.0  | -      | -    | ns   | -                                                                        |

| Lead time<br>before the first<br>working clock<br>edge   | $t_{L}$               | 9.0  | -      | -    | ns   | -                                                                        |

| Tailing time<br>after the last<br>working clock<br>edge  | t <sub>T</sub>        | 9.0  | -      | -    | ns   | -                                                                        |

| Data setup time<br>after DO goes to<br>low impedance     | t <sub>ds</sub>       | -    | -      | 5.0  | ns   | -                                                                        |

| Data hold time<br>before DO goes<br>to high<br>impedance | t <sub>dh</sub>       | -    | -      | 8.0  | ns   | -                                                                        |

| Synchronization time                                     | t <sub>sync</sub>     | 100  | -      | -    | ns   | Synchronization time between two SPI transactions if SPI mode is changed |

| Chip select high phase                                   | t <sub>CS_N_h</sub>   | 15   | -      | -    | ns   | Back to back SPI transactions                                            |

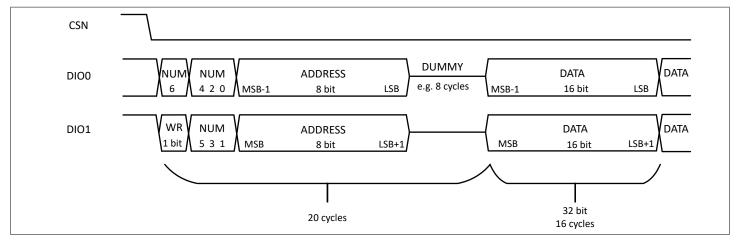

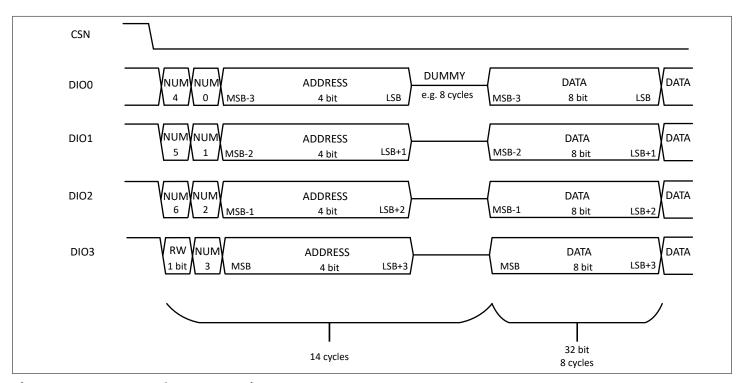

## 3.3.4 SPI Operation Modes

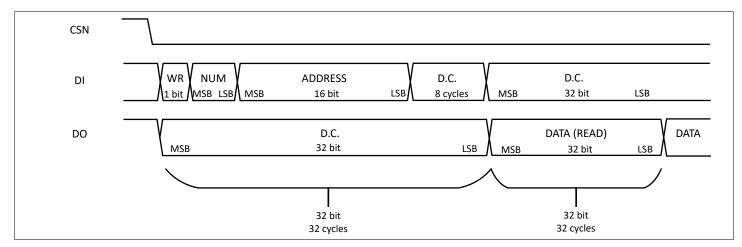

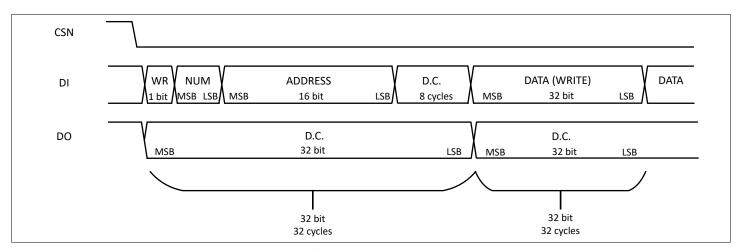

Each SPI transaction consists of three phases. The command, the address and data phase.

The command phase starts with one bit  $\mathbf{WR}$  (read:0<sub>B</sub>, write: 1<sub>B</sub>) to specify the kind of operation, read or write operation. Followed by a seven bit field so called  $\mathbf{NUM}$  to specify the overall number of intended transactions.

Afterwards, there is a two byte wide **ADDRESS** field to define the targeted destination address.

Based on the type of operation, read or write, the device has to switch the direction of its used pins which requires a minimum of five cycles wait time.

Once the configurable wait time is over, the last phase the so-called data phase starts. In this phase the read or write **DATA** is transferred on one, two or four pins based on the selected operation mode.

Note: Only during the data phase, if the transaction type is read and the broad-cast mode is disabled then the output drivers of the respective IO pins are enabled.

By default, the device uses LSB first however, this can be re-configured to MSB first for all modes. If required, the SPI transaction can be paused at any time of the protocol by stopping the SPI clock (CLK). This is possible as the device is only sensitive to SPI clock edges.

The device offers three different modes of operation:

- Standard/single SPI (DIO0 + DIO1) (see Figure 5 and Figure 6)

- Dual SPI (DIO0 + DIO1) (see Figure 7)

- Quad SPI (DIO0 + DIO1 + DIO2 + DIO3) (see Figure 8)

Figure 5 Standard SPI read transaction

Figure 6 Standard SPI write transaction

Figure 7 Dual SPI transaction

18

Figure 8 Quad SPI transaction

4 XOSC

#### 4 XOSC

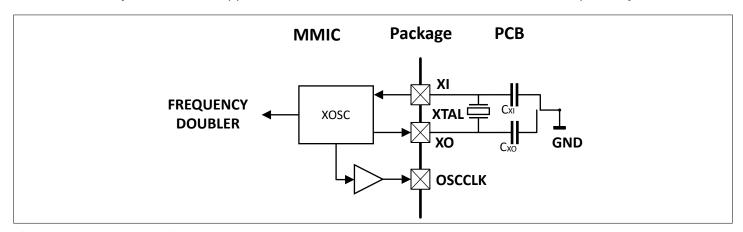

#### 4.1 Overview

The device requires a 80 MHz system clock for proper operation. This system clock can be either provided by an external oscillator via the XI pin or generated by the MMIC itself using the embedded crystal oscillator.

For this a crystal resonator and additional capacitors need to be connected to the XI and XO pins of the device, as shown in Figure 9.

To get the required 80 MHz system frequency it is possible to apply the 80 MHz directly or to use the on-chip frequency doubler circuitry by feeding it with a 40 MHz signal.

The embedded crystal oscillator supports both 40 MHz (38.4 MHz) and 80 MHz (76.8 MHz), respectively.

Figure 9 XOSC interface to external XTAL

### 4.2 XOSC Parameters

#### Table 18 XOSC parameters

$VDD_{PLL} = 1.14$  to 1.26 V,  $VDD_{LE} = 1.71$  to 1.89 V,  $T_b = -20$ °C to +85°C, values verified by CV over DoE

| Parameter                               | Symbol               |      | Values |      | Unit | Note or condition                                                             |

|-----------------------------------------|----------------------|------|--------|------|------|-------------------------------------------------------------------------------|

|                                         |                      | Min. | Тур.   | Max. |      |                                                                               |

| XOSC total load capacitance             | C <sub>XOSC</sub>    | 6    | 8      | 10   | pF   | $C_{XOSC\_Load} \approx ((C_{XI} * C_{XO}) / (C_{XI} + C_{XO})) + C_{PCB}$    |

| XOSC start up<br>time                   | t <sub>STARTUP</sub> | -    | 350    | 500  | μs   | -                                                                             |

| XTAL                                    |                      |      | 1      |      |      |                                                                               |

| XTAL equivalent<br>series<br>resistance | ESR <sub>XTAL</sub>  | -    | 30     | 60   | Ω    | Higher resistance leads to increased phase noise and increased start-up time. |

| XTAL frequency<br>40 MHz                | f <sub>XTAL_40</sub> | 39.9 | 40     | 40.1 | MHz  | Internal frequency doubler must be activated.                                 |

| XTAL frequency<br>80 MHz                | f <sub>XTAL_80</sub> | 79.9 | 80     | 80.1 | MHz  | -                                                                             |

| XTAL voltage                            | V <sub>XTAL_IO</sub> | 0    | 0.9    | 1    | V    | -                                                                             |

(table continues...)

4 XOSC

#### (continued) XOSC parameters Table 18

$VDD_{\rm PLL}$  = 1.14 to 1.26 V,  $VDD_{\rm LF}$  = 1.71 to 1.89 V,  $T_{\rm b}$  = -20°C to +85°C, values verified by CV over DoE

| Parameter                                    | Symbol                      | Values |      |      | Unit | Note or condition                                                                          |

|----------------------------------------------|-----------------------------|--------|------|------|------|--------------------------------------------------------------------------------------------|

|                                              |                             | Min.   | Тур. | Max. |      |                                                                                            |

| External clock v                             | via XI                      |        | 1    |      |      | ·                                                                                          |

| External input<br>clock frequency<br>80 MHz  | f <sub>EXT_OSCCLK</sub>     | 75     | 80   | 85   | MHz  | Input clock frequency of 76.8 MHz or 80 MHz                                                |

| External input<br>clock frequency<br>40 MHz  | f <sub>EXT_OSCCLK/2</sub>   | 37.5   | 40   | 42.5 | MHz  | Input clock frequency of 38.4 MHz or 40 MHz. Internal frequency doubler must be activated. |

| External input<br>clock duty cycle<br>80 MHz | DC <sub>EXT_OSCCLK</sub>    | 45     | 50   | 55   | %    | Input clock frequency of 76.8 MHz or 80 MHz                                                |

| External input<br>clock duty cycle<br>40 MHz | DC <sub>EXT_OSCCLK</sub> /2 | 47.5   | 50   | 52.5 | %    | Input clock frequency of 38.4 MHz or 40 MHz                                                |

| External input<br>clock voltage              | V <sub>EXT_OSCCLK</sub>     | 0      | 0.9  | 1.2  | V    | -                                                                                          |

| External input clock rise time               | $t_{EXT\_OSCCLK,R}$         | -      | -    | 2    | ns   | 20% to 80%                                                                                 |

| External input clock fall time               | $t_{EXT\_OSCCLK,F}$         | -      | -    | 2    | ns   | 20% to 80%                                                                                 |

| External input clock jitter                  | J <sub>EXT_OSCCLK,P</sub>   | -      | 300  | 400  | fs   | -                                                                                          |

| OSCCLK pad                                   | •                           |        | •    |      |      |                                                                                            |

| OSCCLK load capacitance                      | C <sub>OSCCLK</sub>         | -      | -    | 5    | pF   | -                                                                                          |

| OSCCLK<br>equivalent<br>series<br>resistance | ESR <sub>OSCCLK</sub>       | -      | -    | 1    | Ω    | -                                                                                          |

| OSCCLK voltage                               | V <sub>OSCCLK</sub>         | 0      | 0.9  | 0.99 | V    | -                                                                                          |

| OSCCLK clock<br>duty cycle                   | DC <sub>OSCCLK</sub>        | 40     | 50   | 60   | %    | System clock duty cycle                                                                    |

| System clock                                 |                             |        |      |      |      |                                                                                            |

| System clock<br>frequency                    | f <sub>SYSCLK</sub>         | 75     | 80   | 85   | MHz  | -                                                                                          |

| System clock<br>duty cycle                   | DC <sub>SYSCLK</sub>        | 45     | 50   | 55   | %    | -                                                                                          |

## **Preliminary Target Datasheet**

5 RCOSC

## 5 RCOSC

## 5.1 RCOSC Parameters

## Table 19 RCOSC parameters

$VDD_D$  = 1.14 to 1.26 V,  $T_b$  = -20°C to +85°C

| Parameter                | Symbol                     | Values |              |      | Unit | Note or condition                                                    |

|--------------------------|----------------------------|--------|--------------|------|------|----------------------------------------------------------------------|

|                          |                            | Min.   | Тур.         | Max. |      |                                                                      |

| ROSC start up time       | t <sub>STARTUP</sub>       | 10     | 26           | 40   | μs   | Verified by design                                                   |

| RCOSC frequency range    | $f_{RCOSC}$                | 71.0   | 76.8<br>80.0 | 84.0 | kHz  | Target frequency of 76.8 kHz based on f <sub>SYSCLK</sub> = 76.8 MHz |

|                          |                            |        |              |      |      | Target frequency of 80 kHz based on f <sub>SYSCLK</sub> = 80 MHz     |

| RCOSC<br>frequency error | f <sub>RCOSC_error</sub>   | -3     | 0            | 3    | kHz  | Trimming applied                                                     |

| RCOSC duty cycle         | <i>DC</i> <sub>RCOSC</sub> | 47.5   | 50           | 52.5 | %    | -                                                                    |

#### **Preliminary Target Datasheet**

#### 6 PLL

The PLL is designed to generate high performance frequency chirps in the range of 57.0 GHz to 64.0 GHz. The modulation is performed inside the PLL bandwidth (in-band-modulation, 1MHz loop bandwidth) with an analog charge pump based fractional-N RF-PLL architecture. It furthermore features a shape generator with high flexibility to allow different ramp shapes and duration times.

#### **6.1** PLL Parameters

### Table 20 PLL parameters

$VDD_{PLL} = 1.14$  to 1.26 V,  $VDD_{LF} = 1.71$  to 1.89 V,  $T_b = -20$ °C to +85°C, values verified by CV over DoE

| Parameter                        | Symbol                  | Values |      |      | Unit   | Note or condition                                    |

|----------------------------------|-------------------------|--------|------|------|--------|------------------------------------------------------|

|                                  |                         | Min.   | Тур. | Max. |        |                                                      |

| Output<br>frequency range        | $f_{RF}$                | 57.0   | -    | 64.0 | GHz    | For PLL SDM Rhee/DeMuer                              |

| Continous FM chirp bandwidth     | BW                      | 0      | -    | 7    | GHz    | -                                                    |

| Chirp slope                      | Slope                   | -      | -    | 700  | MHz/µs | -                                                    |

| Frequency ramp linearity error   | Error                   | -2     | -    | 2    | MHz    | 5 GHz bandwidth                                      |

| Frequency ramp settling time     | t <sub>PLL_settle</sub> | -      | -    | 6    | μs     | -                                                    |

| PLL phase noise<br>@1MHz offset  | PN <sub>PLL_1MHz</sub>  | -      | -    | -80  | dBc/Hz | Single sideband for specified output frequency range |

| PLL phase noise<br>@5MHz offset  | PN <sub>PLL_5MHz</sub>  | -      | -    | -85  | dBc/Hz | Single sideband for specified output frequency range |

| PLL phase noise<br>@10MHz offset | PN <sub>PLL_10MHz</sub> | -      | -    | -95  | dBc/Hz | Single sideband for specified output frequency range |

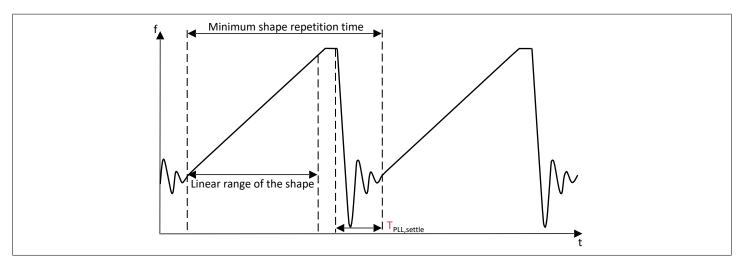

## **6.1.1** Settling Time

The ramp settling time is required by the PLL to damp undershoot and overshoot in case of saw-tooth shapes as illustrated in Figure 10.

V0.50

6 PLL

Figure 10 Chirp settling time

## 6.1.2 Ramp Linearity

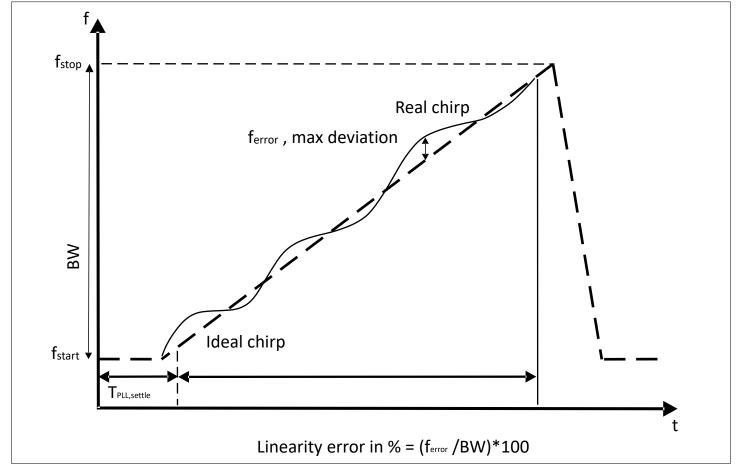

Frequency ramp linearity error is defined to be < 1% of the frequency-modulated (FM) chirp bandwidth (2 GHz). The linearity error is calculated as the deviation from an "ideal" frequency ramp. The specification needs to be fulfilled after the frequency ramp settling time. The assumed worst case FM chirp bandwidth for linearity evaluations is 2 GHz. Figure 11 illustrates the frequency linearity definition.

Figure 11 Frequency linearity definition

## **Preliminary Target Datasheet**

7 RF Frontend

### **7** RF Frontend

In the RF frontend, all features to enable the radar functionality are implemented.

### **7.1** RF FE Parameters

## Table 21 RF FE parameters

$VDD_{\rm RF}$  = 1.14 to 1.26 V,  $VDD_{\rm BB}$  = 1.71 to 1.89 V,  $T_{\rm b}$  = -20°C to +85°C, values verified by CV over DoE

| Parameter                                        | Symbol                   | Values |      |      | Unit | Note or condition                     |

|--------------------------------------------------|--------------------------|--------|------|------|------|---------------------------------------|

|                                                  |                          | Min.   | Тур. | Max. |      |                                       |

| Frequency range                                  | $f_{RF}$                 | 57.0   | -    | 64.0 | GHz  | -                                     |

| Transmitter                                      |                          |        |      |      |      |                                       |

| Transmit output power                            | $P_{TX}$                 | 7      | 11   | 13   | dBm  | Conducted power at pad                |

| Transmit output power variation over temperature | P <sub>TX_Temp</sub>     | 0      | 1.0  | 2.0  | dB   | With maximum PA setting               |

| Transmitter power control dynamic range          | $P_{TX\_D}$              | -      | 15   | -    | dB   | -                                     |

| BPSK phase error                                 | ERR <sub>BPSK</sub>      | -      | -    | 6    | 0    | -                                     |

| Receiver                                         |                          |        |      |      |      |                                       |

| Receiver conversion gain                         | CG <sub>RX</sub>         | 9.5    | 14   | 16   | dB   | at 1 MHz IF offset                    |

| Conversion gain variation over temperature       | CG <sub>RX_Temp</sub>    | -      | 1    | -    | dB   | -                                     |

| Noise figure<br>single sideband<br>RX @100 kHz   | NFSSB <sub>RX_100k</sub> | 11     | 14.5 | 22   | dB   | at RX input (die), Verified by design |

| Noise figure<br>single sideband<br>RX @500 kHz   | NFSSB <sub>RX_500k</sub> | 10     | 13   | 20   | dB   | at RX input (die), Verified by design |

| Noise figure<br>single sideband<br>RX @5 MHz     | NFSSB <sub>RX_5MH</sub>  | 8      | 12.5 | 19   | dB   | at RX input (die), Verified by design |

| Receiver 1dB compression point                   | P-1dB <sub>RX</sub>      | -7     | -5   | -1   | dBm  | -                                     |

| Phase shifter resolution                         | RES <sub>PS</sub>        | -      | 4.5  | -    | 0    |                                       |

(table continues...)

### **Preliminary Target Datasheet**

7 RF Frontend

### Table 21 (continued) RF FE parameters

$VDD_{RF}$  = 1.14 to 1.26 V,  $VDD_{BB}$  = 1.71 to 1.89 V,  $T_b$  = -20°C to +85°C, values verified by CV over DoE

| Parameter           | Symbol           | Values |      | Unit | Note or condition |   |

|---------------------|------------------|--------|------|------|-------------------|---|

|                     |                  | Min.   | Тур. | Max. |                   |   |

| Phase shifter steps | N <sub>PHS</sub> | 0      | -    | 42   | -                 | - |

## 7.2 On-chip Sensor Parameters

Relation between actual chip backside temperature (Temp) and temperature sensor readout in mV (V<sub>T</sub>):

Temp =  $(V_T - b) / k$

## Table 22 On-chip sensor parameters

$VDD_{\rm PLL}$  = 1.14 to 1.26 V,  $VDD_{\rm BB}$  = 1.71 to 1.89 V,  $T_{\rm b}$  = -20°C to +85°C

| Parameter                          | Symbol                |      | Values        |      | Unit    | Note or condition                         |

|------------------------------------|-----------------------|------|---------------|------|---------|-------------------------------------------|

|                                    |                       | Min. | Тур.          | Max. |         |                                           |

| Temperature                        |                       | -    |               |      |         |                                           |

| Temperature sensor slope           | k                     | -    | -3.542<br>967 | -    | mV / °C | -                                         |

| Temperature sensor offset          | b                     | -    | 212.6<br>86   | -    | mV      | -                                         |

| Temperature range                  | $T_{Range}$           | -20  | -             | 85   | °C      | ±9°C                                      |

| Temperature range (high precision) | T <sub>Range_HP</sub> | 30   | 40            | 50   | °C      | ± 5°C, Verified by design                 |

| Power detector                     | •                     | •    |               |      |         |                                           |

| Peak detector accuracy             | PD <sub>PA_acc</sub>  | -2   | -             | 2    | dB      | Over f <sub>RF</sub> , Verified by design |

| Peak detector dynamic range        | PD <sub>PA_dr</sub>   |      | 15            |      | dBm     | -                                         |

8 Analog Baseband

## 8 Analog Baseband

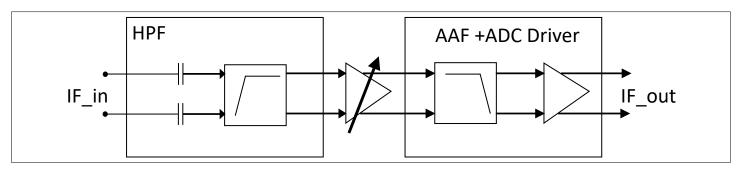

The analog baseband block consists of a high-pass-filter (HPF), a programmable gain amplifier (PGA), an antialiasing-filter (AAF) and a driver for the ADC input, as illustrated in Figure 12.

The HPF is used to remove the direct current (DC) offset at the output of the RX mixer and suppresses the reflected signal from close targets (radome, e.g.).

Figure 12 Baseband simplified block diagram, one for each RX channel

The IF signal is filtered by a HPF. It's a two stage HPF. First stage is selectable between 100kHz and 1MHz, second one is set around 40kHz and can be disabled.

The programable gain amplifier (PGA) provides a minimum voltage gain of 24 dB. The gain can be adjusted in steps of 3 dB each up to a maximum gain of 60 dB.

Afterwards, the PGA is followed by an AAF which cut-off frequency can be set to four different frequencies between 1 and 6 MHz. Followed by an ADC driver amplifier with a gain of 1.

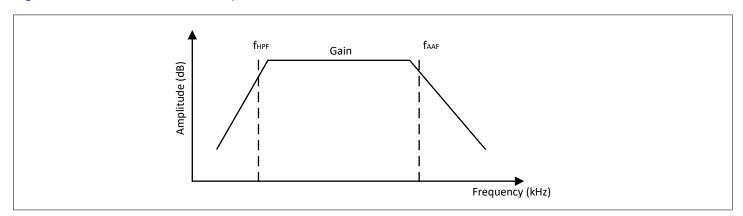

Figure 13 illustrates baseband bandpass characteristic.

Figure 13 Baseband bandpass characteristic

## 8.1 Analog Baseband Current Consumption

#### Table 23 Analog baseband current consumption

$VDD_{BB} = 1.71 \text{ V to } 1.89 \text{ V}, T_b = -20 ^{\circ}\text{C to } +85 ^{\circ}\text{C}$

| Parameter                   | Symbol               | Values |      | Unit | Note or condition |   |

|-----------------------------|----------------------|--------|------|------|-------------------|---|

|                             |                      | Min.   | Тур. | Max. |                   |   |

| ABB current consumption off | I <sub>ABB_OFF</sub> | -      | -    | 0.5  | μΑ                | - |

(table continues...)

#### **Preliminary Target Datasheet**

Table 23 (continued) Analog baseband current consumption

$VDD_{BB} = 1.71 \text{ V to } 1.89 \text{ V}, T_b = -20^{\circ}\text{C to } +85^{\circ}\text{C}$

| Parameter                  | Symbol              | Values |      | Unit | Note or condition |   |

|----------------------------|---------------------|--------|------|------|-------------------|---|

|                            |                     | Min.   | Тур. | Max. |                   |   |

| ABB current consumption on | I <sub>ABB_ON</sub> | -      | 6    | -    | mA                | - |

## 8.2 Analog Baseband HPF Parameters

### Table 24 Analog base band HPF parameters

$VDD_{BB} = 1.71 \text{ V to } 1.89 \text{ V}, T_b = -20 ^{\circ}\text{C to } +85 ^{\circ}\text{C}$

| Parameter | Symbol              |      | Values |      |     | Note or condition                                                   |

|-----------|---------------------|------|--------|------|-----|---------------------------------------------------------------------|

|           |                     | Min. | Тур.   | Max. |     |                                                                     |

| HPF1_0    | f <sub>HPF1_0</sub> | 78   | 100    | 122  | kHz | HPF 3 dB cutoff frequency                                           |

| HPF1_1    | f <sub>HPF1_1</sub> | 273  | 350    | 427  | kHz | HPF 3 dB cutoff frequency                                           |

| HPF1_2    | f <sub>HPF1_2</sub> | 507  | 650    | 793  | kHz | HPF 3 dB cutoff frequency                                           |

| HPF1_3    | f <sub>HPF1_3</sub> | 780  | 1000   | 1220 | kHz | HPF 3 dB cutoff frequency                                           |

| HPF2      | f <sub>HPF2</sub>   | 31   | 40     | 49   | kHz | HPF 3 dB cutoff frequency 2 <sup>nd</sup> HPF stage bypass disabled |

## 8.3 Analog Baseband Gain Parameters

## Table 25 Analog base band gain parameters

$VDD_{BB} = 1.71 \text{ V to } 1.89 \text{ V}, T_b = -20 ^{\circ}\text{C to } +85 ^{\circ}\text{C}$

| Parameter     | Symbol                | Values |      | Unit | Note or condition |                    |

|---------------|-----------------------|--------|------|------|-------------------|--------------------|

|               |                       | Min.   | Тур. | Max. |                   |                    |

| ABB gain      | $G_{ABB}$             | 24     | -    | 60   | dB                | Verified by design |

| ABB gain step | G <sub>ABB_STEP</sub> | 2      | 3    | 4    | dB                | Verified by design |

## 8.4 Analog Baseband AAF Parameters

### Table 26 Analog base band AAF parameters

$VDD_{BB} = 1.71 \text{ V to } 1.89 \text{ V}, T_b = -20 ^{\circ}\text{C to } +85 ^{\circ}\text{C}$

| Parameter | Symbol             | Values |      | Unit | Note or condition |                           |

|-----------|--------------------|--------|------|------|-------------------|---------------------------|

|           |                    | Min.   | Тур. | Max. |                   |                           |

| AAF_0     | f <sub>AAF_0</sub> | 0.83   | 1    | 1.17 | MHz               | AAF 3 dB cutoff frequency |

| AAF_1     | f <sub>AAF_1</sub> | 1.66   | 2    | 2.34 | MHz               | AAF 3 dB cutoff frequency |

(table continues...)

## **Preliminary Target Datasheet**

8 Analog Baseband

## Table 26 (continued) Analog base band AAF parameters

$VDD_{\rm BB}$  = 1.71 V to 1.89 V,  $T_{\rm b}$  = -20°C to +85°C

| Parameter | Symbol             | Values |      | Unit | Note or condition |                           |

|-----------|--------------------|--------|------|------|-------------------|---------------------------|

|           |                    | Min.   | Тур. | Мах. |                   |                           |

| AAF_2     | f <sub>AAF_2</sub> | 4.15   | 5    | 5.85 | MHz               | AAF 3 dB cutoff frequency |

| AAF_3     | f <sub>AAF_3</sub> | 4.98   | 6    | 7.02 | MHz               | AAF 3 dB cutoff frequency |

9 ADC

#### 9 **ADC**

#### **Overview** 9.1

The multichannel ADC (MADC) block consists of one SAR ADC for sensor measurement plus one per RX channel. The ADC captures the differential IF output signals from the ABB and convert it into a digital representation of the same. Figure 14 illustrates the MADC simplified block diagram.

The following table specifies the ADC parameters. All parameters are only valid with executed calibration.

Figure 14 **MADC** simplified block diagram

#### **ADC Parameters** 9.2

#### Table 27 **ADC** parameters

$VDD_A = VDD_{LF} = 1.71 \text{ V to } 1.89 \text{ V}, T_b = -20 ^{\circ}\text{C} \text{ to } +85 ^{\circ}\text{C}, \text{ values verified by CV over DoE}$

| Parameter              | Symbol               | Values |      |      | Unit | Note or condition      |

|------------------------|----------------------|--------|------|------|------|------------------------|

|                        |                      | Min.   | Тур. | Max. |      |                        |

| ADC clock<br>frequency | f <sub>ADC_CLK</sub> | -      | 80   | -    | MHz  | -                      |

| Resolution             | Resolution           | -      | 12   | -    | Bit  | Plus 4 fractional bits |

| Signal to noise ratio  | SNR                  | 55     | 63.5 | -    | dBFS | -                      |

(table continues...)

## **Preliminary Target Datasheet**

9 ADC

## Table 27 (continued) ADC parameters

$VDD_A = VDD_{LF} = 1.71 \text{ V to } 1.89 \text{ V}, T_b = -20 ^{\circ}\text{C} \text{ to } +85 ^{\circ}\text{C}, \text{ values verified by CV over DoE}$

| Parameter                      | Symbol            | Values |      |      | Unit | Note or condition                                                                          |

|--------------------------------|-------------------|--------|------|------|------|--------------------------------------------------------------------------------------------|

|                                |                   | Min.   | Тур. | Max. |      |                                                                                            |

| Spurious free dynamic range    | SFDR              | 58     | 69   | -    | dBFS | -                                                                                          |

| Inter<br>modulation<br>product | IM3               | 58     | 69   | -    | dBFS | -                                                                                          |

| Offset                         | Offset            | -30    | -    | 30   | -    | Absolute value of ADC output (5 LSB's) with applied offset calibration                     |

| Gain                           | G <sub>ADC</sub>  | 0.94   | 1    | 1.06 | -    | @ -6 dBFS input                                                                            |

| Bandwidth                      | BW                | -      | -    | 5    | MHz  | -                                                                                          |

| Sample rate                    | SR                | -      | -    | 20   | MS/s | @ $f_{SYS\_CLK} = f_{ADC\_CLK} = 80 \text{ MHz}$                                           |

| Sampling time                  | $T_{S}$           | -      | 12.5 | -    | ns   | @ $f_{SYS\_CLK} = f_{ADC\_CLK} = 80 \text{ MHz}$                                           |

| Conversion time                | T <sub>Conv</sub> | -      | 37.5 | -    | ns   | @ $f_{SYS\_CLK} = f_{ADC\_CLK} = 80 \text{ MHz}$                                           |

| Calibration time               | T <sub>Cal</sub>  | -      | 100  | 120  | us   | @ $f_{SYS\_CLK} = f_{ADC\_CLK} = 80$ MHz, timing, offset and linearity calibration enabled |

10 Package Information

## 10 Package Information

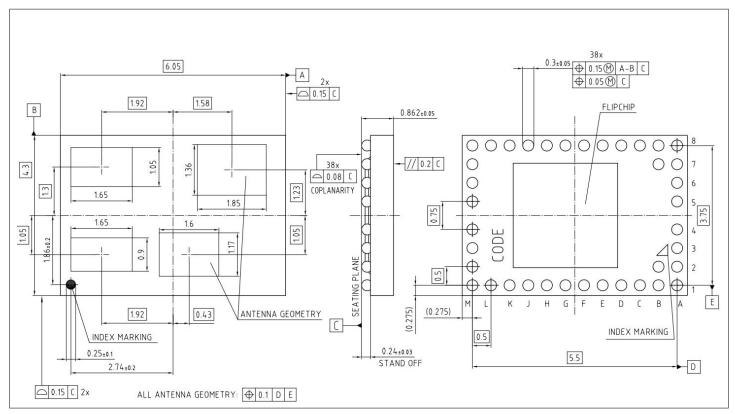

## 10.1 Package

The chip is housed in a laminate package with solder balls of 300 µm diameter and integrates the antennas. According to IPC/JEDEC's J-STD0, the moisture sensitivity level (MSL) is 3.

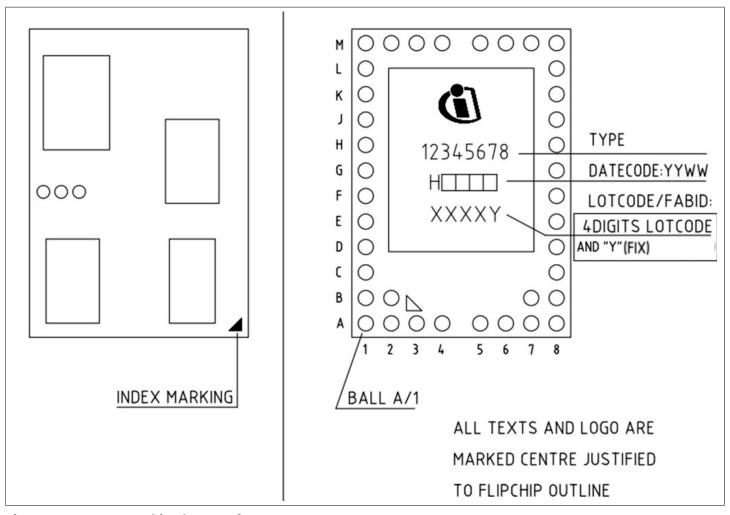

The bottom view of the package is presented in Figure 15. The package size is 6.05 x 4.30 x 0.9 mm<sup>3</sup> with ball pitch of 500 µm. Package outline and marking layout are shown in Figure 16 and Figure 17, respectively.

Package name: PG-VF2BGA-38-1

Figure 15 Device bottom view

#### **Preliminary Target Datasheet**

10 Package Information

Figure 16 Package outline of PG-VF2BGA-38-1

**(infineon**

10 Package Information

Figure 17 Marking layout of PG-VF2BGA-38-1

## 10.2 Built-in Antenna Specification

Antenna performance reported in the following table are ensured by design. Typical antenna behavior is measured on Infineon reference board. Typical antenna beam plots are available in a specific application note and upon specific request.

## 10.2.1 Built-in Antenna Parameters

Table 28 Built-in antenna parameters

| Parameter                        | Symbol           | Values |      |      | Unit | Note or condition                              |

|----------------------------------|------------------|--------|------|------|------|------------------------------------------------|

|                                  |                  | Min.   | Тур. | Max. |      |                                                |

| Bandwidth                        |                  |        |      |      |      |                                                |

| Transmitter antenna bandwidth    | TX <sub>BW</sub> | 57.0   | -    | 64.0 | GHz  | Transmitter bandwidth, Verified by design      |

| Receiver<br>antenna<br>bandwidth | RX <sub>BW</sub> | 57.0   | -    | 64.0 | GHz  | Receiver antenna bandwidth, Verified by design |

(table continues...)

## **Preliminary Target Datasheet**

10 Package Information

## Table 28 (continued) Built-in antenna parameters

| Parameter              | Symbol               | Values |      | Unit | Note or condition |                                                                       |

|------------------------|----------------------|--------|------|------|-------------------|-----------------------------------------------------------------------|

|                        |                      | Min.   | Тур. | Max. |                   |                                                                       |

| Gain                   |                      | '      | •    |      |                   | ·                                                                     |

| TX antenna gain        | G <sub>TX</sub>      | -      | 3.0  | -    | dBi               | Antenna gain of a single TX antenna, Verified by design               |

| RX antenna gain        | $G_{RX}$             | -      | 3.0  | -    | dBi               | Antenna gain of a single RX antenna, Verified by design               |

| Field of view          |                      | •      |      |      |                   |                                                                       |

| Field of view E-plane  | FOV <sub>E</sub>     | -      | 120  | -    | Deg               | Field of view of radar mode in the E-plane, Verified by design        |