## 英飞凌单通道隔离栅极驱动器 IC

### 特性

- 基于电气隔离的无磁芯变压器的单通道栅极驱动器

- 独立输出、参考 GND2 的输出欠压锁定电压或可调输出欠压锁定电压

- 适用于 600 V/650 V/1200 V/1700 V/2300 V IGBT、Si 和 SiC MOSFET

- 典型峰值输出电流高达 6.5 A

- 40 ns 传播延迟，7 ns 器件间匹配（偏差）

- 35 V 绝对最大输出供电电压

- 极高（同类最佳）共模瞬态抗扰度 CMTI > 300 kV/μs

- 主动关断和短路钳位

- 150 mil DSO-8 和 300 mil LDSO-8 封装，CTI > 600

- 3.3 V 或 5 V 输入电源电压

- 适合在高环境温度下运行以及快速开关应用

- UL 1577 认证  $V_{ISO} = 3.0 \text{ kV (rms)}$ ，持续 1 分钟（文件 E311313），适用于 1ED314xMU12F

- UL 1577 认证  $V_{ISO} = 5.7 \text{ kV (rms)}$ ，持续 1 分钟（文件 E311313），以及 IEC 60747-17 ( $V_{IORM} = 1767 \text{ V}$ )（计划中），适用于 1ED314xMC12H

### 潜在应用

- 电动汽车充电桩

- 储能系统

- 太阳能逆变器

- 用于服务器与电信的开关模式电源 (SMPS)

- UPS 系统

- 交流和直流无刷电机驱动器

- 商业供暖、通风和空调 (HVAC) 系统

### 产品验证

根据 JEDEC47/20/22 相关测试，符合工业应用要求

### 描述

EiceDRIVER™ 1ED314xMx12x 栅极驱动器 IC 是高性能电气隔离单通道栅极驱动器，专为驱动 IGBT、MOSFET 和 SiC MOSFET 而设计。这些栅极驱动器 IC 采用 150 mil 8 引脚封装 (1ED314xMU12F) 和 300 mil 8 引脚封装 (1ED314xMC12H)。它们提供高达 6.5 A 的典型输出电流。输入逻辑引脚采用 CMOS 阈值电平，可在 3 V 至 6.5 V 的宽输入电压范围内工作，以支持 3.3 V 微控制器。跨隔离带的数据传输通过采用无磁芯变压器技术实现。所有型号均具有输入和输出欠压锁定 (UVLO) 和主动关断功能。

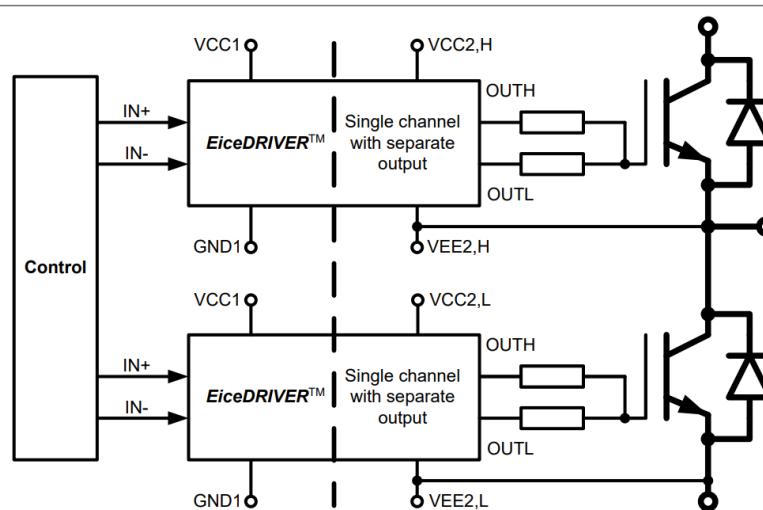

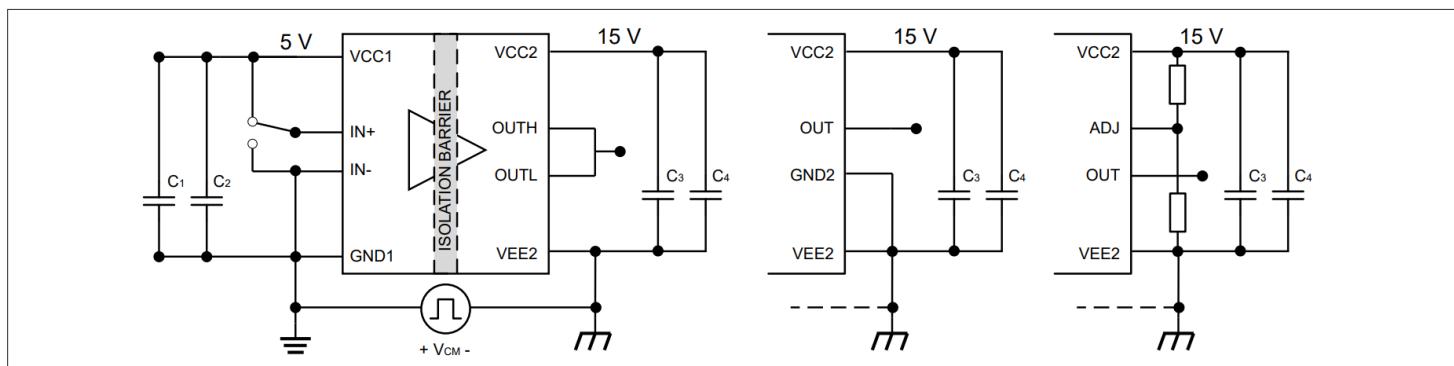

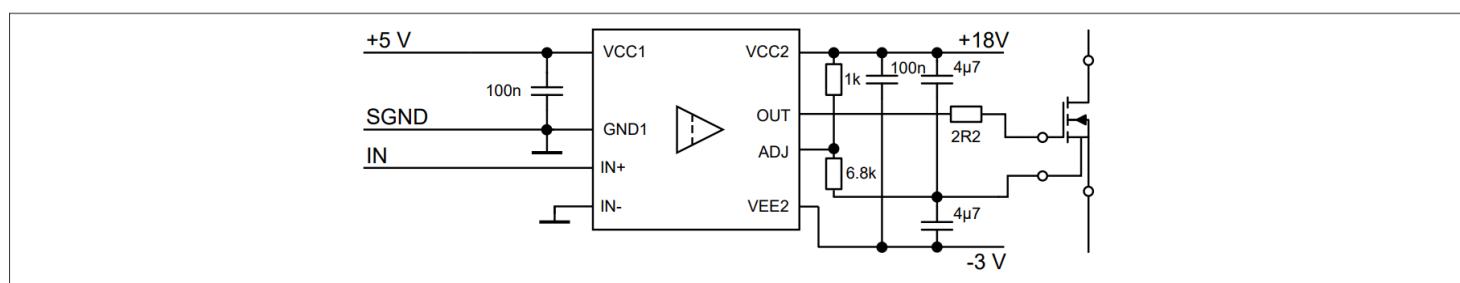

具有独立灌电流和拉电流端子器件的典型应用图

本数据手册的原文使用英文撰写。为方便起见，英飞凌提供了译文；由于翻译过程中可能使用了自动化工具，英飞凌不保证译文的准确性。为确认准确性请务必访问 [infineon.com](http://infineon.com) 参考最新的英文版本（控制文档）。

描述

表1 150 mil 封装的订购信息

| Product type | Typical UVLO<br>( $V_{UVLOL2}/V_{UVLOH2}$ ) | Typical output<br>current<br>source/sink | Output<br>configuration | UL 1577<br>Certification | Package marking |

|--------------|---------------------------------------------|------------------------------------------|-------------------------|--------------------------|-----------------|

| 1ED3140MU12F | 8.5 V / 9.3 V                               | 6 A / 6.5 A                              | Separate outputs        | E311313                  | 3140MU12        |

| 1ED3141MU12F | 11.0 V / 12.0 V                             | 6 A / 6.5 A                              | Separate outputs        | E311313                  | 3141MU12        |

| 1ED3142MU12F | 12.5 V / 13.6 V                             | 6 A / 6.5 A                              | Separate outputs        | E311313                  | 3142MU12        |

表2 300mil封装的订购信息

| Product type | Typical UVLO<br>( $V_{UVLOL2}/V_{UVLOH2}$ ) | Typical output<br>current<br>source/sink | Output<br>configuration    | UL 1577<br>Certification | IEC 60747-17<br>Certification | Package<br>marking |

|--------------|---------------------------------------------|------------------------------------------|----------------------------|--------------------------|-------------------------------|--------------------|

| 1ED3141MC12H | 11.0 V / 12.0 V                             | 6 A / 6.5 A                              | Separate<br>outputs        | E311313                  | Planned                       | 3141MC12           |

| 1ED3142MC12H | 12.5 V / 13.6 V                             | 6 A / 6.5 A                              | Separate<br>outputs        | E311313                  | Planned                       | 3142MC12           |

| 1ED3143MC12H | 11.0 V / 12.0 V                             | 6 A / 6.5 A                              | UVLO referenced<br>to GND2 | E311313                  | Planned                       | 3143MC12           |

| 1ED3144MC12H | 12.5 V / 13.6 V                             | 6 A / 6.5 A                              | UVLO referenced<br>to GND2 | E311313                  | Planned                       | 3144MC12           |

| 1ED3145MC12H | Adjustable                                  | 6 A / 6.5 A                              | Adjustable UVLO            | E311313                  | Planned                       | 3145MC12           |

表3 相关评估板

| Board name            | Gate driver  | Power transistor | Short description                                                                             |

|-----------------------|--------------|------------------|-----------------------------------------------------------------------------------------------|

| EVAL-1ED3142MU12F-SIC | 1ED3142MU12F | IMZA120R020M1H   | Half-bridge board with 1ED3142MU12F gate drivers, paired with CoolSiC™ in PG-TO-247-4 package |

| EVAL-1ED3142MC12H-SIC | 1ED3142MC12H | IMZA120R020M1H   | Half-bridge board with 1ED3142MC12H gate drivers, paired with CoolSiC™ in PG-TO-247-4 package |

| EVAL-1ED3144MC12H-SIC | 1ED3144MC12H | IMZA120R020M1H   | Half-bridge board with 1ED3144MC12H gate drivers, paired with CoolSiC™ in PG-TO-247-4 package |

| EVAL-1ED3145MC12H-SIC | 1ED3145MC12H | IMZA120R020M1H   | Half bridge board with 1ED3145MC12H gate drivers, paired with CoolSiC™ in PG-TO-247-4 package |

## 目录

|                                                            |    |

|------------------------------------------------------------|----|

| <b>特性</b>                                                  | 1  |

| <b>潜在应用</b>                                                | 1  |

| <b>产品验证</b>                                                | 1  |

| <b>描述</b>                                                  | 1  |

| <b>目录</b>                                                  | 3  |

| <b>1 框图参考</b>                                              | 5  |

| <b>2 引脚配置及说明</b>                                           | 7  |

| <b>3 电气特性及参数</b>                                           | 11 |

| 3.1 绝对最大额定值                                                | 11 |

| 3.2 推荐操作条件                                                 | 12 |

| 3.3 电气特性                                                   | 13 |

| 3.3.1 电源                                                   | 13 |

| 3.3.2 逻辑输入                                                 | 14 |

| 3.3.3 栅极驱动器                                                | 15 |

| 3.3.4 动态特性                                                 | 15 |

| 3.3.5 主动关断                                                 | 17 |

| 3.3.6 过温保护                                                 | 17 |

| <b>4 PG-DSO-8 (150 mil) 封装的绝缘特性(UL 1577)</b>               | 18 |

| <b>5 PG-LDSO-8 (300 mil) 封装的绝缘特性(IEC 60747-17、UL 1577)</b> | 19 |

| <b>6 典型特征</b>                                              | 20 |

| <b>7 参数测量</b>                                              | 24 |

| 7.1 CMTI 测量设置                                              | 24 |

| 7.2 欠压锁定(UVLO)                                             | 24 |

| 7.3 传播延迟、上升和下降时间                                           | 25 |

| <b>8 功能说明</b>                                              | 28 |

| 8.1 输入特征                                                   | 28 |

| 8.1.1 输入信号过滤(去毛刺滤波)                                        | 29 |

| 8.1.2 输入引脚的上拉和下拉电阻                                         | 29 |

| 8.1.3 输入电源和欠压锁定(UVLO)                                      | 30 |

| 8.2 输出要素                                                   | 31 |

| 8.2.1 驱动器输出和电源                                             | 33 |

| 8.2.2 输出欠压锁定(UVLO)                                         | 33 |

| 8.2.3 主动关断                                                 | 35 |

| 8.2.4 短路钳位                                                 | 35 |

| 8.2.5 过温保护                                                 | 35 |

| <b>9 应用信息</b>                                              | 36 |

|       |                                  |    |

|-------|----------------------------------|----|

| 9.1   | 典型应用 .....                       | 36 |

| 9.2   | 电源建议 .....                       | 38 |

| 9.3   | <i>IN+</i> 和 <i>IN-</i> 用法 ..... | 39 |

| 9.4   | 栅极电阻的选择 .....                    | 40 |

| 9.5   | 功耗估算 .....                       | 40 |

| 9.5.1 | 栅极驱动器 .....                      | 40 |

| 9.5.2 | 外部栅极电阻 .....                     | 41 |

| 9.6   | 输出 UVLO 电平调整 .....               | 41 |

| 9.7   | 布局指南 .....                       | 42 |

| 10    | 相关链接 .....                       | 45 |

| 11    | 封装尺寸 .....                       | 46 |

|       | 修订记录 .....                       | 50 |

|       | 免责声明 .....                       | 51 |

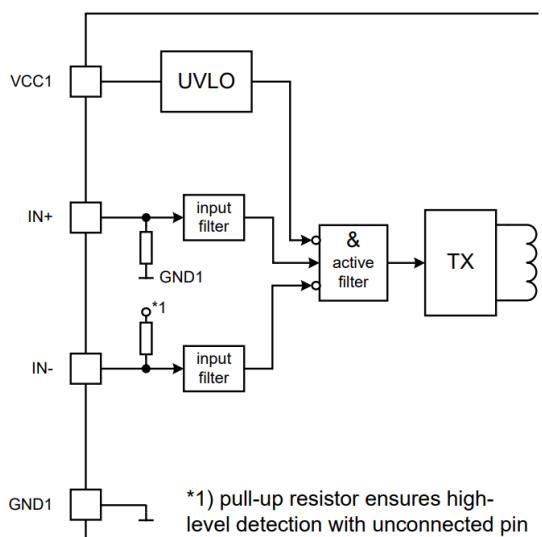

1 框图参考

1 框图参考

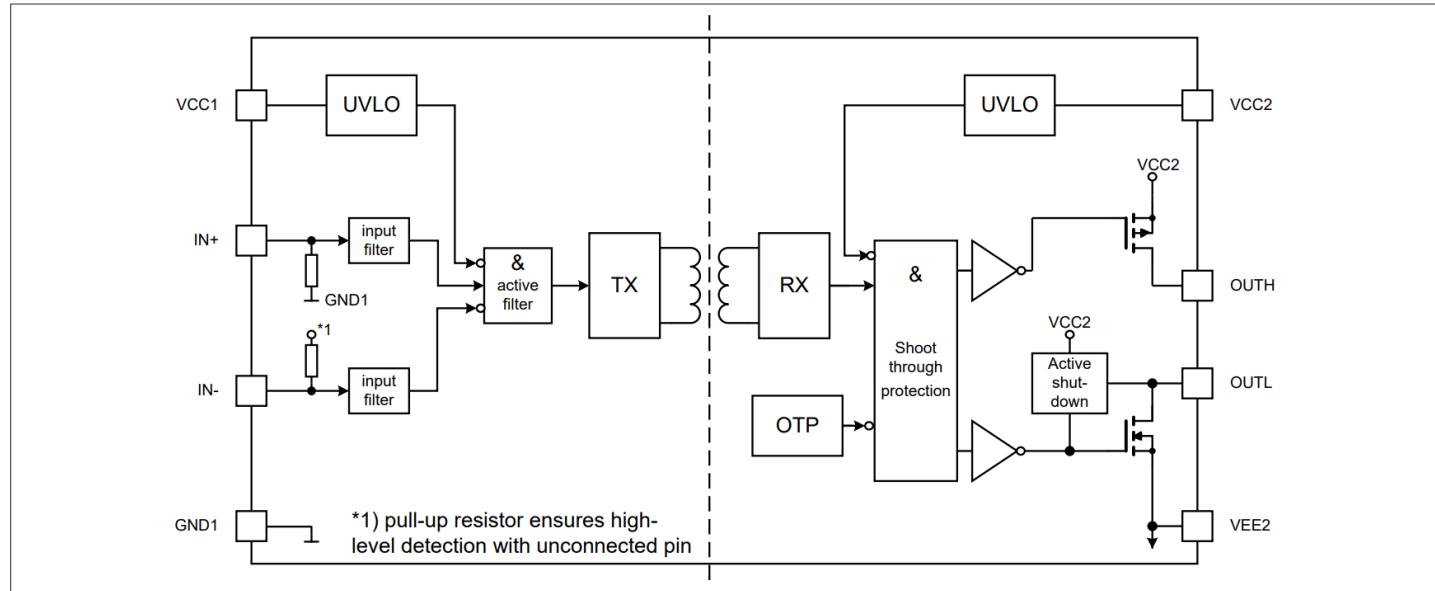

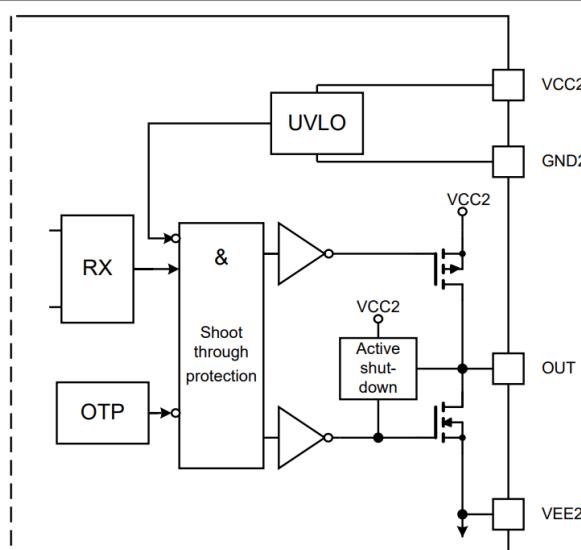

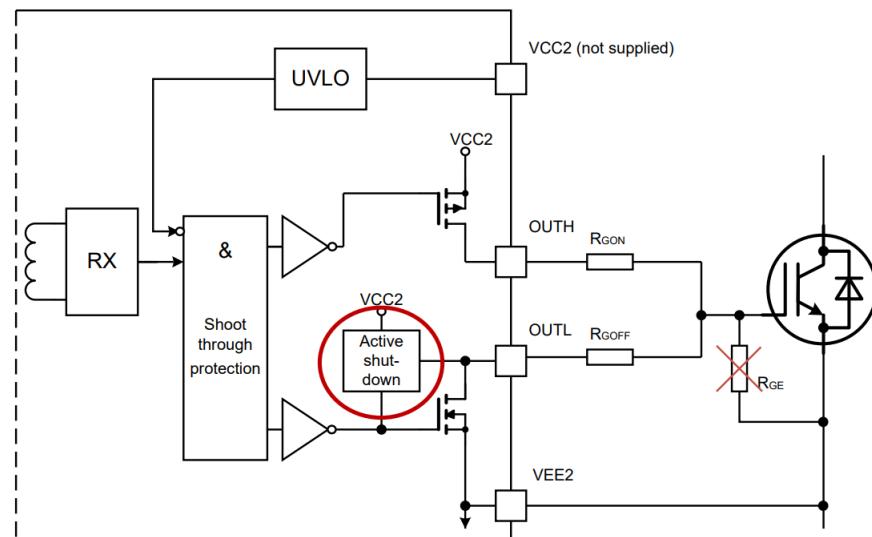

图 2 具有独立灌电流和拉电流引脚器件的框图 (1ED3140、1ED3141 和 1ED3142)

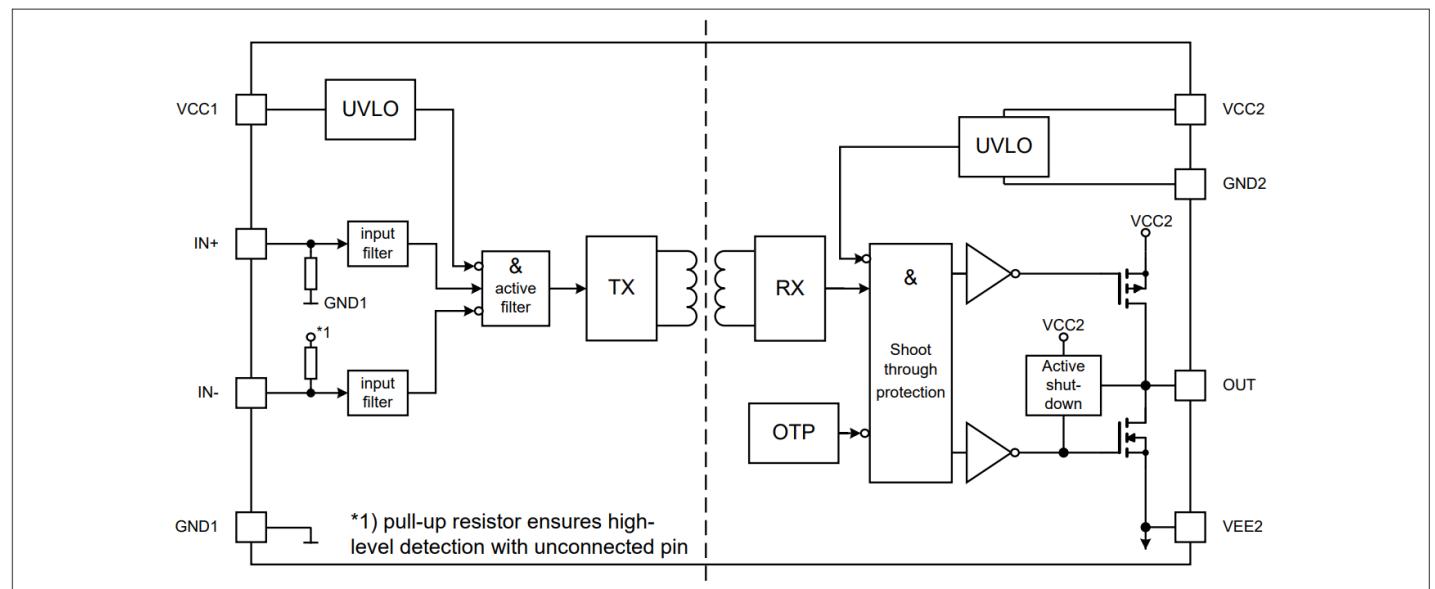

图 3 带有 GND2 引脚的器件 (1ED3143 和 1ED3144) 框图

1 框图参考

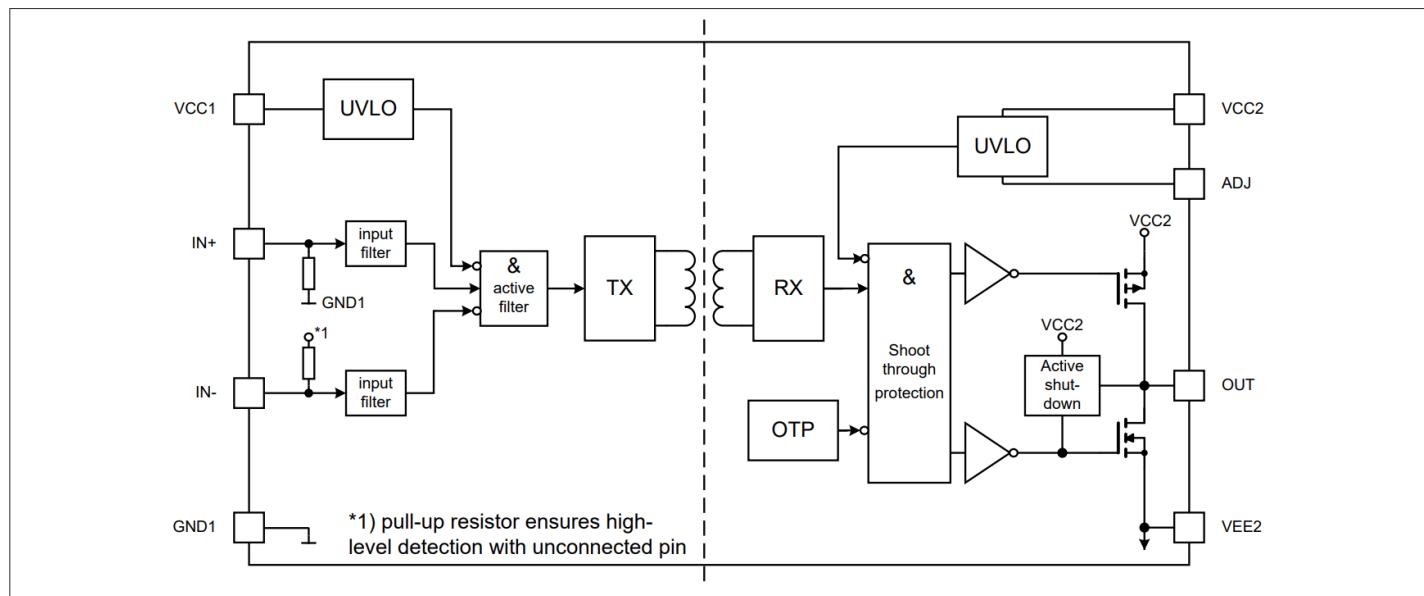

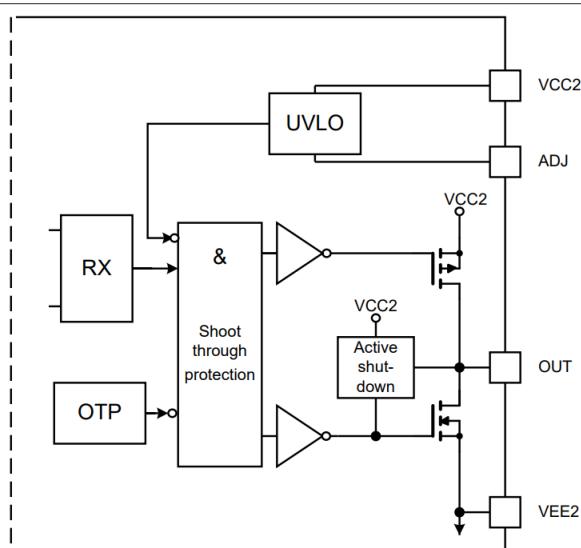

图 4 带 ADJ 引脚的器件框图 (1ED3145)

## 2 引脚配置及说明

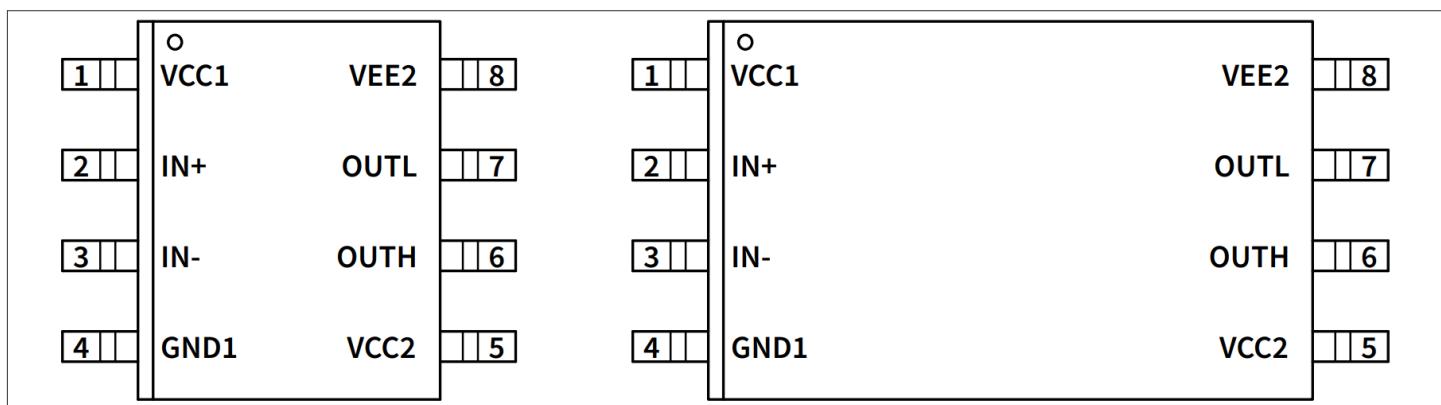

表 4 1ED3140、1ED3141 和 1ED3142 的引脚配置

| Pin No. | Name | Function                                |

|---------|------|-----------------------------------------|

| 1       | VCC1 | Positive power supply input side        |

| 2       | IN+  | Non-inverted driver input (active high) |

| 3       | IN-  | Inverted driver input (active low)      |

| 4       | GND1 | Input side ground                       |

| 5       | VCC2 | Positive power supply output side       |

| 6       | OUTH | Driver sourcing output                  |

| 7       | OUTL | Driver sinking output                   |

| 8       | VEE2 | Output side ground                      |

图 5 1ED3140、1ED3141 和 1ED3142 的引脚排列 (顶视图)

2 引脚配置及说明

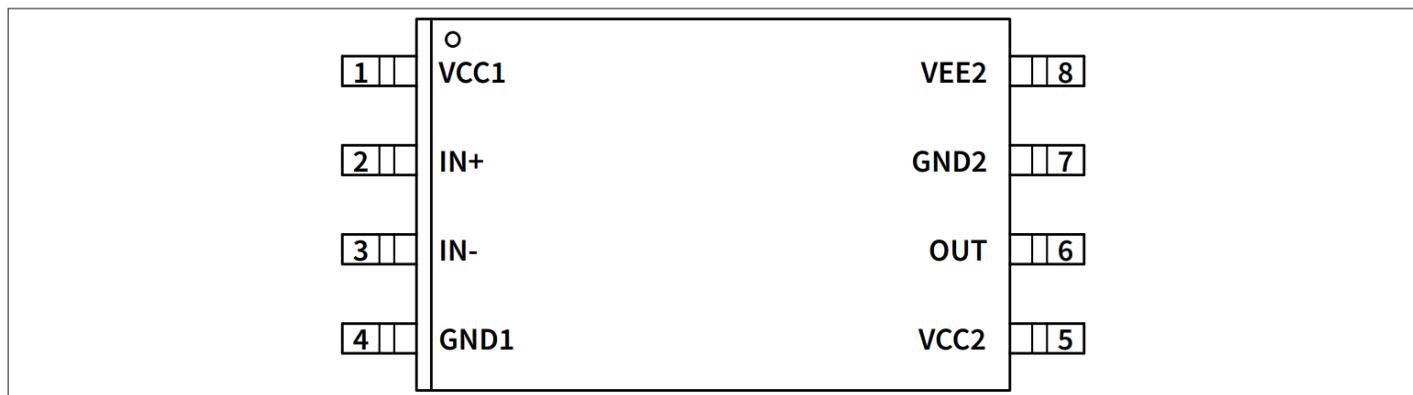

表 5 1ED3143 和 1ED3144 的引脚配置

| Pin No. | Name | Function                                |

|---------|------|-----------------------------------------|

| 1       | VCC1 | Positive power supply input side        |

| 2       | IN+  | Non-inverted driver input (active high) |

| 3       | IN-  | Inverted driver input (active low)      |

| 4       | GND1 | Input side ground                       |

| 5       | VCC2 | Positive power supply output side       |

| 6       | OUT  | Driver sourcing and sinking output      |

| 7       | GND2 | Signal ground output side               |

| 8       | VEE2 | Negative power supply output side       |

图 6 1ED3143 和 1ED3144 的引脚排列 (顶视图)

2 引脚配置及说明

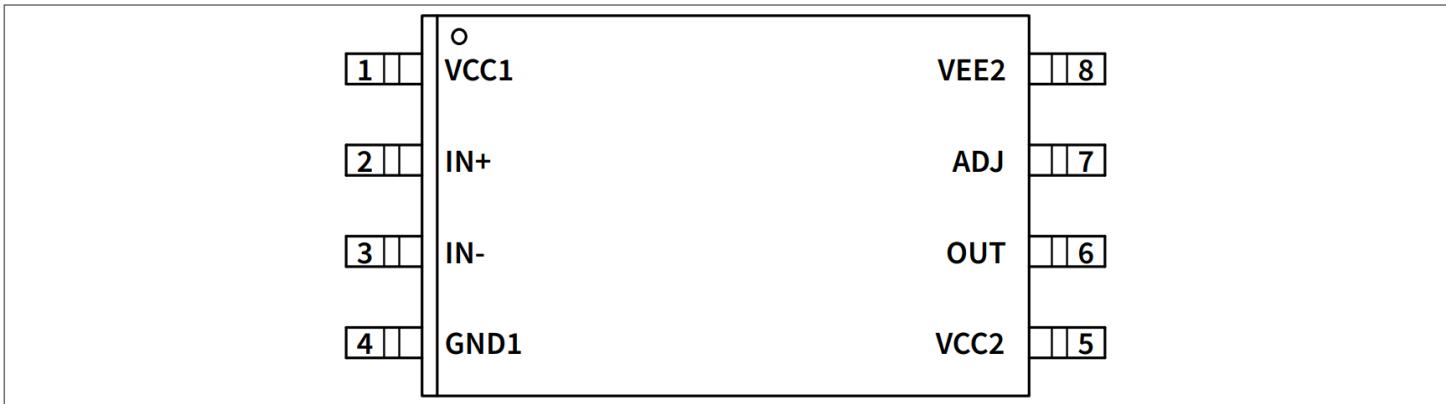

表 6 1ED3145 引脚配置

| Pin No. | Name | Function                                |

|---------|------|-----------------------------------------|

| 1       | VCC1 | Positive power supply input side        |

| 2       | IN+  | Non-inverted driver input (active high) |

| 3       | IN-  | Inverted driver input (active low)      |

| 4       | GND1 | Input side ground                       |

| 5       | VCC2 | Positive power supply output side       |

| 6       | OUT  | Driver sourcing and sinking output      |

| 7       | ADJ  | Adjustable UVLO input                   |

| 8       | VEE2 | Output side ground                      |

图 7 1ED3145 引脚分布 (顶视)

图) 引脚说明

- **VCC1**：输入电源电压。连接至 3.3 V 或 5 V 电源，并通过去耦电容与 **GND1** 相连。使用低 ESR 和低 ESL 电容，并尽可能靠近器件放置。

- **GND1**：输入地。所有输入侧信号 **VCC1**、**IN+** 和 **IN-** 均以此地为参考。

- **IN+**：驱动器输出的同相控制信号。内部滤波器可有效抑制 **IN+** 上的噪声。如果该引脚处于开路状态，内部弱下拉电阻会将该引脚拉至低电平状态，如图 2 所示。

- **IN-**：驱动器输出的反相控制信号。内部滤波器可有效抑制 **IN-** 上的噪声。如果保持开路，内部弱上拉电阻会将该引脚拉至高电平状态，如图 2 所示。

- **VCC2**：输出正电源轨。连接一个去耦电容从此引脚到 **VEE2**。使用低 ESR 和低 ESL 电容，并尽可能靠近器件放置。

- **VEE2**：带 **GND2** 引脚的栅极驱动器的输出负电源轨，不带 **GND2** 引脚的栅极驱动器的输出地。如果采用双极电源（正负电压分别参考 IGBT 发射极或 MOSFET 源极），则此引脚应连接到负电源电压。

- **OUTH**：驱动器拉电流输出引脚，用于为外部晶体管（IGBT 或 MOSFET）的栅极充电。导通状态下，此输出连接至 **VCC2**。此输出由 **IN+** 和 **IN-** 控制，并由 UVLO 事件关闭。

- **OUTL**：驱动器灌电流输出引脚，用于为外部晶体管（IGBT 或 MOSFET）的栅极放电。在关断状态下，此输出连接至 **VEE2**。该输出由 **IN+** 和 **IN-** 控制。发生 UVLO 事件时，**OUTL** 会被主动拉低。如果栅极驱动器输出未供电，主动关断电路会将输出电压保持在低电平。

- **OUT**：驱动器拉电流和灌电流输出引脚，用于为外部晶体管（IGBT 或 MOSFET）的栅极充电和放电。导通状态下，此输出连接至 **VCC2**；关断状态下，此输出连接至 **VEE2**。输出由 **IN+** 和 **IN-** 控制。发生欠压闭锁 (UVLO) 事件时，此输出将关闭，主动关断功能将输出电压保持在低电平。

## 2 引脚配置及说明

- **GND2**：输出侧正负电源电压的参考电压。此引脚连接到IGBT发射极或MOSFET源极。**GND2**是输出侧UVLO电平的参考电压。

- **ADJ**：输出侧欠压闭锁阈值电压调整。**VCC2**和栅极驱动公共地（IGBT发射极或MOSFET源极）之间的电

阻分压器连接到此引脚，用于设置UVLO阈值。

3 电气特性及参数

## 3 电气特性及参数

### 3.1 绝对最大额定值

表 7 绝对最大额定值

超出所列的绝对最大额定值的应力可能会对器件造成永久性损坏。这些仅为应力额定值。不保证器件在这些条件下或任何其他 推荐操作条件之外的情况下工作。长时间暴露于绝对最大额定值条件下可能会影响器件的可靠性。

| Parameter                                 | Symbol          | Values           |      |                  | Unit | Note or condition                                          |

|-------------------------------------------|-----------------|------------------|------|------------------|------|------------------------------------------------------------|

|                                           |                 | Min.             | Typ. | Max.             |      |                                                            |

| Power supply input side voltage           | $V_{VCC1}$      | -0.3             |      | 17               | V    | $V_{VCC1} - V_{GND1}$                                      |

| Power supply output side voltage          | $V_{VCC2}$      | -0.3             |      | 35               | V    | $V_{VCC2} - V_{VEE2}$                                      |

| Positive power supply output side voltage | $V_{VCC2}$      | -0.3             |      | 35               | V    | $V_{VCC2} - V_{GND2}$ , valid only for 1ED3143 and 1ED3144 |

| Negative power supply output side voltage | $V_{VEE2}$      | -35              |      | 0.3              | V    | $V_{VEE2} - V_{GND2}$ , valid only for 1ED3143 and 1ED3144 |

| Gate driver output voltage                | $V_{OUT}$       | $V_{VEE2} - 0.3$ |      | $V_{VCC2} + 0.3$ | V    | valid only for 1ED3143, 1ED3144 and 1ED3145                |

| Gate driver source output voltage         | $V_{OUTH}$      | $V_{VCC2} - 35$  |      | $V_{VCC2} + 0.3$ | V    | valid only for 1ED3140, 1ED3141 and 1ED3142                |

| Gate driver sink output voltage           | $V_{OUTL}$      | $V_{VEE2} - 0.3$ |      | $V_{VEE2} + 35$  | V    | valid only for 1ED3140, 1ED3141 and 1ED3142                |

| Logic input voltages (IN+, IN-)           | $V_{IN}$        | -0.3             |      | 6.5              | V    |                                                            |

| Dynamic logic input voltages (IN+, IN-)   | $V_{INdyn}$     | -5               |      | 15               | V    | <sup>1)</sup> $t_{IN} < 100 \text{ ns}$ , $d < 0.01$       |

| Adjustable UVLO input                     | $V_{ADJ}$       | $V_{VCC2} + 0.3$ |      | $V_{VCC2} - 6$   | V    | valid only for 1ED3145                                     |

| Input to output offset voltage            | $V_{OFFSET}$    |                  |      | 2300             | V    | <sup>2)</sup> $V_{OFFSET} =  V_{VEE2} - V_{GND1} $         |

| ESD robustness - human body model         | $ V_{ESD,HBM} $ |                  |      | 4                | kV   | <sup>3)</sup>                                              |

| ESD robustness - charged device model     | $ESD,CDM$       |                  |      | TC1500           |      | <sup>4)</sup>                                              |

| Junction temperature                      | $T_J$           | -40              |      | 150              | °C   |                                                            |

| Storage temperature                       | $T_{Stg}$       | -55              |      | 150              | °C   |                                                            |

#### PG-DSO-8-72 (150-mil)

|                                                    |                |  |  |     |     |                                                                |

|----------------------------------------------------|----------------|--|--|-----|-----|----------------------------------------------------------------|

| Power dissipation (input side)                     | $P_{D,IN}$     |  |  | 100 | mW  | <sup>5)</sup> $T_A = 85 \text{ °C}$                            |

| Power dissipation (output side)                    | $P_{D,OUT}$    |  |  | 500 | mW  | <sup>6)</sup> $T_A = 85 \text{ °C}$                            |

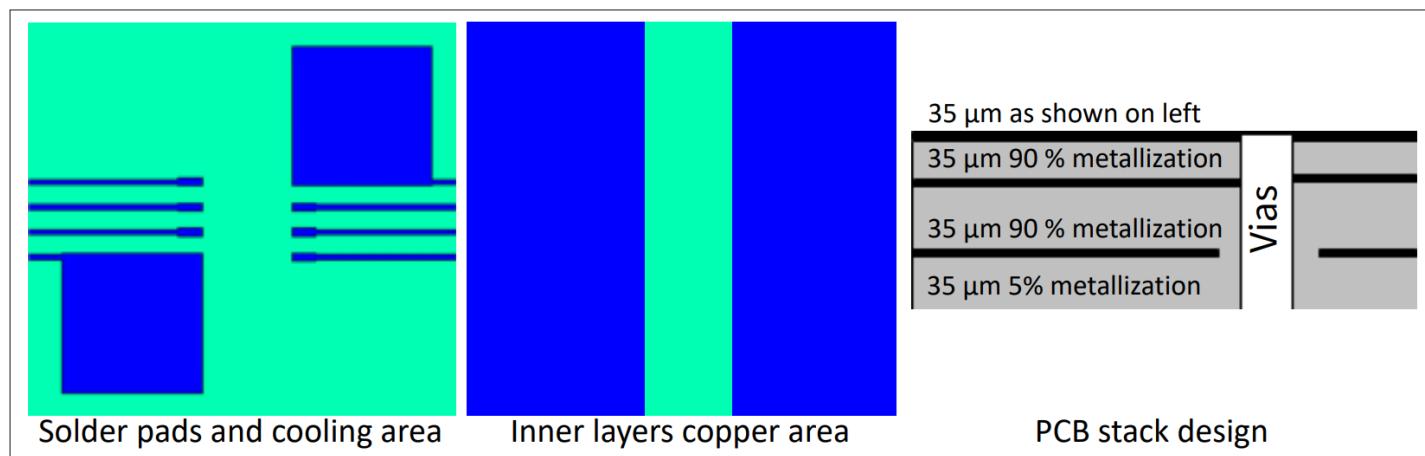

| Thermal resistance junction to ambient             | $R_{THJA,OUT}$ |  |  | 129 | K/W | $T_A = 85 \text{ °C}$ , 2s2p - no vias, $P_J = 500 \text{ mW}$ |

| Characterization parameter junction to package top | $\Psi_{Jtop}$  |  |  | 6.1 | K/W | $T_A = 85 \text{ °C}$ , 2s2p - no vias, $P_J = 500 \text{ mW}$ |

(表格续下页.....)

3 电气特性及参数

表 7 (续) 绝对最大额定值

超出所列的绝对最大额定值的应力可能会对器件造成永久性损坏。这些仅为应力额定值。不保证器件在这些条件下或任何其他 推荐操作条件之外的情况下工作。长时间暴露于绝对最大额定值条件下可能会影响器件的可靠性。

| Parameter                                          | Symbol         | Values |      |      | Unit | Note or condition                                                |

|----------------------------------------------------|----------------|--------|------|------|------|------------------------------------------------------------------|

|                                                    |                | Min.   | Typ. | Max. |      |                                                                  |

| <b>PG-LDSO-8-1 [300-mil]</b>                       |                |        |      |      |      |                                                                  |

| Power dissipation (input side)                     | $P_{D,IN}$     |        |      | 100  | mW   | <sup>7)</sup> $T_A = 85^\circ\text{C}$                           |

| Power dissipation (output side)                    | $P_{D,OUT}$    |        |      | 550  | mW   | <sup>8)</sup> $T_A = 85^\circ\text{C}$                           |

| Thermal resistance junction to ambient             | $R_{thJA,OUT}$ |        |      | 113  | K/W  | $T_A = 85^\circ\text{C}$ , 2s2p - no vias, $P_J = 550\text{ mW}$ |

| Characterization parameter junction to package top | $\Psi_{Jtop}$  |        |      | 5.7  | K/W  | $T_A = 85^\circ\text{C}$ , 2s2p - no vias, $P_J = 550\text{ mW}$ |

1) 参数无需经过生产测试 - 通过设计/特性验证

2) 仅用于功能操作

3) 根据 ANSI/ESDA/JEDEC-JS-001-2017 (通过串联 1.5 kΩ 电阻给 100 pF 电容器放电)。

4) 根据 ANSI/ESDA/JEDEC-JS-002-2014 (TC = 测试条件, 单位: 伏特)

5) IC 输入侧功耗在  $137.1^\circ\text{C}$  以上时线性降额, 下降率为  $7.75\text{ mW}/^\circ\text{C}$

6) IC 输出侧功耗在  $85^\circ\text{C}$  以上时线性降额, 下降率为  $7.75\text{ mW}/^\circ\text{C}$

7) IC 输入侧功耗在  $138.7^\circ\text{C}$  以上时线性降额, 下降率为  $8.85\text{ mW}/^\circ\text{C}$

8) IC 输出侧功耗在  $87.8^\circ\text{C}$  以上时线性降额, 下降率为  $8.85\text{ mW}/^\circ\text{C}$

图8 热特性数据参考布局

该 PCB 布局代表用于 150 mil 封装热特性评估的参考布局。

### 3.2 推荐操作条件

表8 推荐操作条件

| Parameter                       | Symbol     | Values |      |      | Unit | Note or condition     |

|---------------------------------|------------|--------|------|------|------|-----------------------|

|                                 |            | Min.   | Typ. | Max. |      |                       |

| Power supply input side voltage | $V_{VCC1}$ | 3.0    |      | 15   | V    | $V_{VCC1} - V_{GND1}$ |

(表格续下页.....)

表8 (续) 推荐操作条件

| Parameter                                 | Symbol     | Values |      |      | Unit | Note or condition                           |

|-------------------------------------------|------------|--------|------|------|------|---------------------------------------------|

|                                           |            | Min.   | Typ. | Max. |      |                                             |

| Power supply output side voltage          | $V_{VCC2}$ | 9.6    |      | 32   | V    | $V_{VCC2} - V_{VEE2}$ , 1ED3140             |

| Power supply output side voltage          | $V_{VCC2}$ | 12.35  |      | 32   | V    | $V_{VCC2} - V_{VEE2}$ , 1ED3141             |

| Power supply output side voltage          | $V_{VCC2}$ | 14     |      | 32   | V    | $V_{VCC2} - V_{VEE2}$ , 1ED3142             |

| Power supply output side voltage          | $V_{VCC2}$ | 4.35   |      | 32   | V    | $V_{VCC2} - V_{VEE2}$ , 1ED3145             |

| Positive power supply output side voltage | $V_{VCC2}$ | 12.35  |      | 32   | V    | $V_{VCC2} - V_{GND2}$ , 1ED3143             |

| Positive power supply output side voltage | $V_{VCC2}$ | 14     |      | 32   | V    | $V_{VCC2} - V_{GND2}$ , 1ED3144             |

| Negative power supply output side voltage | $V_{VEE2}$ | -16    |      | 0    | V    | $V_{VEE2} - V_{GND2}$ , 1ED3143 and 1ED3144 |

| Logic input voltages (IN+, IN-)           | $V_{IN}$   | -0.3   |      | 5.5  | V    |                                             |

| Ambient temperature                       | $T_A$      | -40    |      | 125  | °C   |                                             |

| Junction temperature                      | $T_J$      | -40    |      | 150  | °C   |                                             |

### 3.3 电气特性

电气特性包括在建议工作条件下，电源电压和温度在范围内的数值分布。电气特性在生产过程中于  $T_A = 25$  °C 下测试。典型值代表在  $V_{VCC1} = 3.3$  V、 $V_{VCC2} - V_{VEE2} = 15$  V 和  $T_A = 25$  °C 下测得的中值。对于 1ED3143 和 1ED3144  $V_{VEE2} - V_{GND2} = 0$  V。特性中的最小值和最大值均通过特性/设计验证。除非另有说明，否则这适用于所有电气特性。

#### 3.3.1 电源

表9 电源

| Parameter                                | Symbol       | Values |      |      | Unit | Note or condition                                   |

|------------------------------------------|--------------|--------|------|------|------|-----------------------------------------------------|

|                                          |              | Min.   | Typ. | Max. |      |                                                     |

| UVLO threshold input side (on)           | $V_{UVLOH1}$ |        | 2.86 | 3.0  | V    | $V_{VCC1} - V_{GND1}$                               |

| UVLO threshold input side (off)          | $V_{UVLOL1}$ | 2.5    | 2.66 |      | V    | $V_{VCC1} - V_{GND1}$                               |

| UVLO hysteresis input side               | $V_{HYS1}$   | 0.1    | 0.2  |      | V    | $V_{UVLOH1} - V_{UVLOL1}$                           |

| Quiescent current input side             | $I_{Q1}$     |        |      | 1.1  | mA   | $IN+ = Low, IN- = Low$                              |

| Quiescent current output side, ON state  | $I_{Q2,ON}$  |        |      | 1.35 | mA   | $IN+ = High, IN- = Low, V_{VCC2} - V_{VEE2} = 15$ V |

| Quiescent current output side, OFF state | $I_{Q2,OFF}$ |        |      | 1.0  | mA   | $IN+ = Low, IN- = High, V_{VCC2} - V_{VEE2} = 15$ V |

#### 1ED3140

|                                  |              |      |      |     |   |                           |

|----------------------------------|--------------|------|------|-----|---|---------------------------|

| UVLO threshold output side (on)  | $V_{UVLOH2}$ |      | 9.3  | 9.6 | V | $V_{VCC2} - V_{VEE2}$     |

| UVLO threshold output side (off) | $V_{UVLOL2}$ | 8.25 | 8.55 |     | V | $V_{VCC2} - V_{VEE2}$     |

| UVLO hysteresis output side      | $V_{HYS2}$   |      | 0.75 |     | V | $V_{UVLOH2} - V_{UVLOL2}$ |

(表格续下页.....)

3 电气特性及参数

表 9 (续) 电源

| Parameter                                   | Symbol           | Values |       |       | Unit    | Note or condition                 |

|---------------------------------------------|------------------|--------|-------|-------|---------|-----------------------------------|

|                                             |                  | Min.   | Typ.  | Max.  |         |                                   |

| <b>1ED3141</b>                              |                  |        |       |       |         |                                   |

| UVLO threshold output side (on)             | $V_{UVLOH2}$     |        | 12    | 12.35 | V       | $V_{VCC2} - V_{VEE2}$             |

| UVLO threshold output side (off)            | $V_{UVLOL2}$     | 10.7   | 11.05 |       | V       | $V_{VCC2} - V_{VEE2}$             |

| UVLO hysteresis output side                 | $V_{HYS2}$       |        | 0.95  |       | V       | $V_{UVLOH2} - V_{UVLOL2}$         |

| <b>1ED3142</b>                              |                  |        |       |       |         |                                   |

| UVLO threshold output side (on)             | $V_{UVLOH2}$     |        | 13.6  | 14    | V       | $V_{VCC2} - V_{VEE2}$             |

| UVLO threshold output side (off)            | $V_{UVLOL2}$     | 12.15  | 12.55 |       | V       | $V_{VCC2} - V_{VEE2}$             |

| UVLO hysteresis output side                 | $V_{HYS2}$       |        | 1.05  |       | V       | $V_{UVLOH2} - V_{UVLOL2}$         |

| <b>1ED3143</b>                              |                  |        |       |       |         |                                   |

| UVLO threshold output side (on)             | $V_{UVLOH2}$     |        | 12    | 12.35 | V       | $V_{VCC2} - V_{GND2}$             |

| UVLO threshold output side (off)            | $V_{UVLOL2}$     | 10.7   | 11.05 |       | V       | $V_{VCC2} - V_{GND2}$             |

| UVLO hysteresis output side                 | $V_{HYS2}$       |        | 0.95  |       | V       | $V_{UVLOH2} - V_{UVLOL2}$         |

| <b>1ED3144</b>                              |                  |        |       |       |         |                                   |

| UVLO threshold output side (on)             | $V_{UVLOH2}$     |        | 13.6  | 14    | V       | $V_{VCC2} - V_{GND2}$             |

| UVLO threshold output side (off)            | $V_{UVLOL2}$     | 12.15  | 12.55 |       | V       | $V_{VCC2} - V_{GND2}$             |

| UVLO hysteresis output side                 | $V_{HYS2}$       |        | 1.05  |       | V       | $V_{UVLOH2} - V_{UVLOL2}$         |

| <b>1ED3145</b>                              |                  |        |       |       |         |                                   |

| Adjustable UVLO threshold output side (on)  | $V_{ADJ,UVLOH2}$ |        | 2     | 2.07  | V       | $V_{VCC2} - V_{ADJ}$              |

| Adjustable UVLO threshold output side (off) | $V_{ADJ,UVLOL2}$ | 1.78   | 1.84  |       | V       | $V_{VCC2} - V_{ADJ}$              |

| Adjustable UVLO hysteresis output side      | $V_{ADJ,HYS2}$   |        | 0.16  |       | V       | $V_{ADJ,UVLOH2} - V_{ADJ,UVLOL2}$ |

| ADJ leakage current                         | $I_{Q,ADJ}$      | 2.4    | 3     | 3.6   | $\mu A$ | $V_{ADJ} = V_{VCC2} - 3 V$        |

### 3.3.2 逻辑输入

表 10 逻辑输入

| Parameter                             | Symbol       | Values |      |      | Unit      | Note or condition                      |

|---------------------------------------|--------------|--------|------|------|-----------|----------------------------------------|

|                                       |              | Min.   | Typ. | Max. |           |                                        |

| IN+, IN- low input threshold voltage  | $V_{IN,L}$   | 1.1    |      |      | V         |                                        |

| IN+, IN- high input threshold voltage | $V_{IN,H}$   |        |      | 2.5  | V         |                                        |

| IN+, IN- low/high hysteresis          | $V_{IN,HYS}$ | 0.5    | 0.8  |      | V         |                                        |

| IN+, IN- input current                | $I_{IN}$     |        |      | 100  | $\mu A$   | $V_{VCC1} = 5 V, V_{IN} \leq V_{VCC1}$ |

| IN+ pull down resistor                | $R_{IN,PD}$  |        | 75   |      | $k\Omega$ |                                        |

| IN- pull up resistor                  | $R_{IN,PU}$  |        | 75   |      | $k\Omega$ |                                        |

3 电气特性及参数

### 3.3.3 栅极驱动器

表 11 栅极驱动器

| Parameter                                           | Symbol          | Values |      |      | Unit     | Note or condition                                                                                     |

|-----------------------------------------------------|-----------------|--------|------|------|----------|-------------------------------------------------------------------------------------------------------|

|                                                     |                 | Min.   | Typ. | Max. |          |                                                                                                       |

| High level output peak current                      | $I_{OUTH}$      | 3.5    | 6    |      | A        | <sup>1)</sup> $V_{VCC2} - V_{VEE2} = 15 \text{ V}$ , IN+ = High, IN- = Low, $C_L = 100 \text{ nF}$    |

| High level output on resistance                     | $R_{DSON,H}$    | 0.3    | 0.9  | 2.1  | $\Omega$ | $I_{OUTH} = 0.1 \text{ A}$                                                                            |

| Low level output peak current                       | $I_{OUTL}$      | 3.5    | 6.5  |      | A        | <sup>1)</sup> $V_{VCC2} - V_{VEE2} = 15 \text{ V}$ , IN+ = Low, IN- = High, $C_L = 100 \text{ nF}$    |

| Low level output on resistance                      | $R_{DSON,L}$    | 0.2    | 0.5  | 1.1  | $\Omega$ | $I_{OUTL} = 0.1 \text{ A}$                                                                            |

| Short circuit clamp voltage between OUT(H) and VCC2 | $V_{CLP\_OUTH}$ |        |      | 1.0  | V        | $V_{OUT(H)} - V_{VCC2}$ , $I_{OUTH} = -500 \text{ mA}$ , $t < 10 \mu\text{s}$ , IN+ = High, IN- = Low |

| Clamp voltage between VEE2 and OUT(L)               | $V_{CLP\_OUTL}$ |        |      | 1.0  | V        | $V_{VEE2} - V_{OUT(L)}$ , $I_{OUTL} = -500 \text{ mA}$ , $t < 10 \mu\text{s}$ , IN+ = Low, IN- = High |

1) 参数无需经过生产测试 - 通过设计/特性验证

### 3.3.4 动态特性

表 12 动态特性

| Parameter                                        | Symbol             | Values |      |      | Unit | Note or condition                                                                                                    |

|--------------------------------------------------|--------------------|--------|------|------|------|----------------------------------------------------------------------------------------------------------------------|

|                                                  |                    | Min.   | Typ. | Max. |      |                                                                                                                      |

| Input to output propagation delay ON             | $t_{PDON}$         | 34     | 40   | 50   | ns   | $V_{VCC2} - V_{VEE2} = 15 \text{ V}$ , $C_L = 100 \text{ pF}$ , valid only for 1ED3140, 1ED3141, 1ED3143 and 1ED3145 |

| Input to output propagation delay ON             | $t_{PDON}$         | 34     | 40   | 50   | ns   | $V_{VCC2} - V_{VEE2} = 18 \text{ V}$ , $C_L = 100 \text{ pF}$ , valid only for 1ED3142 and 1ED3144                   |

| Input to output propagation delay OFF            | $t_{PD OFF}$       | 34     | 40   | 50   | ns   | $V_{VCC2} - V_{VEE2} = 15 \text{ V}$ , $C_L = 100 \text{ pF}$ , valid only for 1ED3140, 1ED3141, 1ED3143 and 1ED3145 |

| Input to output propagation delay OFF            | $t_{PD OFF}$       | 34     | 40   | 50   | ns   | $V_{VCC2} - V_{VEE2} = 18 \text{ V}$ , $C_L = 100 \text{ pF}$ , valid only for 1ED3142 and 1ED3144                   |

| Input to output propagation delay distortion IN+ | $ t_{PDISTO,IN+} $ |        | 0    | 3    | ns   | <sup>1)</sup> $ t_{PD OFF} - t_{PD ON} $                                                                             |

| Input to output propagation delay distortion IN- | $ t_{PDISTO,IN-} $ |        | 0    | 5    | ns   | <sup>1)</sup> $ t_{PD OFF} - t_{PD ON} $                                                                             |

| Input to output, part to part skew               | $t_{SKEW}$         |        |      | 7    | ns   | <sup>1) 2)</sup> $C_L = 100 \text{ pF}$ , valid for same input pin and edge                                          |

| Input to output, part to part skew plus          | $t_{SKEW+}$        |        | 0    | 8    | ns   | <sup>1)</sup> $C_L = 100 \text{ pF}$ , valid for opposite output edge and any input combination                      |

(表格续下页.....)

表 12 (续) 动态特性

| Parameter                                  | Symbol           | Values |      |      | Unit                    | Note or condition                                                                                                                                               |

|--------------------------------------------|------------------|--------|------|------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                            |                  | Min.   | Typ. | Max. |                         |                                                                                                                                                                 |

| Input pulse suppression time (filter time) | $t_{INFLT}$      | 16     |      |      | ns                      | shorter pulses will not propagate to the output                                                                                                                 |

| Minimum input pulse width                  | $t_{IN,min}$     | 27     |      |      | ns                      |                                                                                                                                                                 |

| Rise time                                  | $t_{RISE}$       |        |      | 20   | ns                      | $V_{VCC2} - V_{VEE2} = 15 \text{ V}$ , $C_L = 1 \text{ nF}$ , valid only for 1ED3140, 1ED3141 and 1ED3145                                                       |

| Rise time                                  | $t_{RISE}$       |        |      | 20   | ns                      | $V_{VCC2} - V_{VEE2} = 18 \text{ V}$ , $C_L = 1 \text{ nF}$ , valid only for 1ED3142 and 1ED3144                                                                |

| Fall time                                  | $t_{FALL}$       |        |      | 20   | ns                      | $V_{VCC2} - V_{VEE2} = 15 \text{ V}$ , $C_L = 1 \text{ nF}$ , valid only for 1ED3140, 1ED3141, 1ED3143 and 1ED3145                                              |

| Fall time                                  | $t_{FALL}$       |        |      | 20   | ns                      | $V_{VCC2} - V_{VEE2} = 18 \text{ V}$ , $C_L = 1 \text{ nF}$ , valid only for 1ED3142 and 1ED3144                                                                |

| Input-side start-up time                   | $t_{START,VCC1}$ |        | 2.5  | 10   | $\mu\text{s}$           | <sup>3)</sup> $\text{IN+} = \text{High}$ , $\text{IN-} = \text{Low}$ , $V_{VCC2} > V_{UVLOH2}$ , $C_L = 100 \text{ pF}$                                         |

| Input-side deactivation time               | $t_{STOP,VCC1}$  |        | 2.5  | 10   | $\mu\text{s}$           | <sup>3)</sup> $\text{IN+} = \text{High}$ , $\text{IN-} = \text{Low}$ , $V_{VCC2} > V_{UVLOH2}$ , $C_L = 100 \text{ pF}$                                         |

| Output-side start-up time                  | $t_{START,VCC2}$ |        | 5    | 10   | $\mu\text{s}$           | <sup>3)</sup> $\text{IN+} = \text{High}$ , $\text{IN-} = \text{Low}$ , $V_{VCC1} > V_{UVLOH1}$ , $C_L = 100 \text{ pF}$ , valid for all products except 1ED3145 |

| Output-side start-up time                  | $t_{START,VCC2}$ |        | 8    | 13   | $\mu\text{s}$           | <sup>3)</sup> $\text{IN+} = \text{High}$ , $\text{IN-} = \text{Low}$ , $V_{VCC1} > V_{UVLOH1}$ , $C_L = 100 \text{ pF}$ , valid only for 1ED3145                |

| Output-side deactivation time              | $t_{STOP,VCC2}$  | 0.5    |      | 1.5  | $\mu\text{s}$           | <sup>3)</sup> $\text{IN+} = \text{High}$ , $\text{IN-} = \text{Low}$ , $V_{VCC1} > V_{UVLOH1}$ , $C_L = 100 \text{ pF}$ , valid for all products except 1ED3145 |

| Output-side deactivation time              | $t_{STOP,VCC2}$  | 1.5    |      | 4    | $\mu\text{s}$           | <sup>3)</sup> $\text{IN+} = \text{High}$ , $\text{IN-} = \text{Low}$ , $V_{VCC1} > V_{UVLOH1}$ , $C_L = 100 \text{ pF}$ , valid only for 1ED3145                |

| High-level common-mode transient immunity  | $ CM_H $         | 300    |      |      | $\text{kV}/\mu\text{s}$ | <sup>3)</sup> $V_{CM} = 1500 \text{ V}$ ; $\text{IN-}$ tied to $\text{GND1}$ ; $\text{IN+}$ tied to $\text{VCC1}$                                               |

| Low-level common-mode transient immunity   | $ CM_L $         | 300    |      |      | $\text{kV}/\mu\text{s}$ | <sup>3)</sup> $V_{CM} = 1500 \text{ V}$ ; $\text{IN-}$ tied to $\text{VCC1}$ ; $\text{IN+}$ tied to $\text{GND1}$                                               |

1) 相同环境温度和工作条件下的值。

2) 该参数以前称为输入到输出、器件与器件的传播延迟变化

3) 参数无需经过生产测试 - 通过设计/特性验证

### 3.3.5 主动关断

表 13 主动关断

| Parameter                | Symbol      | Values |      |      | Unit | Note or condition                                                                      |

|--------------------------|-------------|--------|------|------|------|----------------------------------------------------------------------------------------|

|                          |             | Min.   | Typ. | Max. |      |                                                                                        |

| Active shut down voltage | $V_{ACTSD}$ |        |      | 1.8  | V    | $V_{OUTL} - V_{VEE2}$ , $I_{OUTL} = 500$ mA,<br>$VCC2$ open, $OUTH$ connected to $R_G$ |

| Active shut down voltage | $V_{ACTSD}$ |        |      | 1.8  | V    | $V_{OUT} - V_{VEE2}$ , $I_{OUTL} = 500$ mA, $VCC2$ open                                |

### 3.3.6 过温保护

表14 过温保护

| Parameter                              | Symbol       | Values |      |      | Unit | Note or condition  |

|----------------------------------------|--------------|--------|------|------|------|--------------------|

|                                        |              | Min.   | Typ. | Max. |      |                    |

| Overtemperature protection temperature | $T_{OTPOFF}$ |        | 165  | 175  | °C   | <a href="#">1)</a> |

| Overtemperature protection hysteresis  | $T_{OTPHYS}$ |        | 10   |      | °C   | <a href="#">1)</a> |

1) 参数无需经过生产测试 - 通过设计/特性验证

## 4 PG-DSO-8 (150 mil) 封装的绝缘特性 (UL 1577)

该耦合器仅适用于给定安全等级内的额定绝缘。应通过适当的保护电路确保符合安全额定值。

表 15 PG-DSO-8 (150 mil) 封装的绝缘规格

| Description | Symbol | Characteristic | Unit |

|-------------|--------|----------------|------|

|-------------|--------|----------------|------|

### 安全限值

|                                                                                 |          |     |    |

|---------------------------------------------------------------------------------|----------|-----|----|

| Maximum ambient safety temperature                                              | $T_S$    | 150 | °C |

| Maximum input-side power dissipation at $T_A = 25^\circ\text{C}$ <sup>1)</sup>  | $P_{SI}$ | 100 | mW |

| Maximum output-side power dissipation at $T_A = 25^\circ\text{C}$ <sup>2)</sup> | $P_{SO}$ | 970 | mW |

### 封装特定的绝缘特性

|                            |          |       |    |

|----------------------------|----------|-------|----|

| External clearance         | $CLR$    | > 4   | mm |

| External creepage          | $CPG$    | > 4   | mm |

| Comparative tracking index | $CTI$    | > 600 | -  |

| Isolation capacitance      | $C_{IO}$ | 1     | pF |

### 获得 UL 1577 认证 (文件 E311313)

|                                     |                |      |        |

|-------------------------------------|----------------|------|--------|

| Insulation withstand voltage (60 s) | $V_{ISO}$      | 3000 | V(rms) |

| Insulation test voltage (1 s)       | $V_{ISO,TEST}$ | 3600 | V(rms) |

1) IC 输入侧功耗在  $137.1^\circ\text{C}$  以上时线性降额, 系数  $7.75 \text{ mW}/^\circ\text{C}$

2) IC 输出侧功耗在  $25^\circ\text{C}$  以上时线性降额, 系数  $7.75 \text{ mW}/^\circ\text{C}$

5 PG-LDSO-8 (300 mil) 封装的绝缘特性 (IEC 60747-17、UL 1577)

## 5 PG-LDSO-8 (300 mil) 封装的绝缘特性 (IEC 60747-17、UL 1577)

该耦合器仅适用于给定安全等级内的额定绝缘。应通过适当的保护电路确保符合安全额定值。

表 16 PG-LDSO-8 (300 mil) 封装的绝缘规格

| Description                                                                     | Symbol   | Characteristic | Unit |

|---------------------------------------------------------------------------------|----------|----------------|------|

| <b>安全限值</b>                                                                     |          |                |      |

| Maximum ambient safety temperature                                              | $T_s$    | 150            | °C   |

| Maximum input-side power dissipation at $T_A = 25^\circ\text{C}$ <sup>1)</sup>  | $P_{SI}$ | 100            | mW   |

| Maximum output-side power dissipation at $T_A = 25^\circ\text{C}$ <sup>2)</sup> | $P_{SO}$ | 1006           | mW   |

### 封装特定的绝缘特性

|                            |          |       |    |

|----------------------------|----------|-------|----|

| External clearance         | $CLR$    | > 8   | mm |

| External creepage          | $CPG$    | > 8   | mm |

| Comparative tracking index | $CTI$    | > 600 | –  |

| Isolation capacitance      | $C_{IO}$ | < 1   | pF |

### 符合 IEC 60747-17 的加强绝缘 (计划)

|                                                                                                                                                 |             |             |         |

|-------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------|---------|

| Installation classification per EN 60664-1, Table 1<br>for rated mains voltage $\leq 150$ V (rms)                                               |             | I-IV        | –       |

| for rated mains voltage $\leq 300$ V (rms)                                                                                                      |             | I-IV        |         |

| for rated mains voltage $\leq 600$ V (rms)                                                                                                      |             | I-III       |         |

| for rated mains voltage $\leq 1000$ V (rms)                                                                                                     |             | I-II        |         |

| Climatic classification                                                                                                                         |             | 40/125/21   | –       |

| Pollution degree (EN 60664-1)                                                                                                                   |             | 2           | –       |

| Apparent charge, method a<br>$V_{pd(ini),a} = V_{IOTM}, V_{pd(m)} = 1.6 \times V_{IORM}, t_{ini} = 1 \text{ min}, t_m = 10 \text{ s}$           | $q_{pd}$    | < 5         | pC      |

| Apparent charge, method b<br>$V_{pd(ini),b} = V_{IOTM} \times 1.2, V_{pd(m)} = 1.875 \times V_{IORM}, t_{ini} = 1 \text{ s}, t_m = 1 \text{ s}$ | $q_{pd}$    | < 5         | pC      |

| Isolation resistance at $T_{A,max}; V_{IO} = 500$ V <sub>DC</sub> , $T_A = 125$ °C                                                              | $R_{IO}$    | $> 10^{11}$ | Ω       |

| Isolation resistance at $T_s; V_{IO} = 500$ V <sub>DC</sub> , $T_s = 150$ °C                                                                    | $R_{IO\_S}$ | $> 10^9$    | Ω       |

| Maximum rated transient isolation voltage                                                                                                       | $V_{IOTM}$  | 8000        | V(peak) |

| Maximum repetitive isolation voltage                                                                                                            | $V_{IORM}$  | 1767        | V(peak) |

| Maximum working isolation voltage                                                                                                               | $V_{IOWM}$  | 1249        | V(rms)  |

| Impulse voltage                                                                                                                                 | $V_{IMP}$   | 8000        | V(peak) |

| Maximum surge isolation voltage for reinforced isolation<br>$V_{TEST} \geq V_{IMP} \times 1.3$                                                  | $V_{IOSM}$  | 11000       | V(peak) |

### 获得 UL 1577 认证 (文件 E311313)

|                                     |                |      |        |

|-------------------------------------|----------------|------|--------|

| Insulation withstand voltage (60 s) | $V_{ISO}$      | 5700 | V(rms) |

| Insulation test voltage (1 s)       | $V_{ISO,TEST}$ | 6840 | V(rms) |

1) IC 输入侧功耗在 138.7 °C 以上时线性降额, 系数 8.85 mW/°C

2) IC 输出侧功耗在 25°C 以上时线性降额, 系数 8.05 mW/°C

6 典型特征

## 6 典型特征

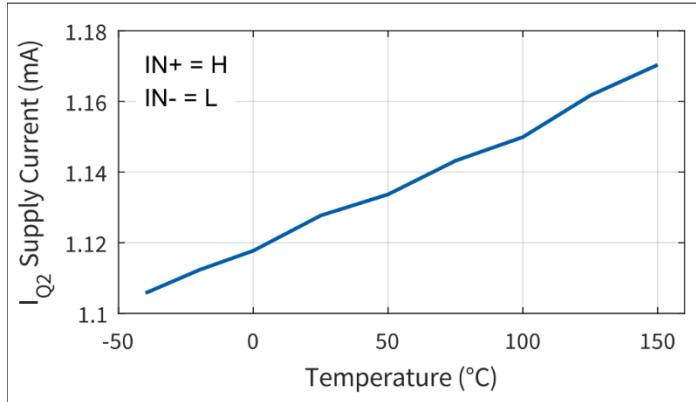

除非另有说明, 测量都是在  $V_{VCC1} = 3.3\text{ V}$ 、  $VCC1$  和  $GND1$  之间放置  $100\text{nF}$  电容

$VCC2$  与  $VEE2$  之间放置  $4.7\mu\text{F}$  电容。

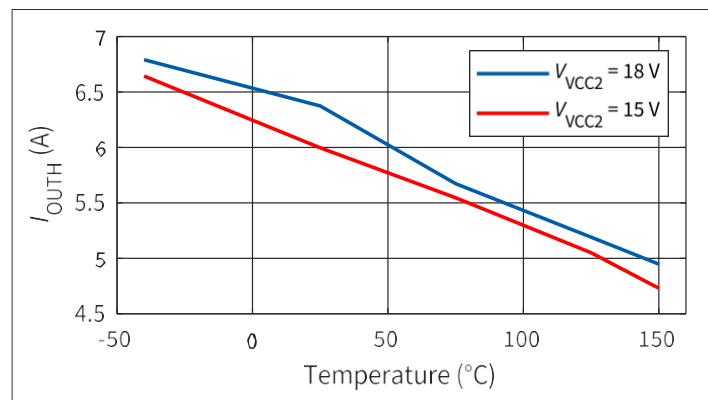

图9 高电平输出峰值电流与温度的关系

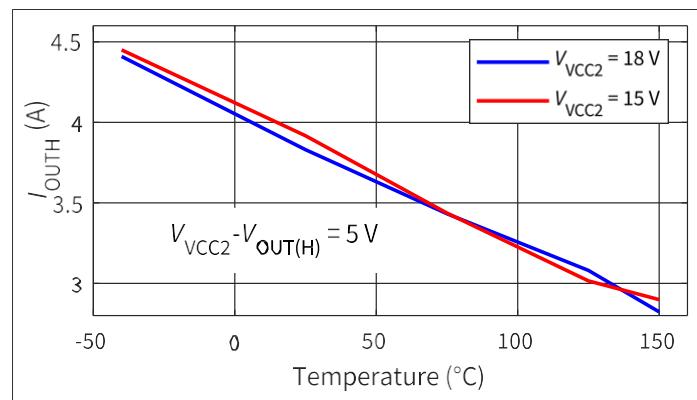

图10 高电平输出电流与温度的关系在  $V_{VCC2} - V_{OUT(H)} = 5\text{ V}$  情况下

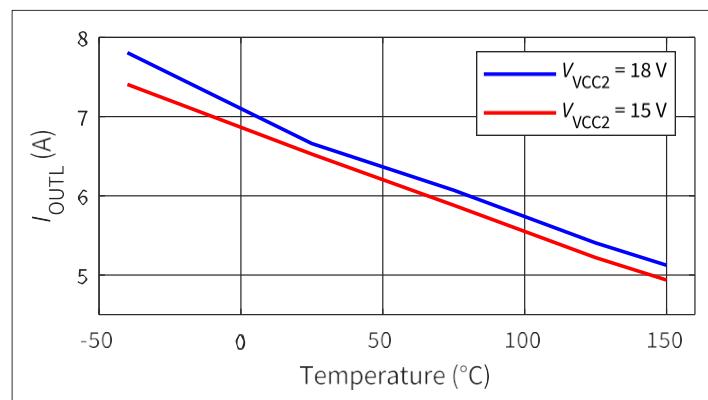

图11 低电平输出峰值电流与温度的关系

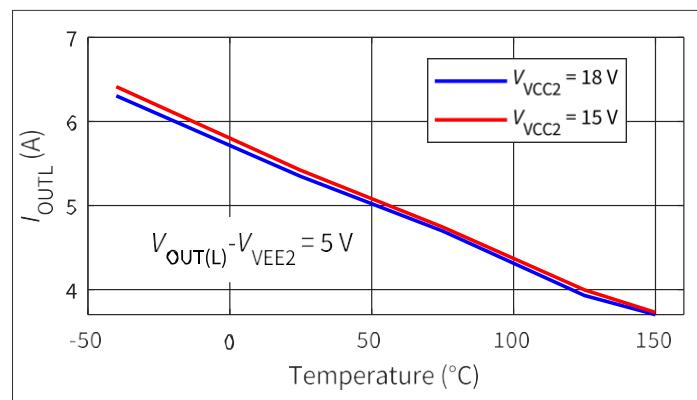

图12 低电平输出电流与温度的关系在  $V_{OUT(L)} - V_{VEE2} = 5\text{ V}$  情况下

6 典型特征

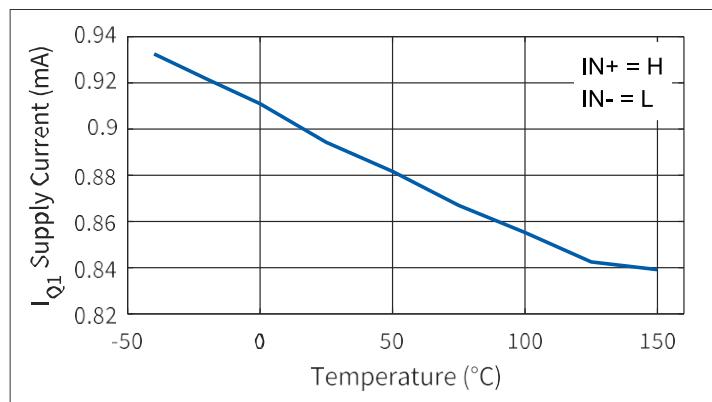

图 13  $I_{Q1}$  电源电流与温度的关系

图 14  $I_{Q1}$  电源电流与温度的关系

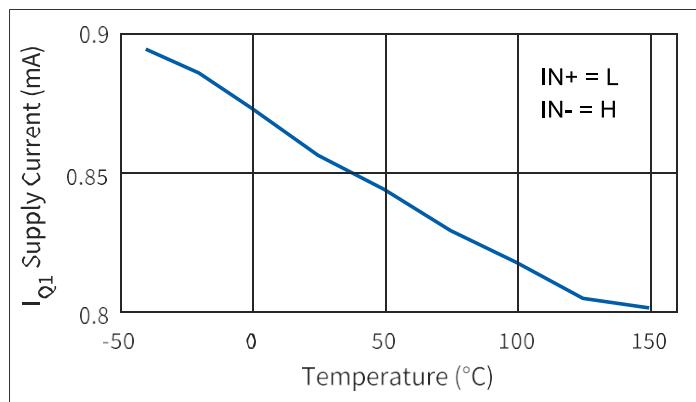

图 15  $I_{Q1}$  电源电流与输入频率的关系

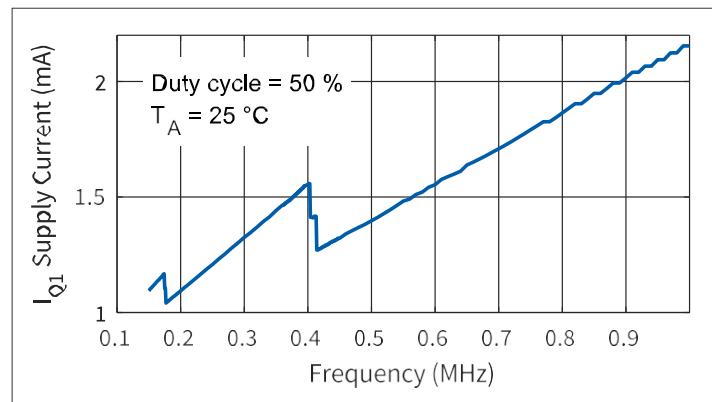

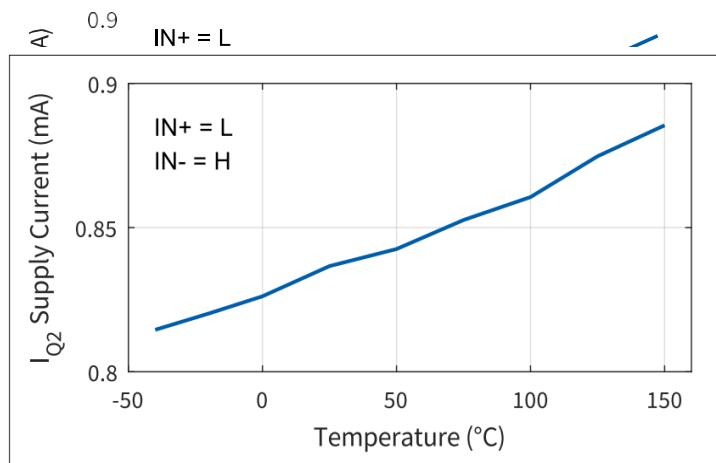

图 16  $I_{Q2}$  电源电流与温度的关系

图 17  $I_{Q2}$  电源电流与温度的关系

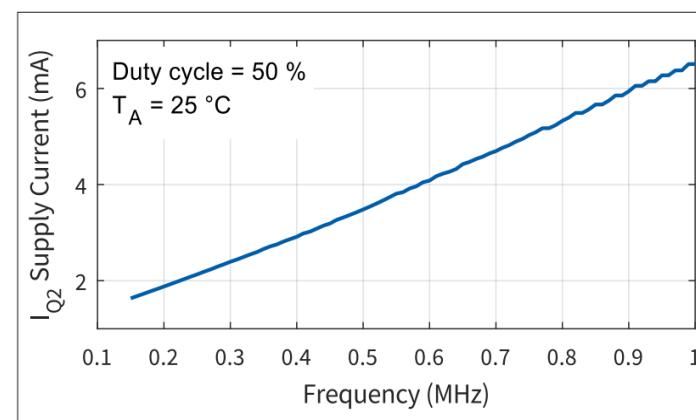

图 18  $I_{Q2}$  电源电流与输入频率的关系

## 6 典型特征

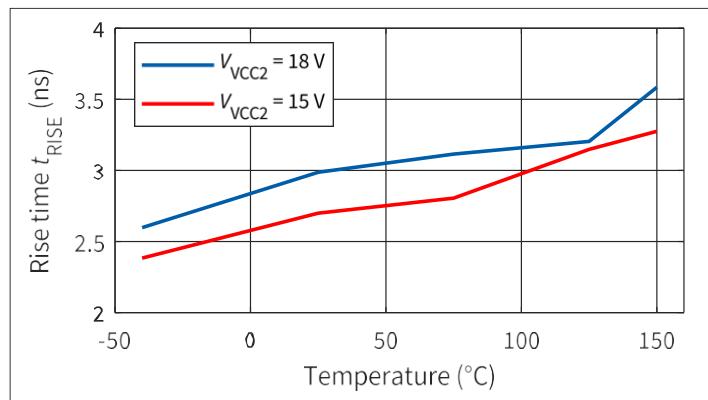

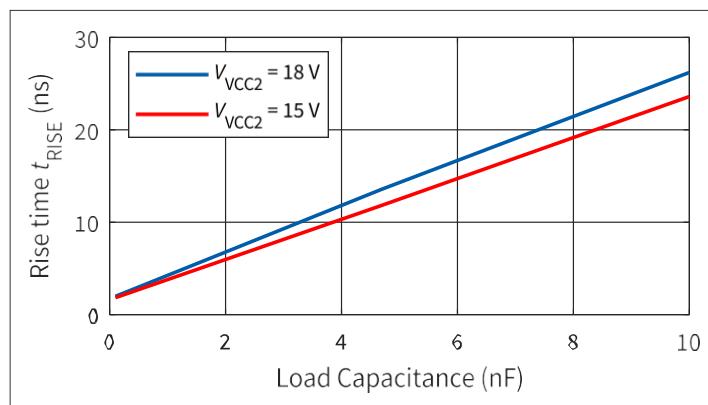

图 19 上升时间  $t_{RISE}$  与温度的关系

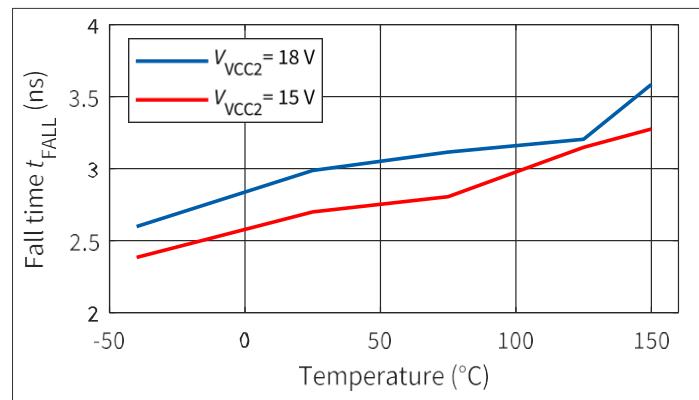

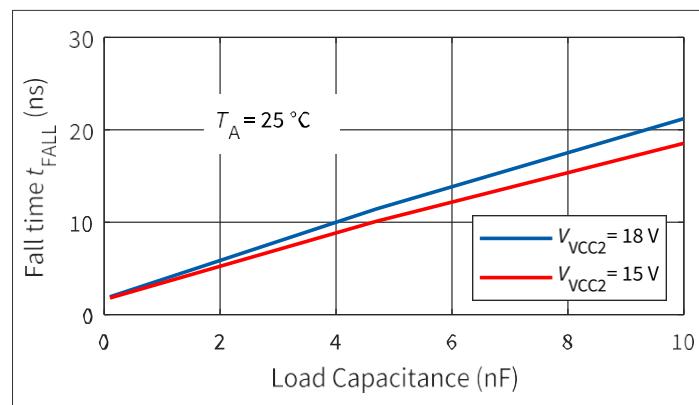

图 20 下降时间  $t_{FALL}$  与温度的关系

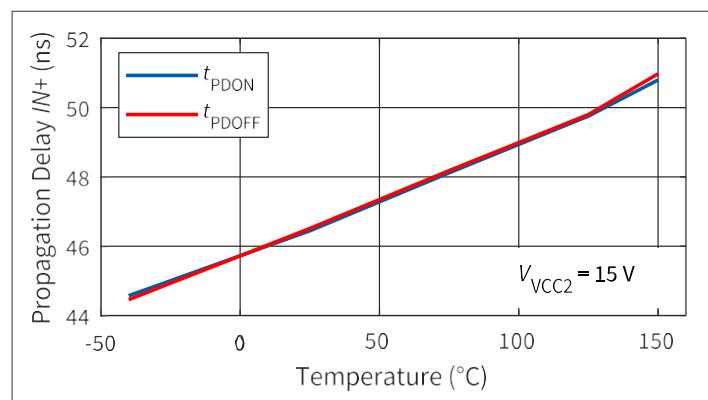

图 21 IN+ 传播延迟与温度的关系 ( $V_{VCC2} = 15\text{ V}$ )

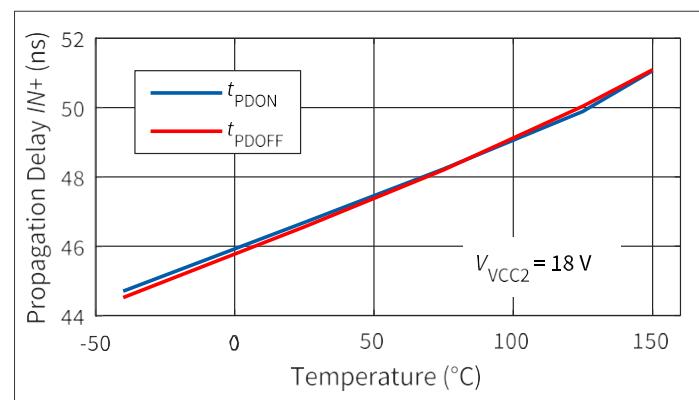

图 22 IN+ 传播延迟与温度的关系 ( $V_{VCC2} = 18\text{ V}$ )

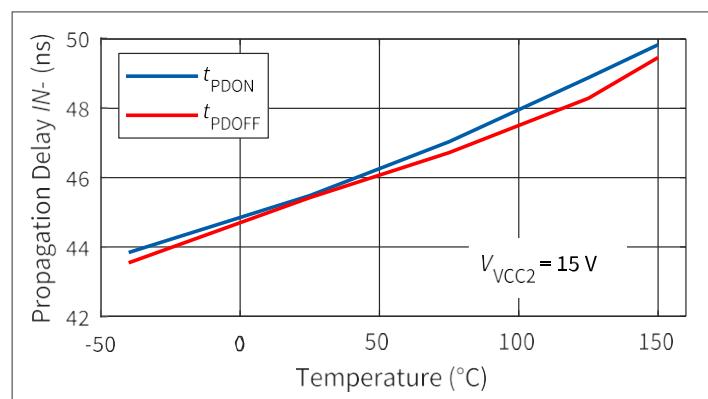

图 23 IN- 传播延迟与温度的关系 ( $V_{VCC2} = 15\text{ V}$ )

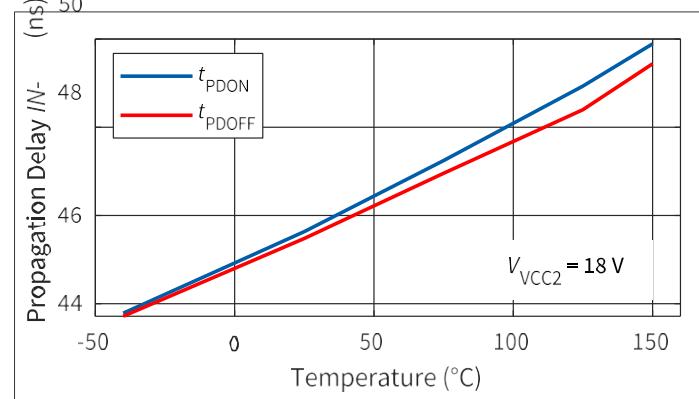

图 24 IN- 传播延迟与温度的关系 ( $V_{VCC2} = 18\text{ V}$ )

6 典型特征

图 25 上升时间  $t_{RISE}$  与负载电容的关系

图 26 下降时间  $t_{FALL}$  与负载电容的关系

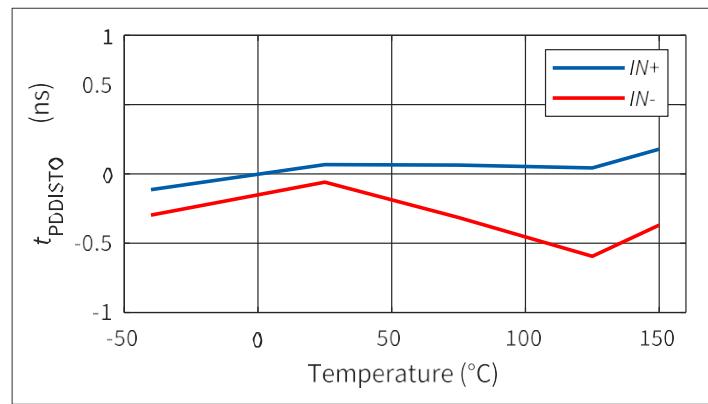

图 27 传播延迟失真

$t_{PDISTO}$  与温度的关系

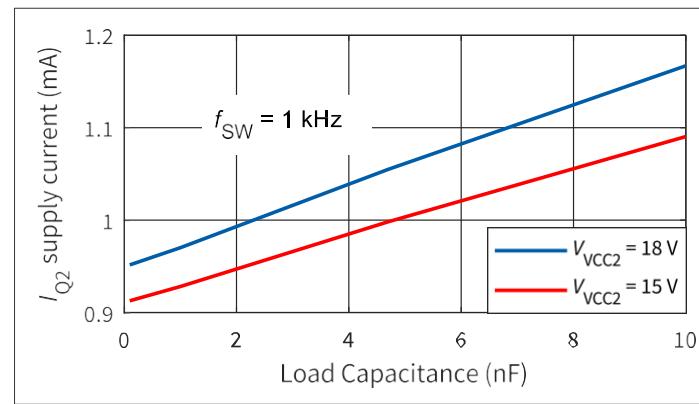

图 28  $I_{Q2}$  电源电流与负载电容

的关系

## 7 参数测量

### 7.1 CMTI 测量设置

图 29 所有型号的 CMTI 测试电路

图 29 显示了用于共模瞬态抗扰度CMTI测量的测试设置。

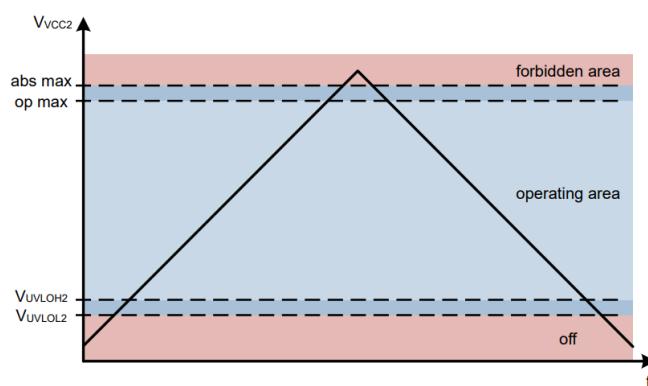

### 7.2 欠压锁定(UVLO)

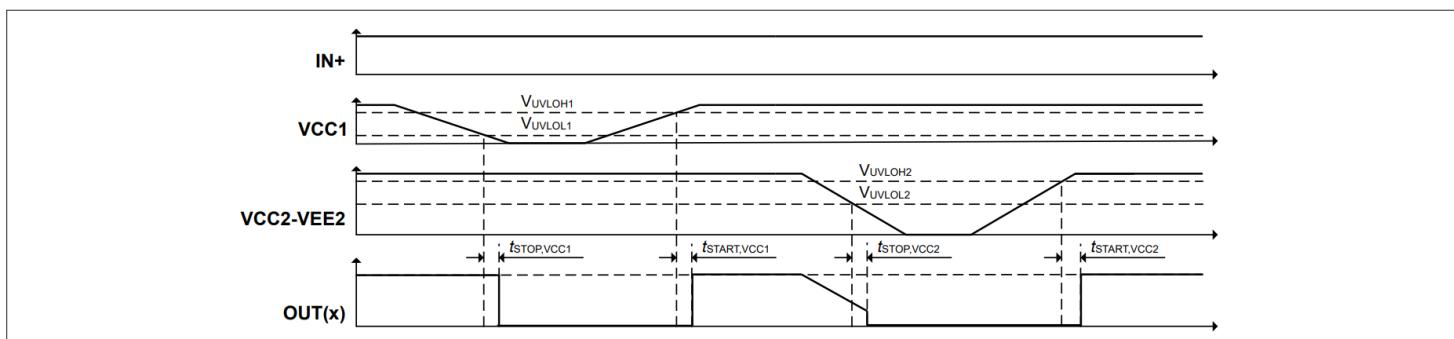

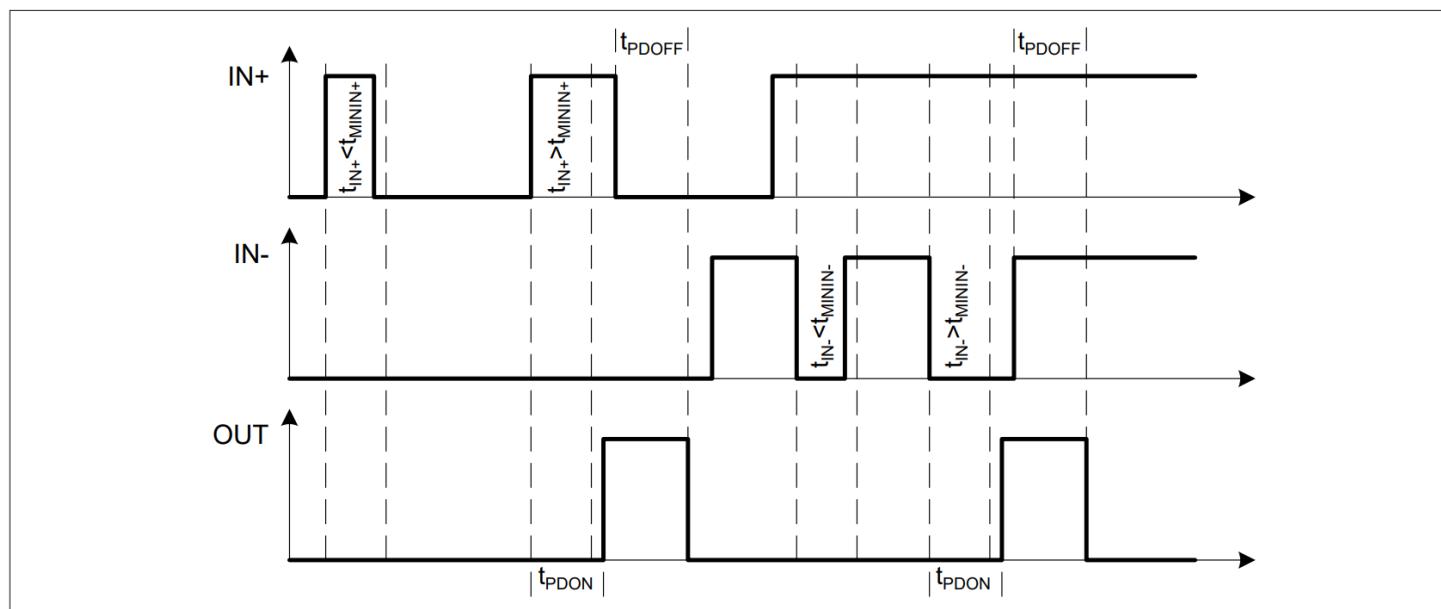

图 30 具有独立输出引脚器件的 UVLO 行为

为确保 IGBT、Si 或 SiC MOSFET 的正确开关，该器件在输入侧和输出侧均配备了独立的欠压锁定功能。只有当两个电源电压均超过各自的 $V_{UVLOH}$ 水平时，器件才会开始工作。

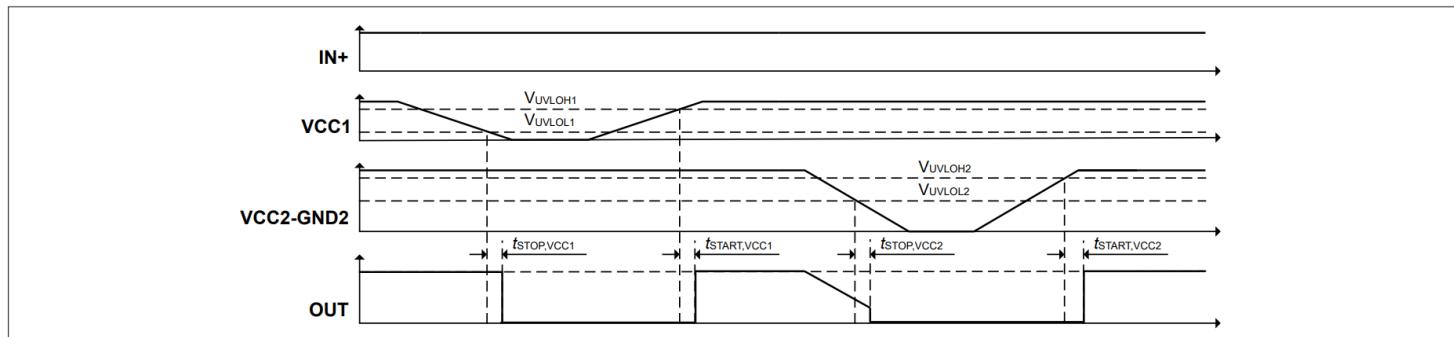

图 31 带有 GND2 引脚型号的 UVLO 行为

## 7 参数测量

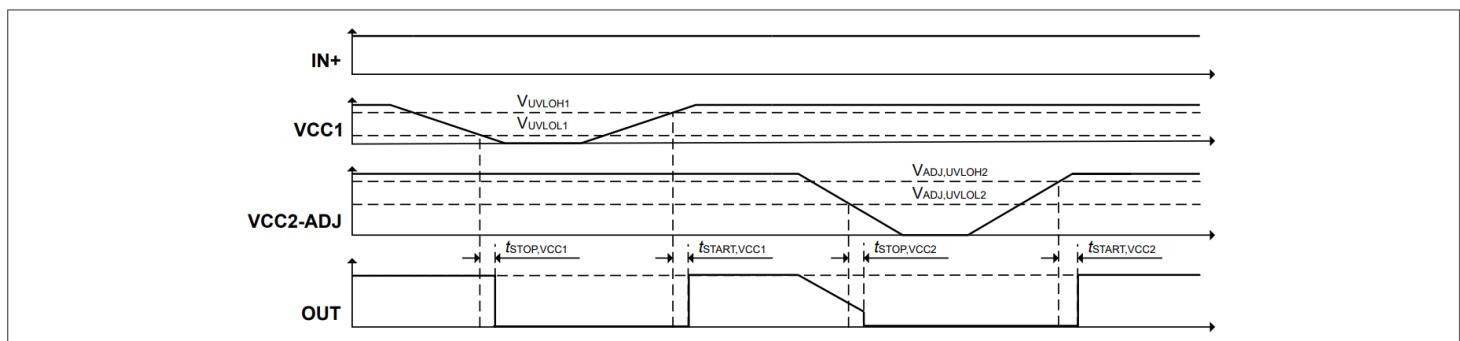

图 32 带有 ADJ 引脚型号的 UVLO 行为

如果输入芯片的电源电压  $V_{VCC1}$  降至  $V_{UVLOL1}$  以下，则在关断之前，会向输出芯片发送关断信号。IGBT、Si 或 SiC MOSFET 将关断，并且  $IN+$  和  $IN-$  处的信号将被忽略，直到  $V_{VCC1}$  再次达到上电电压  $V_{UVLOH1}$  为止。

如果输出芯片的电源电压  $V_{VCC2}$  降至  $V_{UVLOL2}$  以下，则 IGBT、Si 或 SiC MOSFET 将关闭，并且来自输入芯片的信号将被忽略，直到  $V_{VCC2}$  再次达到上电电压  $V_{UVLOH2}$ 。

## 7.3 传播延迟、上升和下降时间

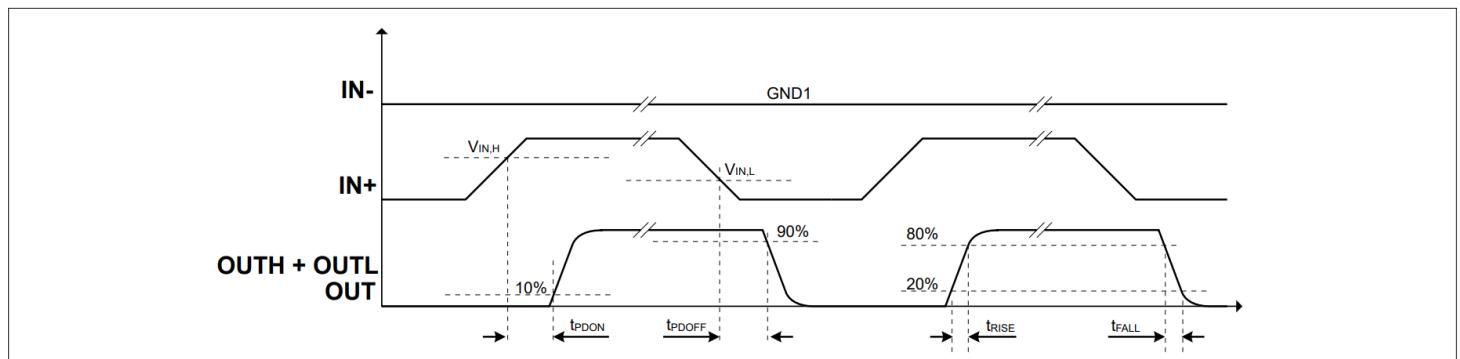

图 33 使用非反相输入的传播延迟、上升时间和下降时间

图 33 和 图34 显示非反相输入  $IN+$  和反相输入  $IN-$  的传播延迟  $t_{PDON}$  和  $t_{PDOFF}$ ，包括上升时间  $t_{RISE}$  和下降时间  $t_{FALL}$  的图表。

图 34 使用反相输入的传播延迟、上升时间和下降时间

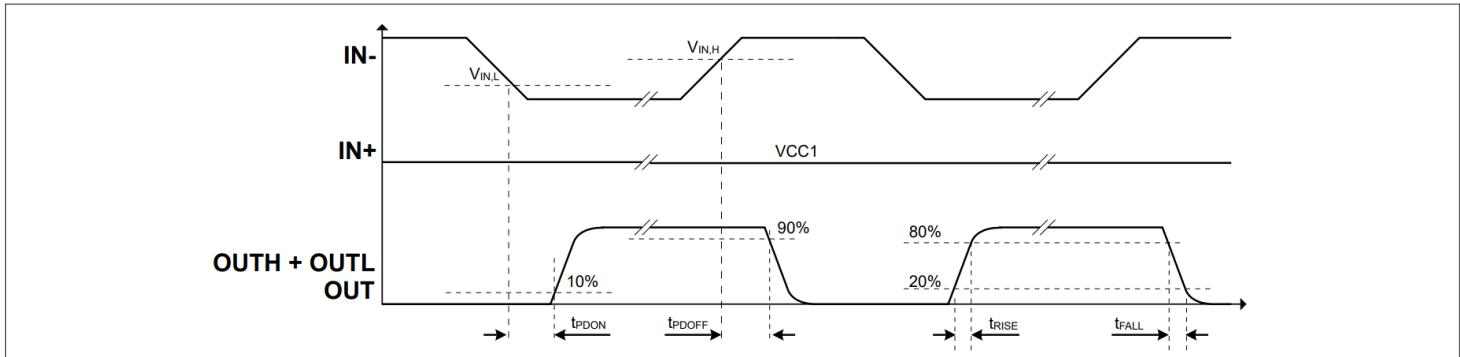

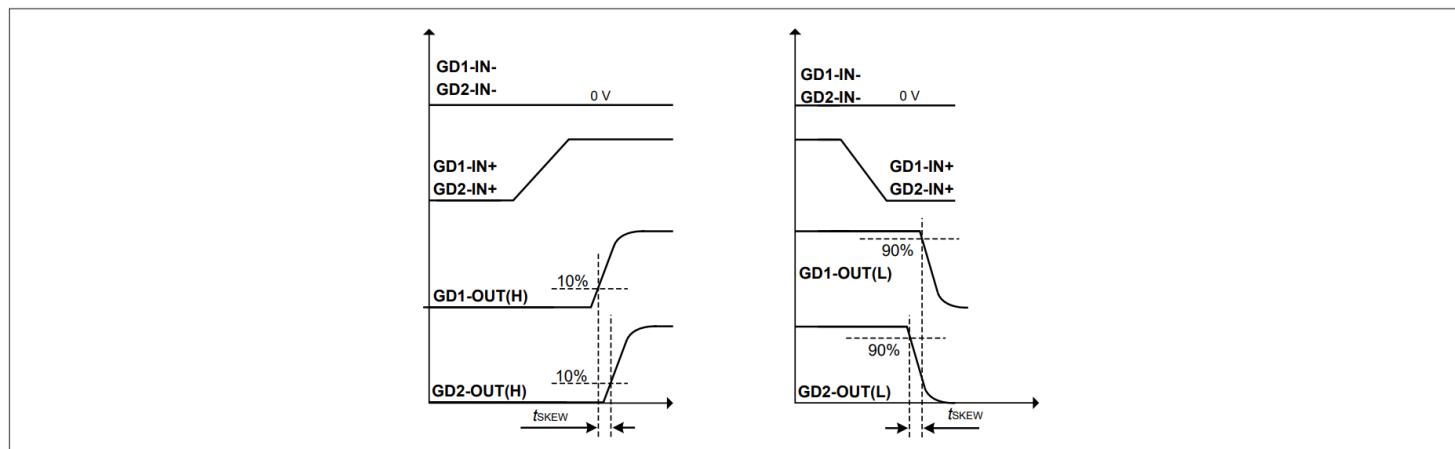

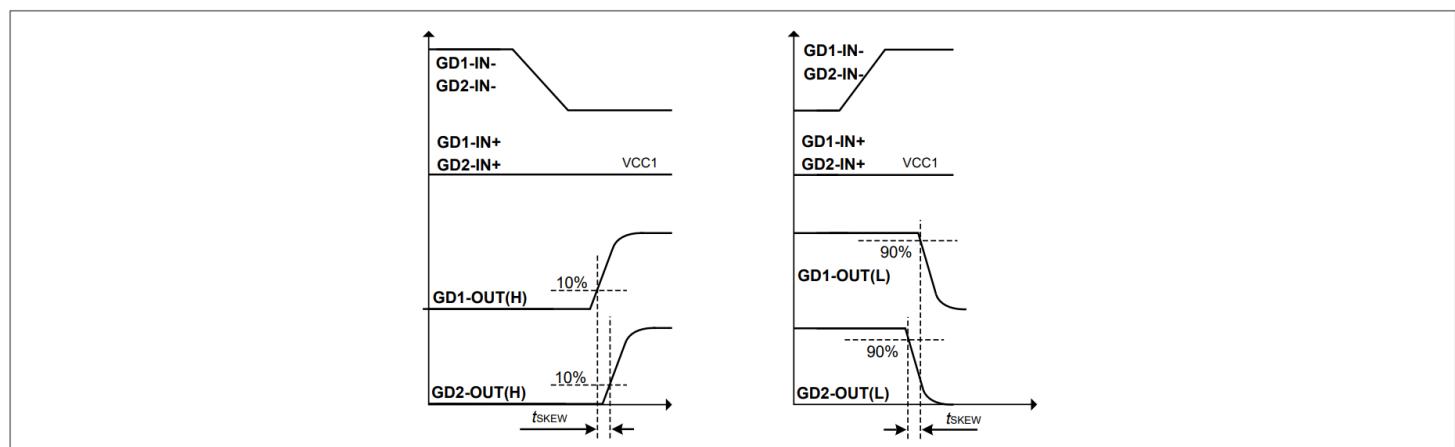

图 35 使用非反相输入的输入到输出、器件与器件的偏差

图 35 和图36 显示同相和反相输入的输入到输出、器件间偏差,  $t_{SKEW}$ 测量值。此参数突出显示了器件间传播延迟的变化, 在并联栅极驱动器时尤为重要。该参数始终假设器件间的工作条件 (温度和电源电压) 相同。

图 36 使用反相输入的输入到输出、器件与器件的偏差

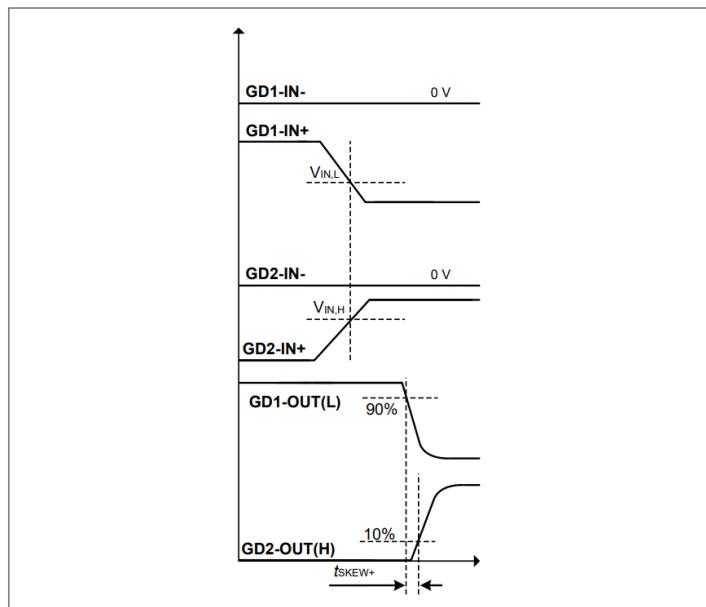

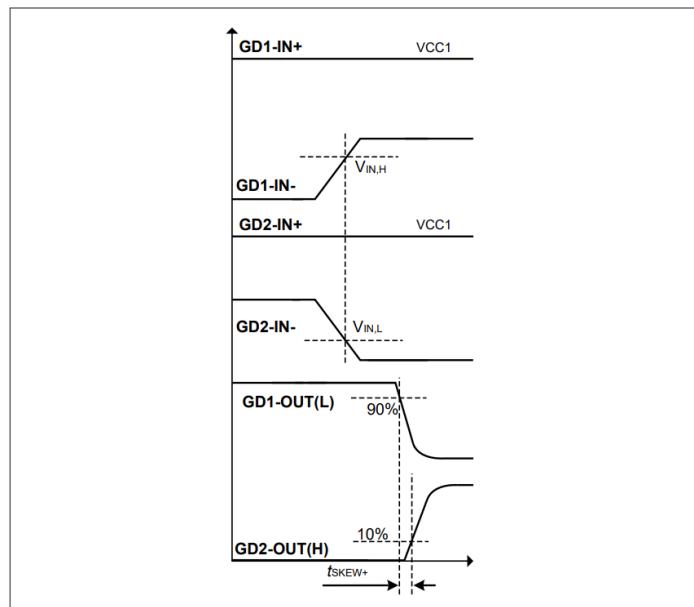

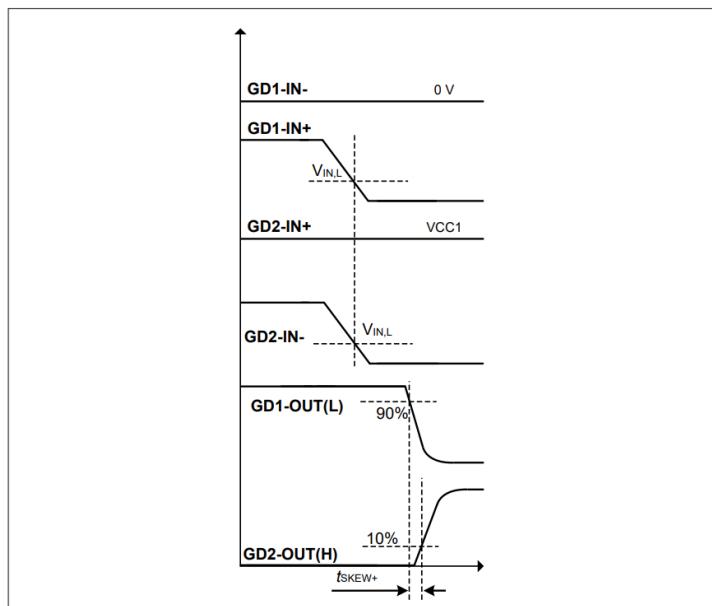

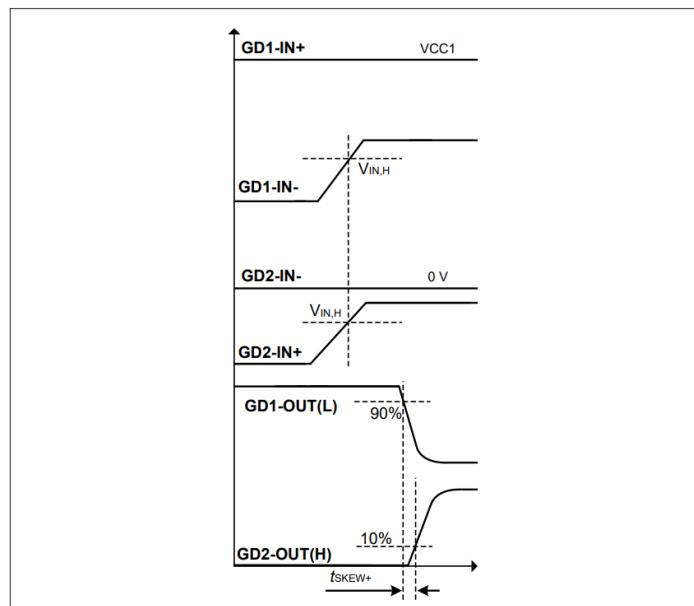

图 37, 图38, 图39 和图40 在所有可能的组合下, 使用输入侧的同相或反相输入, 偏移量 ( $t_{SKEW+}$ )情况。偏移量参数在相同的温度和电源电压下有效。该参数描述了在前述条件下半桥电路中开启和关闭传播延迟之间的差异, 并从栅极驱动器的角度定义了所需的最小死区时间。这在使用互补脉冲驱动时很重要 (例如在半桥电路中) 。

图 37 使用非反相

输入时偏差量

图 38 使用反相

输入时偏差量

图 39

输入时

偏差量

图40

输入时

偏差量

## 8 功能说明

### 8.1 输入特征

栅极驱动器的输入侧有两个输入,  $IN+$  和  $IN-$ , 用于控制信号, 两个电源端子  $VCC1$  和  $GND1$ , 为输入芯片电源。

图41 输入部分框图

栅极驱动器 IC 输入部分由以下功能块组成:

- 输入欠压锁定电路

- 信号滤波

- 反相输入的上拉电阻

- 同相输入下拉电阻

- 信号传输至隔离输出部分

### 8.1.1 输入信号过滤（去毛刺滤波）

驱动器 IC 的输入部分会过滤两个输入信号，以抑制由外部影响触发的短脉冲。

图42 输入脉冲抑制和开启/关闭传播延迟

$IN+$  或  $IN-$  上的任何脉冲，如果短于输入脉冲抑制时间  $t_{INFLT}$ ，将被滤波，不会传输到输出芯片。较长的脉冲将以所示的传播延迟  $t_{PDON}$  和  $t_{PDOFF}$  发送到输出端。这有助于设计，并且在大多数情况下无需使用外部 RC 滤波器来抑制噪声。

### 8.1.2 输入引脚的上拉和下拉电阻

输入上拉或下拉电阻确保在相应输入未连接时处于关断状态。这些电阻的典型值为  $75\text{k}\Omega$ 。即使  $VCC1$  引脚达到允许的最大电压，这些电阻产生的输入电流也保持在  $1\text{mA}$  以下。

上拉和下拉电阻设计用于连接到外部电源或地电位，以永久激活各个驱动器输入。

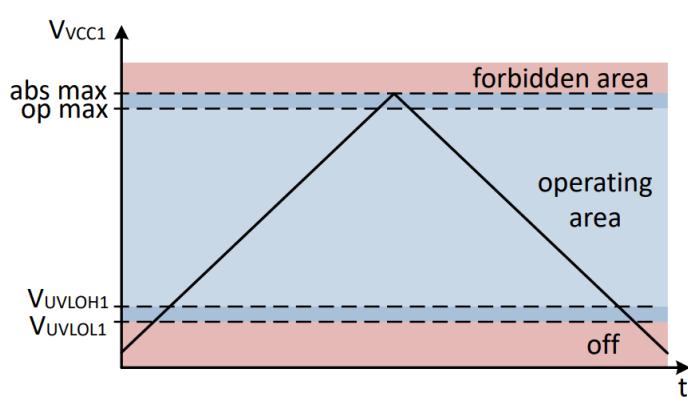

### 8.1.3 输入电源和欠压锁定 (UVLO)

输入电源范围的绝对最大额定值为 -0.3 V 至 17 V。超过绝对最大电压 (abs max) 的静态操作会损坏内部结构，因此是禁止的。

图 43 输入电源和 UVLO 阈值

当  $V_{CC1}$  引脚电压上升至开启欠压锁定阈值 ( $V_{UVLOH1}$ ) 时，输入部分开始工作。它会评估输入信号  $IN+$  和  $IN-$ ，并将其当前状态传输至输出部分。当  $V_{CC1}$  电压下降至关闭欠压锁定阈值 ( $V_{UVLOL1}$ ) 时，无论  $IN+$  或  $IN-$  状态如何，输入部分都会发出最终关闭信号。阈值  $V_{UVLOL1}$  和  $V_{UVLOH1}$  之间的迟滞可确保电源电压接近阈值水平时稳定运行。

任何超过绝对最大电压 (abs max) 额定值的电压过冲都可能损坏驱动器电路。在此区域，电流消耗会急剧增加，导致超出最大允许输入功耗。工作区域定义在开启欠压闭锁阈值 ( $V_{UVLOH1}$ ) 和建议最大工作电压之间。

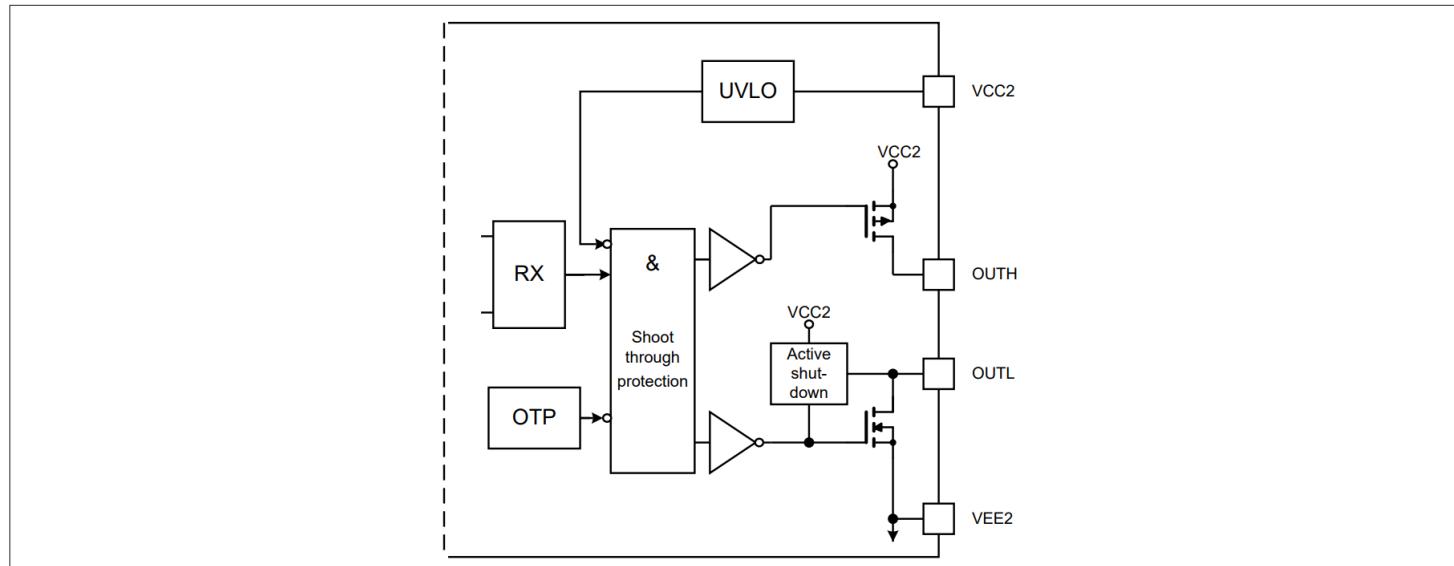

## 8.2 输出要素

本节描述栅极驱动器的输出部分。栅极驱动器 IC 的输出特性包括输出电源的欠压锁定、内部输出级的直通保护电路和主动关断电路。

图 44 具有独立拉电流和灌电流输出引脚型号的输出部分框图

具有独立输出引脚的栅极驱动器 IC 的输出部分由以下功能块组成：

- 输出欠压锁定电路

- 与输入部分隔离的信号接收器

- 拉电流和灌电流输出级

- 主动关断电路

- 过温保护

8 功能说明

图 45 带 GND2 引脚型号的输出部分框图

带有 GND2 引脚的栅极驱动器 IC 的输出部分由以下功能块组成：

- 以 GND2 引脚为参考的输出欠压锁定电路

- 与输入部分隔离的信号接收器

- 拉电流和灌电流输出级在内部连接在一起

- 主动关断电路

- 过温保护

图 46 带 ADJ 引脚型号的输出部分框图

带有 ADJ 引脚的栅极驱动器 IC 的输出部分由以下功能块组成：

- 输出欠压锁定电路，允许使用 ADJ 引脚调整 UVLO 阈值电压

- 与输入部分隔离的信号接收器

- 拉电流和灌电流输出级在内部连接在一起

- 主动关断电路

- 过温保护

## 8.2.1 驱动器输出和电源

驱动器输出部分采用 MOSFETs 提供轨到轨输出, 如图 44、图 45 以及图 46 所示。只要驱动器电源电压稳定, 此功能就能在导通和短路期间保持对栅极电压的严格控制。由于内部压降较低, 只要不超过栅极驱动器的额定电流, IGBT、Si 或 SiC MOSFET 的开关行为主要由栅极电阻控制。此外, 由于大部分能量都消耗在栅极电阻上, 因此它还能降低驱动器的功耗。

栅极驱动器 IC 的拉电流级采用纯 PMOS MOSFET 设计。PMOS 在导通初期提供强电流, 然后维持高栅极电流直至栅极达到  $V_{CC2}$  轨电压, 从而确保 IGBT、Si 或 SiC MOSFET 快速导通。灌电流级由 NMOS 组成。

## 8.2.2 输出欠压锁定(UVLO)

对于所有型号, 输出电源范围均为正绝对最大额定值 35 V。因此, 栅极驱动器 IC 能够向连接的功率器件提供双极栅极电压。

图 47 输出电源和欠压锁定阈值

UVLO 功能可在输出电源电压  $V_{CC2}$  过低时阻止电源开关运行, 从而保护功率器件。在输出电源电压  $V_{CC2}$  正向上升期间, 一旦电压高于 UVLO 阈值 ( $V_{UVLOH2}$ ), 输出级便会根据从栅极驱动器输入端接收到的信号, 通过打开或关闭输出引脚来开始工作。在  $V_{CC2}$  下降期间, 一旦电压低于关断 UVLO 阈值 ( $V_{UVLOL2}$ ), 无论输入部分收到什么信号, 输出部分都会发出关断命令。阈值  $V_{UVLOL2}$  和  $V_{UVLOH2}$  之间的迟滞可确保电源电压接近阈值水平时稳定运行。

对于具有独立输出引脚的型号, 输出电源电压  $V_{CC2}$  是根据电压  $V_{EE2}$  测量的。因此, 对于这些型号, 输出 UVLO 会监控完整的轨到轨电源电压。或者, 对于带有 GND2 引脚的型号,  $V_{CC2}$  是根据接地引脚 GND2 测量的。因此, 对于这些型号, 当输出侧使用双极电源电压时, UVLO 仅监控正电源电压, 并且栅极驱动器会在正电源电压过低时阻止 OUT 引脚导通。因此, 在使用双极电源电压的应用中, 带有 GND2 引脚的型号可为 IGBT、Si 或 SiC MOSFET 提供更有效的 UVLO 保护。

图 48 1ED3145 在单极和双极电源电压下的欠压锁定电平调整

最后，1ED3145 器件允许调节欠压锁定保护生效的电压， $V_{VCC2}$ ，如图46所示，输出 UVLO 功能块具有  $ADJ$  引脚，用于调节欠压锁定电平。栅极驱动器的 UVLO 功能块监控电压  $V_{VCC2}$ ，相对于此  $ADJ$  引脚上的电压。在输出供电电压  $V_{VCC2}$  的正压斜坡上升期间，一旦  $ADJ$  引脚上的电压超过 UVLO 阈值  $V_{ADJ,UVLOH2}$ ，输出级便开始工作，根据从栅极驱动器输入侧收到的信号打开或关闭输出引脚。在供电电压  $V_{VCC2}$  的斜坡下降期间，一旦  $ADJ$  引脚上的电压低于关断 UVLO 阈值  $V_{ADJ,UVLOL2}$ ，输出部分便会启动关断，而不管从输入部分收到的信号如何。阈值  $V_{ADJ,UVLOL2}$  和  $V_{ADJ,UVLOH2}$  之间的滞回可确保供电电压接近阈值水平时的稳定运行。

由电阻  $R_1$  和  $R_2$  组成的电阻分压器用于将  $ADJ$  引脚上的电压设置为所需电平。当使用单极性电源电压时，电阻分压器连接在  $VCC2$  和  $VEE2$  引脚之间。如果应用中使用双极性电源，则电阻分压器连接在  $VCC2$  引脚和系统虚拟地之间，以便 UVLO 模块仅监控正电源电压，并在正电源电压过低时阻止栅极驱动器工作。

$ADJ$  引脚上的电压  $V_{ADJ}$  被设置为当电源电压  $V_{VCC2}$  高于所需的导通电压  $V_{VCC2,ON}$  时，满足以下条件：

$$V_{VCC2} - V_{ADJ} > V_{ADJ,UVLOH2} \text{ (Max.)} \quad (1)$$

因此，电阻  $R_1$  和  $R_2$  的阻值可选择满足如下条件：

$$\frac{R_1}{R_1 + R_2} \times V_{VCC2,ON} > V_{ADJ,UVLOH2} \text{ (Max.)} \quad (2)$$

为了确保栅极驱动器的UVLO功能可靠运行，建议  $R_1$  使用  $1\text{k}\Omega$  至  $10\text{k}\Omega$  之间的电阻值，并将分压器的总电阻限制在  $100\text{k}\Omega$  以下。在噪声环境中，建议  $R_1$  使用接近  $1\text{k}\Omega$  的电阻值。

任何超过绝对最大额定电压的电压过冲都可能损坏驱动器电路。在此区域，电流消耗会急剧增加，从而导致超出最大允许功耗。工作区域定义在开启欠压闭锁阈值 ( $V_{UVLOH2}$ ) 和建议最大工作电压之间。

### 8.2.3 主动关断

主动关闭功能是驱动器的一项保护功能。其设计目的是防止所连接功率器件的自由浮动触发栅极开启。

主动关断功能可在输出芯片未连接到电源或欠压锁定功能生效时，确保 IGBT、Si 或 SiC MOSFET 处于安全关断状态。IGBT、Si 或 SiC MOSFET 栅极通过  $OUT(L)$  引脚钳位至  $VEE2$ 。

图 49 框图显示了具有独立拉电流和灌电流引脚型号的主动关闭功能

如果  $VCC2$  引脚电源缺失或崩溃，驱动器的输出部分将进入主动关断模式。在这种情况下，驱动器使用所连接栅极的浮动电压为内部电路供电。该解决方案比使用外部栅极-发射极电阻  $R_{GE}$  强得多。同时，如果开关上发生快速  $dV/dt$  事件，即使栅极驱动器未通电，也可能产生可能偏置栅极的米勒电流，主动关断电路也会使用该电压自行供电，并主动将栅极拉低。主动关断功能在所有型号中都以类似的方式运行。

### 8.2.4 短路钳位

短路期间，功率晶体管的栅极电压由于米勒电容的反馈而趋于上升。在这种情况下，IC会在内部钳位  $OUT(H)$  引脚上的电压，并将其限制在略高于电源电压  $V_{CC2}$  的值。最大 500 mA 电流可通过此路径反馈至电源，持续 10  $\mu$ s。如果预计电流更大或需要更严格的钳位，则应在  $OUT(H)$  和  $VCC2$  引脚之间添加外部肖特基二极管。

### 8.2.5 过温保护

当 IC 结温超过阈值温度  $T_{OTPOFF}$  时，过温保护会关闭栅极驱动器 IC 的输出，保护应用免遭破坏性故障。然而，需要注意的是，该保护的激活阈值和解除阈值均超过了 IC 的绝对最大结温  $T_J$ 。因此，即使结温超过绝对最大结温，过温保护也无法防止栅极驱动器 IC 损坏。

9 应用信息

注意：英飞凌仅出于礼貌提供此信息，并不承担任何法律义务。以下应用章节中的信息不属于英飞凌组件规范的一部分，英飞凌不保证其准确性或完整性。英飞凌的客户负责确定组件是否适合其用途。客户应验证并测试其设计应用以确认系统功能。

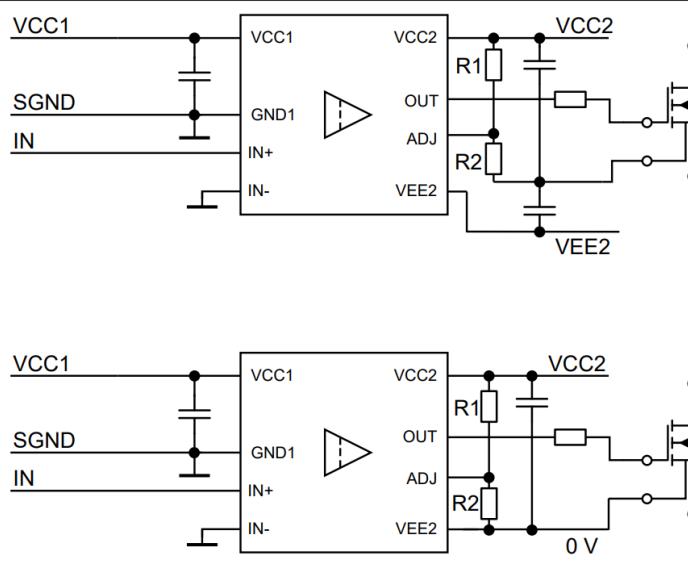

## 9.1 典型应用

本节介绍如何在应用中使用栅极驱动器。

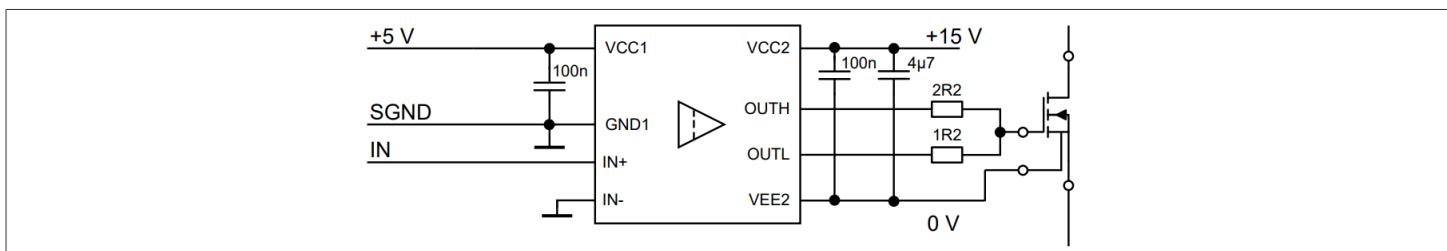

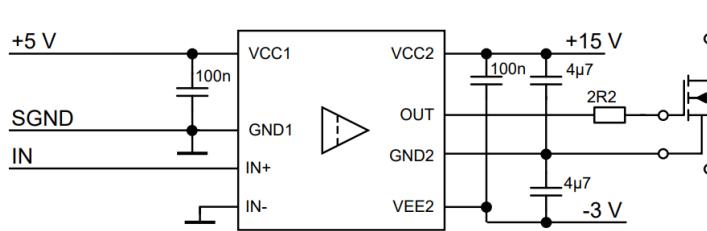

图 50 和图51 展示了一种典型的栅极驱动器应用，其输出端用于拉电流和灌电流。对于这些应用，可以使用单独的栅极电阻来开通和关断功率器件。通过采用独立的源极引脚 $OUTH$ 和吸收引脚 $OUTL$ ，可以优化物料清单 (BOM)，从而为每个功率器件节省一个旁路肖特基二极管。

## 图 50 使用单极电源驱动 SiC MOSFET 的具有拉电流和灌电流引脚型号的电路示例

当使用单极电源串压驱动开关时,  $V_{EE2}$  引脚应直接连接到功率晶体管的源极或发射极, 如图 50 所示。

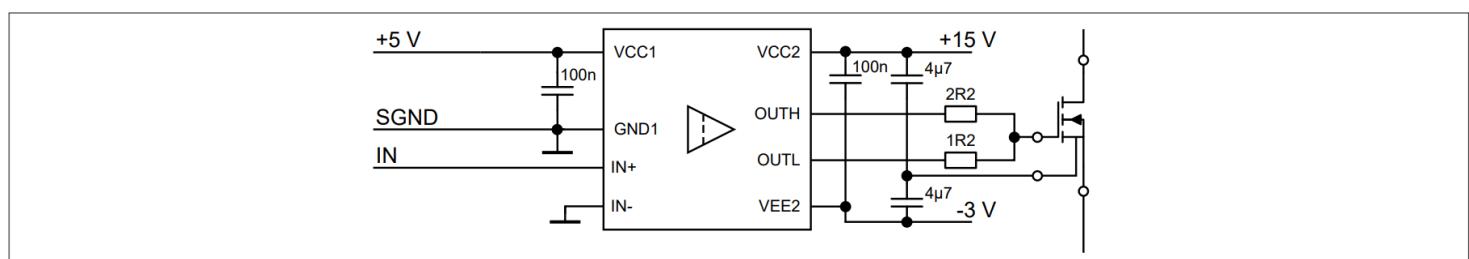

图 51 具有独立拉电流和灌电流引脚型号的双极电源驱动 SiC MOSFET 电路示例

当使用双极性电源电压驱动时，应在连接到VCC2和VEE2引脚的两个电容之间建立虚拟地。然后，该虚拟地应连接到功率晶体管的源极或发射极，如图51所示。

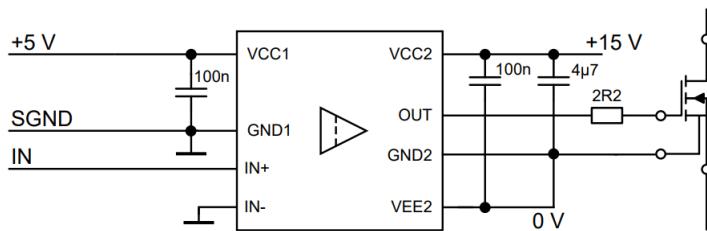

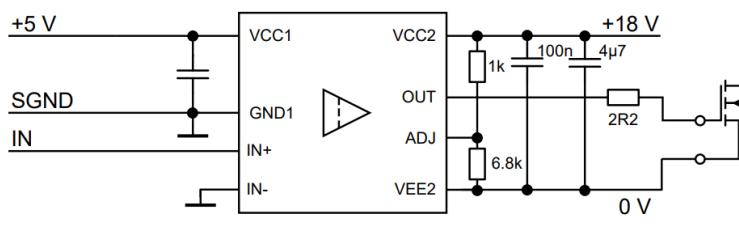

图 52 和图 53 所示为带 GND2 引脚的栅极驱动器的典型应用电路。对于带 GND2 引脚的型号，输出的拉电流和灌电流级内部连接，栅极拉电流和灌电流由 OUT 引脚提供。如果电源开关的导通和关断需要不同的栅极电阻，可以在灌电流路径上使用单独的肖特基旁路二极管。

图 52 使用单极电源驱动 SiC MOSFET 的带有 GND2 引脚器件的电路示例

使用单极性电源电压驱动开关时, GND2 引脚应直接连接到功率晶体管的源极或发射极, 如 [图52](#) 所示。此外, VEE2 引脚应连接到 GND2 引脚。

图 53 使用双极电源驱动 SiC MOSFET 的带有 GND2 引脚器件的电路示例

当使用双极电源驱动开关时, GND2 引脚应连接到功率晶体管的源极或发射极, 如 [图53](#) 所示。

最后, 具有输出侧可调UVLO功能器件的典型应用电路如[图54](#) 和[图55](#) 所示。

图 54 使用单极电源驱动 SiC MOSFET 的带有可调 UVLO 器件的电路示例

当使用单极电源电压驱动开关时, VEE2 引脚应直接连接到功率晶体管的源极或发射极, 如 [图54](#) 所示。连接在 VCC2 和 VEE2 引脚之间的电阻分压器用于调整输出侧 UVLO 阈值

图 55 使用双极电源驱动 SiC MOSFET 的可调 UVLO 器件电路示例

当使用双极电源电压驱动开关时，应在连接到 *VCC2* 和 *VEE2* 引脚的两个电容之间建立虚拟地，如 [图 55](#) 所示。连接在 *VCC2* 和虚拟地之间的电阻分压器用于调整输出侧UVLO阈值。

## 9.2 电源建议

1ED314x 栅极驱动器支持输入和输出侧的宽范围供电电压。这些设备可以在输出侧采用单极和双极电源电压运行，以确保应用中的可靠和安全运行。

为确保栅极驱动器正常工作，需要在电源引脚上放置合适的去耦电容。在输入侧，建议在 *VCC1* 引脚和 *GND1* 引脚之间放置一个 100 nF 的低 ESR 表面贴装多层陶瓷电容。该电容应尽可能靠近引脚放置。

输出侧的去耦电容除了可以隔离电源上的任何干扰外，还能储存功率晶体管开关所需的栅极电流。因此，这些电容的尺寸应适当，以限制功率晶体管开关过程中的压降。使用单极电源时，应在 *VCC2* 引脚和 *VEE2* 引脚之间放置一个至少 4.7  $\mu$ F 的低 ESR 表面贴装多层陶瓷电容，电容大小应靠近引脚。使用双极电源时，建议在 *VCC2* 引脚和虚拟地（功率晶体管的源极或发射极电位）之间或 *GND2* 引脚（如果适用）之间使用至少 4.7  $\mu$ F 的陶瓷电容。同样，建议在 *VEE2* 引脚和虚拟地或 *GND2* 引脚之间使用一个 4.7  $\mu$ F 的电容。根据功率晶体管的栅极电荷以及峰值源极电流和漏极电流，可能需要更大的电容来限制功率晶体管开关过程中的压降。最后，建议在 *VCC2* 和 *VEE2* 引脚之间使用一个 100 nF 的去耦电容，以确保它们之间的短路径能够去耦任何高频噪声。

选择电容器时，重要的是要考虑陶瓷电容器相对于所施加的直流电压的电容下降。

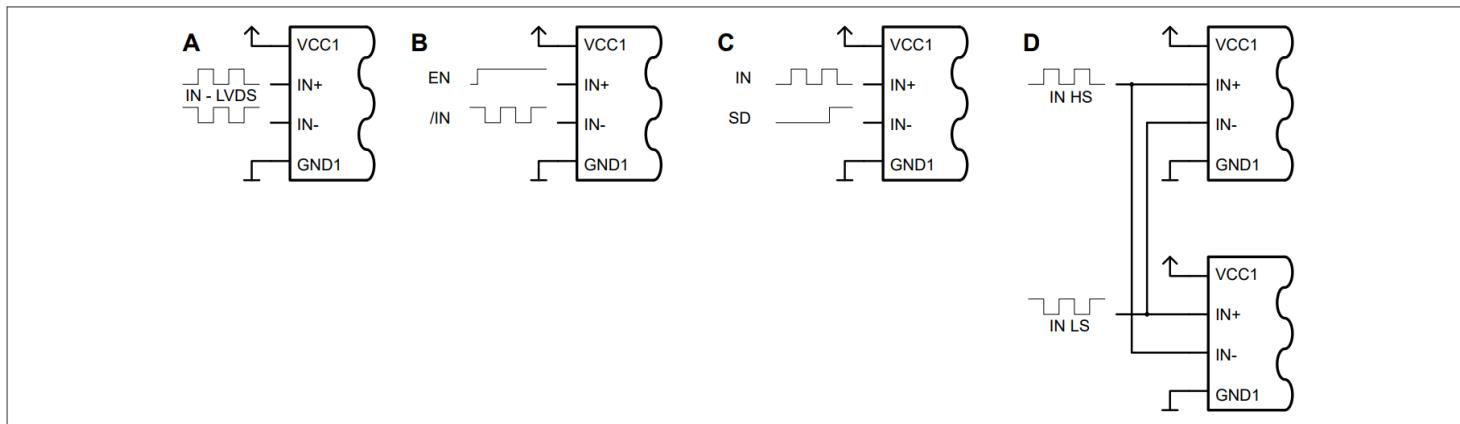

## 9.3 *IN+* 和 *IN-* 用法

反相(*IN-*) 和非反相 (*IN+*) 输入引脚提供了多种可能性来连接 PWM 输入和逻辑信号，以满足各种控制和保护用途。

图 56 *IN+*和*IN-*的使用

除了使用带有差分信号 (A) (*VCC1*和*GND1*电平) 的两个输入之外，仅使用一个输入信号进行实际开关控制，第二个输入可用于诸如启用 (B)、关断 (C) 或联锁 (D) 等功能。

### A) 差分信号

在 *IN+* 和 *IN-* 上施加逻辑电平差分信号，*VCC1* 引脚为正电平，*GND1* 引脚为负电平，可以改善共模噪声抑制。然而，需要注意的是，输入引脚 *IN+* 和 *IN-* 本质上并非真正的差分信号，这些引脚上的信号以输入地 *GND1* 为参考。

### B) 使能

使用 *IN+* 引脚作为使能信号，*IN-* 引脚则通过反相逻辑输入信号控制输出 PWM。这样，该使能信号便可在完整逆变器的各个栅极驱动器 IC 之间共享，从而通过单个控制信号启动运行。

### C) 关机

使用 *IN-* 引脚作为关断信号，*IN+* 引脚则通过同相逻辑输入信号控制输出 PWM。这样，关断信号便可在完整逆变器的各个栅极驱动器 IC 之间共享，从而通过单个控制信号中断操作。

### D) 联锁

半桥配置中经常使用联锁来避免高压直流母线电源的直通电流。将顶部和底部驱动器 IC 的以下输入信号引脚连接在一起可同时抑制两个通道的静态开启：

- 顶部栅极驱动器的非反相输入 (*IN+*) 与底部驱动器的反相输入 (*IN-*)

- 底部栅极驱动器的非反相输入 (*IN+*) 与顶部驱动器的反相输入 (*IN-*)

然而，栅极驱动器和功率开关的动态开关特性仍然可能导致短时直通。为了避免电源开关的开启时间重叠，建议对微控制器的 PWM 生成进行适当的死区时间设置。

## 9.4 棚极电阻的选择

棚极电阻是棚极驱动电路中的关键元件。棚极电阻限制棚极驱动器的拉电流和灌电流，从而控制开启和关闭操作期间相关功率晶体管的开关速度。因此，仔细选择合适的棚极电阻是设计过程中至关重要的考虑因素。选择棚极电阻时需要考虑的一些重要因素包括：

- 优化开关损耗

- 限制关断时功率晶体管漏源电压或集电极发射极电压的过冲和振荡

- 限制导通期间漏极电流或集电极电流的过冲和振荡

- 抑制棚极环路中的寄生电感和电容引起的棚极源极或棚极发射极电压的振荡

作为棚极驱动器选择的起点，可以使用功率晶体管数据表中用于表征导通和关断损耗的棚极电阻。电源条件很少与功率晶体管数据表中使用的电源条件相同。因此，需要应用功率晶体管数据表的值作为优化最终棚极电阻的起点。这里提出的方法对于实际应用和功率晶体管数据表使用相同的峰值棚极电流值。

根据功率晶体管数据表，峰值棚极电流等于：

$$I_{G, \text{pk}} = \frac{\Delta V_{GS}}{R_{G, \text{datasheet}} + R_{G, \text{int}}} = \frac{\Delta V_{GS}}{R_{G, \text{application}} + R_{G, \text{int}}} \quad (3)$$

with  $\Delta V_{GS} = V_{VCC2} - V_{VEE2}$

解该方程中的 $R_G$ 可得出：

$$R_G = \frac{\Delta V_{GS}}{I_{G, \text{pk}}} - R_{G, \text{int}} \quad (4)$$

该方法为棚极电阻的选择提供了一个起点。需要进行进一步评估（例如 EMI 测量）来确定棚极电阻的最终选择，因为它们必须进行调整以适应电路电感、裕度和允许的  $dV/dt$  瞬变。

在确定棚极电阻元件的尺寸时，必须考虑由于功率晶体管的开关而导致的这些电阻中的平均功率耗散（如[第 9.5.2 章](#)所述），以及元件的脉冲功率能力。

## 9.5 功耗估算

### 9.5.1 棚极驱动器

棚极驱动器输入侧损耗主要由静态损耗决定，其计算公式如下：

$$P_{Q1} = V_{VCC1} \cdot I_{Q1} \quad (5)$$

棚极驱动器的输出侧损耗包括标称开关频率和无负载时的静态电流损耗 $P_{Q2}$ 、拉电流损耗 $P_{\text{source}}$ 和灌电流损耗 $P_{\text{sink}}$ ：

$$P_{\text{OUT}} = P_{\text{O}_2} + P_{\text{source}} + P_{\text{sink}} \quad (6)$$

输出侧的静态损耗 $P_{02}$ 可按下式计算：

$$P_{Q2} = (V_{VCC2} - V_{VEE2}) \cdot I_{Q2} \quad (7)$$

开通损耗  $P_{\text{source}}$  和关断损耗  $P_{\text{sink}}$  可以通过使用栅极驱动器输出级内部电阻  $R_{\text{DSO},\text{H}}$  或  $R_{\text{DSO},\text{L}}$ 、外部栅极电阻  $R_{\text{G,ext}}$  和功率晶体管内部栅极电阻  $R_{\text{G,int}}$  之间的电阻分压，以及应用相关的栅极电荷  $Q_{\text{G}}$ 、总栅极驱动电压  $V_{\text{VCC2}} - V_{\text{VEE2}}$  和开关频率  $f_{\text{sw}}$  来估算：

$$P_{\text{source}} = \frac{1}{2} Q_G \cdot f_{\text{sw}} \cdot (V_{\text{VCC2}} - V_{\text{VEE2}}) \cdot \frac{R_{\text{DSON,H}}}{R_{\text{DSON,H}} + R_{G,\text{ext,ON}} + R_{G,\text{int}}} \quad (8)$$

$$P_{\text{sink}} = \frac{1}{2} Q_G \cdot f_{\text{sw}} \cdot (V_{\text{VCC2}} - V_{\text{VEE2}}) \cdot \frac{R_{\text{DSON,L}}}{R_{\text{DSON,L}} + R_{G,\text{ext,OFF}} + R_{G,\text{int}}}$$

此外，栅极驱动器周围的外部组件会使 IC 发热。仅计算损耗和理论结温不足以证明栅极驱动器电路设计是可行的。需要通过测量进行验证，以避免应用中出现意外的影响。例如，可以通过使用红外摄像机来识别热点。

## 9.5.2 外部栅极电阻

可以使用由栅极拉电流的路径和灌电流路径中的电阻分压来估算开通栅极电阻  $R_{G,ext,ON}$  和关断栅极电阻  $R_{G,ext,OFF}$  的损耗，如下所示：

$$P_{\text{source,ext}} = \frac{1}{2} Q_G \cdot f_{\text{sw}} \cdot (V_{\text{VCC2}} - V_{\text{VEE2}}) \cdot \frac{R_{\text{G,ext,ON}}}{R_{\text{DSON,H}} + R_{\text{G,ext,ON}} + R_{\text{G,int}}} \quad (9)$$

$$P_{\text{sink,ext}} = \frac{1}{2} Q_G \cdot f_{\text{sw}} \cdot (V_{\text{VCC2}} - V_{\text{VEE2}}) \cdot \frac{R_{\text{DSON,L}}}{R_{\text{DSON,L}} + R_{\text{G,ext,OFF}} + R_{\text{G,int}}}$$

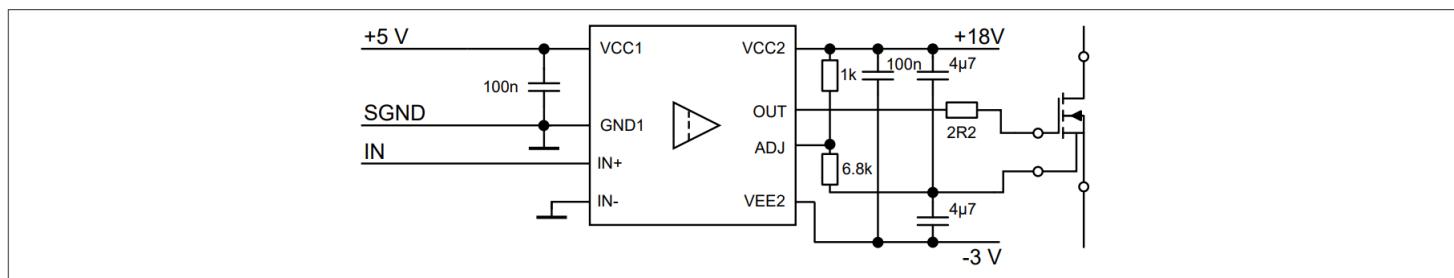

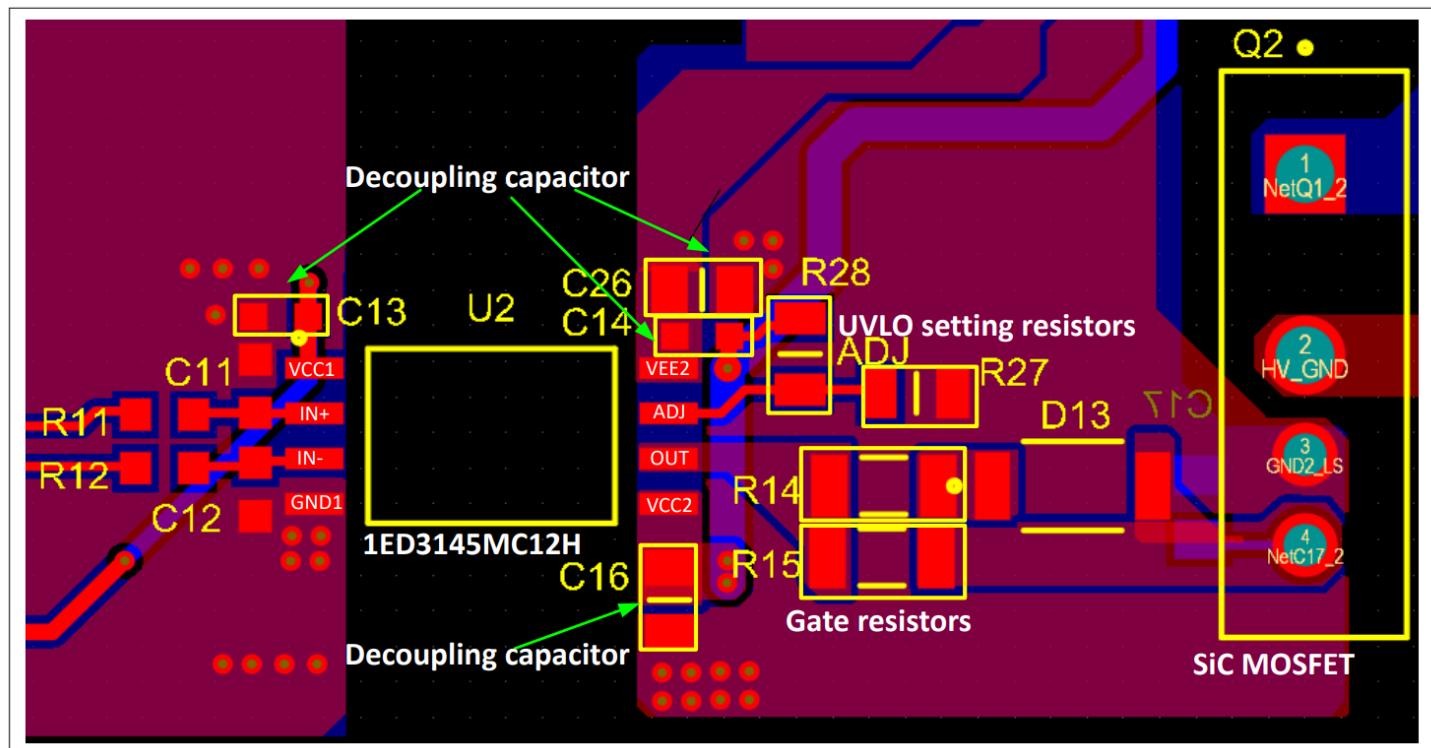

## 9.6 输出UVLO串平调整

如第8.2.2节所述，输出侧UVLO可以设置为所需水平，以增强系统可靠性，尤其是在使用SiC MOSFET时。图57显示了UVLO设置的示例。本例中使用双极电源，其中 $V_{CC2}$ 为18V， $V_{EE2}$ 为-3V（参考开尔文源电压）。

图 57 1ED3145 的 UVLO 电平调整示例

要设置 UVLO，使得当  $V_{CC2}$  超过 16.2 V 时栅极驱动器即可运行：

$$\frac{R_1}{R_1 + R_2} \times V_{VCC2, ON} > V_{ADJ, UVLOH2} (\text{Max.}) \quad (10)$$

$$\frac{R_1}{R_1 + R_2} \times 16.2 \text{ V} > 2.07 \text{ V} \quad (11)$$

选择阻值为 1 kΩ 的电阻  $R_1$  会导致  $R_2$  的阻值为 6.8 kΩ

## 9.7 布局指南

拥有精心设计的 PCB 布局对于实现栅极驱动器的最佳性能至关重要。从而保证整个电力电子转换器以最佳状态运行。创建精心设计的 PCB 布局需要对特定关键因素给予一定程度的关注和考虑。使用 1ED314x 栅极驱动器设计 PCB 布局时应考虑的关键点是：

- 输入侧的低 ESR、低 ESL 去耦电容必须靠近  $VCC1$  和  $GND1$  引脚放置，并与这些引脚连接，以尽可能缩短去耦环路。同样，输出侧的去耦电容也应靠近  $VCC2$  和  $VEE2$  引脚放置，并通过短连接与这些引脚连接。

- 最小化功率晶体管栅极充电和放电电流环路的物理面积至关重要。栅极环路包含具有高  $dV/dt$  和  $di/dt$  的走线，短环路设计可最大限度地减少功率晶体管栅极开启和关闭引起的噪声。此外，短环路设计还可以最大限度地减少栅极环路的杂散电感并提高开关性能。为了实现短栅极环路，栅极驱动器应位于功率晶体管附近，而存储高峰值电流能量的去耦电容器应位于靠近栅极驱动器的位置

- 为了进一步降低栅极环路的杂散电感，可以对栅极环路中的走线使用宽走线。此外，电流的正向路径和返回路径可以在同一 PCB 层上彼此平行布线，或者在相邻的 PCB 层上彼此重叠，以实现最小的杂散电感

- 如果是单极电源，栅极驱动器的  $VEE2$  引脚应连接到功率晶体管的开尔文源极/发射极引脚（如有）。同样，如果是双极电源，去耦电容之间的虚拟地或  $GND2$  引脚应连接到功率晶体管的开尔文源极/发射极引脚。如果没有开尔文引脚，则与源极/发射极的连接应尽可能短，以避免功率晶体管的大电流流入栅极环路。

- 栅极驱动器封装主体下方的区域应保持无任何走线，以确保输入侧和输出侧之间安全隔离的完整性

- 建议将连接到  $IN+$  和  $IN-$  引脚的栅极驱动器的输入信号远离任何噪声走线。虽然 1ED314x 栅极驱动器带有集成输入滤波器，可以滤除输入信号上的高频噪声，但可以将时间常数较小的外部 RC 滤波器放置在靠近这些引脚的位置，以增强滤波效果。此外，建议在输入信号走线下方设置接地层，以屏蔽信号噪声

- 对于具有可调 UVLO 的型号 1ED3145，在设计输出侧 UVLO 电路的布局时必须小心谨慎。UVLO 电路的走线和用于设置 UVLO 的电阻器必须远离功率晶体管开关产生的任何高  $dV/dt$  和  $di/dt$ 。此外，确保栅极环路的高  $dV/dt$  和  $di/dt$  不会耦合到 UVLO 电路中，这一点也至关重要

- 栅极驱动器 IC 在系统运行过程中会产生功耗，如第 9.5.1 章所述。器件产生的热量主要通过 PCB 散热。建议最大限度地增加连接到  $GND1$  和  $VEE2$  引脚的铜箔面积，以便有效地将栅极驱动器的热量散热到 PCB 上。

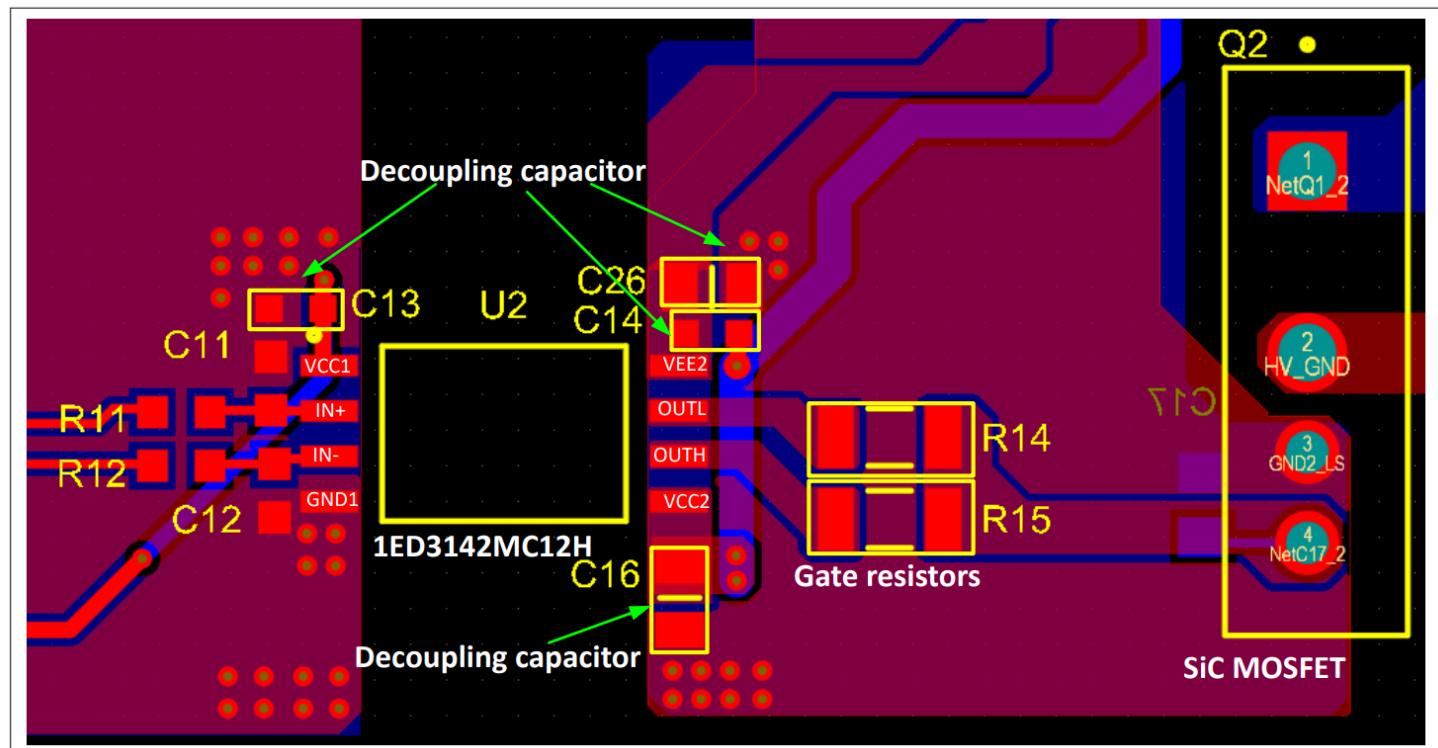

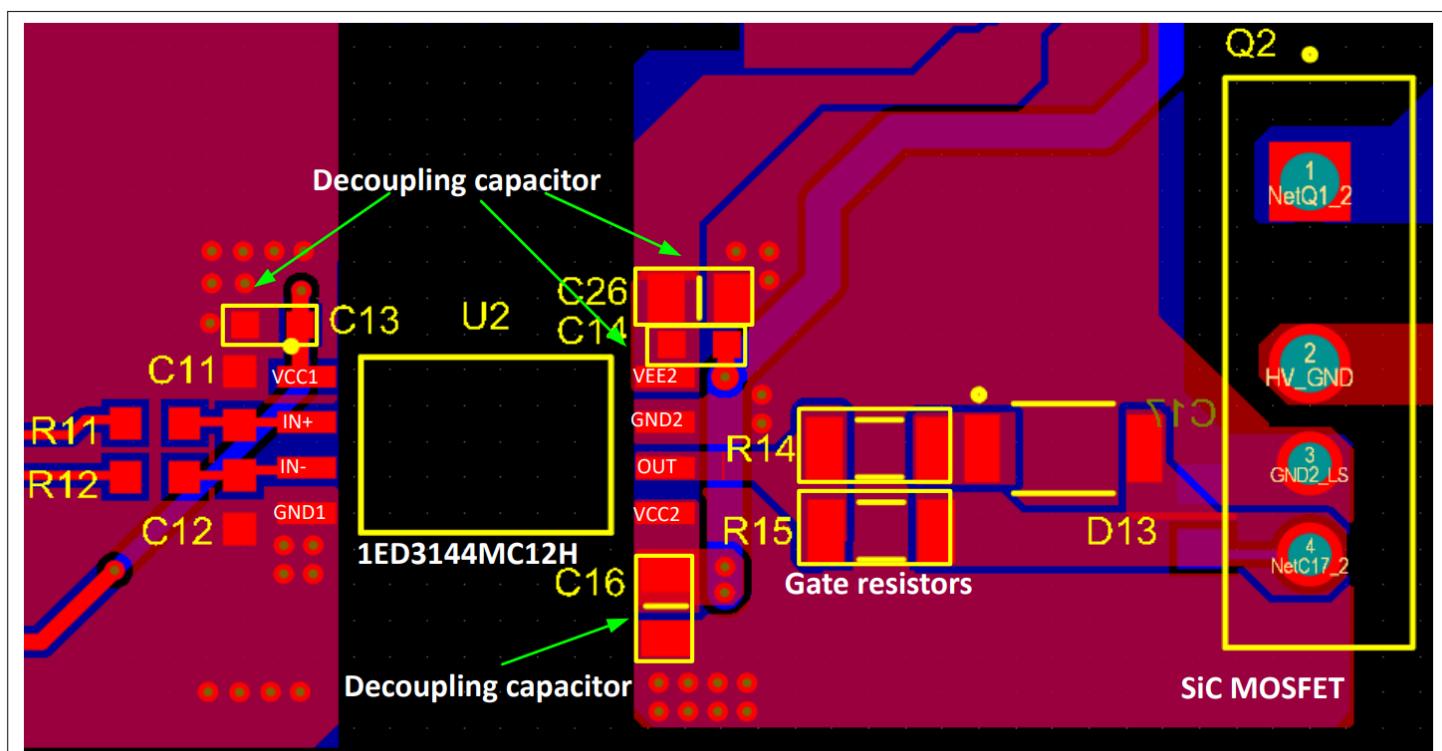

图 58 具有独立输出引脚型号的 PCB 布局示例

图 58, 图 59 和图 60 展示具有分离输出、GND2 引脚、带有可调UVLO 的栅极驱动器的 PCB 布局示例。所有配置的更详细布局可在表3列出的评估板设计文件中找到。

图 59 带 GND2 引脚器件的 PCB 布局示例

图 60 带可调 UVLO 的器件的 PCB 布局示例

## 10 相关链接

**注意：** 请考虑所选功率器件绝缘要求和栅极驱动器IC 功率耗散。

| Product group                    | Product name                       | Description                                                              |

|----------------------------------|------------------------------------|--------------------------------------------------------------------------|

| TRENCHSTOP™<br>IGBT Discrete     | <a href="#">IWH40N65WR6</a>        | 650 V, 40 A IGBT with anti-parallel diode in TO-247-3-HCC                |

|                                  | <a href="#">IHW30N160R5</a>        | 1600 V, 30 A IGBT Discrete with anti-parallel diode in TO-247            |

|                                  | <a href="#">IKW15N120CS7</a>       | 1200 V IGBT7 S7, 15 A IGBT with anti-parallel diode in TO247             |

|                                  | <a href="#">IKQ75N120CS7</a>       | 1200 V IGBT7 S7, 75 A IGBT with anti-parallel diode in TO247-3           |

| CoolSiC™ SiC<br>MOSFET Discrete  | <a href="#">IMBF170R1K0M1</a>      | 1700 V, 1000 mΩ SiC MOSFET in TO-263-7 with extended creepage            |

|                                  | <a href="#">IMZA120R040M1H</a>     | 1200 V, 40 mΩ SiC MOSFET in TO247-4 package                              |

|                                  | <a href="#">IMZA120R014M1H</a>     | 1200 V, 14 mΩ SiC MOSFET in TO247-4 package                              |

|                                  | <a href="#">IMBG120R030M1H</a>     | 1200 V, 30 mΩ SiC MOSFET in TO-263-7 package                             |

|                                  | <a href="#">IMYH200R012M1H</a>     | 2000 V, 12 mΩ SiC MOSFET in TO-247-PLUS with high creepage and clearance |

| CoolSiC™ SiC<br>MOSFET<br>Module | <a href="#">FS33MR12W1M1H_B11</a>  | EasyPACK™ 1B 1200 V, 33 mΩ sixpack module                                |

|                                  | <a href="#">FF17MR12W1M1H_B11</a>  | EasyDUAL™ 1B 1200 V, 17 mΩ half-bridge module                            |

|                                  | <a href="#">FF4MR12W2M1H_B11</a>   | EasyDUAL™ 2B 1200 V, 4 mΩ half-bridge module                             |

|                                  | <a href="#">F4-17MR12W1M1H_B11</a> | EasyPACK™ 1B 1200 V, 17 mΩ fourpack module                               |

| TRENCHSTOP™<br>IGBT Modules      | <a href="#">F4-100R17N3E4</a>      | EconoPACK™ 3 1700 V, 100 A fourpack IGBT module                          |

|                                  | <a href="#">F4-200R17N3E4</a>      | EconoPACK™ 3 1700 V, 200 A fourpack IGBT module                          |

|                                  | <a href="#">FP10R12W1T7_B11</a>    | EasyPIM™ 1B 1200 V, 10 A three phase input rectifier PIM IGBT module     |

|                                  | <a href="#">FS100R12W2T7_B11</a>   | EasyPACK™ 2B 1200 V, 100 A sixpack IGBT module                           |

|                                  | <a href="#">FP150R12KT4_B11</a>    | EconoPIM™ 3 1200V three-phase PIM IGBT module                            |

|                                  | <a href="#">FS200R12KT4R_B11</a>   | EconoPACK™ 3 1200 V, 200 A sixpack IGBT module                           |

11 封装尺寸

11 封装尺寸

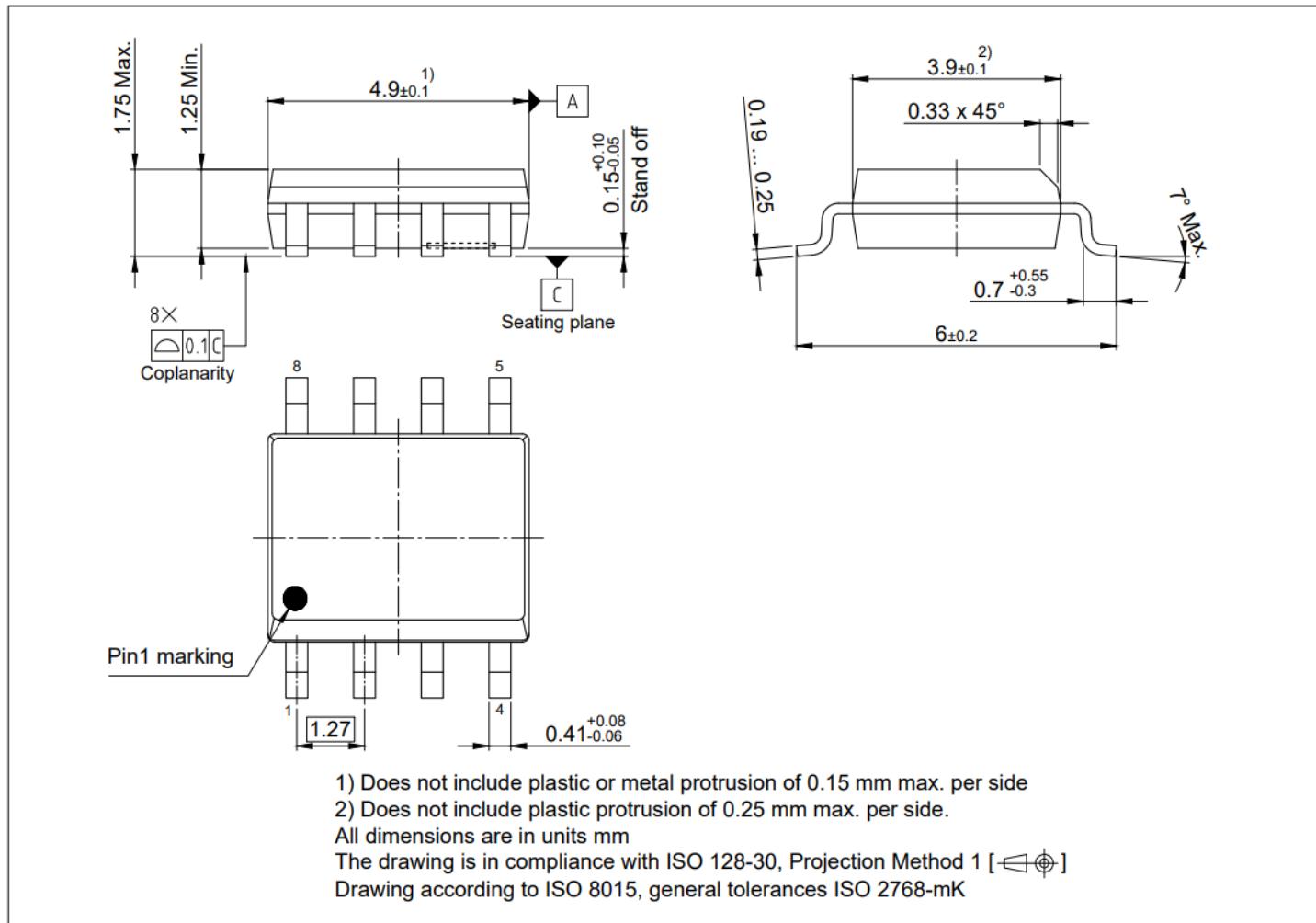

图61

PG-DSO-8 (150 mil) (塑料双列小外形封装, 150 mil)

11 封装尺寸

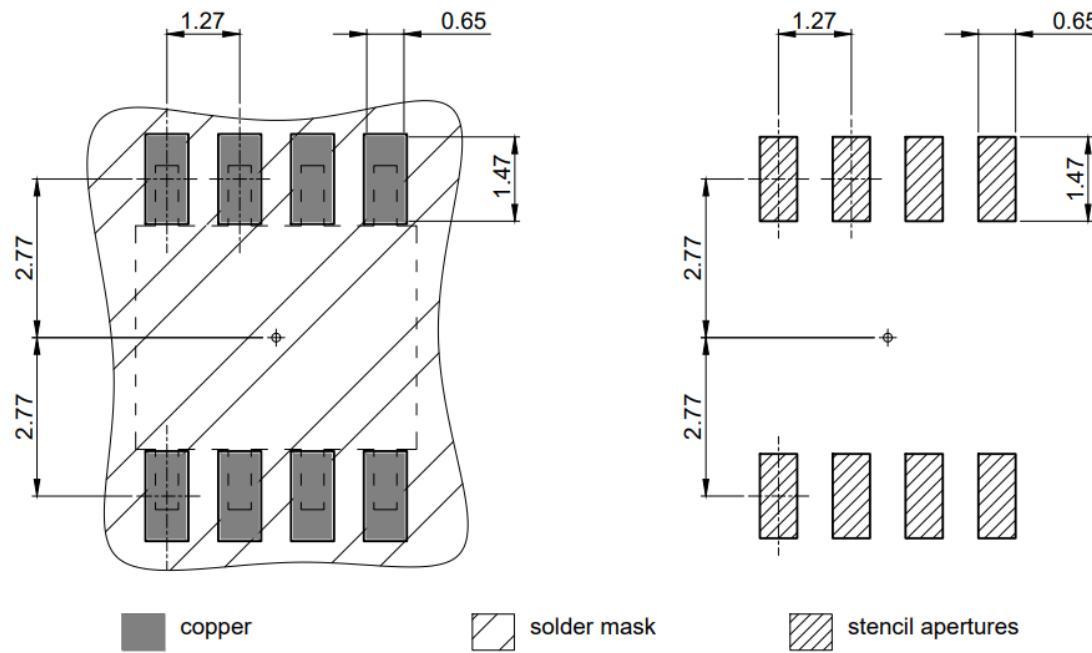

图 62

PG-DSO-8 (150 mil) 推荐封装

11 封装尺寸

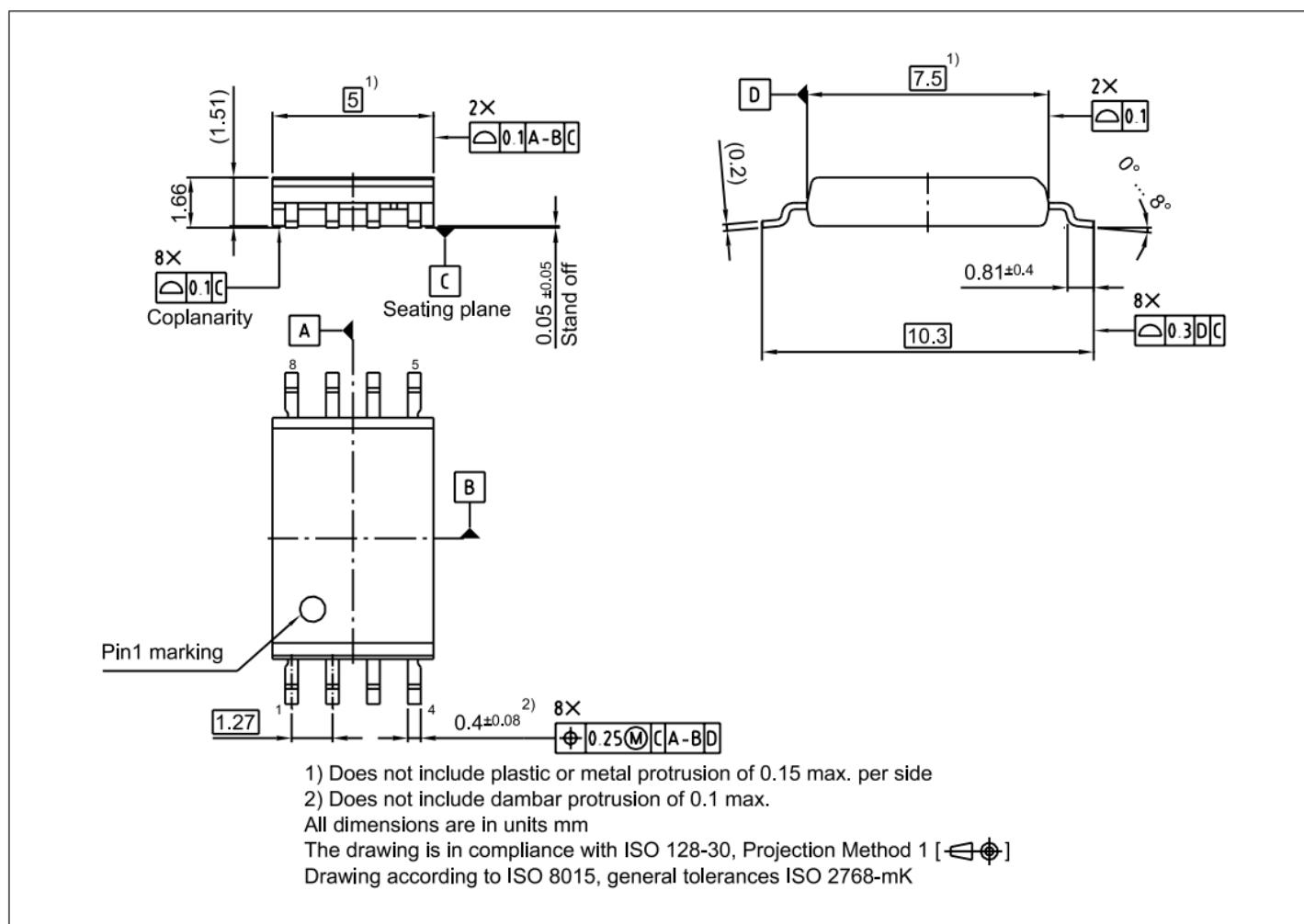

图 63

PG-LDSO-8 (300 mil) (塑料双列小外形封装, 300 mil)

11 封装尺寸

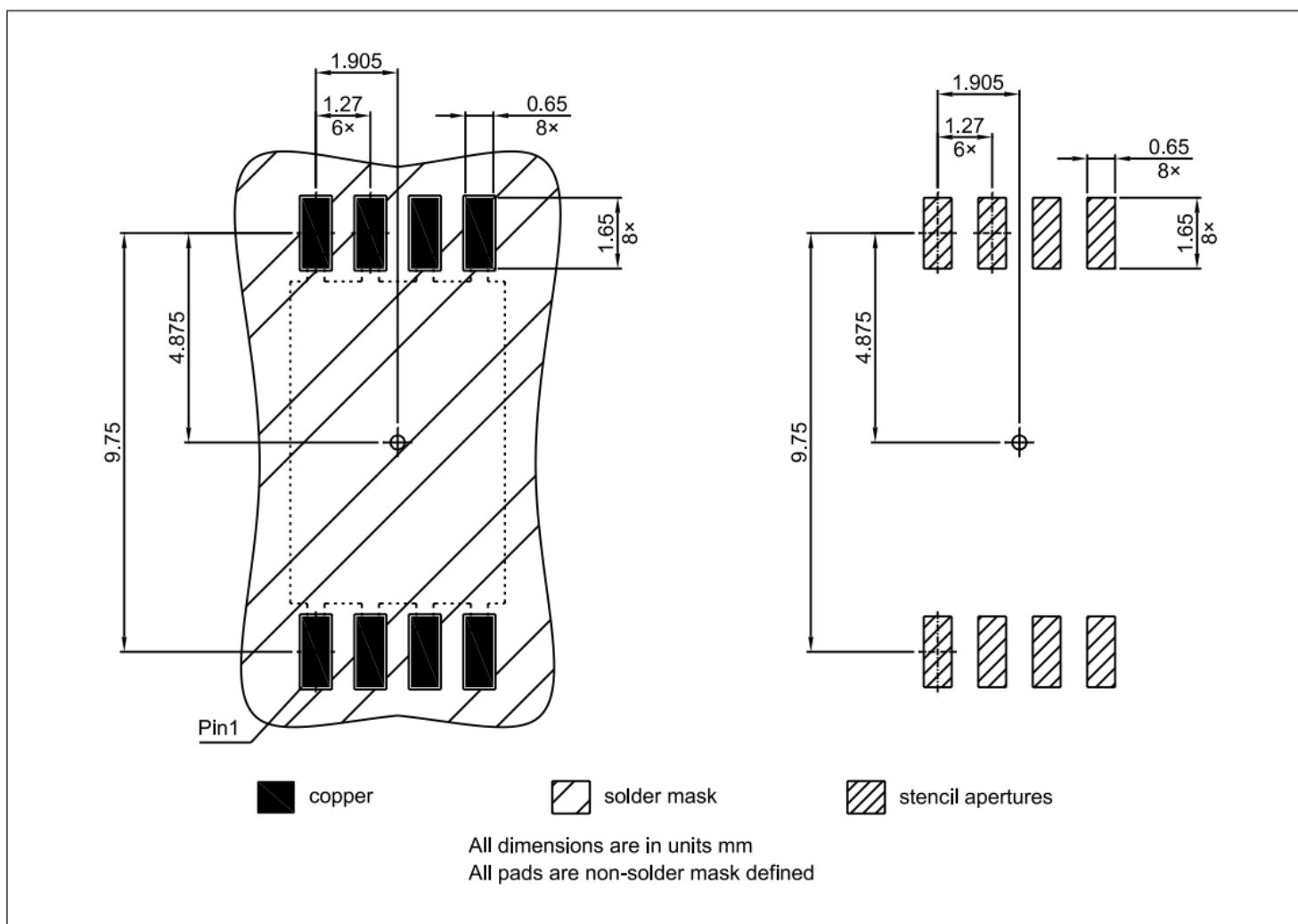

图 64

PG-LDSO-8 (300 mil) 推荐封装

## 修订记录

| Document version | Date of release | Description of changes                                                                                                                                                                  |

|------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| v2.0             | 2024-10-04      | <ul style="list-style-type: none"><li>Initial release of 1ED314xMC12H products</li></ul>                                                                                                |

| v1.20            | 2024-10-01      | <ul style="list-style-type: none"><li>Updated the values of the parameters, <math>t_{PDON}</math>, <math>t_{PDOFF}</math>, <math>t_{INFLT}</math> and <math>t_{IN,min}</math></li></ul> |

| v1.11            | 2023-07-26      | <ul style="list-style-type: none"><li>Removed duplicate parameters from dynamic characteristics and active shut down</li></ul>                                                          |

| v1.10            | 2023-06-26      | <ul style="list-style-type: none"><li>Increased CTI value to 600</li></ul>                                                                                                              |

| v1.0             | 2023-01-15      | <ul style="list-style-type: none"><li>Initial release of 1ED314xMU12F products</li></ul>                                                                                                |

## 免责声明

请注意，本文件的原文使用英文撰写，为方便客户浏览英飞凌提供了中文译文。该中文译文仅供参考，并不可作为任何论点之依据。

由于翻译过程中可能使用了自动化程序，以及语言翻译和转换过程中的差异，最后的中文译文与最新的英文版本原文含义可能存在不尽相同之处。

因此，我们同时提供该中文译文版本的最新英文原文供您阅读，请参见 <http://www.infineon.com>

英文原文和中文译文版本之间若存有任何歧异，以最新的英文版本为准，并且仅认可英文版本为正式文件。

**您如果使用本文件，即表示您同意并理解上述说明。英飞凌不对因翻译过程中可能存在的任何不完整或不准确信息而产生的任何直接或间接损失或损害负责。英飞凌不承担中文译文版本的完整性和准确性责任。如果您不同意上述说明，请不要使用本文件。**

## Trademarks

All referenced product or service names and trademarks are the property of their respective owners.

版本 2025-08-28

**Infineon Technologies AG** 出版，

德国 Neubiberg 85579

版权 © 2025 Infineon Technologies AG

及其关联公司。

保留所有权利。

**Do you have a question about this

document?**

**Email:**

[erratum@infineon.com](mailto:erratum@infineon.com)

## 重要通知

**Infineon Technologies AG** 及其关联公司（以下简称“英飞凌”）销售或提供和交付的产品（可能也包括样品，且可能由硬件或软件或两者组成）

（以下简称“产品”），应遵守客户与英飞凌签订的框架供应合同或其他书面协议的条款和条件，如无上述合同或其他书面协议，则应遵守适用的英飞凌销售条件。只有在英飞凌明确书面同意的情况下，客户的一般条款和条件或对适用的英飞凌销售条件的偏离才对英飞凌具有约束力。

为避免疑义，英飞凌不承担不侵犯第三方权利的所有保证和默示保证，例如对特定用途/目的的适用性或适销性的保证。

英飞凌对与样品、应用或客户对任何产品的具体使用有关的任何信息或本文档中给出的任何示例或典型值概不负责。

本文件中包含的数据仅供具有技术资格和技能的客户代表使用。客户有责任评估产品对预期应用和客户特定用途的适用性，并在预期应用和客户特定用途中验证本文件中包含的所有相关技术数据。客户有责任正确设计、编程和测试预期应用的功能性和安全性，并遵守与其使用相关的法律要求。

除非英飞凌另行明确批准，否则产品不得用于任何因产品故障或使用产品的任何后果可合理预期会导致人身伤害的应用。但是，上述规定并不妨碍客户在英飞凌明确设计和销售的使用领域中使用任何产品，但是客户对应用负有全部责任。

英飞凌明确保留根据适用法律，如《德国版权法》（UrhG）第 44b 条，将其内容用于商业资料和数据探勘（TDM）的权利。

如果产品包含安全功能：

由于任何计算设备都不可能绝对安全，尽管产品采取了安全措施，但英飞凌不保证产品不会被入侵、数据不会被盗或遗失，或不会发生其他漏洞（以下简称“安全漏洞”），英飞凌对任何安全漏洞不承担任何责任。

如果本文档包含或引用软件：

根据美国、德国和世界其他国家的知识产权法律和条约，该软件归英飞凌所有。英飞凌保留所有权利。因此，您只能按照软件附带的软件授权协议的规定使用本软件。

如果没有适用的软件授权协议，英飞凌特此授予您个人的、非排他性的、不可转让的软件知识产权授权（无权转授权）：(a) 对于以源代码形式提供的软件，仅在贵组织内部修改和复制该软件用于英飞凌硬件产品；及(b) 对于以二进制代码（binary code）形式对外向终端用户分发该软件，仅得用于英飞凌硬件产品。禁止对本软件进行任何其他使用、复制、修改、翻译或编译。有关产品、技术、交货条款和条件以及价格的详细信息，请联系离您最近的英飞凌办公室或访问 [https://www.infineon.com](http://www.infineon.com)。