# BGT60LTR11AIP ユーザーガイド

## XENSIV™ 60 GHz レーダー

### 本書について

#### 適応範囲と目的

このユーザーガイドは、データシートとユーザーガイドでの BGT60LTR11AIP の使用方法の詳細を提供することを目的とします。

データシートでは技術データと制限されたデバイス内容のみが記載されているため、このユーザーガイドでは、デバイスの操作方法をより詳細に説明するために、次のことを説明しています。

- すべての異なるビルディングブロック

- さまざまなブロックの操作方法

- SPI レジスタの設定は、真理値表を含むトピックごとにグループ化されています。

#### 対象者

この文書は、インフィニオンの XENSIV™ 60 GHz の BGT60LTR11AIP、およびその派生である BGT60LTR11SAIP と BGT60LTR11BAIP のハードウェア設計を始めようとするエンジニアのためのファームウェアやソフトウェア入門書として機能します。

## 目次

## 目次

|                                                 |           |

|-------------------------------------------------|-----------|

| 本書について .....                                    | 1         |

| 目次 .....                                        | 2         |

| <b>1 はじめに .....</b>                             | <b>4</b>  |

| <b>2 メインコントローラ .....</b>                        | <b>5</b>  |

| 2.1 クアッドステート入力と「アドバンスモード」 .....                 | 6         |

| 2.1.1 クワッドステートの基本 .....                         | 6         |

| 2.1.2 「アドバンスモード」 .....                          | 6         |

| 2.1.3 QS1 .....                                 | 6         |

| 2.1.4 QS2 .....                                 | 7         |

| 2.1.5 QS3 .....                                 | 9         |

| 2.1.6 QS4 .....                                 | 10        |

| 2.2 パワーアップとシーケンス .....                          | 10        |

| 2.2.1 電源投入時 .....                               | 11        |

| 2.2.2 初期化シーケンス .....                            | 11        |

| 2.2.3 自律パルスモードシーケンス .....                       | 13        |

| 2.2.4 自律 CW モードシーケンス .....                      | 17        |

| 2.2.5 SPI モードシーケンス .....                        | 18        |

| 2.2.6 検出器 .....                                 | 18        |

| 2.3 動的制御信号の概要 .....                             | 18        |

| <b>3 SPI インターフェース .....</b>                     | <b>20</b> |

| 3.1 SPI インターフェースの説明 .....                       | 21        |

| 3.1.1 SPI 書き込みモード .....                         | 21        |

| 3.1.2 SPI 読み出しモード .....                         | 21        |

| 3.1.3 SPI バーストモード .....                         | 22        |

| 3.2 SPI レジスタ .....                              | 23        |

| 3.2.1 レジスタの概要 .....                             | 23        |

| 3.2.2 ダイレクトアクセスレジスタ .....                       | 24        |

| 3.2.3 レジスタマップのビットフィールド .....                    | 24        |

| 3.2.4 レジスタ Reg0 - ダイレクトアクセスレジスタ .....           | 26        |

| 3.2.5 レジスタ Reg1 - ダイレクトアクセスレジスタ .....           | 28        |

| 3.2.6 レジスタ Reg2 - 閾値 .....                      | 29        |

| 3.2.7 レジスタ Reg4 - PLL 設定 1 .....                | 30        |

| 3.2.8 レジスタ Reg5 - PLL 設定 2 .....                | 32        |

| 3.2.9 レジスタ Reg6 - PLL 設定 3 .....                | 33        |

| 3.2.10 レジスタ Reg7 - デューティサイクル、タイミング、PD、MPA ..... | 34        |

| 3.2.11 レジスタ Reg8 - 分周器 .....                    | 36        |

| 3.2.12 レジスタ Reg9 - ベースバンド .....                 | 37        |

| 3.2.13 レジスタ Reg10 - ホールド時間 .....                | 39        |

## 目次

|          |                                 |           |

|----------|---------------------------------|-----------|

| 3.2.14   | レジスタ Reg12 - BITE .....         | 39        |

| 3.2.15   | レジスタ Reg13 - Algo 1 .....       | 40        |

| 3.2.16   | レジスタ Reg14 - Algo 2 .....       | 42        |

| 3.2.17   | レジスタ Reg15 - デジタル制御 .....       | 43        |

| 3.2.18   | レジスタ Reg34 - ADC 開始 .....       | 45        |

| 3.2.19   | レジスタ Reg35 - ADC 変換 .....       | 46        |

| 3.2.20   | レジスタ Reg36 - ADC ステータス .....    | 47        |

| 3.2.21   | レジスタ Reg38~53 - ADC の結果 .....   | 48        |

| 3.2.22   | レジスタ Reg56 - 状態とチップバージョン .....  | 49        |

| 3.2.23   | レジスタ GSR0 - SPI ステータスレジスタ ..... | 51        |

| <b>4</b> | <b>AD コンバーター .....</b>          | <b>52</b> |

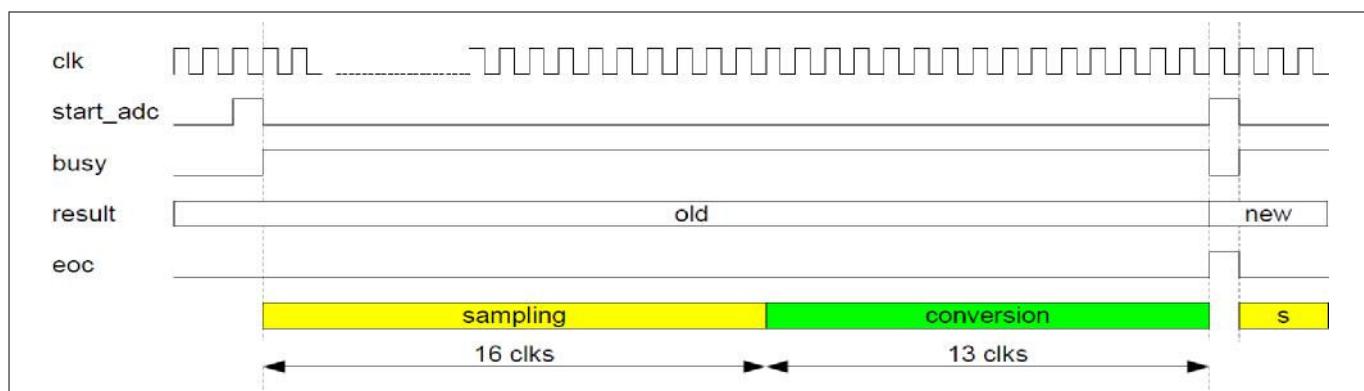

| 4.1      | AD 変換のシーケンス .....               | 52        |

| 4.1.1    | バンドギャップの有効化 .....               | 52        |

| 4.1.2    | ローカル ADC クロックの有効化 .....         | 52        |

| 4.1.3    | ADC を有効化 .....                  | 52        |

| 4.1.4    | ADC 変換の開始 .....                 | 52        |

| 4.1.4.1  | 单一変換 .....                      | 52        |

| 4.1.4.2  | 順次変換 .....                      | 52        |

| 4.2      | ADC 構成 .....                    | 53        |

| 4.2.1    | アナログ入力チャネルゲイン .....             | 53        |

| 4.2.2    | アナログ入力電圧サンプリング .....            | 53        |

| 4.2.3    | ADC フェーズ .....                  | 53        |

| 4.3      | 変換時間 .....                      | 53        |

| 4.4      | ADC のパワーダウンシーケンス .....          | 54        |

| <b>5</b> | <b>検出器 .....</b>                | <b>55</b> |

| 5.1      | デジタル評価 .....                    | 55        |

| 5.2      | ホールド時間 .....                    | 55        |

|          | 改訂履歴 .....                      | 56        |

|          | 免責事項 .....                      | 57        |

## 1 はじめに

### 1 はじめに

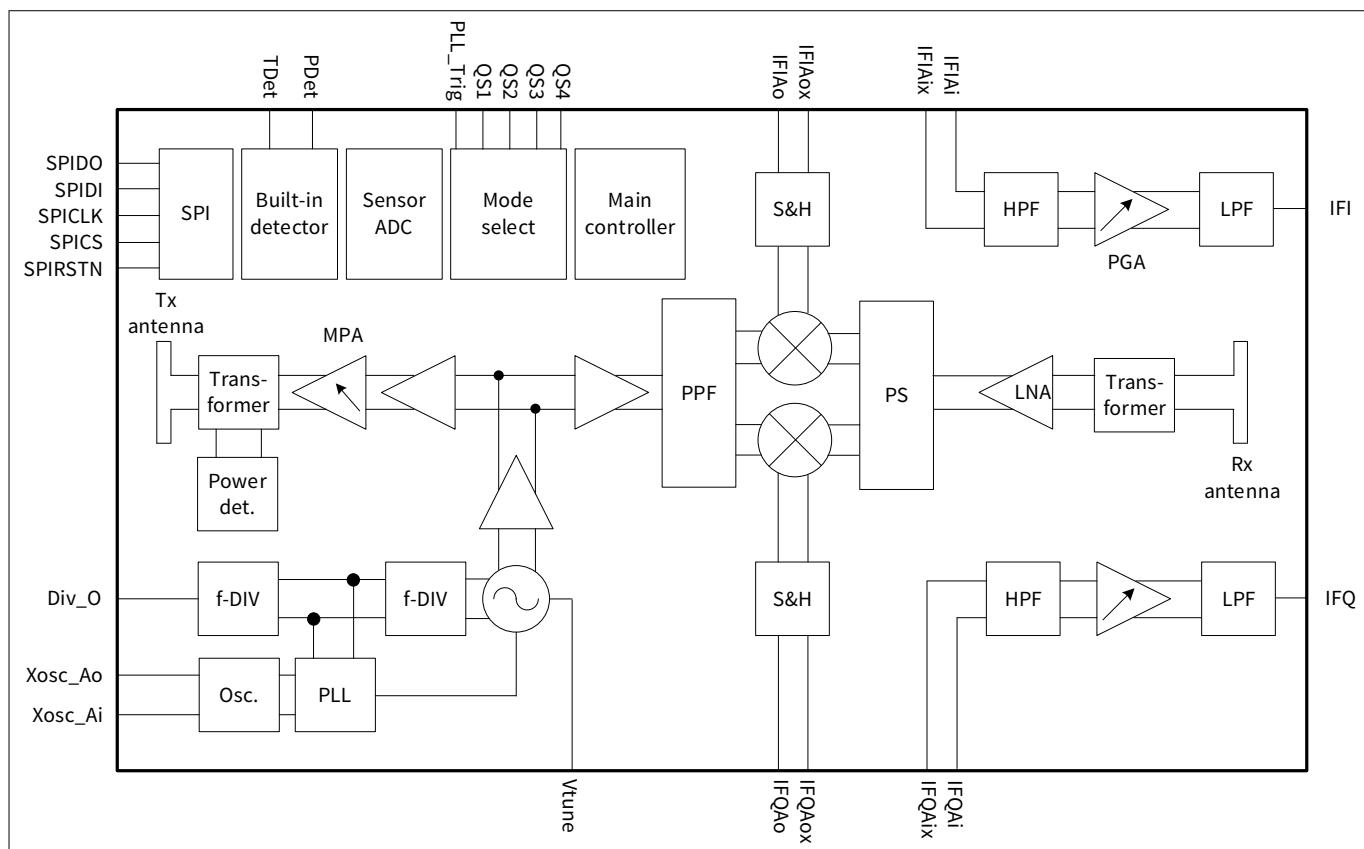

BGT60LTR11AIP は、アンテナ、設定可能な内蔵検出器、および完全に自律的な動作を可能にするステートマシンを含む、完全に統合されたマイクロ波モーションセンサーです。これは、BGT60LTR11AIP および BGT60LTR11SAIP バージョンでは 61 GHz～61.5 GHz、BGT60LTR11BAIP バージョンでは 60.5 GHz～61 GHz の周波数帯域でドップラーモーションセンサーとして動作できるように設計されています。

フェーズロックループ (PLL) を備えた分周器は、電圧制御発振器 (VCO) の周波数を安定させ、連続波 (CW) 動作を可能にします。このデバイスは、完全自律モードと SPI モードの 2 つの動作モードをサポートしています。この異なるモードは、ハードウェアプリセットピンを介して選択できます。

BGT60LTR11AIP には、高周波信号生成用の統合された低位相ノイズプッシュプッシュ VCO があります。送信部は、シリアル・ペリフェラル・インターフェース (SPI) を介して制御し、設定可能/調整可能な出力パワー、ミディアムパワー・アンプで構成されています。送信電力は、統合された電力検出器によって監視されます。パッケージ化されたモノリシックマイクロ波集積回路 (MMIC) は、最大のエリアカバレッジを実現する統合ブロードビームアンテナを備えています。

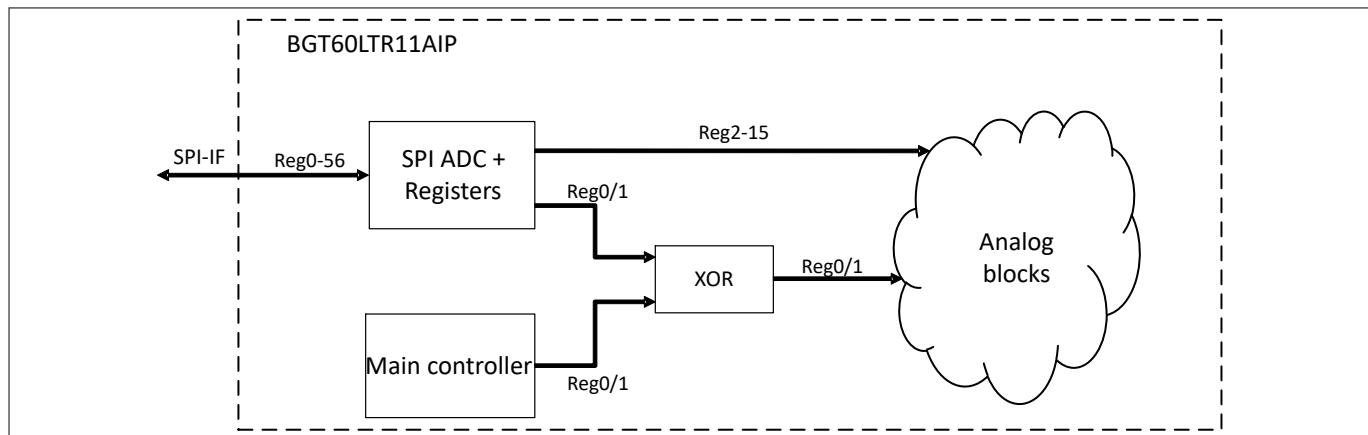

図 1 BGT60LTR11AIP ブロック図

## 2 メインコントローラ

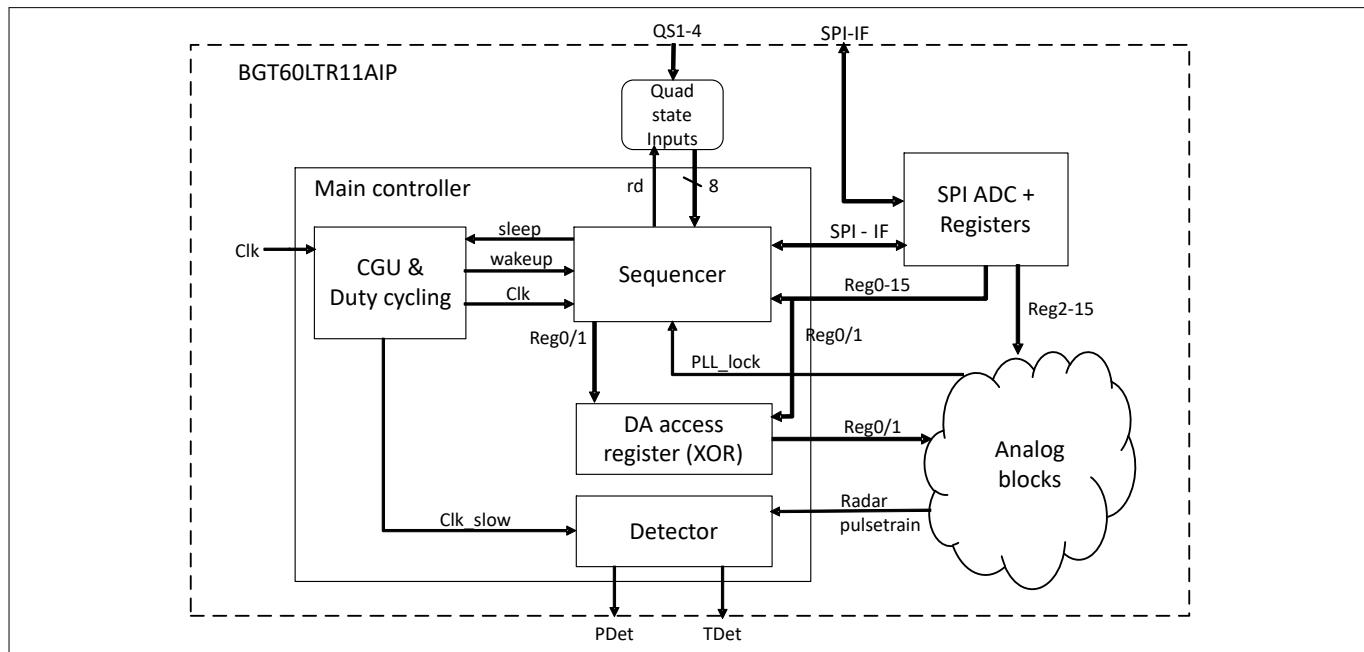

メインコントローラの主な目的は、自動的にパルスおよび CW モードを処理することです。さらに、SPI インターフェースを使用して外部マイクロコントローラからすべてを制御できる SPI モードも利用できます。

図2 メインコントローラのブロック図

初期状態の指示情報は「接近」に設定されています。出力パッド電圧の真理値表を表1に示します。

表 1 出力パッド電圧の真理値表

| 出力パッド電圧 |      | モーション | 接近/離れる |

|---------|------|-------|--------|

| TDet    | PDet |       |        |

| 高       | 高    | No    | 該当なし   |

| 低       | 低    | Yes   | 離れる    |

| 低       | 高    | Yes   | 接近     |

BGT60LTR11AIP は、4 つのクアッドステート入力 QS1-4 を提供します。1 つのクアッドステート入力を使用すると、1 つの入力ピンから 4 つのステートを取得できます。これらのピンは、チップの構成に使用されます。

## 2 メインコントローラ

### 2.1 クアッドステート入力と「アドバンスモード」

デジタルメインコントローラのリセット時および初期化シーケンス中に、チップが開始する設定を決定するため、いくつかのチップ入力ピンがサンプリングされます。

#### 2.1.1 クワッドステートの基本

クワッドステート入力は、1つの入力ピンで4つの異なる状態を設定できます。[表2](#)は、可能な入力状態と、結果として得られるそれぞれの内部信号をバイナリ記述で示しています。クワッドステート入力は、電源投入時のメインコントローラにより初期化シーケンスの開始時点にサンプリングされます。このサンプリング後の変更は無効です。リセットピンをセットするか、soft\_reset ビット (Reg15[15]) の書き込みによってソフトリセットをアクティブにすることで、リサンプリングをトリガーすることができます。

表2 クワッドステート入力の状態

| パッド                      | b1 | b0 |

|--------------------------|----|----|

| ground                   | 0  | 0  |

| open                     | 0  | 1  |

| 100 kΩ ~ V <sub>DD</sub> | 1  | 0  |

| V <sub>DD</sub>          | 1  | 1  |

#### 2.1.2 「アドバンスモード」

デジタルメインコントローラがリセットから立ち上がる間に PLL\_Trig ピンが「0」のとき、チップブートは「ベーシックモード」になります。

PLL\_Trig ピンがチップの起動中に「1」に維持し、チップブートと QS1 が同時に GND または OPEN である場合、「アドバンスモード」は有効になります。またピン SPIDI と SPICLK もパルス繰り返し時間 (PRT) (dc\_rep\_rate (Reg7[11:10])) を決定するためにサンプリングされます。さらに、ピン QS2 と QS3 はセンサー ADC によって測定され、各「平均ウインドウ」の前にそれぞれ 4ビット値に変換されます。

表3 アドバンスモードの PRT

| PLL_Trig | SPIDI | SPICLK | dc_rep_rate | PRT     |

|----------|-------|--------|-------------|---------|

| 0        | *     | *      | 1           | 500 μs  |

| 1        | 0     | 0      | 1           | 500 μs  |

| 1        | 0     | 1      | 3           | 2000 μs |

| 1        | 1     | 0      | 0           | 250 μs  |

| 1        | 1     | 1      | 2           | 1000 μs |

#### 2.1.3 QS1

QS1 は、チップのモード (Autonomous または SPI) を選択するために使用されます。

表4 QS1

| パッド    | b1 | b0 | 動作モード                       |

|--------|----|----|-----------------------------|

| ground | 0  | 0  | 自律 CW モード <a href="#">1</a> |

| (続く)   |    |    |                             |

## 2 メインコントローラ

表 4 (続き) QS1

| パッド               | b1 | b0 | 動作モード                        |

|-------------------|----|----|------------------------------|

| open              | 0  | 1  | 自律パルスモード                     |

| 100 kΩ ~ $V_{DD}$ | 1  | 0  | 外部 9.6MHz クロックが有効になる SPI モード |

| $V_{DD}$          | 1  | 1  | SPI モード                      |

1) 通常の動作モードではありません。FCC、ETSI などのテスト目的のみです。

2.1.4 QS2

QS2 は、ターゲットの同一なレーダー反射断面積に対して検出器の閾値を選択するために使用されます。検出器のしきい値が低いほど、検出範囲が高くなります。[レジスタ Reg2 - 閾値](#)で説明されているレジスタ Reg2 に書き込まれます。

表 5 QS2

| パッド                                       | b1 | b0 | 検出器の閾値 <sup>1)</sup> |

|-------------------------------------------|----|----|----------------------|

| <b>ベーシックモード</b>                           |    |    |                      |

| ground                                    | 0  | 0  | 80                   |

| open                                      | 0  | 1  | 192                  |

| 100 kΩ ~ $V_{DD}$                         | 1  | 0  | 480                  |

| $V_{DD}$                                  | 1  | 1  | 2560                 |

| <b>アドバンスモード</b>                           |    |    |                      |

| $1*V_{DD}/16 - 2*V_{DD}/16$ <sup>2)</sup> | *  | *  | 66                   |

| $2*V_{DD}/16 - 3*V_{DD}/16$               | *  | *  | 80                   |

| $3*V_{DD}/16 - 4*V_{DD}/16$               | *  | *  | 90                   |

| $4*V_{DD}/16 - 5*V_{DD}/16$               | *  | *  | 112                  |

| $5*V_{DD}/16 - 6*V_{DD}/16$               | *  | *  | 136                  |

| $6*V_{DD}/16 - 7*V_{DD}/16$               | *  | *  | 192                  |

| $7*V_{DD}/16 - 8*V_{DD}/16$               | *  | *  | 248                  |

| $8*V_{DD}/16 - 9*V_{DD}/16$               | *  | *  | 320                  |

| $9*V_{DD}/16 - 10*V_{DD}/16$              | *  | *  | 384                  |

| $10*V_{DD}/16 - 11*V_{DD}/16$             | *  | *  | 480                  |

| $11*V_{DD}/16 - 12*V_{DD}/16$             | *  | *  | 640                  |

| $12*V_{DD}/16 - 13*V_{DD}/16$             | *  | *  | 896                  |

| $13*V_{DD}/16 - 14*V_{DD}/16$             | *  | *  | 1344                 |

| $14*V_{DD}/16 - 15*V_{DD}/16$             | *  | *  | 1920                 |

| $15*V_{DD}/16 - 16*V_{DD}/16$             | *  | *  | 2560                 |

1) 検出器の閾値は、0.5m の検出範囲ステップを保証する値を設定します。

## 2 メインコントローラ

-

- 2) サンプリングされた電圧範囲に応じて割り当てられた QS 状態: 例えば、 $1*V_{DD}/16 - 2*V_{DD}/16$  は、 $1*V_{DD}/16$  から  $2*V_{DD}/16$  までを意味します。

-

## 2.1.5 QS3

QS3 は、TDet 出力のホールドタイムを選択するために使用されます。これはターゲットが検出された後、出力ステータスが保持される期間を定義します。[レジスタ Reg10 - ホールド時間](#)で説明されているレジスタ Reg10 に書き込まれます。

表 6 QS3

| パッド                                       | b1 | b0 | 検出ホールドタイム                             |

|-------------------------------------------|----|----|---------------------------------------|

| <b>ベーシックモード</b>                           |    |    |                                       |

| ground                                    | 0  | 0  | 16/32/64/128 ms (dc_rep_rate 内の dep.) |

| open                                      | 0  | 1  | 1 s                                   |

| 100 kΩ ~ $V_{DD}$                         | 1  | 0  | 10 s                                  |

| $V_{DD}$                                  | 1  | 1  | 1 min                                 |

| <b>アドバンスモード</b>                           |    |    |                                       |

| $0*V_{DD}/16 - 1*V_{DD}/16$ <sup>1)</sup> | *  | *  | 100 ms                                |

| $1*V_{DD}/16 - 2*V_{DD}/16$               | *  | *  | 500 ms                                |

| $2*V_{DD}/16 - 3*V_{DD}/16$               | *  | *  | 1 s                                   |

| $3*V_{DD}/16 - 4*V_{DD}/16$               | *  | *  | 2 s                                   |

| $4*V_{DD}/16 - 5*V_{DD}/16$               | *  | *  | 3 s                                   |

| $5*V_{DD}/16 - 6*V_{DD}/16$               | *  | *  | 5 s                                   |

| $6*V_{DD}/16 - 7*V_{DD}/16$               | *  | *  | 10 s                                  |

| $7*V_{DD}/16 - 8*V_{DD}/16$               | *  | *  | 30 s                                  |

| $8*V_{DD}/16 - 9*V_{DD}/16$               | *  | *  | 45 s                                  |

| $9*V_{DD}/16 - 10*V_{DD}/16$              | *  | *  | 1 min                                 |

| $10*V_{DD}/16 - 11*V_{DD}/16$             | *  | *  | 90 s                                  |

| $11*V_{DD}/16 - 12*V_{DD}/16$             | *  | *  | 2 min                                 |

| $12*V_{DD}/16 - 13*V_{DD}/16$             | *  | *  | 5 min                                 |

| $13*V_{DD}/16 - 14*V_{DD}/16$             | *  | *  | 10 min                                |

| $14*V_{DD}/16 - 15*V_{DD}/16$             | *  | *  | 15 min                                |

| $15*V_{DD}/16 - 16*V_{DD}/16$             | *  | *  | 30 min                                |

1) サンプリングされた電圧範囲に応じて割り当てられた QS 状態: 例えば、 $1*V_{DD}/16 - 2*V_{DD}/16$  は、 $1*V_{DD}/16$  から  $2*V_{DD}/16$  までを意味します。

## 2 メインコントローラ

### 2.1.6 QS4

QS4 は、PLL の設定によりデバイスの動作周波数を選択するために使用されます。周波数は、チップのバージョン (BGT60LTR11AIP および BGT60LTR11SAIP または BGT60LTR11BAIP) にも依存します。

表 7 QS4

| パッド                                     | b1 | b0 | VCO 周波数  |

|-----------------------------------------|----|----|----------|

| <b>BGT60LTR11AIP および BGT60LTR11SAIP</b> |    |    |          |

| ground                                  | 0  | 0  | 61.1 GHz |

| open                                    | 0  | 1  | 61.2 GHz |

| 100 kΩ ~ $V_{DD}$                       | 1  | 0  | 61.3 GHz |

| $V_{DD}$                                | 1  | 1  | 61.4 GHz |

| <b>BGT60LTR11BAIP</b>                   |    |    |          |

| ground                                  | 0  | 0  | 60.6 GHz |

| open                                    | 0  | 1  | 60.7 GHz |

| 100 kΩ ~ $V_{DD}$                       | 1  | 0  | 60.8 GHz |

| $V_{DD}$                                | 1  | 1  | 60.9 GHz |

**警告:** 同じ動作周波数で近接で動作しているセンサーは干渉する可能性があります。

## 2.2 パワーアップとシーケンス

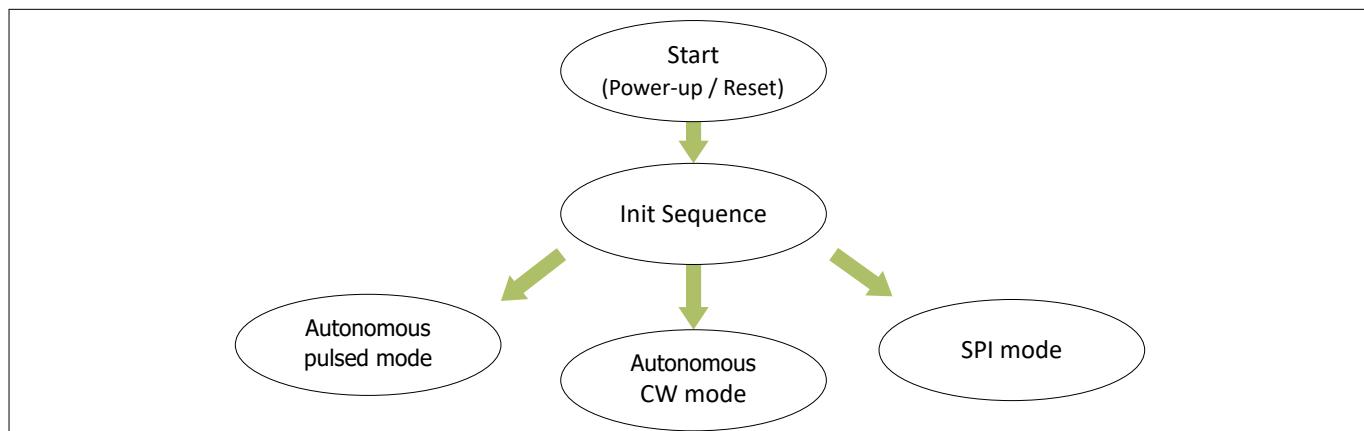

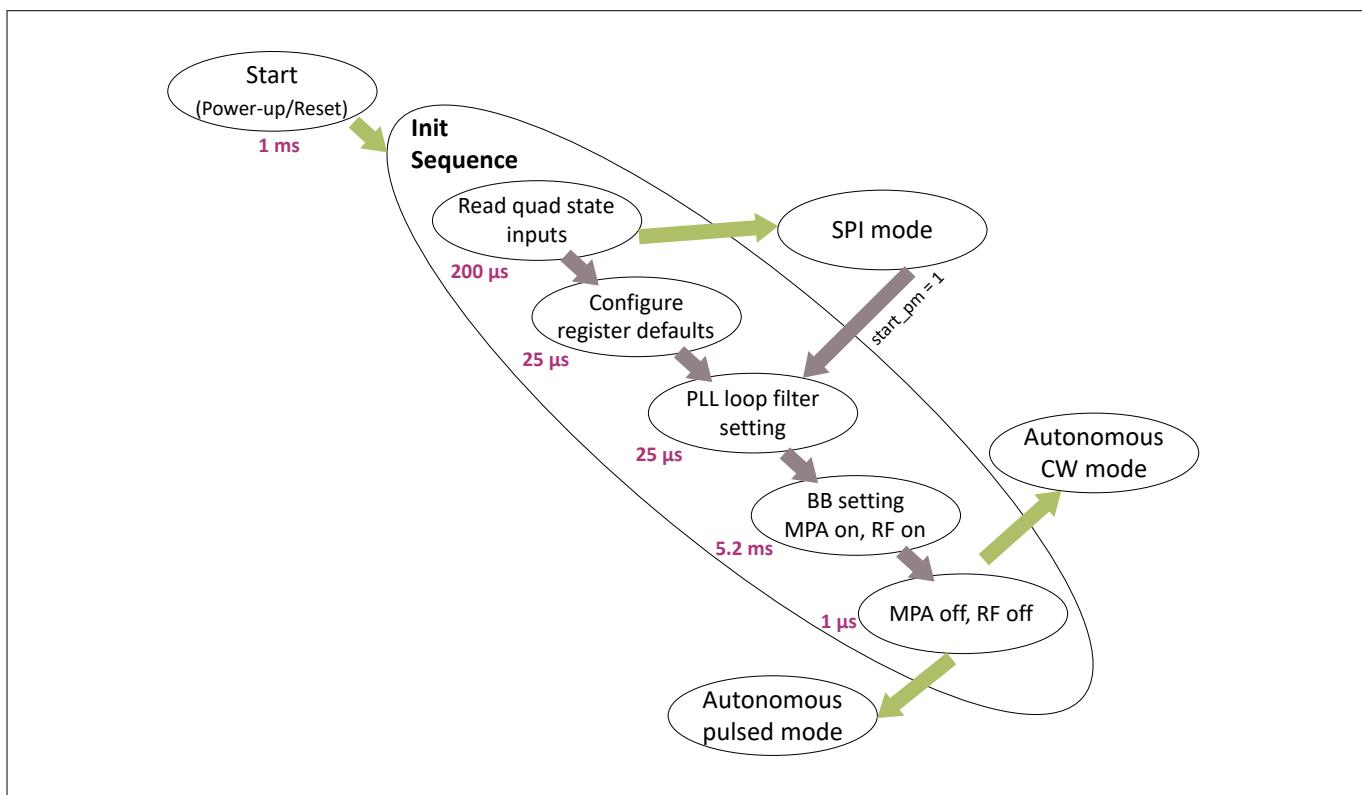

図 3 状態図の概要

クワッドステート入力 QS1 に応じて、3 つの使用可能なモードのいずれかが選択されます。起動時、内部メインコントローラが SPI インターフェースを制御します。したがって、そのフェーズ中または自律 (パルス/CW) モード中に外部からチップをプログラムすることは推奨しません。したがって、SPI アクティビティは、SPI モードの場合にのみ推奨されます。

その理由は、メインコントローラは同期の問題を防止するために、パッド SPICSN がアクティブ (=0) であればに停止されるためです。これは、SPI インターフェースの現在のマスターとは無関係です。したがって、SPI インターフェースを使用しない場合、または外部コントローラが存在しない場合は、パッドを「1」に設定する必要があります。

## 2 メインコントローラ

### 2.2.1 電源投入時

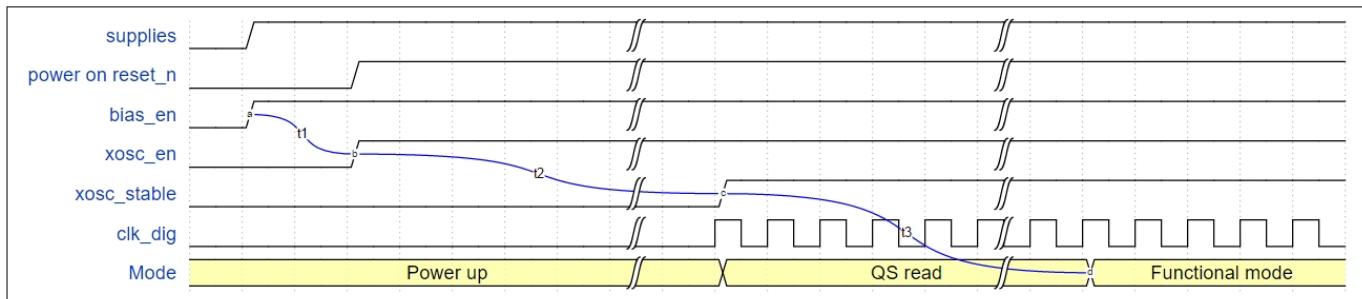

図 4 に、電源投入に関する内部信号を示します。

図 4 電源投入時

供給ランプは  $400\mu\text{s}$  より短くする必要があります。bias\_en は電源に直接接続されているため、同時にランプします。統合されたパワーオンリセットにより、デジタル部分が定義された状態でウェイクアップし、この信号が発振器を起動する xosc\_en にも接続されます。これらの信号の立ち上りエッジ間の時間  $t_1$  は、少なくとも  $9\mu\text{s}$  以上の必要があります。これは、ランプする時間が定義されたとおりになると満たされます。

発信機はメインコントローラのクロックを安定かつ有効化する時間  $t_2$  を必要とし、 $t_2$  は 1 ミリ秒未満です。時間  $t_3$  は QS1-4 入力設定を読み込むために必要とされます。これには  $200\mu\text{s}$  かかります。チップは、SPI パルス/SPI CW モードで、外部から SPI コマンドを受け入れることができます。

### 2.2.2 初期化シーケンス

図 5 初期化シーケンス

## 2 メインコントローラ

初期化シーケンスは、電源投入/リセットの直後に開始されます。これは、次の手順で構成されます。

- 選択された動作モードを知るために、クワッドステート入力を読み出します。これはアナログセトリングに  $200\mu\text{s}$  を必要とします。SPI モードの場合、初期化シーケンスが終了され、メインコントローラが SPI モードに切り替わり、SPI インターフェースの制御が外部マイクロコントローラに切り替わります。

- 自律パルス/CW モードの場合、設定レジスタのデフォルト値が設定され、内部の SPI ADC ブロックの SPI インターフェースを使用して書き込まれます。

- PLL が起動後、ループフィルターのセトルメント中には中電力増幅器 (MPA) はアクティブになりません。 $20\mu\text{s}$  後、MPA がアクティブになり、RF も実行されます。ベースバンド (BB) が安定するまで  $5\text{ ms}$  かかります。

- 自律 CW モードでは、初期化シーケンスが終了し、メインコントローラが CW モードに切り替わります。

- 自律パルスモードの場合、MPA、RF および PLL がオフになり、メインコントローラがパルスモードに切り替わります。

初期化シーケンス終了時にはステータスピットである init\_done (Reg56[13]) が設定されます。

表 8 初期化シーケンスの詳細

| 番号 | コマンド                      | 説明                                                                          |

|----|---------------------------|-----------------------------------------------------------------------------|

| 1  | write Reg1 0x0100         | ビット qs_rd_en を設定                                                            |

| 2  | 2*read Reg55              | 事前に定義された値を 2 回読み出し、十分なクロックサイクルを提供                                           |

| 3  | wait 200 $\mu\text{s}$    | クワッドステート入力を読み出す前に $200\mu\text{s}$ 待機                                       |

| 4  | read quad state inputs    | SPI モード設定時に初期化シーケンスを読み出し、終了                                                 |

| 5  | write Reg1 0x0000         | リセットビット qs_rd_en                                                            |

| 6  | spiwrite Reg4 Reg4_init   | 定義された初期値を書き込み                                                               |

| 7  | spiwrite Reg5 Reg5_init   | 定義された初期値を書き込み                                                               |

| 8  | spiwrite Reg6 Reg6_init   | 定義された初期値を書き込み                                                               |

| 9  | spiwrite Reg7 Reg7_init   | 定義された初期値を書き込み (PLL_Trig, SPICLK, SPIDI ピンから部分的に計算)                          |

| 10 | spiwrite Reg8 Reg8_init   | 定義された初期値を書き込み                                                               |

| 11 | spiwrite Reg9 Reg9_init   | 定義された初期値を書き込み                                                               |

| 12 | spiwrite Reg2 Reg2_init   | 定義された初期値を書き込み (ピン PLL_Trig、クアッドステート(アドバンスモードでのアナログ読み出し)から計算)                |

| 13 | spiwrite Reg10 Reg10_init | 定義された初期値を書き込み (ピン PLL_Trig、クアッドステート(アドバンスモードでのアナログ読み出し)から計算)                |

| 14 | write Reg0 0x311F         | vcobuf_en, vco_en, pll_en, rxbuf_en, txbuf_en, mixi_en, mixq_en, lna_en を設定 |

| 15 | write Reg1 0x1036         | div_bias_en, bb_boost_dis, bb_clk_chop_en, bb_strup_hp, bb_amp_en を設定       |

| 16 | wait PLLen to PLLactive   | 定義された時間 pll_en から pll_active ( $2\mu\text{s}$ ) まで待機                        |

| 17 | write Reg0 0x371F         | pll_active、pll_clk_gate_en を設定                                              |

| 18 | wait for lock detect      | 待機後、SPI の制御を外部に設定                                                           |

| 19 | wait 20 $\mu\text{s}$     | MPA をオフにして PLL ループフィルターをセトリング                                               |

| 20 | write Reg0 0x373F         | mpa_en を設定                                                                  |

(続く)

## 2 メインコントローラ

表 8 (続き) 初期化シーケンスの詳細

| 番号 | コマンド                           | 説明                                                                                          |

|----|--------------------------------|---------------------------------------------------------------------------------------------|

| 21 | wait MPA to sample enable      | MPA が Sample & Hold – mpa2sh_dly (Reg7[5:4]) を有効にするまで設定時間待機                                 |

| 22 | write Reg1 0x1037              | bb_sample_en を設定                                                                            |

| 23 | wait 5 ms                      | ベースバンドがセトリングするまで待機                                                                          |

| 24 | end for autonomous CW mode     | 自律 CW モードの設定時に初期化シーケンスを終了                                                                   |

| 25 | write Reg1 0x1092              | bb_boost_dis, bb_strup_hp, bb_sample_en をリセットし、bb_dig_det_en を設定。<br>100 ns 待機              |

| 26 | write Reg0 0x371F              | mpa_en をリセット                                                                                |

| 27 | wait 20 $\mu$ s                | パルスモード時、最適なリロックのために MPA がアクティブではない状態での PLL のセトリングを許可                                        |

| 28 | write Reg0 0x311F              | pll_active、pll_clk_gate_en をリセット<br>100 ns 待機                                               |

| 29 | write Reg1 0x0092              | div_bias_en をリセット                                                                           |

| 30 | write Reg0 0x0900              | RF オフ、pll_en のみがオン、pll_open_loop が設定される                                                     |

| 31 | end for autonomous pulsed mode | パルスモードの初期化シーケンスを終了し、dc_rep_rate (Reg7[11:10]) で定義されたスリープフェーズでパルスモードを開始。その後、自律パルスモードシーケンスが開始 |

### 2.2.3 自律パルスモードシーケンス

パルスモードでは、VCO, RF, および PLL がオフになった後の短時間だけデバイスがアクティブになります。その後に、ベースバンドは常に動作し続けます。オン/オフレートは約 1:5 から 1:140 の範囲設定が可能です。デフォルト設定は 1:35 ですこれは、デフォルトの繰り返し時間が 500  $\mu$ s で、オン時間が 14  $\mu$ s であるためです。これは、RF および PLL の起動に必要な約 9  $\mu$ s と、デフォルトのサンプル時間として 5  $\mu$ s で構成されます。

表 9 自律パルスモードシーケンスの詳細

|   | コマンド                   | 説明                                                                          |

|---|------------------------|-----------------------------------------------------------------------------|

| 1 | write Reg0 0x391F      | vcobuf_en, vco_en, pll_en, rxbuf_en, txbuf_en, mixi_en, mixq_en, lna_en を設定 |

| 2 | write Reg1 0x1092      | div_bias_en を設定                                                             |

| 3 | wait VCO to PLL        | 定義された時間 VCO が PLL にオンになるのを待機 – vco2pll_dly (Reg7[6])                        |

| 4 | write Reg0 0x3F1F      | pll_active、pll_clk_gate_en を設定                                              |

| 5 | wait for lock detect   |                                                                             |

| 6 | write Reg0 0x3F3F      | mpa_en を設定                                                                  |

| 7 | wait MPA enable to S&H | 定義された時間、MPA が Sample&Hold を有効にするまで待機 – ld2sh_dly (Reg7[5:4])                |

(続く)

## 2 メインコントローラ

表 9 (続き) 自律パルスモードシーケンスの詳細

|    | コマンド                  | 説明                                                                                                                |

|----|-----------------------|-------------------------------------------------------------------------------------------------------------------|

| 8  | write Reg1 0x1093     | bb_sample_en を設定                                                                                                  |

| 9  | sampling running      | 定義された時間待機- dc_on_pulse_len (Reg7[9:8])                                                                            |

| 10 | write Reg1 0x1092     | bb_sample_en をリセット<br>100ns 待機                                                                                    |

| 11 | write Reg0 0x393F     | pll_active、pll_clk_gate_en をリセット<br>100ns 待機                                                                      |

| 12 | write Reg0 0x391F     | mpa_en をリセット<br>100ns 待機                                                                                          |

| 13 | write Reg1 0x0092     | div_bias_on をリセット                                                                                                 |

| 14 | write Reg0 0x0900     | RF がオフで、pll_en のみがオンのままで、pll_open_loop が設定                                                                        |

| 15 | wait for next wake-up | シーケンスは、定義された時間の後に再開されます。<br>dc_rep_rate dc_rep_rate (Reg7[11:10]), dc_rep_rate は、アクティブフェーズ<br>からアクティブフェーズまでを測定します |

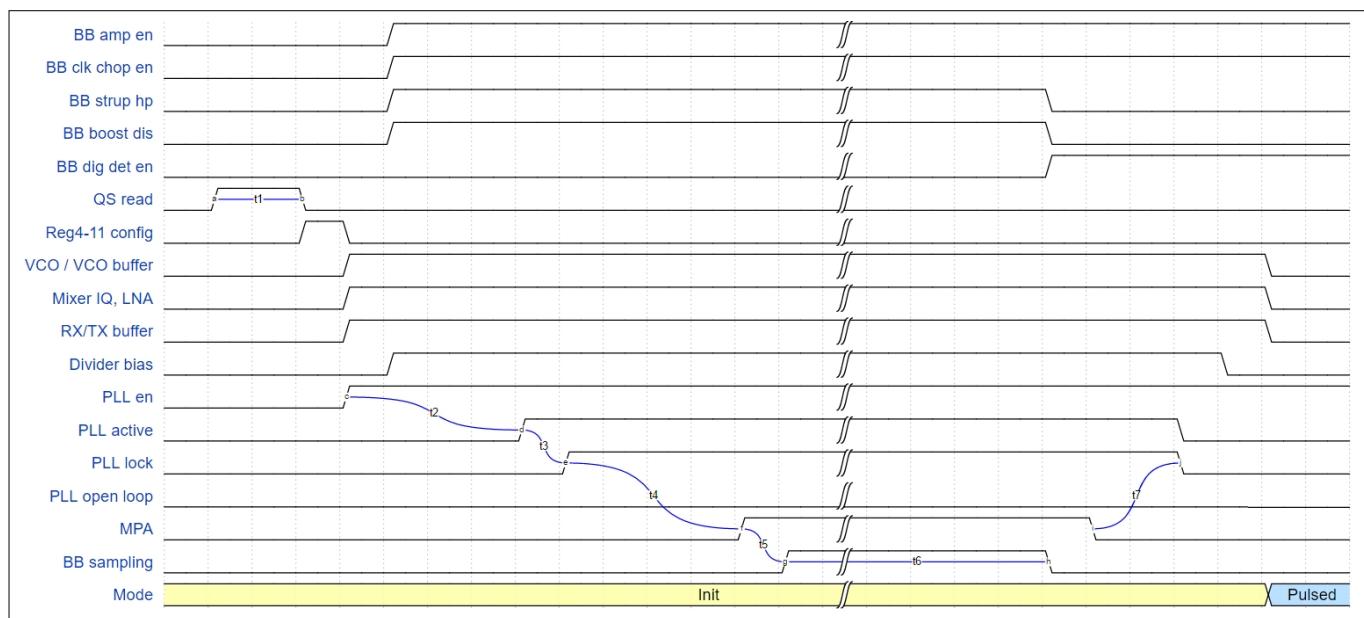

図 6 自律パルスモード - 初期化フェーズ

図 6 に、パルスモード初期化フェーズのすべての制御信号の波形図を示します。

t1: 200  $\mu$ s、クアッドステートの読み出し入力が 1 になるまでに必要な時間。

それぞれのブロックがオン変わる前に、設定レジスタ Reg4-11 が書き込まれます。

## 2 メインコントローラ

- t2: 2  $\mu$ s、PLL がアクティブ状態に設定される前に PLL イネーブルが有効になるのに必要な時間。VCO をオンにした直後に、分周器バイアスをアクティブにする必要があります。

- t3: ~15  $\mu$ s、PLL ロックに必要な時間。

- t4: 20  $\mu$ s、MPA を無効にした状態でのループフィルターのセトリングに必要な時間。

- t5: mpa2sh\_dly (初期値は 1  $\mu$ s)、MPA をアクティブにしてからサンプリングするまでの時間。

- t6: 5ms、ベースバンドのセトリングに必要な時間。

- t7: 20  $\mu$ s、パルスモードで最良の再ロック状態を可能にするために MPA を無効にして PLL がセトリングするのに必要な時間。

これでデジタル検出器がオンになり、カウントが開始され、アナログ検出器が安定するまでさらに 50 ミリ秒かかります。BB は同時にパルスモード用に設定されます。

初期化フェーズでは、PLL と RF は次の順序でオフになります: Sample&Hold / MPA / PLL / Divider bias / RF、各ステップは 100 ns かかる必要があります。MPA を無効にした後、時間  $t_7$  が必要です。信号 pll\_clk\_gate\_en は pll\_active と同じである必要があります。

レジスタは、外部からアクティブパルスモード中にプログラムできますが、次の点を考慮する必要があります。

- アクセスは、レジスタの変更を待つ間、メインコントローラのシーケンサを停止します。bb\_clock\_chop、デジタル検出器、ウェイクアップカウンタはまだ動作中です。

- pll\_en = 1 (Reg0[8]) または pll\_clk\_gate\_en = 1 (Reg0[10]) の場合、PLL レジスタ (Reg4～Reg6) は変更しないでください。

- bb\_dig\_det\_en = 1 (Reg1[7]) の場合、デジタル検出器の設定 (Reg2, Reg10) を変更しないでください。

- ウェイクアップロジックからシーケンサへのウェイクアップパルスの長さは 1.6  $\mu$ s です。SPI アクセスがパルス全体をカバーする場合、次の電源投入フェーズはスキップされます。次のウェイクアップパルスで、次のウェイクアップを発生します。

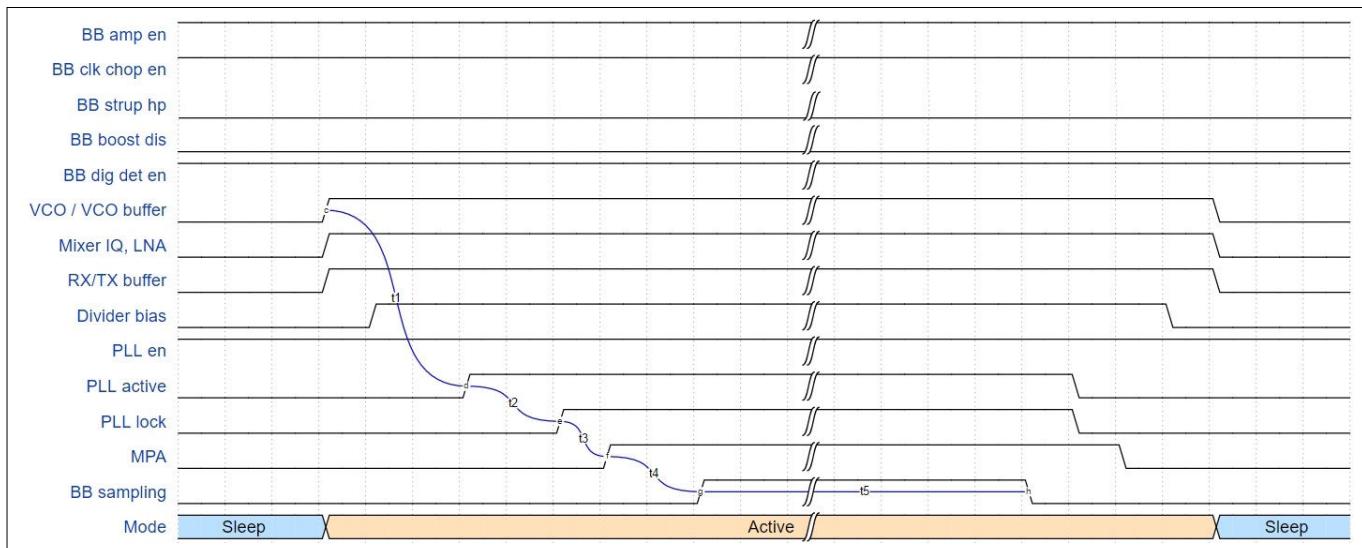

図 7 パルスモード - アクティブフェーズ

図 7 は、スリープフェーズで始まりスリープフェーズで終了する初期化フェーズ後のパルスモードを示します。dc\_rep\_rate (Reg7[11:10]) は、アクティブフェーズの開始から次のアクティブフェーズの開始までの時間を定義します。

## 2 メインコントローラ

- t1: vco2pll\_dly (初期値は 1  $\mu$ s)、VCO を有効にした後に PLL アクティブが設定される時間。VCO をオンにした直後に、分周器バイアスをアクティブにする必要があります。

- t2:  $\sim$ 5  $\mu$ s、PLL がロックに必要な時間。

- t3: 300~400 ns、ロック検出信号の同期と MPA の有効化に必要な時間。

- t4: mpa2sh\_dly (初期値は 1  $\mu$ s)、MPA をアクティブにしてからサンプリングするまでの時間。

- t5: dc\_on\_pulse\_len (初期値は 5  $\mu$ s) Reg7[9:8]、時間どおりにサンプリング。

アクティブフェーズの場合、PLL と RF は次の順序でオフになります: Sample&Hold / PLL / MPA / Divider bias / RF、各ステップは 100 ns かかる必要があります。信号 pll\_clk\_gate\_en は pll\_active と同じである必要があります。

パルスが終了するとすぐに、センサー ADC が開始され、IF 信号が変換されてデジタル検出器により測定されます。

## 2.2.4 自律 CW モードシーケンス

自律連続波モードでは、デバイスはクアッドステート入力どおり設定された状態でアクティブになります。メインコントローラはセンサー ADC のみを使用し、デジタル検出器で IF 信号を測定します。初期化シーケンスは正しいステップで残されたため、CW モードシーケンス自体には 2 つのエントリしか含まれません。1 つは制御信号のみをオフにし、検出器のデジタル部分をオンにするためです。

表 10 自律 CW モードシーケンスの詳細

|   | コマンド              | 説明                                      |

|---|-------------------|-----------------------------------------|

| 1 | write Reg1 0x10B3 | bb_dig_det_en を設定し、bb_strup_hp をリセットします |

| 2 | end               |                                         |

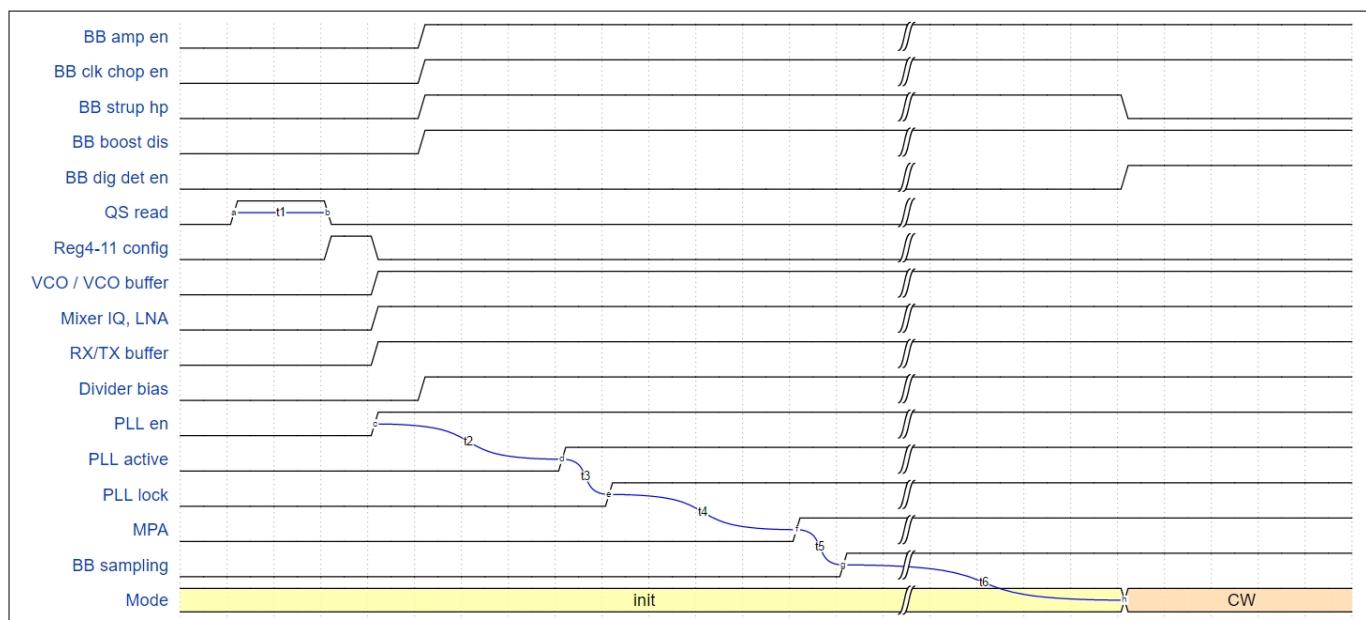

図 8 は、初期化フェーズを含む自律 CW モードを示します。

ベースバンドのセトリングが終了するまでの初期化フェーズは、自律パルスモードの場合と同じです。CW モードでは、ベースバンドとサンプリングは継続的にオンになり、bb\_strup\_hp=0 (Reg1[2]) になります。

図 8 自律 CW モード

## 2.2.5 SPI モードシーケンス

これはマニュアルモードであり、メインコントローラは非アクティブであり、Reg0/1 はメインコントローラによりすべてオフに設定されています。SPI シーケンスは、クアッドステート入力をオフにするだけです。クアッドステート入力 QS1 に応じて、外部 9.6 MHz クロックが有効 (QS1="10") または無効 (QS1="11") になります。

**表 11 SPI モードシーケンスの詳細**

|   | コマンド              | 説明                   |

|---|-------------------|----------------------|

| 1 | write Reg1 0x0000 | qs_rd_en ビットをリセットします |

| 2 | end               |                      |

オプションとして、レジスタを構成し、後でパルスモードまたは CW モードをアクティブにすることもできます。これは、start\_pm (Reg15[14]) を"1"に設定することで実行できます。start\_cw = 0 (Reg15[12]) の場合はパルスモードになり、それ以外の場合は CW モードになります。

外部クロックが有効になっている場合 (QS1="10") 、ビット clk\_ext\_dis (Reg15[13]) を設定することにより、同じ SPI アクセスでオフに切り替えることができます。クロックがオフになると、外部コンポーネントがスリープ状態になるように、さらに 16~32 個のクロックが配信されます。

## 2.2.6 検出器

RF ブロックをオンにすると、検出器をアクティブにできます。ベースバンドのセトリングのために検出器を有効にしてから、さらに 50 ms かかります。この間、出力 TDet と PDet は非アクティブ状態に保たれます。

## 2.3 動的制御信号の概要

**表 12 動的制御信号の概要**

|                             | 自律パルスモード | 自律 CW モード | SPI モード |

|-----------------------------|----------|-----------|---------|

| vcobuf_en, vco_en           | トグル      | 1         | 0       |

| pll_clk_gate_en, pll_active | トグル      | 1         | 0       |

| pll_open_loop               | 0        | 0         | 0       |

| pll_en                      | 1        | 1         | 0       |

| mpa_en                      | トグル      | 1         | 0       |

| rxbuf_en, txbuf_en          | トグル      | 1         | 0       |

| mixi_en, mixq_en            | トグル      | 1         | 0       |

| lna_en                      | トグル      | 1         | 0       |

| div_bias_en                 | トグル      | 1         | 0       |

| qs_rd_en                    | 0        | 0         | 0       |

| bb_dig_det_en               | 1        | 1         | 0       |

| bb_boost_dis                | 0        | 1         | 0       |

| bb_clk_chop_en              | 1        | 1         | 0       |

| bb_strup_hp                 | 0        | 0         | 0       |

| bb_amp_en                   | 1        | 1         | 0       |

(続く)

## 2 メインコントローラ

表 12 (続き) 動的制御信号の概要

|              | 自律パルスモード | 自律 CW モード | SPI モード |

|--------------|----------|-----------|---------|

| bb_sample_en | トグル      | 1         | 0       |

動的制御信号は、アナログブロックとデジタルブロックのオン/オフを切り替えるために使用されます。これらは、(=レジスタ=0/1) ダイレクトアクセスレジスタに配置されています。メインコントローラはフルクロック速度でシーケンスを実行でき、各レジスタアクセスに 100 ns かかります。他のすべてのレジスタの場合、メインコントローラは約 25 クロックサイクル (=2.5  $\mu$ s) 必要とする SPI インターフェースを使用する必要があります。

図 13 に、この概念のブロック図を示します。これらのビットをマニュアルでプログラミングする場合は、排他的論理とロジックを考慮する必要があります。

メインコントローラが 1 つのビットをオフにする場合は、"1"でプログラミングすることで実行できます。メインコントローラが 1 つのビットをオンにする場合は、"0"でプログラミングすることで実行できます。

明確にするためのいくつかの例:

- bb\_clk\_chop\_en をオフにする必要がある場合は、パルスモードと CW モードの場合は"1"、SPI モードの場合は"0"にプログラムする必要があります。

- bb\_boost\_dis をオンにする必要がある場合は、パルスモードと SPI モードの場合は"1"、CW モードの場合は"0"にプログラムする必要があります。

- lna\_en をオフにする必要がある場合は、CW モードは"1"、SPI モードは"0"にプログラムする必要があります。メインコントローラにより継続的にプログラムされるため、パルスモードではオフにできません。"1"でプログラミングすると、ビットが反転するだけです。

### 3 SPI インターフェース

## 3 SPI インターフェース

SPI – Serial Peripheral Interface

- 7 ビットの連続アドレス空間

- 16 ビットの固定ペイロード

- チップセレクト (スレーブ選択) は Low アクティブ

- 外部 SPI マスターから SPI アクセスがない場合、High に保つ必要があります。SPI モードではこのようなアクセスが推奨されています。メインコントローラによって内部的にも使用されるため、このように使用しない場合、SPI インターフェースで競合が発生する可能性があります。

- SPICS=1 の場合、データ出力 SPIDO (別名 MISO) は High-Z です

上記のような競合で引き起こされる問題を回避するために、以下を推奨します。

- SPI を使用しない場合は、SPICSN を High に保ってください。そうしないと、内部シーケンサが続行できず、動作が停止します。

- チップが自律モード (パルス/CW) で動作している間、以下のタイミング制約を考慮する必要があります。**SPIDO を使用可能にするため、ビット「miso\_drv」(Reg15[6])を設定することを強く推奨します!**

- アクセス中は SPICSN を長時間 (1.6  $\mu$ s) ローに駆動してはいけません。これによって、内部使用の SPI を妨げ、シーケンサのタイミングを崩します。これは主に低速のデータレート (16 Mbps 未満) の場合やバーストアクセスに関連しています。

- アクセスを開始する際には、以下の調停プロトコルを使用する必要があります。

1. 初期状態では、SPICSN は High にドライブされています (最小で 100 ns 以上)。

2. SPIDO が Low になるまで待ちます (High は内部シーケンサが SPI を使用していることを意味します)。

- それは長い時間はかかるないはずです。しかし、何かが完全に壊れている場合は、タイムアウトのような問題の検出に役立つ場合があります。「miso\_drv」=0 の場合は、このステップをスキップしてください。

3. SPICSN を Low にドライブする (バスを予約してみてください)。

4. 100ns 以上待ちます (SPICSN の同期に必要な時間)。

5. SPIDO をもう一度チェックしてください。High であれば (シーケンサも SPI を開始し)、ステップ 1 に進んでください。

- それ以外の場合は、ステップ 6 に進んでください。

6. 実際のデータ送信を行ってください。

7. SPICSN を High にドライブしてください (バスを解放)。

- アクティブモード時のタイミングとアービトレーションを制限する代わりに、SPI を内部で使用していないスロットを使用することも可能です。つまり周期的な SPIDO のパターン (周期はサンプルレート) に従って、外部アクセスを調整します。

### 3 SPI インターフェース

#### 3.1 SPI インターフェースの説明

SPI コマンドはデータ入力 SPIDI (シリアルデータ入力) を介して読み込まれ、この入力はマスターから供給されるクロック入力 SPICLK に同期しています。出力ワードは、データ出力 SPIDO (シリアルデータ出力) に同期して表示されます。送信サイクルは、入力信号 SPICSN (chip select not) のアクティブ Low により開始します。SPICLK の最後の立ち上りエッジで、データが書き込まれます。レジスタ・ブロック送信サイクルは、入力信号 SPICSN の立ち上りエッジで終了します。

動作エッジはクロックの立ち上りエッジです。動作エッジごとに SPIDI のステータスが入力レジスタにシフトされます。また、作業エッジごとに、SPIDO バスの状態が出力からシフトされます。SPIDO のタイミングは fast\_mode (Reg15[8]) を"1"に設定することで変更できます。この場合、SPIDO は SPI クロックサイクルの半分だけ遅延します (したがって、代わりに立ち下りエッジで変化します)。これにより、外部 SPI マスターのホールド時間が長くなります (ただし、セットアップ時間は短くなります)。

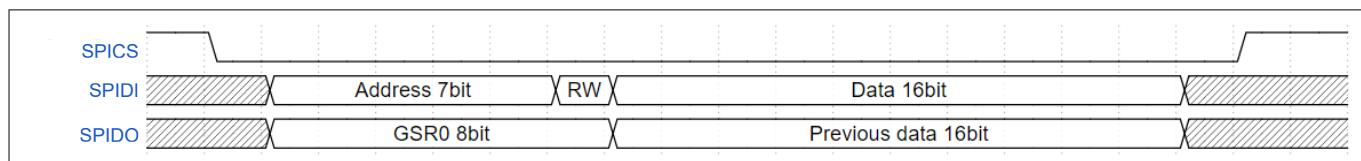

##### 3.1.1 SPI 書き込みモード

書き込み (ライト) アクセスは、SPICSN の立ち下りエッジの後で、MSB を先頭に 7 ビットのアドレスを転送して開始します。続く 8 ビット目 (RW = read/write ビット) が"1"であれば、ライトアクセスであることを示します。その後、16 ビットのペイロードが送信されます。送信順番は MSB が先です。

アドレスと RW ビットを受信すると同時に、グローバルステータスレジスタ GSR0 (8 ビット) が SPIDO (MSB ファースト) でシリアルシフトアウトされます。ペイロードの送信中、前のレジスタの内容が SPIDO でシリアルにシフトアウトされます。

最後に SPICSN の立ち上りエッジでアクセスを終了します。

図 9 SPI 書き込み - MSB、RW = "1"

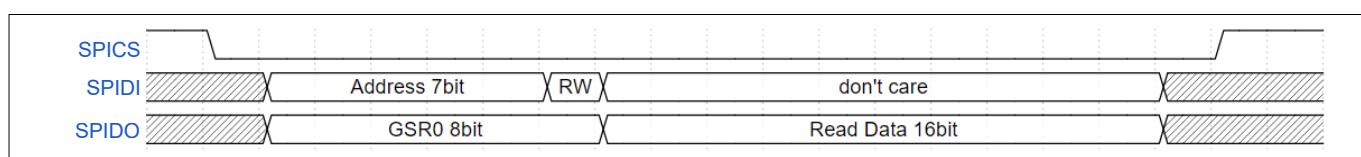

##### 3.1.2 SPI 読み出しモード

読み出し (リード) アクセスは、SPICSN の立ち下りエッジの後で、MSB を先頭に 7 ビットのアドレスを転送して開始します。続く 8 ビット目 (RW = read/write ビット) が"0"であれば、リードアクセスであることを示します。次の 16 ビットデータは、リードアクセスには必要ないため、無視されます。

アドレスと RW ビットを受信すると同時に、グローバルステータスレジスタ GSR0 (8 ビット) が SPIDO (MSB ファースト) でシリアルシフトアウトされます。その後、読み出されたデータは SPIDO でシリアルにシフトアウトされます。最後に SPICSN の立ち上りエッジでアクセスを終了します。

図 10 SPI 読み出し - MSB、RW = "0"

### 3 SPI インターフェース

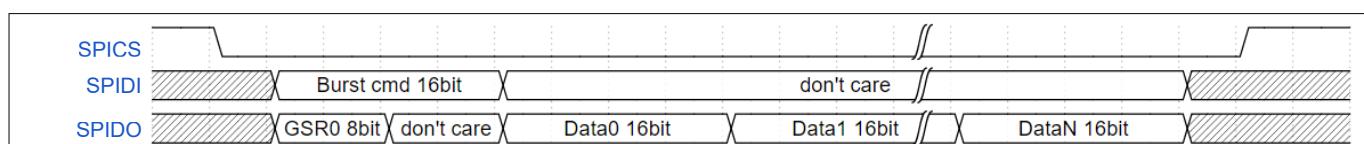

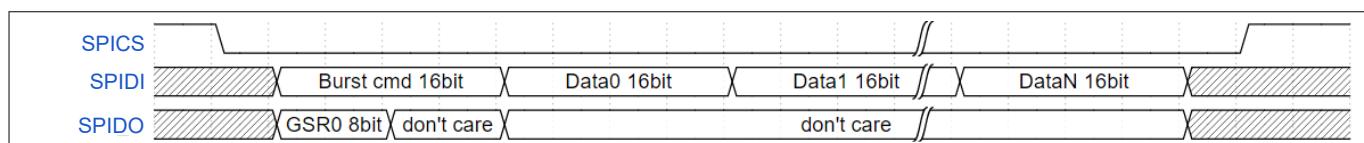

#### 3.1.3 SPI バーストモード

バーストモードは、単一のレジスタだけを読み出すのではなく、複数のレジスタを読み出したり書き出したりするために使用されます。バーストモードコマンドはいくつかのビットフィールドで構成され、表 13 に示されています。

##### バーストコマンドの例:

レジスタ Reg4 にアクセスするためのバーストコマンド (読み出し: 0xFF08、書き込み: 0xFF09)

表 13 バーストモードコマンド

| ビットフィールド | ビット幅 | ビットフィールド名 | 説明                                            |

|----------|------|-----------|-----------------------------------------------|

| 15:8     | 8    | addr/RW   | バースト開始アドレス (常に 0xFF)                          |

| 7:1      | 7    | saddr     | バーストモード開始アドレス                                 |

| 0        | 1    | rwb       | バーストモードの読み出し/書き込み<br>0-バースト読み出し<br>1-バースト書き込み |

##### SPI バーストアクセス

スタートコンディションの後、SPIDI 上に SPI マスターから 16 ビットバーストモードコマンドが送信されます。同時に、ステータスレジスタ GSR0 (8 ビット) と 8 ビットのダミーデータが SPIDO 上でシフトアウトされます。コマンドシーケンスが完了した後、バーストライトモードでは、書き込みバーストデータは SPIDI の SPI マスターからシフトインされるか、読み出しバーストデータはバースト読み出しモードの SPIDO の SPI マスターにシフトアウトされます。

バーストアクセスでは、任意の数の書き込み/読み出しデータブロックを使用できます。アクセスは、SPICS の立ち上りエッジで終了します。

##### バーストモード読み出しシーケンス

バースト読み出しシーケンスでは、SPI マスターはデバイスから読み出します。

図 11 SPI バースト読み出し

##### バーストモードの書き込みシーケンス

バースト書き込みモードでは、SPI マスターがデバイスに書き込みを行います。

図 12 SPI バースト書き込み

3 SPI インターフェース

### 3.2 SPI レジスタ

#### 3.2.1 レジスタの概要

表 14 レジスタの概要

| レジスタ     | モード | 説明                            | リセット値  | 初期化シーケンス後の値<br>(パルススリープ/CW)                                                                                                    |

|----------|-----|-------------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------|

| Reg0     | RW  | Control bits                  | 0x0000 | 0x0900 <sup>1)</sup> / 0x373F <sup>1)</sup>                                                                                    |

| Reg1     | RW  | Control bits                  | 0x0000 | 0x0092 <sup>1)</sup> / 0x10B3 <sup>1)</sup>                                                                                    |

| Reg2     | RW  | Detector threshold            | 0x0000 | QS2 に依存                                                                                                                        |

| Reg3     | RW  | Reserved                      | 0x0000 | 0x0000                                                                                                                         |

| Reg4     | RW  | PLL 1                         | 0x0000 | 0x0F3A                                                                                                                         |

| Reg5     | RW  | PLL 2                         | 0x0000 | QS4 に依存                                                                                                                        |

| Reg6     | RW  | PLL 3                         | 0x0000 | 0x6800                                                                                                                         |

| Reg7     | RW  | Duty cycling, timing, pd, MPA | 0x0000 | 0x0457                                                                                                                         |

| Reg8     | RW  | Divider                       | 0x0000 | 0x0000                                                                                                                         |

| Reg9     | RW  | Baseband                      | 0x0000 | 0x0068                                                                                                                         |

| Reg10    | RW  | Detector hold time            | 0x0000 | QS3 に依存                                                                                                                        |

| Reg11    | RW  | Reserved                      | 0x0000 | 0x0000                                                                                                                         |

| Reg12    | RW  | BITE, AMUX                    | 0x0000 | 0x0000                                                                                                                         |

| Reg13    | RW  | Algo 1                        | 0x0000 | 0x0000                                                                                                                         |

| Reg14    | RW  | Algo 2                        | 0x0000 | 0x0000                                                                                                                         |

| Reg15    | RW  | Digital control               | 0x0000 | 0x0000                                                                                                                         |

| Reg34    | RW  | ADC start                     | 0x0000 | 0x0000                                                                                                                         |

| Reg35    | RW  | ADC convert                   | 0x0000 | 0x0000                                                                                                                         |

| Reg36    | RO  | ADC status                    | 0x0000 | 0x0000                                                                                                                         |

| Reg38-53 | RO  | ADC result channel 0 – 15     | 該当なし   | 該当なし                                                                                                                           |

| Reg56    | RO  | Status and chip version       | 0x0000 | 0x2000,<br>Bit [0:2] chip_version に依存<br>Bit [7:8] QS4 に依存<br>Bit [9:10] QS3 に依存<br>Bit [11:11] QS2 に依存<br>Bit [15:14] QS1 に依存 |

| GSR0     | RO  | 8 ビット SPI ステータスレジスタ           | 0x00   | 0x00                                                                                                                           |

1) これらの値はメインコントローラによって設定されるため、レジスタを読み出すと 0x0000 が output されます。

「実際の」MMIC リセット値は、SPI モードでは変更されないため、SPI モードでのみ読み出せます。自立パルスモードまたは自立 CW モードでは、初期化シーケンスが完了した時に、MMIC リセット値は上書きされます。

### 3 SPI インターフェース

#### 3.2.2 ダイレクトアクセスレジスタ

Reg0 および Reg1 は図 13 に示すようにダイレクトアクセスレジスタです。これらのビットは、メインコントローラから直接制御できます。他のすべてレジスタは、外部オプションのマイコンから SPI でプログラムするか、または電源投入時にメインコントローラから内部的に SPI によってプログラムする必要があります。

SPI からの外部リードアクセスは、常に SPI ADC ブロック内のレジスタをアドレス指定するため、XOR (排他的論理和) の出力に関する情報を読み出すことはできません。リードアクセスは、SPI ADC 内に格納された値を提供します。

図 13 ダイレクトアクセスレジスタ

#### 3.2.3 レジスタマップのビットフィールド

表 15 レジスタマップ

|      |        | 7              | 6             | 5              | 4               | 3             | 2               | 1                   | 0              |

|------|--------|----------------|---------------|----------------|-----------------|---------------|-----------------|---------------------|----------------|

| Reg0 | [15:8] | reserved       |               | vcobuf_en      | vco_en          | pll_open_loop | pll_clk_gate_en | pll_activ_e         | pll_en         |

|      | [7:0]  | reserved       |               | mpa_en         | txbuf_en        | mixq_en       | mixi_en         | lna_en              | rxbuf_en       |

| Reg1 | [15:8] | reserved       |               |                | div_bias_en     | reserved      |                 |                     | qs_rd_en       |

|      | [7:0]  | bb_dig_d et_en | reserved      | bb_boost _dis  | bb_clk_c hop_en | reserved      | bb_strup _hp    | bb_amp_en           | bb_samp_le_en  |

| Reg2 | [15:8] | hprt           | aprt          | dir_mod_e      | thrs            |               |                 |                     |                |

|      | [7:0]  | thrs           |               |                |                 |               |                 |                     |                |

| Reg3 | [15:8] | reserved       |               |                |                 |               |                 |                     |                |

|      | [7:0]  |                |               |                |                 |               |                 |                     |                |

| Reg4 | [15:8] | pll_dft_dmx    |               | reserved       | pll_bias_ dis   | pll_lf_iso    | pll_lf_r4_ sel  | pll_cl_lo op_pmo de | pll_lf_r2_ sel |

|      | [7:0]  | xosc_mo de     | pll_fbdv _cnt | pll_cp_icp_sel |                 |               | pll_cp_m ode    | pll_pfd_rdt_sel     |                |

(続く)

**3 SPI インターフェース**

**表 15 (続き) レジスタマップ**

|              |        | 7               | 6               | 5                   | 4              | 3                 | 2              | 1               | 0                   |

|--------------|--------|-----------------|-----------------|---------------------|----------------|-------------------|----------------|-----------------|---------------------|

| <b>Reg5</b>  | [15:8] | reserved        |                 |                     |                |                   |                | pll_fcw         |                     |

|              | [7:0]  | pll_fcw         |                 |                     |                |                   |                |                 |                     |

| <b>Reg6</b>  | [15:8] | pll_ld_tw_sel   |                 |                     | pll_ld_le<br>n | pll_ld_en         | reserved       |                 |                     |

|              | [7:0]  | reserved        |                 |                     |                |                   |                |                 |                     |

| <b>Reg7</b>  | [15:8] | reserved        |                 |                     |                | dc_rep_rate       |                | dc_on_pulse_len |                     |

|              | [7:0]  | reserved        | vco2pll_d<br>ly | mpa2sh_dly          |                | pd_en             | mpa_ctrl       |                 |                     |

| <b>Reg8</b>  | [15:8] | reserved        |                 |                     |                |                   |                |                 |                     |

|              | [7:0]  | reserved        |                 |                     |                | div_sel           |                | div_out_en      | div_test<br>mode_en |

| <b>Reg9</b>  | [15:8] | reserved        |                 |                     |                |                   |                |                 |                     |

|              | [7:0]  | bb_hp_res       |                 | bb_clk_c<br>hop_sel | bb_lpf_b<br>w  | bb_ctrl_gain      |                |                 |                     |

| <b>Reg10</b> | [15:8] | hold            |                 |                     |                |                   |                |                 |                     |

|              | [7:0]  |                 |                 |                     |                |                   |                |                 |                     |

| <b>Reg11</b> | [15:8] | reserved        |                 |                     |                |                   |                |                 |                     |

|              | [7:0]  |                 |                 |                     |                |                   |                |                 |                     |

| <b>Reg12</b> | [15:8] | reserved        |                 |                     |                |                   |                |                 |                     |

|              | [7:0]  | bb_amux_ctrl    |                 | bb_amux<br>_en      | bite_pd_<br>en | bite_ctrl         |                |                 | bite_en             |

| <b>Reg13</b> | [15:8] | reserved        |                 |                     |                |                   |                |                 |                     |

|              | [7:0]  | phase_win_len   |                 |                     | mean_win_len   |                   |                | prt_mult        |                     |

| <b>Reg14</b> | [15:8] | thrs_offset     |                 |                     |                |                   |                |                 |                     |

|              | [7:0]  | dir_hys_<br>dis | dir_keep        | hold_x32            | swap_iq        | autoblin<br>d_dis | pulse_m<br>on  | phase_thrs      |                     |

| <b>Reg15</b> | [15:8] | soft_rese<br>t  | start_pm        | clk_ext_d<br>is     | start_cw       | fast_pha<br>se    | dir_c2_1       |                 | fastmode            |

|              | [7:0]  | adc_mon         | miso_drv        | mot_pol             | dir_pol        | stat_mux          |                |                 |                     |

| <b>Reg34</b> | [15:8] | reserved        |                 |                     |                |                   |                |                 |                     |

|              | [7:0]  | reserved        |                 |                     |                | adc_en            | bandgap<br>_en | adc_clk_<br>en  |                     |

| <b>Reg35</b> | [15:8] | reserved        |                 |                     |                |                   |                |                 |                     |

|              | [7:0]  | lv_gain         | reserved        |                     | chnr_all       | chnr              |                |                 |                     |

(続く)

### 3 SPI インターフェース

表 15 (続き) レジスタマップ

|       |        | 7                   | 6            | 5        | 4               | 3                | 2        | 1        | 0       |

|-------|--------|---------------------|--------------|----------|-----------------|------------------|----------|----------|---------|

| Reg36 | [15:8] | reserved            |              |          |                 |                  |          |          |         |

|       | [7:0]  | reserved            |              |          |                 |                  |          | adc_read | bandgap |

| Reg38 | [15:0] | ADC 結果レジスタチャネル 0～15 |              |          |                 |                  |          |          |         |

| Reg56 | [15:8] | qs1_s               | init_done    | qs2_s    |                 | qs3_s            |          | qs4_s    |         |

|       | [7:0]  | qs4_s               | advance_mode | reserved | pll_lock_detect | chip_version     |          |          |         |

| GSR0  | [7:0]  | reserved            |              |          |                 | adc_result_ready | reserved |          |         |

#### 3.2.4 レジスタ Reg0 - ダイレクトアクセスレジスタ

初期化シーケンス後の値: 0x0900 (パルスモード)

初期化シーケンス後の値: 0x373F (CW モード)

|                |                 |         |

|----------------|-----------------|---------|

| DAR_REG0_REG   | Address (アドレス): | 0x00H   |

| Reg0 のレジスタ割り当て | リセット値:          | 0x0000H |

|     |           |          |                |                 |            |          |    |

|-----|-----------|----------|----------------|-----------------|------------|----------|----|

| 15  | 14        | 13       | 12             | 11              | 10         | 9        | 8  |

| Res | vcobuf_en | vco_en   | pll_open_lo op | pll_clk_gate_en | pll_active | pll_en   |    |

| rw  | rw        | rw       | rw             | rw              | rw         | rw       | rw |

| 7   | 6         | 5        | 4              | 3               | 2          | 1        | 0  |

| Res | mpa_en    | txbuf_en | mixq_en        | mixi_en         | lna_en     | rxbuf_en |    |

| rw  | rw        | rw       | rw             | rw              | rw         | rw       | rw |

| フィールド         | ビット   | タイプ | 説明                                                                                                                        |

|---------------|-------|-----|---------------------------------------------------------------------------------------------------------------------------|

| Res           | 15:14 | rw  | 未使用。リセット値から変更しないでください。                                                                                                    |

| vcobuf_en     | 13    | rw  | <b>VCO バッファの有効</b><br>0 <sub>D</sub> : VCO バッファをオフ<br>1 <sub>D</sub> : VCO バッファをオン                                        |

| vco_en        | 12    | rw  | <b>VCO の有効</b><br>0 <sub>D</sub> : VCO をオフ<br>1 <sub>D</sub> : VCO をオン                                                    |

| pll_open_loop | 11    | rw  | <b>PLL オープンループクロックゲートの有効</b><br>ロック検出後、PLL をオープンループに切り替えます<br>0 <sub>D</sub> : クローズループ<br>1 <sub>D</sub> : ロック検出後のオープンループ |

(続く)

### 3 SPI インターフェース

(続き)

| フィールド           | ビット | タイプ | 説明                                                                                                                                   |

|-----------------|-----|-----|--------------------------------------------------------------------------------------------------------------------------------------|

| pll_clk_gate_en | 10  | rw  | <b>PLL クロックゲートの有効</b><br>PLL のデジタル部クロックをアクティブにします。PLL 内で同期化<br>0 <sub>D</sub> : PLL デジタルクロックオフ<br>1 <sub>D</sub> : PLL デジタルクロックオン    |

| pll_active      | 9   | rw  | <b>PLL のアクティブ</b><br>ビットが設定時、PLL ロック開始<br>0 <sub>D</sub> : PLL ループオープン<br>1 <sub>D</sub> : PLL ロック開始                                 |

| pll_en          | 8   | rw  | <b>PLL の有効</b><br>このビットは、PLL のバイアス構造を有効にします。pll_en が「1」に限り、PLL 設定レジスタは安定しています。<br>0 <sub>D</sub> : PLL 無効<br>1 <sub>D</sub> : PLL 有効 |

| Res             | 7:6 | rw  | <b>未使用。リセット値から変更しないでください。</b>                                                                                                        |

| mpa_en          | 5   | rw  | <b>ミディアムパワーアンプの有効</b><br>0 <sub>D</sub> : MPA をオフ<br>1 <sub>D</sub> : MPA をオン                                                        |

| txbuf_en        | 4   | rw  | <b>TX バッファの有効</b><br>0 <sub>D</sub> : TX バッファをオフ<br>1 <sub>D</sub> : TX バッファをオン                                                      |

| mixq_en         | 3   | rw  | <b>ミキサー Q の有効</b><br>0 <sub>D</sub> : ミキサー Q をオフ<br>1 <sub>D</sub> : ミキサー Q をオン                                                      |

| mixi_en         | 2   | rw  | <b>ミキサー I の有効</b><br>0 <sub>D</sub> : ミキサー I をオフ<br>1 <sub>D</sub> : ミキサー I をオン                                                      |

| lna_en          | 1   | rw  | <b>LNA の有効</b><br>0 <sub>D</sub> : LNA をオフ<br>1 <sub>D</sub> : LNA をオン                                                               |

| rxbuf_en        | 0   | rw  | <b>RX バッファの有効</b><br>0 <sub>D</sub> : RX バッファをオフ<br>1 <sub>D</sub> : RX バッファをオン                                                      |

### 3 SPI インターフェース

#### 3.2.5 レジスタ Reg1 - ダイレクトアクセスレジスタ

初期化シーケンス後の値: 0x0092 (パルスモード)

初期化シーケンス後の値: 0x10B3 (CW モード)

|                |                 |         |

|----------------|-----------------|---------|

| DAR_REG1_REG   | Address (アドレス): | 0x01H   |

| Reg1 のレジスタ割り当て | リセット値:          | 0x0000H |

|                      |            |                     |                       |            |                    |                  |                     |

|----------------------|------------|---------------------|-----------------------|------------|--------------------|------------------|---------------------|

| 15                   | 14         | 13                  | 12                    | 11         | 10                 | 9                | 8                   |

|                      |            |                     | <b>div_bias_en</b>    |            |                    | <b>Res</b>       | <b>qs_rd_en</b>     |

|                      |            |                     | rw                    | rw         | rw                 | rw               | rw                  |

| 7                    | 6          | 5                   | 4                     | 3          | 2                  | 1                | 0                   |

| <b>bb_dig_det_en</b> | <b>Res</b> | <b>bb_boost_dis</b> | <b>bb_clk_chop_en</b> | <b>Res</b> | <b>bb_strup_hp</b> | <b>bb_amp_en</b> | <b>bb_sample_en</b> |

| rw                   | rw         | rw                  | rw                    | rw         | rw                 | rw               | rw                  |

| フィールド          | ビット   | タイプ | 説明                                                                                                                                                                                            |

|----------------|-------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Res            | 15:13 | rw  | 未使用。リセット値から変更しないでください。                                                                                                                                                                        |

| div_bias_en    | 12    | rw  | 分周器バイアスの有効<br>0 <sub>D</sub> : 分周器バイアスをオフ<br>1 <sub>D</sub> : 分周器バイアスをオン                                                                                                                      |

| Res            | 11:9  | rw  | 未使用。リセット値から変更しないでください。                                                                                                                                                                        |

| qs_rd_en       | 8     | rw  | クワッド状態入力の有効<br>アナログセトリングを可能にするために、入力を読み出しの 200 µs 前にクアッドステート入力を有効にしなければいけません。<br>0 <sub>D</sub> : QS をオフ<br>1 <sub>D</sub> : QS をオン                                                           |

| bb_dig_det_en  | 7     | rw  | デジタルベースバンド検出器の有効<br>検出器のデジタル部分を有効にします。起動/チップリセット後、このビットを最初にオンにした時、検出器のデジタル部分がターゲットヒットのカウントを開始し、アナログ回路のセトリングを可能にするまでは 50 ms かかります。<br>0 <sub>D</sub> : BB 検出器がオフ<br>1 <sub>D</sub> : BB 検出器がオン |

| Res            | 6     | rw  | 未使用。リセット値から変更しないでください。                                                                                                                                                                        |

| bb_boost_dis   | 5     | rw  | ベースバンドサンプルとホールドスイッチブーストの設定<br>0 <sub>D</sub> : SandH ゲート電圧ブーストが有効 (パルスモード)<br>1 <sub>D</sub> : SandH ゲート電圧ブーストが無効 (CW モード)                                                                    |

| bb_clk_chop_en | 4     | rw  | クロックチョップの有効<br>チョッピング用の継続クロック信号を有効にします。<br>0 <sub>D</sub> : クロックオフ<br>1 <sub>D</sub> : クロックオン                                                                                                 |

| Res            | 3     | rw  | 未使用。リセット値から変更しないでください。                                                                                                                                                                        |

(続く)

### 3 SPI インターフェース

(続き)

| フィールド        | ビット | タイプ | 説明                                                                                                                       |

|--------------|-----|-----|--------------------------------------------------------------------------------------------------------------------------|

| bb_strup_hp  | 2   | rw  | <b>ベースバンド起動ブーストモード設定</b><br>0 <sub>D</sub> : 起動ブーストモードが無効<br>1 <sub>D</sub> : 起動ブーストモードが有効                               |

| bb_amp_en    | 1   | rw  | <b>ベースバンドアンプの有効</b><br>0 <sub>D</sub> : ベースバンドアンプが無効<br>1 <sub>D</sub> : ベースバンドアンプが有効                                    |

| bb_sample_en | 0   | rw  | <b>ベースバンドサンプリングの有効</b><br>ミキサー出力のサンプルおよびホールド容量への接続を制御。<br>0 <sub>D</sub> : 切断、ホールドフェーズ<br>1 <sub>D</sub> : 接続、サンプリングフェーズ |

#### 3.2.6 レジスタ Reg2 - 閾値

初期化シーケンス後の値: QS2 に依存

| THOLD_REG2_REG        |             |                 | Address (アドレス): 0x02 <sub>H</sub> |   |   |             |

|-----------------------|-------------|-----------------|-----------------------------------|---|---|-------------|

| Reg2 のレジスタ割り当て        |             |                 | リセット値: 0x0000 <sub>H</sub>        |   |   |             |

| 15 14 13 12 11 10 9 8 |             |                 |                                   |   |   |             |

| <b>hppt</b>           | <b>aprt</b> | <b>dir_mode</b> |                                   |   |   | <b>thrs</b> |

| rw                    | rw          | rw              |                                   |   |   | rw          |

| 7                     | 6           | 5               | 4                                 | 3 | 2 | 1 0         |

| <b>thrs</b>           |             |                 |                                   |   |   |             |

| rw                    |             |                 |                                   |   |   |             |

| フィールド    | ビット | タイプ | 説明                                                                                                                                                                      |

|----------|-----|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| hppt     | 15  | rw  | <b>高いパルスの繰り返し時間</b><br>初期化シーケンスの後、起動時の SPICSN のレベルの逆数。<br>0 <sub>D</sub> : 変更なし<br>1 <sub>D</sub> : PRT は prt_mult (Reg13[1:0]) で乗算されます。これは省電力ですが、方向検知に問題が発生する可能性があります。 |

| aprt     | 14  | rw  | <b>アダプティブパルスの繰り返し時間</b><br>初期値: 1 <sub>D</sub><br>0 <sub>D</sub> : 変更なし<br>1 <sub>D</sub> : PRT はターゲットが検出されない限り、prt_mult (Reg13[1:0]) が乗算されます。これは電力を節約するためです。           |

| dir_mode | 13  | rw  | <b>方向検出モード</b><br>初期値: 1 <sub>D</sub><br>0 <sub>D</sub> : Mode 1, PDet=0, TDet=1 (ターゲットが検出されない)。<br>1 <sub>D</sub> : Mode 2, PDet=1, TDet=1 (ターゲットが検出されない)。             |

(続く)

### 3 SPI インターフェース

(続き)

| フィールド | ビット  | タイプ | 説明                                                                                    |

|-------|------|-----|---------------------------------------------------------------------------------------|

| thrs  | 12:0 | rw  | <b>検出器の閾値設定</b><br>初期化シーケンス後の初期値 (QS2 に従う)<br>内部は 32 で除算され、IF 信号の ADC 結果は LSB に対応します。 |

#### 3.2.7 レジスタ Reg4 - PLL 設定 1

初期化シーケンス後の値: 0x0F3A

pll\_en = 1(Reg0[8])の場合、このレジスタは変更しないでください。

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                        |                       |                   |                       |                          |                        |    |    |   |   |                    |            |                      |                   |                       |                          |                       |  |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |                  |                      |                       |  |  |                     |                        |  |    |    |    |  |  |    |    |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-----------------------|-------------------|-----------------------|--------------------------|------------------------|----|----|---|---|--------------------|------------|----------------------|-------------------|-----------------------|--------------------------|-----------------------|--|----|----|----|----|----|----|----|----|---|---|---|---|---|---|---|---|------------------|----------------------|-----------------------|--|--|---------------------|------------------------|--|----|----|----|--|--|----|----|--|

| PLL_CONFIG1_REG4_REG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | <b>Address (アドレス):</b> | 0x04H                 |                   |                       |                          |                        |    |    |   |   |                    |            |                      |                   |                       |                          |                       |  |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |                  |                      |                       |  |  |                     |                        |  |    |    |    |  |  |    |    |  |

| Reg4 のレジスタ割り当て                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <b>リセット値:</b>          | 0x0000H               |                   |                       |                          |                        |    |    |   |   |                    |            |                      |                   |                       |                          |                       |  |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |                  |                      |                       |  |  |                     |                        |  |    |    |    |  |  |    |    |  |

| <table border="1" style="width: 100%; border-collapse: collapse;"> <tr> <td style="width: 25%;">15</td><td style="width: 25%;">14</td><td style="width: 25%;">13</td><td style="width: 25%;">12</td><td style="width: 25%;">11</td><td style="width: 25%;">10</td><td style="width: 25%;">9</td><td style="width: 25%;">8</td></tr> <tr> <td><b>pll_dft_mux</b></td><td><b>Res</b></td><td><b>pll_bias_di_s</b></td><td><b>pll_lf_iso</b></td><td><b>pll_lf_r4_se_l</b></td><td><b>pll_cl_loop_pmode</b></td><td><b>pll_lf_r2_se_l</b></td><td></td></tr> <tr> <td style="text-align: center;">rw</td><td style="text-align: center;">rw</td></tr> <tr> <td style="text-align: center;">7</td><td style="text-align: center;">6</td><td style="text-align: center;">5</td><td style="text-align: center;">4</td><td style="text-align: center;">3</td><td style="text-align: center;">2</td><td style="text-align: center;">1</td><td style="text-align: center;">0</td></tr> <tr> <td><b>xosc_mode</b></td><td><b>pll_fbdv_c_nt</b></td><td colspan="3" style="text-align: center;"><b>pll_cp_icp_sel</b></td><td><b>pll_cp_mod_e</b></td><td colspan="2" style="text-align: center;"><b>pll_pfd_rdt_sel</b></td></tr> <tr> <td style="text-align: center;">rw</td><td style="text-align: center;">rw</td><td colspan="3" style="text-align: center;">rw</td><td style="text-align: center;">rw</td><td colspan="2" style="text-align: center;">rw</td></tr> </table> |                        |                       | 15                | 14                    | 13                       | 12                     | 11 | 10 | 9 | 8 | <b>pll_dft_mux</b> | <b>Res</b> | <b>pll_bias_di_s</b> | <b>pll_lf_iso</b> | <b>pll_lf_r4_se_l</b> | <b>pll_cl_loop_pmode</b> | <b>pll_lf_r2_se_l</b> |  | rw | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | <b>xosc_mode</b> | <b>pll_fbdv_c_nt</b> | <b>pll_cp_icp_sel</b> |  |  | <b>pll_cp_mod_e</b> | <b>pll_pfd_rdt_sel</b> |  | rw | rw | rw |  |  | rw | rw |  |

| 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 14                     | 13                    | 12                | 11                    | 10                       | 9                      | 8  |    |   |   |                    |            |                      |                   |                       |                          |                       |  |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |                  |                      |                       |  |  |                     |                        |  |    |    |    |  |  |    |    |  |

| <b>pll_dft_mux</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <b>Res</b>             | <b>pll_bias_di_s</b>  | <b>pll_lf_iso</b> | <b>pll_lf_r4_se_l</b> | <b>pll_cl_loop_pmode</b> | <b>pll_lf_r2_se_l</b>  |    |    |   |   |                    |            |                      |                   |                       |                          |                       |  |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |                  |                      |                       |  |  |                     |                        |  |    |    |    |  |  |    |    |  |

| rw                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | rw                     | rw                    | rw                | rw                    | rw                       | rw                     | rw |    |   |   |                    |            |                      |                   |                       |                          |                       |  |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |                  |                      |                       |  |  |                     |                        |  |    |    |    |  |  |    |    |  |

| 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6                      | 5                     | 4                 | 3                     | 2                        | 1                      | 0  |    |   |   |                    |            |                      |                   |                       |                          |                       |  |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |                  |                      |                       |  |  |                     |                        |  |    |    |    |  |  |    |    |  |