A guide for adapting the LLC calculator to design rules based on exact mode analysis of LLC converter

### **About this document**

### **Authors:**

Mladen Ivankovic

Jon Mark Hancock

### Scope and purpose

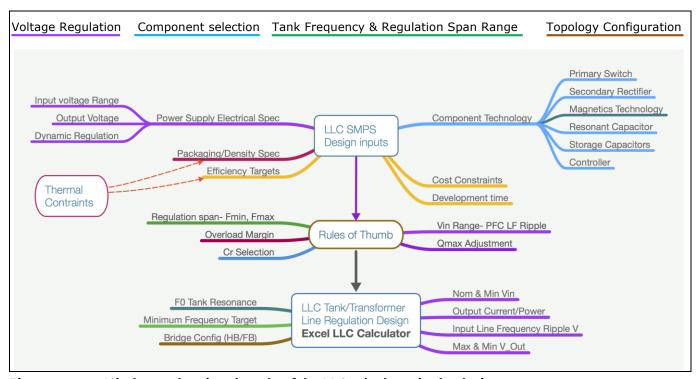

This document is intended to give guidance in the application of Rules of Thumb (ROT) based on exact non-linear analysis of the LLC converter for using the LLC calculator as a design synthesis tool to develop the basic LLC tank parameters based on the SMPS specification requirements. The overall target is minimizing the conduction losses in the LLC by minimizing the RMS currents on both the primary side and secondary side of the LLC converter for a given output power and voltage regulation range requirement (either input or output referred).

- Conventional usage of First Harmonic Approximation (FHA) in the design process appears to result in higher than desirable current on both the primary and secondary sides, especially in low-line conditions, due to the Cr sizing, overall Q of the Cr/Lr network, and generally larger than desirable inductance m-ratio due to FHA simplifications.

- It is possible to develop working alignments which lower both the primary- and secondary-side RMS current, with better overall efficiency over the full load range, and with a more functional control span over the line voltage regulation range.

- Comparisons of different optimization targets and strategies will be presented with analyss of results over line and load range.

Also discussed are issues of dimensioning the tank and transformer gain in consideration of the transition between buck and boost mode, and how that affects both efficiency and the required span of control operation. MathCAD techniques for RMS current factor vs normalized switching frequency are shown, as well as a MathCAD technique for calculating the maximum possible output power for a given tank alignment vs normalized switching frequency.

### Intended audience

This application note is intended for anyone interested in and working on the design of the resonant LLC converter at any power level or application type.

It is a companion to Part II in the LLC Design Webinar series from PMM Academy.

The primary tools discussed are "no-cost" tools such as the vector-based LLC calculator running in Excel, and a parameterized LTspice simulation circuit for tank parameter verification developed for easy configuration and fast simulation (tens of seconds, not tens of minutes). Additional capabilities are described using more expensive tools such as MathCAD and MatLAB with specialty software.

### **About this document**

### **Table of contents**

| Part I          | II: Using the LLC calculator with Rules of Thumb (ROT) and fast verification with LTspice                        | . 1 |

|-----------------|------------------------------------------------------------------------------------------------------------------|-----|

| Abou            | t this document                                                                                                  | . 1 |

| 1               | Myth-busters for the FHA technique                                                                               | . 4 |

| -<br>1.1        | Typical design process using FHA – is GIGO the limiting factor?                                                  |     |

| 1.2             | What is the primary question for optimizing the LLC converter?                                                   |     |

| 1.2.1           | What is the fundamental design goal for the LLC tank?                                                            |     |

| 1.3             | Does linear AC analysis fall short in predicting LLC RMS current?                                                |     |

| 1.3.1           | Mistaken assumption about estimating RMS currents in the tank or output rectifiers – variable                    |     |

|                 | frequency sine wave is not the reality                                                                           |     |

| 2               | Design review of the Infineon/Finepower 12 V 600 W LLC converter                                                 |     |

| <b>-</b><br>2.1 | Overview of the Infineon/Finepower 12 V 600 W LLC converter                                                      |     |

| 2.2             | Supply specifications and LLC tank parameters                                                                    |     |

| 2.3             | FHA predicted gain curves and $F_{min}$ , with $Fr(Hz) = 155$ kHz and $Cr = 66$ nF, $m = 12.5$                   |     |

| 2.4             | Analysis of operating point transitions (boost to buck mode) and impact on $F_{max}$ at 10 percent loa           |     |

| 2.5             | FHA reverse analysis of system parameters to verify operational capability for regulation at low-                | 410 |

| 2.0             | line                                                                                                             | 11  |

| 2.6             | MatLAB as a platform for SMPS design – LLC exact mode analysis with exact transient mode time                    |     |

| 2.0             | diagrams and power margin analysisdiagrams and power margin analysis                                             |     |

| 2.7             | The importance of the resonant capacitor behavior on line and load regulation                                    |     |

| 2.7.1           | Full-load nominal V <sub>in</sub> = 380 V operating condition                                                    |     |

| 2.7.2           | Full-load low-line V <sub>in</sub> = 350 V operating condition                                                   |     |

| 2.8             | Examining the RMS operating currents over the load range for V <sub>in</sub> = 380 V and V <sub>in</sub> = 350 V |     |

| 2.9             | Comparing the power margin and output capability prediction of FHA vs exact calculation                          |     |

| 2.10            | Key points and principles for consideration after review and comparison of FHA calculated                        |     |

| 0               | alignments with alignments optimized based on exact mode calculation                                             | 20  |

| 2.11            | Alternative proposed tank alignments optimizing either light-load RMS current or low-line input                  |     |

|                 | RMS current                                                                                                      |     |

| 2.11.1          |                                                                                                                  |     |

| 2.11.2          |                                                                                                                  |     |

| 2.11.3          |                                                                                                                  |     |

| 2.11.4          |                                                                                                                  |     |

| 2.11.5          |                                                                                                                  |     |

| 2.11.6          |                                                                                                                  |     |

| 2.11.7          | ·                                                                                                                |     |

| 3               | Using a more effective LLC design process to optimize power density and input range capability                   |     |

| 3.1             | Target issues and other problems                                                                                 |     |

| 3.1.1           | Typical core loss and turns count issues affecting transformer size                                              |     |

| 3.2             | Guidelines and boundary conditions for ROT approach                                                              |     |

| 3.2.1           | RMS current to average current ratio at low-line input                                                           |     |

| 3.2.2           | M-ratio for normalized F <sub>min</sub> at low-line input                                                        |     |

| 3.2.3           | Impact of quality factor of Lr+Cr tank and V-Cr limits                                                           |     |

| 3.2.4           | Design power margin                                                                                              |     |

| 3.2.5           | Using WBG switches to advantage – managing an optimal control frequency span for switches                        |     |

|                 | magnetics and output filter                                                                                      |     |

| 3.2.6           | Using a wider input range LLC tank design to reduce bulk capacitor size and volume (target:                      |     |

|                 | improved converter power density)                                                                                | .36 |

| 3.3             | Alternative wide input range designs and their transfer functions                                                |     |

V 1.0

### **About this document**

| 3.3.1   | Design using LLC calculator with FHA with no modification                                       |         |

|---------|-------------------------------------------------------------------------------------------------|---------|

| 3.3.2   | Design using the LLC calculator with ROT modification of Q/load current                         | 40      |

| 3.3.3   | Power margin anaylsis at V <sub>in</sub> = 300 V, 330 V                                         |         |

| 3.3.4   | Comparison of gain and F <sub>min</sub> for wide input range tank designs                       | 43      |

| 3.3.5   | Comparison of power margin, RMS current and V-Cr for the examined alignments                    | 45      |

| 3.4     | Summary: takeways for alignment design guides for ROT and operating characteristics, and        |         |

|         | potential component limitations                                                                 |         |

|         | Recommended design procedure for LLC calculator with ROT                                        | 47      |

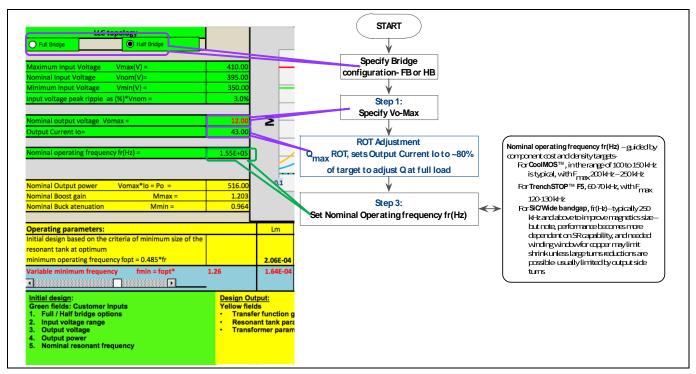

| 4.1     | Where the LLC calculator fits in the design process                                             |         |

| 4.2     | Complete sequence of steps and verification process                                             |         |

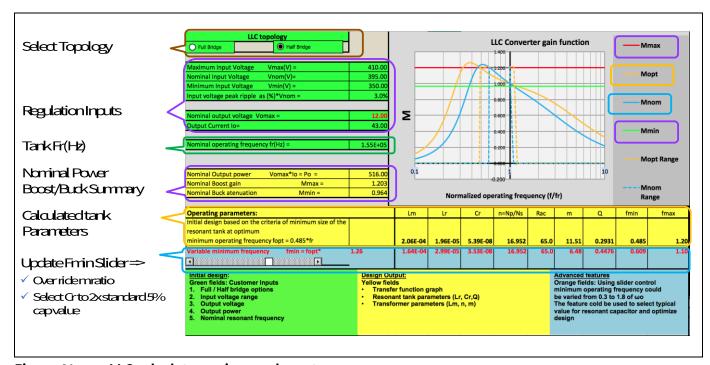

| 4.2.1   | Navigation of the LLC calculator main pane                                                      |         |

| 4.2.2   | Topology and voltage inputs                                                                     |         |

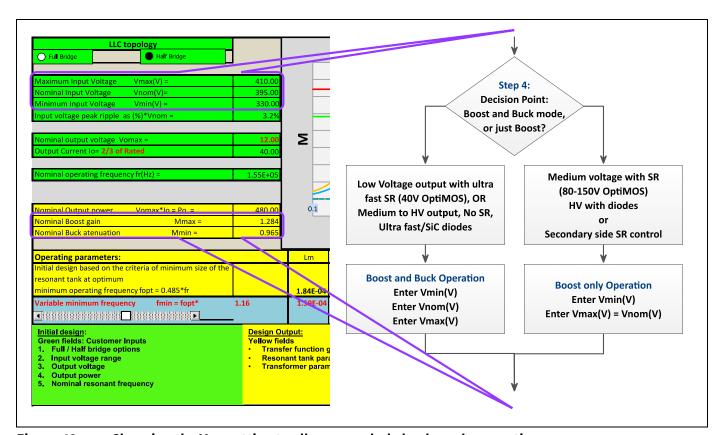

| 4.2.3   | To buck or not to buck? This is the question                                                    |         |

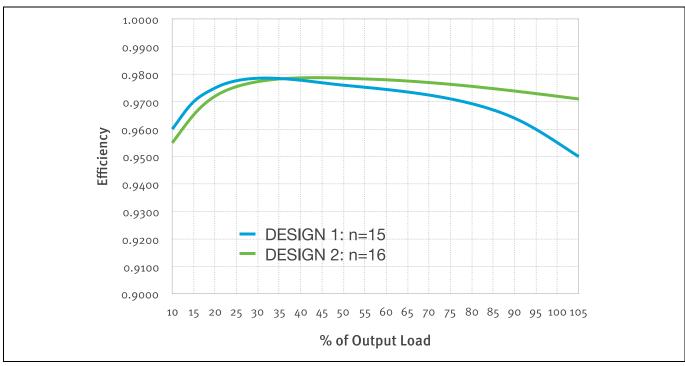

| 4.2.3.1 | Comparing trade-offs in two 12 V 600 W designs, one with V <sub>nom</sub> chosen to optimize li | _       |

|         | but having greater buck mode operation at nominal V <sub>in</sub>                               |         |

| 4.2.3.2 | LTspice simulation for LLC with n = 15 or n = 16                                                |         |

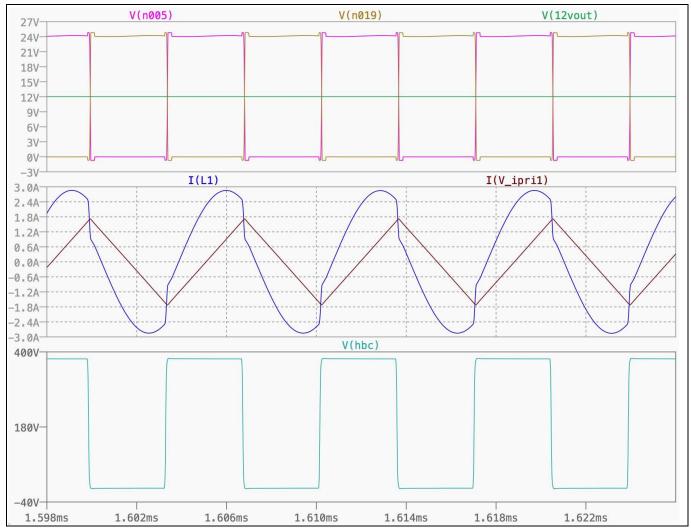

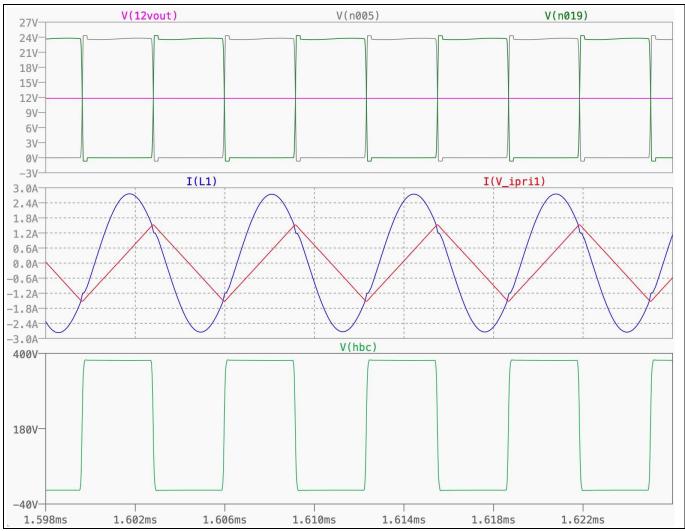

| 4.2.3.3 | Simulation results for LLC with Fr(Hz) = 115 kHz, n = 15 at V <sub>in</sub> = 380 V             |         |

| 4.2.3.4 | Simulation results for LLC with Fr(Hz) = 157 kHz, n = 16 at V <sub>in</sub> = 380 V             |         |

| 4.2.4   | Setting up 12 V 600 W design for mainly boost/DCM operation at nominal Fr(Hz) for up            |         |

|         | input by V <sub>in</sub> and peak input ripple                                                  |         |

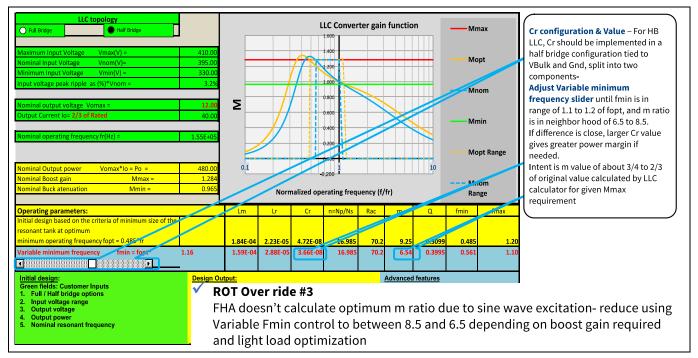

| 4.2.5   | ROT over-ride – m-ratio adjustment                                                              |         |

| 4.2.6   | Check calculated operating and control frequency span                                           |         |

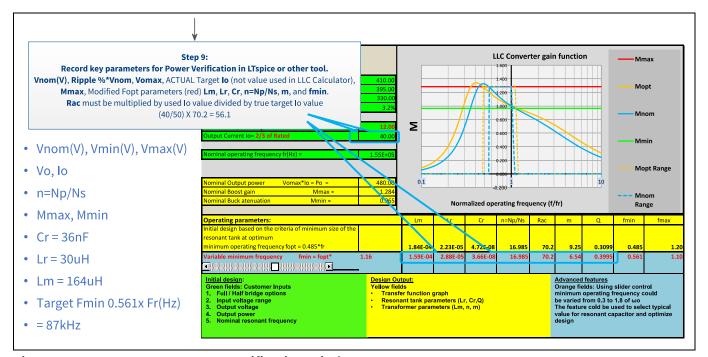

| 4.2.7   | Collect parameters for design verification                                                      | 58      |

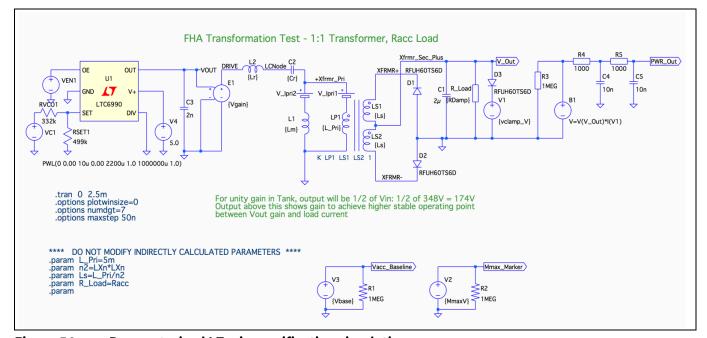

| 5 U     | Jsing LTspice as a fast LLC tank design verification tool                                       | 60      |

| 5.1     | The benefits of a simple parameterized model that runs in tens of seconds, not tens of mi       | าutes60 |

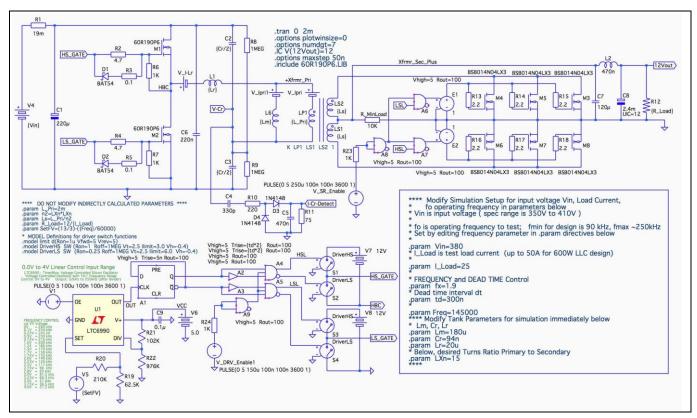

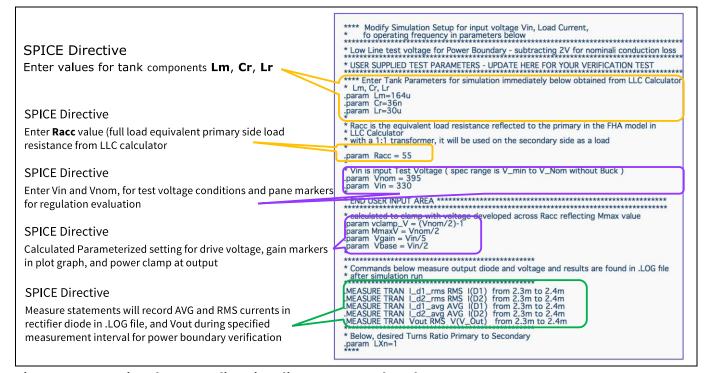

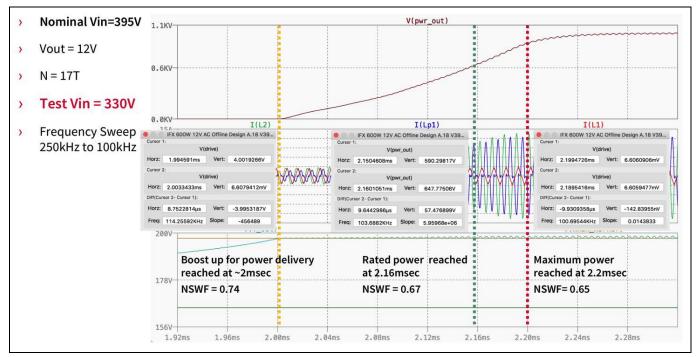

| 5.2     | LTspice circuit example for wide input range parameterized n = 17T design                       | 61      |

| 5.2.1   | Entering values for parameterized SPICE directives on the schematic sheet                       | 62      |

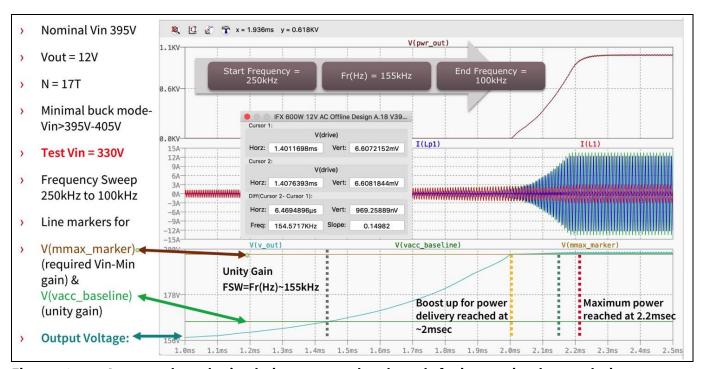

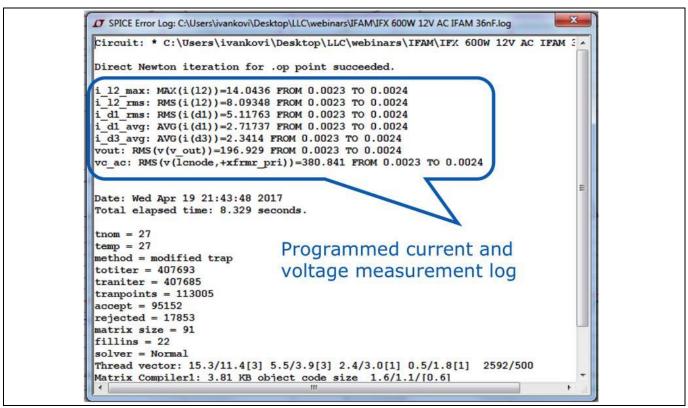

| 5.2.2   | Simulation results ready for evaluation                                                         | 63      |

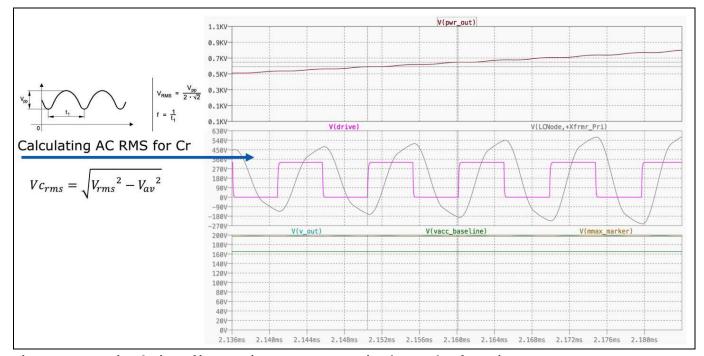

| 5.2.3   | Interactive calculation of total current, power output, etc                                     | 64      |

| 6 S     | iummary                                                                                         | 66      |

| 7 R     | References                                                                                      | 67      |

| Revisio | on history                                                                                      | 68      |

Myth-busters for the FHA technique

### 1 Myth-busters for the FHA technique

FHA is a widely used design method for developing the resonant LLC converter. [1] It will produce an operable design, but the question now being heard more often is, does it produce an optimum design? And based on which considerations? Regulation? Efficiency?

Also, does it provide enough information to inform the designer accurately of how much margin and capability the design has to handle corner cases that may arise? Is there a chance that efficiency and regulation performance might be improved just by a better tank design, with the same semiconductor complement? Not seeking that extra performance margin could be viewed as leaving money on the table from a design engineering viewpoint.

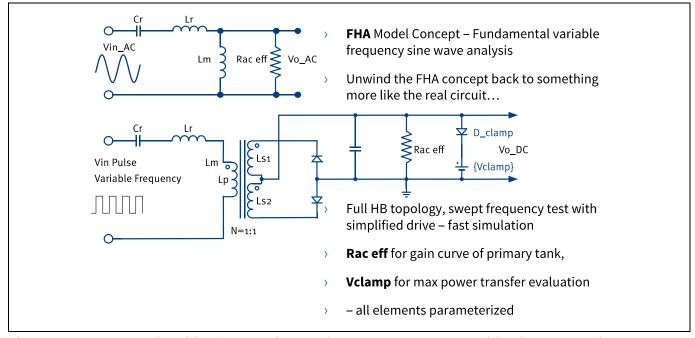

#### 1.1 Typical design process using FHA – is GIGO the limiting factor?

Many suggested variants exist for incorporating the use of FHA into a design synthesis process – the original FHA technique itself merely purports to analyze and describe the operational characteristics of a specific proposed LLC tank configuration, based on certain simplifications, not to specify the means for arriving at that configuration. [2, 3]

Example of the iterative process for using FHA for LLC design Figure 1

Myth-busters for the FHA technique

It can be argued that many of these alternative published procedures may be useful and in some sense "correct" – in the sense of reaching an optimized result within the boundaries of the simplifications of FHA. However, the case can be made that this is only so if the results calculated by the FHA technique are both accurate and sufficient to assess the design being considered. If that is not the case, due to the simplifications and shortcomings of FHA, then the potential for GIGO must be considered carefully. Or an alternative design process must be used, using accurate time-domain based techniques and iterative solutions, which have been published and discussed as early as 2001, but seem largely ignored. [4]

### 1.2 What is the primary question for optimizing the LLC converter?

"One of the really tough things is figuring out what questions to ask... Once you figure out the question, then the answer is relatively easy." – Elon Musk

### 1.2.1 What is the fundamental design goal for the LLC tank?

The basic requirements for an LLC converter are generally very similar to any other voltage regulator circuit:

- Achieve the necessary output voltage regulation vs load current

- Accomplish the above over the necessary line input voltage range, including input voltage drop-outs or surges

As the LLC converter is a regulation topology that can greatly reduce or nearly eliminate switching loss, when properly designed (there is more about this in Part III) then it is also the designer's responsibility to configure the LLC converter to accomplish the above with the minimum RMS current on the primary and secondary sides. If we've essentially eliminated switching loss, then the remaining key to efficiency is minimizing conduction loss from  $I^2 \times R$  losses.

This is presumed straightforward to do, if the converter is operating at or just below resonance all the time, but an examination of line regulation-related issues and the common requirement for systems such as telecoms, battery charges and lighting to have a significant range of output voltage adjustment will show that there are often reasons why this is not possible or desirable. This is due to the requirements for input voltage span and output voltage adjustment. In particular, this may become an issue for higher voltage outputs, and for cases when a required voltage control span is coupled with a need to limit the frequency modulation span due to component or system requirements, while avoiding techniques such as burst mode in order to prevent or limit capacitive mode behavior.

Within these criteria, there may be multiple possible "optimum solutions" depending on the overall system performance targets, including factors such as overall power density and efficiency over a wide load range. The intention of this guide is to highlight factors contributing to optimization in several possible paths; it is up to the designer and specifier to decide which set of trade-offs is optimal for a given commercial application.

Let's take a closer look at some conditions where FHA may not deliver the feedback and information needed by the designer to optimize the system performance.

Myth-busters for the FHA technique

### 1.3 Does linear AC analysis fall short in predicting LLC RMS current?

This is a fundamental issue, and one on which overly simplistic viewpoints still often prevail. In principle, if operating just at resonance, variations on the tank components and Q should not cause significant differences in operating currents. (This ignores for the moment the impact of I-Lm.) But how often is this ideal input voltage the case for a real-world application, such as off-line operation from a PFC front end, with significant line frequency voltage ripple and slow regulation response?

And while for AC-DC off-line applications, the primary-side current is generally not very high, for LV outputs the secondary-side current may be quite large even for mid-range power output requirements (500 W to 600 W). Under these conditions the RMS to average current ratio has considerable bearing on efficiency – and hence, the actual operating normalized switching frequency in relation to the tank resonant frequency.

## 1.3.1 Mistaken assumption about estimating RMS currents in the tank or output rectifiers – variable frequency sine wave is not the reality

Let's consider the basic line regulation scenario – nominal input vs low-line. There are less severe variations of line regulation which are also normally encounted even under nominal conditions – for example, a typical PFC regulator may have up to +/-5 percent line frequency ripple voltage under nominal full-load operation. This can be handled in several ways – such as tuning the LLC for exact resonance at the average, and having it back and forth between buck and boost mode, or considering the peak input voltage, and taking this as the nominal value for operationg at Fr(Hz) (the converter resonant frequency) and going into some value of boost-up in the rest of the "nominal" range.

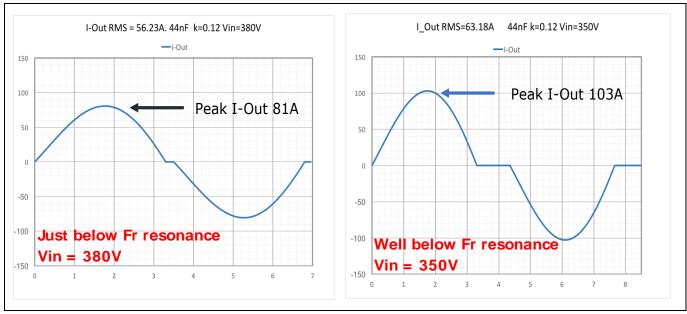

But for now, let's consider a simpler case, just assuming a pure DC nominal line input voltage of 380 V, and a nominal low-line voltage of 350 V. FHA postulates a variable frequency sine wave for the converter analysis, and so shows no difference for the secondary-side RMS to average current between these two cases. But what do things really look like?

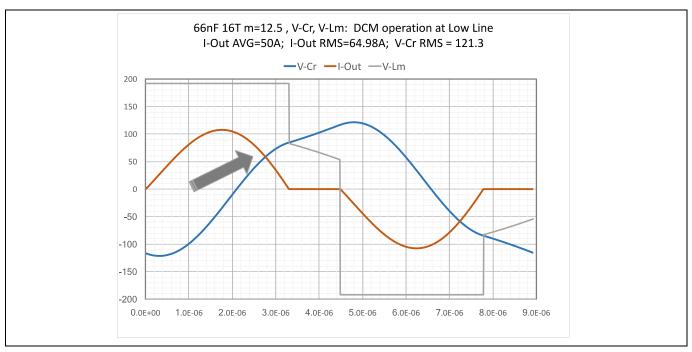

**Figure 2** shows the output current time diagrams for a 12 V/50 A LLC converter running at full load for both line voltage levels – at 380 V and 350 V. Note that the time domain response of the resonant Lr/Cr network does not result in variable frequency sine waves (as for FHA with linear AC analysis), but rather haversine waves at a fixed period defined by the resonant network. As described in the first application note in this series, as the square-wave primary-side drive is lowered in frequency, the converter enters discontinuous or boost mode, and due to the charge pump effect of the primary magnetizing inductance Lm charges up the resonant capacitor so that a higher half-wave resonant current pulse can be delivered each half-cycle.

This results in the peak current at the output rising from 81 A to 103 A, and the output RMS current (for the same average current of 50 A) rising from 56.23 A to 63.18 A, due to Discontinuous Current Mode (DCM) operation. It would be preferable to minimize this additional RMS current and the  $I^2 \times R$  losses it induces on the secondary side.

FHA will not predict this variable RMS factor, as it assumes a variable frequency sine wave exciting the resonant network. So, FHA cannot be used to estimate the RMS output current factor and the variation in conduction loss with different tank designs when not operating exactly at resonance.

Myth-busters for the FHA technique

Figure 2 Comparison of secondary-side current waveforms for 50 A average output current for V<sub>in</sub> of 380 V and 350 V for a 12 V LLC converter

When considering these facts, there are several points to investigate further:

- Viewing the LLC converter with variable frequency linear AC analysis seems to have the potential to miss some important characteristics with regards to predicting the converter behavior and being able to assess and analyze a design prior to construction and testing.

- Charging the resonant capacitor Cr from the square-wave input on the primary side and understanding the impact from the perspective of time-domain behavior may be key to predicting performance capabilities of a given tank design particularly the true maximum gain achievable and the power delivery capability for a specific m-ratio.

- Engineers love to be able to create nice-looking gain plots vs frequency for varied load conditions with various configurations of FHA calculators but is it possible to "game" or modify the design inputs and target criteria so that a FHA-based tool will produce results that more nearly resemble the results from time-consuming exact mode analysis or simulation (or actual hardware)?

- Once such a design is formulated, is it possible to have a low-cost tool that can do calculations or simulations in only tens of seconds to verify the fundamental tank performance in the time domain for gain vs frequency, output current and power margin, incorporating the necessary non-linear characteristics and complexity for a realiastic basic behavioral analysis of the tank?

These are the targets of this work which, will be addressed in the following application note.

Design review of the Infineon/Finepower 12 V 600 W LLC converter

## 2 Design review of the Infineon/Finepower 12 V 600 W LLC converter

### 2.1 Overview of the Infineon/Finepower 12 V 600 W LLC converter

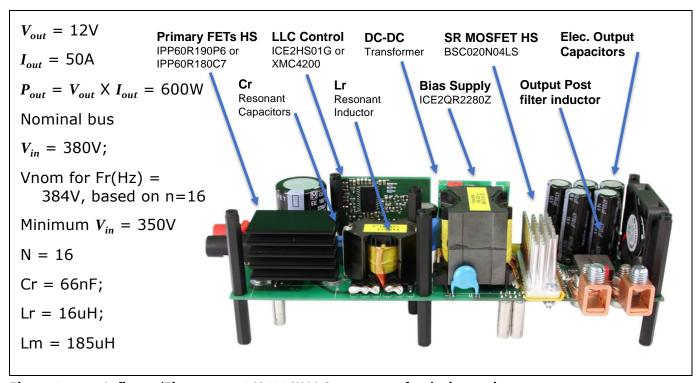

For the purpose of this investigation, we chose to use the Infineon 12 V 600 W LLC design, which is available in several different configurations with different primary-side MOSFETs and either mixed signal control with the ICE2HS01G or digital control with the XMC™ 4200. Options for primary-side MOSFETs have included CoolMOS™ IPP60R190P6 and IPP60R280C7, and now IPP60R170P7. The basic design is the same for these configurations, as shown in **Figure 3**. [5]

Figure 3 Infineon/Finepower 12 V 600 W LLC converter, for design review

### 2.2 Supply specifications and LLC tank parameters

Table 1Design parameters/specifications

| Description                               | Minimum      | Nominal   | Maximum                 |

|-------------------------------------------|--------------|-----------|-------------------------|

| Input voltage                             | 350 V DC     | 380 V DC  | 410 V DC                |

| Output voltage                            | 11.9 V DC    | 12.0 V DC | 12.1 V DC               |

| Output power                              |              |           | 600 W                   |

| Efficiency at 50 percent P <sub>max</sub> | 97.5 percent |           |                         |

| Switching frequency                       | 90 kHz       | 150 kHz   | 250 kHz                 |

| Dynamic output voltage regulation         |              |           | Max. overshoot = 0.1 V  |

| (0 to 90 percent load step)               |              |           | Max. undershoot = 0.3 V |

| $V_{\text{out\_ripple}}$                  |              |           | 150 mV <sub>pk-pk</sub> |

Design review of the Infineon/Finepower 12 V 600 W LLC converter

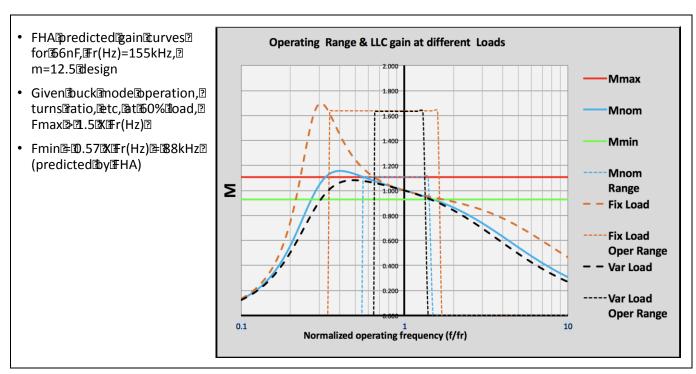

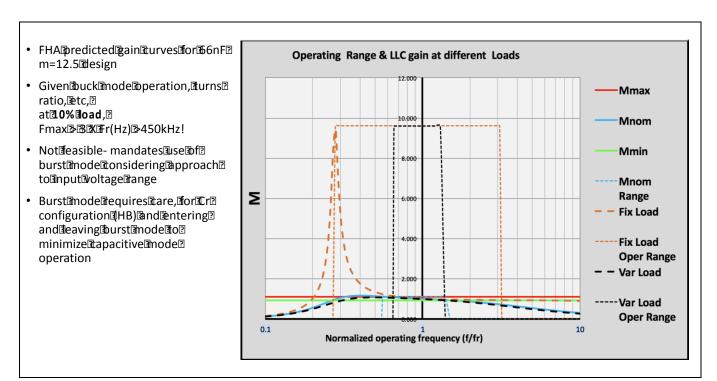

## 2.3 FHA predicted gain curves and F<sub>min</sub>, with Fr(Hz) = 155 kHz and Cr = 66 nF, m = 12.5

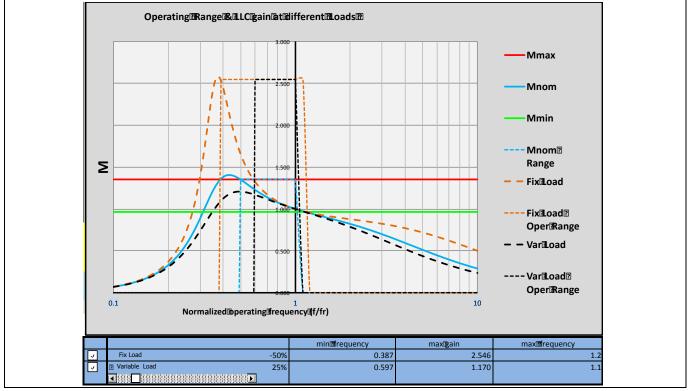

The Excel LLC calculator tool described in the first paper of this series [6, 7] was used to plot FHA gain curves for the Infineon/Finepower 12 W 600 V SMPS design shown in **Figure 3**. This could be called a mixed-mode design, as for the nominal input voltage range it must operate both in boost mode (for input voltage below 384 V) and in buck mode (for input voltage between 385 V and 410 V). The  $M_{nom}$  curve is the predicted full power gain curve for the converter as designed, with the LLC resonant tank values for Cr, Lr and Lm and transformer turns n = 16, as shown in **Figure 4**. Marker lines are used to define the required gain boundaries:

- $M_{max}$  is the peak boost-up gain needed for operation/regulation at minimum  $V_{in} = 350 \text{ V}$

- M<sub>min</sub> is the gain attenuation needed for operation up to 410 V.

Because the gain roll-off in buck mode is quite variable depending on the operating load current (and other parameters, such as the transformer parasitic parallel capacitance) buck mode behavior should be examined carefully under a range of load conditions. In the plot of **Figure 4**, the dashed orange curve for "fixed load" was set to 60 percent load, and under these conditions, the calculated/predicted  $F_{max}$  for  $V_{in}$  = 410 V is 1.5 × the Fr(Hz) tank resonant frequency, or about 230 kHz.

Figure 4 Predicted operating range curves for the Infineon/Finepower 12 V 600 W LLC converter

Design review of the Infineon/Finepower 12 V 600 W LLC converter

## 2.4 Analysis of operating point transitions (boost to buck mode) and impact on F<sub>max</sub> at 10 percent load

At 15 percent load the predicted operating frequency rises to 1.9 × Fr(Hz), which is approximately 294 kHz. It can go even higher for lighter load values such as 10 percent: see **Figure 5**. For silicon power MOSFETs such as CoolMOS™, this will generally dictate using a lower maximum frequency (250 kHz max.) and switching to burst mode operation, and taking some care to avoid or limit capacitive mode operation, which may be possible every time a burst starts up.

Figure 5 Calculated F<sub>max</sub> for 10 percent or less load for the Infineon/Finepower 12 V 600 W LLC converter

Design review of the Infineon/Finepower 12 V 600 W LLC converter

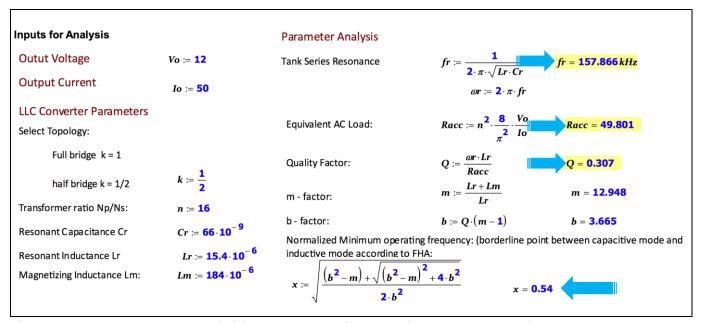

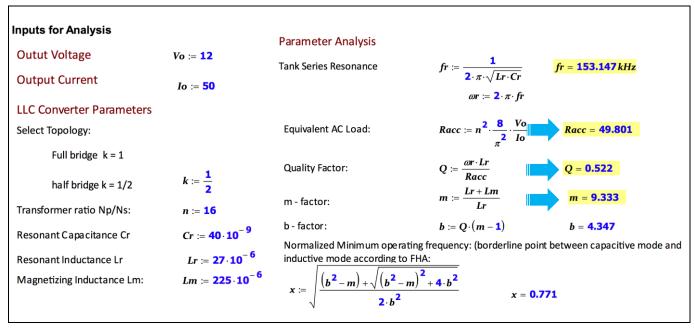

## 2.5 FHA reverse analysis of system parameters to verify operational capability for regulation at low-line

A common design check is to verify a proposed LLC tank design for regulation capability by using what amounts to reverse mode analysis with FHA to calculate the expected minimum operation frequency for regulation at low-line input, and to verify the necessary boost-up gain. This process is shown in **Figures 6 and 7**, using MathCAD, for the Infineon/Finepower 12 V 600 W LLC converter from **Figure 3**.

Figure 6 LLC converter definition and calculation of basic LLC parameters from tank values

Figure 7 FHA reverse analysis of converter regulation capabilities confirming V<sub>in</sub> = 350 V capability

In this calculation series, we verify a number of parameters from the tank configuration:

Design review of the Infineon/Finepower 12 V 600 W LLC converter

- The tank resonant frequency Fr(Hz) Fr(Hz) = 157.8 kHz

- The effective primary-side reflected impedance/resistance seen by the tank,  $R_{acc}$  = 49.8  $\Omega$

- The tank quality factor at full load, **Q** = 0.307

- The predicted minimum operating frequency at full load fo = 85 kHz

- The maximum gain factor  $G_{max} = 1.12$

- The nominal input voltage when the tank is at unity gain: **V**<sub>innom</sub> = 384 V

- The predicted minimum V<sub>in</sub> for which the proposed LLC tank system should be able to provide enough boost-up gain to achieve output regulation, **V**<sub>inmin</sub> = 342.7 V

Reverse FHA analysis predicts that the Infineon/Finepower design fulfills the regulation range requirements for input voltage at low-line  $V_{in}$  = 350 V.

The question to pose, though, is does it do so in an optimal manner, considering a primary goal of minimizing the RMS currents on the primary and secondary side of the converter in order to minimize the conduction losses under most operating conditions?

Design review of the Infineon/Finepower 12 V 600 W LLC converter

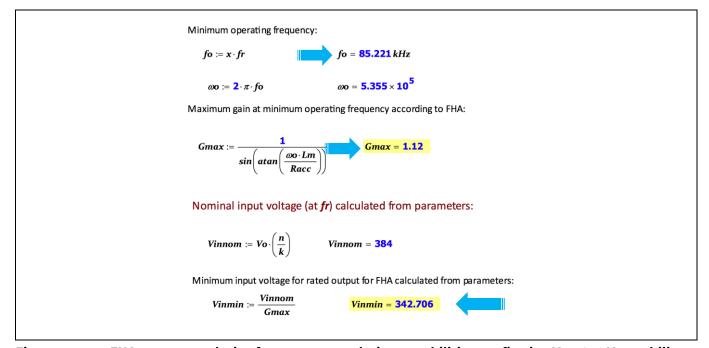

## 2.6 MatLAB as a platform for SMPS design – LLC exact mode analysis with exact transient mode time diagrams and power margin analysis

What appears to be necessary and desirable is to have a baseline of accurate data from simulation or exact mode analysis, which can quantify the true potential behavior of the non-linear LLC tank design with output rectifier – not its approximate behavior using a highly simplified linear model. To this end, software for LLC analysis that runs under MatLAB (**Figure 8**) was obtained from power consultant Patrick Smeets in the Netherlands, based on time-domain analysis, as discussed earlier.

Figure 8 MatLAB environment for calculations and programming

This software supports closed-form exact mode analysis in the DCM region at resonance and below. Ideal components are assumed; the program makes no attempt to model losses in semiconductor switches or magnetic components. The behavior of the resonant tank and transformer on power capability and waveform analysis are the primary concern.

The operational behavior is somewhat different because of the necessity to provide full accurate operating point analysis – so the operating points for load, input voltage and tank characteristics are specified, and the swept parameter is the excitation frequency of the LLC tank, with a typical normalized range of 0.5 of Fr(Hz) to 1 (**Figure 9**).

Design review of the Infineon/Finepower 12 V 600 W LLC converter

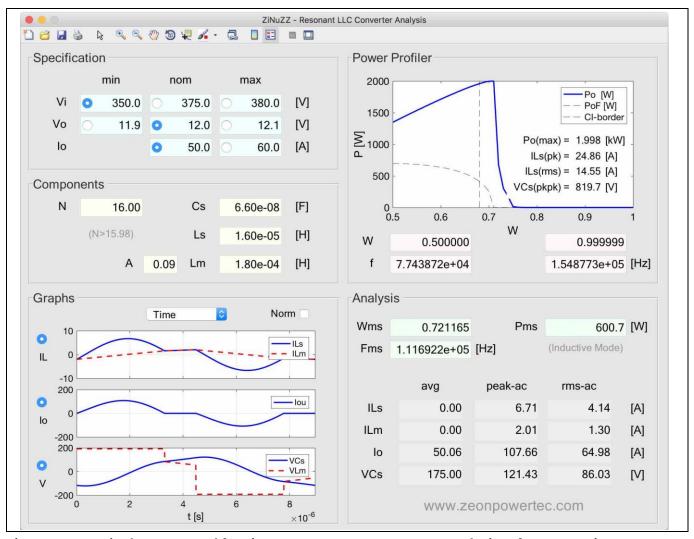

Figure 9 Single-pane panel for ZiNuZZ resonant LLC converter analysis software running on MatLAB

Two panes are used for data entry: "Specification" for the basic input and output voltage and load current parameters, and "Components" for the tank component values (Cs = Cr), (Ls = Lr), Lm, n = transformer turns ratio, and A, the direct ratio of Ls to Lm (not to be confused with the commonly used m-ratio, which would be (Ls+Lm)/Ls. Lm or A may be calculated or entered values. N is shown as a minimum value based on the specification entry, but may be raised to a higher value (such as rounding up for integer turns ratio).

Key operating features and capabilities include:

- Power capability at a given operating point as a function of FSW swept from 0.5 to 1 × Fr(Hz) or a sub-set thereof, with FHA mode and capacitive mode boundary plotted

- Instant operating point waveform analysis:

- Relevant currents and voltages

- State plane trajectories

- Frequency spectrum of output current

- Normalized and absolute scaling

- Instant operating point signal characteristics:

- Relevant currents and voltages including I-Ls (I-Lr), I-Lm, I-O

- Average, peak AC, and RMS AC values

Design review of the Infineon/Finepower 12 V 600 W LLC converter

## 2.7 The importance of the resonant capacitor behavior on line and load regulation

The resonant capacitor Cr serves more than one role. While, along with the resonant inductor Lr, it does define the resonant frequency and Q of the LLC tank, it is also in essence part of a resonant charge pump that defines the output capability of the complete LLC tank for each switching cycle, in conjunction with the magnetizing inductance Lm, which charges it up during the DCM mode dead-time.

Let's look at the LLC time diagrams at both just below the the nominal Fr(Hz) tank frequency, and in low-line boost-up operation.

### 2.7.1 Full-load nominal V<sub>in</sub> = 380 V operating condition

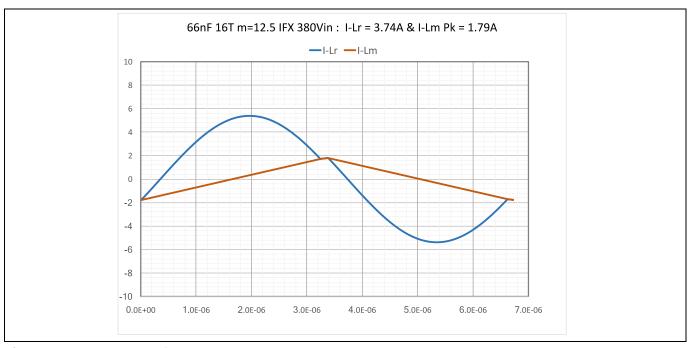

First, for nominal input voltage of 380 V, the tank resonant current from the inductor (I-Lr) and the magnetizing inductance of the transformer (I-Lm) are shown in **Figure 10**, operating at full load at about 155 kHz. There is a short available dead-time interval calculated here of 200 ns, for the resonant switching transition. With the typical programmed dead-time interval of 300 to 350 ns, depending on the CoolMOS™ type, the LLC stage would likely be just nudging into the start of buck mode at this input voltage, depending on the exact value of Cr and Lr, considering the typical component tolerances.

Figure 10 I-Lr, I-Lm for V<sub>in</sub> = 380 V and FL

**Figure 11** shows additional waveforms, including the voltage across Cr, the resonant capacitor, and the output current I-Out. Due to the very short DCM interval, Cr voltage and I-Out are fairly close to sine waves. In this very short DCM/dead-time interval, there is very little time for the magnetizing inductance current to charge up the resonant capacitor, and the gain transfer function of the Cr/Lr tank is essentially unity.

Design review of the Infineon/Finepower 12 V 600 W LLC converter

Figure 11 V-Cr, V-Lm, I-Out for V<sub>in</sub> = 380 V and FL

### 2.7.2 Full-load low-line V<sub>in</sub> = 350 V operating condition

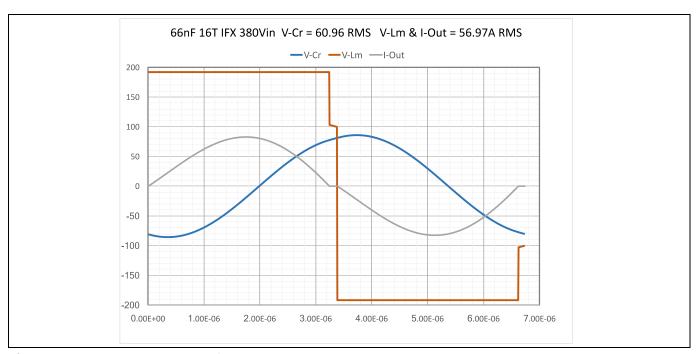

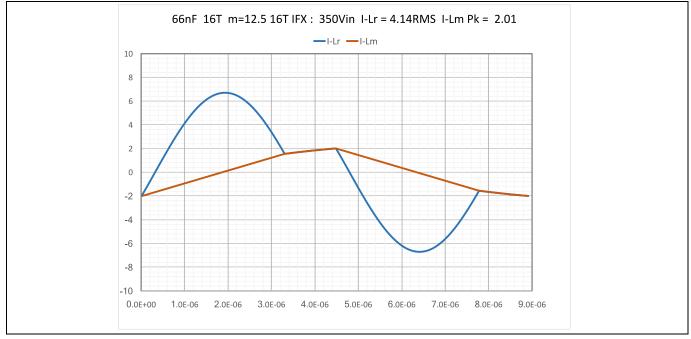

At low-line condition, with  $V_{in}$  = 350 V, the situation looks quite different for the primary-side resonant tank current, as shown in **Figure 12**.

Figure 12 I-Lr, I-Lm for  $V_{in} = 350 \text{ V}$  and FL

Now the DCM interval is fairly long, reflecting a drop in the normalized switching frequency to about 70 percent of Fr(Hz), and the peak I-Lm has risen somewhat, to about 2 A. The peak I-Lr has risen to about 6.8 A, from about 5.6 A at  $V_{in}$  = 380 V.

Design review of the Infineon/Finepower 12 V 600 W LLC converter

**Figure 13** shows clearly the charge pump effect on Cr during the DCM interval, boosting the voltage across Cr by about 60 V, from 80 V to 140 V. This enables a higher power transfer to the secondary side, with a peak current of about 110 A at the output in order to deliver 50 A average, with the RMS output current increasing from 57 A to 65 A.

Figure 13 V-Cr, V-Lm, I-Out for V<sub>in</sub> = 380 V and FL

Design review of the Infineon/Finepower 12 V 600 W LLC converter

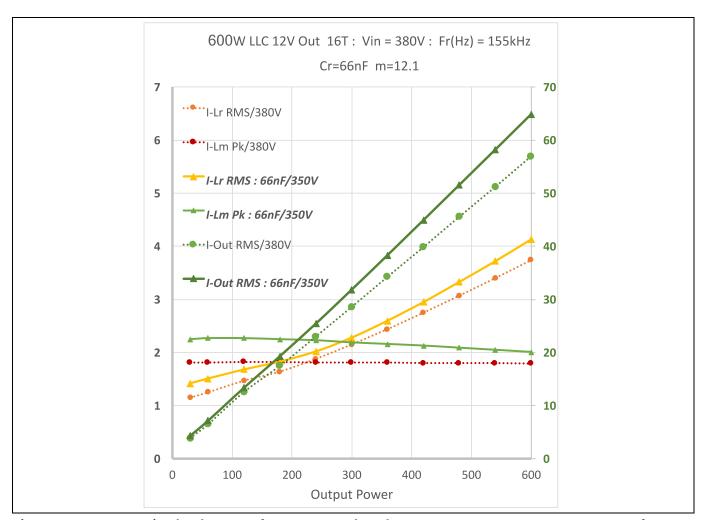

### 2.8 Examining the RMS operating currents over the load range for $V_{in}$ = 380 V and $V_{in}$ = 350 V

A more detailed way to look at this difference in nominal-line vs low-line operating currents is to do an analysis for a multiplicity of operating points, at defined power intervals, from 25 W to 600 W output, and plot the results for both  $V_{in}$  = 380 V and  $V_{in}$  = 350 V.

The results of this are shown in **Figure 14**, which highlights the differences in RMS current for I-Lr, I-Lm Pk and I-Out over the load range, on both the primary and secondary sides. The impact of I-Lm also shows up in the total I-Lr value, which as expected, shows a tip-up at the lower power range due to the relatively fixed current requirement for I-Lm. This is why reducing I-Lm can be important for improving light-load efficiency.

Note that I-Out is plotted on the right-hand side Y-axis to preserve clarity for the lower current data on the primary side, which is plotted on the left-hand Y-axis.

Figure 14 Operating load current for I-Lr, I-Lm-Pk and I-Out over 25 W to 600 W output range for 380 V (dotted) and 350 V (solid)

Design review of the Infineon/Finepower 12 V 600 W LLC converter

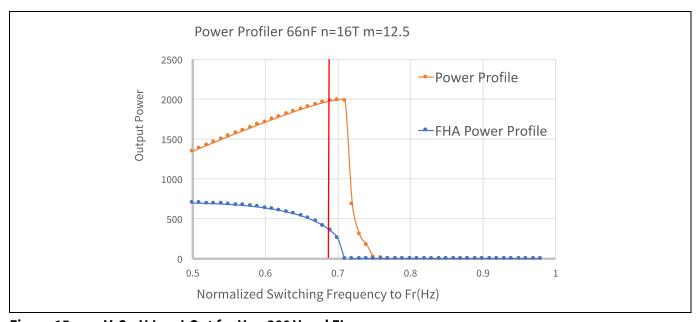

## 2.9 Comparing the power margin and output capability prediction of FHA vs exact calculation

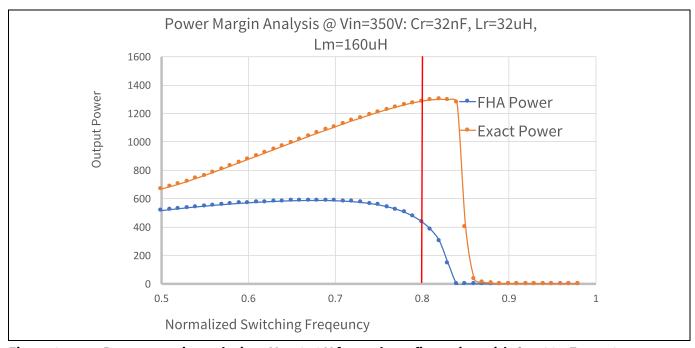

Finally, for our review of the existing 12 V 600 W design, let's take a look at the power margin capability of this design, comparing FHA and exact calculation, as plotted in **Figure 15**. The FHA power capability shows good agreement with the previously calculated reverse FHA analysis, showing an adequate power delivery capability in the area around a normalized switching frequency of 0.55, though not any appreciable extra margin.

On the other hand, exact mode calculation predicts a nearly 2 kW peak power capability in the area of normalized FSW = 0.7, and hardware simulation bears out this number. One might question whether power capability of three times the required nominal output power is really necessary, and if this impacts other aspects of performance. Are there possible benefits to a design which is tuned more accurately for the required output power, with a reasonable safety margin? This question will be explored further in section 2.11.

Figure 15 V-Cr, V-Lm, I-Out for V<sub>in</sub> = 380 V and FL

Design review of the Infineon/Finepower 12 V 600 W LLC converter

# 2.10 Key points and principles for consideration after review and comparison of FHA calculated alignments with alignments optimized based on exact mode calculation

From this and many other calculation and simulation examples which time and space preclude from being included in this paper, some useful principles have emerged to be considered for LLC converter design.

- For a given Fr(Hz) tank resonant frequency, the value of the resonant capacitor Cr directly bears on the power capability of the LLC converter.

- While these results point to the possibility of substantial reductions in the value of Cr, with several attendant benefits, there are practical issues such as power margin and RMS voltage capability of the resonant capacitor Cr, which also should be considered.

- As an arbitrary choice, two power margin levels have been chosen for potential designs:

- "Conservative," with a 100 percent power margin analysis i.e., for a 600 W converter, a tank alignment theoretically capable of 1200 W at low-line input voltage is recommended.

- "Aggressive," with just a 50 percent power margin capability at the rated operating point. This typically results in higher stress on Cr, as well as larger inductor requiements for Lr.

- Component issues around Cr and Lr selection are discussed in Part III of this series.

- Substantial reduction in the value of Cr requires an increase in the value of Lr, which is followed by a comparable increase in Lm for the same tank alignment. This reduces the primary-side I-Lm, with potential efficiency benefits on the primary for light-load operation.

- Reducing the RMS factor on the secondary side requires reducing the m-ratio, to shorten the DCM interval. This in turn decreases the value of Lm, increasing the primary-side loss at light load. However, this may be largely off-set by the reduction of Cr and increase in the value of Lr that are possible with an understanding of usable tank Q based on exact mode analysis instead of FHA.

- Decreasing m-ratios also drive higher charging of Cr, which supports higher output power for a given Cr, and hence, lowering the value of Cr; the drawback is requiring a capacitor technology suited to higher working AC RMS voltage capabilty.

Two conclusions emerge which suggest a useful test to evaluate:

- Conventional usage of FHA in the design process appears to result in higher than desirable current on both the primary and secondary sides, especially in low-line conditions, due to the Cr sizing and overall Q of the Cr/Lr network.

- It should be possible to develop working alignments which lower both the primary and secondary-side RMS current, with better overall efficiency over the full load range, and with a narrower control span over the line voltage regulation range.

This last assumption will be implemented and evaluated in the rest of this application note.

Design review of the Infineon/Finepower 12 V 600 W LLC converter

## 2.11 Alternative proposed tank alignments optimizing either light-load RMS current or low-line input RMS current

Two alternative alignments for the Infineon/Finepower 12 V 600 W LLC converter will be evaluated here – for one, the focus is primarily on improving light-load efficiency, while not compromising any other performance parameter – i.e., low-line efficiency must be as good or better than the original design, full-load nominal-line input performance as good or better, etc. The proposed alignment with m = 9.3 is focused on light-load efficiency, and the m = 6 alignment is focused on low-line efficiency. For these examples, the transformer ratio and operating range for boost mode vs buck mode are not altered.

Table 2 Tank parameters for original Infineon/Finepower 12 V 600 W LLC converter and two alternative alignments

| LLC parameters            | m = 12.5 | m = 9.3 | m = 6  |

|---------------------------|----------|---------|--------|

| Cr                        | 66 nF    | 40 nF   | 32 nF  |

| Lr                        | 16 μΗ    | 27 μΗ   | 32 μΗ  |

| Lm                        | 185 μΗ   | 225 μΗ  | 160 μΗ |

| Transformer turns ratio n | 16       | 16      | 16     |

### 2.11.1 Target: improving light-load efficiency

For this application target, the design direction is to increase the Cr/Lr tank Q to a more suitable target value ( $\sim$ 0.5) while reducing the value of Cr by about 40 percent. While only doing this, and keeping the same m-ratio, would also have reduced I-Lm by 40 percent, a preferred compromise target for the m-ratio for relatively narrow input range that is required (350 V to 384 V in DCM range). An m-ratio of 9.3 was used, cutting the reduction in I-Lm current to just 20 percent, but with some attendant reduction of the RMS factor for output current to be expected at  $V_{in\_min}$  = 350 V. If light-load efficiency is prioritized over low-line behavior, then an m-ratio of 10 to 12 could be considered.

These changes will result in alteration of the tank Q at full load from about 0.31 to 0.522, which by typical FHA calculations probably can't meet low-line regulation. This will be checked along with the actual power magin potential at low-line input.

### 2.11.2 Target: improving low-line efficiency

For this alternative application target, the design requirement is to reduce the RMS current factor of I-Out for minimum  $V_{in}$  = 350 V, while desiring to match as nearly as possible the nominal input voltge RMS current values, and compromising light-load efficiency minimally.

This requires a more aggressive m-ratio in the range of 6 to 7, which also allows further reduction in the value of Cr while still being able to meet regulation targets. Detailed analysis shows that this smaller value for Cr does result in a higher AC RMS voltage and frequency capability, and requires taking more care in component selection. Analysis and simulation show 150 VRMS at 133 kHz for the 32 nF alignment at full load and  $V_{in}$  = 350 V, vs 86 VRMS at 111 kHz. More details will be discussed about this in Part III for component selection.

Design review of the Infineon/Finepower 12 V 600 W LLC converter

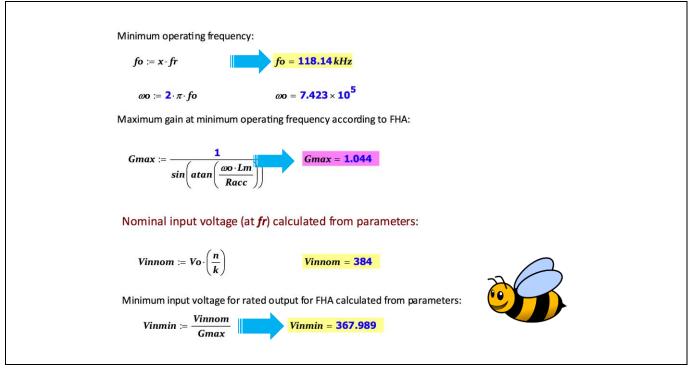

## 2.11.3 Reverse FHA regulation analysis of light-load efficiency optimized design

Reverse analysis using FHA was done for the 40 nF alignment, to confirm the basic calculated parameters for Fr(Hz),  $R_{acc}$ , Q, and m-ratio.

Figure 16 LLC converter definition and calculation of basic LLC parameters from tank values for alignment for enhanced light-load efficiency

Figure 17 FHA reverse analysis of converter regulation capabilities for  $V_{in}$  = 350 V indicates this alignment can't meet regulation targets. The bumblebee cannot fly ... or can it?

Design review of the Infineon/Finepower 12 V 600 W LLC converter

In this reverse FHA calculation for the 40 nF alignment, with m = 9.3, we can verify a number of parameters from the tank configuration:

- The tank resonant frequency **Fr(Hz)** Fr(Hz) = 153 kHz

- The effective primary-side reflected impedance/resistance seen by the tank,  $R_{acc} = 49.8 \Omega$

- The tank quality factor at full load, **Q** = 0.522

- The minimum operating frequency at full load fo = 118 kHz (?)

- The predicted maximum gain factor  $G_{max} = 1.044$  does not meet requirements

- The nominal input voltage when the tank is at unity gain:  $V_{innom}$  = 384 V is as expected

- The minimum  $V_{in}$  for which the proposed LLC tank system should be able to provide enough boost-up gain to achieve output regulation,  $V_{inmin}$  = 368 V does not meet requirements

Reverse FHA analysis predicts the 40 nF/m = 9.3 design doesn't meet the regulation range requirements for input voltage at low-line  $V_{in}$  = 350 V.

Next, we'll look at the predicted capability with exact analysis.

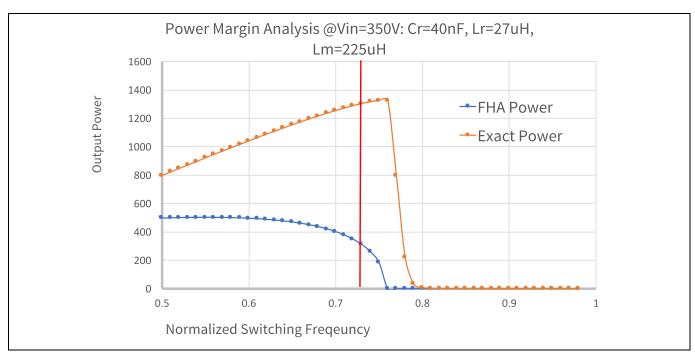

### 2.11.4 Exact power margin analysis for Cr = 40 nF tank design

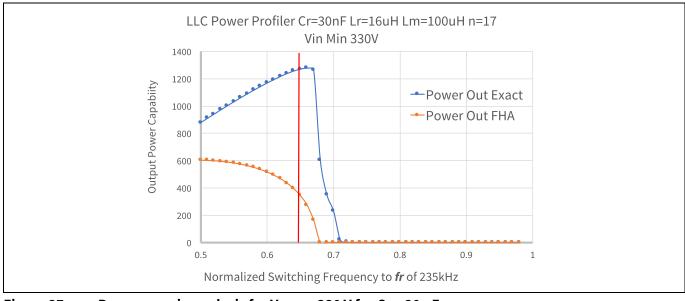

A power profile was prepared for the 40 nf/m = 9.3 alignment including predicted FHA capability. While this tool also confirms that FHA predicts a shortfall in meeting 600 W output requirement, exact analysis shows a theoretical capability (before component losses) of over 1300 W peak, which meets the desired conservative 100 percent margin capability for a 600 W design. This capability was duplicated in full non-linear simulation in LTspice.

Figure 18 Power margin at V<sub>in</sub> = 350 V for tank configuration with Cr = 40 nF, m = 9.3

Design review of the Infineon/Finepower 12 V 600 W LLC converter

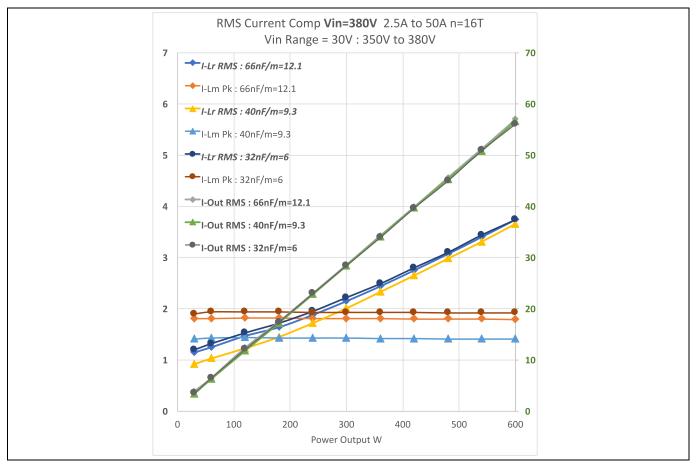

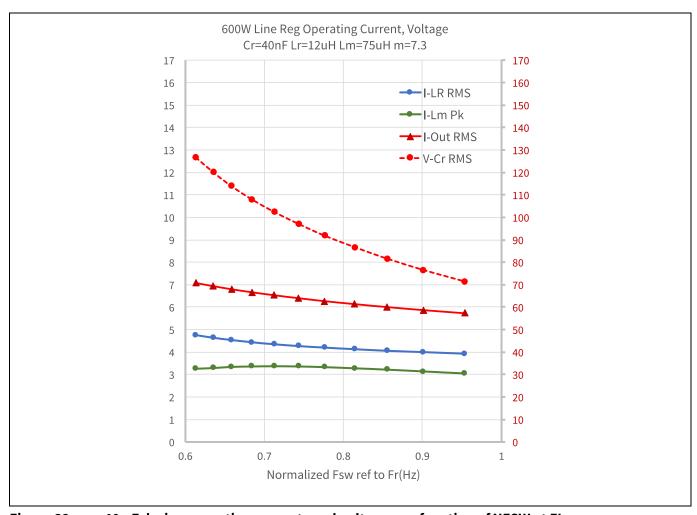

### 2.11.5 Comparison of RMS currents for the three-tank configurations at $V_{in} = 380 \text{ V RMS}$

The next step is to compare the RMS currents for each tank alignment at operating power points from 25 W to 600 W, as was done in **Figure 14** for the original design at  $V_{in} = 380 \text{ V}$  and  $V_{in} = 350 \text{ V}$ .

**Figure 19** shows this for  $V_{in} = 380 \text{ V}$  for the three alignments.

Figure 19 RMS current comparison at V<sub>in</sub> = 380 V

A few points should be noted when interpreting the results:

- Because the input voltage puts the operating frequency nearly at the Fr(Hz) resonance for all alignments, I-Out tracks very closely, as the RMS factor is nearly identical.

- Peak I-Lm tracks as would be expected for the variation in magnetizing inductance Lm, and as expected the 40 nF alignment has the lowest value, and the lowest value for I-Lr RMS current over the entire input voltage range, by about 25 percent.

- The 32 nF tank design tracks just a tiny bit higher on I-Lr current than the nominal 66 nF Cr design, but the I-Out RMS current is calculated as very slightly lower.

- The values are summarized to two decimal places in **Table 3**. The lowest RMS current values are in **bold face**. As might be expected for V<sub>in</sub> = 380 V, the 40 nF alignment outperformed the original 66 nF alignment by varying amounts over the full output range, but especially at light-load conditions. Hoever, at full load and V<sub>in</sub> = 380 V, the 32 nF had the lowest I-out current by nearly 0.5 A compared to 40 nF alignment, and nearly a full ampere compared with the 66 nF alignment.

Design review of the Infineon/Finepower 12 V 600 W LLC converter

Table 3 RMS current comparison of alignments for LLC alignments at V<sub>in</sub> = 380 V

| Operating condition    | 66 nf m = 12.5 | 40 nF m = 9.3 | 32 nF m = 6 |

|------------------------|----------------|---------------|-------------|

| 50 A output: I-Out RMS | 56.97 A        | 56.45 A       | 56.03 A     |

| 50 A output: I-Lr RMS  | 3.74 A         | 3.66 A        | 3.74 A      |

| 50 A output: I-Lm Pk   | 1.79 A         | 1.41 A        | 1.92 A      |

| 20 A output: I-Lr RMS  | 1.88 A         | 1.72 A        | 1.95 A      |

| 10 A output: I-Lr RMS  | 1.47 A         | 1.23 A        | 1.53 A      |

| 10 A output: I-Lm Pk   | 1.82 A         | 1.44 A        | 1.94 A      |

| 2.5 A output: I-LR RMS | 1.15 A         | 0.92 A        | 1.2 A       |

| 2.5 A output: I-Lm Pk  | 1.81 A         | 1.41 A        | 1.9 A       |

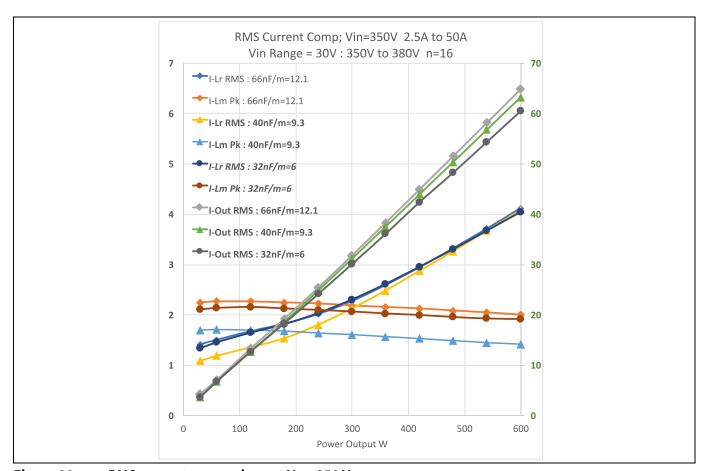

### 2.11.6 Comparison of RMS currents for the three-tank configurations at $V_{in} = 350 \text{ V RMS}$

**Figure 20** graphs and compares the RMS current results for the low-line condition,  $V_{in} = 350 \text{ V}$ . The general trends are similar, but now the I-Out differences for RMS factor are quite pronounced.

Figure 20 RMS current comparison at V<sub>in</sub> = 350 V

• Peak I-Lm tracks similarly, but is higher overall due to the lower operating frequencies, as each design is now operating at F<sub>min</sub>.

Design review of the Infineon/Finepower 12 V 600 W LLC converter

- The 32 nF tank design tracks about the same now for I-Lr current as the nominal 66 nF Cr design, but the I-Out RMS current comes in much lower, about 7 percent less current, which translates to nearly 14 percent less power dissipation due to  $I^2 \times R$ .

- Even the 40 nF design ostensibly optimized for light load comes in 2.5 percent lower on RMS output current at full load, amounting to nearly a 5 percent lower power dissipation if the output-side resistance is equivalent.

- The values are summarized to two decimal places in **Table 3**. The lowest RMS current values are **in bold face**. As might be expected for V<sub>in</sub> = 350 V, the 32 nF alignment out-performed the original 66 nF alignment by a solid percentage for output RMS current over the whole output range, but especially at heavy-load conditions.

- Under light-load conditions, from 1/3 load and less, both the 40 nF and 32 nF alignments have lower predicted RMS current than the original 66 nF alignment.

- In no case did the original FHA-based alignment have lower RMS current than the alternatives at either 380 V input or 350 V input for any output current value.

Table 4 RMS current comparison of alignments for LLC alignments at V<sub>in</sub> = 350 V

| Operating condition    | 66 nF m = 12.5 | 40 nF m = 9.3 | 32 nF m = 6 |

|------------------------|----------------|---------------|-------------|

| 50 A output: I-Out RMS | 64.9 A         | 63.3 A        | 60.55 A     |

| 50 A output: I-Lr RMS  | 4.13 A         | 4.09 A        | 4.05 A      |

| 50 A output: I-Lm Pk   | 2.01 A         | 1.42 A        | 1.92 A      |

| 20 A output: I-Lr RMS  | 25.45 A        | 24.89 A       | 24.19 A     |

| 10 A output: I-Out RMS | 13.37 A        | 12.77 A       | 12.76 A     |

| 10 A output: I-Lm Pk   | 2.27 A         | 1.70 A        | 2.16 A      |

| 2.5 A output: I-Lr RMS | 1.42 A         | 1.09 A        | 1.34 A      |

| 2.5 A output: I-Lm Pk  | 2.25 A         | 1.70 A        | 2.11 A      |

Design review of the Infineon/Finepower 12 V 600 W LLC converter

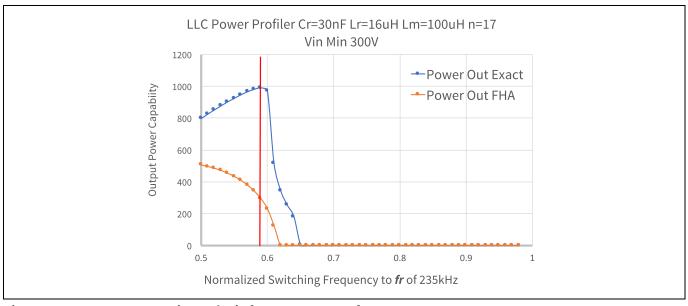

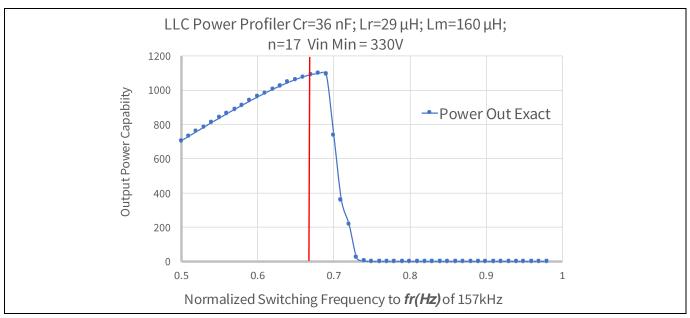

## 2.11.7 Power profile check of 32 nF alignment and FSW<sub>min</sub> comparison of the three alignments

One last cross-check was run, to check the power profile of the 32 nF I-Out optimized alignment, as shown in Figure 21. The results meet the "conservative" alignment criteria with 100 percent power margin, and also highlights that FHA would not show this alignment as regulation capable.

Figure 21 Power margin analysis at  $V_{in} = 350 \text{ V}$  for tank configuration with Cr = 32 nF, m = 6

The normalized and nominal low-line switching frequencies are shown in **Table 5** for each alignment. The  $F_{min}$  moves as expected based on the different m-ratios. Given a higher RMS voltage capability for the resonant cap Cr, the 32 nF alignment can cover a wider input range.

Table 5 Minimum normalized FSW for regulation of three alignments at V<sub>in</sub> = 350 V

| Operating condition    | 66 nF m = 12.5               | 40 nF m = 9.3                | 32 nF m = 6                  |

|------------------------|------------------------------|------------------------------|------------------------------|

| 50 A output: I-Out RMS | FSW <sub>min</sub> = 111 kHz | FSW <sub>min</sub> = 118 kHz | FSW <sub>min</sub> = 133 kHz |

|                        | Normalized FSW = 0.72        | Normalized FSW = 0.77        | Normalized FSW = 0.84        |

Using a more effective LLC design process to optimize power density and input range capability

# 3 Using a more effective LLC design process to optimize power density and input range capability

A closer look at operating gain and power capability targeting a wide input range 12 V 600 W design

A design process which utilizes the LLC tank more effectively also has potential for addressing performance requirements besides optimized efficiency. A common plea from SMPS customers is not for ever higher efficiency, beyond a point, but for greater output power in the same size box. With existing designs already using single-turn windings in some cases, such as the Infineon/Finepower 12 V 600 W LLC converter, conventional approaches with reduction of magnetics component sizes by frequency are not likely to enable the desired improvement in density. How can we reach these system design targets though better LLC tank fundamentals?

### 3.1 Target issues and other problems...

There are a number of concerns and issues that should be discussed in the context of a high-performance LLC design realizable with a more realistic design approach than FHA. Such designs should be applicable in the real world – a majority of LLC evaluation boards on the market seem designed to operate from high-power DC lab supplies, with a narrow input voltage range, and not from an active power factor unit. There are some concerns and requirements that need to be addressed:

- For LV output designs, we are coming up against limitations in transformer size reduction because single-turn output designs are already in use, and the required window area to control conduction losses leaves little opportunity for core volume reduction.

- Other components, such as bulk input caps and EMI filters, are now tending to dominate the volume requirements for AC-DC supplies. Can the design of the LLC converter be leveraged at all to reduce the size of these components?

- Are there ways to usefully optimize the LLC converter design with Wide Band Gap (WBG) switches? Higher frequency by itself is not necessarily a useful feature.

- Output filter size and allowable ripple voltage is another factor that can limit density, depending on the

operating frequency range of the converter large m-ratios don't serve this requirement well, as operating

at minimum V<sub>in</sub> may increase the voltage ripple at the output substantially compared with operating at

Fr(Hz).

### Some potential issues and solutions...

- In the low to medium power area, it may be a challenge to use matrix transformer construction with series windings and paralleled secondaries, but at higher powers this may pay off in reducing primary-side dissipation, and give better ratios of core volume to cooling area.

- Bulk capacitors must smooth the AC ripple current from the active PFC filter, and provide hold-up during a skipped cycle line event. With relatively narrow input voltage range, such as 350 V to 384 V in DCM/boost, to 410 V with buck, larger capacitors are required. If an extended input range is possible, such as 300 V or 330 V to 405 V while purely in DCM/boost mode, then capacitor size can be adjusted or greater power can be delivered from the same volume.

- WBG switches reduce the I-Lm requirements and dead-time, allowing more latitude in the transformer and tank efficiency trade-offs, and safer operation at high frequency in protection modes.

- High-power WBG LLC designs with LL normalized FSW of 0.575 at 350 V stress the output filter capability for smoothing at high frequency with heavy DCM operation due to the much lower ripple frequency. Limiting the control frequency span to a more workable range is mandatory for both filter performance and efficiency.

Using a more effective LLC design process to optimize power density and input range capability

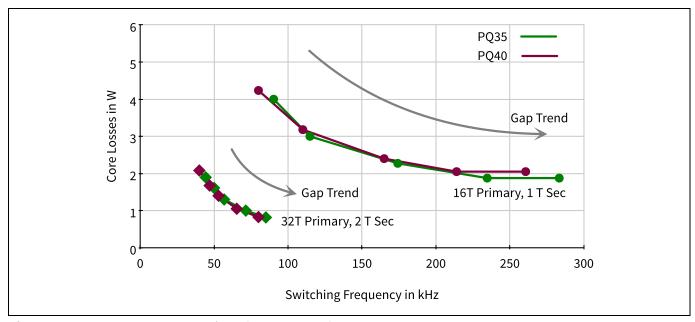

### 3.1.1 Typical core loss and turns count issues affecting transformer size

**Figure 22** highlights the transformer design challenge, showing an overview of approaches that could be considered for 12 V output LLC in the range of 600 W to 1 kW [2]. More turns (32T primary, 2T secondary) will lower the core excitation losses, cutting them in half for a moderate switching frequency below 100 kHz, but will quadruple the winding resistance, due to double the turns and half the wire cross-section. Moving to a PQ40-40 format core will help with the core window area available for windings, but will also increase the core volume, and reduce the cooling surface area in proportion to core and winding losses. This can be a primary argument for at least reducing the primary-side winding requirements by using a series connection of two transformers, and cutting the volt-seconds support requirements for each core in half.

Figure 22 Core loss comparison for PQ cores for 2T secondary and 1T secondary

Using a more effective LLC design process to optimize power density and input range capability

### 3.2 Guidelines and boundary conditions for ROT approach

The boundary conditions and guidelines are intended to inform and modify the use of the LLC calculator program to achieve optimum results for both minimizing RMS currents on the primary and secondary sides and optimizing the frequency control range span and line regulation performance. Topics include:

- a detailed look at the RMS to average current behavior, and how it may inform the ratio of minimum operating frequency to Fr(Hz) resonance frequency

- power margin at minimum V<sub>in</sub> for a given LLC tank configuration

- recommended targets for F<sub>min</sub>.

### 3.2.1 RMS current to average current ratio at low-line input

The inability to identify and predict the true RMS factor for output and input current vs frequency is one of the key weaknesses of FHA-based tools, due to their simplified assumption of a variable frequency sine wave. Let's look at this in detail, regarding its roots in the DCM mode waveforms of the LLC converter operating anywhere below resonance. This was highlighted earlier in **Figure 12** and **Figure 13**, showing the time diagram for input current and output current for the Infineon/Finepower 12 V 600 W LLC converter with V<sub>in</sub> = 350 V.

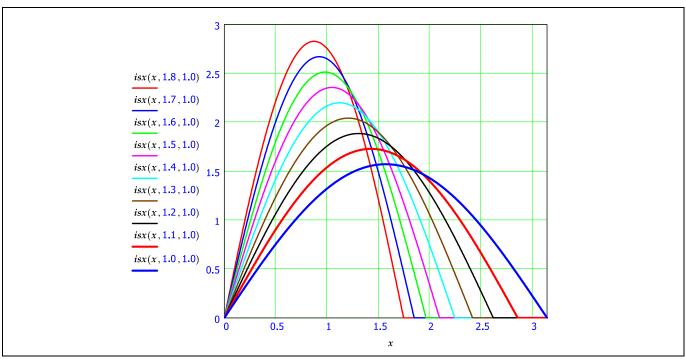

A function in MathCAD shown in **Figure 23** can be used to plot and verify the average and RMS current factor for haversine waveforms with variable haversine period duty cycle in relation to the total period, and a specific average output current *Io*:

$$isx(x, p, Io) := \begin{cases} \frac{Io \times p \times \pi}{1 - cos(p \times \pi)} \times sin(p \times x) & \text{if } \left(x \le \frac{\pi}{p}\right) \land (p < 1) \\ \frac{Io \times p \times \pi}{2} \times sin(p \times x) & \text{if } x \le \frac{\pi}{p} \\ 0 & \text{otherwise} \end{cases}$$

Figure 23 Function for plotting RMS current for haversine wave as a function of ratio of total period to haversine period

If we use this function and plot we can see the analogous effect of DCM mode operation on the peak current for the same average current in **Figure 24**. What is not equivalent to the LLC is that the total period here is fixed, and the haversine wave period is varied; in the LLC, the haversine is fixed and the total period varies. But the RMS factor calculated is the same for the same ratio of haversine period to total period. The period multiplier for the plots is varied from 1 (essentially a sine wave, both periods equal) to 1.8, which corresponds to heavy DCM mode, equivalent to a normalized switching frequency of 0.55 of the resonance frequency Fr(Hz).

Using a more effective LLC design process to optimize power density and input range capability

Figure 24 Plots of haversine waveforms with variable total period ratio to haversine ratio from 1 to 1.8

The average current *Iav* and the RMS current *Irms* can be calculated from these waveforms using two related functions in MathCAD shown in **Figure 25**, to verify that the displayed waveforms are all equivalent to the same average current, and to calculate the RMS current factor increase as a function of the period duty cycle, which impacts the efficiency due to increase of power losses for the same output current. The RMS current defines the true heating factor for the operating current.

Average Current:

$$iav(x, Ipk) := \frac{1}{x \times \pi} \times \int_0^{\pi} f(\alpha, Ipk) d\alpha$$

RMS Current:  $Irms(x, Ipk) := \sqrt{\frac{1}{x \times \pi} \times \int_0^{\pi} f(\alpha, Ipk)^2 d\alpha}$

Figure 25 Calculation of average and RMS current from haversine waveforms of I<sub>pk</sub> with variable DCM interval

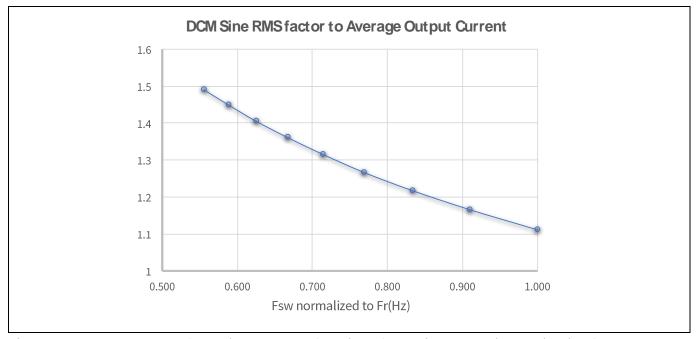

The average current for each parameter set and the RMS current are shown in **Figure 26**, verifying that each waveform dataset for varying duty cycles represents the same average output current, and the RMS current factor is calculated for comparison and plotting in **Figure 27**.

Using a more effective LLC design process to optimize power density and input range capability

| Average Current     | RMS Current              |

|---------------------|--------------------------|

| iav(1.0, 1.571) = 1 | Irms(1.0, 1.571) = 1.111 |

| iav(1.1, 1.728) = 1 | Irms(1.1, 1.730) = 1.166 |

| iav(1.2, 1.885) = 1 | Irms(1.2, 1.885) = 1.217 |

| iav(1.3, 2.042) = 1 | Irms(1.3, 2.042) = 1.266 |

| iav(1.4, 2.2) = 1   | Irms(1.4, 2.2) = 1.315   |

| iav(1.5, 2.357) = 1 | Irms(1.5, 2.357) = 1.361 |

| iav(1.6, 2.514) = 1 | Irms(1.6, 2.514) = 1.405 |

| iav(1.7, 2.671) = 1 | Irms(1.7, 2.671) = 1.449 |

| iav(1.8, 2.828) = 1 | Irms(1.8, 2.828) = 1.49  |

Figure 26 Average current and RMS current results for total period to haversine period ratios of 1 to 1.8 for waveforms created from the function of Figure 23

Figure 27 RMS current factor increase as a function of reducing normalized switching frequency

The best-case RMS factor ratio occurs at resonance, with an RMS to average current ratio of 1.111, or 11 percent greater. At a normalized FSW of 0.55, this rises to 49 percent greater, and at a normalized FSW of 0.5 is about 57 percent greater. For high-output current converters, this should be a clear disincentive to using large m-ratios with a low normalized switching frequency, even for just a fixed output with occasional input under-voltage. For applications such as battery chargers or telecom systems which must regulate over a significant output voltage range, the RMS current factor as a function of normalized switching frequency should be considered carefully in choosing the tank alignment. For higher efficiency, limiting  $F_{min}$  to 0.7 or above is a good strategy.

Using a more effective LLC design process to optimize power density and input range capability

### 3.2.2 M-ratio for normalized F<sub>min</sub> at low-line input

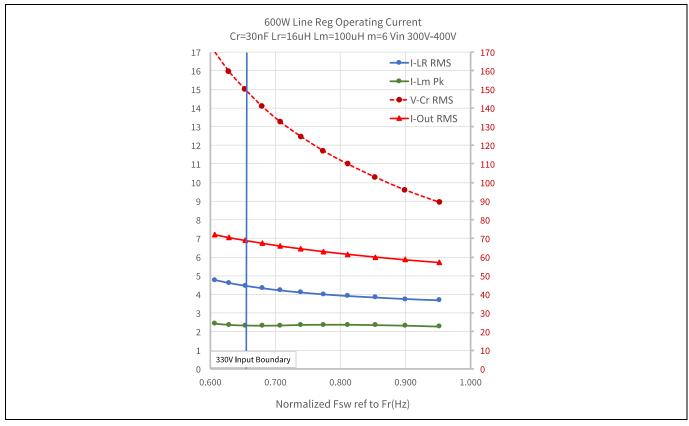

Adjustment of the m-ratio has a first order effect on achieving a specific tank gain and normalized  $F_{min}$ . How does this relate to the examples for the Infineon/Finepower 12 V 600 W LLC converter discussed in the section 2 design review? The RMS factor for the  $V_{in}$  = 350 V condition is about the same at 26 to 27 percent, for the original design (**Figure 15**) with  $F_{min}$  at 0.74 and the light-load optimized design (**Figure 18**) at 0.77. This RMS factor is about 15 percent over the value at the Fr(Hz) resonance.

The difference comes in with the tank Q at the full-load operating point:  $\sim$ 0.3 for the original design with Cr = 66 nF, and  $\sim$ 0.5 for the light-load optimized version with Cr = 40 nF, and which is off-set by the optimized version using a lower m-ratio of 9.3 instead of 12.5. This moves the F<sub>min</sub> up in frequency, reducing the RMS current factor, and increases the M<sub>nom</sub> gain level.

The design with an m-ratio of 6 and Cr = 32 nF has an operating normalized FSW of about 0.84, as shown in **Figure 21**. This does result in a 7 percent reduction in RMS current for the optimized design, and output current-related conduction power dissipation that is 13 percent lower compared with the original version.

While using a wider input voltage range for minimum normalized FSW can have some potential power density benefits for dealing with hold-up times, for a steady-state variation of regulation range such as in battery charger systems such as telecoms or other applications, restricting the normalized FSW to a range of 0.75 or higher may have clear efficiency benefits, and may be a wiser trade-off than optimizing for light-load efficiency. It depends on the desired overall system target. With informed analysis, making that decision is the choice of the designer.

### Lower m-ratios than often calculated via FHA optimization will have several benefits:

- They will result in lower RMS factors for output current, due to higher F<sub>min</sub> at V<sub>in</sub> = V<sub>min</sub>

- They will result in a wider margin from capacitive mode, due to higher  $F_{min}$  at  $V_{in} = V_{min}$

- They will result in more attenuation at light and no load in the buck region

### Suggested ROT starting points for m-ratio and light-load efficiency optimization:

- For a line input range of 10 percent in DCM, (such as 350 V to 385 V) recommended m-ratio is no more than 9 to 10

- For a line input range of 15 percent, (such as 330 V to 390 V) recommended m-ratio is in the range of 7.5 to

- For a line input range up to 20 percent, (such as 315 V to 395 V) recommended m-ratio is in the range of 6.5 to 7.5

- For a line input range up to 25 percent, recommended m-ratio is in the range of 6 to 7, depending on the need for light-load optimization and the RMS voltage capability of Cr. In this case, the performance focus would be bulk capacitor sizing to optimize supply power density, not light-load efficiency, as the I-Lm value wil be higher in order to get the boost-up capability.

For suggested approaches for m-ratio and low-line RMS current factor optimization, much lower m-ratios may be used in some cases, depending on targets for light-load efficiency and low-line efficiency, using m-ratios in the range of 6.5 to 7.5 even for somewhat narrow input range requirements such as 35 V to 40 V. This also may be the preferred choice if some range of output voltage adjustment is required, as for a battery charging system, as the low m-ratio will intrinsically give a greater total regulation range, regardless of how it's distributed at the input or output.

Tank alignments with smaller values of Cr for the same  $V_{in\_min}$  and  $F_{min}$  will result in significantly higher values of RMS voltage on Cr. This can be verified in simulation at  $V_{in} = V_{in\_min}$ , and should be taken into account in

Using a more effective LLC design process to optimize power density and input range capability

selecting the capacitor technology and voltage rating. This will be discussed in more detail in Part III, where component technologies for LLC converters are discussed in detail with application requirements.

### 3.2.3 Impact of quality factor of Lr+Cr tank and V-Cr limits

The quality factor of the Cr-Lr resonant network has a direct bearing on the achievable output power – the higher the capacitance, and hence the lower the Q, the greater the power capability. Cr is key to the output power capability. But using a higher Cr value than necessary sets the inductive components (Lr and Lm) to lower values and increases the I-Lm current, which does not contribute directly to delivered output power near resonance at Fr(Hz). Hence, it is a conductive power loss on the primary.

At larger m-ratios (typically 8 and upward) and moderate input voltage span (with the difference between nominal line and low-line about 10 percent of the nominal line value), using FHA the usable Q to achieve line regulation is about 0.3. In the real world, higher Q can be used and still have good power margin, typically 0.45 to 0.55. Reducing the value of Cr in this way allows corresponding increases in the value of Lm for the same m-ratio, allowing the improvement in light-load efficiency. The reduction in calculated Cr may be from 30 percent up to 40 percent, as seen in the previous example reducing Cr from 66 nF to 40 nF.

At the lower end of generally useful m-ratios, 6 to 7, FHA methods will calculate a higher Q and the potential reduction in Cr may only be 20 percent. This still has a useful impact on reducing I-Lm, and keeping  $F_{min}$  in a higher range more favorable for efficiency than FHA predicts.

Moving in this direction requires care in the selection of the Cr capacitor, as the RMS voltage requirements increase as the value is decreased. For example, in the case of the two additional 155 kHz 12 V 600 W alignments, comparing RMS currents and V-Cr RMS voltage in **Figures 27 to 30**, the smaller Cr requires a 25 percent increase in RMS voltage capability. In typical cases, this may simply require using a HV rating of the same general technology and capacitor value, such as moving from a metalized film capacitor at 630 V DC to the same technology at 1000 V DC or 1200 V DC. This will be examined in more detail in Part III of this series.

### 3.2.4 Design power margin

Power margin cannot be accurately assessed by FHA. As already shown in section **2.11**, it predicts that the LLC tank cannot deliver required power at low-line for designs that are shown capable of delivering up to two times the required power. Simulation or exact mode analysis should be used. In this paper, we describe two general cases for power margin ROT:

- Conservative power margin: with a two-times theoretical capability (100 percent) over nominal full load.

- **Aggressive power margin:** with only 50 percent theoretical capability over nominal full load, using a smaller value of Cr and higher Lm for the same Fr(Hz), and requiring greater RMS voltage capability for the Cr capacitor.

Power margin, light-load optimization and Cr as well as V-Cr operating limits are intrinsically linked:

- Aggressive optimization of Cr also means higher V-Cr operating voltage requirements and smaller power margin.

- This optimization can be used to minimize light-load I-Lm or to minimize RMS factor by raising F<sub>min</sub> for the operating range through using a lower m-ratio.

Using a more effective LLC design process to optimize power density and input range capability

## 3.2.5 Using WBG switches to advantage – managing an optimal control frequency span for switches, magnetics and output filter

WBG switches are in some cases capable of very high switching frequencies, but using that capability indiscriminately may not benefit overall system performance. It is quite possible to develop a 400 kHz nominal Fr(Hz) at 390 V DC input converter, while optimizing for primary-side current using conventional techniques, and arrive at a design with a very wide m-ratio (15 to 17) and a very wide frequency control span requirement. Such a design might support 350 V low-line, but with a normalized FSW of 0.58 ( $\sim$ 230 kHz) with a nominal V<sub>in</sub> of 380 V for normalized FSW of 0.84 (332 kHz), and be operating at the threshold of buck mode and degraded SR behavior at V<sub>in</sub> = 390 V. Over-current conditions or PFC bulk over-shoot then require switching well over 600 kHz. We will show that this is not an optimal design path.

Where WBG switches can excel is in reducing the energy needed for resonant transitions, and then tuning the converter to optimize system performance. Possible approaches include:

- Designing for a narrower frequency control range with a lower Fr(Hz) in line with realistic dead-time (set by I-Lm and Qoss)

- Tuning for a narrower frequency control range with a higher minimum FSW for minimum line input voltage, better RMS factor on output current (0.675 to 0.7 for 330 V LL) and lower HF ripple voltage on output filter

- Designing for nominal Fr(Hz) at 405 V, to stay away from AC-line ripple voltage effects from PFC running at full power at nominal 385 V to 390 V

- Selecting an operating frequency range that can be supported by existing secondary-side synchronous rectifier switching characteristics

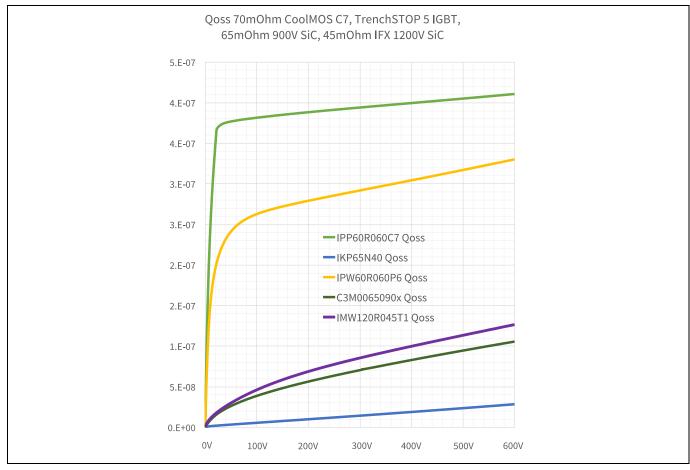

Figure 28  $Q_{oss}$  comparisons of 45 to 70 m $\Omega$  class HV switches – 600 V and higher

Using a more effective LLC design process to optimize power density and input range capability

### 3.2.6 Using a wider input range LLC tank design to reduce bulk capacitor size and volume (target: improved converter power density)

In modern SMPS it's already becoming the case with silicon switches that components not thought of as directly being affected by switching frequency have a great impact on the total volume and achievable power density. While it may not be obvious at first that the converter design can be optimized to reduce the size of those components, such as the bulk hold-up capacitors, this approach is needed to make real progress for both improving density and reducing cost.

Considering the original case study chosen here, the Infineon/Finepower 12V 600 W LLC converter, to what degree can the bulk capacitor size be addressed? A key parameter for selection of the bulk capacitor is the capacitance value needed to provide 10 ms of hold-up time during the loss of AC input power. In turn, this depends heavily on the supported input voltage range for delivering rated output – the wider this input range can be, the smaller the cap value size, as long as other capabilities such as RMS current capability are met.

The required bulk capacitor size can be estimated from the PFC output power, the hold-up time required, the nominal output voltage, and the minimum output voltage:

$$C_{Bulk} = \frac{2 \times Pfc_{Power\_out} \times T_{Holdup}}{V_{Out^2} - V_{min^2}}$$

In **Table 6**, we compare the operating range possibilities and calculated bulk capacitor values for some new potential design alignments, with different alignment trade-offs for wide input range vs light load efficiency. These are not the only possible solutions, but they highlight in several steps the potential for reducing bulk capacitor value and size.

Table 6 Hold-up time 10 ms and bulk capacitor size

| LLC converter description                                                                    | V <sub>in</sub><br>nominal | V <sub>in</sub><br>minimum | Calculated bulk cap value | Bulk cap value in commercial sizes |

|----------------------------------------------------------------------------------------------|----------------------------|----------------------------|---------------------------|------------------------------------|

| Original 12 V/600 W LLC n = 16<br>Cr = 66 nF; Fr(Hz) = 155 kHz; m = 12.5                     | 380 V DC                   | 350 V DC                   | 640 μF                    | 680 μF                             |

| Modified alignment for best light-load<br>Cr = 27 nF; Fr(Hz) = 230 kHz; m = 7.5; n = 17      | 395 V DC                   | 350 V DC                   | 418 μF                    | 470 μF                             |

| Modified alignment 1 for wide range<br>Cr = 30 nF; Fr(Hz) = 230 kHz; m = 7.5; n = 17         | 395 V DC                   | 330 V DC                   | 298 μF                    | 300 μF                             |

| Modified alignment 2 for widest input range<br>Cr = 40 nF; Fr(Hz) = 230 kHz; m = 7.5; n = 17 | 395 V DC                   | 300 V DC                   | 212 μF                    | 220 μF                             |

The bulk capacitor value must be selected from the commercial value equal to or or greater than the calculated value required. For the smaller values, using two capacitors or more in parallel at half the value may be necessary to meet the RMS current requirements at line frequency.

Using a more effective LLC design process to optimize power density and input range capability

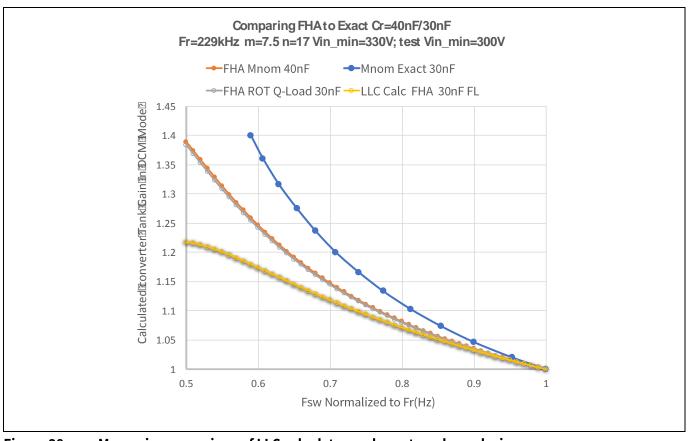

#### 3.3 Alternative wide input range designs and their transfer functions

Some design examples with variations will now be explored, using many of these concepts, to highlight how the LLC calculator may be of use in that process, and to show the achievable correlation in gain parameters between using the LLC calculator with ROT, and exact mode analysis. This wide input range example presents more of a challenge to the LLC design process than a typical 30 V to 40 V line input range example.

This is introduced as a preamble to the walk-through on the ROT procedure in section 4 for using the LLC calculator as a design visualization and synthesis tool.

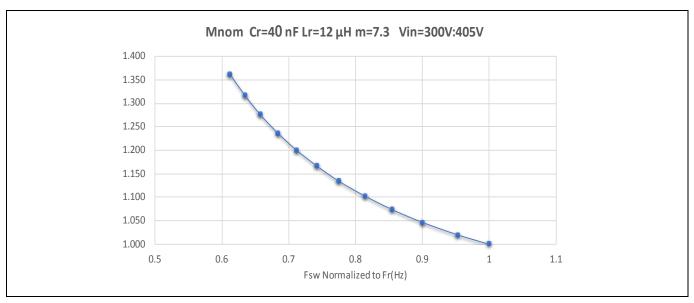

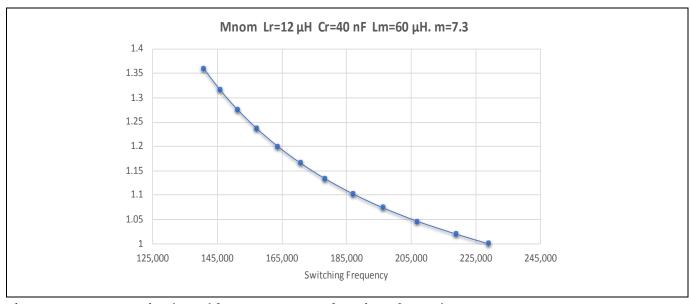

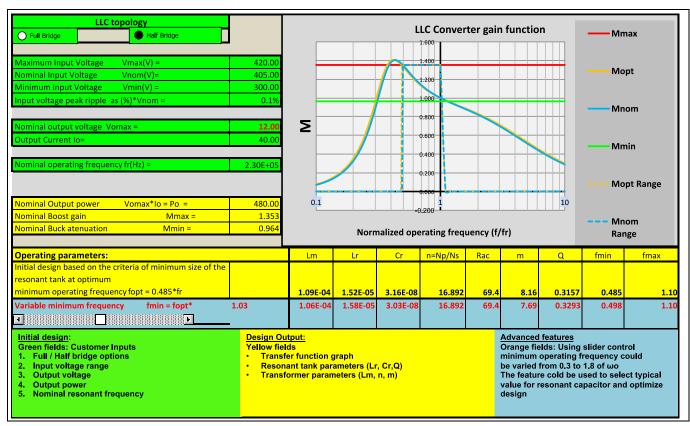

#### 3.3.1 Design using LLC calculator with FHA with no modification

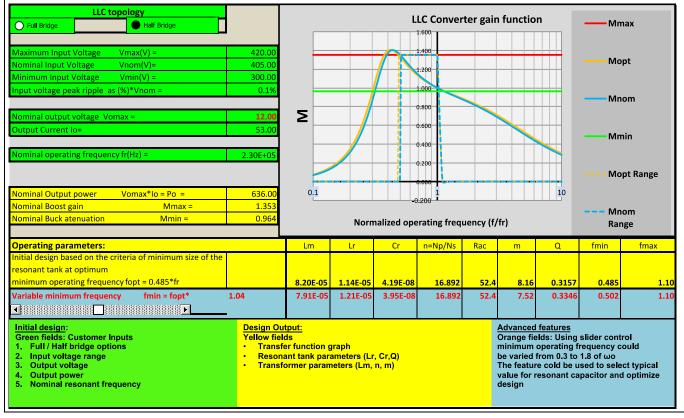

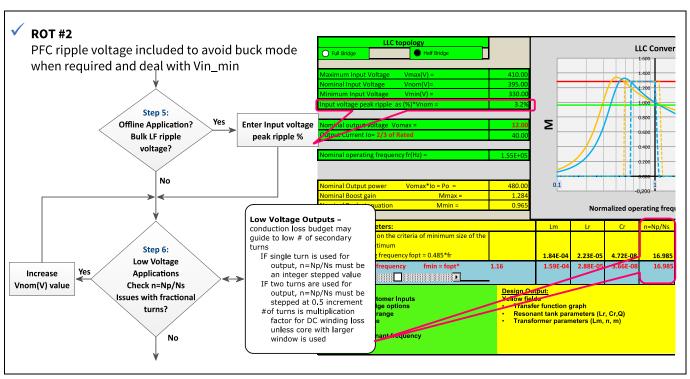

First, let's take a look at the entry and results for using the LLC calculator with only small modifications of input procedure. Consider first the user data entry, as shown in **Figure 29**:

- Nominal input voltage is set to 405 V this sets the desired range for operating at the tank resonance Fr(Hz), and any input capability above that is handled in buck mode. This also defines the operating point for turns ratio in relation to the specified output voltage, at essentially n = 17T.