# EMI 要求を満たすための CoolMOS™ベース電源の最適化

## 本書について

### 適用範囲と目的

効率の向上は、AC-DC スイッチング電源 (SMPS) 設計者にとって重要な考慮事項です。シリコンスーパー・ジャンクション (SJ) MOSFET の性能が向上すると、MOSFET の固有静電容量が低減され、プラグアンドプレイの代替品として使用するとスイッチング速度が速くなります。これにはスイッチング損失が改善されるという利点がありますが、電磁妨害 (EMI) が増加します。このため、一部の設計では、高速スイッチング SJ MOSFET が EMI コンプライアンステストに合格するために、設計中に特別な注意が必要です。

このアプリケーションノートでは、スイッチング MOSFET に関する部品と寄生成分の影響と、MOSFET スイッチングを制御して EMI を改善する方法について説明します。低電力設計は、金属製の筐体やシールドが欠けていることが多く、EMI を緩和する部品はコストが非常に高く追加できないため、EMI にとって最も困難な傾向があります。低消費電力設計では、フライバックコンバータが依然として主要なトポロジであるため、これが主な焦点となります。この原理は他のトポロジにも適用できます。

### 対象者

最新の SJ ベースの CoolMOS™ MOSFET への移行に関心のある SMPS 設計者。

## 目次

## 目次

|                                                         |    |

|---------------------------------------------------------|----|

| 本書について .....                                            | 1  |

| 目次 .....                                                | 2  |

| 1 EMI の概要 .....                                         | 3  |

| 2 フライバックのノイズ源 .....                                     | 5  |

| 2.1 MOSFET のターンオンノイズ .....                              | 6  |

| 2.2 MOSFET のターンオフノイズ .....                              | 7  |

| 2.3 MOSFET のアーリーチャネルシャットダウン .....                       | 9  |

| 2.4 寄生リングングとフェライトビーズ .....                              | 9  |

| 2.5 RCD スナバネットワーク .....                                 | 11 |

| 2.6 ノイズ源の低減に関するまとめ .....                                | 12 |

| 2.7 フライバック/PFC による置換値の推定 .....                          | 13 |

| 3 ノイズの伝送防止 .....                                        | 15 |

| 3.1 フライバック電源の $dI/dt$ および $dV/dt$ を低減するためのレイアウト手法 ..... | 15 |

| 3.2 シャーシグランドではなく、入力バルクコンデンサのリターンに対するヒートシンクの接地 .....     | 15 |

| 3.3 Y コンデンサ .....                                       | 16 |

| 3.4 変圧器のシールド .....                                      | 16 |

| 3.5 周波数変調機能付き可変周波数 PWM コントローラ .....                     | 17 |

| 4 実例 - 45 W アダプタ .....                                  | 19 |

| 5 結論 .....                                              | 20 |

| 6 付録: EMI 測定プロットの読み出し .....                             | 21 |

| 参考資料 .....                                              | 23 |

| 改訂履歴 .....                                              | 24 |

| 免責事項 .....                                              | 25 |

## 1 EMI の概要

### 1 EMI の概要

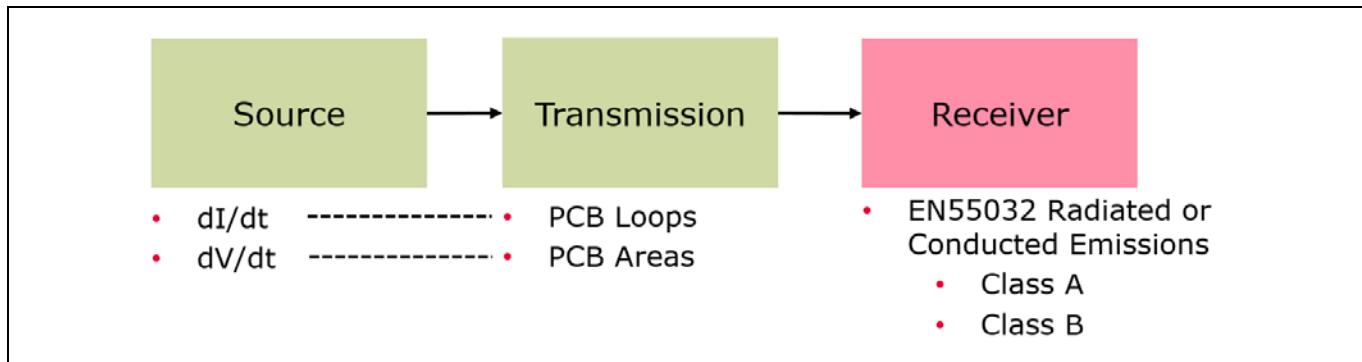

**Figure 1** EMI 経路の基本ブロック: **Source** (ノイズ源), **Transmission** (伝送経路), および **Receiver** (レシーバ)

EMI コンプライアンスは、ノイズの多い電源が無線信号や近くの他の電子機器の動作に干渉しないようにするために重要です。10 kHz を超えるスプリアス信号は、規制に準拠する必要があります。EMI 試験には大きく分けて 2 つのカテゴリがあります。1 つ目は、信号がケーブルを介して直接伝導される伝導性エミッションで、通常は 150 kHz~30 MHz で測定され、2 つ目はアンテナで測定され、通常は 30 MHz~1 GHz で測定される放射性エミッションです。アプリケーションによって法的要件は異なりますが、EMI を参照する場合の主要なカテゴリは次のとおりです。

EMI コンプライアンスは理論的には簡単ですが、システム寄生要素に大きく依存しているため、実際には管理が常に困難であり、システム寄生要素は必ずしもよく知られていません。これらの寄生要素により、純粋に回路定数に基づいてシミュレーションや予測を行うことはほぼ不可能です。EMI は、放射型か伝導型かにかかわらず、ノイズ源、伝送経路、およびレシーバという 3 つの重要な部分があると考えることができます。受信機の設定はアプリケーションの法的規制によって設定されるため、準拠するには、ノイズ源を減らすか、レシーバへの伝送経路を減らすしかありません。

放射妨害波では、ノイズ源は常に時間とともに変化する電流または電圧であり、このレシーバへの結合経路は常に、時間の経過に伴う電流変化のループまたは時間の経過に伴う電圧の変化の領域です。これにより、エンドレシーバへの誘導結合または容量結合のいずれかが発生する可能性があります。伝導性放射では、電流がケーブルを通ってレシーバに流れるときに信号が直接結合し、より高い周波数では、ループと PCB 領域が主電源ケーブルに戻るため、dI/dt および dV/dt による結合も発生します。

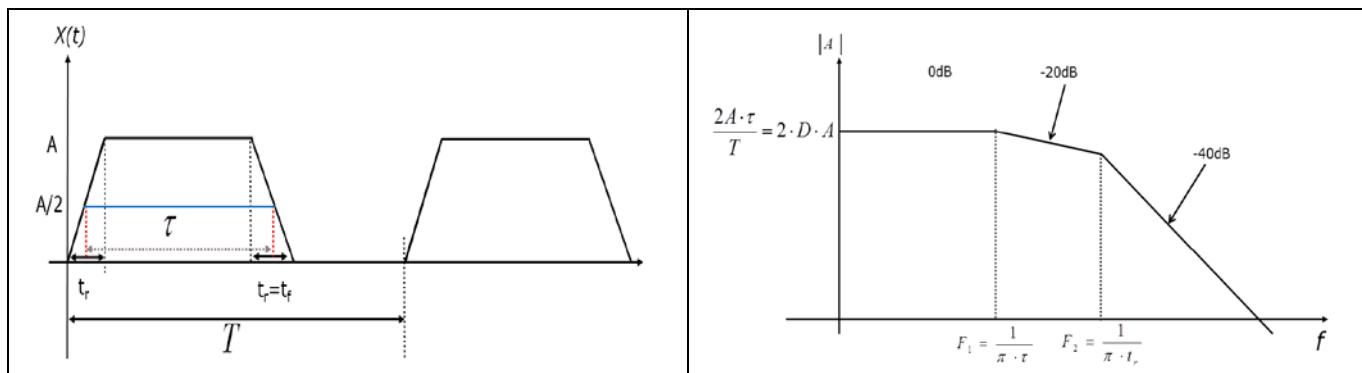

dV/dt と dI/dt を気にする理由を理解するには、以下に示すように、台形波形の高調波成分を見ることが重要です。

**Figure 2** 左: 時間領域の台形波形; 右: 台形波形の高調波成分

## 1 EMI の概要

Figure 2 の右の画像では、台形波形の高調波成分に 2 つの重要なロールオフポイントがあることがわかります。1 つ目は、波形のオン時間の周期に関連しています。立ち上り時間と立ち下り時間は、それぞれ -40 dB/decade のロールオフポイントに対応し、これはシステム全体のノイズに非常に大きな影響を与えます。そのため、設計の中でさまざまな波形の立ち上り時間と立ち下り時間を遅らせることで、ノイズ源を減らすことができます。

$dV/dt$  と  $dI/dt$  を低減する場合の問題は、これらのスイッチング期間中に MOSFET でエネルギーが消費されるため、通常、システムに損失が加わることです。効率を最大化するには、まず外部へのノイズの伝達を減らすことに集中し、最後の手段として MOSFET の速度を落とすことが常に最善です。

このアプリケーションノートでは、MOSFET の  $dV/dt$  と  $dI/dt$  を遅くする方法と、ノイズの伝達を低減するいくつかの手法について説明します。

## 2 フライバックのノイズ源

### 2 フライバックのノイズ源

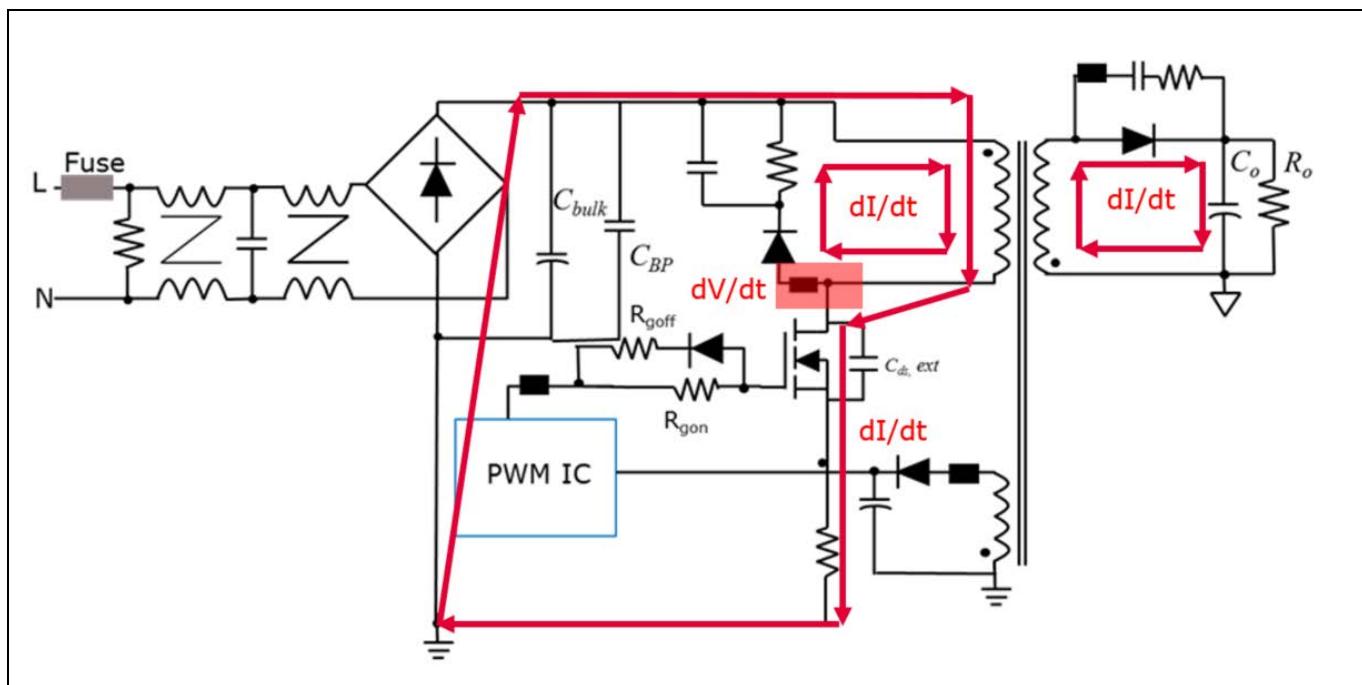

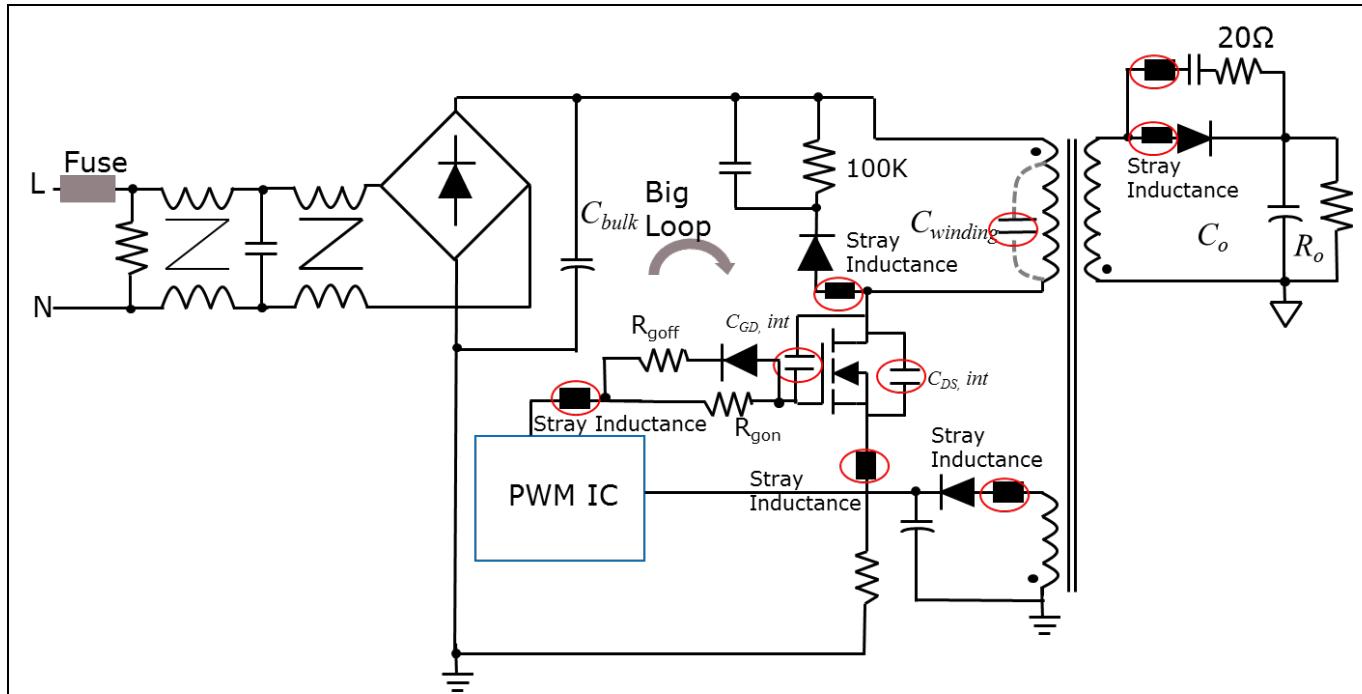

EMI の臨界電流ループと電圧ノードを [Figure 3](#) に示します。

電圧  $dV/dt$  の重要なノードは MOSFET のドレインであり、ノイズがシステム内の他のノードに結合したり、入力および出力電源ケーブルに付着したりするのを防ぐために、設計のレイアウトではこの領域ができるだけ小さく保つ必要があります。

フライバックコンバータで高  $dI/dt$  を実現する重要な電流ループは、出力整流器ループ、MOSFET ターンオン電流ループ、および RCD スナバクランプループです。これらのループはすべて、他のノードやケーブル、外界への誘導結合の量を減らすために、最小限の領域に維持する必要があります。

**Figure 3** 標準的なフライバック電源と主要な  $dV/dt$  ネット、 $dI/dt$  ループ

システム内の重要なループとノードを確認したので、次はターンオンおよびターンオフ時にフライバックコンバータの 1 次側電流ループと電圧ノードの  $dI/dt$  と  $dV/dt$  に影響を与える MOSFET パラメータと周辺部品について見ていきます。

## 2 フライバックのノイズ源

### 2.1 MOSFET のターンオンノイズ

MOSFET のスイッチング動作が外付け部品によってどのように影響を受けるかを確認するために、インフィニオンの 40 W アダプタボード EVAL\_40W\_19V\_FLYB\_P7 をリファレンスとして使用し、ボード上に外付けの定電圧ゲートドライバを配置して 230V AC で動作します。

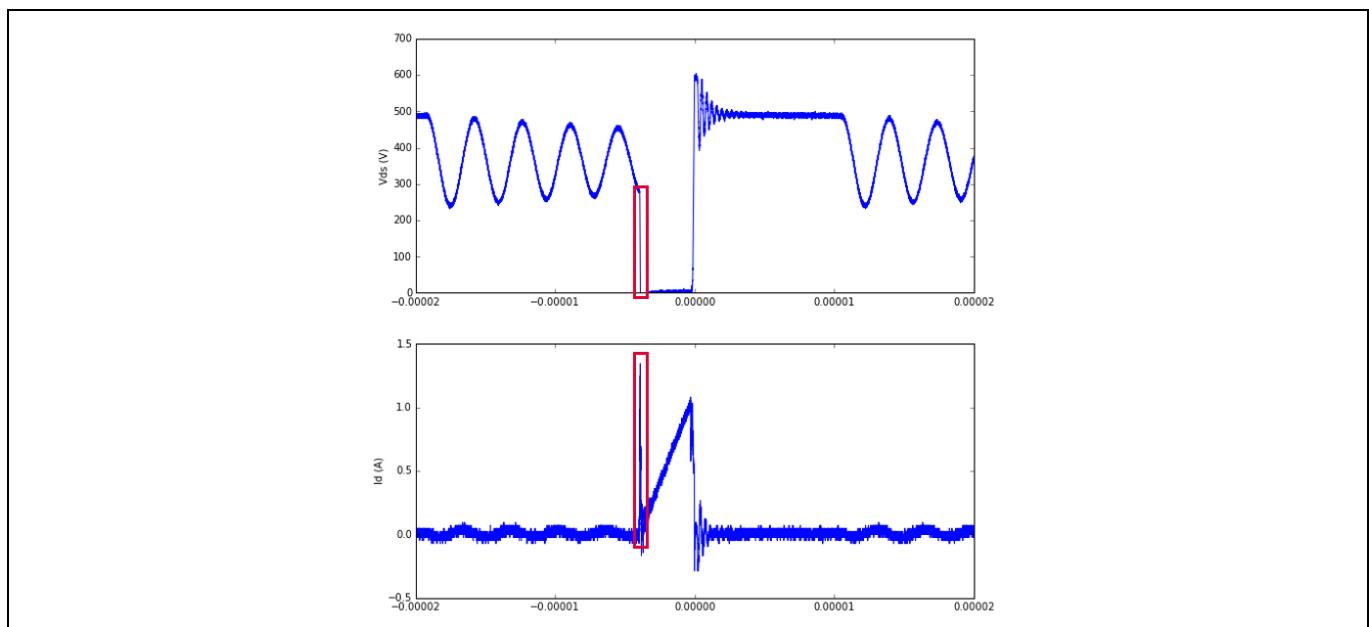

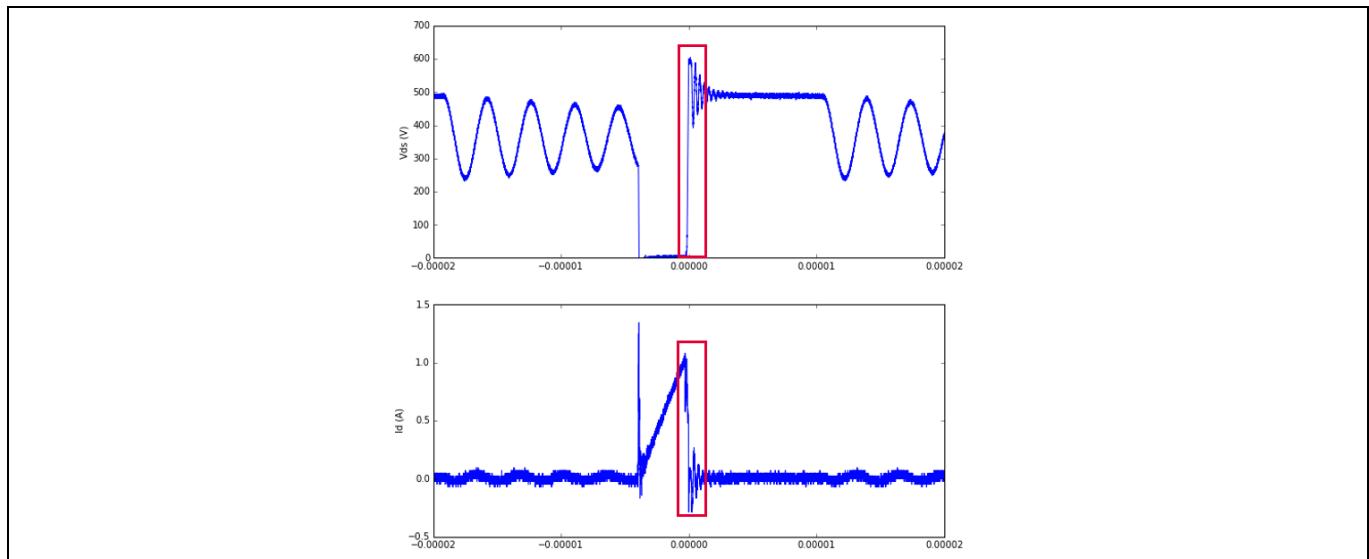

**Figure 4** 標準的なフライバック ターンオンドレインソースの波形(上)と電流波形(下)で、MOSFET のターンオン部分を赤でハイライト

Figure 4 に示す波形は、40 W ボードの波形です。赤枠で示したように、MOSFET がデバイスの出力容量に蓄積されたエネルギーと、システムの寄生容量に蓄積されたエネルギーを放電するために、 $dV/dt$  が発生します。この  $dV/dt$  は対応する放電電流も発生するため、静電容量の放電が速いほど、生成される電流スパイクが高くなります。

電流不連続モード フライバックのターンオンスロープを決定する式は次のとおりです。

$$\frac{dV_{ds}}{dt} = \frac{V_{gs}}{R_{g\_on\_tot} \cdot C_{gd\_tot}}$$

$$I_{drain} = C_{ds_{tot}} \cdot \frac{dV_{ds}}{dt}$$

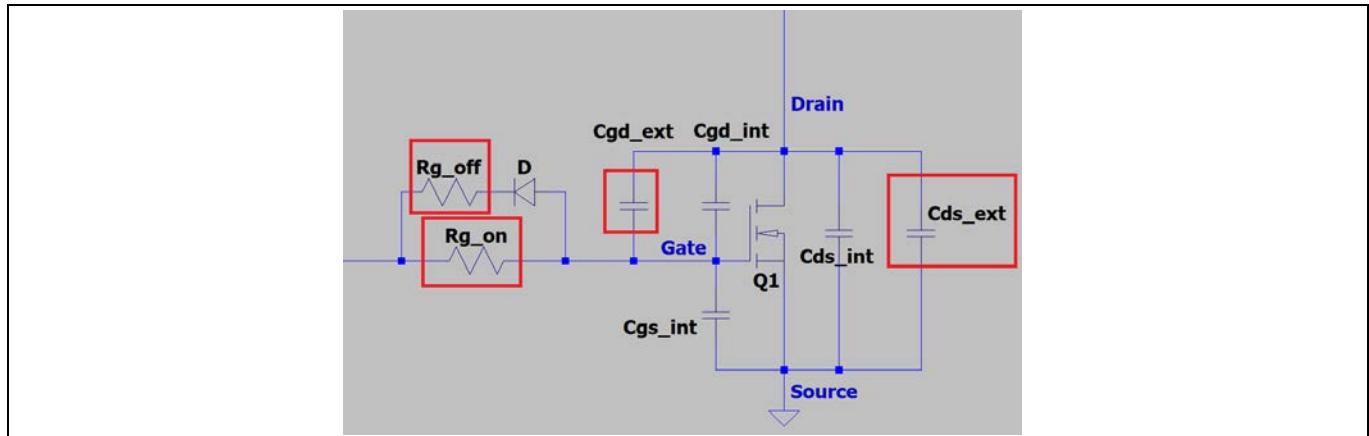

このことから、外付けの  $C_{gd}$  容量を追加するか、ターンオンゲート抵抗を大きくしてターンオンの  $dV/dt$  を遅くすることができます。ターンオン時のスパイク電流は、ゲート抵抗と  $C_{gd}$  によって制御され、総  $C_{ds}$  容量を低減することも有益です。 $C_{gs}$  は MOSFET の  $dV/dt$  または  $di/dt$  に関与しないため、EMI 用の外付け  $C_{gs}$  コンデンサを配置しても意味がないことに注意してください。

## 2 フライバックのノイズ源

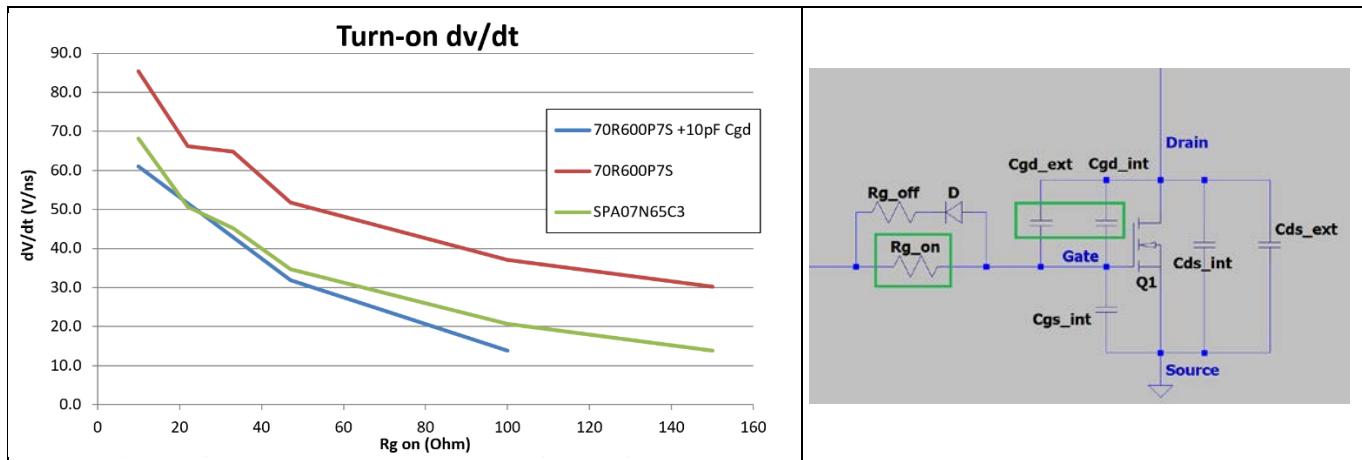

Figure 5 ターンオン dv/dt に及ぼす  $R_{g\_on}$  と  $C_{gd}$  外部 ( $C_{gd\_ext}$ ) の影響

今回 40 W アダプタは、古い技術世代であるため、低速スイッチングリファレンスとして使用するためには、SPA07N65C3 MOSFET で最初にテストしました。総ゲート抵抗は 10 Ωから 150 Ωまで調整しました。 $R_g$  が増加すると、システムの dv/dt が遅くなることがわかります。C3 デバイスを IPA70R600P7S に置き換えると、同じ  $R_g$  外部の dv/dt が増加することがわかります。 $R_g$  が 40 Ωの SPA07N65C3 の dv/dt は 40 V/ns ですが、P7 では 40 V/ns を達成するのに約 90 Ωが必要です。

10 pF 1 kV のセラミックコンデンサを  $C_{gd}$  の外部コンデンサとして追加すると、P7 デバイスのターンオン dv/dt は C3 デバイスとほぼ同じになりますが、効率に悪影響をあたえることに注意してください。

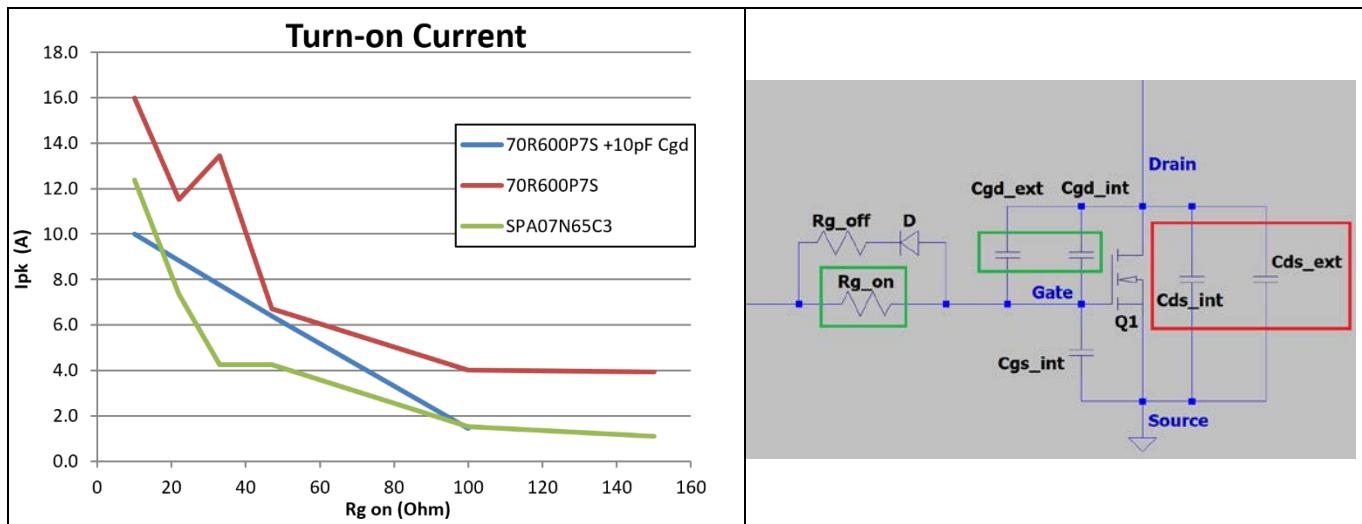

Figure 6  $R_{g\_on}$  と  $C_{gd}$  外部 ( $C_{gd\_ext}$ ) のターンオン di/dt への影響

これで、ターンオン電流のスパイクは dv/dt と同じ傾向をたどります。 $R_{g\_on}$  を大きくすることで、ターンオン電流のスパイクを低減することができ、これによりターンオン電流 di/dt が減少します。次に、10 pF の  $C_{gd}$  を外部に追加すると、P7 の電流スパイクは C3 デバイスとほぼ同じになります。

## 2.2 MOSFET のターンオフノイズ

40 W アダプタでも同じ作業を行い、MOSFET のターンオフノイズを確認しました。

## 2 フライバックのノイズ源

**Figure 7 MOSFET のターンオフ  $dV_{ds}/dt$ 、ターンオフのスロープを赤で強調表示、ターンオフの  $dI/dt$  スロープを赤で強調表示**

Figure 7 に、MOSFET のターンオフ  $dV/dt$  と  $dI/dt$  を示します。ここで、励磁インダクタンスと漏れインダクタンスに蓄積されたエネルギーは、MOSFET とシステム全体の寄生容量の両方の  $C_{ds}$  の出力容量に伝達されます。デバイスの抵抗が制限されている場合、デバイスの  $dV/dt$  は、デバイスのターンオンに使用したのと同じパラメータを使用して制御できます。

$$\frac{dV_{ds}}{dt} = \frac{V_{gs}}{R_{goff\_tot} \cdot C_{gd\_tot}}$$

ここでも、ターンオフ抵抗と  $C_{gd\_total}$  がスイッチング時間に影響をあたえていることがわかります。

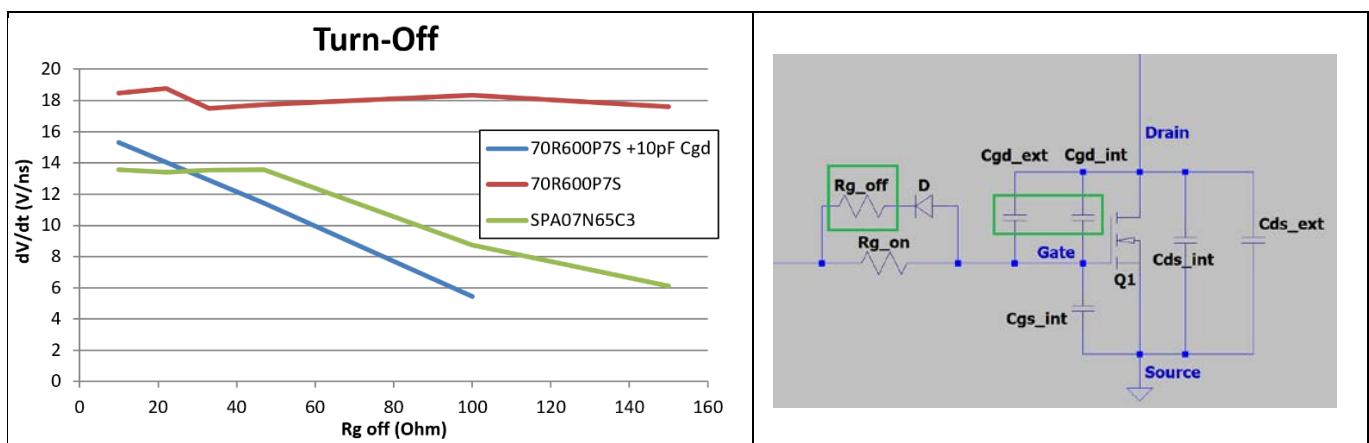

**Figure 8 MOSFET のターンオフ  $dV/dt$  と  $R_{g\_off\_total}$  の関係**

Figure 8 に、40 W アダプタの  $dV/dt$  を、総外部ゲート抵抗を変化させたときのテスト結果を示します。 $R_{g\_off\_total}$  が  $10\Omega$  であっても、最速の  $dV/dt$  は  $18\text{ V/ns}$  であり、少なくとも  $100\Omega$  の外部ゲート抵抗に達するまでターンオンでは見られません。MOSFET のターンオン時には  $dV/dt$  が高くなるため、ターンオフ時の  $dV/dt$  は通常、MOSFET のターンオンほど EMI に大きな影響を与えません。

## 2 フライバックのノイズ源

40 W アダプタで行われたテストでは、外部が 10 pF の  $C_{gd}$  の SPA07N65C3 と IPA70R600P7S の両方が、ゲート抵抗が増加し、dV/dt が低下する傾向に従っていることがわかります。しかし、10 pF のない IPA70R600P7S はこの傾向に従わないため、何か別のことが起こっています。IPA70R600P7S が  $R_{g\_off}$  で制御されていないように見える理由をよりよく理解するには、アーリーチャネルシャットダウン(ECSD)を理解する必要があります。

### 2.3 MOSFET のアーリーチャネルシャットダウン

通常、MOSFET は、デバイスのターンオンと同様に、ターンオフ時に外付けの  $R_g$  と  $C_{gd}$  の合計によって制御されます。特定の条件下では、出力の電圧が上昇し始める前に MOSFET がオフになります。この状態は ECSD です。この状態では、MOSFET は電流源によって充電されるコンデンサのように動作します。ECSD 動作モードが発生している場合、ターンオフの傾きは次式で制御されます。

$$\frac{dV_{ds}}{dt} = \frac{I_{drain}}{C_{ds\_tot}}$$

システムの  $I_{drain}$  は設計によって制約されるため、MOSFET を遅くする唯一の方法は、外付けの  $C_{ds}$  容量を追加することです。

ECSD が発生する地点は、次の式を使用して計算できます。

$$R_{g\_ECSD} < \frac{V_{plateau} \cdot C_{ds\_tot}}{I_{drain} \cdot C_{gd\_tot}}$$

このことから、 $C_{ds\_tot}/C_{gd\_tot}$  の比率が重要な役割を果たしていることがわかり、40 W の測定で外部  $C_{gd}$  のない P7 が制御不能に見えた理由も明らかになります。P7 は C3 デバイスと比較すると  $C_{gd}$  が低いため、外部  $R_g$  が 150 Ωを超えて ECSD になります。これは、ターンオフ効率を向上させるために P7 テクノロジーで意図的に行われていますが、 $R_{g\_off}$  を調整するだけでは P7 が制御不能に見える可能性があります。10 pF  $C_{gd}$  を追加することにより、ECSD 点はより低い  $R_{g\_off}$  に移行し、P7 は C3 デバイスと同様に外部  $R_g$  で制御可能になりました。ECSD 状態でターンオフ時に MOSFET の dV/dt を制御する最良の方法は、外付けの  $C_{ds}$  コンデンサの値を増やすことです。ただし、これはターンオン dI/dt に悪影響をあたえるため、これら 2 つのノイズ源の間でバランスを取る必要があります。

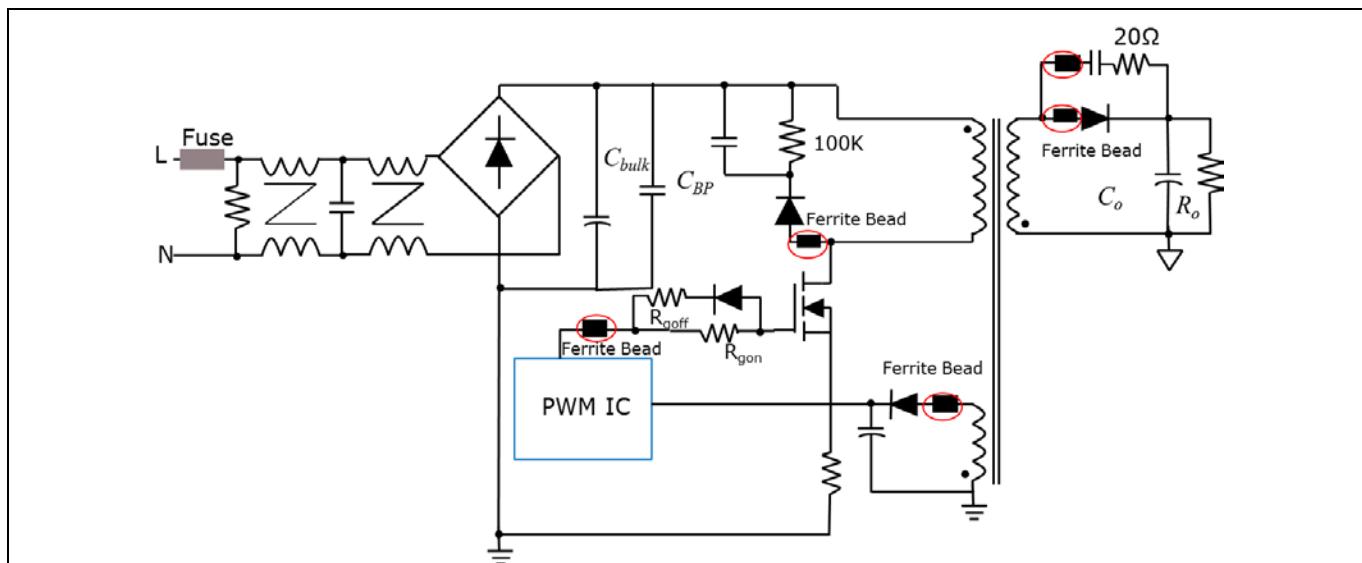

### 2.4 寄生リングングとフェライトビーズ

前項では、MOSFET の dV/dt と dI/dt の基本概念について説明し、これらの過渡現象に関する一般的なネットとループ、およびこれらのノイズ源に影響を与える MOSFET パラメータを見てきました。Figure 9 に、回路全体で異なる寄生特性を持つフライバック電源を示します。

## 2 フライバックのノイズ源

Figure 9 フライバック電源といくつかの関連寄生素子

寄生には、MOSFET のドレインとソースの浮遊インダクタンス、ゲート駆動段の浮遊インダクタンス、トランジスタ出力、出力ダイオード、スナバ段の浮遊インダクタンスなどがあります。一般に数 nH の値である浮遊インダクタンスは、ループ内の  $dI/dt$  に基づいて大きな電圧オーバーシュートを引き起こすことがあります。同様に、浮遊容量には、MOSFET の内部寄生(出力容量と帰還容量を含む)と、そのネットに存在する  $dV/dt$  による電流を発生させるトランジスタ巻線容量が含まれます。これらのノイズ電流と電圧の相互作用は EMI につながります。

前の図から、MOSFET ループに存在するさまざまな  $dI/dt$  セクションは、次の結果をもたらします。

- ゲートの浮遊インダクタンスによるノイズ電圧

- ソースの浮遊インダクタンスによるノイズ電圧

- ドレインの浮遊インダクタンスによるノイズ電圧

- 1 次側の大きなループによるノイズ電圧

$dI/dt$  を遅くするために、既知のインダクタンスが回路に追加されます。この既知のインダクタンスは浮遊インダクタンスと直列であるため、合計値は常に、設計者が知っている加算インダクタンスの範囲内になります。フェライトビーズは、広い周波数範囲にわたって高周波ノイズエネルギーをフィルタリングする受動デバイスです。意図した周波数範囲で抵抗性になり、高周波エネルギーを熱の形で放散します。

ただし、フェライトビーズはシステム内で慎重に使用する必要があります。フェライトビーズを追加しても、周波数による複素インピーダンスであり、一部の周波数ではノイズが低減され、他の周波数ではノイズがさらに悪化する可能性があります。この簡単な例は、フェライトビーズとローパスフィルタリング用のデカップリングコンデンサの組み合わせによる不要な共振です。この場合、より高い周波数をフィルタリングしますが、LC 共振をシステムに導入します。しかし、フェライトビーズの挙動を正しく理解し、考慮することで、これらの問題を回避できます。

ビーズインダクタンス  $L_{bead}$  は次の式で計算されます。

## 2 フライバックのノイズ源

$$L_{bead} = \frac{X_L}{2\pi f}$$

典型的なフェライトビーズのデータシートによると、ビーズが最も誘導性が高い領域は周波数  $f$  を示します。例えば  $f=30$  MHz の場合、30 MHz での  $X_L$  リアクタンスは  $233 \Omega$  であることがわかります。

上記の式により、一般的なフェライトビーズのインダクタンス値 ( $L_{bead}$ ) は  $1.2 \mu\text{H}$  になります。SMPS で使用されるほとんどのフェライトビーズは、 $1.2 \mu\text{H}$  から  $2.2 \mu\text{H}$  の範囲です。

ビーズの寄生容量と DC 抵抗は、目的の周波数でインピーダンスが有効になり、DCR 損失が最小限に抑えられるように、デバイスのデータシートから検証する必要があります。フェライトビーズを正しく実装することは、高周波ノイズとスイッチング過渡現象を低減するための効果的で安価な方法です。

したがって、適切に選択されたフェライトビーズを MOSFET の  $dI/dt$  過渡部に配置することができます。出力および補助電源回路の整流器の逆回復の  $dI/dt$  は、MOSFET の 1 次側のスイッチングによって制御されます。したがって、これらのポイントにビーズを配置すると、 $dI/dt$  効果によって引き起こされる EMI の低減にも役立ちます。

ただし、MOSFET のソースにフェライトビーズを使用するには注意が必要です。EMI では、グランドへのリターンパスをできるだけ低く抑えることが望されます。フェライトビーズを追加することで、MOSFET 全体とノイズの多いドレインパッドがグランドに戻るまでのインピーダンスがさらに高くなり、場合によっては、さらに多くの放射 EMI がシステムに導入される可能性があります。

## 2.5 RCD スナバネットワーク

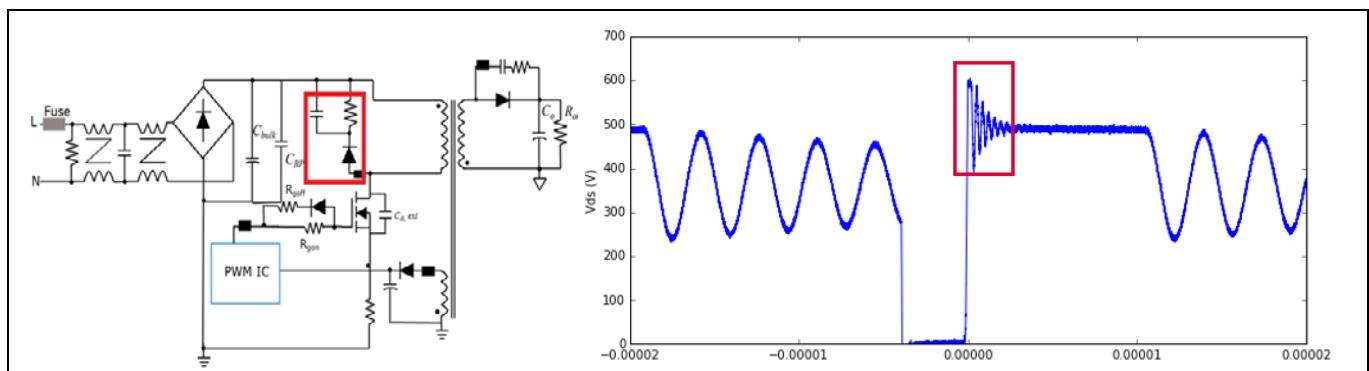

MOSFET の  $dV/dt$  と  $dI/dt$  の他に、EMI ノイズの一般的な発生源はフライバックスナバネットワークです。

Figure 10 左: 赤で示した標準的な RCD スナバネットワーク; 右: スナバと寄生 LC のリンク

スナバが導通を開始すると、 $C_{ds}$  の総容量とトランジスタの漏れインダクタンスの LC リンギングが、主基本波を持つ減衰した正弦波から矩形波に近いものになり、ダイオードの導通には逆回復スパイクと非線形波形が生じます。この波形は、追加の放射ノイズを発生させます。スナバネットワークの EMI を改善するために、RCD スナバネットワークと直列に  $5 \Omega$ ～ $10 \Omega$  を追加し、低速のダイオードを使用すると、スナバネットワークによって生成されるノイズを低減できます。US1K などの超高速ダイオードを使用する代わりに、S1K などの標準ダイオードを使用する必要があります。このダイオードは導通が遅く、逆回復時間が長いため放射ノイズの量が減少します。逆回復時間の増加は、RCD コンデンサに蓄えられるエネルギーを低減するという優れた追加効果があるため、システム効率の向上にも役立ちます。

## 2 フライバックのノイズ源

### 2.6 ノイズ源の低減に関するまとめ

前述したように、MOSFET の動作を遅くすることは、システムの効率を低下させる結果となるため、通常、システムの EMI を改善するための最後の選択肢です。以下の回路構成を用いて、ノイズ源ごとに調整が必要な部品について検討します。

Figure 11 主要な EMI 低減部品を赤で強調表示した基本的な MOSFET 設定

Table 1 MOSFET のスイッチングノイズ源の速度低下

| ターンオン $dV/dt$    | ターンオン $di/dt$    | 制御されたターンオフ $dV/dt$ | ECSD のターンオフ $dV/dt$ |

|------------------|------------------|--------------------|---------------------|

| 外部 $C_{gd}$ を追加  | 外部 $C_{gd}$ を追加  | 外部 $C_{gd}$ を追加    |                     |

| $R_{g\_on}$ を増やす | $R_{g\_on}$ を増やす | $R_{g\_on}$ を増やす   |                     |

|                  | 外部 $C_{ds}$ を減らす |                    | 外部 $C_{ds}$ を増やす    |

上の表からわかるように、外部  $C_{ds}$  は、ターンオンの  $di/dt$  を悪化させ、ターンオフの  $dV/dt$  を良くする効果があります。つまり、通常はバランスが必要であり、ターンオフの  $dV/dt$  を遅くするために外部の  $C_{ds}$  を増やす場合は、同様のターンオンの  $di/dt$  を維持するために外部の  $R_{g\_on}$  または  $C_{gd}$  も増やす必要があります。

システム内のリングを減衰させるための一般的なオプションは、フェライトビーズを次の場所に配置することです。

1. MOSFET ドレイン(フェライトビーズの DC 抵抗に注意)

2. MOSFET ゲート

3. スナバネットワーク

4. 出力ダイオード

5. 出力ダイオード スナバ

## 2 フライバックのノイズ源

Figure 12 MOSFET の  $dI/dt$  低減のための一般的なフェライトビーズ配置ポイント

## 2.7 フライバック/PFC による置換値の推定

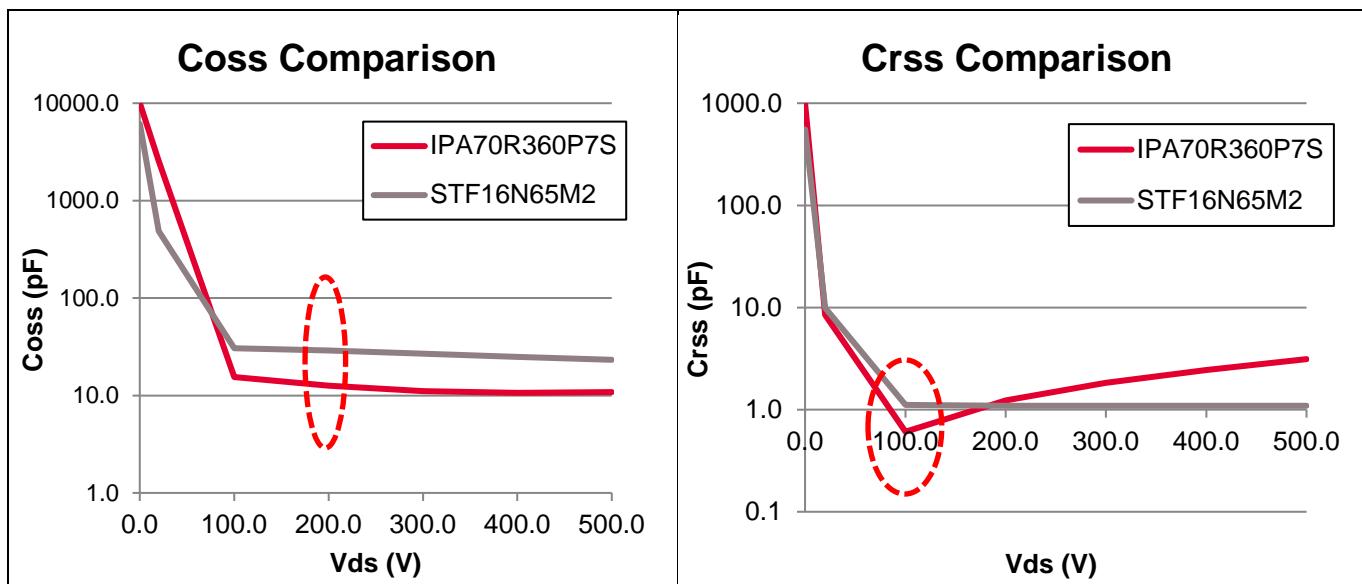

一般的な状況は、古い設計を旧世代のデバイスから新しい世代の CoolMOS™に更新する場合です。この状況では、設計の自由度をあまり高くせずに EMI 要件を満たす必要があるため、同様のターンオン/ターンオフの  $dV/dt$  と  $dI/dt$  を得るために、最初の推定値があると便利です。通常、低消費電力のフライバックの場合、CoolMOS™ P7 は ECSD 状態にあると想定するのが安全であるため、デバイスのデータシートからデータを取得して、次の手法を使用できます。

1. 参照部品と新しい部品の  $C_{oss}$  を取り、 $C_{oss}$  曲線の線形領域の差を取ります。

2. 新世代のデバイスの出力容量は小さいため、その差を外付けの  $C_{oss}$  に追加する必要があります。

3. 古い  $C_{rss}$  のデータシートの  $C_{rss}$  曲線を新しい  $C_{rss}$  で割った比率を取ります。これにより、MOSFET の  $C_{gd}$  の違いがわかります。

4. この古い MOSFET  $C_{gd}$ /新しい MOSFET  $C_{gd}$  の比率に  $R_{g\_on}$  を掛けて、新しい  $R_{g\_on}$  を求めます。

それでは、以下の実際の例を見てみましょう。

Figure 13 IPA70R360P7S および STF16N65M2 の  $C_{oss}$  および  $C_{rss}$  データシートの比較

## 2 フライバックのノイズ源

データシートのグラフの  $C_{oss}$  曲線と  $C_{rss}$  曲線の情報は、IPA70R360P7S データシートと STF16N65M2 データシートの両方から取得されます。

まず、 $C_{oss}$  の値を見ていきます。STF16N65M2 は 200 V で 28.9 pF の静電容量を備えています。IPA70R360P7S は 12.6 pF です。その差は 16.3 pF の静電容量です。PCB にはすでに 47 pF のドレンソース容量の 1 kV の 1206 セラミック コンデンサが取り付けられているため、47 pF + 16.3 pF の場合、47 pF のコンデンサを外付けした STF16N65M2 に合わせるには、合計 63.3 pF のドレンソース容量を外部にする必要があります。最も近い標準静電容量値は 68 pF なので、これが最初に試す値になります。

さて、デバイスの  $C_{rss}$  比を見ると、100 V は M2 デバイスと比較して P7 が最も小さい  $C_{rss}$  であることがわかります。ここで、M2 の静電容量は 1.1 pF ですが、P7 の静電容量は 100 V で 0.6 pF です。元の設計でターンオン抵抗に 100 Ω があった場合、新しいターンオン抵抗で試すのが 180 Ω になるのが妥当です。

このことから、MOSFET を減速するための最初の推定値は、68 pF の  $C_{ds}$  の外部値と 180 Ω の  $R_{g\_on}$  として導き出すことができます。

### 3 ノイズの伝送防止

## 3 ノイズの伝送防止

### 3.1 フライバック電源の $dI/dt$ および $dV/dt$ を低減するためのレイアウト手法

EMI の問題では、まず設計を最適化するために、レイアウト上重要な  $dI/dt$  ループとスイッチノードのクリティカルエリアを常に最小化します。これは、システム効率を低下させることなく、外部へのノイズ伝達を低減するためです。1 次側 MOSFET のループを小さくするには、高周波、高電圧の DC コンデンサ(できればセラミック誘電体)を追加して、有効ループ面積を小さくします。また、SMD セラミックコンデンサは、直列インダクタンスが低く、直列抵抗が高いという利点があるため、電源の入力に使用される大型の電解コンデンサよりもはるかに高い周波数に有効です。これを Figure 3 の  $C_{BP}$  として示します。

Figure 3 に示すようなスイッチングループ領域は最小限に抑える必要があります。次のような回路基板内の意図しないアンテナを減らします。

1. 長い配線 - 高  $dV/dt$  ノードの配線をできるだけ短くします。

2. ビア - PCB を通過するノイズの多いビアごとに、PCB を通過するビアの近くにグランドプレーンがあることを確認して、リターンパスを短くします。

3. コンポーネントのリード線とピン - 短いリード線で浮遊インダクタンスを低減します。

4. ドライバと IC の近くで電源とグランドの間に SMD セラミックデカップリングコンデンサを配置します。

5. 電源プレーンは、PCB の端から戻る必要があります。

6. グランドプレーンまたは電源プレーン内で配線が切断され、意図しない開口部またはスロットアンテナが作成されることは避けてください。

7. 順方向電流と戻り電流の両方が明確に定義された導通経路上にある経路を包含するループアンテナは避けてください。

8. 単層設計では、PCB のエッジの周囲に EMI ガードリングとしてグランドトレースを保持するようにしてください。

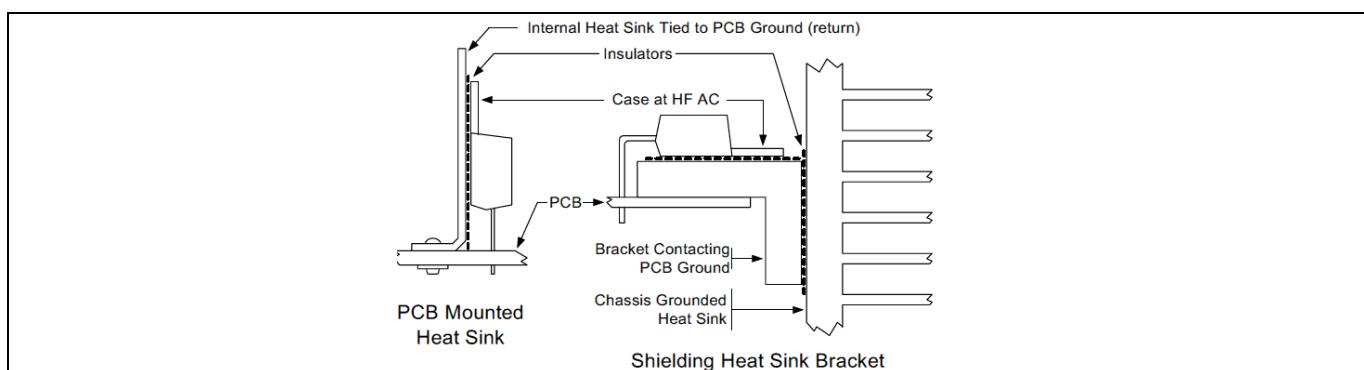

### 3.2 シャーシグランドではなく、入力バルクコンデンサのリターンに対するヒートシンクの接地

ヒートシンクを PCB のグランド/入力バルクコンデンサリターンに接地して、同相ノイズと放射ノイズを低減します。TO-220FP とヒートシンクの容量結合は、EMI に注意すべき重要なループです。

**Figure 14** 容量結合ノイズをシャーシグランドではなく共通回路に迂回させる 2 つのヒートシンク配置

### 3 ノイズの伝送防止

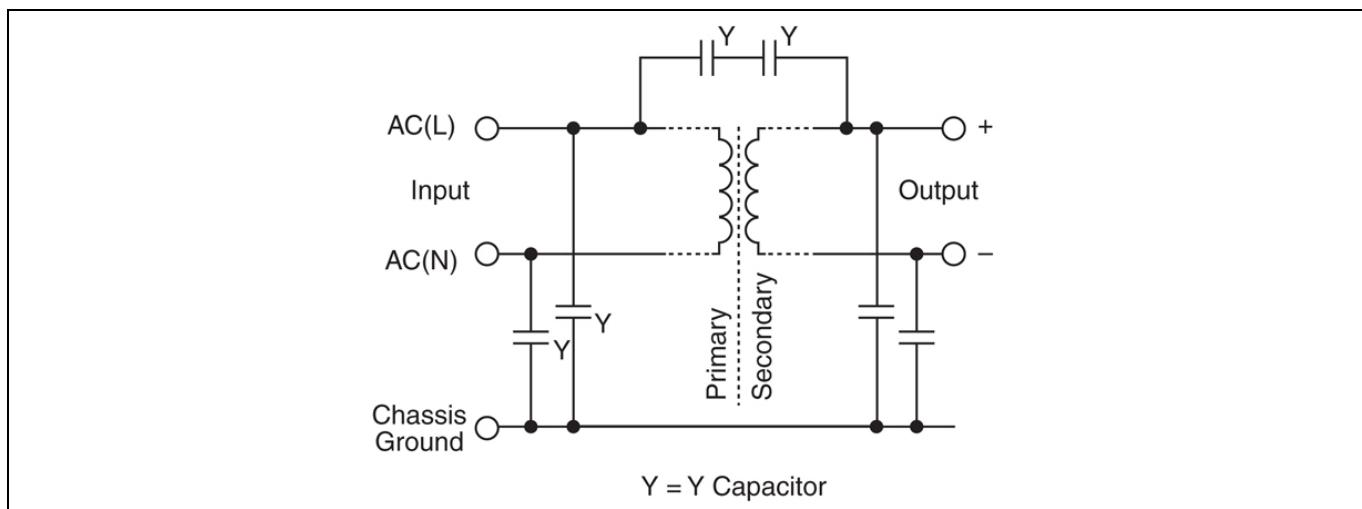

#### 3.3 Y コンデンサ

Figure 9 に示すように、フライバックトランスに寄生巻線容量がある以外に、実用的なトランスには 1 次巻線と 2 次巻線の間に浮遊容量があります。この静電容量は、コンバータのスイッチング動作と相互作用します。入力と出力の間には他の接続がないため、入力と出力の間に高周波電圧が発生します。電源からのケーブルはアンテナとして機能し、スイッチングプロセスによって生成された高周波を伝送します。

高周波のコモンモードノイズを抑制するには、電源の入力側と出力側の間に、フライバックトランスの静電容量よりも大幅に高い静電容量のコンデンサを配置する必要があります。これにより、高周波ノイズを効果的にショートさせ、電源からの漏れを防止します。

充電器などのクラス 2(非アース)電源を設計する場合、これらのコンデンサを入力ライブまたはニュートラル、あるいはその両方に接続する以外に選択肢はありません。しかし、これらのコンデンサの短絡故障は深刻な問題になります。アダプタなどのクラス 1 電源では、主電源と主電源アースの間のコンデンサの故障は、アースへの短絡(基本絶縁の故障に相当)を意味します。クラス 2 の PSU では、コンデンサの故障ははるかに深刻です。これは、ユーザーに直接的かつ深刻な安全上の問題を意味します(二重または強化絶縁の故障に相当)。ユーザーへの危険を防ぐために、コンデンサは短絡障害の可能性が非常に低いように設計する必要があります。

そのため、トランスの寄生容量によるノイズ電圧を絶縁する目的で、特殊なコンデンサが必要になります。これらのコンデンサは「Y コンデンサ」として知られています(一方、X コンデンサは、主電源の通電時と主電源のニュートラルの間で使用されます)。Y コンデンサには、主に Y1 と Y2 の 2 つのサブタイプがあります(Y1 が定格の高いタイプです)。

Figure 15 Y コンデンサを使用してトランスの寄生容量によるノイズを制限

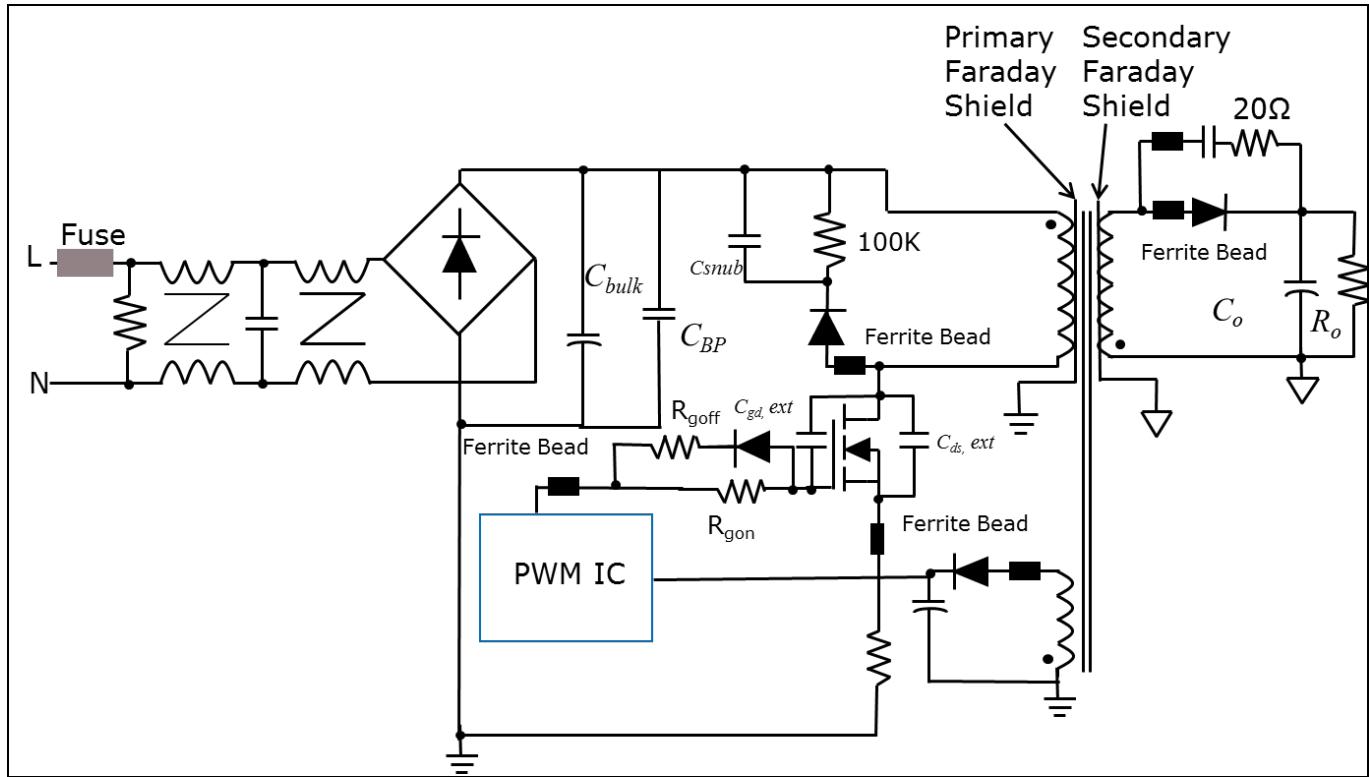

#### 3.4 変圧器のシールド

変圧器は、1 次巻線と 2 次巻線の間にファラデーシールドまたは銅箔を使用して設計できます。1 次グラウンドと 2 次グラウンドに接続されたファラデーシールドにより、ノイズ電圧がそれぞれのグラウンドに安全に戻されます。前項で述べた 1 次側から 2 次側への静電容量を低減し、この静電容量から発生するコモンモードノイズを低減するために効果的に機能します。詳細については、[参考資料セクションのアプリケーションノート\[3\]および\[4\]](#)を参照してください。

### 3 ノイズの伝送防止

Figure 16 1次側と2次側の間の寄生容量によるノイズ結合を最小限に抑えるトランスシールド

### 3.5 周波数変調機能付き可変周波数 PWM コントローラ

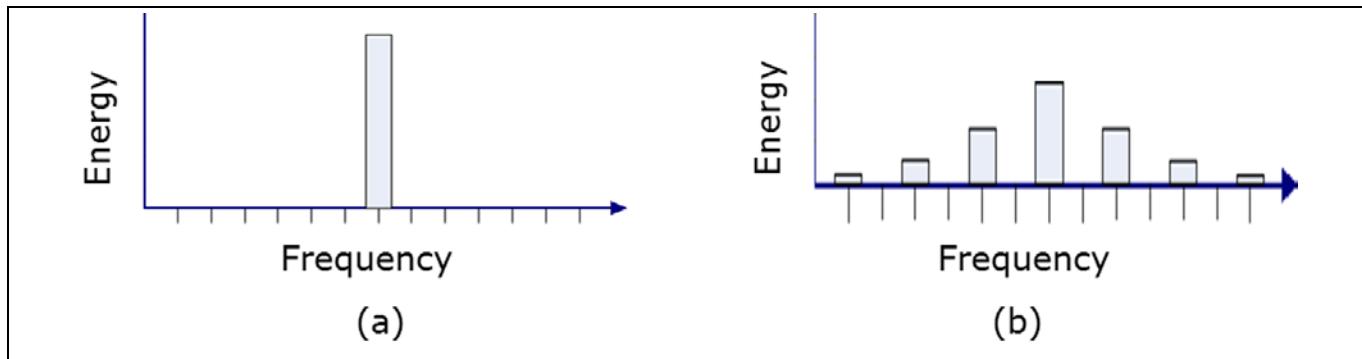

上記で説明した手法とは別に、一定の周波数とデューティサイクル(D)の矩形波によって制御されるフライバックコンバータの場合、EMIを低減するための従来の手法は受動フィルタを使用することで構成されます。これには、サイズ、重量、設計の複雑さ、効率、コストなどの制限があります。最新の可変周波数(VF)または周波数ジッタリングEMI低減技術は、フィルタソリューションで直面する問題を克服するために利用できます。インターリーブ技術は、供給される総電力を均等に共有するために使用されます。VFスペクトラム拡散シグナリングの一般的な考え方を Figure 17 に示します。Figure 17 (a)と(b)ではスペクトル分布が異なりますが、Figure 17 (b)ではピークレベルが低下していますが、全エネルギーは同じです。スイッチング周波数変調(SFM)は、SMPSのEMIを低減する効果的な方法です。この手法は、オリジナルのスペクトラム拡散クロック生成(SSCG)技術に基づいています。SFMを使用すると、EMI高調波の振幅低減と、振幅の小さい側波帶高調波の生成の間にトレードオフがあります。

SMPSのPWMスペクトラム拡散制御原理を以下に説明します。

$f = f_s + \Delta f$ 、ここで  $f_s$  は PWM スイッチの基準周波数です。 $\Delta f$  は追加のスペクトラム拡散信号周波数で、スペクトラム拡散信号の時間領域特性に応じて周波数を変化させます。

## 3 ノイズの伝送防止

Figure 17 VF PWM コントローラを使用したスペクトラム拡散周波数生成

この非線形制御設計アプローチの利点は、回路が単純であることです。多くの IC メーカーの基本的な SMPS 制御回路でさえ、わずか数個の受動部品を追加するだけで使用できます。この方法の主な欠点は、設計者がすべての負荷条件とパラメータ変動における回路性能を慎重に検討し、すべてのケースでスペクトラム拡散動作とシステム全体の安定性を確保する必要があることです。

インフィニオンは、ICE5xSAG など、このような周波数変調技術を採用してコントローラレベルで EMI を低減する PWM コントローラを多数保有しています。

#### 4 実例 – 45 W アダプタ

## 4 実例 – 45 W アダプタ

放射および伝導 EMI 要件を満たし、効率を犠牲にすることなく 45 W アダプタを設計する詳細な説明については、[45 W 19 V adapter reference board](#) [5] に設計プロセスの非常に優れたウォークスルーがあります。この設計では、MOSFET の速度を落とすことではなく、トランスの設計、高周波ループ、およびラインフィルタの設計に重点が置かれており、特定の設計の EMI と効率の両方の要件を満たす方法の概要を示しています。

Figure 18 筐体内の 45W P7 SOT-223 デモボードの底面

Table 2 45 W NB adapter reference board の仕様

|                                                                  |                                   |

|------------------------------------------------------------------|-----------------------------------|

| 入力電圧および周波数                                                       | 90 V AC (60 Hz) ~264 V AC (50 Hz) |

| 出力電圧、電流、および電力                                                    | 19 V/2.37 A/45 W                  |

| アクティブモードの 4 点平均効率<br>(25%, 50%, 75%, 100%負荷)<br>(EU CoC バージョン 6) | 88%以上                             |

| 無負荷消費電力                                                          | 100 mW 未満                         |

| 伝導性エミッショ n (EN 55022 Class B)                                    | QP と平均に 6 dB のマージンで合格             |

| 放射エミッショ n (EN 55022 Class B)                                     | QP に 6 dB のマージンで合格                |

| PCB フォームファクタ (L × W × H)                                         | 86 × 35 × 20 mm                   |

---

## 5 結論

### 5 結論

最新の CoolMOS™ MOSFET を使用して設計する場合、効率の向上やコストの最適化のために、CoolMOS™ SJ MOSFET のスイッチングパラメータに注意する必要があります。スイッチング特性の違いは EMI テストで強調されますが、多くの場合、このアプリケーションノートで説明する手法は、余裕を持って EMI 要件を満たす必要があります。CoolMOS™デバイスを使用した場合の効率と熱性能の大幅な向上は、多くの場合、EMI マージンを満たす必要があるため、低下します。電源設計者は、CoolMOS™デバイスのメリットを効果的に享受するために、効率と EMI の最適なトレードオフを見つける必要があります。

CoolMOS™の  $dI/dt$  および  $dV/dt$  を低減するだけでなく、PCB レイアウトを最適化するシステムソリューションアプローチ、正しい接地を備えた Y コンデンサの使用、正しい接地によるスイッチングトランジistor のシールド、ヒートシンクの接地、および周波数変調オプションを含む可変周波数の PWM コントローラの使用など、効率を犠牲にすることなく EMI を改善するシステムソリューションアプローチを検討することもできます。

## 6 付録: EMI 測定プロットの読み出し

## 6 付録: EMI 測定プロットの読み出し

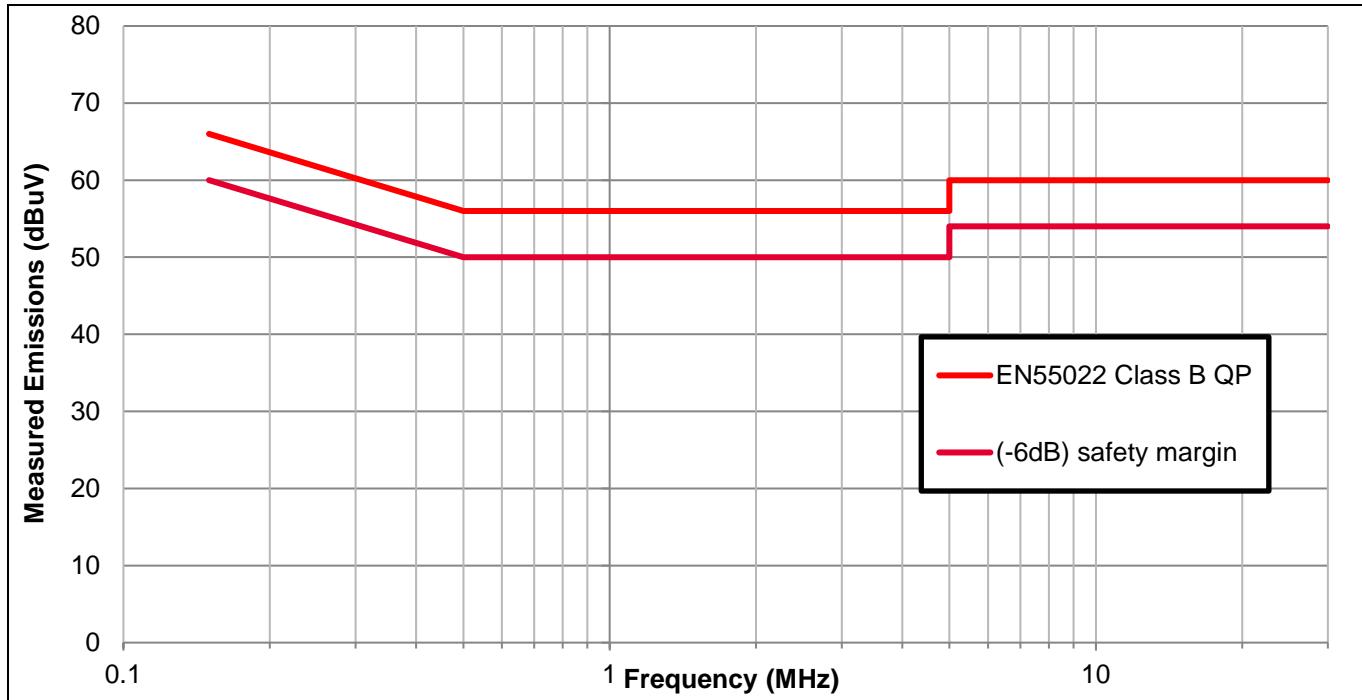

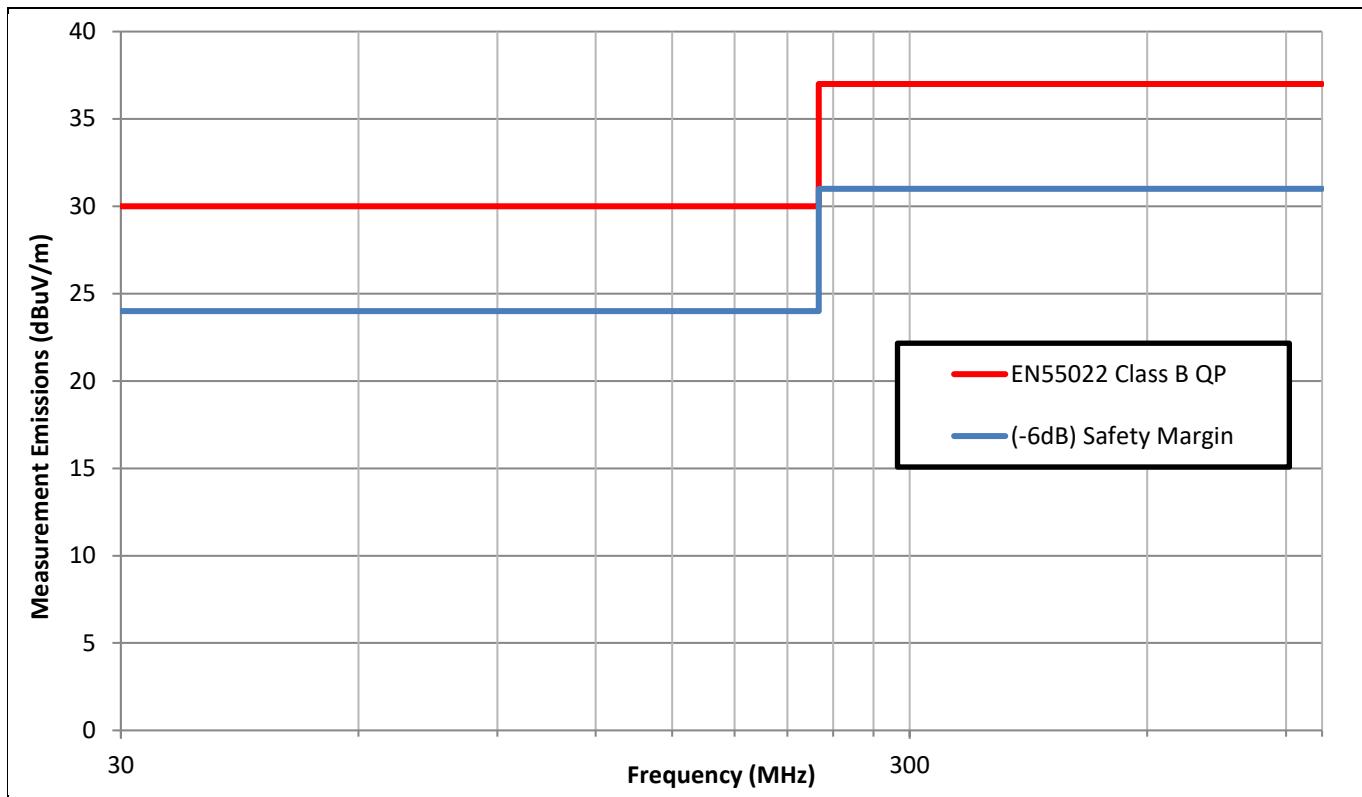

標準的な伝導および放射 EMI 制限線を [Figure 19](#) と [Figure 20](#) に示します。

Figure 19 伝導性エミッション試験の制限 - 150 kHz~30 MHz

Figure 20 放射妨害波試験の制限 - 30 MHz~1 GHz

## 6 付録: EMI 測定プロットの読み出し

スペクトラムアナライザで使用される検出器に基づいて、平均、準ピーク (QP) またはピーク測定値を取得できます。ピーク検出では、常に最高の読み出し値が得られ、次に QP、その後に平均の読み出し値が続きます。したがって、EMI スキャンを迅速に実行するために、ほとんどのエンジニアはピーク検出を好み、その結果を QP リミットと比較します。この条件が満たされると、事実上、追加のヘッドルーム (安全マージン) が達成されます。QP 検出は、ピーク検出テスト (QP リミットを適用した状態) がわずかに不合格になった場合にのみ実行する必要があります。

通常、測定の不正確さや基板間のばらつきなどを考慮して、-6 dB の安全マージンが必要です。通常、QP リミットが満たされている場合、平均リミット (平均検出と平均リミットを使用) も満たされます。約 5 MHz 未満の周波数では、ノイズ電流は主に差動モードになりますが、5 MHz を超える周波数では、ノイズ電流は主にコモンモードになります。20 MHz を超える周波数では、伝導ノイズは誘導ピックアップに起因し、入力ケーブルまたは出力ケーブルからの放射である可能性があります。

---

## 参考資料

### 参考資料

- [1] CoolMOS™ C6 – Mastering the Art of Slowness

<http://www.infineon.com/dgdl/Infineon+-+Application+Note+-+PowerMOSFETs+-+600V+CoolMOS.+-+C6+-+Mastering+the+Art+of+Slowness.pdf?fileId=db3a3043271faefd0127903d130171e1>

- [2] CoolMOS™ C7 – Mastering the Art of Quickness

<http://www.infineon.com/dgdl/Infineon+-+Application+Note+-+650V+CoolMOS+C7+-+Mastering+the+Art+of+Quickness.pdf?fileId=db3a30433e5a5024013e6a966779640b>

- [3] Transformer construction techniques

<http://www.infineon.com/dgdl/an-1024.pdf?fileId=5546d462533600a401535591115e0f6d>

- [4] Meeting EMI-EFT requirements on a system level

<http://www.infineon.com/dgdl/AN-PS0001+Lightning+test.pdf?fileId=db3a304412b407950112b4182a8224f9>

- [5] 45 W 19 V adapter reference board using the 700 V CoolMOS™ P7 in SOT-223 package

[https://www.infineon.com/dgdl/Infineon-Engineering\\_report\\_demo\\_board\\_DEMO\\_45W\\_19V\\_FLYB\\_P7-AN-v01\\_01-EN.pdf?fileId=5546d46261ff5777016242b56c745be0](https://www.infineon.com/dgdl/Infineon-Engineering_report_demo_board_DEMO_45W_19V_FLYB_P7-AN-v01_01-EN.pdf?fileId=5546d46261ff5777016242b56c745be0)

---

## 改訂履歴

### 改訂履歴

| 版数  | 発行日        | 変更内容                                                                                                                                                    |

|-----|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.0 | 2024-11-28 | 本版は英語版 AN_1910_PL52_121340 Optimizing CoolMOS™-based power supplies to meet EMI requirements について、インフィニオン DEVELOPER COMMUNITY の参画者によって日本語に翻訳されたドキュメントです |

## Trademarks

All referenced product or service names and trademarks are the property of their respective owners.

**Edition 2024-11-28**

**Published by**

**Infineon Technologies AG

81726 Munich, Germany**

**© 2024 Infineon Technologies AG.

All Rights Reserved.**

**Do you have a question about this

document?**

**Email:** [erratum@infineon.com](mailto:erratum@infineon.com)

**Document reference**

**AN\_1910\_PL52\_121340\_JA**

## 重要事項

本手引書に記載された本製品の使用に関する手引きとして提供されるものであり、いかなる場合も、本製品における特定の機能性能や品質について保証するものではありません。本製品の使用の前に、当該手引書の受領者は実際の使用環境の下であらゆる本製品の機能及びその他本手引書に記された一切の技術的情報について確認する義務が有ります。インフィニオンテクノロジーズはここに当該手引書内で記される情報につき、第三者の知的所有権の不侵害の保証を含むがこれに限らず、あらゆる種類の一切の保証および責任を否定いたします。

本文書に含まれるデータは、技術的訓練を受けた従業員のみを対象としています。本製品の対象用途への適合性、およびこれら用途に関連して本文書に記載された製品情報の完全性についての評価は、お客様の技術部門の責任にて実施してください。

## 警告事項

技術的要件に伴い、製品には危険物質が含まれる可能性があります。当該種別の詳細については、インフィニオンの最寄りの営業所までお問い合わせください。

インフィニオンの正式代表者が署名した書面を通じ、インフィニオンによる明示の承認が存在する場合を除き、インフィニオンの製品は、当該製品の障害またはその使用に関する一切の結果が、合理的に人的傷害を招く恐れのある一切の用途に使用することはできないこと予めご了承ください。