#### **About this document**

Scope and purpose

This application note provides implementation details for the USB Video Class (UVC) and USB Audio Class (UAC), as well as guidance on developing firmware for UVC and UAC composite device. Conforming to these classes enables a camera and audio device to operate with built-in PC drivers and host applications, such as Windows Camera app, Webcamoid, and VLC media player. This application note also offers insight into using the Infineon product EZ-USB™ FX20 as a composite device to interface with a camera (image sensor)/HDMI frame grabber and microphone/audio to stream uncompressed data into a PC.

This application note describes the synchronous slave FIFO interface of the EZ-USB™ FX20 with the Efinix Ti180 FPGA and provides common trouble shooting methods.

#### Intended audience

This document is primarily intended for individuals who wish to design and implement a composite device (UVC + UAC) using EZ-USB™ FX20 slave FIFO interface and PDM interface with an FPGA.

#### Table of contents

### **Table of contents**

| About    | t this documentt this document                                         | 1  |

|----------|------------------------------------------------------------------------|----|

| Table    | of contents                                                            | 2  |

| 1        | Introduction                                                           | 5  |

| 2        | USB Video Class (UVC) standard                                         | 7  |

| _<br>2.1 | Key features and benefits of USB Video Class (UVC)                     |    |

| 2.2      | UVC version support                                                    |    |

| 2.3      | UVC implementation details                                             |    |

| 2.3.1    | Enumeration using UVC descriptors                                      |    |

| 2.3.2    | Handling UVC requests                                                  |    |

| 2.4      | USB video class requirements                                           |    |

| 2.4.1    | USB descriptors for UVC                                                | 9  |

| 2.4.1.1  | 1 Video control (VC) interface                                         | 10 |

| 2.4.1.2  | Video streaming (VS) interface                                         | 11 |

| 2.4.2    | UVC-specific requests                                                  | 12 |

| 2.4.2.1  | Control requests – Brightness, PTZ control, and extension unit control | 16 |

| 2.4.2.2  | 2 Streaming requests – Probe and commit control                        | 16 |

| 2.4.3    | Video data format: YUY2                                                | 17 |

| 2.4.4    | UVC video data header                                                  | 17 |

| 3        | USB Audio Class (UAC) standard                                         | 20 |

| 3.1      | UAC version support                                                    |    |

| 3.2      | Enumeration using UAC descriptor                                       |    |

| 3.3      | Operational code                                                       |    |

| 3.4      | USB audio class requirements                                           | 22 |

| 3.4.1    | USB descriptors for UAC                                                | 22 |

| 3.4.1.1  | 1 Audio control interface                                              | 22 |

| 3.4.1.2  | 2 Audio streaming (AS) interface                                       | 23 |

| 3.5      | UAC-specific requests                                                  | 23 |

| 4        | UVC + UAC composite device application                                 | 25 |

| 5        | LVDS/LVCMOS interface                                                  | 26 |

| 5.1      | Slave FIFO access sequence and interface timing (LVDS/LVCMOS)          |    |

| 5.1.1    | LVDS RX write sequence                                                 |    |

| 5.2      | GPIF III interface in LVCMOS/LVDS mode                                 | 28 |

| 5.2.1    | LVCMOS WideLink: Port0 and Port1 combined                              |    |

| 5.2.2    | LVCMOS Narrow Link: Port0                                              | 30 |

| 5.2.3    | LVCMOS Narrow Link: Port1                                              | 31 |

| 5.2.4    | LVDS WideLink: Port0 and Port1 combined                                | 32 |

| 5.2.5    | LVDS Narrow Link: Port0                                                | 33 |

| 5.2.6    | LVDS Narrow Link: Port1                                                | 33 |

| 5.3      | Ping-pong DMA buffers                                                  | 34 |

| 5.3.1    | LVCMOS 2-bit SlaveFIFO GPIF III state machine                          | 34 |

| 5.3.2    | LVDS RX GPIF III state machine                                         | 35 |

| 6        | LVCMOS transmitter implementation in FPGA                              | 37 |

| 6.1      | Functional description of FPGA LVCMOS TX                               |    |

| 6.1.1    | Device selection FSM                                                   |    |

| 6.1.2    | LINK training FSM                                                      |    |

| 6.1.3    | LVCMOS data packet transmitter                                         |    |

#### Table of contents

| 7 L              | VDS transmitter implementation in FPGA                                                               | 39             |

|------------------|------------------------------------------------------------------------------------------------------|----------------|

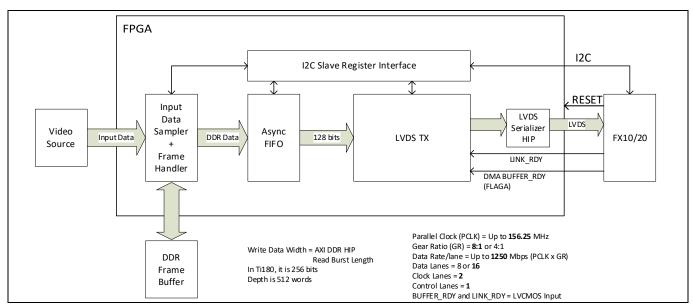

| 7.1              | FPGA LVDS transmitter high level block diagram                                                       | 39             |

| 7.2              | I2C slave register interface                                                                         | 39             |

| 7.2.1            | FPGA I2C register details                                                                            | 40             |

| 7.2.1.1          | Common control and status registers                                                                  | 40             |

| 7.2.1.2          | Device specific registers                                                                            | 42             |

| 7.2.1.3          | Base offset for device specific register                                                             | 45             |

| 7.3              | Functional description of FPGA LVDS TX                                                               | 45             |

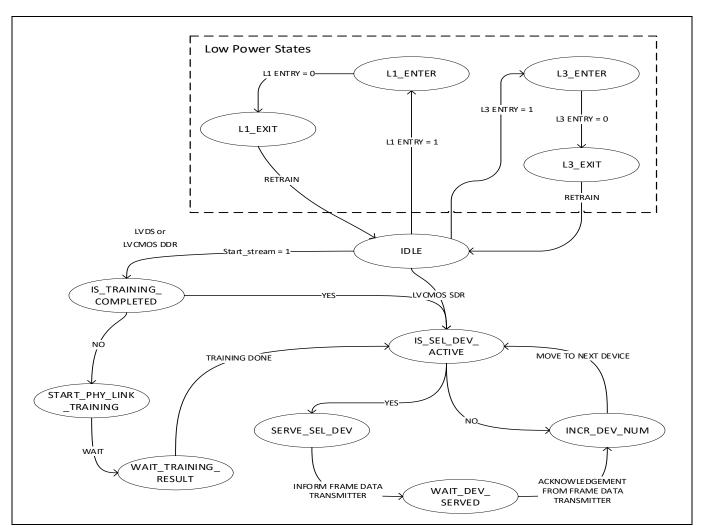

| 7.3.1            | Device selection FSM                                                                                 | 45             |

| 7.3.2            | IDLE                                                                                                 | 46             |

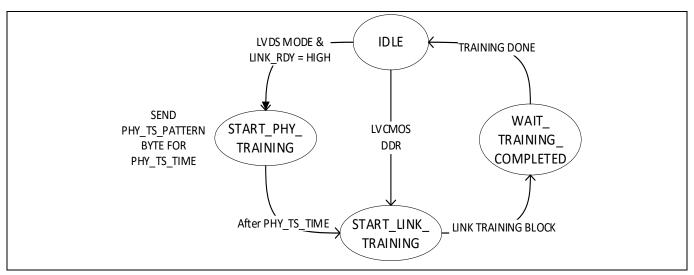

| 7.3.3            | PHY and LINK training FSM                                                                            | 46             |

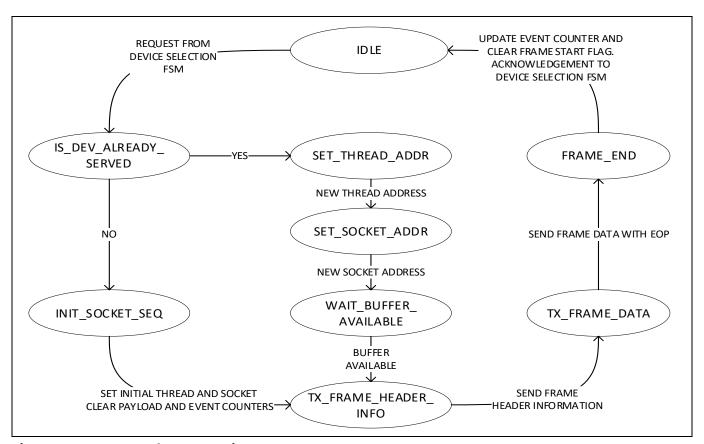

| 7.3.4            | Frame data transmitter FSM                                                                           | 47             |

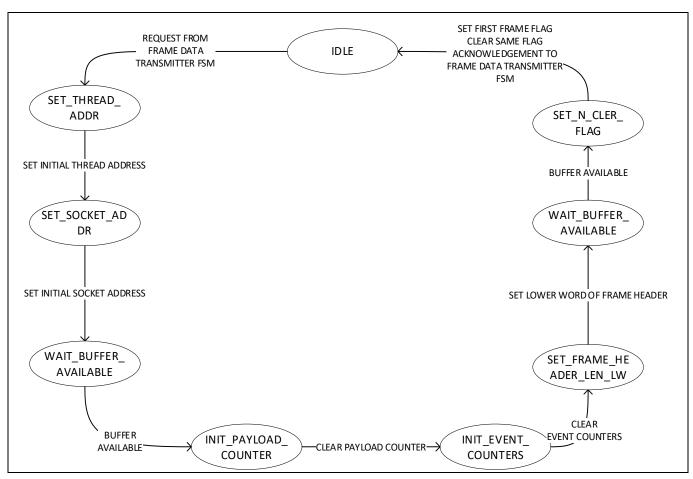

| 7.3.4.1          | Initial socket sequence FSM                                                                          | 48             |

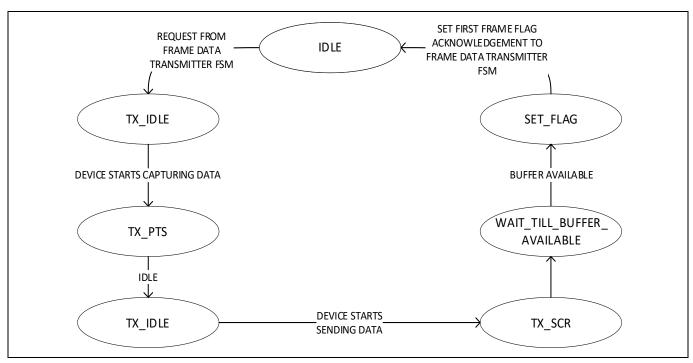

| 7.3.4.2          | Frame header information transmitter FSM                                                             | 49             |

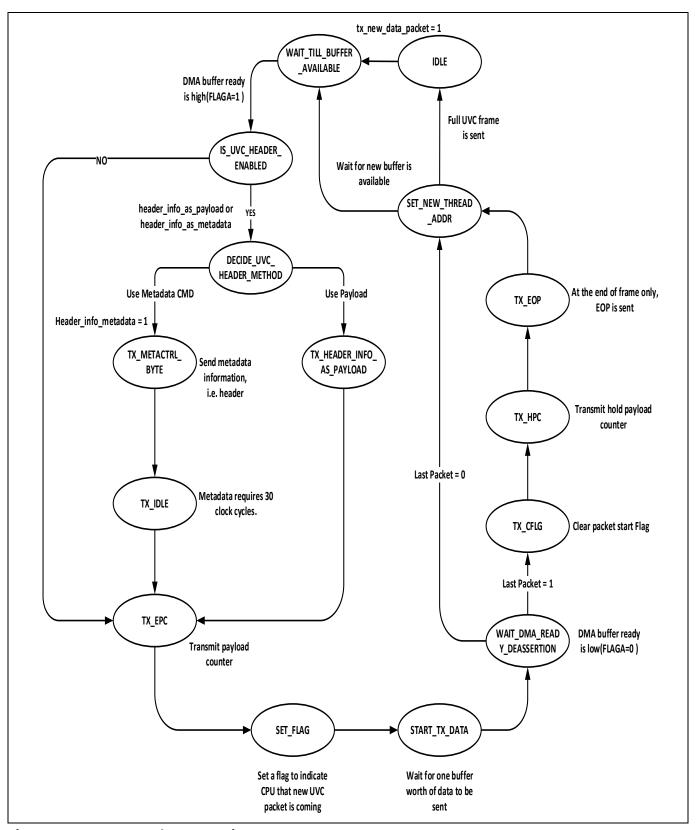

| 7.3.4.3          | LVDS data packet transmitter FSM                                                                     | 50             |

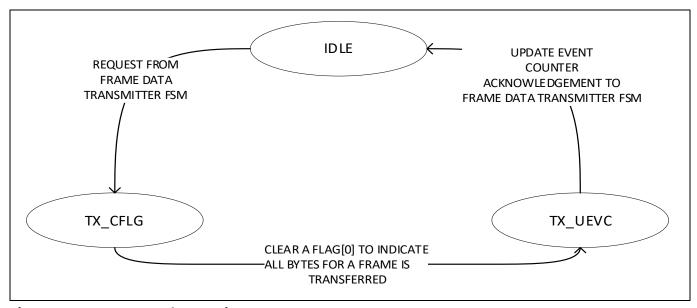

| 7.3.4.4          | Frame end transmitter FSM                                                                            | 52             |

| 8 A              | udio interface                                                                                       | 53             |

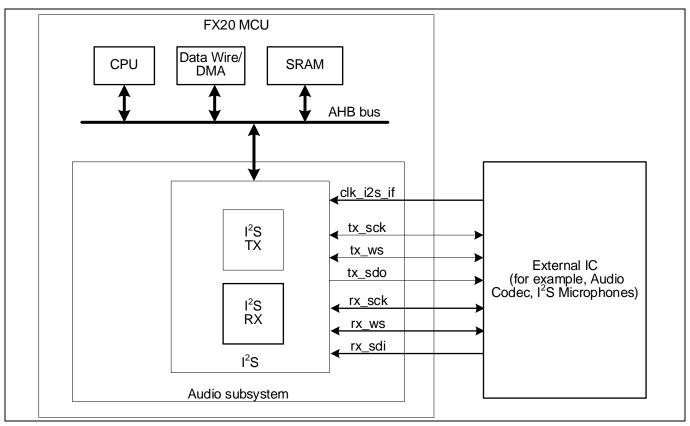

| 8.1              | Direct I2S Rx/Tx support in EZ-USB™ FX20                                                             | 53             |

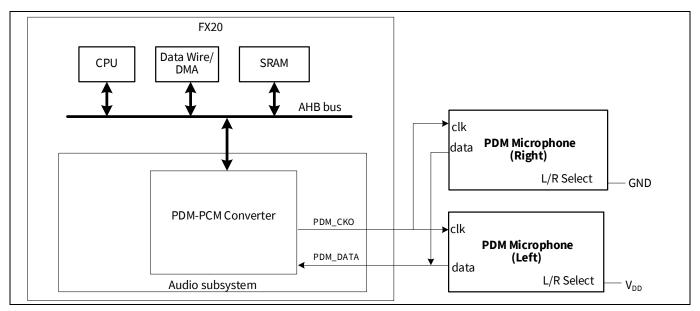

| 8.2              | Built-in PDM to PCM converter support                                                                |                |

| 8.3              | Pin mapping of audio (microphone)                                                                    |                |

| 9 F              | irmware                                                                                              |                |

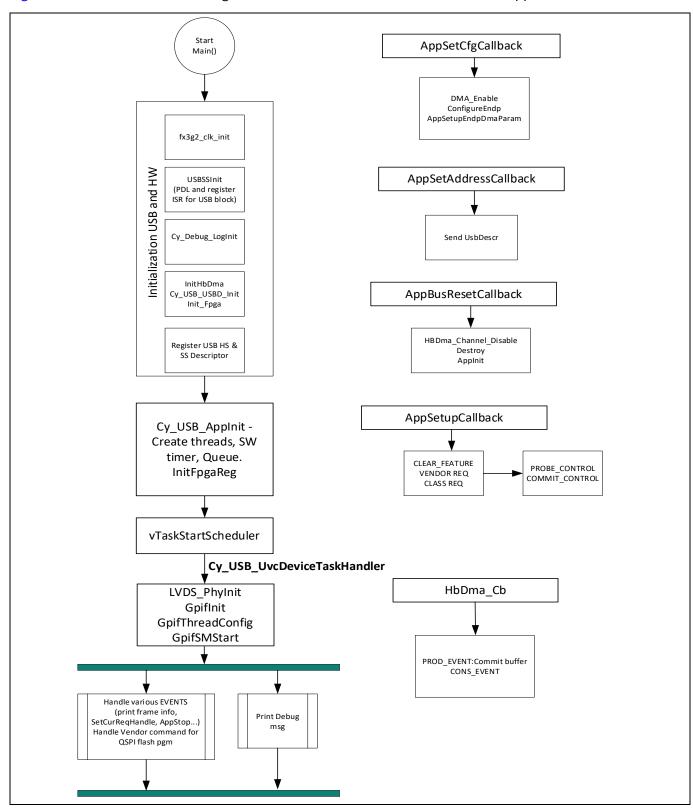

| 9.1              | Application thread (RTOS task)                                                                       |                |

| 9.2              | Firmware flowchart                                                                                   |                |

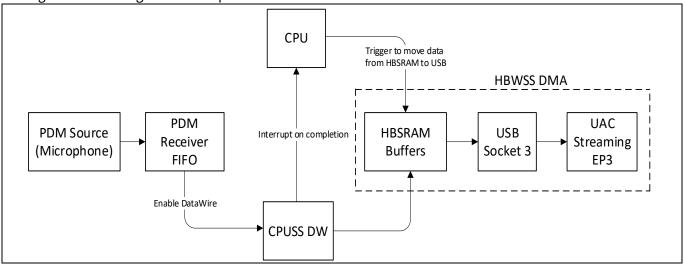

| 9.3              | Audio (PDM) data flow                                                                                |                |

| 9.4              | Enumeration                                                                                          |                |

| 9.5              | Configuring the video source through the I2C interface                                               |                |

| 9.6              | Starting the video streaming                                                                         |                |

| 9.7              | Setting up DMA buffers                                                                               |                |

| 9.8              | Handling the DMA buffers during video streaming                                                      |                |

| 9.9              | Terminating the video streaming                                                                      |                |

| 9.10             | Enabling debug interface using USB FS                                                                |                |

| 10 U             | VC host driver and application                                                                       |                |

| 10.1             | UVC host driver                                                                                      |                |

| 10.2             | UVC host application                                                                                 |                |

|                  | ools                                                                                                 |                |

| 11.1             | USB 3.2 Protocol Analyzer (LeCroy, Wireshark)                                                        |                |

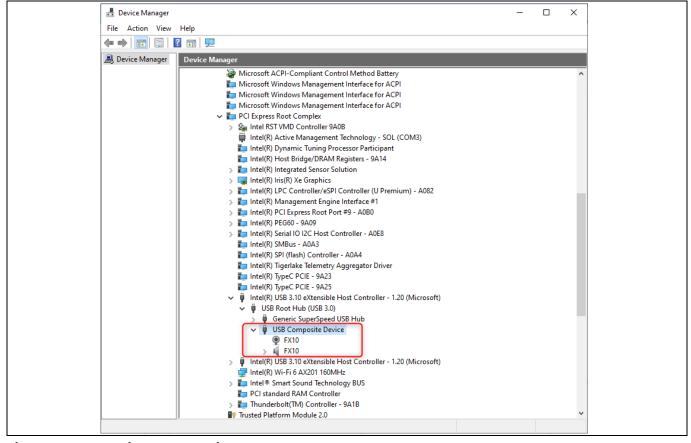

| 11.2             | Device Manager                                                                                       |                |

| 11.3             | Serial terminal (Tera Term, Cool Term, etc.)                                                         |                |

| 11.4             | EZ-USB™ FX Control Center                                                                            |                |

| 11.5             | EZ-USB™ FX20 to FPGA interface                                                                       |                |

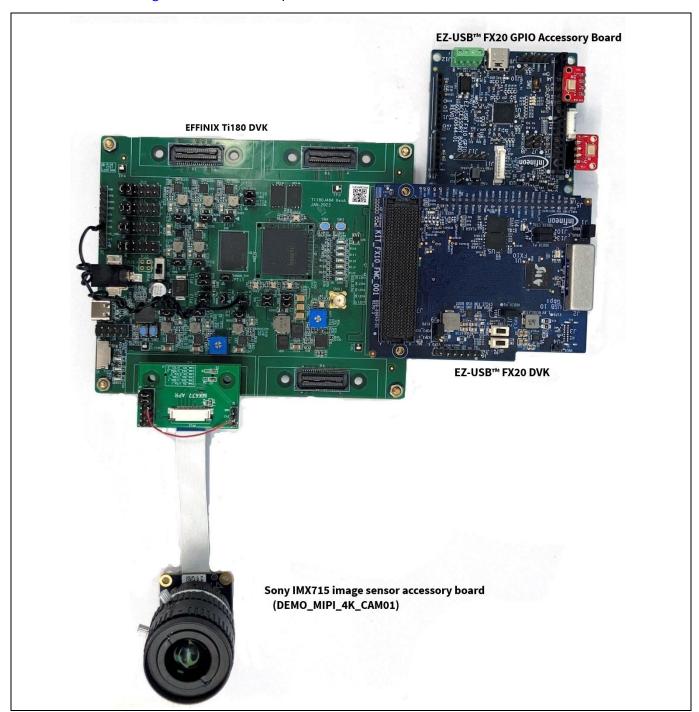

| 11.6             | Hardware and software requirement                                                                    |                |

| 11.7             | Hardware kit                                                                                         |                |

| 11.8             | EFINIX Ti180 FPGA board setup and hardware modification                                              |                |

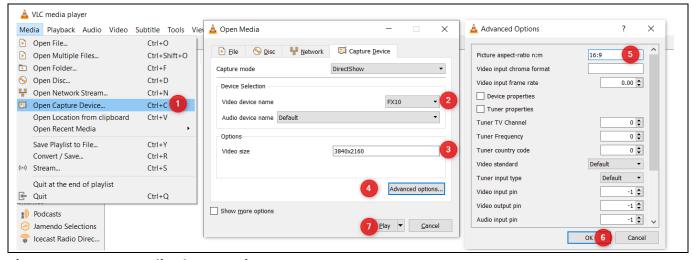

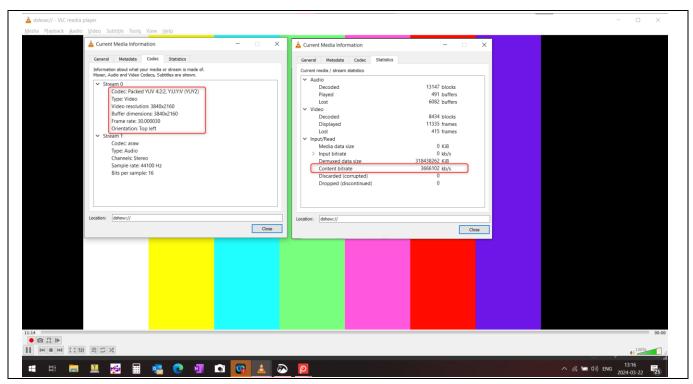

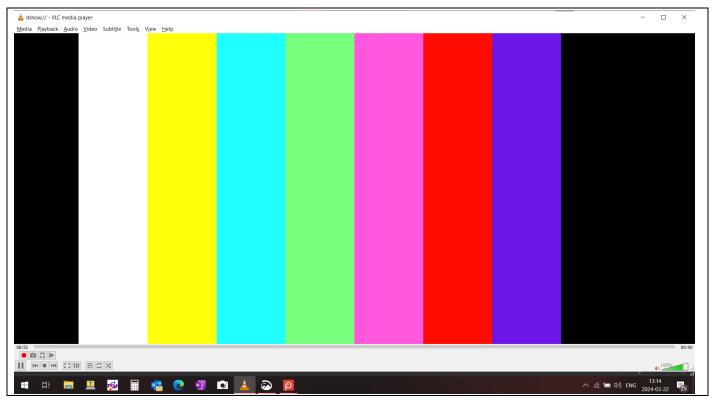

| 11.8.1           | Streaming video using VLC media player                                                               |                |

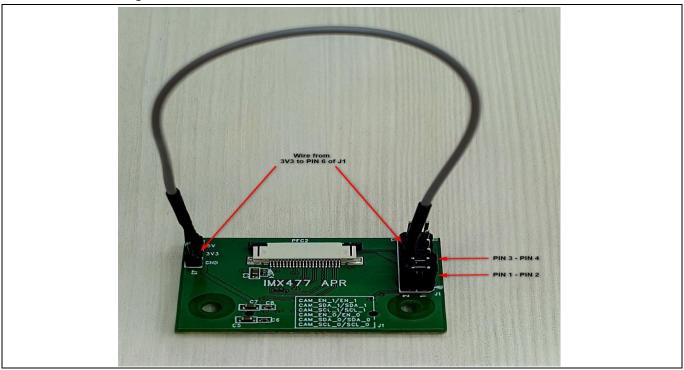

| 11.8.2           | PDM microphone add-on board support                                                                  |                |

|                  | • • • • • • • • • • • • • • • • • • • •                                                              |                |

| <b>12 T</b> 12.1 | roubleshooting                                                                                       |                |

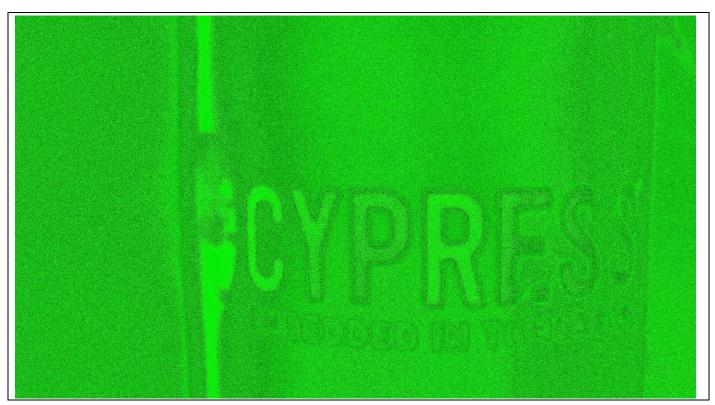

| 12.1             | Black screen viewed in host application                                                              |                |

| 12.2             | Unable to get 4K video streaming at 60 fps (FX10) or 120 fps (FX20)<br>Video freeze during streaming |                |

|                  |                                                                                                      |                |

| Application      | JIT HOLE 5                                                                                           | UUZ-30089 KEV. |

#### **Table of contents**

|       | aimer                      | 82 |

|-------|----------------------------|----|

| Revis | sion history               | 81 |

| Refe  | rences                     | 80 |

|       | Summary                    |    |

|       | FPGA projects              |    |

| 13.1  | EZ-USB™ FX20 firmware      | 78 |

| 13    | Associated project files   | 78 |

|       | Discontinuous audio output |    |

| 12.4  | No audio output            | 75 |

Introduction

#### 1 Introduction

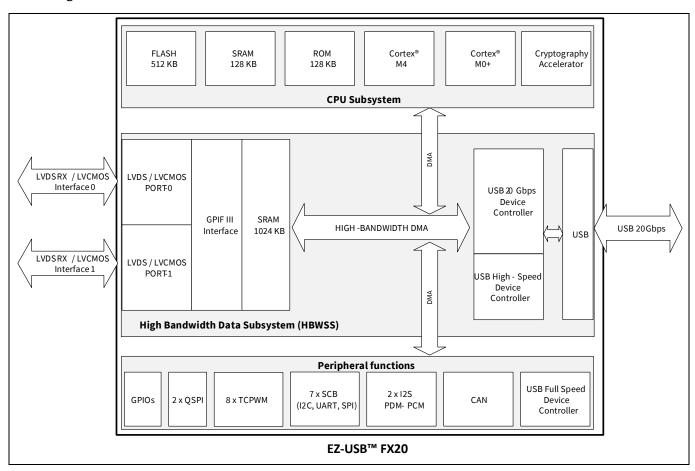

The EZ-USB™ FX20/FX10/FX5N/FX5 is a family of USB peripheral controllers that comply with the USB 3.2 Gen 2x2 specification and are backward compatible with the USB 3.1 and USB 2.0 specification. EZ-USB™ FX20 consist of dual Arm® Cortex®-M4 and M0+ core CPUs, a 512 KB flash, 128 KB SRAM, 128 KB ROM, seven Serial Communication Blocks (SCBs), a cryptography accelerator, and a high bandwidth data subsystem providing DMA data transfers between LVDS/LVCMOS and USB ports at speeds up to 20 Gbps. An additional 1 MB SRAM is included in the high bandwidth data subsystem to provide buffering for USB data. EZ-USB™ FX20 also supports USB Type-C plug orientation detection and flip-mux function without the need for external logic.

For a detailed understanding of the EZ-USB<sup>™</sup> FX device architecture and features, see Figure 1, which shows the block diagram of the device. The architectural reference manual provides a comprehensive description of the device's architecture and functionality, including the operation of each resource in all modes. Additionally, the manual offers specific guidance on the use of associated registers, helping to ensure effective implementation and configuration of the device.

Figure 1 EZ-USB™ FX block diagram

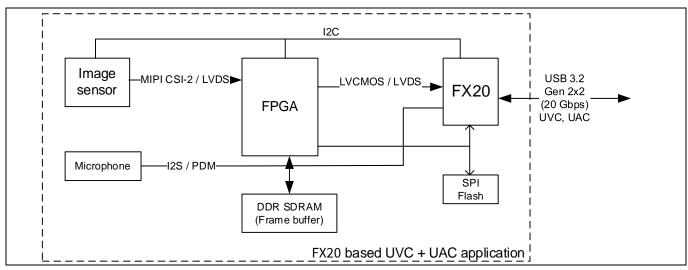

EZ-USB™ FX20 controller is typically used in cameras, video, imaging, and data acquisition. Figure 2 shows EZ-USB™ FX20 controller used in a video and audio application. This Application note provides guidance for implementing a UVC and UAC composite device with EZ-USB™ FX20 controller.

Figure 2 shows an EZ-USB™ FX20 controller connected to a PC equipped with a USB 3.2 Gen 2x2 port. EZ-USB™ FX20 is also connected to an FPGA using the LVDS/LVCMOS interface. The FPGA decodes the image sensor/ISP stream received over MIPI CSI-2/LVDS and sends the video data to EZ-USB™ FX20 over the

#### Introduction

LVDS/LVCMOS interface. The microphone is directly interfaced through Pulse Density Modulation (PDM) port of the EZ-USB™ FX20 controller.

Figure 2 EZ-USB™ FX20 based video and audio application

**USB Video Class (UVC) standard**

### 2 USB Video Class (UVC) standard

USB Video Class (UVC) is a standard introduced by the USB Implementers Forum (USB-IF) that defines the protocol for video streaming functionality over a USB connection. It enables devices, such as webcams, digital camcorders, and other video capturing devices to be quickly recognized and used by computers without the need for special drivers. UVC is an extension of the USB device class specification designed to ensure cross-platform compatibility and plug-and-play functionality. Its standardization simplifies the process of connecting and using video devices, making it a popular choice for manufacturers and end-users alike.

### 2.1 Key features and benefits of USB Video Class (UVC)

- **Plug-and-Play:** One of the main advantages of UVC is its plug-and-play capability. When you connect a UVC-compliant device to a computer, the operating system automatically detects and installs the necessary drivers to support the device, eliminating the need for additional software installation

- **Driverless Operation:** UVC devices do not require specific drivers for each operating system, as modern operating system including Windows, macOS, Linux supports native driver for UVC

- **Stream Control:** UVC defines a standard set of controls for managing video streaming parameters, such as resolution, frame rate, exposure, focus, and white balance. This allows applications and operating systems to adjust the settings of the UVC-compliant camera

- **Interoperability:** With UVC, video streaming devices from different manufacturers can interoperate seamlessly. As long as they adhere to the UVC standard, they should work together without any conflicts

#### 2.2 UVC version support

The UVC specification version has gone through several revisions to improve and expand its capabilities. Each version of UVC introduced new features and enhancements, making it easier to integrate video devices with various host systems without the need for specialized drivers.

- UVC 1.0, The initial release of UVC, was introduced around 2005

- UVC 1.1, released in 2006, brought improvements to UVC 1.0. The size of the processing unit was reduced by one-byte as it does not support analog video standards

- UVC 1.1 includes a new 16-byte GUID field, the length of the MPEG2TS format descriptor was increased to 23 bytes from 7 bytes in UVC 1.0

- UVC 1.5, also known as UVC H.264, was introduced in 2009. UVC 1.1 does not support H.264 compressed video format, while UVC 1.5 supports it and introduced new controls in the camera terminal, processing unit, and encoding unit

Note: The code example attached with this application note supports UVC specification 1.1 and 1.5.

**USB Video Class (UVC) standard**

### 2.3 UVC implementation details

Conforming to the UVC specification requires two EZ-USB™ FX20 code modules:

- Enumeration using UVC descriptors

- Handling UVC requests

### 2.3.1 Enumeration using UVC descriptors

A USB device's capabilities or characteristics are described using descriptors. The code attached to this application note includes a file named fx3g2\_descriptors.c (explained in Section 2.4.1), which contains the UVC enumeration data. The USB specification that defines the format for UVC descriptors is available in the video class section at usb.org. This section gives a high-level overview of the descriptors.

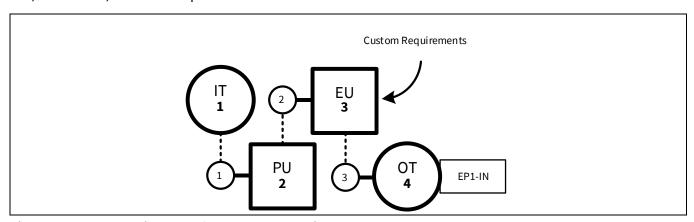

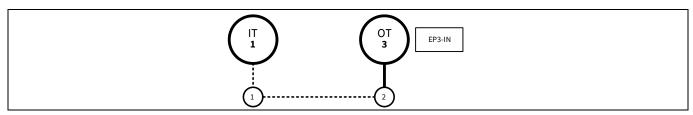

A UVC device comprises four logical elements:

- 1. Input camera terminal (IT)

- 2. Output terminal (OT)

- 3. Processing unit (PU)

- 4. Extension unit (EU)

The elements are connected in the descriptors, as shown in Figure 3. Connections are made between elements by associating terminal numbers in the descriptors. For example, the Input (camera) terminal descriptor declares its ID to be 1, and the processing unit descriptor specifies its input connection to have the ID of 1, logically connecting it to the input terminal. The output terminal descriptor specifies which USB endpoint to use; in this case, BULK-IN endpoint 1.

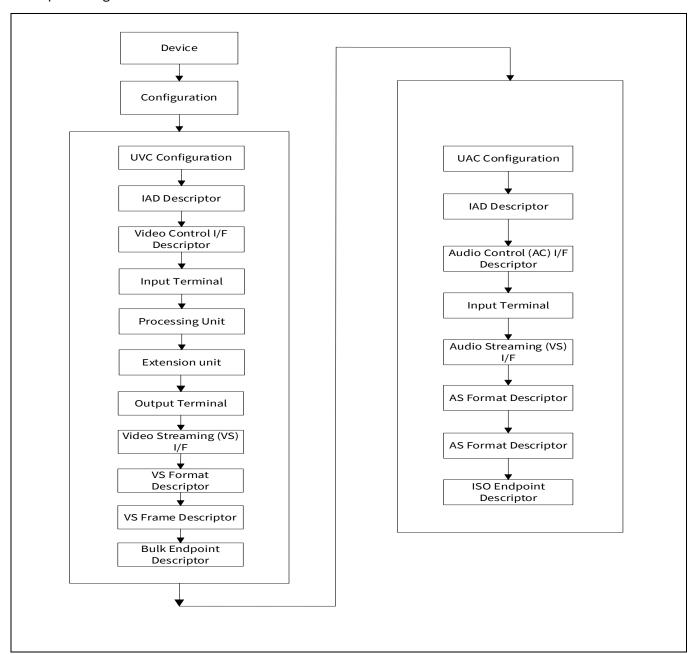

Figure 3 UVC diagram of the camera architecture

The descriptors also include video properties, such as width, height, frame rate, frame size, and bit depth, and control properties, such as brightness, exposure, gain, contrast, pan, tilt, and zoom (PTZ). Apart from the standard video controls, the extension unit provides additional controls based on user requirements.

After successful enumeration, the device will be listed under Camera in the Windows Device Manager.

Note:

The maximum bandwidth achievable using the ISOC-IN endpoint under UVC for USB 3.2 in Windows 7/8 machine is 24 Mbps because the UVC driver limits the BURST to 1 for the ISOC endpoint. But with the Windows 10 machine, BURST can be set to 15 to achieve maximum ISOC bandwidth (10 Gbps). There is no such limitation for BULK endpoint. Therefore, the ISOC-IN endpoint is not used in this project. See this forum for more information.

**USB Video Class (UVC) standard**

### 2.3.2 Handling UVC requests

After the host enumerates the camera, the UVC driver sends a series of requests to the camera to determine operational characteristics. This is called the capability request phase. It precedes the streaming phase, in which the host application starts streaming video. The EZ-USB™FX20 firmware responds to the requests that arrive over the USB control endpoint (EP0).

For example, suppose a UVC device indicates that it supports a brightness control in one of its USB descriptors. During the capability request phase, the UVC driver queries the device to discover the relevant brightness parameters.

When a host application makes a request to change the brightness value, the UVC driver issues a SET control request to change the brightness value (SET\_CUR).

Similarly, when the host application chooses to stream a supported video format/frame rate/frame size, it issues streaming requests. There are two types: PROBE and COMMIT. PROBE requests are used to determine if the UVC device is ready to accept changes to the streaming mode. A streaming mode is a combination of image format, frame size, and frame rate. The COMMIT control is used to configure the hardware with the streaming parameters from the Probe control.

#### 2.4 USB video class requirements

The firmware project for this application note is in the folder named *cyfxuvc\_uac\_an38689*. This section explains how the UVC requirements are satisfied by the example project. UVC requires a device to:

- Enumerate with the UVC-specific USB descriptors.

- Handle SET/GET UVC-specific requests for the UVC control and stream capabilities reported in the USB descriptors.

- Stream video data in a UVC-conformant color format.

- Add a UVC conformant header for every image payload.

Details of these requirements can be found in the UVC Specification v1.5.

#### 2.4.1 USB descriptors for UVC

The fx3g2\_descriptors.c file contains the USB descriptor tables. The byte arrays CyFxUSBHSConfigDscr (Hi-Speed) and CyFxUSBSSConfigDscr (SuperSpeed and SuperSpeed Plus) contain the UVC-specific descriptors. These descriptors implement the following tree of sub-descriptors:

Configuration descriptor

- Interface association descriptor

- Video control (VC) interface descriptor

- VC interface header descriptor

- o Input (camera) terminal descriptor

- o Processing unit descriptor

- Extension unit descriptor

- Output terminal descriptor

- VC status interrupt endpoint descriptor

- Video streaming (VS) interface descriptor

- VS interface input header descriptor

**USB Video Class (UVC) standard**

- VS format descriptor

- VS frame descriptor

- BULK-IN video endpoint descriptor

The configuration descriptor is a standard USB descriptor that defines the functionality of the USB device in its sub-descriptors. The interface association descriptor is used to indicate to the host that the device conforms to a standard USB class. Here, this descriptor reports a UVC-conformant device with two interfaces: video control (VC) interface and video streaming (VS) Interface. Having two separate interfaces makes the UVC device a USB composite device.

#### 2.4.1.1 Video control (VC) interface

The VC interface descriptor and its sub-descriptors report all the control interface-related capabilities. Examples include brightness, contrast, hue, exposure, and PTZ controls.

The VC interface header descriptor is a UVC-specific interface descriptor that points to the VS interfaces to which this VC Interface belongs.

The input (camera) terminal descriptor, the processing unit descriptor, the extension unit descriptor, and the output terminal descriptor contain bitfields that describe features supported by the respective terminal or unit.

The camera terminal controls mechanical (or equivalent digital) features, such as exposure and the PTZ of the device that transmits the video stream.

The processing unit controls image attributes, such as brightness, contrast, and hue of the video being streamed through it.

The extension unit allows vendor-specific features to be added, much like standard USB vendor requests. In this design, the extension unit is empty, but a sample design is implemented, and it can be enabled to get or set the device firmware version. If the extension unit is utilized, the standard host application will not see its features unless the host application is designed to recognize them. A sample host application is provided to get or set the device firmware version. You can design your own extension controls and host application to query these controls. Some features that can be supported include getting the device firmware version and hardware IDs, writing to sensor/image signal processor (ISP) registers, and so on. The device can support more than one extension unit. For more details on the UVC extension unit with the associated firmware project, see 2.4.2.

The output terminal is used to describe an interface between these units (IT, PU, EU) and the host. The VC status interrupt endpoint descriptor is a standard USB descriptor for an Interrupt endpoint. This endpoint can be used to communicate UVC-specific status information. The functionality of this endpoint is outside the scope of this application note.

The UVC specification divides these functionalities so that you can easily structure the implementation of the class-specific control requests. However, the implementation of these functionalities is application-specific. The supported control capabilities are reported in the bitfield bmControls ( $fx3g2\_descriptors.c$ ) of the respective terminal/unit descriptor by setting the corresponding capability bits to '1'. The UVC device driver polls for details about the control on enumeration. The polling for details is carried out over EP0 requests. All such requests, including the video streaming requests, are handled by the Cy\_USB\_AppSetupCallback function in the  $cy\_usb\_app.c$  file.

**USB Video Class (UVC) standard**

### 2.4.1.2 Video streaming (VS) interface

The video streaming interface descriptor and its sub-descriptors report the various frame formats (e.g., uncompressed, MPEG, H.264), frame resolutions (width, height, and bit depth), and frame rates. Based on the values reported, the host application can choose to switch streaming modes by selecting supported combinations of frame formats, frame resolutions, and frame rates.

The VS interface input header descriptor specifies the number of VS format descriptors that follow.

The VS format descriptor contains the images' aspect ratio and the color format, such as uncompressed or compressed.

The VS frame descriptor contains image resolution and all supported frame rates for that resolution. If the camera supports different resolutions, multiple VS frame descriptors follow the VS format descriptor.

The BULK-IN video endpoint descriptor is a standard USB endpoint descriptor that contains information about the bulk endpoint used for streaming video.

This example uses four resolutions with multiple frame rates. Its image characteristics are contained in two descriptor tables and the probe/commit control structure table, as shown in the following tables (only relevant byte offsets are shown).

Table 1 VS format descriptor value

| VS format descriptor byte offset | Characteristic                                              | SuperSpeed Plus value                                                                      | Hi-Speed value                                                                             |

|----------------------------------|-------------------------------------------------------------|--------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|

| 4                                | Number of frame<br>descriptors with the<br>described format | 4                                                                                          | 1                                                                                          |

| 5-20                             | GUID of streaming-<br>encoding format                       | 'Y', 'U', 'Y', '2',0X00,0X00,<br>0X10,0X00,0X80,0X00,<br>0X00,0XAA,0X00,0X38,<br>0X9B,0X71 | 'Y', 'U', 'Y', '2',0X00,0X00,<br>0X10,0X00,0X80,0X00,<br>0X00,0XAA,0X00,0X38,<br>0X9B,0X71 |

| 21                               | Number of bits per pixel                                    | 16                                                                                         | 16                                                                                         |

| 23-24                            | Width to height ratio                                       | 16:9                                                                                       | 4:3                                                                                        |

Table 2 VS frame descriptor value

| VS frame descriptor byte offset | Characteristic                                                 | SuperSpeed value                       | Hi-Speed value                       |

|---------------------------------|----------------------------------------------------------------|----------------------------------------|--------------------------------------|

| 3                               | Frame descriptor index                                         | 1                                      | 1                                    |

| 5-6                             | Width in pixel                                                 | 3840                                   | 640                                  |

| 7-8                             | Height in pixel                                                | 2160                                   | 480                                  |

| 13-16                           | Maximum bit rate at the shortest frame interval in unit of bps | 3840x2160x16x30 fps<br>(16 bits/pixel) | 640x480x16x15 fps<br>(16 bits/pixel) |

| 21-24, also 26-29               | Frame interval in 100 ns units                                 | 0x51615 (30 fps)                       | 0xA2C2A (15 fps                      |

Note that multiple-byte values are listed LSB first (little-endian), so, for example, the frame rate is 0x00051615, which is 33.33 milliseconds, or 30 fps.

**USB Video Class (UVC) standard**

Table 3 Probe/commit structure values

| Probe/commit structure byte offset | Characteristic                 | SuperSpeed value               | Hi-Speed value               |

|------------------------------------|--------------------------------|--------------------------------|------------------------------|

| 2                                  | Format index                   | 1                              | 1                            |

| 3                                  | Frame index                    | 1                              | 1                            |

| 4-7                                | Frame interval in 100 ns units | 0x51615 (30 fps)               | 0xA2C2A (15 fps)             |

| 18-21                              | Maximum image size in bytes    | 3840x2160x2<br>(2 bytes/pixel) | 640x480x2<br>(2 bytes/pixel) |

This design can be adapted to support different image resolutions, such as 1080p, 720p, etc. by modifying the entries in these three tables.

### 2.4.2 UVC-specific requests

The UVC specification uses USB control endpoint EP0 to communicate control and streaming requests to the UVC device. These requests are used to discover and change the attributes of the video-related controls. The UVC specification defines these video-related controls as capabilities. These capabilities allow you to change image properties or to stream video. A capability (first item) can be a video control property, such as brightness, contrast, and hue, or video stream mode properties, such as the color format, frame size, and frame rate. Capabilities are reported via the UVC-specific section of the USB Configuration descriptor. Each of the capabilities has attributes. The attributes of a capability are as follows:

- The minimum value

- The maximum value

- The number of values between the minimum and the maximum

- The default values

- The current value

SET and GET are the two types of UVC-specific requests. SET is used to change the current value of an attribute, while GET is used to read an attribute.

Here is a list of UVC-specific requests:

- SET\_CUR is the only type of SET request

- GET\_CUR reads the current value

- GET\_MIN reads the minimum supported value

- GET\_MAX reads the maximum supported value

- GET\_RES reads the resolution (step value to indicate the supported values between min and max)

- GET\_DEF reads the default value (return the appropriate value to set defaults for any parameter, e.g., default frame resolution, etc.)

- GET\_LEN reads the size of the attribute in bytes

- GET\_INFO queries the status/support for specific capability

The UVC specification defines these requests as either mandatory or optional for a given capability. For example, if the SET\_CUR request is optional for a particular capability, its presence is determined through the GET\_INFO request. If the camera does not support a certain request for a capability, it must indicate this by stalling the control endpoint when the request is issued from the host to the camera.

**USB Video Class (UVC) standard**

There are byte fields in these requests that qualify their target capability. These byte fields have a hierarchy, which follows the same structure as the UVC-specific descriptors described in Section 2.3.1. The first level identifies the interface (video control or video streaming).

If the first level identifies the interface as video control, the second level identifies the terminal or unit, and the third level identifies the capability of that terminal or unit. For example, if the target capability is the brightness control, then:

- First level = video control

- Second level = processing unit

- Third level = brightness control

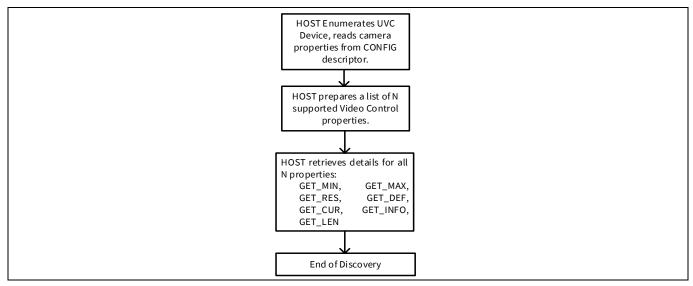

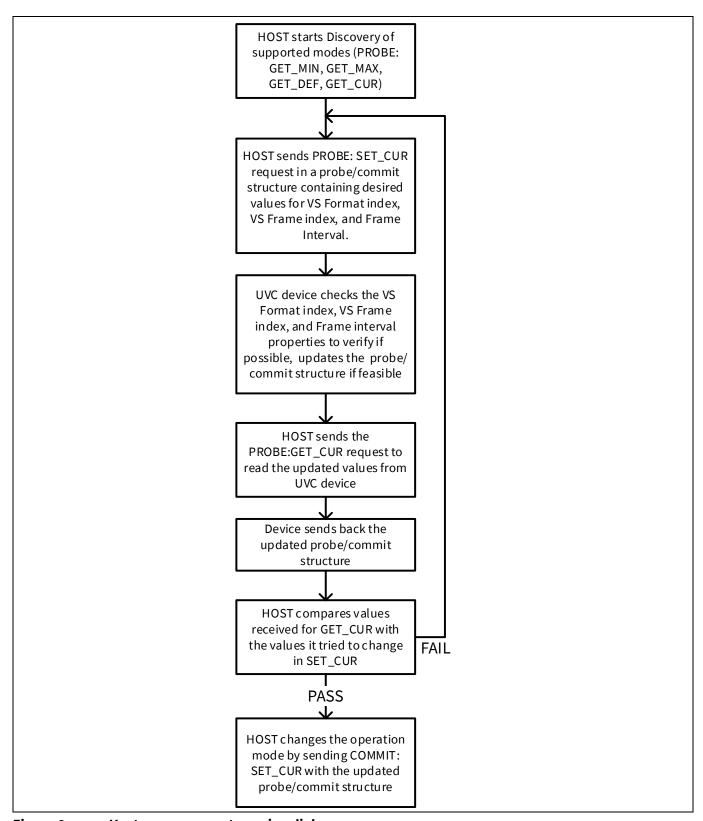

If the first level identifies the interface as video streaming, the second level would be PROBE or COMMIT. There is no third level. When the host wants the UVC device to start streaming or to change the streaming mode, the host first determines if the device supports the new streaming mode. To determine this, the host sends a series of SET and GET requests with the second level set to PROBE. The device either accepts or rejects the change to the streaming mode. If the device accepts the change request, the host confirms it by sending the SET\_CUR request with the second level set to COMMIT. This interaction between the host and the device is illustrated in Figure 4. The following three flowcharts show how the host interacts with a UVC device.

Figure 4 The UVC enumeration and discovery flow figure

When the UVC device is plugged into USB, the host enumerates it and discovers details about the properties supported by the camera (Figure 5).

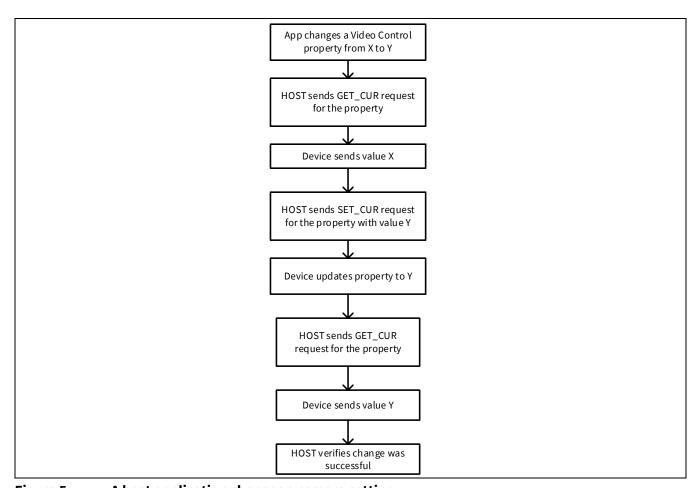

During a video operation, a camera operator may change a camera property, such as brightness, in a display dialog presented by the host application. Figure 6 shows this interaction.

This kind of implementation is a synchronous control transfer. As per the UVC specification, a device can support two kinds of control requests: synchronous control transfer and asynchronous control transfer.

Standard UVC requests like brightness, pan, tilt, and zoom (PTZ) requests take lesser time to complete (less than 10 ms). In this case, UVC device writes to a sensor/ISP register and doesn't wait for any acknowledgment from the sensor/ISP. When host drivers send a SET\_CUR request, the device responds within 10 ms with a success (acknowledge the request) or failure (stall the request). As per UVC specs, this request is synchronous in nature. All standard UVC video control requests can be supported through the **synchronous control transfers**.

**USB Video Class (UVC) standard**

Now assume that a host driver sets an exposure value. As per design implementation, the sensor/ISP responds with an acknowledgement in about 100mS. The device always responds to the SET\_CUR request with a success for the SET\_CUR request and after receiving the acknowledgement from the sensor/ISP, the device loads the control status Interrupt endpoint with a success or failure. This kind of request is an **asynchronous control request**. Note that the asynchronous control request transfers are not handled on this project as all the requests are synchronous in nature.

Note: For more details on how to use the control status interrupt of the video control interface, see

Section 2.4.2.2 "Status Interrupt Endpoint" in the UVC Specification v1.5.

Note: Status interrupt endpoint can be used to handle status interrupt endpoint for hardware-triggered

still capture. For asynchronous video controls, the status interrupt endpoint response can be populated based on Table 2-2: Status Packet Format (VideoControl Interface as the Originator) of the UVC Specification, with appropriate Control selector value (bSelector) based on the queried

video control.

Figure 5 A host application changes a camera setting

Before starting to stream, the host application issues a set of probe requests to discover the possible streaming modes. After the default streaming mode is decided, the UVC driver issues a COMMIT request. This process is shown in Figure 6. At this point, the UVC driver is ready to stream video from the UVC device.

**USB Video Class (UVC) standard**

Figure 6 Host-camera pre-streaming dialog

**USB Video Class (UVC) standard**

### 2.4.2.1 Control requests - Brightness, PTZ control, and extension unit control

Brightness and PTZ controls are implemented in the associated project. PTZ can be turned on by setting the macro value UVC\_PTZ\_EN to '1' in the *cy\_usb\_uvc\_device.h* file. It is important to note that this control may not be supported by the image sensor, and if that is the case, specific hardware must be designed accordingly. Regardless, the firmware implementation for these controls on the USB side remains the same. However, the image sensor implementation might differ. Therefore, only placeholder functions are provided that implement the USB side of these controls, however, so you will need to write code for the image sensor specific PTZ implementation.

Note:

The functions described for UVC controls are implemented in the cy\_usb\_videocontrol.c file. This file is part of the project stored in the cyfxuvc\_an38689 folder, which can be found in the zip file of the source code attached to this application note.

The host application sends video control requests (over EP0) that are targeted to the processing unit for brightness control. All setup requests are handled via the  $Cy\_USB\_AppSetupCallback$  function. This function detects whether the host has sent a UVC-specific request (control or stream) and then handles the specific request in the  $Cy\_USB\_AppSetupCallback$  function and sets an event flag for only SET\_CUR request, labeled as "CY\_USB\_UVC\_DEVICE\_SET\_CUR\_RQT". This flag is processed by the  $Cy\_USB\_UVcDeviceTaskHandler()$  function.

Control requests will trigger the video control request event CY\_USB\_UVC\_DEVICE\_VIDEO\_CNTRL\_RQT flag. The Cy\_USB\_UvcDeviceTaskHandler function looking for any of these flags to be raised, and then it calls the HandleVCInterfaceRequest function in order to decode the video control request. Based on the type of control UVC that is being requested, the appropriate function is called.

Modify the function under *CY\_UVC\_VC\_PROCESSING\_UNIT\_ID* to implement processing unit-related controls (brightness, contrast, hue, and so on). Modify the function under *CY\_UVC\_VC\_CAMERA\_TERMINAL\_ID* to implement camera terminal controls.

The UVC specification includes details on camera terminal, processing unit, and extension unit USB descriptors.

An extension unit control – to Get or Set device firmware version can be implemented in the EZ-USB™ FX20. For more details on how to design a UVC extension unit in the firmware, see Implementing extension unit control in AN75779 example project. The get or set firmware version control allows you to retrieve and update the firmware version. This can be achieved by using the uvc\_extension\_app\_x86.exe (for 32-bit Windows) or uvc\_extension\_app\_x64 (for 64-bit Windows). Guidelines for running the host application is provided in the readme.txt file. The host application is based on Microsoft's Media foundation class and DirectShow APIs. For additional information on the host application, see the forum discussion.

Note:

At this moment, EZ-USB™ FX20 UVC firmware does not support Extension unit control request, it will be added later.

### 2.4.2.2 Streaming requests - Probe and commit control

The Cy\_USB\_AppSetupCallback function is responsible for handling streaming-related requests. When the UVC driver needs to stream video from a UVC device, the first step is to negotiate with the device. In this phase, the driver sends a set of parameters to the device using PROBE requests, which includes GET\_MIN, GET\_MAX, GET\_RES, and GET\_DEF. In response, the EZ-USB<sup>TM</sup> FX20 firmware returns a PROBE structure that, contains the USB descriptor indices of video format and video frame, frame rate, maximum frame size, and payload size (the number of bytes that the UVC driver can fetch in one transfer).

**USB Video Class (UVC) standard**

The switch case for CY\_USB\_UVC\_VS\_PROBE\_CONTROL handles the negotiation phase of the streaming process for either a USB 2.0 or USB 3.2 connection (the properties of the supported video in these modes differ). Note that the reported values for GET\_MIN, GET\_MAX, GET\_DEF, and GET\_CUR are the same because the same streaming mode is supported in either USB 2.0 or USB 3.2. These values would differ if multiple streaming modes needed to be supported.

The switch case for  $CY\_USB\_UVC\_VS\_COMMIT\_CONTROL$  handles the start of the streaming phase. When the host sends a SET\_CUR request for COMMIT control, it indicates that it will start streaming video next. Therefore, when SET\_CUR for COMMIT control is received, it triggers the  $CY\_USB\_UVC\_DEVICE\_SET\_CUR\_RQT$  event. This event, in turn, causes the main application thread's  $CY\_USB\_UVCDeviceTaskHandler$  to call the  $CY\_USB\_UVCSetCurRqtHandler$  function. This function informs the video source about selected video parameters and starts the GPIF III state machine for video streaming.

#### 2.4.3 Video data format: YUY2

The UVC specification supports only a subset of color formats for video data. Therefore, you should choose an image sensor/ISP that streams images in a color format that conforms to the UVC specification. This application note covers an uncompressed color format called YUY2, which is supported by most, but not all, image sensors. The YUY2 color format is a 4:2:2 down-sampled version of the YUV color format. Luminance values Y are sampled for every pixel, but chrominance values U and V are sampled only for even pixels. This creates "macro pixels", each of which describes two image pixels using a total of four bytes. Notice that every other byte is a Y value, and the U and V values represent only even pixels:

Y0, U0, Y1, V0 (first 2 pixels)

Y2, U2, Y3, V2 (next 2 pixels)

Y4, U4, Y5, V4 (next 2 pixels)

See Wikipedia for additional information on color formats.

Note:

If you want to change the video format, the GUID must also be changed in the VS format descriptor. See the Media types for information on the GUIDs for supported formats.

Although a monochrome image is not supported as a part of the UVC specification, an 8-bit monochrome image can be represented in the YUY2 format by sending the monochrome image data as Y values and setting all the U and V values to 0x80.

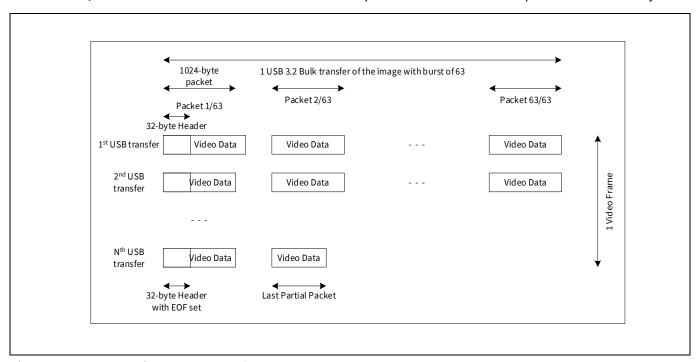

#### 2.4.4 UVC video data header

As per the UVC specification, each video payload sent to the host requires a header. This header contains the information about the properties of the image data being transferred. For instance, it contains a "new frame" bit that the image sensor / ISP controller (EZ-USB™ FX20) toggles for every frame. Additionally, the EZ-USB™ FX20 can include Presentation Time Stamp and Source Clock reference in the header and set an error bit to indicate any issues encountered during the streaming of the current frame. This UVC data header is required for every USB transfer. For more information, see the UVC specification. You can see the format of the UVC video data header in Table 4. The code example used in this application note uses a 32-byte header.

Table 4 UVC video data header format

| Byte offset | Field name | Description                                                                     |

|-------------|------------|---------------------------------------------------------------------------------|

| 0           | HLF        | bHeaderLength - Header length field specifies the length of the header in bytes |

**USB Video Class (UVC) standard**

| Byte offset | Field name | Description                                                                                                                                 |  |

|-------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1           | BFH        | bmHeaderInfo - Bitfield header indicates the type of the image data, status of the video stream and the presence or absence of other fields |  |

| 2-5         | PTS        | dwPresentationTime - Presentation time stamp indicates the source clock time in native device clock units                                   |  |

| 6-11        | SCR        | scrSourceClock - Source clock reference indicates system time clock and USB start-of-frame (SOF) token counter                              |  |

| 12-31       | PAD        | To ensure 32-byte alignment is required for DMA channel creation, zero padding is required                                                  |  |

Note:

See USB\_Video\_Payload\_Frame\_Based\_1.5.pdf section 2.1 Payload Header available in Video Class v1.5 document at www.usb.org.

The Header Length Field (HLF) value is always 32 in the example code provided with this application note. Although the Presentation Time Stamp (PTS) and Source Clock Reference (SCR) fields are optional, the firmware example (Firmware link should be added here) populates these fields with zeros.

Table 5 shows the format of the BFH, which is a part of the UVC video data header.

Table 5 Bitfield header (BFH) format

| Bit offset | Field name | Description                                                                                                        |  |

|------------|------------|--------------------------------------------------------------------------------------------------------------------|--|

| 0          | FID        | Frame identifier bit toggles at each image frame start boundary and stays constant for the rest of the image frame |  |

| 1          | EOF        | End of frame bit indicates the end of a video and is set only in the last USB transfer belonging to an image frame |  |

| 2          | PTS        | Presentation time stamp bit indicates the presence of a PTS field in the UVC video data header (1=present)         |  |

| 3          | SCR        | Source clock reference bit indicates the presence of an SCR field in the UVC video data header (1=present)         |  |

| 4          | RES        | Reserved, set to 0                                                                                                 |  |

| 5          | STI        | Still image bit indicates if the video sample belongs to a still image                                             |  |

| 6          | ERR        | Error bit indicates an error in the device streaming                                                               |  |

| 7          | EOH        | End of header bit, when set, indicates the end of the BFH fields                                                   |  |

The bitfield header (BFH) keeps changing value at the end of a frame.

UVC header insertion can be done in any of the following methods:

- Adding UVC header by firmware

- Adding UVC header by FPGA

- Adding UVC header using insert metadata feature of EZ-USB™ FX20

**Method 1:** In this method, the CPU is involved in adding the UVC header. The DMA channel should be created in manual mode by enabling producer and consumer interrupts.

**Method 2:** In this method, FPGA is preconfigured to insert the header. The FPGA adds the 32-byte UVC header to every payload, which is then sent to the USB host. The DMA channel can be created in Auto mode, and this method can help to get maximum throughput as there is no CPU interaction.

**USB Video Class (UVC) standard**

Method 3: In this mode, the 32-byte UVC header is stored in EZ-USB™ FX20 Metadata Memory, and the DMA Hardware inserts the UVC header to each DMA buffer on receiving the Insert metadata command (INMD) over the control lane and commit it to the USB host without CPU interaction. The DMA channel can be created in Auto mode. See the EZ-USB™ FX20 architecture reference manual to know more details about metadata insertion.

In this project, the UVC header can be inserted by FPGA or EZ-USB™ FX20 by setting the appropriate macros in "cy\_usb\_app.h" header file.

- Set 'MANUAL\_DMA\_CHANNEL' to value '1' and ensure that 'UVC\_HEADER\_BY\_FX20' is updated with value '1'. This will enable the manual DMA channels configuration and UVC header insertion by EZ-USB™ FX20 CPU

- Set 'MANUAL\_DMA\_CHANNEL' to value '0' and ensure that 'UVC\_HEADER\_BY\_FPGA' is updated with value '1'. This will enable the Auto DMA channel configuration and UVC header insertion by the EFINIX Ti180 FPGA

Figure 7 illustrates how the headers are added to the video data. The 32-byte header is added for every USB bulk transfer, and each transfer includes a total of 63 bulk packets. The USB 3.2 bulk packet size is 1024 bytes.

Figure 7 UVC video data transfers

**USB Audio Class (UAC) standard**

### 3 USB Audio Class (UAC) standard

The USB Audio Class (UAC) was introduced to simplify the process by defining a common set of rules and requirements that audio devices must follow to communicate with USB host devices effectively. This standardization ensures that USB audio devices, such as microphones, speakers, headphones, sound cards, and audio interfaces, can be easily connected and used without the need for specialized drivers or software installations.

The USB Audio class (UAC) uses the isochronous transfer type (Endpoint) to stream audio across a USB link. Isochronous transfers are continuous, real-time transfers that have a pre-negotiated bandwidth. Because isochronous transfers do not have an error recovery mechanism or handshaking, they must support streams of error-tolerant data.

Conforming to the UAC requires two EZ-USB™ FX20 code modules:

- Enumeration using UAC descriptors

- Handling UAC requests. Stream Audio data

#### 3.1 UAC version support

The USB Implementers Forum (USB-IF) is responsible for defining and updating the USB Audio specifications. Below is the list of USB audio class version released by USB-IF.

- **USB Audio 1.0:** This was the initial version of the USB Audio specification and was released in 1998. Supports audio data rate up to 96 kHz. Maximum bit depth is 24 bits

- Supported low sample rates and bit depths

- USB Audio Version 1.0 is implemented in the firmware example provided with this application.

- **USB Audio 2.0:** This version was released in 2006 and brought significant improvements over the previous versions. Supports audio data rate up to 192 kHz and supports some feature

- Support for multiple audio channels

- Maximum bit depth is 32 bits

- Support for higher sample rates and bit depths

- Support for asynchronous data transfers

- Support for digital signal processing (DSP)

- Supported more advanced audio devices like external sound cards and audio interfaces

- **USB Audio 3.0:** This version was a proposed update to the specification to support SuperSpeed USB (USB 3.0) capability and was released in 2016. Supports audio data rate up to 384 kHz

- Number of channel supports is 32. Maximum bit depth is 32 bits

- Support USB Type-C

- **USB Audio 4.0:** This version is released in April 2023

### 3.2 Enumeration using UAC descriptor

The code attached to this application note includes a file named fx3g2\_descriptors.c, which is explained in Section 2.3.1 contains the UAC enumeration data. The USB specification that defines the format for UAC descriptors is available in the Audio class section at usb.org. This section gives a high-level overview of the descriptors.

#### **USB Audio Class (UAC) standard**

The endpoint descriptors store stream-related parameters, while the Terminal descriptor stores control-related parameters. The audio functionality is divided into two entities are called Unit and Terminals. The standard UAC specification describes seven different types of standard Unit and Terminals that represent most of the audio functions. In this application note, interfacing the microphone as a UAC device, and it requires two logical elements.

- Input camera terminal (IT)

- Output terminal (OT)

The elements are connected in the descriptors, as shown in Figure 8. Connections are made between elements by associating terminal numbers in the descriptors. For example, the input (Audio) terminal descriptor describes how signals carried over USB are handled, in this case Microphone or Digital audio. The IT declares its ID to be 1, and the Feature unit descriptor specifies that its input connection to have the ID of 1, logically connecting it to the input terminal. The output terminal descriptor specifies which USB endpoint to use, in this case ISOCHRONOUS-IN endpoint 4.

Figure 8 UAC diagram

The descriptor also specifies the type of input audio, such as Microphone or Digital audio.

After successful enumeration, the device will be listed under **Audio input and output** in the **Windows Device Manager**.

#### 3.3 Operational code

When the USB device connects to a USB port, the host retrieves information about the device's capabilities through the control transfers during enumeration. After receiving the information during the enumeration process, the host determine how to communicate with the device. To control the functional behavior of an audio function, the host can manipulate the Units and Terminals inside the audio function via the Audio control interface. The device precedes to streaming phase, during which the host application starts streaming Audio. The EZ-USB™ FX20 firmware commits the audio data to the host over the Audio streaming endpoint (EP4).

For example, suppose a UAC device indicates that it supports a volume control in Feature Unit descriptors. The USB Audio Class defines a standard set of control requests that can be used to control various aspects of the audio function, including volume.

When a host application makes a request to change the audio volume, the host issues a SET control request (SET\_CUR), which contains the parameters that the host wants to set, including the volume level. The audio function responds with a status message indicating whether the request was successful or not to alter the volume.

Similarly, when the host application chooses to control supported audio control (Volume/Mute/Tone Control), it issues a SET control request (SET\_CUR) and GET control request (GET\_CUR) to alter the volume level.

**USB Audio Class (UAC) standard**

### 3.4 USB audio class requirements

The firmware project for this application note is in the folder named *cyfxuvc\_uac\_an38689*. This section explains how the UAC requirements are satisfied by the example project. The UAC requires a device to:

- Enumerate with the UAC-specific USB descriptors.

- Stream audio data in a UAC-conformant audio format.

Details of these requirements are found in the UAC Specification.

#### 3.4.1 USB descriptors for UAC

The fx3g2\_descriptors.c file contains the USB descriptor tables. The byte arrays CyFxUSBHSConfigDscr (Hi-Speed) and CyFxUSBSSConfigDscr (SuperSpeed and Super Speed Plus) contain the UAC-specific descriptors. These descriptors implement the following tree of sub-descriptors:

Configuration descriptor

- Interface association descriptor

- Audio control (AC) interface descriptor

- Input (Audio) terminal descriptor

- Output terminal descriptor

- Audio streaming (AS) interface descriptor

- AS format descriptor

- ISOCHRONOUS-IN video endpoint descriptor

#### 3.4.1.1 Audio control interface

Audio functions are addressed through their audio interfaces. Each audio function has a single Audio Control (AC) interface and can have several Audio Streaming (AS) interfaces. The Audio Control (AC) interface descriptor and its sub-descriptors report all the control interface-related capabilities. Examples include Volume, Mute, Automatic gain control, equalizer, bass boost, and tone controls.

The input (Audio) terminal descriptor, the feature unit descriptor, and the output terminal descriptor contain bitfields that describe features supported by the respective terminal or unit.

The Input Terminal (IT) is used to interface between the audio function's 'outside world' and other Units in the audio function. It serves as a medium for audio information flowing into the audio function and it represents the source of incoming audio data.

The Output Terminal (OT) represents an ending point for audio channels, it is used to describe an interface between IT, FU, and the host. It serves as an outlet for audio information. Its function is to represent a sink of outgoing audio data, for example a speaker built into an audio device or a Line Out connector.

An interrupt endpoint can be used for status returns. This endpoint is optional. All descriptors related to the internals of the audio function are part of the class-specific Audio Control- (AC) interface descriptor. The Audio Control (AC) interface of an audio function may support multiple alternate settings. The functionality of this endpoint is outside the scope of this application note.

The UAC device driver polls for details about the control on enumeration. The polling for details is carried out over EPO requests. All such requests, including the Audio streaming requests, are handled by the Cy USB PDMDeviceTaskHandler function in the cy\_usb\_uac.c file.

**USB Audio Class (UAC) standard**

### 3.4.1.2 Audio streaming (AS) interface

Audio Streaming interfaces are used to interchange digital audio data streams between the Host and the audio function. The Audio streaming interface descriptor and its sub-descriptors report the various Audio stream and Audio data format (e.g., Mono 8-bit PCM to MPEG2 7.1), see USB Audio Data Formats document from USB-IF to know about supported audio data format. The audio device can support multiple configurations. Within each configuration can be multiple interfaces, each interface can possibly having alternate settings.

Table 6 Class specific audio streaming interface

| AS format descriptor byte offset | Characteristic        | SuperSpeed Plus value | Hi-Speed value |

|----------------------------------|-----------------------|-----------------------|----------------|

| 3                                | Terminal link ID      | 2                     | 2              |

| 4                                | Interface delay in ms | 0x01                  | 0x01           |

| 5-6                              | Format - PCM          | 0x0001                | 0x0001         |

Table 7 Class specific audio streaming format descriptor

| AS format descriptor byte offset | Characteristic          | SuperSpeed Plus value | Hi-Speed value |

|----------------------------------|-------------------------|-----------------------|----------------|

| 3                                | Audio format type - PCM | 1                     | 1              |

| 4                                | Number of channels      | 0x02 (Stereo)         | 0x02 (Stereo)  |

| 5                                | Frame size in bytes     | 2                     | 2              |

| 6                                | Bit Resolution          | 0x10                  | 0x10           |

| 8-10                             | Sampling frequency      | 48000 Hz              | 48000 Hz       |

### 3.5 UAC-specific requests

The UAC specification uses USB control endpoint EP0 to communicate control and streaming requests to the UAC device. These requests are used to discover and change the attributes of the audio-related controls. The UAC specification defines these audio-related controls as capabilities. These capabilities allow you to change audio properties, such as Volume, Mute, and equalizer. Capabilities are reported via the UVC-specific section of the USB Configuration descriptor. Each of the capabilities has attributes. The attributes of a capability are as follows:

- The minimum value

- The maximum value

- The number of values between the minimum and the maximum

- The default values

- The current value

SET and GET are the two types of UAC-specific requests. SET is used to change the current value of an attribute, while GET is used to read an attribute.

Note: In this application note, used PDM microphones as input to (IT) and (OT) is USB host. Feature Unit (FU) is not needed for this example.

USB Audio Class (UAC) standard

Note: The Product ID in the Standard Device Descriptor must be changed to support stereo and mono

channel.

**UVC + UAC composite device application**

### 4 UVC + UAC composite device application

A UVC + UAC composite device is an application that enables a device to function as both video and audio device simultaneously, using a single USB connection.

This type of application is often used in devices such as webcams, conference cameras, and other video conferencing equipment. By combining both video and audio capabilities into a single device, it simplifies the setup process and reduces the need for multiple cables and connections.

Figure 9 illustrates how to form a UVC + UAC composite device by combining UVC descriptor and UAC descriptor using the EZ-USB™ FX20.

Figure 9 UVC + UAC composite device descriptor

LVDS/LVCMOS interface

### **5** LVDS/LVCMOS interface

The high bandwidth data subsystem provides DMA data transfers between LVDS/LVCMOS I/O subsystem and the USB 3.2 Gen 2x2 device at speeds up to 20 Gbps. The 1024 KB SRAM is included in this subsystem to provide sufficient buffering for data. This subsystem is also interfaced with the peripheral and system interconnect for data transfers to other low-bandwidth peripherals.

High bandwidth data subsystem I/Os can be configured as LVDS or LVCMOS interfaces.

The LVDS/LVCMOS interface is used to connect to external data sources. This interface enables data transfer over EZ-USB™ FX20's LVDS or LVCMOS I/Os to other peripherals using DMA.

The LVDS/LVCMOS interface is internally split into a physical layer (LVDS/LVCMOS ports), a link layer (GPIF III links), and a high-bandwidth DMA layer.

The data flow path between the ports and the GPIF III interface is referred to as a link, which is a connection that enables data transfer between these components.

The EZ-USB™ FX20 contains two links, both the ports can be configured as independent data paths (or links). Alternatively, two ports can be merged to form a single link, routing data from both ports to the GPIF III interface as a single link (wide link). Figure 11 to Figure 16 shows the interconnect diagram between FPGA and EZ-USB™ FX20 in various configuration mode. In this application we are using WideLink mode as a default configuration, however user can change the configuration by setting / clearing appropriate pre-processor macros in the firmware. See the EZ-USB™ FX20 datasheet section 2.2 and EZ-USB™ FX20 architecture reference manual section 25 to learn more about the features supported, control byte encoding and the configuration supported by the LVCMOS / LVDS interface.

The maximum bandwidth supported by EZ-USB™ FX20 in LVCMOS DDR WideLink receive mode (Input data) is 10 Gbps, 5 Gbps of output data (Transmit mode) throughput and the maximum bandwidth supported in LVDS WideLink receive mode is 20Gbps.

### 5.1 Slave FIFO access sequence and interface timing (LVDS/LVCMOS)

The Slave FIFO interfacing timings depend on the different configurations supported by EZ-USB™ FX20, i.e., LVCMOS (SDR/DDR). See Section 6 "Timing and electrical diagrams" in the EZ-USB™ FX20 datasheet for more details about the timing diagrams for LVCMOS configurations.

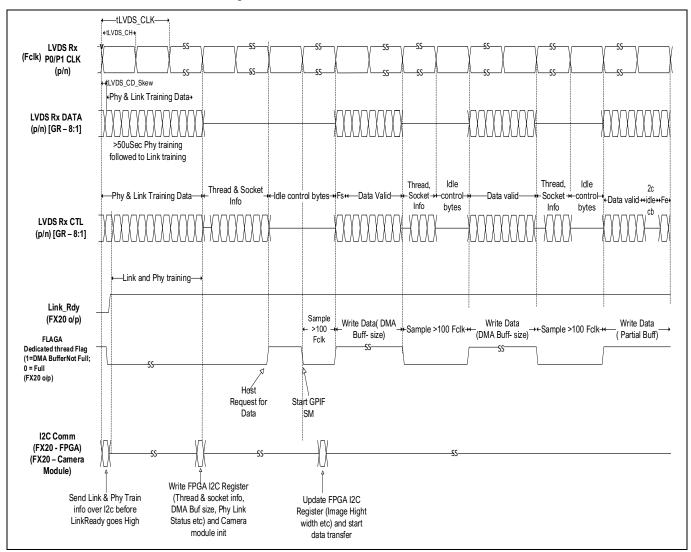

Figure 10 shows the write cycle timing diagram in LVDS receiver (RX) mode. Note that only DMA\_READY (FLAGA) is used to indicate whether the DMA buffer is available or not. Unlike in the EZ-USB™ FX3, PARTIAL\_FLAG(FLAGB) is not used in this application. Master FPGA starts writing the data only when DMA\_READY(FLAGA) is asserted (HIGH).

LVDS/LVCMOS interface

### 5.1.1 LVDS RX write sequence

Figure 10 LVDS RX write cycle timing diagram

The FPGA LVDS TX should be configured before establishing LVDS communication.

EZ-USB™ FX20 should assert the LINK\_READY signal to start the training. Once the LINK\_READY signal is asserted (HIGH), the FPGA will send the PHY training bytes for 50 μs, followed by the LINK training pattern on all data lanes and control lanes for four clock cycles.

The FPGA will receive the PHY and LINK training status, thread and socket information, DMA buffer size, and other video streaming information via I2C communication.

The FPGA uses the received information to configure the EZ-USB™ FX20 thread and socket by sending commands over the LVDS control lane. For more information on LVDS control byte encoding, see Section 25.4 of the EZ-USB™ FX20 architecture manual.

When the host application requests data, the EZ-USB™ FX20 starts the GPIF state machine and enables the DMA channel. This step asserts the DMA\_RDY (FLAGA) signal, indicating that the DMA buffer is available to the FPGA.

The EZ-USB™ FX20 also provides video streaming parameters, including 'image height', 'width', 'frame rate', and 'Start/Stop stream' parameters, over I2C.

#### **LVDS/LVCMOS interface**

After receiving the 'Start/Stop stream' signal (HIGH), the FPGA waits (sampling more than 100 FCLK cycle) for the DMA\_RDY (FLAGA) signal. Once the DMA\_RDY (FLAGA) signal is available, the FPGA starts transmitting the DATA\_CMD command on the control lane and video data bytes on the data lane, which is equal to the DMA buffer size, and waits for the DMA\_RDY (FLAGA) signal to de-assert.

Once the DMA\_RDY signal is de-asserted, the FPGA will send the thread and socket number over the control lane and waits (sampling more than 100 FCLK cycle) for the DMA\_RDY (FLAGA) signal. The received thread and socket number will be used by the FX20 to allocate the thread and sockets.

The above steps for transmitting data are continued until the last buffer. Finally, to terminate the ongoing DMA transfer, the FPGA sends the EOP\_CMD command on the control lane, which allows the EZ-USB™ FX20 to wrap up the DMA buffer and commits the partial data to the host.

#### 5.2 GPIF III interface in LVCMOS/LVDS mode

Figure 11 to Figure 16 show the interconnect diagram between the FPGA and EZ-USB™ FX20 using LVCMOS and LVDS interface with narrow and wide link modes. In this application, the EZ-USB™ FX20 is configured to operate in receive (RX) mode, allowing it to receive colorbar data generated by the FPGA or video stream from a camera module (either THine camera module with built-in ISP or a Sony IMX715 image sensor board). For details on how the firmware is configured to stream video from different sources, see Section 7.2. Note that the FPGA is always in transmit (TX) mode. To understand how FPGA FSM is designed to send video data over the LVCMOS and LVDS interface, see the FPGA Tx implementation Section 6 and section 7.

The number of GPIF threads supported by EZ-USB™ FX20 in WideLink mode is four, and number of GPIF threads supported in narrow link mode is two.

Based on the FPGA TX and EZ-USB™ FX20 RX interface configurations, below configurations have been tested for UVC and UAC composite device implementation:

LVCMOS

LVCMOS WideLink: Port0 and Port1 combined

LVCMOS Narrow Link: Port0LVCMOS Narrow Link: Port1

LVDS

- LVDS WideLink: Port0 and Port1 combined

LVDS Narrow Link: Port0LVDS Narrow Link: Port1

LVDS/LVCMOS interface

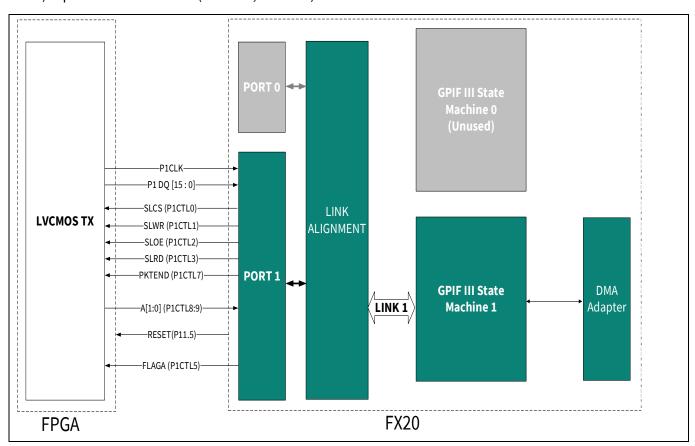

#### 5.2.1 LVCMOS WideLink: Port0 and Port1 combined

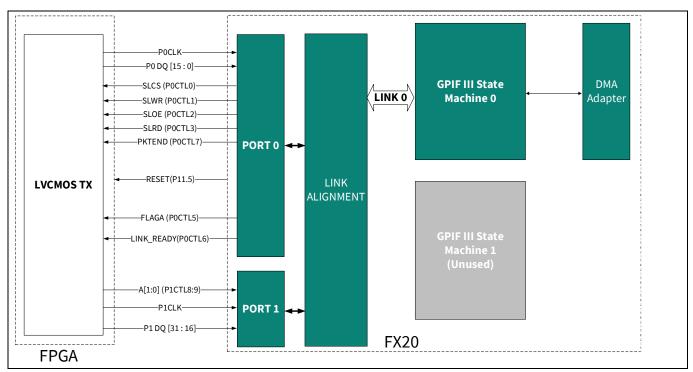

Figure 11 shows the 2-bit SlaveFIFO configuration in LVCMOS WideLink mode, which combines Port0 and Port1 (GPIF Link0 and GPIF Link1). Up to four GPIF threads (Thread0, Thread1, Thread2, Thread3) can be used in this mode.

Figure 11 Interconnect diagram between FPGA and EZ-USB™ FX20 in LVCMOS DDR WideLink mode

LVDS/LVCMOS interface

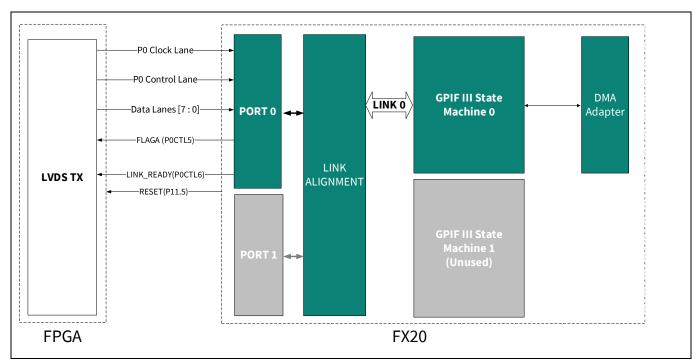

#### 5.2.2 LVCMOS Narrow Link: Port0

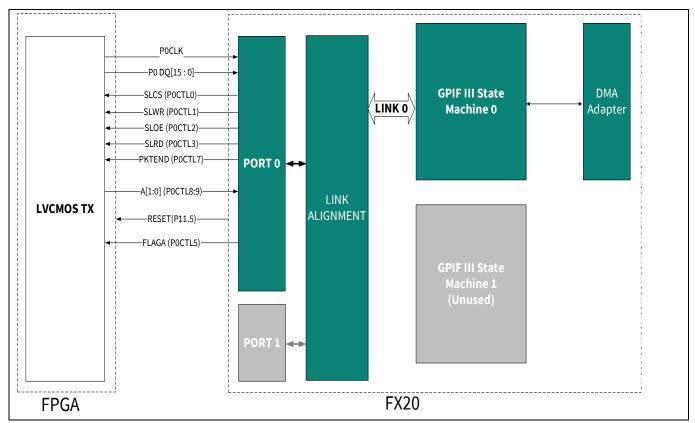

Figure 12 shows the 2-bit SlaveFIFO configuration in LVCMOS Port0 Narrow Link, which uses only Port0 (GPIF Link0). Up to two GPIF threads (Thread0, Thread1) can be used in this mode.

Figure 12 Interconnect diagram between FPGA and EZ-USB™ FX20 in LVCMOS SDR/DDR NarrowLink0 mode

LVDS/LVCMOS interface

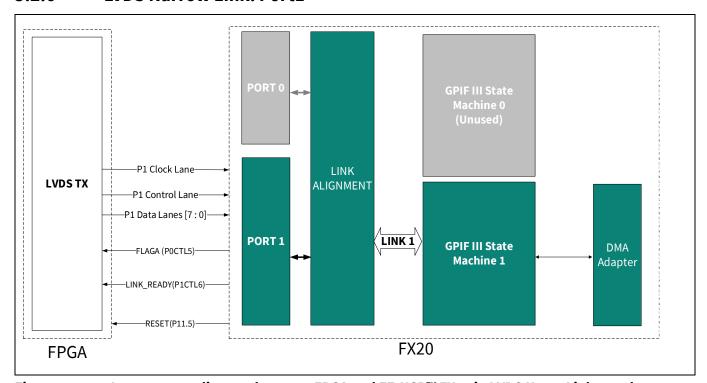

#### 5.2.3 LVCMOS Narrow Link: Port1

Figure 13 shows the 2-bit SlaveFIFO configuration in LVCMOS Port1 Narrow Link, which uses only Port1 (GPIF Link1). Up to two GPIF threads (Thread2, Thread3) can be used in this mode.

Figure 13 Interconnect diagram between FPGA and EZ-USB™ FX20 in LVCMOS SDR / DDR NarrowLink1 mode

Note:

The RESET (P11.5) signal mentioned in the figure 11 to figure 16 is not part of the GPIF state machine, it is handled using the GPIO, externally to reset the FPGA logic/FSMs

It is recommended that the master FPGA master clock be routed to the P0CLK and P1CLK pins of the EZ-USB™ FX20 when configured in LVCMOS WideLink mode.

The control and address signals used in the LVCMOS DDR interface is summarized in the table 8.

Table 8 Control signal usage in LVCMOS DDR receiver state machine

| EZ-USB™ FX20 pin | Function | Description                                                                                                                                                                                                                                                       |

|------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| POCTLO (K4)      | SLCS     | Active-low Chip Selection signal. Should be asserted low by the master FPGA when communication with EZ-USB™ FX20                                                                                                                                                  |

| POCTL1 (J4)      | SLWR     | Active-low Write Enable signal. Should be asserted low by the master FPGA when sending any data to the EZ-USB™ FX20 upon DMA_READY (FLAGA) is asserted (High). The data present on the data lanes will be sampled and stored into the DMA buffer when this signal |

LVDS/LVCMOS interface

| EZ-USB™ FX20 pin | Function          | Description                                                                                                                                                                                                                                                                                                                            |

|------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  |                   | is asserted along with SLCS. Can be combined with PKTEND signal to indicate that this data ends the transfer and the DMA operation should be terminated                                                                                                                                                                                |

| P0CTL2 (K4)      | SLOE              | Active-low Output Enable signal. Not used in this application as data is only being received by EZ-USB™ FX20                                                                                                                                                                                                                           |

| P0CTL3 (G4)      | SLRD              | Active-low Read Enable signal. Not used in this application as data is only being received by EZ-USB™ FX20                                                                                                                                                                                                                             |

| P0CTL5 (E4)      | DMA_READY (FLAGA) | Active-High DMA Ready indication for current Thread.                                                                                                                                                                                                                                                                                   |

| P0CTL7 (F2)      | PKTEND            | Active-low Packet End signal. Should be asserted low when the FPGA master wants to terminate the ongoing DMA transfer. Should be asserted along with SLWR and the last cycle of data to complete transfers with nonempty data. Can be asserted with only SLCS# low and SLWR# high to complete the DMA transfer with zero bytes of data |

| P1CTL9 (B13)     | A0                | LS bit of 2-bit address bus used to select thread                                                                                                                                                                                                                                                                                      |

| P1CTL8 (A13)     | A1                | MS bit of 2-bit address bus used to select thread                                                                                                                                                                                                                                                                                      |

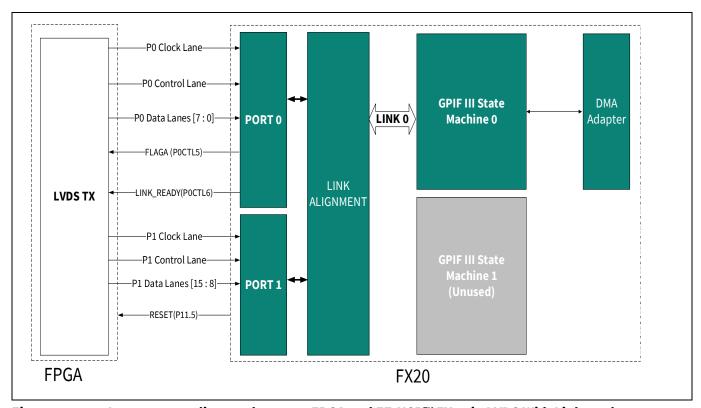

#### 5.2.4 LVDS WideLink: Port0 and Port1 combined

Figure 14 Interconnect diagram between FPGA and EZ-USB™ FX20 in LVDS WideLink mode

It is important to note that, 'P0 Clock Lane' and 'P1 Clock Lane' have to be connected when FX20 is configured to LVDS WideLink mode and same clock as to route to both the LVDS clock lanes.

LVDS/LVCMOS interface

#### 5.2.5 LVDS Narrow Link: Port0

Figure 15 Interconnect diagram between FPGA and EZ-USB™ FX20 in LVDS NarrwLink0 mode

#### 5.2.6 LVDS Narrow Link: Port1

Figure 16 Interconnect diagram between FPGA and EZ-USB™ FX20 in LVDS NarrwLink1 mode

In this application, the POCTL6 control signal serves as the LINK\_READY signal, it initiates the transmission of the PHY and LINK training patterns from FPGA in LVDS mode, and only the LINK training pattern for LVCMOS mode.

**LVDS/LVCMOS interface**

Alternatively, the LINK\_READY signal can be communicated to the FPGA via I2C, SPI, QSPI, UART, GPIO, or GPIF control signals it is not part of the GPIF III state machine.

### 5.3 Ping-pong DMA buffers

The application firmware uses DMA descriptors, and the DMA buffer connections manage data flow. Single / two GPIF threads are employed to fill DMA buffers. These GPIF threads use separate GPIF sockets (acting as producer sockets) and DMA descriptor chains (descriptor chain 1 and descriptor chain 2). The USB socket (acting as a consumer socket) uses a different DMA descriptor chain (descriptor chain 3) to read the data out in the correct order. This example uses singles GPIF thread by default and can be changed to two GPIF threads by setting the *PORTO\_THREAD\_INTLV* flag to '1' in *Makefile*.

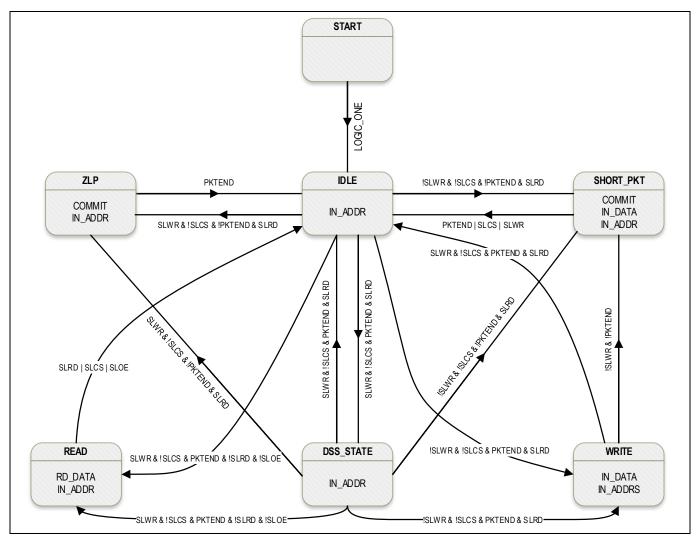

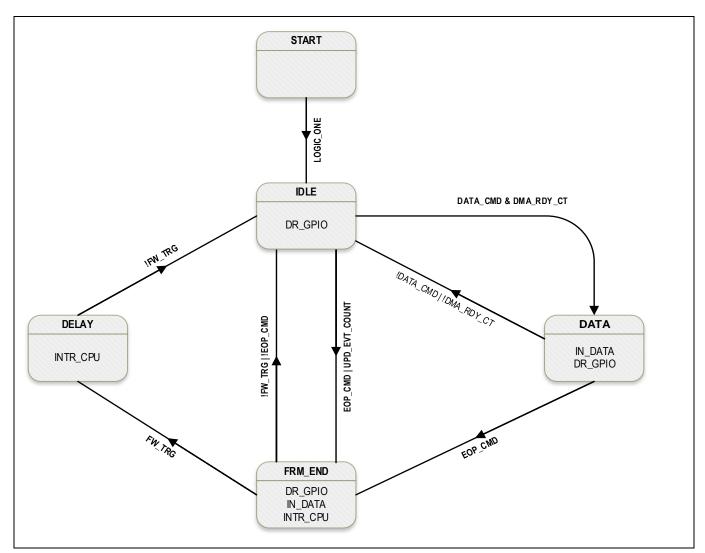

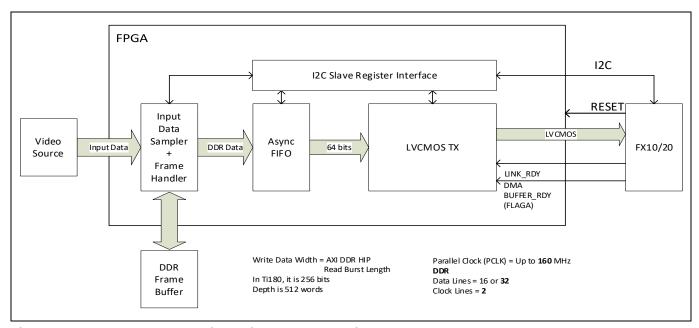

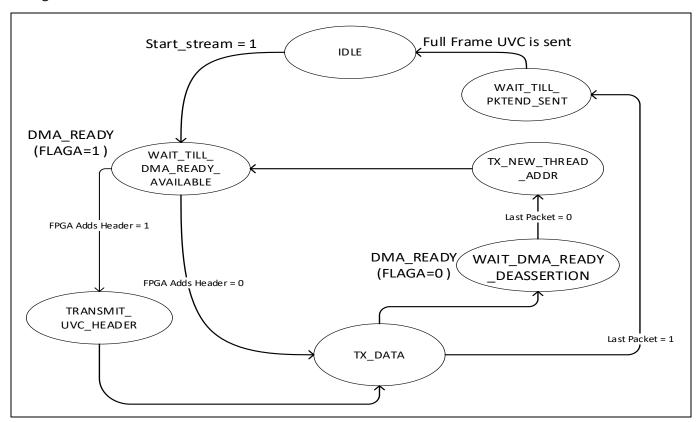

The GPIF III state machine can use either internal control signals or external inputs to select the active GPIF thread. In this example, the switching between GPIF threads is controlled by the external control signals (A0, A1) driven by the FPGA.