#### **About this document**

#### Scope and purpose

This document introduces a 11kW high-efficiency high-density bidirectional three-/single-phase AC-DC power converter, i.e., REF\_11KW\_PFC\_SIC\_QD offered by Infineon. The design can be used in multiple applications, including but not limited to EV charging, onboard charger, and energy storage systems.

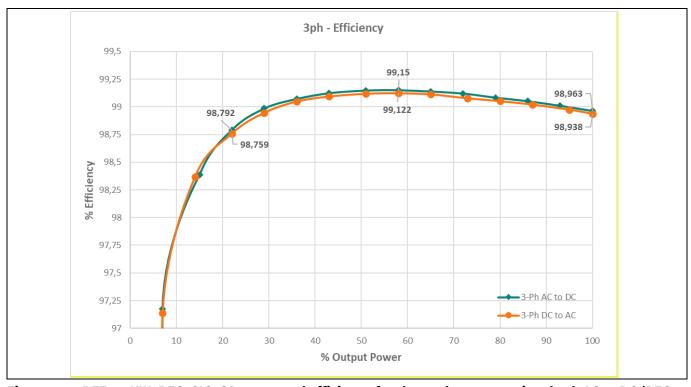

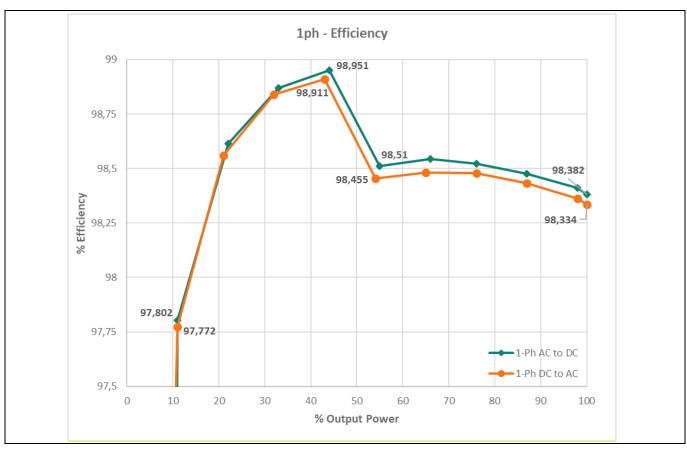

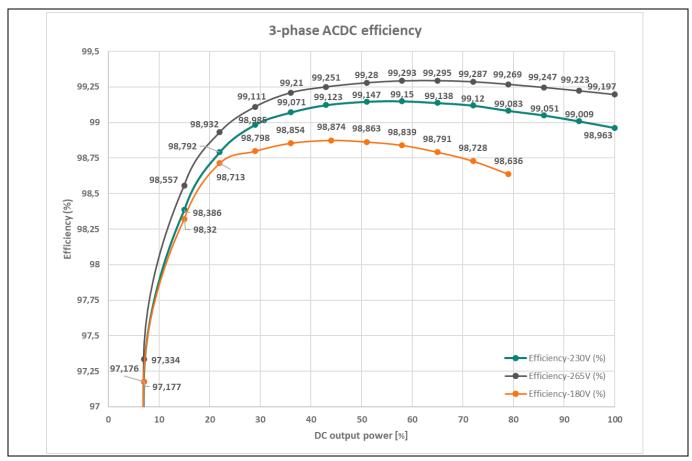

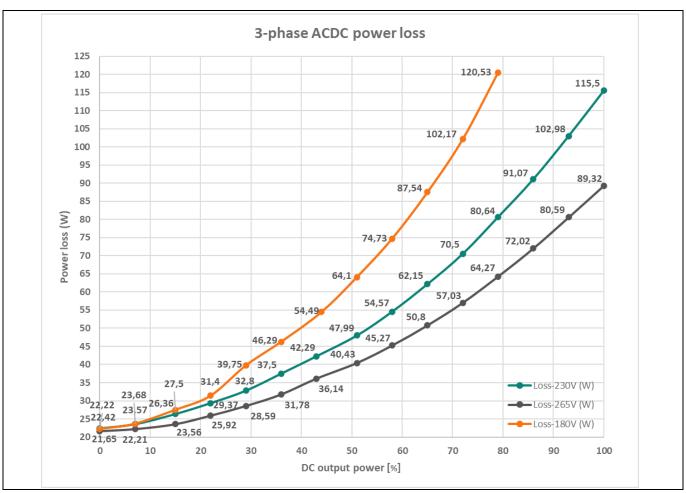

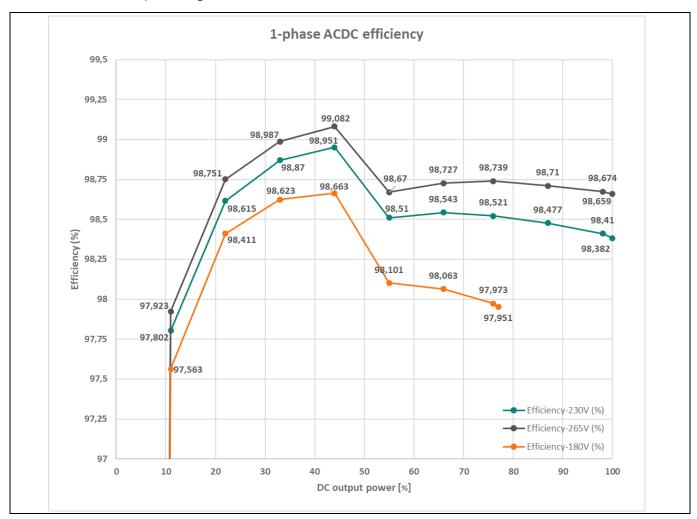

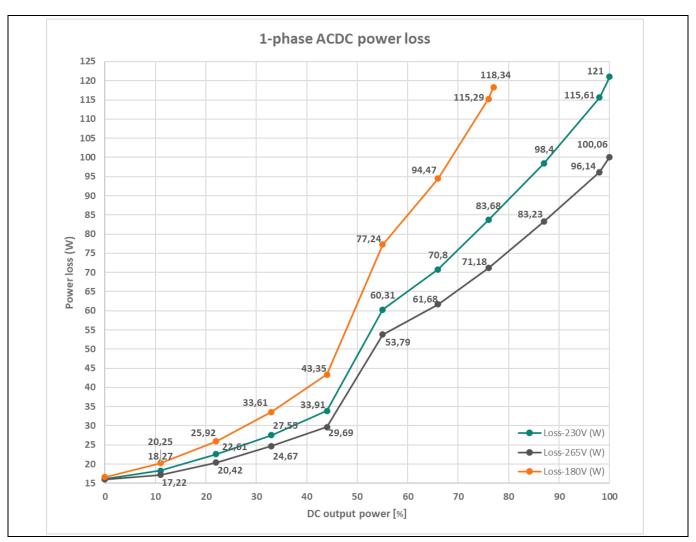

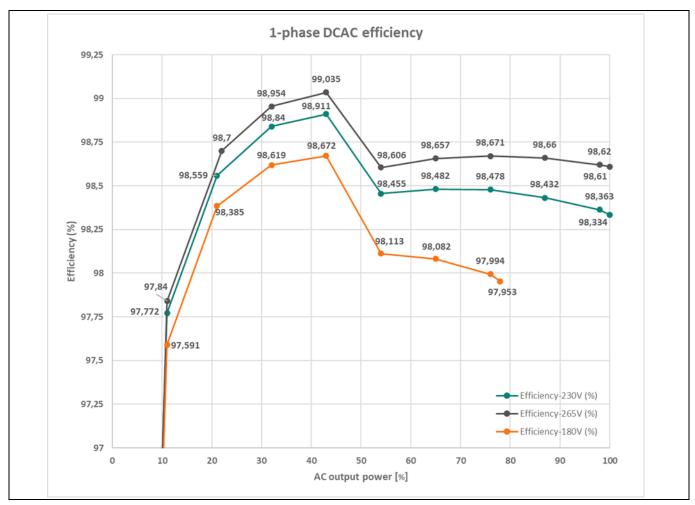

The REF\_11KW\_PFC\_SIC\_QD design can operate under both single-phase and three-phase AC grid with DC-side voltage around 800V. When interfacing three-phase grid, the design can convert steady state maximum power of 11 kW in both power-flow directions, i.e., either PFC mode or inverter mode, with peak efficiency of 99.15 % (PFC) and 99.122 % (inverter) with 230  $V_{RMS}$  grid voltage. When interfacing with single-phase grid, the design can convert steady state maximum power of 7.3 kW in both power-flow directions, with peak efficiency of 98.95 % (PFC) and 98.91 % (inverter).

With the size of 243 mm x 100 mm x 40 mm (excluding cooling plate) and the power density of 11.3 kW/L, i.e., 185 W/in³, REF\_11KW\_PFC\_SIC\_QD demonstrates a viable approach for achieving high power density and efficiency, in the combined three-/single-phase AC-DC power converter unit compared to state-of-the-art solutions. The system solution REF\_11KW\_PFC\_SIC\_QD utilizes Infineon's innovative top-side-cooling package Q-DPAK devices which enables the high-performance metrics. The design is realized by the well-proven three-level active neutral point clamped (3L-ANPC) topology with optimizations on switching loops.

This document describes the converter operation principle, hardware design as well as software design topics and a summary of the experimental results for the complete Infineon solution.

#### Intended audience

The document is intended for R&D engineers, hardware designers, and developers of power electronic systems.

#### **About this document**

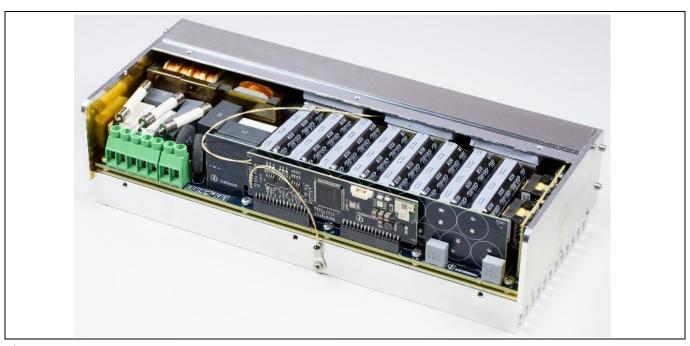

Figure 1 REF\_11KW\_PFC\_SIC\_QD

Figure 2 REF\_11KW\_PFC\_SIC\_QD measured efficiency for three-phase operation, both AC to DC (PFC mode) and DC to AC (inverter mode)

#### **About this document**

Figure 3 REF\_11KW\_PFC\_SIC\_QD measured efficiency for single-phase operation, both AC to DC (PFC mode) and DC to AC (inverter mode)

The key components from Infineon enabling REF\_11KW\_PFC\_SIC\_QD are:

- 750V CoolSiC™ Gen 2, 25 mΩ QDPAK (IMDQ75R025M2H), and EiceDRIVER™ 2EDB9259Y for the fast switching half-bridge

- 650V CoolSiC<sup>™</sup> Gen 2, 20 mΩ QDPAK (IMDQ65R020M2H), and EiceDRIVER<sup>™</sup> 2EDB9259Y for the single-phase power pulsation buffer

- 600 V CoolMOS™ CM8, 16 mΩ QDPAK (IPDQ60R016CM8), EiceDRIVER™ 2EDB9259Y for the line-frequency switching half-bridge

- XMC4400-F100K512 BA microcontroller for the implementation of the digital control

- XENSIV™ TLE4971-A050N5-U-E0001 high precision coreless current sensor for grid current sensing

- Quasi-resonant flyback CoolSET™ IC ICE2QR2280G for auxiliary power supply

- EiceDRIVER™ 2EDN7533R for auxiliary power supply

- OPTIREG™ switcher TLS4120D0EPV33 2.8 MHz synchronous step-down regulator for supplying the 3.3 V rail

- Medium power AF Schottky Diode BAT165

- 60 V N-Channel Small Signal MOSFET BSS138N

#### **Table of contents**

#### **Table of contents**

| Abou  | ıt this document                                                 | 1  |

|-------|------------------------------------------------------------------|----|

| Table | e of contents                                                    | 4  |

| 1     | Introduction                                                     | 6  |

| 1.1   | Overview of feasible topologies                                  |    |

| 1.2   | Introduction to REF_11KW_PFC_SIC_QD                              |    |

| 1.3   | Specifications                                                   | 9  |

| 2     | System overview and description                                  | 12 |

| 2.1   | 3L-ANPC phase leg modulation                                     | 12 |

| 2.1.1 | Operation principle                                              | 13 |

| 2.1.2 | Decoupling capacitor to close switching loop                     | 15 |

| 2.1.3 | Pre-charging of decoupling capacitor during startup              | 16 |

| 2.2   | Three-phase configuration                                        | 17 |

| 2.3   | Single-phase configuration                                       |    |

| 2.3.1 | Basic operational principle of power pulsation buffer            | 19 |

| 2.3.2 | Practical modulation scheme of phase C as power pulsation buffer | 21 |

| 3     | System hardware design                                           | 23 |

| 3.1   | Auxiliary power supply                                           | 24 |

| 3.2   | Capacitor bank voltage balancing circuit                         | 27 |

| 3.3   | Driving configuration                                            | 29 |

| 3.4   | Switching-loop optimization                                      | 30 |

| 3.5   | Thermal design                                                   | 31 |

| 3.5.1 | Standoff height                                                  | 31 |

| 3.5.2 | Avoiding PCB warpage                                             | 32 |

| 3.5.3 | Insulation requirement                                           | 33 |

| 3.6   | Inductor and current sense against stray field                   | 34 |

| 3.7   | Common-mode choke with differential-mode inductance              | 35 |

| 4     | System software design                                           | 37 |

| 4.1   | Three-phase control diagram                                      |    |

| 4.2   | Single-phase control diagram                                     |    |

| 4.3   | DC droop feature                                                 |    |

| 5     | Experimental results                                             | 40 |

| 5.1   | Setup description                                                |    |

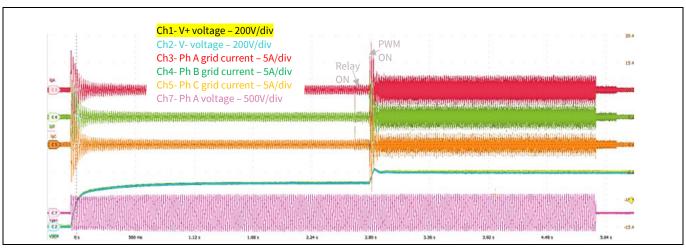

| 5.1   | Converter startup                                                | 41 |

| 5.1.1 | AC to DC (PFC mode) startup                                      | 41 |

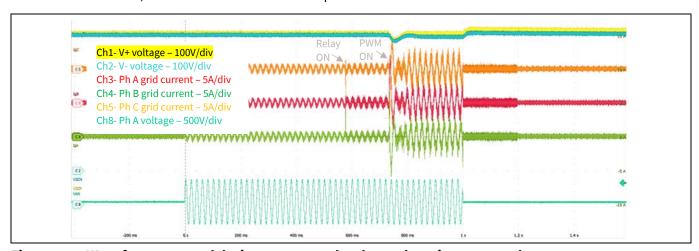

| 5.1.2 | DC to AC (inverter mode) startup                                 | 42 |

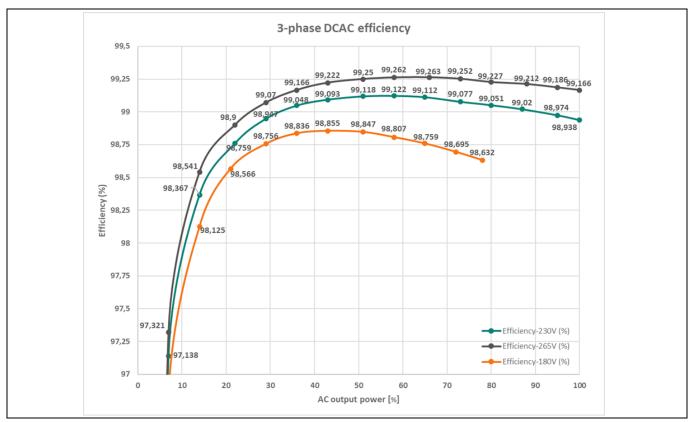

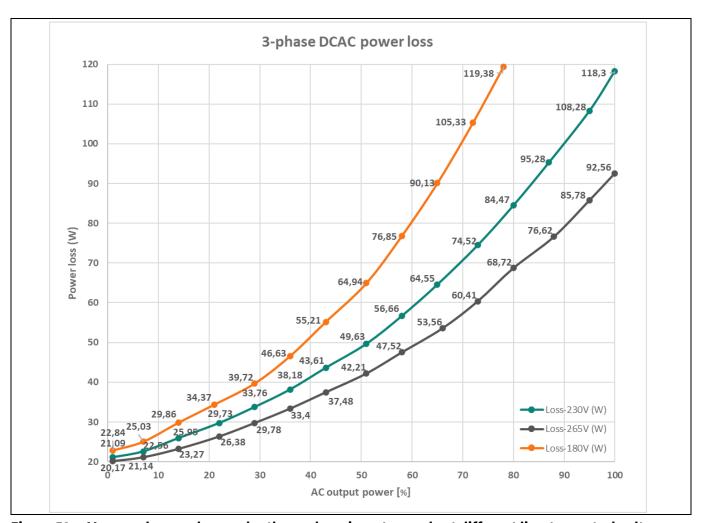

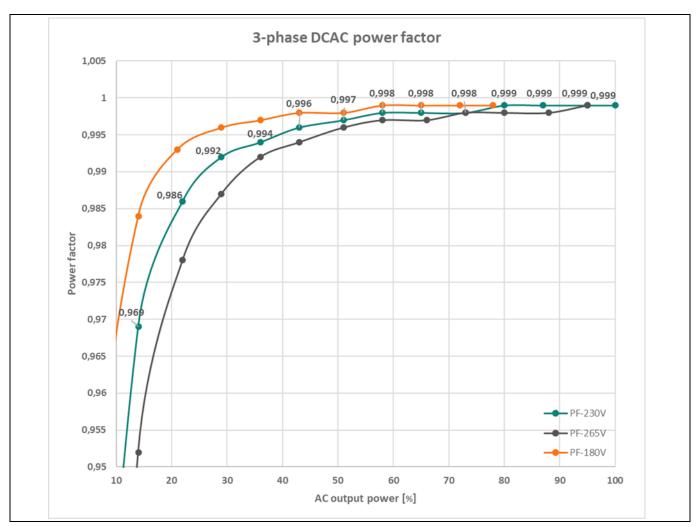

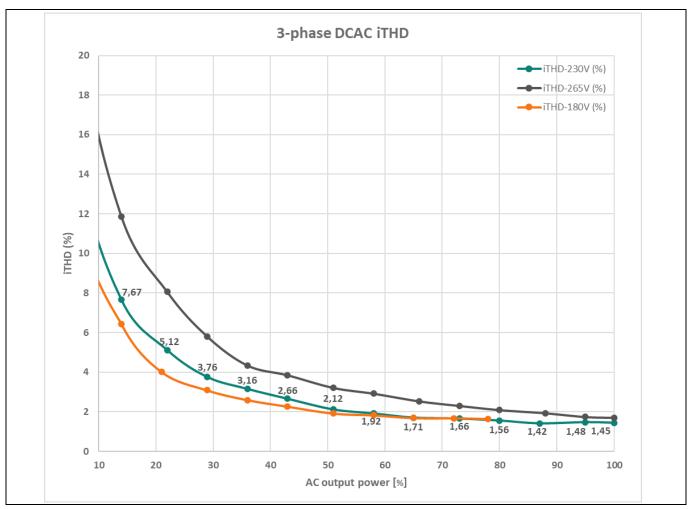

| 5.2   | Three-phase steady-state operation – efficiency, PF, and iTHD    | 43 |

| 5.2.1 | PFC mode                                                         |    |

| 5.2.2 | Inverter mode                                                    | 48 |

| 5.3   | Single-phase steady-state operation – efficiency, PF, and iTHD   | 52 |

| 5.3.1 | PFC mode                                                         | 52 |

| 5.3.2 | Inverter mode                                                    | 57 |

| 5.4   | Dynamic performance                                              | 61 |

| 5.4.1 | Bidirectional power-flow transition                              |    |

| 5.4.2 | Load transients                                                  | 65 |

| 5.5   | Thermal performance                                              | 67 |

| 6     | Summary                                                          | 70 |

V 1.0

#### **Table of contents**

| 7     | Schematics        | 71 |

|-------|-------------------|----|

| 7.1   |                   |    |

| 7.2   |                   |    |

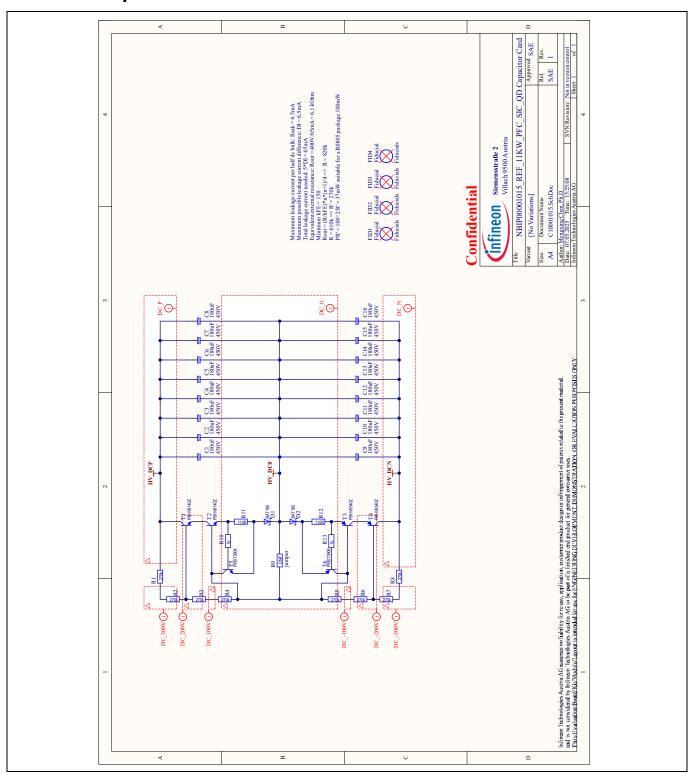

| 7.2.1 | Capacitor card    |    |

| 7.2.2 |                   |    |

| 7.2.3 |                   |    |

| 8     | Bill of Materials | 77 |

| Refei | rences            | 83 |

|       | sion history      |    |

|       | aimer             |    |

Introduction

#### 1 Introduction

In the recent decade, power electronic systems have been developing towards higher efficiency and higher power density, as well as lower system cost. This application note demonstrates a viable system solution (REF\_11KW\_PFC\_SIC\_QD) for 800 VDC based three-/single-phase converters. The demonstrated system solution achieves premium power density and efficiency by introducing multi-level topology and lower voltage rating power semiconductors with better figure-of-merit into the system. The use of 600 – 750 V power semiconductors in the 800 VDC based system makes it possible to switch at a frequency of 65 kHz, reducing the size of magnetics, boosting the efficiency, and increasing the power density. The following subsection overviews the state-of-art topologies and shows the advantages of the selected topology.

#### 1.1 Overview of feasible topologies

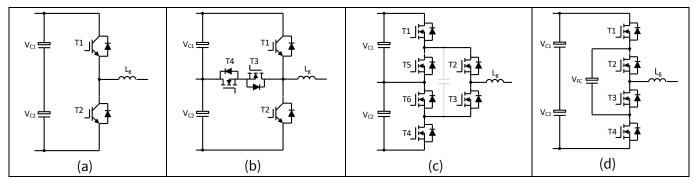

This section compares the four typical topology implementations for an 800 VDC bus system, focusing on practical trade-offs in efficiency, component selection, EMI performance, and implementation complexity.

**Two-level half-bridge (2L-HB) topology:** is the most established and widely adopted AC-DC architecture. It requires high-voltage semiconductors rated for 1200 V (e.g., Si IGBTs or SiC MOSFETs) to support the 800 VDC bus as shown in Figure 4 (a). While it offers a simple design and robust operation, it inherently exhibits high-voltage slew rates (dv/dt), leading to increased EMI, and necessitating a large PFC choke, which can limit power density. Plus, operating the 2L-HB with high frequency (e.g., 65 kHz and above) is not prefered due to the high switching losses. Nevertheless, it is still the mainstream in the market.

Three-level T-type neutral-point-clamped (3L-TNPC) topology: shown in Figure 4 (b) improves upon the 2L-HB by reducing the effective dv/dt, due to its 3-level switching nature. This enables a smaller PFC choke and better EMI behavior. The topology still requires 1200 V-rated devices, similar to the 2L-HB, but provides notable improvements in power density and system performance.

Three-level active-neutral-point-clamped (3L-ANPC) topology: Figure 4 (c) shows the classical NPC architecture by replacing two clamping diodes with actively controlled switches. This modification enhances system efficiency, provides better thermal distribution, and allows more flexible modulation strategies. A key benefit of the 3L-ANPC is that it can be implemented entirely with lower-voltage semiconductors (600 V–750 V), which are more efficient. The 3L-ANPC topology is well proven in the PV systems and multiple modulation schemes exist for this topology, with some approaches using only two high-frequency switches and four line-frequency devices — while maintaining full bidirectional operation and high efficiency.

The three-level flying-capacitor (3L-FC) topology in Figure 4 (d) uses four 600 V-750 V switches and a flying capacitor per phase leg. This architecture enables higher apparent switching frequency (via phase-shift modulation), which leads to further reduction in choke size. In practice, maintaining the flying capacitor voltage at half the DC bus voltage under all operating conditions — especially during startup, surges, or load transients — adds control complexity and may require auxiliary circuitry.

Among the various bidirectional PFC topologies for an 800 V DC bus, the 3L-ANPC stands out as the preferred choice due to its superior performance in terms of efficiency, power density, as well as the robustness. Compared to the traditional 2-Level and other 3-Level topologies, the 3L-ANPC enables the use of lower voltage-rated power devices (600 V−750 V), which significantly reduces switching losses and provides better figure-of-merits on device level. By replacing certain clamping diodes with active switches, it achieves better loss distribution and higher overall system efficiency. When combined with CoolMOS™ super-junction MOSFETs and CoolSiC™ devices, the 3L-ANPC topology delivers exceptional power density and reliability, meeting the stringent requirements of high efficiency, compactness, and robustness.

#### Introduction

Figure 4 Topology candidates for bidirectional AC-DC power converters featuring 800 V<sub>DC</sub> bus in a single leg representation. (a) Two-level half bridge (2L-HB); (b) Three-level T-type neutral-point-clamped (3L-TNPC); (c) Three-level active-neutral-point-clamped (3L-ANPC); (d) Three-level flying-capacitor (3L-FC)

#### 1.2 Introduction to REF\_11KW\_PFC\_SIC\_QD

This reference design shows how to implement a three-level ANPC converter that limits the voltage stress on all the power components to only half of the DC bus voltage, allowing use of power components with better figure-of-merit. The main characteristics of the presented design are:

- Bidirectional 11 kW three-phase/7.3 kW single-phase PFC or inverter power stage using Si/SiC switches

- 600 V- rated switches in 800 V system due to three level toplogy

- Hall-based current sense (high accuracy, stray field suppression, and stability overtemperature)

- High-power/volume density due to high switching frequency (65 kHz) and high efficiency (>98.5% at full load)

- System reliability improvement by low voltage stress on the switches

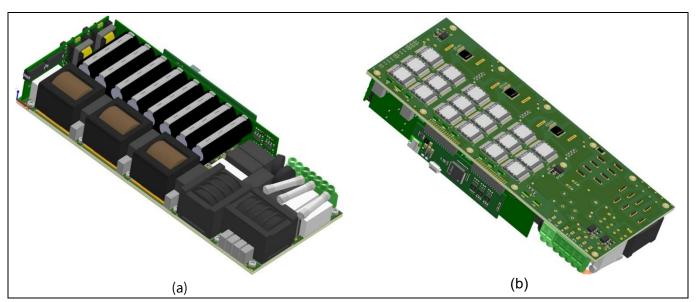

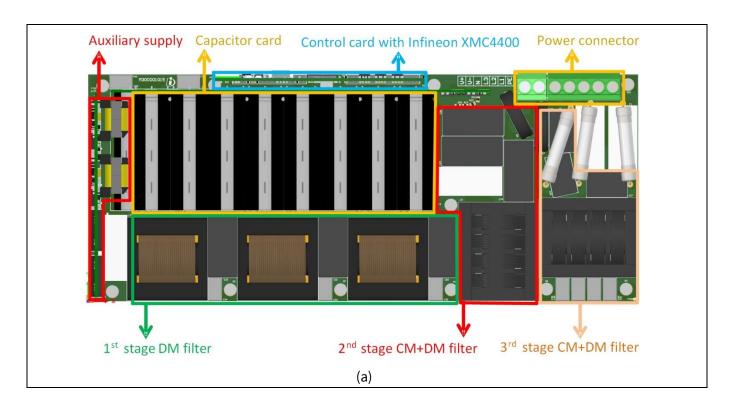

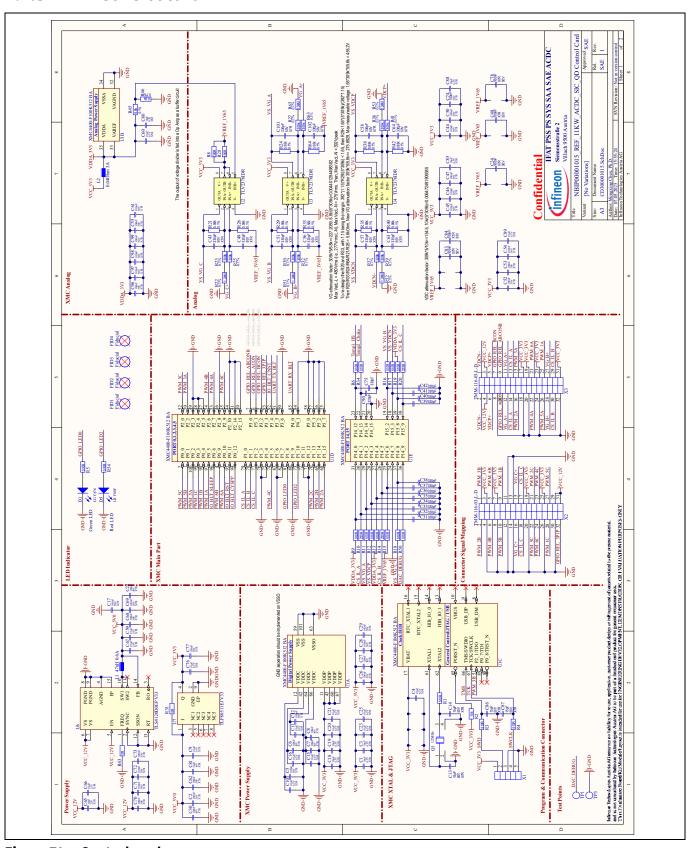

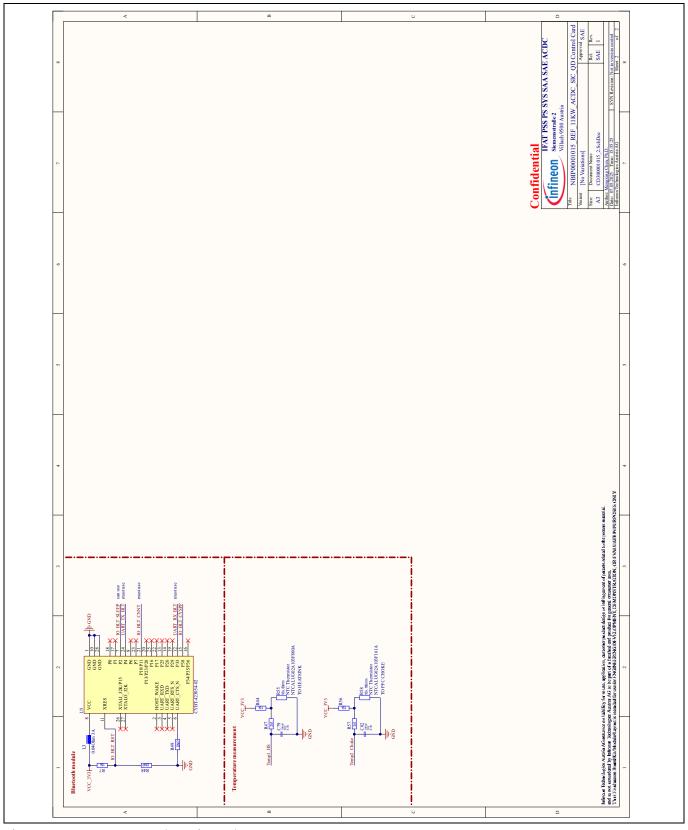

This reference design is built in a compact form factor (Figure 5) with the following sub-assemblies Figure 6):

- Main board (M300001015) comprises EMI filters, driver circuits and power stages attached to heatsink

- Bias supply card (BS200001015) quasi-resonant flyback and ring oscillator circuits for isloated outputs

- Control card (CD300001015) MCU, Bluetooth module, temperature measurement, and regulator IC units

- Capacitor card (C200001015) DC bus capacitors with active voltage balancing circuitry

The reference board REF\_11KW\_PFC\_SIC\_QD bottom side is mounted on heat sink and the top side is covered by a plastic enclosure.

#### Introduction

REF\_11KW\_PFC\_SIC\_QD captured from CAD software; (a) Top view; (b) bottom view Figure 5

#### Introduction

Figure 6 REF\_11KW\_PFC\_SIC\_QD captured from CAD software; (a) Top view with capacitor board assembled; (b) top view with capacitor board removed; (c) bottom view

#### **1.3** Specifications

The specifications of the converter under tested conditions are highlighted in Table 1.

#### Introduction

Table 1 Specification of REF\_11KW\_PFC\_SIC\_QD

| Parameter                               | Symbol                                        | Values                        | ;     |            | Unit | Note/Test condition           |

|-----------------------------------------|-----------------------------------------------|-------------------------------|-------|------------|------|-------------------------------|

|                                         |                                               | Min.                          | Max.  | Тур.       |      |                               |

| 3-Phase AC voltage (RMS)                | V <sub>AC</sub>                               | 318                           | 400   | 480        | ٧    | RMS value                     |

| 1-Phase AC voltage (RMS)                | V <sub>AC</sub>                               | 180                           | 230   | 265        | ٧    | RMS value                     |

| AC frequency                            | f <sub>AC</sub>                               | _                             | 50    | -          | Hz   | -                             |

| Nominal DC bulk voltage                 | V <sub>DC</sub>                               | _                             | 800   | _          | ٧    | -                             |

| AC RMS current (3-phase)                | I <sub>RMS</sub>                              | _                             | 16    | _          | Α    | per phase                     |

| AC RMS current (1-phase)                | I <sub>RMS</sub>                              | _                             | 32    | _          | Α    | total phase current           |

| Output power (3-phase)                  | P <sub>out</sub>                              | _                             | 11000 | _          | W    | -                             |

| Output power (1-phase)                  | P <sub>out</sub>                              | _                             | 7300  | _          | W    | -                             |

| Operating ambient temperature           | Т <sub>АМВ</sub>                              | -                             | 25    | -          | °C   | -                             |

| Peak to peak DC split<br>voltage ripple | $\Delta V_{DC}$                               | _                             | -     | 70         | V    | 1-phase/3-phase maximum       |

| Power density                           | _                                             | _                             | 11.3  | _          | kW/L | Without heatsink              |

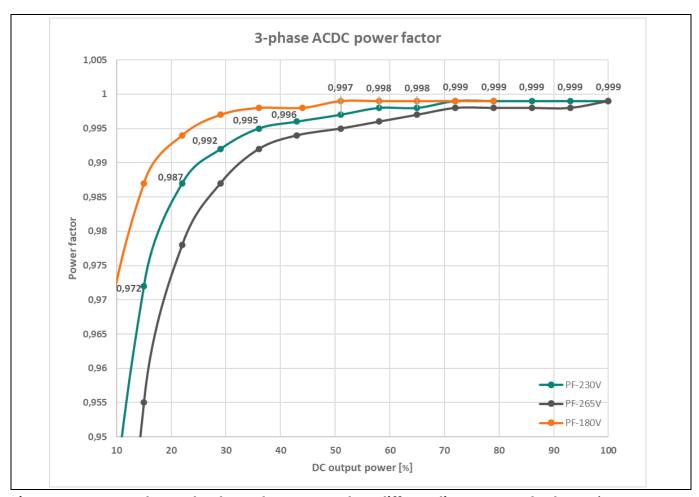

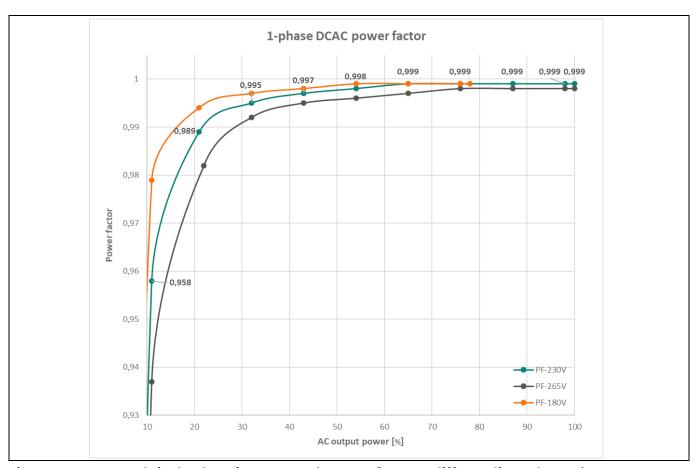

| Power factor (3-phase)                  | PF                                            | 0.95                          | _     | 0.999      | -    | Min: 10% load, Max: full-load |

| Power factor (1-phase)                  | PF                                            | 0.96                          | -     | 0.999      | -    | Min: 10% load, Max: full-load |

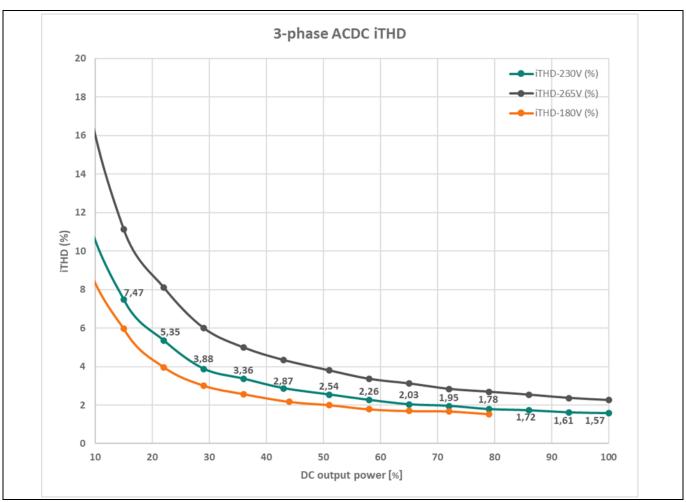

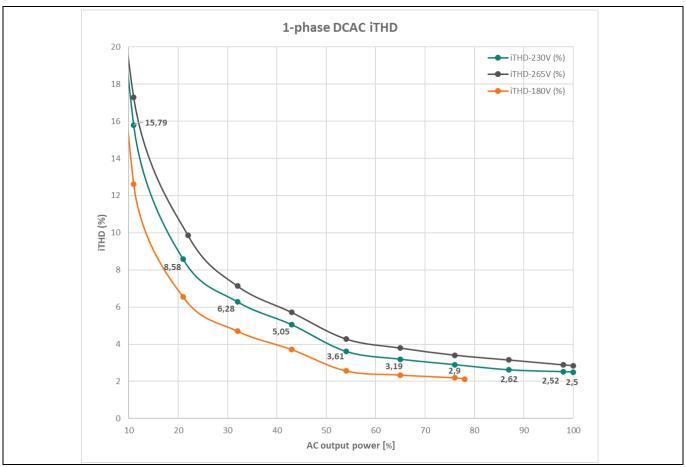

| Input current THD (3-<br>phase)         | iTHD                                          | 1.6                           | -     | 12         | %    | Min: full-load, Max:10% load  |

| Input current THD (1-<br>phase)         | iTHD                                          | 1.4                           | -     | 15         | %    | Min: full-load, Max:10% load  |

| Switching frequency                     | f <sub>SW</sub>                               | _                             | 65    | -          | kHz  | -                             |

| Efficiency performance                  |                                               |                               |       |            |      |                               |

| Efficiency (3-phase PFC)                | p <sub>180V</sub>                             | 97.8                          | 98.63 | 98.87      | %    | Min: 10% load, Typ: full-load |

|                                         | p <sub>230V</sub>                             | 98.3                          | 98.96 | 99.15      | ]    | Max: half-load                |

|                                         | p <sub>265V</sub>                             | 98                            | 99.19 | 99.29      |      |                               |

| Efficiency (3-phase                     | η <sub>180V</sub>                             | 97.25                         | 98.63 | 98.85      | %    | Min: 10% load, Typ: full-load |

| Inverter)                               | p <sub>230V</sub>                             | 97.8                          | 98.83 | 99.12      | ]    | Max: half-load                |

|                                         | p <sub>265V</sub>                             | 98                            | 99.16 | 9.16 99.26 |      |                               |

| Efficiency (1-phase PFC)                | η <sub>180V</sub>                             | 97.5                          | 97.95 | 98.66      | %    | Min: 10% load, Typ: full-load |

|                                         | p <sub>230V</sub>                             | 97.8                          | 98.38 | 98.95      |      | Max: half-load                |

|                                         | η <sub>265V</sub>                             | 97.8                          | 98.66 | 99.08      |      |                               |

| Efficiency (1-phase                     | (1-phase p <sub>180V</sub> 97.5 97.95 98.67 % | Min: 10% load, Typ: full-load |       |            |      |                               |

| Inverter)                               | p <sub>230V</sub>                             | 97.75                         | 98.33 | 98.91      |      | Max: half-load                |

|                                         | p <sub>265V</sub>                             | 97.5                          | 98.6  | 99.03      | ]    |                               |

| Protection limits                       | •                                             |                               | •     | •          | •    | •                             |

| Grid-side AC voltage per<br>phase       | V <sub>AC</sub>                               | 180                           | -     | 265        | V    | RMS, line-to-neutral          |

| Grid-side over-current limit            | OCL                                           | _                             | _     | 35         | Α    | Peak value                    |

#### Introduction

| Parameter                                   | Symbol                | Values |      |      | Unit | Note/Test condition        |

|---------------------------------------------|-----------------------|--------|------|------|------|----------------------------|

|                                             |                       | Min.   | Max. | Тур. |      |                            |

| Split capacitor over-<br>voltage protection | OVP                   | _      | _    | 440  | V    | Each split capacitor       |

| DC-side under voltage protection            | UVP                   | 510    | -    | 750  | V    | Related to V <sub>AC</sub> |

| Inverter mode DC voltage                    | $V_{DC,INV}$          | 750    | _    | 880  | ٧    | Peak value                 |

| Heatsink temperature                        | Temp <sub>HS</sub>    | -      | _    | 90   | °C   | @T <sub>AMB</sub> = 25°C   |

| Inductor temperature                        | Temp <sub>Choke</sub> | _      | _    | 120  | °C   |                            |

System overview and description

#### 2 System overview and description

REF\_11KW\_PFC\_SIC\_QD utilizes the well-proven 3L-ANPC topology. This section provides information on the operation principle of a single 3L-ANPC phase leg along with topics such as switching loop minimization and startup precharging.

Additionally, it also provides information on the two operating modes, i.e., three- and single-phase operation. For single-phase operation, an operation method to mitigate the 50 Hz DC midpoint voltage fluctuation is presented.

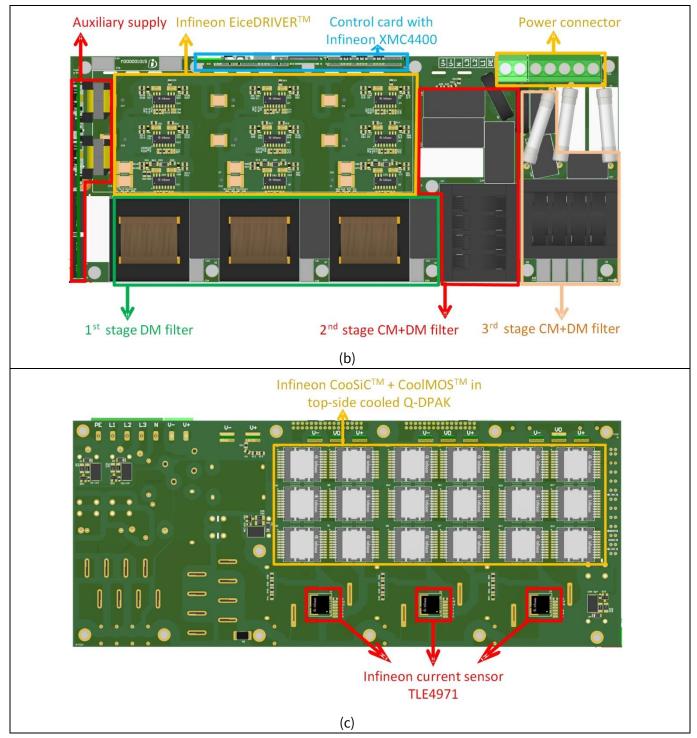

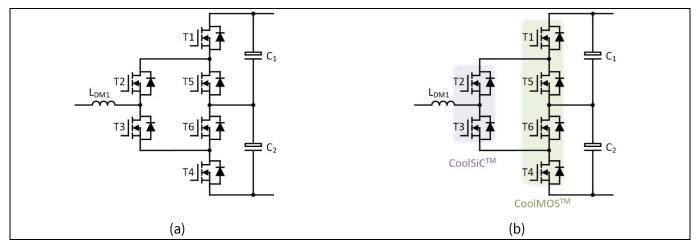

#### 2.1 3L-ANPC phase leg modulation

The 3L-ANPC power stage is inherently capable of bidirectional operation. The single phase-leg representation of the three-level active neutral-point clamped (3L-ANPC) converter implemented in REF\_11kW\_PFC\_SIC\_QD is depicted in Figure 7.

Figure 7 Circuit diagram of a single phase-leg of 3L-ANPC. (a) General drawing without assignment of CoolMOS™ and CoolSiC™; (b) Detailed drawing with assignment of CoolMOS™ and CoolSiC™ for modulation scheme I

#### System overview and description

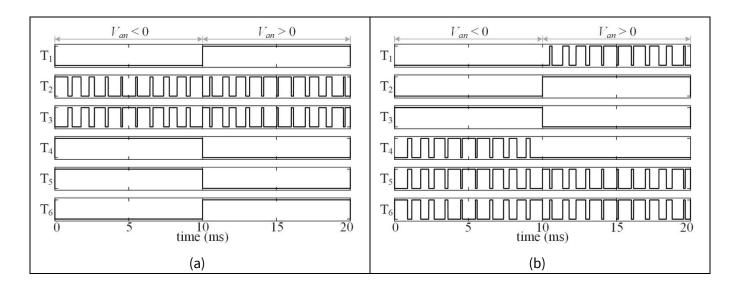

Figure 8 Modulation scheme of 3L-ANPC phase-leg. (a) Modulation scheme I; (b) Modulation scheme II; (c) Modulation scheme III; (d) Modulation scheme IV

Multiple modulation principles of 3L-ANPC converter are depicted in Figure 8 (a) and (d), which can be found in literatures [1]-[7]. These swiching patterns greatly affect the power loss distribution among the six switching devices. Particularly, the modulation scheme IV shown in Figure 8 (d) achieves the so-called switching-frequency-doubling at the swich-node, by applying the phase shift technique to the modulation carrier.

The key difference between them is the number of devices switching at high-frequency, e.g., 65 kHz, and line freuquecy, e.g., 50 Hz. Those under line-frequency switching are implemented with Si-based power semiconductors, e.g., Si IGBT and Si super junction MOSFET, while those under high-frequency switching are implemented with wide-band-gap (WBG) power semiconductors, e.g., SiC MOSFET and GaN HEMT. Therefore, the cost and control complexity of various modulation methods differs. Considering these, this work adopts the simplest modulation pattern with the lowest number of high-frequency devices, i.e., two high-frequency-switching devices and four line-frequency switching devices.

The selected modulation scheme of one single phase-leg is illustrated in Figure 8 (a). With this scheme, the control and modulation complexity as well as the system cost of 3L-ANPC converter is minimized, compared to other schemes. The two devices  $T_2$  and  $T_3$  switch at high frequency, i.e., 65 kHz, which are implemented with 750 V/650 V CoolSiC<sup>TM</sup>. Moreover, the four devices  $T_1$  and  $T_4 - T_6$  commutate at 50 Hz/60 Hz and can be implemented with Si CoolMOS<sup>TM</sup>.

Since those devices bear only the conduction loss, it is very flexible for the power converter designer to scale the power level by selecting the proper  $R_{DSON}$  of the  $CoolMOS^{TM}$ . With the low  $R_{DSON}$  achievable by the  $CoolMOS^{TM}$ , the 3L-ANPC converter with the selected modulation features much lower conduction loss compared to its counterparts. Additionally, the  $R_{DSON}$  selection of  $CoolSiC^{TM}$   $T_2$  and  $T_3$  can be solely optimized based on the balance between switching and conduction losses.

Note: Assuming the DC-bus overall voltage as 800 V, all switching devices can be implemented with 600 V-750 V ratings, which provides better figure-of-merit compared with 1200 V devices.

#### 2.1.1 Operation principle

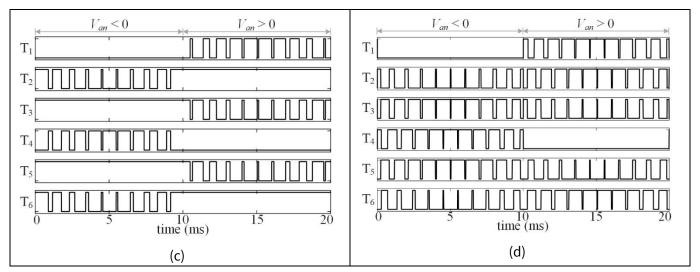

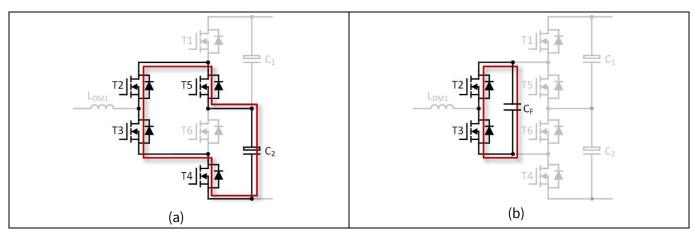

Single phase-leg is considered as shown in Figure 9 and Figure 10 where, Figure 9 demonstrates the operation principle of single ANPC phase leg during the positive line-cycle. The line frequency CoolMOS™ T₁ and T₆

#### System overview and description

switches are kept on during the positive line cycle, whereas the other CoolMOS<sup>TM</sup>  $T_4$  and  $T_5$  switches are kept off. The two high-frequency CoolSiC<sup>TM</sup>  $T_2$  and  $T_3$  switches at 65 kHz in a complimentary way.

In the PFC mode, (i.e., the inductor current flows from the grid-side to the converter-side), when  $T_2$  conducts, the inductor  $L_{DM1}$  current charges the upper bulk capacitor (C1) through  $T_1$  and  $T_2$ . On the other hand, when  $T_3$  conducts, the grid current charges the inductor  $L_{DM1}$  through  $T_6$  and  $T_3$ .

In the inverter mode, (i.e., the inductor current flows from the converter-side to grid-side), when  $T_2$  conducts, the upper bulk capacitor (C1) charges the inductor. On the other hand, when  $T_3$  conducts, the inductor current gets discharged by the grid voltage.

Figure 9 Operation principle of single ANPC phase leg during positive line cycle. (a) When T<sub>2</sub> conducts; (b) When T<sub>3</sub> conducts

Figure 10 Operation principle of single ANPC phase leg during negative line cycle. (a) When T<sub>3</sub> conducts; (b) When T<sub>2</sub> conducts

Figure 10 demonstrates the operation principle of single ANPC phase leg during the negative line cycle. The line frequency CoolMOS<sup>TM</sup>  $T_4$  and  $T_5$  are kept on during the negative line cycle, whereas the other CoolMOS<sup>TM</sup>  $T_1$  and  $T_6$  are kept off. The two high-frequency CoolSiC<sup>TM</sup> switch at 65 kHz in a complimentary manner.

In the PFC mode, (i.e., the inductor current flows from the converter-side to the grid-side), when  $T_3$  conducts, the inductor  $L_{DM1}$  current charges the lower bulk capacitor (C2). On the other hand, when  $T_2$  conducts, the grid charges the inductor  $L_{DM1}$ .

#### System overview and description

In the inverter mode, (i.e., the inductor current flows from the grid-side to converter-side), when  $T_3$  conducts, the lower bulk capacitor (C2) charges the inductor. On the other hand, when  $T_2$  conducts, the grid inductor gets discharged by the grid voltage.

#### 2.1.2 Decoupling capacitor to close switching loop

As mentioned, the adoped modulation method features easy implementation and lowest BOM cost compared with other ANPC modulation methods as it switches the lowest device count in high-frequency. However, one of the significant drawbacks of this method is that the switching loop is relatively long compared to the other modulation methods [7].

As shown in Figure 11 (a), the switching loop consists of switches T<sub>2</sub>, T<sub>3</sub>, T<sub>4</sub>, C2, and T<sub>5</sub>. All the device bonding inductance, the PCB trace inductance, and the ESL of capacitor contributes to the overall switching-loop inductance. This big loop inductance will induce high overshoot voltage on the high-switching-speed SiC MOSFETs. In some cases, the switching dv/dt has to be lowered in order to secure the fast-switching SiC MOSFETs. This disadvantage significantly hinders the benefit of fast-switching CoolSiC™ in the application of the aforementioned ANPC modulation method.

Figure 11 Commutation loop of 3L-ANPC phase leg. (a) Without a decoupling capacitor connected directly to the fast-switching leg T<sub>2</sub>-T<sub>3</sub>; (b) With a decoupling capacitor C<sub>F</sub> connected directly to the fast-switching leg T<sub>2</sub>-T<sub>3</sub>

In reference [8], a RC series snubber circuit is added to the high-frequency switching SiC half-bridge  $(T_2-T_3)$ . The RC circuit provides a low impedance for the switching-transient current. In this way, the swiching loop can be closed without switches  $T_4$ , C2, and  $T_5$ . Therefore, the fast-switching SiC MOSFETs see much less voltage overshoots. In this circuit, the resistor functions to dampen the switching oscillation, as well as to limit the current overshot caused by the switching of line-frequency MOSFETs under the condition when the two bulk voltages are not perfectly equal. However, the resistor can bring additional inductance to the loop. From the power-dense-layout perspective, the insertion of a resistor makes the switching cell no longer compact.

Therefore, in this reference design, only a single decoupling capacitor in the capacitance range of 100 nF to 200 nF (under the applied voltage level) is used across the half bridge formed by  $T_2$  and  $T_3$ . According to experiment results, the decoupling capacitor significantly reduces the switching-loop inductance and limits the  $V_{DS}$  overshoot during switching transients. However, this small decoupling capacitor needs to be properly precharged during startup.

System overview and description

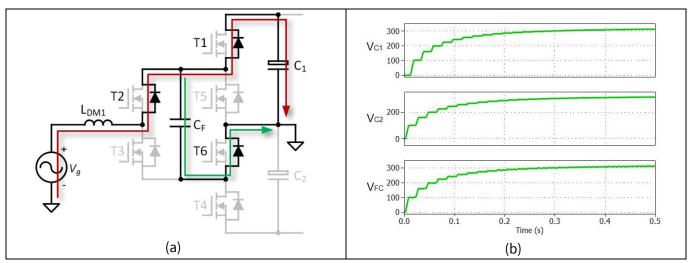

#### 2.1.3 Pre-charging of decoupling capacitor during startup

During the PFC mode (either three phase or single phase) startup, the grid voltage naturally activates the current path through the decoupling capacitor, therefore, the decoupling capacitor can be passively charged. Figure 12 depicts the circuit diagram and simulation waveform during the passive precharge. It can be seen that, during positive line cycle, the current path containing the body diodes of  $T_2$  and  $T_6$ , as well as the decoupling capacitor is activated, and the decoupling capacitor is clamped to the upper bulk capacitor voltage. This is verified with the simulation waveform shown in Figure 12 (b). Then, when the PWM signals are enabled, no voltage difference exists between half-bulk voltage and decoupling capacitor voltage. Therefore, the line-frequency switches  $T_1$ ,  $T_5$ ,  $T_6$ , and  $T_4$  see no inrush current during switching.

Figure 12 Passive pre-charging of the de-coupling capacitor. (a) Circuit diagram during passive precharge; (b) Simulation waveform during passive precharge

However, the grid can only charge the decoupling capacitor to the grid AC peak value. In the case that a DC source with terminal voltage is higher than two times of the grid AC peak voltage, i.e., during the inverter mode startup, high inrush current can be present when the line-frequency devices conducts due to the significant voltage difference between bulk capacitor and decoupling capacitor. Moreover, when the converter is going to operate under islanding mode, there is no voltage source present at the AC side to passively precharge the decoupling capacitor.

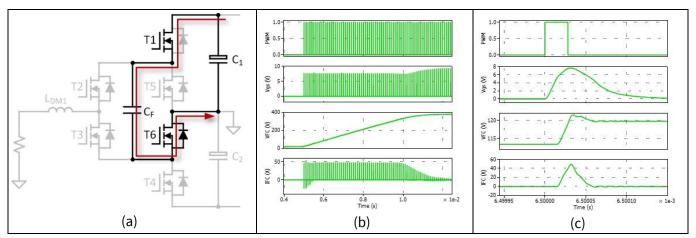

To handle the inverter mode (including islanding mode) startup more safely in REF\_11kW\_PFC\_SIC\_QD, an active pre-charging method is implemented. Figure 13 (a) depicts the circuit diagram during active pre-charge without grid voltage. During the process, device  $T_6$  is kept on, while device  $T_1$  is given short PWM pulses to its gate. In this way, the current path highlighted by the red-solid line is enabled. Figure 13 (b) and (c) present the PWM signal and  $V_{GS}$  of  $T_1$ , as well as the decoupling capacitor voltage and current in an overall and single switching cycle view, respectively.

It is concluded that the decoupling capacitor is slowly precharged to half-DC-link voltage, i.e., 400 V, and the charging current is controlled below 50 A in transient pulses to protect the power semiconductor devices. In the case scenario that the grid voltage is present, the operation of switch pair  $T_1$ - $T_6$  is only valid under positive line cycle, otherwise the inductor  $L_{DM1}$  current is out of regulation.

#### System overview and description

Figure 13 Active pre-charging of the decoupling capacitor. (a) Circuit diagram during active pre-charge; (b) Simulation waveform during active pre-charge; (c) Zoom-in view in one switching cycle

The device pair of  $T_5$ - $T_4$  can also enable the active pre-charging path in an opposite way, where  $T_5$  is constantly ON and  $T_4$  operates with short pulses. Additionally, the operation of device pair  $T_5$ - $T_4$  is only under negative line cycle if grid voltage is present.

To conclude, the active pre-charge method is only needed during the startup-phase of inverter mode operation. During operation of the converter, i.e., all devices switch according to the modulation scheme shown in Figure 13, the decoupling capacitor voltage is synchronized to either the upper or lower DC bulk voltage, therefore, no active control is required.

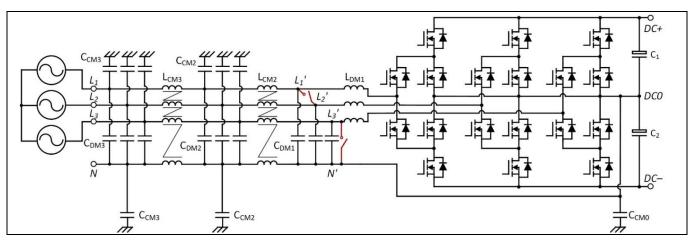

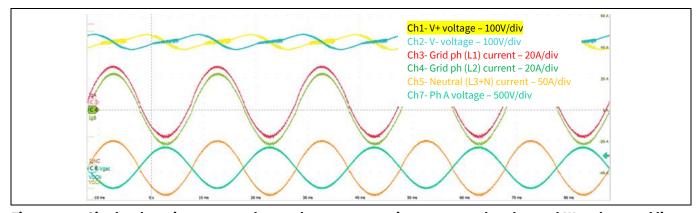

#### 2.2 Three-phase configuration

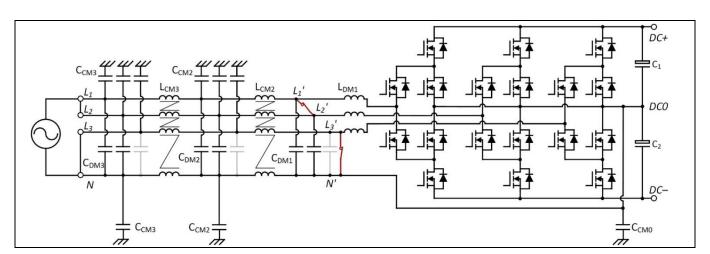

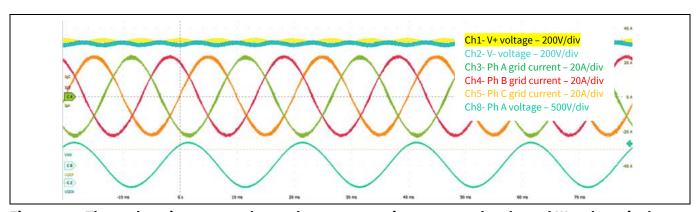

Under three-phase connection, the simplified main power circuit diagram of the system solution REF\_11KW\_PFC\_SIC\_QD is demonstrated in Figure 14. The system is connected to three-phase grid without the need of connecting neutral point (N). The three-phase currents flow through three power lines, i.e., L1L1', L2L2', and L3L3'. All three phase legs of the ANPC converter are active and convert power in both AC-to-DC and DC-to-AC operation modes. The neutral power line NN' is not used for power feeding under three-phase connection. Instead, it is utilized as the return path for current ripples as well as to reduce the common-mode noise between the potential DC0 and protective earth. Only three windings of the 4-winding common-mode-choke are utilized for power transfer.

Note:

In any power flow operation with REF\_11KW\_PFC\_SIC\_QD, leave the N terminal of the board unconnected during three-phase testing.

#### System overview and description

Figure 14 Simplified diagram of REF\_11KW\_PFC\_SIC\_QD in three-phase configuration

As shown in Figure 14, the two relays connected between L1'-L2' and L3'-N' are maintained open during the three-phase operation. The main purpose of these two relays is to short the two power lines L1L1' and L2L2', as well as L3L3' and NN' to maximize the utilization of copper content during single-phase operation.

#### 2.3 Single-phase configuration

The simplified main power diagram of the system solution REF\_11KW\_PFC\_SIC\_QD under single-phase operation is depicted in Figure 15. Being different from the three-phase operation mode, the two relays connected between L1'-L2' and L3'-N' are maintained closed during the single-phase operation. At the grid side, the terminals (L1 and L2) need to be combined with a short-circuited jumper, as well as the terminals L3 and N.

Note: When intending to start the board with single phase AC supply, externally combining the terminals L1 and L2 together, as well as L3 and N together is necessary.

Figure 15 Simplified diagram of REF\_11KW\_PFC\_SIC\_QD in single-phase configration

Only two phase-legs (A and B) of the ANPC converter operate in an interleaved way to convert power in AC-to-DC and DC-to-AC operation modes of single-phase configuration. In this way, all four windings of the common-mode choke are utilized. Power lines L1L1' and L2L2' are used as the active line connection in combination, whereas power lines L3L3' and NN' are combined and utilized as neutral return path. This neutral path is finally connected to the mid-point of the DC-side bulk capacitor (DC0). In this way, the output DC voltage can be easily

#### System overview and description

boosted to 800 V even for single-phase operation. Therefore, no matter the how the grid-side is configured, i.e., either three-phase or single-phase input, the DC side can always maintain 800 V.

Note:

Since there is only phases A and B operating to convert power, 2/3 of the three-phase power can be achieved for single-phase AC input.

However, connecting the AC neutral to the DC midpoint results in a large grid current flowing in and out of the midpoint of bulk capacitor bank. Therefore, the midpoint potential fluctuates significantly with 50 Hz content, which stresses the bulk capacitors and pentionally triggers the over/undervoltage protection of the bulk capacitors. A straightforward method to control this fluctuation is to increase the capacitance of the bulk capacitor banks. However, this would result in increased system volume and weight, which is not preferred for power converters with power density and cost constraints. Therefore, a novel operation method is created and implemented, which is explained in detail in Section 2.3.1.

Note:

During hardware testing, the software is able to automatically detect whether to operate under three-phase or single-phase mode based on phase voltage measurements if the user connects AC terminals following Figure 14 and Figure 15. Hence, there is no user intervention needed for the microcontroller during the start-up phase.

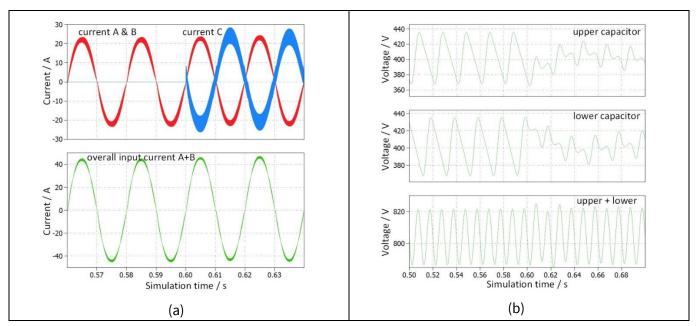

#### 2.3.1 Basic operational principle of power pulsation buffer

As explained in Section 2.3, single phase operation results in the fluctuation of DC midpoint voltage. The simulated waveforms during single phase operation is shown in Figure 16 (simulation time before 0.60 s in the figure). The two phases A and B operate in an interleaved way so that the overall input current in Figure 16 (a) has a reduced ripple at twice the switching-frequency. It can be seen in Figure 16 (b) that both the upper and lower bulk capacitors exhibit a significant voltage ripple, which contain both 50 Hz and 100 Hz harmonics. However, the overall upper and lower voltage only shows 100 Hz voltage ripple. This indicates that the 50 Hz voltage ripple on the upper and lower bulk capacitors are counter phase, which is caused by the grid current flowing in and out of the DC midpoint. This volage ripple especially at 50 Hz stresses the bulk capacitors and potentially triggers the over/undervoltage protection of capacitors.

#### System overview and description

Figure 16 Simulation waveform before and after the operation of phase C as the power pulsation buffer during single-phase operation. (a) Waveforms of separate phase currents and combined input current; (b) Waveforms of separate bulk capacitor voltages and the overall bulk voltage. The capacitance of 1.5 mF for each upper and lower bulk capacitor bank is considered in the simulation

Fortunately, for single phase operation, the yet unused phase leg C of ANPC can be fully utilized to eliminate this 50 Hz voltage fluctuation. To enable this, the relay which connects L3' and N' must be closed, as it is indicated in Figure 15. Then the output of phase leg C is connected back to the DC midpoint via the first differential-mode inductor  $L_{DM1}$  and the relay L3'N'.

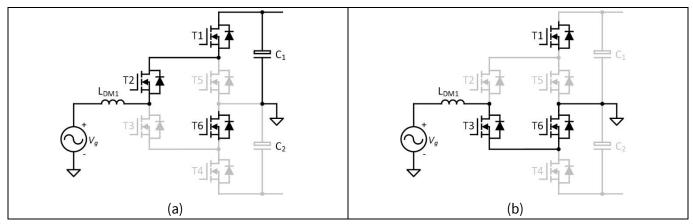

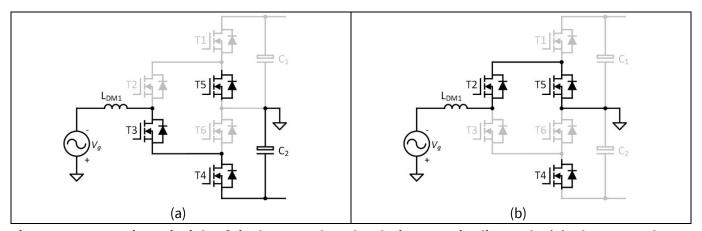

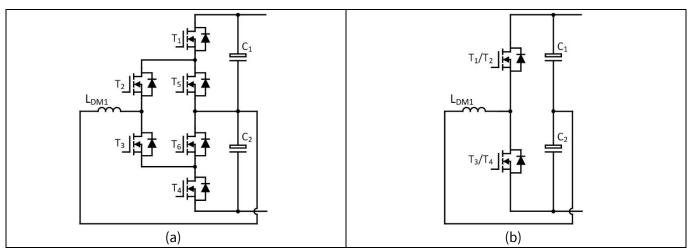

To highlight the operation method of phase C, the circuit diagram for phase C under single-phase operation is shown in Figure 17 (a). The basic operation principle is to turn-on/off switches  $T_1$  and  $T_2$ , as well as  $T_3$  and  $T_4$  simultaneously at high switching frequency, i.e., 65 kHz in this work, and the PWM signals  $T_1/T_2$  and  $T_3/T_4$  are implemented in a complementary way with dead-time inserted. Unlike phase A and B, in order to operate phase C as power pulsation buffer, phase C should be implemented with all CoolSiC<sup>TM</sup> devices. The switches  $T_5$  and  $T_6$  are left un-modulated. Doing so, the three-level ANPC phase leg is operated the same as a two-level leg, which is depicted in Figure 17 (b).

#### System overview and description

Figure 17 (a) Circuit diagram of phase leg C during single phase operation, when relay L3'N' is closed; (b) Analogy to a two-level phase leg

The simplest way of operation is to assign both device combinations  $T_1/T_2$  and  $T_3/T_4$  a 50% conduction duty, so that the voltage on  $C_1$  and  $C_2$  can be equalized, and the 50 Hz voltage fluctuation can be fully eliminated. However, the inductor  $(L_{DM1})$  current is left uncontrolled and the MOSFETs can be damaged due to the high current. This can be managed by controlling the current on the  $L_{DM1}$  inductor in a way that the 50 Hz voltage fluctuation can also be minimized.

As shown in Figure 16 (a), after simulation time 0.6 s, the inductor L<sub>DM1</sub> current of phase C is controlled to be the same magnitude but 180° out of phase to phase A/B current. As shown in Figure 16 (b), after implementing the phase C operation, i.e., after simulation time of 0.6 s, the voltage ripple on upper and lower capacitors are significantly reduced. An FFT analysis confirms that the 50 Hz ripple magnitude is reduced from 60 V peak-to-peak (before operating phase C) to 16 V peak-to-peak (after operating phase C). The 50 Hz voltage ripple can be fully eliminated if high amplitude of sinusoidal current is injected by phase C. However, the MOSFETs and inductor L<sub>DM1</sub> on phase C would bear more dissipation dramatically, which is not preferred from economic perspective. Therefore, the fully elimination of 50 Hz voltage ripple is not applied.

This method is easy to implement as the current controller of phase C is assigned with the counter-phase current reference as of phase A/B. The operation of phase C does not affect the grid current waveform quality since it just enables the current to flow inside the power converter.

#### 2.3.2 Practical modulation scheme of phase C as power pulsation buffer

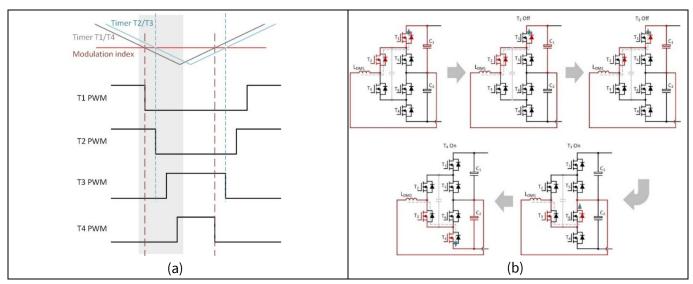

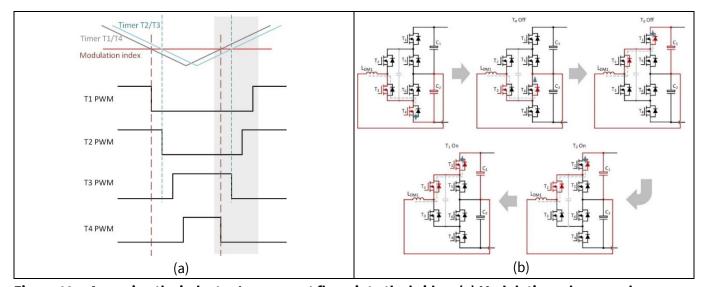

In practice, assigning two switches  $T_1$  and  $T_2$  (or  $T_3$  and  $T_4$ ) exactly the same PWM signal might be problematic due to tolerance of gate driver propagation delay and MOSFETs turn-on delay. Overvoltage on drain-source voltage might occur and damage the MOSFETs if  $T_1$  and  $T_2$  (or  $T_3$  and  $T_4$ ) are not turned-on and off simultaneously. Therefore, a practical modulation scheme must be implemented to prevent device damage. Figure 18 (a) presents the modulation scheme and switching wavefoms during the transition from positive output (both  $T_1$  and  $T_2$  on) to negative output (both  $T_3$  and  $T_4$  on).

Two PWM timers are used with a designed small phase delay of 50 ns, which are noted as timer  $T_1/T_4$  and timer  $T_2/T_3$  in Figure 18 (a). After comparator operations in the PWM generation module in the microcontroller, PWM signals of  $T_1$  and  $T_4$  are generated by timer  $T_1/T_4$  whereas, PWM signals of  $T_2$  and  $T_3$  are generated by timer  $T_2/T_3$ . Moreover, the dead-time between  $T_1$  PWM and  $T_4$  PWM should be set longer than the dead-time between  $T_2$  PWM and  $T_3$  PWM. The resultant switching signals follow the sequence of  $T_1$  off –  $T_2$  off –  $T_3$  on –  $T_4$  on during the transition from positive output to negative output. On the other hand, during the transition from negative output to positive output, the switching signals follow the sequence of  $T_4$  off –  $T_3$  off –  $T_2$  on –  $T_1$  on.

#### System overview and description

The equivalent circuits during transitions from positive to negative output and negative to positive output are shown in Figure 18 (b) and Figure 19 (b), respectively. It is noted that, even MOSFETs  $T_5$  and  $T_6$  are left unmodulated, their body diodes are utilized during the transitions. It is important to follow the switching sequence depicted in Figure 18 (a) and Figure 19 (a) in order to ensure that no overvoltage is applied to any MOSFET. The transition interval during which the switching sequence happens should also be minimized since it does not contribute to the 50 Hz voltage fluctuation reduction.

Figure 18 Assuming the inductor L<sub>DM1</sub> current flows into the bridge. (a) Modulation scheme and switching waveforms during the transition from positive output to negative output; (b) Equivalent circuits during the transition from positive output to negative output

Figure 19 Assuming the inductor L<sub>DM1</sub> current flows into the bridge. (a) Modulation scheme and switching waveforms during the transition from negative output to positive output; (b) Equavalent circuits during the transition from negative output to positive output

System hardware design

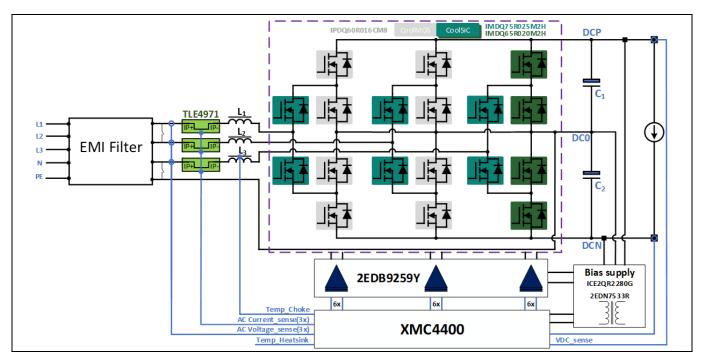

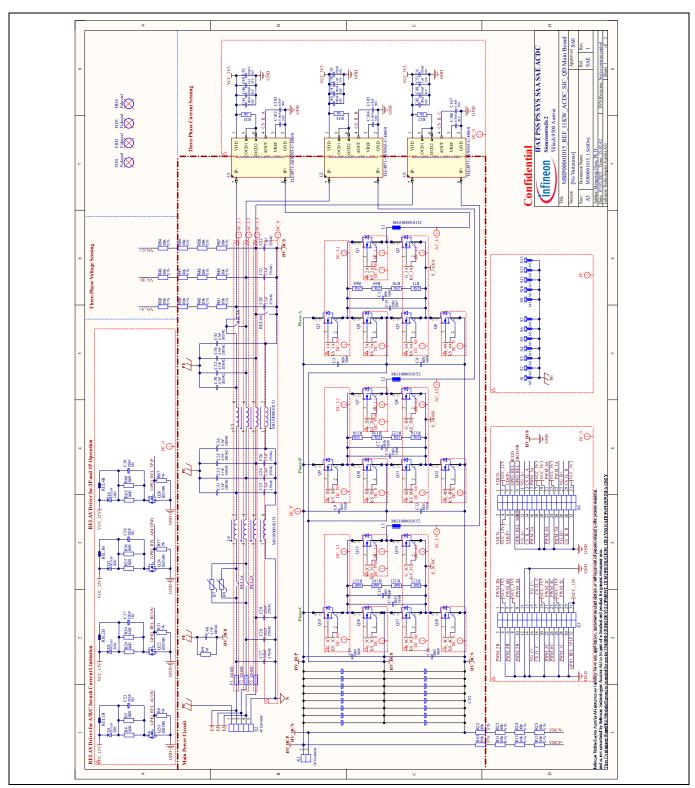

#### 3 System hardware design

To prove the concept of combining CoolMOS™ and CoolSiC™ in a bidirectional 3L-ANPC converter, the system demonstrator REF\_11KW\_PFC\_SIC\_QD is designed with high-efficiency and high-power-density targeting EV charging, OBC, energy storage systems, and other applications.

Key system specifications are mentioned in Figure 20. The system can handle both three-phase and single-phase AC input delivering the output power of 11 kW and 7.3 kW, respectively. The output voltage is maintained as 800 VDC for both single- and three-phase inputs.

Figure 20 shows the simplified architecture of the reference design. The hardward design consists of the following parts:

- CoolMOS™ and CoolSiC™ switches are driven by the dual-channel isolated gate driver EiceDRIVER™

2EDB9259Y. The auxiliary power supply unit is fed from DC bus, i.e., both from positive-half and negative-half DC rails

- Quasi-resonant flyback controller integrated power IC CoolSET™ ICE2QR2280G together with EiceDRIVER™

2EDN7533R in ring oscillator concept are used to generate eleven channels of isolated 18 V bias supplies to

drive all the power switches

- The CoolMOS™ and CoolSiC™ in the top-side cooling (TSC) package Q-DPAK are implemented in the prototype to demonstrate its capability to enable high power density designs

- The system efficiency at full load is boosted by 25 mΩ R<sub>DSON</sub> CoolSiC<sup>™</sup> IMDQ75R025M2H in the high-frequency leg and 16 mΩ R<sub>DSON</sub> CoolMOS<sup>™</sup> IPDQ60R016CM8 devices in low-frequency legs

- The current measurements for current loop control are realized by Infineon's XENSIV™ TLE4971 current sensors. The demonstrator is digitally controlled using Infineon microcontroller XMC4400 series. The peak efficiency can reach upto ~99.2% with the proposed solution

Figure 20 11 kW/800 V 3L-ANPC converter system block diagram

The functionalities implemented are soft-start, PFC, voltage regulation, overvoltage protection (OVP), undervoltage protection (UVP), overcurrent protection (OCP), and bidirectionality modes.

System hardware design

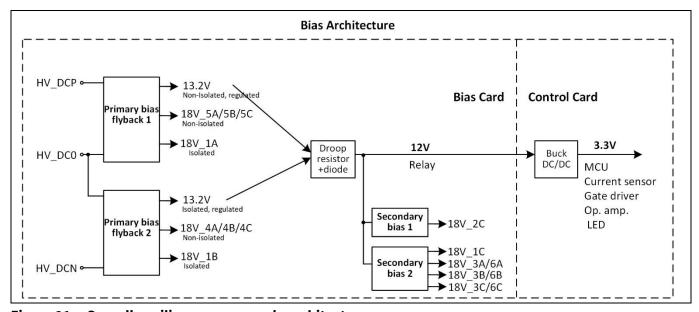

#### 3.1 Auxiliary power supply

All auxiliary power supply channels are located on the daughter card labeled as "BS200001015". Figure 21 demonstrates the overall architecture of auxiliary power supply. The loads on the auxiliary power supply include nine channels of 18 V supply for biasing all MOSFETs, one 12 V bus to power the relay coils, and one 3.3 V bus to power the MCU, current sensor, gate driver logic, operational amplifiers, and LED indicators. The schematic of the auxiliary power board is displayed in Section 7.2.2.

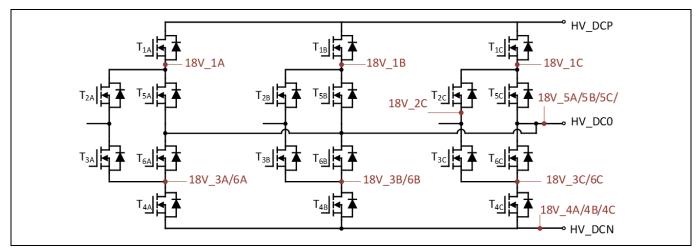

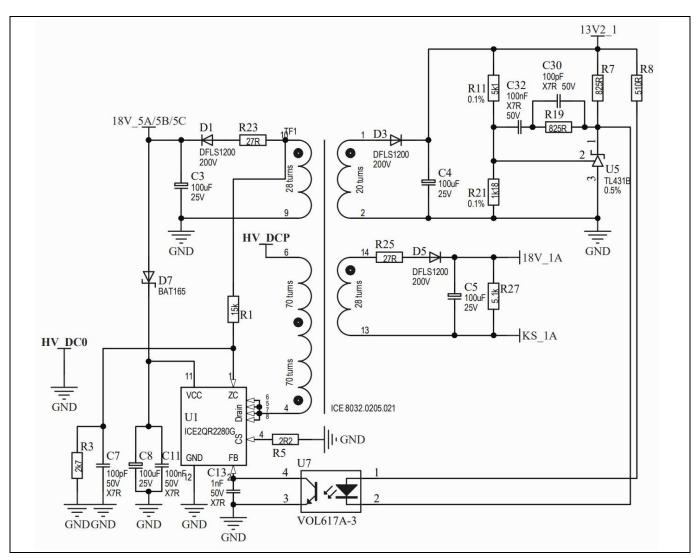

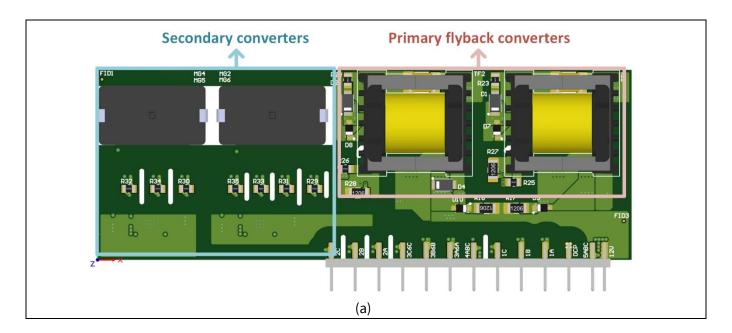

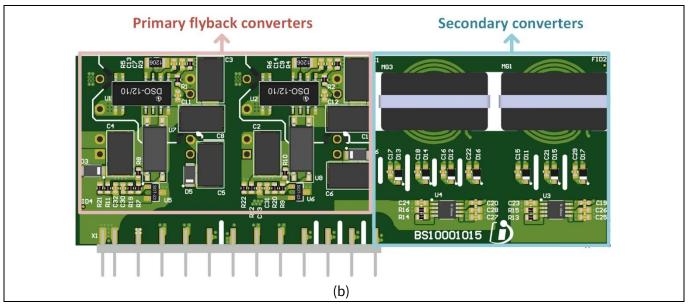

There are different conversion stages on the auxiliary power board. The main stage consists of two flyback converters with Infineon CoolSET™ integrated power management IC ICE2QR2280G. The two flyback converters are fed from the upper and lower DC bulk capacitors respectively, i.e., HV\_DCP(+400 V)-HV\_DCO(0V) and HV\_DCO(0V)-HV\_DCN(-400 V). As demonstrated in Figure 21, each flyback converter has three outputs and only the 13.2 V output is regulated due to its heavy loading. The rest of the two 18 V outputs are fed to bias the MOSFETs. It is to be noted from Figure 22 that the supply channels of 18V\_5A/5B/5C and 18V\_4A/4B/4C refer to the netlables HV\_DCO(0V) and HV\_DCN(-400 V) respectively, and provides driving voltage to the six MOSFETs T5A, T5B, T5C, T4A, T4B, and T4C. The rest outputs from the flyback converter feed the two gates of high-side MOSFETs T1A and T1B. Figure 23 depicts the schematic of a single primary flyback converter.

Figure 21 Overall auxiliary power supply architecture

Figure 22 18 V supply scheme to bias all MOSFETs

V 1.0

#### System hardware design

Figure 23 Single flyback converter schematic

The two 13.2 V outputs from flyback converters are then synthesized together via diode and droop resistor to form a 12 V bus. The purpose of implementing diodes and droop resistors is to equalize the output current and therefore, to support the balancing of two bulk voltages. The 12 V bus powers the relay coils and feeds the 3.3 V output switching regulator using Infineon's OPTIREG™ TLS4120D0EP V33 switching regulator. Additionally, the 12 V bus also feeds the secondary conversion stage.

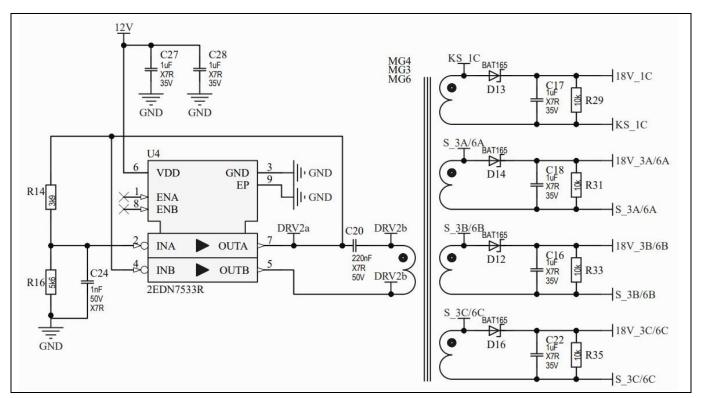

The secondary conversion stage utilizes a novel ring oscillator concept with Infineon's EiceDRIVER™ 2EDN7533R, which generates the rest of the 18 V supply voltages. The planar cores are used to implement this secondary bias converter. The schematic of this secondary converter is diaplayed in Figure 24. For each phase, the MOSFETs T₃ and T₆ can share the same channel of 18 V supply due to that their source pins are tied together. The 18 V driver supply of T2A and T2B are obtained through bootstrapping circuit, which is further discussed in the following sections. Figure 25 (a) and (b) show the front- and back-side of the auxiliary power supply board, respectively. The layout of primary flyback converters and the secondary converters can be clearly identified.

#### System hardware design

Figure 24 Secondary bias converter schematic

System hardware design

Figure 25 Pictures of the auxiliary power supply board captured from CAD design software. (a) Front side; (b) Back side

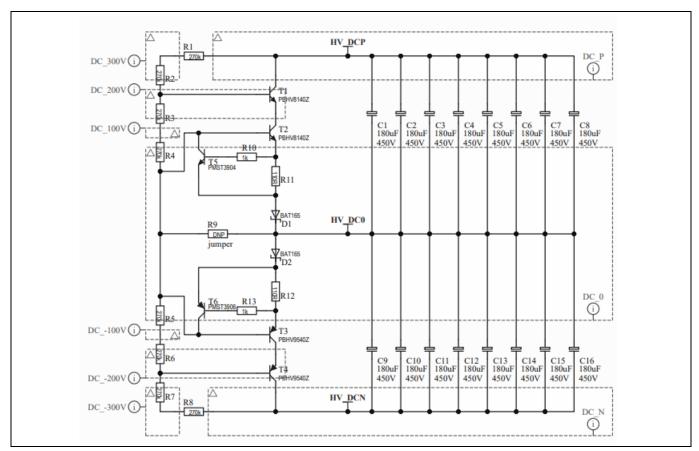

#### 3.2 Capacitor bank voltage balancing circuit

As mentioned in Section 3.1, the two flyback converters are fed from the upper and lower DC bulk capacitor banks. Therefore, the voltage balancing of the upper and lower bulk capacitor banks can be challenging as the two flyback converters may draw unbalanced supply current from the bulk capacitors. The 3L-ANPC converter can actively balance the bulk capacitor voltages by digital control algorithm but this only functions when the ANPC phase-leg is under operation. During the startup and standby phases when the 3L-ANPC phase-legs do not operate, the voltage balancing of the upper and lower bulk capacitors cannot be guaranteed.

Therefore, in this system solution design, a circuit that does not rely on the microcontroller to balance the two bulk voltages is implemented. The schematic of the balancing circuit is displayed in Figure 26. This circuit is also known as active voltage balancer for balancing the mismatch of leakage currents in series connected electrolytic capacitors [9]. Robust high-voltage BJTs are used in cascode configuration to realize the higher gain of the circuit. The circuit also features current limiting function so that the voltage ripple (DC midpoint fluctuation) during single-phase operation would not cause additional power losses. Therefore, the designed circuit features a rejection to AC ripples and only compensates for DC voltage difference between the upper and lower bulk capacitor banks. This ensures the stable operation of the two flyback converters to supply the auxiliary power for the whole system.

#### System hardware design

Figure 26 Bulk capacitor active voltage balancing circuit schematic

System hardware design

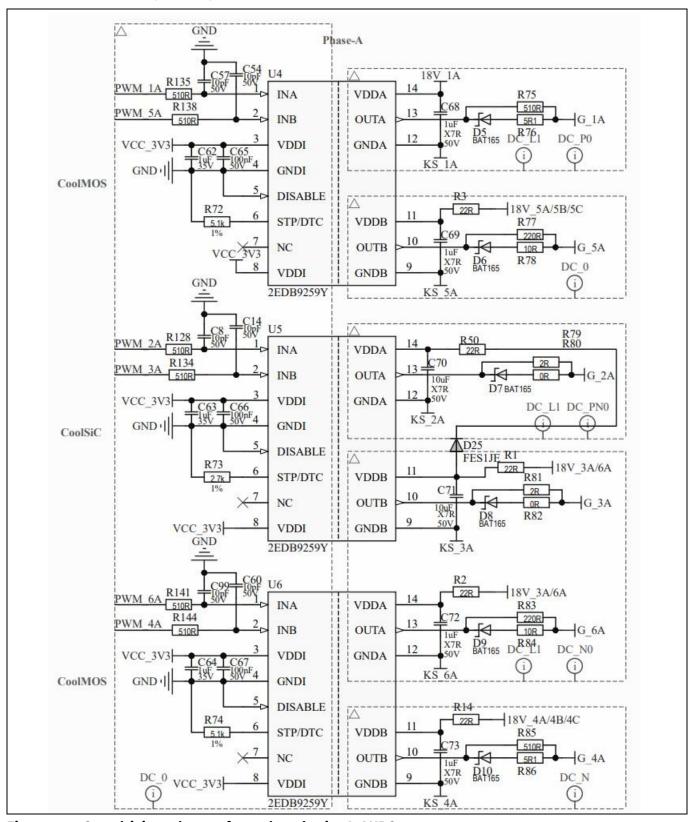

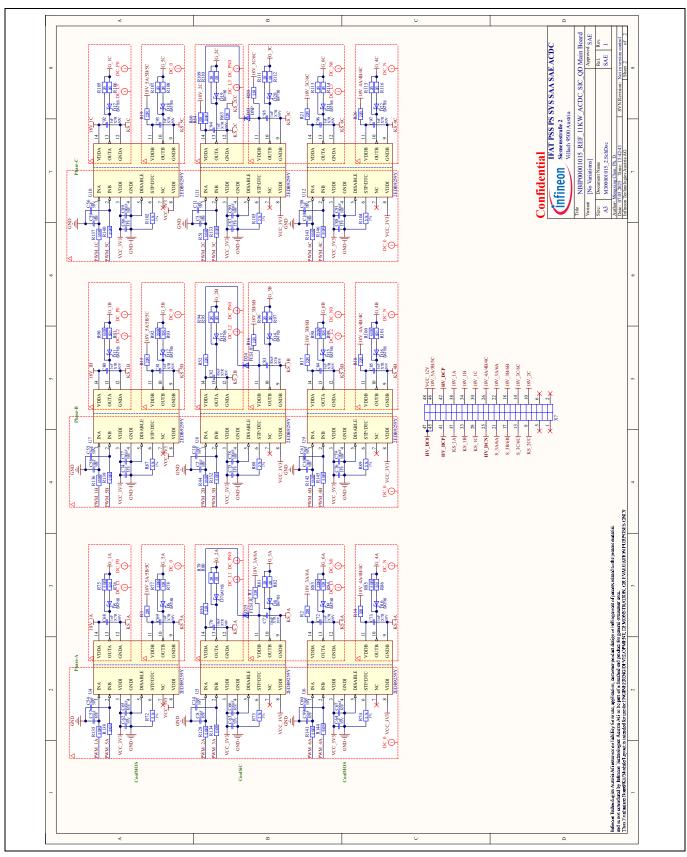

#### 3.3 Driving configuration

Figure 27 Gate driving scheme of one phase leg in 3L-ANPC

Figure 27 shows the gate driving stage of phase-A leg in ANPC converter topology. The dual-channel gate driver 2EDB9259Y is used to drive both CoolSiC™ and CoolMOS™ switches. As mentioned in Section 3.1, switches T1A,

#### System hardware design

T3A, T4A, T5A, and T6A are biased by the auxliary power supply card, whereas the high-side switch T2A is biased by a bootstrap circuit (D25 and R50) from 18V\_3A/6A. In this way, the switching performance of high-side switch T2A can be optimized.

With gate resistances of 2  $\Omega$  for turn-on and 0  $\Omega$  for turn off for switches T2A and T3A, high switching speeds are achieved during the commutation of those complementary SiC devices. A 2.7 k $\Omega$  pull-down resistor is connected to the STP/DTC pin of the gate driver 2EDB9259Y, which drives the fast-switching leg to configure the minium dead-time to be 27 ns. An actual dead-time of 50 ns is controlled by the XMC4400 microcontroller. Note that 22  $\Omega$  damping resistors (R1, R2, R3, and R14) are used in series with all 18 V supplies that are shared by multiple switches. Otherwise, oscillation on 18 V supply can be induced due to the Kelvin-source connection of supply voltage.

The schematic of phase-B driving stage replicates that of phase A. However, the phase-C driving-stage schematic is different than phase A/B because the high-side swtich T2C is supplied directly by the auxiliary power supply card, instead of bootstrapping. This is due to the requirement of synchronous operation of all phase legs during three-phase startup.

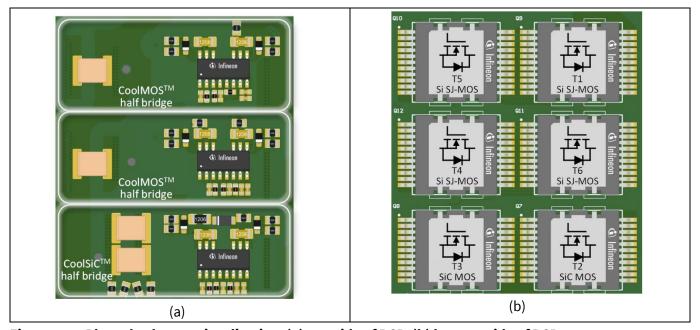

#### 3.4 Switching-loop optimization

Minimizing the switching-loop inductance is crucial when designing the hard-switched bridge-leg. A single ANPC phase leg captured from the PCB CAD software is depicted in Figure 28, visualized from both the top side and bottom side of the PCB, in Figure 28 (a) and (b), respectively. To simplify and modularize the design, a single ANPC phase leg is split into three half bridges, i.e., two CoolMOS™ half-bridges and one CoolSiC™ half-bridge. All utilized MOSFETs are packed in Infineon's innovative top-side cooled package Q-DPAK. As shown in Figure 28 (b), the MOSFETs are mounted on the bottom side of the power PCB, with heatslugs facing downwards to the heatsink.

Figure 28 Phase-leg layout visualization; (a) top-side of PCB; (b) bottom-side of PCB

The top-side cooled package allows all peripheral devices, e.g., gate drive circuit, bootstrap circuit, and decoupling capacitors can be placed on top-side of the PCB, right on top of the MOSFETs. The Q-DPAK therefore, enables compact design and minimum switching area loop inductance. The switching loop in the cross-sectional view is demonstrated in Figure 29 (a), as it is highlighted in red solid line. The power loop layout is done on the bottom and second bottom layers to minimize the loop. The decoupling capacitor is connected Application note

#### System hardware design

to the power loop by placing veritical via arrays. The total loop inductance is estimated to be ~7 nH [10] with the top-side cooled Q-DPAK and the optimized switching loop PCB design.

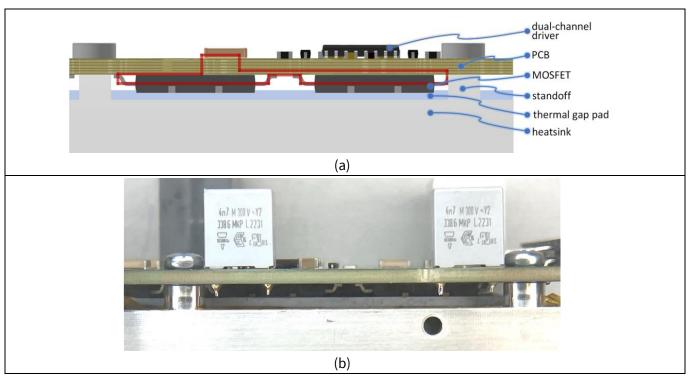

Figure 29 Cross-sectional view of the switching cell. (a) Captured in the PCB CAD software; (b) Real hardware in photo

#### 3.5 Thermal design

When designing the thermal management solutions for Infineon's Q-DPAK packages, there are a variety of thermal interface materials (TIMs), including gap pads, liquid gap fillers, and phase-change materials [11]. Commercially available gap pads are typically composed of pre-cured silicone combined with ceramic powder. These materials are offered in various softness grades, such as soft and ultra-soft, and provide a thermal conductivity range typically between 2 and 10 W/(m·K) or higher. For applications with higher thermal demands, choosing a high thermal conductivity gap pad can significantly improve heat dissipation from the package.

However, thermal conductivity is not the only parameter to consider. Other important characteristics include thickness, material compressibility, and insulation level. Selecting the optimal TIM requires to balance these factors based on the application needs and design constraints.

#### 3.5.1 Standoff height

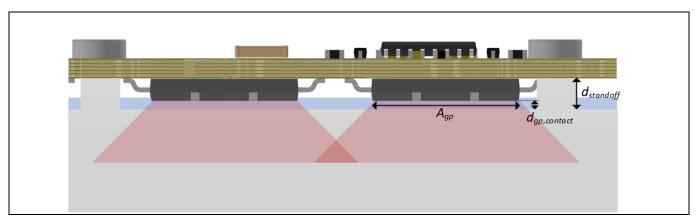

Gap pads typically offer good high-temperature performance, but to maintain consistent thermal performance over time, they require a permanent and reliable contact force. As shown in Figure 29 (a) and (b), and 30, mechanical standoffs with defined heights are used to maintain the spacing between the PCB and heatsink, denoted as  $d_{\text{standoff}}$ . The final compressed thickness of the gap pad  $d_{\text{gp,contact}}$  can be calculated using the following relationship:

$$d_{gp,contact} = d_{standoff} - (d_{gdpak} \pm 0.1 \text{ mm})$$

(1)

#### System hardware design

where,  $d_{qdpak}$  represents the typical package thickness of the Q-DPAK (2.3 mm nominal, with a  $\pm$  0.05 mm tolerance). To ensure continuous mechanical contact between the package and gap pad, the compressed thickness must always be less than the original thickness of the gap pad:

$$d_{gp,contact} < d_{gp,origin}$$

(2)

$$d_{\text{standoff}} < d_{\text{gp,origin}} + (d_{\text{qdpak}} - 0.05 \text{ mm})$$

(3)

For example, if the thermal gap pad has an original thickness of 1.0 mm, the standoff height should be calculated less than 3.25 mm. Considering a gap-pad compression distantce to be 0.15 mm for instance, then the final standoff height should be designed as  $d_{standoff} = 3.1$  mm. Then, the thermal resistance of the gap pad can be estimated as:

$$R_{th,gp} = d_{gp,contact} / (A_{gp} \cdot \lambda_{gp})$$

(4)

$$= (d_{standoff} - (d_{odpak} \pm 0.05 mm)) / (A_{gp} \cdot \lambda_{gp})$$

(5)

where,  $A_{gp}$  and  $\lambda_{gp}$  are the effective heat transfer area and thermal conductivity of the applied gap pad, respectively.

Figure 30 Cross-sectional view of the switching cell

Generally, reducing the standoff height (i.e., increasing compression distance of the gap pad) can effectively lower the thermal resistance between the package and heatsink. However, this increases mechanical stress on the PCB due to higher compression ratio of gap pad. Excessive stress can lead to PCB warpage, which in turn may cause severe issues like solder joint cracking or failure of surface-mounted components, especially multilayer ceramic capacitors.

#### 3.5.2 Avoiding PCB warpage

To prevent PCB warpage in the applications using top-side cooled Q-DPAK packages, three key strategies can be implemented.

The first method is to increase the thickness and to optimize the stackup of the PCB. The main board thickness of PCB used in REF\_11KW\_PFC\_SIC\_QD is ~2.5 mm. In the PCB stackup, the core layers are made of fiberglass-epoxy laminate, and they therefore provide the main structural support and substrate for the PCB. The prepreg layers, on the other hand, act mainly as adhesive and bonding layers during the lamination process. Putting more core layer in the PCB buildup helps to improve the rigidity of the PCB and prevent the PCB from warpage.

The second method is to increase the mechanical support provided to the PCB by the metallic chassis or cooling plate. This is achieved by placing additional height-defining standoffs or spacers near the Q-DPAK device, as shown in Figure 30. These standoffs help to distribute mechanical load more evenly and reduce localized stress caused by gap pad compression.

#### System hardware design

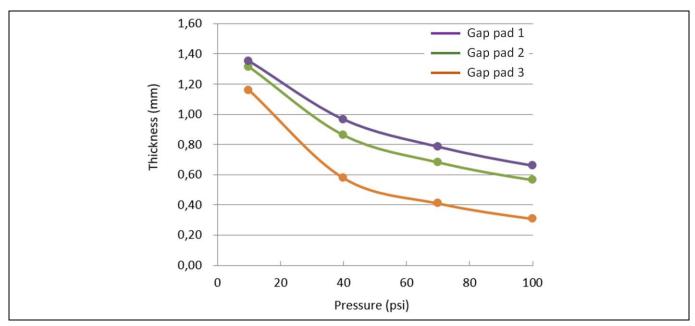

The third method involves selecting a gap pad with higher compressibility, which reduces the mechanical stress transmitted to the PCB. Figure 31 illustrates the compressibility characteristics of three different gap pad materials, expressed as thickness versus applied pressure — a common metric provided by gap pad manufacturers. Among the materials compared, Gap Pad 3 demonstrates the highest compressibility, showing the greatest reduction in thickness under the same applied pressure. This feature makes it more effective in accommodating mechanical tolerances and minimizing stress-induced deformation of the PCB.

Figure 31 Thermal pad material's compressibility vs. thickness vs. pressure curve

#### 3.5.3 Insulation requirement

In addition to thermal conduction, a secondary but equally critical function of gap pads is to provide electrical isolation between the package and the cooling structure (e.g., heatsink or metallic baseplate). This is especially important in applications where the cooling component is electrically connected to protective earth.

Depending on system-level requirements, many power converter designs must withstand high-voltage insulation levels, typically in the range of several kilovolts between active circuitry and protective earth. According to manufacturer specifications, typical dielectric breakdown strengths of commercial gap pad materials range from 5 kV/mm to 10 kV/mm.

Therefore, depending on the system insulation requirement and the selected gap pad's dielectric breakdown voltage, a minimum thickness of gap-pad layer (after pressure application) should be defined. In some cases, an additional insulation layer, such as adhesive Kapton layer, can be applied to the heatsink or chassis to reinforce electrical isolation (commonly referred to as double insulation).

Considering all these aforementioned design factors such as mechanical tolerances, PCB warpage, and insulation requirements, the typical post-compression thickness of the gap pad in practical applications generally falls within the range of 0.5 mm to 1.5 mm. With REF\_11KW\_PFC\_SIC\_QD, the standoff height of 3.1 mm is defined and the 1 mm ultra-soft gap pad FSL-BS from Denka Company Limited is used. The selected gap pad features a thermal conductivity of 3 W/m·K and a premium compressibility of 30 % at 0.1 MPa pressure. The dielectric breakdown voltage of the selected material is reported to be 10 kV/mm. Considering the full-range height tolerance of Q-DPAK, the post-compression thickness of 1 mm gap pad is in the range between 0.6 mm and 0.8 mm.

System hardware design

#### 3.6 Inductor and current sense against stray field

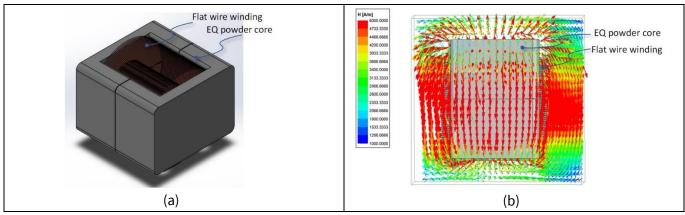

In REF\_11KW\_PFC\_SIC\_QD, each inductor is made with one pair of HTEQ3626A high flux core from Chang Sung Corporation. Helical winding with flat wire with the dimension of 7 mm (width)  $\times$  0.4 mm (thickness), with totally 50 turns wounded, is implemented due to its better window utilization ratio. The achieved initial inductance is tested to be 330  $\mu$ H, and the rated current is designed to be 16  $A_{RMS}$ . A 3D picture of the inductor captured in CAD software is shown in Figure 32 (a).

Figure 32 (a) 3D picture of the inductor captured in CAD software. (b) Simulated stray field strength in the vicinity of the inductor

The EQ-core based inductor solution helps to increase the overall power density as it occupies the least volume compared to other magnetic core shapes, e.g., toroidal etc. However, inevitable stray field can be found in the vicinity of the inductor, because the powder core material features relatively low permeability and the EQ shape increases the chance for the field to leak. Figure 32 (b) depicts the FEM simulation result of stray field surrounding the inductor. This stray field can cause interference to its neighboring components which work on magnetic priniciple, especially the Hall- and magnetoresistive-based current sensors. In theory, all Hall- and magnetoresistive-based current sensors without built-in shielding layer suffer from measurement error due to the stray field. The magnetic interference level increases sharply with higher current flowing through the inductor, and therefore, the current THD value sees significant increase with the increase of output power during the operation.

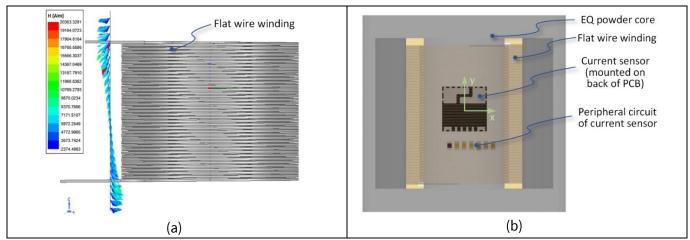

Figure 33 (a) Simulated stray field strength in the plane beneath the inductor, i.e., the PCB plane. The core is hidden for simplicity; (b) The concluded optimal position and orientation for TLE/TLI 4971 current sensor with least stray field interference, visualized from the top-side of inductor

#### System hardware design

Several methods can be applied to mitigate the stray field interference effect. First, the current sensor can be placed away from the inductor, where the stray field density is much less. This method requires more layout area on the PCB and may enlarge the switching-node area significantly if the current sensor is electrically connected between the bridge-leg and inductor. Therefore, this method may not be applicable to all designs.

The second method involves applying external field-shielding component to the current sensor. Doing so, the stray field can be bypassed before it reaches the current sensor. A slight cost would be added due to extra shielding components and the excessive effort for the assembly process.

Finally, since the current sensor typically shows immunity to a certain magnetic field direction, it can be placed in the vincinity of inductor but in a specific location and orientation that the stray field does not affect the sensor output behavior. This method does not require additional components and can be used in designs where the PCB layout needs to be compact. On the other hand, this method requires deep know-how on stray field distribution as well as current sensor behavior.

Therefore, the stray field orientation at the PCB plane (where the current sensor is assembled) is studied, which is shown in Figure 33 (a). It is known that the sensing element is sensitive to stray field in perpendicular to its sensing element. The current sensor should be placed in alignment with the center of the inductor as the perpendicular field at the center of inductor geometry is nearly zero according to Figure 33 (a). During testing, it is noticed that the orientation of current sensor also affects the stray field sensitivity. Finally, the optimal position and orientation of current sensor is concluded in Figure 33 (b), which is visualized from top-side of the inductor, and nearly no stray-field interference can be observed during testing. Rotating the current sensor by 180° still sees the optimum performance, while rotating by 90° sees more sensitive to stray field. The REF\_11KW\_PFC\_SIC\_QD finally adopts the optimal layout shown in Figure 33 (b), and the performance is verified through tested current THD is mentioned in Sections 5.3 and 5.4.

Note:

The recommended optimal orientation only applies to the tested current sensor TLE/TLI 4971 from Infineon because of the package difference and how the sensing element is mounted in the package. Extra validation needs to be conducted if another model of current sensor is used.

In conclusion, this section provides a guideline regarding layouting and placement of Infineon's current sensor TLE/TLI 4971 with EQ-core based power inductor to achieve the lowest level of stray field interference. The concluded optimum layout to achieve the compact PCB layout is demonstrated in Figure 33 (b).

#### 3.7 Common-mode choke with differential-mode inductance

A novel common-mode choke is used in REF\_11KW\_PFC\_SIC\_QD to further improve the power density of the design. The differential-mode inductances are integrated into the common-mode choke, and this allows the REF\_11KW\_PFC\_SIC\_QD to be implemented without dedicated differential-mode inductors.

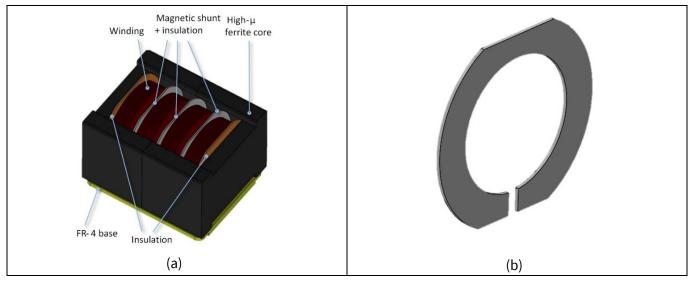

The integration of differential-mode inductance is realized by inserting ferromagnetic material (magnetic shunt) between the adjacent windings in the common-mode choke buildup. This ferromagnetic material provides extra magnetic permeability to the leakage path and therefore, helps to increase the differential-mode inductance. Figure 34 (a) demonstrates the common-mode choke structure utilized in REF\_11KW\_PFC\_SIC\_QD. Two high-permeability ferrite cores (R10K material from DMEGC) are used, each of which is in the shape of PQ35-43A. Four sets of helical flat wires (each in the size of 6 x 0.6 mm, 8 turns) are assembled in the window area. Then, three sets of magnetic shunts with insulation are mounted in between the windings.

The geometry of the magnetic shunt is depicted in Figure 34 (b), which can be easily fitted into the core structure. The magnetic shunt is made from NO 30-16 electric steel sheet thickness of 0.3 mm. The utilized material can significantly increase the leakage path magnetic permeability and does not affect the system

#### System hardware design

efficiency through out the measurement. Multiple pieces of magnetic shunts can be stacked to increase the final differential-mode inductance. Figure 35 shows one of the finished common-mode choke prototypes. For more information on the common-mode choke design, refer to [12].

Figure 34 Common-mode choke buldup used in REF\_11KW\_PFC\_SIC\_QD. (a) The whole common-mode choke captured in 3D CAD design software; (b) Magnetic shunt in ring shape used in the common-mode choke buildup

Figure 35 Finished common-mode choke prototype

System software design

## 4 System software design

#### 4.1 Three-phase control diagram

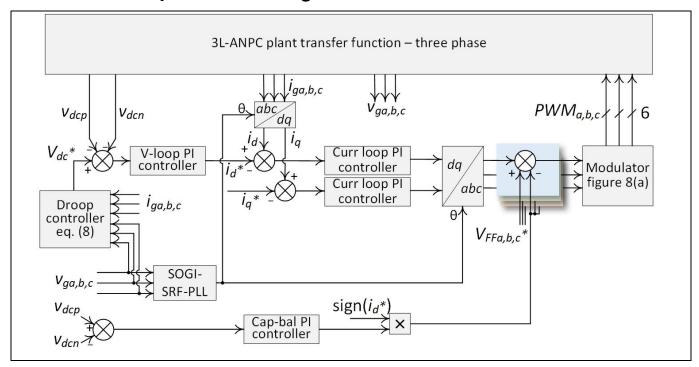

Figure 36 Three-phase control diagram

The three-phase control diagram is demonstrated in Figure 36. The two DC capacitor voltages  $V_{dcp}$  and  $V_{dcn}$  are sampled and compared with the DC volage reference  $V_{dc}^*$ . The DC voltage reference  $V_{dc}^*$  is given by the droop controller, which is displayed in Section 4.3. The outer voltage loop PI controller is implementd in C code to regulate the overall DC-link voltage  $V_{dcp} + V_{dcn}$ , which generates the d-axis current reference  $i_d^*$ . Since the dc-link voltage is controlled, the converter is able to work under both PFC and inverter modes. The well-established dq current control method is utilized with two PI controllers to regulate the d- and q-axis currents [13].

The q-axis current reference  $i_q^*$  is set to zero in this controller implementation. The two modulation voltages in dq axis are then transformed back to abc axis with the angle information from the three-phase second-order generalized integrator phase-locked loop (SOGI-PLL). The grid voltage feed-forward  $V_{FFa,b,c}^*$  is used to improve the dynamic behavior of current regulation. In addition, a capacitor-voltage-balance loop is implemted to control the voltage difference of the upper and lower DC bulk voltages.

System software design

#### 4.2 Single-phase control diagram

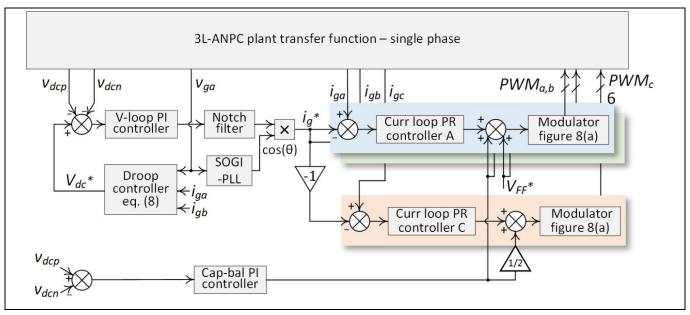

Figure 37 Single-phase control diagram

The single-phase control diagram is demonstrated in Figure 37. The DC voltage reference  $V_{dc}^*$  is given by the droop controller, which is illustrated in Section 4.3. Same as the three-phase control, the overall DC-link voltage is regulated by the voltage-loop PI controller, allowing the power to flow in both directions. The notch filter is implemented in cascade to the PI controller to eliminate the double line-frequency contents appearing normally on the single-phase current reference. During operation, phase currents A and B are sampled and controlled in an interleaved manner to lower the differential mode (DM) noise. Two proportional resonant (PR) controllers are used to regulate the two single-phase currents [14]. In the end, the grid voltage feed-forward and capacitor voltage balancing contents are added to the two current regulation outputs.

Both the three-phase and single-phase control methods are implemented using Infineon's 32-bit XMC440 microcontroller in C code. And all calculations are based on fixed-point arithmetic. The 12-bit ADCs of XMC4400 are deployed to convert the three inductor currents, three grid-side voltages, two DC bulk voltages, and two temperature sense signals into digital values. All the ADC inputs are configured as single-ended mode. The three inductor currents and three grid-side voltages are configured to be sampled in a synchronous way to ensure the balanced control among three phases.

Note:

The control software can self-identify whether to operate under three-phase or single-phase mode by evaluating the input voltages before start-up. The user does not need to re-configure or re-flash the software.

For both single- and three-phase control, the SOGI-PLL and current loop are executed in the frequency of 65 kHz, being the same as the switching frequency of SiC MOSFETs. The voltage loops, including the overall DC-link voltage control, the notch filter, and the DC capacitor voltage balancing control are implemented in the frequency of 6.5 kHz.

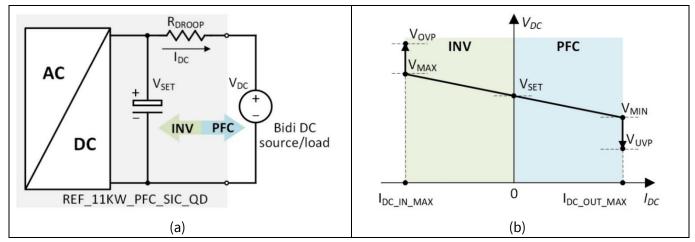

### 4.3 DC droop feature

To enable the bidirectional power flow and a smooth control of power flow direction, as well as power amplitude, a droop feature is implemented to the DC side voltage control. The circuit diagram of droop feature is demonstrated in Figure 38, where  $V_{\text{SET}}$  and  $V_{\text{DC}}$  denote the DC voltage reference (800 V nominal) and actual

#### System software design

bidirectional DC source, respectively. At the DC output/input port of REF\_11KW\_PFC\_SIC\_QD, the existing 800 V bulk capacitance presents a nominal value of 720  $\mu$ F. During the bidirectional testing, directly connecting the DC terminals to the bidirectional DC source without the R<sub>DROOP</sub> is not a preferred option. The capacitive current, which flows between the bulk capacitor and DC source cannot be controlled, because the amount of power is unregulated. The system will run either in steady-state PFC mode (if  $V_{DC} < V_{SET}$ ) or steady-state inverter mode (if  $V_{DC} > V_{SET}$ ). In the case that  $V_{DC}$  is close to  $V_{SET}$ , power flow can oscillate between the PFC mode and inverter mode.

Figure 38 Droop control method. (a) Circuit diagram illustrating the droop feature at DC terminal. The resistor R<sub>DROOP</sub> is a virtual resistor realized by control software; (b) Output V-I curve demonstrating the implemented droop feature

With the  $R_{DROOP}$  inserted between the bulk capacitor and DC source, the DC terminal current  $I_{DC}$  is limited by the Ohm's law:

$$I_{DC} = (V_{SET} - V_{DC}) / R_{DROOP}$$

(6)

With the  $R_{DROOP}$  populated, the V-I characteristic will behave as demonstrated in Figure 38 (b). By adjusing the bidirectional DC source output voltage, not only can the power flow direction be smoothly controlled, but also the power level can be precisely regulated. The  $R_{DROOP}$  value can be determined by the maximum voltage swing as well as the DC input/output current range:

$$R_{DROOP} = (V_{MAX} - V_{MIN}) / (I_{DC\_OUT\_MAX} - I_{DC\_IN\_MAX})$$

$$(7)$$

Taking the three-phase operation mode for instance, the  $V_{MAX}$  and  $V_{MIN}$  are designed to be 811 V and 789 V, respectively with the center point to be  $V_{SET}$  = 800 V. The DC input/output current range are designed to be ± 13.75 A considering the power limit of ± 11 kW. Hence, the actual value of  $R_{DROOP}$  is calculated to be 0.8  $\Omega$ .

The simple way of implementing R<sub>DROOP</sub> is to use a physical power resistor, but this causes additional power losses. In REF\_11KW\_PFC\_SIC\_QD, the droop resistor is realized virtually with the digital control. The XMC<sup>™</sup> microcontroller monitors the actual input/output power from AC side P<sub>AC</sub> and adjust the DC bulk voltage reference automatically following:

$$V_{dc}^* = V_{SET} - R_{DROOP}^* I_{DC} = V_{SET} - R_{DROOP}^* (P_{AC}/V_{SET})$$

(8)

The detailed control diagram including the mentioned droop control are displayed in Figure 35 and Figure 36.

**Experimental results**

### 5 Experimental results

### 5.1 Setup description

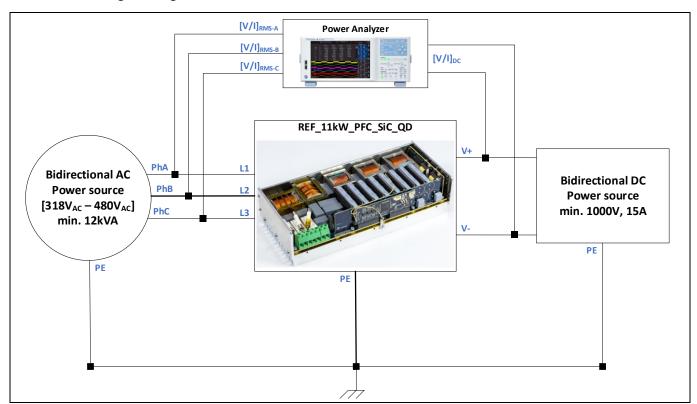

This subsection introduces the experimental setup. It is recommended that all conducted testing follows the test setup introduced in this subsection. Figure 39 shows the test setup for PFC and inverter mode operations with three-phase AC feeding.

The bidirectional AC source phase terminals (A, B, C) are connected to AC terminals (L1, L2, and L3) labelled on REF\_11KW\_PFC\_SIC\_QD.

Note:

The PE line between the AC source and REF\_11KW\_PFC\_SIC\_QD needs to be connected always, and the required current and voltage insulation ratings of cables are followed for safety reasons.

The DC voltage is regulated by the microcontroller following the droop rule introduced in Section 4.3, which allows the user to control both the power conversion and the power-flow direction by changing the DC source/load voltage setting.

Figure 39 Test setup for three-phase operation: both PFC and inverter modes

Note:

Under three-phase operation mode, REF\_11KW\_PFC\_SIC\_QD is designed with AC side three-wire connection without neutral wired. Ensure that during the three-phase operation, the neutral terminal on the board is left unconnected.

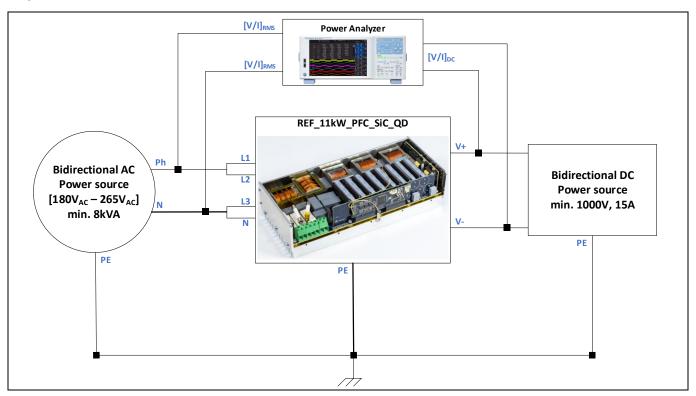

The single-phase test setup is demonstrated in Figure 40. Being different from three-phase setup, during single-phase testing, the L1 and L2 terminals of REF\_11KW\_PFC\_SIC\_QD should be combined (shorted) externally and connected to the phase terminal of the AC source. Additionally, the L3 and N terminals of REF\_11KW\_PFC\_SIC\_QD should be combined externally and connected to the neutral terminal of the AC

#### **Experimental results**

source. The cable connecting either phase or neutral should be at least 32 A rated to deliver 7.3 kW power in single phase.

Figure 40 Test setup for one-phase operation: both PFC and inverter modes

An external fan with 500 mW power supply (<12 V) below the cold plate and four channel power quality analyzer in the setup are required to evaluate the design. In case bidirectional operation is not required, the previous setup can be simplified as follows:

- For PFC mode operation alone, bidirectional source/load can be replaced by unidirectional source/load

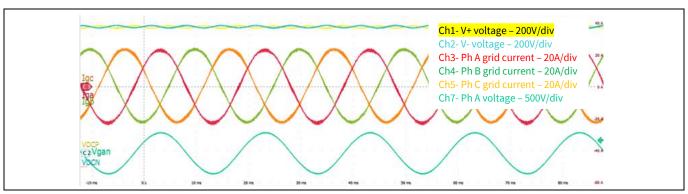

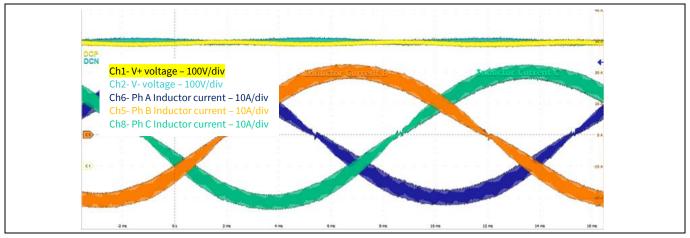

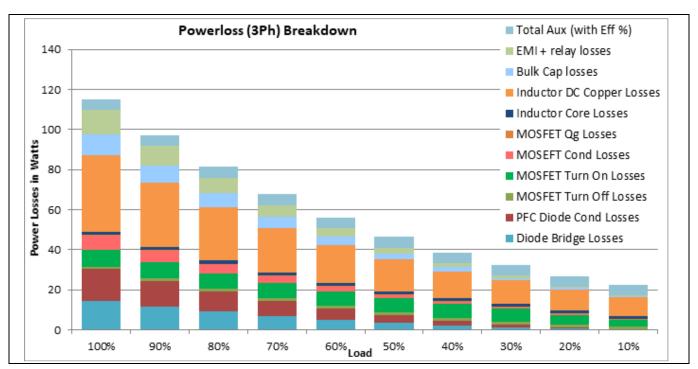

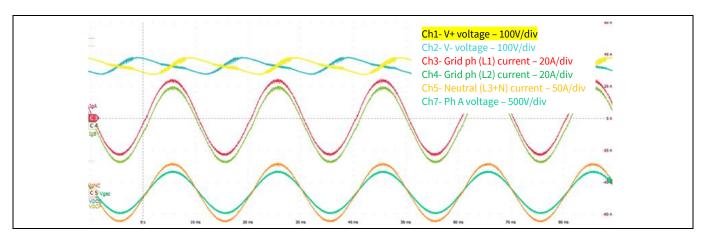

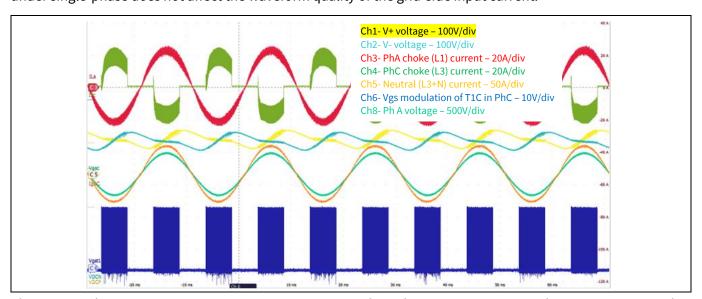

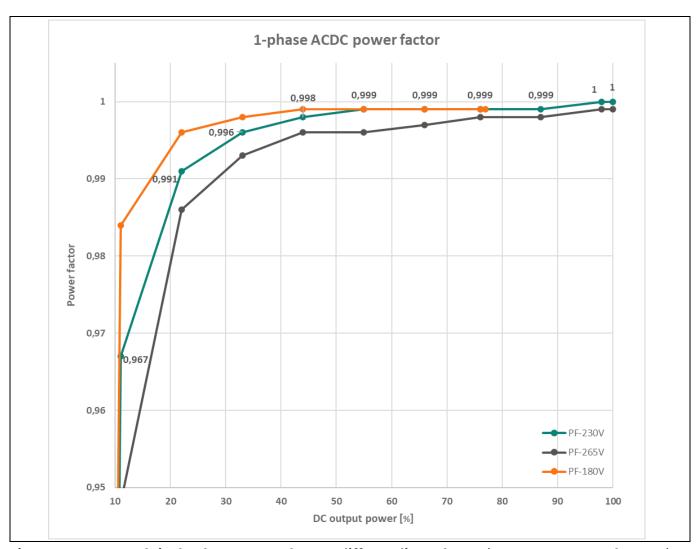

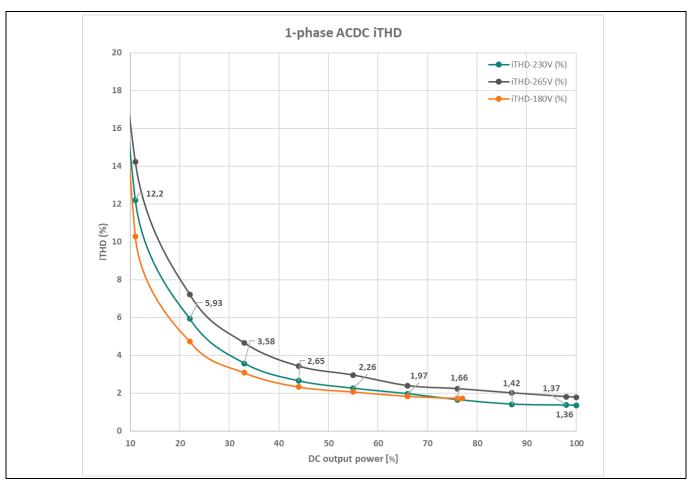

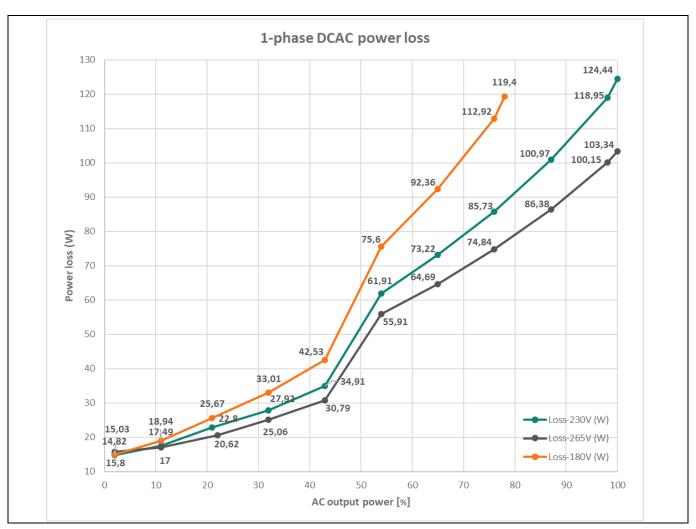

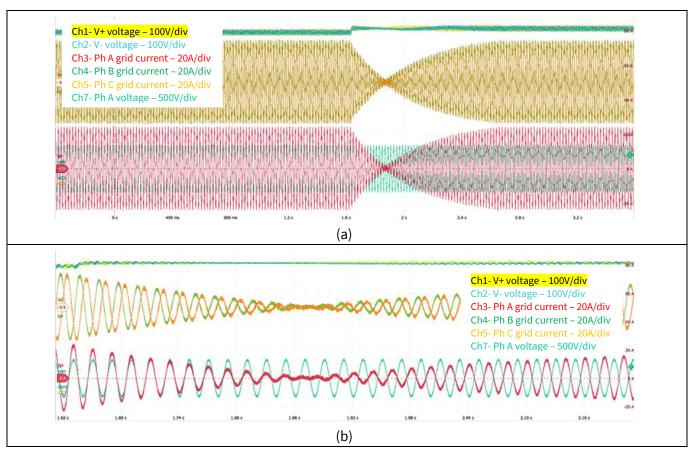

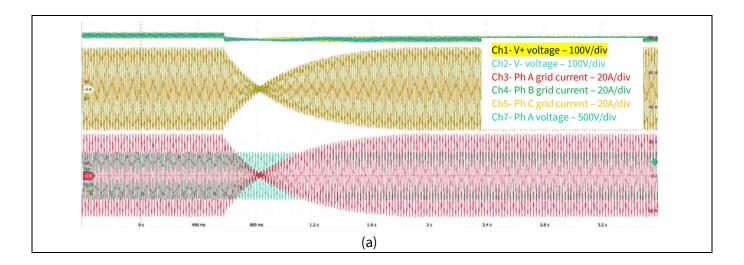

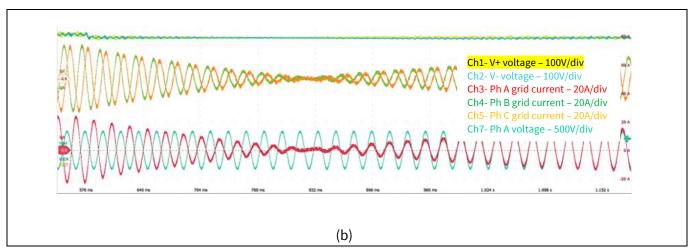

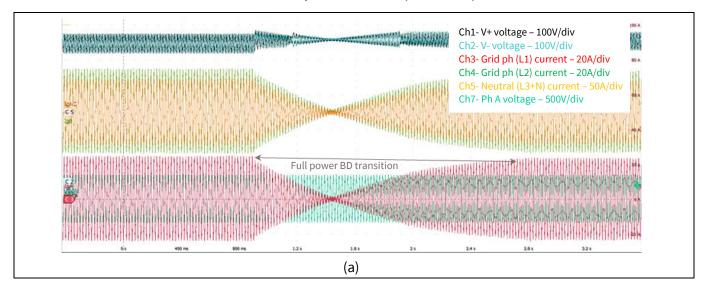

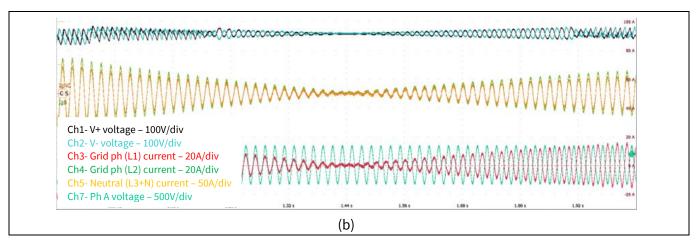

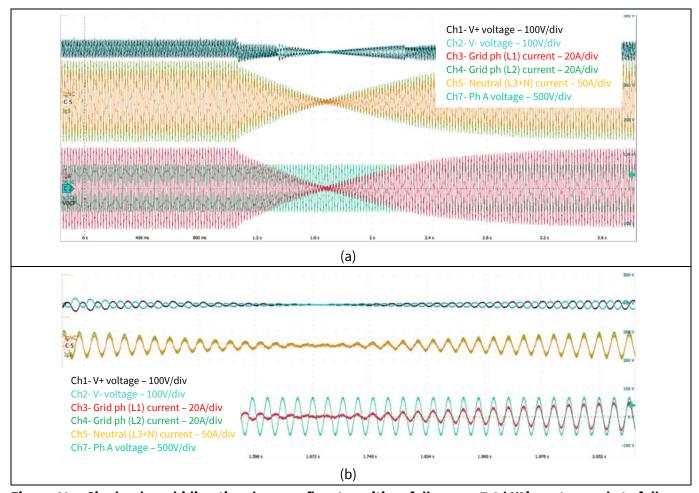

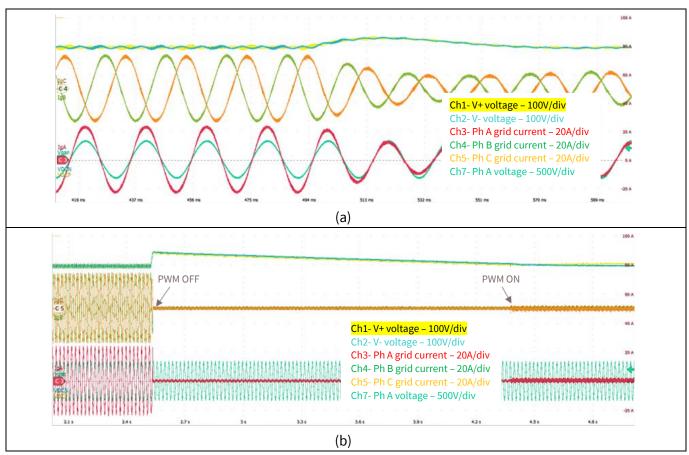

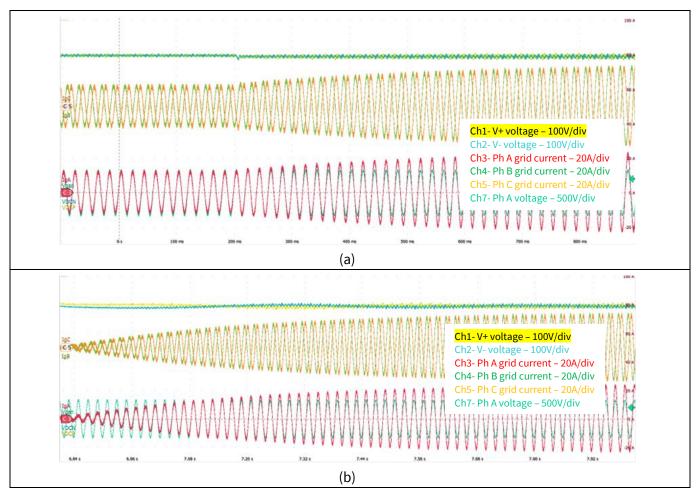

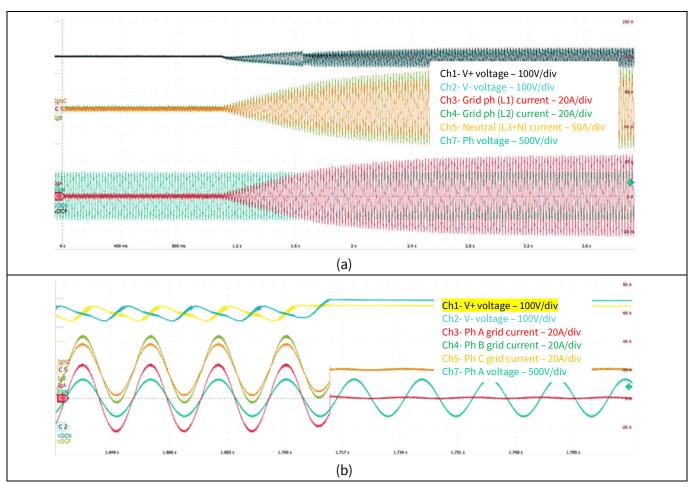

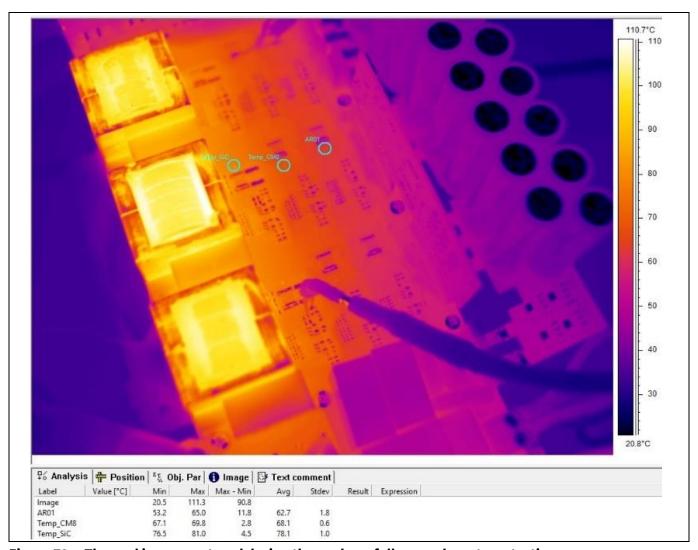

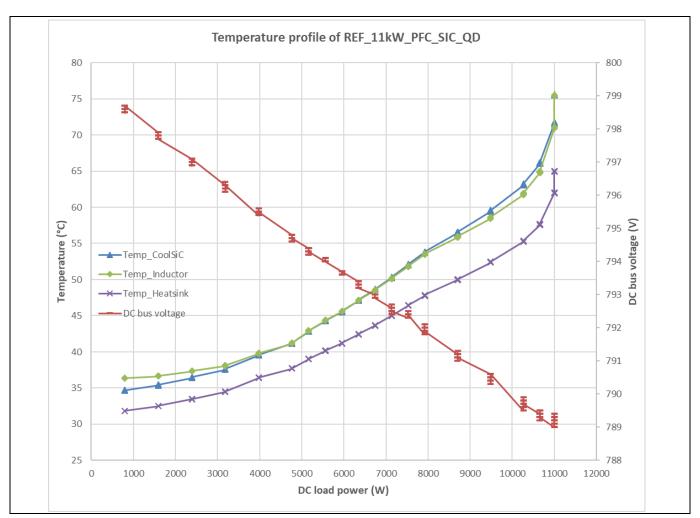

- For inverter mode operation alone, the same replacement can be done with an additional diode in positive rail on the DC side for safety operation