-48 V to 50 V isolated digital power supply using XDPP1100

### **About this document**

### **Scope and purpose**

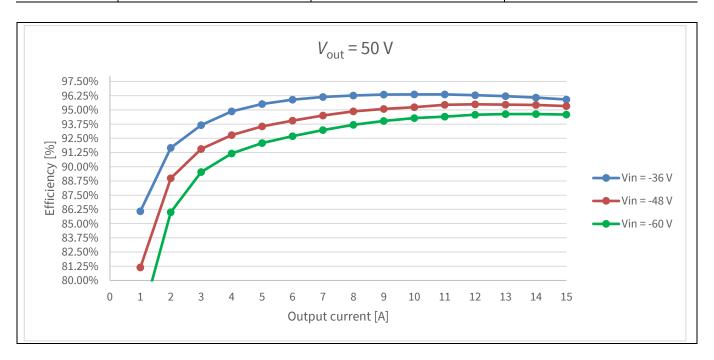

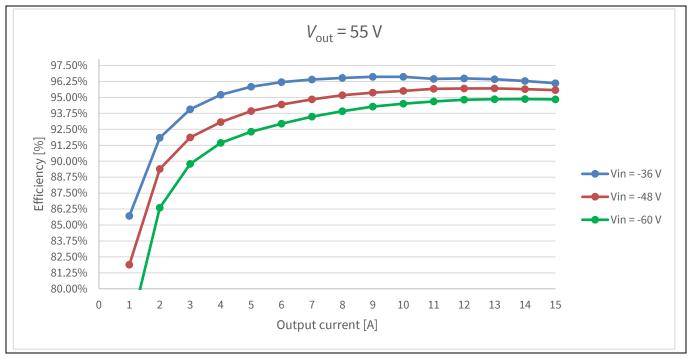

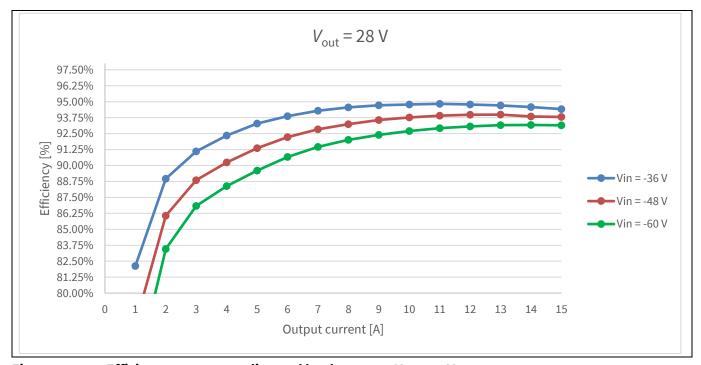

This document introduces a fully functional system solution developed by Infineon, for an isolated DC-DC converter targeting radio frequency power amplifier (RFPA) applications. The converter is made available in the form of a power module, following the industry-standard quarter-brick form factor. This converter is based on a full-bridge topology with full-bridge rectification (FB-FB), providing the required functional isolation. It can deliver up to 750 W output power while regulating +50 V output, from an input ranging from -60 V to -36 V. The converter shows high typical efficiency, up to 95.3 percent at full load at a nominal line of -48 V.

With the rollout of the fifth generation (5G) wireless communication, high-performance power supply units (PSUs) are required to support the demanding power requirements of the network equipment. High power density combined with high efficiency, fast dynamic response, flexibility to adjust output voltage, telemetry, and field upgrade capability are major features that are required besides the highest reliability. Infineon supports these needs by means of a wide portfolio of power discretes showing leading figures of merit (FOMs), other than advanced power management and driver ICs specifically targeting isolated and non-isolated DC-DC converters for telecom applications.

The reference design REF\_750W\_FBFB\_50V includes the following parts from the Infineon product portfolio:

- The latest OptiMOS<sup>TM</sup> 6 80 V MOSFETs, 3.1 m $\Omega$   $R_{DS(on),max}$  (ISCO31N08NM6) as primary-bridge switches

- OptiMOS<sup>TM</sup> 5 150 V, 11 m $\Omega$   $R_{DS(on),max}$  (BSC110N15NS5) as secondary-bridge synchronous rectifiers (SRs) and clamp MOSFETs

- EiceDRIVER™ dual-channel, functional isolated MOSFET gate driver (2EDF7275K) to drive primary FETs as well as SRs and active clamp FETs

- XDP™ integrated digital power controller with PMBus for isolated DC-DC power applications (XDPP1100) implementing advanced digital control and telemetry of the power stage

### Intended audience

This application note is targeted at application engineers and designers of telecom power modules.

## 750 W FB-FB quarter-brick DC-DC converter for RFPA applications -48 V to 50 V isolated digital power supply using XDPP1100

### **Table of contents**

### **Table of contents**

| About            | t this documentt this document                                               | 1  |

|------------------|------------------------------------------------------------------------------|----|

| Table            | of contents                                                                  | 2  |

| 1                | Introduction                                                                 | 4  |

| 1.1              | Background of the application                                                |    |

| 1.2              | Single-stage, isolated solution: system description                          |    |

| 1.3              | Board specification                                                          |    |

| 1.4              | Printed circuit board overview                                               | 9  |

| 1.4.1            | PCB details                                                                  | 9  |

| 1.4.2            | Planar transformer design                                                    |    |

| 1.5              | Schematic files                                                              |    |

| 1.6              | Test fixture board                                                           | 15 |

| 2                | Measures to reduce the drain voltage overshoot in the synchronous rectifiers | 16 |

| 2.1              | Origin of the drain voltage overshoot                                        |    |

| 2.2              | Actively clamping the drain-source voltage in synchronous rectifiers         |    |

| 2.2.1            | Active clamp basics                                                          |    |

| 2.2.2            | Active clamp implementation                                                  |    |

| 3                | XDP™ XDPP1100 digital power controller configuration                         |    |

| 3.1              | Topology and transformer turns ratio                                         |    |

| 3.1.1            | Input voltage (V <sub>IN</sub> ) telemetry by VRSEN                          |    |

| 3.1.2            | Input voltage (V <sub>IN</sub> ) telemetry by PRISEN                         |    |

| 3.1.3            | Feed-forward                                                                 |    |

| 3.1.4            | PID coefficients scaling                                                     |    |

| 3.1.5            | Fast transient response (FTR) and ftr_vin_thresh configuration               |    |

| 3.2              | Output current (I <sub>OUT</sub> ) sense                                     |    |

| 3.3              | Firmware patch and configuration                                             |    |

| 3.3.1            | Load patch                                                                   |    |

| 3.3.1.1          | '                                                                            |    |

| 3.3.1.2          | ·                                                                            |    |

| 3.3.1.3<br>3.3.2 | FW patch handler                                                             |    |

| 3.3.z<br>3.4     | Active clamp switches PWM configuration                                      |    |

| 3.4.1            | Option 1 – use ramp0 (present solution)                                      |    |

| 3.4.2            | Option 2 – use ramp0                                                         |    |

| 3.4.3            | Option 3 – use ramp1                                                         |    |

|                  | Experimental verification                                                    |    |

| <b>-</b><br>4.1  | Test setup                                                                   |    |

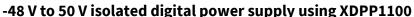

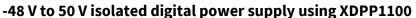

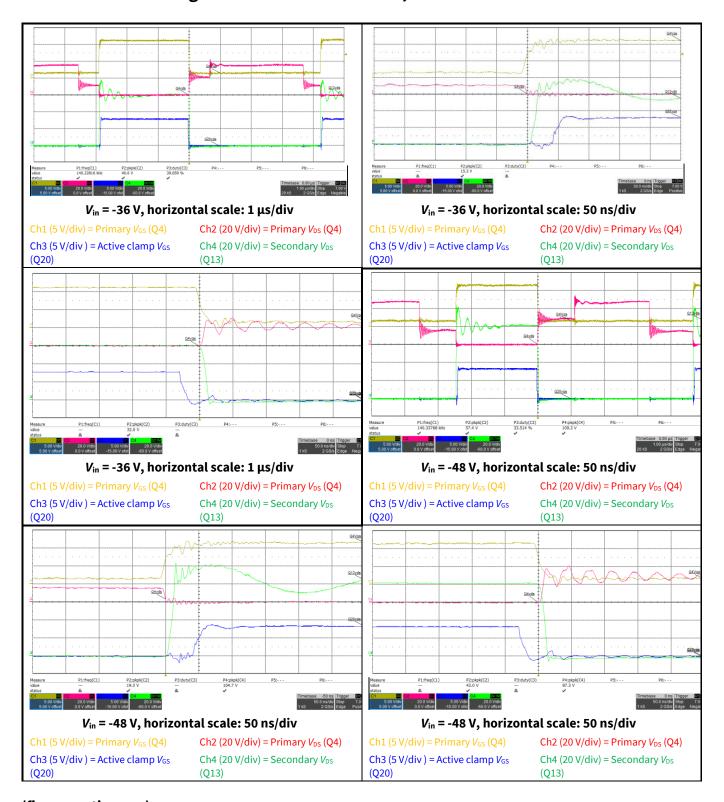

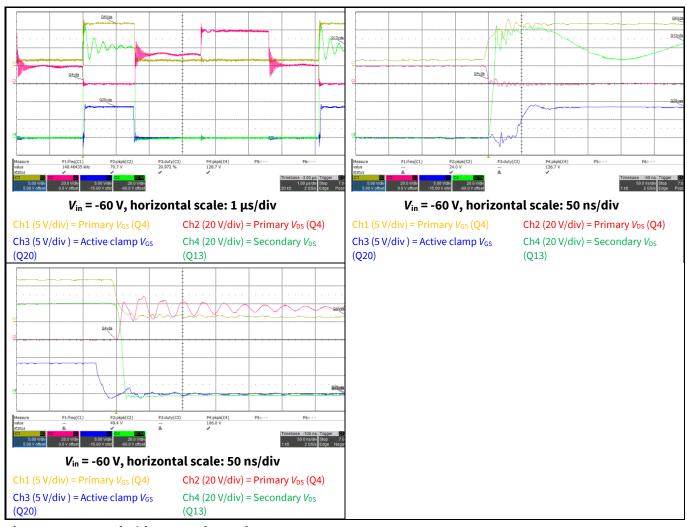

| 4.2              | Operation waveforms                                                          |    |

| 4.2.1            | Steady-state operation                                                       |    |

| 4.2.1.1          | ·                                                                            |    |

| 4.2.2            | Output ripple and noise                                                      |    |

| 4.2.3            | Start-up waveforms                                                           |    |

| 4.2.3.1          | ·                                                                            |    |

| 4.2.4            | Line and load transients                                                     | 53 |

| 4.2.4.1          | 1 Line transients                                                            | 53 |

| 4.2.4.2          | 2 Load transients for V <sub>out</sub> = 50 V                                | 53 |

| 4.3              | Efficiency                                                                   | 54 |

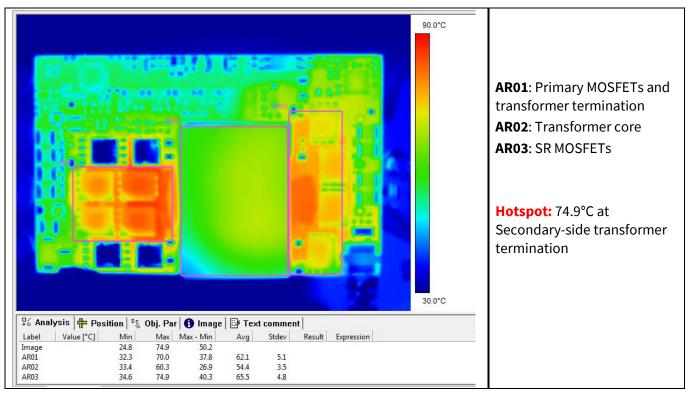

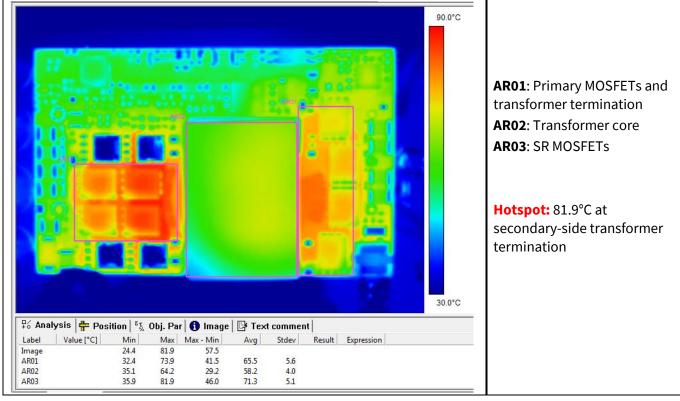

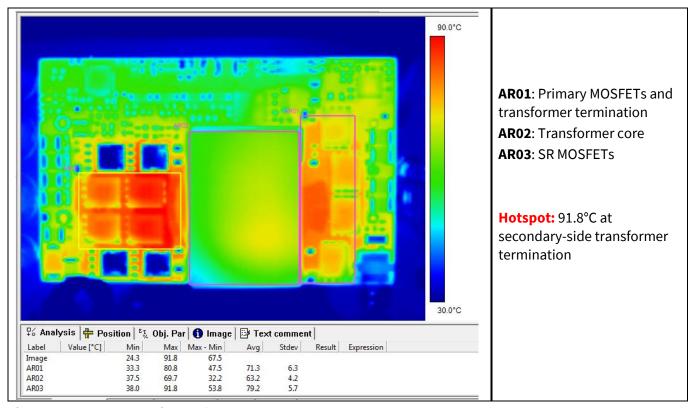

| 4.4              | Thermal images                                                               | 55 |

| 5                | Appendix                                                                     | 58 |

|                  |                                                                              |    |

## 750 W FB-FB quarter-brick DC-DC converter for RFPA applications -48 V to 50 V isolated digital power supply using XDPP1100

### Table of contents

| 5.1      | (R)LC series circuit solution | 58 |

|----------|-------------------------------|----|

| 5.1.1    | Non-damped case               |    |

| 5.1.2    | Damped case                   |    |

| 5.2      | Bill of materials             |    |

| Referen  | ces                           | 62 |

| Revisior | n history                     | 63 |

|          | ner                           |    |

Introduction

### 1 Introduction

### 1.1 Background of the application

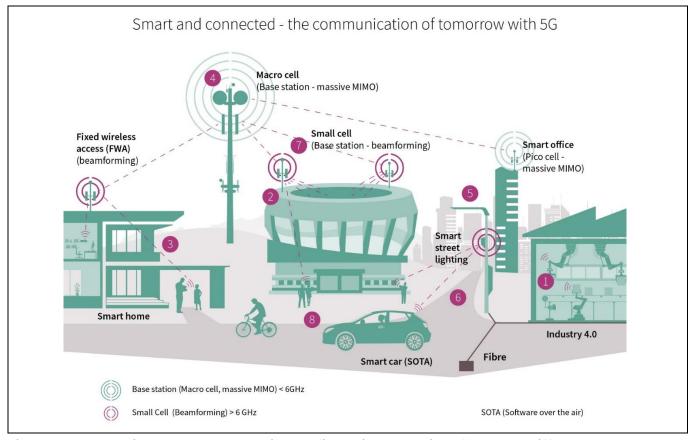

The next development stage of the mobile network is 5G. This new technology allows a significantly higher data capacity and extremely fast response times. This opens a completely new potential applications in an increasingly networked society. To support this, traditional architectures of mobile networks have changed dramatically, in both core network and radio access network (RAN).

Massive multiple input multiple output (MIMO) is one of the main enabling technologies behind 5G RAN. MIMO represents a method adopted for wireless communications using multiple antennas to transmit and receive signals. MIMO has already been exploited in 3G and 4G networks. With 5G, the concept is further developed, by using more antennas (organized in arrays) to exploit the advantages of multipath propagation. These include improved coverage (by means of advanced techniques such as beamforming, null forming and spatial multiplexing) and capacity (capability to handle traffic without compromising performance), finally translating to high user throughput.

In the first phase of the rollout, most of the cellular base stations (BTSs) will be operated at sub-6 GHz frequencies. Massive MIMO arrays at sub-6 GHz dictate the demand for small form factor, highly efficient power amplifiers (RFPAs) to be used. Form factor requirements directly translate into power density requirements. A typical way to increase output power in RPFAs is to increase the supply voltage. Silicon LDMOS technology dominated in RFPA designs for old wireless standards. The supply voltage is 28 V, which gives a good tradeoff between power and efficiency. Silicon LDMOS technology allows easy scaling to higher breakdown voltages by controlling the extension of the epitaxial drift region.

Figure 1 Possible cellular base station configurations conceived for 5G and different usage scenarios

### -48 V to 50 V isolated digital power supply using XDPP1100

#### Introduction

Silicon LDMOS solutions rated for 50 V supply enable doubling of the power density, at the expense of lower efficiency and reduced performance in terms of power gain cut-off frequency. These limit the application of 50 V silicon LDMOS RFPAs mostly to sub-GHz applications, which are not of interest for telecom radios. Furthermore, modulation schemes adopted in 5G lead to signals showing high peak-to-average power ratio (PAPR). This means that deep back-off power operation is needed to maintain linear operation of the amplifier. As a result, RFPAs will also need to be highly efficient when working far from the gain compression point.

To address the demanding requirements in terms of power density and efficiency, while enabling broadband operation, GaN HEMT-based RFPAs have been affirmed as the best-in-class solution for sub-6 GHz 5G base stations. It is evident that GaN – as a compound semiconductor showing both wide-bandgap (WBG) and high electron velocity saturation (i.e., showing a high Johnson's FOM) – represents a preferred solution for high-power, high-frequency applications, solely on the basis of material properties. Wide-bandgap translates into a higher breakdown field (with the possibility to withstand higher supply voltages while retaining small geometries), while high-electron velocity saturation allows high-frequency operation. GaN HEMT-based RFPAs are typically supplied at 50 V (bringing power density benefits) and show high efficiency at higher frequencies (compared to silicon LDMOS) and high-power gain linearity.

The broad adoption of GaN-based RFPAs and the strict specifications that original equipment manufacturers (OEMs) impose in terms of equipment miniaturization, in turn enforce challenging requirements on the PSU subsystem, usually embedded in the antenna itself. New solutions for DC-DC converters targeting GaN RFPAs, regulating 50 V while providing high power density and efficiency – to deal with reduced thermal budget – are needed. Major topologies aimed at RFPA applications are summarized in Table 1.

The Infineon evaluation board REF\_750W\_FBFB\_50V aims to address the application requirements by means of a single-stage, isolated topology. The digitally controlled power supply includes advanced protections for the most reliable operation of the power module. The PMBus communication allows remote telemetry and advanced management of the PSU unit.

The Infineon evaluation board REF\_750W\_FBFB\_50V completes the Infineon solution targeting RFPAs alongside VD\_XDP\_2Ph\_INV\_BUCK\_BOOST, a non-isolated design aimed at 28 V to 56 V LDMOS and GaN RFPAs.

Table 1 Major DC-DC topologies (non-isolated, isolated) adopted in power modules aiming at RFPA applications

| Topology<br>description        | Topology                           | Schematic diagram                                                                                                        | Complexity (cost)    |

|--------------------------------|------------------------------------|--------------------------------------------------------------------------------------------------------------------------|----------------------|

| Single-stage,<br>non-isolated  | ZVS<br>inverting<br>buck-<br>boost | SR <sub>1</sub> + U <sub>out</sub> + <sub>2850</sub> v C <sub>out</sub> + <sub>2850</sub> v                              | Lowest               |

| Single-stage, isolated         | FB-FB                              | Q <sub>1</sub> Q <sub>3</sub> SR <sub>1</sub> SR <sub>3</sub> U  U <sub>in</sub> (1) (1) (1) (1) (1) (1) (1) (1) (1) (1) | Industry<br>standard |

| Focus of this application note |                                    | Q <sub>2</sub> Q <sub>4</sub> SR <sub>2</sub> SR <sub>4</sub>                                                            |                      |

### -48 V to 50 V isolated digital power supply using XDPP1100

#### Introduction

| Topology<br>description | Topology      | Schematic diagram                                                                                                                    | Complexity (cost) |

|-------------------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| Two stages, isolated    | Buck +<br>DCX | Buck (regulated) Q3 Q5 DCX (Open-loop) SR1 SR3 L2 Uout Assort C2 + C2 + C2 + C2 + C3 C4 C5 C5 C6 | Highest           |

### 1.2 Single-stage, isolated solution: system description

This application note will focus on a system solution aimed at addressing the RFPA application requirements by means of a single-stage, isolated topology.

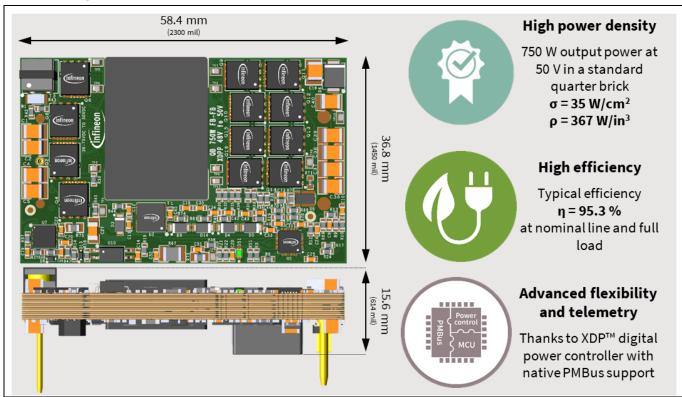

The main features of the Infineon evaluation board REF\_750W\_FBFB\_50V are summarized here:

- **High power density** with 750 W output power in an industry-standard quarter-brick form factor, showing a **low profile** of 15.6 mm

- **Highly efficient** solution with typical efficiency exceeding 95.5 percent at nominal line of -48 V and full load, thanks to synergy between Infineon OptiMOS™ power MOSFETs, showing leading FOMs, and powerful Infineon EiceDRIVER™ ICs

- Advanced digital control thanks to Infineon's XDP™ digital power controller, ensuring high reliability through advanced protections (OVP, OCP, OTP, and more.) and PMBus for advanced power conversion and monitoring

Figure 2 Main features offered by the Infineon REF\_750W\_FBFB\_50V reference design

#### Introduction

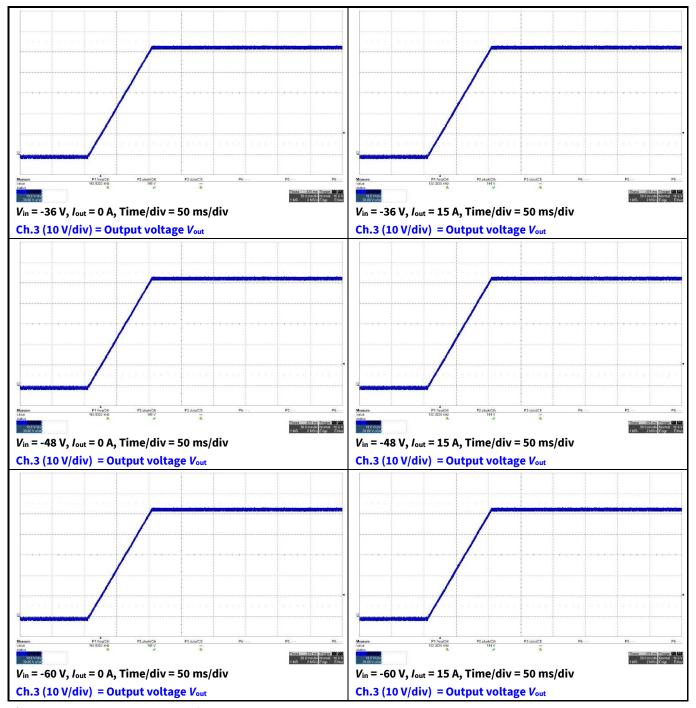

The Infineon evaluation board REF\_750W\_FBFB\_50V operates from an input voltage range of -60 to -36 V DC. The nominal output voltage is +50 V, with a maximum output current of 15 A, corresponding to a maximum output power of 750 W. The board is non-base plated, and it is intended to be operated under forced airflow of approximately 3 m/s (600 LFM). The output is galvanically isolated from the input, allowing versatile grounding configurations.

The 750 W isolated DC-DC converter consists of full-bridge topology with full-bridge synchronous rectification, switching at 140 kHz. The isolation transformer of the main power stage needs to show a step-up ratio, for the converter to be able to regulate the +50 V output rail during low-line conditions of -36 V.

The functionally isolated (coreless transformer technology) gate driver EiceDRIVER™ 2EDF7275K is used on both the primary and secondary side of the converter. This simplifies the bill of materials (BOM), by avoiding the use of digital isolators for the signals traveling across the isolation barrier. On the secondary side, the 2EDF7275K channel-to-channel functional isolation of 1.5 kV enables use of the dual-channel driver as a half-bridge driver. The 3:5 transformer ratio would not allow the choice of a junction-isolated half-bridge driver (like the EiceDRIVER™ 2EDL8024) for the SRs, because a phase voltage as high as 120 V could be expected during the high-line transient conditions.

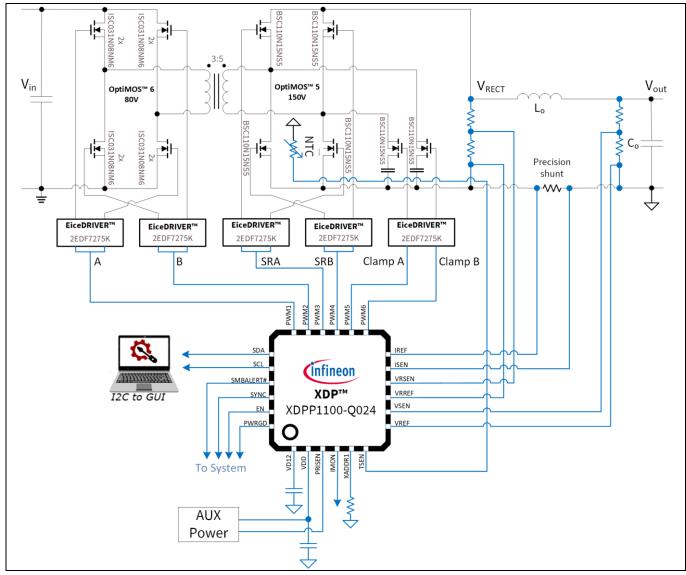

Figure 3 Block diagram of the Infineon REF\_750W\_FBFB\_50V reference design

## 750 W FB-FB quarter-brick DC-DC converter for RFPA applications -48 V to 50 V isolated digital power supply using XDPP1100

#### Introduction

On the primary-side bridge, 80 V power MOSFETs in a SuperSO8 package from the latest OptiMOS™ 6 generation are used. For the secondary-side full-bridge, the 3:5 transformer step-up ratio dictates the need for 150 V rated devices, and OptiMOS™ 5 150 V serve as SRs in this application. To keep the voltage overshoot low enough to stay within the drain-source voltage rating of the SR MOSFETs, an active clamp circuit is introduced. The circuit is identified by a capacitor, to absorb the energy from the power transformer leakage inductance (as well as any other stray inductance in the power loop), properly inserted by means of an actively controlled N-channel MOSFET. The circuit is replicated for both phases of the full-wave rectifier, and the clamp switches are driven by means of an additional 2EDF7275K dual-channel isolated driver.

The control of the power stage is implemented by the Infineon XDP™ XDPP1100-Q024 digital power controller. It has analog/mixed-signal capabilities, on-chip memory, and communication peripherals. The device is specifically optimized for the control of isolated and non-isolated DC-DC converters, such as telecom brick converters. Main features include high-resolution PWM (78.125 ps), state-machine-based digital control loop, dedicated hardware (HW) peripherals (including high-performance voltage and current-sense ADCs), GUI-based system configuration for ease of use, accurate telemetry and PMBus support, and much more. It has a -40°C to 125°C operational temperature range.

The XDPP1100 supports both voltage-mode control (VMC) and peak-current-mode control (PCMC). This reference design adopts VMC. When configured to VMC, flux balancing (supported by HW) is enabled to prevent flux walkaway in the power stage transformer.

The firmware (FW) configuration and patch features are described in chapter 3.

The fully functional reference design was designed as a testing platform, with easy access to probe test points. The simplified block diagram for the board is shown in Figure 3. The full set of specifications for the board is given in the next section.

### 1.3 Board specification

The specifications for the Infineon REF\_750W\_FBFB\_50V isolated quarter-brick DC-DC converter are given in Table 2.

Specifications are given for  $T_a = 25$ °C unless otherwise specified.

Table 2 Specification of the Infineon REF\_750W\_FBFB\_50V evaluation board

| Parameter                                         | Symbol               | Values |      |      | Unit | Note/took condition                                                                     |  |

|---------------------------------------------------|----------------------|--------|------|------|------|-----------------------------------------------------------------------------------------|--|

| Parameter                                         | Symbol               | Min.   | Тур. | Мах. | Unit | Note/test condition                                                                     |  |

| Operating input voltage                           | V <sub>in</sub>      | -36    | -48  | -60  | V    | -                                                                                       |  |

| Input current RMS value (V <sub>out</sub> = 50 V) | $I_{\rm in,RMS}$     | -      | 16.5 | -    | Α    | $V_{\rm in} = -48  \text{V}, P_{\rm out} = 750  \text{W}$                               |  |

|                                                   |                      |        | 22   |      |      | $V_{\rm in} = -36  \text{V}, P_{\rm out} = 750  \text{W}$                               |  |

| Start-up voltage threshold                        | $V_{\rm in(on)}$     | -43    | 1    | -    | V    | -                                                                                       |  |

| Minimum operating voltage after start-up          | $V_{\text{in(off)}}$ | _      | ı    | -34  | V    | -                                                                                       |  |

| Output voltage set-point                          | $V_{ m out,nom}$     | 25     | 50   | 55   | V    | Adjustable setpoint                                                                     |  |

| Output current                                    | I <sub>out</sub>     | -      | -    | 15   | Α    | -                                                                                       |  |

| Output power                                      | $P_{\text{out}}$     | _      | -    | 750  | W    | $V_{\rm out} = 50 \text{ V}, v_{\rm air} = 3 \text{ m/s}$                               |  |

| Efficiency (V <sub>out</sub> = 50 V)              | η                    | _      | 95.3 | -    | %    | $V_{\rm in} = -48  \text{V}, P_{\rm out} = 750  \text{W}$                               |  |

| Power dissipation (V <sub>out</sub> = 50 V)       | P <sub>diss</sub>    | _      | -    | 37   | W    | $V_{\rm in} = -48  \text{V}, P_{\rm out} = 750  \text{W}$                               |  |

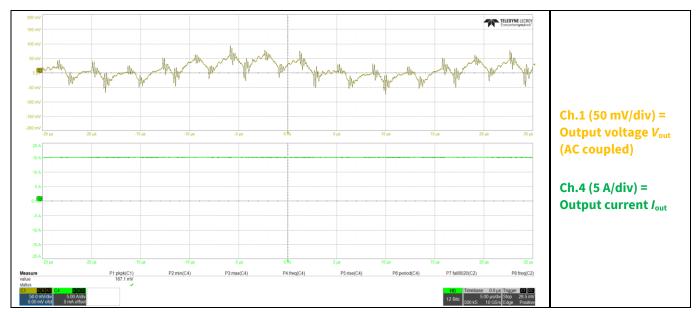

| Output voltage ripple                             | $V_{ m out,ac}$      | _      | _    | 200  | mV   | Peak-to-peak, $V_{\text{out}} = 50 \text{ V}$ , $C_{\text{out,ext}} = 4x56 \mu\text{F}$ |  |

### Introduction

| Davamatav                          | Cyresh al                    | Values |      | l lmit | Note /took one dition |                                                                         |  |

|------------------------------------|------------------------------|--------|------|--------|-----------------------|-------------------------------------------------------------------------|--|

| Parameter                          | Symbol                       | Min.   | Тур. | Max.   | Unit                  | Note/test condition                                                     |  |

| Output voltage set-point tolerance | $\sigma V_{ m out,nom}$      | -1     |      | +1     | %                     | -                                                                       |  |

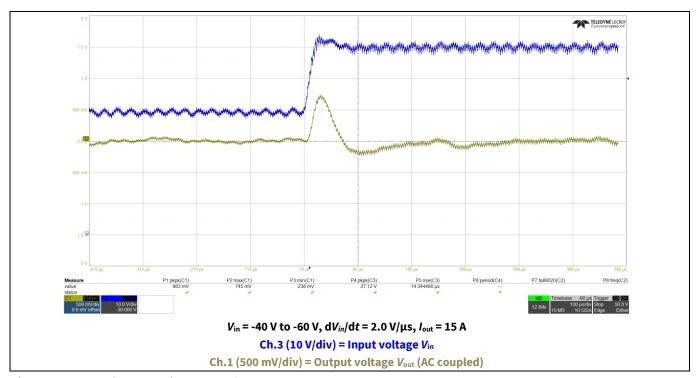

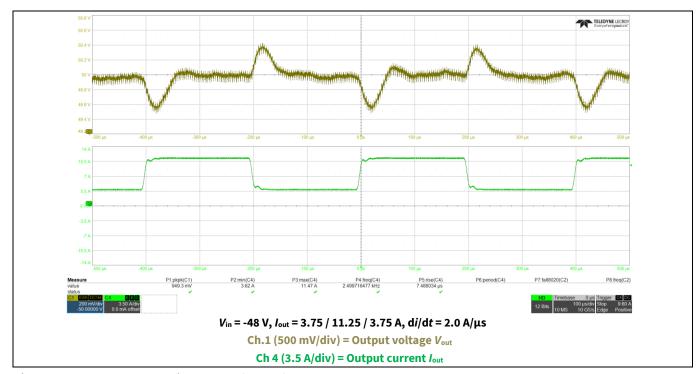

| Output voltage regulation (load)   | $\Delta V_{ m out(load)}$    | _      | -    | 100    | mV                    | $V_{\text{in}} = -48 \text{ V}, 0-100\% \text{ of } I_{\text{out,max}}$ |  |

| Output voltage regulation (line)   | $\Delta V_{ m out(line)}$    | _      | _    | 100    | mV                    | $V_{\rm in}$ = -6036 V, $I_{\rm out}$ = 15 A                            |  |

| Recommended output capacitance     | $C_{\mathrm{out}}$           | 220    | -    | 1000   | μF                    | -                                                                       |  |

| Dynamic load response              | $\Delta V_{ m out(tr,load)}$ | _      | -    |        |                       | $V_{\rm in}$ = -48 V, $V_{\rm out}$ = 50 V, 25%                         |  |

| -Output voltage deviation          | $t_{tr(load)}$               |        |      | ±500   | mV                    | to 75% of $I_{\text{out,max}}$ at 2 A/ $\mu$ s,                         |  |

| -Settling time                     |                              |        |      | 40     | μs                    | $C_{out} = 4x56 \mu F$                                                  |  |

| Switching frequency                | $f_{\sf sw}$                 | _      | 140  | -      | kHz                   | -                                                                       |  |

| Airflourial acity                  | Vair                         | _      | 600  |        | LFM                   | -                                                                       |  |

| Airflow velocity                   |                              |        | 3    |        | m/s                   |                                                                         |  |

| Operating temperature (ambient)    | Ta                           | -40    | _    | 50     | °C                    | -                                                                       |  |

| Functional isolation voltage       | $V_{\rm iso}$                | _      | 1500 | _      | V                     | -                                                                       |  |

### 1.4 Printed circuit board overview

### 1.4.1 PCB details

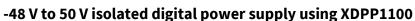

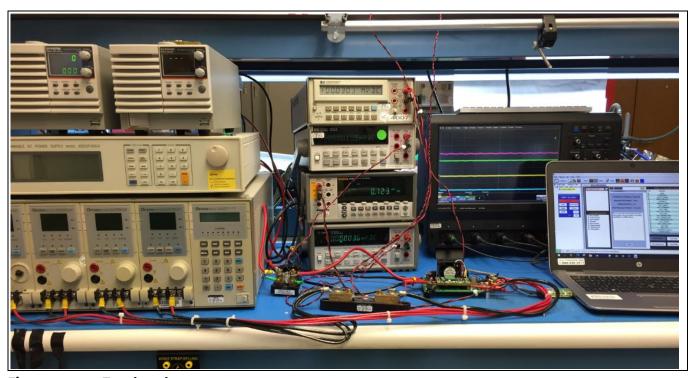

The placement of the components for the main power stage of the Infineon REF\_750W\_FBFB\_50V isolated quarter-brick DC-DC converter is shown in Figure 4.

Figure 4 Top and bottom views of the Infineon REF\_750W\_FBFB\_50V Evaluation Board

### -48 V to 50 V isolated digital power supply using XDPP1100

#### Introduction

The PCB follows the mechanical outline for industry-standard DOSA single-output pin, quarter-brick DC-DC converters. The board outline measures  $L = 58.4 \text{ mm} \times W = 36.8 \text{ mm}$  (2300 mil x 1450 mil).

The PCB is made up of 14 layers. The top and bottom layers have 4 oz thickness, while the middle layers have 6 oz. thickness. The total PCB thickness is 4.72 mm (186 mil).

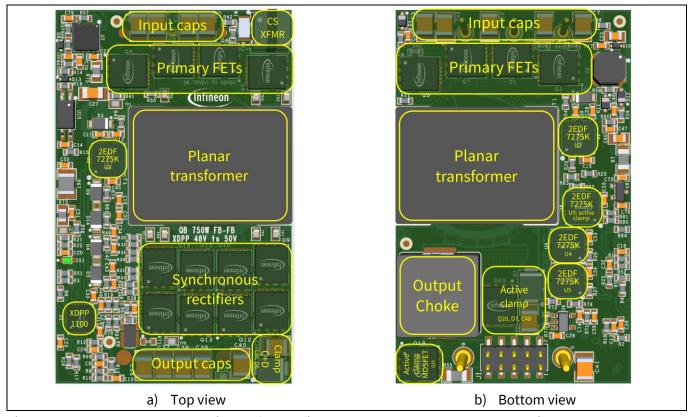

### 1.4.2 Planar transformer design

The main power stage transformer is an integral part of the PCB itself. The primary winding is made up of an effective number of turns equal to three, while the secondary winding is made up of five turns. This defines a turns ratio of 3:5. The transformer step-up ratio is needed to provide the 50 V output regulation at low-line conditions and represents a unique feature for this brick DC-DC module aimed at RFPA applications. In fact, it is typical for brick power modules to show step-down ratios of 3:1 or 4:1 (for example, the Infineon evaluation board REF\_600W\_FBFB\_XDPP1100 – an intermediate bus converter performing 48 V to 12 V conversion – showing a turns ratio of 3:1 [1]). The step-up conversion ratio of 3:5 comes with a number of implications:

- 1. The PCB-integrated magnetic construction requires a higher number of layers compared to a conventional step-down DC-DC power module. Infineon's solution REF\_750W\_FBFB\_50V comes with a PCB stackup that is 14 layers deep, with a total thickness of 4.72 mm. A core with a window height compatible with the total PCB thickness needs to be selected. A standard EQ25 core is chosen for this design.

- 2. The primary-referred secondary current is about 1.67 times larger than the load current. Contrary to the typical case of a step-down brick converter, a larger share of the overall copper losses is expected to affect the primary winding. To minimize these losses, in the interleaved planar construction of the transformer a larger portion of the window area is dedicated to the primary winding. Overall, the primary winding is determined by the parallel connections of three sets of windings, each of them made up of three turns. Primary winding extends to layers 1, 2, 4, 6, 7, 9, 11, 13, and 14. A complete overview of the transformer construction is shown in Figure 5.

Figure 5 Planar transformer construction overview

### -48 V to 50 V isolated digital power supply using XDPP1100

### Introduction

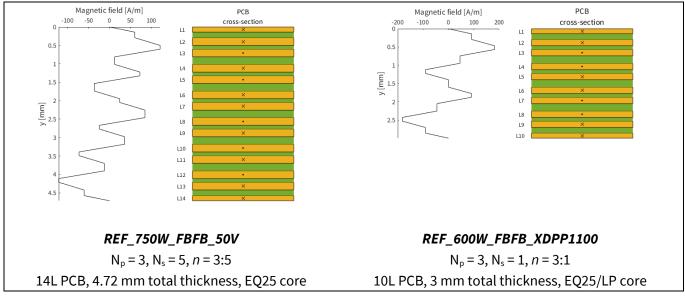

Figure 6 Magnetomotive force (MMF) plots and scale PCB cross-sections for Infineon's REF\_750W\_FBFB\_50V and REF\_600W\_FBFB\_XDPP1100 reference designs

3. The overall transformer secondary-side referred leakage inductance is substantially higher compared to a transformer showing step-down conversion ratio. The comparison of the MMF plots between the Infineon reference designs REF\_750W\_FBFB\_50V (n = 3:5) and REF\_600W\_FBFB\_XDPP1100 (n = 3:1) for the same primary Ampere-turns ( $N_p = 3$ ,  $I_p = 1$  A) suggests a lower primary-referred leakage inductance for the 3:5 solution, as the peak value of the leakage flux is reduced thanks to the more favorable interleaving scheme adopted. A common first approximation that assumes the quasi-static AC operating regime of the transformer, enables to consider a uniform distribution of the current within each conductor cross-section. Then the magnetic field is uniform as well, resulting in a piecewise-linear MMF plot, as shown in Figure 6. The profile of the magnetic field magnitude allows, given the geometry of the core, the computation of the magnetic field energy associated with the leakage fluxes. The magnetic field energy is then associated to an overall primary-referred leakage inductance:

$$\frac{1}{2} \int_{\mathbb{R}^3}^{\square} \mathbf{H} \cdot \mathbf{B} \, dV \approx \frac{1}{2\mu_0} \int_{V_{wdg}}^{\square} H^2 \, dV = W_m = \frac{1}{2} L_{Lk,p} I_p^2 \quad \Rightarrow \quad L_{Lk,p} = \frac{1}{I_p^2 \mu_0} \int_{V_{wdg}}^{\square} H^2 \, dV \tag{1}$$

By evaluating the integral in equation (1) for the two different magnetic structures, it would be possible to obtain a first, rough estimation for the leakage inductances. The integral that should extend to the region of the tri-dimensional space where the magnetic field exists is carried out limited to the winding window volume  $V_{wdg}$ , since the field is negligible within the core because of the high permeability of the ferrite. The trivial solution of the integral is beyond the scope of this document, and the results of the calculations are directly reported in Table 3.

The new reference design REF\_750W\_FBFB\_50V, aimed at RFPA, shows a primary-referred leakage inductance reduced by roughly 40 percent compared to the reference design aimed at 48 V to 12 V conversion. Still, when the overall leakage inductance is concentrated at the secondary side, the step-up ratio of 3:5 leads to a significantly higher value compared to the design showing step-down ratio:

$$L_{Lk,s} = \left(\frac{N_s}{N_p}\right)^2 L_{Lk,p} \tag{2}$$

### -48 V to 50 V isolated digital power supply using XDPP1100

Introduction

Table 3 Estimates for transformer total leakage inductance  $L_{Lk,p(s)}$  according to equations (1) and (2), primary and secondary referred

| Board/reference design | XMFR<br>ratio | Number of layers                       | Primary-referred leakage inductance $L_{Lk,p}$ | Secondary-referred leakage inductance $L_{Lk,s}$ |

|------------------------|---------------|----------------------------------------|------------------------------------------------|--------------------------------------------------|

| REF_750W_FBFB_50V      | 3:5           | 14 (4 oz. top/bottom,<br>6 oz. middle) | 5.8 nH                                         | 16.1 nH                                          |

| REF_600W_FBFB_XDPP1100 | 3:1           | 10 (4 oz. top/bottom,<br>5 oz. middle) | 9.3 nH                                         | 1.0 nH                                           |

Since a high value of the secondary-side referred leakage inductance is heavily impacting the voltage overshoot at the synchronous rectifiers turn-off, some measures need to be taken to reduce the peak drain voltage and keep the MOSFETs operating within the SOA, or the maximum voltage allowed in compliance with the applicable regulations. See chapter 2.

4. The SR devices at the secondary side, arranged in a full-bridge configuration, need to block a voltage up to:

$$V_{s,max} = \left(\frac{N_s}{N_p}\right) |V_{in}|_{|max} = \left(\frac{5}{3}\right) 60 = 100 \text{ V}$$

(3)

Meaning that 150 V devices need to be used to accommodate the voltage overshoot plus derating. Infineon OptiMOS<sup>TM</sup> 5 150 V, showing industry's best FOMs and in particular coming with an excellent FOM<sub>rr</sub> =  $R_{DS(on)} \times Q_{rr}$ , is then the preferred technology for the SR MOSFETs. While the area-specific on-state resistance for OptiMOS<sup>TM</sup> 5 150 V is roughly ten times higher compared to OptiMOS<sup>TM</sup> 6 40 V devices employed in 12 V output brick converters, this is not a matter of concern for the 750 W, 50 V output reference design REF\_750W\_FBFB\_50V, where the output current is limited to 15 A. The area-specific conduction losses for each SR MOSFET can be written:

$$P_{cond} \times (NA) \text{ [W mm}^2\text{]} = [R_{on}A]I_{rms}^2$$

(4)

With A [mm²] being the active silicon area of each device, N the number of paralleled rectifiers and  $[R_{on}A]$  the area-specific on-state resistance FOM of each technology. Considering the same total active area NA allocated for the SRs in both the conventional 12 V output (rated 600 W) and 50 V output (rated 750 W) solutions, the losses end up being roughly the same for both solutions (Table 4).

Table 4 Comparison of area-specific losses with conventional 12 V output brick converter

| Board/reference design | $V_{\mathrm{out}}$ | I <sub>out,max</sub> ≈ I <sub>rms</sub> | SRs technology   | P <sub>cond</sub> x (NA)                                                                                           |

|------------------------|--------------------|-----------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------|

| REF_600W_FBFB_XDPP1100 | 12 V               | 50 A                                    | OptiMOS™ 6 40 V  | $[R_{on}A]_{\text{OptiMOS}^{\text{m}}6\ 40\text{V}}\ (50\ \text{A})^2$                                             |

| REF_750W_FBFB_50V      | 50 V               | 15 A                                    | OptiMOS™ 5 150 V | $\approx 10[R_{on}A]_{\text{OptiMOS}^{\text{TM}}6 \text{ 40V}} \left(\frac{50 \text{ A}}{3.\overline{3}}\right)^2$ |

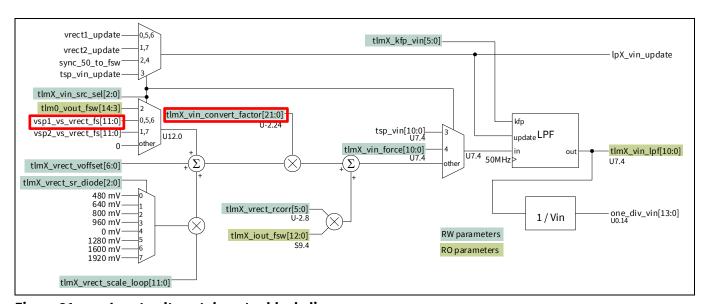

5. The XDP™ XDPP1100 digital power controller is a versatile digital controller that can be employed in various applications, including isolated and non-isolated DC-DC converters. For isolated topologies, the IC has been conceived to support step-down type transformers by default. The controller provides flexibility through firmware, and the same hardware can also be configured to support step-up turns ratios. This can be accomplished by patching the firmware, and the details of the implementations are given in section 3.1.

-48 V to 50 V isolated digital power supply using XDPP1100

Introduction

## 1.5 Schematic files

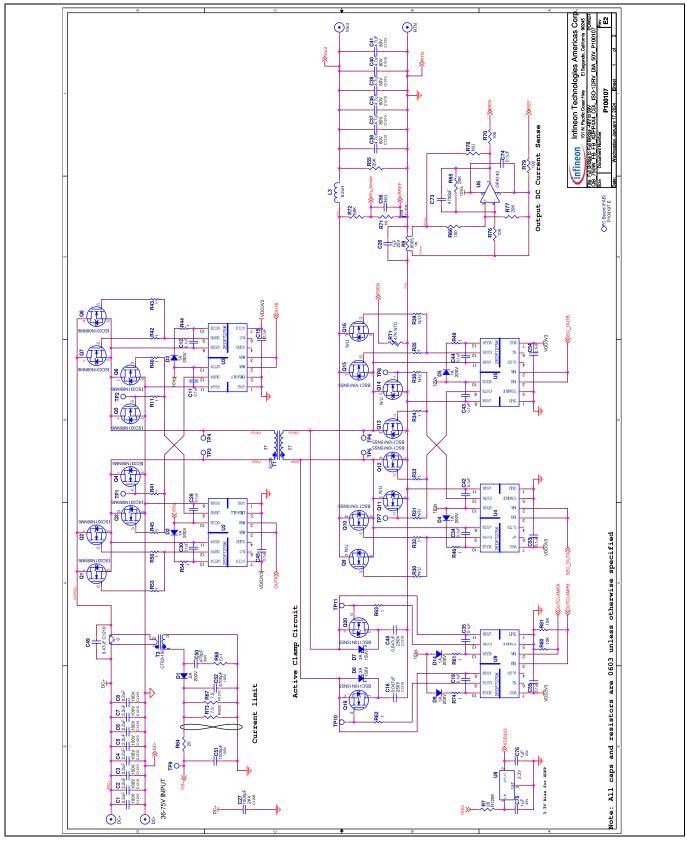

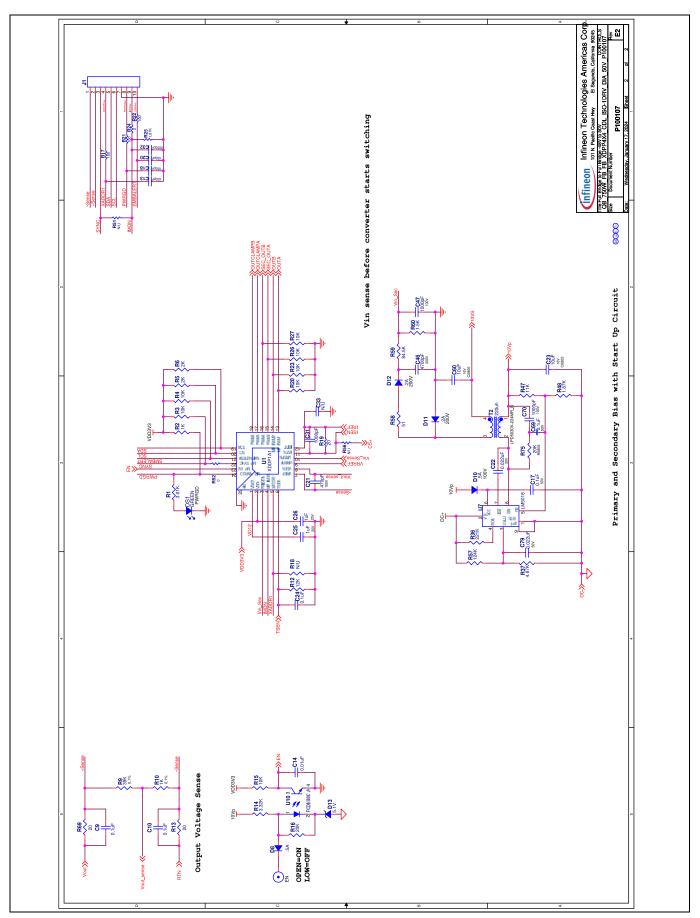

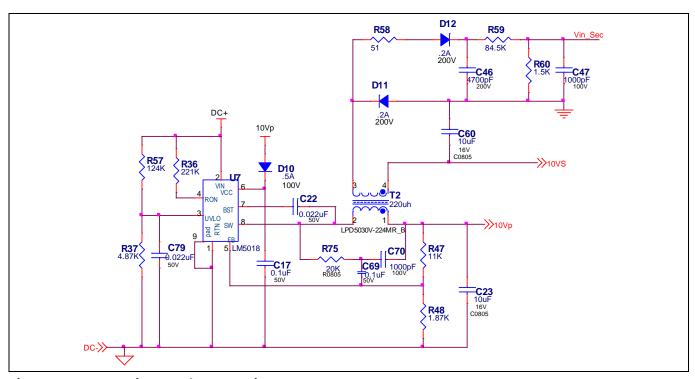

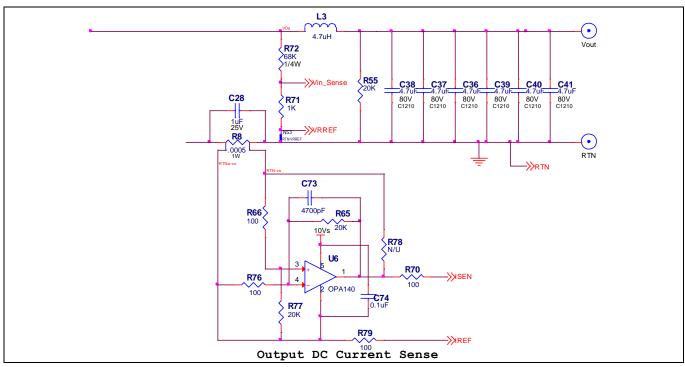

The main power stage schematic is shown in Figure 7, while the control and bias circuit schematic is shown in Figure 8.

Figure 7 Power stage schematic

## -48 V to 50 V isolated digital power supply using XDPP1100 $\,$

### Introduction

Figure 8 Control and bias circuit schematic

### -48 V to 50 V isolated digital power supply using XDPP1100

#### Introduction

The input voltage can be sensed through the auxiliary power supply secondary winding via the PRISEN pin or through the transformer secondary winding via the VRSEN pin. The XDP<sup>TM</sup> XDPP1100 digital power controller allows the user to configure  $V_{IN}$  telemetry from either source.

### 1.6 Test fixture board

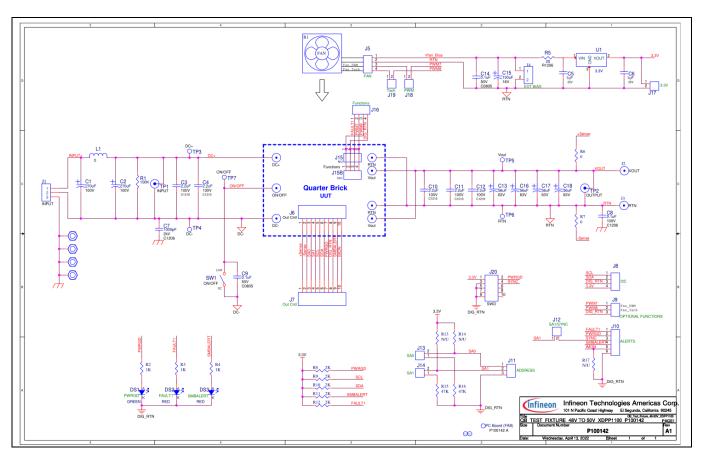

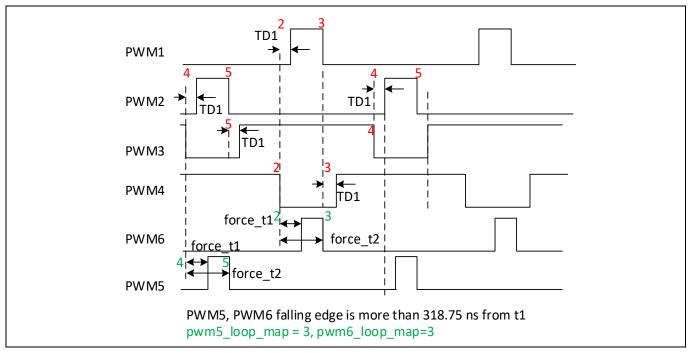

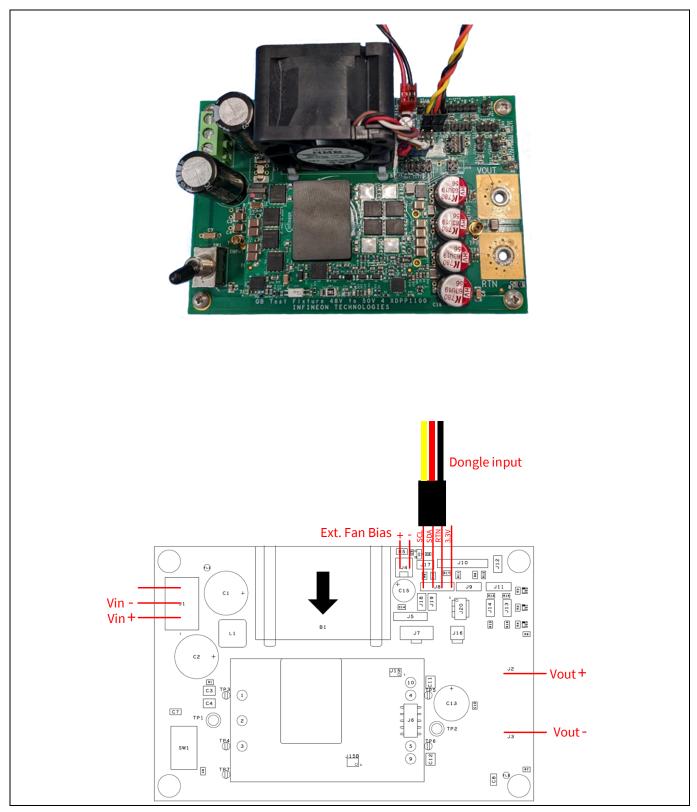

The quarter-brick test fixture is the test platform for the quarter-brick. It provides power connection terminals and communication and debugging ports, as well as a cooling fan.

Figure 9 shows the schematic of the test fixture. It has an I<sup>2</sup>C connector for I<sup>2</sup>C and PMBus communication, and a SWD debugger port for FW debugging. The fan should be biased with an external DC power supply, in the 5 to 12 V range depending on the desired airflow. This bias is necessary to enable communication with the XDPP1100 to the USB dongle: a 3.3 V LDO regulator on the test fixture provides pull-up voltage to the SDA/SCL I<sup>2</sup>C communication bus when 5 to 12 V is applied to the external bias connector.

The switch SW1 at the primary is the enable switch to turn on the quarter-brick unit. Please note that the polarity of the enable switch can be configured by PMBus command ON\_OFF\_CONFIG. If EN "active low" is preferred, the user should write PMBus command ON\_OFF\_CONFIG and choose the polarity to be "active low". When "active low" is selected, the on/off label on the test fixture aligns with the actual on/off status. If "active high" is selected, the on/off label shows the opposite status.

Figure 9 Test fixture board P100142 (50 V<sub>out</sub>) schematic

Attention: The Infineon reference design REF\_750W\_FBFB\_50V is meant to be operated only on test fixture board design no. P100142. Do not try to operate the power module on a different design, or in any design meant for 12 V output quarter-brick units!

-48 V to 50 V isolated digital power supply using XDPP1100

Measures to reduce the drain voltage overshoot in the synchronous rectifiers

## 2 Measures to reduce the drain voltage overshoot in the synchronous rectifiers

### 2.1 Origin of the drain voltage overshoot

To understand the origin of the drain voltage overshoot during synchronous rectifiers turn-off, it is helpful to simplify the topology and focus only on the circuit elements that are mostly impacting on it.

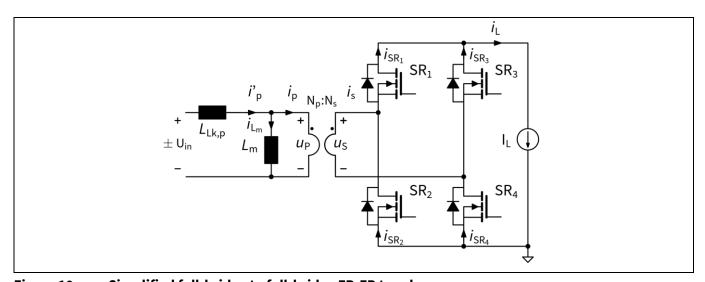

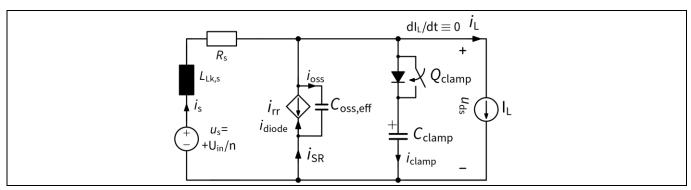

The full-bridge to full-bridge topology in Table 1 can be simplified by removing the primary-side bridge, replacing it with an ideal bipolar voltage source  $\pm U_{\rm in}$ . The transformer is modeled as a linear circuit consisting of an ideal transformer with a turns ratio  $n = N_p$ :  $N_s$ , a magnetizing inductance taking into account the finite permeability of the magnetic core, and a leakage inductance – concentrated on the primary side – modeling the imperfect flux linkage between the windings. Any primary-side power loop stray inductance (PCB and packages) can always be concentrated into the primary-side referred leakage inductance of the power transformer. CCM operation for the output inductor is assumed, and this one is considered big enough to be modeled as a constant current source  $I_L$ . The resulting simplified topology is shown in Figure 10.

Figure 10 Simplified full-bridge to full-bridge FB-FB topology

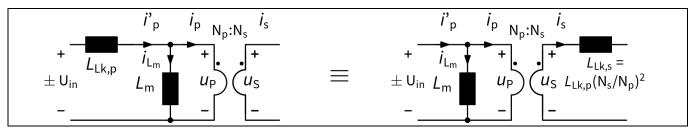

The method summarized by equation (1) enables estimation of the sum of the leakage reactances reported overall on the primary side of the transformer, assuming that the magnetizing inductance  $L_m$  can be considered much larger compared to the primary-reflected secondary leakage inductance. The sum of the leakage reactances can be equivalently concentrated on the secondary port of the transformer. The values of the primary-side and secondary-side referred to overall transformer leakage are linked by the turns ratio squared (Figure 11).

Figure 11 Equivalence of the practical transformer model showing an overall primary (left) or secondary (right) referred leakage inductance

### -48 V to 50 V isolated digital power supply using XDPP1100

### Measures to reduce the drain voltage overshoot in the synchronous rectifiers

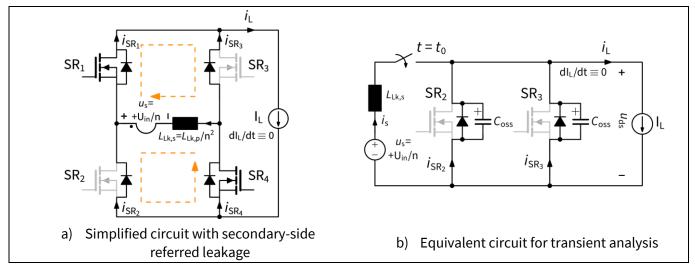

Considering a model for the transformer showing an overall secondary-side referred leakage inductance simplifies the analysis and leads to the circuit shown in Figure 12a. Here, a powering phase which sees the diagonal identified by  $SR_1$  and  $SR_4$  MOSFETs as the active rectification path is considered. The powering phase, starting at  $t = t_0$ , follows a freewheeling phase where all the primary switches are off, and all the SRs are on, sharing the load current  $I_L$ . During the freewheeling phase the transformer is effectively shorted by the SRs, and so the reflected primary voltage is zero, while the primary bridge current  $i^p$  is zero. The primary transformer current  $i^p$  can be considered zero as well, taking the approximation of a large magnetizing inductance. By assuming this, the rectifiers only carry a portion of the load current, otherwise in the practical case of a finite magnetizing inductance  $L_m$ , they also share the non-null magnetization current ( $i^p = i^p$ ). For the sake of clarity, the approximation for  $L^p \to \infty$  is taken. For  $t \ge t_0$  part of the load current carried by the body diodes of  $SR_2$  and  $SR_3$  starts to be transferred to the channel of the active synchronous rectifiers,  $SR_1$  and  $SR_4$ . The di/dt on the output branch is negligible, and so the current transfer is dictated only by the two inner loops of the full-bridge, comprising the four rectifiers, the leakage inductor, and the transformer secondary (Figure 12a). In particular, the di/dt is governed by the total inner loops inductance, that according to the picture coincides with the transformer leakage inductance only, but that also includes the other stray inductances in the power loop:

$$L_{loop} = L_{Lk,s} + L_{stray}$$

where  $L_{stray} = \Sigma(L_s + L_d) + L_{PCB}$  (5)

With  $L_s$  and  $L_d$  being the source and drain package-related inductances for the power MOSFETs. According to the estimate carried out in Table 3, the contribution of  $L_{Lk,s}$  is dominant among  $L_{stray}$  for the reference design REF\_750W\_FBFB\_50V aimed at RFPA applications and again, for the sake of clarity, will be the only contribution considered. Then, assuming equal current sharing among the rectifiers, it can be shown that the current in SR<sub>2</sub> and SR<sub>3</sub> body diodes is ramped down with a rate:

$$\left| \frac{di_{1SR}}{dt} \right| = \frac{U_{in}}{2nNL_{lk,s}} \tag{6}$$

Where  $n = N_p/N_s$  and N is the number of paralleled SRs for each position. From equation (6) it is evident that having a larger value for  $L_{Lk,s}$  results in a current in the rectifiers ramping down at a lower rate, enabling more charge carriers to recombine and resulting in a lower value for the recovered charge  $Q_{rr}$ . Parallelization is also beneficial in this sense since the current density is reduced within each rectifier. Please note that equation (6) assumes that the primary-side MOSFETs will switch so fast they will not limit the current transfer rate.

Figure 12 Minimum circuits needed for the analysis of voltage overshoot in synchronous rectifiers

### -48 V to 50 V isolated digital power supply using XDPP1100

### Measures to reduce the drain voltage overshoot in the synchronous rectifiers

In Figure 12b the circuit of Figure 12a is further simplified and rearranged to perform a simple transient analysis. The complex, buck-isolated topology has been reduced to a simple circuit, which is functionally identical to a simple non-isolated buck converter.

The dead time mode of operation precedes the instant of time  $t = t_0$ , where the synchronous rectifiers  $SR_2$  and  $SR_3$  are in the off-state and their body diodes share the load current. Their drift regions are flooded by carriers sustaining the current flow. At  $t = t_0$  an input voltage step is applied. The current in the rectifiers ramps down according to equation (6). The drain-source voltage is clamped by the body diode to a forward voltage drop, until the diode experiences recovery. In practice, when measuring the drain-to-source voltage with an oscilloscope, a small step in the drain-source voltage is always recorded in the waveform during the current ramp-down phase, and this is related to the stray inductances associated with the package (not shown in the equivalent circuit):

$$u_{ds} = -\underbrace{u_{sd}(i_d)}_{\substack{\text{diode forward} \\ \text{voltage}}} + (L_s + L_d) \frac{U_{in}}{2nNL_{lk,s}} \quad t_0 \le t \le t_1$$

(7)

By ignoring any form of charge storage mechanism within the rectifiers, they would instantaneously turn off as soon as the current reaches zero, let's say at  $t = t_1$ . From this point onward, the drain-to-source voltage is no longer clamped, and it is free to rise. The drain-to-source voltage rises, overshooting the transformer secondary voltage. Let's assume, for a moment, to consider a constant, effective output capacitance for the MOSFETs. Please note that ignoring the voltage dependence of the  $C_{\rm oss}$  is a strong assumption, given that the significant nonlinearity of the output charge characteristic in modern charge-compensated trench MOSFETs would have a severe impact on the voltage overshoot. In a latter section, this assumption will be dropped, so that the effects of the voltage-dependent output capacitance will become clearer.

By studying the forced response of the circuit in Figure 12b one would find that the voltage at the rectifiers would reach two times the transformer secondary voltage, independently of the values of  $L_{Lk,s}$ ,  $C_{oss}$  and the load current  $I_L$ .

$$U_{ds,pk} = \max_{t \ge t_2} u_{ds}(t) = 2U_s \tag{8}$$

This outcome is the result of having neglected any damping action in the circuit and is in accordance with the theory of the non-damped series LC circuit. See section 5.1.1.

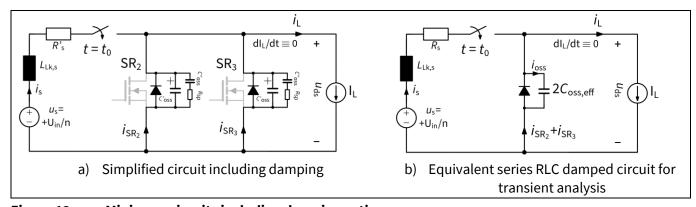

Some non-negligible damping action is always recorded in the circuit. Input capacitors' ESR, primary switches and synchronous rectifiers  $SR_1$  and  $SR_4$   $R_{DS(on)}$ , and transformer and layout-associated AC resistance  $R_{ac}$ , can be combined into an equivalent secondary-referred series resistance  $R'_s$ . In addition, in established charge-compensated field-plate trench MOSFET technologies, including OptiMOS<sup>TM</sup> 5 150 V, an equivalent integral RC snubber can be always referred to the output port of the device [2], as shown in Figure 13a.

Figure 13 Minimum circuits including damping actions

## 750 W FB-FB quarter-brick DC-DC converter for RFPA applications -48 V to 50 V isolated digital power supply using XDPP1100

### Measures to reduce the drain voltage overshoot in the synchronous rectifiers

The combination of the series resistance and the output RC snubber introduces the missing damping action that is needed to explain the experimental observations. The circuit in Figure 13a is a non-elementary series or parallel-like RLC circuit, and its analysis is complex. By applying some elementary impedance transformations (valid only at the natural oscillation frequency), and with minor approximations, the circuit in Figure 13a can be reduced to the equivalent series RLC circuit in Figure 13b.

Again the forced response of the circuit in Figure 13b can be easily obtained (see section 5.1.2), and a closed-form expression for the voltage overshoot at the rectifiers is given in equation (9):

$$U_{ds,OV}[\%] = \exp\left(\frac{-\zeta\pi}{\sqrt{1-\zeta^2}}\right) \times 100\% \tag{9}$$

Where  $\zeta \triangleq R_s/(2L_{Lk,s}\omega_0)$  is the damping ratio, and  $0 \le \zeta \le 1$ .

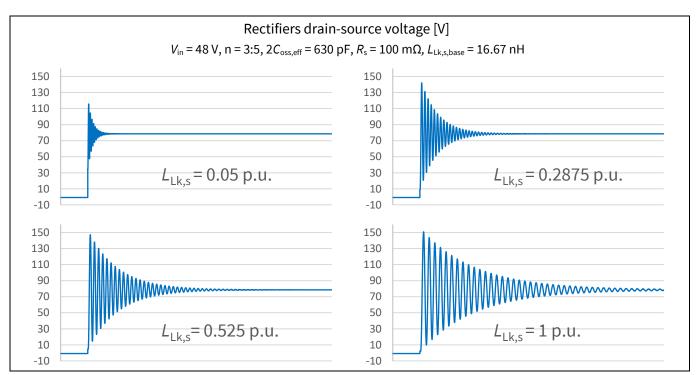

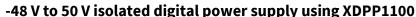

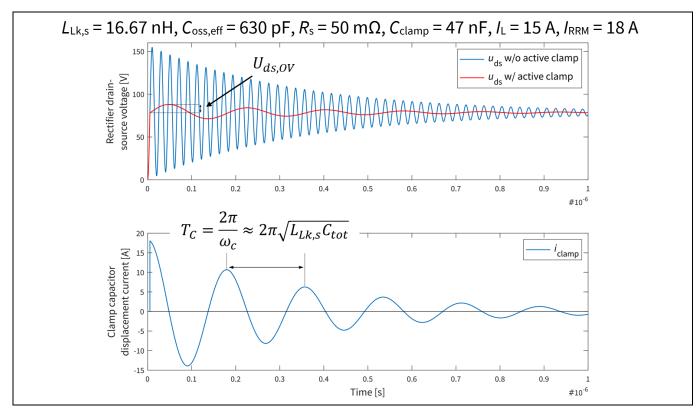

The voltage overshoot is higher for highly underdamped circuits (high quality factor Q), e.g., with the higher value of the leakage inductance. In addition, the oscillations will take longer to extinguish. Drain-source voltages during rectifier turn-off are plotted in Figure 14, having swept the overall, secondary-referred loop inductance (damping ratio). Plots are produced according to equation (52), given in the Appendix.

Figure 14 Forced response plotted for the circuit in Figure 13b, having swept the inductance, resulting in different damping ratios.  $L_{Lk,s}$  is given in p.u. "per unit" of the base inductance value  $L_{Lk,s,base}$ .

While the result in equation (9) recovers at least the dependence on the leakage inductance and the output capacitance, the model is still inadequate to accurately describe the actual turn-off of the rectifier(s).

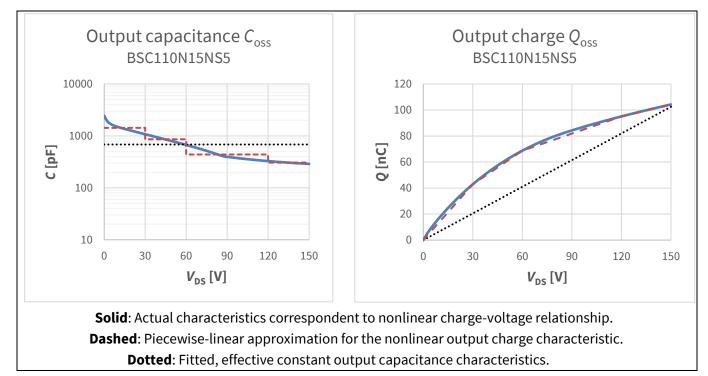

The results reported so far are in fact valid only under the assumption of a constant effective output capacitance  $C_{\rm oss,eff}$ . The relation between output charge and voltage in actual devices is nonlinear, resulting in an anomalous output capacitance  $C_{\rm oss} = C_{\rm oss}(u_{\rm ds})$ . Despite that, a constant output capacitance  $C_{\rm oss,eff}$  can always be fitted to give a response that is in partial agreement (for example, by fitting the natural oscillation frequency) with experimental results or device simulations. This was, for instance, the approach used to produce the plots in Figure 14.

### -48 V to 50 V isolated digital power supply using XDPP1100

Measures to reduce the drain voltage overshoot in the synchronous rectifiers

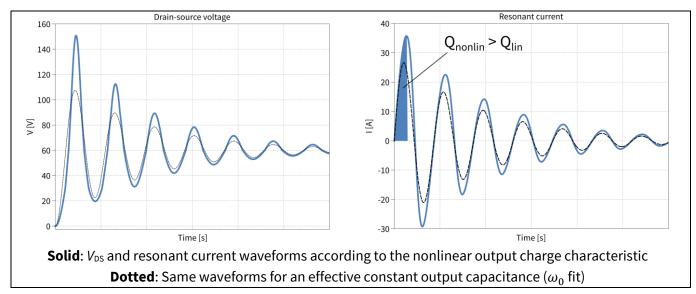

Figure 15 Output capacitance and output charge characteristics for OptiMOS™ 5 150 V BSC110N15NS5 taken as an example

In most of the cases, the impact of the actual voltage-dependent output capacitance in MOSFETs is to produce an overshoot larger than the one predicted by equation (9). In a practical MOSFET, the output capacitance decreases with increasing drain-source voltage (Figure 15). This, in the rectifiers turn-off transient, translates in a drain-source voltage waveform that rises not anymore according to a single eigenfrequency: the drain-source voltage rises more gradually at the beginning of the transient (low  $V_{DS}$ , higher  $C_{OSS}$ ), whereas the waveform becomes progressively steeper once the drain-source voltage increases (lower  $C_{OSS}$ ). Accordingly, the displacement current increases with a faster rate compared to the case of a constant capacitance. This also means that, before the current starts reverting, more charge will be transferred to the output capacitance (depletion layer) resulting in a way higher peak voltage overshoot compared to the linear case (Figure 16).

Figure 16 Turn-off transient comparison for linear and nonlinear output charge characteristic

### -48 V to 50 V isolated digital power supply using XDPP1100

### Measures to reduce the drain voltage overshoot in the synchronous rectifiers

The analytical model presented in Appendix can be directly generalized to predict the overshoot also in a practical scenario, when a piecewise linear approximation is taken for the output charge characteristic (Figure 15). The same approach is pursued, for instance, by a variety of piecewise-linear simulators.

Note:

Infineon's SPICE models for OptiMOS™ Power-Transistors come with a full modeling of the MOSFETs voltage-dependent capacitances, and they must be considered the preferred tool to perform this kind of investigations.

Although the model presented so far does not consider the effects of a load current, in its simplicity it still captures the main dependencies of the voltage overshoot on the circuit parameters. These are found to be the overall secondary-referred loop inductance (including transformer leakage and any other source of stray inductances), the output capacitance of the SR MOSFETs (with its voltage-dependent characteristic), and the power loop resistance.

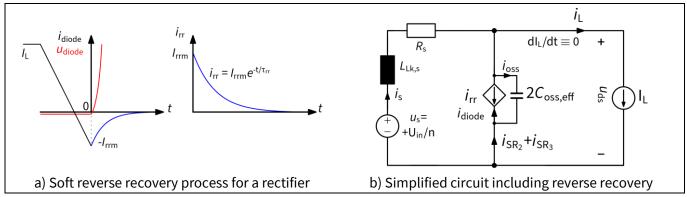

Experimental results clearly show that the voltage overshoot at the rectifiers during turn-off strongly depends on the load current. Despite being modeled on the circuits just discussed; it seems from previous analysis that the voltage overshoot would be completely independent of the load. The dependence on the load current is explained by the presence of a charge storage mechanism within the rectifiers, until now ignored. During the dead time, the drift regions of the SRs are flooded with charge carriers, whose concentration is dependent on the value of the current carried by the rectifier. The higher the forward current, the greater the amount of stored charge. Charge carriers need to be removed from the drift region to create a space charge region that can support the voltage. This process, called *reverse recovery*, prevents the rectifier switching to the reverse blocking state as soon as the current crosses zero. Instead, a reverse current (whose rate is still given by equation (6)) is observed to persist until the drift region is sufficiently depleted from carriers. This happens after a time  $t_a = f(I_L, di/dt, T_j)$  starting from the zero crossing, for which the reverse current reaches its peak value  $I_{rrm}$ . Then the voltage is free to rise according to the formation of a space charge region, while the remaining charge carriers are swept out by means of an exponential decaying (diffusion) current. The whole commutation process is shown in Figure 17a.

While the process is far more complex than described here [3], the modeling proposed is again sufficient and simple enough to highlight the role of the main players contributing to the drain-source voltage overshoot during rectifier turn-off. Again, the approximation for a constant, effective output capacitance for the MOSFETs is taken to keep the analysis as simple as possible.

Let's consider for simplicity t = 0 the instant of time for which the current in the body diode reached the peak reverse recovery current  $I_{rrm}$ . Then the diode can be replaced by a controlled current source  $i_{rr}$  and a parallel capacitance equal to an effective constant output capacitance for the MOSFET (Figure 17b).

Figure 17 Reverse recovery modeling and equivalent simplified circuit for transient analysis

### -48 V to 50 V isolated digital power supply using XDPP1100

### Measures to reduce the drain voltage overshoot in the synchronous rectifiers

The initial conditions for the circuit are given by:

$$\begin{cases} u_{ds}(0) = -U_{sd,f} \approx 0 \\ i_s(0) = I_L + I_{rrm} \end{cases}$$

(10)

The Kirchhoff voltage law for the left-side mesh is written:

$$L_{Lk,s}\frac{d}{dt}\left[I_L + 2C_{oss,eff}\frac{du_{ds}}{dt} + i_{rr}\right] + R_s\left[I_L + 2C_{oss,eff}\frac{du_{ds}}{dt} + i_{rr}\right] + u_{ds} = U_s \tag{11}$$

Where  $i_{rr}$  is a time-varying current source modeling the soft-recovery behavior of the diode (minority-carriers diffusion current), modeled as a decaying exponential:

$$i_{rr}(t) = I_{rrm}e^{-\frac{t}{\tau_{rr}}} \tag{12}$$

The time constant  $\tau_{rr}$  is closely tied to the semiconductor device physics, specifically the characteristic time for the recombination of the charge carriers under high-level injection conditions.

Using (12) in (11) results in (13), a second-order ordinary differential equation for the drain-source voltage  $u_{\rm ds}$ :

$$2L_{Lk,s}C_{oss,eff}\frac{d^{2}u_{ds}}{dt^{2}} + 2R_{s}C_{oss,eff}\frac{du_{ds}}{dt} + u_{ds} = (U_{s} - R_{s}I_{L}) + \left(\frac{L_{Lk,s}}{\tau_{rr}} - R_{s}\right)I_{rrm}e^{-\frac{t}{\tau_{rr}}}$$

(13)

The solution of the homogeneous equation has already been found in the form (see section 5.1.2):

$$u_{ds,hom}(t) = Ae^{-\frac{R_s}{2L_{Lk,s}}t}\sin(\omega t + \Phi)$$

(14)

While the solution must be found in the form of a constant plus an exponential function (having the same eigenvalue as the forcing function):

$$u_{ds,part}(t) = U + U_{rr}e^{-\frac{t}{\tau_{rr}}} \tag{15}$$

By substitution of (15) into (13), and after some manipulation that includes ignoring the effect of the equivalent series resistance, one can solve the two arbitrary constants:

$$\begin{cases} U = U_{s} - R_{s}I_{L} \\ U_{rr} \approx \tau_{rr}I_{rrm}L_{Lk,s}\frac{\omega_{0}^{2}}{1 + \omega_{0}^{2}\tau_{rr}} = Q_{rr}L_{Lk,s}\frac{\omega_{0}^{2}}{1 + \omega_{0}^{2}\tau_{rr}^{2}} \end{cases}$$

(16)

Where the reverse recovery charge  $Q_{rr}$  is given by:

$$Q_{rr} = \int_0^\infty I_{rrm} e^{-\frac{t}{\tau_{rr}}} dt = \tau_{rr} I_{rrm} \tag{17}$$

The general solution is:

$$u_{ds}(t) = u_{ds,hom}(t) + u_{ds,part}(t) = Ae^{-\alpha t}\sin(\omega t + \phi) + U + U_{rr}e^{-\frac{t}{\tau_{rr}}}$$

(18)

The two arbitrary integration constants A and  $\phi$  are found by imposing the initial conditions:

Measures to reduce the drain voltage overshoot in the synchronous rectifiers

$$\begin{cases}

\frac{u_{ds}(0) = 0}{dt} \\

\frac{du_{ds}}{dt}(0) = \frac{i_{oss}(0)}{2C_{oss,eff}} = \frac{i_{s}(0) - i_{rr}(0) - I_{L}}{2C_{oss,eff}} = \frac{I_{L} + I_{rrm} - I_{rrm} - I_{L}}{2C_{oss,eff}} = 0

\end{cases}$$

(19)

Resulting in:

$$\begin{cases}

\phi = -\tan^{-1} \left[ \omega \tau_{rr} \left( 1 + \frac{U}{U_{rr}} \right) \right] \\

U_{rr} \sqrt{1 + (\omega \tau_{rr})^2 \left( 1 + \frac{U}{U_{rr}} \right)^2} \\

A = \frac{U_{rr} \sqrt{1 + (\omega \tau_{rr})^2 \left( 1 + \frac{U}{U_{rr}} \right)^2}}{\omega \tau_{rr}} \approx U + U_{rr}

\end{cases} \tag{20}$$

Finally, the general solution of the problem is then written:

$$u_{ds}(t) = (U_s - R_s I_L) \left[ 1 + e^{\frac{-R_s}{2L_{Lk,s}}t} \sin(\omega t + \phi) \right] + \underbrace{L_{Lk,s}Q_{rr} \frac{\omega_0^2}{1 + \omega_0^2 \tau_{rr}^2} \left[ e^{-\frac{t}{\tau_{rr}}} + e^{-\frac{R_s}{2L_{Lk,s}}t} \sin(\omega t + \phi) \right]}_{\text{Term associated with body diode reverse recovery}}$$

(21)

By direct comparison of equation (21) with the result already found in the Appendix (equation (52)) it shows that an additional term, in phase with the main *RLC* resonance, contributes to the drain-source voltage overshoot on the rectifiers. The additional term is directly proportional to the product of the secondary-referred loop inductance  $L_{Lks}$ , with the reverse recovery charge  $Q_{rr}$ . Since  $Q_{rr}$  is proportional to the load current  $I_L$ , the load dependence of the voltage overshoot is recovered:

$$U_{rr} \propto L_{Lk,s} Q_{rr}(I_L) \tag{22}$$

From equation (21) it is also evident that again, the higher the overall secondary-side referred loop inductance, the higher is the extra voltage overshoot expected because of the reverse recovery. This is far more complex, as a higher value for  $L_{Lk,s}$  results in a lower di/dt on the rectifiers during turn-off, and this helps in reducing  $Q_{rr}$  because more charge carriers have time to recombine within the device. Despite the excellent switching performances ( $Q_{rr}$ ) of OptiMOS<sup>TM</sup> 5 150 V [4], the large  $L_{Lk,s}$  in Infineon REF\_750W\_FBFB\_50V would still give an unacceptably high voltage overshoot at the drain of the rectifiers.

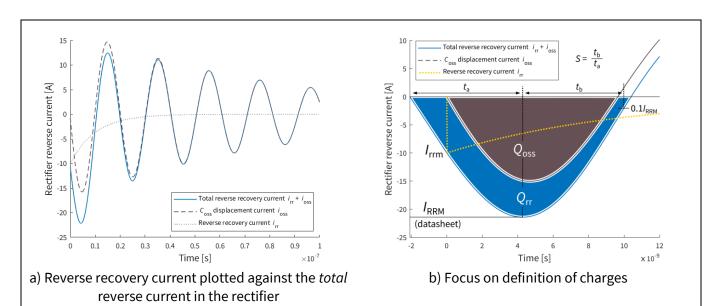

Figure 18 Drain-source voltage for the rectifier with reverse recovery in circuit in Figure 17b

## 750 W FB-FB quarter-brick DC-DC converter for RFPA applications -48 V to 50 V isolated digital power supply using XDPP1100

### Measures to reduce the drain voltage overshoot in the synchronous rectifiers

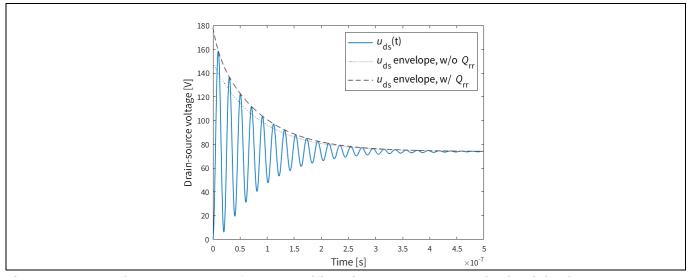

The extra overshoot not only depends on  $Q_{rr}$  but also on the "softness" of the recovery (decay ratio). It would be helpful to analyze the influence of the parameters ( $I_{rrm}$  and  $\tau_{rr}$ ) by focusing on the upper envelope of the drain-source voltage  $\widehat{u_{ds}}(t)$ , having  $\sin(\omega t + \phi) = 1$ :

$$\widehat{u_{ds}}(t) = (U_s - R_s I_L) \left[ 1 + e^{-\frac{R_s}{2L_{Lk,s}}t} \right] + L_{Lk,s} Q_{rr} \frac{\omega_0^2}{1 + \omega_0^2 \tau_{rr}^2} \left[ e^{-\frac{t}{\tau_{rr}}} + e^{-\frac{R_s}{2L_{Lk,s}}t} \right]$$

(23)

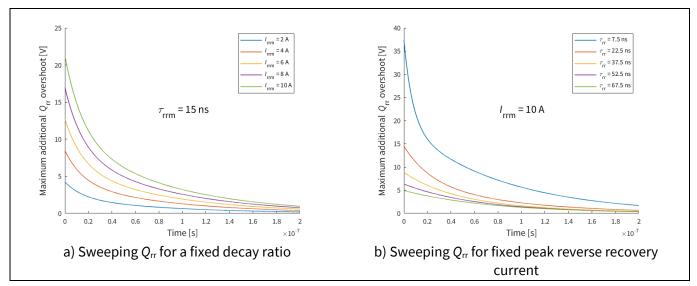

In particular, one can focus only on the term associated with the reverse recovery of the rectifier and plot the upper limit line for the extra overshoot expected. In Figure 19a, a sweep performed on the peak reverse recovery current  $I_{rrm}$  clearly shows the extra voltage overshoot increasing with it. In Figure 19b a sweep is done on the reverse recovery current characteristic time of decay. A smaller value for  $\tau_{rr}$  leads to higher  $di_{rr}/dt$  and higher voltage overshoot. The value of  $\tau_{rr}$ , that is mostly dependent on the silicon technology, affects the "recovery softness factor" (RSF) as defined by JEDEC [5]. To better explain this, it is essential to distinguish between what we called until now "reverse recovery current"  $i_{rr}$  and the "total reverse recovery current": while the former exclusively accounts for minority charge carriers swept out from the drift region, the latter additionally includes the displacement current in the equivalent output capacitance  $C_{oss}$ , associated with the creation of a space charge region able to sustain the voltage. In Figure 20a, the total current  $i_s$  in the rectifier (Figure 17b) is plotted together with the displacement current ( $-i_{oss}$ ) and the reverse recovery current ( $-i_{rr}$ ). The total reverse recovery current is given by  $i_s = -(i_{oss} + i_{rr})$ .

Figure 19 Extra voltage overshoot due to reverse recovery for different  $I_{rrm}$  and  $\tau_{rr}$  (softness)

When it comes to characterizing the switching performances of a MOSFET operated as a synchronous rectifier, it is not possible to distinguish between displacement and reverse recovery (diffusion) currents, as it is only possible to measure the total current at the source terminal. In datasheets, when the recovered charge  $Q_{rr}$  is specified, this always includes a contribution from  $Q_{oss}$ , as it is given as the integral over time of the total current measured at the source terminal. In other words,  $Q_{rr}$  in datasheets specifies the *total* reverse recovery charge and has nothing to do with the definition given by equation (17) that only *models* the amount of minority carrier charge to be swept out from the drift region. Taking Figure 20b as an example, the value given in the datasheets for the reverse recovery charge  $Q_{rr}$  would be the sum of the brown and blue areas, i.e.,  $Q_{rr(datasheet)} = Q_{rr} + Q_{oss}$ . Similar considerations apply for the peak reverse recovery current  $I_{RRM}$ , if specified in datasheets, as this will never correspond to the definition of  $I_{rrm}$  given in equation (12). From Figure 20b it would also now be possible to understand how  $\tau_{rr}$  would affect the softness of the recovery: as a higher value for  $\tau_{rr}$  would slow down the  $I_{rr}$  curve decay, and this has the effect of shifting the blue curve down, the current zero crossing will be delayed accordingly and  $t_b$  will result in a higher number.

## 750 W FB-FB quarter-brick DC-DC converter for RFPA applications -48 V to 50 V isolated digital power supply using XDPP1100

## **(infineon**

Measures to reduce the drain voltage overshoot in the synchronous rectifiers

Figure 20 Reverse recovery current, Coss displacement current and total reverse recovery current

-48 V to 50 V isolated digital power supply using XDPP1100

Measures to reduce the drain voltage overshoot in the synchronous rectifiers

### 2.2 Actively clamping the drain-source voltage in synchronous rectifiers

### 2.2.1 Active clamp basics

There are a variety of solutions typically adopted to keep voltage overshoot on rectifiers under control. Among them it is possible to distinguish between snubbers (made up of passive components only) and voltage clamps making use of controlled switches. Within the passive solutions, both dissipative (simple and polarized RC [6]) and resonant [7] snubbers are used. On the other hand, it is becoming common in modern DC-DC brick power modules to actively clamp the drain-source voltage at the SRs. In any buck or buck-derived topology the drain of the SR MOSFET sees a high impedance (the output filter inductor), meaning that – AC-wise – the drain terminal is left floating, enabling high-frequency oscillations to build up. The idea underlying the active clamp is to tie the drain terminal of the synchronous rectifier to a low impedance voltage source that, in practice, is realized as a large capacitor.

The basic active clamp circuit is shown in Figure 21. The clamp capacitor must be considered pre-charged at its steady-state value, which should be as close as possible to the transformer secondary voltage  $U_s$ .

Figure 21 Simple active clamp circuit

The transient analysis starts at t = 0, for which  $u_{ds}(0) = 0$ ,  $i_s(0) = I_L + I_{rrm}$ . The drain-source voltage rises according to equation (21), although with a slightly slowed-down transient, due to the fact that the equivalent output capacitance of the SR MOSFET now sees in parallel the series combination of the clamp capacitance and the output capacitance of  $Q_{clamp}$ :

$$C_{eq} = 2C_{oss,eff} + \frac{C_{oss,eff}(Q_{clamp})C_{clamp}}{C_{oss,eff}(Q_{clamp}) + C_{clamp}} \approx C_{oss,eff} + C_{oss,eff}(Q_{clamp}) \qquad 0 \le t \le t_1$$

(24)

At a certain instant of time, say  $t = t_1$ , the drain-source voltage would reach the clamp capacitor voltage  $U_{\text{clamp}}$ . This can be estimated by:

$$t_1 = \frac{\sin^{-1}\left(\frac{U_{clamp}}{U + U_{rr}} - 1\right) - \phi}{\omega} \tag{25}$$

Provided that  $t_1$  would result in less than 1/3 of min( $\alpha$ ,  $\tau_{rr}$ ) and where all the above quantities are defined as per equations (13)...(20). This approximation fits well for the case of the Infineon design REF\_750W\_FBFB\_50V.

For  $t > t_1$  the body diode of  $Q_{\text{clamp}}$  will result in it being forward-biased and the clamp capacitor being effectively in parallel with the synchronous rectifier output capacitance:

$$C_{tot} = C_{oss,eff} + C_{clamp} (26)$$

### -48 V to 50 V isolated digital power supply using XDPP1100

### Measures to reduce the drain voltage overshoot in the synchronous rectifiers

The drain-source voltage will show a sharp change of slope and the resonance frequency will change accordingly. The drain source voltage will continue to rise according to the same law described by equation (11), now having an equivalent capacitance given by equation (26).

In the limit for an infinitely large clamp capacitor (voltage source), the peak overshoot results in being clamped exactly at the steady-state value  $U_{\text{clamp}}$ . The voltage overshoot expected for a finite value of the clamp capacitance has instead been estimated as follows. Let's assume for the sake of simplicity that the steady-state voltage for the clamp capacitor would be exactly equal to the transformer secondary voltage:

$$U_{clamp} = U_s \tag{27}$$

Then, when the drain-source voltage would equal  $U_{\text{clamp}}$ , it also happens that the total reverse recovery current in the rectifier would be equal to the peak *total* reverse recovery current. This has always to be true as, looking at the circuit in Figure 17b, the drain-source voltage can only be equal to  $U_s$  when:

$$\frac{di_s}{dt} = 0 \Leftrightarrow \frac{di_{SR}}{dt} = 0 \Leftrightarrow i_{SR} = -I_{RRM}$$

(28)

Where  $I_{RRM}$  stays for the peak *total* reverse recovery current, as already explained in Figure 20b. To estimate the voltage bump at the rectifiers (and at the clamp capacitor) it is then more convenient to study the transient of the circuit in Figure 22, for convenience resetting again t = 0. To keep the analysis straightforward,  $Q_{rr}$  is neglected this time, while its contribution can be always considered as shown in section 2.1.

Figure 22 Simplified circuit for active clamp transient analysis

The initial conditions for the new mode of operation will be:

$$\begin{cases} u_{ds}(0) = u_{\mathcal{C}_{oss,eff}}(0) = u_{\mathcal{C}_{clamp}}(0) = U_{clamp} \\ i_{s}(0) = I_{L} + I_{RRM} \Rightarrow \frac{du_{ds}}{dt}(0) = \frac{I_{RRM}}{C_{tot}} \end{cases}$$

(29)

The drain-source voltage will evolve as described by:

$$u_{ds}(t) \approx (U_s - R_s I_L) + I_{RRM} \sqrt{\frac{L_{Lk,s}}{C_{tot}}} e^{-\frac{R_s}{2L_{Lk,s}}t} \sin(\omega_c t + \phi)$$

(30)

Where:

$$\begin{cases} \omega_c = 1/\sqrt{L_{Lk,s}C_{tot}} \\ \tan \phi \approx \phi = \frac{\sqrt{1-\zeta^2}}{\zeta} \frac{1}{1 + \frac{I_{RRM}}{\alpha R_s C_{tot}I_L}} \end{cases}$$

(31)

### -48 V to 50 V isolated digital power supply using XDPP1100

### Measures to reduce the drain voltage overshoot in the synchronous rectifiers

It is straightforward to find the peak drain-source voltage overshoot expected at the rectifier by finding the maxima of (30). Using the maxima of the envelope is in most of the cases already a reasonable estimation, and this is given by:

$$U_{ds,OV} \approx I_{RRM} \sqrt{\frac{L_{Lk,s}}{C_{tot}}} = \frac{I_{RRM}}{\sqrt{1+k}} \sqrt{\frac{L_{Lk,s}}{C_{oss,eff}}}$$

(32)

Being k a per-unit clamp capacitance normalized to  $C_{oss,eff}$ :

$$C_{clamp} = kC_{oss,eff} \tag{33}$$

This enables sizing of the clamp capacitor according to the maximum allowed overshoot at the rectifiers:

$$k = \left[ \frac{I_{RRM}}{U_{ds,OV}} \sqrt{\frac{L_{Lk,S}}{C_{oss,eff}}} \right]^2 - 1$$

(34)

Depending on the value of the effective output capacitance of the SR MOSFETs, clamp capacitance values 50 to 100 times greater than  $C_{oss}$  can be expected for a design such as Infineon's REF\_750W\_FBFB\_50V.

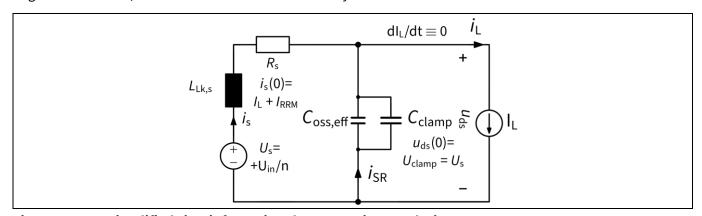

The need for an active device to implement the clamp is evident, because as soon as the clamped drain source voltage reaches its peak, the current in the clamp capacitor will cross zero and the clamp diode will become reverse biased. A path must be provided for the current in the clamp capacitor to reverse and to guarantee the charge balance. In other words, the clamp capacitor needs to be *reset* by the resonance created with the loop inductance. This path is realized by closing  $Q_{\text{clamp}}$  sometime after the clamp diode (typically the integral body diode of  $Q_{\text{clamp}}$ ) starts conducting. Typically, this is done by commanding the turn-on of  $Q_{\text{clamp}}$  after a certain dead time (where equation (25) has to be considered together with other sources of delay) with respect to the primary PWM forcing the turn-off commutation of the rectifiers. Then  $Q_{\text{clamp}}$  turns on, with ZVS taking over the diode current.

To properly reset the capacitor, the active switch clamp on-time must be selected for the current to perform at least one full resonant cycle. The switch must be turned off with the right timing: to avoid high over voltages building up across the loop inductance, the turn-off must occur when the current clamp current  $i_{\text{clamp}}$  (Figure 21) is in its positive half-cycle. To reduce the losses in the clamp, the switch on-time should be maximized (to reduce body diode conduction) and it should be turned off some time before the current zero crossing. This guard-band time should consider the tolerances in components and in PCB manufacturing that would affect the clamp resonant frequency. The minimum on-time to allow proper resetting of the capacitor while minimizing the losses in the clamp should be selected as:

$$t_{on,min}(Q_{clamp}) < \frac{5}{2}\pi\sqrt{L_{Lk,s}C_{tot}} - t_{dt,on} - t_{dt,off}$$

(35)

Where  $t_{dt,on}$  and  $t_{dt,off}$  are the active clamp switch turn-on and turn-off dead times.

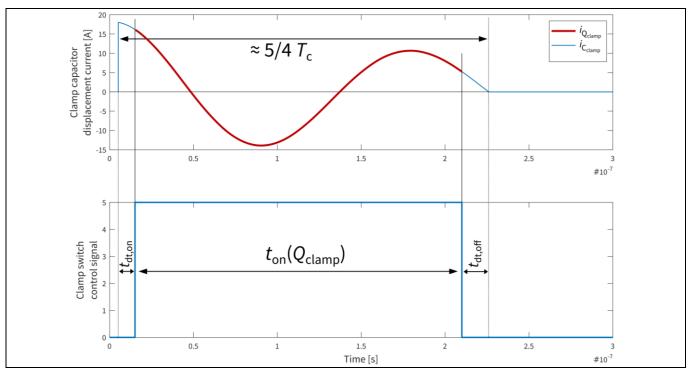

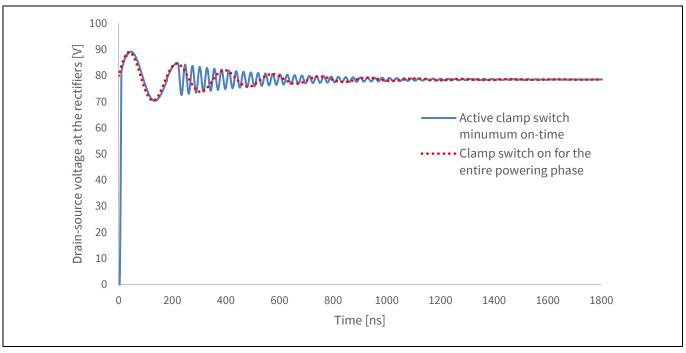

Figure 23 shows how to obtain the expression for the minimum clamp on-time. Meanwhile, Figure 24 shows the effectiveness of the active clamp solution in keeping the voltage overshoot controlled. Figure 24 shows a strategy for which the clamp switch is kept on during the entire powering phase. Depending on the damping ratio, sometimes the on-time given in equation (35) is not sufficient to achieve the charge balance in the clamp capacitor. Whether this would be the case, more than one resonant cycle should be allowed for the reset. The recovered charge  $Q_{rr}$  from the clamp switch would be another element – neglected in this analysis – that would alter the charge balance in the clamp capacitor. Please note that the clamp resonant current is reflected on the primary side through the transformer. Although this is wanted, as the energy stored in the leakage is partially

### -48 V to 50 V isolated digital power supply using XDPP1100

### Measures to reduce the drain voltage overshoot in the synchronous rectifiers

recovered being transferred to the input capacitors, this could compromise the efficiency (larger primary current) or EMC performances of the converter.

Figure 23 Minimum on-time for the clamp switch to achieve clamp capacitor reset while minimizing clamp conduction losses

Figure 24 Effectiveness of active clamp to control voltage overshoot in SRs. This case shows a control strategy for which  $Q_{\text{clamp}}$  is kept on for the entire off-phase of the rectifier

### -48 V to 50 V isolated digital power supply using XDPP1100

Measures to reduce the drain voltage overshoot in the synchronous rectifiers

Figure 25 Simulated waveforms for two different control strategies for the active clamp switch control

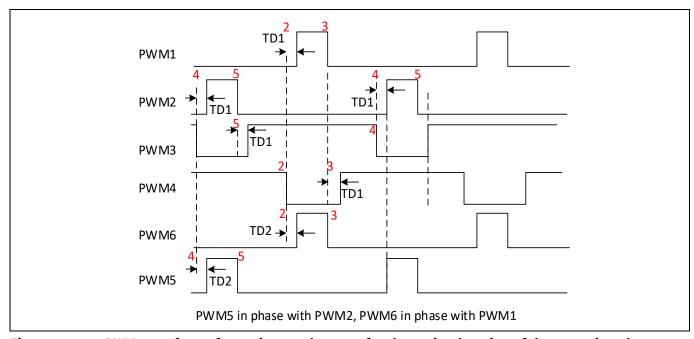

In section 3.4 different options will be given to configure the digital power controller to achieve the desired timing for the clamp, depending on the design. The Infineon reference design REF\_750W\_FBFB\_50V adopts the solution in section 3.4.1, where the active clamp switch is kept on for the entire duration of the powering phase; i.e., the clamp switch and the primary active PWM share the same timing (apart from the necessary dead times).

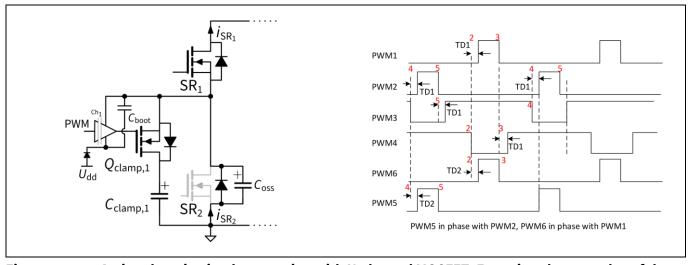

### 2.2.2 Active clamp implementation

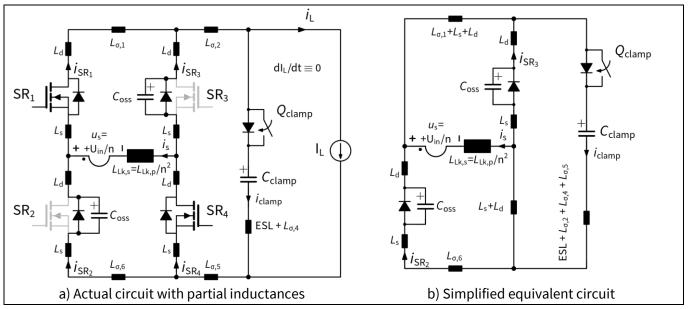

In practice, for the present reference design that is based on a full-bridge topology coming with a full-wave rectifier, there are different ways to implement active clamping of drain-source voltage for rectifiers. The basic implementation in Figure 21 can be traced back to the actual bridge circuit, following the steps taken from the circuit in Figure 12.

In Figure 26 the full-wave rectifier circuit including the active clamp is shown. Partial inductances related to both packages and PCBs are highlighted. These inductances will partially decouple the clamp capacitor from the drain of the rectifiers  $SR_2$  and  $SR_3$  that are experiencing the turn-off conditions. This will limit the effectiveness of the clamp, because high-frequency oscillatory modes will be superimposed on the waveform shown in Figure 24. The amplitude and frequency of these modes will depend on the value of the stray inductances, which should always be minimized by following best practices in PCB layout. A low-ESL clamp capacitor must also be selected in the actual implementation.

The symmetrical nature of the bridge rectifier is broken by the introduction of the clamp, as shown in Figure 26. In a practical layout, this would probably lead to an arrangement where the active clamp circuit sits closer to a bridge leg.

### -48 V to 50 V isolated digital power supply using XDPP1100

Measures to reduce the drain voltage overshoot in the synchronous rectifiers

Figure 26 Full-wave rectifier including stray, partial inductances related to power discrete packages and PCB layout

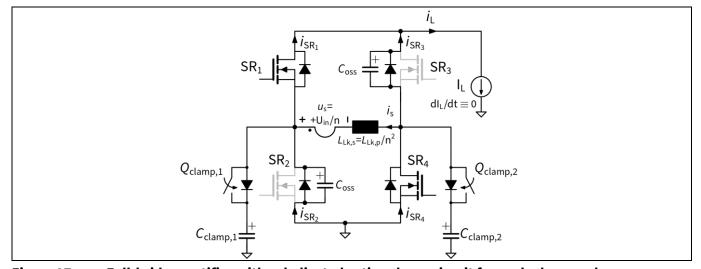

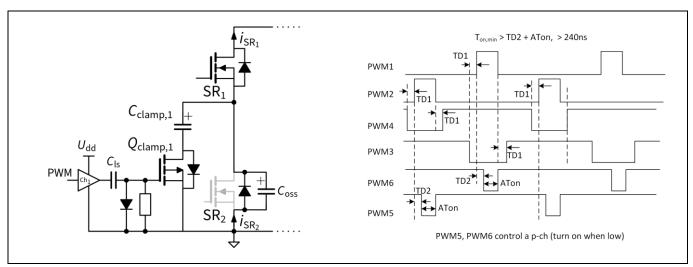

This would again limit the effectiveness of the clamp for the leg. At the cost of almost doubling its BOM, a different clamp circuit can be dedicated to each phase node, to reinstate the symmetry of the circuit (Figure 27).

Figure 27 Full-bridge rectifier with a dedicated active clamp circuit for each phase node

When it comes to an actual realization of the clamp switches, there are two options typically adopted. In both cases, for the Infineon reference design REF\_750W\_FBFB\_50V, the switches should be selected to block voltages as high as 150 V.

P-channel MOSFET: The advantage of using a P-channel MOSFET for the realization of Q<sub>clamp</sub> comes from the possibility of using a single, dual-channel (to drive the clamp switches off both legs) low-side gate driver referred to a secondary power ground. The clamp RMS current is typically low, especially when the clamp on-time is kept at its minimum. So, the penalty in the higher area-specific on-state resistance of a P-channel MOSFET is generally not an issue, and even the smallest surface-mount packages could fit the application.

### -48 V to 50 V isolated digital power supply using XDPP1100

### Measures to reduce the drain voltage overshoot in the synchronous rectifiers

The P-channel MOSFET requires an AC-coupled gate drive scheme, as shown in Figure 28, to implement the required level shifting ( $C_{ls}$ ,  $R_{gs}$ ,  $D_{gs}$ ) for the gate-to-source voltage. The PWM control signal needs to be complementary to the one intended for a conventional N-channel MOSFET drive.

Figure 28 Active clamping implementation with P-channel MOSFET. Focus is only on one leg of the full-bridge

2. *N-channel MOSFET*: Another possible solution uses an N-channel MOSFET for the realization of  $Q_{\text{clamp}}$ . In this case, a broader portfolio of devices can be selected, especially in the 150 V voltage class. The penalty here is paid in the BOM and in the PCB real estate, as the driving requires two high-side drivers or a dual-channel isolated driver. Bootstrapping of two power supplies is also required.

Figure 29 Active clamping implementation with N-channel MOSFET. Focus is only on one leg of the full-bridge

The solution using the N-channel MOSFET is the one chosen for the Infineon reference design REF\_750W\_FBFB\_50V. The clamp MOSFETs are selected to be the same as the SR MOSFETs, namely OptiMOS<sup>TM</sup> 5 150 V, 11 m $\Omega$   $R_{DS(on),max}$  BSC110N15NS5.

Clamp MOSFETs are driven by the dual-channel isolated gate driver EiceDRIVER™ 2EDF7275K.

-48 V to 50 V isolated digital power supply using XDPP1100

XDP™ XDPP1100 digital power controller configuration

## 3 XDP™ XDPP1100 digital power controller configuration

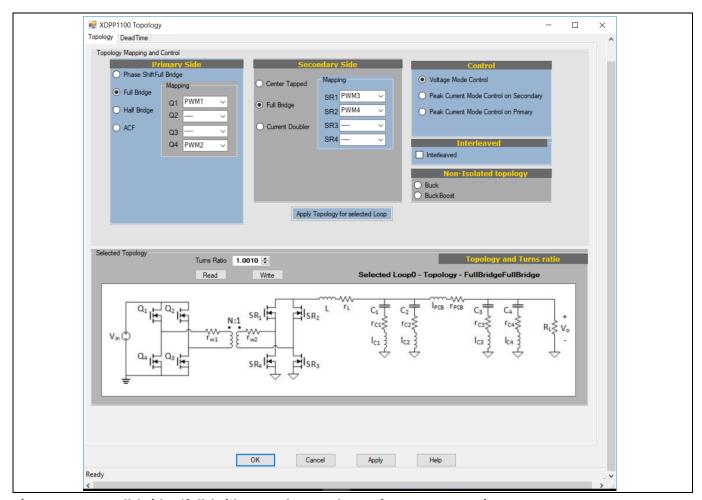

### 3.1 Topology and transformer turns ratio

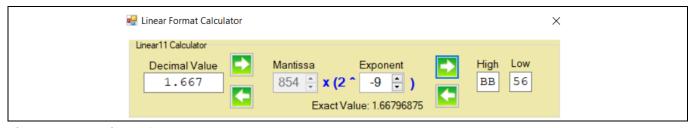

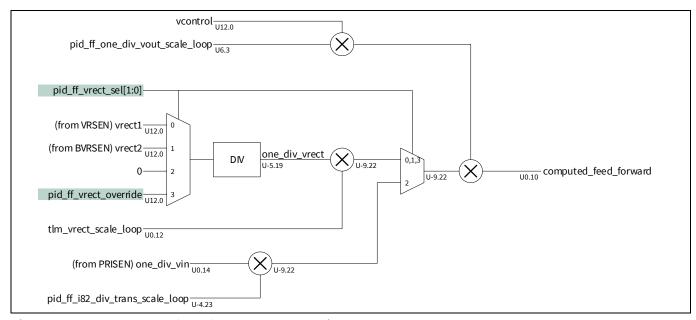

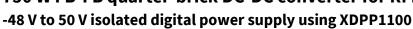

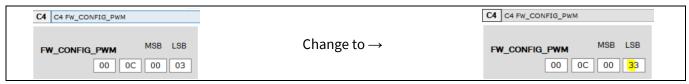

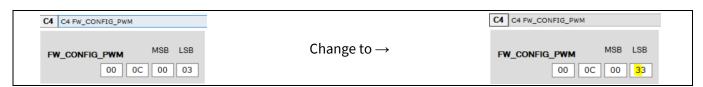

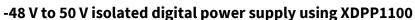

In the XDPP1100 graphical user interface (GUI) "Topology" design tool, configure the topology to full-bridge primary and full-bridge secondary, mapping the PWMs per HW connection. Please note that the XDPP1100 only supports step-down type transformers by default, i.e., the transformer turns ratio  $n = N_p$ :  $N_s$  must be higher than 1. Thus in Figure 30 the transformer turns ratio is set to 1.001.

Figure 30 Full-bridge/full-bridge topology and transformer turns ratio