#### **About this document**

#### Scope and purpose

This application note describes a high-density and high-efficiency PSU targeted towards enterprise server applications and covers the design and implementation of a 2.7 kW dual-stage AC-DC power supply utilizing highly efficient CoolSiC<sup>™</sup> devices. The power stages are digitally controlled by XMC<sup>™</sup> microcontrollers which provide responsive fault protection and stable output regulation.

Additionally, it describes the system in detail, along with critical design guidelines and a control strategy. It also includes setup and testing instructions to help you experience the full benefits of the Infineon products used in the design.

#### Intended audience

This application note is intended for power electronics engineers who want to verify the performance of the following Infineon products in a server power supply application consisting of bridgeless totem-pole power factor correction (PFC) and LLC topologies:

- CoolSiC<sup>™</sup> 650 V, 60 mΩ in bridgeless totem-pole PFC topology

- 600 V CoolMOS™ CM8, 37 mΩ in bridgeless totem-pole PFC topology

- 600 V CoolMOS™ CM8, 24 mΩ in LLC topology

- OptiMOS™ 6 MOSFET technology in LLC synchronous rectification

- Digital control with the XMC<sup>™</sup> family of microcontrollers

- Isolated and non-isolated gate drivers from the EiceDRIVER™ family

- A digital isolator from the ISOFACE™ product family

#### CoolSiC<sup>™</sup> product family

Infineon's CoolSiC™ MOSFETs offer exceptional performance in switching behavior and total losses. These devices are designed to offer high efficiency and optimal reliability, while also boasting a low on-resistance that remains stable and reproducible. Its ability to turn off the device with zero gate bias makes the CoolSiC™ MOSFETs the only true "normally-off" devices.

The CoolSiC<sup>™</sup> family supports applications such as:

- Energy Storage Systems

- Industrial drives

- Motor control and drives

- UPS

# 2.7 kW Titanium server digital power supply with CoolSiC<sup>™</sup> 650 V and XMC<sup>™</sup> MCUs

#### **Table of contents**

### **Table of contents**

| Abou  | ıt this document                                     | 1  |

|-------|------------------------------------------------------|----|

| Table | e of contents                                        | 2  |

| 1     | Introduction                                         | 3  |

| 1.1   | System specifications                                | 4  |

| 2     | Hardware overview                                    | 6  |

| 2.1   | Power supply board description                       | 6  |

| 2.2   | Infineon products                                    | 7  |

| 2.2.1 | CoolSiC™ MOSFETs                                     | 7  |

| 2.2.2 | CoolMOS™ MOSFETs                                     | 8  |

| 2.2.3 | OptiMOS™ MOSFETs                                     | 8  |

| 2.2.4 | XMC™ microcontroller                                 | 8  |

| 2.2.5 | EiceDRIVER™ gate drivers                             | 8  |

| 2.2.6 | ISOFACE™ digital isolator                            | 9  |

| 3     | Hardware design considerations                       | 10 |

| 3.1   | Bridgeless totem-pole PFC                            | 10 |

| 3.1.1 | CoolSiC™ MOSFET selection                            | 11 |

| 3.1.2 | CoolMOS™ MOSFET selection                            | 13 |

| 3.1.3 | PFC inductor design                                  | 13 |

| 3.1.4 | DC bus capacitors                                    | 15 |

| 3.2   | LLC DC-DC converter                                  | 15 |

| 3.2.1 | Primary side CoolMOS™ MOSFET selection               | 16 |

| 3.2.2 | Secondary side OptiMOS™ MOSFET synchronous rectifier | 17 |

| 3.2.3 | LLC transformer                                      | 18 |

| 3.2.4 | ORing FET                                            | 21 |

| 3.2.5 | Losses in LLC capacitors                             | 21 |

| 4     | Control and firmware                                 | 23 |

| 4.1   | PFC control                                          | 23 |

| 4.1.1 | Current control loop                                 | 24 |

| 4.1.2 | Control of the low-frequency half-bridge leg         | 27 |

| 4.1.3 | Voltage control loop                                 | 28 |

| 4.2   | LLC control                                          | 30 |

| 4.3   | Protection features                                  | 33 |

| 5     | Test results                                         | 34 |

| 6     | Summary                                              | 39 |

| 7     | Schematics                                           | 40 |

| 7.1   | Main board schematic                                 | 40 |

| 7.2   | Controller board schematic                           | 41 |

| Refer | rences                                               | 42 |

|       | sion history                                         |    |

Introduction

### 1 Introduction

As the computing power requirements increase, there is a need for higher power availability in the same volume for datacenter server applications.

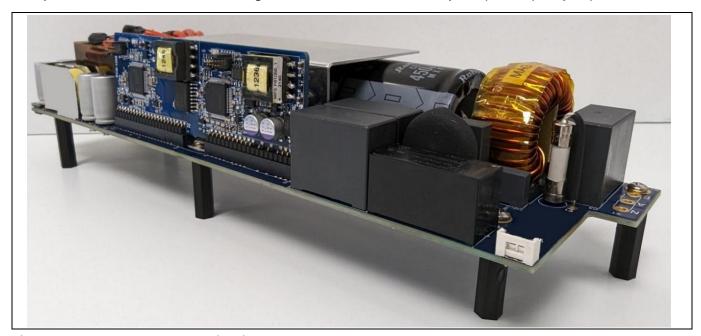

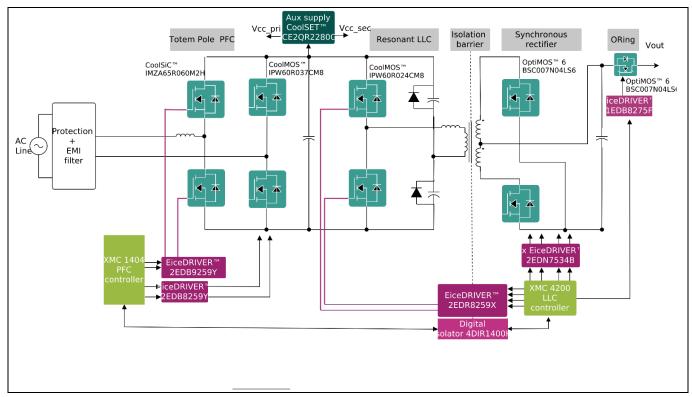

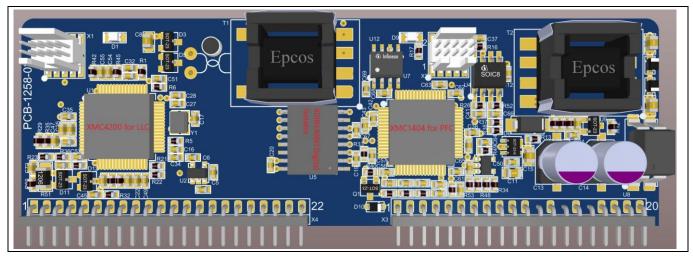

Figure 1 shows the high density 2.7 kW 80 PLUS Titanium server power supply board. Server PSUs are typically two-stage systems consisting of a front-end AC-DC PFC rectifier that draws high-quality power from the grid and provides a constant DC bus for the subsequent DC-DC stage, as shown in Figure 2. The isolated DC-DC stage is implemented with a highly efficient LLC topology, which provides the regulated bus voltage to the downstream server loads. Utilizing the best-in-class Infineon power devices, gate drivers, and microcontrollers, this system meets and exceeds the stringent 80 PLUS Titanium efficiency and power quality requirements.

Figure 1 2.7 kW 80 PLUS Titanium server power supply board

Introduction

Figure 2 Typical PSU system block diagram

### 1.1 System specifications

This reference design has been developed to meet the following requirements:

Table 1 Input requirements

| Parameter             | Value                                     |

|-----------------------|-------------------------------------------|

| Input voltage range   | 180–264 Vac (2700 W), 90–140 Vac (1400 W) |

| Frequency             | 47 Hz to 63 Hz                            |

| Efficiency            | 96% peak, 80 PLUS Titanium                |

| Max input current     | 13.8 A <sub>rms</sub> at 120/208 Vac      |

| Inrush current        | <30 A <sub>pk</sub>                       |

| Surge withstand       | >1 kV L-L, >2 kV L-E (EN 61000-4-5)       |

| Power factor          | >0.9 beginning at 20% load                |

| ITHD, Harmonics       | <10%, EN 61000-3-2                        |

| Hold-up time          | >10 ms at 100% load                       |

| Operating temperature | 0°C to 50°C                               |

V 2.1

# 2.7 kW Titanium server digital power supply with CoolSiC<sup>™</sup> 650 V and XMC<sup>™</sup> MCUs

#### Introduction

Table 2 Output requirements

| Parameter                     | Value                          |  |

|-------------------------------|--------------------------------|--|

| Nominal output voltage        | 12.2 V                         |  |

| Total output regulation range | 11.2 V to 13.2 V               |  |

| Output ripple                 | <180 mVp-p                     |  |

| Output current                | 224/112 A at the high/low line |  |

| Capacitive loading            | 4,000 μF to 38,000 μF          |  |

| Start-up from AC to output    | <2 s                           |  |

| Output rise time              | <100 ms                        |  |

| Operating temperature         | 0°C to 50°C                    |  |

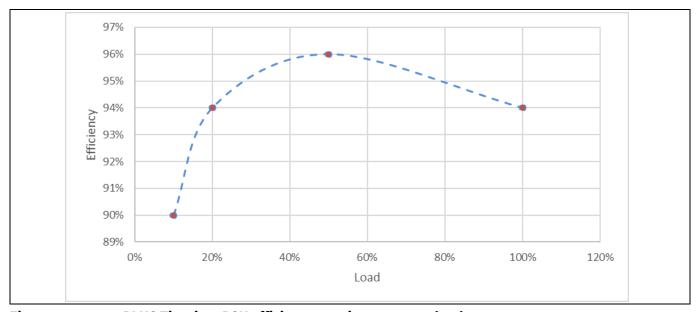

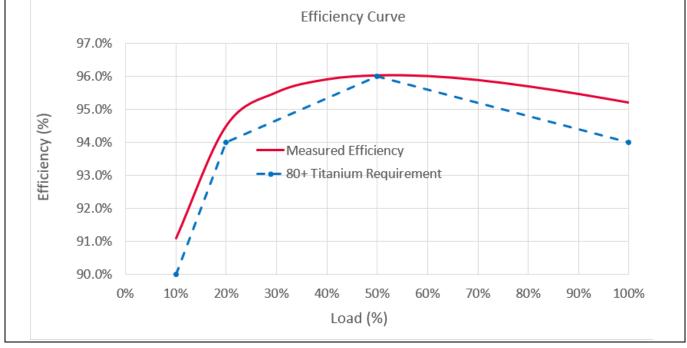

### Table 3 80 PLUS Titanium efficiency requirements

| Percentage of rated load | 10% | 20% | 50% | 100% |

|--------------------------|-----|-----|-----|------|

| 80 PLUS Titanium         | 90% | 94% | 96% | 94%  |

Note: These requirements are measured at Vin = 230 Vac, including bias and fan power.

**Hardware overview**

### 2 Hardware overview

### 2.1 Power supply board description

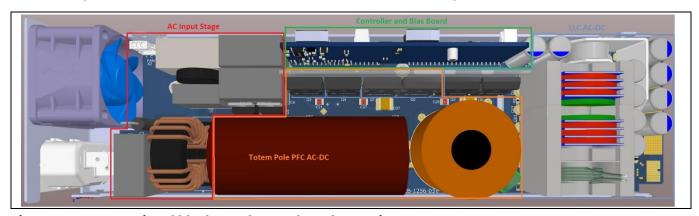

The various functional blocks of the PSU are:

- Input stage, which contains the EMI filter, inrush current limiting, and protection components

- Totem-pole boost power factor correction AC-DC stage

- LLC DC-DC conversion stage

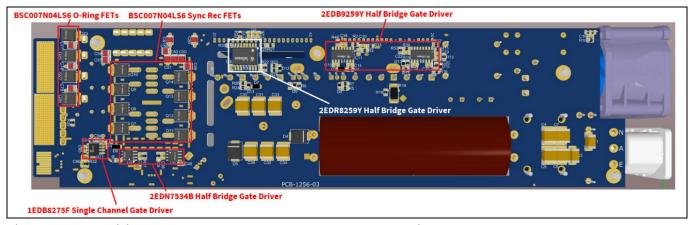

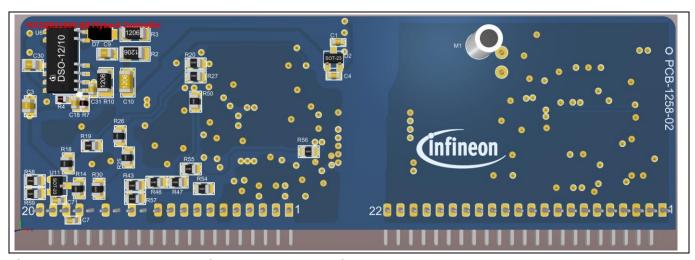

Figure 3 and Figure 4 show the top and bottom views of the 2.7 kW PSU with a power density of 54 W/in<sup>3</sup>.

Additionally, Figure 5 and Figure 6 show the control and bias boards, which contain the MCU to control the PFC and LLC stages, and the bias power supply, which provides housekeeping power for the PSU.

Figure 3 Functional blocks on the PSU board - top view

Figure 4 Critical components on the PSU board - bottom view

**Hardware overview**

Figure 5 Controller and bias board - top view

Figure 6 Controller and bias board – bottom view

### 2.2 Infineon products

#### 2.2.1 CoolSiC™ MOSFETs

The AC-DC rectification with power factor correction is achieved by the implementation of a bridgeless totempole PFC boost converter operating in a continuous conduction mode (CCM). The hard switching nature of a CCM converter necessitates the use of switching devices with low parasitic capacitances and reverse recovery losses. Infineon's CoolSiC<sup>™</sup> 650 V MOSFET meets these requirements and enables the front-end AC-DC rectifier to operate at high efficiencies and quality of power drawn from the grid.

This design uses  $CoolSiC^{TM}$  IMZA65R060M2H 650 V MOSFET in a TO247 4-pin package. The 4-pin package reduces parasitic source inductance effects during driving of the device and enables fast switching with high efficiencies. The excellent thermal behavior of  $CoolSiC^{TM}$  and the low  $R_{DS(on)}$  shift overtemperature enable the use of a higher  $R_{DS(on)}$  device, which typically has lower capacitances. This leads to lower switching losses, ensuring high operating efficiency. A robust fast body diode with a low reverse recovery charge is critical in a hard-switching topology, both in terms of reliability and efficiency. Its superior gate oxide reliability combined with the ease of driving enables the use of standard gate drivers, such as the latest generation of isolated gate drivers from the EiceDRIVER<sup>TM</sup> family.

Hardware overview

#### 2.2.2 CoolMOS™ MOSFETs

The AC rectification leg of the bridgeless totem-pole PFC converter uses CoolMOS™ IPW60R037CM8 600 V MOSFET. Because these switches operate at a slower rate of AC line frequency, it is critical to minimize the conduction losses. IPW60R037CM8 features the best R<sub>DS(on)</sub>\*A figure of merit and significantly minimizes the AC line current conduction losses to enable high efficiency across the load range.

Additionally, the primary side of the DC-DC LLC converter uses CoolMOS<sup>TM</sup> IPW60R024CM8 600 V MOSFET, an ideal fit for high-frequency resonant topologies such as the LLC converter because of its best-in-class reverse recovery charge, lowest  $E_{oss}$ , and  $R_{DS(on)}$  x  $Q_g$  figure of merit. This device features excellent hard commutation ruggedness in the hard switching regions of LLC operation.

### 2.2.3 OptiMOS™ MOSFETs

The LLC synchronous rectification is performed using OptiMOS<sup>TM</sup> 6 BSC007N04LS6 40 V and 0.7 m $\Omega$  MOSFETs. Using MOSFETs for synchronous rectification as opposed to diodes minimizes conduction losses to achieve a high-efficiency and high-power-density power supply. OptiMOS<sup>TM</sup> 6 MOSFETs are optimized for low-voltage, high-current synchronous rectification applications. They have a very low  $R_{DS(on)}$  that minimizes conduction losses. Their low thermal resistance from junction to bottom makes thermal management easy at full loads. They are rated up to 175°C, which helps designers use fewer devices in parallel to spread out losses and heat. The small footprint of the surface mount package further helps in increasing the system power density.

#### 2.2.4 XMC<sup>™</sup> microcontroller

A 32-bit XMC1404 microcontroller digitally controls the bridgeless totem-pole PFC boost converter. XMC1404 is based on an Arm® Cortex®-M0 processor core and is an ideal MCU to address the real-time control needs of a bridgeless TPPFC topology. It contains a fast 12-bit ADC with two samples and hold stages and a 0–5.5 V input range to enable high-resolution sensing for real-time control of the converter. The high-resolution ADC, in conjunction with a 16-bit 96 MHz Capture/Compare Unit 8 (CCU8) timer for PWM, ensures that the PFC controller achieves the goals of high power quality, tight output regulation, and good dynamic line and load response.

The second-stage LLC DC-DC converter is implemented and controlled using the powerful XMC4200 MCU, which is based on Arm® Cortex®-M4 with a built-in DSP instruction set. It comes with a comprehensive set of fast and precise analog/mixed signal, timer/PWM, and communication peripherals. The following are the features of XMC4200 that make it well suited to implement a resonant topology like LLC, which depends on fine adjustment of switching dead times:

- Up to 4x 12-bit ADC with a sample time of 70 ns ensures fast reaction times and tighter control loops

- 4-channel, 150 ps HRPWM timer

- One CCU8 for motor control and power conversion

- High-performance 32-bit Arm® Cortex®-M4 CPU

### 2.2.5 EiceDRIVER™ gate drivers

The following gate drivers from the EiceDRIVER™ family are used in this design:

• 2EDB9259Y is used on the PFC fast legs. This is a dual-channel isolated gate driver IC with floating outputs. The strong 5 A/9 A source/sink dual-channel gate driver comes with a very high 150 V/ns common-mode transient immunity (CMTI) for robust operation with CoolSiC™ MOSFETs in a high-power switching noise environment

#### **Hardware overview**

- 2EDB8259Y is used on the PFC slow legs for driving the CoolMOS™ MOSFETs. This part is similar to 2EDB9259Y, but with a lower UVLO of 8 V to be compatible with the driving levels of CoolMOS™ MOSFET

- 2EDR8259X is used to drive the primary switches in the LLC DC-DC converter. It is a reinforced isolated gate driver IC to drive the LLC primary switches across the isolation boundary because the XMC4200 MCU is located on the low-voltage side. The strong 5 A/9 A source/sink dual-channel gate driver comes with a very high 150 V/ns CMTI for robust operation with CoolMOS™ MOSFETs, CoolGaN™ GIT HEMTs, and a high-power switching noise environment. It features symmetrical operation in a bootstrapped system to reduce the risk of saturation of the main transformer or hard commutation in an LLC

- 2EDN7534B is used to drive the low-voltage synchronous rectifier of the LLC DC-DC converter. This gate

driver comes in a small SOT-23 footprint to increase the power density of the solution. High output current

capability, tight timing specifications, and reduced output startup and shutdown times make the 2EDN

family the first choice for many fast-switching applications

### 2.2.6 ISOFACE™ digital isolator

In this reference design, the XMC1404 PFC controller is located on the high-voltage side, whereas the LLC controller XMC4200 is located on the 12 V side of the board. The communication between these two controllers must be implemented over the reinforced isolation barrier to satisfy system-level safety requirements. The 4DIR1400H digital isolator is a perfect fit for this use case, with the following features:

- High common-mode transient immunity > 100 kV/μs

- VISO of 5700 V<sub>rms</sub> (UL1577), VDE 0884-17

- Wide supply voltage ranges from 2.7 V to 6.5 V (absolute maximum 7.5 V)

- Accurate timing with a 26 ns typical propagation delay and -6/+7 ns spread

- Low power consumption with a maximum 3.3 mA at 3.3 V and 1 Mbps

- The fail-safe default output is low

- Low power consumption

**Hardware design considerations**

### 3 Hardware design considerations

### 3.1 Bridgeless totem-pole PFC

This section describes the design and selection of the critical components of the first-stage bridgeless totem-pole PFC.

Table 4 shows the specifications of the PFC section.

Table 4 PFC specifications

| Parameter           | Value                                     |

|---------------------|-------------------------------------------|

| Input voltage range | 180–264 Vac (2700 W), 90-140 Vac (1400 W) |

| Output voltage      | 385 V                                     |

| Power factor        | >0.9 beginning at 20% load                |

| ITHD, Harmonics     | <10%, EN 61000-3-2                        |

| Hold-up time        | >10 ms at 100% load                       |

| Switching frequency | 65 kHz                                    |

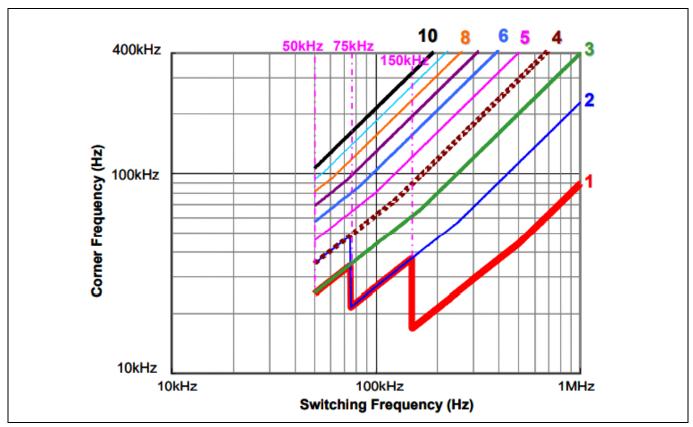

As mentioned in [1], there is a relationship between the single-stage PFC switching frequency and the EMI filter cut-off frequency. From Figure 7, you can see that the optimal switching frequency for a single-stage PFC is just below 75 kHz. For this design, 65 kHz is chosen to ensure that the second harmonic is below the measurement start of 150 kHz and minimize hard switching losses.

Figure 7 Relationship between switching frequency and EMI filter corner frequency (see [1])

**Hardware design considerations**

#### 3.1.1 CoolSiC™ MOSFET selection

As mentioned earlier, CoolSiC™ MOSFET is an ideal fit for a hard-switching topology like the bridgeless totem-pole PFC. The main goal of using a CoolSiC™ MOSFET in this design is to minimize both conduction and switching losses to maximize the efficiency and power density. The CoolSiC™ MOSFET has significantly better figures of merit, which helps it outperform silicon superjunction MOSFETs in topologies that have third-quadrant operation.

The parametric advantage of CoolSiC<sup>TM</sup> MOSFET over silicon SJ MOSFETs is described in detail [2]. This application note also describes the process of selecting the optimum  $R_{DS(on)}$  for a design by considering the power level, switching frequency, and load at which peak efficiency or best thermal performance is desired. For this design, a CoolSiC<sup>TM</sup> IMZA65R060M2H 650 V MOSFET is selected, which has a nominal  $R_{DS(on)}$  of 60 m $\Omega$ .

After selecting an  $R_{DS(on)}$  class, calculate the total losses (conduction plus switching) at the highest loss operating condition to ensure that the losses do not exceed the thermal management capability of the design and satisfy the efficiency criteria.

In the bridgeless totem-pole boost PFC, each CoolSiC™ MOSFET operates as a boost switch during one half of the AC cycle and as a rectifier during the other half. Therefore, according to the following equations, the losses for each half of the AC cycle must be calculated and averaged to find the total loss per device over the full line cycle.

First, define the operating conditions under which the converter needs to be designed and analyzed.

| $V_{in\_rms}$ := 230 $	extbf{\emph{V}}$                                       | Input RMS voltage                    |

|-------------------------------------------------------------------------------|--------------------------------------|

| $V_{in\_pk} \coloneqq V_{in\_rms} \cdot \sqrt{2} = 325.269 \ V$               | Peak of input voltage                |

| $V_{out}\!\coloneqq\!400~	extbf{\emph{V}}$                                    | PFC output voltage                   |

| $F_s = 65 \text{ kHz}$                                                        | PFC switching frequency              |

| $P_{oLLC}\coloneqq 2700~W$                                                    | Full load output power               |

| $\eta_{LLC}\!\coloneqq\!96\%$                                                 | Efficiency of LLC stage at full load |

| $P_{oPFC}\coloneqq rac{P_{oLLC}}{\eta_{LLC}} = 2.813 \; 	extbf{\textit{kW}}$ | PFC stage output power               |

| $T_s \coloneqq \frac{1}{F_s} = 15.385 \; \mu s$                               | Switching period                     |

| DeadTime = 300   ns                                                           | PFC fast leg dead time               |

| $V_g\!\coloneqq\!15~	extbf{V}$                                                | CoolSiC™ gate drive voltage          |

CoolSiC<sup>™</sup> gate drive voltage

#### **Hardware design considerations**

$$Q_q = 19 \, nC$$

CoolSiC<sup>™</sup> gate charge

$$R_{dson} = 0.06 \Omega$$

CoolSiC<sup>™</sup> on state resistance

#### CoolSiC<sup>™</sup> losses as a boost switch

#### **Conduction loss**

$$I_Q \!\coloneqq\! \frac{P_{oPFC}}{V_{in~rms}} \! \cdot \! \sqrt{1 \! - \! \frac{8}{3 \! \cdot \! \pi} \! \cdot \! \frac{V_{in\_pk}}{V_{out}}} \! = \! 6.806~A$$

Boost switch RMS current

$$P_{Q \ cond} := I_Q^2 \cdot R_{dson} \cdot 1.2 = 3.335 \ W$$

Conduction loss including R<sub>DS(on)</sub> temperature coefficient at 125°C

#### **Switching loss**

The method of calculating the switching losses is shown in [2] and is used to estimate the switching losses in this design.

$$I_{Lavg} \coloneqq \frac{P_{oPFC}}{V_{in,rms}} \cdot \frac{2 \cdot \sqrt{2}}{\pi} = 11.009 \ A$$

Average inductor current during switching transitions

$$E_{on\_off} \! \coloneqq \! \left( \! \frac{1.85}{1~\textit{A}} \! \cdot \! I_{Lavg} \! + \! \frac{1.24~\Omega}{R_{dson}} \! \right) \! \cdot \! 10^{-6}~\textit{\textbf{J}} \! = \! \left( 4.103 \cdot 10^{-5} \! \right) \textit{\textbf{J}}$$

Average of turn on and turn off energy

$$P_{Q\_sw} := E_{on\_off} \cdot F_s = 2.667 \ W$$

Switching loss

$$P_{Q GD} = V_g \cdot Q_g \cdot F_s = 0.019 \ W$$

Gate drive loss

#### **Total loss during switch mode**

$$P_{Q\_tot} := P_{Q\_cond} + P_{Q\_sw} + P_{Q\_GD} = 6.021 \ W$$

#### CoolSiC™ MOSFET losses as a boost rectifier

During the other AC half cycle, the same CoolSiC™ MOSFET that acts as the switch during the previous half cycle now operates as a synchronous boost rectifier. Initially, the current flows through the body diode during the dead time, resulting in body diode VI loss. At high switching frequencies, the dead time becomes a larger percentage of the total period and account this loss in the total loss calculation. Another benefit of CoolSiC™ MOSFET over superjunction MOSFETs is that the dead time can be minimized to reduce this loss component because of the fast rise and fall times. The CoolSiC™ MOSFET channel turns on after the dead time, resulting in conduction loss. Losses during this mode of operation are calculated as:

#### **Hardware design considerations**

#### **Conduction loss**

$$I_D \coloneqq \sqrt{\frac{16}{3 \cdot \pi} \cdot \frac{P_{oPFC}^{\phantom{oPFC}^2}}{V_{in\_pk} \cdot V_{out}}} = 10.159 \; \textbf{A}$$

Boost rectifier RMS current

$$P_{D \ cond} := I_D^2 \cdot R_{dson} \cdot 1.2 = 7.431 \ W$$

Conduction loss including R<sub>DS(on)</sub> temperature coefficient at 125°C

$$P_{revcond} = 2 \cdot I_{Lavg} \cdot V_{SD} \cdot DeadTime \cdot F_s = 1.846 \ W$$

Conduction loss during dead time

$$P_{D\_GD} := V_g \cdot Q_g \cdot F_s = 0.019 \ W$$

Gate drive loss

#### Total loss as a rectifier

$$P_{D\_tot} \coloneqq P_{D\_cond} + P_{revcond} + P_{D\_GD} = 9.296 \ \textbf{W}$$

#### Total loss per device over a full AC line cycle

$$P_{CoolSiC\_tot} = \frac{P_{Q\_tot} + P_{D\_tot}}{2} = 7.658 W$$

#### 3.1.2 CoolMOS™ MOSFET selection

In a bridgeless totem-pole boost PFC, the diode bridge line rectifier is replaced by active switches, specifically superjunction MOSFETs, to eliminate the diode conduction loss. The only loss component in these devices will be the channel conduction loss. These devices operate at low line frequencies; therefore, switching losses are neglected.

$$R_{dsonSi} = 0.037 \Omega$$

CoolMOS™ MOSFET on state resistance

$$I_{SiRMS} = \frac{P_{oPFC}}{\sqrt{2} \cdot V_{in\ rms}} = 8.647\ A$$

RMS current at line frequency

$$P_{Sicond}\!\coloneqq\!\!I_{SiRMS}^{\phantom{Sicond}2}\!\cdot\!R_{dsonSi}\!\cdot\!1.5\!=\!4.149~\textbf{W}$$

Conduction loss of each line rectifying CoolMOS™ MOSFET at 125°C

### 3.1.3 PFC inductor design

The maximum amount of allowable ripple determines the required inductance. The amount of ripple also impacts the magnitude of differential and common mode conducted EMI, so it must be carefully chosen while keeping the overall size in mind. For this design, a ripple value of around 20% was chosen. The resulting inductance value obtained from calculations is 250  $\mu$ H at full load and at the peak of the AC sine wave.

#### **Hardware design considerations**

As shown in Figure 8, this inductor is implemented using two stacked cores of Edge material from Magnetics, Inc., which has a permeability ( $\mu$ ) of 60 and an A $_{L}$  of 61 nH/T $^{2}$ . A two-layer winding of 60 turns provides the required inductance of around 250  $\mu$ H under the above-mentioned conditions. The Edge material maintains its permeability over a wide range of DC bias and therefore is a great fit for PFC applications where minimizing inductance droop over the AC sinusoidal current is important. Compared to other powder iron cores, Edge material has significantly lower losses. These two crucial features help in designing a compact inductor for a high-density converter.

Figure 8 PFC inductor

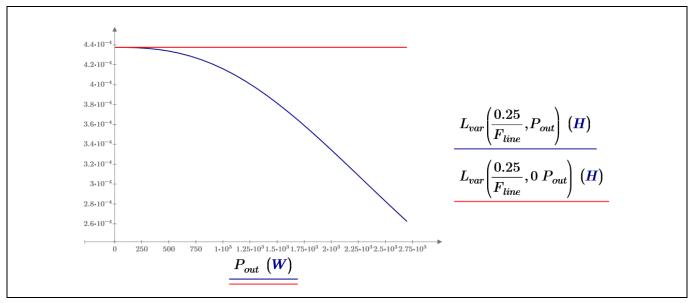

The detailed calculation to understand inductance variation, core, and copper losses can be obtained from [1]. Figure 9 shows that the inductance varies from around 440  $\mu$ H at no load to 260  $\mu$ H at full load and peak of the AC line, satisfying the ripple requirements. The high inductance at no load and at AC zero crossing ensures a CCM operation, resulting in a high power factor, low total harmonic distortion, and low EMI across the entire line and load range.

Figure 9 Inductance variation across the AC line cycle and load

The DC resistance of an assembled inductor is around 50 m $\Omega$ . This leads to a copper loss of 8.5 W at a maximum line current of 13 A. For this design, the core losses in the inductor at full load are around 1.6 W.

**Hardware design considerations**

### 3.1.4 DC bus capacitors

The DC bus capacitor value is calculated based on two criteria: the maximum allowable double-line frequency ripple and the ability to hold up the bus voltage above a minimum value for at least 10 ms during an AC line drop-out condition. The greater of these two values must be selected to satisfy both conditions. In this design, two (2)  $680~\mu F$  capacitors are selected to provide enough capacitance to satisfy the AC line drop-out requirements.

#### 3.2 LLC DC-DC converter

The LLC resonant converter is a very popular topology in the server SMPS space due to its numerous advantages. It is an isolated soft switching topology where both zero-voltage switching (ZVS) and zero-current switching (ZCS) can be achieved to drastically minimize switching losses. The capability to operate with ZVS and ZCS provides many benefits. Soft switching reduces EMI significantly in the system. Reduced switching losses also mean that the converter can be operated at a high frequency, reducing the size of the transformer and capacitors to achieve high power density. Another benefit of this topology is that it can maintain soft switching over a wide range of loads, which enables high efficiency over the load range, satisfying the stringent OCP Titanium efficiency requirements as shown in Figure 10.

Figure 10 80 PLUS Titanium PSU efficiency requirement over load range

Despite the several performance benefits of the LLC resonant converter, adoption of this topology outside of the server space has been low due to challenges in designing the hardware and developing closed-loop controls. This application note shows that these challenges can be overcome and the high-performance benefits of this topology can be realized using Infineon products such as CoolMOS™ MOSFETs and XMC™ microcontrollers.

The process of hardware design and component selection for an LLC resonant converter is described in detail in [3] and [4]. The following sections will quantify the conduction and switching losses of the primary and secondary MOSFETs. These loss numbers justify the selection of the MOSFETs in this design to meet the efficiency requirements as seen in the previous section.

**Hardware design considerations**

### 3.2.1 Primary side CoolMOS™ MOSFET selection

With optimized dead time control, the LLC resonant converter can achieve soft switching for both turn-on and turn-off transitions over the majority of the operating range. This allows a designer to use cost-effective and high-performance CoolMOS<sup>TM</sup> MOSFETs. However, it is important to pay attention to a few parameters during the selection process to achieve a balance between low on-state resistance and low switching parasitics. In this aspect, CoolMOS<sup>TM</sup> MOSFET offers the best figure of merit to achieve both low conduction loss and soft switching. The device chosen for this design is the IPW60R024CM8, which is a 600 V, 24 m $\Omega$  device with excellent switching characteristics. The comparison between different  $R_{DS(on)}$  classes of CFD7 CoolMOS<sup>TM</sup> MOSFET in an LLC converter of similar power is shown in [4]. Based on the analysis, a 24 m $\Omega$  device is a good fit for this 2.7 kW LLC design. The CM8 device offers superior performance to CFD7 devices because of its best-inclass reverse recovery charge, lowest  $E_{oss}$ , and  $R_{DS(on)}$  x  $Q_g$  figure of merit.

#### **LLC operating conditions**

$V_0 = 12 V$  LLC output Voltage

fsw = 72 kHzLLC resonant frequency

$P_{oLLC} \coloneqq 2700~W$  Full load output power

n≔15 Transformer turns ratio

#### **Primary MOSFET conduction loss**

$IpriFET_rms := 13 A$

| Ipra LI_rms = 15 A                                                  | Primary RMS current                       |

|---------------------------------------------------------------------|-------------------------------------------|

| $Rds_pri := 24 \cdot 10^{-3} \cdot \Omega \cdot 1.4 = 0.034 \Omega$ | Primary switches on state resistance 75°C |

$PpriFET\_cond := IpriFET\_rms^2 \cdot Rds\_pri \cdot 2 = 11.357 W$  Primary switches conduction loss

### **Primary MOSFET body diode conduction loss**

$Prpi\_bodydiode := Iturnoff \cdot Vf \cdot Tdeadtime \cdot fsw \cdot 2 = 0.346 \ W$

| Iturnoff := 12 A       | Turn-off RMS current                 |

|------------------------|--------------------------------------|

| <i>Vf</i> :=1 <i>V</i> | Forward voltage of MOSFET body diode |

| Tdeadtime := 200 ns    | Switch dead time                     |

**Hardware design considerations**

#### **Primary MOSFET turn off loss**

$$Ppri\_turnoff := \frac{Vin \cdot Iturnoff}{4} \cdot 40 \ ns \cdot fsw \cdot 2 = 6.653 \ W$$

#### **Primary MOSFET gate drive loss**

$$Vdrv_pri := 12 \cdot V$$

Gate drive voltage

$$Qg\_pri = 122 \cdot 10^{-9} C$$

Gate charge

$$Ppri\_driving = Qg\_pri \cdot Vdrv\_pri \cdot fsw \cdot 2 = 0.211 \ W$$

#### **Total primary switch loss**

$Ppri\_FET \coloneqq PpriFET\_cond + Prpi\_bodydiode + Ppri\_turnoff + Ppri\_driving = 18.566 \ \textbf{W}$

### 3.2.2 Secondary side OptiMOS™ MOSFET synchronous rectifier

The optimum selection of MOSFETs for the secondary-side synchronous rectifier has been described in detail in [5]. The device selection depends primarily on minimizing and balancing both conduction and switching losses. Selecting a device with low  $R_{DS(on)}$  to minimize conduction losses is critical due to the high output current in this design. As seen in the PFC design section, the switching loss comprises several loss components that arise from the switching transition characteristics of the device, such as the gate charge, turn on, and turn off energy. The OptiMOS<sup>TM</sup> 6 series of MOSFETs offers an excellent selection of low  $R_{DS(on)}$  classes along with low parasitics, which minimize switching losses. The LLC converter operates mostly in a soft switching region, which inherently minimizes the switching loss. Due to this benefit, the designer has the freedom to select a low  $R_{DS(on)}$  device to minimize conduction losses while still keeping switching losses low.

#### **Secondary MOSFET loss calculation:**

#### **Secondary MOSFET conduction loss**

$$Rds\_sec := 0.7 \cdot 10^{-3} \cdot \Omega \cdot 1.5 = 0.001 \Omega$$

Secondary switches on state resistance 75°C

$IsecFET_rms := 174 A$

Secondary RMS current

$PsecFET\_cond := IsecFET\_rms^2 \cdot \frac{Rds\_sec}{8} \cdot 2 = 7.947 \text{ W}$

Secondary switches conduction loss

V 2.1

#### **Hardware design considerations**

#### **Secondary MOSFET body diode conduction loss**

Iturnon\_SR  $\rightleftharpoons$  25 A Turn on current of

the synchronous rectifier (SR) FETs

$Iturnoff\_SR := 60 A$ Turn off current of

the SR FETs

$Vf_sec := 1 V$  SR FETs diode

forward voltage

Tdiode\_on = 400 ns

Diode conduction

time between turn off and turn on

Tdiode\_off:=400 ns

Diode conduction

time between turn on and turn off

$Psec\_bodydiode \coloneqq (Iturnon\_SR \cdot Vf\_sec \cdot Tdiode\_on + Iturnoff\_SR \cdot Vf\_sec \cdot Tdiode\_off) \cdot fsw \cdot 2 = 4.896 \ \textbf{\textit{W}} \\ \text{SR FETs body} \\ \text$

diode losses

#### **Secondary MOSFET gate driving loss**

$Vdrv\_sec = 6 \cdot V$  SR FET gate drive

voltage

$Qg\_sec := \frac{118 \cdot 10^{-9} \cdot C}{10 \text{ V}} \cdot 6 \text{ V} = (7.08 \cdot 10^{-8}) \text{ C}$ SR FET gate

charge

$Psec\_driving = Qg\_sec \cdot Vdrv\_sec \cdot fsw \cdot 16 = 0.489 \ W$  SR FET gate

driving loss

#### **Total secondary switch loss**

$Psec\_FET \coloneqq PsecFET\_cond + Psec\_bodydiode + Psec\_driving = 13.333 \ \textit{\textbf{W}}$

#### 3.2.3 LLC transformer

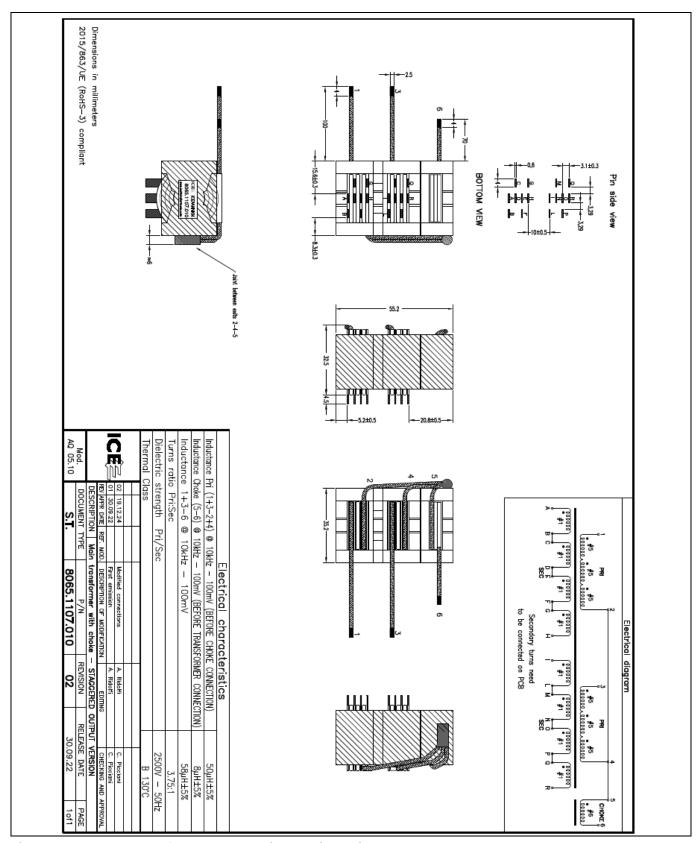

The transformer material selection and construction are optimized to minimize AC and DC losses and achieve high power density. The primary consists of two 15-turn litz wire windings in parallel, and the center-tapped secondary consists of four 1-turn copper foil windings in parallel, as shown in Figure 11. The resonant inductor has a 6-turn litz wire winding.

### **Hardware design considerations**

Figure 11 LLC transformer schematic and dimensions

### **Hardware design considerations**

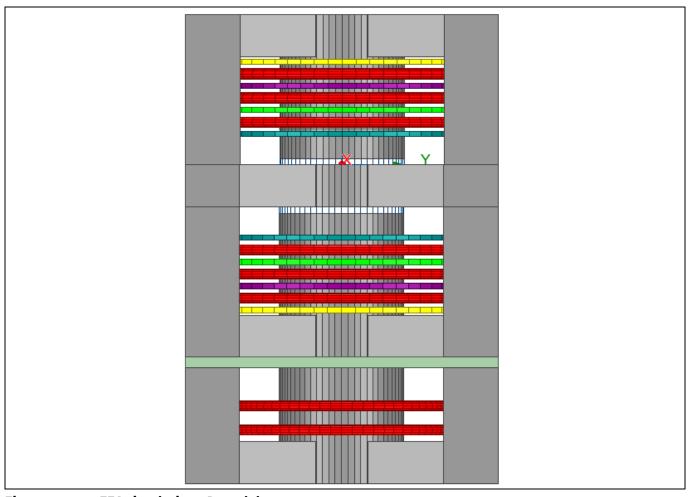

A FEA simulation was carried out to optimize the core and winding structure. Figure 12 shows the 3D model of the FEA simulation schematic of the transformer.

Figure 12 FEA simulation 3D model

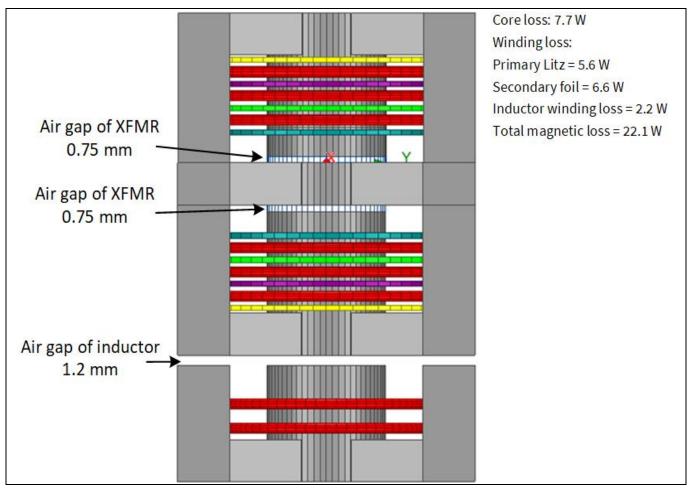

This modeling and analysis are used to select the core structure that provides the lowest loss solution. As seen from the results of the FEA simulation in Figure 13, the optimized transformer design results in a total power loss of close to 22 W at the highest load condition.

#### **Hardware design considerations**

Figure 13 FEA simulation results

### 3.2.4 ORing FET

The primary criteria for selecting an ORing FET is low  $R_{DS(on)}$ , and in this design, the same FET that was used for synchronous rectification is chosen as the ORing FET.

#### **Conduction loss in the ORing FET**

$$PoringFET := \left(\frac{P}{Vo}\right)^2 \cdot \frac{Rds\_sec}{8} = 6.645 \text{ W}$$

### 3.2.5 Losses in LLC capacitors

#### Loss in resonant capacitor

$$ICr_rms := 10 A$$

$$ESR\_Cr = \frac{2 \cdot 10^{-3} \cdot \Omega}{3} = (6.667 \cdot 10^{-4}) \Omega$$

$$PCr := ICr\_rms^2 \cdot ESR\_Cr \cdot 2 = 0.133 W$$

#### **Hardware design considerations**

#### Loss in output capacitor

$$ICo\_rms := 110 A$$

$$ESR\_Co := \frac{2 \cdot 10^{-3} \cdot \Omega}{36} = (5.556 \cdot 10^{-5}) \Omega$$

$$PCo := ICo\_rms^2 \cdot ESR\_Co = 0.672$$

W

LLC output capacitor RMS current

LLC output capacitor ESR

Power loss in LLC output capacitor

#### **Total capacitor losses**

$$Pcap := PCr + PCo = 0.806 W$$

An additional loss component is the termination, bus bars, and PCB trace loss due to the high output current. In this design, it is assumed to be around 15 W.

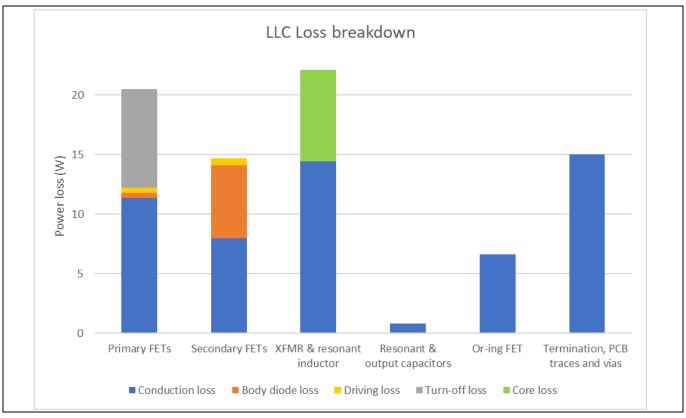

Figure 14 shows the estimated total losses in the LLC block at full load along with the loss breakdown.

$Ploss \coloneqq Ppri\_FET + Psec\_FET + Pmag + PoringFET + Pcap + Pother = 76.449 \ \textbf{W}$

Figure 14 LLC loss breakdown

**Control and firmware**

### 4 Control and firmware

### 4.1 PFC control

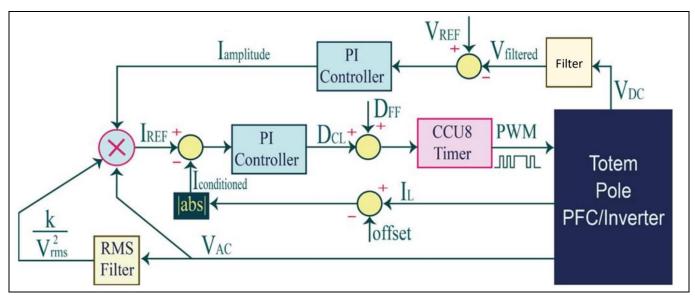

The structure of the PFC controller is shown in Figure 15. The goal of this controller is to regulate the PFC output voltage at the DC bus setpoint and control the input current shape so that a high-power-factor operation is achieved. This voltage must be regulated over line and load variations and controlled during transient events within a certain margin. This is achieved by first sensing the output voltage via hardware sensing and the ADC of XMC1404.

The output of the ADC is compared to the setpoint, and the error is fed to the PI controller, which generates the amplitude of the reference current. This current reference amplitude is multiplied by the instantaneous AC voltage to generate a sinusoidal reference for the average inductor current. This is compared against the measured average inductor current, and the error is the input to the inner current loop PI controller. The current PI controller uses the error to generate the closed-loop duty cycle value  $D_{CL}$ , which is then summed with the feed-forward duty cycle value  $D_{FF}$  to generate the final duty that shapes the inductor current as well as regulates the output voltage. The CCU8 timer uses this duty value to generate PWM signals used to drive the totem-pole PFC fast leg.

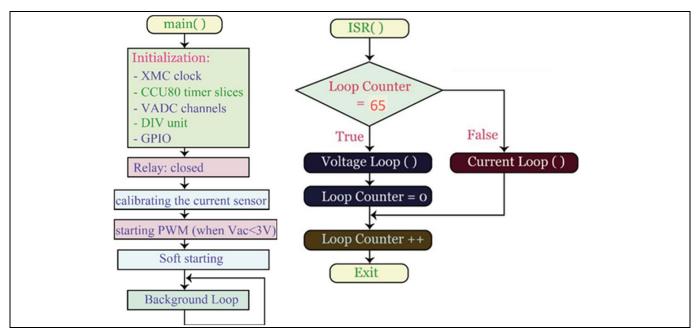

Figure 15 Control architecture of the bridgeless totem-pole PFC

Figure 16 depicts the digital implementation of the above architecture on the XMC1404 microcontroller. In the beginning, the MCU peripherals are initialized. The next step is to limit the inrush current during the charging of the DC bus capacitor. The relay is kept open for 300 ms to allow the inrush current to pass through an NTC and stay under the maximum limit. The relays are closed following this to bypass the NTC and eliminate the conduction loss during steady-state operation. The current sensor is then calibrated before the PWMs are enabled for a soft start to charge the DC bus capacitors to the final regulated voltage value. Both the voltage and current loops are implemented in one interrupt service routine (ISR).

#### **Control and firmware**

Figure 16 Main control loop and interrupt service routine implemented in XMC1404

#### 4.1.1 Current control loop

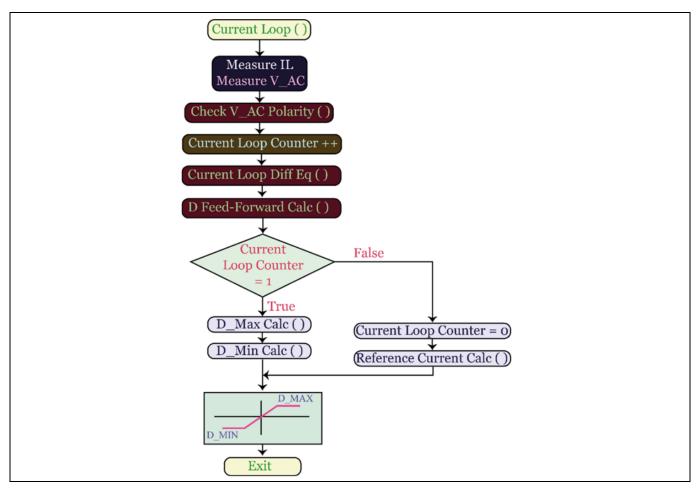

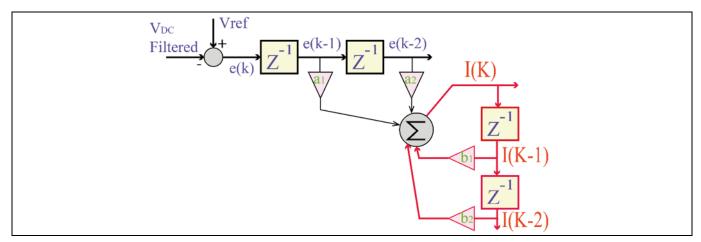

The current and voltage measurements are captured once the current loop starts. The RMS value of the AC voltage is obtained by processing the measured AC voltage through an RMS filter. This value is used to determine the feed-forward duty cycle to counteract abrupt changes in AC voltage, thereby improving line regulation. The current loop difference equation is used to calculate the closed loop duty cycle and the feed-forward duty cycle, as shown in Figure 17. The voltage loop also uses the measured and filtered DC voltage to implement the voltage difference equation. The maximum and minimum duty cycle values are determined in this loop based on the instantaneous AC voltage and the allowed maximum and minimum DC voltages. This limits the peak overshoot and undershoot values of the voltage during load transients.

**Control and firmware**

Figure 17 Current control loop in XMC1404

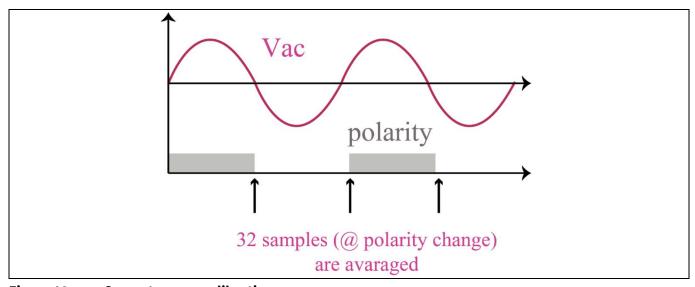

The controller also performs a zero calibration of the current sensing and measuring chain to cancel out any offset in the sensor, amplifier, and ADC signal chain. This is done by measuring 32 successive current samples during the zero crossing of 16 input voltage cycles. These values are averaged and used as a zero-current reference, as shown in Figure 18.

Figure 18 Current sensor calibration

#### **Control and firmware**

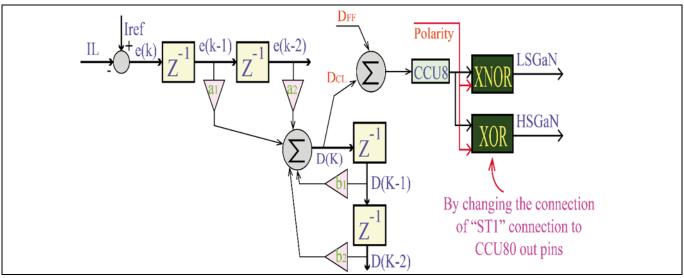

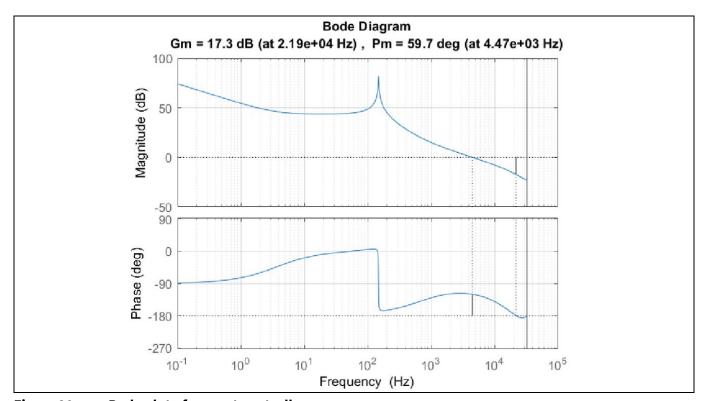

Figure 19 shows the digital implementation of the current controller. The final duty cycle is fed to the PWM timer CCU8. The main boost switch and the synchronous rectifier switch are determined based on the AC voltage polarity. Figure 20 shows the frequency response characteristics of the current controller. It has a gain crossover frequency of 4.5 kHz, and the phase margin is greater than 50°.

Figure 19 Digital implementation of current control and compensation

Figure 20 Bode plot of current controller

**Control and firmware**

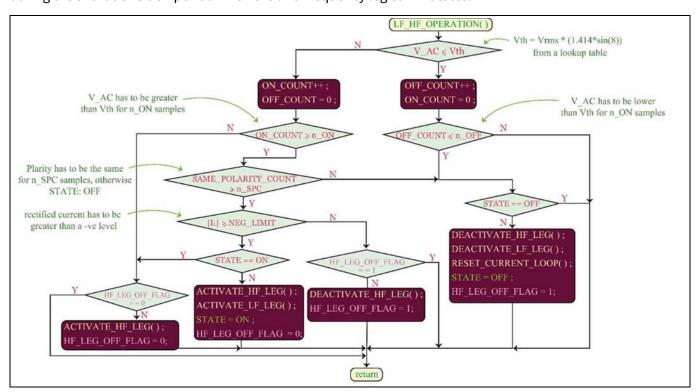

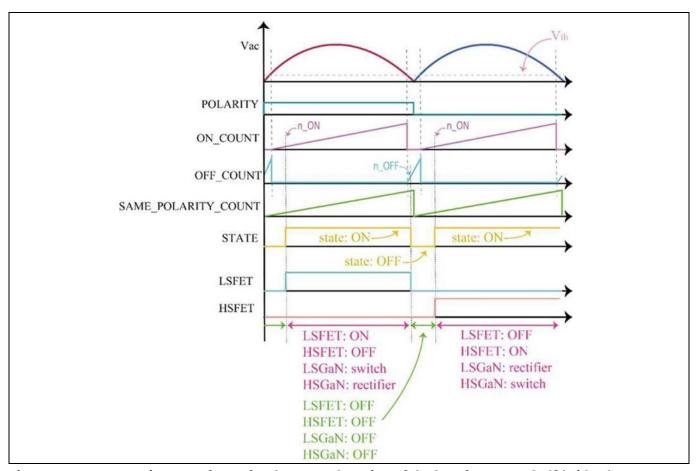

### 4.1.2 Control of the low-frequency half-bridge leg

The line frequency half-bridge switches change state during every zero crossing of the AC cycle. This is determined by measuring the AC voltage and comparing it with a threshold set near zero. A timing hysteresis is utilized to ensure smooth and accurate switching without any jitters. The high-frequency leg is also disabled during the short transition period when the line-frequency leg commutates.

Figure 21 State-diagram for the control of the low-frequency half-bridge leg

Figure 22 shows the operating waveforms of the line frequency half-bridge leg.

# 2.7 kW Titanium server digital power supply with CoolSiC<sup>™</sup> 650 V and XMC<sup>™</sup> MCUs

#### **Control and firmware**

Figure 22 Operating waveforms for the control section of the low-frequency half-bridge leg

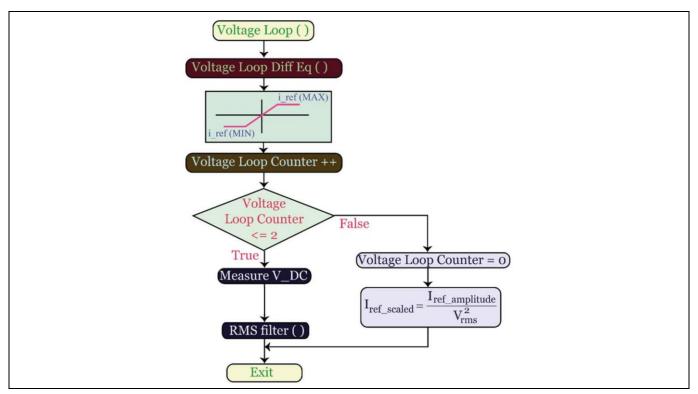

### 4.1.3 Voltage control loop

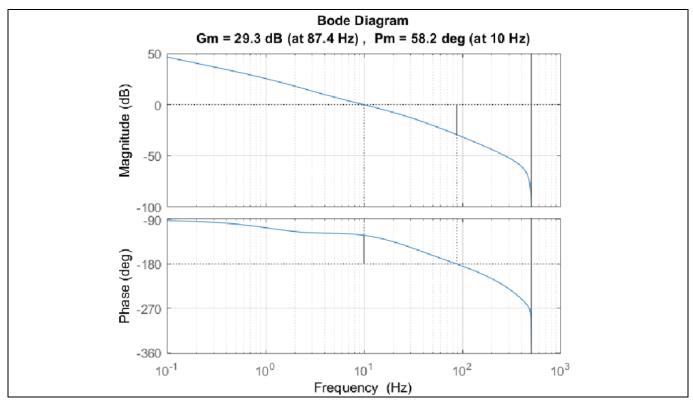

The flow of the outer voltage control loop is shown in Figure 23, and the digital implementation is shown in Figure 24. It has a gain crossover frequency of 10 Hz in order to not react to the line frequency component of the output voltage. It has a phase margin greater than 50°, as shown in Figure 25.

**Control and firmware**

Figure 23 Voltage control loop in XMC1404

Figure 24 Digital implementation of voltage control and compensation

**Control and firmware**

Figure 25 Bode plot of voltage controller

#### 4.2 LLC control

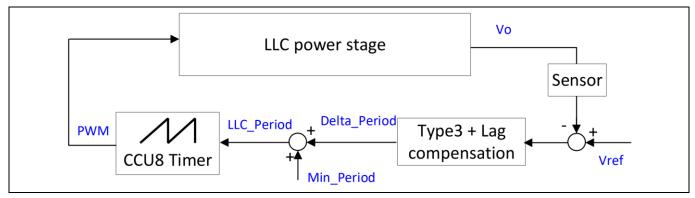

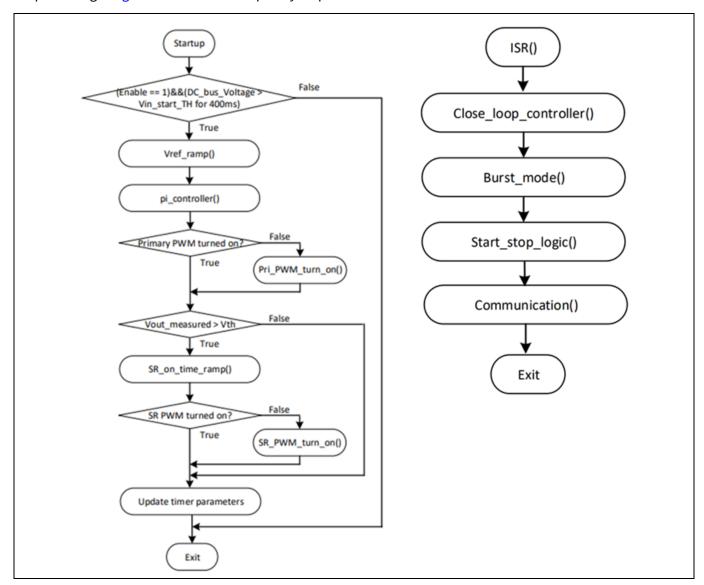

Figure 26 shows the structure of the LLC controller. The goal of this controller is to regulate the output voltage to the setpoint under all line and load conditions during steady-state and transient operations. This is achieved by first sensing the output voltage and comparing it to the setpoint. The resulting error is then passed on to type 3 and the lag compensator. The compensator outputs a delta period, which is appended to the minimum period, resulting in the final LLC period. This period is fed to the CCU8 timer of the XMC4200 microcontroller, which generates the PWM signals for the LLC power stage.

Figure 26 Control architecture of LLC converter

Figure 27 shows the digital implementation or flow of the controller. At startup, the DC bus voltage is checked to ensure that it is greater than the turn-on threshold. Once confirmed, the reference voltage is ramped up from 0 to 12 V. A slow PI controller is used during startup. At the beginning, the PI controller is saturated, and the initial switching frequency is limited to the maximum frequency. Then the switching frequency starts decreasing as Vref increases. Only primary PWM is turned on during the Vref ramp. When the measured output

#### **Control and firmware**

voltage rises close to a threshold (for example, 11.6 V), a soft start of SR PWM happens. SR on time gradually ramps from zero to the maximum value, which is half the resonance period when below resonance or half the switching period when above resonance with some delays.

This LLC controller is executed in an interrupt service routine running at a rate of 30 kHz. Other functions are also included in this ISR, such as burst mode, decisions on starting or stopping operations, and communication.

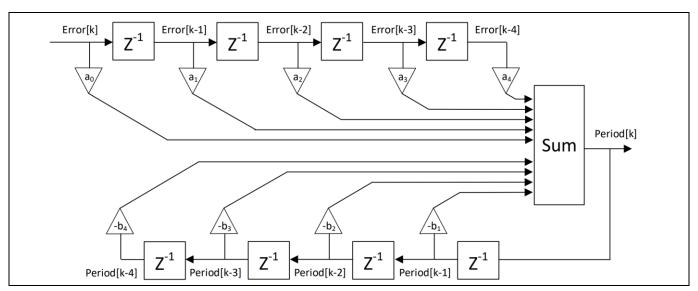

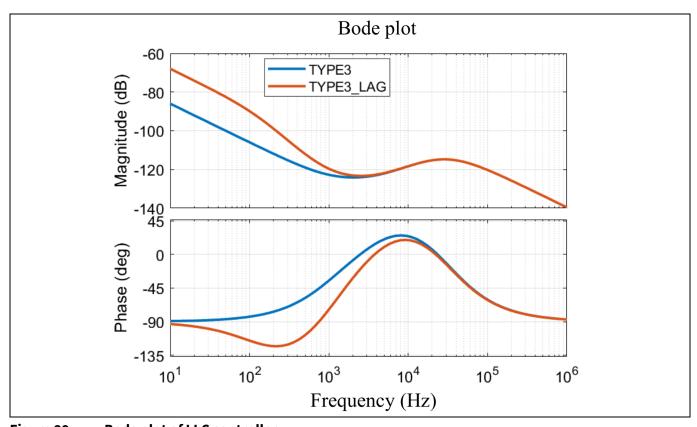

Figure 28 shows the digital implementation of the Type 3 + lag compensation controller. The additional lag compensation is to reduce the double-line frequency ripple component, which comes from the PFC, in the output voltage. Figure 29 shows the frequency response of the LLC controller.

Figure 27 Main control loop and the interrupt service routine (ISR)+

#### **Control and firmware**

Figure 28 Digital implementation of type 3 + lag compensation

Figure 29 Bode plot of LLC controller

**Control and firmware**

### **4.3** Protection features

The PFC and LLC circuit blocks are protected against failures due to electrical and thermal overstress. Critical signals are sensed through instrumentation and input to the ADC channels of the two microcontrollers. A failure is detected when the ADC output exceeds the set threshold. The protection features, thresholds, and responses are listed in Table 5.

**Table 5** Protection features

| Protection          | Protection threshold |  |

|---------------------|----------------------|--|

| PFC protections     |                      |  |

| AC overvoltage      | 275 V <sub>rms</sub> |  |

| AC overcurrent      | 32 A <sub>pk</sub>   |  |

| Output overvoltage  | 435 V                |  |

| LLC protections     |                      |  |

| Input undervoltage  | 300 V                |  |

| Primary overcurrent | 40 A <sub>pk</sub>   |  |

| Overtemperature     | ~120°C               |  |

| Output overvoltage  | 15 V                 |  |

**Test results**

### 5 Test results

The PSU was tested extensively to validate the electrical performance over steady-state and transient operating conditions as defined in the requirement specifications.

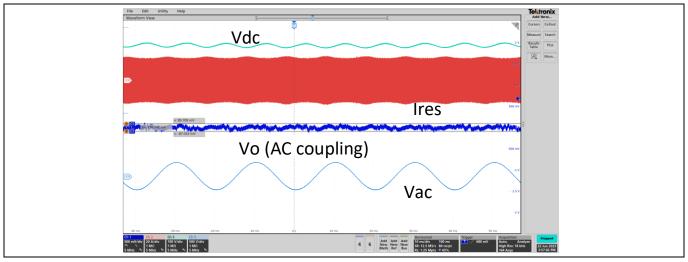

Figure 30 shows the PSU operation at steady-state output. The AC-coupled output voltage waveform shows a ripple of 176 mV<sub>pp</sub>, which is below the maximum allowed limit. This validates a stable hardware and control loop design to achieve regulated output voltage with low ripple.

Figure 30 Steady state output voltage ripple (test condition: Vac = 230 V, f = 50 Hz, full load)

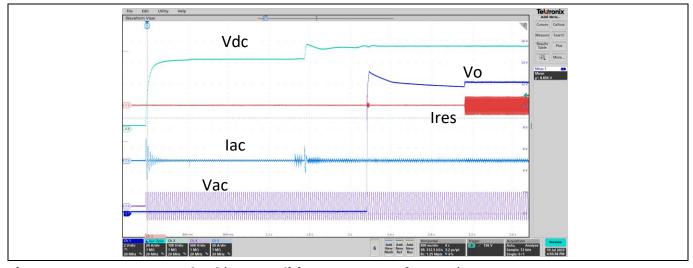

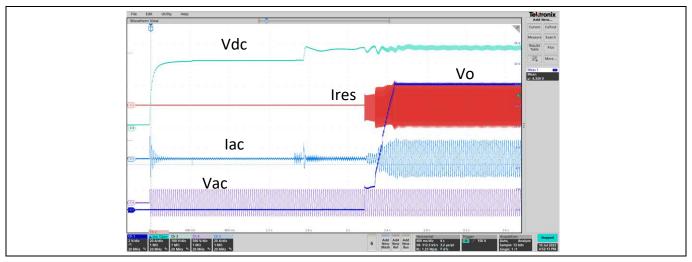

Figure 31 shows the startup performance under no load conditions. As seen, the converter starts up with a minimum overshoot at the output, which settles and regulates in a short amount of time. There is a short period of PWM shutdown caused by burst operation due to the no-load condition. Figure 32 shows the same operation at full load conditions with excellent control of the output voltage without any operation abnormalities. These waveforms show the performance of the digital controller for the two stages, implemented with the XMC™ microcontrollers, providing stable control during transient operation.

Figure 31 Startup at no load (test condition: Vac = 230 V, f = 50 Hz)

**Test results**

Figure 32 Startup at full load (test condition: Vac = 230 V, f = 50 Hz)

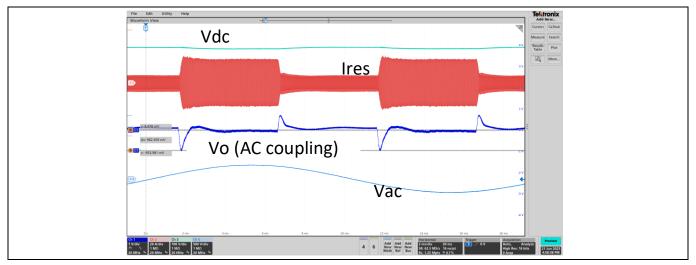

Continuing with transient operation, Figure 33 shows the testing of the PSU during load steps from 5% to 105%, during which the output voltage overshoots and undershoots must be limited below 1.3 V. As seen in the waveform, the output voltage overshoot and undershoot are below 1 V, which meets the regulatory requirements under this operating condition.

Figure 33 Transient operation (test condition: Vac = 230 V, f = 50 Hz, 5% load to 105% load, 2.5 A/us slew rate)

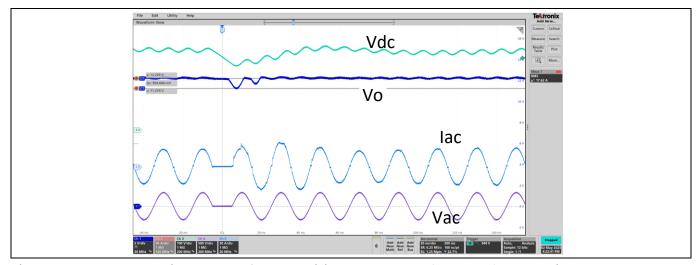

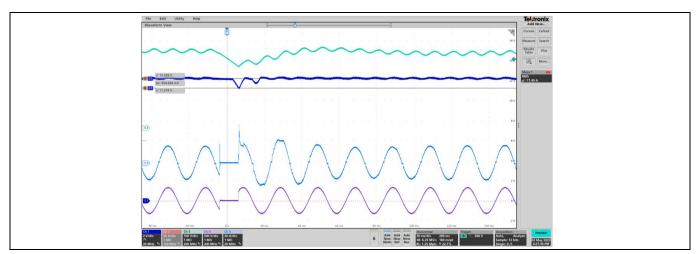

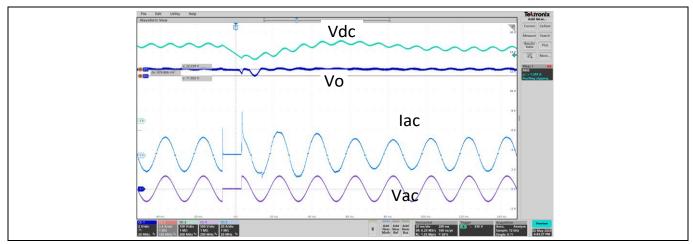

In server applications, the operation of the PSU under abnormal line conditions is critical in maintaining regulated power for the downstream loads. One of the requirements is to provide output voltage and power within the specified limits during AC line drop-out conditions. The regulations state that the PSU must continue to provide regulated output for the duration of the AC line dropout of at least 10 ms. Figure 34, Figure 35, and Figure 36 show the PSU output voltage performance during AC line drop-out conditions at 0-, 45-, and 90-degree angles of the AC voltage. The output voltage undershoot and overshoot are well controlled during this operation.

**Test results**

Figure 34 10 ms AC line dropout (test condition: Vac = 230 V, f = 50 Hz, full load, line dropout at 0 degree angle)

Figure 35 10 ms AC line dropout at 100% load (test condition: Vac = 230 V, f = 50 Hz, full load, line dropout at 45 degree angle)

Figure 36 10 ms AC line dropout at 100% load (test condition: Vac = 230 V, f = 50 Hz, full load, line dropout at 90 degree angle)

#### **Test results**

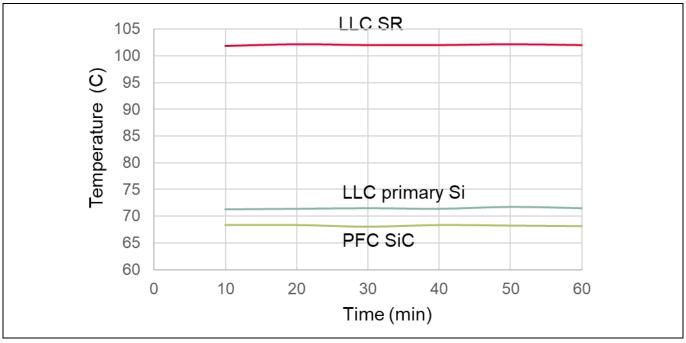

Figure 37 shows the thermal performance of critical components at full load. The temperatures are well below the absolute maximum limits of the components, demonstrating the high electrical efficiency and optimum thermal design of the PSU.

Figure 37 Thermal measurements within the enclosure (test condition: Vac = 230 V, f = 50 Hz, full load)

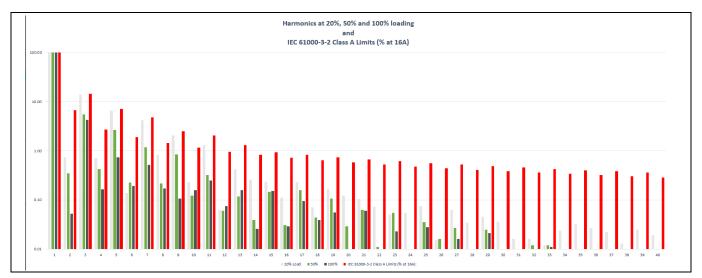

To qualify as an 80 PLUS Titanium server PSU, the design must exceed the efficiency requirements at specified load points, as shown in Table 3. Figure 38 shows that this design meets and exceeds the efficiency requirements. Figure 39 shows that the PSU harmonic emissions are below the IEC 61000-3-2 requirements for maximum harmonics injected back into the AC line.

Figure 38 Converter efficiency at 230 V AC input

Test results

Figure 39 Harmonics measurement of the converter compared to IEC 61000-3-2 limit

Summary

### 6 Summary

This application note introduces a 2.7 kW enterprise server PSU implemented with Infineon's industry-leading products. It achieves a peak efficiency of 96.11% and a low harmonic content to meet the stringent requirements. Excellent electrical and thermal performances are achieved by using best-in-class CoolSiC™ and CoolMOS™ MOSFETs in the PFC and LLC blocks. The high power factor and excellent power quality of the totem-pole PFC are achieved through digital control using XMC1404. The LLC achieves tight regulation and excellent transient load performance using the XMC4200 for digital control.

Test results show compliance with target specifications and regulations to meet the 80 PLUS Titanium standards.

# 2.7 kW Titanium server digital power supply with CoolSiC<sup>™</sup> 650 V and XMC<sup>™</sup> MCUs

Schematics

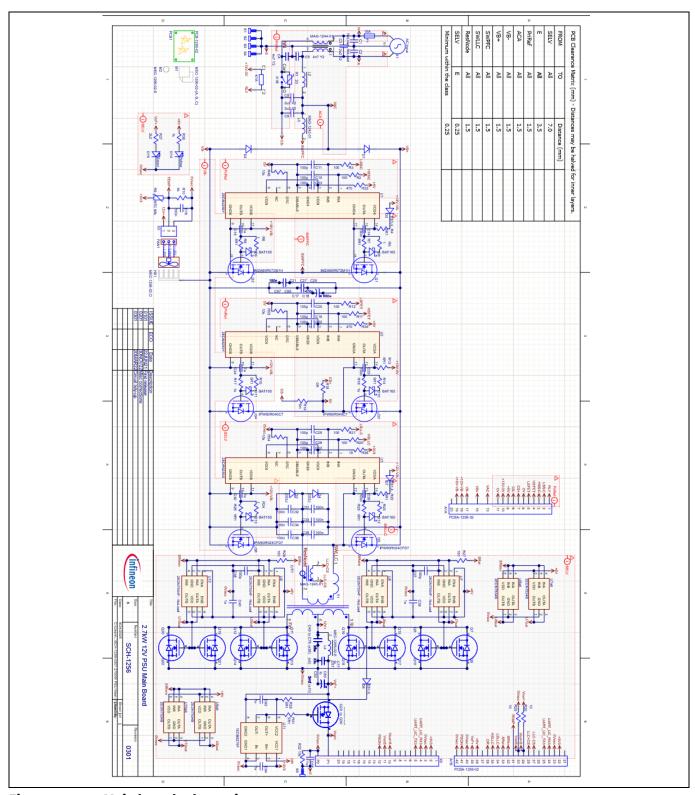

### **7** Schematics

### 7.1 Main board schematic

Figure 40 Main board schematic

V 2.1

# 2.7 kW Titanium server digital power supply with CoolSiC<sup>™</sup> 650 V and XMC<sup>™</sup> MCUs

**Schematics**

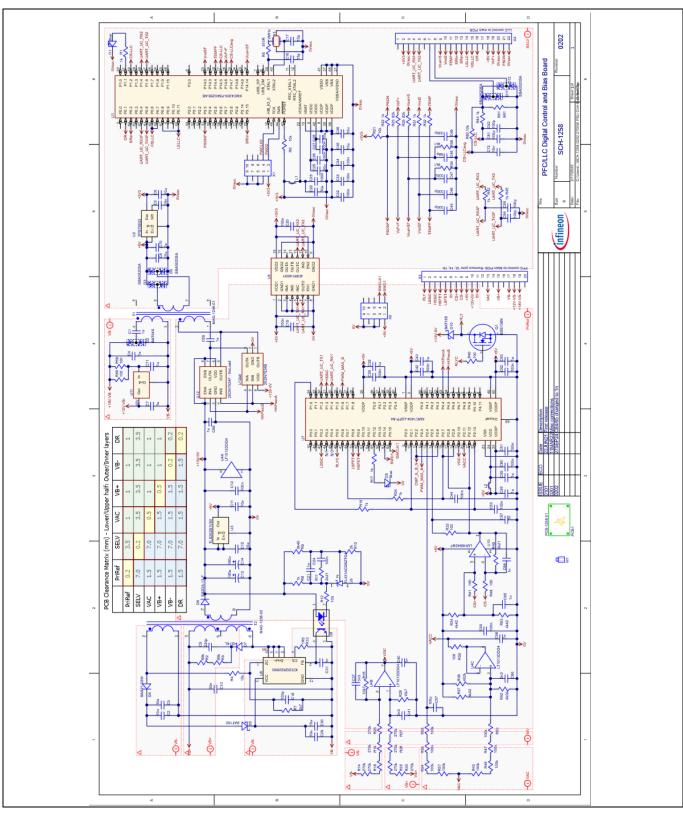

### 7.2 Controller board schematic

Figure 41 Controller board schematic

References

### References

- [1] Virginia Polytechnic Institute and State University: *Investigation on Interleaved Boost Converters and Applications*; Available online

- [2] Infineon Technologies AG: CoolSiC™ totem-pole PFC design guide and power loss modeling; Available online

- [3] Infineon Technologies AG: Resonant LLC Converter: Operation and Design 250W 33Vin 400Vout Design Example; Available online

- [4] Infineon Technologies AG: 3300 W 52 V LLC with 600 V CoolMOS™ CFD7 and XMC™; Available online

- [5] Infineon Technologies AG: Optimum MOSFET Selection for Synchronous Rectification; Available online

# 2.7 kW Titanium server digital power supply with CoolSiC<sup>™</sup> 650 V and XMC<sup>™</sup> MCUs

**Revision history**

### **Revision history**

| Document revision | Date       | Description of changes                                                                                                                                  |

|-------------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| V 1.0             | 2023-11-02 | Initial release                                                                                                                                         |

| V 2.0             | 2025-04-09 | Updated CoolSiC <sup>™</sup> devices to G2 counterparts and CoolMOS <sup>™</sup> devices to CM8 counterparts. Updated calculations and impacted results |

| V 2.1             | 2025-07-21 | Updated magnetics winding diagram. Updated calculation and impacted results                                                                             |

#### **Trademarks**

All referenced product or service names and trademarks are the property of their respective owners.

Edition 2025-07-21 Published by

Infineon Technologies AG 81726 Munich, Germany

© 2025 Infineon Technologies AG. All Rights Reserved.

Do you have a question about this document?

Email: erratum@infineon.com

Document reference AN190407

#### Important notice

The information contained in this application note is given as a hint for the implementation of the product only and shall in no event be regarded as a description or warranty of a certain functionality, condition or quality of the product. Before implementation of the product, the recipient of this application note must verify any function and other technical information given herein in the real application. Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind (including without limitation warranties of non-infringement of intellectual property rights of any third party) with respect to any and all information given in this application note.

The data contained in this document is exclusively intended for technically trained staff. It is the responsibility of customer's technical departments to evaluate the suitability of the product for the intended application and the completeness of the product information given in this document with respect to such application.

#### Narnings

Due to technical requirements products may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies office.

Except as otherwise explicitly approved by Infineon Technologies in a written document signed by authorized representatives of Infineon Technologies, Infineon Technologies' products may not be used in any applications where a failure of the product or any consequences of the use thereof can reasonably be expected to result in personal injury.