# アプリケーション・ノート：AN-1123

## ブートストラップ・ネットワーク分析： 内蔵ブートストラップ機能に焦点を当てる

著 **Andrea Merello**

### 目次

|                                                   | ページ |

|---------------------------------------------------|-----|

| 1. はじめに .....                                     | 2   |

| 2. ブートストラップ・トポロジに関する理論的な考察 .....                  | 3   |

| 2.1 ブートストラップ抵抗の寄与 .....                           | 4   |

| 2.2 ブートストラップ・コンデンサの寄与 .....                       | 4   |

| 3. 内蔵ブートストラップ FET を使用する<br>ブートストラップ回路のサイジング ..... | 9   |

| 4. 負荷電流なしでのテスト・ベンチ測定 .....                        | 12  |

| 5. 負荷を変化させてブートストラップ回路を考察する .....                  | 16  |

| 6. 内蔵ブートストラップの制限 .....                            | 19  |

| 7. 結論 .....                                       | 20  |

本書の目的は、ゲート・ドライバ IC で、内蔵ブートストラップ機能を使用する場合のトポロジに焦点を当てながら、ブートストラップのサイジングの理論と実際について理解を深めることにあります。

© インターナショナル・レクティファイアー・ジャパン

この文献の無断複製・転載を禁じます。

## 1. はじめに

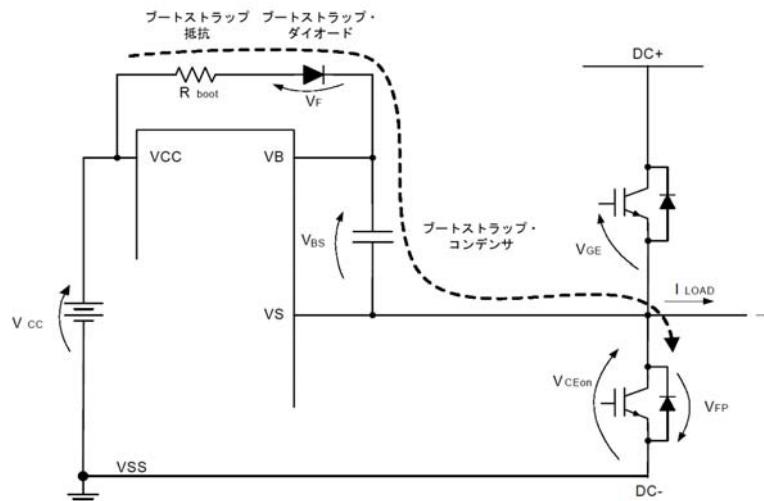

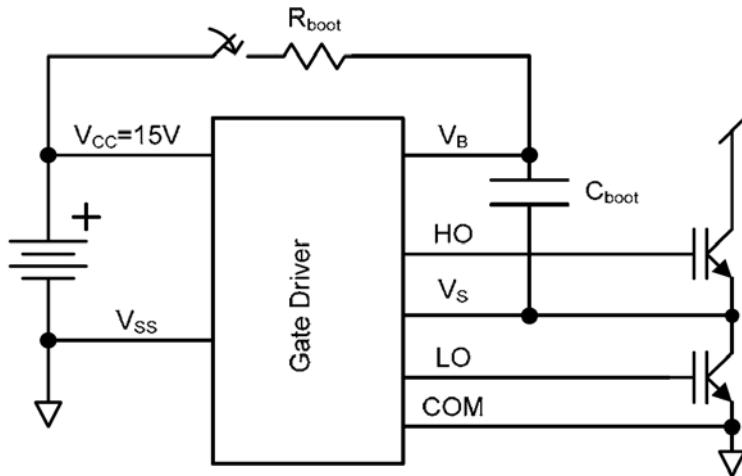

ゲート・ドライバICのハイサイドのドライブ回路に電源を供給するために幅広く使用される方法の1つに、ブートストラップ電源があります。ブートストラップ電源は、ブートストラップ・ダイオードとブートストラップ・コンデンサで構成されます。この回路を、図1に示します。

図1. ブーストストラップ電源

この電源供給方法には、シンプルで低成本という利点があります。ただし、ブートストラップ・コンデンサを充電する必要があるため、電力変換器のデューティ・サイクルと電源スイッチのオンタイムが制限される可能性があります。これらの制限は、適切なコンデンサとブートストラップ抵抗を選択することで、大幅に緩和することができます。

ブートストラップ・コンデンサ ( $V_{BS}$ ) が達成可能な最大電圧は、図 1 に示すブートストラップ回路の素子に依存します。 $R_{BOOT}$  の電圧降下、ブートストラップ・ダイオードの  $V_F$ 、ローサイドのスイッチ（スイッチを流れる電流の方向によって  $V_{CEOON}$  または  $V_{FP}$ ）の電圧降下、および存在すれば、ローサイドのスイッチのエミッタと DC レールの間に配置されたシャント抵抗（図 1 には示されていない）の電圧降下のすべてを考慮に入れる必要があります。

本書の目的は、ゲート・ドライバ IC で、内蔵ブートストラップ・ダイオードを使用する場合のトポロジに焦点を当てながら、ブートストラップのサイジングの理論と実際について理解を深めることにあります。<sup>1</sup>

<sup>1</sup> 本書では内蔵ブートストラップ・ダイオードを、抵抗と理想的なスイッチが直列に接続された簡単な方法で示します。また、ブートストラップ・ダイオードは、「ブートストラップFET」とも呼ばれ、シリコン設計における実際の物理実装を示す場合に使用されます。

## 2. ブートストラップ・トポロジに関する理論的な考察

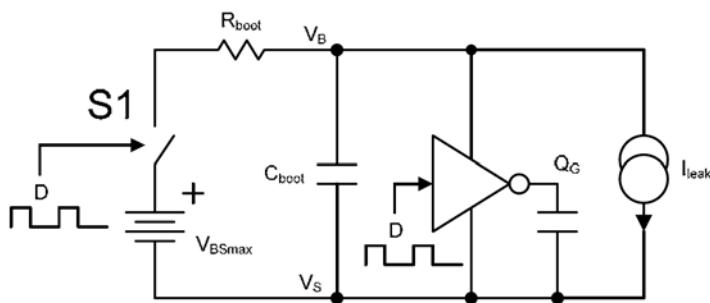

ハーフ・ブリッジのトポロジで使用されるブートストラップ回路のサイジングについて詳細に検討する前に、いくつかの予備的考察を理解しておく必要があります。以下の簡略化した回路図が予備的考察の理解を深めるのに役立ちます（図2を参照）。

ブートストラップ回路（図2を参照）のこの表現によって、S1スイッチ状態の関数あるいはそのデューティ・サイクル（ $D = \text{デューティ・サイクル} = T_{\text{ON}}/T \equiv 1 - D^*$ <sup>2</sup>）の関数としての  $V_{\text{BS}}$  動作の計算や、ゲート充電、漏れ電流、ブートストラップ抵抗、ブートストラップ・コンデンサの計算が簡単になります。

図 2. 簡略化したブートストラップ回路図

一般に  $V_{\text{BSMAX}}$  は、供給電圧（図1の  $V_{\text{CC}}$ ）にブートストラップ回路の静的降下を加算または減算した値を表します。

引き続いて行う考察では、スイッチS1のデューティ・サイクルが定常状態に達し、その後も一定に保たれていることを前提にします。つまり、式が示すのは、時間が経過してもデューティ・サイクルが一定であるという条件のもとでの有効な結果です。

その後、システムのAC応答を処理する（つまり、デューティ・サイクルが時間の経過とともに変化する）場合について、いくつか重要な考察を行います。

### 「静的な」式：1 サイクルの PWM における $V_{\text{BS}}$ 動作：

ブートストラップ・コンデンサ ( $C_{\text{BOOT}}$ ) によって発生する電圧 ( $V_{\text{BS}}$ ) は一般に、（図 2 に基づく）2つの寄与要因によって示されます。1つ目は、理想的なスイッチ (S1) がオン ( $T_{\text{ON}}$ ) のときにブートストラップ抵抗で発生する電圧降下によって示されます。2つ目は、システムのスイッチングにより印加されるリップルの特性です。ACリップルの振幅は主に、ブートストラップ・コンデンサのサイジングによって確定され、その計算はS1がオフ ( $T_{\text{OFF}}$ ) のときに行われます。この後の考察では、 $V_{\text{BSMAX}}$  は、最大取得可能な  $V_{\text{BS}}$  の値として定義します。図2では、これは  $V_{\text{BSMAX}}$  ジェネレータで表されます。

<sup>2</sup>  $T_{\text{ON}}$  は、ローサイドの IGBT のゲート信号がアクティブである期間を表すスイッチのオンタイムです。

## 2.1 ブートストラップ抵抗の寄与

スイッチング期間 ( $T_S$ ) に供給電圧 ( $V_{BSMAX}$ ) から回路に供給する必要がある総電荷量は、式 1 で示されます。

$$Q_{TOT}^* = Q_G^* + I_{leak} \cdot T_S \quad (\text{式1})$$

変数  $Q_G$  は、パワー・デバイスのゲートとゲート・ドライバのレベル・シフターが必要とする総電荷量として定義されます。また  $I_{LEAK}$  は、ゲート・ドライバのハイサイドの回路に供給する必要がある DC 電流を元に算出します。

$S_1$  が PWM 波形によって駆動されること、さらにブートストラップ抵抗を通して電荷が供給されるのは  $T_{ON}$  のときのみであることを考慮に入れると、ブートストラップ抵抗を流れる平均電流は、式 2 で計算した値になります。

$$\bar{I} = \frac{Q_G^* + I_{leak} \cdot T_S}{T_{ON}} = \frac{Q_G^* \cdot f + I_{leak}}{D} \quad (\text{式2})$$

$$(f = \frac{1}{T_S}; D = \frac{T_{ON}}{T_S})$$

$R_{BOOT}$  の平均電圧降下は、式3で定義されます。

$$V_{Rboot} = \frac{Q_G^* \cdot f + I_{leak}}{D} \cdot R_{boot} \quad (\text{式3})$$

## 2.2 ブートストラップ・コンデンサの寄与

ブートストラップ・コンデンサからハイサイドの回路に供給される総電荷量は、式 4 で計算できます。

$$Q_{TOT} = Q_G^* + I_{leak} \cdot T_{off} = Q_G^* + I_{leak} \cdot (1 - D) \cdot T_S \quad (\text{式4})$$

$V_{BS}$  のリップル振幅は、式 5 を利用して求めることができます。

$$\Delta V_{BS} = \frac{Q_{TOT}}{C_{boot}} \quad (\text{式5})$$

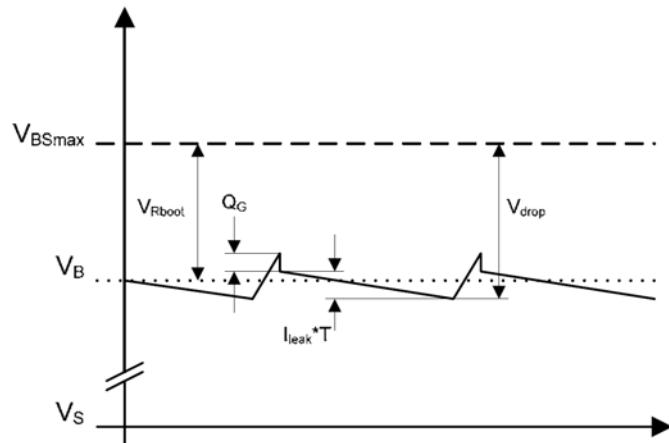

$V_{BS}$  の形状は、図 3 では時間の関数として表されます。ここでは、さまざまな寄与因子が識別されています。式 6 で与えられる  $V_{drop}$  の計算（図 3 を参照）。

$$V_{drop} = V_{Rboot} + \Delta V_{BS}/2^3 \text{ (式6)}$$

上の式が有効である条件は、 $V_{Rboot}$  が  $\Delta V_{BS}/2$  よりも大きくなるために、デューティ・サイクルが十分低い場合のみです。この条件が発生するのは、ブートストラップ・コンデンサを完全に充電するための再充電時間を十分確保できる場合です（この計算では、4 つの時定数の  $\Delta t$  の後に、コンデンサが完全に充電されることを前提にします）。式 7 は、デューティ・サイクルの境界条件を示します。

$$D < \frac{4 \cdot R_{boot} \cdot C_{boot}}{T_s} \text{ (式7)}$$

図 3.  $V_{BS}$  波形

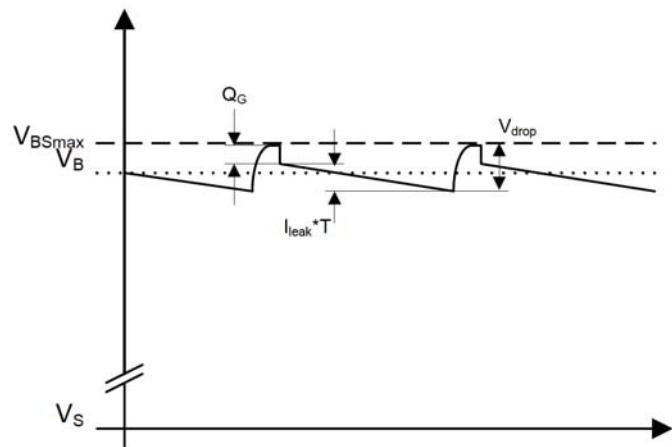

$D > \frac{4 \cdot R_{boot} \cdot C_{boot}}{T_s}$  の場合は常に、式 6 は無効になり、 $V_{drop}$  は、図 4 に示すように、 $\Delta V_{BS}$  と等しくなります。

$$V_{drop} = \Delta V_{BS} \text{ (式8)}$$

考慮する必要がある重要な事項は、 $V_{BS}$  リップルがブートストラップ・コンデンサにのみ依存するのに対し、最大到達  $V_{BS}$  ( $V_{BSMAX}$ ) からの平均電圧降下 ( $V_{drop}$ ) は、ブートストラップ抵抗にのみ依存することです。

<sup>3</sup>  $V_{drop}$  は、ブートストラップ回路のすべての素子（ここでは説明を省略）を考慮に入れた場合に到達可能な最大値 ( $V_{BSMAX}$ ) からの  $V_{BS}$  の降下を表します。これらの素子については、後で詳しく解説します。

図 4.  $D \gg \frac{4 \cdot R_{boot} \cdot C_{boot}}{T_S}$  の場合の  $V_{drop}$

( $\Delta V_{BS}$  を無視するために) かなり大容量のブートストラップ・コンデンサを使用する場合でも、 $V_{Rboot}$  降下が大きくなることがあるので注意する必要があります。 $V_{BS}$  降下に対するこの寄与によって、与えられたブートストラップ抵抗の最小許容デューティ・サイクルに、制限が固定されます。式 9 は、 $\Delta V_{BS}$  寄与を無視したときの  $D_{MIN}$  を示し、さらに、 $V_{drop}$  が、供給からの最大許容降下を示します。

$$D_{MIN} = \frac{Q_G^* \cdot f + I_{leak} \cdot R_{boot}}{V_{drop}} \quad (\text{式9})$$

例 :

$Q_G^* = 40\text{nC}$ 、 $f = 20\text{kHz}$ 、 $I_{leak} = 200\mu\text{A}$ 、 $R_{boot} = 220\Omega$ 、 $V_{drop} = 2\text{V}$  ( $V_{BS} = V_{CC} - V_{drop} = 13\text{V}$ )。最小許容デューティ・サイクルは 11% です。

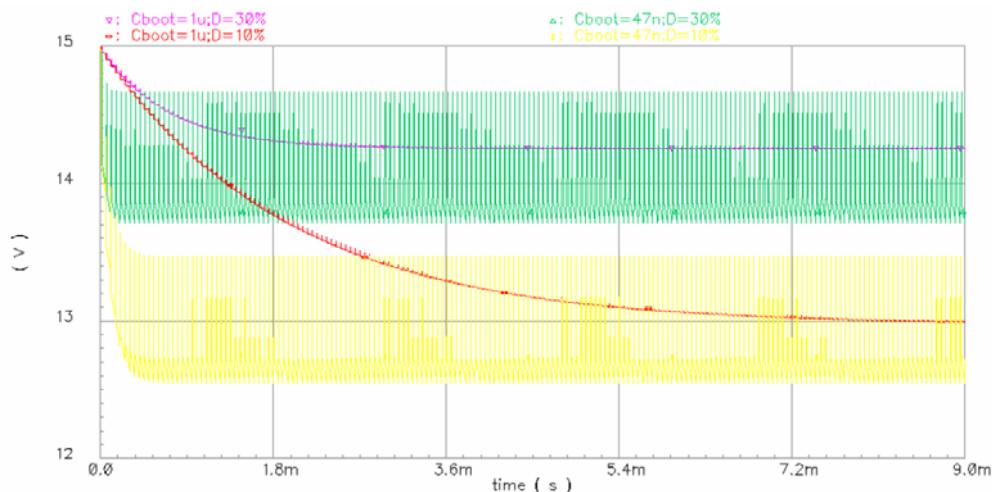

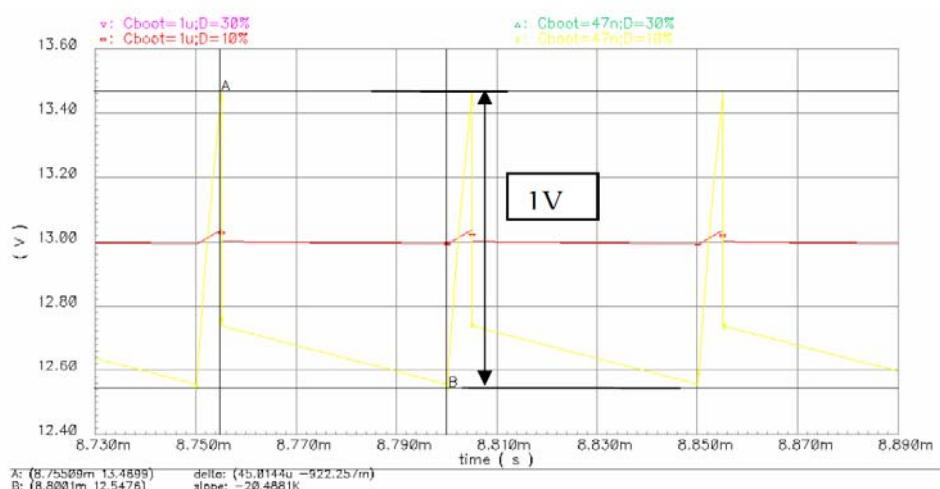

以下のパラメータを使用してシミュレーションを実行し、結果を図 5 と図 6 に示してあります。このシミュレーションでは、 $R_{boot} = 220\Omega$ 、 $Q_G = 40\text{nC}$ 、 $I_{leak} = 200\mu\text{A}$ 、 $f = 1/T_S = 20\text{kHz}$ 、 $D_{MIN}$  デューティ・サイクルは  $D = 10\%$  か  $D = 30\%$  のいずれか、 $C_{boot} = 47\text{nF}$  または  $1\mu\text{F}$  (あらかじめ  $V_{BSmax} = 15\text{V}$  に充電しておく)。

以下に、 $C_{boot}$  が  $47\text{nF}$  に等しく、デューティ・サイクルが 10% の場合の計算例を示します。

$$D = 10\% << \frac{4 \cdot R_{boot} \cdot C_{boot}}{T_S} = \frac{4 \cdot 220\Omega \cdot 1\mu\text{F}}{50\mu\text{s}} = 82.7\%$$

その結果、

$$V_{drop} = V_{Rboot} + \Delta V_{BS} / 2$$

最悪の場合 ( $D = 10\%$ ) の予想される  $V_{Rboot}$  は以下のとおりです。

$$V_{Rboot} = \frac{40nC \cdot 20kHz + 200\mu A}{10\%} \cdot 220\Omega = 2.2V$$

予想されるリップル ( $C_{boot} = 47nF$ ) は以下のとおりです。

$$\Delta V_{BS} = \frac{40nC \cdot 200\mu A \cdot (1-10\%) \cdot 50\mu s}{47nF} = 1V$$

$$V_{drop} = V_{Rboot} + \Delta V_{BS} / 2 = 2.7V \Rightarrow V_{BS} = 12.3V$$

### 動的応答：

図 5 と図 6 にプロットされるシミュレーションは、 $47nF$  または  $1\mu F$  に等しい  $C_{boot}$  と  $10\%$  または  $30\%$  に等しいデューティ・サイクルで表示されます。緑色と黄色の曲線は、 $47nF$  ブートストラップ・コンデンサの  $V_{BS}$  を表します。紫色と赤色の曲線は、 $1\mu F$  ブートストラップ・コンデンサの  $V_{BS}$  を表します。

図 6 は、さまざまなブートストラップ・コンデンサの影響を示します。 $V_{BS}$  リップルのみが影響を受けます（平均値は実際には一定に保たれます）。

図 5 は、 $15V$  ( $D = 100\%$ ) にフル充電されたブートストラップ・コンデンサから開始するシステムのステップ応答を示します。特にこの図は、平均  $V_{BS}$  が、式 10 で算出した時定数の单極システムと同様の動作を行うことを示します。

$$\tau = \frac{R_{boot} \cdot C_{boot}}{D} \quad (\text{式10})$$

デューティ・サイクルとシステムのステップ応答とのこの関係によって、低デューティ・サイクルでは、時定数 ( $\tau$ ) が大きくなる（それによって、応答も遅くなる）ことが分かり、高デューティ・サイクルでは、応答が速くなることが分かります。

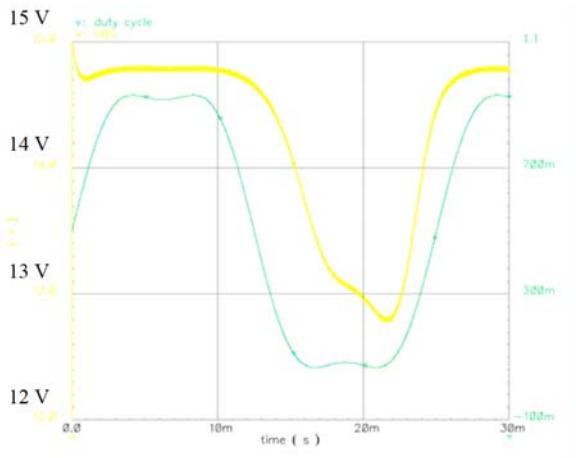

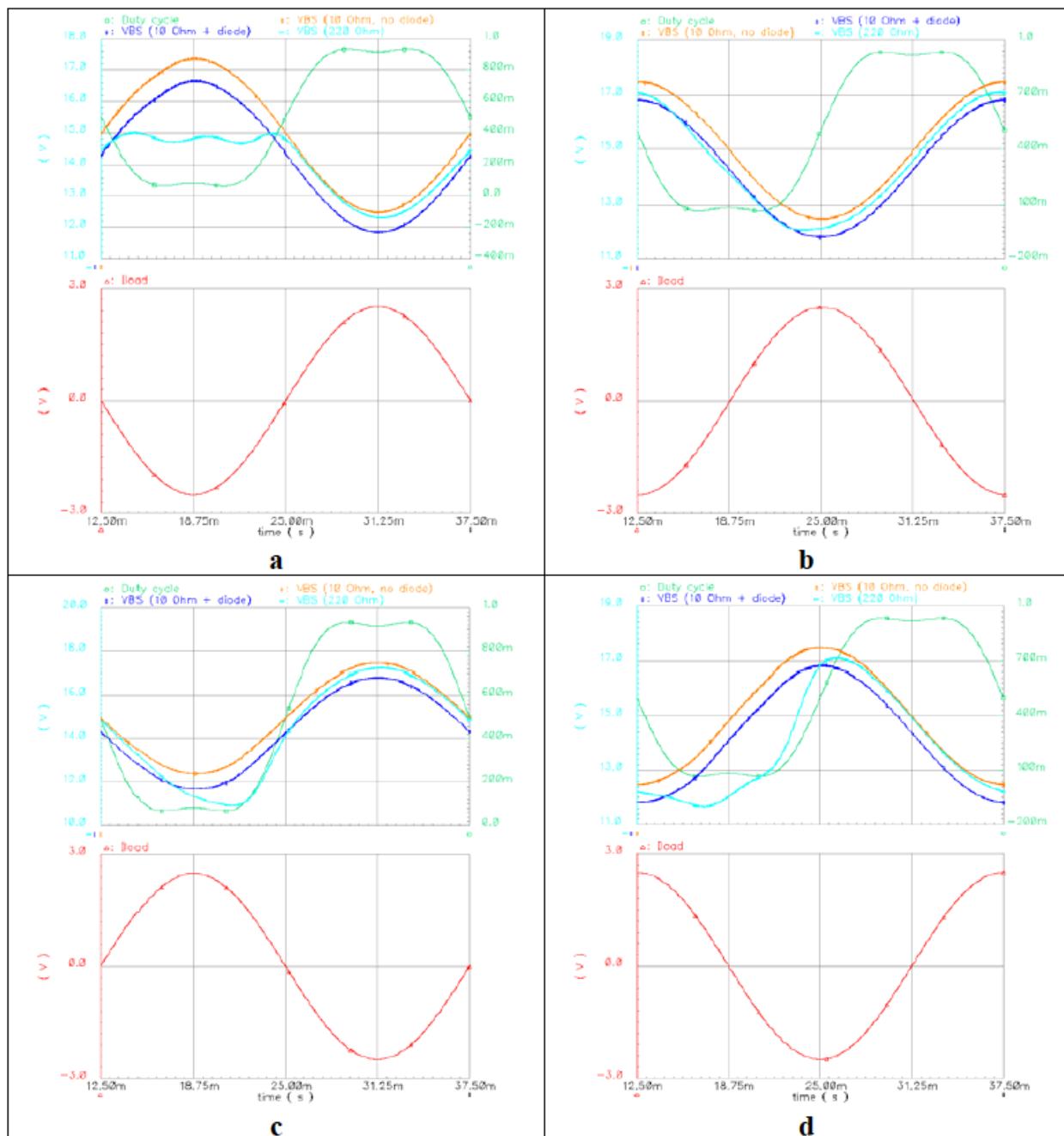

この動作は、デューティ・サイクルの変化に対する適応フィルタとして働きます。これはより詳細なシミュレーション（図 7 を参照）で確認できます。そのシミュレーションでは、デューティ・サイクルによって変調される正弦波（ $40Hz$  基本波と第三高調波）が回路に供給されます ( $T_s = 50\mu s$ 、電気周波数 =  $f_e$ ）。

図5では、パラメータは、 $R_{boot} = 220\Omega$ 、 $C_{boot} = 1\mu F$ 、および  $D = 10\%$  です。

$$\tau = \frac{220 \cdot 1\mu F}{0.1} = 2.2ms \rightarrow f_{\tau} = \frac{1}{2\pi\tau} = 72Hz$$

$R_{boot} = 220\Omega$ 、 $C_{boot} = 1\mu F$ 、および  $D = 10\%$  の組み合わせも示されています。

$$\tau = \frac{200 \cdot 1 \mu F}{0.3} = 733 \mu s \rightarrow f_{\tau} = \frac{1}{2\pi\tau} = 217 \text{Hz}$$

図 5. ブートストラップ回路のパラメトリック・シミュレーション：

S1 デューティ・サイクルとブートストラップ・コンデンサ

図 7. S1 デューティ・サイクル の 40Hz 正弦波と第三高調波の変調<sup>4</sup>

欠点として、低デューティ・サイクルでは、 $Q_{TOT} = Q_G^* + I_{leak} \cdot T_{off} = Q_G^* + I_{leak} \cdot (1 - D) \cdot T_S$  が増大します。この場合、大きい方のブートストラップ・コンデンサがリップルを制御し、平均時定数を増大します。

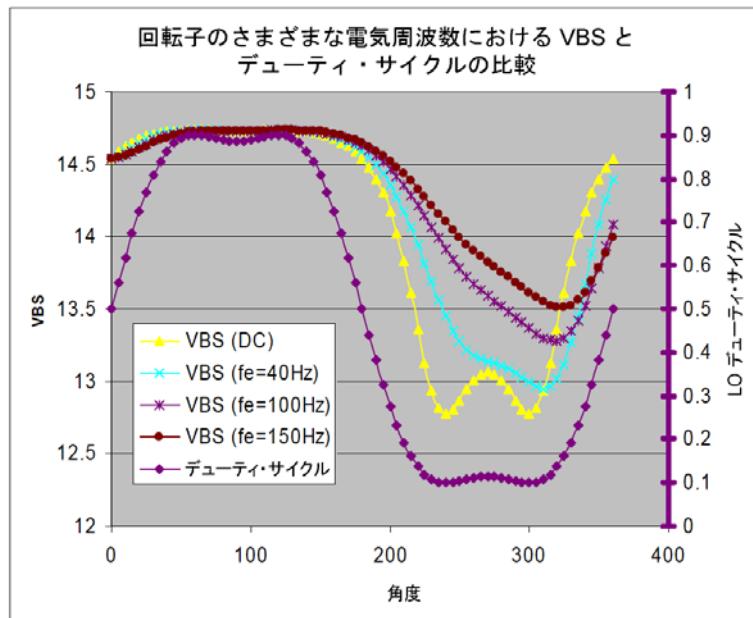

システムの動的応答には、特に興味深いものがあります。図 8 は、さまざまな電気周波数の予想される（算出された）VBS です。デューティ・サイクルは、0° から 360° まで変化する角度（ $2\pi f_e$  に等しい。ここで、 $f_e$  は回転子の電気周波数）の関数（正弦波 + 第三高調波）で表現されます。

同じプロットに、さまざまな  $f_e$  から得た VBS 電圧が表示されます。この図で注目すべきは、黄色の曲線の VBS (DC) が、前に述べた静的な式（式 3、5、6、8）から得た曲線を表していることです。青緑色の曲線は、図 7 のシミュレーションに示すように、 $f_e = 40\text{Hz}$  から得ています。

### 3. 内蔵ブートストラップ FET を使用するブートストラップ回路のサイジング

図 1 に示すように、ブートストラップ回路には、ブートストラップ抵抗とブートストラップ・コンデンサを選定するときに考慮に入れる必要があるコンポーネントがいくつか含まれています。内蔵ブートストラップ機能（内蔵ブートストラップ FET など）と組み合わせてゲート・ドライバを使用する場合は、外部ブートストラップ・ダイオードは（ほとんどのアプリケーションで）使用されず、回路解析時に通常考慮する  $V_F$  の代わりにブートストラップ FET の電圧降下を考慮に入れます。考慮に入れる必要がある他の素子には、電源スイッチ（IGBT など）、スイッチと並列に接続されるフリーホイール・ダイオード、DC レールで使用するシャント抵抗、ローサイドのスイッチと DC レールを直列に接続して使用するシャント抵抗があります。

<sup>4</sup> 前頁と同じデータ :  $R_{boot} = 220\Omega$ 、 $Q_G = 40\text{nC}$ 、 $I_{leak} = 200\mu\text{A}$ 、 $f = 1/T_S = 20\text{kHz}$

図 8. 回転子のさまざまな電気周波数において予想される  $V_{BS}$  降下

前述の手順に従って、 $V_{BSmax}$ （図 2 と図 5 を参照）を以下のように計算できます。

$$V_{BSmax} = V_{CC} - V_{CE} \quad (\text{式11: ブートストラップ FET})$$

または

$$V_{BSmax} = V_{CC} - V_F - V_{CE} \quad (\text{式12: ブートストラップ・ダイオード})$$

ここで、 $V_{CC}$  はローサイドの電源電圧、 $V_F$  はブートストラップ・ダイオードの順降下、 $V_{CE}$  は、IGBT での電圧降下（電流がパワー・デバイスを流れる場合）またはフリーホイール・ダイオードの順方向バイアスの電圧降下（この場合は、 $V_{BSMAX}$  が増大するマイナスの寄与）です。最悪の場合、サイジングでは、 $V_{CE}$  は、ローサイドの IGBT の  $V_{CEon}$  で表されます。

以下の設計例では、図 9 に示すシステムを考察します。ここで、ブートストラップ FET は、理想的なスイッチと抵抗で表されます。

ブートストラップ回路の定数選定するには、まず、ハイサイドの IGBT がオンのときの最小電圧降下 ( $V_{drop}$ ) を求めます。最小ゲート電圧を IGBT のゲート ( $V_{GEmin}$ ) に供給する必要があることを考慮に入れると、 $V_{drop}$  は、 $V_{BS}$  供給の最大可能電圧降下であり、以下の式で定義されます。

$$V_{drop} \leq V_{CC} - V_{GEmin} - V_{CEon} \quad (\text{式13})$$

図 9. 理想的なスイッチと  $R_{boot}$  で表されるブートストラップ FET

IR 社のゲート・ドライバは、ハイサイドのゲート駆動に低電圧ロックアウト (UVLO) 保護を装備し、ここで  $V_{BS}$  電圧を監視して、最小しきい値を確保します。すなわち、 $V_{BS}$  がこのしきい値を下回ると、UVLO 保護が関与して、ゲート・ドライバ IC を無効にします。したがって、最小  $V_{GE}$  は、ハイサイド電圧立下り不足電圧しきい値 ( $V_{BSUV-}$ ) よりも高くななければなりません。

$$V_{GEmin} > V_{BSUV}$$

ローサイドのスイッチがオフのときにブートストラップ・コンデンサ電圧 ( $V_{BS}$ ) の放電に寄与する以下の要因について考慮する必要があります。

- ターンオン時に IGBT が必要とするゲート電荷 ( $Q_G$ )

- IGBT のゲートとソース間の漏れ電流 ( $ILK_{GE}$ )

- フローティング部の静止電流 ( $IQBS$ )

- フローティング部の漏れ電流 ( $ILK$ )

- ブートストラップ・ダイオード逆バイアス漏れ ( $ILK_{DIODE}$ )

- 内部のレベル・シフターが必要とする電荷 ( $QLS$ )

- ブートストラップ・コンデンサ漏れ電流 ( $ILK_{CAP}$ )

- ハイサイドの最大オンタイム ( $(1-D_{MIN}) * Ts$ 。ここで、 $D_{MIN}$  は最小デューティ・サイクル)

$ILK_{CAP}$  は、電解コンデンサを使用する場合のみ関連し、他のタイプのコンデンサを使用する場合は無視できます。少なくとも 1 つの低 ESR セラミック・コンデンサを使用することを強くお勧めします（電解コンデンサと低 ESR セラミック・コンデンサを並列に接続して使用すると、効率がよくなることがあります）。

ブートストラップ・コンデンサから放電される総電荷量は、 $Q_{TOT}$  (式 4 を参照) と呼ばれ、式 14 で算出できます。

$$Q_{TOT} = Q_G + Q_{LS} + (I_{LK\_GE} + I_{QBS} + I_{LK} + I_{LK\_CAP}) \cdot (1 - D_{MIN}) \cdot T_S = Q_G^* + I_{leak} \cdot (1 - D_{MIN}) \cdot T_S \quad (\text{式14})$$

ブートストラップ・コンデンサは、 $C_{boot} > \frac{Q_{TOT}}{V_{drop}}$  を使用し、以下を検証することで選択できます。

$$V_{drop} = \Delta V_{BS} \quad (\text{図 4 を参照})$$

上の式を検証できない場合、 $V_{drop}$  は、 $V_{drop} = V_{Rboot} + \Delta V_{BS} / 2$  で計算できます。式 3 の公式と  $V_{drop}$  の既知の値を使用すれば、 $V_{BS}$  は、 $V_{BSmin} = V_{CC} - V_{CEon} - V_{drop}$  で求めることができます。ただし、 $V_{GEmin}$  要件を忘れないでください。

#### 4. 負荷電流なしでのテスト・ベンチ測定

内蔵ブートストラップ回路の動作または性能についてより適切な例を提供するために、いくつかの実験例の比較を入れました。以下では、以下の 3 つの比較を示します。

- 10Ω ブートストラップ抵抗と外部ブートストラップ・ダイオードの回路

- 内蔵ブートストラップ回路

- 内蔵ブートストラップ回路と外部ブートストラップ・コンポーネントの並列

テスト条件 :

- PWM=20kHz

- $C_{boot}=1\mu F$

- 基本周波数 = 25Hz

- 最小パルス = 560ns (変調指数 = 97.7%)

- 負荷電流なし

- ゲート・ドライバ IC : IR2136 (外部ブートストラップ・トポロジ) または IRS2136D (内蔵ブートストラップ)

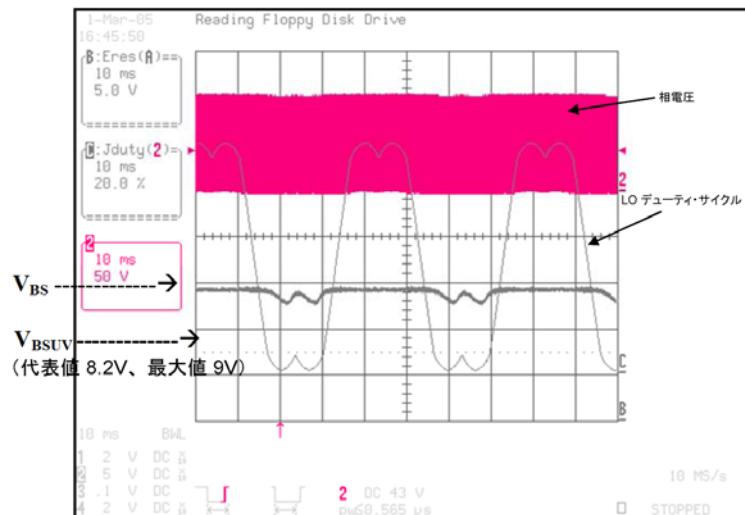

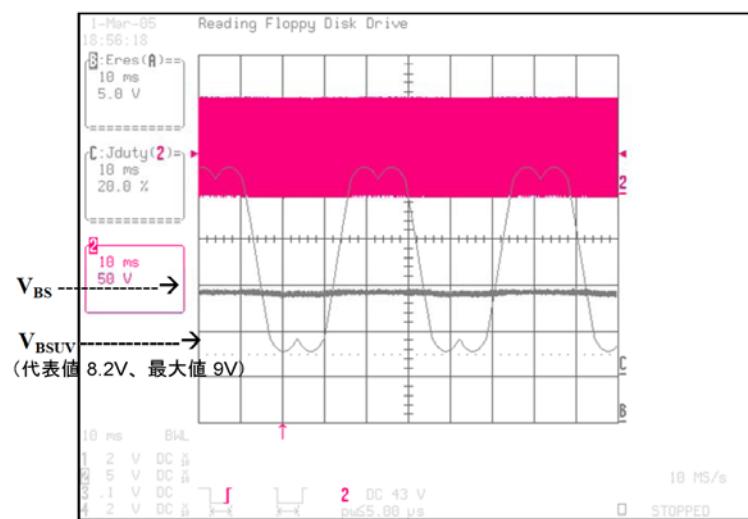

図 10.  $10\Omega$  とダイオードの外部ブートストラップ回路（最小パルス 560ns）

図 11. 内蔵ブートストラップ回路（最小パルス 560ns）

内蔵ブートストラップ・ネットワークが、25Hz の基本周波数でフィルタリング効果を提供するという興味深いことを確認できます（図 11 を参照）。同じ図から、V<sub>BS</sub> が、ブートストラップ・ダイオードの順降下の損失を出さずに、ほぼ 15V に達していることも確認できます。

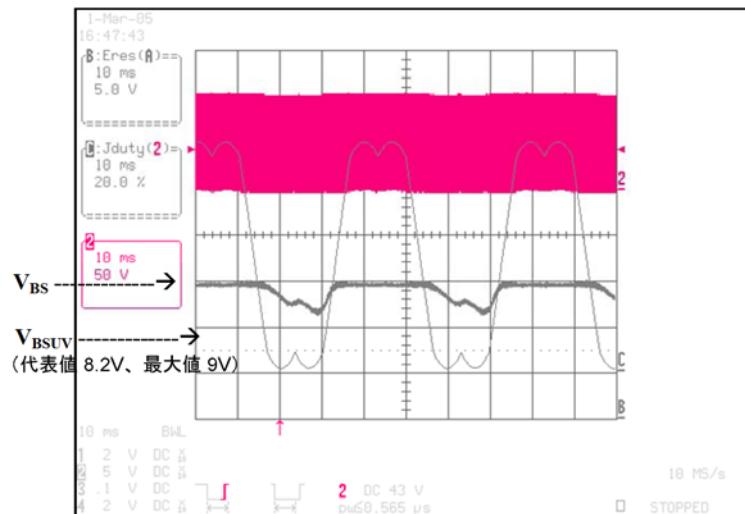

この 2 つ目の例では、最小パルスが 5μs に上昇し、変調指数が 80% に下降しています。

図 12. 外部ブートストラップ・コンポーネント（最小パルス 560ns）と並列に接続された内蔵ブートストラップ回路

テスト条件：

- PWM=20kHz

- Cboot=1μF

- 基本周波数 = 25Hz

- 最小パルス = 5μs (変調指数 = 80%)

- 負荷電流なし

- ゲート・ドライバ IC : IR2136 (外部ブートストラップ・トポロジ) または IRS2136D (内蔵ブートストラップ)

図 13. 10Ω 抵抗とダイオードの外部ブートストラップ回路（最小パルス 5μs）

図 14. 内蔵ブートストラップ回路（最小パルス 5μs）

図 15. 外部ブートストラップ・コンポーネント（最小パルス 5μs）と

並列に接続された内蔵ブートストラップ回路

変調指数が低い場合に、内蔵ブートストラップ回路は、25°C での外部ブートストラップ回路から得た結果と同程度のよい結果を出しています。

## 5. 負荷を変化させてブートストラップ回路を考察する

これまでの例では、テストは、負荷に流れる電流（正または負）の影響を考慮に入れていませんでした。負荷電流は、 $V_{BSMAX}$  の値に影響を与えます。この影響について、引き続き考察します。

考察する状況は 3 つあります。1 つ目は、 $I_{LOAD}$  が 0 未満の場です。

- $I_{LOAD} < 0$  : 負荷電流がローサイドの IGBT に流れ、一定の  $V_{CEon}$  を発生する

$$V_{BSmax} = V_{CC}(-V_F) - V_{CEon} \quad (\text{式15})$$

この場合は、 $V_{BSMAX}$  の最小値を確認します。これは、ブートストラップ・コンデンサのサイジングの最悪の場合を表します。ローサイドの IGBT の  $V_{CEON}$  が、 $V_s$  ノードをプルアップし、ブートストラップ供給の充電に利用可能な電圧を減少させます。IGBT と直列に接続したシャント抵抗を使用する回路では、その電圧降下が結果にも影響することがあります。

相電流と相電圧間の小さな位相シフトを考察すると（位相のデューティ・サイクルが高く、ブートストラップ・コンデンサの充電に時間がかかるときに起こる現象）、 $V_{CEON}$  の大きさによっては、誘起される電圧降下が減少することがあります。

2 つ目は、負荷電流が 0 で、スイッチの電圧降下を無視できる場合です。この状況は既に本書で考察し、電流のゼロ交差時に起こります。

- $I_{LOAD} = 0$  : IGBT がオンのときでも IGBT には負荷がかからず、 $V_{CE}$  を無視できる

$$V_{BSmax} = V_{CC}(-V_F) \quad (\text{式16})$$

3 つ目は、負荷電流が正で、スイッチの電圧降下が、フリーホイール・ダイオードから生じる降下によって起こる場合です。

- $I_{LOAD} > 0$  : 負荷電流がフリーホイール・ダイオードを流れる

$$V_{BSmax} = V_{CC}(-V_F) + V_{FP} \quad (\text{式17})$$

この場合は、 $V_{BSMAX}$  の値が最大になります。 $I_{LOAD}$  がフリーホイール・ダイオードに流れ、その電圧降下が、 $V_{BS}$  の充電に利用可能な電圧を上昇させます。同じ考察を  $I_{LOAD} < 0$  の場合にも行うことができます。ただし、この場合、（ $V_{BSMAX}$  の上昇によって促進される）現象は、デューティ・サイクルの最短時に起こります。

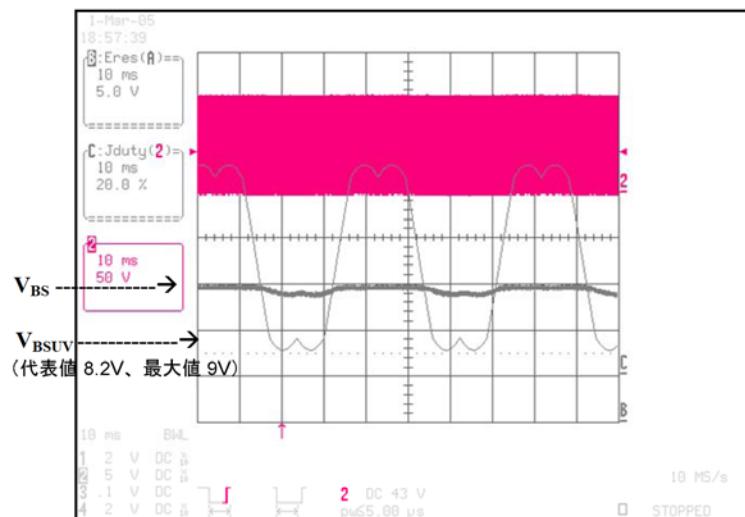

図 16 は、印加電圧によって負荷電流が位相シフトを起こす場合のシミュレーション結果を示します。プロットが示すのは、デューティ・サイクル（緑色）、シミュレーションされた VBS 電圧（青色 = 200Ω ブートストラップ抵抗、青緑色 = 10Ω ブートストラップ抵抗とダイオード、オレンジ色 = 達成可能な最大 VBS ）、および位相に正で入る負荷電流（赤色）です。

図 16. 可変デューティ・サイクルと負荷電流位相による VBS のシミュレーション

シミュレーションのパラメータは以下のとおりです。

$IQBS = 150\mu A$

$ILK = 50\mu A$

$QLS = 1.2nC$

$QG = 40nC$

$TS = 50\mu s (f=20kHz)$

$VF = 1V$

$Rboot = 220\Omega$

$VCC = 15V$

$VCEon = 3V$

$VGEmin = 10V$

$DMIN = 10\% \text{ (PWM キャリアの最小デューティ・サイクル)}$

シミュレーションの回路図は、（正弦波を持つように理想化された） $VCEON$  と  $VFP$  の影響を考察できるように、図 2 の回路に変更を加えています。

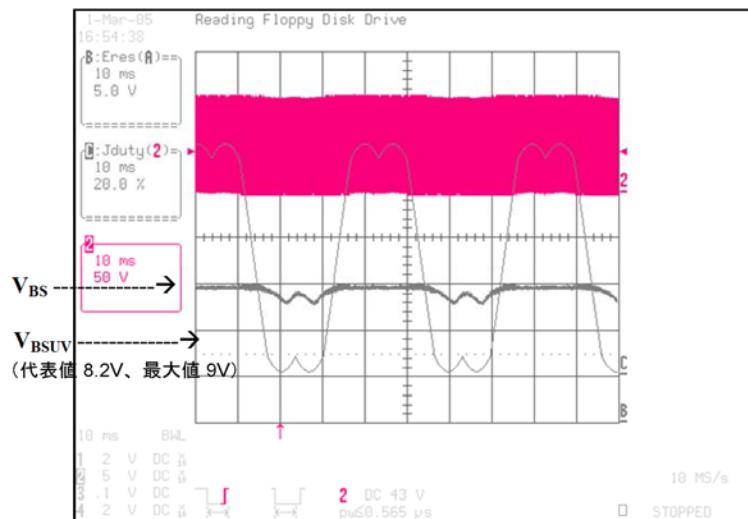

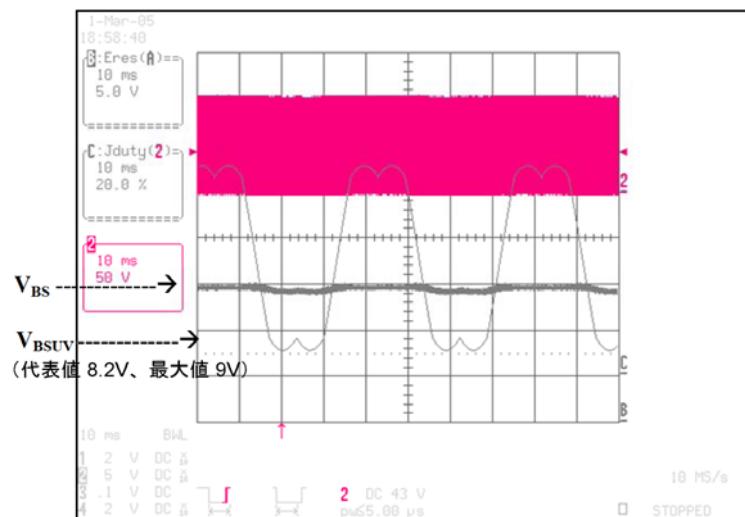

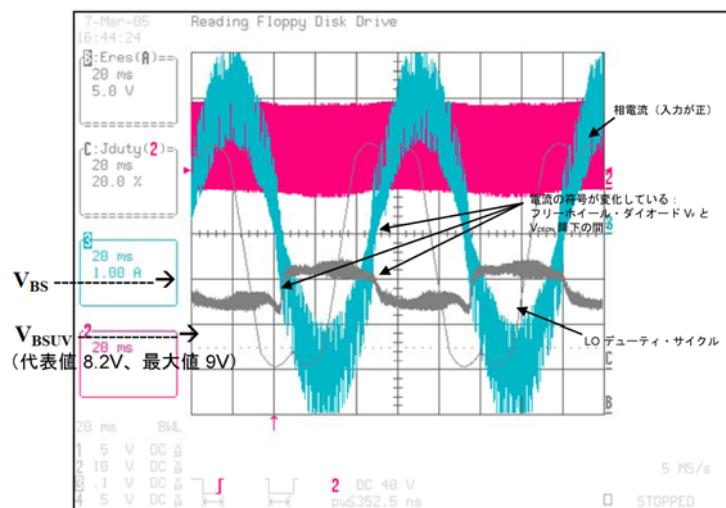

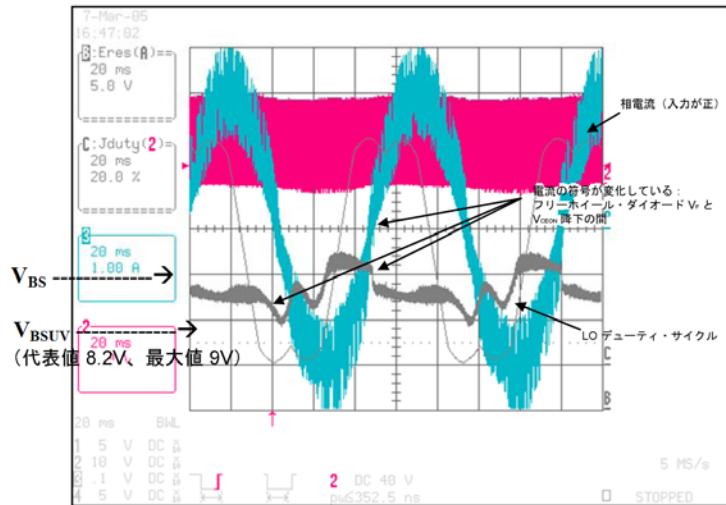

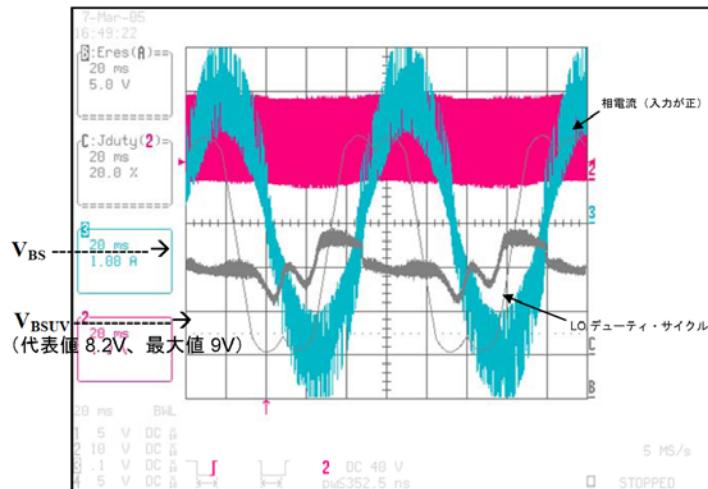

ここで、一連のテスト測定を検証して、 $VBS$  動作が変調と位相遅れ（電流と電圧間）の関数として理解できることを示します。テスト条件を以下に示します（前のテスト条件と少し異なります）。

- PWM=20kHz

- $Cboot=1\mu F$

- 基本周波数 = 11Hz

- 最小パルス = 367ns ( $m = 98.5\%$ )

- 負荷電流（インバータ段の方向が正）= 5A 最大振幅

図 17. 10Ω + 外部ダイオードのブートストラップ回路

図 18. 内蔵ブートストラップ回路

図 19. 17V V<sub>cc</sub> 供給の内蔵ブートストラップ回路

## 6. 内蔵ブートストラップの制限

これまで考察したブートストラップ FET では、LO がアクティブである（また、Vs ピンが V<sub>SS</sub> に結合している）ときのみ、ブートストラップ FET がオンであることを前提としました。この動作原理は、無駄時間の浪費につながります。この時間は、ローサイドのフリー・ホイールの再循環時にブートストラップ・コンデンサを再充電するために使用できます。外部ブートストラップ・ダイオードを使用するトポロジでは、このような問題は起きません。ほとんどの場合（モーター駆動用途では通常、3μs 未満の無駄時間と約 20kHz の最大スイッチング周波数が発生します）、充電で生じる損失は無視できます。

内蔵ブートストラップに関係するもう 1 つの制限は、補完のないスイッチング方式に対してです。

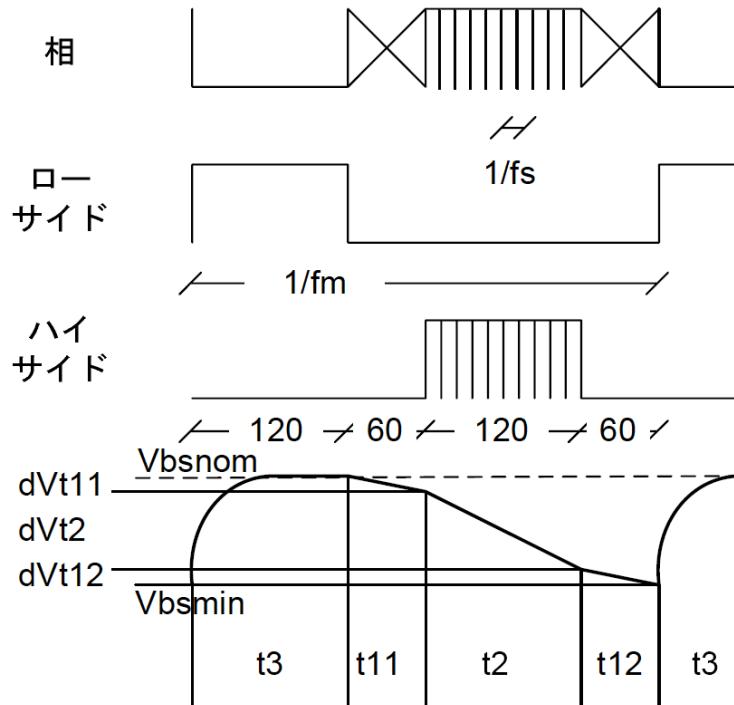

図 20. 補完のない 6 段階スイッティング方式の  $V_{BS}$  電圧の動作

例として、ハイサイドの IGBT を細かく分割し、ローサイドの IGBT をオフにした 6 段階のスイッティング方式を考察しました（図 20 を参照）。 $V_{BS}$  が充電されるのは、ローサイドの IGBT がオン（ $t_3$ ）のときのみであり、 $C_{boot}$  の充電は、ハイサイドのスイッティング期間（ $t_2$ ）には絶対にリフレッシュされません。

この問題を解決する方法は、ハイサイドのスイッチを細かく分割しながら、ローサイドを補完的な方法でスイッティングすることです。これにより、ブートストラップ・コンデンサのリフレッシュが可能になります。補完的なスイッティングでは、第 2 節で示した式を適用します。

IR 社は、補完のない PWM 方式に適応する内蔵ブートストラップのさまざまな起動戦略もデバイスに提供します。このトピックについては、本書では考察しません。

## 7. 結論

ここでは、フローティング供給の充電に対するブートストラップ抵抗とブートストラップ・コンデンサの影響について考察しました。抵抗のブートストラップ回路が引き起こす主な問題は、アプリケーションのために得る最小デューティ・サイクルに影響が出る平均電圧降下です。この影響があるっても、正弦波駆動用の内蔵ブートストラップ・トポロジは使用できます。

獲得した式は一般には有効ですが、内蔵ブートストラップ・トポロジが設計要件に適合するかどうかを実際に使用して検証する必要があります。

本書では主に、3相空間ベクトル（または、3相正弦波 + 第三高調波）の変調を使用するアプリケーションについて解説しています。他の変調（2相空間ベクトル、6段階など）については、個別に考察する必要があります。

ブーストストラップ機能の統合は、外部コンポーネントの数を減らし(HV ダイオード×3 + 抵抗×1)、基板上の面積を節約するという利点を低コストのアプリケーションにもたらします。このソリューションは特に、高い集積度を必要とするモジュールにお勧めします。