## サイプレスはインフィニオンテクノロジーズになりました

この表紙に続く文書には「サイプレス」と表記されていますが、これは同社が最初にこの製品を開発したからです。新規および既存のお客様いずれに対しても、引き続きインフィニオンがラインアップの一部として当該製品をご提供いたします。

### 文書の内容の継続性

下記製品がインフィニオンの製品ラインアップの一部として提供されたとしても、それを理由としてこの文書に変更が加わることはありません。今後も適宜改訂は行いますが、変更があった場合は文書の履歴ページでお知らせします。

### 注文時の部品番号の継続性

インフィニオンは既存の部品番号を引き続きサポートします。ご注文の際は、データシート記載の注文部品番号をこれまで通りご利用下さい。

**S6BP203A**

# ASSP, 42V, 2.4A, 同期整流式昇降圧 DC/DCコンバータIC

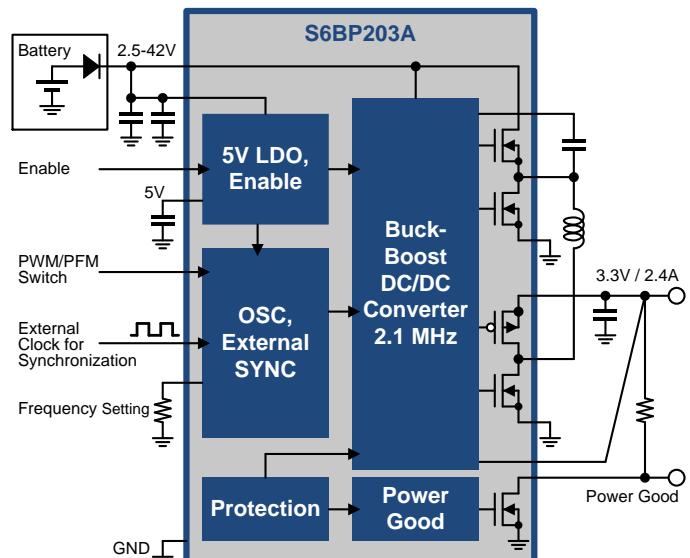

S6BP203A は、4 つのスイッチング FET を内蔵した 1-Ch 昇降圧 DC/DC コンバータ IC です。本 IC は広範囲な入力電圧 2.5V~42V と最大 2.4A の出力電流を供給できます。本製品は軽負荷時に自動で PFM 動作へ切換る動作を有しており、非常に低い 50  $\mu$ A の休止電流による超高効率を実現しています。自動車のコールドクランク条件から最大 42V のロードダンプ条件に対し、1 ms の遷移時間で安定した出力電圧を供給します。そのため、本製品は自動車向け、産業機器向けの用途の電源に適しています。本製品は SYNC 機能を持ち合わせており、外部クロック信号を入力できる SYNC\_IN が選択可能で、200 kHz から 400 kHz の範囲のクロック信号が外部から入力された場合、FET は外部クロック信号に同期してスイッチング動作します。外部からクロック信号を与えられない場合、FET は内部クロック信号を基準にスイッチング動作します。外付け抵抗により内部クロック信号は 200 kHz から 2.1 MHz の範囲で設定可能です。本製品には外付けの出力電圧設定抵抗や位相補償部品が不要であるため、外部部品点数と部品実装面積を削減できます。本製品は、入力低電圧時誤動作防止 (入力 UVLO: 入力 Under Voltage Lockout)、出力低電圧保護 (出力 UVP: 出力 Under Voltage Protection)、出力過電圧保護 (出力 OVP: 出力 Over Voltage Protection)、出力過電流保護 (出力 OCP: 出力 Over Current Protection)、過熱保護 (TSD: Thermal Shutdown) の 5 種の保護機能を搭載しています。さらに、出力電圧 (VOUT 端子) の状態を示すパワーグッド (PG: Power Good) 機能を搭載しています。出力電圧が PG 電圧に到達した時点で PG 信号を出力させます。

## 特長

- 広範囲な入力電圧範囲: 2.5V~42V

- 出力電圧: 3.3V

- 広範囲な動作周波数範囲: 200 kHz~2.1 MHz

- 外部クロック同期範囲: 200 kHz~400 kHz

- SYNC 機能

- SYNC IN: 外部クロック入力

(外部クロック未入力時、内部クロック動作)

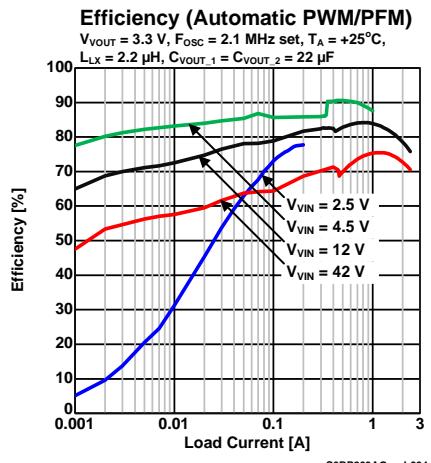

- 軽負荷時 PFM 動作による超高効率

(MODE 端子ローレベル選択時)

- PWM/PFM 自動切換え動作と PWM 固定動作は MODE 端子で選択可能

- スイッチング FET 内蔵

- 同期整流式カレントモード制御

- 停止電流: 1  $\mu$ A 以下

- 休止電流: 50  $\mu$ A

- パワーグッド監視

- ウィンドウコンパレータによる出力電圧監視

- パワーオンリセット時間: 14 ms

- 負荷依存のないソフトスタート時間: 0.9 ms

(スイッチング周波数 2.1 MHz 設定時)

- 高度保護機能

- 入力低電圧時誤動作防止

- 出力低電圧保護: 92.0%

- 出力過電圧保護: 108.0%

- 出力過電流保護

- 過熱保護

- 小型ETSSOP16パッケージ (放熱パッドタイプ): 5 mm × 6.4 mm

- AEC-Q100 規格に準拠 (Grade-1)

## アプリケーション

- 先進運転支援システム

(ADAS: Advanced Driver Assistance Systems)

- インストルメントクラスタ

- 車載機器

- 産業機器

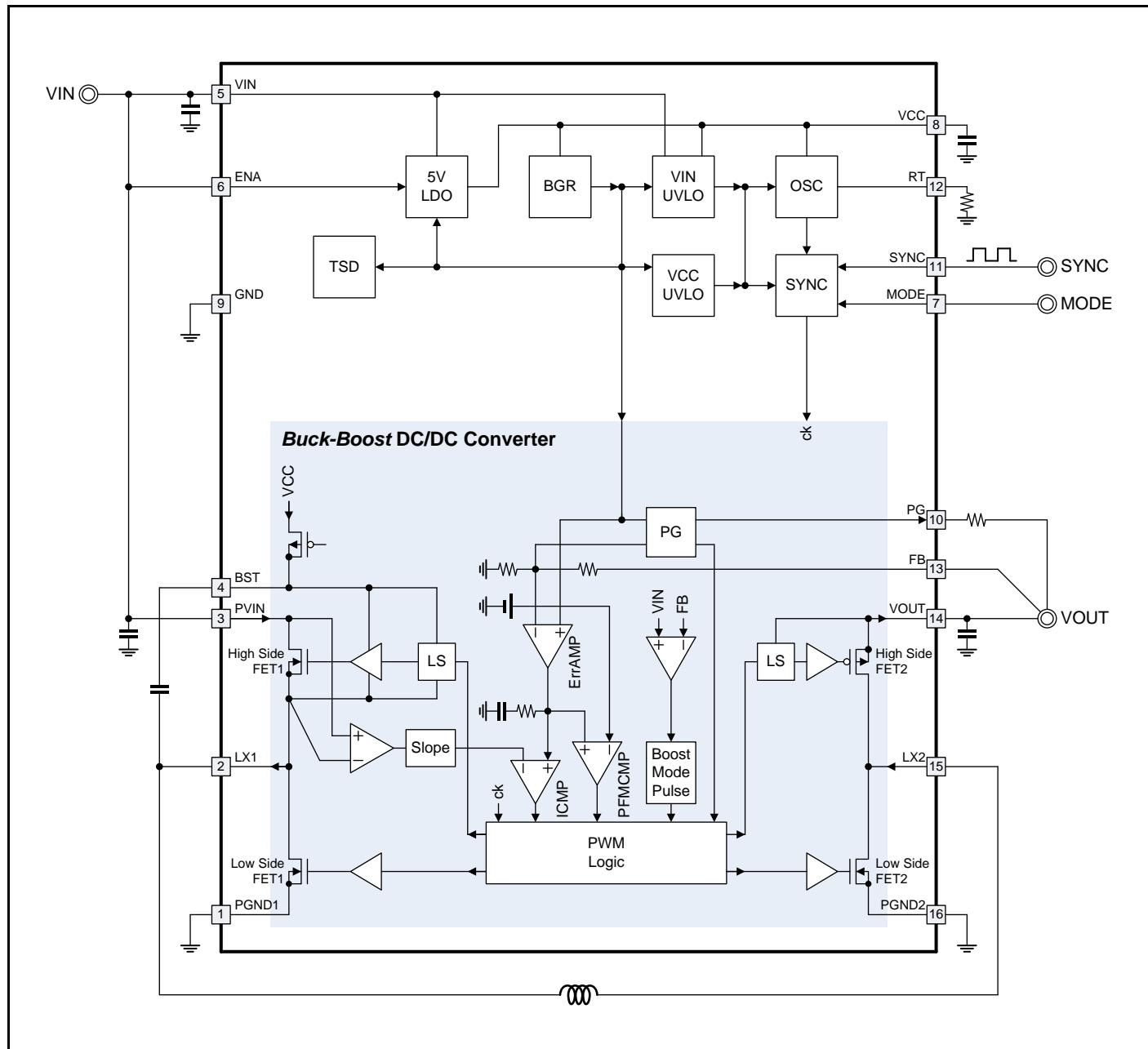

## ブロック図

## 詳細情報

サイプレスは、[www.cypress.com/pmic](http://www.cypress.com/pmic) に大量のデータを掲載しており、ユーザがデザインに適切な PMIC デバイスを選択し、デバイスをデザインに迅速で効果的に統合する手助けをしています。以下は、S6BP203A の要約です。

■概要: [車載 PMIC ポートフォリオ](#)、[車載 PMIC ロードマップ](#)

■製品セレクタ:

□ [S6BP203A](#):

1-Ch 車載向け昇降圧 PMIC

■アプリケーションノート: サイプレスは、S6BP203A アプリケーションノートを提供しています。以下は、S6BP203A 用の推奨アプリケーションノートです。

□ [AN99497](#): 電源システムの部品選定

□ [AN201006](#): 熱の検討とパラメータ

■評価キット取扱説明書:

□ [S6SBP203A8FVA1001](#):

S6BP203A 評価キット取扱説明書

■関連製品:

□ [S6BP201A](#), [S6BP202A](#):

1-Ch 車載向け昇降圧 PMIC

□ [S6BP401A](#):

6-Ch 車載 ADAS 向け PMIC

□ [S6BP501A](#), [S6BP502A](#):

3-Ch 車載クラスタ向け PMIC

## 目次

|                            |    |

|----------------------------|----|

| <b>特長</b> .....            | 1  |

| <b>アプリケーション</b> .....      | 1  |

| <b>ブロック図</b> .....         | 1  |

| <b>詳細情報</b> .....          | 2  |

| 1. 端子配列図 .....             | 4  |

| 2. 端子機能説明 .....            | 4  |

| 3. アーキテクチャブロック図 .....      | 6  |

| 4. 絶対最大定格 .....            | 7  |

| 5. 推奨動作条件 .....            | 7  |

| 6. 電気的特性 .....             | 8  |

| 7. 機能説明 .....              | 9  |

| 7.1 保護機能 .....             | 9  |

| 7.2 保護機能一覧表 .....          | 10 |

| 8. 応用回路例・部品表 .....         | 11 |

| 9. アプリケーションノート .....       | 12 |

| 9.1 動作条件の設定 .....          | 12 |

| 10. 参考データ .....            | 14 |

| 11. 使用上の注意 .....           | 16 |

| 12. RoHS 指令に対応した品質管理 ..... | 16 |

| 13. オーダ型格 .....            | 16 |

| 14. パッケージ・外形寸法図 .....      | 17 |

| 15. 主な変更内容 .....           | 18 |

| 改訂履歴 .....                 | 18 |

| セールス、ソリューションおよび法律情報 .....  | 19 |

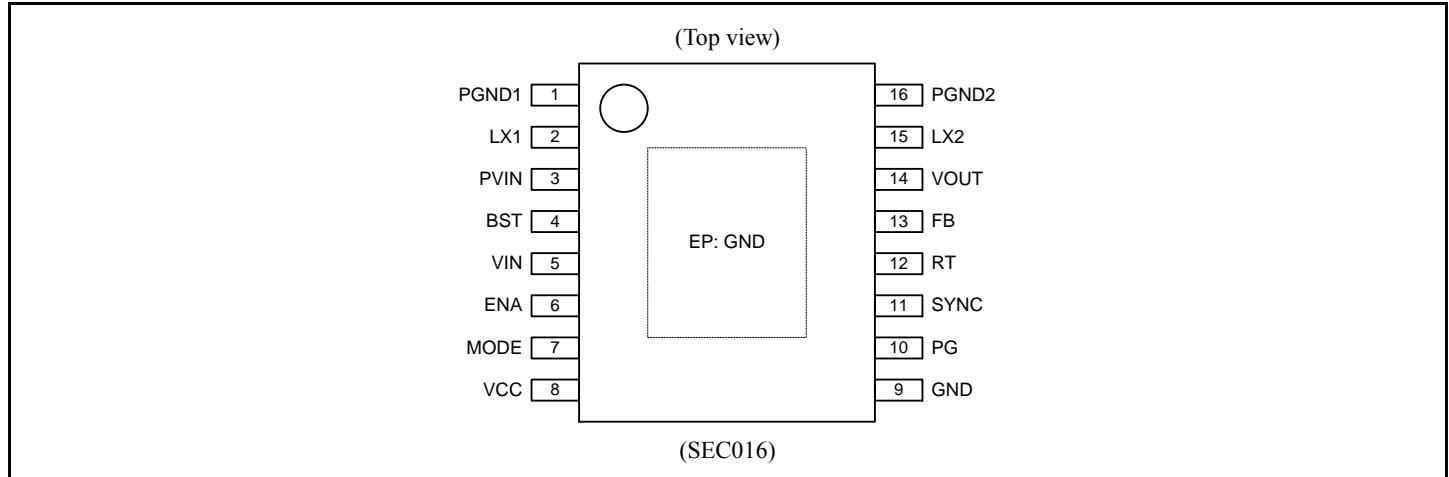

## 1. 端子配列図

Figure 1-1 端子配列図

## 2. 端子機能説明

Table 2-1 端子機能説明

| 端子番号 | 端子記号  | I/O | 機能説明                                                             |

|------|-------|-----|------------------------------------------------------------------|

| 1    | PGND1 | —   | 内蔵スイッチング FET 用接地端子                                               |

| 2    | LX1   | O   | インダクタ接続端子                                                        |

| 3    | PVIN  | I   | PWM コントローラおよびスイッチング FET 用電源端子                                    |

| 4    | BST   | I   | 昇圧容量接続端子                                                         |

| 5    | VIN   | I   | 電源端子                                                             |

| 6    | ENA   | I   | DC/DC コンバータイネーブル端子                                               |

| 7    | MODE  | I   | PFM/PWM 動作制御端子<br>MODE 端子の設定は「9.1 動作条件の設定」を参照                    |

| 8    | VCC   | O   | 内部基準電圧 LDO 出力端子, VCC 容量接続端子                                      |

| 9    | GND   | —   | 接地端子                                                             |

| 10   | PG    | O   | パワーグッド用オープンドレイン出力端子<br>使用時は VOUT 端子に接続してください<br>未使用時はオープンとしてください |

| 11   | SYNC  | I   | 外部クロック入力端子<br>SYNC 端子の設定は「9.1 動作条件の設定」を参照                        |

| 12   | RT    | O   | 内部クロック (スイッチング周波数) 用抵抗接続端子<br>設定抵抗値は「9.1 動作条件の設定」を参照             |

| 13   | FB    | I   | 出力電圧フィードバック端子                                                    |

| 14   | VOUT  | O   | DC/DC コンバータ出力端子                                                  |

| 15   | LX2   | O   | インダクタ接続端子                                                        |

| 16   | PGND2 | —   | 内蔵スイッチング FET 用接地端子                                               |

| EP   | GND   | —   | 接地端子                                                             |

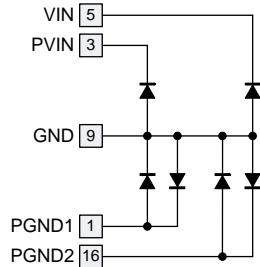

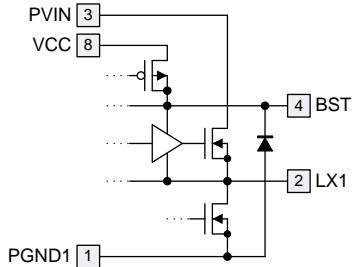

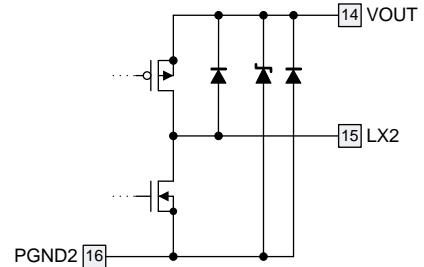

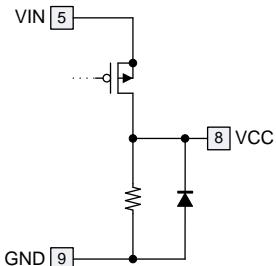

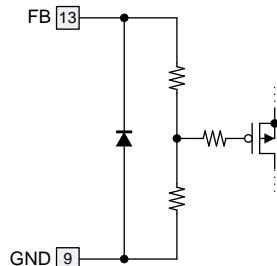

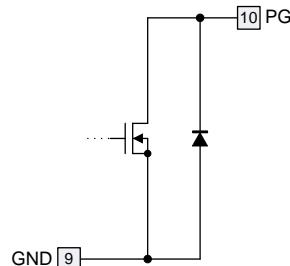

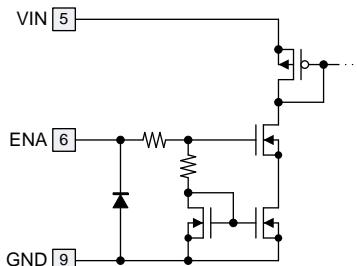

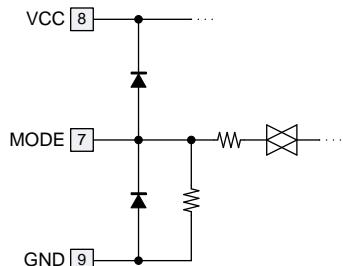

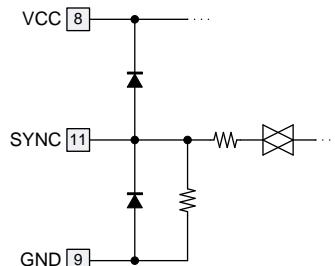

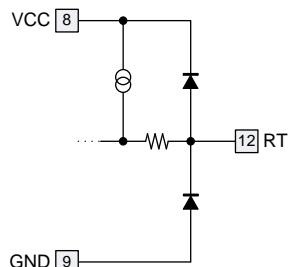

Figure 2-1 入出力端子等価回路図

<VIN pin, PVIN pin>

<LX1 pin, BST pin>

<VOUT pin, LX2 pin>

<VCC pin>

<FB pin>

<PG pin>

<ENA pin>

<MODE pin>

<SYNC pin>

<RT pin>

### 3. アーキテクチャブロック図

Figure 3-1 アーキテクチャブロック図

#### 4. 絶対最大定格

| 項目        | 記号                  | 条件                           | 定格値  |                  | 単位 |

|-----------|---------------------|------------------------------|------|------------------|----|

|           |                     |                              | 最小   | 最大               |    |

| 電源電圧 (*1) | V <sub>VIN</sub>    | VIN 端子                       | -0.3 | +48.0            | V  |

|           | V <sub>PVIN</sub>   | PVIN 端子                      | -0.3 | +48.0            | V  |

|           | V <sub>VCC</sub>    | VCC 端子                       | -0.3 | +6.9             | V  |

| 端子電圧 (*1) | V <sub>BST</sub>    | BST 端子                       | -0.3 | +48.0            | V  |

|           | V <sub>LX1</sub>    | LX1 端子                       | -2.0 | +48.0            | V  |

|           | V <sub>LX2</sub>    | LX2 端子                       | -2.0 | +6.9             | V  |

|           | V <sub>FB</sub>     | FB 端子                        | -0.3 | V <sub>VCC</sub> | V  |

|           | V <sub>RT</sub>     | RT 端子                        | -0.3 | V <sub>VCC</sub> | V  |

|           | V <sub>MODE</sub>   | MODE 端子                      | -0.3 | V <sub>VCC</sub> | V  |

|           | V <sub>SYNC</sub>   | SYNC 端子                      | -0.3 | V <sub>VCC</sub> | V  |

|           | V <sub>ENA</sub>    | ENA 端子                       | -0.3 | +48.0            | V  |

|           | V <sub>PG</sub>     | PG 端子                        | -0.3 | +6.9             | V  |

| 差分電圧 (*1) | V <sub>BST-LX</sub> | BST-LX1 端子間                  | -0.3 | +6.9             | V  |

|           | V <sub>GND</sub>    | GND-PGND1 端子間, GND-PGND2 端子間 | -0.3 | +0.3             | V  |

| PG 出力電流   | I <sub>PG</sub>     | PG 端子                        | -3   | 0                | mA |

| 許容損失 (*1) | P <sub>D</sub>      | T <sub>a</sub> ≤±25°C        | 0    | 3324 (*2)        | mW |

| 保存温度      | T <sub>STG</sub>    | -                            | -55  | +150             | °C |

\*1: PGND1 = PGND2 = GND = 0V 時

\*2: 76.2 mm × 114.3 mm の 4 層 FR-4 基板に本製品を実装時

#### ＜注意事項＞

- 絶対最大定格を超えるストレス (電圧, 電流, 温度など) の印加は、半導体デバイスを破壊する可能性があります。したがって、定格を一項目でも超えることのないようご注意ください。

#### 5. 推奨動作条件

| 項目        | 記号                   | 条件                           | 規格値   |       |       | 単位 |

|-----------|----------------------|------------------------------|-------|-------|-------|----|

|           |                      |                              | 最小    | 標準    | 最大    |    |

| 電源電圧 (*1) | V <sub>VIN</sub>     | VIN 端子                       | 5.0   | 12.0  | 42.0  | V  |

|           |                      |                              | 2.5   | 12.0  | 42.0  | V  |

| 端子電圧 (*1) | V <sub>BST</sub>     | BST 端子                       | 0.0   | -     | 47.5  | V  |

|           | V <sub>LX1</sub>     | LX1 端子                       | -1.0  | +12.0 | +42.0 | V  |

|           | V <sub>LX2</sub>     | LX2 端子                       | -1.0  | -     | +5.5  | V  |

|           | V <sub>FB</sub>      | FB 端子                        | 0.0   | -     | 5.5   | V  |

|           | V <sub>MODE</sub>    | MODE 端子                      | 0.0   | -     | 5.5   | V  |

|           | V <sub>SYNC</sub>    | SYNC 端子                      | 0.0   | -     | 5.5   | V  |

|           | V <sub>ENA</sub>     | ENA 端子                       | 0.0   | 12.0  | 42.0  | V  |

|           | V <sub>PG</sub>      | PG 端子                        | 0.0   | -     | 5.5   | V  |

|           | V <sub>BST-LX1</sub> | BST-LX1 端子間                  | 0.0   | -     | 5.5   | V  |

| 差分電圧 (*1) | V <sub>GND</sub>     | GND-PGND1 端子間, GND-PGND2 端子間 | -0.05 | 0.00  | +0.05 | V  |

|           | I <sub>PG</sub>      | PG 端子 (吸い込み電流)               | 0     | -     | 1     | mA |

| BST 容量値   | C <sub>BST</sub>     | BST-LX1 端子間                  | 0.068 | 0.100 | 0.470 | μF |

| VCC 容量値   | C <sub>VCC</sub>     | VCC-GND 端子間                  | 2.2   | 4.7   | 10.0  | μF |

| RT 抵抗値    | R <sub>RT</sub>      | RT-GND 端子間, 内部クロック使用時        | 22    | -     | 270   | kΩ |

| 動作周囲温度    | T <sub>a</sub>       | -                            | -40   | +25   | +125  | °C |

\*1: PGND1 = PGND2 = GND = 0V 時

#### ＜注意事項＞

- 推奨動作条件は、半導体デバイスの正常な動作を確保するための条件です。電気的特性の規格値は、すべてこの条件の範囲内で保証されます。常に推奨動作条件下で使用してください。

- この条件を超えて使用すると、信頼性に悪影響を及ぼすことがあります。

- データシートに記載されていない項目、使用条件、論理の組合せでの使用は、保証していません。

- 記載されている以外の条件での使用をお考えの場合は、必ず事前に営業部門までご相談ください。

## 6. 電気的特性

VIN = PVIN = 12V, ENA = 5V (特に記載がない場合には推奨動作条件下における電気的特性)

| 項目                         | 記号                  | 条件                      | 規格値                                                                                    |          |          | 単位                  |

|----------------------------|---------------------|-------------------------|----------------------------------------------------------------------------------------|----------|----------|---------------------|

|                            |                     |                         | 最小                                                                                     | 標準       | 最大       |                     |

| 昇降圧 DC/DC<br>コンバータ<br>ブロック | VOUT 出力電圧           | V <sub>VOUT</sub>       | I <sub>VOUT</sub> = 0A,                                                                | 3.251    | 3.300    | 3.349 V             |

|                            | FB 入力抵抗値            | R <sub>FB</sub>         | EN = 0V, Ta = +25°C                                                                    | 2.53     | 3.17     | 3.80 MΩ             |

|                            | スイッチング FET<br>オン抵抗  | R <sub>H</sub> SIDEFET1 | LX1 = -30 mA (PVIN-LX1 端子間)                                                            | —        | 150      | — mΩ                |

|                            |                     | R <sub>L</sub> SIDEFET1 | LX1 = 30 mA (LX1-PGND1 端子間)                                                            | —        | 150      | — mΩ                |

|                            |                     | R <sub>H</sub> SIDEFET2 | LX2 = -30 mA (VOUT-LX2 端子間)                                                            | —        | 150      | — mΩ                |

|                            |                     | R <sub>L</sub> SIDEFET2 | LX2 = 30 mA (LX2-PGND2 端子間)                                                            | —        | 150      | — mΩ                |

|                            | スイッチング FET<br>リーク電流 | I <sub>LEAK</sub>       | —                                                                                      | —        | —        | 5 μA                |

|                            | ソフトスタート時間           | T <sub>SS</sub>         | R <sub>RT</sub> = 22 kΩ                                                                | 0.855    | 0.9      | 0.945 ms            |

|                            | 最大出力電流              | I <sub>VOUT</sub>       | PVIN ≥ 7.5V, Ta = 25°C                                                                 | 2.4 (*1) | —        | — A                 |

|                            |                     |                         | PVIN = 4.5V, Ta = 25°C                                                                 | 1.0 (*1) | —        | — A                 |

|                            | 電流リミット              | I <sub>LIMIT</sub>      | PVIN = 12V, L = 2.2 μH                                                                 | 2.4 (*1) | —        | — A                 |

| 5V LDO<br>ブロック             | VCC 出力電圧            | V <sub>VCC</sub>        | VIN = 12V                                                                              | 4.9      | 5.0      | 5.1 V               |

| VIN UVLO<br>ブロック           | VIN UVLO 立下り閾値      | V <sub>UVLOVINHL</sub>  | VIN 入力電圧立下り時                                                                           | 2.30     | 2.40     | 2.50 V              |

|                            | VIN UVLO 立上り閾値      | V <sub>UVLOVINLH</sub>  | VIN 入力電圧立上り時                                                                           | 4.55     | 4.75     | 4.95 V              |

| VCC UVLO<br>ブロック           | VCC UVLO 立下り閾値      | V <sub>UVLOVCCHL</sub>  | VCC 入力電圧立下り時                                                                           | 2.30     | 2.40     | 2.50 V              |

|                            | VCC UVLO 立上り閾値      | V <sub>UVLOVCCCLH</sub> | VCC 入力電圧立上り時                                                                           | 4.55     | 4.75     | 4.95 V              |

| ENA 端子                     | イネーブル条件             | V <sub>ENA</sub>        | イネーブル電圧範囲                                                                              | 1.10     | —        | V <sub>VIN</sub> V  |

|                            |                     | V <sub>DSB</sub>        | ディセーブル電圧範囲                                                                             | 0.0      | —        | 0.2 V               |

|                            | ENA 入力電流            | I <sub>ENA</sub>        | V <sub>ENA</sub> = 12V                                                                 | —        | 1        | 3 μA                |

| MODE 端子                    | MODE 入力電圧           | V <sub>MODE_L</sub>     | PWM/PFM 自動切換え動作                                                                        | 0.0      | —        | 0.4 V               |

|                            |                     | V <sub>MODE_H</sub>     | PWM 固定動作                                                                               | 2.0      | —        | V <sub>VOUT</sub> V |

|                            | MODE 入力電流           | I <sub>MODE</sub>       | MODE = 5.0V                                                                            | —        | 5        | 10 μA               |

| OSC ブロック                   | スイッチング周波数           | FOSC                    | R <sub>RT</sub> = 22 kΩ                                                                | 2.0      | 2.1      | 2.2 MHz             |

|                            |                     |                         | R <sub>RT</sub> = 270 kΩ                                                               | 180      | 200      | 220 kHz             |

| SYNC ブロック<br>(SYNC_IN)     | SYNC 入力閾値電圧         | V <sub>SYNC_L</sub>     | —                                                                                      | 0.0      | —        | 0.4 V               |

|                            |                     | V <sub>SYNC_H</sub>     | —                                                                                      | 2.0      | —        | V <sub>VOUT</sub> V |

|                            | SYNC 入力周波数          | V <sub>SYNC_L</sub>     | —                                                                                      | 200      | —        | 400 kHz             |

|                            | SYNC 入力<br>デューティ比   | V <sub>SYNC_H</sub>     | —                                                                                      | +20      | +50      | +80 %               |

|                            | SYNC リーク電流          | I <sub>LKSYNC</sub>     | V <sub>SYNC</sub> = 5.0V                                                               | —        | 5        | 10 μA               |

| PG ブロック<br>(UVP, OVP)      | VOUT UVP 立下り閾値      | P <sub>GUVPHL</sub>     | 出力電圧に対する立下り閾値                                                                          | 90.5     | 92.0     | 93.5 %              |

|                            | VOUT UVP 立上り閾値      | P <sub>GUVP LH</sub>    | 出力電圧に対する立上り閾値                                                                          | 91.5     | 93.0     | 94.5 %              |

|                            | VOUT OVP 立上り閾値      | P <sub>GOVPLH</sub>     | 出力電圧に対する立上り閾値                                                                          | 106.5    | 108.0    | 109.5 %             |

|                            | VOUT OVP 立下り閾値      | P <sub>GOVPHL</sub>     | 出力電圧に対する立下り閾値                                                                          | 105.5    | 107.0    | 108.5 %             |

|                            | リーク電流               | I <sub>LKPG</sub>       | V <sub>PWRGD</sub> = 5.0V, V <sub>ENA</sub> = 0V                                       | 0        | —        | 1 μA                |

|                            | ローレベル出力電圧           | V <sub>OLPG</sub>       | I <sub>PGSINK</sub> = 1 mA                                                             | 0.025    | 0.05     | 0.15 V              |

|                            | 異常検出時遅延時間           | T <sub>PPG</sub>        | パワー停止時                                                                                 | —        | 7 (*1)   | 12 (*1) μs          |

|                            | パワーオンリセット時間         | T <sub>RPG</sub>        | パワーグッド時                                                                                | 9.1      | 14.0     | 18.9 ms             |

| 過熱保護<br>ブロック<br>(TSD)      | 停止温度                | T <sub>TSDH</sub>       | —                                                                                      | —        | 165 (*1) | — °C                |

|                            |                     | T <sub>TSDL</sub>       | ヒステリシス                                                                                 | —        | 10 (*1)  | — °C                |

| 電源電流                       | 停止電流                | I <sub>VINSDN</sub>     | VIN 入力電流, V <sub>ENA</sub> = 0V                                                        | —        | 1        | 5 μA                |

|                            | 休止電流                | I <sub>VINQ</sub>       | VIN 入力電流,<br>V <sub>ENA</sub> = 12V, I <sub>VOUT</sub> = 0A,<br>MODE/SYNC/PG 端子 = OPEN | —        | 50       | 70 μA               |

\*1: 電気的特性は、統計的特性評価および代替試験により確認しています。

## 7. 機能説明

### 7.1 保護機能

#### 入力低電圧時誤動作防止 (入力 UVLO)

入力 UVLO は下記に示した状態から IC の誤動作を防止し、後段デバイスを保護する機能です。

- 電源投入時の過渡状態

- 入力電圧の瞬時低下

このような誤動作を防止するため、本機能は VIN 入力電圧と VCC 電圧を監視しています。VIN もしくは VCC どちらかの電圧が UVLO 立下り閾値 2.4V (標準値) 以下まで低下すると、IC は VOUT 電圧出力を停止させ、UVLO 状態となります。VIN と VCC 双方の電圧が UVLO 立上り閾値 4.75V (標準値) 以上になると、IC は UVLO 状態から解除され通常動作に復帰します。

#### 出力低電圧保護 (出力 UVP)

出力 UVP は出力電圧が低下したことを監視し PG 端子で通知する機能です。

出力電圧が出力電圧設定値に対し UVP 立下り閾値 ( $P_{GUVPHL}$ ) 低下した場合、PG 電圧をローレベルに固定します。IC は UVP 状態となるが、UVP 状態下では DC/DC スイッチング動作を継続します。

出力電圧が出力電圧設定値より UVP 立上り閾値 ( $P_{GUVPLH}$ ) 以上に再び上昇すると、IC は UVP 状態から解除され、PG 電圧をハイレベルに固定します。

#### 出力過電圧保護 (出力 OVP)

出力 OVP は VOUT 出力電圧が上昇したことを監視しスイッチング動作を停止させる機能です。これは過電圧から後段デバイスを保護します。また、VOUT の状態は PG 端子で通知されます。

出力電圧が出力電圧設定値に対し OVP 立上り閾値 ( $P_{GOVPLH}$ ) 上昇した場合、PG 端子電圧をローレベルに固定します。IC は OVP 状態となり、ハイ側 FET のスイッチング動作は停止します。出力電圧が出力電圧設定値より VOUT OVP 立下り閾値 ( $P_{GOVPHL}$ ) 以下に再び降下すると、IC は OVP 状態から解除され、スイッチング動作を再開します。PG 端子電圧は再びハイレベルに固定されます。

#### 出力過電流保護 (出力 OCP)

出力 OCP は過大な負荷電流を制限することで後段デバイスを保護する機能です。

#### 過熱保護 (TSD)

TSD は IC を熱破壊から保護するための機能です。接合部温度が +165°C (標準値) に達するとハイ側 FET とロー側 FET のスイッチングを停止し、IC は TSD 状態となります。接合部温度が +155°C (標準値) 以下になると IC は TSD 状態から解除され、電源供給を再開させます。

## 7.2 保護機能一覧表

各保護機能が働いた場合の状態を下記の表に示します。

**Table 7-1 保護機能一覧表**

| 機能                       | ENA 端子<br>設定 | PG<br>端子出力 | DC/DC<br>コンバータ動作 | 備考                                                                                                 |

|--------------------------|--------------|------------|------------------|----------------------------------------------------------------------------------------------------|

| 停止動作                     | L            | Hi-Z (*1)  | 停止               | PG 端子は VOUT 端子にプルアップ抵抗を介して接続することを推奨しています。<br>ENA 端子がロー・レベルの際には VOUT 端子は 0V になるため、PG 端子は 0V を出力します。 |

| 通常動作                     | H            | Hi-Z (*1)  | スイッチング           | –                                                                                                  |

| 入力低電圧時誤動作防止<br>(入力 UVLO) | H            | L          | 停止               | UVLO 状態から解除後、ソフトスタートで自動復帰します。                                                                      |

| 出力低電圧保護<br>(出力 UVP)      | H            | L          | スイッチング           | –                                                                                                  |

| 出力過電圧保護<br>(出力 OVP)      | H            | L          | 停止               | –                                                                                                  |

| 出力過電流保護<br>(出力 OCP)      | H            | L          | スイッチング           | OCP は出力電圧を垂加させる動作です。                                                                               |

| 過熱保護<br>(TSD)            | H            | L          | 停止               | TSD 解除後、ソフトスタートで自動復帰します。                                                                           |

\*1: PG 端子はオープン・ドレインです。内部 MOSFET は OFF 状態。

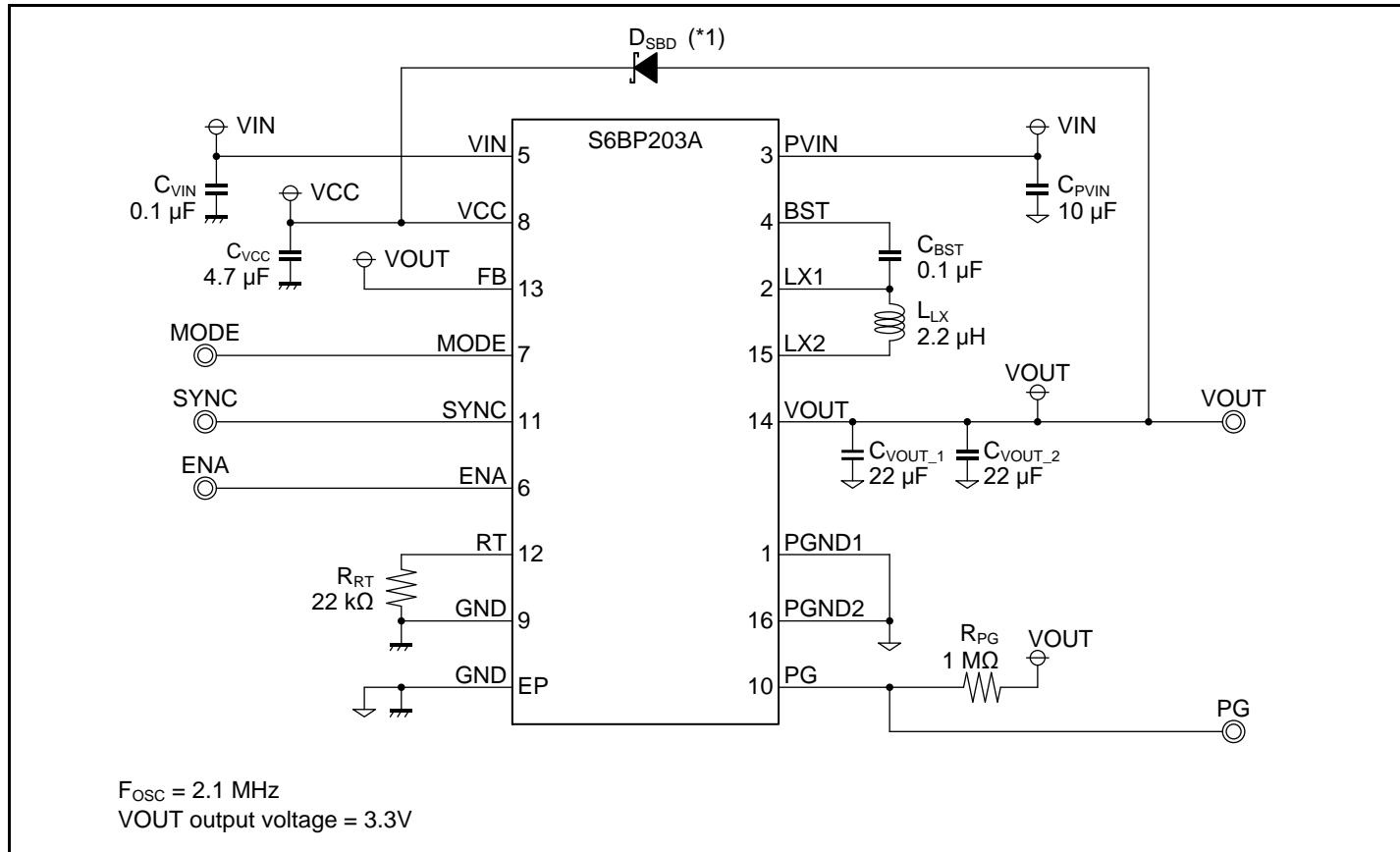

## 8. 応用回路例・部品表

Figure 8-1 応用回路例

\*1:  $VIN \leq 3.3V$  で使用する際は  $D_{SBD}$  が必要です。また、高温条件では  $D_{SBD}$  のリーク電流 ( $I_R$ ) が増加します。PWM/PFM 自動切り換え動作 (MODE = L, SYNC = L) 状況下では、 $D_{SBD}$  のリーク電流に応じた負荷を VOUT 端子に接続してください。

Table 8-1 部品表

| 記号                               | 項目                 | 値                 | 型格                   | ベンダ | パッケージサイズ (W×L×H[mm]) | 備考                               |

|----------------------------------|--------------------|-------------------|----------------------|-----|----------------------|----------------------------------|

| $C_{VIN}$ ,<br>$C_{BST}$         | セラミック容量            | 0.1 $\mu\text{F}$ | CGA2B3X7R1H104K050BB | TDK | 1.0×0.5×0.5          | X7R, 定格電圧: 50 Vdc                |

| $C_{PVIN}$                       | セラミック容量            | 10 $\mu\text{F}$  | CGA9N3X7R1H106K230KB | TDK | 5.7×5.0×2.3          | X7R, 定格電圧: 50 Vdc                |

| $C_{VCC}$                        | セラミック容量            | 4.7 $\mu\text{F}$ | CGA4J3X7R1C475K125AB | TDK | 2.0×1.25×1.25        | X7R, 定格電圧: 16 Vdc                |

| $C_{VOUT\_1}$ ,<br>$C_{VOUT\_2}$ | セラミック容量            | 22 $\mu\text{F}$  | CGA6P1X7R1C226M250AC | TDK | 3.2×2.5×2.5          | X7R, 定格電圧: 16 Vdc                |

| $L_{LX}$                         | インダクタ              | 2.2 $\mu\text{H}$ | CLF7045T-2R2N-D      | TDK | 7.2×6.9×4.5          | DCR: 14.6 mΩ, $Idc_{max}$ : 5.5A |

| $R_{RT}$                         | 抵抗                 | 22 kΩ             | RK73H1JTTD2202F      | KOA | 0.8×1.6×0.45         | —                                |

| $R_{PG}$                         | 抵抗                 | 1 MΩ              | RK73H1JTTD1004F      | KOA | 0.8×1.6×0.45         | —                                |

| $D_{SBD}$                        | ショットキー<br>バリアダイオード | —                 | MBR140SF             | ON  | 1.65×2.7×0.95        | —                                |

TDK: TDK 株式会社

KOA: コーア株式会社

ON: オン・セミコンダクタ・コーポレーション

## 9. アプリケーションノート

### 9.1 動作条件の設定

#### DC/DC コンバータ動作設定

DC/DC コンバータの動作状態は MODE 端子と SYNC 端子によって設定されます。

Table 9-1 DC/DC コンバータ動作設定

| MODE 端子 | SYNC 端子 (信号入力) | DC/DC コンバータの動作状態            |

|---------|----------------|-----------------------------|

| L (*3)  | L (*3)         | 内部クロック信号による PWM/PFM 自動切換動作  |

|         | 外部クロック入力 (*5)  | 外部クロック信号と同期した PWM 固定動作 (*2) |

|         | H (*4)         | 使用禁止 (*1)                   |

| H (*4)  | L (*3)         | 内部クロック信号による PWM 固定動作        |

|         | 外部クロック入力 (*5)  | 外部クロック信号と同期した PWM 固定動作 (*2) |

|         | H (*4)         | 使用禁止 (*1)                   |

\*1: SYNC 端子がハイレベルの場合、休止電流 ( $I_{VINO}$ ) が上昇します。

\*2: RT 抵抗値 ( $R_{RT}$ ) を  $330\text{ k}\Omega$  に設定してください。

\*3: GND1 端子または GND2 端子電圧を印加してください。

\*4: VOUT 端子電圧を印加してください。

\*5: ハイレベル時は VOUT 端子電圧を印加してください。ローレベル時は GND1 端子または GND2 電圧を印加してください。

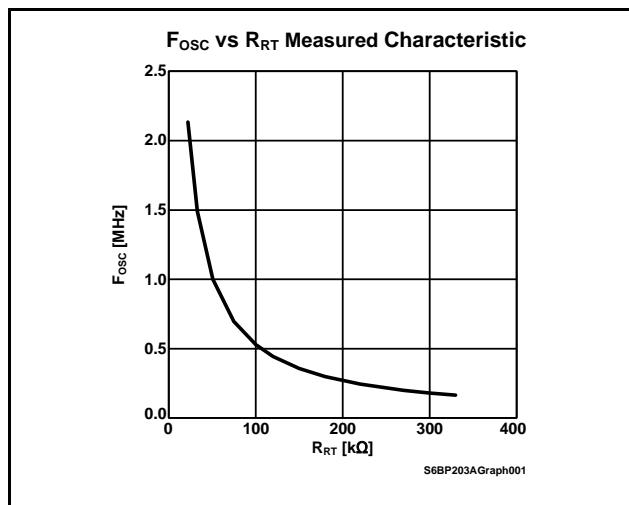

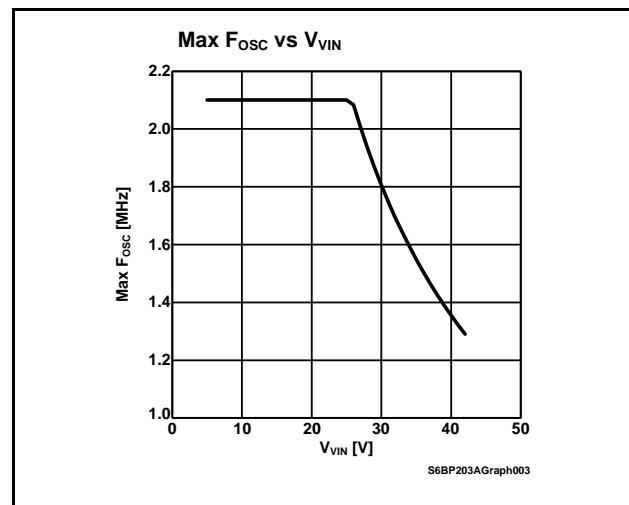

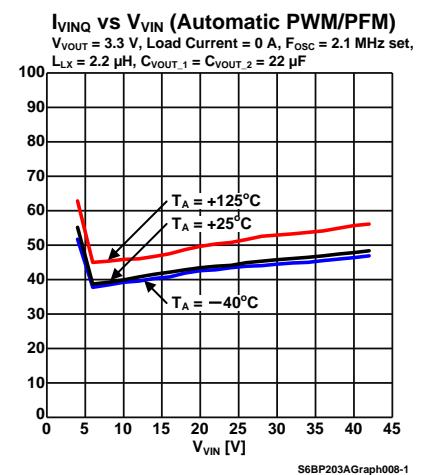

#### スイッチング周波数 (内部クロック) の設定

スイッチング周波数 (内部クロック) は RT 端子に接続するタイミング抵抗 ( $R_{RT}$ ) で設定できます。Figure 9-1 の範囲でタイミング抵抗を設定してください。また、入力電圧によりスイッチング周波数が制限されます。Figure 9-2 の範囲でスイッチング周波数を設定してください。

Figure 9-1  $F_{osc}$  vs  $R_{RT}$  の実測特性

Figure 9-2 最大  $F_{osc}$  vs  $V_{VIN}$

下記の式で参考値を算出できます。

$$F_{osc} [\text{Hz}] \approx \frac{1}{R_{RT} \times 21.7 \times 10^{-12}}$$

F<sub>osc</sub> : スイッチング周波数 [Hz]

R<sub>RT</sub> : タイミング抵抗値 [Ω]

### ソフトスタート時間の設定

ソフトスタート時間は、RT 端子に接続するタイミング抵抗 ( $R_{RT}$ ) で決まります。

$$T_{SS} \text{ [s]} = \frac{1}{F_{osc}} \times 2 \times 1024$$

$T_{SS}$  : ソフトスタート時間 [s]

$F_{osc}$  : スイッチング周波数 [Hz]

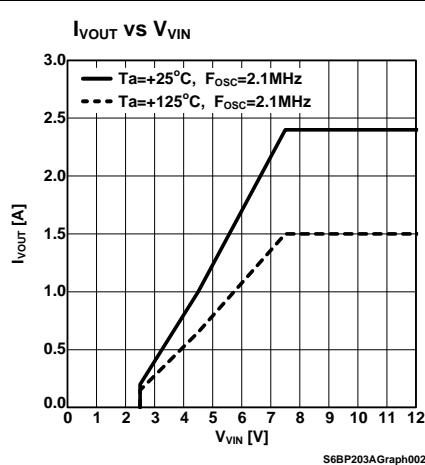

### VOUT 最大出力電流の検討

VOUT 端子の最大出力電流が以下のグラフの範囲内であることを確認してください。

Figure 9-3  $I_{VOUT}$  vs  $V_{VIN}$

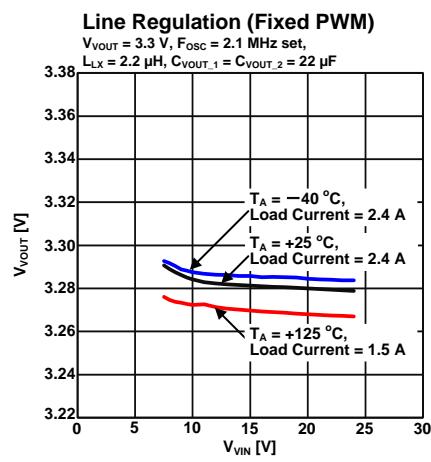

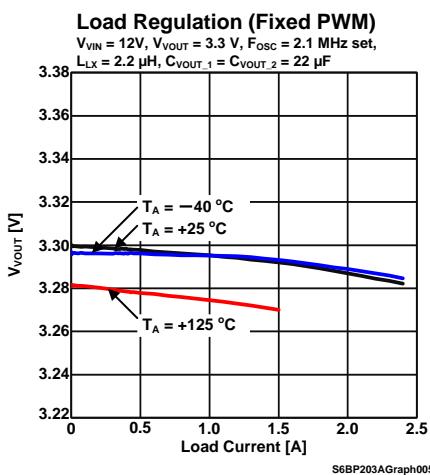

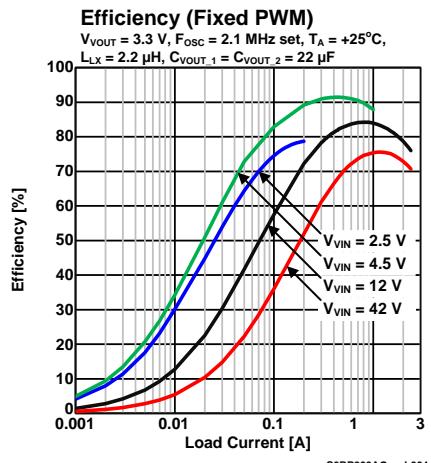

## 10. 参考データ

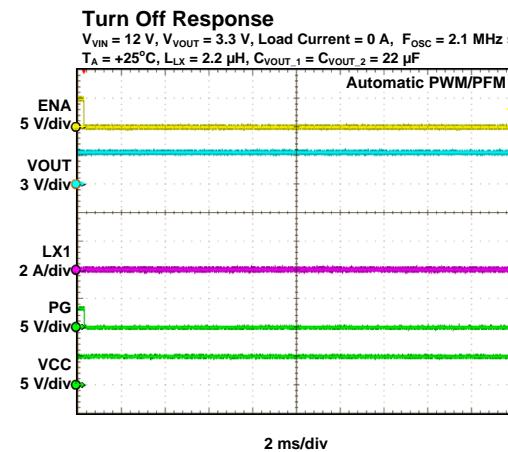

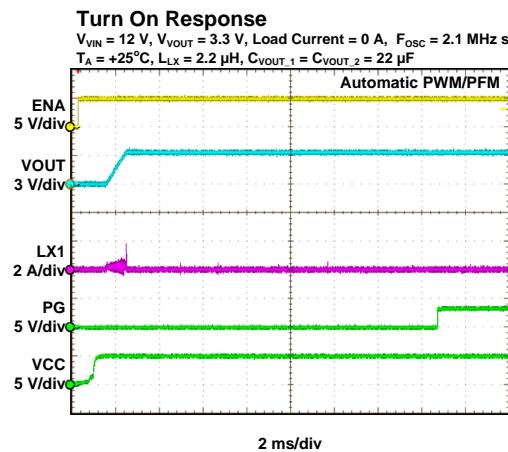

下記は、「8. 応用回路例・部品表」の条件で測定した参考データです。

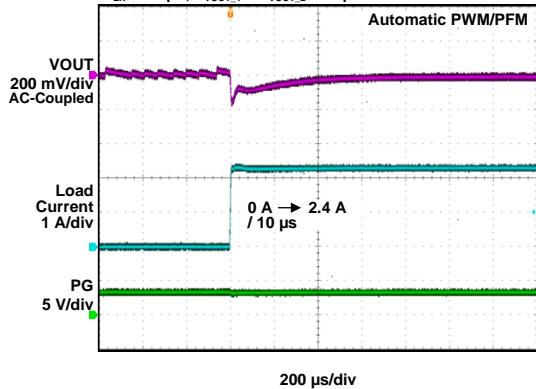

**Load Transient Response**

$V_{IN} = 12 \text{ V}$ ,  $V_{OUT} = 3.3 \text{ V}$ ,  $F_{OSC} = 2.1 \text{ MHz}$  set,  $T_A = +25^\circ\text{C}$ ,

$L_{LX} = 2.2 \mu\text{H}$ ,  $C_{VOUT\_1} = C_{VOUT\_2} = 22 \mu\text{F}$

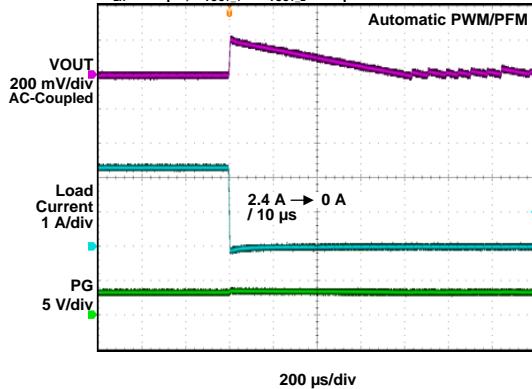

**Load Transient Response**

$V_{IN} = 12 \text{ V}$ ,  $V_{OUT} = 3.3 \text{ V}$ ,  $F_{OSC} = 2.1 \text{ MHz}$  set,  $T_A = +25^\circ\text{C}$ ,

$L_{LX} = 2.2 \mu\text{H}$ ,  $C_{VOUT\_1} = C_{VOUT\_2} = 22 \mu\text{F}$

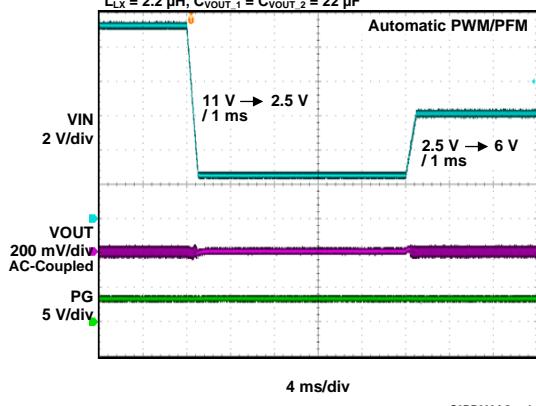

**Cold Crank Line Transient Response**

$V_{OUT} = 3.3 \text{ V}$ , Load Current = 0.2 A,  $F_{OSC} = 2.1 \text{ MHz}$  set,  $T_A = +25^\circ\text{C}$ ,

$L_{LX} = 2.2 \mu\text{H}$ ,  $C_{VOUT\_1} = C_{VOUT\_2} = 22 \mu\text{F}$

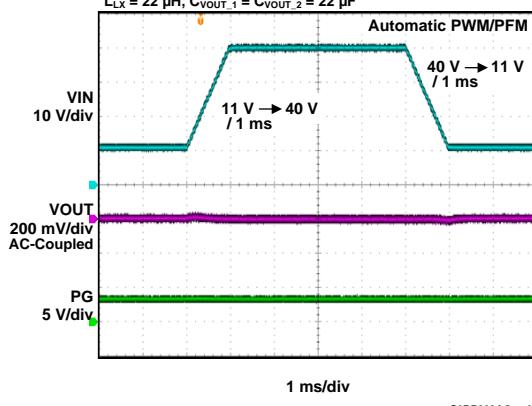

**Load Dump Line Transient Response**

$V_{OUT} = 3.3 \text{ V}$ , Load Current = 2.4 A,  $F_{OSC} = 200 \text{ kHz}$  set,  $T_A = +25^\circ\text{C}$ ,

$L_{LX} = 22 \mu\text{H}$ ,  $C_{VOUT\_1} = C_{VOUT\_2} = 22 \mu\text{F}$

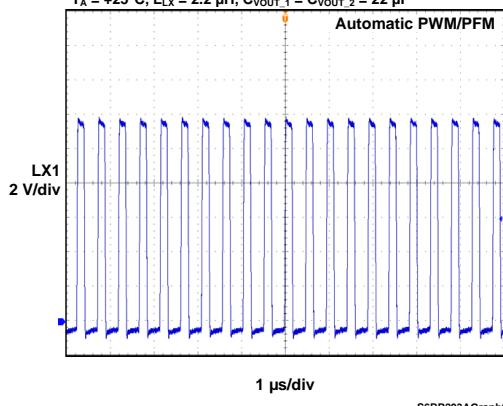

**Switching Waveform**

$V_{IN} = 12 \text{ V}$ ,  $V_{OUT} = 3.3 \text{ V}$ , Load Current = 2.4 A,  $F_{OSC} = 2.1 \text{ MHz}$  set,

$T_A = +25^\circ\text{C}$ ,  $L_{LX} = 2.2 \mu\text{H}$ ,  $C_{VOUT\_1} = C_{VOUT\_2} = 22 \mu\text{F}$

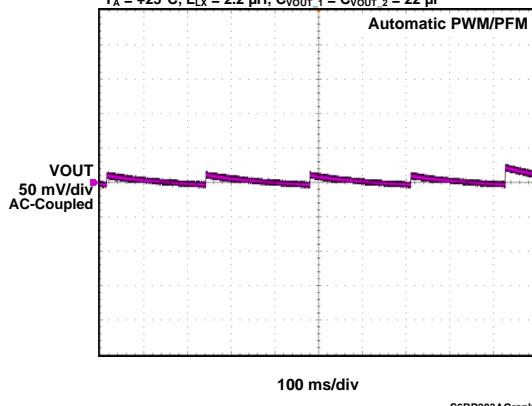

**Ripple Waveform**

$V_{IN} = 12 \text{ V}$ ,  $V_{OUT} = 3.3 \text{ V}$ , Load Current = 0 A,  $F_{OSC} = 2.1 \text{ MHz}$  set,

$T_A = +25^\circ\text{C}$ ,  $L_{LX} = 2.2 \mu\text{H}$ ,  $C_{VOUT\_1} = C_{VOUT\_2} = 22 \mu\text{F}$

## 11. 使用上の注意

プリント基板のアースラインは、共通インピーダンスを考慮し設計してください。

### 静電気対策を行ってください。

- 半導体を入れる容器は、静電気対策を施した容器か導電性の容器をご使用ください。

- 実装後のプリント基板を保管・運搬する場合は、導電性の袋か容器に収納してください。

- 作業台、工具、測定機器は、アースを取ってください。

- 作業する人は、人体とアースの間に  $250\text{ k}\Omega\sim1\text{ M}\Omega$  の抵抗を直列に入れてください。

### 負電圧を印加しないでください。

-0.3V 以下の負電圧を印加した場合、LSI の寄生トランジスタが動作し誤動作を起こすことがあります。

## 12. RoHS 指令に対応した品質管理

本製品は、RoHS 指令に対応し、鉛・カドミウム・水銀・六価クロムと、特定臭素系難燃剤 PBB と PBDE の基準を遵守しています。

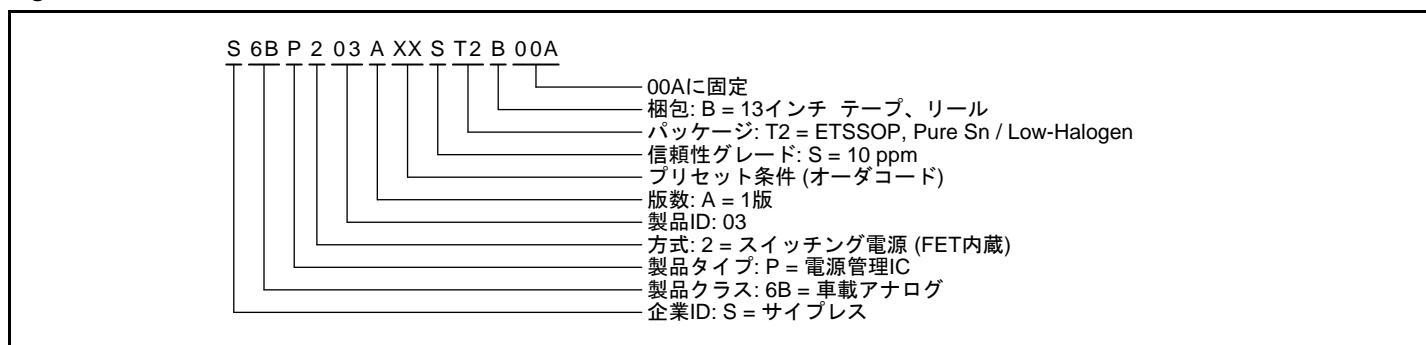

## 13. オーダ型格

Table 13-1 オーダ型格

| オーダコード | 型格 (MPN)          | パッケージ                                                          |

|--------|-------------------|----------------------------------------------------------------|

| 8F     | S6BP203A8FST2B00A | プラスチック・ETSSOP16 (0.65 mm ピッチ), 16 ピン<br>(Package Code: SEC016) |

MPN: Marketing Part Number

Figure 13-1 オーダ型格の定義

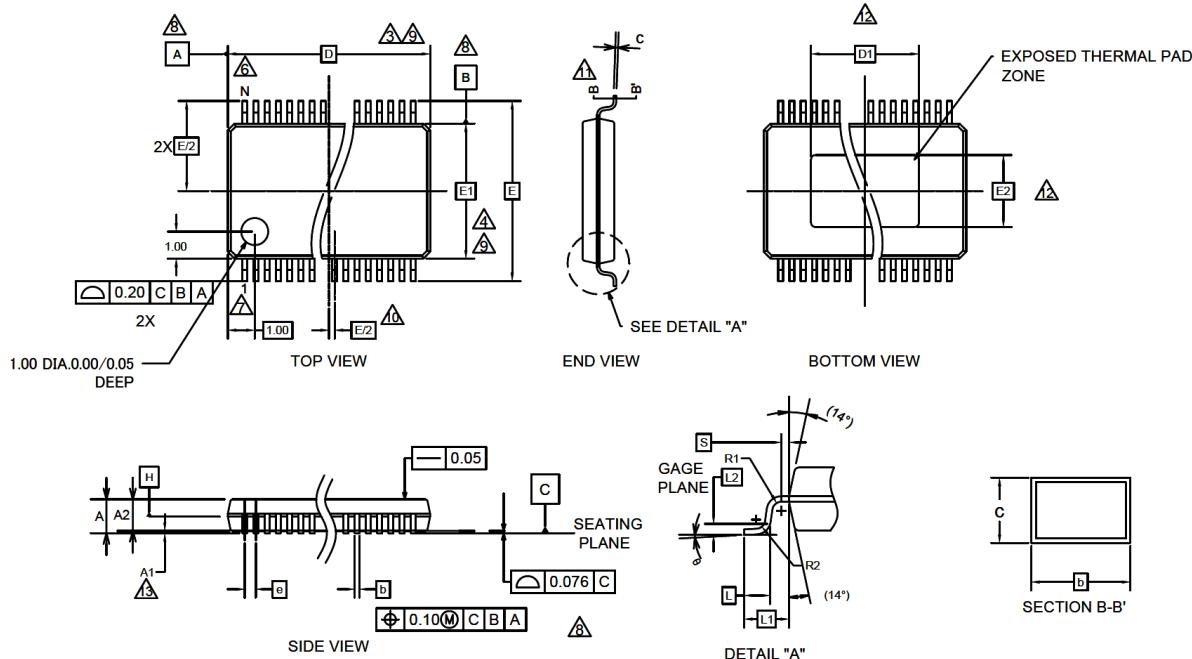

## 14. パッケージ・外形寸法図

Package Code: SEC016

| SYMBOL         | DIMENSIONS |      |      |

|----------------|------------|------|------|

|                | MIN.       | NOM. | MAX. |

| A              | -          | -    | 1.10 |

| A1             | 0.05       | -    | 0.15 |

| A2             | 0.85       | 0.90 | 0.95 |

| D              | 4.90       | 5.00 | 5.10 |

| E1             | 4.30       | 4.40 | 4.50 |

| E              | 6.40 BSC   |      |      |

| D1             | 2.90       | 3.00 | 3.10 |

| E2             | 2.90       | 3.00 | 3.10 |

| S              | 0.20       | -    | -    |

| R1             | 0.09       | -    | -    |

| R2             | 0.09       | -    | -    |

| θ              | 0°         | -    | 8°   |

| c              | 0.09       | -    | 0.20 |

| b              | 0.19       | -    | 0.30 |

| L              | 0.50       | 0.60 | 0.70 |

| L <sub>1</sub> | 1.00 REF   |      |      |

| L <sub>2</sub> | 0.25 BSC   |      |      |

| e              | 0.65 BSC   |      |      |

| N              | 16         |      |      |

NOTE:

1. ALL DIMENSIONS ARE IN MILLIMETERS.

2. DIMENSIONING & TOLERANCES PER ASME. Y14.5M-1994.

3. DIMENSION 'D' DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS. MOLD FLASH, PROTRUSIONS OR GATE BURRS SHALL NOT EXCEED 0.15 PER SIDE.

4. DIMENSION 'E1' DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION SHALL NOT EXCEED 0.25 PER SIDE.

5. DIMENSION 'b' DOES NOT INCLUDE DAMBER PROTRUSION. ALLOWABLE DAMBER PROTRUSIONS SHALL BE 0.07mm TOTAL IN EXCESS OF THE 'b' DIMENSION AT MAXIMUM MATERIAL CONDITION. DAMBER CANNOT BE LOCATED ON THE LOWER RADIUS OF THE FOOT. MINIMUM SPACE BETWEEN PROTRUSION AND ADJACENT LEAD SHOULD BE 0.08mm FOR 0.65mm PITCH, 0.08mm FOR 0.50mm PITCH AND 0.07mm FOR 0.40mm PITCH PACKAGES.

6. 'N' IS THE MAXIMUM NUMBER OF TERMINAL POSITIONS FOR THE SPECIFIED PACKAGE LENGTH.

7. TERMINAL NUMBERS ARE SHOWN FOR REFERENCE ONLY.

8. DATUMS A AND B TO BE DETERMINED AT DATUM PLANE H.

9. DIMENSIONS 'D' AND 'E1' TO BE DETERMINED AT DATUM PLANE H.

10. THIS DIMENSION APPLIES ONLY TO VARIATIONS WITH AN EVEN NUMBER OF LEADS PER SIDE FOR VARIATION WITH AN ODD NUMBER OF LEADS PER SIDE, THE "CENTER" LEAD MUST BE COINCIDENT WITH THE PACKAGE CENTERLINE, DATUM A.

11. CROSS SECTION B-B' TO BE DETERMINED AT 0.10 TO 0.25MM FROM THE LEAD TIP.

12. DIMENSIONS "D1" AND "E2" ARE THERMALLY ENHANCED VARIATIONS. END USER SHOULD VERIFY AVAILABLE SIZE OF EXPOSED PER FOR SPECIFIC DEVICE APPLICATION "D1" AND "E2" DIMENSIONS DO NOT INCLUDE MOLD FLASH.

13. A1 IS DEFINED AS THE VERTICAL CLEARANCE FROM THE SEATING PLANE TO THE LOWEST POINT ON THE PACKAGE BODY.

PACKAGE OUTLINE, 16 LEAD ETSSOP

SEC016

002-10769 Rev. \*\*

## 15. 主な変更内容

Spansion Publication Number: S6BP203A\_DS405-00031

| ページ             | 場所       | 変更箇所                                                                                                          |

|-----------------|----------|---------------------------------------------------------------------------------------------------------------|

| Preliminary 0.1 | —        | 初版                                                                                                            |

| Preliminary 0.2 | —        | —                                                                                                             |

| 12              | 10. 機能説明 | 「出力過電圧保護 (出力 OVP)」の説明を修正<br>「VOUT OVP 立上り閾値 (P <sub>GOVPHL</sub> )」 → 「VOUT OVP 立下り閾値 (P <sub>GOVPHL</sub> )」 |

注意事項: 以降の変更点に関しては、「改訂履歴」を参照してください。

## 改訂履歴

文書名: S6BP203A ASSP 42V, 2.4A 同期整流式昇降圧 DC/DC コンバータ IC

文書番号: 002-08535

| 版  | ECN 番号  | 変更者  | 発行日        | 変更内容                                   |

|----|---------|------|------------|----------------------------------------|

| ** | —       | HIXT | 09/04/2015 | New Spec.                              |

| *A | 5056152 | HIXT | 12/18/2015 | これは英語版の 002-08534 Rev. *A を翻訳した日本語版です。 |

| *B | 5164348 | HIXT | 03/08/2016 | これは英語版の 002-08534 Rev. *B を翻訳した日本語版です。 |

| *C | 5843028 | MASG | 08/03/2017 | Adapted Cypress new logo.              |

| *D | 5969949 | HIXT | 11/20/2017 | これは英語版の 002-08534 Rev. *D を翻訳した日本語版です。 |

## セールス、ソリューションおよび法律情報

### ワールドワイドな販売と設計サポート

サイプレスは、事業所、ソリューションセンター、メーカー代理店、および販売代理店の世界的なネットワークを保持しています。お客様の最寄りのオフィスについては、[サイプレスのロケーションページ](#)をご覧ください。

#### 製品

|                               |                                                                    |

|-------------------------------|--------------------------------------------------------------------|

| ARM® Cortex® Microcontrollers | <a href="http://cypress.com/arm">cypress.com/arm</a>               |

| 車載用                           | <a href="http://cypress.com/automotive">cypress.com/automotive</a> |

| クロック&パッファ                     | <a href="http://cypress.com/clocks">cypress.com/clocks</a>         |

| インターフェース                      | <a href="http://cypress.com/interface">cypress.com/interface</a>   |

| IoT(モノのインターネット)               | <a href="http://cypress.com/iot">cypress.com/iot</a>               |

| メモリ                           | <a href="http://cypress.com/memory">cypress.com/memory</a>         |

| マイクロコントローラ                    | <a href="http://cypress.com/mcu">cypress.com/mcu</a>               |

| PSoC                          | <a href="http://cypress.com/psoc">cypress.com/psoc</a>             |

| 電源用 IC                        | <a href="http://cypress.com/pmic">cypress.com/pmic</a>             |

| タッチ センシング                     | <a href="http://cypress.com/touch">cypress.com/touch</a>           |

| USB コントローラ                    | <a href="http://cypress.com/usb">cypress.com/usb</a>               |

| ワイヤレス                         | <a href="http://cypress.com/wireless">cypress.com/wireless</a>     |

#### PSoC® ソリューション

[PSoC 1](#) | [PSoC 3](#) | [PSoC 4](#) | [PSoC 5LP](#) | [PSoC 6](#)

#### サイプレス開発者コミュニティ

[フォーラム](#) | [WICED IOT Forums](#) | [Projects](#) | [ビデオ](#) | [ブログ](#) | [トレーニング](#) | [Components](#)

#### テクニカルサポート

[cypress.com/support](http://cypress.com/support)

Arm and Cortex are registered trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere.

© Cypress Semiconductor Corporation, 2015-2017. 本書面は、Cypress Semiconductor Corporation 及び Spansion LLC を含むその子会社（以下「Cypress」という。）に帰属する財産である。本書面（本書面に含まれ又は言及されているあらゆるソフトウェア若しくはファームウェア（以下「本ソフトウェア」という。）を含む）は、アメリカ合衆国及び世界のその他の国における知的財産法令及び条約に基づき Cypress が所有する。Cypress はこれらの法令及び条約に基づく全ての権利を留保し、本段落で特に記載されているものを除き、その特許権、著作権、商標権又はその他の知的財産権のライセンスを一切許諾しない。本ソフトウェアにライセンス契約書が伴っておらず、かつ Cypress との間で別途本ソフトウェアの使用方法を定める書面による合意がない場合、Cypress は、(1) 本ソフトウェアの著作権に基づき、(a) ソースコード形式で提供されている本ソフトウェアについて、Cypress ハードウェア製品と共に用いるためにのみ、かつ組織内部でのみ、本ソフトウェアの修正及び複製を行うこと、並びに (b) Cypress のハードウェア製品ユニットに用いるためにのみ、（直接又は再販売者及び販売代理店を介して間接のいずれかで）本ソフトウェアをバイナリコード形式で外部エンドユーザーに配布すること、並びに (2) 本ソフトウェア（Cypress により提供され、修正がなされていないもの）が抵触する Cypress の特許権のクレームに基づき、Cypress ハードウェア製品と共に用いるためにのみ、本ソフトウェアの作成、利用、配布及び輸入を行うことについての非独占的で譲渡不能な一身専属のライセンス（サプライセンスの権利を除く）を付与する。本ソフトウェアのその他の使用、複製、修正、変換又はコンパイルを禁止する。

**適用される法律により許される範囲内で、Cypress は、本書面又はいかなる本ソフトウェア若しくはこれに伴うハードウェアに關しても、明示又は默示をとわず、いかなる保証（商品性及び特定の目的への適合性の默示の保証を含むがこれらに限られない）も行わない。**適用される法律により許される範囲内で、Cypress は、別途通知することなく、本書面を変更する権利を留保する。Cypress は、本書面に記載のある、いかなる製品若しくは回路の適用又は使用から生じる一切の責任を負わない。本書面で提供されたあらゆるサンプルデザイン情報又はプログラムコードを含む）は、参照目的のために提供されたものである。この情報で構成するあらゆるアリケーション及びその結果としてのあらゆる製品の機能性及び安全性を適切に設計、プログラム、かつテストすることは、本書面のユーザーの責任において行われるものとする。Cypress 製品は、兵器、兵器システム、原子力施設、生命維持装置若しくは生命維持システム、蘇生用の設備及び外科的移植を含むその他の医療機器若しくは医療システム、汚染管理若しくは有害物質管理の運用のために設計され若しくは意図されたシステムの重要な構成部分としての使用、又は装置若しくはシステムの不具合が人身傷害、死亡若しくは物的損害を生じさせるようなその他の使用（以下「本目的外使用」という。）のためには設計、意図又は承認されていない。重要な構成部分とは、それの不具合が装置若しくはシステムの不具合を生じさせるか又はその安全性若しくは実効性に影響すると合理的に予想できるような装置若しくはシステムのあらゆる構成部分をいう。Cypress 製品はそれら一切から本書により免除される。Cypress は Cypress 製品の本目的外使用から生じ又は本目的外使用に関連するいかなる請求、損害又はその他の責任についても、Cypress はその全部又は一部をとわず一切の責任を負わず、かつ Cypress はそれら一切から本書により免責される。Cypress は Cypress 製品の本目的外使用から生じ又は本目的外使用に関連するあらゆる請求、費用、損害及びその他の責任（人身傷害又は死亡に基づく請求を含む）から免責補償される。

Cypress, Cypress のロゴ、Spansion, Spansion のロゴ及びこれらの組み合わせ、WICED, PSoC, CapsSense, EZ-USB, F-RAM、及び Traveo は、米国及びその他の国における Cypress の商標又は登録商標である。Cypress のより完全な商標のリストは、[cypress.com](http://cypress.com) を参照すること。その他の名称及びブランドは、それぞれの権利者の財産として権利主張がなされている可能性がある。