### **Features**

- · High speed

- $t_{AA} = 10 \text{ ns}$

- Embedded error-correcting code (ECC) for single-bit error correction

- · Low active and standby currents

- I<sub>CC</sub> = 90 mA typical at 100 MHz

- I<sub>SB2</sub> = 20 mA typical

- Operating voltage range: 2.2 V to 3.6 V

- 1.0-V data retention

- Transistor-transistor logic (TTL) compatible inputs and outputs

- ERR pin to indicate 1-bit error detection and correction

- Available in Pb-free 44-pin TSOP II package

### **Functional description**

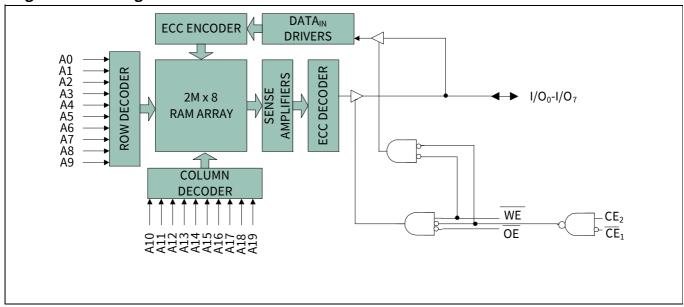

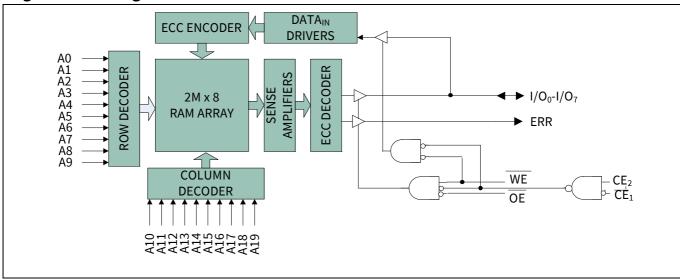

The CY7C1059H and CY7C1059HE are dual chip enable high-performance CMOS fast static RAM devices with embedded ECC. The CY7C1059H device is available in standard pin configurations. The CY7C1059HE device includes a single bit error indication pin (ERR) that signals the host processor in the case of an ECC error-detection and correction event.

To write to the device, take chip enables ( $\overline{CE}_1$  LOW and  $\overline{CE}_2$  HIGH) and write enable ( $\overline{WE}$ ) input LOW. Data on the eight I/O pins (I/O<sub>0</sub> through I/O<sub>7</sub>) is then written into the location specified on the address pins (A<sub>0</sub> through A<sub>20</sub>).

To read from the device, take chip enables  $(\overline{CE}_1 \text{ LOW})$  and  $CE_2 \text{ HIGH}$  and output enable  $(\overline{OE})$  LOW while forcing the write enable  $(\overline{WE})$  HIGH. Under these conditions, the contents of the memory location specified by the address pins will appear on the I/O pins. See **Truth table – CY7C1059H/CY7C1059HE on page 18** for a complete description of read and write modes. The input and output pins  $(I/O_0 \text{ through } I/O_7)$  are placed in a high impedance state when the device is deselected  $(\overline{CE}_1 \text{ HIGH})$  or  $CE_2 \text{ LOW}$ , the outputs are disabled  $(\overline{OE} \text{ HIGH})$ , or during a write operation  $(\overline{CE}_1 \text{ LOW})$ ,  $CE_2 \text{ HIGH}$ , and  $CE_2 \text{ LOW}$ .

On CY7C1059HE devices, the detection and correction of a single-bit error in the accessed location is indicated by the assertion of the ERR output (ERR = High)  $^{[1]}$ .

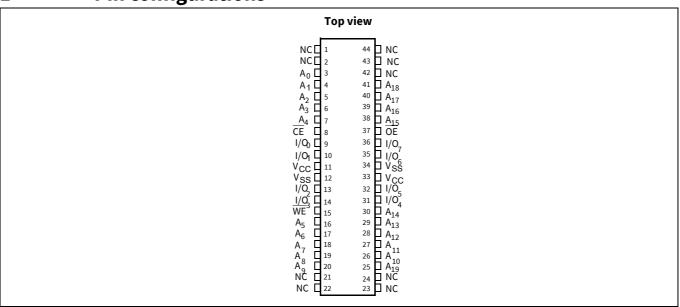

All I/Os (I/O<sub>0</sub> through I/O<sub>7</sub>) are placed in a high impedance state when the device is deselected ( $\overline{\text{CE}}_1$  HIGH or  $\overline{\text{CE}}_2$  LOW), and control signals are de-asserted ( $\overline{\text{CE}}_1$  /  $\overline{\text{CE}}_2$ ,  $\overline{\text{OE}}$ , WE). CY7C1059H and CY7C1059HE devices are available in a 44-pin TSOP II package with center power and ground (revolutionary) pinout package.

#### Note

1. Automatic write back on error detection feature is not supported in this device.

Logic block diagram - CY7C1059H

# Logic block diagram - CY7C1059H

### Logic block diagram - CY7C1059HE

Table of contents

### Table of contents

| Features                              |    |

|---------------------------------------|----|

| Functional description                |    |

| Logic block diagram - CY7C1059H       | 2  |

| Logic block diagram - CY7C1059HE      |    |

| Table of contents                     |    |

| 1 Pin configurations                  | 4  |

| 2 Product portfolio                   | 5  |

| 3 Maximum ratings                     | 6  |

| 4 Operating range                     | 7  |

| 5 DC electrical characteristics       | 8  |

| 6 Capacitance                         | g  |

| 7 Thermal resistance                  | 10 |

| 8 AC test loads and waveforms         | 11 |

| 9 Data retention                      | 12 |

| 9.1 Data retention characteristics    | 12 |

| 9.2 Data retention waveform           | 12 |

| 10 AC switching characteristics       | 13 |

| 11 Switching waveforms                | 15 |

| 12 Truth table - CY7C1059H/CY7C1059HE | 18 |

| 13 ERR output- CY7C1059HE             | 19 |

| 14 Ordering information               |    |

| 14.1 Ordering code definitions        | 20 |

| 15 Package diagram                    |    |

| 16 Acronyms                           |    |

| 17 Document conventions               |    |

| 17.1 Units of measure                 | 23 |

| Revision history                      | 24 |

Pin configurations

# 1 Pin configurations

Figure 1 44-pin TSOP II<sup>[2]</sup>

### Note

2. NC pins are not connected on the die.

2021-11-02

infineon

Product portfolio

# 2 Product portfolio

### Table 1 Product portfolio

|              | Footures and                       |            | V <sub>CC</sub> range<br>(V) |       | Power dissipation                                           |     |                                   |     |  |

|--------------|------------------------------------|------------|------------------------------|-------|-------------------------------------------------------------|-----|-----------------------------------|-----|--|

| Product      | Features and options (see the "Pin | Range      |                              | Speed | Operating I <sub>CC</sub> ,<br>(mA)<br>f = f <sub>max</sub> |     | Standby, I <sub>SB2</sub><br>(mA) |     |  |

|              | configurations" on page 4 section) |            | (V)                          | (ns)  |                                                             |     |                                   |     |  |

|              | on page 4 section)                 |            |                              |       | <b>Typ</b> [3]                                              | Max | <b>Typ</b> [3]                    | Max |  |

| CY7C1059H30  | Dual-chip enable                   | Industrial | 2.2 V-3.6 V                  | 10    | 90                                                          | 110 | 20                                | 30  |  |

| CY7C1059HE30 | Dual-chip enable and ERR output    |            | 2.2 V-3.6 V                  | 10    | 90                                                          | 110 | 20                                | 30  |  |

#### Note

3. Typical values are included for reference only and are not guaranteed or tested. Typical values are measured at  $V_{CC}$  = 1.8 V (for  $V_{CC}$  range of 1.65 V-2.2 V),  $V_{CC}$  = 3 V (for  $V_{CC}$  range of 2.2 V-3.6 V), and  $V_{CC}$  = 5 V (for  $V_{CC}$  range of 4.5 V-5.5 V),  $V_{CC}$  = 25°C.

infineon

Maximum ratings

# 3 Maximum ratings

| Exceeding maximum ratings may impair the useful life of the device. These user guid | delines are not tested.          |

|-------------------------------------------------------------------------------------|----------------------------------|

| Storage temperature                                                                 | 65°C to +150°C                   |

| Ambient temperature with power applied                                              | –55°C to +125°C                  |

| Supply voltage on V <sub>CC</sub> relative to GND                                   | 0.5 V to +6.0 V                  |

| DC voltage applied to outputs in high Z state [4]                                   | 0.5 V to V <sub>CC</sub> + 0.5 V |

| DC input voltage [4]                                                                | 0.5 V to V <sub>CC</sub> + 0.5 V |

| Current into outputs (LOW)                                                          | 20 mA                            |

| Static discharge voltage (MIL-STD-883, method 3015)                                 | >2001 V                          |

| Latch up current                                                                    | > 140 mA                         |

#### Note

4.  $V_{IL(min)} = -2.0 \text{ V}$  and  $V_{IH(max)} = V_{CC} + 2 \text{ V}$  for pulse durations of less than 20 ns.

infineon

Operating range

# 4 Operating range

### Table 2 Operating range

| Grade      | Ambient temperature | V <sub>CC</sub> |  |

|------------|---------------------|-----------------|--|

| Industrial | -40°C to +85°C      | 2.2 V to 3.6 V  |  |

DC electrical characteristics

#### **DC** electrical characteristics 5

#### **DC** electrical characteristics Table 3

Over the operating range of -40°C to 85°C

| Parameter        | Description Test conditions                        |                | 10 ns                                                                                                                                                                                                                                 |                     |      | 11             |                       |      |

|------------------|----------------------------------------------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|----------------|-----------------------|------|

|                  | Desc                                               | cription       | lest conditio                                                                                                                                                                                                                         | Test conditions     |      | <b>Typ</b> [6] | Max                   | Unit |

| V <sub>OH</sub>  | Output                                             | 2.2 V to 2.7 V | $V_{CC}$ = Min, $I_{OH}$ = -1.0 mA                                                                                                                                                                                                    |                     | 2.0  | -              | -                     | V    |

|                  | HIGH<br>voltage                                    | 2.7 V to 3.0 V | $V_{CC}$ = Min, $I_{OH}$ = -4.0 mA                                                                                                                                                                                                    |                     | 2.2  | -              | -                     |      |

|                  | 1011000                                            | 3.0 V to 3.6 V | $V_{CC} = Min, I_{OH} = -4.0 \text{ mA}$                                                                                                                                                                                              |                     | 2.4  | -              | -                     |      |

| V <sub>OL</sub>  | Output                                             | 2.2 V to 2.7 V | V <sub>CC</sub> = Min, I <sub>OL</sub> = 2 mA                                                                                                                                                                                         |                     | -    | -              | 0.4                   |      |

|                  | LOW<br>voltage                                     | 2.7 V to 3.6 V | V <sub>CC</sub> = Min, I <sub>OL</sub> = 8 mA                                                                                                                                                                                         |                     | -    | -              | 0.4                   |      |

| V <sub>IH</sub>  | Input                                              | 2.2 V to 2.7 V | -                                                                                                                                                                                                                                     |                     | 2.0  | -              | V <sub>CC</sub> + 0.3 |      |

|                  | HIGH<br>voltage                                    | 2.7 V to 3.6 V | -                                                                                                                                                                                                                                     |                     | 2.0  | -              | V <sub>CC</sub> + 0.3 |      |

| V <sub>IL</sub>  | Input LOW                                          | 2.2 V to 2.7 V | -                                                                                                                                                                                                                                     |                     | -0.3 | -              | 0.6                   |      |

|                  | voltage <sup>[5]</sup>                             | 2.7 V to 3.6 V | -                                                                                                                                                                                                                                     |                     | -0.3 | _              | 0.8                   |      |

| I <sub>IX</sub>  | Input leaka                                        | ge current     | $GND \le V_{IN} \le V_{CC}$                                                                                                                                                                                                           |                     | -1.0 | _              | +1.0                  | μΑ   |

| I <sub>OZ</sub>  | Output leal                                        | kage current   | $GND \le V_{OUT} \le V_{CC}$ , output                                                                                                                                                                                                 | t disabled          | -1.0 | _              | +1.0                  |      |

| I <sub>CC</sub>  | Operatings                                         | supply current |                                                                                                                                                                                                                                       | f = 100 MHz         | ı    | 90.0           | 110.0                 | mA   |

|                  |                                                    |                | CMOS levels                                                                                                                                                                                                                           | f=66.7 MHz          | ı    | 70.0           | 80.0                  |      |

| I <sub>SB1</sub> | Automatic CE power<br>down current – TTL<br>inputs |                | $\begin{aligned} &\text{Max V}_{\text{CC}}, \overline{\text{CE}} \ge \text{V}_{\text{IH}}^{[7]}, \\ &\text{V}_{\text{IN}} \ge \text{V}_{\text{IH}} \text{ or V}_{\text{IN}} \le \text{V}_{\text{IL}}, f = f_{\text{I}} \end{aligned}$ | XAM                 | 1    | _              | 40.0                  |      |

| I <sub>SB2</sub> | Automatic<br>down curre<br>inputs                  |                | $\begin{aligned} &\text{Max V}_{\text{CC}}, \overline{\text{CE}} \ge \text{V}_{\text{CC}} - 0.2 \text{ V} \\ &\text{V}_{\text{IN}} \ge \text{V}_{\text{CC}} - 0.2 \text{ V or V}_{\text{IN}} \le 0 \end{aligned}$                     | [7]<br>0.2 V, f = 0 | -    | 20.0 [6]       | 30.0                  |      |

<sup>5.</sup> V<sub>IL(min)</sub> = -2.0 V and V<sub>IH(max)</sub> = V<sub>CC</sub> + 2 V for pulse durations of less than 20 ns.

6. Typical values are included for reference only and are not guaranteed or tested. Typical values are measured at V<sub>CC</sub> = 3 V (for V<sub>CC</sub> range of 2.2 V-3.6 V) T<sub>A</sub> = 25°C.

7. For all <u>dual</u> chip enable <u>de</u>vices, CE is the logical combination of CE<sub>1</sub> and CE<sub>2</sub>. When CE<sub>1</sub> is LOW and CE<sub>2</sub> is HIGH, CE is LOW; when CE<sub>1</sub> is HIGH or CE<sub>2</sub> is LOW, CE is HIGH.

**(infineon**

Capacitance

# 6 Capacitance

### Table 4 Capacitance

| Parameter [8]    | Description       | Test conditions                                    | 44-pin TSOP II | Unit |

|------------------|-------------------|----------------------------------------------------|----------------|------|

| C <sub>IN</sub>  | Input capacitance | $T_A = 25$ °C, $f = 1$ MHz, $V_{CC} = V_{CC(typ)}$ | 10             | pF   |

| C <sub>OUT</sub> | I/O capacitance   |                                                    | 10             |      |

### Note

8. Tested initially and after any design or process changes that may affect these parameters.

**infineon**

Thermal resistance

### 7 Thermal resistance

### Table 5 Thermal resistance

| Parameter <sup>[9]</sup> | Description                              | Test conditions                                                         | 44-pin TSOP II | Unit |

|--------------------------|------------------------------------------|-------------------------------------------------------------------------|----------------|------|

| $\Theta_{JA}$            | Thermal resistance (junction to ambient) | Still air, soldered on a 3 × 4.5 inch, four-layer printed circuit board | 66.93          | °C/W |

| $\Theta$ <sub>JC</sub>   | Thermal resistance (junction to case)    |                                                                         | 13.09          |      |

### Note

<sup>9.</sup> Tested initially and after any design or process changes that may affect these parameters.

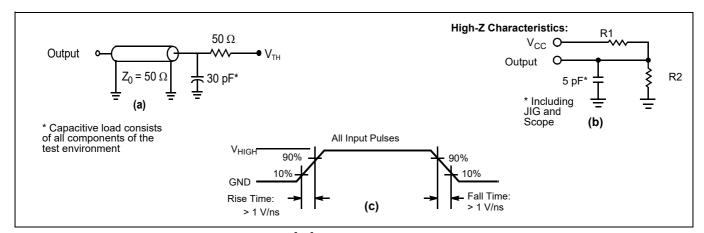

AC test loads and waveforms

### 8 AC test loads and waveforms

Figure 2 AC test loads and waveforms [10]

Table 6 AC test loads and waveforms

| Parameters        | 1.8 V | 3.0 V | 5.0 V | Unit |

|-------------------|-------|-------|-------|------|

| R1                | 1667  | 317   | 317   | Ω    |

| R2                | 1538  | 351   | 351   | Ω    |

| V <sub>TH</sub>   | 0.9   | 1.5   | 1.5   | V    |

| V <sub>HIGH</sub> | 1.8   | 3     | 3     | V    |

#### Note

10. Full device AC operation assumes a 100- $\mu$ s ramp time from 0 to  $V_{CC}(min)$  and 100- $\mu$ s wait time after  $V_{CC}$  stabilization.

Data retention

### 9 Data retention

### 9.1 Data retention characteristics

### **Table 7** Data retention characteristics

Over the operating range of -40°C to 85°C

| Parameter                          | Description                          | Description Conditions                                                                                             |      |      | Unit |

|------------------------------------|--------------------------------------|--------------------------------------------------------------------------------------------------------------------|------|------|------|

| $V_{DR}$                           | V <sub>CC</sub> for data retention   | -                                                                                                                  | 1.0  | -    | V    |

| I <sub>CCDR</sub>                  | Data retention current               | $V_{CC} = V_{DR}, \overline{CE} \ge V_{CC} - 0.2 V^{[11]}, V_{IN} \ge V_{CC} - 0.2 V \text{ or } V_{IN} \le 0.2 V$ | -    | 30.0 | mA   |

| t <sub>CDR</sub> <sup>[12]</sup>   | Chip deselect to data retention time | -                                                                                                                  | 0    | -    | ns   |

| t <sub>R</sub> <sup>[12, 13]</sup> | Operation recovery time              | V <sub>CC</sub> ≥ 2.2 V                                                                                            | 10.0 | -    |      |

|                                    |                                      | V <sub>CC</sub> < 2.2 V                                                                                            | 15.0 | -    |      |

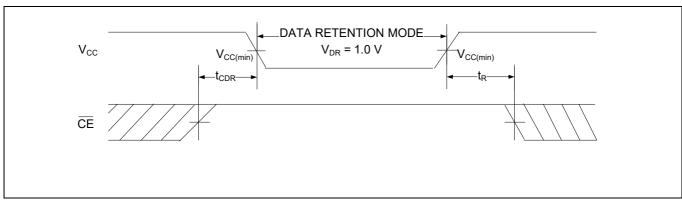

### 9.2 Data retention waveform

Figure 3 Data retention waveform<sup>[11]</sup>

<sup>11.</sup> For all <u>dual</u> chip enable <u>devices</u>,  $\overline{\text{CE}}$  is the logical <u>combination</u> of  $\overline{\text{CE}}_1$  and  $\overline{\text{CE}}_2$ . When  $\overline{\text{CE}}_1$  is LOW and  $\overline{\text{CE}}_2$  is HIGH,  $\overline{\text{CE}}$  is LOW; when  $\overline{\text{CE}}_1$  is HIGH or  $\overline{\text{CE}}_2$  is LOW,  $\overline{\text{CE}}$  is HIGH.

<sup>12.</sup> This parameter is guaranteed by design and is not tested.

<sup>13.</sup> Full device operation requires linear  $V_{CC}$  ramp from  $V_{DR}$  to  $V_{CC(min.)} \ge 100 \,\mu s$  or stable at  $V_{CC(min.)} \ge 100 \,\mu s$ .

**(infineon**

AC switching characteristics

### 10 AC switching characteristics

### Table 8 AC switching characteristics

Over the operating range of -40°C to 85°C

| Parameter [14]     | Description                                                | 10    | ns   | 11   |

|--------------------|------------------------------------------------------------|-------|------|------|

| Parameter          | Description                                                | Min   | Max  | Unit |

| Read cycle         |                                                            | ,     |      | -    |

| t <sub>POWER</sub> | V <sub>CC</sub> stable to first access <sup>[15, 16]</sup> | 100.0 | -    | μς   |

| t <sub>RC</sub>    | Read cycle time                                            | 10.0  | -    | ns   |

| t <sub>AA</sub>    | Address to data / ERR valid                                | _     | 10.0 |      |

| t <sub>OHA</sub>   | Data / ERR hold from address change                        | 3.0   | -    |      |

| t <sub>ACE</sub>   | CE LOW to data / ERR valid <sup>[17]</sup>                 | _     | 10.0 |      |

| t <sub>DOE</sub>   | OE LOW to data / ERR valid                                 | _     | 5.0  |      |

| t <sub>LZOE</sub>  | OE LOW to low Z [18, 19, 20]                               | 0     | -    |      |

| t <sub>HZOE</sub>  | OE HIGH to high Z [18, 19, 20]                             | _     | 5.0  |      |

| t <sub>LZCE</sub>  | CE LOW to low Z [17, 18, 19, 20]                           | 3.0   | -    |      |

| t <sub>HZCE</sub>  | CE HIGH to high Z [17, 18, 19, 20]                         | -     | 5.0  |      |

| t <sub>PU</sub>    | CE LOW to power-up [16, 17]                                | 0     | -    |      |

| t <sub>PD</sub>    | CE HIGH to power-down [16, 17]                             | _     | 10.0 |      |

Write cycle [21, 22]

- 14.Test conditions assume signal transition time (rise/fall) of 3 ns or less, timing reference levels of 1.5 V (for  $V_{CC} \ge 3$  V) and  $V_{CC} \ge 3$  V), and input pulse levels of 0 to 3 V (for  $V_{CC} \ge 3$  V) and 0 to  $V_{CC}$  (for  $V_{CC} < 3$  V). Test conditions for the read cycle use output loading shown in part (a) of **Figure 2 on page 11**, unless specified otherwise.

- $15.t_{POWER}$  gives minimum amount of time that the power supply is at stable  $V_{CC}$  until first memory access is performed.

- 16. These parameters are guaranteed by design and are not tested.

- 17. For all <u>dual</u> chip enable <u>devices</u>,  $\overline{CE}$  is the logical <u>combination</u> of  $\overline{CE}_1$  and  $\overline{CE}_2$ . When  $\overline{CE}_1$  is LOW and  $\overline{CE}_2$  is HIGH,  $\overline{CE}_1$  is LOW; when  $\overline{CE}_1$  is HIGH or  $\overline{CE}_2$  is LOW,  $\overline{CE}_1$  is HIGH.

- 18. $t_{HZOE}$ ,  $t_{HZCE}$ ,  $t_{HZWE}$ ,  $t_{LZOE}$ ,  $t_{LZOE}$ , and  $t_{LZWE}$  are specified with a load capacitance of 5 pF as in (b) of **Figure 2 on page 11**. Transition is measured  $\pm 200$  mV from steady state voltage.

- 19.At any temperature and voltage condition,  $t_{HZCE}$  is less than  $t_{LZCE}$ ,  $t_{HZBE}$  is less than  $t_{LZDE}$ , and  $t_{HZWE}$  is less than  $t_{LZWE}$  for any device.

- 20. Tested initially and after any design or process changes that may affect these parameters.

- 21. The internal write time of the memory is defined by the overlap of  $\overline{WE} = V_{IL}$ ,  $\overline{CE} = V_{IL}$ . These signals must be LOW to initiate a write, and the HIGH transition of any of these signals can terminate the operation. The input data setup and hold timing should be referenced to the edge of the signal that terminates the write.

- 22. The minimum write pulse width for write cycle No.2 (WE Controlled, OE LOW) should be sum of t<sub>H7WE</sub> and t<sub>SD</sub>.

**infineon**

AC switching characteristics

#### **Table 8** AC switching characteristics (continued)

Over the operating range of -40°C to 85°C

| Parameter [14]    | Description                   | 10   | ns  | Unit |

|-------------------|-------------------------------|------|-----|------|

| - Farailleter -   | Description                   | Min  | Max | Unit |

| t <sub>WC</sub>   | Write cycle time              | 10.0 | _   | ns   |

| t <sub>SCE</sub>  | CE LOW to write end [17]      | 7.0  | _   |      |

| t <sub>AW</sub>   | Address setup to write end    | 7.0  | -   |      |

| t <sub>HA</sub>   | Address hold from write end   | 0    | _   |      |

| t <sub>SA</sub>   | Address setup to write start  | 0    | _   |      |

| t <sub>PWE</sub>  | WE pulse width                | 7.0  | _   |      |

| t <sub>SD</sub>   | Data setup to write end       | 5.0  | _   |      |

| t <sub>HD</sub>   | Data hold from write end      | 0    | _   |      |

| t <sub>LZWE</sub> | WE HIGH to low Z [18, 19, 20] | 3.0  | _   |      |

| t <sub>HZWE</sub> | WE LOW to high Z [18, 19, 20] | -    | 5.0 |      |

- 14.Test conditions assume signal transition time (rise/fall) of 3 ns or less, timing reference levels of 1.5 V (for  $V_{CC} \ge 3$  V) and  $V_{CC}/2$  (for  $V_{CC} < 3$  V), and input pulse levels of 0 to 3 V (for  $V_{CC} \ge 3$  V) and 0 to  $V_{CC}$  (for  $V_{CC} < 3$  V). Test conditions for the read cycle use output loading shown in part (a) of **Figure 2 on page 11**, unless specified otherwise.

- $15.t_{POWER}$  gives minimum amount of time that the power supply is at stable  $V_{CC}$  until first memory access is performed.

- 16. These parameters are guaranteed by design and are not tested.

- 17. For all dual chip enable devices,  $\overline{CE}$  is the logical combination of  $\overline{CE}_1$  and  $\overline{CE}_2$ . When  $\overline{CE}_1$  is LOW and  $\overline{CE}_2$  is HIGH,  $\overline{CE}_1$  is LOW; when  $\overline{CE}_1$  is HIGH or  $\overline{CE}_2$  is LOW,  $\overline{CE}_1$  is HIGH.

- 18.  $t_{HZOE}$ ,  $t_{HZCE}$ ,  $t_{HZWE}$ ,  $t_{LZOE}$ , and  $t_{LZWE}$  are specified with a load capacitance of 5 pF as in (b) of **Figure 2 on page 11**. Transition is measured  $\pm 200$  mV from steady state voltage.

- 19.At any temperature and voltage condition,  $t_{HZCE}$  is less than  $t_{LZCE}$ ,  $t_{HZBE}$  is less than  $t_{LZBE}$ ,  $t_{HZOE}$  is less than  $t_{LZWE}$  for any device.

- 20. Tested initially and after any design or process changes that may affect these parameters.

- 21. The internal write time of the memory is defined by the overlap of  $\overline{WE} = V_{IL}$ ,  $\overline{CE} = V_{IL}$ . These signals must be LOW to initiate a write, and the HIGH transition of any of these signals can terminate the operation. The input data setup and hold timing should be referenced to the edge of the signal that terminates the write.

- 22. The minimum write pulse width for write cycle No.2 (WE Controlled, OE LOW) should be sum of t<sub>HZWE</sub> and t<sub>SD</sub>.

Switching waveforms

# 11 Switching waveforms

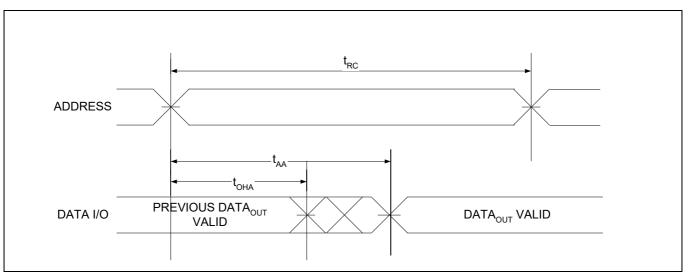

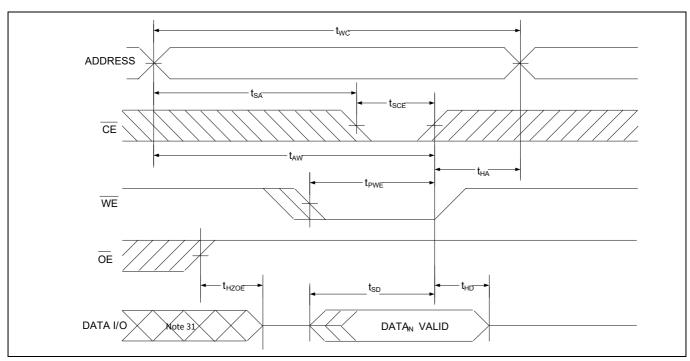

Figure 4 Read cycle No. 1 of CY7C1059H (address transition controlled)<sup>[23, 24]</sup>

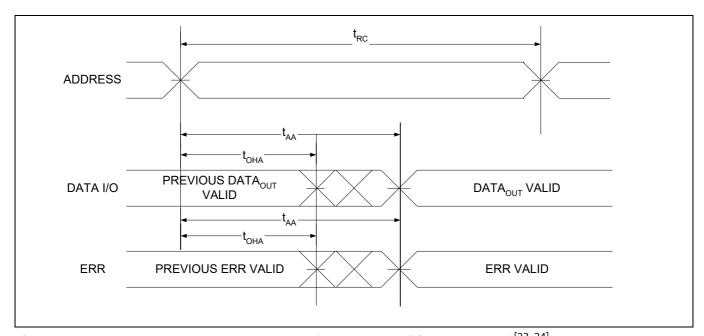

Figure 5 Read cycle No. 2 of CY7C1059HE (address transition controlled) [23, 24]

#### **Notes**

23.<u>The</u> device is continuously selected,  $\overline{OE} = V_{IL}$ ,  $\overline{CE} = V_{IL}$ . 24.WE is HIGH for read cycle.

infineon

Switching waveforms

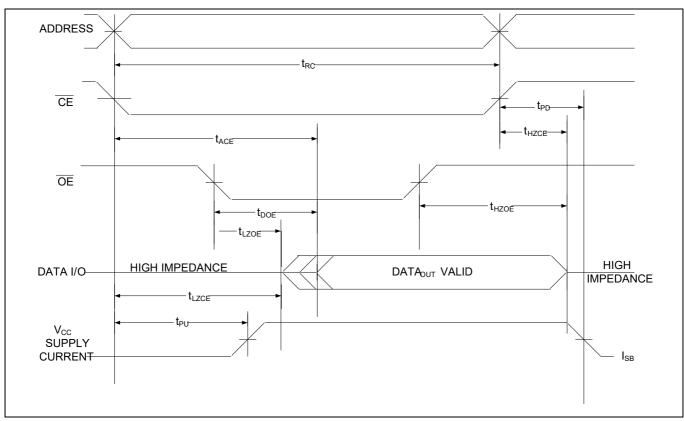

Figure 6 Read cycle No. 3 ( $\overline{OE}$  controlled,  $\overline{WE}$  HIGH) [25,  $\overline{26, 27}$ ]

#### **Notes**

27. Address valid prior to or coincident with CE LOW transition.

<sup>25.</sup>For al<u>l dual chip enable devices, CE</u> is the logical <u>combination of CE</u><sub>1</sub> and CE<sub>2</sub>. When CE<sub>1</sub> is LOW and CE<sub>2</sub> is <u>HIGH</u>, CE is LOW; when CE<sub>1</sub> is HIGH or CE<sub>2</sub> is LOW, CE is HIGH.

26.WE is HIGH for read cycle.

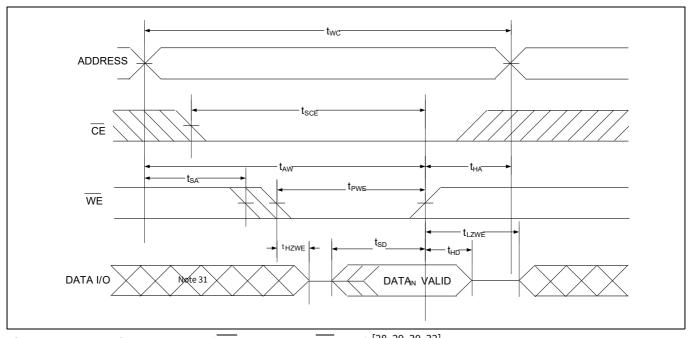

Switching waveforms

Figure 7 Write cycle No. 1 (CE Controlled) [28, 29, 30]

Figure 8 Write Cycle No. 2 (WE Controlled, OE Low) [28, 29, 30, 32]

- 28. For all <u>dual</u> chip enable <u>devices</u>,  $\overline{CE}$  is the logical <u>combination</u> of  $\overline{CE}_1$  and  $\overline{CE}_2$ . When  $\overline{CE}_1$  is LOW and  $\overline{CE}_2$  is HIGH,  $\overline{CE}_1$  is LOW; when  $\overline{CE}_1$  is HIGH or  $\overline{CE}_2$  is LOW,  $\overline{CE}_1$  is HIGH.

- 29. The internal write time of the memory is defined by the overlap of  $\overline{WE} = V_{IL}$ ,  $\overline{CE} = V_{IL}$ . These signals must be LOW to initiate a write, and the HIGH transition of any of these signals can terminate the operation. The input data setup and hold timing should be <u>referenced</u> to the edge of the signal that terminates the write.

- 30. Data I/O is in high impedance state if  $\overline{CE} = V_{IH}$ , or  $\overline{OE} = V_{IH}$ .

- 31. During this time I/O are in output put state. Do not apply input signals.

- 32. The minimum write cycle width should be sum of  $t_{HZWE}$  and  $t_{SD}$ .

infineon

Truth table - CY7C1059H/CY7C1059HE

# 12 Truth table - CY7C1059H/CY7C1059HE

Table 9 Truth table - CY7C1059H/CY7C1059HE

| ¯CE <sub>1</sub> | CE <sub>2</sub> | OE     | WE                | I/O <sub>0</sub> -I/O <sub>7</sub> | Mode                       | Power                      |

|------------------|-----------------|--------|-------------------|------------------------------------|----------------------------|----------------------------|

| Н                | X [33]          | X [33] | X <sup>[33]</sup> | High Z                             | Power-down                 | Standby (I <sub>SB</sub> ) |

| X [33]           | L               | X [33] | X <sup>[33]</sup> | High Z                             | Power-down                 | Standby (I <sub>SB</sub> ) |

| L                | Н               | L      | Н                 | Data out                           | Read all bits              | Active (I <sub>CC</sub> )  |

| L                | Н               | X [33] | L                 | Data in                            | Write all bits             | Active (I <sub>CC</sub> )  |

| L                | Н               | Н      | Н                 | High Z                             | Selected, outputs disabled | Active (I <sub>CC</sub> )  |

#### Note

<sup>33.</sup> The input voltage levels on these pins should be either at  $V_{IH}$  or  $V_{IL}$ .

infineon

ERR output- CY7C1059HE

# 13 ERR output- CY7C1059HE

### Table 10 ERR output - CY7C1059HE

| Output [34] | Mode                                                     |  |

|-------------|----------------------------------------------------------|--|

| 0           | Read operation, no single bit error in the stored data.  |  |

| 1           | Read operation, single bit error detected and corrected. |  |

| High Z      | Device deselected or outputs disabled or write operation |  |

#### Note

34.ERR is an Output pin.If not used, this pin should be left floating.

infineon

Ordering information

# 14 Ordering information

Table 11 Ordering information

| Speed<br>(ns) | Voltage<br>range | Ordering code      | Package<br>diagram | Package type<br>(All Pb-free) | ERR pin /<br>ball | Operating range |

|---------------|------------------|--------------------|--------------------|-------------------------------|-------------------|-----------------|

| 10            | 2.2 V-3.6 V      | CY7C1059H30-10ZSXI | 51-85087           | 44-pin TSOP II                | No                | Industrial      |

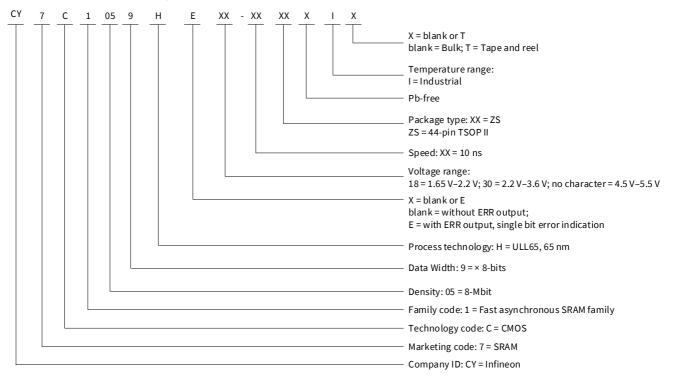

### 14.1 Ordering code definitions

Package diagram

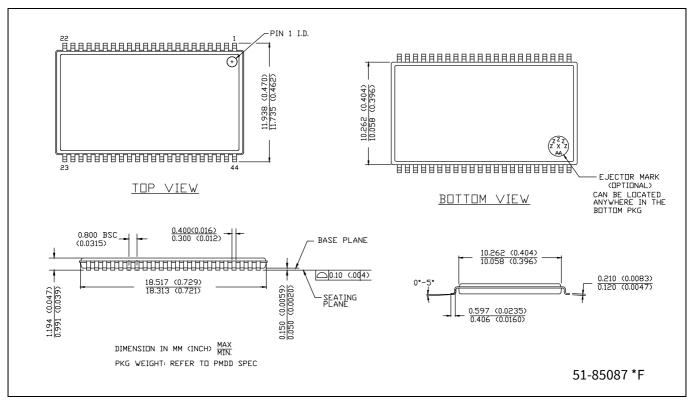

# 15 Package diagram

Figure 9 44-pin TSOP II (18.4 × 10.2 × 1.194 mm) Z54-II package outline, 51-85087

infineon

Acronyms

# 16 Acronyms

### Table 12 Acronyms

| Acronym | Description                             |  |  |

|---------|-----------------------------------------|--|--|

| CE      | chip enable                             |  |  |

| CMOS    | complementary metal oxide semiconductor |  |  |

| I/O     | input/output                            |  |  |

| ŌĒ      | output enable                           |  |  |

| SRAM    | static random access memory             |  |  |

| TSOP    | thin small outline package              |  |  |

| TTL     | transistor-transistor logic             |  |  |

| VFBGA   | very fine-pitch ball grid array         |  |  |

| WE      | write enable                            |  |  |

**i**nfineon

**Document conventions**

# 17 Document conventions

### 17.1 Units of measure

Table 13 Unit of measure

| Symbol | Unit of measure |  |

|--------|-----------------|--|

| °C     | degree celsius  |  |

| MHz    | megahertz       |  |

| μΑ     | microampere     |  |

| μs     | microsecond     |  |

| mA     | milliampere     |  |

| mm     | millimeter      |  |

| ns     | nanosecond      |  |

| Ω      | ohm             |  |

| %      | percent         |  |

| pF     | picofarad       |  |

| V      | volt            |  |

| W      | watt            |  |

**Revision history**

### **Revision history**

| Document version | Date of release | Description of changes |

|------------------|-----------------|------------------------|

| **               | 2021-11-02      | Initial release        |

#### **Trademarks**

All referenced product or service names and trademarks are the property of their respective owners.

Edition 2021-11-02 Published by Infineon Technologies AG 81726 Munich, Germany

© 2021 Infineon Technologies AG. All Rights Reserved.

Do you have a question about this document?

Go to www.cypress.com/support

Document reference 002-34169 Rev. \*\*

#### IMPORTANT NOTICE

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics ("Beschaffenheitsgarantie").

With respect to any examples, hints or any typical values stated herein and/or any information regarding the application of the product, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation warranties of non-infringement of intellectual property rights of any third party.

In addition, any information given in this document is subject to customer's compliance with its obligations stated in this document and any applicable legal requirements, norms and standards concerning customer's products and any use of the product of Infineon Technologies in customer's applications.

The data contained in this document is exclusively intended for technically trained staff. It is the responsibility of customer's technical departments to evaluate the suitability of the product for the intended application and the completeness of the product information given in this document with respect to such application.

For further information on the product, technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies office (www.infineon.com).

#### WARNINGS

Due to technical requirements products may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies office.

Except as otherwise explicitly approved by Infineon Technologies in a written document signed by authorized representatives of Infineon Technologies, Infineon Technologies' products may not be used in any applications where a failure of the product or any consequences of the use thereof can reasonably be expected to result in personal injury.