Marking/Step: (E)ES-AB

32-bit single-chip microcontroller 10581AERRA

#### About this document

#### Scope and purpose

This document describes the deviations of the device from the current user documentation, to support the assessment of the effects of these deviations on your custom hardware and software implementations. Please take note of the following information:

- This errata sheet applies to all temperature and frequency versions and to all memory size variants, unless explicitly noted otherwise. For a derivative synopsis, see the latest datasheet or user manual

- Multiple device variants are covered in this one document. If an issue is related to a particular module, and this module is not specified for a specific device variant, then the issue does not apply to that device variant

- For example, issues with the identifier "EMEM" (extension memory) do not apply to devices for which no extension memory is specified ("EMEM" is used only as a generic example and may not be a feature of the device that this document covers)

- Devices marked with EES or ES are engineering samples which may not be completely tested in all functional and electrical characteristics and are therefore only suitable for evaluation

- The specific test conditions for EES and ES are documented in a separate status sheet

- Some of the errata have workarounds which may be supported by the tool vendors. Some corresponding compiler switches may need to be set. Please refer to the respective documentation of your compiler

- To understand the effect of issues relating to the on-chip debug system, please refer to the respective debug tool vendor documentation

#### **Current documentation**

- AURIX<sup>™</sup> TC4Dx user manual

- TC4Dx A-step COM Datasheet

- TriCore<sup>™</sup> TC1.8 architecture manual volume 1

- TriCore<sup>™</sup> TC1.8 architecture manual volume 2

- AURIX<sup>™</sup> TC4x architecture reference

- AURIX<sup>™</sup> TC4x debug and trace

- AURIX™ TC4Dx Safety Manual

**Note**: Please contact your nearest Infineon sales office for additional information.

#### **Conventions used in this document**

Each erratum identifier follows the pattern [Module]\_[Arch].[Type][Number]:

- [Module] = subsystem, peripheral, or function affected by the erratum

- [Arch] = microcontroller architecture where the erratum was initially detected

- AI = Architecture Independent

- TC = TriCore™

- [Type] = category of deviation

- [none] = Functional deviation

Marking/Step: (E)ES-AB

# infineon

### About this document

- P = Parametric deviation

- H = Application hint

- [Number] = ascending sequential number within the three previous fields

**Note**: [Number] As this sequence is used over several derivatives, including already solved deviations, gaps can occur inside this numbering sequence

# Marking/Step: (E)ES-AB

## **Table of contents**

## **Table of contents**

|   | About this document                                          | 1   |

|---|--------------------------------------------------------------|-----|

|   | Table of contents                                            | 3   |

| 1 | Errata overview                                              | 4   |

| 2 | Functional deviations                                        | 12  |

| 3 | Parametric deviations                                        | 78  |

| 4 | Application hints                                            | 80  |

| 5 | Legacy issues carried over from previous product generations | 106 |

|   | Revision history                                             | 128 |

|   | Disclaimer                                                   | 121 |

Marking/Step: (E)ES-AB

# infineon

### 1 Errata overview

# 1 Errata overview

List of errata referenced in this document.

#### Table 1 Functional deviations

| Issue title                                                                                                                                  | Change | Page |

|----------------------------------------------------------------------------------------------------------------------------------------------|--------|------|

| [ADC_TC.030] Missing access errors for specific ADC registers                                                                                |        | 12   |

| [CANXL_AI.001] Wrong TX messages sequence when using TX priority queue slot 0-7                                                              |        | 12   |

| [CANXL_AI.002] Wrong Tx descriptor fetch after TX-scan in specific condition                                                                 |        | 13   |

| [CCU_TC.011] Arbitrary SRI clock security error alarm                                                                                        |        | 14   |

| [CCU_TC.012] Sporadic CCUSTAT.LCK after writing SYSPLLCON1 or PERPLLCON1                                                                     |        | 15   |

| [CCU_TC.013] Functional problem of amplitude regulation in OSC module                                                                        |        | 16   |

| [CCU_TC.015] MPLL accumulated jitter violation                                                                                               |        | 17   |

| [CCU_TC.016] Amplitude regulation in kHz XTAL might be unstable                                                                              |        | 17   |

| [CCU_TC.017] Unexpected alarm when activating KDIV monitors                                                                                  |        | 17   |

| [CCU_TC.018] fTPB to feGTM relation in divider ratio table to be changed to fTBP to feGTM_half relation                                      |        | 19   |

| [CCU_TC.020] Short pulse on output clock when changing KDIV                                                                                  |        | 19   |

| [CCU_TC.021] Mismatch in divider value information and register description                                                                  |        | 20   |

| [CCU_TC.022] Update divider ratio table fFSI/fSPB                                                                                            |        | 20   |

| [CCU_TC.023] Inconsistency between SYSPLLCON1 register description and SYSPLL functional description                                         |        | 21   |

| [CCU_TC.025] Allowed divider ratios between $f_{SRICS}$ and $f_{FSI}$ is missing                                                             |        | 22   |

| [CCU_TC.026] UM correction for CPB bitfield                                                                                                  |        | 22   |

| [CCU_TC.028] Remove SUP mode from TC4xx UM Clock part                                                                                        |        | 23   |

| [CPU_TC.134] FPU conversion instructions assert invalid flag before rounding                                                                 |        | 23   |

| [CPU_TC.144] Retriggering of CFI lockstep self-test fails                                                                                    |        | 24   |

| [CPU_TC.146] Potential performance issue when quad-word (128-bit) load or store instructions are followed by loop instruction (LOOP, LOOP.U) |        | 25   |

| [CPU_TC.147] CPUCS reset values when CSRM debug enabled                                                                                      |        | 26   |

| [CPU_TC.148] No APU protection on internal path from CPU to local scratchpad RAMs                                                            |        | 27   |

| [CPU_TC.149] Incorrect reference to PSW.CDC in DBGSR description                                                                             |        | 29   |

| [DAP_TC.012] Timeout counters when MWBE = 1, waiting time greater than programmed                                                            |        | 29   |

| [DAP_TC.013] Update table DAP/JTAG interface pins' on-chip pull device setting                                                               |        | 30   |

| [DMA_TC.069] Spurious DMA lockstep alarms                                                                                                    |        | 30   |

| [DMA_TC.070] DMA resource partition overflow error status is unreliable                                                                      |        | 31   |

| [DRE_TC.001] Pending requests in registers COBL_BPR0/1 cannot be cleared                                                                     |        | 31   |

| [DRE_TC.002] Pending requests in register CIBL_BPR cannot be cleared                                                                         |        | 32   |

Marking/Step: (E)ES-AB

# infineon

## 1 Errata overview

## Table 1 (continued) Functional deviations

| Issue title                                                                                                                      | Change | Page |

|----------------------------------------------------------------------------------------------------------------------------------|--------|------|

| [DRE_TC.003] Frame loss in multi-cast due to CRE abort sequence on the CAN side on the previous multi-cast transfer              |        | 32   |

| [DRE_TC.005] ETH2CAN - ACF_CAN_ADDR/LE_ACF_CAN_ADDR field not being reset                                                        |        | 33   |

| [DRE_TC.006] Inconsistency between GETH and LETH while triggering error interrupt by the DRE                                     |        | 33   |

| [DRE_TC.008] Forwarding ID (FID) wrongly assembled for LETH                                                                      |        | 34   |

| [eGTM_AI.530] GTM_AEI: AEI_READY erroneously set                                                                                 |        | 34   |

| [eGTM_TC.005] Kernel reset corner case causes AXI hang-up                                                                        |        | 34   |

| [eGTM_TC.006] eGTM wrapper cannot be switched off (CLC) when soft suspend is active                                              |        | 35   |

| [ERAY_TC.001] Wrong reset behavior SSH-ERAY                                                                                      | new    | 35   |

| [GETH_AI.029] CBS credit not decremented during the IPG phase of transmission                                                    |        | 36   |

| [GETH_AI.032] Time Aware Shaper (TAS) additional IPG in case of back-to-back packet transmission                                 |        | 37   |

| [GETH_AI.033] Received packet not routed to the programmed VLAN filter fail queue                                                |        | 37   |

| [GETH_AI.034] Minimum inter packet gap of the MAC transmitter mismatches the programmed non-standard value MII speed modes       |        | 38   |

| [GETH_AI.035] Receive interrupt watchdog clock-based timer not reset on other timers timeout and receive inter triggering events |        | 39   |

| [GETH_AI.036] MAC incorrectly starts packet transmission before threshold number of bytes are available in the transmit queue    |        | 39   |

| [GETH_AI.037] Receive DMA stops operation when packet flush initiation and exit from suspend mode overlap                        |        | 40   |

| [GETH_AI.038] Unintended closure of receive descriptor when intermediate descriptor contains definition error                    |        | 40   |

| [GETH_AI.039] Transmit packet not terminated when underflow occurs in MII speed modes                                            |        | 41   |

| [GETH_AI.040] Rx DMA stall due to incomplete context descriptor closure                                                          | new    | 41   |

| [GETH_AI.041] RX DMA stall with varying RX packet length and active Tx DMA in forwarding port                                    | new    | 42   |

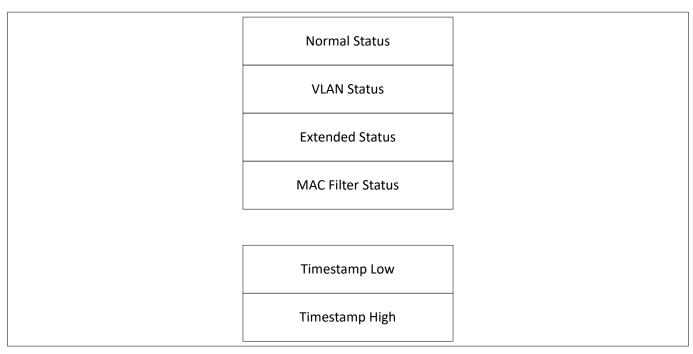

| [GETH_AI.042] RX frames stall in case of normal status word only                                                                 | new    | 42   |

| [GETH_AI.045] Bridge is padding extra 8 bytes in forwarding packet due to delayed word acceptance in the egress port             | new    | 43   |

| [HSPHY_TC.005] Loss of Receive Ethernet communication during temperature change                                                  |        | 43   |

| [LETH_AI.005] CBS credit not decremented during the IPG phase of transmission                                                    |        | 44   |

| [LETH_AI.008] Time Aware Shaper (TAS) additional IPG in case of back-to- back packet transmission                                |        | 45   |

# Marking/Step: (E)ES-AB

# infineon

## 1 Errata overview

## Table 1 (continued) Functional deviations

| Issue title                                                                                                                                                    | Change | Page |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------|

| [LETH_AI.010] Reading back contents of the register 10BT1S_PLCA_TIMER, the TOT and BT bitfields are swapped                                                    |        | 46   |

| [LETH_AI.011] 10BT1S Delayed transmission after TO starts as follower                                                                                          | new    | 46   |

| [LETH_AI.013] Long COMMIT without TRANSMIT                                                                                                                     | new    | 47   |

| [LETH_AI.014] 10BT1S Incorrect encoding of first bit after TX command                                                                                          | new    | 47   |

| [LETH_AI.015] 10BT1S Unintended dropping of next received packet when preceding corrupted SILENCE symbol resembles any of the SSD/ESD/HB/BEACON symbols        | new    | 48   |

| [LETH_AI.016]PLCA cycle time between 2 BEACON deviates from expected value                                                                                     | new    | 48   |

| [LETH_AI.017] Incorrect description of register bit-field Portj_B10T1S_PLCA_Sts.PS                                                                             | new    | 49   |

| [LETH_AI.018] RX frames stall in case of normal status word only                                                                                               | new    | 49   |

| [LETH_AI.019] 10BT1S PLCA_R bit of Portj_B10T1S_PLCA_Ctrl register is not self clearing                                                                        | new    | 51   |

| [LETH_AI.020] 10BT1S Coordinator transmits the packet without BEACON (during unintended TO)                                                                    | new    | 51   |

| [LETH_AI.022] 10BT1S Unintended dropping of next received packet when first of the two SYNC symbols right shifted by one bit position resembles the SSD symbol | new    | 52   |

| [LETH_AI.023] Incorrect access type is specified for bit-fields in register Portj_B10T1S_PLCA_Sts                                                              | new    | 52   |

| [LETH_AI.024] Transmit timestamp is not properly transferred in descriptor if TxDMA channel is mapped to any queue except TxQ0 and bridge is enabled.          | new    | 53   |

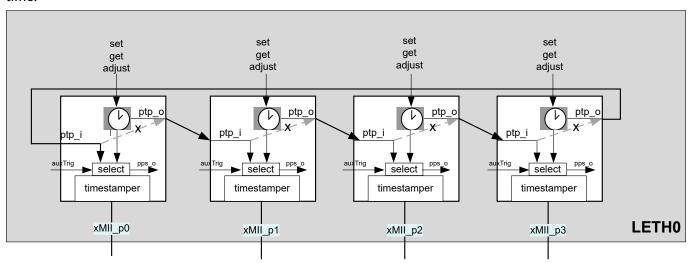

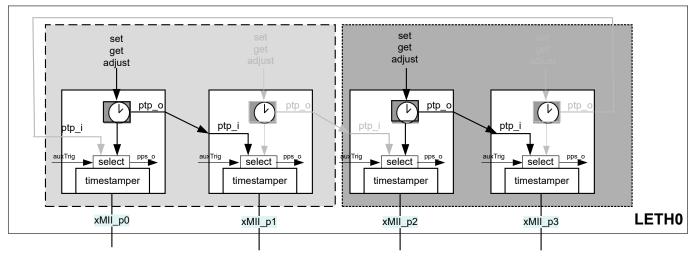

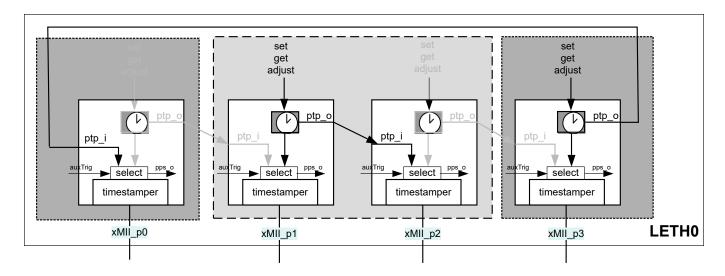

| [LETH_TC.010] Missing PTP time sync concept among all LETH0 MAC ports                                                                                          |        | 53   |

| [LETH_TC.013] LETH0 PPS output for some PORT pins is inverted                                                                                                  |        | 55   |

| [LETH_TC.015] FRP last instruction index is not updated correctly in receive descriptor (RDES2)                                                                |        | 56   |

| [LETH_TC.017] Layers of LETH0_P3 MDIO mapped in P13.6 for TC4Dx                                                                                                |        | 57   |

| [LMU_TC.003] LMU can lock up when writes immediately follow a protection modification                                                                          |        | 57   |

| [MCDS_TC.069] COUNT field of FIFOOVRCNT wraps around and does not saturate                                                                                     |        | 58   |

| [MCDS_TC.070] FIFOPRE[11:5] consideration for PRE and PRE-POST mode decision                                                                                   |        | 58   |

| [MCDS_TC.071] Multick not working as expected                                                                                                                  |        | 59   |

| [MCDS_TC.072] Unexpected VM change STATE messages                                                                                                              |        | 59   |

| [MCDS_TC.073] VM change STATE message after IP message instead of before                                                                                       |        | 59   |

| [MCDS_TC.075] Wrong first tline after TRIF FIFO overrun                                                                                                        |        | 60   |

| [MCDS_TC.077] MCDS_TSUEMUCNT not counting                                                                                                                      |        | 60   |

| [MCDS_TC.078] Wrong configuration of DMA0 Trace                                                                                                                | new    | 61   |

Marking/Step: (E)ES-AB

# infineon

## 1 Errata overview

## Table 1 (continued) Functional deviations

| Issue title                                                                                                                     | Change  | Page |

|---------------------------------------------------------------------------------------------------------------------------------|---------|------|

| [MSC_TC.018] TFIP is used to select service request output line SR0-3 for time frame Manchester interrupt TFMI instead of TFMIP |         | 61   |

| [MSC_TC.019] MSC alternate SRI clock source feature is not functional                                                           |         | 61   |

| [MSC_TC.025] Slow channel feature is not functional                                                                             |         | 62   |

| [MSC_TC.026] PPDE field considered when EXEN=1 and EXEN=0 as well                                                               |         | 62   |

| [PCIE_AI.002] L1 PM Substates Capabilities Register fields are not HWINIT                                                       |         | 62   |

| [PCIE_AI.003] PME retransmission time not satisfied                                                                             |         | 63   |

| [PCIE_AI.004] DMA Configuration Register access failure                                                                         |         | 63   |

| [PCIE_AI.005] TLP with ECRC error not handled as advisory non-fatal error                                                       | changed | 64   |

| [PCIE_AI.006] Data transfer completes without channel status update                                                             |         | 64   |

| [PCIE_AI.007] Updating PCIe common reference clock configuration                                                                | new     | 65   |

| [PMS_TC.020] XRAM uncorrectable error alarm issue                                                                               |         | 65   |

| [PMS_TC.029] Resets MONBISTSTAT                                                                                                 |         | 66   |

| [PMS_TC.030] clk_xtal is not synchronous for one cycle after transition from STANDBY1 to RUN mode                               |         | 66   |

| [PMS_TC.032] HPBG trimming via SCR_SCU_PMSHPBG_BGTRIM                                                                           |         | 66   |

| [PORTS_TC.010] P20.6 is in Pull up mode even if HWCFG[6]=0                                                                      |         | 67   |

| [PORTS_TC.011] PCSRSEL=1 blocks the emergency stop signal                                                                       |         | 67   |

| [PPU_AI.003] Single stepping might lead to problems                                                                             |         | 68   |

| [PPU_TC.002] Trace flush is not working                                                                                         |         | 68   |

| [PPU_TC.005] External event (CTRL.REQWU) only cleared after second wait event instruction executes                              | changed | 69   |

| [SAFETY_TC.031] Test procedure update for SM[HW]:SRI:ERROR_HANDLING and SM[HW]:LLI:ERROR_HANDLING                               |         | 69   |

| [SAFETY_TC.032] Wrong register name in GETH:ISR_MONITOR                                                                         |         | 69   |

| [SAFETY_TC.033] Wrong alarm name and reaction for LMU REDUNDANCY SM                                                             |         | 70   |

| [SAFETY_TC.034] Missing double-bit error alarm for DMI and STU access to VDSP memory                                            | new     | 70   |

| [SCR_TC.026] I2C does not support multi-master systems                                                                          |         | 71   |

| [SCR_TC.029] I2C does not support Software reset (I2C_SRST.SRST)                                                                |         | 71   |

| [SCR_TC.030] Incorrect baud rate after clock stretching                                                                         |         | 72   |

| [SCR_TC.032] [I2C] Slave does not return to IDLE state after receiving NACK in transmit mode                                    |         | 72   |

| [SCR_TC.034] [I2C] Slave does not return to IDLE state after sending NACK to the data byte of a general call                    |         | 73   |

| [SCR_TC.035] [OCDS] debugging of SCR reset does not work                                                                        |         | 73   |

Marking/Step: (E)ES-AB

# infineon

### 1 Errata overview

## Table 1 (continued) Functional deviations

| Issue title                                                                                                              | Change  | Page |

|--------------------------------------------------------------------------------------------------------------------------|---------|------|

| [SDMMC_AI.003] Nst timing violation for STOP command                                                                     | new     | 73   |

| [SMM_TC.006] Port issue if port pin configured to reset at the end of reset                                              |         | 74   |

| [SMU_TC.016] FS timing status not updated                                                                                |         | 74   |

| [SMU_TC.019] Missing P33.8 EMS A input in pin definition tables                                                          | new     | 75   |

| [SRI_TC.004] Writes to reserved address space are overwriting DOM0_ACCEN registers with a similar offset from their base |         | 75   |

| [TRIF_TC.001] TME target address needs to be 32-byte aligned                                                             |         | 75   |

| [VMT_TC.004] Wrong register value shown in MBIST chapter                                                                 | new     | 76   |

| [xSPI_TC.002] Clock low to CS high (tCKLCSH) timing JESD251C specification violation                                     | changed | 77   |

#### Table 2 Parametric deviations

| Issue title                                              | Change | Page |

|----------------------------------------------------------|--------|------|

| [CCU_TC.P003] CLOCK Parameter changing (XTAL1 amplitude) |        | 78   |

| [DAP_TC.P003] DAP pin driver strength not sufficient     |        | 78   |

| [MSC_TC.P003] LVDS and SS timing update                  |        | 78   |

## Table 3 Application hints

| Issue title                                                                                                                                          | Change | Page |

|------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------|

| [ADC_TC.H047] Unexpected global service request after GLSRCFGx reconfiguration                                                                       |        | 80   |

| [ADC_TC.H049] CHy_STAT register triggers arbitration issue                                                                                           |        | 80   |

| [ADC_TC.H051] Single EMUX input per TMADC instance                                                                                                   | new    | 80   |

| [ASCLIN_TC.H010] Incomplete reset isolation                                                                                                          |        | 80   |

| [CCU_TC.H019] Amplitude regulation in OSC module                                                                                                     |        | 81   |

| [CDSP_TC.H001] Application reset impacts CDSP debug registers                                                                                        |        | 81   |

| [CDSP_TC.H002] Incomplete reset isolation                                                                                                            |        | 81   |

| [CPU_TC.H025] Avoiding unbounded delays in store buffer residency                                                                                    | new    | 81   |

| [CPU_TC.H026] Spurious lockstep error triggered on TriCore™ if DSPR is accessed by CPU or slave before DSPR-MBIST                                    | new    | 92   |

| [DRE_TC.H002] Throughput performance drop for GETH or LETH to LETH forwarding via DRE                                                                |        | 92   |

| [GETH_AI.H005] The MMC_Rx_Packet_SMD_Err_Cntr counter incorrectly updated in internal Loopback mode                                                  |        | 93   |

| [GETH_AI.H006] Packets received in the highest numbered queue not sent to the software after the packet to be duplicated to multiple DMAs is dropped |        | 93   |

| [GETH_TC.H007] Incomplete reset isolation                                                                                                            |        | 94   |

| [HSPHY_TC.H004] Problem with clk_sram during application reset                                                                                       |        | 94   |

Marking/Step: (E)ES-AB

# infineon

## 1 Errata overview

## Table 3 (continued) Application hints

| Issue title                                                                                                                | Change | Page |

|----------------------------------------------------------------------------------------------------------------------------|--------|------|

| [HSPHY_TC.H007] Missing register description in the user manual to configure Rx adaption control                           |        | 95   |

| [HSPHY_TC.H008] Incorrect Initialization sequence for SGMII leading to alarms                                              |        | 95   |

| [HSSL_TC.H002] Incomplete reset isolation                                                                                  |        | 96   |

| [LETH_AI.H001] Combination of forwarding and reception to host on Port0 does not works as expected                         | new    | 96   |

| [LETH_TC.H001] Incomplete reset isolation                                                                                  |        | 96   |

| [LETH_TC.H002] DMA channel locks up when time stamping is enabled and context descriptor is not available                  |        | 97   |

| [MCDS_TC.H008] Trace start from halt after reset state with two MCDS instances                                             |        | 97   |

| [MCDS_TC.H009] Fan comparators do not trigger in case of multiple discontinuities                                          |        | 97   |

| [MCMCAN_TC.H014] Incomplete reset isolation                                                                                |        | 98   |

| [MCMCAN_TC.H015] CRE ERRCTRL Register Wrong Access Mode                                                                    |        | 98   |

| [MSC_TC.H016] Incomplete reset isolation                                                                                   |        | 98   |

| [PACKAGE_TC.H009] Max. compressive force during customer housing mounting                                                  |        | 99   |

| [PCIE_AI.H001] In non-D0 power state, the controller does not handle the Cpl TLP as an unexpected completion               | new    | 99   |

| [PCIE_TC.H002] Region upper address register (RGNUA) value is evaluated as "less or equal" instead of "strictly less than" |        | 99   |

| [PCIE_TC.H003] Interrupt detection should clear its internal status                                                        |        | 100  |

| [PCIE_TC.H005] Register write error response is not evaluated                                                              |        | 100  |

| [PCIE_TC.H006] Incomplete reset isolation                                                                                  |        | 101  |

| [PCIE_TC.H007] Outbound traffic is not blocked in hardware when MSE=0 nor when BME = 0                                     |        | 101  |

| [PMS_TC.H020] Standby RAM address missing in PMS documentation                                                             |        | 101  |

| [PPU_AI.H001] Unclear statement in the user manual with respect to vector memory ECC errors                                |        | 102  |

| [PSI5S_TC.H002] Incomplete reset isolation                                                                                 |        | 102  |

| [PSI5_TC.H003] Incomplete reset isolation                                                                                  |        | 102  |

| [QSPI_TC.H010] Incomplete reset isolation                                                                                  |        | 103  |

| [QSPI_TC.H012] HS mode functionality is not supported for all baud-rate configurations                                     |        | 103  |

| [SAFETY_TC.H021] Remove AA step designator from package specific data                                                      |        | 103  |

| [SCR_TC.H017] I2C clock synchronization in slave mode (clock stretching)                                                   |        | 103  |

| [SCR_TC.H018] Do not use master mode stop bit (I2C_CNTR.STP=1) in slave mode                                               |        | 104  |

| [SCR_TC.H021] I2C Clock stretching                                                                                         |        | 104  |

Marking/Step: (E)ES-AB

# infineon

## 1 Errata overview

## Table 3 (continued) Application hints

| Issue title                                                           | Change | Page |

|-----------------------------------------------------------------------|--------|------|

| [SCR_TC.H022] OCDS SCR reset during monitor mode                      |        | 104  |

| [SENT_TC.H008] Incomplete reset isolation                             |        | 104  |

| [xSPI_TC.H001] XIP write is not supported                             |        | 105  |

| [xSPI_TC.H002] 8bit and 16bit XIP read issue through un-cached memory |        | 105  |

### Table 4 Legacy issues

| Issue title                                                                                                                                                                       | Change | Page |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------|

| [CPU_TC.H024] Usage of atomic instructions SWAPMSK.W and LDMST to access registers with bit-fields that can also be updated by hardware (rwh)                                     |        | 106  |

| [DMA_TC.071] Daisy Chain request is lost when repeat triggers too soon                                                                                                            |        | 107  |

| [eGTM_AI.516] SPE-RTL: IRQ raised on disabled inputs                                                                                                                              |        | 107  |

| [eGTM_AI.517] (A)TOM: Missing edge on output signal (A)TOM_OUT                                                                                                                    |        | 108  |

| [eGTM_AI.H803] SPEC-(A)TOM: Missing priority information for register update                                                                                                      |        | 109  |

| [FlexRay_AI.087] After reception of a valid sync frame followed by a valid non-sync frame in the same static slot the received sync frame may be ignored                          |        | 109  |

| [FlexRay_AI.088] A sequence of received WUS may generate redundant SIR.WUPA/B events                                                                                              |        | 110  |

| [FlexRay_AI.089] Rate correction set to zero in case of SyncCalcResult=MISSING_TERM                                                                                               |        | 110  |

| [FlexRay_AI.090] Flag SFS.MRCS is set erroneously although at least one valid sync frame pair is received                                                                         |        | 111  |

| [FlexRay_AI.091] Incorrect rate and / or offset correction value if second Secondary Time Reference Point (STRP) coincides with the action point after detection of a valid frame |        | 111  |

| [FlexRay_AI.092] Initial rate correction value of an integrating node is zero if pMicroInitialOffsetA,B = 0x00                                                                    |        | 112  |

| [FlexRay_AI.093] Acceptance of start-up frames received after reception of more than gSyncNodeMax sync frames                                                                     |        | 112  |

| [FlexRay_AI.094] Sync frame overflow flag EIR.SFO may be set if slot counter is greater than 1024                                                                                 |        | 112  |

| [FlexRay_AI.095] Register RCV displays wrong value                                                                                                                                |        | 113  |

| [FlexRay_AI.096] Noise following a dynamic frame that delays idle detection may fail to stop slot                                                                                 |        | 113  |

| [FlexRay_AI.097] Loop back mode operates only at 10 MBit/s                                                                                                                        |        | 114  |

| [FlexRay_AI.099] Erroneous cycle offset during start-up after abort of start-up or normal operation                                                                               |        | 114  |

| [FlexRay_AI.100] First WUS following received valid WUP may be ignored                                                                                                            |        | 115  |

| [FlexRay_AI.101] READY command accepted in READY state                                                                                                                            |        | 115  |

Marking/Step: (E)ES-AB

## 1 Errata overview

# Table 4 (continued) Legacy issues

| Issue title                                                                                                                                       | Change | Page |

|---------------------------------------------------------------------------------------------------------------------------------------------------|--------|------|

| [FlexRay_AI.102] Slot status vPOC!SlotMode is reset immediately when entering HALT state                                                          |        | 115  |

| [FlexRay_Al.103] Received messages not stored in Message RAM when in Loop Back<br>Mode                                                            |        | 116  |

| [FlexRay_AI.104] Missing start-up frame in cycle 0 at coldstart after FREEZE or READY command                                                     |        | 116  |

| [FlexRay_AI.105] RAM select signals of IBF1/IBF2 and OBF1/OBF2 in RAM test mode                                                                   |        | 117  |

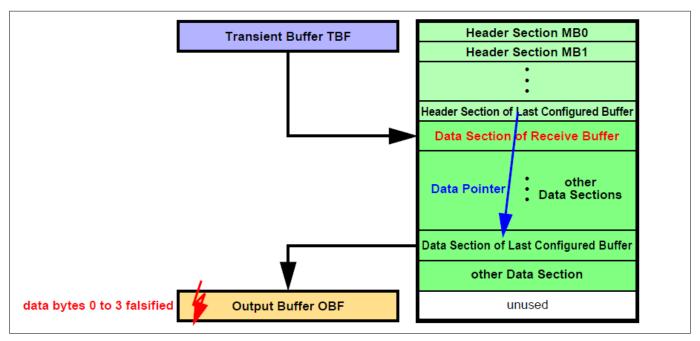

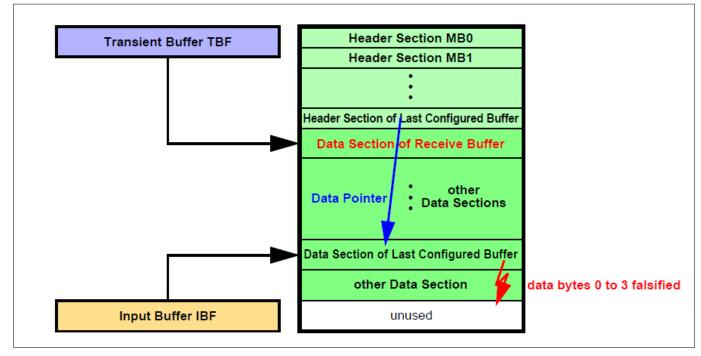

| [FlexRay_AI.106] Data transfer overrun for message transfers Message RAM to Output<br>Buffer (OBF) or from Input Buffer (IBF) to Message RAM      |        | 117  |

| [FlexRay_AI.H004] Only the first message can be received in External Loop Back mode                                                               |        | 119  |

| [FlexRay_AI.H005] Initialization of internal RAMs requires one eray_bclk cycle more                                                               |        | 120  |

| [FlexRay_AI.H006] Transmission in ATM/Loopback mode                                                                                               |        | 120  |

| [FlexRay_AI.H007] Reporting of coding errors via TEST1.CERA/B                                                                                     |        | 120  |

| [FlexRay_AI.H009] Return from test mode operation                                                                                                 |        | 120  |

| [FlexRay_AI.H010] Driver software must launch CLEAR_RAMS command before reading from E-Ray RAMs                                                   |        | 121  |

| [FlexRay_AI.H011] Behavior of interrupt flags in FlexRay™ Protocol Controller (E-Ray)                                                             |        | 121  |

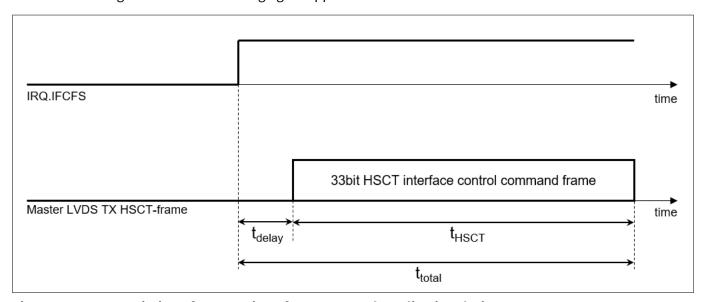

| [HSCT_TC.H010] Interface control command timing on the LVDS ports                                                                                 |        | 122  |

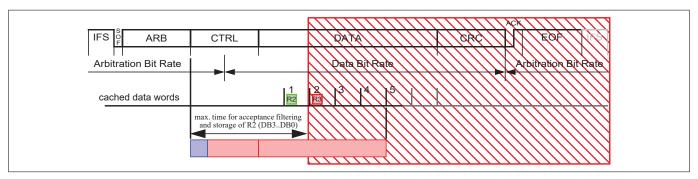

| [MCMCAN_AI.025] Sporadic data corruption (payload) in case acceptance filtering is not finished before reception of data R3 (DB7DB4) is completed |        | 123  |

| [MSC_TC.027] De-feature of ABRA for MSC                                                                                                           |        | 125  |

| [QSPI_TC.006] Baud rate error detection in slave mode (error indication in current frame)                                                         |        | 126  |

| [SDMMC_AI.002] Transfer complete interrupt not generated post ADMA3 transfer                                                                      |        | 126  |

| [SDMMC_AI.H001] Packet buffer is not fully utilized for the write traffic                                                                         |        | 126  |

| [SENT_TC.H009] Unexpected NNI error behavior                                                                                                      |        | 127  |

| [SMU_TC.015] SMU alarm emulation might trigger unwanted active alarm reaction                                                                     |        | 127  |

#### 2 Functional deviations

### 2 Functional deviations

### 2.1 [ADC\_TC.030] Missing access errors for specific ADC registers

#### **Description**

Missing access errors for the following ADC registers:

- CLKEN CDSP

- TMADCx\_SWTRCFG

- TMADCx\_RESFCLR

- TMADCx ERRFCLR

- TMADCx\_BNDFCLR

- TMADCx\_RESFSET

- CDSP BNDCF

- CDSP\_BNDFCL

- CDSP GLOBHCD

- CDSP GLOBRCD

- CDSP\_GLOBRD

- CDSP\_OSCCDSPA

- CDSP OSCCDSPB

- CDSP\_RESEVy

- CDSP\_RESEVCLRy

- CDSP\_WUERREV

- CDSP\_WUERRCL

- CDSP\_DSPa\_BOUNDSEL

#### Scope

**ADC** registers

#### **Effects**

8-bit or 16-bit accesses to the register may result in unpredictable register content, but they do not get flagged with bus errors to the Communication Peripheral Bus (COMPB).

#### Workaround

Limit access to the registers listed above to 32-bit access.

# 2.2 [CANXL\_AI.001] Wrong TX messages sequence when using TX priority queue slot 0-7

#### **Description**

#### Definition:

- PQ(N) defines the TX Priority Queue slot N

- FQ(N) defines the TX FIFO Queue N

- TX-Scan is the internal TX message arbitration. Two internal buffers are used to store TX messages with the highest priority

Application assumptions for the description:

• The PQ(N) is running concurrently with the FQ(N)

v1.0

Marking/Step: (E)ES-AB

# infineon

#### 2 Functional deviations

- The FQ(N) message is currently transmitted to the TX CAN bus and is stored in the first internal buffer

- The PQ(N) message is waiting to be sent as the next candidate for transmission (previous result of the TX-Scan). This message is stored in the second internal buffer

- The next message in the FQ(N) has a higher priority than the message in PQ(N)

The issue is caused by a missing check in the Message Handler during TX-Scan. In order to keep going with the same FQ, the TX-Scan considers not only the current, but also the next TX message. In some cases, this next message may have been already selected by the TX-Scan and stored in one of the two internal buffers. Therefore, the Message Handler keeps going with the same FQ, one message after the other. Although TX messages may have identical queue number N, it could be either a PQ(N) or a FQ(N) message. In current implementation, only the message queue number is considered. If the next message of the FQ(N) has the higher priority and the PQ(N) message is already in one of the two internal buffers, the TX-Scan selects the PQ(N), as the queue numbers are identical. There is no issue for FQ(N) and PQ(M) messages in the internal buffers, the next message in the FQ(N) will replace the PQ(M) message.

#### Scope

The problem occurs for the internal TX message arbitration, called TX-Scan. If a TX message from a PQ(N) (that is already selected as next candidate for transmission) has a lower priority than a new TX message in the PQ(N), then the PQ(N) message will start transmission first.

#### **Effects**

TX message ordering may not be correct according to the TX message priority.

Note:

This issue has no safety impact since any delay of transmission caused by this issue can be detected using the existing safety mechanisms.

#### Workaround

Do not use FQ and PQ with the same number. If FQ(N) is used, do not use the PQ(N). As an example: if FQ(1), FQ(2) and FQ(5) are used, do not use PQ(1), PQ(2) and PQ(5). On the other hand, PQ(8) up to PQ(31) can be used without any restrictions.

# 2.3 [CANXL\_AI.002] Wrong Tx descriptor fetch after TX-scan in specific condition

#### **Description**

#### Definition:

- PQ(Z) defines the TX Priority Queue slot Z

- FQ(N) defines the TX FIFO Queue N

- TXDESCN[i] defines the current TX Descriptor at the index i in the FQ(N)

- TXDESCM[k] defines the current TX Descriptor at the index k in the FQ(M)

- TX-Scan is the internal TX message arbitration. Two internal buffers are used to store the two TX messages with the highest priority

#### Here are the application assumptions:

- The FQ(N) is running concurrently with either a FQ(M) or a PQ(Z) or both

- Either the TXDESCM[k] or PQ(Z) is having higher priority against the TXDESCN[i]

- The FQ(N) has only one valid TX descriptor TXDESCN[i] left to execute, the TXDESCN[i+1] is invalid at that time

Marking/Step: (E)ES-AB

# **(infineon**

#### 2 Functional deviations

- The TXDESCN[i] is selected by the TX-Scan for transmission, leading to the upload of the TXDESCN[i+1] (which is invalid) in the local memory

- Due to the CAN bus arbitration, or a CAN bus OFF or an error on physical link, the TXDESCN[i] is not transmitted

The FQ(M) with a TXDESCM[k] valid or a PQ(Z) is started. The TXDESCN[i] currently selected by the TX-Scan is preempted by the TXDESCM[k] or PQ(Z). When the TXDESCM[k] or PQ(Z) message is sent, the FQ(N) gets the priority back and sends the message defined in TXDESCN[i]. At that time, an internal status to define the next descriptor, is wrongly updated. As the TXDESCN[i+1] in local memory is invalid, the FQ(N) goes immediately on hold. When the TXDESCN[i+1] is set valid, the software can restart the FQ(N). It turns out that the TXDESCN[i+2] is fetched in place of the TXDESCN[i+1].

#### Scope

The problem occurs for a FQ(N), if the following conditions are met:

- TXDESCN[i] from FQ(N) is selected by the TX-Scan and provided to the CAN bus, but not transmitted due to CAN bus arbitration or a CAN bus OFF or error on physical link

- TXDESCN[i+1] is invalid at the time TXDESCN[i] has been selected for transmission. As a result, the invalid TXDESCN[i+1] is uploaded to the local memory and will not be updated without a restart

- TXDESCM[k] from FQ(M) or a PQ(Z) is having higher priority over the TXDESC[i]

#### **Effects**

We have to consider two scenarios when the FQ(N) restarts:

- 1. TXDESCN[i+1] and TXDESCN[i+2] are valid: When the FQ(N) restarts, the rolling counter value defined in the TXDESCN[i+2] does not match the one expected from TXDESCN[i+1]. This mismatch leads to a safety error and an interrupt (DECERR) can be triggered, if enabled

- 2. TXDESCN[i+1] is valid and TXDESCN[i+2] is invalid: When the FQ(N) restarts, the FQ(N) is set right away to on hold (TXDESCN[i+2] is invalid), while a valid message is defined in TXDESCN[i+1]. The message in TXDESCN[i+1] is not considered for transmission. No error is generated as there are no checks done for an invalid descriptor. Nevertheless, a functional interrupt can be generated for an invalid descriptor detection

#### Workaround

Whatever the strategy for managing the FQ(N) (interrupts or polling), the following workaround is valid: If the FQ(N) is on hold and the FQ(N) current address pointer is pointing to a valid TX descriptor TXDESCN[i], restart the FQ(N). If the safety mechanism is enabled, and a safety error triggers, check safety and status registers to identify a TX\_DESC\_REQ\_ERR and verify that the TXDESCN[i+1] and TXDESCN[i+2] are valid.

Despite the occurrence of such issue, the TXFQN is still working properly.

# 2.4 [CCU\_TC.011] Arbitrary SRI clock security error alarm

#### Description

The security clock monitor is mentioned in the feature list of the CLOCK chapter in the user manual. This monitor is supposed to send an alarm named "SRI Clock Security Error" to the SMU\_CS when the  $f_{\rm SRI}$  clock becomes higher than its design limit.

The defect is that this monitor can activate an alarm even when  $f_{SRI}$  never exceeds the allowed maximum frequency.

**Note**: For alarm index mapping, please refer to the device specific alarm mapping tables in the SMU chapter "Alarm mapping table for ALMCS\*".

Marking/Step: (E)ES-AB

#### 2 Functional deviations

#### Scope

SMU\_CS

#### **Effects**

The alarm "SRI Clock Security Error" is activated in SMU\_CS although  $f_{SRI}$  never left the allowed frequency range. Its occurrence is unpredictable. It can be already set at application start after any reset, or occur during application run-time.

#### Workaround

The generated alarm shall be ignored. That is, no SMU CS error reaction will be configured.

#### 2.5 [CCU\_TC.012] Sporadic CCUSTAT.LCK after writing SYSPLLCON1 or PERPLLCON1

#### Description

A clock register lock mechanism was implemented for TC4xx. As the clocking system contains several registers that are updated by a posting mechanism, it is necessary to maintain data coherency using a "lock" while the posted write transaction is ongoing and the register write takes effect at the final destination. This bit in the CCUSTAT register indicates if the posting mechanism is active, that means ongoing and not finished yet. While it is set, write access to the respective registers will not be executed without further notification to the application.

One clock output of the PLL ( $f_{PLL1}$  or  $f_{PLL2}$  or  $f_{PLL3}$ ) may not be working (no clock) or having wrong clock frequencies (wrong Kx divider setting). This issue may occur in the initialization phase or reconfiguration phase of the clock settings. The Kx-DIV will never release the CCU lock again and all clock configuration registers are locked and can not be accessed anymore.

The issue can be detected by polling the CCU lock bit at least for 100 µs. When in this time the clock is not recovering, a system reset needs to be executed to recover from the issue.

The issue can occur on any of the PLL clock outputs.

#### Scope

All PLL output paths

#### **Effects**

The wrong frequency (wrong K-Divider) or dead clock at one of the PLL output paths, and the lock of the clock configuration register can only be restored by a system reset.

#### Workaround

To avoid this potential issue, the following configuration sequence for the K-dividers must be executed always for the configuration or re-configuration of any PLL.

#### PLL configuration phase:

1. PLL off

Errata sheet

- 2. Check for CCU lock: CLOCK CCUSTAT.B.LCK == 0 with a timeout of at least 100 µs

- 3. Configure K-dividers in xPLLCON1 register

- Set KxPREDIV = div by 2 (xPLLCON1.KxPREDIV = div by 2)

- b. Check for CCU lock: CLOCK CCUSTAT.B.LCK == 0 with a timeout of at least 100 µs (only for PerPLL)

- Set KxDIV = 0x01 (xPLLCON1.KxDIV = 0x01) c.

- d. Check for CCU lock: CLOCK CCUSTAT.B.LCK == 0 with a timeout of at least 100 µs (only for PerPLL)

v1.0

### Marking/Step: (E)ES-AB

# **(infineon**

#### 2 Functional deviations

- **e.** Set other PLL parameters as described in the user manual

- f. Check for CCU lock: CLOCK\_CCUSTAT.B.LCK == 0 with a timeout of at least 100 µs (only for PerPLL)

- **4.** PLL on (power PLL)

- 5. Check for CCU lock: CLOCK\_CCUSTAT.B.LCK == 0 with a timeout of at least 100 μs

- **6.** Check if PLL is powered: xPLLSTAT.PWRSTAT == 1 with a timeout at least 100 μs

- **7.** Wait for 1ms to avoid jitter

- 8. Check for PLL lock: xPLLSTAT.PLLLOCK == 1 with a timeout at least 100 μs

- **9.** Configure KxPREDIV (if necessary)

- **a.** Set KxPREDIV to final value

- 10. Wait for 10µs and check for CCU lock: CLOCK CCUSTAT.B.LCK == 0 with a timeout of at least 100 µs

- 11. Configure KxDIV

- a. Set KxDIV to final value

- **b.** Check for CCU lock: CLOCK\_CCUSTAT.B.LCK == 0 with a timeout of at least 100 μs

#### Changing the KxDIV value during run time (KxPREDIV is not allowed to change during run time)

- 1. Check for PLL lock: xPLLSTAT.PLLLOCK == 1 with a timeout at least 100 μs

- 2. Check for CCU lock: xLOCK CCUSTAT.B.LCK == 0 with a timeout at least 100 µs

- **3.** Configure K-dividers in xPLLCON1 register

- **a.** KxDIV = 0x01 (xPLLCON1.KxDIV = 0x01)

- **4.** Wait for 10μs and check for CCU lock: CLOCK\_CCUSTAT.B.LCK == 0 with a timeout of at least 100 μs

- 5. Configure KxDIV

- a. Set KxDIV to final value

- **b.** Check for CCU lock: CLOCK\_CCUSTAT.B.LCK == 0 with a timeout of at least 100 μs

# 2.6 [CCU\_TC.013] Functional problem of amplitude regulation in OSC module

#### **Description**

The amplitude regulation for the internal crystal (main) oscillator is implemented as a peak detection. Once the XTAL1 pin voltage reaches the threshold the regulator is activated and will decrease the oscillator gain permanently (till the next oscillator power-down/power-up cycle). Therefore, the amplitude regulation is defeatured in TC4Dx.

#### Scope

The maximum peak-to-peak amplitude on pin is affected.

#### **Effects**

During the amplitude regulation operation, once the maximum amplitude threshold is reached, the event is latched and will stay active for the entire power-up cycle, even if the amplitude would drop below specified minimum limit.

Further amplitude reduction over time might be caused by temperature change.

The possibility of unwanted peak-detection events by external disturbances cannot be totally ruled out (EMC related issue).

#### Workaround

With the bit-field GAINSEL in the OSCCON register the amplitude can be manually configured. The default value is maximum gain (GAINSEL=11). Based on the crystal matching report, the amplitude can be reduced with two intermediate gain configurations (GAINSEL=10/01) or reduced to the minimum gain configuration (GAINSEL=00).

Marking/Step: (E)ES-AB

#### 2 Functional deviations

## 2.7 [CCU\_TC.015] MPLL accumulated jitter violation

#### Description

SYSPLL and PerPLL show high accumulated RMS jitter. The distribution shows an oscillation (violating the limit: 100 ps), before settling to a lower value.

#### Scope

SYSPLL and PerPLL

#### **Effects**

Violation of internal spec limit. No performance issue. Accumulated peak jitter limits are not affected.

#### Workaround

No workaround - no impact on technical performance.

### 2.8 [CCU\_TC.016] Amplitude regulation in kHz XTAL might be unstable

#### **Description**

The amplitude regulation of the kHz OSC might be unstable at low temperatures (-40°C).

#### Scope

Real Time Clock (RTC) if the external crystal 32 kHz is used (RTC\_CON0.RTCCLKSEL = 1).

#### **Effects**

At lower temperatures (-40°C) the amplitude regulation might be unstable.

#### Workaround

Please do not activate the amplitude regulation via the RTC\_CON0.REGEN bit (REGEN=0). Per default, the amplitude regulation is deactivated.

# 2.9 [CCU\_TC.017] Unexpected alarm when activating KDIV monitors

#### **Description**

The KDIV monitors of the System PLL and Peripheral PLL can raise false alarm after enabling the monitor.

#### Scope

All devices are affected. Depends on clock configuration of System PLL or Peripheral PLL.

The issue occurs in:

- System PLL: K2-PREDIV is 1.2 or 1.6 or K3-PREDIV is not equal to 2.0

- Peripheral PLL: K2/K4-PREDIV is 1.2 or 1.6 or K3-PREDIV is not equal to 2.0

#### **Effects**

KDIV monitor raises sporadic false alarms directly after monitor enable when the clock was started.

#### Workaround

If the PPU is not used, the KDIV-3 Monitor of the System PLL should be disabled.

v1.0

### Marking/Step: (E)ES-AB

# infineon

#### 2 Functional deviations

The following sequence should be always included for every monitor enable. It is reducing the probability of the failure. With every loop the issue probability is reduced significantly.

After start-up of the PLL:

- **1.** Activate System PLL and Peripheral PLL KDIV Monitors

- **2.** Wait 1µs

- a. Deactivate System PLL monitors if affected

- 1. Clear alarm in STDBY SMU for System PLL

- **2.** Set restart mon = 1

- **b.** Deactivate affected Peripheral PLL monitors if affected

- 1. Step through all three monitors and only deactivate affected monitor (see details in MONSTAT register below)

- 2. Clear alarm in SMU for Peripheral PLL

- **3.** Set restart mon = 1

- **c.** If restart\_mon = 1:

- 1. Wait 1us

- **2.** Activate System PLL and Peripheral PLL KDIV Monitors

- **3.** Increment retry\_counter

- **4.** step\_counter = 0

- **5.** restart\_mon = 0

- **d.** Increment step\_counter

- e. Wait 1us

- Go to a. if step\_counter <= 100 and retry\_counter < MAX\_RETRIES (Infineon recommends MAX\_RETRIES = 8)</p>

- 3. If retry\_counter is above the maximum defined loops: Real KDIV issue assumed. Raise alarm flag of KDIV Monitor

The following settings needs to be avoided for both PLLs and under all circumstances:

- K3-PREDIV = 1.0 (higher KDIV-3 Monitor failure rate)

- It is recommended to enable the KDIV-Monitors on backup-clock

The following clock setting is recommended for maximum performance mode with a minimal issue probability:

#### Table 5 System PLL configuration

| System<br>PLLCON1 | K3-PREDIV | K3-DIV | K2-PREDIV | K2-DIV | f <sub>DCO [MHz]</sub> | f <sub>PLL0 [MHz]</sub> | f <sub>PPU [MHz]</sub> |

|-------------------|-----------|--------|-----------|--------|------------------------|-------------------------|------------------------|

| 1101 <sub>H</sub> | 1.1       | 2      | 1.0       | 2      | 1000                   | 500                     | 454.55                 |

#### Table 6 Peripheral PLL configuration

| Peripher<br>al<br>PLLCON<br>1 | K2-<br>PREDIV | K2-DIV | K3-<br>PREDIV | K3-DIV | K4-<br>PREDIV | K4-DIV | f <sub>DCO</sub><br>[MHz] | f <sub>PLL1</sub><br>[MHz] | f <sub>PLL2</sub><br>[MHz] | f <sub>PLL3</sub><br>[MHz] |

|-------------------------------|---------------|--------|---------------|--------|---------------|--------|---------------------------|----------------------------|----------------------------|----------------------------|

| 03A104 <sub>H</sub>           | 1             | 5      | 2             | 2      | 1             | 4      | 800                       | 160                        | 200                        | 200                        |

#### Table 7 MONSTAT register

| Field | Bits | Туре | Description                                                |

|-------|------|------|------------------------------------------------------------|

| KDIV1 | 8    | 1    | PER_PLL1 K-divider<br>monitor status 0 no<br>alarm 1 alarm |

Marking/Step: (E)ES-AB

# infineon

#### 2 Functional deviations

Table 7 (continued) MONSTAT register

| Field | Bits | Туре | Description                                          |

|-------|------|------|------------------------------------------------------|

| KDIV2 | 9    | rh   | PER_PLL2 K-divider monitor status 0 no alarm 1 alarm |

| KDIV3 | 10   | rh   | PER_PLL3 K-divider monitor status 0 no alarm 1 alarm |

Note:

The mentioned bit-fields in the MONSTAT register above will be made visible in the next user manual update.

# 2.10 [CCU\_TC.018] fTPB to feGTM relation in divider ratio table to be changed to fTBP to feGTM\_half relation

#### **Description**

The table "Divider ratio restrictions" in the CLOCK chapter is wrongly showcasing the relation between fTPB and feGTM to be >=1.

This relation of frequencies is instead targeting fTPB and feGTMhalf.

**Note**: feGTMhalf is always half the frequency of feGTM

The correct row of the table is shown below

#### Table 8 Divider ratio restrictions

| Clock A | Clock B   | Allowed values | Recommended<br>value for 400MHz<br>use-case | Recommended<br>value for 500MHz<br>use-case |

|---------|-----------|----------------|---------------------------------------------|---------------------------------------------|

| fTPB    | feGTMhalf | n>=1           | 1                                           | 1                                           |

#### Scope

Divider ratio restrictions.

#### **Effects**

The wrong relation currently in the user manual is restricting the feGTM to the maximum of fTPB which is 250 MHz.

#### Workaround

Apply the shown clock ratio of fTPB:feGTMhalf instead of fTPB:feGTM.

# 2.11 [CCU\_TC.020] Short pulse on output clock when changing KDIV

#### **Description**

Changing K-DIVS on the fly could cause a short pulse.

#### Scope

System PLL and Peripheral PLL output signals are affected.

v1.0

Marking/Step: (E)ES-AB

#### 2 Functional deviations

#### **Effects**

Short pulse will be distributed to the IPs. Clear effect cannot be judged.

#### Workaround

Changing K-DIVIDER on the fly must be avoided at all circumstances.

Therefore, frequency throttling for start-up behavior must be avoided.

Please use SystemPLL to start-up the ramp oscillator.

Please use PeripheralPLL to start-up direct frequency step to the target frequency.

# 2.12 [CCU\_TC.021] Mismatch in divider value information and register description

#### **Description**

CCU system clock options table shows incorrect value for FSI2DIV. The table is corrected as follows:

#### Table 9 CCU system clock options

| CCU               | Clock source                     |                             |                             |                             |           |

|-------------------|----------------------------------|-----------------------------|-----------------------------|-----------------------------|-----------|

| clock<br>output   | f <sub>BACK</sub> (system reset) | <b>f</b> <sub>PLL0</sub> 2) | <b>f</b> <sub>BACK</sub> 3) | <b>f</b> <sub>RAMP</sub> 4) | Off<br>5) |

| $f_{\text{FSI2}}$ | ÷ FSI2DIV=1                      | ÷ SRIDIV<br>FSI2DIV=1       | ÷ SRIDIV<br>FSI2DIV=1       | ÷ SRIDIV<br>FSI2DIV=1       |           |

<sup>1)</sup> Set by system reset, CLKSELS =  $01_B$

#### Scope

CLOCK\_SYSCCUCON0

#### **Effects**

There is a mismatch between the table CCU system clock options clock output  $f_{\rm FSI2}$ , and the documented FSI2DIV After Boot-FW Value in the register description of CLOCK\_SYSCCUCON0 in chapter System CCU clock control register 0 in table Reset values of CLOCK\_SYSCCUCON0.

#### Workaround

No workaround, only correction to the table.

# 2.13 [CCU\_TC.022] Update divider ratio table fFSI/fSPB

#### **Description**

The divider ratio restrictions table has an incorrect entry. The table is corrected as follows:

v1.0

<sup>2)</sup> Set by SW at anytime, CLKSELS =  $00_B$

<sup>3)</sup> Set by HW due to clock emergency switch, set by SW at anytime, CLKSELS =  $01_B$

<sup>4)</sup> Set by SW at anytime, set by HW during application reset or clock emergency switch execution, CLKSELS = 10<sub>B</sub>

<sup>5)</sup> Set by SW through respective divider or clock selection setting

# infineon

#### 2 Functional deviations

Table 10 Divider ratio restrictions

| Clock A   | Clock B   | Allowed values | Recommended value for 400 MHz use-case <sup>1)</sup> | Recommended value for 500 MHz use-case <sup>2)</sup> |  |

|-----------|-----------|----------------|------------------------------------------------------|------------------------------------------------------|--|

| $f_{FSI}$ | $f_{SPB}$ | n ≥ 1          | n = 2                                                | n = 2                                                |  |

<sup>1)</sup> The recommended defaults apply for a system source clock frequency of f<sub>source0</sub> = 400 MHz only.

#### Scope

CLOCK\_SYSCCUCONO.

#### **Effects**

The divider ratio restrictions table has an incorrect entry.

#### Workaround

No workaround, only correction to the table.

# 2.14 [CCU\_TC.023] Inconsistency between SYSPLLCON1 register description and SYSPLL functional description

#### **Description**

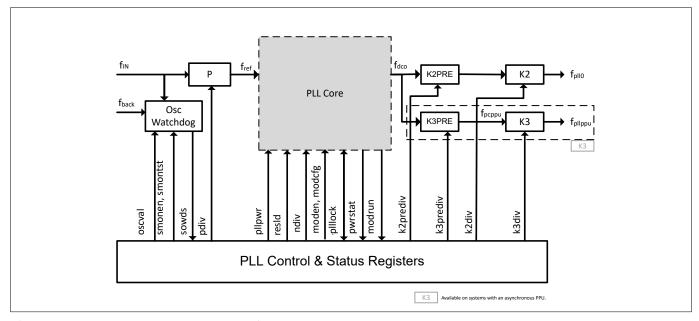

There is an inconsistency between CLOCK\_SYSPLLCON1 register description and the Functional description chapter of the SYSPLL. K2PRE is added to the figure with the recommendation to only use the K2PRE = 1.0 predivider value. The description is corrected as follows:

Figure 1 System PLL block diagram

#### Scope

CLOCK\_SYSPLLCON1.

<sup>2)</sup> The recommended defaults apply for a system source clock frequency of f<sub>source0</sub> = 500 MHz only.

Marking/Step: (E)ES-AB

#### 2 Functional deviations

#### **Effects**

There is an inconsistency between CLOCK\_SYSPLLCON1 register description and the Functional description chapter of the SYSPLL.

#### Workaround

No workaround, only correction to the description.

# 2.15 [CCU\_TC.025] Allowed divider ratios between $f_{SRICS}$ and $f_{FSI}$ is missing

#### **Description**

The Divider ratio restrictions table is missing a line for Clock A =  $f_{SRICS}$  and Clock B =  $f_{FSI}$ . The table is corrected as follows:

#### Table 11 Divider ratio restrictions

| Clock A     | Clock B   | Allowed values           |       | Recommended value for 500 MHz use-case <sup>2)</sup> |

|-------------|-----------|--------------------------|-------|------------------------------------------------------|

| $f_{SRICS}$ | $f_{FSI}$ | $n = 1, 2, 3, 4, 5^{3)}$ | n = 4 | n = 5                                                |

- 1) The recommended defaults apply for a system source clock frequency of  $f_{\text{source0}}$  = 400 MHz only.

- 2) The recommended defaults apply for a system source clock frequency of  $f_{\text{source0}}$  = 500 MHz only.

- 3) Note that  $f_{SRICS}/f_{FSI}=1$  is not supported by all devices. Please refer to the device specific chapters for further restrictions.

- Do not apply values that would lower  $f_{\text{FSI}}$  below its reset value which is 100 MHz. This is needed to guarantee a graceful shutdown operation.

#### Scope

CLOCK\_SYSCCUCONO.

#### **Effects**

The Divider ratio restrictions table is missing a line for Clock A =  $f_{SRICS}$  and Clock B =  $f_{FSI}$ .

#### Workaround

No workaround, only correction to the table.

# 2.16 [CCU\_TC.026] UM correction for CPB bitfield

#### **Description**

The description of CLOCK\_SYSCCUCON0.CPBDIV is missing a note with respect to the impact of setting CPBDIV to 0. The description is corrected by adding a note that setting CLOCK\_SYSCCUCON0.CPBDIV to 0 can lead to a bus error.

#### Scope

CLOCK SYSCCUONO.

Marking/Step: (E)ES-AB

# infineon

#### 2 Functional deviations

#### **Effects**

The description of CLOCK\_SYSCCUCON0.CPBDIV is missing a note with respect to the impact of setting CPBDIV to 0.

#### Workaround

No workaround, only correction to the description.

#### 2.17 [CCU\_TC.028] Remove SUP mode from TC4xx UM Clock part

#### Description

The Crystal oscillator control register description incorrectly shows the bitfield SUPM. The bitfield SUPM is reserved and must not be used. This reference is now removed from the register description and replaced with bitfield RSVD11.

| 31           | 30               | 29                 | 28                 | 27         | 26         | 25  | 24  | 23  | 22        | 21         | 20         | 19               | 18               | 17               | 16               |

|--------------|------------------|--------------------|--------------------|------------|------------|-----|-----|-----|-----------|------------|------------|------------------|------------------|------------------|------------------|

| C            | )                | CLKS<br>ELP<br>HY2 | CLKS<br>ELP<br>HY0 | 0          | RSV<br>D26 | IN: | SEL |     | )         | RSV<br>D21 | RSV<br>D20 | X2CA<br>P3E<br>N | X2CA<br>P2E<br>N | X2CA<br>P1E<br>N | X2CA<br>P0E<br>N |

| r            |                  | rw                 | rw                 | r          | rw         | r   | w   |     | r         | rw         | rw         | rw               | rw               | rw               | rw               |

| 15           | 14               | 13                 | 12                 | 11         | 10         | 9   | 8   | 7   | 6         | 5          | 4          | 3                | 2                | 1                | 0                |

| X1CA<br>P3EN | X1CA<br>P2E<br>N | X1CA<br>P1E<br>N   | X1CA<br>P0E<br>N   | RSV<br>D11 | MODE       |     | HYS | CTL | HYSE<br>N | RSV<br>D4  | RS         | /D2              | GAIN             | ISEL             |                  |

| rw           | rw               | rw                 | rw                 | rw         |            | rw  |     | r   | w         | rw         | rw         | r                | w                | r                | W                |

#### Scope

CLOCK\_OSCCON.

#### **Effects**

The Crystal oscillator control register description incorrectly shows the bitfield SUPM.

#### Workaround

No workaround, the incorrect reference is removed form the register description.

# 2.18 [CPU\_TC.134] FPU conversion instructions assert invalid flag before rounding

#### **Description**

FPU conversion instructions (from floating-point to unsigned integer format) raise the invalid flag incorrectly prior to rounding, which deviates from the IEEE 754-2019 standard.

#### **Expected behavior**

According to the standard, the invalid flag should only be raised if the rounded result is outside the range of the target.

Marking/Step: (E)ES-AB

#### 2 Functional deviations

#### **Observed behavior**

When converting from floating-point to unsigned integer (FTOU, FTOUZ, DFTOU or DFTOUZ) or unsigned long (DFTOUL or DFTOULZ), all negative numbers are forced to zero and the invalid flag is set regardless of the rounding settings.

#### Workaround

When trapping on invalid is configured (FPU\_SYNC\_TRAP\_CON.FIE==1), TriCore™ raises a coprocessor synchronous trap (CSE) when an invalid condition is detected. The trap handler should check that the FI condition is due to a relevant conversion instruction by checking the value in FPU\_SYN\_TRAP\_OPC. The trap handler should then check the rounding mode and input operand value in order to detect whether the conversion involved a negative value that would round to 0 or not.

If the rounded value would be 0, then emulation of the instruction (by placing 0 in the destination GPR, resetting FPU\_SYNC\_TRAP\_CON.TST, and returning to the instruction after the FPU conversion operation) should occur. If the rounded result value would not be zero then the original invalid operation processing should proceed.

When trapping on invalid is not configured (FPU\_SYNC\_TRAP\_CON.FIE==0), no traps are raised and PSW.FI is always set when an invalid condition is detected. For a conversion involving a negative value that rounds to 0, PSW.FI will be set when it should not.

In this case there is no good workaround as the detection of an invalid condition can only be done in software.

### 2.19 [CPU\_TC.144] Retriggering of CFI lockstep self-test fails

#### **Description**

The TC1.8 CPU NVM interface lockstep incorporates a hardware-based self-test. The self-test function of the core NVM interface (triggered by setting CFILCLTEST.LCLT= $\mathbf{1}_B$ ) provides the application software with the ability to generate a lockstep alarm.

If the application software requires to test the lockstep logic multiple times during the same power-on cycle, setting the LCLT bit-field multiple times will not result in additional tests or alarms, after the initial usage. While the bit-field (write only with automatic hardware clearing) reads back a  $0_{\rm B}$ , the internal state machine is not correctly reset after an initial test.

#### Scope

This problem is limited to multiple testing of the CFI lockstep alarm in between power-on reset.

#### **Effects**

No further CFI lockstep test, or lockstep alarm is possible without an explicit clear of the associated lockstep test register.

#### Workaround

After triggering the hardware-based self-test function, the application software must write 0 to the lockstep test register (CFILCLTEST.LCLT= $0_B$ ). This ensures that any subsequent test will occur.

### Marking/Step: (E)ES-AB

# infineon

#### 2 Functional deviations

# 2.20 [CPU\_TC.146] Potential performance issue when quad-word (128-bit) load or store instructions are followed by loop instruction (LOOP, LOOP.U)

#### **Description**

A quad-word (128-bit) load (LD.DD) or store (ST.DD) instruction immediately followed by a loop instruction (LOOP, LOOP.U) can result in non-optimal performance depending on the memories addressed. One or two stall cycles are inserted between a quad-word (128-bit) load or store and the subsequent loop instruction. This is not the case when smaller size load or store operations are immediately followed by a loop instruction. Depending on the memories accessed this may or may not increase the cycles per loop iteration by up to one or two cycles. If the iteration cycles are increased then maximum bandwidth will be reduced.

In the following two examples, used to copy data between two memory locations, a[4] contains the address of the source memory location, a[5] contains the address of the destination memory, and a[2] contains the number of iterations minus 1. In Example 1, which uses quad-word (128-bit) instructions, the loop instruction stalls for one or two additional cycles per iteration compared to an equivalent copy using only double-word (64-bit) load and store operations as used in Example 2.

Example 1: Copy based on quad-word operations

```

.label128

ld.dd e0/e2, [a4+]16

st.dd [a5+]16, e0/e2

loop a2, .label128

```

Example 2: Copy based on double-word operations

```

.label64

ld.d e0, [a4+]8

st.d [a5+]8, e0

loop a2, .label64

```

If the source and destination memories are local or cached remote memories, the additional stall cycles increase the loop iteration time accordingly. However, if the destination memory is anything else (non-cached remote DSPR, remote DLMU or LMU) then some or all of the stalls before the LOOP instruction will not add to the number of cycles per loop iteration. In addition, if the source memory is not local and is non-cached, while the stalls before the LOOP instruction do add to the loop iteration count, the copy bandwidth is still much higher than the 64-bit version.

#### Scope

The erratum is limited to quad-word (128-bit) load or store instructions immediately followed by a loop instruction (LOOP, LOOP.U), used for targeting local, or cached memory locations for both source and destination.

#### **Effects**

Loops using quad-word (128-bit) load or store can have a longer execution time than equivalent ones using double-word (64-bit) load or stores.

#### Workaround

Only when targeting local or cacheable memory locations, within loops, for example implementing memcpy(), loops using double-word (64-bit) load or stores are recommended over quad-word (128-bit) ones.

Loops using quad word (128-bit) load or store should be used to target memories where the benefit of the quad-word accesses outweigh the small number of stall cycles. This is the case when accessing a non-local memory with non-cached naturally aligned accesses. This is because a single 128-bit external transfer is significantly faster than two 64-bit ones.

# Marking/Step: (E)ES-AB

#### 2 Functional deviations

#### [CPU\_TC.147] CPUCS reset values when CSRM debug enabled 2.21

#### **Description**

When CSRM debugging is allowed, the CPUCS ACCEN and CPUCS\_CFICS ACCEN registers are updated by the CSRM\_FW to grant Cerberus read and write access to all the instance resources. This difference under CSRM debug is not documented in the user manual.

The following table shows the correct reset values of the ACCEN registers visible to the application software when CSRM debugging is allowed:

CPUCS and CPU\_CFICS after Boot-FW reset values when CSRM debug is allowed Table 12

| Register name               | Reset value           |

|-----------------------------|-----------------------|

| CPU_CFICS_ACCENPFSFRCFG_WRB | 00004000 <sub>H</sub> |

| CPU_CFICS_ACCENPFSFRCFG_RDA | 10003000 <sub>H</sub> |

| CPU_CFICS_ACCENPFSFRCFG_RDB | 00004000 <sub>H</sub> |

| CPU_CFICS_ACCENPFSFR_WRB    | 00004000 <sub>H</sub> |

| CPU_CFICS_ACCENPFSFR_RDA    | 10003000 <sub>H</sub> |

| CPU_CFICS_ACCENPFSFR_RDB    | 00004000 <sub>H</sub> |

| CPUCS_ACCENSPRCFG_WRA       | 10003000 <sub>H</sub> |

| CPUCS_ACCENSPRCFG_WRB       | 00004000 <sub>H</sub> |

| CPUCS_ACCENSPRCFG_RDA       | 10003000 <sub>H</sub> |

| CPUCS_ACCENSFRCFG_WRA       | 10003000 <sub>H</sub> |

| CPUCS_ACCENSFRCFG_WRB       | 00004000 <sub>H</sub> |

| CPUCS_ACCENSFRCFG_RDA       | 10003000 <sub>H</sub> |

| CPUCS_ACCENSFRCFG_RDB       | 00004000 <sub>H</sub> |

| CPUCS_ACCENSPR0_WRA         | 10003000 <sub>H</sub> |