#### LITIX™ Pixel Rear Multi-channel LED driver

#### **Features**

- 16 channel device with integrated and protected output stages, optimized to drive LEDs

- High regulated output current up to 76.5 mA per channel

- Parallel output operation for higher load currents

- 16 independent 6-bit output current configurations from 5.625 mA to 76.5 mA

- 16 independent 14-bit PWM engines from 100 Hz up to 2 kHz

- · Configurable thermal derating

- Configurable Short and Single-LED-Short thresholds

- Open load detection mechanism

- Digital feedback of external two voltage measurements (NTC/PTC)

- Integrated HSLI transceiver, CAN-FD physical-layer compatible up to 2 MBit/s

- Developed according to ISO26262 with process complying to ASIL-B

#### **Potential applications**

- Open-drain LED driver with high-speed lighting interface (HSLI UARToverCAN)

- Automotive rear light functions such as tail, stop and sequential (dynamic) turn indicator

- Animated light functions like "welcome/goodbye" functions

- Interior lighting functions for ambient lighting (RGB color control), illumination and dash board lighting

- LED panels for industrial applications and instrumentation

#### **Product validation**

Qualified for automotive applications. Product validation according to AEC-Q100.

#### **Description**

The TLD7002-16ES is a 16 channel device with integrated and protected output stages. It is designed to control LEDs with a current up to 76.5 mA as linear current sink (LCS). The power stages can be configured in parallel for higher load currents. Each individual power output stage is configured to a 6-bit current set value stored in the OTP. 16 independent and individual PWM configurations can be set. A high-speed lighting interface is used for device OTP programming, configuration, control and diagnostic feedback.

#### **Datasheet**

#### Description

| Parameter                                  | Symbol               | Values                           |

|--------------------------------------------|----------------------|----------------------------------|

| Power supply operating voltage             | $V_{S(OP)}$          | 6.0 V 20 V                       |

| Maximum output voltage                     | V <sub>OUT_max</sub> | 35 V                             |

| Nominal load current (Linear current sink) | I <sub>L_NOM</sub>   | 76.5 mA, $V_{LED} = 5 \text{ V}$ |

| Output current accuracy (> 10,125 mA)      | $A_{IOUT,L}$         | ±4.5%                            |

| Minimum dropout voltage                    | V <sub>dr_min</sub>  | 600 mV at 50 mA                  |

Further features include the following:

- · Configurable thermal derating to protect the LED load at high ambient temperature conditions

- Configurable LED Open, Short and Single-LED-Short thresholds for LED fault detection

- Digital feedback of external NTC/PTC temperature measurement and up to two separate LED forward voltage measurements

- High-speed lighting interface for LED control

- Integrated HSLI transceiver, CAN-FD physical-layer compatible and electrical characteristics compliant to ISO11898-2:2016

- Protocol based on UART with baud rate up to 2 MBit/s

- Integrated transceiver with very low electromagnetic emission (EME) allows the use without additional common mode choke

- Developed according to ISO26262 with process complying to ASIL-B

- Optimized for Electromagnetic Compatibility (EMC)

- · Optimized for high immunity against Electromagnetic Interference (EMI)

- Green Product (RoHS compliant)

- · AEC Qualified

#### Safety relevant features:

- Configurable V<sub>FWD</sub> monitoring

- · Programmable output current monitoring

- PWM duty cycle monitoring

- · HSLI bus watchdog

- GPINn PWM warning

- Integrated load diagnostic features for open load, short circuit, single LED short, short between two adjacent strings detection.

- Programmable safe state in case of loss of communication

- · Internal over temperature sensor

- · Internal clock monitoring

- Individual fault and status flags readable via HSLI

- · Configurable fault management and common open-drain output error pin ERRN

| Product type | Package     | Marking    |  |

|--------------|-------------|------------|--|

| TLD7002-16ES | PG-TSDSO-24 | TLD7002-16 |  |

# **Datasheet**

# **Table of contents**

|       | Table of contents                       | 3  |

|-------|-----------------------------------------|----|

| 1     | Block diagram and terms                 | 6  |

| 1.1   | Block diagram                           | 6  |

| 1.2   | Terms                                   | 6  |

| 2     | Pin configuration                       | 7  |

| 2.1   | Pin configuration                       | 7  |

| 2.2   | Pin description                         | 7  |

| 3     | General product characteristics         | 9  |

| 3.1   | Absolute maximum ratings                | 9  |

| 3.2   | Functional range                        | 11 |

| 3.3   | Thermal resistance                      | 12 |

| 4     | Power supply                            | 13 |

| 4.1   | Power mode states                       | 13 |

| 4.2   | Idle mode                               | 14 |

| 4.3   | Init mode                               | 14 |

| 4.4   | Fail-off mode                           | 15 |

| 4.5   | Fail-safe mode                          | 15 |

| 4.6   | Active mode                             | 15 |

| 4.7   | OTP mode                                | 16 |

| 4.8   | OTP programming mode                    | 16 |

| 4.9   | OTP emulation mode                      | 16 |

| 4.10  | Electrical characteristics power supply | 17 |

| 5     | General Purpose Input (GPI)             | 21 |

| 5.1   | Overview and features                   | 21 |

| 5.2   | Digital Input                           | 21 |

| 5.3   | Direct drive                            | 21 |

| 5.4   | Output enable                           | 22 |

| 5.5   | Analog input                            | 22 |

| 5.6   | GPIN PWM decoding                       | 22 |

| 5.7   | Electrical characteristics              | 23 |

| 6     | Power Stage                             | 25 |

| 6.1   | Features                                | 25 |

| 6.2   | Current sink operation                  | 25 |

| 6.3   | HSLI configurable output current        | 25 |

| 6.4   | PWM Generator                           | 25 |

| 6.4.1 | PWM function                            | 26 |

| 6.4.2 | PWM frequency                           | 26 |

| 6.4.3 | PWM duty cycle                          | 26 |

3

# **Datasheet**

Table of contents

| 6.4.4 | PWM duty cycle configuration - linear or power-law relation | 26 |

|-------|-------------------------------------------------------------|----|

| 6.4.5 | PWM phase shift                                             | 27 |

| 6.5   | Power shift                                                 | 28 |

| 6.6   | Parallel output configuration                               | 29 |

| 6.7   | Thermal overload                                            | 29 |

| 6.8   | Thermal derating                                            | 29 |

| 6.8.1 | Thermal derating with integrated temperature sensor         | 29 |

| 6.8.2 | Thermal derating with GPIN0                                 | 30 |

| 6.9   | Thermal overload retry strategy                             | 31 |

| 6.10  | Normal and fast switching mode                              | 31 |

| 6.11  | Electrical characteristics                                  | 32 |

| 7     | Load Diagnostic                                             | 36 |

| 7.1   | Features                                                    | 36 |

| 7.2   | VFWD measurement                                            | 36 |

| 7.3   | VGPIN measurement                                           | 36 |

| 7.4   | VLED measurement                                            | 37 |

| 7.5   | VS measurement                                              | 37 |

| 7.6   | Minimum VOUT measurement                                    | 37 |

| 7.7   | Voltage regulator feedback                                  | 38 |

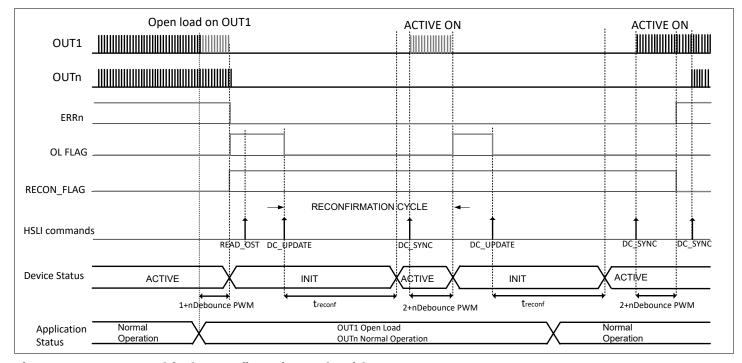

| 7.8   | Open load detection                                         | 38 |

| 7.9   | Single LED Short (SLS) detection                            | 38 |

| 7.10  | OUT_SHORT_WRN, CUR_WRN, DC_WRN, VFWD_WRN warnings           | 38 |

| 7.11  | Diagnostic group                                            | 39 |

| 7.12  | Configurable fault management                               | 39 |

| 7.13  | Load fault reconfirmation cycle                             | 40 |

| 7.14  | Diagnostic enable                                           | 41 |

| 7.15  | Diagnostic sample delay                                     | 42 |

| 7.16  | Load diagnostic debouncing                                  | 42 |

| 7.17  | ERRN reaction                                               | 42 |

| 7.18  | ERRN report                                                 | 43 |

| 7.19  | ERRn reporting sources                                      | 43 |

| 7.20  | HSLI diagnostic flag handling                               | 44 |

| 7.21  | Electrical characteristics                                  | 45 |

| 8     | отр                                                         | 46 |

| 8.1   | Features                                                    | 46 |

| 8.2   | Electrical characteristics                                  | 46 |

| 9     | Communication interface                                     | 47 |

| 9.1   | Protocol layer - High Speed Lighting Interface              | 47 |

| 9.1.1 | General description                                         | 47 |

| 9.1.2 | Main features                                               | 47 |

| 9.1.3 | Frame structure                                             | 47 |

|       |                                                             |    |

4

# **Datasheet**

#### Table of contents

| 9.1.4        | HSLI interframe delay                                 | 47 |

|--------------|-------------------------------------------------------|----|

| 9.1.5        | Slave response bus idle time                          |    |

| 9.1.6        | UART byte field                                       |    |

| 9.1.7        | HSLI baud rate auto detection                         |    |

| 9.1.8        | HSLI bit timing                                       |    |

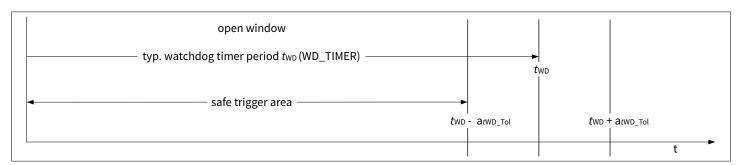

| 9.1.9        | HSLI watchdog timeout                                 |    |

| 9.1.10       | Electrical characteristics                            |    |

| 9.1.11       | Master Frame Types                                    |    |

| 9.1.11.1     | Overview                                              |    |

| 9.1.11.2     | DC_SYNC - broadcast duty cycle update synchronization |    |

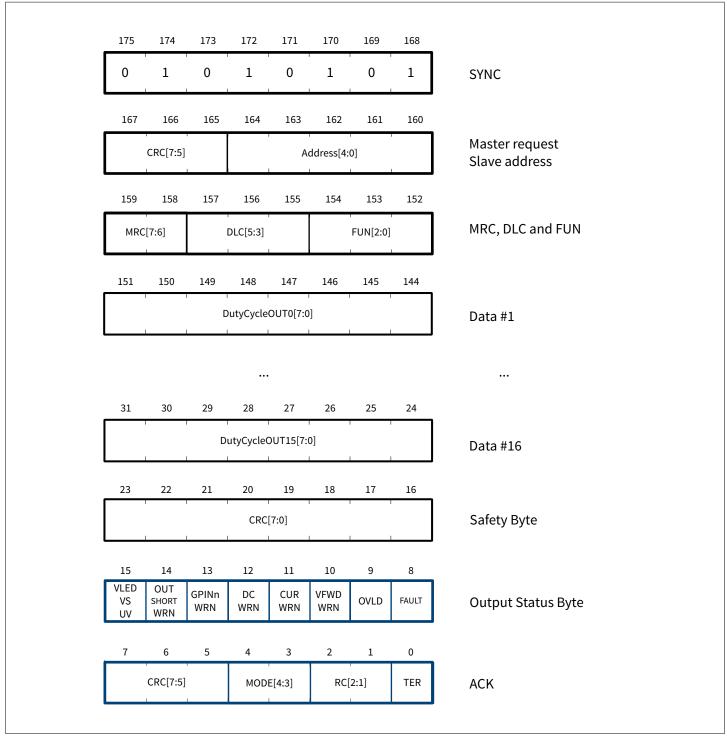

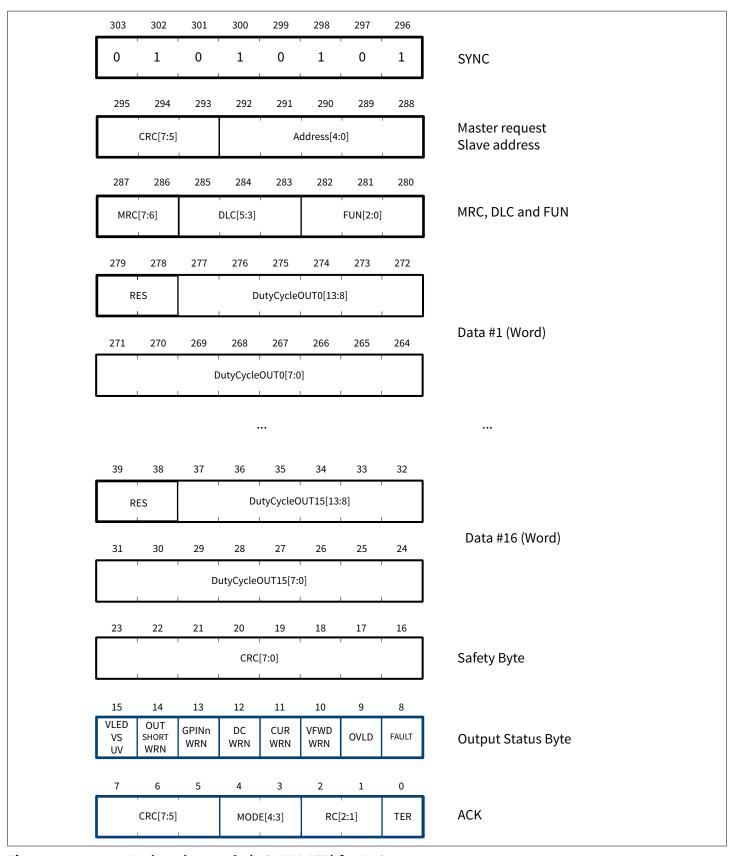

| 9.1.11.3     | DC_UPDATE - update duty cycle shadow register         |    |

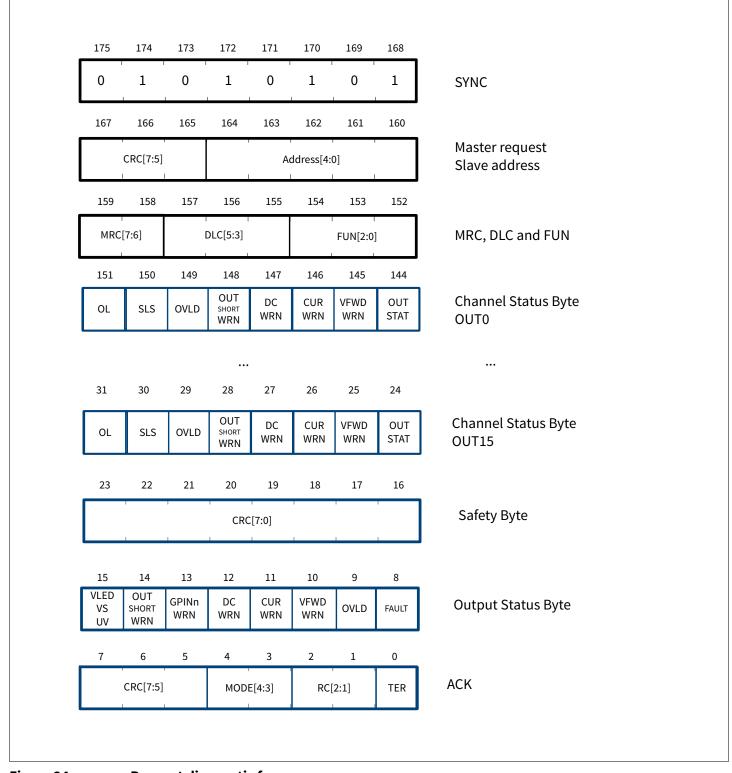

| 9.1.11.4     | READ_OST - request diagnostic                         |    |

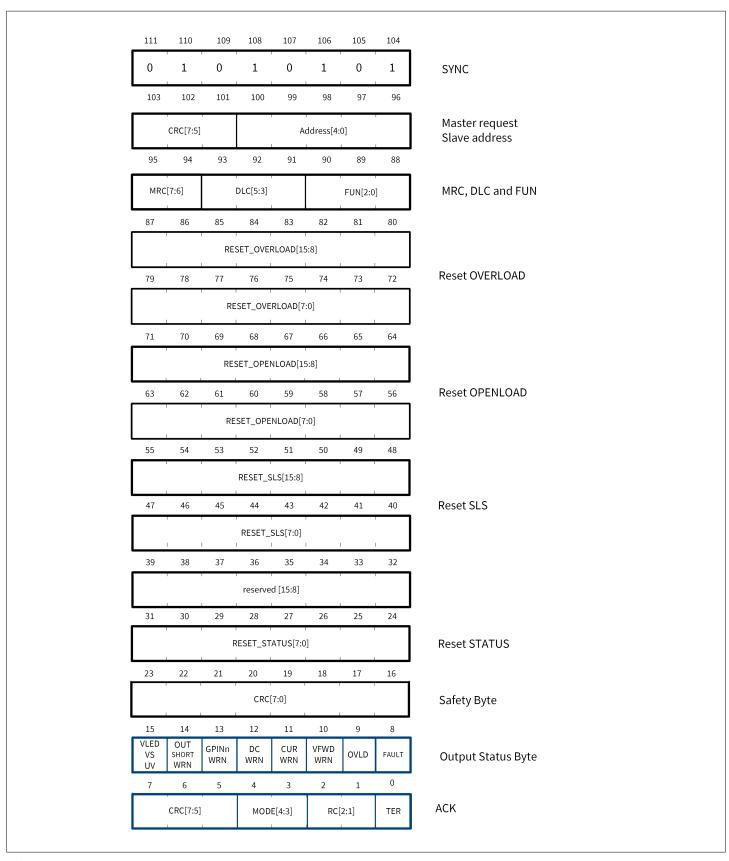

| 9.1.11.5     | HWCR frame                                            |    |

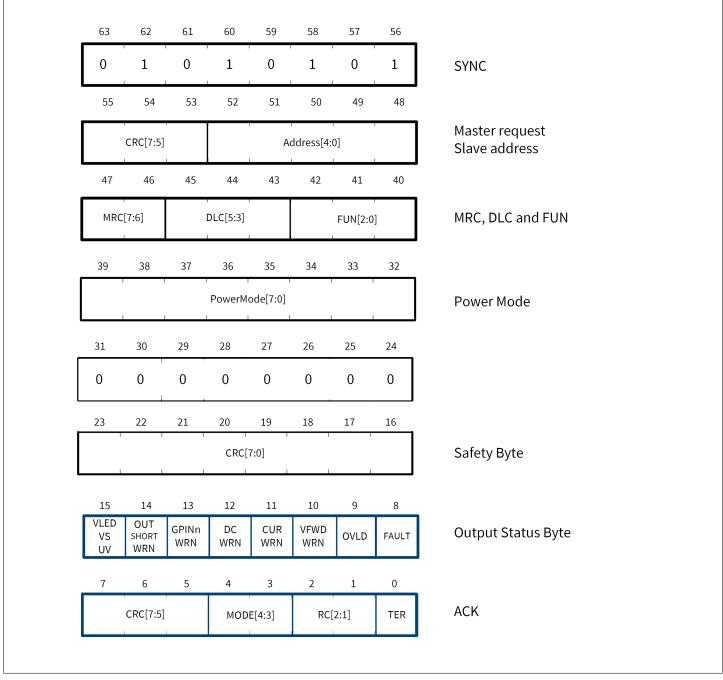

| 9.1.11.6     | PM_CHANGE - power mode change                         |    |

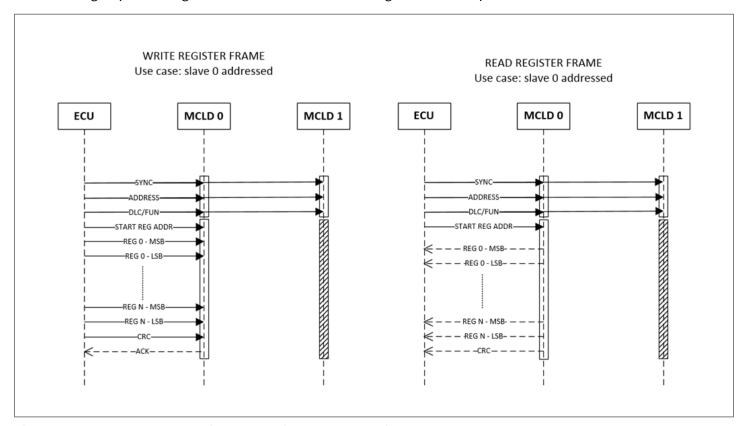

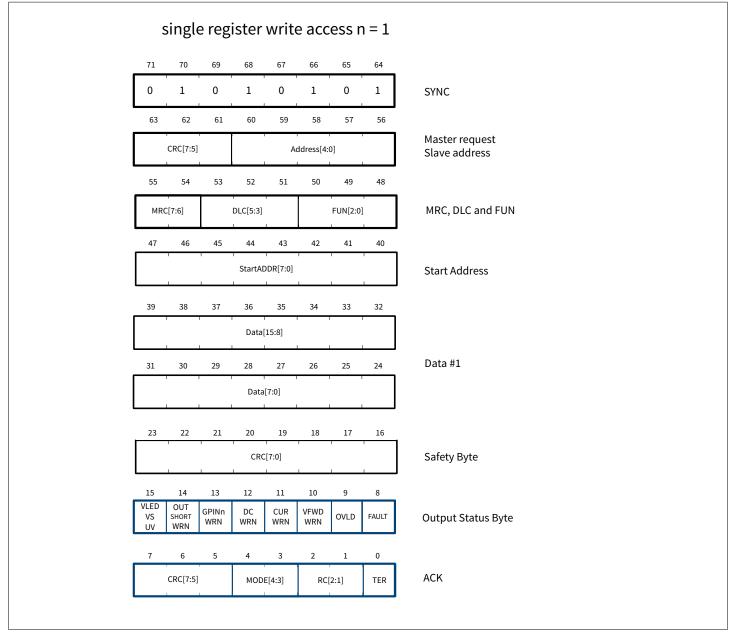

| 9.1.11.7     | WRITE_REG - Write register                            |    |

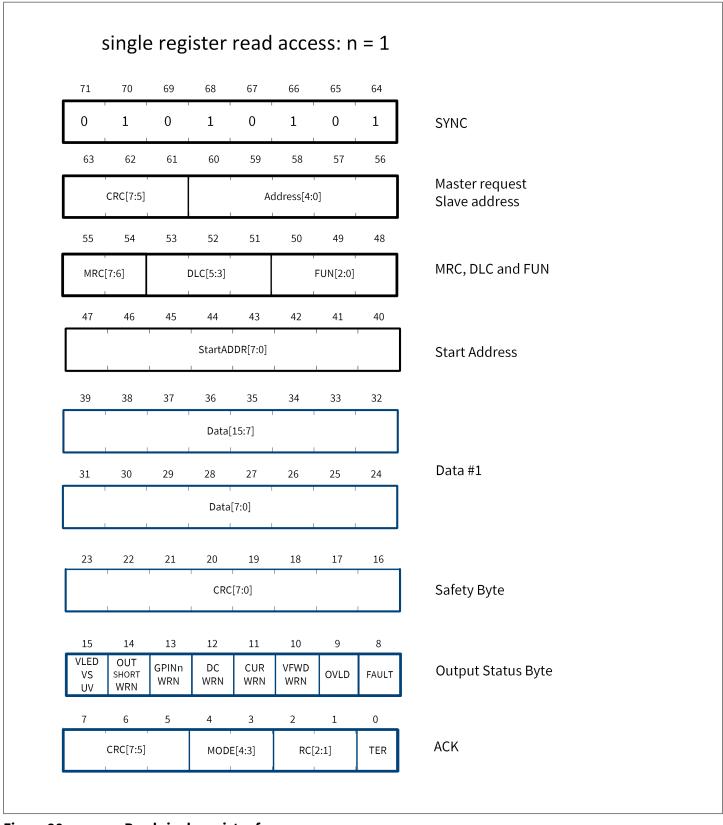

| 9.1.11.8     | READ_REG - Read register                              |    |

| 9.1.11.9     | SYNC_BREAK                                            |    |

| 9.1.11.10    | Handling of invalid frame requests                    | 66 |

| 9.1.11.11    | CRC overview                                          | 66 |

| 9.1.11.12    | Byte Field Description                                | 67 |

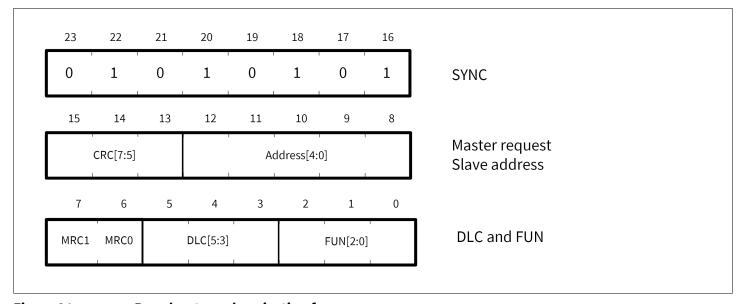

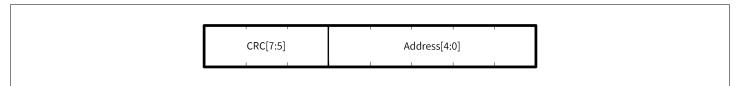

| 9.1.11.12.1  | MASTER_REQ_ADDR                                       | 67 |

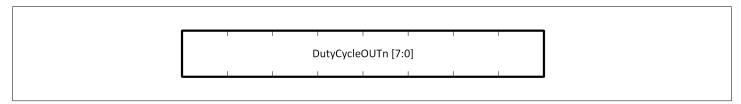

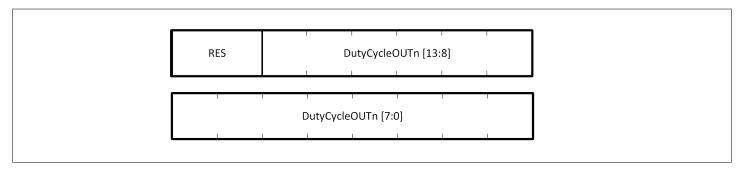

| 9.1.11.12.2  | DutyCycleOUTn byte                                    | 68 |

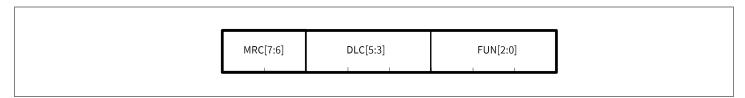

| 9.1.11.12.3  | MRC_DLC_FUN byte                                      | 68 |

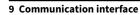

| 9.1.11.12.4  | StartADDR byte                                        | 69 |

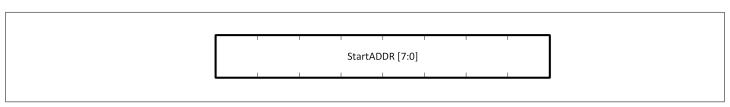

| 9.1.11.12.5  | Data Word                                             | 70 |

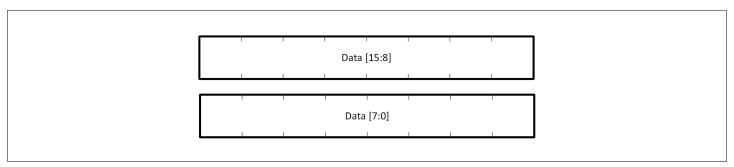

| 9.1.11.12.6  | Power Mode                                            | 70 |

| 9.1.11.12.7  | Output Status Byte                                    | 71 |

| 9.1.11.12.8  | Channel status Byte – OUTn                            | 72 |

| 9.1.11.12.9  | RESET diagnostic words                                | 73 |

| 9.1.11.12.10 | ACK byte                                              | 75 |

| 9.2          | Physical layer                                        | 75 |

| 9.2.1        | CAN-FD compliance                                     | 75 |

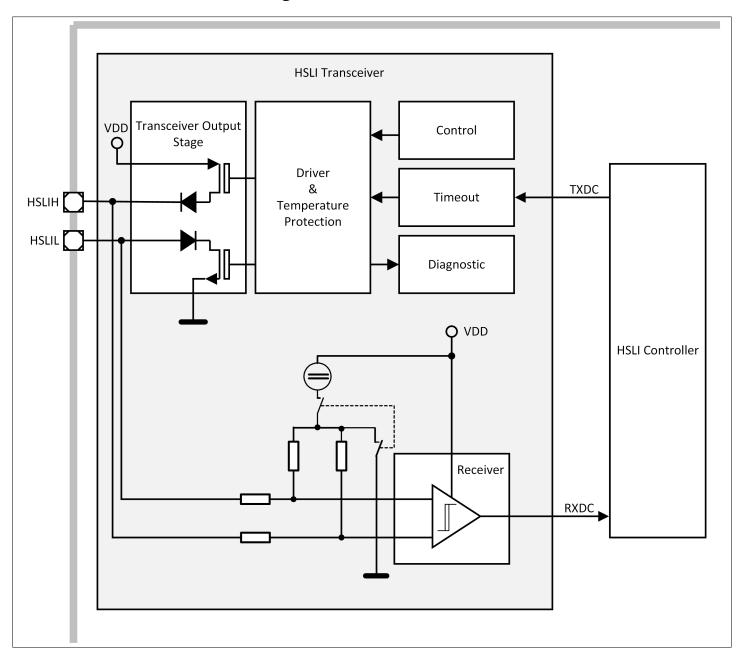

| 9.2.2        | Transceiver block diagram                             | 76 |

| 9.2.3        | Electrical characteristics                            | 77 |

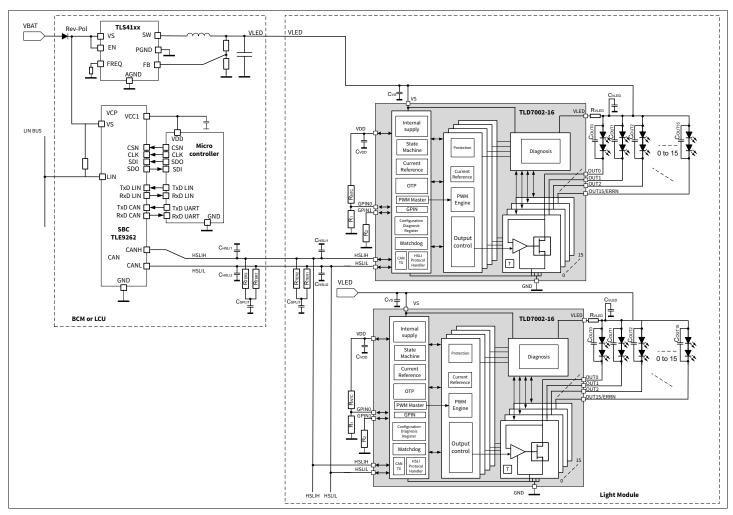

| 10           | Application Information                               | 79 |

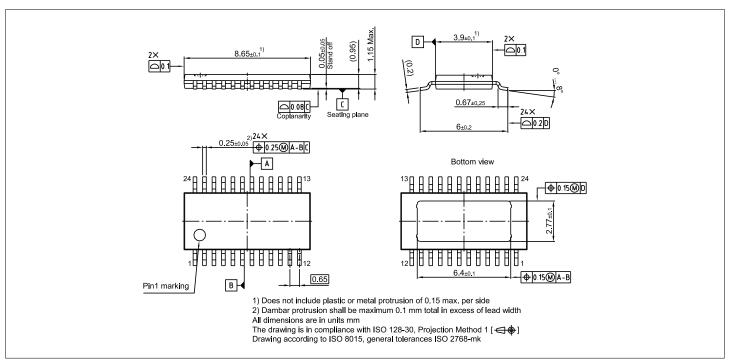

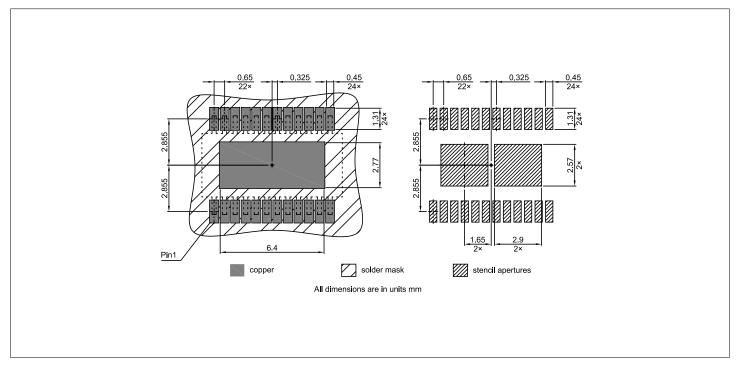

| 11           | Package dimensions                                    | 80 |

|              | Revision history                                      | 81 |

|              | Disclaimer                                            | 82 |

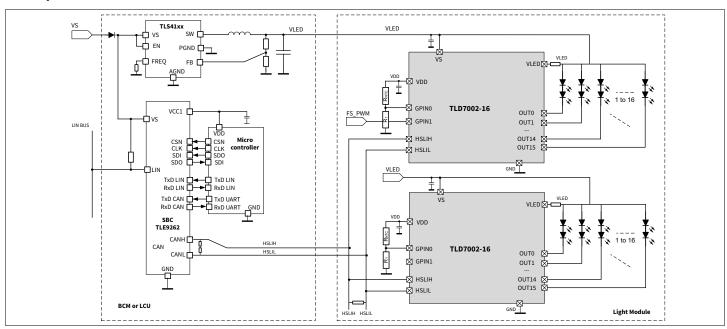

1 Block diagram and terms

# 1 Block diagram and terms

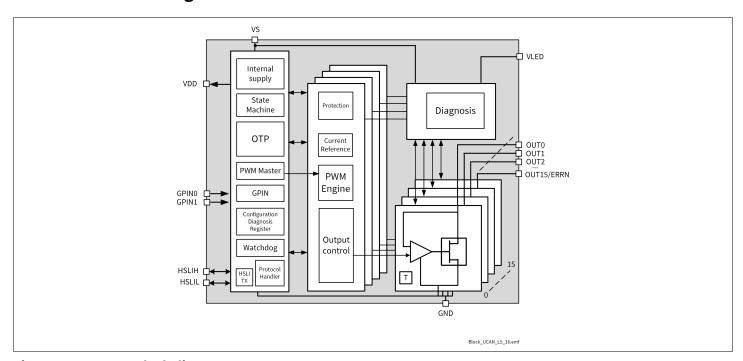

# 1.1 Block diagram

Figure 1 Block diagram

#### 1.2 Terms

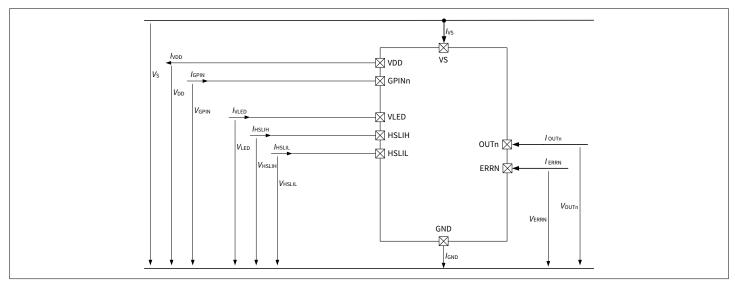

Figure 2 shows all terms used in this datasheet, with associated convention for positive values.

Figure 2 Terms and definitions

OUTn: n denotes the channel number from 0 to 15 GPINn: n denotes the GPIN number from 0 to 1

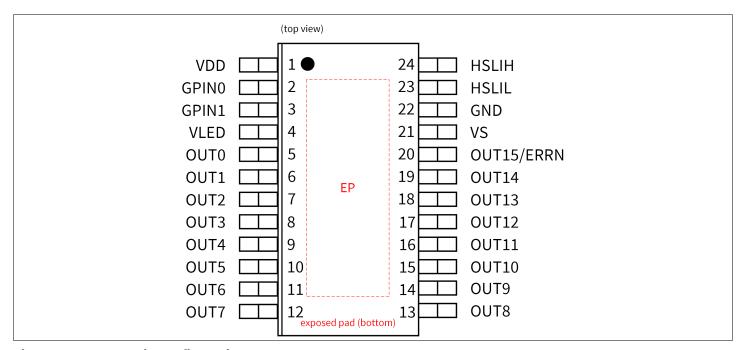

2 Pin configuration

# 2 Pin configuration

# 2.1 Pin configuration

Figure 3 Pin configuration

# 2.2 Pin description

Table 1 Pin description

| Pin | Symbol    | Function                                                                                                                                                                                                            |

|-----|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 21  | VS        | Power supply voltage                                                                                                                                                                                                |

|     |           | Supply for internal biasing and can be used for differential forward voltage measurement of the LED load                                                                                                            |

| 1   | VDD       | Digital GPIN supply voltage output                                                                                                                                                                                  |

|     |           | Can be used as voltage reference for NTC/PTC thermistors and acts as HSLI bus voltage reference, thus as supply for the transceiver                                                                                 |

| 22  | GND       | Ground                                                                                                                                                                                                              |

|     |           | Ground potential. Connect externally close to the chip                                                                                                                                                              |

| -   | EP        | Exposed pad                                                                                                                                                                                                         |

|     |           | Connect to external heat spreading Cu area, either electrical GND or floating potential. Recommendation is to use the GND layer of a PCB with thermal vias, The exposed pad is not replacing the electrical GND pin |

| 520 | OUT0OUT15 | Output channel                                                                                                                                                                                                      |

|     |           | Open drain linear current sink. Connect to the target load                                                                                                                                                          |

| 20  | ERRN      | ERROR flag I/O                                                                                                                                                                                                      |

|     |           | Open drain active low error flag. Connect to a pull-up resistor                                                                                                                                                     |

#### **Datasheet**

2 Pin configuration

#### Table 1 (continued) Pin description

| Pin | Symbol       | Function                                                                   |

|-----|--------------|----------------------------------------------------------------------------|

| 2,3 | GPIN0, GPIN1 | General purpose input                                                      |

|     |              | Can be used for voltage measurement or as function activation input source |

| 4   | VLED         | Analog input                                                               |

|     |              | Can be used for differential forward voltage measurement of the LED load   |

| 24  | HSLIH        | High-speed lighting interface high level I/O                               |

|     |              | "high" in "dominant" state                                                 |

| 23  | HSLIL        | High-speed lighting interface low level I/O                                |

|     |              | "low" in "dominant" state                                                  |

Note:

Unused output pins (OUTn) shall be left open with duty cycle set to 0 or connected to GND via 100k  $\Omega$ . A single resistor can be shared for multiple unused outputs.

Unused HSLI pins shall be left open or connected to GND via a resistor higher than 10k Ohm.

Unused GPINn pins shall be connected to GND via a resistor higher than 10k Ohm.

A resistor in series to VLED from 2k Ohm up to 5k Ohm shall be used to limit the current on the pins in case of a short between VLED and GPIN1 or Short between OUT0 and VLED.

Unused VLED pin shall be connected to VS through the previously mentioned resistor.

#### **Datasheet**

3 General product characteristics

# **3** General product characteristics

# 3.1 Absolute maximum ratings

## Table 2 Absolute maximum ratings

$T_J$  = -40°C to +150°C; all voltages with respect to ground, positive currents flowing as described in Figure 2 (unless otherwise specified).

| Parameter                              | Symbol             |      | Values |       |    | Note or condition                                                                                      | P-      |

|----------------------------------------|--------------------|------|--------|-------|----|--------------------------------------------------------------------------------------------------------|---------|

|                                        |                    | Min. | Тур.   | Max.  |    |                                                                                                        | Number  |

| Supply pins                            |                    | 1    |        | -     | _  | ,                                                                                                      |         |

| Power supply voltage                   | V <sub>S</sub>     | -0.3 | _      | 28    | V  | _                                                                                                      | PRQ-362 |

| Power supply load<br>dump voltage      | V <sub>S(LD)</sub> | _    | -      | 35    | V  | suppressed Load Dump acc. to ISO16750-2 (2010). $R_i = 2 \Omega$                                       | PRQ-686 |

| Digital supply voltage                 | $V_{DD}$           | -0.3 | _      | 5.5   | V  | -                                                                                                      | PRQ-363 |

| Digital supply current                 | I <sub>DD</sub>    | 0    | -      | 10    | mA | Not subject to production test - specified by design                                                   | PRQ-364 |

| Output pins                            |                    |      |        |       |    |                                                                                                        |         |

| Power output voltage                   | V <sub>OUT</sub>   | -0.3 | _      | 35    | ٧  | -                                                                                                      | PRQ-365 |

| Power output current                   | I <sub>OUT</sub>   | 0    | -      | 85    | mA | Not subject to production test - specified by design                                                   | PRQ-366 |

| GPIN/VLED pins                         |                    | 1    | 1      |       |    |                                                                                                        |         |

| Voltage at pin GPIN0,<br>GPIN1         | $V_{GPIN}$         | -0.3 | _      | VDD   | V  | -                                                                                                      | PRQ-367 |

| Current at pin GPIN0,<br>GPIN1         | I <sub>GPIN</sub>  | 0    | -      | 13.75 | mA | Not subject to production test - specified by design sum of current on GPIN0 and GPIN1 limited to 20mA | PRQ-368 |

| <br>Voltage at pin VLED                | $V_{LED}$          | -0.3 | _      | 35    | V  | _                                                                                                      | PRQ-369 |

| HSLI pins                              | LLD                |      |        |       |    |                                                                                                        |         |

| Voltage at pin HSLIL,<br>HSLIH         | V <sub>HSLI</sub>  | -40  | -      | 40    | V  |                                                                                                        | PRQ-756 |

| Temperatures                           |                    |      |        |       |    |                                                                                                        |         |

| Junction temperature (table continues) | T <sub>J</sub>     | -40  | -      | 150   | °C | Not subject to production test - specified by design                                                   | PRQ-370 |

#### **Datasheet**

3 General product characteristics

#### Table 2 (continued) Absolute maximum ratings

$T_J$  = -40°C to +150°C; all voltages with respect to ground, positive currents flowing as described in Figure 2 (unless otherwise specified).

| Parameter                                          | Symbol                    |      | Values |      | Unit | Note or condition                                                                  | P-<br>Number |

|----------------------------------------------------|---------------------------|------|--------|------|------|------------------------------------------------------------------------------------|--------------|

|                                                    |                           | Min. | Тур.   | Max. |      |                                                                                    |              |

| ESD susceptibility                                 |                           |      |        |      | ·    |                                                                                    |              |

| ESD susceptibility all pins (HBM)                  | V <sub>ESD(HBM)</sub>     | -2   | -      | 2    | kV   | ESD susceptibility,<br>Human Body Model<br>"HBM" according to<br>AEC Q100-002;     | PRQ-540      |

|                                                    |                           |      |        |      |      | Not subject to production test - specified by design                               |              |

| ESD susceptibility<br>HSLIH, HSLIL vs GND<br>(HBM) | V <sub>ESD(HBM)</sub>     | -8   | _      | 8    | kV   | ESD susceptibility,<br>Human Body Model<br>"HBM" according to<br>AEC Q100-002;     | PRQ-665      |

|                                                    |                           |      |        |      |      | Not subject to production test - specified by design                               |              |

| ESD susceptibility all pins (CDM)                  | V <sub>ESD(CDM)</sub>     | -500 | -      | 500  | V    | ESD susceptibility,<br>Charged Device Model<br>"CDM" according to<br>AEC Q100-011; | PRQ-542      |

|                                                    |                           |      |        |      |      | Not subject to production test - specified by design                               |              |

| ESD susceptibility corner pins (CDM)               | V <sub>ESD(CDM)_</sub> CR | -750 | -      | 750  | V    | ESD susceptibility,<br>Charged Device Model<br>"CDM" according to<br>AEC Q100-011; | PRQ-543      |

|                                                    |                           |      |        |      |      | Not subject to production test - specified by design                               |              |

#### Notes:

- 1. Stresses above the ones listed here may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

- 2. Integrated protection functions are designed to prevent IC destruction under fault conditions described in the data sheet. Fault conditions are considered as "outside" normal operating range. Protection functions are not designed for continuous repetitive operation.

3 General product characteristics

#### **Functional range** 3.2

#### Table 3 **Functional range**

$T_J = -40$ °C to +150°C, all voltages with respect to ground, positive currents flowing as described in Figure 2 (unless otherwise specified)

| Parameter                                           | Symbol               |      | Values |       |    | Note or condition                                                                                                | P-       |

|-----------------------------------------------------|----------------------|------|--------|-------|----|------------------------------------------------------------------------------------------------------------------|----------|

|                                                     |                      | Min. | Тур.   | Max.  |    |                                                                                                                  | Number   |

| Supply pins                                         |                      |      |        |       |    |                                                                                                                  | <u>'</u> |

| Power supply voltage operating range                | V <sub>SOP</sub>     | 6    | 9      | 20    | V  | -                                                                                                                | PRQ-373  |

| Extended power<br>supply voltage<br>operating range | $V_{SOPEXT}$         | 6    | 9      | 29    | V  | t ≤ 1 min with parameter deviations                                                                              | PRQ-763  |

| VS capacitor range                                  | C <sub>VS</sub>      | 100  | 470    | _     | nF | X7R                                                                                                              | PRQ-374  |

| VDD capacitor range                                 | $C_{VDD}$            | 4700 | _      | 13000 | nF |                                                                                                                  | PRQ-375  |

| VLED capacitor range                                | C <sub>VLED</sub>    | _    | 470    | _     | nF | X7R                                                                                                              | PRQ-376  |

| Temperatures                                        |                      |      |        |       |    |                                                                                                                  |          |

| Junction temperature                                | $T_{J}$              | -40  | _      | 150   | °C | -                                                                                                                | PRQ-377  |

| Output stage                                        |                      |      |        |       |    |                                                                                                                  |          |

| VLED operating range                                | $V_{\text{LED(OP)}}$ | 2    | 9      | 20    | V  | -                                                                                                                | PRQ-660  |

| Output voltage operating range                      | V <sub>OUT(OP)</sub> | 0.6  | -      | 20    | V  | -                                                                                                                | PRQ-378  |

| Output current per<br>channel                       | <b>Г</b> оит         | 0    | -      | 76.5  | mA | Code 0x00 = 5.625<br>mA, Code 0x3F = 76.5<br>mA;<br>OUT.DC = 0 % results<br>into 0 mA and power<br>stage is off. | PRQ-379  |

| Output capacitor range                              | C <sub>OUT</sub>     | 0    | _      | 100   | nF | _                                                                                                                | PRQ-380  |

| Output inductance range                             | L <sub>OUT</sub>     | 0    | -      | 2     | μН | 10 nF < C <sub>OUT</sub> ≤ 100 nF                                                                                | PRQ-381  |

| Output inductance range                             | L <sub>OUT</sub>     | 0    | -      | 1     | μH | C <sub>OUT</sub> < 10 nF                                                                                         | PRQ-382  |

#### **Datasheet**

3 General product characteristics

#### 3.3 Thermal resistance

#### Table 4 Thermal resistance

| Parameter                                          | Symbol             |      | Values |      |     | Note or condition                                                               | P-      |

|----------------------------------------------------|--------------------|------|--------|------|-----|---------------------------------------------------------------------------------|---------|

|                                                    |                    | Min. | Тур.   | Max. |     |                                                                                 | Number  |

| Thermal characterization parameter Junction-to-Top | $\Psi_{JTOP}$      | -    | 3      | 5    | K/W | Not subject to production test - specified by design.                           | PRQ-618 |

| Thermal resistance junction to soldering point     | R <sub>thJSP</sub> | -    | 3      | 5    | K/W | simulated at exposed pad; Not subject to production test - specified by design. | PRQ-619 |

| Thermal resistance junction to ambient             | R <sub>thJA</sub>  | -    | 28     | 30   | K/W | Not subject to production test - specified by design.                           | PRQ-383 |

#### Note:

Specified  $R_{\rm th}$  values are according to Jedec JESD51-2,-5,-7 at natural convection on FR4 2s2p board; the product (chip + package) was simulated on a 76.2 x 114.3 x 1.5 mm board with 2 inner copper layers (2 x 70  $\mu$ m Cu, 2 x 35  $\mu$ m Cu). Where applicable a thermal via array under the exposed pad contacted the first inner copper layer. Simulation done at  $T_{\rm AMB}$  = 85°C with all channels on,  $P_{\rm DISSIPATION}$  = 2 W and a homogeneous temperature distribution across the device.

Thermal characterisation parameter Junction-to-Top is calculated as:  $\Psi_{JTOP} = (T_J - T_{Top})/P$  where P is the total power dissipation of the package, not only the power dissipated on the device top surface.  $\Psi_{JTOP}$  can be adopted to estimate the junction temperature from the package top temperature (measured by e.g. a thermo-couple or by Infrared camera) according to the formula below:  $T_J = T_{Top} + \Psi_{JTOP} * P$

4 Power supply

#### 4 Power supply

The device is supplied by VS, which is used for the internal logic and the supply for the power output stages. Moreover, the high-speed lighting bus bias voltage  $V_{\rm DD}$  is generated internally from VS and available on the VDD pin. VS has an undervoltage detection circuit, which prevents the activation of the power output stages and diagnosis in case the applied voltage is below the undervoltage threshold.

#### 4.1 Power mode states

The device has the following operation modes:

- Idle (unsupplied and reset)

- Init mode

- Active mode

- OTP mode with substates for programming or emulation

- Fail-safe mode

- · Fail-off mode

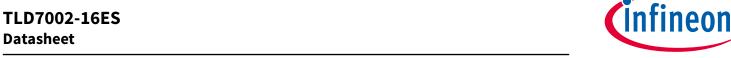

The state diagram including the possible transitions is shown below. The behavior of the device as well as some parameters may change depending on the operation mode of the device.

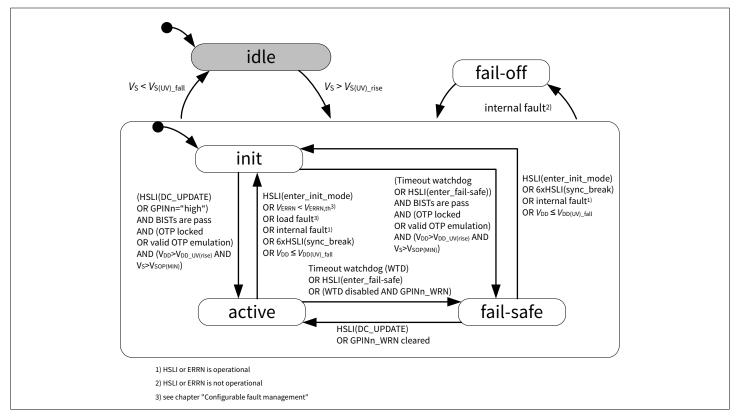

The state diagrams are shown in Figure 4 and Figure 5.

Note: ADC readings, and all the diagnostic related to it, are available only in ACTIVE, FAIL-SAFE and OTP modes.

Figure 4 Power supply operation modes

4 Power supply

Figure 5 Power supply operation modes for OTP programming and emulation

#### 4.2 Idle mode

In the idle mode

- all output channels are switched OFF and

- the device is reset including configuration and fault registers and

- the HSLIH and HSLIL bus interface pins are floating.

The device enters into Idle mode if the power supply voltage  $V_S < V_{S(UV)\_fall}$  OR internal fault via fail-off mode occurred.

#### 4.3 Init mode

The following functions are available in init mode:

- Sending and receiving HSLI frames if  $V_{DD} > V_{DD(UV)_rise}$

- VDD output voltage is available

- · BIST safety mechanism are executed

- Power output stages are commanded to off, means the DC = 0%.

The device enters into init mode in  $t_{IDLE2INIT}$  if:

$V_{S} > V_{S(UV)_{rise}}$

OR in  $t_{\mathsf{INIT}}$  if:

#### **Datasheet**

4 Power supply

the device is in active mode AND

- an internal fault occurred and HSLI or ERRn is operational OR

- $V_{\rm DD} < V_{\rm DD(UV) fall}$

OR

PM\_CHANGE(enter\_init\_mode) frame is received via the HSLI bus

OR

6 times sync\_break is received via the HSLI bus as described in Chapter 9.1.11.9 to reset the device

OR

the device is in active mode AND a load fault has been detected

OR

the device is in active mode AND ERRN is active when  $V_{\text{ERRN}} < V_{\text{ERRN,th}}$ .

#### 4.4 Fail-off mode

In the fail-off mode the device is reset, all output channels are switched OFF and the HSLIH and HSLIL bus interface pins are floating.

The device enters into fail-off mode in  $t_{\text{FAIL OFF}}$  in case of an internal fault when HSLI or ERRN is not operational.

#### 4.5 Fail-safe mode

In fail-safe mode each output stage enters the desired safe state either ON or OFF.

The device enters into fail-safe mode in  $t_{\text{ACTIVE2FAILSAFE}}$

- if the device is in active mode and the timeout watchdog is triggered OR

- if the device is in init mode and the timeout watchdog is triggered OR

- if the device received an PM\_CHANGE(enter\_fail-safe) via the HSLI bus OR

- if the GPIN warning occurs and the watchdog timeout is disabled.

The device exits the fail-safe mode into init mode in  $t_{\text{FAILSAFE2INIT}}$  if

- the device received a valid PM\_CHANGE(enter\_init\_mode) frame via the HSLI OR

- a 6 consecutive HSLI sync break frames trigger a device reset.

The device exits the fail-safe mode into active mode in  $t_{\text{FAILSAFE2ACTIVE}}$  if

- the device received a valid DC\_UPDATE frame via the HSLI OR

- GPIN warning cleared via HSLI HWCR frame

The safe state is set on the FAIL-SAFE MODE OTP register.

If the device reaches the fail-safe state, the duty cycle values and the output current of all and only the outputs enabled in fail-safe state will be updated with the content of the OTP registers (OTP failsafe/GPIN0 DC register and OTP ISET register).

#### 4.6 Active mode

The device enters into active mode within  $t_{INIT2ACTIVE}$  if:

- the device is in init OR fail-safe mode AND

- BISTs are pass in init mode AND

- OTP is configured and locked OR OTP emulation is valid AND

- the device received a valid DC\_UPDATE command via the HSLI bus OR an activation request via GPINn AND

15

V<sub>DD</sub>>V<sub>DD</sub> UV(rise) AND V<sub>S</sub>>V<sub>SOP(MIN)</sub>

#### **Datasheet**

4 Power supply

Valid commands means no CRC-3 for master request, CRC-8 error and no frame structure error occurred.

#### 4.7 **OTP** mode

In this mode the LCU can program or emulate the OTP configuration.

Following functions are available in OTP mode:

- Sending and receiving HSLI frames if  $V_{DD} > V_{DD(UV)}$  rise

- VDD output voltage is available

- internal fault monitoring

The device enters into OTP mode in  $t_{INIT2OTP}$  if:

- the device is in init mode AND

- the device received a valid enter\_OTP\_mode frame via the HSLI bus

#### 4.8 **OTP programming mode**

The following functions are available in OTP programming mode:

- sending and receiving HSLI frames if  $V_{DD} > V_{DD(UV)}$  rise

- VDD output voltage is available

- internal fault monitoring

The device enters into OTP programming mode in  $t_{\text{OTP2PRG}}$  if:

- the device is in OTP mode AND

- the device received a WRITE\_REG(write\_OTP) via the HSLI bus AND

- GPIN0 is set to "high".

In this programing mode the LCU can program the OTP configuration register and store them permanently in the OTP. In order to program the OTP, supply voltage on VS pin must remain within the VS PROG voltage range during the entire programming procedure. The OTP is locked and secured if the LCU successfully writes all the OTP registers and the correct CRC protection word.

Note:

Datasheet

In case GPIN0=LOW and a valid passphrase is sent, the device remains in OTP mode. A HSLI power mode change frame is required to move the device to init mode.

#### 4.9 **OTP** emulation mode

The following functions are available in OTP emulation mode:

- sending and receiving HSLI frames if  $V_{DD} > V_{DD(UV)}$  rise

- VDD output voltage is available

- internal fault monitoring

The device enters into OTP emulation mode in  $t_{OTP2PRG}$  if:

- the device is in OTP mode AND

- the device received a WRITE REG(emu OTP) via the HSLI bus AND

- GPINO is set as digital input and a "high" voltage level applied.

In this emulation mode, the LCU can program a volatile copy of the OTP.

This volatile copy is not stored in the OTP.

The device generates a CRC protection word for the volatile copy of the OTP and this is compared to the CRC protection word received from the LCU.

#### **Datasheet**

4 Power supply

The OTP volatile copy is used until the next power-up sequence in case the LCU CRC protection word matches to the OTP emulation checksum.

Note:

In case GPIN0=LOW and a valid passphrase is sent, the device remains in OTP mode. A HSLI power mode change frame is required to move the device to init mode.

# 4.10 Electrical characteristics power supply

#### Table 5 Electrical characteristics

$V_S$  = 6 V to 20 V,  $T_J$  = -40°C to +150°C, all voltages with respect to ground, positive currents flowing as described in Figure 2 (unless otherwise specified). Typical values:  $V_S$  = 9 V,  $T_J$  = 25°C

| Parameter                                             | Symbol                  | Values |      |      | Unit | Note or condition                                                                                                                                                                                                                                                                          | P-      |

|-------------------------------------------------------|-------------------------|--------|------|------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

|                                                       |                         | Min.   | Тур. | Max. |      |                                                                                                                                                                                                                                                                                            | Number  |

| Power supply                                          |                         |        |      |      |      |                                                                                                                                                                                                                                                                                            |         |

| Power supply<br>undervoltage<br>shutdown rising edge  | V <sub>S(UV)_rise</sub> | 2.8    | 3.75 | 4.5  | V    | -                                                                                                                                                                                                                                                                                          | PRQ-387 |

| Power supply<br>undervoltage<br>shutdown falling edge | V <sub>S(UV)_fall</sub> | 1.85   | 2.5  | 2.9  | V    | -                                                                                                                                                                                                                                                                                          | PRQ-388 |

| Power supply current consumption in init mode         | I <sub>VS(INIT)</sub>   | -      | -    | 8    | mA   | no bus communication; no load on VDD; init mode; LP_INIT='0'; ERRN disabled                                                                                                                                                                                                                | PRQ-667 |

| Power supply current consumption in init mode LP_INIT | I <sub>VS(INIT)</sub>   |        | 3.2  | 4.5  | mA   | no bus communication; no load on VDD; init mode; LP_INIT='1'; $V_S > 8 \text{ V}$ ; $f_{PWM}$ configured to 300 Hz; GPIN0 configured as analog input; GPIN1 configured as digital input; $T_J \leq 85^{\circ}\text{C}$ ; ERRN disabled; Not subject to production test-specified by design | PRQ-879 |

#### **Datasheet**

# Table 5 (continued) Electrical characteristics

$V_S$  = 6 V to 20 V,  $T_J$  = -40°C to +150°C, all voltages with respect to ground, positive currents flowing as described in Figure 2 (unless otherwise specified). Typical values:  $V_S$  = 9 V,  $T_J$  = 25°C

| Parameter                                                          | Symbol                    |      | Values |      |    | Note or condition                                                                                                                                                                        | P-      |

|--------------------------------------------------------------------|---------------------------|------|--------|------|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

|                                                                    |                           | Min. | Тур.   | Max. |    |                                                                                                                                                                                          | Number  |

| Power supply current consumption in active mode                    | I <sub>VS(ACTIVE)</sub>   | -    | 15     | 20   | mA | no bus<br>communication; all<br>output channels ON;<br>active mode;<br>no load on VDD                                                                                                    | PRQ-389 |

| Power supply current consumption in active mode with communication | / <sub>VS(ACTIVE)</sub>   | -    | -      | 21   | mA | active mode, HSLI communication, DC_UPDATE and DC_SYNC frame sent with 100 fps at 1 Mbit/s, all output channels on; no load on VDD; Not subject to production test - specified by design | PRQ-691 |

| Power supply current consumption in programming modes              | I <sub>VS(PRG)</sub>      | -    | 40     | 70   | mA | OTP programming mode; OTP programming emulation mode; no load on VDD;                                                                                                                    |         |

| Power supply current consumption in fail-safe mode                 | I <sub>VS(Failsafe)</sub> | -    | 15     | 20   | mA | no bus<br>communication;<br>Fail-safe mode;<br>no load on VDD                                                                                                                            | PRQ-392 |

#### **Datasheet**

## Table 5 (continued) Electrical characteristics

$V_S$  = 6 V to 20 V,  $T_J$  = -40°C to +150°C, all voltages with respect to ground, positive currents flowing as described in Figure 2 (unless otherwise specified). Typical values:  $V_S$  = 9 V,  $T_J$  = 25°C

| Parameter                                 | Symbol                     | Values |      |                                  | Unit | Note or condition                                                                                                                                                                          | P-      |

|-------------------------------------------|----------------------------|--------|------|----------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

|                                           |                            | Min.   | Тур. | Max.                             |      |                                                                                                                                                                                            | Number  |

| Internal voltage regula                   | ator and oscilla           | ator   |      |                                  |      |                                                                                                                                                                                            |         |

| VDD output voltage                        | $V_{ m VDD}$               | 4.9    | 5    | 5.1                              | V    | Not subject to production test - specified by design 0 < I <sub>VDD</sub> ≤ 10 mA; init mode; active mode; fail-safe mode; OTP mode; OTP programming mode; OTP programming emulation mode; | PRQ-393 |

| VDD undervoltage<br>shutdown falling edge | V <sub>DD(UV)_fall</sub>   | 3.8    | 4.25 | 4.5                              | V    | -                                                                                                                                                                                          | PRQ-693 |

| VDD undervoltage<br>shutdown rising edge  | V <sub>DD(UV)_rising</sub> | 4.5    | 4.75 | 4.9                              | V    |                                                                                                                                                                                            | PRQ-730 |

| Absolute oscillator<br>frequency accuracy | af <sub>OSC</sub>          | -1     | -    | 1                                | %    | -20°C $\leq$ T <sub>J</sub> $<$ 125°C, not<br>subject to production<br>test;<br>$a_{fOSC} = f_{OSCmax}$ -<br>$f_{OSCmin}/f_{OSCaverage}$                                                   | PRQ-726 |

| Timings                                   |                            |        |      |                                  |      |                                                                                                                                                                                            |         |

| Idle to Init delay                        | t <sub>IDLE2INIT</sub>     | -      | -    | 5                                | ms   | C <sub>VDD</sub> ≤ 4.7 μF                                                                                                                                                                  | PRQ-668 |

| Init to Active delay                      | t <sub>INIT2ACTIVE</sub>   | -      | _    | 250                              | μs   | GPIN is processed after HSLI communication is finished; Not subject to production test - specified by design                                                                               | PRQ-394 |

| Init mode delay                           | t <sub>INIT</sub>          | -      | -    | 250 + 2<br>(1/f <sub>PWM</sub> ) | μs   | Not subject to production test - specified by design                                                                                                                                       | PRQ-694 |

| Fail-off mode delay  (table continues)    | t <sub>fail_off</sub>      | _      | -    | 250                              | μs   | Not subject to production test - specified by design                                                                                                                                       | PRQ-765 |

#### **Datasheet**

# Table 5 (continued) Electrical characteristics

$V_S$  = 6 V to 20 V,  $T_J$  = -40°C to +150°C, all voltages with respect to ground, positive currents flowing as described in Figure 2 (unless otherwise specified). Typical values:  $V_S$  = 9 V,  $T_J$  = 25°C

| Parameter                   | Symbol                        |      | Values |                                  | Unit | Note or condition                                                                                                                                                    | P-      |

|-----------------------------|-------------------------------|------|--------|----------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

|                             |                               | Min. | Тур.   | Max.                             |      |                                                                                                                                                                      | Number  |

| Init to OTP delay           | t <sub>INIT2OTP</sub>         | -    | -      | 1                                | ms   | Not subject to production test - specified by design                                                                                                                 | PRQ-728 |

| OTP to programming<br>delay | t <sub>OTP2PRG</sub>          | -    | _      | 1                                | ms   | transition to OTP programming mode; transition to OTP programming emulation mode; Not subject to production test - specified by design                               | PRQ-395 |

| Active to fail-safe delay   | t <sub>ACTVE2FAILSAFE</sub>   | -    | -      | 4                                | ms   | I <sub>OUT</sub> ≥ 90% of desired output current after watchdog timeout triggered;  f <sub>PWM</sub> ≥ 300 Hz;  Not subject to production test - specified by design | PRQ-397 |

| Fail-safe to init delay     | t <sub>FAILSAFE2INIT</sub>    | -    | -      | 250 + 2<br>(1/f <sub>PWM</sub> ) | μs   | Not subject to production test - specified by design                                                                                                                 | PRQ-398 |

| Fail-safe to active delay   | t <sub>FAILSAFE2</sub> ACTIVE | -    | -      | 250                              | μs   | Not subject to production test - specified by design                                                                                                                 | PRQ-855 |

5 General Purpose Input (GPI)

# 5 General Purpose Input (GPI)

#### 5.1 Overview and features

The device provides two general purpose input pins GPIN0 and GPIN1. The GPINs can be used as

- digital input for direct drive feature to operate the device without the HSLI interface

- analog inputs connected to the internal ADC multiplexer for external NTC/PTC measurements

Accepted input signals for the direct drive feature can be either static voltage level or PWM decoded duty cycle

### 5.2 Digital Input

The GPINn pins integrate an internal pull-down function when set as digital input, where the pull-down current is defined by  $I_{PD}$ .

The digital input is set by default on GPIN0 and disabled on GPIN1. If the GPINn is used as analog input, the pull-down current is disabled as described in Chapter 5.5.

If GPINn is set as digital input it can be used to move the device in active mode. This is valid also if no outputs are mapped to GPINn. An activation request is either a static input high voltage level (Vih) or a PWM input high duty cycle (dc\_hi) with GPINn set as digital input.

#### 5.3 Direct drive

The direct drive function can be used to operate the device without the HSLI interface. A valid PWM signal on GPIN overwrites the HSLI request. One or both inputs drive one to all power output channels defined with a GPINn to OUTn mapping stored in the OTP.

| GPIN0OUTn MAP - Group0 | GPIN1OUTn MAP - Group1 |

|------------------------|------------------------|

| 0b aaaa aaaa aaaa      | 0b bbbb bbbb bbbb      |

Definition for a,b

Each GPIN is mapped to one set of 16 duty cycle configuration with a resolution of 8-bit. The configuration is stored in the OTP. The GPINO duty cycle configuration shares the fail-safe duty cycle configuration.

In case two GPINs are mapped to the same OUTn both GPINs demands are combined by a logical OR.

A GPIN1 ON demand has higher priority than a GPIN0 ON demand to resolve the duty cycle configuration conflict.

#### **Application example:**

${\sf GPIN1}$  is used to active a stop light function, where OUTn is configured to 100% duty cycle

GPINO is used to active a tail light function, where OUTn is configured to 6% duty cycle

#### Table 6 Application example

| GPIN0 (tail light) | GPIN1 (stop light) | Output duty cycle |

|--------------------|--------------------|-------------------|

| Low                | Low                | 0%                |

| Low                | High               | 100%              |

| High               | Low                | 6%                |

| High               | High               | 100%              |

The device resolves duty cycle request conflicts between GPIN activation and HSLI activation according to following table:

<sup>&</sup>quot;0" ... input is not mapped to the corresponding power output stage

<sup>&</sup>quot;1" ... input is mapped to the corresponding power output stage

#### **Datasheet**

5 General Purpose Input (GPI)

Table 7 GPIN priority configuration

| Output<br>mapped to<br>GPIN | GPIN         | GPINn_WRN | HSLI_WDT      | Priority configuration |

|-----------------------------|--------------|-----------|---------------|------------------------|

| no                          | _            | -         | not triggered | HSLI                   |

| no                          | _            | _         | triggered     | Fail-safe (OTP)        |

| no                          | _            | _         | disabled      | HSLI                   |

| yes                         | static low   | _         | not triggered | HSLI                   |

| yes                         | static low   | _         | triggered     | Fail-safe (OTP)        |

| yes                         | static low   | _         | disabled      | GPIN, output OFF       |

| yes                         | static high  | _         | _             | GPIN, output ON        |

| yes                         | PWM low      | no        | not triggered | HSLI                   |

| yes                         | PWM low      | no        | triggered     | Fail-safe (OTP)        |

| yes                         | PWM low      | no        | disabled      | GPIN, output OFF       |

| yes                         | PWM high     | no        | _             | GPIN, output ON        |

| yes                         | PWM low/high | yes       | not triggered | HSLI                   |

| yes                         | PWM low/high | yes       | triggered     | Fail-safe (OTP)        |

| yes                         | PWM low/high | yes       | disabled      | Fail-safe (OTP)        |

**Note:** In case of a transition from GPIN control back to HSLI control a DC\_SYNC frame is needed to synchronize to the last configured duty cycle.

**Note:** The table is referring to duty cycle priority only. The output current instead is set by the output current configuration volatile register in active mode while in fail safe it is taken from the OTP current values.

#### 5.4 Output enable

The GPINO enables or disables all power output stages if the ouput enable (OE) feature is configured via the OTP. The output power stages are enabled if the GPINO="high", disabled if the GPINO="low".

A "high" state is when VGPIN0  $\geq V_{IH}$  OR as in case of a PWM encoding as described in Chapter 5.6.

A "low" state is when VGPIN0  $\leq V_{IL}$  OR as in case of a PWM encoding as described in Chapter 5.6.

The output enable function is not effective for

- OUT15, when used as ERRn

- OUT0, when used as DCDC feedback channel.

# 5.5 Analog input

The GPINs can be configured with the OTP as analog input pins for external voltage measurements, (e.g. for external NTC/PTC temperature measurements).

The pull-down function is disabled in case the GPINn is configured as analog input pin.

The GPIN ADC measurement is described in Chapter 7.3.

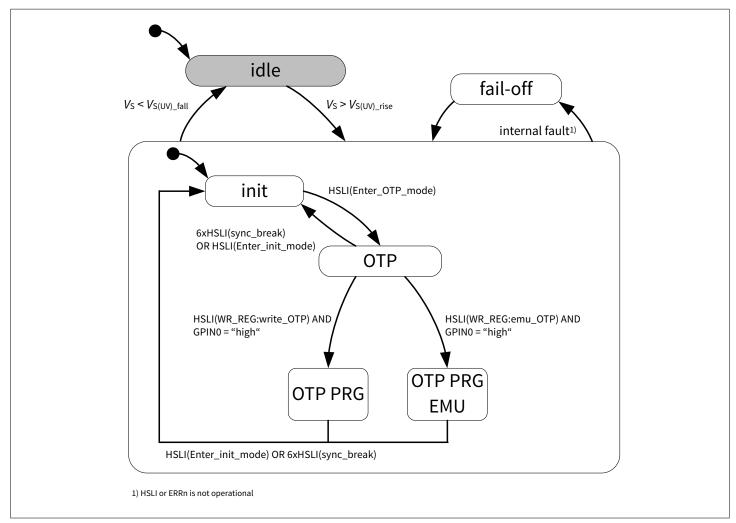

# 5.6 GPIN PWM decoding

The GPINs can decode an input PWM signal with a frequency of  $f_{PWM\_GPINn}$  where

a duty cycle dc<sub>10</sub> is detected as OFF activation OR

#### **Datasheet**

#### 5 General Purpose Input (GPI)

- a duty cycle dcHI is detected as ON activation OR

- a duty cycle outbound of  $dc_{10}$  OR  $dc_{HI}$  is detected as fault and reported via the HSLI interface or ERRn.

The GPIN decoding can be enabled or disabled via the OTP configuration for each GPINn.

In case of active mode the GPIN warning flag (GPINn\_WRN) is reported via the HSLI output status byte OR activating ERRN with a PWM.DC = 100%.

In case of fail-safe mode the fault state is reported by activating ERRN with a PWM.DC = 100%.

A GPIN warning on ERRN is reported, when fault management configuration is set to "0" - no state change.

Note:

The device interprets an immediate warning recovery as OFF activation. At least two GPIN PWM periods are required to detect an ON activation after a GPIN warning.

The GPIN WRN flag is cleared with an explicit HWCR frame from LCU.

Note:

If both GPINs are used for direct control and GPIN decoding enabled a phase shift between 10 µs and 1/fPWM and same frequency are required.

If the phase shift constraint is not granted, a GPIN short (GPIN\_SHORT) is detected by the device and reported in the output status byte FAULT bit.

Figure 6 GPIN PWM decoding scheme

#### 5.7 Electrical characteristics

#### Table 8 Electrical characteristics

$V_S = 6 \text{ V to } 20 \text{ V}$ ,  $T_J = -40 ^{\circ}\text{C}$  to +150  $^{\circ}\text{C}$ , all voltages with respect to ground, positive currents flowing as described in Figure 2 (unless otherwise specified). Typical values:  $V_S = 9 \text{ V}$ ,  $T_J = 25 ^{\circ}\text{C}$

| Parameter                  | Symbol           |      | Values |         |    | Note or condition                                                        | P-      |

|----------------------------|------------------|------|--------|---------|----|--------------------------------------------------------------------------|---------|

|                            |                  | Min. | Тур.   | Max.    |    |                                                                          | Number  |

| GPINn                      |                  |      |        |         |    |                                                                          |         |

| Input low voltage          | V <sub>IL</sub>  | 0    | _      | 0.8     | V  | -                                                                        | PRQ-407 |

| Input high voltage         | V <sub>IH</sub>  | 2.0  | -      | 5.5     | V  | Internally clamped to 5.5 V if the input current is ≤ I <sub>GPINn</sub> | PRQ-408 |

| Analog input voltage range | V <sub>AIN</sub> | 0    | _      | VDD+0.3 | V  | -                                                                        | PRQ-409 |

| Input pull-down current    | I <sub>PD</sub>  | 3    | 10     | 25      | μΑ | V <sub>GPIN</sub> = 5 V                                                  | PRQ-411 |

#### **Datasheet**

5 General Purpose Input (GPI)

# Table 8 (continued) Electrical characteristics

$V_S$  = 6 V to 20 V,  $T_J$  = -40°C to +150°C, all voltages with respect to ground, positive currents flowing as described in Figure 2 (unless otherwise specified). Typical values:  $V_S$  = 9 V,  $T_J$  = 25°C

| Parameter                  | Symbol              |      | Values |      |    | Note or condition                                         | P-      |  |

|----------------------------|---------------------|------|--------|------|----|-----------------------------------------------------------|---------|--|

|                            |                     | Min. | Тур.   | Max. |    |                                                           | Number  |  |

| Input leakage current      | I <sub>IL</sub>     | -10  | -      | 10   | μΑ | V <sub>GPIN</sub> = 5 V;<br>configured as analog<br>input | PRQ-412 |  |

| PWM decoding               |                     | ·    | -      | '    | -  |                                                           | -       |  |

| GPINn PWM decode frequency | $f_{ m PWM\_GPINn}$ | 25.5 | -      | 2000 | Hz | Not subject to production test - specified by design      | PRQ-670 |  |

| Input low duty cycle       | dc <sub>LO</sub>    | 12.5 | 25     | 37.5 | %  | Not subject to PRO production test - specified by design  |         |  |

| Input high duty cycle      | dc <sub>HI</sub>    | 62.5 | 75     | 87.5 | %  | Not subject to production test - specified by design      | PRQ-672 |  |

#### **6** Power Stage

#### 6.1 Features

- 16 output power stages

- one master PWM frequency ranging from 100 Hz to 2 kHz for LED dimming

- 16 individual configurable edge-aligned PWM engines with 14-bit duty cycle resolution

- one configurable 5-bit phase shift function for improved EME and supply stabilization

- parallel output operation

- integrated thermal overload protection

- thermal protection by derating of the output current

- 16 independent 6-bit configurable global output current configuration ranging from 5.625 mA to 76.5 mA

# 6.2 Current sink operation

The output stage sinks an individual configurable 6-bit output current I<sub>OUT</sub> where the desired output current is configurable via the OTP or via HSLI in runtime.

The following table is related to the configurable output current configurations:

Table 9 Output current configurations

| I <sub>OUT</sub> step | I <sub>OUT</sub> [mA] |

|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| 0                     | 5.625                 | 16                    | 23.625                | 32                    | 41.625                | 48                    | 59.625                |

| 1                     | 6.75                  | 17                    | 24.75                 | 33                    | 42.75                 | 49                    | 60.75                 |

| 2                     | 7.875                 | 18                    | 25.875                | 34                    | 43.875                | 50                    | 61.875                |

| 3                     | 9                     | 19                    | 27                    | 35                    | 45                    | 51                    | 63                    |

| 4                     | 10.125                | 20                    | 28.125                | 36                    | 46.125                | 52                    | 64.125                |

| 5                     | 11.25                 | 21                    | 29.25                 | 37                    | 47.25                 | 53                    | 65.25                 |

| 6                     | 12.375                | 22                    | 30.375                | 38                    | 48.375                | 54                    | 66.375                |

| 7                     | 13.5                  | 23                    | 31.5                  | 39                    | 49.5                  | 55                    | 67.5                  |

| 8                     | 14.625                | 24                    | 32.625                | 40                    | 50.625                | 56                    | 68.625                |

| 9                     | 15.75                 | 25                    | 33.75                 | 41                    | 51.75                 | 57                    | 69.75                 |

| 10                    | 16.875                | 26                    | 34.875                | 42                    | 52.875                | 58                    | 70.875                |

| 11                    | 18                    | 27                    | 36                    | 43                    | 54                    | 59                    | 72                    |

| 12                    | 19.125                | 28                    | 37.125                | 44                    | 55.125                | 60                    | 73.125                |

| 13                    | 20.25                 | 29                    | 38.25                 | 45                    | 56.25                 | 61                    | 74.25                 |

| 14                    | 21.375                | 30                    | 39.375                | 46                    | 57.375                | 62                    | 75.375                |

| 15                    | 22.5                  | 31                    | 40.5                  | 47                    | 58.5                  | 63                    | 76.5                  |

# 6.3 HSLI configurable output current

The 6-bit output current *I*<sub>OUT</sub> can be configured also runtime via the HSLI in init mode, OTP programming emulation mode and active mode.

25

#### 6.4 PWM Generator

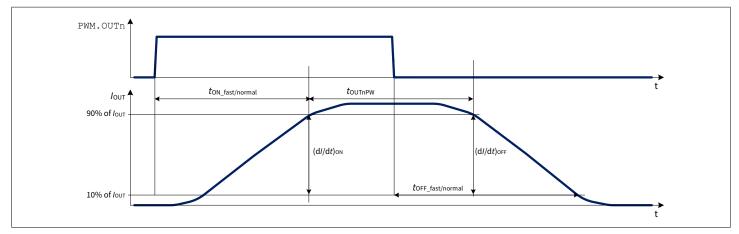

#### 6.4.1 PWM function

The device operates each power output stage with a PWM function containing

- one configurable duty cycle per channel

- one global PWM frequency and

- one global PWM phase shift

The device sinks current on HSLI request or GPIN request on each output channel in ≤tON time.

This delay depends on the PWM frequency and on the phase shift according to the following approximate formula:  $t_{ON}=1/f_{PWM}+n^*t_{PHS}$

## 6.4.2 PWM frequency

The PWM engine operates with one master PWM frequency setting  $f_{PWM}$  stored in the OTP. The configuration steps should cover multiples of 50 Hz and 60 Hz in the range from 100 Hz to 2 kHz according to following table:

Table 10 Configuration example

| Step | Frequency [Hz] | Step | Frequency [Hz] |

|------|----------------|------|----------------|

| 0    | 99.90          | 8    | 662.08         |

| 1    | 200.32         | 9    | 723.38         |

| 2    | 239.65         | 10   | 781.25         |

| 3    | 300.48         | 11   | 899.50         |

| 4    | 359.78         | 12   | 1199.00        |

| 5    | 399.89         | 13   | 1502.40        |

| 6    | 539.03         | 14   | 1799.00        |

| 7    | 600.96         | 15   | 1997.00        |

## 6.4.3 PWM duty cycle

The PWM engine provides 16 individual configurable edge-aligned PWM duty cycle settings configurable

- via the OTP in fail-safe mode OR

- the HSLI interface in active mode

- GPINn direct control as described in Chapter 5.3

The updated duty cycle values are applied to the power stages synchronous to the internal PWM period. e.g. the power output duty cycle change is seen latest after one PWM period  $(1/f_{PWM})$  independently if the change was triggered by the HSLI, fail-safe mode or GPINn control.

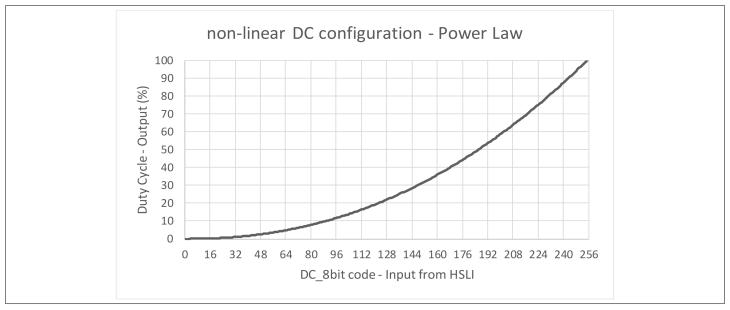

# 6.4.4 PWM duty cycle configuration - linear or power-law relation

The duty cycle setting can be configured as

- non-linear 8-bit duty cycle configuration by using the DC\_UPDATE frame and DLC=0x4, which is related to the 8-bit configuration with a power law relation to the 14-bit resolution OR

- linear 14-bit duty cycle configuration by using the DC UPDATE frame and DLC=0x6.

The applied power law is defined as:

DC\_14bit =  $16383 * (DC_8bit/255)^{1/gamma}$ , where gamma is set to 0.4545 and the result is round up away from 0. The graphical representation is shown in Figure 7.

#### **Datasheet**

6 Power Stage

DC\_14bit ... duty cycle in 14-bit representation DC\_8bit ... duty cycle in 8-bit representation

Figure 7 Power law - 8-bit to 14-bit

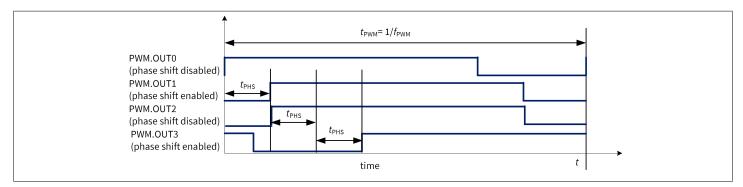

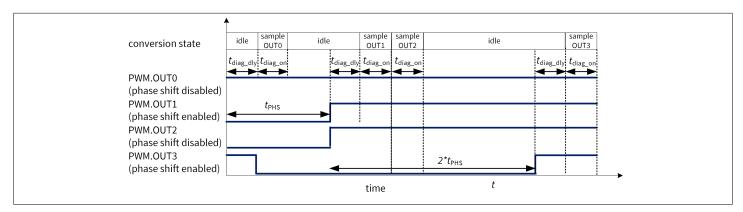

#### 6.4.5 PWM phase shift

The PWM generator provides one global 5-bit PWM phase shift configuration stored in the OTP.

The phase shift can be enabled or disabled for each power output stage via the OTP.

In case the phase shift is enabled,  $OUT_n$  turns on with a delay of  $t_{PHS}$ =n \*  $n_{PSH}$ \*1/ $f_{PWM}$ , where n=0 to 15.

In case the phase shift is disabled,  $OUT_n$  turns on simultaneously with  $OUT_{n-1}$ . Both cases are shown in following Figure 8.

The 5-bit phase-shift configuration is related to the 14-bit duty cycle reference from bits 9:5 as shown in table below. This results into a phase shift range of  $n_{PSH}$  referred to the PWM period.

Table 11 Duty cycle to phase shift bit weight relation

| bit | Duty cycle<br>(14-bit) | Phase shift<br>(5-bit) | bit | Duty cycle<br>(14-bit) | Phase shift<br>(5-bit) |

|-----|------------------------|------------------------|-----|------------------------|------------------------|

| 13  | х                      |                        | 06  | х                      | х                      |

| 12  | х                      |                        | 05  | х                      | х                      |

| 11  | х                      |                        | 04  | х                      |                        |

| 10  | х                      |                        | 03  | х                      |                        |

| 09  | х                      | х                      | 02  | х                      |                        |

| 08  | х                      | х                      | 01  | х                      |                        |

| 07  | х                      | х                      | 00  | х                      |                        |

Figure 8 Timing diagram and parameter for PWM pulse

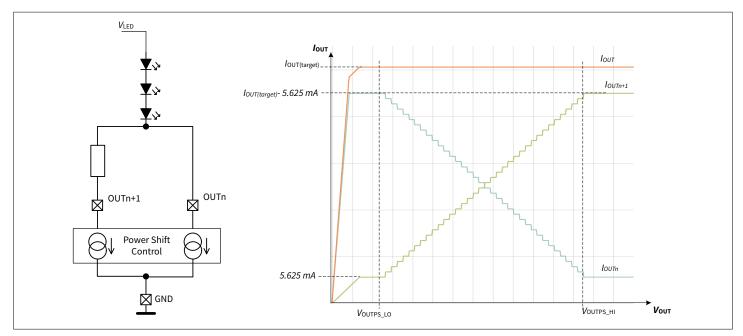

#### 6.5 Power shift

The device can limit the internal power dissipation by balancing one load current branch with two power stages and an external resistance.

The primary output channel OUTn and secondary output channel OUTn+1 provide the output current  $I_{\text{OUT}} = I_{\text{OUTn}} + I_{\text{OUTn+1}}$ , where  $I_{\text{OUTn+1}}$  linearly increases with OUTn voltage, starting from  $V_{\text{OUTPS\_LO}}$ , until  $V_{\text{OUTPS\_HI}}$  threshold is reached. If  $V_{\text{OUTn}} > V_{\text{OUTPS\_HI}}$  then  $I_{\text{OUTn+1}} = I_{\text{OUT}} - 5.625$  mA and  $I_{\text{OUTn}} = 5.625$  mA. The sum of  $I_{\text{OUTn}}$  and  $I_{\text{OUTn+1}}$  remains constant while  $V_{\text{OUTn}}$  rises.

V<sub>OUTPS\_LO</sub> is calculated as following:

$V_{OUTPS\_LO} = (1 + V_{OUTPS\_HI} \cdot 5,625mA / IOUT) / (1 + 5,625mA / IOUT)$

The external resistance is connected to the secondary output channel, and it shall be selected according to:

$R = (V_{OUTPS HI} - V_{OUTPS LO}) / (I_{OUT} - 5.625 mA)$

The primary and secondary output channels are defined according to following table:

Table 12 Primary and secondary output channels

| Primary | Secondary |

|---------|-----------|

| OUT0    | OUT1      |

| OUT2    | OUT3      |

| OUT8    | OUT9      |

| OUT10   | OUT11     |

The power shift threshold  $V_{\text{OUTPS\_HI}}$  is programmable by a 2-bit OTP register with 4 options as shown below with an accuracy of a  $\alpha_{\text{VOUT PS}}$  per configuration step.

Table 13 V<sub>OUTPS HI</sub> configuration steps

| Configuration step | V <sub>OUTPS_HI</sub> |

|--------------------|-----------------------|

| 0                  | 2 V                   |

| 1                  | 3 V                   |

| 2                  | 6 V                   |

| 3                  | 10 V                  |

The power shift needs to be enabled via the OTP configuration. When using the power shift feature, it necessary to send the same duty cycle update requests to both involved channels.

Figure 9 Power shift principle

In case the thermal derating feature is enabled, or in Fail Safe condition, the power shift feature is not available. Therefore it is recommended set the secondary output to disabled in the OTP fail-safe enable bit.

The target output current, which is the sum of the primary and the secondary channels, shall be set in the primary channel OTP current register.

The secondary channel OTP current register shall be set to the minimum value.

In case faulty management configuration is set to 1 the power shift feature shall be disabled.

# 6.6 Parallel output configuration

Up to all output stages can be used in parallel to achieve a higher output current without any dedicated configuration needs.

#### 6.7 Thermal overload

The output stage integrates an individual thermal overload protection (thermal shutdown).

The output stage turns off if the junction temperature exceeds  $T_{\text{J(ABS)}}$  with a hysteresis of  $T_{\text{HYS(ABS)}}$  and reports the thermal overload event in a fault register.

The LCU can poll the OVLD flag in the output status byte or by reading the channel status byte OUTn with the READ\_OST command. The OVLD flag is cleared after the fault has been acknowledged with an explicit HWCR frame from the LCU.

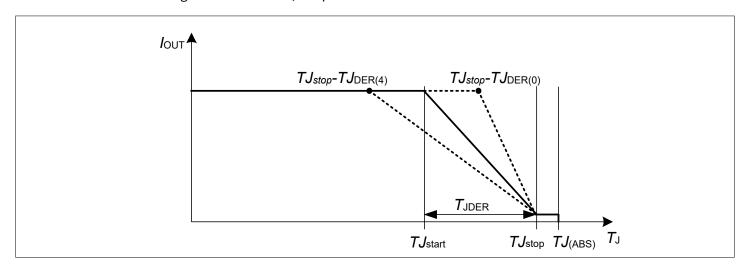

# 6.8 Thermal derating

# 6.8.1 Thermal derating with integrated temperature sensor

The output stage provides a configurable thermal derating (thermal foldback) of the output current based on the integrated device temperature measurement. Each output stage starts to decrease the current linearly when  $T_J \ge T_{Jstart}$  until  $T_{Jstop}$  is reached, where

$$I_{OUTDER} = I_{OUT} - (T_J - T_{Jstart}) \times k_{DER}$$

(1)

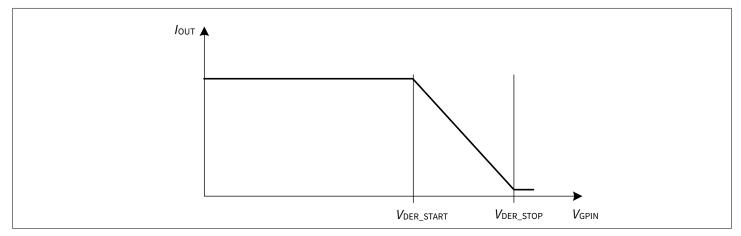

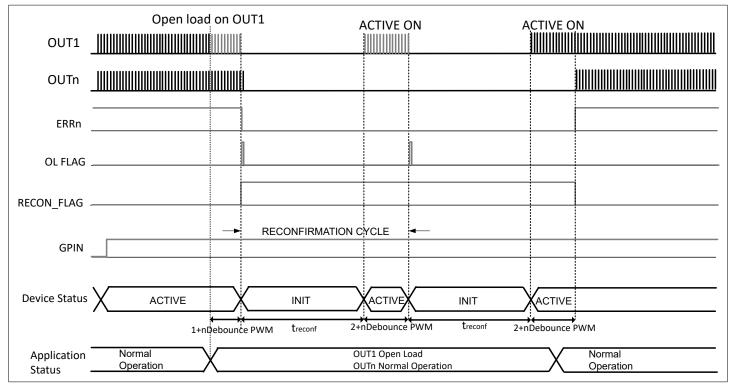

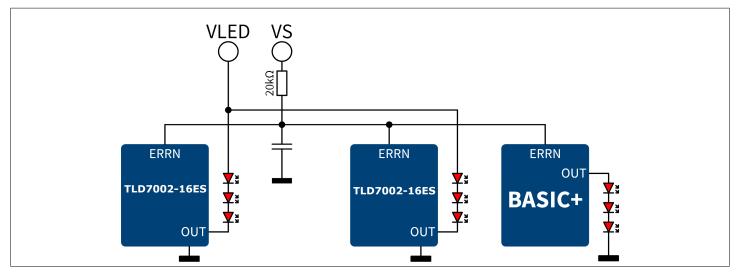

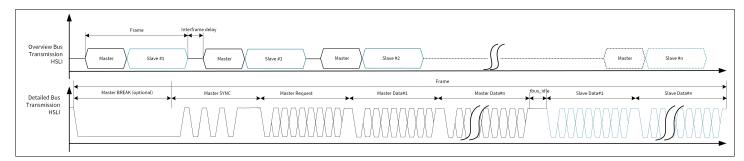

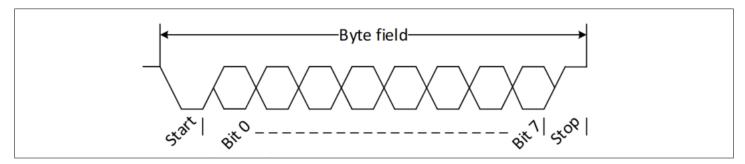

$$k_{DER} = \frac{(I_{OUT} - 5.625mA)}{T_{JDER}} \tag{2}$$