# 1 G ビット (128 MB)/512 M ビット (64 MB) GL-T MIRRORBIT™ フラッシュ

パラレル , 3.0V

## 概要

サイプレス S29GL01GT/512T は、45 nm プロセス テクノロジを用いて製造される、MIRRORBIT™ フラッシュ製品です。ページ アクセス時間 15 ns という高速アクセスと、これに対応した 100 ns という高速ランダム アクセス時間を実現しています。一度の動作で最大 256 ワード /512 バイトのプログラム可能な書き込みバッファを備え、標準のプログラミング アルゴリズムに比べて効果的な高速プログラミングを実現しています。このような特長を備えたこれらのデバイスは、大容量、高性能、そして低消費電力を必要とする今日の組込みアプリケーションに最適です。

## 特長

- 45nm の MIRRORBIT™ 技術

- 単一電源 ( $V_{CC}$ ) による読み出し / プログラム / 消去 (2.7 V ~ 3.6 V)

- 汎用性がある I/O 機能

- 広範な I/O 電圧 ( $V_{IO}$ ): 1.65 V ~  $V_{CC}$

- ×8/×16 データ バス

- 非同期 32 バイト ページ読み出し

- 512 バイト プログラミング バッファ

- ページの倍数単位で、最大 512 バイトまでのプログラミング

- 単一ワードと同一ワードでの複数プログラムを選択可能

- 自動エラー チェックと訂正 (ECC) – 1 ビット エラー訂正の内部ハードウェア ECC

- セクタ消去

- ユニフォーム 128 KB セクタ

- プログラム / 消去動作のための一時停止 / 再開コマンド

- ステータス レジスタ、データ ポーリング、およびレディ / ビジー ピンによるデバイス状態の特定

- セクタの高度な保護 (ASP)

- セクタごとの揮発性および不揮発性の保護方式

- 個別の 2048 バイト OTP (ワンタイムプログラム) アレイ

- 4 つのロック可能な領域 (SSR0 ~ SSR3)

- SSR0 は工場出荷時ロック設定

- SSR3 はパスワードによる読み出し保護

- 共通フラッシュインターフェース (CFI) パラメーター テーブル

- 温度範囲 / グレード

- 産業用 (-40°C ~ +85°C)

- 産業用プラス (-40°C ~ +105°C)

- 拡張 (-40°C ~ +125°C)

- 車載用, AEC-Q100 グレード 3 (-40°C ~ +85°C)

- 車載用, AEC-Q100 グレード 2 (-40°C ~ +105°C)

- 100,000 プログラム / 消去サイクル

- 20 年のデータ保持期間

## 性能要約

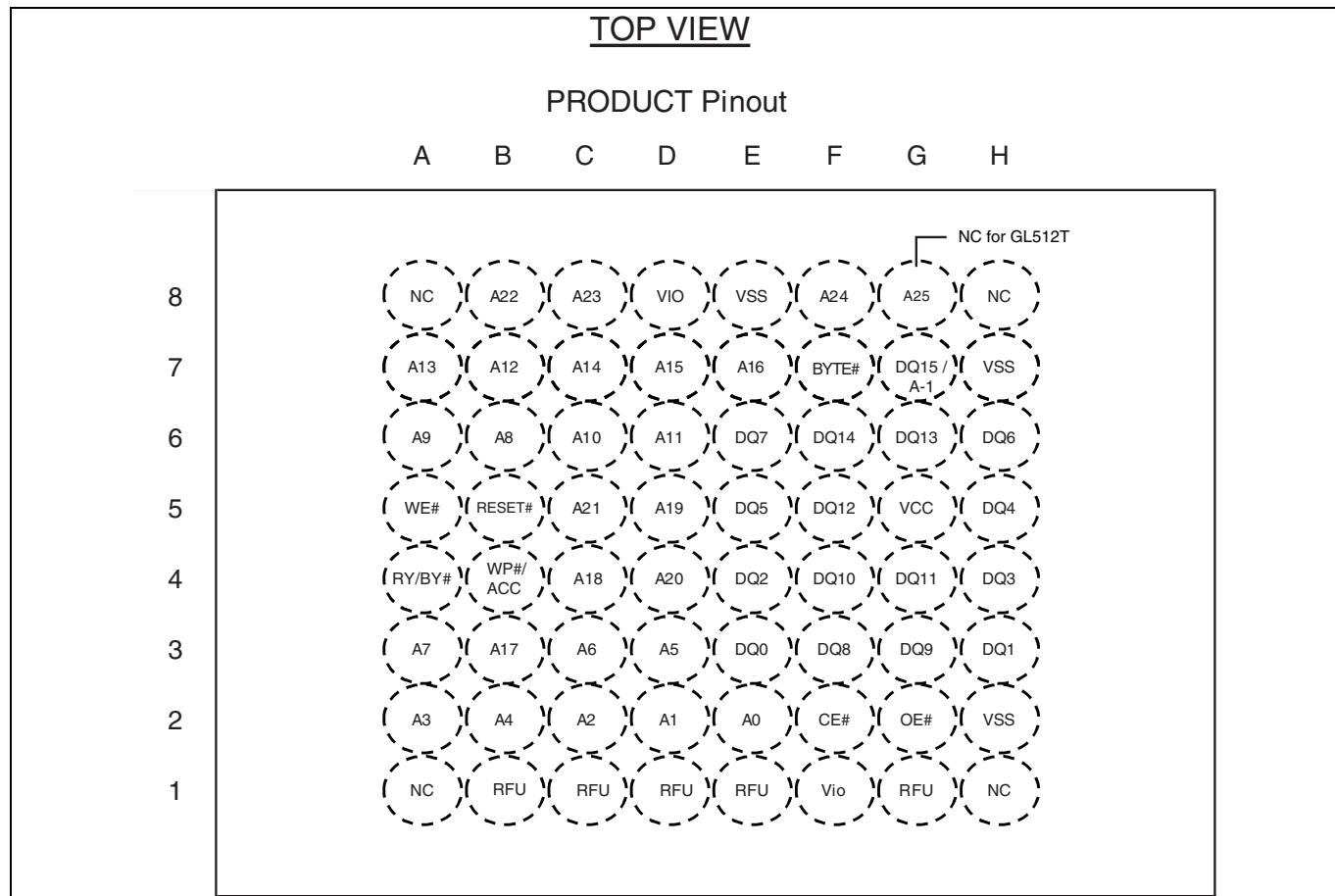

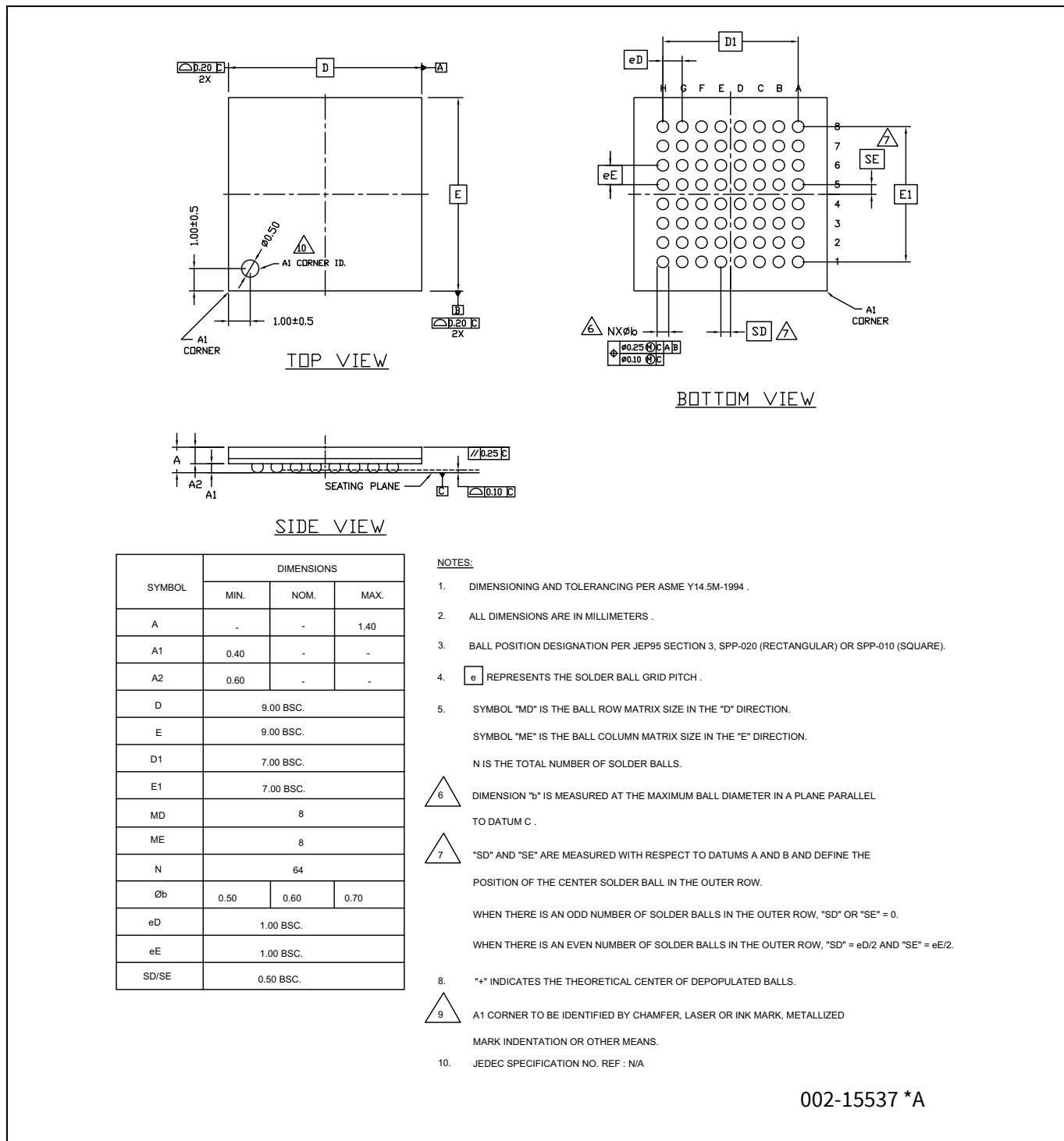

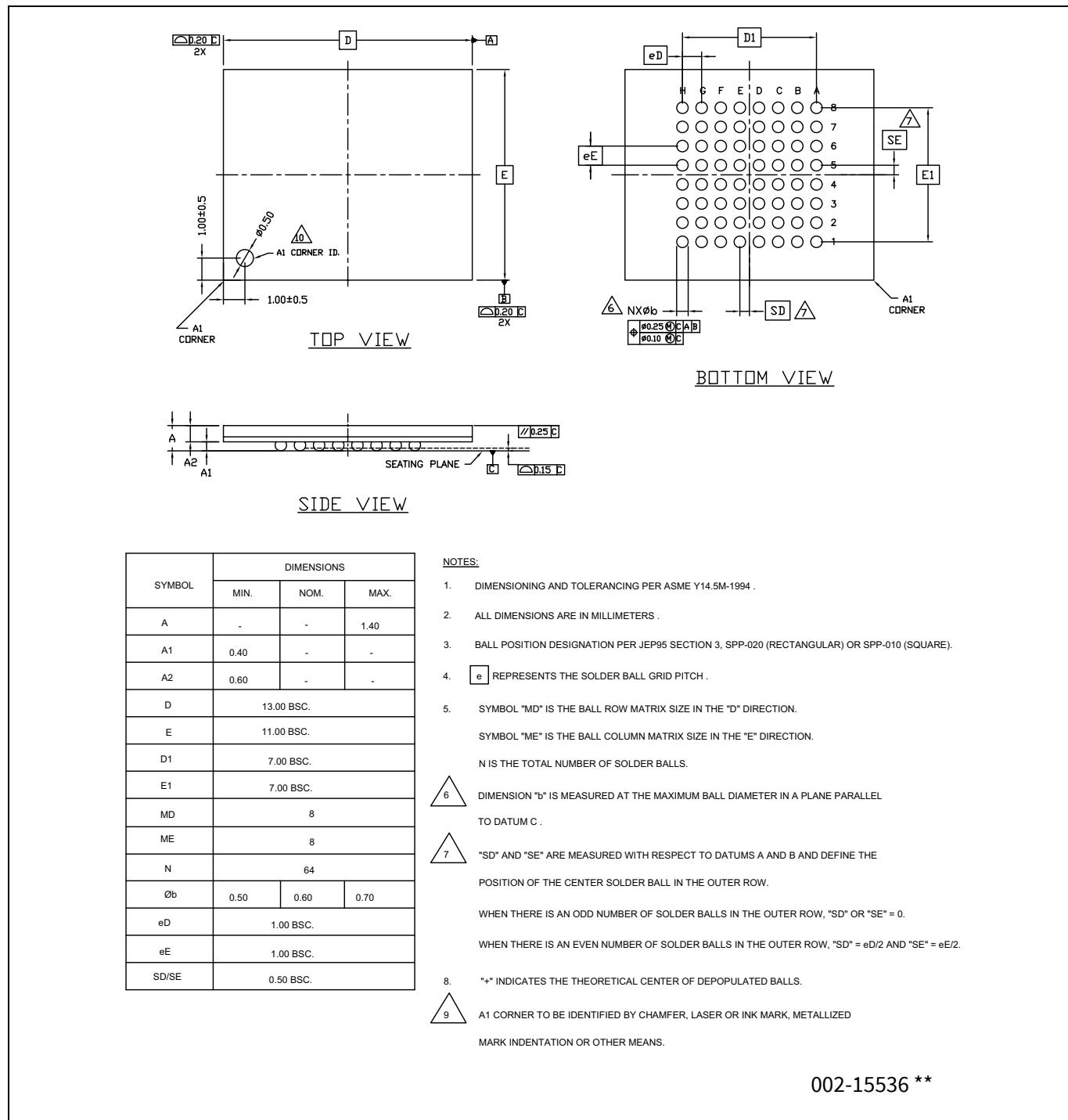

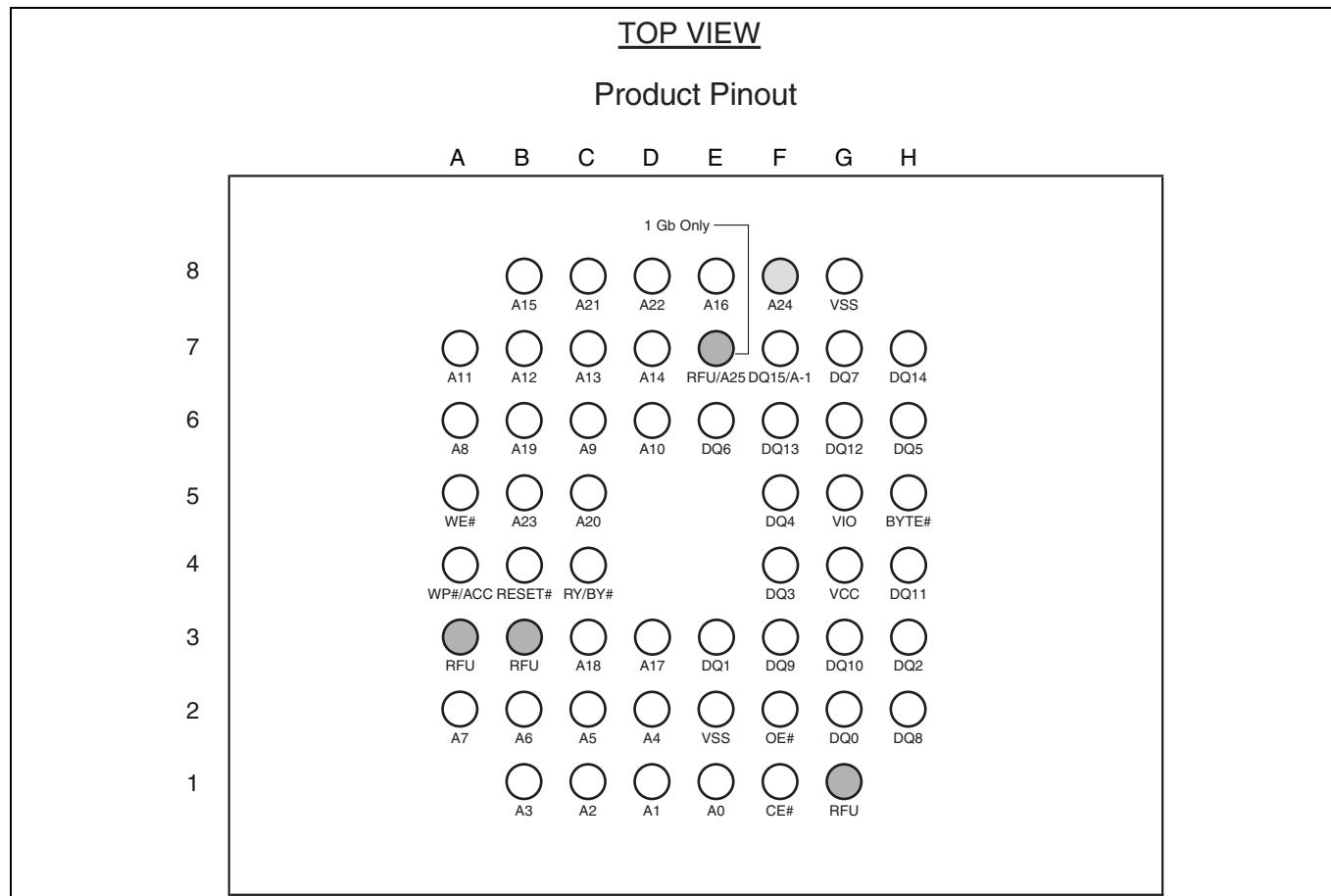

## ・パッケージオプション

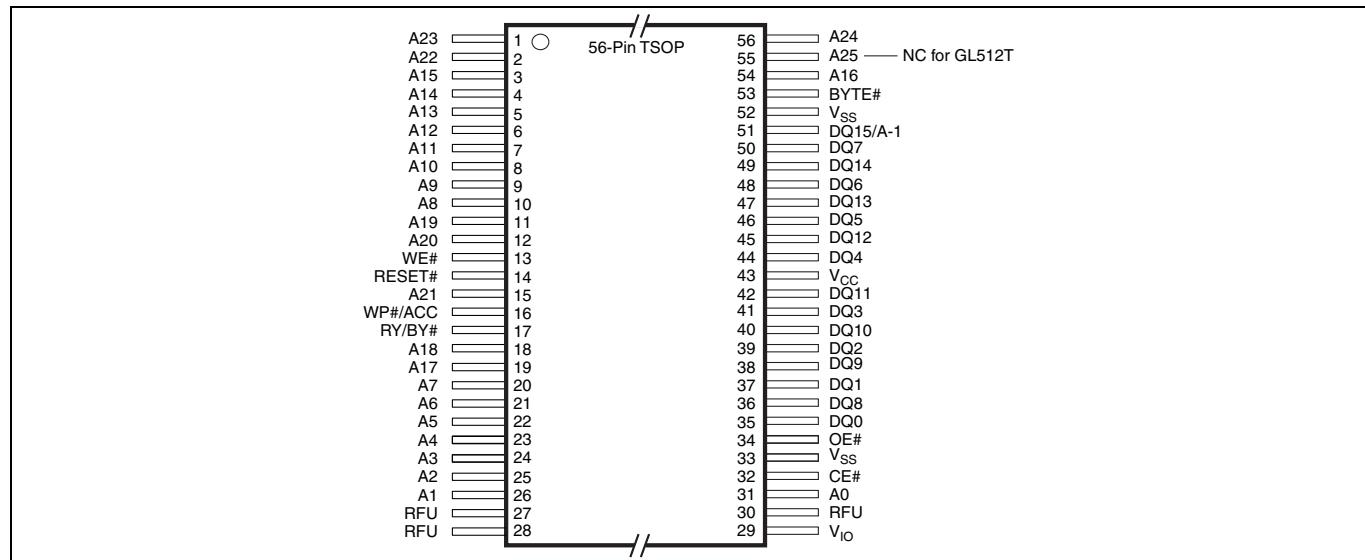

- 56 ピン TSOP

- 64 ボール LAA 強化 BGA, 13 mm × 11 mm

- 64 ボール LAE 強化 BGA, 9 mm × 9 mm

- 56 ボール VBU 強化 BGA, 9 mm × 7 mm

## 性能要約

## 動作温度範囲 -40°C ~ +85°C の性能要約

| 最大読み出しアクセス時間 |                      |                          |                          |                         |                         |

|--------------|----------------------|--------------------------|--------------------------|-------------------------|-------------------------|

| メモリ容量        | 電圧範囲                 | ランダムアクセス時間 ( $t_{ACC}$ ) | ページアクセス時間 ( $t_{PACc}$ ) | CE# アクセス時間 ( $t_{CE}$ ) | OE# アクセス時間 ( $t_{OE}$ ) |

| 512 Mb       | フル $V_{CC} = V_{IO}$ | 100                      | 15                       | 100                     | 25                      |

|              | 汎用 I/O $V_{IO}$      | 110                      | 25                       | 110                     | 35                      |

| 1 Gb         | フル $V_{CC} = V_{IO}$ | 100                      | 15                       | 100                     | 25                      |

|              | 汎用 I/O $V_{IO}$      | 110                      | 25                       | 110                     | 35                      |

## 動作温度範囲 -40°C ~ +105°C の性能要約

| 最大読み出しアクセス時間 |                      |                          |                          |                         |                         |

|--------------|----------------------|--------------------------|--------------------------|-------------------------|-------------------------|

| メモリ容量        | 電圧範囲                 | ランダムアクセス時間 ( $t_{ACC}$ ) | ページアクセス時間 ( $t_{PACc}$ ) | CE# アクセス時間 ( $t_{CE}$ ) | OE# アクセス時間 ( $t_{OE}$ ) |

| 512 Mb       | フル $V_{CC} = V_{IO}$ | 110                      | 15                       | 110                     | 25                      |

|              | 汎用 I/O $V_{IO}$      | 120                      | 25                       | 120                     | 35                      |

| 1 Gb         | フル $V_{CC} = V_{IO}$ | 110                      | 15                       | 110                     | 25                      |

|              | 汎用 I/O $V_{IO}$      | 120                      | 25                       | 120                     | 35                      |

## 動作温度範囲 -40°C ~ +125°C の性能要約

| 最大読み出しアクセス時間 |                      |                          |                          |                         |                         |

|--------------|----------------------|--------------------------|--------------------------|-------------------------|-------------------------|

| メモリ容量        | 電圧範囲                 | ランダムアクセス時間 ( $t_{ACC}$ ) | ページアクセス時間 ( $t_{PACc}$ ) | CE# アクセス時間 ( $t_{CE}$ ) | OE# アクセス時間 ( $t_{OE}$ ) |

| 512 Mb       | フル $V_{CC} = V_{IO}$ | 120                      | 15                       | 120                     | 25                      |

|              | 汎用 I/O $V_{IO}$      | 130                      | 25                       | 130                     | 35                      |

| 1 Gb         | フル $V_{CC} = V_{IO}$ | 120                      | 15                       | 120                     | 25                      |

|              | 汎用 I/O $V_{IO}$      | 130                      | 25                       | 130                     | 35                      |

性能要約

標準的なプログラム / 消去速度

| 動作                    | -40°C ~ +85°C | -40°C ~ +105°C | -40°C ~ +125°C |

|-----------------------|---------------|----------------|----------------|

| バッファプログラミング (512 バイト) | 1.14 MBps     | 1.14 MBps      | 1.14 MBps      |

| セクタ消去 (128 KB)        | 245 KBps      | 245 KBps       | 245 KBps       |

最大消費電流

| 動作                       | -40°C ~ +85°C | -40°C ~ +105°C | -40°C ~ +125°C |

|--------------------------|---------------|----------------|----------------|

| アクティブ読み出し (5 MHz, 30 pF) | 60 mA         | 60 mA          | 60 mA          |

| プログラム                    | 100 mA        | 100 mA         | 100 mA         |

| 消去                       | 100 mA        | 100 mA         | 100 mA         |

| スタンバイ                    | 100 µA        | 200 µA         | 215 µA         |

## 目次

## 目次

|                                                 |    |

|-------------------------------------------------|----|

| <b>概要</b>                                       | 1  |

| <b>特長</b>                                       | 1  |

| <b>性能要約</b>                                     | 2  |

| <b>目次</b>                                       | 4  |

| <b>1 製品概要</b>                                   | 6  |

| <b>2 アドレス空間オーバーレイ</b>                           | 8  |

| 2.1 フラッシュメモリアレイ                                 | 10 |

| 2.2 デバイス ID および CFI (ID-CFI) ASO                | 11 |

| 2.3 ステータスレジスタ ASO                               | 12 |

| 2.4 データポーリングステータス ASO                           | 12 |

| 2.5 SSR ASO                                     | 13 |

| 2.6 セクタ保護の制御                                    | 14 |

| 2.7 ECC ステータス ASO                               | 15 |

| <b>3 データ保護</b>                                  | 16 |

| 3.1 デバイス保護方式                                    | 16 |

| 3.2 コマンド保護                                      | 16 |

| 3.3 SSR (OTP)                                   | 16 |

| 3.4 セクタ保護方式                                     | 17 |

| <b>4 読み出し動作</b>                                 | 22 |

| 4.1 非同期読み出し                                     | 22 |

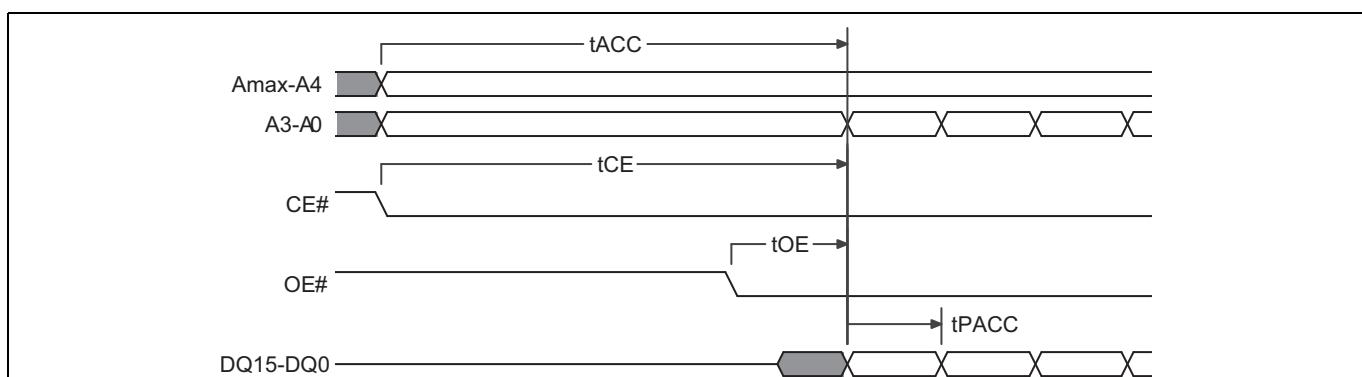

| 4.2 ページモード読み出し                                  | 22 |

| <b>5 組込み動作</b>                                  | 23 |

| 5.1 組込みアルゴリズムコントローラー (EAC)                      | 23 |

| 5.2 プログラムと消去のまとめ                                | 24 |

| 5.3 自動 ECC                                      | 25 |

| 5.4 コマンドセット                                     | 27 |

| 5.5 ステータス監視                                     | 43 |

| 5.6 エラータイプおよびクリア手順                              | 50 |

| 5.7 組込みアルゴリズム性能表                                | 53 |

| <b>6 データの完全性</b>                                | 56 |

| 6.1 消去可能回数                                      | 56 |

| 6.2 データ保持                                       | 56 |

| <b>7 ソフトウェアインターフェースリファレンス</b>                   | 57 |

| 7.1 コマンドのまとめ                                    | 57 |

| 7.2 デバイス ID と共にフラッシュインターフェース (ID-CFI) の ASO マップ | 64 |

| <b>8 信号の説明</b>                                  | 69 |

| 8.1 アドレスとデータの設定                                 | 69 |

| 8.2 入出力のまとめ                                     | 69 |

| 8.3 ワード / バイト設定                                 | 70 |

| 8.4 汎用 I/O 機能                                   | 70 |

| 8.5 レディ / ビジー # (RY/BY#)                        | 70 |

| 8.6 ハードウェアリセット                                  | 70 |

| <b>9 信号プロトコル</b>                                | 71 |

| 9.1 インターフェースの状態                                 | 71 |

| 9.2 ハードウェアデータ保護状態での電源切斷                         | 72 |

| 9.3 低消費電力モード                                    | 72 |

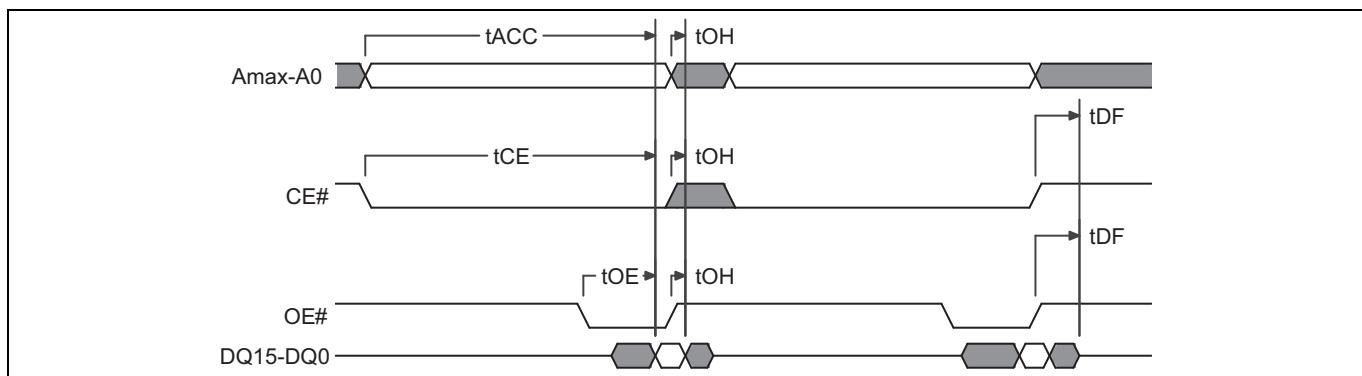

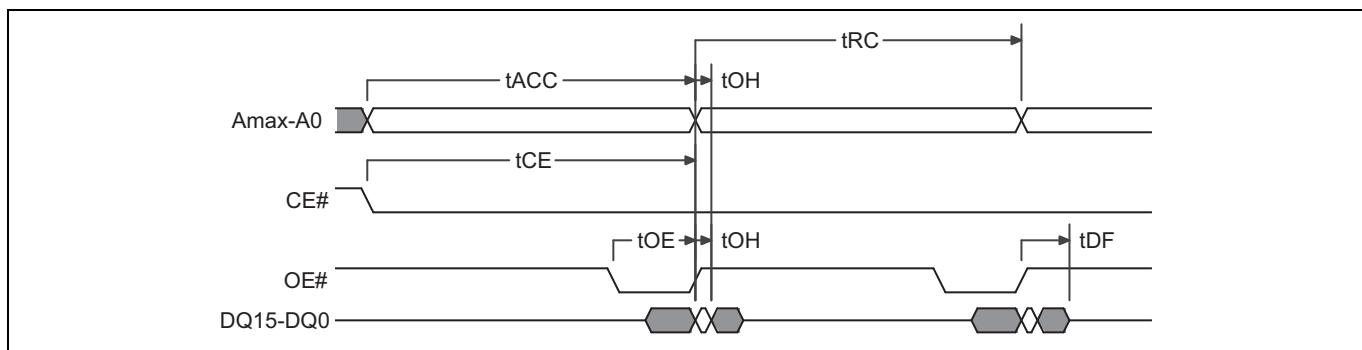

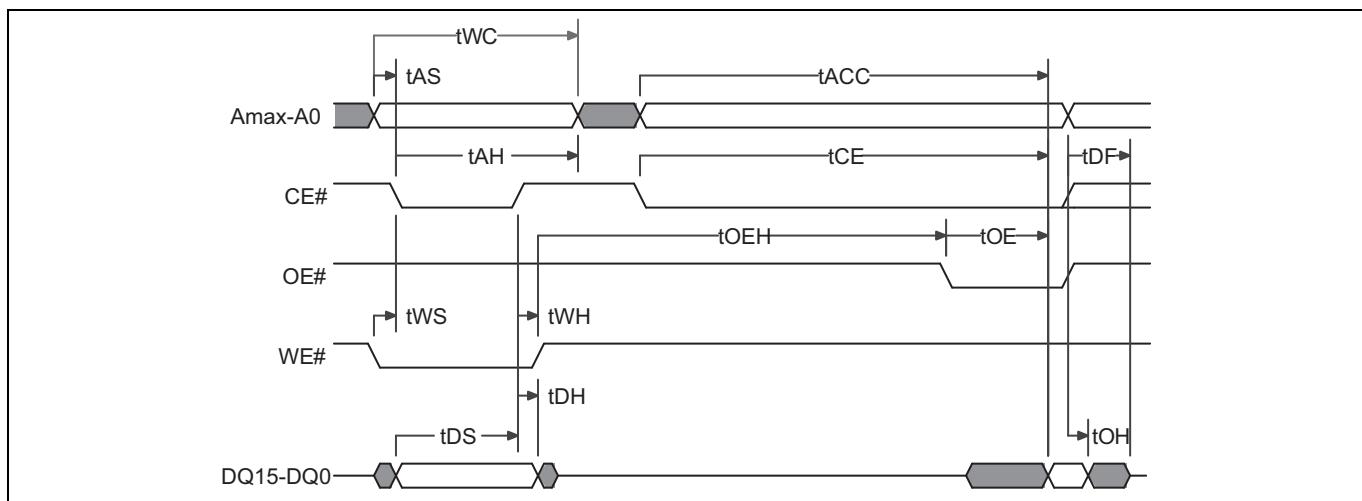

| 9.4 読み出し                                        | 73 |

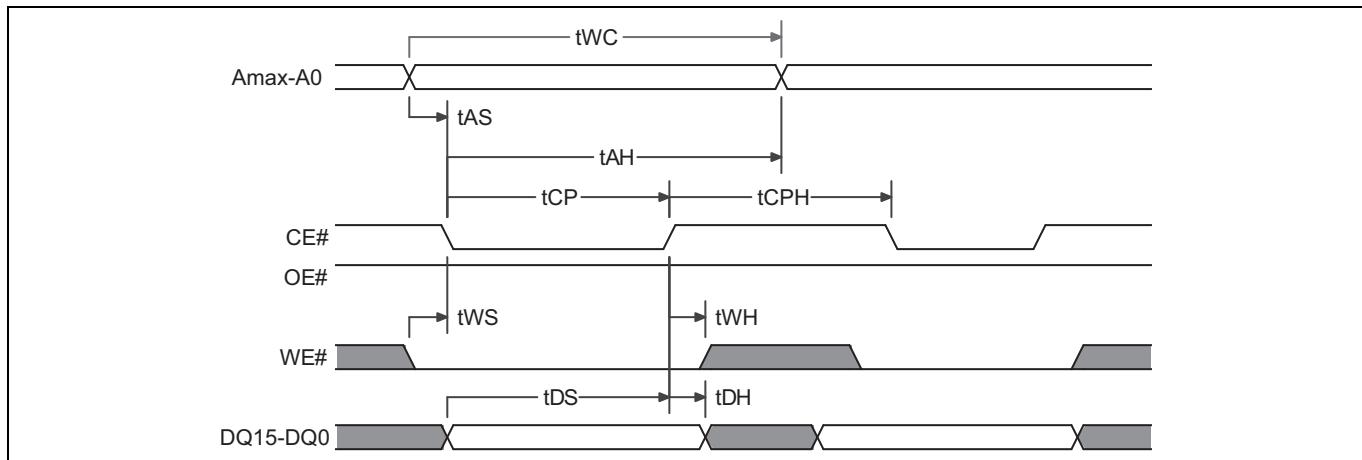

| 9.5 書き込み                                        | 74 |

| <b>10 電気的仕様</b>                                 | 75 |

| 10.1 絶対最大定格                                     | 75 |

| 10.2 熱抵抗                                        | 75 |

目次

|                                        |            |

|----------------------------------------|------------|

| 10.3 ラッチアップ特性 .....                    | 75         |

| 10.4 動作範囲 .....                        | 76         |

| 10.5 DC 電気的特性 .....                    | 79         |

| 10.6 静電容量特性 .....                      | 81         |

| <b>11 タイミング仕様 .....</b>                | <b>84</b>  |

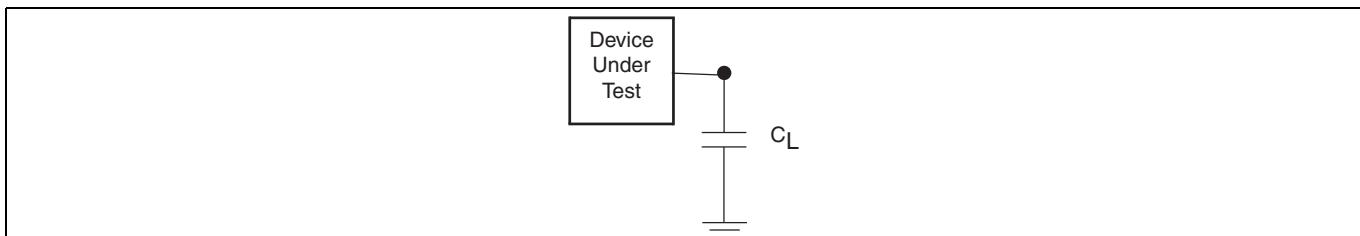

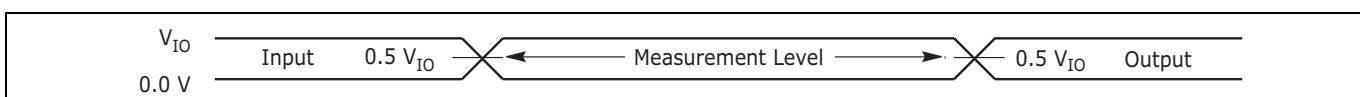

| 11.1 波形遷移の要点 .....                     | 84         |

| 11.2 AC テスト条件 .....                    | 85         |

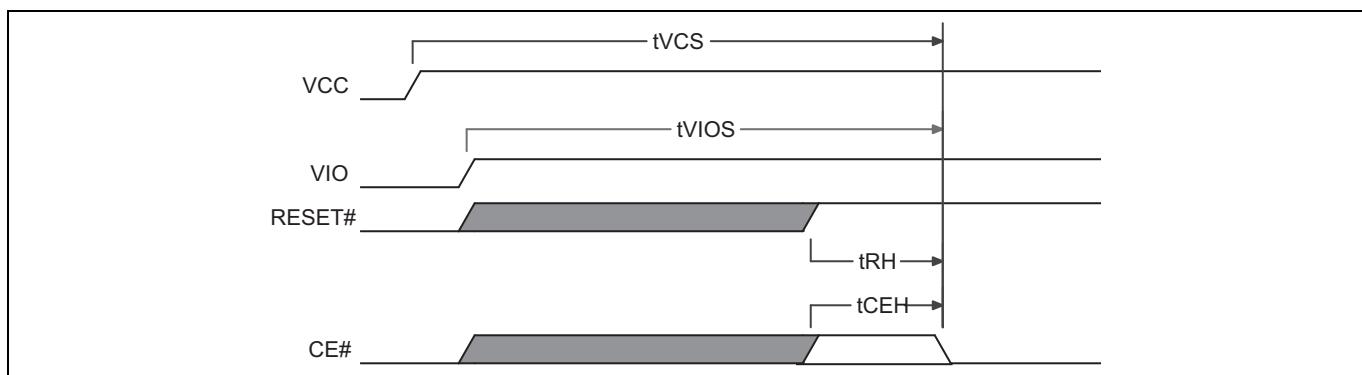

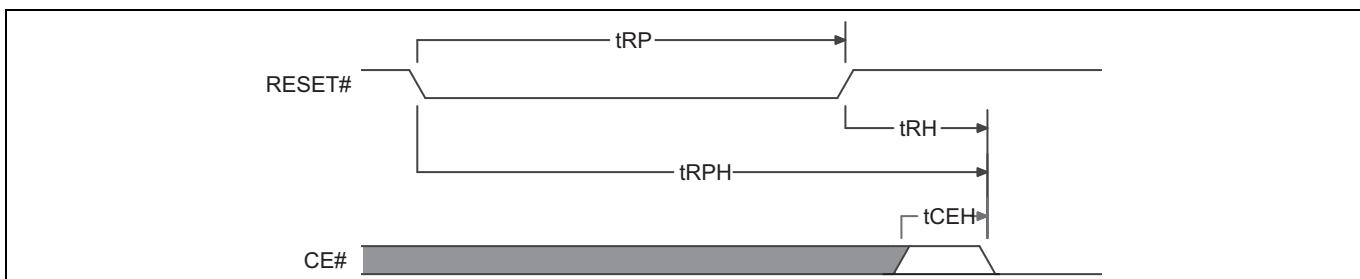

| 11.3 パワーオンリセット (POR) とウォームリセット .....   | 86         |

| 11.4 AC 電気的特性 .....                    | 89         |

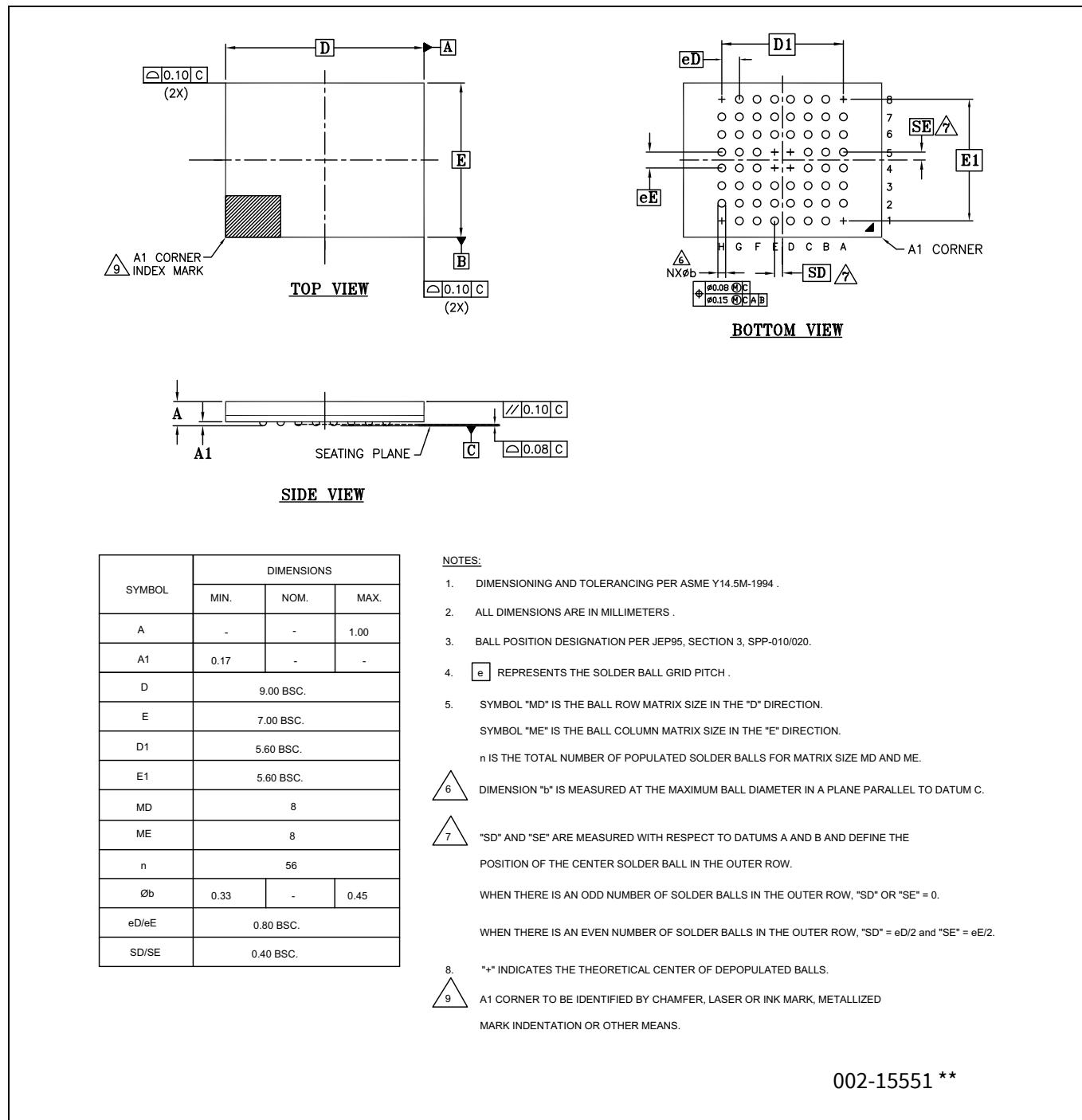

| <b>12 物理インターフェース .....</b>             | <b>106</b> |

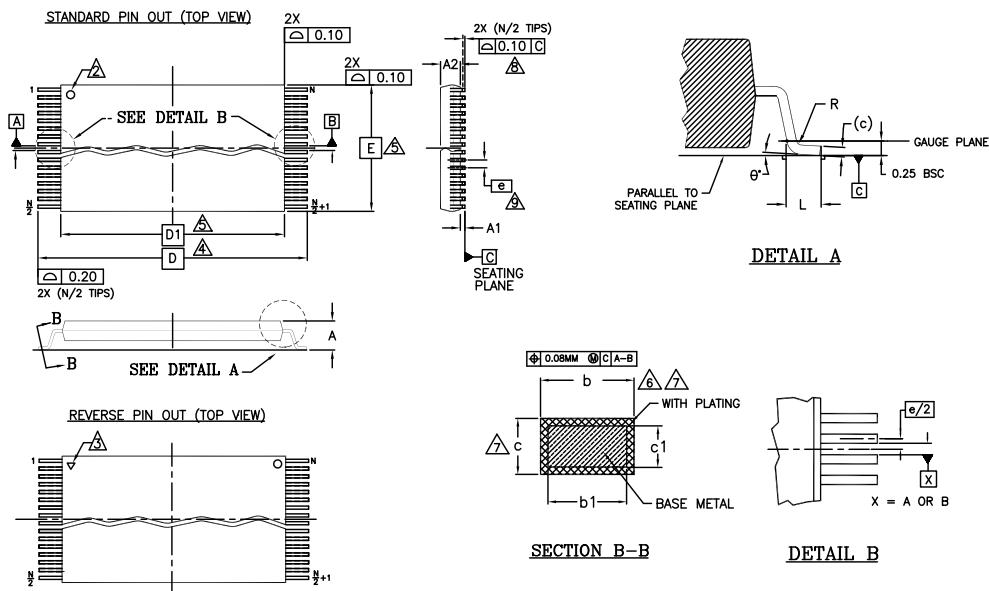

| 12.1 56 ピン TSOP .....                  | 106        |

| 12.2 64 ボール FBGA .....                 | 108        |

| 12.3 56 ボール FBGA .....                 | 111        |

| <b>13 FBGA パッケージの取扱注意事項 .....</b>      | <b>113</b> |

| <b>14 注文情報 .....</b>                   | <b>114</b> |

| 14.1 有効な組合せ – 標準 .....                 | 114        |

| 14.2 有効な組合せ – 車載用グレード / AEC-Q100 ..... | 117        |

| <b>改訂履歴 .....</b>                      | <b>120</b> |

| <b>免責事項 .....</b>                      | <b>121</b> |

## 1 製品概要

GL-T ファミリは、512M ビット～1G ビットの、3.0V コア、汎用 I/O、不揮発性フラッシュメモリデバイスで構成されます。これらのデバイスは 8 ビット(バイト)/16 ビット(ワード)幅のデータバスを持ち、バイト/ワード境界アドレスのみを使用します。すべての読み出しアクセスは各バス転送サイクルで 8/16 ビットのデータを供給します。すべての書き込みアクセスは各バス転送サイクルから 8/16 ビットのデータを受け取ります。

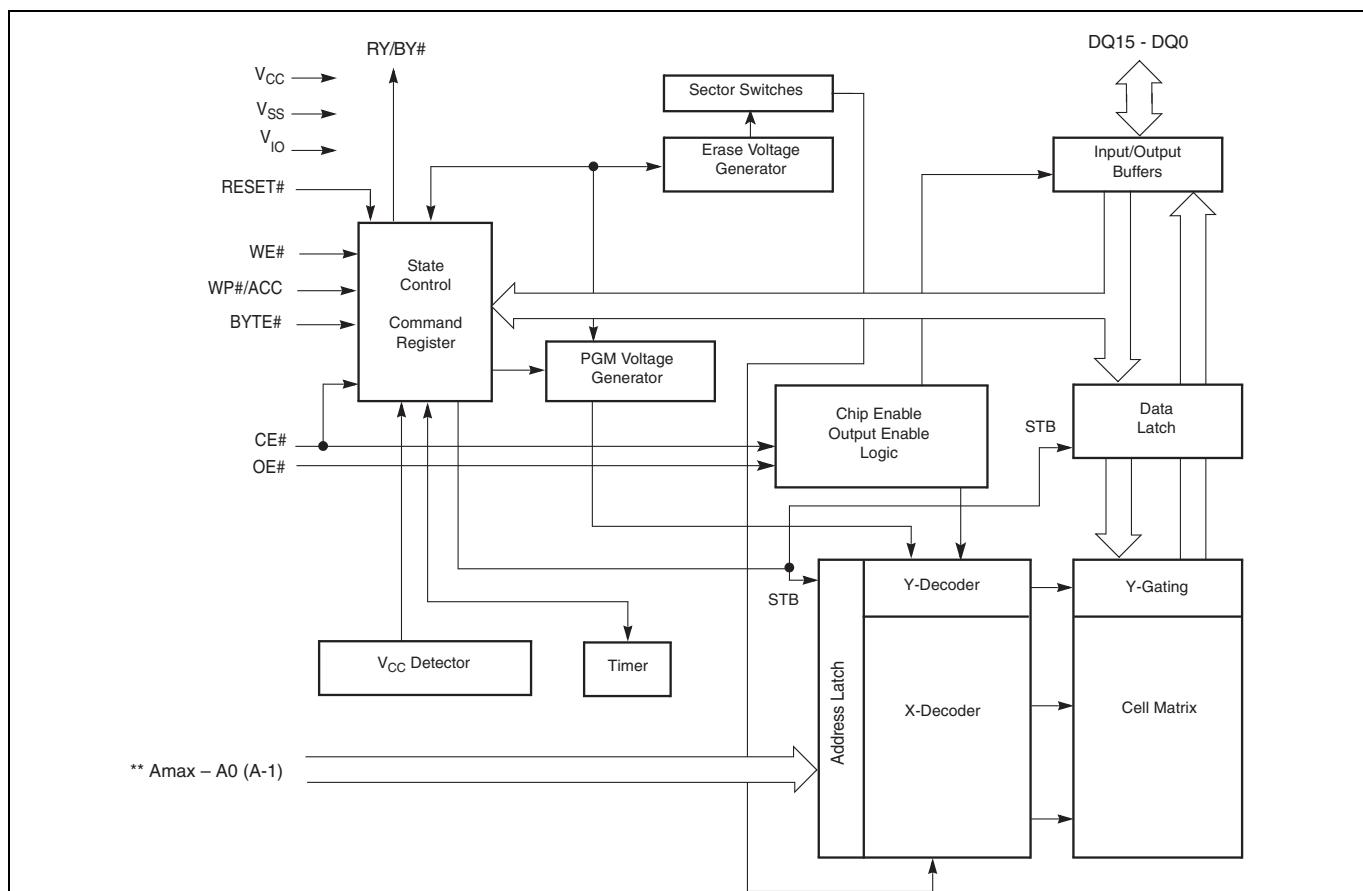

Figure 1 ブロック ダイヤグラム <sup>[1]</sup>

GL-T ファミリは、XIP (eXecute In Place) 技術とデータストレージフラッシュメモリの両方の最良の機能を組み合わせています。このファミリは、データストレージフラッシュの高密度かつ高速のプログラム速度とともに、XIP フラッシュの高速ランダムアクセスを有しています。

任意のランダムな場所への読み出しアクセスは、デバイス容量と I/O 供給電圧に応じて、100 ns ~ 120 ns です。各々の(最初の)ランダムアクセスで、ページと呼ばれる 32 バイトにアラインされたデータグ ループをすべて読み出します。同一ページ内の他のワードは、ワードアドレスの下位 4 ビットのみを変更して読み出しが可能です。同一ページ内でのアクセスには 15 ns ~ 25 ns を要します。これはページモード読み出しと呼ばれています。上位ワードアドレスビットを変更すると、異なるページに移動し、新しい初期アクセスが開始されます。すべての読み出しアクセスは非同期です。

### 注:

1. Amax GL01GT = A25, Amax GL512T = A24

**Table 1 S29GL-T アドレス マップ**

| タイプ            | ×16                               |          | ×8                                |          |

|----------------|-----------------------------------|----------|-----------------------------------|----------|

|                | カウント                              | アドレス     | カウント                              | アドレス     |

| ページ内のアドレス      | 16                                | A3-A0    | 32                                | A3-A1    |

| 書き込みバッファ内のアドレス | 256                               | A7-A0    | 256                               | A7-A1    |

| ページ            | セクタあたり 4096                       | A15-A4   | セクタあたり 4096                       | A15-A4   |

| 書き込みバッファ ライン   | セクタあたり 256                        | A15-A8   | セクタあたり 256                        | A15-A8   |

| セクタ            | 1024 (1 G ビット)<br>512 (512 M ビット) | Amax-A16 | 1024 (1 G ビット)<br>512 (512 M ビット) | Amax-A16 |

デバイス制御ロジックは、ホストインターフェース コントローラー (HIC) と組込みアルゴリズム コントローラー (EAC) の 2 つの並行する操作セクションに分かれています。HIC はデバイス入力の信号レベルをモニターし、かつ必要に応じてデバイス出力を駆動し、ホストシステムとのデータ読み出しと書き込み転送を実行します。HIC は読み出し転送で、現在入力されたアドレス空間からデータを出力し、書き込み転送アドレスとデータ情報を EAC コマンドメモリに配置し、また、電源遷移、ハードウェアリセットおよび書き込み転送を EAC に通知します。EAC は、書き込み転送後、コマンドメモリを参照して適切なコマンドシーケンスを検出し、関連する組込みアルゴリズムを実行します。

メモリアレイ内の不揮発性データの書換えには、組込みアルゴリズム (EA) と呼ばれる複雑な動作シーケンスを実行する必要があります。アルゴリズムはデバイス内部の EAC によって完全に管理されています。メインアルゴリズムは、メインアレイデータのプログラミングと消去を実行します。ホストシステムはフラッシュデバイスのアドレス空間にコマンドコードを書き込みます。お EAC はコマンドを受け取り、コマンドを完了するのに必要なすべてのステップを実行し、EA の進行中にステータス情報を提供します。

各メモリビットの消去済み状態はロジック 1 です。プログラミングにより論理 1 (HIGH) から論理 0 (LOW) に変更します。消去動作のみがロジック 0 から 1 に変更できます。消去動作は、セクタと呼ばれる、128KB にアラインされた一連のデータグループに対して実行される必要があります。インフィニオンからの出荷する時点では、すべてのセクタは消去されています。

プログラミングは 512 バイトの書き込みバッファを介して行われます。x16 タイプでは、プログラミング動作を開始する前に、書き込みバッファの任意の位置に 1 ~ 256 ワードを書き込みます。フラッシュメモリアレイ内では、512 バイトにアラインされた各々の 512 バイトのデータグループをライン (Line) と呼びます。また、x8 タイプでは、プログラム動作を開始する前に、書き込みバッファ内の任意の位置に 1 ~ 256 バイトを書き込みます。プログラミング動作は揮発性データを書き込みバッファから不揮発性メモリアレイのラインに転送します。この動作は書き込みバッファプログラミングと呼ばれます。

デバイスが、書き込みバッファにロードされた 32 バイト整列のデータページを 512 バイトフラッシュアレイ ラインに転送する時、内部ロジックはページ用の ECC コードを、ホストシステムソフトウェアには見えないメモリアレイの一部にプログラムします。内部ロジックはすべてのアレイ読み出し動作の初期アクセス中に ECC 情報をチェックします。必要があれば、ECC 情報は初期アクセス時間中に 1 ビットエラーを訂正します。

リセット後、または書き込みバッファを使用する動作の完了後は、書き込みバッファの値がすべて 1 になります。バッファ書き込みコマンドによって 0 に書き込まれていない位置は、デフォルトにより「1」の値のままでです。書き込みバッファ内の「1」は、プログラミング動作内にメモリアレイのデータに影響しません。

書き込みバッファにロードされた各データのページは、メモリアレイのラインに転送されます。

ASP (Advanced Sector Protection) という高度なセクタ保護機能セットによって、セクタはそれぞれ独立にプログラムと消去動作から保護されます。ASP では、プログラムと消去動作から保護されるセクタを選択するために、いくつかの、ハードウェアおよびソフトウェア制御の、揮発性と不揮発性の手法を提供しています。

## 2 アドレス空間 オーバーレイ

いくつかの個々のアドレススペースがあり、フラッシュメモリデバイスのアドレス範囲内に表示されることがあります。ひとつのアドレス空間が常時表示されます(アクセスできます)。

- **フラッシュメモリアレイ**: データ格納用のメイン不揮発性メモリアレイであり、非同期読み出し動作によってランダムにアクセスできます。

- **ID/CFI**: サイプレスの工場でプログラムされたデバイス特性情報のために使用されるメモリアレイです。この領域には、デバイス識別(ID)と共通フラッシュインターフェース(CFI)の情報テーブルが含まれています。

- **セキュアシリコン領域(SSR)**: インフィニオンの工場でプログラムされた恒久データおよびカスタマープログラミング可能な恒久データのために使用される1回書き込み可能な(OTP)不揮発性メモリアレイです。

- **ロックレジスタ**: ASP機能を設定しSSRをロックするため使用されるOTP不揮発性ワードです。

- **恒久的保護ビット(PPB)**: セクタごとに1ビットを有する不揮発性メモリアレイです。プログラムされると、各ビットは該当するセクタを消去とプログラミングから保護します。

- **PPBロック**: PPBビットのプログラミングと消去を有効化または無効化する揮発性レジスタビットです。

- **アレイパスワード**: パスワードモードのセクタ保護を使用する際にPPBロックビットの状態を変更可能にするために使用される64ビットパスワード格納用のOTP型不揮発性アレイです。

- **SSR3パスワード**: SSR3の読み出しを可能にするために使用される64ビットパスワード格納用のOTP型不揮発性アレイです。

- **ダイナミック保護ビット(DYB)**: 挥発性アレイであり、セクタごとに1ビットを占めます。セットされると、各ビットは該当するセクタを消去とプログラミングから保護します。

- **ステータスレジスタ**: 組込みアルゴリズムステータスを表示するために使用する揮発性レジスタです。

- **データポーリングステータス**: レガシーソフトウェア互換で、組込みアルゴリズムステータスを表示するための代替方法として使用される揮発性レジスタです。

- **ECCステータス**: 選択されたページの読み出し中に行われたすべてのエラー検出または訂正措置のステータスを提供します。

メインフラッシュメモリアレイは次のデフォルトアドレス空間ですが、任意の一時点での他の1つのアドレス空間によってオーバーレイすることができます。各代替アドレス空間はアドレス空間オーバーレイ(ASO)と呼ばれています。

各ASOは、フラッシュデバイスのアドレス範囲全体を置き換え(オーバーレイ)します。特定のASOアドレスマップで定義されていないアドレス範囲は、将来に使用するために確保されます。ASOアドレスマップ範囲外のすべての読み出しアクセスは、有効ではない(未定義)データを返します。その位置はアクティブ駆動されたデータを表示しますが、「1」にせよ「0」にせよ、その意味は未定義です。

任意の時にフラッシュデバイスのアドレス空間に表示される内容を決定する4つのデバイス動作モードがあります。

- 読み出しモード

- データポーリングモード

- ステータスレジスタ(SR)モード

- アドレス空間オーバーレイ(ASO)モード

## アドレス空間 オーバーレイ

読み出しモードでは、フラッシュメモリアレイ全体が、ホストシステムのメモリコントローラーによって直接読み出せます。電源投入時、ハードウェアリセット後、コマンドリセット後、または組込みアルゴリズム(EA)が一時停止された後は、メモリデバイスの組込みアルゴリズムコントローラー(EAC)の制御下でデバイスが読み出しモードになります。読み出しアクセスとコマンド書き込み動作は読み出しモードで実行可能です。EAが一時停止されている時に、読み出しモードにおいてコマンドのサブセットが許容されます。

どのモードでも、ステータスレジスタ読み出しコマンドを発行してデバイスのアドレス空間内のあらゆるワードアドレスでステータスレジスタASOを表示させられます。このステータスレジスタASOモードでは、デバイスインターフェースは読み出しアクセスだけに対応し、書き込みアクセスはすべて無視されます。デバイスへの次の読み出しアクセスは、ステータスレジスタの内容にアクセスし、ステータスレジスタASOを終了し、ステータスレジスタ読み出しコマンドが受信された以前の(呼び出し)モードに戻ります。

EAモードでは、EACは不揮発性メモリアレイのプログラミングまたは消去のような組込みアルゴリズムを実行します。EAモード中には、フラッシュデバイスアドレス空間全体がデータポーリング状態ASOで置換されるため、どのメインフラッシュメモリアレイも読み出せません。データポーリング状態は、デバイスアドレス空間内のすべてのワード位置でも発生します。

EAモードでは、プログラム/消去一時停止コマンド、またはステータスレジスタ読み出しコマンドのみが実行可能です。他のコマンドはすべて無視されます。したがって、EAモードから他のASOに入ることはできません。

組込みアルゴリズム(EA)が一時停止されると、デバイスがそのEAを一時停止させるまでデータポーリングASOが認識できます。EAが一時停止しているとき、データポーリングASOは終了し、フラッシュアレイデータが利用できます。一時停止されたEAが再開されると、EAが再度一時停止になるか終了するまで、データポーリングASOが再びアクセスされます。組込みアルゴリズムが実行されると、データポーリングASOは終了し、デバイスは(組込みアルゴリズムが開始された)前の(呼び出し)モードに移行します。

ASOモードでは、残りのオーバーレイアドレス空間の1つがアクセス(メインのフラッシュアレイアドレスマップにオーバーレイ)されます。いつも一度に移行できるASOは1つだけです。デバイスへのコマンドは、現在アクセス中のASOに作用します。個々のASOに対して特定のコマンドのみが有効です。これらは表の各ASO関連のセクション、[Table 23](#)にリストアップされています。

以下のASOは1から0へ変更するようにプログラム可能な不揮発データを持っています。

- セキュアシリコン領域

- ロックレジスタ

- 恒久的保護ビット(PPB)

- パスワード

- PPB ASOのみ0から1へ変更するために消去可能な不揮発データを持つ

ある不揮発性ASOがアクセスされている間にプログラムコマンドまたは消去コマンドが発行されると、EAはそのASO上で動作します。EAがアクティブの間はASOは読み出し不可です。EAが完了すると、ASOに入っている状態のままで再度読み出し可能になります。EAがこれらの任意のASOで動作している間は、一時停止コマンドと再開コマンドが無視されます。

アドレス空間 オーバーレイ

## 2.1 フラッシュメモリアレイ

S29GL-T ファミリはセクタサイズ 128 kB の同一のセクタアーキテクチャを有しています。下表に異なるデバイスのセクタアーキテクチャを示します。

**Table 2 S29GL01GT セクタおよびメモリアドレスマップ**

| セクタサイズ<br>(KB) | セクタ数 | セクタ範囲  | アドレス範囲<br>(16 ビット) | アドレス範囲<br>(8 ビット) | 備考        |

|----------------|------|--------|--------------------|-------------------|-----------|

| 128            | 1024 | SA0    | 0000000h-000FFFFh  | 0000000h-001FFFFh | セクタ開始アドレス |

|                |      | :      | :                  | :                 | -         |

|                |      | SA1023 | 3FF0000h-3FFFFFFh  | 7FE0000h-7FFFFFFh | セクタ終了アドレス |

**Table 3 S29GL512T セクタおよびメモリアドレスマップ**

| セクタサイズ<br>(KB) | セクタ数 | セクタ範囲 | アドレス範囲<br>(16 ビット) | アドレス範囲<br>(8 ビット) | 備考        |

|----------------|------|-------|--------------------|-------------------|-----------|

| 128            | 512  | SA0   | 0000000h-000FFFFh  | 0000000h-001FFFFh | セクタ開始アドレス |

|                |      | :     | :                  | :                 | -         |

|                |      | SA511 | 1FF0000h-1FFFFFFh  | 3FE0000h-3FFFFFFh | セクタ終了アドレス |

注: 上記の表は、デバイス全体のセクタ関連情報を 1 ページで示すために圧縮した表現になっています。明示的にリストアップされていない(GL512T の SA1 ~ SA510 のような) セクタおよびそのアドレスの範囲は、同じサイズの他のすべてのセクタの場合と同じパターンを形成するようなセクタ開始アドレスと終了アドレスを有します。例えば、すべての 128 kB セクタは、x16 タイプでは XXX0000h ~ XXXFFFFh で、x8 タイプでは XXX0000h ~ XXX1FFF のパターンを有します。

## 2.2 デバイス ID および CFI (ID-CFI) ASO

システムに搭載されたフラッシュメモリの種類を識別するために、システムに対する2つの従来方式があります。1つは従来自動選択(Auto Select)として呼ばれていたもので、現在ではデバイス識別(ID)と呼ばれています。もう1つの方法は、共通フラッシュインターフェース(CFI)と呼ばれています。

IDに関しては、1つのコマンドを使用してアドレス空間オーバーレイを有効にし、その最大16ワードの位置を読み出すことで、JEDEC製造者識別(ID)、デバイスID、およびいくつかの構成情報と保護ステータス情報をフラッシュメモリから取得します。システムはこの製造者IDとデバイスIDを用いて、フラッシュデバイスと一緒に使用する適切なドライバーソフトウェアを選択できます。

CFIもまた、コマンドを使ってアドレス空間オーバーレイを有効にし、フラッシュメモリの構成や動作方法の基本情報についての拡張可能なテーブルを読み出せます。この方法を用いると、使用するそれぞれのメモリデバイス特性を念頭において、ドライバーソフトウェアが記述される必要はありません。その代わりに、ドライバーソフトウェアは多くの異なるデバイスを扱うためにより一般的な方法で記述されますが、ドライバーの動作をCFIテーブルの情報に基づいて最適化します。

これまで、これら2つのアドレス空間は個別のコマンドを使用し、そして個別のオーバーレイでした。しかし、これら2つのアドレス空間のマッピングは重複しないので、単一のアドレス空間に組み合わせ、単一のオーバーレイに共に表示できます。自動選択(ID)またはCFIオーバーレイにアクセス(入る)するために使用されるどちらの従来のコマンドも、今回組み合わせたID-CFIアドレスマップを表示させます。

表示されるID-CFIアドレスマップは、フラッシュアレイ全体をオーバーレイします。

ID-CFIアドレスマップは、選択したセクタの位置0を始点とします。ID-CFI ASOの最大定義アドレスを超えて選択したセクタの最大アドレスまでの位置は未定義のデータを有します。ID-CFIへアクセスするためのコマンドは前の世代のメモリに使用されたものと同じアドレスとデータ値を使用して、JEDEC製造者ID(自動選択)とCFI情報にそれぞれアクセスします。

**Table 4 ID-CFIアドレスマップ概要**

| ワードアドレス            | バイトアドレス             | 説明               | 読み出し / 書き込み |

|--------------------|---------------------|------------------|-------------|

| (SA)+0000h ~ 000Fh | (SA)+0000h ~ 001Fh  | デバイスID(従来の自動選択値) | 読み出し専用      |

| (SA)+0010h ~ 0079h | (SA)+0020h ~ 00F2h  | CFIデータ構造         | 読み出し専用      |

| (SA)+0080h ~ FFFFh | (SA)+00F3h ~ 1FFFFh | 未定義              | 読み出し専用      |

完全なアドレスマップについては[Table 25](#)を参照してください。

### 2.2.1 デバイスID

JEDEC (Joint Electron Device Engineering Council) の標準 JEP106T は、準拠メモリ用の製造者IDを定義します。共通の業界使用法が、メモリデバイスから製造者IDとデバイス固有IDを読み出す方法とフォーマットを定義しました。製造者IDとデバイスID情報は、主に、プログラミング機器が、対応するプログラミングアルゴリズムを有するデバイスと自動的にマッチするように意図されています。インフィニオンはこの32バイトのアドレス空間内に追加フィールドを加えました。

元の業界フォーマットは、x8, x16, x32等のどのメモリデータバス幅でも動作するように構成されました。IDコード値は従来はバイト幅ですが、バス幅アドレス境界に位置しています。これはデバイスアドレス入力のインクリメントが、常に、データバスの最下位バイトに位置するIDコード付きの、連続するバイト、ワード、またはダブルワード位置を読み出すためです。デバイスのデータバスはワード幅のため、各コードバイトは各ワード位置の下半分に位置しています。元の業界フォーマットでは上位バイトが常に0でした。インフィニオンはこのフォーマットを変更して、アドレス空間のいくつかのワードにおいて両方のバイトを使用するようにしました。デバイスIDのアドレスマップの詳細については[Table 25](#)を参照してください。

アドレス空間 オーバーレイ

## 2.2.2 共通フラッシュメモリインターフェース

JEDEC CFI 仕様 (JESD68.01) は、フラッシュメモリデバイスから読み出し可能な標準化されたデータ構造を定義し、ベンダー仕様のソフトウェアアルゴリズムを全デバイスファミリで使用可能としています。データ構造には、さまざまな電気的パラメーターとタイミングパラメーター、およびデバイスがサポートする特別な機能などのシステム設定の情報が含まれます。そのため、ソフトウェアサポートは、デバイスに依存せず、デバイス ID にも依存せず、フラッシュデバイスファミリ全体に対して上位下位互換性があります。

システムは、[デバイス ID と共通フラッシュインターフェース \(ID-CFI\) の ASO マップ](#)に示すように、選択したセクタ内のアドレスにある CFI 情報を読み出せます。

デバイス ID 情報のように、CFI 情報は x8, x16, x32 などのすべてのメモリデータバス幅で動作するように構成されています。コード値は常にバイト幅ですが、データバス幅アドレス境界に位置されます。よって、デバイスアドレスのインクリメントは、常にデータバスの最下位バイトに位置するコード付きの連続するバイト、ワード、またはダブルワード位置を読み出します。データバスはワード幅のため、各コードバイトは各ワード位置の下半部に位置し、上位バイトは常に '0' です。

詳細は、CFI 仕様バージョン 1.4 (またはそれ以降) および JEDEC 発行文献 JEP137-A および JESD68.01 の資料を参照してください。JEDEC 標準については、JEDEC ([www.jedec.org](http://www.jedec.org)) にお問い合わせください。

## 2.3 ステータスレジスタ ASO

ステータスレジスタ ASO は、組込みアルゴリズム (EA) のレジスタ化された揮発性状態を示す単一のワードを含みます。ステータスレジスタ読み出しコマンドが発行されると、現時点のステータスが (WE# の立ち上りエッジで) レジスタに取り込まれ、ASO が有効になります。ステータスレジスタの内容はすべてのワード位置に現れます。最初の読み出しアクセスは、ステータスレジスタ ASO 状態 (CE# または OE# の立ち上りエッジを有する) を終了し、ステータスレジスタ読み出しコマンドの発行時点に使用されていたアドレス空間のマップに戻ります。書き込みコマンドはステータスレジスタ ASO 状態を終了しません。

## 2.4 データポーリングステータス ASO

データポーリングステータス ASO は、EA の進行状態を示す揮発性メモリの単一のワードを含みます。データポーリングステータス ASO 状態への遷移は、EA を開始するコマンドシーケンスの最後の書き込みサイクルの直後に行われます。EA を開始するコマンドは以下です。

- ・ワードプログラム

- ・バッファからフラッシュへのプログラム

- ・チップ消去

- ・セクタ消去

- ・消去の再開 / プログラム再開

- ・プログラム再開拡張方式

- ・ブランクチェック

- ・ロックレジスタプログラム

- ・パスワードプログラム

- ・PPB プログラム

- ・全 PPB 消去

- ・消去ステータス評価

データポーリングによるステータスワードは、デバイスのアドレス空間のすべてのワード位置に現れます。EA が完了するとデータポーリングステータス ASO は終了し、デバイスアドレス空間は EA が開始された時点のアドレスマップモードに戻ります。

## 2.5 SSR ASO

SSR は、1回のみプログラム可能で更なる変更からは永久に保護される追加メモリ領域、つまり1回書き込み可能(OTP)領域を提供します。SSRの長さは2048バイトです。その内容は、工場用ロックセキュアシリコン領域(SSR0)が512バイト、カスタマー用ロックセキュアシリコン領域(SSR1とSSR2)が1024バイト、および読み出しパスワード付きのカスタマー用ロックセキュアシリコン領域(SSR3)が512バイトです。

SSR0は、更なるプログラミングを防止するために、ロックされた状態で出荷されています。SSR1とSSR2はそれぞれが個別のロックビットを持つOTPで、一度ロックされるとその領域への更なるプログラミングは不可です。SSR3はOTPで、SSR3パスワードがないとこの領域の読み出しやプログラミングにはSSR3パスワードが必要です。SSR3は一度ロックされると更なるプログラミングは実行できません。

セキュアシリコンエントリコマンドの実行中に提供されるセクタアドレスは、SSRのアドレスマップによってオーバーレイされるフラッシュメモリアレイセクタを選択します。SSRは選択したセクタ内の位置0からオーバーレイされます。将来の互換性のため、セクタ0のアドレスを使用することを推奨します。SSR ASO状態の間、他のすべてのセクタの内容は、読み出し動作のためのメモリコアデータです。ASO領域外のプログラミングは許可されません。

**Table 5 SSR**

| ワードアドレス範囲        | バイトアドレス範囲         | 内容                             | 領域   | サイズ    |

|------------------|-------------------|--------------------------------|------|--------|

| (SA)+0000h～00FFh | (SA)+0000h～01FFh  | 工場ロック用セキュアシリコン領域               | SSR0 | 512バイト |

| (SA)+0100h～01FFh | (SA)+0200h～03FFh  | カスタマーロック用セキュアシリコン領域            | SSR1 | 512バイト |

| (SA)+0200h～02FFh | (SA)+0400h～05FFh  | カスタマーロック用セキュアシリコン領域            | SSR2 | 512バイト |

| (SA)+0300h～03FFh | (SA)+0600h～07FFh  | 読み出しパスワード付きカスタマーロック用セキュアシリコン領域 | SSR3 | 512バイト |

| (SA)+0400h～FFFFh | (SA)+0800h～1FFFFh | 未定義                            | 該当なし | 126 KB |

## 2.6 セクタ保護の制御

### 2.6.1 ロック レジスタ ASO

ロック レジスタ ASO は、OTP メモリのシングルワードを含みます。ASO モードに遷移すると、ロック レジスタがデバイス アドレス空間のすべてのワード位置に割り付けられます。しかし、将来の互換性のため、ロック レジスタに対する読み出しありはプログラミングは、デバイス アドレス空間の位置 0 でのみ行うことを推奨します。

### 2.6.2 恒久的保護ビット (PPB) ASO

PPB ASO は、デバイス内の各セクタに対応するフラッシュメモリアレイの 1 ビットを含みます。PPB ASO モードに遷移すると、セクタの PPB ビットがそのセクタ内のアドレスの最下位ビット (LSB) に割り付けられます。セクタ内の任意のアドレスを読み出すと、LSB がそのセクタの不揮発性保護状態を示すデータを表示します。ただし、将来の互換性のため、PPB ビットの読み出しありはプログラミングをセクタのアドレス '0' でのみ行うことを推奨します。このビットが '0' の場合、セクタはプログラミングおよび消去動作から保護されます。このビットが '1' の場合、セクタは PPB で保護されません。セクタは ASP の他の機能でも保護されることがあります。

### 2.6.3 PPB ロック ASO

PPB ロック ASO は、揮発性メモリのシングルビットを含みます。このビットは、PPB ASO のビットがプログラミングまたは消去されることを制御します。このビットが 0 の場合、PPB ASO はプログラミングおよび消去動作から保護されます。このビットが 1 の場合、PPB ASO は保護されません。PPB ロック ASO モードに遷移すると、PPB ロックビットがデバイス アドレス空間内の各アドレスの最下位ビット (LSB) に割り付けられます。ただし、将来の互換性のため、PPB ロックビットに対する読み出しありはプログラミングを、デバイスのアドレス '0' でのみ行うことを推奨します。

### 2.6.4 パスワード ASO

パスワード ASO は、OTP メモリの 4 ワードを含みます。パスワード ASO モードに遷移すると、パスワードがデバイス アドレス空間内のアドレス '0' から出力されます。第 4 ワードより上位のアドレスのデータは未定義です。

### 2.6.5 ダイナミック保護ビット (DYB) ASO

DYB ASO は、デバイス内の各セクタに対応する揮発性メモリアレイの 1 ビットを含みます。DYB ASO モードに遷移すると、セクタの DYB ビットはそのセクタの各アドレスの最下位ビット (LSB) に割り付けられます。セクタ内の任意のアドレスを読み出すと、セクタの不揮発性保護状態を示す LSB のあるデータを表示します。しかし、将来の互換性のため、DYB ビットに対する読み出し、セットまたはクリアは、セクタのアドレス 0 でのみ行うことを推奨します。このビットが '0' の場合、セクタはプログラミングおよび消去動作から保護されます。このビットが '1' の場合、セクタは DYB で保護されません。セクタは ASP の他の機能で保護されることがあります。

アドレス空間 オーバーレイ

## 2.7 ECC ステータス ASO

システムは、読み出しモード中に ECC ステータス エントリ コマンド シーケンスを発行することで、ECC ステータス ASO にアクセスできます。ECC ステータス ASO は、ECC 機能の有効または無効ステータス、または選択されたページの読み出し中に ECC 機能が 1 ビット エラーを訂正したか否かの情報を提供します。**自動 ECC** は、ECC 機能についてより詳細に説明します。

ECC ステータス ASO では以下の動作が行えます。

- 選択したページの ECC ステータスの読み出し

- ASO 終了

### 2.7.1 ECC ステータス

ECC ステータス ASO の内容は、選択された ECC ページについて、ECC ロジックが、32 バイトデータの ECC ページで、ECC ページ 8 ビット ECC コードでエラーを訂正したか否かを、またはその ECC ユニットで ECC が無効になっていることを示します。**Table 23** と **Table 24** に示す ECC ステータス読み出しコマンドで指定したアドレスは ECC ページを選択します。

**Table 6** ECC ステータス ワード - 上位バイト

| ビット | 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 名称  | RFU |

| 値   | X   | X   | X   | X   | X   | X   | X   | X   |

**Table 7** ECC ステータス ワード - 下位バイト

| ビット | 7   | 6   | 5   | 4   | 3                        | 2                                | 1                                | 0   |

|-----|-----|-----|-----|-----|--------------------------|----------------------------------|----------------------------------|-----|

| 名称  | RFU | RFU | RFU | RFU | 16 ワード ページで ECC 有効       | ECC ビットの 1 ビット エラー訂正済み           | データ ビットの 1 ビット エラー訂正済み           | RFU |

| 値   | X   | X   | X   | X   | 0 = ECC 有効<br>1 = ECC 無効 | 0 = エラー訂正なし<br>1 = 1 ビット エラー訂正済み | 0 = エラー訂正なし<br>1 = 1 ビット エラー訂正済み | X   |

### 3 データ保護

デバイスは、どのセクタでの悪意によるもしくは偶発的な変更をハードウェア手段によって防ぐためのいくつかの機能を提供します。

#### 3.1 デバイス保護方式

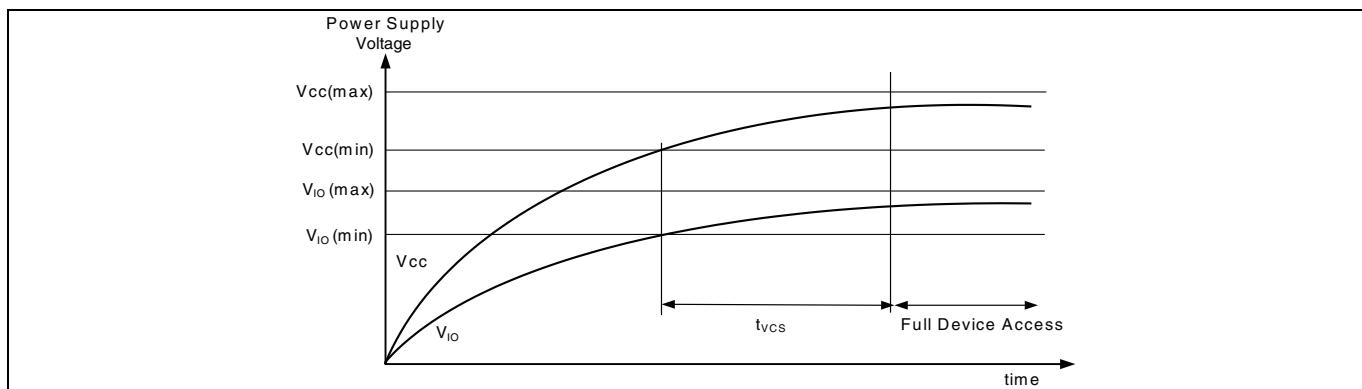

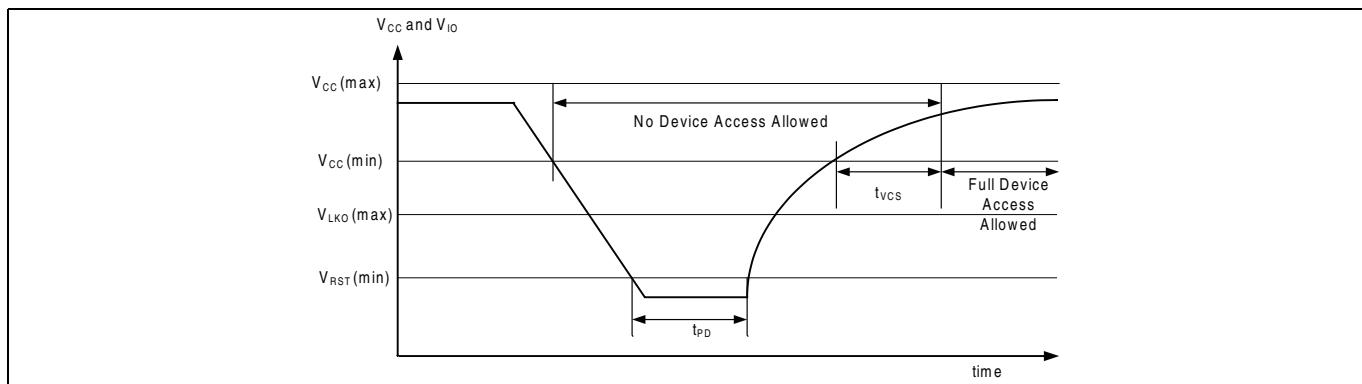

##### 3.1.1 電源投入時の書き込み禁止

RESET#, CE#, WE#, OE# は、Power-On-Reset(POR) 中は無視されます。POR 時には、デバイスは選択できず、WE# の立ち上りエッジでコマンドを受け付けず、出力をさせません。ホストインターフェースコントローラー (HIC) と組込みアルゴリズムコントローラー (EAC) は、POR 時には、スタンバイ状態にリセットされ、アレイデータ読み出し準備ができます。CE# または OE# は POR ( $t_{VCS}$ ) の終了前に  $V_{IH}$  に達する必要があります。

POR の終了時、デバイスの条件は以下のとおりです。

- すべての内部設定情報がロードされている

- デバイスは読み出しモードになっている

- ステータスレジスタはデフォルト値になっている

- DYB ASO 内のすべてのビットは全セクタを非保護の設定になっている

- 書き込みバッファはすべて 1 の値でロードされている

- EAC はスタンバイ状態になっている

##### 3.1.2 低 $V_{CC}$ 時の書き込み禁止

$V_{CC}$  が  $V_{LKO}$  未満になると、HIC はすべての書き込みサイクルを受信せず、EAC がリセットされます。これにより、 $V_{CC}$  電圧投入時と切断時にデータは保護されます。 $V_{CC}$  が  $V_{LKO}$  以上の場合、意図しない書き込みを回避するために、システムは適切な信号を制御ピンに供給する必要があります。

#### 3.2 コマンド保護

EA はコマンドシーケンスを EAC コマンドメモリに書き込むことで開始されます。コマンドメモリアレイはホストシステムからの読み出しあり不可で、ASO を有しません。各ホストインターフェース書き込みは、デバイスに対するコマンドまたはコマンドシーケンスの一部です。EAC は、書き込みが適切なコマンドシーケンスの一部かどうかを判断するために、各書き込み転送のアドレスとデータを確認します。正しいコマンドシーケンスが完了すると、EAC は適切な EA を開始します。

誤ったアドレスやデータ値を書き込むか、または不適切なシーケンスで書き込むことにより、EAC を通常、スタンバイ状態に戻します。ただし、不適切なコマンドシーケンスによりデバイスが不定状態になることがあります。この場合には、システムはリセットコマンドを書き込むか、または場合によりハードウェアリセット(RESET# 信号を LOW に駆動する)を行い、EAC をスタンバイ状態(ランダム読み出し可能状態)に復帰させる必要があります。

各書き込みで提供されるアドレスは、その書き込みがデバイスに対するコマンドであることを識別するように、ビットパターンを含んでいます。アドレスの上位部分は、コマンド動作が実行されるセクタアドレスを選択することもできます。セクタアドレス(SA)は Amax から A16 までのフラッシュアドレスビット(システムバイトアドレス信号 Amax から A16)を含みます。コマンドビットパターンは、A10～A0 のフラッシュアドレスビット(システムバイトアドレス信号 A11 から A1)に配置されます。

各書き込みにおけるデータは、書き込みをコマンドとして識別するためのビットパターン、実行されるコマンド動作を識別するコード、または動作を実行するために必要な提供情報です。デバイスにより受け付けられるコマンドの一覧については、[Table 23](#) を参照してください。

#### 3.3 SSR (OTP)

セキュアシリコン領域の説明については [SSR ASO](#) を参照してください。許可されるコマンドの説明については [セキュアシリコン領域 ASO](#) を参照してください。

## 3.4 セクタ保護方式

### 3.4.1 書き込み保護信号

$WP\# = V_{IL}$  の場合は、他の ASP 設定に関係なく、最下位または最上位アドレスのセクタがプログラム動作や消去動作から保護されます。最下位と最上位セクタのどちらかは選択したデバイスオーダー オプション(モデル)に依存します。 $WP\# = V_{IH}$  の場合、最下位または最上位アドレスのセクタは  $WP\#$  信号によって保護されませんが、他の ASP 設定の要素により保護されることがあります。 $WP\#$  は内部プルアップを持っており、何も接続しないと  $V_{IH}$  となります。組込み動作中に  $WP\#$  は  $V_{IL}$  と  $V_{IH}$  の間で変化させてはいけません。

### 3.4.2 高度セクタ保護 (ASP)

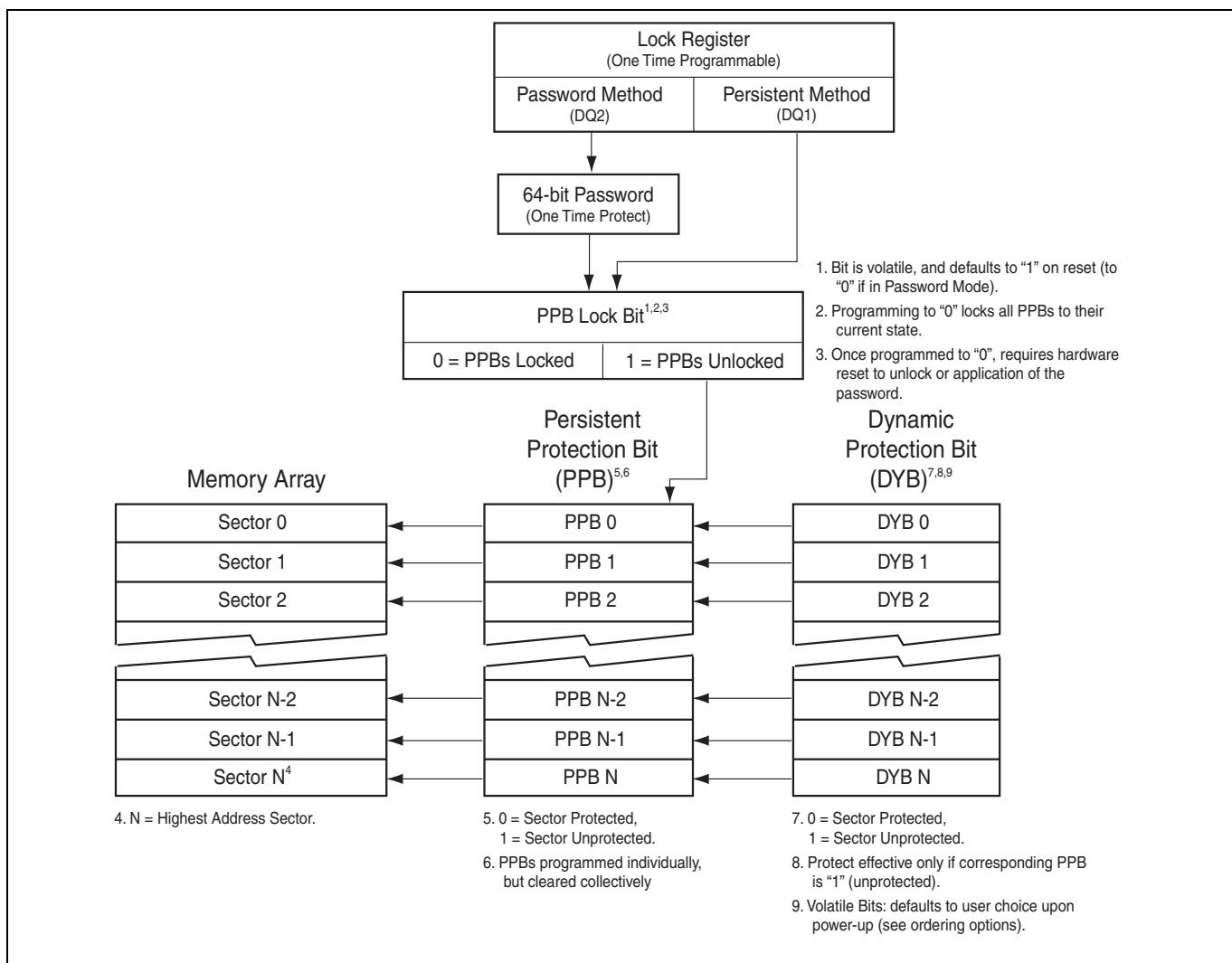

ASP は、1つのセクタまたはすべてのセクタで、プログラムや消去の動作を個別に無効または有効にするために使用される、独立したハードウェアおよびソフトウェア方式の一式です。ここでは、メモリアレイに保存されたデータのさまざまな保護方法を記載します。これらの方の概要を [Figure 2](#) に示します。

Figure 2 ASP の概要

## データ保護

いずれのメインのフラッシュアレイセクタにも、不揮発性(PPB)と揮発性(DYB)の保護ビットが整備されています。それらのビットのどちらかが‘0’であると、セクタはプログラム動作や消去動作から保護されます。

PPBビットは、PPBロックビットが‘0’の場合にプログラムや消去から保護されます。PPBロックビットの状態を管理する方式には、恒久保護およびパスワード保護の2つがあります。

恒久保護方式では、PORまたはハードウェアリセット時にPPBロックビットが‘1’にセットされ、PPBビットがデバイスリセットによって保護されなくなります。PPBビットを保護するためにPPBロックビットを‘0’にクリアするためのコマンドがあります。恒久保護方式では、PPBロックビットをセットするコマンドがないため、PPBロックビットは、次の電源切断またはハードウェアリセットまで、‘0’のままでです。恒久保護方式では、ブートコードにより、PPBのプログラミングまたは消去によってセクタ保護を変更するオプションを設定し、次にPPBロックビットを消去することで、その後の通常のシステム動作の間の更なる変更からPPBを保護します。これはブートコード制御によるセクタ保護とも呼ばれます。

パスワード方式では、PORまたはハードウェアリセットの間、PPBロックビットを‘0’にクリアしてPPBを保護します。パスワード方式では、64ビットのパスワードを恒久的にプログラムし、隠せます。隠しパスワードと比較するためのパスワードを供給するために1個のコマンドが使用されます。パスワードが一致した場合、PPBロックビットはPPBを保護解除するために‘1’に設定されます。PPBロックビットを‘0’に消去するために、あるコマンドが使用されます。

PPBロック管理方法の選択は、ロックレジスタのOTPビットのプログラミングによって行われ、使用方法がそれに応じて恒久的に選択されます。

ロックレジスタはSSR保護用のOTPビットも含んでいます。

PPBビットは消去され、そのためインフィニオンからの出荷時にはすべてのメインフラッシュアレイのセクタがすべて非保護です。セキュアシリコン領域は、注文時のオーダーオプション(モデル)によって、工場にて保護するか非保護のままにできます。

### 3.4.3 PPBロック

PPBロックはすべてのPPBビットを保護するための揮発性ビットです。‘0’にクリアすると、すべてのPPBをロックし、‘1’に設定するとPPBの変更を許可します。PPBロックビットはデバイスあたりに1つのみ割り当てられます。

PPBロックコマンドを使用してこのビットを‘0’にクリアします。PPBロックビットは、必ずすべてのPPBを所望の設定にした後で、‘0’にクリアされなければなりません。

恒久保護モードでは、PORまたはハードウェアリセットの間は、PPBロックが‘1’にセットされます。クリアされると、ソフトウェアコマンドシーケンスではPPBロックをセットできません。別のハードウェアリセットまたは電源投入でPPBロックビットをセットする必要があります。

パスワード保護モードでは、PORまたはハードウェアリセットの間に、PPBロックが‘0’にクリアされます。PPBロックは、パスワードロック解除コマンドシーケンスによってのみ‘1’に設定できます。

PPBロックはPPBロックビットクリアのコマンドで消去できます。

### 3.4.4 恒久的保護ビット(PPB)

PPBは、別の不揮発性フラッシュアレイに配置されます。各セクタごとに1つのPPBビットが割り当てられます。PPBが‘0’の場合、その対応するセクタはプログラムおよび消去動作から保護されます。PPBは個別にプログラムされますが、グループとして消去される必要があります。これは、個々のワードがメインアレイでプログラム可能であるがセクタ全体が一括での消去を必要とすることと同様です。消去前のプリプログラミングと検証はEACを行います。

PPBビットのプログラミングには、通常のワードプログラミングのための時間が必要です。PPBビットのプログラミング動作またはPPB消去動作中は、動作が完了するまで、データポーリング状態DQ6トグルビット1がトグルします。すべてのPPBを消去するには、通常のセクタ消去時間が必要です。

PPBロックが‘0’の場合、PPBプログラムまたは消去コマンドは実行されず、PPBのプログラミングまたは消去することなくタイムアウトします。

所定のセクタのPPBの保護状態は、PPB ASOに遷移した時にPPB状態読み出しコマンドを実行することによって確認されます。

### 3.4.5 ダイナミック保護ビット (DYB)

DYB は、揮発性でセクタ固有であり、個別に変更できます。DYB は、消去した PPB を持つセクタのみにに対して保護を制御します。セクタの PPB が ‘1’ の場合には、DYB セットまたは消去コマンド シーケンスを発行すると、DYB はそれに応じて ‘0’ に設定されるかまたは ‘1’ に消去され、それに伴って各セクタは保護か非保護の状態に置かれます。この機能により、ソフトウェアで簡単にセクタを予期せぬ書換えから保護でき、同時に変更が必要な場合に簡単な保護解除することが出来ます。

DYB は、必要に応じて ‘0’ にセットするかまたは ‘1’ にクリアできます。

### 3.4.6 セクタ保護状態の概要

各セクタは以下の保護状態があります。

- ロック解除 - セクタは非保護です。簡単なコマンドで保護を変更できます。パワーサイクルまたはハードウェアリセット後は非保護のデフォルト状態となります。

- 動的ロック - セクタは保護され、保護は簡単なコマンドで変更できます。パワーサイクルまたはハードウェアリセットの間は、保護状態は保存されません。

- 恒久的ロック - セクタは保護されます。PPB ロック ビットが ‘1’ にセットされた場合のみ、保護を変更できます。保護状態は不揮発性で、パワーサイクルまたはハードウェアリセットの間は保存されます。保護状態を変更するには、PPB ビットをプログラムするかまたは消去する必要があります。

**Table 8 セクタ保護状態**

| 保護ビット値  |     |     | セクタ状態                     |

|---------|-----|-----|---------------------------|

| PPB ロック | PPB | DYB |                           |

| 1       | 1   | 1   | 非保護 - PPB と DYB は変更可能     |

| 1       | 1   | 0   | 保護 - PPB と DYB は変更可能      |

| 1       | 0   | 1   | 保護 - PPB と DYB は変更可能      |

| 1       | 0   | 0   | 保護 - PPB と DYB は変更可能      |

| 0       | 1   | 1   | 非保護 - PPB は変更不可、DYB は変更可能 |

| 0       | 1   | 0   | 保護 - PPB は変更不可、DYB は変更可能  |

| 0       | 0   | 1   | 保護 - PPB は変更不可、DYB は変更可能  |

| 0       | 0   | 0   | 保護 - PPB は変更不可、DYB は変更可能  |

### 3.4.7 ロック レジスタ

ロック レジスタは、SSR の保護を制御し PPB ロック ビットの管理方法(保護モード)を決定するための、不揮発性 OTP ビットを持っています。

**Table 9 ロック レジスタ**

| ビット     | デフォルト値 | 名称                          |

|---------|--------|-----------------------------|

| 15 ~ 12 | 1      | 予約済み                        |

| 11      | 1      | SSR 領域 3 パスワード保護モード ロック ビット |

| 10      | 1      | SSR 領域 3( カスタマー ) ロック ビット   |

| 9       | 1      | SSR 領域 2( カスタマー ) ロック ビット   |

| 8       | 0      | 予約済み                        |

| 7       | 1      | 予約済み                        |

| 6       | 1      | SSR 領域 1( カスタマー ) ロック ビット   |

| 5       | 1      | 予約済み                        |

| 4       | 1      | 予約済み                        |

| 3       | 1      | 予約済み                        |

| 2       | 1      | パスワード保護モード ロック ビット          |

| 1       | 1      | 恒久的保護モード ロック ビット            |

| 0       | 0      | SSR 領域 0( 工場 ) ロック ビット      |

一度ロックすると、SSR の保護された部分をロック解除する方法はなく、この保護された SSR のメモリ空間のいずれのビットも変更できないため、SSR の保護ビットを使用する際には十分注意する必要があります。SSR が保護されると、この領域へのプログラムのあらゆる試みに対しては、プログラムする領域が保護されている旨のステータスが表示され、どのようなプログラミングの試みも成功しません。領域 0, 1, 2 および 3 のインジケータビットは、それぞれロックレジスタのビット位置 0, 6, 9, および 10 に配置されています。

工場出荷時は、すべてのデバイスはデフォルトの恒久保護方式になっており、電力が印加されたときはすべてのセクタが非保護になっています。デバイスプログラマやホストシステムは、その後セクタ保護方式を選択できます。1回プログラミング方式、不揮発性ビット、それらのいずれかをプログラミングすると、その箇所をそのモードで恒久的にロックします。

#### 恒久保護モード ロック ビット (DQ1)

パスワード保護モード ロック ビット (DQ2) 両方のロック ビットをプログラミングのために同時に選択すると、動作は中止されます。パスワード モード ロック ビットがプログラムされると、恒久的モード ロック ビットは恒久に無効とされ、保護方式に対する変更は許可されません。同様に、恒久的モード ロック ビットをプログラムすると、パスワード モードは恒久的に無効となります。

パスワード モードを選んだ場合は、対応するロック レジスタ ビットを設定する前に、パスワードをプログラムしてください。パスワード保護モード ロック ビット (DQ2) を設定するとパスワードのプログラミングや読み出し能力が無効になります。

ロック レジスタのプログラミング時間は、通常のワード プログラミングに要する時間と同じです。ロック レジスタ プログラミング EA の間、データ ポーリング状態 DQ6 トグル ビット I は、プログラミングが完了するまでトグルします。システムはまた、ステータス レジスタを読み出すことで、ロック レジスタのプログラミング状態を決定できます。これらのステータス ビットについては、[ステータス レジスタ](#) を参照してください。

DQ2 または DQ1、および DQ6 または DQ0 の各ビットを同時にプログラムする必要はありません。これにより、デバイス保護スキームを選択前後に、ユーザーが SSR をロックできます。ロック ビットをプログラムする場合、予約済みビットは '1'(マスク済み) でなくてはいけません。

### 3.4.8 恒久保護モード

恒久保護方式は、POR またはハードウェアリセットの間に PPB ロック ビットが ‘1’ にセットされ、PPB ビットがデバイスリセットによって保護されません。PPB を保護するために PPB ロック ビットを ‘0’ にクリアするためのコマンドがあります。恒久保護方式では、PPB ロック ビットを ‘1’ にセットするコマンドがないため、次の電源切断またはハードウェアリセットまで PPB ロック ビットは ‘0’ のままで。

### 3.4.9 パスワード保護モード

#### 3.4.9.1 PPB パスワード保護モード

PPB パスワード保護モードを使用すると、PPB ロックを設定するための 64 ビットのパスワードを要求することによって、恒久的セクタ保護モードよりもむしろ高いセキュリティ レベルを実現できます。このパスワード要件に加えて、電源投入とリセット後、電源投入時の保護を確実にするために PPB ロックは ‘0’ にクリアされます。完全なパスワードを入力してパスワードロック解除コマンドを正常に実行すると、PPB ロックが ‘1’ にセットされ、セクタの PPB の変更が可能になります。

パスワード保護の注意：

- パスワード プログラム コマンドでプログラムできるのは、0 だけです。

- インフィニオン出荷時はパスワードはすべて 1 です。パスワードは自身のメモリ空間内にあり、パスワード プログラムとパスワード読み出しコマンドの使用によりアクセス可能です。

- あらゆる 64 ビット パスワードの組合せがパスワードとして有効です。

- パスワードをプログラムして検証したら、パスワードの読み出しや書き換えを防ぐためには、パスワード モード ロック ビットをセットする必要があります。

- パスワード モード ロック ビットをプログラムすると、データバス上で 64 ビット パスワードの読み出しができなくなり、さらなるパスワードのプログラミングもできません。パスワード領域に対するさらなる読み出しコマンドは無効にされます(データは 1 として読み出されます)。パスワード保護モード ロック ビットがプログラムされた後に、パスワードが何であるかを確認する方法はありません。パスワードの検証ができるのは、パスワード保護モードを選択する前のみです。プログラミング動作はすべて失敗となり、その結果はロックしたセクタでの通常のプログラム障害として報告されます。

- パスワード モード ロック ビットは消去できません。

- ロック解除の機能を動作させるためには、正確なパスワードを入力する必要があります。

- アドレスはどのような順序でもロードできますが、一致の成功のためには 4 ワードすべてが必要です。

- パスワードアドレス / データをロードする間に、セクタアドレス(Amax ~ A16)とワードラインアドレス(A15 ~ A8)が ‘0’ と比較されます。セクタアドレスまたはワードラインアドレスが一致しない場合、書き込みサイクルの最後にエラーが報告されます。ステータスレジスタは、プログラムステータスピットが ‘1’ にセットされ、書き込みバッファ中止ステータスピットが ‘1’ にセットされ、プログラミング動作が失敗したことを表して、レディ状態に戻ります。データポーリング状態は、DQ7 がパスワード ロック解除コマンドの最後のワード内の DQ7 ビットの補数に設定され、DQ6 がトグルして、アクティブ状態のままでです。RY/BY# は LOW のままで。

- 特定のアドレスとデータは、プログラム バッファからフラッシュ コマンドが与えられた後に比較されます。内部の設定値と一致しない場合、プログラミング動作が失敗したことを示すプログラム状態ビットが ‘1’ に設定されて、ステータスレジスタはレディ状態に戻ります。データポーリング状態は、DQ7 がパスワード ロック解除コマンドの最後のワード内の DQ7 ビットの補数に設定され、DQ6 がトグルして、アクティブ状態のままでです。RY/BY# は LOW のままで。誤ったパスワードによるこのエラーの場合、デバイスは  $t_{PPB}$  の待ち時間を必要とし、ソフトウェアリセットコマンドが、パスワード ASO を適切に終了するためのパスワード ASO 終了コマンドの前に、エラーをクリアする必要があります。そうしないと、デバイスはパスワード ASO のままで。

- デバイスは、有効な 64 ビットのパスワードがデバイスに与えられた後に PPB ロックを設定するために  $t_{PPB}$  の時間が必要です。このため、ハッカーが正しいパスワードに一致させようとして 64 ビットの組合せを実行するには、非現実的な長さの時間(5800 万年)かかります。EA ステータス チェック方式は、いつ EAC が新規パスワード コマンドを受付ける準備ができるかの判定にも使用できます。

- パスワード モード ロック ビットの設定後にパスワードを失くした場合、PPB ロックをクリアする方法はありません。

読み出し動作

## 4 読み出し動作

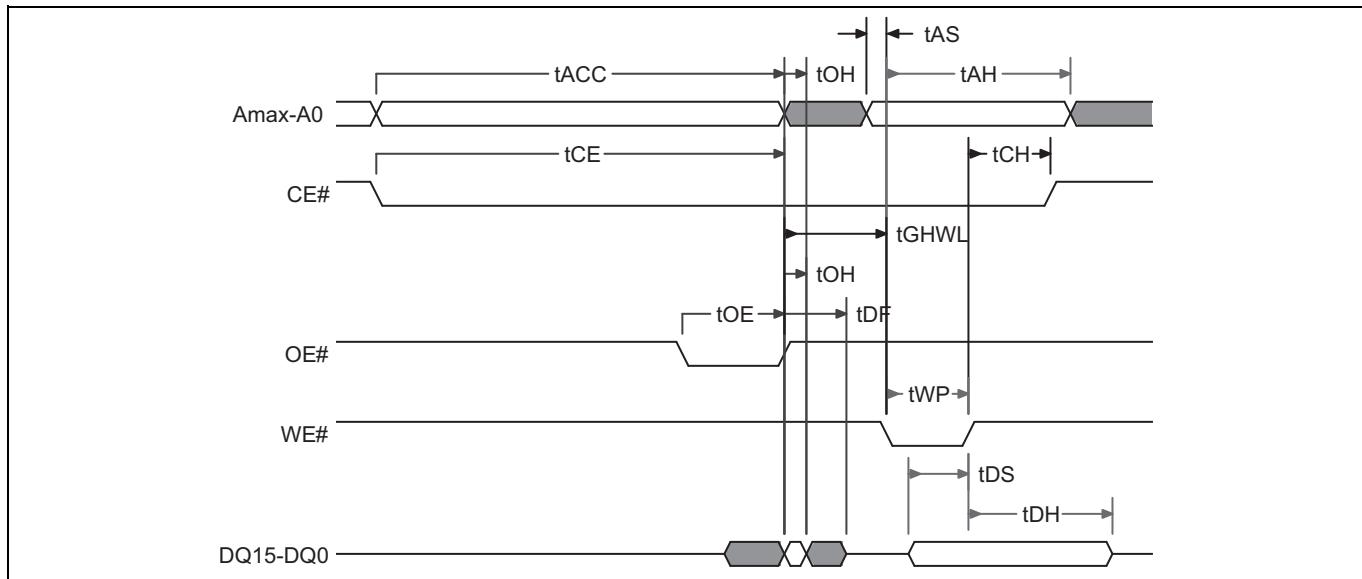

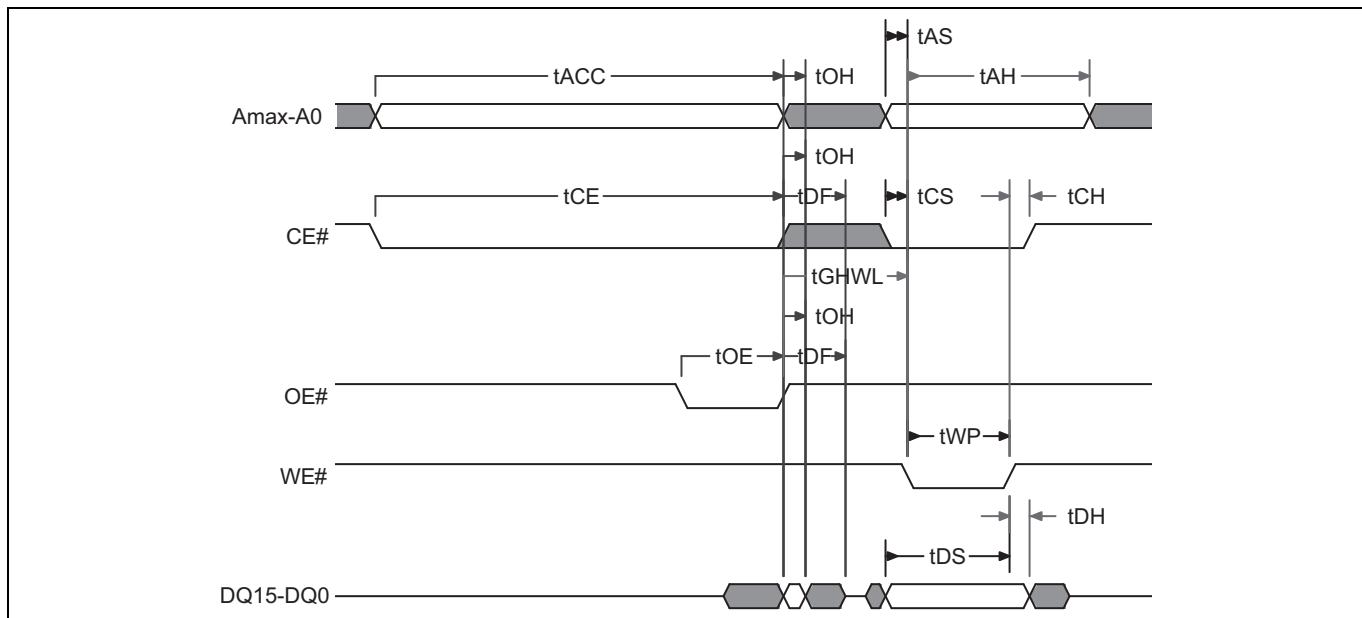

### 4.1 非同期読み出し

それぞれの読み出しアクセスをメモリ内の任意の場所に対して実行できます(ランダムアクセス)。それぞれのランダムアクセスはセルフタイム式であり、CE# またはアドレスが確定してから有効なデータが出力されるまでの時間( $t_{ACC}$  または  $t_{CE}$ )と同じレイテンシで実行されます。

### 4.2 ページモード読み出し

それぞれのランダム読み出しが 32 バイトからなる「ページ」全体に並列でアクセスします。同じページ内の後続の読み出しが、より速い読み出しアクセス速度により行われます。ページは上位アドレスビット(A<sub>max</sub> ~ A<sub>4</sub>)によって選択されますが、そのページの特定のワードは最下位アドレスビットA<sub>3</sub> ~ A<sub>0</sub>(x8 タイプでは A<sub>3</sub> ~ A<sub>1</sub>)によって選択されます。上位アドレスビットは一定に保持され、同じページの異なるワードを選択するためには A<sub>3</sub> ~ A<sub>0</sub>(x8 タイプでは A<sub>3</sub> ~ A<sub>1</sub>)だけが変更されます。これは非同期アクセスであり、CE# と OE# の両方が LOW、および非同期ページアクセス時間( $t_{PACC}$ )が満たされた場合に、そのデータが DQ15 ~ DQ0(x8 タイプでは DQ7 ~ DQ0)に現れます。後続のアクセスのために CE# が HIGH になってから LOW になると、ランダム読み出しアクセスが実行され、その実行時間( $t_{ACC}$  または  $t_{CE}$ )も必要とされます。

組込み動作

## 5 組込み動作

### 5.1 組込みアルゴリズム コントローラー (EAC)

EAC は、フラッシュメモリアレイをプログラムし、消去するためのコマンドをホストシステムから受信し、不揮発性メモリの状態を変更するのに必要な複雑な操作をすべて実行します。これにより、ホストシステムはプログラムおよび消去のプロセスを管理する必要がなくなります。

EAC の動作は以下の 4 カテゴリに分けられます。

- スタンバイ (読み出しモード)

- アドレス空間の切替え

- 組込みアルゴリズム (EA)

- 高度セクタ保護 (ASP) の管理

#### 5.1.1 EAC スタンバイ

スタンバイ モードでは、消費電流を大幅に低減できます。コマンドが処理されず、組込みアルゴリズムが進行中でないとき、EAC はスタンバイ モードに入ります。組込みアルゴリズムの実行中にデバイスを非選択とする ( $CE\# = HIGH$ ) と、その動作が完了するまでデバイスは依然としてアクティブ電流を消費します ( $I_{CC3}$ )。DC 電気的特性の  $I_{CC4}$  はホストインターフェースと EAC の両方がスタンバイ状態にあるときのスタンバイ電流の仕様を示しています。

#### 5.1.2 アドレス空間の切替え

特定のアドレスとデータ配列 (コマンド シーケンス) を書き込むと、メモリデバイスアドレス空間をメイン フラッシュアレイからアドレス空間オーバーレイ (ASO) の 1 つに切り替えます。

組込みアルゴリズムは、現時点で有効になっている (入っている) ASO で表示されている情報に基づいて動作します。システムが ASO 終了コマンドを発行する、ハードウェアリセットを実行する、またはデバイスの電源が切られるまで、システムは ASO へのアクセスを継続します。ASO 終了コマンドは、ASO からメイン フラッシュアレイのアドレス空間に切り替えます。特定の ASO が有効の時に受信されたコマンドは、コマンド定義テーブルの ASO 開始と ASO 終了コマンドの間にリストアップされています。すべてのコマンドシーケンスのアドレスとデータの要件については、[コマンドのまとめ](#) を参照してください。

#### 5.1.3 組込みアルゴリズム (EA)

メモリアレイ内の不揮発性データの書換えには、EA と呼ばれる複雑な動作シーケンスを実行する必要があります。これらのアルゴリズムはデバイス内部の EAC によって完全に管理されています。メインアルゴリズムは、メインアレイのデータと ASO のプログラミングと消去を実行します。ホストシステムはフラッシュデバイスのアドレス空間にコマンドコードを書き込みます。EAC はコマンドを受け取り、コマンドを完了するのに必要なすべてのステップを実行し、EA の進行中にステータス情報を提供します。

組込み動作

## 5.2 プログラムと消去のまとめ

フラッシュのデータビットは、セクタと呼ばれる大きなグループで並行して消去されます。消去動作は、セクタ内の各データビットを論理1状態(HIGH)に設定します。フラッシュデータビットは、消去状態(論理1)からプログラム状態(論理0, LOW)に個別にプログラミングできます。**'0'**のデータビットを**'1'**にプログラムすることはできません。後続の読み出し結果から、そのデータが**'0'**のままであることが分かります。**'0'**から**'1'**に変換できるのは消去動作のみです。同じワード位置を別の0ビットで複数回プログラムすると、直前のデータとプログラミング中の新しいデータとの論理積となります。プログラム動作と消去動作の時間を**組込みアルゴリズム性能表**に示します。

プログラムと消去動作を一時停止できます。

- 消去動作を一時停止することで消去動作中に(消去セクタ以外の)別のセクタのプログラミングや読み出しを行えます。消去一時停止中は他の消去動作を開始できません。

- プログラム動作を一時停止することで、(プログラミング中のライン以外の)別の位置の読み出しを行えます。

- プログラム動作の一時停止中は、他のプログラム動作または消去動作を開始できません。つまり、プログラム動作の一時停止中はプログラムコマンドと消去コマンドが無視されます。

- 間に挟んだプログラム動作または読み出しアクセスが完了すると、一時停止している消去動作やプログラム動作が再開されます。デバイスが別のコマンドを実行していない場合は、一時停止後に隨時に再開できます。

- プログラム動作と消去動作は、必要に応じて何度も中断できますが、プログラム動作または消去動作を進捗させ完了させるためには、再開コマンドと次の一時停止コマンドの間に、**組込みアルゴリズム性能表**に示す  $t_{PRS}$  または  $t_{ERS}$  以上の時間を要します。

- EAが完了すると、EACはEAが開始された動作状態(消去一時停止, EACスタンバイ,...)とアドレス空間に戻ります。

システムは、ステータスレジスタを読み出すか、またはデータポーリングステータスを使うことにより、プログラム動作または消去動作のステータスを決定できます。これらのステータスビットについては、**ステータスレジスタ**を参照してください。詳細については**データポーリングステータス**を参照してください。

組込みプログラムアルゴリズムの実行中にデバイスに書き込まれるコマンドは、プログラム一時停止(x51h), ステータス読み出しコマンド(x70h), および消去一時停止 / プログラミング一時停止コマンド(xB0h)以外は無視されます。

組込み消去アルゴリズムの実行中にデバイスに書き込まれるコマンドは、ステータス読み出し(x70h)および消去一時停止 / プログラミング一時停止コマンド(xB0h)以外は無視されます。

ハードウェアリセットが発生すると、進行中のプログラム / 消去動作が直ちに終了し、 $t_{RPH}$ 時間後に読み出しモードに戻ります。データの完全性を確保するためには、デバイスがアイドル状態に戻ったら、終了した動作を再実行します。

性能と信頼性の理由で、読み出しとプログラミングは32バイトのページ上で内部的に行われます。**DC電気的特性**の  $I_{CC3}$  は書き込み(組込みアルゴリズム)動作時のアクティブ電流仕様を示します。

組込み動作

### 5.2.1 プログラムの粒度

S29GL-Tは、ワードプログラミングと、書き込みバッファプログラミングの、2つのプログラミング方式をサポートしています。各ページはどちらかの方法でプログラミングできます。異なる方式でプログラムされたページは、産業用温度バージョン (-40°C ~ +85°C) では、同じラインに混在する場合があります。産業用プラスバージョン (-40°C ~ +105°C) および拡張バージョン (-40°C ~ +125°C) では、デバイスは消去間に各32バイトのページごとに1回のプログラム動作だけをサポートしており、シングルワードプログラミングコマンドはサポートされません。

ワードプログラミングは、コマンドによって提供されたワードのデータを検査し、コマンドのデータワードの0と一致させるようにアドレス指定したメモリアレイのワードに0をプログラムします。

書き込みバッファプログラミングは、書き込みバッファを検査し、書き込みバッファの0と一致させるようにアドレス指定したメモリアレイのページに0をプログラムします。なお、書き込みバッファのすべてをデータで満たす必要はありません。最少単一ビット、複数ビット、單一ワード、複数ワード、1ページ、複数ページ、またはバッファすべてのプログラミング動作が可能です。書き込みバッファ方式を使用すると、プログラムコマンドを書き込む時のホストシステムのオーバーヘッドが削減され、プログラム動作時のメモリデバイスの内部オーバーヘッドが削減されるため、書き込みバッファによるプログラミングはより効率的になり、ワードプログラミングコマンドによって個別ワードをプログラムする方式よりプログラム時間がさらに短縮されます。

### 5.2.2 追加プログラミング

ワードプログラミングか書き込みバッファによるプログラミングのいずれかの方式で、同じワード位置を複数回プログラムして、追加分だけ1を0に変更できます。同じページで複数回のプログラミング動作を行うと、そのページのECCが無効になることに注意してください。

## 5.3 自動ECC

### 5.3.1 ECCの概要

自動ECC機能は、通常プログラム、消去および読み出し動作でトランスペアレントに（存在が意識されず）機能します。デバイスがデータページを書き込みバッファからメモリアレイに転送する時、内部ECCロジックはページ用のECCコードを、ホストシステムには見えないメモリアレイの一部にプログラムします。デバイスは各初期ページアクセス中にページデータとECCコードを評価します。必要があれば、内部ECCロジックは初期アクセス時間中に1ビットエラーを訂正します。

特定のページに複数回プログラムすると、そのページのECC機能が無効になります。次回にホストシステムがページを含むセクタを消去するまで、そのページのECC機能は無効のままです。ホストシステムは複数のプログラム動作に続いてそのページに格納されたデータを読み出せますが、ECCは無効になっており、そのページのエラーを検出または訂正是されません。

### 5.3.2 プログラムおよび消去のまとめ

性能と信頼性の理由で、読み出しとプログラム動作は32バイトのページ上で並行して行われます。デバイスは、初めてプログラムされる時、各ページにECCコードを追加することによって各ページにECCを提供します。ECCコードは自動で、ホストシステムにトランスペアレントです。

組込み動作

### 5.3.3 ECC の実装

メインフラッシュアレイの各 32 バイトページおよび各 32 バイト OTP 領域には、関連する ECC コードがあります。内部 ECC ロジックは、読み出しアクセス中に、ページまたは関連する ECC コードで 1 ビットエラーを検出し、訂正できます。

ページに適用される最初の書き込みバッファプログラム動作では、そのページの ECC コードをプログラムします。特定のページに対して後続のプログラム動作が 2 回以上行われると、そのページの ECC 機能が無効になります。これにより、ビットまたはワードのプログラミングが可能ですが、同じページに複数のプログラム動作を行うと、インクリメンタル プログラミングが行われるページで ECC 機能が無効になることにご注意ください。ECC が無効になったページを含むセクタを消去すると、そのページの ECC 機能が再び有効になります。

ECC 機能は自動で、ユーザーにトランスペアレントです。自動 ECC 機能がトランスペアレントであることにより、各ページにデータを 1 回書き込む標準的なプログラム動作でのデータの完全性が向上します。また ECC 機能は、単一ワード プログラミングと、同じページまたはワードが複数回プログラムされるビットウォーキングを可能にすることによって、前世代の GL ファミリ製品とのソフトウェア互換性を容易にします。ページの自動 ECC が無効になった時、ECC 機能はそのページから読み出されたデータでエラーを検出または訂正しません。

### 5.3.4 ワード プログラミング

ワード プログラミングは、メインフラッシュメモリアレイの任意の場所に単一ワードをプログラムします。同じ 32 バイトページに複数のワードをプログラムすると、そのページで自動 ECC 保護が無効になります。そのページを含むセクタを消去すると、そのページでの複数のワード プログラム動作に続いて自動 ECC は再び有効になります。

### 5.3.5 書き込みバッファ プログラミング

各書き込みバッファプログラム動作では、1 ビット～512 バイトのプログラミングが可能です。32 バイトのページは自動 ECC 保護を機能させる最小のプログラム粒度です。同じページに複数回プログラムすると、そのページの自動 ECC 機能が無効になります。インフィニオンは、書き込みバッファ プログラミング動作で、1 度の動作で複数ページをプログラムし、各ページに 1 回だけ書き込むことを推奨します。これにより、各ページで自動 ECC 保護は有効のままであります。最高の性能を得るには、512 バイト境界に整列された 512 バイトのライン全体でプログラムしてください。

組込み動作

## 5.4 コマンドセット

### 5.4.1 プログラム方式

#### 5.4.1.1 ワード プログラミング

ワード プログラミングは、メイン フラッシュ メモリ アレイの任意の場所に単一ワードをプログラムするために使用されます。

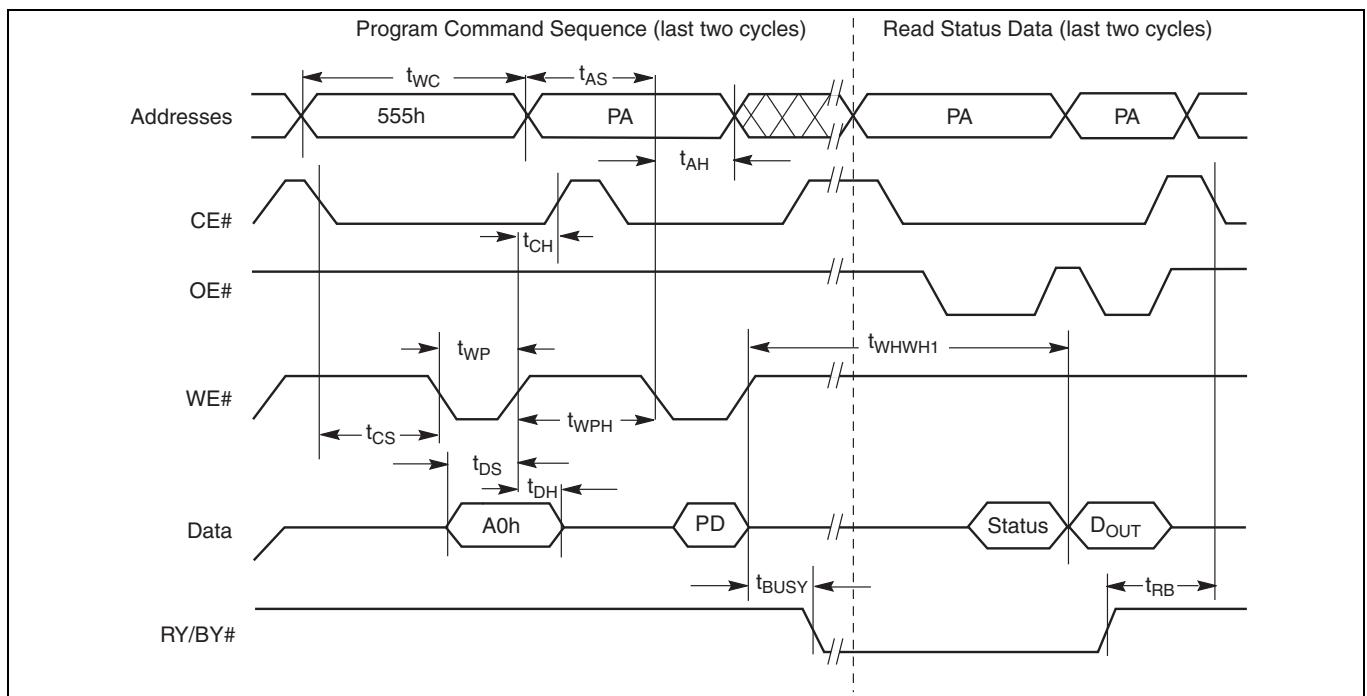

ワード プログラミング コマンドは 4 回の書き込みサイクルのシーケンスです。プログラム コマンド シーケンスは、2 つのアンロック書き込みサイクルを書き込むことから開始され、その後に、プログラム 設定コマンドが続きます。プログラム アドレスとデータが次に書き込まれ、このようにして順番に組込みワード プログラム アルゴリズムが開始します。システムは、更なる制御やタイミングを提供する必要はありません。デバイスは自動的にプログラム パルスを生成し、内部でプログラムされたセルのマージンを検証します。ワード プログラムの組込みアルゴリズムが完了すると、EAC はスタンバイ モードに戻ります。

システムは、データポーリング ステータスを使用するか、ステータス レジスタを読み出すか、または RY/BY# 出力をモニターすることで、プログラム動作のステータスを決定できます。これらのステータスピットについては、[ステータス レジスタ](#)を参照してください。これらのステータスピットについては、[データ ポーリング ステータス](#)を参照してください。ワード プログラミング動作の図については、

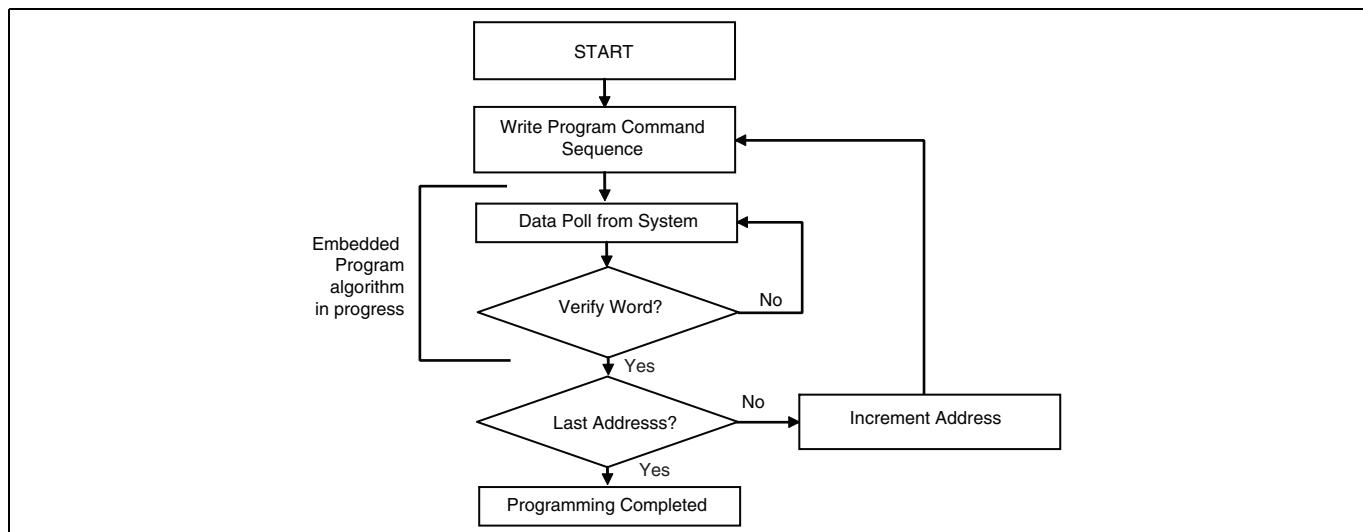

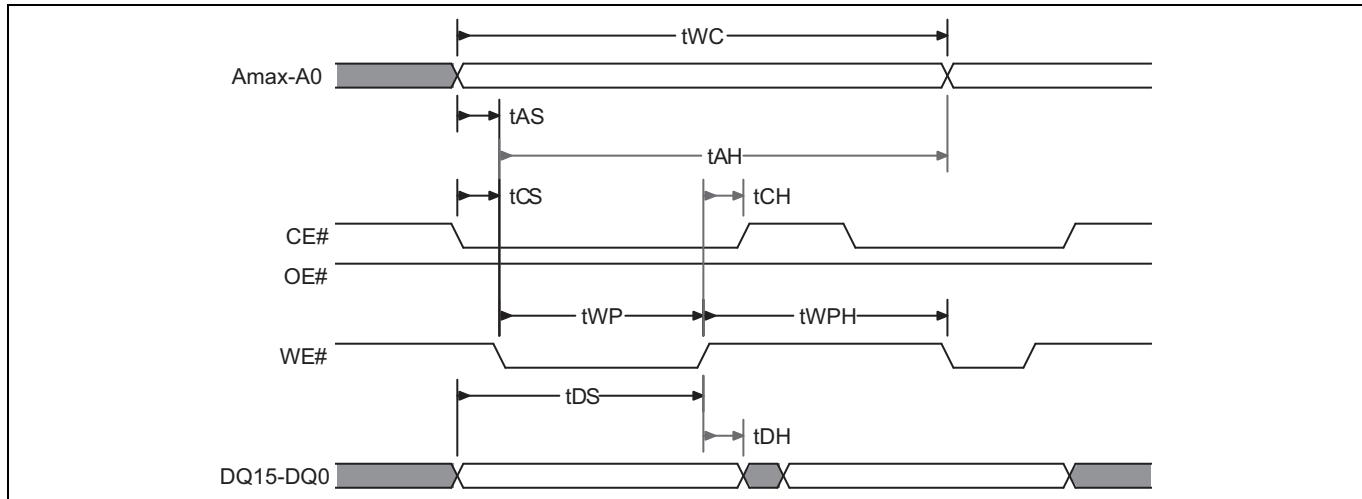

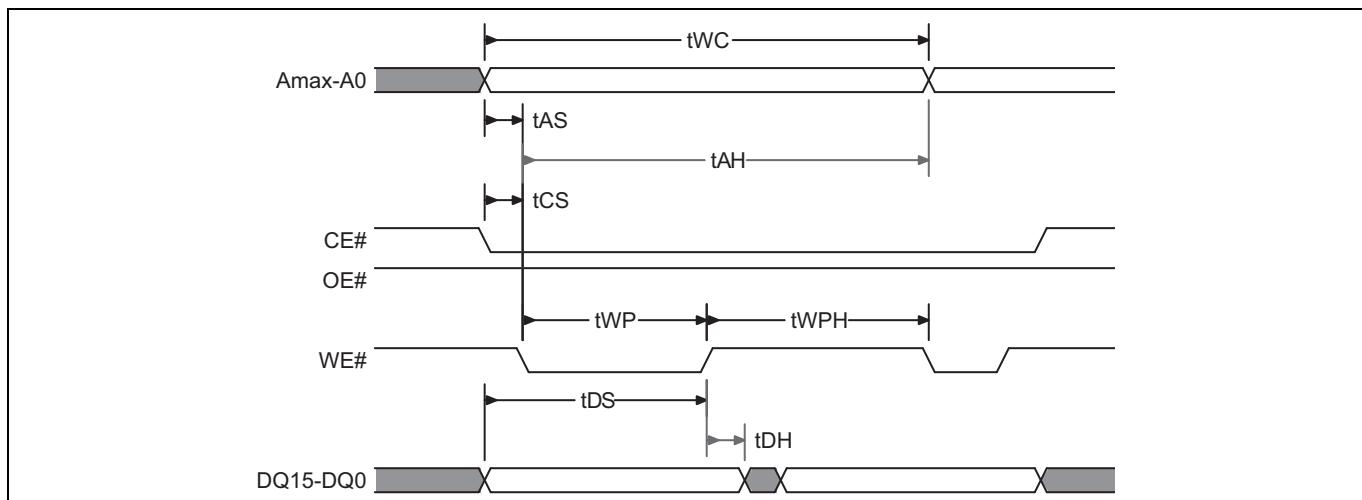

**Figure 3** を参照してください。

組込みプログラム アルゴリズムの実行中は、プログラム一時停止コマンドを除き、デバイスに書き込むコマンドはすべて無視されます。ハードウェアリセット (RESET# = V<sub>IL</sub>) により、プログラム動作が瞬時に終了し、tRPH 時間後にデバイスが読み出しモードに戻ることに注意してください。データの完全性を確保するためには、デバイスがハードウェアリセット動作を完了したら、プログラム コマンド シーケンスを再度実行する必要があります。

ワード プログラミング コマンドの修正済みバージョン (アンロック書き込みサイクルがない) は、ロックレジスタ、パスワード、および PPB ASO またはアンロックバイパスモードに入ったときに、プログラミングのために使用されます。PPB ロックと DYBASO に入るときに揮発性ビットを変更するためにもそのコマンドは使用されます。プログラム コマンド シーケンスについては、[Table 23](#) を参照してください。

**Figure 3** ワード プログラム動作

組込み動作

#### 5.4.1.2 書き込みバッファプログラミング

書き込みバッファは、512 バイトの境界（ライン）にアラインされた 512 バイトのアドレス範囲内のデータをプログラムするために使用されます。このように、完全な書き込みバッファプログラミング動作はライン境界に整列される必要があります。512 バイト以下のプログラミング動作は、任意のワード境界で開始できますが、ライン境界を越えられません。書き込みバッファプログラミング動作の開始時は、バッファ内のすべてのビット位置が 1 (FFFFh ワード) です。したがって、ロードされなかつたすべての位置は、既存のデータが保持されます。アドレスマップについては、[製品概要](#)を参照してください。

書き込みバッファプログラミングでは、1 回の動作で最大 512 バイトまでプログラミングできます。各書き込みバッファプログラミング動作は、1 ビットから 512 バイトまでプログラミングできます。複数ページに書き込んで、各ページは 1 回だけ書き込むことを推奨します。最高の性能を得るには、512 バイト境界に整列された 512 バイトのライン全体でプログラムしてください。

書き込みバッファプログラミングは、メインフラッシュアレイまたは SSR ASO のみサポートされます。書き込みバッファプログラム動作は、最初に 2 つのアンロックサイクルを書き込むことで開始されます。この後、プログラミングが発生しているセクタアドレス (SA) で、3 回目の書き込みサイクル（バッファ書き込みコマンド）が続けます。次にシステムは、「ワード位置数 - 1」の値を書き込みます。これにより、デバイスは、データをロードした書き込みバッファアドレス数を認識でき、それによりバッファからフラッシュへのプログラムの確認コマンドの実行タイミングを確定できるようになります。セクタアドレスは、バッファ書き込みコマンドと、ワード数書き込みコマンドで一致する必要があります。プログラム対象のセクタはロック解除（非保護）になる必要があります。

この後、システムは開始アドレス / データのペアを書き込みます。この開始アドレスはプログラムされる最初のアドレス / データのペアであり、書き込みバッファのラインアドレスを選択します。セクタアドレスは、バッファのセクタアドレス書き込みと一致する必要があります。そうでない場合は、動作が中止され、中止状態に遷移します。すべての後続アドレス / データのペアは、連続した順序でなければいけません。すべての書き込みバッファアドレスは同じライン内にある必要があります。システムがこの範囲外のデータをロードしようとすると、動作は中止され、中止状態に遷移します。

カウンタ値は、データのロード動作のたびに減少します。データ書き込みをカウントダウンしている間は、毎回の書き込みは書き込みバッファにロードされるデータと見なされるため、注意してください。書き込みバッファロード中は、すべてのコマンドが実行不可能です。書き込みバッファのロードを停止する唯一の方法は、プログラミング動作のラインにないアドレスで書き込むことです。この無効なアドレスを受信すると、バッファ書き込みコマンドは直ちに中止します。

書き込みバッファ位置の指定した数をロードしたら、システムはセクタアドレスにおいて、バッファからフラッシュコマンドを書き込まなければいけません。デバイスはその後ビジー状態になります。組込みプログラムアルゴリズムは正しいデータパターンを得るために、データを自動的にプログラムし検証します。これらの動作中に、システムは更なる制御やタイミングを提供する必要はありません。書き込みバッファ位置の不正な数がロードされた場合、動作は中止され、中止状態に遷移します。ワードカウントの最後にバッファからフラッシュへのプログラムのコマンドが書き込まれずに、別のコマンドやデータが書き込まれると、動作は中止されます。

書き込みバッファの組込みプログラミング動作は、プログラム一時停止コマンドにより一時停止できます。組込みプログラムアルゴリズムが完了すると、EAC はプログラム動作が開始したときの EAC スタンバイまたは消去一時停止スタンバイの状態に戻ります。

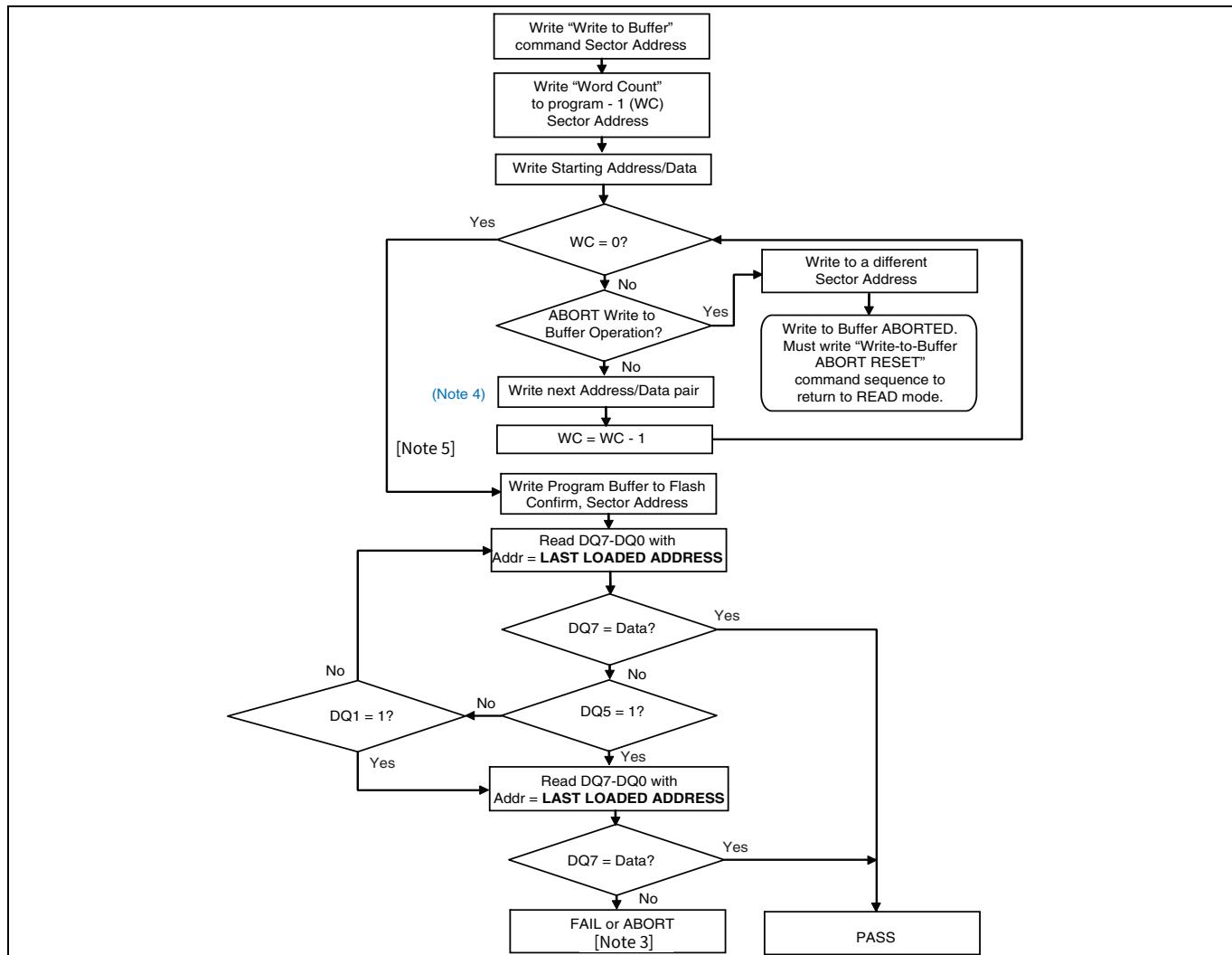

システムは、データポーリングステータスを使用するか、ステータスレジスタを読み出すか、または RY/BY# 出力をモニターすることでプログラム動作のステータスを確定できます。これらのステータスビットについては、[ステータスレジスタ](#)および[データポーリングステータス](#)を参照してください。プログラム動作図については、[Figure 4](#) を参照してください。

書き込みバッファプログラミングシーケンスは、以下の条件で中止されます。

- ・バッファサイズ (255) を越えるワードカウント値をロードする。

- ・バッファ書き込みコマンドで指定したラインにないアドレスを書き込む。

- ・ワードカウント数書き込みで指定したデータワードがロードされた後に、バッファからフラッシュへのプログラムのコマンドが発行されない。

バッファ書き込みコマンドの強制終了を引き起こす何らかの条件が発生すると、動作は直ちに中止し、ステータスレジスタのビット位置 4 (PSB = 1) に、バッファ書き込み中止のビット位置 3 (WBASB = 1) によ

## 組込み動作

るプログラム失敗が報告されます。その後、プログラム動作が成功すると、この失敗の状態はクリアされます。またはクリアステータスレジスタが実行されて、PSBステータスピットがクリアされます。

書き込みバッファプログラミングシーケンスは、ハードウェアリセットまたはパワー サイクルにより停止させられます。しかし、両方法のどちらかを使用すると、プログラムされた領域は、データ値が無効または不安定な中間的な状態になってしまいます場合があります。この場合は、同じデータで同じ領域を再プログラムするか、または消去してデータ値を正しくプログラムまたは消去する必要があります。

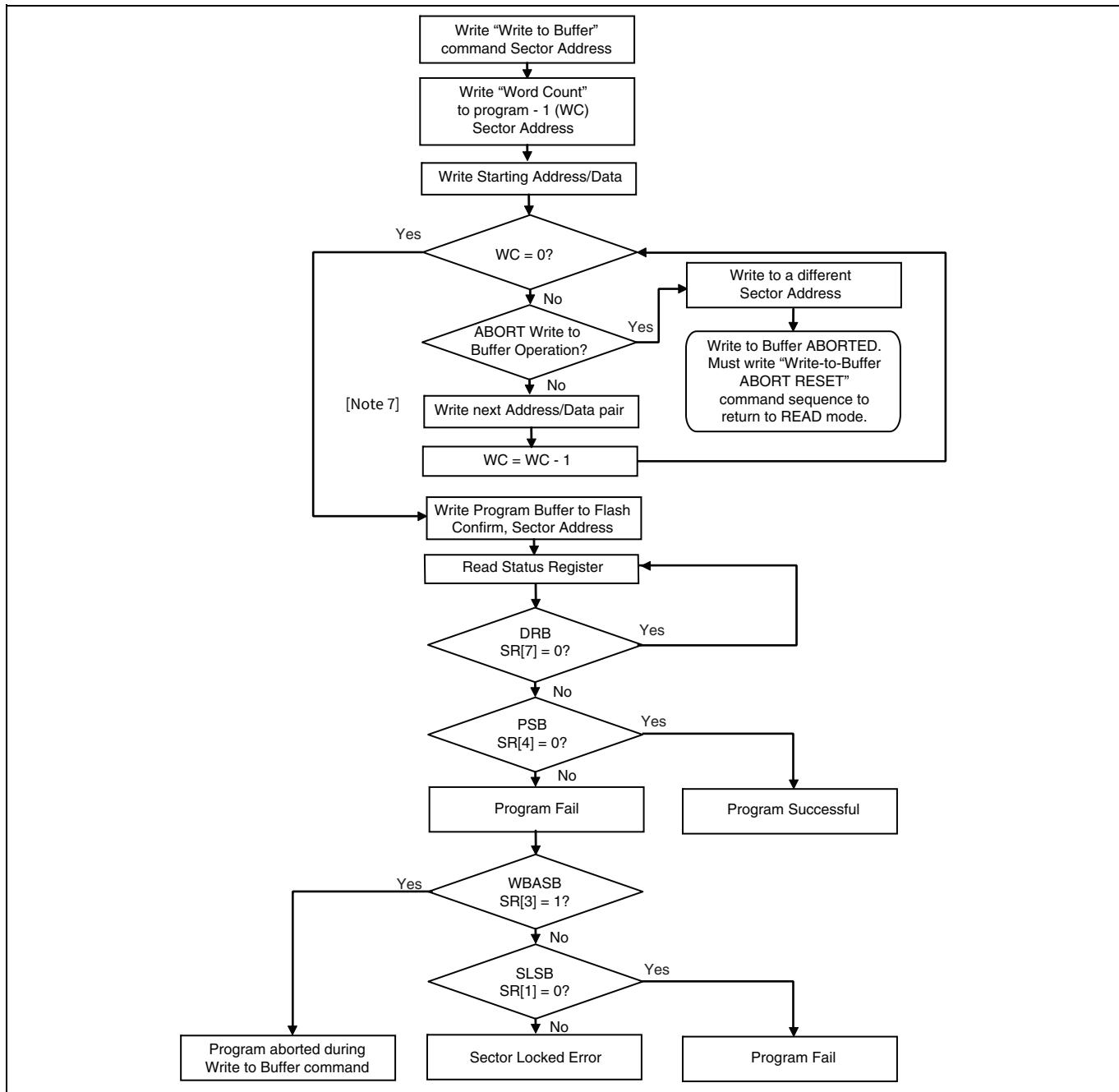

Figure 4 データポーリング状態での書き込みバッファプログラミング動作

### 注:

2. DQ7 が DQ5 と同時に変化する場合があるため、DQ5=1 の場合でも DQ7 を再チェックする必要があります。

3. DQ5=1 でこのフローチャートの位置に到達した場合は、デバイスは FAILED です。DQ1=1 でこのフローチャートの位置に到達した場合、バッファ書き込み動作は ABORTED されます。いずれの場合も、デバイスを READ モードに戻すには、デバイスに適切な RESET コマンドを書き込む必要があります。DQ1=1 の場合は、書き込みバッファプログラミング中止リセット、DQ5=1 の場合は、ソフトウェア RESET または書き込みバッファプログラミング中止リセットを実行します。

4. 書き込みバッファプログラミングに必要なコマンドシーケンスについては、Table 23 を参照してください。

5. セクタ アドレスが指定されたとき、指定したセクタのいずれのアドレスも受け入れ可能になります。ただし、バッファ書き込みのアドレス位置にデータをロードする場合、すべてのアドレスは選択された書き込みバッファページ内にある必要があります。

組込み動作

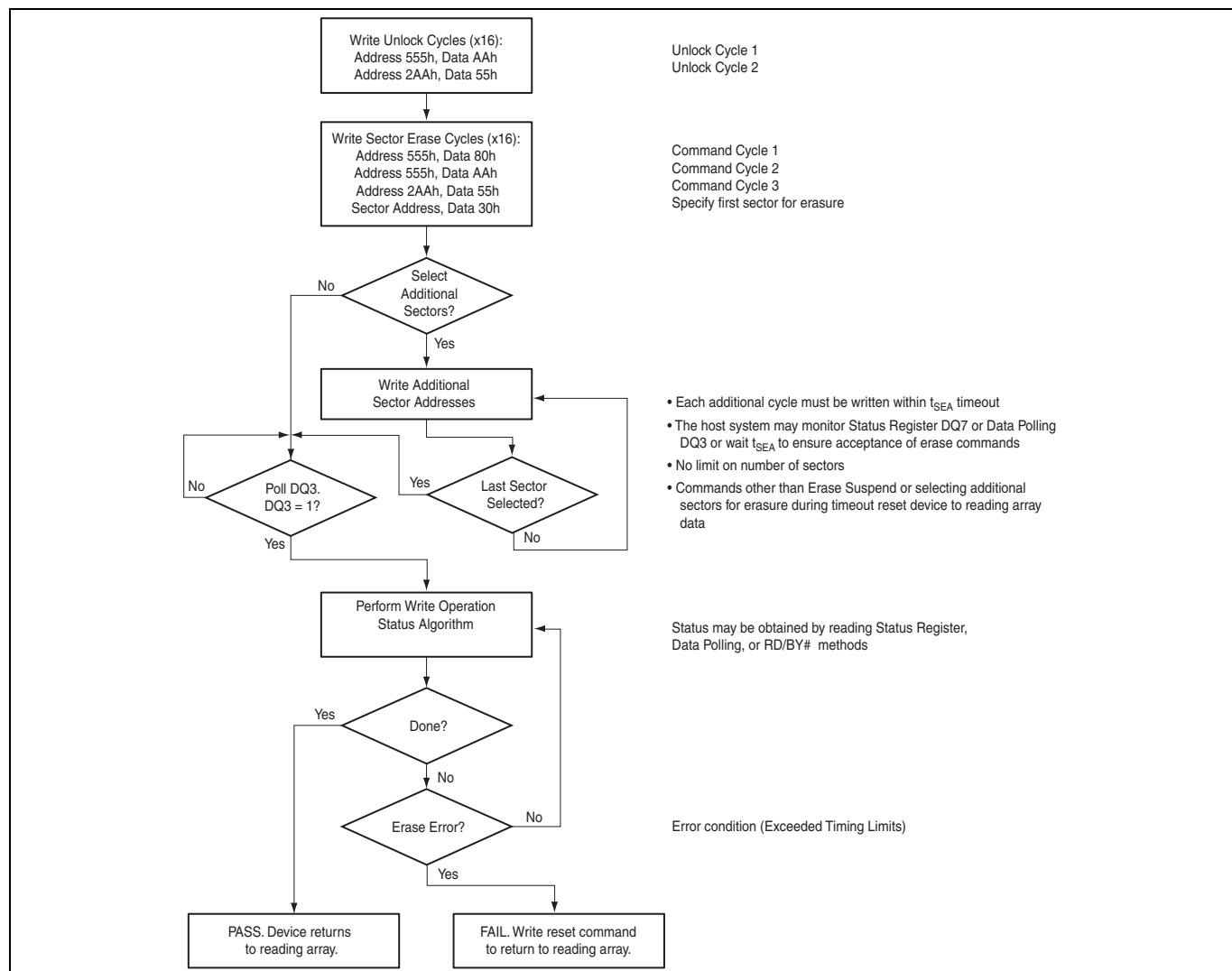

Figure 5 ステータス レジスタでの書き込みバッファ プログラミング動作

注:

6. 書き込みバッファ プログラミングに必要なコマンド シーケンスについては、Table 23 を参照してください。

7. セクタ アドレスが指定されたとき、指定したセクタのいずれのアドレスも受け入れ可能になります。ただし、バッファ書き込みのアドレス位置にデータをロードする場合、すべてのアドレスは選択された書き込みバッファ ページ内にある必要があります。

組込み動作

Table 10 書き込みバッファプログラミングのコマンドシーケンス

| シーケンス                                                                               | ×16    |       | ×8     |     | 備考                                                      |

|-------------------------------------------------------------------------------------|--------|-------|--------|-----|---------------------------------------------------------|

|                                                                                     | アドレス   | データ   | アドレス   | データ |                                                         |

| ロック解除コマンド 1 を発行                                                                     | 555    | AA    | AAA    | AA  |                                                         |

| ロック解除コマンド 2 を発行                                                                     | 2AA    | 55    | 555    | 55  |                                                         |

| セクタアドレスでのバッファへの書き込みコマンドを発行                                                          | SA     | 0025h | SA     | 25h |                                                         |

| セクタアドレスでのロケーション数を発行<br>例:<br>WC が 0 の場合、プログラム対象ワード数は 1<br>WC が 1 の場合、プログラム対象ワード数は 2 | SA     | WC    | SA     | WC  | WC = プログラム対象ワード数 - 1<br>(×8 モードでは、WC = プログラム対象バイト数 - 1) |

| 開始アドレス / データペアをロード                                                                  | 開始アドレス | PD    | 開始アドレス | PD  | 書き込みバッファページを選択し、最初のアドレス / データペアをロード                     |

| 次のアドレス / データペアをロード                                                                  | WBL    | PD    | WBL    | PD  | すべてのアドレスは選択した書き込みバッファページの境界内にあり、シーケンシャルにロードされる必要がある     |

| 最後のアドレス / データペアをロード                                                                 | WBL    | PD    | WBL    | PD  | すべてのアドレスは選択した書き込みバッファページの境界内にあり、シーケンシャルにロードされる必要がある     |

| セクタアドレスでの書き込みバッファプログラム確認を発行                                                         | SA     | 0029h | SA     | 29h | このコマンドはロードされた最後の書き込みバッファロケーションに続く必要があります。そうでないと、動作が中止する |

| デバイスがビジーになる                                                                         |        |       |        |     |                                                         |

**凡例:**

SA = セクタアドレス (セクタアドレスにないビットは「ドントケア」です。セクタ内の任意のアドレスで十分です。)

WBL = 書き込みバッファの位置 (開始アドレスによって指定された書き込みバッファラインの境界内である必要があります。)

WC = ワードカウント

PD = プログラムデータ

組込み動作

### 5.4.2 プログラム一時停止 / プログラム再開コマンド

プログラム一時停止コマンドにより、システムは組込みのプログラミング動作を中断し、一時停止されていない他のラインからデータを読み出せます。プログラミング実行中にプログラム一時停止コマンドを書き込むと、デバイスは  $t_{PSL}$  ( プログラム一時停止レイテンシ ) の間、そのプログラミング動作を停止してステータスビットを更新します。プログラム一時停止コマンドを書き込む際にアドレスはドントケアです。

プログラム一時停止に使用できるコマンドは 2 つあります。それは、従来の組合せである消去 / プログラム一時停止コマンド (B0h コマンドコード ) と、個別のプログラム一時停止コマンド (51h コマンドコード ) です。プログラム再開用にも 2 つのコマンドがあります。それは、従来の組合せである消去 / プログラム再開コマンド (30h コマンドコード ) と、個別のプログラム再開コマンド (50h コマンドコード ) です。プログラミングの時には、個別のプログラム一時停止コマンドとプログラム再開コマンドを使用し、消去一時停止と再開の時には、従来の組合せのコマンドを使用することを推奨します。

プログラミング動作が一時停止した後は、システムは一時停止されていない任意のラインからアレイデータを読み出せるようになります。消去が一時停止している間も、プログラムしている間には、プログラム一時停止コマンドの発行が可能です。この場合には、消去一時停止またはプログラム一時停止状態になっていないどのアドレスからも、データを読み出せます。

プログラム再開コマンドを書き込まれた後は、デバイスはプログラミング動作に戻り、ステータスビットが更新されます。システムは、ステータスレジスタを読み出すか、またはデータポーリングにより、プログラム動作のステータスを確定できます。これらのステータスビットについては、[ステータスレジスタ](#)を参照してください。詳細については[データポーリングステータス](#)を参照してください。

プログラム一時停止中に有効なアクセスとコマンドは以下のとおりです。

- 消去一時停止していないセクタからの読み出し

- プログラム一時停止していないラインからの読み出し

- ステータス読み出しコマンド

- ステータスレジスタのクリア

- ASO 終了またはコマンドセット終了

- プログラム再開コマンド

システムはプログラム一時停止モードを終了するためにプログラム再開コマンドを書き込んで、プログラミング動作を継続する必要があります。続けてプログラム再開コマンドを書き込んでも無視されます。デバイスがプログラミング動作を再開した後は、プログラム一時停止コマンドを再度書き込みます。

プログラム動作は、必要に応じて何度も中断できますが、プログラム動作を進捗させ完了させるためには、再開コマンドと次の一時停止コマンドの間は組込みアルゴリズムコントローラー (EAC) に示す  $t_{PRS}$  以上の時間を要します。

プログラム一時停止と再開は、ASO に入っている間はサポートされません。

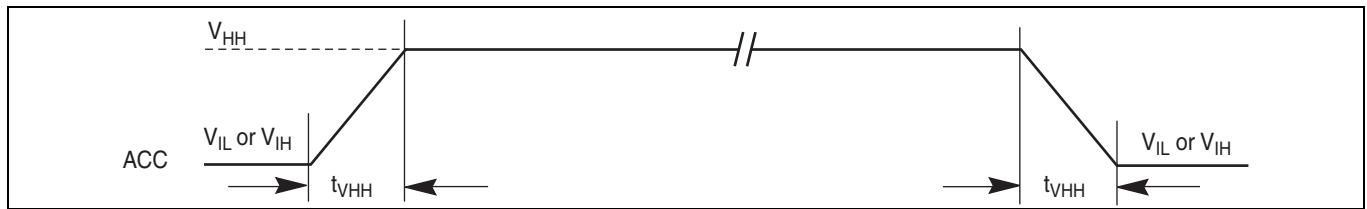

### 5.4.3 アクセラレーションプログラミング

デバイスは、システムが WP#/ACC または ACC のピン上で  $V_{HH}$  をアサートした時に、プログラム動作をサポートします。WP#/ACC や ACC のピンが  $V_{IH}$  または  $V_{IL}$  に戻ると、デバイスはアクセラレーションプログラミングモードを終了し通常のモードに戻ります。WP#/ACC は  $V_{HH}$  に耐えられますが、プログラム機能を高めるようには設計されていません。システムがこの入力に  $V_{HH}$  をアサートすると、デバイスは自動的にアンロックバイパスモードに入ります。その後、システムはロック解除のバイパスモードによって提供された書き込みバッファロードコマンドシーケンスを使用できます。アンロックバイパスモード中にバッファ書き込み中止リセットが必要な場合、デバイスをリセットするためには完全な 3 サイクルのリセットコマンドシーケンスを使用しなければならないことに注意してください。組込みプログラム動作の完了後に ACC 入力上の  $V_{HH}$  を切断すると、デバイスは通常の動作に戻ります。アクセラレーションプログラミング以外の動作を行う場合、WP#/ACC ピンを  $V_{HH}$  にセットしないでください。そうでないと、デバイスに損傷を与える可能性があります。WP# は内部プルアップを持っており、何も接続しないと  $V_{IH}$  となります。アクセラレーションプログラミングは室温でのみ実行できます。

- WP#/ACC を  $V_{HH}$  に上昇させる前に、セクタをロック解除する必要があります。

- 電源投入シーケンスの完了後に、WP#/ACC が  $V_{HH}$  を印加することを推奨します。また、 $V_{CC}/V_{IO}$  の電源低下の前に、WP#/ACC の印加を  $V_{HH}$  から  $V_{IH}/V_{IL}$  にすることを推奨します。

組込み動作

#### 5.4.4 アンロックバイパス

このデバイスは、プログラミングコマンドを短縮化するために、アンロックバイパスモードを備えています。デバイスがアンロックバイパスモードになると、データプログラミングのために、通常の4サイクルの代わりに2つの書き込みサイクルだけが必要です。デバイスはまた、バッファ書き込みコマンドもサポートし、4+の書き込みサイクルのみを要します。

このモードでは、通常のプログラムコマンドシーケンスで必要な最初の2つのアンロックサイクルが不要になるため、トータルのプログラミング時間が短縮されます。[コマンドのまとめ](#)にこのアンロックバイパスコマンドシーケンスの要件を示します。

アンロックバイパスモード中では、読み出し、プログラム、書き込みバッファプログラミング、バッファ書き込み中止リセット、ステータスレジスタ読み出し、ステータスレジスタクリア、ソフトリセット、アンロックバイパスセクタ消去、アンロックバイパスチップ消去、アンロック消去一時停止/再開、アンロックバイパス一時停止/再開、およびアンロックバイパスリセットコマンドのみが有効です。アンロックバイパスモードを終了するには、2サイクルのアンロックバイパスリセットコマンドシーケンスを実行します。最初のサイクルアドレスは「ドントケア」で、データは90hです。2番目のサイクルにはデータ00hだけが必要です。その後、セクタは読み出しモードに戻ります。

#### ソフトウェア関数およびサンプルコード

以下はアンロックバイパスへのエントリ、プログラムおよび終了関数を使用したCソースコードの例です。インフィニオンフラッシュメモリソフトウェア開発ガイドラインは、[Infineon Low Level Driver User's Guide](#)を参照してください。

**Table 11 アンロックバイパスエントリ (LLD 関数 = lld\_UnlockBypassEntryCmd)**

| サイクル | 説明       | 動作   | バイトアドレス    | ワードアドレス    | データ   |

|------|----------|------|------------|------------|-------|

| 1    | アンロック    | 書き込み | ベース + AAAh | ベース + 555h | 00AAh |

| 2    | アンロック    | 書き込み | ベース + 555h | ベース + 2AAh | 0055h |

| 3    | エントリコマンド | 書き込み | ベース + AAAh | ベース + 555h | 0020h |

```

/* Example: Unlock Bypass Entry Command */

*( (UINT16 *)base_addr + 0x555 ) = 0x00AA; /* write unlock cycle 1 */

*( (UINT16 *)base_addr + 0x2AA ) = 0x0055; /* write unlock cycle 2 */

*( (UINT16 *)base_addr + 0x555 ) = 0x0020; /* write unlock bypass command */

/* At this point, programming only takes two write cycles. */

/* Once you enter Unlock Bypass Mode, do a series of like */

/* operations (programming or sector erase) and then exit */

/* Unlock Bypass Mode before beginning a different type of */

/* operations. */

```

**Table 12 アンロックバイパスプログラム (LLD 関数 = lld\_UnlockBypassProgramCmd)**

| サイクル | 説明          | 動作   | バイトアドレス    | ワードアドレス    | データ      |

|------|-------------|------|------------|------------|----------|

| 1    | プログラムセットアップ | 書き込み | ベース + XXXh | ベース + XXXh | 00A0h    |

| 2    | プログラムコマンド   | 書き込み | プログラムアドレス  | プログラムアドレス  | プログラムデータ |

```

/* Example: Unlock Bypass Program Command */

/* Do while in Unlock Bypass Entry Mode! */

*( (UINT16 *)base_addr ) = 0x00A0; /* write program setup command */

*( (UINT16 *)pa ) = data; /* write data to be programmed */

/* Poll until done or error. */

/* If done and more to program, */

/* do above two cycles again. */

```

**Table 13 アンロックバイパスリセット (LLD 関数 = lld\_UnlockBypassResetCmd)**

| サイクル | 説明        | 動作   | バイトアドレス    | ワードアドレス    | データ   |

|------|-----------|------|------------|------------|-------|

| 1    | リセットサイクル1 | 書き込み | ベース + XXXh | ベース + XXXh | 0090h |

| 2    | リセットサイクル2 | 書き込み | プログラムアドレス  | プログラムアドレス  | 0000h |

```

/* Example: Unlock Bypass Exit Command */

*( (UINT16 *)base_addr ) = 0x0090;

*( (UINT16 *)base_addr ) = 0x0000;

```

### 5.4.5 消去ステータス評価 (EES)

EES コマンドは、アドレス指定されたセクタの最後の消去動作が正常に完了した（すなわち「信頼できる」）かを確認します。EES コマンドは、電力喪失、リセット、または消去動作中の電力喪失、リセット、または不良による消去動作不良を検出するために使用されます。

任意のセクタで EES を開始するには、EAC がスタンバイ状態になっている時に、そのセクタのアドレス 555h に 35h を書き込みます。

デバイスがプログラミング中、消去中、または一時停止中は、EES コマンドが書き込まれない場合があります。

EES コマンドは、動作の間、対象アレイの読み出しを許可しません。

ステータスレジスタまたはポーリング方法 (DQ6 トグルのみ) を使用して、デバイスがビジーか完了済みかを確定します。完了済みの場合、ステータスレジスタ読み出しを使い、セクタが信頼できるかを確認します。該当するセクタが信頼できると、ステータスレジスタのビット 5 (SR[5]) が '0' にクリアされます。該当するセクタが信頼できない場合、SR[5] は '1' にセットされ、RD/BY# は LOW のままに維持されます。デバイスをスタンバイ状態に戻すためには、ソフトウェアリセット /ASO 終了コマンドか、またはステータスレジスタクリアコマンドが必要です。

EES が完了すると、EAC はスタンバイ状態に戻ります。

SR での消去状態を完了し更新するために、EES コマンドは  $t_{EES}$  を要します。EES コマンドの完了時点を決定するためには、DRB ビット (SR[7]) を読み出すことができます。あるセクタが (SR[5]=1) で消去されないことが見いだされると、そのセクタ内のデータ記憶の信頼性を確保するために、セクタを再び消去しなければいけません。

組込み動作

## 5.4.6 ブランク チェック

ブランク チェック コマンドにより、選択したメイン フラッシュ アレイ セクタが現在消去されている（すなわち「信頼でき」かつ「ブランク」である）かどうかを確認できます。ブランク チェック 中は、ブランク チェック コマンドにより、対象アレイの読み出しが許可されません。このコマンドの実行中に対象アレイを読み出すと、ポーリング データが返されます。

任意のセクタでブランク チェック を開始するには、EAC がスタンバイ 状態にになっている時に、そのセクタのアドレス 555h に 33h を書き込みます。

デバイスがプログラミング中、消去中、または一時停止中は、ブランク チェック コマンドが書き込まれない場合があります。

ステータス レジスタ または ポーリング 方法（組込み 消去動作に相当）を使用して、デバイスがビジーか完了済みかを決定します。

完了済みの場合、ステータス レジスタ と ポーリング 方法によって、該当するセクタがブランク（消去動作が正常に終了したこと）か、またはそのセクタが消去されていないことを示します。セクタが空白の場合、ステータス レジスタ の ビット 5 (SR[5]) は '0' にクリアされます。セクタが空白でない場合、SR[5] は '1' にセットされ、RD/BY# は LOW のままに維持されます。デバイスをスタンバイ 状態に戻すためには、ソフトウェアリセット /ASO 終了コマンドか、またはステータス レジスタ クリア コマンドを必要とします。

消去されなかったビットを発見すると、デバイスは直ちに動作を停止して、結果を報告します。

ブランク チェック が完了すると、EAC はスタンバイ 状態に戻ります。

## 5.4.7 消去方式

### 5.4.7.1 チップ 消去

チップ 消去機能は、メインの フラッシュ メモリ アレイ 全体を消去します。消去の前にデバイスをプリ プログラムする必要はありません。電気的な消去を行う前に、組込み 消去アルゴリズム は メモリ 全体を オール 0 データ パターン に 自動的に プログラミング して 検証 します。チップ 消去 が 正常に 完了 すると、デバイス内のすべての 領域 が FFFFh を 含みます。これらの動作中に、システムは 更なる 制御 や タイミング を 提供する 必要 は ありません。チップ 消去 コマンド シーケンス を 開始 するためには、最初に 2 つの アンロック サイクル を 書き込んで、次に セットアップ コマンド を 書き込みます。さらに、追加の 2 つの アンロック 書き込み サイクル の 後に チップ 消去 コマンド を 書き込み、順番に 組込み 消去アルゴリズム を 実行 します。6 番目の サイクル の 最後で WE# が HIGH になると、RY/BY# は LOW になります。

組込み 消去アルゴリズム が 完了 すると、EAC はスタンバイ 状態に戻ります。組込み 消去動作 の 実行 中 は、デバイスからのデータの読み出しが許可されないことに 注意 してください。システムは、RY/BY# や ステータス レジスタ を 読み出すか、または データ ポーリング を 使用して、消去動作のステータスを 確定 できます。RY/BY# について は、[レディ / ビジー # \(RY/BY#\)](#) を 参照 してください。これらのステータス ビット について は、[ステータス レジスタ](#) を 参照 してください。 詳細 について は [データ ポーリング ステータス](#) を 参照 してください。

チップ 消去動作 が 開始 すると、ステータ読み出し、ハードウェアリセット、またはパワーサイクル のみ が 有効 です。他のコマンド は すべて 無視 されます。ただし、ハードウェアリセット または パワーサイクル を 実行 すると、消去動作 が 直ちに 終了 し、t<sub>RPH</sub> 時間 後 に 読み出し モード に 戻る ます。チップ 消去動作 が 終了 した 場合 は、データの完全性を 確保 する ため に、デバイス が アイドル 状態 に 戻った 則、チップ 消去 コマンド シーケンス を 再 実行 する 必要 が あります。

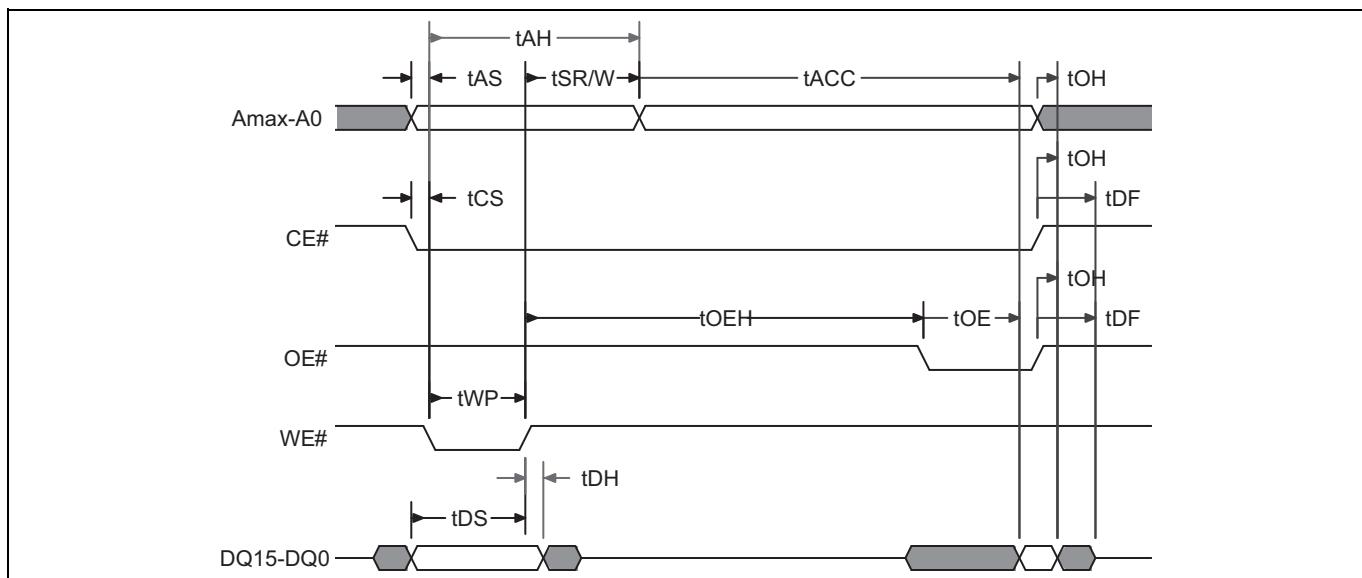

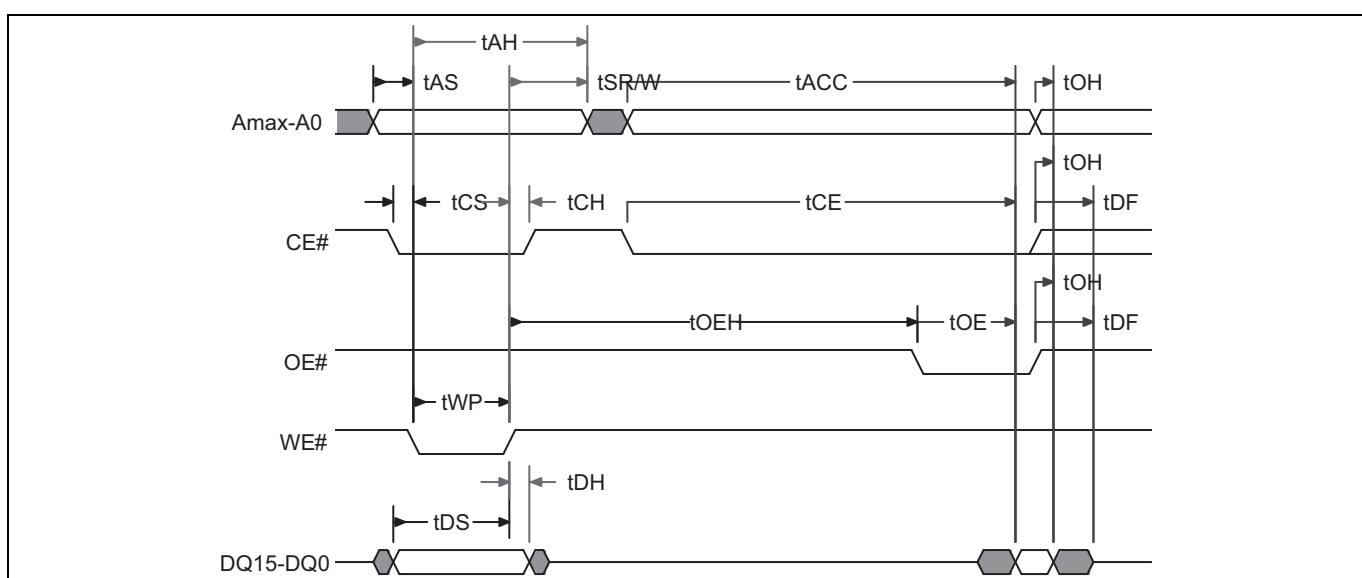

パラメーターとタイミング図について は、[Table 18, 非同期書き込み動作](#)、および [代替 CE# により制御される書き込み動作](#) を 参照 してください。

ASP DYB および PPB ビット によって 保護された セクタ は 消去 されません。[高度セクタ保護 \(ASP\)](#) を 参照 してください。セクタ が チップ 消去 で 保護 さ れて いる 場合 は、チップ 消去 は、保護された セクタ を スキップ し、次の セクタ の 消去 を 続行 します。保護された セクタ での 失敗 し た 消去 によつて は、ステータス レジスタ の 消去ステータス ビット と セクタ ロック ビット は '1' に セット されません。

組込み動作

### 5.4.7.2 セクタ消去

セクタ消去機能は、メモリアレイ内の 1 つのセクタを消去します。デバイスは消去の前にプリプログラムするシステムを必要としません。電気的な消去を行う前に、組込み消去アルゴリズムはセクタ全体をすべてオール 0 パターンに対して自動的にプログラミングして検証します。セクタ消去が正常に完了すると、消去されたセクタ内のすべての領域が FFFFh を含みます。これらの動作中に、システムは更なる制御やタイミングを提供する必要はありません。セクタ消去コマンドシーケンスを開始するためには、最初に 2 つのアンロックサイクルを書き込んで、次にセットアップコマンドを書き込みます。さらに、追加の 2 つのアンロック書き込みサイクルの後に消去されるセクタのアドレスとセクタ消去コマンドが続きます。6 番目のサイクルの最後で WE# が HIGH になると、RY/BY# は LOW になります。

コマンドシーケンスを書き込むと、 $t_{SEA}$  のセクタ消去タイムアウトが発生します。このタイムアウト期間中には、別のセクタアドレスとセクタ消去コマンドを書き込みます。タイムアウト期間中は無効なコマンドは無視されます。セクタ消去バッファはどの順番でもロードでき、セクタの数は 1 セクタから全セクタまでです。これらの追加サイクルの間の時間は  $t_{SEA}$  未満でなければいけません。そうしないと、消去動作が開始されます。タイムアウト時間を過ぎた後のセクタ消去アドレスおよびコマンドは、受け入れられる場合もあり、そうでない場合もあります。この間はプロセッサの割込みを禁止して、すべてのコマンドを受け入れできるようになります。最後のセクタ消去コマンドを書き込んだ後、割込みを有効にできます。消去動作中は、セキュアシリコンセクタ、自動選択および CFII 機能は使用できないことに留意ください。この場合、システムはコマンドシーケンスと追加のアドレス、コマンドを再度書き込まなければいけません。

システムは、RY/BY#、ステータスレジスタを読み出すか、またはデータポーリングを使用して、消去動作のステータスを確定できます。RY/BY# については、[レディ / ビジー # \(RY/BY#\)](#) を参照してください。これらのステータスピットについては、[ステータスレジスタ](#) を参照してください。詳細については[データポーリングステータス](#) を参照してください。

セクタ消去動作が開始すると、ステータスレジスタ読み出しコマンドと消去一時停止コマンドが有効となります。他のコマンドはすべて無視されます。ただし、ハードウェアリセットを実行すると、直ちに消去動作が終了し、 $t_{RPH}$  時間後に読み出しモードに戻ることに留意ください。セクタ消去動作が終了した場合は、データの完全性を確保するためにデバイスの動作がリセットされたら、セクタ消去コマンドシーケンスを再実行する必要があります。

ASP DYB および PPB ビット、またはパスワード保護によって保護されたセクタは消去されません。[高度セクタ保護 \(ASP\)](#) を参照してください。マルチセクタ消去の間セクタが保護される場合は、セクタ消去は保護されたセクタをスキップし、次のセクタの消去を続行します。保護されたセクタでの失敗した消去により、ステータスレジスタの消去ステータスピットとセクタロックビットは '1' にセットされません。パラメーターとタイミング図については、[組込みアルゴリズムコントローラ \(EAC\)](#) を参照してください。ASP DYB および PPB ビットによって保護されたセクタは消去されません。[高度セクタ保護 \(ASP\)](#) を参照してください。

組込み動作

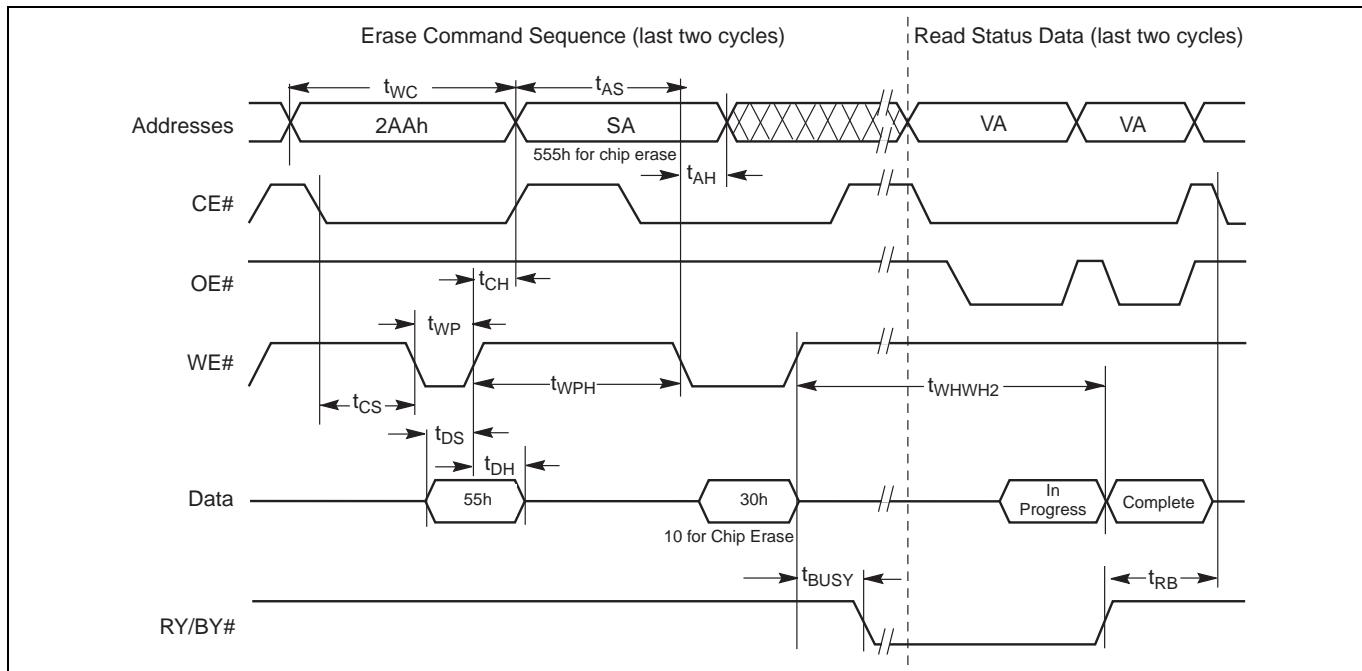

Figure 6 セクタ消去動作 [8]

注:

8. x8 バスサイクルに対してはコマンドのまとめを参照してください。

組込み動作

#### 5.4.8 消去一時停止 / 消去再開

消去一時停止コマンドを実行すると、システムはセクタ消去動作を中断して、メインフラッシュアレイからデータを読み出すか、メインフラッシュアレイに対してプログラミングできるようになります。このコマンドはセクタ消去またはセクタプログラムの動作中にのみ有効です。チップ消去動作中に書き込んでも、消去一時停止コマンドは無視されます。

セクタ消去中に消去一時停止コマンドが書き込まれると、デバイスは消去動作を中止してステータスビットを更新するために最大  $t_{ESL}$  (消去一時停止レイテンシ) を要します。

消去動作が中止した後、製品は消去一時停止モードに入ります。このとき、システムは、メインフラッシュアレイからデータを読み出すか、データをプログラミングできるようになります。消去一時停止対象セクタ内のいずれかのアドレスから読み出すと、不確定なデータを生じます。システムは、ステータスレジスタを読み出すか、またはデータポーリングにより、セクタが消去中か消去一時停止中かを確定できます。これらのステータスビットについては、[ステータスレジスタ](#)を参照してください。詳細については[データポーリングステータス](#)を参照してください。

消去一時停止のプログラム動作が完了すると、EAC は消去一時停止状態に戻ります。通常のプログラム動作と同じように、システムはステータスレジスタを読み出することで、プログラム動作の状態を確認できます。

消去一時停止中にプログラム不良が発生した場合は、ステータスレジスタクリアまたはソフトウェアリセットコマンドが、デバイスを消去一時停止状態に復帰させます。そのメモリアレイに再度プログラムする場合は、その前に消去を再開し完了させる必要があります。

以下は消去一時停止中に有効なアクセスとコマンドです。

- 一時停止状態でないセクタからの読み出し

- 一時停止状態でないセクタへのプログラム

- ステータスレジスタ読み出し

- ステータスレジスタクリア

- 消去再開コマンド

セクタ消去動作を再開させるには、消去再開コマンドを書き込む必要があります。デバイスは消去動作に戻り、ステータスビットが更新されます。また、この後に再開コマンドの書き込みも無視されます。チップが消去動作を再開した後に、消去一時停止コマンドを再度書き込みます。

ASOに入っている間は、消去一時停止と消去再開はサポートされません。

組込み動作

## 5.4.9 ASO エントリおよび ASO 終了

### 5.4.9.1 ID-CFI ASO

システムは読み出しモード中に ID-CFI エントリ コマンド シーケンスを実行することで、ID-CFI ASO にアクセスできます。詳細については [Table 25](#) を参照してください。

ID-CFI ASO では以下の動作が行えます。

- エントリ コマンドで使用した同じ SA を使用した ID-CFI ASO の読み出し

- セクタ アドレス (SA) + 2h でのセクタ保護状態の読み出し。位置 2h は、アドレス指定したセクタにおけるセクタ保護の現在の状態を揮発性情報で提供します。位置 2h にあるワードのビット 0 には、アドレス指定したセクタに関する PPB および DYC ビットの論理 NAND が示されます。このように、セクタが PPB=0 または DYC=0 ビットによって保護設定されていると、表示される状態が保護設定となります (1=セクタ保護、0=セクタ保護解除)。

- ASO 終了

以下は CFI エントリおよび終了関数を使用した C ソースコードの例です。インフィニオン フラッシュメモリ用ソフトウェア開発のガイドラインは、[Infineon Low Level Driver User's Guide](#) を参照してください。

```

/* Example: CFI Entry command */

*( (UINT16 *)base_addr + 0x55 ) = 0x0098; /* write CFI entry command */

/* Example: CFI Exit command */

*( (UINT16 *)base_addr + 0x000 ) = 0x00F0; /* write cfi exit command */

```

### 5.4.9.2 ステータス レジスタ ASO

ステータス レジスタ ASO は、組込みアルゴリズム (EA) のレジスタ化された揮発性状態を示す单一のワードを含みます。ステータス レジスタ読み出しコマンドが発行されると、現時点のステータスが (WE# の立ち上りエッジで) レジスタに取り込まれ、ASO が有効になります。ステータス レジスタの内容はすべてのワード位置に割り付けられます。最初の読み出しアクセスにより、ステータス レジスタ ASO 状態が (CE# または OE# の立ち上りエッジで) 終了し、ステータス レジスタ読み出しコマンドの発行時に使用されていたアドレス空間のマップに戻ります。なお、書き込みコマンドではステータス レジスタ ASO 状態は終了しません。

### 5.4.9.3 セキュアシリコン領域 ASO

システムは、読み出しモード中にセキュアシリコン領域エントリ コマンド シーケンスを実行することで、セキュアシリコン領域にアクセスできます。このエントリ コマンドはコマンド内のセクタ アドレス (SA) を使用し、どのセクタがオーバレイされるかを確認します。

セキュアシリコン領域 ASO では次の動作が行えます。

- セキュアシリコン領域の読み出し

- ワードまたは書き込みバッファプログラミング コマンドを使用して、カスタマー セキュアシリコン領域のプログラムが可能になります。アンロックバイパスコマンドおよび ACC の使用は許可されません。

- ASO 終了 (ソフトウェア下位互換性のために、レガシーのセキュアシリコン終了コマンドを使用)

- ASO 終了 (すべての ASO に共通の終了コマンドを使用。一貫した終了方式の代替)

- SSR の領域 3 読み出しパスワードモードを使用する際の推奨手順は次のとおりです。

- SSR の領域 3 に所望のデータをプログラミング

- ロック レジスタのビット 10 を '0' にクリア (更なるプログラミング動作を無効にする)

- SSR の領域 3 のパスワードをプログラミング

- ロック レジスタのビット 11 を '0' にクリア。これは、SSR 領域 3 の読み出しが可能になる前にパスワードを適用する必要があるため、SSR の領域 3 のパスワード機能が有効にする。

組込み動作

#### **5.4.9.4 ロックレジスタ ASO**

システムは、読み出しモード中にロックレジスタエントリコマンドシーケンスを実行することで、ロックレジスタにアクセスできます。このエントリコマンドは、エントリコマンドからのセクタアドレスを使用しません。デバイスアドレス空間のワード位置0にロックレジスタが割り付けられます。デバイスアドレス空間の他のすべての位置は未定義となります。

ロックレジスタASOでは以下の動作が行えます。

- デバイスのアドレス位置0を使用した、ロックレジスタの読み出し

- 修正されたワードプログラミングコマンドを使用した、カスタマーロックレジスタのプログラム

- ASO終了(ソフトウェア下位互換性のために、レガシーのコマンドセット終了コマンドを使用)

- ASO終了(すべてのASOに共通の終了コマンドを使用。一貫した終了方式の代替)

#### **5.4.9.5 ECCステータス ASO**

システムは、読み出しモード中にECCステータスエントリコマンドシーケンスを実行することで、ECCステータスASOにアクセスできます。ECCステータスASOは、特定のページのECC機能の有効または無効ステータス、または選択されたページでECCロジックが1ビットエラーを訂正したかの情報を提供します。

ECCステータスASOでは以下の動作が行えます。

- 選択したページのECCステータスの読み出し

#### **5.4.9.6 パスワード ASO**

システムは、読み出しモード中にパスワードエントリコマンドシーケンスを実行することで、パスワードASOにアクセスできます。このエントリコマンドは、エントリコマンドからのセクタアドレスを使用しません。パスワードは、デバイスアドレス空間のワード位置0～3に割り付けられます。デバイスアドレス空間の他のすべての位置は未定義となります。

パスワードASOでは以下の動作が行えます。

- (ロックされていない場合に)デバイスのアドレス位置0～3を使用したパスワード読み出し

- 修正されたワードプログラミングコマンドを使用した、パスワードのプログラム

- パスワードアンロックコマンドを使用したPPBロックビットのロック解除

- ASO終了(ソフトウェア下位互換性のために、レガシーのコマンドセット終了コマンドを使用)

- ASO終了(すべてのASOに共通の終了コマンドを使用。一貫した終了方式の代替)

#### **5.4.9.7 PPB ASO**

システムは、読み出しモード中にPPBエントリコマンドシーケンスを実行することで、PPBASOにアクセスできます。このエントリコマンドは、エントリコマンドからのセクタアドレスを使用しません。セクタのPPBビットはそのセクタ内のすべてのワード位置のビット0に割り付けられます。

PPBASOでは以下の動作が可能です。

- セクタ内の任意のワードのビット0にある、セクタのPPB保護ステータスの読み出し

- 修正されたワードプログラミングコマンドを使用した、PPBビットのプログラム

- PPB消去コマンドを使用したすべてのPPBビットの消去

- ASO終了(ソフトウェア下位互換性のために、レガシーのコマンドセット終了コマンドを使用)

- ASO終了(すべてのASOに共通の終了コマンドを使用。一貫した終了方式の代替)

組込み動作

#### 5.4.9.8 PPB ロック ASO

システムは、読み出しモード中に PPB ロックエントリコマンドシーケンスを実行することで、PPB ロック ASO にアクセスできます。このエントリコマンドは、エントリコマンドからのセクタアドレスを使用しません。グローバル PPB ロックビットはデバイスのすべてのワード位置のビット 0 に割り付けられます。

PPB ロック ASO では以下の動作が可能です。

- デバイスアドレス空間の任意のワードのビット 0 にある、PPB ロック保護ステータスの読み出し

- 修正されたワードプログラミングコマンドを使用した、PPB ロックビットの設定

- ASO 終了(ソフトウェア下位互換性のために、レガシーのコマンドセット終了コマンドを使用)

- ASO 終了(すべての ASO に共通の終了コマンドを使用。一貫した終了方式の代替)

#### 5.4.9.9 DYB ASO

システムは、読み出しモード中に DYB エントリコマンドシーケンスを実行することで、DYB ASO にアクセスできます。このエントリコマンドは、エントリコマンドからのセクタアドレスを使用しません。セクタの DYB ビットが、そのセクタ内のすべてのワード位置のビット 0 に割り付けられます。

DYB ASO では次の動作が行えます。

- セクタ内の任意のワードのビット 0 にあるセクタの DYB 保護ステータスの読み出し

- 修正されたワードプログラミングコマンドを使用した、DYB ビットの設定

- 修正されたワードプログラミングコマンドを使用した、DYB ビットのクリア

- ASO 終了(ソフトウェア下位互換性のために、レガシーのコマンドセット終了コマンドを使用)

- ASO 終了(すべての ASO に共通の終了コマンドを使用。一貫した終了方式の代替)

#### 5.4.9.10 ソフトウェア(コマンド)リセット / ASO 終了

ソフトウェアリセットはコマンドセット([Table 23](#) を参照してください)の一部で、EAC をスタンバイ状態に復帰させる働きもします。必ず、以下の条件の場合に使用してください。

- ASO モードを終了

- タイムアウト発生時に、データポーリング用のタイムアウトビット(DQ5)をクリア

ソフトウェアリセットを実行しても EA モードへの影響はありません。プログラミングまたは消去が開始された後は、その動作が完了するまでリセットコマンドは無視されます。ソフトウェアリセットを実行しても出力への影響はありません。ソフトウェアリセットの第一の役割は、ASO モードから、または失敗したプログラム動作や消去動作から、読み出しモードに復帰されることです。

ソフトウェアリセットを実行すると、無効なコマンドシーケンスに由来する未定義状態から読み出しモードに戻ることがあります。一部の未定義状態から通常動作に復帰させるには、ハードウェアリセットが必要になる場合があります。

ソフトウェアリセットのレイテンシの要件はありません。リセットコマンドは、 $t_{WPH}$  の間に実行されます。

組込み動作

### 5.4.9.11 連続性チェック機能

連続性チェックは、パッケージのコネクタから個々のダイパッドおよびDDPでの個々のダイへの接続に関する基本的なテストを提供します。この機能は、いくつかのコマンドの最初に用いられるレガシーのアンロックサイクルシーケンスの拡張です。アンロックシーケンスとは、アドレスとデータラインの下位部分に1と0のパターンを交互に、1回目と2回目は反転したパターンを書き込むような、2回の書き込みのことです。連続性チェックを実行するためには、これらのパターンはすべてのアドレス(Amax ~ '0')とデータライン(DQ15 ~ '0')をカバーするように拡張されます。論理比較回路は、2つの書き込みサイクルで反転された1と0の交互パターンを検出します。

DDPの場合、A26入力は書き込み対象のダイを選択するために使用されます。正しいパターンが検出されると、ステータスレジスタのビット0が'1'にセットされます。ステータスレジスタクリアのコマンドは、ステータスレジスタのビット0を'0'にクリアします。

下表に、x16の單一ダイ(例:GL01GT)の連続性チェックのシーケンスを示します。

**Table 14 単一ダイの連続性チェックシーケンス**

| 段階              | アクセスタイプ | アドレスA26 | アドレスA25 ~ A0 | データ  | 備考                                                        |

|-----------------|---------|---------|--------------|------|-----------------------------------------------------------|

| セットアップ          | 書き込み    | 該当なし    | XXXX555      | XX71 | ダイゼロステータスをクリア                                             |

|                 | 書き込み    | 該当なし    | 555          | XX70 | ダイゼロにステータスレジスタ読み出しコマンドを書き込む                               |

|                 | 読み出し    | 該当なし    | x            | RD   | ステータスビットゼロ=0であることを確認するためにダイゼロからステータスを読み出す                 |

| 連続性パターン         | 書き込み    | 該当なし    | 2AAAA55      | FF00 | 1番目の連続性サイクル                                               |

|                 | 書き込み    | 該当なし    | 15555AA      | 00FF | 2番目の連続性サイクル                                               |

| 検出された連続性パターンを検証 | 書き込み    | 該当なし    | 555          | XX70 | ダイゼロにステータスレジスタ読み出しコマンドを書き込む                               |

|                 | 読み出し    | 該当なし    | x            | RD   | 検出された連続性パターンに対するステータスビットゼロ=1であることを確認するためにダイゼロからステータスを読み出す |

下表に、x8の單一ダイ(例:GL01GT)の連続性チェックのシーケンスを示します。

**Table 15 単一ダイの連続性チェックシーケンス**

| 段階              | アクセスタイプ | アドレスA26 | アドレスA25 ~ A0 | データ | 備考                                                        |

|-----------------|---------|---------|--------------|-----|-----------------------------------------------------------|

| セットアップ          | 書き込み    | 該当なし    | XXXX555      | 71  | ダイゼロステータスをクリア                                             |

|                 | 書き込み    | 該当なし    | AAA          | 70  | ダイゼロにステータスレジスタ読み出しコマンドを書き込む                               |

|                 | 読み出し    | 該当なし    | x            | RD  | ステータスビットゼロ=0であることを確認するためにダイゼロからステータスを読み出す                 |

| 連続性パターン         | 書き込み    | 該当なし    | 55554AB      | FF  | 1番目の連続性サイクル                                               |

|                 | 書き込み    | 該当なし    | 2AAAB54      | 00  | 2番目の連続性サイクル                                               |

| 検出された連続性パターンを検証 | 書き込み    | 該当なし    | 555          | 70  | ダイゼロにステータスレジスタ読み出しコマンドを書き込む                               |

|                 | 読み出し    | 該当なし    | x            | RD  | 検出された連続性パターンに対するステータスビットゼロ=1であることを確認するためにダイゼロからステータスを読み出す |

組込み動作

## 5.5 ステータス監視

EA ステータスの監視には 3 方式があります。前世代の S29GL フラッシュファミリでは、データポーリングおよび Ready/Busy# (RY/BY#) 信号と呼ばれる方式を使用していました。これらの方程式は、S29GL-T ファミリでもサポートされています。1 つの追加された方程式は、ステータスレジスタを読み出すことです。

### 5.5.1 ステータスレジスタ

プログラムおよび消去動作のステータスは、単一 16 ビットのステータスレジスタによって提供されます。ステータスレジスタ読み出しコマンドが書き込まれた後に、ステータスレジスタ情報の読み出しアクセスが続きます。ステータスレジスタ読み出しコマンドが発行されると、現時点のステータスが (WE# の立ち上りエッジで) レジスタに取り込まれ、ASO が有効になります。ステータスレジスタの内容が、メモリアドレス空間のすべてでエイリアス (オーバーレイ) されます。ステータスレジスタ ASO での有効な読み出し (CE# と OE# が LOW) アクセスは ( $t_{CEPH}/t_{OEPEH}$  での CE# または OE# の立ち上りエッジで) ASO を終了し、ステータスレジスタ読み出しコマンドが発行された時に使用中のアドレス空間マップに戻ります。x8 モードでは、CE# と OE# を LOW に維持し、かつ A1 での遷移をすることで、ステータスレジスタへの 1 回のアクセスによりステータスレジスタ全体 (上位バイトと下位バイトの両方) を読み出せます。書き込み動作が無視され、デバイスはステータスレジスタ ASO に留まります。ステータスレジスタには、直前に完了した組込みアルゴリズム (EA) の結果 (成功または失敗) に関するビットが、次のように示されます。

- 消去ステータス (ビット 5)

- プログラムステータス (ビット 4)

- 書き込みバッファ中断 (ビット 3)

- セクタロック済みステータス (ビット 1)

- 検出された連続性チェックパターン (ビット 0)

また、処理中の EA の現時点の状態に関するビットが次のように示されます。

- デバイスビジー (ビット 7)

- 消去一時停止 (ビット 6)

- プログラム一時停止 (ビット 2)

現時点の状態に関するビットは、EA が現在処理中か、サスペンド (一時停止) 中か、完了かを示します。上位 8 ビット (ビット 15:8) は予約済みです。これらのビットは未定義の HIGH または LOW の値を持っており、この値は、あるステータス読み出しから別のステータス読み出しに変わり得ます。これらのビットは、ドントケアのビットとして扱うべきであり、どのようなソフトウェア読み込み状態によても無視されます。

ステータスレジスタビット 3=0 の場合、ソフトウェアリセットコマンドはステータスレジスタのビット [5, 4, 1, 0] を 0 にクリアします。現時点の状態ビットはそれに影響されません。

クリアステータスレジスタコマンドは、ステータスレジスタのビット [5, 4, 3, 1, 0] を 0 にクリアしますが、現時点の状態ビットには影響しません。

組込み動作

Table 16 ステータス レジスタ

| ビット番号                          | 15:8    | 7                         | 6                                          | 5                            | 4                                   | 3                                                       | 2                                     | 1                                     | 0                                                 |

|--------------------------------|---------|---------------------------|--------------------------------------------|------------------------------|-------------------------------------|---------------------------------------------------------|---------------------------------------|---------------------------------------|---------------------------------------------------|

| ビットの説明                         | 予約済み    | デバイス レディ ビット              | 消去一時停止 ステータス ビット <sup>[9]</sup>            | 消去ス テータス ビット <sup>[10]</sup> | プログラム ステータス ビット <sup>[11, 12]</sup> | 書き込み バッファ中 止ステータス ビット                                   | プログラ ム一時停 止ステー タスビッ 特 <sup>[13]</sup> | セクタ ロックス テータス ビット <sup>[14, 15]</sup> | 連続性 チェック                                          |

| ビット名                           | Note 18 | DRB                       | ESSB                                       | ESB                          | PSB                                 | WBASB                                                   | PSSB                                  | SLSB                                  | CC                                                |

| リセット ステータス <sup>[16, 17]</sup> | X       | 1                         | 0                                          | 0                            | 0                                   | 0                                                       | 0                                     | 0                                     | 0                                                 |

| ビギーステータス                       | 無効      | 0                         | 無効                                         | 無効                           | 無効                                  | 無効                                                      | 無効                                    | 無効                                    | 無効                                                |

| レディステータス                       | X       | 1 <sup>[19, 20, 21]</sup> | 0=一時停止中 消去無し <sup>[22]</sup><br>1=一時停止中 消去 | 0=消去が 成功<br>1=消去が 失敗         | 0=プログラ ムが成功<br>1=プログラ ムが失敗          | 0=プログ ラムの中止 無し<br>1=バッ ファへの書 き込みコマ ンドの実行 中にプログ ラムの中止 あり | 0=プログ ラム一時 停止無し<br>1=プログ ラムが一 時停止中    | 0=動作中 のセクタ ロック無 し<br>1=セクタ ロックに よるエラー | 0=連続性 チェックパ ターンが検 出されない<br>1=連続性 チェックパ ターンが検 出される |

## 注:

9. 消去一時停止中は、一時停止されたセクタやキュー内のセクタへのプログラミングは無視され、エラーは報告されません。

10. ESB は最新の消去操作の結果(正常または異常)を反映します。

11. PSB は最新のプログラム操作の結果(正常または異常)を反映します。

12. プログラム一時停止コマンド発行時、ユーザーは DRB が '1' になるまでステータスの読み出しを継続する必要があります。

13. プログラム再開コマンドを実行すると PSSB は '0' にクリアされます。

14. SLSB は、セクタがロックされているため、プログラムまたは消去動作が失敗したことを示します。

15. SLSB は最新のプログラム動作または消去動作の状態を反映します。

16. すべてのビットは、コールドリセットまたはウォームリセットによりリセットの状態になります。

17. ステータスレジスタクリアコマンドまたはリセットコマンドにより、ビット 5, 4, 3, 1 は '0' にクリアされます。

18. ビット 15~8 は将来の使用のために予約済みで、「0」または「1」の値を表示します。状態をチェックする時はこれらのビットを無視(マスク)する必要があります。

19. デバイスに実行中の組込みアルゴリズムがない場合、ビット 7 は '1' です。

20. ビット 6~1 は、ビット 7 が '1' の場合にのみ有効です。

21. プログラム一時停止コマンド発行時、ユーザーは DRB が '1' になるまでステータスの読み出しを継続する必要があります。

22. 消去再開コマンドにより ESSB は '0' にクリアされます。

組込み動作

## 5.5.2 データポーリングステータス

アクティブな組込みアルゴリズム中は、EAC はデータポーリング ASO に切り替わり、あらゆる読み出しアクセスに対して EA ステータスを表示します。1ワードのステータス情報がデバイスアドレス空間のすべてのロケーションでエイリアスされます。ステータスワードには、1つの EA のステータスを判定するためのビットが複数あります。これらは、ある EA が実行の間に、読み出しアクセス中にデータバス上に現れるため、DQ ビットと呼ばれます。DQ ビット 15 ~ 8, DQ4, および DQ0 は、予約済みであり、未定義データを提供します。ステータス監視ソフトウェアは予約済みのビットをマスクし、それらをドントケアとして取り扱う必要があります。X8 モードではデータポーリングの実行中に A1 が無視されます。[Table 17](#) および次の節では残りのビットの機能について説明します。

### 5.5.2.1 DQ7: Data# ポーリング

Data# ポーリングビット (DQ7) は、組込みアルゴリズムが実行中であるか、完了しているかを、ホストシステムに示します。Data# ポーリングは、プログラム / 消去コマンド シーケンスの最後の WE# パルスの立ち上がりエッジの後に有効になります。Data# ポーリングは、書き込みバッファプログラミング中に、書き込みバッファページでプログラムされている最後のワードに対してのみ有効です。書き込みバッファページにプログラムしようとする最後のワード以外のどのようなワードの Data# ポーリングステータスを読み出しても、誤ったステータス情報を返します。

組込みプログラムアルゴリズムが実行されている間、デバイスは、DQ7 にプログラムされたデータビットの補数を、DQ7 に出力します。この DQ7 の状態は、消去一時停止間のプログラミングにも当てはまります。組込みプログラムアルゴリズムが完了すると、デバイスはプログラムされたデータビットを、プログラムされた最後のワードのビット 7 に出力します。プログラム一時停止の場合は、アレイデータの読み出しのみが可能です。プログラムアドレスが保護されたセクタ内のアドレスである場合、DQ7 の Data# ポーリングは  $t_{DP}$  の間アクティブになり、その後デバイスはアレイデータ読み出しに戻ります。

組込み消去、消去ステータス評価、またはブランクチェックアルゴリズムを実行している間、Data# ポーリングは DQ7 に '0' を出力します。アルゴリズムが完了するか、デバイスが消去一時停止モードに入ると、Data# ポーリングは DQ7 に '1' を出力します。これは、組込みプログラムアルゴリズム用に説明した補数 / 真のデータ出力に類似しています：消去関数はセクタ内のすべてのビットを '1' に変更します。その前に、デバイスは補数または '0' を出力します。有効なステータス情報を DQ7 に読み出すために、システムは、消去の対象として選択されたセクタ内にあるアドレスを指定する必要があります。

消去コマンド シーケンスが書き込まれた後、消去のために選択されたセクタが保護されている場合、DQ7 の Data# ポーリングは  $t_{DP}$  の間アクティブとなり、その後、デバイスはアレイデータ読み出しに戻ります。

組込みプログラムまたは消去動作が完了する直前に、出力イネーブル (OE#) が LOW にアサートされている間は、DQ7 が DQ6 ~ DQ0 と非同期的に変化することがあります。つまり、デバイスが、ステータス情報の提供から、DQ7 の有効なデータに切り替える場合があります。システムが DQ7 出力をサンプリングするタイミングによっては、ステータス情報または有効なデータのいずれかを読み出すことになります。また、デバイスがプログラムまたは消去動作を完了し、かつ DQ7 に有効なデータが出力されている場合でも、DQ6 ~ DQ0 から出力されるデータが無効のままである場合があります。ただし、次の読み出しサイクル時には有効なデータが DQ7 ~ DQ0 に出力されます。

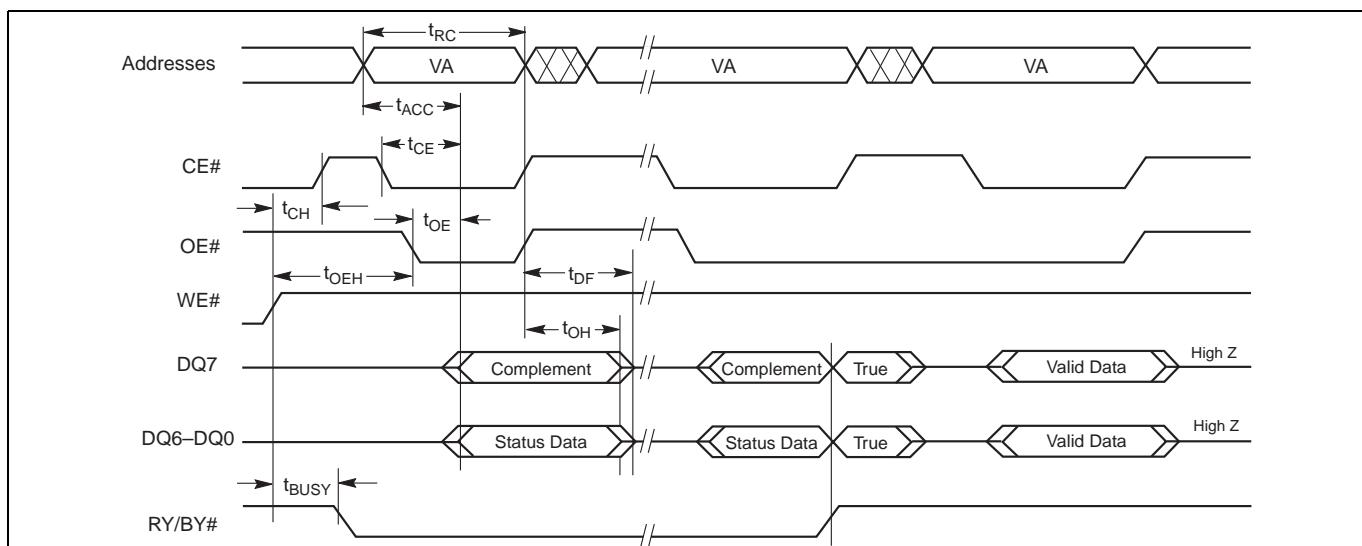

システムは、DQ7 が補数から真のデータに変更されていることを検出すると、その後の読み出しサイクルで DQ15 ~ DQ0 (x8 モードでは、Dq7 ~ DQ0) にある有効なデータを読み出せます。これは、出力イネーブル (OE#) が LOW にアサートされていると、DQ7 が DQ6 ~ DQ0 と非同期的に変化することがあるためです。このことを [Figure 29](#) に示します。[Figure 17](#) に、DQ7 の Data# ポーリングにより得られる出力を示します。また、[Figure 4](#) に書き込みバッファプログラミングに使用される Data# ポーリングアルゴリズムを示します。

有効な DQ7 データポーリングステータスは、以下から読み出せます。

- 書き込みバッファプログラミング動作用の書き込みバッファにロードされた最後のワードのアドレス

- 単一ワードプログラミング動作の位置

- 消去、消去ステータス評価、またはブランクチェック対象のセクタ内の位置

- または、チップ消去時の任意のセクタ内の位置

組込み動作

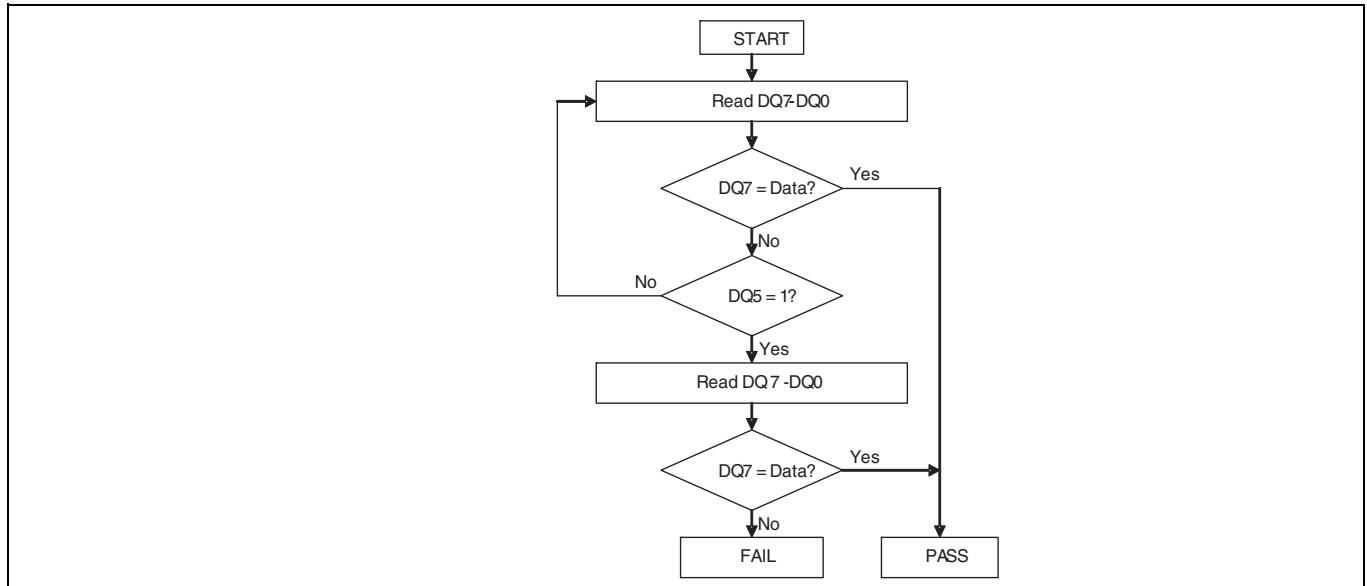

Figure 7 Data# ポーリング アルゴリズム [23]

注:

23.DQ7 が DQ5 と同時に変化する場合があるため、DQ5=1 の場合でも、DQ7 を再チェックする必要があります。

組込み動作

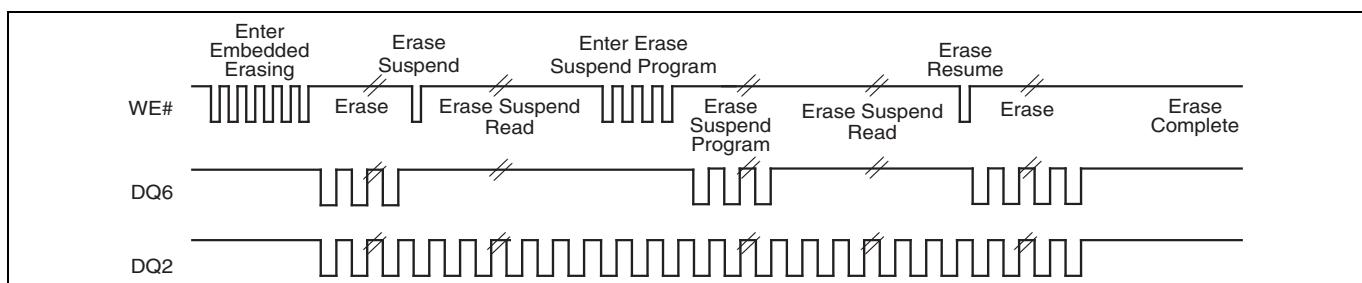

### 5.5.2.2 DQ6: トグルビット I

DQ6 に出力されるトグルビット I は、組込みプログラムまたは消去アルゴリズムが実行中であるか、完了しているか、あるいは、デバイスがプログラム一時停止または消去一時停止モードになっているかを示します。トグルビット I は任意のアドレスで読み出せて、コマンドシーケンスの最後の WE# パルスの立ち上がりエッジの後(プログラムまたは消去動作の前)に有効になります。

組込みプログラムまたは消去アルゴリズム動作の実行中、任意のアドレスへの次の読み出しサイクルで DQ6 がトグルします。(システムは、OE# または CE# のいずれかを使い、読み出しサイクルを制御できます。) 動作が完了すると、DQ6 がトグルを停止します。

消去コマンドシーケンスを書き込んだ後、消去の対象として選択したセクタが保護されている場合、DQ6 は  $t_{DP}$  の間トグルし、その後、EAC はスタンバイ(読み出しモード)に戻ります。選択したセクタが保護されていない場合、組込み消去アルゴリズムは保護されないセクタを消去します。

システムは、DQ6 と DQ2 を一緒に使い、セクタが消去動作中か、あるいは消去一時停止中かを調べられます。デバイスが消去実行中の場合(つまり、組込み消去アルゴリズムが実行中の場合)、DQ6 はトグルします。デバイスがプログラム一時停止モードまたは消去一時停止モードに入ると、DQ6 はトグルを停止します。ただし、どのセクタが消去動作中または消去一時停止中かを決めるために、システムは DQ2 を使用する必要があります。その替わりに DQ7 も使用できます([DQ7: Data# ポーリング](#)を参照してください)。

DQ6 は、消去一時停止プログラムモードの間もトグルし、組込みプログラムアルゴリズムが完了すればトグルを停止します。

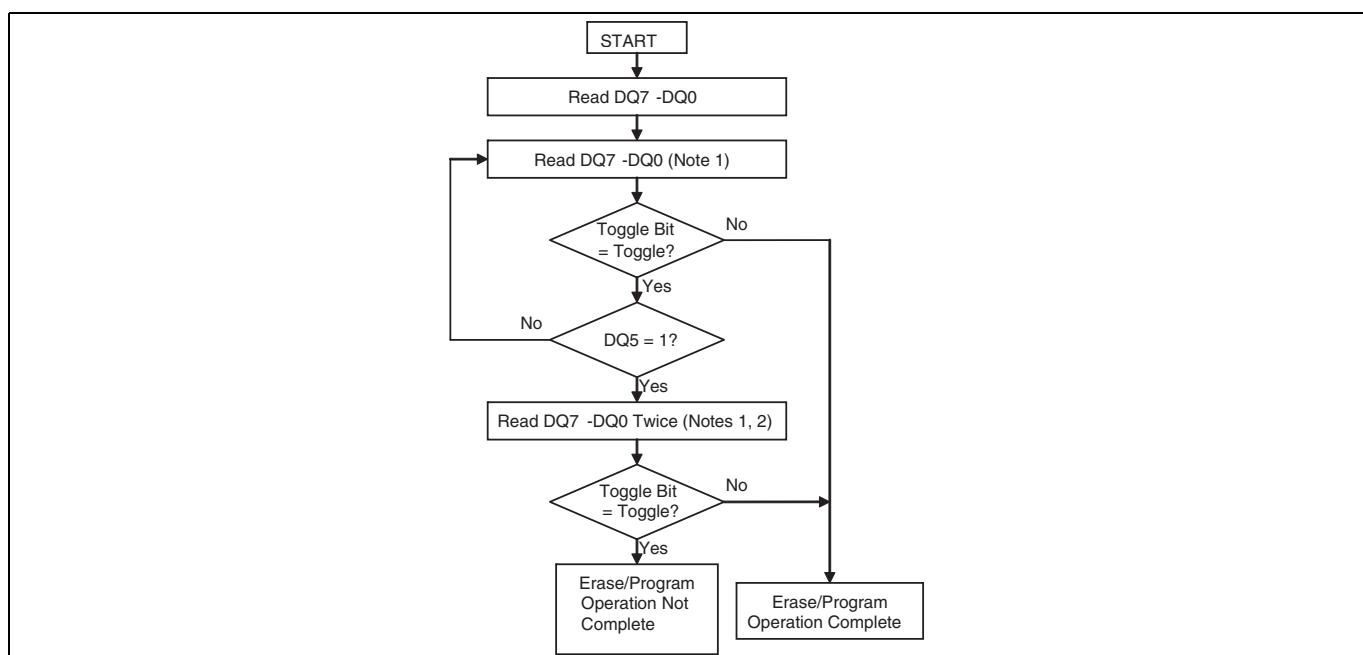

[Table 17](#) に、DQ6 のトグルビット I の出力を示します。[Figure 8](#) に、トグルビットのアルゴリズムをフローチャート形式で示します。[トグルビット DQ6/DQ2 の読み出し](#) ではアルゴリズムを説明します。また、[Figure 8](#) に、トグルビットタイミング図を示します。[DQ2: トグルビット II](#) も参照してください。

### 5.5.2.3 DQ3: セクタ消去タイマー

セクタ消去コマンドシーケンスを書き込んだ後、システムは DQ3 を読み出して、消去動作が開始したかを調べられます。詳細については、[セクタ消去](#) を参照してください。(セクタ消去タイマーは、チップ消去コマンドには適用されません。) 消去の対象として追加のセクタを選択する場合、セクタ消去コマンドの後で全タイムアウトも適用されます。タイムアウトの期間が経過した時に、DQ3 は '0' から '1' に切り替わります。システムからの追加のセクタ消去コマンドの書き込み間隔が必ず  $t_{SEA}$  未満になるならば、システムは DQ3 を監視する必要はありません。

セクタ消去コマンドを書き込んだ後、システムは DQ7 (Data# ポーリング)、または DQ6 (トグルビット I) の状態を読み出して、デバイスがコマンドシーケンスを受け取ったことを確認し、そして DQ3 を読み出す必要があります。DQ3 が '1' の場合は、組込み消去アルゴリズムが開始しています。消去操作が完了するまで、これ以降のコマンドは(消去一時停止コマンドを除き)無視されます。DQ3 が '0' の場合、デバイスは更なるセクタ消去コマンドを受け取ります。コマンドが受け取られたことを確認するため、それぞれの後続のセクタ消去コマンドの前後で、システムソフトウェアは DQ3 の状態をチェックしなければいけません。2回目の状態チェックで DQ3 が HIGH の場合は、最後に書き込んだコマンドを受け取っていない可能性があります。[Table 17](#) に、他のステータスビットとの関連の DQ3 のステータスを示します。

### 5.5.2.4 DQ2: トグルビット II

DQ2 から出力されるトグルビット II は、DQ6 と一緒に使用することにより、指定されたセクタが消去動作中である(つまり、組込み消去アルゴリズムの実行中である)か、またはそのセクタが消去一時停止中であるかを示します。トグルビット II は、コマンドシーケンスの最後の WE# パルスの立ち上りエッジの後に有効になります。

消去の対象として選択されたセクタ(またはマルチセクタ消去中の消去の対象として選択されたすべてのセクタ)内のアドレスをシステムが読み出すと、DQ2 はトグルします。(システムは、OE# または CE# のいずれかを使い、読み出しサイクルを制御できます。) ただし、DQ2 は、セクタが消去中であるか、消去一時停止中であるかを区別できません。これと対照的に、DQ6 はデバイスが消去動作中か、消去一時停止中かを示しますが、セクタが消去の対象として選択されたかを区別できません。したがって、セクタならびにモード情報を得るには、これらのステータスビットが両方とも必要となります。DQ2 と DQ6 の出力の相違については、[Table 17](#) を参照してください。[Figure 7](#) に、トグルビットのアルゴリズムをフローチャート形式で示し、[トグルビット DQ6/DQ2 の読み出し](#) でアルゴリズムを説明します。

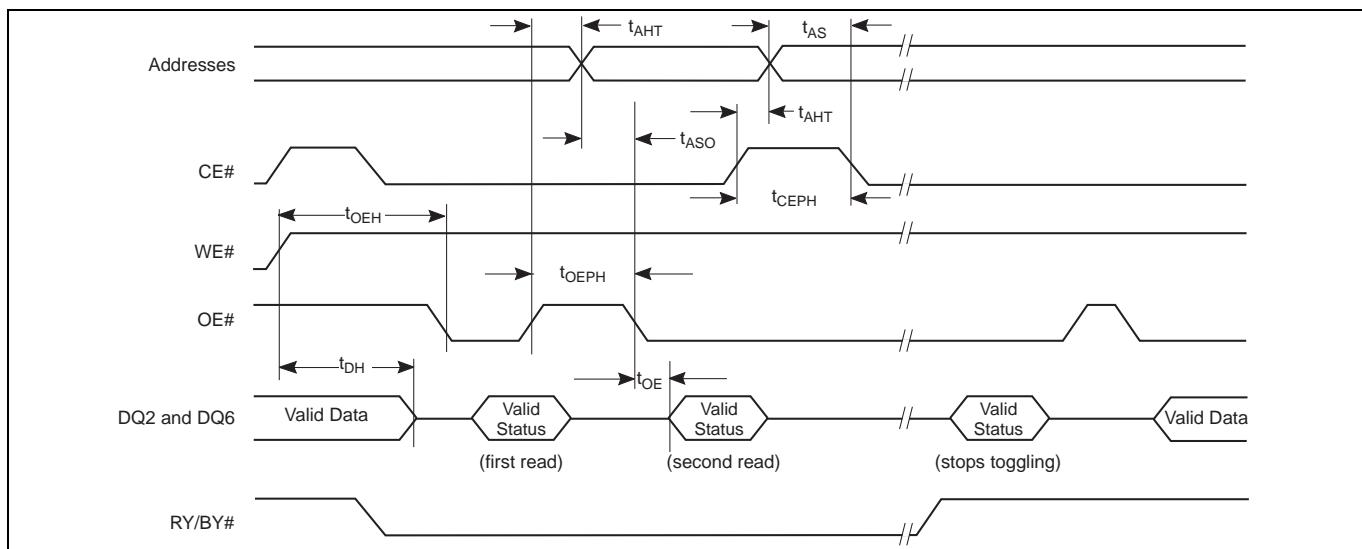

[Figure 8](#) にトグルビットのタイミング図を示します。

組込み動作

### 5.5.2.5 トグルビット DQ6/DQ2 の読み出し