# 512Mb/1Gb SEMPER™ フラッシュ

オクタルインターフェース, 1.8 V/3.0 V

## 機能

- 各メモリアレイセルに 2 データビットを保存するインフィニオン 45 nm MIRRORBIT™ 技術

- セクタアーキテクチャオプション

- ユニフォーム: アドレス空間はすべて 256 KB セクタで構成

- ハイブリッド:

- コンフィギュレーション 1: アドレス空間は、最上部または最下部でグループ化された 32 の 4 KB セクタと、残りの部分にある全 256 KB セクタで構成

- コンフィギュレーション 2: アドレス空間は、最上部と最下部の両方で均等に分割された 32 の 4 KB セクタと、残りの部分にある全 256 KB セクタで構成

- 256 または 512 バイトのページプログラムバッファ

- 1024 バイト (32×32 バイト) の OTP セキュアシリコンアレイ

- オクタルインターフェース (8S-8S-8S, 8D-8D-8D)

- JEDEC eXpandedシリアルペリフェラルインターフェース (SPI) (JESD251) 準拠

- SDR オプションは最大 200 MBps (200 MHz クロック速度)

- DDR オプションは最大 400 MBps (200 MHz クロック速度)

- データストローブ (DS) をサポートし、高速システムでの読み出しデータキャプチャを簡素化

- 安全性機能

- ISO26262 ASIL B 準拠および ASIL D 対応の安全性機能

- インフィニオン Endurance Flex アーキテクチャ: 高耐久性および長期データ保持のパーティションを提供

- インターフェース CRC: ホストコントローラーと SEMPER™ フラッシュデバイス間の通信インターフェースでエラーを検出

- データ整合性 CRC: メモリアレイでエラーを検出

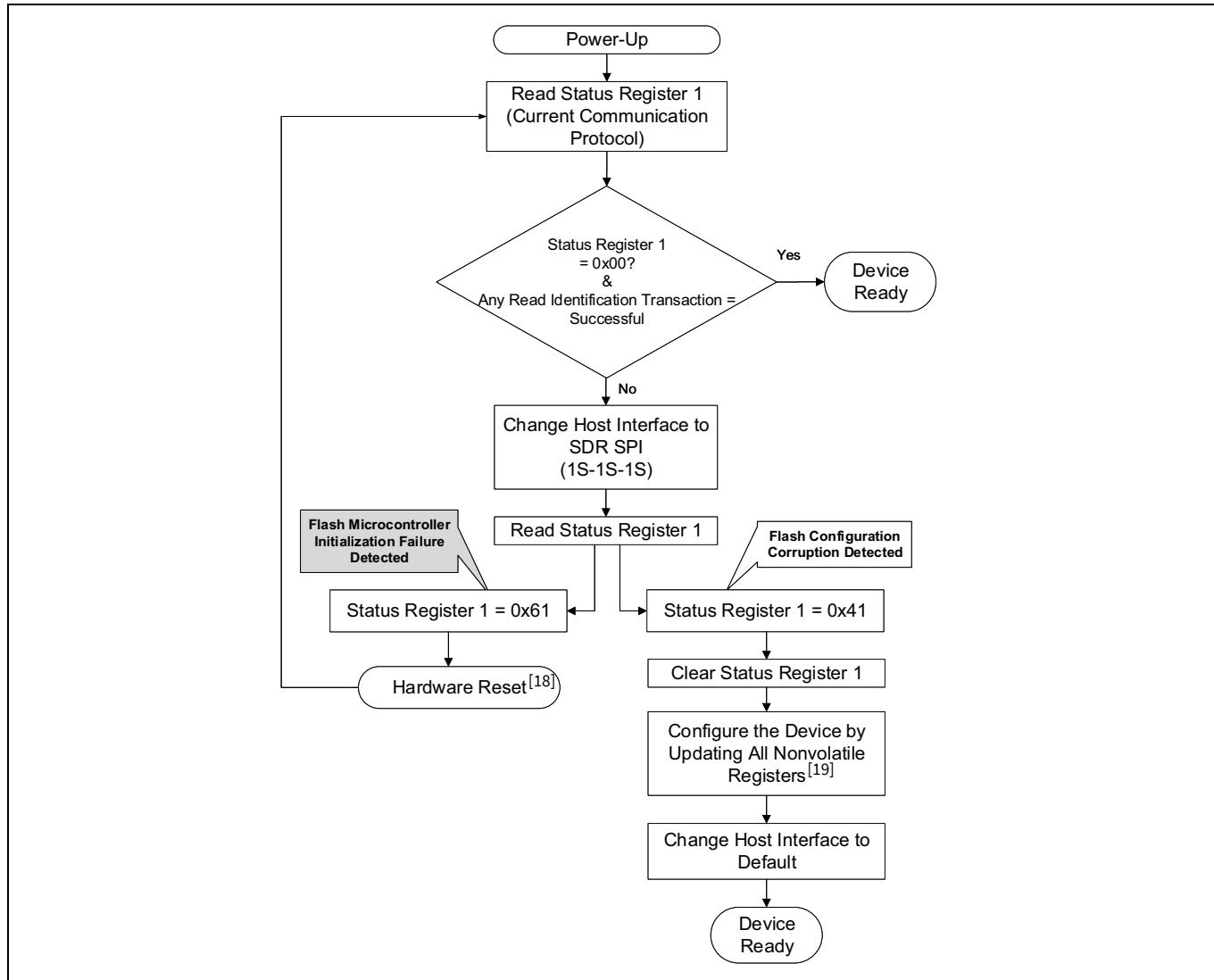

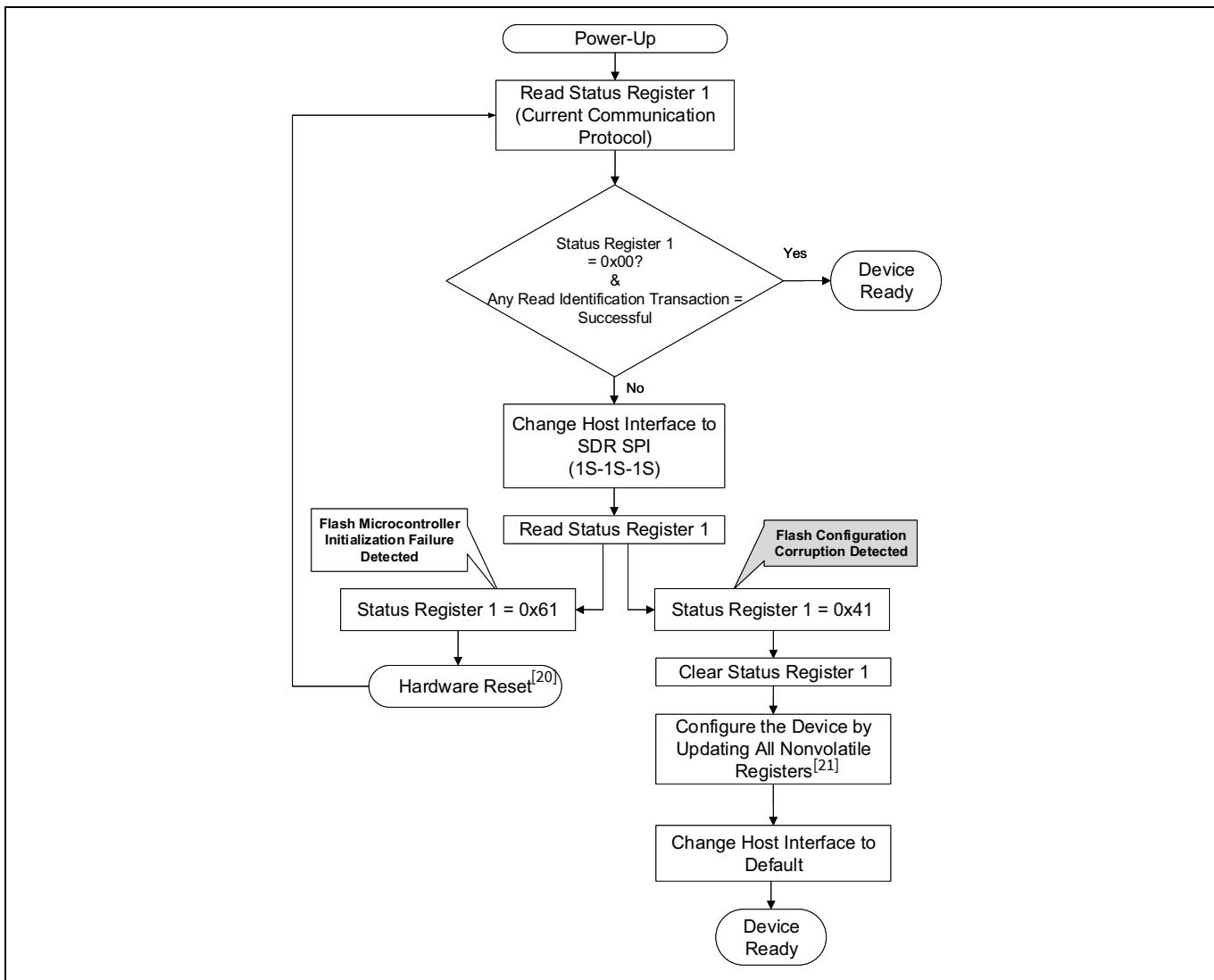

- セーフブート: デバイスの初期化失敗を報告し、コンフィギュレーション破損を検出し、回復オプションを提供

- 内蔵エラー訂正コード (ECC): メモリアレイデータでシングルビットエラー訂正およびダブルビットエラー検出 (SECDED) を実行

- 消去中の電力喪失を示すセクタ消去ステータスインジケータ

- 保護機能

- メモリアレイとデバイスコンフィギュレーションのレガシーブロック保護 (LBP)

- 個別メモリアレイセクタ単位での高度セクタ保護 (ASP)

- オートブート: 電源投入後のメモリアレイへの即時アクセスを有効化

- CS# シグナリング方式 (JEDEC) または個別の RESET# ピンによるハードウェアリセット

- デバイス機能と特長を記述するシリアルフラッシュ検出可能パラメーター (SFDP)

- デバイス ID, メーカー ID, 固有 ID

- データ整合性

- 512 Mb デバイス

- メインアレイは最小 1,280,000 回のプログラム / 消去サイクル

- 1Gb デバイス

- メインアレイは最小 2,560,000 回のプログラム / 消去サイクル

- すべてのデバイス

- 4 KB セクタは最小 300,000 回のプログラム / 消去サイクル

- 少なくとも 25 年間のデータ保持

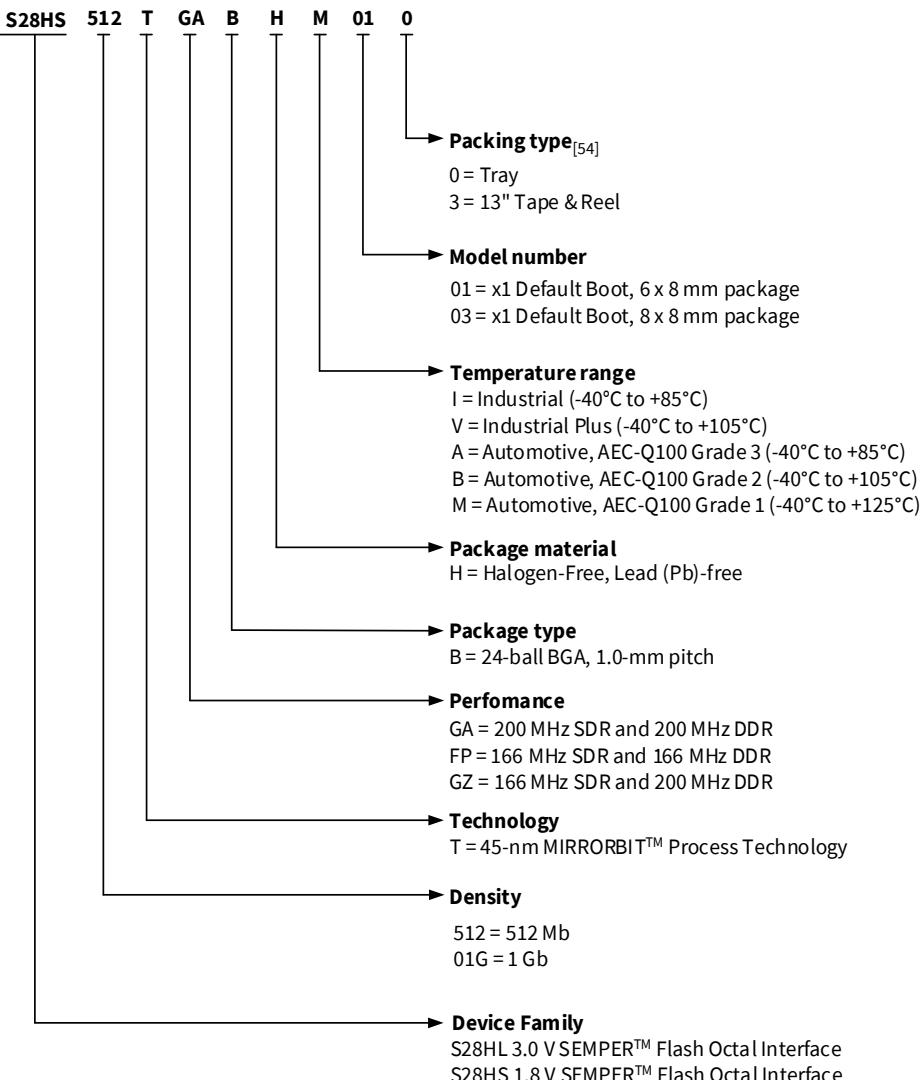

## 性能要約

- 電源電圧

- 1.7 V ~ 2.0 V (HS-T)

- 2.7 V ~ 3.6 V (HL-T)

- グレード / 温度範囲

- 産業用 (-40°C ~ +85°C)

- 産業用プラス (-40°C ~ +105°C)

- 車載向け AEC-Q100 グレード 3 (-40°C ~ +85°C)

- 車載向け AEC-Q100 グレード 2 (-40°C ~ +105°C)

- 車載向け AEC-Q100 グレード 1 (-40°C ~ +125°C)

- パッケージ

- 512 Mb: 24 ボール BGA 6x8mm

- 1Gb: 24 ボール BGA 8x8mm

## 性能要約

**Table 1 最大読み出し速度**

| トランザクション               | 初期アクセス レイテンシ<br>(サイクル) | クロック レート (MHz) | MBps  |

|------------------------|------------------------|----------------|-------|

| SPI 読み出し               | 0                      | 50             | 6.25  |

| SPI 高速読み出し             | 10                     | 166            | 20.75 |

| SDR オクタル読み出し<br>(HS-T) | 16                     | 200            | 200   |

| SDR オクタル読み出し<br>(HL-T) | 14                     | 166            | 166   |

| DDR オクタル読み出し<br>(HS-T) | 23                     | 200            | 400   |

| DDR オクタル読み出し<br>(HL-T) | 20                     | 166            | 332   |

**Table 2 標準プログラムと消去速度**

| 動作                                      | KBps    |

|-----------------------------------------|---------|

| 256 B ページ プログラム (4 KB セクタ /256 KB セクタ ) | 595/533 |

| 512 B ページ プログラム (4 KB セクタ /256 KB セクタ ) | 753/898 |

| 256 KB セクタ消去                            | 331     |

| 4 KB セクタ消去                              | 95      |

**Table 3 標準消費電力**

| 動作                | HL-T 電流 (mA) | HS-T 電流 (mA)  |

|-------------------|--------------|---------------|

| SDR 読み出し (50 MHz) | 10           | 10            |

| SDR 読み出し (オクタル)   | 75 (166 MHz) | 156 (200 MHz) |

| DDR 読み出し (オクタル)   | 75 (166 MHz) | 156 (200 MHz) |

| プログラム             | 50           | 50            |

| 消去                | 50           | 50            |

| スタンバイ             | 0.014        | 0.011         |

| ディープパワーダウン        | 0.0022       | 0.0013        |

データ整合性

## データ整合性

**Table 4** プログラム / 消去 (PE) 可能回数 - 高耐久性 (256 KB セクタ)

| パーティション内のセクタ数            | 最小 PE サイクル数        | 最小データ保持期間 | 単位 |

|--------------------------|--------------------|-----------|----|

|                          | 512 Mb および 1 Gb 製品 |           |    |

| 512 (1 Gb デバイスのデフォルト値)   | 2,560,000          |           |    |

| 508                      | 2,540,000          |           |    |

| 504                      | 2,520,000          |           |    |

| ...                      | ...                |           |    |

| 256 (512 Mb デバイスのデフォルト値) | 1,280,000          | 2         | 年  |

| 252                      | 1,260,000          |           |    |

| ...                      | ...                |           |    |

| 28                       | 140,000            |           |    |

| 24                       | 120,000            |           |    |

| 20                       | 100,000            |           |    |

注: 最小サイクル数は高耐久性パーティション全体に対するものです。

**Table 5** プログラム / 消去可能回数 - 長期データ保持パーティション (256 KB セクタ)

| 最小 PE サイクル数 | 最小データ保持期間 | 単位 |

|-------------|-----------|----|

| 500         | 25        | 年  |

注: 最小サイクル数は各々のセクタに対するものです。

**Table 6** 4 KB セクタおよび不揮発性レジスタアレイのプログラム / 消去可能回数

| フラッシュメモリタイプ                                                     | 最小サイクル数                                                                  | 単位      | 最小データ保持期間 | 単位 |

|-----------------------------------------------------------------|--------------------------------------------------------------------------|---------|-----------|----|

| 4 KB セクタのプログラム / 消去サイクル数                                        | 500                                                                      |         | 25        | 年  |

|                                                                 | 300,000                                                                  |         | 2         |    |

| 恒久的な保護ビット (PPB) アレイまたは不揮発性レジスタアレイのプログラム / 消去サイクル数               | 注: 上記の書き換え可能回数を達成するためには、プログラムまたは消去動作中に電力喪失イベントをセクタあたり 300 回に制限する必要があります。 | PE サイクル |           |    |

| 注: 不揮発性レジスタへの書き込みトランザクションを実行するたびに、不揮発性レジスタアレイ全体で PE サイクルが発生します。 | 500                                                                      |         | 25        |    |

## 目次

|                                             |     |

|---------------------------------------------|-----|

| 機能 .....                                    | 1   |

| 性能要約 .....                                  | 2   |

| データ整合性 .....                                | 3   |

| 目次 .....                                    | 4   |

| 1 ピン配置および信号の説明 .....                        | 6   |

| 2 インターフェースの概要 .....                         | 8   |

| 2.1 概要 .....                                | 8   |

| 2.2 信号プロトコル .....                           | 10  |

| 2.3 トランザクションプロトコル .....                     | 11  |

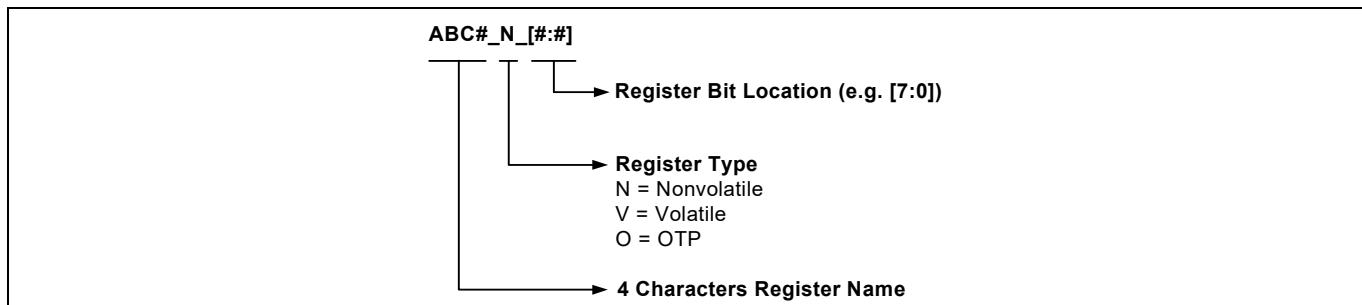

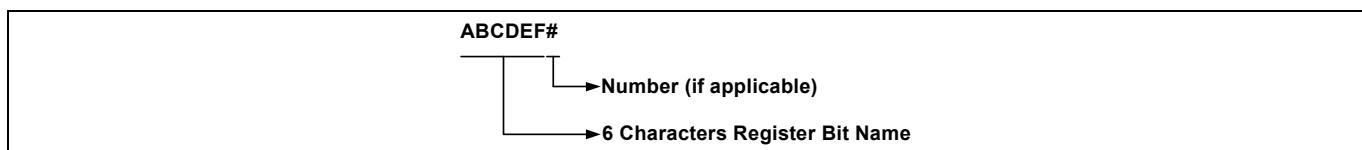

| 2.4 レジスタ命名規則 .....                          | 19  |

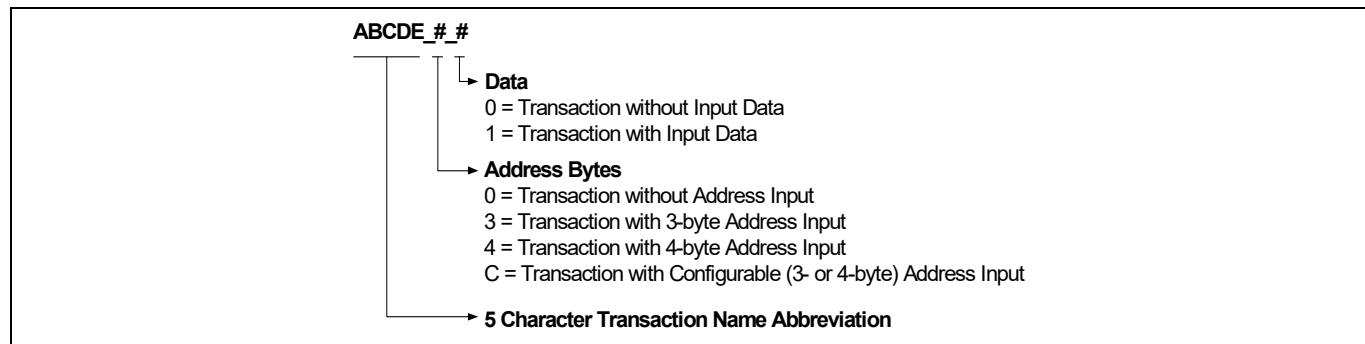

| 2.5 トランザクション命名規則 .....                      | 20  |

| 3 アドレス空間マップ .....                           | 21  |

| 3.1 SEMPER™ フラッシュメモリアレイ .....               | 21  |

| 3.2 ID アドレス空間 .....                         | 23  |

| 3.3 JEDEC JESD216 SDFP 空間 .....             | 23  |

| 3.4 SSR アドレス空間 .....                        | 24  |

| 3.5 レジスタ .....                              | 25  |

| 4 機能 .....                                  | 27  |

| 4.1 エラー検出と訂正 .....                          | 27  |

| 4.2 Endurance Flex アーキテクチャ (ウェアレベリング) ..... | 31  |

| 4.3 インターフェース CRC .....                      | 36  |

| 4.4 データ整合性 CRC .....                        | 39  |

| 4.5 データ保護スキーム .....                         | 40  |

| 4.6 セーフブート .....                            | 50  |

| 4.7 オートブート .....                            | 54  |

| 4.8 読み出しトランザクション .....                      | 55  |

| 4.9 書き込みトランザクション .....                      | 59  |

| 4.10 プログラム .....                            | 62  |

| 4.11 消去 .....                               | 64  |

| 4.12 組込み動作の一時停止と再開 .....                    | 66  |

| 4.13 リセット .....                             | 70  |

| 4.14 電力モード .....                            | 74  |

| 4.15 電源投入と電源切断 .....                        | 76  |

| 5 レジスタ .....                                | 78  |

| 5.1 レジスタ命名規則 .....                          | 78  |

| 5.2 ステータスレジスタ 1 (STR1x) .....               | 79  |

| 5.3 ステータスレジスタ 2 (STR2x) .....               | 83  |

| 5.4 コンフィギュレーションレジスタ 1 (CFR1x) .....         | 85  |

| 5.5 コンフィギュレーションレジスタ 2 (CFR2x) .....         | 88  |

| 5.6 コンフィギュレーションレジスタ 3 (CFR3x) .....         | 90  |

| 5.7 コンフィギュレーションレジスタ 4 (CFR4x) .....         | 93  |

| 5.8 コンフィギュレーションレジスタ 5 (CFR5x) .....         | 96  |

| 5.9 インターフェース CRC イネーブルレジスタ (ICEV) .....     | 97  |

| 5.10 インターフェース CRC チェック値レジスタ (ICRV) .....    | 97  |

| 5.11 メモリアレイデータ整合性チェック CRC レジスタ (DCRV) ..... | 98  |

| 5.12 ECC ステータスレジスタ (ESCV) .....             | 98  |

| 5.13 ECC アドレストラップレジスタ (EATV) .....          | 100 |

| 5.14 ECC エラー検出カウントレジスタ (ECTV) .....         | 101 |

| 5.15 高度セクタ保護レジスタ (ASPO) .....               | 102 |

| 5.16 ASP パスワード レジスタ (PWDO) .....            | 104 |

| 5.17 ASP PPB ロック レジスタ (PPLV) .....          | 105 |

目次

|                                                     |            |

|-----------------------------------------------------|------------|

| 5.18 ASP PPB アクセス レジスタ (PPAV) .....                 | 105        |

| 5.19 ASP ダイナミック ブロック アクセス レジスタ (DYAV) .....         | 106        |

| 5.20 オートブート レジスタ (ATBN) .....                       | 106        |

| 5.21 セクタ消去カウント レジスタ (SECV) .....                    | 108        |

| 5.22 INT# ピン コンフィギュレーション レジスタ (INCV) - オクタルのみ ..... | 108        |

| 5.23 INT# ピン ステータス レジスタ (INSV) - オクタルのみ .....       | 110        |

| 5.24 Endurance Flex アーキテクチャ選択 レジスタ (EFXx) .....     | 111        |

| <b>6 トランザクション テーブル .....</b>                        | <b>114</b> |

| 6.1 SPI (1S-1S-1S) トランザクション テーブル .....              | 114        |

| 6.2 オクタル (8S-8S-8S, 8D-8D-8D) トランザクション テーブル .....   | 118        |

| <b>7 電気的特性 .....</b>                                | <b>123</b> |

| 7.1 絶対最大定格 [35] .....                               | 123        |

| 7.2 動作範囲 .....                                      | 123        |

| 7.3 熱抵抗 .....                                       | 124        |

| 7.4 静電容量特性 .....                                    | 124        |

| 7.5 ラッチアップ仕様 .....                                  | 124        |

| 7.6 DC 特性 .....                                     | 124        |

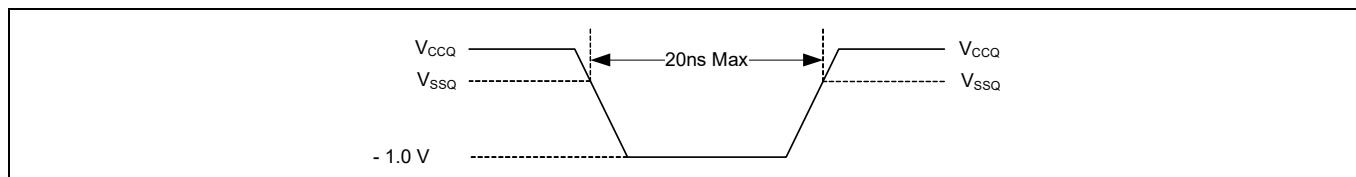

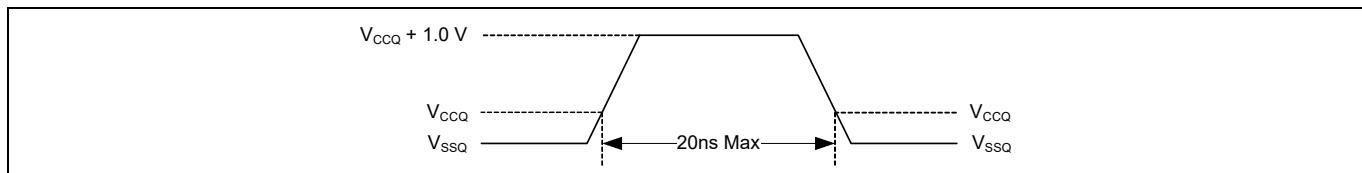

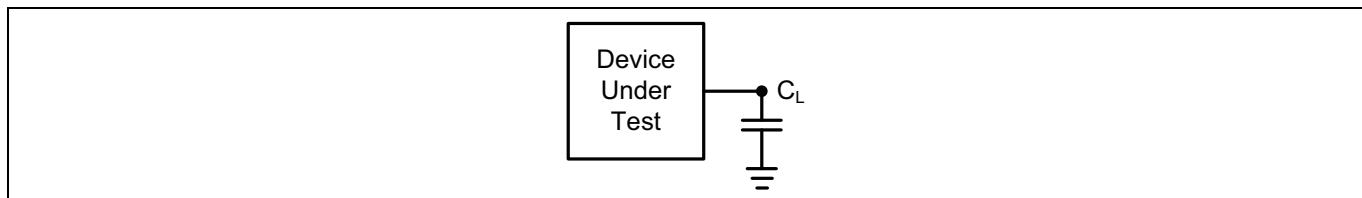

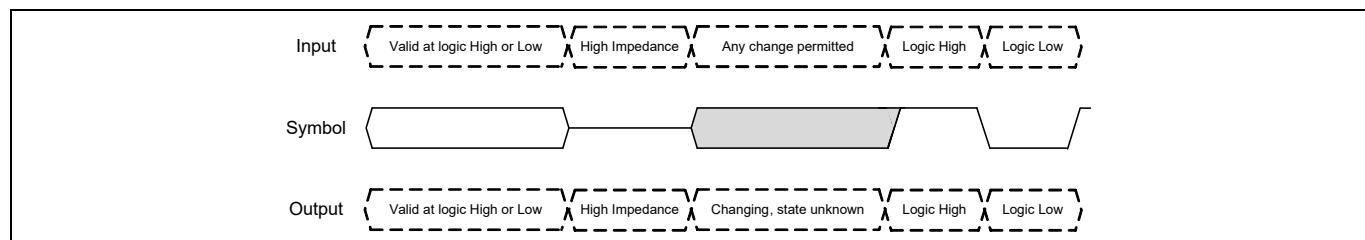

| 7.7 AC テスト条件 .....                                  | 128        |

| <b>8 タイミング特性 .....</b>                              | <b>129</b> |

| 8.1 タイミング波形 .....                                   | 136        |

| <b>9 デバイス ID .....</b>                              | <b>139</b> |

| 9.1 JEDEC SFDP レビジョン D .....                        | 139        |

| 9.2 メーカーおよびデバイス ID .....                            | 166        |

| 9.3 固有デバイス ID .....                                 | 166        |

| <b>10 パッケージ図 .....</b>                              | <b>167</b> |

| <b>11 注文情報 .....</b>                                | <b>169</b> |

| 11.1 有効な組合せ – 標準グレード .....                          | 170        |

| 11.2 有効な組合せ – 車載向けグレード /AEC-Q100 .....              | 171        |

| 改訂履歴 .....                                          | 172        |

| 免責事項 .....                                          | 173        |

## 1 ピン配置および信号の説明

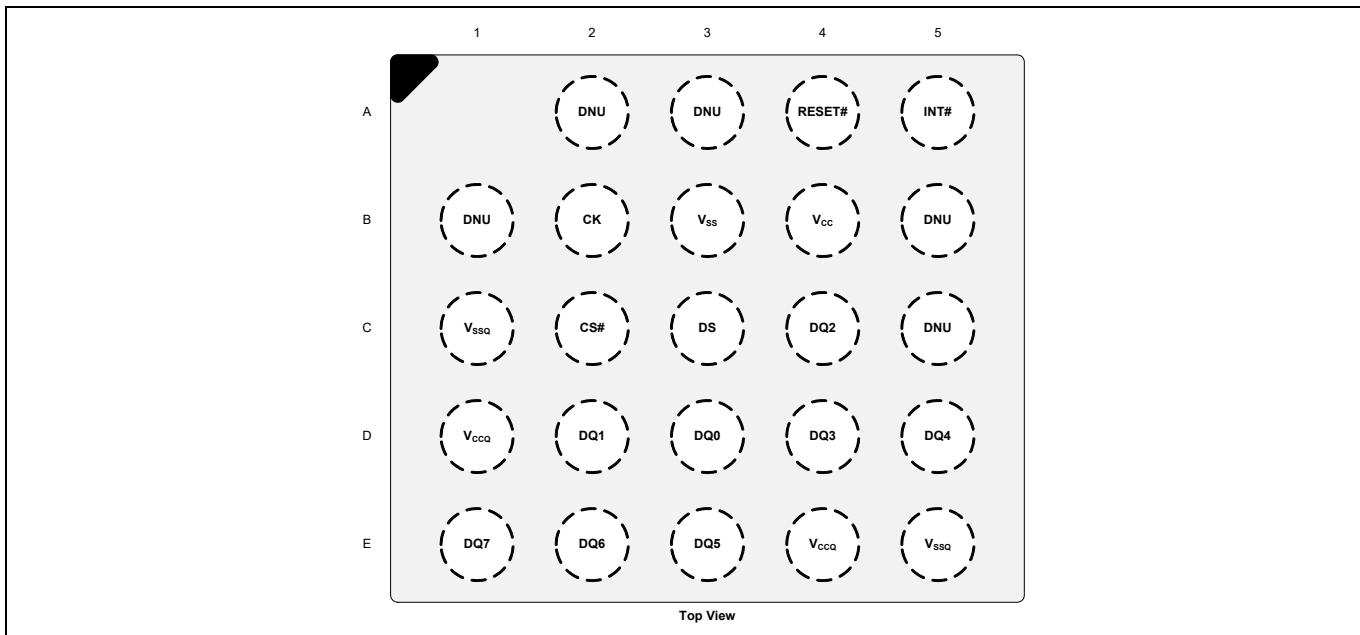

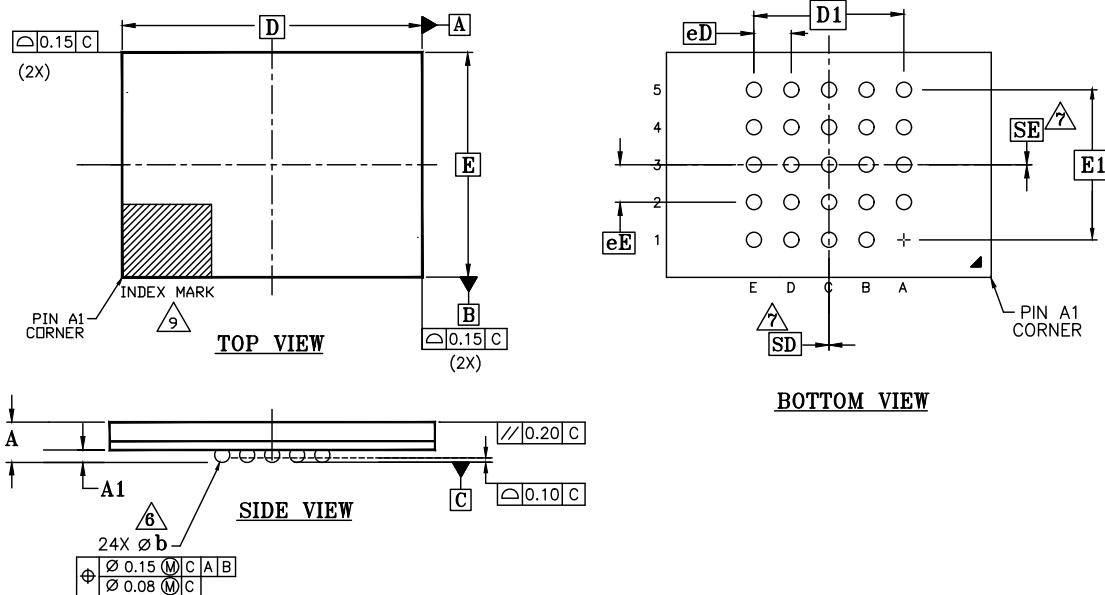

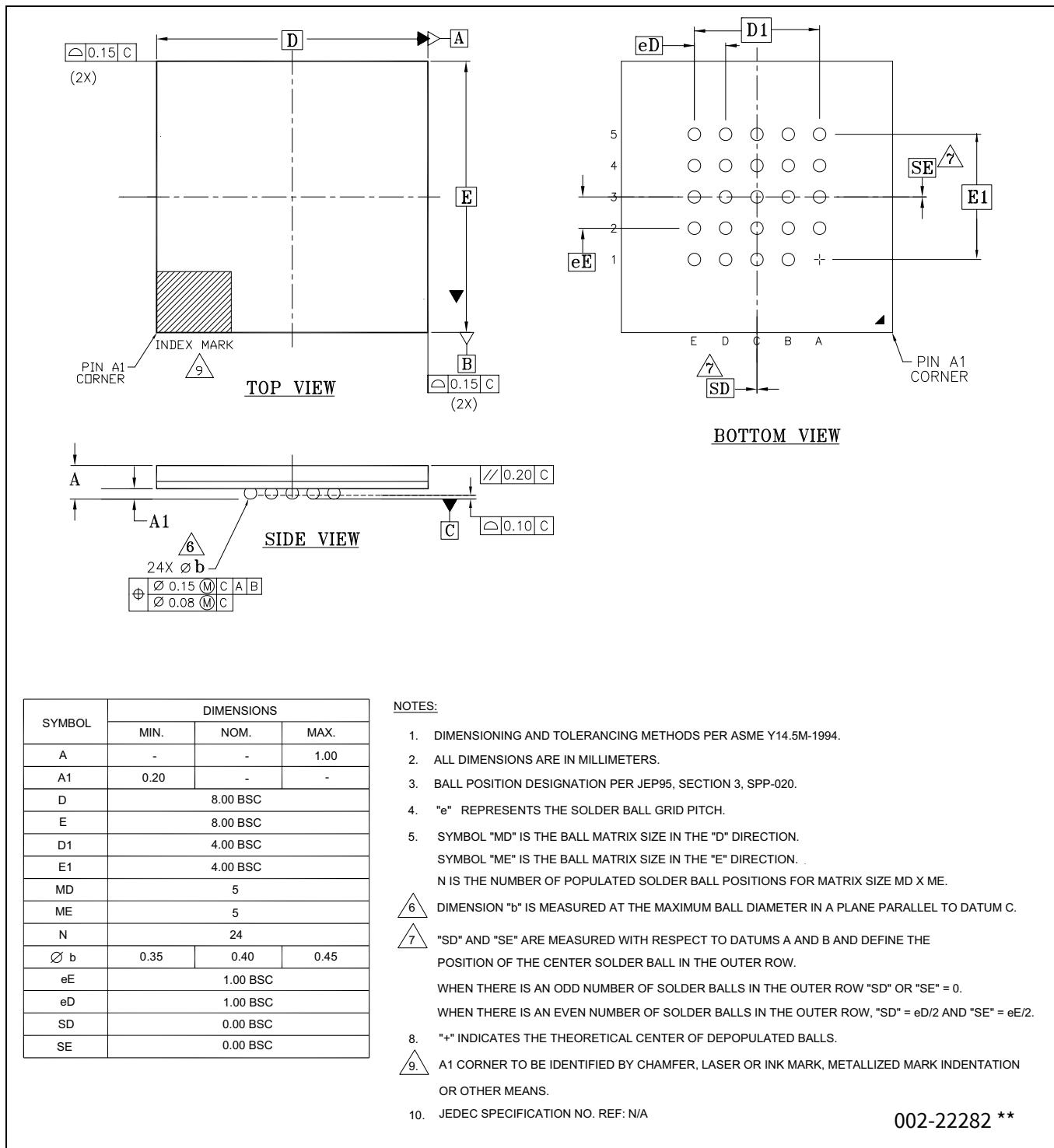

**Figure 1 24 ボール BGA ピン配置 [1]**

### 注

1. BGA パッケージのフラッシュメモリデバイスは超音波洗浄にさらされると損傷する場合があります。パッケージ本体を長時間にわたって温度 150°C 以上の環境にさらすと、パッケージあるいはデータの整合性あるいはその両方が損なわれることがあります。

ピン配置および信号の説明

Table 7 信号の説明

| 記号               | タイプ           | 必須 / オプション | 説明                                                                                                                                                                                                                                                                               |

|------------------|---------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CS#              | 入力            | 必須         | チップ選択 (CS#):すべてのバストランザクションは CS# の HIGH から LOW への遷移で開始され、CS# の LOW から HIGH への遷移で終了します。CS# を LOW にすると、デバイスはアクティブモードになります。CS# が HIGH になると、内部組込み動作が実行中でないかぎり、デバイスはスタンバイモードになります。他のすべての入力ピンは無視され、出力ピンは高インピーダンス状態になります。ピンコンフィギュレーションで専用 RESET# ピンがあるデバイスでは、CS# が HIGH であってもアクティブのままです。 |

| CK               |               |            | クロック (CK):クロックはシリアルインターフェースのタイミングを提供します。トランザクションはクロックの立ち上りエッジでラッ奇されます。SDR プロトコルでは、コマンド、アドレスおよびデータ入力がクロックの立ち上りエッジでラッ奇され、クロックの立ち下りエッジでデータが出力されます。DDR プロトコルでは、コマンド、アドレスおよびデータ入力がクロックの両エッジでラッ奇され、データがクロックの両エッジで出力されます。                                                               |

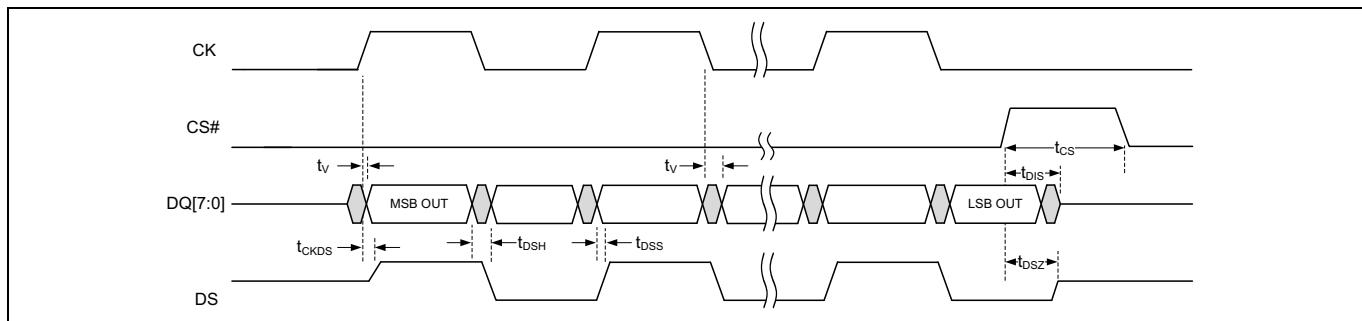

| DS               | 出力            |            | 読み出しデータストローブ (DS): DS はデータ読み出し動作のみに使用され、SDR/DDR モードで出力データが有効であることを示します。CS# が LOW のとき、読み出しトランザクション中に、DS は CS# が HIGH になるまでデータ出力を同期化するようにトグルします。                                                                                                                                   |

| DQ[7:0]          | 入力 / 出力       |            | シリアルデータ (DQ[7:0]): 双方向信号であり、コマンド、アドレス、およびデータ情報を転送します。<br>レガシー (x1) SPI インターフェース : DQ[0] は入力 (SI)、DQ[1] は出力 (SO) です。<br>オクタル (x8) インターフェース : DQ[7:0] は入力と出力です。                                                                                                                    |

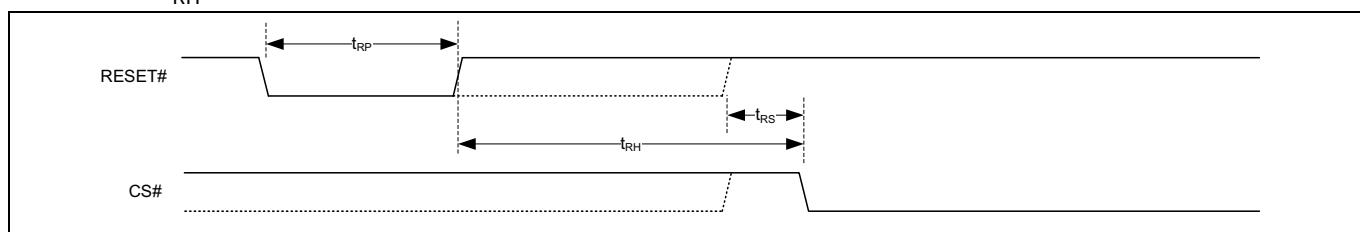

| RESET#           | 入力 (弱プルアップ)   | オプション      | ハードウェアリセット (RESET#): LOW のとき、デバイスは自己初期化してアレイ読み出し状態に戻ります。RESET# が LOW のとき、DS と DQ[7:0] は高インピーダンス状態になります。RESET# は弱プルアップが含まれており、RESET# を未接続のままにすると、それ自身で HIGH 状態にプルアップされます。                                                                                                         |

| INT#             | 出力 (オープンドレイン) |            | システム割込み (INT#): LOW のとき、デバイスは内部イベントが発生したことを示します。この信号はデバイスがチップ内イベントが発生したことを示すためにシステムレベルの割込みとして使用されます。INT# はオープンドレイン出力です。INT# 出力の推奨プルアップ抵抗は 5 kΩ ~ 10 kΩ です。                                                                                                                       |

| V <sub>CC</sub>  | 電源            | 必須         | コア電源                                                                                                                                                                                                                                                                             |

| V <sub>CCQ</sub> |               |            | 入力 / 出力用の電源                                                                                                                                                                                                                                                                      |

| V <sub>SS</sub>  | グランド          | 必須         | コアグランド                                                                                                                                                                                                                                                                           |

| V <sub>SSQ</sub> | 電源            |            | 入力 / 出力グランド                                                                                                                                                                                                                                                                      |

| DNU              | -             | -          | 使用禁止                                                                                                                                                                                                                                                                             |

## 2 インターフェースの概要

### 2.1 概要

SEMPER™ フラッシュ オクタル製品ファミリは、JEDEC JESD251 eXpanded SPI (xSPI) 仕様に準拠した、高速 CMOS、MIRRORBIT™ NOR フラッシュ デバイスです。SEMPER™ フラッシュは、ASIL-B に準拠および ASIL-D に対応するために ISO 26262 規格による機能安全用に設計されています。

オクタルインターフェースを備えた SEMPER™ フラッシュ デバイスは、オクタルペリフェラルインターフェース (OPI) とレガシー x1 シリアルペリフェラルインターフェース (SPI) の両方をサポートします。両インターフェースはトランザクションを逐次的に転送し、インターフェース接続信号の数を減らします。SPI は SDR、OPI は SDR と DDR の両方をサポートします。

デバイスからの読み出し動作はバースト指向です。読み出しトランザクションはラップバーストカリニアバースト方式で行うよう設定できます。ラップバーストは単一ページから読み出しますが、リニアバーストはメモリアレイ全体を読み出します。

各メモリビットの消去済み状態は論理 1 です。プログラム動作により論理 1 (HIGH) から論理 0 (LOW) に変更します。消去動作だけがメモリビットを「0」から「1」に変更できます。消去動作はセクタ全体 (4KB または 256KB) に対して行わなければいけません。

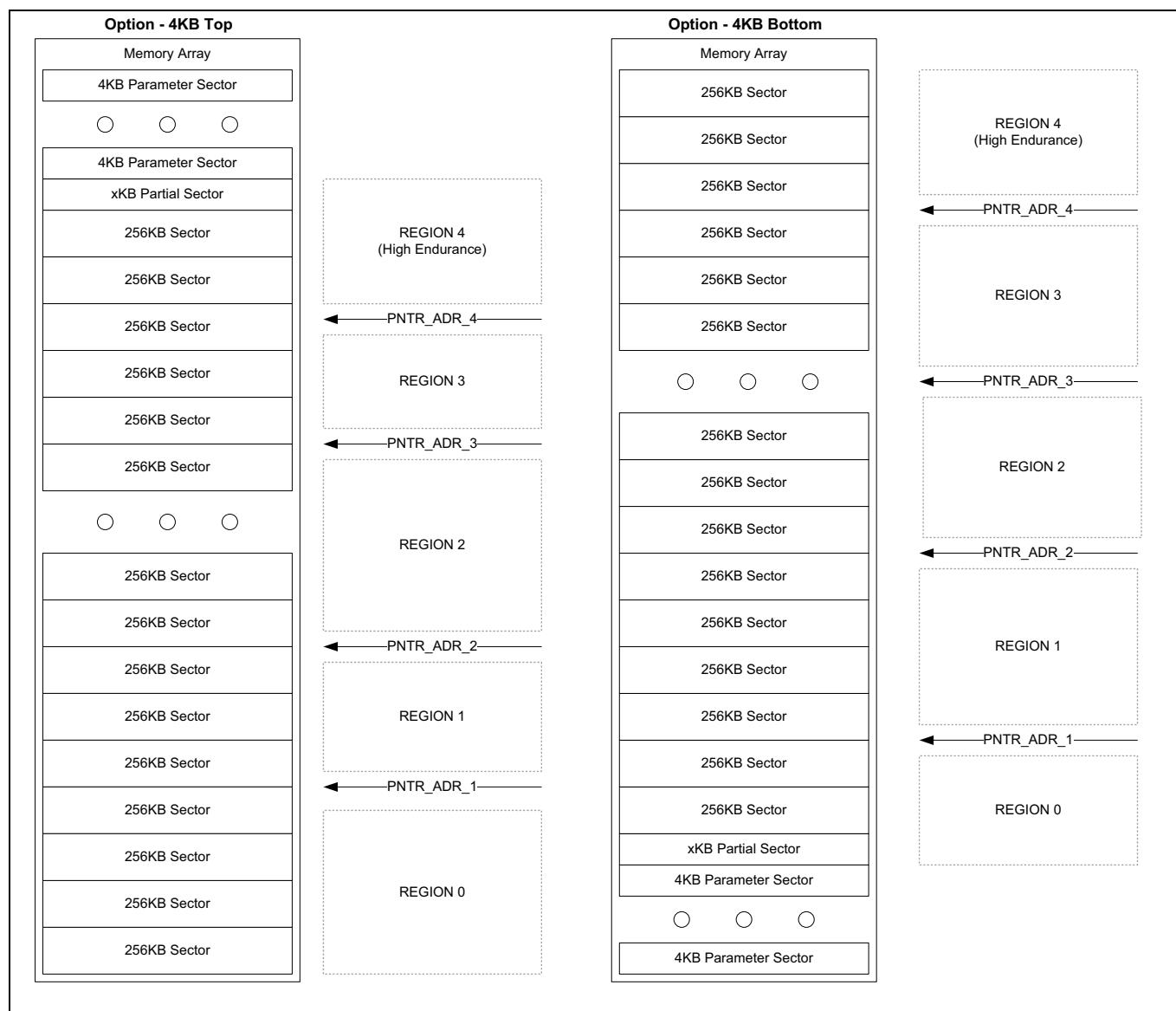

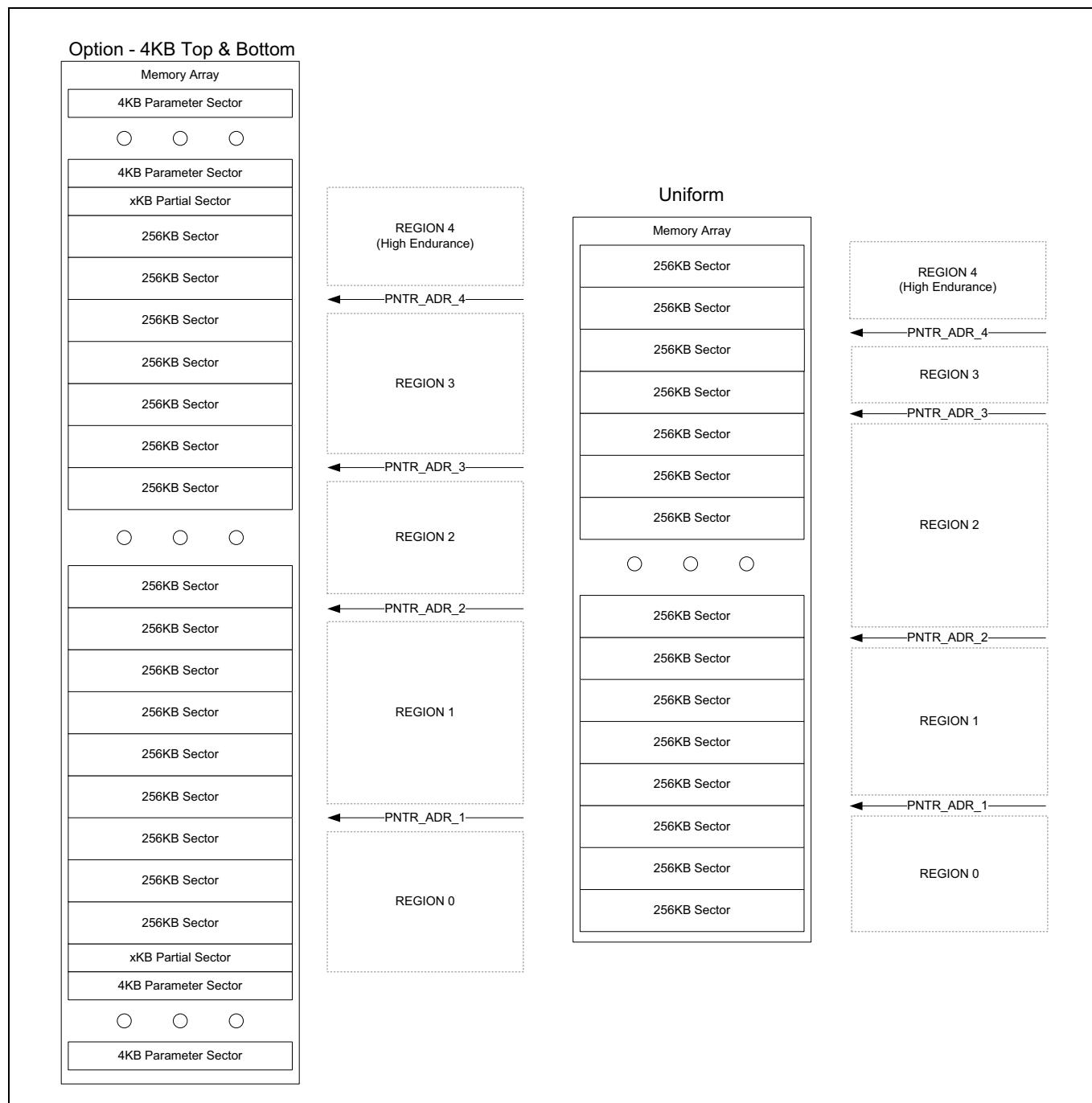

SEMPER™ フラッシュは柔軟性のあるセクタアーキテクチャを提供します。アドレス空間は、ユニフォーム 256 KB セクタアレイあるいはハイブリッド コンフィギュレーション 1 (32 個の 4 KB セクタが上部と下部にグループされ、残りのセクタがすべて 256 KB)、またはハイブリッド コンフィギュレーション 2 (32 個の 4 KB セクタが上下で均等に分けられ、残りのセクタがすべて 256 KB) のどちらかに設定できます。

単一のプログラム動作で使用するページプログラム バッファは、256 バイトまたは 512 バイトのどちらかに設定できます。512 バイト オプションでは、最大のプログラムスループットが得られます。

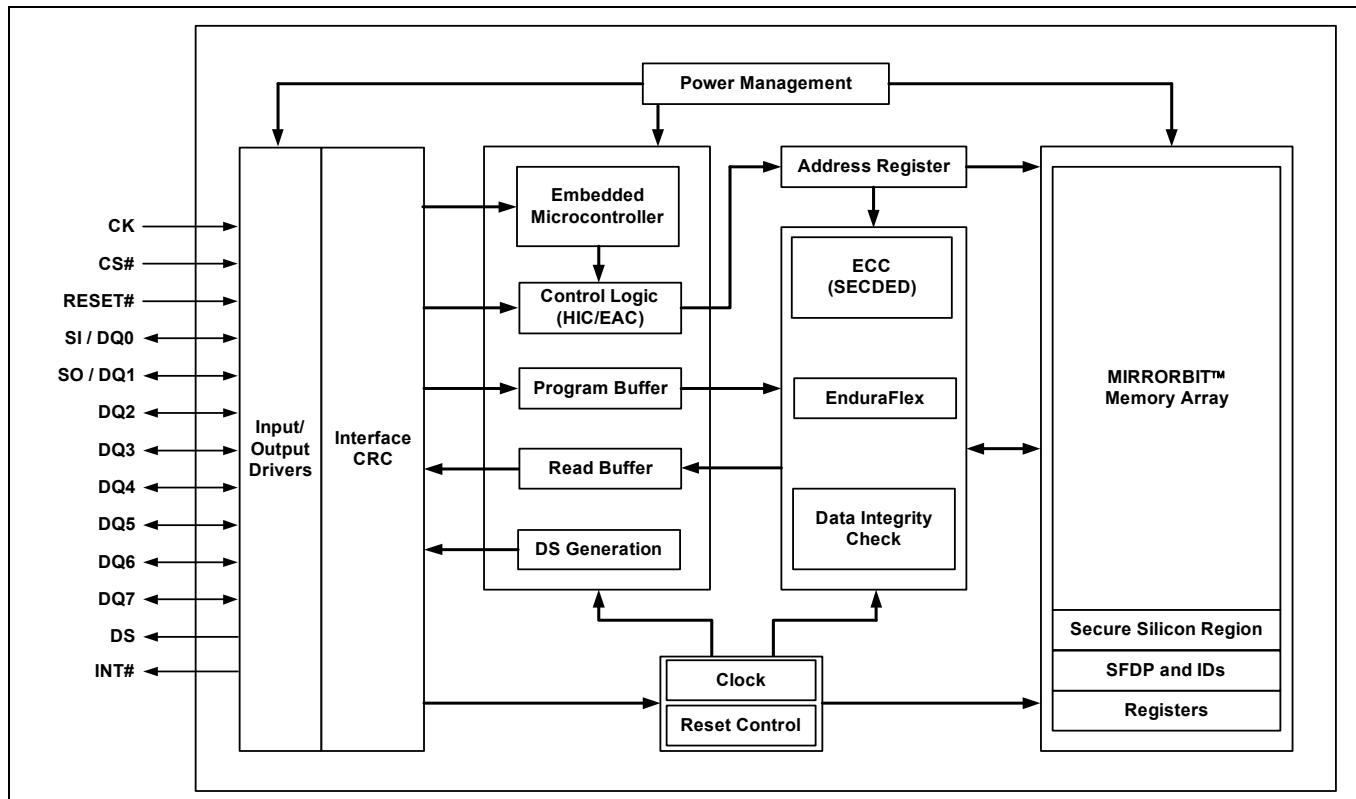

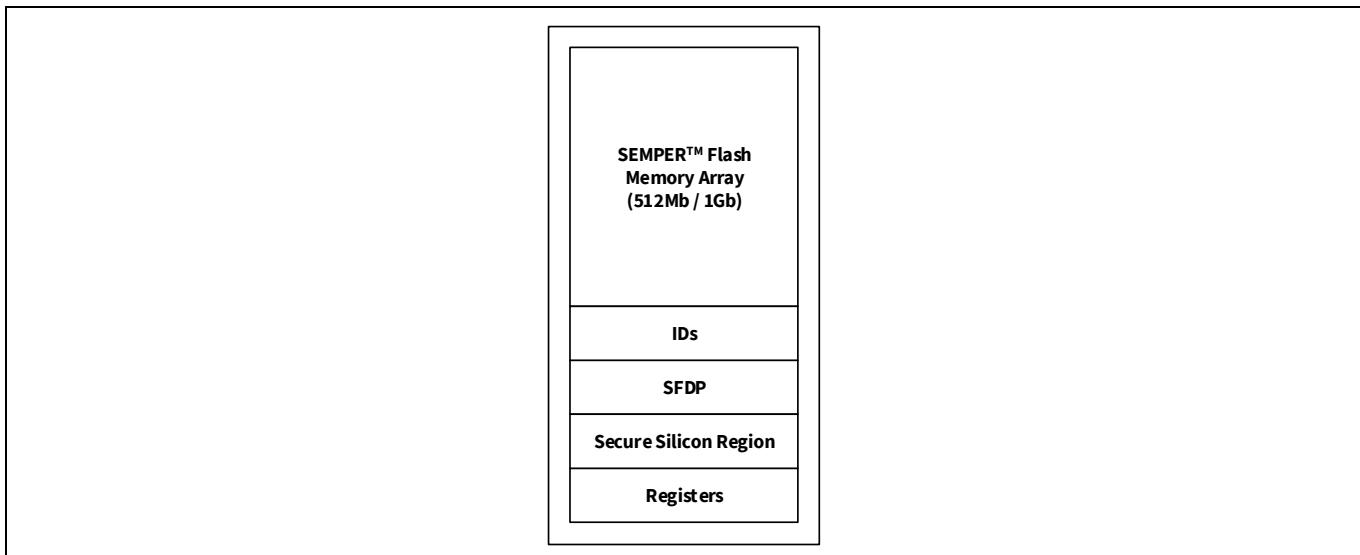

Figure 2 論理ブロック ダイヤグラム

## インターフェースの概要

オクタルインターフェースを備えた SEMPER™ フラッシュファミリは、複数の容量、1.8 V と 3.0 V コアと I/O 電圧オプションを含みます。

デバイス制御ロジックは、ホストインターフェースコントローラー (HIC) と組込みアルゴリズムコントローラー (EAC) の 2 つの並行して動作するセクションに分かれています。HIC はデバイス入力の信号レベルを監視し、かつ必要に応じてデバイス出力を駆動し、データ読み出し、ホストシステムとのデータ読み出し、プログラム、書き込み転送を実行します。HIC は読み出し転送で、アクセス中のアドレス空間からデータを出力し、書き込み転送アドレスとデータ情報を EAC コマンドメモリに配置し、また、電源遷移および書き込み転送を EAC に通知します。EAC は、プログラムまたは書き込み転送後に、コマンドシーケンスが適正かどうかについてコマンドメモリをチェックして、そして関連する組込みアルゴリズムを実行します。

メモリアレイ内の不揮発性データの書き換えのためには、組込みアルゴリズム (EA) の一部である一連の動作を必要とします。アルゴリズムは内部の EAC によって完全に管理されています。主要なアルゴリズムは、メインアレイデータのプログラムと消去を実行します。ホストシステムはフラッシュデバイスにコマンドコードを書き込みます。EAC はコマンドを受け取り、トランザクションを完了するために必要なすべてのステップを実行し、EA の進行中にステータス情報を提供します。

CK, CS#, SI/DQ0, SO/DQ1 および DQ[7:2] の必須 SPI 信号に加え、オクタルインターフェースデバイスを備えた SEMPER™ フラッシュは、RESET#、DS および INT# 信号も含みます。RESET# が LOW から HIGH に遷移すると、デバイスは内部のパワーオンリセット (POR) 後のデフォルト状態に戻ります。データストローブ (DS) が読み出しトランザクション中に出力データと同期化されるため、ホストシステムは高いクロック周波数動作でデータをキャプチャできます。INT# は、デバイスマスターに割込みを提供するオープンドレイン出力で、プログラムまたは消去動作の終了時にデバイスがビジーからレディに遷移する時点を示すか、または読み出し中の ECC エラーの検出を示します。

インフィニオン EnduraFlex アーキテクチャにより、システム設計者は特定のアプリケーション用に NOR フラッシュの耐久性とデータ保持期間をカスタマイズすることができます。ホストは高耐久性または長期データ保持用のパーティションを定義し、最大 100 万回以上のサイクルまたは 25 年のデータ保持期間を実現します。

オクタルインターフェースを備えた SEMPER™ フラッシュデバイスは、メモリアレイのプログラム中に組込みハミングエラー訂正コードを生成することでエラー検出と訂正をサポートします。その後、この ECC コードは読み出し中に 1 ビットと 2 ビットエラーの検出および 1 ビットの訂正に使用されます。

オクタルインターフェースを備えた SEMPER™ フラッシュデバイスは、ホストシステムにデバイスの状態を提供する診断機能を内蔵しています。

- プログラムおよび消去動作 : プログラムまたは消去の成功、失敗および一時停止状態の報告

- エラー検出と訂正 : アドレストラップおよびエラー カウントを含む 1 ビットおよび / または 2 ビットエラーステータス

- データ整合性チェック : メモリアレイ内容に対するエラー検出

- インターフェース CRC: デバイスインターフェースに対するエラー検出

- セーフブート : 適切なフラッシュデバイス初期化およびコンフィギュレーション破損からの回復の報告

- セクタ消去ステータス : セクタごとの消去の成功と失敗状態の報告

- セクタ消去カウンター : セクタごとの消去サイクルのカウント

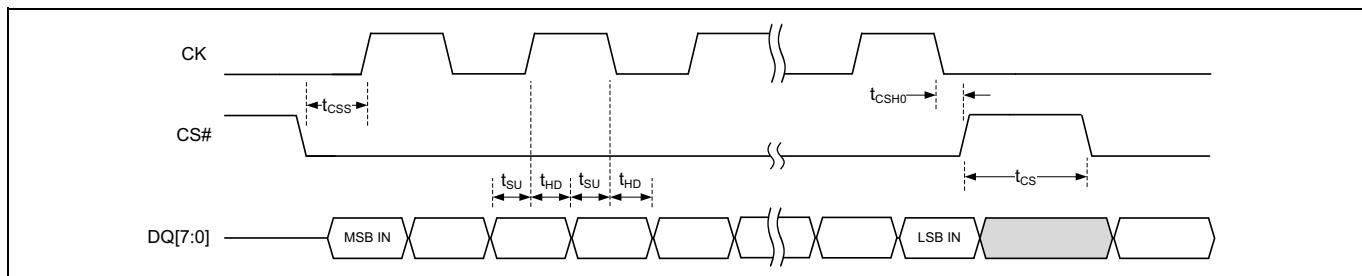

## 2.2 信号プロトコル

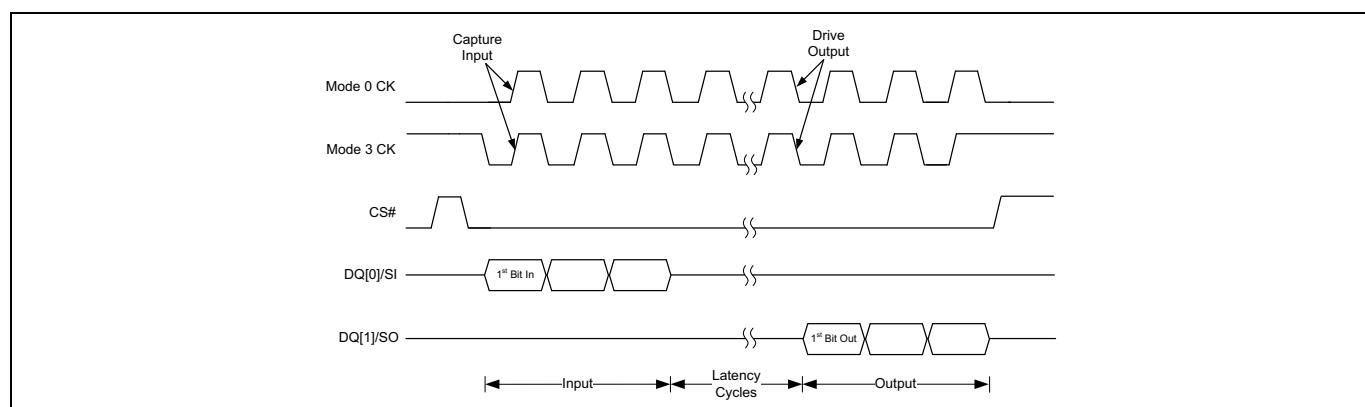

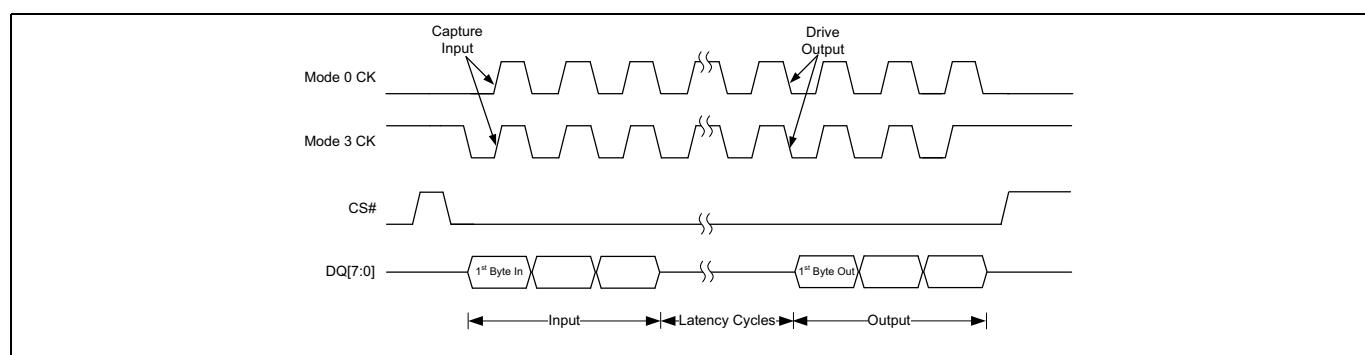

### 2.2.1 オクタルと SPI を備える SEMPER™ フラッシュのクロック モード

オクタルインターフェースを備える SEMPER™ フラッシュは、以下の 2 つのクロック モードのどちらかで、組込みマイクロ コントローラ (バス マスター) により駆動されます。

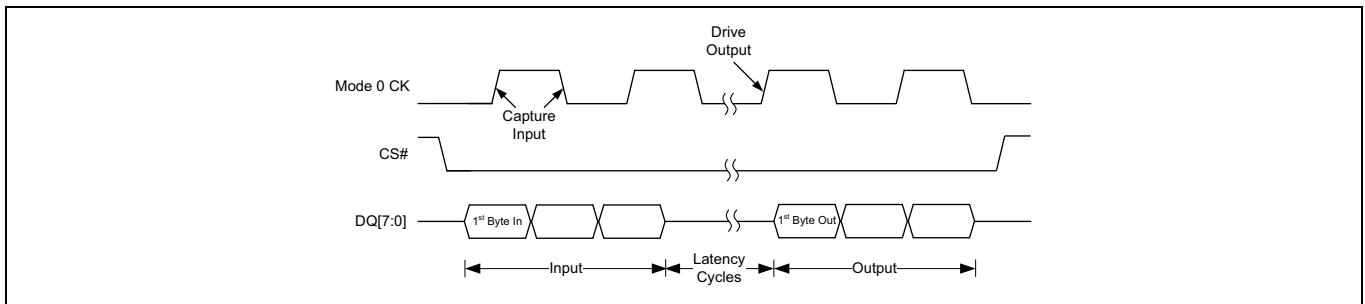

- モード 0: クロックの極性は CS# の立ち下りでは LOW であり、キャプチャ入力では HIGH になるまで LOW のままでです。

- モード 3: クロックの極性は CS# の立ち下りで HIGH であり、キャプチャ入力では LOW から HIGH になります。

両方のモードでデータは、SDR プロトコルの場合 CK 信号の立ち上りエッジで、DDR プロトコルの場合 CK 信号の両エッジでデバイスにラッチされます。SDR プロトコルの出力データは CK クロック信号の立ち下りエッジで、DDR プロトコルの出力データは CK クロック信号の立ち上りエッジで、使用可能になります。

2 つのモードの異なる点は、バス マスターがスタンバイ モードであり、データを転送しない時のクロック極性です。

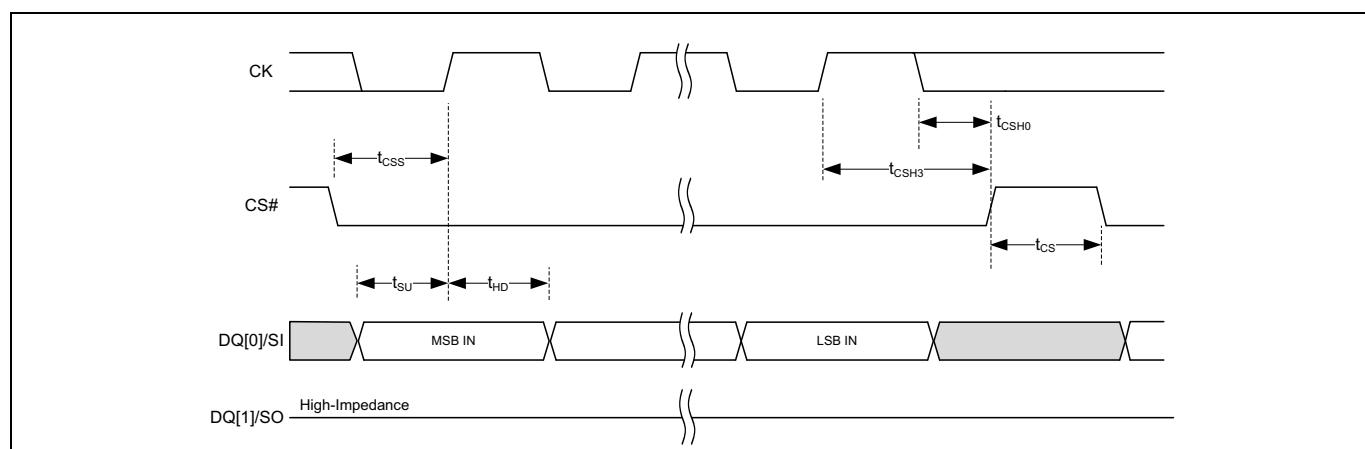

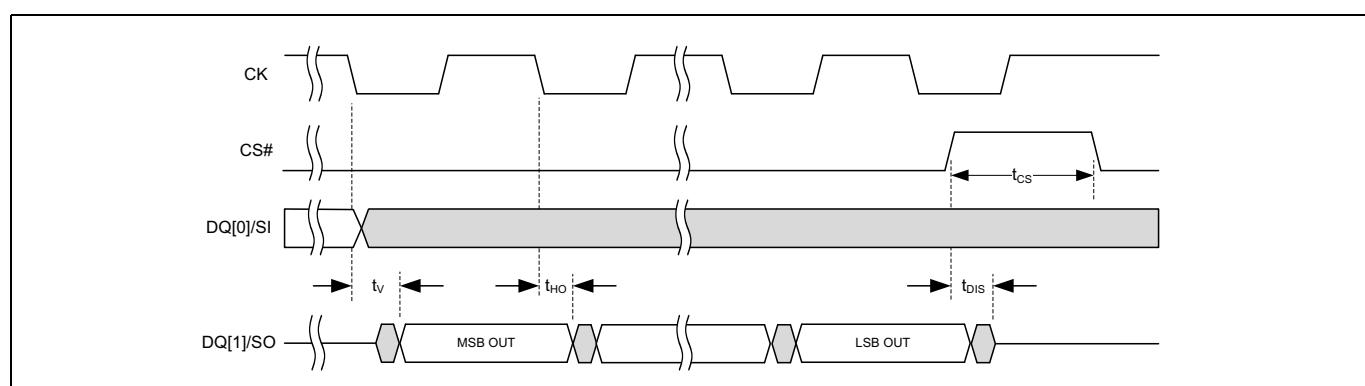

Figure 3 サポートされる SPI SDR モード

Figure 4 サポートされるオクタル SDR モード

## インターフェースの概要

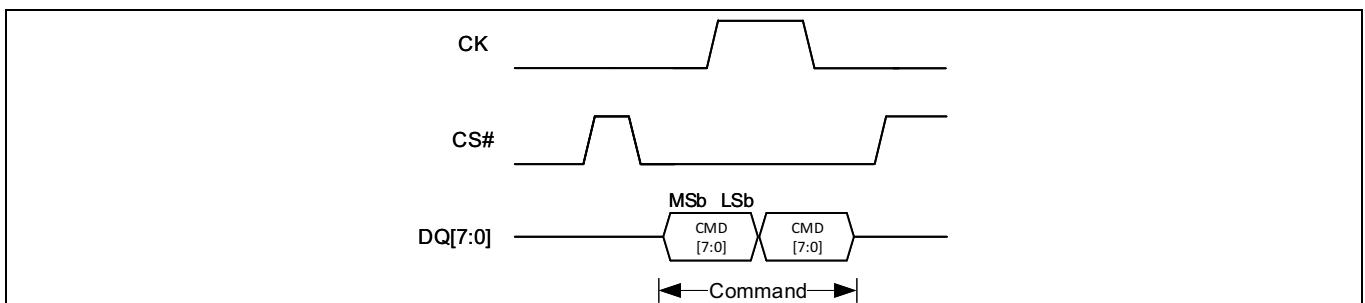

SEMPER™ フラッシュ オクタル DDR モード動作では、クロック モード 0 のみがサポートされます。

**Figure 5** サポートされるオクタル DDR モード

## 2.3 トランザクションプロトコル

### トランザクション

- CS# がアクティブ (LOW) のとき、データ (DQ) 信号上でまずコマンド情報、次にアドレスおよびデータがホストからフラッシュデバイスに転送されている間、クロック信号 (CK) はトグルします。フラッシュデバイスからホストへの読み出しデータ、またはホストからフラッシュデバイスへの書き込みデータの転送中にクロックはトグルし続けます。ホストは所望のデータ量を転送した後、CS# を非アクティブ (HIGH) に駆動します。CS# がアクティブである期間は、バス上のトランザクションと呼ばれます。

- CS# が非アクティブのとき、CK はトグルする必要がありません。

- コマンド転送はすべてのトランザクションの開始時に行われます。アドレス、レイテンシサイクルおよびデータ転送フェーズはオプションで、それらの存在はプロトコルモードまたは転送されるコマンドに依存します。

### トランザクションキャプチャ

- CK はホストとメモリの間の各ビットまたは各ビットグループの転送を示します。コマンド、アドレスおよび書き込みデータビットの転送は、SDR トランザクションでは CK の立ち上りエッジで、DDR トランザクションではすべての CK エッジで行われます。

注：

- プログラムまたは消去(組込み動作)中に、フラッシュメモリアレイを読み出そうとすると無視されます。組込み動作はそれに影響されず、実行が継続されます。組込み動作中、ごく限られたコマンドセットは受け入れられます。それらは 66 ページの “組込み動作の一時停止と再開” で説明されています。

### プロトコル用語

- トランザクション中に使用される DQ 信号の数は、現在のプロトコルモードまたは転送されるコマンドによって異なります。レイテンシサイクルは DQ 信号を情報転送に使用しません。プロトコルモードオプションは、コマンド、アドレスおよびデータフェーズで使用されるデータレートおよび DQ 幅 (DQ 信号の数) によって示されます。形式は次のとおりです。

WR-WR-WR、ここでは：

- 最初の WR はコマンドビットの幅とレート

- 2 番目の WR はアドレスビットの幅とレート

- 3 番目の WR はデータビットの幅とレート

- ビット幅の値は 1 または 8 のいずれかです。R の値は、SDR の場合は S で、DDR の場合は D です。SDR の場合では、転送値はクロックサイクルの立ち上りエッジと立ち下りエッジの両方で同じです。DDR は、各クロックの立ち上りエッジと立ち下りエッジで、異なる転送値を持ちます。

## インターフェースの概要

### • 例 :

- 1S-1S-1S は、コマンドが 1 ビット幅の SDR、アドレスが 1 ビット幅の SDR、データが 1 ビット幅の SDR であることを意味します。

- 8D-8D-8D は、コマンド、アドレスおよびデータ転送はいずれも 8 ビット幅の DDR であることを意味します。

## プロトコル定義

### • オクタルインターフェースを備える SEMPER™ フラッシュ向けに定義されているプロトコルモード :

1.1S-1S-1S: コマンド転送、アドレス転送およびデータ転送中に 1 つの DQ 信号が使用されます。すべてのフェーズは SDR です。

2.8S-8S-8S: コマンド転送、アドレス転送およびデータ転送中に 8 つの DQ 信号が使用されます。すべてのフェーズは SDR です。

3.8D-8D-8D: コマンド転送、アドレス転送およびデータ転送中に 8 つの DQ 信号が使用されます。すべてのフェーズは DDR です。

## 1S-1S-1S プロトコル

- 1S-1S-1S モードはパワーオンリセット (POR) の後に推奨されるデフォルトのプロトコルですが、フラッシュデバイスはクアッドモードにリセットするように設定できます。

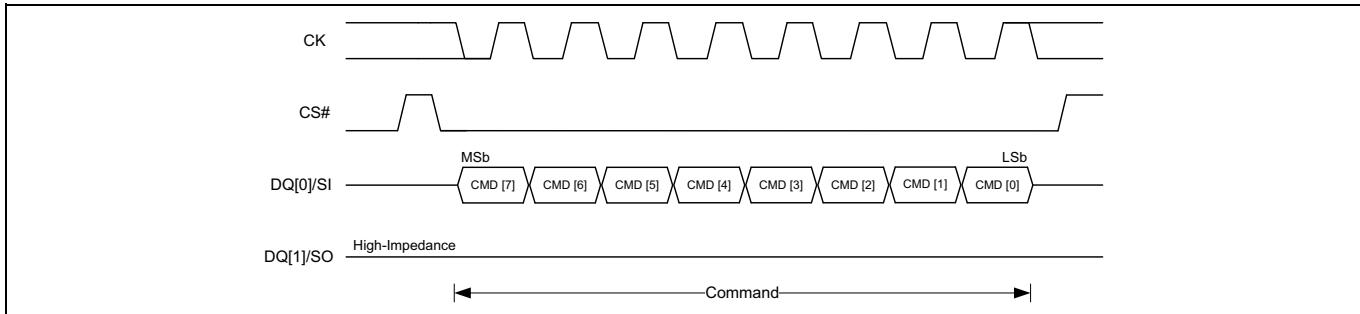

- 各トランザクションは 8 ビット (1 バイト) コマンドで始まります。コマンドは、情報転送のタイプ、または実行するデバイスの動作を選択します。

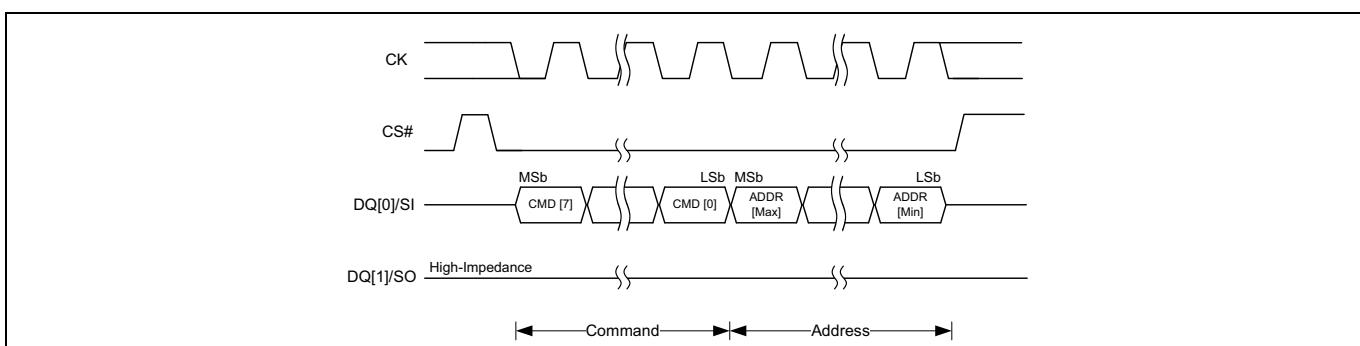

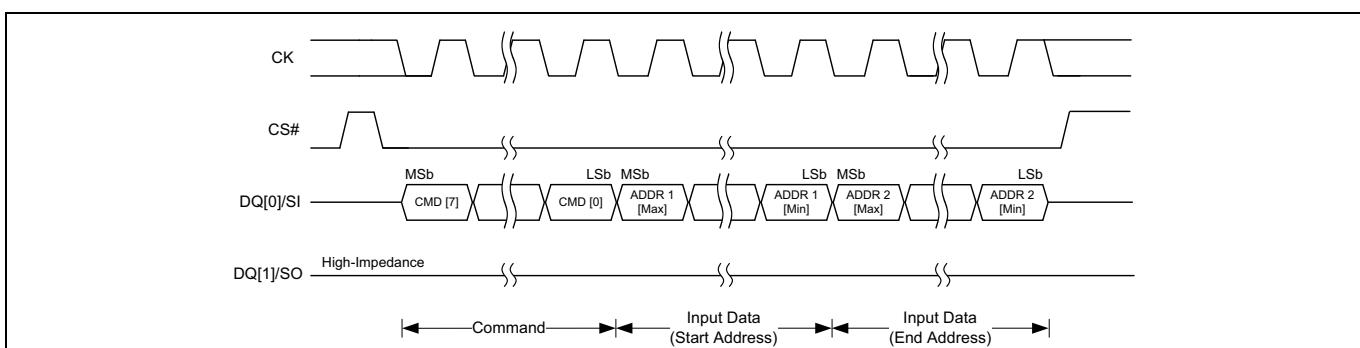

- このプロトコルは、SI/DQ[0] を使用してホストからフラッシュデバイスへ、SO/DQ[1] を使用してフラッシュデバイスからホストへ情報を転送します。各 DQ ライン上で、情報は各バイト内で最上位ビット (MSb) から最下位ビット (LSb) へ順に配置されます。シーケンシャルアドレスバイトは最上位から最下位に順に転送されます。シーケンシャルデータバイトは最下位アドレスから最上位アドレスへ順に転送されます。

- 1S-1S-1S プロトコルでは、DQ[7:2] はデータ転送期間中に使用されません。そのため、DQ[7:2] 信号は高インピーダンスになります。

## 8S-8S-8S と 8D-8D-8D プロトコル

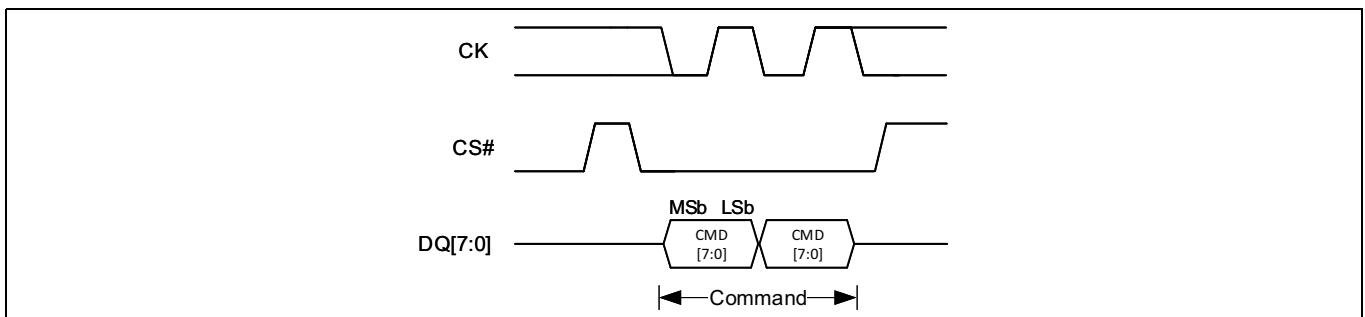

- 各トランザクションは 16 ビット (2 つの同じバイト) コマンドで始まります。コマンドは、情報転送のタイプ、または実行するデバイスの動作を選択します。

### • 4 バイトアドレスのみサポートします。

- このプロトコルは DQ[7:0] 信号を使用します。アドレスバイトの LSb ビットは DQ[0] 信号に、その次のビットは DQ[1] 信号に順に配置されます。シーケンシャルアドレスバイトは最上位から最下位に順に転送されます。SDR でのシーケンシャルデータバイトは、最下位アドレスから最上位アドレスへの順で転送されます。DDR でのシーケンシャルデータバイトはバイトペア (ワード) でのみ転送され、バイト順序は、バイトがそのプロトコルモードで書き込まれるまたはプログラムされる順序に依存します。シーケンシャルデータバイトは最下位アドレスから最上位アドレスへ順に転送されます。

- このプロトコルでは、読み出しへトランザクションのデータ転送期間中、データストローブ (DS) 信号がフラッシュデバイスによって駆動され、遷移は DQ 信号データ遷移によって同期されます (DDR でエッジ揃え、SDR プロトコルで中央揃え)。DS はその他のデータ出力と同じタイミング特性を持つ追加の出力信号として使用されますが、あらゆるデータビットが転送されることで遷移が保証されます。

13 ページの “シリアルペリフェラルインターフェース (SPI、1S-1S-1S)” に、すべてのトランザクションフォーマットをプロトコルモードで示しています。

### 2.3.1 シリアルペリフェラルインターフェース (SPI、1S-1S-1S)

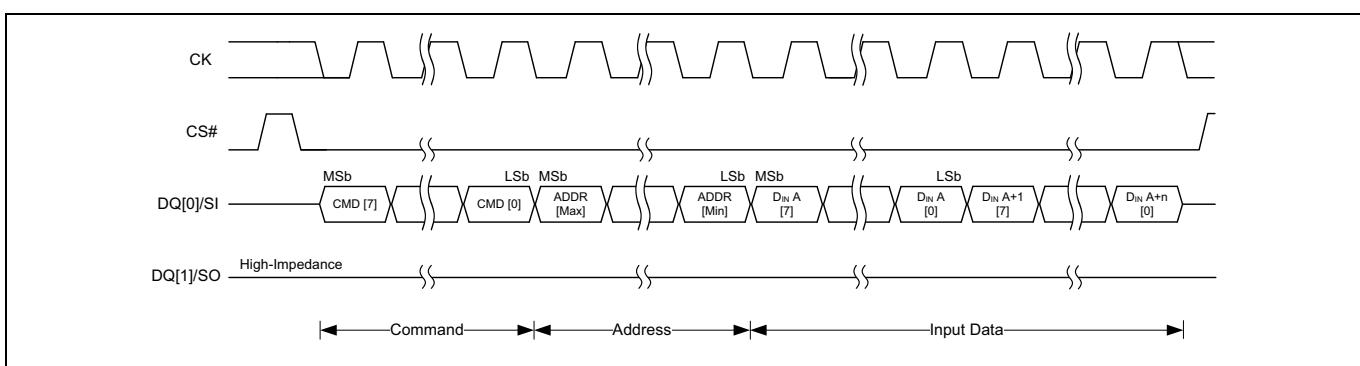

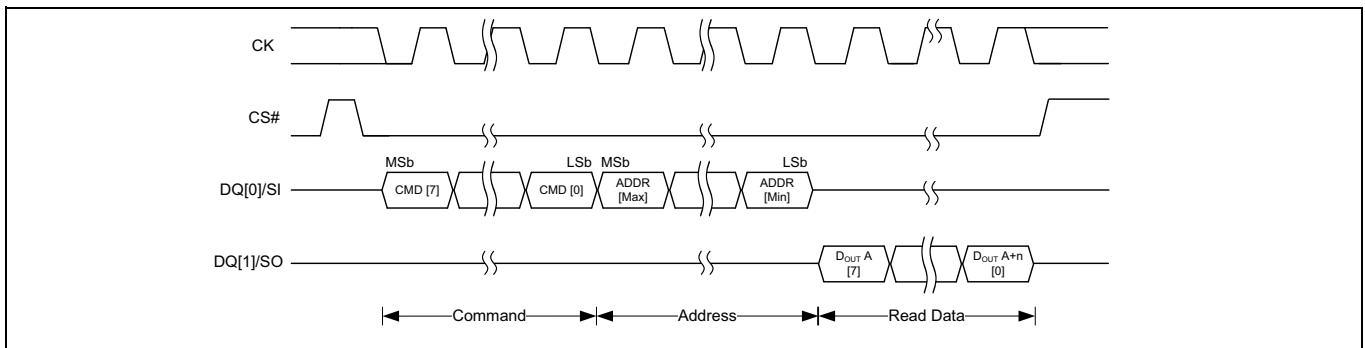

Figure 6 コマンド入力のある SPI トランザクション

Figure 7 コマンド入力のある SPI トランザクション

Figure 8 コマンドと 2 アドレス入力のある SPI トランザクション

Figure 9 コマンド , アドレスおよびデータ入力のある SPI プログラム トランザクション

## インターフェースの概要

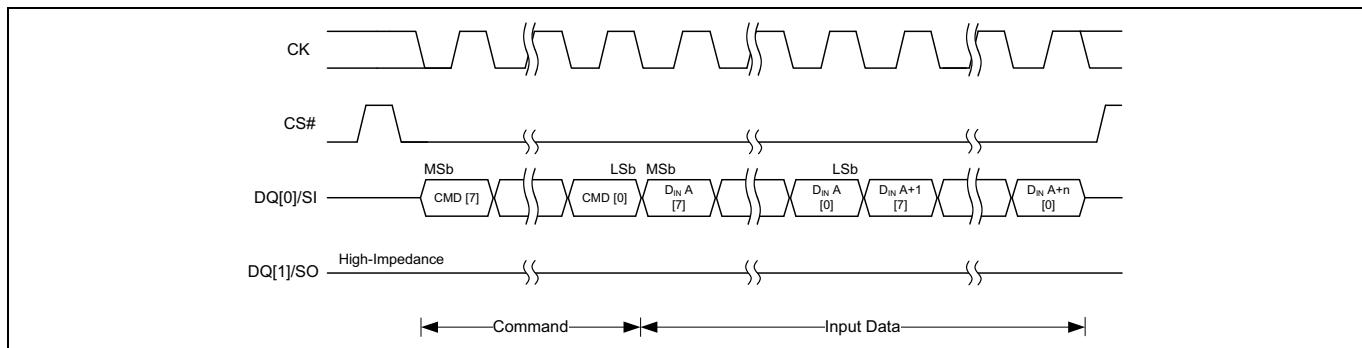

**Figure 10** コマンドとデータ入力のある SPI プログラム トランザクション

**Figure 11** コマンド入力のある SPI 読み出しトランザクション(出力レイテンシ有り)

**Figure 12** コマンドとアドレス入力のある SPI 読み出しトランザクション(出力レイテンシ有り)

### インターフェースの概要

**Figure 13** コマンドとアドレス入力のある SPI 読み出しトランザクション(出力レイテンシ無し)

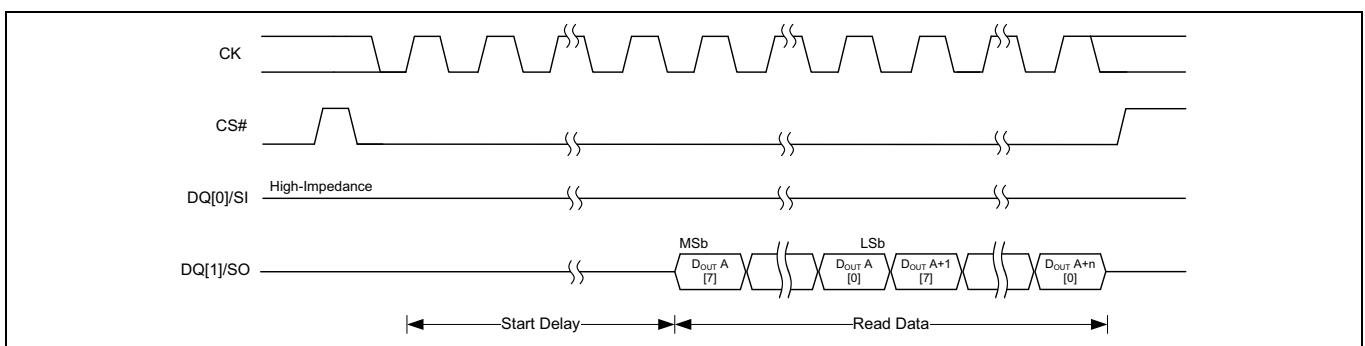

**Figure 14** 出力データシーケンスのある SPI トランザクション(オートブート)

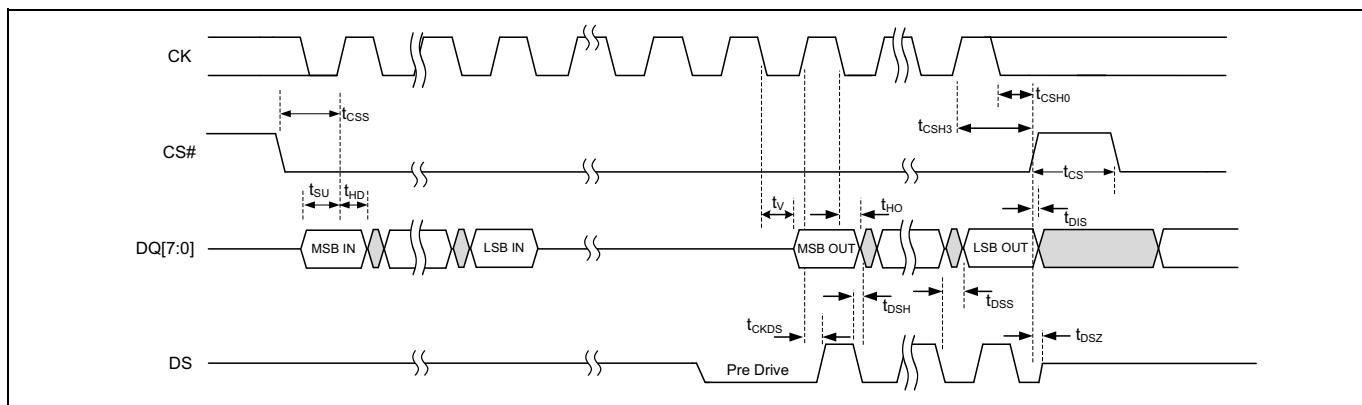

### 2.3.2 オクタルペリフェラルインターフェース(オクタル, 8S-8S-8S および 8D-8D-8D)

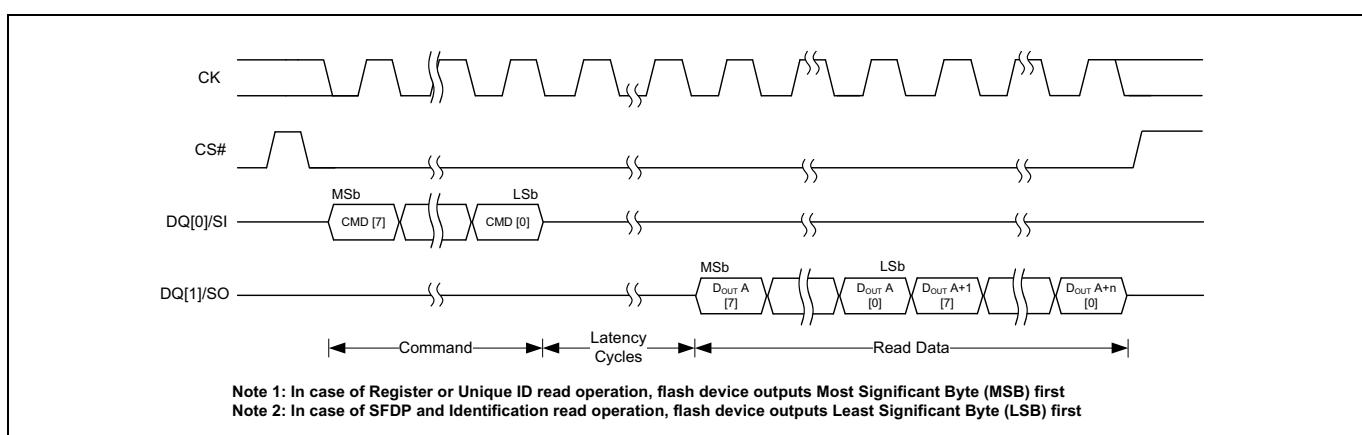

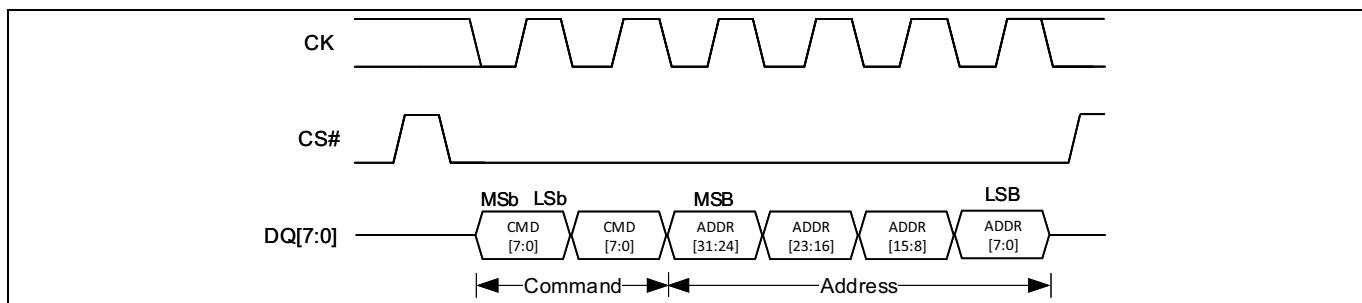

**Figure 15** コマンド入力のあるオクタル SDR トランザクション

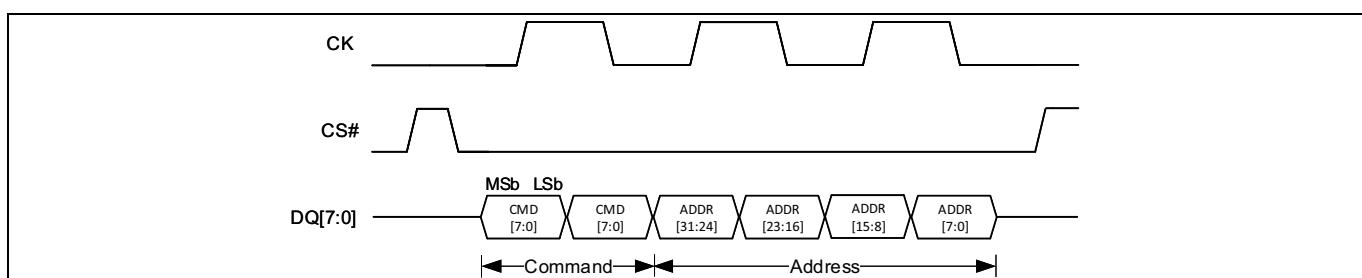

**Figure 16** コマンド入力のあるオクタル DDR トランザクション

## インターフェースの概要

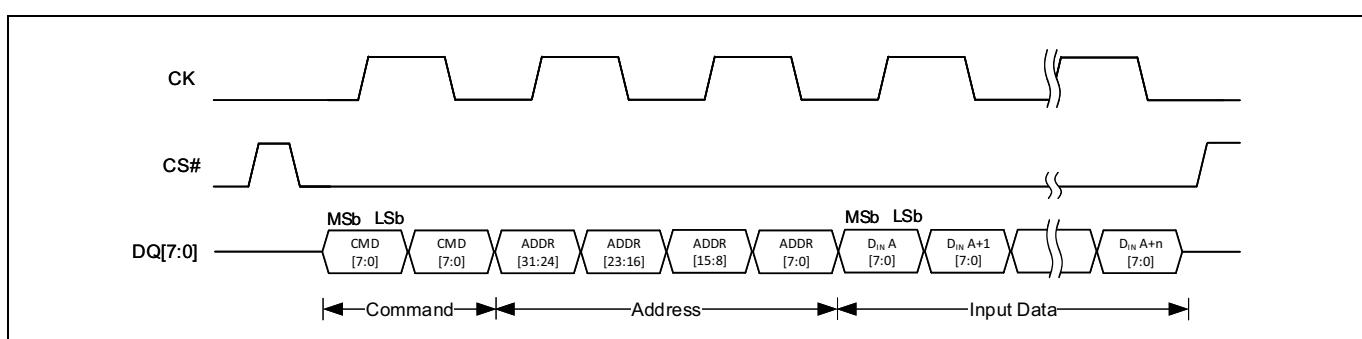

Figure 17 コマンドとアドレス入力のあるオクタル SDR トランザクション

Figure 18 コマンドとアドレス入力のあるオクタル DDR トランザクション [2]

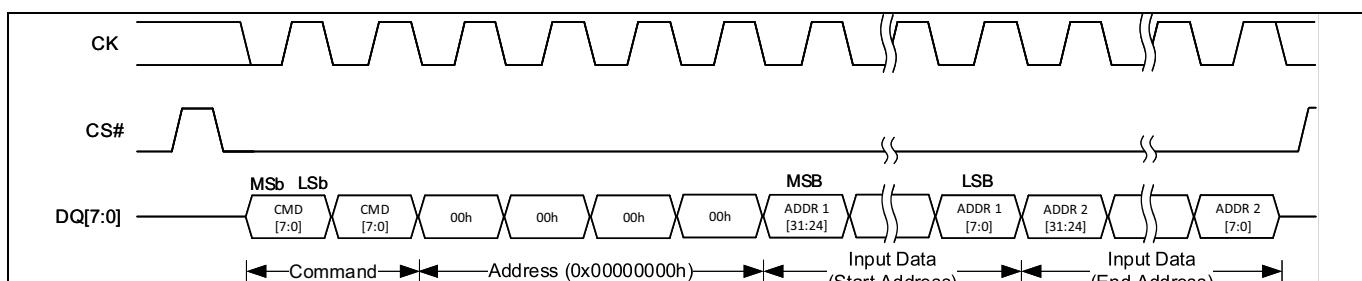

Figure 19 コマンドと 2 つのアドレス入力のあるオクタル SDR トランザクション

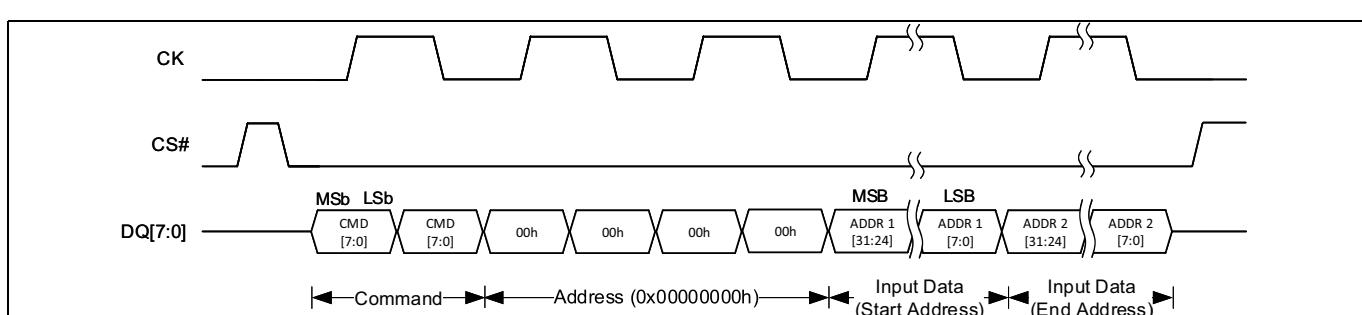

Figure 20 コマンドと 2 つのアドレス入力のあるオクタル DDR トランザクション

## 注

2. アドレス入力を必要とするあらゆるオクタル DDR トランザクションではアドレスの LSb は常に 0 です。

## インターフェースの概要

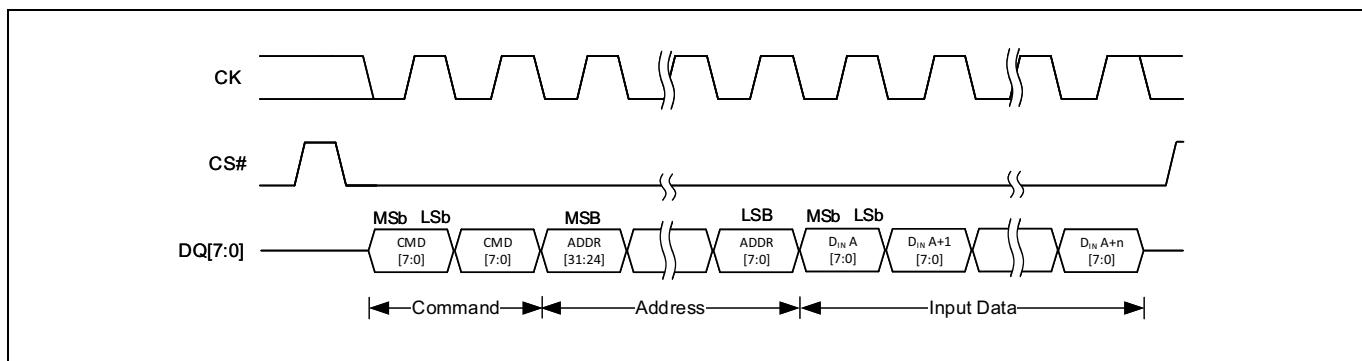

**Figure 21** コマンド , アドレスおよびデータ入力のあるオクタル SDR プログラムトランザクション

**Figure 22** コマンド , アドレスおよびデータ入力のあるオクタル DDR プログラムトランザクション

[3]

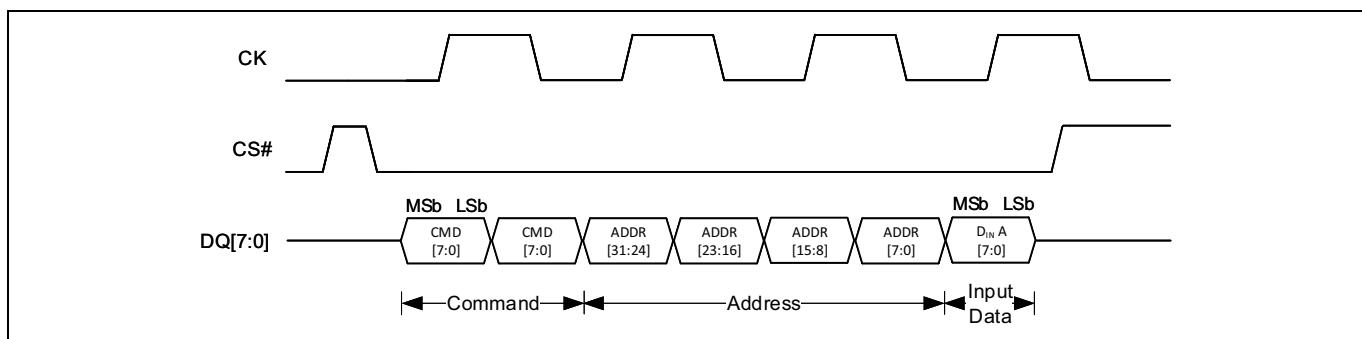

**Figure 23** コマンド , アドレスおよびシングルバイトデータ入力のあるオクタル DDR プログラムトランザクション

[3]

## 注

3. アドレス入力を必要とするあらゆるオクタル DDR トランザクションではアドレスの LSb は常に 0 です。

## インターフェースの概要

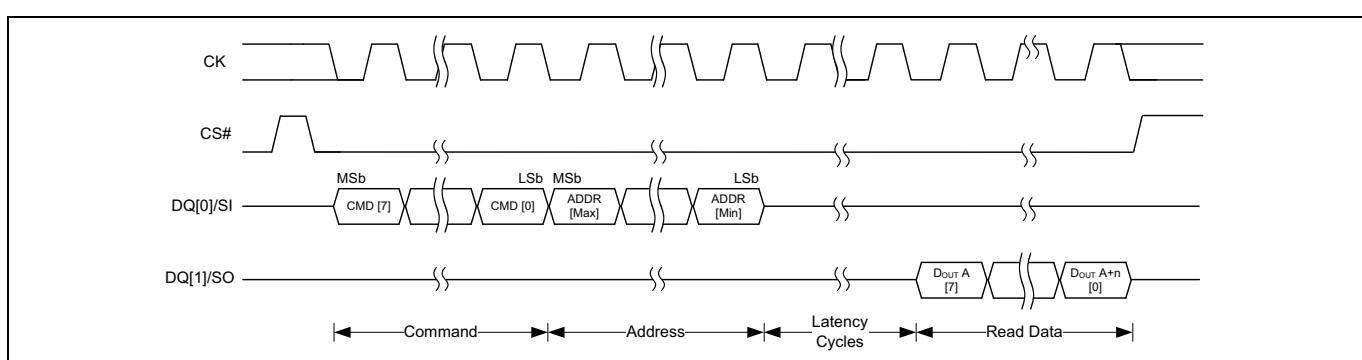

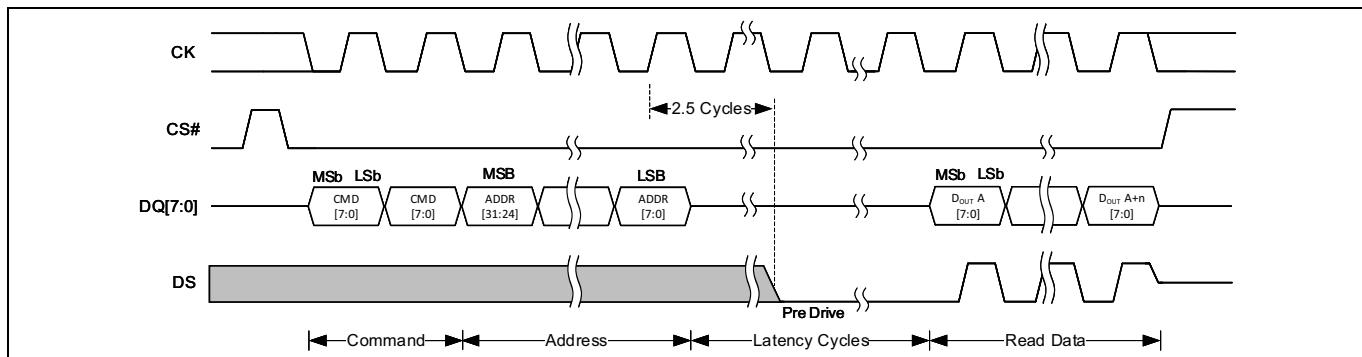

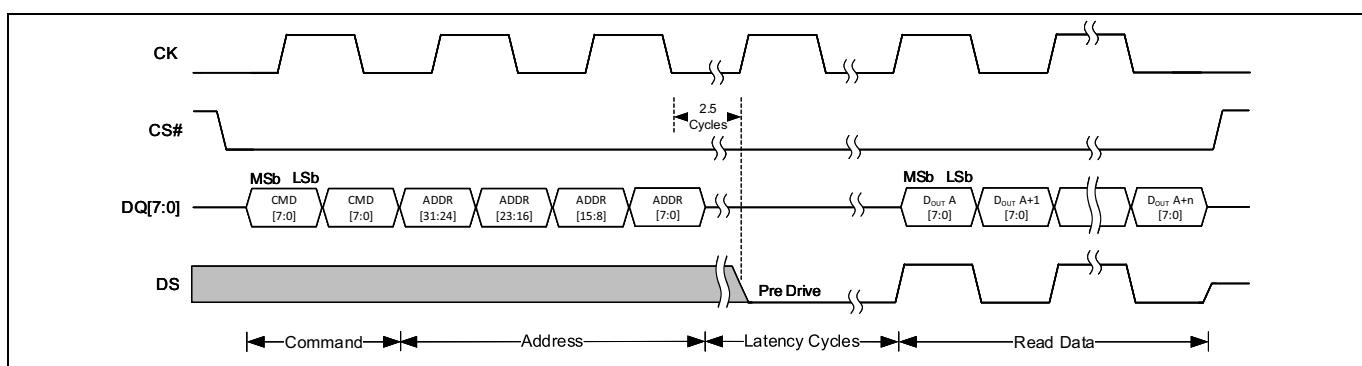

Figure 24 コマンドとアドレス入力のある SDR 読み出しトランザクション(出力レイテンシ有り)

Figure 25 コマンドとアドレス入力のあるオクタル DDR 読み出しトランザクション(出力レイテンシ有り)[4,5]

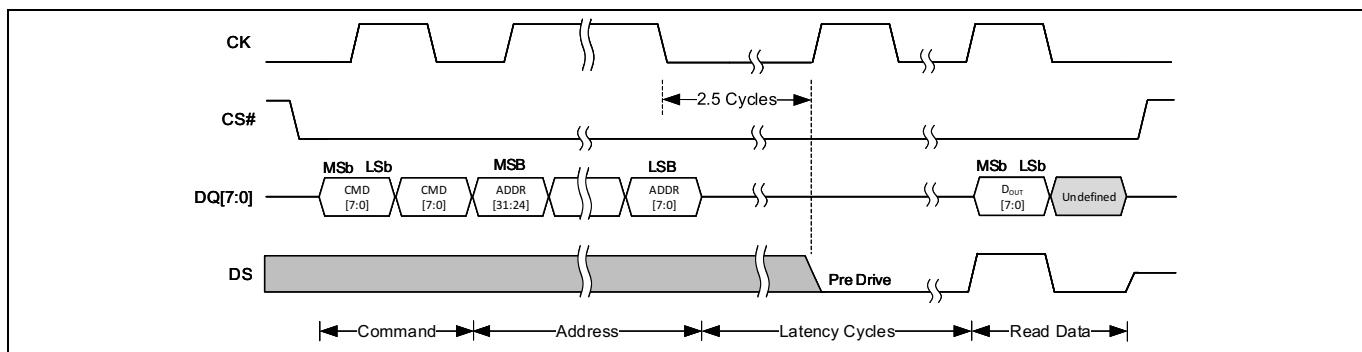

Figure 26 コマンドとアドレス入力のあるオクタル DDR シングルバイト読み出しトランザクション(出力レイテンシ有り)[6]

## 注

4. アドレス入力を必要とするあらゆるオクタル DDR トランザクションではアドレスの LSb は常に 0 です。

5. インターフェース CRC 読み出しトランザクションはオクタル DDR でのみサポートされます。

6. アドレス入力を必要とするあらゆるオクタル DDR トランザクションではアドレスの LSb は常に 0 です。

## インターフェースの概要

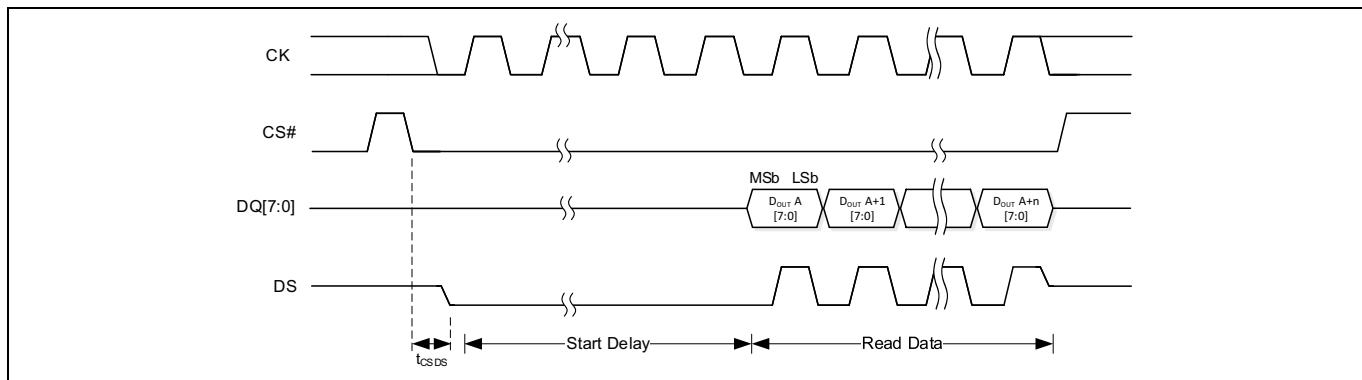

**Figure 27** 出力データシーケンスのあるオクタル SDR トランザクション(オートブート)

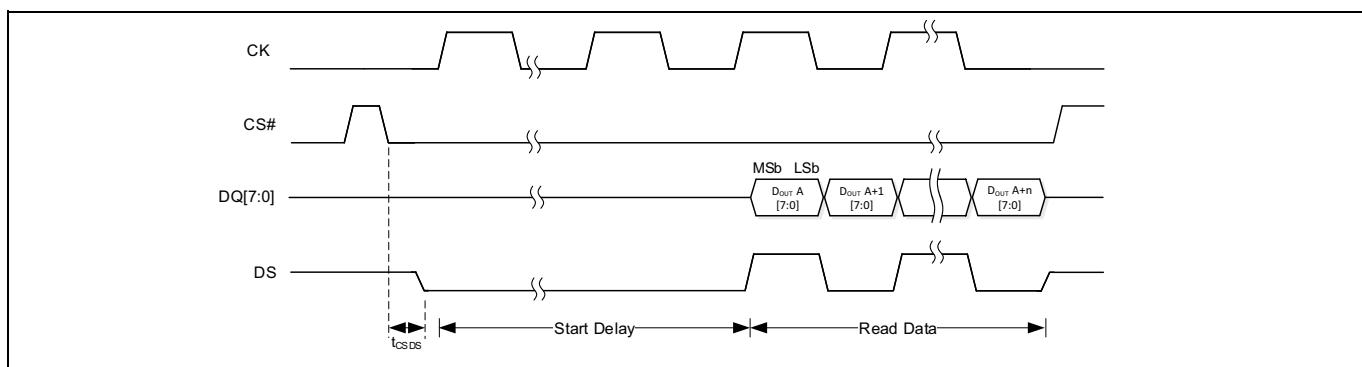

**Figure 28** 出力データシーケンスのあるオクタル DDR トランザクション(オートブート)

## 2.4 レジスタ命名規則

**Figure 29** レジスタ命名規則

**Figure 30** レジスタビット命名規則

## 2.5 トランザクション命名規則

**Figure 31 トランザクション命名規則**

### 3 アドレス空間マップ

HL-T/HS-T ファミリは、メモリ容量が 512 Mb または 1 Gb のデバイスを有効にするために 32 ビット(4 バイト)アドレスと同様に 24 ビットアドレスをサポートします。4 バイトアドレスにより、最大 4GB(32Gb) のアドレス空間を直接アドレス指定することが可能になります。アドレス バイト オプションは、対応するコンフィギュレーション レジスタに書き込むことで変更できます。また、4 バイトアドレス モードに入る(EN4BA\_0\_0)ためおよびモードから出る(EX4BA\_0\_0)ための個別のトランザクションもあります。

Figure 32 HL-T/HS-T アドレス空間マップ概要

#### 3.1 SEMPER™ フラッシュメモリアレイ

メイン フラッシュ アレイは物理セクタと呼ばれるユニットに分けられています。

HL-T/HS-T ファミリのセクタアーキテクチャは以下のオプションに対応しています。

- 256 KB ユニフォーム セクタ オプション対応の 512 Mb, 1 Gb

- ハイブリッド セクタ オプション対応の 512 Mb, 1 Gb

- アドレス空間の最上部または最下部にある 32 の 4 KB セクタおよび 1 つの 128 KB セクタと、256 KB の残りのセクタの物理セット

- アドレス空間の最上部と最下部の両方にある 16 の 4KB セクタおよび 1 つの 192 KB セクタと、256 KB の残りのセクタの物理セット

コンフィギュレーション レジスタ 1 および コンフィギュレーション レジスタ 3 内のセクタアーキテクチャ選択ビットの組合せは、HL-T/HS-T ファミリの異なるセクタアーキテクチャ オプションをサポートします。詳細については 78 ページの “[レジスタ](#)” を参照してください。

アドレス空間マップ

**Table 8 256KB ユニフォームセクタアドレスマップ<sup>[7]</sup>**

| セクタ<br>サイズ<br>(KB) | S28HL01GT および S28HS01GT |           |                                    | S28HL512T および S28HS512T |           |                                    |

|--------------------|-------------------------|-----------|------------------------------------|-------------------------|-----------|------------------------------------|

|                    | セクタ<br>数                | セクタ<br>範囲 | バイトアドレス範囲<br>(セクタ開始アドレス～セクタ終了アドレス) | セクタ<br>数                | セクタ<br>範囲 | バイトアドレス範囲<br>(セクタ開始アドレス～セクタ終了アドレス) |

| 256                | 512                     | SA00      | 00000000h ~ 0003FFFFh              | 256                     | SA00      | 00000000h ~ 0003FFFFh              |

|                    |                         | :         | :                                  |                         | :         | :                                  |

|                    |                         | SA511     | 07FC0000h ~ 07FFFFFFh              |                         | SA255     | 03FC0000h ~ 03FFFFFFh              |

注

7. コンフィギュレーション : CFR3N[3] = 1。

**Table 9 最下部のハイブリッドコンフィギュレーション 1:32 の 4KB セクタと 256KB ユニフォームセクタのアドレスマップ<sup>[8]</sup>**

| セクタ<br>サイズ<br>(KB) | S28HL01GT および S28HS01GT |           |                                    | S28HL512T および S28HS512T |           |                                    |

|--------------------|-------------------------|-----------|------------------------------------|-------------------------|-----------|------------------------------------|

|                    | セクタ<br>数                | セクタ<br>範囲 | バイトアドレス範囲<br>(セクタ開始アドレス～セクタ終了アドレス) | セクタ<br>数                | セクタ<br>範囲 | バイトアドレス範囲<br>(セクタ開始アドレス～セクタ終了アドレス) |

| 4                  | 32                      | SA00      | 00000000h ~ 00000FFFh              | 32                      | SA00      | 00000000h ~ 00000FFFh              |

|                    |                         | :         | :                                  |                         | :         | :                                  |

|                    |                         | SA31      | 0001F000h ~ 0001FFFFh              |                         | SA31      | 0001F000h ~ 0001FFFFh              |

| 128                | 1                       | SA32      | 00020000h ~ 0003FFFFh              | 1                       | SA32      | 00020000h ~ 0003FFFFh              |

| 256                | 511                     | SA33      | 00040000h ~ 0007FFFFh              | 255                     | SA33      | 00040000h ~ 0007FFFFh              |

|                    |                         | :         | :                                  |                         | :         | :                                  |

|                    |                         | SA543     | 07FC0000h ~ 07FFFFFFh              |                         | SA287     | 03FC0000h ~ 03FFFFFFh              |

注

8. コンフィギュレーション : CFR3N[3] = 0, CFR1N[6] = 0, CFR1N[2] = 0。

**Table 10 最上部のハイブリッドコンフィギュレーション 1:32 の 4KB セクタと 256KB ユニフォームセクタのアドレスマップ<sup>[9]</sup>**

| セクタ<br>サイズ<br>(KB) | S28HL01GT および S28HS01GT |           |                                    | S28HL512T および S28HS512T |           |                                    |

|--------------------|-------------------------|-----------|------------------------------------|-------------------------|-----------|------------------------------------|

|                    | セクタ<br>数                | セクタ<br>範囲 | バイトアドレス範囲<br>(セクタ開始アドレス～セクタ終了アドレス) | セクタ<br>数                | セクタ<br>範囲 | バイトアドレス範囲<br>(セクタ開始アドレス～セクタ終了アドレス) |

| 256                | 511                     | SA00      | 00000000h ~ 0003FFFFh              | 255                     | SA00      | 00000000h ~ 0003FFFFh              |

|                    |                         | :         | :                                  |                         | :         | :                                  |

|                    |                         | SA510     | 07F80000h ~ 07FBFFFFh              |                         | SA254     | 03F80000h ~ 03FBFFFFh              |

| 128                | 1                       | SA511     | 07FC0000h ~ 07FDFFFFh              | 1                       | SA255     | 03FC0000h ~ 03FDFFFFh              |

| 4                  | 32                      | SA512     | 07FE0000h ~ 07FE0FFFh              | 32                      | SA256     | 03FE0000h ~ 03FE0FFFh              |

|                    |                         | :         | :                                  |                         | :         | :                                  |

|                    |                         | SA543     | 07FFF000h ~ 07FFFFFFh              |                         | SA287     | 03FFF000h ~ 03FFFFFFh              |

注

9. コンフィギュレーション : CFR3N[3] = 0, CFR1N[6] = 0, CFR1N[2] = 1。

**Table 11** ハイブリッドコンフィギュレーション 2: 最下位 16 と最上位 16 の 4KB セクタのアドレスマップ<sup>[10]</sup>

| セクタ<br>サイズ<br>(KB) | S28HL01GT および S28HS01GT |           |                                    | S28HL512T および S28HS512T |           |                                    |

|--------------------|-------------------------|-----------|------------------------------------|-------------------------|-----------|------------------------------------|

|                    | セクタ<br>数                | セクタ<br>範囲 | バイトアドレス範囲<br>(セクタ開始アドレス～セクタ終了アドレス) | セクタ<br>数                | セクタ<br>範囲 | バイトアドレス範囲<br>(セクタ開始アドレス～セクタ終了アドレス) |

| 4                  | 16                      | SA00      | 00000000h ~ 00000FFFh              | 16                      | SA00      | 00000000h ~ 00000FFFh              |

|                    |                         | :         | :                                  |                         | :         | :                                  |

|                    |                         | SA15      | 0000F000h ~ 0000FFFFh              |                         | SA15      | 0000F000h ~ 0000FFFFh              |

| 192                | 1                       | SA16      | 00010000h ~ 0003FFFFh              | 1                       | SA16      | 00010000h ~ 0003FFFFh              |

| 256                | 510                     | SA17      | 00040000h ~ 0007FFFFh              | 254                     | SA17      | 00040000h ~ 0007FFFFh              |

|                    |                         | :         | :                                  |                         | :         | :                                  |

|                    |                         | SA526     | 07F80000h ~ 07FBFFFFh              |                         | SA270     | 03F80000h ~ 03FBFFFFh              |

| 192                | 1                       | SA527     | 07FC0000h ~ 07FEFFFFh              | 1                       | SA271     | 03FC0000h ~ 03FEFFFFh              |

| 4                  | 16                      | SA528     | 07FF0000h ~ 07FF0FFFh              | 16                      | SA272     | 03FF0000h ~ 03FF0FFFh              |

|                    |                         | :         | :                                  |                         | :         | :                                  |

|                    |                         | SA543     | 07FFF000h ~ 07FFFFFFh              |                         | SA287     | 03FFF000h ~ 03FFFFFFh              |

#### 注

10. コンフィギュレーション : CFR3N[3] = 0, CFR1N[6] = 1。

上記の表は参考としていくつかのセクタを使用する要約された表です。明示的にリストされていないアドレス範囲があります。すべての 4KB セクタのパターンは xxxx000h ~ xxxxFFFh です。すべての 256KB セクタのパターンは xxx00000h ~ xxx3FFFFh, xxx40000h ~ xxx7FFFFh, xx80000h ~ xx9FFFFh, または xxD0000h ~ xx9FFFFh です。

### 3.2 ID アドレス空間

メモリのこの特別な領域は、メーカー ID, デバイス ID, および固有 ID に割り当てられます。

- メーカー ID は JEDEC によって割り当てられます (Table 94 を参照してください)。

- デバイス ID はインフィニオンによって割り当てられます (Table 94 を参照してください)。

- 64 ビット固有番号は固有デバイス ID アドレス空間の 8 バイトにあります。固有 ID は、各デバイスに固有のソフトウェア読み出し可能シリアル番号として使用できます。 (Table 95 を参照)

ID のために定義されるアドレス空間がなく、対応するトランザクションを提供することでのみ読み出せます。ID を読み出すためにトランザクションにアドレスは必要ありません。このアドレス空間内のデータは読み出し専用データです。

### 3.3 JEDEC JESD216 SFDP 空間

SFDP 規格は、内部パラメーター テーブルの標準的な一式でこのシリアルフラッシュ デバイスの機能と特長を記述する一貫性のある方法を提供します。ホストシステムソフトウェアはこれらのパラメーター テーブルを問い合わせ、異なる機能に対応するために必要な調整を可能にします。SFDP アドレス空間には、SFDP データ構造を識別し、各パラメーターへのポインタを提供する、アドレス 0 から始まるヘッダが含まれています。SFDP アドレス空間はインフィニオンによってプログラムされ、ホストシステムに対しては読み出し専用です (Table 90 ~ Table 93 を参照してください)。

**Table 12** SFDP アドレスマップ概要

| バイトアドレス | 説明                                       |

|---------|------------------------------------------|

| 0000h   | JEDEC JESD216 SFDP 空間の位置 0 - SFDP ヘッダの開始 |

| ,,,     | SFDP ヘッダの残りの部分に続いて未定義の空間                 |

**Table 12 SFDP アドレスマップ概要( 続き )**

| バイトアドレス | 説明                                                   |

|---------|------------------------------------------------------|

| 0100h   | SFDP パラメーター テーブルの開始。SFDP パラメーター テーブルのデータは 0100h で始まる |

| ...     | SFDP パラメーター テーブルの残りの部分に続いてさらなるパラメーターまたは未定義空間         |

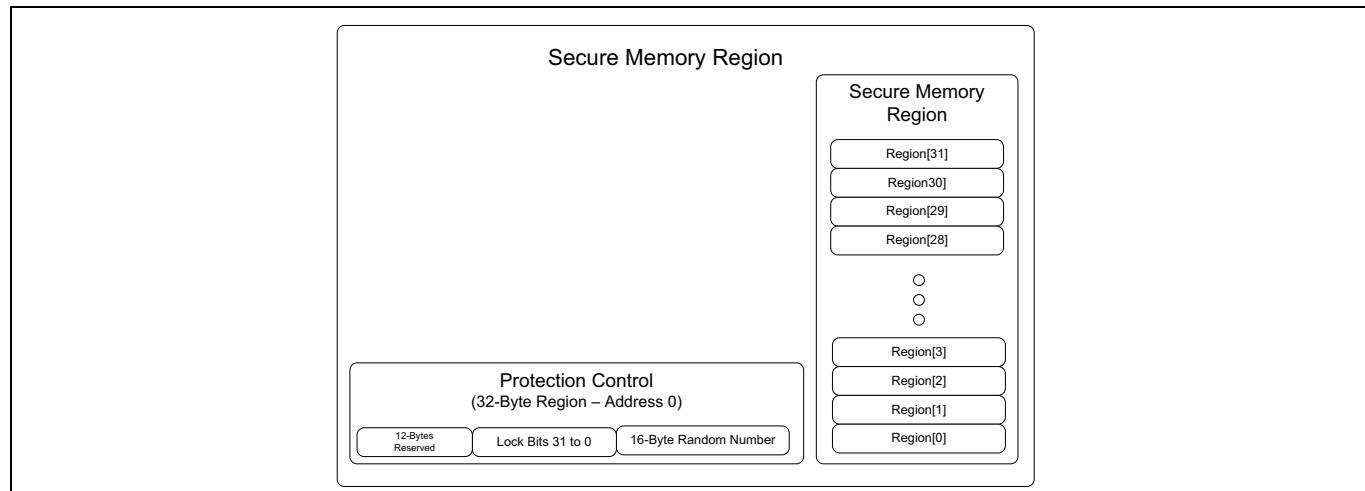

### 3.4 SSR アドレス空間

各 HS/L-T family メモリデバイスは OTP アドレス空間である 1024 バイトの SSR を持っています。このアドレス空間はメイン フラッシュアレイから分かれています。SSR 領域は 32 の領域に分割され、それが単独にロックでき、32 バイト整列長です。

アドレス 0 から始まる 32 バイトの領域では、

- 16 最下位バイトは 128 ビットの乱数を含みます。この乱数に対する書き込み、消去またはプログラムは不可であり、行おうとすると PRGERR フラグが返されます。

- 次の 4 バイトは、セキュア領域ごとに 1 ビット(合計 32 ビット)を提供し、いったん「0」にセットされたら、書き込み、消去またはプログラムから恒久的に保護します。

- 他のすべてのバイトは予約されています。

残りの領域は、インフィニオン出荷時に消去され、追加の恒久的なデータのプログラミングに使用できます。

**Table 13 SSR アドレスマップ**

| 領域    | バイトアドレス範囲   | 目次                                                                                                               | 工場出荷初期状態             |  |

|-------|-------------|------------------------------------------------------------------------------------------------------------------|----------------------|--|

| 領域 0  | 000h        | インフィニオンによりプログラムされた乱数の LSB                                                                                        | インフィニオンによりプログラムされた乱数 |  |

|       | ...         | ...                                                                                                              |                      |  |

|       | 00Fh        | インフィニオンによりプログラムされた乱数の MSB                                                                                        |                      |  |

|       | 010h ~ 013h | 領域ロックビット<br>バイト 10h [ビット 0] = 「0」のとき、領域 0 をプログラムから保護します。<br>...<br>バイト 13h [ビット 7] = 「0」のとき、領域 31 をプログラムから保護します。 | 全バイト = FFh           |  |

|       | 014h ~ 01Fh | 将来使用するために予約済み (RFU)                                                                                              |                      |  |

| 領域 1  | 020h ~ 03Fh | ユーザー プログラミング用に使用可能                                                                                               |                      |  |

| 領域 2  | 040h ~ 05Fh |                                                                                                                  |                      |  |

| ...   | ...         |                                                                                                                  |                      |  |

| 領域 31 | 3E0h ~ 3FFh |                                                                                                                  |                      |  |

アドレス空間マップ

### 3.5 レジスタ

レジスタは、HS/L-T family メモリデバイスの動作方法を設定する、またはデバイス動作のステータスを報告するために使用される小さなグループのメモリセルです。レジスタは特定のコマンドおよびアドレスでアクセスされます。Table 14 に、本フラッシュメモリデバイスの利用可能なレジスタのアドレスマップを示します。

Table 14 レジスタ アドレス マップ

| 機能                                    | レジスタタイプ                                        | レジスタ名                     | 揮発性コンポーネントアドレス<br>(16進数) | 不揮発性コンポーネントアドレス<br>(16進数) |

|---------------------------------------|------------------------------------------------|---------------------------|--------------------------|---------------------------|

| デバイスステータス                             | ステータス レジスタ 1                                   | STR1N[7:0],<br>STR1V[7:0] | 0x00800000               | 0x00000000                |

|                                       | ステータス レジスタ 2                                   | STR2V[7:0]                | 0x00800001               | 該当なし                      |

| デバイスコンフィギュレーション                       | コンフィギュレーション レジスタ 1                             | CFR1N[7:0],<br>CFR1V[7:0] | 0x00800002               | 0x00000002                |

|                                       | コンフィギュレーション レジスタ 2                             | CFR2N[7:0],<br>CFR2V[7:0] | 0x00800003               | 0x00000003                |

|                                       | コンフィギュレーション レジスタ 3                             | CFR3N[7:0],<br>CFR3V[7:0] | 0x00800004               | 0x00000004                |

|                                       | コンフィギュレーション レジスタ 4                             | CFR4N[7:0],<br>CFR4V[7:0] | 0x00800005               | 0x00000005                |

|                                       | コンフィギュレーション レジスタ 5                             | CFR5N[7:0],<br>CFR5V[7:0] | 0x00800006               | 0x00000006                |

| インターフェース CRC                          | インターフェース CRC イネーブル レジスタ                        | ICEV[7:0]                 | 0x00800008               | 該当なし                      |

| インフィニオン Endurance Flex アーキテクチャ選択 レジスタ | インフィニオン Endurance Flex アーキテクチャ選択 レジスタ 0 [1:0]  | EFX0O[7:0]                |                          | 0x00000050                |

|                                       | インフィニオン Endurance Flex アーキテクチャ選択 レジスタ 1 [7:0]  | EFX1O[7:0]                |                          | 0x00000052                |

|                                       | インフィニオン Endurance Flex アーキテクチャ選択 レジスタ 1 [10:8] | EFX1O[10:8]               |                          | 0x00000053                |

|                                       | インフィニオン Endurance Flex アーキテクチャ選択 レジスタ 2 [7:0]  | EFX2O[7:0]                |                          | 0x00000054                |

|                                       | インフィニオン Endurance Flex アーキテクチャ選択 レジスタ 2 [10:8] | EFX2O[10:8]               |                          | 0x00000055                |

|                                       | インフィニオン Endurance Flex アーキテクチャ選択 レジスタ 3 [7:0]  | EFX3O[7:0]                |                          | 0x00000056                |

| インフィニオン Endurance Flex アーキテクチャ        | インフィニオン Endurance Flex アーキテクチャ選択 レジスタ 3 [10:8] | EFX3O[10:8]               |                          | 0x00000057                |

|                                       | インフィニオン Endurance Flex アーキテクチャ選択 レジスタ 4 [7:0]  | EFX4O[7:0]                |                          | 0x00000058                |

|                                       | インフィニオン Endurance Flex アーキテクチャ選択 レジスタ 4 [10:8] | EFX4O[10:8]               |                          | 0x00000059                |

アドレス空間マップ

**Table 14 レジスタ アドレス マップ ( 続き )**

| 機能         | レジスタタイプ                         | レジスタ名       | 揮発性コンポーネントアドレス (16進数) | 不揮発性コンポーネントアドレス (16進数) |

|------------|---------------------------------|-------------|-----------------------|------------------------|

| 割込みピン      | 割込みコンフィギュレーション レジスタ             | INCV[7:0]   | 0x00800068            |                        |

|            | 割込みステータス レジスタ                   | INSV[7:0]   | 0x00800067            |                        |

| エラー訂正      | ECC ステータス レジスタ                  | ESCV[7:0]   | 0x00800089            | 該当なし                   |

|            | ECC エラー検出カウント レジスタ [7:0]        | ECTV[7:0]   | 0x0080008A            |                        |

|            | ECC エラー検出カウント レジスタ [15:8]       | ECTV[15:8]  | 0x0080008B            |                        |

|            | ECC アドレス トラップ レジスタ [7:0]        | EATV[7:0]   | 0x0080008E            |                        |

|            | ECC アドレス トラップ レジスタ [15:8]       | EATV[15:8]  | 0x0080008F            |                        |

|            | ECC アドレス トラップ レジスタ [23:16]      | EATV[23:16] | 0x00800040            |                        |

|            | ECC アドレス トラップ レジスタ [31:24]      | EATV[31:24] | 0x00800041            |                        |

|            | オートブート レジスタ [7:0]               | ATBN[7:0]   | 該当なし                  | 0x000000042            |

| オートブート     | オートブート レジスタ [15:8]              | ATBN[15:8]  |                       | 0x000000043            |

|            | オートブート レジスタ [23:16]             | ATBN[23:16] |                       | 0x000000044            |

|            | オートブート レジスタ [31:24]             | ATBN[31:24] |                       | 0x000000045            |

| 消去カウント     | セクタ消去カウント レジスタ [7:0]            | SECV[7:0]   | 0x00800091            | 該当なし                   |

|            | セクタ消去カウント レジスタ [15:8]           | SECV[15:8]  | 0x00800092            |                        |

|            | セクタ消去カウント レジスタ [23:16]          | SECV[23:16] | 0x00800093            |                        |

| データ整合性チェック | データ整合性チェック CRC レジスタ [7:0]       | DCRV[7:0]   | 0x00800095            | 該当なし                   |

|            | データ整合性チェック CRC レジスタ [15:8]      | DCRV[15:8]  | 0x00800096            |                        |

|            | データ整合性チェック CRC レジスタ [23:16]     | DCRV[23:16] | 0x00800097            |                        |

|            | データ整合性チェック CRC レジスタ [31:24]     | DCRV[31:24] | 0x00800098            |                        |

| 保護とセキュリティ  | 高度セクタ保護 レジスタ [7:0]              | ASPO[7:0]   | 該当なし                  | 0x000000030            |

|            | 高度セクタ保護 レジスタ [15:8]             | ASPO[15:8]  |                       | 0x000000031            |

|            | ASP PPB ロック レジスタ ( 持続的保護 ブロック ) | PPLV[7:0]   | 0x0080009B            | 該当なし                   |

|            | ASP パスワード レジスタ [7:0]            | PWDO[7:0]   | 該当なし                  | 0x000000020            |

|            | ASP パスワード レジスタ [15:8]           | PWDO[15:8]  |                       | 0x000000021            |

|            | ASP パスワード レジスタ [23:16]          | PWDO[23:16] |                       | 0x000000022            |

| 保護とセキュリティ  | ASP パスワード レジスタ [31:24]          | PWDO[31:24] |                       | 0x000000023            |

|            | ASP パスワード レジスタ [39:32]          | PWDO[39:32] |                       | 0x000000024            |

|            | ASP パスワード レジスタ [47:40]          | PWDO[47:40] |                       | 0x000000025            |

|            | ASP パスワード レジスタ [55:48]          | PWDO[55:48] |                       | 0x000000026            |

|            | ASP パスワード レジスタ [63:56]          | PWDO[63:56] |                       | 0x000000027            |

## 4 機能

### 4.1 エラー検出と訂正

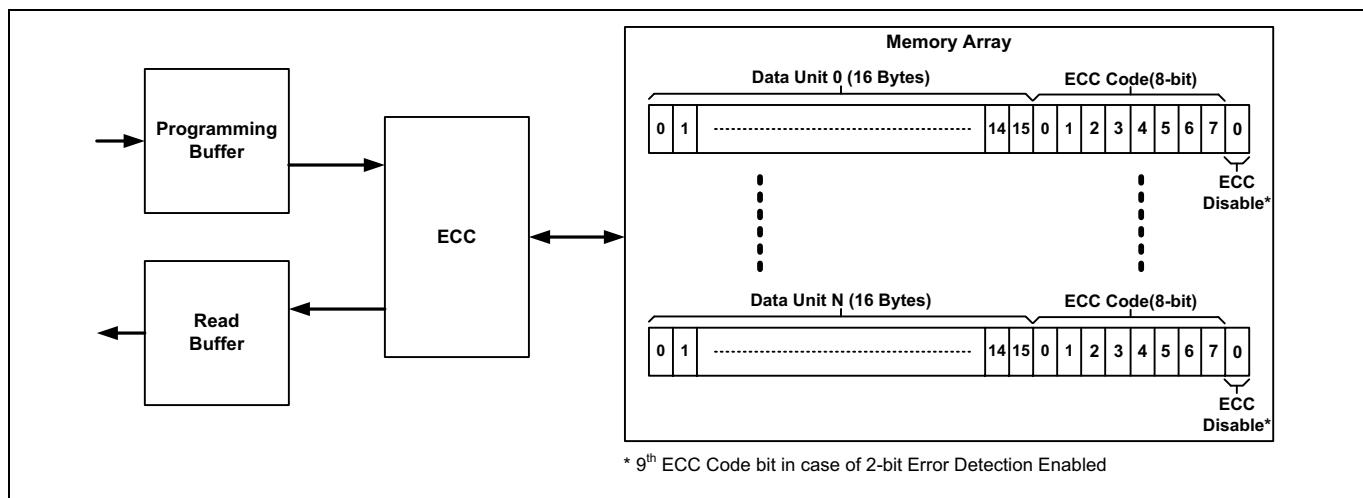

HL-T/HS-T ファミリのデバイスは、メモリアレイのプログラム中に組込みハミングエラー訂正コードを生成することで、エラー検出と訂正をサポートします。その後、この ECC コードは読み出し中にエラーの検出と修正に使用されます。ECC は 16 バイトデータユニットをベースとしています。16 バイトデータユニットがプログラムバッファにロードされ、(消去後の) プログラム用に 128 ビットのフラッシュメモリアレイラインに転送されるとき、各データユニットごとの 8 ビットエラー訂正コード (ECC) も、ホストシステムソフトウェアに見えないメモリアレイの部分にプログラムされます。その後、この ECC 情報は各フラッシュアレイの読み出し動作中にチェックされます。データユニット内のいかなる 1 ビットエラーも ECC ロジックによって訂正されます。16 バイトデータユニットは、ECC が有効である最小のプログラム粒度です。

あるデータ量が最初に 16 バイトデータユニット内にプログラムされたとき、ECC 値はデータユニット全体に対してセットされます。消去を行わず、その後に追加のデータが同じデータユニットにプログラムされた場合、データユニットの ECC は無効にされ、1 ビット ECC ディセーブルビットがセットされます。データユニットに対して ECC を再び有効にするためにはセクタ消去が必要となります。

これらは、ユーザーに対してトランスペアレント (透明) な自動動作です。ECC 機能の透明性は、各データユニットに一回のデータ書き込みを行う標準的なプログラム動作に対するデータの信頼性を向上させます。また同時に、シングルバイトプログラムおよび同じデータユニットが複数回プログラムされるビットウォーキング (この場合、ECC は無効) を可能にすることで、旧世代の製品とのソフトウェア互換性を可能にします。

Figure 33 16 バイト ECC データユニットの例

SEMPER™ NOR フラッシュはデフォルト ECC コンフィギュレーションとして 2 ビットエラー検出をサポートします。このコンフィギュレーションでは、データユニット内のどの 1 ビットエラーも訂正され、どの 2 ビットエラーも検出され報告されます。16 バイトユニットデータは、2 ビットエラー検出のために 9 ビットエラー訂正コードを必要とします。2 ビットエラー検出が有効にされたとき、(消去を行わず) 同じデータユニットに対するバイトプログラム、ビットウォーキングや複数回のプログラム動作は不可であり、プログラムエラーとなります。ECC モードを 1 ビットエラー検出から 2 ビットエラー検出に、または 2 ビットエラー検出から 1 ビットエラー検出に変更すると、メモリアレイ内のすべてのデータが無効になります。ECC モードを変更する際、まずホストはデバイス内のすべてのセクタを消去する必要があります。プログラムされたデータを消去せずに ECC モードを変更した場合、その後の読み出し動作は未定義の動作となります。

#### 4.1.1 ECC エラー報告

ECC エラーを検出したとき、5 つの方法でホストシステムに通知できます。

- ECC データユニットステータスは、データユニット内の 1 ビットまたは 2 ビットエラーの状態を提供します。

- ECC ステータスレジスタは、最後の ECC クリアまたはリセット後の、1 ビットまたは 2 ビットエラーの状態を示します。

- アドレストラップレジスタは、メモリアレイ読み出し中の POR またはリセットの後に発生する最初の ECC エラーのアドレス位置をキャプチャします。

- ECC エラー検出カウンターは、読み出し中にデータユニットに発生した 1 ビットまたは 2 ビットエラーの数を記録します。

- 割込み(INT#)出力は、データ読み出し中のいつ 1 ビットまたは 2 ビットエラーが検出されたかを示すために有効にされます。

##### 4.1.1.1 ECC データユニットステータス(EDUS)

- 各データユニットの ECC ステータスは 8 ビット ECC データユニットステータスによって提供されます。

- ECC ステータストランザクションは、アドレス指定されたデータユニットの ECC ステータスを出力します。ECC データユニットステータスの内容は、選択されたデータユニットに対して、訂正済みの 1 ビットエラーまたは検出済みの 2 ビットエラーがあるか、またはそのデータユニットに対する ECC が無効にされたかを示します。

**Table 15 ECC データユニットステータス**

| ビット       | フィールド名 | 機能                 | 読み出し / 書き込み (R/W)<br>N = 不揮発性<br>V = 挥發性 | 工場出荷時設定 (2 進) | 説明                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------|--------|--------------------|------------------------------------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EDUS[7:4] | RESRVD | 将来使用するために予約済み      | V=>R                                     | 0000          | これらのビットは将来使用するために予約されています。                                                                                                                                                                                                                                                                                                                                                                |

| EDUS[3]   | ECC2BD | 2 ビット ECC エラー検出フラグ | V=>R                                     | 0             | <p>このビットは、2 ビット ECC エラー検出が有効な場合(CFR4V[3]=1)、2 ビットエラーがデータユニットで検出されたかどうかを示します。</p> <p>2 ビットエラー検出が無効な場合(CFR4V[3]=0)、ECC2BD ビットは常に「0」になります。</p> <p>注: 2 ビットエラー検出が有効(CFR4V[3]=1)の場合、シングルバイトプログラミングまたはすでに部分的にプログラミングされたデータユニットでビットウォーキングを実行している間、ECCOFF ビットは 1b に設定されません。このようなバイトプログラミングまたはビットウォーキングを実行しようとすると、プログラムエラーが発生します。</p> <p>選択オプション:<br/>1=2 ビットエラーが検出されました。<br/>0=エラーが発生しませんでした。</p> |

| EDUS[2]   | RESRVD | 将来使用するために予約済み      | V=>R                                     | 0             | このビットは将来使用するために予約されています。                                                                                                                                                                                                                                                                                                                                                                  |

**Table 15 ECC データ ユニット ステータス ( 続き )**

| ビット     | フィールド名 | 機能                       | 読み出し / 書き込み (R/W)<br>N = 不揮発性<br>V = 挥発性 | 工場出荷時設定 (2進) | 説明                                                                                                                                                               |

|---------|--------|--------------------------|------------------------------------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EDUS[1] | ECC1BC | 1 ビット ECC エラー検出と訂正 フラグ   | V=>R                                     | 0            | <p>このビットはエラーがデータ ユニットで訂正されたかどうかを示します。</p> <p>選択オプション:</p> <p>1=1 ビット エラーがアドレス指定されたデータ ユニットで訂正されました。</p> <p>0=アドレス指定されたデータ ユニットで訂正された 1 ビット エラーはありませんでした。</p>     |

| EDUS[0] | ECCOFF | データ ユニット ECC オフ / オン フラグ | V=>R                                     | 0            | <p>このビットは ECC シンドロームがデータ ユニットでオフになっているかどうかを示します。</p> <p>選択オプション:</p> <p>1=選択されたデータ ユニットで ECC はオフです。</p> <p>0=選択されたデータ ユニットで ECC はオンです。</p> <p>依存性 : CFR4x[3]</p> |

#### 4.1.1.2 ECC ステータス レジスタ (ECSV)

- 8 ビットの ECC ステータス レジスタは、最後の ECC クリアまたはリセット後の通常読み出し中に発生した 1 ビットまたは 2 ビット エラーの状態を示します。ECC ステータス レジスタはユーザーがプログラマ可能な不揮発性ビットを持っていません。定義されたすべてのビットは揮発性読み出し専用ビットです。これらのビットのデフォルト状態はハードウェアにより設定されます。

- ECC ステータス レジスタは任意レジスタ読み出しトランザクションによってアクセスできます。任意レジスタ読み出しに基づく ECSV の正しいシーケンスは次のとおりです。

- 任意の読み出しトランザクションを使用してデータをメモリアレイから読み出します。

- ECSV はデバイスによって更新されます。

- ECSV の任意レジスタ読み出しは最後のクリアまたはリセット後のあらゆる ECC イベントの状態を提供します。

- ECSV は、POR,CS# シグナリング リセット, ハードウェア / ソフトウェア リセット, または ECC ステータス レジスタ クリア トランザクションによってクリアされます。

#### 4.1.1.3 ECC エラー アドレス トラップ (EATV)

- フラッシュ アレイ読み出し中に初めて発生した ECC エラーの ECC データ ユニット アドレスをキャプチャするための 32 ビット レジスタが用意されています。POR、ハードウェア リセットまたは ECC クリア トランザクション後に最初に発生した有効なエラー タイプ (CFR4N[3] での選択によって「2 ビットのみ」または「1 ビットか 2 ビット」) のアドレスのみがキャプチャされます。EATV レジスタは読み出しトランザクションの間にのみ更新されます。

EATV レジスタは、エラーが検出されたときにアクセスされたアドレスを格納します。不良ビットはレジスタで示された正確なアドレスに見つけられないことがあります。エラーが検出された整列済みの 16 バイト ECC データ ユニット内に見つけられます。単一の読み出し動作中に複数の ECC データ ユニットにエラーが見つかった場合、最初の不良の ECC ユニットのアドレスのみが EATV レジスタにキャプチャされます。

## 機能

2 ビット エラー検出が有効でなく、同じ ECC ユニットが複数回プログラムされた場合、その ECC ユニットの ECC エラー検出が無効にされ、エラーが認識できないのでアドレスをトラップできません。ECC ステータス レジスタ (ECSV) ビット 3 または 4 が 1 の場合、アドレス トラップ レジスタは有効なアドレスを持ちます。

- アドレス トラップ レジスタは任意レジスタ読み出しトランザクションで読み出されます。

- ECC ステータス レジスタ クリアトランザクション、POR または CS# シグナリング / ハードウェア / ソフトウェアリセットは、アドレス トラップ レジスタをクリアします。

### 4.1.1.4 ECC エラー検出カウンター (ECTV)

- フラッシュメモリアレイからデータが読み出されるときに発生した 1 ビットまたは 2 ビットエラーの数をカウントするための 16 ビットレジスタが用意されています。メインアレイで認識されたエラーのみが、エラー検出カウンターを増分させます。ECTV レジスタは読み出しトランザクションの間にのみ更新されます。ECC ステータス読み出しトランザクションは ECTV レジスタに影響しません。

16 ビット エラー検出カウンターは FFFFh を越えて増分しませんが、ECC は動作を継続します。

注：連続した読み出し動作中に、1 ビットまたは 2 ビット エラーが検出されると、クロックがトグルし続け、メモリデバイスはデータアドレスの増分および DQ 信号上の新データの配置を継続することができます。エラーが発生した追加のデータユニットは CS# が HIGH に戻されるまでカウントされます。

読み出しトランザクション中は、エラーが発生したデータユニットごとに 1 つのエラーのみがカウントされます。各読み出しトランザクションでは、対象のデータユニットへの読み出しが新しく行われます。もし複数の読み出しトランザクションがエラーのある同じデータユニットにアクセスしたら、エラー カウンターはデータユニットが読み出されるたびに増分します。

2 ビット エラー検出が有効でなく、同じデータユニットが複数回プログラムされた場合、そのデータユニットの ECC エラー検出が無効にされ、エラーが認識されず、カウントされません。

- ECC エラー検出カウント レジスタは、任意レジスタ読み出しトランザクションで読み出されます。

- POR、CS# シグナリング / ハードウェア / ソフトウェアリセットまたは ECC ステータス レジスタ クリアトランザクションでは、ECTV レジスタは「0」にセットされます。

### 4.1.1.5 INT# 出力

- HL-T/HS-T は、フラッシュデバイス内にイベントが発生したことをホストシステムに通知する INT# 出力ピンをサポートします。ユーザーは、以下のときにアクティブ (LOW) に遷移するよう INT# 出力ピンを設定できます。

- 2 ビット ECC エラーの検出時

- 1 ビット ECC エラーの検出時

- ビジー状態からレディ状態への遷移時

INT# ピンは BGA パッケージでのみ利用可能です。動作は INT# 出力 (通常は HIGH) が有効になった状態で割込みコンフィギュレーション レジスタ (INCV) によって制御されます。割込みコンフィギュレーション レジスタは、INT# 出力ピンで HIGH から LOW への遷移をトリガーするように内部イベントが有效地にされるタイミングを決定します。

割込みステータス レジスタ (INSV) は、INSV が最後にクリアされた以降生じた有効な内部イベントを示します。

有効にされると、INT# 出力ピンは有効なイベントの発生時に HIGH から LOW に遷移します。ホストが INT# が LOW 状態に遷移したことを認識すると、INSV レジスタが読み出され、どの内部イベントが原因であるかを判定します。POR、ハードウェアリセット、ソフトウェアリセット、DPD 終了、または CS# シグナリングリセット中の INT# 出力の状態は無効です。

- INCV および INSV は SPI とオクタルインターフェースの任意レジスタ読み出しトランザクションによりアクセスできます。INCV への任意レジスタ書き込みトランザクションは、オクタルインターフェースでのみサポートされています。

## 機能

- 以下の方法で、INT# 出力を（外部プルアップ抵抗で HIGH に戻る）HIGH 状態に戻させます。

- 割込みコンフィギュレーションレジスタのビット 7 に「1」をロードすることで、INT# 出力を無効にします。

- 出力を LOW にするどの内部イベントが生じたかを示す INSV ビット中の適切なビットを（「1」を書き込むことで）リセットします。LOW 状態にあって INSV 内で有効にされたすべての INSV ビットは、INT# 出力が HIGH に戻る前にリセットされる必要があります。

- INT# 出力も、CS# シグナリングリセット、ハードウェアリセット (RESET#=LOW) または POR によりデフォルト状態（無効、High-Z）に戻されます。ハードウェアリセットおよび POR は、割込みコンフィギュレーションレジスタをデフォルト状態（全割込みが無効）に戻すことで、すべての割込みを無効にします。

- ECC イベントの後に ECC ステータスレジスタをクリアすると、INT# 出力を強制的に HIGH 状態にします。

### 4.1.2 ECC に関するレジスタとトランザクション

Table 16 ECC に関するレジスタとトランザクション

| 関連するレジスタ                                              | 関連する SPI トランザクション (Table 81 を参照してください) | 関連するオクタルトランザクション (Table 82 を参照してください) |

|-------------------------------------------------------|----------------------------------------|---------------------------------------|

| コンフィギュレーションレジスタ 4 (CFR4N, CFR4V) (Table 58 を参照してください) | 任意レジスタ読み出し (RDARG_C_0)                 | 任意レジスタ読み出し (RDARG_4_0)                |

| ECC ステータスレジスタ (ECSV) (Table 64 を参照してください)             | 書き込みイネーブル (WRENB_0_0)                  | 書き込みイネーブル (WRENB_0_0)                 |

| ECC アドレストラップレジスタ (EATV) (Table 65 を参照してください)          | 任意レジスタ書き込み (WRARG_C_1)                 | 任意レジスタ書き込み (WRARG_4_1)                |

| ECC エラー検出カウントレジスタ (ECTV) (Table 66 を参照)               | ECC ステータス読み出し (RDECC_4_0)              | ECC ステータス読み出し (RDECC_4_0)             |

| 割込みコンフィギュレーションレジスタ (INCV) (Table 74 を参照してください)        | ECC ステータスレジスタクリア (CLECC_0_0)           | ECC ステータスレジスタクリア (CLECC_0_0)          |

| 割込みステータスレジスタ (INSV) (Table 75 を参照してください)              | -                                      | -                                     |

## 4.2 Endurance Flex アーキテクチャ（ウェアレベリング）

インフィニオン Endurance Flex アーキテクチャでは、高耐久性が長期データ保持に設定可能な領域にメインメモリアレイを分割できます。Endurance Flex は、ウェアレベリングプールの一部であるすべてのセクタにプログラム / 消去サイクルが均等に分布される高耐久性領域にウェアレベリングを実装します。これは、個々のセクタの早期摩耗を防止し、デバイスの信頼性を大きく向上させます。

アーキテクチャ上では、Endurance Flex のウェアレベリングアルゴリズムは論理セクタの物理セクタへのマッピングに基づいています。製品の寿命期間中に、このマッピングはすべての物理セクタにおけるプログラム / 消去サイクルの均等な分布を維持するように変更されます。論理から物理へのマッピング情報は、セクタがアップされたときに更新される専用フラッシュアレイに格納されます。セクタアップは、消去トランザクションが発行されると行われます。

Endurance Flex の高耐久性領域は少なくとも 20 セクタのセットを必要とします。長期データ保持期間、高耐久性、または両方の領域の設定に柔軟性を提供するために、4 ポインタアーキテクチャが用意されています。工場出荷時の設定では、すべてのポインタを無効にしており、ウェアレベリングの一部としてすべてのセクタを高耐久性として指定しています。4 ポインタを使用して最大 5 つの領域を形成し、それぞれを長期データ保持または高耐久性に設定できます。

Figure 34 は Endurance Flex アーキテクチャの概要を提供します。異なるセクタアーキテクチャに基づいた 5 つの可能な領域を示します。

注：4KB セクタは Endurance Flex アーキテクチャの一部ではありません。

機能

## Figure 34 Endurance Flex アーキテクチャ概要

機能

**Figure 35 Endurance Flex アーキテクチャ概要 ( 続き )**

**Table 17 領域定義 [11, 12, 13, 14]**

| 領域 | 下限          | 上限          |

|----|-------------|-------------|

| 0  | セクタ 0       | アドレス ポインタ 1 |

| 1  | アドレス ポインタ 1 | アドレス ポインタ 2 |

| 2  | アドレス ポインタ 2 | アドレス ポインタ 3 |

| 3  | アドレス ポインタ 3 | アドレス ポインタ 4 |

| 4  | アドレス ポインタ 4 | 最上位セクタ      |

注

11. ポインタ アドレスは以下の規則に従う必要があります。

ポインタ 4 アドレス > ポインタ 3 アドレス

ポインタ 3 アドレス > ポインタ 2 アドレス

ポインタ 2 アドレス > ポインタ 1 アドレス

12. 4KB セクタは含まれません。

13. 高耐久性領域と長期データ保持領域は、デバイスが最初に電源投入されたときに設定する必要があります。これらは一度設定されると、変更できません。

14. いずれの高耐久性領域もその最小サイズは 20 セクタです。

#### 4.2.1 コンフィギュレーション 1: 最大耐久性 - 1 高耐久性領域

最大耐久性は、すべての 256KB セクタを高耐久性として指定することで達成できます。すべてのセクタは Endurance Flex ポインタ アーキテクチャを使用して高耐久性として指定する必要があります。最大耐久性のポインタ コンフィギュレーションを、Table 18 に示します。

**Table 18 最大耐久性コンフィギュレーションのための Endurance Flex ポインタ値 [15]**

| ポインタ番号 | ポインタアドレス EPTADn[8:0] | 領域タイプ ERGNTn | ポインタイネーブル番号 EPTEBn | グローバル領域選択 GBLSEL | ウェアレベリングイネーブル WRLVEN |

|--------|----------------------|--------------|--------------------|------------------|----------------------|

| 0      | 該当なし                 | 該当なし         | 該当なし               | 1'b1             | 1'b1                 |

| 1      | 9'b1111111111        | 1'b1         | 1'b1               | 該当なし             | 該当なし                 |

| 2      | 9'b1111111111        |              |                    |                  |                      |

| 3      | 9'b1111111111        |              |                    |                  |                      |

| 4      | 9'b1111111111        |              |                    |                  |                      |

注

15. これもデバイスのデフォルト コンフィギュレーションです。

#### 4.2.2 コンフィギュレーション 2: 2 領域選択 - 1 長期データ保持領域と 1 高耐久性領域

長期データ保持または高耐久性のセクタは Endurance Flex ポインタアーキテクチャを使用して指定する必要があります。領域 0 は長期データ保持として指定され、16 セクタからなります。領域 1 は高耐久性として指定され、240 セクタからなります。2 領域コンフィギュレーションのポインタセットアップを、Table 19 に示します。定義されるポインタの数は、構成される領域の数に基づきます。

**Table 19 2 領域コンフィギュレーションのための Endurance Flex ポインタ値**

| ポインタ番号 | ポインタアドレス<br><b>EPTADn[8:0]</b> | 領域タイプ<br><b>ERGNtN</b> | ポインティネーブル番号<br><b>EPTEBn</b> | グローバル領域選択<br><b>GBLSEL</b> | ウェアアレベリングイネーブル<br><b>WRLVEN</b> |

|--------|--------------------------------|------------------------|------------------------------|----------------------------|---------------------------------|

| 0      | 該当なし                           | 該当なし                   | 該当なし                         | 1'b0                       | 1'b1                            |

| 1      | 9'b000010000                   | 1'b1                   | 1'b0                         |                            |                                 |

| 2      |                                |                        |                              |                            |                                 |

| 3      | 9'b1111111111                  | 1'b1                   | 1'b1                         | 該当なし                       | 該当なし                            |

| 4      |                                |                        |                              |                            |                                 |

#### 4.2.3 Endurance Flex に関するレジスタとトランザクション

**Table 20 Endurance Flex に関するレジスタとトランザクション**

| 関連するレジスタ                                                                                                                    | 関連する SPI トランザクション<br>(Table 81 を参照してください) | 関連するオクタルトランザクション (Table 82 を参照してください) |

|-----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|---------------------------------------|

| Endurance Flex アーキテクチャ選択レジスタ (EFX40, EFX30, EFX20, EFX10, EFX00) (111 ページの “Endurance Flex アーキテクチャ選択レジスタ (EFXx)” を参照してください) | 任意レジスタ読み出し (RDARG_C_0)                    | 任意レジスタ読み出し (RDARG_4_0)                |

|                                                                                                                             | 任意レジスタ書き込み (WRARG_C_1)                    | 任意レジスタ書き込み (WRARG_4_1)                |

#### 4.3 インターフェース CRC

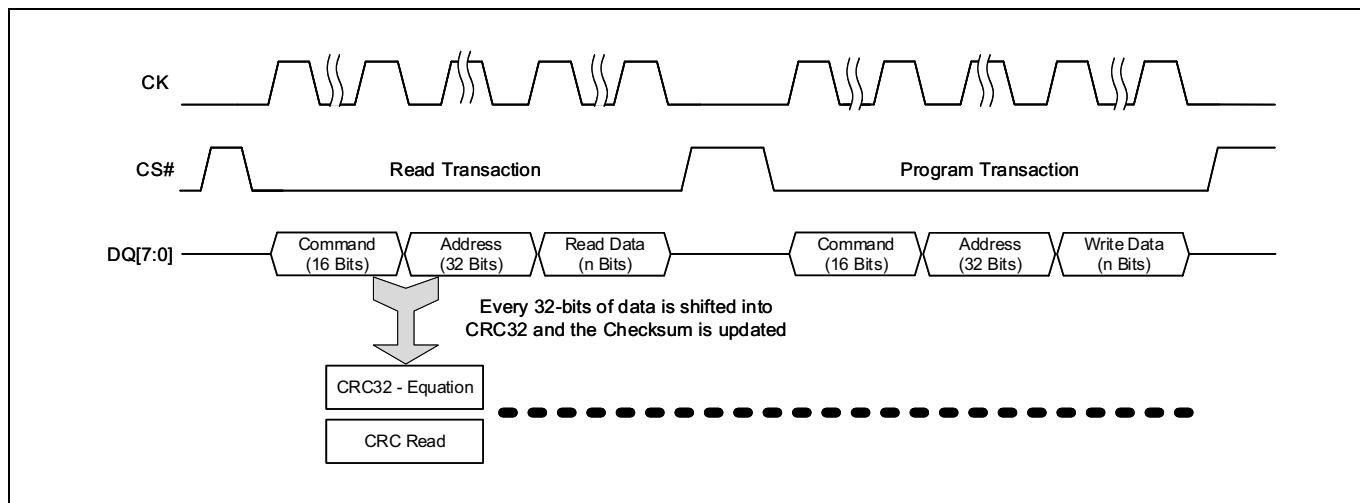

インターフェース CRC は、ホストとデバイス間の通信に対するハードウェア加速の CRC 計算を実行し、転送される情報の整合性を確実にします。CRC は、デバイスで生データへの誤った変更を検出するため一般に使用されるエラー検出コードです。インターフェース CRC 保護はコンフィギュレーションオプションです (ICEV[0] - ITCRCE)。

HL-T/HS-T デバイス ファミリのインターフェース CRC 方式は、CRC チェック値を検証し適切な処置を取るために、ホストに全面的に依存します。デバイスは、ホストがインターフェース CRC 読み出しトランザクション (RDCRC\_4\_0) を使用して読み出す CRC チェック値を計算します。計算結果のチェック値は、CS# が LOW の間のすべてのトランザクション内容、すなわち、コマンド、アドレスおよびデータを含みます。この CRC チェックサムは、単一のトランザクションまたは一連のトランザクションのいずれに対しても生成できます。唯一の制限は、スレーブが CRC チェックサムを計算するデータサイズは  $2^{32}$  ビットより小さくなければならないことです。

ホストも同じトランザクションシーケンスに対して CRC チェック値を計算する必要があります。準備ができたとき、ホストはデバイスが計算した CRC チェック値を読み出し、自分が計算したものと比較します。不一致の場合、ホストは完全なトランザクションシーケンスを繰り返すを選択できます。

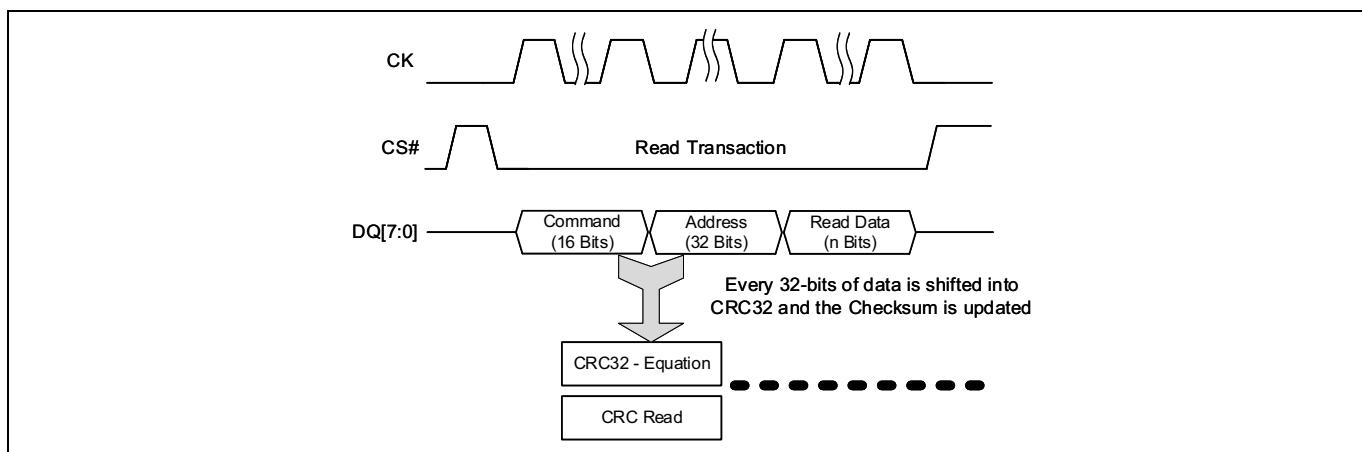

Figure 36 CRC 計算の概要

注：

- CRC 読み出しトランザクションの終了時、デバイスは CRC チェック値をリセットし、CRC 多項式を再初期化します。

- CRC32 多項式 :  $X^{32} + X^{28} + X^{27} + X^{26} + X^{25} + X^{23} + X^{22} + X^{20} + X^{19} + X^{18} + X^{14} + X^{13} + X^{11} + X^{10} + X^9 + X^8 + X^6 + 1$

- ホストとデバイスの CRC 多項式は同一でなければなりません。

- インターフェース CRC はオクタル DDR プロトコルでのみサポートされます。

- インターフェース CRC チェック値は以下の条件で 0xFFFFFFFFh にリセットされます。

- POR

- ハードウェアリセット

- ソフトウェアリセット

- CS# シグナリングリセット

- インターフェース CRC チェック値の読み出し

- ディープパワー ダウンの終了

注：

- コマンドが正常に受信される前にトランザクションが中止された場合、すなわち、転送の長さが、早い CS# デアサートのため短縮された場合、転送されたデータは CRC チェック値にクロック入力されま

## 機能

すが、もはや保証されません。インターフェース CRC を使用する際、有効なアボートされていないトランザクションのみが使用されなければなりません。

- インターフェース CRC 値は揮発性ステータス レジスタの読み出しの前に読み出す必要があります、また揮発性ステータス レジスタの読み出しの後にインターフェース CRC 値をクリアする必要があります。

- インターフェース CRC が無効のとき、インターフェース CRC レジスタ値は不定になります。インターフェース CRC 機能を無効にする前にインターフェース CRC レジスタを読み出し、CRC 計算を再初期化するためにインターフェース CRC 機能を有効にした後にもう一度読み出すことを推奨します。

### 4.3.1 読み出し

読み出し動作は、CS#=LOW のときにホストが READ トランザクションを指定したときに行われます。その後、デバイスはアドレスに基づいてメモリからのデータを提供します。新しい READ トランザクションを発行することなく、連続したアドレスに対して任意のバイト数で読み出し(バースト読み出し)が可能です。

トランザクション保護のために、デバイスは CRC32 多項式を使用してトランザクションシーケンス全体(CS# LOW 状態)に対して CRC を実行します。CS# を HIGH にすると、CRC 計算は停止され、チェック値は CRC レジスタにラッチされます。ホストが複数回の READ トランザクションを実行した場合、デバイスは毎回の CS# LOW サイクルの間に CRC チェック値の更新を継続します。

**Figure 37 CRC による読み出し保護**

注: 連続したインターフェース CRC 読み出しトランザクションは、リセットされる CRC チェックサム値を示しません。各インターフェース CRC レジスタ読み出しトランザクションの終了時、インターフェース CRC レジスタはリセットされ、少なくとも 3 クロック サイクルの間の有効な入力データによるトランザクションが行われた後に、レジスタそれ自体を新しい CRC チェックサム値で更新します。

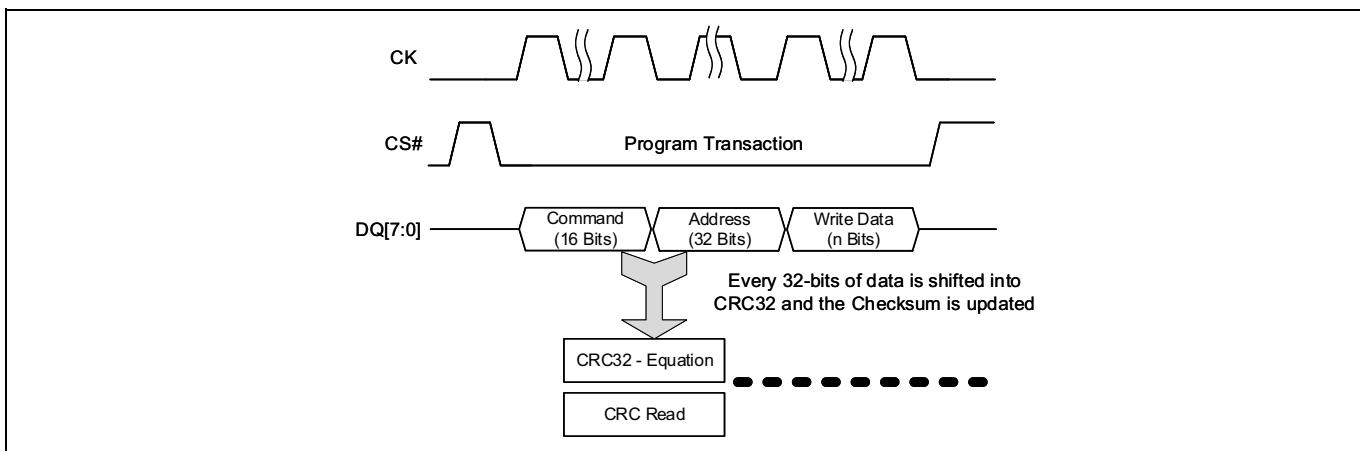

### 4.3.2 プログラム / 消去

プログラム動作は、CS#=LOW のときにホストがプログラム トランザクションを指定したときに行われます。新しいプログラム トランザクションを発行することなく、連続したアドレスに対して最大 256 バイト /512 バイトの書き込み(バースト書き込み)が可能です。消去動作は、CS#=LOW の間に、ホストが消去トランザクションを指定したときに行われます。単一のセクタもデバイス全体も消去できます。

トランザクション保護のために、スレーブ デバイスは、CRC32 多項式を使用して、命令シーケンス全体(CS# LOW 状態)に対して CRC を実行します。プログラム / 消去トランザクションを完了するために CS# を HIGH にすると、CRC 計算は停止され、チェックサムは CRC レジスタにラッチされます。ホストが複数回のプログラム / 消去トランザクションを実行した場合、スレーブは毎回の CS# LOW サイクルの間に CRC チェックサムの更新を継続します。

Figure 38 CRC によるプログラム保護

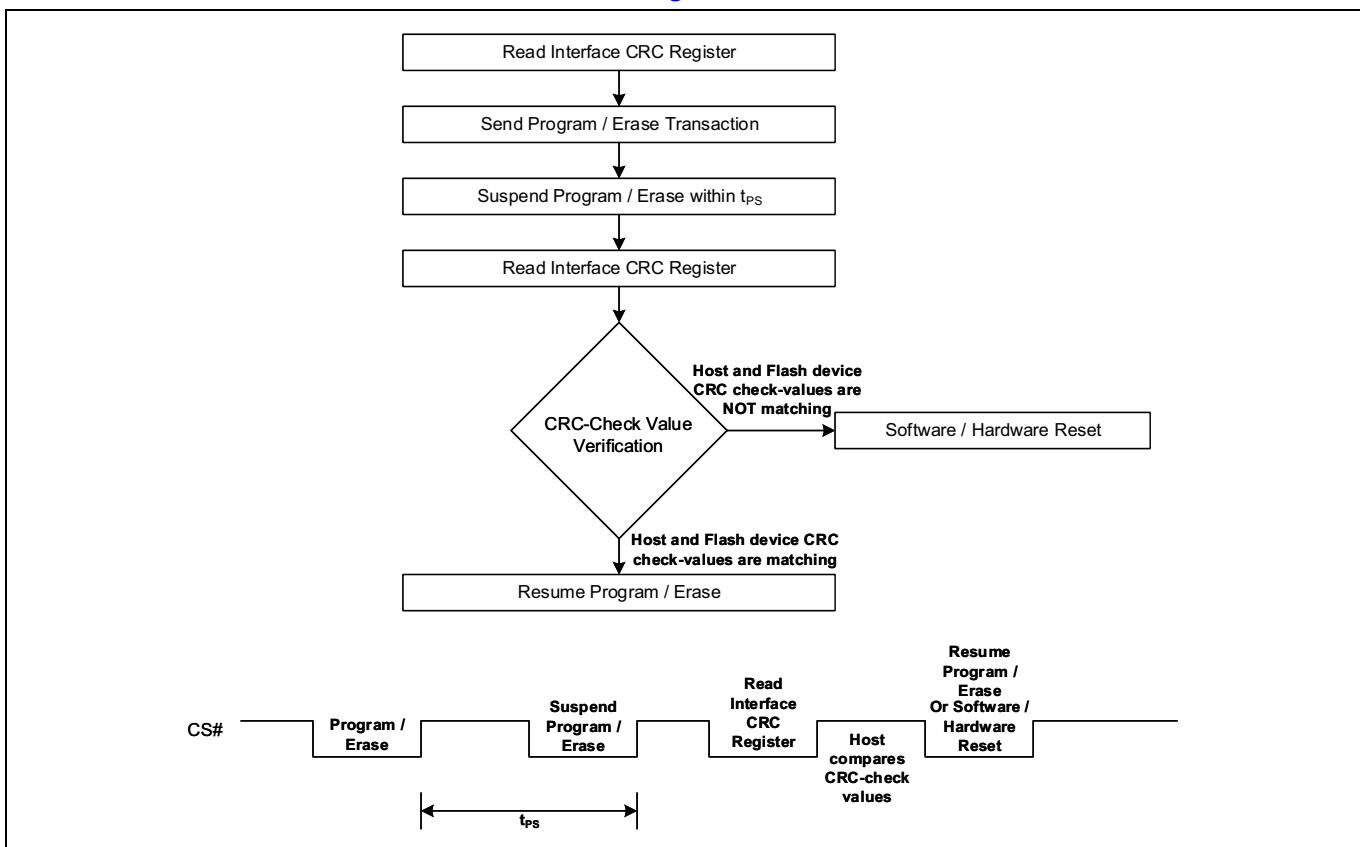

ホストデバイスは読み出しインターフェース CRC トランザクションを使用し、スレーブデバイスからの CRC チェックサムを読み出します。スレーブデバイスは RDCRC\_4\_0 トランザクションを CRC チェックサムの一部として含み、その後チェックサムデータをデータバス上に配置します。ホストデバイスが、スレーブからの CRC チェックサムの受信時に、ホストデバイス自体が計算した CRC チェックサムとの不一致を検出した場合、ホストデバイスはスレーブデバイスにプログラム / 消去トランザクションを再発行できます。フラッシュでは、CRC チェックサムエラーに起因する同じ位置への複数回のプログラム / 消去は、アクセス可能回数に影響します。Figure 39 に、この問題の解決策を示します。

Figure 39 プログラムおよび消去トランザクションのインターフェース CRC フロー

#### 4.3.3 インターフェース CRC に関するレジスタとトランザクション

Table 21 インターフェース CRC に関するレジスタとトランザクション

| 関連するレジスタ                                        | 関連する SPI トランザクション<br>(Table 81 を参照してください) | 関連するオクタルトランザクション (Table 82 を参照してください) |

|-------------------------------------------------|-------------------------------------------|---------------------------------------|

| インターフェース CRC イネーブルレジスタ (ICEV)<br>(Table 61 を参照) | 該当なし                                      | インターフェース CRC レジスタ読み出し (RDCRC_4_0)     |

#### 4.4 データ整合性 CRC

HL-T/HS-T ファミリ デバイスは、メモリアレイ内のユーザー定義アドレス範囲に対してハードウェア 加速の CRC 計算を実行するために一連のトランザクションを備えています。計算はプログラムや消去と同じような組込み動作のもう一つのタイプであり、計算実行中はデバイスがビジーになります。CRC 動作は、インターフェース CRC と同じ CRC32 多項式を使用して、CRC チェック値を計算します。

CRC32 多項式 :  $x^{32} + x^{28} + x^{27} + x^{26} + x^{25} + x^{23} + x^{22} + x^{20} + x^{19} + x^{18} + x^{14} + x^{13} + x^{11} + x^{10} + x^9 + x^8 + x^6 + 1$

チェック値の生成シーケンスは、DICHK\_4\_1 トランザクションの入力で開始します。このトランザクションは、CRC 計算の対象となるアドレス範囲の開始を定義する CRC 開始アドレス レジスタに開始アドレスをロードすることを含みます。また、CRC 終了アドレス レジスタに終了アドレスをロードすることも含みます。CS# を HIGH にすると、CRC 計算が始まります。CRC プロセスは、開始アドレスと終了アドレスの間に格納されているデータのチェック値を計算します。

計算期間中、デバイスはビジー状態 (STR1V[0] - RDYBSY = 1) に入ります。チェック値の計算が完了すると、デバイスはレディ状態 (STR1V[0] - RDYBSY = 0) に戻り、計算結果のチェック値は読み出し可能になります。チェック値はデータ整合性 CRC レジスタ (DCRV[31:0]) に格納され、任意レジスタ読み出しトランザクションを使用して読み出せます。

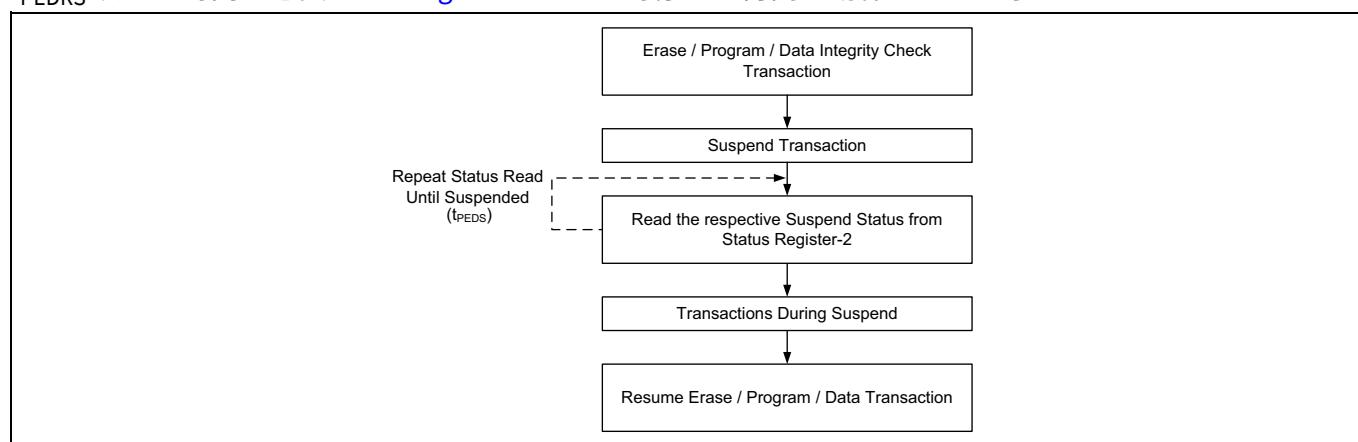

チェック値の計算はデバイスがスタンバイ状態のときにのみ開始できます。始まった計算は、メモリアレイからデータを読み出すために CRC 一時停止トランザクション (SPEPD\_0\_0) で一時停止できます。一時停止状態では、ステータス レジスタ 2 の CRC 一時停止ステータスピットがセットされます (STR2V[4] - DICRCS = 1)。いったん一時停止されたら、ホストはステータス レジスタを読み出したり、メモリアレイからデータを読み出したり、CRC 再開トランザクション RSEPD\_0\_0 で CRC 計算を再開できます。

終了アドレス (ENDADD) は、開始アドレス (STRADD) より少なくとも 4 アドレス高くなければなりません。[ENDADD < STRADD+3] の場合、チェック値の計算は中止され、デバイスはレディ状態に戻ります (STR1V[0] - RDYBSY = 0)。データ整合性 CRC 中止ステータスピットはセットされ (STR2V[3] - DICRCA = 1)、中止状態を示します。DICRCA ピットはセットされたら、ソフトウェアリセットまたは後続の有効な CRC コマンド実行でクリアできます。[ENDADD < STRADD+3] の場合、チェック値は不定のデータを保持します。

注 : CRC チェック値の計算中に無効なトランザクションがあると、チェック値データが壊れことがあります。

#### 4.4.1 データ整合性チェックに関するレジスタとトランザクション

Table 22 データ整合性 CRC に関するレジスタとトランザクション

| 関連するレジスタ                                          | 関連する SPI トランザクション<br>(Table 81 を参照してください) | 関連するオクタルトランザクション (Table 82 を参照してください)    |

|---------------------------------------------------|-------------------------------------------|------------------------------------------|

| ステータス レジスタ 1 (STR1N, STR1V) (Table 47 を参照してください)  | データ整合性チェック (DICHK_4_1)                    | データ整合性チェック (DICHK_4_1)                   |

| ステータス レジスタ 2 (STR2V) (Table 50 を参照してください)         | 消去 / プログラム / データ整合性 チェック一時停止 (SPEPD_0_0)  | 消去 / プログラム / データ整合性 チェック一時停止 (SPEPD_0_0) |

| データ整合性 CRC チェック値 レジスタ (DCRV) (Table 63 を参照してください) | 消去 / プログラム / データ整合性 チェック再開 (RSEPD_0_0)    | 消去 / プログラム / データ整合性 チェック再開 (RSEPD_0_0)   |

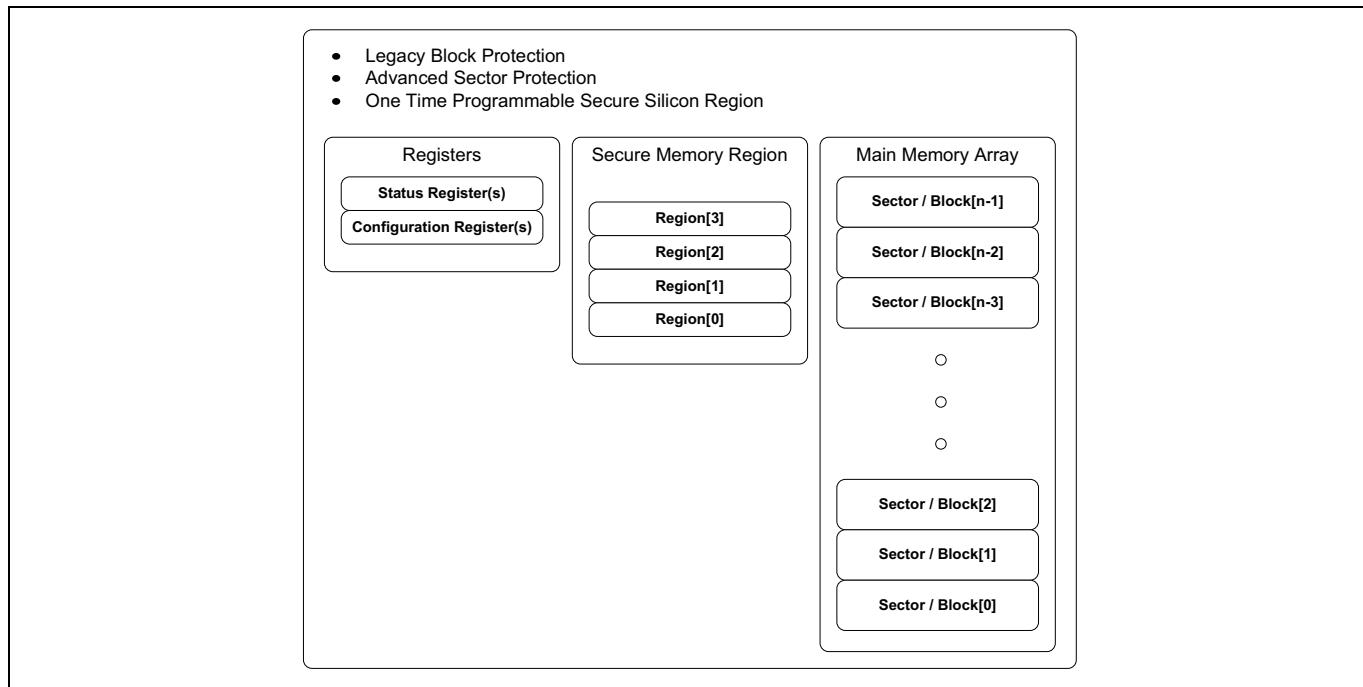

## 4.5 データ保護スキーム

データ保護は、保存されているデータおよびデバイスコンフィギュレーションへの誤った変更を防止するためには必要です。誤った変更には、メモリアレイの誤った消去やプログラムだけでなく、デバイスの機能を変化させる可能性のあるコンフィギュレーションレジスタへの書き込みも含まれます。保護スキームは、単一のセクタやセクタグループ、メモリアレイの一部または全体を対象とする3つのタイプがあります。Figure 40に、異なる保護スキームと該当するデータ領域の概要を示します。

Figure 40 データ保護およびセキュリティ(書き込み/プログラム/消去)スキーム

### 4.5.1 レガシー ブロック保護 (LBP)

レガシー ブロック保護 (LBP) はブロックベースのデータ保護スキームです。LBP は、レガシーシリアル NOR フラッシュ デバイスとの互換性をサポートします。LBP は、ステータスとコンフィギュレーション レジスタを保護することにより、メモリアレイおよびデバイス コンフィギュレーション内のデータを保護します。

#### 4.5.1.1 メモリアレイ保護

メモリアレイの保護は、ステータス レジスタ 1 (STR1N[4:2]/STR1V[4:2] - LBPROT[2:0]) およびコンフィギュレーション レジスタ 1 (CFR1N[5]/CFR1V[5] - TBPROT) のビットの組合せによるブロック サイズの選択に依存します。Table 23 は、LBP メモリアレイのブロック選択の概要を示します。

Table 23 レガシー ブロック メモリアレイ保護の選択

| CFR1N[5]/<br>CFR1V[5]<br>TBPROT | STR1N[4]/<br>STR1V[4]<br>LBPROT[2] | STR1N[3]/<br>STR1V[3]<br>LBPROT[1] | STR1N[2]/<br>STR1V[2]<br>LBPROT[0] | メモリアレイ<br>ブロック<br>サイズ | 512 Mb (KB) | 1 Mb (KB) |

|---------------------------------|------------------------------------|------------------------------------|------------------------------------|-----------------------|-------------|-----------|

| 0                               | 0                                  | 0                                  | 0                                  | 無                     | 0           | 0         |

| 0                               | 0                                  | 0                                  | 1                                  | 上位 1/64               | 1024        | 2048      |

| 0                               | 0                                  | 1                                  | 0                                  | 上位 1/32               | 2048        | 4096      |

| 0                               | 0                                  | 1                                  | 1                                  | 上位 1/16               | 4096        | 8192      |

| 0                               | 1                                  | 0                                  | 0                                  | 上位 1/8                | 8192        | 16384     |

| 0                               | 1                                  | 0                                  | 1                                  | 上位 1/4                | 16384       | 32768     |

| 0                               | 1                                  | 1                                  | 0                                  | 上位 1/2                | 32768       | 65536     |

Table 23 レガシー ブロック メモリアレイ保護の選択( 続き )

| CFR1N[5]/<br>CFR1V[5]<br>TBPROT | STR1N[4]/<br>STR1V[4]<br>LBPROT[2] | STR1N[3]/<br>STR1V[3]<br>LBPROT[1] | STR1N[2]/<br>STR1V[2]<br>LBPROT[0] | メモリアレイ<br>ブロック<br>サイズ | 512 Mb (KB) | 1 Mb (KB) |

|---------------------------------|------------------------------------|------------------------------------|------------------------------------|-----------------------|-------------|-----------|

| 0                               | 1                                  | 1                                  | 1                                  | 全セクタ                  | 65536       | 131072    |

| 1                               | 0                                  | 0                                  | 0                                  | 無                     | 0           | 0         |

| 1                               | 0                                  | 0                                  | 1                                  | 下位 1/64               | 1024        | 2048      |

| 1                               | 0                                  | 1                                  | 0                                  | 下位 1/32               | 2048        | 4096      |

| 1                               | 0                                  | 1                                  | 1                                  | 下位 1/16               | 4096        | 8192      |

| 1                               | 1                                  | 0                                  | 0                                  | 下位 1/8                | 8192        | 16384     |

| 1                               | 1                                  | 0                                  | 1                                  | 下位 1/4                | 16384       | 32768     |

| 1                               | 1                                  | 1                                  | 0                                  | 下位 1/2                | 32768       | 65536     |

| 1                               | 1                                  | 1                                  | 1                                  | 全セクタ                  | 65536       | 131072    |

#### 4.5.1.2 コンフィギュレーション保護

LBP はコンフィギュレーションレジスタ 1 (CFR1N[4, 0]/CFR1V[4, 0] - PLPROT, TLPROT) で選択ビットを持っています。これらの選択ビットはステータスとコンフィギュレーションレジスタを恒久的または一時的に保護し、したがってデバイスのコンフィギュレーションを保護します。一時的保護は、次の電源切断、ハードウェアリセット、または CS# シグナリング リセットまで有効なままです。

Table 24 オプション 2 - レガシー ブロック コンフィギュレーション保護の選択<sup>[16]</sup>

| CFR1N[4]/CFR1V[4]<br>PLPROT | CFR1N[0]/CFR1V[0]<br>TLPROT | レジスタ保護ステータス                                                                 |

|-----------------------------|-----------------------------|-----------------------------------------------------------------------------|

| 0                           | 0                           | ステータスとコンフィギュレーションレジスタは保護されません。                                              |

| 1                           | X                           | ステータスとコンフィギュレーションレジスタは恒久的に保護されます (TBPROT, LBPROT[2:0], SP4KBS, TB4KBS)。     |

| 0                           | 1                           | ステータスとコンフィギュレーションレジスタは次の電源切断まで保護されます (TBPROT, LBPROT[2:0], SP4KBS, TB4KBS)。 |

注

16. コンフィギュレーションを保護することで、保護のために選択されたメモリアレイ ブロックも保護されます。

#### 4.5.1.3 レガシー ブロック保護のフローチャート

LBP 保護スキームのフローチャートを、Figure 41 に示します。

Figure 41 レガシー ブロック保護のフローチャート

#### 4.5.1.4 LBP に関するレジスタとトランザクション

Table 25 LBP に関するレジスタとトランザクション

| 関連するレジスタ                                               | 関連する SPI トランザクション (Table 81 を参照してください) | 関連するオクタルトランザクション (Table 82 を参照してください) |

|--------------------------------------------------------|----------------------------------------|---------------------------------------|

| ステータス レジスタ 1 (STR1N, STR1V) (Table 47 を参照してください)       | 任意レジスタ読み出し (RDARG_C_0)                 | 任意レジスタ読み出し (RDARG_4_0)                |

| コンフィギュレーション レジスタ 1 (CFR1N, CFR1V) (Table 51 を参照してください) | 任意レジスタ書き込み (WRARG_C_1)                 | 任意レジスタ書き込み (WRARG_4_1)                |

|                                                        | ステータス レジスタ 1 読み出し (RDSR1_0_0)          | ステータス レジスタ 1 読み出し (RDSR1_4_0)         |

|                                                        | 書き込みイネーブル (WRENB_0_0)                  | 書き込みイネーブル (WRENB_0_0)                 |

#### 4.5.2 高度セクタ保護 (ASP)

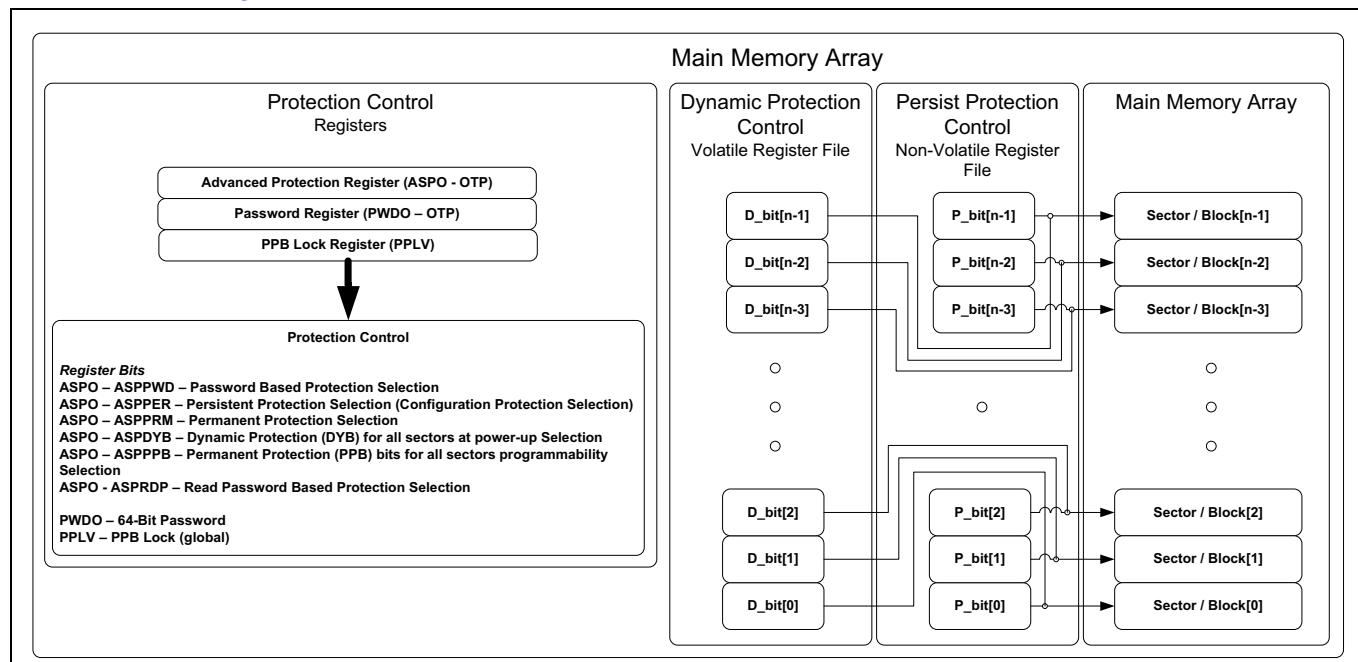

高度セクタ保護スキームでは、消去やプログラムを防止するために揮発性または不揮発性ロック機能によって個々のメモリアレイセクタを独立して制御できます。不揮発性ロック コンフィギュレーションもロックされるか、またはパスワードで保護されます。

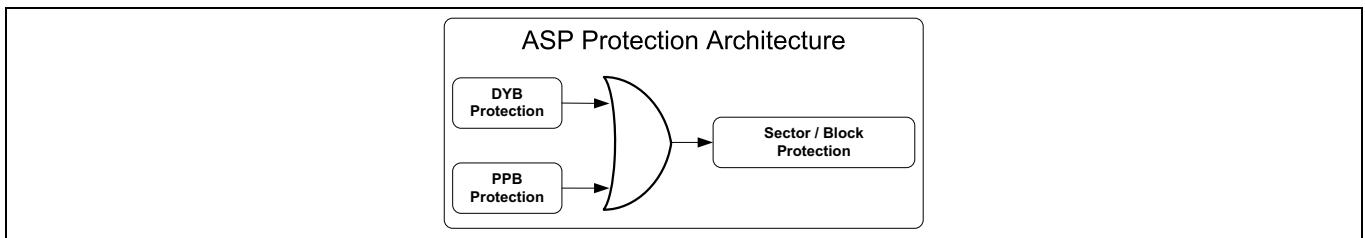

メインメモリアレイのセクタは、揮発性 (DYB) と不揮発性 (PPB) の保護ビットペアにより消去やプログラムから保護されます。各 DYB/PPB ビットペアは個別に、該当セクタを保護するために「0」にセットされ、該当セクタの保護を解除するために「1」にクリアされます。DYB 保護ビットは何回でもセットおよびクリアできますが、不揮発性の PPB ビットそれは対応する技術的な耐久性要件を満たす必要があります。Figure 42 に、ASP の概要を示します。

Figure 42 高度セクタ保護 (不揮発性)

**Figure 43 DYB と PPB の保護制御**

ASP は、設計やシステムのニーズに応じて採用される複数のデータ保護スキームを作り出す豊富なコンフィギュレーションオプションセットを提供します。それらのコンフィギュレーションオプションは、43 ページの “[コンフィギュレーション保護](#)”～48 ページの “[ASP に関するレジスタとトランザクション](#)”で説明します。

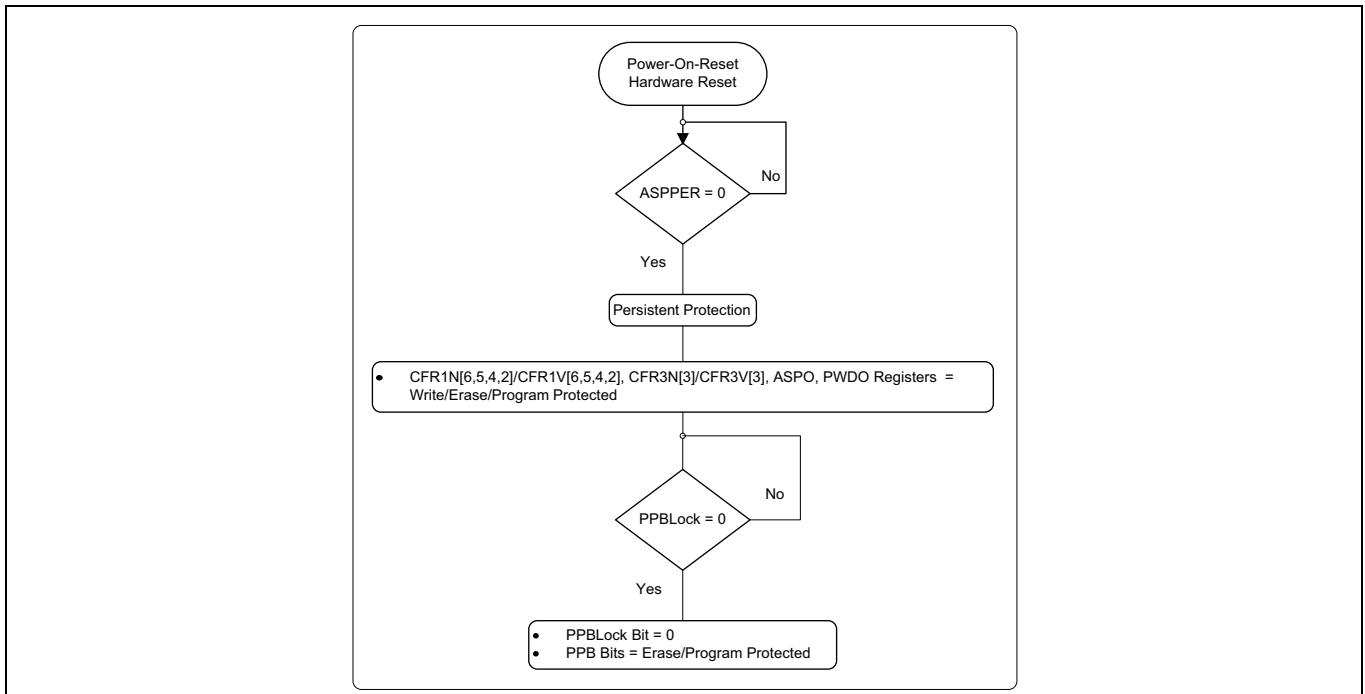

#### 4.5.2.1 コンフィギュレーション保護

ASP は持続的保護スキームを用いてデバイスのコンフィギュレーションを保護します。高度セクタ保護レジスタのビット 1 (ASPO[1] - ASPPER) は持続的保護スキームを選択し、次のレジスタまたはレジスタビットを書き込みやプログラムから保護します。

- CFR1V[6,5,4,2]/CFR1N[6,5,4,2] - SP4KBS, TBPROT, PLPROT, TB4KBS

- CFR3N[3]/CFR3V[3] - UNHYSA

- ASPO[15:0]

- PWDO[63:0]

持続的保護スキームのフローチャートを、[Figure 44](#) に示します。

**Figure 44 持続的保護スキームのフローチャート**

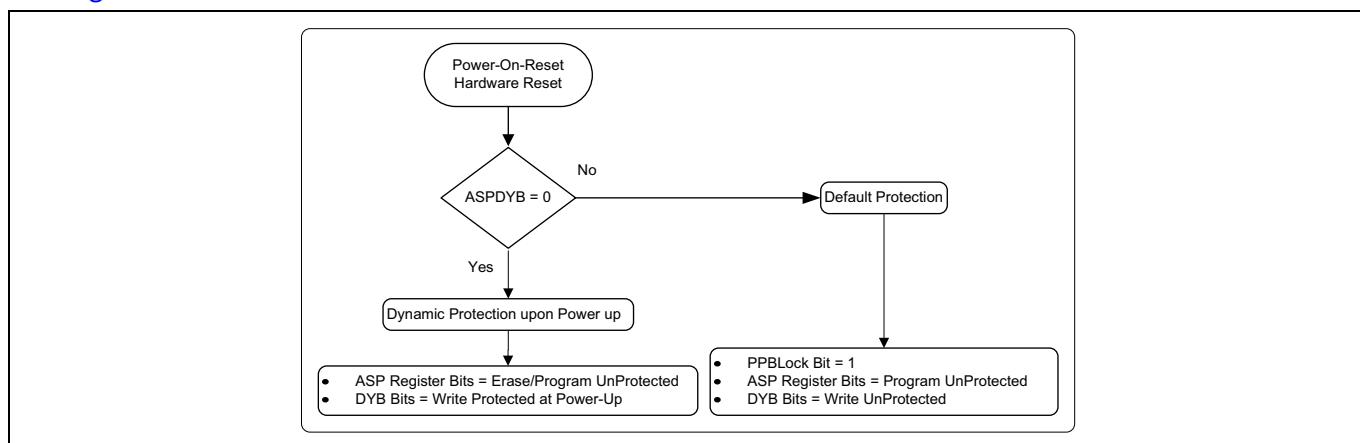

#### 4.5.2.2 ダイナミック DYB ( 挿発性 ) セクタ保護

ダイナミック保護ビット (DYB) は挿発性で各セクタに固有であり、個別に変更できます。DYB は、PPB がクリアされたセクタに対してのみ保護を制御します。DYB 書き込みトランザクションを実行することで、DYB を「0」にセットするか、または「1」にクリアし、各セクタはそれぞれ保護または非保護の状態になります。この機能により、ソフトウェアが意図しない変更からセクタを簡単に保護できますが、変更が必要なときには保護を簡単に取り除くことを妨げません。DYB は、何度でも必要なだけ、「0」にセットまたは「1」にクリアできます。

ダイナミックセクタ保護スキームでは、電源投入時にすべての DYB 挿発性保護ビットを「0」にリセットするオプション(保護済み)があり、基本的にはすべてのセクタを消去やプログラムから保護します。高度セクタ保護レジスタのビット 4 (ASPO[4] - ASPDYB) を選択すると、電源投入保護スキームですべてのセクタに対してダイナミック保護 (DYB) を選択します。これらの DYB ビットは、必要に応じて個別に「1」にセットできます。電源投入時の保護を示すダイナミックセクタ保護スキームのフローチャートを、Figure 45 に示します。

Figure 45 ダイナミックセクタ保護スキームのフローチャート

#### 4.5.2.3 恒久的 / 一時的 PPB ( 不揮発性 ) セクタ保護

各不揮発性ビット (PPB) は個別のメモリセクタに対する不揮発性保護を提供します。すなわち、対応するビットが「1」にクリアされるまでメモリセクタはロックされたまま(保護が有効)です。ASP で PPB ベースの不揮発性選択を制御するためには、恒久的および一時的と呼ばれる 2 つのオプションが用意されています。

#### 4.5.2.4 恒久的 PPB 保護スキーム

PPB は、個別の不揮発性フラッシュアレイに配置されます。セクタごとに 1 つの PPB ビットが割り当てられます。PPB が「0」にプログラムされた場合、該当するセクタはプログラムおよび消去動作から保護されます。PPB は個別にプログラムされますが、グループとして消去される必要があります。これは、個々のワードがメインアレイでプログラム可能であるが PPB セクタ全体が一括での消去を必要とすることと同様です。PPB ビットのプログラムには、通常のワードプログラム時間が必要です。PPB ビットプログラムまたは PPB ビット消去の間に、ステータスレジスタにアクセスしていつ動作が完了したかを確認できます。すべての PPB を消去するためには、標準のセクタ消去時間が必要です。

恒久的 PPB ベースの保護スキームは、その名のとおり、恒久的であり変更されることはありません。PPB アーキテクチャがいったん決定されたら、高度セクタ保護レジスタのビット 0 (ASPO[0]) を選択することにより、すべての PPB ビットに対して恒久的保護が有効になり、基本的にはすべての PPB 消去とプログラム動作が無効になります。ASPO は書き込みまたはプログラムからも保護されます。

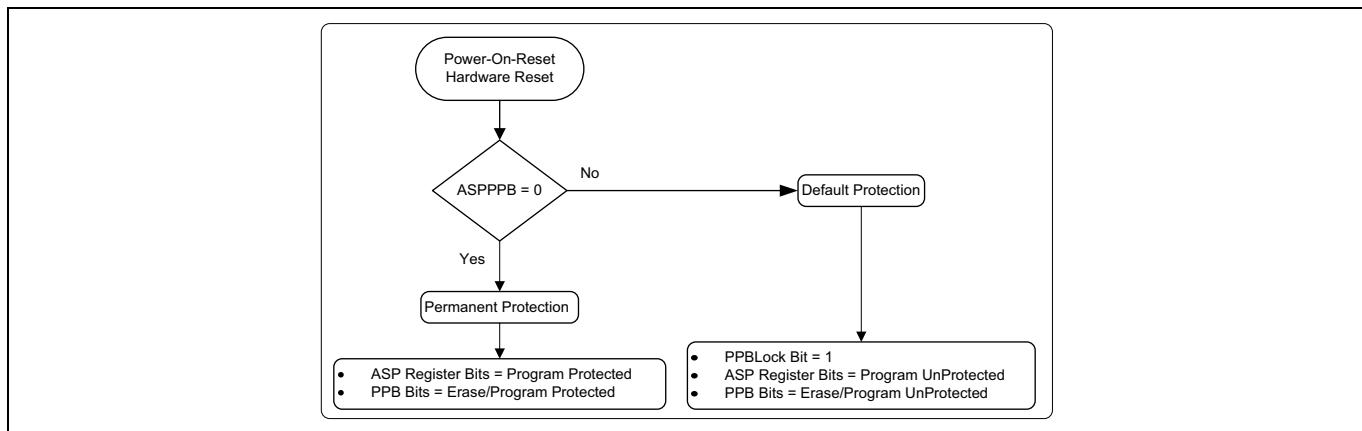

恒久的 PPB 保護スキームのフローチャートを、Figure 46 に示します。

Figure 46 恒久的 PPB セクタ保護のフローチャート

#### 4.5.2.5 一時的 PPB 保護スキーム

PPB ベースの不揮発性保護アーキテクチャは一時的にロックできます。その間、個別の PPB ビットの消去とプログラムは禁止されます。持続的保護ロックビット (PPBLock) は、すべての PPB ビットを保護するための揮発性ビットです。「0」にクリアすると、すべての PPB をロックし、「1」にセットすると PPB の変更を許可します。PPB ロックビットはデバイスあたり 1 つのみです。PPB ロックトランザクション (WRPLB\_0\_0) を使用してこのビットを「0」にクリアします。PPB ロックビットは、すべての PPB を所望の設定にした後にのみ「0」にクリアしなければなりません。PPB ロックビットは、POR またはハードウェアリセット時に「1」にセットされます。PPB ロックトランザクションでクリアされた場合、PPBLock をセットできるソフトウェアコマンドシーケンスはなく、別のハードウェアリセットまたは電源投入のみが PPBLock をセットできます。

注 : 一時的 PPB 保護では、ASP コンフィギュレーションは必要とされません。

#### 4.5.2.6 パスワード保護スキーム

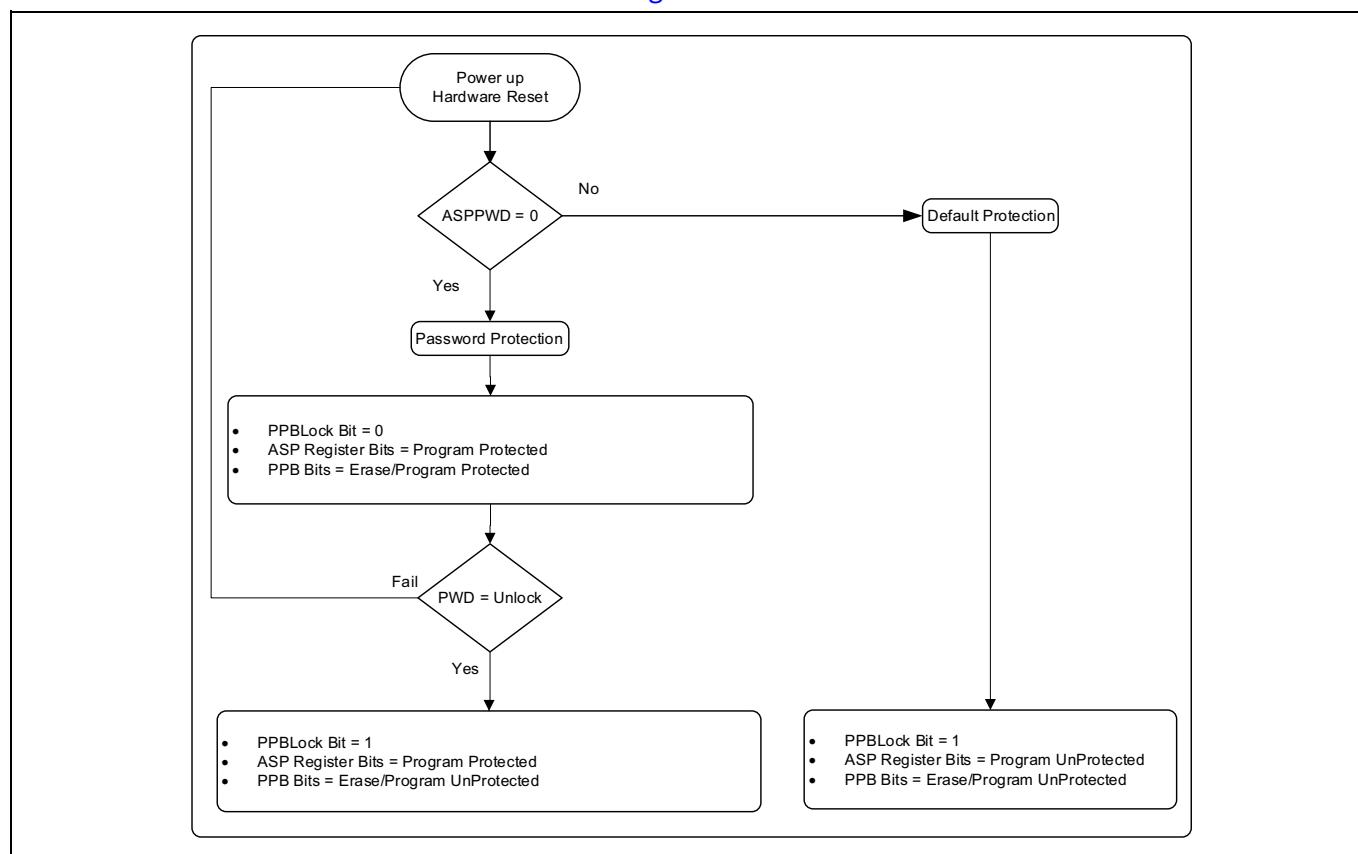

パスワード保護スキームは、PPB ロックをセットするために 64 ビットのパスワードを必要とすることにより、更なる高いレベルのセキュリティを実現します。このパスワード要件に加えて、電源投入またはハードウェアリセット後、電源投入時の保護を確実にするために PPB ロックは「0」にクリアされます。完全なパスワードを入力してパスワードロック解除コマンドを正常に完了すると、PPB ロックビットが「1」にセットされ、セクタの PPB の変更が可能になります。パスワード保護スキームは高度セクタ保護レジスタのビット 2 (ASPO[2] - ASPPWD) により選択されます。パスワード保護スキームは ASPO を書き込みやプログラムからも保護します。

注：パスワード保護スキームを選択する前にパスワードをプログラムする必要があります。パスワードロック解除の SPI トランザクション (PWDUL\_0\_1) またはオクタルトランザクション (PWDUL\_4\_1) が比較のためのパスワードを提供するために使用されます。

パスワード保護スキームのフローチャートを、Figure 47 に示します。

Figure 47 パスワード保護スキームのフローチャート

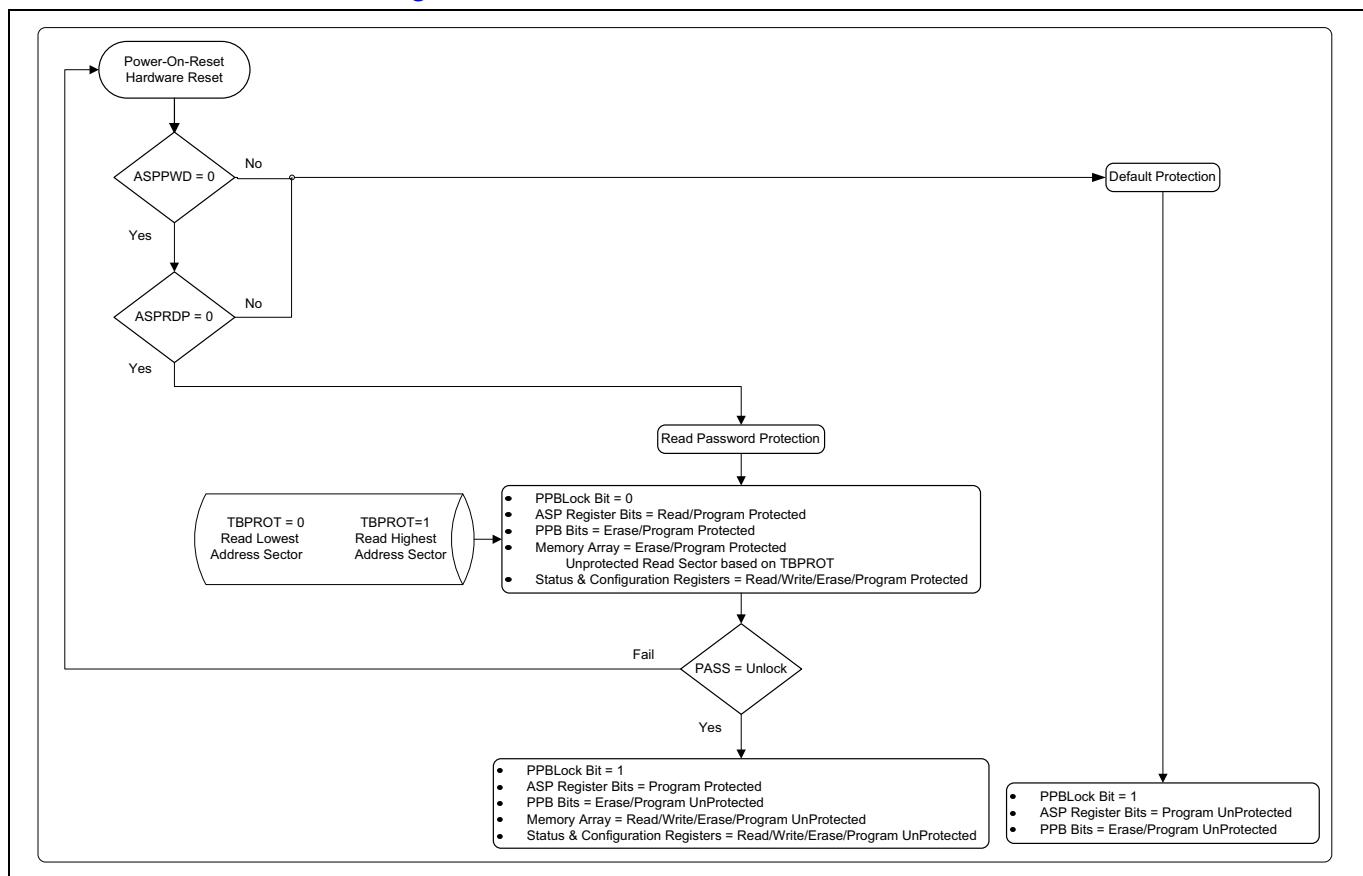

#### 4.5.2.7 パスワード読み出し保護スキーム

パスワード読み出し保護スキームはパスワード保護スキームに代わり、最も優れたデータ保護を実現します。パスワード読み出し保護スキームでは、フラッシュメモリアレイは読み出し、プログラムおよび消去から保護されます。パスワードロック解除トランザクションが正常に完了するまでは、コンフィギュレーションレジスタ1のビット5(CFR1x[5] - TBPROT)によって選択された最下位または最上位(256KB)セクタアドレス範囲のみが読み出せます。読み出しトランザクションで提供されたセクタアドレスに関係なく、「0」は最上位セクタから、「1」は最下位セクタから選択します。アレイの読み出し保護部分からの読み出しへは、読み出し可能なセクタにリダイレクトします。

注：パスワード読み出し保護スキームを選択する前にパスワードをプログラムする必要があります。パスワードロック解除のSPIトランザクション(PWDUL\_0\_1)またはオクタルトランザクション(PWDUL\_4\_1)が比較のためのパスワードを提供するために使用されます。パスワード読み出し保護スキームのフローチャートを、Figure 48に示します。

Figure 48 パスワード読み出し保護スキームのフローチャート

#### 4.5.2.8 PPB ビット - OTP 選択

ASP は、PPB 消去トランザクション (ERPPB\_0\_0) を永久に無効にするコンフィギュレーションオプションを提供しています。これにより、すべての PPB ビットがワンタイムプログラマブルになります。このオプションを使用すれば、PPB 保護はいったん選択されたら変更できなくなります。高度セクタ保護レジスタのビット 3 (ASPO[3] - ASPPP) を選択することで PPB ビットが OTP になります。

#### 4.5.2.9 一般的な ASP ガイドライン

- 持続的保護 (ASPPER) およびパスワード保護 (ASPPWD) は相互に排他的であり、一つのオプションしかプログラムできません。

- パスワード読み出し保護 (ASPRDP) は、必要な場合、パスワード保護 (ASPPWD) と同時にプログラムする必要があります。

- いったんパスワードがプログラムされ検証されたら、パスワードの読み出しを防ぐために、パスワード保護スキーム (ASPPWD) を「0」にプログラムする必要があります。

- パスワード読み出し保護スキームおよびパスワード保護スキームが有効になった（すなわち、ASPO[5] - ASPRDP、ASPO[2] - ASPPWD が「0」にプログラムされた）場合、パスワードロック解除シーケンスに正しいパスワードが正常に入力されるまで、すべてのアドレスがブートセクタにリダイレクトされます。正しいパスワードが入力されると、パスワード読み出し保護モードが無効になり、すべてのアドレス指定が適切な位置を選択します。

- パスワード読み出し保護モードがアクティブの場合、メモリ空間のプログラムまたはレジスタへの書き込みは許可されません。

#### 4.5.2.10 ASP に関するレジスタとトランザクション

Table 26 ASP に関するレジスタとトランザクション

| 関連するレジスタ                                              | 関連する SPI トランザクション<br>(Table 81 を参照してください) | 関連するオクタルトランザクション (Table 82 を参照してください) |

|-------------------------------------------------------|-------------------------------------------|---------------------------------------|

| 高度セクタ保護レジスタ<br>(ASPO) (Table 67 を参照してください)            | ダイナミック保護ビット読み出し (RDDYB_4_0)               | ダイナミック保護ビット読み出し (RDDYB_4_0)           |

| コンフィギュレーションレジスタ 1 (CFR1N, CFR1V) (Table 51 を参照してください) | ダイナミック保護ビット書き込み (WRDYB_4_1)               | ダイナミック保護ビット書き込み (WRDYB_4_1)           |

|                                                       | 持続的保護ビット読み出し (RDPPB_4_0)                  | 持続的保護ビット読み出し (RDPPB_4_0)              |

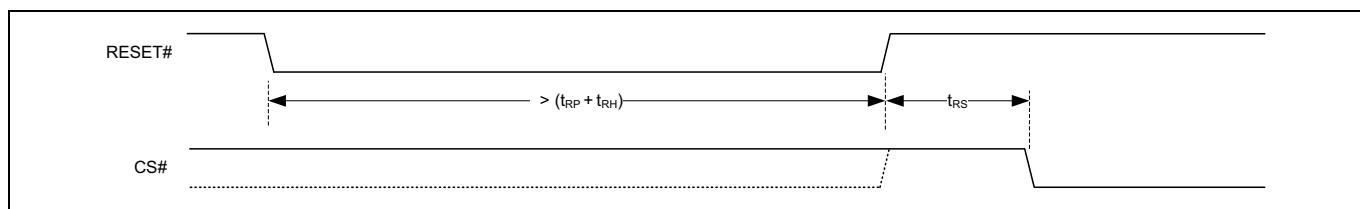

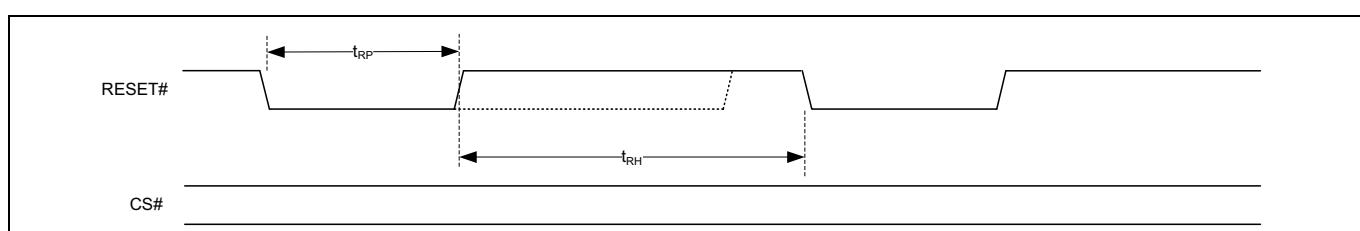

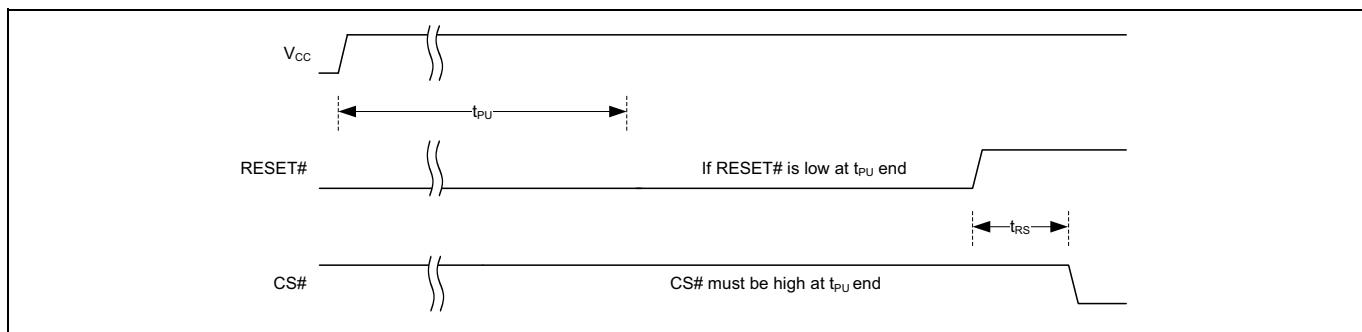

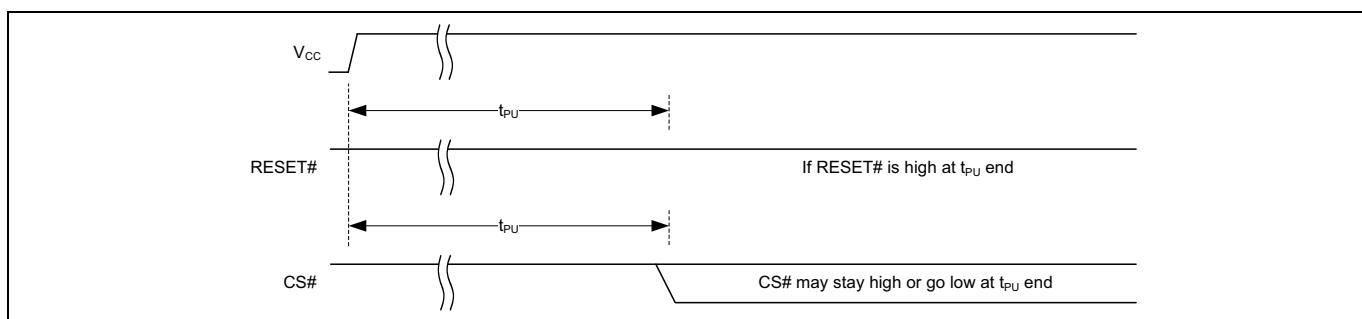

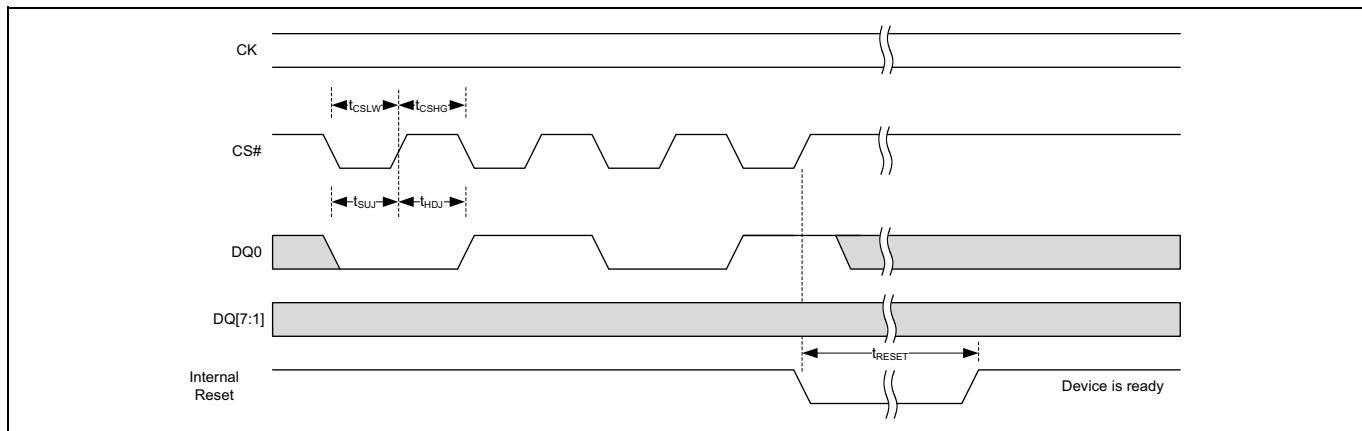

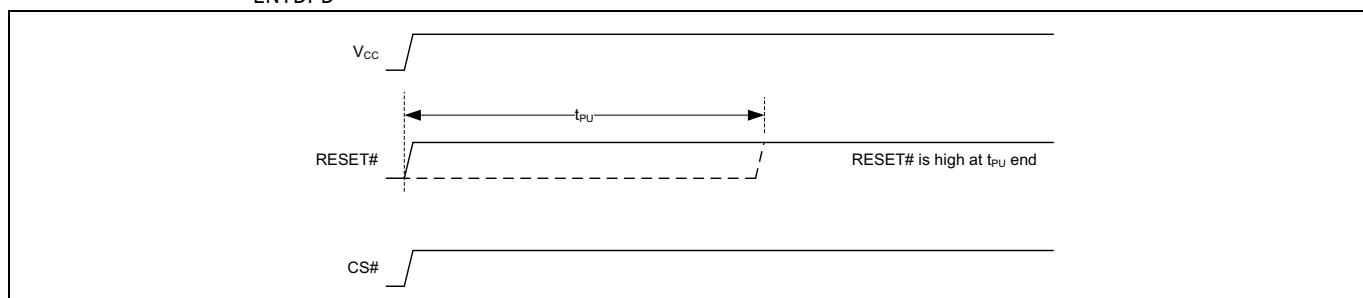

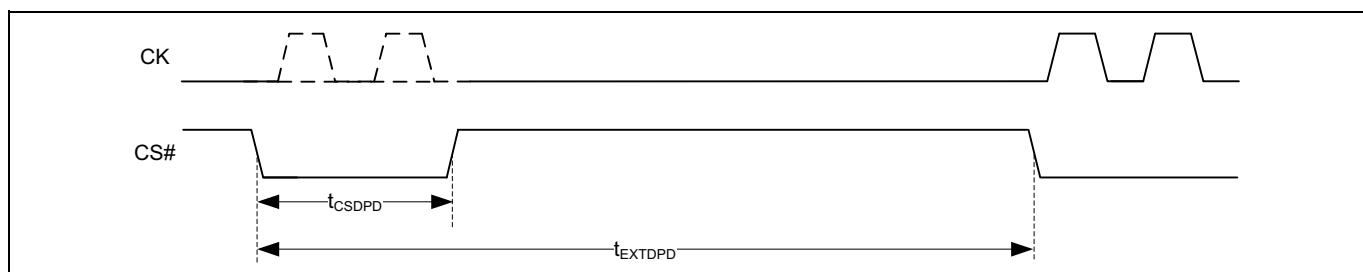

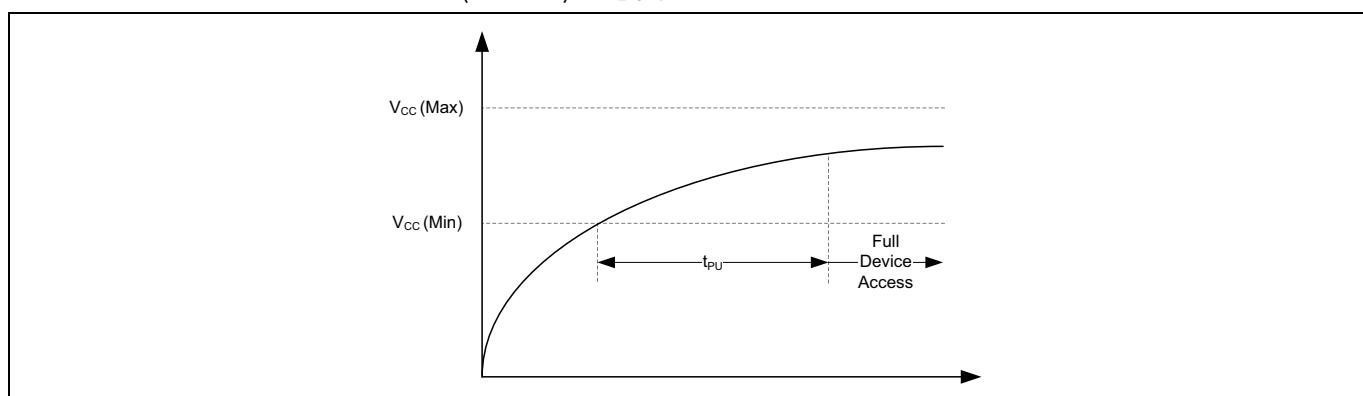

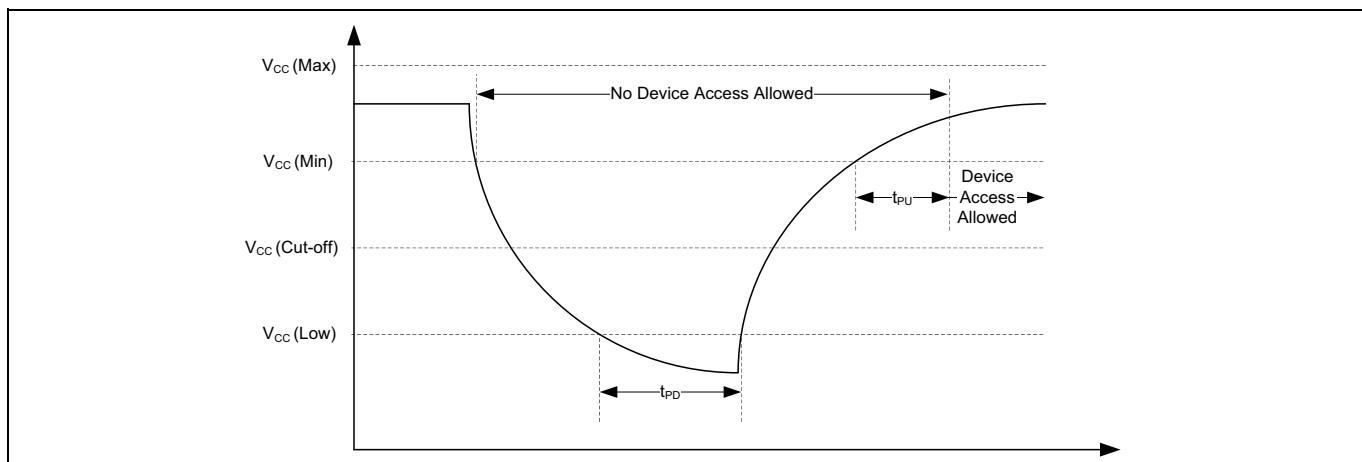

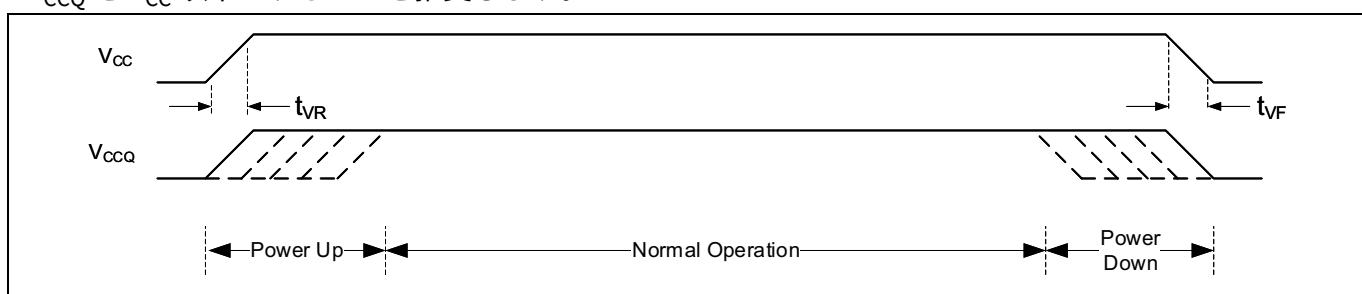

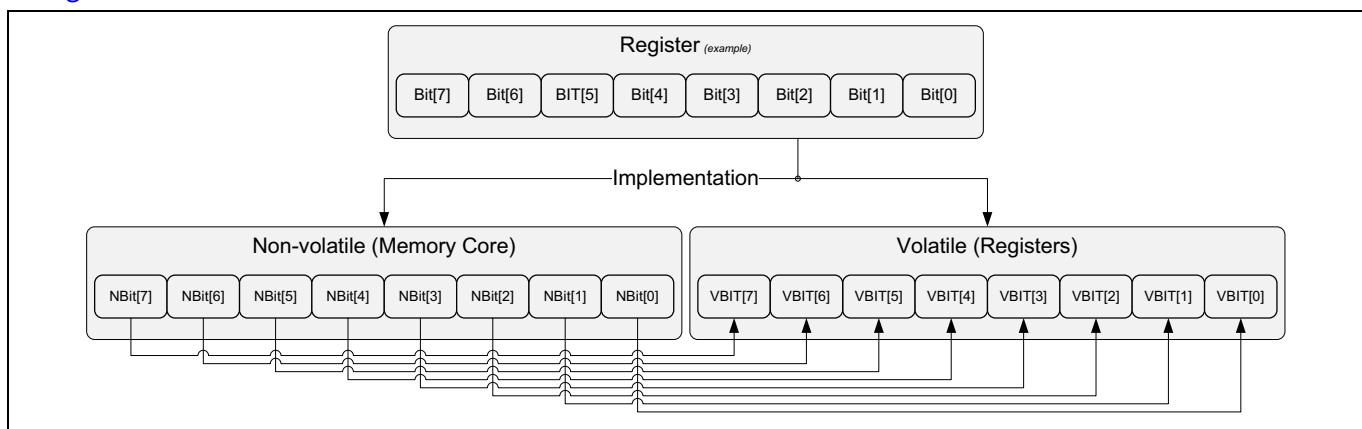

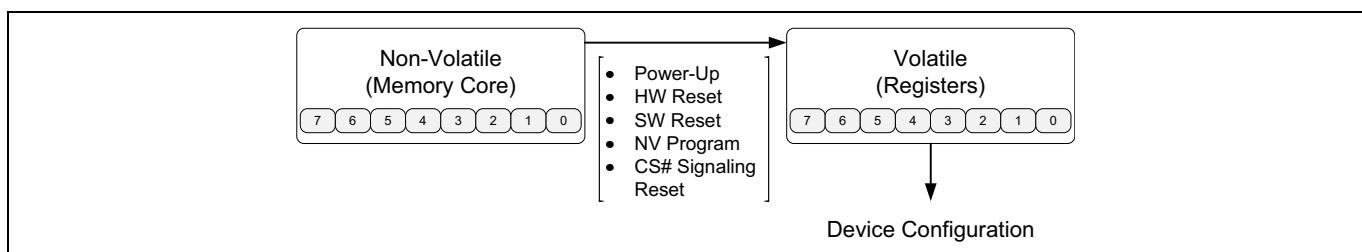

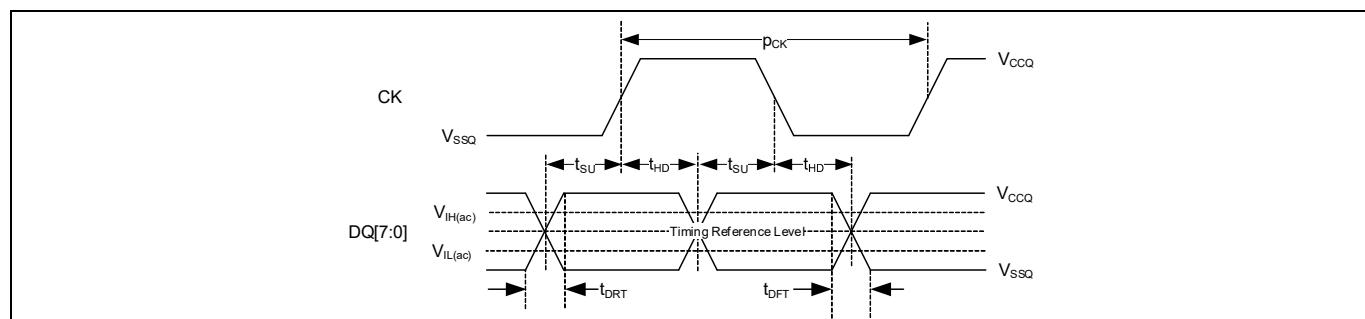

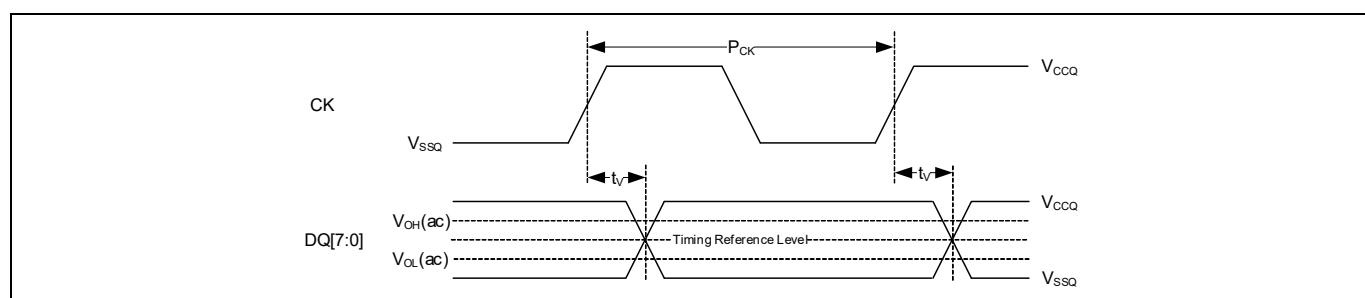

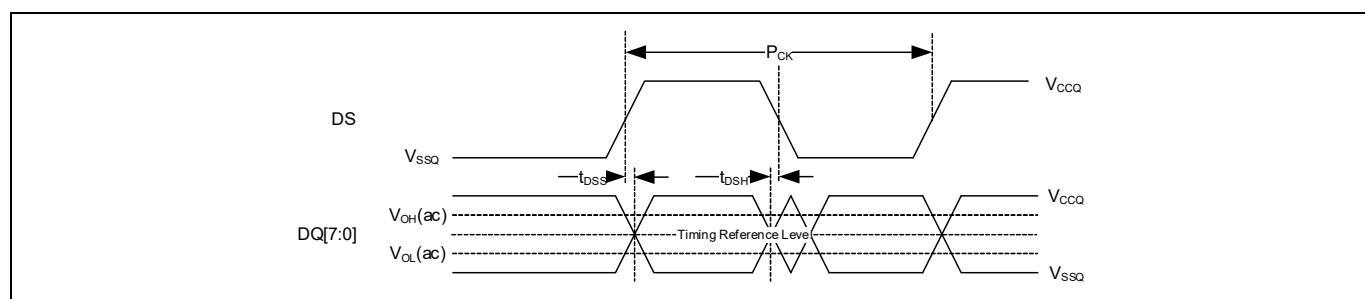

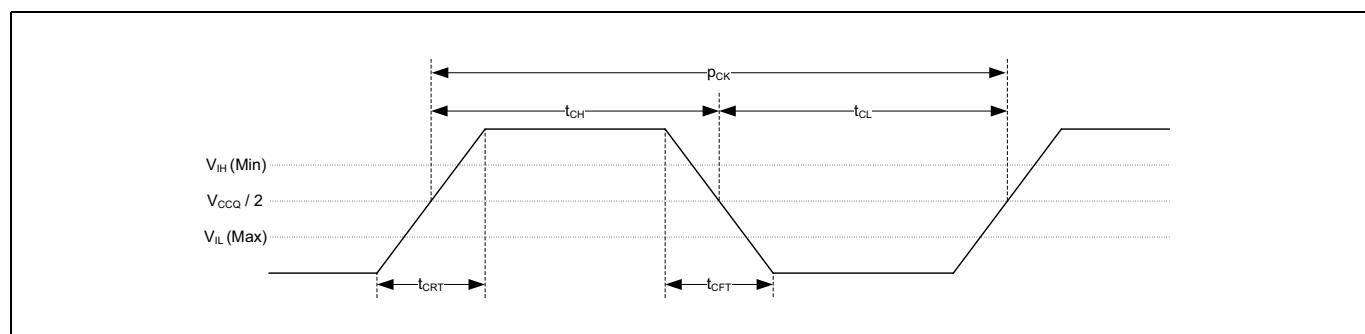

|                                                       | 持続的保護ビットプログラム (PRPPB_4_0)                 | 持続的保護ビットプログラム (PRPPB_4_0)             |