# 64Mb HYPERRAM™ セルフリフレッシュ DRAM (PSRAM)

オクタル xSPI, 1.8V/3.0V

## 特長

- インターフェース

- xSPI (オクタル) インターフェース

- 1.8V/3.0V インターフェース対応

- シングルエンド クロック (CK) - 11 本のバス信号

- オプションの差動クロック (CK, CK#) - 12 本のバス信号

- チップセレクト (CS#)

- 8 ビット データバス (DQ[7:0])

- ハードウェアリセット (RESET#)

- 双方向読み出し書き込みデータストローブ (RWDS)

- すべてのトランザクションの開始時においてリフレッシュ レイテンシを示す出力

- 読み出しトランザクション中に読み出しデータストローブとしての出力

- 書き込みトランザクション中に書き込みデータマスクとしての入力

- オプションとしての DDR 中央読み出しきストローブ (DCARS)

- 読み出しトランザクションの間、RWDS は CK から位相シフトされた第 2 のクロックによりオフセット

- 位相シフト クロックは、RWDS 遷移エッジを読み出しデータのタイミング内に移動するために使用

- 性能、消費電力、およびパッケージ

- 200MHz の最大クロックレート

- DDR - クロックの両エッジでデータを転送

- 最大 400MBps (3,200Mbps) のデータスループット

- 設定可能なバースト特性

- リニアバースト

- ラップバースト長:

- 16 バイト (8 クロック)

- 32 バイト (16 クロック)

- 64 バイト (32 クロック)

- 128 バイト (64 クロック)

- ハイブリッド オプション - 1 回のラップバーストの後にリニアバーストが続く

- 設定可能な出力駆動強度

- 電力モード

- ハイブリッドスリープモード

- ディープパワーダウン

- アレイリフレッシュ

- 部分的メモリアレイ (1/8, 1/4, 1/2 など)

- 全体

- パッケージ

- 24 ボール FBGA

- 動作温度範囲

- 産業用 (I): -40°C ~ +85°C

- 産業用プラス (V): -40°C ~ +105°C

- 車載向け, AEC-Q100 グレード 3: -40°C ~ +85°C

- 車載向け, AEC-Q100 グレード 2: -40°C ~ +105°C

- 技術

- 38nm DRAM

性能要約

## 性能要約

| 読み出しトランザクションタイミング                  | 単位     |

|------------------------------------|--------|

| 1.8V $V_{CC}/V_{CCQ}$ での最大クロック レート | 200MHz |

| 3.0V $V_{CC}/V_{CCQ}$ での最大クロック レート |        |

| 最大アクセス時間 ( $t_{ACC}$ )             | 35ns   |

| 最大消費電流                                             | 単位          |

|----------------------------------------------------|-------------|

| バースト読み出し / 書き込み (200MHz, 1.8V でのリニアバースト)           | 25mA        |

| バースト読み出し / 書き込み (200MHz, 3.0V でのリニアバースト)           | 30mA        |

| スタンバイ ( $CS\# = V_{CC} = 3.6V, 105^\circ C$ )      | 360 $\mu A$ |

| ディープパワーダウン ( $CS\# = V_{CC} = 3.6V, 105^\circ C$ ) | 15 $\mu A$  |

| スタンバイ ( $CS\# = V_{CC} = 2.0V, 105^\circ C$ )      | 330 $\mu A$ |

| ディープパワーダウン ( $CS\# = V_{CC} = 2.0V, 105^\circ C$ ) | 12 $\mu A$  |

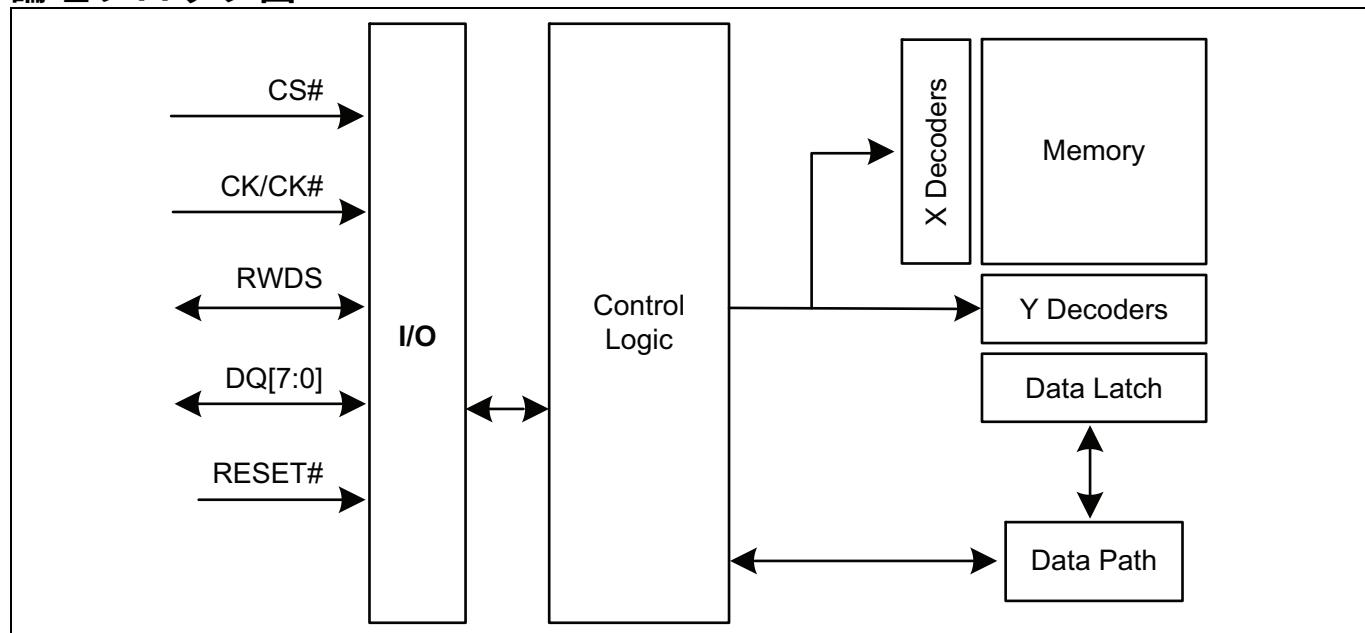

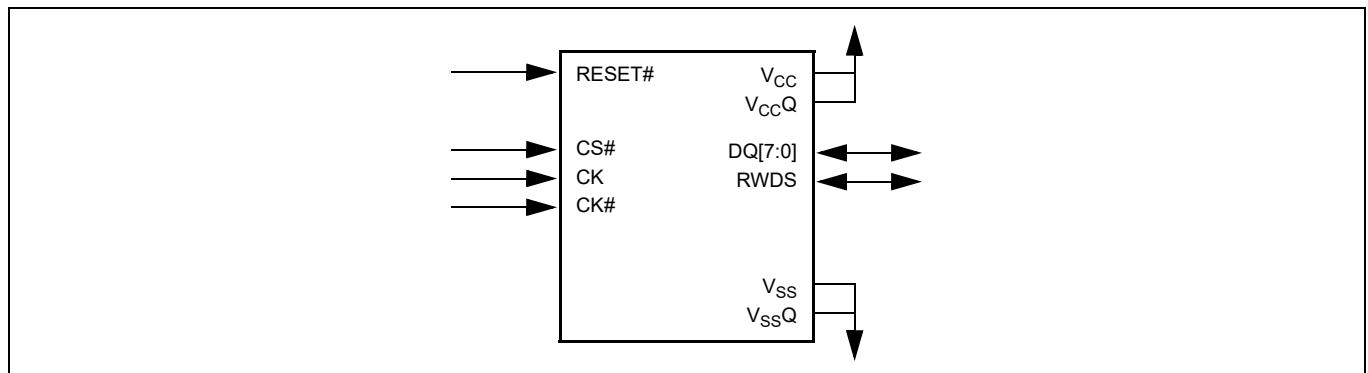

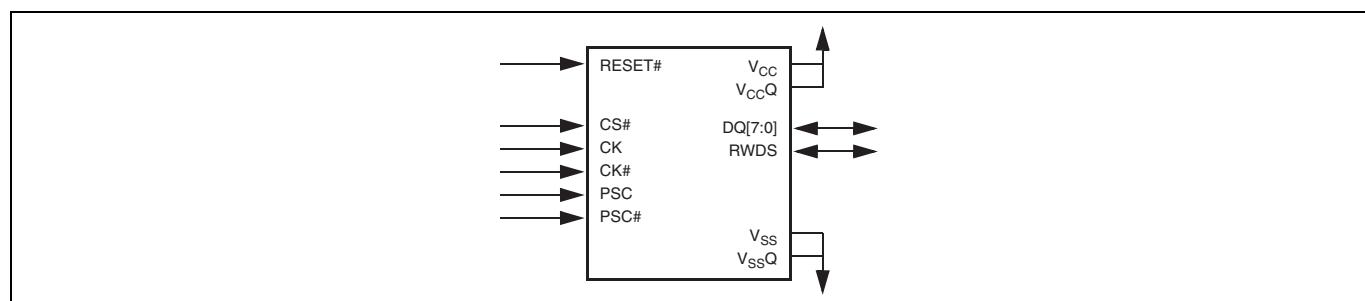

## 論理ブロック図

## 目次

|                                      |           |

|--------------------------------------|-----------|

| <b>1 概要説明</b>                        | <b>5</b>  |

| 1.1 xSPI (オクタル) インターフェース             | 5         |

| <b>2 製品概要</b>                        | <b>8</b>  |

| 2.1 xSPI (オクタル) インターフェース             | 8         |

| <b>3 信号の説明</b>                       | <b>9</b>  |

| 3.1 入出力の要約                           | 9         |

| <b>4 xSPI (オクタル) トランザクションの詳細</b>     | <b>10</b> |

| 4.1 コマンド / アドレス / データビットの割り当て        | 11        |

| 4.2 リセット イネーブル トランザクション              | 12        |

| 4.3 リセット トランザクション                    | 12        |

| 4.4 ID 読み出し トランザクション                 | 13        |

| 4.5 ディープパワーダウン トランザクション              | 14        |

| 4.6 読み出し トランザクション                    | 15        |

| 4.7 書き込み トランザクション                    | 16        |

| 4.8 書き込み イネーブル トランザクション              | 16        |

| 4.9 書き込み ディセーブル トランザクション             | 17        |

| 4.10 任意レジスタ読み出し トランザクション             | 17        |

| 4.11 任意レジスタ書き込み トランザクション             | 18        |

| 4.12 メモリ読み出し / 書き込み トランザクション中のデータ配置  | 19        |

| 4.13 レジスタ読み出し / 書き込み トランザクション中のデータ配置 | 20        |

| <b>5 メモリ空間</b>                       | <b>21</b> |

| 5.1 xSPI (オクタル) インターフェース             | 21        |

| 5.2 メモリ容量と行境界                        | 21        |

| <b>6 レジスタ空間アクセス</b>                  | <b>22</b> |

| 6.1 xSPI (オクタル) インターフェース             | 22        |

| 6.2 デバイス ID レジスタ                     | 22        |

| 6.2.1 デバイスのコンフィギュレーション レジスタ          | 28        |

| <b>7 インターフェース仕様</b>                  | <b>29</b> |

| <b>8 低消費電力モード</b>                    | <b>30</b> |

| 8.1 インターフェーススタンバイ                    | 30        |

| 8.2 アクティブクロック停止                      | 30        |

| 8.3 ハイブリッドスリープ                       | 31        |

| 8.4 ディープパワーダウン                       | 32        |

| <b>9 電気的仕様</b>                       | <b>33</b> |

| 9.1 絶対最大定格                           | 33        |

| 9.1.1 入力信号オーバーシュート                   | 33        |

| 9.2 ラッチアップ特性                         | 34        |

| 9.3 動作範囲                             | 34        |

| 9.3.1 温度範囲                           | 34        |

| 9.3.2 電源電圧                           | 34        |

| 9.4 DC 電気的特性                         | 35        |

| 9.4.1 静電容量特性                         | 37        |

| 9.5 電源投入時の初期化                        | 38        |

| 9.6 電源切断                             | 39        |

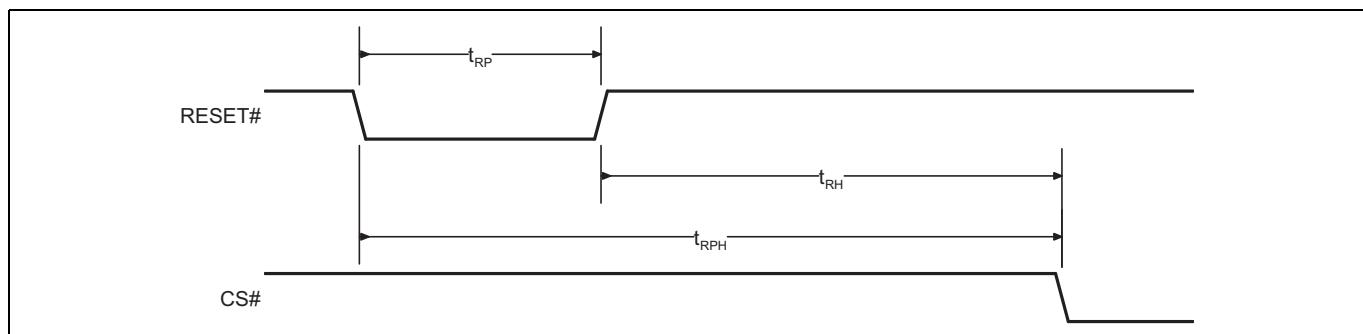

| 9.7 ハードウェアリセット                       | 40        |

| 9.8 ソフトウェアリセット                       | 40        |

| <b>10 タイミング仕様</b>                    | <b>42</b> |

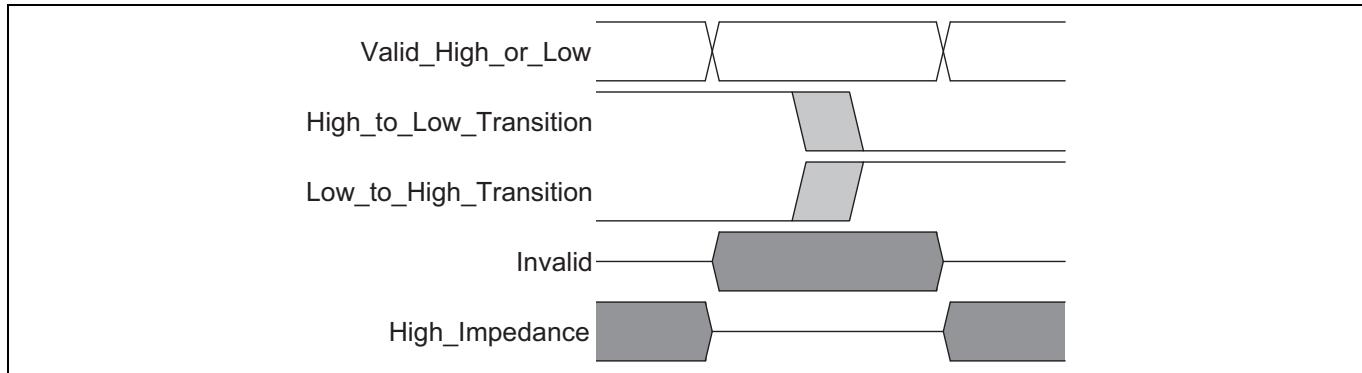

| 10.1 スイッチング波形の要素                     | 42        |

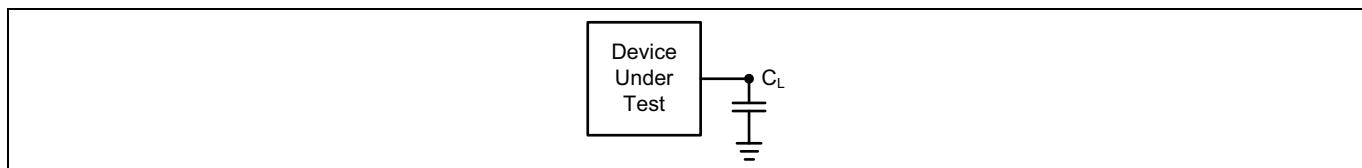

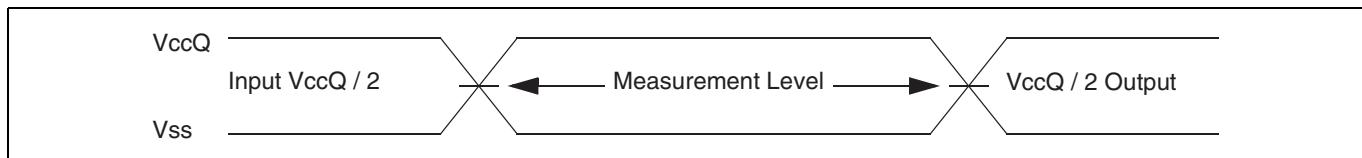

| 10.2 AC テスト条件                        | 42        |

| 10.3 CLK 特性                          | 43        |

| 10.4 AC 電気的特性                        | 44        |

目次

|                                                                    |           |

|--------------------------------------------------------------------|-----------|

| 10.4.1 読み出しトランザクション .....                                          | 44        |

| 10.4.2 書き込みトランザクション .....                                          | 46        |

| <b>11 物理インターフェース .....</b>                                         | <b>47</b> |

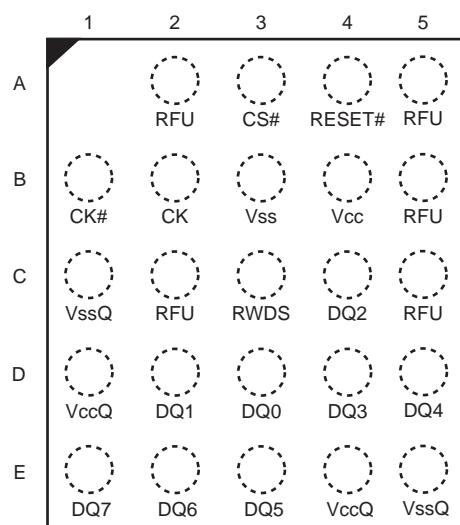

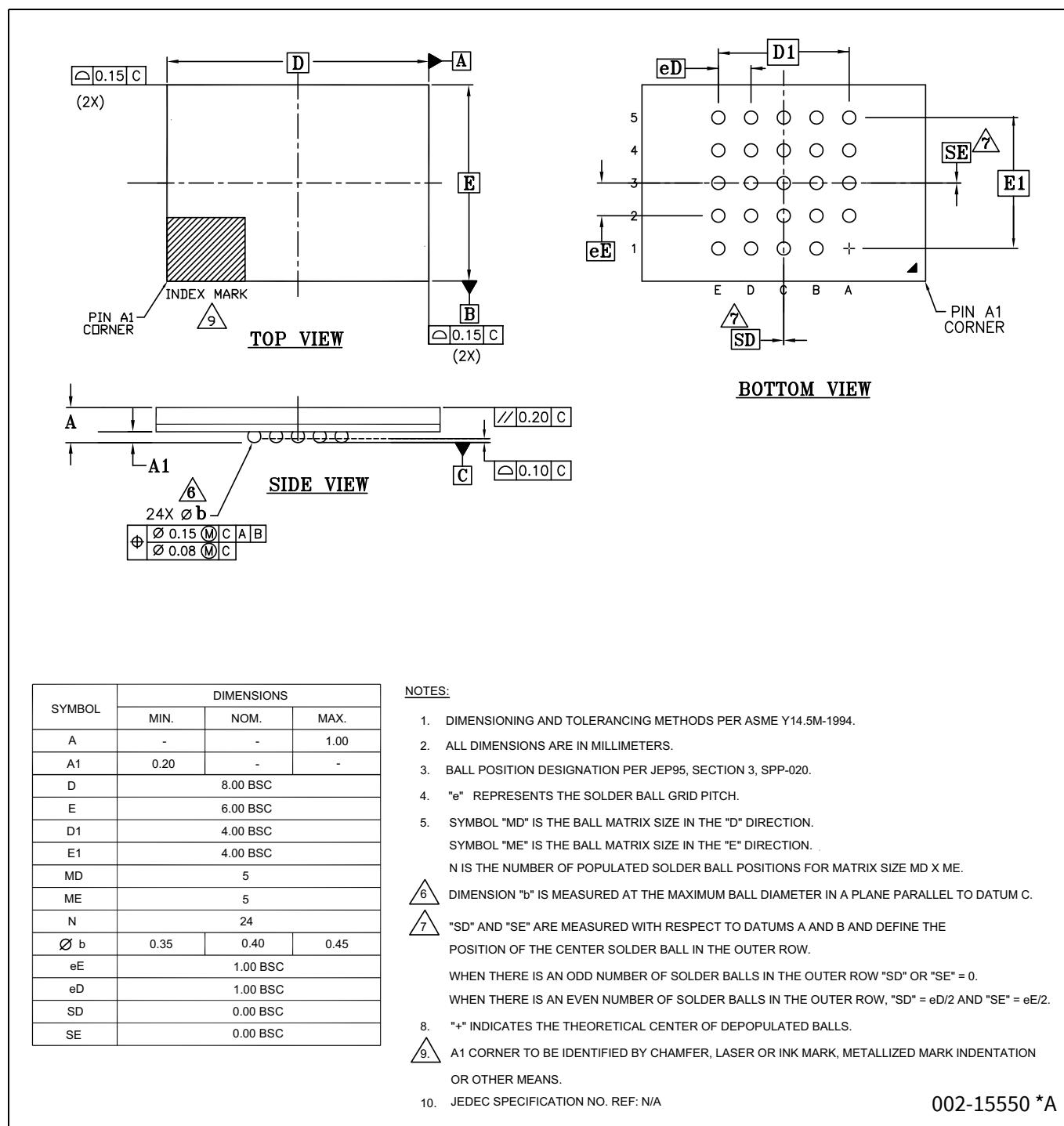

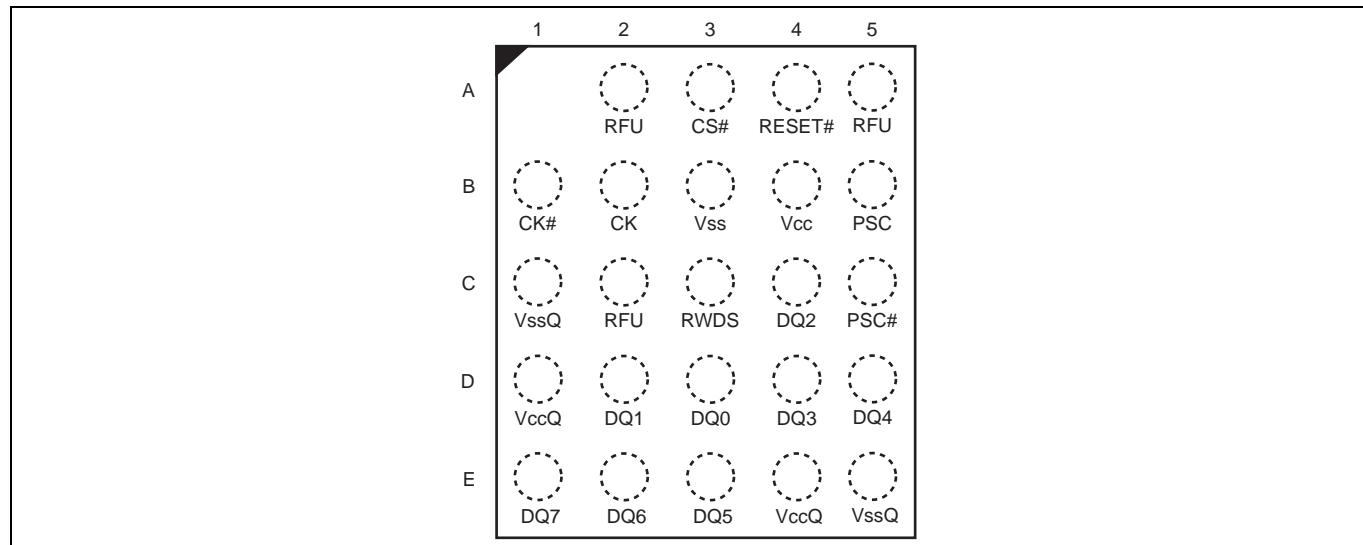

| 11.1 FBGA 24 ボール 5x5 アレイ フットプリント .....                             | 47        |

| 11.2 パッケージ図 .....                                                  | 48        |

| <b>12 DDR 中央揃え読み出しきストローブ (DCARS) 機能 .....</b>                      | <b>49</b> |

| 12.1 DCARS を備えた xSPI HYPERRAM™ 製品の信号説明 .....                       | 49        |

| 12.2 DCARS を備えた HYPERRAM™ 製品 – FBGA 24 ボール , 5x5 アレイ フットプリント ..... | 51        |

| 12.3 DCARS を備えた HYPERRAM™ メモリのタイミング .....                          | 51        |

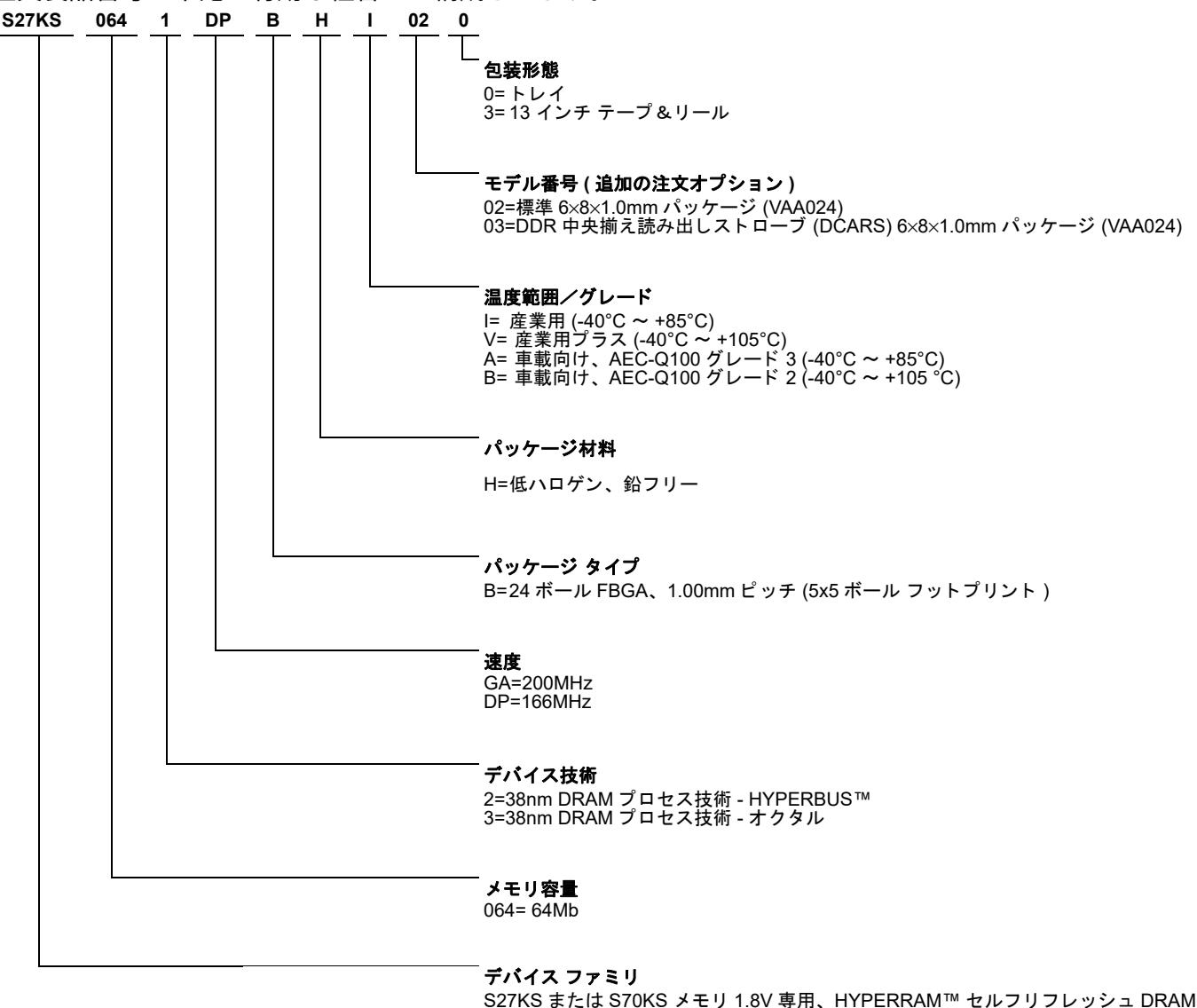

| <b>13 注文情報 .....</b>                                               | <b>53</b> |

| 13.1 注文製品番号 .....                                                  | 53        |

| 13.2 有効な組合せ .....                                                  | 54        |

| 13.3 有効な組合せ – 車載向けグレード / AEC-Q100 .....                            | 54        |

| <b>14 略語 .....</b>                                                 | <b>55</b> |

| <b>15 本書の表記法 .....</b>                                             | <b>56</b> |

| 15.1 測定単位 .....                                                    | 56        |

| 改訂履歴 .....                                                         | 57        |

## 1 概要説明

Infineon® の 64Mb HYPERRAM™ デバイスは、xSPI (オクタル) インターフェースを備えた高速 CMOS、セルフリフレッシュ DRAM です。DRAM アレイは周期的にリフレッシュが必要なダイナミックセルを使用します。デバイス内のリフレッシュ制御ロジックは、メモリが xSPI インターフェースマスター (ホスト) によってアクティブに読み出しまだ書き込みされていないときに DRAM アレイ上のリフレッシュ動作を管理します。ホストがリフレッシュ動作を管理する必要がないため、ホストからは DRAM アレイがリフレッシュなしにデータを保持するスタティックセルを使用しているように見えます。したがって、このメモリは擬似スタティック RAM (PSRAM) として、より正確に記述されます。

DRAM セルは読み出し / 書き込みトランザクション中にリフレッシュできないため、ホストが読み出し / 書き込みのバースト転送長を制限して、必要に応じて内部ロジックのリフレッシュ動作を行えるようにする必要があります。メモリがリフレッシュ動作を必要とした場合、ホストはトランザクションの期間を制限し、新しいトランザクションの開始時に追加の初期アクセス レイテンシを許可する必要があります。

### 1.1 xSPI (オクタル) インターフェース

xSPI (オクタル) は、8 個の I/O をサポートする、SPI 互換の少信号数の DDR インターフェースです。xSPI (オクタル) の DDR プロトコルでは、DQ 入出力信号のクロックサイクルごとに 2 データ バイトが転送されます。xSPI (オクタル) での読み出し / 書き込みトランザクションは、内部 RAM アレイにおける一連の 1 クロックサイクルの 16 ビット幅データ転送と、DQ 信号上の 2 つの 1/2 クロックサイクルの 8 ビット幅データ転送で構成されます。すべての入出力は LV-CMOS 互換です。デバイスは異なる注文製品番号 (OPN) で、アレイ ( $V_{CC}$ ) および I/O バッファ ( $V_{CCQ}$ ) の電源電圧として 1.8V  $V_{CC}/V_{CCQ}$  または 3.0V  $V_{CC}/V_{CCQ}$  (公称) に対応しています。

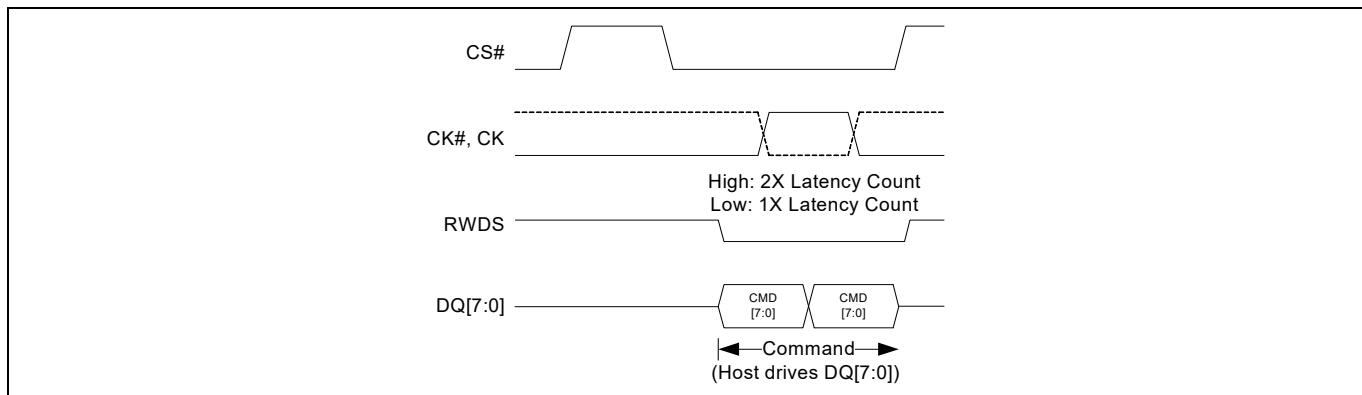

xSPI (オクタル) の各トランザクションにはコマンドは必須ですが、アドレスとデータはオプションです。トランザクションは以下に示す構造です。

- 各トランザクションは CS# が LOW になることで開始し、CS# が HIGH に戻ることで終了します。

- シリアルクロック (CK) はホストとメモリの間の各ビットまたは各ビットグループの転送を示します。すべての転送は、CK エッジごとに発生します (DDR モード)。

- 各トランザクションには、実行するデバイス動作のタイプを選択する 16 ビット コマンドがあります。16 ビット コマンドは、2 つの 8 ビット オペコードに基づいています。同じ 8 ビットのオペコードがクロックの両エッジで送信されます。

- コマンドは単独であるか、またはその後にデータアクセスのためにデバイス内のメモリ位置を選択するアドレスビットが続く場合があります。

- 読み出しトランザクションは、アドレスビットの後にレイテンシ期間が必要であり、0～数 CK サイクル続きます。CK は、読み出しトランザクションのレイテンシ期間中にトグルし続ける必要があります。トランザクションのコマンドおよびアドレス部分で、メモリは RWDS 信号を HIGH 状態に駆動することで、初期レイテンシ期間に挿入される必要なリフレッシュ時間 ( $t_{RFH}$ ) に追加のレイテンシ期間が必要かどうかを示します。

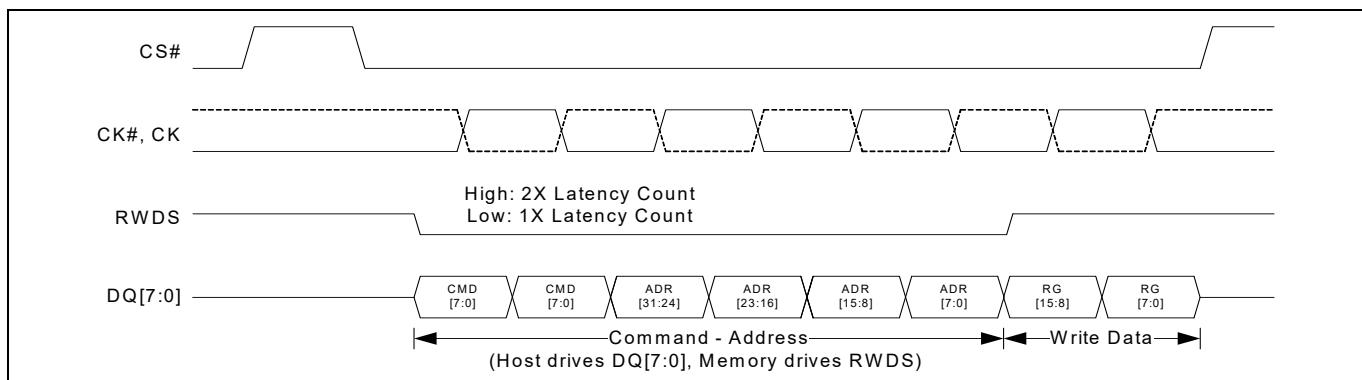

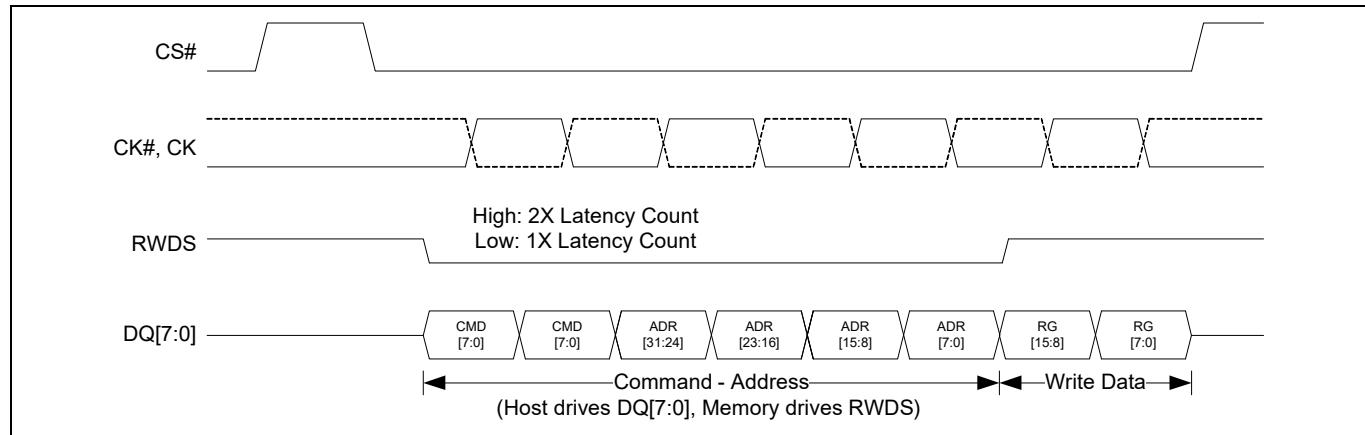

- レジスタへの書き込みトランザクションにはレイテンシ期間は必要ありません。

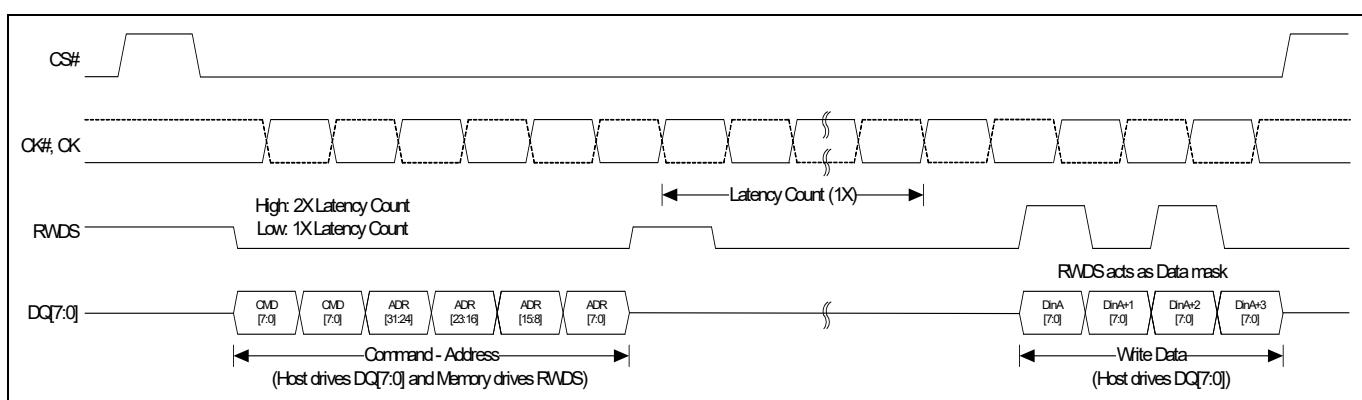

- メモリアレイへの書き込みトランザクションは、アドレスビットの後にレイテンシ期間が必要であり、0～数 CK サイクル続きます。CK は、書き込みトランザクションのレイテンシ期間中にトグルし続ける必要があります。トランザクションのコマンドおよびアドレス部分で、メモリは RWDS 信号を HIGH 状態に駆動することで、初期レイテンシ期間に挿入される必要なリフレッシュ時間 ( $t_{RFH}$ ) に追加のレイテンシ期間が必要かどうかを示します。

- すべてのトランザクションで、コマンドおよびアドレスビットは最上位ビット (MSb) ファースト方式でデバイスにシフトインされます。データビットの個々のデータビットも、MSb ファースト方式でデバイスにシフトインされます / デバイスからシフトアウトされます。すべてのデータビットは、最下位アドレスビットが最初に転送されます。

概要説明

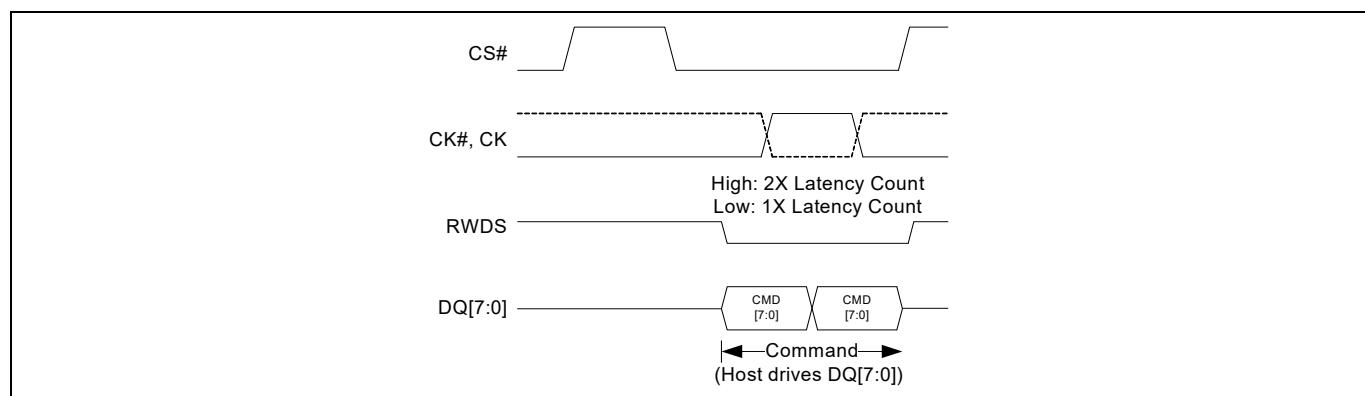

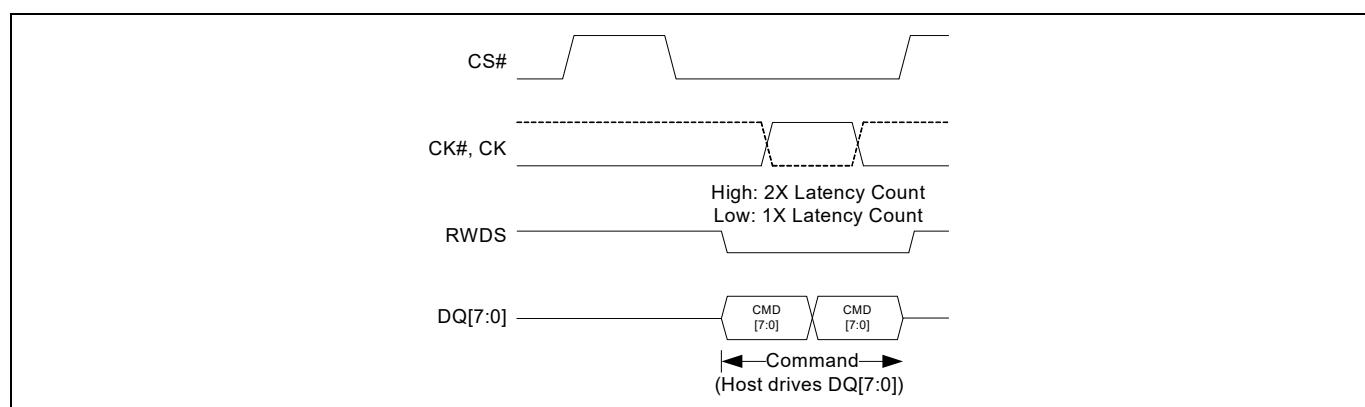

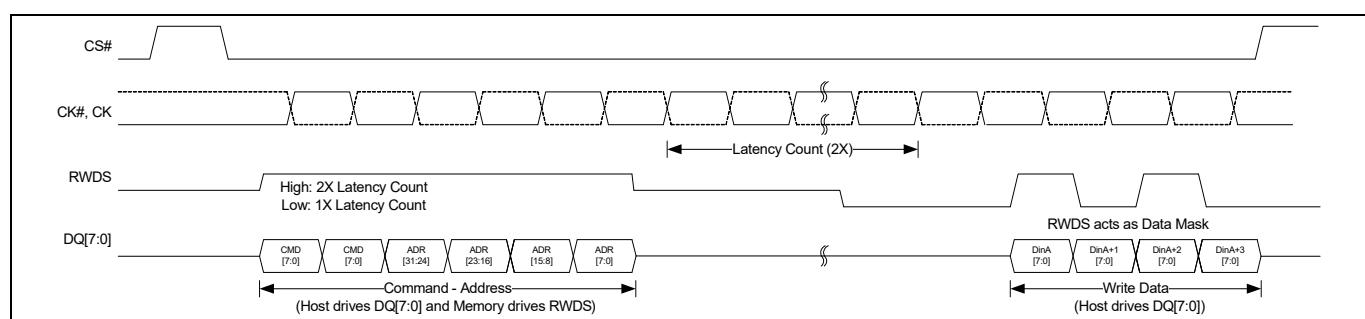

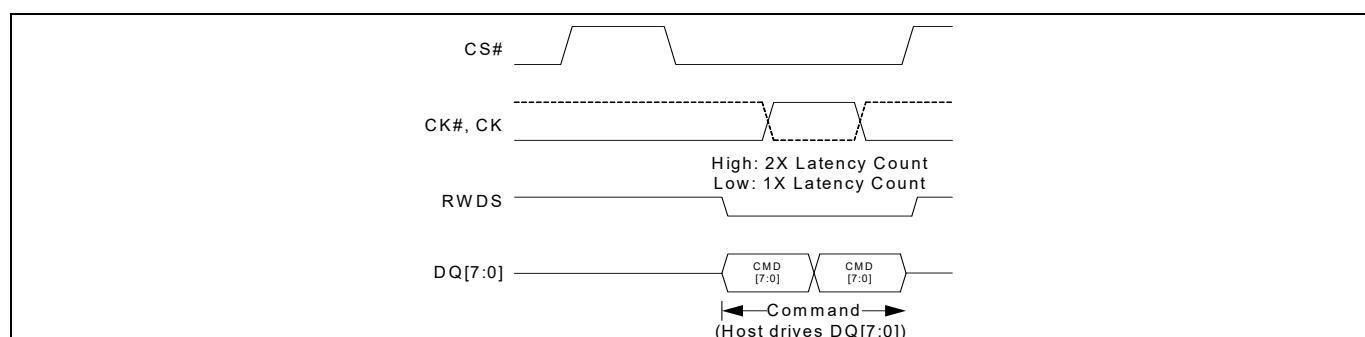

Figure 1 xSPI ( オクタル ) を介したコマンドのみのトランザクション (DDR)

Figure 2 xSPI ( オクタル ) を介したレイテンシ無し書き込みトランザクション (DDR) ( レジスタ書き込み )<sup>[1]</sup>

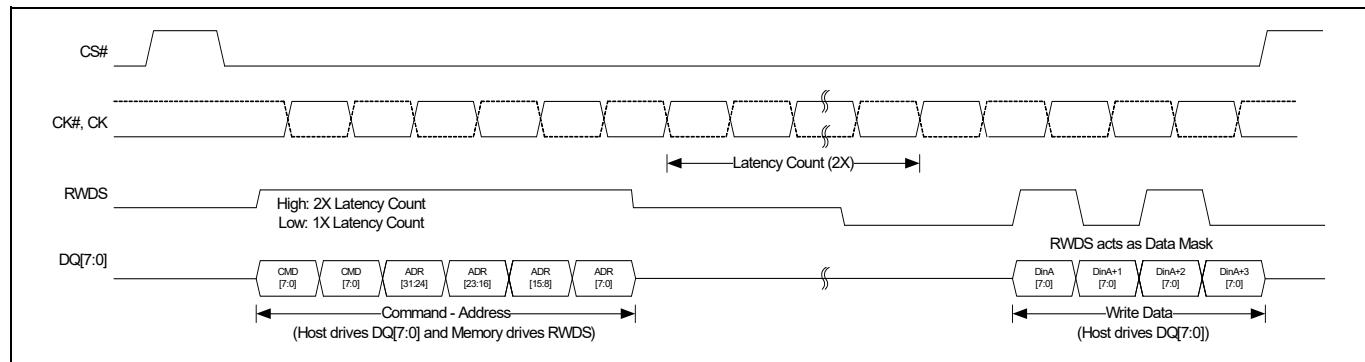

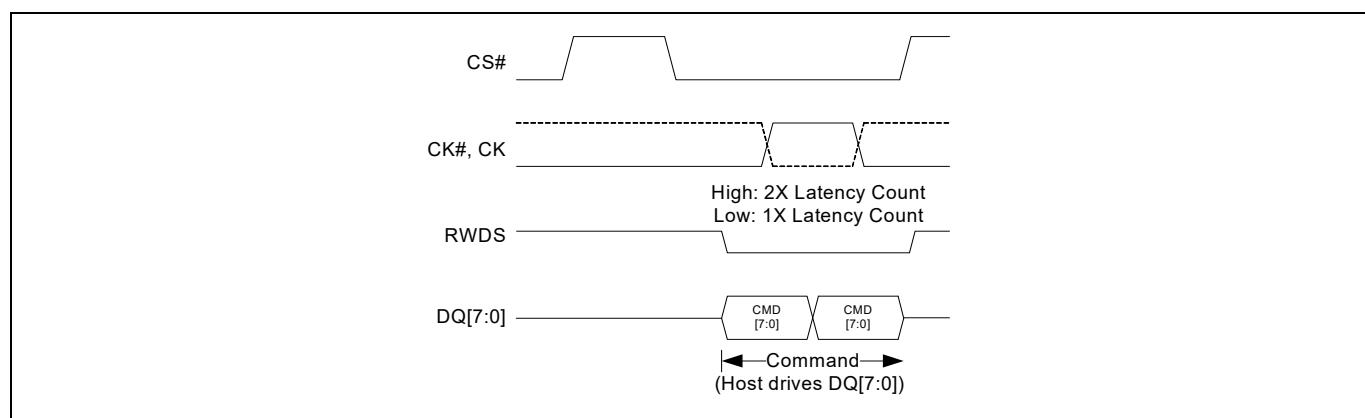

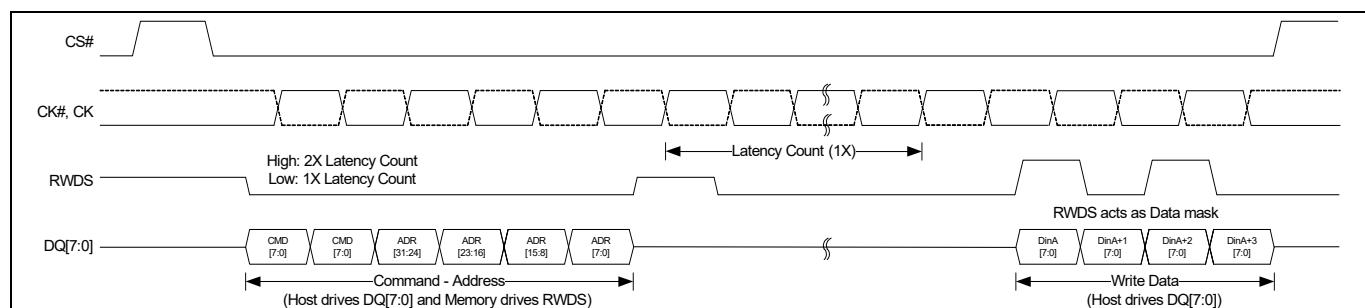

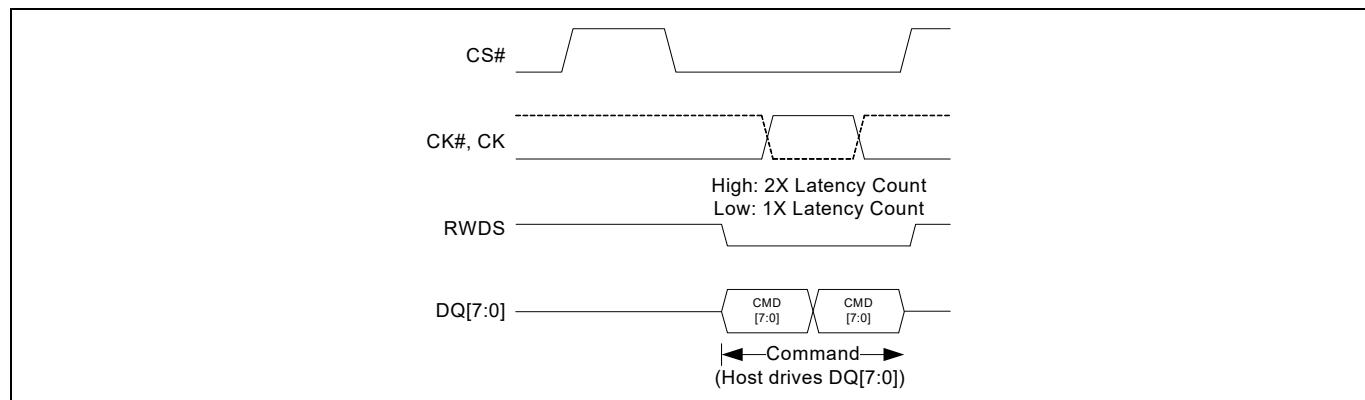

Figure 3 xSPI ( オクタル ) を介した 1 倍レイテンシの書き込みトランザクション (DDR) ( メモリア レイ書き込み )<sup>[2, 3]</sup>

注 :

1. 遅延の無い書き込みトランザクションは、レジスタ書き込みのみに使用されます。

2. RWDS はホストによって駆動されます。

3. DinA および DinA+2 のデータはマスクされます。

概要説明

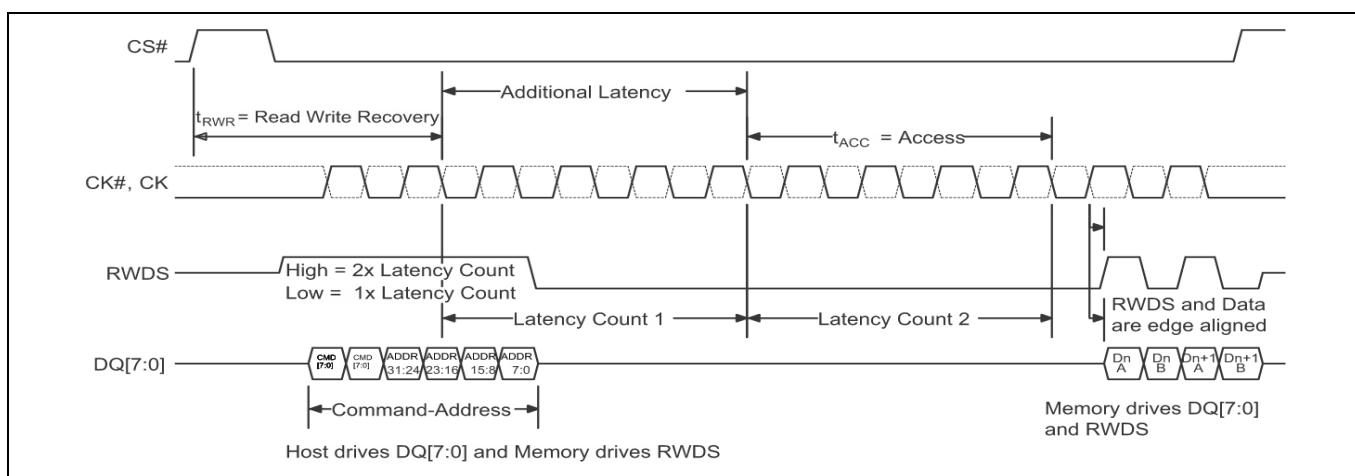

Figure 4 xSPI (オクタル) を介した 2 倍レイテンシの書き込みトランザクション (DDR) (メモリア

レイ書き込み)<sup>[4, 5]</sup>

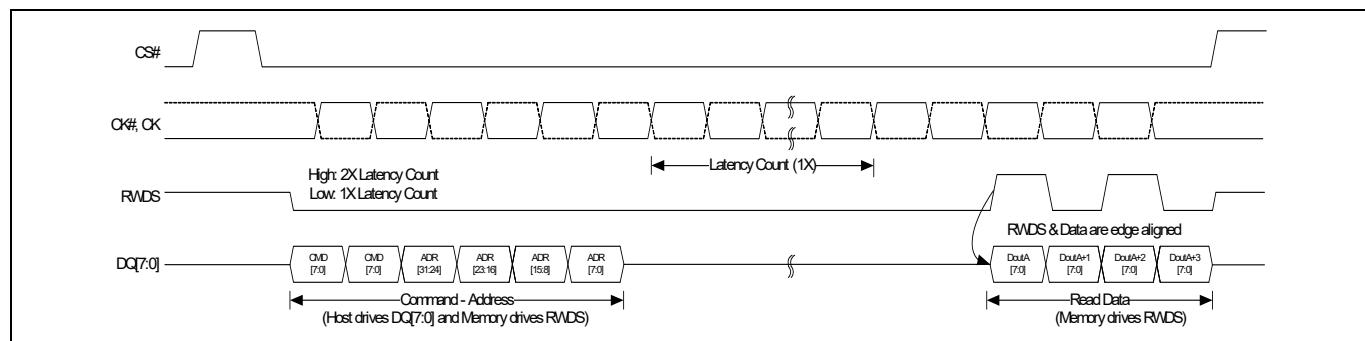

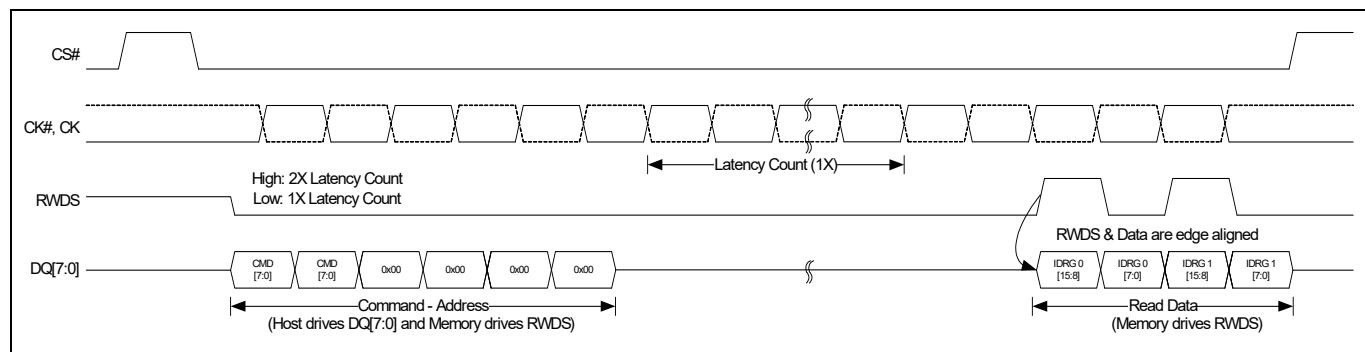

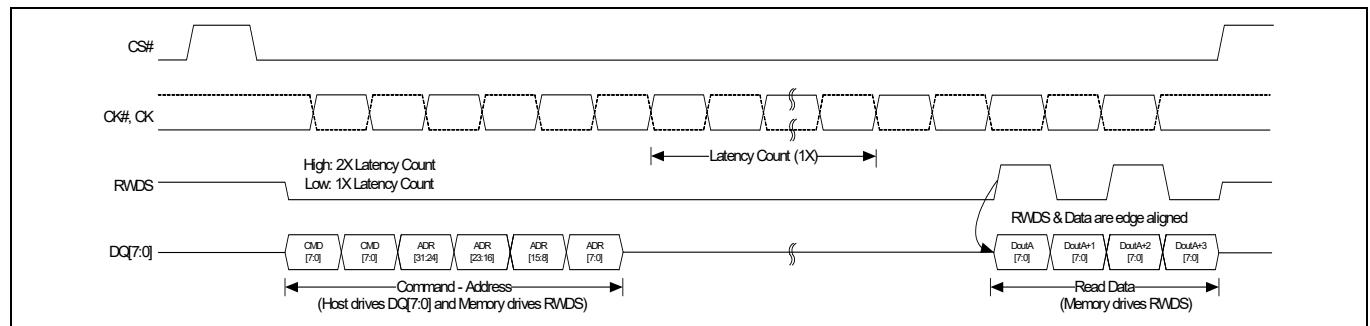

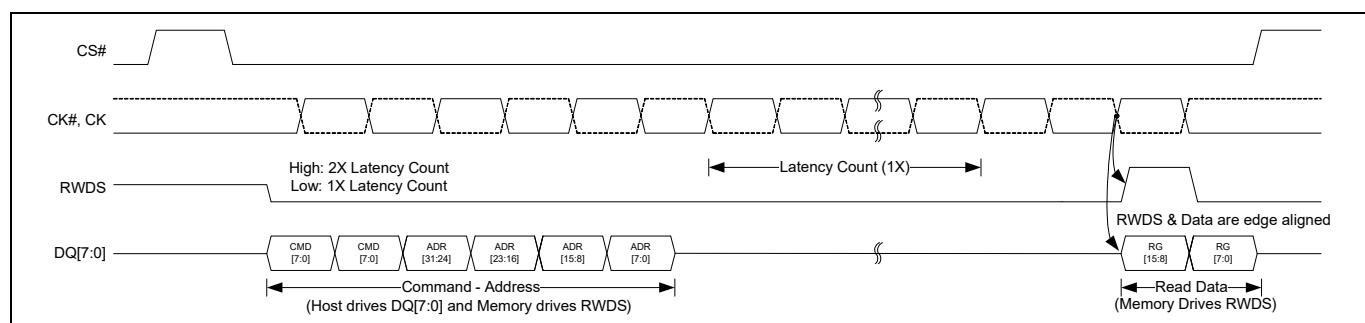

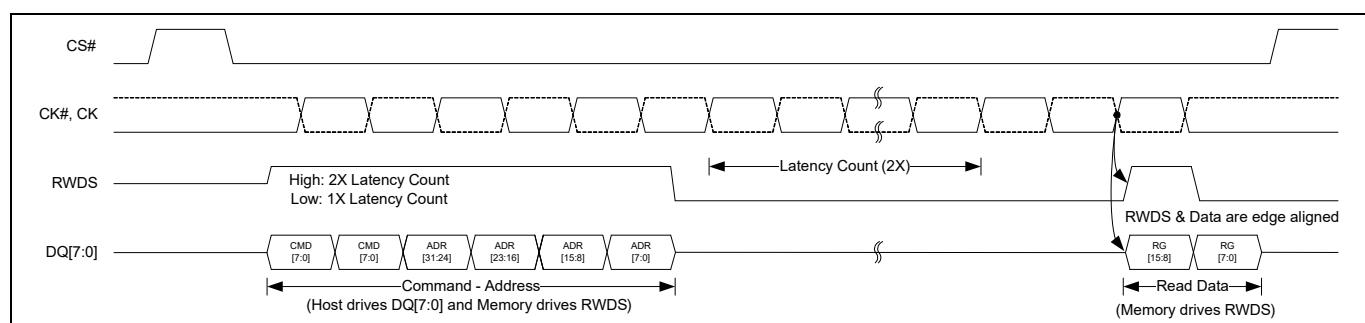

Figure 5 xSPI (オクタル) を介した 1 倍レイテンシの読み出しトランザクション (DDR) (すべての

読み出し)<sup>[6]</sup>

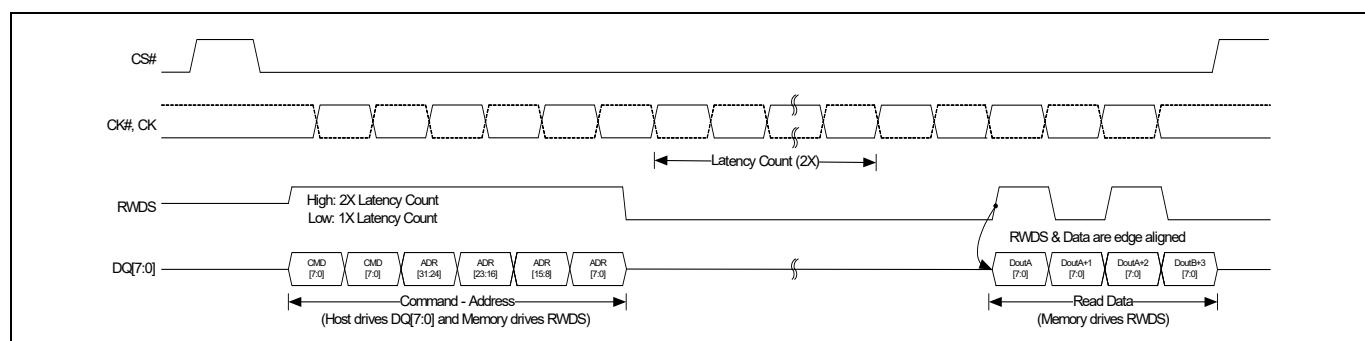

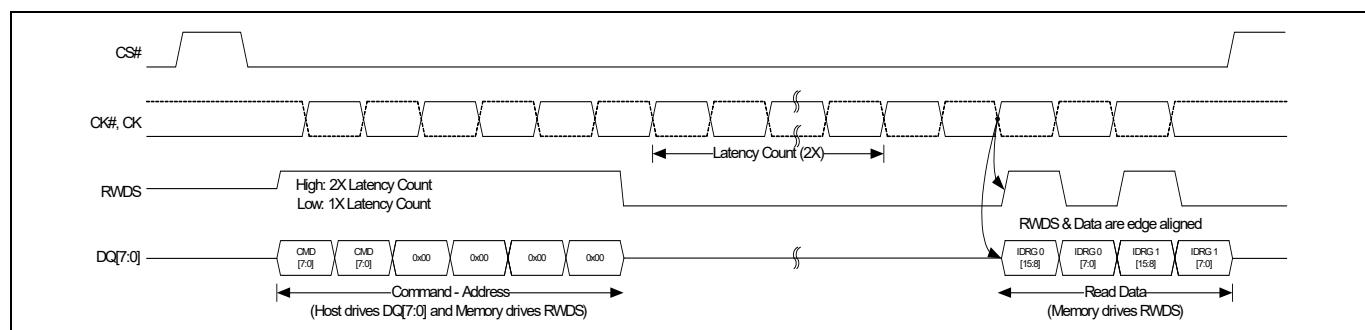

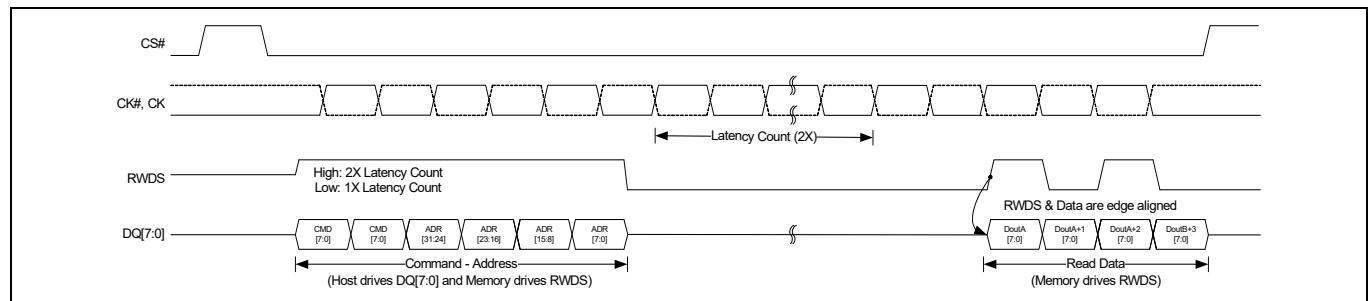

Figure 6 xSPI (オクタル) を介した 2 倍レイテンシの読み出しトランザクション (DDR) (すべての

読み出し)<sup>[7]</sup>

注:

4. RWDS は、コマンド サイクルとアドレス サイクル中に HYPERRAM™ によって 2 倍のレイテンシで駆動され、その後のデータマスキングのためにホストによって駆動されます。

5. DinA および DinA+2 のデータはマスクされます。

6. RWDS はデータと位相が揃えられて、HYPERRAM™ によって駆動されます。

7. RWDS は、コマンドとアドレス サイクル中に HYPERRAM™ によって 2 倍のレイテンシで駆動され、その後データと位相が揃えられて再び駆動されます。

## 2 製品概要

64Mb HYPERRAM™ デバイスは、1.8V または 3.0V のアレイと I/O の同期セルフリフレッシュダイナミック RAM (DRAM) です。HYPERRAM™ デバイスはホストシステムに xSPI (オクタル) スレーブインターフェースを提供します。xSPI (オクタル) インターフェースは 8 ビット (1 バイト) 幅の DDR データバスを持ち、ワード幅 (16 ビットデータ) のアドレス境界のみを使用します。読み出しトランザクションはクロックサイクルごとに 16 ビット (クロックエッジごとに 8 ビット) のデータを提供します。書き込みトランザクションはクロックサイクルごとに 16 ビット (クロックエッジごとに 8 ビット) のデータを使用します。

Figure 7 xSPI (オクタル) HYPERRAM™ インターフェース [8]

### 2.1 xSPI (オクタル) インターフェース

読み出し / 書き込みトランザクションは、対象の行 / 列アドレスを定義するために 3 クロックサイクル、そして  $t_{ACC}$  の初期アクセスレイテンシが必要です。トランザクションの CA 部分の間、RWDS 信号を HIGH に駆動することで、メモリは必要なリフレッシュ時間 ( $t_{RFH}$ ) に対する追加のレイテンシが初期レイテンシに挿入されるかを示します。読み出し (または書き込み) トランザクション中、初期のデータ値が出力 (または入力) された後、後続のクロックサイクルで追加のデータがラップまたはリニアシーケンスに従って行から読み出されます (または行に書き込まれます)。リニアバーストモードに設定されている場合、デバイスはメモリアレイから次の連続する行を自動的にフェッチして、連続リニアバーストをサポートします。読み出し / 書き込みデータ転送が進行中に同時にアレイ内の次の行にアクセスすると、400MBps の持続データ速度を実現できるリニアシーケンシャルバーストを実行できます (1 バイト (8 ビットデータバス) \*2 (データクロックエッジ) \*200MHz=400MBps)。

#### 注:

8. CK# はオプションとして差動クロックモードで使用されます。

### 3 信号の説明

#### 3.1 入出力の要約

**Table 1** に xSPI ( オクタル ) HYPERRAM™ 信号を示します。アクティブ Low 信号名の末尾にはハッシュ記号 (#) が付いています。

**Table 1** 入出力の要約 <sup>[10]</sup>

| 記号                      | タイプ                             | 説明                                                                                                                                                                                                                                           |

|-------------------------|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CS#                     | マスター出力 ,<br>スレーブ入力              | <b>チップセレクト</b> : バストランザクションは HIGH から LOW への遷移で開始し、LOW から HIGH への遷移で終了します。マスター デバイスには、スレーブごとに個別の CS# があります。                                                                                                                                   |

| CK, CK#[ <sup>9</sup> ] |                                 | <b>差動クロック</b> : コマンド , アドレス , およびデータ情報は CK と CK# 信号の交差に対して出力されます。差動クロックの使用はオプションです。<br><b>シングルエンドクロック</b> : CK# は使用されず、シングルエンド CK のみが使用されます。クロックがフリー ランである必要はありません。                                                                          |

| DQ[7:0]                 | 入力 / 出力                         | <b>データ入力 / 出力</b> : コマンド , アドレス , およびデータ情報は、読み出しと書き込みトランザクション中にこれらの信号上で転送されます。                                                                                                                                                               |

| RWDS                    | 入力 / 出力                         | <b>読み出し / 書き込みデータストローブ</b> : あらゆるバストランザクションのコマンド / アドレス部分では、RWDS はスレーブ出力となり、追加の初期レイテンシが必要かどうかを示します。読み出しデータ転送中、RWDS はスレーブ出力となり、データは RWDS とエッジが揃えられます。書き込みトランザクションのデータ転送中、RWDS はスレーブ入力となり、データマスクとして機能します。<br>(HIGH= 追加レイテンシあり、LOW= 追加レイテンシなし ) |

| RESET#                  | マスター出力 ,<br>スレーブ入力 ,<br>内部プルアップ | <b>ハードウェアリセット</b> : LOW のとき、デバイスは自己初期化し、スタンバイ状態に戻ります。RESET# が LOW のとき、RWDS と DQ[7:0] は HIGH-Z 状態になります。スレーブ RESET# 入力は弱プルアップに接続している、すなわち、RESET# が未接続の場合に HIGH 状態にプルアップされます。                                                                   |

| V <sub>CC</sub>         | 電源                              | アレイの電源                                                                                                                                                                                                                                       |

| V <sub>CCQ</sub>        |                                 | 入力 / 出力の電源                                                                                                                                                                                                                                   |

| V <sub>SS</sub>         |                                 | アレイのグランド                                                                                                                                                                                                                                     |

| V <sub>SSQ</sub>        |                                 | 入力 / 出力のグランド                                                                                                                                                                                                                                 |

| RFU                     | 未接続                             | <b>将来使用するために予約済み</b> : 内部で接続される場合と接続されない場合があり、将来的な互換性維持のため、この信号 / ボールの位置は未接続のままとし、PCB のルーティングチャネルで使用しないでください。この信号 / ボールは将来的に信号によって使用される場合があります。                                                                                              |

#### 注:

9. CK# はオプションの接続で差動クロック モードで使用されます。ホスト コントローラーに接続しない場合、CK# 入力ピンを開放のままにせず、V<sub>CCQ</sub> または V<sub>SSQ</sub> に接続してください。

10. オプションの DCARS のピン配置とピンの説明は、[DDR 中央揃え読み出しきストローブ \(DCARS\) 機能](#)に記載されています。

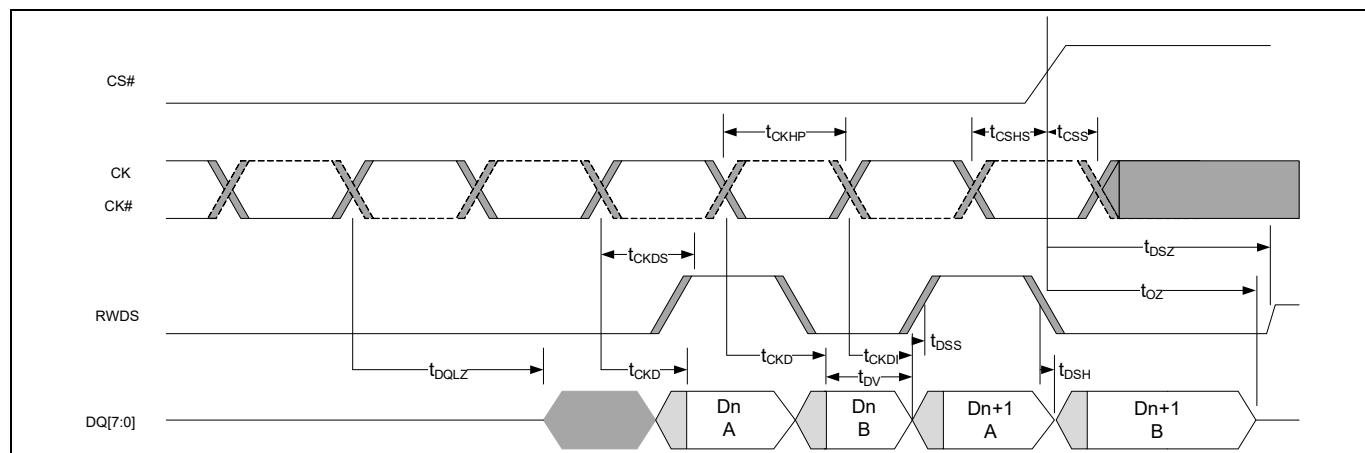

## 4 xSPI (オクタル) トランザクションの詳細

xSPI (オクタル) マスターはクロックがアイドルの間に CS# を LOW に駆動することでトランザクションを開始します。その後、CA ワードが転送される間にクロックがトルグし始めます。

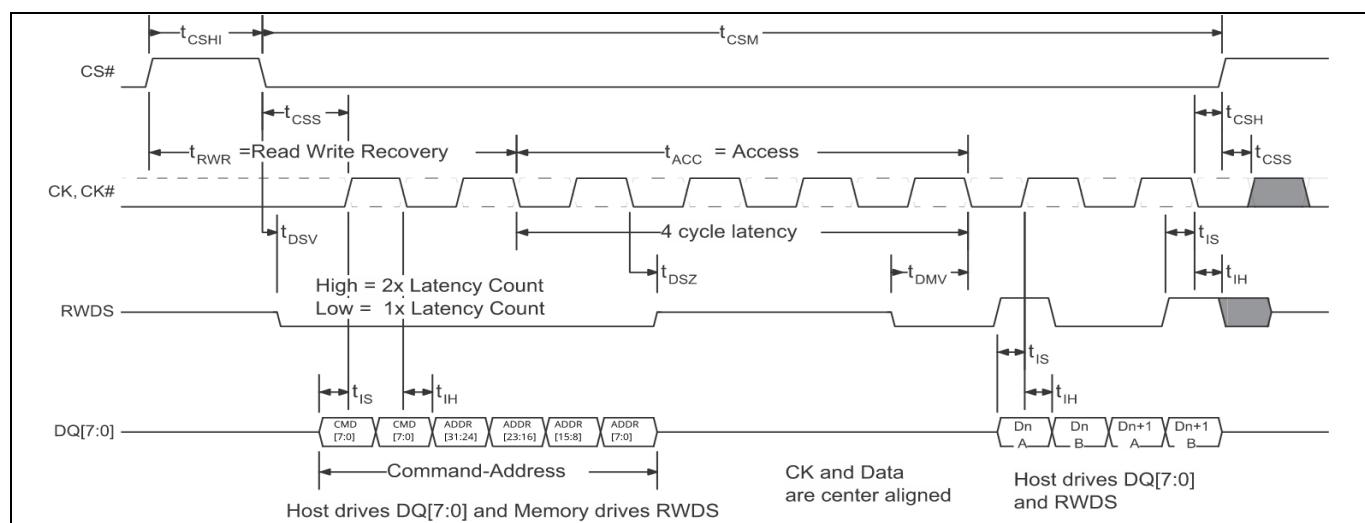

メモリ読み出し / 書き込みトランザクションの場合、xSPI (オクタル) マスターは、コンフィギュレーションレジスタ 0 のレイテンシ数設定で定義されたサイクル数の間クロック供給を継続します (レジスタ書き込みトランザクションでは、レイテンシは不要です)。特定のクロック周波数に必要な初期レイテンシ数は、RWDS に基づいています。CA サイクル中に RWDS が LOW の場合、1 つのレイテンシが挿入されます。CA サイクル中に RWDS が HIGH の場合、追加のレイテンシ カウントが挿入されます。これらのレイテンシクロック サイクルが完了すると、RWDS の遷移を開始すると同時に対象データの出力を開始します。

読み出しデータ転送中、読み出しデータは RWDS のすべての遷移とエッジが揃えられて出力されます。CS# が LOW の間にホストがクロックの遷移を継続する限り、データは引き続き出力されます。バーストトランザクションは、メモリが分散型リフレッシュを実行するのを妨げるほど長くしないでください。

書き込みデータ転送中、書き込みデータはクロックエッジでの中央揃えです。メモリは各ワードの最初のデータ バイトを CK の立ち上りエッジで取り込んで、第 2 バイトを CK の立ち下りエッジで取り込みます。RWDS はデータマスクとしてホストマスターインターフェースにより駆動されます。データの書き込み中で RWDS が HIGH の場合、バイトがマスクされ、アレイは変更されません。データの書き込み中で RWDS が LOW の場合、データがアレイに配置されます。書き込みデータ転送中にマスターが RWDS を駆動しているため、マスターも HYPERRAM™ デバイスも書き込みトランザクションのデータ転送部分内のレイテンシの必要性を示せません。許容される書き込みデータ バースト長の設定も、コンフィギュレーションレジスタ 0 に示されています。

ラップバーストはバースト長の範囲内でラップし続け、リニアバーストは行の境界を越えて順次にデータを出力します。リニアバースト読み出しがアレイの最後のアドレスに達した後、最終アドレスを越えてバーストを継続すると、アドレス範囲の先頭からデータが提供されます。クロックがアイドルの間に CS# を HIGH にすることで読み出し転送をいつでも終了できます。

クロックがフリー ランである必要はありません。CS# が HIGH の間にクロックはアイドル状態のままであることがあります。

## 4.1 コマンド / アドレス / データ ビットの割り当て

Table 2 コマンド セット<sup>[11-15]</sup>

| コマンド                    | コード  | CA データ | アドレス<br>(バイト) | レイテンシ<br>サイクル | データ<br>(バイト) | 必要条件   |

|-------------------------|------|--------|---------------|---------------|--------------|--------|

| <b>ソフトウェアリセット</b>       |      |        |               |               |              |        |

| REST ENABLE             | 0x66 | 8-0-0  | 0             | 0             | 0            |        |

| RESET                   | 0x99 | 8-0-0  | 0             | 0             | 0            | リセット有効 |

| <b>ID</b>               |      |        |               |               |              |        |

| READ ID <sup>[11]</sup> | 0x9F | 8-8-8  | 4 (0x00)      | 3-7           | 4            |        |

| <b>電力モード</b>            |      |        |               |               |              |        |

| DEEP POWER DOWN         | 0xB9 | 8-0-0  | 0             | 0             | 0            |        |

| <b>メモリアレイ読み出し</b>       |      |        |               |               |              |        |

| READ (DDR)              | 0xEE | 8-8-8  | 4             | 3-7           | 1 ~ ∞        |        |

| <b>メモリアレイ書き込み</b>       |      |        |               |               |              |        |

| WRITE (DDR)             | 0xDE | 8-8-8  | 4             | 3-7           | 1 ~ ∞        | 書き込み有効 |

| <b>書き込み有効化 / 無効化</b>    |      |        |               |               |              |        |

| WRITE ENABLE            | 0x06 | 8-0-0  | 0             | 0             | 0            |        |

| WRITE DISABLE           | 0x04 | 8-0-0  | 0             | 0             | 0            |        |

| <b>レジスタ読み出し</b>         |      |        |               |               |              |        |

| READ ANY REGISTER       | 0x65 | 8-8-8  | 4             | 3-7           | 2            |        |

| <b>レジスタ書き込み</b>         |      |        |               |               |              |        |

| WRITE ANY REGISTER      | 0x71 | 8-8-8  | 4             | 0             | 2            | 書き込み有効 |

**注:**

- 11.2つのIDレジスタの内容が一緒に(IDレジスタ0に続いてIDレジスタ1)読み出されます。

- 12.書き込みイネーブルは、メモリまたはレジスタ値の不注意な変更に対する保護を提供します。書き込みトランザクションを後で実行できるようにする内部書き込みイネーブルラッチ(WEL)をセットします。

- 13.書き込みディセーブルは、書き込みトランザクションの実行を無効にするために使用できます。これは、内部書き込みイネーブルラッチ(WEL)をリセットします。

- 14.WELラッチは、メモリ書き込みトランザクションが正常に終了した後、「1」にセットされたままになります。電源切断/電源投入シーケンスまたはハードウェア/ソフトウェアリセット後、WELラッチは「0」にクリアされます。

- 15.レジスタ書き込みトランザクションが正常に終了すると、内部WELラッチは「0」にクリアされます。

## 4.2 リセットイネーブルトランザクション

リセットイネーブルトランザクションは、リセットトランザクションの直前に必要です。リセットイネーブルに続くなりセット以外のトランザクションは、リセットイネーブル条件をクリアし、後のリセットトランザクションが認識されないようにします。

Figure 8 リセットイネーブルトランザクション (DDR)

## 4.3 リセットトランザクション

リセットイネーブルの直後にリセットトランザクションを実行することで、ソフトウェアリセットプロセスを開始します。

Figure 9 リセットトランザクション (DDR)

#### 4.4 ID 読み出しトランザクション

ID 読み出しトランザクションは、デバイス ID レジスタ 0 および 1 への読み出しアクセスを提供します。これらのレジスタには、メーカー ID とデバイス ID が含まれます。データ読み出しシーケンスは次のとおりです。

Table 3 ID 読み出しのデータシーケンス

| アドレス空間 | バイト順      | バイト位置 | ワード データ ビット | DQ |

|--------|-----------|-------|-------------|----|

| レジスタ 0 | ビッグエンディアン | A     | 15          | 7  |

|        |           |       | 14          | 6  |

|        |           |       | 13          | 5  |

|        |           |       | 12          | 4  |

|        |           |       | 11          | 3  |

|        |           |       | 10          | 2  |

|        |           |       | 9           | 1  |

|        |           |       | 8           | 0  |

|        | ビッグエンディアン | B     | 7           | 7  |

|        |           |       | 6           | 6  |

|        |           |       | 5           | 5  |

|        |           |       | 4           | 4  |

|        |           |       | 3           | 3  |

|        |           |       | 2           | 2  |

|        |           |       | 1           | 1  |

|        |           |       | 0           | 0  |

| レジスタ 1 | ビッグエンディアン | A     | 15          | 7  |

|        |           |       | 14          | 6  |

|        |           |       | 13          | 5  |

|        |           |       | 12          | 4  |

|        |           |       | 11          | 3  |

|        |           |       | 10          | 2  |

|        |           |       | 9           | 1  |

|        |           |       | 8           | 0  |

|        | ビッグエンディアン | B     | 7           | 7  |

|        |           |       | 6           | 6  |

|        |           |       | 5           | 5  |

|        |           |       | 4           | 4  |

|        |           |       | 3           | 3  |

|        |           |       | 2           | 2  |

|        |           |       | 1           | 1  |

|        |           |       | 0           | 0  |

## xSPI (オクタル) トランザクションの詳細

Figure 10 1倍レイテンシの ID 読み出しトランザクション (DDR)<sup>[16]</sup>Figure 11 2倍レイテンシの ID 読み出しトランザクション (DDR)<sup>[17]</sup>

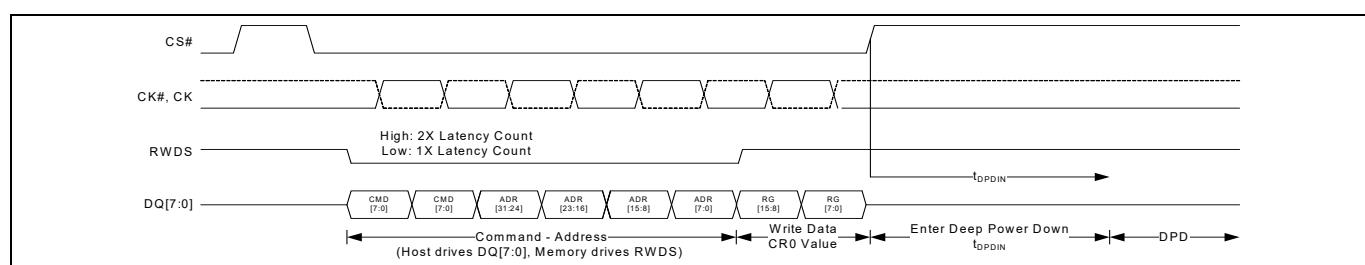

## 4.5 ディープパワーダウントランザクション

ディープパワーダウントランザクションは、デバイスを最低消費電力状態であるディープパワーダウン状態に移行させます。CR0[15]に「0」を書き込むことでも、デバイスをディープパワーダウン状態にします。ディープパワーダウン状態では、すべてのレジスタの内容が失われ、デバイスはデフォルト状態で起動します。

Figure 12 ディープパワーダウントランザクション (DDR)

## 注:

16. RWDS はデータと位相が揃えられて、HYPERRAM™ によって駆動されます。

17. RWDS は、コマンドとアドレスサイクル中に HYPERRAM™ によって 2 倍のレイテンシで駆動され、その後データと位相が揃えられて再び駆動されます。

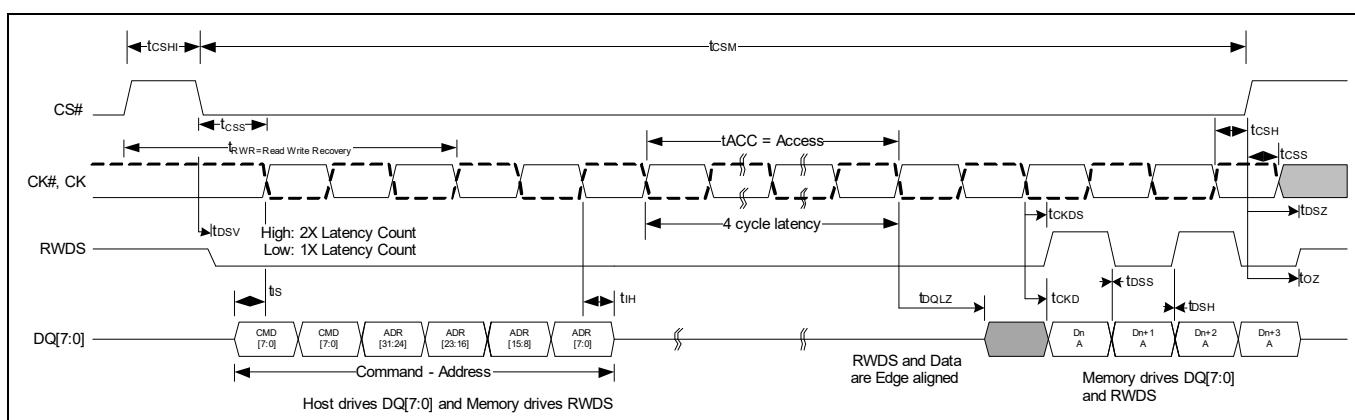

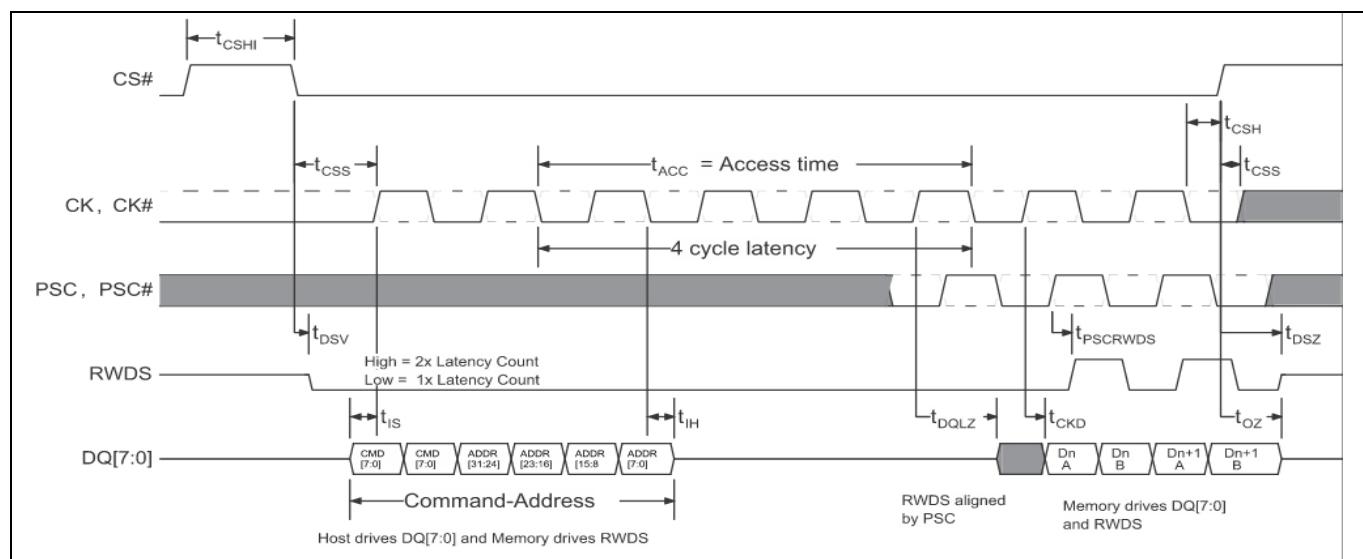

## 4.6 読み出しトランザクション

読み出しトランザクションはメモリアレイからデータを読み出します。このトランザクションには、デバイスの内部回路が、アドレス指定されたメモリ位置にアクセスするための十分な時間を与えるレイテンシ要件 (ダミーサイクル) があります。これらのレイテンシサイクル中に、ホストはデータバス DQ[7:0] をトライステートにできます。

Figure 13 1 倍レイテンシの ID 読み出しトランザクション (DDR)<sup>[18]</sup>

Figure 14 2 倍レイテンシの ID 読み出しトランザクション (DDR)<sup>[19]</sup>

### 注:

18. RWDS はデータと位相が揃えられて、HYPERRAM™ によって駆動されます。

19. RWDS は、コマンドとアドレスサイクル中に HYPERRAM™ によって 2 倍のレイテンシで駆動され、その後データと位相が揃えられて再び駆動されます。

20. RWDS はホストによって駆動されます。

21. DinA および DinA+2 のデータはマスクされます。

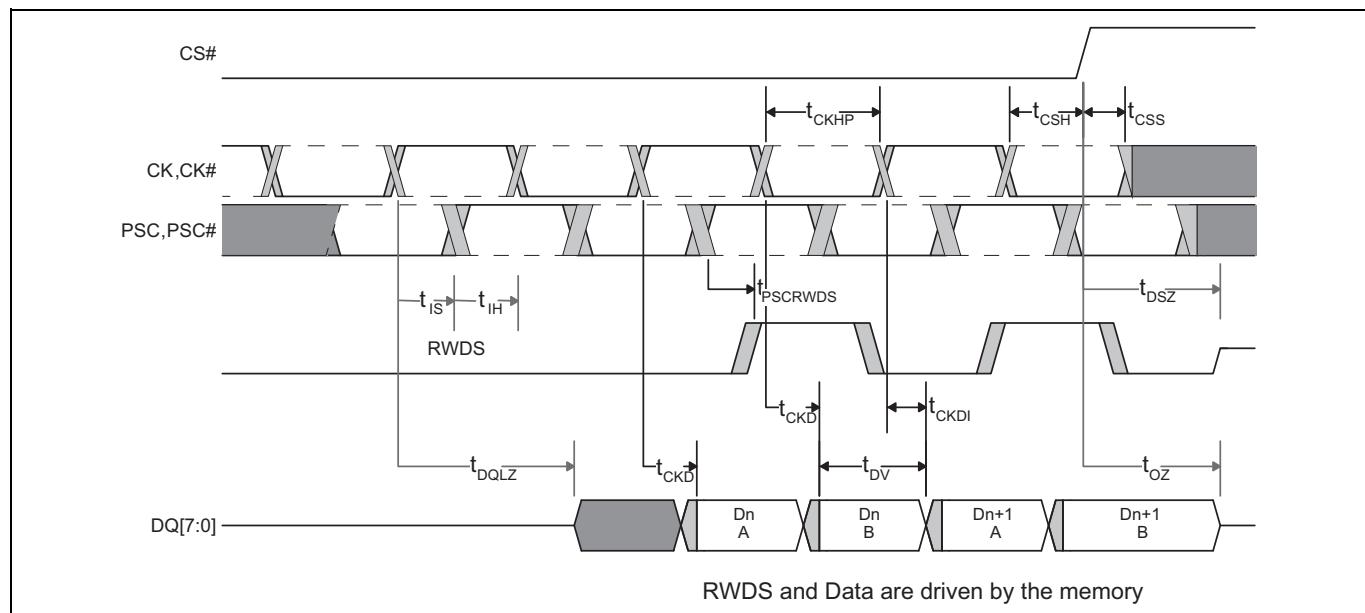

## 4.7 書き込みトランザクション

書き込みトランザクションは、メモリアレイにデータを書き込みます。このトランザクションには、デバイスの内部回路が、アドレス指定されたメモリ位置にアクセスするために十分な時間を与えるレイテンシ要件 (ダミーサイクル) があります。これらのレイテンシサイクル中にホストはデータバス DQ[7:0] をトライステートにできます。

WEL ラッチをセットする書き込みイネーブルトランザクションは、最初の書き込みの前に実行する必要があります。WEL ラッチは、メモリ書き込みトランザクションが正常に終了した後、「1」にセットされたままになります。メモリアレイへの不注意な書き込みを防ぐために、書き込みディセーブルトランザクションによってリセットする必要があります。

Figure 15 1倍レイテンシの書き込みトランザクション (DDR)<sup>[22, 23]</sup>

Figure 16 2倍レイテンシの書き込みトランザクション (DDR)<sup>[22, 23]</sup>

## 4.8 書き込みイネーブルトランザクション

書き込みイネーブルトランザクションは、メモリアレイまたはレジスタのデータを変更するトランザクションの前に実行する必要があります。

Figure 17 書き込みイネーブルトランザクション (DDR)

注:

22. RWDS は、コマンドサイクルとアドレスサイクル中に HYPERRAM™ によって 2 倍のレイテンシで駆動され、その後データマスキングのためにホストによって駆動されます。

23. DinA および DinA+2 のデータはマスクされます。

## 4.9 書き込みディセーブルトランザクション

書き込みディセーブルトランザクションは、メモリアレイまたはレジスタへのデータ書き込みを禁止します。

Figure 18 書き込みディセーブルトランザクション (DDR)

## 4.10 任意レジスタ読み出しトランザクション

任意レジスタ読み出しトランザクションは、デバイスのすべてのレジスタを読み出します。このトランザクションには、デバイスの内部回路が、アドレス指定されたレジスト位置にアクセスするための十分な時間を与えるレイテンシ要件(ダミーサイクル)があります。これらのレイテンシサイクル中にホストはデータバス DQ[7:0] をトライステートにできます。

Figure 19 1倍レイテンシの任意レジスタ読み出しトランザクション (DDR)<sup>[24]</sup>

Figure 20 2倍レイテンシの任意レジスタ読み出しトランザクション (DDR)<sup>[25]</sup>

注:

24. RWDS はデータと位相が揃えられて、HYPERRAM™ によって駆動されます。

25. RWDS は、コマンドとアドレスサイクル中に HYPERRAM™ によって 2 倍のレイテンシで駆動され、その後のデータと位相が揃えられて再び駆動されます。

#### 4.11 任意レジスタ書き込みトランザクション

任意レジスタ書き込みトランザクションは、デバイスのレジスタに書き込みます。レイテンシ要件 (ダミーサイクル) はありません。

Figure 21 xSPI (オクタル) レイテンシなし書き込みトランザクション (DDR) (レジスタ書き込み)<sup>[26, 27]</sup>

#### 注:

- 26. 遅延のない書き込みトランザクションは、レジスタ書き込みにのみ使用されます。

- 27. RWDS のデータマスクはサポートされません。

#### 4.12 メモリ読み出し / 書き込みトランザクション中のデータ配置

メモリ読み出し / 書き込み中のデータ配置はホストに依存します。デバイスは、書き込まれた(書き込み)データを出力します(読み出し)。したがって、メモリアレイではビッグエンディアンとリトルエンディアンの両方がサポートされます。

Table 4 メモリ読み出し / 書き込み中のデータ配置

| アドレス空間                                                                                                                                                                                    | バイト順      | バイト位置 | ワードデータビット | DQ | ビット順 |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-------|-----------|----|------|--|--|

| メモリ                                                                                                                                                                                       | ビッグエンディアン | A     | 15        | 7  |      |  |  |

|                                                                                                                                                                                           |           |       | 14        | 6  |      |  |  |

|                                                                                                                                                                                           |           |       | 13        | 5  |      |  |  |

|                                                                                                                                                                                           |           |       | 12        | 4  |      |  |  |

|                                                                                                                                                                                           |           |       | 11        | 3  |      |  |  |

|                                                                                                                                                                                           |           |       | 10        | 2  |      |  |  |

|                                                                                                                                                                                           |           |       | 9         | 1  |      |  |  |

|                                                                                                                                                                                           |           |       | 8         | 0  |      |  |  |

|                                                                                                                                                                                           | リトルエンディアン | B     | 7         | 7  |      |  |  |

|                                                                                                                                                                                           |           |       | 6         | 6  |      |  |  |

|                                                                                                                                                                                           |           |       | 5         | 5  |      |  |  |

|                                                                                                                                                                                           |           |       | 4         | 4  |      |  |  |

|                                                                                                                                                                                           |           |       | 3         | 3  |      |  |  |

|                                                                                                                                                                                           |           |       | 2         | 2  |      |  |  |

|                                                                                                                                                                                           |           |       | 1         | 1  |      |  |  |

|                                                                                                                                                                                           |           |       | 0         | 0  |      |  |  |

| メモリ空間でデータにアクセスしている場合:<br>各読み出し / 書き込みワードの最初のバイトは「A」バイト、2番目は「B」バイトです。<br>AおよびBバイトのワードのビットは、データの書き込み方法に依存します。ワード下位アドレスビット7～0がAバイトの位置に書き込まれ、ビット15～8がBバイトの位置に書き込まれる場合、またはその逆の場合、同じ順序で読み出されます。 |           |       |           |    |      |  |  |

| そのため、メモリ空間はリトルエンディアンまたはビッグエンディアンの順で格納され、読み出されます。                                                                                                                                          |           |       |           |    |      |  |  |

#### 4.13 レジスタ読み出し / 書き込みトランザクション中のデータ配置

レジスタ読み出し / 書き込み中のデータ配置はビッグエンディアンです。

Table 5 レジスタ読み出し / 書き込み中のデータ配置

| アドレス空間 | バイト順      | バイト位置 | ワードデータビット | DQ | ビット順                                                                                                                                                                                               |

|--------|-----------|-------|-----------|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| レジスタ   | ビッグエンディアン | A     | 15        | 7  | レジスタ空間でデータにアクセスしている場合:<br>xSPI (オクタル) での読み出しトランザクション中、クロックサイクルごとに 2 バイトが転送されます。上位バイト A (ワード [15:8]) は RWDS の立ち上りエッジと立ち下りエッジの間で転送されます (エッジ揃え)。下位バイト B (ワード [7:0]) は RWDS の立ち下りエッジと立ち上りエッジの間で転送されます。 |

|        |           |       | 14        | 6  |                                                                                                                                                                                                    |

|        |           |       | 13        | 5  |                                                                                                                                                                                                    |

|        |           |       | 12        | 4  |                                                                                                                                                                                                    |

|        |           |       | 11        | 3  |                                                                                                                                                                                                    |

|        |           |       | 10        | 2  |                                                                                                                                                                                                    |

|        |           |       | 9         | 1  |                                                                                                                                                                                                    |

|        |           |       | 8         | 0  |                                                                                                                                                                                                    |

|        | ビッグエンディアン | B     | 7         | 7  | 書き込み中、上位バイト A (ワード [15:8]) は CK の立ち上りエッジで転送され、下位バイト B (ワード [7:0]) CK の立ち下りエッジで転送されます。したがって、レジスタにはデバイスに依存する固定ビット位置と意味の定義があるため、レジスタ空間は常にビッグエンディアンで読み書きされます。                                          |

|        |           |       | 6         | 6  |                                                                                                                                                                                                    |

|        |           |       | 5         | 5  |                                                                                                                                                                                                    |

|        |           |       | 4         | 4  |                                                                                                                                                                                                    |

|        |           |       | 3         | 3  |                                                                                                                                                                                                    |

|        |           |       | 2         | 2  |                                                                                                                                                                                                    |

|        |           |       | 1         | 1  |                                                                                                                                                                                                    |

|        |           |       | 0         | 0  |                                                                                                                                                                                                    |

## 5 メモリ空間

### 5.1 xSPI ( オクタル ) インターフェース

Table 6 メモリ空間アドレスマップ ( バイトベース - 最下位ビット A(0) が常に「0」にセットされた 8 ビット )

| ユニットタイプ     | カウント           | システムバイトアドレスビット | アドレスビット | 備考                                     |

|-------------|----------------|----------------|---------|----------------------------------------|

| 64Mb デバイスの行 | 8192 ( 行 )     | A22 ~ A10      | 22 ~ 10 | -                                      |

| 行           | 1 ( 行 )        | A9 ~ A4        | 9 ~ 4   | 512 ( 16 ビットワード )<br>または 1KB           |

| ハーフページ      | 16 ( バイトアドレス ) | A3 ~ A0        | 3 ~ 0   | 16 バイト ( 8 ワード )<br>A0 は常に「0」にセットされます。 |

### 5.2 メモリ容量と行境界

デバイスの DRAM アレイ サイズ ( 容量 ) は、ID0 レジスタの行アドレスビット数と列アドレスビット数 フィールドに示された行と列アドレスに使用されるシステムアドレスの総ビット数で判定できます。例えば、64Mb HYPERRAM™ デバイスは 10 列アドレスビットと 13 行アドレスビットがあり、合計で 23 アドレスビット ( バイトアドレス ) =  $2^{23} = 8\text{MB}$  ( 4M ワード ) があります。10 列アドレスビットは、各行には  $2^{10} = 1024$  ワード = 1KB があります。行アドレスビット数は、各アレイのリフレッシュ間隔以内に 8196 行がリフレッシュされることを示します。行数はリフレッシュ間隔の計算に使用されます。

レジスタ空間アクセス

## 6 レジスタ空間アクセス

### 6.1 xSPI (オクタル) インターフェース

Table 7 レジスタ空間アドレスマップ(アドレスビットA0は常に「0」にセット)

| レジスタ                           | アドレス(バイトアドレス指定可能)                    |

|--------------------------------|--------------------------------------|

| ID レジスタ 0 (ID0[15:0])          | 0x00000000                           |

| ID レジスタ 1 (ID1[15:0])          | 0x00000002                           |

| コンフィギュレーションレジスタ 0 (ID0[15:0])  | 0x00000004                           |

| コンフィギュレーションレジスタ 1 (ID1[15:0])  | 0x00000006                           |

| ダイメーカー情報レジスタ<br>(レジスタ0～レジスタ17) | 0x00000008, 0x0000000A to 0x0000002A |

### 6.2 デバイス ID レジスタ

CS#がLOWのときに選択されたデバイスに関する情報を提供する2つの読み出し専用不揮発性ワードレジスタがあります。デバイス情報フィールドは以下を識別します。

- メーカー

- タイプ

- メモリ容量

- 行アドレスビット数

- 列アドレスビット数

- リフレッシュタイプ

Table 8 ID レジスタ 0 (ID0) のビット割り当て

| ビット     | 機能        | 設定(2進)                                                                                          |

|---------|-----------|-------------------------------------------------------------------------------------------------|

| [15:14] | 予約済み      | 00 - Default                                                                                    |

| 13      | 予約済み      | 0 - Default                                                                                     |

| [12:8]  | 行アドレスビット数 | 00000 - 1個の行アドレスビット<br>...<br>11111 - 32個の行アドレスビット<br>...<br>01100 - 64Mb - 13個の行アドレスビット(デフォルト) |

| [7:4]   | 列アドレスビット数 | 0000 - 1個の列アドレスビット<br>...<br>1000 - 9個の列アドレスビット(デフォルト)<br>...<br>1111 - 16個の列アドレスビット            |

| [3:0]   | メーカー      | 0000 - 予約済み<br>0001 - Infineon®(デフォルト)<br>0010 ~ 1111 - 予約済み                                    |

Table 9 ID レジスタ 1 (ID1) のビット割り当て

| ビット    | 機能      | 設定(2進)                                           |

|--------|---------|--------------------------------------------------|

| [15:4] | 予約済み    | 0000_0000_0000(デフォルト)                            |

| [3:0]  | デバイスタイプ | 0001 - HYPERRAM™ 2.0<br>0000, 0010 ~ 1111 - 予約済み |

## 6.2.1 デバイスのコンフィギュレーションレジスタ

### 6.2.1.1 コンフィギュレーションレジスタ 0 (CR0)

コンフィギュレーションレジスタ 0 (CR0) は、HYPERRAM™ デバイスの電力状態とアクセス プロトコルの動作条件の定義に使用されます。設定可能な特性は以下のとおりです。

- ・ラップバースト長(長さを 16, 32, 64, または 128 バイトに揃えたデータグループ)

- ・ラップバーストタイプ

- レガシー ラップ(選択した長さを持つ揃えたグループ内でラップ アラウンドのあるシーケンシャル アクセス)

- ハイブリッド ラップ(1回のレガシー ラップ後に次のシーケンシャルグループの開始でリニア バーストを使用)

- ・初期レイテンシ

- ・可変レイテンシ

- アレイの読み出し / 書き込みトランザクションが固定レイテンシを用いるか可変レイテンシを用いるかを設定します。固定レイテンシを選択した場合、メモリは常に 1 つのリフレッシュ レイテンシを指定し、それに応じて読み出しデータ転送を遅延させます。可変レイテンシを選択した場合、新しいトランザクションが開始すると同時にリフレッシュが必要となるときにのみリフレッシュ レイテンシが追加されます。

- ・出力駆動強度

- ・ディープ パワーダウン (DPD) モード

Table 10 コンフィギュレーションレジスタ 0 (CR0) のビット割り当て

| CR0 ビット | 機能             | 設定 (2 進)                                                                                                                                                                                                                                                             |

|---------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [15]    | ディープパワー ダウン有効化 | 1-通常動作 (デフォルト)。HYPERRAM™は DPO 終了後にこの値を自動的に「1」にセット<br>0-「0」を書き込むと、デバイスはディープパワーダウンに入る                                                                                                                                                                                  |

| [14:12] | 駆動強度           | 000 - 34Ω (デフォルト)<br>001 - 115Ω<br>010 - 67Ω<br>011 - 46Ω<br>100 - 34Ω<br>101 - 27Ω<br>110 - 22Ω<br>111 - 19Ω                                                                                                                                                        |

| [11:8]  | 予約済み           | 1-予約済み (デフォルト)<br>将来使用のために予約済み。このレジスタに書き込むとき、将来の互換性維持のためこれらのビットを「1」にセットする必要があります。                                                                                                                                                                                    |

| [7:4]   | 初期レイテンシ        | 0000 - 133 の Max 周波数での 5 クロック レイテンシ<br>0001 - 166 の Max 周波数での 6 クロック レイテンシ<br>0010 - 200MHz/166MHz の Max 周波数での 7 クロック レイテンシ (デフォルト)<br>0011 - 予約済み<br>0100 - 予約済み<br>...<br>1101 - 予約済み<br>1110 - 85 の Max 周波数での 3 クロック レイテンシ<br>1111 - 104 の Max 周波数での 4 クロック レイテンシ |

| [3]     | 固定レイテンシ 有効化    | 0-可変レイテンシ - CA サイクル中の RWDS に応じて初期レイテンシの 1 倍または 2 倍<br>1-固定レイテンシ。初期レイテンシの 2 倍 (デフォルト)                                                                                                                                                                                 |

| [2]     | ハイブリッド バースト有効化 | 0: ハイブリッド バーストシーケンスに従うラップ バーストシーケンス<br>1: レガシー ラップ バースト方式でのラップ バーストシーケンス (デフォルト)                                                                                                                                                                                     |

| [1:0]   | バースト長          | 00 - 128 バイト<br>01 - 64 バイト<br>10 - 16 バイト<br>11 - 32 バイト (デフォルト)                                                                                                                                                                                                    |

## ラップ バースト

ラップ バーストトランザクションは、設定されたワード グループの長さと一致したワード境界に揃えたワード グループ内のメモリにアクセスします。ラップ アクセス グループは 16, 32, 64, または 128 バイトの揃えと長さとして設定できます。ラップ トランザクション中に、アクセスはグループ内で CA によって選択された位置から開始し、設定されたワード グループ揃えの境界の終わりまで継続してから、グループの始まりにラップ アラウンドした後、開始位置まで続きます。ラップ バーストは一般的に、クリティカルワード ファースト方式で命令またはデータをキャッシュ ラインに書き込ませる読み出しアクセスに使用されます。

## ハイブリッド バースト

ハイブリッド バーストの始まりは対象アドレスのラップ バースト グループの長さ内でラップしてから、ラップ グループの終わりの後にある次のデータ ハーフページまで続きます。継続したアクセスは、CS# を HIGH にすることで転送を終了するまでリニア バースト順序で実行されます。ラップ バーストと、次

レジスタ空間アクセス

のバーストグループの始まりから開始するリニアバーストの混成により、単一のアクセスで複数のシーケンシャルアドレス キャッシュ ラインにデータが書き込まれます。

最初のキャッシュ ラインはクリティカルなワードから書き込まれます。その後、最初のラインを処理中にメモリ内の次のシーケンシャルラインを読み出してキャッシュに格納できます。

Table 11 CR0[2] によるラップバーストシーケンスの制御

| ビット    | デフォルト値 | 設定の詳細                                                                                              |

|--------|--------|----------------------------------------------------------------------------------------------------|

| CR0[2] | 1b     | ハイブリッドバースト有効化<br>CR0[2]=0: ハイブリッドバーストシーケンスに従うラップバーストシーケンス<br>CR0[2]=1: レガシーラップバースト方式でのラップバーストシーケンス |

Table 12 ラップバーストシーケンス例 (アドレス指定)

| バーストタイプ   | ラップ境界(バイト)               | 開始アドレス(16進) | データワードのバイトアドレス(16進)シーケンス                                                                                                                                                                                                                 |

|-----------|--------------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ハイブリッド 64 | 1回の64バイトのラップ後にリニアバーストが続く | XXXXXX02    | 02, 04, 06, 08, 0A, 0C, 0E, 10, 12, 14, 16, 18, 1A, 1C, 1E, 20, 22, 24, 26, 28, 2A, 2C, 2E, 30, 32, 34, 36, 38, 3A, 3C, 3E, 00<br>(ラップバースト完了。最初の64バイトのラップグループの終了時点以降リニアバーストを実行)<br>40, 42, 44, 46, 48, 4A, 4C, 4E, 50, 52, ...           |

| ハイブリッド 64 | 1回の64バイトのラップ後にリニアバーストが続く | XXXXXX2E    | 2E, 30, 32, 34, 36, 38, 3A, 3C, 3E, 00, 02, 04, 06, 08, 0A, 0C, 0E, 10, 12, 14, 16, 18, 1A, 1C, 1E, 20, 22, 24, 26, 28, 2A, 2C, (ラップバースト完了。最初の64バイトのラップグループの終了時点以降リニアバーストを実行)<br>40, 42, 44, 46, 48, 4A, 4B, 4C, 4D, 4E, 4F, 50, 52, ... |

| ハイブリッド 16 | 1回の16バイトのラップ後にリニアバーストが続く | XXXXXX02    | 02, 04, 06, 08, 0A, 0C, 0E, 00<br>(ラップバースト完了。最初の16バイトのラップグループの終了時点以降リニアバーストを実行)<br>10, 12, 14, 16, 18, 1A, ..                                                                                                                            |

| ハイブリッド 16 | 1回の16バイトのラップ後にリニアバーストが続く | XXXXXX0C    | 0C, 0E, 00, 02, 04, 06, 08, 0A<br>(ラップバースト完了。最初の16バイトのラップグループの終了時点以降リニアバーストを実行)<br>10, 12, 14, 16, 18, 1A, ...                                                                                                                           |

| ハイブリッド 32 | 1回の32バイトのラップ後にリニアバーストが続く | XXXXXX0A    | 0A, 0C, 0E, 10, 12, 14, 16, 18, 1A, 1C, 1E, 00, 02, 04, 06, 08<br>(ラップバースト完了。最初の32バイトのラップグループの終了時点以降リニアバーストを実行)<br>20, 22, 24, 26, 28, 2A, ...                                                                                           |

| ラップ 64    | 64                       | XXXXXX02    | 02, 04, 06, 08, 0A, 0C, 0E, 10, 12, 14, 16, 18, 1A, 1C, 1E, 20, 22, 24, 26, 28, 2A, 2C, 2E, 30, 32, 34, 36, 38, 3A, 3C, 3E, 00, ...                                                                                                      |

| ラップ 64    | 64                       | XXXXXX2E    | 2E, 30, 32, 34, 36, 38, 3A, 3C, 3E, 00, 02, 04, 06, 08, 0A, 0C, 0E, 10, 12, 14, 16, 18, 1A, 1C, 1E, 20, 22, 24, 26, 28, 2A, 2C, 2E, 30, ....                                                                                             |

| ラップ 16    | 16                       | XXXXXX02    | 02, 04, 06, 08, 0A, 0C, 0E, 00, ...                                                                                                                                                                                                      |

| ラップ 16    | 16                       | XXXXXX0C    | 0C, 0E, 00, 02, 04, 06, 08, 0A, ...                                                                                                                                                                                                      |

| ラップ 32    | 32                       | XXXXXX0A    | 0A, 0C, 0E, 10, 12, 14, 16, 18, 1A, 1C, 1E, 00, 02, 04, 06, 08, ...                                                                                                                                                                      |

| リニア       | リニアバースト                  | XXXXXX02    | 02, 04, 06, 08, 0A, 0C, 0E, 10, 12, 14, 16, 18, 1A, 1C, 1E, 20, 22, ...                                                                                                                                                                  |

## 初期レイテンシ

メモリ空間への読み出し / 書き込みのトランザクションまたはレジスタ空間への読み出しトランザクションは、CA で選択された行を開くためにいくつかの初期レイテンシを要します。この初期レイテンシは tACC です。tACC を満たすために必要なレイテンシクロック数は、クロック入力周波数に応じて 3 ~ 7クロックの間で変化します。CR0[7:4] の値は初期レイテンシのクロック数を選択します。初期設定値は 7クロックであり、ホストシステムがより最適な低い初期レイテンシを設定する前に最大 200MHz までの周波数で動作することを可能とします。

メモリ空間への読み出し / 書き込みトランザクションまたはレジスタ空間への読み出しトランザクションが開始すると同時に分配型リフレッシュが必要となるとき、RWDS 信号は CA の期間中に HIGH になり、選択された行を開く前にリフレッシュ動作が完了するための追加の初期レイテンシが挿入されていることを示します。

レジスタ空間への書き込みトランザクションは常に初期レイテンシがありません。RWDS は CA 期間中に HIGH または LOW です。レジスタデータをキャプチャするために必要な初期レイテンシがないため、RWDS の CA 期間中の論理レベルは CA の直後のレジスタデータの配置に影響しません。リフレッシュ動作はレジスタデータのキャプチャと並行してメモリアレイで実行できます。

## 固定レイテンシ

コンフィギュレーションレジスタのオプションビット CR0[3] は、すべてのメモリ空間への読み出し / 書き込みトランザクションまたはレジスタ空間への読み出しトランザクションに必要な初期レイテンシを同じにします。このためには、CA 期間中常に RWDS を HIGH に駆動して 2つの初期レイテンシ期間が必要であることを指定します。この固定レイテンシは分配型リフレッシュの必要性にかかわらず、単に固定の(決定的な)初期レイテンシをすべてのトランザクションタイプに提供します。固定レイテンシはデフォルトの POR またはリセットコンフィギュレーションです。システムは、このコンフィギュレーションビットをクリアして固定レイテンシを無効にし、リフレッシュ用の追加のレイテンシが必要となるときにのみ RWDS を HIGH に駆動して可変レイテンシを有効にできます。

## 駆動強度

DQ と RWDS 信号ラインの負荷、長さ、インピーダンスはシステム デザインによって異なります。コンフィギュレーションレジスタビット CR0[14:12] を使うと、DQ[7:0] 信号と RWDS 信号の出力インピーダンスを調整して DQ 信号と RWDS 信号のインピーダンスをシステム条件に適合させ、オーバーシュートやアンダーシュート、リングインなど高速信号の動作を最小限にできます。デフォルトの POR またはリセットコンフィギュレーション値は 000b であり、出力インピーダンスオプションの中間点を選択します。

指定されたインピーダンス値は、標準的なシリコンプロセス条件、定格動作電圧 (1.8V または 3.0V)、50°C でのフルアップとフルダウン両方のドライバの Typ 値です。インピーダンス値はプロセス、電圧および温度 (PVT) 条件によって Typ 値と異なることがあります。プロセスが遅く、電圧が低く、温度が高いほどインピーダンスは高くなります。プロセスが速く、電圧が高く、温度が低いほどインピーダンスは低くなります。

各システム デザインでは、動作電圧と温度範囲にわたってデータのシグナルインテグリティを評価して、動作条件に最適な駆動強度を選択する必要があります。

## ディープパワーダウン

HYPERRAM™ デバイスがシステムの動作に必要ない場合、CR0[15] に「0」を書き込むことで、デバイスをディープパワーダウン (DPD) という非常に低消費電力な状態に移行させられます。CR0[15] を「0」にクリアすると、デバイスは  $t_{DPDIN}$  時間内に DPD 状態に移行し、すべてのリフレッシュ動作が停止します。DPD 状態の間、RAM に格納されたデータは失われます(リフレッシュなしで無効になります)。DPD を終了するには、CS# を LOW に駆動してから HIGH に駆動すること、POR またはリセットが必要です。DPD モードでは、CS# と RESET# 信号のみが監視されます。詳細は [ディープパワーダウン](#) を参照してください。

### 6.2.1.2 コンフィギュレーションレジスタ 1

コンフィギュレーションレジスタ 1(CR1) は、HYPERRAM™ デバイスのリフレッシュ アレイ サイズ、リフレッシュ レート、ハイブリッド スリープを定義するために使用されます。設定可能な特性は以下のとおりです。

- 部分的アレイ リフレッシュ

- ハイブリッド スリープ状態

- リフレッシュ レート

Table 13 コンフィギュレーションレジスタ 1(CR1) のビット割り当て

| CR1 ビット | 機能            | 設定 (2 進)                                                                                                                                                |

|---------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| [15:8]  | 予約済み          | FFh - 予約済み (デフォルト)<br>これらのビットは常に FFh に設定                                                                                                                |

| [7]     | バースト タイプ      | 1 - リニア バースト (デフォルト)<br>0 - ラップ バースト                                                                                                                    |

| [6]     | マスター クロック タイプ | 1 - シングル エンド - CK (デフォルト)<br>0 - 差分 - CK#, CK                                                                                                           |

| [5]     | ハイブリッド スリープ   | 1 - デバイスがハイブリッド スリープ状態に移行<br>0 - 通常動作 (デフォルト)                                                                                                           |

| [4:2]   | 部分的アレイ リフレッシュ | 000 - アレイ全体 (デフォルト)<br>001 - アレイの下位 1/2<br>010 - アレイの下位 1/4<br>011 - アレイの下位 1/8<br>100 - なし<br>101 - アレイの上位 1/2<br>110 - アレイの上位 1/4<br>111 - アレイの上位 1/8 |

| [1:0]   | 分散型リフレッシュ間隔   | 10 - $1\mu\text{s}$ $t_{CSM}$ (産業用プラス温度範囲デバイス)<br>11 - 予約済み<br>00 - 予約済み<br>01 - $4\mu\text{s}$ $t_{CSM}$ (産業用温度範囲デバイス)                                 |

#### バースト タイプ

リニアとラップの 2 つのバースト タイプが、HYPERRAM™ の xSPI (オクタル) モードでサポートされます。CR1[7] は使用するタイプを選択します。

#### マスター クロック タイプ

シングル エンドと差動の 2 つのクロック タイプがサポートされます。CR1[6] は使用するタイプを選択します。

#### 部分的アレイ リフレッシュ

部分的アレイ リフレッシュ コンフィギュレーションは HYPERRAM™ のリフレッシュ動作を CR1[5:3] で指定されたメモリアレイの部分に制限します。これにより、スタンバイ電流が削減されます。デフォルトのコンフィギュレーションでは、アレイ全体がリフレッシュされます。

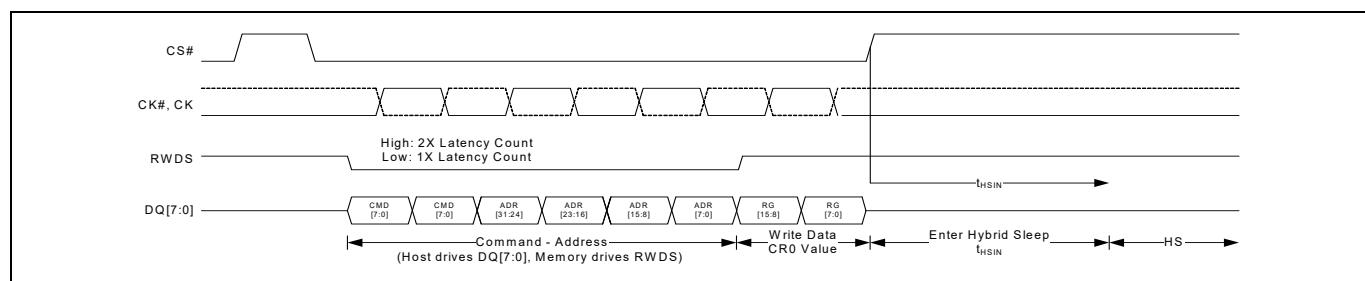

#### ハイブリッド スリープ (HS)

HYPERRAM™ デバイスがシステムの動作に必要なく、デバイスのデータを保持する必要がある場合、デバイスをハイブリッド スリープ状態にして、さらに消費電力を節約できます。CR1[5] に「0」を書き込むことにより、デバイスをハイブリッド スリープ状態にします。CS# を LOW にすると、デバイスは HS 状態を終了し、CR1[5] を「1」にセットします。また、POR またはハードウェアリセットによっても、デバイスはハイブリッド スリープ状態を終了します。POR またはハードウェアリセットは、メモリコアデータが失われる可能性があるリフレッシュを無効にすることに注意してください。

### 分散型リフレッシュ間隔

DRAM アレイはすべてのビットの定期的なリフレッシュが必要です。これは、ホストシステムが特定の制限時間内に各行内の 1 つの位置を読み出し / 書き込みすることで行われます。読み出し / 書き込みのアクセスにより、その行のビットは内部バッファにコピーされます。アクセスの終了時、バッファに格納されたビットはメモリ内の行に書き戻されるため、DRAM メモリセル内のビット行が再充電 (リフレッシュ) されます。

HYPERRAM™ デバイスは自動的に行をリフレッシュするセルフリフレッシュロジックを内蔵しています。メモリがホストシステムによってアクティブに読み出し / 書き込みされていないときのみ、行の自動リフレッシュを実行できます。リフレッシュロジックは、その時点でリフレッシュが必要な場合、アクティブな読み出し / 書き込みの終了を待ってからリフレッシュを実行します。リフレッシュが完了する前に新しい読み出し / 書き込みが開始する場合、メモリは CA 期間中に RWDS を HIGH に駆動して新しいアクセスの開始時に追加の初期レイテンシが必要となることを示します。これにより、新しいアクセスが開始する前にリフレッシュ動作が完了できます。

**Table 14** に示すように、メモリアレイ全体の必要なリフレッシュ間隔は温度によって異なります。これは、すべての行を更新する必要がある時間です。すべての行のリフレッシュは、各間隔の開始時に一括してアクセスすること、あるいは 1 回にいくつかの行のグループを、各間隔を通して分散された形でのリフレッシュ (バーストリフレッシュ) をすること、あるいは間隔にわたって均等に分配された単一行のリフレッシュとしても実行できます。セルフリフレッシュロジックは間隔内で單一行のリフレッシュ動作を分散することで、バーストリフレッシュの実行でメモリが長い期間ビジーになることはなく、これによりホストアクセスが長い期間遅延されることはありません。

**Table 14** 温度ごとのアレイリフレッシュ間隔

| デバイスの温度 (°C) | アレイリフレッシュ間隔 (ms) | アレイ行数 | 推奨 $t_{CSM}$ (μs) |

|--------------|------------------|-------|-------------------|

| 85           | 64               | 8192  | 4                 |

| 105          | 16               | 8192  | 1                 |

分配型リフレッシュ方式は、ホストがメモリの必要な分配型リフレッシュを行えなくなるほど長いバーストトランザクションを実行しないことを必要とします。このことから、リフレッシュロジックがトランザクション同士間にリフレッシュを挿入できるように読み出し / 書き込みトランザクションの長さの上限値が設定されます。この上限値は CS# の最大 LOW 時間 ( $t_{CSM}$ ) と呼ばれます。 $t_{CSM}$  値は、アレイリフレッシュ間隔をアレイ内の行数で割ってから、結果を半分に減らすことで計算されます。これにより、分配型リフレッシュが必要とされる直前に開始する最大長のホストアクセスが原因で分配型リフレッシュ間隔が完全に見逃されることを防止できます。 $t_{CSM}$  が必要な分散型リフレッシュ間隔の半分にセットされた値であるため、リフレッシュ動作を遅延させる一連の最大長のホストアクセスは、リフレッシュ間隔を行数で割った値の 2 倍である速度でリフレッシュ動作に追いつきます。

ホストシステムは、各トランザクションを  $t_{CSM}$  に違反する前に終了することで  $t_{CSM}$  の要件を満たす必要があります。このためには、ホストメモリコントローラロジックは  $t_{CSM}$  の制限に達すると長いトランザクションを分割するか、またはホストシステムハードウェアあるいはソフトウェアは  $t_{CSM}$  よりも長い単一読み出し / 書き込みトランザクションを実行しません。

**Table 14** に示したように、低温ではアレイリフレッシュ間隔が長くなるため、 $t_{CSM}$  が増加し、その結果、より長いトランザクションを実行できるようになります。ホストシステムは、最大動作温度に対して表からの  $t_{CSM}$  値を使用することもでき、分散型リフレッシュ間隔を長くするためにシステムの温度センサーで現時点の動作温度も判定できます。

## 7 インターフェース状態

Table 15 に、信号の値の要件を、インターフェースの状態ごとに示します。

Table 15 インターフェース状態

| インターフェース状態                          | $V_{CC}/V_{CCQ}$                  | CS# | CK, CK# | DQ7-DQ0                  | RWDS             | RESET# |

|-------------------------------------|-----------------------------------|-----|---------|--------------------------|------------------|--------|

| 電源切断                                | $< V_{LKO}$                       | X   | X       | HIGH-Z                   | HIGH-Z           | X      |

| パワーオン(コールド)リセット                     | $\geq V_{CC}/V_{CCQ} \text{ min}$ | X   | X       | HIGH-Z                   | HIGH-Z           | X      |

| ハードウェア(ウォーム)リセット                    | $\geq V_{CC}/V_{CCQ} \text{ min}$ | X   | X       | HIGH-Z                   | HIGH-Z           | L      |

| インターフェーススタンバイ                       | $\geq V_{CC}/V_{CCQ} \text{ min}$ | H   | X       | HIGH-Z                   | HIGH-Z           | H      |

| CA                                  | $\geq V_{CC}/V_{CCQ} \text{ min}$ | L   | T       | マスター出力有効                 | Y                | H      |

| 読み出し初期アクセスレイテンシ(データバスターンアラウンド周期)    | $\geq V_{CC}/V_{CCQ} \text{ min}$ | L   | T       | HIGH-Z                   | L                | H      |

| 書き込み初期アクセスレイテンシ(RWDSターンアラウンド周期)     | $\geq V_{CC}/V_{CCQ} \text{ min}$ | L   | T       | HIGH-Z                   | HIGH-Z           | H      |

| 読み出しデータ転送                           | $\geq V_{CC}/V_{CCQ} \text{ min}$ | L   | T       | スレーブ出力有効                 | スレーブ出力有効ZまたはT    | H      |

| 初期レイテンシありの書き込みデータ転送                 | $\geq V_{CC}/V_{CCQ} \text{ min}$ | L   | T       | マスター出力有効                 | マスター出力有効XまたはT    | H      |

| 初期レイテンシなしの書き込みデータ転送 <sup>[28]</sup> | $\geq V_{CC}/V_{CCQ} \text{ min}$ | L   | T       | マスター出力有効                 | スレーブ出力LまたはHIGH-Z | H      |

| アクティブクロック停止 <sup>[29]</sup>         | $\geq V_{CC}/V_{CCQ} \text{ min}$ | L   | アイドル    | マスターまたはスレーブ出力有効またはHIGH-Z | Y                | H      |

| ディープパワーダウン                          | $\geq V_{CC}/V_{CCQ} \text{ min}$ | H   | XまたはT   | HIGH-Z                   | HIGH-Z           | H      |

| ハイブリッドスリープ                          | $\geq V_{CC}/V_{CCQ} \text{ min}$ | H   | XまたはT   | HIGH-Z                   | HIGH-Z           | H      |

### 凡例

L =  $V_{IL}$

H =  $V_{IH}$

X =  $V_{IL}$  または  $V_{IH}$

Y =  $V_{IL}$  または  $V_{IH}$  または  $V_{OL}$  または  $V_{OH}$

Z =  $V_{OL}$  または  $V_{OH}$

L/H = 立ち上りエッジ

H/L = 立ち下りエッジ

T = 情報転送中にトグル

アイドル = CK が LOW、CK# が HIGH

有効 = すべてのバス信号が L または H レベルに安定している

### 注:

28. 初期レイテンシのない(ゼロ初期レイテンシ)書き込み動作には、RWDS用のターンアラウンド期間がありません。HYPERRAM™ デバイスは CA期間中に常に RWDSを駆動して、延長レイテンシが必要かどうかを示します。CA期間の直後にマスター書き込みデータが続くため、HYPERRAM™ デバイスは RWDSをLOWに駆動し続けるか、または RWDSをHIGH-Z状態にすることがあります。レイテンシのない書き込み期間中に、マスターは RWDSを駆動してはいけません。レイテンシのない書き込みは、RWDSをデータマスク機能として使用しません。書き込みデータのすべてのバイトが書き込まれます(フルワード書き込み)。

29. アクティブクロック停止は **アクティブクロック停止** で説明します。DPDは **ハイブリッドスリープ** で

## 8 低消費電力モード

### 8.1 インターフェーススタンバイ

スタンバイは、デバイスがホストによってデータ転送用に選択されていない (CS#=HIGH) とき、インターフェースにとってのデフォルトの低消費電力状態です。この状態では、CS# と RESET# 以外のすべての入出力は無視されます。

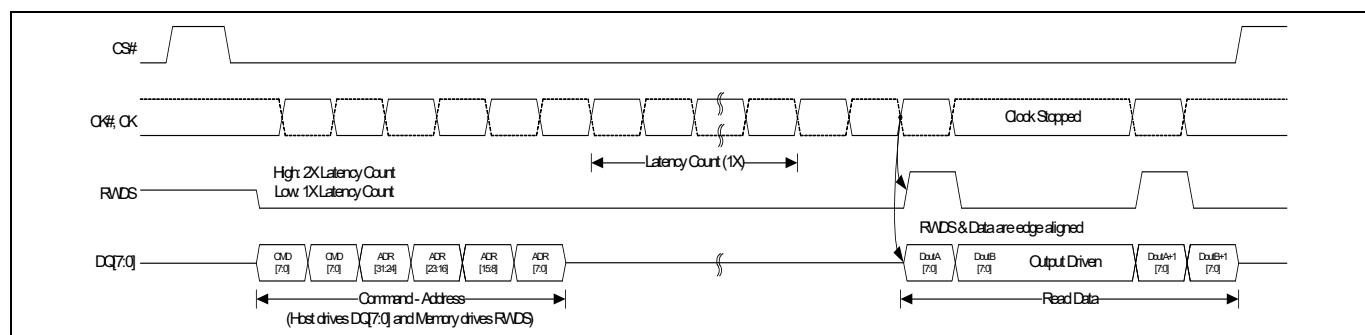

### 8.2 アクティブクロック停止

設計注記: アクティブクロック停止機能は、サポートされるかどうかを判定するためにデバイスの特性評価を保留しています。

アクティブクロック停止状態では、読み出し / 書き込み動作のデータ転送部分の間、デバイスインターフェースの消費エネルギーを  $I_{CC6}$  レベルに低減します。クロックが  $[t_{ACC}+30\text{ns}]$  にわたって安定状態に維持されると、デバイスは自動的にこの状態に入ります。アクティブクロック停止状態では、読み出しデータはラッチされ、常にデータバスに出力されます。 $I_{CC6}$  については [DC 電気的特性](#) を参照してください。

アクティブクロック停止状態により、ホストシステムクロックが停止してデータ転送を一時停止するときに消費電流を減少できます。このような拡張されたデータ転送サイクル中に CS# が LOW にある場合がありますが、メモリデバイスのホストインターフェースは  $[t_{ACC}+30\text{ns}]$  が経過した後にアクティブクロック停止時の電流レベルになります。これにより、データ転送が停止された場合、デバイスは低電流状態に入ります。クロックのトグルによりデータ転送が再開されると、アクティブ読み書き電流に戻ります。アクティブクロック停止状態は  $t_{CSM}$  の制限に違反して使用してはいけません。CS# は  $t_{CSM}$  が違反される前に HIGH になる必要があります。クロックは LOW 状態にある限り、アクティブトランザクションのどの部分でも停止できます。レジスタアクセス中にはクロックを停止しないことを注意してください。

Figure 22 読み出しトランザクション中のアクティブクロック停止 (DDR)<sup>[30]</sup>

注:

30.RWDS は CA サイクル中に LOW です。追加レイテンシがスレーブによって必要とされる時点で読み出しトランザクションが開始しないため、この読み出しトランザクションでは読み出しデータのアクセス用に 1 つの初期レイテンシがあります。

### 8.3 ハイブリッドスリープ

ハイブリッドスリープ(HS)状態では、消費電流が削減されます( $I_{HS}$ )。CR1[5]に「0」を書き込むことでHS状態に入れます。デバイスは  $t_{HSIN}$  の間消費電力を減少させます。メモリ空間とレジスタ空間のデータはHS状態中に保持されます。CS#をLOWにすると、デバイスはHS状態を終了し、CR1[5]を「1」にセットします。また、PORまたはハードウェアリセットによっても、デバイスはハイブリッドスリープ状態を終了します。PORまたはハードウェアリセットは、メモリコアデータが失われる可能性があるリフレッシュを無効にすることに注意してください。スタンバイ状態に復帰するためには  $t_{EXITHS}$  の時間がかかります。これらのイベントのいずれかでHSを終了した後、デバイスの状態はハイブリッドスリープに入る状態と同じです。

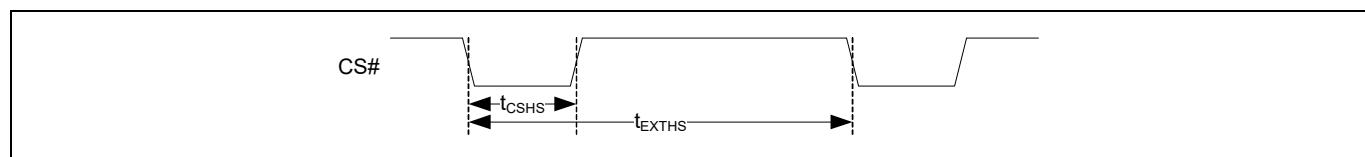

Figure 23 HS トランザクション開始

Figure 24 HS トランザクション終了

Table 16 ハイブリッドスリープタイミングパラメーター

| パラメーター      | 説明                                               | Min | Max  | 単位      |

|-------------|--------------------------------------------------|-----|------|---------|

| $t_{HSIN}$  | ハイブリッドスリープ CR1[5]=0 レジスタ書き込みから DPD 電力レベルになるまでの時間 | -   | 3    | $\mu s$ |

| $t_{CSHS}$  | HS を終了する CS# パルス幅                                | 60  | 3000 | ns      |

| $t_{EXTHS}$ | CS# ハイブリッドスリープ終了からスタンバイになるまでのウェイクアップ時間           | -   | 100  | $\mu s$ |

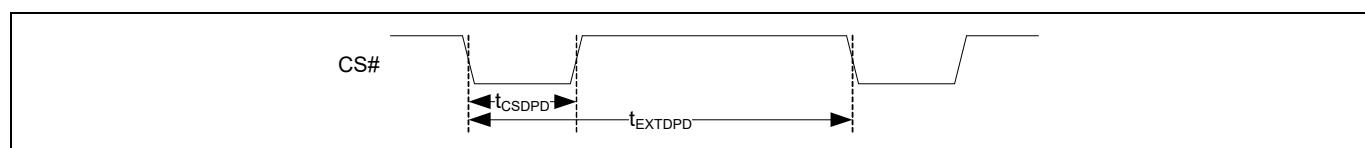

## 8.4 ディープパワーダウン

ディープパワーダウン (DPD) 状態では、消費電流は可能な限り低レベル ( $I_{DPD}$ ) で駆動されます。CR0[15] に「0」を書き込むことで DPD 状態に入れます。デバイスは  $t_{DPDIN}$  の間消費電力を減少させ、すべてのリフレッシュ動作を停止します。DPD 状態の間、メモリ空間に格納されたデータは失われます(リフレッシュなしで無効になります)。CS# を LOW に駆動してから HIGH に駆動することにより、デバイスは DPD 状態を終了します。また、POR またはハードウェアリセットによってもデバイスは DPD 状態を終了します。スタンバイ状態に復帰するためには  $t_{EXTDPD}$  の時間がかかります。POR の後にスタンバイ状態に復帰するには  $t_{VCS}$  時間かかります。これは、どの POR においても同様です。これらのイベントのいずれかで DPD を終了した後、デバイスの状態は POR を実行した後の状態と同じです。

注: xSPI (オクタル) では、ディープパワーダウントランザクションまたは任意レジスタ書き込みトランザクションを使用して DPD を開始できます。

Figure 25 DPD トランザクション開始

Figure 26 DPD トランザクション終了

Table 17 ディープパワーダウンタイミングパラメーター

| パラメーター       | 説明                                                 | Min | Max  | 単位 |

|--------------|----------------------------------------------------|-----|------|----|

| $t_{DPDIN}$  | ディープパワーダウン CR0[15]=0 のレジスタ書き込みから DPD 電力レベルになるまでの時間 | -   | 3    | μs |

| $t_{CSDPD}$  | DPD を終了する CS# パルス幅                                 | 200 | 3000 | ns |

| $t_{EXTDPD}$ | CS# ディープパワーダウン終了からスタンバイになるまでのウェイクアップ時間             | -   | 150  | μs |

注:

- 31.サポートされた MCP の完全なリストについては、[注文情報](#)を参照してください。

- 32.追加のリーク電流が VCCQ DIE\_STK[1:0] 接続で生成されません。

電気的仕様

## 9 電気的仕様

### 9.1 絶対最大定格

|                                    |                                   |

|------------------------------------|-----------------------------------|

| プラスチック パッケージの保存温度                  | -65 °C ~ +150 °C                  |

| 通電時の周囲温度                           | -65 °C ~ +115 °C                  |

| グランドに対する電圧                         |                                   |

| すべての信号 <sup>[33]</sup>             | -0.5V ~ +(V <sub>CC</sub> + 0.5V) |

| 出力短絡電流 <sup>[34]</sup>             | 100 mA                            |

| V <sub>CC</sub> , V <sub>CCQ</sub> | -0.5V ~ +4.0V                     |

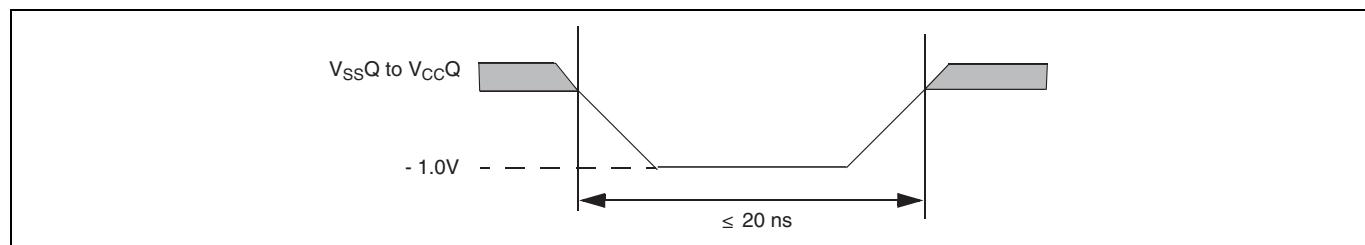

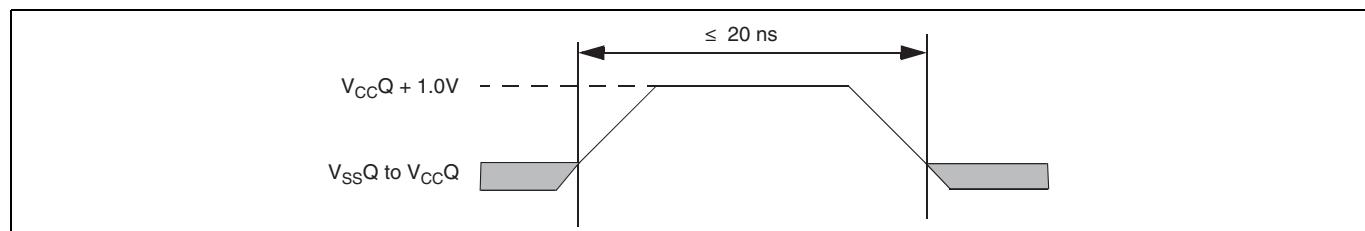

#### 9.1.1 入力信号オーバーシュート

DC 条件において、入力または I/O 信号は V<sub>SS</sub> と V<sub>CC</sub> の電圧範囲内にあることが必要です。電圧変動中、入力または I/O は最大 20ns の間 [V<sub>SS</sub>-1.0V] までの負オーバーシュート、または [V<sub>CC</sub>+1.0V] までの正オーバーシュートの可能性があります。

Figure 27 最大負オーバーシュート波形

Figure 28 最大正オーバーシュート波形

#### 注:

33. 入力または I/O 信号の最小 DC 電圧は -1.0V です。電圧変動時、入力または I/O 信号は最大 20ns の間 [V<sub>SS</sub>-1.0V] までアンダーシュートする可能性があります。Figure 27 を参照してください。入力または I/O 信号の最大 DC 電圧は [V<sub>CC</sub>+1.0V] です。電圧変動時、入力または I/O 信号は最大 20ns の間 [V<sub>CC</sub>+1.0V] までオーバーシュートする可能性があります。Figure 28 を参照してください。

34. 複数の出力は同時にグランドに短絡できません。短絡時間は 1 秒を超えてはいけません。

電気的仕様

## 9.2 ラッチアップ特性

Table 18 ラッチアップ仕様<sup>[36]</sup>

| 説明                                | Min  | Max             | 単位 |

|-----------------------------------|------|-----------------|----|

| すべての入力専用接続での $V_{SSQ}$ を基準とした入力電圧 | -1.0 | $V_{CCQ} + 1.0$ | V  |

| すべての I/O 接続で $V_{SSQ}$ を基準とした入力電圧 | -1.0 | $V_{CCQ} + 1.0$ |    |

| $V_{CCQ}$ 電流                      | -100 | +100            | mA |

## 9.3 動作範囲

動作範囲は、デバイスの正常な機能が保証される範囲を定めたものです。

### 9.3.1 温度範囲

| パラメーター | 記号    | デバイス                      | 仕様  |     | 単位 |

|--------|-------|---------------------------|-----|-----|----|

|        |       |                           | Min | Max |    |

| 周囲温度   | $T_A$ | 産業用 (I)                   | -40 | 85  | °C |

|        |       | 産業用プラス (V)                |     | 105 |    |

|        |       | 車載向け, AEC-Q100 グレード 3 (A) |     | 85  |    |

|        |       | 車載向け, AEC-Q100 グレード 2 (B) |     | 105 |    |

### 9.3.2 電源電圧

| 説明                 | Min | Max | 単位 |

|--------------------|-----|-----|----|

| 1.8V $V_{CC}$ 電源電圧 | 1.7 | 2.0 | V  |

| 3.0V $V_{CC}$ 電源電圧 | 2.7 | 3.6 |    |

#### 注:

- 35.絶対最大定格に記載されたものを越えるストレスの印加は、デバイスを完全に破壊する可能性があります。ただし、これはストレスのみに対する定格です。上記の条件あるいは本データシートの動作説明の各節に記載されている条件を越える条件におけるデバイスの機能動作は保証されません。長時間にわたってデバイスを絶対最大定格条件に放置すると、デバイスの信頼性に影響を与えます。

36. $V_{CC}/V_{CCQ}$  の電源電圧を除外します。テスト条件:  $V_{CC}=V_{CCQ}$ 、1度に1つの接続をテストし、テストされていないピンは  $V_{SS}$  に接続します。

## 9.4 DC 電気的特性

Table 19 DC 電気的特性 (CMOS 互換)

| パラメーター      | 説明                                                | テスト条件                                                                                                | 64Mb     |                     |               | 単位            |

|-------------|---------------------------------------------------|------------------------------------------------------------------------------------------------------|----------|---------------------|---------------|---------------|

|             |                                                   |                                                                                                      | Min      | Typ <sup>[37]</sup> | Max           |               |

| $I_{LI1}$   | 入力リーク電流<br>3.0V デバイスリセット信号 HIGH のみ                | $V_{IN} = V_{SS} \sim V_{CC}$ ,<br>$V_{CC} = V_{CC} \text{ max}$                                     | -        | 2                   | 15            | $\mu\text{A}$ |

| $I_{LI2}$   | 入力リーク電流<br>1.8V デバイスリセット信号 HIGH のみ                | $V_{IN} = V_{SS} \sim V_{CC}$ ,<br>$V_{CC} = V_{CC} \text{ max}$                                     |          |                     |               |               |

| $I_{LI3}$   | 入力リーク電流<br>3.0V デバイスリセット信号 LOW のみ <sup>[38]</sup> | $V_{IN} = V_{SS} \sim V_{CC}$ ,<br>$V_{CC} = V_{CC} \text{ max}$                                     |          |                     |               |               |

| $I_{LI4}$   | 入力リーク電流<br>1.8V デバイスリセット信号 LOW のみ <sup>[38]</sup> | $V_{IN} = V_{SS} \sim V_{CC}$ ,<br>$V_{CC} = V_{CC} \text{ max}$                                     |          |                     |               |               |

| $I_{CC1}$   | $V_{CC}$ アクティブ読み出し電流                              | $CS\# = V_{IL}$ , @200 MHz,<br>$V_{CC} = 2.0\text{V}$                                                | 15       | 25                  | 30            | $\text{mA}$   |

|             |                                                   | $CS\# = V_{IL}$ , @166 MHz,<br>$V_{CC} = 3.6\text{V}$                                                |          | 28                  |               |               |

|             |                                                   | $CS\# = V_{SS}$ , @200 MHz,<br>$V_{CC} = 3.6\text{V}$                                                |          | 30                  |               |               |

| $I_{CC2}$   | $V_{CC}$ アクティブ書き込み電流                              | $CS\# = V_{IL}$ , @200 MHz,<br>$V_{CC} = 2.0\text{V}$                                                | 15       | 25                  | 30            | $\text{mA}$   |

|             |                                                   | $CS\# = V_{IL}$ , @166 MHz,<br>$V_{CC} = 3.6\text{V}$                                                |          | 28                  |               |               |

|             |                                                   | $CS\# = V_{SS}$ , @200 MHz,<br>$V_{CC} = 3.6\text{V}$                                                |          | 30                  |               |               |

| $I_{CC4I}$  | $V_{CC}$ スタンバイ電流<br>(-40°C ~ +85°C)               | $CS\# = V_{IH}$ , $V_{CC} = 2.0\text{V}$<br>$CS\# = V_{IH}$ , $V_{CC} = 3.6\text{V}$                 | 80<br>90 | 220<br>250          | 350<br>360    | $\mu\text{A}$ |

| $I_{CC4IP}$ | $V_{CC}$ スタンバイ電流<br>(-40°C ~ +105°C)              | $CS\# = V_{IH}$ , $V_{CC} = 2.0\text{V}$<br>$CS\# = V_{IH}$ , $V_{CC} = 3.6\text{V}$                 |          | 330<br>360          |               |               |

| $I_{CC5}$   | リセット電流                                            | $CS\# = V_{IH}$ ,<br>$RESET\# = V_{IL}$ ,<br>$V_{CC} = V_{CC} \text{ max}$                           | -        | 1                   | 8<br>12<br>35 | $\text{mA}$   |

| $I_{CC6I}$  | アクティブクロック停止時の電流<br>(-40°C ~ +85°C)                | $CS\# = V_{IL}$ ,<br>$RESET\# = V_{IH}$ ,<br>$V_{CC} = V_{CC} \text{ max}$                           | 5        | 8                   |               |               |

| $I_{CC6IP}$ | アクティブクロック停止時の電流<br>(-40°C ~ +105°C)               | $CS\# = V_{IL}$ ,<br>$RESET\# = V_{IH}$ ,<br>$V_{CC} = V_{CC} \text{ max}$                           | 8        | 12                  |               |               |

| $I_{CC7}$   | 電源投入時の $V_{CC}$ 電流 <sup>[37]</sup>                | $CS\# = V_{IH}$ ,<br>$V_{CC} = V_{CC} \text{ max}$ ,<br>$V_{CC} = V_{CCQ} = 2.0\text{V}$ または<br>3.6V | -        | 35                  |               |               |

| $I_{DPD}$   | 3.0V でのディープパワーダウン電流<br>(-40°C ~ +85°C)            | $CS\# = V_{IH}$ , $V_{CC} = 3.6\text{V}$                                                             | -        | -                   | 12            | $\mu\text{A}$ |

| $I_{DPD}$   | 1.8V でのディープパワーダウン電流<br>(-40°C ~ +85°C)            | $CS\# = V_{IH}$ , $V_{CC} = 2.0\text{V}$                                                             |          |                     | 10            |               |

注:

37.完全にテストされているわけではありません。

38.RESET# が LOW のとき、デバイスは DPD 状態を終了し、ICC5 リセット電流を流し始め、RESET# 期間中の  $I_{LI}$  が小さくなります。

Table 19 DC 電気的特性 (CMOS 互換) (Continued)

| パラメーター    | 説明                                      | テスト条件                               | 64Mb                   |                     |                       | 単位      |

|-----------|-----------------------------------------|-------------------------------------|------------------------|---------------------|-----------------------|---------|

|           |                                         |                                     | Min                    | Typ <sup>[37]</sup> | Max                   |         |

| $I_{DPD}$ | 3.0V でのディープパワーダウン電流<br>(-40°C ~ +105°C) | CS# = $V_{IH}$ , $V_{CC} = 3.6V$    | -                      | -                   | 15                    | $\mu A$ |

| $I_{DPD}$ | 1.8V でのディープパワーダウン電流<br>(-40°C ~ +105°C) | CS# = $V_{IH}$ , $V_{CC} = 2.0V$    |                        |                     | 12                    |         |

| $I_{HS}$  | 3.0V でのハイブリッドスリープ電流<br>(-40°C ~ +85°C)  | CS# = $V_{IH}$ , $V_{CC} = 3.6V$    |                        | 35                  | 230                   |         |

| $I_{HS}$  | 1.8V でのハイブリッドスリープ電流<br>(-40°C ~ +85°C)  | CS# = $V_{IH}$ , $V_{CC} = 2.0V$    |                        | 25                  | 200                   |         |

| $I_{HS}$  | 3.0V でのハイブリッドスリープ電流<br>(-40°C ~ +105°C) | CS# = $V_{IH}$ , $V_{CC} = 3.6V$    |                        | 35                  | 310                   |         |

| $I_{HS}$  | 1.8V でのハイブリッドスリープ電流<br>(-40°C ~ +105°C) | CS# = $V_{IH}$ , $V_{CC} = 2.0V$    |                        | 25                  | 300                   |         |

| $V_{IL}$  | 入力 LOW 電圧                               | -                                   | $-0.15 \times V_{CC}Q$ | -                   | $0.35 \times V_{CC}Q$ | $V$     |

| $V_{IH}$  | 入力 HIGH 電圧                              |                                     |                        |                     | $1.15 \times V_{CC}Q$ |         |

| $V_{OL}$  | 出力 LOW 電圧                               | $DQ[7:0]$ に対して<br>$I_{OL}=100\mu A$ | -                      |                     | 0.20                  |         |

| $V_{OH}$  | 出力 HIGH 電圧                              | $DQ[7:0]$ に対して<br>$I_{OH}=100\mu A$ | $V_{CC}Q-0.20$         |                     | -                     |         |

注:

37.完全にテストされているわけではありません。

38.RESET# が LOW のとき、デバイスは DPD 状態を終了し、ICC5 リセット電流を流し始め、RESET# 期間中の  $I_L$  が小さくなります。

#### 9.4.1 静電容量特性

Table 20 1.8V での静電容量特性 [39, 40, 41]

| 説明                    | パラメーター | 64Mb | 単位 |

|-----------------------|--------|------|----|

|                       |        | Max  |    |

| 入力静電容量 (CK, CK#, CS#) | CI     | 3.0  | pF |

| デルタ入力静電容量 (CK, CK#)   | CID    | 0.25 |    |

| 出力静電容量 (RWDS)         | CO     | 3.0  |    |

| IO 静電容量 (DQx)         | CIO    | 3.0  |    |

| IO 静電容量デルタ (DQx)      | CIOD   | 0.25 |    |

Table 21 3.0V での静電容量特性 [39, 40, 41]

| 説明                    | パラメーター | 64Mb | 単位 |

|-----------------------|--------|------|----|

|                       |        | Max  |    |

| 入力静電容量 (CK, CK#, CS#) | CI     | 3.0  | pF |

| デルタ入力静電容量 (CK, CK#)   | CID    | 0.25 |    |

| 出力静電容量 (RWDS)         | CO     | 3.0  |    |

| IO 静電容量 (DQx)         | CIO    | 3.0  |    |

| IO 静電容量デルタ (DQx)      | CIOD   | 0.25 |    |

#### 注:

- 39.これらの値は設計保証であり、サンプルベースでのみテストされます。

- 40.接点の静電容量は、ベクタネットワークアナライザーを用いた静電容量測定 JEP147 手順に従って測定されます。 $V_{CC}$ 、 $V_{CCQ}$  を印加し、他のすべての信号（テスト中の信号以外）を開放にします。DQ 信号を高インピーダンス状態にする必要があります。

- 41.システム内の信号伝播時間整合を実現するために、CK, CK#, RWDS, および DQx 信号の静電容量値は同程度でなければならないことに注意してください。アクティブ (LOW) になる CS# と DQ バスに出力されるデータ間には重要なタイミング関係がないため、CS# の静電容量値はそこまで重要ではありません。

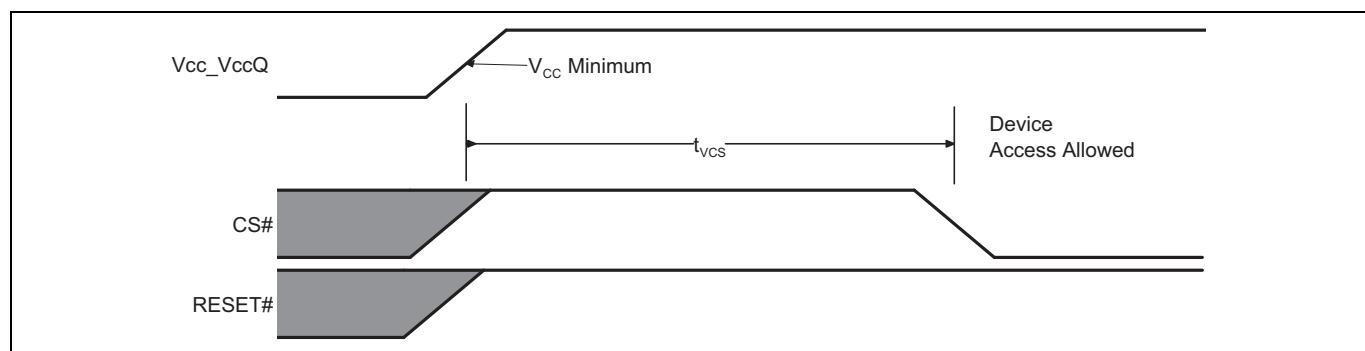

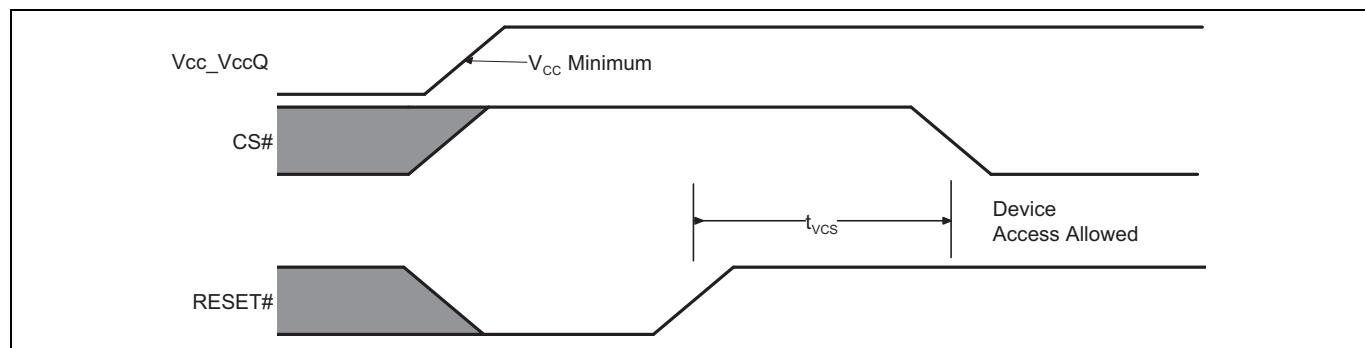

## 9.5 電源投入時の初期化

HYPERRAM™ 製品は、電源投入時の初期化プロセスを起動する電圧センサーを内蔵しています。 $V_{CC}$  と  $V_{CCQ}$  は同時に印加する必要があります。電源電圧が  $V_{CC}(\text{Min})$  以上の安定したレベルに達した後、デバイスは自己初期化プロセスを完了するために  $t_{VCS}$  時間を要します。

電源投入時にデバイスは選択できません。電源投入時に  $V_{CC}(\text{Min})$  に達するまで CS# は  $V_{CCQ}$  に印加された電圧に応じて変化しなければなりません。その後、CS# は  $t_{VCS}$  の追加の遅延時間の間 HIGH を維持する必要があります。 $V_{CCQ}$  とチップセレクト (CS#) を接続する簡単なプルアップ抵抗を使用すると安全かつ適切な電源投入を保証できます。

電源投入時に RESET# が LOW である場合、デバイスは RESET# が HIGH になるまで  $t_{VCS}$  期間の開始を遅延させます。 $t_{VCS}$  期間は、DRAM アレイのリフレッシュ動作を実行して初期化するために使用されます。

初期化が完了すると、デバイスは通常動作が開始できます。

Figure 29 RESET# が HIGH 時の電源投入

Figure 30 RESET# が LOW 時の電源投入

Table 22 電源投入およびリセット パラメーター [42, 43, 44]

| パラメーター    | 説明                                                                 | Min | Max | 単位 |

|-----------|--------------------------------------------------------------------|-----|-----|----|

| $V_{CC}$  | 1.8V $V_{CC}$ 電源電圧                                                 | 1.7 | 2.0 | V  |

| $V_{CC}$  | 3.0V $V_{CC}$ 電源電圧                                                 | 2.7 | 3.6 |    |

| $t_{VCS}$ | $V_{CC}$ と $V_{CCQ} \geq \text{Min}$ かつ RESET# HIGH から最初のアクセスまでの時間 | -   | 150 | μs |

### 注:

42. 電源投入時のリセット時間 ( $t_{VCS}$ ) 中はバス トランザクション (読み出しと書き込み) は禁止されます。

43.  $V_{CCQ}$  は、 $V_{CC}$  と同じ電圧でなければいけません。

44.  $V_{CC}$  ランプレートは非線形である場合があります。

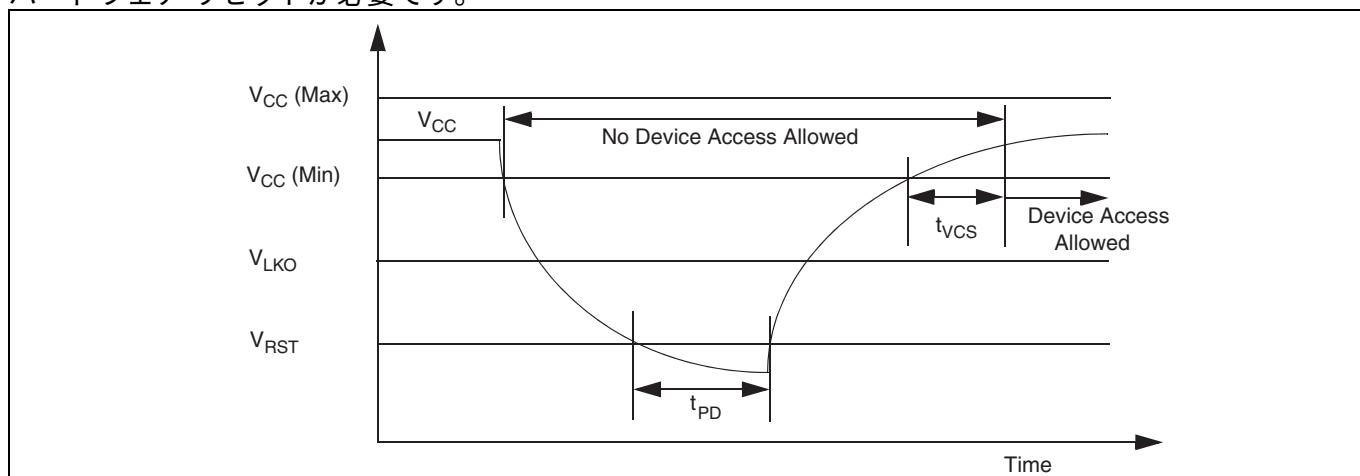

## 9.6 電源切斷

HYPERRAM™ デバイスは、アレイ電源 ( $V_{CC}$ ) が  $V_{CC}$  ロックアウト電圧 ( $V_{LKO}$ ) 以下となったときに電源切斷とみなされます。電源電圧が  $V_{SS}$  レベルまで低下する変動の間は、 $V_{CCQ}$  は  $V_{CC}$  以下を保つ必要があります。 $V_{LKO}$  レベルでは、HYPERRAM™ デバイスのコンフィギュレーションまたはアレイデータは失われています。

$V_{CC}$  は常に  $V_{CCQ}$  以上 ( $V_{CC} \geq V_{CCQ}$ ) であることが必要です。

電源切斷時または電源電圧が  $V_{LKO}$  を下回ったとき、アレイ電源電圧も電源切斷期間 ( $t_{PD}$ ) の間  $V_{CC}$  リセット ( $V_{RST}$ ) 以下である必要があります。これにより、電源電圧が再び  $V_{CCMin}$  まで上昇したとき、デバイスが正しく初期化します。Figure 31 を参照してください。

電圧低下時に、 $V_{CC}$  が  $V_{LKO}$  を上回ったままの場合は、デバイスは初期化状態のままとなり、 $V_{CC}$  が再度  $V_{CCMin}$  を上回ったとき正常に動作します。 $V_{CC}$  が  $t_{PD}$  期間以上  $V_{RST}$  を下回らない場合、POR プロセスが実行される保証はありません。この場合は、デバイスが正しく初期化されていることを確認するためにハードウェアリセットが必要です。

Figure 31 電源切斷または電圧低下

以下では電源切斷仕様の HYPERRAM™ デバイスに依存する側面を説明します。

Table 23 1.8V でのパワーダウン電圧とタイミング [45]

| 記号        | パラメーター                                    | Min | Max | 単位 |

|-----------|-------------------------------------------|-----|-----|----|

| $V_{CC}$  | $V_{CC}$ 電源電圧                             | 1.7 | 2.0 | V  |

| $V_{LKO}$ | デバイスの電圧がこれを下回ると再初期化が必要となる $V_{CC}$ ロックアウト | 1.5 | -   |    |

| $V_{RST}$ | 初期化を確実に行うために必要な $V_{CC}$ 低電圧              | 0.7 | -   |    |

| $t_{PD}$  | $V_{CC} \leq V_{RST}$ の期間                 | 50  | -   | μs |

Table 24 3.0V でのパワーダウン電圧とタイミング [45]

| 記号        | パラメーター                                    | Min | Max | 単位 |

|-----------|-------------------------------------------|-----|-----|----|

| $V_{CC}$  | $V_{CC}$ 電源電圧                             | 2.7 | 3.6 | V  |

| $V_{LKO}$ | デバイスの電圧がこれを下回ると再初期化が必要となる $V_{CC}$ ロックアウト | 2.4 | -   |    |

| $V_{RST}$ | 初期化を確実に行うために必要な $V_{CC}$ 低電圧              | 0.7 | -   |    |

| $t_{PD}$  | $V_{CC} \leq V_{RST}$ の期間                 | 50  | -   | μs |

### 注:

45.  $V_{CC}$  ランプレートは非線形である場合があります。

## 9.7 ハードウェアリセット

RESET# 入力は、デバイスをスタンバイ状態に復帰させるハードウェアによる方法を提供します。

$t_{RPH}$  の間、デバイスは  $I_{CC5}$  電流を消費します。RESET# が継続的に  $t_{RPH}$  を超えて LOW に保持される場合、デバイスは CMOS スタンバイ電流 ( $I_{CC4}$ ) を消費します。RESET# が LOW の間 ( $t_{RP}$  期間中) および  $t_{RPH}$  期間中、バス トランザクションは許可されません。

ハードウェアリセットは以下を行います。

- コンフィギュレーションレジスタをデフォルト値に戻させます

- RESET# が LOW の間にセルフリフレッシュ動作を停止させ、メモリアレイデータが無効とみなされます

- デバイスにハイブリッドスリープ状態を強制的に終了させます

- デバイスにディープパワーダウン状態を強制的に終了させます

RESET# が HIGH に戻った後、セルフリフレッシュ動作が再開します。RESET# が LOW の間にセルフリフレッシュ動作が停止され、セルフリフレッシュ行カウンターが初期設定値にリセットされるため、

**Table 14** に示した必要なアレイリフレッシュ間隔以内にリフレッシュされない行がある場合があります。これは、ハードウェアリセット中またはその直後に DRAM アレイデータが失われる可能性があります。ホストシステムは、ハードウェアリセット後に DRAM アレイデータが失われたと想定し、必要なデータをリロードします。

Figure 32 ハードウェアリセットタイミング図

Table 25 電源投入およびリセットパラメーター

| パラメーター    | 説明                              | Min | Max | 単位 |

|-----------|---------------------------------|-----|-----|----|

| $t_{RP}$  | RESET# パルス幅                     | 200 | -   | ns |

| $t_{RH}$  | RESET# (HIGH) と CS# (LOW) の間の時間 |     |     |    |

| $t_{RPH}$ | RESET# LOW から CS# LOW までの時間     | 400 |     |    |

## 9.8 ソフトウェアリセット

ソフトウェアリセットは、デバイスをスタンバイ状態に復帰させるソフトウェアによる方法を提供します。 $t_{SR}$  の間、デバイスは  $I_{CC5}$  電流を消費します。

ソフトウェアリセットは以下を行います。

- コンフィギュレーションレジスタをデフォルト値に戻させます

- ソフトウェアリセットプロセスの間にセルフリフレッシュ動作を停止させ、メモリアレイデータが無効とみなされます

ソフトウェアリセットが終了した後、セルフリフレッシュ動作が再開します。セルフリフレッシュ動作が停止され、セルフリフレッシュ行カウンターが初期設定値にリセットされるため、**Table 14** に示した必要なアレイリフレッシュ間隔以内にリフレッシュされない行があります。これは、ソフト

ウェアリセット中またはその直後に DRAM アレイデータが失われる可能性があります。ホストシステムは、ソフトウェアリセット後に DRAM アレイデータが失われたと想定し、必要なデータをリロードします。

Table 26 ソフトウェアリセットタイミング

| パラメーター   | 説明                                                  | Min | Max | 単位 |

|----------|-----------------------------------------------------|-----|-----|----|

| $t_{SR}$ | ソフトウェアリセットトランザクション<br>CS# HIGH からデバイスがスタンバイに入るまでの時間 | -   | 400 | ns |

## 10 タイミング仕様

以下ではタイミング仕様の HYPERRAM™ デバイスに依存する側面を説明します。

### 10.1 スイッチング波形の要素

### 10.2 AC テスト条件

Figure 33 テスト セットアップ

Table 27 テスト仕様<sup>[47]</sup>

| パラメーター                                       | 全速度バージョン        | 単位   |

|----------------------------------------------|-----------------|------|

| 出力負荷静電容量, $C_L$                              | 15              | pF   |

| 入力の立ち上りと立ち下りの最小スルーレート (1.8V) <sup>[46]</sup> | 1.13            | V/ns |

| 入力の立ち上りと立ち下りの最小スルーレート (3.0V) <sup>[46]</sup> | 2.06            |      |

| 入力パルス レベル                                    | 0.0 ~ $V_{CCQ}$ | V    |

| 入力タイミング測定基準レベル                               | $V_{CCQ}/2$     |      |

| 出力タイミング測定基準レベル                               |                 |      |

Figure 34 入力波形および測定レベル<sup>[48]</sup>

#### 注:

- 46.すべての AC タイミングはこの入力のスルーレートを前提とします。

- 47.入力および出力タイミングは  $V_{CCQ}/2$  または CK/CK# の交差を基準とします。

- 48.差動 CK/CK# ペアの入力タイミングはクロック交差のポイントから測定されます。

### 10.3 CLK 特性

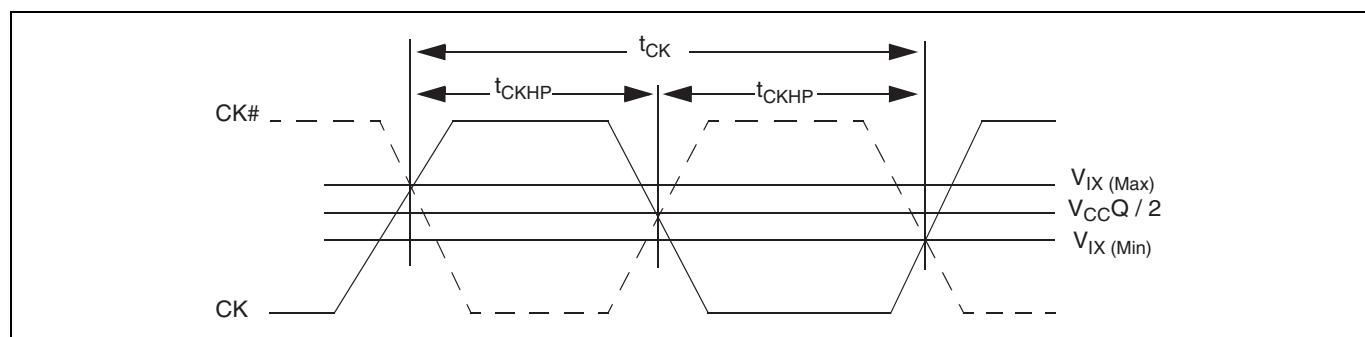

Figure 35 クロック特性

Table 28 クロックタイミング [49, 50, 51]

| パラメーター [52, 53]                                                    | 記号         | 200MHz |      | 166MHz |      | 単位       |

|--------------------------------------------------------------------|------------|--------|------|--------|------|----------|

|                                                                    |            | Min    | Max  | Min    | Max  |          |

| CK 周期                                                              | $t_{CK}$   | 5      | -    | 6      | -    | ns       |

| CK 半周期 - デューティ サイクル                                                | $t_{CKHP}$ | 0.45   | 0.55 | 0.45   | 0.55 | $t_{CK}$ |

| 周波数での CK 半周期<br>Min = 0.45 $t_{CK}$ Min<br>Max = 0.55 $t_{CK}$ Min | $t_{CKHP}$ | 2.25   | 2.75 | 2.7    | 3.3  | ns       |

Table 29 クロックの AC/DC 電気的特性 [54, 55]

| パラメーター    | 記号           | Min                  | Max                  | 単位 |

|-----------|--------------|----------------------|----------------------|----|

| DC 入力電圧   | $V_{IN}$     | -0.3                 | $V_{CCQ} + 0.3$      | V  |

| DC 差動入力電圧 | $V_{ID(DC)}$ | $V_{CCQ} \times 0.4$ | $V_{CCQ} + 0.6$      |    |

| AC 差動入力電圧 | $V_{ID(AC)}$ | $V_{CCQ} \times 0.6$ | $V_{CCQ} \times 0.6$ |    |

| AC 差動交差電圧 | $V_{IX}$     | $V_{CCQ} \times 0.4$ | $V_{CCQ} \times 0.6$ |    |

#### 注:

49.±5% のクロックジッタが許容されます。

50.最小周波数 (最大  $t_{CK}$ ) は、CS# の最大 Low 時間 ( $t_{CSM}$ )、初期レイテンシ、およびバースト長に依存します。

51.CK および CK# 入力スルーレートは  $\geq 1V/ns$  (差動的に測定される場合は  $2V/ns$ ) でなければいけません。

52.CK# は 1.8V デバイスでのみ使用され、破線の波形として表示されます。

53.3V デバイスは、シングルエンドのクロック入力を使用します。

54. $V_{ID}$  は CK の入力レベルと CK# の入力レベルの差の大きさです。

55. $V_{IX}$  の期待値は、送信デバイスの  $V_{CCQ}/2$  であり、 $V_{CCQ}$  の DC レベルの変化に追随しなければなりません。

## 10.4 AC 電気的特性

### 10.4.1 読み出しトランザクション

Table 30 HYPERRAM™ 固有読み出しタイミング パラメーター

| パラメーター                                                                                                                        | 記号                                  | 200MHz |      | 166MHz |       | 単位 |

|-------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|--------|------|--------|-------|----|

|                                                                                                                               |                                     | Min    | Max  | Min    | Max   |    |

| トランザクション同士間のチップセレクト HIGH 時間 (1.8V)                                                                                            | t <sub>CSHI</sub>                   | 6      | -    | 6      | -     | ns |