## サイプレスはインフィニオンテクノロジーズになりました

この表紙に続く文書には「サイプレス」と表記されていますが、これは同社が最初にこの製品を開発したからです。新規および既存のお客様いずれに対しても、引き続きインフィニオンがラインアップの一部として当該製品をご提供いたします。

### 文書の内容の継続性

下記製品がインフィニオンの製品ラインアップの一部として提供されたとしても、それを理由としてこの文書に変更が加わることはありません。今後も適宜改訂は行いますが、変更があった場合は文書の履歴ページでお知らせします。

### 注文時の部品番号の継続性

インフィニオンは既存の部品番号を引き続きサポートします。ご注文の際は、データシート記載の注文部品番号をこれまで通りご利用下さい。

S27KL0641/S27KS0641

S70KL1281/S70KS1281

## 3.0V/1.8V 64M ビット (8M バイト) HyperRAM™ セルフリフレッシュDRAM

### 特長

#### HyperRAM™ ロー シグナル カウント インターフェース

- 3.0 V I/O、11 本のバス信号

- シングルエンド クロック (CK)

- 1.8 V I/O、12 本のバス信号

- 差動クロック (CK, CK#)

- チップ セレクト (CS#)

- 8 ビット データ バス (DQ[7:0])

- 読み出し書き込みデータ ストローブ (RWDS)

- 双方向データ ストローブ／マスク

- すべてのトランザクションの開始時においてリフレッシュ レイテンシを示す出力

- 読み出しトランザクション中の読み出しデータ ストローブ としての出力

- 書き込みトランザクション中の書き込みデータ マスクとしての入力

- RWDS DCARS タイミング

- 読み出しトランザクションの間、RWDS は CK から位相シフトされた第 2 のクロックによりオフセットされる。

- 位相シフトクロックは、RWDS 遷移エッジを読み出しデータのタイミング内に移動するために使用

#### 高性能

- 最大 333 MBps

- ダブル データ レート (DDR) – クロック サイクルごとに 2 回のデータ転送

- $V_{CC} 1.8 \text{ V}$  時、166 MHz クロック レート (333 MBps)

- $V_{CC} 3.0 \text{ V}$  時、100 MHz クロック レート (200 MBps)

- 連続バースト トランザクション

- 設定可能なバースト特性

- ラップされるバースト長：

- 16 バイト (8 クロック)

- 32 バイト (16 クロック)

- 64 バイト (32 クロック)

- 128 バイト (64 クロック)

- リニア バースト

- ハイブリッド オプション - 1 回のラップ バーストの後にリニア バーストが続く

- 各トランザクションでラップ バーストまたはリニア バーストの方式を選択可能

- 設定可能な出力駆動強度

- 低消費電力モード

- ディープ パワーダウン

- パッケージ

- 24 ボール FBGA

### 性能要約

| 読み出しトランザクション タイミング                                |         |

|---------------------------------------------------|---------|

| 1.8 V $V_{CC}/V_{CCQ}$ での最大クロック レート               | 166 MHz |

| 3.0 V $V_{CC}/V_{CCQ}$ での最大クロック レート               | 100 MHz |

| 最大アクセス時間、(166 MHz での $t_{ACC}$ )                  | 36 ns   |

| 166MHz での最初のワードまでの最大 CS# アクセス時間 (リフレッシュ レイテンシを除く) | 56 ns   |

| 最大消費電流                                      | 64 MB  | 128 MB |

|---------------------------------------------|--------|--------|

| バースト読み出し／書き込み<br>(166 MHz、1.8 V でのリニア バースト) | 60 mA  | 72 mA  |

| パワー オン リセット                                 | 50 mA  | 100 mA |

| スタンバイ (CS# = High、3 V、105°C)                | 300 µA | 600 µA |

| ディープ パワー ダウン (CS# = High、3 V、105°C)         | 40 µA  | N/A    |

| スタンバイ (CS# = High、1.8 V、105°C)              | 300 µA | 600 µA |

| ディープ パワー ダウン (CS# = High、1.8 V、105°C)       | 20 µA  | N/A    |

Not Recommended for New Designs (NRND)

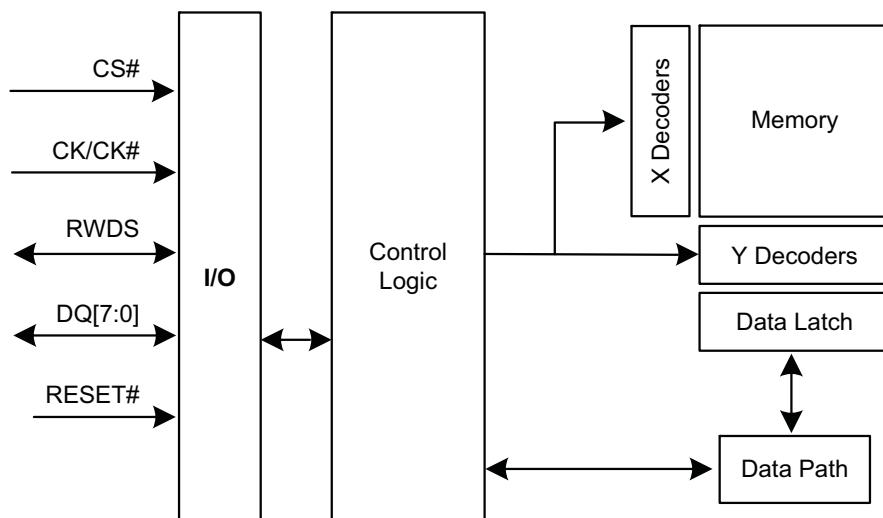

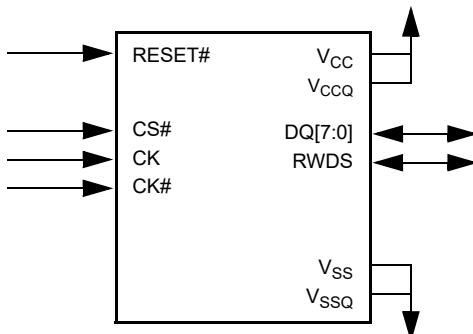

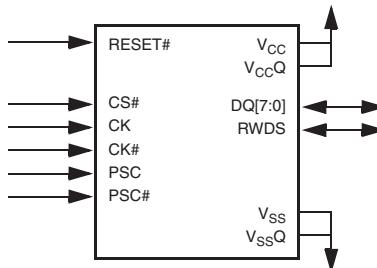

## 論理ブロック図

### ブロックダイヤグラム—64 Mb

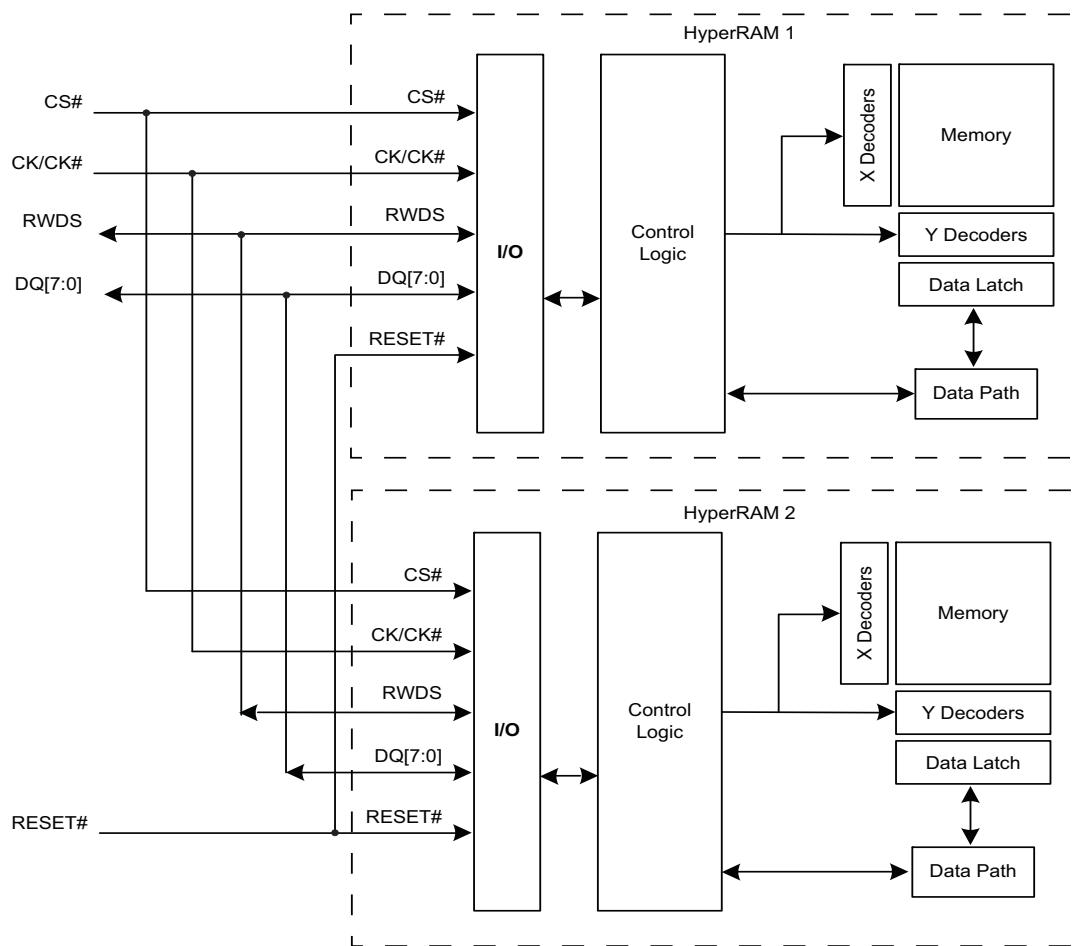

### ブロックダイヤグラム—128 Mb

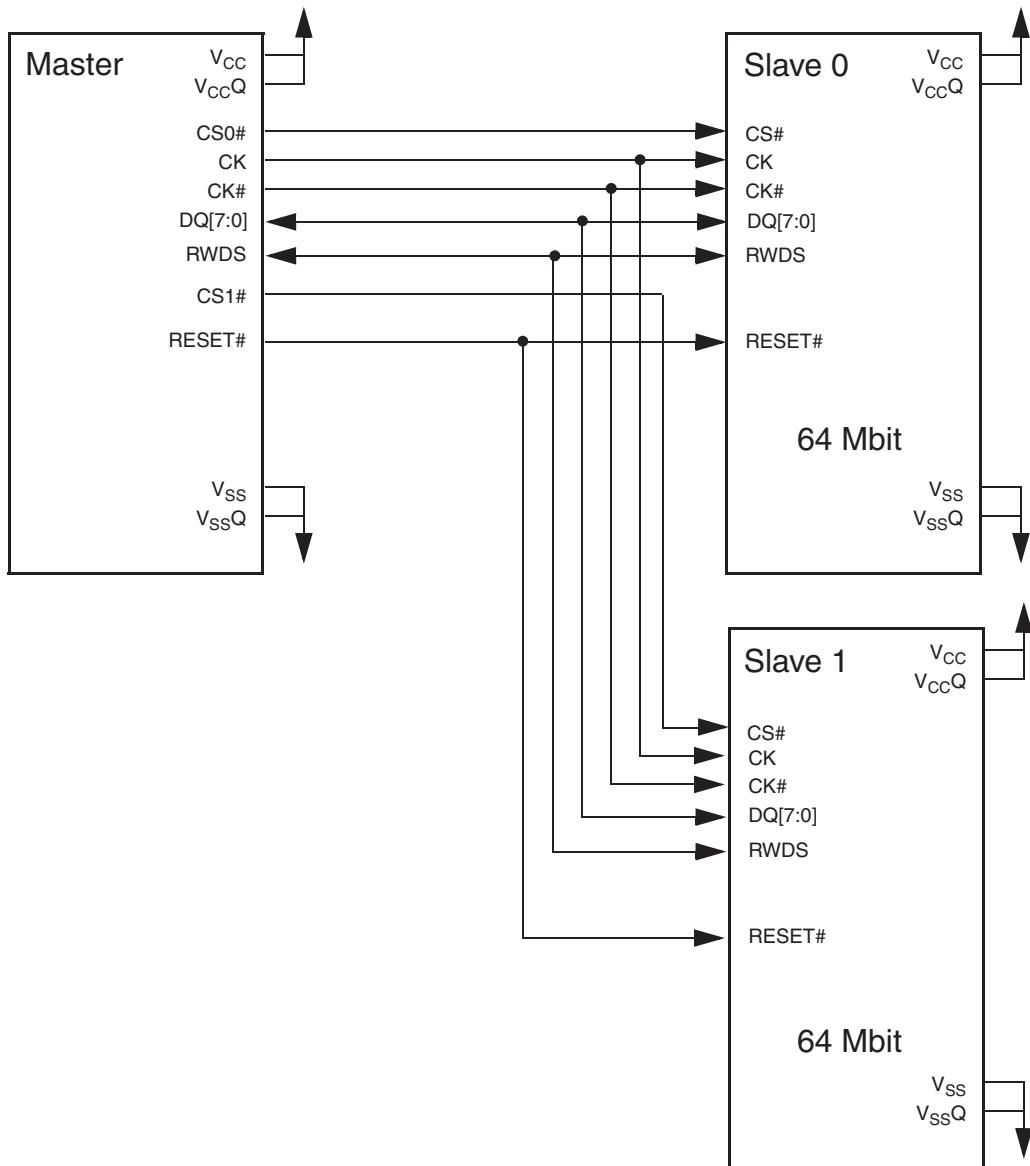

## HyperRAM ブロックダイヤグラム

オプション信号を含めた HyperRAM 接続

## 目次

|                                          |           |

|------------------------------------------|-----------|

| <b>概要</b> .....                          | <b>5</b>  |

| <b>製品概要</b> .....                        | <b>8</b>  |

| <b>HyperRAM 信号の説明</b> .....              | <b>9</b>  |

| 入出力の要約 .....                             | 9         |

| コマンド／アドレス ビットの割り当て .....                 | 10        |

| 読み出しトランザクション .....                       | 14        |

| 初期レイテンシ有りの書き込みトランザクション（メモリ コア書き込み） ..... | 15        |

| 初期レイテンシ無しの書き込みトランザクション（レジスタ書き込み） .....   | 17        |

| <b>メモリ空間</b> .....                       | <b>18</b> |

| <b>レジスタ空間</b> .....                      | <b>18</b> |

| デバイス識別レジスタ .....                         | 19        |

| レジスタ空間へのアクセス .....                       | 20        |

| <b>インターフェースの状態</b> .....                 | <b>26</b> |

| 省電力モード .....                             | 27        |

| <b>電気的仕様</b> .....                       | <b>29</b> |

| 絶対最大定格 .....                             | 29        |

| ラッチアップ特性 .....                           | 30        |

| 動作範囲 .....                               | 30        |

| DC 特性 .....                              | 31        |

| 電源投入時の初期化 .....                          | 33        |

| 電源切断 .....                               | 34        |

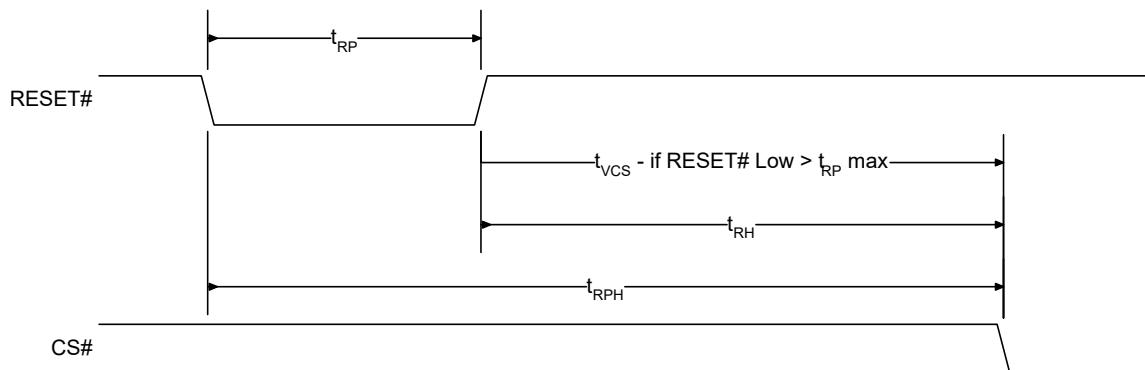

| ハードウェア リセット .....                        | 35        |

|                                                           |           |

|-----------------------------------------------------------|-----------|

| <b>タイミング仕様</b> .....                                      | <b>36</b> |

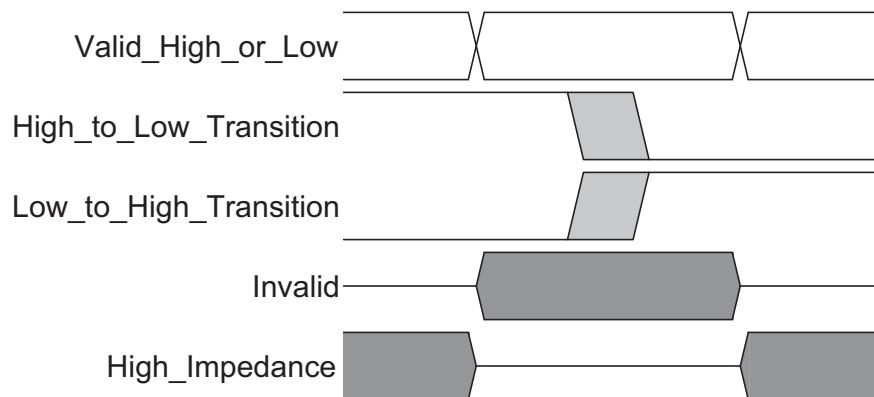

| 波形切り替えの基本事項 .....                                         | 36        |

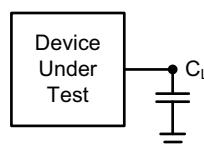

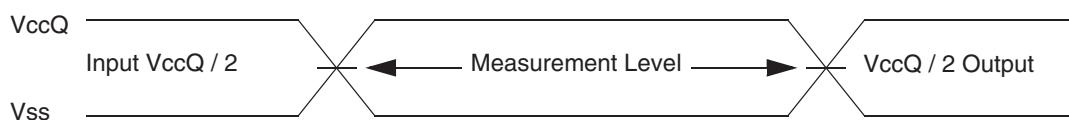

| AC テスト条件 .....                                            | 36        |

| AC 特性 .....                                               | 37        |

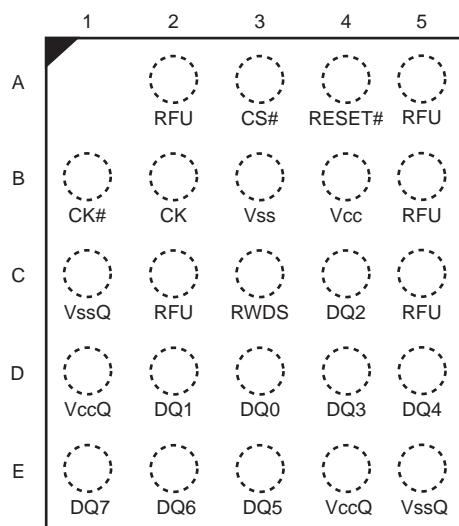

| <b>物理インターフェース</b> .....                                   | <b>40</b> |

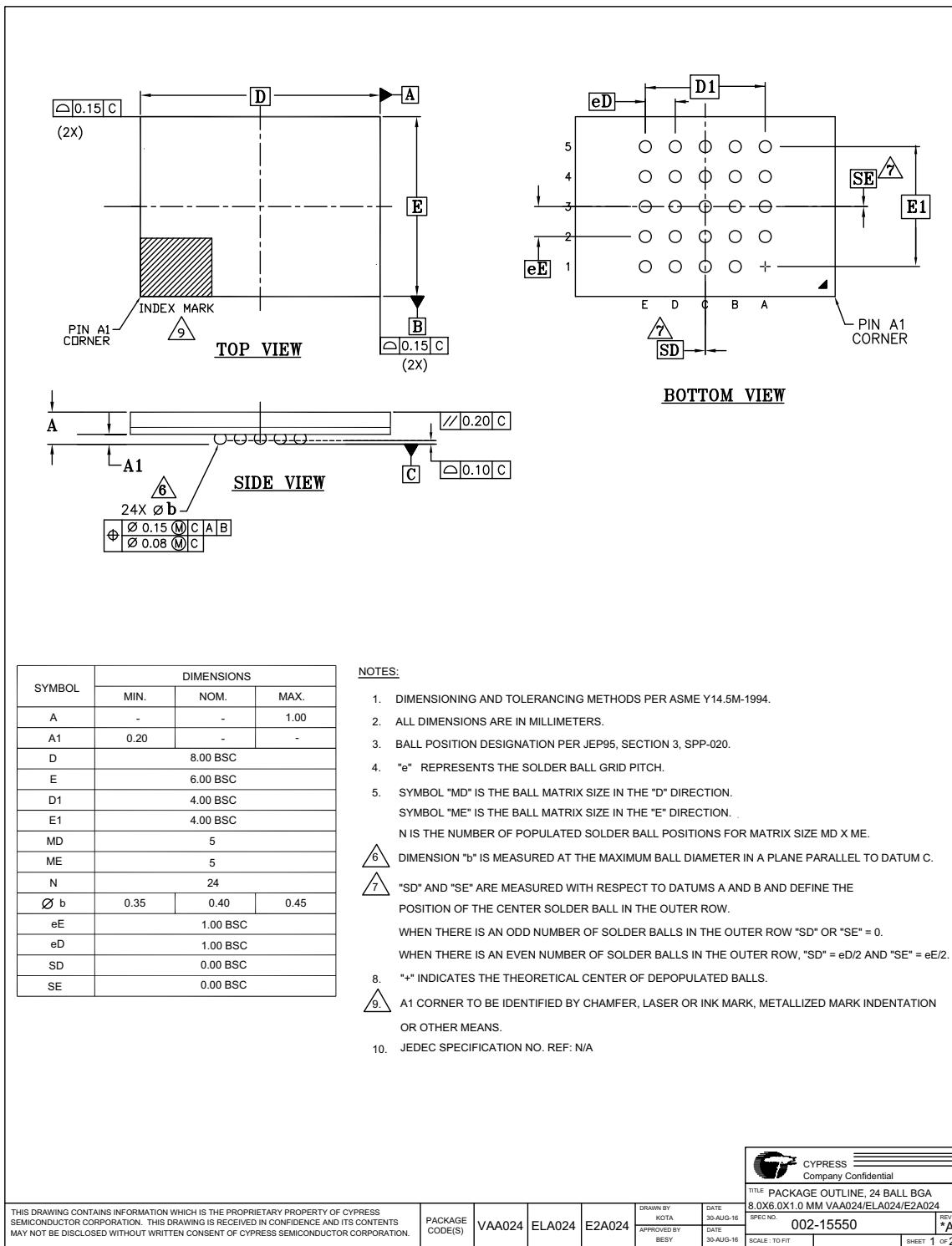

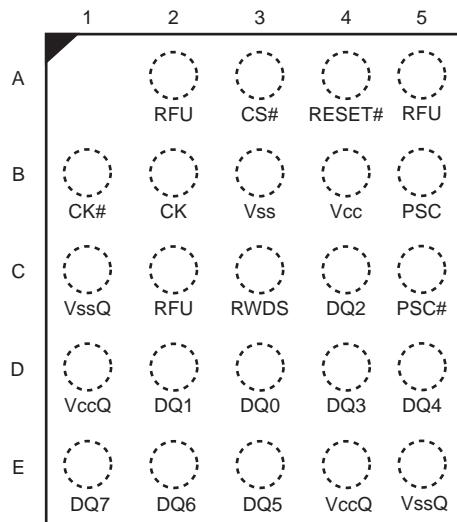

| FBGA 24 ボール 5×5 のアレイ フットプリント .....                        | 40        |

| 外形図 .....                                                 | 41        |

| <b>DDR 中央挿入読み出しひストローブ (DCARS) の機能</b> .....               | <b>42</b> |

| DCARS を持つ HyperRAM 製品の信号説明 .....                          | 42        |

| DCARS を持つ HyperRAM 製品 — FBGA 24 ボール、5×5 アレイ フットプリント ..... | 43        |

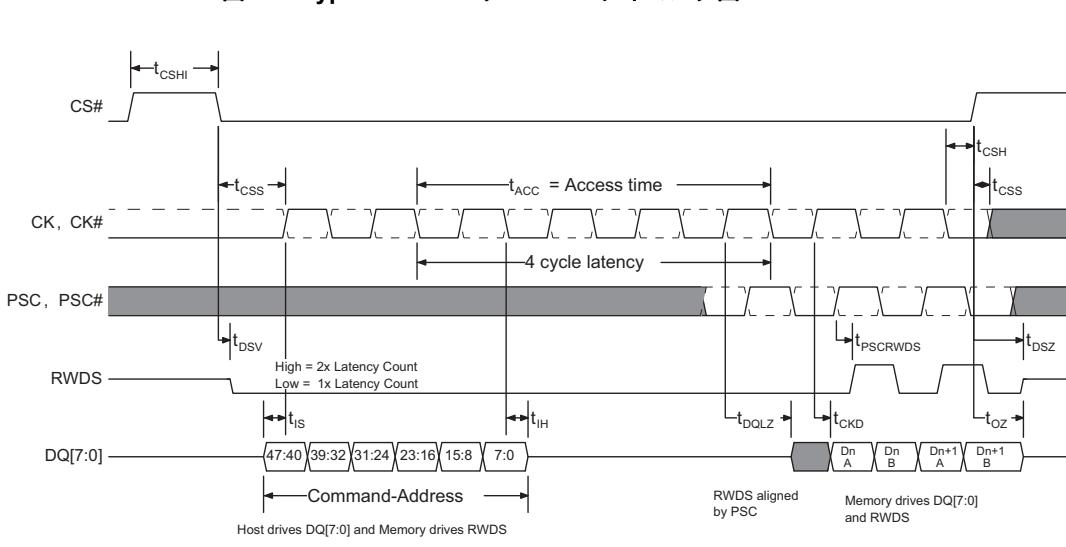

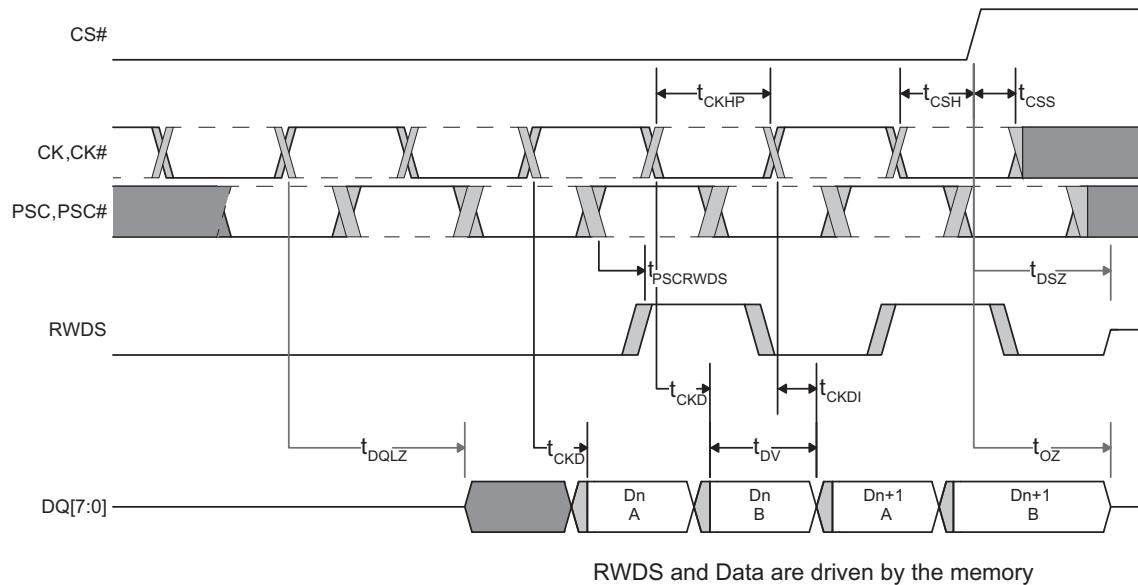

| DCARS を持つ HyperRAM メモリのタイミング .....                        | 43        |

| <b>注文情報</b> .....                                         | <b>45</b> |

| 注文製品番号 .....                                              | 45        |

| 有効な組合せ .....                                              | 46        |

| 有効な組み合わせ — 車載向けグレード／AEC-Q100 .....                        | 48        |

| <b>改訂履歴</b> .....                                         | <b>50</b> |

| <b>セールス、ソリューションおよび法律情報</b> .....                          | <b>51</b> |

| ワールドワイド販売と設計サポート .....                                    | 51        |

| 製品 .....                                                  | 51        |

| PSoC® ソリューション .....                                       | 51        |

| サイプレス開発者コミュニティ .....                                      | 51        |

| テクニカルサポート .....                                           | 51        |

## 1. 概要

サイプレス 64M ビット HyperRAM™ デバイスは HyperBus インターフェースを備えた高速 CMOS、セルフリフレッシュ ダイナミック RAM (DRAM) です。サイプレス 128M ビット HyperRAM™ デバイスは 64M ビット HyperRAM デバイスを 1 つのパッケージにしたデュアルダイスチック品です。

ランダム アクセス メモリ (RAM) アレイは周期的なりフレッシュが必要なダイナミック セルを使用します。デバイス内のリフレッシュ制御ロジックは、RAM が HyperBus インターフェース マスター (ホスト) によってアクティブに読み書きされていない時に RAM アレイ上のリフレッシュ動作を管理します。ホストがリフレッシュ動作を管理する必要がないため、ホストからは DRAM アレイは、リフレッシュなしにデータを保持するスタティック セルを使用しているように見えます。したがって、メモリは擬似スタティック RAM (PSRAM) とも見なされます。

読み出しあり書き込みトランザクション中に DRAM セルをリフレッシュできないため、内部ロジックによるリフレッシュ動作が必要となる場合、ホストは必要な内部ロジックによるリフレッシュをブロックするほど長い読み書きバースト転送を実行してはいけません。メモリのリフレッシュ動作が必要となる場合、ホストはトランザクションの期間を制限し、新しいトランザクションの始まりに追加の初期アクセス レイテンシを許可する必要があります。

HyperBus は少ない信号数のダブルデータ レート (DDR) インターフェースで、高速読み書きスループットを達成します。DDR プロトコルでは、クロック サイクルごとに 2 データ バイトが DQ 入出力信号上で転送されます。HyperBus の読み書きトランザクションは、内部 HyperRAM コア内の一連の 16 ビット幅で 1 クロック サイクルのデータ転送です。それぞれの転送は DQ 信号上の 2 つの対応する 8 ビット幅で 0.5 クロック サイクルのデータ転送からなります。すべての入出力は LV-CMOS に準拠します。

注文製品番号 (OPN) デバイス バージョンはコア ( $V_{CC}$ ) と IO バッファ ( $V_{CCQ}$ ) の電源電圧として 1.8V または 3.0V (定格) を使用できます。

コマンド、アドレスとデータ情報は 8 つの HyperBus DQ[7:0] 信号を介して転送されます。クロックは、DQ 信号でコマンド、アドレスまたはデータを受信する際に、HyperBus スレーブによる情報の取り込みに使用されます。コマンドまたはアドレス値はクロック遷移の中央揃えになっています。

各トランザクションは CS# とコマンド アドレス (CA) 信号のアサートから始まり、その後に 6 個の CA バイトを転送するためにクロック遷移が開始します。その後初期アクセス レイテンシと読み出し／書き込みデータ転送が続いて、CS# のデアサートで終了します。

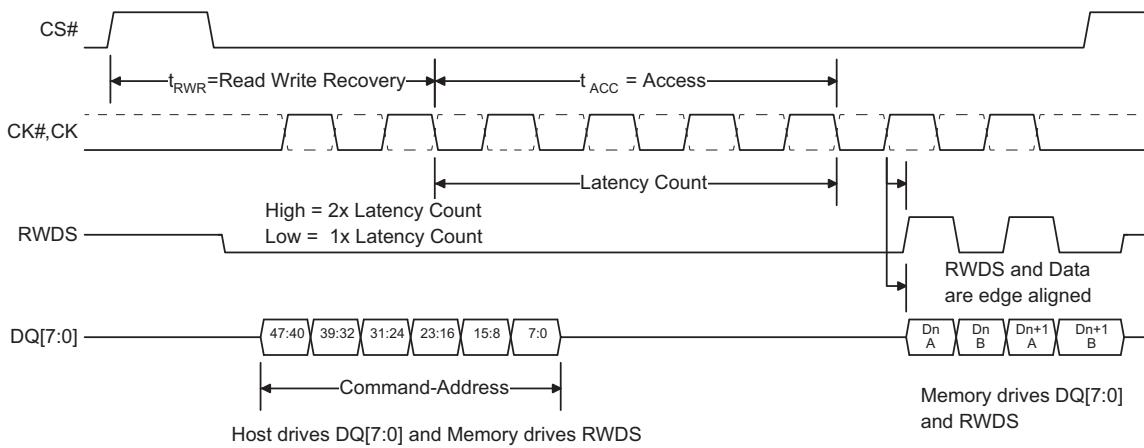

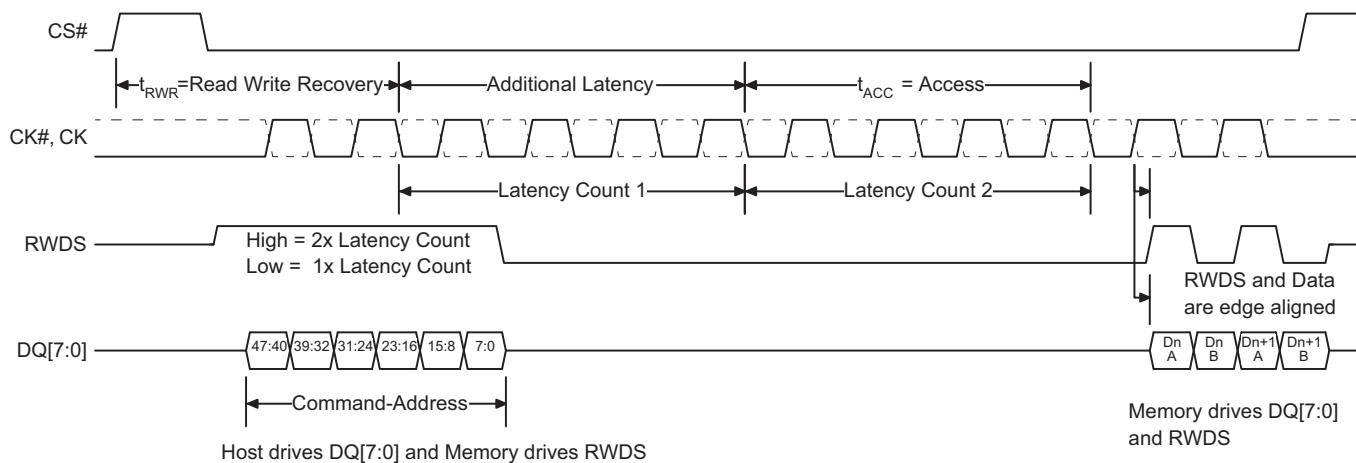

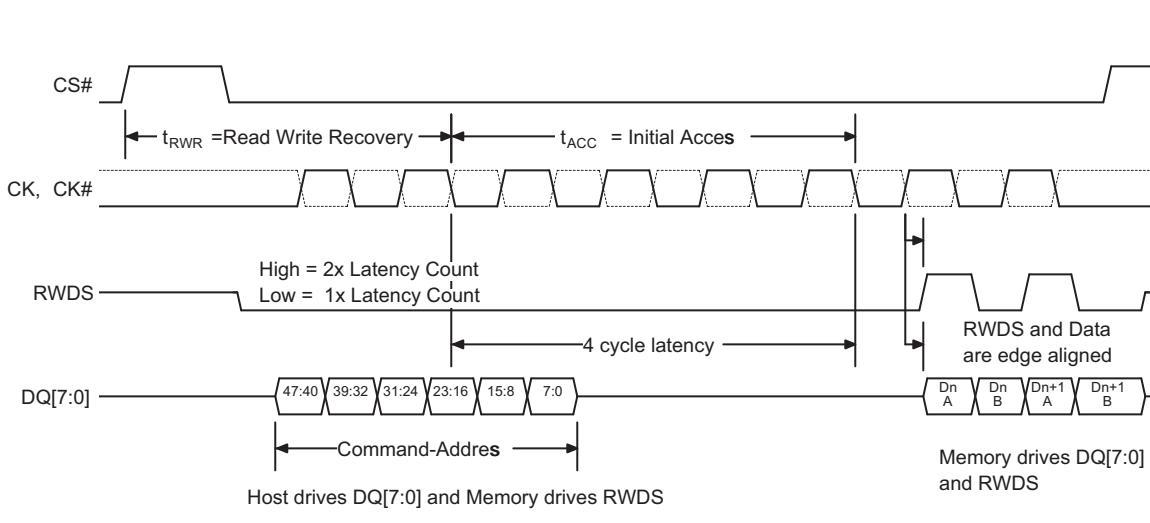

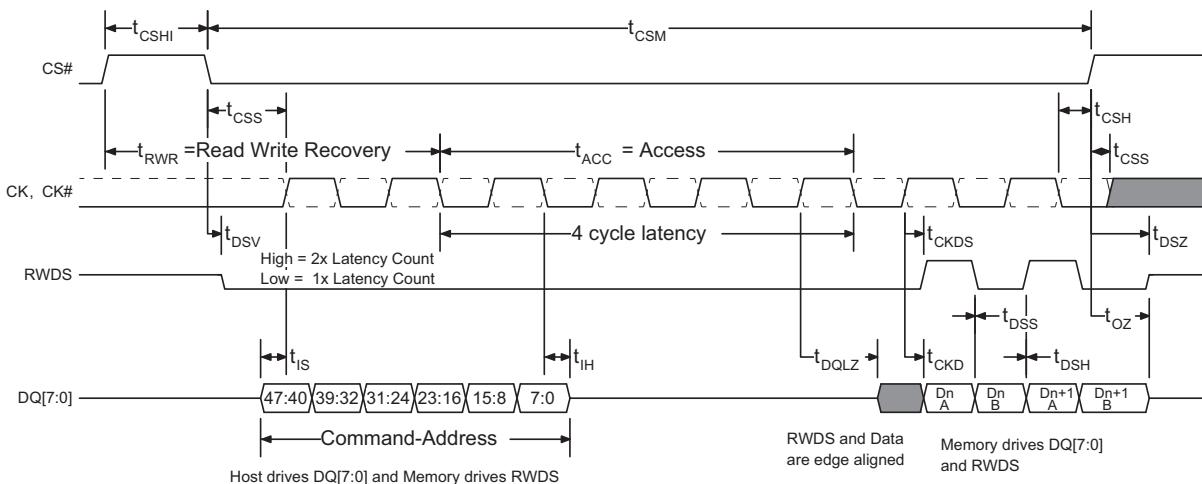

図 1. 読み出しトランザクション、シングル初期レイテンシ カウント

読み書きデータ ストローブ (RWDS) は以下のことを示す双方向信号です :

- 読み出しトランザクションで HyperRAM デバイスからマスター デバイスまでのデータ転送が開始する時点 (初期読み出し レイテンシ)

- 読み出しトランザクションでデータが HyperRAM デバイスからマスター デバイスまで転送されている時 (ソース同期読み出し データ ストローブとして)

- 書き込みトランザクションでマスター デバイスから HyperRAM デバイスまでのデータ転送が開始する時点 (初期書き込み レイテンシ)

- 書き込みデータ転送中のデータ マスク

読み書きトランザクションの CA 転送部分中、RWDS は HyperRAM デバイスからの出力として機能し、トランザクションに追加の初期アクセス レイテンシが必要となるかを示します。

読み出しデータ転送中、RWDS はデータ値が RWDS の遷移と同時に変化する読み出しデータ ストローブ信号です。

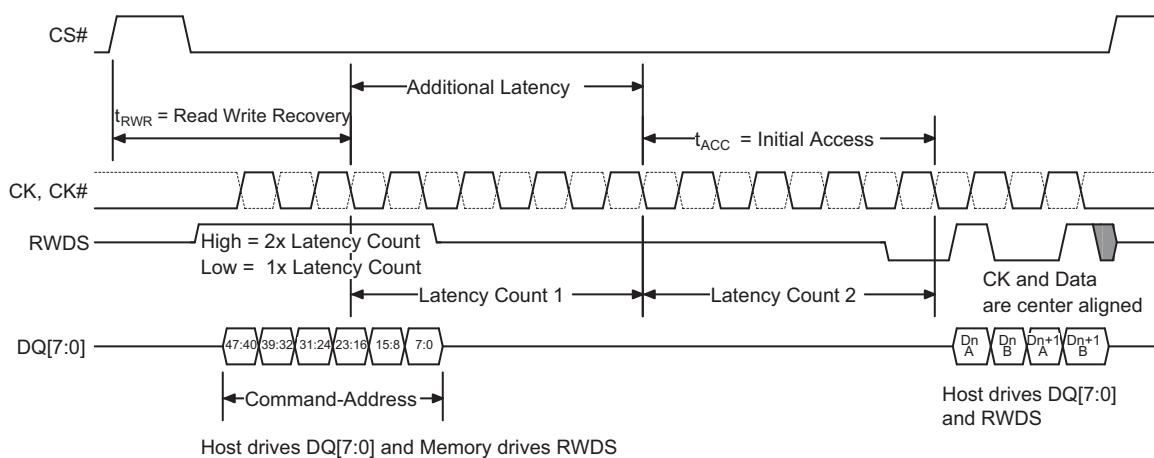

**図 2. 読み出しトランザクション、追加のレイテンシ カウント**

書き込みデータ転送中、RWDS は各データバイトの転送が RWDS の HIGH でマスクされる（無効でメモリ内のバイト位置の変更ができない）か、RWDS の LOW でマスクされない（有効でメモリに書き込まれる）かを示します。データ マスクはメモリ内の書き込みデータをバイトに揃えるか、または単一のバーストライトでワードに揃わない複数書き込みの結合のために、ホストによって使用されます。書き込みトランザクション中は、データはクロック遷移と中央揃えになります。

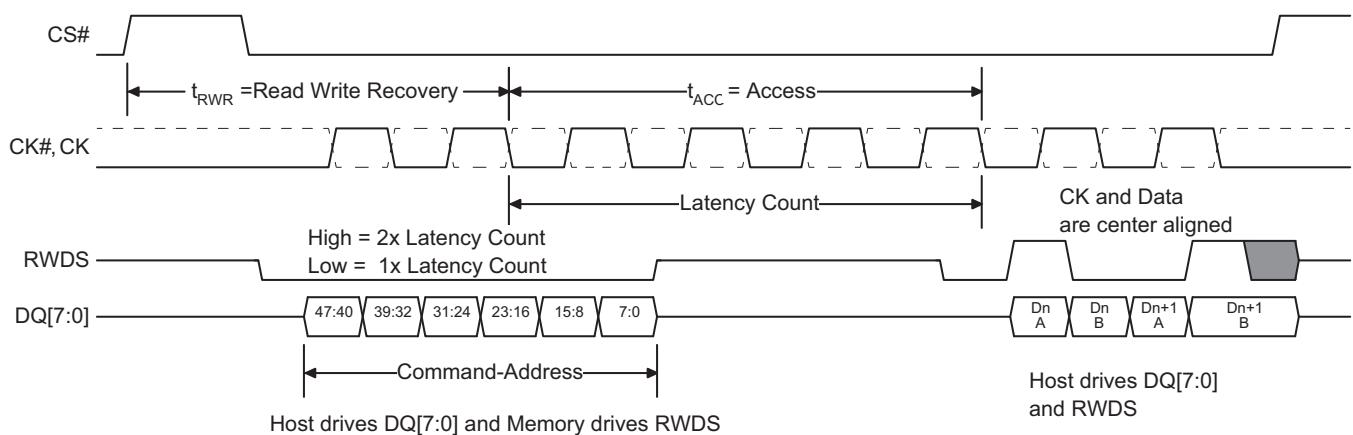

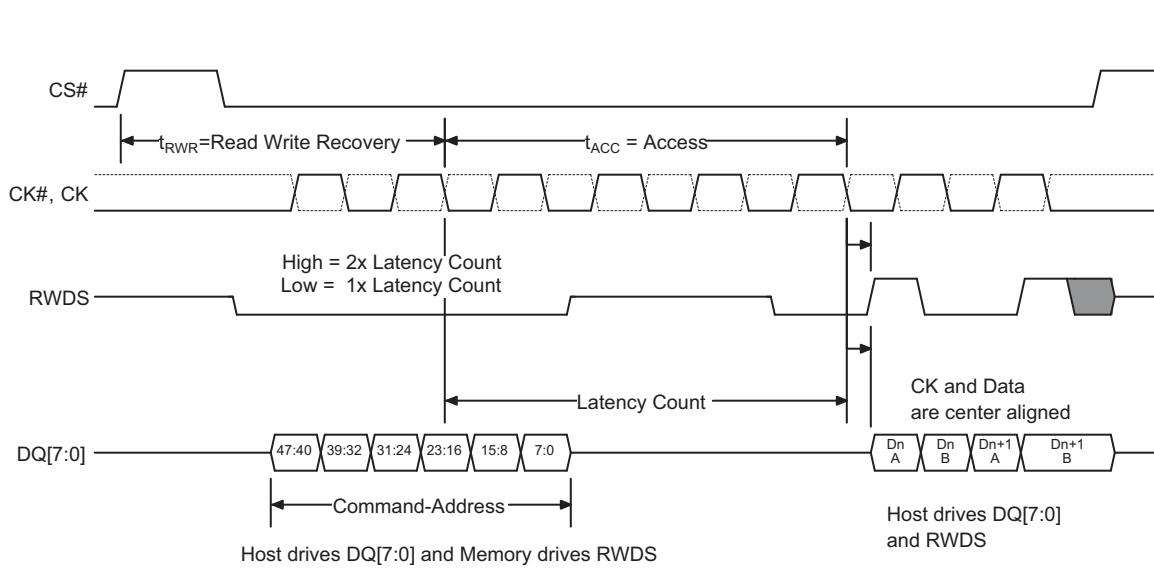

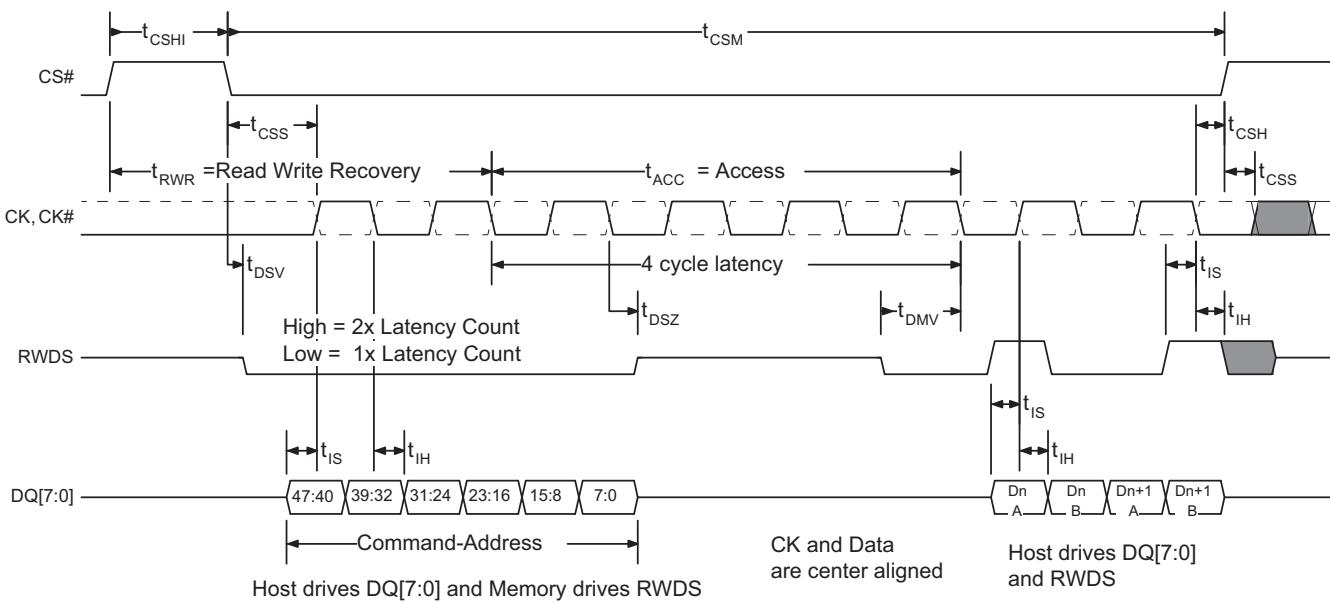

**図 3. 書き込みトランザクション、シングル初期レイテンシ カウント**

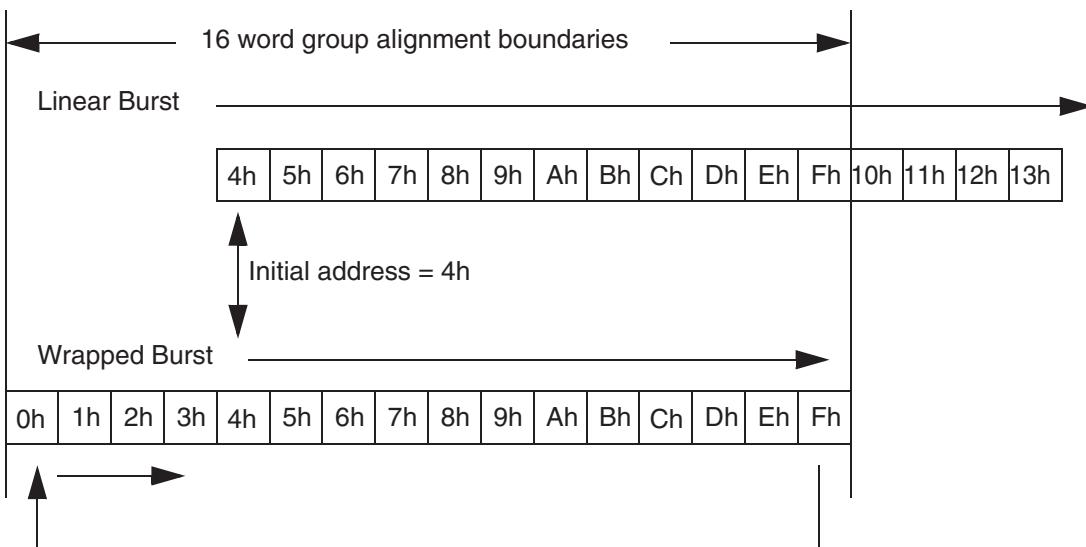

読み書きトランザクションはバースト指向で、クロック サイクルごとに次の連続的なワードを転送します。各々の読み書きトランザクションはラップ バーストカリニア バースト シーケンスで行えます。

**図 4. リニア バースト シーケンス対ラップ バースト シーケンス**

ラップ トランザクションでは、アクセスは選択した位置から開始し、設定したワード グループ揃えの境界の終わりまで継続してから、グループの開始位置までラップし、最初の開始位置に戻るまで続けます。ラップ バーストは一般的に、クリティカルワード優先のキャッシュ ライン フィルの読み出しトランザクションに使用されます。リニア トランザクションでは、アクセスは選択した位置から開始して、トランザクションが終了する (CS# が HIGH に戻る) まで順次に継続します。リニア トランザクションは一般的に、グラフィック画像などの大量の隣接データの転送に使用されます。各トランザクション コマンドがそのトランザクションのバースト シーケンスのタイプを選択するため、必要に応じてラップとリニア バースト トランザクションをダイナミックに混合できます。

## 2. 製品概要

64M ビットおよび 128M ビット HyperRAM デバイスは、1.8V または 3.0V のコアと I/O がある同期セルフリフレッシュ ダイナミック RAM (DRAM) です。HyperRAM デバイスはホストシステムに HyperBus スレーブ インターフェースを提供します。HyperBus は 8 ビット (1 バイト) 幅の DDR データバスを持ち、ワード幅 (16 ビット データ) のアドレス境界のみを使用します。読み出しトランザクションはクロック サイクルごとに 16 ビット (クロック エッジごとに 8 ビット) のデータを提供します。書き込みトランザクションはクロック サイクルごとに 16 ビット (クロック エッジごとに 8 ビット) のデータを受理します。

図 5. HyperRAM インターフェース

読み出しと書き込みトランザクションはターゲット行アドレスとバースト タイプを定義するのに 2 クロック サイクルを要し、その後初期アクセス レイテンシ  $t_{ACC}$  を要します。トランザクションのコマンドアドレス (CA) 部分の間 RWDS 信号を HIGH に駆動することで、メモリは必要なリフレッシュ時間 ( $t_{RFH}$ ) に対する追加のレイテンシが初期レイテンシに挿入されるかを示します。CA 期間中の 3 番目のクロック サイクルでターゲット行内のターゲット ワード アドレスが指定されます。読み出し (または書き込み) トランザクション中、初期のデータ値が出力 (入力) された後、後続のクロック サイクルで追加のデータはラップまたはリニアシーケンスに従って行から読み出されます (行に書き込まれます)。リニア バースト モードに設定した場合、デバイスは連続リニア バーストをサポートするために自動的にメモリ アレイから次のシーケンシャル行をフェッチします。読み出しあとは書き込みデータ転送が進行中に同時にアレイ内の次の行にアクセスすると、333Mbps の持続データ速度を実現できるリニア シーケンシャル バーストを実行できます (1 バイト (8 ビット データ バス) \* 2 (データ クロック エッジ) \* 166MHz = 333Mbps)。

### 3. HyperRAM 信号の説明

#### 3.1 入出力の要約

表 1 に HyperRAM 信号を示します。アクティブ LOW の信号名の末尾にはハッシュ記号 (#) が付いています。

表 1. 入出力の要約

| 記号               | 種類                    | 説明                                                                                                                                                                                                                        |

|------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CS#              | マスター出力、スレーブ入力         | チップ セレクト。バス トランザクションは HIGH から LOW への移行で開始。バス トランザクションは LOW から HIGH への移行で終了。マスター デバイスは各スレーブ用に個別の CS# を用意                                                                                                                   |

| CK, CK#          | マスター出力、スレーブ入力         | 差動クロック。コマンド、アドレスとデータ情報は CK と CK# 信号の交差に対してタイミングが定義される出力。差動クロックは 1.8V/I/O のデバイスで使用されるシングルエンド クロック。3.0V のデバイスでは CK# は使用されず、シングルエンド CK のみが使用される。<br>クロックがフリー ランニングである必要はない                                                   |

| DQ[7:0]          | 入力／出力                 | データの入力／出力。コマンド、アドレスおよびデータ情報は読み出しと書き込みトランザクション中にこれらの信号上に転送される                                                                                                                                                              |

| RWDS             | 入力／出力                 | 読み出し／書き込みデータ ストローブ。すべてのバス トランザクションのコマンド／アドレス部分の間は RWDS がスレーブ出力であり、追加の初期レイテンシが必要かどうかを示す。読み出しデータ転送中はスレーブ出力となり、データは RWDS とタイミングエッジが揃う。書き込みトランザクションのデータ転送中はスレーブ入力となり、データ マスクとして機能。<br>(HIGH = 追加のレイテンシ有り ; LOW = 追加のレイテンシ無し ) |

| RESET#           | マスター出力、スレーブ入力、内部プルアップ | ハードウェアリセット。LOW の時、スレーブ デバイスは自己初期化してスタンバイ状態に戻る。RESET# が LOW の時、RWDS と DQ[7:0] は High-Z 状態に移る。スレーブ RESET# 入力は弱プルアップを含み、RESET# が未接続にされると、HIGH 状態にプルアップされる                                                                    |

| V <sub>CC</sub>  | 電源                    | 電源                                                                                                                                                                                                                        |

| V <sub>CCQ</sub> | 電源                    | 入力／出力電源                                                                                                                                                                                                                   |

| V <sub>SS</sub>  | 電源                    | グランド                                                                                                                                                                                                                      |

| V <sub>SSQ</sub> | 電源                    | 入力／出力グランド                                                                                                                                                                                                                 |

| RFU              | 未接続                   | 予約。内部での接続または非接続に関わらず、この信号 / 端子は未接続のままにしてください。また将来的な互換性のために PCB ルーティングチャネルで使用しないでください。この信号 / 端子は将来的に使用される可能性があります。                                                                                                         |

### 3.2 コマンド／アドレス ビットの割り当て

すべての HyperRAM バス トランザクションは読み出しと書き込みの 2 種類に分けられます。バス トランザクションはクロックがアイドル状態 (CK=LOW で CK#=HIGH) の状態の CS# の LOW への遷移でスタートします。最初の 3 クロック サイクルでは、3 ワードのコマンド／アドレス (CA0, CA1, CA2) 情報が転送されて、トランザクションの特性を定義します。コマンド／アドレス ワードは最初の 6 つのクロック エッジを使用して DDR タイミングで示されます。以下の特性はコマンド／アドレス情報で定義されます：

- 読み出しましたは書き込みトランザクション

- アドレス空間：メモリ アレイ空間またはレジスタ空間

- レジスタ空間は、デバイスの特性を識別し、HyperBus インターフェースでの読み書き転送のスレーブ固有の動作を決定するデバイス識別 (ID) レジスタとコンフィギュレーション レジスタ (CR) にアクセスするために使用されます。

- トランザクションは、リニア バースト シーケンスまたはラップ バースト シーケンスのどちらを使用するか。

- 対象の行 (およびハーフページ) アドレス (上位アドレス)

- 対象の列 (ハーフページ内のワード) アドレス (下位アドレス)

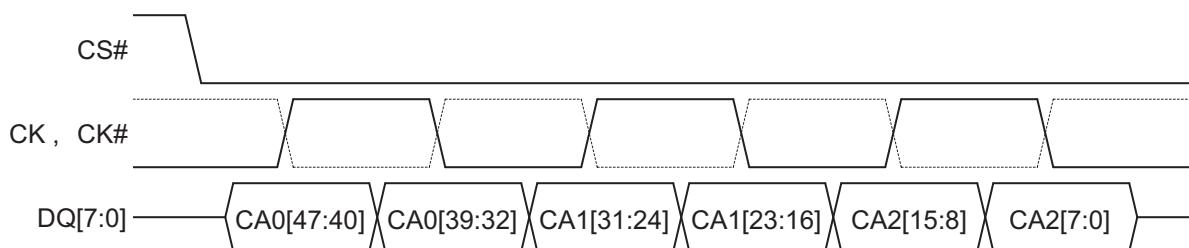

図 6. コマンドアドレスのシーケンス <sup>[1, 2, 3]</sup>

表 2. DQ 信号に対するコマンドアドレス ビットの割り当て

| 信号    | CA0[47:40] | CA0[39:32] | CA1[31:24] | CA1[23:16] | CA2[15:8] | CA2[7:0] |

|-------|------------|------------|------------|------------|-----------|----------|

| DQ[7] | CA[47]     | CA[39]     | CA[31]     | CA[23]     | CA[15]    | CA[7]    |

| DQ[6] | CA[46]     | CA[38]     | CA[30]     | CA[22]     | CA[14]    | CA[6]    |

| DQ[5] | CA[45]     | CA[37]     | CA[29]     | CA[21]     | CA[13]    | CA[5]    |

| DQ[4] | CA[44]     | CA[36]     | CA[28]     | CA[20]     | CA[12]    | CA[4]    |

| DQ[3] | CA[43]     | CA[35]     | CA[27]     | CA[19]     | CA[11]    | CA[3]    |

| DQ[2] | CA[42]     | CA[34]     | CA[26]     | CA[18]     | CA[10]    | CA[2]    |

| DQ[1] | CA[41]     | CA[33]     | CA[25]     | CA[17]     | CA[9]     | CA[1]    |

| DQ[0] | CA[40]     | CA[32]     | CA[24]     | CA[16]     | CA[8]     | CA[0]    |

注：

1. 図に HyperBus 上のすべてのトランザクションの初期の 3 クロック サイクルを示します。

2. 差動クロックの CK# は破線の波形で示されます。

3. コマンドアドレス情報は読み出しと書き込みトランザクションの両方の間にクロックと「中央挿え」となります。

**表3. コマンド／アドレス ビットの割り当て** [4, 5, 6, 7, 8]

| CA ビット # | ビット名        | ビット機能                                                                                                                                                                    |

|----------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 47       | R/W#        | トランザクションを読み出しましたは書き込みとして識別。<br>R/W#=1 は読み出しトランザクションを、<br>R/W#=0 は書き込みトランザクションを示す                                                                                         |

| 46       | アドレス空間 (AS) | 読み書きトランザクションがメモリ空間またはレジスタ空間のどちらにアクセスするかを示す。<br>AS=0 はメモリ空間を示す<br>AS=1 はレジスタ空間を示す<br>レジスタ空間はデバイス ID とコンフィギュレーション レジスタにアクセスするために使用される                                      |

| 45       | バースト タイプ    | バーストがリニアかラップであるかを示す。<br>バースト タイプ =0 はラップ バーストを、<br>バースト タイプ =1 はリニア バーストを示す                                                                                              |

| 44 ~ 16  | 行と上位列アドレス   | 対象アドレスの行と上位列要素：システム ワード アドレス ビット A31 ~ A3。<br>ホスト コントローラー マスター インターフェースは、特定のデバイス容量に使用されない上位行のアドレス ビットを 0 にセットする必要がある。行のサイズ、およびそれによる行と列のアドレス間のアドレス ビット境界はスレーブ デバイスによって異なる |

| 15 ~ 3   | 予約済み        | 将来の列アドレス拡張用に予約済み。<br>予約済み ビットは、現時点の HyperBus デバイスではドントケア ビットであるが、将来の互換性維持のためにホスト コントローラー マスター インターフェースによって 0 にセットする必要がある                                                 |

| 2 ~ 0    | 下位列アドレス     | 対象アドレスの下位列要素：ハーフ ページ内の開始ワードを選択するシステム ワード アドレス ビット A2 ~ 0                                                                                                                 |

**注：**

- 行は内部メモリアレイ構造に関連するワードのグループであり、行の境界を越える時に追加のレイテンシが RWDS によって挿入されることがあります。これはデバイスに依存する動作であり、詳細については各 HyperBus デバイスのデータシートをご参照ください。また、行数は HyperRAM メモリ用の分散リフレッシュ間隔の計算に使用できます。

- ページは 16 ワード (32 バイト) 長の、デバイスの内部読み出しましたは書き込みアクセスに揃ったユニットであり、ページの境界を越える時に追加のレイテンシが RWDS によって挿入されることがあります。これはデバイスに依存する動作であり、詳細については各 HyperBus デバイスのデータシートをご参照ください。

- 列アドレスはバーストトランザクションが開始する行内のワード位置を選択します。列アドレスは上位部分と下位部分に分けられています。上位部分は 8 ワード (16 バイト) ハーフページを選択し、下位部分は読み出しましたは書き込みトランザクション バーストが開始するハーフページ内のワードを選択します。

- 行と上位列 (ハーフ ページ) アドレス ビットがスレーブ インターフェースによって取り込まれると、初期読み出しアクセス時間が開始します。連続リニア読み出しバーストはメモリ デバイスが内部で 16 バイトのハーフページにアクセスをインターリープすることで有効になります。

- HyperBus プロトコルアドレス空間の境界について以下を仮定します：

29 の行と上位列アドレス ビット

3 の下位列アドレス ビット

各アドレスが 1 ワード幅 (16 ビット = 2 バイト) のデータ値を選択。

29+3=32 アドレス ビット = 4G アドレスをサポートする 8G バイト (64G ビット) の最大アドレス空間

列アドレスの将来の拡張で 29 の行と上位列 +16 の下位列アドレス ビット = 35 テラワード = 70 テラバイトのアドレス空間が可能です。

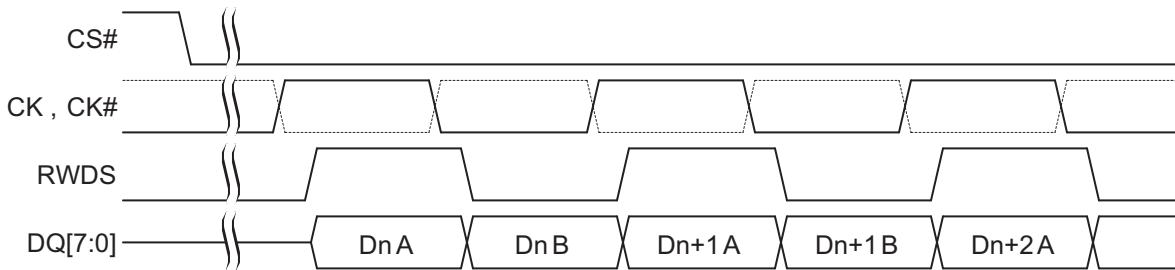

**図 7. 読み出しトランザクション中のデータ配置** [9, 10, 11, 12, 13]

**注：**

- 図に HyperBus 上の読み出しトランザクションの一部を示します。差動クロックの CK# は破線の波形で示されます。

- データは、読み出しトランザクションの間に読み出しデータストローブとして機能する RWDS と「エッジ揃え」となります。

- データは常にフルワード インクリメントで転送されます (ワード単位の転送)。

- ワード アドレスは各クロック サイクルでインクリメントします。各ワードではバイト A が RWDS の立ち上がりエッジと立ち下がりエッジの間にあり、その後に RWDS の立ち下がりエッジと立ち上がりエッジの間にあるバイト B が続けます。

- 各バイト内のデータ ビットは常に上位から下位の順で配置され、ビット 7 が DQ7 にあり、ビット 0 が DQ0 にあります。

**表 4. 読み出しましたは書き込みトランザクション中のデータ ビットの配置**

| アドレス空間 | バイト順      | バイト位置 | ワードデータビット | DQ | ビット順                                                                                                                                                                                                            |

|--------|-----------|-------|-----------|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| メモリ    | ビッグエンディアン | A     | 15        | 7  | データがメモリ空間でアクセスされている時:<br>読み出されるかまたは書き込まれる各ワードの1番目のバイトが「A」バイトで、<br>2番目のバイトが「B」バイト。<br>AとBバイト内のワードのビットはデータが書き込まれる方法によって異なる。<br>ワードの下位アドレスビット7~0がAバイト位置に、ビット15~8がBバイト位置に書き込まれるかまたはその逆に書き込まれる場合、これらのビットが同じ順で読み出される。 |

|        |           |       | 14        | 6  |                                                                                                                                                                                                                 |

|        |           |       | 13        | 5  |                                                                                                                                                                                                                 |

|        |           |       | 12        | 4  |                                                                                                                                                                                                                 |

|        |           |       | 11        | 3  |                                                                                                                                                                                                                 |

|        |           |       | 10        | 2  |                                                                                                                                                                                                                 |

|        |           |       | 9         | 1  |                                                                                                                                                                                                                 |

|        |           |       | 8         | 0  |                                                                                                                                                                                                                 |

|        | リトルエンディアン | B     | 7         | 7  | そのため、メモリ空間はリトルエンディアンまたはビッグエンディアンの順で格納され、読み出される。                                                                                                                                                                 |

|        |           |       | 6         | 6  |                                                                                                                                                                                                                 |

|        |           |       | 5         | 5  |                                                                                                                                                                                                                 |

|        |           |       | 4         | 4  |                                                                                                                                                                                                                 |

|        |           |       | 3         | 3  |                                                                                                                                                                                                                 |

|        |           |       | 2         | 2  |                                                                                                                                                                                                                 |

|        |           |       | 1         | 1  |                                                                                                                                                                                                                 |

|        |           |       | 0         | 0  |                                                                                                                                                                                                                 |

|        | ビッグエンディアン | A     | 7         | 7  | データがメモリ空間でアクセスされている時:<br>読み出されるかまたは書き込まれる各ワードの1番目のバイトが「A」バイトで、<br>2番目のバイトが「B」バイト。<br>AとBバイト内のワードのビットはデータが書き込まれる方法によって異なる。<br>ワードの下位アドレスビット7~0がAバイト位置に、ビット15~8がBバイト位置に書き込まれるかまたはその逆に書き込まれる場合、これらのビットが同じ順で読み出される。 |

|        |           |       | 6         | 6  |                                                                                                                                                                                                                 |

|        |           |       | 5         | 5  |                                                                                                                                                                                                                 |

|        |           |       | 4         | 4  |                                                                                                                                                                                                                 |

|        |           |       | 3         | 3  |                                                                                                                                                                                                                 |

|        |           |       | 2         | 2  |                                                                                                                                                                                                                 |

|        |           |       | 1         | 1  |                                                                                                                                                                                                                 |

|        |           |       | 0         | 0  |                                                                                                                                                                                                                 |

|        | リトルエンディアン | B     | 15        | 7  |                                                                                                                                                                                                                 |

|        |           |       | 14        | 6  |                                                                                                                                                                                                                 |

|        |           |       | 13        | 5  |                                                                                                                                                                                                                 |

|        |           |       | 12        | 4  |                                                                                                                                                                                                                 |

|        |           |       | 11        | 3  |                                                                                                                                                                                                                 |

|        |           |       | 10        | 2  |                                                                                                                                                                                                                 |

|        |           |       | 9         | 1  |                                                                                                                                                                                                                 |

|        |           |       | 8         | 0  |                                                                                                                                                                                                                 |

**表 4. 読み出しままたは書き込みトランザクション中のデータビットの配置(続き)**

| アドレス空間 | バイト順      | バイト位置 | ワードデータビット | DQ | ビット順                                                                                                                                                                                     |

|--------|-----------|-------|-----------|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| レジスタ   | ビッグエンディアン | A     | 15        | 7  | データがレジスタ空間でアクセスされている時:<br>HyperBus上の読み出しままたは書き込みトランザクションの間は各クロックサイクルで2バイトが転送される。上位バイトA(ワード[15:8])はRWDSの立ち上がりエッジと立ち下がりエッジの間で転送される(エッジ揃え)。下位バイトB(ワード[7:0])はRWDSの立ち下がりエッジと立ち上がりエッジの間で転送される。 |

|        |           |       | 14        | 6  |                                                                                                                                                                                          |

|        |           |       | 13        | 5  |                                                                                                                                                                                          |

|        |           |       | 12        | 4  |                                                                                                                                                                                          |

|        |           |       | 11        | 3  |                                                                                                                                                                                          |

|        |           |       | 10        | 2  |                                                                                                                                                                                          |

|        |           |       | 9         | 1  |                                                                                                                                                                                          |

|        |           |       | 8         | 0  |                                                                                                                                                                                          |

|        | ビッグエンディアン | B     | 7         | 7  | 書き込みの間は、上位バイトA(ワード[15:8])がCK立ち上がりエッジで転送され、下位バイトB(ワード[7:0])がCK立ち下がりエッジで転送される。<br>したがって、レジスタがデバイス依存の固定したビット位置と意味の定義を有するため、レジスタ空間は常にビッグエンディアンの順で読み書きされる                                     |

|        |           |       | 6         | 6  |                                                                                                                                                                                          |

|        |           |       | 5         | 5  |                                                                                                                                                                                          |

|        |           |       | 4         | 4  |                                                                                                                                                                                          |

|        |           |       | 3         | 3  |                                                                                                                                                                                          |

|        |           |       | 2         | 2  |                                                                                                                                                                                          |

|        |           |       | 1         | 1  |                                                                                                                                                                                          |

|        |           |       | 0         | 0  |                                                                                                                                                                                          |

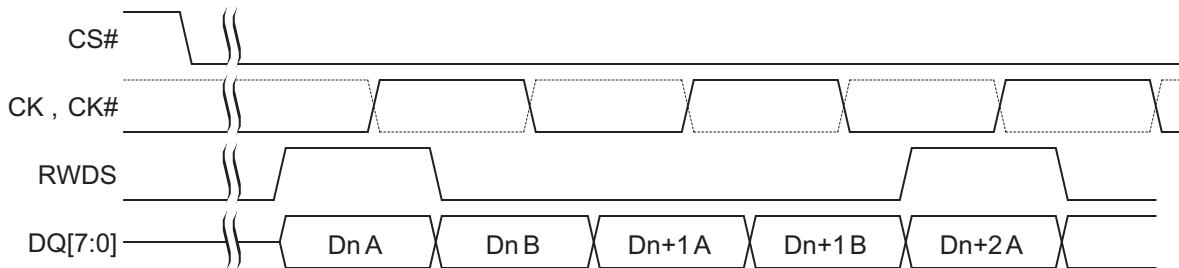

**図 8. 書き込みトランザクション中のデータ配置** [14, 15, 16, 17]

**注:**

14. 図にHyperBus上の書き込みトランザクションの一部を示します。

15. 書き込みトランザクション中は、データはクロックと「中央揃え」となります。

16. 初期レイテンシありの書き込みデータ転送の間、RWDSはデータマスクとして機能します。アラインされていない3バイトのデータの書き込みの最初と最後のバイトのマスクを示します。

17. 初期レイテンシ無しの書き込みデータ転送の間にRWDSはマスターによって駆動されません。この場合、データのフルワードが常に書き込まれます。この場合、RWDSがスレーブによってLOWに駆動されるか、またはHigh-Z状態のままにされています。

### 3.3 読み出しトランザクション

HyperBus マスターはクロックがアイドルの間に CS# を LOW に駆動することでトランザクションを開始します。その後、コマンドアドレス CA ワードが転送される間にクロックがトルグし始めます。

CA0 では、CA[47] = 1 は読み出しトランザクションが実行されることを示します。CA[46] = 0 はメモリ空間が、CA[46] = 1 はレジスタ空間が読み出されていることを示します。CA[45] はバースト タイプ（ラップまたはリニア）を示します。行と上位列のアドレスが CA0 と CA1 (CA[47:16]) に提供され次第、読み出しトランザクションは内部のアレイアクセスを開始できます。CA2 (CA[15:0]) は選択した行内の対象ワード アドレスを指定します。ただし、いくつかの HyperBus デバイスでは前のトランザクションの終了と新しいアクセスの開始の間に一定の最小時間を必要とします。この時間は読み出し - 書き込み - 復帰時間 ( $t_{RWR}$ ) と呼ばれています。 $t_{RWR}$  が経過した後に CA1 転送が完了する時点だけにマスター インターフェースは CS# を LOW に駆動し始める必要があります。

HyperBus マスターはその後、コンフィギュレーション レジスタ 0 で設定された待ち時間数によって定義されたサイクル数、クロックを続けます。特定のクロック周波数のために必要な初期待ち時間カウントは RWDS に基づきます。CA サイクル中に RWDS が LOW の場合、1 つのレイテンシが挿入されます。CA サイクル中に RWDS が HIGH の場合、追加のレイテンシ カウントが挿入されます。これらのレイテンシ クロック サイクルが完了すると、メモリは読み書きデータストローブ (RWDS) の遷移を開始すると同時に対象データの出力を開始します。

新しいデータは RWDS の遷移ごとにこのエッジと揃う出力となります。CS# が LOW の間にホストがクロックを遷移し続ける限り、データは引き続き出力されます。なお、HyperRAM デバイスは、メモリアレイ境界を越えるとき、ワード間のレイテンシを挿入するため、ワードの配信間に、RWDS LOW で RWDS 遷移を停止することがあります。

ラップ バーストはバースト長の範囲内でラップし続け、リニア バーストは行の境界を越えて順次にデータを出力します。リニア バースト読み出しがアレイ内の最終アドレスに達した後、最終アドレス以降でバーストを継続すると未定義のデータを出力します。クロックがアイドルの間に CS# を HIGH にすることで読み出し転送をいつでも終了できます。

クロックがフリー ランニングである必要はありません。CS# が HIGH の間にクロックはアイドル状態のままになります。

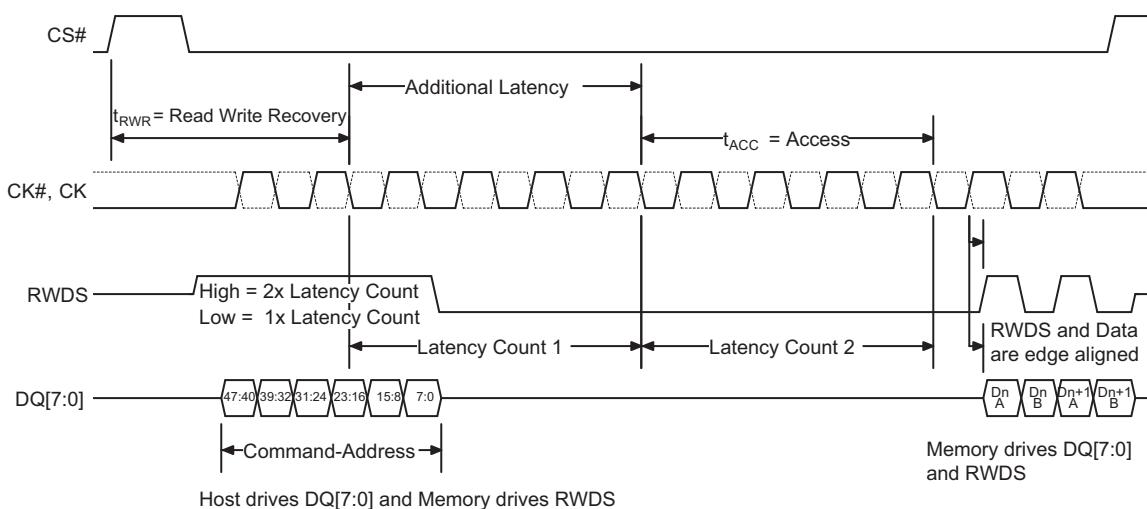

図 9. 追加の初期レイテンシ有りの読み出しトランザクション [18, 19, 20, 21, 22, 23, 24, 25]

#### 注:

18. トランザクションは CK=LOW と CK#=HIGH の間の CS# の立ち下がりで開始します。

19. CS# は新しいトランザクションが開始する前に HIGH に復帰しなければなりません。

20. CK# は CK 信号の相補信号です。3.0 V デバイスはシングルエンド クロック (CK 信号のみ) を使用します。CK# は差動クロックを提供するために 1.8V のデバイスで CK とともに使用されます。差動クロックの CK# は破線の波形で示されます。

21. CA[23:16] が取り込まれると読み出しアクセス アレイは開始します。

22. 読み出しレイテンシはコンフィギュレーション レジスタ内の初期レイテンシ値で定義されます。

23. この読み出しトランザクションの例では初期レイテンシ カウントが 4 クロック サイクルに設定されています。

24. この読み出しトランザクションでは、CA 転送中に RWDS が HIGH になることは対象のデータの出力をさらに 4 クロック サイクル遅延させます。

25. メモリ デバイスは読み出しトランザクション中に RWDS を駆動します。

**図 10. 追加の初期レイテンシ無しの読み出しトランザクション** <sup>[26]</sup>

### 3.4 初期レイテンシ有りの書き込みトランザクション（メモリ コア書き込み）

HyperBus マスターはクロックがアイドルの間に CS# を LOW に駆動することでトランザクションを開始します。その後、コマンドアドレス CA ワードが転送される間にクロックがトルグし始めます。

CA0 では、CA[47] = 0 は書き込みトランザクションが実行されることを示します。CA[46] = 0 はメモリ空間が書き込み中であることを示します。CA[45] はバーストタイプ（ラップまたはリニア）を示します。行と上位列のアドレスが CA0 と CA1 (CA[47:16]) に提供され次第、書き込みトランザクションは内部のアレイアクセスを開始できます。CA2 (CA[15:0]) は選択した行内の対象ワードアドレスを識別します。ただし、いくつかの HyperBus デバイスでは前のトランザクションの終了と新しいアクセスの開始の間に一定の最小時間を必要とします。この時間は読み出し - 書き込み - 復帰時間 ( $t_{RWR}$ ) と呼ばれています。 $t_{RWR}$  が経過した後に CA1 転送が完了する時点だけにマスターインターフェースは CS# を LOW に駆動し始めます。

HyperBus マスターはその後、コンフィギュレーションレジスタ 0 に設定する待ち時間数によって定義されたサイクル数のために、クロックを続けます。特定のクロック周波数のために必要な初期待ち時間カウントは RWDS に基づきます。CA サイクル中に RWDS が LOW の場合、1 つのレイテンシが挿入されます。このサイクル中に RWDS が HIGH の場合、追加のレイテンシカウントが挿入されます。

このレイテンシ クロック サイクルが経過した後、HyperBus マスターは対象のデータを出力し始めます。書き込みデータはクロック エッジと中央揃えとなります。メモリは各ワードの最初のバイトデータを CK の立ち上がりエッジで取り込んで、第 2 バイトを CK の立ち下がりエッジで取り込みます。

CA クロック サイクル中に RWDS はメモリによって駆動されます。

書き込みデータ転送中に、RWDS はホスト マスターインターフェースによってデータマスクとして駆動されます。データの書き込み中で RWDS が HIGH の時、バイトがマスクされ、アレイは変更されません。データの書き込み中で RWDS が LOW の時、データがアレイに入れられます。書き込みデータ転送中にマスターが RWDS を駆動しているため、マスター デバイスも HyperRAM デバイスも書き込みトランザクションのデータ転送部分内のレイテンシの必要性を示せません。許容される書き込みデータバースト長の設定は、コンフィギュレーションレジスタ 0 に示されています。

CS# が LOW の間に HyperBus マスターがクロックを遷移し続ける限り、データは引き続き転送されます。レガシーフォーマットのラップ バーストはバースト長以内でラップし続けます。ハイブリッド ラップは 1 回ラップしてから、次のラップ境界でスタートするリニア バーストに切り替わります。リニア バーストはページ境界を越える連続的なデータを受け入れます。クロックがアイドルの間に CS# を HIGH にすることで書き込み転送をいつでも終了できます。

リニア バースト書き込みがメモリアレイ空間の最後のアドレスに到達したとき、バーストの継続はアドレス範囲の先頭に書き込まれます。

クロックがフリー ランニングである必要はありません。CS# が HIGH の間にクロックはアイドル状態のままになることがあります。

#### 注：

26. RWDS は CA サイクル中に LOW です。追加のレイテンシがスレーブによって要求される時点で読み出しトランザクションが開始しないため、この読み出しトランザクションでは読み出しデータのアクセスに 1 つの初期レイテンシ カウントがあります。

図 11. 追加の初期レイテンシ有りの書き込みトランザクション [27, 28, 29, 30, 31, 32, 33]

図 12. 追加の初期レイテンシ無しの書き込みトランザクション [27, 30, 32, 33, 34]

**注:**

27. トランザクションは CK が LOW、CK# が HIGH 状態で開始する必要があります。

28. CS# は新しいトランザクションが開始する前に HIGH に復帰しなければなりません。

29. コマンドアドレスの間に、RWDS はメモリで駆動され、追加のレイテンシサイクルが必要かどうかを示します。

30. この例では、RWDS は追加のレイテンシサイクルの必要を示しています。

31. コマンドアドレスサイクルの終了時点で、メモリは、ホスト HyperBus マスターが RWDS を駆動しはじめられるように、RWDS の駆動を停止します。マスターは初期レイテンシが終了する前、データマスク事前期間をスレーブに提供するために、RWDS を有効な LOW 状態に駆動する必要があります。

32. データの転送中、RWDS はホストで駆動され、データのどのバイトがマスクされるべきかまたはアレイにロードされるべきかを示します。

33. この図は、RWDS がバイト B0 と A1 に非整列ワード書き込みをするためにバイト A0 と B1 をマスクしている状況を示しています。

34. この例では、RWDS は追加のレイテンシサイクルが必要ではないと示しています。

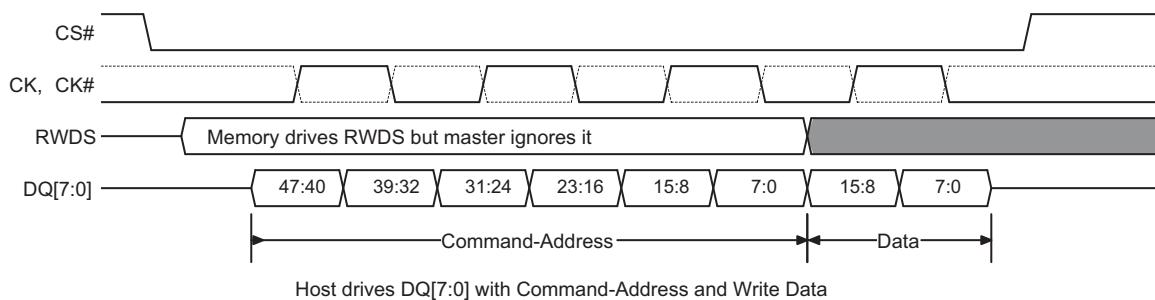

### 3.5 初期レイテンシ無しの書き込みトランザクション（レジスタ書き込み）

書き込みトランザクションは、トランザクション属性を示すコマンド／アドレス情報を提供する最初の 3 クロック サイクルから開始します。CA0 は書き込みトランザクションが次に実行されることを示す一方、アドレス空間およびバースト種類（ラップカリニア）も示します。

初期レイテンシ無しでの書き込みは、レジスタ空間を書き込むために使用されます。レイテンシ無しで HyperRAM デバイスの書き込みトランザクションは、CA サイクルが書き込みデータ転送によって続くことを意味します。初期レイテンシの無し書き込み処理に RWDS 用のターン アラウンド期間はありません。HyperRAM デバイスはコマンドアドレス期間中に常に RWDS を駆動して、初期レイテンシのあるトランザクションに延長レイテンシが必要とされるかを示します。しかし、HyperRAM デバイスはトランザクションが読み出しであるか、またはレジスタ空間への書き込みかどうかを知る前に、HyperRAM デバイスは最初の CA バイトの受信前に RWDS は駆動されます。レイテンシ無しの書き込みの場合、CA 期間中の RWDS の状態は初期のゼロレイテンシに影響しません。この場合にコマンドアドレス期間の直後にマスター書き込みデータが続くため、書き込みデータ転送中に HyperRAM デバイスは RWDS を LOW に駆動し続けるか、または RWDS を High-Z 状態にすることがあります。レイテンシ無しの書き込み期間中に、マスターは RWDS を駆動してはいけません。レイテンシ無しの書き込みには RWDS をデータ マスク機能として使用しません。書き込みデータのすべてのバイトが書き込まれます（フルワード書き込み）。

各ワードでの最初のデータ バイトは CK の立ち上がりエッジに、第 2 のデータ バイトは CK の立ち下がりエッジに現れます。書き込みデータはクロック入力と中央揃えです。クロックがアイドルの間に CS# を HIGH にすることで書き込み転送をいつでも終了できます。クロックがフリー ランニングである必要はありません。

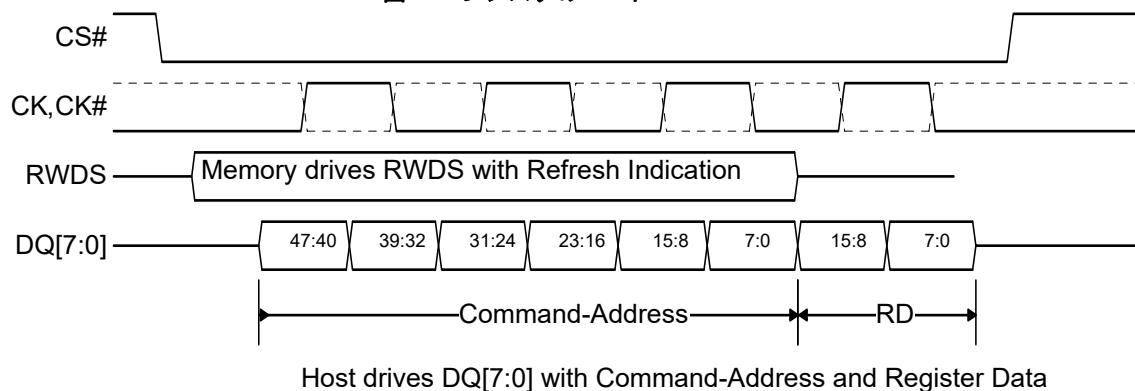

図 13. 初期レイテンシ無しの書き込み動作

## 4. メモリ空間

CA[46] = 0 の時、読み書きトランザクションは DRAM メモリ アレイにアクセスします。

表 5. メモリ空間アドレス マップ

| 単位タイプ              | カウント         | システム ワード アドレス ビット | CA ビット  | 備考                                                 |

|--------------------|--------------|-------------------|---------|----------------------------------------------------|

| 128 M ビット デバイスでのダイ | 2            | A22               | 35      | CA 35 (A22) = 0, ボトム ダイ<br>CA 35 (A22) = 1, トップ ダイ |

| 64M ビット デバイス の行    | 8192 (行)     | A21 ~ A9          | 34 ~ 22 |                                                    |

| 行                  | 1 (行)        | A8 ~ A3           | 21 ~ 16 | 512 (ワード アドレス)<br>1K バイト                           |

| ハーフページ             | 8 (ワード アドレス) | A2 ~ A0           | 2 ~ 0   | 16 バイト                                             |

## 5. レジスタ空間

CA[46] = 1 の時、読み書きトランザクションはレジスタ空間にアクセスします。

表 6. レジスタ空間のアドレス マップ<sup>[35]</sup>

| レジスタ                     | システム アドレス | —  | —  | —  | 31 ~ 27     | 26 ~ 19 | 18 ~ 11 | 10 ~ 3  | —      | 2 ~ 0 |

|--------------------------|-----------|----|----|----|-------------|---------|---------|---------|--------|-------|

|                          | CA ビット    | 47 | 46 | 45 | 44 ~ 40     | 39 ~ 32 | 31 ~ 24 | 23 ~ 16 | 15 ~ 8 | 7 ~ 0 |

| 識別レジスタ 0 (読み出し専用)        |           |    |    |    | C0h または E0h | 00h     | 00h     | 00h     | 00h    | 00h   |

| 識別レジスタ 1 (読み出し専用)        |           |    |    |    | C0h または E0h | 00h     | 00h     | 00h     | 00h    | 01h   |

| コンフィギュレーション レジスタ 0 の読み出し |           |    |    |    | C0h または E0h | 00h     | 01h     | 00h     | 00h    | 00h   |

| コンフィギュレーション レジスタ 0 の書き込み |           |    |    |    | 60h         | 00h     | 01h     | 00h     | 00h    | 00h   |

| コンフィギュレーション レジスタ 1 の読み出し |           |    |    |    | C0h または E0h | 00h     | 01h     | 00h     | 00h    | 01h   |

| コンフィギュレーション レジスタ 1 の書き込み |           |    |    |    | 60h         | 00h     | 01h     | 00h     | 00h    | 01h   |

注:

35. 読み出しの場合、CA45 はラップまたはリニア読み出しを示すために 0 または 1 です。書き込みの場合、リニア シングル ワード レジスタの書き込みのみがサポートされているため、CA45 は 1 でなければなりません。

## 5.1 デバイス識別レジスタ

CS# が LOW の時選択されたデバイスの情報を提供する読み出し専用かつ不揮発性のワード レジスタが 2 本あります。デバイス情報フィールドは以下を識別します：

- メーカー

- 種類

- メモリ容量

- 行アドレス ビット数

- 列アドレス ビット数

表 7. ID レジスタ 0 のビット割り当て

| ビット     | 機能         | 設定 (2 進)                                                                                |

|---------|------------|-----------------------------------------------------------------------------------------|

| 15 ~ 14 | 64 M ビット   | 予約済み                                                                                    |

|         | 128 M ビット  | ダイアドレス：<br>00 = ダイ 1<br>01 = ダイ 2                                                       |

| 13      | Reserved   | 0 - default                                                                             |

| 12 ~ 8  | 行アドレス ビット数 | 00000: 1 行アドレス ビット<br>...<br>11111: 32 行アドレス ビット<br>01100: 64 M ビット<br>01101: 128 M ビット |

| 7 ~ 4   | 列アドレス ビット数 | 0000: 1 列アドレス ビット<br>...<br>1111: 16 列アドレス ビット                                          |

| 3 ~ 0   | メーカー       | 0000 - 予約済み<br>0001 - サイプレス<br>0010 ~ 1111 - 予約済み                                       |

表 8. ID レジスタ 1 のビット割り当て

| ビット    | 機能       | 設定 (2 進)                                |

|--------|----------|-----------------------------------------|

| 15 ~ 4 | 予約済み     | 0000_0000_0000b (デフォルト)                 |

| 3 ~ 0  | デバイス タイプ | 0000: HyperRAM 1.0<br>0001 ~ 1111: 予約済み |

### 5.1.1 容量および行境界

デバイスの DRAM アレイ サイズ (容量) は、ID0 レジスタの行アドレス ビット数と列アドレス ビット数フィールドに示された行と列アドレスに使用されるシステム アドレスの総ビット数で判定できます。例えば、64M ビット HyperRAM デバイスは 9 列アドレス ビットと 13 行アドレス ビットがあり、合計で 22 ワード アドレス ビット =  $2^{22}$  = 4M ワード = 8M バイトがあります。9 列アドレス ビットは、各行には  $2^9 = 512$  ワード = 1K バイトがあることを示します。行アドレス ビット数は、各アレイのリフレッシュ間隔以内に 8196 行がリフレッシュされることを示します。行数はリフレッシュ間隔の計算に使用されます。

## 5.2 レジスタ空間へのアクセス

レジスタの初期設定値は電源投入時またはハードウェアリセット時にロードされます。レジスタはデバイスがスタンバイ状態にある時いつでも変更できます。

図 14 に示すように単一の 16 ビットワード書き込みトランザクションによりレジスタをロードできます。CA[47] = 0 は書き込みトランザクションを示し、CA[46] = 1 はレジスタ空間への書き込みを示し、CA[45] = 1 はリニア書き込みを示し、CA フィールドの下位ビットはレジスタアドレスを示します。

図 14. レジスタのロード [36, 37, 38, 39]

各レジスタは個別のシングルワード書き込みトランザクションで書き込まれます。レジスタ書き込みトランザクションにはレイテンシがなく、単一のデータワードはコマンドアドレスの直後に続きます。RWDS は、メモリアレイのリフレッシュが進行中であるかを示すために CA サイクル中常にメモリによって駆動されるため、書き込み中にはホストによって駆動されません。レジスタ空間への書き込みはメモリアレイでなくレジスタに直接アクセスするため、進行中のアレイリフレッシュに関する初期書き込みレイテンシはありません。レジスタ書き込みでは、レジスタの両バイトは常に書き込まれており、マスクされないため、RWDS はデータマスクとして使用されません。

予約済みレジスタフィールドは初期設定値で書き込む必要があります。予約済みフィールドに初期設定値以外の値を書き込むと、未定義の結果となることがあります。

レジスタの読み出しが、CA[46] = 1 にセットしてレジスタ空間を選択し、1つの 16 ビット読み出しへトランザクションを実行することで行われます。1つ以上のワードを読み出す場合、各読み出しで同じレジスタ値が繰り返されます。1つのみのレジスタ値が読み出されるため、CA[45] バーストタイプは「ドントケア」です。レジスタ内容はアレイデータの読み出しと同じ方法で返されますが、コマンドアドレス期間中の RWDS の状態に応じて 1 つか 2 つのレイテンシがあります。レイテンシ数はコンフィギュレーションレジスタ 0 の読み出しレイテンシフィールド (CR0[7:4]) で定義されます。

**注意事項** : 128M ビットデュアルダイス택クのすべてのコンフィギュレーションレジスタについて、同様に設定することを推奨します。

注:

36. レジスタ空間への書き込み中にはホストは RWDS を駆動してはいけません。

37. RWDS 信号は、メモリアレイがリフレッシュされているかに応じてコマンドアドレス期間中にメモリによって駆動されます。このリフレッシュの指定はレジスタデータの書き込みに影響を与えるません。CS# が LOW になった直後、CA[47:46] が受信される前に、RWDS は駆動されてトランザクションがレジスタ空間への書き込みであることを示しますが、これに対して RWDS のリフレッシュ指定は関係しません。

38. レジスタ値は常に CA 値の直後に提供され、リフレッシュレイテンシによって遅らせられることはありません。

39. RWDS 信号はコマンドアドレス期間後に High-Z に戻ります。レジスタデータはマスクされることはありません。レジスタデータの両データバイトは選択したレジスタにロードされます。

### 5.2.1 コンフィギュレーション レジスタ 0

コンフィギュレーション レジスタ 0 (CR0) は、HyperRAM デバイスの電力モードとアクセス プロトコルの動作条件の定義に用いられます。設定可能な特性は以下の通りです：

- ラップ バースト長 (長さが 16、32、64 または 128 バイトの揃えたデータ グループ)

- ラップ バースト タイプ

- レガシー ラップ (選択した長さを持つ揃えたグループ内でラップ アラウンドによるシーケンシャル アクセス)

- ハイブリッド ラップ (1 回のレガシー ラップ後に次のシーケンシャル グループの開始でリニア バーストを使用)

- 初期レイテンシ

- 可変レイテンシ

- アレイ読み出しまだ書き込みトランザクションが固定レイテンシを用いるか可変レイテンシを用いるかの設定。固定レイテンシを選択した場合、メモリは常に 1 つのリフレッシュ レイテンシを指定し、それに応じて読み出しデータ転送を遅延させます。可変レイテンシを選択した場合、新しいトランザクションが開始すると同時にリフレッシュが必要となる時にのみリフレッシュ レイテンシが追加されます。

- 出力駆動強度

- ディープ パワー ダウン モード

表 9. コンフィギュレーション レジスタ 0 のビット割り当て

| CR0 ビット | 機能                            | 設定 (2 進)                                                                                                                                                                                              |

|---------|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15      | ディープ パワー ダウン イネーブル (64 M ビット) | 1: 通常動作 (デフォルト)<br>0: CR[15] に 0 を書き込むと、デバイスがディープ パワー ダウン モードに入る                                                                                                                                      |

|         | 予約 (128 M ビット)                | 128M ビット デュアルスタック用として予約                                                                                                                                                                               |

| 14 ~ 12 | 駆動強度                          | 000: 34Ω (デフォルト)<br>001: 115Ω<br>010: 67Ω<br>011: 46Ω<br>100: 34Ω<br>101: 27Ω<br>110: 22Ω<br>111: 19Ω                                                                                                 |

| 11 ~ 8  | 予約済み                          | 1 - 予約済み (デフォルト)<br>将来の使用のために予約済み。このレジスタに書き込む時、将来の互換性維持のためにこれらのビットを 1 にセットする必要がある                                                                                                                     |

| 7 ~ 4   | 初期レイテンシ                       | 0000: 5 クロック レイテンシ - 133 MHz<br>0001: 6 クロック レイテンシ - 166 MHz (デフォルト)<br>0010: 予約済み<br>0011: 予約済み<br>0100: 予約済み<br>...<br>1101 - 予約済み<br>1110 - 3 クロック レイテンシ - 83 MHz<br>1111 - 4 クロック レイテンシ - 100 MHz |

| 3       | 固定レイテンシ イネーブル (64 M ビット)      | 0: 可変レイテンシ。CA サイクル中の RWDS によって初期レイテンシの 1 倍または 2 倍<br>1 - 固定レイテンシ。初期レイテンシの 2 倍 (デフォルト)                                                                                                                 |

|         | 予約 (128 M ビット)                | 1: 固定レイテンシ。初期レイテンシの 2 倍 (デフォルト)                                                                                                                                                                       |

| 2       | ハイブリッド バースト イネーブル             | 0: ハイブリッド バースト シーケンスに従うラップ バースト シーケンス<br>1: レガシー ラップ バースト方法でのラップ バースト シーケンス (デフォルト)                                                                                                                   |

| 1 ~ 0   | バースト長                         | 00: 128 バイト<br>01: 64 バイト<br>10: 16 バイト<br>11 - 32 バイト (デフォルト)                                                                                                                                        |

### 5.2.1.1 ラップ バースト

ラップ バースト トランザクションは、ワード グループの長さと一致したワード境界に揃えたワード グループ内のメモリにアクセスします。ラップ アクセスグループは長さが 16、32、64 または 128 バイトの揃えたグループに設定できます。ラップ トランザクション中に、アクセスはグループ内でコマンドアドレスによって選択された位置から開始し、設定されたワード グループ揃えの境界の終わりまで継続してから、グループの始まりに戻って、開始位置まで続けます。ラップ バーストは一般的に、クリティカル ワード ファースト方式で命令またはデータをキャッシュ ラインに書き込ませる読み出しアクセスに使用されます。

### 5.2.1.2 ハイブリッド バースト

ハイブリッド バーストの始まりはターゲット アドレスのラップ バースト グループの長さ内でラップし、ラップ グループの終了アドレスの後にある次のデータのハーフページに続けます。継続したアクセスは、CS# を HIGH にすることで転送を終了するまでリニア バースト順序で実行されます。ラップ バーストと、次のバースト グループの始まりから開始するリニア バーストの混成により、単一のアクセスで複数のシーケンシャル アドレス キャッシュ ラインにデータが書き込まれます。最初のキャッシュ ラインはクリティカルなワードから書き込まれます。その後、最初のラインを処理中にメモリ内の次のシーケンシャル ラインを読み出してキャッシュに格納できます。

表 10. ラップ バースト シーケンスの CR0[2] 制御

| ビット | デフォルト値 | 名称                                                                                                           |

|-----|--------|--------------------------------------------------------------------------------------------------------------|

| 2   | 1      | ハイブリッド バースト イネーブル<br>CR[2]=0: ハイブリッド バースト シーケンスに従うラップ バースト シーケンス<br>CR[2]=1: レガシー ラップ バースト方法でのラップ バースト シーケンス |

表 11. ラップ バースト シーケンス例<sup>[40]</sup>

| バーストの選択<br>CA[45] | バースト<br>タイプ<br>CR0[2:0] | ラップ境界<br>(バイト)                | 開始アドレス<br>(16 進) | アドレス シーケンス (16 進)<br>(ワード)                                                                                                                                                                                                                                                                                           |

|-------------------|-------------------------|-------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0                 | 000<br>ハイブリッド<br>128    | 1 回の 128 バイトのラップ後にリニア バーストが続く | XXXXXX03         | 03、04、05、06、07、08、09、0A、0B、0C、0D、0E、0F、10、11、12、13、14、15、16、17、18、19、1A、1B、1C、1D、1E、1F、20、21、22、23、24、25、26、27、28、29、2A、2B、2C、2D、2E、2F、30、31、32、33、34、35、36、37、38、39、3A、3B、3C、3D、3E、3F、00、01、02<br>(ラップ バーストを完了。最初の 128 バイトのラップ グループの終了時点以降リニア バーストを実行)<br>40、41、42、43、44、45、46、47、48、49、4A、4B、4C、4D、4E、4F、50、51、... |

| 0                 | 001<br>ハイブリッド<br>64     | 1 回の 64 バイトのラップ後にリニア バーストが続く  | XXXXXX03         | 03、04、05、06、07、08、09、0A、0B、0C、0D、0E、0F、10、11、12、13、14、15、16、17、18、19、1A、1B、1C、1D、1E、1F、00、01、02、<br>(ラップ バーストを完了。最初の 64 バイトのラップ グループの終了時点以降リニア バーストを実行)<br>20、21、22、23、24、25、26、27、28、29、2A、2B、2C、2D、2E、2F、30、31、...                                                                                                 |

| 0                 | 001<br>ハイブリッド<br>64     | 1 回の 64 バイトのラップ後にリニア バーストが続く  | XXXXXX2E         | 2E、2F、30、31、32、33、34、35、36、37、38、39、3A、3B、3C、3D、3E、3F、20、21、22、23、24、25、26、27、28、29、2A、2B、2C、2D、<br>(ラップ バーストを完了。最初の 64 バイトのラップ グループの終了時点以降リニア バーストを実行)<br>40、41、42、43、44、45、46、47、48、49、4A、4B、4C、4D、4E、4F、50、51、...                                                                                                 |

| 0                 | 010<br>ハイブリッド<br>16     | 1 回の 16 バイトのラップ後にリニア バーストが続く  | XXXXXX02         | 02、03、04、05、06、07、00、01、<br>(ラップ バーストを完了。最初の 16 バイトのラップ グループの終了時点以降リニア バーストを実行)<br>08、09、0A、0B、0C、0D、0E、0F、10、11、12、...                                                                                                                                                                                              |

注:

40. 128Mビット デュアル ダイ スタックでは、ダイの境界をまたぐリニア バーストはサポートされていません。

**表 11. ラップ バースト シーケンス例<sup>[40]</sup>(続き)**

| バーストの選択 |          | バースト タイプ   | ラップ境界 (バイト)                | 開始アドレス (16進) | アドレス シーケンス (16進)<br>(ワード)                                                                                                                                                                           |

|---------|----------|------------|----------------------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CA[45]  | CR0[2:0] |            |                            |              |                                                                                                                                                                                                     |

| 0       | 010      | ハイブ リッド 16 | 1回の 16 バイトのラップ後にリニアバーストが続く | XXXXXX0C     | 0C、0D、0E、0F、08、09、0A、0B、(ラップ バーストを完了。最初の 16 バイトのラップ グループの終了時点以降リニアバーストを実行)<br>10、11、12、13、14、15、16、17、18、19、1A、...                                                                                  |

| 0       | 011      | ハイブ リッド 32 | 1回の 32 バイトのラップ後にリニアバーストが続く | XXXXXX0A     | 0A、0B、0C、0D、0E、0F、00、01、02、03、04、05、06、07、08、09、...                                                                                                                                                 |

| 0       | 011      | ハイブ リッド 32 | 1回の 32 バイトのラップ後にリニアバーストが続く | XXXXXX1E     | 1E、1F、10、11、12、13、14、15、16、17、18、19、1A、1B、1C、1D、...                                                                                                                                                 |

| 0       | 100      | ラップ 128    | 128                        | XXXXXX03     | 03、04、05、06、07、08、09、0A、0B、0C、0D、0E、0F、10、11、12、13、14、15、16、17、18、19、1A、1B、1C、1D、1E、1F、20、21、22、23、24、25、26、27、28、29、2A、2B、2C、2D、2E、2F、30、31、32、33、34、35、36、37、38、39、3A、3B、3C、3D、3E、3F、00、01、02、... |

| 0       | 101      | ラップ 64     | 64                         | XXXXXX03     | 03、04、05、06、07、08、09、0A、0B、0C、0D、0E、0F、10、11、12、13、14、15、16、17、18、19、1A、1B、1C、1D、1E、1F、00、01、02、...                                                                                                 |

| 0       | 101      | ラップ 64     | 64                         | XXXXXX2E     | 2E、2F、30、31、32、33、34、35、36、37、38、39、3A、3B、3C、3D、3E、3F、20、21、22、23、24、25、26、27、28、29、2A、2B、2C、2D、...                                                                                                 |

| 0       | 110      | ラップ 16     | 16                         | XXXXXX02     | 02、03、04、05、06、07、00、01、...                                                                                                                                                                         |

| 0       | 110      | ラップ 16     | 16                         | XXXXXX0C     | 0C、0D、0E、0F、08、09、0A、0B、...                                                                                                                                                                         |

| 0       | 111      | ラップ 32     | 32                         | XXXXXX0A     | 0A、0B、0C、0D、0E、0F、00、01、02、03、04、05、06、07、08、09、...                                                                                                                                                 |

| 0       | 111      | ラップ 32     | 32                         | XXXXXX1E     | 1E、1F、10、11、12、13、14、15、16、17、18、19、1A、1B、1C、1D、...                                                                                                                                                 |

| 1       | XXX      | リニア        | リニアバースト                    | XXXXXX03     | 03、04、05、06、07、08、09、0A、0B、0C、0D、0E、0F、10、11、12、13、14、15、16、17、18、...                                                                                                                               |

注:

40. 128Mビット デュアル ダイ スタックでは、ダイの境界をまたぐリニアバーストはサポートされていません。

### 5.2.1.3 初期レイテンシ

メモリ空間への読み書きトランザクションまたはレジスタ空間への読み出しトランザクションは、コマンドアドレスによって選択された行を開くためにいくつかの初期レイテンシを要します。この初期レイテンシは  $t_{ACC}$  です。 $t_{ACC}$  を満たすために必要なレイテンシクロック数は、HyperBus 周波数に依存し、3 ~ 6 クロックの間で変化します。CR0[7:4] の値は初期レイテンシのクロック数を選択します。初期設定値は 6 クロックであり、ホストシステムがより最適な低い初期レイテンシを設定する前に最大 166MHz までの周波数で動作することを可能とします。

メモリ空間への読み書きトランザクションまたはレジスタ空間への読み出しトランザクションが開始すると同時に分配リフレッシュが必要となる時、RWDS 信号はコマンドアドレスの期間中に HIGH になり、行を開く前にリフレッシュ動作が完了するための追加の初期レイテンシが挿入されることを示します。

レジスタ空間への書き込みトランザクションは常に初期レイテンシがありません。RWDS はコマンドアドレス期間中に HIGH または LOW です。レジスタデータを取り込むのに必要な初期レイテンシがないため、RWDS のコマンドアドレス期間中の論理レベルはコマンドアドレスの直後のレジスタデータの書き込みに影響を与えません。リフレッシュ動作はレジスタデータのキャプチャと平行してメモリアレイで実行できます。

### 5.2.1.4 固定レイテンシ

コンフィギュレーションレジスタオプションビット CR0[3] は、すべてのメモリ空間への読み書きトランザクションまたはレジスタ空間への読み出しトランザクションに必要な初期レイテンシを同じにします。このためには、コマンドアドレス期間中常に RWDS を HIGH に駆動して 2 つの初期レイテンシ期間が必要であることを指定します。この固定レイテンシは分配リフレッシュの必要性にかかわらず、単に固定（決定的）初期レイテンシをすべてのトランザクションタイプに提供します。固定レイテンシオプションを使うと、一部の HyperBus メモリコントローラーのデザインを簡素化できるか、またはトランザクションの決定的な性能を保証できます。固定レイテンシはデフォルトの POR またはリセットコンフィギュレーションです。システムは、このコンフィギュレーションビットをクリアして固定レイテンシを無効にし、リフレッシュ用の追加のレイテンシが必要となる時にのみ RWDS が HIGH に駆動される可変レイテンシを有効にできます。

**注意事項** : 128M ビットデュアルダイス택크は、固定レイテンシのみサポートしています。

### 5.2.1.5 駆動強度

DQ 信号ラインの負荷、長さ、インピーダンスはシステムデザインによって異なります。コンフィギュレーションレジスタビット CR0[14:12] を使うと、DQ[7:0] 信号の出力インピーダンスを調整して DQ 信号インピーダンスをシステム条件に適合させ、オーバーシュートやアンダーシュート、リングングなど高速信号の動作を最小限にできます。デフォルトの POR またはリセットコンフィギュレーション値は 000b であり、出力インピーダンスオプションの中間点を選択します。

指定されたインピーダンス値は、標準的なシリコンプロセス条件、定格動作電圧 (1.8V または 3V)、50°C でのプルアップとプルダウン両方のドライバの Typ 値です。インピーダンス値はプロセス、電圧および温度 (PVT) 条件によって Typ 値の最大  $\pm 80\%$  まで異なることがあります。プロセスが遅く、電圧が低く、温度が高いほどインピーダンスは高くなります。プロセスが速く、電圧が高く、温度が低いほどインピーダンスは低くなります。

各システムデザインでは、動作電圧と温度範囲にわたってデータのシグナルインテグリティを評価して、動作条件に最適な駆動強度を選択する必要があります。

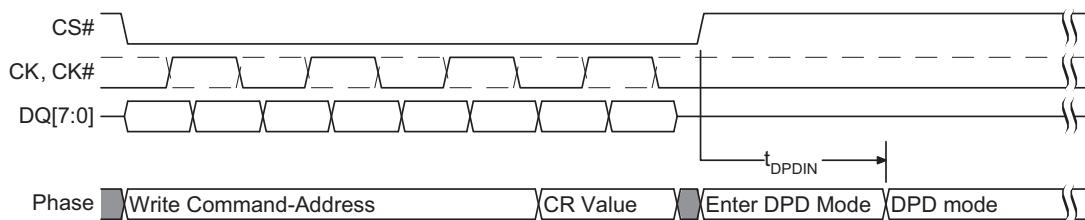

### 5.2.1.6 ディープパワーダウン

HyperRAM デバイスがシステムの動作には必要ない場合、CR0[15] に 0 を書き込むことで、デバイスをディープパワーダウン (DPD) という非常に低消費電力モードに移行させられます。CR0[15] を 0 にクリアすると、デバイスは  $t_{DPDIN}$  の時間内に DPD モードに移行し、すべてのリフレッシュ動作が停止します。DPD モードの間、RAM に格納されたデータは失われます（リフレッシュなしで無効になります）。CS# を LOW に駆動してから HIGH に駆動するデバイスへの次のアクセス、POR、またはリセットによりデバイスは DPD モードを終了します。スタンバイモードに復帰するのには  $t_{DPDOUT}$  の時間がかかります。詳細は、27 ページの 6.1.3 節ディープパワーダウンをご参照ください。

**注意事項** : ディープパワーダウンオプションは、128M ビットデュアルダイス택크ではサポートされていません。

### 5.2.2 コンフィギュレーションレジスタ 1

コンフィギュレーションレジスタ 1 (CR1) は HyperRAM デバイスの分配リフレッシュ間隔を定義するために使用されます。コア DRAM アレイはすべてのビットの定期的なリフレッシュが必要です。これは、ホストシステムが特定の期限以内に各行内の 1 つの位置を読み書きすることで行えます。読み書きアクセスは 1 行のビットを内部バッファにコピーします。アクセスの終了時、バッファに格納されたビットはメモリ内の行に戻って書き込まれるため、DRAM メモリセル内のビット行が再充電（リフレッシュ）されます。

ただし、ホストシステムには一般的に、メモリのあらゆる行を定期的に読み出し、メモリアレイ全体のリフレッシュ間隔以内に各行がアクセスされるかを追跡するよりも良いやり方を持っています。HyperRAM デバイスはセルフリフレッシュロジックを内蔵しています。このロジックは自動的に行をリフレッシュし、ホストシステムがメモリをリフレッシュする必要がなくなります。メモリがホストシステムによってアクティブに読み書きされない時にのみ行の自動リフレッシュを実行できます。リフレッシュが必要な時点でアクティブな読み書きが行われている場合は、リフレッシュロジックはこの読み書きの完了を待ちます。リフレッシュが完了する前に新しい読み書きが開始する場合、メモリはコマンドアドレス期間中に RWDS を HIGH に駆動して新しいアクセスの開始時に追加の初期レイテンシが必要となることを示します。これにより、新しいアクセスが開始する前にリフレッシュ動作が完了できます。

25 ページの表 12 温度に応じたアレイリフレッシュ間隔に示すように、メモリアレイ全体の必要なリフレッシュ間隔は温度によって異なります。この時間以内にすべての行をリフレッシュする必要があります。すべての行のリフレッシュは、各間隔の開始時に、一群の塊としてのアクセスをすること、あるいは 1 回にいくつかの行のグループを、各間隔を通して分散された形でのリフレッシュ（バーストリフレッシュ）をすること、あるいは間隔にわたって均等に分配された單一行のリフレッシュとしても実行できます。セルフリフレッシュロジックは間隔にわたって單一行のリフレッシュ動作を分配することで、バーストリフレッシュの実行でメモリが長い期間ビジーになることはなく、これによってホストアクセスが長い期間遅延されることはありません。

**表 12. 温度に応じたアレイ リフレッシュ間隔**

| デバイス温度 (°C) | アレイ リフレッシュ間隔 (ms) | 行数   | 推奨の $t_{CMS}$ (μs) |

|-------------|-------------------|------|--------------------|

| 85          | 64                | 8192 | 4                  |

| 105         | 16                | 8192 | 1                  |

**表 13. コンフィギュレーション レジスタ 1 のビット割り当て**

| CR1 ビット | 機能         | 設定 (2 進)                                                                                                          |

|---------|------------|-------------------------------------------------------------------------------------------------------------------|

| 15 ~ 2  | 予約済み       | 000000h: 予約済み (デフォルト)<br>将来使用のために予約済み。レジスタに書き込む時、将来の互換性のためこれらのビットを 0 にクリアする必要がある                                  |

| 1 ~ 0   | 分散リフレッシュ間隔 | 10b: デフォルト<br>産業用温度範囲のデバイスは 4μs<br>産業用拡張温度範囲のデバイスは 1μs<br>11b: デフォルトの 1.5 倍<br>00b: デフォルトの 2 倍<br>01b: デフォルトの 4 倍 |

分配リフレッシュ方法は、ホストが、メモリが必要な分配リフレッシュを行えなくなるほど長いバースト トランザクションを実行しないことを必要とします。このことから、リフレッシュ ロジックがトランザクション間にリフレッシュを挿入できるように読み書きトランザクションの長さの上限値が設定されます。この上限値は CS# の最大 LOW 時間 ( $t_{CMS}$ ) と呼ばれます。 $t_{CMS}$  値は、アレイリフレッシュ間隔をアレイ内の行数で割ってから、結果を半分に減らすことで計算されます。これにより、分配リフレッシュが実行される直前に開始する最大長のホスト アクセスが原因で分配リフレッシュ間隔が完全に見逃されることを防止できます。 $t_{CMS}$  が必要なリフレッシュ間隔の半分にセットされた値であるため、リフレッシュ動作を遅延させる一連の最大長のホスト アクセスは、リフレッシュ間隔を行数で割った値の 2 倍である速度でリフレッシュ動作に追いつきます。

ホスト システムは、各トランザクションを  $t_{CMS}$  に違反する前に終了することで  $t_{CMS}$  の要件を満たす必要があります。このためには、ホスト メモリ コントローラ ロジックは  $t_{CMS}$  の限界に達すると長いトランザクションを分割するか、またはホスト システム ハードウェアまたはソフトウェアは  $t_{CMS}$  よりも長い単一読み書きトランザクションを実行しません。

25 ページの表 12 に示したように、低温ではアレイ リフレッシュ間隔が長くなるため、 $t_{CMS}$  が増加し、その結果、より長いトランザクションを実行できるようになります。ホスト システムは、最大動作温度に対応する表の  $t_{CMS}$  値を使うこともでき、分配リフレッシュ間隔を長くするためにシステム内の温度センサーで現時点の動作温度を判定することもできます。

またホスト システムは、すべてのリフレッシュ動作に対して明示的に責任を持つ形で、 $t_{CMS}$  を効果的に増加できます。この場合はより長いトランザクションで取り逃がされた分配リフレッシュに追いつくために複数のシーケンシャル行に対してバースト リフレッシュ読み出しを実行します。

## 6. インターフェースの状態

表 14 には、インターフェース信号値の要件を、インターフェースの状態ごとに示します。

表 14. インターフェース状態

| インターフェース状態                           | $V_{CC} / V_{CCQ}$           | CS# | CK、CK#  | DQ7 ~ DQ0                 | RWDS                | RESET# |

|--------------------------------------|------------------------------|-----|---------|---------------------------|---------------------|--------|

| ハードウェアによるデータ保護付きパワーオフ ( フラッシュメモリ )   | $< V_{LKO}$                  | X   | X       | High-Z                    | High-Z              | X      |

| パワーオン ( コールド ) リセット                  | $\geq V_{CC} / V_{CCQ\ min}$ | X   | X       | High-Z                    | High-Z              | X      |

| ハードウェア ( ウォーム ) リセット                 | $\geq V_{CC} / V_{CCQ\ min}$ | X   | X       | High-Z                    | High-Z              | L      |

| インターフェーススタンバイ                        | $\geq V_{CC} / V_{CCQ\ min}$ | H   | X       | High-Z                    | High-Z              | H      |

| コマンドアドレス                             | $\geq V_{CC} / V_{CCQ\ min}$ | L   | T       | マスター出力有効                  | X                   | H      |

| 読み出し初期アクセス レイテンシ ( データバスターンアラウンド周期 ) | $\geq V_{CC} / V_{CCQ\ min}$ | L   | T       | High-Z                    | L                   | H      |

| 書き込み初期アクセス レイテンシ ( RWDS ターンアラウンド周期 ) | $\geq V_{CC} / V_{CCQ\ min}$ | L   | T       | High-Z                    | High-Z              | H      |

| 読み出しデータ転送                            | $\geq V_{CC} / V_{CCQ\ min}$ | L   | T       | スレーブ出力有効                  | スレーブ出力有効<br>X または T | H      |

| 初期レイテンシ有りの書き込みデータ転送                  | $\geq V_{CC} / V_{CCQ\ min}$ | L   | T       | マスター出力有効                  | マスター出力有効<br>X または T | H      |

| 初期レイテンシ無しの書き込みデータ転送 <sup>[41]</sup>  | $\geq V_{CC} / V_{CCQ\ min}$ | L   | T       | マスター出力有効                  | スレーブ出力 L または High-Z | H      |

| アクティブクロック停止 <sup>[42]</sup>          | $\geq V_{CC} / V_{CCQ\ min}$ | L   | アイドル    | マスター / スレーブ出力有効または High-Z | X                   | H      |

| ディープパワーダウン <sup>[42]</sup>           | $\geq V_{CC} / V_{CCQ\ min}$ | H   | X または T | スレーブ出力 High-Z             | High-Z              | H      |

注:

41. 初期レイテンシのない ( ゼロ初期レイテンシ ) 書き込み処理に RWDS 用のターンアラウンド期間はありません。HyperRAM デバイスはコマンドアドレス期間中に常に RWDS を駆動して、延長レイテンシが必要かどうかを示します。コマンドアドレス期間の直後にマスター書き込みデータが続くため、HyperRAM デバイスは RWDS を LOW に駆動し続けるか、または RWDS を High-Z 状態にすることがあります。レイテンシ無しの書き込み期間中に、マスターは RWDS を駆動してはいけません。レイテンシ無しの書き込みには RWDS をデータマスク機能として使用しません。書き込みデータのすべてのバイトが書き込まれます ( フルワード書き込み )。

42. アクティブクロックストップは 27 ページの 6.1.2 節 アクティブクロックストップに表示します。DPD は 27 ページの 6.1.3 節 ディープパワーダウンで説明されています。

凡例

$L = V_{IL}$

$H = V_{IH}$

$X = V_{IL}$  または  $V_{IH}$

$L/H$  = 立ち上がりエッジ

$H/L$  = 立ち下がりエッジ

T = 情報転送中にトグル

アイドル = CK が LOW、CK# が HIGH

有効 = すべてのバス信号が L または H レベルに安定している

## 6.1 省電力モード

### 6.1.1 インターフェーススタンバイ

スタンバイは、デバイスがホストによってデータ転送用に選択されていない (CS#= HIGH) 時のインターフェースに対する初期設定の低消費電力状態です。この状態では、CS# と RESET# 以外のすべての入出力は無視されます。

### 6.1.2 アクティブクロックストップ

アクティブクロックストップモードでは、読み書き動作のデータ転送部分の間、デバイスインターフェースの消費エネルギーを  $I_{CC6}$  レベルに低減します。クロックが  $t_{ACC} + 30\text{ns}$  にわたって安定状態に維持されると、デバイスは自動的にこのモードに入ります。アクティブクロックストップモードでは、読み出しデータはラッチされ、常にデータバスに出力されます。 $I_{CC6}$  は 31 ページの 7.4 節 DC 特性に示されます。

アクティブクロックストップモードにより、ホストシステムクロックが停止してデータ転送を一時停止する時に消費電流を減少させられます。このような拡張されたデータ転送サイクル中に CS# が LOW にある場合がありますが、メモリデバイスのホストインターフェースは  $t_{ACC} + 30\text{ns}$  が経過した後にアクティブクロックストップ電流レベルになります。これにより、データ転送が中止された場合、デバイスは低電流モードに入ります。クロックのトグルによりデータ転送が再開されると、アクティブ読み書き電流に戻ります。アクティブクロックストップモードは  $t_{CSM}$  の限界に違反して使用しないでください。CS# は  $t_{CSM}$  が違反される前に HIGH になる必要があります。

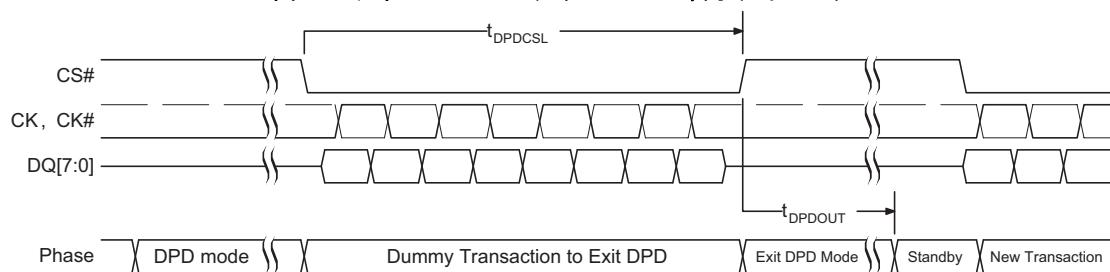

### 6.1.3 ディープパワーダウン

ディープパワーダウン (DPD) モードでは、消費電流は可能な限り低いレベル ( $i_{DPD}$ ) にされます。CR0[15] に 0 を書き込むとデバイスは DPD モードに入ります。デバイスは  $t_{DPDIN}$  の間消費電力を減少させ、すべてのリフレッシュ動作を停止します。DPD モードの間、メモリ空間に格納されたデータは失われます (リフレッシュなしで無効になります)。CS# を LOW に駆動してから HIGH に駆動するデバイスへの次のアクセスで、デバイスは DPD モードを終了します。CS# を LOW に駆動してから HIGH に駆動し、DPD モードを終了するための読み書きトランザクションは、デバイスによって無視されるダミートランザクションです。また、POR またはハードウェアリセットでもデバイスは DPD モードを終了します。DPD モードでは、CS# と RESET# 信号のみ監視されます。ダミートランザクションまたはリセットの後にスタンバイモードに復帰するには  $t_{DPDOUT}$  時間かかります。POR の後に DPD モードからスタンバイモードに復帰するには  $t_{VCS}$  時間かかります。これはどの POR においても同様です。それらのイベントのいずれかで DPD を終了した後、デバイスの状態は POR を実行した後の状態と同じです。

表 15. ディープパワーダウンモードのタイミングパラメーター

| パラメーター       | 説明                                                     | Min | Max | 単位            |

|--------------|--------------------------------------------------------|-----|-----|---------------|

| $t_{DPDIN}$  | ディープパワーダウンレジスタの CR0[15] に 0 を書き込んでから DPD 電力レベルに入るまでの時間 | 10  | -   | $\mu\text{s}$ |

| $t_{DPDCSL}$ | ディープパワーダウンモードの終了を発生させる CS# LOW 期間                      | 200 | -   | ns            |

| $t_{DPDOUT}$ | CS# が LOW から HIGH になってからスタンバイウェイクアップ開始までの時間            | -   | 150 | $\mu\text{s}$ |

図 15. ディープパワーダウンへの移行タイミング

**図 16. ディープパワー ダウンの CS# 終了タイミング**

**注:**

43. ディープパワー ダウン オプションは、128M ビット デュアル ダイ スタックではサポートされていません。

## 7. 電気的仕様

### 7.1 絶対最大定格

|                        |                                   |

|------------------------|-----------------------------------|

| プラスチック パッケージの保存温度      | -65°C ~ +150°C                    |

| 通電時の周囲温度               | -65°C ~ +115°C                    |

| グランドに対する電圧             |                                   |

| すべての信号 <sup>[44]</sup> | -0.5V ~ +(V <sub>CC</sub> + 0.5V) |

| 出力短絡電流 <sup>[45]</sup> | 100mA                             |

| V <sub>CC</sub>        | -0.5V ~ +4.0V                     |

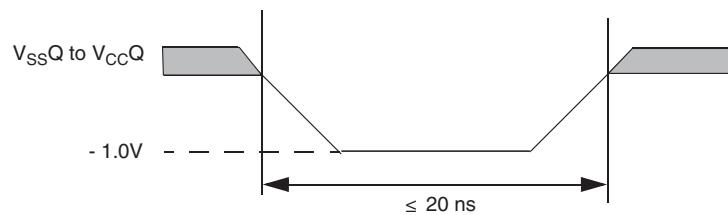

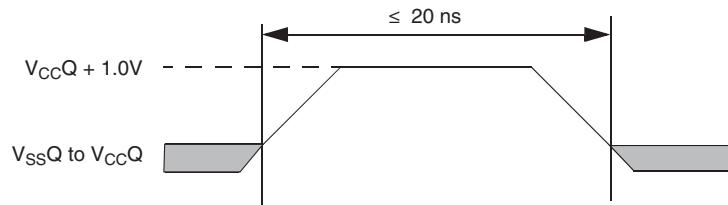

#### 7.1.1 入力信号オーバーシュート

DC 条件において、入力または I/O 信号は V<sub>SS</sub> と V<sub>DD</sub> の電圧範囲以内にあることが必要です。電圧変動の間、入力または I/O は最大 20ns の期間で、V<sub>SS</sub> -1.0V にアンダーシュートするか、または V<sub>DD</sub> +1.0V にオーバーシュートする可能性があります。

図 17. 最大ネガティブ オーバーシュート波形

図 18. 最大ポジティブ オーバーシュート波形

#### 注:

44. 入力または I/O 信号の最小 DC 電圧 -1.0V。電圧変動の間、入力または I/O 信号は、最大 20ns の期間で  $V_{SS} \sim -1.0V$  までアンダーシュートする可能性があります。図 17 をご参照ください。入力または I/O 信号の最大 DC 電圧 -  $V_{CC} + 1.0V$ 。電圧変動の間、入力または I/O 信号は、最大 20ns の期間で  $V_{CC} + 1.0V$  までオーバーシュートする可能性があります。図 18 をご参照ください。

45. 複数の出力を同時にグランドに短絡することはできません。短絡時間は 1 秒を超えてはなりません。

46. 絶対最大定格に記載されている動作範囲を超えて動作すると、デバイスに恒久的な損傷を与える場合があります。ただし、これはストレスのみに対する定格です。上記の条件あるいは本データシートの動作説明の各節に記載されている条件を超える条件におけるデバイスの機能動作は保証されません。長時間にわたってデバイスを絶対最大定格条件に放置すると、デバイスの信頼性に影響を与えます。

## 7.2 ラッチアップ特性

表 16. ラッチアップ仕様<sup>[47]</sup>

| 説明                                  | Min  | Max             | 単位 |

|-------------------------------------|------|-----------------|----|

| すべての入力のみの接続での、 $V_{SSQ}$ を基準とした入力電圧 | -1.0 | $V_{CCQ} + 1.0$ | V  |

| すべての I/O 接続での、 $V_{SSQ}$ を基準とした入力電圧 | -1.0 | $V_{CCQ} + 1.0$ |    |

| $V_{CCQ}$ 電流                        | -100 | +100            | mA |

注：

47. 電源電圧  $V_{CC}/V_{CCQ}$  を除外します。テスト条件： $V_{CC} = V_{CCQ} = 1.8V$ 、一度に 1 つの接続をテストし、テストされていないピンは  $V_{SS}$  に接続。

## 7.3 動作範囲

動作範囲は、デバイスの正常な機能が保証される範囲を定めたものです。

### 7.3.1 溫度範囲

| パラメーター | 記号    | デバイス                     | 仕様  |     | 単位 |

|--------|-------|--------------------------|-----|-----|----|

|        |       |                          | Min | Max |    |

| 周囲温度   | $T_A$ | 産業用 (I)                  | -40 | 85  | °C |

|        |       | 産業用拡張 (V)                | -40 | 105 |    |

|        |       | 車載向け、AEC-Q100 グレード 3 (A) | -40 | 85  |    |

|        |       | 車載向け、AEC-Q100 グレード 2 (B) | -40 | 105 |    |

### 7.3.2 電源電圧

|                        |              |

|------------------------|--------------|

| $V_{CC}$ および $V_{CCQ}$ | 1.7V ~ 1.95V |

| $V_{CC}$ および $V_{CCQ}$ | 2.7V ~ 3.6V  |

### 7.3.3 热抵抗

| パラメーター        | 説明               | 試験条件                                 | 24-ball BGA | 単位   |

|---------------|------------------|--------------------------------------|-------------|------|

| $\Theta_{JA}$ | 熱抵抗<br>(周囲への接合)  | 静止空気、101.5 mm×105 mm にはんだ付け<br>4層PCB | 51          | °C/W |

| $\Theta_{JB}$ | 熱抵抗<br>(ボディへの接合) |                                      | 33          |      |

| $\Theta_{JC}$ | 熱抵抗<br>(ベースへの接合) |                                      | 26          |      |

## 7.4 DC 特性

表 17. DC 特性 (CMOS 互換性)

| パラメーター             | 説明                                                  | テスト条件                                                                                                 | 64 M ピット |                     |       | 128 M ピット |                     |       | 単位 |

|--------------------|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------|----------|---------------------|-------|-----------|---------------------|-------|----|

|                    |                                                     |                                                                                                       | Min      | Typ <sup>[48]</sup> | Max   | Min       | Typ <sup>[48]</sup> | Max   |    |

| I <sub>LI</sub>    | 入力リーク電流<br>3V デバイス リセット信号 High のみ                   | V <sub>IN</sub> = V <sub>SS</sub> ~ V <sub>CC</sub> 、<br>V <sub>CC</sub> = V <sub>CC</sub> max        | -        | -                   | -0.1  | -         | -                   | -0.2  | μA |

| I <sub>LI</sub>    | 入力リーク電流<br>1.8V デバイス リセット信号 High のみ                 | V <sub>IN</sub> = V <sub>SS</sub> ~ V <sub>CC</sub> 、<br>V <sub>CC</sub> = V <sub>CC</sub> max        | -        | -                   | -0.1  | -         | -                   | -0.2  | μA |

| I <sub>LI</sub>    | 入力リーク電流<br>3V デバイス リセット信号 Low のみ (49)               | V <sub>IN</sub> = V <sub>SS</sub> ~ V <sub>CC</sub> 、<br>V <sub>CC</sub> = V <sub>CC</sub> max        | -        | -                   | +20.0 | -         | -                   | +40.0 | μA |

| I <sub>LI</sub>    | 入力リーク電流<br>1.8V デバイス リセット信号 Low のみ (49)             | V <sub>IN</sub> = V <sub>SS</sub> ~ V <sub>CC</sub> 、<br>V <sub>CC</sub> = V <sub>CC</sub> max        | -        | -                   | +20.0 | -         | -                   | +40.0 | μA |

| I <sub>CC1</sub>   | V <sub>CC</sub> アクティブ読み出し電流                         | CS# = V <sub>IL</sub> (166MHz、<br>V <sub>CC</sub> = 1.9V)                                             | -        | 20                  | 60    | -         | 29                  | 72    | mA |

|                    |                                                     | CS# = V <sub>IL</sub> (100MHz、V <sub>CC</sub> = 3.6V)                                                 | -        | 20                  | 35    | -         | 32                  | 47    | mA |

| I <sub>CC2</sub>   | V <sub>CC</sub> アクティブ書き込み電流                         | CS# = V <sub>IL</sub> (166MHz、<br>V <sub>CC</sub> = 1.9V)                                             | -        | 15                  | 60    | -         | 23                  | 72    | mA |

|                    |                                                     | CS# = V <sub>IL</sub> (100MHz、V <sub>CC</sub> = 3.6V)                                                 | -        | 15                  | 35    | -         | 27                  | 47    | mA |

| I <sub>CC4I</sub>  | 産業用温度 (-40°C ~ +85°C)<br>V <sub>CC</sub> スタンバイ電流    | CS#、V <sub>CC</sub> = V <sub>CC</sub> Max                                                             | -        | 135                 | 200   | -         | 286                 | 400   | μA |

| I <sub>CC4IP</sub> | 産業用拡張温度 (-40°C ~ +105°C)<br>V <sub>CC</sub> スタンバイ電流 | CS#、V <sub>CC</sub> = V <sub>CC</sub> Max                                                             | -        | 135                 | 300   | -         | 312                 | 600   | μA |

| I <sub>CC5</sub>   | リセット電流                                              | CS# = V <sub>IH</sub> 、RESET# =<br>V <sub>IL</sub> 、<br>V <sub>CC</sub> = V <sub>CC</sub> Max         | -        | 10                  | 20    | -         | 20                  | 40    | mA |

| I <sub>CC6I</sub>  | 産業用温度 (-40°C ~ +85°C)<br>アクティブ クロック ストップ電流          | CS# = V <sub>IL</sub> 、RESET# =<br>V <sub>IH</sub> 、<br>V <sub>CC</sub> = V <sub>CC</sub> Max         | -        | 5.3                 | 8     | -         | 11                  | 16    | mA |

| I <sub>CC6IP</sub> | 産業用拡張温度 (-40°C ~ +105°C) アクティブ クロック ストップ電流          | CS# = V <sub>IL</sub> 、RESET# =<br>V <sub>IH</sub> 、<br>V <sub>CC</sub> = V <sub>CC</sub> Max         | -        | 5.3                 | 12    | -         | 12                  | 24    | mA |

| I <sub>CC7</sub>   | 電源投入時の V <sub>CC</sub> 電流 <sup>[48]</sup>           | CS# = H、V <sub>CC</sub> = V <sub>CC</sub> max、<br>V <sub>CC</sub> = V <sub>CCQ</sub> = 1.95V または 3.6V | -        | -                   | 35    | -         | -                   | 70    | mA |

| I <sub>DPD</sub>   | 3V 85°C でのディープ パワー ダウン電流                            | CS#、V <sub>CC</sub> = 3.6V、T <sub>A</sub> = 85°C                                                      | -        | -                   | 20    | -         | -                   | N/A   | μA |

| I <sub>DPD</sub>   | 1.8V 85°C でのディープ パワー ダウン電流                          | CS#、V <sub>CC</sub> = 1.9V、T <sub>A</sub> = 85°C                                                      | -        | -                   | 10    | -         | -                   | N/A   | μA |

| I <sub>DPD</sub>   | 3V 105°C でのディープ パワー ダウン電流                           | CS#、V <sub>CC</sub> = 3.6V、T <sub>A</sub> = 105°C                                                     | -        | -                   | 40    | -         | -                   | N/A   | μA |

注:

48. 100% テストされているわけではありません。

49. RESET# の LOW は DPD モードを終了し、I<sub>CC5</sub> リセット電流を引き込み、僅かな Reset# の LOW 期間中は I<sub>LI</sub> を消費。

**表 17. DC 特性 (CMOS 互換性) ( 続き )**

| パラメーター    | 説明                          | テスト条件                                           | 64 M ピット            |                      |                      | 128 M ピット           |                      |                      | 単位      |

|-----------|-----------------------------|-------------------------------------------------|---------------------|----------------------|----------------------|---------------------|----------------------|----------------------|---------|

|           |                             |                                                 | Min                 | Typ <sup>[48]</sup>  | Max                  | Min                 | Typ <sup>[48]</sup>  | Max                  |         |

| $I_{DPD}$ | 1.8V 105°C でのディープ パワー ダウン電流 | $CS\#$ 、 $V_{CC} = 1.9V$ 、 $T_A = 105^{\circ}C$ | -                   | -                    | 20                   | -                   | -                    | N/A                  | $\mu A$ |

| $V_{IL}$  | 入力 LOW 電圧                   |                                                 | -0.5                | -                    | $0.3 \times V_{CC}$  | -0.5                | -                    | $0.3 \times V_{CC}$  | V       |

| $V_{IH}$  | 入力 HIGH 電圧                  |                                                 | $0.7 \times V_{CC}$ | -                    | $V_{CC} + 0.3$       | $0.7 \times V_{CC}$ | -                    | $V_{CC} + 0.3$       | V       |

| $V_{OL}$  | 出力 LOW 電圧                   | $DQ[7:0]$ に対して $I_{OL} = 100\mu A$              | -                   | -                    | $0.15 \times V_{CC}$ | -                   | -                    | $0.15 \times V_{CC}$ | V       |

| $V_{OH}$  | High 出力電圧                   | $DQ[7:0]$ に対して $I_{OH} = 100\mu A$              | -                   | $0.85 \times V_{CC}$ | -                    | -                   | $0.85 \times V_{CC}$ | -                    | V       |

注:

48. 100% テストされているわけではありません。

49.  $RESET\#$  の LOW は DPD モードを終了し、 $I_{CC5}$  リセット電流を引き込み、僅かな  $Reset\#$  の LOW 期間中は  $I_{LI}$  を消費。

#### 7.4.1 高静電容量特性

**表 18. 1.8V での静電容量特性** [50, 51, 52]

| 説明                  | パラメーター | Min | Max  | 単位 |

|---------------------|--------|-----|------|----|

| 入力静電容量 (CK、CK#、CS#) | CI     | 3   | 4.5  | pF |

| デルタ入力静電容量 (CK、CK#)  | CID    | -   | 0.25 | pF |

| 出力静電容量 (RWDS)       | CO     | 3   | 4    | pF |

| IO 静電容量 (DQx)       | CIO    | 3   | 4    | pF |

| IO 静電容量デルタ (DQx)    | CIOD   | -   | 0.5  | pF |

注:

50. これらの値は設計保証であり、サンプル ベースでのみテストされます。

51. 接点の静電容量は、ベクタ ネットワーク アナライザーを用いた静電容量測定 JEP147 手順に従って測定されます。 $V_{CC}$ 、 $V_{CCQ}$  を印加し、他のすべての信号 ( テスト中の信号以外 ) を開放にします。DQ 信号を High-Z 状態にする必要があります。

52. システム内の信号伝播時間整合を実現するために、CK、CK#、RWDS、DQx 信号の静電容量値は同程度でなければならないことに注意してください。アクティブ (LOW) になる CS# と DQ バスに出力されるデータ間には重要なタイミング関係がないため、CS# の静電容量値はそこまで重要ではありません。

**表 19. 3.0V での静電容量特性** [53, 54, 55]

| 説明               | パラメーター | Min | Max | 単位 |

|------------------|--------|-----|-----|----|

| 入力静電容量 (CK、CS#)  | CI     | 3   | 4.5 | pF |

| 出力静電容量 (RWDS)    | CO     | 3   | 4   | pF |

| IO 静電容量 (DQx)    | CIO    | 3   | 4   | pF |

| IO 静電容量デルタ (DQx) | CIOD   | -   | 0.5 | pF |

注:

53. これらの値は設計保証であり、サンプル ベースでのみテストされます。

54. 接点の静電容量は、ベクタ ネットワーク アナライザーを用いた静電容量測定 JEP147 手順に従って測定されます。 $V_{CC}$ 、 $V_{CCQ}$  を印加し、他のすべての信号 ( テスト中の信号以外 ) を開放にします。DQ 信号を高インピーダンス状態にする必要があります。

55. CK、RWDS、DQx 信号の静電容量値は同等になり、システム内の信号伝播時間整合を実現する必要があります。アクティブ (LOW) になる CS# と DQ バスに出力されるデータ間には重要なタイミング関係がないため、CS# の静電容量値はそこまで重要ではありません。

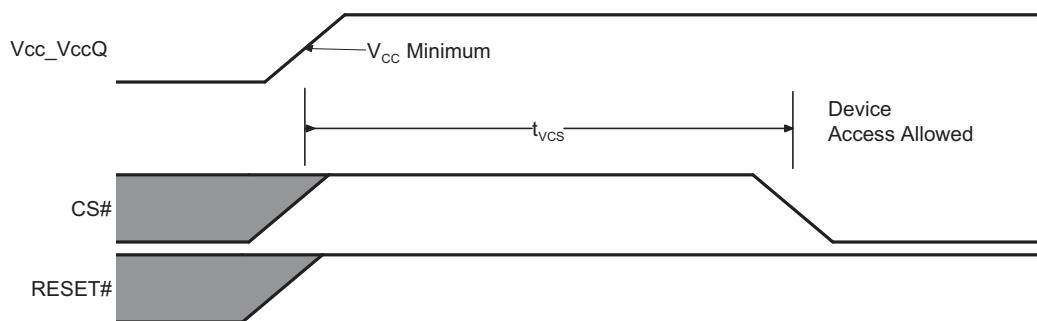

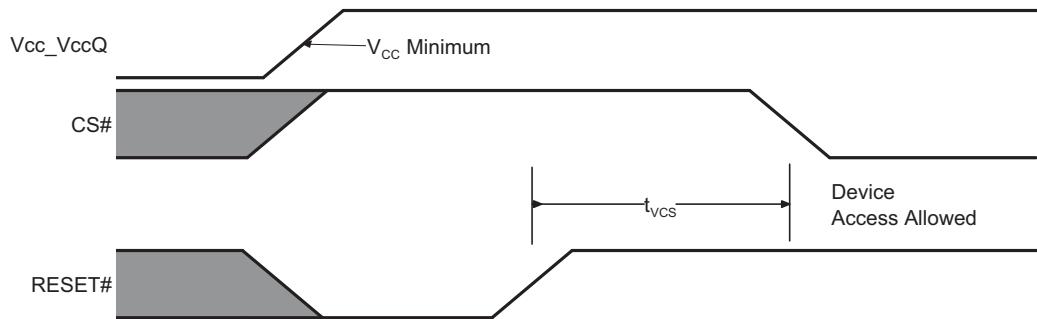

## 7.5 電源投入時の初期化

HyperRAM 製品は、電源投入時の初期化プロセスを起動する電圧センサーを内蔵しています。 $V_{CC}$  と  $V_{CCQ}$  は同時に印加する必要があります。電源電圧が  $V_{CC}$  (Min) 以上の安定したレベルに達した後、デバイスは自己初期化プロセスを完了するのに  $t_{VCS}$  時間を要します。

電源投入時にデバイスを選択することはできません。電源投入時に  $V_{CC}$  (Min) に達するまで CS# は  $V_{CCQ}$  印加された電圧に応じて変化しなければなりません。その後、CS# は  $t_{VCS}$  の追加の遅延時間の間 HIGH を維持する必要があります。 $V_{CCQ}$  とチップセレクト (CS#) を接続する簡単なプルアップ抵抗を使用すると安全かつ適切な電源投入を保証できます。

電源投入時に RESET# が LOW である場合、デバイスは RESET# が HIGH になるまで  $t_{VCS}$  時間の開始を遅延させます。 $t_{VCS}$  期間は、DRAM アレイのリフレッシュ動作を実行して初期化するために使用されます。

初期化が完了すると、デバイスは通常動作の準備ができます。

図 19. RESET# が HIGH 時の電源投入

図 20. RESET# が LOW 時の電源投入

表 20. 電源投入およびリセット パラメーター [56, 57, 58]

| パラメーター    | 説明                                                          | Min | Max  | 単位 |

|-----------|-------------------------------------------------------------|-----|------|----|

| $V_{CC}$  | 1.8V $V_{CC}$ 電源電圧                                          | 1.7 | 1.95 | V  |

| $V_{CC}$  | 3V $V_{CC}$ 電源電圧                                            | 2.7 | 3.6  | V  |

| $t_{VCS}$ | $V_{CC}$ と $V_{CCQ} \geq$ Min かつ RESET# HIGH から最初のアクセスまでの時間 | -   | 150  | μs |

注：

56. 電源投入時のリセット時間 ( $t_{VCS}$ ) 中はバス トランザクション (読み出しと書き込み) は禁止されます。

57.  $V_{CCQ}$  は、 $V_{CC}$  と同じ電圧でなければなりません。

58.  $V_{CC}$  ランプ レートは非線形である場合があります。

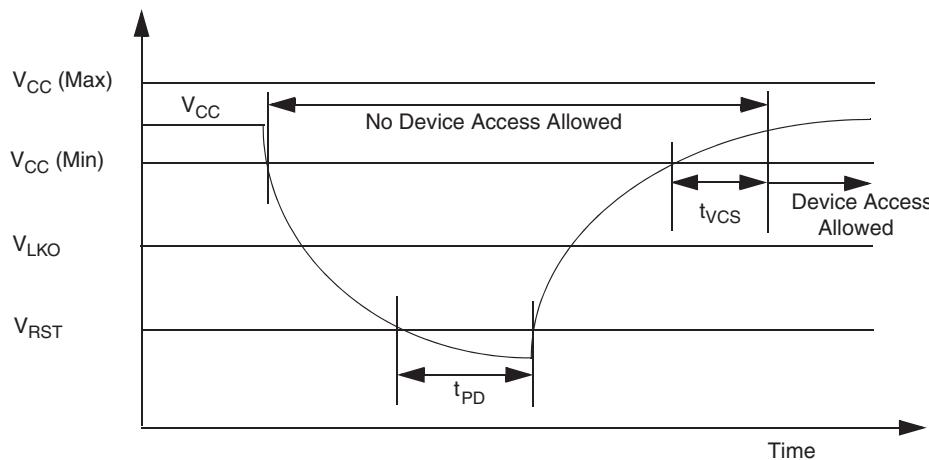

## 7.6 電源切斷

HyperRAM デバイスは、コア電源供給 ( $V_{CC}$ ) が  $V_{CC}$  ロックアウト電圧 ( $V_{LKO}$ ) 以下となった時に電源切斷とみなされます。電源電圧が  $V_{SS}$  レベルまで低下する変動の間は、 $V_{CCQ}$  は  $V_{CC}$  以下を保つ必要があります。 $V_{LKO}$  レベルでは、HyperRAM デバイスのコンフィギュレーションまたはアレイデータは失われています。

$V_{CC}$  は常に  $V_{CCQ}$  ( $V_{CC} \geq V_{CCQ}$ ) 以上であることが必要です。

電源切斷時または電源電圧が  $V_{LKO}$  を下回った時、コア電源供給の電圧も電源切斷期間 ( $t_{PD}$ ) 中  $V_{CC}$ Reset ( $V_{RST}$ ) 以下である必要があります。これにより、電源供給が再び  $V_{CC}$  の最小値まで上昇した時、部品が正しく初期化します。図 21 をご参照ください。

電圧低下時に、 $V_{CC}$  が  $V_{LKO}$  を上回ったままの場合は、部品は初期化状態のままとなり、 $V_{CC}$  が再度  $V_{CC}$  の最小値を上回った時正常に動作します。 $V_{CC}$  が  $t_{PD}$  期間以上  $V_{RST}$  を下回らない場合、POR プロセスが実行される保証はありません。この場合は、HyperBus デバイスが正しく初期化されていることを確認するためにハードウェアリセットが必要です。

図 21. 電源切斷または電圧低下

以下の節は電源切斷仕様の HyperRAM デバイスに依存した側面を説明します。

表 21. 1.8V でのパワーダウン電圧とタイミング [59]

| 記号        | パラメーター                                  | Min | Max  | 単位      |

|-----------|-----------------------------------------|-----|------|---------|

| $V_{CC}$  | $V_{CC}$ 電源電圧                           | 1.7 | 1.95 | V       |

| $V_{LKO}$ | $V_{CC}$ のロックアウト電圧。電圧がこれを下回ると再初期化が必要となる | 1.7 | -    | V       |