## 特殊特性

### HyperRAM™ 低电平信号计数接口

- 3.0 V I/O, 11 个总线信号

- 单端时钟 (CK)

- 1.8 V I/O, 12 个总线信号

- 差分时钟 (CK、CK#)

- 芯片选择 (CS#)

- 8 位数据总线 (DQ[7:0])

- 读写数据选通 (RWDS)

- 双向数据选通 / 掩码

- 在开始执行任何操作时作为输出, 用于指示刷新延迟

- 在读取过程中作为输出, 其功能是读取数据选通

- 在写入过程中作为输入, 其功能是写入数据掩码

- RWDS DCARS 时序

- 在读取过程中, 与 CK 相移的第二时钟是 RWDS 的偏移

- 相移的时钟用于将 RWDS 切换沿移动到读数据眼图范围内

### 高性能

- 高达 333 MB/s

- 双数据速率 (DDR): 每个时钟周期内进行两个数据传输

- $V_{CC} = 1.8$  V 时, 时钟频率可达 166 MHz (相应速率为 333 MB/s)

- $V_{CC} = 3.0$  V 时, 时钟频率可达 100 MHz (相应速率为 200 MB/s)

- 顺序突发操作

- 可配置突发特性

- 循环突发长度:

- 16 个字节 (8 个时钟周期)

- 32 个字节 (16 个时钟周期)

- 64 个字节 (32 个时钟周期)

- 128 个字节 (64 个时钟周期)

- 线性突发

- 混合选项 — 循环突发后接线性突发

- 在每一个操作中指定循环或线性突发类型

- 可配置输出驱动强度

- 封装

- 24-ball FBGA

## 性能总结

| 读取操作时序                                    |         |

|-------------------------------------------|---------|

| $V_{CC}/V_{CCQ} = 1.8$ V 时的最大时钟频率         | 166 MHz |

| $V_{CC}/V_{CCQ} = 3.0$ V 时的最大时钟频率         | 100 MHz |

| 最长访问时间, (时钟频率为 166 MHz 时的 $t_{ACC}$ )     | 36 ns   |

| 时钟频率为 166 MHz 时访问第一个字的最长 CS# 时间 (不包括刷新延迟) | 56 ns   |

| 最大电流消耗                                 |        |

|----------------------------------------|--------|

| 突发读取或写入 (频率为 166 MHz、电压为 1.8 V 下的线性突发) | 60 mA  |

| 上电复位                                   | 50 mA  |

| 待机模式 (CS# = 高电平、3 V、105°C)             | 300 µA |

| 深度掉电模式 (CS# = 高电平、3 V、105°C)           | 40 µA  |

| 待机模式 (CS# = 高电平、1.8 V、105°C)           | 300 µA |

| 深度掉电模式 (CS# = 高电平、1.8 V、105°C)         | 20 µA  |

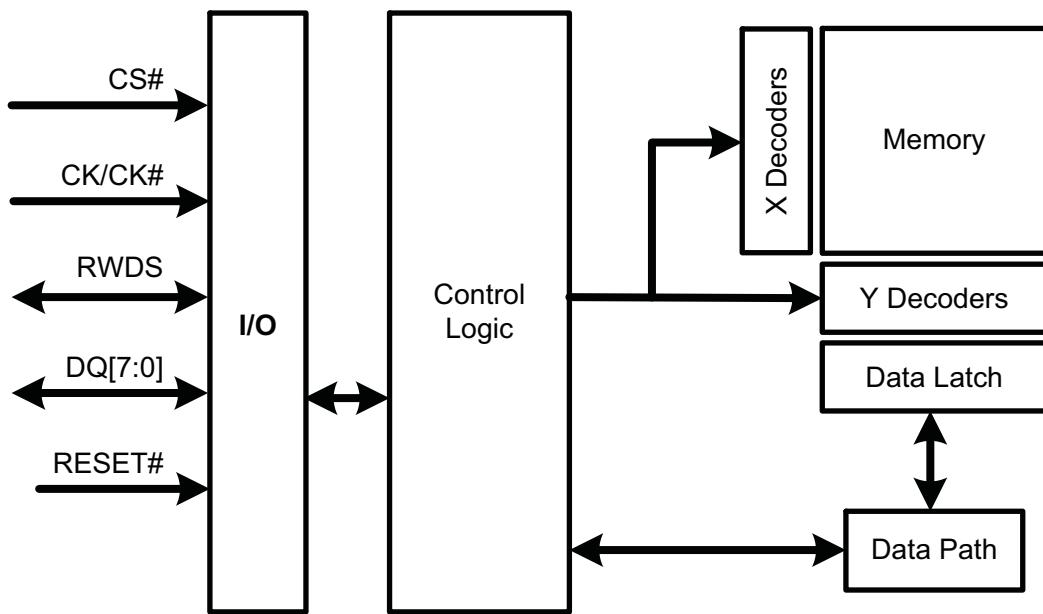

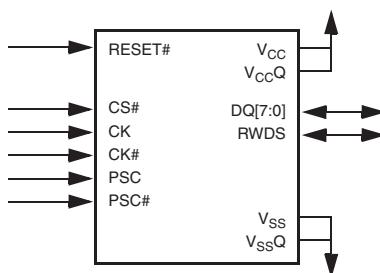

## 逻辑框图

## 目录

|                          |    |                                                         |    |

|--------------------------|----|---------------------------------------------------------|----|

| <b>1. 概述</b>             | 4  | <b>9.7 硬件复位</b>                                         | 36 |

| <b>2. HyperRAM 产品概述</b>  | 7  | <b>10. 时序规范</b>                                         | 37 |

| <b>3. HyperRAM 信号描述</b>  | 8  | 10.1 切换波形的关键                                            | 37 |

| 3.1 输入 / 输出简介            | 8  | 10.2 交流测试条件                                             | 37 |

| 3.2 命令 / 地址位分配           | 9  | 10.3 交流特性                                               | 38 |

| 3.3 读取操作                 | 13 | <b>11. 物理接口</b>                                         | 41 |

| 3.4 包含初始延迟的写入操作（存储器内核写入） | 14 | 11.1 FBGA 24 球 5 x 5 阵列封装                               | 41 |

| 3.5 无初始延迟的写入操作（寄存器写入）    | 16 | 11.2 物理框图                                               | 42 |

| <b>4. 存储器空间</b>          | 17 | <b>12. DDR 中心对齐读取选通功能</b>                               | 43 |

| <b>5. 寄存器空间</b>          | 17 | 12.1 带有 DCARS 信号说明的 HyperRAM 产品                         | 43 |

| 5.1 器件标识寄存器              | 17 | 12.2 具有 DCARS 的 HyperRAM 产品 — FBGA 24 球型焊盘，<br>5x5 阵列封装 | 44 |

| 5.2 寄存器空间访问              | 18 | 12.3 HyperRAM 存储器 DCARS 时序                              | 44 |

| <b>HyperRAM 器件硬件接口</b>   |    |                                                         |    |

| <b>6. 接口状态</b>           | 25 | <b>13. 订购信息</b>                                         | 46 |

| 6.1 节能模式                 | 25 | 13.1 订购器件型号                                             | 46 |

| <b>7. HyperRAM 连接说明</b>  | 27 | 13.2 有效组合                                               | 47 |

| 7.1 其它封装连接信号摘要           | 27 | 13.3 有效组合 — 汽车级 /AEC-Q100                               | 48 |

| 7.2 HyperRAM 框图          | 28 | <b>14. 修订记录</b>                                         | 49 |

| <b>8. 接口状态</b>           | 29 | 文档修订记录页                                                 | 49 |

| <b>9. 电气规范</b>           | 30 | <b>销售、解决方案和法律信息</b>                                     | 50 |

| 9.1 最大绝对额定值              | 30 | 全球销售和设计支持                                               | 50 |

| 9.2 栓锁特性                 | 31 | 产品                                                      | 50 |

| 9.3 工作范围                 | 31 | PSoC® 解决方案                                              | 50 |

| 9.4 直流特性                 | 32 | 赛普拉斯开发者社区                                               | 50 |

| 9.5 上电初始化                | 33 | 技术支持                                                    | 50 |

| 9.6 掉电                   | 35 |                                                         |    |

## 1. 概述

赛普拉斯的 64 Mb HyperRAM™ 产品系列是一个高速 CMOS，自刷新的动态 RAM (DRAM) 器件，并且它拥有一个 HyperBus 接口。随机存取存储器 (RAM) 阵列使用了要求定期刷新的动态单元。当 HyperBus 接口主设备 (主机) 未对存储器进行任何读或写操作时，器件内部的刷新控制逻辑将监控 RAM 数组的刷新操作。由于不需要通过主机进行任何刷新操作，因此，从主机角度来看，DRAM 使用静态单元来保持数据而不需要进行刷新。因此，也可以将该存储器视为伪静态 RAM (PSRAM)。

由于在读或写操作周期内 DRAM 单元不能进行刷新，所以主机进行读或写操作占用的时长也受到限制，以确保所需的内部逻辑刷新操作不会受到阻塞。开始新的数据传输时，如果存储器需要进行刷新操作，那么主机需要限制操作的时长，并要允许附加的初始访问延迟。

HyperBus 是低信号计数的双数据速率 (DDR) 接口，可提供较高的吞吐量用于进行读和写操作。每一个时钟周期内，DDR 接口协议支持在 DQ 输入 / 输出信号上传输两个数据字节。HyperBus 的每一个读取或写入操作包含一系列的 16 位宽且为一个时钟周期长的数据传输 (位于内部 HyperRAM 核心中) 以及相应的两个 8 位宽、半个时钟周期长的数据转换 (位于 DQ 信号上)。所有输入和输出均与 LV-CMOS 兼容。拥有订购器件编号 (OPN) 的器件版本适用于 1.8 V 或 3.0 V (额定值) 的内核电源电压 ( $V_{CC}$ ) 和 IO 缓冲区的电源电压 ( $V_{CCQ}$ )。

命令、地址和数据信息通过 8 个 HyperBus DQ[7:0] 信号传输。在 DQ 信号上接收命令、地址或数据时，HyperBus 从器件使用时钟来捕获信息。命令或地址值与时钟沿中心对齐。

每个操作的流程为：首先输出有效的 CS# 和命令 - 地址 (CA) 信号，然后时钟开始交替传输 6 个 CA 字节，接下来经过初始访问延迟、执行读或写数据传输，最后输出无效的 CS#。

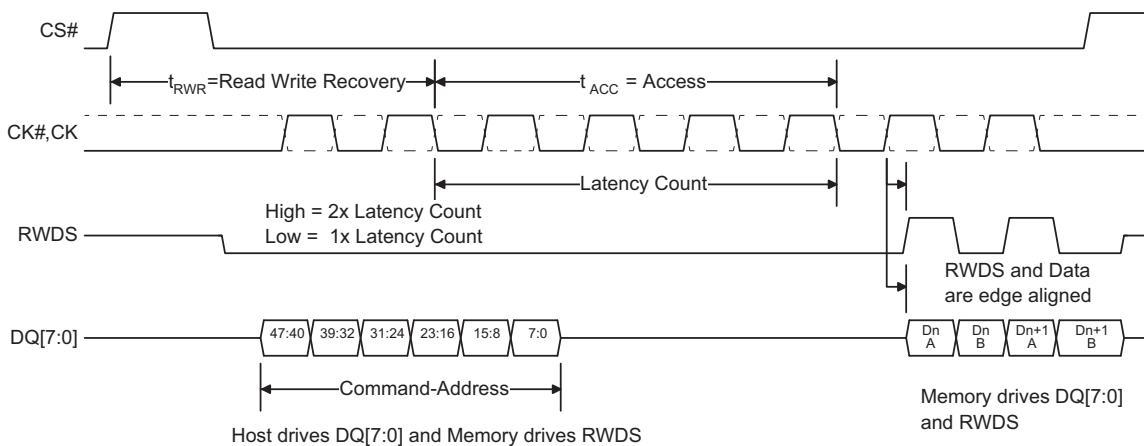

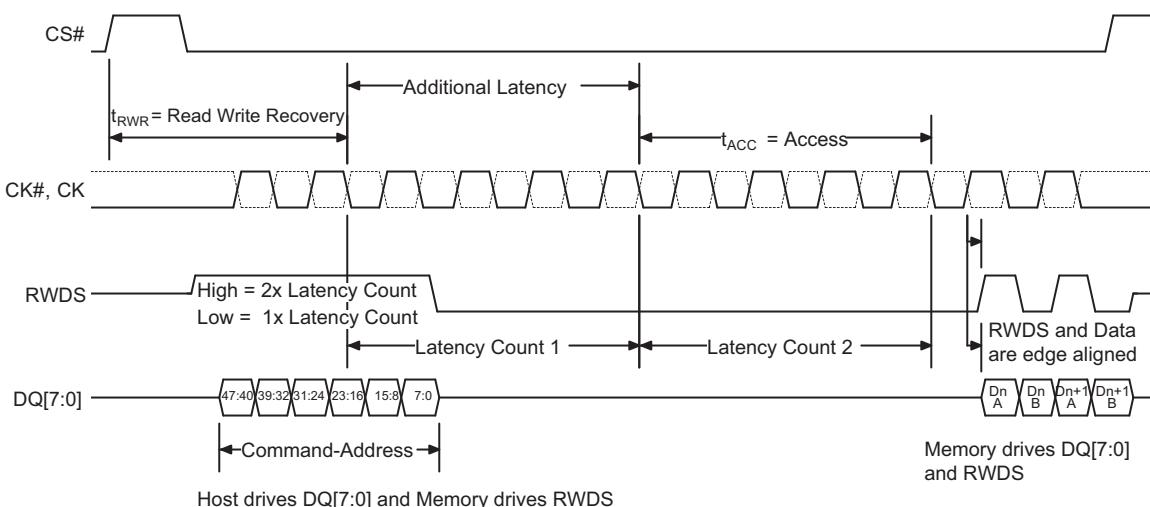

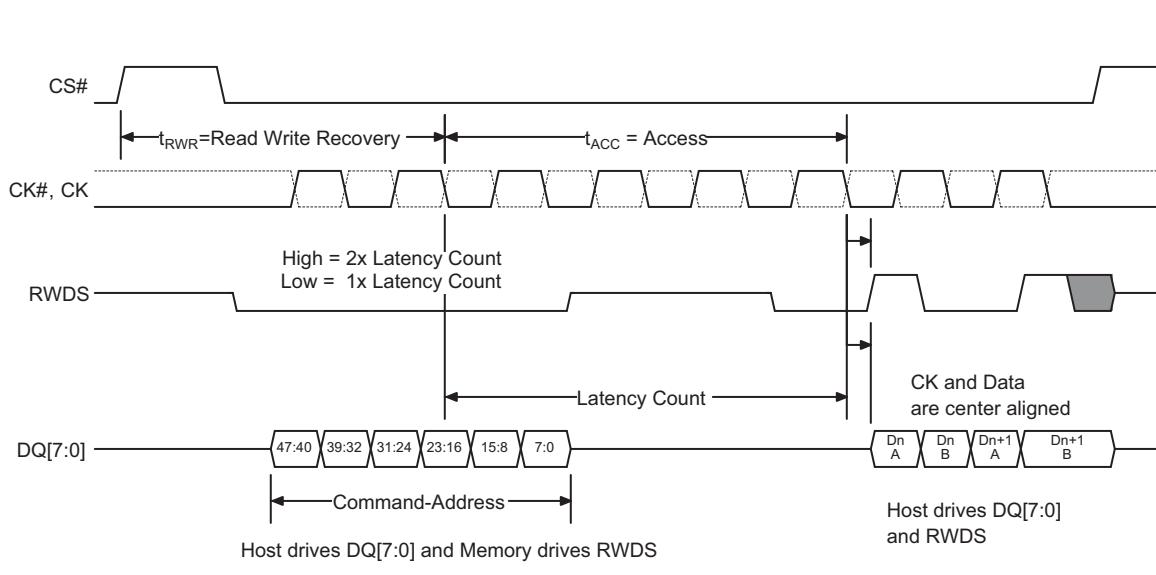

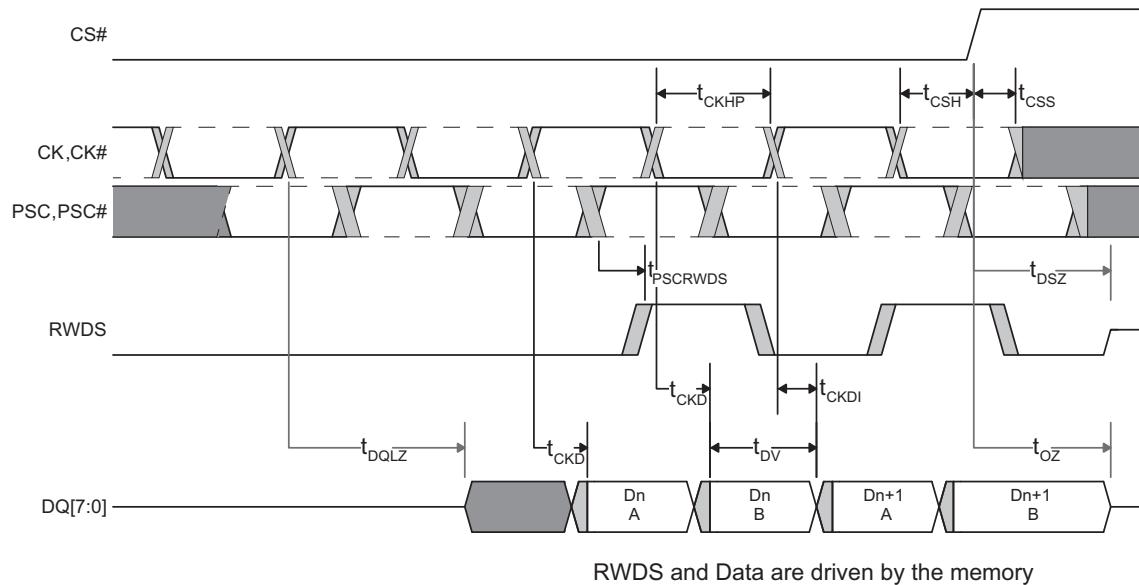

图 1.1 读操作 (单初始延迟计数)

读 / 写数据选通 (RWDS) 是一个双向信号，用于指示下列内容：

- 读取期间内，数据从 HyperRAM 器件开始传输到主设备的时间 (初始读取延迟)

- 读取期间内，数据从 HyperRAM 器件传输到主设备的时间 (源同步读取数据选通)

- 写入期间内，数据从主设备开始传输到 HyperRAM 器件的时间 (初始写延迟)

- 写入数据传输中的数据掩码

在读取或写入操作的 CA 传输过程中，RWDS 作为 HyperRAM 器件的输出，表示操作是否需要附加初始访问延迟。

在读取数据传输中，RWDS 作为读数据选通，数据边沿与 RWDS 的转换对齐。

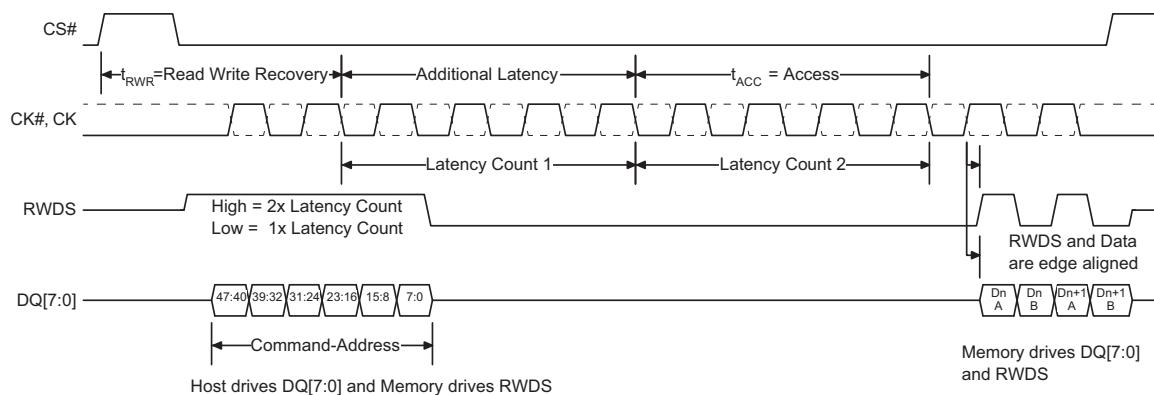

图 1.2 读取操作（附加延迟计数）

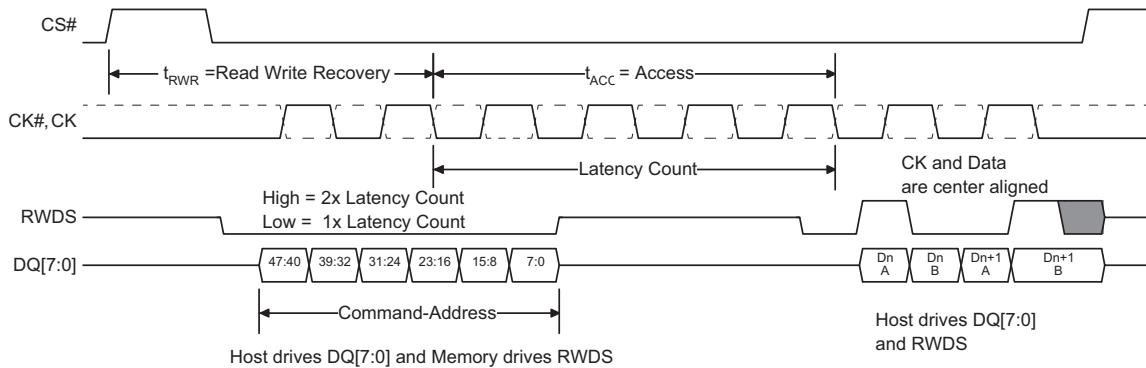

在写入数据传输中, RWDS 用于指示每个数据字节传输是在 RWDS 的高电平状态下被屏蔽(无效并防止改变字节在存储器中的位置)还是在 RWDS 的低电平状态下未被屏蔽(有效, 并被写入到存储器内)。主机可以通过数据屏蔽对存储器内的写入数据进行字节对齐, 或合并单一突发写入中并非字对齐的写数据。在写入操作期间, 数据中心与时钟转换沿对齐。

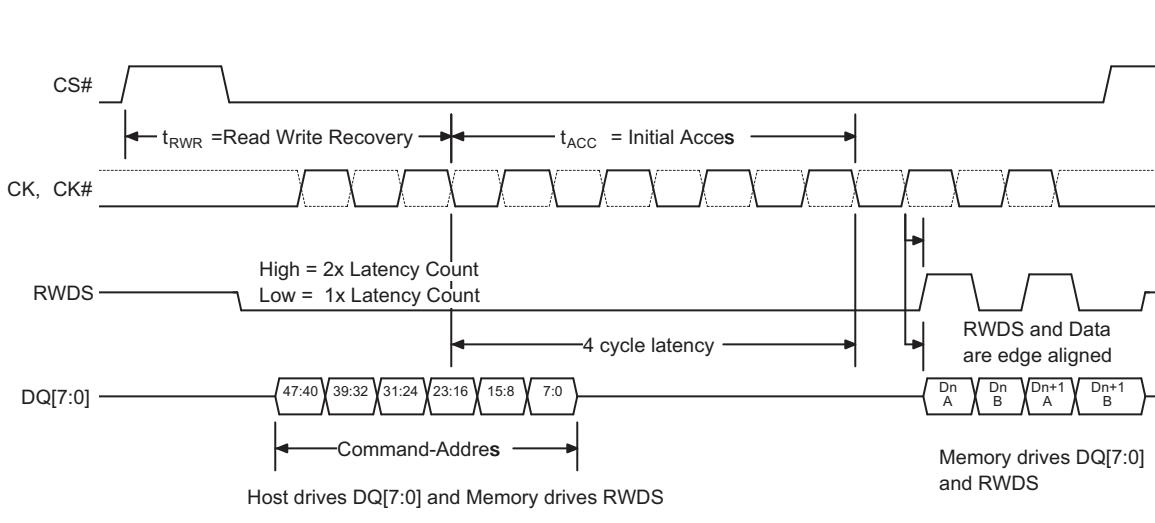

图 1.3 写入操作（单初始延迟计数）

读取和写入操作均是突发序列, 在每个时钟周期内会传输下一个字。每个读取或写入操作都可以使用循环或线性突发序列

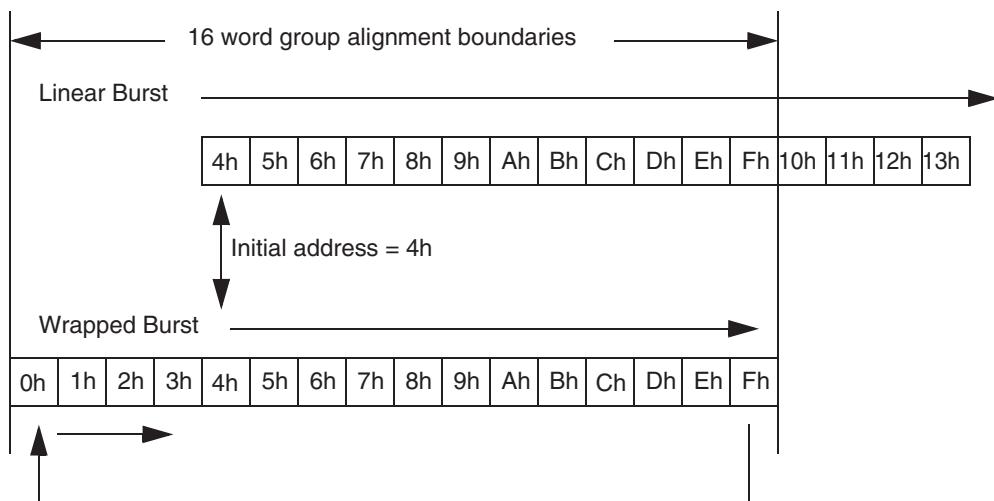

图 1.4 线性与循环突发序列

循环操作期间，访问将从选定的位置开始，持续到已配置的字组对齐边界的边沿，然后返回到组的起始位置，并再次从选定位置开始执行。循环突发一般用于临界字第一高速缓存行填充的读取操作。在线性操作期间，访问从一个选定的地址开始，并且按顺序连续进行，直到 CS# 返回高电平、操作终止为止。该操作通常用于执行连续的大容量数据传输，如图形图像传输。由于每个操作命令将选择相对应的突发序列类型，因此，需要时可动态使用循环和线性突发序列。

## 2. HyperRAM 产品概述

64 Mb HyperRAM 器件是一款使用 1.8 V/3.0 V 内核和 I/O 并且能够进行同步自刷新的动态 RAM (DRAM)。本产品系列支持 HyperBus 从设备接口，用于连接主机系统。HyperBus 拥有一个 8 位 (一个字节) 宽的 DDR 数据总线，但地址是字地址 (16 位数据)。执行读取操作时，每一个时钟周期内将传输 16 位数据 (在时钟上下沿各传输 8 位)。执行写入操作时，每一个时钟周期内将传输 16 位数据 (在时钟上下沿各传输 8 位)。

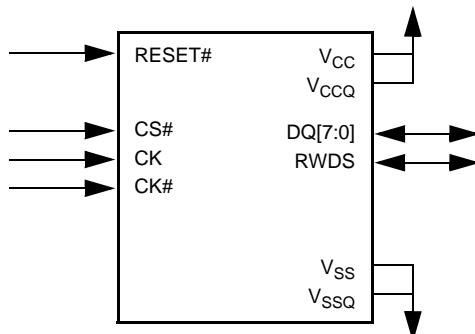

图 2.1 HyperRAM 接口

读取和写入操作需要占用两个时钟周期来定义目标行地址、突发类型，以及时长为  $t_{ACC}$  的初始访问延迟。在某个操作的命令 - 地址 (CA) 传输过程中，通过将 RWDS 信号设置为高电平，存储器可以指示初始延迟是否需要添加额外的刷新时间 ( $t_{RFH}$ )。在 CA 传输期间，第三个时钟周期将指定目标行上目标字的地址。在读取 (或写入) 期间，输出 (或输入) 初始数据值后，在下一个时钟周期内可使用循环或线性序列从行中读取附加数据 (或将其写入到行中)。配置为线性突发模式时，器件将从存储器数组中自动提取下一行，以实现连续的线性突发序列。通过在读取或写入数据传输的同时访问阵列中的下一行，可以实现线性顺序突发操作，并提供高达 333 MB/s 的持续数据传输率 (一个字节 (8 位数据总线) \* 2 (数据时钟沿) \* 166 MHz = 333 MB/s)。

### 3. HyperRAM 信号描述

#### 3.1 输入 / 输出简介

表 3.1 中显示的是有关 HyperRAM 信号的信息。低电平有效信号的名称带有一个井字符 (#) 作为后缀。

表 3.1 I/O 简介

| 符号               | 类型           | 说明                                                                                                                                |

|------------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------|

| CS#              | 主出从入         | 片选。该引脚从高电平转为低电平时，将启动总线传输。相反，当该引脚从低电平转为高电平时，将终止总线传输。主设备为每个从设备提供了一个独立的 CS#。                                                         |

| CK、 CK#          | 主出从入         | 差分时钟。命令、地址和数据信息在 CK 和 CK# 信号交叉点输出。差分时钟用于 1.8 V 的 I/O 器件。<br>单端时钟。3.0 V 器件不使用 CK#，仅使用了一个单端 CK。<br>不要求使用自由运行时钟。                     |

| DQ[7:0]          | 输入 / 输出      | 数据输入 / 输出。进行读写操作期间，将通过这些信号来传输命令、地址和数据信息。                                                                                          |

| RWDS             | 输入 / 输出      | 读写数据选通。在所有总线操作的命令 / 地址部分中，RWDS 是一个从输出，并表示是否需要附加初始延迟。读取数据传输期间的从设备为输出，数据与 RWDS 边沿对齐。在写入数据传输期间，从输入作为数据掩码使用。<br>(高 = 附加延迟，低 = 无附加延迟)。 |

| RESET#           | 主出从入<br>内部上拉 | 硬件复位。当该信号处于低电平状态时，从设备会自初始化，并返回到待机状态。当 RESET# 处于低电平状态时，RWDS 和 DQ[7:0] 将进入高阻态。从设备 RESET# 输入包含一个弱上拉电阻，如果 RESET# 保持未连接状态，它将被上拉到高电平状态。 |

| V <sub>CC</sub>  | 电源电压         | 内核电源电压。                                                                                                                           |

| V <sub>CCQ</sub> | 电源电压         | 内核输入 / 输出电源电压。                                                                                                                    |

| V <sub>SS</sub>  | 电源电压         | 内核接地电压。                                                                                                                           |

| V <sub>SSQ</sub> | 电源电压         | 内核输入 / 输出电源电压。                                                                                                                    |

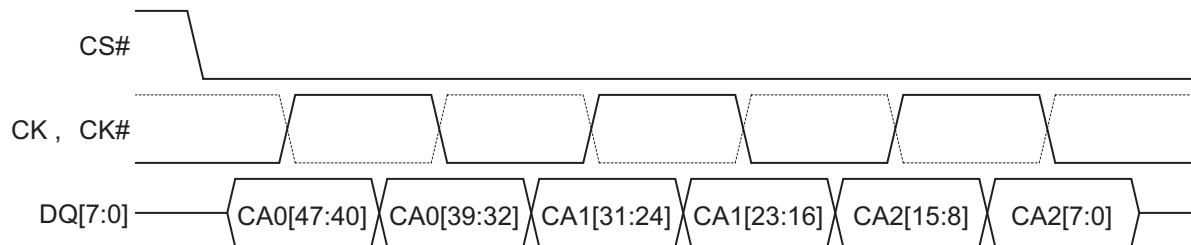

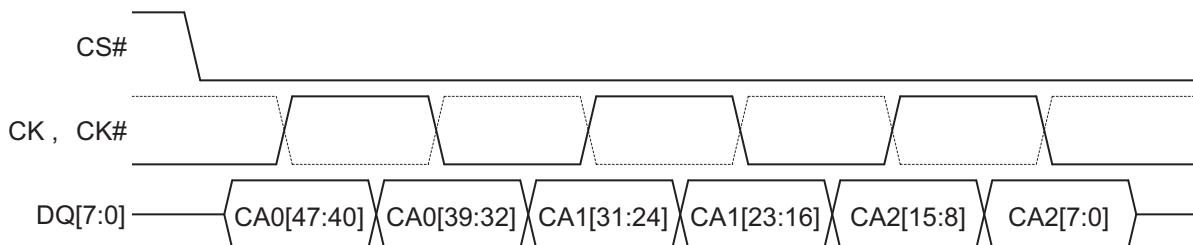

### 3.2 命令 / 地址位分配

所有 HyperRAM 总线数据操作都可分为读取或写入操作两类。一个总线数据操作在 CS# 为低电平并且时钟处于闲置状态（CK 为低电平且 CK# 为高电平）时开始。在前三个时钟周期内，将传输三个命令 / 地址（CA0、CA1、CA2）信息字来定义操作特性。命令 / 地址字按 DDR 时序进行传输，并使用前六个时钟边沿。命令 / 地址信息定义了以下操作特性：

- 读取操作还是写入操作

- 地址空间：存储器阵列空间还是寄存器空间

- 寄存器空间用于访问器件标志（ID）寄存器和配置寄存器（CR），以便指定器件特性并确定 HyperBus 接口上读取和写入传输中针对从设备的行为。

- 传输操作使用线性还是循环突发序列。

- 目标行（和半页）地址（上行地址）

- 目标列（半页中的字）地址（下列地址）

图 3.1 命令 - 地址序列

**注意：**

1. 上图显示的是 HyperBus 上所有数据操作的最前三个时钟周期。

2. 差分时钟的 CK# 用虚线波形显示。

3. 在读取和写入操作中，命令 - 地址信息均与时钟中心对齐。

表 3.2 DQ 信号的命令 - 地址位分配

| 信号    | CA0[47:40] | CA0[39:32] | CA1[31:24] | CA1[23:16] | CA2[15:8] | CA2[7:0] |

|-------|------------|------------|------------|------------|-----------|----------|

| DQ[7] | CA[47]     | CA[39]     | CA[31]     | CA[23]     | CA[15]    | CA[7]    |

| DQ[6] | CA[46]     | CA[38]     | CA[30]     | CA[22]     | CA[14]    | CA[6]    |

| DQ[5] | CA[45]     | CA[37]     | CA[29]     | CA[21]     | CA[13]    | CA[5]    |

| DQ[4] | CA[44]     | CA[36]     | CA[28]     | CA[20]     | CA[12]    | CA[4]    |

| DQ[3] | CA[43]     | CA[35]     | CA[27]     | CA[19]     | CA[11]    | CA[3]    |

| DQ[2] | CA[42]     | CA[34]     | CA[26]     | CA[18]     | CA[10]    | CA[2]    |

| DQ[1] | CA[41]     | CA[33]     | CA[25]     | CA[17]     | CA[9]     | CA[1]    |

| DQ[0] | CA[40]     | CA[32]     | CA[24]     | CA[16]     | CA[8]     | CA[0]    |

**表 3.3 命令 / 地址位分配**

| CA 位 # | 位名        | 位功能                                                                                                       |

|--------|-----------|-----------------------------------------------------------------------------------------------------------|

| 47     | R/W#      | 表示读或写操作。<br>R/W# = 1, 表示读操作<br>R/W# = 0, 表示写操作                                                            |

| 46     | 地址空间 (AS) | 表示所执行的读 / 写访问是对存储器还是对寄存器空间进行的。<br>AS = 0, 表示对存储器空间进行操作<br>AS = 1, 表示对寄存器空间进行操作<br>寄存器空间可用于访问器件 ID 和配置寄存器。 |

| 45     | 突发类型      | 表示突发类型是线性的还是循环的。<br>突发类型 = 0, 表示循环突发<br>突发类型 = 1, 表示线性突发                                                  |

| 44-16  | 行地址与高位列地址 | 指出目标地址的行地址和高位列地址组件：系统中的字地址位 (A31-A3)<br>需要通过主机控制器的主接口将未使用的高位行地址位设置为 0。行大小以及行与列地址之间的地址位边界与从设备相关。           |

| 15-3   | 保留        | 留给列地址的扩展部分使用<br>在当前的 HyperBus 器件中无需关注保留位，但考虑到将来的兼容性要求，应通过主机控制器的主接口将其设置为 0。                                |

| 2-0    | 低位列地址     | 目标地址的低位列组件：系统中的字地址位 (A2-A0) 在半页的范围内选择起始字。                                                                 |

**注意：**

1. 行是一组与内部存储器阵列结构相关的字。当访问跨过行边界时，可以通过 RWDS 插入额外延迟。该特性取决于器件，更多相关信息，请查阅 HyperBus 器件数据手册。另外，可以使用行数来计算 HyperRAM 器件的分布式刷新间隔。

2. 页是器件内部进行读取或写入访问的单位。页的长度为 16 字 (32 个字节) 并且是对齐的。当访问跨过页边界时，可以通过 RWDS 插入额外延迟。该特性取决于器件，更多相关信息，请查阅 HyperBus 器件数据手册。

3. 列地址用于选择突发操作在行内的起始字位置。列地址被分为上列和下列两部分。上列地址选择半页 8 字 (16 字节)，下列地址则选择半页内读取或写入操作突发开始的字。

4. 从接口捕捉到行和上列 (半页) 地址位时，便开始了读取操作的初始访问时间。存储器器件允许连续线性的读取突发对 16 字节半页内部进行交叉访问。

**5. HyperBus 协议地址空间限制，假设：**

29 个行和上列地址位

3 个下列地址位

每个地址选择一个字长 (16 位 = 2 字节) 的数据值

$29 + 3 = 32$  地址位 = 4 G 地址，最大支持 8 GB (64 Gb) 地址空间

将来扩展型的列地址可以支持 29 个行和上列地址位 + 16 个下列地址位 = 35 万亿字 = 70 TB 地址空间。

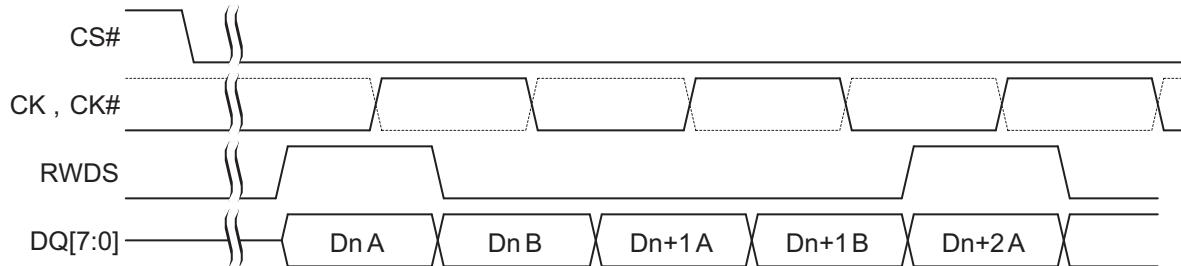

**图 3.2 某个读取操作期间的数据放置**

**注意：**

1. 上图显示的是 HyperBus 上读取操作的一部分。差分时钟的 CK# 用虚线表示。

2. 在读取操作中，RWDS 作为读取数据选通使用，它与数据边沿对齐。

3. 数据传输单位按整字递增 (也称为字粒度传输)。

4. 字地址按每个时钟周期递增。对于每个字，字节 A 在 RWDS 上升沿和下降沿间被传输，接下来在 RWDS 下降沿和上升沿间传输字节 B。

5. 每个字节中的数据位按从高到低的顺序放置，位 7 对应于 DQ7，位 0 对应于 DQ0。

**表 3.4** 读或写传输期间数据位的放置

| 地址空间 | 字节顺序 | 字节位置 | 字数据位 | DQ | 位序 |

|------|------|------|------|----|----|

| 存储器  | 字节大端 | A    | 15   | 7  |    |

|      |      |      | 14   | 6  |    |

|      |      |      | 13   | 5  |    |

|      |      |      | 12   | 4  |    |

|      |      |      | 11   | 3  |    |

|      |      |      | 10   | 2  |    |

|      |      |      | 9    | 1  |    |

|      |      |      | 8    | 0  |    |

|      | 字节小端 | B    | 7    | 7  |    |

|      |      |      | 6    | 6  |    |

|      |      |      | 5    | 5  |    |

|      |      |      | 4    | 4  |    |

|      |      |      | 3    | 3  |    |

|      |      |      | 2    | 2  |    |

|      |      |      | 1    | 1  |    |

|      |      |      | 0    | 0  |    |

|      | 字节小端 | A    | 7    | 7  |    |

|      |      |      | 6    | 6  |    |

|      |      |      | 5    | 5  |    |

|      |      |      | 4    | 4  |    |

|      |      |      | 3    | 3  |    |

|      |      |      | 2    | 2  |    |

|      |      |      | 1    | 1  |    |

|      |      |      | 0    | 0  |    |

|      | 字节大端 | B    | 15   | 7  |    |

|      |      |      | 14   | 6  |    |

|      |      |      | 13   | 5  |    |

|      |      |      | 12   | 4  |    |

|      |      |      | 11   | 3  |    |

|      |      |      | 10   | 2  |    |

|      |      |      | 9    | 1  |    |

|      |      |      | 8    | 0  |    |

在存储器空间中访问数据时：

先对每字的 A 字节执行读或写操作，然后才对 B 字节执行读 / 写操作。

在 A 和 B 字节中，每字中的位取决于数据是如何写入的。如果将字的小端地址位 7-0 写入到 A 字节的位置，将位 15-8 写入 B 字节的位置，或反过来写入，那么需要使用相同顺序进行读回。

可按小端或大端顺序对存储器空间进行写入或读取操作。

**表 3.4** 读或写传输期间数据位的放置 (续)

| 地址空间 | 字节顺序 | 字节位置 | 字数据位 | DQ | 位序                                                                                                                                         |

|------|------|------|------|----|--------------------------------------------------------------------------------------------------------------------------------------------|

| 寄存器  | 字节大端 | A    | 15   | 7  | 在寄存器空间中访问数据时：<br>对于 HyperBus 的读取传输，每个时钟周期内将传输两个字节。大端字节 A (Word[15:8]) 在 RWDS 的上升沿和下降沿之间被传输 (边沿对齐)。小端字节 B (Word[7:0]) 在 RWDS 的下降沿和上升沿之间被传输。 |

|      |      |      | 14   | 6  |                                                                                                                                            |

|      |      |      | 13   | 5  |                                                                                                                                            |

|      |      |      | 12   | 4  |                                                                                                                                            |

|      |      |      | 11   | 3  |                                                                                                                                            |

|      |      |      | 10   | 2  |                                                                                                                                            |

|      |      |      | 9    | 1  |                                                                                                                                            |

|      |      |      | 8    | 0  |                                                                                                                                            |

|      |      | B    | 7    | 7  | 在写操作期间，大端字节 A (Word[15:8]) 在时钟的上升沿上被传输，小端字节 B (Word[7:0]) 在时钟的下降沿上被传输。<br>始终按高端字节顺序对寄存器空间进行读 / 写操作，因为这些寄存器具有固定的与器件相关的位位置和定义。               |

|      |      |      | 6    | 6  |                                                                                                                                            |

|      |      |      | 5    | 5  |                                                                                                                                            |

|      |      |      | 4    | 4  |                                                                                                                                            |

|      |      |      | 3    | 3  |                                                                                                                                            |

|      |      |      | 2    | 2  |                                                                                                                                            |

|      |      |      | 1    | 1  |                                                                                                                                            |

|      |      |      | 0    | 0  |                                                                                                                                            |

**图 3.3** 写入操作期间的数据放置

**注意：**

1. 上图显示的是 HyperBus 上写入操作的一部分。

2. 在写入操作期间，数据与时钟中心对齐。

3. 在带有初始延迟的写入数据传输期间，RWDS 作为数据掩码使用。第一和最后的字节被屏蔽，用于描述三字节的非对齐写入数据。

4. 在零初始延迟的写入数据传输期间，RWDS 未被主设备驱动。在这种情况下，会一直写入整字数据。从设备可以将 RWDS 驱动为低电平或使之处于高阻态。

### 3.3 读取操作

HyperBus主设备在时钟处于闲置状态时会将CS#驱动为低电平，启动一个数据操作。然后时钟开始切换，同时传输命令-地址CA字。

在CA[0]中，CA[47] = 1时，则正在执行读取操作。CA[46] = 0，表示将读取存储器空间；或者CA[46] = 1，表示将读取寄存器空间。CA[45]指定突发类型（循环还是线性）。一旦行和高位列地址被传输到CA0和CA1（CA[47:16]），读操作可以进行内部存储阵列访问。CA2（CA[15:0]）指定所进行内的目标字地址。但是，有些器件要求两个数据操作之间保留最长时间，这段时间被称为读-写恢复时间（t<sub>RWR</sub>）。只有满足t<sub>RWR</sub>后完成CA1传输时，主接口才需要将CS#驱动为低电平。

这时，HyperBus主接口会根据配置寄存器0中延迟计数设置所定义的周期数继续计时。而某个特定时钟频率所需的初始延迟计数取决于RWDS。在CA周期中，如果RWDS为低电平，则需要插入一个延迟周期。在CA周期中，如果RWDS为高电平，则需要插入一个附加的延迟计数。完成这些延迟周期后，存储器开始同时翻转读-写数据选通（RWDS）并输出目标数据。

新数据输出与RWDS每次转换都是边沿对齐的。CS#为低电平状态时，只要主机仍然切换时钟，便会继续输出数据。但HyperRAM器件可能在各字传输期间以及RWDS为低电平时停止RWDS转换，以便在超出某个存储器阵列边界时在各字间插入延迟。

循环突发只在突发长度内进行循环，而线性突发将按顺序输出数据，甚至会超出行界限。线性突发读取到阵列中最后的地址时，如果继续读取并且超出最后地址，那么会获得未定义的数据。在时钟处于闲置状态时，将CS#驱动为高电平可以随时停止读取传输。

不要求时钟处于自由运行状态。CS#为高电平时，时钟可保持闲置状态。

图 3.4 读取操作（包含附加初始延迟）

#### 注意：

1. 在CS#为下降沿、CK为低电平，并且CK#为高电平时，将启动数据操作。

2. 必须使CS#返回到高电平状态，才能启动一个新操作。

3. CK#是CK信号的反相信号。3 V器件使用单端时钟（CK），在1.8 V器件上CK#与CK一起使用，用于提供差分时钟。差分时钟的CK#用虚线波形显示。

4. CA[23:16]被捕捉后，将立即开始读取访问存储阵列。

5. 读取延迟由配置寄存器中的初始延迟值定义的。

6. 在该读取操作示例中，初始延迟被设置为四个时钟周期。

7. 在该读取操作中，CA周期内RWDS的高电平状态会使目标数据输出延迟四个时钟周期。

8. 在读取操作过程中，存储器驱动了RWDS。

图 3.5 读取操作（无附加初始延迟）

**注意:**

1. RWDS 在 CA 周期中为低电平状态。在该读取操作中，读取数据访问存在一个单初始延迟计数，因为读取操作开始时，从接口并不要求添加延迟。

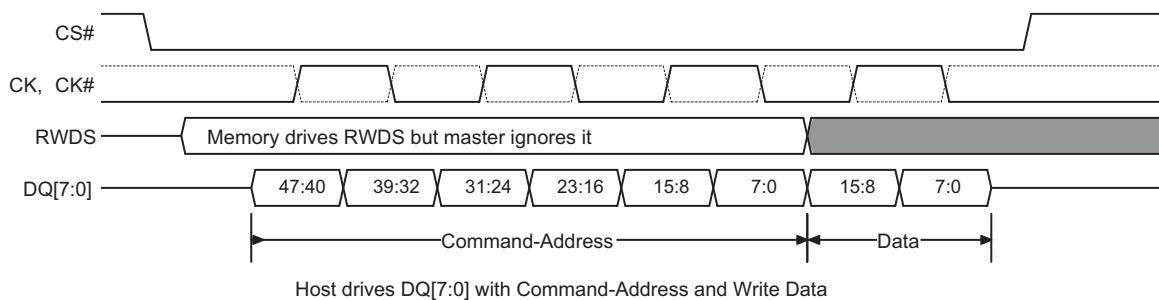

### 3.4 包含初始延迟的写入操作（存储器内核写入）

HyperBus 主设备在时钟处于闲置状态时会将 CS# 驱动为低电平，从而启动一次数据操作。时钟开始切换，命令 - 地址 CA 字被传输。

在 CA0 中，CA[47] = 0，表示将要执行一个写入操作。CA[46] = 0 表示将写入存储器空间内。CA[45] 指定突发类型（循环还是线性）。一旦行和高位列地址被传输到 CA0 和 CA1 (CA[47:16])，写入操作便可以进行内部阵列访问。CA2 (CA[15:0]) 指定所选行内的目标字地址。但是，一些 HyperBus 设备要求两个数据操作之间存在一段最小的等待时间。这段时间被称为读 - 写 - 恢复时间 ( $t_{RWR}$ )。只有满足  $t_{RWR}$  后完成 CA1 传输时，主接口才需要将 CS# 驱动为低电平。

这时，HyperBus 主接口会根据配置寄存器 0 中延迟计数设置所定义的周期数继续计时。而某个特定时钟频率所需的初始延迟计数取决于 RWDS。在 CA 周期中，如果 RWDS 为低电平，则需要插入一个延迟周期。在 CA 周期中，如果 RWDS 为高电平，则需要插入一个附加的延迟计数。

完成这些延迟周期后，HyperBus 主接口将开始输出目标数据。写入数据中心与时钟边沿对齐。每个字中的第一个数据字节会在 CK 上升沿上被存储器捕捉，第二个数据字节会在 CK 下降沿上被捕捉。

在 CA 时钟周期中，存储器会驱动 RWDS。

在写入数据传输过程中，主机主接口驱动 RWDS，将其作为数据掩码使用。RWDS 为高电平时，写入数据字节被屏蔽，并且存储阵列不会改变。RWDS 为低电平时，写入数据将被放入到存储阵列中。由于主设备在写入数据传输期间驱动 RWDS，所以主设备和 HyperRAM 器件都不会在执行写操作的数据传输过程中要求延迟。进行配置寄存器 0 时也对可用的写数据突发长度设置进行了定义。

当 CS# 为低电平时，只要 HyperBus 主设备仍然切换时钟，便会继续传输数据。传统格式的循环突发会在突发长度内继续进行循环。混合循环突发将执行一次循环操作，然后在下一个循环边界上切换为线性突发。线性突发持续接收数据，甚至超出页边界。在时钟处于闲置状态时，可随时通过将 CS# 驱动为高电平来停止写入传输。

当某个线性突发的写入操作到达存储器阵列最后地址时，继续执行突发会写入到地址范围的起始位置。

不要求时钟处于自由运行状态。CS# 为高电平时，时钟可保持闲置状态。

图 3.6 写入操作（包含附加初始延迟）

**注意:**

- 必须将 CK 驱动为低电平，并将 CK# 驱动为高电平，以启动数据传输操作。

- 必须将 CS# 返回到高电平状态，才能启动一个新操作。

- 在命令 - 地址期间，RWDS 被存储器驱动，以表示是否要求附加延迟周期。

- 在该示例中，RWDS 表示要求附加初始延迟。

- 命令 - 地址周期结束时，存储器不再驱动 RWDS，转由主机 HyperBus 主设备驱动 RWDS。主设备要在初始延迟周期结束前将 RWDS 驱动为有效的低电平状态，为从设备提供数据掩码前导周期。

- 数据传输过程中，RWDS 由主机驱动，表示数据字节被屏蔽还是被加载到存储阵列内。

- 上图显示的是 RWDS 屏蔽字节 A0 和字节 B1，向字节 B0 和 A1 执行非对齐字写操作。

图 3.7 写入操作（无附加初始延迟）

**注意:**

- 在命令 - 地址期间，RWDS 被存储器驱动，并表示是否要求附加延迟周期。

- 在该示例中，RWDS 表示不要求附加延迟。

- 命令 - 地址周期结束时，存储器不再驱动 RWDS，转由主机 HyperBus 主接口驱动 RWDS。主设备要在初始延迟周期结束前将 RWDS 驱动为有效的低电平状态，为从设备提供数据掩码前导周期。

- 数据传输过程中，RWDS 由主机驱动，表示数据字节被屏蔽还是被加载到存储阵列内。

- 上图显示的是 RWDS 屏蔽字节 A0 和字节 B1，向字节 B0 和 A1 执行非对齐字写操作。

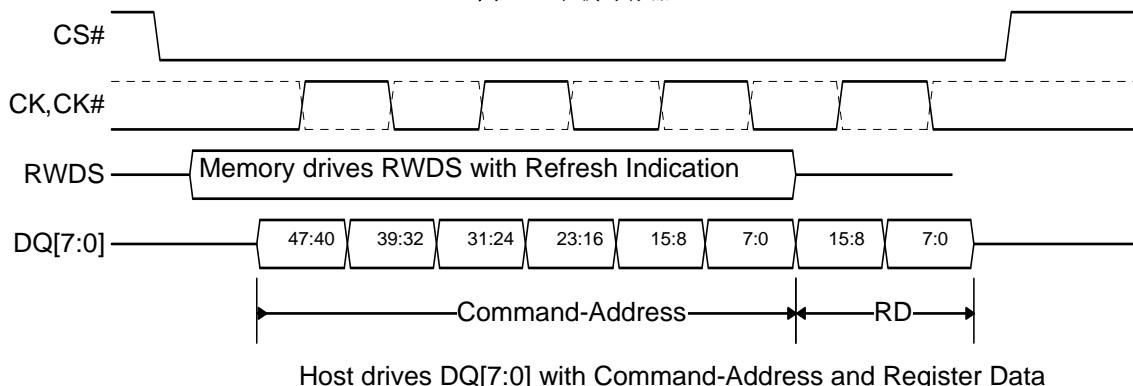

### 3.5 无初始延迟的写入操作（寄存器写入）

写入操作的最前三个时钟周期用于提供表示操作特性的命令 / 地址信息。CA0 用于指示将执行的操作是写操作，并且指明操作的地址空间和突发类型（循环还是线性）。

无初始延迟的写操作适用于对寄存器空间进行写入操作的场合。无延迟的 HyperRAM 寄存器写入操作指的是在 CA 时钟周期后执行写数据传输。对于零初始延迟的写入操作，RWDS 不存在返回周期。HyperRAM 器件在命令 - 地址周期中会一直驱动 RWDS，用于表示包含初始延迟的数据传输操作是否需要增加延迟时间。但 HyperRAM 器件接收到第一个 CA 字节前，也就是在 HyperRAM 器件确认数据操作需要进行的是读操作还是写操作前，已经驱动了 RWDS。如果操作是零延迟的写入操作，那么 CA 传输期间的 RWDS 状态并不会影响它的初始延迟。在这种情况下，由于主设备写数据紧挨着 CA 周期，所以 HyperRAM 器件在写数据传输期间可能仍将 RWDS 驱动为低电平或将它转换到高阻态。在零延迟写入操作中，不要通过主设备驱动 RWDS。零延迟的写入操作不会将 RWDS 作为数据掩码使用。写入数据的所有字节均被写入（整字写入）。

每个字中的第一个数据字节在 CK 上升沿上被传输，第二个数据字节在 CK 下降沿上被传输。写入数据与时钟输入是中心对齐的。在时钟处于闲置状态时，可随时通过将 CS# 驱动为高电平来停止写入传输。不要求时钟处于自由运行状态。

图 3.8 写入操作（无初始延迟）

## 4. 存储器空间

CA[46] 为 0, 表示对 DRAM 存储器阵列进行读取或写入操作。

表 4.1 存储空间地址映射

| 单位类型        | 计数       | 系统字地址位   | CA 位    | 注意                |

|-------------|----------|----------|---------|-------------------|

| 64 Mb 器件中的行 | 8192 (行) | A21 - A9 | 34 - 22 |                   |

| 行           | 1 (行)    | A8 - A3  | 21 - 16 | 512 (字地址)<br>1 KB |

| 半页          | 8 (字地址)  | A2 - A0  | 2 - 0   | 16 个字节            |

## 5. 寄存器空间

CA[46] 为 1, 表示对寄存器进行读取或写入操作。

表 5.1 寄存器空间地址映射

| 寄存器             | 系统地址      | —  | —  | —  | 31-27 | 26-19 | 18-11 | 10-3  | —    | 2-0 |

|-----------------|-----------|----|----|----|-------|-------|-------|-------|------|-----|

|                 | CA 位      | 47 | 46 | 45 | 44-40 | 39-32 | 31-24 | 23-16 | 15-8 | 7-0 |

| 标识寄存器 0<br>(只读) | C0h 或 E0h |    |    |    |       | 00h   | 00h   | 00h   | 00h  | 00h |

| 标识寄存器 1<br>(只读) | C0h 或 E0h |    |    |    |       | 00h   | 00h   | 00h   | 00h  | 01h |

| 配置寄存器 0 读取      | C0h 或 E0h |    |    |    |       | 00h   | 01h   | 00h   | 00h  | 00h |

| 配置寄存器 0 写入      | 60h       |    |    |    |       | 00h   | 01h   | 00h   | 00h  | 00h |

| 配置寄存器 1 读取      | C0h 或 E0h |    |    |    |       | 00h   | 01h   | 00h   | 00h  | 01h |

| 配置寄存器 1 写入      | 60h       |    |    |    |       | 00h   | 01h   | 00h   | 00h  | 01h |

**注意:**

1. CA45 可为 0 或 1, 它们分别表示循环或线性读取操作。由于仅支持线性单字存储器写入, 所以 CA45 必须为 1。

### 5.1 器件标识寄存器

共存在两个只读的非易失性字寄存器, 可在 CS# 为低电平时提供所选定器件的相关信息。器件信息字段指出:

- 制造商

- 类型

- 大小

- 行地址位计数

- 列地址位计数

表 5.2 ID 寄存器 0 位分配

| 位     | 功能     | 设置 (二进制数值)                                |

|-------|--------|-------------------------------------------|

| 15:14 | 保留     | 保留                                        |

| 13    | 保留     | 0 — 默认值                                   |

| 12-8  | 行地址位计数 | 00000 — 一个行地址位<br>...<br>11111 — 32 个行地址位 |

**表 5.2 ID 寄存器 0 位分配 (续)**

| 位   | 功能     | 设置 (二进制数值)                                   |

|-----|--------|----------------------------------------------|

| 7-4 | 列地址位计数 | 0000 — 一个列地址位<br>...<br>1111 — 16 个列地址位      |

| 3-0 | 制造商    | 0000 — 保留<br>0001 — 赛普拉斯<br>0010 ~ 1111 — 保留 |

**表 5.3 ID 寄存器 1 位分配**

| 位    | 功能   | 设置 (二进制数值)                          |

|------|------|-------------------------------------|

| 15-4 | 保留   | 0000_0000_0000b (默认)                |

| 3-0  | 器件类型 | 0000 — HyperRAM<br>0001 到 1111 — 保留 |

### 5.1.1 容量与行边界

通过系统的行和列地址位的总数 (由 ID0 寄存器内行地址位计数和列地址位计数字段中所指出的)，可确定器件的 DRAM 数组大小 (容量)。例如：拥有 9 个列地址位和 13 个行地址位的 64 Mb HyperRAM，可拥有总共  $2^{22} = 4$  百万字 = 8 MB。9 个列地址位指的是每一行有  $2^9 = 512$  字 = 1 KB。行地址位计数指出每一刷新间隔时间内需要对 8196 个行进行刷新。行计数用于计算刷新间隔。

## 5.2 寄存器空间访问

寄存器的默认值在上电或硬件复位时被下载。器件处于待机状态时，可随时改变寄存器的值。

装载寄存器是通过单个 16 位字写入操作进行，如图 5.1 所示。CA[47] 为 ‘0’ 表示写入操作，CA[46] 为 ‘1’ 表示写入到寄存器，CA[45] 为 ‘1’ 表示进行线性写入操作，CA 字段中的其他低位指出了寄存器的地址。

**图 5.1 下载寄存器**

**注意：**

1. 写入寄存器时，主机不能驱动 RWDS 信号。

2. 在 CA 期间，存储器会根据存储器阵列的刷新情况来驱动 RWDS 信号。刷新操作的指示并不影响寄存数据的写入。RWDS 在 CS# 转为低电平后立即被驱动，是在 CA[47:46] 被输入，指示对寄存器空间进行写入前发生 (对于该写入操作，RWDS 刷新指示是无效的)。

3. 在 CA 值后紧接着提供了寄存器的值，并不需要经过刷新延迟。

4. 完成 CA 过程，RWDS 信号将返回到高阻抗状态。寄存器数据始终不被屏蔽。寄存器的两个数据字节均被装载到所选的寄存器内。

每个寄存器进行一个独立的单字写入操作。寄存器的写入操作是无延迟的，在命令 - 地址后立即传输单个数据字。写入操作期间，**RWDS** 并非由主机驱动，该信号是由存储器在 **CA** 周期内驱动的，用于指出存储器阵列是否在刷新。寄存器写入操作是直接对寄存器（而不是存储器阵列）进行的，因此不存在有关阵列刷新操作的初始写入延迟。在写寄存器时，因为寄存器的两个字节总是被写入，不被屏蔽，因此 **RWDS** 信号不用来屏蔽数据。

寄存器的保留字段必须写入相应的默认值。向这些字段写入其他数值会生成未定义的结果。

对寄存器进行的读取是单个 16 位的操作，在此，**CA[46] = 1**，用于指示操作是对寄存器空间进行的。如果对多于 1 个字进行读取，那么在每一次字读取，同样的寄存器值将被重复。**CA[45]**，即突发类型，为“无需关注”，因为仅对单个寄存器值进行读取。寄存器的内容以读取阵列数据同样的方式被返回，根据 **RWDS** 在 **CA** 周期内的状态，需要一个或两个延迟周期。延迟周期数量是由配置寄存器 0 读取延迟字段 (**CR0[7:4]**) 定义的。

## 5.2.1 配置寄存器 0

配置寄存器 0 (CR0) 用于定义 HyperRAM 器件的功耗模式和访问协议的工作条件。可配置以下特性：

- 循环突发长度 (16、32、64 或 128 字节对齐和长度的数据组)

- 循环突发类型

- 传统循环 (顺序访问，并按选择的长度和对齐的数据组进行循环)

- 混合循环 (进行传统循环一次，然后从下一个数据组的开头进行线性突发操作)

- 初始延迟

- 变量延迟

- 读取或写入操作是否采用固定或变量延迟。如果选择固定延迟，则存储器会始终指定刷新延迟，并会根据该拖延来执行数据读取操作。如果选择的是变量延迟，那么启动新的数据操作时，只有需要刷新时才会添加刷新延迟。

- 输出驱动强度

- 深度掉电模式

表 5.4 配置寄存器 0 位分配

| CR0 位 | 功能     | 设置 (二进制数值)                                                                                                                                    |

|-------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| 15    | 深度掉电使能 | 1 — 正常操作 (默认设置)<br>0 — 向 CR[15] 上写入 0 会使器件进入深度掉电状态                                                                                            |

| 14-12 | 驱动强度   | 000 — 34 Ω (默认值)<br>001 — 115 Ω<br>010 — 67 Ω<br>011 — 46 Ω<br>100 — 34 Ω<br>101 — 27 Ω<br>110 — 22 Ω<br>111 — 19 Ω                           |

| 11-8  | 保留     | 1 — 保留 (默认值)<br>保留供将来使用。对该寄存器进行写操作时，要将这些位设置为 1 来满足将来的兼容性需要。                                                                                   |

| 7-4   | 初始延迟   | 0000 — 5 个时钟周期延迟<br>0001 — 6 个时钟周期延迟 (默认值)<br>0010 — 保留<br>0011 — 保留<br>0100 — 保留<br>...<br>1101 — 保留<br>1110 — 3 个时钟周期延迟<br>1111 — 4 个时钟周期延迟 |

| 3     | 固定延迟使能 | 0 — 变量延迟 — 它是初始延迟的一倍或两倍，具体取决于 CA 周期中 RWDS 信号的状态。<br>1 — 固定为初始延迟的两倍 (默认值)                                                                      |

**表 5.4** 配置寄存器 0 位分配 (续)

| CR0 位 | 功能     | 设置 (二进制数值)                                                   |

|-------|--------|--------------------------------------------------------------|

| 2     | 混合突发使能 | 0: 循环突发序列位于混合突发序列后<br>1: 传统的循环突发序列 (默认)                      |

| 1-0   | 突发长度   | 00 — 128 字节<br>01 — 64 字节<br>10 — 16 字节<br>11 — 32 字节 (默认设置) |

### 5.2.1.1 循环突发

循环突发操作是对存储空间内字边界对齐的某个数据组进行访问，该数据组的长度与寄存器中配置的数据组长度匹配。循环访问组的对齐和长度可配置为 16、32、64 或 128 个字节。在循环操作中，访问将从命令 - 地址在字组中选定的位置开始，一直连续到已配置的字组对齐边界的最后部分，然后返回到字组的起始位置，继续访问到所选的起始位置。循环突发一般用于特定的读取访问，这种访问是按临界字为第一传输部分的方式来填充命令或数据缓存行。

### 5.2.1.2 混合突发

混合突发操作先是在目标地址按照配置的循环突发字组长度进行循环突发操作，然后继续访问循环字组边界后面的半页数据。随后执行的数据访问是线性突发序列访问，直到 CS# 为高电平停止传输为止。混合突发是一个循环突发，随后是从下一个字组开始的线性突发，这样允许在一次访问中可填充多个连续地址的缓存行。第一个缓存行从临界字开始填充的。然后在处理第一行时，可以将存储器中的下一行读取到缓存内。

**表 5.5** CR0[2] — 控制循环突发序列

| 位 | 默认值 | 名称                                                          |

|---|-----|-------------------------------------------------------------|

| 2 | 1   | 混合突发使能<br>CR[2] = 0: 循环突发序列位于混合突发序列后<br>CR[2] = 1: 传统循环突发序列 |

**表 5.6** 循环突发序列示例

| 突发选择   |          | 突发类型   | 循环边界<br>(字节)                                          | 起始地址<br>(十六进制<br>格式) | 地址序列 (十六进制格式)<br>(字)                                                                                                                                                                                                                                                                                                  |

|--------|----------|--------|-------------------------------------------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CA[45] | CR0[2:0] |        |                                                       |                      |                                                                                                                                                                                                                                                                                                                       |

| 0      | 000      | 混合 128 | 对最前面的<br>128 个字节进<br>行一次循环<br>突发操作，<br>然后进行线<br>性突发操作 | XXXXXX03             | 03、04、05、06、07、08、09、0A、0B、0C、0D、0E、0F、10、11、<br>12、13、14、15、16、17、18、19、1A、1B、1C、1D、1E、1F、20、<br>21、22、23、24、25、26、27、28、29、2A、2B、2C、2D、2E、2F、<br>30、31、32、33、34、35、36、37、38、39、3A、3B、3C、3D、3E、<br>3F、00、01、02<br>(循环操作完成后，从前 128 个字节的循环组后开始线性操作)<br>40、41、42、43、44、45、46、47、48、49、4A、4B、4C、4D、4E、<br>4F、50、51、..... |

| 0      | 001      | 混合 64  | 对最前面的<br>64 个字节进<br>行一次循环<br>突发操作，<br>然后进行线<br>性突发操作  | XXXXXX03             | 03、04、05、06、07、08、09、0A、0B、0C、0D、0E、0F、10、11、<br>12、13、14、15、16、17、18、19、1A、1B、1C、1D、1E、1F、00、<br>01、02，<br>(循环操作完成后，从前 64 个字节的循环组后开始线性操作)<br>20、21、22、23、24、25、26、27、28、29、2A、2B、2C、2D、2E、<br>2F、30、31、.....                                                                                                         |

**表 5.6 循环突发序列示例 (续)**

| 突发选择   |          | 突发类型   | 循环边界<br>(字节)<br>(十六进制<br>格式)       | 地址序列 (十六进制格式)<br>(字) |                                                                                                                                                                                                       |

|--------|----------|--------|------------------------------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CA[45] | CR0[2:0] |        |                                    |                      |                                                                                                                                                                                                       |

| 0      | 001      | 混合 64  | 对最前面的 64 个字节进行一次循环突发操作, 然后进行线性突发操作 | XXXXXX2E             | 2E、2F、30、31、32、33、34、35、36、37、38、39、3A、3B、3C、3D、3E、3F、20、21、22、23、24、25、26、27、28、29、2A、2B、2C、2D,<br>(循环操作完成后, 从前 64 个字节的循环组后开始线性操作)<br>40、41、42、43、44、45、46、47、48、49、4A、4B、4C、4D、4E、4F、50、51、.....    |

| 0      | 010      | 混合 16  | 对最前面的 16 个字节进行一次循环突发操作, 然后进行线性突发操作 | XXXXXX02             | 02、03、04、05、06、07、00、01,<br>(循环操作完成后, 从前 16 个字节的循环组后开始线性操作)<br>08、09、0A、0B、0C、0D、0E、0F、10、11、12、.....                                                                                                 |

| 0      | 010      | 混合 16  | 对最前面的 16 个字节进行一次循环突发操作, 然后进行线性突发操作 | XXXXXX0C             | 0C、0D、0E、0F、08、09、0A、0B,<br>(循环操作完成后, 从前 16 个字节的循环组后开始线性操作)<br>10、11、12、13、14、15、16、17、18、19、1A、.....                                                                                                 |

| 0      | 011      | 混合 32  | 对最前面的 32 个字节进行一次循环突发操作, 然后进行线性突发操作 | XXXXXX0A             | 0A、0B、0C、0D、0E、0F、00、01、02、03、04、05、06、07、08、09、.....                                                                                                                                                 |

| 0      | 011      | 混合 32  | 对最前面的 32 个字节进行一次循环突发操作, 然后进行线性突发操作 | XXXXXX1E             | 1E、1F、10、11、12、13、14、15、16、17、18、19、1A、1B、1C、1D、.....                                                                                                                                                 |

| 0      | 100      | 循环 128 | 128                                | XXXXXX03             | 03、04、05、06、07、08、09、0A、0B、0C、0D、0E、0F、10、11、12、13、14、15、16、17、18、19、1A、1B、1C、1D、1E、1F、20、21、22、23、24、25、26、27、28、29、2A、2B、2C、2D、2E、2F、30、31、32、33、34、35、36、37、38、39、3A、3B、3C、3D、3E、3F、00、01、02、..... |

| 0      | 101      | 循环 64  | 64                                 | XXXXXX03             | 03、04、05、06、07、08、09、0A、0B、0C、0D、0E、0F、10、11、12、13、14、15、16、17、18、19、1A、1B、1C、1D、1E、1F、00、01、02、.....                                                                                                 |

| 0      | 101      | 循环 64  | 64                                 | XXXXXX2E             | 2E、2F、30、31、32、33、34、35、36、37、38、39、3A、3B、3C、3D、3E、3F、20、21、22、23、24、25、26、27、28、29、2A、2B、2C、2D、.....                                                                                                 |

| 0      | 110      | 循环 16  | 16                                 | XXXXXX02             | 02、03、04、05、06、07、00、01、.....                                                                                                                                                                         |

| 0      | 110      | 循环 16  | 16                                 | XXXXXX0C             | 0C、0D、0E、0F、08、09、0A、0B、.....                                                                                                                                                                         |

| 0      | 111      | 循环 32  | 32                                 | XXXXXX0A             | 0A、0B、0C、0D、0E、0F、00、01、02、03、04、05、06、07、08、09、.....                                                                                                                                                 |

| 0      | 111      | 循环 32  | 32                                 | XXXXXX1E             | 1E、1F、10、11、12、13、14、15、16、17、18、19、1A、1B、1C、1D、.....                                                                                                                                                 |

| 1      | XXX      | 线性     | 线性突发                               | XXXXXX03             | 03、04、05、06、07、08、09、0A、0B、0C、0D、0E、0F、10、11、12、13、14、15、16、17、18、.....                                                                                                                               |

### 5.2.1.3 初始延迟

对于存储器空间的读和写操作或寄存器空间的读操作，打开命令-地址所选的行时需要初始延迟。该初始延迟时间即为 $t_{ACC}$ 。HyperBus频率决定了满足 $t_{ACC}$ 的延迟时钟周期数量，该数量的范围为3到6。 $CR0[7:4]$ 的值选择了初始延迟所需的时钟周期数量。默认设置是6个周期，这样允许主机系统在设置一个更优化的低初始延迟值之前，可工作在最大工作频率（166 MHz）。

在存储器空间读写操作或寄存器空间读操作开始时，如果需要一个分布的刷新操作，**RWDS**信号在命令-地址期间将转为高电平，用于指示需要添加初始的延迟，以保证刷新操作能够在打开所选行之前完成。

寄存器写入操作始终不存在初始延迟。在命令-地址期间，**RWDS**可能是高电平，也可能是低电平。**RWDS**在命令-地址传输期间的状态不会影响到在命令-地址后立即写入寄存器数据，因为并不需使用初始延迟来捕获寄存器数据。存储器阵列的刷新操作可以和寄存器数据捕获同时进行。

### 5.2.1.4 固定延迟

通过配置寄存器选项位 $CR0[3]$ ，可使存储器空间读写操作与寄存器空间读操作的初始延迟相同。设置该位后，在命令-地址周期中，**RWDS**将驱动为高电平，表示要求两个初始延迟周期。该固定初始延迟与是否有分布刷新的要求无关，它为所有类型的操作提供了一个固定（确定性）的初始延迟。该固定延迟有助于简化HyperBus存储器控制器设计，并保证确定性操作的实现。固定延迟是默认的POR或复位配置。系统可以将该配置位清零来禁用固定延迟，并使用变量初始延迟，当因为刷新需要额外初始延迟时，驱动**RWDS**为高电平。

### 5.2.1.5 驱动强度

**DQ**信号线负载、长度和阻抗都会因系统设计的不同而异。通过配置寄存器位 $CR0[14:12]$ ，可以根据系统条件调整**DQ[7:0]**信号输出阻抗，从而最小化高速信号的行为，如过冲、下冲和振荡。默认POR或复位配置值是000b，选择使用可用输出阻抗的中间值。

所表示的阻抗值是上拉和下拉驱动器在典型的芯片处理的条件，在额定操作电压（1.8 V或3 V）和50°C下的典型值。过程、电压和温度（PVT）条件不同时，阻抗值的变动范围可达典型值的±80%。在过程较慢、电压较低或温度较高的条件下，阻抗值会增加。在过程较快、电压较高或温度较低的条件下，阻抗值会下降。

所有的系统设计都需要估计数据信号在合适的操作电压和温度范围内的完整性，以便选择最佳的驱动强度设置。

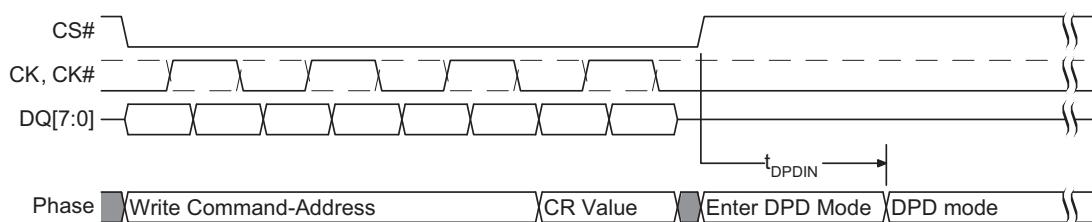

### 5.2.1.6 深度掉电

系统操作不需使用HyperRam时，可通过向 $CR0[15]$ 内写入0，将器件设置在低功耗模式（深度掉电（DPD））。 $CR0[15]$ 被清零时，器件将在 $t_{DPDIN}$ 时长内处于DPD模式，所有刷新操作均被停止。在该模式下，**RAM**的数据被丢失（无效，并且不被刷新）。对器件进行的下一次访问（将**CS#**从低电平驱动为高电平）、POR或复位操作，都会将器件从该模式唤醒。器件需要经过 $t_{DPDOUT}$ 时长来返回到待机模式。有关的详细信息，请参见第25页上的6.1.3、深度掉电章节。

## 5.2.2 配置寄存器 1

配置寄存器 1 (CR1) 定义了 HyperRAM 器件的分布刷新间隔。需要定期刷新内核 DRAM 阵列中的所有位。该操作是在指定的时间内，主机系统通过读取或写入每一行中的一个位置来完成的。读取或写入访问会将某行中的各位复制到内部缓冲区内。访问结束时，缓冲区中的位被回写到存储器的行内，进而对 DRAM 存储器单元中的行位进行充电 (刷新)。

然而，定期读取存储器中的每一行和跟踪整个存储器阵列中的每一行在刷新间隔中是否得到了刷新会占用主机系统的大量时间。HyperRAM 器件拥有能够自动刷新各行的自刷新逻辑，这样减少了主机对存储器进行的刷新操作。行自动刷新仅在主机系统未对存储器进行读取或写入操作时实现。在该过程中，如果要进行刷新，则刷新逻辑要等待有效的读取或写入操作结束后才能进行。进行刷新时，如果发生了读写操作，那么在命令 - 地址期间，存储器会将 RWDS 信号置为高电平来表示需要添加一段附加的初始延迟时间，以保证在进行新的访问前，刷新操作已经完成。

整个存储器阵列所需的刷新间隔随着温度不同而变化，如第 23 页上的表 5.7、与温度相应的阵列刷新间隔所示。在这段时间内，所有行都需要得到刷新。对所有行进行的刷新操作可按照两种方式实现：在每一段刷新间隔内的开头进行一些列的访问，同时刷新一组多行 (突发刷新)，或在整个间隔时间内分步对一个行进行。自刷新逻辑在整个刷新间隔内对一个行进行了分布刷新，这样避免了存储器要用较长时间进行突发刷新操作，进而避免突发操作长时间延迟主机访问的现象。

**表 5.7** 与温度相应的阵列刷新间隔

| 器件温度 (°C) | 阵列刷新时间间隔 (ms) | 阵列行  | 推荐的 $t_{CMS}$ (μs) |

|-----------|---------------|------|--------------------|

| 85        | 64            | 8192 | 4                  |

| 105       | 16            | 8192 | 1                  |

**表 5.8** 配置寄存器 1 位分配

| CR1 位 | 功能     | 设置 (二进制值)                                                                                                                 |

|-------|--------|---------------------------------------------------------------------------------------------------------------------------|

| 15-2  | 保留     | 000000h — 保留 (默认值)<br>保留供将来使用。对该寄存器进行写操作时，要将这些位设置为 0 来满足将来的兼容性需要。                                                         |

| 1-0   | 分布刷新间隔 | 10b — 默认设置为<br>4 μs (针对使用于工业级温度范围的器件)<br>1 μs (针对使用于扩展工业级温度范围的器件)<br>11b — 默认值的 1.5 倍<br>00b — 默认值的 2 倍<br>01b — 默认值的 4 倍 |

该模式要求主机不进行过长的突发操作，以保证存储器能够进行所需的分布刷新。这样便设置好了读取和写入操作的数据长度上限，从而保证刷新逻辑可在各操作之间添加一个刷新操作。该限制被称为最大 CS# 低电平时间 ( $t_{CMS}$ )  $t_{CMS}$  等于阵列刷新间隔除以阵列中行的数量以后减半，这样可保证在发生最长的主机访问操作时，其后面的分布刷新间隔不被漏掉。由于  $t_{CMS}$  等于所需的分布刷新间隔的一半，延迟刷新操作的最长主机访问系列能够在等于刷新间隔除以行数后的两倍速度下满足刷新操作。

主机系统需要遵守  $t_{CMS}$  限制，即违反  $t_{CMS}$  之前，所有操作需要停止。达到  $t_{CMS}$  的限制时，通过使用主机存储器控制器逻辑将较长的操作分解开，或保证主机系统硬件或软件不会执行长于  $t_{CMS}$  时间的单独读取或写入操作，可以达到该目的。

如第 23 页上的表 5.7、与温度相应的阵列刷新间隔中所示，温度越低，阵列刷新间隔越长。因此，可通过增加  $t_{CMS}$ ，以实现时间较长的操作。主机系统可使用表中与最大工作温度相应的  $t_{CMS}$  值，或通过系统中的温度传感器确定当前的工作温度，以便设置更长的分布刷新间隔。

主机系统也可以主动通过对各个行执行所有的刷新操作和突发刷新读取，来延长  $t_{CMS}$ ，进而满足因较长的操作而被漏掉的分布刷新。

## HyperRAM 器件硬件接口

欲了解 HyperFlash 存储器产品中 HyperBus 硬件接口的总体概述, 请参考 HyperBus 规范中的内容。下面部分介绍了硬件接口中有关 HyperRAM 器件方面的内容。

### 6. 接口状态

#### 6.1 节能模式

##### 6.1.1 接口待机模式

待机是器件在没有被主机选择用于数据传输时 (CE# 为高电平) 一种默认的低功耗接口状态。在该状态下, 除 CS# 和 RESET# 外, 所有输入和输出均被忽略。

##### 6.1.2 有效时钟停止

在进行数据读或写操作传输期间, 使用工作时钟停止模式会使器件的接口电流消耗下降到  $I_{CC6}$ 。时钟在  $t_{ACC} + 30\text{ ns}$  期间保持稳定, 则器件将自动进入该模式。在该模式下, 读取数据被锁存并输出在数据总线。 $I_{CC6}$  如第 32 页上的 9.4、直流特性章节所示。

主机系统时钟停止以暂停数据传输时, 进入该模式有助于降低所消耗的电流。即使在这些延长的数据传输周期内 CE# 可能为低电平, 存储设备主机接口经过  $t_{ACC} + 30\text{ ns}$  时间后也会切换到工作时钟停止电流。这样, 停止数据传输时, 器件会进入低电流消耗模式。切换时钟重新启动数据传输时, 会恢复有效的读取或写入电流。违反了  $t_{CSM}$  限制时, 不能使用工作时钟停止模式。违反  $t_{CSM}$  限制前, CS# 要为高电平。

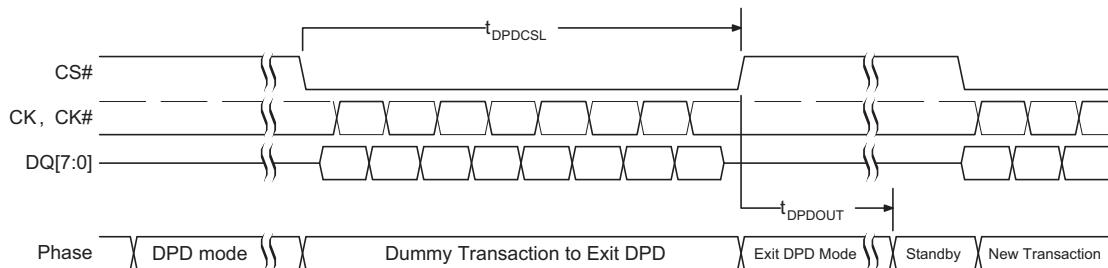

##### 6.1.3 深度掉电

深度掉电 (DPD) 模式下, 所消耗的电流最低 ( $i_{DPD}$ )。通过向 CR0[15] 写入 ‘0’, 可以进入 DPD 模式。器件在  $t_{DPDIN}$  时间内降低功耗, 所有刷新操作均被停止。在该模式下, 存储器中的数据被丢失 (无效, 并不被刷新)。对器件进行的下一次访问 (将 CS# 从低电平驱动为高电平) 会使器件退出 DPD 模式。将 CS# 从低电平驱动为高电平的读或写操作是虚拟的, 器件会忽略该操作。POR 或硬件复位也会使器件退出 DPD 模式。在 DPD 模式下, 仅监控 CS# 和 RESET# 信号。虚拟操作后或复位后返回到待机模式需要经过  $t_{DPDOUT}$  的时间。POR 后返回到待机模式需要使用  $t_{VCS}$  时间, 该时间与其他 POR 相同。因其他事件退出 DPD 模式后, 器件进入的状态与 POR 事件后的相似。

表 6.1 深度掉电时序参数

| 参数           | 说明                                          | 最小值 | 最大值 | 单位            |

|--------------|---------------------------------------------|-----|-----|---------------|

| $t_{DPDIN}$  | 从进入深度掉电模式 (向寄存器 CR[15] 位写入零) 到电流下降为 DPD 的时间 | 10  | -   | $\mu\text{s}$ |

| $t_{DPDCSL}$ | 使器件退出深度掉电模式 (DPD) 的 CS# 低电平时间               | 200 | -   | ns            |

| $t_{DPDOUT}$ | CS# 从低电平转为高电平, 用于将器件从待机模式唤醒所需要的时间           | -   | 150 | $\mu\text{s}$ |

图 6.1 深度掉电进入时序

图 6.2 深度掉电 CS# 退出时序

## 7. HyperRAM 连接说明

下面是其它封装连接信号的说明内容。

### 7.1 其它封装连接信号摘要

**表 7.1 其它封装连接信号摘要**

| 符号        | 类型   | 说明                                                                          |

|-----------|------|-----------------------------------------------------------------------------|

| $V_{CC}$  | 电源电压 | 内核电源电压。                                                                     |

| $V_{CCQ}$ | 电源电压 | 输入 / 输出电源电压。                                                                |

| $V_{SS}$  | 电源电压 | 内核接地电压。                                                                     |

| $V_{SSQ}$ | 电源电压 | 输入 / 输出接地电压。                                                                |

| NC        | 无连接  | 内部无连接。信号 / 球形焊盘在印刷电路板 (PCB) 中的位置可以用作路线通道的一部分。                               |

| RFU       | 无连接  | 保留供将来使用可以内部连接或不连接, 但考虑到未来的兼容性, 不应连接信号/球形焊盘位置或被PCB 路线通道使用。信号 / 球形焊盘未来可供信号使用。 |

| DNU       | 保留   | 请勿使用。保留给赛普拉斯使用。信号 / 球形焊盘被内部连接。信号 / 球形焊盘在 PCB 上必须悬空。                         |

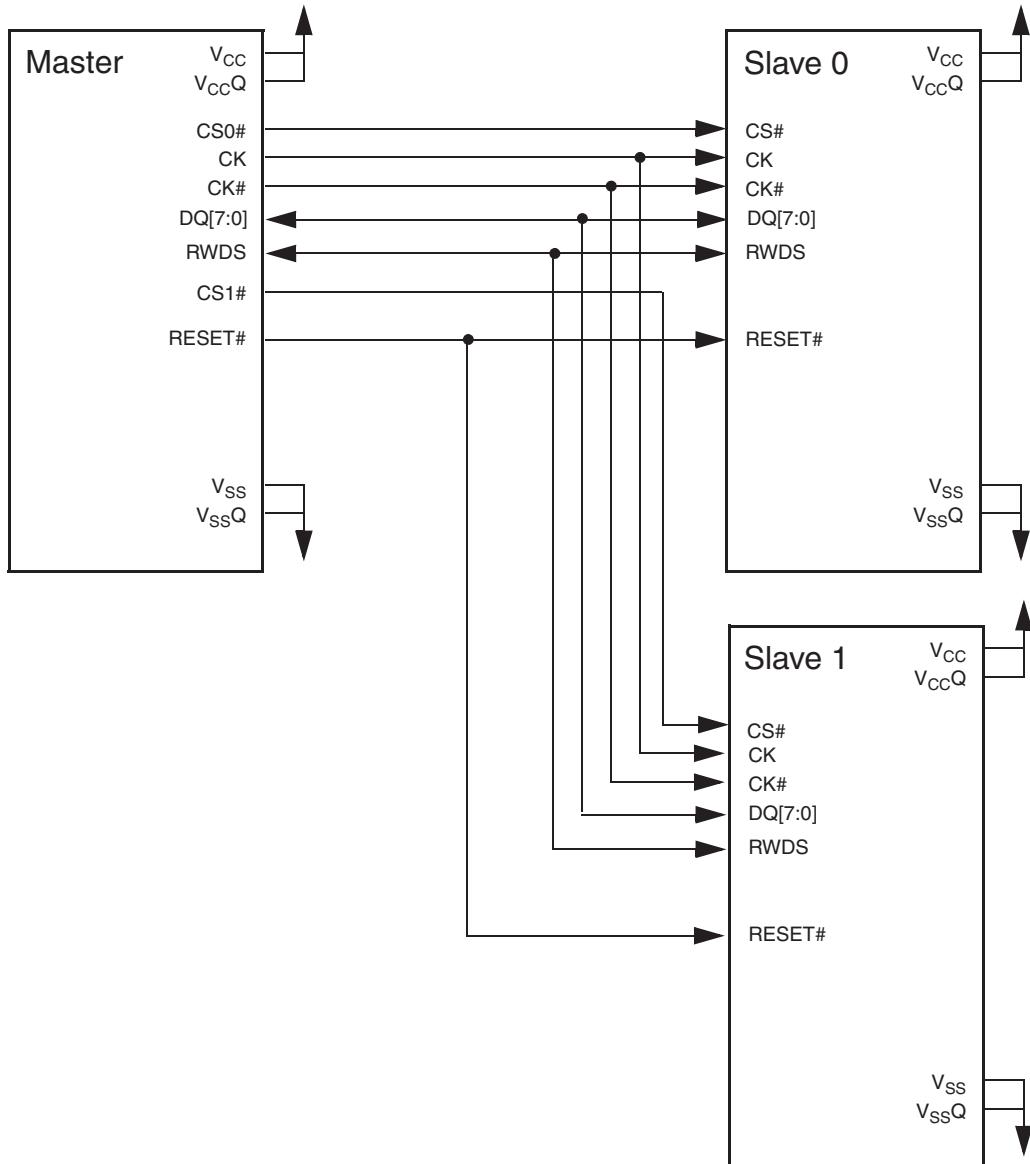

## 7.2 HyperRAM 框图

图 7.1 HyperRAM 连接 (包括可选信号)

## 8. 接口状态

接口状态表描述了每个接口状态所需的信号值。

**表 8.1** 接口状态

| 接口状态                         | $V_{CC} / V_{CCQ}$                  | CS# | CK, CK# | D7-D0             | RWDS        | RESET# |

|------------------------------|-------------------------------------|-----|---------|-------------------|-------------|--------|

| 具有硬件数据保护特性的关电源状态 (Flash 存储器) | $< V_{LKO}$                         | X   | X       | 高阻态               | 高阻态         | X      |

| 上电 (冷) 复位                    | $\geq V_{CC} / V_{CCQ} \text{ min}$ | X   | X       | 高阻态               | 高阻态         | X      |

| 硬件 (热) 复位                    | $\geq V_{CC} / V_{CCQ} \text{ min}$ | X   | X       | 高阻态               | 高阻态         | L      |

| 接口待机状态                       | $\geq V_{CC} / V_{CCQ} \text{ min}$ | H   | X       | 高阻态               | 高阻态         | H      |

| 命令 - 地址                      | $\geq V_{CC} / V_{CCQ} \text{ min}$ | L   | T       | 主输出有效             | X           | H      |

| 读初始访问延迟 (数据总线转换周期)           | $\geq V_{CC} / V_{CCQ} \text{ min}$ | L   | T       | 高阻态               | L           | H      |

| 写初始访问延迟 (RWDS 转换周期)          | $\geq V_{CC} / V_{CCQ} \text{ min}$ | L   | T       | 高阻态               | 高阻态         | H      |

| 读数据传输                        | $\geq V_{CC} / V_{CCQ} \text{ min}$ | L   | T       | 从输出有效             | 从输出有效 X 或 T | H      |

| 带有初始延迟的写数据传输                 | $\geq V_{CC} / V_{CCQ} \text{ min}$ | L   | T       | 主输出有效             | 主输出有效 X 或 T | H      |

| 无初始延迟的写数据传输 (2)              | $\geq V_{CC} / V_{CCQ} \text{ min}$ | L   | T       | 主输出有效             | 从输出 L 或高阻态  | H      |

| 有效时钟停止 (3)                   | $\geq V_{CC} / V_{CCQ} \text{ min}$ | L   | 空闲      | 主 / 从输出有效 / 处于高阻态 | X           | H      |

| 深度掉电 (3)                     | $\geq V_{CC} / V_{CCQ} \text{ min}$ | H   | X 或 T   | 从输出处于高阻态          | 高阻态         | H      |

**图标**

$L = V_{IL}$

$H = V_{IH}$

$X = V_{IL} \text{ 或 } V_{IH}$

$L/H = \text{上升沿}$

$H/L = \text{下降沿}$

$T = \text{信息传输过程中进行切换}$

$\text{闲置} = \text{CK 为低电平且 CK# 为高电平}$

$\text{有效} = \text{所有总线信号都有稳定的低或高电平}$

**注意:**

1. 当 RSTO# 或 INT# 开漏输出为高阻态时, 主设备所提供的上拉阻抗或外部电阻会将信号上拉到高电平状态。

2. 无初始延迟 (具有零初始延迟) 的写入操作, 没有 RWDS 的回转周期。HyperRAM 器件在命令 - 地址周期中一直会驱动 RWDS, 从而表示是否需要增加延迟。由于主设备写数据紧挨着命令 - 地址周期, 所以 HyperRAM 器件会一直将 RWDS 驱动为低电平或将其转换为高阻态。在零延迟写入操作中, 主设备不能驱动 RWDS。零延迟的写入操作不会将 RWDS 作为数据掩码使用。写入数据的所有字节均被写入 (整字写入)。

3. 第 25 页上的 6.1.2、有效时钟停止章节中描述了工作时钟停止的内容。第 25 页上的 6.1.3、深度掉电章节描述了 DPD。

## 9. 电气规范

### 9.1 最大绝对额定值

|                 |                                     |

|-----------------|-------------------------------------|

| 塑料封装存储温度        | -65 °C ~ +150 °C                    |

| 通电时的环境温度        | -65°C ~ +115 °C                     |

| 对地电压            |                                     |

| 所有信号 (1)        | -0.5 V ~ +(V <sub>CC</sub> + 0.5 V) |

| 输出短路电流 (2)      | 100 mA                              |

| V <sub>CC</sub> | -0.5 V ~ +4.0 V                     |

#### 注意:

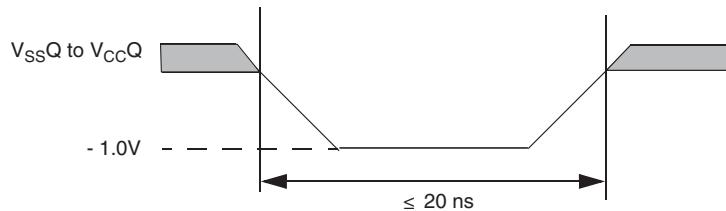

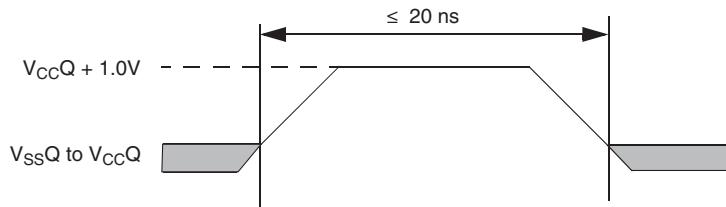

1. 输入或 I/O 信号上的最小直流电压是 -1.0 V。在电压转换期间，输入或 I/O 信号可能低于 V<sub>SS</sub>，降到 -1.0 V，时间最长为 20 ns。请参见图 9.1。输入或 I/O 信号上的最大直流电压是 V<sub>CC</sub> +1.0 V。在电压转换期间，输入或 I/O 信号可能升到 V<sub>CC</sub> +1.0 V，时间最长为 20 ns。请参考图 9.2。

2. 每一次只能有一个输出对地短接。短接时间不能超过一秒。

3. 如果使用大于最大绝对额定值中所列出的数值，可能造成永久性损害。这只是压力额定值；并不暗示器件在这些值或者在此数据手册操作部分所示值之上的任何其他情形下能正常运行。如果让芯片长时间运行于绝对最大额定值状态，会影响芯片的可靠性。

#### 9.1.1 输入信号过冲

在直流条件下，输入或 I/O 应处于从 V<sub>SS</sub> 到 V<sub>DD</sub> 之间的范围内。在电压转换期间，输入或 I/O 信号可能低于 V<sub>SS</sub>，降到 -1.0 V 或升到 V<sub>DD</sub> +1.0 V，时间最长为 20 ns。

图 9.1 最大负过冲波形

图 9.2 最大正过冲波形

## 9.2 栓锁特性

表 9.1 栓锁规范

| 说明                             | 最小值  | 最大值             | 单位 |

|--------------------------------|------|-----------------|----|

| 在所有输入连接上相对于 $V_{SSQ}$ 的输入电压    | -1.0 | $V_{CCQ} + 1.0$ | V  |

| 在所有 I/O 连接上相对于 $V_{SSQ}$ 的输入电压 | -1.0 | $V_{CCQ} + 1.0$ | V  |

| $V_{CCQ}$ 电流                   | -100 | +100            | mA |

**注意:**

1. 不包括  $V_{CC}/V_{CCQ}$  电源。测试条件:  $V_{CC} = V_{CCQ} = 1.8$  V, 每一次检测一个连接,  $V_{SS}$  下的连接不进行检测。

## 9.3 工作范围

工作范围定义了部分限制值, 使用这些值可保证器件正常运行。

### 9.3.1 温度范围

| 参数   | 符号    | 器件                     | 规范  |     | 单位 |

|------|-------|------------------------|-----|-----|----|

|      |       |                        | 最小值 | 最大值 |    |

| 环境温度 | $T_A$ | 工业级 (I)                | -40 | 85  | °C |

|      |       | 扩展的工业级 (V)             | -40 | 105 |    |

|      |       | 汽车级, AEC-Q100 等级 3 (A) | -40 | 85  |    |

|      |       | 汽车级, AEC-Q100 等级 2 (B) | -40 | 105 |    |

### 9.3.2 供电电压

|                      |                |

|----------------------|----------------|

| $V_{CC}$ 和 $V_{CCQ}$ | 1.7 V ~ 1.95 V |

| $V_{CC}$ 和 $V_{CCQ}$ | 2.7 V ~ 3.6 V  |

## 9.4 直流特性

表 9.2 直流特性 (CMOS 兼容)

| 参数          | 说明                                              | 测试条件                                                                                      | 最小值                 | 典型值<br>(1)           | 最大值                  | 单位      |

|-------------|-------------------------------------------------|-------------------------------------------------------------------------------------------|---------------------|----------------------|----------------------|---------|

| $I_{L1}$    | 输入漏电流<br>(仅在 3 V 器件复位信号为高电平时有效)                 | $V_{IN} = V_{SS}$ 到 $V_{CC}$ ,<br>$V_{CC} = V_{CC\max}$                                   | -                   | -                    | -0.1                 | $\mu A$ |

| $I_{L1}$    | 输入漏电流<br>(仅在 1.8 V 器件复位信号为高电平时有效)               | $V_{IN} = V_{SS}$ 到 $V_{CC}$ ,<br>$V_{CC} = V_{CC\max}$                                   | -                   | -                    | -0.1                 | $\mu A$ |

| $I_{L1}$    | 输入漏电流<br>(仅在 3 V 器件复位信号为低电平时) (2)               | $V_{IN} = V_{SS}$ 到 $V_{CC}$ ,<br>$V_{CC} = V_{CC\max}$                                   | -                   | -                    | +20.0                | $\mu A$ |

| $I_{L1}$    | 输入漏电流<br>(仅在 1.8 V 器件复位信号为低电平时) (2)             | $V_{IN} = V_{SS}$ 到 $V_{CC}$ ,<br>$V_{CC} = V_{CC\max}$                                   | -                   | -                    | +20.0                | $\mu A$ |

| $I_{CC1}$   | 相当于 $V_{CC}$ 的有效读取电流                            | $CS\# = V_{IL}$ , 166 MHz, $V_{CC} = 1.9$ V                                               | -                   | 20                   | 60                   | $mA$    |

|             |                                                 | $CS\# = V_{IL}$ , 100 MHz, $V_{CC} = 3.6$ V                                               | -                   |                      |                      |         |

| $I_{CC2}$   | 相当于 $V_{CC}$ 的有效写入电流                            | $CS\# = V_{IL}$ , 166 MHz, $V_{CC} = 1.9$ V                                               | -                   | 15                   | 60                   | $mA$    |

|             |                                                 | $CS\# = V_{IL}$ , 100 MHz, $V_{CC} = 3.6$ V                                               | -                   |                      |                      |         |

| $I_{CC4I}$  | 工业级温度 (-40 °C ~ +85 °C) 下相当于 $V_{CC}$ 的待机电流     | $CS\#, V_{CC} = V_{CC\max}$                                                               | -                   | 135                  | 200                  | $\mu A$ |

| $I_{CC4IP}$ | 扩展的工业级温度 (-40 °C ~ +105 °C) 下相当于 $V_{CC}$ 的待机电流 | $CS\#, V_{CC} = V_{CC\max}$                                                               | -                   | 135                  | 300                  | $\mu A$ |

| $I_{CC5}$   | 复位电流                                            | $CS\# = V_{IH}$ , RESET# = $V_{IL}$ ,<br>$V_{CC} = V_{CC\max}$                            | -                   | 10                   | 20                   | $mA$    |

| $I_{CC6I}$  | 工业级温度 (-40 °C ~ +85 °C) 下的有效时钟停止电流              | $CS\# = V_{IL}$ , RESET# = $V_{IH}$ ,<br>$V_{CC} = V_{CC\max}$                            | -                   | 5.3                  | 8                    | $mA$    |

| $I_{CC6IP}$ | 扩展的工业级温度 (-40 °C ~ +105 °C) 下的工作时钟停止电流          | $CS\# = V_{IL}$ , RESET# = $V_{IH}$ ,<br>$V_{CC} = V_{CC\max}$                            | -                   | 5.3                  | 12                   | $mA$    |

| $I_{CC7}$   | 上电期间 $V_{CC}$ 的电流 (1)                           | $CS\#$ 为高电平, $V_{CC} = V_{CC\max}$ ,<br>$V_{CC} = V_{CCQ} = 1.95$ V 或 3.6 V<br>(注意 9.4.1) | -                   | -                    | 35                   | $mA$    |

| $I_{DPD}$   | 3 V、85°C 条件下的深度掉电电流                             | $CS\#, V_{CC} = 3.6$ V, $T_A = 85$ °C                                                     | -                   | -                    | 20                   | $\mu A$ |

| $I_{DPD}$   | 1.8 V、85°C 条件下的深度掉电电流                           | $CS\#, V_{CC} = 1.9$ V, $T_A = 85$ °C                                                     | -                   | -                    | 10                   | $\mu A$ |

| $I_{DPD}$   | 3 V、105°C 条件下的深度掉电电流                            | $CS\#, V_{CC} = 3.6$ V, $T_A = 105$ °C                                                    | -                   | -                    | 40                   | $\mu A$ |

| $I_{DPD}$   | 1.8 V、105°C 条件下的深度掉电电流                          | $CS\#, V_{CC} = 1.9$ V, $T_A = 105$ °C                                                    | -                   | -                    | 20                   | $\mu A$ |

| $V_{IL}$    | 输入低电压                                           |                                                                                           | -0.5                | -                    | $0.3 \times V_{CC}$  | V       |

| $V_{IH}$    | 输入高电压                                           |                                                                                           | $0.7 \times V_{CC}$ | -                    | $V_{CC} + 0.3$       | V       |

| $V_{OL}$    | 输出低电压                                           | $I_{OL} = 100 \mu A$ (DQ[7:0])                                                            | -                   | -                    | $0.15 \times V_{CC}$ | V       |

| $V_{OH}$    | 输出高电压                                           | $I_{OH} = 100 \mu A$ (DQ[7:0])                                                            | -                   | $0.85 \times V_{CC}$ | -                    | V       |

注意:

1. 并非 100% 经过了测试。

2. 将 RESET# 置为低电平可使器件退出 DPD 模式, 并接收  $I_{CC5}$  复位电流, 从而使  $I_{L1}$  的值在 Reset# 为低电平期间降至很小。

### 9.4.1 电容特性

表 9.3 1.8 V 电容特性

| 说明                | 参数   | 最小值 | 最大值  | 单位 |

|-------------------|------|-----|------|----|

| 输入电容 (CK、CK#、CS#) | Cl   | 3   | 4.5  | pF |

| 输入电容差值 (CK、CK#)   | CID  | -   | 0.25 | pF |

| 输出电容 (RWDS)       | CO   | 3   | 4    | pF |

| I/O 电容 (DQx)      | CIO  | 3   | 4    | pF |

| IO 电容 Delta (DQx) | CIOD | -   | 0.5  | pF |

**注意:**

1. 这些值仅由设计保证，并且只进行过示例测试。

2. 接触电容值是通过 JEP147 过程获得的，该过程使用了向量网络分析仪进行电容测量。使用了  $V_{CC}$  和  $V_{CCQ}$ ，所有信号（待测信号除外）均处于悬空状态。DQ 应处于高阻抗状态。

3. 请注意，要求 CK、CK#、RWDS 和 DQx 信号的电容相同，从而保证系统中信号传输时间匹配。CS# 的电容值不是关键因素，因为 CS# 有效（为低电平）和数据在 DQ 总线上传输之间不存在关键的时序要求。

表 9.4 3.0 V 电容特性

| 说明                | 参数   | 最小值 | 最大值 | 单位 |

|-------------------|------|-----|-----|----|

| 输入电容 (CK、CS#)     | Cl   | 3   | 4.5 | pF |

| 输出电容 (RWDS)       | CO   | 3   | 4   | pF |

| I/O 电容 (DQx)      | CIO  | 3   | 4   | pF |

| IO 电容 Delta (DQx) | CIOD | -   | 0.5 | pF |

**注意:**

1. 这些值仅由设计保证，并且只进行过示例测试。

2. 接触电容值是通过 JEP147 过程获得的，该过程使用了向量网络分析仪进行电容测量。使用了  $V_{CC}$  和  $V_{CCQ}$ ，所有信号（待测信号除外）均处于悬空状态。DQ 应处于高阻抗状态。

3. 请注意，要求 CK、RWDS 和 DQx 信号的电容相同，从而保证系统中信号传输时间匹配。CS# 的电容没有上述引脚的电容重要，因为 CS# 变为有效状态（低电平）与数据出现在 DQ 总线上之间的时序不很重要。

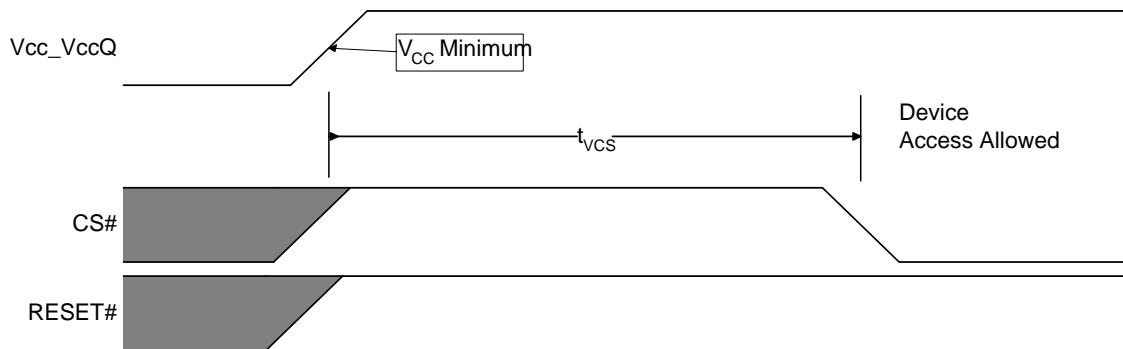

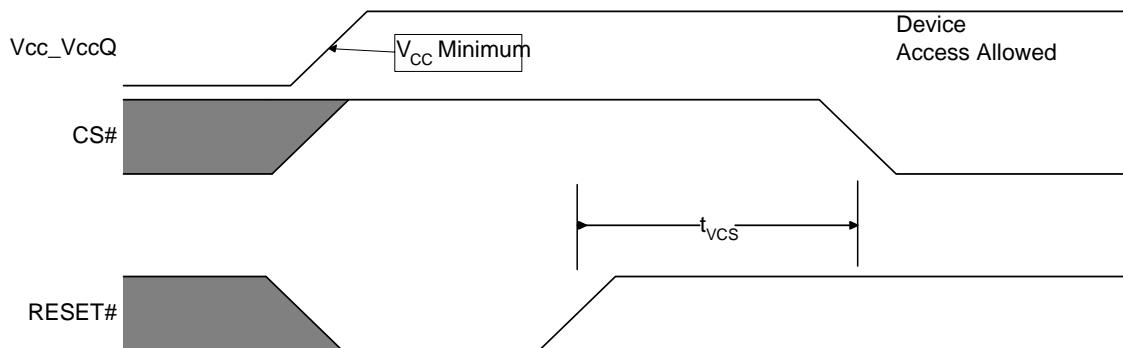

### 9.5 上电初始化

HyperRAM 系列产品拥有一个片上电压传感器，用于启动上电初始化过程。需要同时使用  $V_{CC}$  和  $V_{CCQ}$ 。当电源达到不低于  $V_{CC}$ （最小值）的稳定电平时，器件需要经过  $t_{VCS}$  时间来完成其自身的初始化过程。

在上电过程中不能选择器件。上电过程中，CS# 需要遵循  $V_{CCQ}$ ，直到达到  $V_{CC}$  (min) 为止，此后，CS# 需要在  $t_{VCS}$  的时间内保持为高电平。为安全和适当上电操作起见， $V_{CCQ}$  和片选 (CS#) 之间可使用一个简单的上拉电阻。

在上电过程中，如果 RESET# 为低电平，则器件将延迟  $t_{VCS}$  时间，直到 RESET# 为高电平为止。 $t_{VCS}$  周期主要用于对 DRAM 数组进行刷新，以便实现初始化操作。

初始化操作完成后，器件可以进行正常的操作。

图 9.3 上电过程 (RESET# 为高电平)

图 9.4 上电过程 (RESET# 为低电平)

表 9.5 上电和复位参数

| 参数        | 说明                                                           | 最小值 | 最大值  | 单位      |

|-----------|--------------------------------------------------------------|-----|------|---------|

| $V_{CC}$  | 1.8 V 的 $V_{CC}$ 电源                                          | 1.7 | 1.95 | V       |

| $V_{CC}$  | 3 V 的 $V_{CC}$ 电源                                            | 2.7 | 3.6  | V       |

| $t_{VCS}$ | 从 $V_{CC}$ 和 $V_{CCQ} \geq$ 最小值且 $RESET\#$ 为高电平到开始执行第一次访问的时间 | —   | 150  | $\mu s$ |

**注意:**

1. 在上电复位期间 ( $t_{VCS}$ ), 不允许进行总线操作 (读和写操作)。

2. 要求  $V_{CCQ}$  和  $V_{CC}$  电压相同。

3.  $V_{CC}$  的升降速率可能是非线性的。

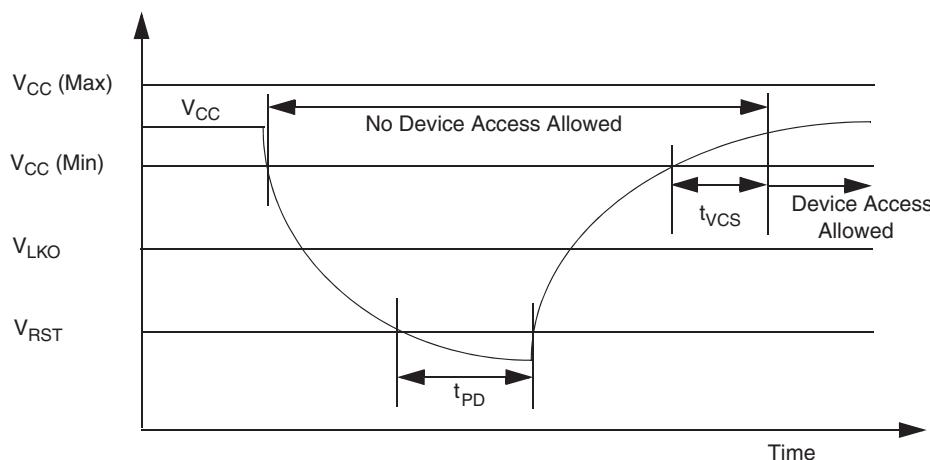

## 9.6 掉电

内核供电电压 ( $V_{CC}$ ) 下降到  $V_{CC}$  锁定电压以下 ( $V_{LKO}$ ) 时, HyperRAM 器件被视为掉电。当  $V_{CC}$  低于  $V_{LKO}$  时, HyperFlash 存储器阵列受保护, 以防止对它进行写入或擦除操作。这样可防止在电源转换期间 Flash 存储器的内容被篡改。电源降到  $V_{SS}$  的过程中,  $V_{CCQ}$  需要保持在不高于  $V_{CC}$  的电压电平。在  $V_{LKO}$  电压下, HyperRAM 的配置或存储阵列数据将被丢失。

$V_{CC}$  不能小于  $V_{CCQ}$  ( $V_{CC} \geq V_{CCQ}$ )。

在掉电状态或电压降到  $V_{LKO}$  以下时, 内核供电电压也需要在掉电时间 ( $t_{PD}$ ) 内低于  $V_{CC}$  复位 ( $V_{RST}$ ), 这样, 在供电电压上升超过  $V_{CC}$  最小值时, 器件才会正常初始化。请参见图 9.5。

如果在电压下降过程中,  $V_{CC}$  保持为高于  $V_{LKO}$  的状态, 那么当  $V_{CC}$  再次超过  $V_{CC}$  最小值时, 器件将被初始化, 并正常运行。如果  $V_{CC}$  未下降到  $V_{RST}$  以下, 并在保持该状态超过  $t_{PD}$  时间, 则无法保证 POR 过程能被执行。在这种情况下, 需要进行硬件复位才可保证 HyperBus 器件被正常初始化。

图 9.5 掉电或电压下降

下面部分介绍了掉电规范中有关 HyperRAM 器件方面的内容。

表 9.6 1.8 V 下电电压和时序

| 符号        | 参数                               | 最小值 | 最大值  | 单位      |

|-----------|----------------------------------|-----|------|---------|

| $V_{CC}$  | $V_{CC}$ 电源                      | 1.7 | 1.95 | V       |

| $V_{LKO}$ | $V_{CC}$ 锁定电压, 低于该电压时需要重新进行初始化操作 | 1.7 | -    | V       |

| $V_{RST}$ | 保证初始化操作能够发生的 $V_{CC}$ 低电压        | 0.8 | -    | V       |

| $t_{PD}$  | $V_{CC} \leq V_{RST}$ 的时间        | 30  | -    | $\mu s$ |

注意:

1.  $V_{CC}$  的升降速率可能是非线性的。

表 9.7 3.0 V 下电电压和时序

| 符号        | 参数                               | 最小值 | 最大值 | 单位      |

|-----------|----------------------------------|-----|-----|---------|

| $V_{CC}$  | $V_{CC}$ 电源                      | 2.7 | 3.6 | V       |

| $V_{LKO}$ | $V_{CC}$ 锁定电压, 低于该电压时需要重新进行初始化操作 | 2.7 | -   | V       |

| $V_{RST}$ | 保证初始化操作能够发生的 $V_{CC}$ 低电压        | 0.8 | -   | V       |

| $t_{PD}$  | $V_{CC} \leq V_{RST}$ 的时间        | 50  | -   | $\mu s$ |

注意:

1.  $V_{CC}$  的升降速率可能是非线性的。

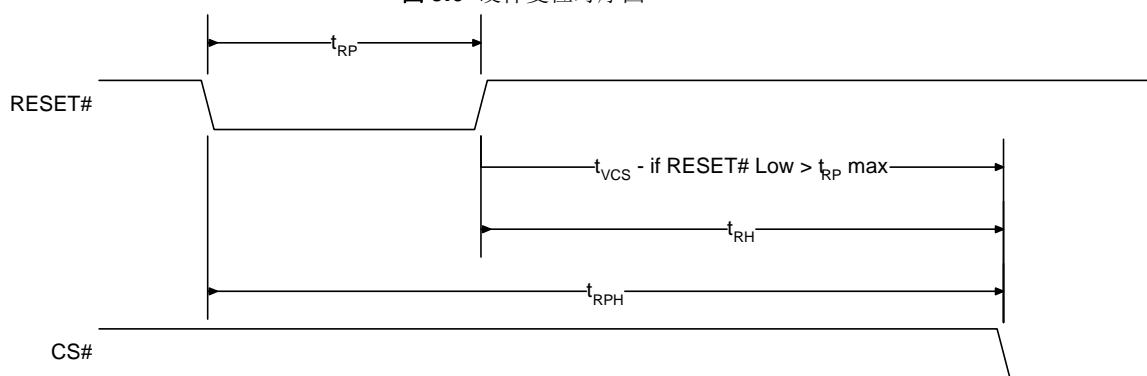

## 9.7 硬件复位

RESET# 输入提供了一种硬件复位方法，通过该方法可使设备返回到待机状态。

在  $t_{RP}$  期间，器件消耗的电流为  $I_{CC5}$ 。经过  $t_{RPH}$  时间，如果 RESET# 保持为低电平，则器件将消耗 CMOS 待机电流 ( $I_{CC4}$ )。RESET# 为低电平时 ( $t_{RP}$  期间内)，和  $t_{RPH}$  期间内，不能进行总线操作。

硬件复位会：

- 将所有配置寄存器恢复到各自的默认值。

- 停止自刷新操作（当 RESET# 为低电平时），

- 并会强制使器件退出深度掉电模式。

RESET# 返回到高电平时，自刷新操作将恢复。由于在 RESET# 为低电平期间，自刷新操作被停止，并且自刷新行计数器恢复为默认值，所以在第 23 页上的表 5.7、与温度相应的阵列刷新间隔中显示的阵列刷新间隔中会存在某些行得不到刷新。这样，在硬件复位过程中或之后，DRAM 阵列数据可能被丢失。硬件复位后，主机系统假设 DRAM 阵列数据已丢失，并重新下载所需的数据。

图 9.6 硬件复位时序图

表 9.8 上电和复位参数

| 参数        | 说明                         | 最小值 | 最大值 | 单位 |

|-----------|----------------------------|-----|-----|----|

| $t_{RP}$  | RESET# 脉冲宽度                | 200 | -   | ns |

| $t_{RH}$  | 从 RESET# 为高电平到 CS# 为低电平的时间 | 200 | -   | ns |

| $t_{RPH}$ | 从 RESET# 为低电平到 CS# 为低电平的时间 | 400 | -   | ns |

## 10. 时序规范

下面部分介绍了时序规范中有关 HyperRAM 器件方面的内容。

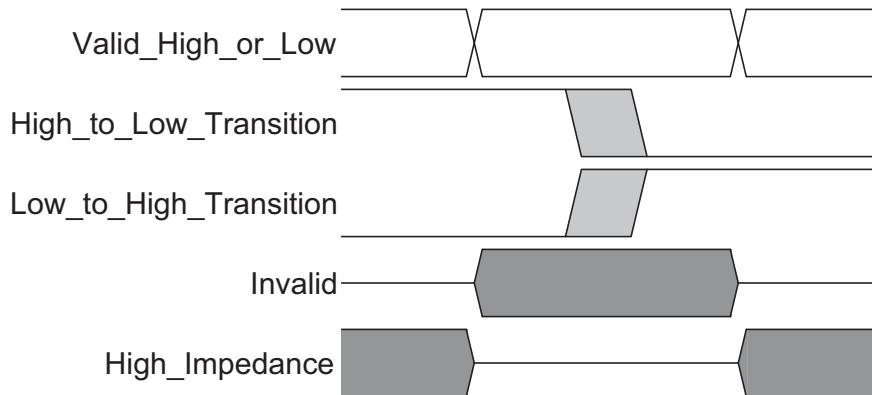

### 10.1 切换波形的关键

### 10.2 交流测试条件

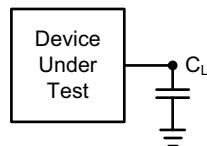

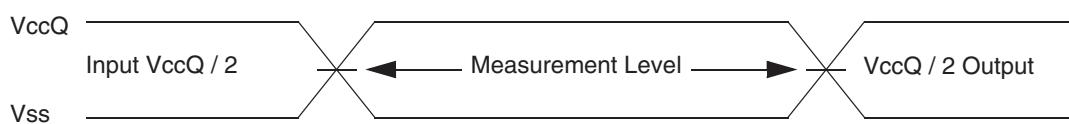

图 10.1 测试设置

表 10.1 测试规范

| 参数                 | 所有速度            | 单位   |

|--------------------|-----------------|------|

| 输出负载电容, $C_L$      | 20              | pF   |

| 最小输入上升和下降斜率 (注意 1) | 2.0             | V/ns |

| 输入脉冲电平             | 0.0 ~ $V_{CCQ}$ | V    |

| 输入时序测量参考电平         | $V_{CCQ}/2$     | V    |

| 输出时序测量参考电平         | $V_{CCQ}/2$     | V    |

**注意：**

- 所有交流时序均假定输入压摆率为 2V/ns。CK/CK# 差分压摆率至少为 4V/ns。

- 输入和输出时序参照  $V_{CCQ}/2$  或 CK/CK# 的交叉点。

图 10.2 输入波形和测量电平

**注意：**

- 差分对 CK/CK# 的输入时序是通过测量时钟交叉得到的。

## 10.3 交流特性

### 10.3.1 读取操作

表 10.2 HyperRAM 特定 1.8 V 读取时序参数

| 参数                                                                                                                                 | 符号         | 166 MHz |       | 133 MHz |      | 100 MHz |      | 单位 |

|------------------------------------------------------------------------------------------------------------------------------------|------------|---------|-------|---------|------|---------|------|----|

|                                                                                                                                    |            | 最小值     | 最大值   | 最小值     | 最大值  | 最小值     | 最大值  |    |

| 两个操作之间的片选为高电平的时间                                                                                                                   | $t_{CSHI}$ | 6       | —     | 7.5     | —    | 10.0    | —    | ns |

| HyperRAM 读 - 写恢复时间                                                                                                                 | $t_{RWR}$  | 36      | —     | 37.5    | —    | 40      | —    | ns |

| 从片选建立到下一个时钟上升沿的时间                                                                                                                  | $t_{CSS}$  | 3       | —     | 3       | —    | 3       | —    | ns |

| 数据选通有效时间                                                                                                                           | $t_{DSV}$  | —       | 12    | —       | 12   | —       | 12   | ns |

| 输入建立时间                                                                                                                             | $t_{IS}$   | 0.6     | —     | 0.8     | —    | 1.0     | —    | ns |

| 输入保持时间                                                                                                                             | $t_{IH}$   | 0.6     | —     | 0.8     | —    | 1.0     | —    | ns |

| HyperFlash 读取初始访问时间                                                                                                                | $t_{ACC}$  | —       | 96    | —       | 96   | —       | 96   | ns |

| HyperRAM 读取初始访问时间                                                                                                                  |            | 36      | —     | 37.5    | —    | 40      | —    | ns |

| 从时钟有效到 DQ 为低阻态的时间                                                                                                                  | $t_{DQLZ}$ | 0       | —     | 0       | —    | 0       | —    | ns |

| 从时钟转换到数据有效的时间                                                                                                                      | $t_{CKD}$  | 1       | 5.5   | 1       | 5.5  | 1       | 5.5  | ns |

| 从时钟转换到数据无效的时间                                                                                                                      | $t_{CKDI}$ | 0       | 4.6   | 0       | 4.5  | 0       | 4.3  | ns |

| 数据有效<br>( $t_{DV} \min = (t_{CKHP} \min - t_{CKD} \max + t_{CKDI} \max)$ 和 $(t_{CKHP} \min - t_{CKD} \min + t_{CKDI} \min)$ 中的更小者) | $t_{DV}$   | 1.7     | —     | 2.375   | —    | 3.3     | —    | ns |

| 从时钟转换到 RWDS 有效的时间                                                                                                                  | $t_{CKDS}$ | 1       | 5.5   | 1       | 5.5  | 1       | 5.5  | ns |

| 从 RWDS 转换到 DQ 有效的时间                                                                                                                | $t_{DSS}$  | -0.45   | +0.45 | -0.6    | +0.6 | -0.8    | +0.8 | ns |

| 从 RWDS 转换到 DQ 无效的时间                                                                                                                | $t_{DSH}$  | -0.45   | +0.45 | -0.6    | +0.6 | -0.8    | +0.8 | ns |

| 时钟下降沿后的片选保持时间                                                                                                                      | $t_{CSH}$  | 0       | —     | 0       | —    | 0       | —    | ns |

| 从片选无效到 RWDS 为高阻态的时间                                                                                                                | $t_{DSZ}$  | —       | 6     | —       | 6    | —       | 6    | ns |

| 从片选无效到 DQ 为高阻态的时间                                                                                                                  | $t_{OZ}$   | —       | 6     | —       | 6    | —       | 6    | ns |

| HyperRAM 片选的最大低电平时间<br>(工业级温度)                                                                                                     | $t_{CSM}$  | —       | 4.0   | —       | 4.0  | —       | 4.0  | us |

| HyperRAM 片选的最大低电平时间<br>(扩展型的工业级温度)                                                                                                 |            | —       | 1.0   | —       | 1.0  | —       | 1.0  | us |

| 刷新时间                                                                                                                               | $t_{RFH}$  | 36      | —     | 37.5    | —    | 40      | —    | ns |

**表 10.3** HyperRAM 特定 3.0 V 读取时序参数

| 参数                                                                                                                              | 符号         | 100 MHz |      | 单位 |

|---------------------------------------------------------------------------------------------------------------------------------|------------|---------|------|----|

|                                                                                                                                 |            | 最小值     | 最大值  |    |

| 两个操作之间的片选为高电平的时间                                                                                                                | $t_{CSHI}$ | 10.0    | —    | ns |

| HyperRAM 读 - 写恢复时间                                                                                                              | $t_{RWR}$  | 40      | —    | ns |

| 从片选建立到底一个时钟上升沿的时间                                                                                                               | $t_{CSS}$  | 3       | —    | ns |

| 数据选通有效时间                                                                                                                        | $t_{DSV}$  | —       | 12   | ns |

| 输入建立时间                                                                                                                          | $t_{IS}$   | 1.0     | —    | ns |

| 输入保持时间                                                                                                                          | $t_{IH}$   | 1.0     | —    | ns |

| HyperFlash 读取初始访问时间                                                                                                             | $t_{ACC}$  | —       | 96   | ns |

| HyperRAM 读取初始访问时间                                                                                                               |            | 40      | —    | ns |

| 从时钟有效沿到数据为低阻态的时间                                                                                                                | $t_{DQLZ}$ | 0       | —    | ns |

| 从 HyperFlash 时钟转换到数据输入 / 输出有效的时间                                                                                                | $t_{CKD}$  | 1       | 6.5  | ns |

| 从 HyperRAM 时钟转换到 DQ 有效的时间                                                                                                       |            | 1       | 7    | ns |

| 从 HyperFlash 时钟转换到数据输入 / 输出无效的时间                                                                                                | $t_{CKDI}$ | 0       | 4.7  | ns |

| 从 HyperRAM 时钟转换到 DQ 无效的时间                                                                                                       |            | 0.5     | 5.2  | ns |

| 数据有效 ( $t_{DV} \min = (t_{CKHP} \min - t_{CKD} \max + t_{CKDI} \max)$ 和 $(t_{CKHP} \min - t_{CKD} \min + t_{CKDI} \min)$ 中的更小者) | $t_{DV}$   | 2.7     | —    | ns |

| 从时钟转换到 RWDS 有效的时间                                                                                                               | $t_{CKDS}$ | 1       | 7    | ns |

| 从 RWDS 转换到 DQ 有效的时间                                                                                                             | $t_{DSS}$  | -0.8    | +0.8 | ns |

| 从 RWDS 转换到 DQ 无效的时间                                                                                                             | $t_{DSH}$  | -0.8    | +0.8 | ns |

| 时钟下降沿后的片选保持时间                                                                                                                   | $t_{CSH}$  | 0       | —    | ns |

| 从片选无效到 RWDS 为高阻态的时间                                                                                                             | $t_{DSZ}$  | —       | 7    | ns |

| 从片选无效到 DQ 为高阻态的时间                                                                                                               | $t_{OZ}$   | —       | 7    | ns |

| HyperRAM 片选的最大低电平时间 (工业级温度)                                                                                                     | $t_{CSM}$  | —       | 4.0  | us |

| HyperRAM 片选的最大低电平时间 (扩展型的工业级温度)                                                                                                 |            | —       | 1.0  | us |

| 刷新时间                                                                                                                            | $t_{RFH}$  | 40      | —    | ns |

### 10.3.2 写入操作

表 10.4 1.8 V 写入时序参数

| 参数                      | 符号        | 166 MHz |     | 133 MHz |     | 100 MHz |     | 单位      |

|-------------------------|-----------|---------|-----|---------|-----|---------|-----|---------|

|                         |           | 最小值     | 最大值 | 最小值     | 最大值 | 最小值     | 最大值 |         |

| 读 - 写恢复时间               | $t_{RWR}$ | 36      | —   | 37.5    | —   | 40      | —   | ns      |

| 访问时间                    | $t_{ACC}$ | 36      | —   | 37.5    | —   | 40      | —   | ns      |

| 刷新时间                    | $t_{RFH}$ | 36      | —   | 37.5    | —   | 40      | —   | ns      |

| 片选信号的最大低电平时间 — 工业级温度    | $t_{CSM}$ | —       | 4.0 | —       | 4.0 | —       | 4.0 | $\mu s$ |

| 片选信号的最大低电平时间 — 扩展的工业级温度 |           | —       | 1.0 | —       | 1.0 | —       | 1.0 | $\mu s$ |

表 10.5 3.0 V 写入时序参数

| 参数                      | 符号        | 100 MHz |     | 单位      |

|-------------------------|-----------|---------|-----|---------|

|                         |           | 最小值     | 最大值 |         |

| 读 - 写恢复时间               | $t_{RWR}$ | 40      | —   | ns      |

| 访问时间                    | $t_{ACC}$ | 40      | —   | ns      |

| 刷新时间                    | $t_{RFH}$ | 40      | —   | ns      |

| 片选信号的最大低电平时间 — 工业级温度    | $t_{CSM}$ | —       | 4.0 | $\mu s$ |

| 片选信号的最大低电平时间 — 扩展的工业级温度 |           | —       | 1.0 | $\mu s$ |

## 11. 物理接口

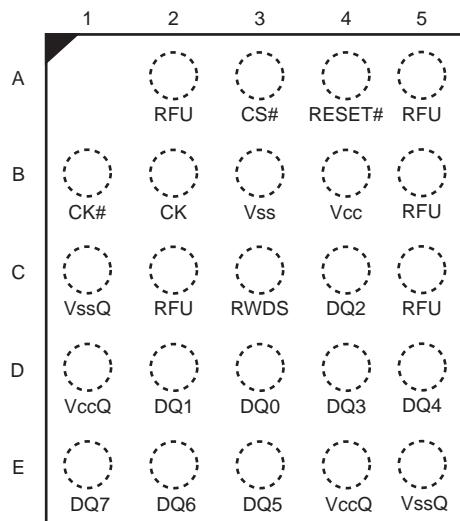

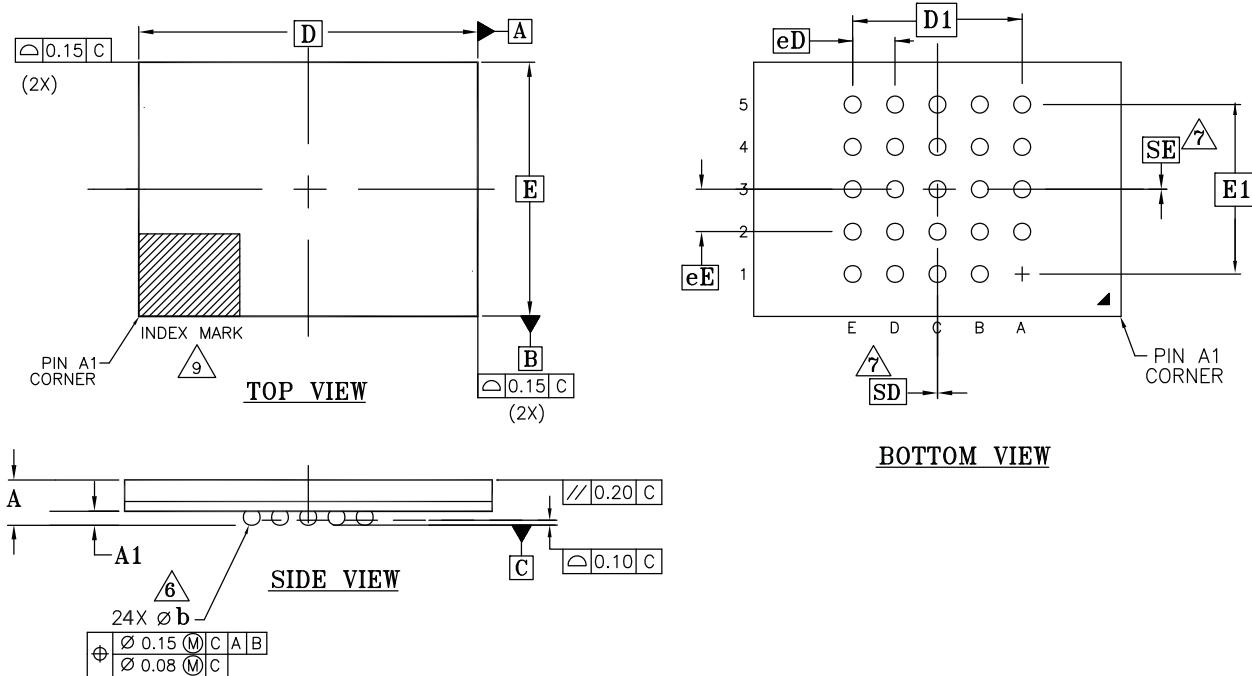

### 11.1 FBGA 24 球 5 x 5 阵列封装

HyperRAMM 存储器提供的封装规格为：加强型的球栅阵列（FBGA）、1 mm 的引脚间距、24 球、5 x 5 球阵列。它的尺寸为 6 mm x 8 mm。

图 11.1 24-FBGA、6 x 8 mm、5x5 球型焊盘封装，顶视图

**注意：**

1. 在 1.8 V 器件上，B1 被分配给 CK#。

2. 在 3.0V 器件上，B1 是 RFU。

## 11.2 物理框图

### 11.2.1 加强型的球栅阵列 (BGA) 24 球 6 x 8 x 1.0 mm (VAA024)

| PACKAGE         |           | VAA 024                   |      |                          | NOTE |  |

|-----------------|-----------|---------------------------|------|--------------------------|------|--|

| JEDEC           |           | N/A                       |      |                          |      |  |

|                 |           | 8.00 mm x 6.00 mm PACKAGE |      |                          |      |  |

| SYMBOL          | MIN       | NOM                       | MAX  | NOTE                     |      |  |

| A               | ---       | ---                       | 1.00 | PROFILE                  |      |  |

| A1              | 0.20      | ---                       | ---  | BALL HEIGHT              |      |  |

| [D]             | 8.00 BSC. |                           |      | BODY SIZE                |      |  |

| [E]             | 6.00 BSC. |                           |      | BODY SIZE                |      |  |

| [D1]            | 4.00 BSC. |                           |      | MATRIX FOOTPRINT         |      |  |

| [E1]            | 4.00 BSC. |                           |      | MATRIX FOOTPRINT         |      |  |

| MD              | 5         |                           |      | MATRIX SIZE D DIRECTION  |      |  |

| ME              | 5         |                           |      | MATRIX SIZE E DIRECTION  |      |  |

| N               | 24        |                           |      | BALL COUNT               |      |  |

| $\varnothing b$ | 0.35      | 0.40                      | 0.45 | BALL DIAMETER            |      |  |

| [eE]            | 1.00 BSC. |                           |      | BALL PITCH               |      |  |

| [eD]            | 1.00 BSC. |                           |      | BALL PITCH               |      |  |

| SD              | 0.00 BSC. |                           |      | SOLDER BALL PLACEMENT    |      |  |

| SE              | 0.00 BSC. |                           |      | SOLDER BALL PLACEMENT    |      |  |

|                 | A1        |                           |      | DEPOPULATED SOLDER BALLS |      |  |

#### NOTES:

1. DIMENSIONING AND TOLERANCING METHODS PER ASME Y14.5M-1994.

2. ALL DIMENSIONS ARE IN MILLIMETERS.

3. BALL POSITION DESIGNATION PER JEP95, SECTION 3, SPP-020.

4. [e] REPRESENTS THE SOLDER BALL GRID PITCH.

5. SYMBOL "MD" IS THE BALL MATRIX SIZE IN THE "D" DIRECTION.

SYMBOL "ME" IS THE BALL MATRIX SIZE IN THE "E" DIRECTION.

6. N IS THE TOTAL NUMBER OF POPULATED SOLDER BALL POSITIONS FOR MATRIX SIZE MD X ME.

7. DIMENSION "b" IS MEASURED AT THE MAXIMUM BALL DIAMETER IN A PLANE PARALLEL TO DATUM C.

8. "SD" AND "SE" ARE MEASURED WITH RESPECT TO DATUMS A AND B AND DEFINE THE POSITION OF THE CENTER SOLDER BALL IN THE OUTER ROW.

9. WHEN THERE IS AN ODD NUMBER OF SOLDER BALLS IN THE OUTER ROW "SD" OR "SE" = 0.

10. WHEN THERE IS AN EVEN NUMBER OF SOLDER BALLS IN THE OUTER ROW, "SD" =  $eD/2$  AND "SE" =  $eE/2$ .

11. "+" INDICATES THE THEORETICAL CENTER OF DEPOPULATED BALLS.

12. A1 CORNER TO BE IDENTIFIED BY CHAMFER, LASER OR INK MARK, METALLIZED MARK INDENTATION OR OTHER MEANS.

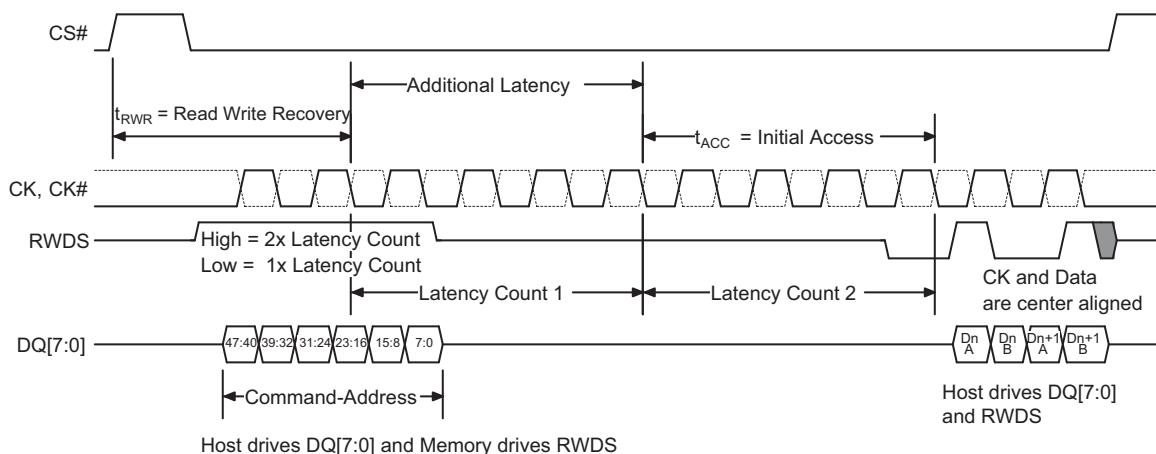

## 12. DDR 中心对齐读取选通功能

HyperRAM 器件提供了一个可选功能，允许与读取数据输出相关的 RWDS 信号的独立时滞（相移）。某些特定器件提供了该功能，具体情况取决于订购器件型号（OPN）。

如果器件提供了 DDR 中心对齐读取选通（DCARS）功能，另外一对差分时钟信号 PSC/PSC#（而不是 CK/CK#）将作为 RWDS 边沿的参考。该时钟通常是 CK/CK# 的复制时钟（它们之间的相移值为 90°），用来将 RWDS 边沿放置在 DQ 信号有效的数据窗口的中心内。然而，CK/CK# 和 PSC/PSC# 之间的其他相移值可用于优化 RWDS 的边沿位置，使其落在 DQ 信号有效的窗口内，这样 RWDS 会根据 RWDS 边沿情况提供所需的数据建立和保持时间。

在写操作期间不使用 PSC/PSC#。在写操作过程中，可以分别将 PSC 和 PSC# 驱动为低电平和高电平，也可以将这两者都驱动为低电平。

仅在 HyperBus 器件（内核额定电压和 I/O 电压 1.8 V）中使用 PSC/PSC# 差分时钟。内核额定电压和 I/O 电压 3 V 的 HyperBus 器件只使用 PSC 单端时钟。

### 12.1 带有 DCARS 信号说明的 HyperRAM 产品

图 12.1 具有 DCARS 信号图的 HyperBus 产品

#### 信号描述

| 符号               | 类型      | 说明                                                                                                                                                                                                                           |

|------------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CS#              | 输入      | 片选。当该信号从高电平转为低电平时，初始化 HyperBus 传输。当该信号从低电平转为高电平时，结束 HyperBus 传输。                                                                                                                                                             |

| CK、CK#           | 输入      | 差分时钟。命令 - 地址 / 数据信息可以是输入也可以是输出，具体取决于 CK 和 CK# 信号之间的关系。3.0 V 的器件不使用 CK#，它仅使用一个单端 CK。                                                                                                                                          |

| PSC、PSC#         | 输入      | 相移时钟。使用 PSC/PSC# 能够避免 RWDS 信号（与 CK/CK# 输入相关）时滞的影响。PSC# 仅适用于 1.8 V 的器件。在写操作过程中，可以分别将 PSC 和 PSC# 驱动为高电平和低电平，也可以将这两个信号都驱动为低电平。                                                                                                  |

| RWDS             | 输出      | 读写数据选通。读取操作期间输出的数据字节根据 CK、CK# 转移到 PSC、PSC# 的相移情况和 RWDS 对齐。PSC、PSC# 可以引起 RWDS 的转换，因此可以使用 CK、CK# 到 PSC、PSC# 的相移将 RWDS 边沿放置在数据有效窗口内。在写操作过程中，RWDS 为输入，其功能是作为数据掩码。在所有总线传输的起始，RWDS 是一个输出，它表示是否需要额外的初始延迟计数（1 = 附加延迟计数，0 = 无附加延迟计数）。 |

| DQ[7:0]          | 输入 / 输出 | 数据输入 / 输出。在读写操作期间，通过这些 DQ 信号传输命令 - 地址 / 数据信息。                                                                                                                                                                                |

| RESET#           | 输入      | 硬件复位。当该信号处于低电平状态时，器件将进行自初始化并返回到空闲态。当 RESET# 为低电平时，RWDS 和 DQ[7:0] 将进入高阻态。RESET# 在内部已经有一个弱上拉，如果 RESET# 未连接，它将被上拉到高电平状态。                                                                                                        |

| V <sub>CC</sub>  | 电源电压    | 内核电源电压。                                                                                                                                                                                                                      |

| V <sub>CCQ</sub> | 电源电压    | 输入 / 输出电源。                                                                                                                                                                                                                   |

| V <sub>SS</sub>  | 电源电压    | 内核接地电压。                                                                                                                                                                                                                      |

| V <sub>SSQ</sub> | 电源电压    | 输入 / 输出接地电压。                                                                                                                                                                                                                 |

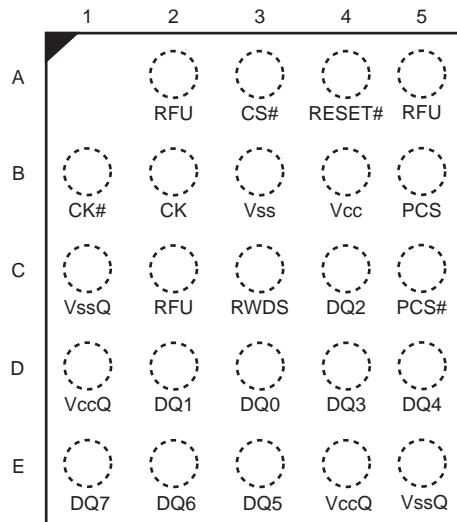

## 12.2 具有 DCARS 的 HyperRAM 产品 — FBGA 24 球型焊盘，5x5 阵列封装

图 12.2 24-FBGA, 5x5 球型焊盘封装, 顶视图

**注意:**

1. B1 是 3.0 V 器件上的一个 RFU, 而在 1.8 V 器件上它被分配给 CK#.

2. B1 在 3.0 V 器件上作为 RFU, 而在 1.8 V 器件上被分配给 PCS#.

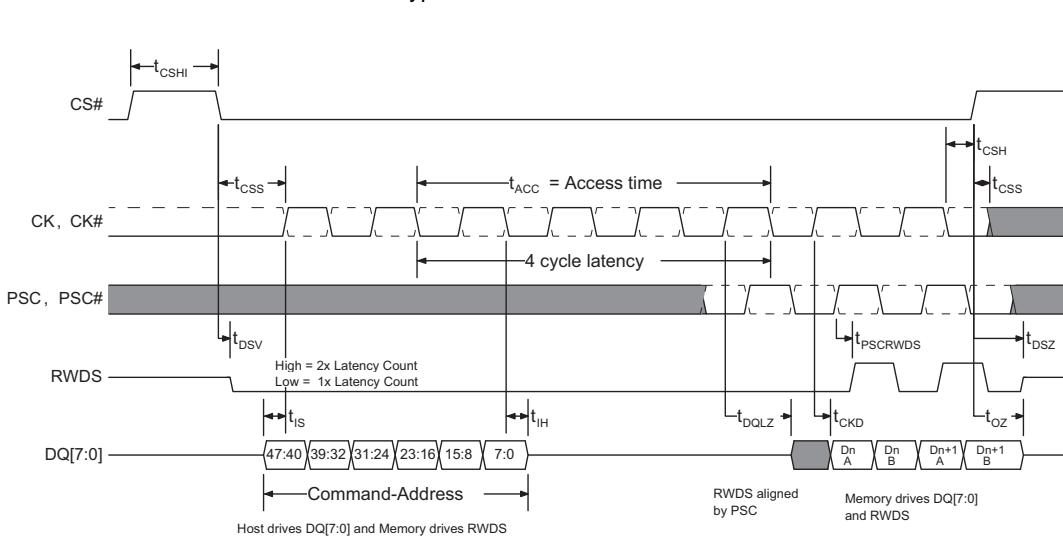

## 12.3 HyperRAM 存储器 DCARS 时序

HyperRAM 读操作时序参数会因器件、电压范围和温度范围的不同而存在差异。并非所有时序参数都被显示在该补充文档内。请参考单独的器件数据手册, 了解当前的所有时序参数信息。本文档所介绍的全部实例说明和参数仅用于定义 DCARS 功能以及说明相移时钟、RWDS 和数据之间的关系。

图 12.3 HyperRAM 存储器的 DCARS 时序图

**注意:**

1. 必须将 CK 设置为低电平, 并将 CK# 设置为高电平, 才能启动操作。必须将 CS# 返回到高电平状态才能启动一个新操作。

2. CK# 和 PSC# 仅适用于 1.8 V 的器件。3 V 的器件使用了一个单端 CK 和 PSC 输入。

3. 在读取操作过程中, 存储器将驱动 RWDS。

4. 该示例演示了一个四个时钟的延迟, 同时不需要额外的初始延迟。

**图 12.4 DCARS 数据有效时序**

**注意:**

- 该图进一步显示了第 43 页上的图 12.1 具有 DCARS 信号图的 HyperBus 产品的数据传输部分, 从而可以更加详细地显示受时钟抖动影响的数据有效周期, 以及时钟和数据之间的延迟是未确定的。

- CK# 和 PSC# 仅适用于 1.8 V 的器件。3 V 的器件使用了一个单端 CK 和 PSC 输入。

- CK 和 PSC 之间的延迟 (相移) 是由 HyperBus 主设备接口 (主机) 控制的, 该相移值通常介于 40 到 140 度之间, 以便将 RWDS 边沿放置在数据有效窗口内, 并使 RWDS 具有足够的数据建立和保持时间。RWDS 的数据建立和保持时间的要求由 HyperBus 主设备接口设计确定, 并且不能使用 HyperBus 从设备时序参数进行寻址。

- HyperBus 的时序参数 ( $t_{CKD}$  和  $t_{CKDI}$ ) 定义了数据有效期内的起始和结束位置。 $t_{CKD}$  和  $t_{CKDI}$  值成对出现 (这些值可能因相同的比率而不同), 这是因为在相同的电压和温度的条件下 RWDS 和数据均是来自同一器件的输出。

**DCARS 读取时序 (电压为 3.0 V)**

| 参数                             | 符号                      | 100 MHz |      | 单位 |

|--------------------------------|-------------------------|---------|------|----|

|                                |                         | 最小值     | 最大值  |    |

| HyperRAM 从 PSC 转换到 RWDS 转换的时间  | $t_{PSCRWDS}$           | 1       | 7    | ns |

| CK 有效到 DQ 有效与 PSC 到 RWDS 间的时间差 | $t_{PSCRWDS} - t_{CKD}$ | -1.0    | +0.5 | ns |

**注意:**

- 采样值, 并非 100% 经过测试。

**DCARS 读取时序 (电压为 1.8 V)**

| 参数                                  | 符号                      | 133 MHz |      | 100 MHz |      | 单位 |

|-------------------------------------|-------------------------|---------|------|---------|------|----|

|                                     |                         | 最小值     | 最大值  | 最小值     | 最大值  |    |

| HyperRAM 从 PSC 转换到 RWDS 转换的时间       | $t_{PSCRWDS}$           | 1       | 5.5  | 1       | 5.5  | ns |

| 从 CK 有效到 DQ 有效与从 PSC 到 RWDS 之间的时间偏差 | $t_{PSCRWDS} - t_{CKD}$ | -1.0    | +0.5 | -1.0    | +0.5 | ns |

**注意:**

- 采样值, 并非 100% 经过了测试。

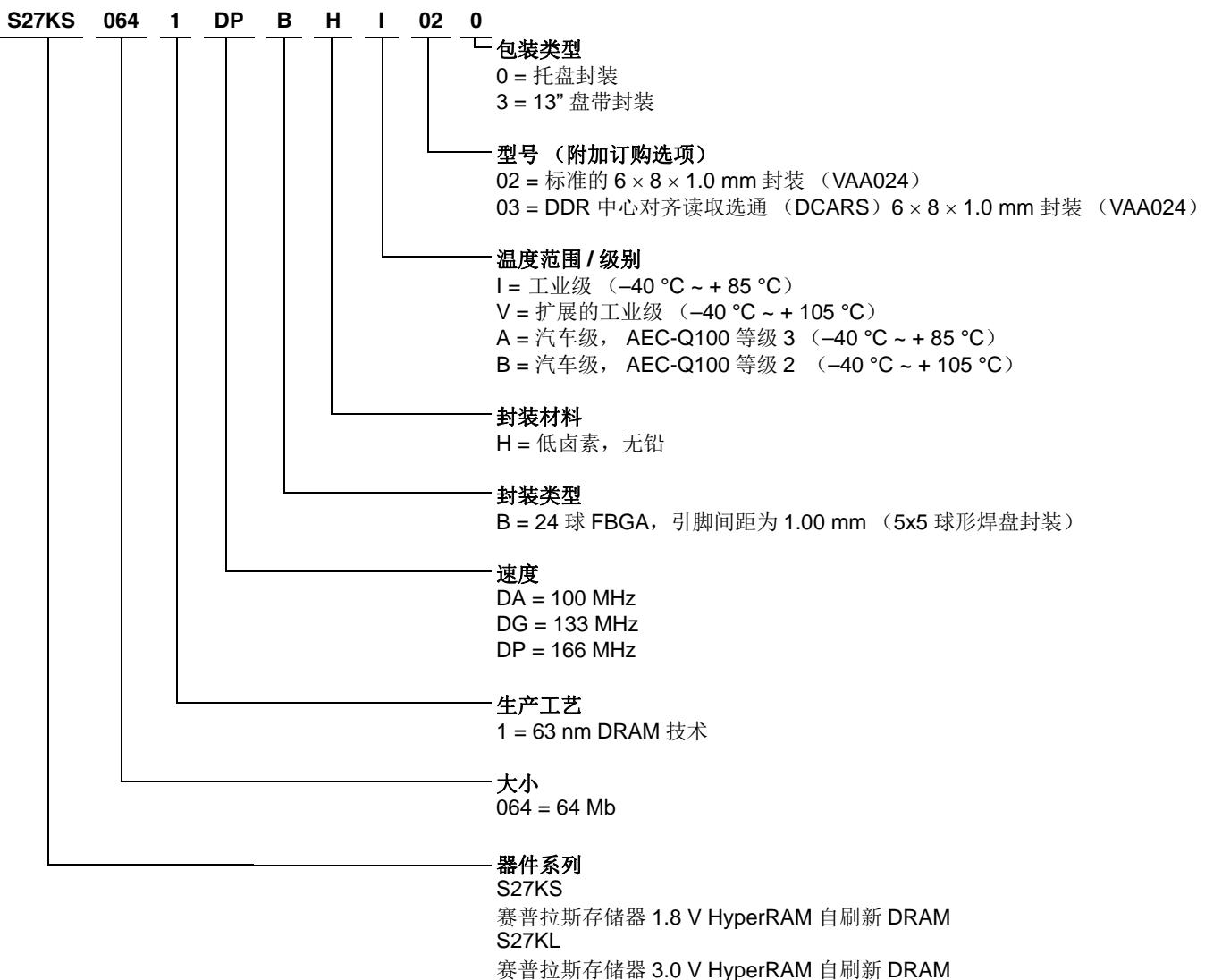

## 13. 订购信息

### 13.1 订购器件型号

订购器件型号由以下有效组合构成:

## 13.2 有效组合