# 英飞凌 64 Mb (8 MB) FS-S 闪存存储器

SPI Multi-I/O, 1.8 V

## 特性

- 具有多线I/O的串行外设接口(SPI)

- SPI时钟极性和相位模式0和3

- 具有双倍数据速率(DDR)选项

- 具有扩展地址：24或32位地址选项

- 串行指令集和封装与S25FL1-K、S25FL-P和S25FL-S SPI系列兼容

- 多线I/O指令集和封装与S25FL1-K S25FL-P和S25FL-S SPI系列兼容

- 读取

- 指令：Normal, Fast, Dual Output, Dual I/O, Quad Output, Quad I/O, DDR Quad I/O

- 模式：回卷突发、持续突发(XIP)、QPI

- 串行闪存可发现参数(SFDP)和通用闪存接口(CFI)，用于配置信息

- 编程

- 256或512字节的页编程缓冲区

- 编程挂起和恢复

- 自动ECC – 内部硬件1位纠错功能

- 擦除

- 混合扇区选项

- 八个4 KB扇区和一个32 KB扇区的物理配置位于地址空间的顶部或底部，所有剩余扇区均为64 KB

- 统一扇区选项

- 统一的64 KB或256 KB块，可与更高容量和未来产品实现软件兼容

- 擦除挂起和恢复

- 擦除状态评估

- 周期寿命

- 最低100,000次编程-擦除周期

- 数据保留

- 最短数据保留时间为20年

- 加密特性

- 1024字节的一次性写入(OTP)空间

- 功能块保护：

- 状态寄存器位用于控制对连续扇区范围的编程或擦除的保护。

- 硬件和软件控制选项

- 高级扇区保护(ASP)

- 由引导代码或密码控制的单独扇区保护

- 读取访问的密码控制选项

- 技术

- 采用Eclipse架构的65纳米MIRRORBIT™技术

- 带CMOS I/O的单电源电压

- 1.7 V至2.0 V

本数据手册的原文使用英文撰写。为方便起见，英飞凌提供了译文；由于翻译过程中可能使用了自动化工具，英飞凌不保证译文的准确性。为确认准确性，请务必访问infineon.com参考最新的英文版本（控制文档）。

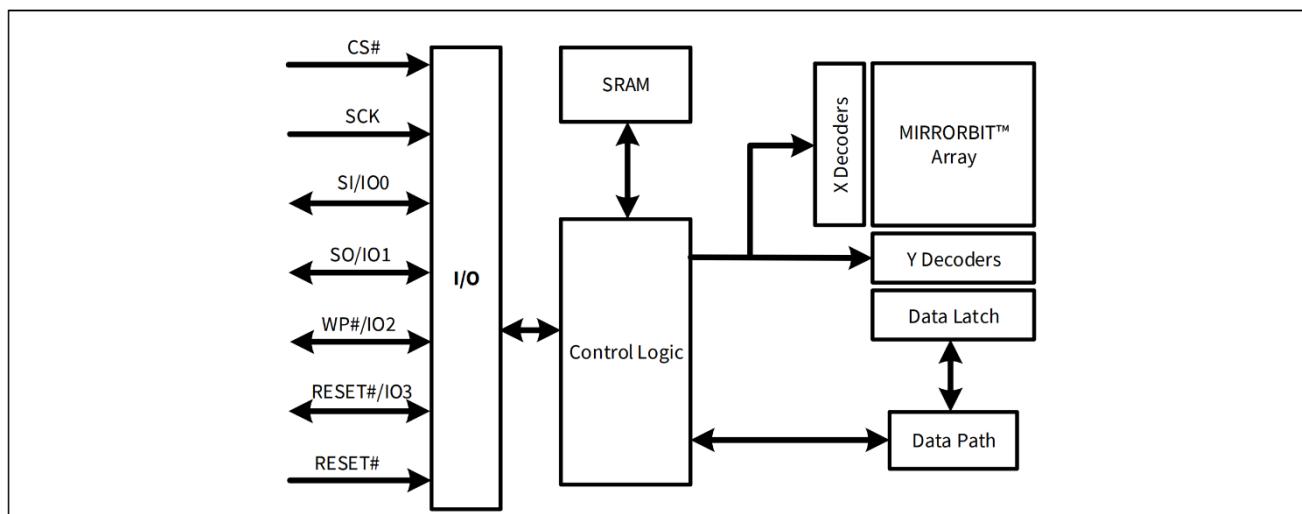

## 逻辑框图

### • 温度范围

- 工业级 (-40°C ~ +85°C)

- 扩展的工业级 (-40°C ~ +105°C)

- 扩展 (-40°C ~ +125°C)

- 汽车级, AEC-Q100 3 级 (-40°C ~ +85°C)

- 汽车级, AEC-Q100 2 级 (-40°C ~ +105°C)

- 汽车级, AEC-Q100 1 级 (-40°C ~ +125°C)

### • 封装 (全部无铅)

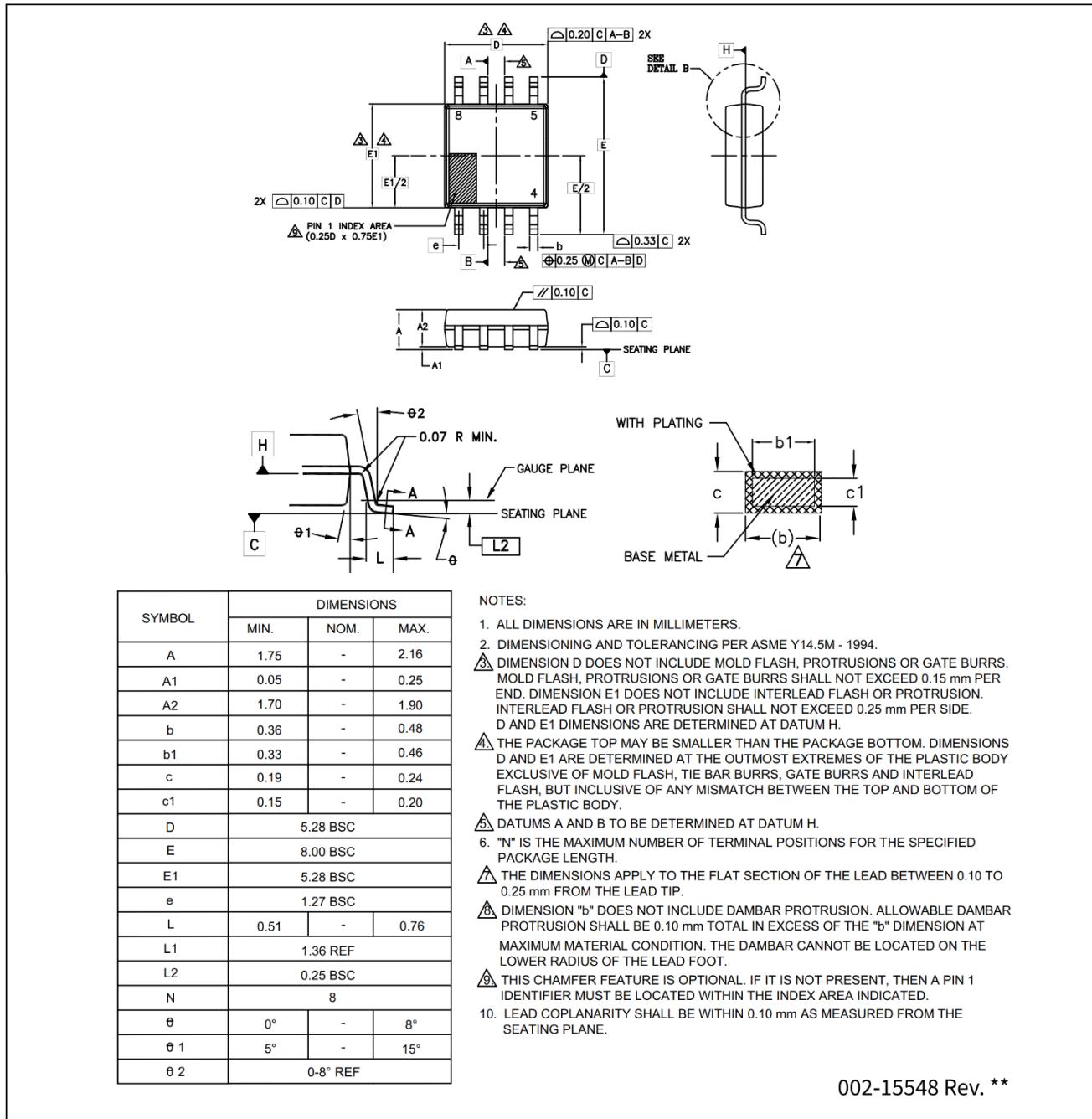

- 8-lead SOIC 208 mil (SOC008)

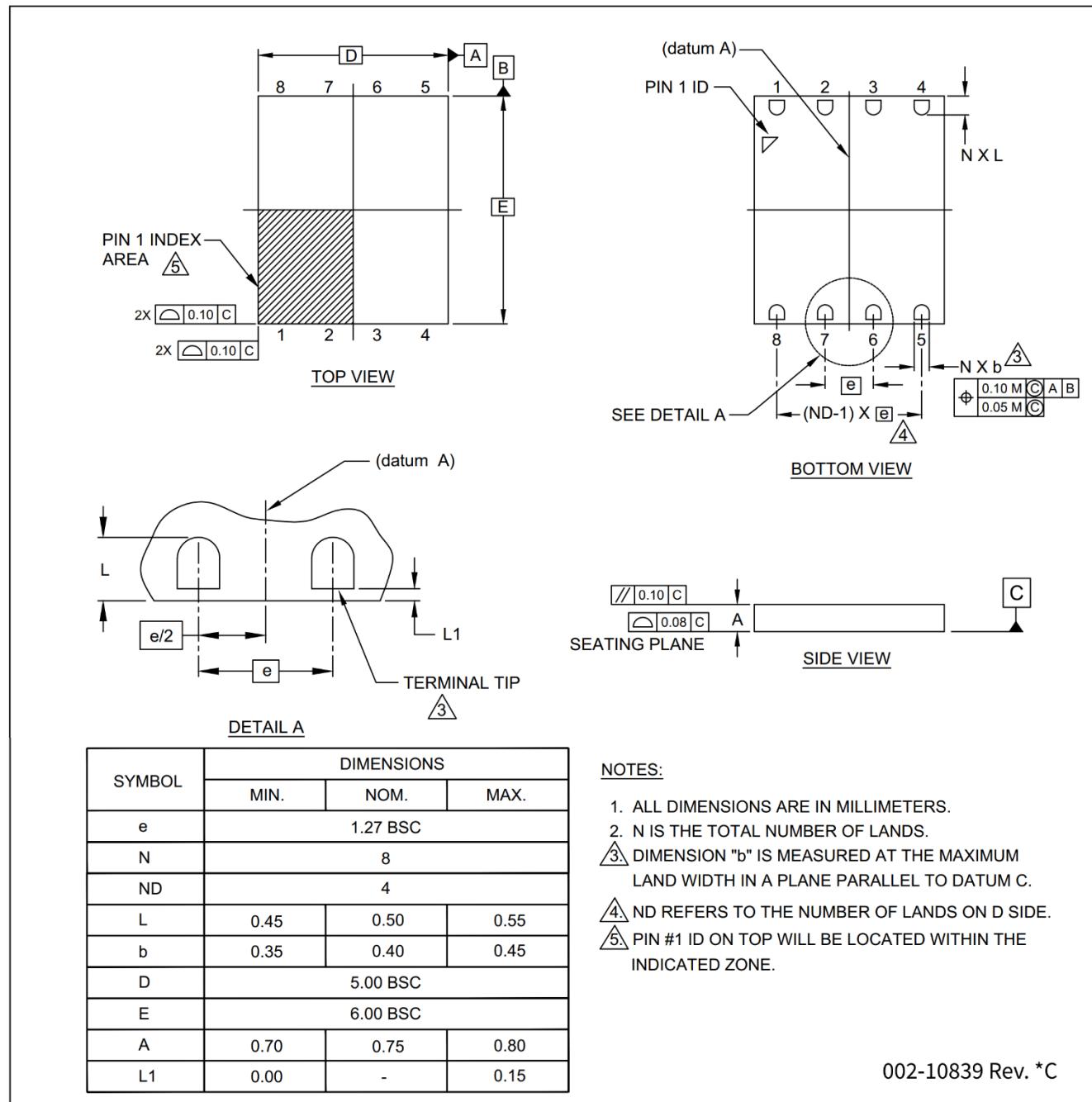

- LGA 5×6mm (W9A008)

- BGA-24 6 × 8 mm

- 5 × 5 ball (FAB024) 封装

## 逻辑框图

## 性能总结

**表 1** 最大读取率

| Command           | Clock rate (MHz) | MBps |

|-------------------|------------------|------|

| Read              | 50               | 6.25 |

| Fast Read         | 133              | 16.5 |

| Dual Read         | 133              | 33   |

| Quad Read         | 133              | 66   |

| DDR Quad I/O Read | 80               | 80   |

**表 2** 典型编程和擦除速率

| Operation                                         | KBps |

|---------------------------------------------------|------|

| Page programming (256 bytes page buffer)          | 712  |

| Page programming (512 bytes page buffer)          | 1080 |

| 4 KB physical sector erase (Hybrid sector option) | 16   |

| 64 KB sector erase                                | 275  |

| 256 KB sector erase                               | 275  |

性能总结

**表 3 典型消耗电流 -40°C 至 +85°C**

| Operation            | Current (mA) |

|----------------------|--------------|

| Serial read 50 MHz   | 10           |

| Serial read 133 MHz  | 22           |

| Quad read 133 MHz    | 60           |

| Quad DDR read 80 MHz | 70           |

| Program              | 60           |

| Erase                | 60           |

| Standby              | 0.025        |

| Deep power down      | 0.006        |

## 目录

|                                            |           |

|--------------------------------------------|-----------|

| <b>特性</b> .....                            | <b>1</b>  |

| <b>逻辑框图</b> .....                          | <b>2</b>  |

| <b>性能总结</b> .....                          | <b>2</b>  |

| <b>目录</b> .....                            | <b>4</b>  |

| <b>1 概述</b> .....                          | <b>9</b>  |

| 1.1 概述.....                                | 9         |

| 1.2 迁移说明.....                              | 9         |

| 1.2.1 特性比较.....                            | 9         |

| 1.2.2 与前几代产品的已知差异.....                     | 10        |

| <b>2 支持多线输入 / 输出的串行外设接口(SPI-MIO)</b> ..... | <b>13</b> |

| <b>3 引脚分配和信号描述</b> .....                   | <b>14</b> |

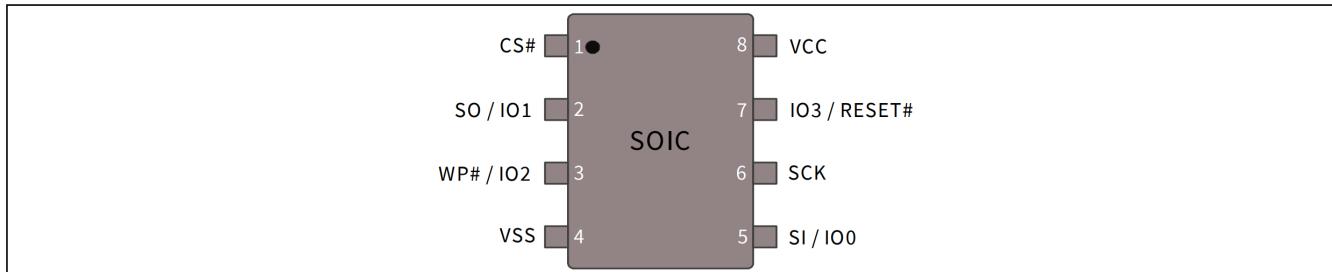

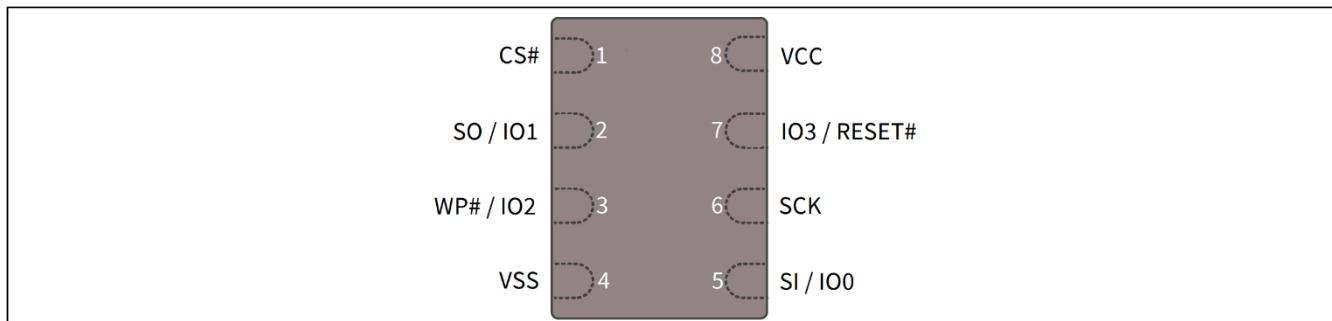

| 3.1 包含 8 个连接点的封装.....                      | 14        |

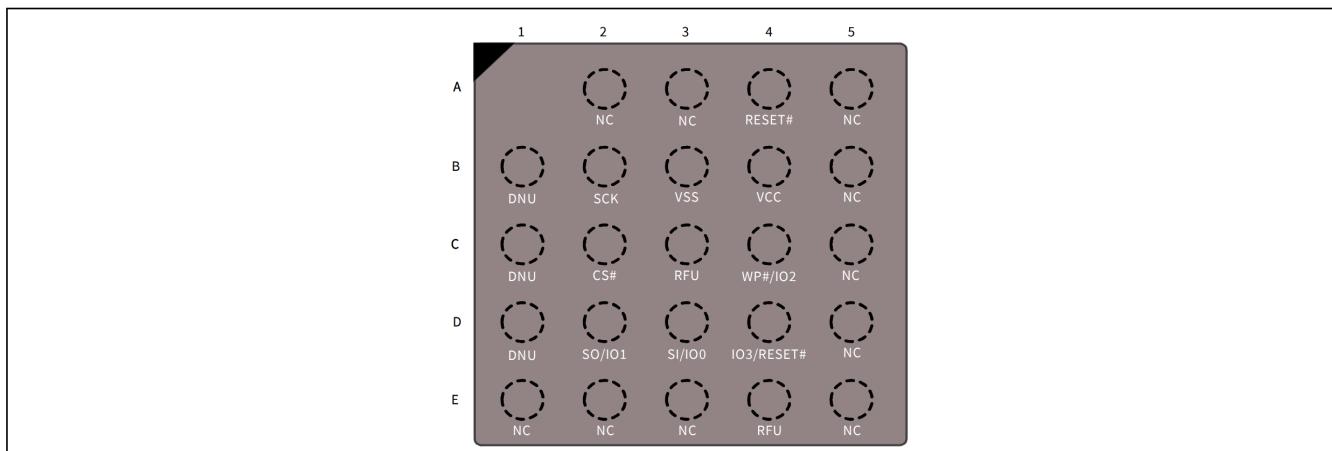

| 3.1.1 BGA ball 封装.....                     | 15        |

| 3.2 关于FBGA的特殊处置说明.....                     | 14        |

| 3.3 输入/输出简介.....                           | 15        |

| 3.4 多线输入 / 输出 (MIO) .....                  | 16        |

| 3.5 串行时钟 (SCK) .....                       | 16        |

| 3.6 片选 (CS #) .....                        | 16        |

| 3.7 串行输入 (SI) /IO0.....                    | 16        |

| 3.8 串行输出 (SO) /IO1 .....                   | 16        |

| 3.9 写保护 (WP#) /IO2.....                    | 17        |

| 3.10 IO3 RESET#.....                       | 17        |

| 3.11 RESET# .....                          | 17        |

| 3.12 电源 (V <sub>CC</sub> ).....            | 18        |

| 3.13 地线 (V <sub>SS</sub> ) .....           | 18        |

| 3.14 未连接 (NC) .....                        | 18        |

| 3.15 预留以供将来使用 (RFU) .....                  | 18        |

| 3.16 请勿使用 (DNU) .....                      | 18        |

| 3.17 系统框图.....                             | 18        |

| <b>4 信号协议</b> .....                        | <b>20</b> |

| 4.1 SPI 时钟模式 .....                         | 20        |

| 4.1.1 单倍数据速率 (SDR) .....                   | 20        |

| 4.1.2 双倍数据速率 (DDR) .....                   | 20        |

| 4.2 命令协议 .....                             | 21        |

| 4.2.1 指令时序示例 .....                         | 23        |

| 4.3 接口状态 .....                             | 26        |

| 4.3.1 VCC 断电 .....                         | 27        |

| 4.3.2 低电压硬件数据保护 .....                      | 27        |

| 4.3.3 上电 (冷) 复位 .....                      | 27        |

| 4.3.4 硬件 (热) 复位 .....                      | 27        |

| 4.3.5 接口待机 .....                           | 27        |

| 4.3.6 指令周期 (传统 SPI 模式) .....               | 27        |

| 4.3.7 指令周期 (QPI 模式) .....                  | 28        |

| 4.3.8 单线输入周期 – 主控到存储器传输 .....              | 28        |

| 4.3.9 单线延时 (虚拟) 周期 .....                   | 28        |

| 4.3.10 单线输出周期 – 存储器到主控传输 .....             | 28        |

| 4.3.11 双线输入周期 - 主控到存储器传输 .....             | 28        |

| 4.3.12 双线延时 (虚拟) 周期 .....                  | 28        |

| 4.3.13 双线输出周期 – 存储器到主控传输 .....             | 29        |

| 4.3.14 QPP 或者 QOR 地址输入周期 .....             | 29        |

| 4.3.15 四线输入周期 - 主控到存储器传输 .....             | 29        |

## 目录

|                                               |           |

|-----------------------------------------------|-----------|

| 4.3.16 四线延时 (虚拟) 周期.....                      | 29        |

| 4.3.17 四线输出周期 – 存储器到主控传输。.....                | 29        |

| 4.3.18 DDR 四线输入周期 – 主控到存储器传输 .....            | 29        |

| 4.3.19 DDR 延时周期.....                          | 30        |

| 4.3.20 DDR 四线输出周期 – 存储器到主控传输 .....            | 30        |

| 4.4 配置寄存器对接口的影响.....                          | 31        |

| 4.5 数据保护.....                                 | 31        |

| 4.5.1 上电.....                                 | 31        |

| 4.5.2 低功耗.....                                | 31        |

| 4.5.3 时钟脉冲计数.....                             | 31        |

| 4.5.4 深度掉电 (DPD) .....                        | 31        |

| <b>5 时序规范 .....</b>                           | <b>32</b> |

| 5.1 波形切换.....                                 | 32        |

| 5.2 交流测试条件.....                               | 32        |

| 5.2.1 电容特性.....                               | 33        |

| 5.3 复位.....                                   | 33        |

| 5.3.1 上电 (冷) 复位.....                          | 33        |

| 5.3.2 RESET # 和 IO3_RESET# 输入启动硬件 (热) 复位..... | 34        |

| 5.4 SDR AC 特征.....                            | 36        |

| 5.4.1 时钟时序.....                               | 37        |

| 5.4.2 输入/输出時序 .....                           | 37        |

| 5.5 DDR AC 特征.....                            | 39        |

| 5.5.1 DDR 输入时序.....                           | 39        |

| 5.5.2 DDR 输出时序.....                           | 40        |

| 5.5.3 使用 DLP 的 DDR 数据有效时序.....                | 40        |

| <b>6 地址空间映射.....</b>                          | <b>42</b> |

| 6.1 概述.....                                   | 42        |

| 6.1.1 扩展地址.....                               | 42        |

| 6.1.2 多个地址空间.....                             | 42        |

| 6.2 闪存存储器阵列.....                              | 42        |

| 6.3 ID-CFI 地址空间.....                          | 45        |

| 6.3.1 英飞凌编程的唯一ID .....                        | 45        |

| 6.4 JEDEC JESD216 串行闪存可发现参数 (SDFP) 空间 .....   | 45        |

| 6.5 OTP 地址空间.....                             | 45        |

| <b>7 寄存器 .....</b>                            | <b>47</b> |

| 7.1 状态寄存器 1.....                              | 48        |

| 7.1.1 状态寄存器 1 非易失性 (SR1NV) .....              | 48        |

| 7.1.2 状态寄存器 1 易失性 (SR1V) .....                | 49        |

| 7.2 状态寄存器 2 易失性 (SR2V) .....                  | 51        |

| 7.3 配置寄存器 1.....                              | 52        |

| 7.3.1 配置寄存器 1 非易失性 (CR1NV) .....              | 52        |

| 7.3.2 配置寄存器 1 易失性 (CR1V) .....                | 53        |

| 7.4 配置寄存器 2.....                              | 55        |

| 7.4.1 配置寄存器 2 非易失性 (CR2NV) .....              | 55        |

| 7.4.2 配置寄存器 2 易失性 (CR2V) .....                | 58        |

| 7.5 配置寄存器 3.....                              | 59        |

| 7.5.1 配置寄存器 3 非易失性 (CR3NV) .....              | 59        |

| 7.5.2 配置寄存器 3 易失性 (CR3V) .....                | 60        |

| 7.6 配置寄存器 4.....                              | 61        |

| 7.6.1 配置寄存器 4 非易失性 (CR4NV) .....              | 61        |

| 7.6.2 配置寄存器 4 易失性 (CR4V) .....                | 62        |

| 7.7 ECC 状态寄存器 (ECCSR) .....                   | 62        |

| 7.8 ASP 寄存器 (ASPR) .....                      | 63        |

## 目录

|                                                    |           |

|----------------------------------------------------|-----------|

| 7.9 密码寄存器 (PASS) .....                             | 64        |

| 7.10 PPB 锁存寄存器 (PPBL) .....                        | 64        |

| 7.11 PPB 访问寄存器 (PPBAR) .....                       | 64        |

| 7.12 DYB 访问寄存器 (DYBAR) .....                       | 65        |

| 7.13 SPI DDR 数据学习寄存器 .....                         | 65        |

| <b>8 嵌入式算法性能表.....</b>                             | <b>45</b> |

| <b>9 数据保护 .....</b>                                | <b>67</b> |

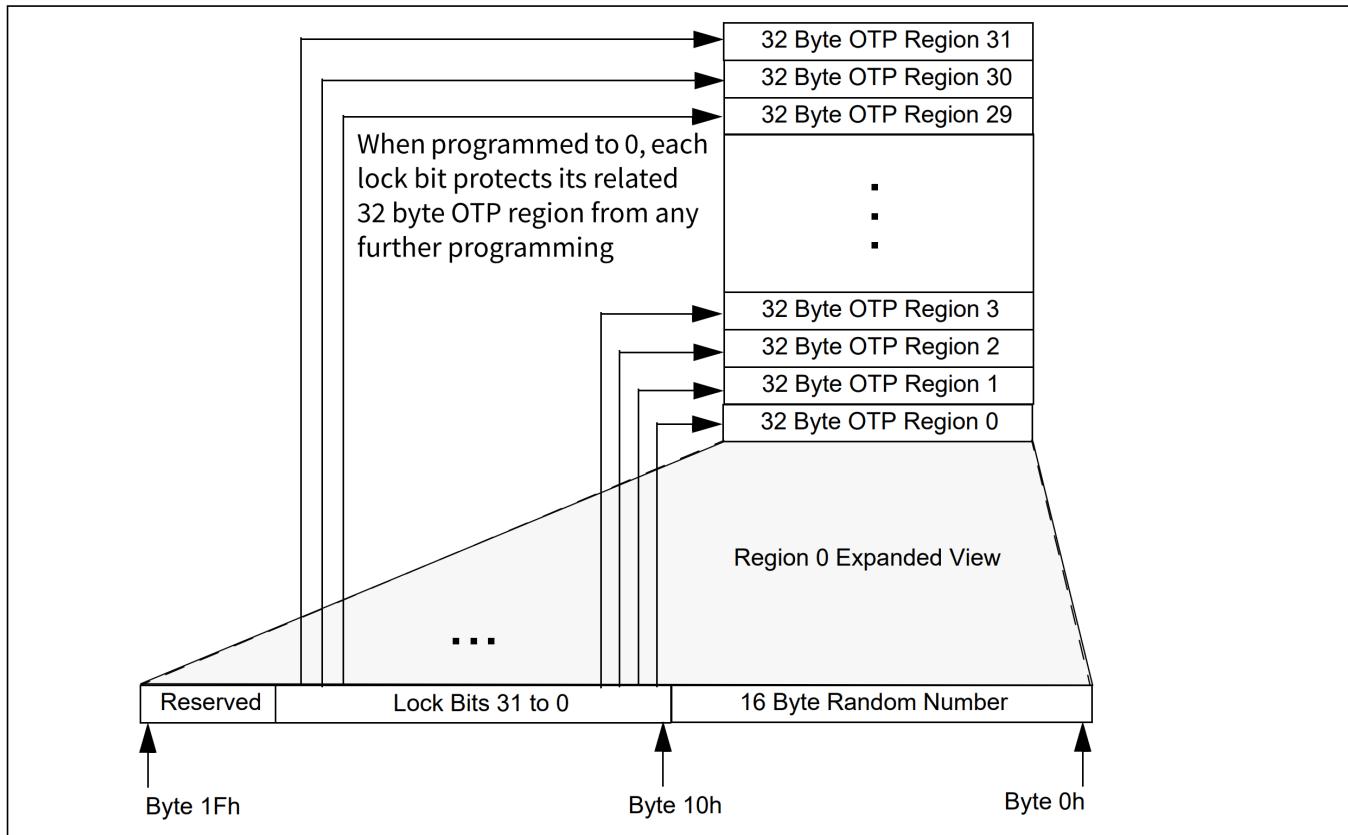

| 9.1 安全存储区域 .....                                   | 67        |

| 9.1.1 读取 OTP 存储空间 .....                            | 67        |

| 9.1.2 编程 OTP 存储空间 .....                            | 67        |

| 9.1.3 英飞凌编程的随机数字 .....                             | 67        |

| 9.1.4 锁存字节 .....                                   | 67        |

| 9.2 写使能指令 .....                                    | 68        |

| 9.3 功能块保护 .....                                    | 68        |

| 9.3.1 冻结位 .....                                    | 69        |

| 9.3.2 写入保护信号 .....                                 | 69        |

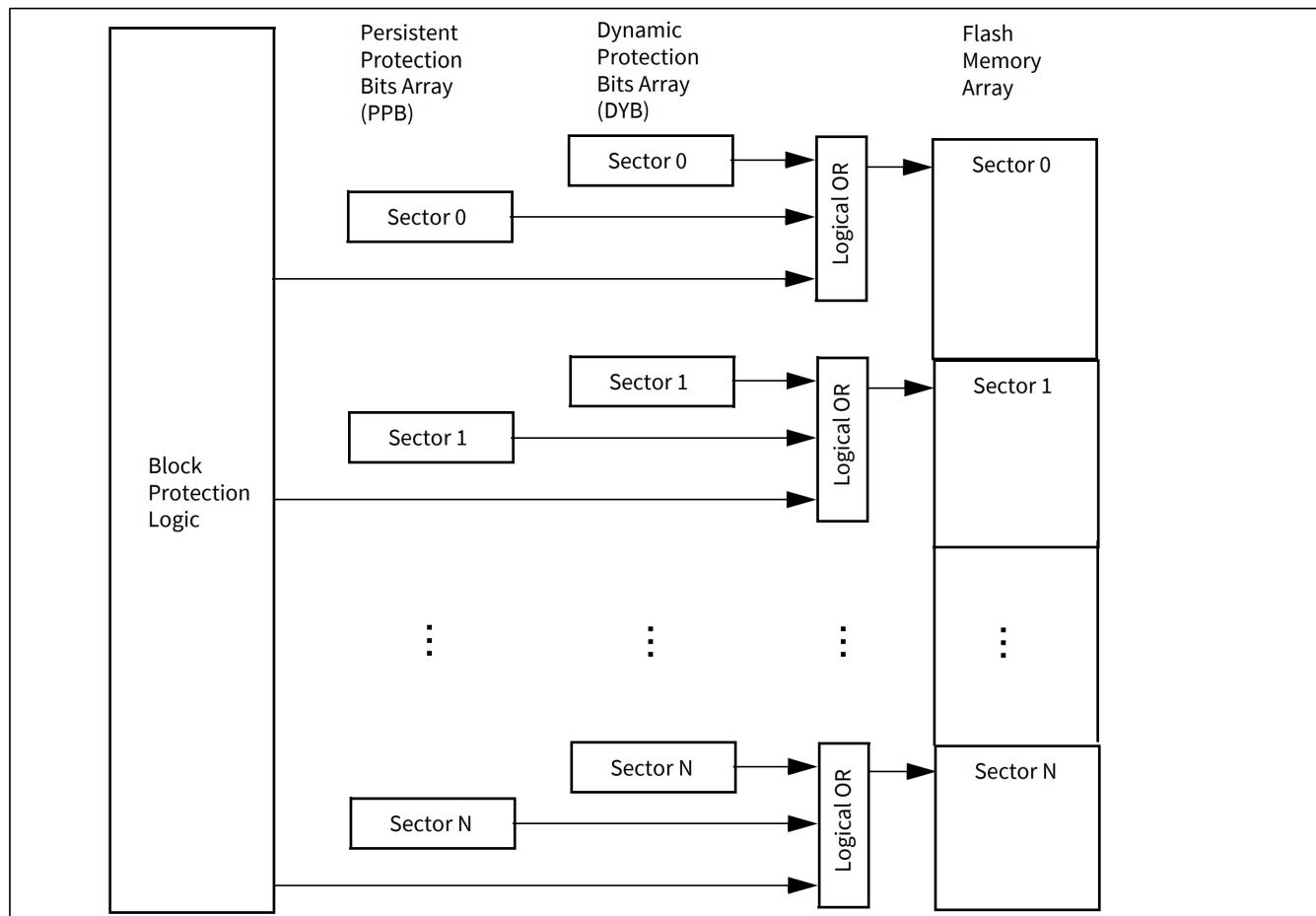

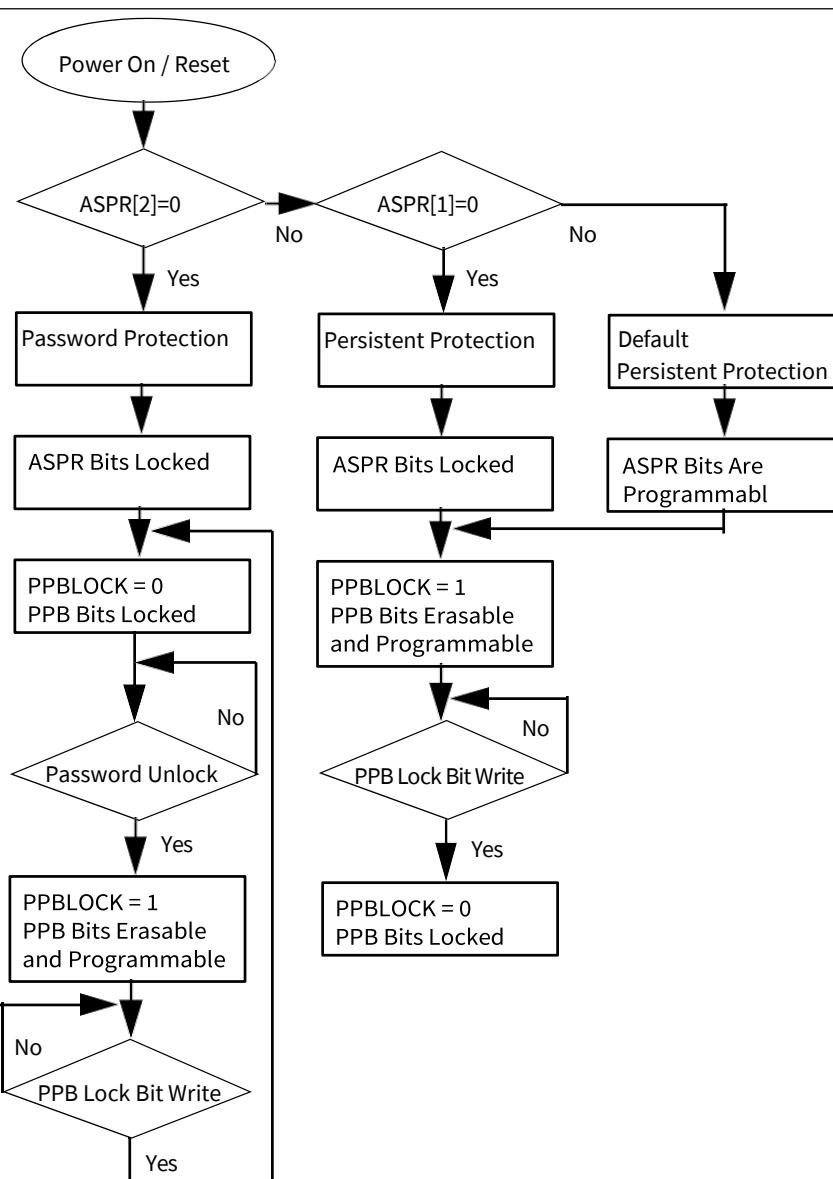

| 9.4 高级扇区保护 .....                                   | 69        |

| 9.4.1 ASP 存储器 .....                                | 72        |

| 9.4.2 持久保护位 (PPB) .....                            | 73        |

| 9.4.3 动态保护位 .....                                  | 73        |

| 9.4.4 PPB 锁存位 (PPBL[0]) .....                      | 73        |

| 9.4.5 扇区保护状态汇总 .....                               | 73        |

| 9.4.6 持久保护模式 .....                                 | 74        |

| 9.4.7 密码保护模式 .....                                 | 74        |

| 9.5 推荐的保护流程 .....                                  | 75        |

| <b>10 命令 .....</b>                                 | <b>76</b> |

| 10.1 命令汇总 .....                                    | 78        |

| 10.1.1 扩展寻址 .....                                  | 78        |

| 10.1.2 按功能分类命令汇总 .....                             | 80        |

| 10.1.3 读取器件标识 .....                                | 82        |

| 10.1.4 寄存器读或写 .....                                | 82        |

| 10.1.5 读取闪存阵列 .....                                | 83        |

| 10.1.6 编程闪存阵列 .....                                | 83        |

| 10.1.7 擦除闪存阵列 .....                                | 84        |

| 10.1.8 OTP、功能块保护和高级扇区保护 .....                      | 84        |

| 10.1.9 复位 .....                                    | 84        |

| 10.1.10 深度掉电模式 .....                               | 84        |

| 10.1.11 预留 .....                                   | 84        |

| 10.2 器件识别命令 .....                                  | 84        |

| 10.2.1 读取器件标识 (RDID 9Fh) .....                     | 84        |

| 10.2.2 四线读取标识 (RDQID AFh) .....                    | 85        |

| 10.2.3 读取串行闪存可发现参数 (RSFDP 5Ah) .....               | 86        |

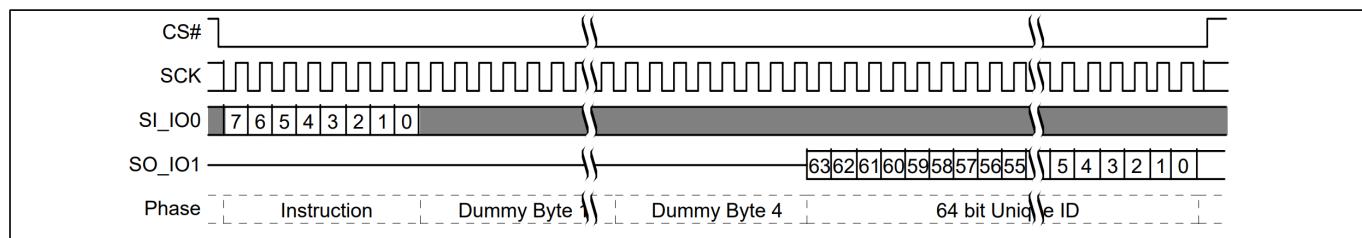

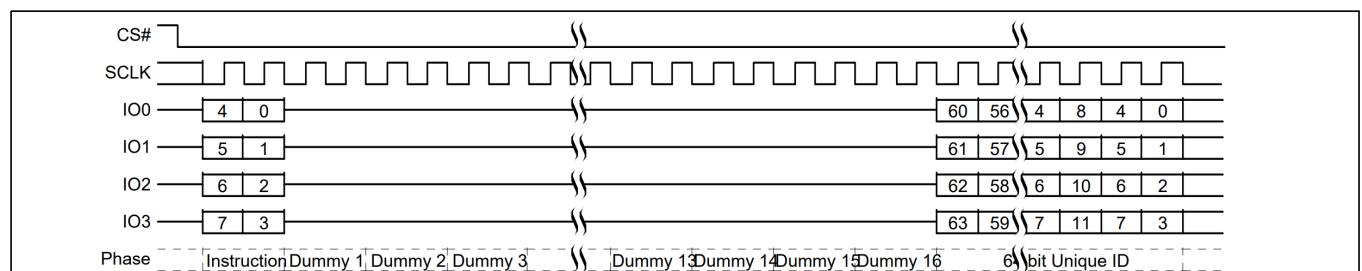

| 10.2.4 读取唯一ID (RUID 4Ch) .....                     | 87        |

| 10.3 寄存器访问指令 .....                                 | 87        |

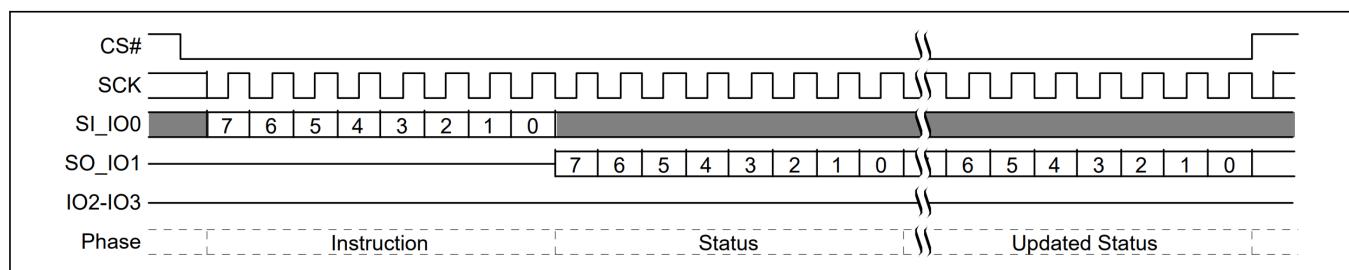

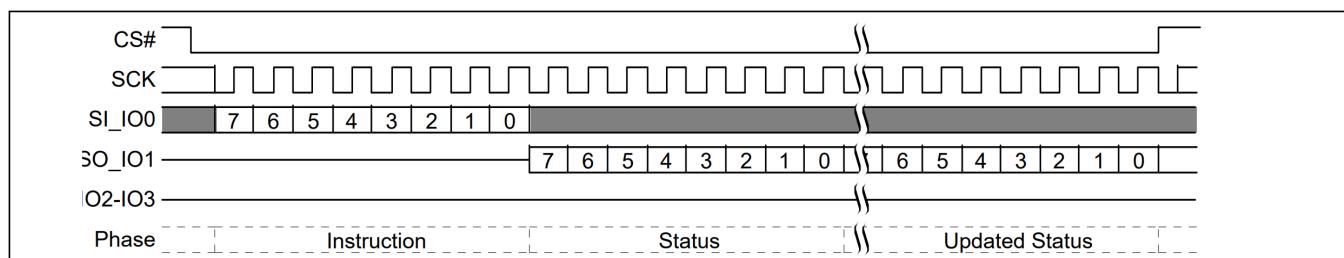

| 10.3.1 读取状态寄存器-1 (RDSR1 05h) .....                 | 87        |

| 10.3.2 读取状态寄存器-2 (RDSR2 07h) .....                 | 88        |

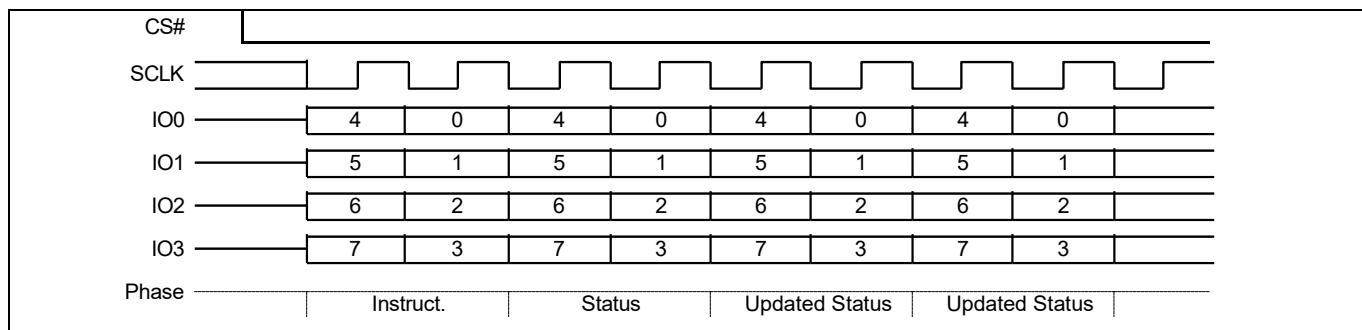

| 10.3.3 读取配置寄存器 (RDCR 35h) .....                    | 88        |

| 10.3.4 写入寄存器 (WRR) 01h) .....                      | 89        |

| 10.3.5 写使能 (WREN 06h) .....                        | 90        |

| 10.3.6 写禁止使能 (WRDI 04h) .....                      | 91        |

| 10.3.7 清除状态寄存器 (CLSR 30h 或者 82h) .....             | 91        |

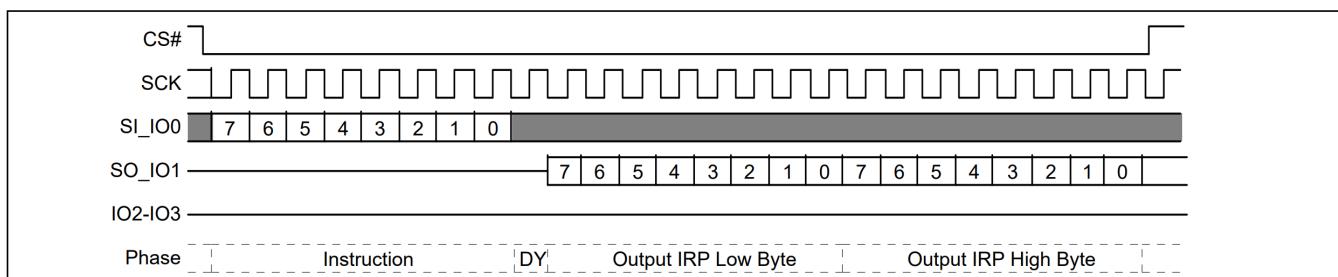

| 10.3.8 ECC 状态寄存器读取 (ECCRD 19h 或者 4EECRD 18h) ..... | 92        |

| 10.3.9 编程 NVDLR (PNVDLR 43h) .....                 | 93        |

## 目录

|                                                     |            |

|-----------------------------------------------------|------------|

| 10.3.10 写入 VDLR (WVDLR 4Ah) .....                   | 94         |

| 10.3.11 数据学习类型码读取 (DLPRD 41h) .....                 | 94         |

| 10.3.12 进入 4 字节地址模式 (4BAM B7h) .....                | 94         |

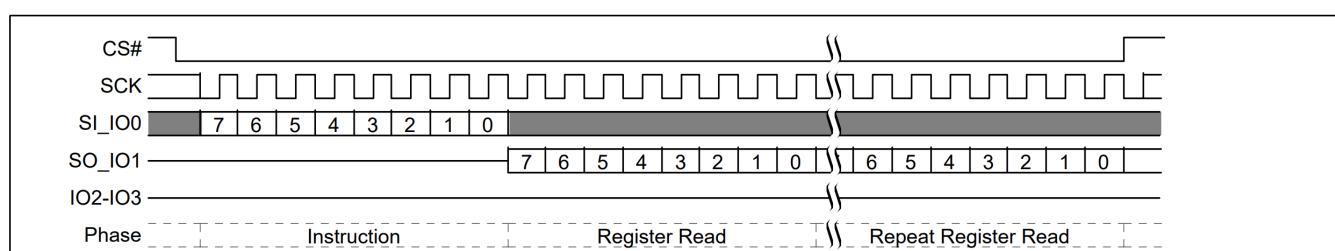

| 10.3.13 读取任何寄存器 (RDAR 65h) .....                    | 95         |

| 10.3.14 写入任何寄存器 (WRAR 71h) .....                    | 97         |

| 10.3.15 设置突发长度 (SBL C0h) .....                      | 97         |

| 10.4 读取闪存阵列指令 .....                                 | 99         |

| 10.4.1 读取 (READ 03h 或者 4READ 13h) .....             | 100        |

| 10.4.2 快速读取 (FAST_READ 0Bh 或者 4FAST_READ 0Ch) ..... | 101        |

| 10.4.3 双线输出读取 (DOR 3Bh 或 4DOR 3Ch) .....            | 102        |

| 10.4.4 四线输读取 (QOR 6Bh 或 4Q 或 6Ch) .....             | 103        |

| 10.4.5 双线 I/O 读取 (DIOR BBh 或者 4DIOR BCCh) .....     | 104        |

| 10.4.6 四线 I/O 读取 (QIOR EBh 或 4QIOR ECCh) .....      | 106        |

| 10.4.7 DDR 四线 I/O 读取 (EDh, EEh) .....               | 108        |

| 10.5 编程闪存阵列指令 .....                                 | 110        |

| 10.5.1 编程粒度 .....                                   | 110        |

| 10.5.2 页编程 (PP 02h 或者 4PP 12h) .....                | 111        |

| 10.5.3 四线页编程 (QPP 32h 或者 4QPP 34h) .....            | 113        |

| 10.6 擦除闪存阵列命令 .....                                 | 114        |

| 10.6.1 参数扇区擦除 (P4E 20h 或者 4P4E 21h) .....           | 114        |

| 10.6.2 扇区擦除 (SE) 8h 或者 4SE DCh) .....               | 115        |

| 10.6.3 批量擦除 (BE 60h 或者 C7h) .....                   | 116        |

| 10.6.4 评估擦除状态 (EES) D0h) .....                      | 117        |

| 10.6.5 擦除或者编程挂起 (EPS 85h, 75h, B0h) .....           | 118        |

| 10.6.6 擦除或者编程恢复 (EPR 7Ah, 8Ah, 30h) .....           | 122        |

| 10.7 一次性编程阵列命令 .....                                | 123        |

| 10.7.1 OTP 编程 (OTPP 42h) .....                      | 123        |

| 10.7.2 OTP 读取 (OTPR 4Bh) .....                      | 123        |

| 10.8 高级扇区保护命令 .....                                 | 124        |

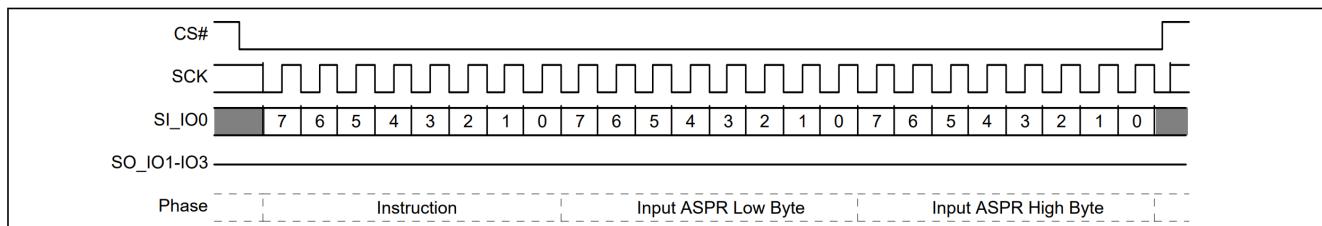

| 10.8.1 ASP 读取 (ASPRD 2Bh) .....                     | 124        |

| 10.8.2 ASP 编程 (ASPP 2Fh) .....                      | 124        |

| 10.8.3 DYB 读取 (DYBRD FAh 或者 4DYBRD E0h) .....       | 125        |

| 10.8.4 DYB 写入 (DYBWR FBh 或者 4DYBWR E1h) .....       | 126        |

| 10.8.5 PPB 读取 (PPBRD FCh 或者 4PPBRD E2h) .....       | 127        |

| 10.8.6 PPB 编程 (PPBP FDh 或者 4PPBP E3h) .....         | 127        |

| 10.8.7 PPB 擦除 (PPBE E4h) .....                      | 128        |

| 10.8.8 PPB 锁存位读取 (PLBRD A7h) .....                  | 128        |

| 10.8.9 PPB 锁存位写入 (PLBWR A6h) .....                  | 129        |

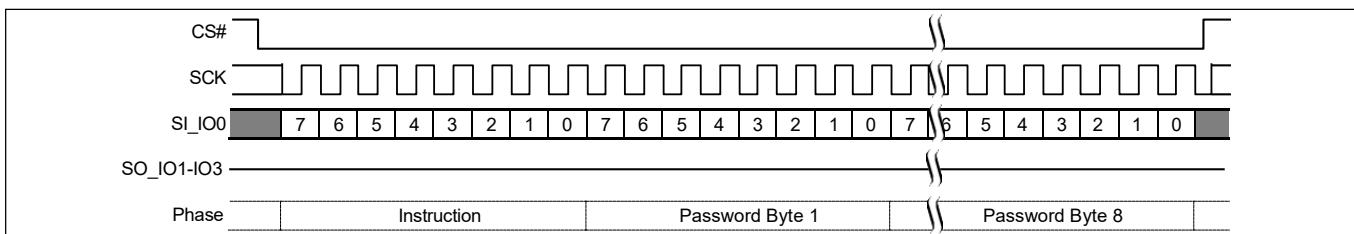

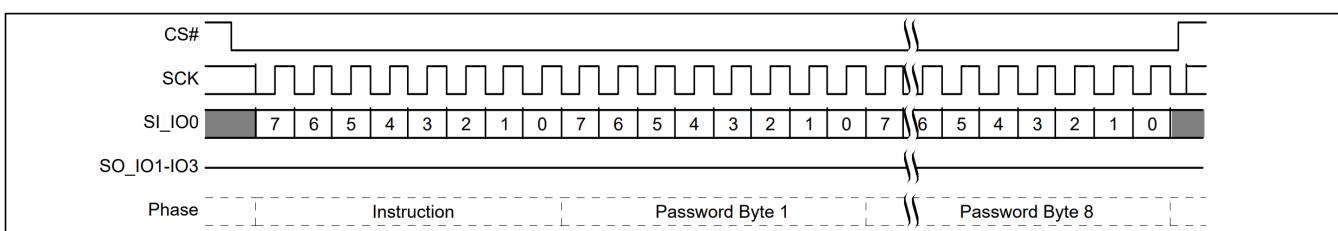

| 10.8.10 密码读取 (PASSRD) E7h) .....                    | 129        |

| 10.8.11 密码编程 (PASSP E8h) .....                      | 130        |

| 10.8.12 密码解锁 (PASSU E9h) .....                      | 130        |

| 10.9 复位命令 .....                                     | 131        |

| 10.9.1 软件复位使能 (RSTEN 66h) .....                     | 131        |

| 10.9.2 软件复位 (RST 99h) .....                         | 131        |

| 10.9.3 传统软件复位 (RESET F0h) .....                     | 132        |

| 10.9.4 模式位复位 (MBR FFh) .....                        | 132        |

| 10.10 DPD 指令 .....                                  | 132        |

| 10.10.1 进入深度掉电 (DPD B9h) .....                      | 132        |

| 10.10.2 深度掉电释放 (RES ABh) .....                      | 133        |

| <b>11 数据完整性 .....</b>                               | <b>134</b> |

| 11.1 擦除耐久性 .....                                    | 134        |

| 11.2 数据保存 .....                                     | 134        |

| <b>12 电气规格参数 .....</b>                              | <b>135</b> |

## 目录

|                                                      |            |

|------------------------------------------------------|------------|

| 12.1 最大绝对额定值.....                                    | 135        |

| 12.2 闩锁特性.....                                       | 135        |

| 12.3 热阻抗.....                                        | 135        |

| 12.4 工作范围.....                                       | 135        |

| 12.4.1 供电电压.....                                     | 135        |

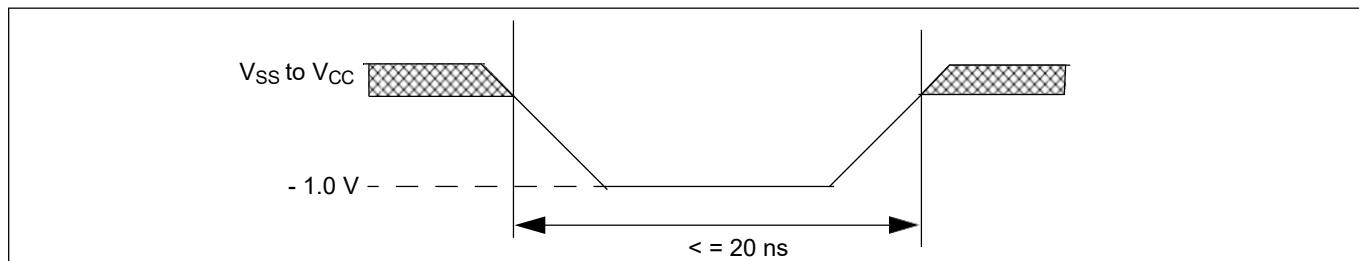

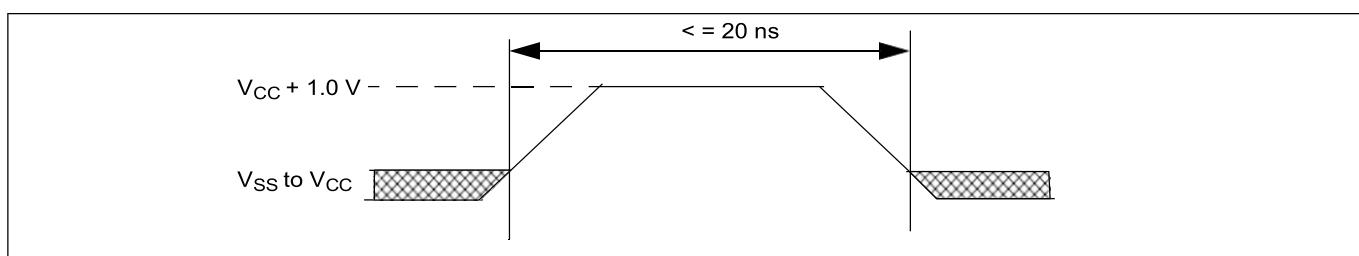

| 12.4.2 温度范围.....                                     | 136        |

| 12.4.3 输入信号过冲.....                                   | 136        |

| 12.5 上电和断电.....                                      | 137        |

| 12.6 DC特性.....                                       | 139        |

| 12.6.1 工业.....                                       | 139        |

| 12.6.2 工业Plus.....                                   | 140        |

| 12.6.3 扩展.....                                       | 141        |

| 12.6.4 工作电源和待机电源模式.....                              | 141        |

| 12.6.5 深度掉电功率模式 (DPD) .....                          | 142        |

| <b>13 器件标识.....</b>                                  | <b>143</b> |

| 13.1 OTP 存储空间地址映射 .....                              | 143        |

| 13.2 器件 ID 和公共接口 (ID-CFI) 地址映射 – 标准 .....            | 144        |

| 13.2.1 字段定义.....                                     | 144        |

| 13.3 串行闪存可发现参数 (SFDP) 地址映射 .....                     | 151        |

| 13.3.1 JEDEC SFDP Rev B 报文头表 .....                   | 151        |

| 13.3.2 JEDEC SFDP Rev B 参数表 .....                    | 153        |

| <b>14 初始交付状态 .....</b>                               | <b>172</b> |

| <b>15 封装图 .....</b>                                  | <b>173</b> |

| 15.1 SOIC 8-引脚, 208 mil body width (SOC008).....     | 173        |

| 15.2 LGA 8-引脚 5 x 6 mm (W9A008).....                 | 174        |

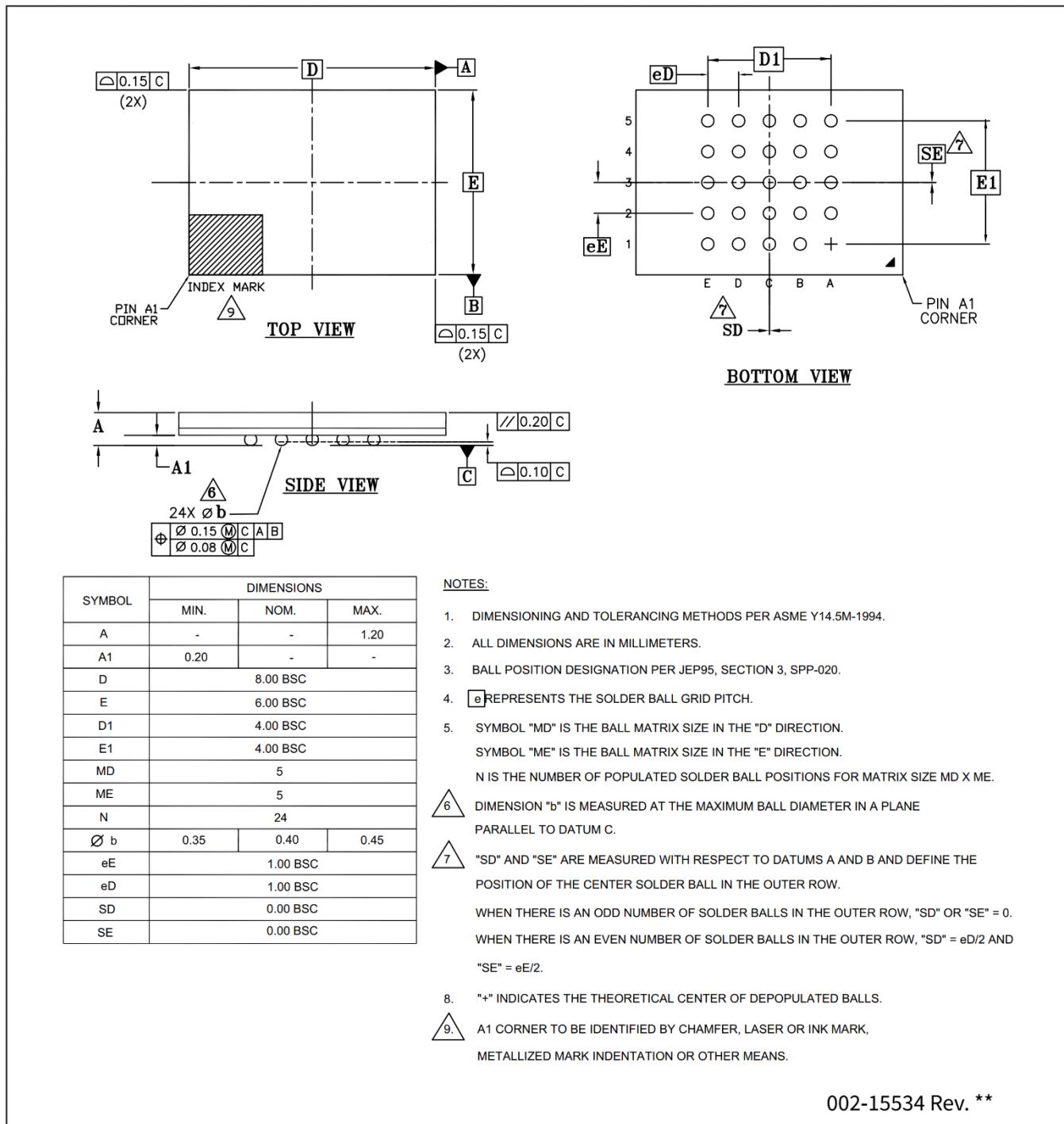

| 15.3 Ball grid array 24-ball 6 x 8 mm (FAB024) ..... | 175        |

| <b>16 订购信息 .....</b>                                 | <b>176</b> |

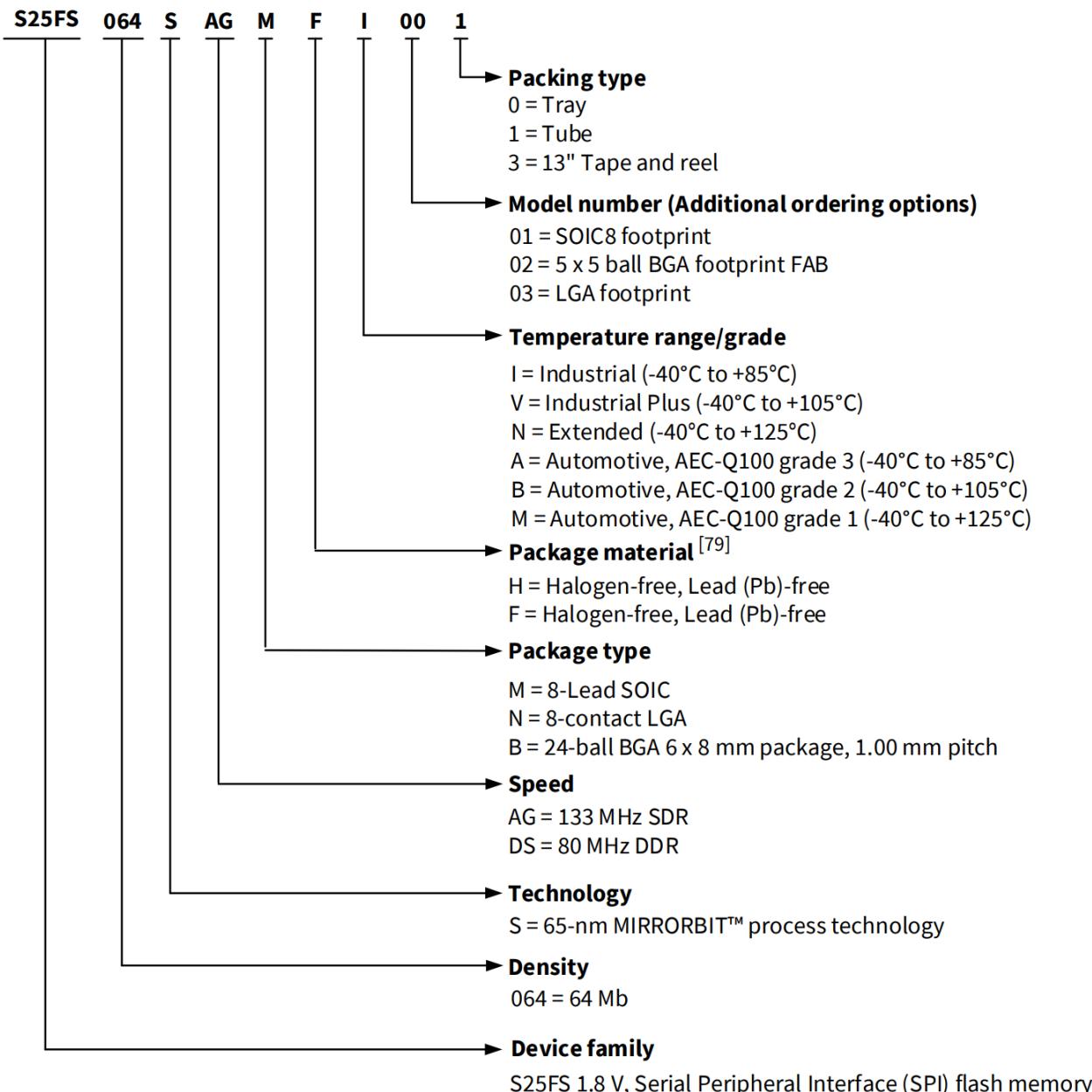

| 16.1 订购部件编号 .....                                    | 176        |

| 16.2 有效组合 – 标准 .....                                 | 177        |

| 16.3 有效组合 – 汽车级/AEC-Q100 .....                       | 177        |

| <b>修订记录.....</b>                                     | <b>178</b> |

## 概述

# 1 概述

## 1.1 概述

英飞凌FS-S 器件系列是非易失性闪存存储器产品，它们采用了以下两种技术

- MIRRORBIT™技术 - 在每个存储器晶体管中存储两个数据位

- Eclipse 架构——显著提高编程和擦除性能

- 65nm 光刻技术

FS-S 系列产品通过串行外设接口(SPI)连接主机系统。该产品支持传统 SPI 的一比特串行输入和输出（即单线 I/O 或 SIO）、可选的两比特（即双线 I/O 或 DIO）、四比特宽（四线 I/O 或 QIO）以及四线外设接口（QPI）命令。另外，它还为 QIO 和 QPI 提供了双倍数据速率（DDR）命令支持，在时钟的双边沿上传送地址和读取数据。

FS-S Eclipse 架构具有页编程指示灯，允许在一次操作中编程多达 512 字节，从而比上一代SPI编程或擦除算法实现更快的有效编程和擦除。

直接从闪存执行代码通常称为就地执行 (XIP)。通过使用支持更高时钟速率的 FS-S 系列器件，并使用四线或 DDR-四线指令，指令读取传输速率可以匹配或超过传统的并行接口、异步、NOR闪存，显着减少信号脚数量。

FS-S 产品系列为各种移动或嵌入式应用提供了容量大、灵活性高且速度快等性能。对于空间、信号连接和功率有限的系统来说，它们是绝佳的解决方案。它们是将代码映射到 RAM、直接执行代码 (XIP) 以及存储可重新编程数据的理想选择。

## 1.2 迁移说明

### 1.2.1 特性比较

FS-S 系列的指令集和封装与先前的 FL-S、FL1-K 和 FL-P 系列相兼容。然而，电源和接口电压标称值为 1.8V。

**表 4 英飞凌SPI系列比较**

| Parameter                  | FS-S                      | FS-S                | FL-S                                   | FL-P              |

|----------------------------|---------------------------|---------------------|----------------------------------------|-------------------|

| Technology node            | 65 nm                     | 65 nm               | 65 nm                                  | 90 nm             |

| Architecture               | MIRRORBIT™ Eclipse        | MIRRORBIT™ Eclipse  | MIRRORBIT™ Eclipse                     | MIRRORBIT™        |

| Release date               | In Production             | 2H2015              | In Production                          | In Production     |

| Density                    | 128 Mb, 256 Mb,<br>512 Mb | 64 Mb               | 128 Mb, 256 Mb,<br>512 Mb              | 32 Mb–256 Mb      |

| Bus width                  | x1, x2, x4                | x1, x2, x4          | x1, x2, x4                             | x1, x2, x4        |

| Supply Voltage             | 1.7 V–2.0 V               | 1.7 V–2.0 V         | 2.7 V–3.6 V /<br>1.65 V–3.6 V $V_{IO}$ | 2.7 V–3.6 V       |

| Normal read speed<br>(SDR) | 6 MB/s (50 MHz)           | 6 MB/s (50 MHz)     | 6 MB/s (50 MHz)                        | 5 MB/s (40 MHz)   |

| Fast read speed<br>(SDR)   | 16.5 MB/s (133 MHz)       | 16.5 MB/s (133 MHz) | 16.5 MB/s (133 MHz)                    | 13 MB/s (104 MHz) |

#### 注释：

1. FL-P 列表示 FL129P MIO SPI 器件（适用于 128 Mb 容量），FL128P 不支持 MIO、OTP 或 4 KB 扇区。

2. 64 KB 扇区擦除选项仅适用于 128 Mb/256 Mb 密度 FL-P、FL-S 和 FS-S 设备。

3. 欲了解详细信息，请参考单独的数据手册。

## 概述

表 4 英飞凌 SPI 系列比较 (续)

| Parameter                    | FS-S                                 | FS-S                                 | FL-S                                 | FL-P                      |

|------------------------------|--------------------------------------|--------------------------------------|--------------------------------------|---------------------------|

| Dual read speed (SDR)        | 33 MB/s (133 MHz)                    | 33 MB/s (133 MHz)                    | 26 MB/s (104 MHz)                    | 20 MB/s (80 MHz)          |

| Quad read speed (SDR)        | 66 MB/s (133 MHz)                    | 66 MB/s (133 MHz)                    | 52 MB/s (104 MHz)                    | 40 MB/s (80 MHz)          |

| Quad read speed (DDR)        | 80 MB/s (80 MHz)                     | 80 MB/s (80 MHz)                     | 66 MB/s (66 MHz)                     | -                         |

| Program buffer size          | 256 B/512 B                          | 256 B/512 B                          | 256 B/512 B                          | 256 B                     |

| Erase sector size            | 64 KB/256 KB                         | 64 KB/256 KB                         | 64 KB/256 KB                         | 64 KB/256 KB              |

| Parameter sector size        | 4 KB (option)                        | 4 KB (option)                        | 4 KB (option)                        | 4 KB                      |

| Sector erase rate (typ.)     | 500 KB/s                             | 500 KB/s                             | 500 KB/s                             | 130 KB/s                  |

| Page programming rate (typ.) | 1.0 MB/s (256 B)<br>1.2 MB/s (512 B) | 1.0 MB/s (256 B)<br>1.2 MB/s (512 B) | 1.2 MB/s (256 B)<br>1.5 MB/s (512 B) | 170 KB/s                  |

| OTP                          | 1024 B                               | 1024 B                               | 1024 B                               | 506 B                     |

| Advanced sector protection   | Yes                                  | Yes                                  | Yes                                  | No                        |

| Auto boot mode               | No                                   | No                                   | Yes                                  | No                        |

| Erase suspend/resume         | Yes                                  | Yes                                  | Yes                                  | No                        |

| Program suspend/resume       | Yes                                  | Yes                                  | Yes                                  | No                        |

| Operating temperature        | -40°C to +85°C/<br>+105°C            | -40°C to +85°C/<br>+105°C/+125°C     | -40°C to +85°C/<br>+105°C            | -40°C to +85°C/<br>+105°C |

## 注释：

1. FL-P 列表示 FL129P MIO SPI 器件（适用于 128 Mb 容量），FL128P 不支持 MIO、OTP 或 4 KB 扇区。

2. 64 KB 扇区擦除选项仅适用于 128 Mb/256 Mb 容量 FL-P、FL-S 和 FS-S 设备。

3. 欲了解详细信息，请参考单独的数据手册。

## 1.2.2 与前几代产品的已知差异

## 1.2.2.1 错误报告

如果在受保护的扇区上尝试进行编程或擦除，FL-K 和 FL-P 存储器要么没有错误状态位，要么不设置它们。FS-S 和 FL-S 系列确实具有针对编程和擦除操作的错误报告状态位。当发生内部编程或擦除故障，或尝试对受保护的扇区进行编程或擦除时，可以置位这些。在这些情况下，程序或擦除操作未按照指令的要求完成。SR1V 中的 P\_ERR 或 E\_ERR 位以及 WIP 位将被置位为 1 并保持为 1。清除状态寄存器指令必须发送到清零，复位错误并将器件返回到待机状态。

## 1.2.2.2 安全硅区 (OTP)

一次性编程 (OTP) 区域的 FS-S 大小和地址映射 (地址映射) 与 FL-K 和 FL-P 代不同。OTP 各部分的保护方法也不同。更多详细信息，请参阅第 67 页的“[安全存储区域](#)”。

## 概述

### 1.2.2.3 配置寄存器冻结位

配置寄存器 1 Freeze 位 CR1V[0]，锁定功能块保护位（SR1NV[4:2] 和 SR1V[4:2]）、TBPARM\_O 位（CR1NV[2]）和 TBPROT\_O 位（CR1NV[5]）的状态，与前几代一样。在 FS-S 和 FL-S 系列中，冻结位还锁定配置寄存器 1 BPNV\_O 位（CR1NV[3]）和安全硅区域（OTP）区域的状态。

### 1.2.2.4 扇区被擦除的指令

仅支持在 FS-S 器件地址空间顶部或底部的 4 KB 参数扇区上使用 4 KB 扇区的指令。

不支持 8 KB 区域（两个 4 KB 扇区）的指令。

不支持 32 KB 区域（八个 4 KB 扇区）的指令。

当选择统一 64 KB 扇区的配置选项或使用 4 KB 参数扇区与 64 KB 统一扇区的混合配置选项时，支持 FS-S 64 KB 扇区的扇区指令（SE）。当使用混合选项时，64 KB 擦除指令可用于将 8 个 4 KB 扇区组的相邻的 32 KB 地址空间连接起来。在这种情况下，64 KB 收获指令是挽救 64 KB 扇区，该扇区被八个 4 KB 扇区部分覆盖，而不影响 4 KB 扇区。这提供了对 32 KB 地址空间的擦除控制，而无需强制擦除 4 KB 扇区。这与 FL-S 家族中实现的行为不同。在 FL-S 家族中，64 KB 扇区指令可以应用于 4 KB 扇区的 64 KB 功能块，从而在一次操作中完成参数扇区的整个功能块。在 FS-S 中，扇区参数并不能填满整个 64 KB 功能块，因此仅使用 4 KB 扇区参数（20h）来填充参数扇区。

当使用 256 KB 统一逻辑扇区的配置选项时，256 KB 扇区的擦除命令将取代 64 KB 擦除命令。

### 1.2.2.5 深度掉电模式

FS-S 家族器件支持深度掉电（DPD）函数。

### 1.2.2.6 WRR 单寄存器写入

在一些传统的 SPI 设备中，只有一个数据字节的写寄存器（WRR）指令会更新状态寄存器 1 和清除配置寄存器 1 中的一些位，包括四线模式位。这可能会导致意外退出四核模式。当提供单个数据字节时，FS-S 家族仅更新状态寄存器 1。在这种情况下，配置寄存器 1 不会被修改。

### 1.2.2.7 不支持输入保持功能

在一些传统的 SPI 设备中，IO3 输入具有替换功能，作为 HOLD# 输入，用于暂停信息传输而不停止串行时钟。FS-S 家族不支持该功能。

### 1.2.2.8 不支持其他旧指令

- DDR 快速读取

- DDR 双线 I/O 读取

## 概述

### 1.2.2.9 新特性

FS-S系列为英飞凌SPI类别存储器引入了新功能：

- 用于内核和 I/O 电压的单个 1.8 V 电源。

- 可配置初始读取延时（虚拟周期数）以获得更快的初始读取时间或更高的时钟速率读取指令

- QPI (QPI, 4-4-4) 读取模式，其中所有传输均为 4 位宽，包括指令

- JEDEC JESD216 Rev B 标准、串行闪存可发现参数 (SDFP)，提供器件特性和配置信息。

- 评估扇区状态指令以确定扇区上的最后一个操作是否成功完成。该指令可用于检测由于掉电或其他原因导致的不完整的擦除。该指令有助于存储器文件系统软件在电源丢失后进行文件系统恢复。

- 高级扇区保护 (ASP) 永久保护。此外，当选择两种 ASP 保护模式之一时，所有寄存器中的所有 OTP 配置位都受到保护，不能进一步编程，从而所有 OTP 配置设置都是永久的。OTP 地址空间不受选择 ASP 保护模式的保护。冻结位 (CR1V[0]) 可用于保护 OTP 地址空间。

支持多线输入 / 输出的串行外设接口 (SPI-MIO)

## **2 支持多线输入 / 输出的串行外设接口 (SPI-MIO)**

许多存储设备通过各自的并行控制线、地址线和数据信号线连接到其主控系统，需要大量的信号连接和更大的封装尺寸。由于大量信号交换，因此信号连接的数量越多，功耗也越高；较大的封装尺寸会增加成本。FS-S 系列通过 6 个信号将所有控制、地址和数据信息串行传输给主机系统，因此可以减少信号连接的数量。这样可以降低存储器封装的成本和信号交换的功耗，减少主机信号连接的数量，主机可以节省连接以供其他功能使用。

FS-S 系列使用了业界标准的单比特 SPI，同时支持可选的扩展命令，用于进行两比特（双线）或 4 比特（四线）宽的串行传输。这种多宽度接口被称为 SPI Multi-I/O 或 SPI-MIO。

引脚分布和信号描述

## 3 引脚分配和信号描述

### 3.1 包含 8 个连接点的封装

图1 8引脚塑料小外型封装（SOIC8）

图2 8-pad LGA 5×6 (W9A008) , 顶视图<sup>[4]</sup>

#### 3.1.1 BGA ball 封装

图3 24-BGA, 5x5 ball 封装 (FAB024) , 顶视图<sup>[4]</sup>

### 3.2 关于FBGA封装的特殊处置说明

如果使用超声波清洁方法，BGA 封装中的闪存存储器器件可能被损坏。如果封装体长时间暴露在 150°C 以上的温度下，封装和/或数据完整性可能会受到损害。

#### 注释：

4. RESET# 输入上连接着一个内部上拉电阻。如果未使用四线模式和硬件复位模式，则在系统中，该输入会保持为未连接状态。

### 3.3 输入/输出简介

**表 5 信号描述**

| Signal name     | Type     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESET#          | Input    | <b>Hardware Reset:</b> LOW = Device resets and returns to standby state, ready to receive a command. The signal has an internal pull-up resistor and may be left unconnected in the host system if not used.                                                                                                                                                                                                                                                                                                                                                             |

| SCK             | Input    | <b>Serial Clock</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| CS#             | Input    | <b>Chip Select</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| SI / IO0        | I/O      | <b>Serial Input</b> for single bit data commands or IO0 for Dual or Quad commands.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| SO / IO1        | I/O      | <b>Serial Output</b> for single bit data commands. IO1 for Dual or Quad commands.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| WP# / IO2       | I/O      | <b>Write Protect</b> when not in Quad mode (CR1V[1] = 0 and SR1NV[7] = 1).<br><b>IO2</b> when in Quad mode (CR1V[1] = 1).<br>The signal has an internal pull-up resistor and may be left unconnected in the host system if not used for Quad commands or write protection. If write protection is enabled by SR1NV[7] = 1 and CR1V[1] = 0, the host system is required to drive WP# HIGH or LOW during a WRR or WRAR command.                                                                                                                                            |

| IO3_RESET#      | I/O      | <b>IO3</b> in Quad-I/O mode, when Configuration Register-1 QUAD bit, CR1V[1] = 1, and CS# is LOW.<br><b>RESET#</b> when enabled by CR2V[5]=1 and not in Quad-I/O mode, CR1V[1] = 0, or when enabled in quad mode, CR1V[1] = 1 and CS# is HIGH.<br>The signal has an internal pull-up resistor and may be left unconnected in the host system if not used for Quad commands or RESET#.                                                                                                                                                                                    |

| V <sub>CC</sub> | Supply   | <b>Power Supply.</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| V <sub>SS</sub> | Supply   | <b>Ground.</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| NC              | Unused   | <b>Not Connected.</b> No device internal signal is connected to the package connector nor is there any future plan to use the connector for a signal. The connection may safely be used for routing space for a signal on a Printed Circuit Board (PCB).<br>However, any signal connected to an NC must not have voltage levels higher than V <sub>CC</sub> .                                                                                                                                                                                                            |

| RFU             | Reserved | <b>Reserved for Future Use.</b> No device internal signal is currently connected to the package connector but there is potential future use of the connector for a signal. It is recommended to not use RFU connectors for PCB routing channels so that the PCB may take advantage of future enhanced features in compatible footprint devices.                                                                                                                                                                                                                          |

| DNU             | Reserved | <b>Do Not Use.</b> A device internal signal may be connected to the package connector. The connection may be used by Infineon for test or other purposes and is not intended for connection to any host system signal. Any DNU signal related function will be inactive when the signal is at V <sub>IL</sub> . The signal has an internal pull-down resistor and may be left unconnected in the host system or may be tied to V <sub>SS</sub> . Do not use these connections for PCB signal routing channels. Do not connect any host system signal to this connection. |

**注释：**

- 具有内部上拉或下拉的输入内部驱动小于 2uA。仅在上电期间，电流才会较大，为 150 uA，持续 4 us。

引脚分布和信号描述

### 3.4 多线输入/输出 (MIO)

传统 SPI 单比特命令（即单 IO 或 SIO）只能通过串行输入（SI）信号将主机的数据发送到存储器内。数据会通过串行输出（SO）信号从存储器内串行回送给主机。

双线或四线输入 / 输出（I/O）命令只能通过 SI/IO0 信号将指令发送给存储器。地址或数据以 IO0 和 IO1 上的位对或 IO0、IO1、IO2 和 IO3 上的四个位（半字节）组的形式从主控发送到存储器。数据同样可以按照双比特一组的方式通过 IO0 和 IO1 从存储器回送给主机，也可以按照四比特（半字节）一组的方式通过 IO0、IO1、IO2 和 IO3 被回送。

QPI 模式允许以四比特（半字节）一组的方式将所有指令、地址和数据通过 IO0、IO1、IO2 和 IO3 从主机传送到存储器内。数据返回主控的方式类似 IO0、IO1、IO2、IO3 上的四位半字节。

### 3.5 串行时钟（SCK）

该输入信号为 SPI 接口提供了同步参考。可以在 SCK 信号的上升沿上锁存指令、地址或数据。在 SDR 指令中，数据输出在 SCK 的下降沿之后发生变化，在 DDR 指令中，数据输出在每个边沿之后发生变化。

### 3.6 片选（CS#）

片选信号指示命令正在向器件传输信息或从器件传输信息，包括与存储器器件相关其他信号。

CS# 信号为高逻辑状态时，不会选择芯片，所有输入信号均被忽略，并且所有输出信号均为高阻抗。除非正在进行内部嵌入式操作，否则器件将处于待机功率模式。嵌入式操作由状态寄存器 1 Write-In-Progress 位 (SR1V[1]) 置位显示为 1，直到操作完成。嵌入式操作的示例包括：编程、擦除或写入寄存器 (WRR) 等操作。

将 CS# 输入驱动为低逻辑状态可以启用器件，使器件进入工作模式。上电后，必须等到 CS# 的下降沿到来后才能执行其他命令。

### 3.7 串行输入（SI）/IO0

该输入信号用于将数据串行传输到器件中。它接收指令、地址和要写入闪存的数据。各个数值在串行 SCK 时钟信号的上升沿上被锁存。

在执行双线和四线命令过程中，SI 变成 IO0（一个输入和输出），用于接收指令、地址和数据（数值在串行 SCK 时钟信号的上升沿上被锁存），并在 SCK 下降沿上（若执行 SDR 命令）或在任意一个边沿上（若执行 DDR 命令）移出数据。

### 3.8 串行输出（SO）/IO1

该输出信号用于将数据串行传输出器件。数据在串行 SCK 时钟信号的下降沿移出。

在执行双线和四线命令过程中，SO 变成 IO1（一个输入和输出），用于接收地址和数据（数值在串行 SCK 时钟信号的上升沿上被锁存），并在 SCK 下降沿上（若执行 SDR 命令）或在任意边沿上（若执行 DDR 命令）移出数据。

## 引脚分布和信号描述

### 3.9 写保护 (WP#) / IO2

当 WP# 被驱动为低电平 ( $V_{IL}$ ) 时，在 WRAR 指令期间，当状态寄存器-1 (SR1NV[7]) 的状态寄存器写入无效，不使能 (SRWD\_NV) 位置为 1 时，无法写入状态寄存器-1 或配置寄存器-1 相关寄存器。在这种情况下，WRR 指令被忽略，选择 SR1NV、SR1V、CR1NV 或 CR1V 的 WRAR 指令被忽略，并且没有错误置位。

这样可以防止传统的块保护设置发生更改。因此，如果在 WRR 或 WRAR 指令期间 SRWD\_NV 设置位为 1 期间 WP# 为低电平，则受功能块保护特性保护的闪存区域中的所有数据字节也受到硬件保护，以防止数据修改。

当 Quad 模式启用时 (CR1V[1] = 1)，WP# 功能不可用。在四线模式下，WP# 功能被作为输入和输出 IO2，用于接收地址和要编程的数据（数值在串行 SCK 时钟信号的上升沿时被锁存）并在 SCK 下降沿时（若执行 SDR 命令）移出数据或在任意一个边沿时（若执行 DDR 命令）移出数据。

WP# 具有内部上拉电阻；未连接时，WP# 处于  $V_{IH}$ ，如果不用于四线模式或写保护模式，则可以在主控系统中保持未连接状态。

### 3.10 IO3\_RESET#

IO3 在四线模式 (CR1V[1] = 1) 下用于输入和输出，用于接收地址和要编程的数据（数值在串行 SCK 时钟信号的上升沿时被锁存）并在 SCK 下降沿时（若执行 SDR 命令）移出数据或在任意一个边沿时（若执行 DDR 命令）移出数据。

通过写入配置寄存器 2 的非易失性位 7 (CR2NV[7] = 1) 来启用 IO3\_RESET# 功能时，IO3\_RESET# 也可用于初始化硬件复位功能。如果器件并非处于四线模式 (114、144、444)，即 CR1V[1] = 0，或 CS# 为高电平，则只能将该输入作为 RESET# 使用。当使用四线 I/O 模式时，CR1V[1] = 1，并且通过 CS 低电平选择器件，IO3\_RESET# 仅用作 IO3 进行信息传输。CS# 为高电平时，IO3/RESET# 不能传送信息，只能将它作为复位输入使用。在四线模式 CS 为高电平期间，调节复位操作，复位功能在四线模式期间仍然可用。

当系统进入复位状态时，必须将 CS# 信号驱动为高电平（作为复位过程的一部分），并将 IO3\_RESET# 信号驱动为低电平。CS# 变为高电平时，IO3\_RESET# 输入从 IO3 切换为复位输入。然后，当 CS 保持高电平且 IO3\_RESET# 信号

保持低电平持续  $t_{RP}$ 。如果不打算复位，则系统需要在数据传输到存储器结束时将驱动为高电平的同时，主动将 IO3\_Reset# CS 驱动为高电平。在将数据传输到主控系统之后，存储器将在  $t_{CS}$  期间将 IO3 驱动为高电平。这将确保 IO3\_RESET# 不会悬空或被内部或外部无源的上拉缓慢拉为高电平。因此，不会由于 IO3\_RESET# 在  $t_{RP}$  结束之前未被识别为高电平而触发意外复位。

当复位特性被禁用时 (CR2V[5] = 0)，IO3\_RESET# 输入复位功能被禁用。

IO3\_RESET# 输入具有一个内部上拉电阻；如果四线模式或复位功能未使用该输入，则在主机系统中它可以保持为不连接状态。如果主机系统将 IO3/RESET# 信号驱动为高电平，然后停止驱动该信号，则通过使用内部上拉电阻将它保持为高电平。

请注意，如果多个 SPI-MIO 存储器中有任意一个工作于四线 I/O 模式，那么它们不能共享 IO3\_RESET# 输入，因为来自一个选定存储器或向其发送的 IO3 可用作第二个非选定存储器（其共享了同一个 IO3\_RESET# 信号）的复位信号。

### 3.11 RESET#

RESET# 输入提供一种硬件复位方法，可使器件返回待机状态。当 RESET# 保持逻辑低 ( $V_{IL}$ ) 至少  $t_{RP}$  时间时，则器件将启动硬件复位过程。

当 RESET# 输入从  $V_{IH}$  转换至  $V_{IL}$  并持续  $> t_{RP}$  时，将启动复位操作。器件将以与上电复位相同的方式复位寄存器状态，但不会经历 POR 期间执行的完整复位过程。硬件复位过程需要  $t_{RPH}$  时间才能完成。RESET# 可随时置为低电平。

RESET# 具有一个内部上拉电阻；如果不使用该引脚，则在主机系统中它可以保持为不连接状态。如果主机系统将复位信号驱动为高电平，然后停止驱动该信号，则通过使用内部上拉电阻将该信号保持为高电平。

## 引脚分布和信号描述

RESET# 输入在所有封装中均不可用。器件的 RESET# 输入不可用时，它将被锁定为非活动状态。

当使用 RESET# 且不处于 QIO 或 QPI 模式时，请勿使用 IO3/RESET# 引脚。

### 3.12 电源 ( $V_{CC}$ )

$V_{CC}$  是所有器件内部逻辑的电压源。它是用于所有器件内部功能（包括读取、编程和擦除）的单一电压。

### 3.13 地 ( $V_{SS}$ )

$V_{SS}$  器件内核、输入信号接收器和输出驱动器的公共电压开漏和接地参考。

### 3.14 未连接 (NC)

没有任何器件内部信号被连接到封装引脚，将来也不计划用于信号连接。该连接可安全地用于印刷电路板 (PCB) 上的信号的布线空间。

### 3.15 预留以供将来使用 (RFU)

当前没有任何器件内部信号被连接到封装引脚，预留供将来使用。不建议将 RFU 连接到 PCB 电路板上的任何信号，以便 PCB 可以在尺寸兼容的器件中实现未来的增强型特性。

### 3.16 请勿使用 (DNU)

器件的内部信号可能被连接到封装引脚。该连接可能被 Infineon 用于测试或其他目的，并不用于连接到任何主控系统信号。DNU 引脚处于低电平 ( $V_{IL}$ ) 时，与该引脚相关的所有功能均无效。该引脚使用了一个内部下拉电阻，在主机系统中可以保持它为未连接状态或将其连接到  $V_{SS}$ 。请勿将该 DNU 引脚连接到 PCB 板上的任意信号。请勿将主机系统的任何信号连接到该引脚。

### 3.17 系统框图

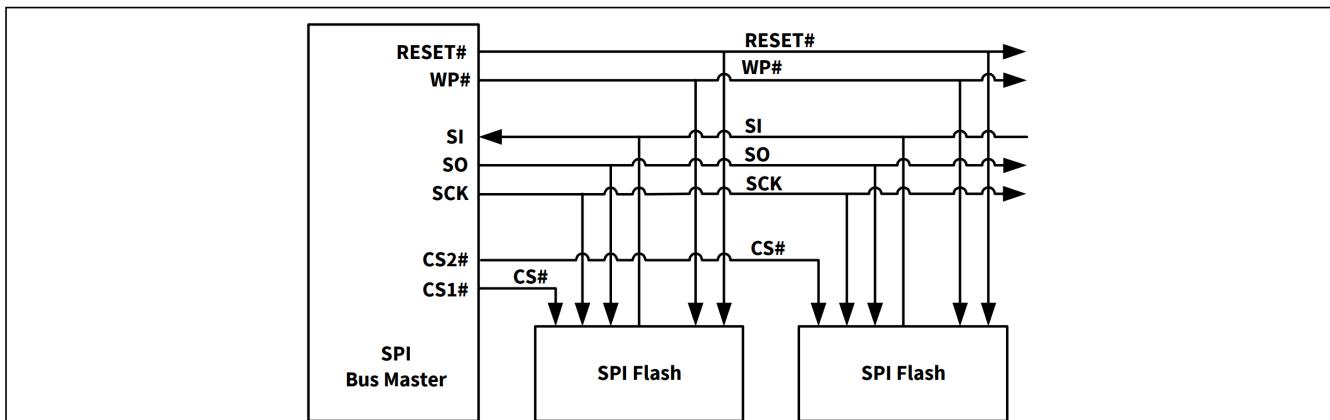

图 4 SPI总线上的总线主控和存储设备 – 单比特数据路径

## 引脚分布和信号描述

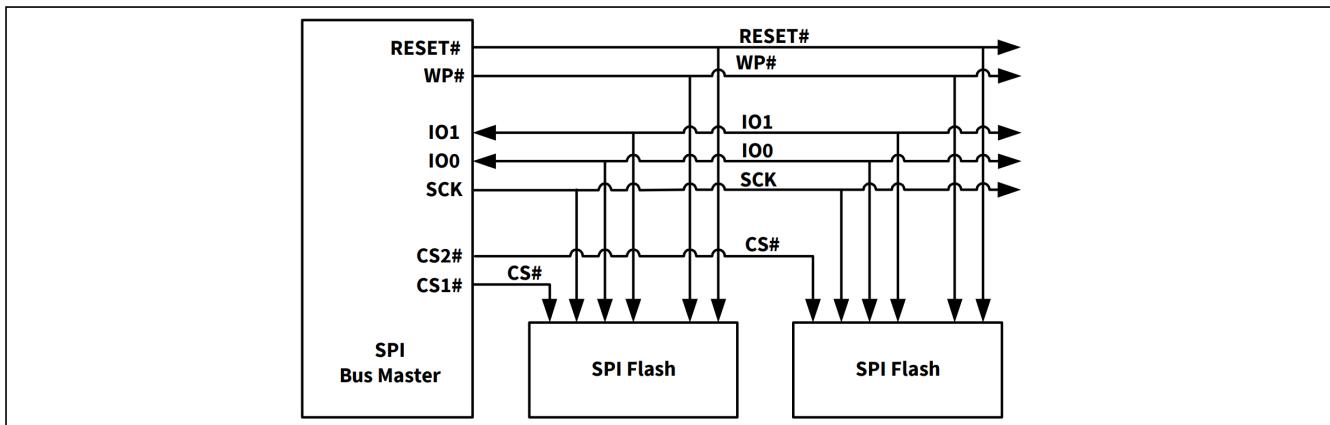

图 5 SPI总线上的总线主控和存储设备 – 双比特数据路径

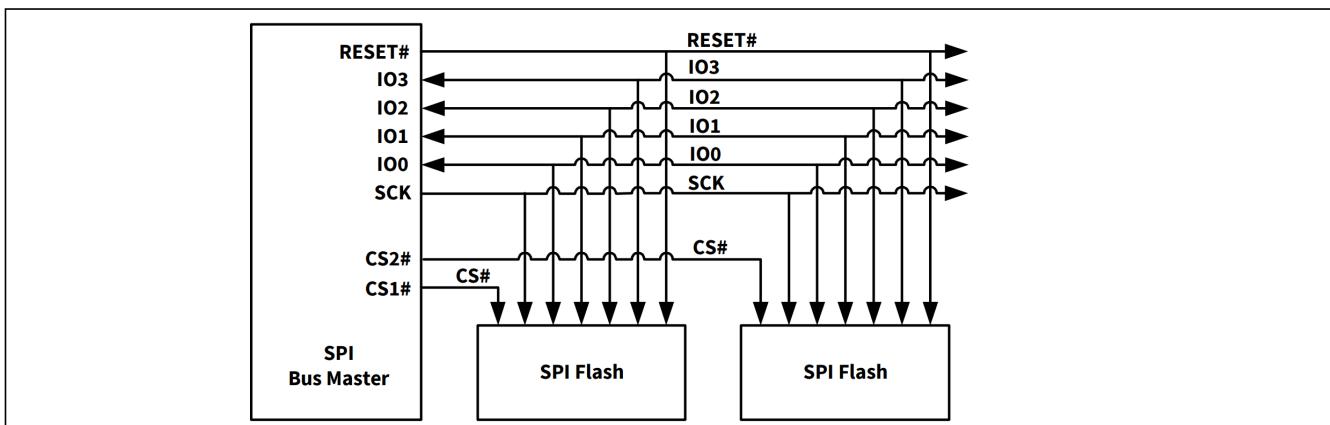

图 6 SPI 总线上的总线主设备和存储器件之间的关系 – 四比特数据路径 - 单独 RESET#

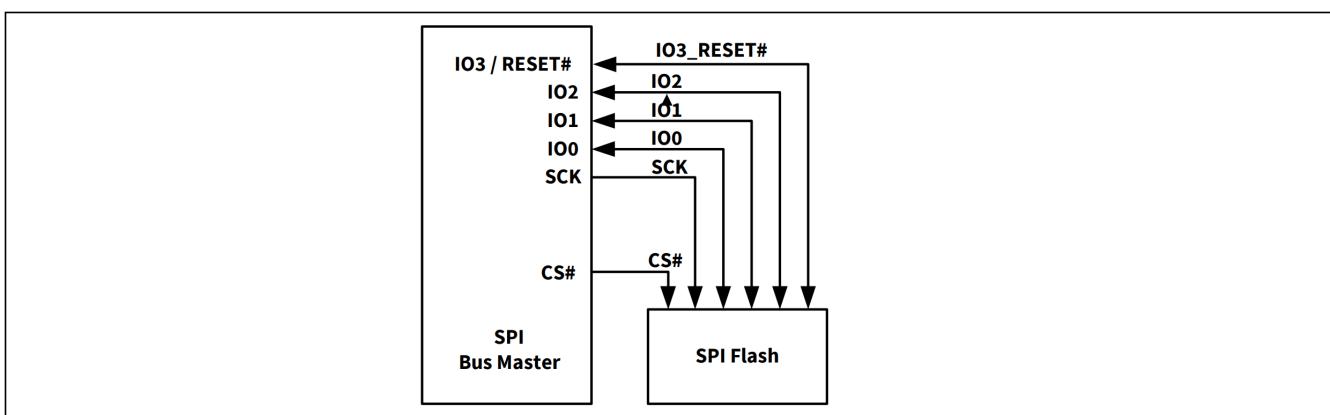

图 7 SPI 总线上的总线主设备和存储器件之间的关系 – 四比特数据路径 - IO3\_RESET#

## 信号协议

# 4 信号协议

## 4.1 SPI 时钟模式

### 4.1.1 单倍数据速率 (SDR)

FS-S 系列可由嵌入式微处理器（总线主机）以以下两种时钟模式驱动。

- 模式 0，时钟极性 (CPOL) = 0，时钟相位 (CPHA) = 0

- 模式 3，CPOL = 1 且 CPHA = 1

在这两种模式中，器件的输入数据总是在 SCK 信号的上升沿上被锁存，输出数据总是在 SCK 时钟信号的下降沿上可用。

两种模式的区别在于总线主机处于待机模式且不传输任何数据时的时钟极性。

- 当 CPOL = 0、CPHA = 0 时，SCK 将保持逻辑低电平状态

- 当 CPOL = 1、CPHA = 1 时，SCK 将保持逻辑高电平状态

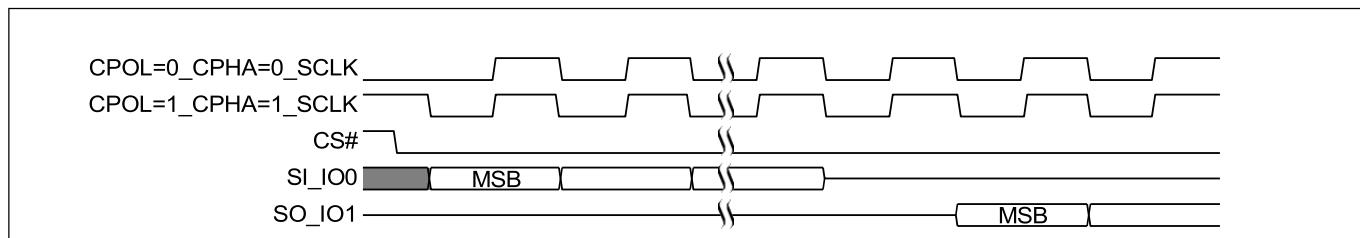

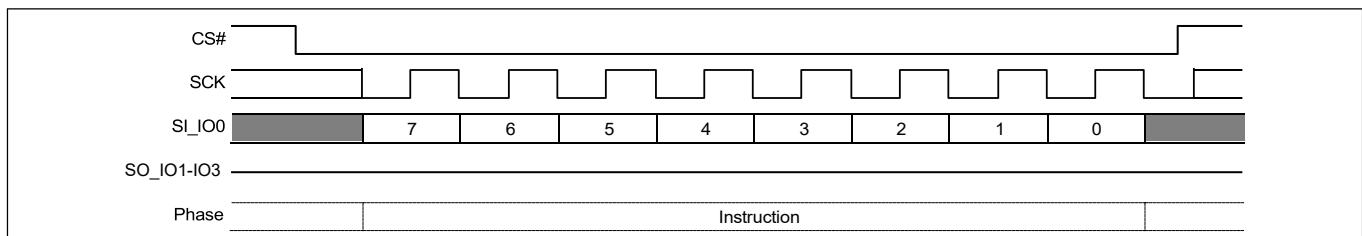

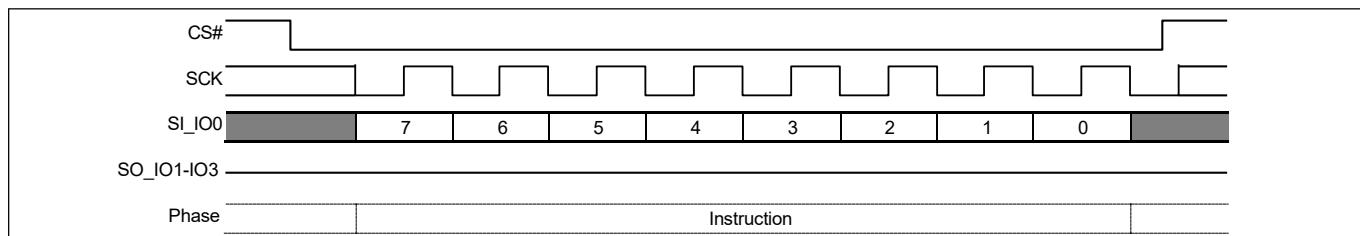

图 8 支持 SPI SDR 模式

本文档其余部分的时序图通常通过在 CS# 下降时将 SCK 显示为高电平和低电平来显示为模式 0 和模式 3。在某些情况下，时序图可能通过显示 SCK 在 CS# 下降沿时的低电平来显示唯一的模式 0。而模式 3 的时序图只是表示在 CS# 的下降沿上时钟信号为高电平，因此模式 3 不需要从 CS# 下降沿后到 SCK 上升沿前的建立和保持时间。

SCK 周期是从一个 SCK 的下降沿到下一个 SCK 的下降沿进行测量（计数）得到的。在模式 0 下，由于开始执行某个命令时 SCK 已经处于低电平状态，因此执行命令时的第一个 SCK 周期指的是从 CS# 的下降沿到第一个 SCK 下降沿。

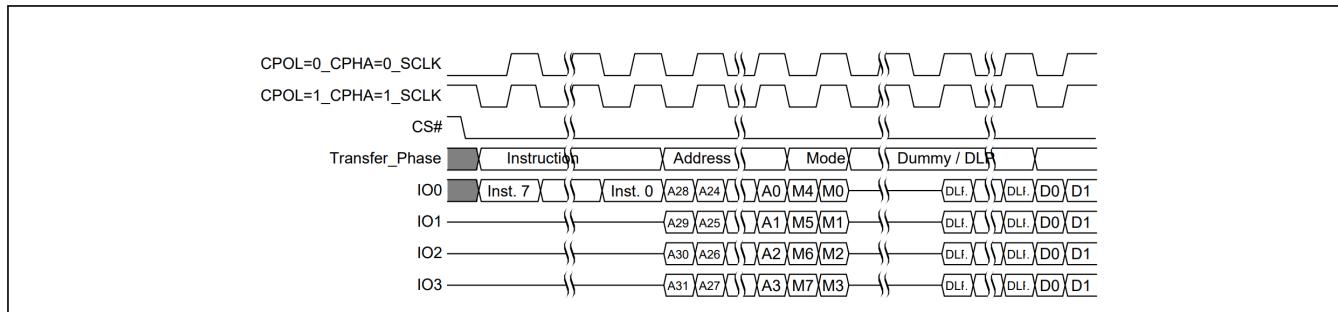

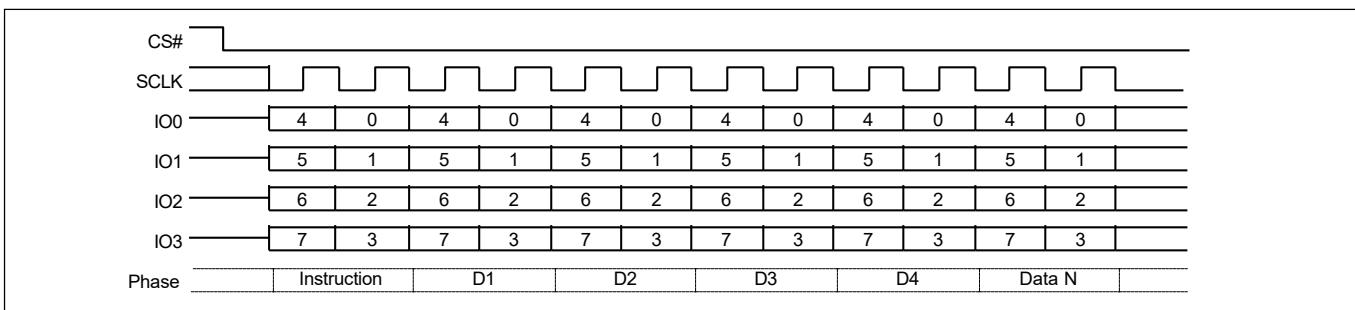

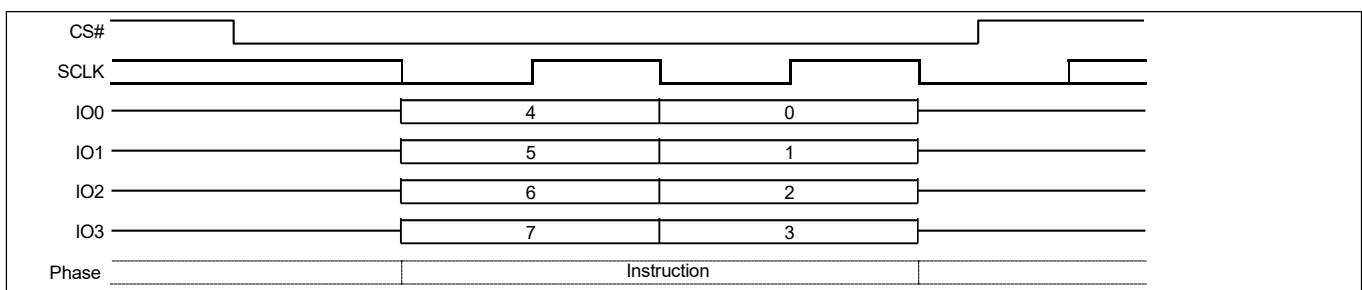

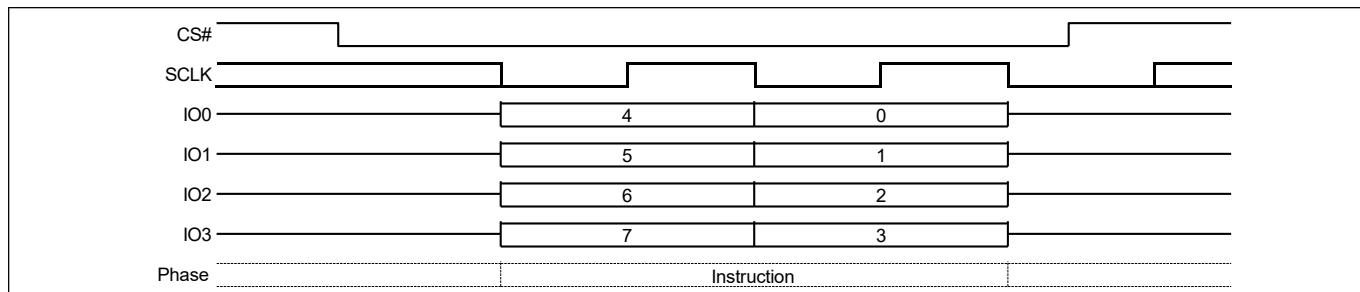

### 4.1.2 双倍数据速率 (DDR)

DDR 指令也支持模式 0 和模式 3。与 SDR 指令相同，在 DDR 指令中，指令位也是在时钟的上升沿被锁存。但是指令后的地址和输入数据则在 SCK 的双边沿上被锁存。第一个地址位被锁存于最后一个指令位结束后的下降沿之后的第一个 SCK 上升沿。第一个输出数据位则在最后访问延时（虚拟）周期结束后的下降沿上被发送。

与 SDR 命令相同，SCK 周期也是从一个 SCK 下降沿到下一个 SCK 下降沿进行测量（计数）得到的。在模式 0 下，由于开始执行某个命令时 SCK 已经处于低电平状态，因此执行命令时的第一个 SCK 周期指的是从 CS# 的下降沿到第一个 SCK 下降沿。

## 信号协议

图 9 支持 SPI DDR 模式

## 4.2 命令协议

主控系统与FS-S系列存储设备之间的所有通讯都是以称为“命令”的单元的形式进行的。

所有指令都以一个8位指令开始，该指令选择要执行的信息传输类型或器件操作。命令还可能具有地址、指令修饰符、延时时间、到存储器的数据传输或从闪存的数据传输。所有指令、地址和数据信息在主控系统和存储器器件之间顺序传输。

命令协议也通过字符命名法进行分类，使用三个字符来标记三个指令阶段的传输宽度：

- 指令

- 地址和指令修饰符（连续读取模式位）；

- Data

单比特命令只通过 SI 信号依次传输指令和地址或数据。数据可以通过 SO 信号串行发送回主控。对于单比特宽指令，单比特宽地址和修饰符、单比特数据的结构，被称为 1-1-1 命令协议。

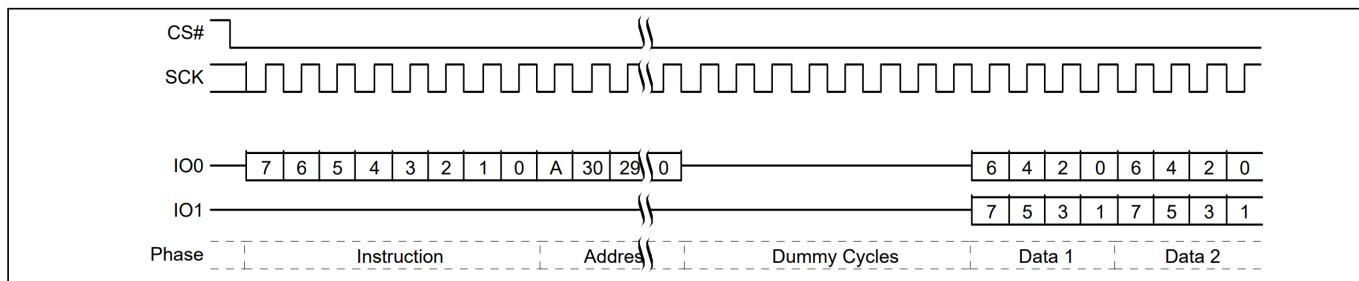

双线输出或四线输出命令从主机端通过 SI (IO0) 将地址和虚拟周期依次进行发送。数据可以按双比特一组的方式通过 IO0 和 IO1 从存储器回送到主机，也可以按四比特（半字节）一组的方式通过 IO0、IO1、IO2 和 IO3 回送。对于双线输出和四线输出命令，这种结构分别被称为 1-1-2 和 1-1-4 命令协议。

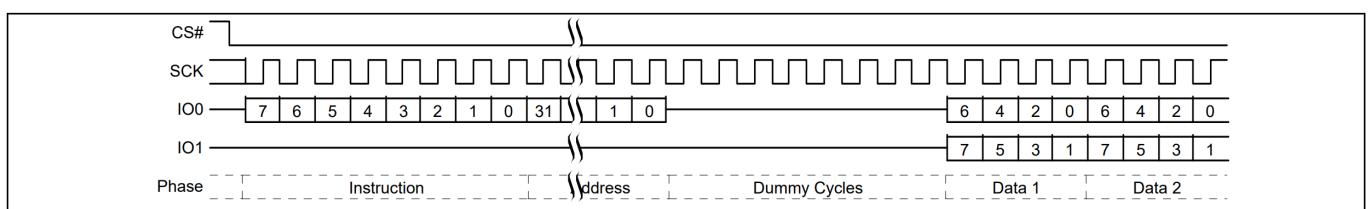

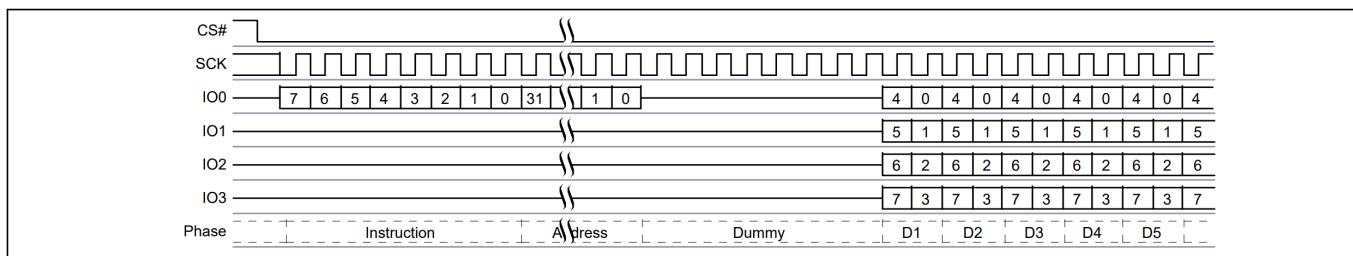

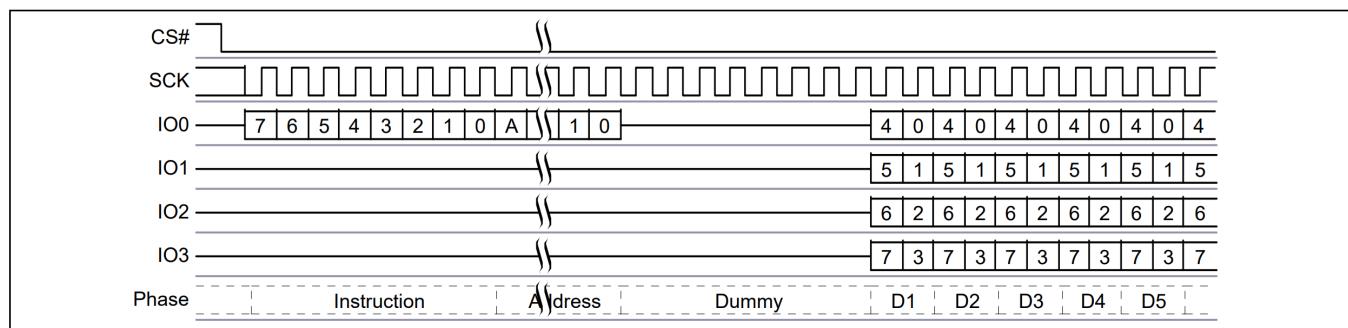

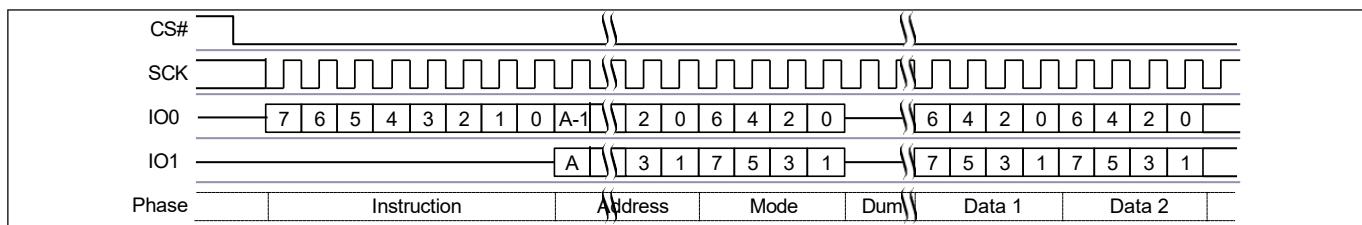

双线或四线输入 / 输出 (I/O) 命令会按双比特一组的方式通过 IO0 和 IO1 将主机的数据传输给存储器，或按四比特（半字节）一组的方式通过 IO0、IO1、IO2 和 IO3 传输给存储器。数据返回到主控的方式类似于 IO0 和 IO1 上的位对，或者 IO0、IO1、IO2 和 IO3 上的四位（半字节）组。对于双线 I/O 和四线 I/O 命令，这种结构分别被称为 1-2-2 和 1-4-4 命令协议。

FS-S 系列也支持 QPI 模式，在该模式下所有信息（包括指令、地址、修饰符和数据）都以 4 比特的宽度传输。这被称为 4-4-4 命令协议。

命令结构如下：

- 每个命令都在 CS# 的下降沿开始执行，并在 CS# 的上升沿结束。主机通过一个命令将片选 (CS#) 信号驱动为低电平，从而能够选择储存器。

- 串行时钟 (SCK) 标记主控和存储器之间每个位或一组位的传输。

- 每个命令都以一个八位（字节）指令开始。该指令选择要执行的信息传输类型或器件操作。指令传输发生在 SCK 上升沿。然而，一些读取指令被先前的读取命令修改，使得该指令是从先前的指令隐含的。这被称为连续读取模式。器件处于连续读取模式时，由于该指令和用于初始化连续读取模式的读取命令相同，所以各个指令位不会在开始执行命令时被传输。在连续读取模式中，指令将以读取地址开始。因此，连续读取模式从一系列相同类型的读取命令中的每个读取命令中删除八个指令位。

## 信号协议

- 该指令可以是独立的，也可以跟随地址位以选择器件中多个地址空间之一内的位置。该指令决定所使用的地址空间。地址可以是 24 位或 32 位、字节边界、地址。地址传输发生在 SDR 指令中的 SCK 上升沿，或 DDR 指令中的每个 SCK 边沿。

- 在传统 SPI 模式下，指令之后的所有传输的宽度均由发送的指令决定。以下表示的可能是其中一种传输类型：仅通过串行输入（SI）或串行输出（SO）信号单比特传输；通过 IO0 和 IO1 信号每次（双线）传输将以双比特的形式进行传输；或通过 IO0-IO3 信号每次（四线）以 4 比特的形式传输。在双比特或四比特组中，最低有效位位于 IO0 上。其他更高有效位则按照权值大小，通过 IO 信号的编号有序放置。单比特或并行位组按照从最高有效位到最低有效位的顺序进行传输。

- 在 QPI 模式下，所有信息都按照 4 比特宽（四线传输）通过 IO0-IO3 信号进行发送

- 双线和四线 I/O 读指令在发送地址后将发送一个指令修饰符（称为连续读取模式位），以指明下一个命令的类型与之前的命令相同，而它并不是明确的命令。这些模式位用于初始化或结束连续读取模式。这些模式位用于初始化或结束连续读取模式。因此，下一条命令只会提供新地址和模式位，并不提供指令字节。当某个命令序列中重复了相同的命令类型时，会减少发送每一个命令所需要的时间。模式位传输发生在 SDR 指令中的 SCK 上升沿，或 DDR 指令中的每个 SCK 边沿。

- 地址或模式位后面可能跟有要存储在存储器器件中的写入数据，或者后面可能是读取数据返回到主控之前的读取延时时间。

- 在 SDR 指令中，写入数据位的传输发生在 SCK 上升沿，或者在 DDR 指令中发生在每个 SCK 沿。

- SCK 会在读访问的延迟周期内继续进行切换。延时可能是零到几个 SCK 周期（也称为虚拟周期）。在读取延时周期结束时，第一个读取数据位在最后一个读取延时周期结束时的 SCK 下降沿时输出。第一个读取的数据位被作为在下一个 SCK 上升沿时传输到主控端。在 SDR 指令中，后续每次传输都发生在下一个 SCK 上升沿，而在在 DDR 指令中，发生在每个 SCK 边沿。

- 如果指令返回读取数据到主控，器件将继续发送数据传输，直到主控将 CS 信号拉高。在读取数据时序中的任何传输之后，CS# 信号都可以被驱动为高电平。这将终止指令。

- 在没有返回数据的指令结束时，主控将 CS 输入驱动为高电平。在独立指令或传输的最后一个写入数据字节的第八位之后，CS# 信号必须变为高电平。也就是说，当 CS# 信号驱动为低电平后的位数恰好是八位的倍数时，CS# 信号必须驱动为高电平。如果 CS# 信号没有在指令或写入数据的八位边界处准确变为高电平，则该命令将被拒绝并且不会执行。

- 所有指令、地址和模式位首先移入具有最高有效位的器件。数据位首先从器件最高有效位（数据字左最位）移入和移出。所有数据都以字节为单位传输，首先发送最低地址字节。后续数据字节按从最低到最高字节地址的顺序发送，即字节地址递增。

- 在编程、擦除或写入周期（嵌入式操作）期间读取闪存阵列的所有尝试都将被忽略。嵌入的操作将继续执行，不会受到任何影响。嵌入操作期间只能接受非常有限的指令配置位。这些在单独的指令描述中进行了讨论。

- 根据指令的不同，执行时间也会有所不同。可以使用从正在执行的指令中读取状态信息的指令来确定指令何时完成执行以及指令是否成功。

信号协议

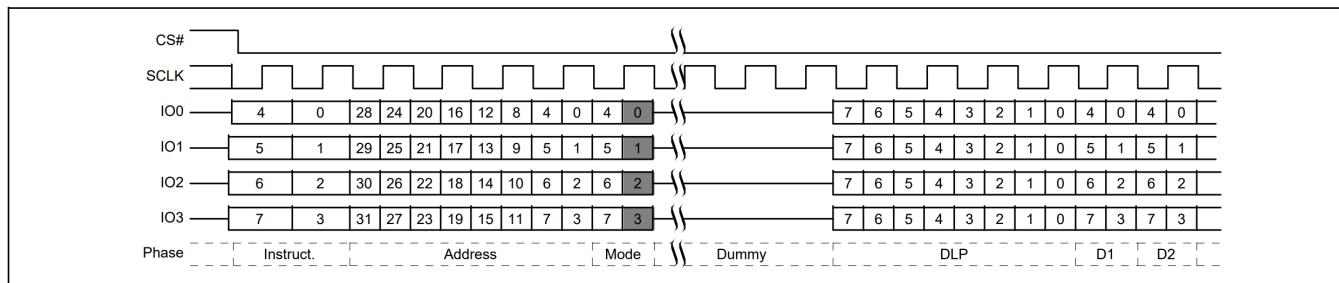

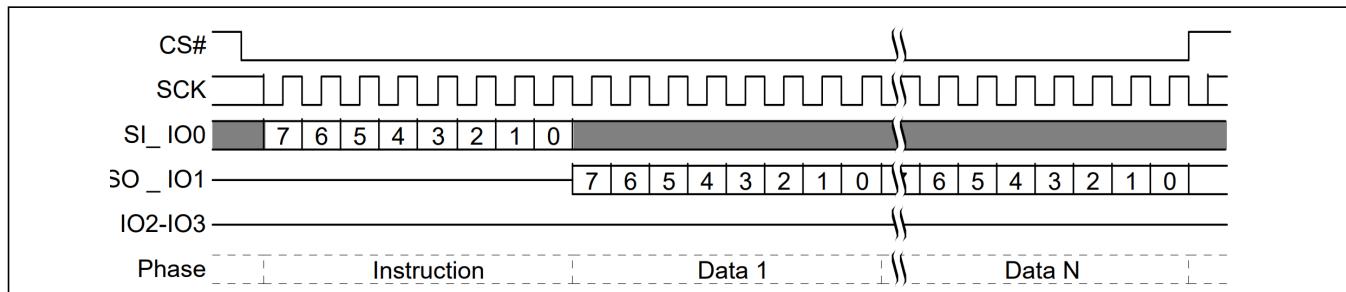

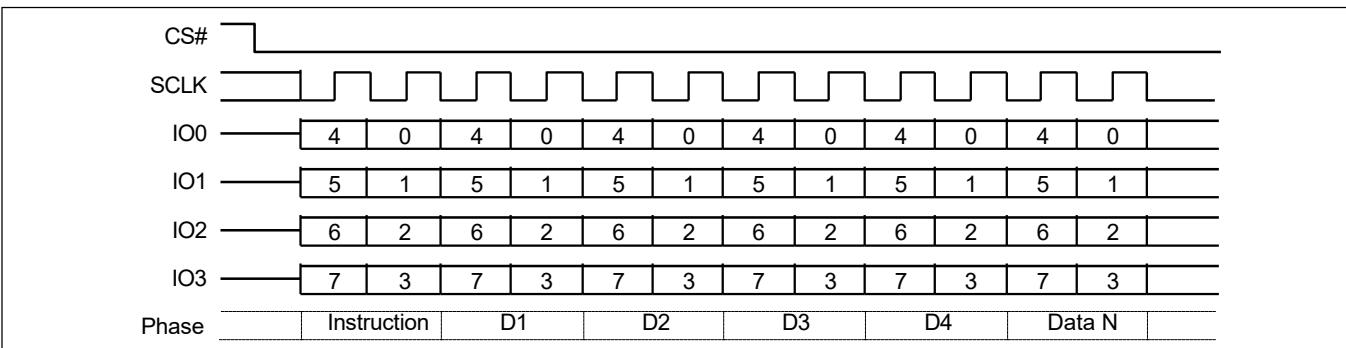

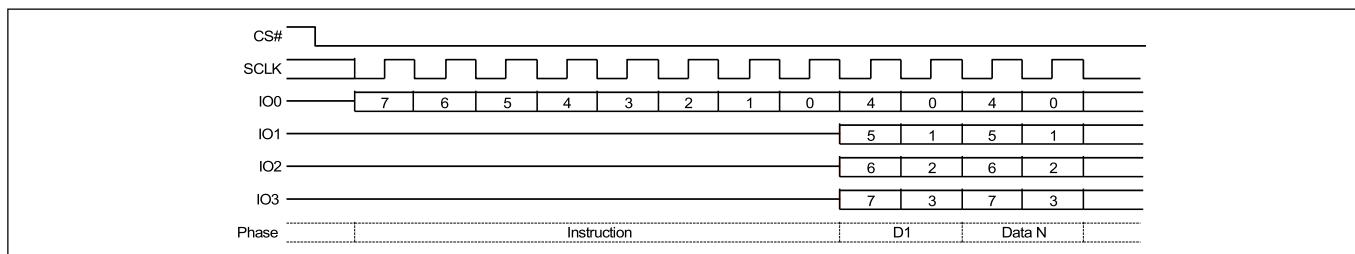

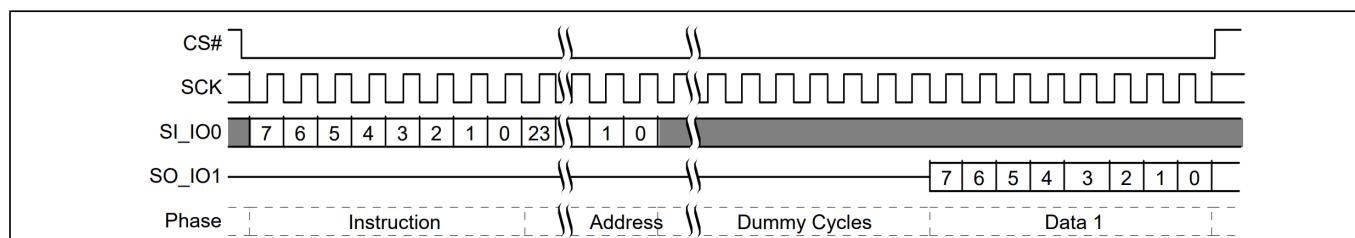

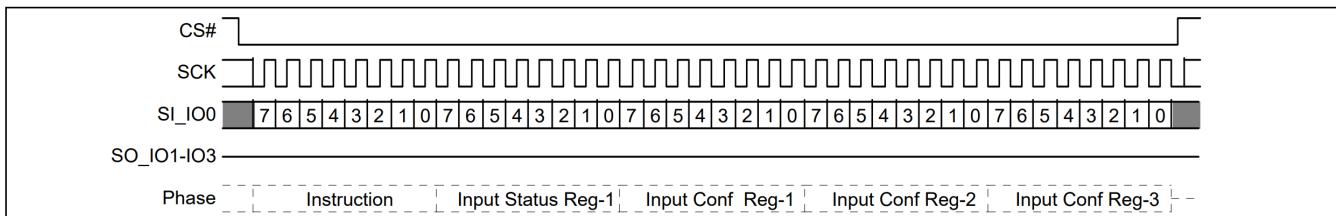

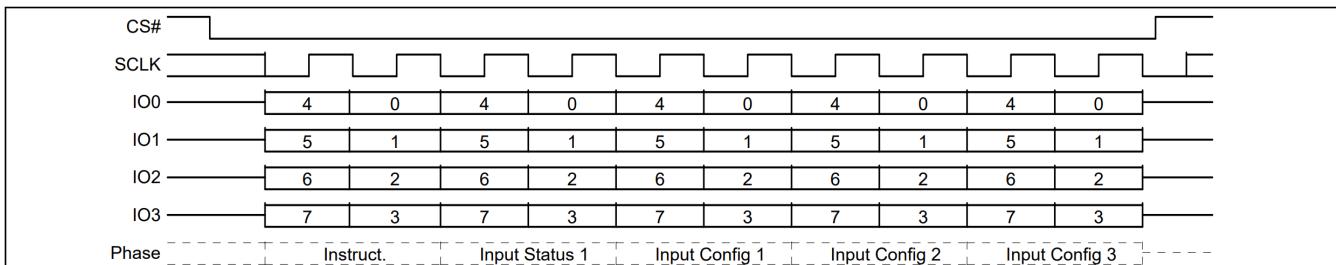

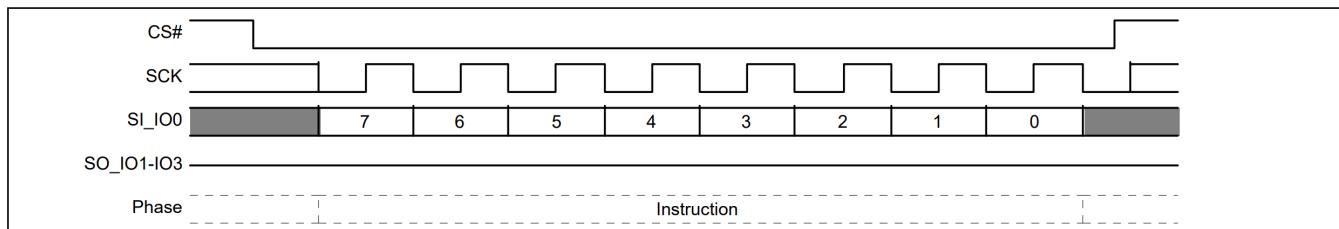

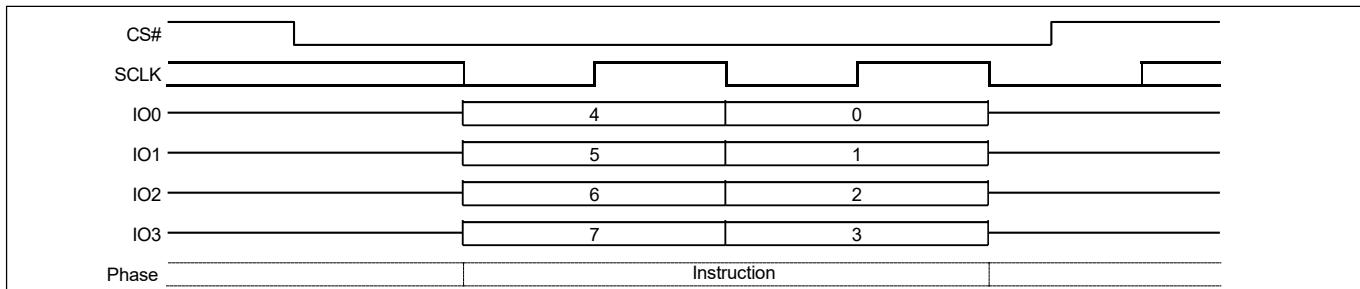

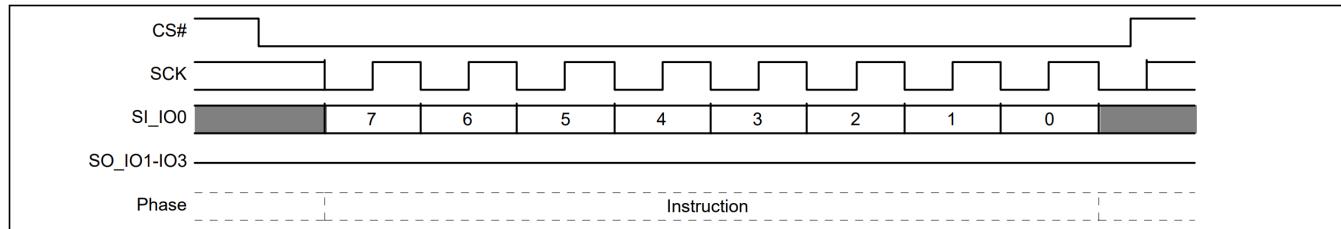

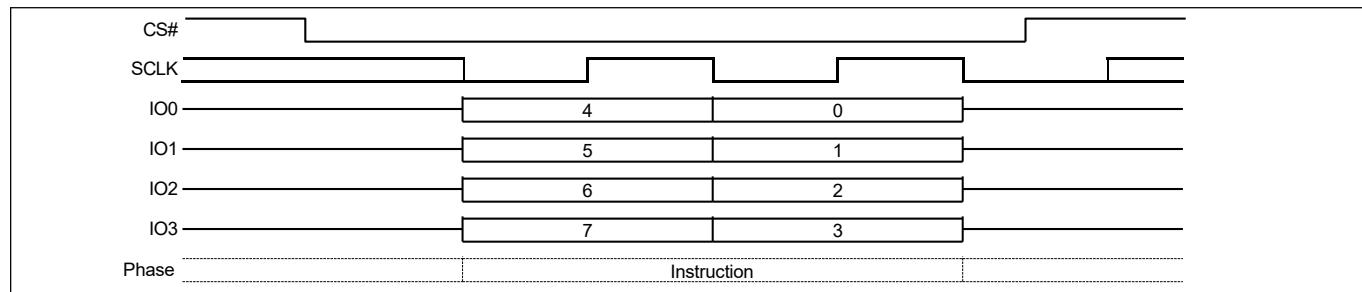

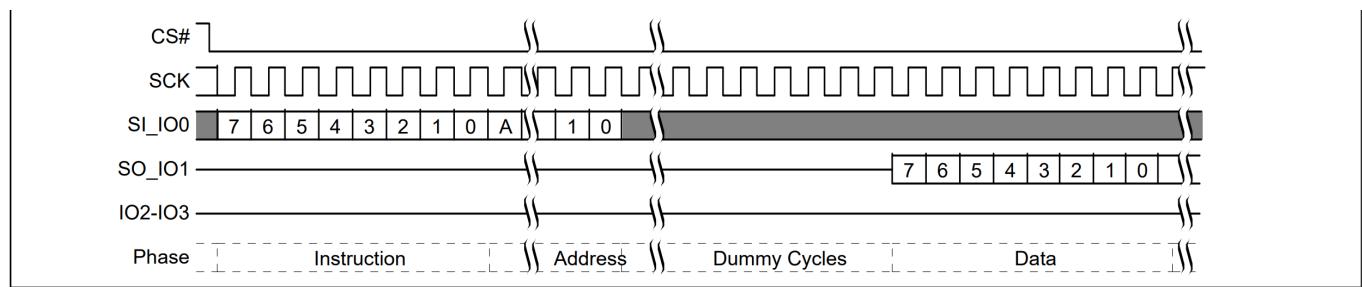

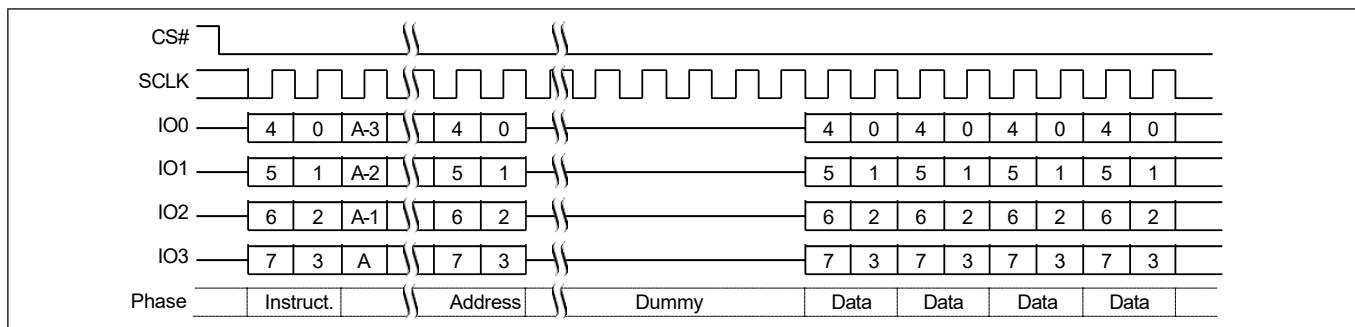

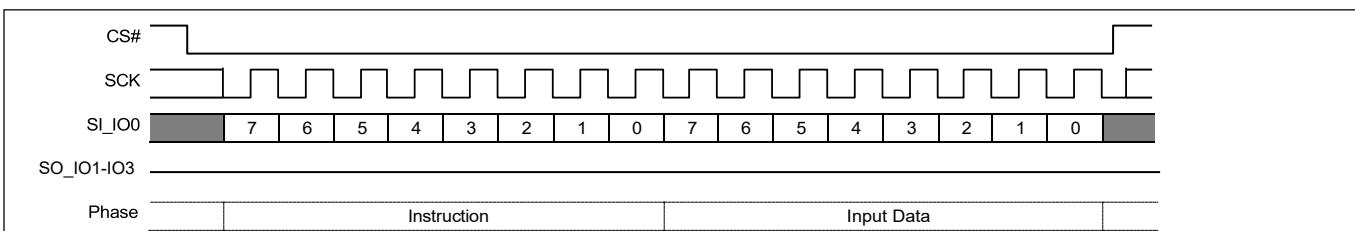

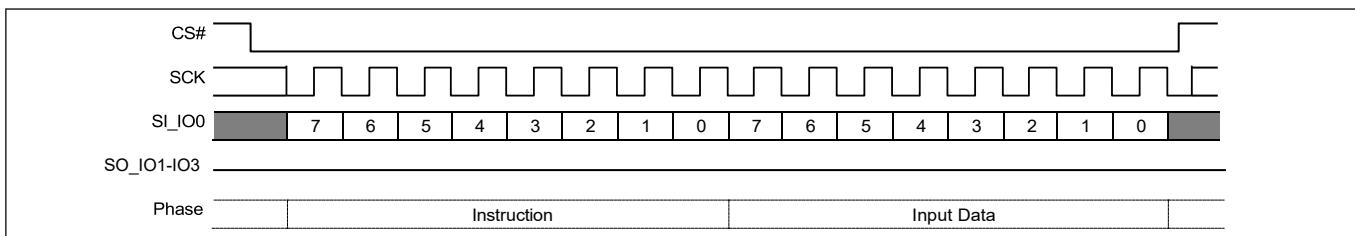

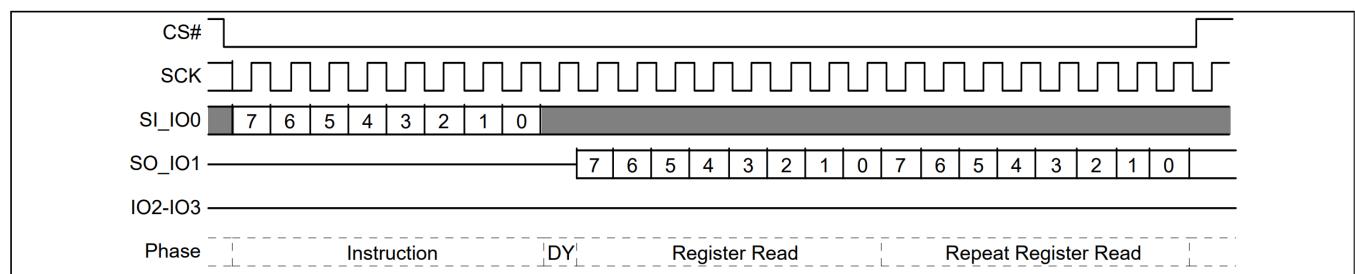

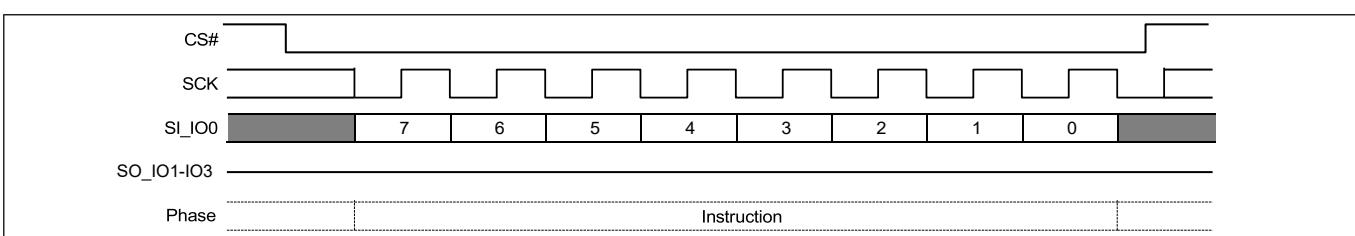

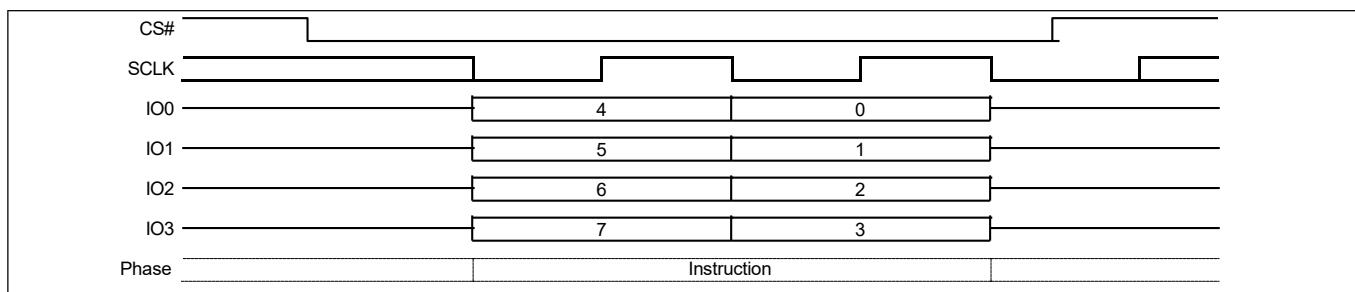

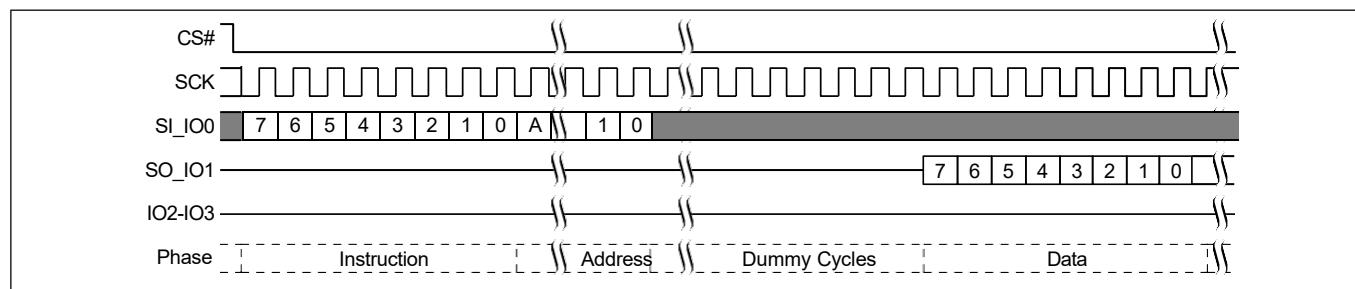

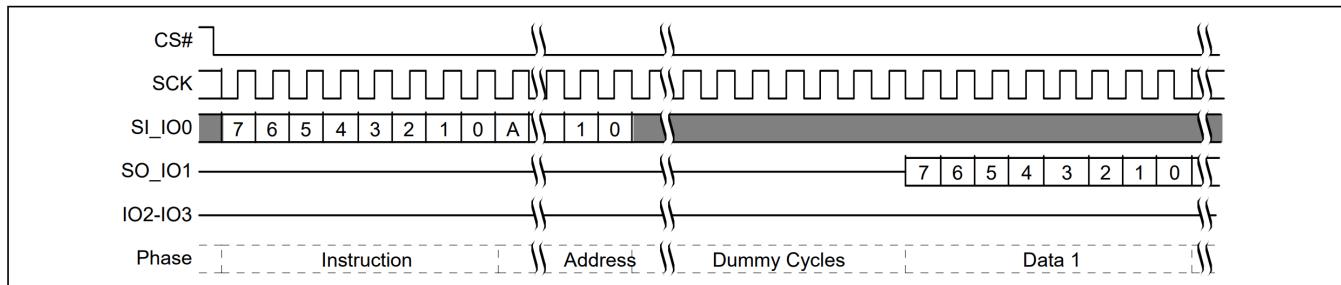

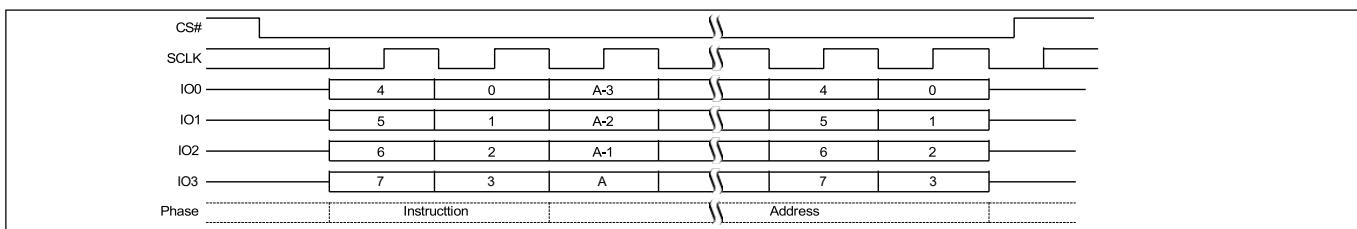

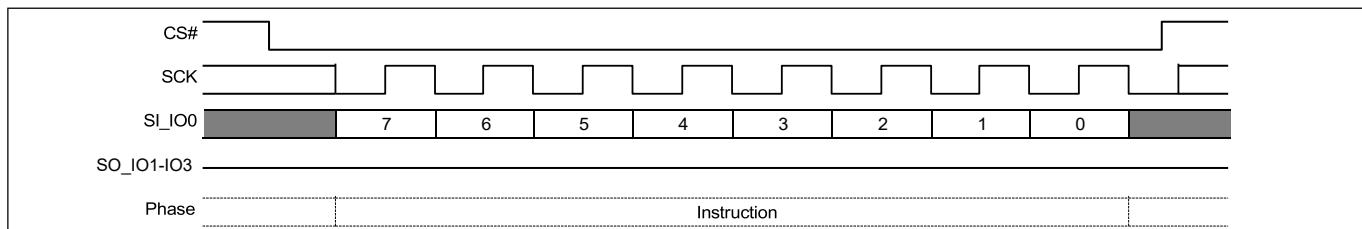

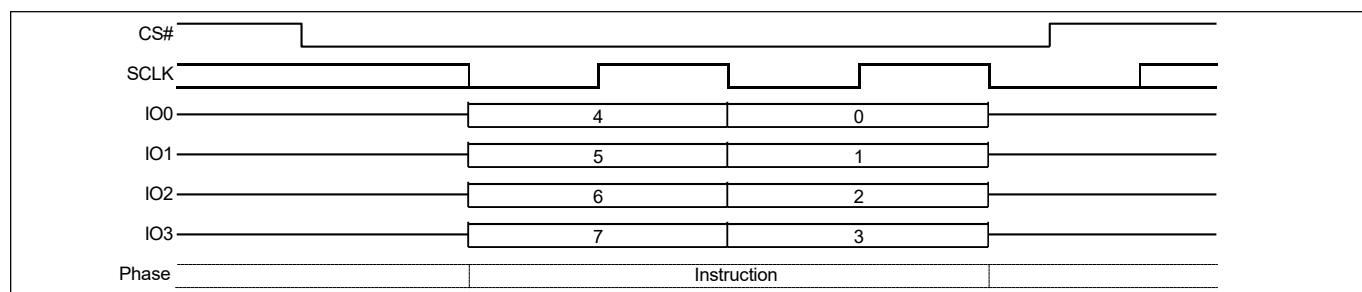

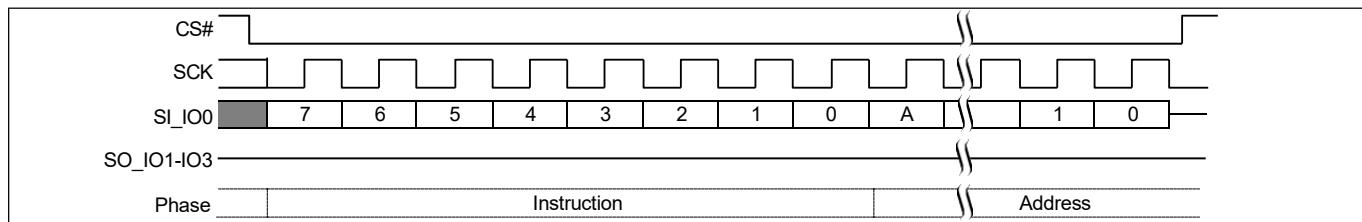

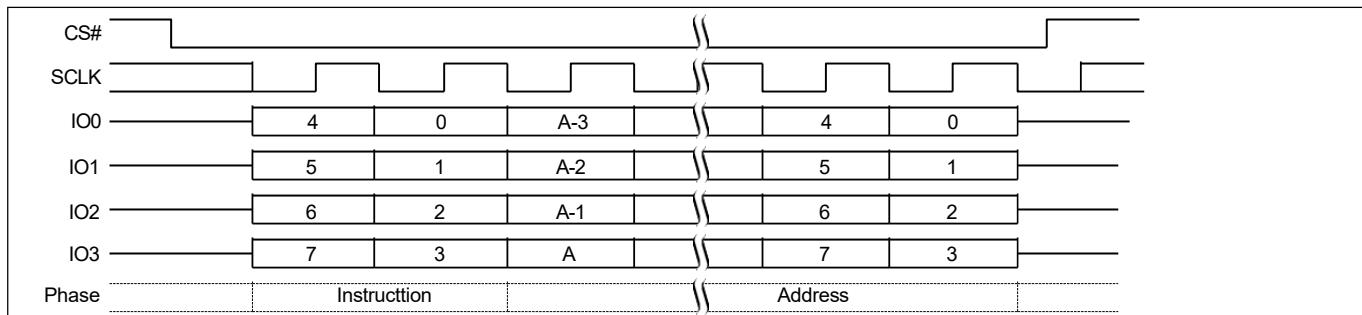

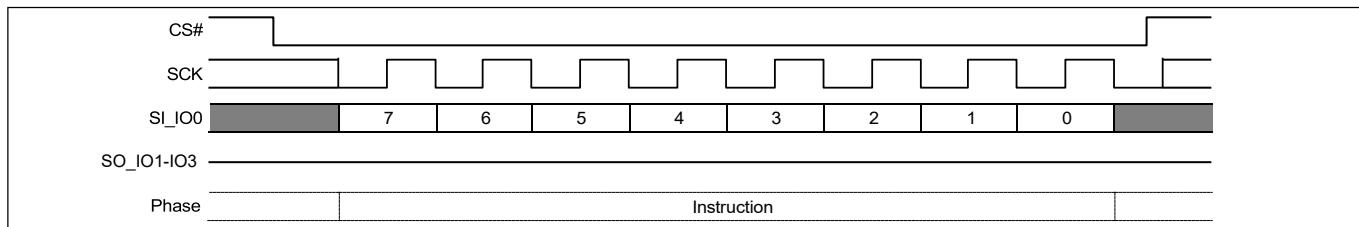

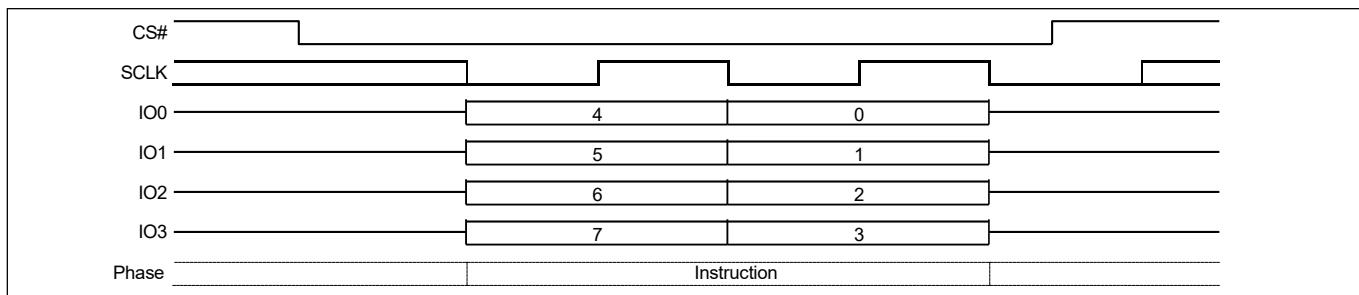

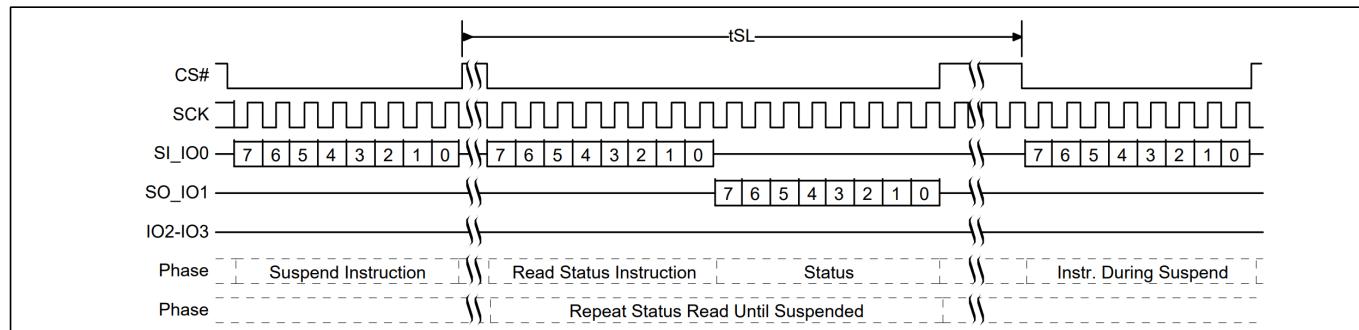

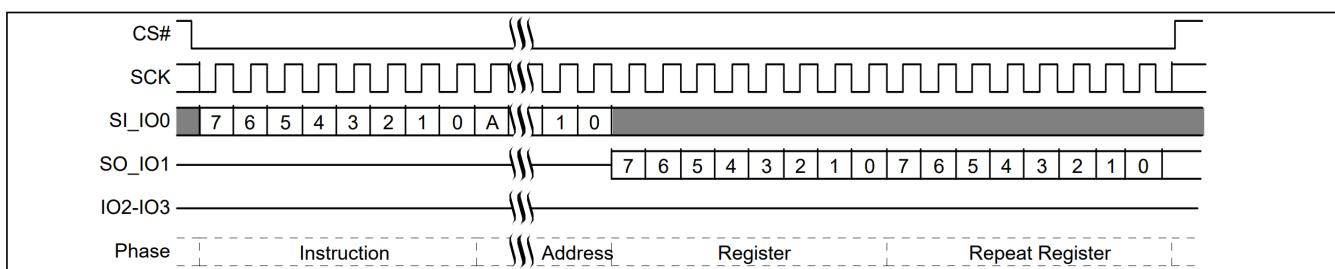

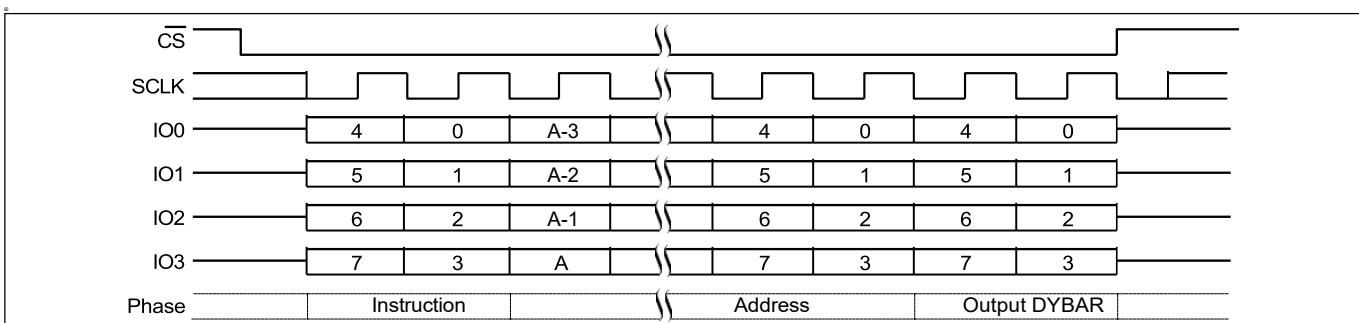

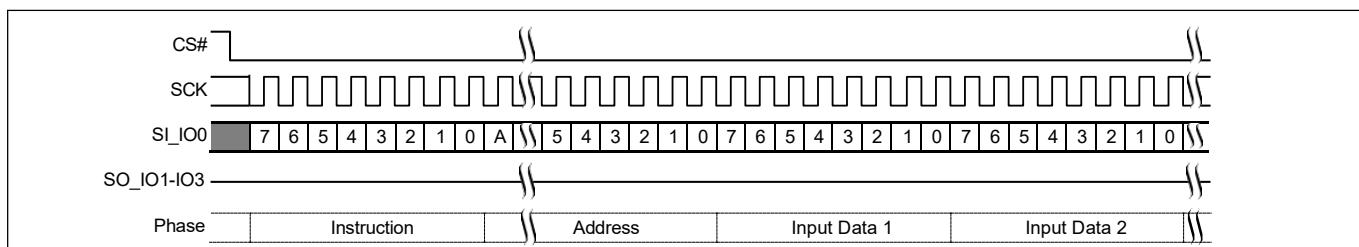

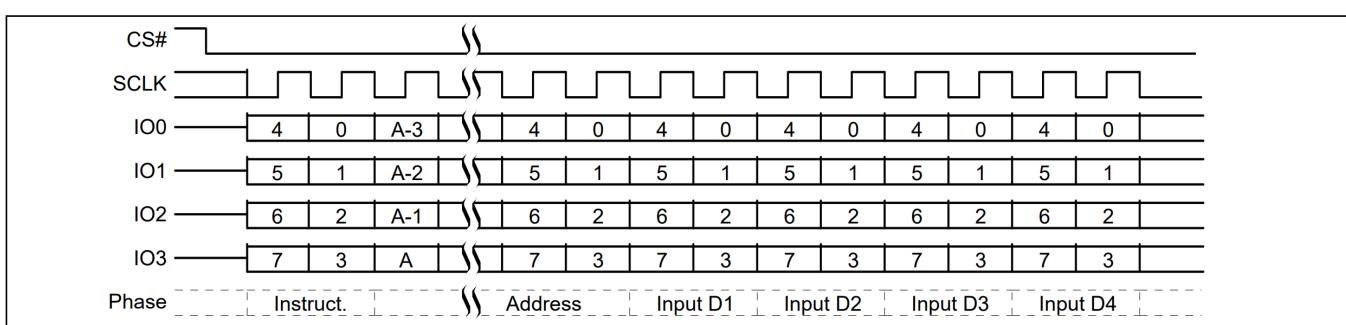

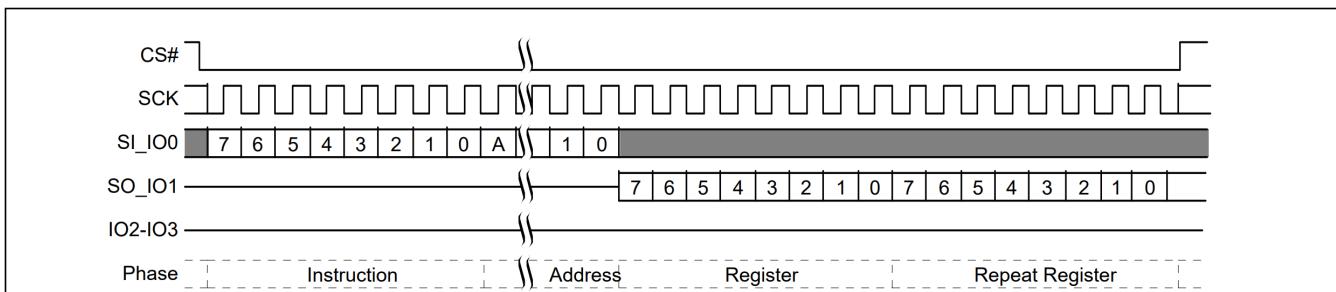

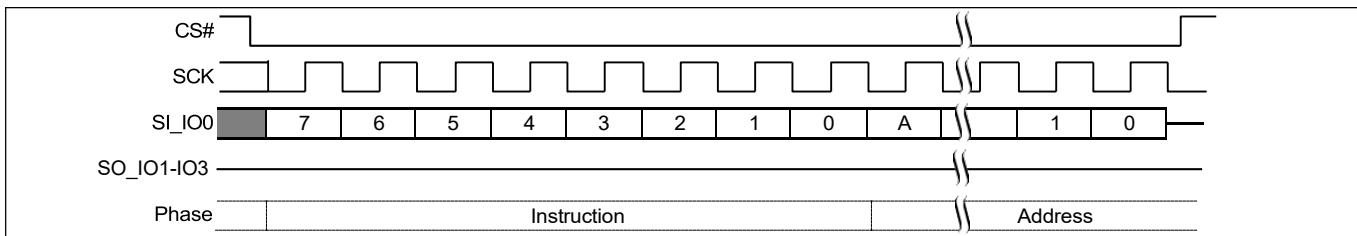

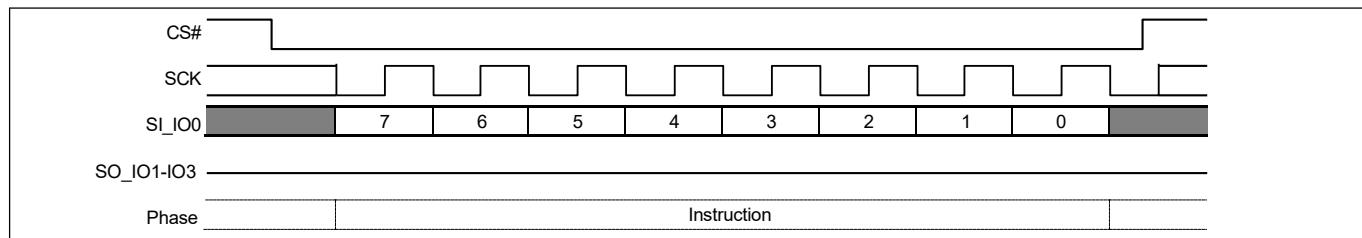

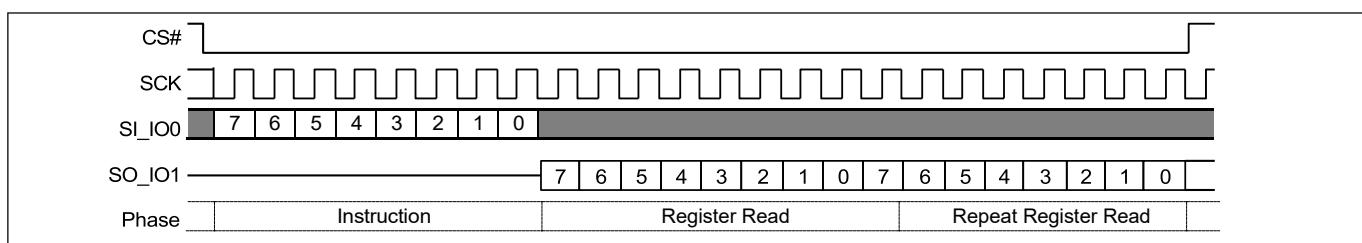

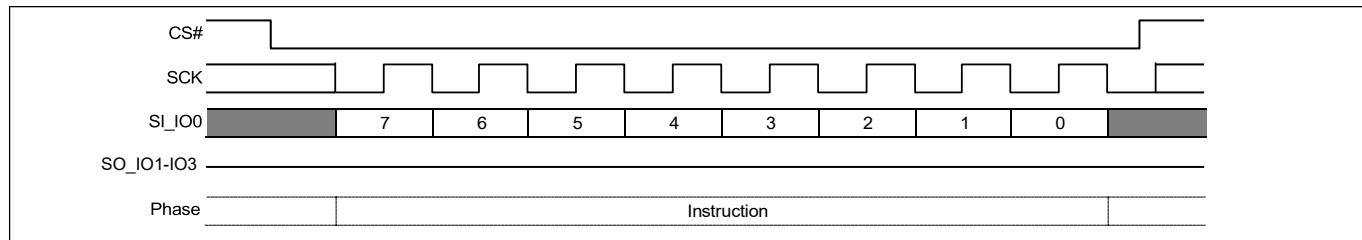

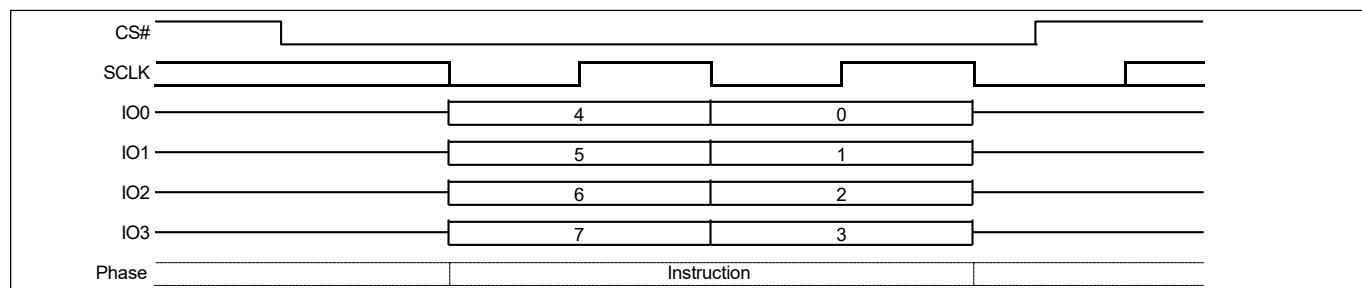

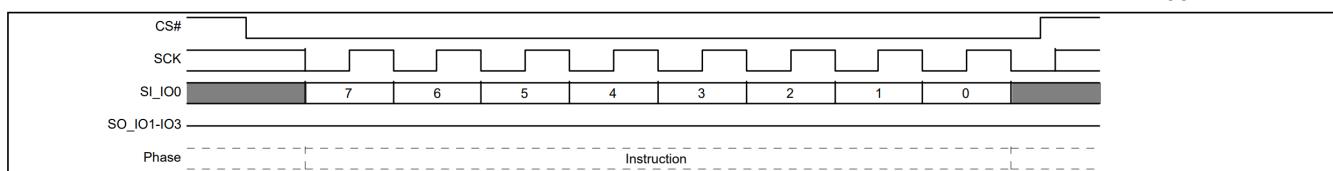

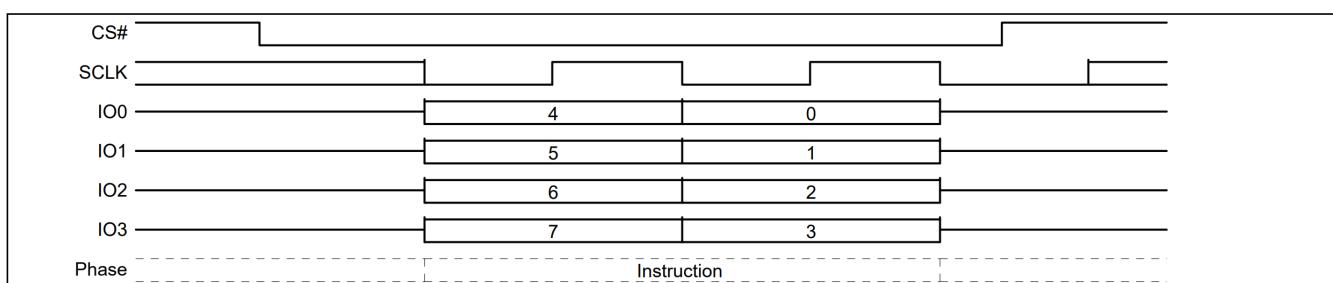

#### 4.2.1 指令时序示例

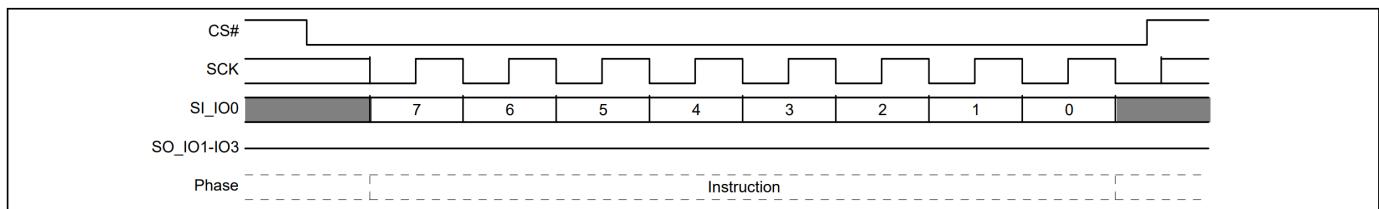

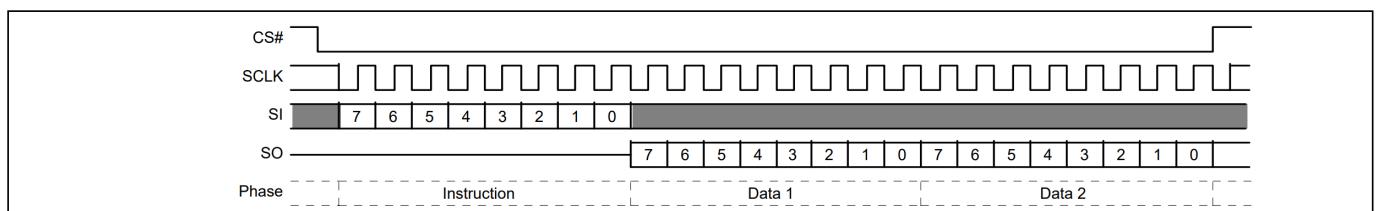

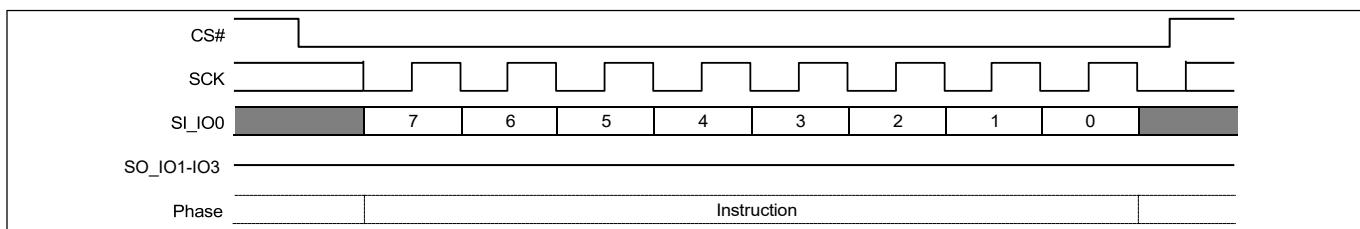

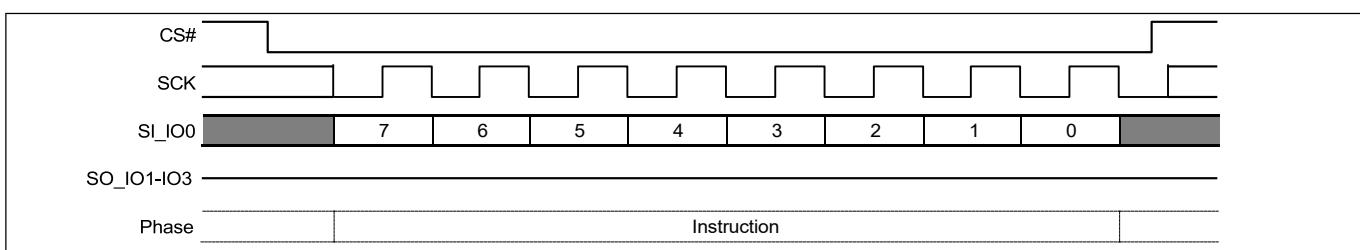

图 10 独立指令命令

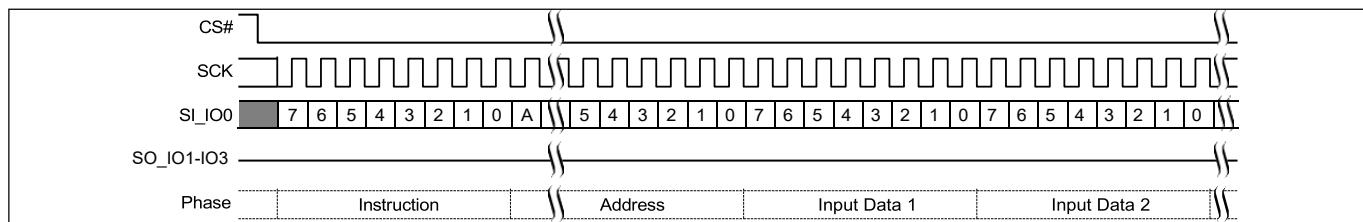

图 11 单线输入命令

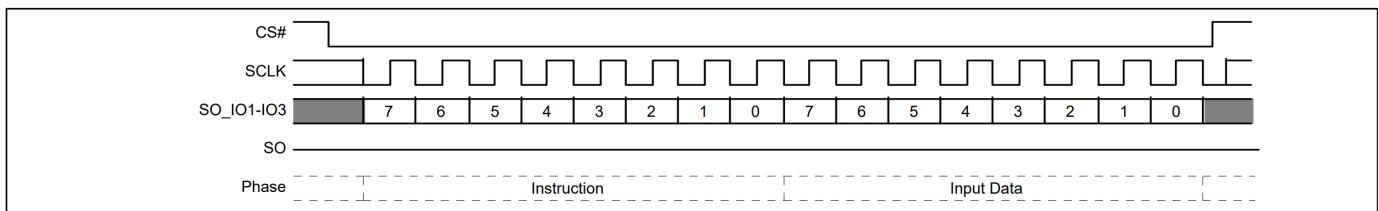

图 12 无延时的单线位宽的输出命令

图 13 带延时的单线位宽的I/O 命令

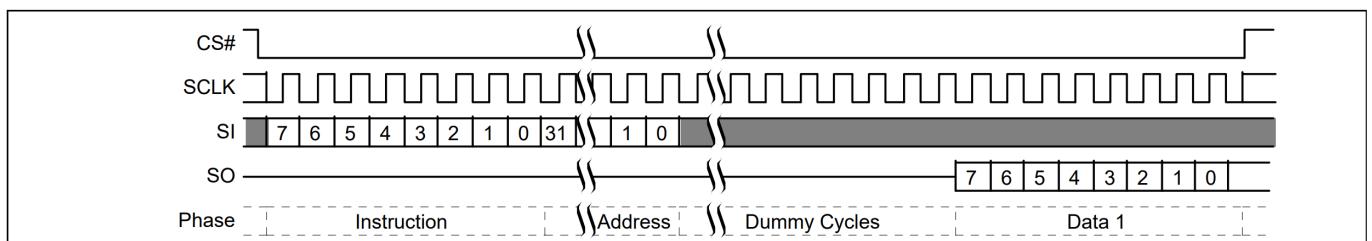

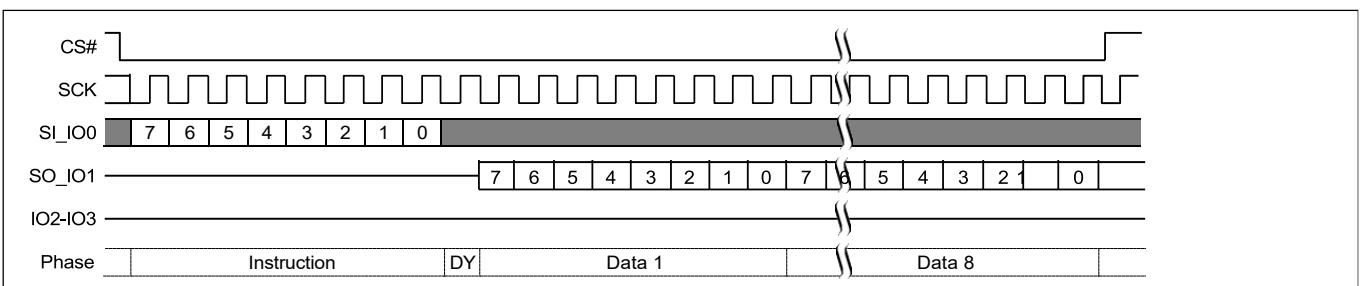

图 14 双线输出读取命令

## 信号协议

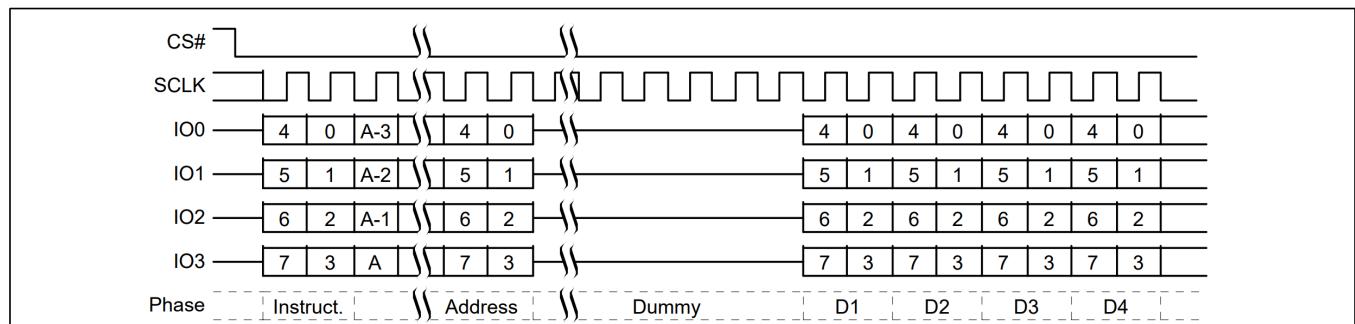

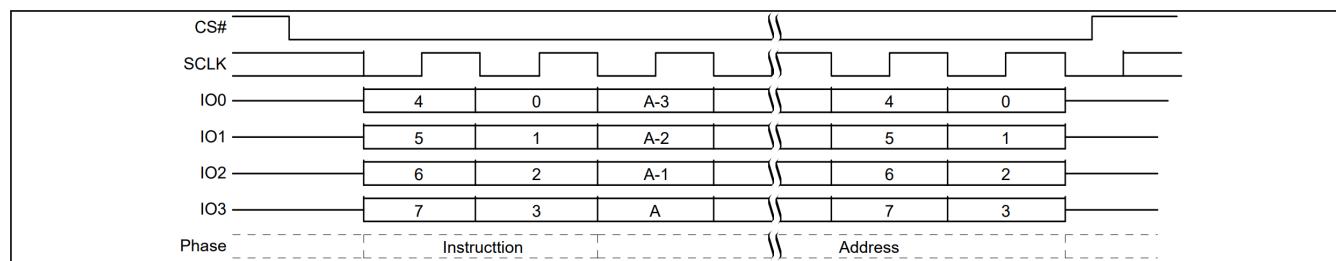

图 15 四线输出读取命令

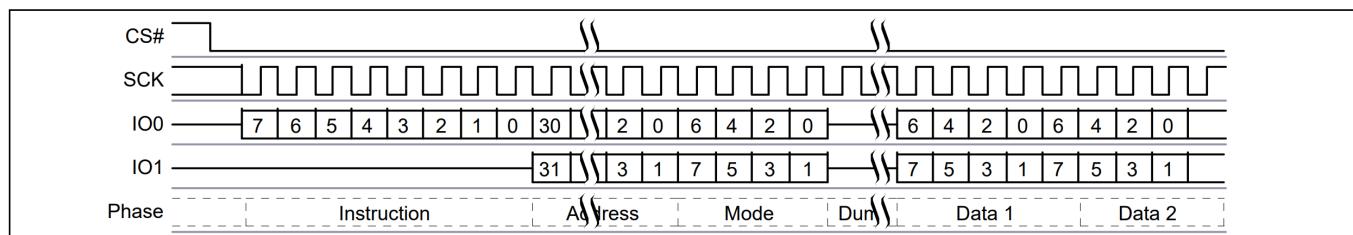

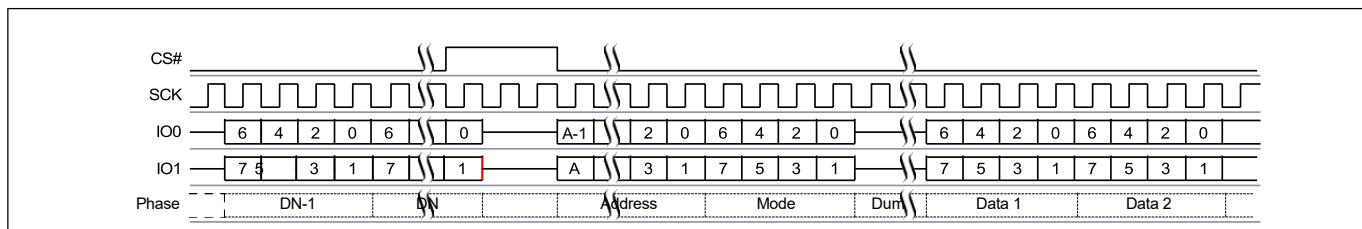

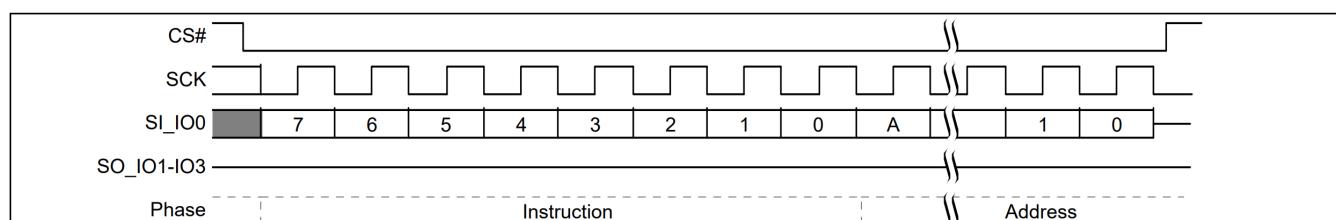

图 16 双线I/O 指令

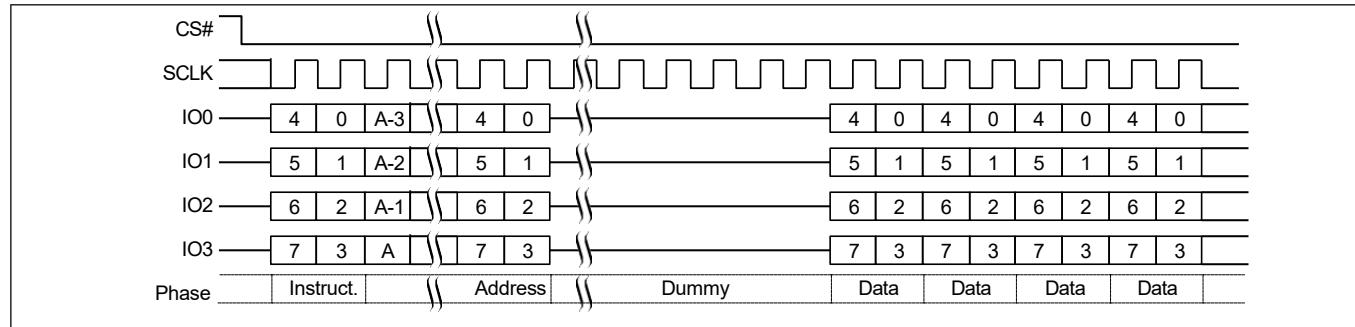

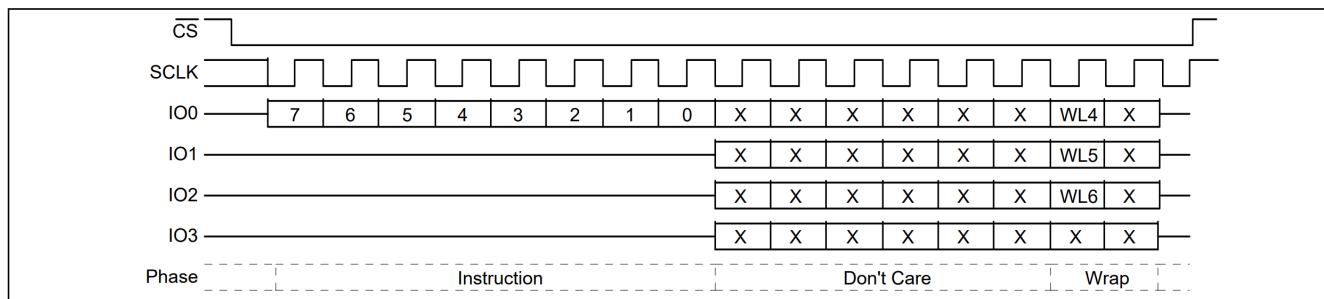

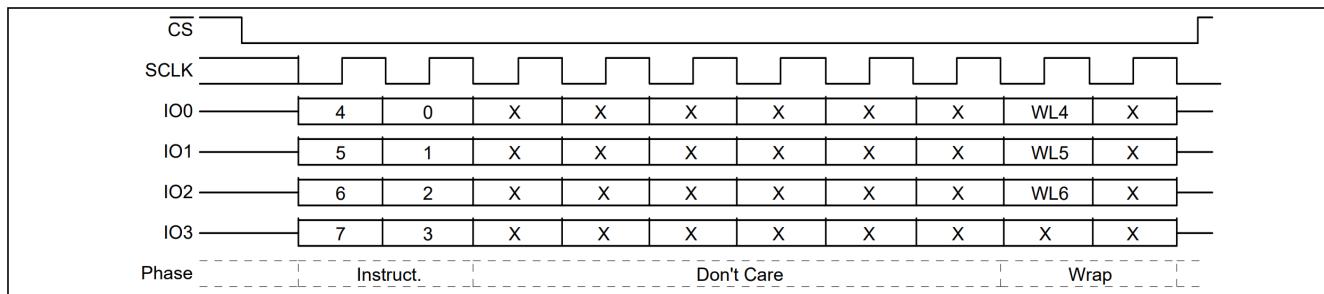

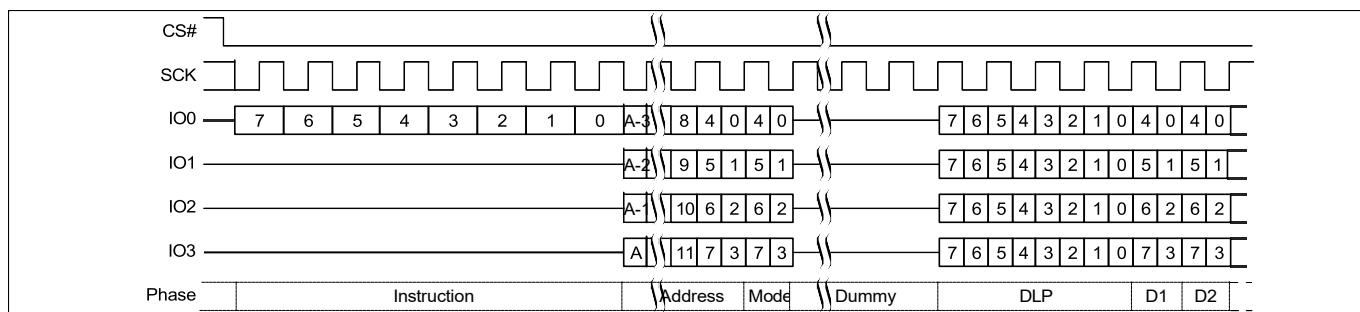

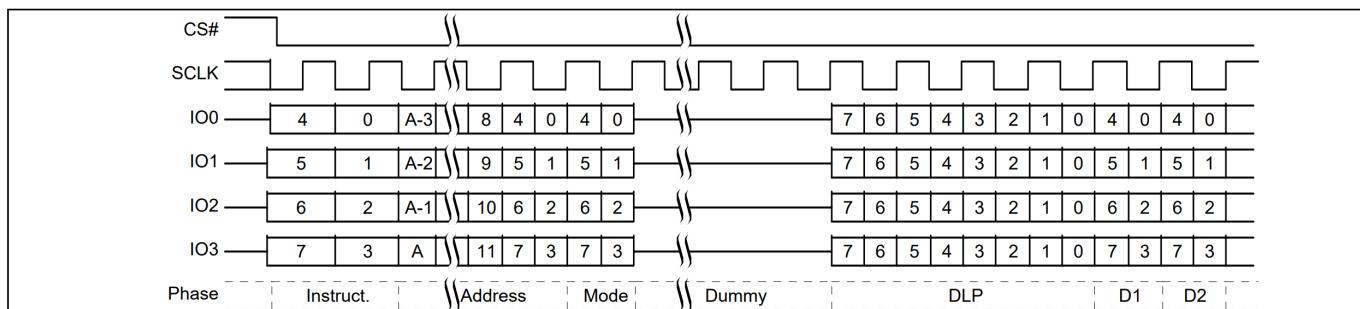

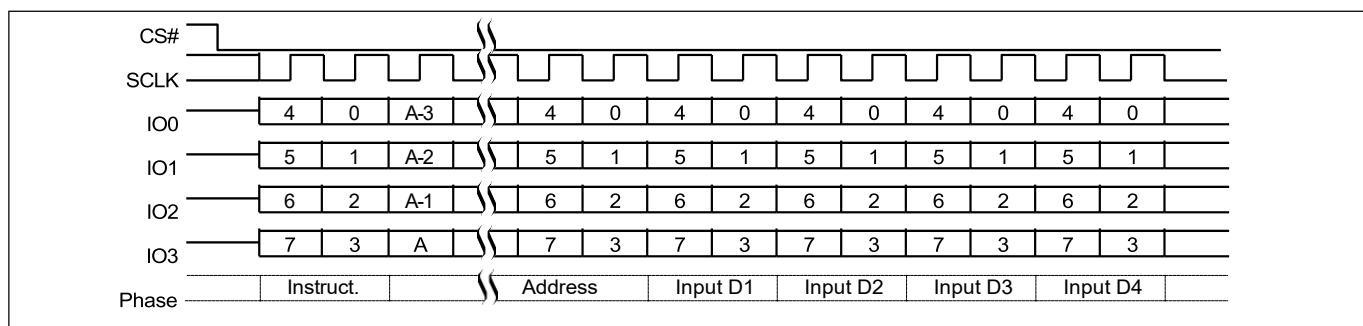

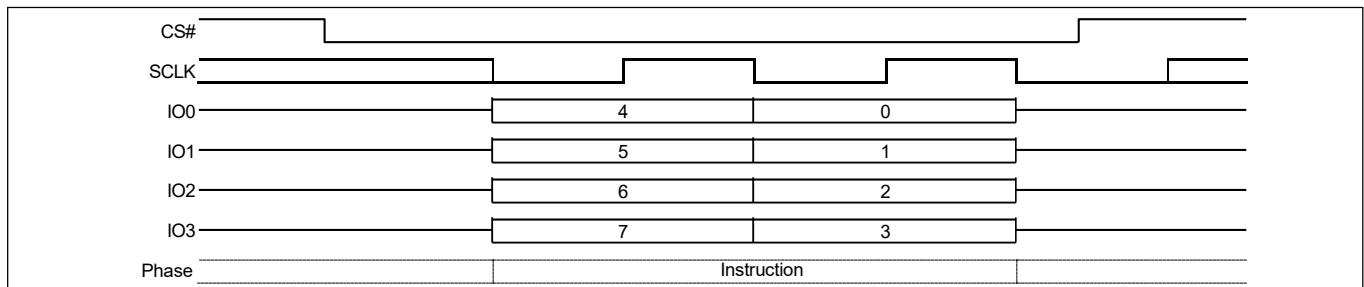

图 17 四线 I/O 指令<sup>[6]</sup>

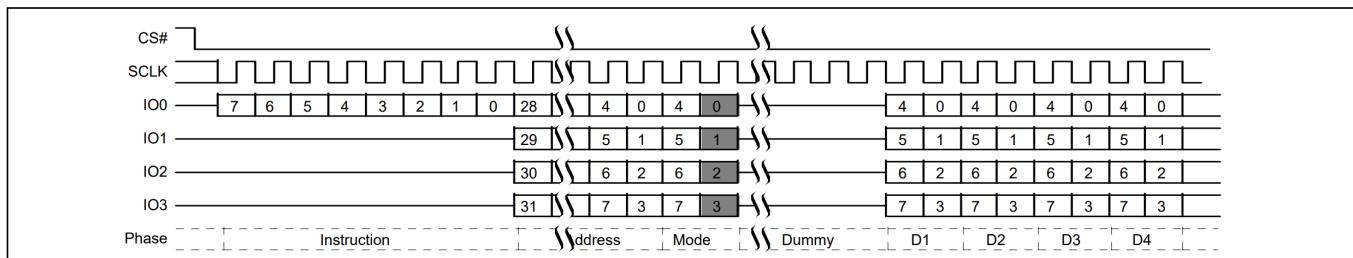

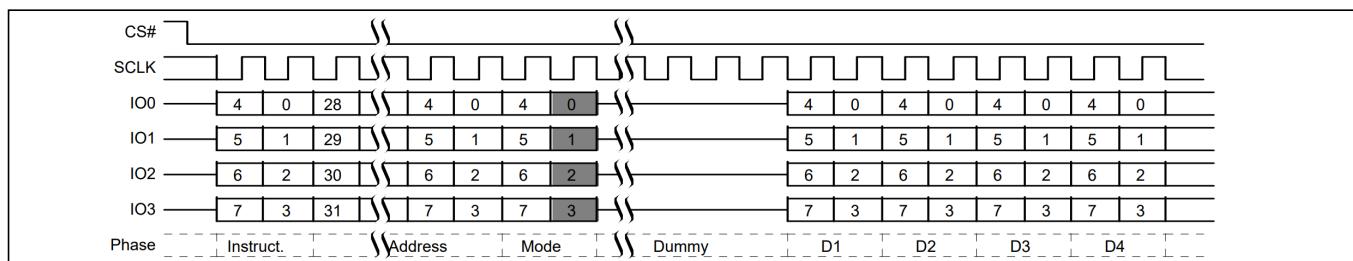

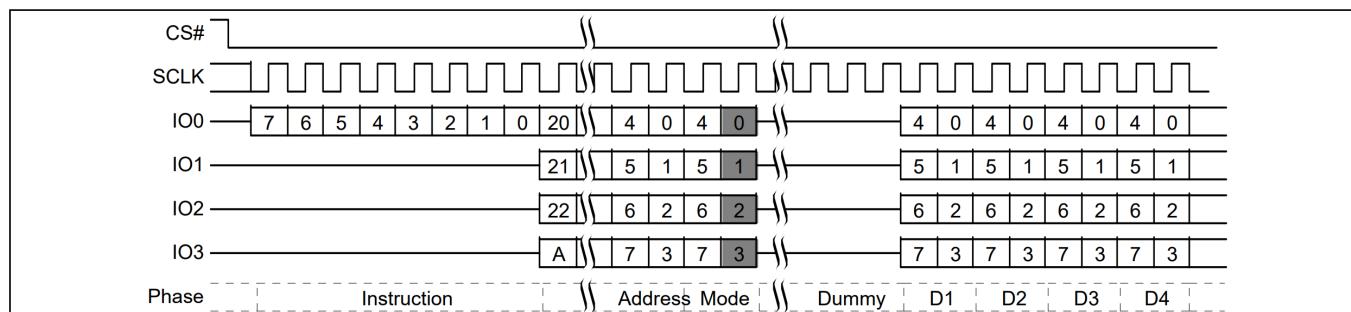

图 18 QPI 模式下的四路 I/O 读取命令<sup>[6]</sup>

### 注释：

6. 灰色位是可选的，在该周期中主机无需发送这些位。

## 信号协议

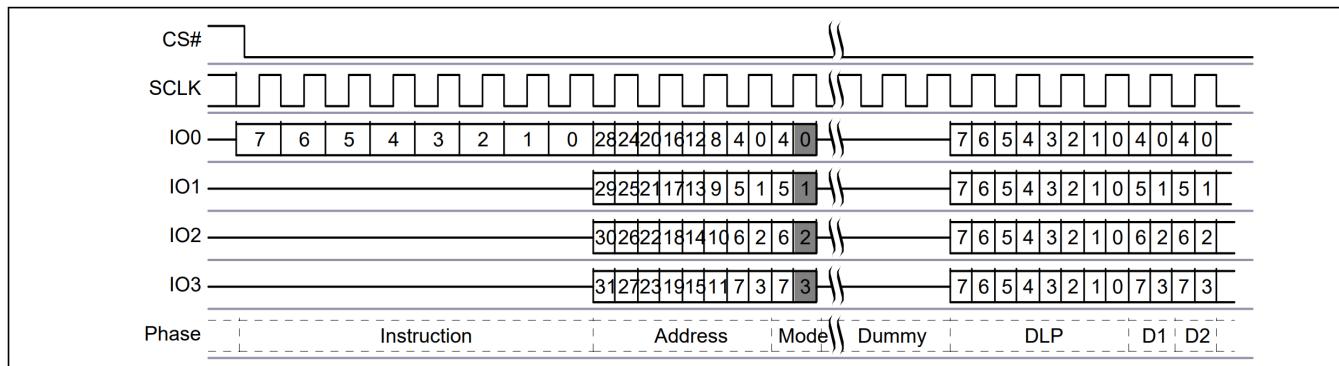

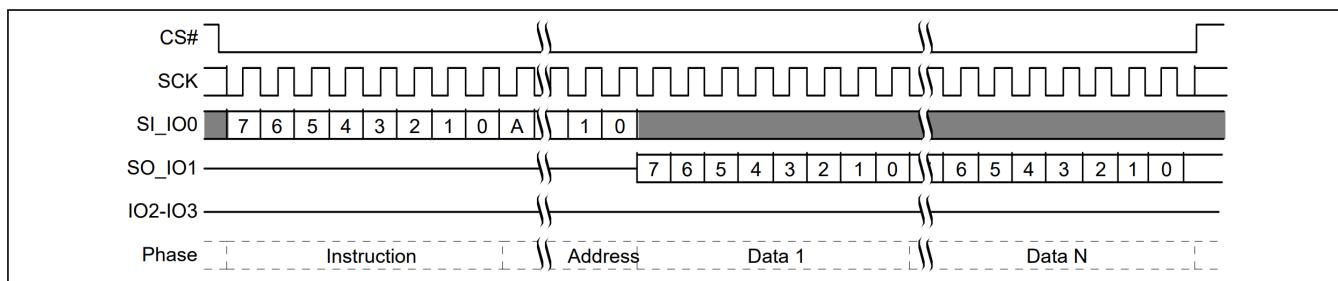

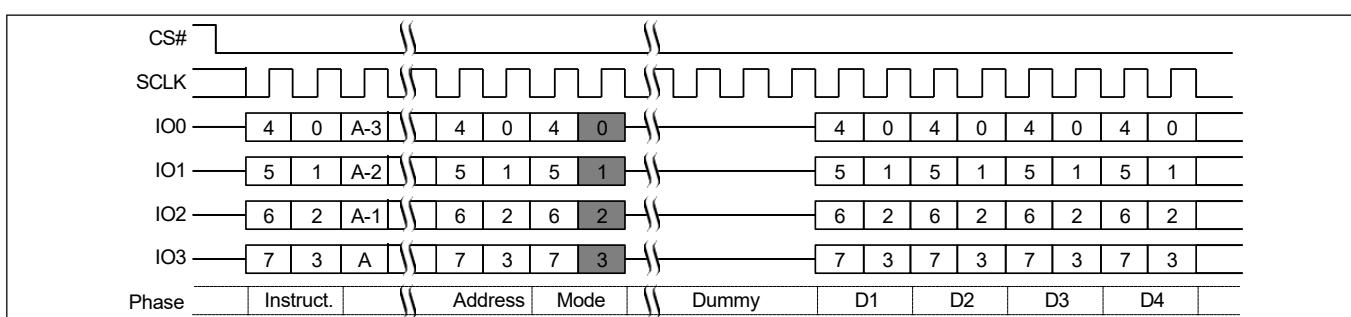

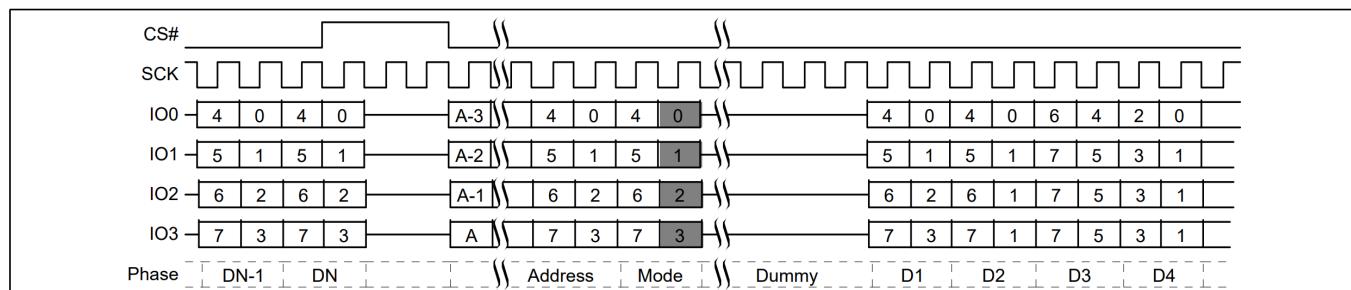

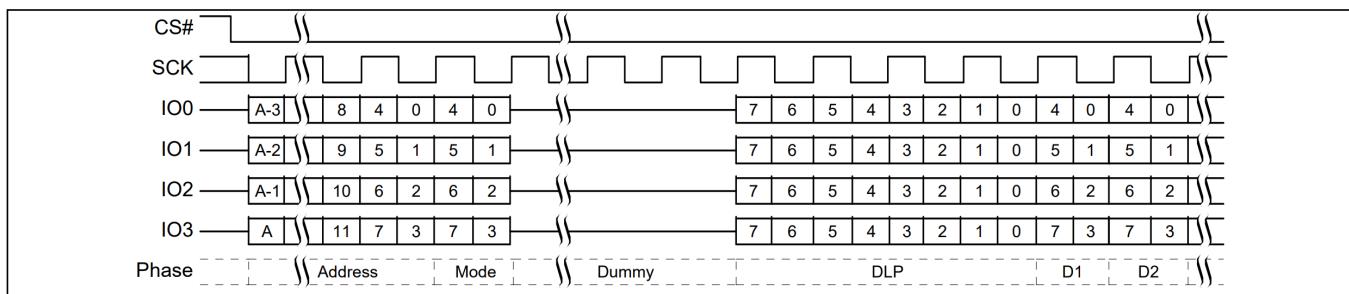

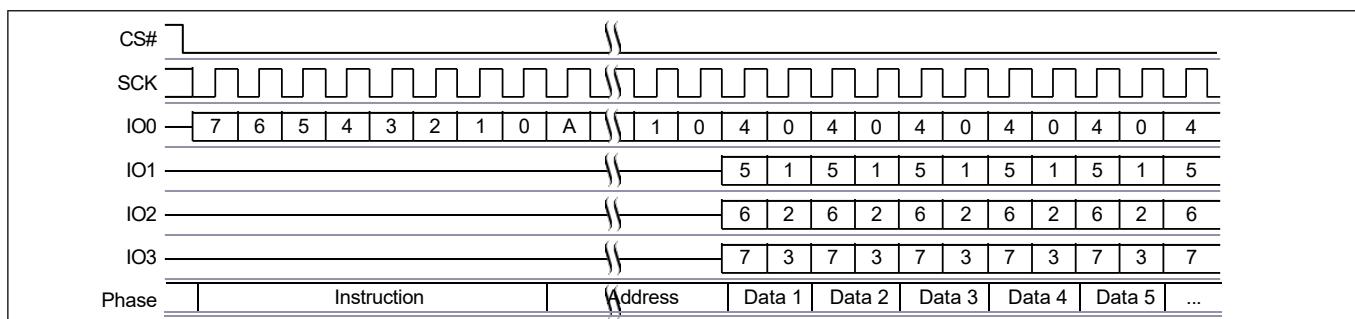

**图 19 DDR 四线I/O 读取命令<sup>[7]</sup>**

**图 20 DDR 四线I/O 读取命令 QPI 模式<sup>[7]</sup>**

“命令”在76页中提供了特定于每个指令的附加序列图。

## 注释：

7. 灰色位是可选的，在该周期中主机无需发送这些位。

信号协议

## 4.3 接口状态

本节介绍与 SPI 接口行为相关的输入和输出信号电平。

**表 6 接口状态汇总**

| Interface state                                  | V <sub>CC</sub>             | SCK | CS# | RESET# | IO3_RESET# | WP#/IO2 | SO/IO1  | SI/IO0  |

|--------------------------------------------------|-----------------------------|-----|-----|--------|------------|---------|---------|---------|

| Power-off                                        | < V <sub>CC</sub> (low)     | X   | X   | X      | X          | X       | X       | X       |

| Low power<br>Hardware data protection            | < V <sub>CC</sub> (cut-off) | X   | X   | X      | X          | X       | Z       | X       |

| Power-on (cold) reset                            | ≥ V <sub>CC</sub> (min)     | X   | HH  | X      | X          | X       | Z       | X       |

| Hardware (warm) reset non-Quad mode              | ≥ V <sub>CC</sub> (min)     | X   | X   | HL     | HL         | X       | Z       | X       |

| Hardware (warm) reset Quad mode                  | ≥ V <sub>CC</sub> (min)     | X   | HH  | HL     | HL         | X       | Z       | X       |

| Interface standby                                | ≥ V <sub>CC</sub> (min)     | X   | HH  | HH     | X          | X       | Z       | X       |

| Instruction cycle (legacy SPI)                   | ≥ V <sub>CC</sub> (min)     | HT  | HL  | HH     | HH         | HV      | Z       | HV      |

| Single input cycle<br>Host to Memory transfer    | ≥ V <sub>CC</sub> (min)     | HT  | HL  | HH     | HH         | X       | Z       | HV      |

| Single latency (dummy) cycle                     | ≥ V <sub>CC</sub> (min)     | HT  | HL  | HH     | HH         | X       | Z       | X       |

| Single output cycle<br>Memory to Host transfer   | ≥ V <sub>CC</sub> (min)     | HT  | HL  | HH     | HH         | X       | MV      | X       |

| Dual input cycle<br>Host to Memory transfer      | ≥ V <sub>CC</sub> (min)     | HT  | HL  | HH     | HH         | X       | HV      | HV      |

| Dual latency (dummy) cycle                       | ≥ V <sub>CC</sub> (min)     | HT  | HL  | HH     | HH         | X       | X       | X       |

| Dual output cycle<br>Memory to Host transfer     | ≥ V <sub>CC</sub> (min)     | HT  | HL  | HH     | HH         | X       | MV      | MV      |

| Quad input cycle<br>Host to Memory transfer      | ≥ V <sub>CC</sub> (min)     | HT  | HL  | HH     | HV         | HV      | HV      | HV      |

| Quad latency (dummy) cycle                       | ≥ V <sub>CC</sub> (min)     | HT  | HL  | HH     | X          | X       | X       | X       |

| Quad output cycle<br>Memory to Host transfer     | ≥ V <sub>CC</sub> (min)     | HT  | HL  | HH     | MV         | MV      | MV      | MV      |

| DDR quad input cycle<br>Host to Memory transfer  | ≥ V <sub>CC</sub> (min)     | HT  | HL  | HH     | HV         | HV      | HV      | HV      |

| DDR latency (dummy) cycle                        | ≥ V <sub>CC</sub> (min)     | HT  | HL  | HH     | MV or Z    | MV or Z | MV or Z | MV or Z |

| DDR quad output cycle<br>Memory to Host transfer | ≥ V <sub>CC</sub> (min)     | HT  | HL  | HH     | MV         | MV      | MV      | MV      |

### 图标：

Z = 无驱动 - 悬空信号

HL = 主控驱动 V<sub>IL</sub>

HH = 主控驱动 V<sub>IH</sub>

HV = HL 或 HH

X = HL 或 HH 或 Z

HT = HL 和 HH 之间切换

ML = 存储器驱动 V<sub>IL</sub>

MH = 存储器驱动 V<sub>IH</sub>

MV = ML 或 MH

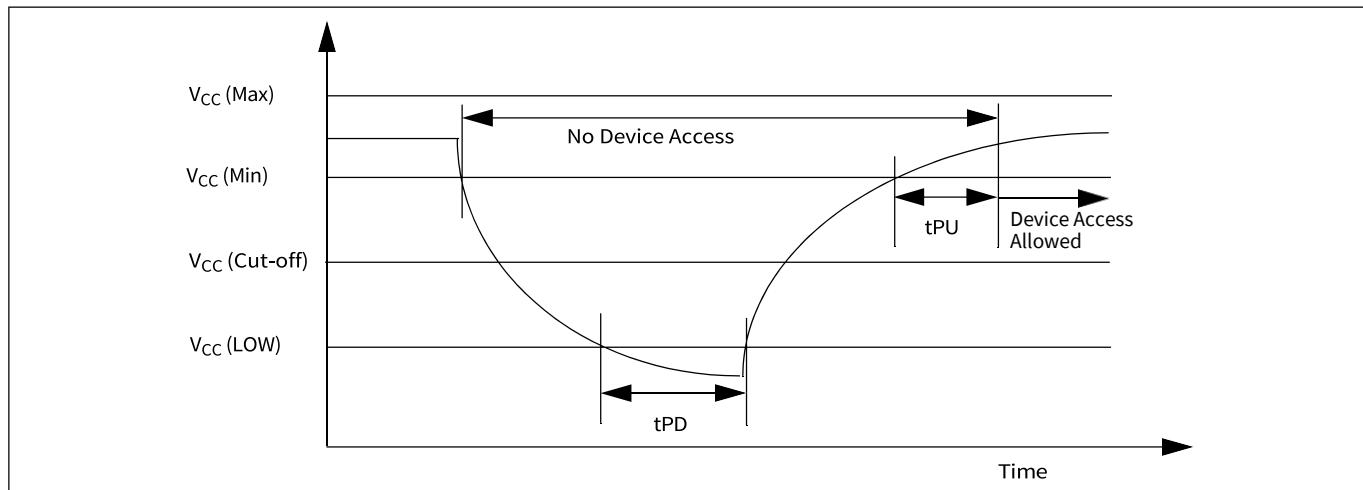

### 4.3.1 **V<sub>CC</sub> 断电**

当内核供电电压等于或低于V<sub>CC(LOW)</sub>电压时，器件被认为已断电。器件不会对外部信号做出反应，并且会被阻止执行任何编程和擦除操作。

### 4.3.2 **低压硬件数据保护**

当V<sub>CC</sub>小于V<sub>CC (Cut-off)</sub>时，存储器器件将忽略指令，以确保当内核供电电压超出工作范围时，编程和擦除操作无法启动。

### 4.3.3 **上电（冷）复位**

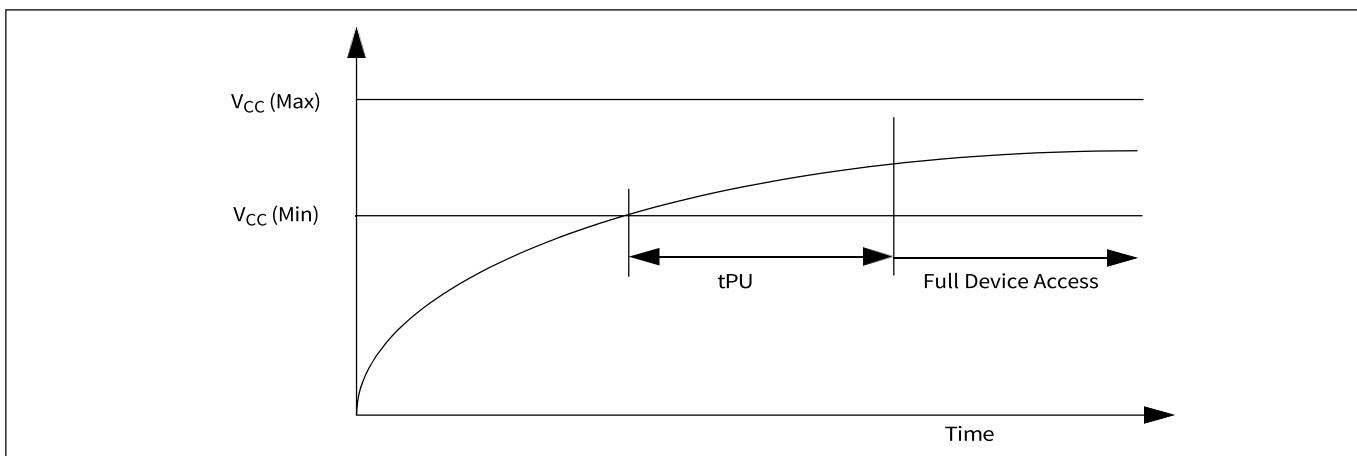

当内核电压源保持在V<sub>CC</sub> (低电平) 或以下并持续 $\geq t_{PD}$ 时间，然后上升到 $\geq V_{CC}$  (最低值) 时，器件将开始其上电复位 (POR) 过程。POR 持续到 $t_{PU}$ 结束。在 $t_{PU}$ 期间，器件对外部输入信号没有反应，也不驱动任何输出。 $t_{PU}$ 结束后，器件转换到待机状态并可以接受指令。有关POR的更多信息，请参阅“[上电复位 \(冷\) 复位](#)”(33页)

### 4.3.4 **硬件（热）复位**

当器件不处于任何四线或QPI模式或处于任何四线模式或QPI模式且CS为高电平时，提供了一个配置选项，允许IO3\_RESET#用作硬件复位输入。在某些封装上的四线或QPI模式下，提供单独的复位输入(复位#)。当IO3\_RESET#或RESET#被驱动为低电平并持续 $t_{RP}$ 时间时，器件启动硬件复位过程。该过程持续 $t_{RPH}$ 时间。在 $t_{RPH}$ 结束以及RESET#( $t_{RH}$ )上升后的复位保持时间结束后，器件将转换为接口待机状态并可接受指令。有关硬件复位的更多信息，请参阅“[RESET# 和 IO3\\_RESET# 输入启动硬件（热）复位](#)”(34页)。

### 4.3.5 **接口待机**

当CS#为高电平时，SPI接口处于待机状态。除RESET#之外的输入将被忽略。接口等待新指令的开始。当CS#变为低电平以开始新命令时，下一个接口状态是指令周期。

在接口待机状态下，如果没有嵌入式算法正在运行，存储器器件将消耗待机电流(I<sub>SB</sub>)。如果嵌入式算法正在运行，则将消耗相关电流，直到运算结束，此时整个器件恢复到待机电流消耗状态。

FS-S系列器件支持深度掉电(DPD)模式。如果器件已通过DPD(B9h)指令置于DPD模式，则接口备用电流为(I<sub>DPD</sub>)。仅当器件未执行嵌入式算法(如状态寄存器1易失性写入进行中(WIP)位清零(SR1V[0]=0)所示)时，才接受DPD指令。在DPD模式下，器件会忽略除从DPD释放(RES ABh)指令，该指令将在t<sub>RES</sub>延迟后将器件返回到接口待机状态。

### 4.3.6 **指令周期（传统 SPI 模式）**

当主控驱动指令的最高有效位(MSB)且CS变为低电平时，器件在SCK的下一个上升沿捕获开始新指令的指令的最高有效位(MSB)。在SCK的每个后续上升沿，该器件捕获8位指令的下一个较低有效位。主控保持CS低电平，并根据指令需要驱动写保护(WP#)和IO3\_RESET#/RESET#信号。但是，WP#仅在WRR或WRAR指令或任何其他影响状态寄存器、配置寄存器和DLR寄存器的指令的指令周期内才相关，否则将被忽略。当器件未处于四线模式(CR1V[1]=0)或QPI模式(CR2V[3]=0)且不需要硬件复位时，IO3\_RESET#被驱动为高电平。

每条指令选择操作的地址空间，和使用的传输格式在命令其他部分。传输格式可以是单线I/O、双线I/O、四线I/O或DDR四线I/O。预期的下一个接口状态取决于收到的指令。

有些指令是独立的，不需要与存储器进行地址或数据传输。主控在SCK上升沿后返回CS高电平，作为该指令中指令的第8位。在这种情况下，下一个接口状态是接口待机。

### 4.3.7 指令周期 (QPI 模式)

在 QPI 模式下，当 CR2V[6]=0 时，指令每个时钟周期传输 4 位。在此模式下，指令周期与四线输出周期相同。请参阅“[四线输入周期 - 主控到存储器传输](#)”(29 页)

### 4.3.8 单线输入周期-主控到存储器的传输

几条指令通过单个串行输入 (SI) 信号将信息从主控器件传送到存储器器件。主控保持RESET#为高电平，CS为低电平，并根据指令的需要驱动SI。储器不驱动串行输出(SO) 信号。

预期的下一个接口状态取决于指令。一些指令使用额外的单输入周期继续向存储器发送地址或数据。其他可能转换为单线延时，或直接转换为单线、双线或四线输出周期状态。

### 4.3.9 单线延时 (虚拟) 周期

读指令可能有零到几个延时周期，在此期间读数据在传输到主控之前从主队列读取。延迟周期数由配置寄存器 (CR3V[3:0]) 中的延迟代码决定。在延时周期内，主控保持 RESET# 和 IO3\_RESET# 高电平，CS 低电平，SCK 切换。写保护 (WP#) 信号被忽略。主控可能会在这些周期内驱动 SI 信号，或者主控可能会让 SI 处于浮动状态。在延时周期内，存储器不使用 SI 或其他 I/O 信号上驱动的任何数据。在延时周期内，存储器不会驱动串行输出 (SI) 或 I/O 信号。

下一个接口状态取决于指令结构，即延时周期数，以及读取是单线、双线还是四线。

### 4.3.10 单线输出周期-存储器到主控的传输

多个指令通过单个串行输出 (SO) 信号将信息传回主控。主控保持RESET#和IO3\_RESET#为高电平，CS为低电平。写保护 (WP#) 信号被忽略。存储器忽略串行输入 (SI) 信号。存储器用数据驱动 SO。

下一个接口状态继续为单线输出周期，直到主控将 CS 返回为高电平结束指令。

### 4.3.11 双线输入周期-主控至存储器的传输

双线读取I/O 指令在每个周期传输两位地址或模式位到存储器。主控保持RESET#和IO3\_RESET#为高电平，CS为低电平。写保护 (WP#) 信号被忽略。主机驱动地址为SI /IO0和SO/IO1。

地址和模式位传送之后的下一个接口状态是双延时周期（有延时要求）；如果不需要延时，则为双线输出周期。

### 4.3.12 双线延时 (虚拟) 周期

读指令可能有零到几个延时周期，在此期间读数据在传输到主控之前从主队列读取。延迟周期数由配置寄存器 (CR3V[3:0]) 中的延迟代码决定。在延时周期内，主控保持 RESET# 和 IO3\_RESET# 为高电平，CS 为低电平，SCK 继续切换。写保护 (WP#) 信号被忽略。主控可能会在这些周期内驱动 SI / IO0 和 SO / IO1 信号，或者主控可能会让 SI / IO0 和 SO / IO1 处于悬空状态。在延时周期内，存储器不使用 SI / IO0 和 SO / IO1 上驱动的任何数据。主机必须在最后一个延迟周期结束时的 SCK 下降沿停止驱动 SI / IO0 和 SO / IO1。建议主控在所有延时周期内停止驱动它们，以便在延时周期结束时存储器开始驱动之前，主控驱动程序有足够的关闭时间。这样可以防止信号方向改变时主控与存储器之间的驱动器冲突。在延时周期内，存储器不会驱动 SI / IO0 和 SO / IO1 信号。

最后一个延时周期之后的下一个接口状态是双线输出周期。

信号协议

#### **4.3.13 双线输出周期-储存器到主控的传输**

双线读取输出和线读取 I/O 在每个周期向主控返回两位数据。主控保持RESET#和IO3\_RESET#为高电平，CS为低电平。写保护（WP#）信号被忽略。存储器在 SCK 下降沿的双输出周期内将数据驱动到 SI/IO0 和 SO/IO1 信号上。

下一个接口状态继续为双线输出周期，直到主控将 CS 返回为高电平结束指令。

#### **4.3.14 QPP 或 QOR 地址输入周期**

四线页编程和四线输出读取指令仅在 IO0 上将地址发送到存储器。其它 IO 信号被忽略。主控保持RESET#和IO3\_RESET#为高电平，CS为低电平，驱动IO0。

对于 QPP，地址传送后的下一个接口状态是四线输入周期。对于 QOR，如果需要延时周期，则地址后的下一个接口状态为四线延时周期；如果不需要延时，则为四线输出周期。

#### **4.3.15 四线输入周期 - 主控至储存器的传输**

四线 I/O 读取命令在每个周期向存储器传输四个地址或模式位。在 QPI 模式下，四线 I/O 读取和页编程指令在每个周期（包括指令周期）向存储器传输四个数据位。主控保持CS低电平，驱动IO信号。

对于四线 I/O 读取，在传送地址位和模式位之后下一个接口状态，如果需要延时周期则为四线延时周期，如果不需要延时则为四线输出周期。对于 QPI 模式页编程命令，主控在传送要写入的数据后，返回 CS#为高电平，且接口返回待机状态。

#### **4.3.16 四线延时（虚拟）周期**

读指令可能有零到几个延时周期，在此期间读数据在传输到主控之前从主队列读取。延时周期数由配置寄存器 (CR3V[3:0]) 中的延时编码决定。在延时周期内，主控保持CS低电平并继续切换SCK。主控可能会在这些周期内驱动 IO 信号，或者主控可能会让 IO 处于浮动状态。在延时周期内，存储器不使用任何通过 IO 驱动的数据。主控必须在最后一个延时周期结束时的下降沿停止驱动 IO 信号。建议主控在所有延时周期内停止驱动它们，以便在延时周期结束时存储器开始驱动之前，主控驱动程序有足够的关闭时间。这样可以防止信号方向改变时主控与存储器之间的驱动器冲突。在延时周期内，存储器不会驱动 IO 信号。

最后一个延时周期之后的下一个接口状态是四线输出周期。

#### **4.3.17 四线输出周期 - 内存到主控的传输**

Quad-O 和 Quad I/O 读取在每个周期向主控返回四位数据。主控维持CS#低位。存储器在四线输出周期内驱动 IO0-IO3 信号上的数据。

下一个接口状态继续为四线输出循环，直到主控将 CS 返回为高电平并结束指令。

#### **4.3.18 DDR 四线输入周期 - 主控到内存传输**

DDR 四线 I/O 读取命令通过所有 IO 信号将地址和模式位发送到存储器。在每个周期中，SCK 的上升沿传输 4 位，下降沿传输 4 位。主控维持CS#低位。

传送地址位和模式位之后的下一个接口状态是 DDR 延时周期。

#### **4.3.19 DDR 延时周期**

DDR 读指令可能有一到几个延时周期，在此期间读数据在传输到主控之前从主队列中读取。延时周期数由配置寄存器 (CR2V[3:0]) 中的延时编码决定。在延时周期内，主控保持CS低电平。主控可能不会在这些周期内驱动 IO 信号。这样在存储器开始驱动之前，主控驱动器就有足够的时间关闭。这样可以防止信号方向改变时主控与存储器之间的驱动器冲突。存储器有一个选项，可以在最后 4 个延时周期内使用数据学习类型码 (DLP) 驱动所有 IO 信号。当延时周期少于 5 个时，不应启用 DLP 选项，以便在存储器开始驱动 DLP 之前至少有一个高阻态周期用于 IO 信号的转变。当延时周期超过 4 个时，存储器直到最后四个延时周期才会驱动 IO 信号。

最后一个延时周期之后的下一个接口状态是 DDR 单线输出周期或四线输出周期，取决于指令。

#### **4.3.20 DDR 四线输出周期 - 内存到主控的传输**

DDR 四线I/O 读取命令将所有 IO 信号上的位返回至主控。在每个周期中，SCK 的上升沿传输 4 位，下降沿传输 4 位。主控维持CS#低位。

下一个接口状态继续为 DDR 四线输出周期，直到主控将 CS 返回为高电平并结束指令。

## 4.4 配置寄存器对接口的影响

配置寄存器 2 易失性位 3 至 0 (CR2V[3:0]) 用于除读取指令和读取 SDFP (RSFDP) 指令之外的所有读取指令的延时。读取始终具有零延时周期。RSFDP 有 8 个延时周期。可变延时也用于 OTPR、ECCRD 和 RDAR 指令。配置寄存器位 1 (CR1V[1]) 选择是使能四线模式，以将 WP# 切换到 IO2 功能，将 RESET# 切换到 IO3 功能，从而允许四线 I/O 读取和 QPI 模式命令。DDR 四线 I/O 读取命令必须选择四线模式。DDR 四线 I/O 读取命令必须选择四线模式。

## 4.5 数据保护

一些防止对存储数据进行意外更改的基本保护完全由硬件设计提供和控制。下面将对此进行描述。其他软件管理保护方法在文档的软件部分讨论。

### 4.5.1 上电

当内核供电电压等于或低于  $V_{CC(LOW)}$  电压时，器件被认为已断电。器件不会对外部信号做出反应，并且会被阻止执行任何编程和擦除操作。

在上电复位 (POR) 期间，将继续阻止编程和擦除操作，因为直到退出 POR 到待机状态时才接受任何指令。

### 4.5.2 低功耗

当  $V_{CC}$  小于  $V_{CC(\text{Cut-off})}$  时，存储器器件将忽略指令，以确保当磁心供电电压超出工作范围时，编程和擦除操作无法启动。

### 4.5.3 时钟脉冲计数

器件在执行之前验证所有非易失的存储器和寄存器数据修改指令是否由时钟计数组成，该计数是八位传输（字节边界）的倍数。不以 8 位（字节）边界结尾的命令将被忽略，并且该命令不会设置任何错误状态。

### 4.5.4 深度掉电 (DPD)

在 DPD 模式下，该器件仅响应 DPD 恢复指令 (RES ABh)。在 DPD 模式期间，所有其他指令都会被忽略，从而保护存储器免受编程和擦除操作的影响。如果 IO3\_RESET# 功能已启用 (CR2V[5] = 1) 或 RESET# 是有效的，则 IO3\_RESET# 或 RESET# 变为低电平将启动硬件复位并从 DPD 模式释放器件。

时序规范

## 5 时序规范

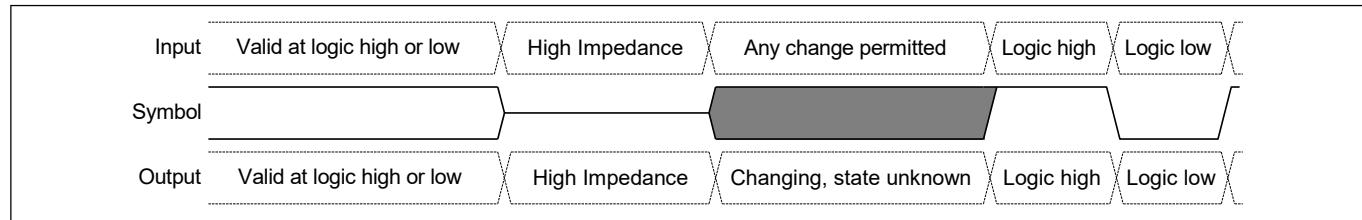

### 5.1 波形切换

图 21 波形元素含义

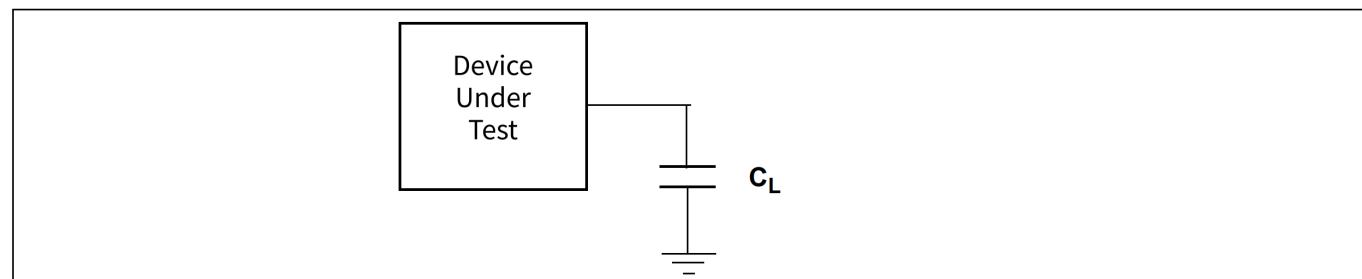

### 5.2 交流测试条件

图 22 测试设置

表 7 AC测量条件

| Symbol | Parameter                 | Min                 | Max          | Unit |   |

|--------|---------------------------|---------------------|--------------|------|---|

| $C_L$  | Load capacitance          | -                   | 30           | pF   |   |

|        | Input pulse voltage       | $0.2 \times V_{CC}$ | $0.8 V_{CC}$ | V    |   |

|        | Input slew rate           | 0.23                | 1.25         | V/ns |   |

|        | Input rise and fall times | 0.9                 | 5            | ns   |   |

|        | Input timing ref voltage  | $0.5 V_{CC}$        |              |      | V |

|        | Output timing ref voltage | $0.5 V_{CC}$        |              |      | V |

注释：

8. 输入斜率是在  $V_{CC}$  最大时从输入脉冲最小值到最大值测得的。例如： $(1.9 V \times 0.8) - (1.9 V \times 0.2) = 1.14 V$ ;

$1.14 V / 1.25 V/ns = 0.9 ns$  上升或下降时间。

9. AC特性表假设时钟和数据信号具有相同的斜率（斜率）。

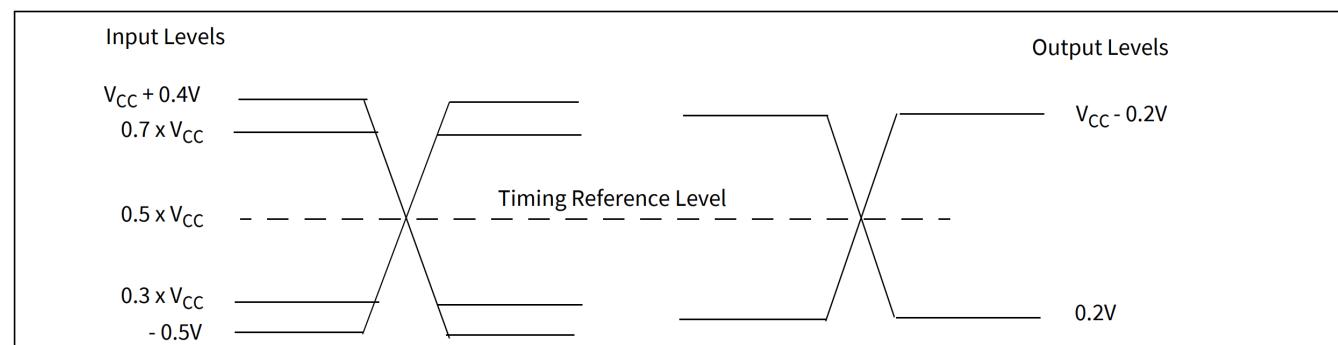

图 23 输入、输出和时序的参考标准

时序规范

## 5.2.1 电容特性

表 8 电容值

|           | Parameter                                           | Test conditions | Package  | Min | Max  | Unit |

|-----------|-----------------------------------------------------|-----------------|----------|-----|------|------|

| $C_{IN}$  | Input capacitance (applies to SCK, CS#, IO3/RESET#) | 1 MHz           | SOIC     | —   | 12.5 | pF   |

|           |                                                     |                 | LGA, BGA | —   | 8    |      |

| $C_{OUT}$ | Output capacitance (applies to All I/O)             | 1 MHz           | SOIC     | —   | 12   | pF   |

|           |                                                     |                 | LGA, BGA | —   | 8    |      |

## 5.3 RESET(复位)

### 5.3.1 上电(冷)复位(POR)

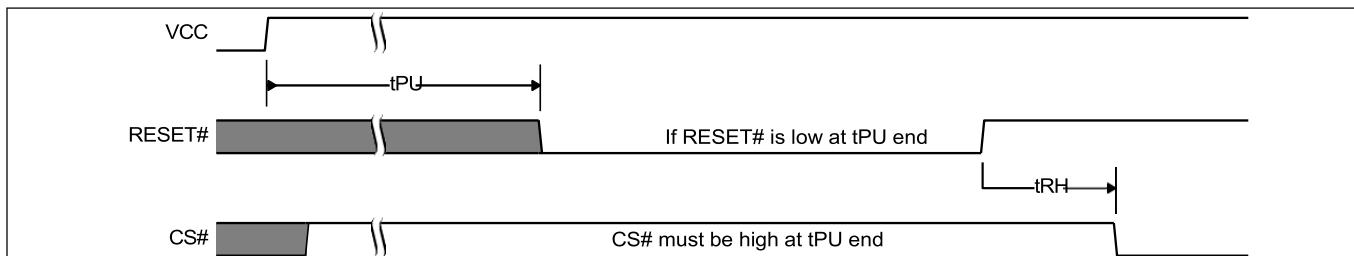

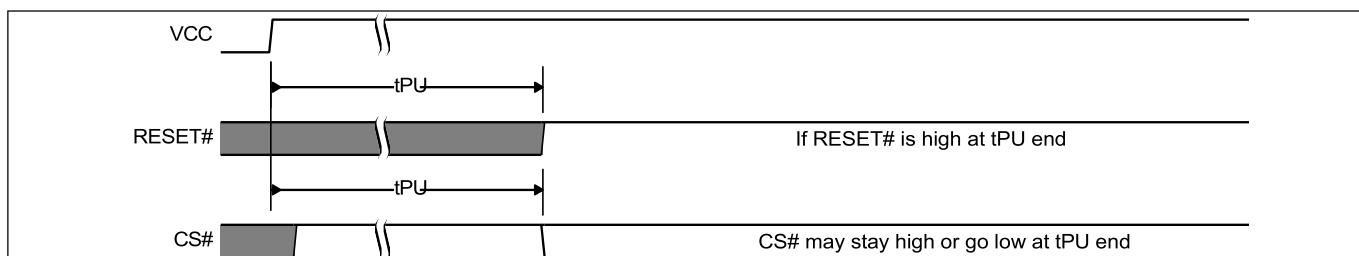

该器件执行上电复位(POR)过程，直到 $V_{CC}$ 上升到 $V_{CC}$ 最小阈值以上后，参见图 122，表 58。上电期间( $t_{PU}$ )不得选择该器件(CS#随 $V_{CC}$ 变为高电平)，即在 $t_{PU}$ 结束之前不得向该器件发送指令。

RESET#和IO3\_RESET#在POR期间会被忽略，但必须处于高电平或低电平。如果RESET#或IO3\_RESET#在POR期间为低电平，并在 $t_{PU}$ 时间结束后保持低电平，则CS必须在RESET#和IO3\_RESET#返回高电平后保持高电平直至 $t_{RH}$ 时间。RESET#和IO3\_RESET#必须返回高电平并持续超过 $t_{RS}$ 时间，然后才能返回低电平以启动硬件复位。

IO3\_RESET#输入仅在四线或QPI模式未启用(CR1V[1]=0或CR2V[6]=0)且CS处于高电平的时间超过 $t_{CS}$ 时间时用作RESET#信号。

图 24 POR 结束时复位低电平

图 25 POR 结束时复位高电平

图 26 POR 跟随硬件复位

## 时序规范

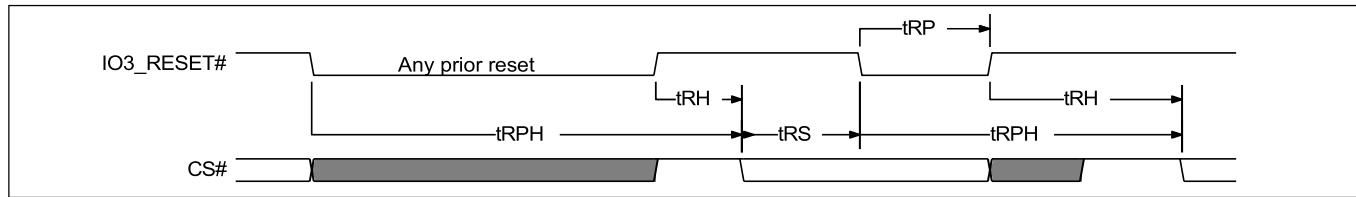

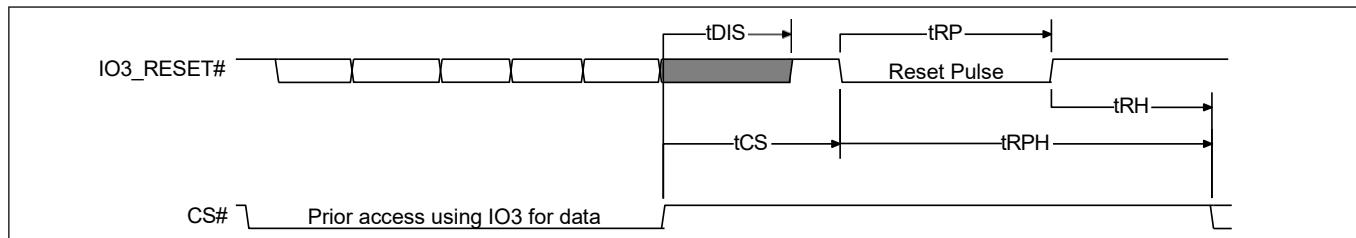

### 5.3.2 RESET# 和 IO3\_RESET# 输入启动硬件（热）复位

RESET# 和 IO3\_RESET# 输入可以作为 RESET# 信号。两种输入均可根据条件启动复位操作。

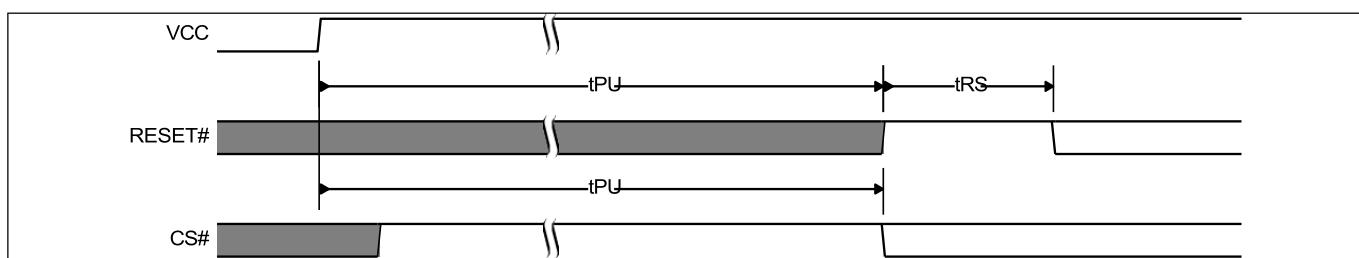

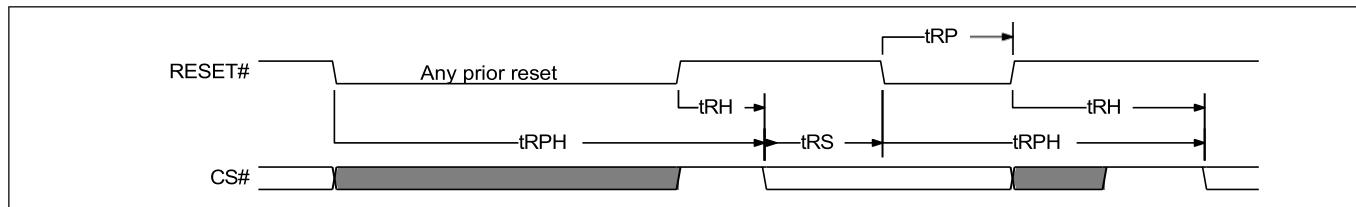

当  $V_{IH}$  到  $V_{IL}$  的转换持续时间大于  $t_{RP}$  时，RESET# 输入将启动复位操作。器件将以与上电复位相同的方式复位寄存器状态，但不会经历 POR 期间执行的完整复位过程。硬件复位过程需要  $t_{RPH}$  的时间才能完成。RESET# 输入仅适用于 BGA 球形封装。

当 CS 保持高电平时间超过  $t_{CS}$  时间，或者四线或 QPI 模式未启用时，IO3\_RESET# 输入将在以下情况下启动复位操作：CR1V[1] = 0 或 CR2V[6] = 0。IO3\_RESET# 输入内部上拉至  $V_{CC}$ ，如果不使用四线或 QPI 模式，则可以悬空。CS# 变为高电平后的  $t_{CS}$  延迟为闪存或主控系统提供时间，以便在 CS# 为低电平期间，将 IO3 用作四线或 QPI 模式 I/O 信号后将其驱动为高电平。内部上拉至  $V_{CC}$  将保持 IO3\_RESET# 为高电平，直到主控系统开始驱动 IO3\_RESET#。在 CS 保持高电平  $t_{CS}$  期间，IO3\_RESET# 输入将被忽略，以避免意外的复位操作。如果将 CS# 驱动为低电平以启动新指令，则 IO3\_RESET# 将用作 IO3。

当器件未处于四线或 QPI 模式时，或者当 CS# 为高电平时，IO3\_RESET# 从  $V_{IH}$  转换为  $V_{IL} > t_{RP}$ ，在  $t_{CS}$  之后，器件将以与上电复位相同的方式复位寄存器状态，但不会经历 POR 期间执行的完整复位过程。

硬件复位过程需要  $t_{RPH}$  时间才能完成。如果 POR 过程在上电期间 ( $t_{PU}$ ) 因任何原因未能正确完成，则 RESET# 变为低电平将启动完整的 POR 过程，而不是硬件复位过程，并且需要  $t_{PU}$  时间才能完成 POR 过程。软件复位指令 (RSTEN 66h 后跟 RST 99h) 与 RESET# 和 IO3\_RESET# 的状态无关。如果 RESET# 和 IO3\_RESET# 为高电平或未连接，并且发出软件复位指令，则器件将执行软件复位。

IO3\_RESET# 的注意事项：

- 如果 RESET# 和 IO3\_RESET# 输入选项均可用，则系统中仅使用一个复位选项。通过设置 CR2NV[7] = 0 (参见表 26) 将 IO3\_RESET# 设置为只能作为 IO3 操作，IO3\_RESET# 输入复位操作可以禁止使能。如果未将 RESET# 输入连接或绑定到  $V_{IH}$ ，则 RESET# 输入可能无法使用。

- RESET# 或 IO3\_RESET# 必须在  $t_{PU}$  或  $t_{RPH}$  之后的  $t_{RS}$  内保持高电平，然后再次变为低电平以启动硬件复位。

- 当 IO3\_RESET# 被驱动为低电平至少一段最短时间 ( $t_{RP}$ ) 后，在  $t_{CS}$  后，器件将终止任何正在进行的操作，使所有输出处于高阻状态，并在  $t_{RPH}$  持续时间内忽略所有读/写指令。器件将接口重置为待机状态。

- 如果四线或 QPI 模式以及 IO3\_RESET# 是启用的，则主控系统不应在  $t_{CS}$  期间驱动 IO3 低电平，以避免 IO3 上的驱动器争用。紧接着以四线或 QPI 模式将数据传输到主控的指令 (例如四线 I/O 读取) 后，存储器会在  $t_{CS}$  期间将 IO3\_RESET# 驱动为高电平，以避免意外的复位操作。紧接着以四线模式将数据传输到存储器的指令 (例如页编程) 后，主控系统应在  $t_{CS}$  期间将 IO3\_RESET# 驱动为高电平，以避免意外的复位操作。

- 如果四线模式未启用，并且在 IO3\_RESET# 置为低电平时 CS# 为低电平，则 CS# 必须在  $t_{RPH}$  期间返回高电平，然后才能在  $t_{RH}$  之后再次置为低电平。

**表 9 硬件复位参数**

| Parameter | Description                                                     | Limit | Time | Unit    |

|-----------|-----------------------------------------------------------------|-------|------|---------|

| $t_{RS}$  | Reset setup - Prior reset end and RESET# HIGH before RESET# LOW | Min   | 50   | ns      |

| $t_{RPH}$ | Reset pulse hold - RESET# LOW to CS# LOW                        | Min   | 35   | $\mu$ s |

注释：

- 上电 ( $t_{PU}$ ) 期间，RESET# 和 IO3\_RESET# 低电平将被忽略。如果 Reset# 在  $t_{PU}$  结束时被置为低电平，则器件将保持复位状态， $t_{RH}$  将决定 CS# 何时变为低电平。

- 如果四线模式启用，则  $t_{CS}$  期间忽略 IO3\_RESET# 低电平。

- $t_{RP}$  和  $t_{RH}$  的总和不能小于  $t_{RPH}$ 。

## 时序规范

**表 9 硬件复位参数 (续)**

| Parameter | Description                             | Limit | Time | Unit |

|-----------|-----------------------------------------|-------|------|------|

| $t_{RP}$  | RESET# Pulse width                      | Min   | 200  | ns   |

| $t_{RH}$  | Reset hold - RESET# HIGH before CS# LOW | Min   | 50   | ns   |

### 注释:

10. 上电 ( $t_{PU}$ ) 期间, RESET# 和 IO3\_RESET# 低电平将被忽略。如果 Reset# 在  $t_{PU}$  结束时被置为低电平, 则器件将保持复位状态,  $t_{RH}$  将决定 CS# 何时变为低电平。

11. 如果四线模式启用, 则  $t_{CS}$  期间忽略 IO3\_RESET# 低电平。

12.  $t_{RP}$  和  $t_{RH}$  的总和不能小于  $t_{RPH}$ 。

**图 27 使用 RESET# 输入进行硬件复位**

**图 28 当四线或 QPI 模式未启用且 IO3\_RESET# 启用时的硬件复位**

**图 29 当四线或 QPI 模式和 IO3\_RESET# 启用时的硬件复位**

时序规范

## 5.4 SDR AC 特性

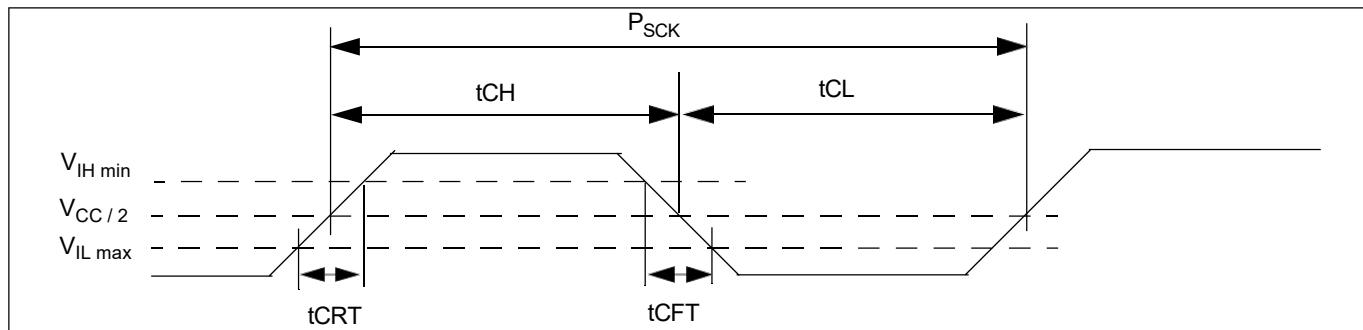

**表 10 SDR AC 特性**

| Symbol              | Parameter                                                                                                                                                              | Min                            | Max                                                               | Unit |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|-------------------------------------------------------------------|------|

| $F_{SCK, R}$        | SCK clock frequency for READ and 4READ instructions                                                                                                                    | DC                             | 50                                                                | MHz  |

| $F_{SCK, C}$        | SCK clock frequency for the following dual and quad commands: DOR, 4DOR, DIOR, 4DIOR, QOR, 4QOR, QIOR, 4QIOR                                                           | DC                             | 133                                                               | MHz  |

| $P_{SCK}$           | SCK clock period                                                                                                                                                       | $1/F_{SCK}$                    |                                                                   |      |

| $t_{WH}, t_{CH}$    | Clock HIGH time                                                                                                                                                        | $50\% P_{SCK} - 5\%$           | $50\% P_{SCK} + 5\%$                                              | ns   |

| $t_{WL}, t_{CL}$    | Clock LOW time                                                                                                                                                         | $50\% P_{SCK} - 5\%$           | $50\% P_{SCK} + 5\%$                                              | ns   |

| $t_{CRT}, t_{CLCH}$ | Clock rise time (slew rate)                                                                                                                                            | 0.1                            | -                                                                 | V/ns |

| $t_{CFT}, t_{CHCL}$ | Clock fall time (slew rate)                                                                                                                                            | 0.1                            | -                                                                 | V/ns |

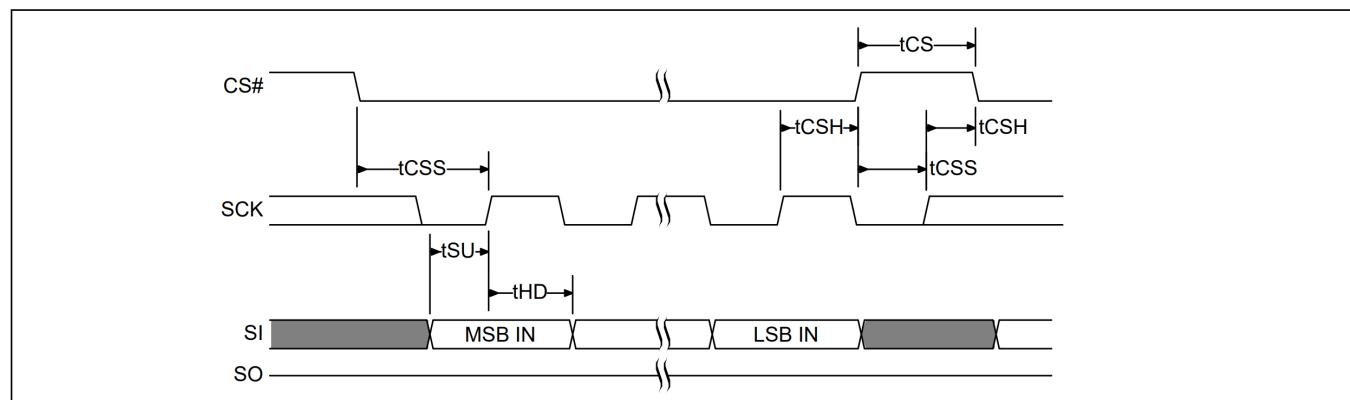

| $t_{CS}$            | CS# HIGH time (read instructions)<br>CS# HIGH time (read instructions when reset feature and quad mode are both enabled)<br>CS# HIGH time (program/erase instructions) | 10<br>20 <sup>[17]</sup><br>50 | -                                                                 | ns   |

| $t_{CSS}$           | CS# active setup time (relative to SCK)                                                                                                                                | 2                              | -                                                                 | ns   |

| $t_{CSH}$           | CS# active hold time (relative to SCK)                                                                                                                                 | 3                              | -                                                                 | ns   |

| $t_{SU}$            | Data in setup time                                                                                                                                                     | 2                              | -                                                                 | ns   |

| $t_{HD}$            | Data in hold time                                                                                                                                                      | 3                              | -                                                                 | ns   |

| $t_V$               | Clock LOW to output valid                                                                                                                                              |                                | 8 <sup>[14]</sup><br>6 <sup>[15]</sup><br>6.5 <sup>[15, 18]</sup> | ns   |

| $t_{HO}$            | Output hold time                                                                                                                                                       | 1                              | -                                                                 | ns   |

| $t_{DIS}$           | Output disable time <sup>[16]</sup><br>Output disable time (when reset feature and quad mode are both enabled)                                                         | -                              | 8<br>20 <sup>[17]</sup>                                           | ns   |

| $t_{WPS}$           | WP# setup time <sup>[13]</sup>                                                                                                                                         | 20                             | -                                                                 | ns   |

| $t_{WPH}$           | WP# hold time <sup>[13]</sup>                                                                                                                                          | 100                            | -                                                                 | ns   |

| $t_{DPD}$           | CS# HIGH to power-down mode                                                                                                                                            | -                              | 3                                                                 | μs   |

| $t_{RES}$           | CS# HIGH to standby mode without electronic signature read                                                                                                             | -                              | 30                                                                | μs   |

**注释：**

13. 仅适用于当 SRWD 置位为 1 时对 WRR 或 WRAR 指令的约束。

14. 完整  $V_{CC}$  范围和  $CL = 30 \text{ pF}$ 。

15. 完整  $V_{CC}$  范围和  $CL = 15 \text{ pF}$ 。

16. 输出 HI-Z 定义为数据不再驱动的点。

17. 当复位特性和四线模式启用时 (CR2V[5] = 1 且 CR1V[1] = 1) ,  $t_{CS}$  和  $t_{DIS}$  需要额外的时间。

18. SOIC 封装。

时序规范

## 5.4.1 时钟时序

图 30 时钟时序

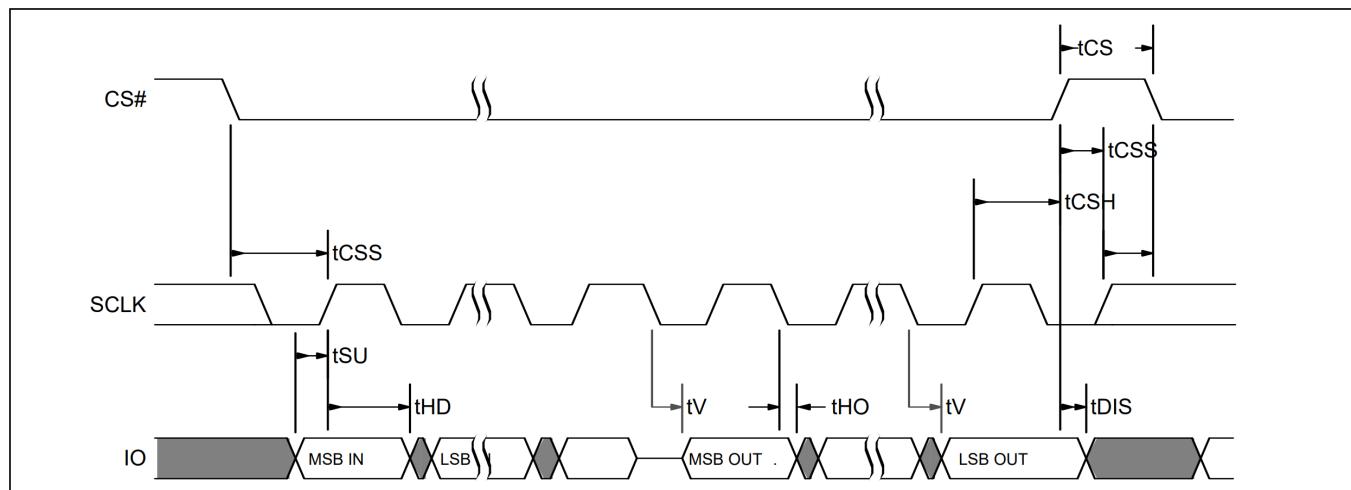

## 5.4.2 输入/输出时序

图 31 SPI单线的一个输入操作

图 32 SPI单线的一个输出操作

## 时序规范

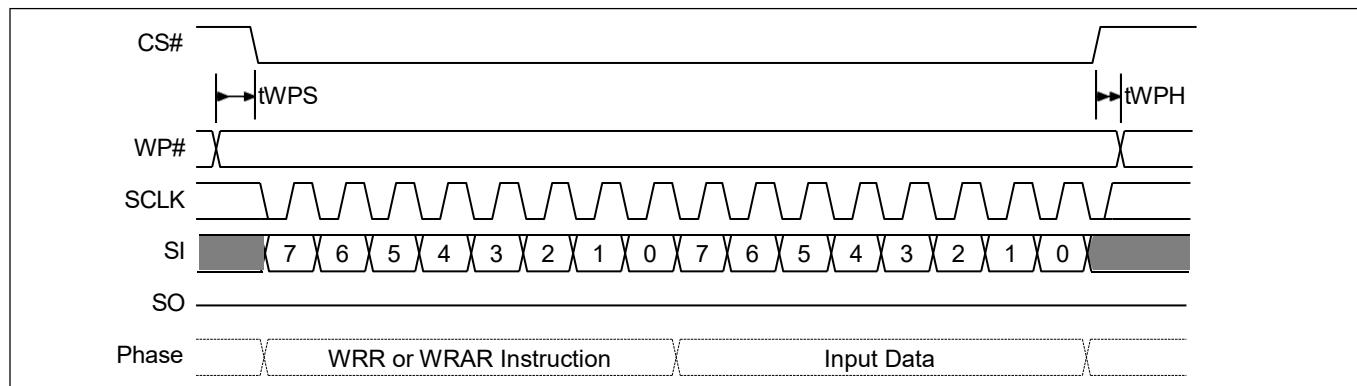

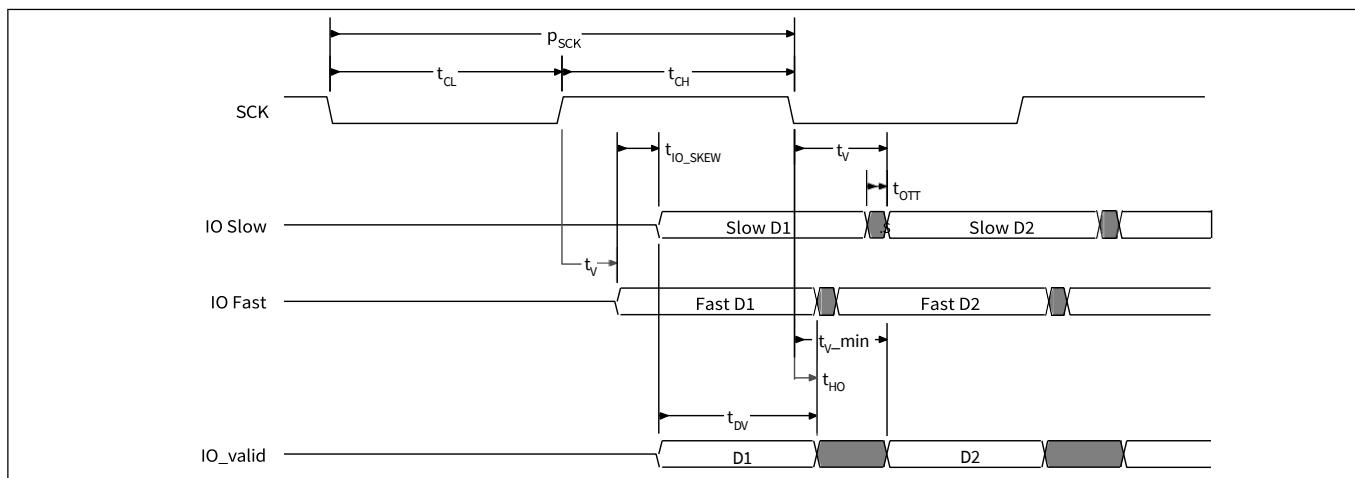

图 33 SDR MIO时序

图 34 WP#输入时序

时序规范

## 5.5 DDR AC 特性

表 11 DDR AC 特性

| Symbol           | Parameter                                                                                            | Min           | Max                                            | Unit |

|------------------|------------------------------------------------------------------------------------------------------|---------------|------------------------------------------------|------|

| $F_{SCK, R}$     | SCK clock frequency for DDR READ instruction                                                         | DC            | 80                                             | MHz  |

| $P_{SCK, R}$     | SCK clock period for DDR READ instruction                                                            | $1/F_{SCK}$   | -                                              | ns   |

| $t_{WH}, t_{CH}$ | Clock HIGH time                                                                                      | 45% $P_{SCK}$ | -                                              | ns   |

| $t_{WL}, t_{CL}$ | Clock LOW time                                                                                       | 45% $P_{SCK}$ | -                                              | ns   |

| $t_{CS}$         | CS# HIGH time (Read instructions)<br>CS# HIGH time (Read instructions when reset feature is enabled) | 10<br>20      | -                                              | ns   |

| $t_{CSS}$        | CS# active setup time (Relative to SCK)                                                              | 2             | -                                              | ns   |

| $t_{CSH}$        | CS# active hold time (Relative to SCK)                                                               | 3             | -                                              | ns   |

| $t_{SU}$         | IO in setup time                                                                                     | 1.5           | -                                              | ns   |

| $t_{HD}$         | IO in hold time                                                                                      | 1.5           | -                                              | ns   |

| $t_V$            | Clock LOW to output valid                                                                            | 1.5           | 6.0 <sup>[19]</sup><br>6.5 <sup>[19, 21]</sup> | ns   |

| $t_{HO}$         | Output hold time                                                                                     | 1.5           | -                                              | ns   |

| $t_{DIS}$        | Output disable time<br>Output disable time (when reset feature is enabled)                           | -             | 8<br>20                                        | ns   |

| $t_{IO\_skew}$   | First IO to last IO data valid time <sup>[20]</sup>                                                  | -             | 600<br>700 <sup>[21]</sup>                     | ps   |

| $t_{DPD}$        | CS# HIGH to power-down mode                                                                          | -             | 3                                              | μs   |

| $t_{RES}$        | CS# HIGH to standby mode without electronic signature read                                           | -             | 30                                             | μs   |

注释：

19. CL = 15 pF。

20. 未经测试。

21. SOIC封装。

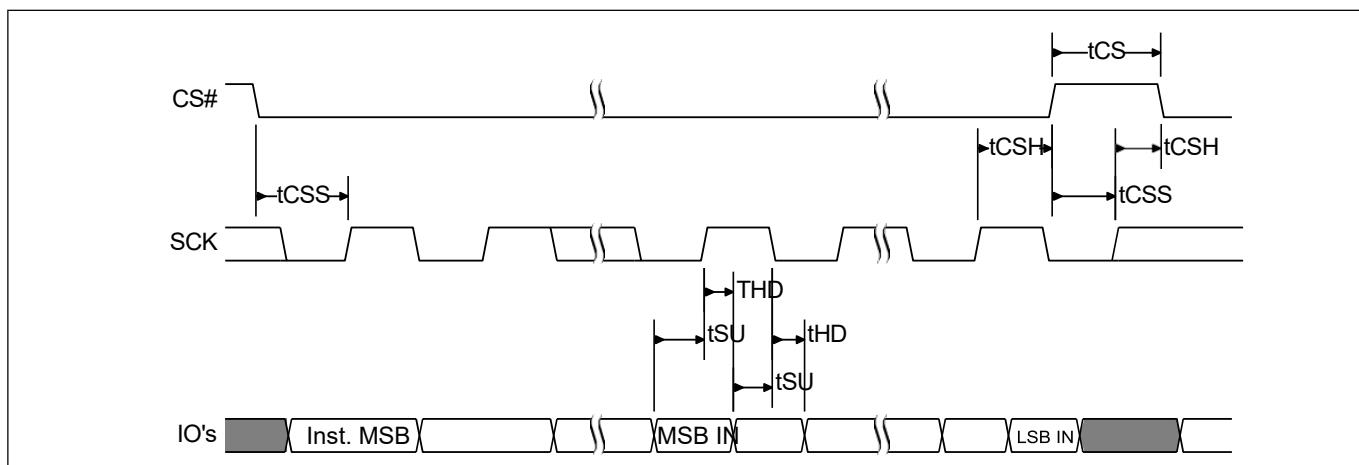

### 5.5.1 DDR 输入时序

图 35 SPI DDR输入时序

时序规范

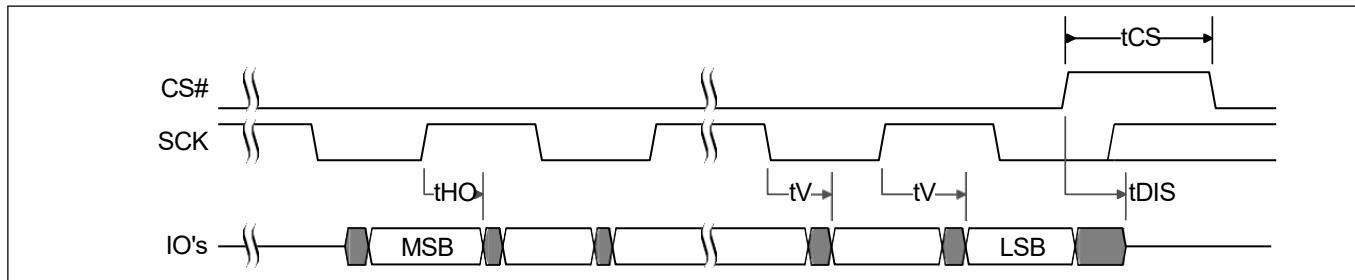

### 5.5.2 DDR 输出时序

图 36 SPI DDR 输出时序

### 5.5.3 使用 DLP 的 DDR 数据有效时序

图 37 SPI DDR 数据有效窗口

最小数据有效窗口 ( $t_{DV}$ ) 和  $t_V$  最小值可按如下方式计算：

$$t_{DV}^{[25]} = \text{Minimum half clock cycle time } (t_{CLH})^{[22]} - t_{OTT}^{[24]} - t_{IO\_SKEW}^{[23]}$$

$$t_{V\_min} = t_{HO} + t_{IO\_SKEW} + t_{OTT}$$

**注释：**

22.  $t_{CLH}$  是  $t_{CL}$  或  $t_{CH}$  中较短的持续时间。

23.  $t_{IO\_SKEW}$  是所有 IO 信号的最小  $t_V$  (输出有效) 与最大  $t_V$  (输出有效) 之间的最大差异 (增量)。

24.  $t_{OTT}$  是每个 IO 上从一个有效数据值到下一个有效数据值的最大输出转换时间。 $t_{OTT}$  取决于系统电平考虑因素，包括：

- a. 存储器器件的输出阻抗 (驱动强度)。

- b. IO 上的系统级寄生效应 (主要是总线容值)。

c. 主控存储控制器输入  $V_{IH}$  和  $V_{IL}$  电平，在该电平下可以识别 0 到 1 和 1 到 0 的转换。

d.  $t_{OTT}$  不是经过英飞凌测试的规格，它依赖于系统，必须由系统设计人员根据上述考虑来推导。

25.  $t_{DV}$  是数据有效窗口。

## 时序规范

### 示例：

80 MHz 时钟频率 = 12.5 ns 时钟周期，DDR 操作和 45% 或更高的占空比

$$t_{CLH} = 0.45 \times PSCK = 0.45 \times 12.5 \text{ ns} = 5.625 \text{ ns}$$

总线阻抗为 45 ohm，电容值为 22 pf，湿度基准为 0.75V<sub>CC</sub>时，从 0 到 1 的上升时间或从 1 到 0 的下降时间为 1.4<sup>[27]</sup> x 阻容时间 (Tau) <sup>[26]</sup> = 1.4 x 0.99 ns = 1.39 ns

$$t_{OTT} = \text{上升时间} + \text{下降时间} = 1.39 \text{ ns} + 1.39 \text{ ns} = 2.78 \text{ ns}.$$

数据有效窗口

$$t_{DV} = t_{CLH} - t_{IO\_SKEW} - t_{OTT} = 5.625 \text{ ns} - 400 \text{ ps} - 2.78 \text{ ns} = 2.45 \text{ ns}$$

t<sub>V</sub> 最小值

$$t_{V\_min} = t_{HO} + t_{IO\_SKEW} + t_{OTT} = 1.0 \text{ ns} + 400 \text{ ps} + 2.78 \text{ ns} = 4.38 \text{ ns}$$

### 注释：

26.Tau = R (输出阻抗) x C (负载电容值)。

27.电压上升至 V<sub>CC</sub>的 75% 的 Tau 时间乘数。

## 地址空间映射

# 6 地址空间映射

## 6.1 概述

### 6.1.1 扩展地址

FS-S 系列支持 32 位 (4 字节) 地址，可实现比仅支持 24 位 (3 字节) 地址的上一代（传统） SPI 设备更高容量的设备。24 位字节分辨率地址只能访问 16 MB (128 Mb) 最大容量。32 位字节分辨率地址允许直接寻址高达 4 GB (32 Gb) 的地址空间，并允许软件兼容从 4 MB (32 Mb) 到 4 GB (32 Gb) 的器件。

为了向后兼容软件，旧指令继续支持 24 位地址。扩展 32 位地址有两种实现方式：

- 扩展地址模式 – 通过主控系统对易失性配置寄存器位操作，可将所有旧指令更改为 32 位地址。

- 4 字节地址指令 – 执行旧功能和新功能，总是需要 32 位地址。

扩展地址模式的默认条件，在上电或复位后，由非易失性配置位控制。默认的扩展地址模式可能是 24 位或 32 位地址的置位。这使得传统软件能够兼容器件的前 128 Mb 访问，或者使器件能够直接以 32 位地址模式启动。

FS-S 系列的 64Mb 容量成员以相同的方式支持扩展地址功能，但实质上忽略任何地址的位 31 至 23 或 22，因为闪存阵列仅需要 23 位或 22 位地址。这使得从 64Mb 密度到更高容量设备的简单迁移成为可能，而无需改变软件的地址处理方面。

### 6.1.2 多个地址空间

许多指令操作都在主线上。地址空间上的一些指令操作与主存储器阵列分开。每个单独的地址空间使用完整的 24 位或 32 位地址，但可能仅定义可用地址空间的一小部分。

## 6.2 闪存存储器阵列

主要的闪存存储器阵列被分为以物理扇区为擦除单位。

FS-S 系列物理扇区可以配置为地址空间顶部或底部的八个 4 KB 参数扇区的混合组合，其余扇区中除一个之外的所有扇区大小统一。由于八个 4 KB 参数扇区组总体上小于统一扇区，因此该组 4 KB 物理扇区分别覆盖（替换）最高或最低地址统一扇区的顶部或底部 32 KB。

参数扇区擦除指令 (20h 或 21h) 必须用于单独擦除 4 KB 扇区。扇区（统一功能块）擦除指令 (D8h 或 DCh) 必须用于擦除任何剩余的扇区，包括未被参数扇区覆盖的最高或最低地址扇区的部分。统一的功能块擦除指令对扇区参数没有影响。

配置寄存器 1 非易失性位 2 (CR1NV[2]) 等于 0 覆盖最低地址统一扇区底部的参数扇区。CR1NV[2] = 1 将参数扇区覆盖在最高地址统一扇区的顶部。参见 [寄存器](#) 了解更多信息。

还有一个配置选项可以从地址映射中删除 4 KB 参数扇区，以便所有扇区的大小都统一。配置寄存器 3 易失性位 3 (CR3V[3]) 等于 0 表示选择具有 4 KB 参数扇区的混合扇区架构。CR3V[3] = 1 选择没有参数扇区的统一扇区架构。统一的物理扇区是：

- 64 KB 或 256 KB

设备还可以配置为使用扇区（统一功能块）指令来擦除 256 KB 逻辑块，而不是单独的 64 KB 物理扇区。此配置选项 (CR3V[1] = 1) 允许低容量设备模拟与使用 256 KB 物理内存的系列中高容量产品相同的扇区擦除行为。这可以简化向家族中更高容量成员的软件迁移。

## 地址空间映射

**表 12 S25FS064S 扇区和内存地址映射, 底部 4 KB 扇区**

| <b>Sector size (KB)</b> | <b>Sector count</b> | <b>Sector range</b> | <b>Address range<br/>(Byte address)</b> | <b>Notes</b>                                                   |

|-------------------------|---------------------|---------------------|-----------------------------------------|----------------------------------------------------------------|

| 4                       | 8                   | SA00                | 0000000h–<br>0000FFFFh                  | Sector starting<br>address<br>—<br>Sector<br>ending<br>address |

|                         |                     | :                   | :                                       |                                                                |

|                         |                     | SA07                | 00007000h–<br>00007FFFFh                |                                                                |

| 32                      | 1                   | SA08                | 00008000h–<br>0000FFFFh                 |                                                                |

| 64                      | 127                 | SA09                | 00010000h–<br>0001FFFFh                 |                                                                |

|                         |                     | :                   | :                                       |                                                                |

|                         |                     | SA135               | 007F0000h–<br>007FFFFFFh                |                                                                |

**表 13 S25FS064S 扇区和内存地址映射, 顶部 4 KB 扇区**

| <b>Sector size (KB)</b> | <b>Sector count</b> | <b>Sector range</b> | <b>Address range<br/>(Byte address)</b> | <b>Notes</b>                                        |

|-------------------------|---------------------|---------------------|-----------------------------------------|-----------------------------------------------------|

| 64                      | 127                 | SA00                | 0000000h–000FFFFh                       | Sector<br>starting<br>—<br>Sector ending<br>address |

|                         |                     | :                   | :                                       |                                                     |

|                         |                     | SA126               | 007E0000h–<br>007EFFFFh                 |                                                     |

| 32                      | 1                   | SA127               | 007F0000h–<br>007F7FFFh                 |                                                     |

| 4                       | 8                   | SA128               | 007F8000h–<br>007F8FFFh                 |                                                     |

|                         |                     | :                   | :                                       |                                                     |

|                         |                     | SA135               | 007FF0000h–<br>007FFFFFFh               |                                                     |

**表 14 S25FS064S 扇区和内存地址映射, 统一的 64 KB 块**

| <b>Sector size (KB)</b> | <b>Sector count</b> | <b>Sector range</b> | <b>Address range<br/>(Byte address)</b> | <b>Notes</b>                                                   |

|-------------------------|---------------------|---------------------|-----------------------------------------|----------------------------------------------------------------|

| 64                      | 128                 | SA00                | 0000000h–<br>0000FFFFh                  | Sector starting<br>address<br>—<br>Sector<br>ending<br>address |