# 128 Mb (16 MB) / 256 Mb (32 MB) FL-L 闪存

SPI multi-I/O, 3.0 V

## 概述

FL-L 器件系列是非易失性闪存存储器产品，它们采用了以下技术：

- 浮栅技术

- 65nm 光刻技术

FL-L 系列产品通过串行外设接口 (SPI) 连接主机系统。该产品支持传统 SPI 的一比特串行输入和输出 (即单线 I/O 或 SIO)、可选的两比特 (即双线 I/O 或 DIO)、四比特宽 (四线 I/O 或 QIO) 以及四线外设接口 (QPI) 命令。另外，它还为 QIO 和 QPI 提供了双倍数据速率 (DDR) 命令支持，在时钟的双边沿上传送地址和读取数据。

该产品具有页编程缓冲区，允许在一次操作中最多编程 256 个字节，并提供单独的 4 KB 大小的扇区、32 KB 半块、64 KB 块或整个芯片擦除功能。

FL-L 系列器件支持更高的时钟频率和四线命令，因此指令读取的传输率能够等于或超过传统的并行接口、异步、NOR 闪存存储器，同时可明显降低信号连接的计数。

FL-L 产品系列为各种移动或嵌入式应用提供了容量大、灵活性高且速度快等性能。该产品系列为空间，信号连接，功耗有限的系统提供了一个理想的存储解决方案。这些存储器的灵活性和性能比普通串行闪存器件好很多。它们是用于将代码传送到 RAM，直接执行代码 (XIP) 和存储可重新编程的数据的理想选择。

## 特性

- 具有多个 I/O 的串行外设接口 (SPI)

- 支持时钟极性以及相位模式 0 和 3

- 具有双倍数据速率 (DDR) 选项

- 具有四线外设接口 (QPI) 选项

- 具有扩展地址：24 或 32 位地址选项

- 串行命令子集和封装与 S25FL-A、S25FL1-K、S25FL-P、S25FL-S 以及 S25FS-S SPI 系列兼容

- 多个 I/O 命令子集和封装与 S25FL-A、S25FL1-K、S25FL-P、S25FL-S 以及 S25FS-S SPI 系列兼容

- 读取

- 命令：普通、快速、双线 I/O、四线 I/O、双线输出、四线输出、DDR 四线 I/O

- 模式：模式：回卷突发、持续突发 (XIP)、QPI

- 串行闪存可发现参数 (SFDP) 用于配置信息

- 编程结构

- 256 字节页编程缓冲区

- 256 Mb (32 MB)/128 Mb (16 MB)，3.0 V FL-L 闪存存储器

- 编程挂起和恢复

- 擦除结构

- 4 KB 扇区擦除

- 32 KB 半块擦除

- 64 KB 扇区擦除

- 芯片擦除

- 擦除挂起和恢复

- 100,000 万次编程 / 擦除周期 (最小值)

- 最短数据保留时间为 20 年

特性

• 安全特性

- 具有状态和配置寄存器保护

- 主闪存阵列外有四个安全区域，每个大小为 256 字节。

- 传统块保护：块范围块范围

- 单独和区域保护

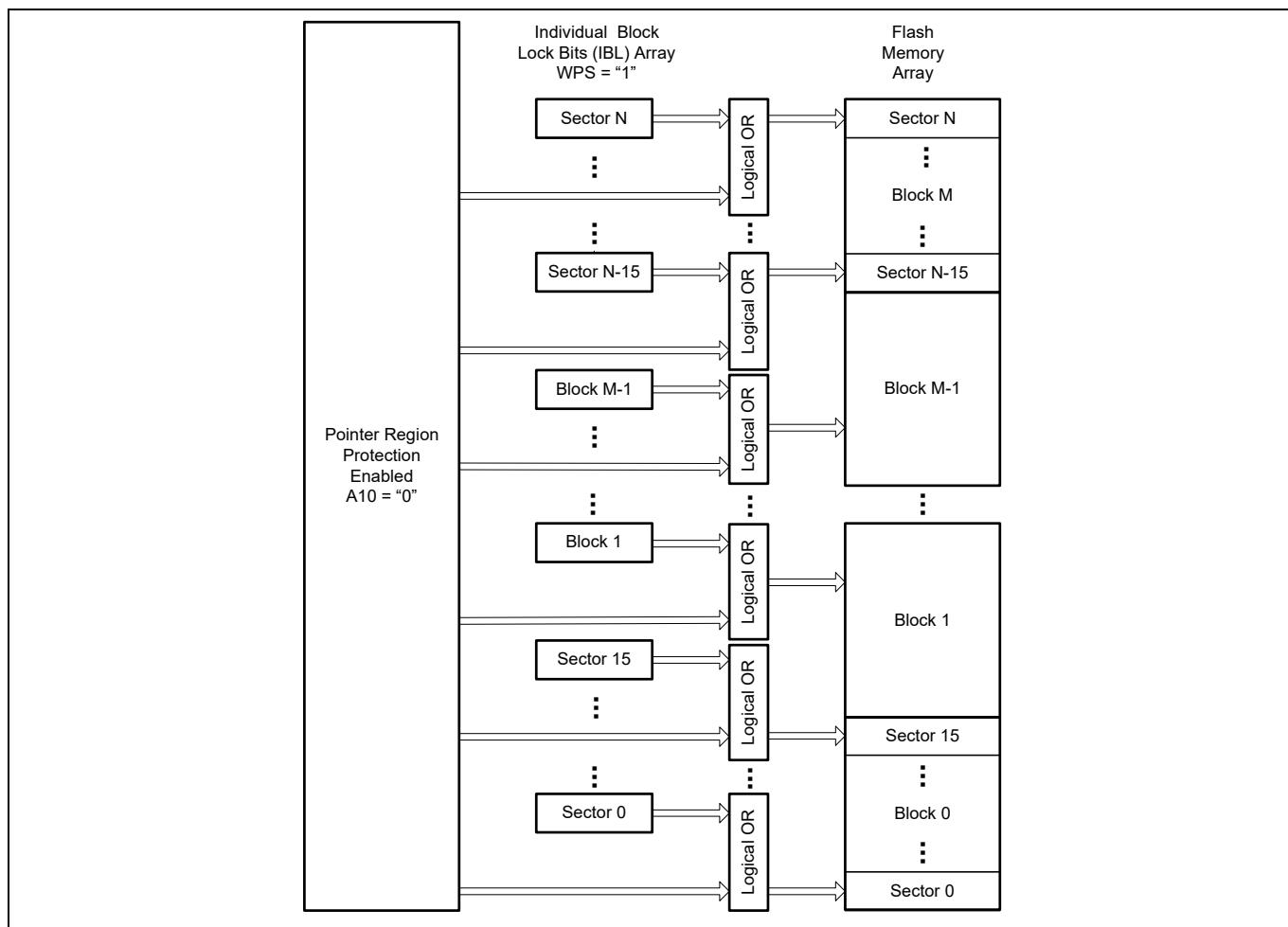

- 单独块锁定：易失性单独扇区 / 块保护

- 指针区域：非易失性扇区 / 块范围

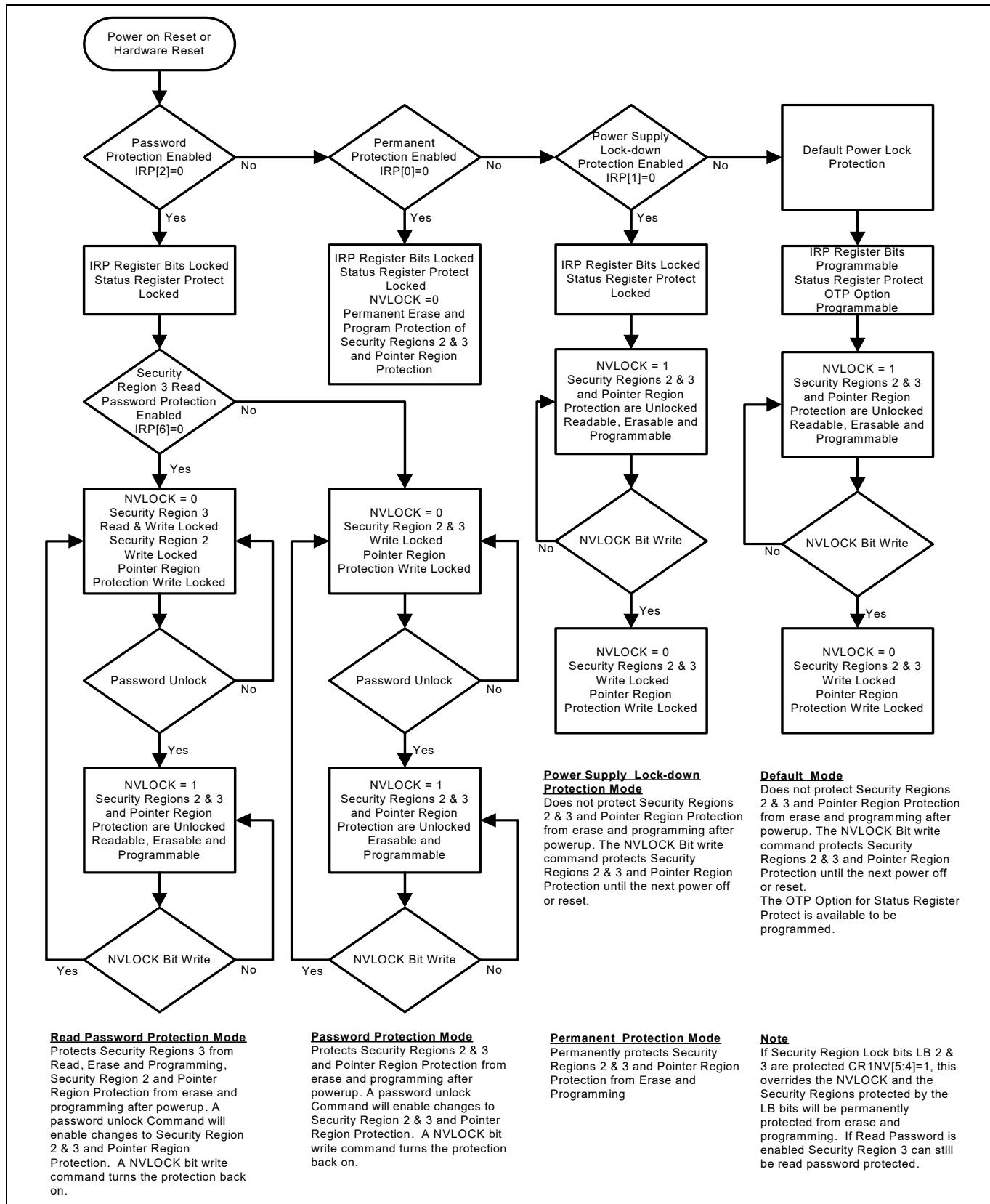

- 安全区域 2 和 3 以及指针区域的电源锁定、密码和永久保护

• 技术

- 65 nm 浮栅技术

- CMOS I/O 的单个供电电压

- 2.7 V ~ 3.6 V

• 温度范围 / 级别

- 工业级 (-40 °C 到 +85 °C)

- 扩展的工业级 (-40 °C 到 +105 °C)

- 汽车级, AEC-Q100 等级 3 (-40 °C 到 +85 °C)

- 汽车级, AEC-Q100 等级 2 (-40 °C 到 +105 °C)

- 汽车级, AEC-Q100 等级 1 (-40 °C 到 +125 °C)

• 封装类型 (所有均无铅)

- 8-pin SOIC 208 mil (SOC008) – 仅 S25FL128L 提供

- WSON 5 × 6 mm (WND008) – 仅 S25FL128L 提供

- WSON 6 × 8 mm (WNG008) – S25FL256L 和 S25FL128L

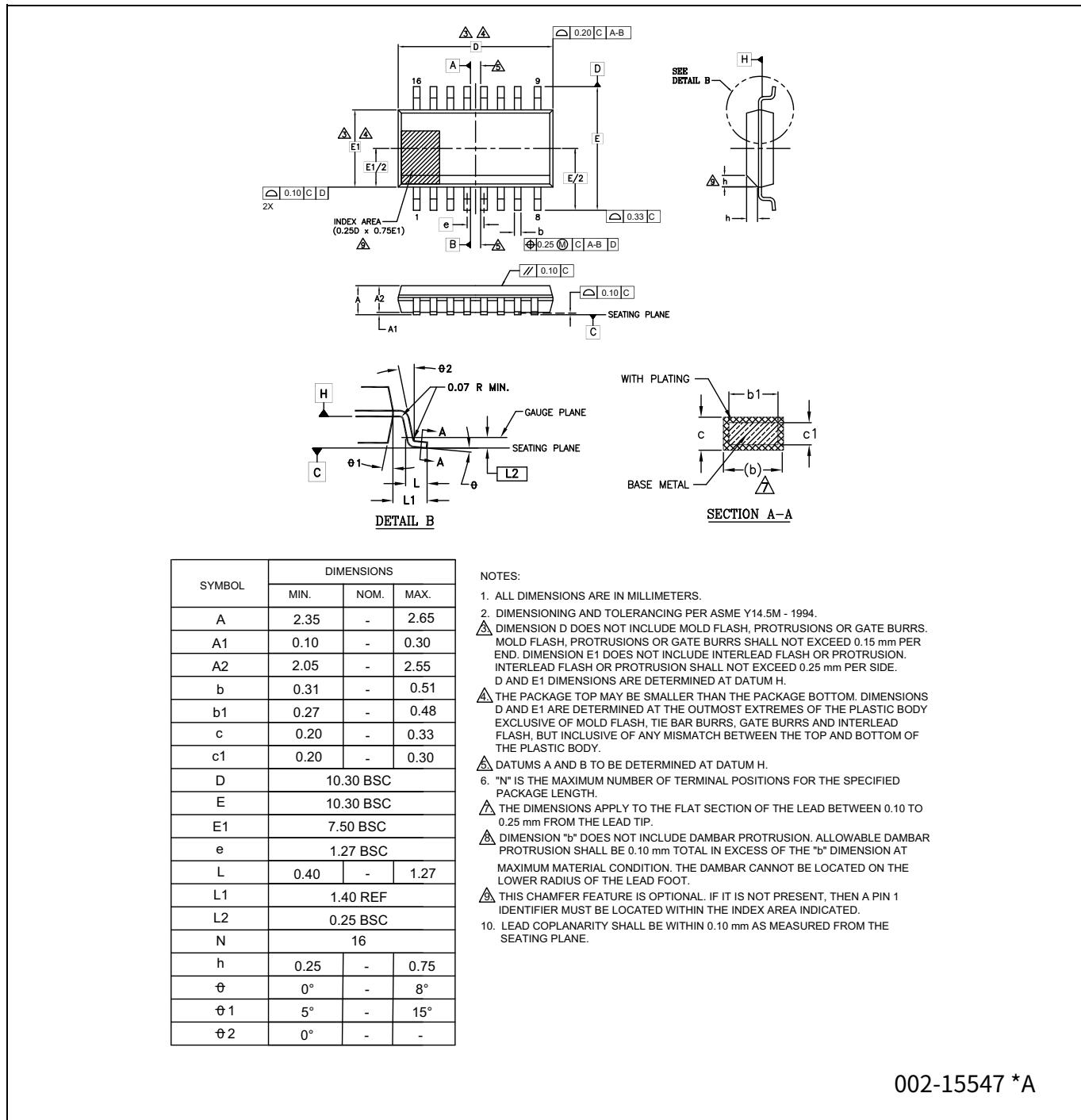

- 16-SOIC 300 mil (SO3016)

- BGA-24 6 × 8 mm

- 5 × 5 ball (FAB024) 封装

- 4 × 6 ball (FAC024) 封装

性能摘要

## 性能摘要

### 最大读取速度 SDR

| 命令   | 时钟速率 (MHz) | Mbps |

|------|------------|------|

| 读取   | 50         | 6.25 |

| 快速读取 |            | 16.5 |

| 双线读取 | 133        | 33   |

| 四线读取 |            | 66   |

### 最大读取速度 DDR

| 指令       | 时钟速率 (MHz) | Mbps |

|----------|------------|------|

| DDR 四线读取 | 66         | 66   |

### 典型的编程和擦除速率

| 操作         | KBps |

|------------|------|

| 页编程        | 854  |

| 4 KB 扇区擦除  | 80   |

| 32 KB 半块擦除 | 168  |

| 64 KB 块擦除  | 237  |

### 典型的电流消耗, -40°C 到 +85°C

| 操作                               | 典型电流 | 单位 |

|----------------------------------|------|----|

| 快速读取 (时钟频率为 5 MHz)               | 10   |    |

| 快速读取 (时钟频率为 10 MHz)              | 10   |    |

| 快速读取 (时钟频率为 20 MHz)              | 10   |    |

| 快速读取 (时钟频率为 50 MHz)              | 15   |    |

| 快速读取 (时钟频率为 108 MHz)             | 25   |    |

| 快速读取 133 MHz                     | 30   |    |

| 四线 I/O/QPI 读取 (时钟频率为 108 MHz)    | 25   | mA |

| 四线 I/O/QPI 读取 (时钟频率为 133 MHz)    | 30   |    |

| 四线 I/O/QPI DDR 读取 (时钟频率为 33 MHz) | 15   |    |

| 四线 I/O/QPI DDR 读取 (时钟频率为 66 MHz) | 30   |    |

| 编程                               | 40   |    |

| 擦除                               | 40   |    |

| 待机 SPI                           | 20   |    |

| 待机 QPI                           | 60   | µA |

| 深度掉电                             | 2    |    |

目录

|                                       |    |

|---------------------------------------|----|

| <b>目录</b>                             |    |

| <b>概述</b>                             | 1  |

| <b>特性</b>                             | 1  |

| <b>性能摘要</b>                           | 3  |

| <b>目录</b>                             | 4  |

| <b>1 产品概述</b>                         | 6  |

| 1.1 移植时注意事项                           | 6  |

| <b>2 引脚分布</b>                         | 8  |

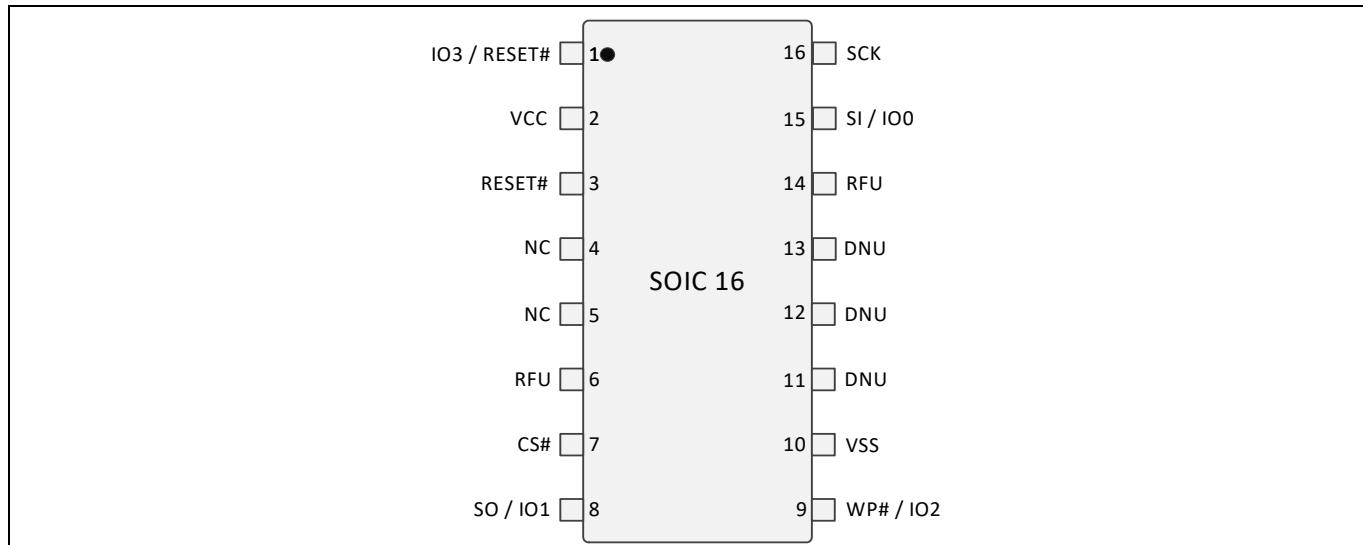

| 2.1 SOIC 16 引脚                        | 8  |

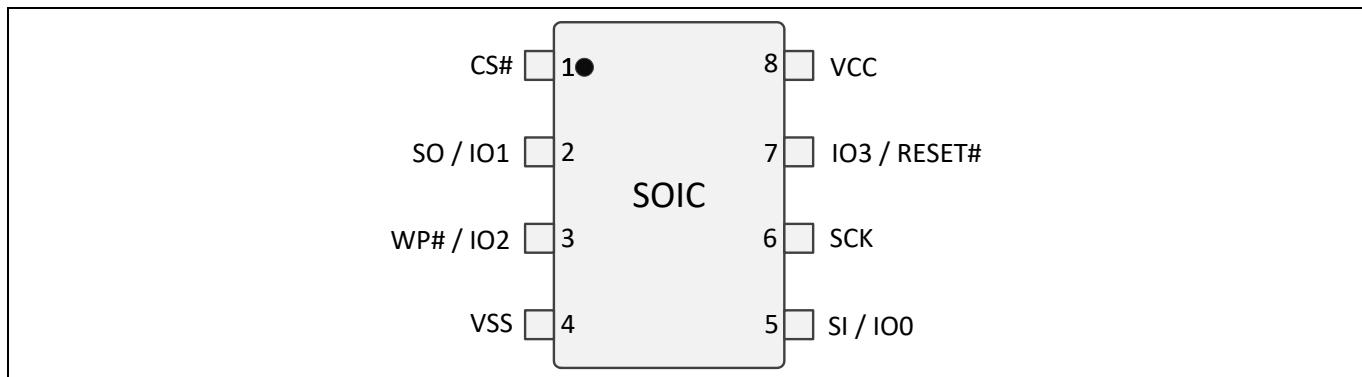

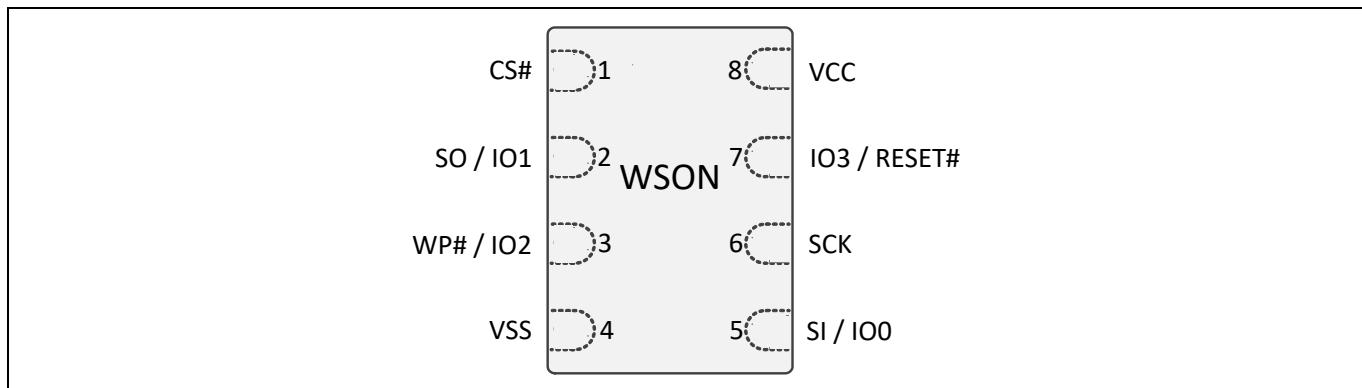

| 2.2 包含 8 个连接点的封装                      | 9  |

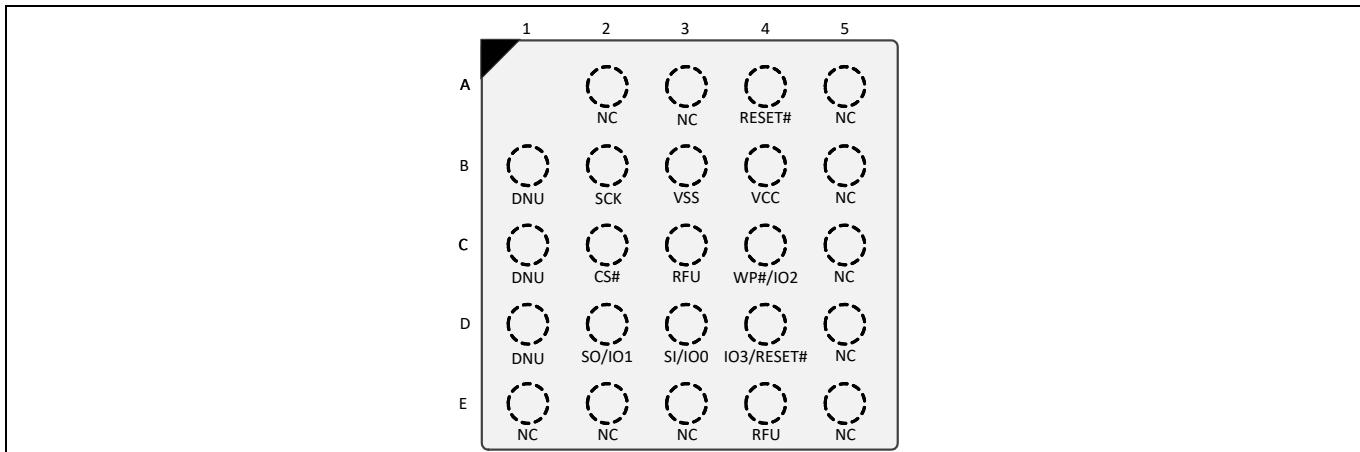

| 2.3 BGA 球形焊盘封装                        | 10 |

| 2.4 FBGA 封装的特殊处理指令说明                  | 10 |

| <b>3 信号说明</b>                         | 11 |

| 3.1 支持多输入 / 输出的串行外设接口 (SPI-MIO)       | 11 |

| 3.2 输入 / 输出简介                         | 11 |

| 3.3 多路输入 / 输出 (MIO)                   | 12 |

| 3.4 串行时钟 (SCK)                        | 12 |

| 3.5 芯片选择 (CS#)                        | 12 |

| 3.6 串行输入 (SI) /IO0                    | 12 |

| 3.7 串行输出 (SO) /IO1                    | 13 |

| 3.8 写保护 (WP#) /IO2                    | 13 |

| 3.9 IO3 / RESET#                      | 13 |

| 3.10 RESET#                           | 14 |

| 3.11 供电电压 ( $V_{CC}$ )                | 14 |

| 3.12 供电与信号接地 ( $V_{SS}$ )             | 14 |

| 3.13 无连接 (NC)                         | 14 |

| 3.14 预留供将来使用 (RFU)                    | 14 |

| 3.15 请勿使用 (DNU)                       | 14 |

| <b>4 框图</b>                           | 15 |

| 4.1 系统框图                              | 15 |

| <b>5 信号协议</b>                         | 17 |

| 5.1 SPI 时钟模式                          | 17 |

| 5.2 命令协议                              | 18 |

| 5.3 接口状态                              | 23 |

| 5.4 数据保护                              | 26 |

| <b>6 地址空间映射</b>                       | 28 |

| 6.1 概述                                | 28 |

| 6.2 闪存存储器阵列                           | 29 |

| 6.3 ID 地址空间                           | 30 |

| 6.4 JEDEC JESD216 串行闪存可发现参数 (SFDP) 空间 | 30 |

| 6.5 安全区域地址空间                          | 30 |

| 6.6 寄存器                               | 31 |

| <b>7 数据保护</b>                         | 53 |

| 7.1 安全区域                              | 53 |

| 7.2 深度掉电                              | 53 |

| 7.3 写入启用命令                            | 54 |

| 7.4 写入保护信号                            | 54 |

| 7.5 状态寄存器保护 (SRP1、SRP0)               | 54 |

| 7.6 阵列保护                              | 56 |

| 7.7 单独和区域保护                           | 64 |

| <b>8 命令</b>                           | 69 |

| 8.1 命令集汇总                             | 69 |

## 目录

|                                     |            |

|-------------------------------------|------------|

| 8.2 标识命令 .....                      | 76         |

| 8.3 寄存器访问命令 .....                   | 80         |

| 8.4 读取闪存阵列命令 .....                  | 95         |

| 8.5 编程闪存阵列命令 .....                  | 104        |

| 8.6 擦除闪存阵列命令 .....                  | 106        |

| 8.7 安全区域阵列命令 .....                  | 114        |

| 8.8 单块锁定命令 .....                    | 116        |

| 8.9 指针区域命令 .....                    | 121        |

| 8.10 单独和区域保护 (IRP) 命令 .....         | 122        |

| 8.11 复位命令 .....                     | 129        |

| 8.12 深度掉电命令 .....                   | 130        |

| <b>9 数据完整性 .....</b>                | <b>133</b> |

| 9.1 擦除次数 .....                      | 133        |

| 9.2 数据保留时间 .....                    | 133        |

| <b>10 软件接口参考 .....</b>              | <b>134</b> |

| 10.1 JEDEC JESD216B 串行闪存可发现参数 ..... | 134        |

| 10.2 器件 ID 地址映射 .....               | 144        |

| 10.3 初始供应状态 .....                   | 144        |

| <b>11 电气规范 .....</b>                | <b>145</b> |

| 11.1 最大绝对额定值 .....                  | 145        |

| 11.2 闩锁特性 .....                     | 145        |

| 11.3 热阻 .....                       | 145        |

| 11.4 工作范围 .....                     | 146        |

| 11.5 上电和掉电 .....                    | 147        |

| 11.6 DC 特性 .....                    | 149        |

| <b>12 时序规范 .....</b>                | <b>153</b> |

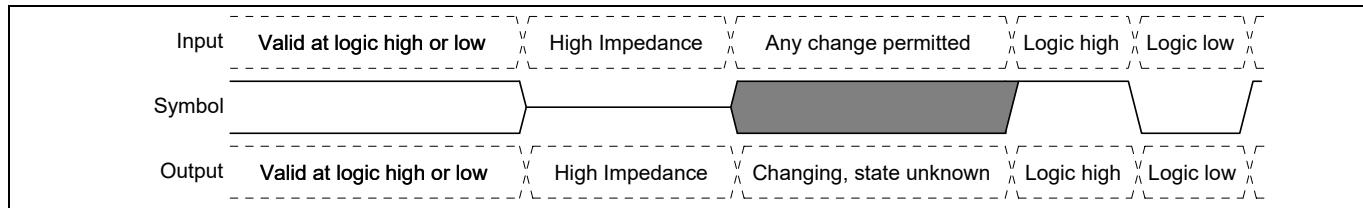

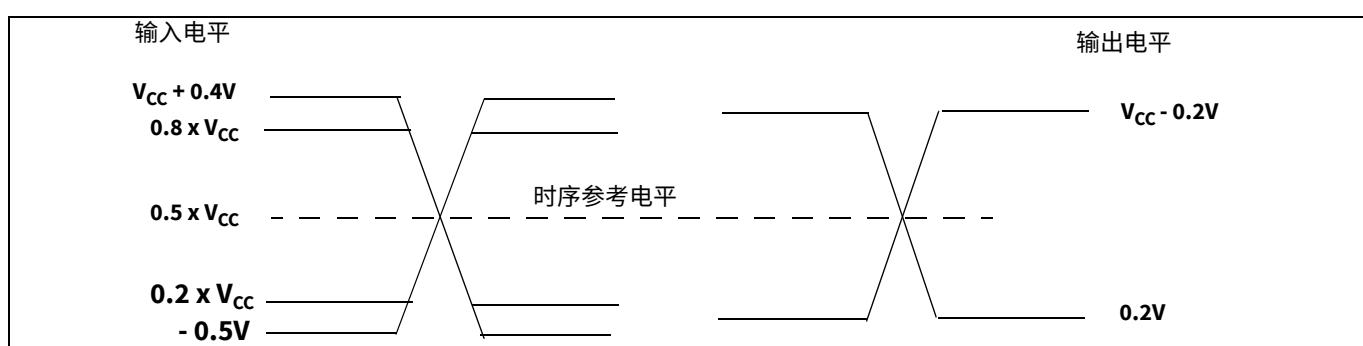

| 12.1 切换波形的关键 .....                  | 153        |

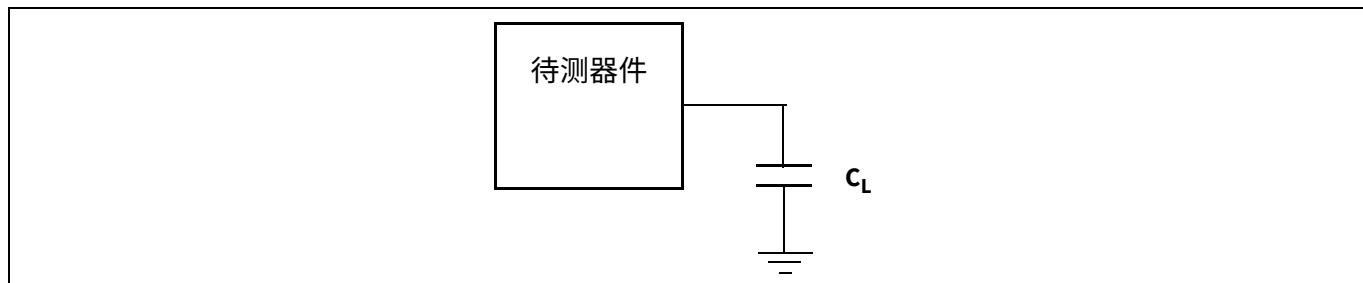

| 12.2 AC 测试条件 .....                  | 153        |

| 12.3 复位 .....                       | 154        |

| 12.4 SDR AC 特性 .....                | 157        |

| 12.5 DDR AC 特性 .....                | 160        |

| 12.6 嵌入式算法性能表 .....                 | 163        |

| <b>13 订购信息 .....</b>                | <b>164</b> |

| 13.1 订购器件型号 .....                   | 164        |

| 13.2 有效组合 — 标准 .....                | 165        |

| 13.3 有效组合 — 汽车级 /AEC-Q100 .....     | 166        |

| <b>14 封装图 .....</b>                 | <b>167</b> |

| 修订记录 .....                          | 176        |

产品概述

## 1 产品概述

### 1.1 移植时注意事项

#### 1.1.1 特性比较

FL-L 系列的指令集和封装与先前的 FL-S、FL1-K 和 FL-P 系列相兼容。

表 1 英飞凌 SPI 系列比较 (1/2)

| 参数               | FL-L                                                   | FL-S                                 | FL1-K                               | FL-P              |

|------------------|--------------------------------------------------------|--------------------------------------|-------------------------------------|-------------------|

| 技术节点             | 65-nm                                                  | 65-nm                                | 90-nm                               | 90-nm             |

| 架构               | 浮栅                                                     | MIRRORBIT™ Eclipse                   | 浮栅                                  | MIRRORBIT™        |

| 出厂日期             | 生产中                                                    | 生产中                                  | 生产中                                 | 生产中               |

| 容量               | 256 Mb                                                 | 128 Mb–1 Gb                          | 4 Mb–64 Mb                          | 32 Mb–256 Mb      |

| 总线带宽             | ×1、×2、×4                                               | ×1、×2、×4                             | ×1、×2、×4                            | ×1、×2、×4          |

| 供电电压             | 2.7 V–3.6 V                                            | 2.7 V–3.6 V / 1.65 V–3.6 V $V_{IO}$  | 2.7 V–3.6 V                         | 2.7 V–3.6 V       |

| 正常读取速度           | 6 MBps (50 MHz)                                        | 6 MBps (50 MHz)                      | 6 MBps (50 MHz)                     | 5 MBps (40 MHz)   |

| 快速读取速度           | 16.5 MBps (133 MHz)                                    | 17 MBps (133 MHz)                    | 13 MBps (108 MHz)                   | 13 MBps (104 MHz) |

| 双线读取速度           | 33 MBps (133 MHz)                                      | 26 MBps (104 MHz)                    | 26 MBps (108 MHz)                   | 20 MBps (80 MHz)  |

| 四线读取速度           | 66 MBps (133 MHz)                                      | 52 MBps (104 MHz)                    | 52 MBps (108 MHz)                   | 40 MBps (80 MHz)  |

| 四线读取速度 (DDR)     | 66 MBps (66 MHz)                                       | 80 MBps (80 MHz)                     | –                                   | –                 |

| 编程缓冲区大小          | 256B                                                   | 256B / 512B                          | 256B                                | 256B              |

| 擦除扇区 / 块大小       | 4 KB / 32 KB / 64 KB                                   | 64 KB / 256 KB                       | 4 KB / 64 KB                        | 64 KB / 256 KB    |

| 参数扇区大小           | –                                                      | 4 KB (选项)                            | –                                   | 4 KB              |

| 扇区 / 块擦除速率 (典型值) | 80 KBps (4 KB)<br>168 KBps (32 KB)<br>237 KBps (64 KB) | 500 KBps                             | 136 KBps (4 KB)<br>437 KBps (64 KB) | 130 KBps          |

| 页编程速率 (典型值)      | 854 KBps (256 B)                                       | 1.2 MBps (256 B)<br>1.5 MBps (512 B) | 365 KBps                            | 170 KBps          |

| 安全区域 /OTP        | 1024B                                                  | 1024B                                | 768B (3 × 256B)                     | 506B              |

## 产品概述

**表 1 英飞凌 SPI 系列比较 (2/2)**

| 参数              | FL-L                                                 | FL-S                             | FL1-K        | FL-P                             |

|-----------------|------------------------------------------------------|----------------------------------|--------------|----------------------------------|

| 单独和区域保护或高级的扇区保护 | 支持                                                   | 支持                               | 不支持          |                                  |

| 擦除挂起 / 恢复       |                                                      |                                  | 支持           | 不支持                              |

| 编程挂起 / 恢复       |                                                      |                                  |              |                                  |

| 工作温度            | -40 到 +85 °C<br>-40 °C 到 +105 °C<br>-40 °C 到 +125 °C | -40 到 +85 °C<br>-40 °C 到 +105 °C | -40 到 +85 °C | -40 到 +85 °C<br>-40 °C 到 +105 °C |

## 注释

- 欲了解详细信息，请参考单独的数据手册。

引脚分布

## 2 引脚分布

### 2.1 SOIC 16 引脚

图 1 16 引脚 SOIC 封装 (SO3016), 俯视图

#### 注释

2. RESET# 和 IO3 / RESET# 输入间连接着一个内部上拉电阻。如果未使用四线模式、模式和硬件复位模式，则在系统中，这些输入会保持为未连接状态。

引脚分布

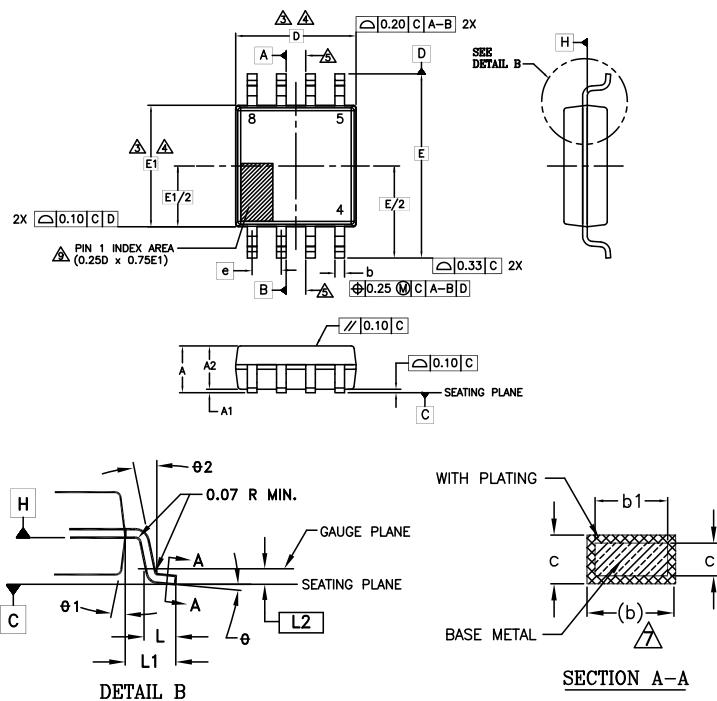

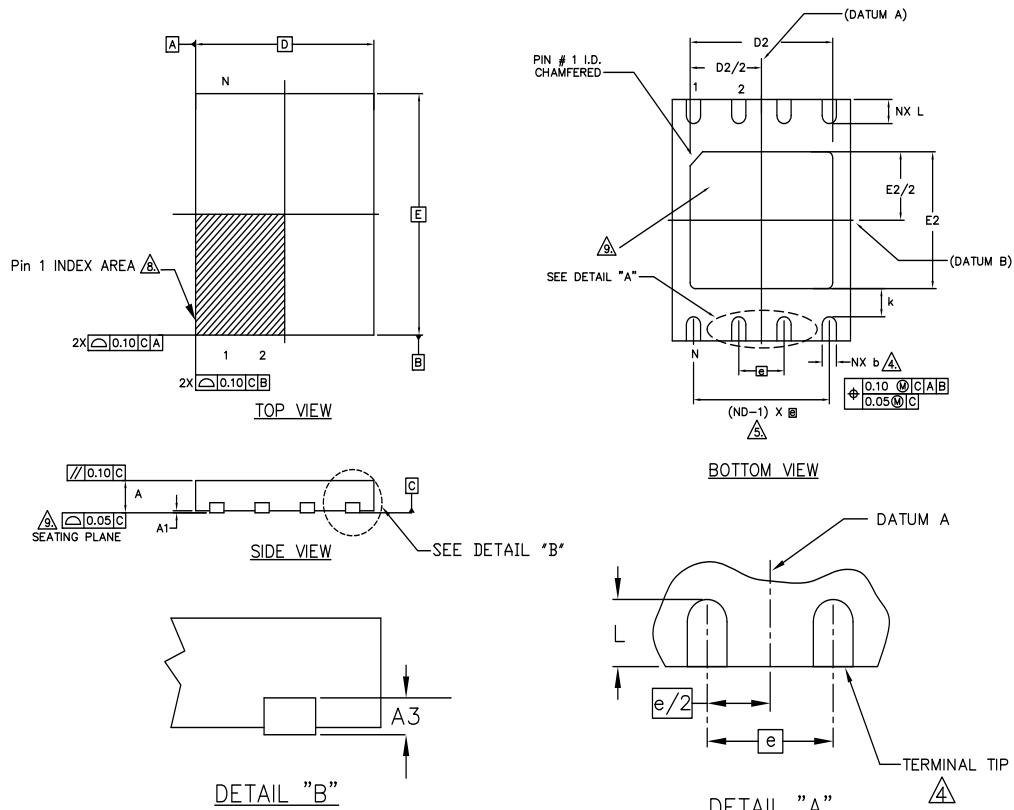

## 2.2 包含 8 个连接点的封装

图 2 8 引脚塑料小外型封装 (SOIC8)

图 3 包含 8 个连接点的封装 (WSON 6 x 8) (WSON 5 x 6) , 俯视图

### 注释

3. RESET# 输入上连接着一个内部上拉电阻。如果未使用四线模式和硬件复位模式，则在系统中，该输入会保持为未连接状态。

引脚分布

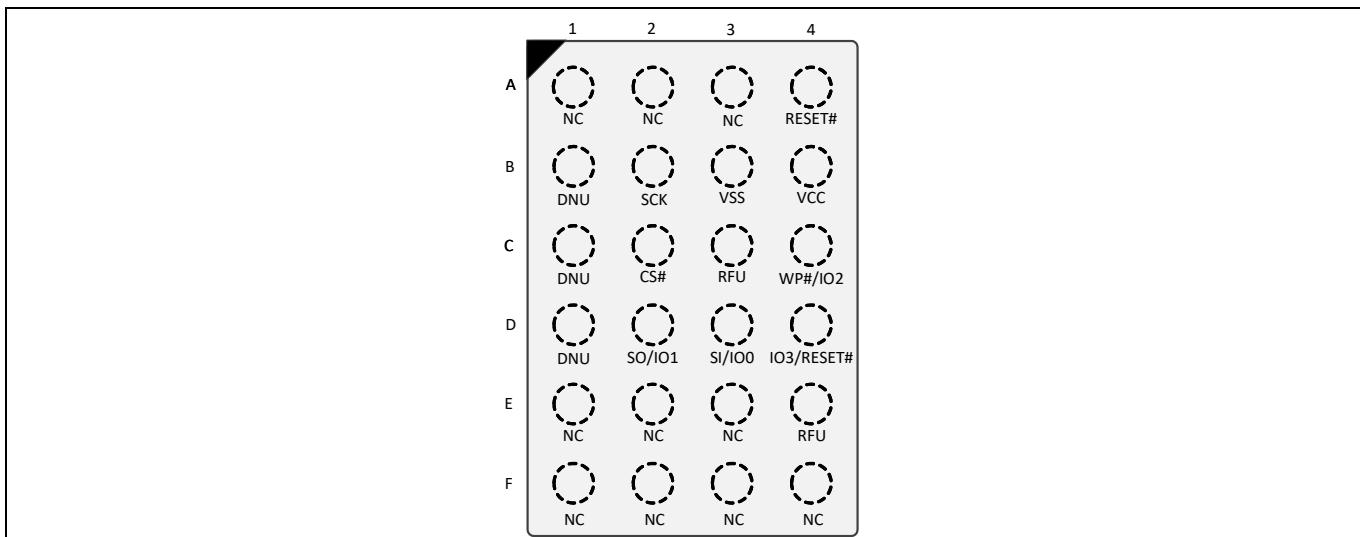

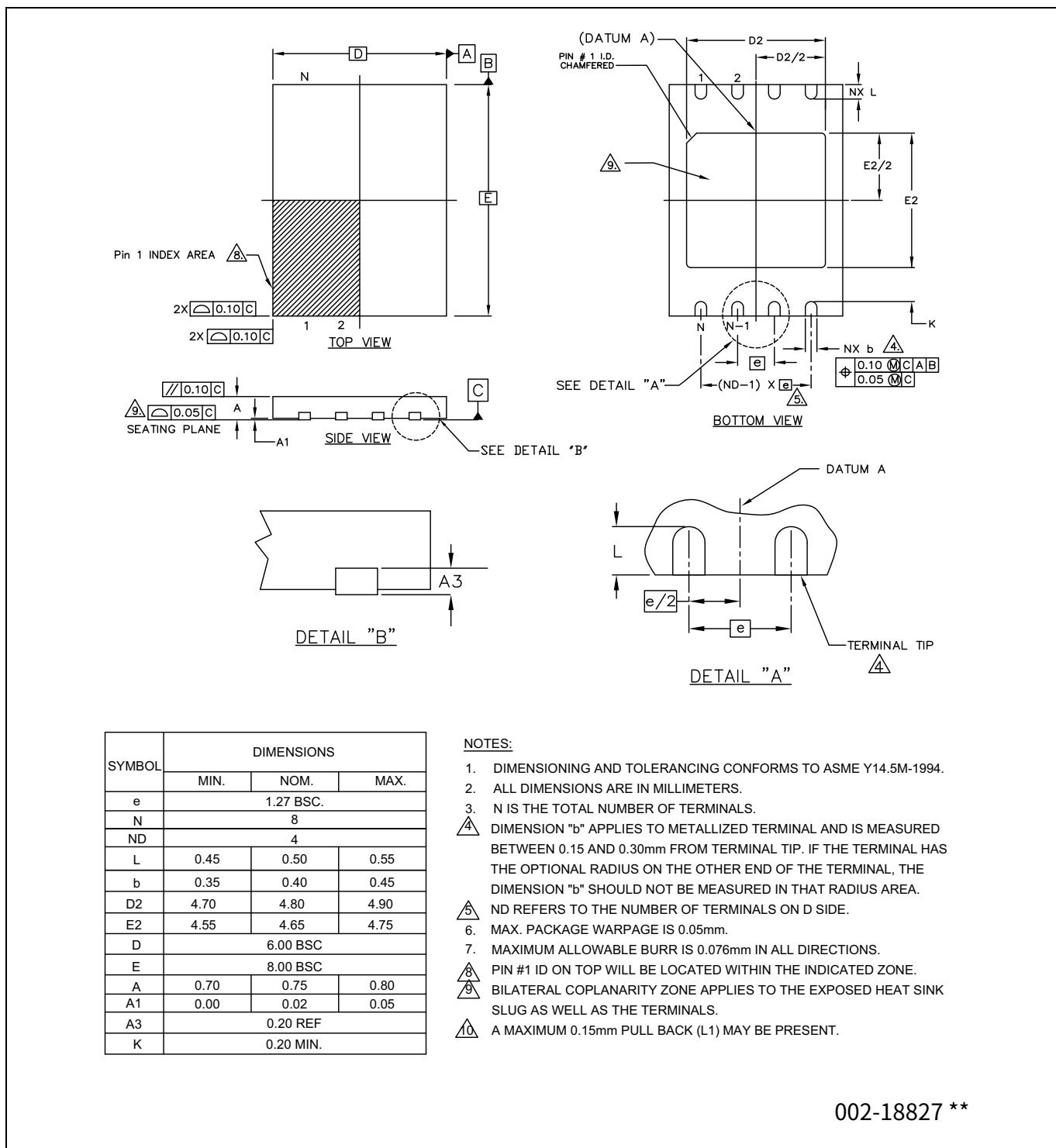

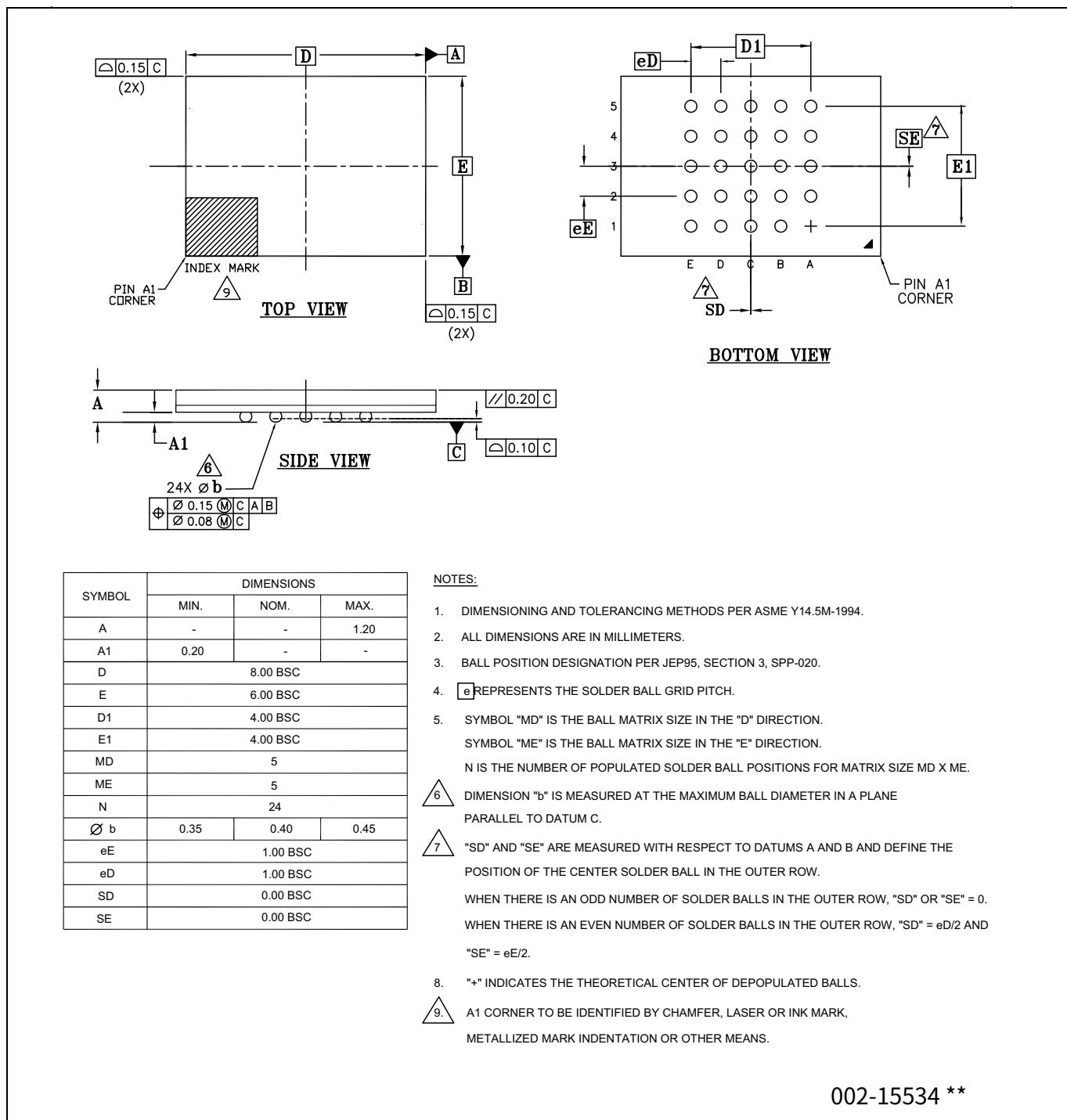

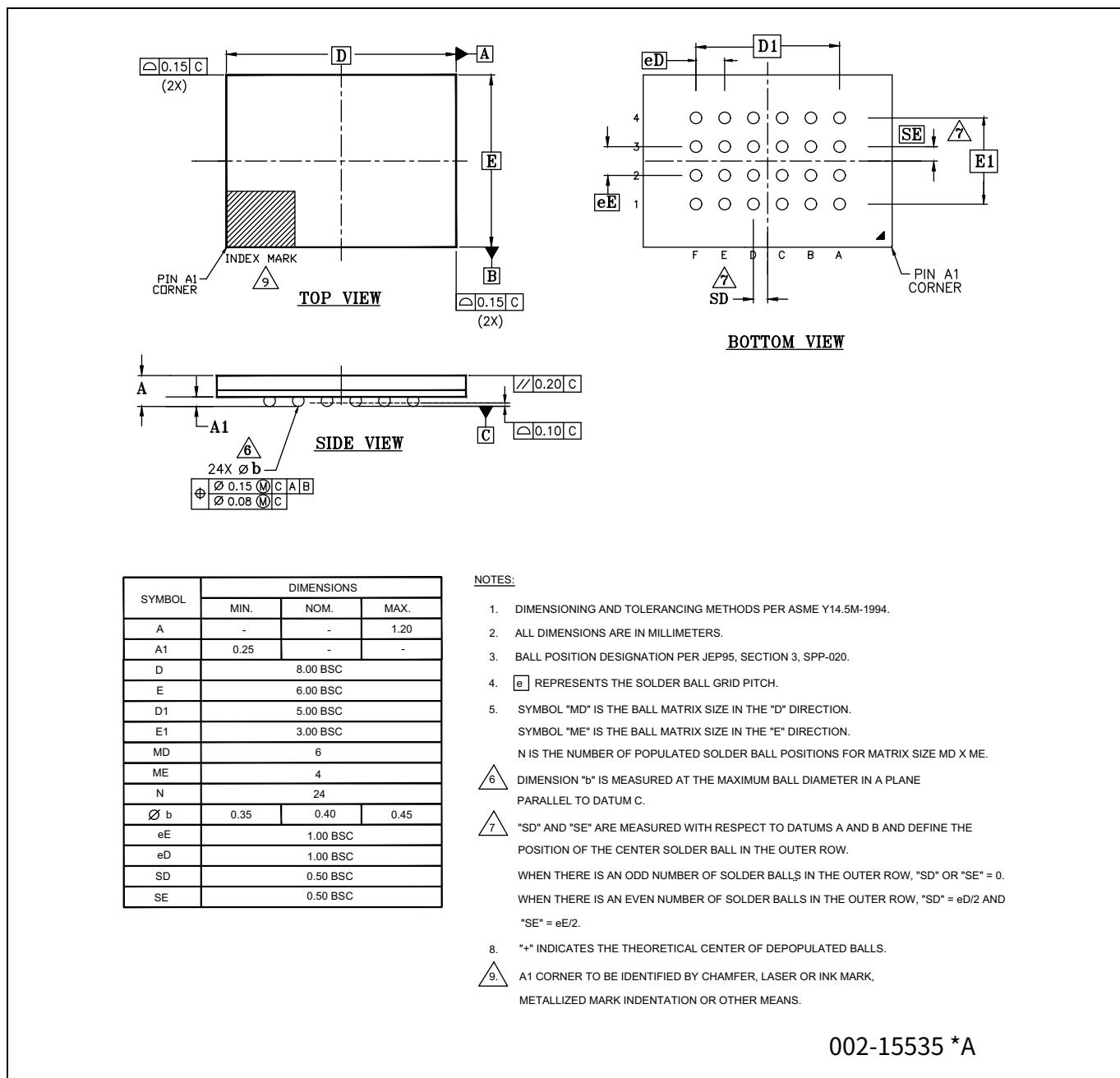

## 2.3 BGA 球形焊盘封装

图 4 24-BGA, 5x5 球型焊盘封装 (FAB024), 俯视图

图 5 24-BGA, 4x6 球型焊盘封装 (FAC024), 俯视图

## 2.4 FBGA 封装的特殊处理指令说明

如果使用超声波清洁方法, BGA 封装中的闪存存储器器件可能被损坏。如果将封装长期放置在温度高于 150°C 的地方, 封装和 / 或数据的完整性可能受到损坏。

### 注释

4. 信号连接的相对位置与 FAC024 BGA 相同, 因此单 PCB 封装可以使用两个封装中的任何一个。

5. RESET# 输入上连接着一个内部上拉电阻。如果未使用四线模式和硬件复位模式, 则在系统中, 该输入会保持为未连接状态。

6. RESET# 输入上连接着一个内部上拉电阻。如果未使用四线模式和硬件复位模式, 则在系统中, 该输入会保持为未连接状态。

信号说明

### 3 信号说明

#### 3.1 支持多输入 / 输出的串行外设接口 (SPI-MIO)

具有独立的并行控制、地址和数据信号的多个存储器件与其主机系统连接时，需要大量的信号连接和更大的封装。由于大量信号交换，因此信号连接的数量越多，功耗也越高；较大的封装尺寸会增加成本。

FL-L 系列通过 6 个信号将所有控制、地址和数据信息串行传输给主机系统，因此可以减少信号连接的数量。这样可以降低存储器封装的成本和信号交换的功耗，减少主机信号连接的数量，主机可以节省连接以供其他功能使用。

FL-L 系列使用了业界标准的单比特 SPI，同时支持可选的扩展命令，用于进行两比特（双线）或 4 比特（四线）宽的串行传输。这种多宽度接口被称为 SPI Multi-I/O 或 SPI-MIO。

#### 3.2 输入 / 输出简介

表 2 信号表 (1/2)

| 信号名称            | 类型  | 说明                                                                                                                                                                                                                         |  |

|-----------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| RESET#          | 输入  | 硬件复位。该信号为低电平时，器件复位并返回待机状态，准备接收命令。该信号具有一个内部上拉电阻；在主机系统中如果不使用该信号，可以保持它为未连接状态。                                                                                                                                                 |  |

| SCK             |     | 串行时钟。                                                                                                                                                                                                                      |  |

| CS#             |     | 芯片选择。                                                                                                                                                                                                                      |  |

| SI / IO0        | I/O | 单比特数据命令的串行输入或双线 / 四线命令的 IO0。                                                                                                                                                                                               |  |

| SO / IO1        |     | 单比特数据命令的串行输出。双线或四线命令的 IO1。                                                                                                                                                                                                 |  |

| WP# / IO2       |     | 不在四线模式 (CR1V[1] = 0 和 SR1NV[7] = 1) 下时，为写保护。<br>在四线模式 (CR1V[1] = 1) 下，为 IO2。<br>该信号具有一个内部上拉电阻。在主机系统中，如果不使用四线模式或不用于写保护，可以保持它为未连接状态。如果通过设置 SR1NV[7] = 1 和 CR1V[1] = 0 启用了写保护功能，那么在执行 WRR 或 WRAR 命令期间，主机系统需要将 WP# 驱动为高电平或低电平。 |  |

|                 |     | 在四线 I/O 模式下，当配置寄存器 1 的 QUAD 位 CR1V[1] = 1 时，或在 QPI 模式下，当 CS# 为低电平并且配置好寄存器 2 的 QPI 位 CR2V[3] = 1 时，该信号将为 IO3。                                                                                                               |  |

| IO3 / RESET#    |     | 当 CR2V[7] = 1，并且处于非四线 I/O 模式 (CR1V[1] = 0) 时，或在四线模式下 (CR1V[1] = 1) CS# 为高电平时，该信号为 RESET#。<br>该信号具有一个内部上拉电阻；在主机系统如果不使用四线模式或不用于 RESET#，可以保持未连接状态。                                                                            |  |

| V <sub>CC</sub> | 电源  | 供电电源。                                                                                                                                                                                                                      |  |

| V <sub>SS</sub> |     | 接地电源。                                                                                                                                                                                                                      |  |

| NC              | 未使用 | 未连接。没有任何器件内部信号被连接到封装引脚，将来也不计划用于信号连接。该连接可能安全地用作印刷电路板 (PCB) 上的信号路由空间。然而，连接到 NC 的任何信号电压电平不能大于 V <sub>CC</sub> 。                                                                                                               |  |

信号说明

表 2 信号表 (2/2)

| 信号名称 | 类型 | 说明                                                                                                                                                                                                     |

|------|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RFU  | 预留 | 预留供将来使用。当前没有任何器件内部信号连接到封装引脚，但是将来可能使用。不建议将 RFU 连接到 PCB 电路板上的任何信号，以便 PCB 可以在尺寸兼容的器件中实现未来的增强型特性。                                                                                                          |

| DNU  | 预留 | 请勿使用。器件的内部信号可能被连接到封装引脚。英飞凌可能会使用该引脚进行测试或其他用途，该引脚不应与任何主机系统信号连接。DNU 引脚处于低电平 ( $V_{IL}$ ) 时，与该引脚相关的所有功能均无效。该引脚使用了一个内部下拉电阻，在主机系统中可以保持它为未连接状态或将其连接到 $V_{SS}$ 。请勿将该 DNU 引脚连接到 PCB 板上的任意信号。请勿将主机系统的任何信号连接到该引脚。 |

### 注释

7. 使用内部上拉或下拉电阻的输入驱动引起的电流低于  $2 \mu\text{A}$ 。只有在上电过程中，该电流才最大（在  $4 \mu\text{s}$  内为  $150 \mu\text{A}$ ）。如果采用普通的工艺技术、 $V_{CC} = 3.3 \text{ V}$ ，若温度 =  $-40^\circ\text{C}$ ，则上拉或下拉电阻的阻值为  $\sim 4.5 \text{ M}\Omega$ ；若温度 =  $90^\circ\text{C}$  时，阻值为  $\sim 6.6 \text{ M}\Omega$ 。

## 3.3 多路输入 / 输出 (MIO)

传统 SPI 单比特命令（即单 IO 或 SIO）只能通过串行输入 (SI) 信号将主机的数据发送到存储器内。数据会通过串行输出 (SO) 信号从存储器内串行回送给主机。

双线或四线输入 / 输出 (I/O) 命令只能通过 SI/IO0 信号将指令发送给存储器。地址或数据可按双比特一组的方式通过 IO0 和 IO1 从主机发送到存储器内，也可以按照四比特（半字节）一组的方式通过 IO0、IO1、IO2 和 IO3 发送。数据同样可以按照双比特一组的方式通过 IO0 和 IO1 从存储器回送给主机，也可以按照四比特（半字节）一组的方式通过 IO0、IO1、IO2 和 IO3 被回送。

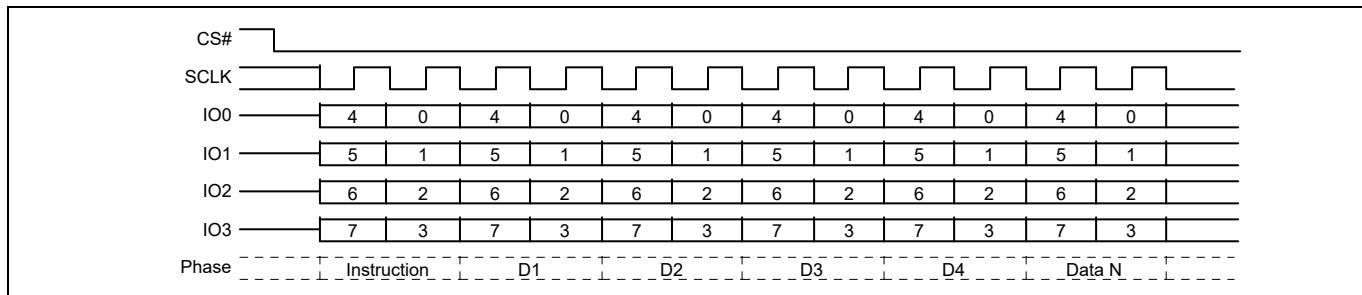

QPI 模式允许以四比特（半字节）一组的方式将所有指令、地址和数据通过 IO0、IO1、IO2 和 IO3 从主机传送到存储器内。数据同样可以按四比特（半字节）一组的方式通过 IO0、IO1、IO2 和 IO3 回送到主机内。

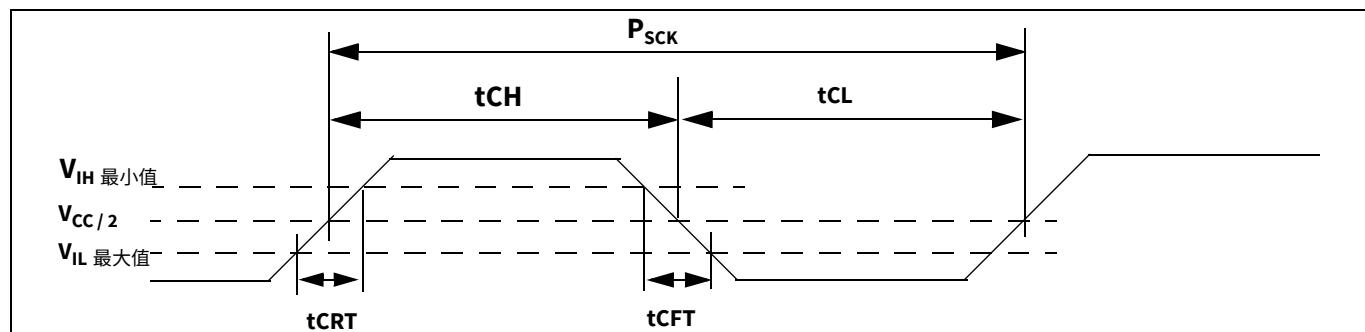

## 3.4 串行时钟 (SCK)

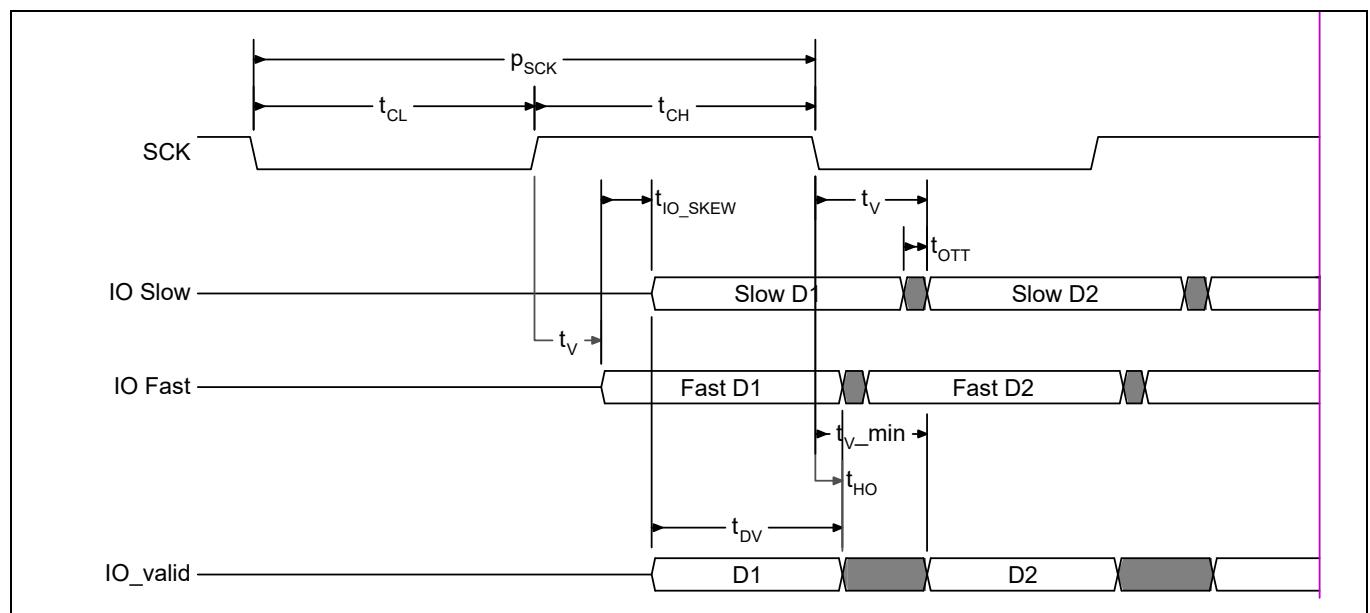

该输入信号为 SPI 接口提供了同步参考。可以在 SCK 信号的上升沿上锁存指令、地址或数据。在 SDR 命令中，数据输出会在 SCK 的下降沿后发生变化。

## 3.5 芯片选择 (CS#)

芯片选择信号指出某条命令正在向器件或从器件传输信息，并指示存储器件的相关信号。

当 CS# 信号为高逻辑状态时，不会选择芯片，所有输入信号均被忽略，并且所有输出信号均为高阻抗。除非正在进行某个内部嵌入式操作，否则器件会处于待机模式。嵌入式操作是从状态寄存器 ‘1’ 的正在写入位 (SR1V[0]) 被设置为 1 到完成该操作为止。嵌入式操作的示例包括：编程、擦除或写入寄存器 (WRR) 等操作。

将 CS# 输入驱动为低逻辑状态可以启用器件，使器件进入工作模式。上电后，必须等到 CS# 的下降沿到来后才能执行其他命令。

## 3.6 串行输入 (SI) /IO0

该输入信号用于将数据串行传输给器件。它接收指令、地址和要写入闪存的数据。各个数值在串行 SCK 时钟信号的上升沿上被锁存。在执行双线和四线命令过程中，SI 变成 IO0（一个输入和输出），用于接收指令、地址和数据（数值在串行 SCK 时钟信号的上升沿上被锁存），并在 SCK 下降沿上（若执行 SDR 命令）或在任意一个边沿上（若执行 DDR 命令）移出数据。

信号说明

### 3.7 串行输出 (SO) /IO1

该输出信号用于串行传输器件中的数据。在串行 SCK 时钟信号的下降沿上移出数据。在执行双线和四线命令过程中，SO 变成 IO1（一个输入和输出），用于接收地址和数据（数值在串行 SCK 时钟信号的上升沿上被锁存），并在 SCK 下降沿上（若执行 SDR 命令）或在任意边沿上（若执行 DDR 命令）移出数据。

### 3.8 写保护 (WP#) /IO2

将 WP# 驱动为低电平 ( $V_{IL}$ ) 时，如果将状态寄存器 1 (SR1NV[7]) 或 (SR1V[7]) 的状态寄存器保护位 0 (SRP0\_NV) 或 (SRP0) 设置为 ‘1’，便不能再写入到状态寄存器、配置寄存器或 DLR 寄存器内。在这种情况下，会忽略选择 SR1NV、SR1V、CR1NV、CR1V、CR2NV、CR2V、CR3NV、DLRNV 和 DLRV 的命令，并且不会报告任何错误。

这样可以防止传统的块保护设置发生更改。因此，如果执行某个命令来修改状态寄存器、配置寄存器或 DLR 寄存器时，WP# 为低电平，并且 SRP0\_NV 为 1，那么受传统块保护的存储器区域中的全部数据字节也受硬件保护，这样便不能修改这些字节。同样可以防止对安全区域锁定 (LB3-LB0) 进行编程。

启用四线模式 (CR1V[1] = 1) 或 QPI 模式 (CR2V[3] = 1) 时，会禁用 WP# 的功能。当启用四线或 QPI 模式 (CR2V[3] = 1) 时，WP# 将被 IO2 输入 / 输出替换，用于接收地址和数据（数值在串行 SCK 时钟信号的上升沿上被锁存），并在 SCK 下降沿上（若执行 SDR 命令）或在任意边沿上（若执行 DDR 命令）移出数据。

WP# 具有一个内部上拉电阻；未连接时，WP# 为高电平 ( $V_{IH}$ )，如果四线模式、QPI 模式或保护功能未使用该引脚，则在主机系统中它可以被保持为不连接状态。

### 3.9 IO3 / RESET#

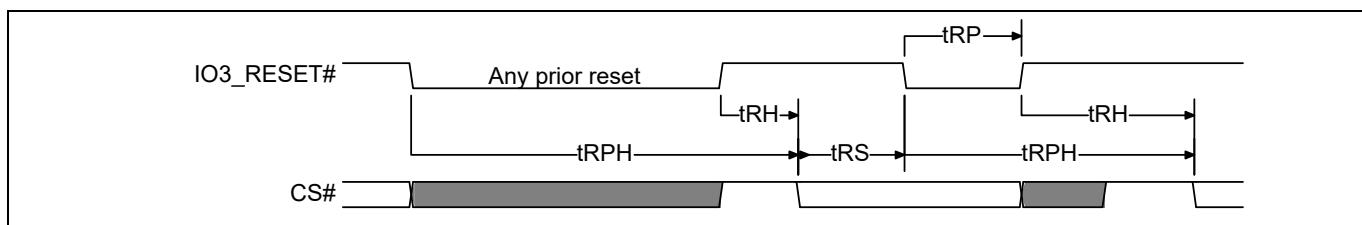

当启用四线模式 (CR1V[1] = 1) 或 QPI 模式 (CR2V[3] = 1) 时，会将 IO3 作为输入 / 输出使用，用于接收地址和数据（数值在串行 SCK 时钟信号的上升沿上被锁存），并在 SCK 下降沿上（若执行 SDR 命令）或在任意边沿上（若执行 DDR 命令）移出数据。

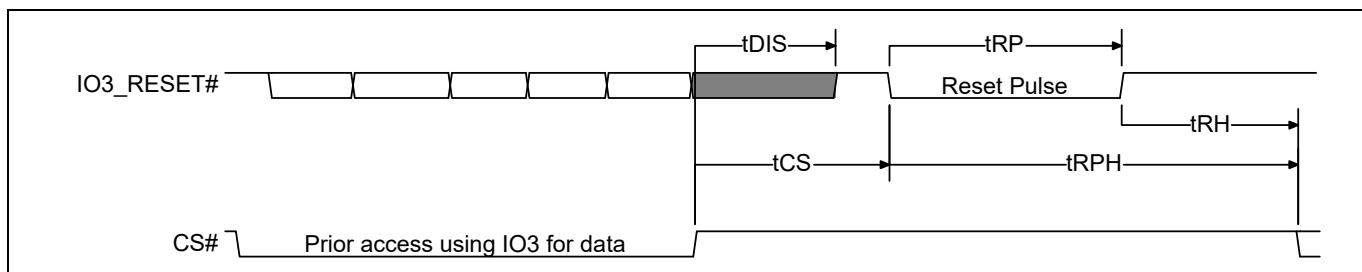

通过写入配置寄存器 2 的非易失性位 7 (CR2NV[7] = 1) 来启用 IO3/RESET# 功能时，IO3/RESET# 也可用于初始化硬件复位功能。如果器件并非处于四线模式 (114、144、444)，即 CR1V[1] = 0，或 CS# 为高电平，则只能将该输入作为 RESET# 使用。如果启用了四线模式 (CR1V[1] = 1) 或 QPI 模式 (CR2V[3] = 1)，或通过将 CS# 设置为低电平来选择器件，则只能将 IO3/RESET# 作为 IO3 传送信息。CS# 为高电平时，IO3/RESET# 不能传送信息，只能将它作为复位输入使用。在四线模式下 (114、144、444)，如果在 CS# 为高电平时，则复位功能在该模式 (114、144、444) 下仍可用。

当系统进入复位状态时，必须将 CS# 信号驱动为高电平（作为复位过程的一部分），并将 IO3/RESET# 信号驱动为低电平。CS# 变为高电平时，IO3/RESET# 输入从 IO3 切换为复位输入。当 CS# 保持为高电平和 IO3/RESET# 信号保持为低电平 ( $t_{RP}$ ) 时，会检测到复位条件。如果不需要进行复位操作，则系统必须在向存储器发送数据的操作结束时将 IO3/RESET# 和 CS# 驱动为高电平。将数据发送给主机系统后，存储器会驱动 IO3 为高电平，使之在  $t_{CS}$  的时间内保持高电平。这样可确保 IO3/RESET# 不进入悬空状态，也不会被内部或外部被动上拉电阻慢慢地上拉到高电平。因此， $t_{RP}$  时间结束前 IO3/RESET# 不会被视为高电平，从而也不会触发意外的复位事件。

CR2V[7] = 0 时，IO3/RESET# 输入的复位功能被禁用。

IO3/RESET# 输入具有一个内部上拉电阻；如果四线模式或复位功能未使用该输入，则在主机系统中它可以保持为不连接状态。如果主机系统将 IO3/RESET# 信号驱动为高电平，然后停止驱动该信号，则通过使用内部上拉电阻将它保持为高电平。

请注意，如果多个 SPI-MIO 存储器中有任意一个工作于四线 I/O 模式，那么它们不能共享 IO3/RESET# 输入，因为来自一个选定存储器或向其发送的 IO3 可用作第二个非选定存储器（其共享了同一个 IO3/RESET# 信号）的复位信号。

信号说明

### **3.10      RESET#**

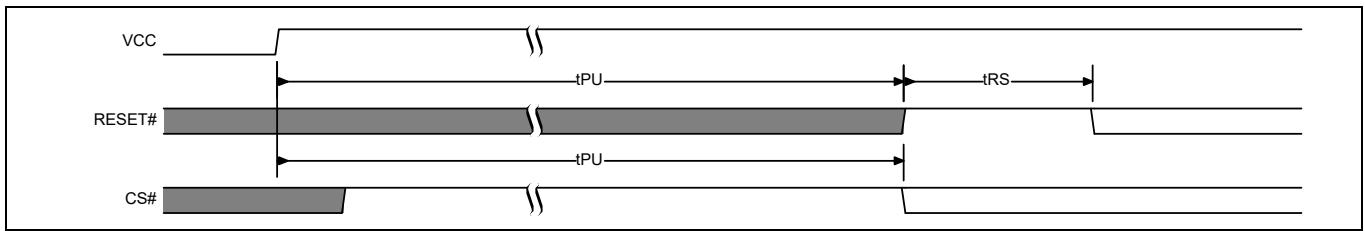

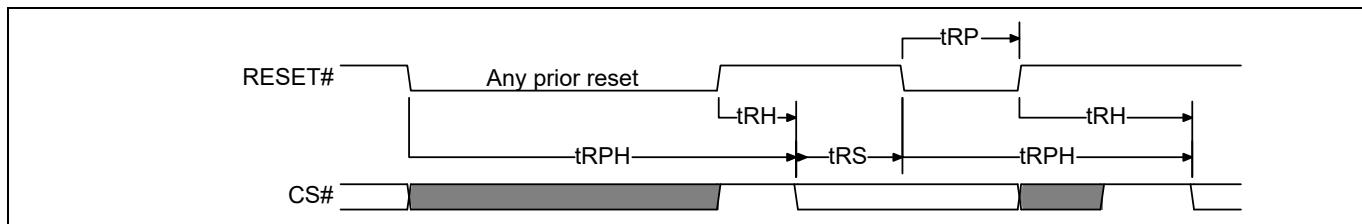

RESET# 输入提供了一种硬件复位方法，该方法可使器件返回待机状态，准备好接收命令。如果将 RESET# 驱动为逻辑低 ( $V_{IL}$ ) 的时间不小于  $t_{RP}$  时长，则器件将启动硬件复位过程。

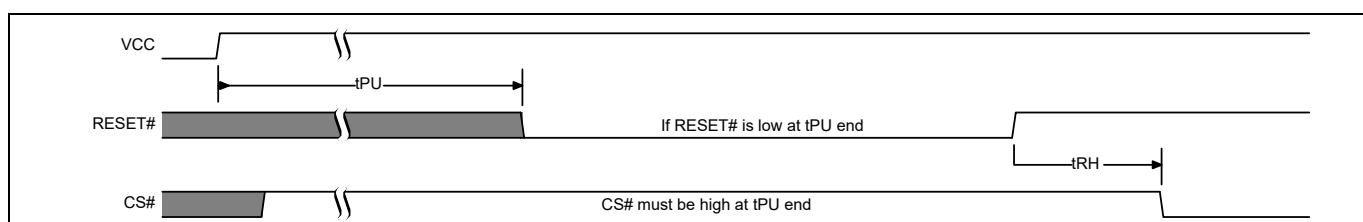

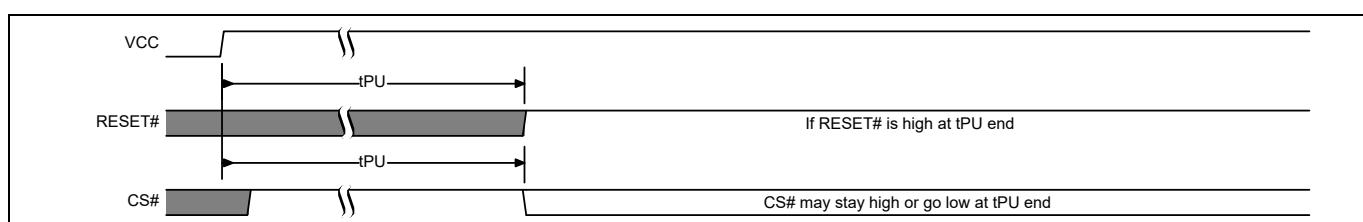

给器件上电并经过  $t_{PU}$  时间后，RESET# 也会导致相同的初始化过程。

此外，可随时将 RESET# 置为低电平。为了确保数据的完整性，一旦器件准备好接收某个命令序列时，需要重新对由硬件复位中断的操作进行初始化。

RESET# 具有一个内部上拉电阻；如果不使用该引脚，则在主机系统中它可以保持为不连接状态。如果主机系统将复位信号驱动为高电平，然后停止驱动该信号，则通过使用内部上拉电阻将该信号保持为高电平。

RESET# 输入在所有封装中均不可用。器件的 RESET# 输入不可用时，它将被锁定为非活动状态。

### **3.11      供电电压 ( $V_{CC}$ )**

$V_{DD}$  是所有器件内部逻辑的供电电压。这种单个电压用于器件的所有内部功能（包括读取、编程和擦除操作）。

### **3.12      供电与信号接地 ( $V_{SS}$ )**

$V_{SS}$  器件内核、输入信号接收器和输出驱动器的公共电压开漏和接地参考。

### **3.13      无连接 (NC)**

没有任何器件内部信号被连接到封装引脚，将来也不计划用于信号连接。该连接可能安全地用作印刷电路板 (PCB) 上的信号路由空间。

### **3.14      预留供将来使用 (RFU)**

当前没有任何器件内部信号被连接到封装引脚，预留供将来使用。不建议将 RFU 连接到 PCB 电路板上的任何信号，以便 PCB 可以在尺寸兼容的器件中实现未来的增强型特性。

### **3.15      请勿使用 (DNU)**

器件的内部信号可能被连接到封装引脚。英飞凌可能会使用该引脚进行测试或其他用途，该引脚不应与任何主机系统信号连接。DNU 引脚处于低电平 ( $V_{IL}$ ) 时，与该引脚相关的所有功能均无效。该引脚使用了一个内部下拉电阻，在主机系统中可以保持它为未连接状态或将其连接到  $V_{SS}$ 。请勿将该 DNU 引脚连接到 PCB 板上的任意信号。请勿将主机系统的任何信号连接到该引脚。

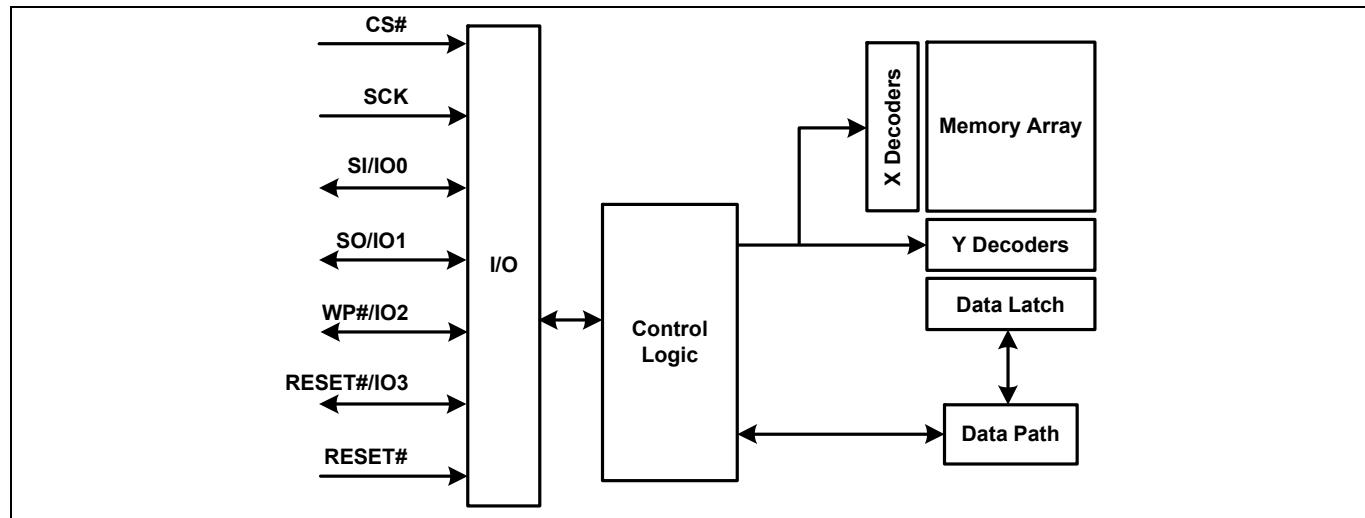

框图

## 4 框图

图 6 逻辑框图

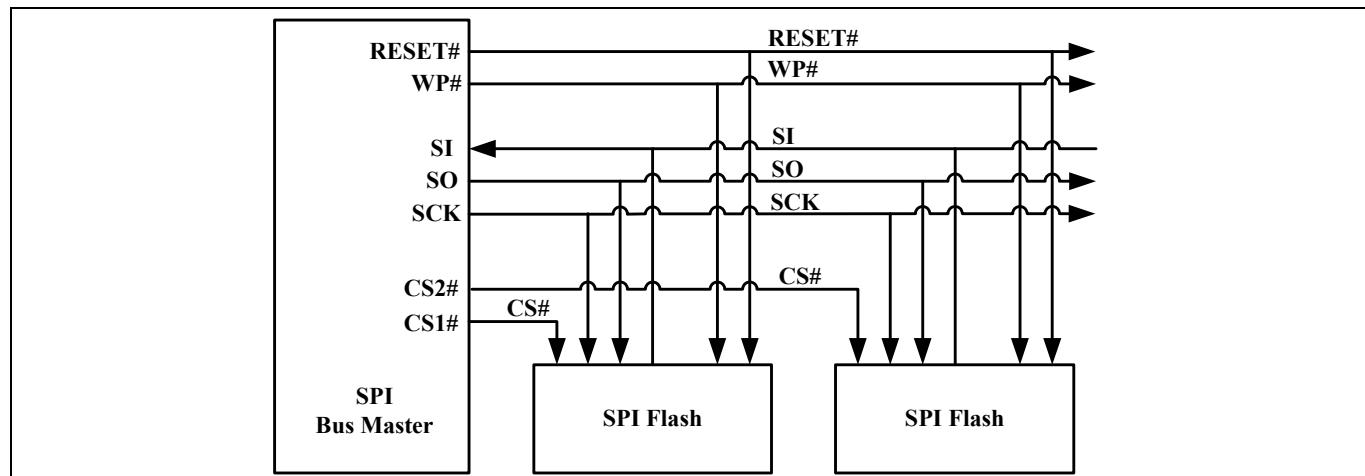

### 4.1 系统框图

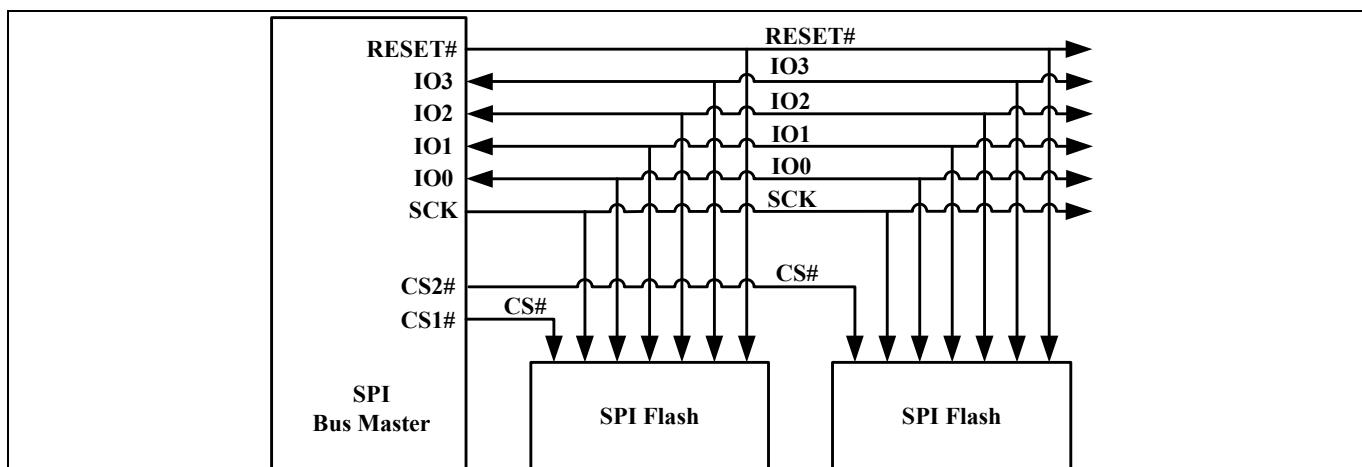

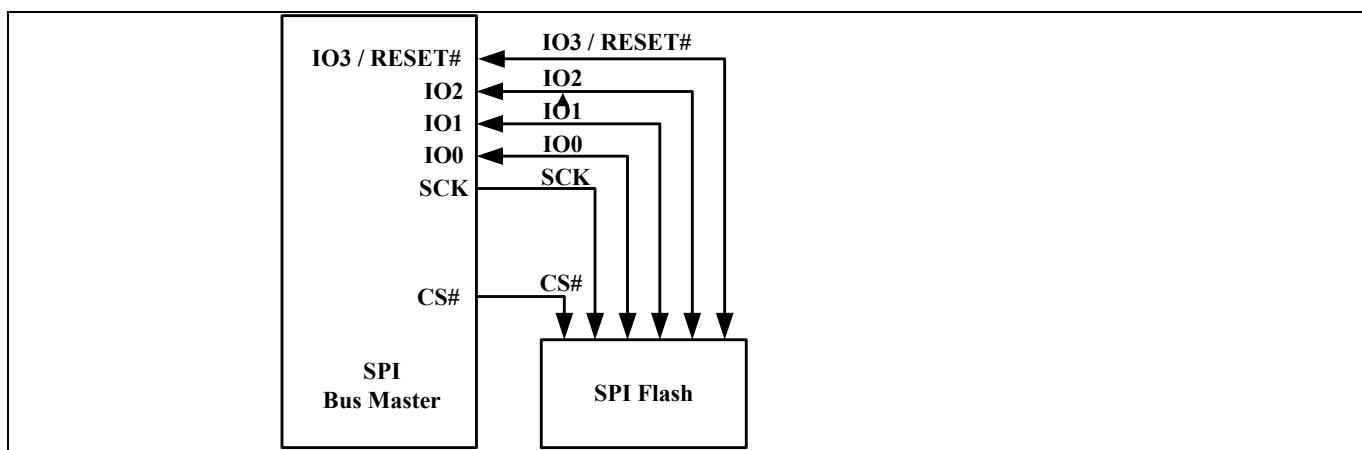

图 7 SPI 总线上的总线主设备和存储器件之间的关系 — 单比特数据路径

框图

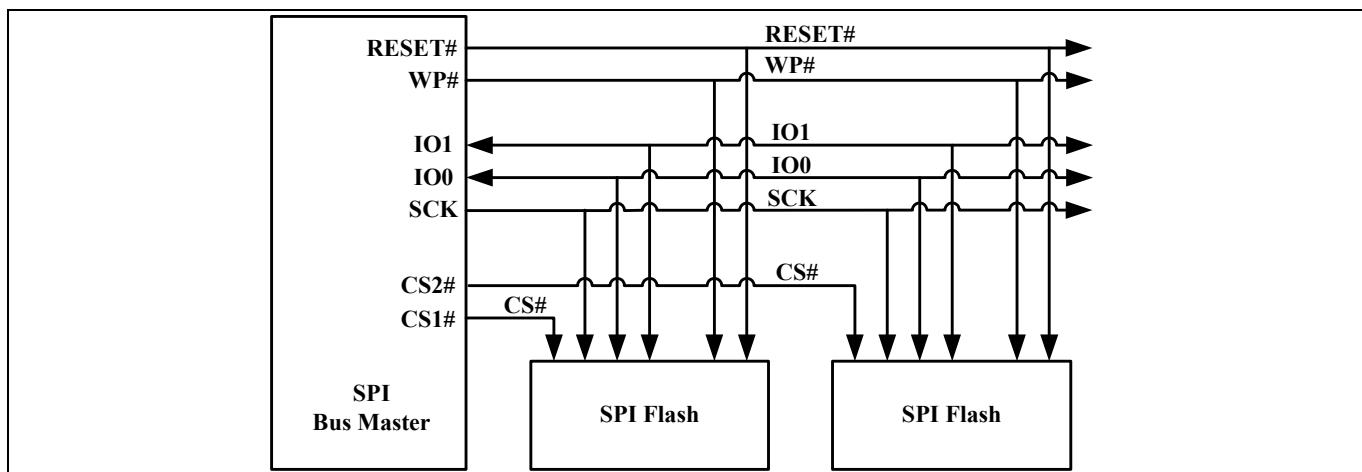

图 8 SPI 总线上的总线主设备和存储器件之间的关系 – 双比特数据路径

图 9 SPI 总线上的总线主设备和存储器件之间的关系 – 四比特数据路径 - 单独 RESET#

图 10 SPI 总线上的总线主设备和存储器件之间的关系 – 四比特数据路径 - IO3/RESET#

信号协议

## 5 信号协议

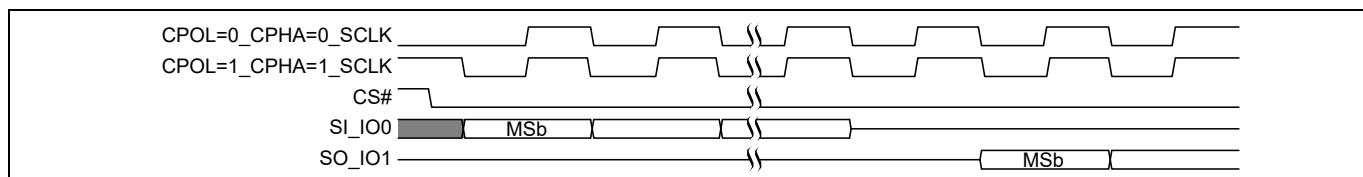

### 5.1 SPI 时钟模式

#### 5.1.1 单倍数据速率 (SDR)

通过嵌入式微控制器（总线主设备）可以将 FL-L 系列驱动到以下任意一种时钟模式。

- 模式 0: 时钟极性 (CPOL) = 0、时钟相位 (CPHA) = 0

- 模式 3: CPOL = 1、CPHA = 1

在这两种模式中，器件的输入数据总是在 SCK 信号的上升沿上被锁存，输出数据总是在 SCK 时钟信号的下降沿上可用。

两种模式间的区别主要是：当总线主设备处于待机模式并且不传输数据时的时钟极性。

- CPOL = 0、CPHA = 0 时，SCK 将处于逻辑低状态

- CPOL = 1、CPHA = 1 时，SCK 将处于逻辑高状态

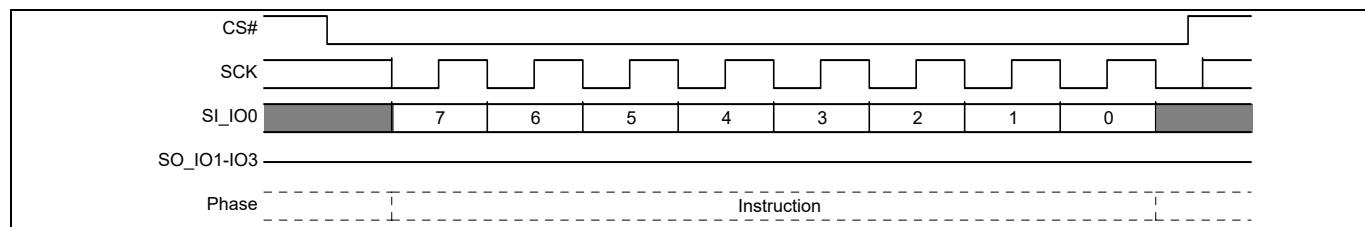

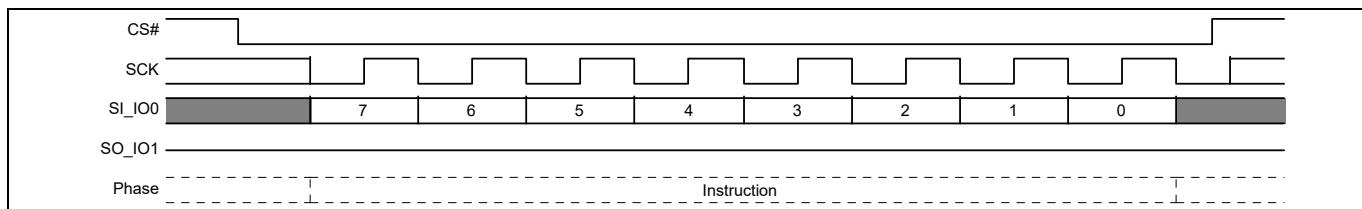

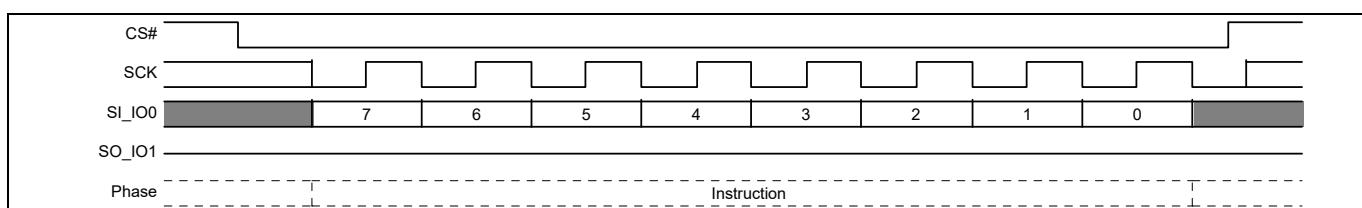

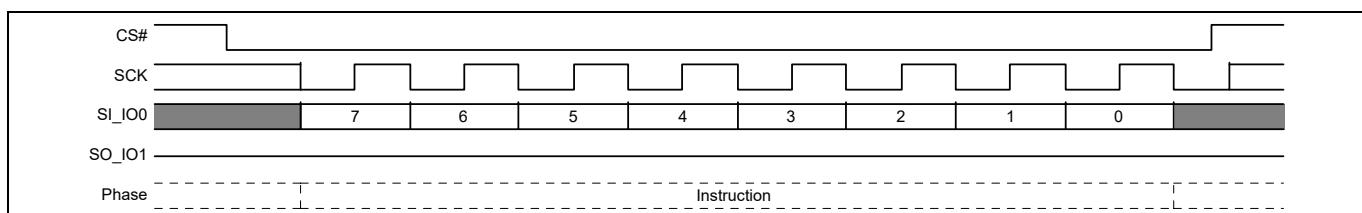

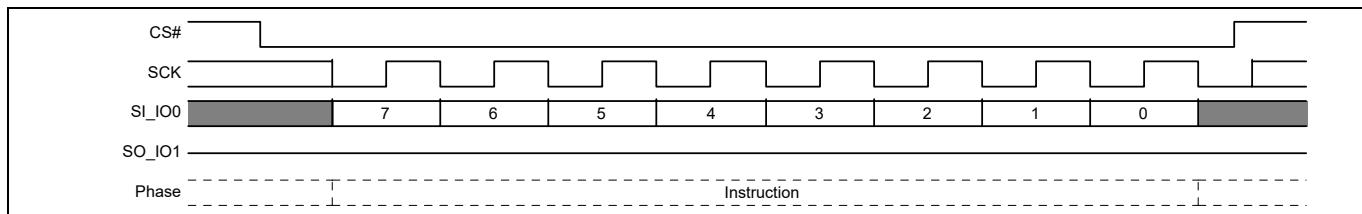

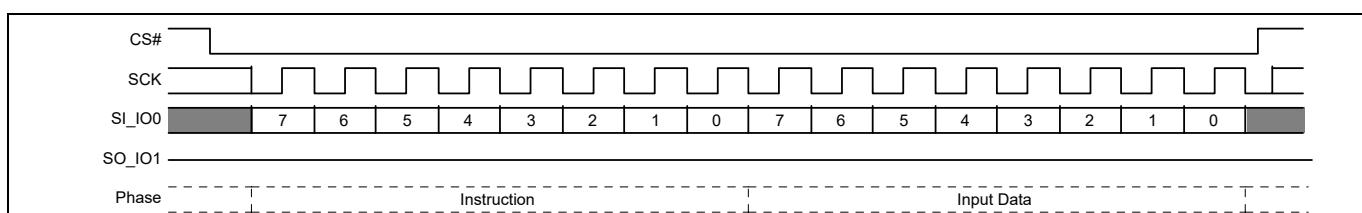

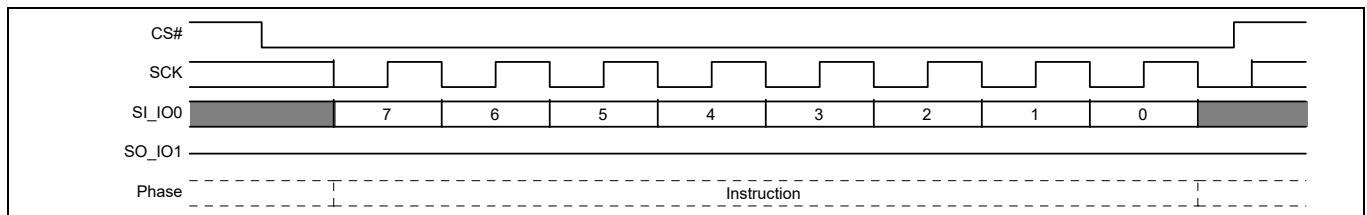

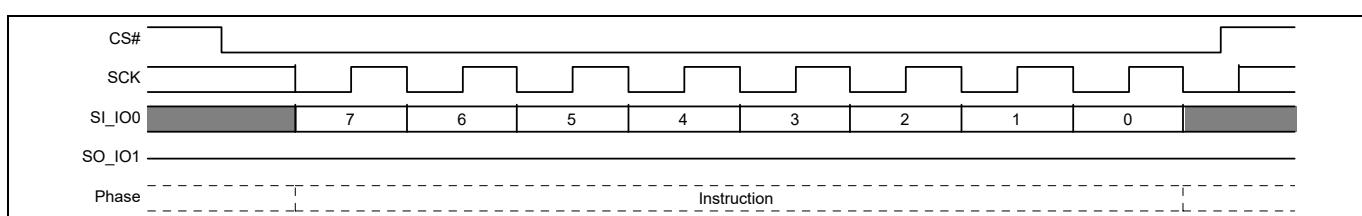

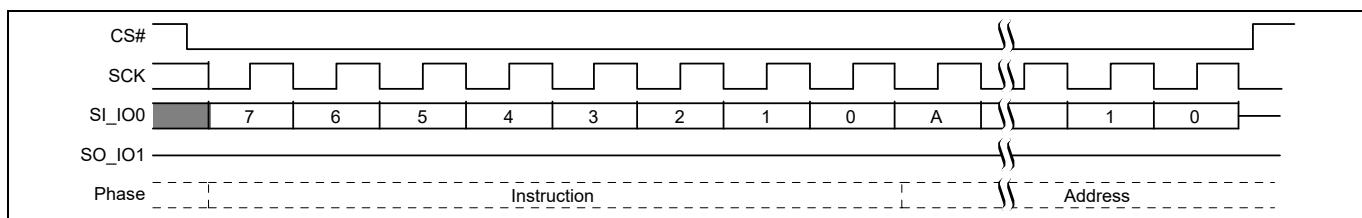

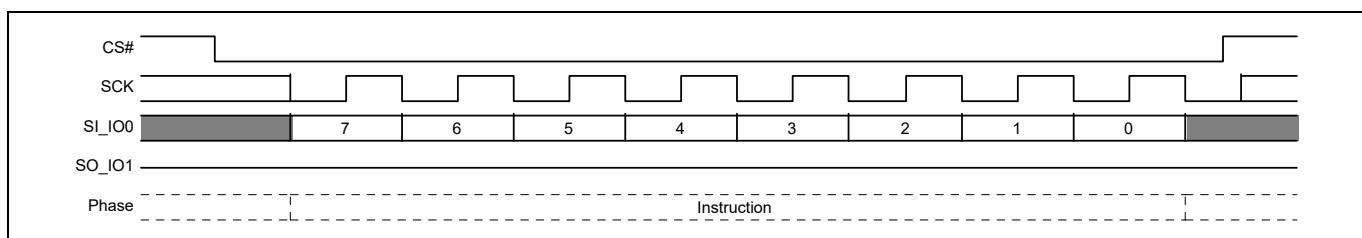

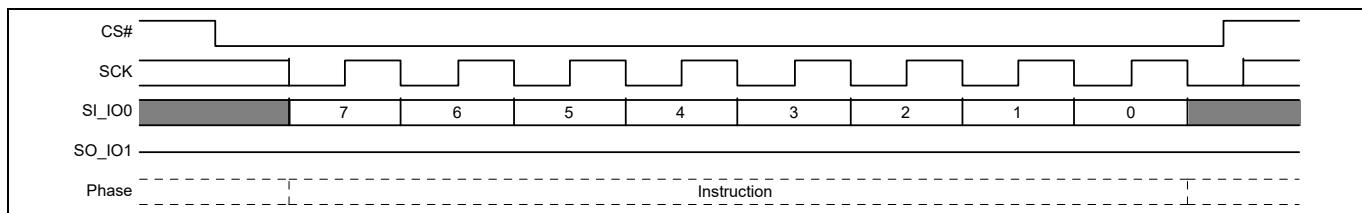

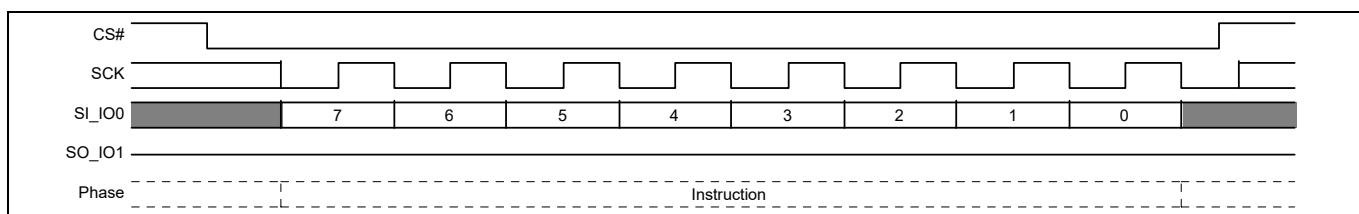

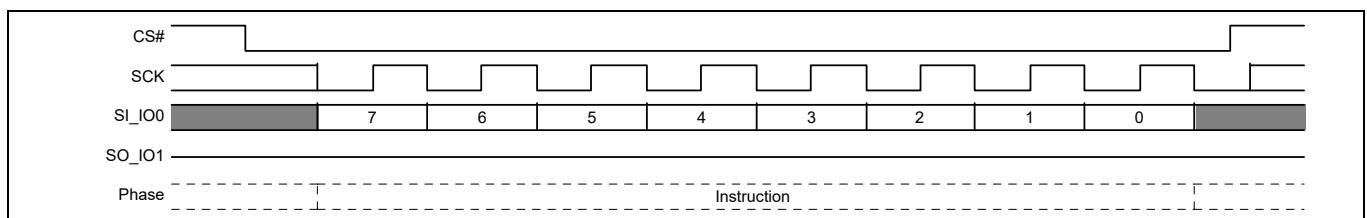

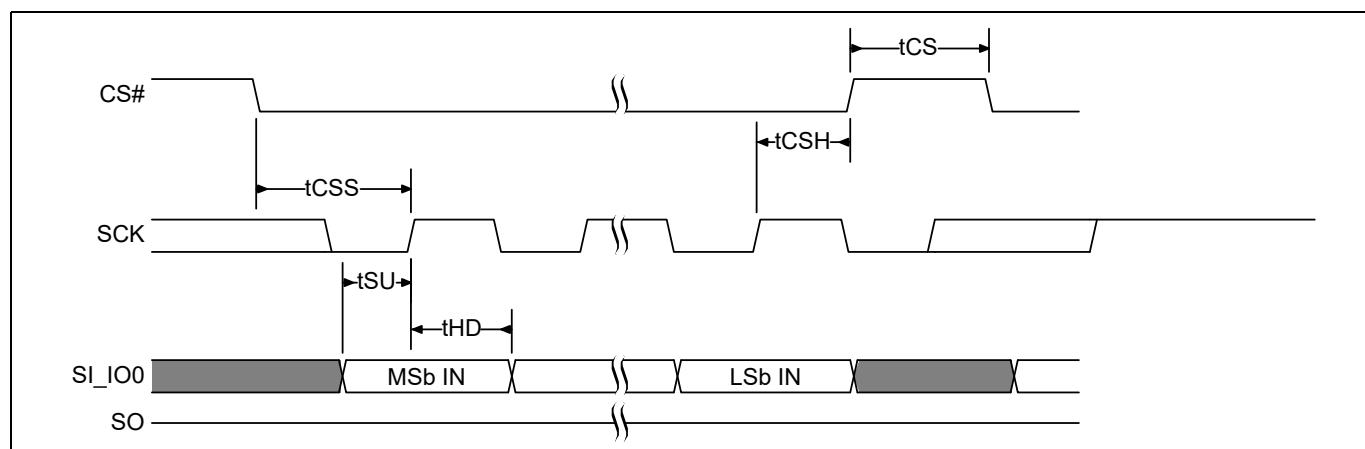

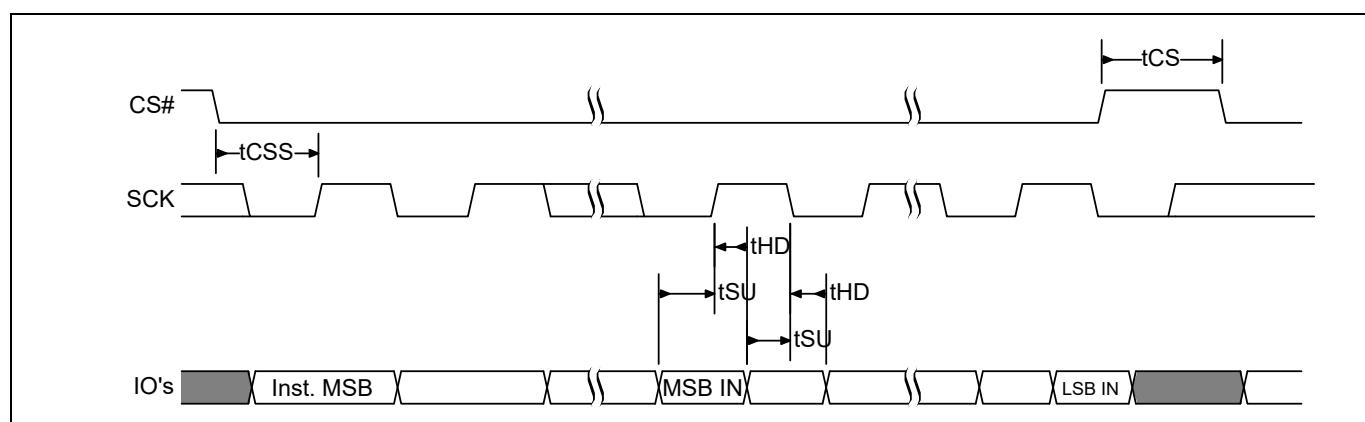

图 11 支持 SPI SDR 模式

整个文档其余部分的时序图通常都是通过显示 SCK 在 CS# 下降沿时的高和低电平来显示模式 0 和模式 3 的。在某些情况下，时序图可能通过显示 SCK 在 CS# 下降沿时的低电平来显示唯一的模式 0。而唯一的模式 3 的时序图只是表示在 CS# 的下降沿上时钟信号为高电平，因此模式 3 不需要从 CS# 下降沿后到 SCK 上升沿前的建立和保持时间。

SCK 周期是从一个 SCK 下降沿到下另一个 SCK 下降沿进行测量（计数）得到的。在模式 0 下，由于开始执行某个命令时 SCK 已经处于低电平状态，因此执行命令时的第一个 SCK 周期指的是从 CS# 的下降沿到第一个 SCK 下降沿。

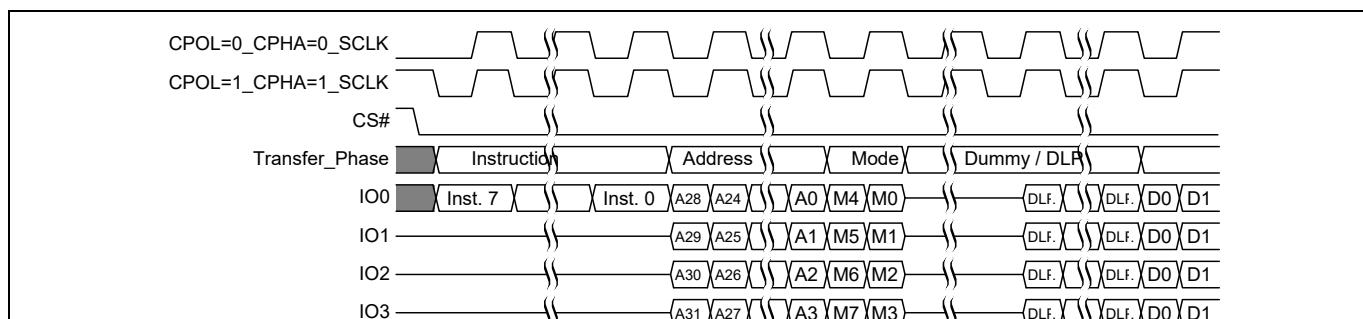

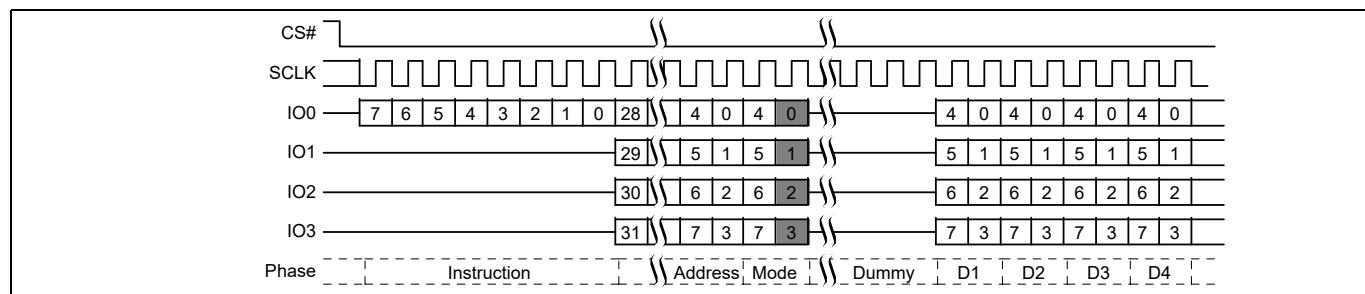

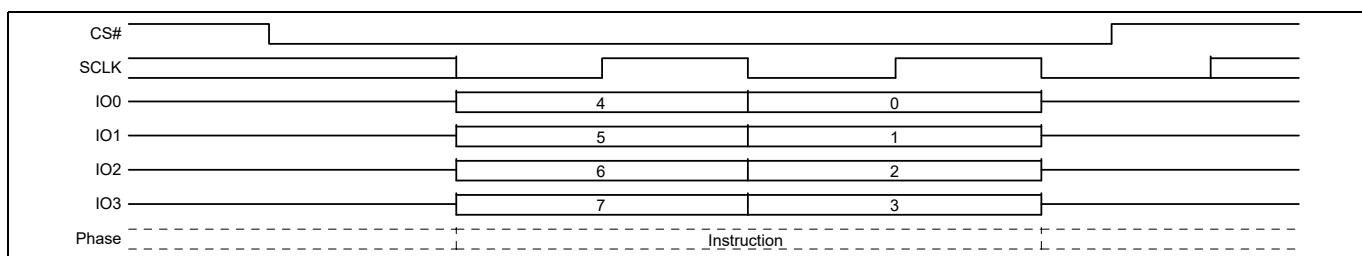

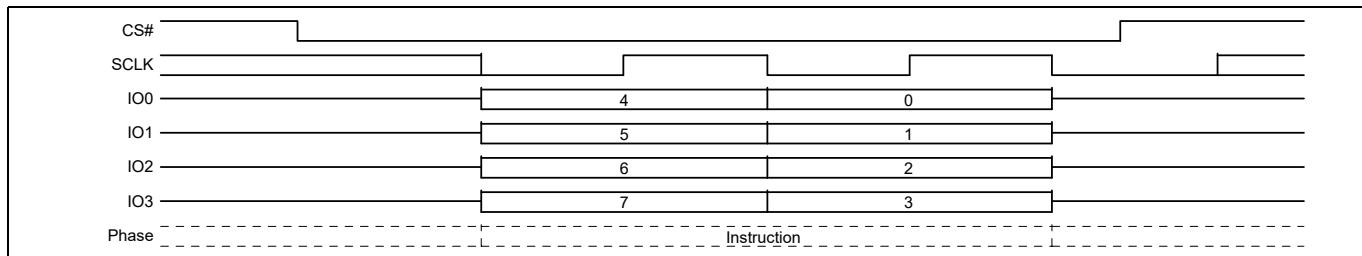

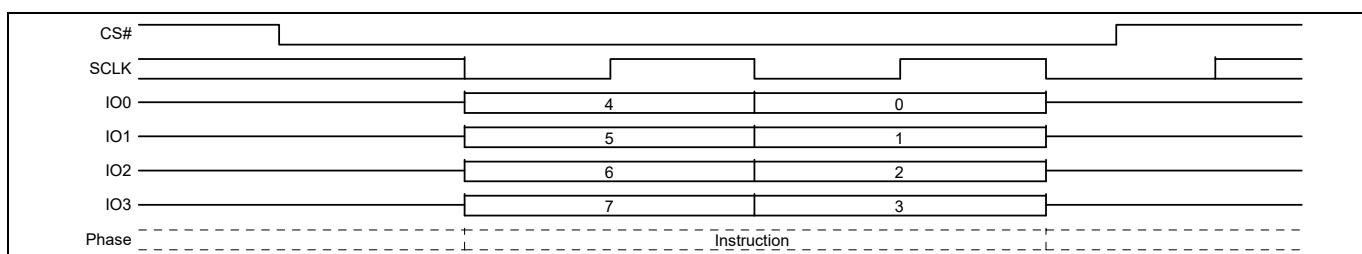

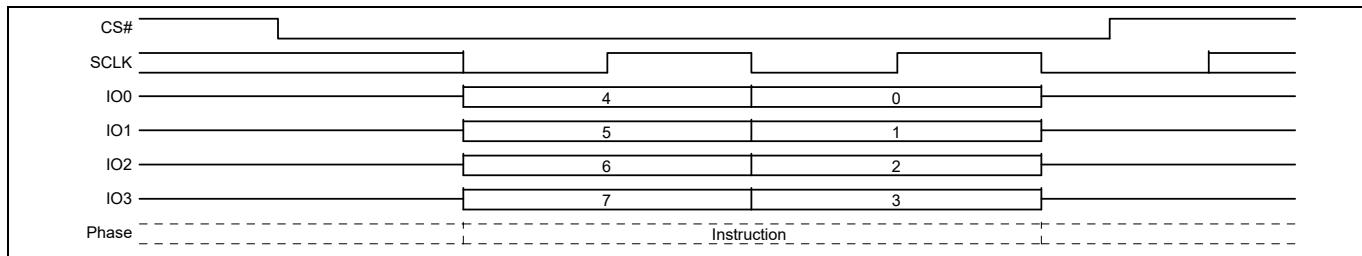

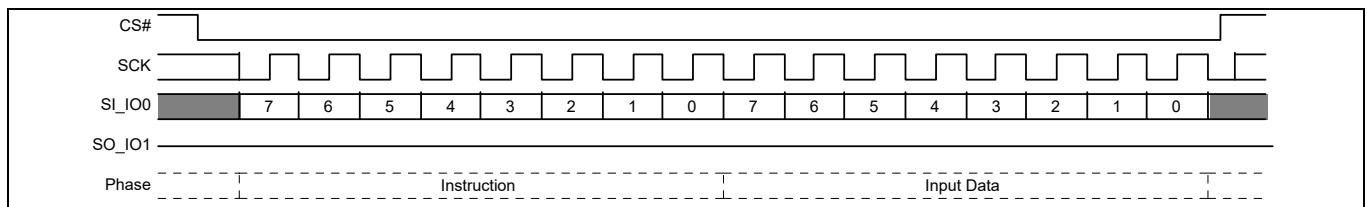

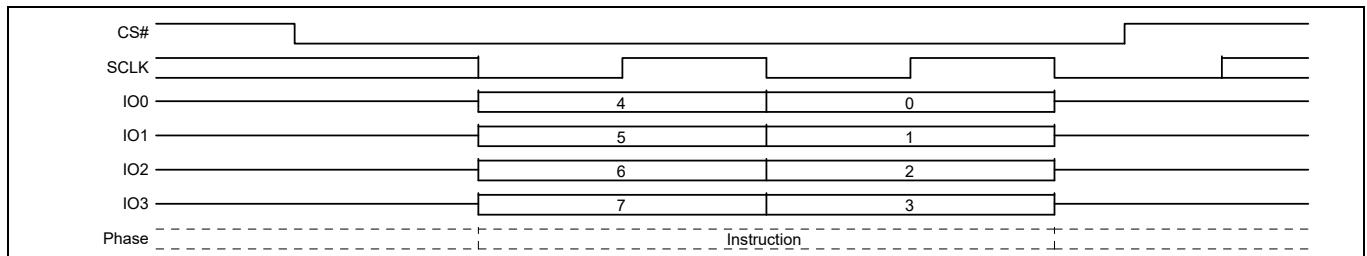

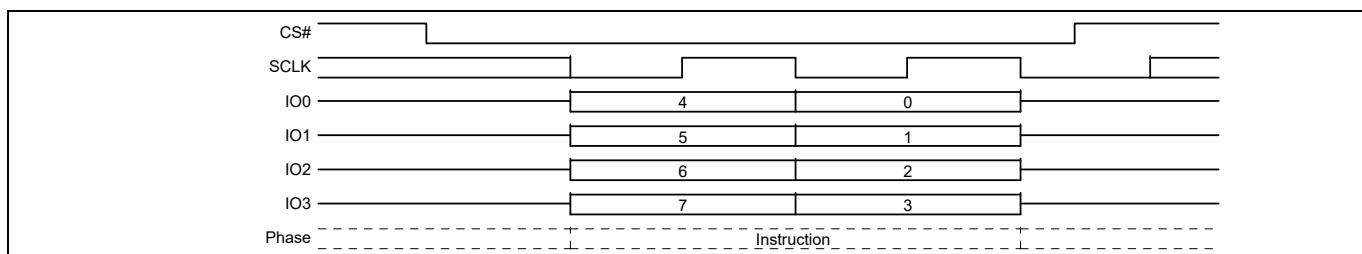

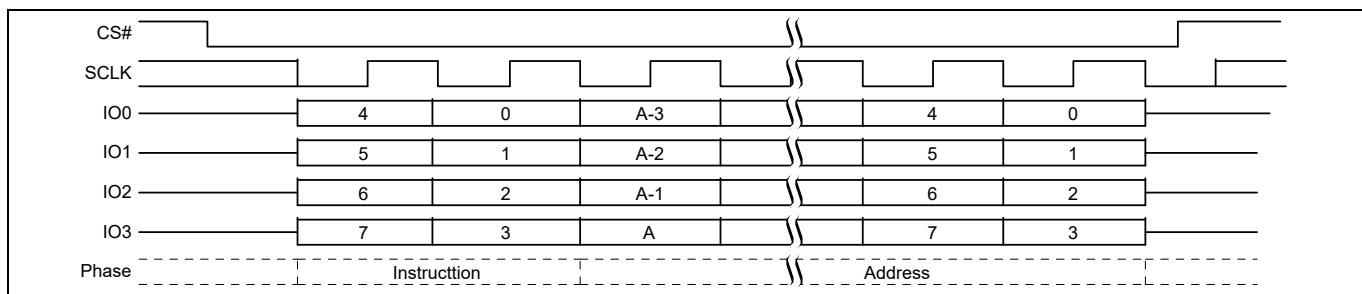

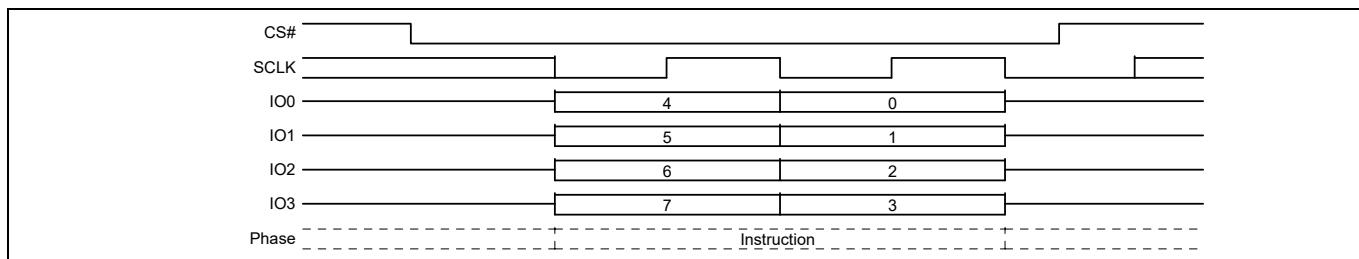

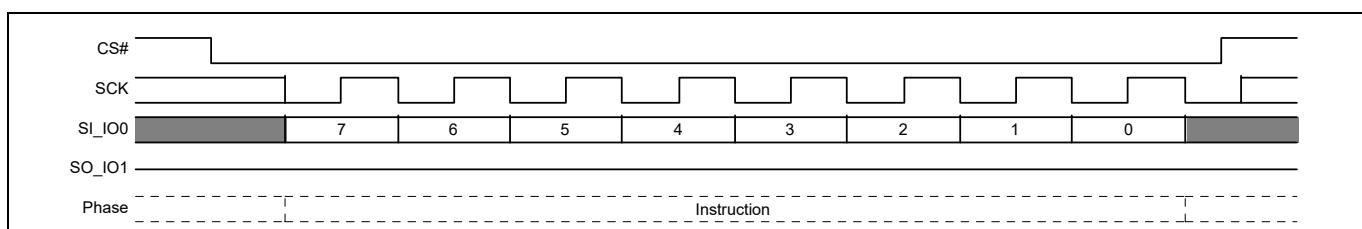

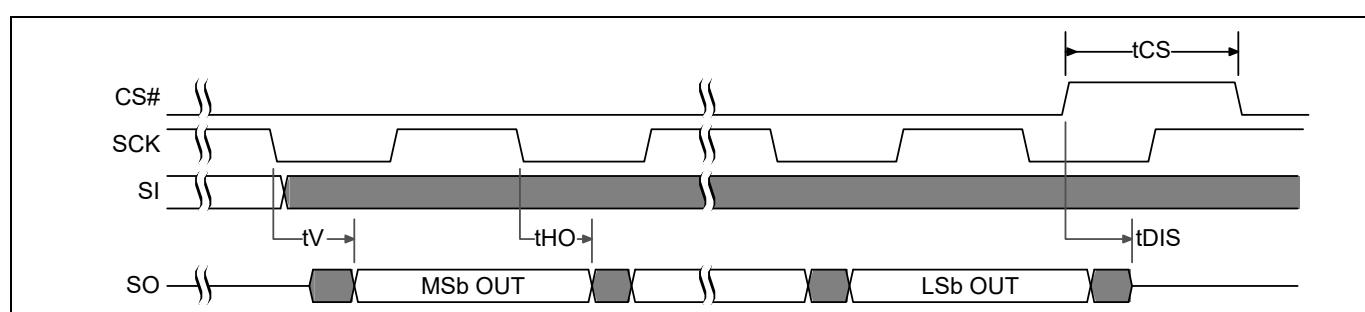

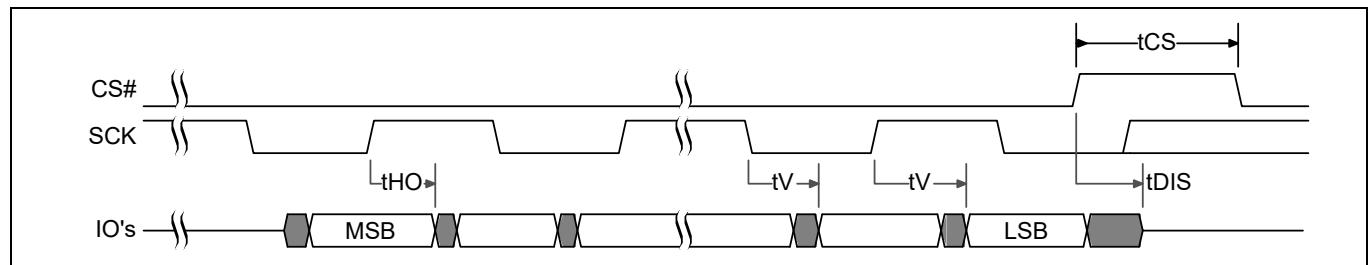

#### 5.1.2 双倍数据速率 (DDR)

DDR 命令也支持模式 0 和模式 3。与 SDR 命令相同，在 DDR 命令中，指令位也是在时钟的上升沿上被锁存的。但是指令后的地址和输入数据则在 SCK 的双边沿上被锁存。最后指令位在 SCK 的下降沿上被锁存之后，第一个地址位会在随后的第一个 SCK 上升沿上被锁存。第一个输出数据位则在最后访问延迟（虚拟）周期结束后的下降沿上被发送。

与 SDR 命令相同，SCK 周期也是从一个 SCK 下降沿到下一个 SCK 下降沿进行测量（计数）得到的。在模式 0 下，由于开始执行某个命令时 SCK 已经处于低电平状态，因此执行命令时的第一个 SCK 周期指的是从 CS# 的下降沿到第一个 SCK 下降沿。

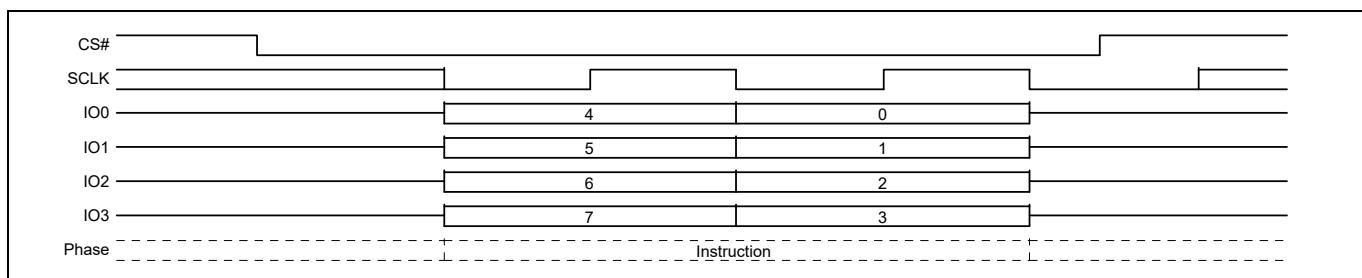

图 12 支持 SPI DDR 模式

信号协议

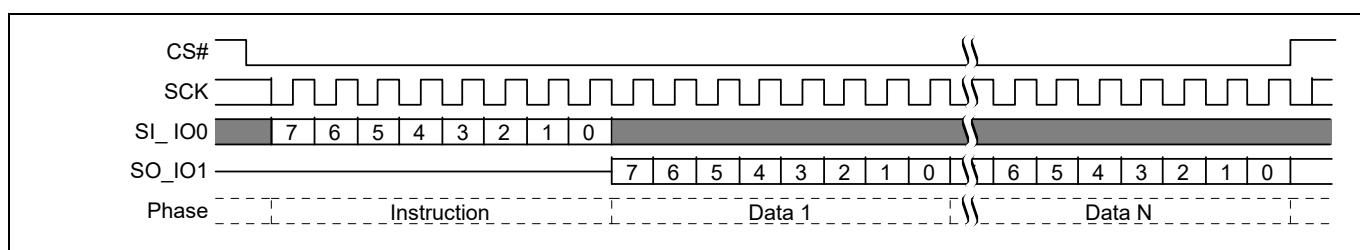

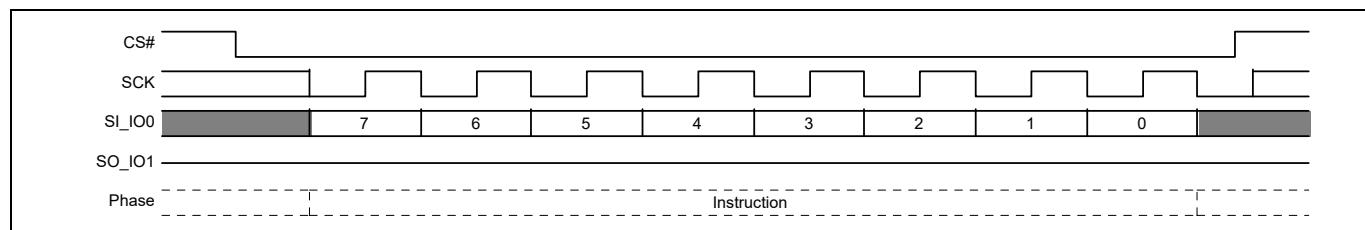

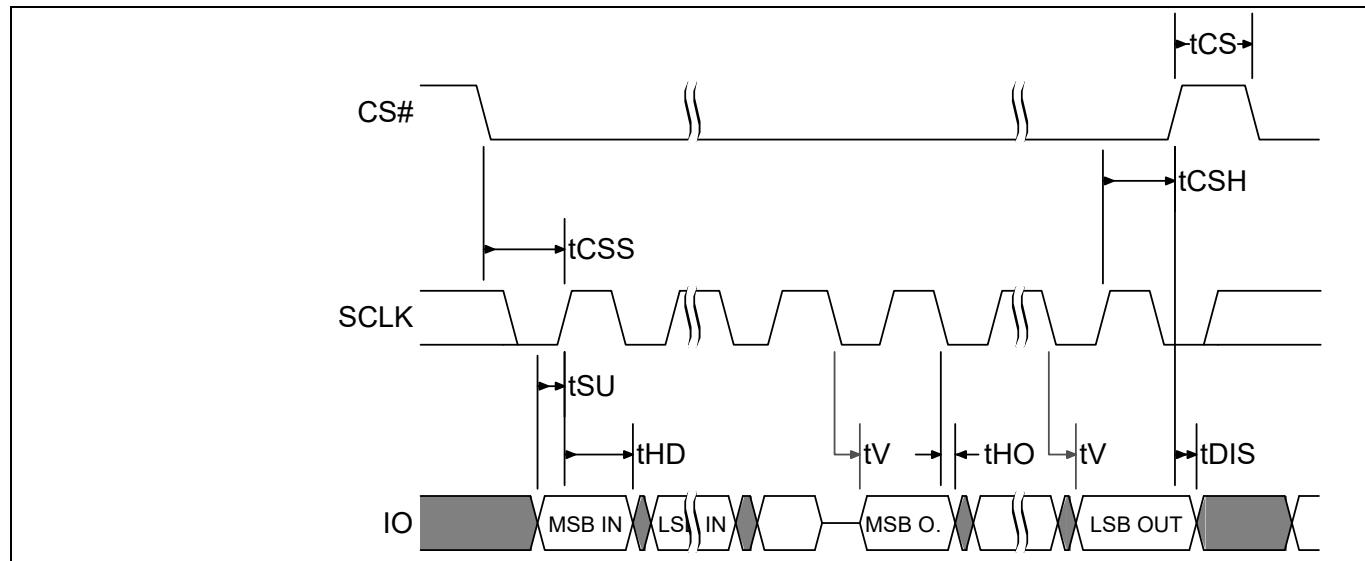

## 5.2 命令协议

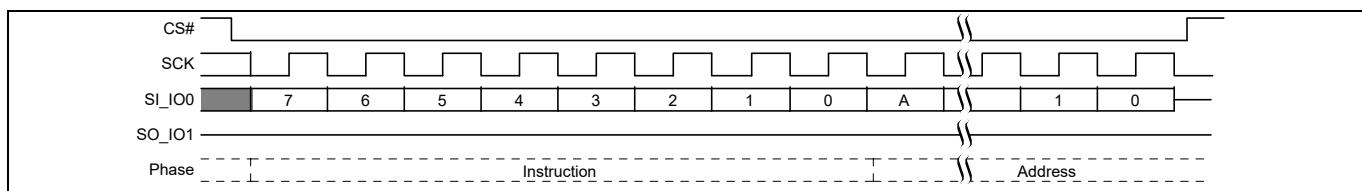

主机系统和 FL-L 存储器件系列之间都是以单位 (unit) 形式 (称为命令) 进行通信的。如需了解所有命令的定义和详情, 请参阅第 69 页的 "命令"。

所有命令都以一个 8 位指令开始, 该指令用于选择信息传输类型或器件需要执行的操作。命令可能也具有一个地址、指令修饰符、延迟周期、传送到存储器, 或者是从存储器传送的数据。主机系统和存储器件之间的所有指令、地址和数据信息都是连续传输的。

通过一个使用 3 个数字的数字命令法来划分命令协议, 以便能参考三个命令阶段的发送宽度。

- 指令;

- 地址和指令修饰符 (连续读取模式位);

- 数据。

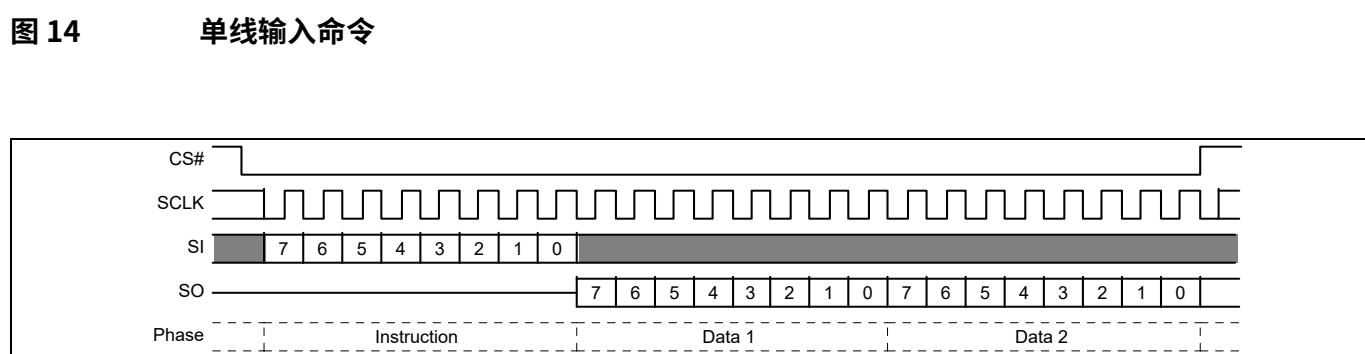

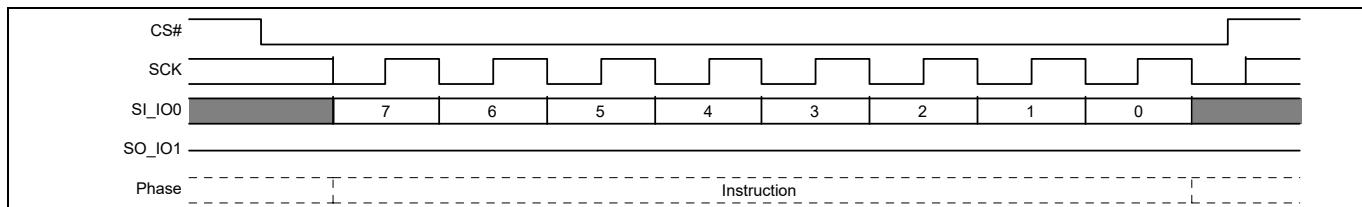

单比特命令只通过 SI 信号依次传输指令和地址或数据。数据会通过 SO 信号从存储器串行回送到主机内。对于单比特宽指令, 单比特宽地址和修饰符、单比特数据的结构, 被称为 1-1-1 命令协议。

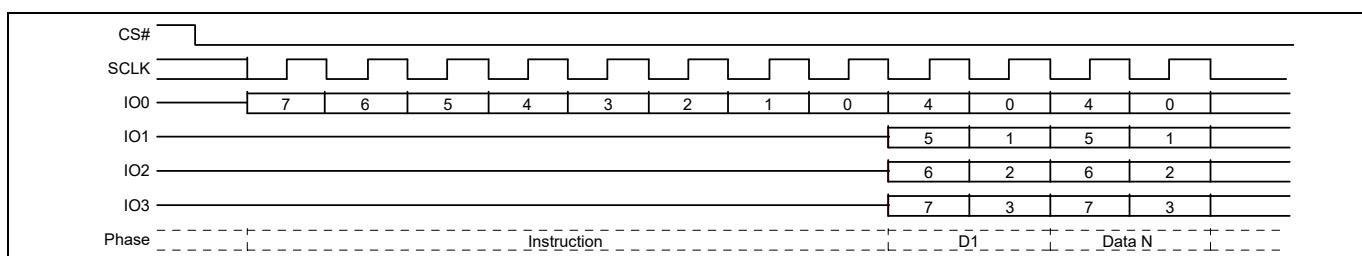

双线输出或四线输出命令从主机端通过 SI (IO0) 将地址和虚拟周期依次进行发送。数据可以按双比特一组的方式通过 IO0 和 IO1 从存储器回送到主机, 也可以按四比特 (半字节) 一组的方式通过 IO0、IO1、IO2 和 IO3 回送。对于双线输出和四线输出命令, 这种结构分别被称为 1-1-2 和 1-1-4 命令协议。

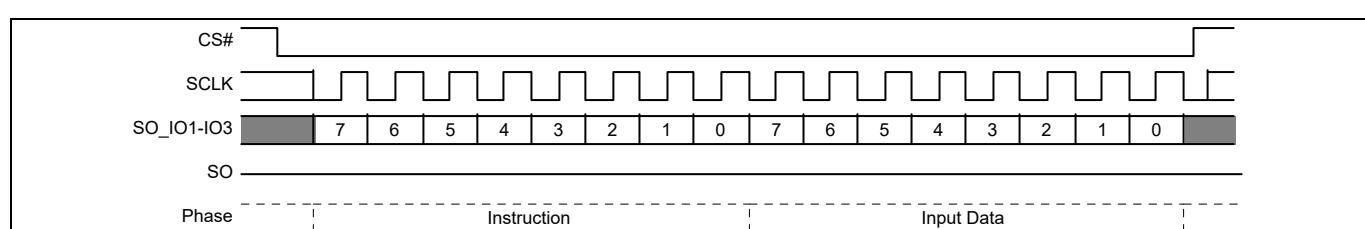

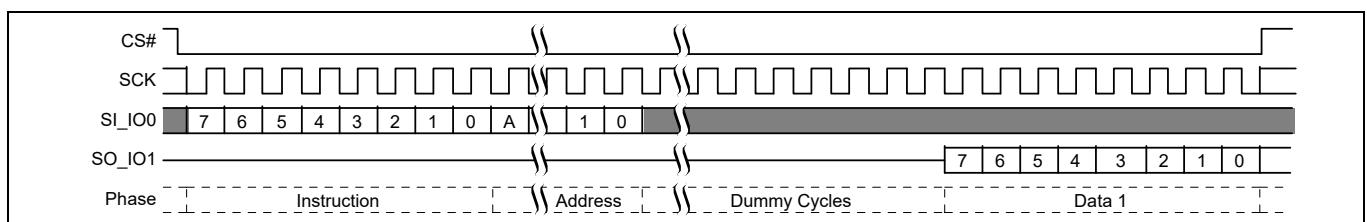

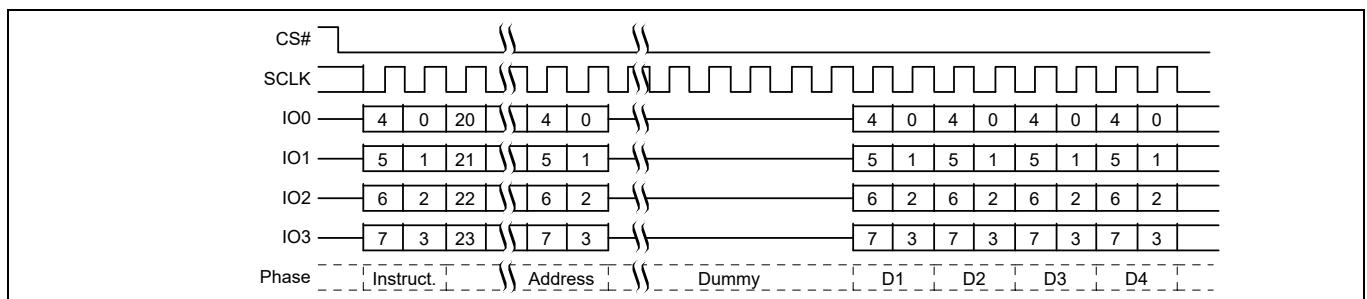

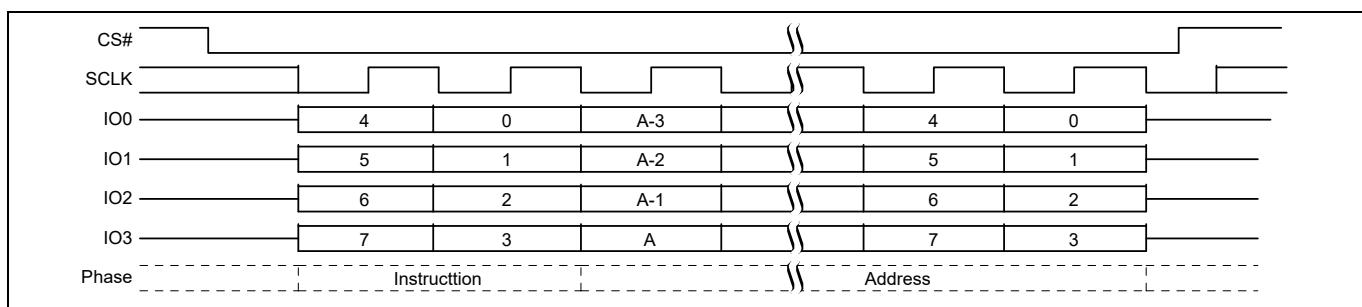

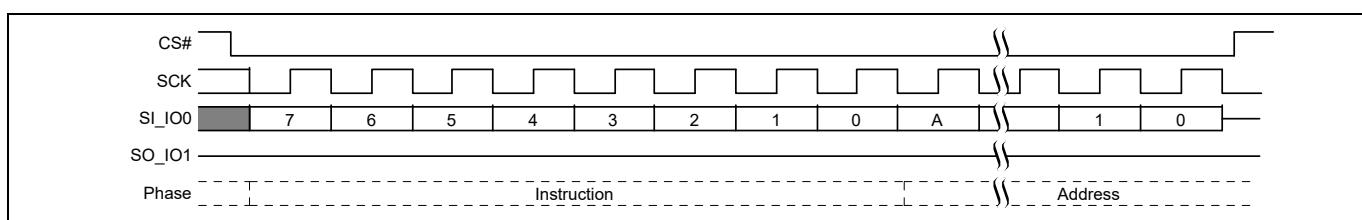

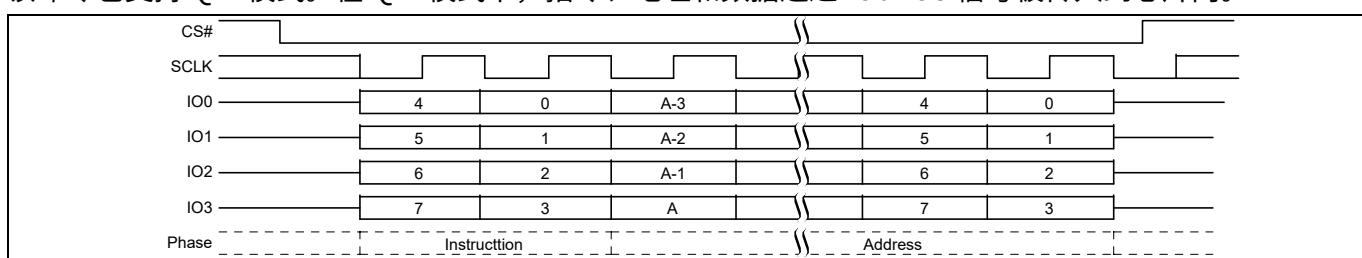

双线或四线输入 / 输出 (I/O) 命令会按双比特一组的方式通过 IO0 和 IO1 将主机的数据传输给存储器, 或按四比特 (半字节) 一组的方式通过 IO0、IO1、IO2 和 IO3 从主机发送, 然后传送虚拟周期。数据也可以按照同样的方式回送给主机。对于双线 I/O 和四线 I/O 命令, 这种结构分别被称为 1-2-2 和 1-4-4 命令协议。

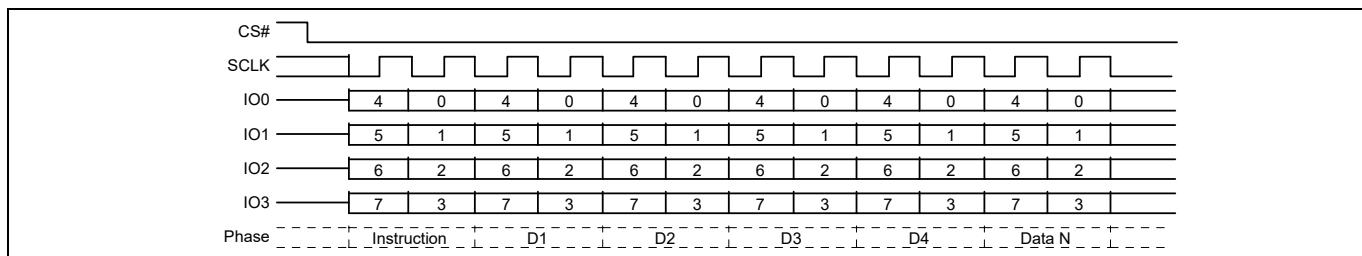

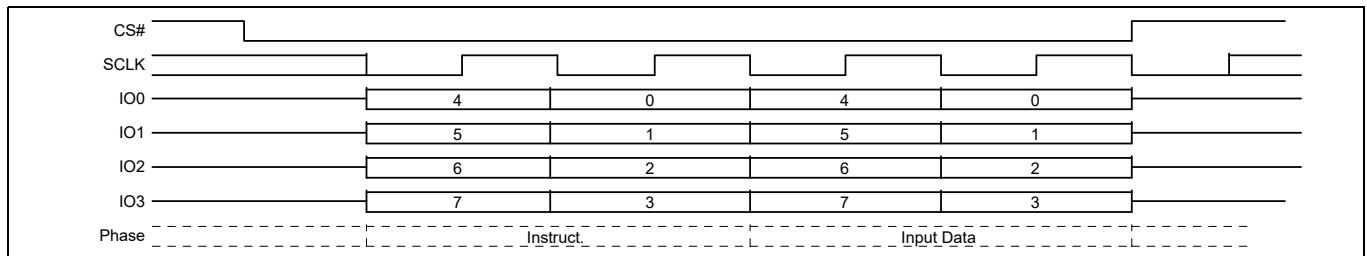

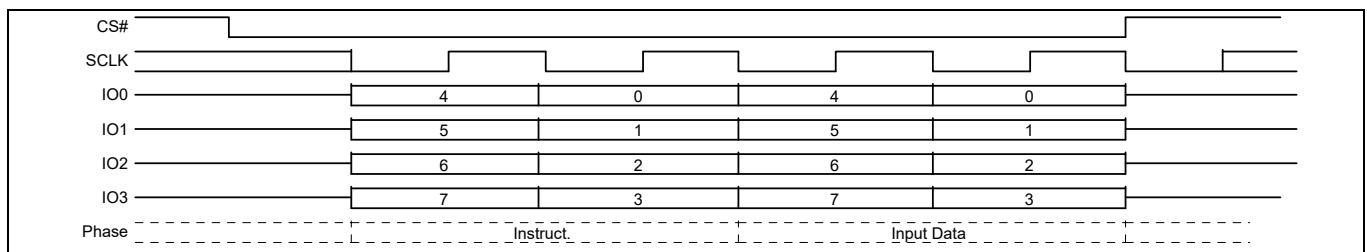

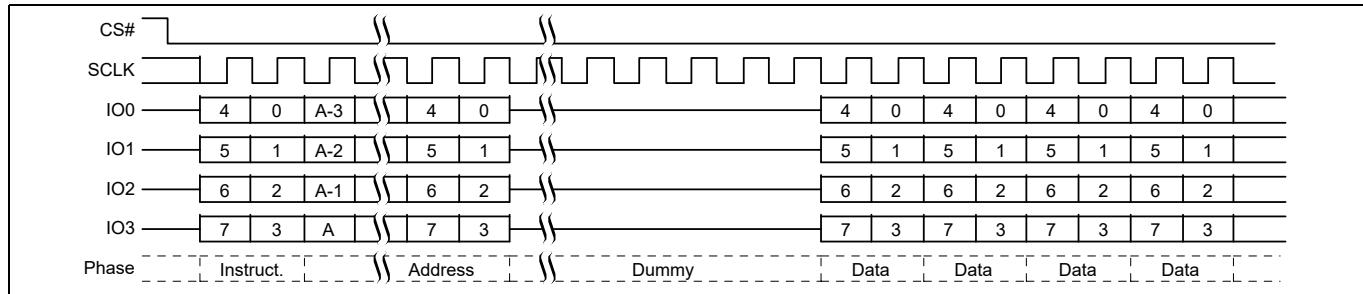

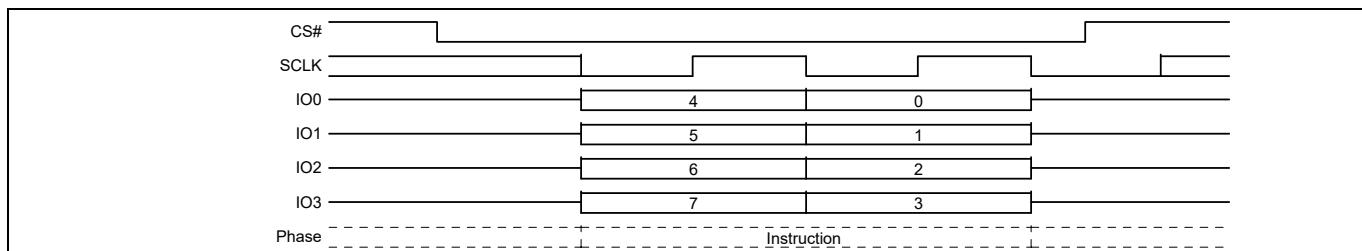

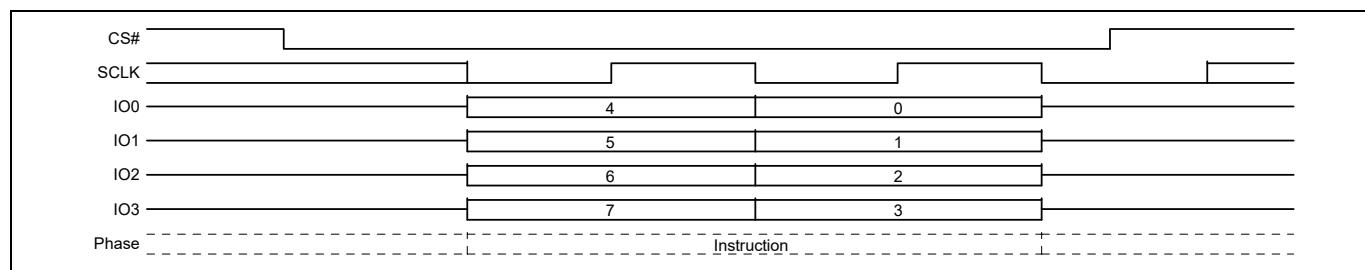

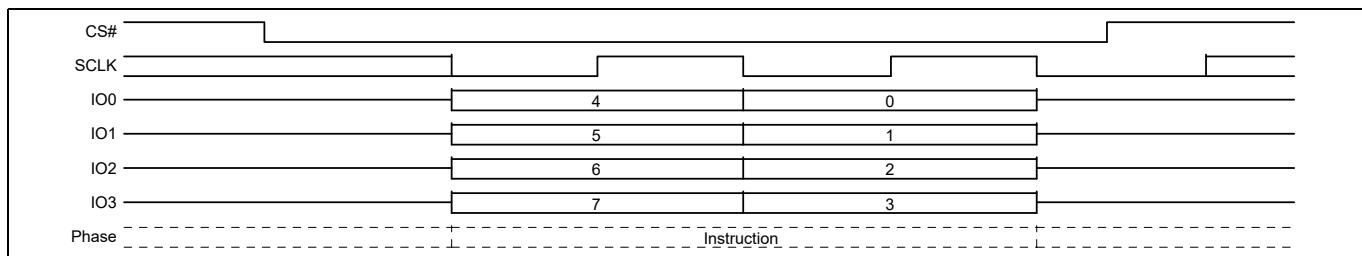

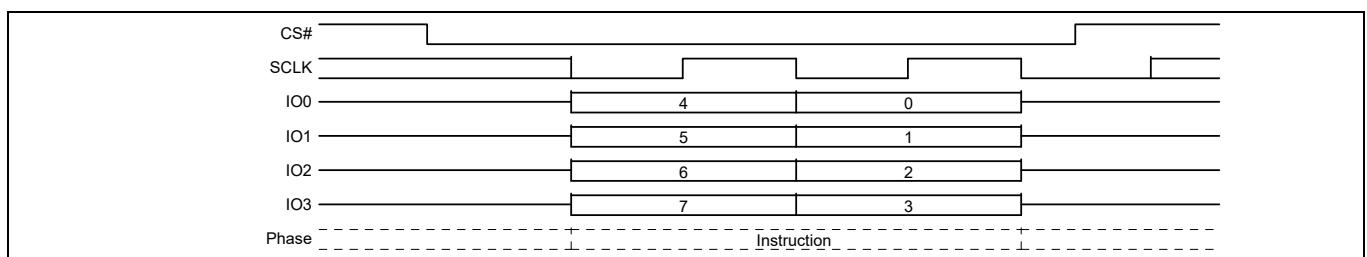

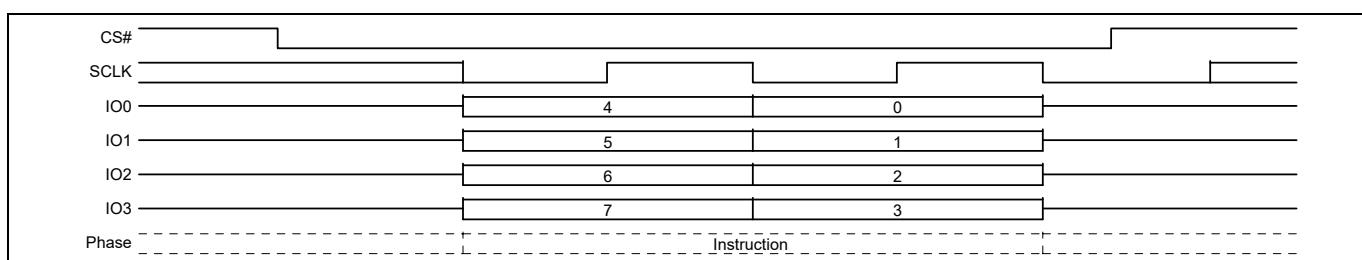

FL-L 系列也支持 QPI 模式, 在该模式下所有信息 (包括指令、地址、修饰符和数据) 都以 4 比特的宽度传输。这种形式被称为 4-4-4 命令协议。

命令的结构如下:

- 每个命令都在 CS# 的下降沿开始执行, 并在 CS# 的上升沿结束。主机通过一个命令将芯片选择 (CS#) 信号驱动为低电平, 从而能够选择器件。

- 串行时钟 (SCK) 标记了主机和存储器之间所传输的单个位或一组位。

- 每个命令都以一个 8 位 (一个字节) 的指令开始。该指令用于选择信息传输类型或需要执行的器件操作。该指令在 SCK 的上升沿上进行传送。但某些读命令被前一个读命令修改, 因此该指令要从更早的命令中显示。这种形式被称为连续读取模式。器件处于连续读取模式时, 由于该指令和用于初始化连续读取模式的读取命令相同, 所以各个指令位不会在开始执行命令时被传输。在该模式下, 命令会从读取地址开始。因此, 连续读取模式会将处于相同类型的读取命令中的每个读命令内的 8 个指令位删除。

- 该指令可以单独在设备的某些地址空间中选择一个位置, 或者跟着地址位一起选择。该指令用于确定所使用的地址空间。地址可能是 24 位或 32 位 (字节边界) 的地址。地址会在 SCK 的上升沿 (若执行 SDR 命令) 或在 SCK 双边沿上 (若执行 DDR 命令) 得到传送。

- 在传统的 SPI 模式下, 传输指令后所有传输宽度都由已发送的指令确定。以下表示的可能是其中一种传输类型: 仅通过串行输入 (SI) 或串行输出 (SO) 信号传输单比特; 通过 IO0 和 IO1 信号每次 (双线) 传输将以双比特的形式进行发送; 或通过 IO0-IO3 信号每次 (四线) 传输以 4 比特的形式执行。在双比特或四比特组中, 最低有效位是通过 IO0 信号发送的。其他更高有效位则按照权值大小通过编号更高的 IO 信号发送。单比特或并行比特组则按照从最高有效位到最低有效位的顺序进传输。

- 在 QPI 模式下, 所有信息都按照 4 比特宽 (四线传输) 通过 IO0-IO3 信号进行发送。

- 双线和四线 I/O 读指令在发送地址后将发送一个指令修饰符 (称为连续读取模式位), 以指明下一个命令的类型与之前的命令相同, 而它并不是明确的命令。这些模式位用于初始化或结束连续读取模式。因此, 下一条命令只会提供新地址和模式位, 并不提供指令字节。当某个命令序列中重复了相同的命令类型时, 会减少发送每一个命令所需要的时间。模式位会在 SCK 的上升沿 (若执行 SDR 命令) 或在 SCK 双边沿上 (若执行 DDR 命令) 进行传送。

- 地址或模式位发送之后可以接着发送将被写入存储器的数据, 可以是一个读延迟周期 (数据返回给主机前)。

- 写入数据位传输会在 SCK 的上升沿 (若执行 SDR 命令) 或在 SCK 双边沿上 (若执行 DDR 命令) 锁存。

## 信号协议

- SCK 会在读访问的延迟周期内继续进行切换。该延迟（又称为虚拟周期）可能为 0 到几个 SCK 周期。最后的读取延迟周期结束后，第一次读取的数据位会在 SCK 下降沿上被输出。第一次读取的数据位被认为是在下一个 SCK 下降沿上传输给主机的。将在 SCK 的下一个上升沿（若执行 SDR 命令）或在 SCK 的任一沿上（若执行 DDR 命令）进行下一次传输操作。

- 如果命令将读数据返回给主机，则存储器件会继续发送数据，直到主机将 CS# 信号驱动为高电平为止。结束读取数据序列中任一个传输操作后，都可以将 CS# 信号驱动为高电平。这样会终止命令。

- 命令被终止时，不会再返回数据，此时主机可将 CS# 输入信号驱动为高电平。传输单独指令的第八位或最后写数据字节的第八位后，CS# 信号必须变为高电平。这样，当位数量在 CS# 被驱动为低电平后是 8 位的整数倍时，必须将 CS# 信号驱动为高电平。如果 CS# 信号在指令或写入数据的 8 位边界后没有变为高电平，该命令将被拒绝，并且不能执行该命令。

- 所有指令、地址和模式位均被移入到器件内，并且先发送最高有效位（MSB）。数据位都被移入到器件，或从器件移出，并且要先传输 MSB。所有数据都以字节为单位进行传输，并且先发送最低地址字节。随后的数据字节按照从最低到最高字节地址的顺序（即字节地址递增）进行发送。

- 在编程、擦除或写周期（嵌入式操作）中，尝试读取闪存阵列的操作均被忽略。嵌入式操作仍继续进行而不受任何影响。执行嵌入式操作时只接受少数命令集。这些信息会在单独命令的说明部分进行介绍。

- 执行时间会因命令不同而发生变化。提供用于读取某个执行命令的状态信息的命令，可确定命令结束的时间，并且确定该命令是否被成功执行。

信号协议

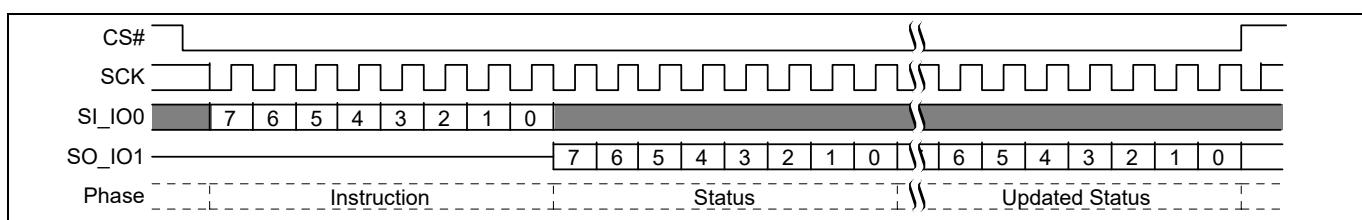

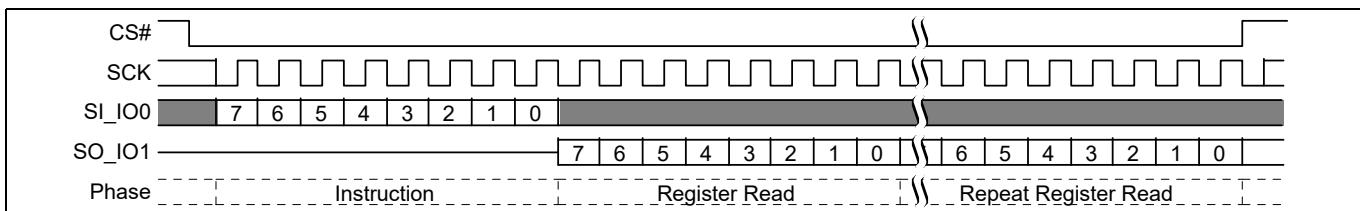

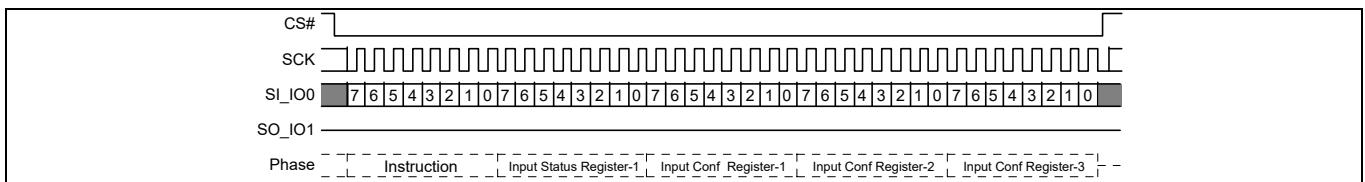

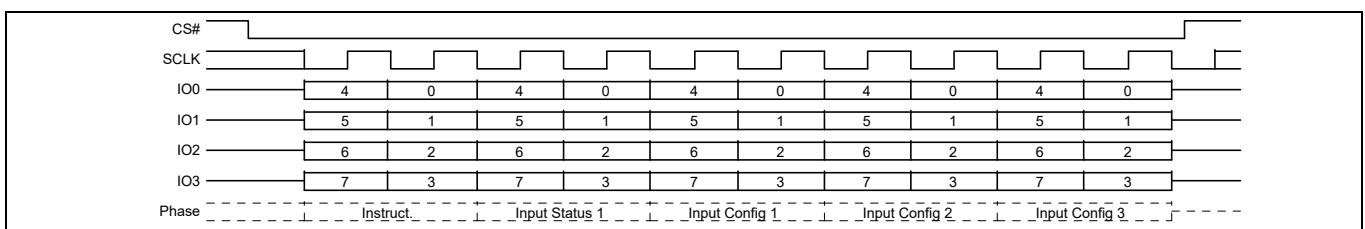

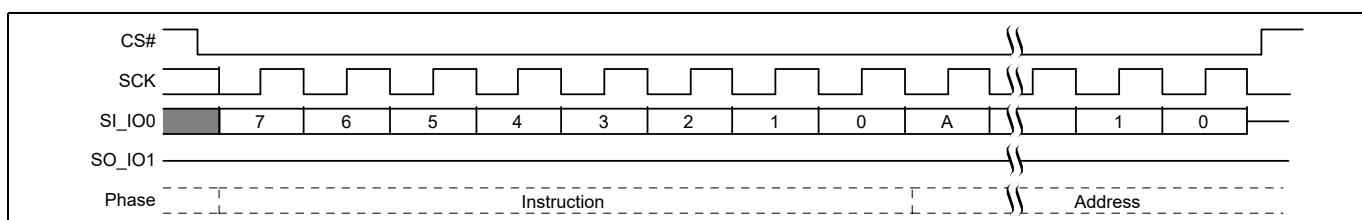

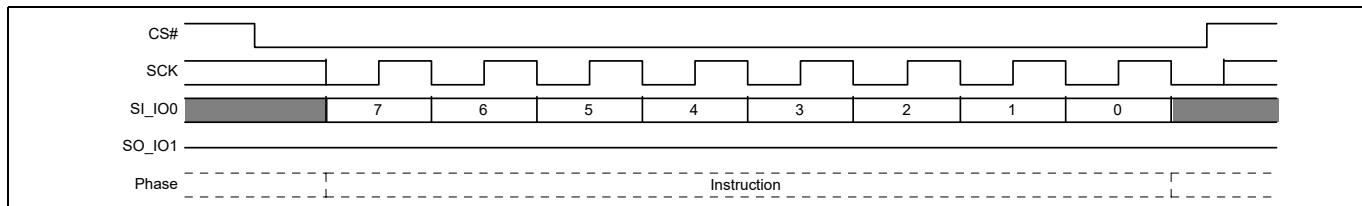

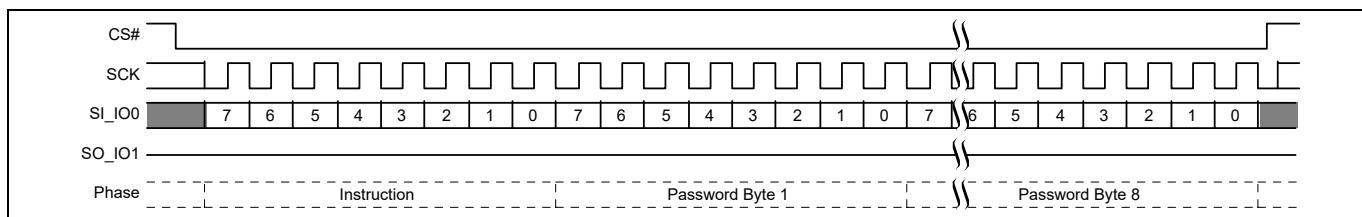

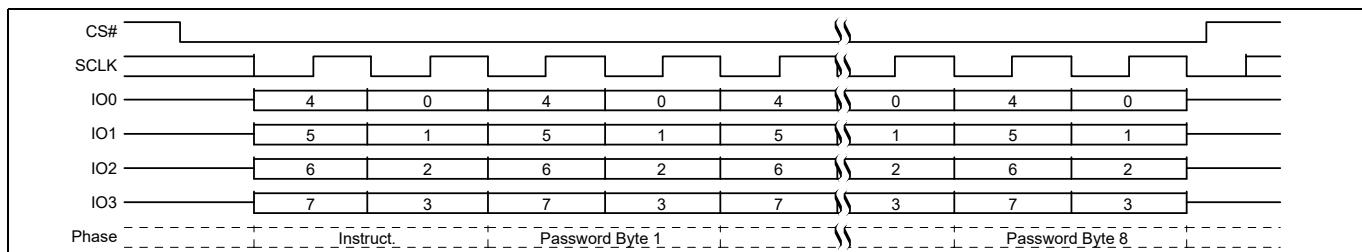

### 5.2.1 命令顺序示例

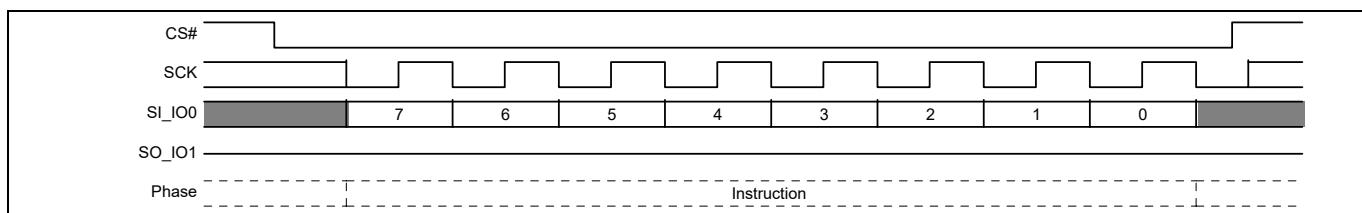

信号协议

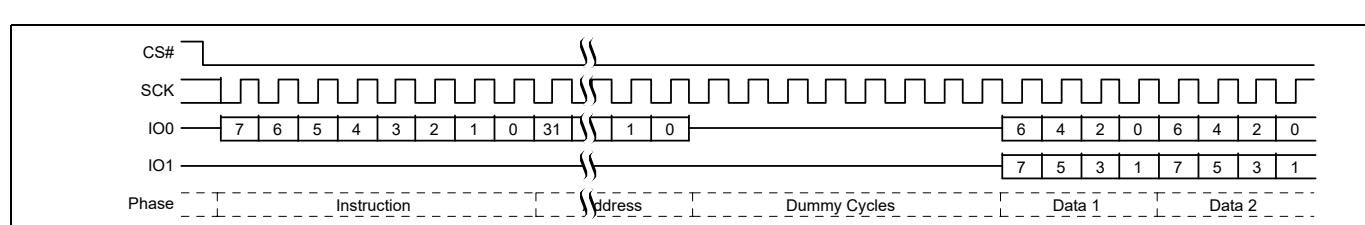

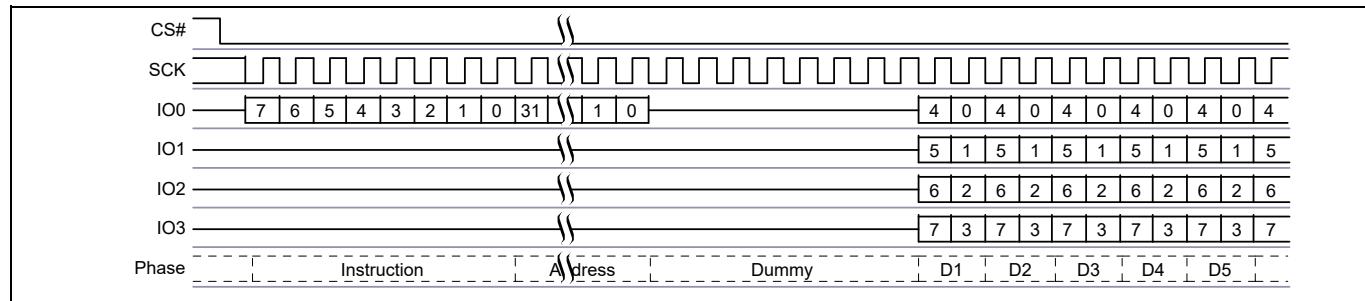

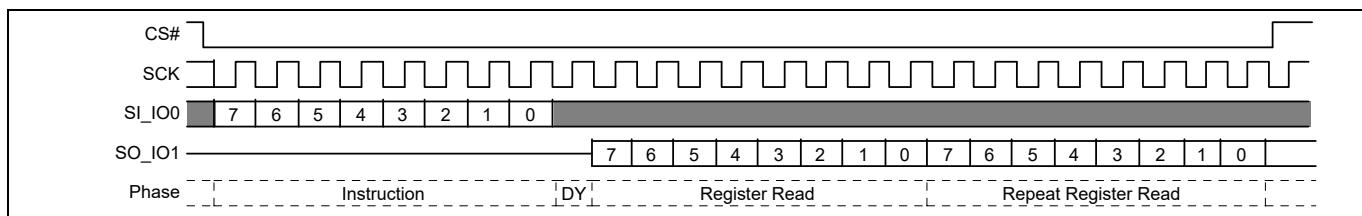

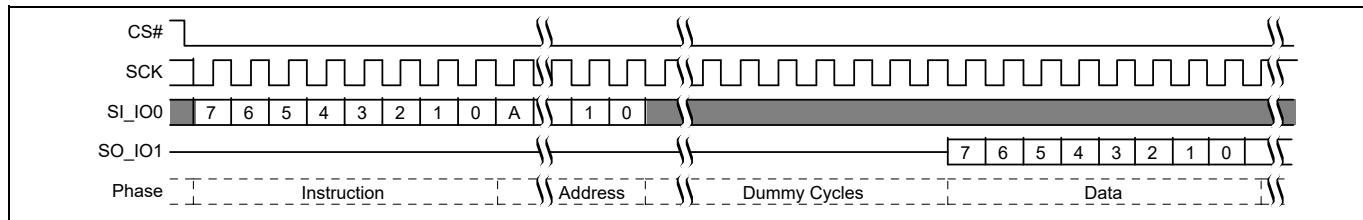

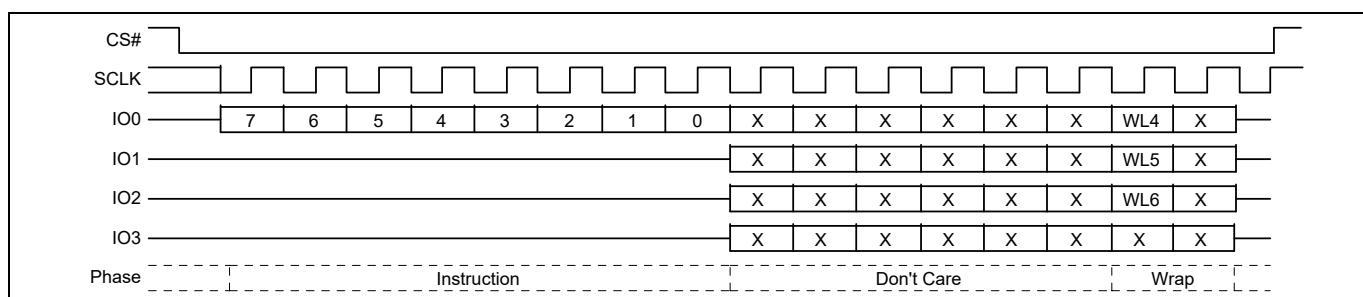

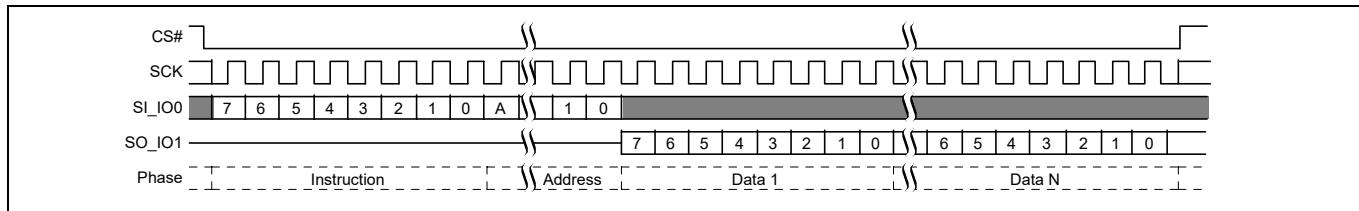

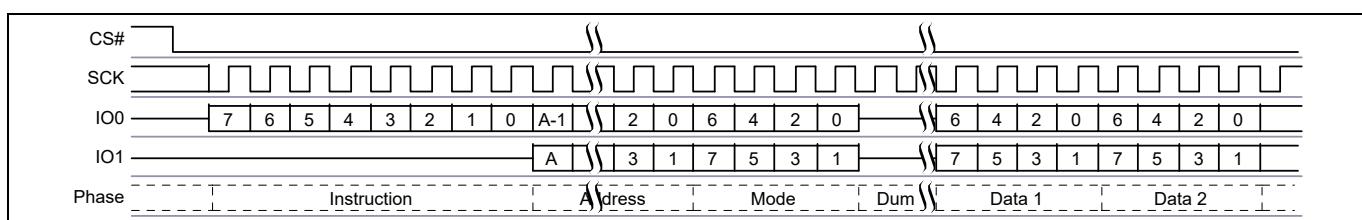

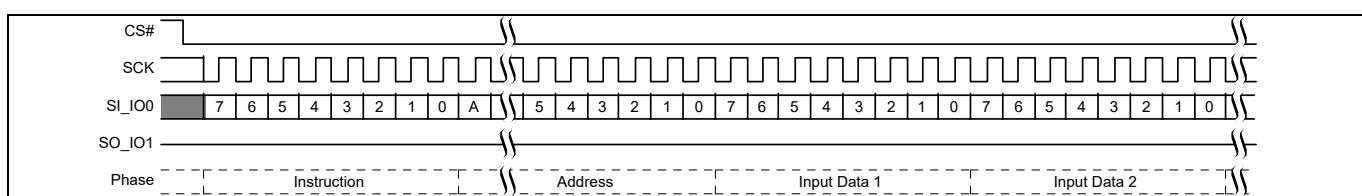

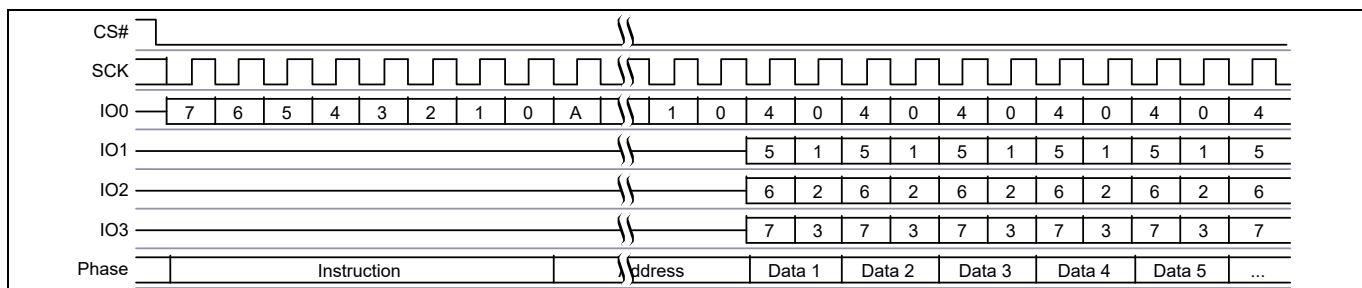

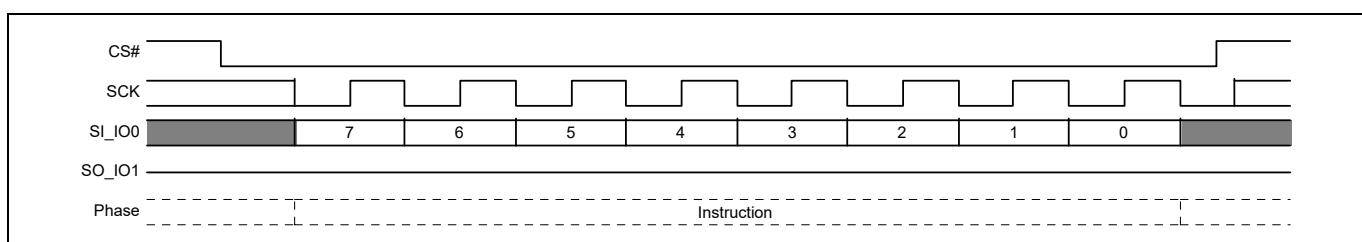

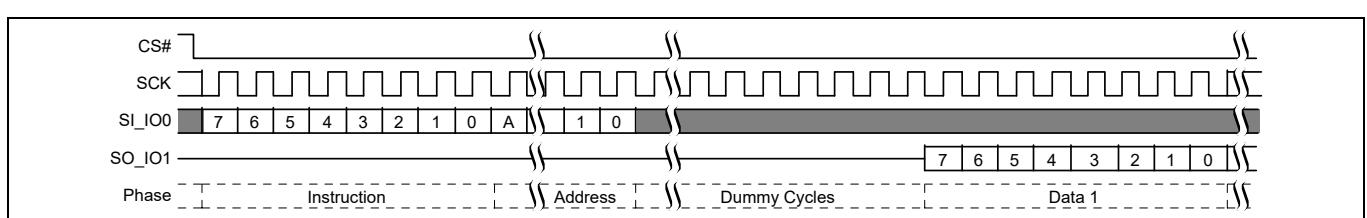

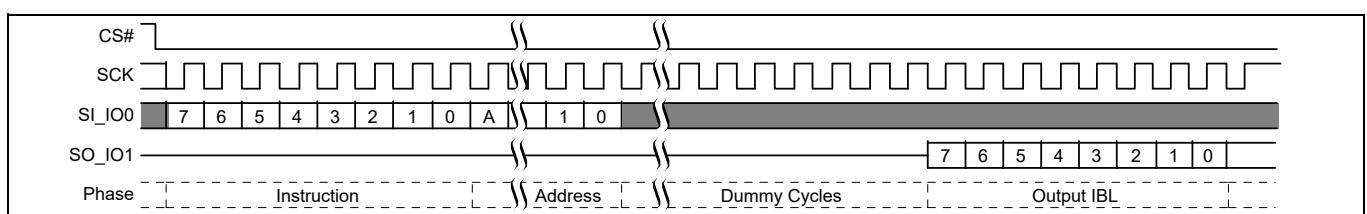

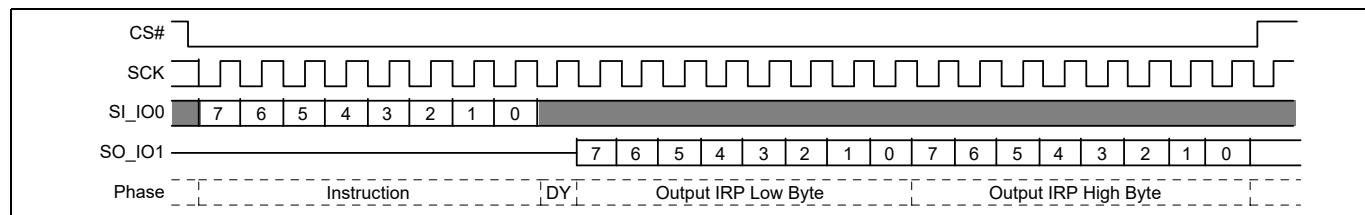

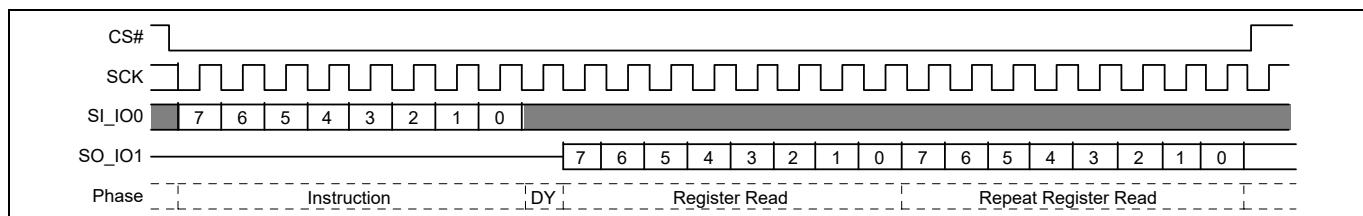

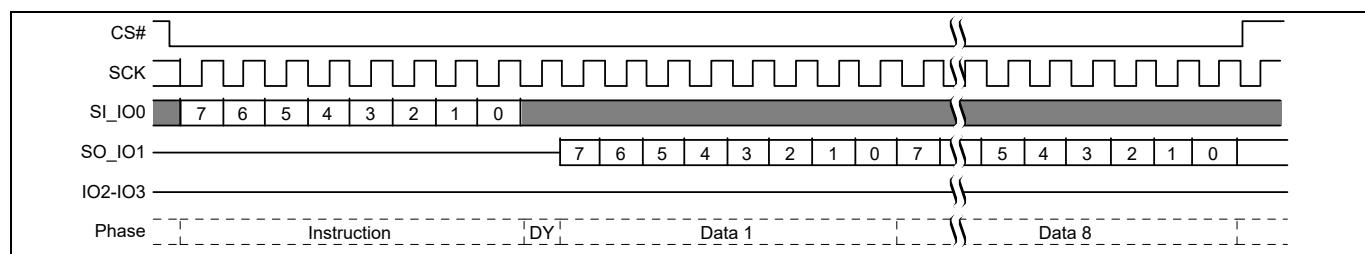

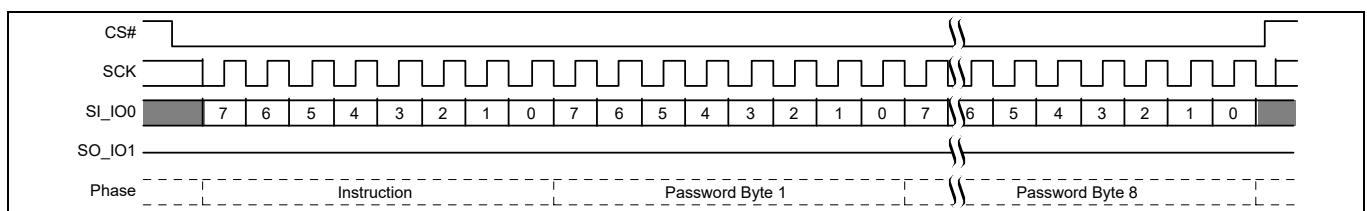

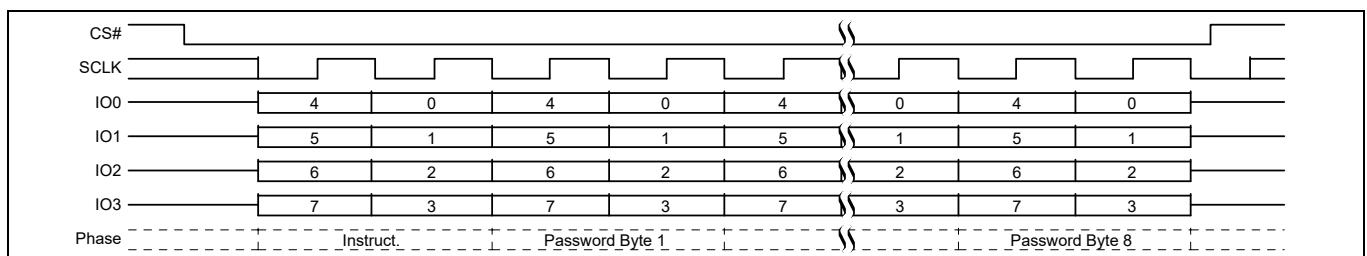

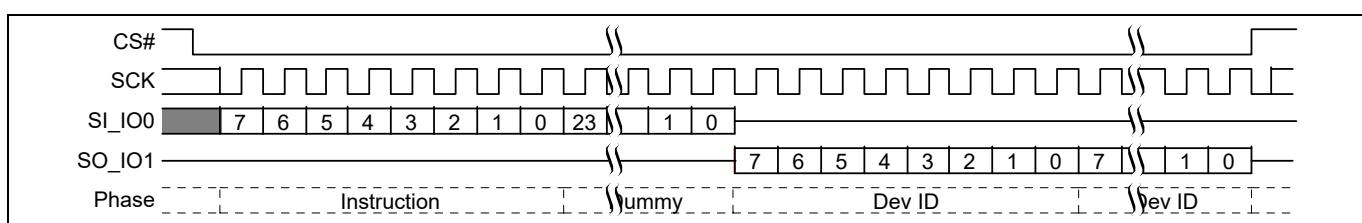

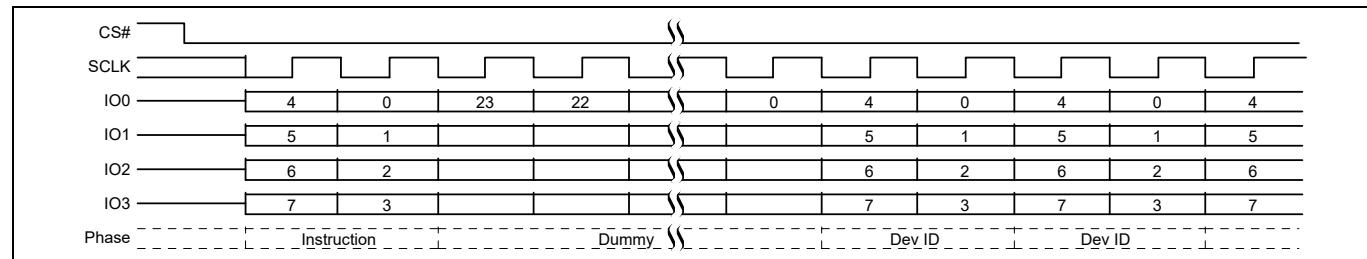

图 18 四线输出读命令

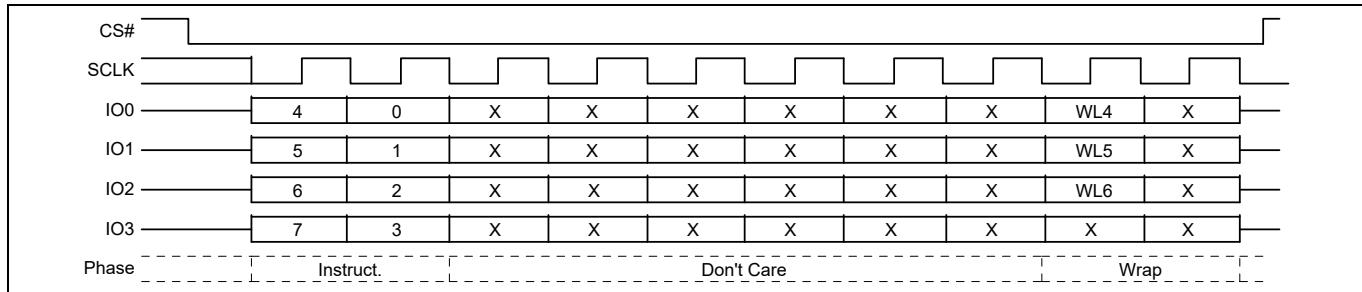

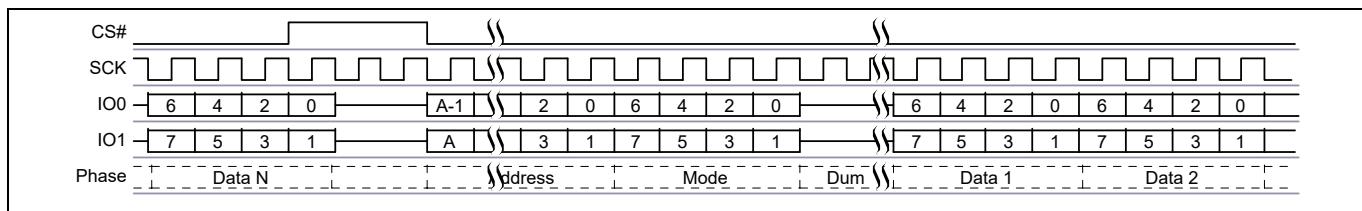

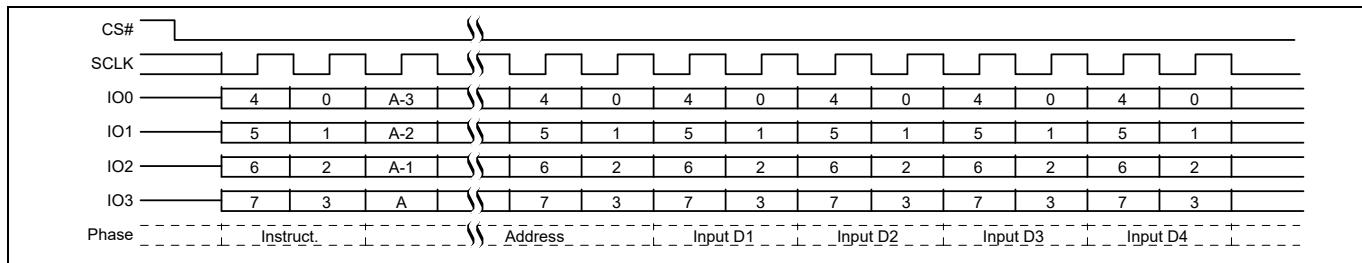

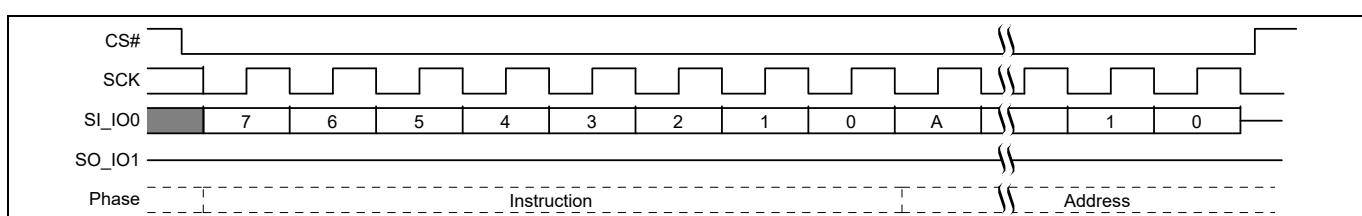

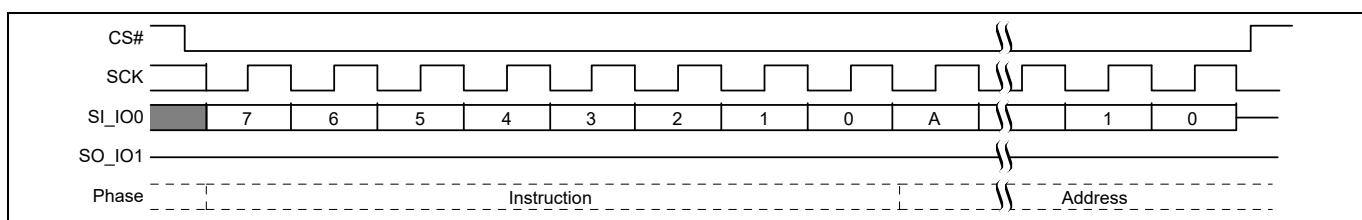

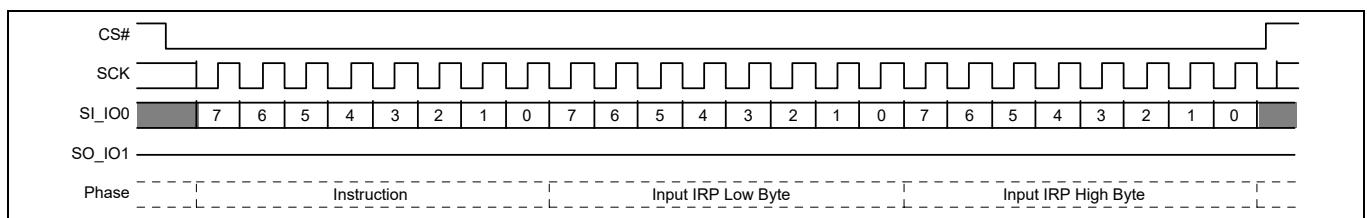

图 19 双线 I/O 命令

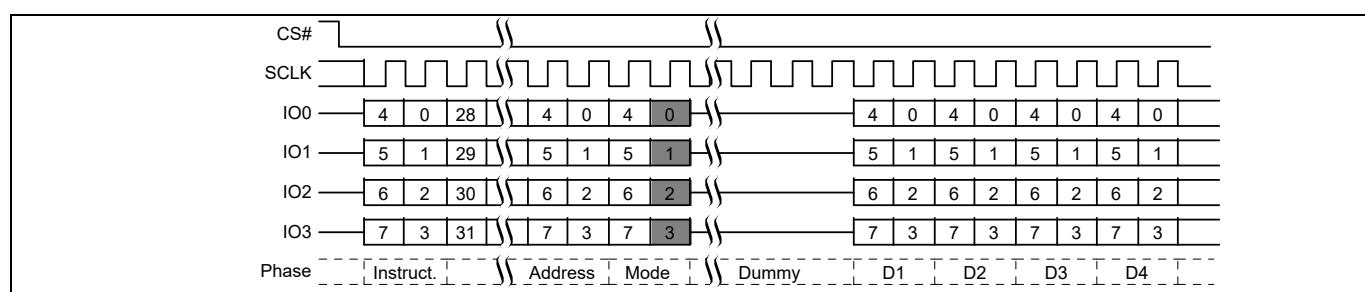

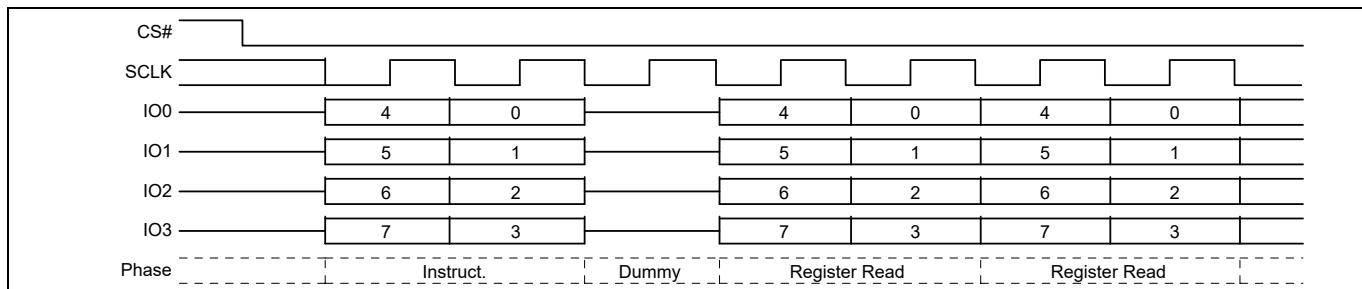

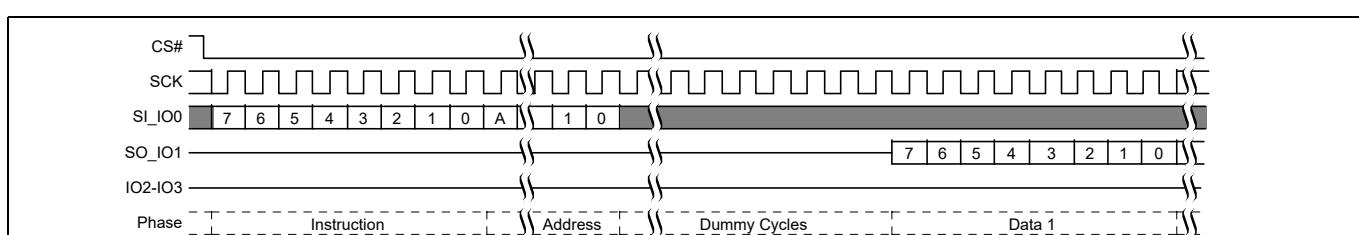

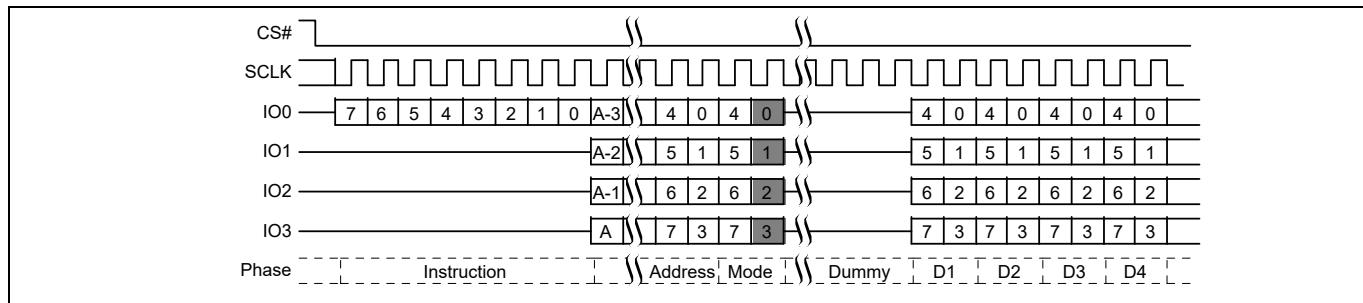

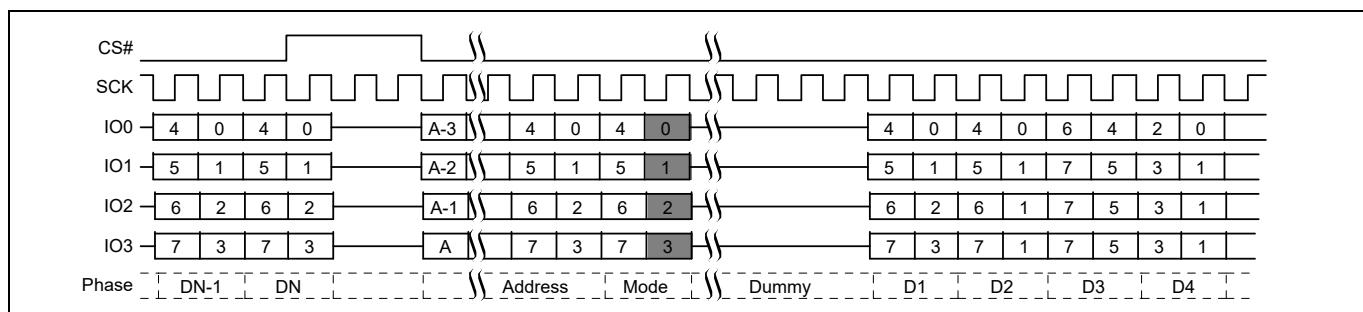

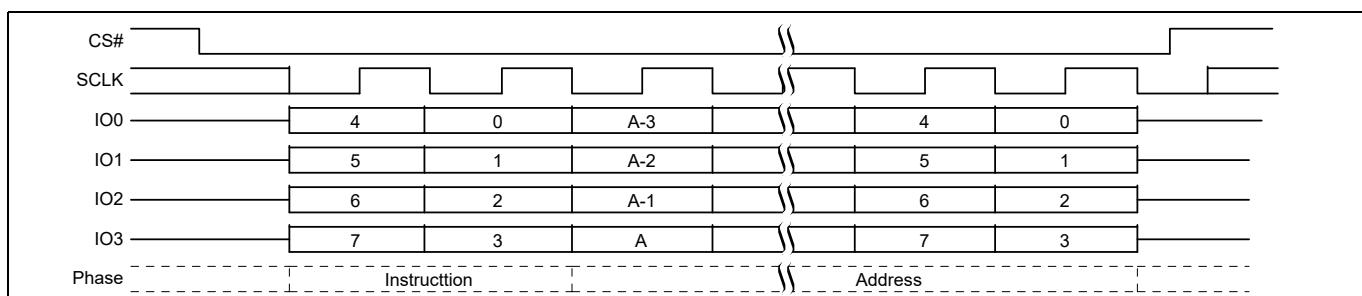

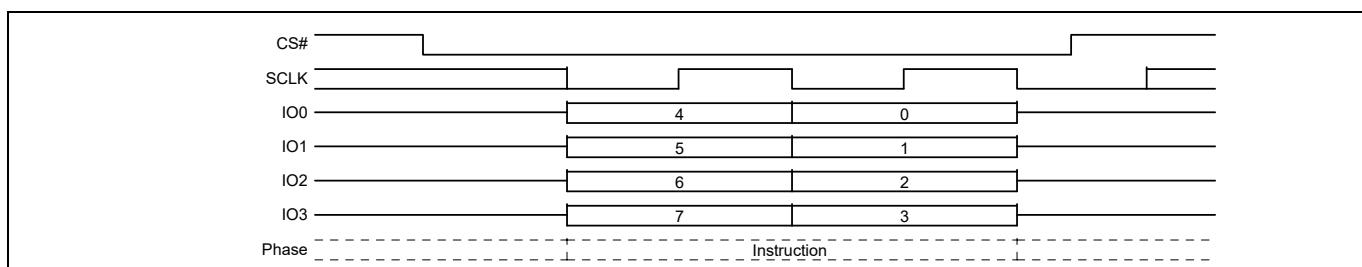

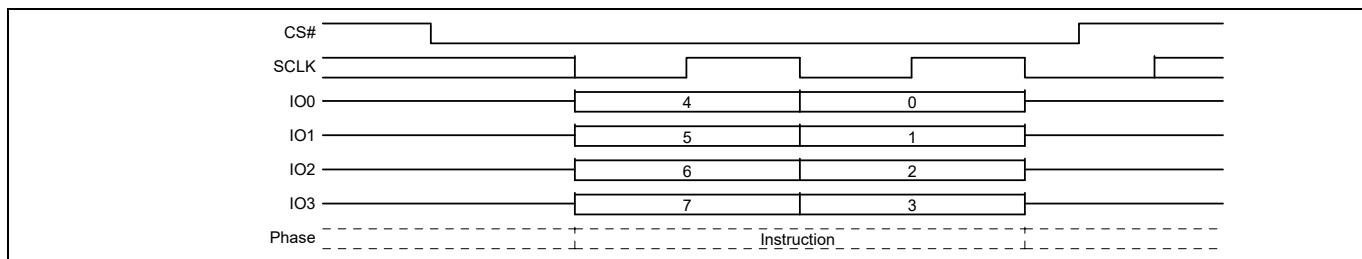

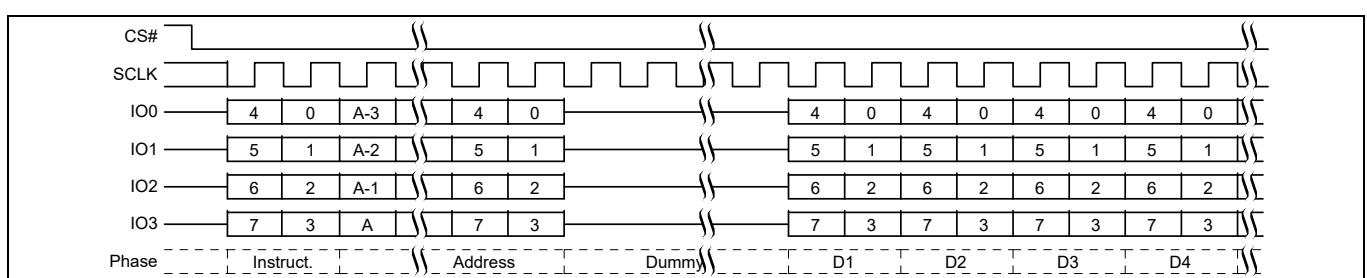

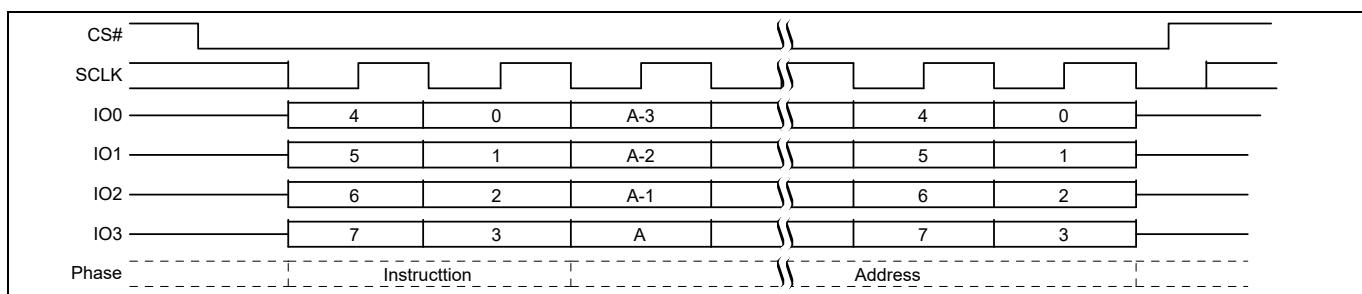

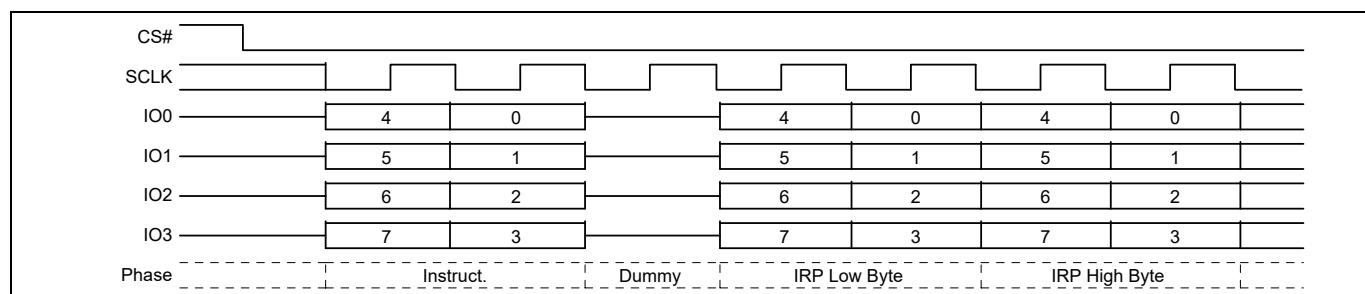

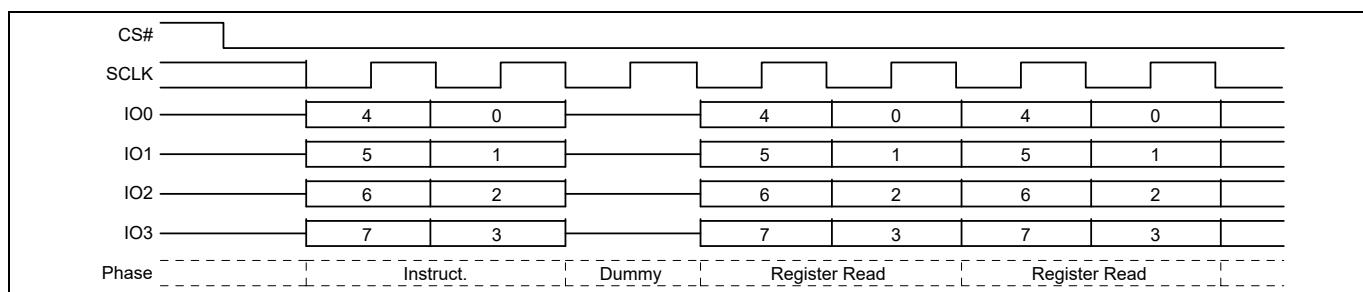

图 20 四线 I/O 命令 [8]

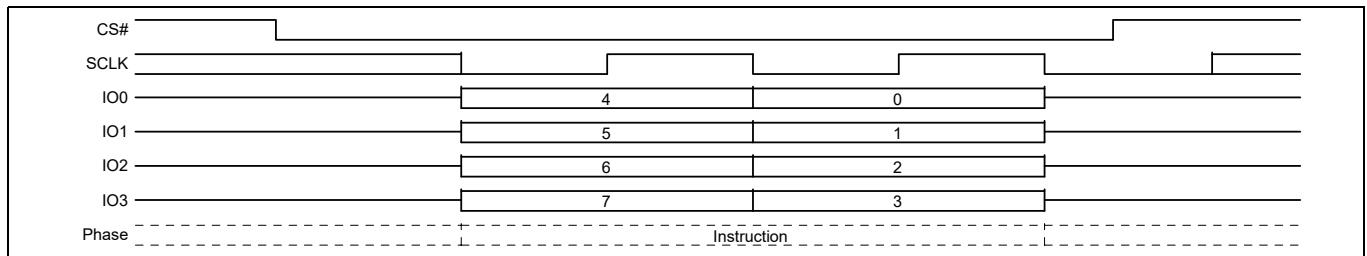

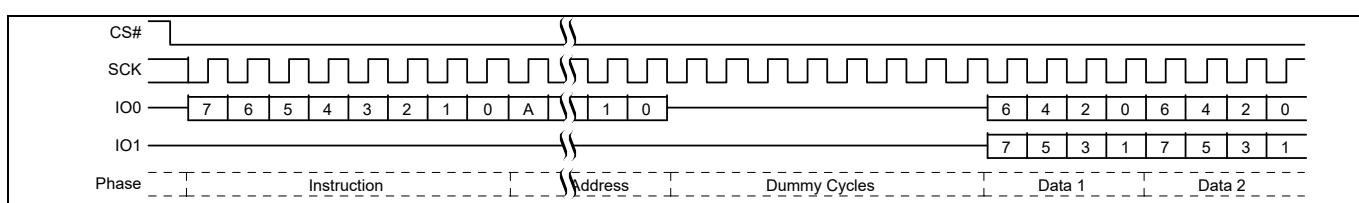

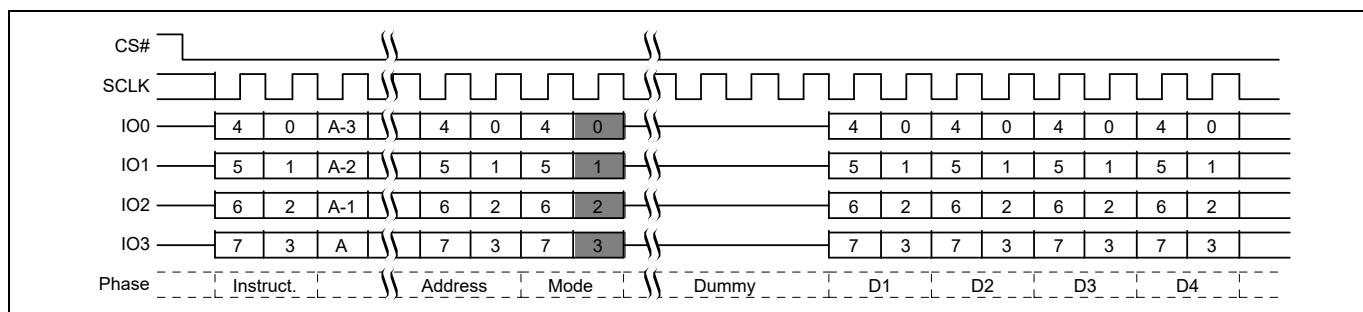

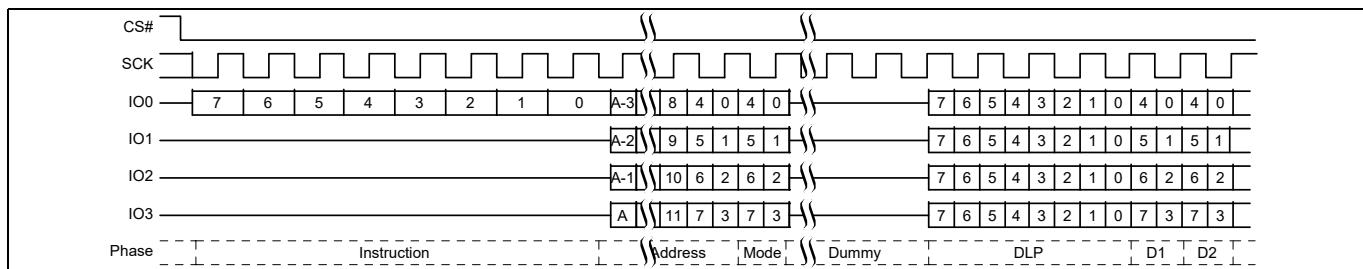

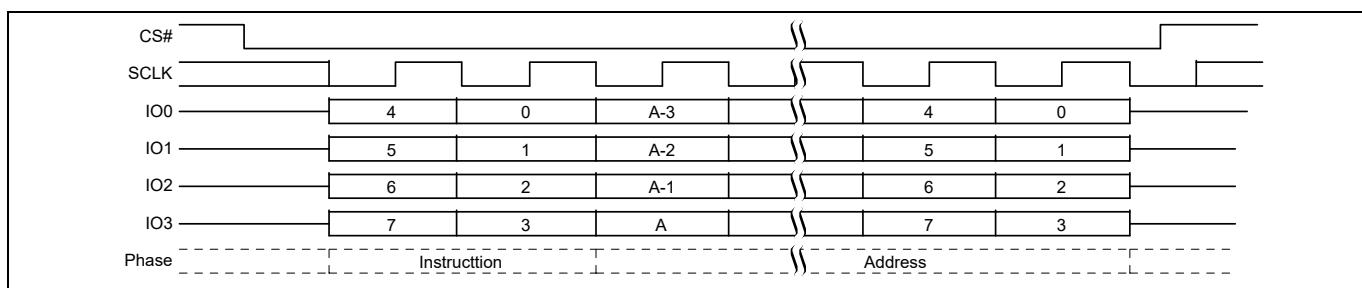

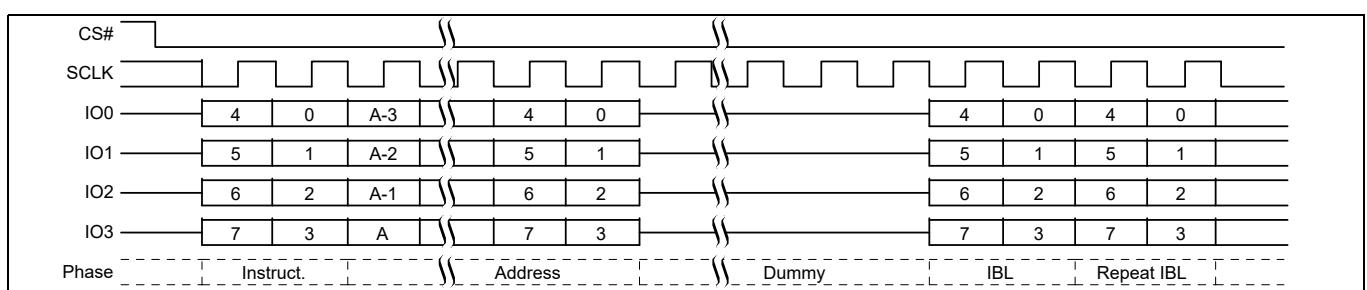

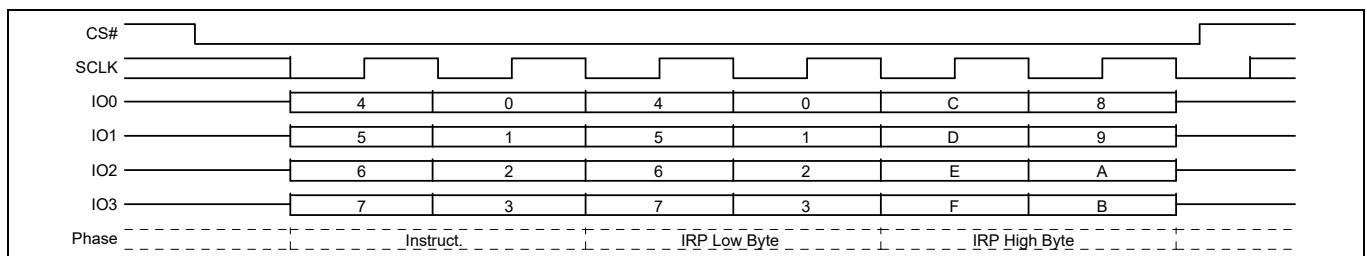

图 21 在 QPI 模式下的四线 I/O 读命令 [8]

### 注释

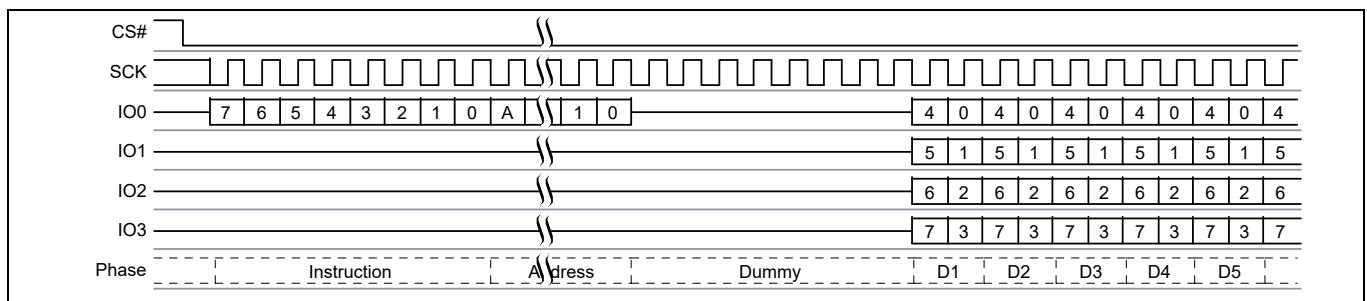

8. 灰色显示的是可选位，在该周期中主机无需发送这些位。

## 信号协议

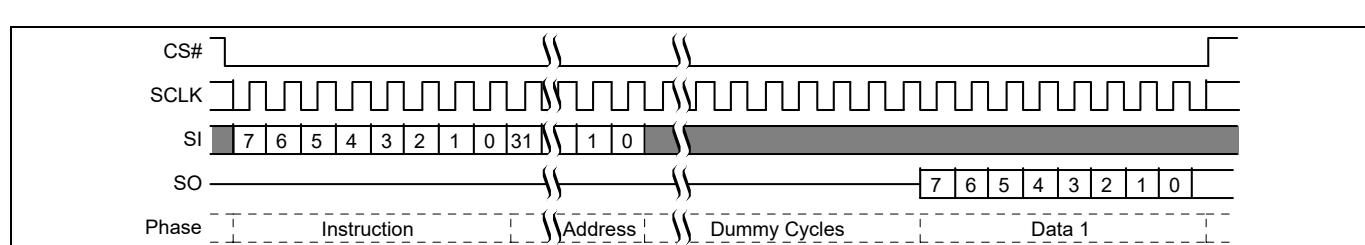

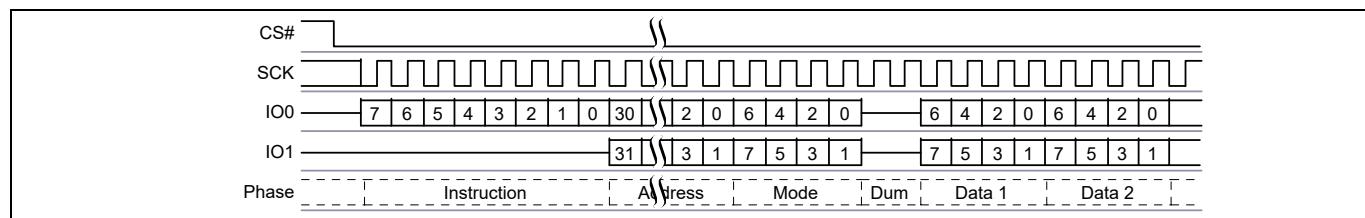

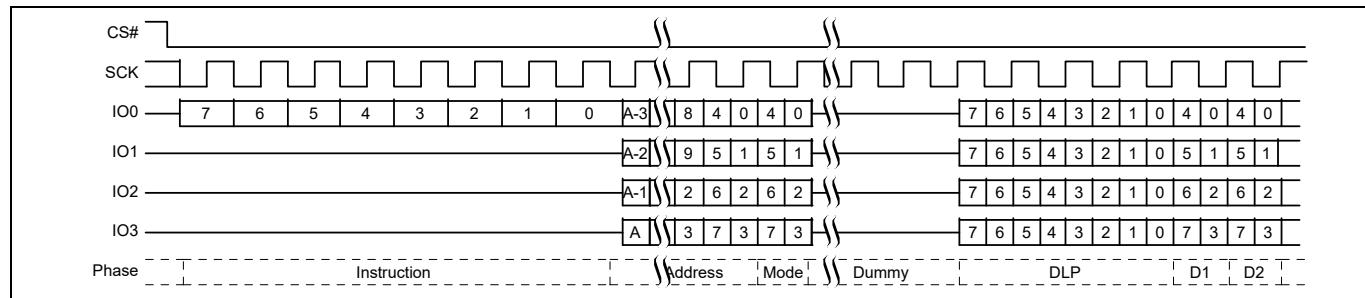

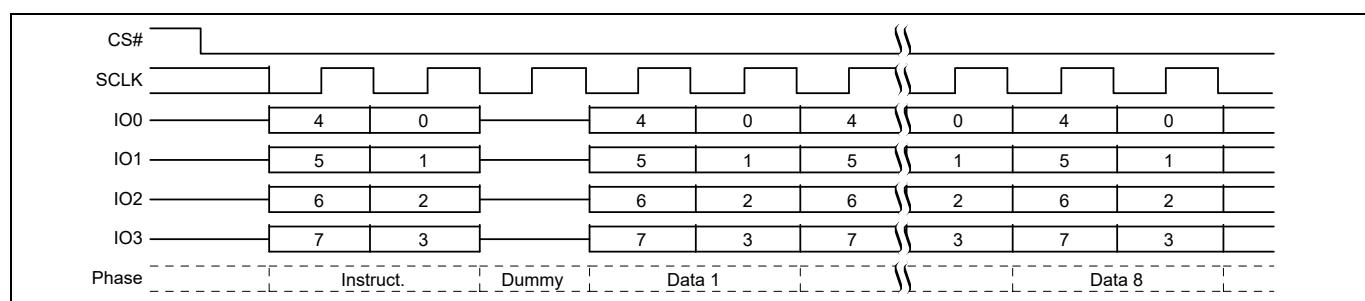

图 22 DDR 双线 I/O 读命令

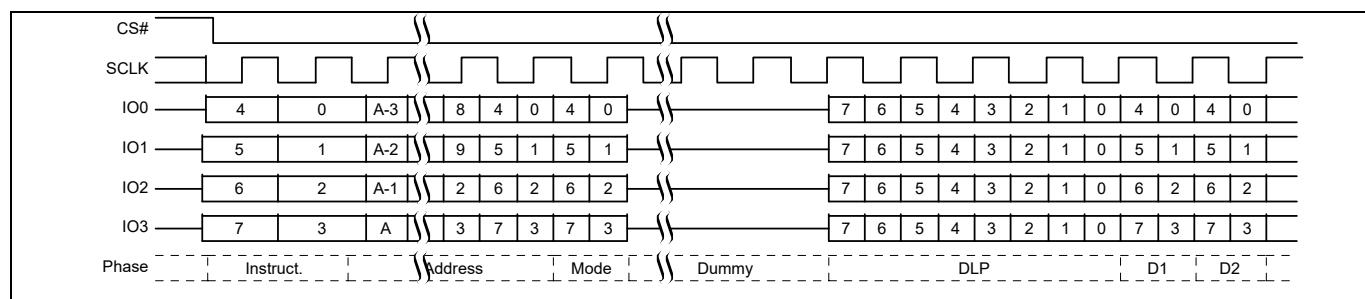

图 23 在 QPI 模式下的 DDR 四线 I/O 读命令

有关每个命令的其他序列框图，请参阅[第 69 页的 "命令"](#)。

信号协议

### 5.3 接口状态

本节将说明与 SPI 接口状态相应的输入和输出信号电平。

表 3 接口状态汇总

| 接口状态                     | $V_{CC}$         | SCK                 | CS# | RESET# | IO3 / RESET# | WP# / IO2 | SO / IO1 | SI / IO0 |

|--------------------------|------------------|---------------------|-----|--------|--------------|-----------|----------|----------|

| 断电                       | $< V_{CC}$ (低电平) | $\geq V_{CC}$ (最小值) | X   | X      | X            | X         | Z        | X        |

| 低电压硬件数据保护                | $< V_{CC}$ (关闭)  |                     | HH  |        |              |           |          |          |

| 上电 (冷) 复位                |                  |                     | X   | HL     | HL           |           |          |          |

| 硬件 (热) 复位无四线模式           |                  |                     | HH  |        |              |           |          |          |

| 硬件 (热) 复位四线模式            |                  |                     |     |        |              |           |          |          |

| 接口待机状态                   |                  |                     |     |        |              |           |          |          |

| 指令周期 (传统 SPI)            |                  |                     |     |        |              | HV        |          |          |

| 单线输入周期<br>从主机到存储器的传输     |                  |                     |     |        |              |           | HV       |          |

| 单线延迟 (虚拟) 周期             |                  |                     |     |        |              |           |          | X        |

| 单线输出周期<br>从存储器到主机的传输     |                  |                     |     |        |              | MV        |          |          |

| 双线输入周期<br>从主机到存储器的传输     |                  |                     | HT  | HL     | HH           | HV        | HV       |          |

| 双线延迟 (虚拟) 周期             |                  |                     |     |        |              | X         | X        |          |

| 双线输出周期<br>从存储器到主机的传输     |                  |                     |     |        |              | MV        | MV       |          |

| 四线输入周期<br>从主机到存储器的传输     |                  |                     |     |        |              | HV        | HV       |          |

| 四线延迟 (虚拟) 周期             |                  |                     |     |        |              | X         | X        |          |

| 四线输出周期<br>从存储器到主机的传输     |                  |                     |     |        |              | MV        | MV       |          |

| DDR 四线输入周期<br>从主机到存储器的传输 |                  |                     |     |        |              | HV        | HV       |          |

| DDR 延迟 (虚拟) 周期           |                  |                     |     |        |              | X         | X        |          |

| DDR 四线输出周期<br>从存储器到主机的传输 |                  |                     |     |        |              | MV        | MV       |          |

注意：

Z = 无驱动信号 – 悬空信号

HL = 由主机驱动的  $V_{IL}$

HH = 由主机驱动的  $V_{IH}$

HV = HL 或 HH

X = HL 或 HH 或 Z

HT = 在 HL 和 HH 间切换

ML = 由存储器驱动的  $V_{IL}$

MH = 由存储器驱动的  $V_{IH}$

MV = ML 或 MH

信号协议

### 5.3.1 断电

当内核供电电压不大于  $V_{CC\_Low}$  电压时，器件被视为断电。这时，器件不对外部信号做出响应，防止对该器件执行的所有编写或擦除操作。

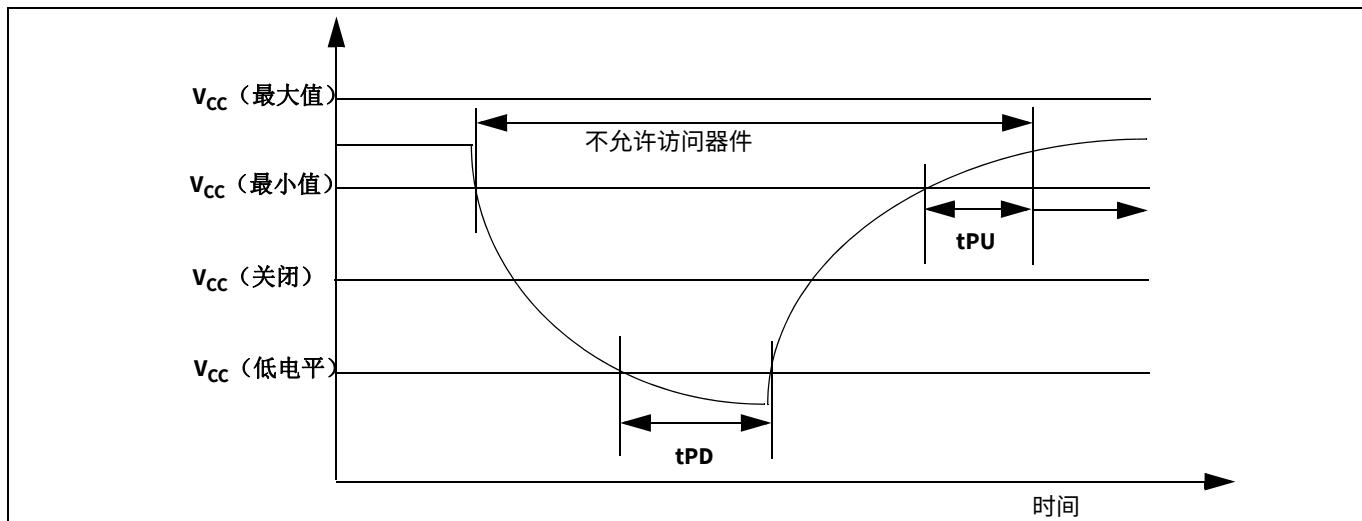

### 5.3.2 低功耗时的硬件数据保护

如果  $V_{CC}$  小于  $V_{CC\_Cut-off}$ ，那么存储器器件会忽略各条命令，以保证内核供电电压在工作范围外时不会启动编写和擦除操作。如果内核电压在  $\geq t_{PD}$  时间内保持不超过  $V_{CC\_Low}$ ，然后上升到  $\geq V_{CC\_Minimum}$  时，器件将开始执行上电复位 (POR) 程序。继续执行 POR 程序，直到  $t_{PU}$  时间结束为止。在  $t_{PU}$  期间，器件不会对外部输入信号做出响应，也不会驱动任何输出。经过  $t_{PU}$  时间后，器件将切换到接口待机状态，并能够接受各条命令。如需进一步了解 POR，请参阅第 154 页的“[上电 \(冷\) 复位](#)”。

### 5.3.3 硬件 (热) 复位

这是一个配置选项，器件并不处于任何一种四线或 QPI 模式时，或者器件处于四线模式或 QPI 模式并且 CS# 为高电平时，则通过该选项，可以将 IO3/RESET# 作为硬件复位输入使用。在四线模式或 QPI 模式下，某些封装中会提供单独的复位输入 (RESET#)。在  $t_{RP}$  期间，如果 IO3 / RESET# 或 RESET# 被置为低电平，则器件将启动硬件复位程序。继续执行该程序  $t_{RPH}$  时间。经过  $t_{RPH}$  时间以及在 RESET# 上升后的复位保持时间 ( $t_{RH}$ ) 后，器件将切换到接口待机状态，并能够接受各条命令。如需进一步了解硬件复位，请参阅第 154 页的“[复位](#)”。

### 5.3.4 接口待机

如果 CS# 为高电平，则 SPI 接口处于待机状态。其他输入 (RESET# 除外) 均被忽略。接口会保持等待状态，直到开始执行新命令为止。当 CS# 转为低电平以启动一条新命令时，下一个接口状态是指令周期。在接口待机状态下，如果不执行任何嵌入式算法，存储器器件将消耗待机电流 ( $I_{SB}$ )。如果正在执行某个嵌入式算法，那么将消耗相应的电流，直到完成该算法为止，此时整个器件将消耗待机电流。

### 5.3.5 指令周期 (传统 SPI 模式)

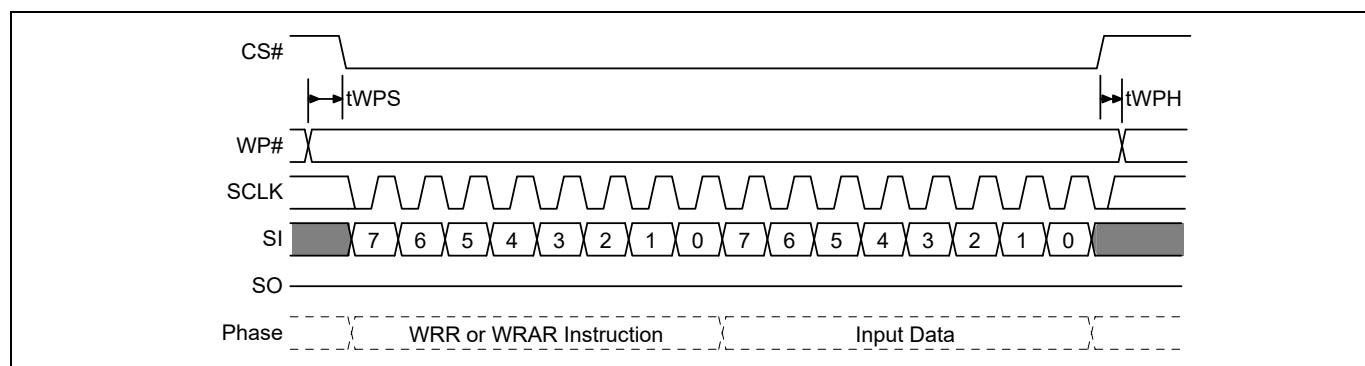

当主机驱动了一个指令的最高有效位 (MSb) 且 CS# 转为低电平时，在 SCK 的下一个上升沿上，器件将捕获指令 (开始新命令) 的最高有效位。在后面每一个 SCK 的上升沿上，器件都将捕获 8 位指令的下一个较低有效位。主机保持 CS# 为低电平并驱动写保护 (WP#) 和 IO3/RESET# 信号以供指令使用。不过，仅在处理 WRR 或 WRAR 命令或任何影响状态寄存器、配置寄存器和 DLR 寄存器命令的指令周期内，WP# 才被验证。除非执行这些指令周期期间，否则 WP# 将被忽略。如果器件未处于四线模式 (CR1V[1] = 0) 或 QPI 模式 (CR2V[3] = 0)，并且不需要硬件复位，则 IO3/RESET# 被置为高电平。

每个指令选择了用于操作的地址空间和在执行命令的其余部分期间使用的传输格式。传输格式可能为单线、双线 I/O、四线 I/O、双线 I/O、四线 I/O 或 DDR 四线 I/O。下一个接口的状态取决于所接收到的指令。

一些命令可以独立使用，无需将地址或数据传输到存储器或传输存储器的地址或数据。经过 SCK (在这种命令中指令的第八位) 上升沿后，主机将 CS# 返回高电平状态。在这种情况下，下一个接口状态是接口待机。

### 5.3.6 指令周期 (QPI 模式)

在 QPI 模式下，如果 CR2V[3] = 1，则在每个周期内各条指令能够传输 4 比特。在该模式下，指令周期与四线输入周期相同 (请参阅第 25 页的“[QPP 或 QOR 地址输入周期](#)”。

### 5.3.7 单线输入周期 — 从主机到存储器的传输

将单线串行输入 (SI) 信号上的指令从主机发送到存储器器件后，一些命令会传输信息。主机保持 RESET# 为高电平、CS# 为低电平，并驱动 SI 以供命令使用。存储器不会驱动串行输出 (SO) 信号。

下一个期望接口的状态取决于该指令。通过使用额外的单线输入周期，某些指令会连续将地址或数据发送给存储器。其他指令可能会切换到单线延迟状态，或直接转到单线、双线或四线输出周期状态。

### 5.3.8 单线延迟 (虚拟) 周期状态

读取命令可能没有延迟周期，也可能有若干个延迟周期，在这些周期内，直到发送到主机前，主闪存存储器阵列内的数据都被读取。配置寄存器 (CR3V[3:0]) 中的延迟代码决定了延迟周期的数量。在延迟周

## 信号协议

期内，主机会保持 RESET# 和 IO3/RESET# 为高电平、CS# 为低电平，SCK 会进行切换。写保护 (WP#) 信号被忽略。在这些周期内，主机可能会驱动 SI 信号，或者将 SI 保持为悬空状态。在延迟周期内，存储器不会使用在 SO 或其他 I/O 信号上所驱动的任意数据。在延迟周期内，存储器不会驱动串行输出 (SO) 或其它 I/O 信号。

下一个接口状态取决于命令结构，例如，延迟周期数量以及读取方式是单线、双线或四线宽度。

### 5.3.9 单线输出周期 — 从存储器到主机的传输

通过单线串行输出 (SO) 信号，若干个命令会将信息返回到主机。主机将保持 RESET# 和 IO3/RESET# 为高电平、CS# 为低电平。写保护 (WP#) 信号被忽略。存储器忽略了串行输入 (SI) 信号。存储器使用数据驱动 SO 信号。

下一个接口状态仍是单线输出周期，直到主机通过将 CS# 返回到高电平状态来结束命令为止。

### 5.3.10 双线输入周期 — 从主机到存储器的传输

每个周期内，双线读取 I/O 命令都会将两个地址或模式位传送给存储器。主机将保持 RESET# 和 IO3/RESET# 为高电平、CS# 为低电平。写保护 (WP#) 信号被忽略。主机将驱动 SI / IO0 和 SO / IO1 上的地址。

传输地址和模式位后，下一个接口状态是双线延迟周期（若需要延迟周期）或双线输出周期（若无需延迟周期）。

### 5.3.11 双线延迟（虚拟）周期

读取命令可能没有延迟周期，也可能会有若干个延迟周期，在这些周期内，直到发送到主机前，主闪存存储器阵列内的数据都被读取。配置寄存器 (CR3V[3:0]) 中的延迟代码决定了延迟周期的数量。在延迟周期内，主机会保持 RESET# 和 IO3/RESET# 为高电平、CS# 为低电平，SCK 会持续切换。写保护 (WP#) 信号被忽略。在这些周期内，主机可能驱动 SI / IO0 和 SO / IO1 信号，或者将这些信号保持为悬空状态。在延迟周期内，存储器不会使用在 SI / IO0 和 SO / IO1 或者其他 I/O 信号上所驱动的任意数据。最后的延迟周期结束时，主机必须停止驱动 SCK 的下降沿上 SI / IO0 和 SO / IO1 信号。在所有延迟周期内，建议停止主机对这些信号的驱动操作，以便在延迟周期结束时存储器开始驱动前，有足够时间使主机驱动器停止传输操作。这样做，如果信号方向发生改变，则能够防止主机和存储器间发生冲突。在延迟周期内，存储器不会驱动 SI / IO0 和 SO / IO1 信号。

最后延迟周期结束后，下一个接口状态是双线输出周期。

### 5.3.12 双线输出周期 — 从存储器到主机的传输

在每个周期内，双线读取输出和双线读取 I/O 命令会将数据（2 位）返回到主机内。主机将保持 RESET# 和 IO3/RESET# 为高电平、CS# 为低电平。写保护 (WP#) 信号被忽略。在双线输出周期内，在 SCK 的下降沿上，存储器将驱动 SI / IO0 和 SO / IO1 信号上的数据。

下一个接口状态仍是双线输出周期，直到主机通过使 CS# 返回高电平状态来结束命令为止。

### 5.3.13 QPP 或 QOR 地址输入周期

四线页编程和四线输出读取命令仅在 IO0 信号上将地址发送到存储器。其他 IO 信号均被忽略。主机将保持 RESET# 和 IO3/RESET# 为高电平、CS# 为低电平，并驱动 IO0。

QPP 命令发送地址后，下一个接口状态将是四线输入周期。QOR 传输地址后，下一个接口状态是四线延迟周期（若需要延迟周期）或四线输出周期（若无需延迟周期）。

### 5.3.14 四线输入周期 — 从主机到存储器的传输

每个周期内，四线 I/O 读取命令都将四个地址位或模式位传输到存储器中。在 QPI 模式下，每个周期（包括指令周期）内，四线 I/O 读取和页编程命令都会将四个数据位传输到存储器内。主机会保持 CS# 为低电平，并驱动 IO 信号。

四线 I/O 读取命令传输地址和模式位后，下一个接口状态是四线延迟周期（若需要延迟周期）或四线输出周期（若无需延迟周期）。在 QPI 模式下，页编程命令传输需要编程的数据后，主机会使 CS# 返回高电平状态，而且接口会返回待机状态。

信号协议

### 5.3.15 四线延迟（虚拟）周期

读取命令可能不存在延迟周期，也可能存在若干个延迟周期。在这些周期内，数据先从主闪存存储器阵列内被读取，然后才被发送给主机。配置寄存器 (CR3V[3:0]) 中的延迟代码决定了延迟周期的数量。在延迟周期内，主机会保持 CS# 为低电平，并持续切换 SCK。在这些周期内，主机可能驱动 IO 信号，或者将 IO 保持为悬空状态。在延迟周期内，存储器不会使用 IO 信号上所驱动的任意数据。最后的延迟周期结束时，主机必须停止驱动下降沿上的 IO 信号。在所有延迟周期内，建议停止主机对这些信号的驱动操作，以便在延迟周期结束时存储器开始驱动前，有足够时间使主机驱动器停止传输操作。这样做，如果信号方向发生改变，则能够防止主机和存储器间发生冲突。在延迟周期内，存储器不会驱动 IO 信号。

最后延迟周期结束后，下一个接口状态是四线输出周期。

### 5.3.16 四线输出周期 – 从存储器到主机的传输

每个周期内，四线 O 和四线 I/O 读取命令会将 4 位的数据返回给主机。主机保持 CS# 为低电平。在四线输出周期期间，存储器会驱动 IO0-IO3 信号上的数据。

下一个接口状态仍是四线输出周期，直到主机使 CS# 返回高电平状态而使命令结束为止。

### 5.3.17 DDR 四线输入周期 – 从主机到存储器的传输

DDR 四线 I/O 读取命令会通过所有 IO 信号将地址和模式位发送给存储器。每个周期内，在 SCK 的上升沿上传输 4 比特，在下降沿上传输 4 比特。主机保持 CS# 为低电平。

传输地址和模式位后，下一个接口状态是 DDR 延迟周期。

### 5.3.18 DDR 延迟周期

DDR 读取命令可能具有一个或若干个延迟周期，在这些周期内，数据被发送给主机前，主闪存存储器阵列内的数据将被读取。配置寄存器 (CR3V[3:0]) 中的延迟代码决定了延迟周期的数量。在延迟周期内，主机会保持 CS# 为低电平。此外，主机不会驱动 IO 信号。因此，在存储器开始驱动前，有足够的空间使主机驱动器停止传输操作。这样做，如果信号方向发生改变，能够防止主机和存储器间发生冲突。在最后 4 个延迟周期内，存储器可以选择使用一个数据学习模式 (DLP) 驱动所有 IO 信号。如果延迟周期数小于 5，则不应该启用 DLP 选项。因此，在存储器开始驱动 DLP 前，至少有一个高阻抗的周期以等待 IO 信号经过处理并返回。如果有大于 4 个延迟周期，则存储器不会驱动 IO 信号，直到最后四个延迟周期为止。

最后延迟周期结束后，下一个接口状态是 DDR 四线输出周期，具体情况取决于指令。

### 5.3.19 DDR 四线输出周期 – 从存储器到主机的传输

DDR 四线 I/O 读取命令会通过所有 IO 信号将数据位发送给主机。每个周期内，在 SCK 的上升沿上传输 4 比特，在下降沿上传输 4 比特。主机保持 CS# 为低电平。

下一个接口状态仍是 DDR 四线输出周期，直到主机使 CS# 返回高电平状态而使命令结束为止。

## 5.4 数据保护

硬件设计提供并管理着某些基本的保护功能，用于防止对存储数据进行意外的更改。具体内容请参阅第 53 页的“[数据保护](#)”。其它软件管理的保护方式将在本文档的第 53 页的“[数据保护](#)”章节中进行讨论。

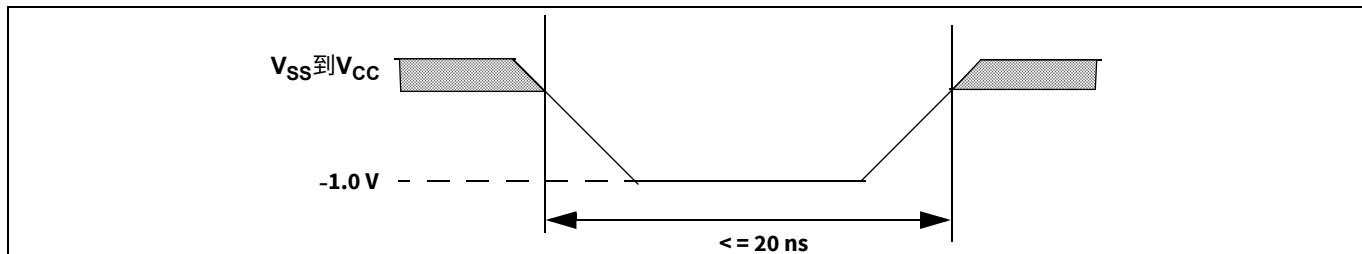

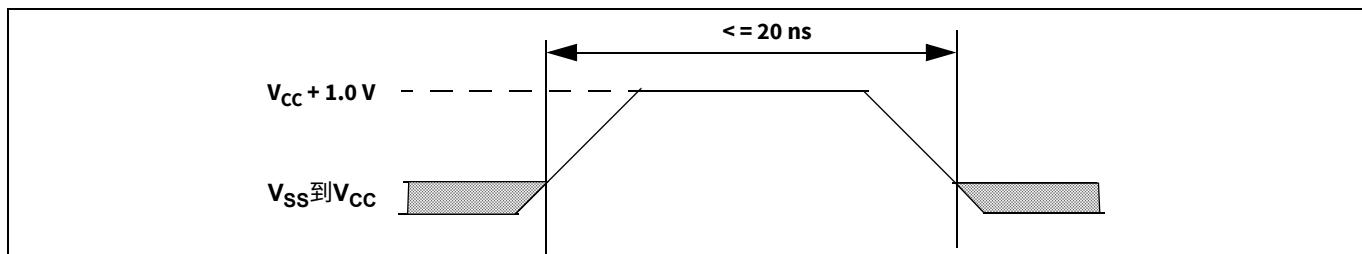

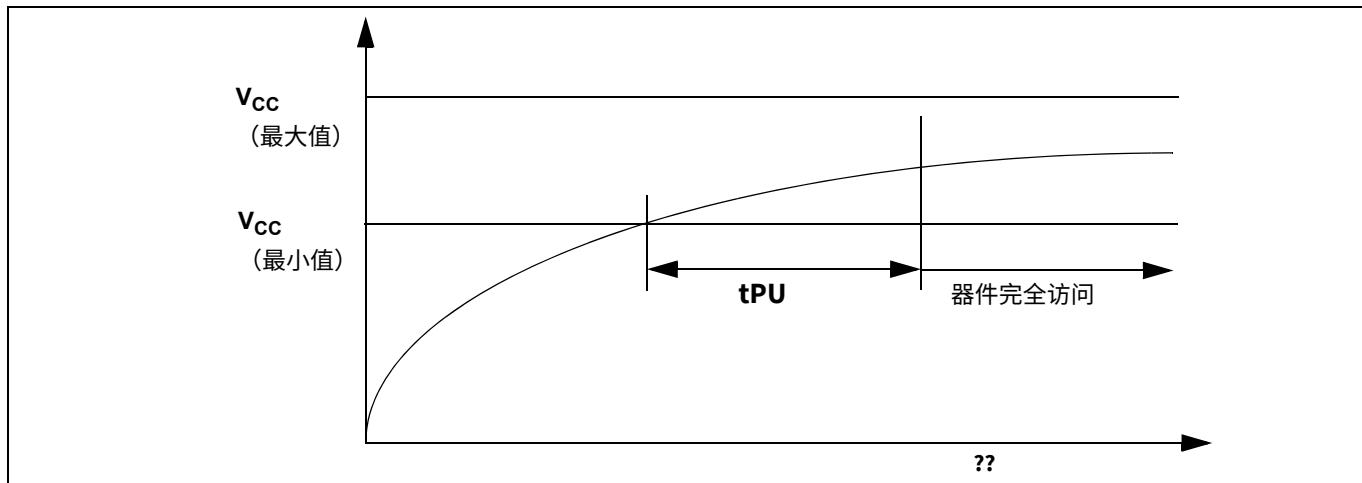

### 5.4.1 上电

发生上电 (CS# 的电压必须采用 V<sub>CC</sub> 上的电压) 时，不能选择器件，直到 V<sub>CC</sub> 准确满足以下值：

- 上电时为 V<sub>CC</sub> (最小值) 并在 t<sub>PU</sub> 的更长延迟期间持续保持该值

用户不能输入任何命令，直到 V<sub>CC</sub> 上升超过 V<sub>CC</sub> 最小阈值后再经过 t<sub>PU</sub> 的有效延迟时间结束为止 (见 [图 131](#))。但是在 t<sub>PU</sub> 期间，如果 V<sub>CC</sub> 返回到低于 V<sub>CC</sub> (最小值) 的电平状态，将不能保证器件正常操作。在 t<sub>PU</sub> 结束前，不应该发出任何命令。

### 5.4.2 低功耗

如果 V<sub>CC</sub> 小于 V<sub>CC</sub> (Cut-off)，那么存储器器件会忽略各条命令，以保证内核供电电压在工作范围外时不会启动编写和擦除操作。

信号协议

### **5.4.3 时钟脉冲数量**

器件会验证所有修改非易失性存储器和寄存器数据的命令是否包含了一个时钟脉冲数量。执行这些命令前，该时钟脉冲数量是 8 的倍数（字节边界）。不在 8 位（字节）边界上结束的命令将被忽略，该命令不存在任何错误状态。

### **5.4.4 深度掉电（DPD）**

在 DPD 模式下，器件仅对从 DPD 模式恢复的命令（RES ABh）发出响应。在该模式下，所有其他命令均被忽略，从而防止对存储器执行编程和擦除操作。如果启用了 IO3/RESET# 功能（CR2V[7] = 1）或者 RESET# 有效，那么通过将 IO3/RESET# 或 RESET# 设置为低电平状态便可以启动硬件复位并使器件退出 DPD 模式。

## **6 地址空间映射**

### **6.1 概述**

#### **6.1.1 扩展地址**

FL-L 系列支持 32 位（4 个字节）地址。这样，同前一代（旧版）SPI 器件相比，器件容量更高（前代 SPI 器件仅支持 24 位（3 个字节）地址。对于 24 位的字节分辨率系统，地址寄存器允许对 16 MB（128 Mb）的地址空间进行访问。对于 32 位、字节分辨率，地址寄存器允许直接访问 4 GB（32 Gb）大的地址空间。

传统的命令仍支持 24 位地址，以实现软件向后兼容。通过以下两种方法可以获取扩展的 32 位地址：

- 扩展地址模式：一个易失性配置寄存器位，它更改了所有传统命令，以获取由主机系统提供的 32 位地址。

- 字节地址命令：执行传统的和新的功能，从而能够获取 32 位地址。

上电或复位后，扩展地址模式的默认条件是由非易失性配置位控制的。可将默认的扩展地址模式设置为 24 或 32 位地址。这样可以对器件的前 128 Mb 空间进行传统的软件兼容访问，并允许器件在 32 位地址模式下直接启动。

#### **6.1.2 多地址空间**

许多命令在主闪存存储器阵列上运行。某些命令在独立于主闪存阵列的地址空间内运行。每个单独地址空间使用了整个 24 或 32 位地址，但只定义可用地址空间的一小部分。

地址空间映射

## 6.2 闪存存储器阵列

主闪存阵列被分为大小统一的擦除单位，这些单位被称为物理块（64 KB）、半块（32 KB）和扇区（4 KB）。

表 4 S25FL256L 扇区地址映射

| 块大小<br>(KB) | 块数量 | 块范围   | 半块<br>大小<br>(KB) | 半块<br>数量 | 半块<br>范围    | 扇区<br>容量<br>(KB) | 扇区<br>数量 | 扇区<br>范围   | 地址范围<br>(字节地址)    | 注意     |

|-------------|-----|-------|------------------|----------|-------------|------------------|----------|------------|-------------------|--------|

| 64          | 1   | BA00  | 32               | 1        | HBA00       | 4                | 1        | SA00       | 0000000h-0000FFFh | 扇区起始地址 |

|             |     |       |                  |          | :           | :                | :        | :          | :                 | —      |

|             |     |       | 32               | 2        | HBA01       | 4                | 16       | SA15       | 000F000h-000FFFFh | —      |

| :           | :   | :     | :                | :        | :           | :                | :        | :          | :                 | —      |

| 64          | 512 | BA511 | 32               | 1023     | HBA10<br>22 | 4                | 8176     | SA817<br>5 | 1FF0000h-1FF0FFFh | —      |

|             |     |       |                  |          | :           | :                | :        | :          | :                 | —      |

|             |     |       | 32               | 1024     | HBA10<br>23 | 4                | 8192     | SA819<br>1 | 1FFF000h-1FFFFFFh | 扇区结束地址 |

表 5 S25FL128L 扇区地址映射

| 块大小<br>(KB) | 块数量 | 块范围   | 半块<br>大小<br>(KB) | 半块<br>数量 | 半块<br>范围   | 扇区<br>容量<br>(KB) | 扇区<br>数量 | 扇区<br>范围   | 地址范围<br>(字节地址)   | 注意     |

|-------------|-----|-------|------------------|----------|------------|------------------|----------|------------|------------------|--------|

| 64          | 1   | BA00  | 32               | 1        | HBA0<br>0  | 4                | 1        | SA00       | 000000h-0000FFFh | 扇区起始地址 |

|             |     |       |                  |          | :          | :                | :        | :          | :                | —      |

|             |     |       | 32               | 2        | HBA0<br>1  | 4                | 16       | SA15       | 00F000h-00FFFFh  | —      |

| :           | :   | :     | :                | :        | :          | :                | :        | :          | :                | —      |

| 64          | 256 | BA255 | 32               | 511      | HBA5<br>10 | 4                | 4080     | SA407<br>9 | FF0000h-FF0FFFh  | —      |

|             |     |       |                  |          | :          | :                | :        | :          | :                | —      |

|             |     |       | 32               | 512      | HBA5<br>11 | 4                | 4096     | SA409<br>5 | FFF000h-FFFFFFh  | 扇区结束地址 |

地址空间映射

## 6.3 ID 地址空间

RDID 命令 (9Fh) 从单独的闪存存储器地址空间内读取信息，以获取器件标识 (ID)。如需了解定义 ID 地址空间内容的表格，请参阅第 144 页的 "器件 ID 地址映射"。该 ID 地址空间由英飞凌编程，主机系统只能对其执行读取操作。

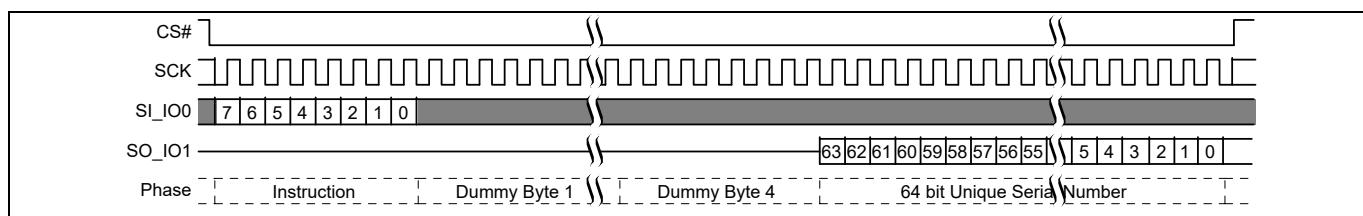

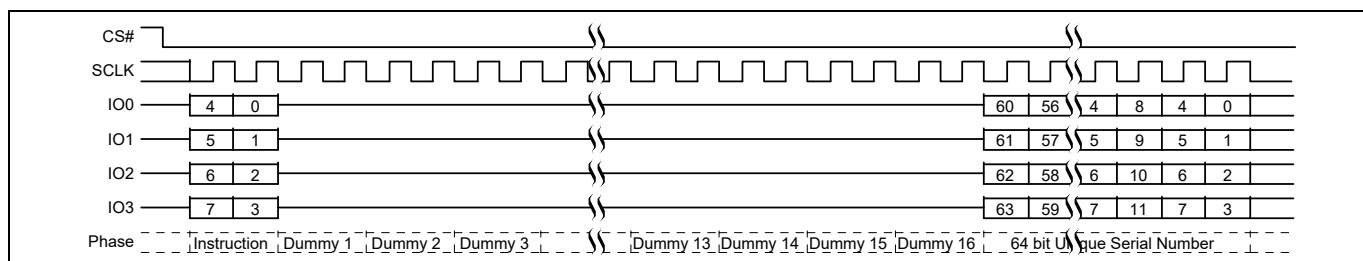

### 6.3.1 器件的唯一 ID

64 位唯一编号位于唯一器件 ID 地址空间中的 8 个字节内，具体请参阅表 50。该唯一 ID 可以作为每个器件的唯一软件可读序列号。

## 6.4 JEDEC JESD216 串行闪存可发现参数 (SFDP) 空间

根据串行闪存可发现参数的 JEDEC JESD216 标准，RSFDP 命令 (5Ah) 从单独闪存存储器地址空间读取信息，以获取器件标识、特性和配置信息。ID 地址空间被组合为某个 SFDP 参数。如需了解定义 SFDP 地址空间内容的表格，请参阅第 134 页的 "JEDEC JESD216B 串行闪存可发现参数"。该 SFDP 地址空间由英飞凌编程，主机系统只能对其执行读取操作。

## 6.5 安全区域地址空间

每个 FL-L 系列存储器器件具有一个独立于主闪存阵列的 1024 字节安全区域地址空间。该安全区域分为四个可独立锁定的 256 字节区域。安全区域存储器空间包含某些信息，这些信息暂时被保护或长期锁定，因此无法对其进行其他的编程或擦除操作。

从英飞凌出厂时，这些区域的数据字节被擦除为 FFh。当该区域不被保护或锁定时，可以对其进行编程和擦除操作，就像对其他闪存存储器地址空间进行的操作一样。可以独立擦除每个区域。安全区域锁定位 (CR1NV[5:2]) 位于配置寄存器 1 内。安全区域锁定位是一次性可编程 (OTP) 位。编程这些位后（设置为 1），一个锁定位将长期防止对相关区域进行其他的擦除或编程操作。

保护寄存器 (PR) NVLock 位暂时防止对区域 2 和区域 3 进行编程或擦除操作。NVLock 位是易失性位，通过使用 IRP 逻辑和各种命令可以设置或清除它。请参阅第 50 页的 "保护寄存器 (PR)"。

IRP 寄存器 (IRP[2]) 中的安全区域密码保护位用于防止对区域 2 和区域 3 进行编程和擦除操作，直到提供一个密码为止。IRP 寄存器 (IRP[6]) 中的安全区域读取保护位用于防止对区域 3 进行读取操作，直到提供一个密码为止。尝试读取防止读操作的区域时，将返回无效和未定义的数据。请参阅第 48 页的 "单独和区域保护寄存器 (IRP)"。

尝试擦除或编程受保护或被锁定的区域时，会导致结果失败，并且 SR2V[6:5] 中的 P\_ERR 或 E\_ERR 位被设置为 '1'。（如需了解详细信息，请参阅第 37 页的 "易失性状态寄存器 2 (SR2V)"）。

**表 6 安全区域地址映射**

| 区域   | 字节地址范围 (十六进制) | 初始供应状态 (十六进制) |

|------|---------------|---------------|

| 区域 0 | 000 到 OFF     | 所有字节 = FF     |

| 区域 1 | 100 到 1FF     |               |

| 区域 2 | 200 到 2FF     |               |

| 区域 3 | 300 到 3FF     |               |

地址空间映射

## 6.6 寄存器

寄存器是存储器单元的小组，用于配置 FL-L 系列存储器器件的运行方式以及报告器件的运行状态。通过使用特殊命令可以访问这些寄存器。使用于每个寄存器的命令（和十六进制指令代码）被注释在每个寄存器的说明内。

在旧版的 SPI 存储器器件中，独立寄存器位可以是同一个寄存器中易失性、非易失性或一次性可编程（OTP）位的混合体。在某些配置选项中，寄存器位的类型会发生改变，例如，从非易失性变为易失性。

FL-L 系列使用单独的非易失性或易失性存储器单元组（区域）来实现不同类型的寄存器位。然而，FL-L 系列兼容了传统寄存器和各种命令并且它们始终有效。当传统寄存器具有易失性位或读取传统寄存器的命令具有 0 读取延迟时，每个传统寄存器有非易性和易失性版本。当读取这种寄存器时，将提供该寄存器的易失性版本。在上电复位（POR）、硬件复位或软件复位期间，寄存器的非易失性版本被复制为易失性版本，以提供易失性寄存器的默认状态。当写入非易失性寄存器位时，寄存器的非易失性版本将被擦除并编程新的位值，而且寄存器的易失性版本将更新非易失性版本的新内容。当编程 OTP 位时，寄存器的非易失性版本将被编程，而且寄存器易失性版本中的相应位被更新。当写入易失性寄存器位时，只有寄存器易失性版本中的相应位被更新。

每一位的类型注释均位于每个寄存器的说明内。每一位的默认状态指的是执行上电复位、硬件复位或软件复位后的状态（如果它是易失性位）。如果该位是非易失性或 OTP 位，那么其默认状态便是器件从赛普拉斯出厂时该位的值。写入非易失性寄存器时，必须特别注意电源供电的稳定（没有中断）。这样才能保证将正确的数据写入寄存器。

### 6.6.1 状态寄存器 1

#### 6.6.1.1 非易失性状态寄存器 1 (SR1NV) S25FL256L

相关命令：非易失性寄存器的写启用（WREN 06h）、写禁用（WRDI 04h）、写入寄存器（WRR 01h）、读取任何寄存器（RDAR 65h）、写入任何寄存器（WRAR 71h）。

表 7 非易失性状态寄存器 1 (SR1NV)

| 位 | 字段名称      | 功能             | 类型     | 默认状态  | 描述                        |

|---|-----------|----------------|--------|-------|---------------------------|

| 7 | SRP0_NV   | 状态寄存器保护 0 默认设置 | 非易失性   | 0     | 为 SRP0 提供默认状态。            |

| 6 | TBPROT_NV | TBPROT 默认设置    | 非易失性   | 0     | 为 TBPROT 提供默认状态。          |

| 5 | BP_NV3    | 传统块保护默认设置      | 非易失性   | 0000b | 为 BP 位提供默认状态。             |

| 4 | BP_NV2    |                |        |       |                           |

| 3 | BP_NV1    |                |        |       |                           |

| 2 | BP_NV0    |                |        |       |                           |

| 1 | WEL_D     | WEL 的默认设置      | 非易失性只读 | 0     | 为 WEL 状态位提供默认状态。用户不能编程该位。 |

| 0 | WIP_D     | WIP 的默认设置      | 非易失性只读 | 0     | 为 WIP 状态位提供默认状态。用户不能编程该位。 |

## 地址空间映射

状态寄存器保护非易失性 (SRP0\_NV) SR1NV[7]: 为 SRP0 提供默认状态 (见第 54 页的 "状态寄存器保护 (SRP1、SRP0)" )。

顶部或底部保护位 (TBPROT\_NV) SR1NV[6]: 为 TBPROT 提供默认状态。

传统模块保护位 (BP\_NV3、BP\_NV2、BP\_NV1、BP\_NV0) SR1NV[5:2]: 为 BP\_3 到 BP\_0 位提供默认状态。

写启用锁存的默认位 (WEL\_D) SR1NV[1]: 为 SR1V[1] 中的 WEL 状态提供默认状态。该位由英飞凌编程, 用户不可编程。

正在写入的默认位 (WIP\_D) SR1NV[0]: 为 SR1V[0] 中的 WIP 状态提供默认状态。为 SR1V[0] 中的 WIP 状态提供默认状态。该位由英飞凌编程, 用户不可编程。

### 6.6.1.2 易失性状态寄存器 1 (SR1V) S25FL256L

相关命令: 相关命令: 读取状态寄存器 1 (RDSR1 05h)、易失性寄存器的写启用 (WRENV 50h)、写入寄存器 (WRR 01h)、清除状态寄存器 (CLSR 30h)、读取任何寄存器 (RDAR 65h)、写入任何寄存器 (WRAR 71h)。通过使用 RDSR1 命令可以显示该寄存器。

**表 8 S25FL256L 易失性状态寄存器 1 (SR1V)**

| 位 | 字段名称   | 功能           | 类型    | 默认状态  | 说明                                                                                                                                                                        |  |

|---|--------|--------------|-------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 7 | SRP0   | 状态寄存器保护 0    | 易失性   | SR1NV | 1 = 通过执行任意影响到 SR1NV、SR1V、CR1NV、CR1V、CR2NV、CR2V、CR3NV、DLRNV 和 DLRV 的命令, WP# 为低电平时 SR1NV、SR1V、CR1NV、CR1V、CR2NV、CR2V、CR3NV、DLRNV 和 DLRV 的锁定状态<br>0 = 即使 WP# 为低电平, 也不进行寄存器保护。 |  |

| 6 | TBPROT | 顶部或底部相对保护    | 易失性   |       | 1 = 从底部 (低地址) 开始执行块保护<br>0 = 从顶部 (高地址) 开始执行 BP                                                                                                                            |  |

| 5 | BP3    | 传统块保护<br>易失性 | 易失性   |       | 防止对所选的扇区 (块) 范围进行编程或擦除操作。                                                                                                                                                 |  |

| 4 | BP2    |              |       |       |                                                                                                                                                                           |  |

| 3 | BP1    |              |       |       |                                                                                                                                                                           |  |

| 2 | BP0    |              |       |       |                                                                                                                                                                           |  |

| 1 | WEL    | 写启用锁存        | 易失性只读 |       | 0 = 不启用写入, 不可执行嵌入式操作; 1 = 启用写入, 可执行嵌入式操作<br>该位不受 WRR 或 WRAR 的影响, 但受 WREN、WRENV、WRDI 和 CLSR 命令的影响。                                                                         |  |

| 0 | WIP    | 正在执行写入操作     | 易失性只读 |       | 1 = 器件处于忙碌状态, 正在执行编程或擦除等嵌入式操作<br>0 = 器件已经处于待机模式, 可以接收命令<br>该位不受 WRR 或 WRAR 的影响, 它仅提供 WIP 状态。                                                                              |  |

## 地址空间映射

状态寄存器保护 0 (SRP0) SR1V[7]: 当该位为 1 并且 WP# 输入为低电平时，器件将处于硬件保护模式。当该位为 ‘1’ 并且 WP# 输入为低电平时，器件将处于硬件保护模式。在该模式下，由于这些寄存器都被配置为只读的，所以更改状态寄存器或配置寄存器的所有命令均被忽略，并且不被执行。因此，可有效地锁存状态寄存器和配置寄存器 SR1NV、SR1V、CR1NV、CR1V、CR2NV、CR2V、CR3NV、DLRNV 和 DLRV 位。如果 WP# 为高电平，便能够更改状态寄存器和配置寄存器 SR1NV、SR1V、CR1NV、CR1V、CR2NV、CR2V、CR3NV、DLRNV 和 DLRV。如果 SRP0 为 ‘0’，WP# 无效，则可能更改状态寄存器和配置寄存器 SR1NV、SR1V、CR1NV、CR1V、CR2NV、CR2V、CR3NV、DLRNV 和 DLRV。WP# 不会影响任何其他寄存器的写操作。SRP0 跟踪该位 (SRP0\_NV) 非易失性版本的更改。当启用 QPI 或 QIO 模式 (CR2V[3] 或 CR1V[1] = 1) 时，内部 WP# 信号电平为 1，这是因为启用其中某个模式时，WP# 外部输入将作为 IO2 使用。这样可以有效地关闭硬件保护。这时，寄存器 SR1NV、SR1V、CR1NV、CR1V、CR2NV、CR2V、CR3NV、DLRNV 和 DLRV 被解锁，您可以对这些寄存器进行写操作 (见第 54 页的 “[状态寄存器保护 \(SRP1、SRP0\)](#)”)。

TBPROT SR1V[6]: 该位定义了状态寄存器中传统模块保护位 BP3、BP2、BP1 和 BP0 的参考点。如状态寄存器部分中所述，通过使用 BP3-0 位，用户可以选择保护阵列的某一部分 (1/64、1/4、1/2 等等) 或整个阵列。将 TBPROT 设置为 ‘0’ 时，传统模块保护被定义为从该阵列的顶部 (最大地址) 开始。将 TBPROT 设置为 ‘1’ 时，传统模块保护被定义为从该阵列的底部 (0 地址) 开始。TBPROT 跟踪该位 (TBPROT\_NV) 非易失性版本的更改。

传统模块保护 (BP3、BP2、BP1、BP0) SR1V[5:2]: 这些位定义了防止编程和擦除操作的主闪存阵列区域。如需了解 BP 位值如何选择受保护的存储器阵列区域，请参阅[第 57 页的 “传统块保护”](#)。

写启用锁存 (WEL) SR1V[1]: 必须将 WEL 位设置为 ‘1’，这样才能启用编程、写入或擦除操作，并能够防止对存储器或寄存器值进行意外更改。执行写启用 (WREN) 命令会将写启用锁存位置 ‘1’，这样便能执行后面所有的编程、擦除或写命令。通过写禁用 (WRDI) 命令，将写启用锁存位置 ‘0’，这样可以防止执行编程、擦除和写命令。编程、写入或擦除操作成功后，WEL 位将被清除为 ‘0’。如果这些操作失败，WEL 位将保持设置状态，应该使用 CLSR 命令清除它。掉电 / 上电序列、硬件复位或软件复位发生后，写启用锁存位将被设置为 WEL\_D。WRR 或 WRAR 命令不会影响该位的状态。

正在写入 (WIP) SR1V[0]: 表示器件是否正在执行编程、写入、擦除或其他操作，器件在这段时间内会忽略新的操作命令。当该位被设置为 ‘1’ 时，器件会执行一个操作。当 WIP 为 ‘1’ 时，仅接收读取状态寄存器 (RDSR1、RDSR2)、读取任何寄存器 (RDAR)、擦除 / 编程暂停 (EPS)、清除状态寄存器 (CLSR)、读取配置寄存器 (RDCR1、RDCR2、RDCR3) 和软件复位 (RST 99h 前面的 RSTEN 66h) 等命令。只有正在对存储器阵列进行擦除或编程操作时，才能接受 EPS 命令。当 WIP=1 时，状态寄存器 E\_ERR 和 P\_ERR 位将被更新。当 P\_ERR 或 E\_ERR 位为 ‘1’ 时，WIP 位将保持设置为 1，以表示器件的繁忙状态并且无法接收新的操作命令。必须接收清除状态寄存器 (CLSR) 命令，这样可以使器件返回待机模式。将 WIP 位清除为 0 时，表示没有任何操作正在进行。这是一个只读位。

地址空间映射

### 6.6.1.3 易失性状态寄存器 1 (SR1NV) S25FL128L,

相关命令：非易失性寄存器的写启用 (WREN 06h)、写禁用 (WRDI 04h)、写入寄存器 (WRR 01h)、读取任何寄存器 (RDAR 65h)、写入任何寄存器 (WRAR 71h)。

表 9 S25FL128L 状态寄存器 1 非易失性 (SR1NV)

| 位 | 字段名称      | 功能                | 类型         | 默认状态 | 描述                            |

|---|-----------|-------------------|------------|------|-------------------------------|

| 7 | SRP0_NV   | 状态寄存器保护 0<br>默认设置 | 非易失性       | 0    | 为 SRP0 提供默认状态。                |

| 6 | SEC_NV    | 扇区 / 块保护          | 非易失性       | 0    | 为 SEC 提供默认状态                  |

| 5 | TBPROT_NV | TBPROT 默认设置       | 非易失性       | 0    | 为 TBPROT 提供默认状态。              |

| 4 | BP_NV2    | 传统块保护默认设<br>置     | 非易失性       | 000b | 为 BP 位提供默认状态。                 |

| 3 | BP_NV1    |                   |            |      |                               |

| 2 | BP_NV0    |                   |            |      |                               |

| 1 | WEL_D     | WEL 的默认设置         | 非易失性<br>只读 | 0    | 为 WEL 状态位提供默认状态。用户不<br>能编程该位。 |

| 0 | WIP_D     | WIP 的默认设置         | 非易失性<br>只读 | 0    | 为 WIP 状态位提供默认状态。用户不<br>能编程该位。 |

状态寄存器保护非易失性位 (SRP0\_NV) SR1NV[7]: 为 SRP0 提供默认状态。请参阅 [第 54 页的 "状态寄存器保护 \(SRP1、SRP0\)"](#)。

扇区 / 块保护位 (SEC\_NV) SR1NV[6]: 为 SEC 提供默认状态。

顶部或底部保护位 (TBPROT\_NV) SR1NV[5]: 为 TBPROT 提供默认状态。

传统模块保护 (BP\_NV3、BP\_NV2、BP\_NV1、BP\_NV0) SR1NV[4:2]: 为 BP\_2 到 BP\_0 位提供默认状

态。

写启用锁存默认 (WEL\_D) SR1NV[1]: 为 SR1V[1] 中的 WEL 状态提供默认状态。该位由英飞凌编程，用

户不可编程。

正在写入的默认位 (WIP\_D) SR1NV[0]: 为 SR1V[0] 中的 WIP 状态提供默认状态。该位由英飞凌编程，

用户不可编程。

地址空间映射

### 6.6.1.4 易失性状态寄存器 1 (SR1V) S25FL128L

相关命令：读取状态寄存器 1 (RDSR1 05h)、易失性寄存器的写启用 (WRENV 50h)、写入寄存器 (WRR 01h)、清除状态寄存器 (CLSR 30h)、读取任何寄存器 (RDAR 65h)、写入任何寄存器 (WRAR 71h)。通过使用 RDSR1 命令可以显示该寄存器。

表 10 S25FL128L 状态寄存器 1 易失性 (SR1V)

| 位 | 字段名称   | 功能        | 类型    | 默认状态  | 说明                                                                                                                                                                           |  |  |

|---|--------|-----------|-------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 7 | SRP0   | 状态寄存器保护 0 | 易失性   | SR1NV | 1 = WP# 为低电平时，通过不执行影响 SR1NV、SR1V、CR1NV、CR1V、CR2NV、CR2V、CR3NV、DLRNV 和 DLRV 的任何命令，可以锁定 SR1NV、SR1V、CR1NV、CR1V、CR2NV、CR2V、CR3NV、DLRNV 和 DLRV 的当前状态<br>0 = 即使 WP# 为低电平，也不进行寄存器保护。 |  |  |

| 6 | SEC    | 扇区 / 块保护  |       |       | 0 = BP2-BP0 保护 64 kB 块<br>1 = BP2-BP0 保护 4 kB 扇区                                                                                                                             |  |  |

| 5 | TBPROT | 顶部或底部相对保护 |       |       | 1 = 从底部 (低地址) 开始执行块保护<br>0 = 从顶部 (高地址) 开始执行块保护                                                                                                                               |  |  |

| 4 | BP2    | 传统块保护易失性  |       |       | 防止对所选的扇区 (块) 范围进行编程或擦除操作。                                                                                                                                                    |  |  |

| 3 | BP1    |           |       |       |                                                                                                                                                                              |  |  |

| 2 | BP0    |           |       |       |                                                                                                                                                                              |  |  |

| 1 | WEL    | 写启用锁存     | 易失性只读 |       | 0 = 不启用写入，不可执行嵌入式操作<br>1 = 启用写入，可执行嵌入式操作<br>该位不受 WRR 或 WRAR 的影响，但受 WREN、WRENV、WRDI 和 CLSR 命令的影响。                                                                             |  |  |

| 0 | WIP    | 正在执行写入操作  |       |       | 1 = 器件处于忙碌状态，正在执行编程或擦除等嵌入式操作<br>0 = 器件已经处于待机模式，可以接收命令<br>该位不受 WRR 或 WRAR 的影响，它仅提供 WIP 状态。                                                                                    |  |  |

状态寄存器保护 0 (SRP0) SR1V[7]: 当该位为 1 并且 WP# 输入为低电平时，器件将处于硬件保护模式。当该位为 ‘1’ 并且 WP# 输入为低电平时，器件将处于硬件保护模式。因此，可有效地锁存状态寄存器和配置寄存器 SR1NV、SR1V、CR1NV、CR1V、CR2NV、CR2V、CR3NV、DLRNV 和 DLRV 位。如果 WP# 为高电平，则可能更改状态寄存器和配置寄存器 SR1NV、SR1V、CR1NV、CR1V、CR2NV、CR2V、CR3NV、DLRNV 和 DLRV，并且更改配置寄存器 SR1NV、SR1V、CR1NV、CR1V、CR2NV、CR2V、CR3NV、DLRNV 和 DLRV。WP# 不会影响其它任何寄存器的写操作。SRP0 跟踪该位 (SRP0\_NV) 非易失性版本的更改。当启用 QPI 或 QIO 模式 (CR2V[3] 或 CR1V[1] = 1) 时，内部 WP# 信号电平为 ‘1’。这是因为启用其中某个模式时，WP# 外部输入将作为 IO2 使用。这样可以有效地关闭硬件保护。这时，寄存器 SR1NV、SR1V、CR1NV、CR1V、CR2NV、CR2V、CR3NV、DLRNV 和 DLRV 被解锁，您可以对这些寄存器进行写操作 (见第 54 页的 “[状态寄存器保护 \(SRP1、SRP0\)](#)”)。

## 地址空间映射

扇区 / 块保护 (SEC) SR1V[6]: 位决定了块保护位 (BP2、BP1、BP0) 将保护大小为 4 kB 的扇区 (SEC = “1” ) 还是大小为 64 kB 的块 (SEC = “0” )。如需了解 SEC 位值如何选择受保护的存储器阵列区域, 请参阅[第 57 页的“传统块保护”](#)。

TBPROT SR1V[5]: 该位定义了状态寄存器中传统块保护位 BP2、BP1 和 BP0 的参考点。如状态寄存器部分中所述, 通过使用 BP2-0 位, 用户可以选择保护阵列的某一部分 (1/64、 $\frac{1}{4}$ 、 $\frac{1}{2}$  等等) 或整个阵列。将 TBPROT 设置为 ‘0’ 时, 传统模块保护被定义为从该阵列的顶部 (最大地址) 开始。将 TBPROT 设置为 ‘1’ 时, 传统模块保护被定义为从该阵列的底部 (0 地址) 开始。TBPROT 跟踪该位 (TBPROT\_NV) 非易失性版本的更改。

传统块保护位 (BP2、BP1、BP0) SR1V[4:2]: 这些位定义了防止编程和擦除操作的主闪存阵列区域。如需了解 BP 位值如何选择受保护的存储器阵列区域, 请参阅[第 57 页的“传统块保护”](#)。

写启用锁存 (WEL) SR1V[1]: 必须将 WEL 位设置为 ‘1’ , 这样才能启用编程、写入或擦除操作, 并能够防止对存储器或寄存器值进行意外更改。执行写启用 (WREN) 命令会将写启用锁存位置 ‘1’ , 这样便能执行后面所有的编程、擦除或写命令。通过写禁用 (WRDI) 命令, 将写启用锁存位置 ‘0’ , 这样可以防止执行编程、擦除和写命令。编程、写入或擦除操作成功后, WEL 位将被清除为 ‘0’ 。如果这些操作失败, WEL 位将保持设置状态, 应该使用 CLSR 命令清除它。掉电 / 上电序列、硬件复位或软件复位发生后, 写启用锁存位将被设置为 WEL\_D。WRR 或 WRAR 命令不会影响该位的状态。

正在写入 (WIP) SR1V[0]: 表示器件是否正在执行编程、写入、擦除或其他操作, 器件在这段时间内会忽略新的操作命令。当该位被设置为 ‘1’ 时, 器件执行一个操作。当 WIP 为 ‘1’ 时, 仅接收读取状态寄存器 (RDSR1、RDSR2)、读取任何寄存器 (RDAR)、擦除 / 编程挂起 (EPS)、清除状态寄存器 (CLSR) 和软件复位 (RSTEN 66h 后面紧跟着 RST 99h) 等命令。只有正在对存储器阵列进行擦除或编程操作时, 才能接受 EPS 命令。当 WIP = 1 时, 状态寄存器 E\_ERR 和 P\_ERR 位将被更新。当 P\_ERR 或 E\_ERR 位为 ‘1’ 时, WIP 位将保持设置为 ‘1’ , 以表示器件的繁忙状态并且无法接收新的操作命令。必须接收清除状态寄存器 (CLSR) 命令, 这样可以使器件返回待机模式。将 WIP 位清除为 0 时, 表示没有任何操作正在进行。这是一个只读位。

地址空间映射

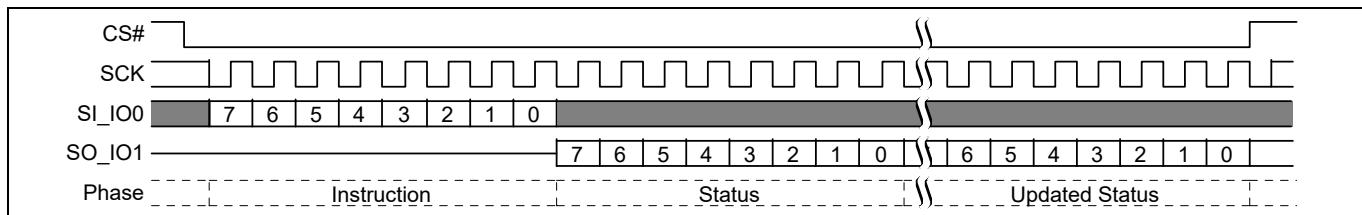

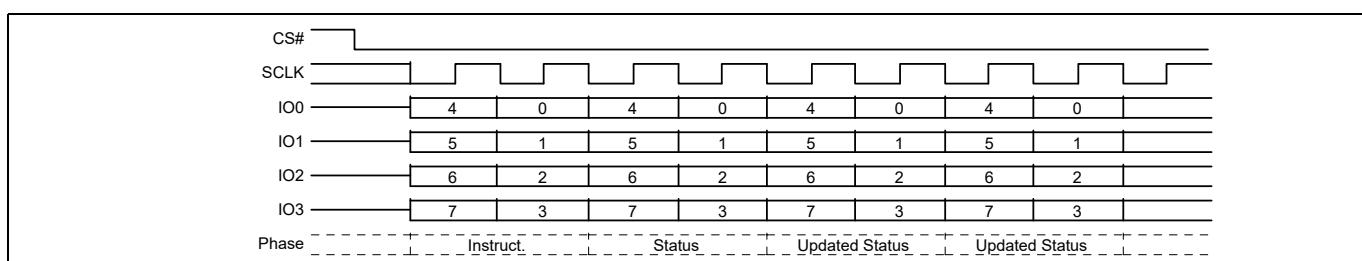

## 6.6.2 易失性状态寄存器 2 (SR2V)

相关命令：读取状态寄存器 2 (RDSR2 07h)、读取任何寄存器 (RDAR 65h)。状态寄存器 2 中没有用户可编程的非易失性位，它的所有定义位都是易失性只读状态位。这些位的默认状态是由硬件设置的。

**表 11 易失性状态寄存器 2 (SR2V)**

| 位 | 字段名称  | 功能      | 类型        | 默认状态                            | 描述                              |  |  |

|---|-------|---------|-----------|---------------------------------|---------------------------------|--|--|

| 7 | RFU   | 预留      | 易失性<br>只读 | 0                               | 预留供将来使用                         |  |  |

| 6 | E_ERR | 发生了擦除错误 |           |                                 | 1 = 发生错误<br>0 = 无错误             |  |  |

| 5 | P_ERR | 发生了编程错误 |           |                                 |                                 |  |  |

| 4 | RFU   | 预留      |           |                                 | 预留供将来使用                         |  |  |

| 3 |       |         |           |                                 |                                 |  |  |

| 2 |       |         |           |                                 |                                 |  |  |

| 1 | ES    | 擦除挂起    | 易失性只读     | 1 = 处于擦除挂起模式。<br>0 = 未处于擦除挂起模式。 |                                 |  |  |

| 0 | PS    | 编程挂起    |           |                                 | 1 = 处于编程挂起模式。<br>0 = 未处于编程挂起模式。 |  |  |

擦除错误位 (E\_ERR) SR2V[6]：擦除错误位用于指出擦除操作的成功或失败。当擦除错误位被设置为‘1’时，则表示最后擦除操作有错误。当用户尝试擦除受保护的单独主存储器扇区或一个被锁定的安全区域时，该位将被设置。如果在执行命令期间找到受保护的扇区时，芯片擦除命令将设置 E\_ERR。将擦除错误位设置为‘1’时，通过使用清除状态寄存器 (CLSR) 命令可以将该位清除为 0。这是一个只读位，不受 WRR 或 WRAR 命令的影响。

编程错误 (P\_ERR) SR2V[5]：编程错误位用于指出编程操作的成功或失败。将编程错误位设置为‘1’时，则表示最后编程操作有错误。当用户尝试对受保护的主存储器扇区或一个被锁定的安全区域进行编程时，该位将被置位。将编程错误位设置为‘1’时，通过使用清除状态寄存器 (CLSR) 命令可以将该位清除为 0。这是一个只读位，不受 WRR 或 WRAR 命令的影响。

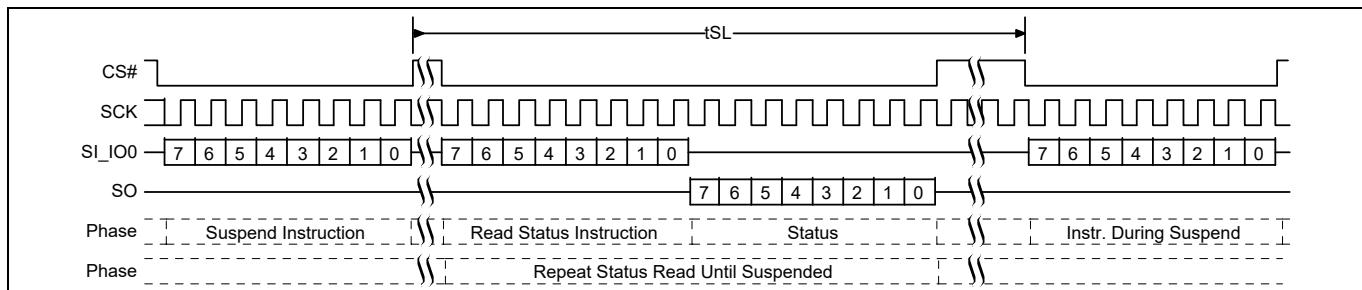

擦除挂起位 (ES) SR2V[1]：擦除挂起位用于指出器件是否进入擦除挂起模式。该状态位不支持用户写入。当擦除挂起位为‘1’时，器件将处于擦除挂起模式。当擦除挂起位为‘0’时，则器件不处于擦除挂起模式。如需详细了解擦除挂起 / 恢复命令，请参阅第 110 页的“[编程或擦除挂起 \(PES 75h\)](#)”。

编程挂起 (PS) SR2V[0]：编程挂起位用于指出器件是否处于编程挂起模式。该状态位不支持用户写入。当编程挂起位为‘1’时，则器件处于编程挂起模式。当编程挂起位为‘0’时，则器件不处于编程挂起模式。如需了解更多信息，请查阅第 110 页的“[编程或擦除挂起 \(PES 75h\)](#)”。

地址空间映射

### 6.6.3 配置寄存器 1

配置寄存器 1 用于控制某些接口和数据保护功能。通过使用带有十六个输入周期的 WRR 命令或通过使用 WRAR 命令可以更改这些寄存器位。

#### 6.6.3.1 非易失性配置寄存器 1 (CR1NV)

相关命令：非易失性寄存器的写启用 (WREN 06h)、写入寄存器 (WRR 01h)、读取任何寄存器 (RDAR 65h)、写入任何寄存器 (WRAR 71h)。

**表 12 非易失性配置寄存器 1 (CR1NV)**

| 位 | 字段名称    | 功能                | 类型         | 默认状态 | 说明                                                                                                                                                          |  |

|---|---------|-------------------|------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 7 | SUS_D   | 挂起状态默认设置          | 非易失性<br>只读 | 0    | 为挂起状态提供默认状态。用户不能编程该位。                                                                                                                                       |  |

| 6 | CMP_NV  | 补充保护默认设置          | 非易失性       |      | 为 CMP 提供默认状态。                                                                                                                                               |  |

| 5 | LB3     | 安全区域锁定位           | OTP        |      | 安全区域 3:0 的 OTP 锁定位 3:0<br>0 = 安全区域未被锁定<br>1 = 安全区域永久性被锁定                                                                                                    |  |

| 4 | LB2     |                   |            |      |                                                                                                                                                             |  |

| 3 | LB1     |                   |            |      |                                                                                                                                                             |  |

| 2 | LB0     |                   |            |      |                                                                                                                                                             |  |

| 1 | QUAD_NV | 四线默认设置            | 非易失性       |      | 为 QUAD 提供默认状态。                                                                                                                                              |  |

| 0 | SRP1_D  | 状态寄存器保护 1<br>默认设置 | OTP        |      | 当 IRP[2:0] = “111” 时，可以编程 SRP1_D 位。<br>锁定 SR1NV、SR1V、CR1NV、<br>CR1V、CR2NV、CR2V、CR3NV、<br>DLRNV 和 DLRV 的当前状态<br>1 = 寄存器永久锁定<br>0 = POR 发生后，寄存器不受 SRP1<br>的保护 |  |

挂起擦除 / 编程状态位 (SUS\_D) CR1NV[7]: 为 CR1V[7] 中的 SUS 位提供默认状态。用户不能编程该位。

补充保护位 (CMP\_NV) CR1NV[6]: 为 CR1V[6] 中的 CMP 位提供默认状态。

安全区域锁定位 (LB3、LB2、LB1、LB0) CR1NV[5:2]: 提供安全区域的 OTP 写保护控制。将 LB 位设置为 1 时，将不能对安全区域进行其他编程或擦除操作。

四线数据宽度非易失性位 (QUAD\_NV) CR1NV[1]: 为 CR1V[1] 中的 QUAD 位提供默认状态。WRR 或 WRAR 命令会影响该位的状态。CR1NV[1] = 1 时，在上电或复位时将默认运行四线数据宽的命令。

状态寄存器保护 1 默认位 (SRP1\_D) CR1NV[0]: 为 CR1V[0] 中的 SRP1 位提供默认状态。当 IRP[2:0] = 111 时，用户可以对 SRP1\_D OTP 位进行编程。当 SRP1\_D = “1” 时，寄存器 SR1NV、SR1V、CR1NV、CR1V、CR2NV、CR2V、CR3NV、DLRNV 和 DLRV 被永久性锁定。请参阅 [第 54 页的“状态寄存器保护 \(SRP1、SRP0\)”](#)。

地址空间映射

### 6.6.3.2 易失性配置寄存器 1 (CR1V)

相关命令：读取配置寄存器 1 (RDCR1 35h)、易失性的写启用 (WRENV 50h)、写入寄存器 (WRR 01h)、读取任何寄存器 (RDAR 65h)、写入任何寄存器 (WRAR 71h)。通过使用 RDCR1 命令可以显示该寄存器。

表 13 易失性配置寄存器 1 (CR1V)

| 位 | 字段名称 | 功能               | 类型        | 默认状态  | 说明                                                                                               |  |

|---|------|------------------|-----------|-------|--------------------------------------------------------------------------------------------------|--|

| 7 | SUS  | 挂起状态             | 易失性<br>只读 | CR1NV | 1 = 擦除 / 编程挂起<br>0 = 擦除 / 编程不挂起                                                                  |  |

| 6 | CMP  | 补充保护             | 易失性       |       | 0 = 正常保护映射<br>1 = 转换保护映射                                                                         |  |

| 5 | LB3  | 安全区域锁定的<br>易失性副本 | 易失性<br>只读 |       | 用户不可写入<br>请参见 CR1NV[5:2]<br>安全区域 3:0 的 OTP 锁定位 3:0<br>0 = 安全区域未被锁定<br>1 = 安全区域永久性被锁定             |  |

| 4 | LB2  |                  |           |       |                                                                                                  |  |

| 3 | LB1  |                  |           |       |                                                                                                  |  |

| 2 | LB0  |                  |           |       |                                                                                                  |  |

| 1 | QUAD | 四线 I/O 模式        | 易失性       |       | 1 = 四线<br>0 = 双线或串行                                                                              |  |

| 0 | SRP1 | 状态寄存器保护 1        |           |       | 锁定 SR1NV、SR1V、CR1NV、CR1V、<br>CR2NV、CR2V、CR3NV、DLRNV 和<br>DLRV 的当前状态<br>1 = 寄存器被锁定<br>0 = 寄存器未被锁定 |  |

挂起状态位 (SUS) CR1V[7]: 挂起状态位用于确定器件是否进入擦除或编程挂起模式。该状态位不支持用户写入。将挂起状态位置为 ‘1’ 时，器件将进入擦除或编程挂起模式。将挂起状态位清除为 ‘0’ 时，表示器件不处于擦除或编程挂起模式。如需详细了解擦除 / 编程挂起 / 恢复命令，请参阅[第 110 页的“编程或擦除挂起 \(PES 75h\)”](#)。

补充保护位 (CMP) CR1V[6]: CMP 与 TBPROT、BP3、BP2、BP1 和 BP0 位一起被使用，用于为阵列保护映射提供更高的灵活性，这样可以为半个到整个阵列的空间提供保护。

LB[3:0] CR1V[5:2]: 这些位是 CR1NV 的相关 OTP 位的易失性复制。它们跟踪相关 OTP 版本的更改。

四线数据宽度 (QUAD) CR1V[1]: 设置为 1 时，这些位将器件的数据宽度切换到 4 比特四线模式。当 CS# 为低电平时，WP# 变为 IO2，IO3/RESET# 变为有效的 I/O 信号。当 CS# 为高电平时，WP# 变为 IO2，IO3/RESET# 变为有效的 I/O 信号。当 CS# 为高电平时，IO3/RESET# 变为 RESET# 输入。WP# 输入不被监控，因此它会正常运行，并且它被内部设置为高电平（无效）。可以正常执行串行和双线 I/O 读取命令，但在使用不同的数据路径宽度切换各个命令时不用为这些命令驱动 WP# 输入。同样，在执行这些命令期间，不需要驱动 IO3/RESET#（CS# 为低电平）。当使用读取四线输出、读取四线 I/O 和读取 DDR 四线 I/O 命令时，必须将 QUAD 位设置为 1。QIO 模式的易失性寄存器写操作拥有  $(t_{QEN})$  时间以将器件接口切换到 QIO 模式和  $(t_{QEX})$  时间，从而能够将器件切换到 SPI 模式。因此，能以 QIO 协议方式立即发送以下命令。通过 QPIEN 和 QPIEX 命令进入 / 退出 QPI 模式，或将 CR2V[3] 设置为 1 时，将使用四线数据宽度模式（无论 QUAD 位的状态如何）。

状态寄存器保护 1 (SRP1) CR1V[0]: 将 SRP1 位设置为 1 时，将通过防止对 SR1NV、SR1V、CR1NV、CR1V、CR2NV、CR2V、CR3NV、DLRNV 和 DLRV 寄存器进行的写操作保护这些寄存器的状态。

请参阅[第 54 页的“状态寄存器保护 \(SRP1、SRP0\)”](#)。

## 地址空间映射

如果 SRP1 位保持清除为 0, SR1NV、SR1V、CR1NV、CR1V、CR2NV、CR2V、CR3NV、DLRNV 和 DLRV 寄存器不受 SRP1 的保护。然而, 这些寄存器可能受 SRP0 (SR1V[7]) 和 WP# 输入的保护。

将一个逻辑 1 写入到 SRP1 位后, 只能通过断电到上电周期或硬件复位将其清除为逻辑 0。软件复位将不影响到 SRP1 位的状态。

CR1V[0] SRP1 位是易失性的。上电后, SRP1 的默认状态由 CR1NV[0] 中的 SRP1\_D 决定。通过使用单个 WRR 或 WRAR 命令可以同时设置 SRP1 位并更新 CR1V 中的其他值。

## 6.6.4 配置寄存器 2

配置寄存器 2 控制某些接口功能。通过使用读取任何寄存器和写入任何寄存器命令可以读取和更改这些寄存器位。该寄存器的非易失性版本允许为这些控制设置 POR、硬件复位或软件复位状态。在正常操作期间, 该寄存器的易失性版本控制着功能状态。

### 6.6.4.1 非易失性配置寄存器 2 (CR2NV)

相关命令: 非易失性寄存器的写启用 (WREN 06h)、写入寄存器 (WRR 01h)、读取任何寄存器 (RDAR 65h)、写入任何寄存器 (WRAR 71h)。

**表 14 非易失性配置寄存器 2 (CR2NV)**

| 位 | 字段名称    | 功能        | 类型   | 默认状态 | 说明                                                                                                                                                            |  |

|---|---------|-----------|------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 7 | IO3R_NV | IO3_Reset | 非易失性 | 0    | 1 = 启用 – 当 CS# 为高电平或四线模式被禁用 (CR1V[1] = 0) 或 QPI 被禁用 (CR3V[3] = 0) 时, IO3_RESET 作为 IO3/RESET# 输入使用<br>0 = 禁用 – IO3 不具有其他功能, 硬件复位被禁用。为 IO3 / RESET# 功能启用提供默认状态。 |  |

| 6 | OI_NV   | 输出阻抗      |      | 1    | 提供默认输出阻抗状态。<br>请参阅 <b>表 15</b> 。                                                                                                                              |  |

| 5 |         |           |      | 0    | 预留供将来使用                                                                                                                                                       |  |

| 4 | RFU     | 预留        |      | 0    | 1 = 启用 – 使用 QPI (4-4-4) 协议<br>0 = 禁用 – 使用传统 SPI 协议, 指令始终在 SI 线上串行传输为 QPI 模式提供默认状态。                                                                            |  |

| 3 | QPI_NV  | QPI       |      | 0    | 为 WPS 提供默认状态<br>0 = 传统保护<br>1 = 单块锁定                                                                                                                          |  |

| 2 | WPS_NV  | 写保护选择     |      | 0    | 为地址长度提供默认状态<br>1 = 4 字节地址<br>0 = 3 字节地址                                                                                                                       |  |

| 1 | ADP_NV  | 上电时的地址长度  |      | 0    | 预留供将来使用                                                                                                                                                       |  |

| 0 | RFU     | 预留        |      | 0    |                                                                                                                                                               |  |

## 地址空间映射

IO3\_Reset 非易失性位 CR2NV[7]: 该位控制 IO3 信号性能的 POR、硬件复位或软件复位状态。由于传统 SPI 器件封装中的信号数量和连接有限，所以几乎所有传统 SPI 器件都没有硬件复位输入信号。当没有将 IO3 信号用于传输主机系统和存储器之间的信息时，FL-L 允许将 IO3 信号作为硬件复位输入使用。通过使用该非易失性 IO3\_Reset 配置位，可以立即启动器件，并且 IO3 作为 RESET# 信号使用。

输出阻抗非易失性位 CR2NV[6:5]: 这些位控制 IO 信号输出阻抗（驱动强度）的 POR、硬件复位或软件复位状态。通过多个驱动强度可以使输出阻抗与系统印刷电路板环境相互匹配，从而能够尽量降低过冲和振铃。这些非易失性输出阻抗配置位允许器件使用合适的驱动强度立即启动。

**表 15 输出阻抗控制**

| CR2NV[6:5] 阻抗选项 | 对 $V_{SS}$ 的典型阻抗 ( $\Omega$ ) | 对 $V_{CC}$ 的典型阻抗 ( $\Omega$ ) | 注意 |

|-----------------|-------------------------------|-------------------------------|----|

| 00              | 18                            | 21                            | -  |

| 01              | 26                            | 28                            |    |

| 10              | 47                            | 45                            |    |

| 11              | 71                            | 64                            |    |

QPI 非易失性位 CR2NV[3]: 该位为所有命令的预期指令宽度控制 POR、硬件复位或软件复位状态。传统 SPI 命令始终在 SI (IO0) 信号上以 1 位宽度（串行 I/O）发送指令。FL-L 系列也支持 QPI 模式。在该模式下，主机系统和存储器之间的所有传输在 IO0 到 IO3 上实现，传输宽度为 4 比特，包括所有指令。该非易失性 QPI 配置位允许器件在 QPI 模式下立即启动），而不是在传统串行指令模式下进行。转到 QPI 模式的建议流程是先使用 QPIEN (38h) 命令，WRR 或 WRAR 命令也可以将 CR2V[3] 设置为 1 (QPI 模式)。QIO 模式的易失性寄存器写操作拥有 ( $t_{QEN}$ ) 时间，用于将器件接口切换到 QIO 模式和 ( $t_{QEX}$ ) 时间，从而能够将器件切换到 SPI 模式。因此，能以 QPI 协议方式立即发送以下命令。通过使用 WRAR 命令将 CR2NV[3] 编程为 1，然后轮询 SR1V[0]，以确定编程操作是否完成。同样，使用 QPIEX (F5h) 命令退出 QPI 模式。也可以使用 WRR 或 WRAR 命令将 CR2V[3] 清除为 0。

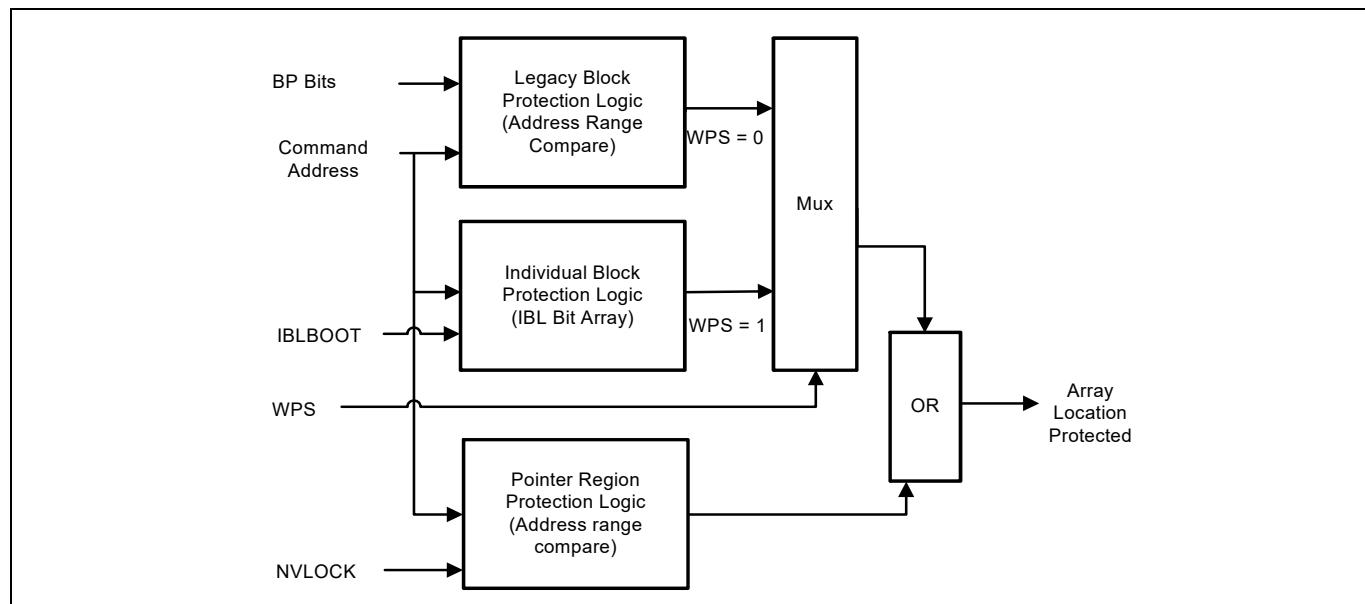

写保护选择非易失性 CR2NV[2]: 该位控制写保护方法的 POR、硬件复位或软件复位状态。在启用该非易失性配置位的情况下，当器件启动时，将启用单独模块锁存保护（而不是传统的模块保护）。

上电时的地址长度、非易失性 CR2NV[1]: 该位为所有命令的预期地址长度控制 POR、硬件复位或软件复位状态。这些命令需要地址而且这些地址不被固定为 3 字节或 4 字节地址。多数传统的 SPI 命令需要一个地址，这些命令通常使用 3 字节（24 位）地址。如果器件容量超过 128 Mb，将需要一个 4 字节（32 位）地址来访问整个存储器阵列。通过使用地址长度配置位可以将所有 3 字节地址命令更改为所期待的 4 字节地址。如需了解命令地址长度，请参阅表 39。该非易失性地址长度配置位允许器件在 4 字节地址模式立即启动，而不是在传统的 3 字节地址模式下进行。

地址空间映射

#### 6.6.4.2 易失性配置寄存器 2 (CR2V)

相关命令：读取配置寄存器 2 (RDCR2 15h)、读取任何寄存器 (RDAR 65h)、易失性的写启用 (WRENV 50h)、写入寄存器 (WRR 01h)、写入任何寄存器 (WRAR 71h)、进入 4 字节地址模式 (4BEN B7h)、退出 4 字节地址模式 (4BEX E9h)、进入 QPI (38h)、退出 QPI (F5h)。通过使用 RDCR2 命令可以显示该寄存器。通过使用 RDCR2 命令可以显示该寄存器。

表 16 易失性配置寄存器 2 (CR2V)

| 位 | 字段名称 | 功能        | 类型  | 默认状态     | 说明                                                                                                                                      |  |  |

|---|------|-----------|-----|----------|-----------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 7 | IO3R | IO3_Reset | 易失性 | CR2NV    | 1 = 启用 — 当 CS# 为高电平或四线模式被禁用 (CR1V[1] = 0) 或 QPI 被禁用 (CR3V[3] = 0) 时，IO3 作为 RESET# 输入使用。<br>0 = 禁用 — IO3 没有其他功能，IO3/RESET# 输入的硬件复位功能被禁用。 |  |  |

| 6 | OI   | 输出阻抗      |     |          | 请参阅表 15。                                                                                                                                |  |  |

| 5 |      |           |     |          | 预留供将来使用                                                                                                                                 |  |  |

| 4 | RFU  | 预留        |     |          | 1 = 启用 — 使用 QPI (4-4-4) 协议<br>0 = 禁用 — 使用传统 SPI 协议，指令始终在 SI 线上串行传输                                                                      |  |  |

| 3 | QPI  | QPI       |     |          | 0 = 传统块保护<br>1 = 单块锁定                                                                                                                   |  |  |

| 2 | WPS  | 写保护选择     |     |          | 只读状态位<br>1 = 4 字节地址<br>0 = 3 字节地址                                                                                                       |  |  |

| 1 | ADP  | 上电时的地址长度  |     |          | 当前地址模式<br>1 = 4 字节地址<br>0 = 3 字节地址                                                                                                      |  |  |

| 0 | ADS  | 地址长度状态    | 易失性 | CR2NV[1] |                                                                                                                                         |  |  |

IO3 复位 CR2V[7]: 该位控制 IO3/RESET# 信号的状态。当 CS# 为高电平或四线模式 (CR1V[1] = 0) 被禁用或 QPI (CR3V[3] = 0) 被禁用时，在正常操作期间，通过易失性 IO3 复位配置位，可将 IO3 作为 RESET# 输入使用。

输出阻抗位 CR2V[6:5]: 这些位控制 IO 信号输出阻抗 (驱动强度)。通过使用该易失性输出阻抗配置位，用户可以在正常操作期间调整驱动强度。

QPI CR2V[3]: 该位控制所有命令的预期指令宽度。通过使用易失性 QPI 配置位，在正常操作期间，器件可以进入和退出 QPI 模式。将该位设置为 QPI 模式时，四线模式将有效，无论 QIO 模式 (CR1V[1]) 的设置如何。将该位清除为传统的 SPI 模式时，QUAD 位不受影响。通过使用 QPIEN (38h) 命令可以将 QPI CR2V[3] 位设置为 ‘1’，通过使用 QPIEX (F5h) 命令可以将其设置为 ‘0’。

表 17 QPI 和 QIO 模式控制位

| QPI CR2V[3] | QUAD CR1V[1] | 说明                                                                      |

|-------------|--------------|-------------------------------------------------------------------------|

| 0           | 0            | SIO 模式：单线和双线读取，WP#/IO2 输入作为 WP# 引脚使用，IO3/RESET# 输入作为 RESET# 引脚使用        |

| 0           | 1            | QIO 模式：单线、双线和四线读取，WP#/IO2 输入作为 IO2 使用，IO3/RESET# 输入作为 IO3 或 RESET# 引脚使用 |

| 1           | X            | QPI 模式：四线读取，WP#/IO2 输入作为 IO2 使用，IO3/RESET# 输入作为 IO3 或 RESET# 引脚使用       |

## 地址空间映射

写保护选择位 CR2V[2]: 通过该位可以选择阵列保护方法，具体请参阅第 57 页的 "传统块保护" 或第 62 页的 "单块锁定 (IBL) 保护"。通过易失性配置位，用户可以在正常操作期间更改保护方法。

上电 (ADP) CR2V[1] 时的地址长度：该位为只读位，它显示了上电复位、硬件复位或软件复位后所有命令的地址长度。该位为只读位，它显示了上电复位、硬件复位或软件复位后所有命令的地址长度。这些命令需要地址，并且这些地址不被固定为 3 字节或 4 字节地址。

地址长度状态 (ADS) CR2V[0]: 该位控制所有命令的预期地址长度。这些命令需要地址，这些地址不被固定为 3 字节或 4 字节地址。如需了解命令地址长度，请参阅表 39。通过易失性地址长度配置位，用户可以在正常操作期间更改地址的长度。4 字节地址模式 (4BEN) 命令直接将该位设置为 4 字节地址模式，(4BEX) 退出命令将该位设置回 3 字节地址模式。更新地址长度非易失性 CR2NV[1] 位时，该位也被更新。

## 6.6.5 配置寄存器 3

配置寄存器 3 控制着主闪存阵列读命令的连续回卷状态和读取延迟。连续回卷配置不会影响读取非主闪存阵列的区域的命令，如：读取寄存器或安全区域的命令。由于在 POR、硬件复位或软件复位期间寄存器的内容被复制到寄存器的易失性版本内，因此该寄存器的非易失性版本允许设置该控制操作的启动状态。正常操作期间，该寄存器的易失性版本控制功能的性能。

通过使用读取配置 3 (RDCR3 33h)、写入寄存器 (WRR 01h)、读取任何寄存器 (RDAR 65h)、写入任何寄存器 (WRAR 71h) 命令可以对这些寄存器位进行读取和更改操作。通过使用设置连续长度 (77h) 命令也可以写入该寄存器的易失性版本。

### 6.6.5.1 非易失性配置寄存器 3 (CR3NV)

相关命令：非易失性寄存器的写启用 (WREN 06h)、写入寄存器 (WRR 01h)、读取任何寄存器 (RDAR 65h)、写入任何寄存器 (WRAR 71h)。

**表 18 非易失性配置寄存器 3 (CR3NV)**

| 位 | 字段名称  | 功能       | 类型    | 默认状态 | 说明                                                          |

|---|-------|----------|-------|------|-------------------------------------------------------------|

| 7 | RFU   | 预留       | WL_NV | 0    | 预留供将来使用                                                     |

| 6 |       |          |       | 1    | 00 = 8 字节回卷<br>01 = 16 字节回卷<br>10 = 32 字节回卷<br>11 = 64 字节回卷 |

| 5 |       | 回卷长度默认设置 |       | 1    |                                                             |

| 4 | WE_NV | 回卷启用默认设置 |       | 1    | 0 = 回卷启用<br>1 = 回卷禁用                                        |

| 3 |       |          | RL_NV | 1    | 0 到 15 个延迟 (虚拟) 周期 (随后读地址或连续模式位)。                           |

| 2 |       |          |       | 0    |                                                             |

| 1 |       | 读取延迟默认设置 |       | 0    |                                                             |

| 0 |       |          |       | 0    |                                                             |

回卷长度非易失性位 CR3NV[6:5]: 这些位控制着回卷读取长度和对齐的 POR、硬件复位或软件复位状态。

回卷启用非易失性位 CR3NV[4]: 该位控制着回卷启用的 POR、硬件复位或软件复位状态。受回卷启用影响的命令包括：读取四线 I/O、读取 QPI、读取 DDR 四线 I/O 和读取 DDR QPI。该配置位允许器件在回卷突发 (wrapped burst) 读取模式下立即启动，而不是在传统的连续读取模式下进行。

## 地址空间映射

读取延迟非易失性 CR3NV[3:0]：这些位控制着所有可变延迟读取命令中读取延迟（虚拟周期）的 POR、硬件复位或软件复位状态。以下读取命令在地址或模式的结束和读取数据开始返回到主机之间有一个可变的延迟周期：

- 对于以下命令，所有时钟频率的延迟均为：一个虚拟周期。如果默认延迟代码为‘0’，该延迟为一个虚拟周期。

- 数据学习模式读取 DLPRD (1-1-1) 或 (4-4-4)

- IRP 读取 IRPRD (1-1-1) 或 (4-4-4)

- 保护寄存器读取 PRRD (1-1-1) 或 (4-4-4)

- 密码读取 PASSRD (1-1-1) 或 (4-4-4)

- 命令的延迟 / 时钟频率如[表 19](#) 和[表 20](#) 所示。如果默认延迟代码为 0，该延迟为 8 个虚拟周期。

- 快速读取 FAST\_READ (1-1-1)

- 四线 O 读取 QOR、4QOR (1-1-4)

- 双线 O 读取 DOR、4DOR (1-1-2)

- 双线 I/O 读取 DIOR、4DIOR (1-2-2)

- 四线 I/O 读取 QIOR、4QIOR (1-4-4) 或 (4-4-4)

- DDR 四线 I/O 读取 DDRQIOR、4DDRQIOR (1-4-4)

- 安全区域读取 SECRR (1-1-1) 或 (4-4-4)

- 读取任何寄存器 RDAR (1-1-1) 或 (4-4-4)

- 读取串行闪存可发现参数 RSFDP (1-1-1) 或 (4-4-4)

非易失性读延迟配置位设置需要使用的读延迟（虚拟周期）数量，因此可以使用主机系统的合适读延迟立即启动器件

地址空间映射

表 19 延迟代码（周期）与频率

| 延迟代码 | 读取命令最大频率 (MHz)  |                       |                         |                       |                         |                             |                                            |

|------|-----------------|-----------------------|-------------------------|-----------------------|-------------------------|-----------------------------|--------------------------------------------|

|      | 快速读取<br>(1-1-1) | 双线输出<br>读取<br>(1-1-2) | 双线 I/O<br>读取<br>(1-2-2) | 四线输出<br>读取<br>(1-1-4) | 四线 I/O<br>读取<br>(1-4-4) | 四线 I/O<br>读取 QPI<br>(4-4-4) | DDR<br>四线 I/O<br>(1-4-4)<br>QPI<br>(4-4-4) |

| 0    | 模式周期<br>= 0     | 模式周期<br>= 0           | 模式周期<br>= 4             | 模式周期<br>= 0           | 模式周期<br>= 2             | 模式周期<br>= 2                 | 模式周期<br>= 1                                |

|      | 虚拟周期<br>= 8     | 虚拟周期<br>= 8           | 虚拟周期<br>= 8             | 虚拟周期<br>= 8           | 虚拟周期<br>= 8             | 虚拟周期<br>= 8                 | 虚拟周期<br>= 8                                |

| 1    | 50              | 50                    | 75                      | 35                    | 35                      | 35                          | 20                                         |

| 2    | 65              | 65                    | 85                      | 45                    | 45                      | 45                          | 25                                         |

| 3    | 75              | 75                    | 95                      | 55                    | 55                      | 55                          | 35                                         |

| 4    | 85              | 85                    | 108                     | 65                    | 65                      | 65                          | 45                                         |

| 5    | 95              | 95                    | 108                     | 75                    | 75                      | 75                          | 55                                         |

| 6    | 108             | 105                   | 108                     | 85                    | 85                      | 85                          | 60                                         |

| 7    | 108             | 108                   | 133                     | 95                    | 95                      | 95                          | 66                                         |

| 8    | 108             | 108                   | 133                     | 108                   | 108                     | 108                         | 66                                         |

| 9    | 133             | 133                   | 133                     | 115                   | 115                     | 115                         | 66                                         |

| 10   | 133             | 133                   | 133                     | 115                   | 115                     | 115                         | 66                                         |

| 11   | 133             | 133                   | 133                     | 120                   | 120                     | 120                         | 66                                         |

| 12   | 133             | 133                   | 133                     | 120                   | 120                     | 120                         | 66                                         |

| 13   | 133             | 133                   | 133                     | 133                   | 133                     | 133                         | 66                                         |

| 14   | 133             | 133                   | 133                     | 133                   | 133                     | 133                         | 66                                         |

| 15   | 133             | 133                   | 133                     | 133                   | 133                     | 133                         | 66                                         |

地址空间映射

表 20 延迟代码（周期）与频率

| 延迟代码 0 | 读取命令最大频率 (MHz)  |                     |                |                    |                       |                           |

|--------|-----------------|---------------------|----------------|--------------------|-----------------------|---------------------------|

|        | 读取任何寄存器 (1-1-1) | 读取任何寄存器 QPI (4-4-4) | 安全区域读取 (1-1-1) | 安全区域读取 QPI (4-4-4) | 读取 SFDP RSFDP (1-1-1) | 读取 SFDP RSFDP QPI (4-4-4) |

|        | 模式周期 = 0        | 模式周期 = 0            | 模式周期 = 0       | 模式周期 = 0           | 模式周期 = 0              | 模式周期 = 0                  |

|        | 虚拟周期 = 8        | 虚拟周期 = 8            | 虚拟周期 = 8       | 虚拟周期 = 8           | 虚拟周期 = 8              | 虚拟周期 = 8                  |