# 128 Mb (16 MB) / 256 Mb (32 MB) FL-L フラッシュ シユ

SPI マルチI/O, 3.0V

## 概要

FL-L ファミリ デバイスはフラッシュ不揮発性メモリの製品であり、以下の技術を使用しています。

- フローティングゲート技術

- 65 nm プロセス リソグラフィー

FL-L ファミリはシリアルペリフェラルインターフェース (SPI) を介して、ホストシステムに接続します。従来の SPI シングルビットシリアル入出力 (シングルI/O または SIO) だけでなく、任意の 2ビット (デュアルI/O または DIO) および 4ビット幅クアッドI/O (QIO) とクアッドペリフェラルインターフェース (QPI) コマンドもサポートされます。さらに、アドレスと読み出しデータをクロックの両方のエッジで転送する、QIO および QPI 用のダブルデータレート (DDR) 読み出しこマンドもサポートします。

アーキテクチャは1回の動作で最大 256 バイトをプログラムすることを可能にするページプログラミング バッファを備えており、個別の 4 KB セクタ, 32 KB ハーフ ブロック, 64 KB ブロック, またはチップ全体の消去機能を提供します。

より高いクロック レートをサポートしクアッド コマンドを備える FL-L ファミリのデバイスを使用することにより、命令読み出し転送速度は従来のパラレルインターフェース、非同期 NOR フラッシュメモリの転送速度以上となり、信号数を著しく減少させています。

FL-L ファミリ製品は高容量に加えて、数多くのモバイルや組込みアプリケーションに必要な柔軟性および高速処理性能を提供します。スペース、信号接続、および消費電力が限られているシステムに理想的なストレージソリューションを提供します。これらのメモリは通常のシリアル フラッシュ デバイスと比べて、はるかに優れた柔軟性および処理性能を提供します。これらは RAM へのコード シャドーイング、コードの直接実行 (XIP)、および再プログラム可能なデータ保存に理想的です。

## 特長

- マルチ I/O を備えた SPI

- クロック極性と位相モード 0 と 3

- ダブルデータ レート (DDR) オプション

- クアッドペリフェラルインターフェース (QPI) オプション

- 拡張アドレス指定: 24 ビットまたは 32 ビット アドレス指定オプション

- S25FL-A, S25FL1-K, S25FL-P, S25FL-S, S25FS-S SPI ファミリと互換性のあるシリアルコマンド サブセットおよびフットプリント

- S25FL-P, S25FL-S, S25FS-S SPI ファミリと互換性のあるマルチ I/O コマンド サブセットおよびフットプリント

- 読み出し

- コマンド: 通常、高速、デュアルI/O、クアッドI/O、デュアルO、クアッドO、DDR クアッドI/O

- モード: バーストラップ、連続(XIP)、QPI

- コンフィギュレーション情報用のシリアル フラッシュ検出可能なパラメーター (SFDP)

- プログラムアーキテクチャ

- 256 バイトのページ プログラム バッファ

- 256 Mb (32 MB)/128 Mb (16 MB), 3.0 V FL-L フラッシュメモリ

- プログラム一時停止と再開

- 消去アーキテクチャ

- ユニフォーム 4 KB セクタ消去

- ユニフォーム 32 KB ハーフ ブロック消去

- ユニフォーム 64 KB ブロック消去

- チップ消去

- 消去の一時停止と再開

- 100,000 プログラム / 消去 サイクル (Min)

- 20 年のデータ保持期間 (Min)

- セキュリティ機能

- ステータスおよびコンフィギュレーション レジスタ保護

- メイン フラッシュ アレイから独立した各 256 バイトの 4 つのセキュリティ領域

- レガシー ブロック保護 : ブロック範囲

- 個別および領域保護

- 個別 ブロック ロック : 振発性個別セクタ / ブロック

- ポインター領域 : 不揮発性セクタ / ブロック範囲

- セキュリティ領域 2 と 3 およびポインター領域の電源ロックダウン, パスワード, または永久的保護

- 技術

- 65nm フローティング ゲート技術

- 単一電源電圧、CMOS I/O

- 2.7 V ~ 3.6 V

- 温度範囲 / グレード

- 産業用 (-40°C ~ +85°C)

- 産業用 プラス (-40°C ~ +105°C)

- 車載向け, AEC-Q100 グレード 3 (-40°C ~ +85°C)

- 車載向け, AEC-Q100 グレード 2 (-40°C ~ +105°C)

- 車載向け, AEC-Q100 グレード 1 (-40°C ~ +125°C)

- パッケージ (すべて鉛フリー)

- 8 ピン SOIC 208mil (SOC008) – S25FL128L のみ

- WSON 5×6mm (WND008) – S25FL128L のみ

- WSON 6×8mm (WNG008) – S25FL256L, および S25FL128L

- 16 ピン SOIC 300mil (SO3016)

- BGA-24 6×8mm

- 5×5 ボール (FAB024) フットプリント

- 4×6 ボール (FAC024) フットプリント

## 性能要約

## 最大 SDR 読み出し速度

| コマンド     | クロック レート (MHz) | MBps |

|----------|----------------|------|

| 読み出し     | 50             | 6.25 |

| 高速読み出し   |                | 16.5 |

| デュアル読み出し |                | 33   |

| クアッド読み出し |                | 66   |

## 最大 DDR 読み出し速度

| コマンド         | クロック レート (MHz) | MBps |

|--------------|----------------|------|

| DDR クアッド読み出し | 66             | 66   |

## 標準プログラム / 消去速度

| 動作              | KBps |

|-----------------|------|

| ページ プログラム       | 854  |

| 4KB セクタ消去       | 80   |

| 32KB ハーフ ブロック消去 | 168  |

| 64KB ブロック消去     | 237  |

## 標準消費電流, -40°C ~ +85°C

| 動作                            | 標準電流 | 単位 |

|-------------------------------|------|----|

| 高速読み出し 5MHz                   | 10   | mA |

| 高速読み出し 10MHz                  | 10   |    |

| 高速読み出し 20MHz                  | 10   |    |

| 高速読み出し 50MHz                  | 15   |    |

| 高速読み出し 108MHz                 | 25   |    |

| 高速読み出し 133MHz                 | 30   |    |

| クアッド I/O / QPI 読み出し 108MHz    | 25   |    |

| クアッド I/O / QPI 読み出し 133MHz    | 30   |    |

| クアッド I/O / QPI DDR 読み出し 33MHz | 15   |    |

| クアッド I/O / QPI DDR 読み出し 66MHz | 30   |    |

| プログラム                         | 40   | μA |

| 消去                            | 40   |    |

| スタンバイ SPI                     | 20   |    |

| スタンバイ QPI                     | 60   |    |

| ディープ パワーダウン                   | 2    |    |

## 目次

|                                                       |           |

|-------------------------------------------------------|-----------|

| <b>概要</b> .....                                       | <b>1</b>  |

| <b>特長</b> .....                                       | <b>1</b>  |

| <b>性能要約</b> .....                                     | <b>3</b>  |

| <b>目次</b> .....                                       | <b>4</b>  |

| <b>1 製品概要</b> .....                                   | <b>6</b>  |

| 1.1 デバイス ファミリ移行時の注意事項 .....                           | 6         |

| <b>2 端子配置図</b> .....                                  | <b>7</b>  |

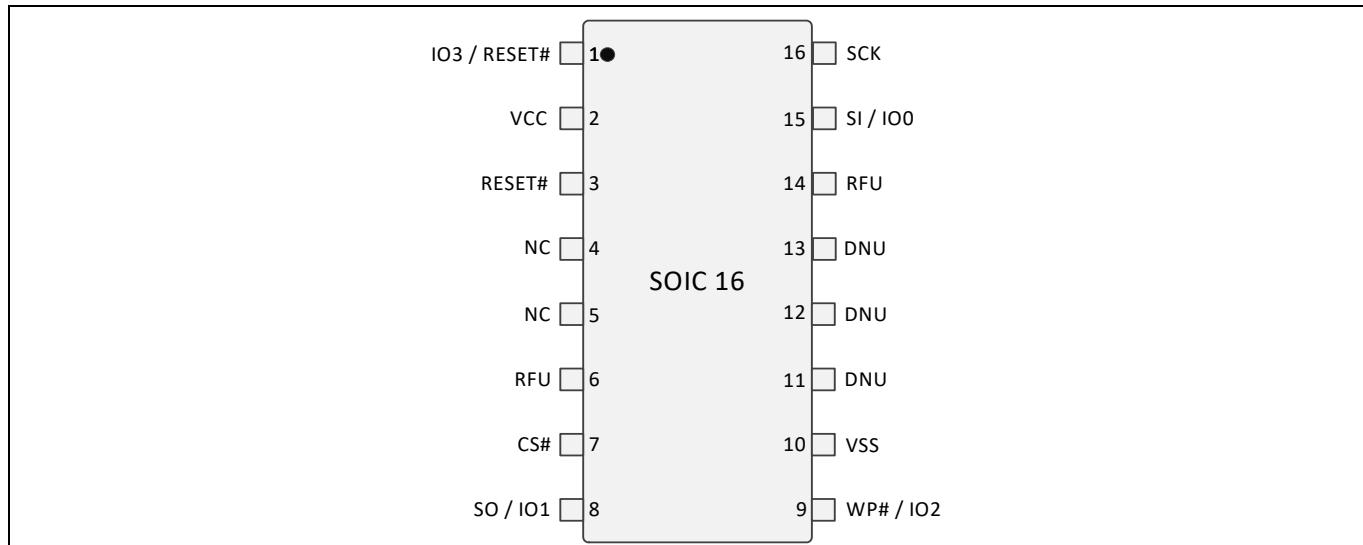

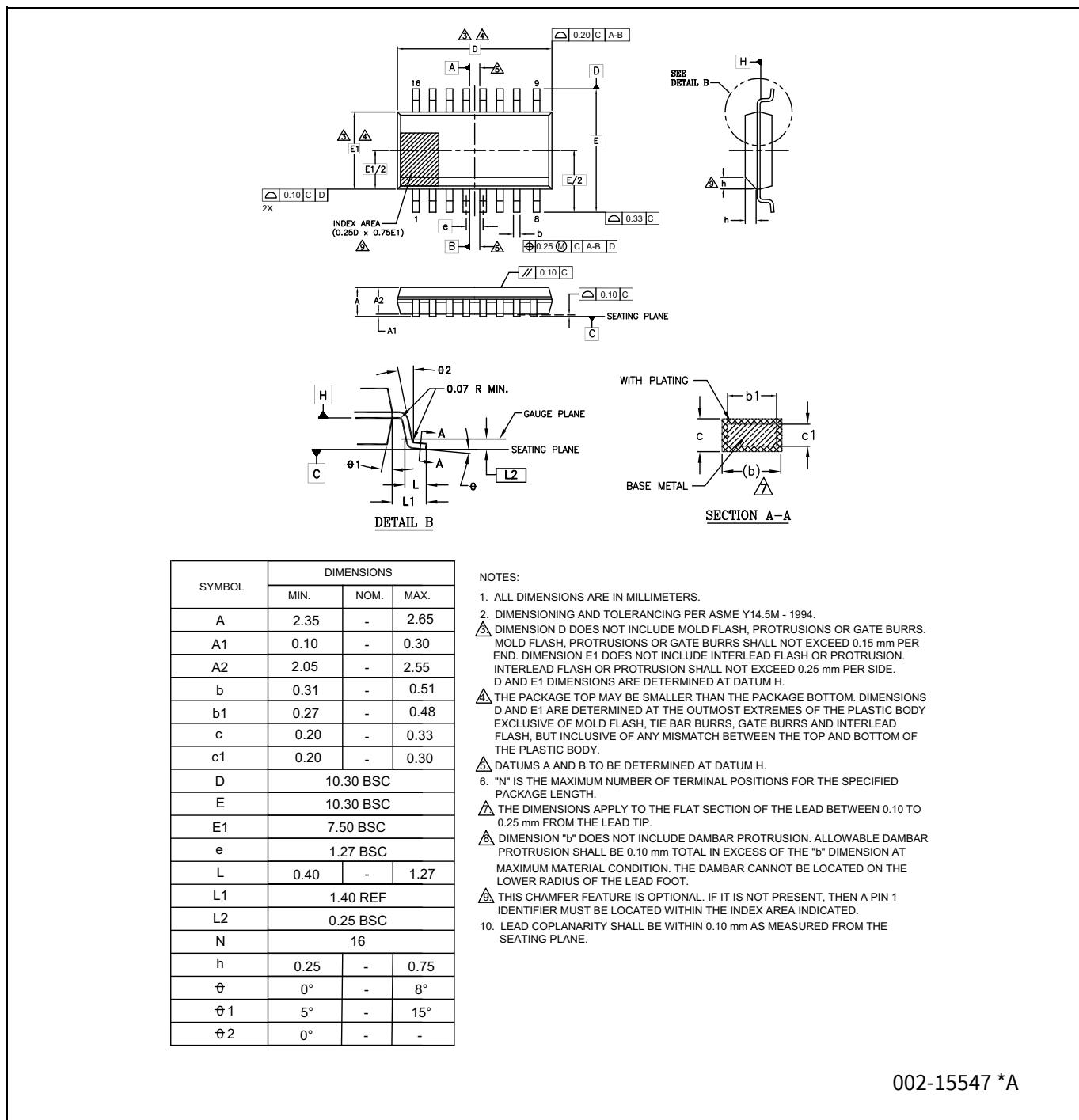

| 2.1 SOIC 16 リード .....                                 | 7         |

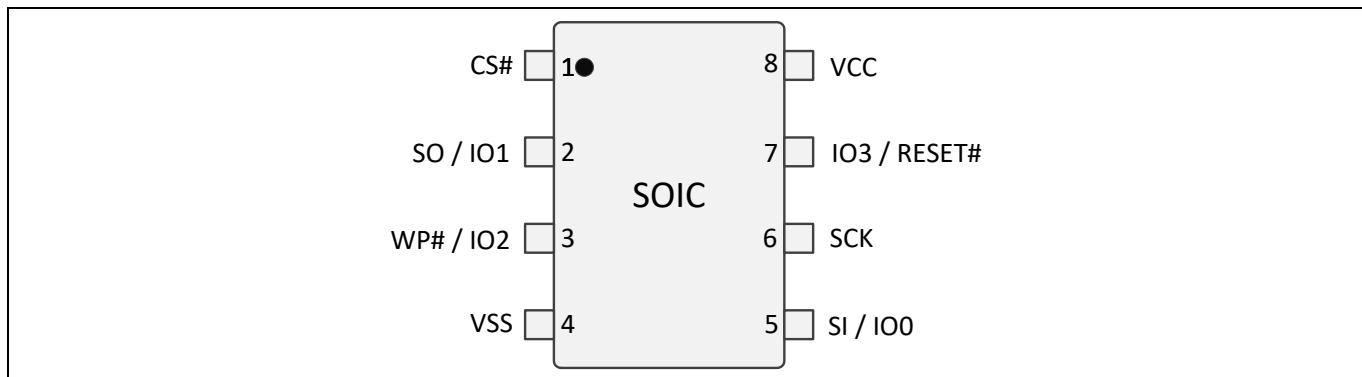

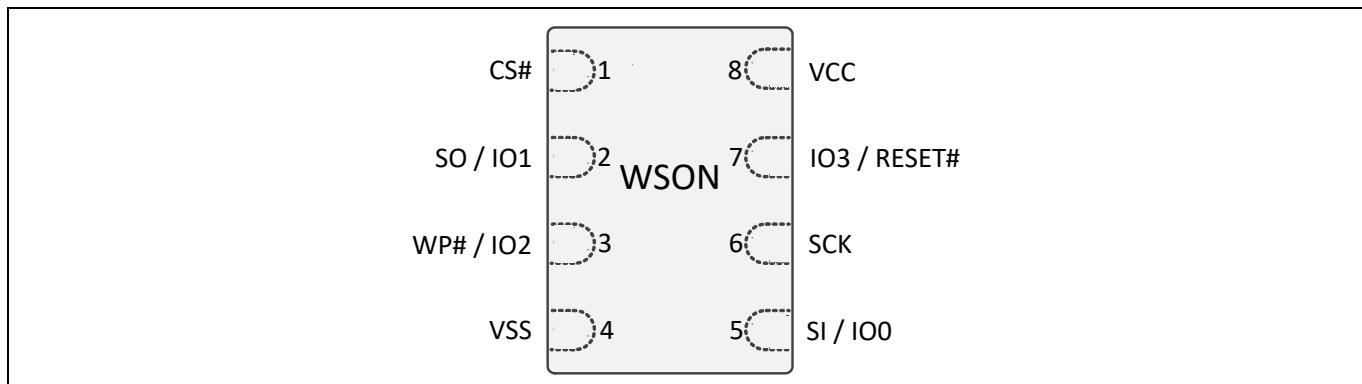

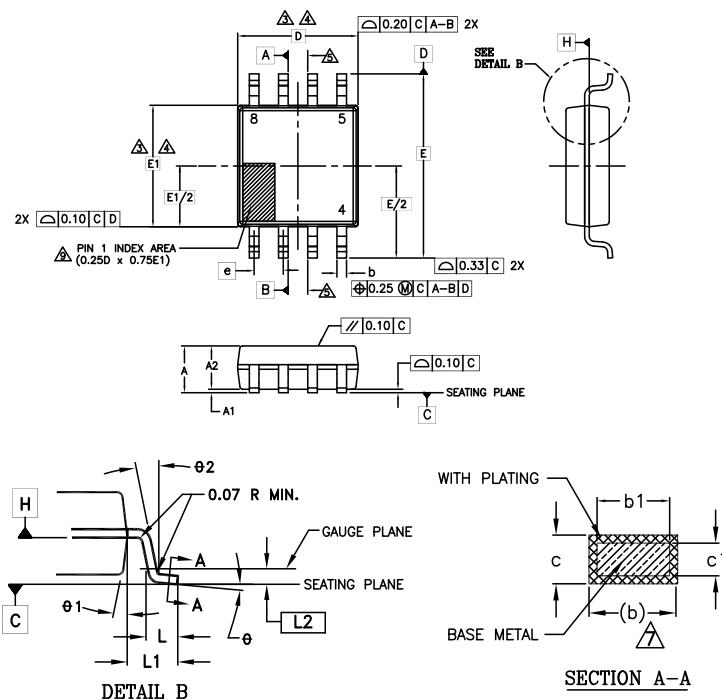

| 2.2 8 コネクタ パッケージ .....                                | 8         |

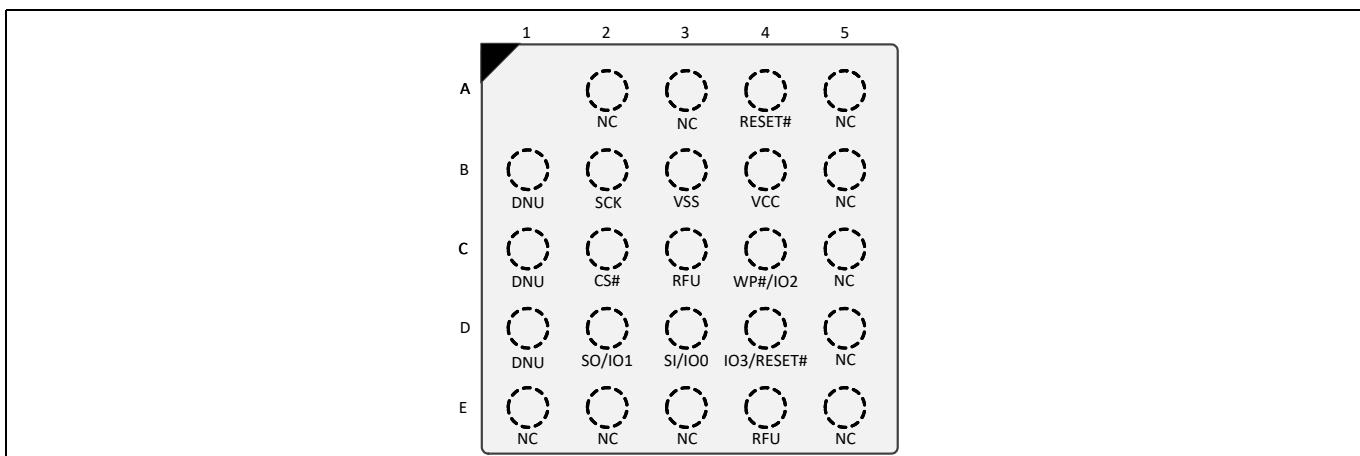

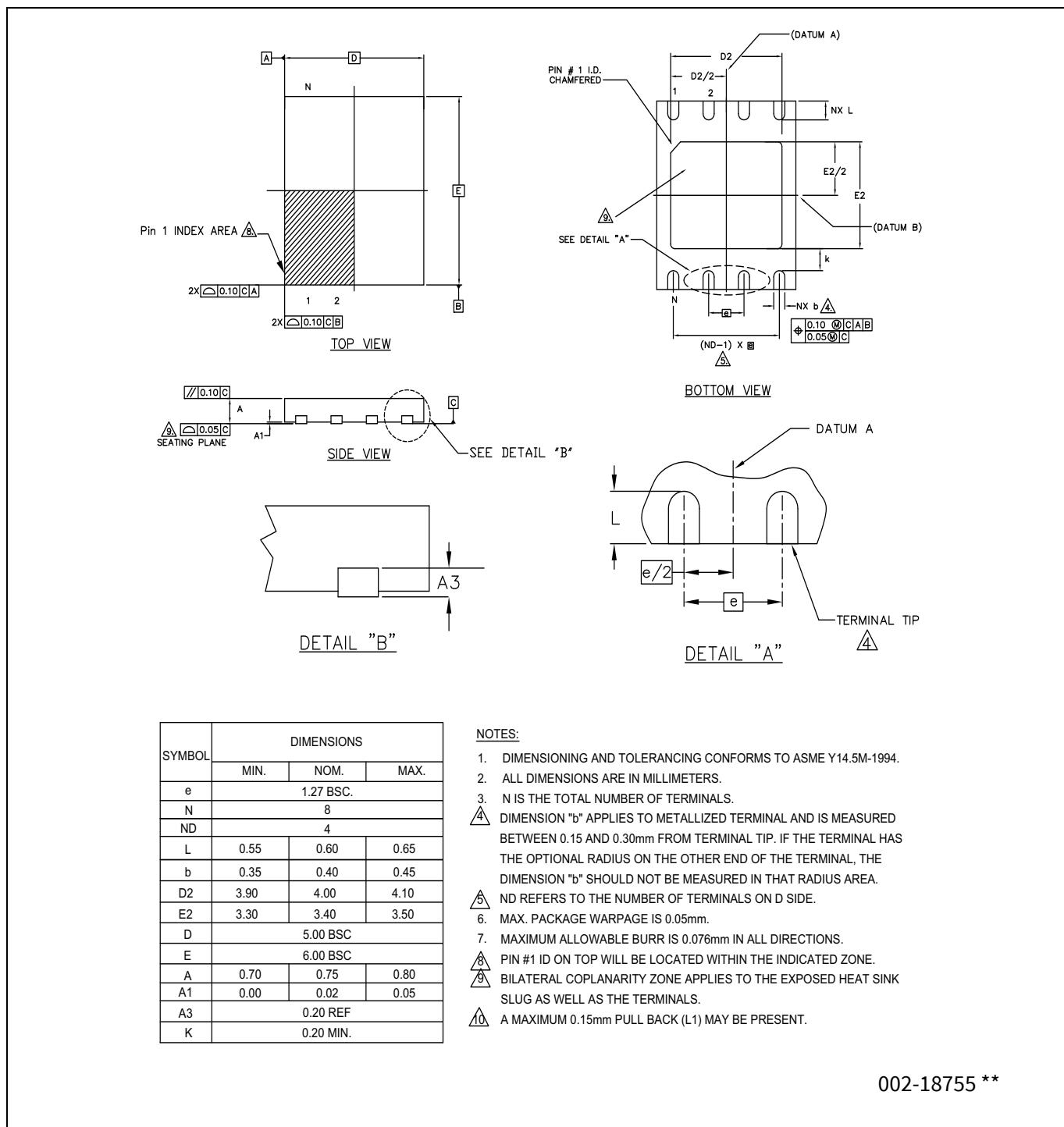

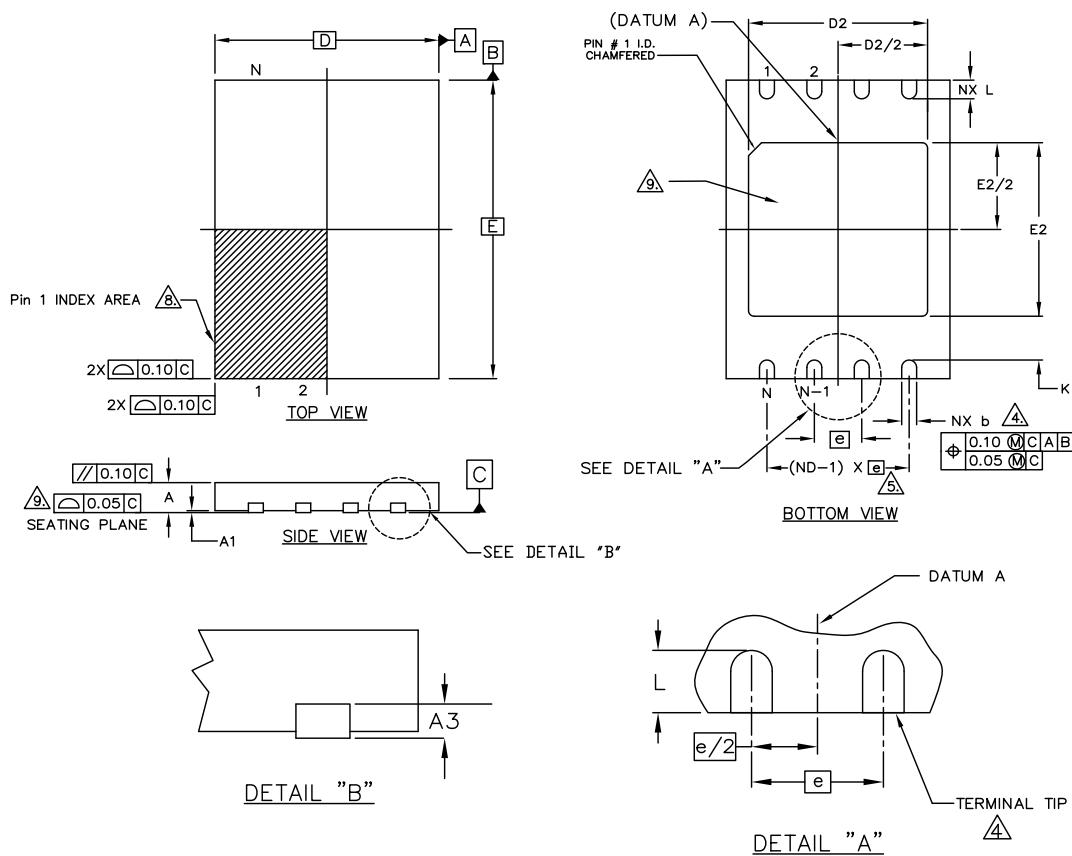

| 2.3 BGA ボール フットプリント .....                             | 9         |

| 2.4 FBGA パッケージの取扱注意事項 .....                           | 9         |

| <b>3 信号の説明</b> .....                                  | <b>10</b> |

| 3.1 複数の入力 / 出力を備えるシリアルペリフェラルインターフェース (SPI-MIO) .....  | 10        |

| 3.2 入出力の要約 .....                                      | 11        |

| 3.3 マルチ入力 / 出力 (MIO) .....                            | 12        |

| 3.4 シリアル クロック (SCK) .....                             | 12        |

| 3.5 チップセレクト (CS#) .....                               | 12        |

| 3.6 シリアル入力 (SI) / IO0 .....                           | 12        |

| 3.7 シリアル出力 (SO) / IO1 .....                           | 12        |

| 3.8 書き込み保護 (WP#) / IO2 .....                          | 13        |

| 3.9 IO3 / RESET# .....                                | 13        |

| 3.10 RESET# .....                                     | 14        |

| 3.11 電源電圧 (V <sub>CC</sub> ) .....                    | 14        |

| 3.12 電源および信号グランド (V <sub>SS</sub> ) .....             | 14        |

| 3.13 未接続 (NC) .....                                   | 14        |

| 3.14 将来に使用するために予約済み (RFU) .....                       | 14        |

| 3.15 使用禁止 (DNU) .....                                 | 14        |

| <b>4 ブロック図</b> .....                                  | <b>15</b> |

| 4.1 システム ブロック図 .....                                  | 15        |

| <b>5 信号プロトコル</b> .....                                | <b>17</b> |

| 5.1 SPI クロック モード .....                                | 17        |

| 5.2 コマンド プロトコル .....                                  | 19        |

| 5.3 インターフェース状態 .....                                  | 24        |

| 5.4 データ保護 .....                                       | 28        |

| <b>6 アドレス空間マップ</b> .....                              | <b>29</b> |

| 6.1 概要 .....                                          | 29        |

| 6.2 フラッシュメモリアレイ .....                                 | 30        |

| 6.3 ID アドレス空間 .....                                   | 31        |

| 6.4 JEDEC JESD216 シリアルフラッシュ検出可能パラメーター (SFDP) 空間 ..... | 31        |

| 6.5 セキュリティ領域アドレス空間 .....                              | 31        |

| 6.6 レジスタ .....                                        | 32        |

| <b>7 データ保護</b> .....                                  | <b>54</b> |

| 7.1 セキュリティ領域 .....                                    | 54        |

| 7.2 ディープパワー ダウン .....                                 | 54        |

| 7.3 書き込みイネーブルのコマンド .....                              | 55        |

| 7.4 書き込み保護信号 .....                                    | 55        |

| 7.5 ステータスレジスタ保護 (SRP1, SRP0) .....                    | 56        |

| 7.6 アレイ保護 .....                                       | 57        |

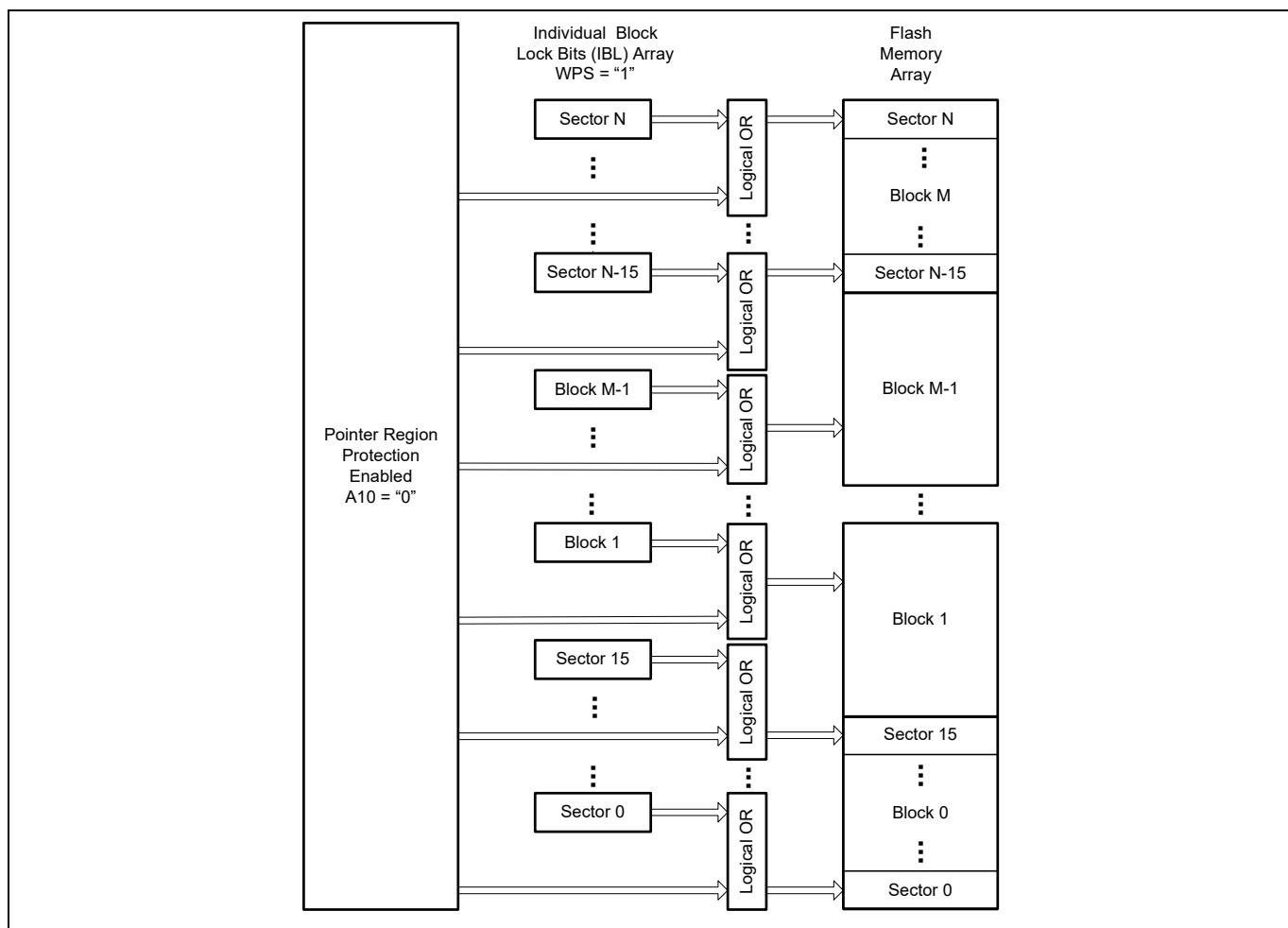

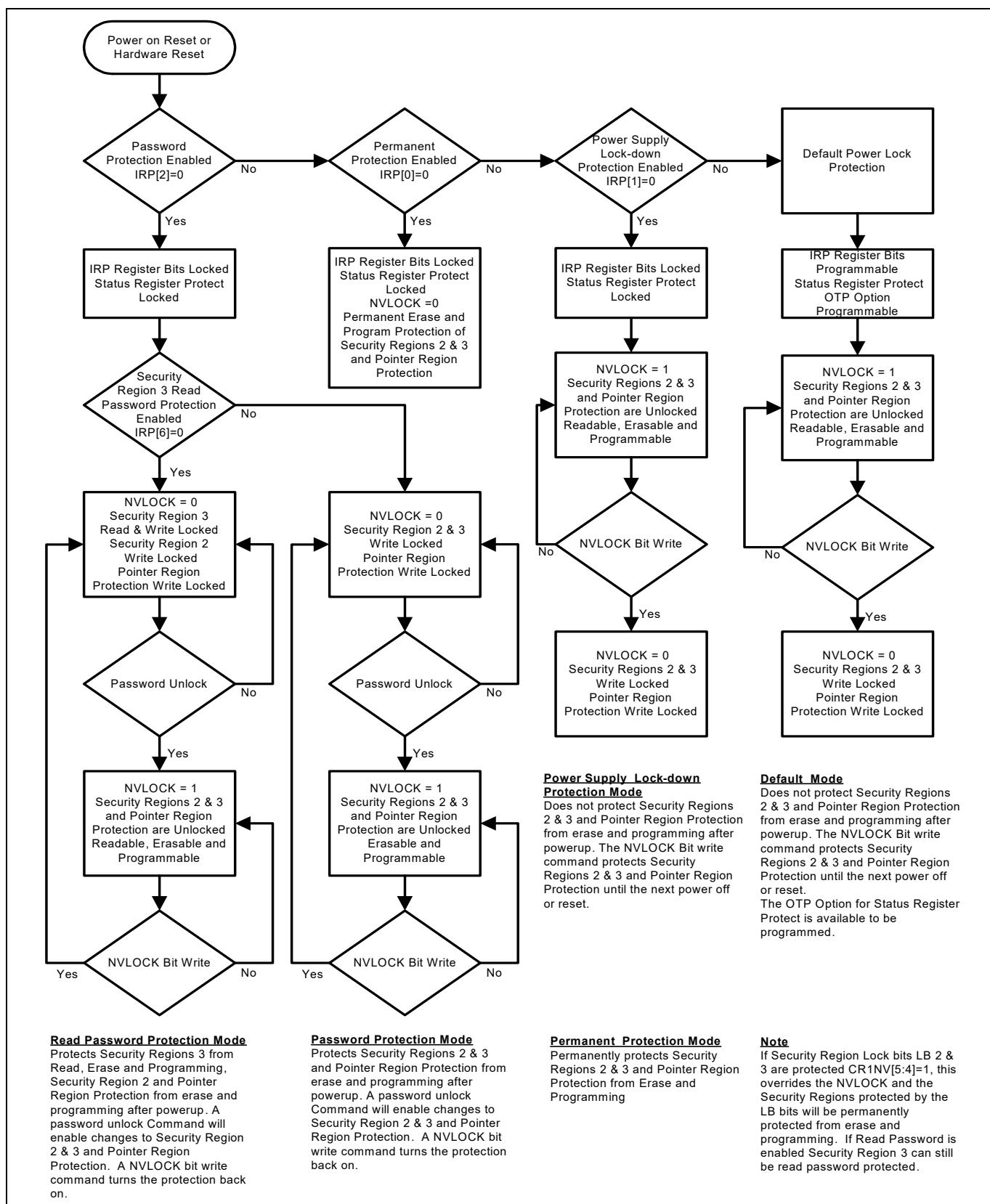

| 7.7 個別および領域保護 .....                                   | 64        |

| <b>8 コマンド</b> .....                                   | <b>69</b> |

| 8.1 コマンド セットのまとめ .....                                | 69        |

|                                                |            |

|------------------------------------------------|------------|

| 8.2 ID のコマンド .....                             | 75         |

| 8.3 レジスタ アクセス コマンド .....                       | 79         |

| 8.4 メモリアレイ読み出しのコマンド .....                      | 94         |

| 8.5 プログラム フラッシュアレイのコマンド .....                  | 103        |

| 8.6 フラッシュアレイの消去コマンド .....                      | 105        |

| 8.7 セキュリティ領域アレイのコマンド .....                     | 114        |

| 8.8 個別ブロックのコマンド .....                          | 116        |

| 8.9 ポインター領域のコマンド .....                         | 121        |

| 8.10 個別および領域保護 (IRP) のコマンド .....               | 122        |

| 8.11 リセットのコマンド .....                           | 129        |

| 8.12 ディープパワーダウンのコマンド .....                     | 130        |

| <b>9 データの完全性 .....</b>                         | <b>133</b> |

| 9.1 消去可能回数 .....                               | 133        |

| 9.2 データ保持 .....                                | 133        |

| <b>10 ソフトウェアインターフェースリファレンス .....</b>           | <b>134</b> |

| 10.1 JEDEC JESD216B シリアル フラッシュ検出可能パラメーター ..... | 134        |

| 10.2 デバイス ID アドレス マップ .....                    | 144        |

| 10.3 工場出荷時の初期状態 .....                          | 144        |

| <b>11 電気的特性 .....</b>                          | <b>145</b> |

| 11.1 絶対最大定格 .....                              | 145        |

| 11.2 ラッチャップ仕様 .....                            | 145        |

| 11.3 熱抵抗 .....                                 | 145        |

| 11.4 動作範囲 .....                                | 146        |

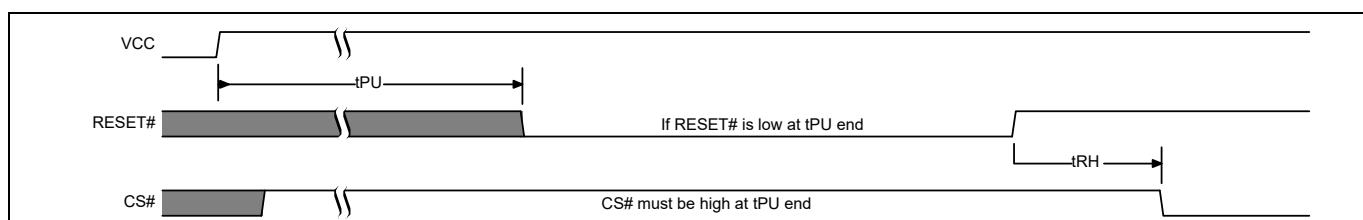

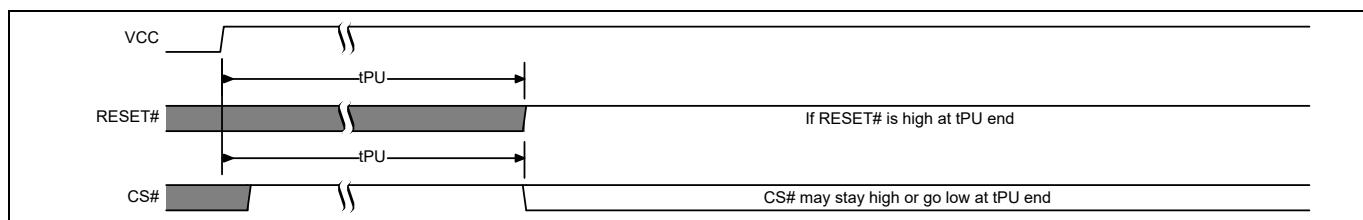

| 11.5 電源投入および電源切斷 .....                         | 147        |

| 11.6 DC 電気的特性 .....                            | 149        |

| <b>12 タイミング仕様 .....</b>                        | <b>153</b> |

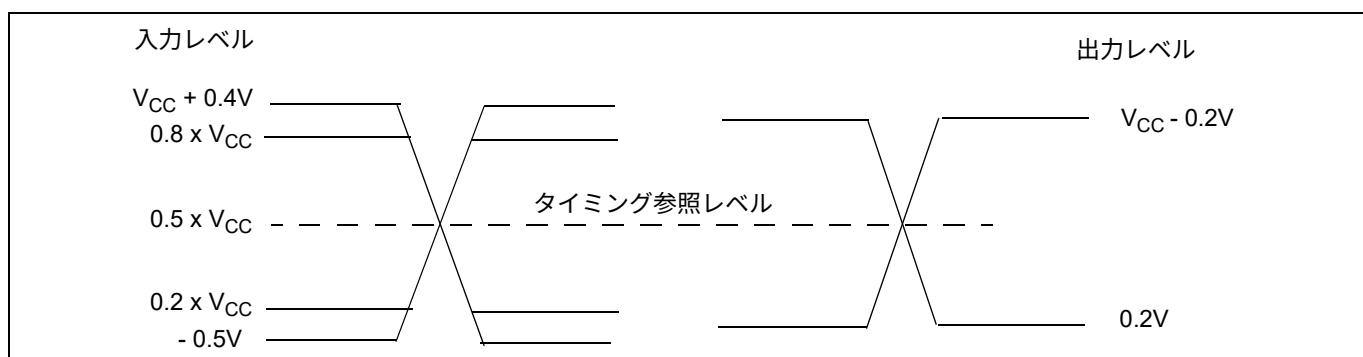

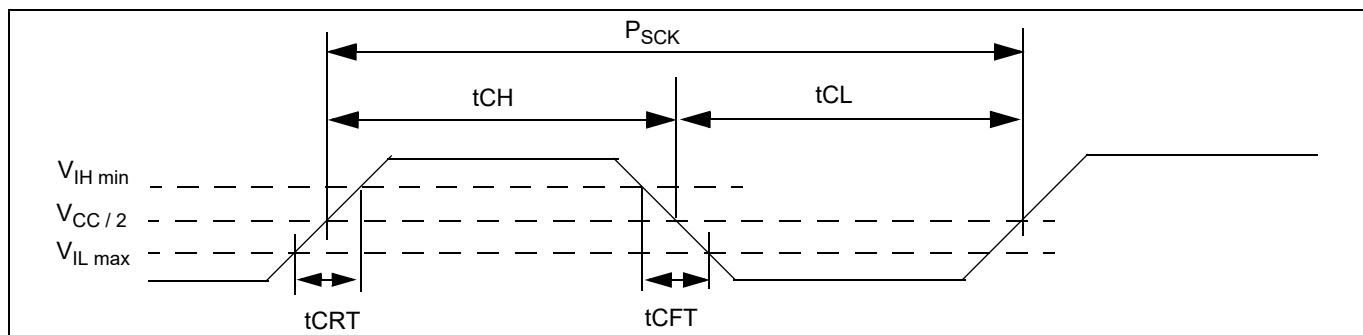

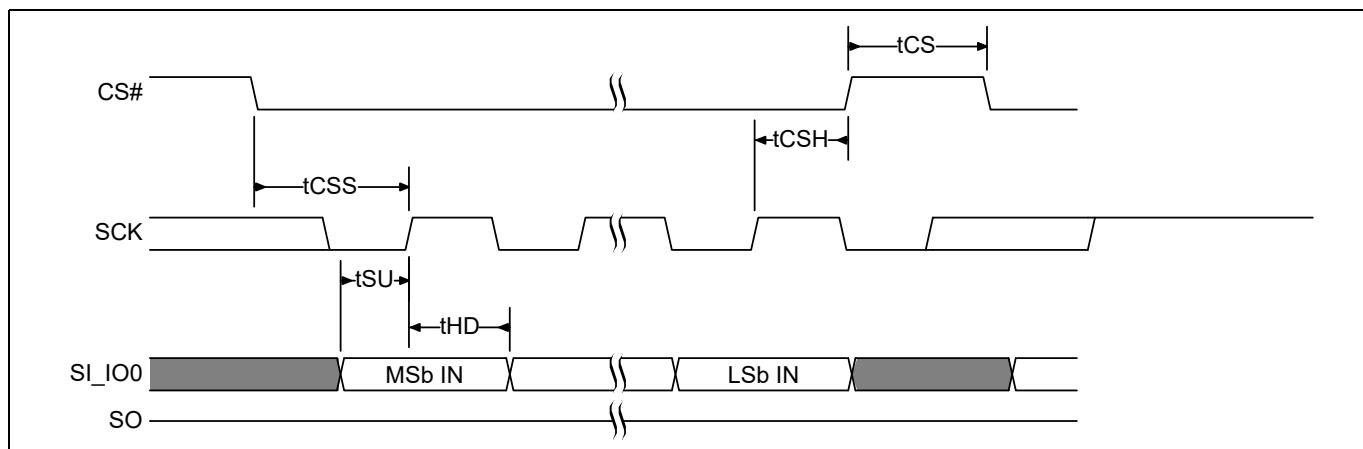

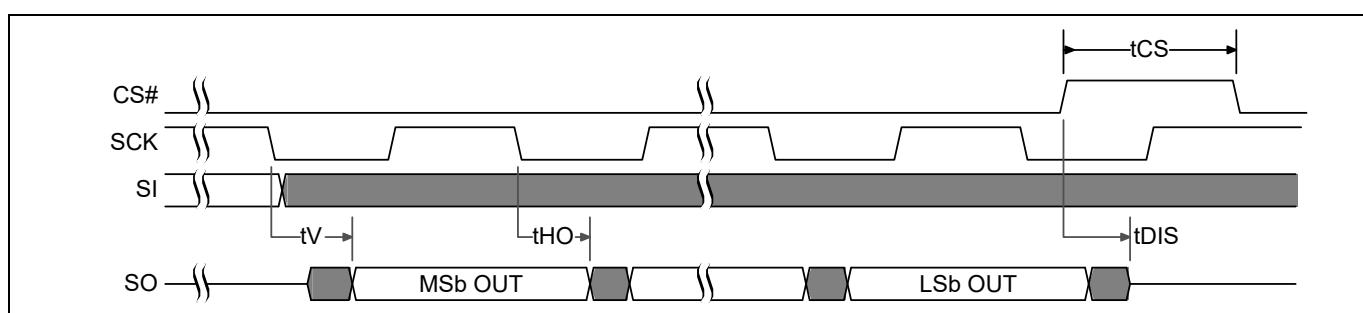

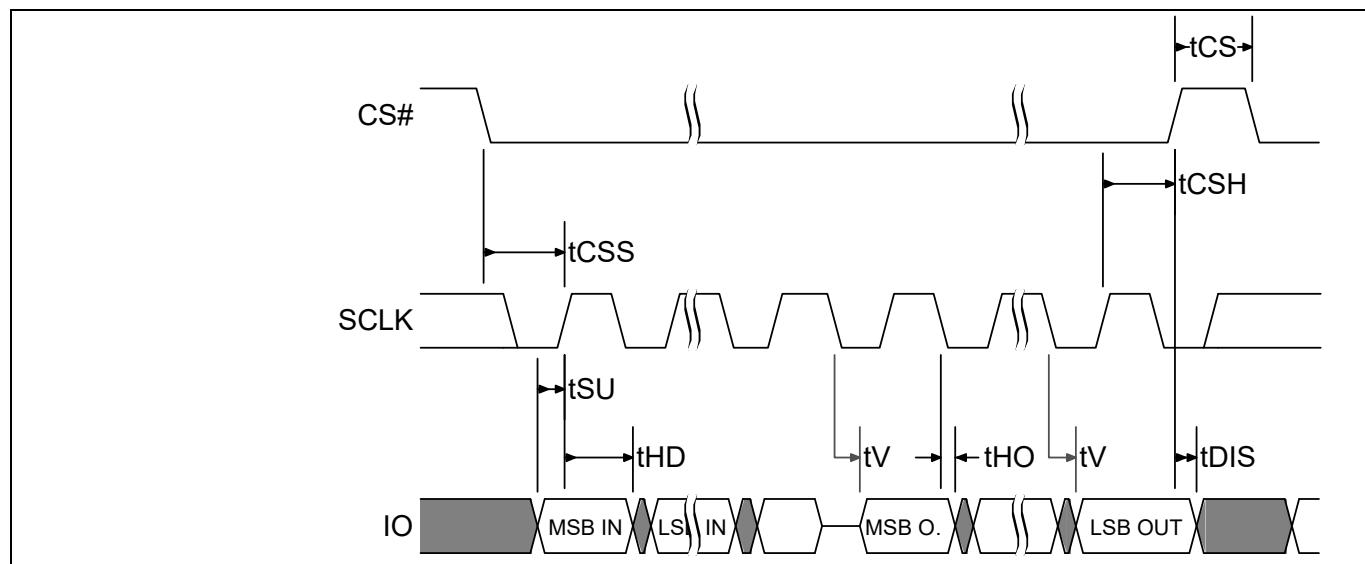

| 12.1 スイッチング波形の要素 .....                         | 153        |

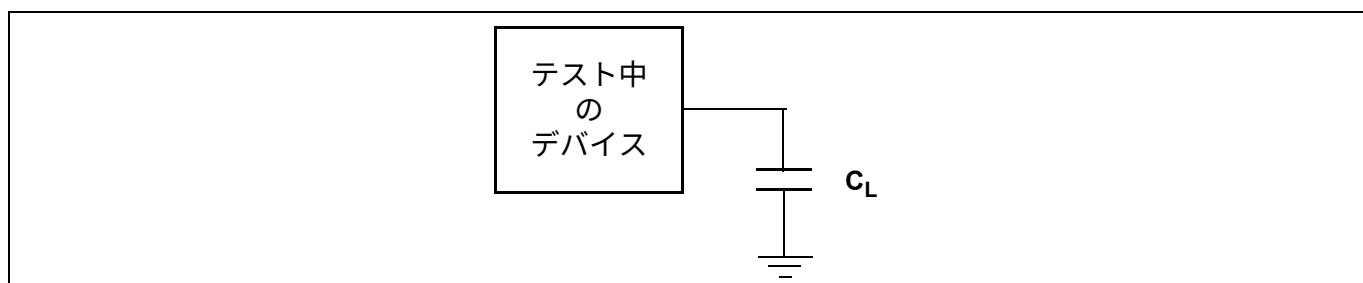

| 12.2 AC テスト条件 .....                            | 153        |

| 12.3 リセット .....                                | 154        |

| 12.4 SDR AC 特性 .....                           | 157        |

| 12.5 DDR AC 特性 .....                           | 160        |

| 12.6 組込みアルゴリズム性能表 .....                        | 163        |

| <b>13 注文情報 .....</b>                           | <b>164</b> |

| 13.1 注文製品番号 .....                              | 164        |

| 13.2 有効な組合せ – 標準 .....                         | 165        |

| 13.3 有効な組合せ – 車載向けグレード / AEC-Q100 .....        | 166        |

| <b>14 パッケージ図 .....</b>                         | <b>167</b> |

| 改訂履歴 .....                                     | 173        |

| 免責事項 .....                                     | 174        |

## 1 製品概要

### 1.1 デバイス ファミリ移行時の注意事項

#### 1.1.1 機能比較

FL-L ファミリは前世代の FL-S, FL1-K, FL-P ファミリとコマンド サブセットおよびファットプリントの互換性があります。

**Table 1 Infineon SPI ファミリの比較**

| パラメーター                     | FL-L                                              | FL-S                                   | FL1-K                           | FL-P                            |

|----------------------------|---------------------------------------------------|----------------------------------------|---------------------------------|---------------------------------|

| 技術ノード                      | 65nm                                              | 65nm                                   | 90nm                            | 90nm                            |

| アーキテクチャ                    | フローティング<br>ゲート                                    | MIRRORBIT™<br>Eclipse                  | フローティング<br>ゲート                  | MIRRORBIT™                      |

| リリース予定                     | 量産中                                               | 量産中                                    | 量産中                             | 量産中                             |

| メモリ容量                      | 256Mb                                             | 128Mb ~ 1Gb                            | 4Mb ~ 64Mb                      | 32Mb ~ 256Mb                    |

| バス幅                        | ×1, ×2, ×4                                        | ×1, ×2, ×4                             | ×1, ×2, ×4                      | ×1, ×2, ×4                      |

| 電源電圧                       | 2.7V ~ 3.6V                                       | 2.7V ~ 3.6V /<br>1.65V ~ 3.6V $V_{IO}$ | 2.7V ~ 3.6V                     | 2.7V ~ 3.6V                     |

| 通常読み出し速度                   | 6MBps (50MHz)                                     | 6MBps (50MHz)                          | 6MBps (50MHz)                   | 5MBps (40MHz)                   |

| 高速読み出し速度                   | 16.5MBps<br>(133MHz)                              | 17MBps (133MHz)                        | 13MBps (108MHz)                 | 13MBps (104MHz)                 |

| デュアル読み出し速度                 | 33MBps (133MHz)                                   | 26MBps (104MHz)                        | 26MBps (108MHz)                 | 20MBps (80MHz)                  |

| クアッド読み出し速度                 | 66MBps (133MHz)                                   | 52MBps (104MHz)                        | 52MBps (108MHz)                 | 40MBps (80MHz)                  |

| クアッド読み出し速度 (DDR)           | 66MBps (66MHz)                                    | 80MBps (80MHz)                         | -                               | -                               |

| プログラム バッファ サイズ             | 256B                                              | 256B / 512B                            | 256B                            | 256B                            |

| 消去セクタ / ブロック サイズ           | 4KB / 32KB / 64KB                                 | 64KB / 256KB                           | 4KB / 64KB                      | 64KB / 256KB                    |

| パラメーター セクタ サイズ             | -                                                 | 4KB (オプション)                            | -                               | 4KB                             |

| セクタ / ブロック 消去 サイズ<br>(Typ) | 80KBps (4KB)<br>168KBps (32KB)<br>237KBps (64KB)  | 500KBps                                | 136KBps (4KB)<br>437KBps (64KB) | 130KBps                         |

| ページ プログラム速度 (Typ)          | 854KBps (256B)                                    | 1.2MBps (256B)<br>1.5MBps (512B)       | 365KBps                         | 170KBps                         |

| セキュリティ 領域 /OTP             | 1024B                                             | 1024B                                  | 768B (3 × 256B)                 | 506B                            |

| 個別および領域保護<br>または高度セクタ保護    | 有                                                 | 有                                      | 無                               | 無                               |

| 消去一時停止 / 再開                |                                                   |                                        | 有                               |                                 |

| プログラム一時停止 / 再開             |                                                   |                                        | 有                               | 無                               |

| 動作温度                       | -40°C ~ +85°C<br>-40°C ~ +105°C<br>-40°C ~ +125°C | -40°C ~ +85°C<br>-40°C ~ +105°C        | -40°C ~ +85°C                   | -40°C ~ +85°C<br>-40°C ~ +105°C |

#### 注:

- 詳細情報は、個別のデータシートを参照してください。

## 2 端子配置図

### 2.1 SOIC 16 リード

Figure 1 16 リード SOIC パッケージ (SO3016), 上面図

注:

- RESET# 入力と IO3/RESET# 入力は内部プルアップ抵抗に接続しており、クアッド モードとハード ウエア リセットが使用されない場合はシステム開放のままにできます。

## 2.2 8 コネクタパッケージ

Figure 2 8 ピン プラスチック小型パッケージ (SOIC8)

Figure 3 8 コネクタ パッケージ (WSON 6 x 8) (WSON 5 x 6), 上面図

注:

- RESET# 入力は内部プルアップ抵抗に接続しており、クアッド モードとハードウェアリセットが使用されない場合はシステムで開放のままにできます。

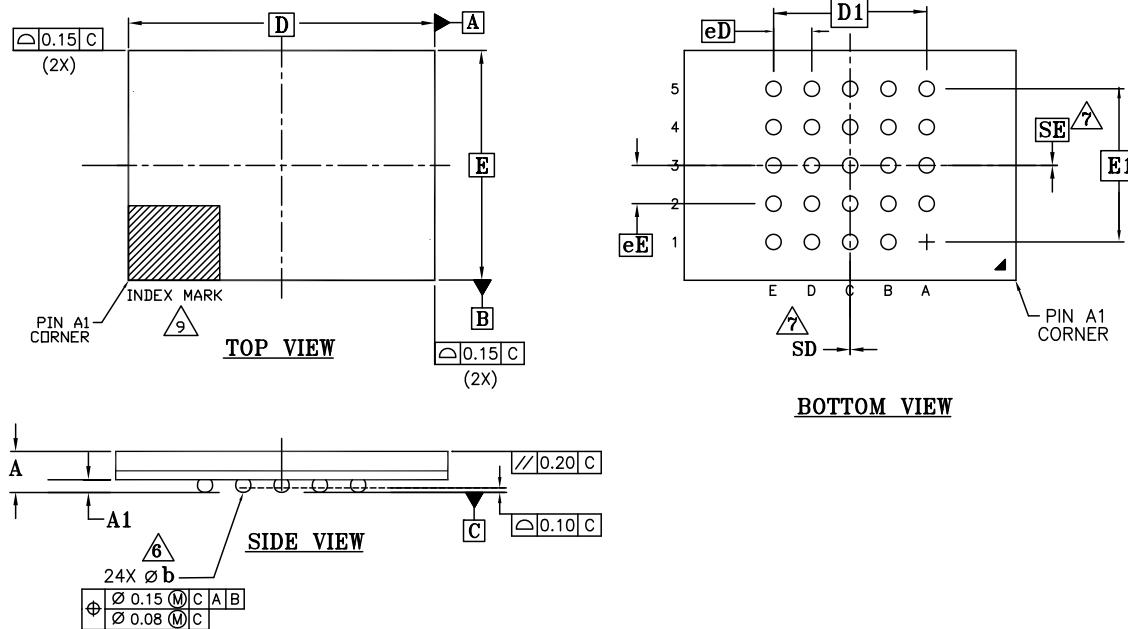

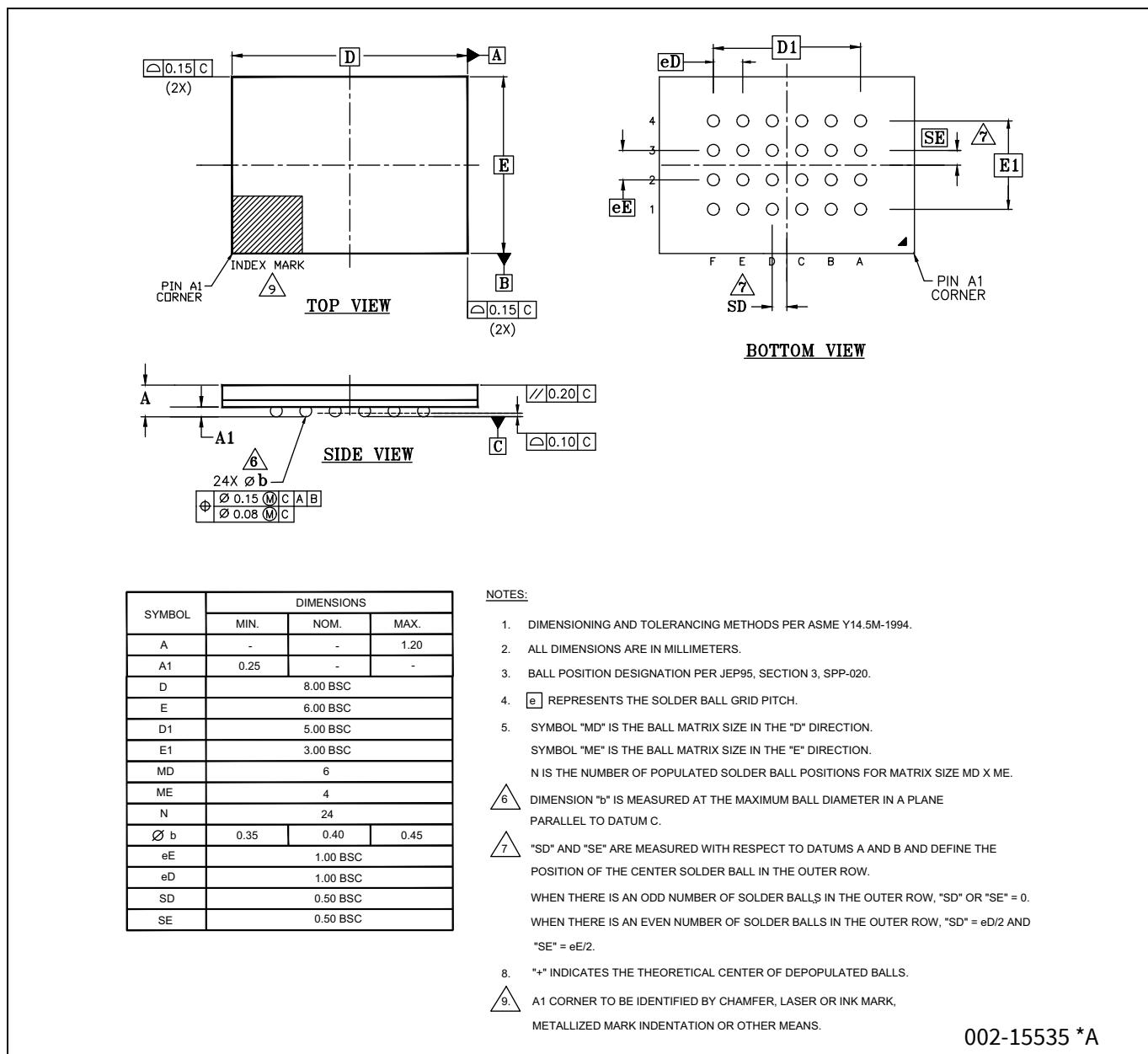

## 2.3 BGA ボール フットプリント

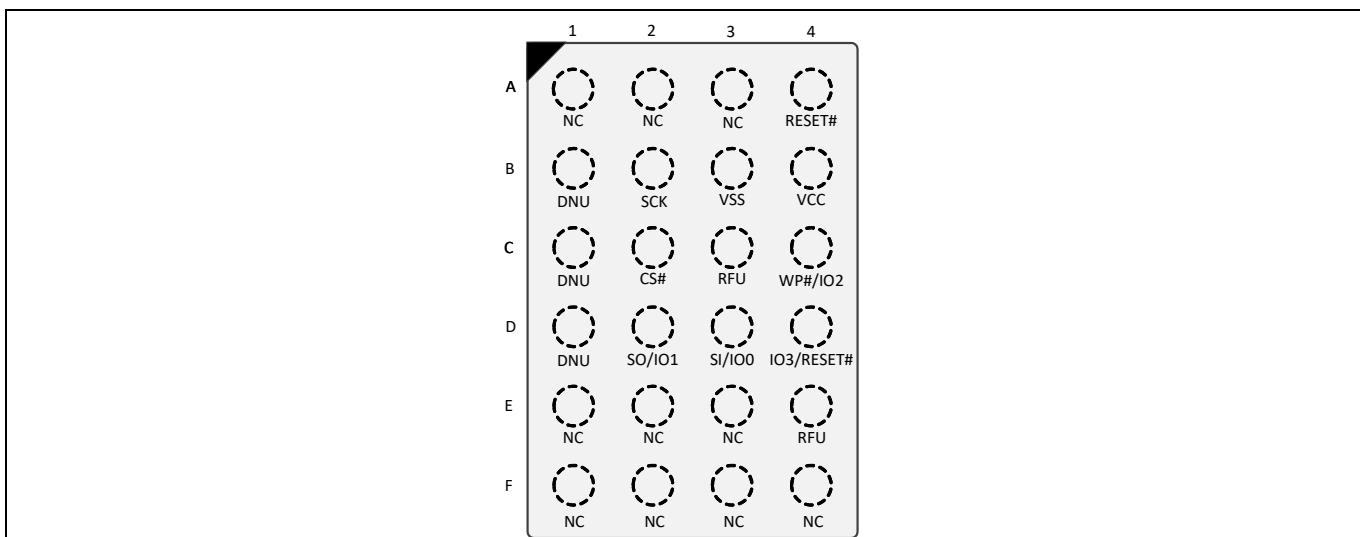

Figure 4 24 ボール BGA, 5 x 5 ボール フットプリント (FAB024), 上面図

Figure 5 24 ボール BGA, 4 x 6 ボール フットプリント (FAC024), 上面図

## 2.4 FBGA パッケージの取扱注意事項

BGA パッケージのフラッシュ メモリ デバイスは超音波洗浄にさらされると損傷する場合があります。パッケージ本体を長時間にわたって温度 150°C 以上の環境に放置すると、パッケージならびにデータの完全性が損なわれることがあります。

注:

- 信号接続は FAC024 BGA と同じ相対位置にあるため、プリント基板の単一のフットプリントでいずれのパッケージにも使用できます。

- RESET# 入力は内部プルアップ抵抗に接続しており、クアッド モードとハードウェアリセットが使用されない場合はシステムで開放のままにできます。

- RESET# 入力は内部プルアップ抵抗に接続しており、クアッド モードとハードウェアリセットが使用されない場合はシステムで開放のままにできます。

### 3 信号の説明

#### 3.1 複数の入力 / 出力を備えるシリアルペリフェラルインターフェース (SPI-MIO)

多くのメモリデバイスは、別々のパラレル制御、アドレス、およびデータ信号でホストシステムに接続し、多数の信号接続とより大きいパッケージサイズを必要とします。接続が多いほど信号スイッチングが多くなるため、消費電力は増加します。パッケージが大きいほどコストは高くなります。

FL-L ファミリはすべての制御、アドレス、およびデータ情報を 6 信号を介して順次転送することで、ホストシステムへの接続に必要な信号数を減らします。これにより、メモリパッケージのコストを削減し、信号スイッチングに必要な電力を削減するほか、ホスト接続数を削減し、その他の機能を使用できるようにホストコネクタを解放します。

FL-L ファミリは業界標準のシングルビット SPI を使用し、2 ビット (デュアル) と 4 ビット (クアッド) 幅のシリアル転送用のオプションの拡張コマンドにも対応しています。複数幅インターフェースは SPI マルチ I/O (SPI-MIO) と呼ばれます。

### 3.2 入出力の要約

Table 2 信号一覧

| 信号名          | タイプ  | 説明                                                                                                                                                                                                                                                                                                                         |

|--------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESET#       | 入力   | ハードウェアリセット: Low にすると、デバイスはリセットし、スタンバイ状態に復帰し、コマンドを受け入れられます。信号は内部プルアップ抵抗に接続され、ホストシステムで使用されない場合は開放のままにできます。                                                                                                                                                                                                                   |

| SCK          |      | シリアルクロック                                                                                                                                                                                                                                                                                                                   |

| CS#          |      | チップセレクト                                                                                                                                                                                                                                                                                                                    |

| SI / IO0     | I/O  | シングルビットデータコマンド用のシリアル入力、またはデュアル / クアッドコマンド用の IO0 です。                                                                                                                                                                                                                                                                        |

| SO / IO1     |      | シングルビットデータコマンド用のシリアル出力、またはデュアル / クアッドコマンド用の IO1 です。                                                                                                                                                                                                                                                                        |

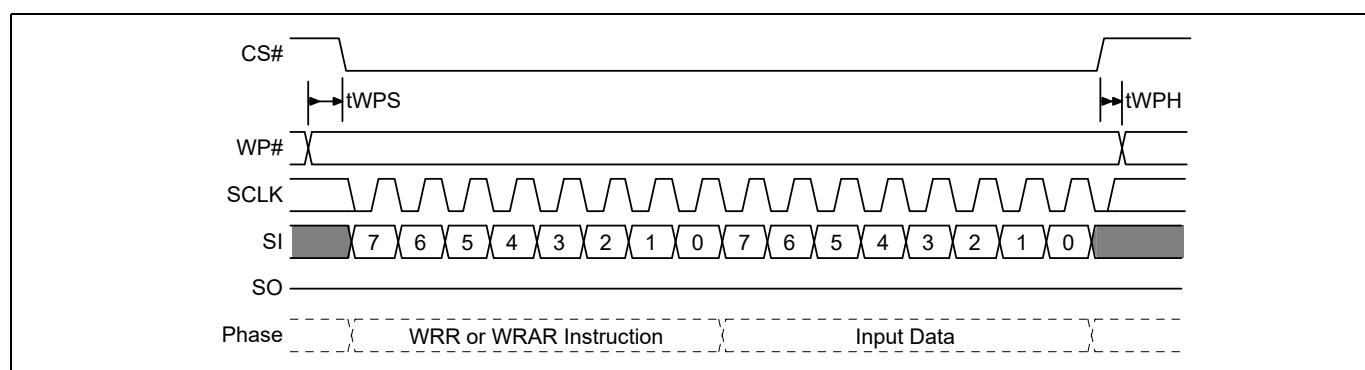

| WP# / IO2    |      | クアッドモードでない (CR1V[1]=0、SR1NV[7]=1) 場合は書き込み保護です。<br>クアッドモードである (CR1V[1]=1) 場合は IO2 です。<br>信号は内部プルアップ抵抗に接続され、ホストシステムでクアッドコマンドまたは書き込み保護に使用されない場合は開放のままにできます。SR1NV[7]=1、CR1V[1]=0 にセットすることで書き込み保護を有効にする場合、ホストシステムは WRR または WRAR コマンドの実行中に WP# を HIGH または LOW に駆動する必要があります。                                                      |

| IO3 / RESET# |      | クアッド I/O モードである (コンフィギュレーションレジスタ 1 の QUAD ビット CR1V[1]=1) 場合、または QPI モードで (コンフィギュレーションレジスタ 2 の QPI ビット CR2V[3]=1)、CS# が LOW である場合は IO3 です。<br>CR2V[7]=1 により有効にされ、クアッド I/O モードでない (CR1V[1]=0) 場合、またはクアッドモード (CR1V[1]=1) で、CS# が HIGH である場合は RESET# です。<br>信号は内部プルアップ抵抗に接続され、ホストシステムでクアッドコマンドまたは RESET# に使用されない場合は開放のままにできます。 |

| $V_{CC}$     | 電源   | 電源                                                                                                                                                                                                                                                                                                                         |

| $V_{SS}$     |      | グランド                                                                                                                                                                                                                                                                                                                       |

| NC           | 未使用  | 未接続: デバイスの内部信号はパッケージコネクタに接続されず、信号にコネクタを使用する計画もありません。接続はプリント基板 (PCB) 上で信号の配線スペース向けに安全に使用できます。ただし、NC に接続されたすべての信号は電圧レベルが $V_{CC}$ 以下でなければなりません。                                                                                                                                                                              |

| RFU          | 予約済み | 将来使用するために予約済み: 現時点ではパッケージコネクタに接続しているデバイスの内部信号はありませんが、将来コネクタを信号に使用する可能性があります。RFU コネクタを PCB 配線チャネルに使用しないことを推奨します。それによって、PCB はフットプリントの互換性があるデバイスの将来の拡張機能を活用できます。                                                                                                                                                              |

| DNU          |      | 使用禁止: デバイスの内部信号がパッケージコネクタに接続される可能性があります。接続はインフィニオンによってテスト用または他の目的で使用され、ホストシステムの信号に接続するためのものではありません。DNU 信号が $V_{IL}$ のとき、DNU 信号に関連するすべての機能は無効になります。信号は内部プルダウン抵抗に接続され、ホストシステムで開放のままにされるか、または $V_{SS}$ に接続できます。これらの接続を PCB 信号配線チャネルに使用しないでください。ホストシステム信号をこれらの信号に接続しないでください。                                                   |

#### 注:

7. 内部でプルアップまたはプルダウン接続された入力の消費電流は、 $2\mu A$  未満です。電源投入時のみ、最大電流は  $4\mu A$  の間、 $150\mu A$  です。プルアップまたはプルダウン抵抗は、標準プロセスで  $V_{CC} = 3.3V$ 、 $-40^\circ C$  の場合は約  $4.5M\Omega$ 、 $90^\circ C$  の場合は約  $6.6M\Omega$  です。

### 3.3 マルチ入力 / 出力 (MIO)

従来の SPI シングルビット幅コマンド (シングルまたは SIO) はシリアル入力 (SI) 信号のみで、情報をホストからメモリへ送信します。データはシリアル出力 (SO) 信号でホストへ順次戻されます。

デュアルまたはクアッド入出力 (I/O) コマンドは SI / IO0 信号のみで命令をメモリに送信します。アドレス、またはデータは IO0 と IO1 信号上でビットペア、または IO0, IO1, IO2, IO3 信号上で 4 ビット (ニブル) グループでホストからメモリへ送信されます。データは同様に IO0 と IO1 信号上でビットペア、または IO0, IO1, IO2, IO3 信号上で 4 ビット (ニブル) グループでホストへ戻されます。

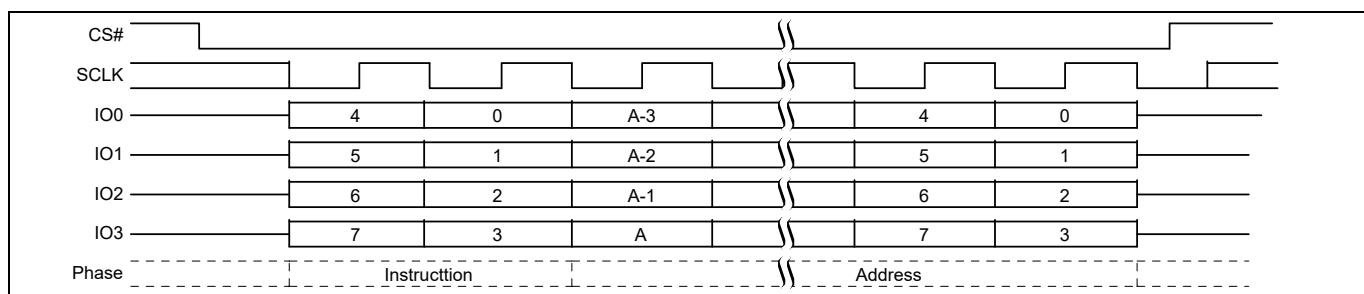

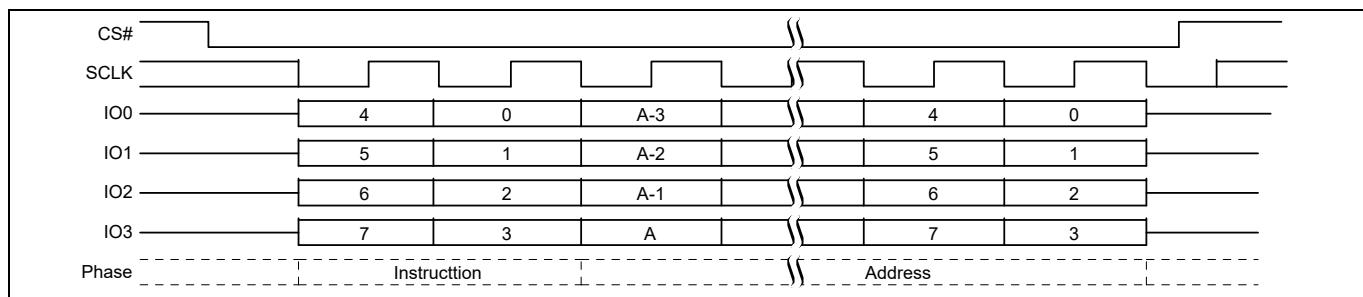

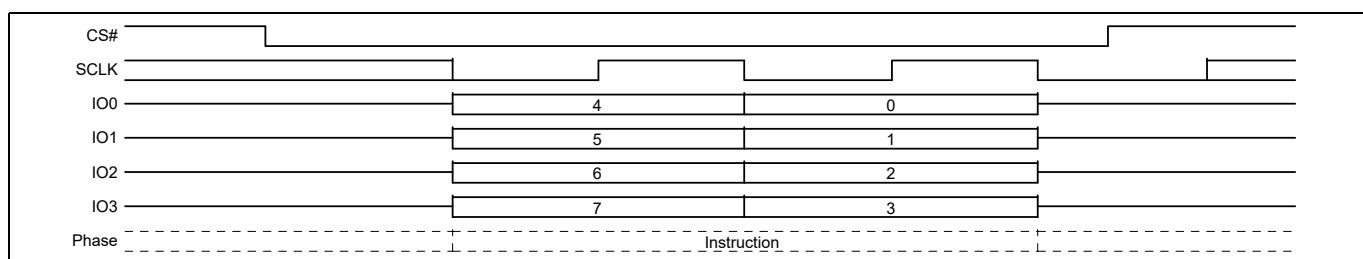

QPI モードでは、すべての命令、アドレスおよびデータが IO0, IO1, IO2, IO3 信号上で 4 ビット (ニブル) グループでホストからメモリへ送信されます。データは同様に IO0, IO1, IO2, IO3 信号上で 4 ビット (ニブル) グループでホストへ戻されます。

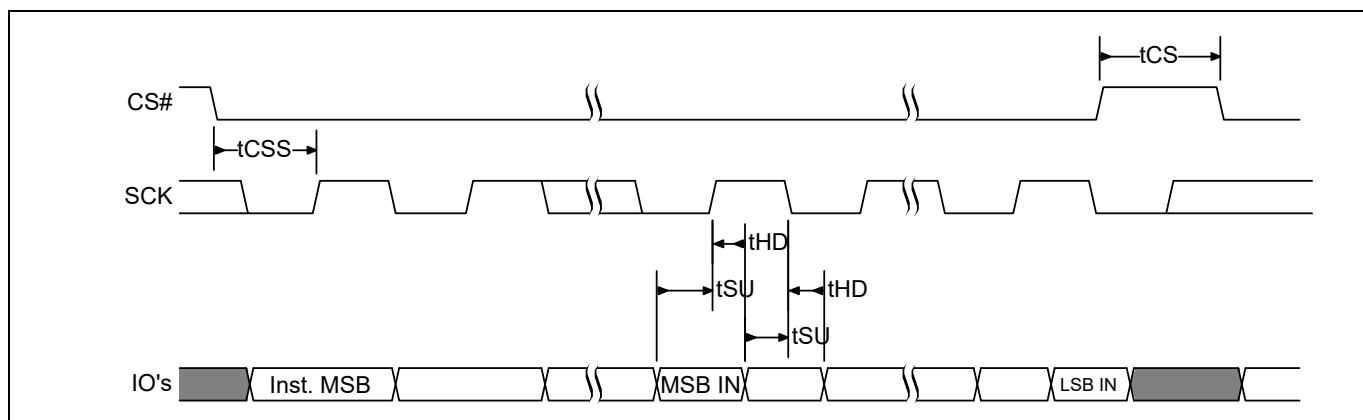

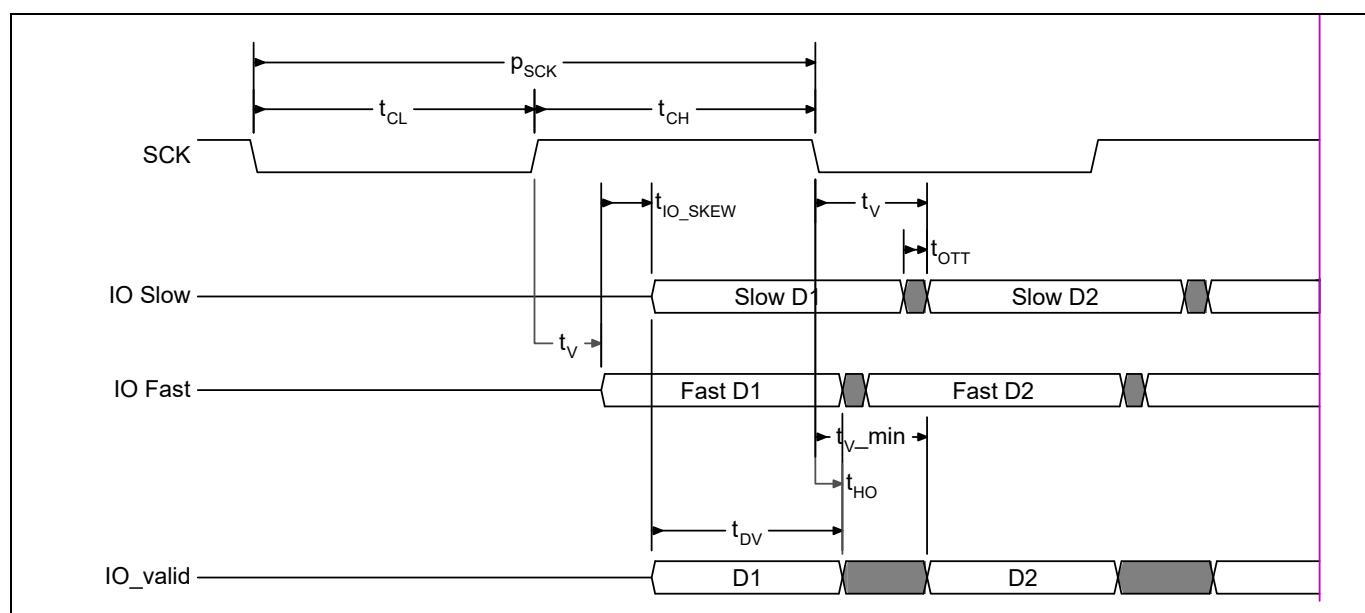

### 3.4 シリアルクロック (SCK)

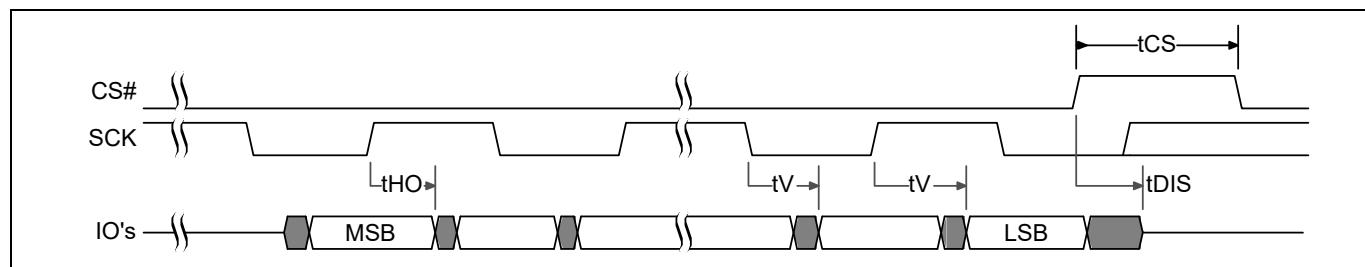

入力信号は SPI インターフェースに同期基準を提供します。命令、アドレス、またはデータ入力は SCK 信号の立ち上りエッジでラッチされます。SDR コマンドでは、データ出力は SCK の立ち下りエッジの後に変化します。

### 3.5 チップセレクト (CS#)

チップセレクト信号は、コマンドがデバイスからまたはデバイスへ情報を送信し、その他の信号がメモリデバイスに関連している時点を示します。

CS# 信号が論理 HIGH のとき、デバイスは選択されず、すべての入力信号は無視され、すべての出力信号は高インピーダンスです。内部の組込み動作がまだ実行中である場合を除き、デバイスはスタンバイ電力モードに入ります。組込み動作は、完了するまで、ステータスレジスタ 1 の「書き込み中」ビット (SR1V[0]) が「1」にセットされることにより示されます。組込み動作の例としてはプログラム、消去、レジスタ書き込み (WRR) 動作があります。

CS# 入力を論理 LOW にすると、デバイスは有効になり、アクティブ電力モードになります。電源投入後、あらゆるコマンドが開始する前に CS# の立ち下りエッジが必要です。

### 3.6 シリアル入力 (SI) / IO0

入力信号はデータをデバイスに順次転送するために使用されます。命令、アドレス、およびプログラムされるデータを受信します。値はシリアル SCK クロック信号の立ち上りエッジでラッチされます。デュアルとクアッドコマンドの実行中、SI は IO0 となります。命令、アドレス、プログラムされるデータ (シリアル SCK クロック信号の立ち上りエッジでラッチされる値) の受信、およびデータのシフトアウト (SDR コマンドの場合は SCK の立ち下りエッジで、DDR コマンドの場合は SCK のすべてのエッジで) のための入出力です。

### 3.7 シリアル出力 (SO) / IO1

出力信号はデータをデバイスからシリアル転送するために使用されます。データはシリアル SCK クロック信号の立ち下りエッジでシフトアウトされます。デュアルとクアッドコマンドの実行中、SO は IO1 となります。アドレスとプログラムされるデータ (シリアル SCK クロック信号の立ち上りエッジでラッチされる値) の受信、およびデータのシフトアウト (SDR コマンドの場合は SCK の立ち下りエッジで、DDR コマンドの場合は SCK のすべてのエッジで) のための入出力です。

### 3.8 書き込み保護 (WP#) / IO2

WP# が LOW (VIL) に駆動されると、ステータスレジスタ 1 のステータスレジスタ保護 0 ビット SRP0\_NV または SRP0 (SR1NV[7] または SR1V[7]) が「1」にセットされた場合、ステータスレジスタ、コンフィギュレーションレジスタまたは DLR レジスタに書き込めません。この場合、SR1NV, SR1V, CR1NV, CR1V, CR2NV, CR2V, CR3NV, DLRNV, および DLRV を選択するコマンドは無視され、エラーがセットされません。

これにより、レガシー ブロック保護設定の変更を防止します。結果として、SRP0\_NV が 1 にセットされており、かつステータスレジスタ、コンフィギュレーションレジスタまたは DLR レジスタを変更するコマンドが実行されている間、WP# が LOW である場合、レガシー ブロック保護機能により保護されるメモリ領域のすべてのデータ バイトはハードウェアによってもデータの変更から保護されます。同様に、セキュリティ領域ロック ビット (LB3 ~ LB0) はプログラムから保護されます。

クアッド モードが有効 (CR1V[1]=1) であるか、または QPI モードが有効 (CR2V[3]=1) である場合、WP# 機能は使用できません。クアッド モードまたは QPI モードが有効 (CR2V[3]=1) の間、WP# 機能は IO2 に置き換えられます。アドレスとプログラムされるデータ (SCK 信号の立ち上りエッジでラッチされる値) の受信およびデータのシフトアウト (SDR コマンドの場合は SCK の立ち下りエッジで、DDR コマンドの場合は SCK のすべてのエッジで) のための入出力です。

WP# は内部のプルアップ抵抗に接続されています。外部に接続されていないとき、WP# は  $V_{IH}$  であり、クアッド モード、QPI モードまたは保護に使用されない場合、ホストシステムで開放にできます。

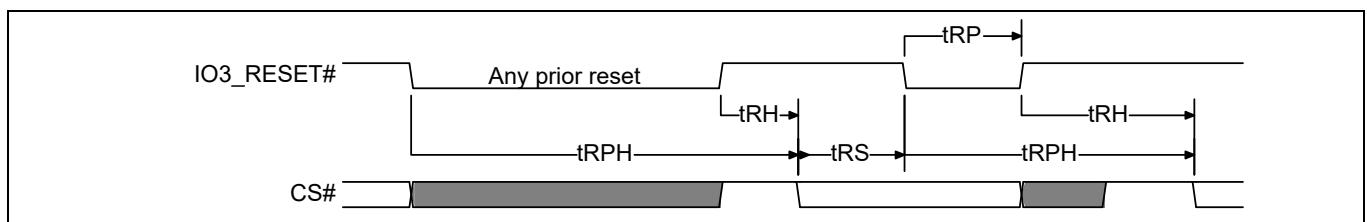

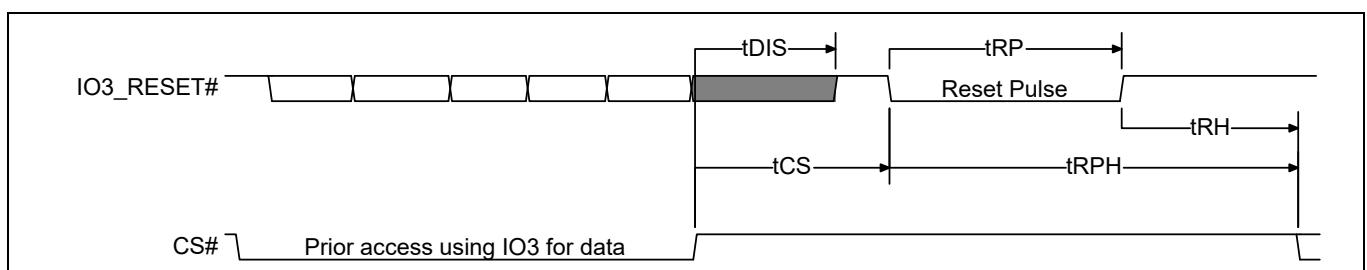

### 3.9 IO3 / RESET#

クアッド モード (CR1V[1]=1) または QPI モードが有効 (CR2V[3]=1) の間、IO3 はアドレスとプログラムされるデータ (SCK 信号の立ち上りエッジでラッチされる値) の受信およびデータのシフトアウト (SDR コマンドの場合は SCK の立ち下りエッジで、DDR コマンドの場合は SCK のすべてのエッジで) のための入出力に使用されます。

IO3/RESET# 機能が不揮発性コンフィギュレーションレジスタ 2 のビット 7 の書き込み (CR2NV[7]=1) により有効にされた場合、IO3/RESET# 入力はハードウェアリセット機能を開始するために使用できます。デバイスがクアッド モード (114, 144, 444) でないか (CR1V[1]=0)、または CS# が HIGH の場合、入力は RESET# としてのみ扱われます。クアッド モードのとき (CR1V[1]=1)、または QPI モードが有効 (CR2V[3]=1) であり、かつデバイスが CS# LOW で選択されている場合、IO3/RESET# は情報転送のために IO3 としてのみ使用されます。CS# が HIGH の場合、IO3/RESET# は情報転送のために使用されず、リセット入力として使用されます。クアッド モード (114, 144, 444) の間、CS# HIGH 時のリセット動作を調整することで、リセット機能を有効のままにできます。

システムがリセットの状態に入る場合、CS# 信号はリセットプロセスの一部として HIGH に駆動しなければならず、IO3/RESET# 信号は LOW に駆動されます。CS# が HIGH になったとき、IO3/RESET# 入力は IO3 である状態からリセット入力に遷移します。その後、CS# が HIGH のままであり、かつ IO3/RESET# 信号が  $t_{RP}$  の間 LOW のままである場合、リセット状態は検出されます。リセットを意図しない場合、メモリへのデータ転送の終わりに、CS# が HIGH に維持されているとき、システムは積極的に IO3/RESET# を HIGH に駆動する必要があります。データをホストシステムへ転送した後、メモリは  $t_{CS}$  の間 IO3 を HIGH に駆動します。これにより、IO3/RESET# は開放の状態にならず、内部あるいは外部のパッシブ プルアップ抵抗によって HIGH にゆっくりプルアップされません。したがって、 $t_{RP}$  が経過する前に IO3/RESET# が HIGH として認識されることによる意図されないリセットはトリガーされません。

CR2V[7]=0 のとき、IO3/RESET# 入力リセット機能は無効です。

IO3/RESET# 入力は内部プルアップ抵抗に接続しており、クアッド モードまたはリセット機能に使用されない場合、ホストシステムで開放にできます。ホストシステムによる IO3/RESET# 信号の HIGH 駆動から信号の駆動停止の後、内部プルアップ抵抗が IO3/RESET# 信号を HIGH のままに維持します。

いずれかの SPI-MIO メモリがクアッド I/O モードで動作している場合、IO3/RESET# は 2 つ以上の SPI-MIO メモリによって共有できないことに注意してください。理由は、1 つの選択されたメモリから駆動されている IO3 が、同じ IO3/RESET# 信号を共有している 2 番目の選択されないメモリによってリセット信号と認識される場合があるからです。

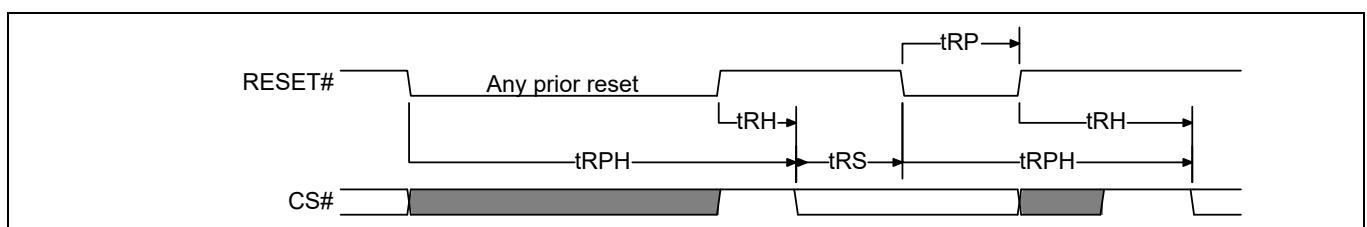

### 3.10 RESET#

RESET# 入力は、デバイスをハードウェア的にスタンバイ状態にリセットして、コマンドを受信できるようにします。RESET# が少なくとも  $t_{RP}$  の 1 周期の間論理 LOW ( $V_{IL}$ ) に駆動されたとき、デバイスはハードウェアリセットプロセスを開始します。

RESET# は、電源投入時と同じ初期化プロセスを行い、 $t_{PU}$  時間を要します。

RESET# はいつでも LOW にアサートできます。データ完全性を保証するために、デバイスがコマンドシーケンスを受けられるようになると、ハードウェアリセットにより中断された動作を再実行する必要があります。

RESET# は内部プルアップ抵抗に接続しており、ホストシステムで使用されない場合は開放のままにすることがあります。ホスト

システムによる RESET 信号の HIGH 駆動から信号の駆動停止の後、内部プルアップ抵抗が RESET 信号を HIGH のままに維持します。

パッケージオプションによって、RESET# 入力は利用できない場合があります。使用されないとき、デバイスの RESET# 入力は無効な状態にされます。

### 3.11 電源電圧 ( $V_{CC}$ )

$V_{CC}$  はすべてのデバイスの内部ロジックの電圧ソースです。読み出し、プログラム、消去を含むデバイスのすべての内部機能に使用される単一の電圧です。

### 3.12 電源および信号グランド ( $V_{SS}$ )

$V_{SS}$  はデバイスコア、入力信号レシーバ、および出力ドライバー用の共通電圧ドレインとグランドリファレンス電圧です。

### 3.13 未接続 (NC)

デバイスの内部信号はパッケージコネクタに接続されず、信号にコネクタを使用する計画もありません。接続はプリント基板 (PCB) 上で信号の配線スペース向けに安全に使用できます。

### 3.14 将来に使用するために予約済み (RFU)

現時点ではパッケージコネクタに接続しているデバイスの内部信号はありませんが、将来コネクタを使用する可能性があります。RFU コネクタを PCB 配線チャネルに使用しないことを推奨します。それによって、PCB はフットプリントの互換性があるデバイスの将来の拡張機能を活用できます。

### 3.15 使用禁止 (DNU)

デバイスの内部信号がパッケージコネクタに接続される可能性があります。接続はインフィニオンによってテスト用または他の目的で使用され、ホストシステムの信号に接続するためのものではありません。DNU 信号が  $V_{IL}$  のとき、DNU 信号に関連するすべての機能は無効になります。信号は内部プルダウン抵抗に接続され、ホストシステムで開放のままにされるか、または  $V_{SS}$  に接続できます。これらの接続を PCB 信号配線チャネルに使用しないでください。ホストシステム信号をこれらの信号に接続しないでください。

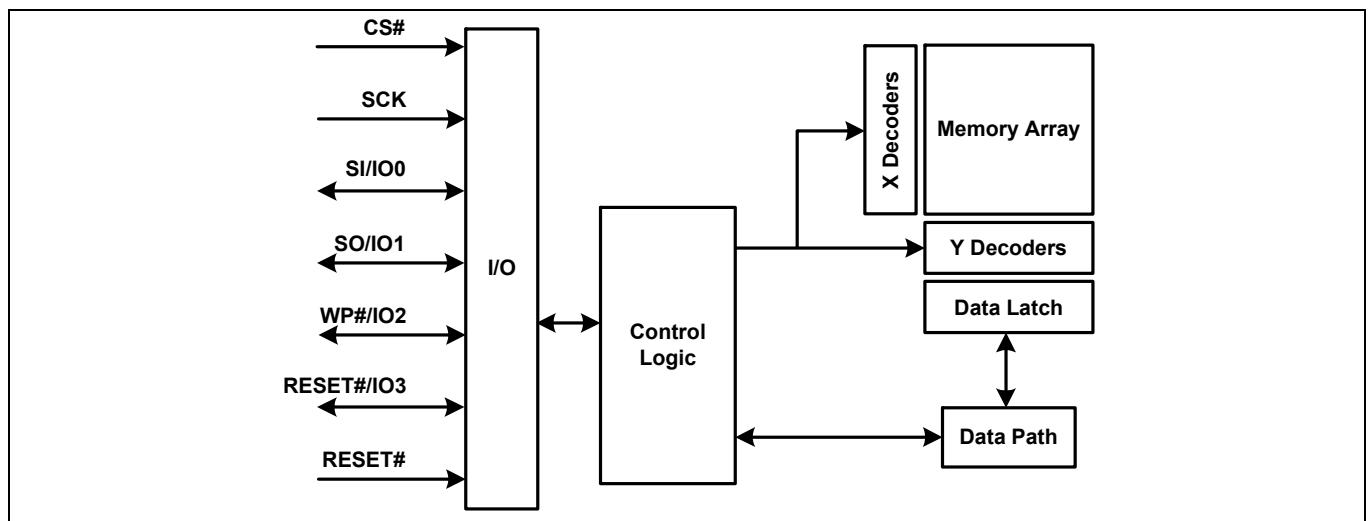

## 4 ブロック図

Figure 6 論理ブロック図

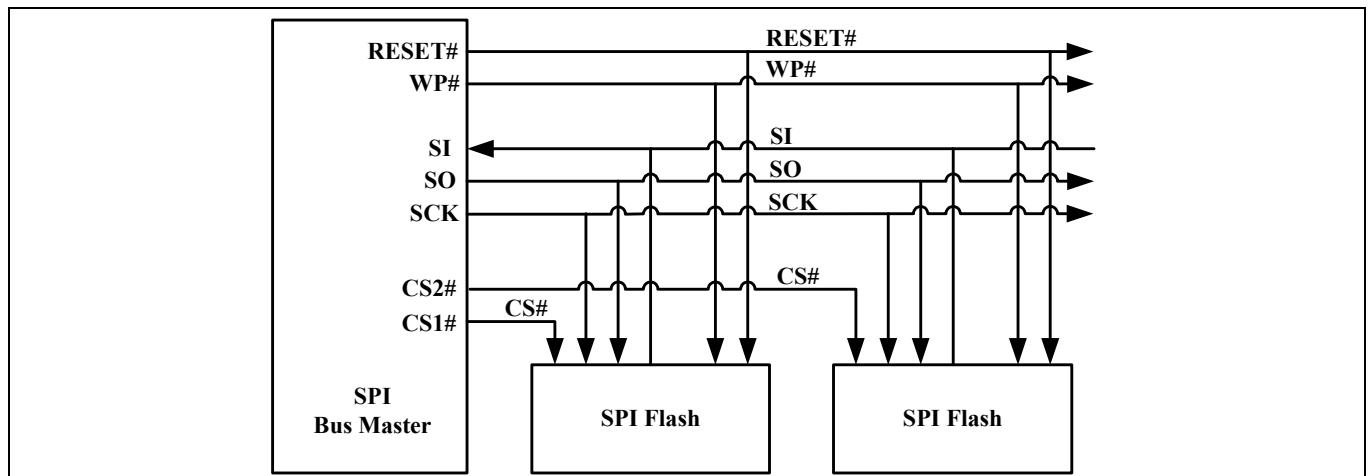

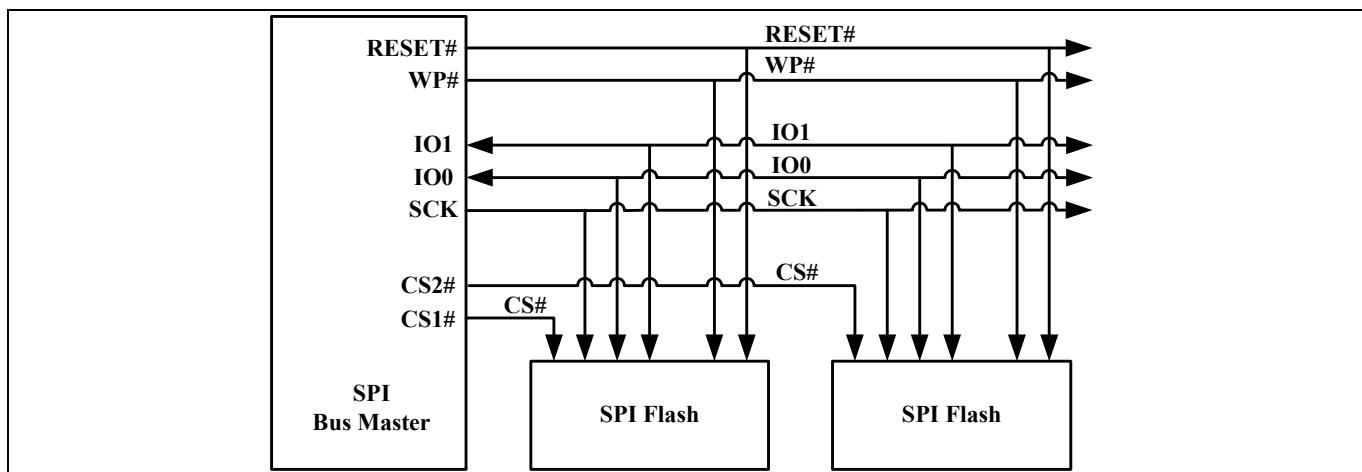

### 4.1 システム ブロック図

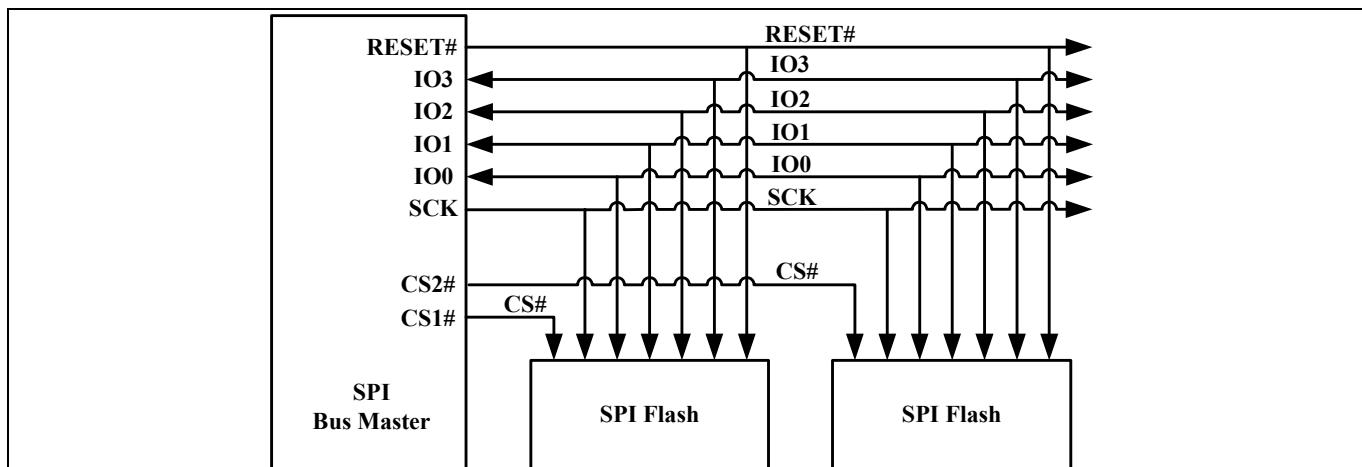

Figure 7 SPI バス上のバス マスターおよびメモリ デバイス - シングル ビット データ パス

Figure 8 SPI バス上のバスマスターおよびメモリデバイス - デュアルビットデータバス

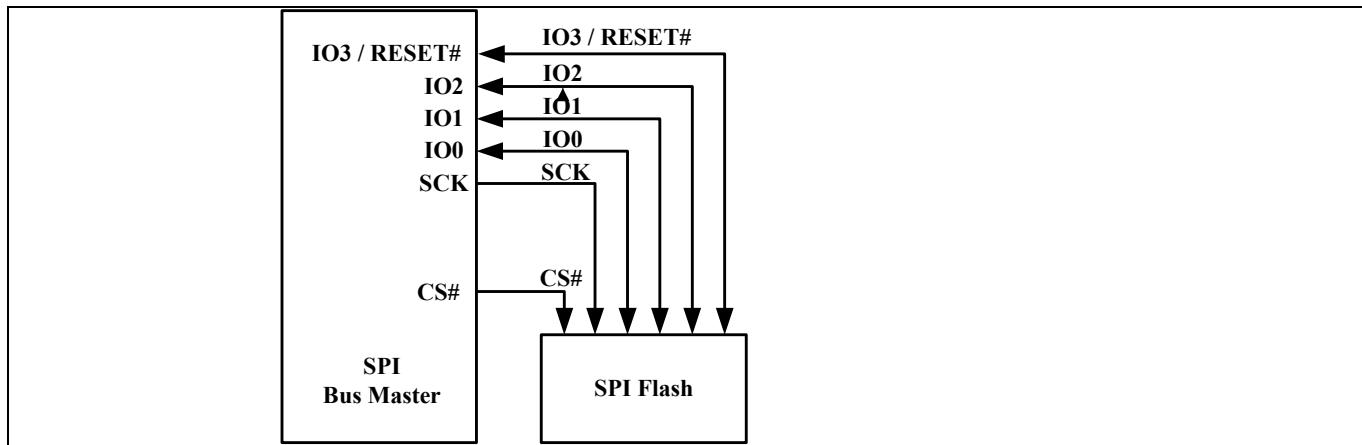

Figure 9 SPI バス上のバスマスターおよびメモリデバイス - クアッドビットデータバス - 個別 RESET#

Figure 10 SPI バス上のバスマスターおよびメモリデバイス - クアッドビットデータバス - I/O3 / RESET#

## 5 信号プロトコル

### 5.1 SPI クロック モード

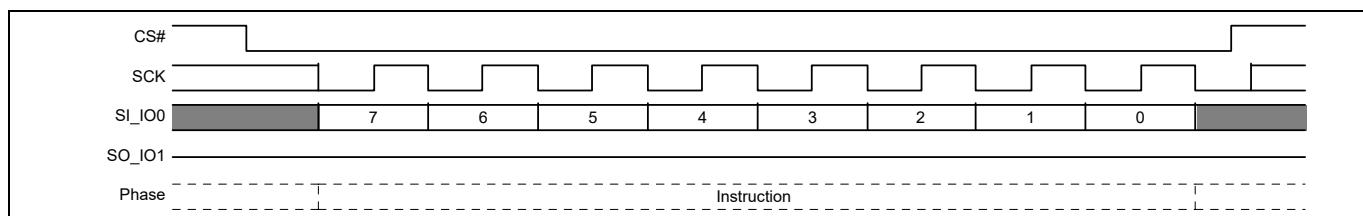

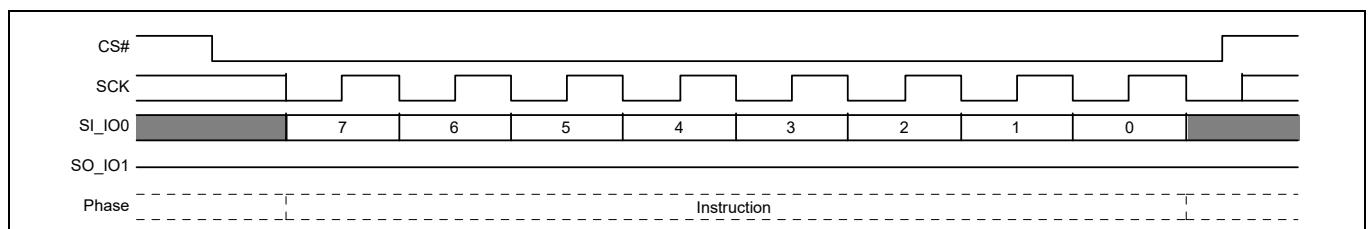

#### 5.1.1 シングルデータ レート (SDR)

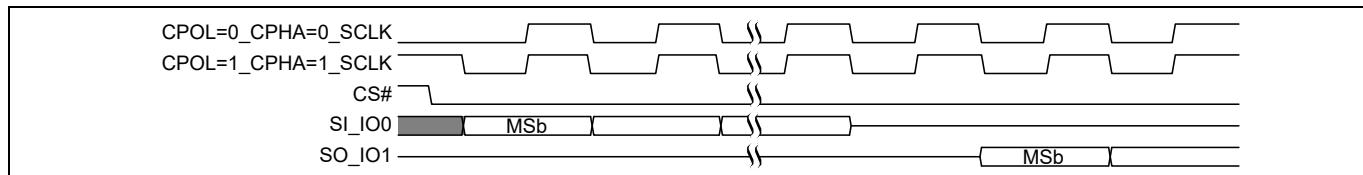

FL-L ファミリは以下の 2 つのクロック モードのどちらかで、組込みマイクロコントローラー (バス マスター) によって駆動されます。

- モード 0: クロック極性 (CPOL) = 0、クロック位相 (CPHA) = 0

- モード 3: CPOL = 1、CPHA = 1

2 つのモードでは、デバイスへの入力データは常に SCK 信号の立ち上りエッジでラッチされ、出力データは常に SCK クロック信号の立ち下りエッジで得られます。

2 つのモードの異なる点は、バス マスターがスタンバイ モードであり、データを転送しないときのクロック極性です。

- CPOL=0、CPHA=0 のとき、SCK は論理 LOW の状態にあります。

- CPOL=1、CPHA=1 のとき、SCK は論理 HIGH の状態にあります。

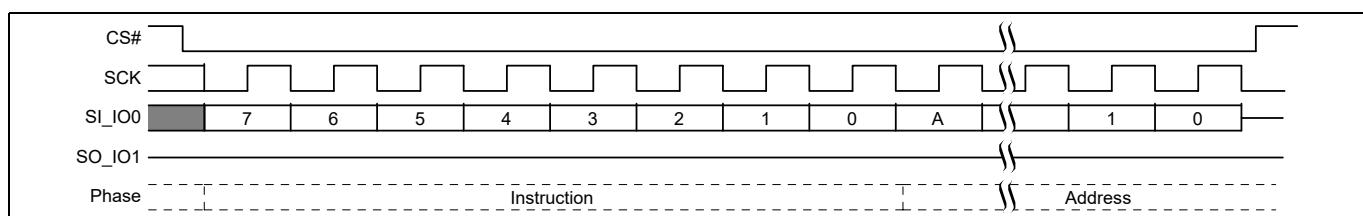

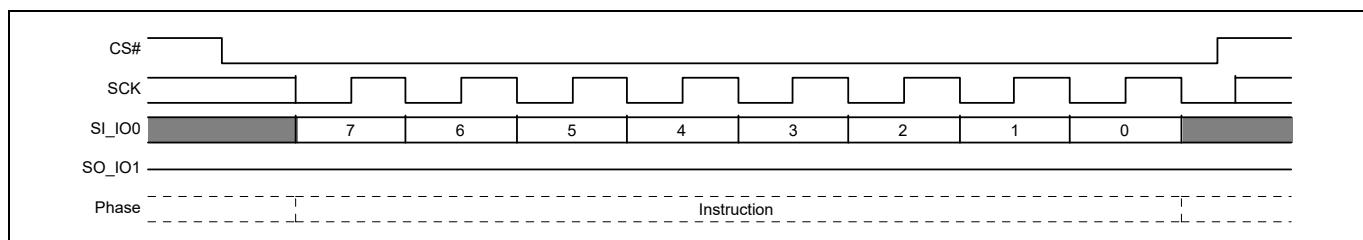

Figure 11 対応する SPI SDR モード

本書の以降のタイミング図は、CS# の立ち下がりのときに SCK が HIGH と LOW の両方として表示することにより、一般的にモード 0 とモード 3 の両方として示されます。場合によっては、タイミング図はモード 0 (CS# の立ち下り時に SCK が LOW) のみを示します。その場合において、モード 3 のタイミングは単に CS# の立ち下りのときにクロックが HIGH であることを意味し、CS# の立ち下りエッジまでの SCK の立ち上りエッジのセットアップまたはホールド時間はモード 3 に必要がありません。

SCK サイクルは SCK の 1 つの立ち下りエッジから次の立ち下りエッジまで測定 (カウント) されます。モード 0 では、SCK がコマンドの開始時にすでに LOW であるため、コマンドの最初の SCK サイクルの始まりは CS# の立ち下りエッジから SCK の最初の立ち下りエッジまで測定されます。

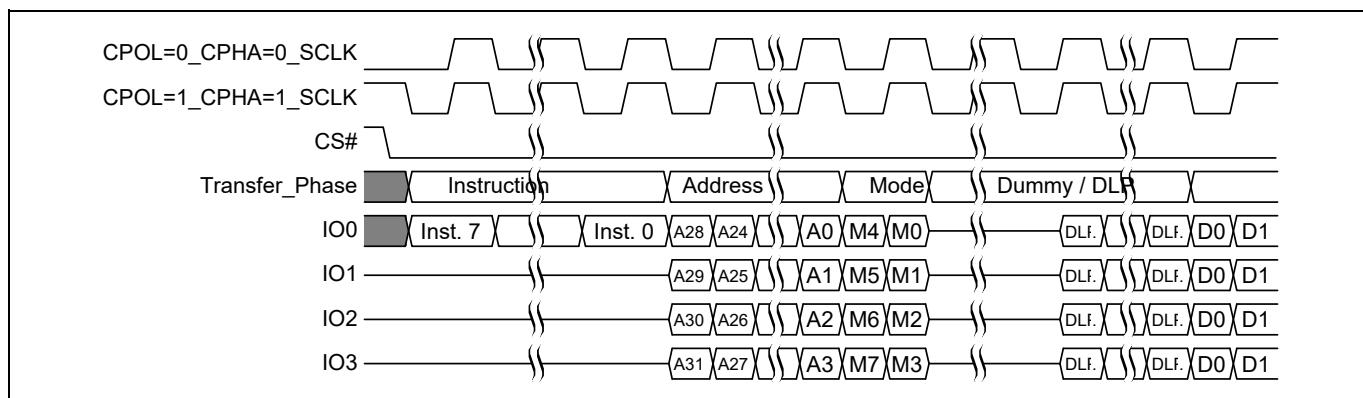

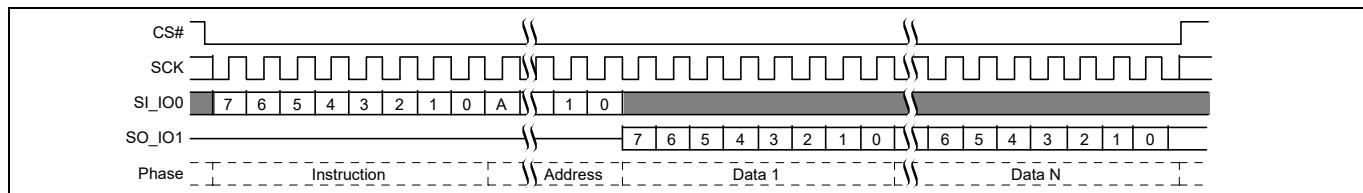

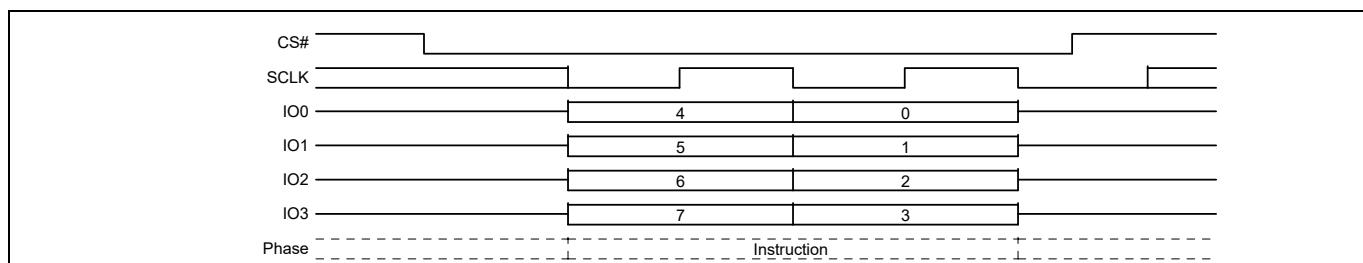

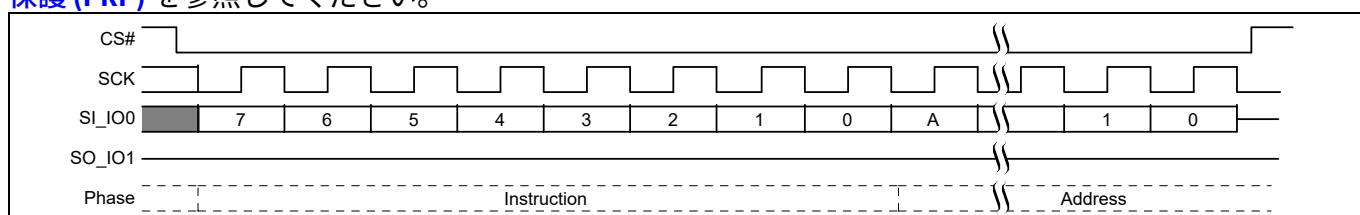

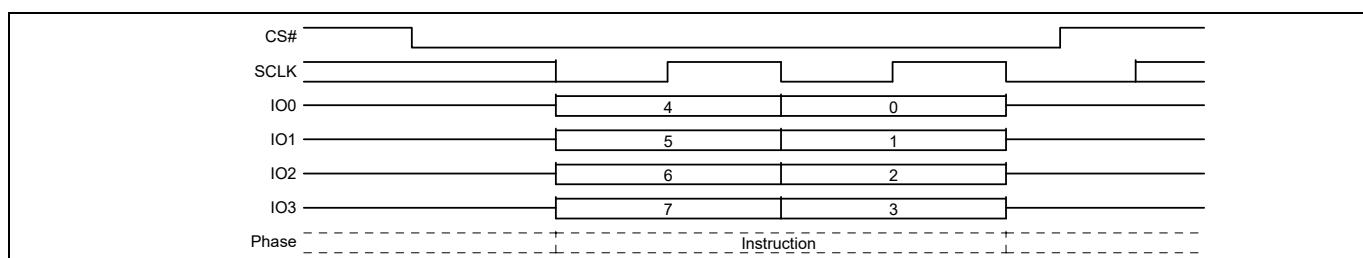

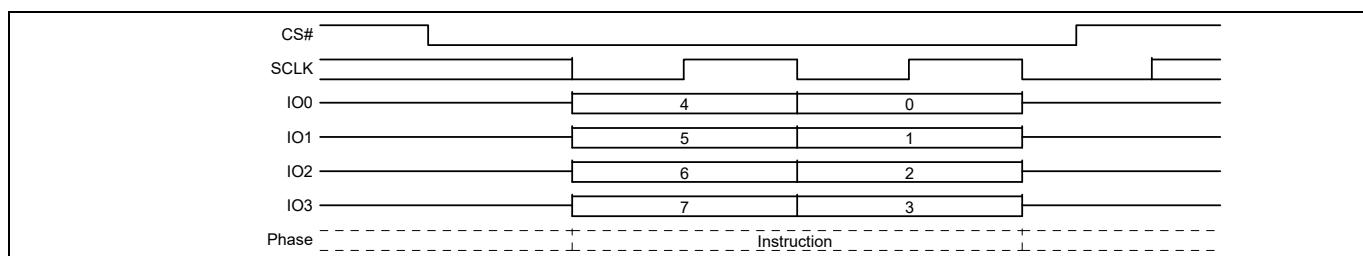

### 5.1.2 ダブルデータレート (DDR)

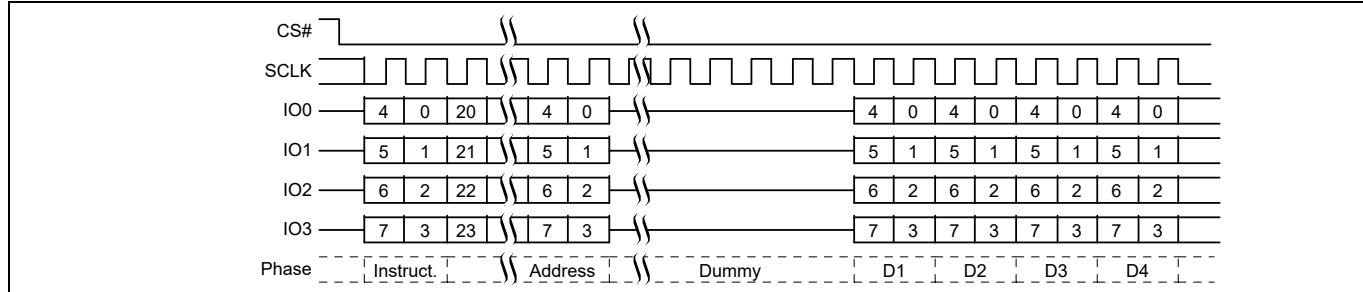

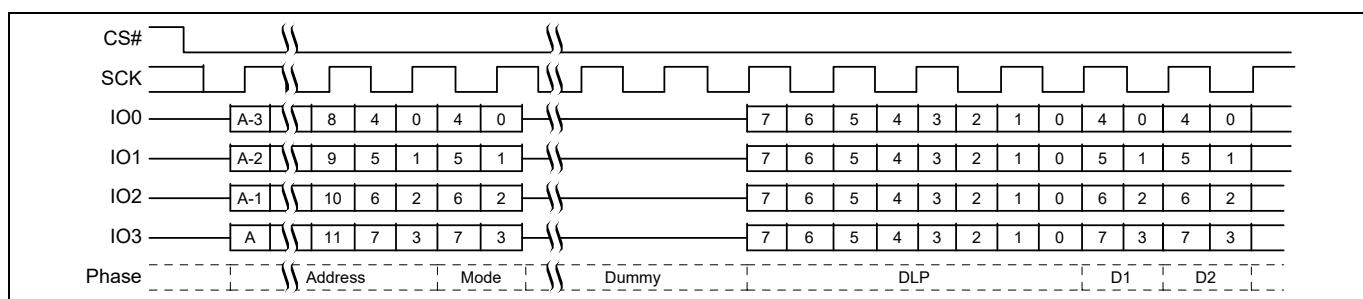

モード 0 とモード 3 は DDR コマンドにも対応します。SDR コマンドと同様に DDR コマンドでは、命令ビットは常にクロックの立ち上りエッジでラッチされます。ただし、命令の後に続くアドレスおよび入力データは SCK の立ち上りエッジと立ち下りエッジの両方でラッチされます。最初のアドレスビットは、直前の命令ビットの終わりの立ち下りエッジの後に続く SCK の最初の立ち上りエッジでラッチされます。出力データの最初のビットは、直前のアクセスレイテンシ (ダミー) サイクルの最後の立ち下りエッジで駆動されます。

SDR コマンドと同様に、SCK サイクルは SCK の 1 つの立ち下りエッジから次の立ち下りエッジまで測定 (カウント) されます。モード 0 では、SCK がコマンドの開始時にすでに LOW であるため、コマンドの最初の SCK サイクルの始まりは CS# の立ち下りエッジから SCK の最初の立ち下りエッジまで測定されます。

Figure 12 対応する SPI DDR モード

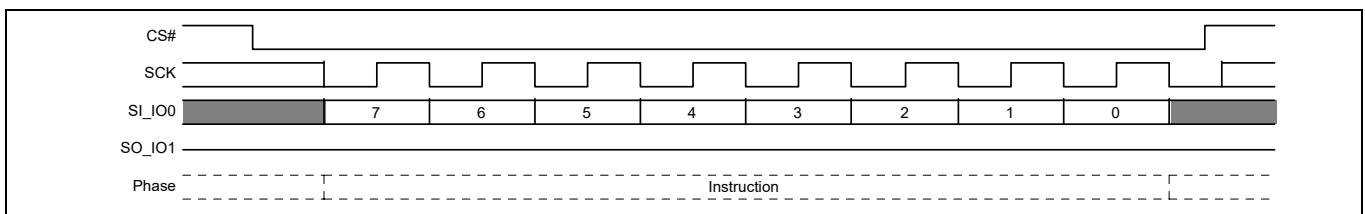

## 5.2 コマンド プロトコル

ホストシステムと FL-L ファミリメモリデバイスの間のすべての通信はコマンドの形で行われます。すべてのコマンドの定義および詳細は [コマンド](#) を参照してください。

すべてのコマンドは、情報転送のタイプまたは実行するデバイスの動作を選択する 8 ビットの命令で始まります。コマンドには、アドレス、命令修飾子、レイテンシ周期、メモリへのデータ転送、またはメモリからのデータ転送もあります。すべての命令、アドレス、およびデータ情報はホストシステムとメモリデバイスの間で順次に転送されます。

コマンドプロトコルは、下記 3 つのコマンドフェーズの転送幅を示すために 3 つの番号を使用する数値命名により分類されます。

- 命令

- アドレスおよび命令修飾子 (連続読み出しモード ビット)

- データ

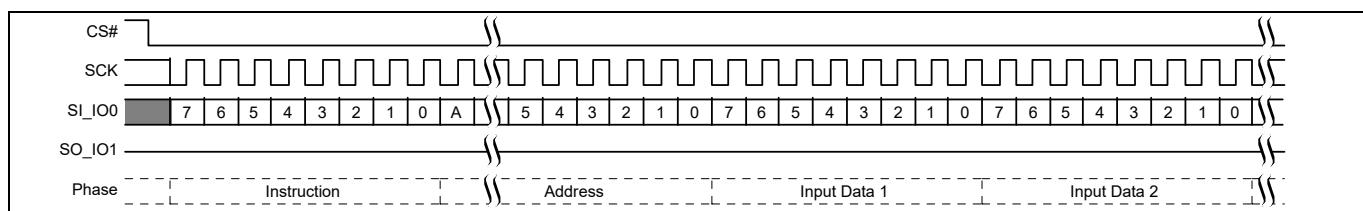

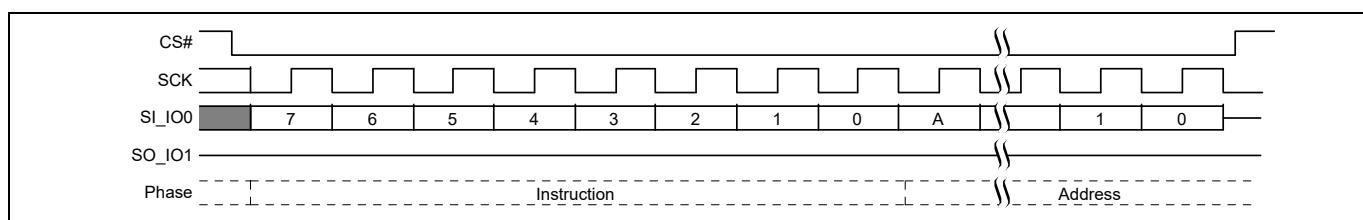

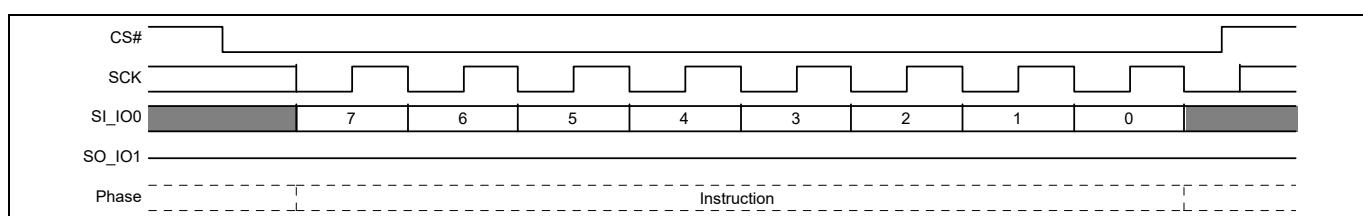

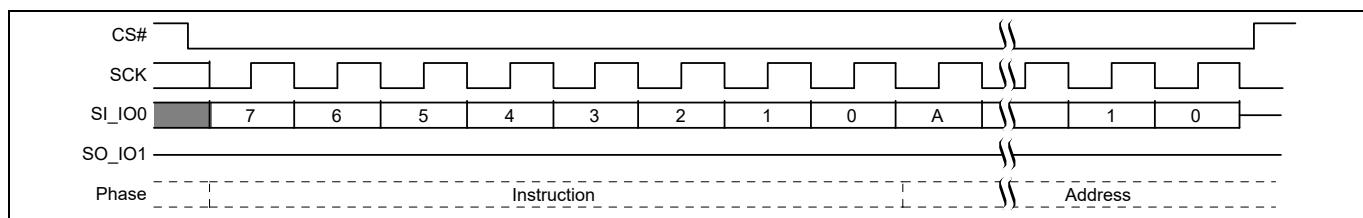

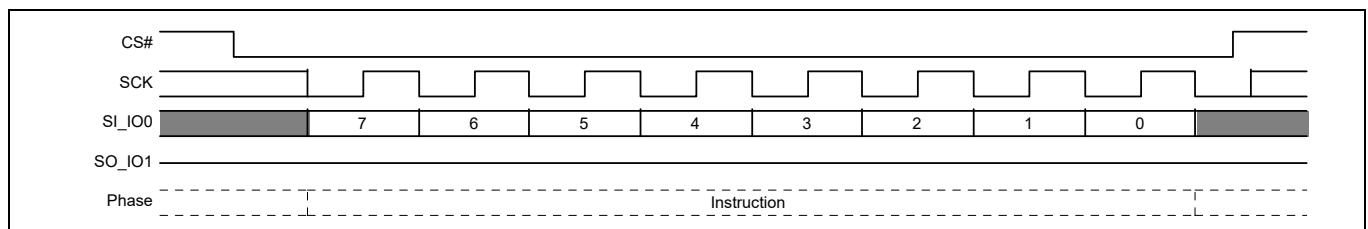

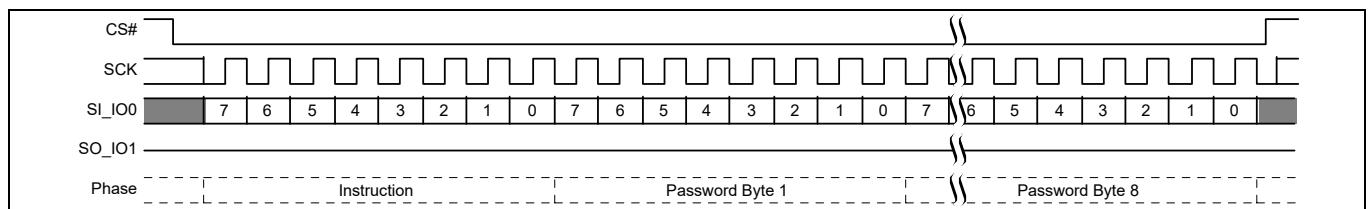

シングルビット幅コマンドは命令で開始し、SI 信号のみで送信されるアドレスまたはデータを提供します。データは SO 信号でホストへ順次戻されることがあります。シングルビット幅命令、シングルビット幅アドレスおよび修飾子、シングルビットデータ用の 1-1-1 コマンドプロトコルと呼ばれます。

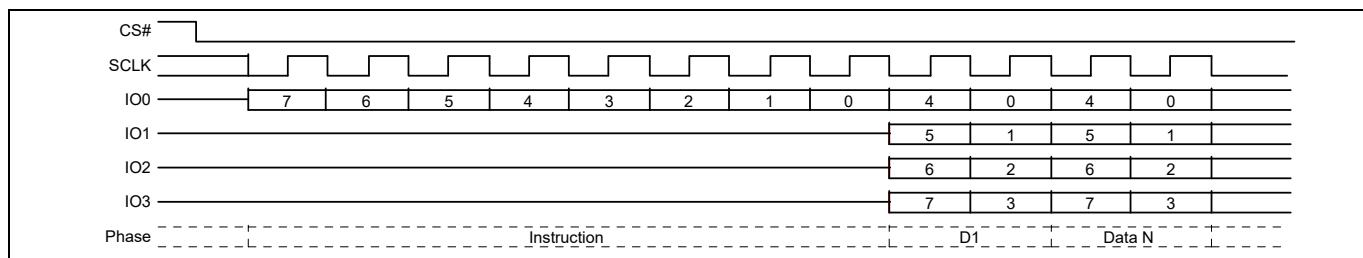

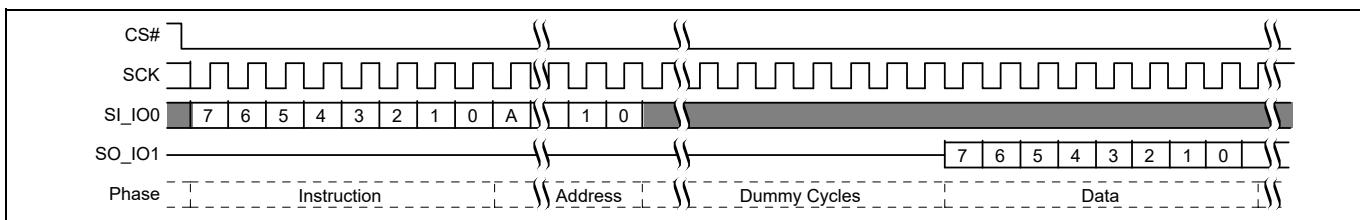

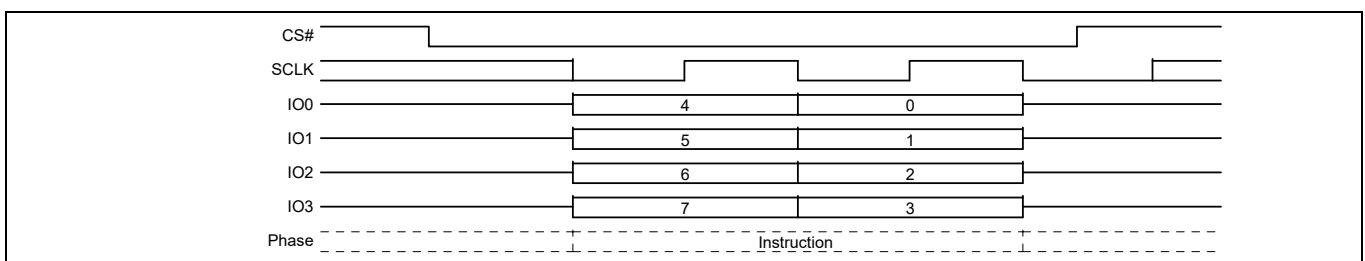

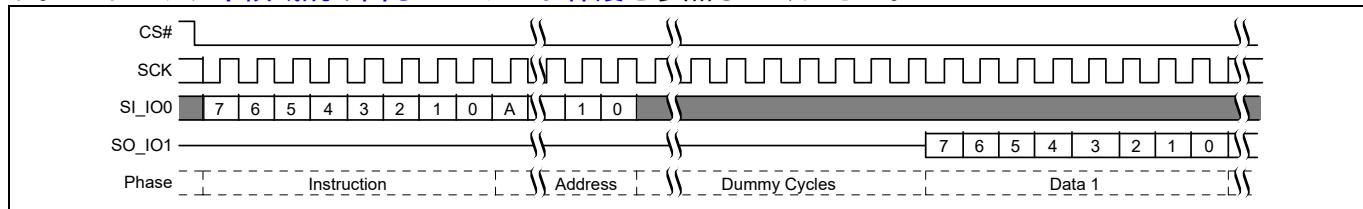

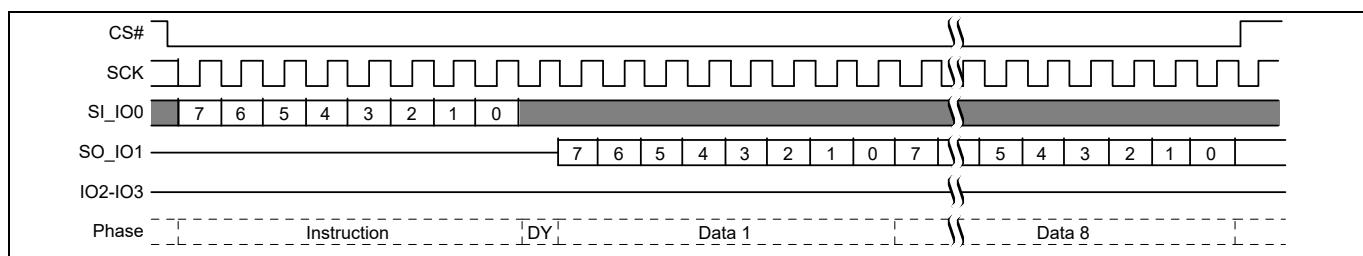

デュアル出力またはクアッド出力のコマンドは SI (I00) 上でシリアルとしてホストから送信されるアドレスを提供してからダミーサイクルを提供します。データは I00 と I01 信号上でビットペア、または I00, I01, I02, I03 信号上で 4 ビット (ニブル) グループでホストへ戻されます。デュアル出力用の 1-1-2 コマンドプロトコル、またはクアッド出力用の 1-1-4 コマンドプロトコルと呼ばれます。

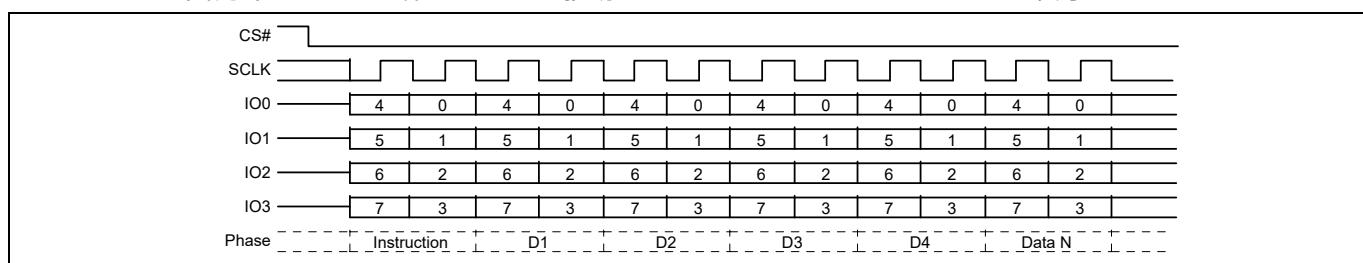

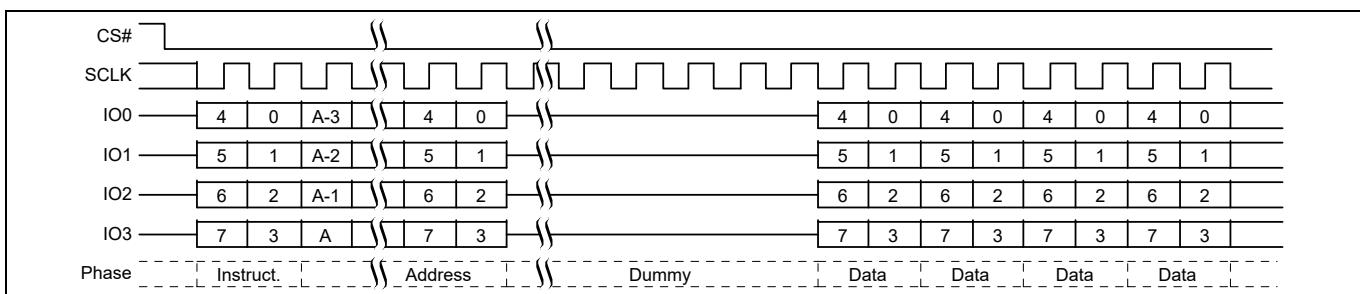

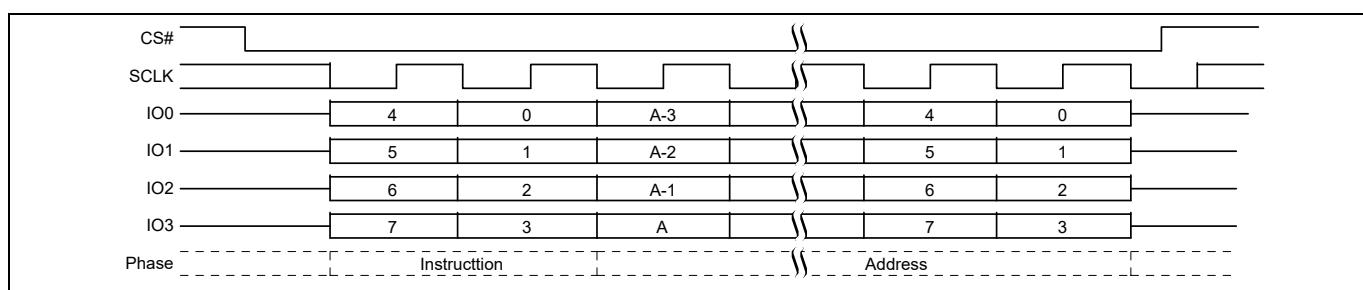

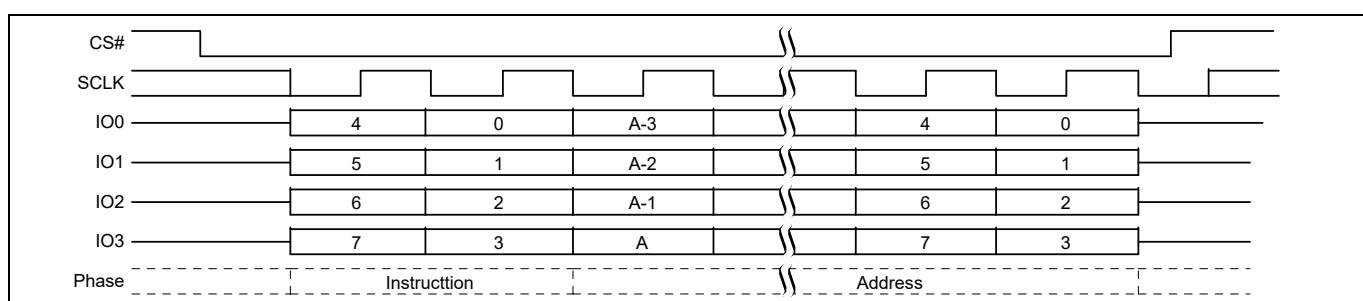

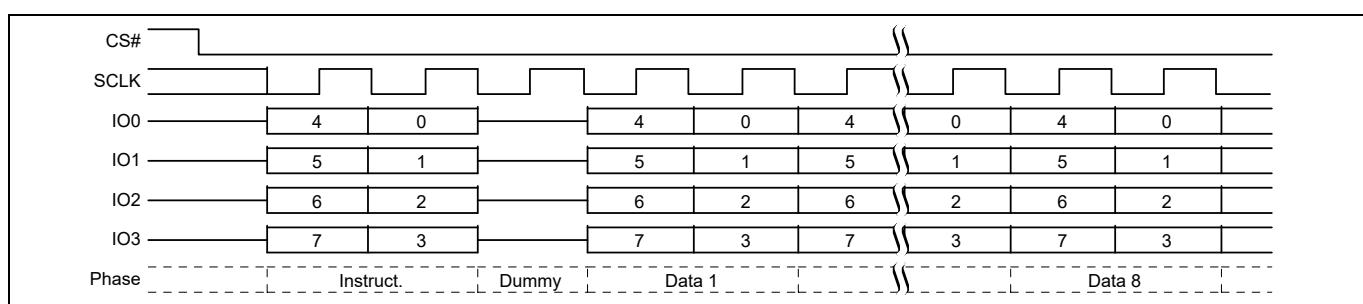

デュアルまたはクアッド入出力 (I/O) コマンドは、I00 と I01 信号上でビットペア、または I00, I01, I02, I03 信号上で 4 ビット (ニブル) グループとしてホストから送信されるアドレスを提供してからダミーサイクルを提供します。データは同様に I00 と I01 信号上でビットペア、または I00, I01, I02, I03 信号上で 4 ビット (ニブル) グループでホストへ戻されます。デュアル I/O 用の 1-2-2 コマンドプロトコル、またはクアッド I/O 用の 1-4-4 コマンドプロトコルと呼ばれます。

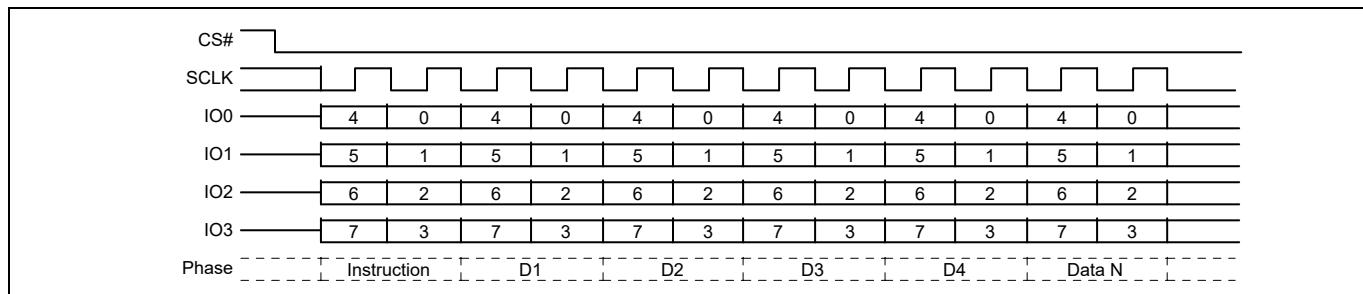

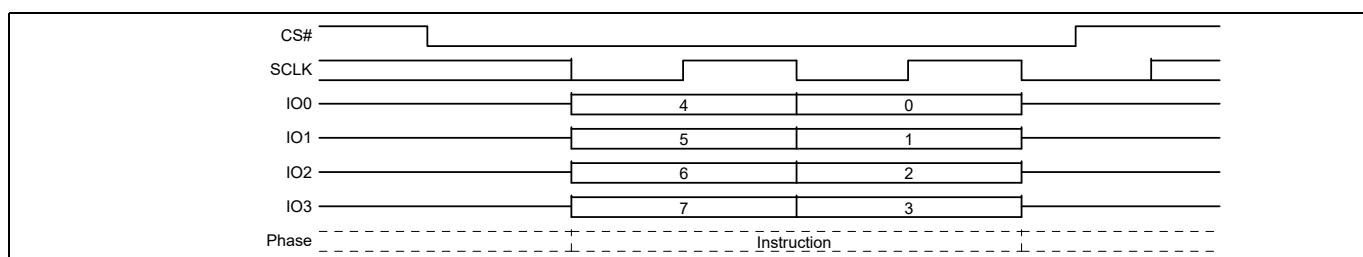

FL-L ファミリは、命令、アドレス、修飾子、およびデータを含み、すべての情報が 4 ビットの幅で転送される QPI モードにも対応します。4-4-4 コマンドプロトコルと呼ばれます。

コマンドは以下のとおり構成されます。

- 各コマンドは CS# が LOW になることで開始され、CS# が HIGH に戻ることで終了されます。メモリデバイスはホストがコマンドを通してチップセレクト (CS#) 信号を LOW に駆動することで選択されます。

- シリアルクロック (SCK) はホストとメモリの間の各ビットまたは各ビットグループの転送を示します。

- 各コマンドは 8 ビット (バイト) の命令で始まります。命令は、情報転送のタイプ、または実行するデバイスの動作を選択します。命令の転送は SCK の立ち上りエッジで実行されます。ただし、いくつかの読み出しコマンドは、命令が前のコマンドから默示的に示されるように、前の読み出しコマンドにより修正されます。連続読み出しモードと呼ばれます。デバイスが連続読み出しモードにあるとき、命令は連続読み出しモードを開始した読み出しコマンドと同じであるため、命令ビットはコマンドの始まりには送信されません。連続読み出しモードでは、コマンドは読み出しアドレスで開始されます。したがって、連続読み出しモードは一連の同じタイプの読み出しコマンドの各読み出しコマンドから 8 命令ビットを取り除きます。

- 命令は単独であるか、またはその後にデバイスの 1 つのアドレス空間内の位置を選択するアドレスビットが続きます。命令は使用されるアドレス空間を決定します。アドレスは 24 ビットまたは 32 ビットのバイト境界アドレスです。アドレス転送は SDR コマンドでは SCK の立ち上りエッジで、DDR コマンドでは SCK の両エッジで実行されます。

- レガシー SPI モードでは、命令の後に続くすべての転送の幅は送信される命令により決められます。その次の転送は SI あるいはシリアル出力 (SO) 信号のみでのシングルビットシリアル転送であり続けるか、I00 と I01 信号上の 1 回の (デュアル) 転送当たりに 2 ビットグループで、または I00 ～ I03 信号上の 1 回の (クアッド) 転送当たりに 4 ビットグループで実行されます。デュアルまたはクアッドのグループでは、最下位ビットは I00 信号上有ります。そのビットに比べて上位である各ビットはより高い番号付きの I/O 信号に有意の順序で (上位から下位へ) 配置されます。シングルビットまたはパラレルビットグループは LSb からの順で転送されます。

- QPI モードでは、すべての転送の幅は I00～I03 信号上の 4 ビット幅 ( クアッド ) 転送です。

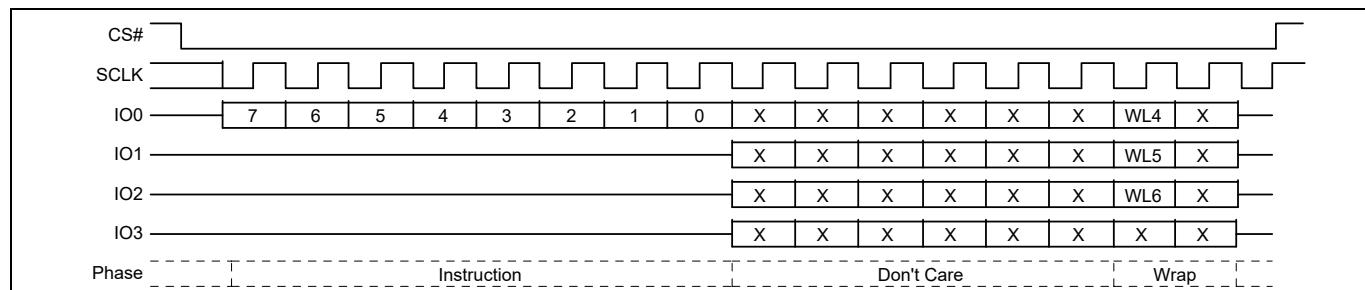

- デュアルおよびクアッド I/O 読み出し命令は、次のコマンドが默示の命令 ( 明示的な命令でなく ) と同じタイプであるかどうかを示すために、アドレスの後に、連続読み出しモードビットと呼ばれる命令修飾子を送信します。モードビットは連続読み出しモードを開始させるか、または終了させます。そのため、連続読み出しモードでは、次のコマンドは命令のバイトを提供せずに新しいアドレスおよびモードビットのみを提供します。これにより、一連のコマンドで同じタイプのコマンドが繰り返された場合、各コマンドの送信に必要な時間を削減できます。モードビットの転送は SDR コマンドの場合、SCK の立ち上りエッジで行われ、DDR コマンドの場合、すべての SCK エッジで行われます。

- アドレスまたはモードビットの後、メモリデバイスに保存される書き込みデータが続くか、または読み出しデータがホストに戻される前に読み出しレイテンシ周期が続く場合があります。

- 書き込みデータビットの転送は SDR コマンドの場合、SCK の立ち上りエッジで行われ、DDR コマンドの場合、すべての SCK エッジで行われます。

- SCK はすべての読み出しアクセス レイテンシ期間中は継続的にトグルします。レイテンシは 0 から数個の SCK サイクルです ( ダミーサイクルとも呼ばれています )。最後の読み出しレイテンシサイクルの終わりに、最初の読み出しデータビットが SCK 立ち下りエッジで出力から駆動されます。最初の読み出しデータビットは次の SCK 立ち上りエッジでホストへ転送されるものと見なされます。その次の転送は SDR コマンドの場合、次の SCK の立ち上りエッジで行われ、DDR コマンドの場合、すべての SCK エッジで行われます。

- コマンドが読み出しデータをホストへ戻す場合、デバイスはホストが CS# 信号を HIGH にするまで、継続的にデータを送信します。CS# 信号は読み出しデータシーケンスの任意の転送の後、HIGH に駆動できます。これにより、コマンドは終了します。データを戻さないコマンドの終わりに、ホストは CS# 入力を HIGH に駆動します。CS# 信号はスタンダードアロン命令または転送される最後の書き込みデータバイトの 8 ビット目の転送後に HIGH にしなければいけません。すなわち、CS# 信号を HIGH に駆動するのは LOW に駆動された後のビット数が 8 ビットの整数倍となる場合に限ります。CS# 信号が命令または書き込みデータの 8 ビット境界で、すなわち、バイトアドレスインクリメント ) の順序で送信されません。

- すべての命令、アドレス、およびモードビットは MSb からデバイスにシフトインされます。デバイスからのデータビットのシフトイン / シフトアウトは MSb から行われます。すべてのデータ転送はバイトの単位で、最下位アドレスバイトから行われます。その次のデータバイトは最下位アドレスバイトから最上位アドレスバイトまで ( すなわち、バイトアドレスインクリメント ) の順序で送信されます。

- プログラム、消去、または書き込みサイクル ( 組込み動作 ) 中に、フラッシュメモリアレイを読み出そうとすると無視されます。組込み動作は何の影響も受けず、実行が継続されます。組込み動作中、ごく限られたコマンドセットは受け入れられます。各々のコマンド説明で記述します。

- コマンドによって実行時間が異なります。いつコマンドの実行が完了したか、およびコマンドが正常に完了したかどうかを判断するために、実行中のコマンドからステータス情報を読み出すコマンドが使用できます。

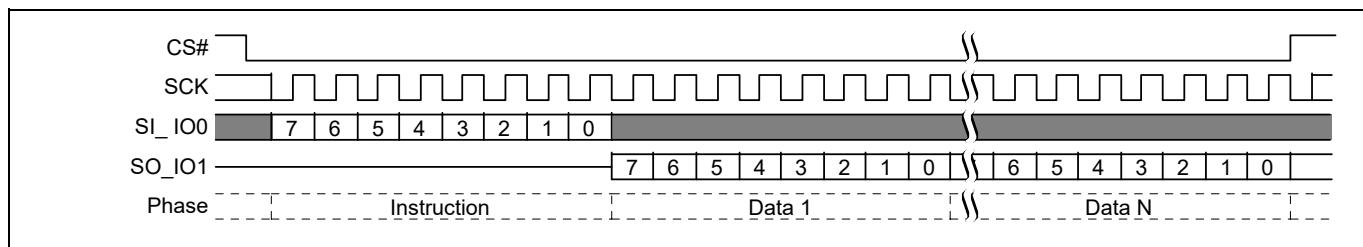

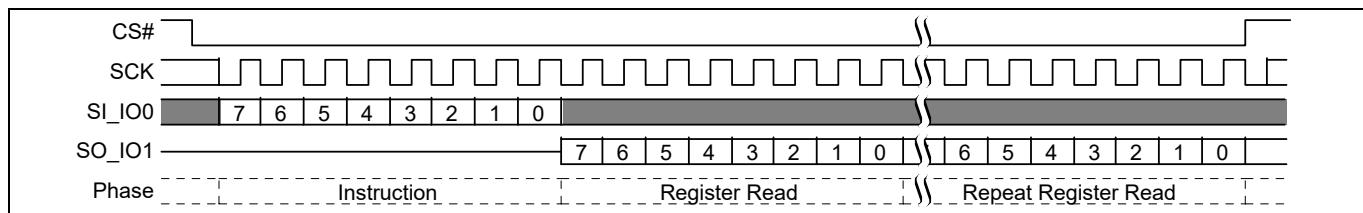

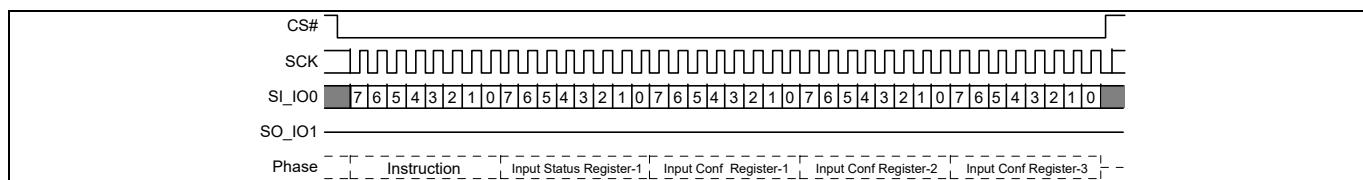

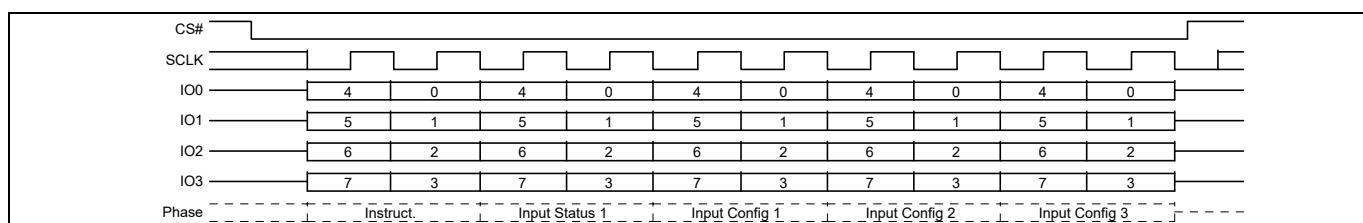

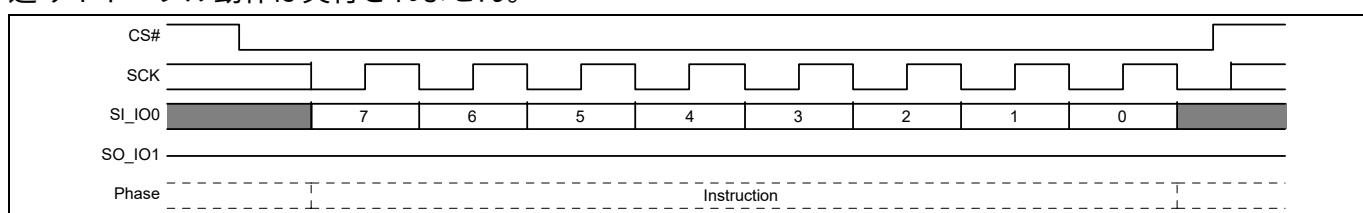

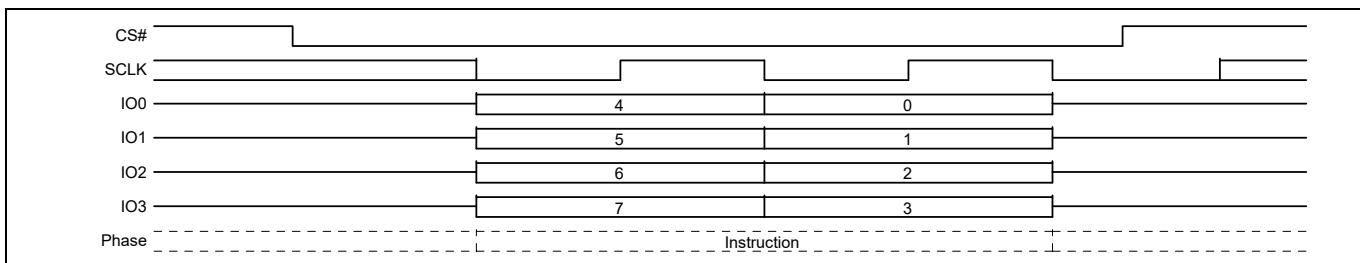

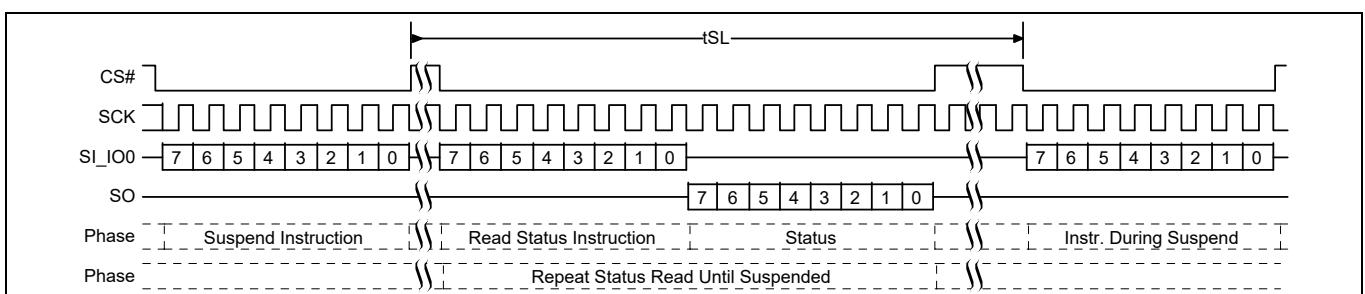

### 5.2.1 コマンドシーケンス例

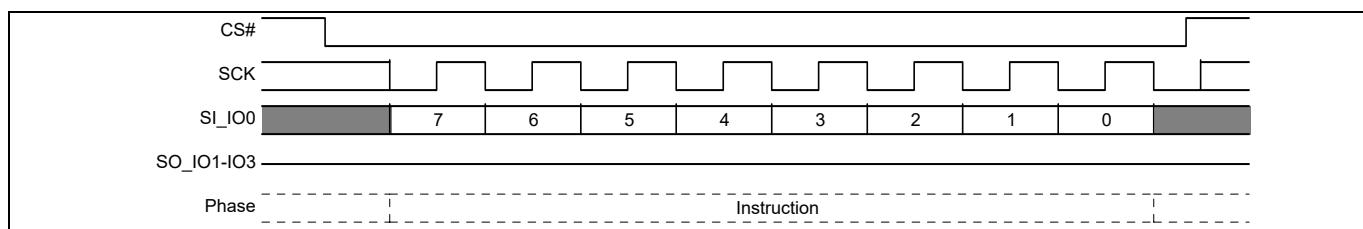

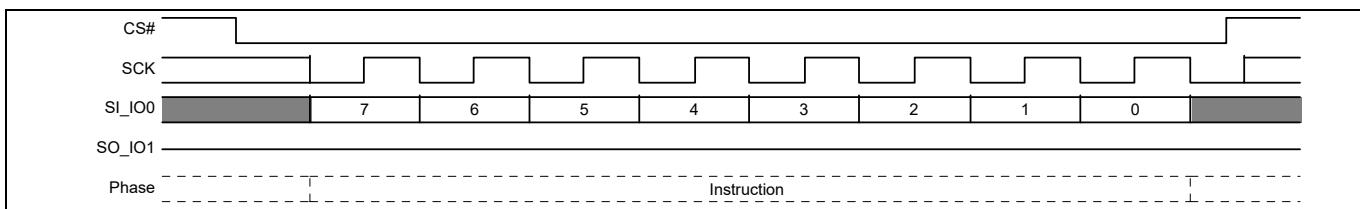

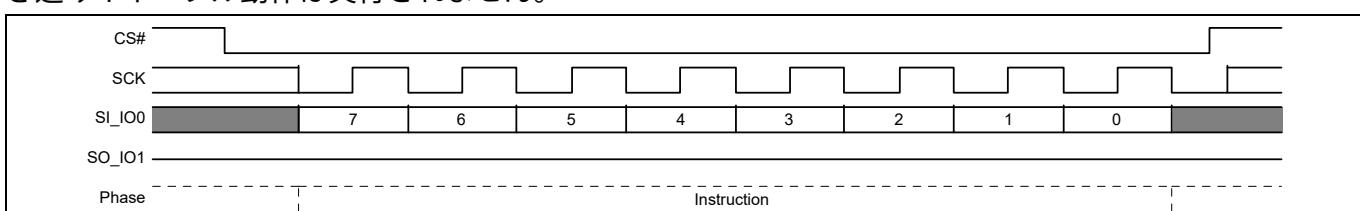

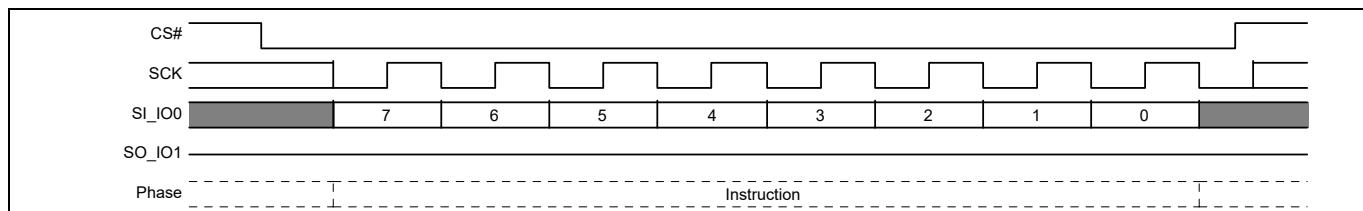

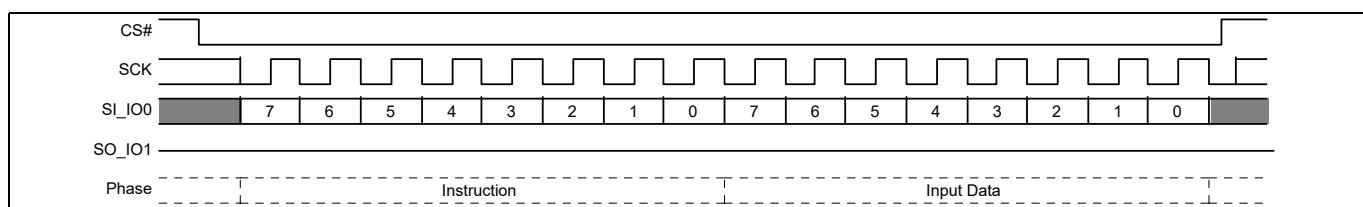

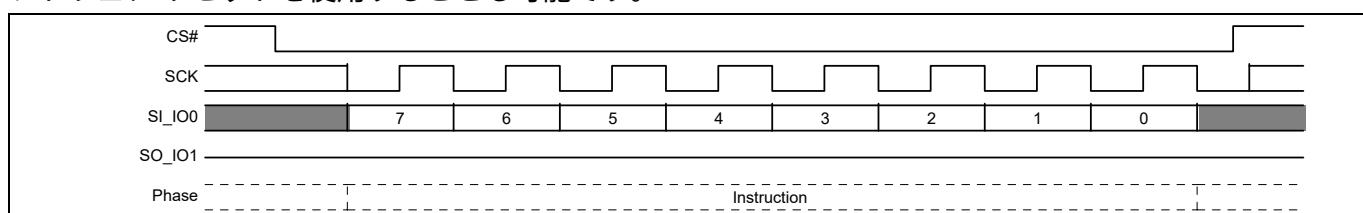

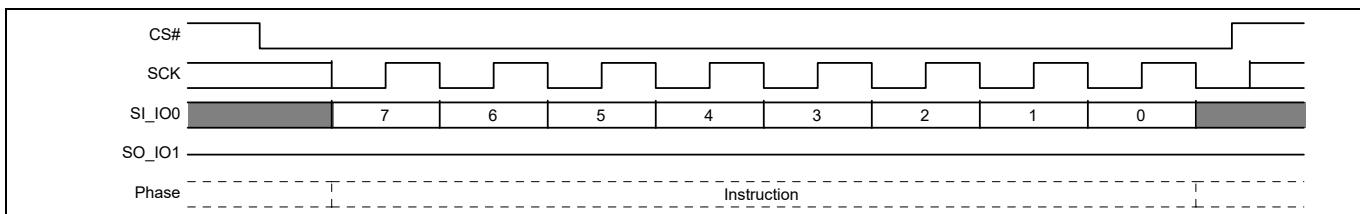

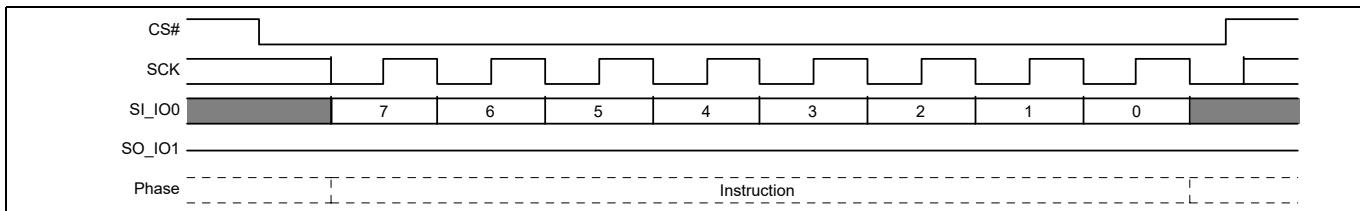

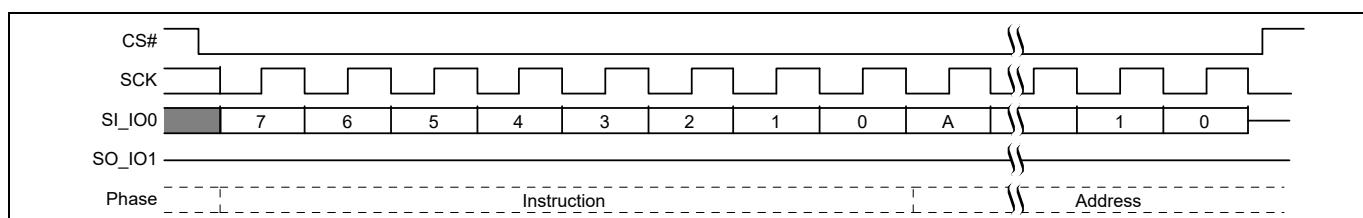

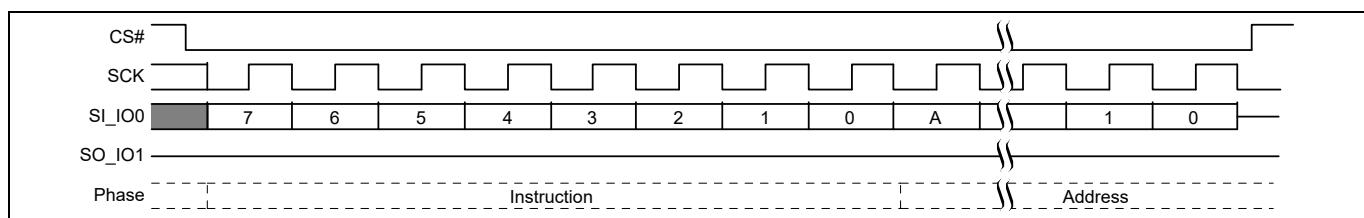

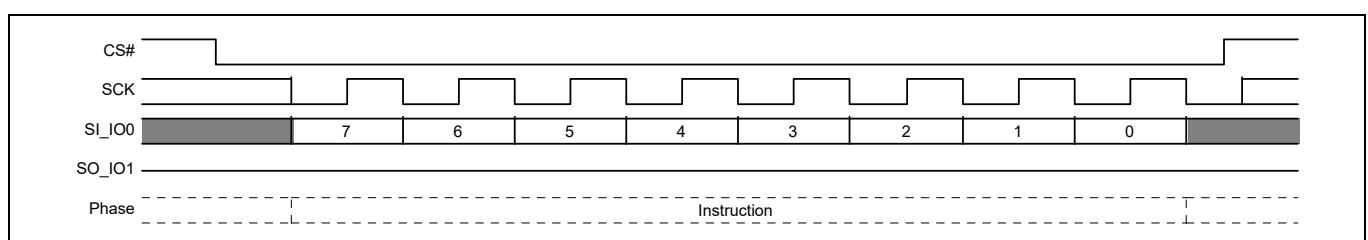

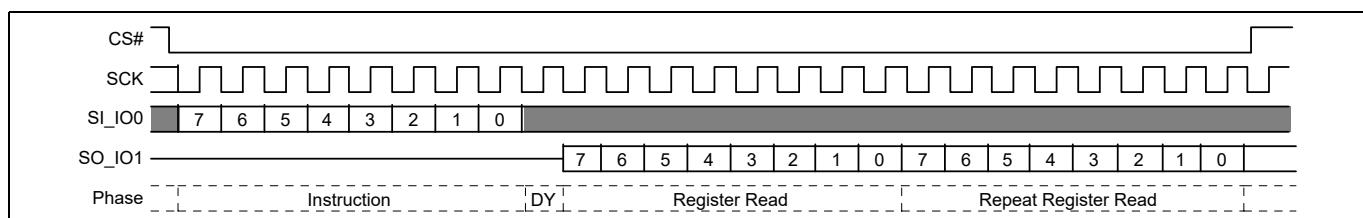

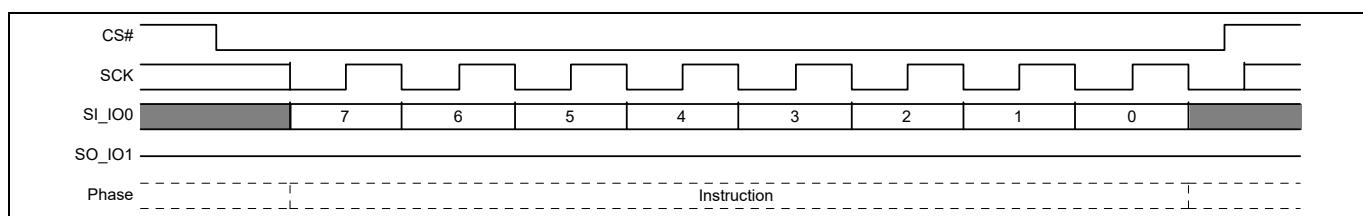

Figure 13 スタンドアロン命令コマンド

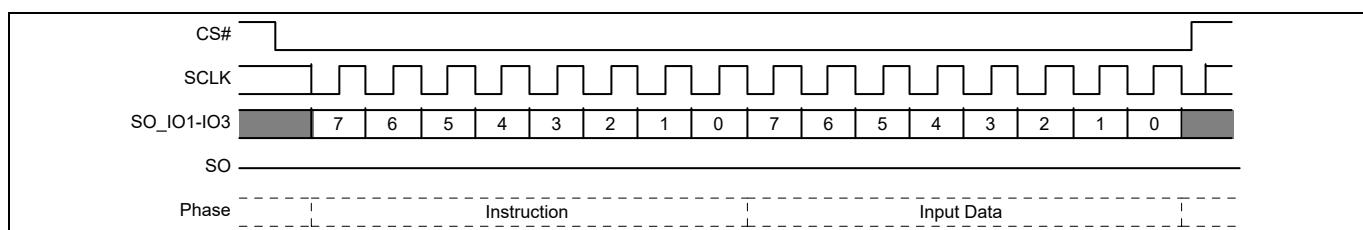

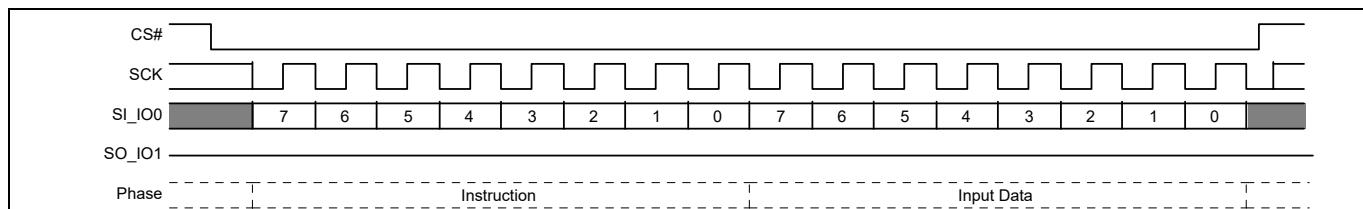

Figure 14 シングルビット幅の入力コマンド

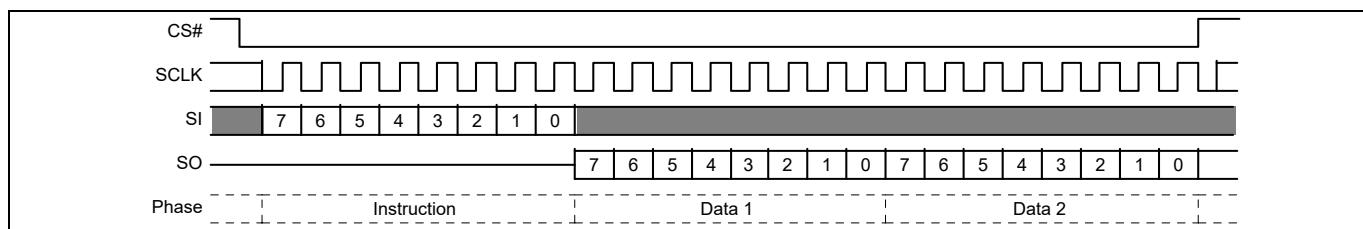

Figure 15 レイテンシなしのシングルビット幅の出力コマンド

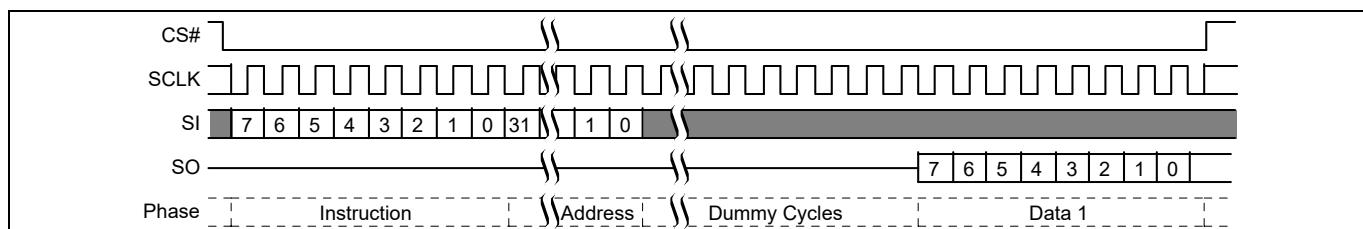

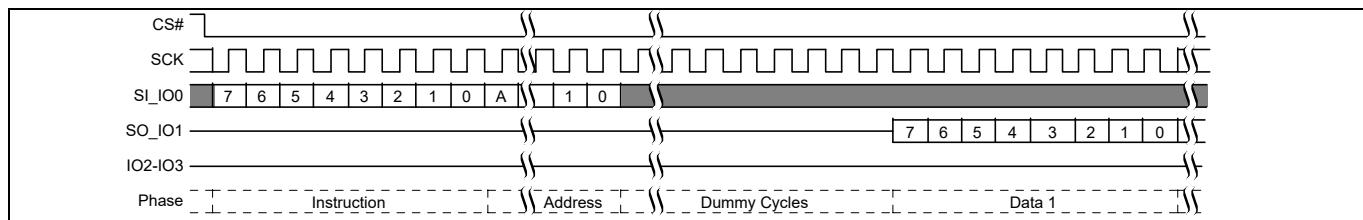

Figure 16 レイテンシ付きのシングルビット幅の I/O コマンド

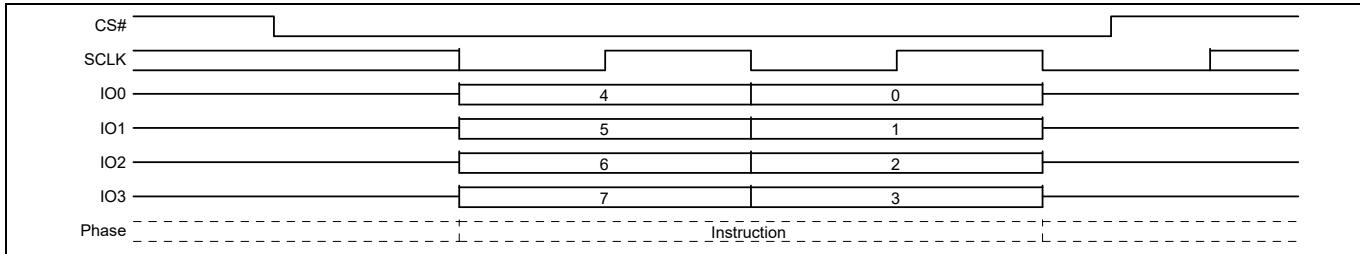

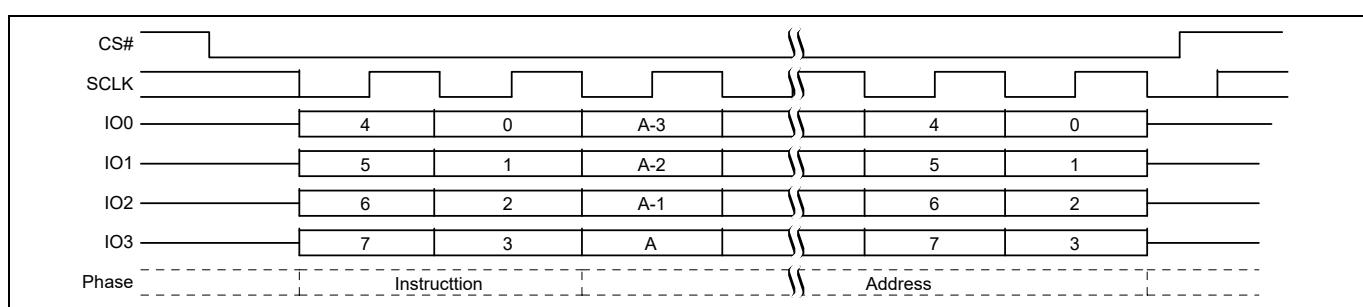

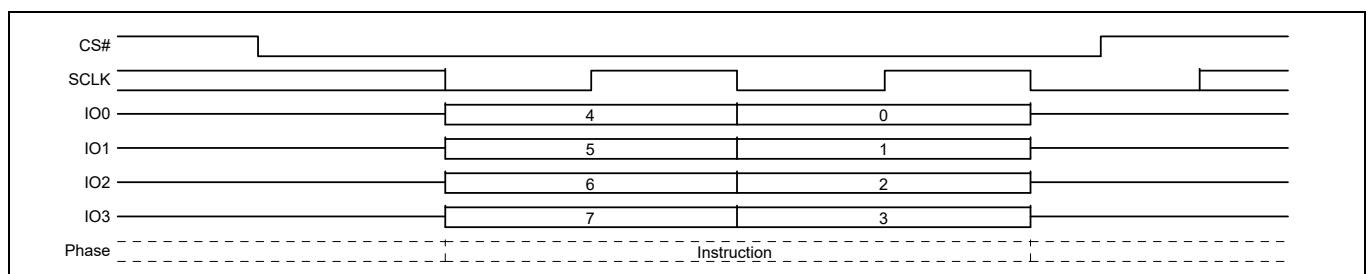

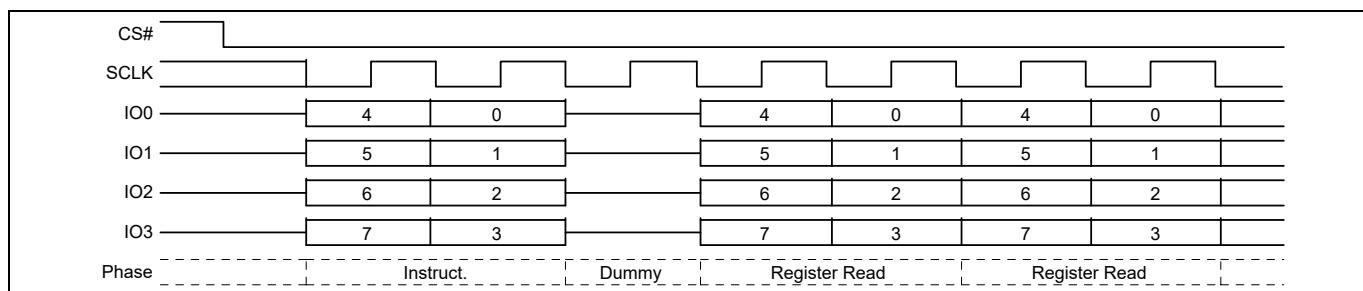

Figure 17 デュアル出力の読み出しコマンド

Figure 18 クアッド出力の読み出しコマンド

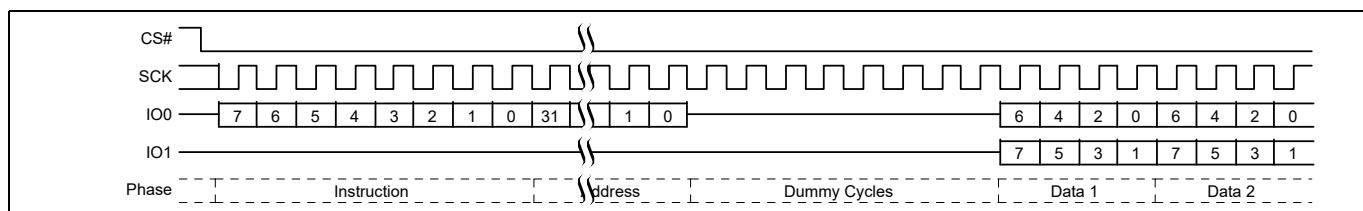

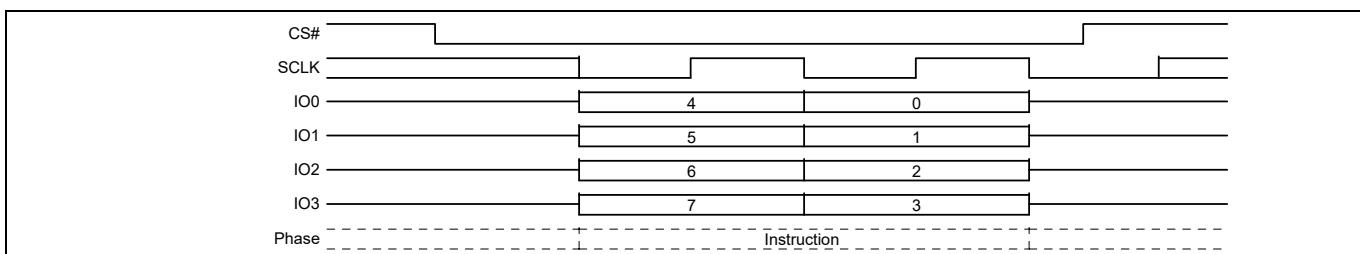

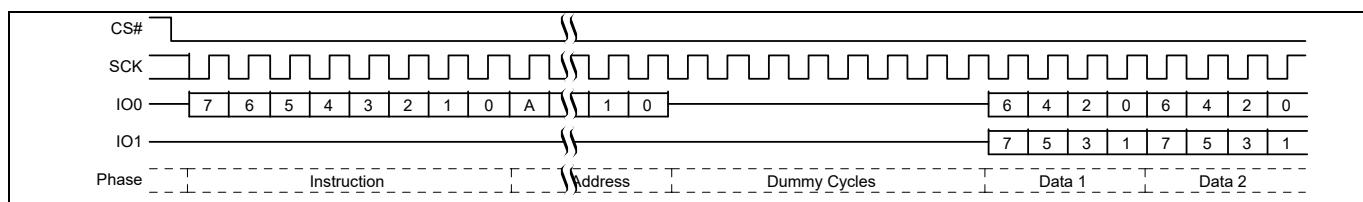

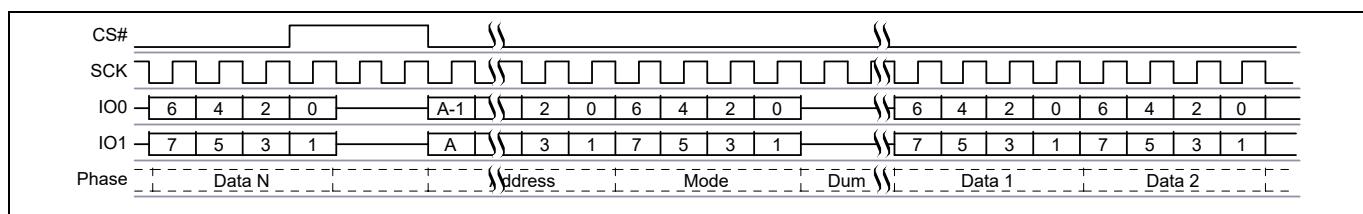

Figure 19 デュアル I/O コマンド

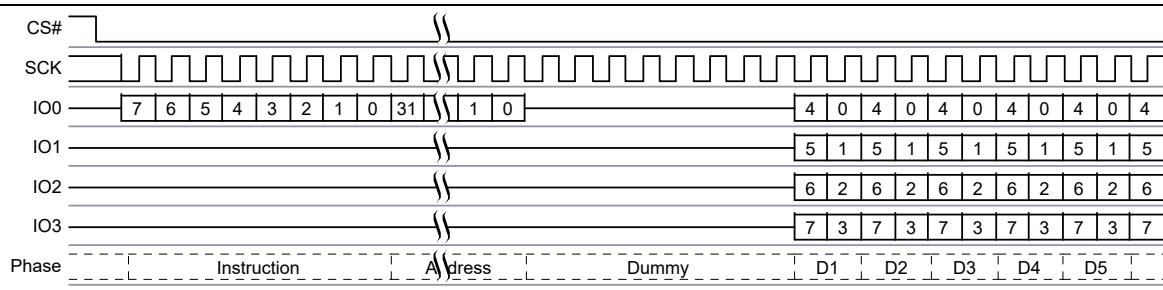

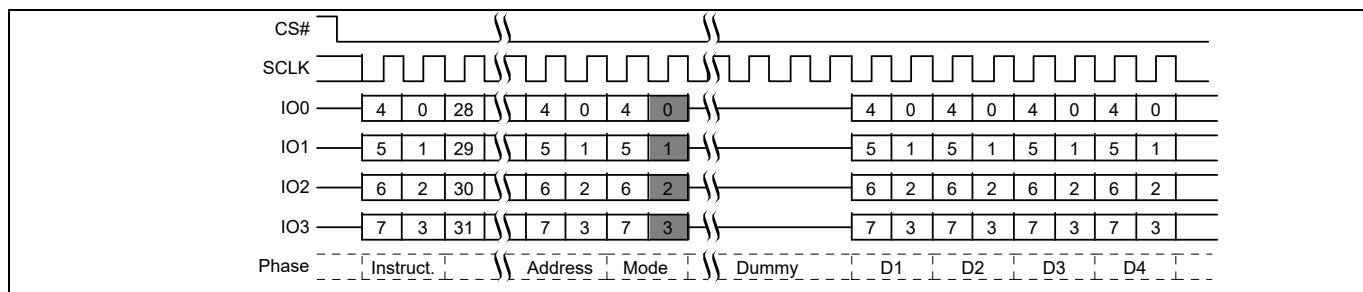

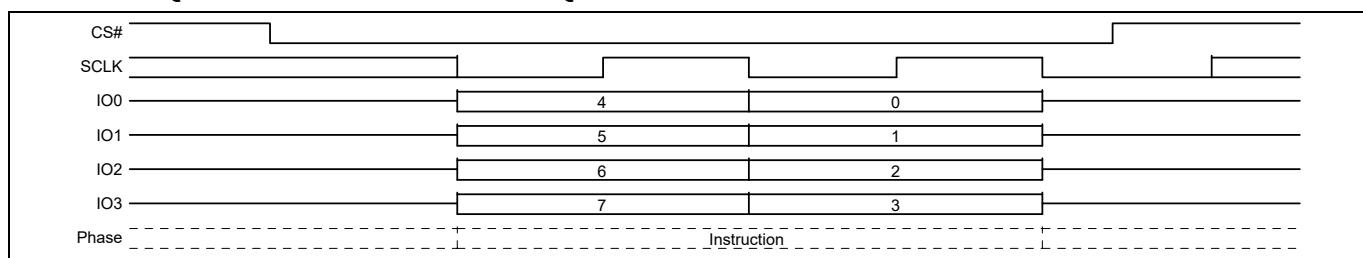

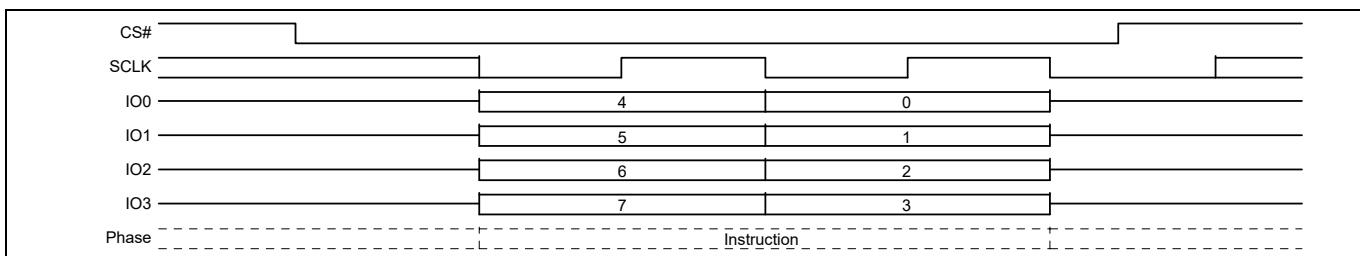

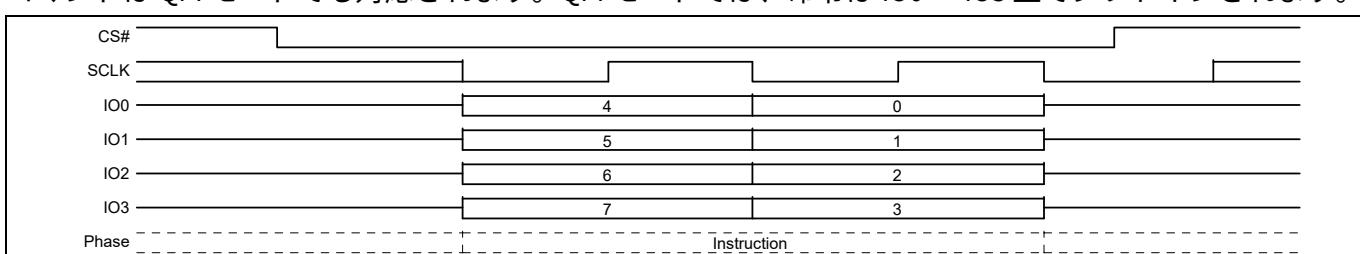

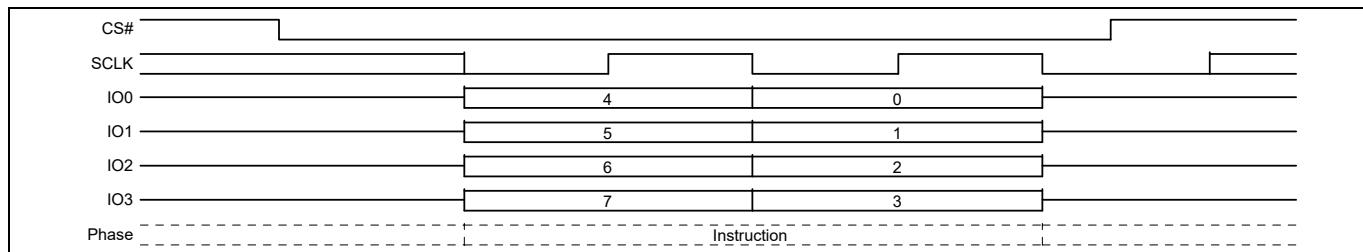

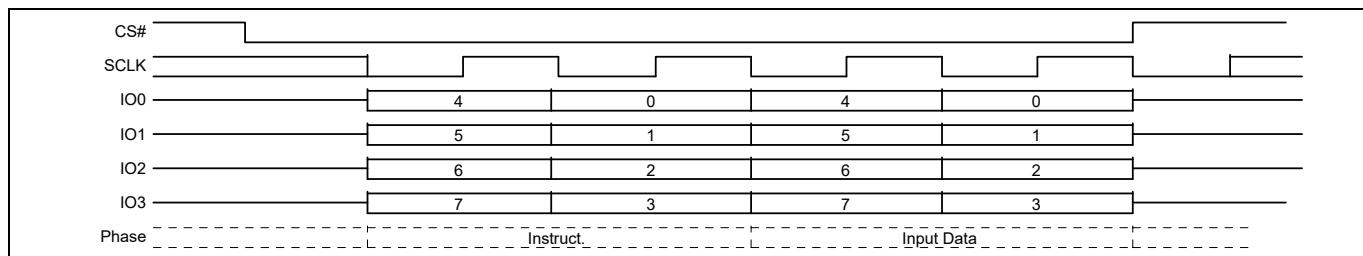

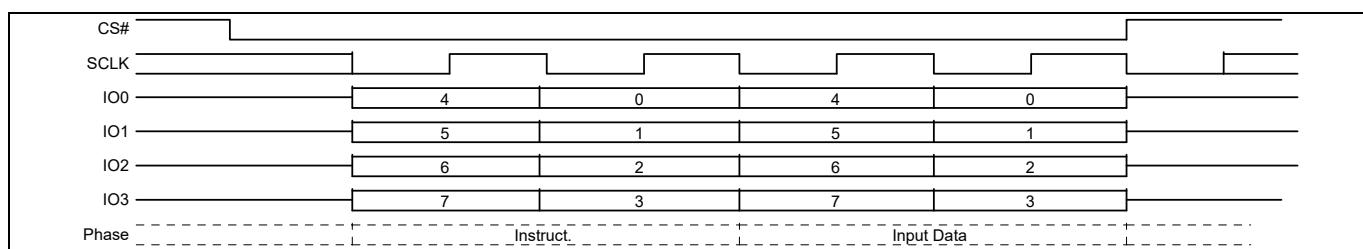

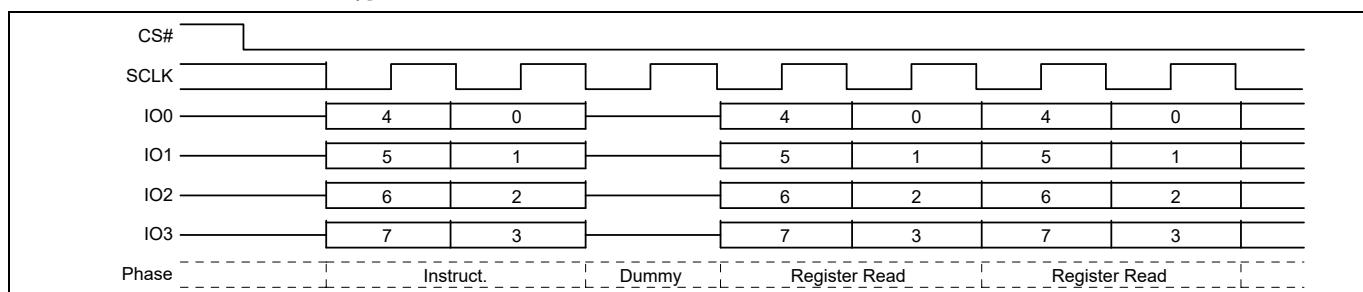

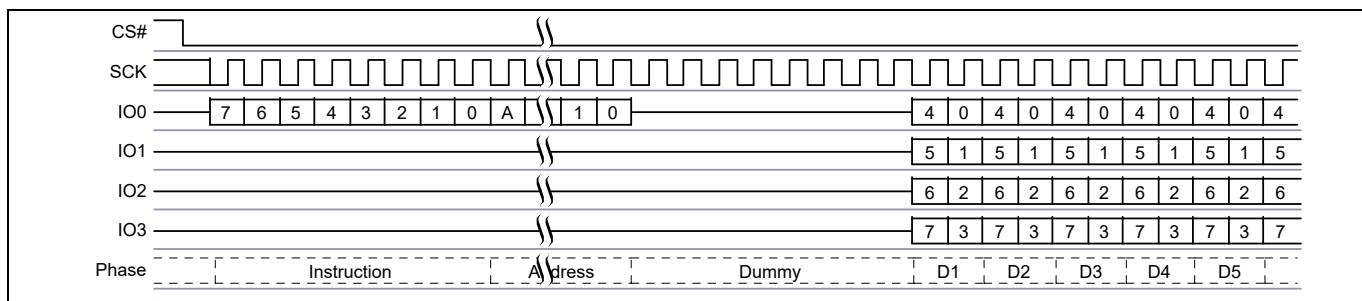

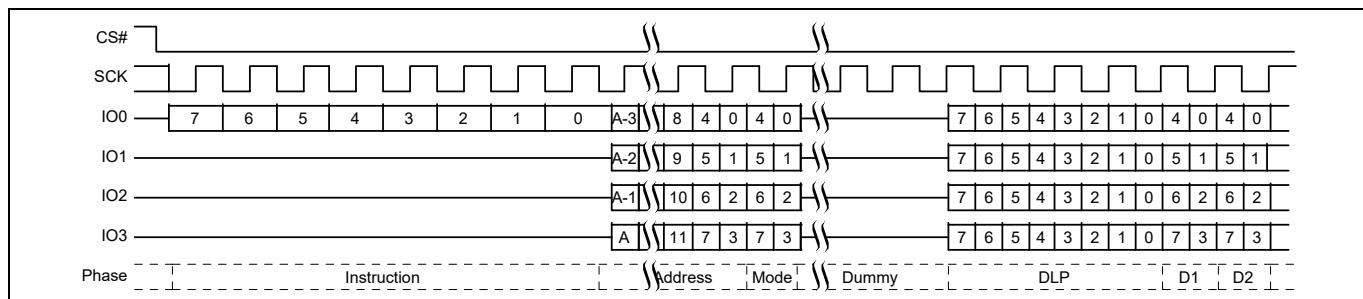

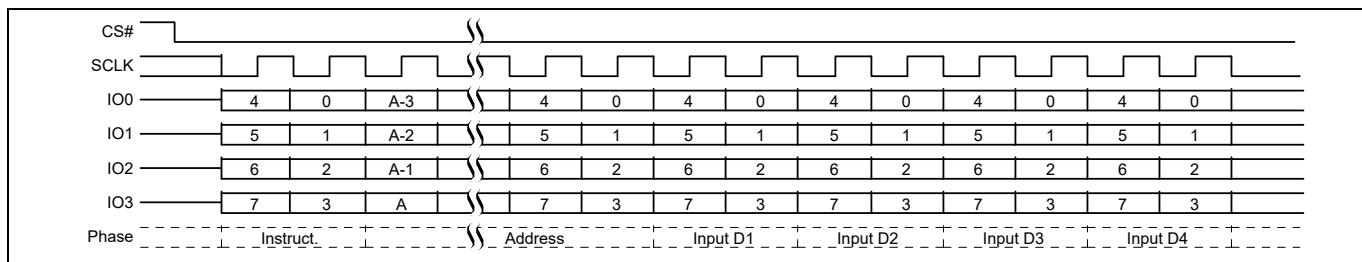

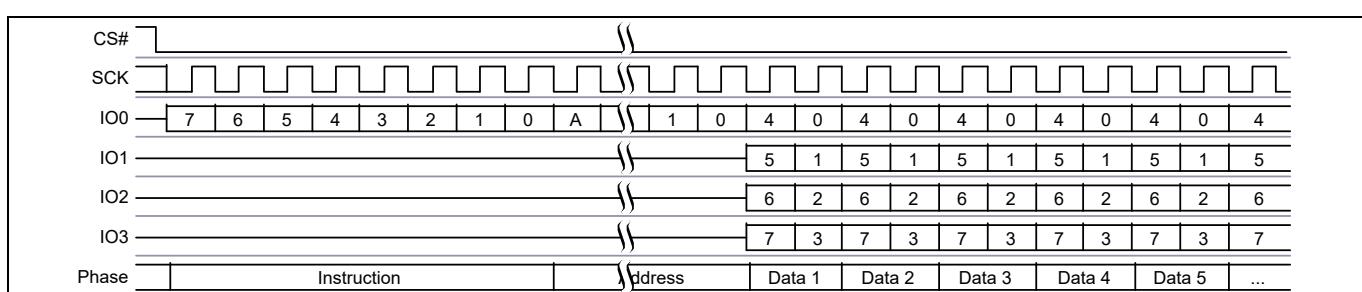

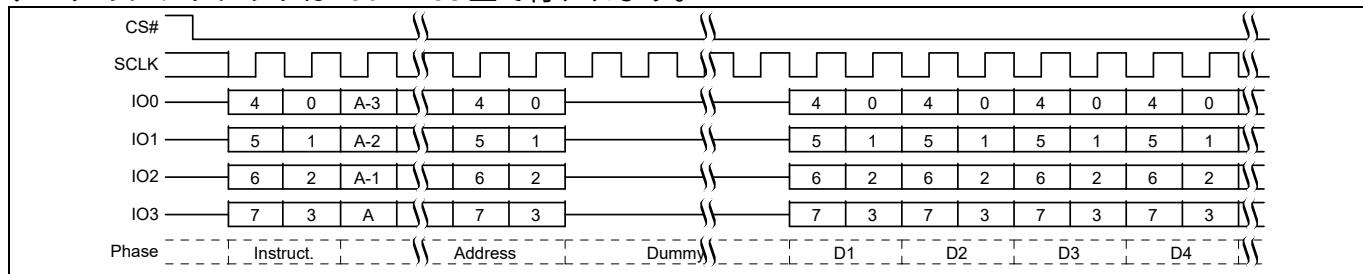

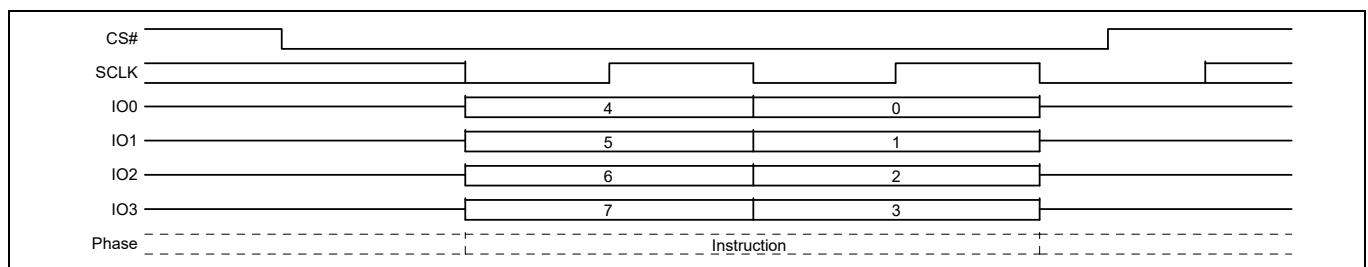

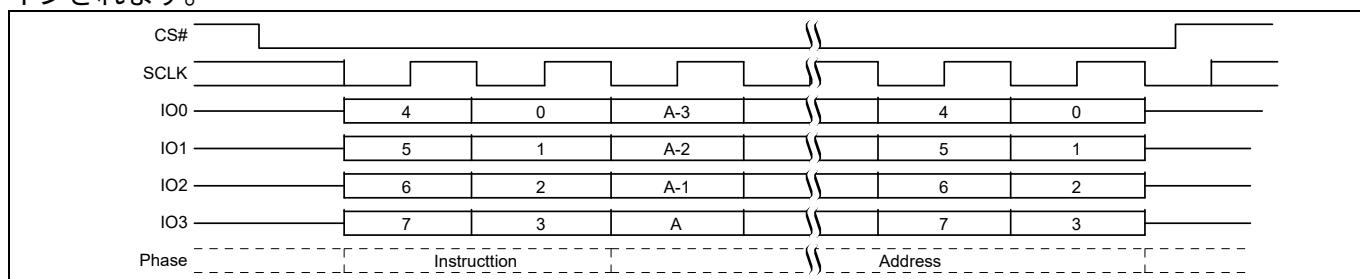

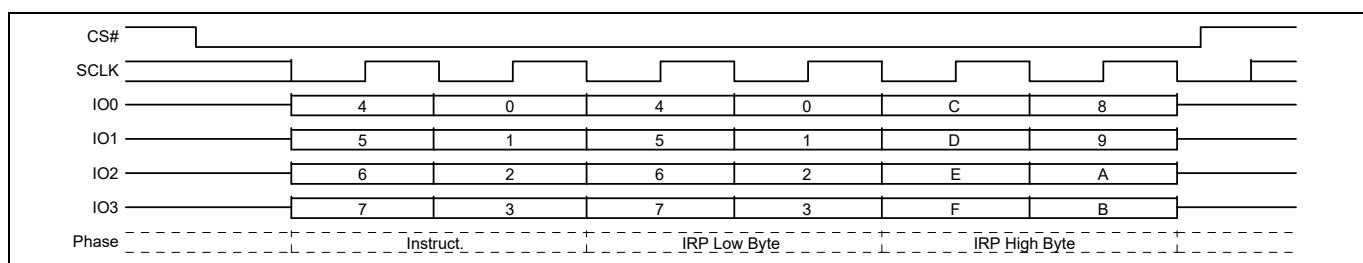

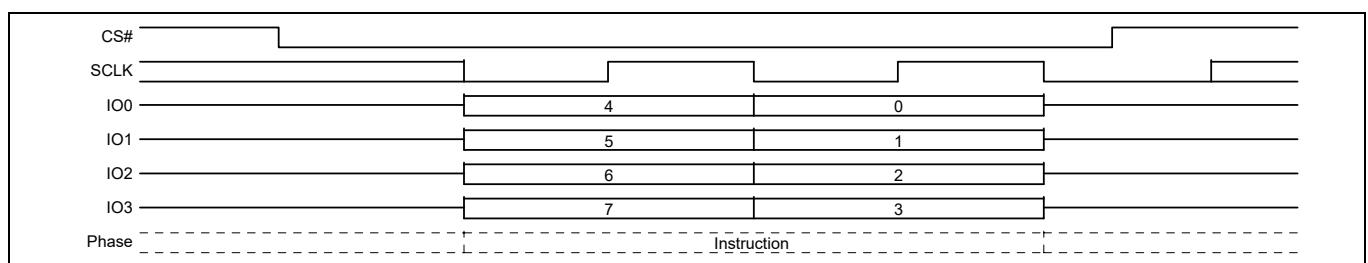

Figure 20 クアッド I/O コマンド [8]

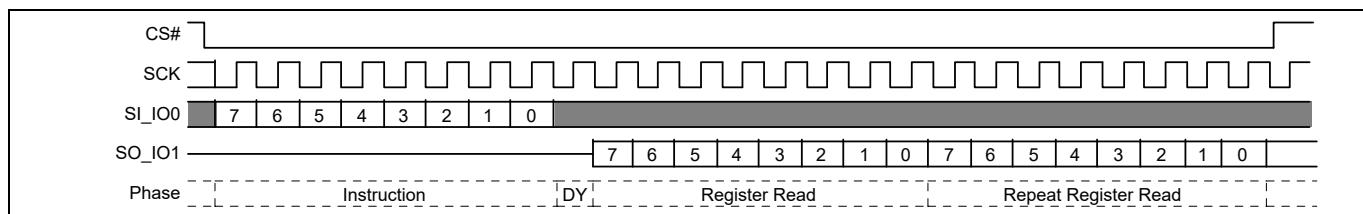

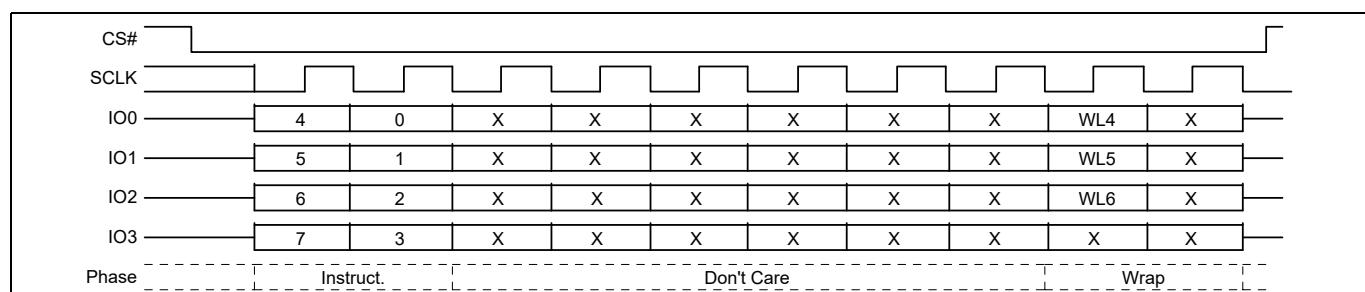

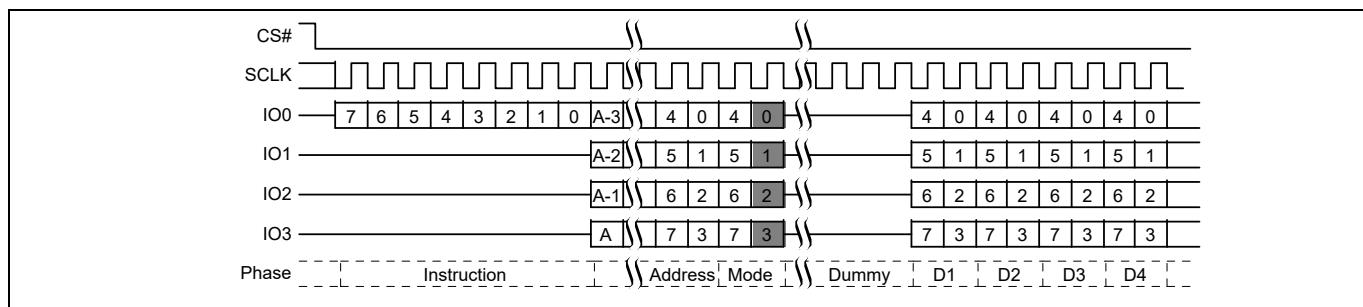

Figure 21 クアッド I/O 読み出しコマンド - QPI モード [8]

**注:**

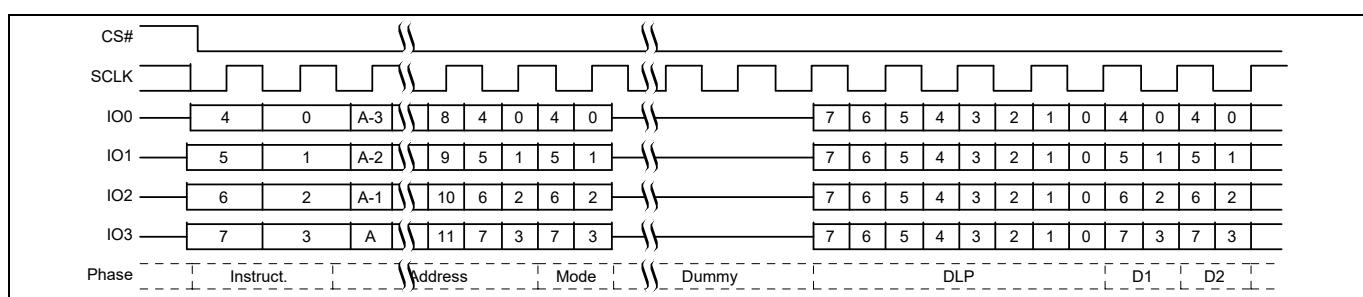

8. 灰色のビットはオプションのビットであり、ホストはそのサイクル中にそれらのビットを駆動する必要がありません。

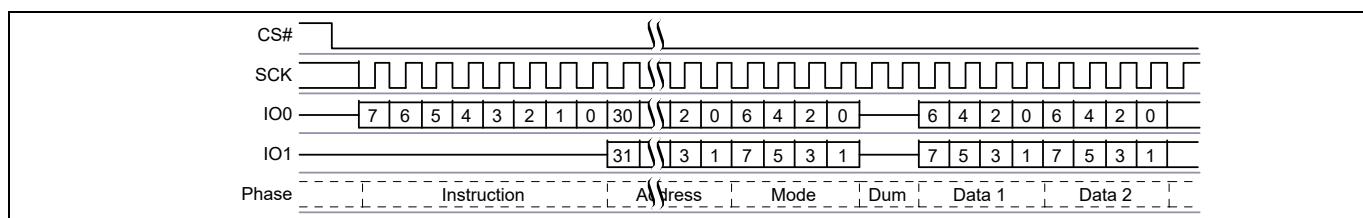

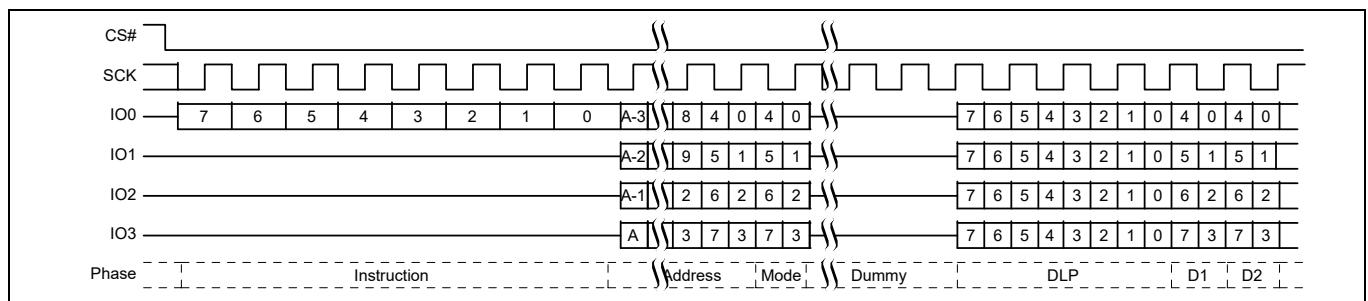

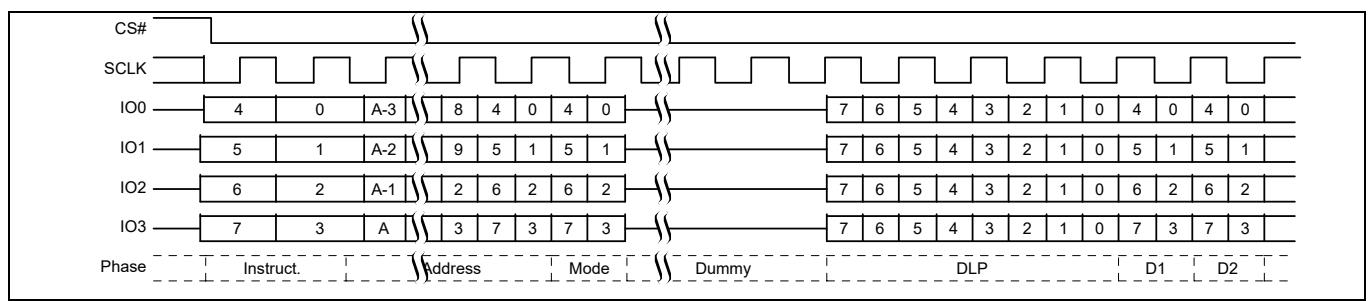

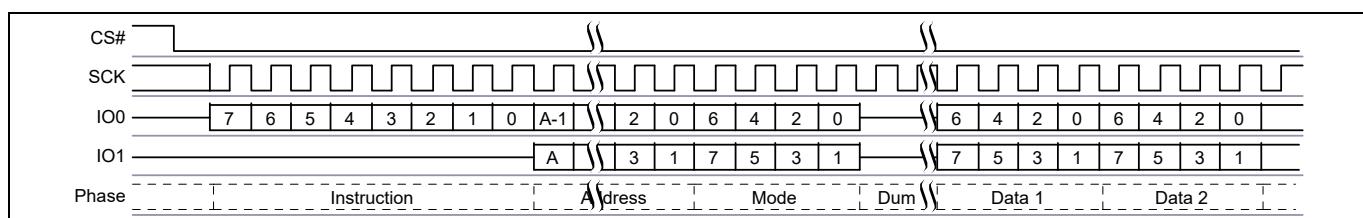

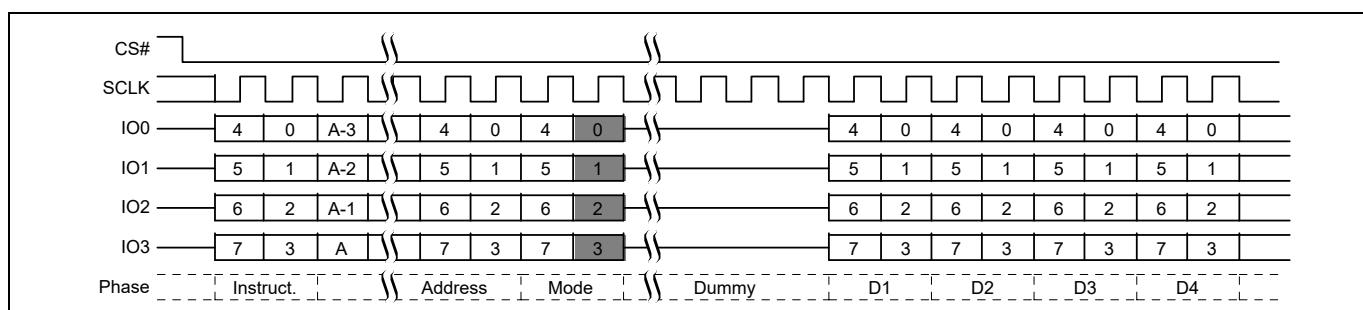

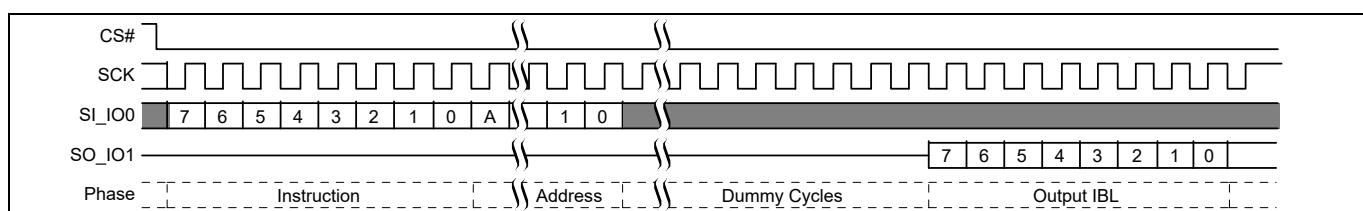

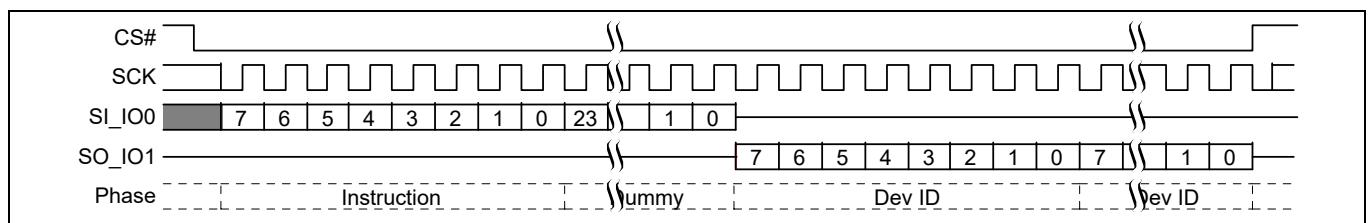

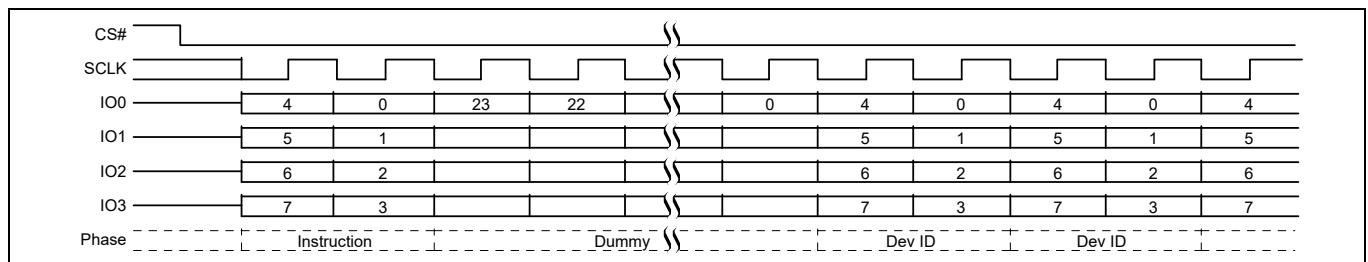

Figure 22 DDR クアッド I/O 読み出しコマンド

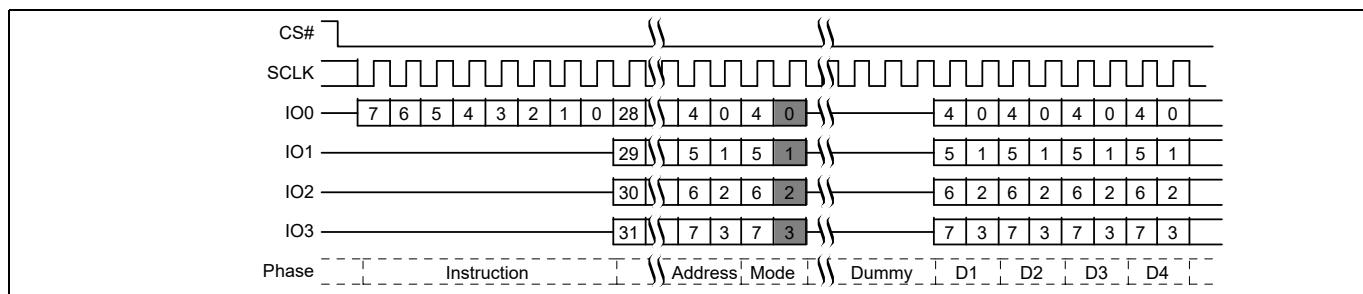

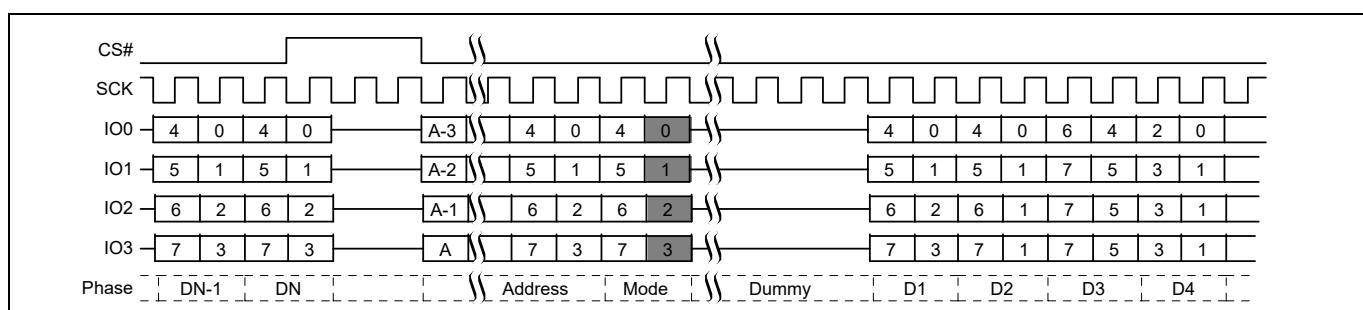

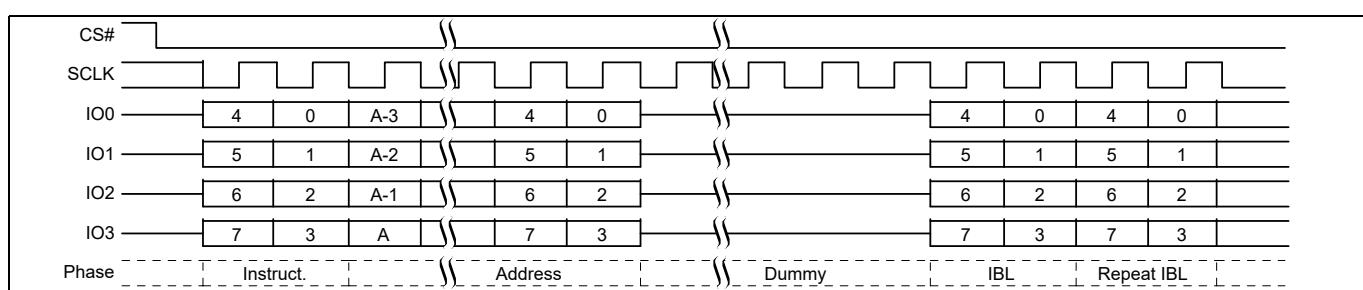

Figure 23 DDR クアッド I/O 読み出しコマンド - QPI モード

各コマンド特定の更なるシーケンス図は [コマンド](#) で記述されます。

### 5.3 インターフェース状態

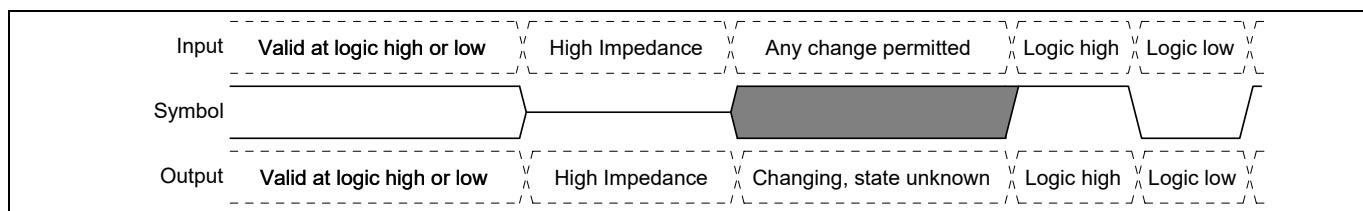

ここでは、SPI インターフェース動作に関連する入力と出力の信号レベルについて説明します。

Table 3 インターフェース状態のまとめ

| インターフェース状態                       | V <sub>CC</sub>            | SCK | CS# | RESET# | IO3 / RESET# | WP# / IO2 | SO / IO1 | SI / IO0 |

|----------------------------------|----------------------------|-----|-----|--------|--------------|-----------|----------|----------|

| 電源切斷                             | <V <sub>CC</sub> (low)     |     | X   |        | X            |           |          |          |

| 低消費電力<br>ハードウェア データ保護            | <V <sub>CC</sub> (cut-off) |     | HH  |        | X            |           |          |          |

| パワーオン (コールド) リセット                |                            | X   | X   |        |              | X         |          | X        |

| ハードウェア (ウォーム) リセット、非<br>クアッド モード |                            |     | HL  |        | HL           |           | Z        |          |

| ハードウェア (ウォーム) リセット、ク<br>アッド モード  |                            |     | HH  |        |              |           |          |          |

| インターフェーススタンバイ                    |                            |     |     |        |              |           |          |          |

| 命令サイクル<br>(レガシー SPI)             |                            |     |     |        |              | HV        |          |          |

| シングル入力サイクル<br>ホストからメモリへの転送       |                            |     |     |        |              |           | HV       |          |

| シングル レイテンシ (ダミー) サイクル            |                            |     |     |        |              |           |          |          |

| シングル出力サイクル<br>メモリからホストへの転送       |                            |     |     |        |              |           | X        |          |

| デュアル入力サイクル<br>ホストからメモリへの転送       | ≥V <sub>CC</sub> (min)     |     |     |        |              |           | MV       |          |

| デュアル レイテンシ (ダミー) サイクル            |                            |     |     |        |              |           | HV       | HV       |

| デュアル出力サイクル<br>メモリからホストへの転送       |                            |     |     |        |              |           | X        | X        |

| クアッド入力サイクル<br>ホストからメモリへの転送       |                            |     |     |        |              |           | MV       | MV       |

| クアッド レイテンシ (ダミー) サイクル            |                            |     |     |        |              |           | HV       | HV       |

| クアッド出力サイクル<br>メモリからホストへの転送       |                            |     |     |        |              |           | X        | X        |

| DDR クアッド入力サイクル<br>ホストからメモリへの転送   |                            |     |     |        |              |           | MV       | MV       |

| DDR レイテンシ (ダミー) サイクル             |                            |     |     |        |              |           | HV       | HV       |

| DDR クアッド出力サイクル<br>メモリからホストへの転送   |                            |     |     |        |              |           | X        | X        |

|                                  |                            |     |     |        |              |           | MV       | MV       |

凡例

Z = ドライバーなし - 開放信号

HL = ホスト駆動 V<sub>IL</sub>

HH = ホスト駆動 V<sub>IH</sub>

HV = HL または HH

X = HL または HH または Z

HT = HL と HH の間トグル

ML = メモリ駆動 V<sub>IL</sub>

MH = メモリ駆動 V<sub>IH</sub>

MV = ML または MH

### 5.3.1 電源切斷

コア電源電圧が  $V_{CC(Low)}$  電圧以下の場合、デバイスは電源切斷と見なされます。デバイスは外部信号に反応せず、あらゆるプログラムまたは消去動作を実行できないようにされます。

### 5.3.2 低消費電力のハードウェアデータ保護

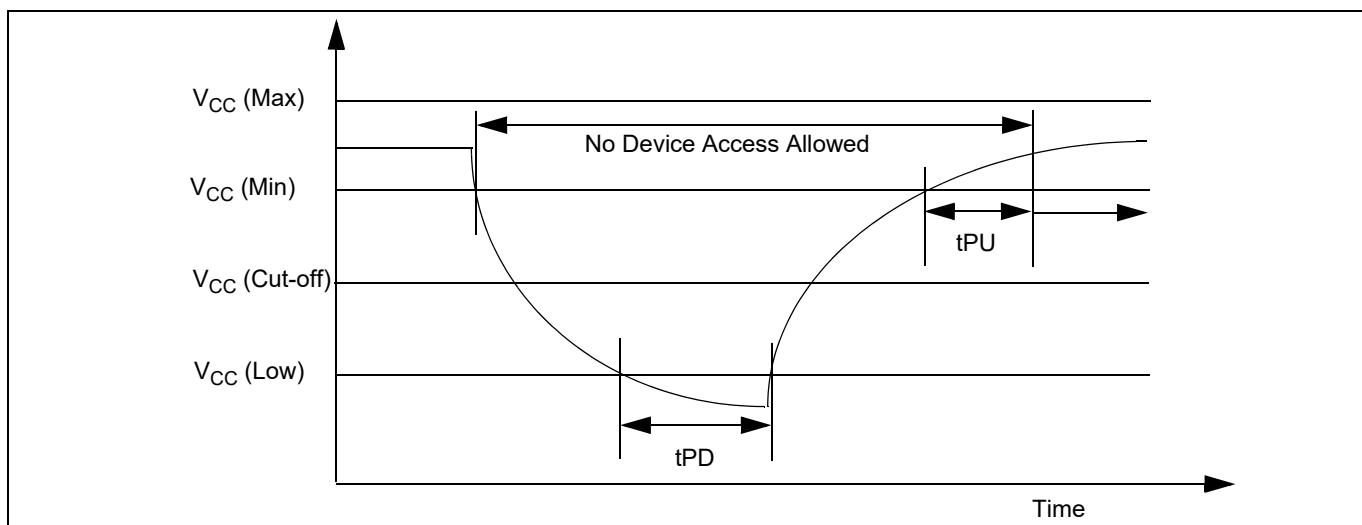

$V_{CC}$  が  $V_{CC(Cut-off)}$  を下回った場合、コア電源電圧が動作範囲外にあるときにプログラムおよび消去動作が開始できないようにするために、メモリデバイスはコマンドを無視します。コア電源電圧が  $t_{PD}$  時間以上で  $V_{CC(Low)}$  電圧以下に維持してから  $V_{CC(Minimum)}$  以上に上がった場合、デバイスはパワーオンリセット (POR) プロセスを開始します。 $t_{PU}$  の終わりまで POR は続きます。 $t_{PU}$  時間中に、デバイスは外部入力信号に反応せず、出力も駆動しません。 $t_{PU}$  が経過した後、デバイスはインターフェーススタンバイ状態に移行して、コマンドを受け入れられるようになります。POR の詳細は [パワーオン \(コールド\) リセット](#) を参照してください。

### 5.3.3 ハードウェア (ウォーム) リセット

デバイスがクアッドモードまたはQPIモードにないとき、またはデバイスがクアッドモードまたはQPIモードにありかつCS#がHIGHのとき、IO3/RESET#をハードウェアリセット入力として使用できるようになるための設定オプションが提供されます。クアッドモードおよびQPIモードでは、いくつかのパッケージで別のリセット入力が提供されます(RESET#)。IO3/RESET# または RESET# を  $t_{RP}$  時間 LOW に駆動した後、デバイスはハードウェアリセットのプロセスを開始します。プロセスは  $t_{RPH}$  時間続きます。 $t_{RPH}$  と、RESET#の立ち上りの後に繰り返しリセットホールド時間( $t_{RH}$ )が両方とも経過した後、デバイスはインターフェーススタンバイ状態に移行して、コマンドを受け入れられるようになります。ハードウェアリセットの詳細は [リセット](#) を参照してください。

### 5.3.4 インターフェーススタンバイ

CS#がHIGHであるとき、SPIインターフェースはスタンバイ状態です。RESET#以外の入力は無視されます。インターフェースは新しいコマンドの開始を待ちます。CS#が新しいコマンドを開始するためにLOWになると、次のインターフェース状態は命令サイクルです。

インターフェーススタンバイ状態の間、進行中の組み込みアルゴリズムがない場合、メモリデバイスはスタンバイ電流( $I_{SB}$ )を消費します。進行中の組み込みアルゴリズムがある場合、対応する電流はアルゴリズムが終了するまで消費されます。その後、デバイス全体の消費電流はスタンバイ電流に戻ります。

### 5.3.5 命令サイクル (レガシー SPI モード)

ホストが命令のMSbを駆動し、かつCS#がLOWになると、SCKの次の立ち上りエッジでデバイスは新しいコマンドを開始する命令のMSbを取り込みます。SCKの各々の次の立ち上りエッジでデバイスは、8ビット命令の次の下位ビットを取り込みます。ホストはCS#をLOWに維持し、書き込み保護(WP#)とIO3/RESET#信号を命令の必要に応じて駆動します。しかし、WP#は、WRR, WRARコマンド、またはステータスレジスタ、コンフィギュレーションレジスタ、およびDLRレジスタに影響を与える他のコマンドの命令サイクル中にのみ有効です。それ以外では無視されます。デバイスがクアッドモードでもなく(CR1V[1]=0)QPIモードでもない(CR2V[3]=0)、かつハードウェアリセットが不要なとき、IO3\_RESET#はHIGHに駆動されます。

各命令は、操作するアドレス空間と、コマンドの残りで使用する転送フォーマットを選択します。転送フォーマットは、シングル、デュアル出力、クアッド出力、デュアルI/O、クアッドI/O、またはDDRクアッドI/Oです。起こりうる次のインターフェース状態は、受け取った命令によって異なります。

いくつかの命令はスタンドアロンであり、メモリからのアドレスまたはデータ転送を必要としません。ホストはこのようなコマンドでの命令の8番目のビットのためのSCKの立ち上りエッジ後にCS#をHIGHに戻します。この場合、次のインターフェース状態はインターフェーススタンバイです。

### 5.3.6 命令サイクル (QPI モード)

QPIモードでは、CR2V[3]=1のとき、命令は1サイクルごとに4ビット転送されます。このモードでは、命令サイクルはクアッド入力サイクルと同様です。[QPP](#) または [QOR](#) アドレス入力サイクルを参照してください。

### 5.3.7 シングル入力サイクル – ホストからメモリへの転送

いくつかのコマンドは、シングルシリアル入力 (SI) 信号上で命令の後に情報をホストからメモリ デバイスに転送します。ホストは RESET# を HIGH に、CS# を LOW に維持し、コマンドの必要に応じて SI を駆動します。メモリはシリアル出力 (SO) 信号を駆動しません。

予期される次のインターフェース状態は、命令によって異なります。いくつかの命令は、追加のシングル入力サイクルを使用して、メモリにアドレスまたはデータを送信し続けます。他の命令はシングル レイテンシ状態に遷移するか、またはシングル、デュアル、およびクアッドの出力サイクル状態に直接遷移します。

### 5.3.8 シングル レイテンシ (ダミー) サイクル

読み出しコマンドは、0～数レイテンシ サイクルがあります。それらのサイクルの間、読み出しデータはメイン フラッシュ メモリアレイから読み出されてから、ホストに転送されます。レイテンシ サイクル数は、コンフィギュレーション レジスタ (CR3V[3:0]) 内のレイテンシ コードによって決まります。レイテンシ サイクル中に、ホストは RESET# と IO3/RESET# を HIGH に、CS# を LOW に維持し、SCK はトグルします。書き込み保護 (WP#) 信号は無視されます。ホストは、これらのサイクル中に SI 信号を駆動するか、または SI を開放のままにします。メモリは、レイテンシ サイクル中に SO またはその他の I/O 信号上で駆動されるデータを使用しません。レイテンシ サイクル中にメモリはシリアル出力 (SO) または I/O 信号を駆動しません。

次のインターフェース状態はコマンドの構造 (すなわち、レイテンシ サイクル数と、読み出しがシングル、デュアル、またはクアッド幅であるか) によって異なります。

### 5.3.9 シングル出力サイクル – メモリからホストへの転送

いくつかのコマンドは、シングルシリアル出力 (SO) 信号上でホストに情報を送り返します。ホストは RESET# と IO3/RESET# を HIGH に、CS# を LOW に維持します。書き込み保護 (WP#) 信号は無視されます。メモリはシリアル入力 (SI) 信号を無視します。メモリはデータを SO に駆動します。

ホストが CS# を HIGH に戻して、コマンドを終了させるまでは、次のインターフェース状態はシングル出力サイクルのままです。

### 5.3.10 デュアル入力サイクル – ホストからメモリへの転送

デュアル I/O 読み出しコマンドは、各サイクルで 2 つのアドレスまたはモード ビットをメモリに転送します。ホストは RESET# と IO3/RESET# を HIGH に、CS# を LOW に維持します。書き込み保護 (WP#) 信号は無視されます。ホストは SI/IO0 および SO/IO1 の上でアドレスを駆動します。

アドレスおよびモード ビットの送信後の次のインターフェース状態は、レイテンシ サイクルが必要であればデュアル レイテンシ サイクルであり、レイテンシが必要でなければデュアル出力サイクルです。

### 5.3.11 デュアル レイテンシ (ダミー) サイクル

読み出しコマンドは、0～数レイテンシ サイクルがあります。それらのサイクルの間、読み出しデータはメイン フラッシュ メモリアレイから読み出されてから、ホストに転送されます。レイテンシ サイクル数は、コンフィギュレーション レジスタ (CR3V[3:0]) 内のレイテンシ コードによって決まります。レイテンシ サイクル中に、ホストは RESET# と IO3/RESET# を HIGH に、CS# を LOW に維持し、SCK はトグルし続けます。書き込み保護 (WP#) 信号は無視されます。ホストは、これらのサイクル中に SI/IO0 および SO/IO1 信号を駆動するか、または SI/IO0 および SO/IO1 を開放のままにします。メモリは、レイテンシ サイクル中に SI/IO0 および SO/IO1 上で駆動されるいかなるデータも使用しません。ホストは、最後のレイテンシ サイクルの終了時に SCK の立ち下りエッジで SI/IO0 および SO/IO1 の駆動を停止する必要があります。メモリがレイテンシ サイクルが終了後駆動を開始する前に、ホスト ドライバーがオフになるのに十分な時間を持つように、ホストがすべてのレイテンシ サイクルでそれらの信号の駆動を停止することが推奨されます。そうすることにより、信号方向が変わるとのホストとメモリとのドライバー衝突を防ぎます。メモリは、レイテンシ サイクル中に SI/IO0 および SO/IO1 信号を駆動しません。最後のレイテンシ サイクルの後に続く次のインターフェース状態はデュアル出力サイクルです。

### 5.3.12 デュアル出力サイクル – メモリからホストへの転送

デュアル出力読み出しとデュアル I/O 読み出しは、各サイクルごとに 2 データビットをホストに戻します。ホストは RESET# と IO3/RESET# を HIGH に、CS# を LOW に維持します。書き込み保護 (WP#) 信号は無視されます。デュアル出力サイクル中に、メモリは SCK の立ち下りエッジで SI/I00 および SO/I01 信号上でデータを駆動します。

ホストが CS# を HIGH に戻して、コマンドを終了させるまでは、次のインターフェース状態はデュアル出力サイクルのままでです。

### 5.3.13 QPP または QOR アドレス入力サイクル

クアッドページプログラムおよびクアッド出力読み出しコマンドは I00 上でのみ、メモリにアドレスを送信します。他の IO 信号は無視されます。ホストは RESET# と IO3/RESET# を HIGH に、CS# を LOW に維持し、I00 を駆動します。

QPP の場合、アドレス送信後の次のインターフェース状態はクアッド入力サイクルです。QOR の場合、アドレス送信後の次のインターフェース状態は、レイテンシサイクルが必要であればクアッドレイテンシサイクルであり、レイテンシが必要でなければクアッド出力サイクルです。

### 5.3.14 クアッド入力サイクル – ホストからメモリへの転送

クアッド I/O 読み出しコマンドは、各サイクルで 4 つのアドレスまたはモードビットをメモリに転送します。QPI モードでは、クアッド I/O 読み出しとページプログラムコマンドは、命令サイクルを含む各サイクルでメモリに 4 データビットを転送します。ホストは CS# を LOW に維持し、IO 信号を駆動します。

クアッド I/O 読み出しの場合、アドレスおよびモードビットの送信後の次のインターフェース状態は、レイテンシサイクルが必要であればクアッドレイテンシサイクルであり、レイテンシが必要でなければクアッド出力サイクルです。QPI モードページプログラムの場合、ホストはプログラムされるデータの送信後に CS# を HIGH に戻し、インターフェースはスタンバイ状態に戻ります。

### 5.3.15 クアッド レイテンシ (ダミー) サイクル

読み出しコマンドは、0 ~ 数レイテンシサイクルがあります。それらのサイクルの間、読み出しデータはメインフラッシュメモリアレイから読み出されてから、ホストに転送されます。レイテンシサイクル数は、コンフィギュレーションレジスタ (CR3V[3:0]) 内のレイテンシコードによって決まります。レイテンシサイクル中に、ホストは CS# を LOW に維持し、SCK をトグルし続けます。ホストはこれらのサイクル中に IO 信号を駆動するか、または IO を開放のままにします。メモリはレイテンシサイクル中に IO 上で駆動されるいかなるデータも使用しません。ホストは最後のレイテンシサイクルの終了時に立ち下りエッジでの IO 信号の駆動を停止する必要があります。メモリがレイテンシサイクルが終了後駆動を開始する前に、ホストドライバーがオフになるのに十分な時間を持つように、ホストがすべてのレイテンシサイクルでそれらの信号の駆動を停止することが推奨されます。そうすることにより、信号方向が変わるときのホストとメモリとのドライバー衝突を防ぎます。レイテンシサイクル中にメモリは IO 信号を駆動しません。

最後のレイテンシサイクルの次のインターフェース状態はクアッド出力サイクルです。

### 5.3.16 クアッド出力サイクル – メモリからホストへの転送

クアッド出力とクアッド I/O 読み出しは、各サイクルごとに 4 データビットをホストに戻します。ホストは CS# を LOW に維持します。メモリはクアッド出力サイクル中に I00 ~ I03 信号上でデータを駆動します。

ホストが CS# を HIGH に戻して、コマンドを終了させるまでは、次のインターフェース状態はクアッド出力サイクルのままでです。

### 5.3.17 DDR クアッド入力サイクル – ホストからメモリへの転送

DDR クアッド I/O 読み出しコマンドは、すべての IO 信号上でアドレスおよびモードビットをメモリに送信します。各サイクルで 4 ビットは SCK の立ち上りエッジで、4 ビットは立ち下りエッジで転送されます。ホストは CS# を LOW に維持します。

アドレスとモードビットの送信後の次のインターフェース状態は DDR レイテンシサイクルです。

### 5.3.18 DDR レイテンシ サイクル

DDR 読み出しコマンドは 1～数レイテンシ サイクルがあります。それらのサイクルの間、読み出しデータはメイン フラッシュ メモリアレイから読み出されてから、ホストに転送されます。レイテンシ サイクル数は、コンフィギュレーション レジスタ (CR3V[3:0]) 内のレイテンシ コードによって決まります。レイテンシ サイクル中に、ホストは CS# を LOW に維持します。これらのサイクル中にホストは IO 信号を駆動しません。よって、メモリが駆動を開始する前に、ホスト ドライバーはオフになるのに十分な時間があります。そうすることにより、信号方向が変わるときのホストとメモリとのドライバー衝突を防ぎます。メモリは最後の 4 レイテンシ サイクル中にデータ ラーニング パターン (DLP) を使ってすべての IO 信号を駆動するオプションがあります。5 レイテンシ サイクル未満の場合、DLP オプションを有効にしてはいけません。その理由は、メモリが DLP の駆動を開始する前に IO 信号のターン アラウンドのために高インピーダンスのサイクルが少なくとも 1 つあるようになります。4 サイクルより多くのレイテンシがある場合、メモリはレイテンシの最後の 4 サイクルまで IO 信号を駆動しません。

最後のレイテンシ サイクルの後に続く次のインターフェース状態は命令に応じて DDR クアッド出力 サイクルです。

### 5.3.19 DDR クアッド出力 サイクル – メモリからホストへの転送

DDR クアッド I/O 読み出しコマンドはすべての IO 信号上でビットをホストに戻します。各サイクルで 4 ビットは SCK の立ち上りエッジで、4 ビットは立ち下りエッジで転送されます。ホストは CS# を LOW に維持します。

ホストが CS# を HIGH に戻して、コマンドを終了させるまでは、次のインターフェース状態は DDR クアッド出力 サイクルのままです。

## 5.4 データ保護

保存されたデータへの意図的でない変更に対するいくつかの基本的な保護は単にハードウェア デザインで提供かつ制御されます。それらは [データ保護](#) で説明されます。ソフトウェアで制御する他の保護方法は本書の [データ保護](#) で説明されます。

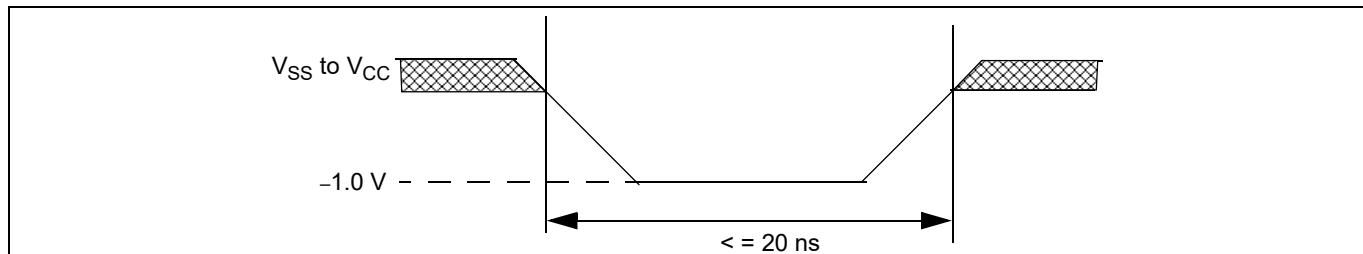

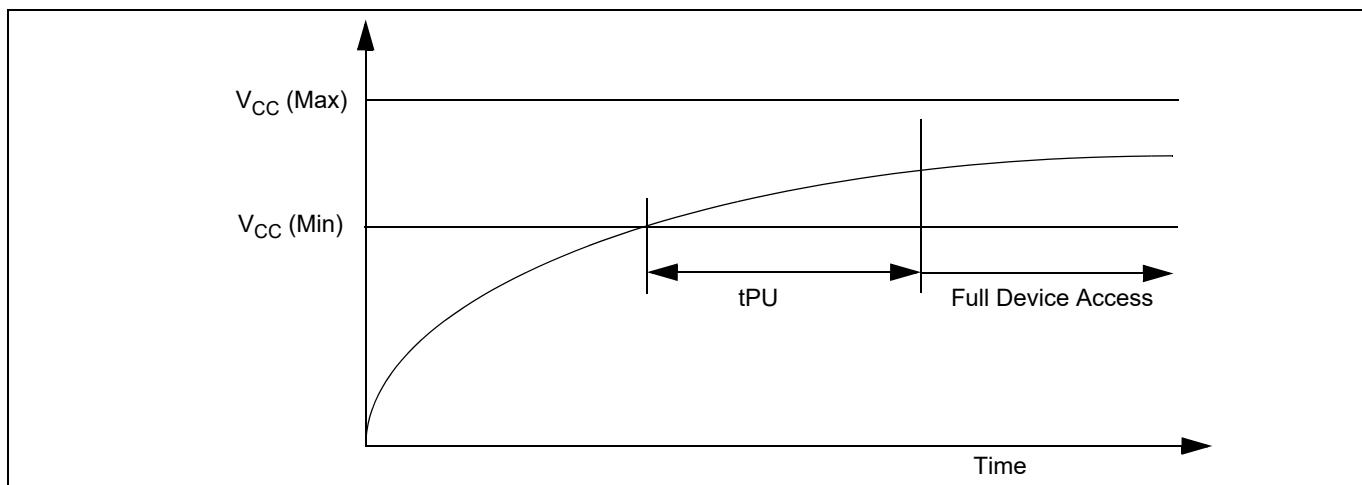

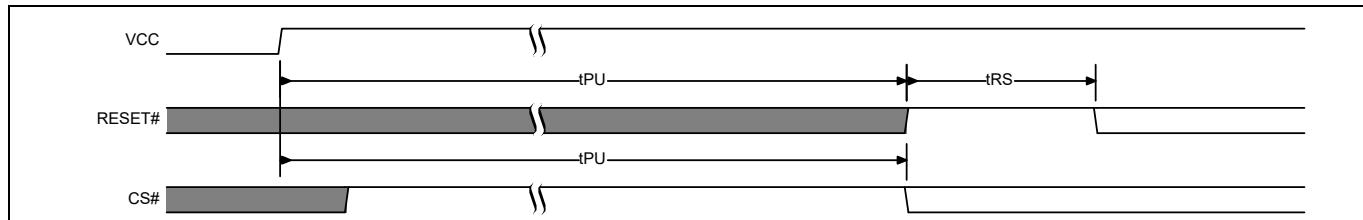

### 5.4.1 電源投入

電源投入時に、以下のように  $V_{CC}$  が正しい値に達するまでデバイスを選択してはいけません（すなわち、CS# は  $V_{CC}$  に印加する電圧に応じる必要があります）。

- 電源投入後、 $t_{PU}$  の遅延時間が経過した後に  $V_{CC}$  (min)

ユーザーは、 $V_{CC}$  が最小  $V_{CC}$  閾値を超えてから  $t_{PU}$  の有効遅延が経過するまで、あらゆるコマンドを入力してはいけません。Figure 131 を参照してください。ただし、 $t_{PU}$  中に  $V_{CC}$  が  $V_{CC}$  (min) を下回った場合、デバイスの正常な動作は保証されません。 $t_{PU}$  の終了まで、コマンドをデバイスに送信しないようしてください。

### 5.4.2 低消費電力

$V_{CC}$  が  $V_{CC}$  (Cut-off) を下回った場合、コア電源電圧が動作範囲外にあるときにプログラムおよび消去動作が開始できないようにするために、メモリ デバイスはコマンドを無視します。

### 5.4.3 クロック パルス カウント

デバイスは、コマンドを実行する前に、すべての不揮発性メモリとレジスタ データ変更のコマンドが、8 ビット転送の倍数（バイト境界）であるクロック パルス カウントを含むことを確認します。8 ビット（バイト）境界で終わらないコマンドは無視され、そのコマンドに対してエラー状態が設定されません。

### 5.4.4 ディープ パワーダウン (DPD)

DPD モードでは、デバイスは DPD 終了コマンド (RES ABh) のみに応答します。他のコマンドは DPD モードの間は無視されます。それによって、メモリはプログラムおよび消去動作から保護されます。IO3/RESET# 機能が有効になったとき (CR2V[7]=1)、または RESET# がアクティブになったとき、IO3/RESET# または RESET# が LOW になると、ハードウェア リセットが開始され、デバイスを DPD モードから解放します。

## 6 アドレス空間マップ

### 6.1 概要

#### 6.1.1 拡張アドレス

FL-L ファミリは 32 ビット (4 バイト) アドレスに対応しており、24 ビット (3 バイト) アドレスだけに対応した前世代 (レガシー) の SPI デバイスに比べると、より高容量のデバイスを可能にします。24 ビット、バイト分解能のアドレスは、16MB (128Mb) の最大容量までしかアクセスできません。一方、32 ビット、バイト分機能のアドレスは最大 4GB (32Gb) までのアドレス空間を直接アドレス指定できます。

レガシー コマンドはソフトウェア下位互換性のために 24 ビット アドレスの対応を継続しています。拡張 32 ビット アドレスは次の 2 つの方法によって有効にされます。

- **拡張アドレス モード** : すべてのレガシー コマンドを、ホストシステムから供給される 32 ビット アドレスを期待するものに変更する、揮発性コンフィギュレーション レジスタ ビットです。

- **4 バイトアドレス コマンド** : レガシー 機能と常に 32 ビット アドレスを期待する新機能の両方を実行します。

電源投入またはリセット後の拡張アドレス モードのデフォルト状態は不揮発性コンフィギュレーション ビットによって制御されます。デフォルト拡張アドレス モードは 24 または 32 ビットのアドレスに設定できます。これにより、デバイスの最初の 128Mb へのレガシー ソフトウェア互換アクセスが可能になるか、またはデバイスが 32 ビット アドレス モードで直接起動できます。

#### 6.1.2 複数のアドレス空間

多くのコマンドはメイン フラッシュ メモリ アレイ上で動作します。メイン フラッシュ アレイから独立したアドレス空間で動作するコマンドもいくつかあります。それぞれ独立したアドレス空間は完全な 24 ビットか 32 ビット アドレスを使用しますが、利用可能なアドレス空間の小さな部分のみを定義することができます。

## 6.2 フラッシュメモリアレイ

メインフラッシュアレイは、物理ブロック (64KB)、ハーフブロック (32KB) およびセクタ (4KB) と呼ばれるユニフォーム消去ユニットに分割されています。

Table 4 S25FL256L セクタアドレスマップ

| ブロックサイズ (KB) | ブロック数 | ブロック範囲 | ハーフブロックサイズ (KB) | ハーフブロック数 | ハーフブロック範囲 | セクタサイズ (KB) | セクタ数 | セクタ範囲  | アドレス範囲 (バイトアドレス)    | 備考        |

|--------------|-------|--------|-----------------|----------|-----------|-------------|------|--------|---------------------|-----------|

| 64           | 1     | BA00   | 32              | 1        | HBA00     | 4           | 1    | SA00   | 0000000h ~ 0000FFFh | セクタ開始アドレス |

|              |       |        |                 |          |           | :           | :    | :      | :                   | —         |

|              |       |        | 32              | 2        | HBA01     | 4           | 16   | SA15   | 000F000h ~ 000FFFFh | —         |

| :            | :     | :      | :               | :        | :         | :           | :    | :      | :                   | —         |

| 64           | 512   | BA511  | 32              | 1023     | HBA1022   | 4           | 8176 | SA8175 | 1FF0000h ~ 1FF0FFFh | —         |

|              |       |        |                 |          |           | :           | :    | :      | :                   | —         |

|              |       |        | 32              | 1024     | HBA1023   | 4           | 8192 | SA8191 | 1FFF000h ~ 1FFFFFFh | セクタ終了アドレス |

Table 5 S25FL128L セクタアドレスマップ

| ブロックサイズ (KB) | ブロック数 | ブロック範囲 | ハーフブロックサイズ (KB) | ハーフブロック数 | ハーフブロック範囲 | セクタサイズ (KB) | セクタ数 | セクタ範囲  | アドレス範囲 (バイトアドレス)   | 備考        |

|--------------|-------|--------|-----------------|----------|-----------|-------------|------|--------|--------------------|-----------|

| 64           | 1     | BA00   | 32              | 1        | HBA00     | 4           | 1    | SA00   | 000000h ~ 000FFFh  | セクタ開始アドレス |

|              |       |        |                 |          |           | :           | :    | :      | :                  | —         |

|              |       |        | 32              | 2        | HBA01     | 4           | 16   | SA15   | 00F000h ~ 00FFFFh  | —         |

| :            | :     | :      | :               | :        | :         | :           | :    | :      | :                  | —         |

| 64           | 256   | BA255  | 32              | 511      | HBA510    | 4           | 4080 | SA4079 | FF0000h ~ FF0FFFh  | —         |

|              |       |        |                 |          |           | :           | :    | :      | :                  | —         |

|              |       |        | 32              | 512      | HBA511    | 4           | 4096 | SA4095 | FFF000h ~ FFFFFFFh | セクタ終了アドレス |

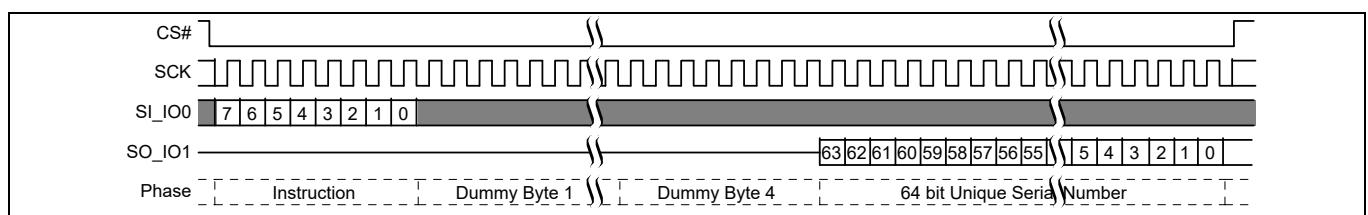

## 6.3 ID アドレス空間

RDID コマンド (9Fh) はデバイス識別子 (ID) のために個別のフラッシュメモリアドレス空間から情報を読み出します。ID アドレス空間の内容を定義する表は、[デバイス ID アドレスマップ](#)を参照してください。ID アドレス空間はインフィニオンによってプログラムされ、ホストシステムからは読み出し専用です。

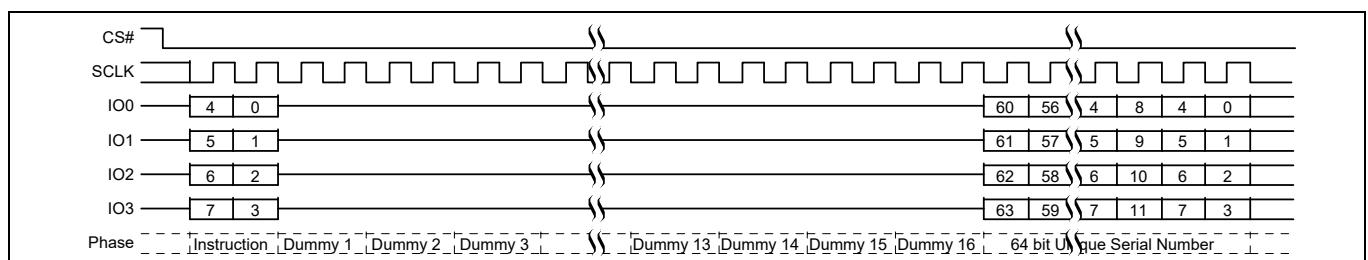

### 6.3.1 固有デバイス ID

64 ビットの固有の番号が固有デバイス ID アドレス空間の 8 バイトに位置しています。[Table 52](#) を参照してください。固有 ID はデバイス固有のソフトウェア読み出し可能なシリアル番号として使用できます。

## 6.4 JEDEC JESD216シリアルフラッシュ検出可能パラメーター (SFDP) 空間

RSFDP コマンド (5Ah) はシリアルフラッシュ検出可能パラメーター向けの JEDEC JESD216 規格に準拠して、デバイス ID, 機能, およびコンフィギュレーション情報のために個別のフラッシュメモリアドレス空間から情報を読み出します。ID アドレス空間は SFDP パラメーターの 1 つとして組み込まれています。SFDP アドレス空間の内容を定義する表は、[JEDEC JESD216Bシリアルフラッシュ検出可能パラメーター](#)を参照してください。SFDP アドレス空間はインフィニオンによってプログラムされ、ホストシステムからは読み出し専用です。

## 6.5 セキュリティ領域アドレス空間

各 FL-L ファミリメモリデバイスにはメインフラッシュアレイから独立した 1024 バイトのセキュリティ領域アドレス空間があります。セキュリティ領域エリアは 4 つの単独にロック可能な 256 バイトの領域に分割されています。セキュリティ領域のメモリ空間は、プログラムまたは消去から一時的に保護される情報または永久的にロックされる情報を格納するためのものです。

インフィニオンから出荷されるときに領域のデータ バイトは FFh に消去されています。保護またはロックされていないとき、領域は他のフラッシュメモリアドレス空間と同じようにプログラムと消去ができます。それぞれの領域を個別に消去できます。セキュリティ領域ロックビット (CR1NV[5:2]) はコンフィギュレーションレジスタ 1 に位置しています。セキュリティ領域ロックビットはワンタイムプログラマブル (OTP) のビットであり、プログラム (1 にセット) された後、ロックビットは関連領域を消去またはプログラムから永久的に保護します。

また領域 2 と領域 3 は、保護レジスタ (PR) の NVLOCK ビットによってプログラムと消去からの一時的な保護機能があります。NVLOCK ビットは揮発性ビットであり、IRP ロジックとコマンドによってセットまたはクリアされます。[保護レジスタ \(PR\)](#) を参照してください。

IRP レジスタでのセキュリティ領域パスワード保護ビット (IRP[2]) はパスワードが提供されるまで領域 2 と領域 3 をプログラムおよび消去動作から保護することを可能にします。IRP レジスタでのセキュリティ領域読み出し保護ビット (IRP[6]) はパスワードが提供されるまで領域 3 を読み出し動作から保護することを可能にします。読み出し保護領域から読み出そうとすると、無効で未定義のデータが返されます。[個別および領域保護レジスタ \(IRP\)](#) を参照してください。

ロックまたは保護された領域で消去またはプログラムしようとすると、動作が失敗し、SR2V[6:5] での P\_ERR ビットまたは E\_ERR ビットが 1 にセットされます (詳細は[揮発性ステータス レジスタ 2 \(SR2V\)](#) を参照してください)。

**Table 6** セキュリティ領域アドレスマップ

| 領域   | バイトアドレス範囲 (16 進) | 工場出荷初期状態 (16 進) |

|------|------------------|-----------------|

| 領域 0 | 000 ~ 0FF        | 全バイト = FF       |

| 領域 1 | 100 ~ 1FF        |                 |

| 領域 2 | 200 ~ 2FF        |                 |

| 領域 3 | 300 ~ 3FF        |                 |

## 6.6 レジスタ

レジスタは、FL-L ファミリメモリデバイスの動作方法を設定する、またはデバイス動作のステータスを報告するために使用される小さなメモリセルグループです。レジスタは特定のコマンドによりアクセスされます。レジスタに使用されるコマンド (と 16 進の命令コード) は各レジスタの説明に記載しています。

レガシー SPI メモリデバイスでは、個別レジスタビットは同じレジスタ内で、揮発性、不揮発性、またはワンタイムプログラマブル (OTP) ビットが混在されています。コンフィギュレーションオプションによってはレジスタビットのタイプは変更可能です (例えば、不揮発性から揮発性に変更できます)。

FL-L ファミリは異なるレジスタビットのタイプを実装するために個別の不揮発性または揮発性メモリセルグループ (領域) を使用します。ただし、レガシーソフトウェアとの互換性のために、レガシー レジスタとコマンドは以前と変わらず対応され、動作し続けます。レガシー レジスタに揮発性ビットがある場合、またはレガシー レジスタを読み出すコマンドの読み出しレイテンシがゼロの場合、各レガシー レジスタには不揮発性と揮発性バージョンが存在します。そのようなレジスタが読み出されるとき、レジスタの揮発性バージョンが提供されます。パワー オン リセット (POR)、ハードウェア リセットまたはソフトウェア リセットの間、揮発性レジスタのデフォルト状態を提供するために、レジスタの不揮発性バージョンは揮発性バージョンにコピーされます。不揮発性レジスタビットが書き込まれたとき、レジスタの不揮発性バージョンは消去され、新しいビット値でプログラムされ、その後、揮発性バージョンは不揮発性バージョンの新しい内容で更新されます。OTP ビットがプログラムされると、レジスタの不揮発性バージョンがプログラムされ、レジスタの揮発性バージョン中の適切なビットが更新されます。揮発性レジスタビットが書き込まれたとき、レジスタの揮発性バージョンのみは適切なビットが更新されます。

各ビットのタイプはそれぞれのレジスタの説明に記載されています。ビットが揮発性である場合、各ビットのデフォルト状態はパワー オン リセット、ハードウェア リセット、またはソフトウェア リセットの後の状態です。ビットは不揮発性または OTP である場合、デフォルト状態はインフィニオンから出荷されたときのビット値です。不揮発性レジスタに書き込む際には、正しいデータがレジスタに書き込まれることを保証する、途切れないと安定した電源が必要となることに特に注意してください。

### 6.6.1 ステータス レジスタ 1

#### 6.6.1.1 不揮発性ステータス レジスタ 1 (SR1NV) S25FL256L

関連コマンド: 不揮発性書き込みイネーブル (WREN 06h), 書き込みディセーブル (WRDI 04h), レジスタ書き込み (WRR 01h), 任意レジスタ読み出し (RDAR 65h), 任意レジスタ書き込み (WRAR 71h)。

Table 7 不揮発性ステータス レジスタ 1 (SR1NV)

| ビット | フィールド名    | 機能                   | タイプ         | 初期状態  | 説明                                         |

|-----|-----------|----------------------|-------------|-------|--------------------------------------------|

| 7   | SRP0_NV   | ステータス レジスタ保護 0 デフォルト | 不揮発性        | 0     | SRP0 のデフォルト状態を示します。                        |

| 6   | TBPROT_NV | TBPROT デフォルト         | 不揮発性        | 0     | TBPROT のデフォルト状態を示します。                      |

| 5   | BP_NV3    | レガシーブロック保護デフォルト      | 不揮発性        | 0000b | BP ビットのデフォルト状態を示します。                       |

| 4   | BP_NV2    |                      |             |       |                                            |

| 3   | BP_NV1    |                      |             |       |                                            |

| 2   | BP_NV0    |                      |             |       |                                            |

| 1   | WEL_D     | WEL デフォルト            | 不揮発性 読み出し専用 | 0     | WEL ステータスのデフォルト状態を示します。ユーザーによってプログラムできません。 |

| 0   | WIP_D     | WIP デフォルト            | 不揮発性 読み出し専用 | 0     | WIP ステータスのデフォルト状態を示します。ユーザーによってプログラムできません。 |

不揮発性ステータス レジスタ (SRP0\_NV) **SR1NV[7]**: SRP0 のデフォルト状態を示します。ステータス レジスタ保護 (SRP1, SRP0) を参照してください。

最上部 / 最下部保護 (TBPROT\_NV) **SR1NV[6]**: TBPROT のデフォルト状態を示します。

レガシー ブロック保護 (BP\_NV3, BP\_NV2, BP\_NV1, BP\_NV0) **SR1NV[5:2]**: BP\_3 ~ BP\_0 のビットのデフォルト状態を示します。

書き込みイネーブル ラッチ デフォルト (WEL\_D) **SR1NV[1]**: SR1V[1] での WEL ステータスのデフォルト状態を示します。ビットはインフィニオンによってプログラムされ、ユーザーはプログラムできません。

書き込み中デフォルト (WIP\_D) **SR1NV[0]**: SR1V[0] での WIP ステータスのデフォルト状態を示します。ビットはインフィニオンによってプログラムされ、ユーザーはプログラムできません。

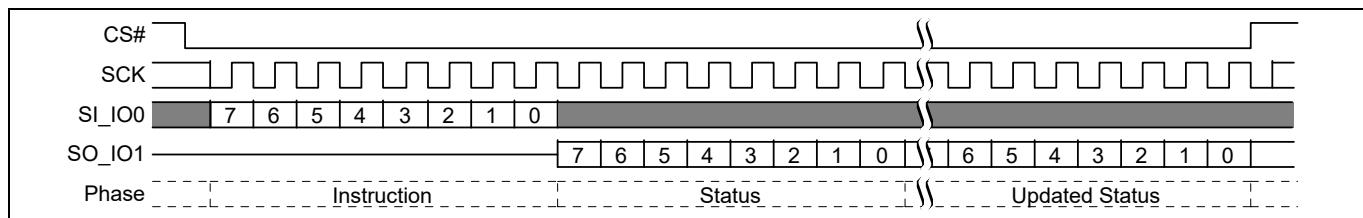

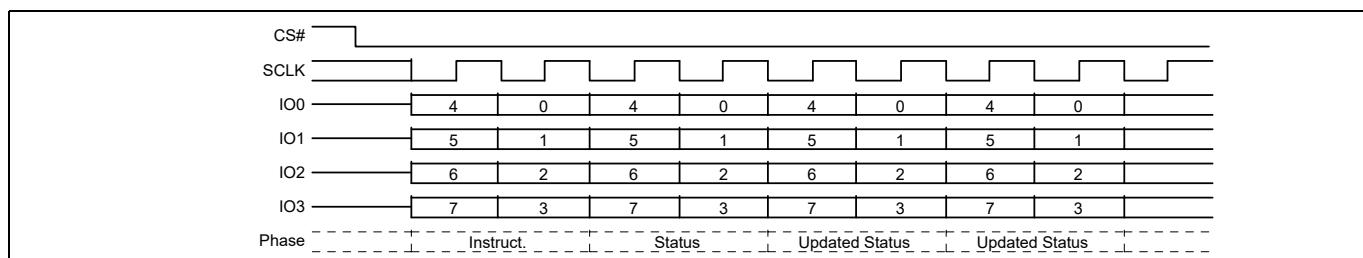

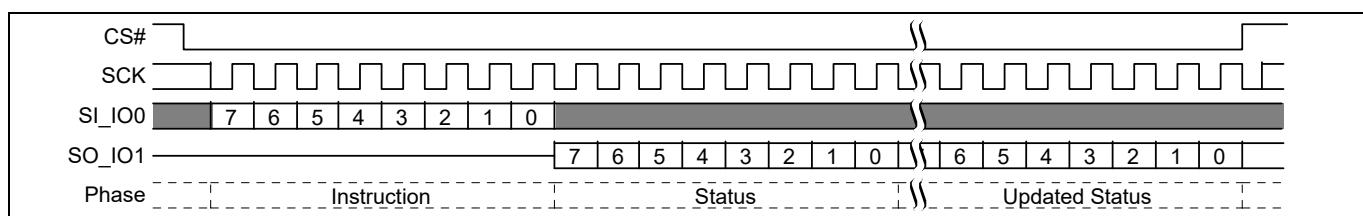

### 6.6.1.2 挥発性ステータス レジスタ 1 (SR1V) S25FL256L

関連コマンド : ステータス レジスタ 1 読み出し (RDSR1 05h)、揮発性 レジスタ の書き込みイネーブル (WRENV 50h)、レジスタ書き込み (WRR 01h)、ステータス レジスタ クリア (CLSR 30h)、任意 レジスタ 読み出し (RDAR 65h)、任意 レジスタ書き込み (WRAR71h)。RDSR1 コマンドの実行で表示される レジスタ です。

Table 8 S25FL256L 挥発性ステータス レジスタ 1 (SR1V)

| ビット | フィールド名 | 機能                   | タイプ         | 初期状態  | 説明                                                                                                                                                                                                     |  |

|-----|--------|----------------------|-------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 7   | SRP0   | ステータス レジスタ 保護 0      | 揮発性         | SR1NV | 1=WP# が LOW のとき、SR1NV, SR1V, CR1NV, CR1V, CR2NV, CR2V, CR3NV, DLRNV, DLRV に影響するなどのコマンドも実行しないことで、SR1NV, SR1V, CR1NV, CR1V, CR2NV, CR2V, CR3NV, DLRNV, DLRV の状態をロックします。<br>0=WP# が LOW になってもレジスタを保護しません。 |  |

| 6   | TBPROT | 最上部 / 最下部 関連 保護      | 揮発性         |       | 1=BP が最下部 (低いアドレス) から開始します。<br>0=BP が最上部 (高いアドレス) から開始します。                                                                                                                                             |  |

| 5   | BP3    | レガシー ブロック ラッチ 挥発性 保護 | 揮発性         |       | セクタ (ブロック) の選択した範囲をプログラム / 消去から保護します。                                                                                                                                                                  |  |

| 4   | BP2    |                      |             |       |                                                                                                                                                                                                        |  |

| 3   | BP1    |                      |             |       |                                                                                                                                                                                                        |  |

| 2   | BP0    |                      |             |       |                                                                                                                                                                                                        |  |

| 1   | WEL    | 書き込みイネーブル ラッチ        | 揮発性 読み出し 専用 |       | 0=書き込みは無効で、組込み動作は開始できません。<br>1=書き込みは有効で、組込み動作は開始できます。<br>ビットは WRR または WRAR コマンドに影響されず、WREN, WRENV, WRDI, および CLSR コマンドにのみ影響されます。                                                                       |  |

| 0   | WIP    | 書き込み中                | 揮発性 読み出し 専用 |       | 1=デバイスはビジーであり、プログラムや消去などの組み込み動作が処理中です。<br>0=デバイスはスタンバイ モードでレディであり、コマンドを受け入れられます。<br>このビットは WRR または WRAR コマンドに影響されず、WIP 状態のみを示します。                                                                      |  |

**ステータス レジスタ保護 0 (SRP0) SR1V[7]:** ビットが「1」にセットされ、WP# 入力が LOW に駆動されると、デバイスはハードウェア保護モードに入ります。このモードでは、ステータス レジスタまたはコンフィギュレーション レジスタを変更するコマンドはすべて無視され、実行のためには受け入れられず、ステータス レジスタとコンフィギュレーション レジスタ SR1NV, SR1V, CR1NV, CR1V, CR2NV, CR2V, CR3NV, DLRNV, および DLRV を読み出し専用 レジスタにすることで、レジスタのビットの状態を効果的にロックします。WP# が HIGH の場合、ステータス レジスタおよびコンフィギュレーション レジスタ SR1NV, SR1V, CR1NV, CR1V, CR2NV, CR2V, CR3NV, DLRNV, および DLRV は変更可能です。SRP0 が 0 であれば、WP# が無効になり、ステータス レジスタおよびコンフィギュレーション レジスタ SR1NV, SR1V, CR1NV, CR1V, CR2NV, CR2V, CR3NV, DLRNV, および DLRV は変更可能です。WP# は他のレジスタの書き込みに影響しません。SRP0 は不揮発性バージョン (SRP0\_NV) に対する変更を追跡します。QPI または QIO モードが有効 (CR2V[3] または CR1V[1] が 1) になる場合、WP# の外部入力が IO2 として使用されるため、内部の WP# 信号 レベルは 1 になります。これにより、ハードウェア保護機能が効果的にオフにされます。SR1NV, SR1V, CR1NV, CR1V, CR2NV, CR2V, CR3NV, DLRNV, および DLRV レジスタはロックされずに書き込み可能になります。 [ステータス レジスタ保護 \(SRP1, SRP0\)](#) を参照してください。

**TBPROT SR1V[6]:** ビットは、ステータス レジスタのレガシー ブロック保護 ビット (BP3, BP2, BP1, BP0) の参照点を定義します。ステータス レジスタの節で説明したとおり、BP3 ~ 0 のビットを使用すると、ユーザーはアレイの一部 (1/64, 1/4, 1/2 など) から全部までオプションとして保護できます。TBPROT が「0」にセットされた場合、レガシー ブロック保護の開始アドレスは最上部 (最大アドレス) になります。TBPROT が「1」にセットされた場合、レガシー ブロック保護の開始アドレスは最下部 (ゼロアドレス) になります。TBPROT は不揮発性バージョン (TBPROT\_NV) に対する変更を追跡します。

**レガシー ブロック保護 (BP3, BP2, BP1, BP0) SR1V[5:2]:** ビットは、プログラムおよび消去コマンドから保護されるメイン フラッシュ アレイ領域を定義します。BP ビット値が保護対象のメモリ アレイ領域を選択する方法については、[レガシー ブロック保護](#) を参照してください。

**書き込みイネーブル ラッチ (WEL) SR1V[1]:** メモリやレジスタ値への不注意による意図しない変更に対する保護手段として、プログラム、書き込み、または消去動作を可能にするためには WEL ビットを「1」にセットする必要があります。書き込みイネーブル (WREN) コマンドを実行すると、書き込みイネーブル ラッチを「1」にセットし、その後のすべてのプログラム、消去、または書き込みコマンドの実行を可能にします。書き込みディセーブル (WRDI) コマンドは書き込みイネーブル ラッチを「0」にセットし、すべてのプログラム、消去および書き込みコマンドの実行を防止します。WEL ビットはプログラム、書き込み、または消去動作が正常に終了すると「0」にクリアされます。処理が正常に終了しない場合、WEL ビットはセットされたままとなり、CLSR コマンドでクリアする必要があります。電源切断 / 電源投入 シーケンス、ハードウェアリセット、またはソフトウェアリセットの後、書き込みイネーブル ラッチは WEL\_D にセットされます。WRR または WRAR コマンドはこのビットには影響しません。

**書き込み中 (WIP) SR1V[0]:** デバイスがプログラム、書き込み、消去動作、またはその他の動作を実行しているかどうかを示し、この間は新しい動作コマンドを無視します。このビットが「1」にセットされると、デバイスは処理の実行でビジーになっていることを示します。WIP が「1」のときに許可されるコマンドは、ステータス レジスタ読み出し (RDSR1, RDSR2), 任意 レジスタ読み出し (RDAR), 消去 / プログラム一時停止 (EPS), ステータス レジスタクリア (CLSR), コンフィギュレーション レジスタ読み出し (RDCR1, RDCR2, RDCR3), およびソフトウェアリセット (RSTEN 66h の後に RST 99h が続く) コマンドだけです。EPS コマンドは、メモリ アレイが消去やプログラム中のみ許可されます。ステータス レジスタの E\_ERR と P\_ERR ビットは WIP が「1」のときに更新されます。P\_ERR または E\_ERR ビットが「1」にセットされたとき、WIP ビットは「1」にセットされたままで、デバイスがまだビジーの状態で新しい動作のコマンドを受信できないことを示します。デバイスをスタンバイ モードに戻らせるためにステータス レジスタクリア (CLSR) コマンドを受信しなければいけません。WIP ビットが「0」にクリアされたとき、進行中の処理はありません。これは、読み出し専用 ビットです。

### 6.6.1.3 不揮発性ステータス レジスタ 1 (SR1NV) S25FL128L

関連コマンド: 不揮発性書き込みイネーブル (WREN 06h), 書き込みディセーブル (WRDI 04h), レジスタ書き込み (WRR 01h), 任意レジスタ読み出し (RDAR 65h), 任意レジスタ書き込み (WRAR 71h)。

Table 9 S25FL128L 不揮発性ステータス レジスタ 1 (SR1NV)

| ビット | フィールド名    | 機能                       | タイプ                | 初期状態 | 説明                                                 |

|-----|-----------|--------------------------|--------------------|------|----------------------------------------------------|

| 7   | SRP0_NV   | ステータス レジスタ<br>保護 0 デフォルト | 不揮発性               | 0    | SRP0 のデフォルト状態を示します。                                |

| 6   | SEC_NV    | セクタ / ブロック保<br>護         | 不揮発性               | 0    | SEC のデフォルト状態を示します。                                 |

| 5   | TBPROT_NV | TBPROT デフォルト             | 不揮発性               | 0    | TBPROT のデフォルト状態を示しま<br>す。                          |

| 4   | BP_NV2    | レガシーブロック保<br>護デフォルト      | 不揮発性               | 000b | BP ビットのデフォルト状態を示し<br>ます。                           |

| 3   | BP_NV1    |                          |                    |      |                                                    |

| 2   | BP_NV0    |                          |                    |      |                                                    |

| 1   | WEL_D     | WEL デフォルト                | 不揮発性<br>読み出し<br>専用 | 0    | WEL ステータスのデフォルト状態<br>を示します。ユーザーによってプ<br>ログラムできません。 |

| 0   | WIP_D     | WIP デフォルト                | 不揮発性<br>読み出し<br>専用 | 0    | WIP ステータスのデフォルト状態を<br>示します。ユーザーによってプロ<br>グラムできません。 |

不揮発性ステータス レジスタ保護 (SRP0\_NV) SR1NV[7]: SRP0 のデフォルト状態を示します。ステータス レジスタ保護 (SRP1, SRP0) を参照してください。

セクタ / ブロック保護 (SEC\_NV) SR1NV[6]: SEC のデフォルト状態を示します。

最上部 / 最下部保護 (TBPROT\_NV) SR1NV[5]: TBPROT のデフォルト状態を示します。

レガシーブロック保護 (BP\_NV3, BP\_NV2, BP\_NV1, BP\_NV0) SR1NV[4:2]: BP\_2 ~ BP\_0 ビットのデフォルト状態を示します。

書き込みイネーブル ラッチ デフォルト (WEL\_D) SR1NV[1]: SR1V[1] での WEL ステータスのデフォルト状態を示します。ビットはインフィニオンによってプログラムされ、ユーザーはプログラムできません。

書き込み中デフォルト (WIP\_D) SR1NV[0]: SR1V[0] での WIP ステータスのデフォルト状態を示します。ビットはインフィニオンによってプログラムされ、ユーザーはプログラムできません。

### 6.6.1.4 振発性ステータス レジスタ 1 (SR1V) S25FL128L

関連コマンド: ステータス レジスタ 1 読み出し (RDSR1 05h), 振発性 レジスタの書き込み イネーブル (WRENV 50h), レジスタ書き込み (WRR 01h), ステータス レジスタクリア (CLSR 30h), 任意 レジスタ読み出し (RDAR 65h), 任意 レジスタ書き込み (WRAR71h)。RDSR1 コマンドの実行で表示される レジスタです。

Table 10 S25FL128L 振発性ステータス レジスタ 1 (SR1V)

| ビット | フィールド名 | 機能                | タイプ        | 初期状態  | 説明                                                                                                                                                                                                          |  |

|-----|--------|-------------------|------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 7   | SRP0   | ステータス レジスタ保護 0    | 揮発性        | SR1NV | 1=WP# が LOW のとき、SR1NV, SR1V, CR1NV, CR1V, CR2NV, CR2V, CR3NV, DLRNV および DLRV に影響する他のコマンドも実行しないことで、SR1NV, SR1V, CR1NV, CR1V, CR2NV, CR2V, CR3NV, DLRNV および DLRV の状態をロックします。<br>0=WP# が LOW になってもレジスタを保護しません。 |  |

| 6   | SEC    | セクタ / ブロック保護      | 揮発性        |       | 0=BP2 ~ BP0 は 64kB ブロックを保護します。<br>1=BP2 ~ BP0 は 4kB セクタを保護します。                                                                                                                                              |  |

| 5   | TBPROT | 最上部 / 最下部 関連保護    | 揮発性        |       | 1=BP が最下部 (低いアドレス) から開始します。<br>0=BP が最上部 (高いアドレス) から開始します。                                                                                                                                                  |  |

| 4   | BP2    | レガシーブロック保護<br>揮発性 | 揮発性        |       | セクタ (ブロック) の選択した範囲をプログラム / 消去から保護します。                                                                                                                                                                       |  |

| 3   | BP1    |                   |            |       |                                                                                                                                                                                                             |  |

| 2   | BP0    |                   |            |       |                                                                                                                                                                                                             |  |

| 1   | WEL    | 書き込み イネーブル ラッチ    | 揮発性 読み出し専用 |       | 0=書き込みは無効で、組み込み動作は開始できません。<br>1=書き込みは有効で、組み込み動作は開始できます。<br>このビットは WRR または WRAR コマンドに影響されず、WREN, WRENV, WRDI および CLSR コマンドにのみ影響されます。                                                                         |  |

| 0   | WIP    | 書き込み中             | 揮発性 読み出し専用 |       | 1=デバイスはビジーであり、プログラムや消去などの組み込み動作が処理中です。<br>0=デバイスはスタンバイモードでレディであり、コマンドを受け入れられます。<br>このビットは WRR または WRAR コマンドに影響されず、WIP 状態のみを示します。                                                                            |  |

ステータス レジスタ保護 0 (SRP0) SR1V[7]: ビットが「1」にセットされ、WP# 入力が LOW に駆動されると、デバイスはハードウェア保護モードになります。このモードでは、ステータス レジスタまたはコンフィギュレーション レジスタを変更するコマンドはすべて無視され、実行のためには受け入れられず、ステータス レジスタとコンフィギュレーション レジスタ SR1NV, SR1V, CR1NV, CR1V, CR2NV, CR2V, CR3NV, DLRNV および DLRV を読み出し専用 レジスタにすることで、レジスタのビットの状態を効果的にロックします。WP# が HIGH の場合、ステータス レジスタおよびコンフィギュレーション レジスタ SR1NV, SR1V, CR1NV, CR1V, CR2NV, CR2V, CR3NV, DLRNV および DLRV は変更可能です。WP# は他の レジスタの書き込みに影響しません。SRP0 は不揮発性 バージョン (SRP0\_NV) に対する変更を追跡します。QPI または QIO モードが有効 (CR2V[3] または CR1V[1] が 1) になる場合、WP# の外部入力が IO2 として使用されるため、内部の WP# 信号レベルは 1 になります。これにより、ハードウェア保護機能が効果的にオフにされます。SR1NV, SR1V, CR1NV, CR1V, CR2NV, CR2V, CR3NV, DLRNV および DLRV レジスタはロックされずに書き込み可能になります。[ステータス レジスタ保護 \(SRP1, SRP0\)](#) を参照してください。

セクタ / ブロック保護 (SEC) SR1V[6]: ビットは、ブロック保護 ビット (BP2, BP1, BP0) が 4kB セクタ (SEC=「1」) または 64kB ブロック (SEC=「0」) を保護するかを制御します。SEC ビット値が保護対象のメモリ アレイ 領域をどのように選択するかは、[レガシーブロック保護](#) を参照してください。

**TBPROT SR1V[5]:** ビットは、ステータス レジスタのレガシー ブロック保護ビット (BP2, BP1, BP0) の参照点を定義します。ステータス レジスタの節で説明したとおり、BP2～0 ビットを使用すると、ユーザーはアレイの一部 (1/64, 1/4, 1/2 など) から全部までオプションとして保護できます。TBPROT が「0」にセットされた場合、レガシー ブロック保護の開始アドレスは最上部(最大アドレス)になります。TBPROT が「1」にセットされた場合、レガシー ブロック保護の開始アドレスは最下部(ゼロアドレス)になります。TBPROT は不揮発性バージョン (TBPROT\_NV) に対する変更を追跡します。

**レガシー ブロック保護 (BP2, BP1, BP0) SR1V[4:2]:** ビットは、プログラムおよび消去コマンドから保護されるメイン フラッシュアレイ領域を定義します。BP ビット値が保護対象のメモリアレイ領域を選択する方法については、[レガシー ブロック保護](#)を参照してください。

**書き込みイネーブル ラッチ (WEL) SR1V[1]:** メモリやレジスタ値への不注意による意図しない変更に対する保護手段として、プログラム、書き込み、または消去動作を可能にするためには WEL ビットを「1」にセットする必要があります。書き込みイネーブル (WREN) コマンドを実行すると、書き込みイネーブル ラッチを「1」にセットし、その後のすべてのプログラム、消去、または書き込みコマンドの実行を可能にします。書き込みディセーブル (WRDI) コマンドは書き込みイネーブル ラッチを「0」にセットし、すべてのプログラム、消去および書き込みコマンドの実行を防止します。WEL ビットはプログラム、書き込み、または消去動作が正常に終了すると「0」にクリアされます。処理が正常に終了しない場合、WEL ビットはセットされたままとなり、CLSR コマンドでクリアする必要があります。電源切断 / 電源投入 シーケンス、ハードウェアリセット、またはソフトウェアリセットの後、書き込みイネーブル ラッチは WEL\_D にセットされます。WRR または WRAR コマンドはこのビットには影響しません。

**書き込み中 (WIP) SR1V[0]:** デバイスがプログラム、書き込み、消去動作、またはその他の動作を実行しているかどうかを示し、この間は新しい動作コマンドを無視します。このビットが「1」にセットされると、デバイスは処理の実行でビジーになっていることを示します。WIP が「1」のときに許可されるコマンドは、ステータス読み出し (RDSR1 または RDSR2)、任意レジスタ読み出し (RDAR)、消去 / プログラム一時停止 (EPS)、ステータス レジスタクリア (CLSR)、およびソフトウェアリセット (RSTEN 66h の後に RST 99h が続く) コマンドだけです。EPS コマンドは、メモリアレイが消去やプログラム中のみ許可されます。ステータス レジスタの E\_ERR と P\_ERR ビットは WIP が「1」のときに更新されます。P\_ERR または E\_ERR ビットが「1」にセットされたとき、WIP ビットは「1」にセットされたままで、デバイスがまだビジーの状態で新しい動作のコマンドを受信できないことを示します。デバイスをスタンバイ モードに戻らせるためにステータス レジスタクリア (CLSR) コマンドを受信しなければなりません。WIP ビットが「0」にクリアされたとき、進行中の処理はありません。読み出し専用ビットです。

## 6.6.2 振発性ステータス レジスタ 2 (SR2V)

関連コマンド: ステータス レジスタ 2 読み出し (RDSR2 07h)、任意レジスタ読み出し (RDAR 65h)。ステータス レジスタ 2 はユーザー プログラム可能な不揮発性ビットを持っていません。定義されたすべてのビットは揮発性読み出し専用の状態にあります。ビットのデフォルト状態はハードウェアにより設定されます。

**Table 11** 挥発性ステータス レジスタ 2 (SR2V)

| ビット | フィールド名 | 機能           | タイプ       | 初期状態 | 説明                                              |

|-----|--------|--------------|-----------|------|-------------------------------------------------|

| 7   | RFU    | 予約済み         |           | 0    | 将来使用するため予約済み                                    |

| 6   | E_ERR  | 消去エラー発生      | 揮発性読み出し専用 |      | 1 = エラーは発生<br>0 = エラーがありません                     |

| 5   | P_ERR  | プログラミングエラー発生 | 揮発性読み出し専用 |      |                                                 |

| 4   | RFU    | 予約済み         | 揮発性読み出し専用 |      | 将来使用するため予約済み                                    |

| 3   |        |              |           |      |                                                 |

| 2   |        |              |           |      |                                                 |

| 1   | ES     | 消去一時停止       | 揮発性読み出し専用 |      | 1 = 消去一時停止モードです。<br>0 = 消去一時停止モードではありません。       |

| 0   | PS     | プログラム一時停止    | 揮発性読み出し専用 |      | 1 = プログラム一時停止モードです。<br>0 = プログラム一時停止モードではありません。 |

**消去エラー (E\_ERR) SR2V[6]:** 消去エラービットは消去動作が成功したか失敗したかを示すために使用されます。消去エラービットが「1」にセットされたとき、直前の消去動作にエラーが発生したことを示します。また、ユーザーが個別の保護されたメインメモリセクタまたはロックされたセキュリティ領域を消去しようとするときにもビットはセットされます。チップ消去コマンド実行中に保護されたセクタを検出すると、E\_ERR ビットはセットされます。消去エラービットが「1」のとき、ステータスレジスタクリア (CLSR) コマンドで「0」にクリアできます。読み出し専用ビットであり、WRR または WRAR コマンドに影響されません。

**プログラムエラー (P\_ERR) SR2V[5]:** プログラムエラービットはプログラム動作が成功したか失敗したかを示すために使用されます。プログラムエラービットが「1」にセットされたとき、直前のプログラム動作にエラーが発生したことを示します。また、ユーザーが保護されたメインメモリセクタまたはロックされたセキュリティ領域をプログラムしようとするときにもビットはセットされます。プログラムエラービットが「1」のとき、ステータスレジスタクリア (CLSR) コマンドで「0」にクリアできます。読み出し専用ビットであり、WRR または WRAR コマンドに影響されません。

**消去一時停止 (ES) SR2V[1]:** 消去一時停止ビットは、いつデバイスが消去一時停止モードに入るかを決めるために使用されます。ステータスピットであり、ユーザーは書き込めません。消去一時停止ビットが「1」にセットされたとき、デバイスは消去一時停止モードになります。消去一時停止ビットが「0」にクリアされたとき、デバイスは消去一時停止モードになりません。消去一時停止 / 再開コマンドの詳細は、[プログラムまたは消去一時停止 \(PES 75h\)](#) を参照してください。

**プログラム一時停止 (PS) SR2V[0]:** プログラム一時停止ビットは、いつデバイスがプログラム一時停止モードに入るかを決めるために使用されます。ステータスピットであり、ユーザーは書き込めません。プログラム一時停止ビットが「1」にセットされたとき、デバイスはプログラム一時停止モードになります。プログラム一時停止ビットが「0」にクリアされたとき、デバイスはプログラム一時停止モードになりません。詳細は[プログラムまたは消去一時停止 \(PES 75h\)](#) を参照してください。

### 6.6.3 コンフィギュレーションレジスタ 1

コンフィギュレーションレジスタ 1 は一定のインターフェースとデータ保護機能を制御します。レジスタビットは 16 入力サイクルの WRR コマンドや WRAR コマンドを使用して変更できます。

#### 6.6.3.1 不揮発性コンフィギュレーションレジスタ 1 (CR1NV)

関連コマンド: 不揮発性書き込みイネーブル (WREN 06h), レジスタ書き込み (WRR 01h), 任意レジスタ読み出し (RDAR 65h), 任意レジスタ書き込み (WRAR 71h)。

Table 12 不揮発性コンフィギュレーションレジスタ 1 (CR1NV)

| ビット | フィールド名  | 機能                         | タイプ                | 初期状態 | 説明                                                                                                                                                                                         |  |

|-----|---------|----------------------------|--------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 7   | SUS_D   | 一時停止<br>ステータス<br>デフォルト     | 不揮発性<br>読み出し<br>専用 | 0    | 一時停止ステータスの初期状態を示します。ユーザーによってプログラムできません。                                                                                                                                                    |  |

| 6   | CMP_NV  | 補完的保護<br>デフォルト             | 不揮発性               |      | CMP の初期状態を示します。                                                                                                                                                                            |  |

| 5   | LB3     | セキュリティ<br>領域<br>ロック ビット    | OTP                |      | セキュリティ領域 3:0 の OTP ロック ビット 3:0<br>0=セキュリティ領域がロックされません。<br>1=セキュリティ領域が永久的にロックされます。                                                                                                          |  |

| 4   | LB2     |                            |                    |      |                                                                                                                                                                                            |  |

| 3   | LB1     |                            |                    |      |                                                                                                                                                                                            |  |

| 2   | LB0     |                            |                    |      |                                                                                                                                                                                            |  |

| 1   | QUAD_NV | クアッド<br>デフォルト              | 不揮発性               |      | QUAD の初期状態を示します。                                                                                                                                                                           |  |

| 0   | SRP1_D  | ステータス<br>レジスタ保護 1<br>デフォルト | OTP                |      | IRP[2:0]=「111」のとき、SRP1_D ビット<br>はプログラムできます。<br>SR1NV, SR1V, CR1NV, CR1V, CR2NV, CR2V,<br>CR3NV, DLRNV, DLRV の現時点の状態を<br>ロックします。<br>1=レジスタが永久的にロックされます。<br>0=POR 後、レジスタは SRP1 で保護されま<br>せん。 |  |

消去 / プログラム一時停止ステータス (SUS\_D) CR1NV[7]: CR1V[7] での SUS ビットのデフォルト状態を示します。ユーザーによってプログラムできません。

補完的保護 (CMP\_NV) CR1NV[6]: CR1V[6] での CMP ビットのデフォルト状態を示します。

セキュリティ領域ロック ビット (LB3, LB2, LB1, LB0) CR1NV[5:2]: セキュリティ領域の OTP 書き込み保護制御を示します。LB ビットが「1」にセットされたとき、対応するセキュリティ領域に対するプログラムや消去動作はできなくなります。

クアッド データ幅 不揮発性 (QUAD\_NV) CR1NV[1]: CR1V[1] での QUAD ビットのデフォルト状態を示します。WRR または WRAR コマンドはこのビットに影響を与えます。CR1NV[1] を「1」にプログラムすると、電源投入時やリセット時にクアッド データ幅コマンドはデフォルトで許可されます。

ステータス レジスタ保護 1 デフォルト (SRP1\_D) CR1NV[0]: R1V[0] での SRP1 ビットのデフォルト状態を示します。IRP[2:0] が「111」の場合、SRP1\_D OTP ビットはユーザー プログラム可能です。SRP1\_D が「1」の場合、SR1NV, SR1V, CR1NV, CR1V, CR2NV, CR2V, CR3NV, DLRNV, および DLRV レジスタは永久的にロックされます。ステータス レジスタ保護 (SRP1, SRP0) を参照してください。

### 6.6.3.2 振発性コンフィギュレーションレジスタ 1 (CR1V)

関連コマンド: コンフィギュレーションレジスタ 1 読み出し (RDCR1 35h), 振発性レジスタの書き込みイネーブル (WRENV 50h), レジスタ書き込み (WRR 01h), 任意レジスタ読み出し (RDAR 65h), 任意レジスタ書き込み (WRAR 71h)。RDCR1 コマンドの実行で表示されるレジスタです。

Table 13 振発性コンフィギュレーションレジスタ 1 (CR1V)

| ビット | フィールド名 | 機能                       | タイプ       | 初期状態  | 説明                                                                                                                              |  |

|-----|--------|--------------------------|-----------|-------|---------------------------------------------------------------------------------------------------------------------------------|--|

| 7   | SUS    | 一時停止ステータス                | 振発性読み出し専用 | CR1NV | 1= 消去 / プログラムが一時停止されます。<br>0= 消去 / プログラムが一時停止されません。                                                                             |  |

| 6   | CMP    | 補完的保護                    | 振発性       |       | 0= 通常保護マップ<br>1= 反転保護マップ                                                                                                        |  |

| 5   | LB3    | セキュリティ領域ロックビットの振発性コピー    | 振発性読み出し専用 |       | ユーザーによって書き込めません。<br>CR1NV[5:2] を参照してください。<br>セキュリティ領域 3:0 の OTP ロックビット 3:0<br>0= セキュリティ領域がロックされません。<br>1= セキュリティ領域が永久的にロックされます。 |  |

| 4   | LB2    |                          |           |       |                                                                                                                                 |  |

| 3   | LB1    |                          |           |       |                                                                                                                                 |  |

| 2   | LB0    |                          |           |       |                                                                                                                                 |  |

| 1   | QUAD   | クアッド I/O モード             | 振発性       |       | 1= クアッド<br>0= デュアルまたはシリアル                                                                                                       |  |

| 0   | SRP1   | ステータスレジスタ保護 <sup>1</sup> |           |       | LSR1NV, SR1V, CR1NV, CR1V, CR2NV, CR2V, CR3NV, DLRNV, DLRV の現時点の状態をロックします。<br>1= レジスタはロックされます。<br>0= レジスタはロック解除されます。            |  |

一時停止ステータス (SUS) CR1V[7]: 一時停止ステータスビットは、いつデバイスが消去またはプログラム一時停止モードにあるかを決めるために使用されます。ステータスビットであり、ユーザーは書き込めません。一時停止ステータスビットが「1」にセットされたとき、デバイスは消去またはプログラム一時停止モードになります。一時停止ステータスビットが「0」にクリアされたとき、デバイスは消去またはプログラム一時停止モードになりません。消去 / プログラム一時停止 / 再開コマンドの詳細は、[プログラムまたは消去一時停止 \(PES 75h\)](#) を参照してください。

補完的保護 (CMP) CR1V[6]: TBPROT, BP3, BP2, BP1, BP0 ビットとともに CMP を使用すると、アレイの半分から全部まで保護できる柔軟性をアレイ保護マップに提供します。

LB[3:0] CR1V[5:2]: ビットは CR1NV の該当する OTP ビットの振発性バージョンです。ビットの該当する OTP バージョンに対する変更を追跡します。

クアッドデータ幅 (QUAD) CR1V[1]: ビットは 1 にセットされると、デバイスのデータ幅を 4 ビットクアッドモードに切り替えます。つまり、WP# は IO2 になり、IO3/RESET# は CS# が LOW のときアクティブな I/O 信号になり、CS# が HIGH のとき RESET# 入力になります。WP# 入力は通常機能が監視されず、内部で HIGH (非アクティブ) にセットされます。シリアルおよびデュアル I/O 読み出しのコマンドはまだ正常に動作しますが、異なるデータバス幅を使ってコマンドを切り替える際はコマンドのために WP# 入力を駆動する必要がありません。同様に、CS# が LOW のとき、それらのコマンドの実行中に IO3/RESET# を駆動する必要がありません。クアッド出力読み出し、クアッド I/O 読み出し、および DDR クアッド I/O 読み出しコマンドを使用する際、QUAD ビットを「1」にセットする必要があります。QIO モードでの振発性レジスタ書き込みは、短くて明確に定義された時間を要します。デバイスインターフェースを QIO モードに切り替えるためには  $t_{QEN}$ 、デバイスを SPI モードに戻らせるためには  $t_{QEX}$  を要します。その後、後続するコマンドは直ちに QIO プロトコルで送信できます。QPI モードは QPIEN および QPIEX コマンド、または CR2V[3] ビットを「1」にセットすることで開始 / 終了される一方、クアッドデータ幅モードは QUAD ビットの設定にかかわらず使用されます。

ステータスレジスタ保護 1(SRP1) CR1V[0]: SRP1 ビットは 1 にセットされたとき、SR1NV, SR1V, CR1NV, CR1V, CR2NV, CR2V, CR3NV, DLRNV、および DLRV レジスタへの書き込み動作を防止することで、レジスタの現時点の状態を保護します。

[ステータスレジスタ保護 \(SRP1, SRP0\)](#) を参照してください。

SRP1 ビットを論理 0 にする限り、SR1NV, SR1V, CR1NV, CR1V, CR2NV, CR2V, CR3NV, DLRNV、および DLRV レジスタは SRP1 により保護されません。ただし、レジスタは SRP0 (SR1V[7]) および WP# 入力により保護が可能です。

SRP1 ビットが一度論理 1 にセットされると、パワー サイクルまたはハードウェアリセットでのみ論理 0 にクリアできます。ソフトウェアリセットは SRP1 ビットの状態に影響を与えません。

CR1V[0] SRP1 は揮発性ビットであり、電源投入後の SRP1 の初期状態は CR1NV[0] での SRP1\_D から得られます。SRP1 ビットは CR1V 内の他の値の更新と同時に WRR または WRAR コマンドの実行で設定できます。

## 6.6.4 コンフィギュレーションレジスタ 2

コンフィギュレーションレジスタ 2 は一定のインターフェース機能を制御します。レジスタビットは任意レジスタ読み出しと任意レジスタ書き込みコマンドを実行することで読み出され変更が可能です。レジスタの不揮発性バージョンにより、POR, ハードウェアリセット、またはソフトウェアリセットの制御状態を設定できます。レジスタの揮発性バージョンは通常動作での機能を制御します。

### 6.6.4.1 不揮発性コンフィギュレーションレジスタ 2 (CR2NV)

関連コマンド: 不揮発性書き込みイネーブル (WREN 06h), レジスタ書き込み (WRR 01h), 任意レジスタ読み出し (RDAR 65h), 任意レジスタ書き込み (WRAR 71h)。

Table 14 不揮発性コンフィギュレーションレジスタ 2 (CR2NV)

| ビット | フィールド名  | 機能          | タイプ  | 初期状態 | 説明                                                                                                                                                                                                     |  |

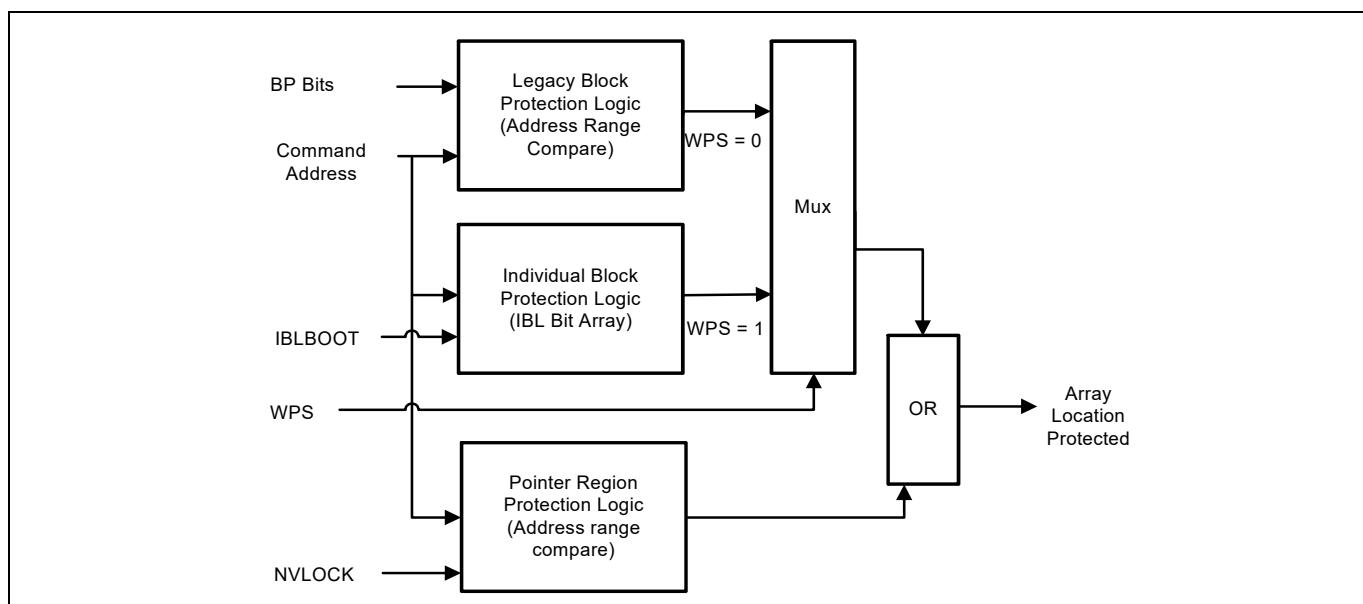

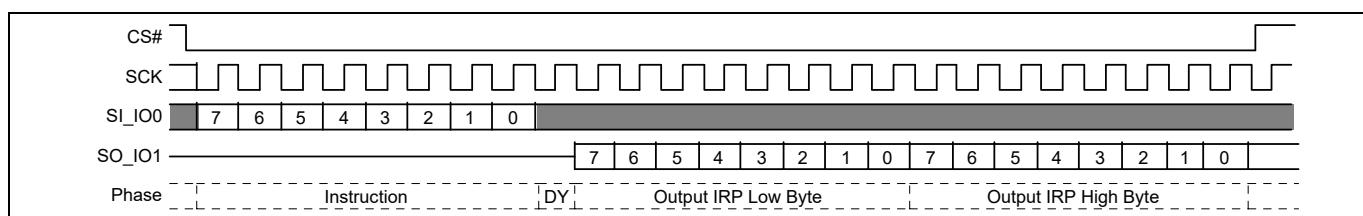

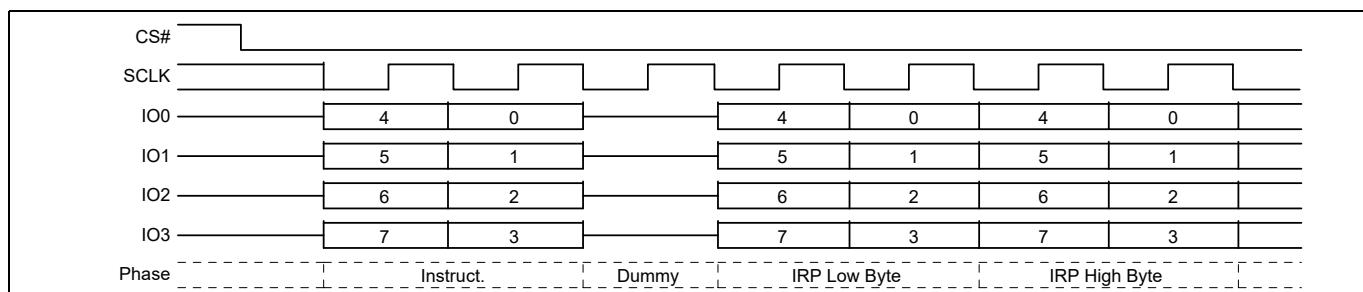

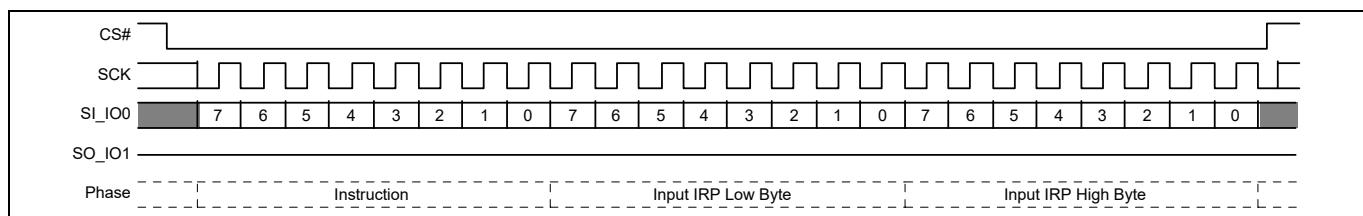

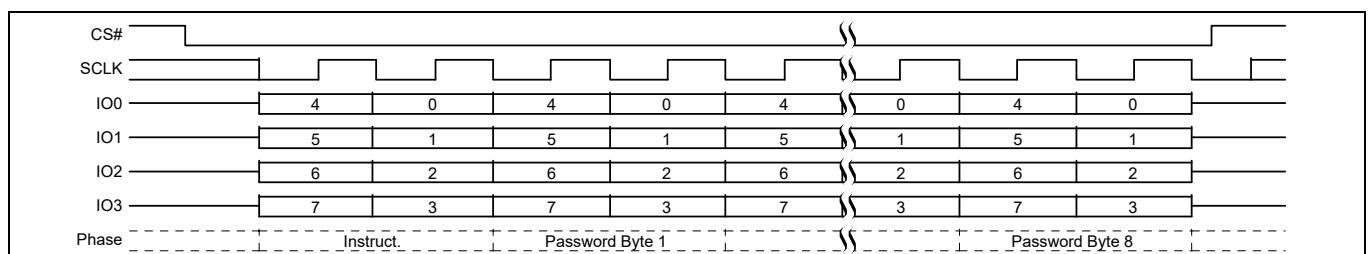

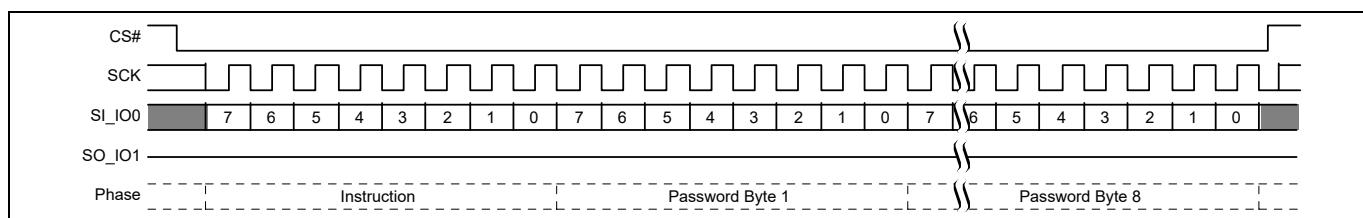

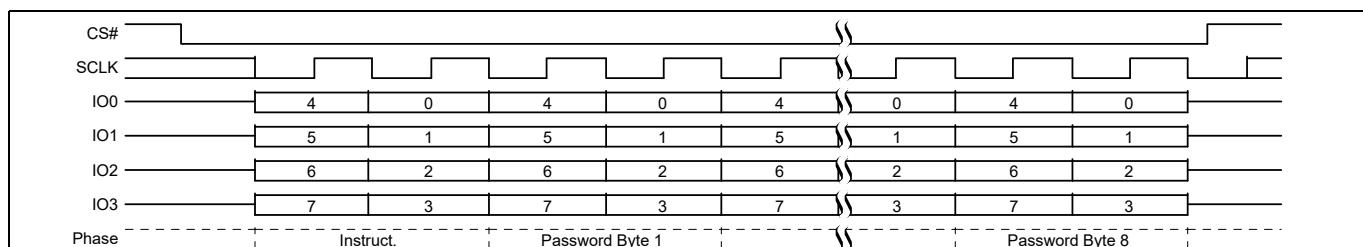

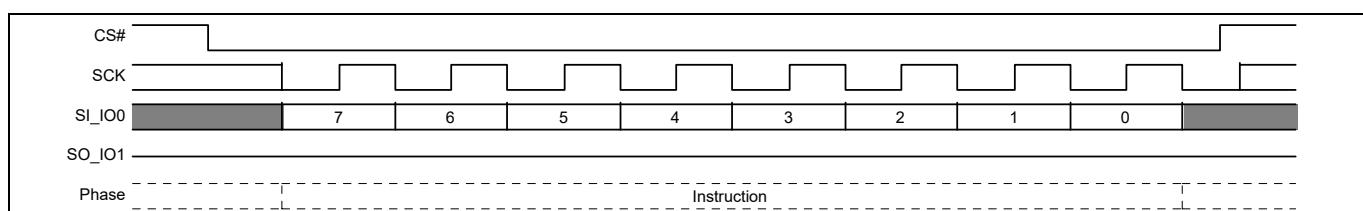

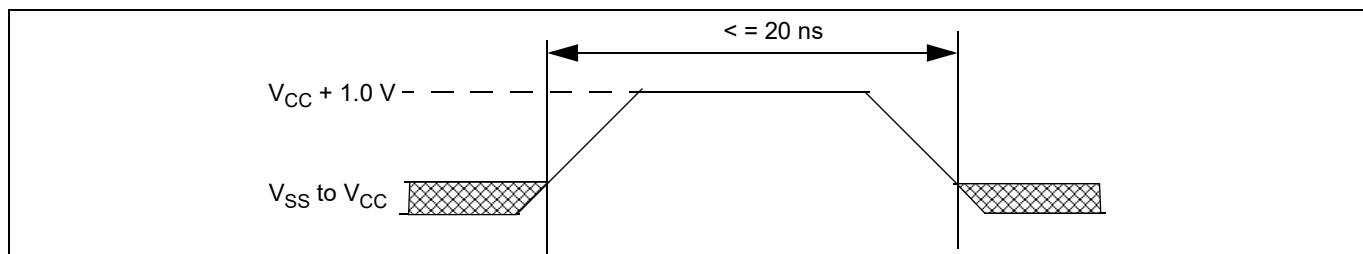

|-----|---------|-------------|------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|