## サイプレスはインフィニオンテクノロジーズになりました

この表紙に続く文書には「サイプレス」と表記されていますが、これは同社が最初にこの製品を開発したからです。新規および既存のお客様いずれに対しても、引き続きインフィニオンがラインアップの一部として当該製品をご提供いたします。

### 文書の内容の継続性

下記製品がインフィニオンの製品ラインアップの一部として提供されたとしても、それを理由としてこの文書に変更が加わることはありません。今後も適宜改訂は行いますが、変更があった場合は文書の履歴ページでお知らせします。

### 注文時の部品番号の継続性

インフィニオンは既存の部品番号を引き続きサポートします。ご注文の際は、データシート記載の注文部品番号をこれまで通りご利用下さい。

## 特長

- 16K×8 構成の 128K ビット強誘電体 RAM (F-RAM)

- 高耐久性 : 100 兆 ( $10^{14}$ ) 回の読み出し／書き込み

- 151 年のデータ保持 (13 ページの [データ保持期間およびアクセス可能回数](#) を参照)

- NoDelay™ 書き込み

- 高い信頼性がある強誘電体プロセス

- 高速 2 線式シリアルインターフェース (I<sup>2</sup>C)

- 最大周波数 3.4MHz<sup>[1]</sup>

- シリアル EEPROM からの置き換え

- 100kHz ~ 400kHz の従来のタイミングに対応

- デバイス ID

- メーカー ID および製品 ID

- 低消費電力

- 100kHz での 175μA の有効電流

- 150μA のスタンバイ電流

- 8μA のスリープモード電流

- 低電圧動作 : V<sub>DD</sub>=2.0V ~ 3.6V

- 産業用途向け温度範囲 : -40°C ~ +85°C

- 8 ピン小型外形集積回路 (SOIC) パッケージ

- RoHS 準拠

## 機能概要

FM24V01A は高度な強誘電体プロセスを使用する 128K ビットの不揮発性メモリです。F-RAM は不揮発性であり、RAM と同

様に読み出し／書き込みを実行します。また EEPROM とその他の不揮発性メモリによる複雑さ、オーバーヘッド、システムレベルの信頼性関連問題を回避し、151 年間にわたって信頼できるデータ保持ができます。

EEPROM と違って、FM24V01A はバス速度で書き込み動作を実行します。書き込み遅延は発生しません。データは、各バイトがデバイスに正常に転送された直後にメモリ アレイに書き込まれます。次のバスサイクルはデータポーリングを必要とせず開始できます。また本製品は他の不揮発性メモリと比較して多くの書き込み可能回数を提供します。さらに、F-RAM 書き込み動作が書き込み回路用に内部で電源電圧を増加することを必要としないため、書き込み中に F-RAM は EEPROM より消費電力が低いです。FM24V01A は  $10^{14}$  回の読み出し／書き込みサイクル、すなわち EEPROM に比べ 1 億倍の書き込みサイクルに対応できます。

これらの能力により、FM24V01A は、頻繁で急速書き込みを必要とする不揮発性メモリの用途に理想的なものです。用途例は、書き込み回数を重視するデータロギングから、EEPROM の長い書き込み時間によりデータ損失が発生することがある厳しい産業用制御まで説明します。機能の組合せにより、システムオーバーヘッドを低減させながらより頻繁なデータ書き込みを可能にします。

FM24V01A はハードウェア置き換えるため、シリアル EEPROM を使用するユーザーに大幅な利点を提供します。デバイスは読み出し専用デバイス ID を内蔵します。これにより、ホストは、メーカー、製品の容量、製品のリビジョンを判断できます。デバイス仕様は、-40°C ~ +85°C の産業用温度範囲において保証されます。

関連リソースに関しては、[こちら](#)を参照してください。

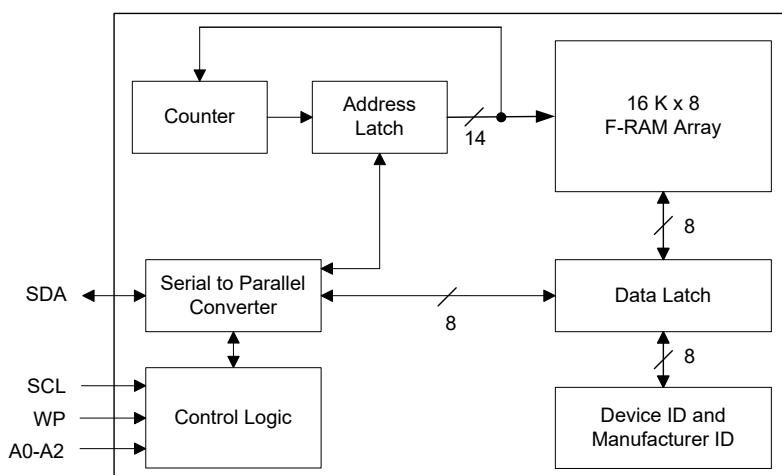

## ロジックブロックダイヤグラム

### 注記

1. FM24V01A は、I<sub>OL</sub> のファストモードプラス (Fm+, 1MHz) および、V<sub>hys</sub> のハイスピードモード (Hs-mode, 3.4MHz) において、NXP I<sup>2</sup>C 仕様に合いません。詳細は 12 ページの [DC 電気的特性](#) の表を参照してください。

## 目次

|                           |    |

|---------------------------|----|

| ピン配置 .....                | 3  |

| ピンの定義 .....               | 3  |

| 機能概要 .....                | 4  |

| メモリーアーキテクチャ .....         | 4  |

| 2線式インターフェース .....         | 4  |

| STOP条件 (P) .....          | 5  |

| START条件 (S) .....         | 5  |

| データ／アドレス転送 .....          | 5  |

| アクノリッジ／ノー アクノリッジ .....    | 6  |

| 高速モード (Hsモード) .....       | 6  |

| スレーブ デバイス アドレス .....      | 7  |

| アドレス指定の概要 .....           | 7  |

| データ転送 .....               | 7  |

| メモリの動作 .....              | 8  |

| 書き込み動作 .....              | 8  |

| 読み出し動作 .....              | 9  |

| スリープ モード .....            | 10 |

| デバイスID .....              | 11 |

| 最大定格 .....                | 12 |

| 動作範囲 .....                | 12 |

| DC電気的特性 .....             | 12 |

| データ保持期間およびアクセス可能回数 .....  | 13 |

| 静電容量 .....                | 13 |

| 熱抵抗 .....                 | 13 |

| ACテストの負荷および波形 .....       | 13 |

| ACテスト条件 .....             | 13 |

| ACスイッチング特性 .....          | 14 |

| パワー サイクル タイミング .....      | 15 |

| 注文情報 .....                | 16 |

| 注文コードの定義 .....            | 16 |

| パッケージ図 .....              | 17 |

| 略語 .....                  | 18 |

| 本書の表記法 .....              | 18 |

| 測定単位 .....                | 18 |

| 改訂履歴 .....                | 19 |

| セールス、ソリューションおよび法律情報 ..... | 20 |

| ワールドワイドな販売と設計サポート .....   | 20 |

| 製品 .....                  | 20 |

| PSoC®ソリューション .....        | 20 |

| サイプレス開発者コミュニティ .....      | 20 |

| テクニカル サポート .....          | 20 |

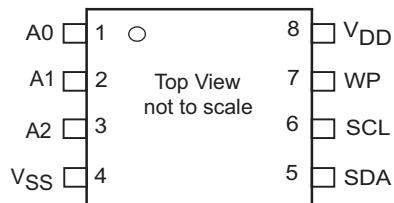

## ピン配置

図 1. 8 ピン SOIC ピン配置

## ピンの定義

| ピン名             | 入出力   | 説明                                                                                                                                                          |

|-----------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A0 ~ A2         | 入力    | デバイス選択アドレス 0 ~ 2: これらのピンは同じ 2 線式バス上で最大 8 個の同様なデバイスの内から 1 つを選択するのに使用。デバイスを選択するには、3 本のピンのアドレス値がスレーブ アドレスの対応ビットと一致する必要がある。アドレスピンは内部でプルダウン                      |

| SDA             | 入力／出力 | シリアルデータアドレス: 2 線式インターフェース用の双方向ピン。オープンドレインであり、2 線式バス上の他のデバイスとワイヤード ANDされるよう意図されている。入力バッファはノイズ耐性に対応するようにシュミットトリガーを備え、出力ドライバは立ち下りエッジでのスロープ制御を備える。外付けプルアップ抵抗が必要 |

| SCL             | 入力    | シリアルクロック: 2 線式インターフェース用のシリアルクロックピン。データは立ち下りエッジでデバイスからクロック出力され、立ち上りエッジでデバイスにクロック入力。SCL 入力もノイズ耐性用にシュミットトリガー入力を備える                                             |

| WP              | 入力    | 書き込み保護: WP が V <sub>DD</sub> に接続された時、メモリマップ全体内のアドレスが書き込みから保護。WP がグランドに接続された時、すべてのアドレスには書き込み可能。このピンは内部でプルダウン                                                 |

| V <sub>SS</sub> | 電源    | デバイスのグランド。システムのグランドに接続する必要がある                                                                                                                               |

| V <sub>DD</sub> | 電源    | デバイスの電源入力                                                                                                                                                   |

## 機能概要

FM24V01A はシリアル F-RAM メモリです。メモリアレイは  $16,384 \times 8$  ビットに論理構成され、業界標準 2 線式 ( $I^2C$ ) インターフェースを介してアクセスされます。F-RAM の機能動作はシリアル EEPROM に似ています。同じピン配置の FM24V01A とシリアル EEPROM の主な相違点は F-RAM の優れた書き込み性能、高いアクセス回数、低消費電力です。

## メモリアーキテクチャ

FM24V01A のアクセスには、8 データビットごとの 16K の位置をアドレス指定します。これら 8 つのデータビットは順次シフトイン／シフトアウトされます。アドレスは、スレーブアドレス（他の非メモリデバイスと区別するため）と 2 バイトアドレスを含む 2 線式プロトコルを使ってアクセスされます。アドレス範囲の上位 2 ビットは「ドントケア」値です。14 ビットのアドレスで、一意的に各バイトアドレスを指定します。

メモリ動作のためのアクセス時間は基本的にシリアルプロトコルに必要な時間以外は 0 です。つまり、メモリは 2 線式バスの速度で読み書きされます。シリアル EEPROM とは異なり、書き込み処理がバス速度で行われるので、デバイスの書き込み準備を知るためにポーリングする必要はありません。新しいバストランザクションがデバイスに送り込まれるまでに書き込み動作は完了します。これは [ページ 8 メモリの動作](#)で詳しく説明します。

## 2 線式インターフェース

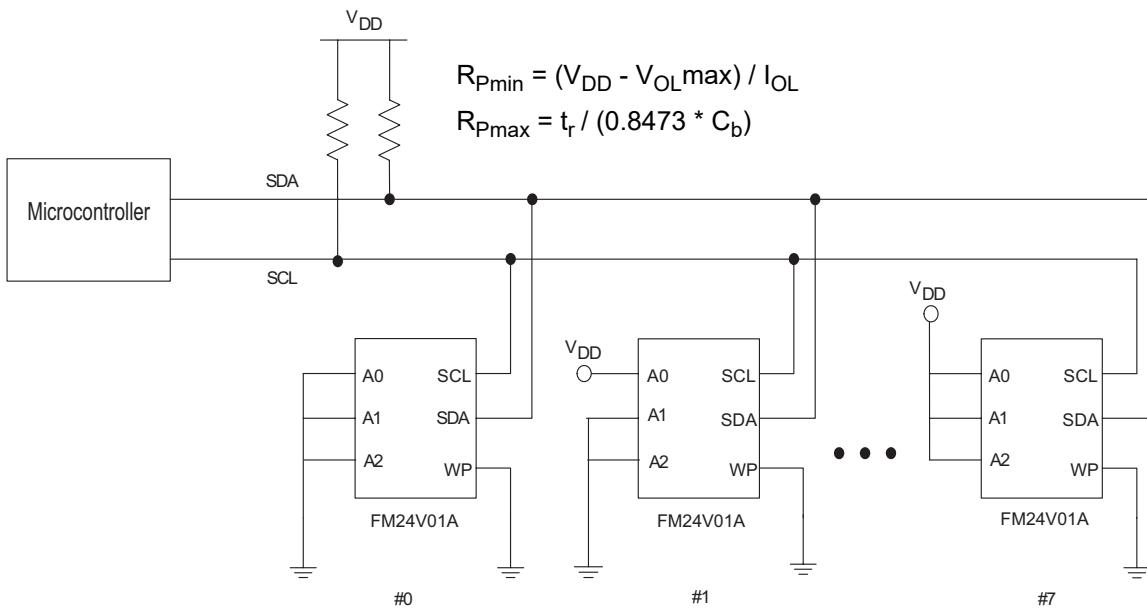

FM24V01A は少ないピン数または小さい基板面積を使って双方向 2 線式バスプロトコルを使用します。[図 2](#) には、マイクロコントローラー ベースのシステム内で FM24V01A 使用した標準的なシステムコンフィギュレーションを示します。業界標準 2 線式バスは多くのユーザーによく知られていますが、本節でも説明します。

慣例では、データをバス上に送信するデバイスはトランスマッタとなり、このデータのターゲットデバイスはレシーバです。バスを制御しているデバイスはマスターです。マスターは、すべての動作用のクロック信号の生成を行います。制御されているバス上のデバイスはスレーブです。FM24V01A は常にスレーブデバイスです。

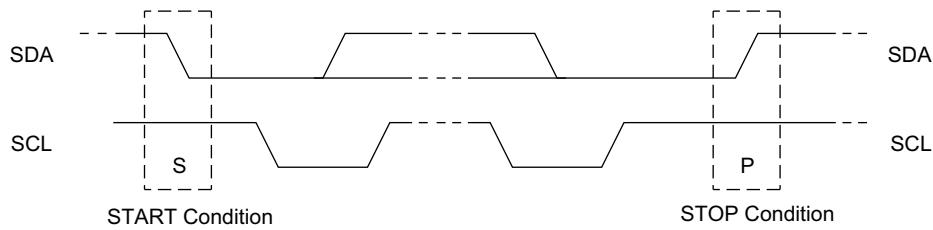

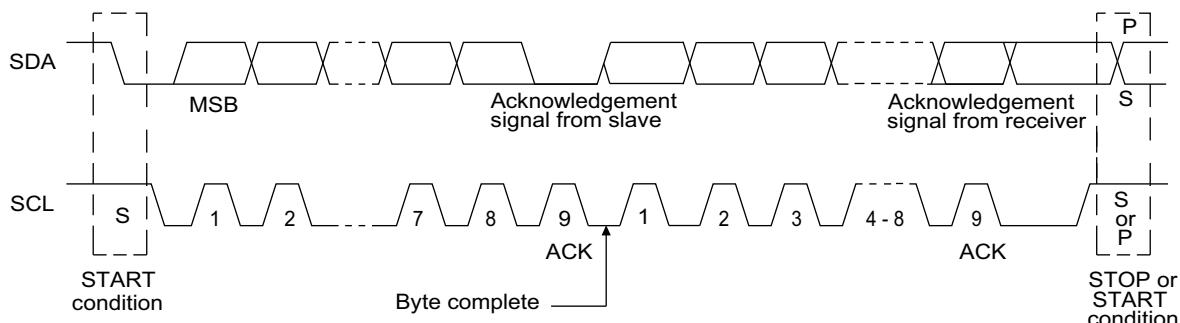

バスプロトコルは SDA と SCL 信号の遷移ステートにより制御されます。START、STOP、データビット、アクノリッジの 4 つの条件があります。[ページ 5 の図 3](#) と [ページ 5 の図 4](#) には、4 つのステートを指定する信号条件を示します。詳しいタイミング図は電気的仕様の節に示します。

FM24V01A は、 $I_{OL}$  のファストモードプラス ( $F_m+$ , 1MHz) および、 $V_{hys}$  のハイスピードモード ( $H_s$ -mode, 3.4MHz) において、NXP I<sup>2</sup>C 仕様に合いません。詳細については [12 ページの DC 電気的特性](#) の表を参照してください。

図 2. シリアル ( $I^2C$ ) F-RAM を使ったシステムコンフィギュレーション

## STOP 条件 (P)

STOP 条件は、SCL 信号が HIGH の時、バス マスターが SDA を LOW から HIGH に駆動する時に指定されます。FM24V01A を使用したすべての動作は STOP 条件で終わる必要があります。動作中に STOP がアサートされると、動作は中止されます。マスターは STOP 条件をアサートするために SDA (メモリ読み出しでない) を制御する必要があります。

## START 条件 (S)

START 条件は SCL 信号が HIGH の時、バス マスターが SDA を HIGH から LOW に駆動する時に指定されます。START 条件はすべてのコマンドの前に発生する必要があります。いつでも START 条件をアサートすることで進行中の動作を中止できます。START 条件を使って動作を中止すると、FM24V01A が新しい動作の準備ができるようになります。

動作中に電源が  $V_{DD}$  の最小値の仕様を下回ると、システムは他の動作を行う前に START 条件を発行する必要があります。

図 3. START および STOP 条件

## データ／アドレス転送

すべてのデータ転送 (アドレスを含む) は SCL が HIGH の時に行われます。上記の 3 つの条件下の場合以外、SDA 信号は SCL が HIGH の時に変化してはいけません。

図 4. I<sup>2</sup>C バス上のデータ転送

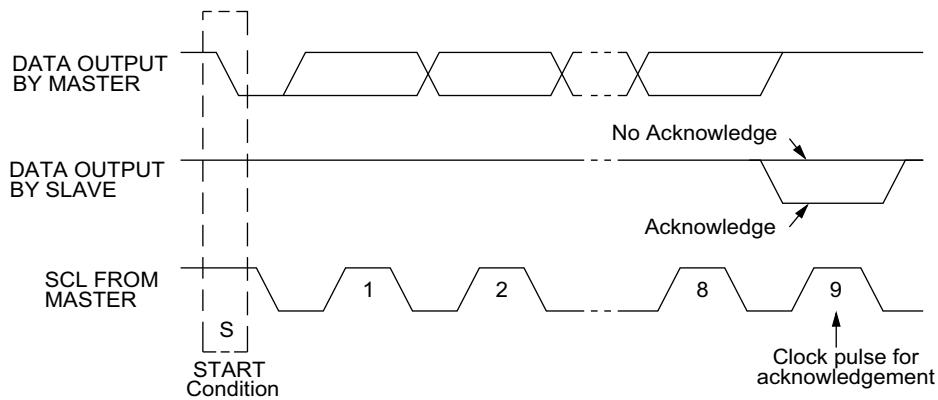

### アクノリッジ/ノーアクノリッジ

アクノリッジは、すべてのトランザクションで8番目のデータビットが転送された後に行われます。この状態の間、トランスマッタは SDA バスを解放してレシーバがバスを駆動できるようにします。レシーバは SDA 信号を LOW に駆動してバイトの受信をアクノリッジします。レシーバが SDA を LOW に駆動しない場合、状態がノーアクノリッジとなり、動作は中止されます。

レシーバは 2 つの明確な理由でアクノリッジに失敗します。1つ目は、バイト転送が失敗することです。この場合、ノーアクノリッジ状態は、デバイスが再びアドレス指定されるように現

時点の動作を中断します。これにより、最後のバイトが通信エラーの発生時に復帰できるようになります。

二つ目の理由は、レシーバが意図的に動作を終了させるようにアクノリッジしないことです。これは最も一般的な理由です。例えば読み出し中に、レシーバがアクノリッジ信号（クロック）を送信している限り、FM24V01A はデータをバス上に置きます。読み出し動作が完了し、これ以上のデータが不要になつた時、レシーバは最後のバイトをアクノリッジしてはなりません。レシーバが最後のバイトをアクノリッジしてしまうと、マスターが STOP などの新しいコマンドを発行する一方で FM24V01A は次のクロックでバスを駆動しようとすることになります。

図 5. I<sup>2</sup>C バス上のアクノリッジ

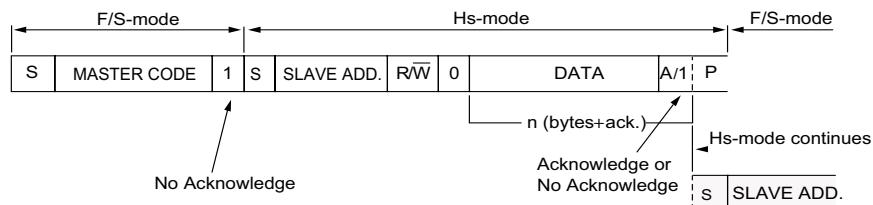

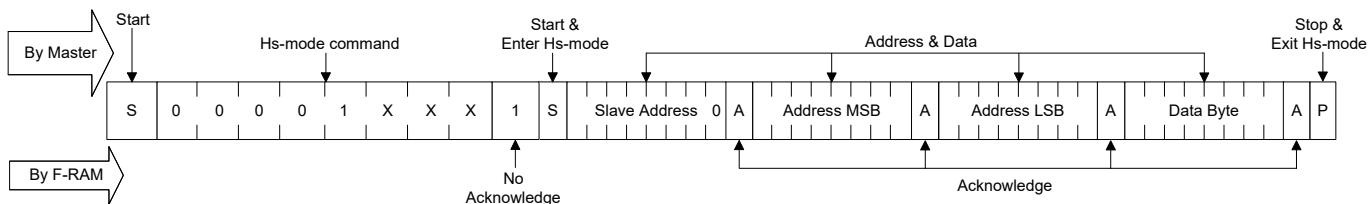

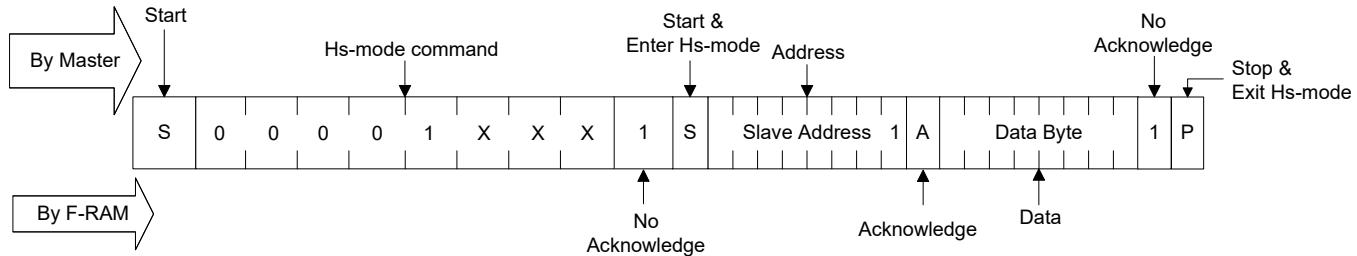

### 高速モード (Hs モード)

FM24V01A は 3.4MHz 高速モードをサポートします。デバイスを高速モードにするには、マスターコード (00001XXXb) を発行する必要があります。すると、マスターとスレーブ間の通

信速度は 3.4MHz まで加速できるようになります。STOP 条件により Hs モードが終了します。シングルバイトおよびマルチバイトの読み書きがサポートされます。

図 6. Hs モードにおけるデータ転送フォーマット

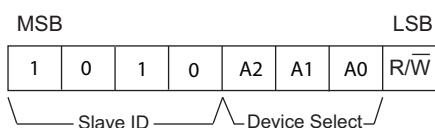

## スレーブ デバイス アドレス

START 条件後に FM24V01A が期待する最初のバイトはスレーブ アドレスです。図 7 に示すように、スレーブ アドレスはデバイス タイプまたはスレーブ ID、デバイス選択アドレス ビット、およびトランザクションが読み出しか書き込みであるかを指定するビットから成ります。

ビット7～4はデバイス タイプ(スレーブID)であり、FM24V01Aの場合は1010bにセットする必要があります。これらのビットにより、他の機能タイプのデバイスが同じアドレス範囲で2線式バス上に存在できます。ビット3～1はデバイス選択アドレスビットです。これらはデバイスを選択するために外部アドレスピンの対応する値に一致する必要があります。各デバイスに異なるアドレスを割り当てることで、最大8個のFM24V01Aデバイスが同じ2線式バス上に存在できます。ビット0は読み出し／書き込みビット(R/W)です。R/W='1'は読み出し動作を示し、R/W='0'は書き込み動作を示します。

図7. メモリスレーブデバイスアドレス

## アドレス指定の概要

FM24V01A が（レシーバとして）スレーブ アドレスをアクノリッジした後、マスターは書き込み動作のためにメモリアドレスをバス上に置けます。アドレスは 2 バイトを必要とします。完全な 14 ビット アドレスは内部でラッチされます。各アクセスにより、ラッチされたアドレス値が自動的にインクリメントされます。現時点のアドレスはラッチに保持されている値です。これは、新たに書き込みされた値または最近のアクセスのアドレス後に続くアドレスです。現時点のアドレスは、電源が入っている限り、または新しい値が書き込みされるまで保持されます。読み出しあはいつも現時点のアドレスを使用します。以下で説明するように書き込み動作を行うことで、ランダムな読み出しアドレスをロードできます。

各データ バイトの送信後、アクノリッジの直前に、FM24V01A は内部アドレス ラッチをインクリメントします。これにより、追加のアドレス指定なしで次の連続バイトにアクセスできます。最後のアドレス (3FFFh) に達した後、アドレス ラッチは 0000h に戻ります。一度の読み出しありは書き込み動作でアクセスできるバイト数の制限はありません。

データ転送

アドレス バイトが送信された後、バス マスターと FM24V01A 間のデータ転送を開始できます。読み出し動作では、FM24V01A は8データビットをバス上に置いてマスターからのアクノリッジを待ちます。アクノリッジ信号が送信された場合、FM24V01A は次の連続バイトを転送します。アクノリッジ信号が送信されない場合、FM24V01A は読み出し動作を終了します。書き込み動作では、FM24V01A はマスターから 8 データ ビットを受け入れてアクノリッジ信号を送信します。すべてのデータ転送は MSB(最上位ビット) ファースト方式で行われます。

## メモリの動作

FM24V01A は、他の 2 線式インターフェース メモリ製品によく似ている方法で動作するように設計されています。主な相違点は、F-RAM 技術の優れた書き込み性能に起因します。これらの改善は、書き込み中に FM24V01A と類似のコンフィギュレーションの EEPROM のいくつかの相違点となります。完全な書き込みと読み出し動作は次の節で詳しく説明します。

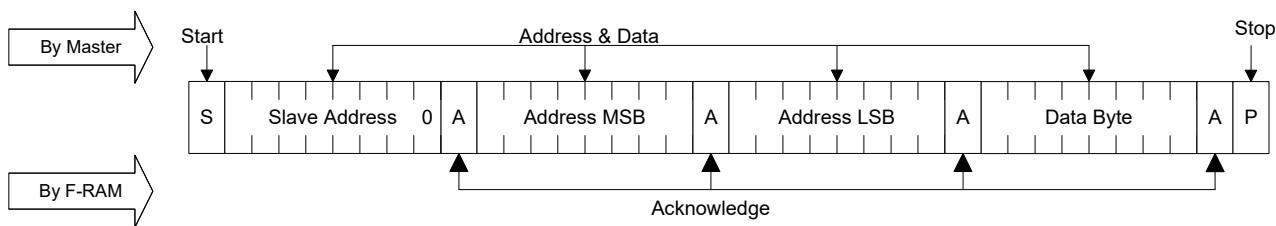

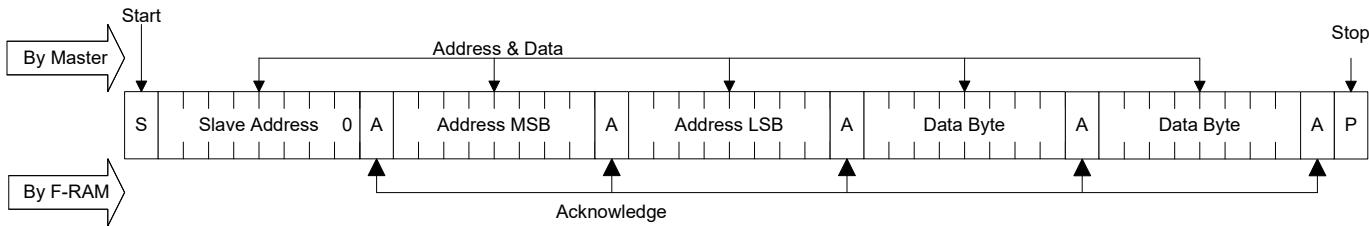

### 書き込み動作

すべての書き込みはスレーブ アドレス、それからメモリ アドレスで始まります。バス マスターはスレーブ アドレスの LSB (R/W ビット) を「0」にセットすることで書き込み動作であることを示します。アドレス指定した後、バス マスターは 1 データ バイトずつメモリに送信して、メモリはアクノリッジ条件を生成します。連続バイトはいくつでも書き込めます。アドレス範囲の終わりに内部で達した場合、アドレス カウンタは 3FFFh から 0000h にラップアップします。

他の不揮発性メモリ技術と異なり、F-RAM は事実上書き込み遅延はありません。基本的なメモリの読み出しと書き込みのアクセス時間が同じなので、バスを介して遅延がないことが感じられます。全体のメモリ動作サイクルは、1 つのバス サイクル以

内で行われます。このため、読み出しと書き込みを含むすべての動作は書き込みの直後に行えます。書き込みが完了するかを判定するために EEPROM で使用される技術であるアクノリッジ ポーリングは不要になり、常にレディー状態を返します。

内部では、8 番目のビットが転送された後に実際のメモリ書き込みが行われます。この書き込みはアクノリッジ信号が送信される前に完了します。このため、ユーザーはメモリ内容を変更せずに書き込みを中止したい場合、8 番目のデータ ビットの前に START または STOP 条件を使用する必要があります。FM24V01A はページ バッファリングを使用しません。

メモリ アレイは WP ピンを使用して書き込みから保護できます。WP ピンを HIGH 状態 ( $V_{DD}$ ) にセットすると、すべてのアドレスを書き込みから保護できます。FM24V01A は保護されたアドレスへ書き込まれたデータ バイトをアクノリッジしません。また、これらのアドレスに書き込もうとしてもアドレス カウンタはインクリメントされません。WP を LOW 状態 ( $V_{SS}$ ) にセットすると、書き込み保護が無効になります。WP は内部でプルダウンされます。

**図 8** と **図 9** は、ファストモードプラス (Fm+) でのシングルバイトとマルチバイト書き込みサイクルを示します。**図 10** は、Hs モードでのシングルバイト書き込みサイクルを示します。

図 8. シングルバイト書き込み

図 9. マルチバイト書き込み

図 10. Hs モード バイト書き込み

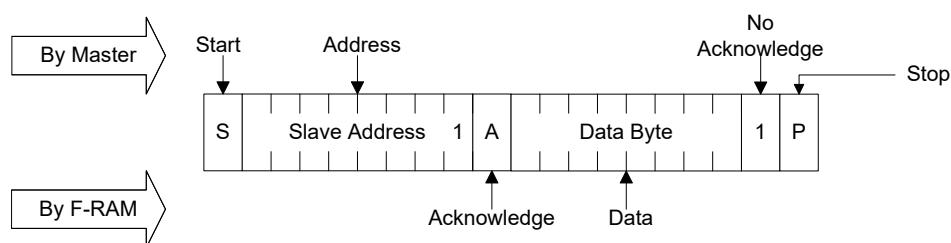

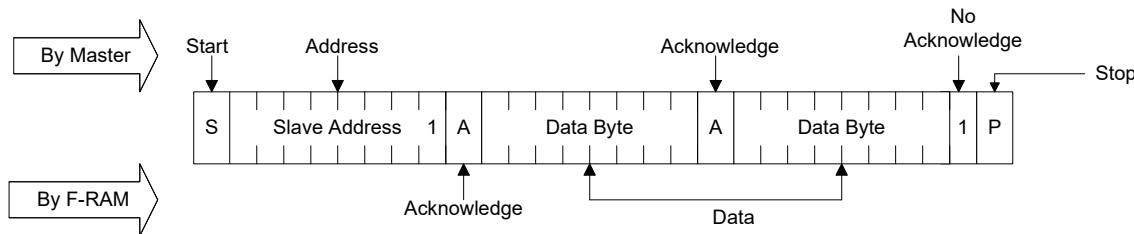

## 読み出し動作

読み出し動作は2つの基本タイプがあります。現時点のアドレス読み出しと選択的なアドレス読み出しだけです。現時点のアドレス読み出しへは、FM24V01Aは内部アドレスラッ奇を使用してアドレスを提供します。選択的な読み出しへは、ユーザーはアドレスを特定の値にセットする手順を行います。

### 現時点のアドレスと連続読み出し

前述のように、FM24V01Aは内部アドレスラッ奇を使用して読み出し動作にアドレスを提供します。現時点のアドレス読み出しへは、アドレスラッ奇内の既存の値を読み出し動作の開始点として使用します。システムは、最近の動作のアドレス直後に続くアドレスから読み出します。

現時点のアドレス読み出しを行うために、バスマスターはLSBが「1」にセットされたスレーブアドレスを提供します。これは読み出し動作が要求されたことを示します。完全なスレーブアドレスを受信した後、FM24V01Aは次のクロックで現時点のアドレスからデータをシフトアウトし始めます。現時点のアドレスは内部アドレスラッ奇で保持される値です。

現時点のアドレスで始まり、バスマスターはバイトをいくつでも読み出せます。したがって、連続読み出しへは単に複数のバ

ト転送と伴った現時点のアドレス読み出しだけです。各バイトの後、内部アドレスカウンタはインクリメントされます。

注：バスマスターがバイトをアクノリッジするたびに、これはFM24V01Aが次の連続バイトを読み出す必要があることを示します。

読み出し動作を正常に終了する4つの方法があります。読み出しを正常に終了しない場合、FM24V01Aが追加のデータをバス上に読み出そうとするためバス競合が発生する可能性が高いです。4つの有効な方法は以下のとおりです。

1. バスマスターは9番目のクロックサイクルでノーアクノリッジ信号を発行し、10番目のクロックサイクルでSTOP条件を発行します。これは推奨された方法であり、下図に示します。

2. バスマスターは9番目のクロックサイクルでノーアクノリッジ信号を発行し、10番目のクロックサイクルでSTART条件を発行します。

3. バスマスターは9番目のクロックサイクルでSTOP条件を発行します。

4. バスマスターは9番目のクロックサイクルでSTART条件を発行します。

図11. 現時点のアドレス読み出し

図12. 連続読み出し

図13. Hsモードでの現時点のアドレス読み出し

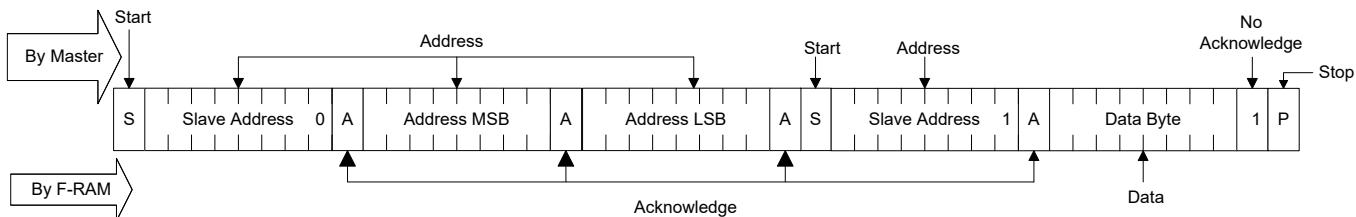

### 選択性な(ランダムな)読み出し

ランダムなアドレス位置を読み出し動作の開始点に選択性できるようにする簡単な方法があります。これは、書き込み動作の最初3バイトを使って内部アドレスをセットし、それから読み出し動作を行うことで実現します。

選択性な読み出しを行うために、バスマスターは LSB ( $R/W$ ) が 0 にセットされたスレーブアドレスを送信します。これは書き

込み動作を示します。書き込みプロトコルに従って、バスマスターはそれに続き、内部アドレスラッチにロードされるアドレスバイトを送信します。FM24V01A がアドレスをアクノリッジした後、バスマスターは START 条件を発行します。これにより、書き込み動作が中止されると同時に、 LSB が「1」にセットされたスレーブアドレスで読み出しコマンドが発行されます。これでの動作は現時点のアドレス読み出しどなります。

**図 14. 選択性な(ランダムな)読み出し**

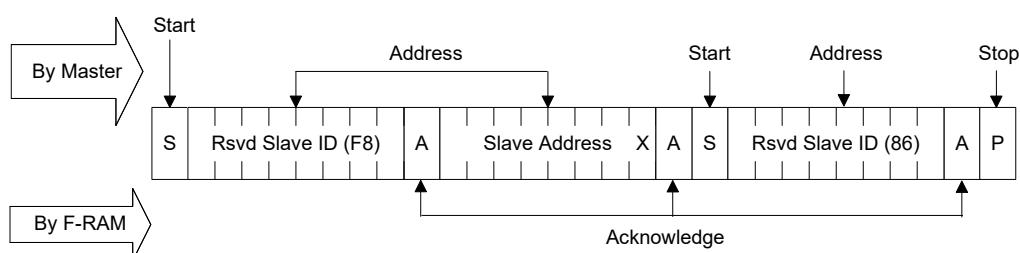

### スリープモード

スリープモードという低消費電力モードが FM24V01A デバイスに実装されています。スリープコマンド 86h がクロック入力されると、デバイスはこの低消費電力モードに移行します。以下のように、スリープモードに入ります。

1. マスターが START コマンドを送信します。

2. マスターが予約済みスレーブ ID 0xF8 を送信します。

3. FM24V01A は ACK を送信します。

4. マスターは、識別する必要とするスレーブデバイスの I<sup>2</sup>C バススレーブアドレスを送信します。最後のビットは「ドントケア」値 (R/W ビット) です。1つのデバイス (I<sup>2</sup>C バススレーブアドレスを持っているもの) のみがこのビットをアクノリッジしなければなりません。

5. FM24V01A は ACK を送信します。

6. マスターは Re-START コマンドを送信します。

7. マスターが予約済みスレーブ ID 0x86 を送信します。

8. FM24V01A は ACK を送信します。

9. マスターは、デバイスがスリープモードに入る事を確保するために、STOP 信号を送信します。

一旦スリープモードに入ると、デバイスは  $I_{ZZ}$  電流を引き出しますが、I<sup>2</sup>C ピンを監視し続けます。一旦マスターが FM24V01A によって識別されたスレーブアドレスを送信すると、デバイスは、 $t_{REC}$  時間 (最大 400μs) 以内に「ウェイクアップ」して、通常動作の準備ができます。デバイスの準備ができているかどうかを判断する別の方法として、マスターは読み出しされた書き込みコマンドを送信して ACK を待ちます。ウェイクアップしている間、デバイスは準備ができるまでにマスターに NACK を返します。

**図 15. スリープモードへの移行**

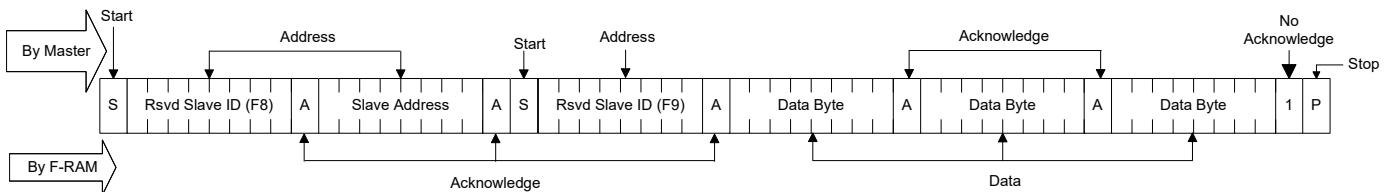

## デバイス ID

FM24V01A デバイスは、メーカー、製品 ID、ダイリビジョンの 3 データ バイトを用意することでデバイスを識別する手段を組み込んでいます。デバイス ID は読み出し専用です。次のように、デバイス ID をアクセスできます。

1. マスターが START コマンドを送信します。

2. マスターが予約済みスレーブ ID 0xF8 を送信します。

3. FM24V01A は ACK を送信します。

4. マスターは、識別する必要があるスレーブ デバイスの I<sup>2</sup>C バス スレーブ アドレスを送信します。最後のビットは「ドント ケア」値 (R/W ビット) です。1つのデバイス (I<sup>2</sup>C バス スレーブ アドレスを持っているもの) のみがこのビットを アクノリッジしなければなりません。

5. FM24V01A は ACK を送信します。

6. マスターは Re-START コマンドを送信します。

7. マスターが予約済みスレーブ ID 0xF9 を送信します。

8. FM24V01A は ACK を送信します。

9. デバイス ID の読み出しあは、12 ビットのメーカー ID、次に 9 ビットのパート ID、それから 3 ビットのダイリビジョン の順で行われます。

10. マスターは、最後のビットを NACK することでデバイス ID の読み出しシーケンスを終了します。従って、スレーブ デバイスのステート マシンがリセットされ、マスターが STOP コマンドを送信できるようになります。

注：デバイス ID の読み出しあは、NACK コマンドを送信することであつても停止できます。

表 1. デバイス ID

| デバイス ID<br>(3 バイト) | デバイス ID の説明         |                   |                  |                  |

|--------------------|---------------------|-------------------|------------------|------------------|

|                    | 23 ~ 12<br>(12 ビット) | 11 ~ 8<br>(4 ビット) | 7 ~ 3<br>(5 ビット) | 2 ~ 0<br>(3 ビット) |

|                    | 製品 ID               |                   |                  |                  |

|                    | 容量                  | バージョン             | ダイリビジョン          |                  |

| 004101h            | 000000000100        | 0001              | 00000            | 001              |

注：製品 ID ビット 0 と 4 は予約済みです。

図 16. デバイス ID の読み出し

## 最大定格

|                                                         |                                         |

|---------------------------------------------------------|-----------------------------------------|

| 最大定格を超えると、デバイスの寿命が短くなる可能性があります。これらのユーザー ガイドラインは試験されません。 |                                         |

| 保存温度                                                    | -65°C ~ +125°C                          |

| 最大累積保存時間                                                |                                         |

| 周囲温度 125°C                                              | 1000 h                                  |

| 周囲温度 85°C                                               | 10 年                                    |

| 電源供給時の周囲温度                                              | -55°C ~ 125°C                           |

| $V_{SS}$ を基準とした $V_{DD}$ の電源電圧                          | -1.0V ~ +4.5V                           |

| 入力電圧 *                                                  | -1.0V ~ +4.5V、 $V_{IN} < V_{DD} + 1.0V$ |

| High-Z 状態の出力<br>に印加される DC 電圧                            | -0.5V ~ $V_{DD} + 0.5V$                 |

| 任意のピンの過渡電圧、グランド電位基準<br>(<20ns)                          | -2.0V ~ $V_{DD} + 2.0V$                 |

## DC 電気的特性

### 動作範囲

| パラメータ           | 説明                              | テスト条件                                                                              | Min                              | Typ <sup>[2]</sup>  | Max                  | 単位      |

|-----------------|---------------------------------|------------------------------------------------------------------------------------|----------------------------------|---------------------|----------------------|---------|

| $V_{DD}$        | 電源                              |                                                                                    | 2.0                              | 3.3                 | 3.6                  | V       |

| $I_{DD}$        | 平均 $V_{DD}$ 電流                  | $SCL = V_{DD} - 0.2V$ と $V_{SS}$ の間でトグル。<br>他の入力は $V_{SS}$ または $V_{DD} - 0.2V$ を印加 | $f_{SCL} = 100kHz$               | -                   | -                    | $\mu A$ |

|                 |                                 |                                                                                    | $f_{SCL} = 1MHz$                 | -                   | -                    | $\mu A$ |

|                 |                                 |                                                                                    | $f_{SCL} = 3.4MHz$               | -                   | -                    | $\mu A$ |

| $I_{SB}$        | $V_{DD}$ スタンバイ電流                | $SCL = SDA = V_{DD}$ 。他の入力は、 $V_{SS}$ または $V_{DD}$ に接続。STOP コマンドを発行                | -                                | 90                  | 150                  | $\mu A$ |

| $I_{ZZ}$        | スリープ モード電流                      | $SCL = SDA = V_{DD}$ 。他の入力は、 $V_{SS}$ または $V_{DD}$ に接続。STOP コマンドを発行                | -                                | 5                   | 8                    | $\mu A$ |

| $I_{LI}$        | 入力リーコンデンサー電流<br>(WP、A2 ~ A0 以外) | $V_{SS} \leq V_{IN} \leq V_{DD}$                                                   | -1                               | -                   | +1                   | $\mu A$ |

|                 | 入力リーコンデンサー電流<br>(WP、A2 ~ A0)    | $V_{SS} \leq V_{IN} \leq V_{DD}$                                                   | -1                               | -                   | +100                 | $\mu A$ |

| $I_{LO}$        | 出力リーコンデンサー電流                    | $V_{SS} \leq V_{OUT} \leq V_{DD}$                                                  | -1                               | -                   | +1                   | $\mu A$ |

| $V_{IH}$        | 入力 HIGH 電圧 (SDL、SDA)            |                                                                                    | 0.7× $V_{DD}$                    | -                   | $V_{DD}(\max) + 0.3$ | V       |

|                 | 入力 HIGH 電圧 (WP、A2 ~ A0)         |                                                                                    | 0.7× $V_{DD}$                    | -                   | $V_{DD} + 0.3$       | V       |

| $V_{IL}$        | 入力 LOW 電圧                       |                                                                                    | -0.3                             | -                   | 0.3× $V_{DD}$        | V       |

| $V_{OL}^{[3]}$  | 出力 LOW 電圧                       | $I_{OL} = 3mA$                                                                     | -                                | -                   | 0.4                  | V       |

|                 |                                 | $I_{OL} = 6mA$                                                                     | -                                | -                   | 0.6                  | V       |

| $R_{in}^{[4]}$  | 入力抵抗 (WP、A2 ~ A0)               | $V_{IN} = V_{IL(\max)}$ の場合                                                        | 50                               | -                   | -                    | kΩ      |

|                 |                                 | $V_{IN} = V_{IH(\min)}$ の場合                                                        | 1                                | -                   | -                    | MΩ      |

| $V_{hys}^{[5]}$ | シミュレート トリガ入力のヒステリシス             |                                                                                    | $f_{SCL} = 100kHz, 400kHz, 1MHz$ | 0.05× $V_{DD}$      | -                    | V       |

|                 |                                 |                                                                                    | $f_{SCL} = 3.4MHz$               | $0.1 \times V_{DD}$ | -                    | V       |

### 注

2. 標準値は 25 °C、 $V_{DD}=V_{DD}(\text{typ})$ 。100% 試験されているわけではありません。

3. FM24V01A は、0.4V の  $V_{OL}$  時の 20mA の  $I_{OL}$  のファストモードプラス ( $Fm+$ , 1MHz) において、NXP I<sup>2</sup>C 仕様に合いません。

4. 入力プルダウン回路は、入力電圧が  $V_{IL}$  以下の時に強くなり (50kΩ)、入力電圧が  $V_{IH}$  以上の時に弱くなります (1MΩ)。

5. FM24V01A は、0.1× $V_{DD}$  の  $V_{hys}$  のハイスピードモード (Hs-mode, 3.4MHz) において、NXP I<sup>2</sup>C 仕様に合いません。

## データ保持期間およびアクセス可能回数

| パラメーター   | 説明      | テスト条件                  | Min       | Max | 単位   |

|----------|---------|------------------------|-----------|-----|------|

| $T_{DR}$ | データ保持期間 | $T_A=85^\circ\text{C}$ | 10        | —   | 年    |

|          |         | $T_A=75^\circ\text{C}$ | 38        | —   |      |

|          |         | $T_A=65^\circ\text{C}$ | 151       | —   |      |

| $NV_C$   | アクセス回数  | 動作温度範囲内                | $10^{14}$ | —   | サイクル |

## 静電容量

| パラメーター [6] | 説明                | テスト条件                                                            | Max | 単位 |

|------------|-------------------|------------------------------------------------------------------|-----|----|

| $C_{IO}$   | 入力／出力ピン静電容量 (SDA) | $T_A=25^\circ\text{C}, f=1\text{MHz}, V_{DD}=V_{DD}(\text{typ})$ | 8   | pF |

| $C_I$      | 入力ピン静電容量          |                                                                  | 6   | pF |

## 熱抵抗

| パラメーター [6]    | 説明                | テスト条件                                        | 8 ピン SOIC | 単位   |

|---------------|-------------------|----------------------------------------------|-----------|------|

| $\Theta_{JA}$ | 熱抵抗<br>(接合部から周囲)  | 熱抵抗を測定するテスト条件は EIA/JESD51 で標準化されたテスト方法と手順に従う | 146       | °C/W |

| $\Theta_{JC}$ | 熱抵抗<br>(接合部からケース) |                                              | 48        | °C/W |

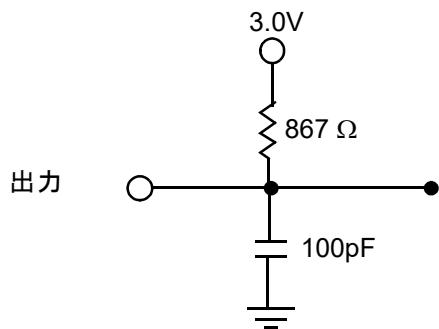

## AC テストの負荷および波形

図 17. AC テストの負荷および波形

## AC テスト条件

- 入力パルス レベル .....  $V_{DD}$  の 10% および 90%

- 入力の立ち上りと立ち下り時間 ..... 10ns

- 入力と出力タイミングの参照レベル .....  $0.5 \times V_{DD}$

- 出力負荷容量 ..... 100pF

### 注

6. これらのパラメーターは設計保証であり、テストは行われていません。

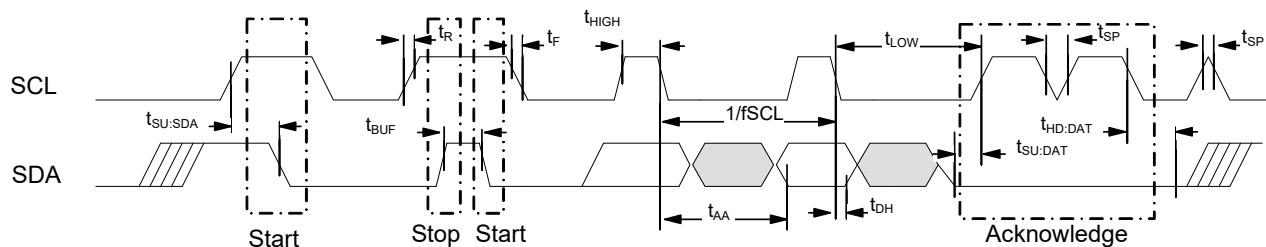

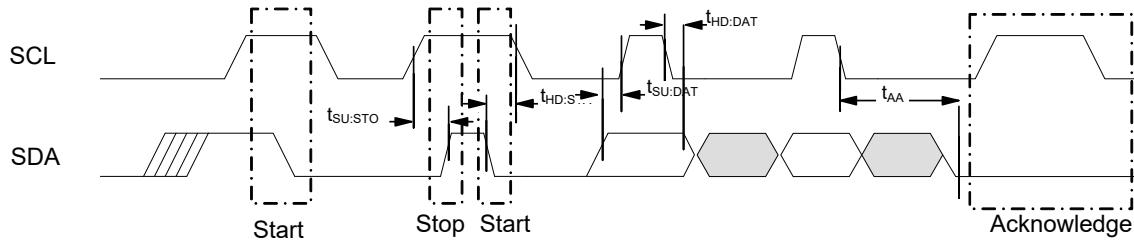

## AC スイッチング特性

### 動作範囲

| パラメーター <sup>[7]</sup>    |               | 説明                                                         | ファストモードプラス(Fm+) <sup>[9]</sup> |     | Hs モード <sup>[9]</sup> |     | 単位  |

|--------------------------|---------------|------------------------------------------------------------|--------------------------------|-----|-----------------------|-----|-----|

| サイプレス<br>パラメーター          | 代替の<br>パラメーター |                                                            | Min                            | Max | Min                   | Max |     |

| $f_{SCL}$ <sup>[8]</sup> |               | SCL クロック周波数                                                | —                              | 1.0 | —                     | 3.4 | MHz |

| $t_{SU;STA}$             |               | 反復 START 用の START 条件セットアップ時間                               | 260                            | —   | 160                   | —   | ns  |

| $t_{HD;STA}$             |               | START 条件ホールド時間                                             | 260                            | —   | 160                   | —   | ns  |

| $t_{LOW}$                |               | クロック LOW 周期                                                | 500                            | —   | 160                   | —   | ns  |

| $t_{HIGH}$               |               | クロック HIGH 周期                                               | 260                            | —   | 60                    | —   | ns  |

| $t_{SU;DAT}$             | $t_{SU;DATA}$ | データ入力セットアップ時間                                              | 50                             | —   | 10                    | —   | ns  |

| $t_{HD;DAT}$             | $t_{HD;DATA}$ | データ入力ホールド時間                                                | 0                              | —   | 0                     | 70  | ns  |

| $t_{DH}$                 |               | データ出力ホールド時間 (SCL=V <sub>IL</sub> の時から)                     | 0                              | —   | 0                     | —   | ns  |

| $t_R$ <sup>[10]</sup>    | $t_r$         | 入力立ち上り時間                                                   | —                              | 120 | 10                    | 80  | ns  |

| $t_F$ <sup>[10]</sup>    | $t_f$         | 入力立ち下り時間                                                   | 20×(V <sub>DD</sub> /5.5V)     | 120 | 10                    | 80  | ns  |

| $t_{SU;STO}$             |               | STOP 条件セットアップ時間                                            | 260                            | —   | 160                   | —   | ns  |

| $t_{AA}$                 | $t_{VD;DATA}$ | SCL LOW から SDA データ出力有効までの時間                                | —                              | 450 | —                     | 130 | ns  |

| $t_{VD;ACK}$             |               | ACK 出力有効時間                                                 | —                              | 450 | —                     | 130 | ns  |

| $t_{OF}$ <sup>[10]</sup> |               | V <sub>IH</sub> (min) から V <sub>IL</sub> (max) までの出力立ち下り時間 | 20×(V <sub>DD</sub> /5.5V)     | 120 | —                     | 80  | ns  |

| $t_{BUF}$                |               | 新規送信前のバス空き時間                                               | 500                            | —   | 300                   | —   | ns  |

| $t_{SP}$                 |               | SCL、SDA 上のノイズ抑制時定数                                         | 0                              | 50  | —                     | 5   | ns  |

図 18. 読み出しのバスタイミング図

図 19. 書き込みのバスタイミング図

### 注

7. テスト条件は、10ns 以下の信号遷移時間、V<sub>DD</sub>/2 のタイミング リファレンス レベル、0 ~ V<sub>DD</sub>(typ) の入力パルス レベル、指定された I<sub>OL</sub> の出力負荷、ページ 13 の図 17 に示している 100pF の負荷容量を想定しています。

8. スピード関連の仕様は、DC から f<sub>SCL</sub>(max) への動作の連続曲線に沿って保証された特性点です。

9. バス負荷 (Cb) の考慮事項 : I<sup>2</sup>C クロック周波数 (SCL) が 1MHz の場合は Cb<550pF ; SCL が 3.4MHz の場合は Cb<100pF。

10. これらのパラメーターは設計保証であり、テストは行われていません。

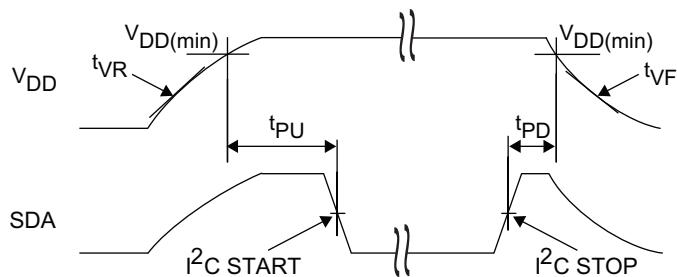

## パワー サイクル タイミング

### 動作範囲

| パラメーター              | 説明                                                | Min | Max | 単位   |

|---------------------|---------------------------------------------------|-----|-----|------|

| $t_{PU}$            | 電源投入時の $V_{DD(min)}$ から最初のアクセス (START 条件) までの時間   | 250 | –   | μs   |

| $t_{PD}$            | 最後のアクセス (STOP 条件) から電源切断時 ( $V_{DD(min)}$ ) までの時間 | 0   | –   | μs   |

| $t_{VR}^{[11, 12]}$ | $V_{DD}$ 電源投入時のランプ レート                            | 50  | –   | μs/V |

| $t_{VF}^{[11, 12]}$ | $V_{DD}$ 電源切断のランプ レート                             | 100 | –   | μs/V |

| $t_{REC}$           | スリープ モードからの復帰時間                                   | –   | 400 | μs   |

図 20. パワー サイクル タイミング

### 注

11.  $V_{DD}$  波形上の任意の点で測定した傾きです。

12. これらのパラメーターは設計保証であり、テストは行われていません。

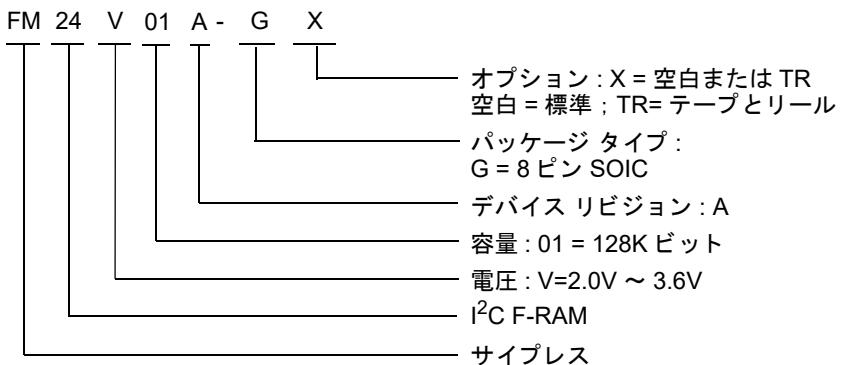

## 注文情報

| 注文コード        | パッケージ図   | パッケージ タイプ | 動作範囲 |

|--------------|----------|-----------|------|

| FM24V01A-G   | 51-85066 | 8 ピン SOIC | 産業用  |

| FM24V01A-GTR | 51-85066 | 8 ピン SOIC |      |

これらすべての部品は鉛フリーです。これらの部品の在庫状況については、最寄りのサイプレスの販売代理店にお問い合わせください。

## 注文コードの定義

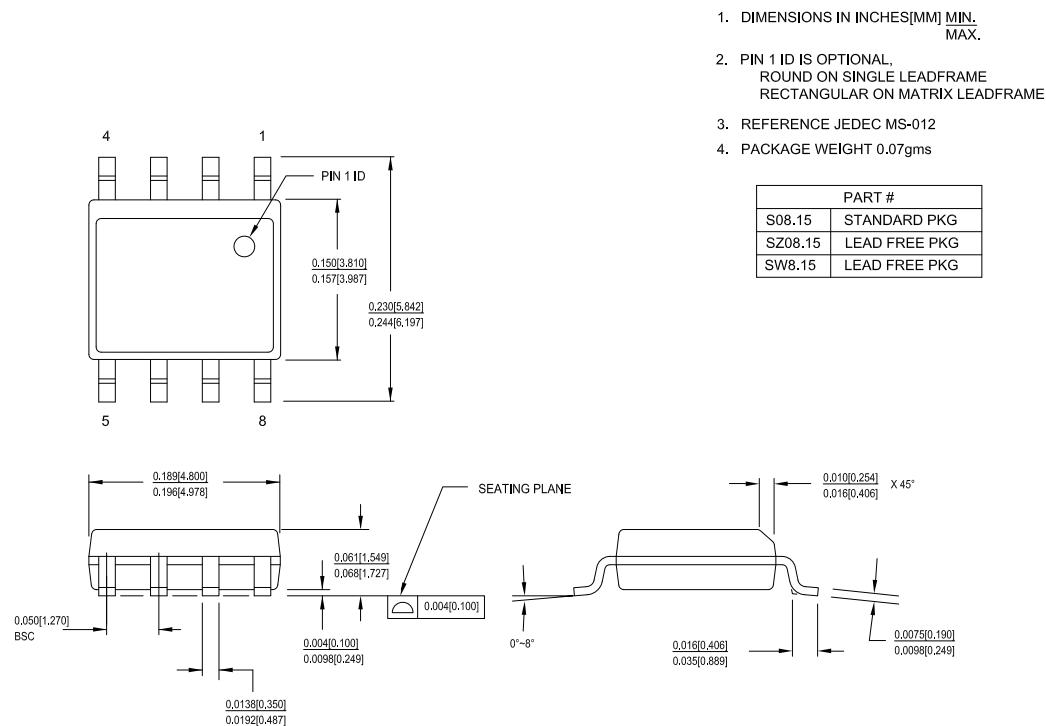

## パッケージ図

図 21. 8 ピン SOIC (150mil) パッケージの外形、51-85066

51-85066 \*I

## 略語

| 略語               | 説明                                                                       |

|------------------|--------------------------------------------------------------------------|

| ACK              | Acknowledge ( アクノリッジ )                                                   |

| CMOS             | Complementary Metal Oxide Semiconductor<br>( 相補型金属酸化膜半導体 )               |

| EIA              | Electronic Industries Alliance ( 米国電子工業会 )                               |

| I <sup>2</sup> C | Inter-Integrated Circuit<br>( インター インテグレーテッド サーキット )                     |

| I/O              | Input/Output ( 入力／出力 )                                                   |

| JEDEC            | Joint Electron Devices Engineering Council<br>( 半導体技術協会 ( 旧電子機器技術評議会 ) ) |

| LSB              | Least Significant Bit ( 最下位ビット )                                         |

| MSB              | Most Significant Bit ( 最上位ビット )                                          |

| NACK             | No Acknowledge ( ノー アクノリッジ )                                             |

| RoHS             | Restriction of Hazardous Substances<br>( 特定有害物質使用制限指令 )                  |

| R/W              | Read/Write ( 読み出し／書き込み )                                                 |

| SCL              | Serial Clock Line ( シリアル クロック ライン )                                      |

| SDA              | Serial Data Access ( シリアル データ アクセス )                                     |

| SOIC             | Small Outline Integrated Circuit<br>( 小型外形集積回路 )                         |

| WP               | Write Protect ( 書き込み保護 )                                                 |

## 本書の表記法

### 測定単位

| 記号  | 測定単位     |

|-----|----------|

| °C  | 摂氏温度     |

| Hz  | ヘルツ      |

| Kb  | 1024 ビット |

| kHz | キロヘルツ    |

| kΩ  | キロオーム    |

| MHz | メガヘルツ    |

| MΩ  | メガオーム    |

| μA  | マイクロアンペア |

| μs  | マイクロ秒    |

| mA  | ミリアンペア   |

| ms  | ミリ秒      |

| ns  | ナノ秒      |

| Ω   | オーム      |

| %   | パーセント    |

| pF  | ピコファラド   |

| V   | ボルト      |

| W   | ワット      |

## 改訂履歴

文書名 : FM24V01A、128K ビット (16K × 8) シリアル (I<sup>2</sup>C) F-RAM

文書番号 : 001-93818

| 版  | ECN 番号  | 発行日        | 変更内容                                           |

|----|---------|------------|------------------------------------------------|

| ** | 4478645 | 09/03/2014 | これは英語版 001-90869 Rev. *A を翻訳した日本語版 Rev. ** です。 |

| *A | 5574184 | 01/04/2017 | これは英語版 001-90869 Rev. *I を翻訳した日本語版 Rev. *A です。 |

| *B | 6906138 | 06/29/2020 | これは英語版 001-90869 Rev. *K を翻訳した日本語版 Rev. *B です。 |

## セールス、ソリューションおよび法律情報

### ワールドワイドな販売と設計サポート

サイプレスは、事業所、ソリューションセンター、メーカー代理店、および販売代理店の世界的なネットワークを保持しています。お客様の最寄りのオフィスについては、[サイプレスのロケーションページ](#)をご覧ください。

#### 製品

Arm® Cortex® Microcontrollers

[cypress.com/arm](http://cypress.com/arm)

車載用

[cypress.com/automotive](http://cypress.com/automotive)

クロック & バッファ

[cypress.com/clocks](http://cypress.com/clocks)

インターフェース

[cypress.com/interface](http://cypress.com/interface)

IoT (モノのインターネット)

[cypress.com/iot](http://cypress.com/iot)

メモリ

[cypress.com/memory](http://cypress.com/memory)

マイクロコントローラ

[cypress.com/mcu](http://cypress.com/mcu)

PSoC

[cypress.com/psoc](http://cypress.com/psoc)

電源用 IC

[cypress.com/pmic](http://cypress.com/pmic)

タッチ センシング

[cypress.com/touch](http://cypress.com/touch)

USB コントローラー

[cypress.com/usb](http://cypress.com/usb)

ワイヤレス

[cypress.com/wireless](http://cypress.com/wireless)

#### PSoC® ソリューション

[PSoC 1](#) | [PSoC 3](#) | [PSoC 4](#) | [PSoC 5LP](#) | [PSoC 6 MCU](#)

#### サイプレス開発者コミュニティ

[コミュニティ](#) | [サンプルコード](#) | [Projects](#) | [ビデオ](#) | [ブログ](#) | [トレーニング](#) | [Components](#)

#### テクニカル サポート

[cypress.com/support](http://cypress.com/support)

© Cypress Semiconductor Corporation, 2014-2020. 本書面は、Cypress Semiconductor Corporation 及び Spansion LLC を含むその子会社（以下「Cypress」という。）に帰属する財産である。本書面（本書面に含まれ又は言及されているあらゆるソフトウェア若しくはファームウェア（以下「本ソフトウェア」という。）を含む）は、アメリカ合衆国及び世界のその他の国における知的財産法令及び条約に基づき Cypress が所有する。Cypress はこれらの法令及び条約に基づく全ての権利を留保し、本段落で特に記載されているものを除き、その特許権、著作権、商標権又はその他の知的財産権のライセンスを一切許諾しない。本ソフトウェアにライセンス契約書が伴っておらず、かつ Cypress との間で別途本ソフトウェアの使用方法を定める書面による合意がない場合、Cypress は、(1) 本ソフトウェアの著作権に基づき、(a) ソースコード形式で提供されている本ソフトウェアについて、Cypress ハードウェア製品と共に用いるためにのみ、かつ組織内部でのみ、本ソフトウェアの修正及び複製を行うこと、並びに (b) Cypress のハードウェア製品ユニットに用いるためにのみ、（直接又は再販売者及び販売代理店を介して間接のいずれかで）本ソフトウェアをバイナリコード形式で外部エンコードユーザーに配布すること、並びに (2) 本ソフトウェア（Cypress により提供され、修正がなされていないもの）が抵触する Cypress の特許権のクレームに基づき、Cypress ハードウェア製品と共に用いるためにのみ、本ソフトウェアの作成、利用、配布及び輸入を行うことについての非独占的で譲渡不能な一身専属のライセンス（サプライセンスの権利を除く）を付与する。本ソフトウェアのその他の使用、複製、修正、変換又はコンパイルを禁止する。

適用される法律により許される範囲内で、Cypress は、本書面又はいかなる本ソフトウェア若しくはこれに伴うハードウェアに關しても、明示又は默示をとわず、いかなる保証（商品性及び特定の目的への適合性の默示の保証を含むがこれらに限られない）も行わない。いかなるコンピューティングデバイスも絶対に安全ということはない。従って、Cypress のハードウェアまたはソフトウェア製品に講じられたセキュリティ対策にもかかわらず、Cypress は、Cypress 製品への権限のないアクセスまたは使用といったセキュリティ違反から生じる一切の責任を負わない。加えて、本書面に記載された製品には、エラッタと呼ばれる設計上の欠陥またはエラーが含まれている可能性があり、公表された仕様とは異なる動作をする場合がある。適用される法律により許される範囲内で、Cypress は、別途通知することなく、本書面を変更する権利を留保する。Cypress は、本書面に記載のある、いかなる製品若しくは回路の適用又は使用から生じる一切の責任を負わない。本書面で提供されたあらゆる情報（あらゆるサンプルデザイン情報又はプログラムコードを含む）は、参照目的のためにのみに提供されたものである。この情報で構成するあらゆるアプリケーション及びその結果としてのあらゆる製品の機能性及び安全性を適切に設計、プログラム、かつテストすることは、本書面のユーザーの責任において行われるものとする。Cypress 製品は、兵器、兵器システム、原子力施設、生命維持装置若しくは生命維持システム、蘇生用の設備及び外科的移植を含むその他の医療機器若しくは医療システム、汚染管理若しくは有害物質管理の運用のために設計され若しくは意図されたシステムの重要な構成部分としての使用、又は装置若しくはシステムの不具合が人身傷害、死亡若しくは物的損害を生じさせるようなその他の使用（以下「本目的外使用」という。）のためには設計、意図又は承認されていない。重要な構成部分とは、それの不具合が装置若しくはシステムの不具合を生じせるか又はその安全性若しくは実効性に影響すると合理的に予想できるような装置若しくはシステムのあらゆる構成部分をいう。Cypress 製品のあらゆる本目的外使用から生じ、若しくは本目的外使用に関連するいかなる請求、損害又はその他の責任についても、Cypress はその全部又は一部をとわず一切の責任を負わず、かつ Cypress はそれら一切から本書により免除される。Cypress は Cypress 製品の本目的外使用から生じ又は本目的外使用に関連するあらゆる請求、費用、損害及びその他の責任（人身傷害又は死亡に基づく請求を含む）から免責補償される。

Cypress, Cypress のロゴ、Spansion, Spansion のロゴ及びこれらの組み合わせ、WICED, PSoC, CapSense, EZ-USB, F-RAM、及び Traveo は、米国及びその他の国における Cypress の商標又は登録商標である。Cypress のより完全な商標のリストは、[cypress.com](http://cypress.com) を参照すること。その他の名称及びブランドは、それぞれの権利者の財産として権利主張がなされている可能性がある。