## 特長

- 2K×8 構成の 16K ビット強誘電体 RAM (F-RAM)

- 高いアクセス可能回数: 100兆( $10^{14}$ )回の読み出し／書き込み

- 151年のデータ保持 (データ保持期間およびアクセス可能回数表を参照)

- NoDelay<sup>TM</sup> 書き込み

- 高い信頼性がある強誘電体プロセス

- 高速 2 線式シリアル インターフェース (I<sup>2</sup>C)

- 最大 1MHz の周波数

- シリアル (I<sup>2</sup>C) EEPROM からの置き換え

- 100kHz ~ 400kHz の従来のタイミングに対応

- 低消費電力

- 100kHz で 100 $\mu$ A のアクティブ電流

- 4 $\mu$ A (typ) のスタンバイ電流

- 電圧動作: V<sub>DD</sub>=4.5V ~ 5.5V

- 産業用途向け温度範囲: -40 °C ~ +85 °C

- 8 ピン小型外形集積回路 (SOIC) パッケージ

- RoHS 準拠

## 機能概要

FM24C16B は高度な強誘電体プロセスを使用する 16K ビットの不揮発性メモリです。強誘電体 RAM (F-RAM) は、不揮発性であり、RAM 同様に読み出し／書き込みを実行します。また EEPROM とその他の不揮発性メモリによる複雑さ、オーバーヘッド、システム レベルの信頼性関連問題を回避し、151 年間にわたって信頼できるデータ保持ができます。

EEPROM と違って、FM24C16B はバス速度で書き込み動作を実行します。書き込み遅延は発生しません。データは、各バイトがデバイスに正常に転送された直後にメモリ アレイに書き込まれます。次のバス サイクルはデータ ポーリングを必要とせず開始できます。また本製品は他の不揮発性メモリと比較して多くのアクセス回数を提供しています。合わせて、F-RAM は書き込み動作に内部昇圧回路を必要としないため、書き込み中の消費電力は EEPROM より低くなります。FM24C16B は  $10^{14}$  回の読み出し／書き込みサイクル、即ち EEPROM に比べ 1 億倍のアクセス回数に対応できます。

これらの能力により、FM24C16B は頻繁で急速書き込みを必要とする不揮発性メモリの用途に理想的なものになります。用途は、書き込みサイクル回数を重視するデータ ロギングから、EEPROM の長い書き込み時間によりデータ損失が発生することがある厳しい産業用制御まで及びます。機能の組み合わせにより、システム オーバーヘッドを低減させながらより頻繁なデータ書き込みを可能にします。

FM24C16B はハードウェア置き換えができるため、シリアル (I<sup>2</sup>C) EEPROM を使用するユーザーに大幅な利点を提供します。デバイス仕様は、産業用温度 -40 °C ~ +85 °C の範囲において保証されます。

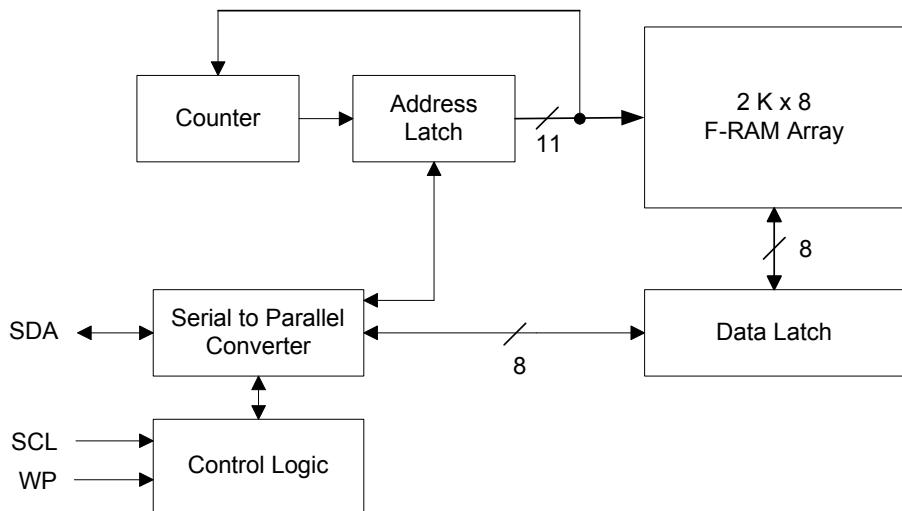

## ロジック ブロック図

## 目次

|                           |    |

|---------------------------|----|

| ピン配置                      | 3  |

| ピンの機能                     | 3  |

| 概要                        | 4  |

| メモリーアーキテクチャ               | 4  |

| I <sup>2</sup> C インターフェース | 4  |

| STOP 条件 (P)               | 4  |

| START 条件 (S)              | 4  |

| データ／アドレス転送                | 5  |

| アクリッジ／ノーアクリッジ             | 5  |

| スレーブ デバイス アドレス            | 6  |

| アドレス指定の概要 (ワード アドレス)      | 6  |

| データ転送                     | 6  |

| メモリの動作                    | 6  |

| 書き込み動作                    | 6  |

| 読み出し動作                    | 7  |

| アクセス可能回数                  | 8  |

| 最大定格                      | 9  |

| 動作範囲                      | 9  |

| DC 電気的特性                  | 9  |

| データ保持期間およびアクセス可能回数        | 10 |

| 容量                        | 10 |

| 熱抵抗                       | 10 |

| AC テストの負荷と波形              | 10 |

| AC テスト条件                  | 10 |

| AC スイッチング特性               | 11 |

| パワー サイクル タイミング            | 12 |

| 注文情報                      | 13 |

| 注文コードの定義                  | 13 |

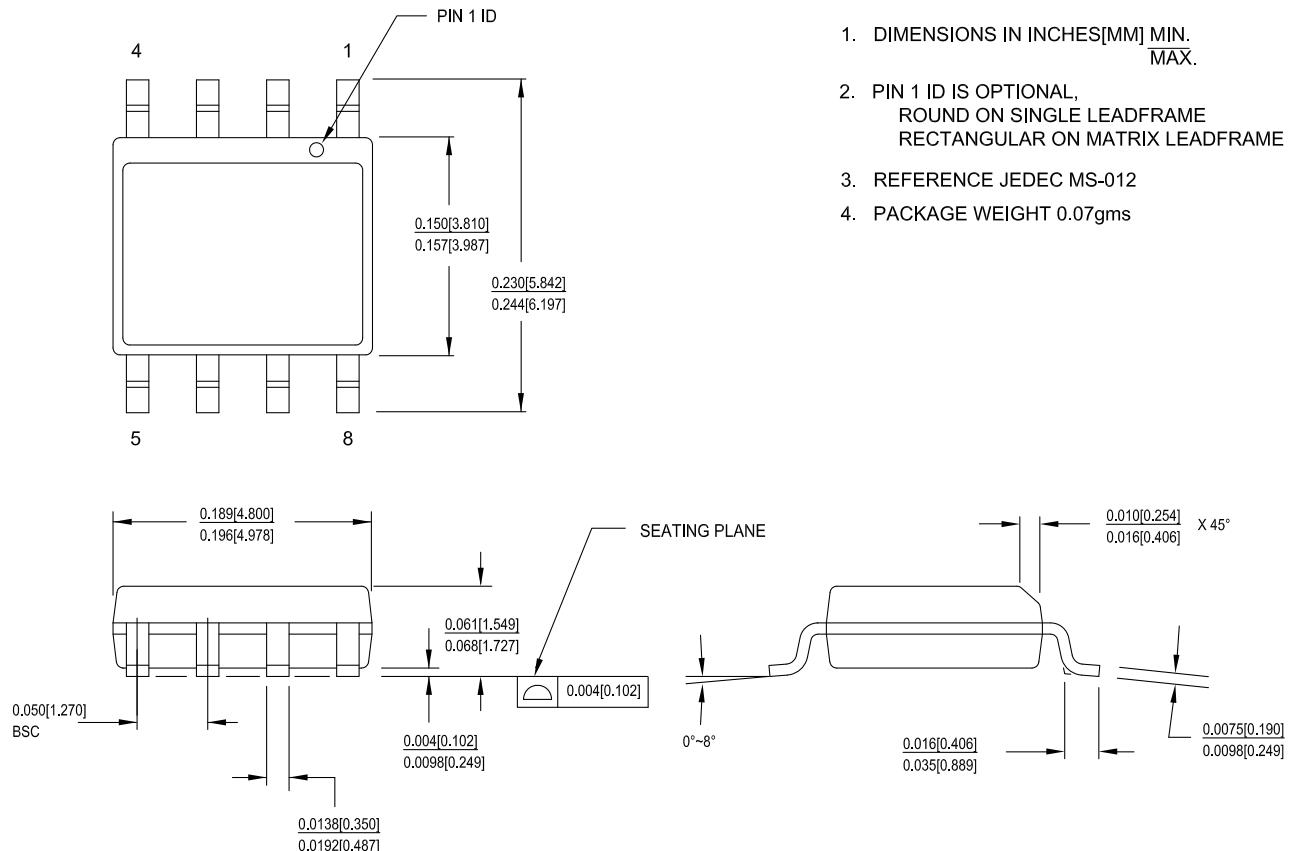

| パッケージ図                    | 14 |

| 略語                        | 15 |

| 本書の表記法                    | 15 |

| 測定単位                      | 15 |

| 改訂履歴                      | 16 |

| セールス、ソリューションおよび法律情報       | 17 |

| ワールドワイドな販売と設計サポート         | 17 |

| 製品                        | 17 |

| PSoC® ソリューション             | 17 |

| サイプレス開発者コミュニティ            | 17 |

| テクニカル サポート                | 17 |

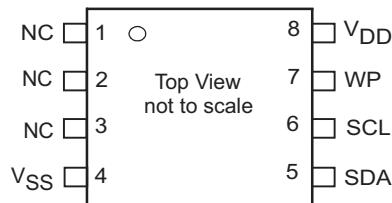

## ピン配置

図 1. 8 ピン SOIC ピン配置

## ピンの機能

| ピン名             | 入出力   | 説明                                                                                                                                                                                       |

|-----------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SDA             | 入力／出力 | シリアル データ／アドレス：I <sup>2</sup> C インターフェースの双方向ピン。オーブンドレインであり、I <sup>2</sup> C バス上の他のデバイスとワイヤード ANDされるよう意図されている。入力バッファはノイズ耐性のためにシミュット トリガーを備え、出力ドライバは立ち下がりエッジでのスロープ制御を備えている。外付けプルアップ抵抗が必要である |

| SCL             | 入力    | シリアル クロック：I <sup>2</sup> C インターフェースのシリアル クロック ピン。データは立ち下がりエッジでデバイスからクロック出力され、立ち上がりエッジでデバイスにクロック入力される                                                                                     |

| WP              | 入力    | 書き込み保護：WP が V <sub>DD</sub> に接続された時、メモリ マップ全体のアドレスが書き込みから保護される。WP がグランドに接続された時、すべてのアドレスが書き込み可能になる。このピンは内部でプルダウンされている                                                                     |

| V <sub>SS</sub> | 電源    | デバイスのグランドで、システムのグランドに接続する必要がある                                                                                                                                                           |

| V <sub>DD</sub> | 電源    | デバイスの電源入力                                                                                                                                                                                |

## 概要

FM24C16B はシリアル F-RAM メモリです。メモリアレイは 2,048×8 ビットに論理構成され、業界標準 I<sup>2</sup>C インターフェースを介してアクセスされます。F-RAM の機能動作はシリアル (I<sup>2</sup>C) EEPROM に似ています。FM24C16B と同じピン配置のシリアル (I<sup>2</sup>C) EEPROM の主な相違点は F-RAM の優れた書き込み性能、高いアクセス回数、低消費電力です。

## メモリアーキテクチャ

FM24C16B のアクセスには、8 データビット毎に 2Kヶ所の位置をアドレス指定します。これら 8 つのデータビットは順次シフトイン／シフトアウトされます。アドレスは、スレーブアドレス (他の非メモリデバイスと区別するため)、行アドレスビット、セグメントアドレスを含む I<sup>2</sup>C プロトコルを使ってアクセスされます。行アドレスは、256 行のいずれかを指定する 8 ビットからなります。3 ビットのセグメントアドレスは、8 セグメントのいずれかを指定します。11 ビットのアドレスで、一意に各バイトアドレスを指定します。

メモリ動作に対応したアクセス時間は基本的にシリアルプロトコルに必要な時間以外は 0 です。つまり、メモリは I<sup>2</sup>C バスの速度で読み書きされます。シリアル (I<sup>2</sup>C) EEPROM とは異なり、書き込み処理がバス速度で行われるので、デバイスの書き込み準備を知るためにポーリングする必要はありません。新しいバストランザクションがデバイスに送り込まれるまでに書き込み動作は完了します。これはインターフェースの項で詳しく説明されています。

書き込み動作は完了します。これはインターフェースの項で詳しく説明されています。

FM24C16B が簡単な内部パワーオンリセット回路以外に他の電源管理回路を備えていないことに注意してください。誤動作を防止するために、ユーザーは V<sub>DD</sub> がデータシートに記載された許容誤差以内であることを保証しなければなりません。

## I<sup>2</sup>C インターフェース

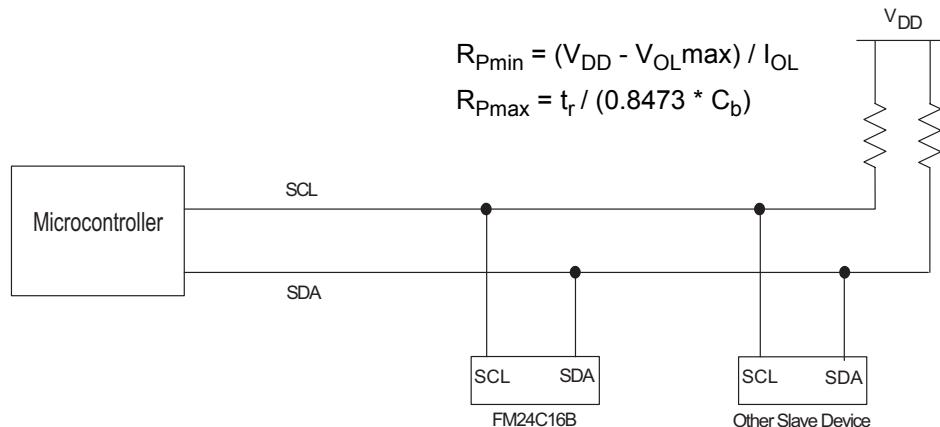

FM24C16B はピン数が少なく、小さい基板面積で済む双方向 I<sup>2</sup>C バスプロトコルを使用しています。図 2 には、マイクロコントローラーベースのシステム内で FM24C16B を使用した標準的なシステムコンフィギュレーションを示します。多くのユーザーによく知られている業界標準 I<sup>2</sup>C バスは本節で説明します。

慣例では、データをバス上に送信するデバイスはトランシミタとなり、このデータのターゲットデバイスはレシーバとなります。バスを制御しているデバイスがマスターとなります。マスターは、すべての動作用のクロック信号の生成を行います。制御されているバス上のデバイスはスレーブとなります。FM24C16B は常にスレーブデバイスです。

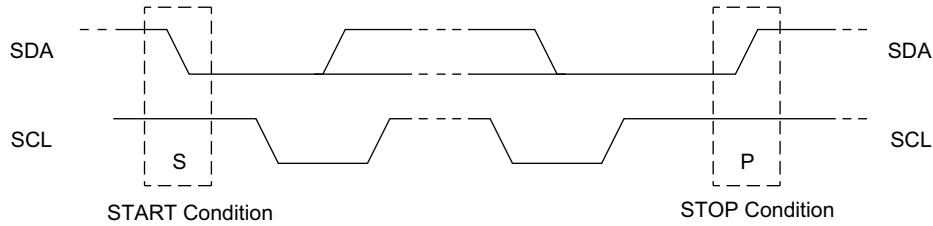

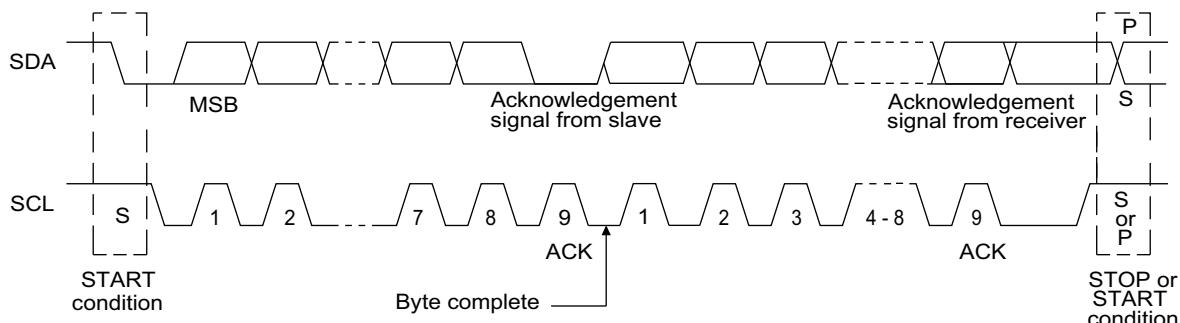

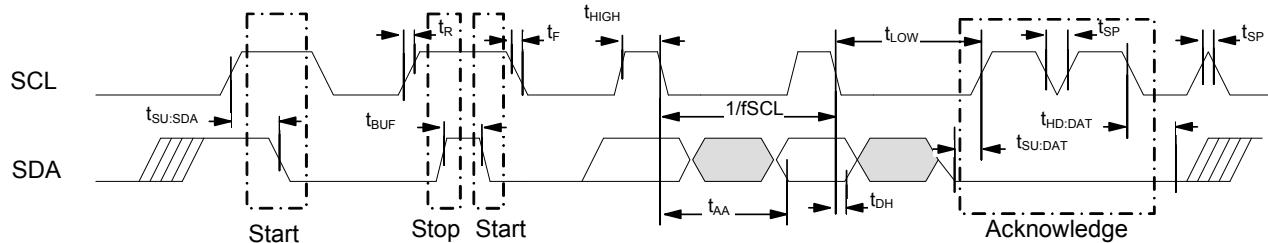

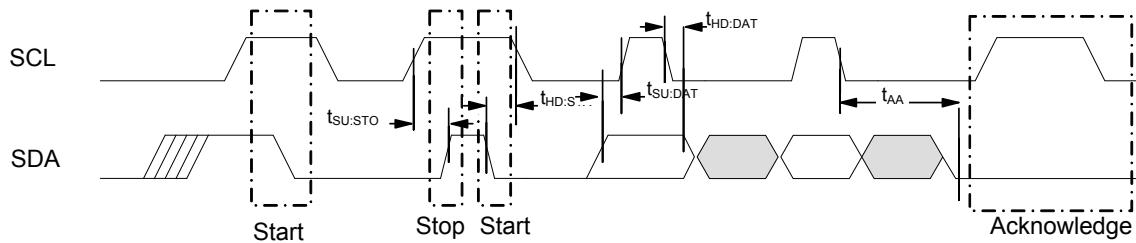

バスプロトコルは SDA と SCL 信号の遷移ステートにより制御されます。START、STOP、データビット、アクノリッジの 4 つの条件があります。図 3 と図 4 には、4 つのステートを指定する信号条件を示します。詳しいタイミング図は電気的仕様の項に示します。

図 2. シリアル (I<sup>2</sup>C) nvSRAM を用いたシステムコンフィギュレーション

## STOP 条件 (P)

STOP 条件は、SCL 信号が HIGH の時、バスマスターが SDA を LOW から HIGH に駆動する時に指定されます。FM24C16B を使用した全ての動作は STOP 条件で終わります。動作中に STOP がアサートされると、動作は中止されます。マスターは STOP 条件をアサートするために SDA を制御する必要があります。

## START 条件 (S)

START 条件は SCL 信号が HIGH の時、バスマスターが SDA を HIGH から LOW に駆動する時に指定されます。START 条件はすべてのコマンドの前に発生する必要があります。START 条件を任意にアサートして進行中の動作を中止することができます。START 条件を使って動作を中止すると、FM24C16B が新しい動作の準備ができるようになります。

動作中に電源が指定された V<sub>DD</sub> の最小値を下回ると、システムは他の動作を行う前に START 条件を発行します。

**図 3. START 条件と STOP 条件**

**図 4. I<sup>2</sup>C バス上のデータ転送**

### データ／アドレス転送

すべてのデータ転送(アドレスを含む)はSCLがHIGHの時に行われます。上記の2つの条件下の場合以外、SDA信号はSCLがHIGHの時に変化しません。

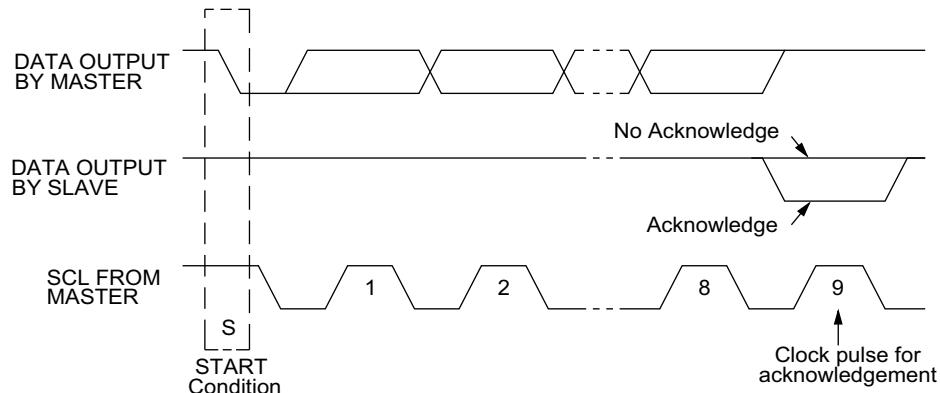

### アクノリッジ／ノーアクノリッジ

アクノリッジは、任意のトランザクションで8番目のデータビットが転送された後に行われます。この状態の間、トランスマッタはSDAバスを解放してレシーバがバスを駆動できるようにします。レシーバはSDA信号をLOWに駆動してバイトの受信を認識します。レシーバがSDAをLOWに駆動しない場合、条件がノーアクノリッジとなり、動作は中止されます。

レシーバは、2つの異なる理由でアクノリッジに失敗します。1番目の理由は、バイト転送が失敗することです。この場合、ノーアクノリッジ条件は、デバイスが再びアドレス指定されるよう現時点の動作を中断します。これにより、最後のバイトが通信エラーの発生時に回復できるようになります。

2番目の理由は、レシーバが意図的に動作を終了させるためにアクノリッジしないことです。これは最も一般的な理由です。例えば読み出し中に、レシーバがアクノリッジ(とクロック)信号を送信している限り、FM24C16Bはデータをバスに送信します。読み出し動作が完了しこれ以上のデータが不要になった時、レシーバは最後のバイトをアクノリッジしてはいけません。レシーバが最後のバイトをアクノリッジする場合、マスターがSTOPなどの新しいコマンドを発行する一方でFM24C16Bは次のクロックでバスを駆動しようとすることになります。

**図 5. I<sup>2</sup>C バス上のアクノリッジ**

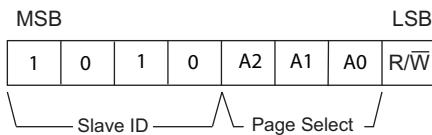

## スレーブ デバイス アドレス

START 条件後に FM24C16B が待ち受けている最初のバイトはスレーブ アドレスです。図 6 に示すように、スレーブ アドレスはデバイス タイプ、アクセスされるメモリ ページ、およびトランザクションが読み出しか書き込みであるかを指定するビットから成ります。

ビット 7 ~ 4 はデバイス タイプであり、FM24C16B の場合は 1010b にセットする必要があります。これらのビットにより、他の機能タイプが同じアドレス範囲の I<sup>2</sup>C バス上に存在することができます。ビット 3 ~ 1 はページ選択です。これは動作の対象とする 256 バイトのメモリ ブロックを指定します。ビット 0 は読み出し／書き込みビット (R/W) です。R/W=「1」は読み出し動作を示し、R/W=「0」は書き込み動作を示します。

図 6. メモリ スレーブ デバイス アドレス

## アドレス指定の概要 (ワード アドレス)

FM24C16B がレシーバとしてスレーブ アドレスをアクノリッジした後、マスターは書き込み動作のためにワード アドレスをバスに送信できます。ワード アドレスはアドレスの下位 8 ビットです。3 ビットのページ選択ビットと組み合わされ、書き込むバイトを指定します。完全な 11 ビット アドレスは内部でラッチされます。3 ビットのページ選択アドレスが内部でラッチされていますが、読み出し動作にワード アドレスはありません。読み出しへはアドレスラッチに内部的に保持された下位 8 ビットを常に使用します。即ち、読み出しへは、最後に動作したアドレスの次のアドレスから読み出します。以下で説明するように書き込み動作を行うことで、ランダムな読み出しアドレスをロードすることができます。

各データ バイトの送信後、アクノリッジの直前に、FM24C16B は内部アドレス ラッチをインクリメントします。これにより、再度アドレスを指定することなく連続する次のバイトにアクセスすることができます。最後のアドレス (7FFh) に達した後、アドレス ラッチは 000h に戻ります。一度の読み出しほとばは書き込み動作でアクセスできるバイト数の制限はありません。

## データ転送

アドレス バイトが送信された後、バス マスターと FM24C16B 間のデータ転送を開始できます。読み出し動作では、FM24C16B は 8 データ ビットをバスに送信してマスターからのアクノリッジを待ちます。アクノリッジ信号が送信された場合、FM24C16B は次の連続バイトを転送します。アクノリッジ信号が送信されない場合、FM24C16B は読み出し動作を終了し

ます。書き込み動作では、FM24C16B はマスターから 8 データ ビットを受信してアクノリッジ信号を送信します。すべてのデータ転送は、MSB (最上位ビット) から始まります。

## メモリの動作

FM24C16B は、他の I<sup>2</sup>C インターフェース メモリ製品によく似ている方法で動作するように設計されています。主な相違点は、F-RAM 技術の優れた書き込み性能に由来します。これらの改善により、書き込み処理の面で FM24C16B と似たコンフィギュレーションの EEPROM と幾つかの相違点があります。書き込みと読み出し動作は以下で詳しく説明します。

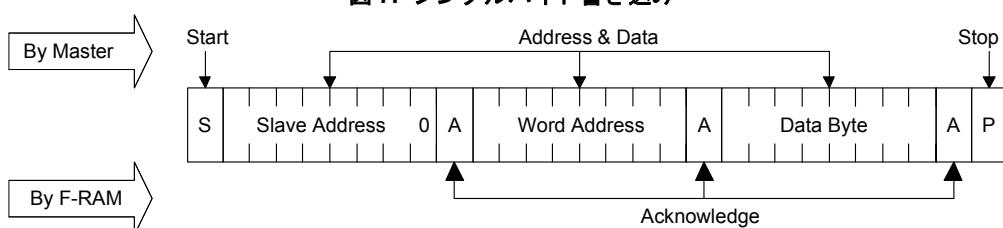

### 書き込み動作

すべての書き込みはスレーブ アドレス、それからワード アドレスで始まります。バス マスターはスレーブ アドレスの LSB (R/W ビット) を「0」にセットすることで書き込み動作を示します。アドレス指定した後、バス マスターは 1 データ バイトずつメモリに送信して、メモリはアクノリッジ条件を生成します。連続して 1 バイトずつでも書き込めます。内部でアドレス範囲の最高値に達すると、アドレス カウンタは 7FFh から 000h に戻ります。

他の不揮発性メモリ技術と異なり、F-RAM は事実上書き込み遅延はありません。基本的なメモリの読み出しと書き込みのアクセス時間が同じなので、バスを介して認識されるデバイス遅延はありません。全体のメモリ動作は、1 つのバス サイクル以内で行われます。このため、読み出しと書き込みを含むすべての動作は書き込みの直後に行うことができます。書き込み完了を判定するために EEPROM で使用される技術であるアクノリッジ ポーリング (acknowledge polling) は不要になり、常にレディー状態を返します。

内部では、8 番目のビットが転送された後に実際のメモリ書き込みが行われます。この書き込みはアクノリッジ信号が送信される前に完了します。このため、ユーザーはメモリ内容を変更せずに書き込みを中止したい場合、8 番目のデータ ビットの前に START または STOP 条件を使用する必要があります。FM24C16B はページ バッファリングを使用しません。

メモリ アレイは WP ピンを使用して書き込みから保護できます。WP ピンを HIGH 状態 (V<sub>DD</sub>) にセットすると、すべてのアドレスを書き込みから保護できます。FM24C16B は保護されたアドレスへ書き込まれたデータ バイトにアクノリッジしません。また、これらのアドレスに書き込もうとしてもアドレス カウンタはインクリメントされません。WP を LOW 状態 (V<sub>SS</sub>) にセットすると、書き込み保護が無効になります。WP は内部でブルダウンされています。

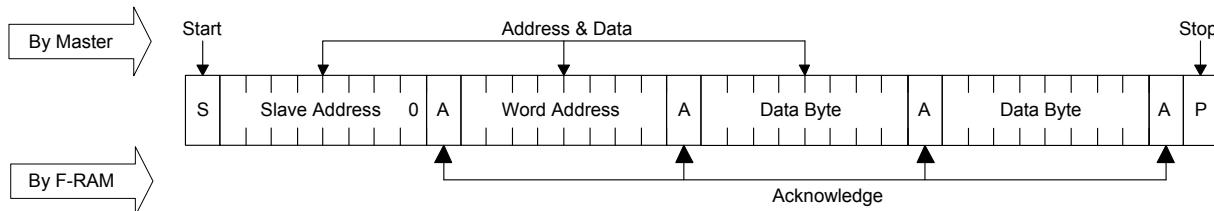

以下の図 7 と図 8 は 1 バイトと複数バイトの書き込みサイクルを示します。

図 7. シングルバイト書き込み

**図 8. マルチバイト書き込み**

### 読み出し動作

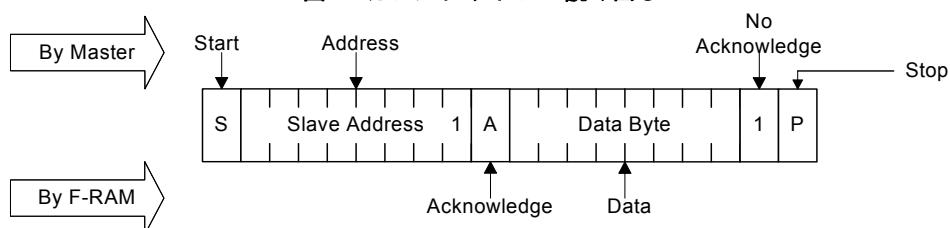

読み出し動作には、カレント アドレス読み出しと選択的アドレス読み出しの 2 つの基本的なタイプがあります。カレント アドレス読み出しでは、FM24C16B は内部アドレス ラッチを使用して下位 8 アドレス ビットを提供します。選択的読み出しでは、ユーザーはこれらの下位アドレス ビットを特定の値に設定する手順を行います。

#### カレント アドレスと連続読み出し

前述のように、FM24C16B は内部ラッチを使用して読み出し動作に下位 8 アドレス ビットを提供します。カレント アドレス読み出しは、アドレス ラッチにある値を読み出し動作の開始点として使用します。システムは、最後に動作したアドレスの次のアドレスから読み出します。

カレント アドレス読み出しを行うために、バス マスターは LSB を「1」にセットしたスレーブ アドレスを送信します。これは読み出し動作が要求されたことを示します。スレーブ アドレス内にある 3 ビットのページ選択ビットは読み出し動作のメモリ ブロックを指定します。スレーブ アドレスを受信した後、FM24C16B は次のクロックでカレント アドレスのデータをシフトアウトし始めます。カレント アドレスは、スレーブ アドレスの 3 ビットと内部アドレス ラッチに保持された 8 ビットと組み合わせたものです。

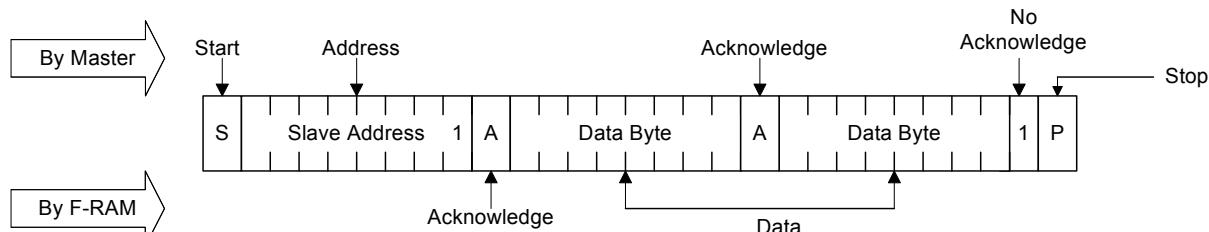

カレント アドレスを冒頭に、バス マスターはバイトをいくつでも読み出せます。従って連続読み出しは単に複数バイトを転

送するカレント アドレス読み出しです。各バイトの転送後、内部アドレス カウンタはインクリメントされます。

**注** バス マスターがバイトにアクノリッジすると、FM24C16B は次の連続バイトを読み出す準備をします。

読み出し動作を正常に終了するには 4 つの方法があります。読み出しを正常に終了しない場合、FM24C16B がデータをバス上に読み出そうとするためバス競合が発生する可能性があります。4 つの有効な方法は以下の通りです。

1. バス マスターは 9 番目のクロック サイクルでノーアクノリッジ信号を発行し、10 番目のクロック サイクルで STOP 条件を発行します。これは推奨される方法です。下図に示します。

2. バス マスターは 9 番目のクロック サイクルでノーアクノリッジ信号を発行し、10 番目のクロック サイクルで START 条件を発行します。

3. バス マスターは 9 番目のクロック サイクルで STOP 条件を発行します。

4. バス マスターは 9 番目のクロック サイクルで START 条件を発行します。

内部アドレスが 7FFh に達すると、次の読み出しサイクルで 000h に戻ります。以下の図 9 と図 10 はカレント アドレス読み出しの正常な動作を示します。

**図 9. カレント アドレス読み出し**

**図 10. 順次読み出し**

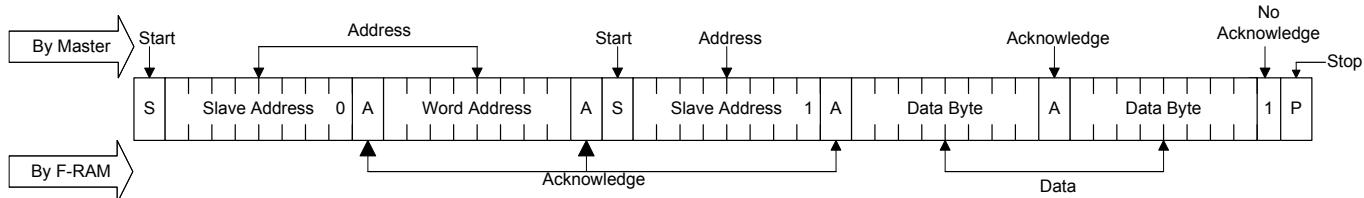

### 選択的 (ランダム) 読み出し

ランダムなアドレスを読み出し動作の開始点に設定する簡単な方法があります。これは、書き込み動作の冒頭 2 バイトを使って内部アドレスをセットし、続いて読み出し動作を行うことで実現します。

選択的読み出しを行うために、バス マスターは LSB (R/W) が 0 にセットされたスレーブ アドレスを送信します。これは書き込み動作を示します。書き込みプロトコルに従って、バス マス

ターはそれに続き、内部アドレス ラッチにロードされるワードアドレス バイトを送信します。FM24C16B がワード アドレスをアクノリッジした後、バス マスターは START 条件を発行します。これにより、書き込み動作が中止されると同時に、 LSB が「1」にセットされたスレーブ アドレスで読み出しコマンドが発行されます。動作はカレント アドレス読み出しとなります。

図 11. 選択的 (ランダム) 読み出し

### アクセス可能回数

FM24C16B は読み出しと格納メカニズムを併いた動作します。このため、アクセス回数は各読み出しままたは書き込みサイクルに適用されます。F-RAM のアーキテクチャは、行と列のアレイに基づいています。1 回の読み出しままたは書き込みで、1 回のアクセスサイクルが行を単位として消費されます。FM24C16B では、各行は 64 ビット幅です。8 バイト毎に行の境界があります。

す。頻繁にアクセスされるデータを異なる行に配置することでアクセス回数を最適化できます。いずれにしても、FRAM の読み出しと書き込みのアクセス回数は 1MHz の I<sup>2</sup>C 速度では実質的に無制限です。同じ行に毎秒 3000 回アクセスしても、1 兆回のアクセスサイクルが終わるまでの期間は 10 年以上になります。

## 最大定格

|                                                         |                                                       |

|---------------------------------------------------------|-------------------------------------------------------|

| 最大定格を超えると、デバイスの寿命が短くなる可能性があります。これらのユーザー ガイドラインは試験されません。 |                                                       |

| 保存温度                                                    | -55 °C ~ +125 °C                                      |

| 最大接合部温度                                                 | 95 °C                                                 |

| V <sub>SS</sub> を基準とした V <sub>DD</sub> の電源電圧            | -1.0V ~ +7.0V                                         |

| 入力電圧                                                    | -1.0V ~ +7.0V, V <sub>IN</sub> <V <sub>DD</sub> +1.0V |

| High-Z 状態の出力                                            |                                                       |

| に与えることができる DC 電圧                                        | -0.5V ~ V <sub>DD</sub> +0.5V                         |

| グランド電位を基準にした                                            |                                                       |

| 任意のピンの過渡電圧 (<20ns)                                      | -2.0V ~ V <sub>DD</sub> +2.0V                         |

| パッケージ許容電力損失 (T <sub>A</sub> =25 °C)                     | 1.0W                                                  |

## DC 電気的特性

### 動作範囲において

| 記号                              | 項目                    | テスト条件                                                                                                        | Min                      | Typ <sup>[1]</sup> | Max                  | 単位  |

|---------------------------------|-----------------------|--------------------------------------------------------------------------------------------------------------|--------------------------|--------------------|----------------------|-----|

| V <sub>DD</sub>                 | 電源                    |                                                                                                              | 4.5                      | 5.0                | 5.5                  | V   |

| I <sub>DD</sub>                 | 平均 V <sub>DD</sub> 電流 | SCL が V <sub>DD</sub> -0.3V と V <sub>SS</sub> の間でトグル。<br>他の入力に V <sub>SS</sub> または V <sub>DD</sub> -0.3V を印加 | f <sub>SCL</sub> =100kHz | -                  | -                    | 100 |

|                                 |                       |                                                                                                              | f <sub>SCL</sub> =400kHz | -                  | -                    | 200 |

|                                 |                       |                                                                                                              | f <sub>SCL</sub> =1MHz   | -                  | -                    | 400 |

| I <sub>SB</sub>                 | スタンバイ電流               | SCL=SDA=V <sub>DD</sub> 。他の全ての入力は、V <sub>SS</sub> または V <sub>DD</sub> に接続。STOP コマンドが発行済み                     | -                        | 4                  | 10                   | μA  |

| I <sub>LI</sub>                 | 入力リーク電流 (WP 以外)       | V <sub>SS</sub> ≤V <sub>IN</sub> ≤V <sub>DD</sub>                                                            | -1                       | -                  | +1                   | μA  |

|                                 | 入力リーク電流 (WP)          | V <sub>SS</sub> ≤V <sub>IN</sub> ≤V <sub>DD</sub>                                                            | -1                       | -                  | +100                 | μA  |

| I <sub>LO</sub>                 | 出力リーク電流               | V <sub>SS</sub> ≤V <sub>IN</sub> ≤V <sub>DD</sub>                                                            | -1                       | -                  | +1                   | μA  |

| V <sub>IH</sub>                 | 入力 HIGH 電圧            |                                                                                                              | 0.7×V <sub>DD</sub>      | -                  | V <sub>DD</sub> +0.3 | V   |

| V <sub>IL</sub>                 | 入力 LOW 電圧             |                                                                                                              | -0.3                     | -                  | 0.3×V <sub>DD</sub>  | V   |

| V <sub>OL</sub>                 | 出力 LOW 電圧             | I <sub>OL</sub> =3mA                                                                                         | -                        | -                  | 0.4                  | V   |

| R <sub>in</sub> <sup>[2]</sup>  | 入力抵抗 (WP)             | V <sub>IN</sub> =V <sub>IL</sub> (Max) の場合                                                                   | 40                       | -                  | -                    | kΩ  |

|                                 |                       | V <sub>IN</sub> =V <sub>IH</sub> (Min) の場合                                                                   | 1                        | -                  | -                    | MΩ  |

| V <sub>HYS</sub> <sup>[3]</sup> | 入力ヒステリシス              |                                                                                                              | 0.05×V <sub>DD</sub>     | -                  | -                    | V   |

### 注

- 標準値は 25 °C、V<sub>DD</sub>=V<sub>DD</sub>(typ) でのものです。全数検査ではありません。

- 入力プルダウン回路は、入力電圧が V<sub>IL</sub> を上回っている時に重くなり (40kΩ)、入力電圧が V<sub>IH</sub> 以上の時に軽くなります (1MΩ)。

- これらのパラメータは設計保証であり、テストは行われていません。

## データ保持期間およびアクセス可能回数

| 記号       | 項目      | テスト条件                  | Min       | Max | 単位   |

|----------|---------|------------------------|-----------|-----|------|

| $T_{DR}$ | データ保持期間 | $T_A=85^\circ\text{C}$ | 10        | —   | 年    |

|          |         | $T_A=75^\circ\text{C}$ | 38        | —   |      |

|          |         | $T_A=65^\circ\text{C}$ | 151       | —   |      |

| $NV_C$   | アクセス回数  | 動作温度範囲内                | $10^{14}$ | —   | サイクル |

## 容量

| 記号 <sup>[4]</sup> | 説明           | テスト条件                                                            | Max | 単位 |

|-------------------|--------------|------------------------------------------------------------------|-----|----|

| $C_O$             | 出力ピン容量 (SDA) | $T_A=25^\circ\text{C}, f=1\text{MHz}, V_{DD}=V_{DD}(\text{typ})$ | 8   | pF |

| $C_I$             | 入力ピン容量       |                                                                  | 6   | pF |

## 熱抵抗

| 記号 <sup>[4]</sup> | 項目                | テスト条件                                               | 8 ピン SOIC | 単位                        |

|-------------------|-------------------|-----------------------------------------------------|-----------|---------------------------|

| $\Theta_{JA}$     | 熱抵抗<br>(接合部から周囲)  | テスト条件は、EIA/JESD51 に準拠する熱インピーダンスを測定するための標準試験方法と手順に従う | 147       | $^\circ\text{C}/\text{W}$ |

| $\Theta_{JC}$     | 熱抵抗<br>(接合部からケース) |                                                     | 47        | $^\circ\text{C}/\text{W}$ |

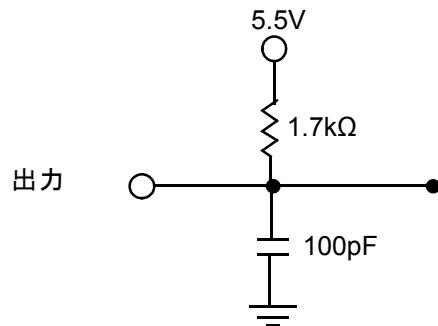

## AC テストの負荷と波形

図 12. AC テストの負荷と波形

## AC テスト条件

- 入力パルス レベル .....  $V_{DD}$  の 10% と 90%

- 入力の立ち上がりと立ち下がり時間 ..... 10ns

- 入力と出力タイミングの基準レベル .....  $0.5 \times V_{DD}$

- 出力負荷容量 ..... 100pF

### 注

- 4. これらのパラメータは設計保証であり、テストは行われていません。

## AC スイッチング特性

動作範囲において

| 記号 <sup>[5]</sup>        | 異なる表記         | 説明                                     | Min | Max  | Min | Max | Min  | Max  | 単位  |

|--------------------------|---------------|----------------------------------------|-----|------|-----|-----|------|------|-----|

| $f_{SCL}$ <sup>[6]</sup> |               | SCL クロック周波数                            | —   | 0.1  | —   | 0.4 | —    | 1.0  | MHz |

| $t_{SU:STA}$             |               | 反復 START 用の START 条件セットアップ時間           | 4.7 | —    | 0.6 | —   | 0.25 | —    | μs  |

| $t_{HD:STA}$             |               | START 条件ホールド時間                         | 4.0 | —    | 0.6 | —   | 0.25 | —    | μs  |

| $t_{LOW}$                |               | クロック LOW 時間                            | 4.7 | —    | 1.3 | —   | 0.6  | —    | μs  |

| $t_{HIGH}$               |               | クロック HIGH 時間                           | 4.0 | —    | 0.6 | —   | 0.4  | —    | μs  |

| $t_{SU:DAT}$             | $t_{SU:DATA}$ | データ入力セットアップ時間                          | 250 | —    | 100 | —   | 100  | —    | ns  |

| $t_{HD:DAT}$             | $t_{HD:DATA}$ | データ入力ホールド時間                            | 0   | —    | 0   | —   | 0    | —    | ns  |

| $t_{DH}$                 |               | データ出力ホールド時間 (SCL=V <sub>IL</sub> の時から) | 0   | —    | 0   | —   | 0    | —    | ns  |

| $t_r^{[7]}$              | $t_r$         | 入力立ち上がり時間                              | —   | 1000 | —   | 300 | —    | 300  | ns  |

| $t_f^{[7]}$              | $t_f$         | 入力立ち下がり時間                              | —   | 300  | —   | 300 | —    | 100  | ns  |

| $t_{SU:STO}$             |               | STOP 条件セットアップ時間                        | 4.0 | —    | 0.6 | —   | 0.25 | —    | μs  |

| $t_{AA}$                 | $t_{VD:DATA}$ | SCL LOW から SDA データ出力有効までの時間            | —   | 3    | —   | 0.9 | —    | 0.55 | μs  |

| $t_{BUF}$                |               | 新規送信前のバス空き時間                           | 4.7 | —    | 1.3 | —   | 0.5  | —    | μs  |

| $t_{SP}$                 |               | SCL、SDA 上のノイズ抑制時定数                     | —   | 50   | —   | 50  | —    | 50   | ns  |

図 13. 読み出し動作バスタイミング図

図 14. 書き込み動作バスタイミング図

注

5. テスト条件は、信号遷移時間が 10ns 以下、タイミングの基準レベルが  $V_{DD}/2$ 、入力パルス レベルが  $0V \sim V_{DD}$  (typ)、規定された  $I_{OL}$  を与える出力負荷と負荷容量が図 12 に示す通りであることを前提にしています。

6. スピード関連の仕様は、DC から  $f_{SCL}$  (max) への動作の連続曲線に沿って保証された特性点です。

7. これらのパラメータは設計保証であり、テストは行われていません。

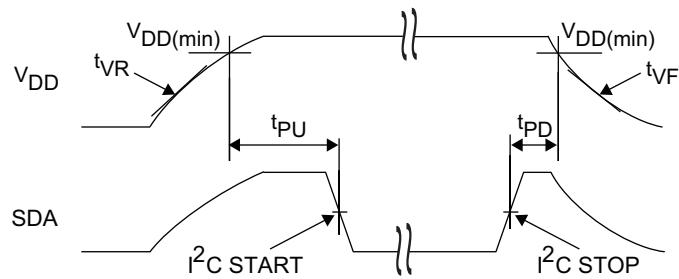

## パワー サイクル タイミング

動作範囲において

| 記号                | 説明                                                | Min | Max | 単位   |

|-------------------|---------------------------------------------------|-----|-----|------|

| $t_{PU}$          | 電源投入時の $V_{DD(min)}$ から最初のアクセス (START 条件) までの時間   | 1   | –   | ms   |

| $t_{PD}$          | 最後のアクセス (STOP 条件) から電源切断時 ( $V_{DD(min)}$ ) までの時間 | 0   | –   | μs   |

| $t_{VR}^{[8, 9]}$ | $V_{DD}$ 電源投入時の変化速度                               | 30  | –   | μs/V |

| $t_{VF}^{[8, 9]}$ | $V_{DD}$ 電源切断時の変化速度                               | 30  | –   | μs/V |

図 15. パワー サイクル タイミング

注

8.  $V_{DD}$  波形上の任意の点で測定した傾きです。

9. 設計保証です。

## 注文情報

| 注文コード        | パッケージ図    | パッケージ タイプ | 動作範囲 |

|--------------|-----------|-----------|------|

| FM24C16B-G   | 001-85066 | 8 ピン SOIC | 産業用  |

| FM24C16B-GTR |           |           |      |

これらすべての部品は鉛フリーです。在庫状況については、最寄りのサイプレスの販売代理店にお問い合わせください。

## 注文コードの定義

FM 24 C 16 B - G TR

オプション：

空白 = 標準； T= テープとリール

パッケージ タイプ : G=8 ピン SOIC

ダイバージョン =B

メモリ容量 : 16=16k ビット

電圧 : C=4.5V ~ 5.5V

I<sup>2</sup>C F-RAM

サイプレス

## パッケージ図

図 16. 8 ピン SOIC (150mil) パッケージの外形、51-85066

51-85066 \*F

**略語**

| 略語               | 説明                                                                    |

|------------------|-----------------------------------------------------------------------|

| ACK              | Acknowledge ( アクノリッジ )                                                |

| CMOS             | Complementary Metal Oxide Semiconductor ( 相補型金属酸化膜半導体 )               |

| EIA              | Electronic Industries Alliance ( 米国電子工業会 )                            |

| I <sup>2</sup> C | Inter-Integrated Circuit ( インター インテグレーテッド サーキット )                     |

| I/O              | Input/Output ( 入力／出力 )                                                |

| JEDEC            | Joint Electron Devices Engineering Council ( 半導体技術協会 ( 旧電子機器技術評議会 ) ) |

| LSB              | Least Significant Bit ( 最下位ビット )                                      |

| MSB              | Most significant bit ( 最上位ビット )                                       |

| NACK             | No Acknowledge ( ノー アクノリッジ )                                          |

| RoHS             | Restriction of Hazardous Substances ( 特定有害物質使用制限指令 )                  |

| R/W              | Read/Write ( 読み出し／書き込み )                                              |

| SCL              | Serial Clock Line ( シリアル クロック ライン )                                   |

| SDA              | Serial Data Access ( シリアル データ アクセス )                                  |

| SOIC             | Small Outline Integrated Circuit ( 小型外形集積回路 )                         |

| WP               | Write Protect ( 書き込み保護 )                                              |

**本書の表記法**

**測定単位**

| 記号  | 測定単位     |

|-----|----------|

| °C  | 摂氏温度     |

| Hz  | ヘルツ      |

| Kb  | 1024 ビット |

| kHz | キロヘルツ    |

| kΩ  | キロオーム    |

| MHz | メガヘルツ    |

| MΩ  | メガオーム    |

| μA  | マイクロアンペア |

| μs  | マイクロ秒    |

| mA  | ミリアンペア   |

| ms  | ミリ秒      |

| ns  | ナノ秒      |

| Ω   | オーム      |

| %   | パーセント    |

| pF  | ピコファラッド  |

| V   | ボルト      |

| W   | ワット      |

## 改訂履歴

文書名 : FM24C16B、16K ビット (2K × 8) シリアル (I<sup>2</sup>C) F-RAM

文書番号 : 001-93860

| Rev. | ECN 番号  | 発行日        | 変更者  | 変更内容                                                          |

|------|---------|------------|------|---------------------------------------------------------------|

| **   | 4480499 | 09/25/2014 | HZEN | これは英語版 001-84450 Rev. *F からを翻訳した日本語版 001-93860 Rev. **<br>です。 |

## セールス、ソリューションおよび法律情報

### ワールドワイドな販売と設計サポート

サイプレスは、事業所、ソリューションセンター、メーカー代理店および販売代理店の世界的なネットワークを保持しています。お客様の最寄りのオフィスについては、[サイプレスのロケーションページ](#)をご覧ください。

#### 製品

|             |                                                                                                                                      |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------|

| 車載用         | <a href="http://cypress.com/go/automotive">cypress.com/go/automotive</a>                                                             |

| クロック & バッファ | <a href="http://cypress.com/go/clocks">cypress.com/go/clocks</a>                                                                     |

| インターフェース    | <a href="http://cypress.com/go/interface">cypress.com/go/interface</a>                                                               |

| 照明 & 電力制御   | <a href="http://cypress.com/go/powerpsoc">cypress.com/go/powerpsoc</a><br><a href="http://cypress.com/go/plc">cypress.com/go/plc</a> |

| メモリ         | <a href="http://cypress.com/go/memory">cypress.com/go/memory</a>                                                                     |

| PSoC        | <a href="http://cypress.com/go/psoc">cypress.com/go/psoc</a>                                                                         |

| タッチ センシング   | <a href="http://cypress.com/go/touch">cypress.com/go/touch</a>                                                                       |

| USB コントローラー | <a href="http://cypress.com/go/USB">cypress.com/go/USB</a>                                                                           |

| ワイヤレス／RF    | <a href="http://cypress.com/go/wirelessFM24VN10">cypress.com/go/wirelessFM24VN10</a>                                                 |

#### PSoC® ソリューション

|                                                                            |

|----------------------------------------------------------------------------|

| <a href="http://psoc.cypress.com/solutions">psoc.cypress.com/solutions</a> |

| <a href="#">PSoC 1   PSoC 3   PSoC 4   PSoC 5LP</a>                        |

#### サイプレス開発者コミュニティ

|                        |                       |                     |                     |                        |

|------------------------|-----------------------|---------------------|---------------------|------------------------|

| <a href="#">コミュニティ</a> | <a href="#">フォーラム</a> | <a href="#">ブログ</a> | <a href="#">ビデオ</a> | <a href="#">トレーニング</a> |

|------------------------|-----------------------|---------------------|---------------------|------------------------|

#### テクニカル サポート

|                                                                    |

|--------------------------------------------------------------------|

| <a href="http://cypress.com/go/support">cypress.com/go/support</a> |

|--------------------------------------------------------------------|

© Cypress Semiconductor Corporation, 2013 - 2014. 本文書に記載される情報は、予告なく変更される場合があります。Cypress Semiconductor Corporation (サイプレス セミコンダクタ社) は、サイプレス製品に組み込まれた回路以外のいかなる回路を使用することに対して一切の責任を負いません。サイプレス セミコンダクタ社は、特許またはその他の権利に基づくライセンスを譲渡することも、または含意することもありません。サイプレス製品は、サイプレスとの書面による合意に基づくものでない限り、医療、生命維持、救命、重要な管理、または安全の用途のために使用することを保証するものではなく、また使用することを意図したものでもありません。さらにサイプレスは、誤動作や故障によって使用者に重大な傷害をもたらすことが合理的に予想される生命維持システムの重要なコンポーネントとしてサイプレス製品を使用することを許可していません。生命維持システムの用途にサイプレス製品を供することは、製造者がそのような使用におけるあらゆるリスクを負うことを意味し、その結果サイプレスはあらゆる責任を免除されることを意味します。

全てのソースコード（ソフトウェアおよび／またはファームウェア）はサイプレス セミコンダクタ社（以下「サイプレス」）が所有し、全世界の特許権保護（米国およびその他の国）、米国の著作権法ならびに国際協定の条項により保護され、かつそれらに従います。サイプレスが本書面によりライセンサーに付与するライセンスは、個人的、非独占かつ譲渡不能のライセンスであり、適用される契約で指定されたサイプレスの集積回路と併用されるライセンサーの製品のみをサポートするカスタムソフトウェアおよび／またはカスタム ファームウェアを作成する目的に限って、サイプレスのソースコードの派生著作物をコピー、使用、変更そして作成するためのライセンス、ならびにサイプレスのソースコードおよび派生著作物をコンパイルするためのライセンスです。上記で指定された場合を除き、サイプレスの書面による明示的な許可なくして本ソースコードを複製、変更、変換、コンパイル、または表示することは全て禁止します。

免責条項：サイプレスは、明示的または默示的を問わず、本資料に関するいかなる種類の保証も行いません。これには、商品性または特定目的への適合性の默示的な保証が含まれますが、これに限定されません。サイプレスは、本文書に記載される資料に対して今後予告なく変更を加える権利を留保します。サイプレスは、本文書に記載されるいかなる製品または回路を適用または使用したことによって生ずるいかなる責任も負いません。サイプレスは、誤動作や故障によって使用者に重大な傷害をもたらすことが合理的に予想される生命維持システムの重要なコンポーネントとしてサイプレス製品を使用することを許可していません。生命維持システムの用途にサイプレス製品を供することは、製造者がそのような使用におけるあらゆるリスクを負うことを意味し、その結果サイプレスはあらゆる責任を免除されることを意味します。

ソフトウェアの使用は、適用されるサイプレス ソフトウェア ライセンス契約によって制限され、かつ制約される場合があります。