## 72M ビット QDR™-IV SRAM

### 特長

- 72M ビットの容量 (4M×18、2M×36)

- 1334MT/s の総合ランダム トランザクション レート <sup>[1]</sup>

- 667MHz の最大動作周波数

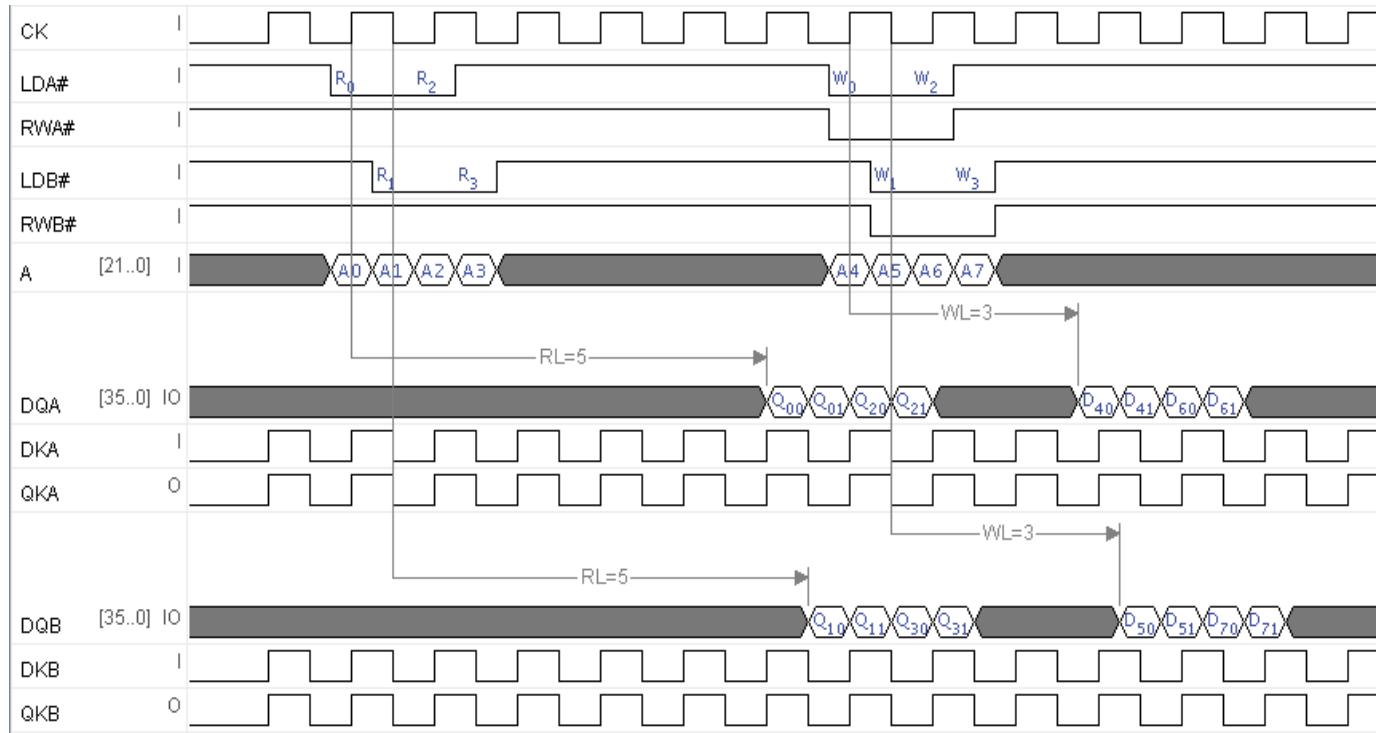

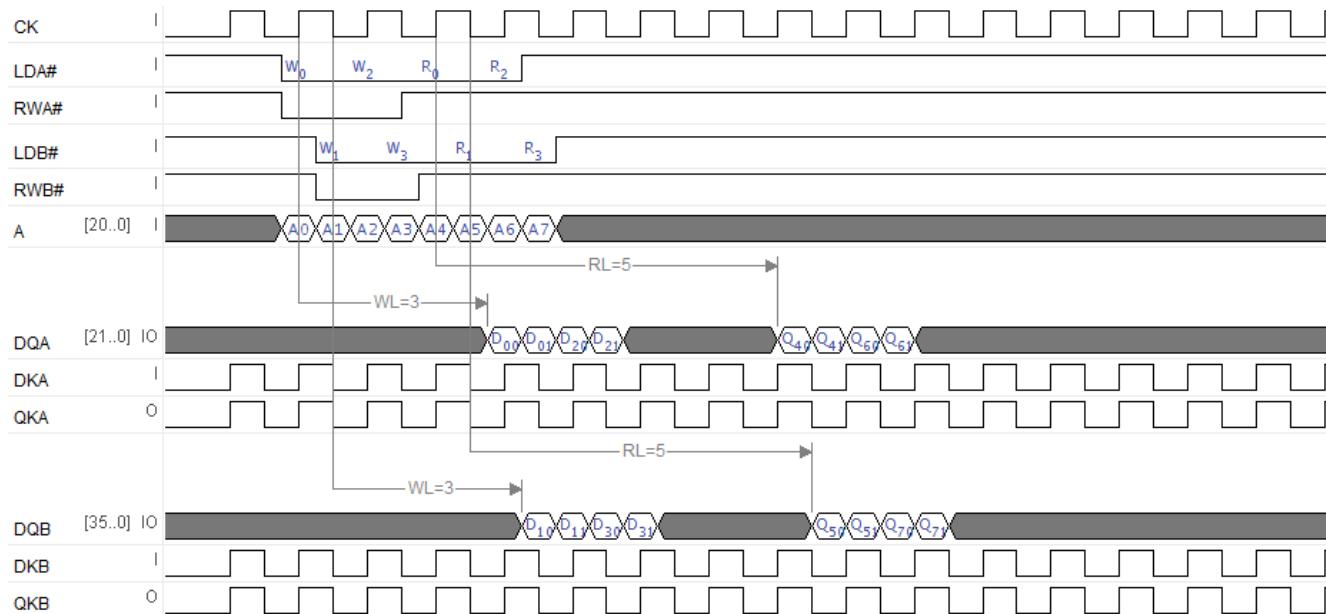

- 5.0 クロック サイクルの読み出しレイテンシ、3.0 クロック サイクルの書き込みレイテンシ

- 2 ワード バーストのアクセス

- 独立した 2 つの双方向データ ポート

- ダブル データ レート (DDR) データ ポート

- 両ポートで同時読み出し／書き込み処理をサポート

- 両データ ポートを制御するシングル アドレス ポート

- DDR アドレス信号方式

- シングル データ レート (SDR) 制御信号方式

- 高速トランシーバ ロジック (HSTL) およびスタブ直列終端 ロジック (SSTL)

- I/O  $V_{DDQ}$ =1.2V±50mV または 1.25V±50mV

- 疑似オープン ドレイン (POD) 信号方式 (JESD8-24 準拠)

- I/O  $V_{DDQ}$ =1.1V±50mV または 1.2V±50mV

- コア電圧

- $V_{DD}$  = 1.3V ± 40 mV

- オンダイ終端 (ODT)

- クロック、アドレス／コマンド、データ入力をプログラム 可能

- ZQ ピンを使った出力インピーダンス内部自己較正

- スイッチング ノイズと消費電力を減少させるバス反転

- アドレスとデータバスで機能のオン／オフをプログラム 可能

- アドレス バス パリティー エラー保護

- ビット毎のデスキュー トレーニング シーケンス

- ソフト エラー レート (SER) を低減するためのエラー訂正 コード (ECC) を内蔵

### セレクションガイド

| 項目      | QDR-IV<br>1334 (MT/s) |      | QDR-IV<br>1200 (MT/s) |      | 単位  |

|---------|-----------------------|------|-----------------------|------|-----|

| 最大動作周波数 | 667                   | 600  | 600                   | 600  | MHz |

| 最大動作電流  | ×18                   | 2500 | 2300                  | 2300 | mA  |

|         | ×36                   | 3200 | 2700                  | 2700 |     |

### 注

1. RTR (ランダム トランザクション レート) は、メモリで実行できる完全なランダム メモリ アクセス (読み出しままたは書き込み) の回数として定義されます。RTR の単位は百万トランザクション / 秒 (MT/s) です。

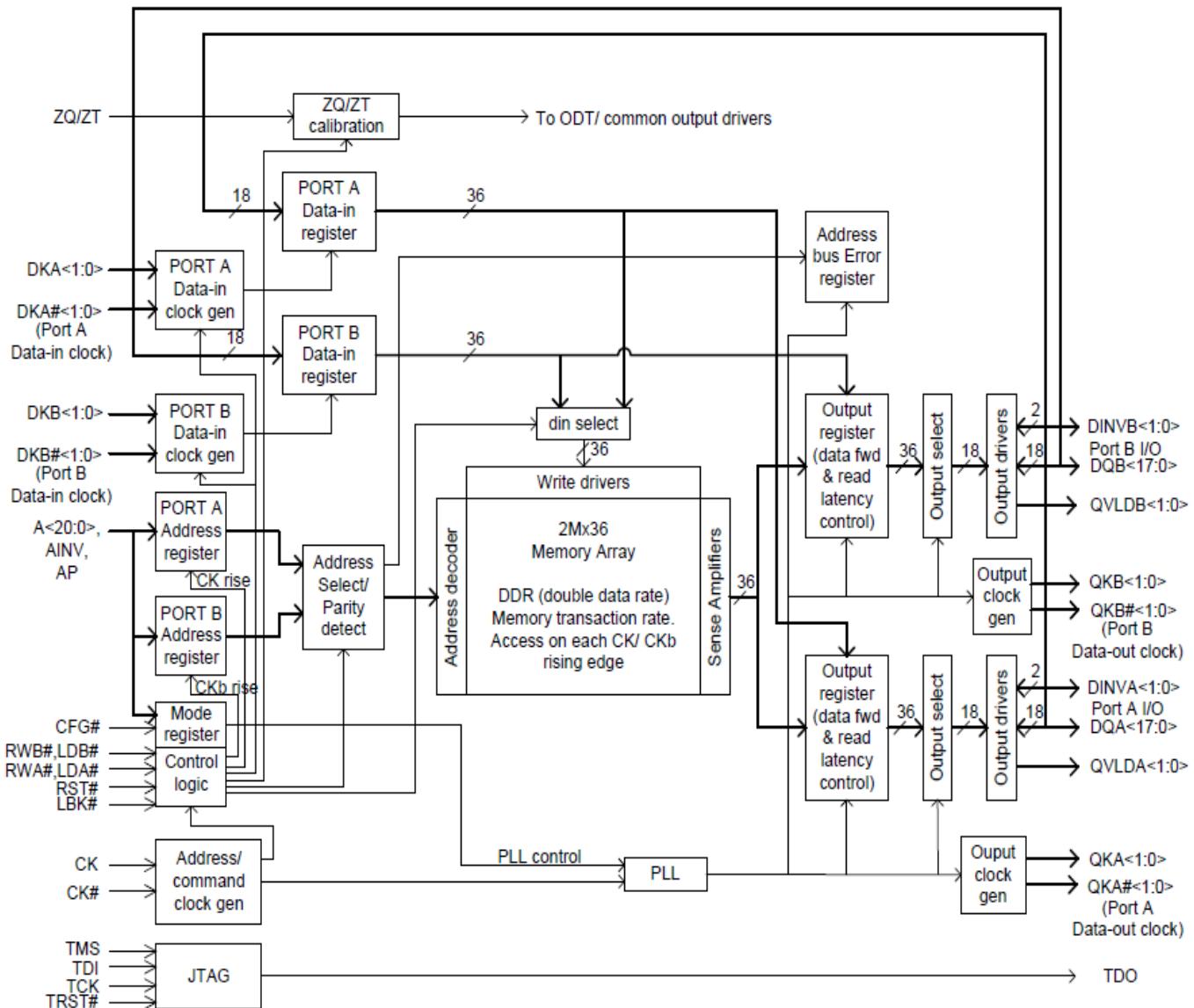

**ブロック図 – CY7C4021KV13**

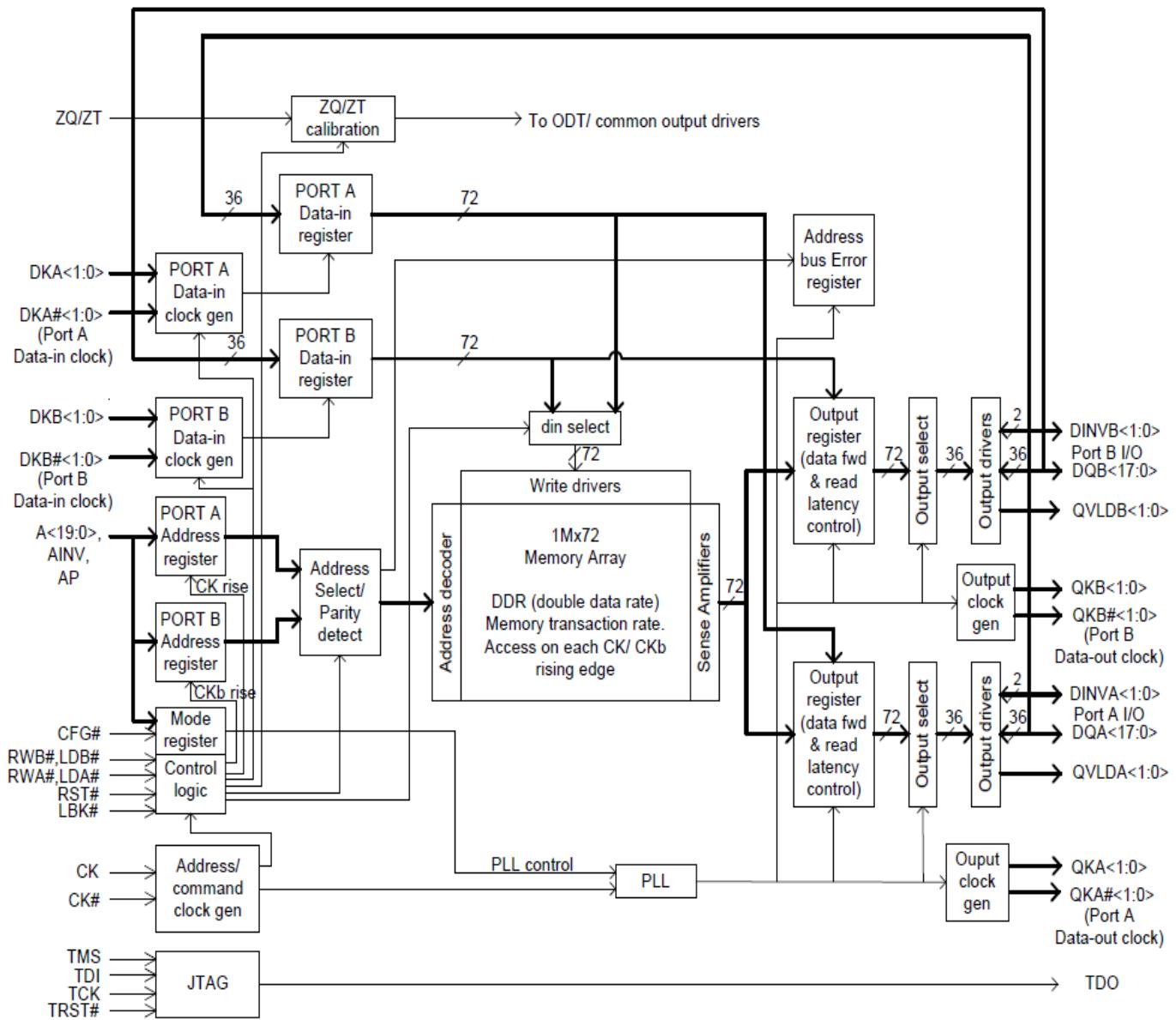

**ブロック図 – CY7C4041KV13**

## 目次

|                                                |           |

|------------------------------------------------|-----------|

| ピン配置 .....                                     | 5         |

| ピンの機能 .....                                    | 7         |

| 機能の概要 .....                                    | 9         |

| コマンド サイクル .....                                | 9         |

| 読み出しと書き込みデータ サイクル .....                        | 9         |

| アドレスおよびデータ バス反転 .....                          | 9         |

| アドレス パリティ .....                                | 10        |

| ポート イネーブル .....                                | 10        |

| オンダイ終端 (ODT) 動作 .....                          | 10        |

| JTAG 動作 .....                                  | 10        |

| 電源投入およびリセット .....                              | 10        |

| 動作モード .....                                    | 11        |

| デスクьюトレーニング シーケンス .....                        | 11        |

| 入出力の信号規格 .....                                 | 12        |

| 初期化 .....                                      | 12        |

| コンフィギュレーション レジスタ .....                         | 14        |

| コンフィギュレーション レジスタの説明 .....                      | 14        |

| コンフィギュレーション レジスタの定義 .....                      | 14        |

| I/O 形式およびポート イネーブル ビットの定義 .....                | 17        |

| ODT 終端ビットの定義 .....                             | 18        |

| 駆動能力ビットの定義 .....                               | 19        |

| <b>IEEE 1149.1シリアル バウンダリ スキャン (JTAG) .....</b> | <b>20</b> |

| Test Access Port (テスト アクセス ポート) .....          | 20        |

| TAP レジスタ .....                                 | 20        |

| TAP 命令セット .....                                | 20        |

| <b>TAP コントローラ状態遷移図 .....</b>                   | <b>22</b> |

| <b>TAP コントローラのブロック図 .....</b>                  | <b>23</b> |

| <b>TAP 電気的特性 .....</b>                         | <b>24</b> |

|                                  |           |

|----------------------------------|-----------|

| TAP AC スイッチング特性 .....            | 24        |

| TAP タイミング図 .....                 | 25        |

| ID レジスタの定義 .....                 | 26        |

| スキャン レジスタ サイズ .....              | 26        |

| 命令コード .....                      | 26        |

| バウンダリ スキャン順序 .....               | 27        |

| 最大定格 .....                       | 30        |

| 動作範囲 .....                       | 30        |

| 中性子ソフト エラー耐性 .....               | 30        |

| 電気的特性 .....                      | 30        |

| 静電容量 .....                       | 32        |

| 熱抵抗 .....                        | 32        |

| AC テストの負荷と波形 .....               | 32        |

| スイッチング特性 .....                   | 33        |

| スイッチング波形 .....                   | 35        |

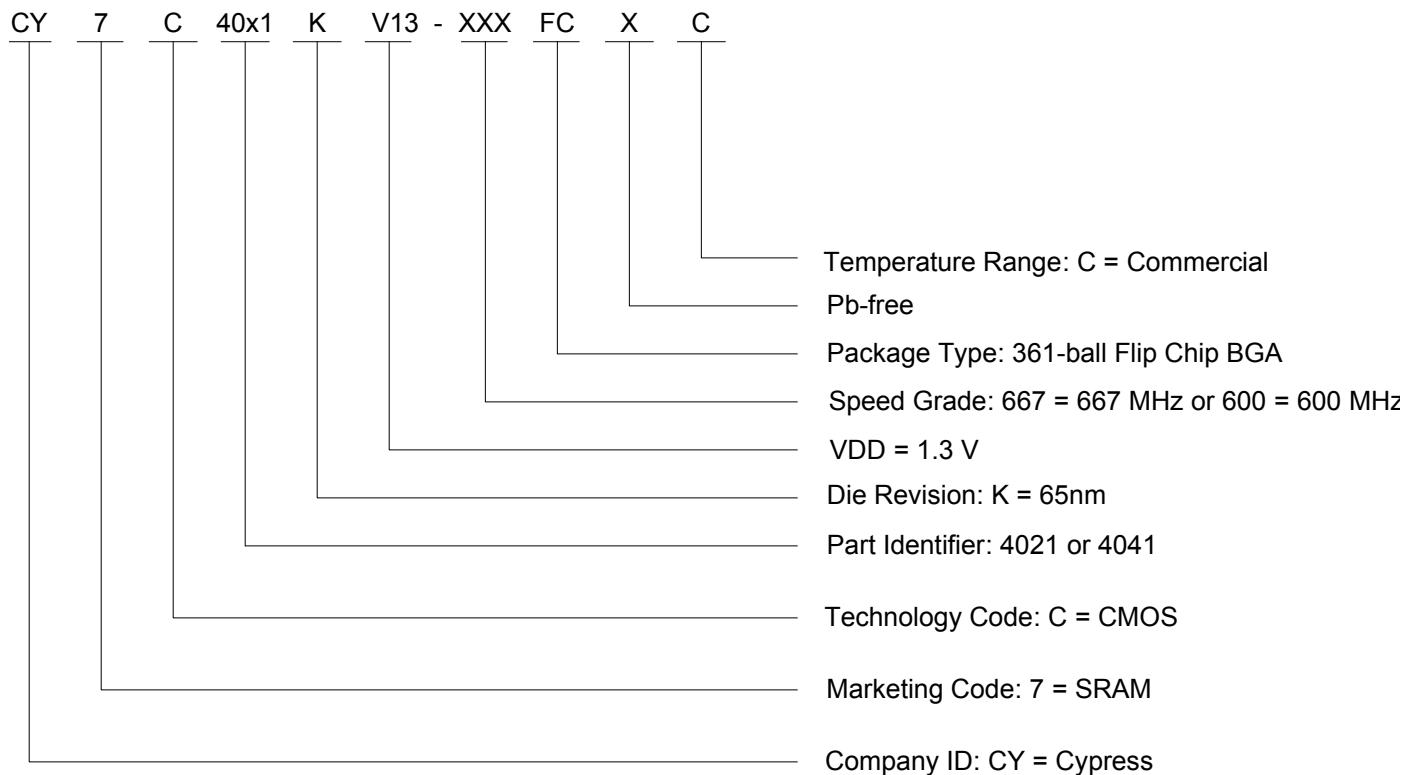

| <b>注文情報 .....</b>                | <b>42</b> |

| 注文コードの定義 .....                   | 42        |

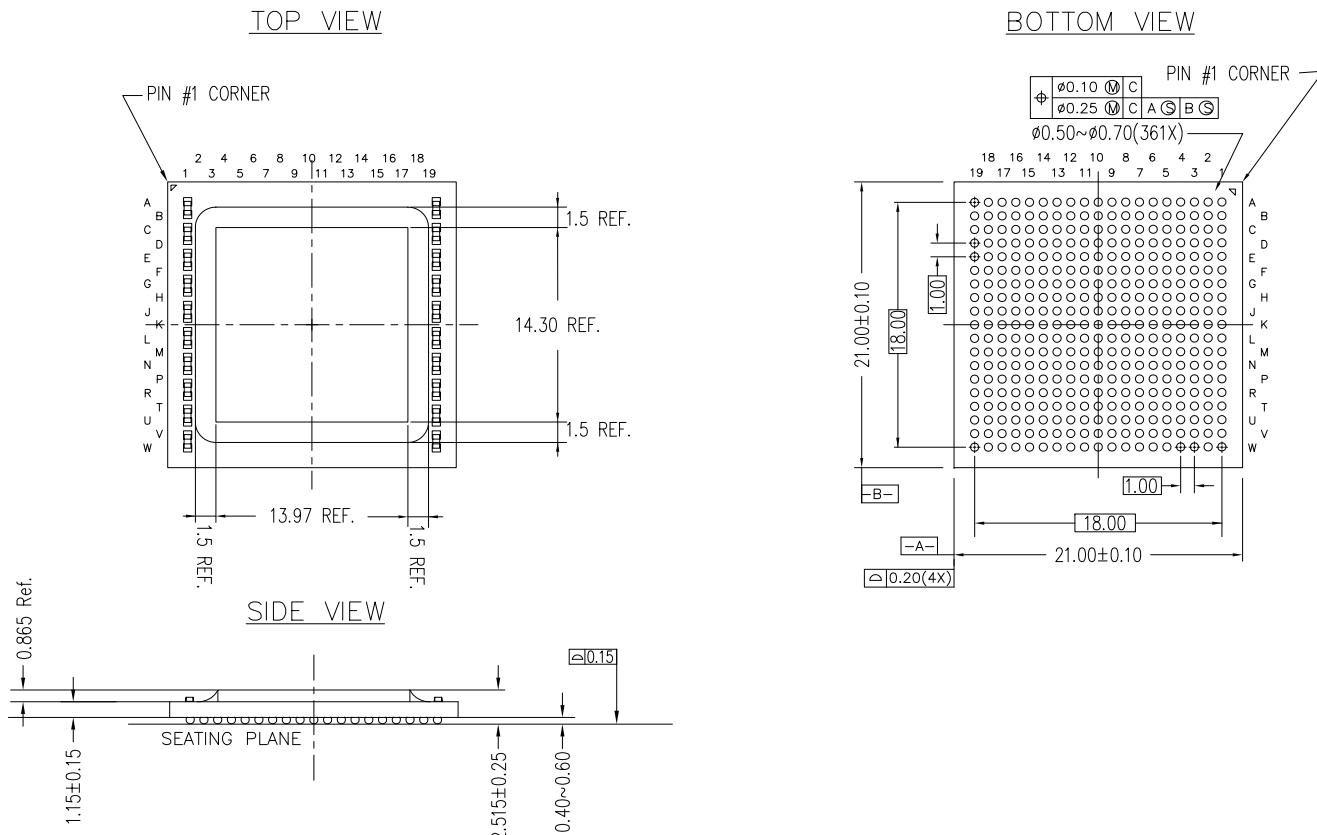

| 外形図 .....                        | 43        |

| 略語 .....                         | 44        |

| <b>本書の表記法 .....</b>              | <b>44</b> |

| 測定単位 .....                       | 44        |

| <b>改訂履歴 .....</b>                | <b>45</b> |

| <b>セールス、ソリューションおよび法律情報 .....</b> | <b>46</b> |

| ワールドワイドな販売と設計サポート .....          | 46        |

| 製品 .....                         | 46        |

| PSoC® ソリューション .....              | 46        |

| サイプレス開発者コミュニティ .....             | 46        |

| テクニカルサポート .....                  | 46        |

## ピン配置

図 1. 361 ポール FCBGA ピン配置

CY7C4021KV13 (4M×18)

|   | 1    | 2     | 3       | 4     | 5     | 6     | 7     | 8       | 9        | 10    | 11        | 12      | 13     | 14     | 15     | 16     | 17      | 18   | 19   |

|---|------|-------|---------|-------|-------|-------|-------|---------|----------|-------|-----------|---------|--------|--------|--------|--------|---------|------|------|

| A | VSS  | VDDQ  | VSS     | DQA 5 | VDDQ  | DQA 7 | VSS   | DQA 8   | VSS      | LBK0# | VSS       | DQA 17  | VSS    | DQA 16 | VDDQ   | DQA 14 | VSS     | VDDQ | VSS  |

| B | VDD  | DNU   | VDDQ    | VSS   | DNU   | VDDQ  | DQA 1 | VDDQ    | VDD      | LBK1# | VDD       | VDDQ    | DQA 10 | VDDQ   | DNU    | VSS    | VDDQ    | DNU  | VDD  |

| C | VSS  | VDDQ  | QvId A0 | QKA0  | VSS   | DQA 2 | VDDQ  | DQA 0   | VSS      | VDDQ  | VSS       | DQA 9   | VDDQ   | DQA 11 | VSS    | QKA1   | QvId A1 | VDDQ | VSS  |

| D | VDD  | VSS   | QKA0#   | VDDQ  | DQA 3 | VSS   | DQA 4 | DINV A0 | VDD      | CFG#  | VDD       | DINV A1 | DQA 13 | VSS    | DQA 12 | VDDQ   | QKA1#   | VSS  | VDD  |

| E | VSS  | DNU   | VDDQ    | VREF  | VSS   | VDDQ  | VSS   | VDD     | VSS      | VDD   | VSS       | VDD     | VSS    | VDDQ   | VSS    | VREF   | VDDQ    | DNU  | VSS  |

| F | VDDQ | VSS   | DKA0#   | DKA0  | DQA 6 | VSS   | VDDQ  | A13     | VDD      | A0    | VDD       | A14     | VDDQ   | VSS    | DQA 15 | DKA1   | DKA1#   | VSS  | VDDQ |

| G | VSS  | DNU   | VSS     | DNU   | VDDQ  | VDD   | A3    | VSS     | A21 144M | A1    | A22 288M  | VSS     | A4     | VDD    | VDDQ   | DNU    | VSS     | DNU  | VSS  |

| H | VDD  | VSS   | DNU     | VSS   | DNU   | VSS   | VSS   | LDA#    | VDDQ     | RWA#  | VDDQ      | LDB#    | VSS    | VSS    | DNU    | VSS    | DNU     | VSS  | VDD  |

| J | VSS  | DNU   | VDDQ    | DNU   | VSS   | VDD   | A5    | VSS     | A19 36M  | CK    | A20 72M   | VSS     | A6     | VDD    | VSS    | DNU    | VDDQ    | DNU  | VSS  |

| K | TDI  | TRST# | TCK     | VSS   | VDD   | VSS   | VDD   | VREF    | VDDQ     | CK#   | VDDQ      | VREF    | VDD    | VSS    | VDD    | VSS    | TMS     | RST# | TDO  |

| L | VSS  | DNU   | VDDQ    | DNU   | VSS   | VDD   | A7    | VDD     | A17      | RWB#  | A18 18M   | VDD     | A8     | VDD    | VSS    | DNU    | VDDQ    | DNU  | VSS  |

| M | VDD  | VSS   | DNU     | VSS   | DNU   | VSS   | VSS   | A11     | VDDQ     | AINV  | VDDQ      | A12     | VSS    | VSS    | DNU    | VSS    | DNU     | VSS  | VDD  |

| N | VSS  | DNU   | VSS     | DNU   | VDDQ  | VDD   | A9    | VSS     | A23 576M | A2    | A24 1152M | VSS     | A10    | VDD    | VDDQ   | DNU    | VSS     | DNU  | VSS  |

| P | VDDQ | VSS   | DKB0#   | DKB0  | DQB 6 | VSS   | VDDQ  | A15     | VDD      | AP    | VDD       | A16     | VDDQ   | VSS    | DQB 15 | DKB1   | DKB1#   | VSS  | VDDQ |

| R | VSS  | DNU   | VDDQ    | VREF  | VSS   | VDDQ  | VSS   | VDD     | VSS      | VDD   | VDD       | VSS     | VDDQ   | VSS    | VREF   | VDDQ   | DNU     | VSS  | VDD  |

| T | VDD  | VSS   | QKB0#   | VDDQ  | DQB 3 | VSS   | DQB 4 | DINV B0 | VDD      | DNU   | VDD       | DINV B1 | DQB 13 | VSS    | DQB 12 | VDDQ   | QKB1#   | VSS  | VDD  |

| U | VSS  | VDDQ  | QvId B0 | QKB0  | VSS   | DQB 2 | VDDQ  | DQB 0   | VSS      | VDDQ  | VSS       | DQB 9   | VDDQ   | DQB 11 | VSS    | QKB1   | QvId B1 | VDDQ | VSS  |

| V | VDD  | DNU   | VDDQ    | VSS   | DNU   | VDDQ  | DQB 1 | VDDQ    | VDD      | PE#   | VDD       | VDDQ    | DQB 10 | VDDQ   | DNU    | VSS    | VDDQ    | DNU  | VDD  |

| W | VSS  | VDDQ  | VSS     | DQB 5 | VDDQ  | DQB 7 | VSS   | DQB 8   | VSS      | ZQ/ZT | VSS       | DQB 17  | VSS    | DQB 16 | VDDQ   | DQB 14 | VSS     | VDDQ | VSS  |

## ピン配置

図 2. 361 ポール FCBGA ピン配置

CY7C4041KV13 (2M×36)

|   | 1    | 2      | 3       | 4      | 5      | 6     | 7     | 8       | 9         | 10    | 11        | 12      | 13     | 14     | 15     | 16     | 17      | 18     | 19   |

|---|------|--------|---------|--------|--------|-------|-------|---------|-----------|-------|-----------|---------|--------|--------|--------|--------|---------|--------|------|

| A | VSS  | VDDQ   | VSS     | DQA 5  | VDDQ   | DQA 7 | VSS   | DQA 8   | VSS       | LBK0# | VSS       | DQA 26  | VSS    | DQA 25 | VDDQ   | DQA 23 | VSS     | VDDQ   | VSS  |

| B | VDD  | DQA 13 | VDDQ    | VSS    | DQA 17 | VDDQ  | DQA 1 | VDDQ    | VDD       | LBK1# | VDD       | VDDQ    | DQA 19 | VDDQ   | DQA 35 | VSS    | VDDQ    | DQA 31 | VDD  |

| C | VSS  | VDDQ   | QvId A0 | QKA0   | VSS    | DQA 2 | VDDQ  | DQA 0   | VSS       | VDDQ  | VSS       | DQA 18  | VDDQ   | DQA 20 | VSS    | QKA1   | QvId A1 | VDDQ   | VSS  |

| D | VDD  | VSS    | QKA0#   | VDDQ   | DQA 3  | VSS   | DQA 4 | DINV A0 | VDD       | CFG#  | VDD       | DINV A1 | DQA 22 | VSS    | DQA 21 | VDDQ   | QKA1#   | VSS    | VDD  |

| E | VSS  | DQA 14 | VDDQ    | VREF   | VSS    | VDDQ  | VSS   | VDD     | VSS       | VDD   | VSS       | VDD     | VSS    | VDDQ   | VSS    | VREF   | VDDQ    | DQA 32 | VSS  |

| F | VDDQ | VSS    | DKA0#   | DKA0   | DQA 6  | VSS   | VDDQ  | A13     | VDD       | A0    | VDD       | A14     | VDDQ   | VSS    | DQA 24 | DKA1   | DKA1#   | VSS    | VDDQ |

| G | VSS  | DQA 15 | VSS     | DQA 16 | VDDQ   | VDD   | A3    | VSS     | A21 288M  | A1    | A22 576M  | VSS     | A4     | VDD    | VDDQ   | DQA 34 | VSS     | DQA 33 | VSS  |

| H | VDD  | VSS    | DQA 9   | VSS    | DQA 10 | VSS   | VSS   | LDA#    | VDDQ      | RWA#  | VDDQ      | LDB#    | VSS    | VSS    | DQA 28 | VSS    | DQA 27  | VSS    | VDD  |

| J | VSS  | DQA 11 | VDDQ    | DQA 12 | VSS    | VDD   | A5    | VSS     | A19 72M   | CK    | A20 144M  | VSS     | A6     | VDD    | VSS    | DQA 30 | VDDQ    | DQA 29 | VSS  |

| K | TDI  | TRST#  | TCK     | VSS    | VDD    | VSS   | VDD   | VREF    | VDDQ      | CK#   | VDDQ      | VREF    | VDD    | VSS    | VDD    | VSS    | TMS     | RST#   | TDO  |

| L | VSS  | DQB 11 | VDDQ    | DQB 12 | VSS    | VDD   | A7    | VDD     | A17       | RWB#  | A18 36M   | VDD     | A8     | VDD    | VSS    | DQB 30 | VDDQ    | DQB 29 | VSS  |

| M | VDD  | VSS    | DQB 9   | VSS    | DQB 10 | VSS   | VSS   | A11     | VDDQ      | AINV  | VDDQ      | A12     | VSS    | VSS    | DQB 28 | VSS    | DQB 27  | VSS    | VDD  |

| N | VSS  | DQB 15 | VSS     | DQB 16 | VDDQ   | VDD   | A9    | VSS     | A23 1152M | A2    | A24 2304M | VSS     | A10    | VDD    | VDDQ   | DQB 34 | VSS     | DQB 33 | VSS  |

| P | VDDQ | VSS    | DKB0#   | DKB0   | DQB 6  | VSS   | VDDQ  | A15     | VDD       | AP    | VDD       | A16     | VDDQ   | VSS    | DQB 24 | DKB1   | DKB1#   | VSS    | VDDQ |

| R | VSS  | DQB 14 | VDDQ    | VREF   | VSS    | VDDQ  | VSS   | VDD     | VSS       | VDD   | VSS       | VDD     | VSS    | VDDQ   | VSS    | VREF   | VDDQ    | DQB 32 | VSS  |

| T | VDD  | VSS    | QKB0#   | VDDQ   | DQB 3  | VSS   | DQB 4 | DINV B0 | VDD       | DNU   | VDD       | DINV B1 | DQB 22 | VSS    | DQB 21 | VDDQ   | QKB1#   | VSS    | VDD  |

| U | VSS  | VDDQ   | QvId B0 | QKB0   | VSS    | DQB 2 | VDDQ  | DQB 0   | VSS       | VDDQ  | VSS       | DQB 18  | VDDQ   | DQB 20 | VSS    | QKB1   | QvId B1 | VDDQ   | VSS  |

| V | VDD  | DQB 13 | VDDQ    | VSS    | DQB 17 | VDDQ  | DQB 1 | VDDQ    | VDD       | PE#   | VDD       | VDDQ    | DQB 19 | VDDQ   | DQB 35 | VSS    | VDDQ    | DQB 31 | VDD  |

| W | VSS  | VDDQ   | VSS     | DQB 5  | VDDQ   | DQB 7 | VSS   | DQB 8   | VSS       | ZQ/ZT | VSS       | DQB 26  | VSS    | DQB 25 | VDDQ   | DQB 23 | VSS     | VDDQ   | VSS  |

## ピンの機能

| 名称                                                | I/O    | 説明                                                                                                                                                                                                                                                                                                                                                     |

|---------------------------------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CK、CK#                                            | 入力クロック | アドレス／コマンド入力クロック。CK および CK# は差動クロック入力です。制御およびアドレス入力信号は CK の立ち上がりエッジと立ち下りエッジの両方でサンプリングされます。CK の立ち上りエッジではポート A 用に制御およびアドレス入力をサンプリングし、CK の立ち下りエッジではポート B 用に制御およびアドレス入力をサンプリングします。CK# は CK と 180 度位相が逆っています。                                                                                                                                                |

| A[x:0]                                            | 入力     | アドレス入力。読み出し、書き込み動作中に CK、CK# クロックの立ち上がりエッジでサンプリングされます。このアドレス入力は両ポートの読み出し、書き込み動作に使用されます。3 本の下位アドレスピン (A0、A1、A2) でアクセスするバンクを選択します。このアドレスピンはバンクアドレスピンとしても知られています。<br>(×36) データ幅の場合、アドレス入力 A[19:0] が使用され、A[24:20] は予備です。<br>(×18) データ幅の場合、アドレス入力 A[20:0] が使用され、A[24:21] は予備です。<br>予備のアドレス入力は無接続であり、ハイレベルかローレベルに固定されるかフローティング状態にされます。                        |

| AP                                                | 入力     | アドレスパリティ入力。アドレスピンを介して偶数パリティを提供するのに使用されます。<br>(×36) データ幅の場合、AP はアドレス入力 A[20:0] に対応します。<br>(×18) データ幅の場合、AP はアドレス入力 A[21:0] に対応します。                                                                                                                                                                                                                      |

| PE#                                               | 出力     | アドレスパリティエラー フラグ。アドレスパリティエラーが検出された時に、ローレベルにアサートされます。アサートされると、コンフィギュレーションレジスタのコマンドによりクリアされるまで、PE# がローレベルのままになります。                                                                                                                                                                                                                                        |

| AINV                                              | 入力     | アドレスとアドレスパリティ入力用のアドレス反転ピン。<br>(×36) データ幅の場合、AINV はアドレス入力 A[20:0] とアドレスパリティ入力 (AP) に対応します。<br>(×18) データ幅の場合、AINV はアドレス入力 A[21:0] とアドレスパリティ入力 (AP) に対応します。                                                                                                                                                                                               |

| DKA[1:0]、<br>DKA#[1:0]、<br>DKB[1:0]、<br>DKB#[1:0] | 入力     | データ入力クロック。<br>DKA[0]/DKA#[0] は、×36 データ幅構成の場合は DQA[17:0] 入力、×18 データ幅構成の場合は DQA[8:0] 入力を制御します。<br>DKA[1]/DKA#[1] は、×36 データ幅構成の場合は DQA[35:18] 入力、×18 データ幅構成の場合は DQA[17:9] 入力を制御します。<br>DKB[0]/DKB#[0] は、×36 データ幅構成の場合は DQB[17:0] 入力、×18 データ幅構成の場合は DQB[8:0] 入力を制御します。<br>DKB[1]/DKB#[1] は、×36 データ幅構成の場合は DQB[35:18] 入力、×18 データ幅構成の場合は DQB[17:9] 入力を制御します。 |

| QKA[1:0]、<br>QKA#[1:0]、<br>QKB[1:0]、<br>QKB#[1:0] | 出力     | データ出力クロック。<br>QKA[0]/QKA#[0] は、×36 データ幅構成の場合は DQA[17:0] 出力、×18 データ幅構成の場合は DQA[8:0] 出力を制御します。<br>QKA[1]/QKA#[1] は、×36 データ幅構成の場合は DQA[35:18] 出力、×18 データ幅構成の場合は DQA[17:9] 出力を制御します。<br>QKB[0]/QKB#[0] は、×36 データ幅構成の場合は DQB[17:0] 出力、×18 データ幅構成の場合は DQB[8:0] 出力を制御します。<br>QKB[1]/QKB#[1] は、×36 データ幅構成の場合は DQB[35:18] 出力、×18 データ幅構成の場合は DQB[17:9] 出力を制御します。 |

| DQA[x:0]、<br>DQB[x:0]                             | 入力／出力  | データ入出力。双方向データバス<br>(×36) データ幅 - DQA <sub>[35:0]</sub> ; DQB <sub>[35:0]</sub><br>(×18) データ幅 - DQA <sub>[17:0]</sub> ; DQB <sub>[17:0]</sub>                                                                                                                                                                                                            |

| LDA#、<br>LDB#                                     | 入力     | 同期ロード入力。LDA# は CK クロックの立ち上がりエッジで、LDB# は立ち下りエッジでサンプリングされます。LDA# はデータポート A 用のコマンド、LDB# はデータポート B 用のコマンドを有効にします。LDx# は、LDx# がローレベルの時にコマンドを有効にし、LDx# がハイレベルの時にコマンドを無効にします。コマンドが無効の時、新たなコマンドは無視されますが内部動作は継続します。                                                                                                                                             |

## ピンの機能

| 名称                       | I/O    | 説明                                                                                                                                                                           |

|--------------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RWA#、<br>RWB#            | 入力     | <b>同期読み出し／書き込み入力。</b> RWA# 入力は CK クロックの立ち上がりエッジで、RWB# は立ち下がりエッジでサンプリングされます。RWA# 入力は、読み出しままたは書き込み動作を選択するのに LDA# 入力と共に使用されます。同様に、RWB# 入力は読み出しか書き込み動作を選択するために LDB# 入力と共に使用されます。 |

| QVLDA[1:0]<br>QVLDB[1:0] | 出力     | <b>出力データ有効インジケータ。</b> QVLD ピンは出力データが有効であることを示します。QVLD は QKx、QKx# と同時に変化します。                                                                                                  |

| ZQ/ZT                    | 入力     | <b>出力インピーダンスマッチング入力。</b> この入力は、デバイス出力をシステムデータバスのインピーダンスに整合するのに使用されます。                                                                                                        |

| CFG#                     | 入力     | コンフィギュレーション ビット。このピンは異なるモード レジスタを設定するのに使用されます。                                                                                                                               |

| RST#                     | 入力     | <b>ローアクティブ非同期 RST。</b> このピンは、RST# がローレベルの時にアクティブであり、RST# がハイレベルの時に非アクティブです。RST# ピンは内部プルダウン抵抗を持ちます。                                                                           |

| LBK0#、<br>LBK1#          | 入力     | 制御およびアドレス、コマンド、クロックの信号に対するデスキュー用のループバック モード。                                                                                                                                 |

| TMS                      | 入力     | <b>JTAG 用のテスト モード選択入力ピン。</b> JTAG 機能が回路で使用されない場合、このピンは未接続でも構いません。                                                                                                            |

| TDI                      | 入力     | <b>JTAG 用のテスト データ入力ピン。</b> JTAG 機能が回路で使用されない場合、このピンは未接続でも構いません。                                                                                                              |

| TCK                      | 入力     | <b>JTAG 用のテスト クロック入力ピン。</b> JTAG 機能が回路で使用されない場合、このピンは VSS に接続しなければなりません。                                                                                                     |

| TDO                      | 出力     | <b>JTAG 用のテスト データ出力ピン。</b> JTAG 機能が回路で使用されない場合、このピンは未接続でも構いません。                                                                                                              |

| TRST#                    | 入力     | <b>JTAG 用のテスト リセット入力ピン。</b> JTAG 機能がシステムで使用されない場合、このピンは VDD に接続しなければなりません。TRST# 入力は JTAG モードにのみ適用可能です。                                                                       |

| DNU                      | 該当なし   | <b>未使用。</b> 未使用ピン。                                                                                                                                                           |

| VREF                     | リファレンス | <b>基準電圧入力。</b> 入力、出力および AC 測定ポイントの参照レベルを設定するのに使用される静的入力です。                                                                                                                   |

| VDD                      | 電源     | デバイスコアへの電源入力。                                                                                                                                                                |

| VDDQ                     | pll 電源 | デバイス出力回路への電源入力。                                                                                                                                                              |

| VSS                      | グランド   | デバイスのグランド。                                                                                                                                                                   |

## 機能の概要

QDR-IV HP SRAM は、2つの独立した双方向データポートを備えた2ワードバースト同期SRAMです。以下の節はQDR-IV HP SRAMの動作を説明します。

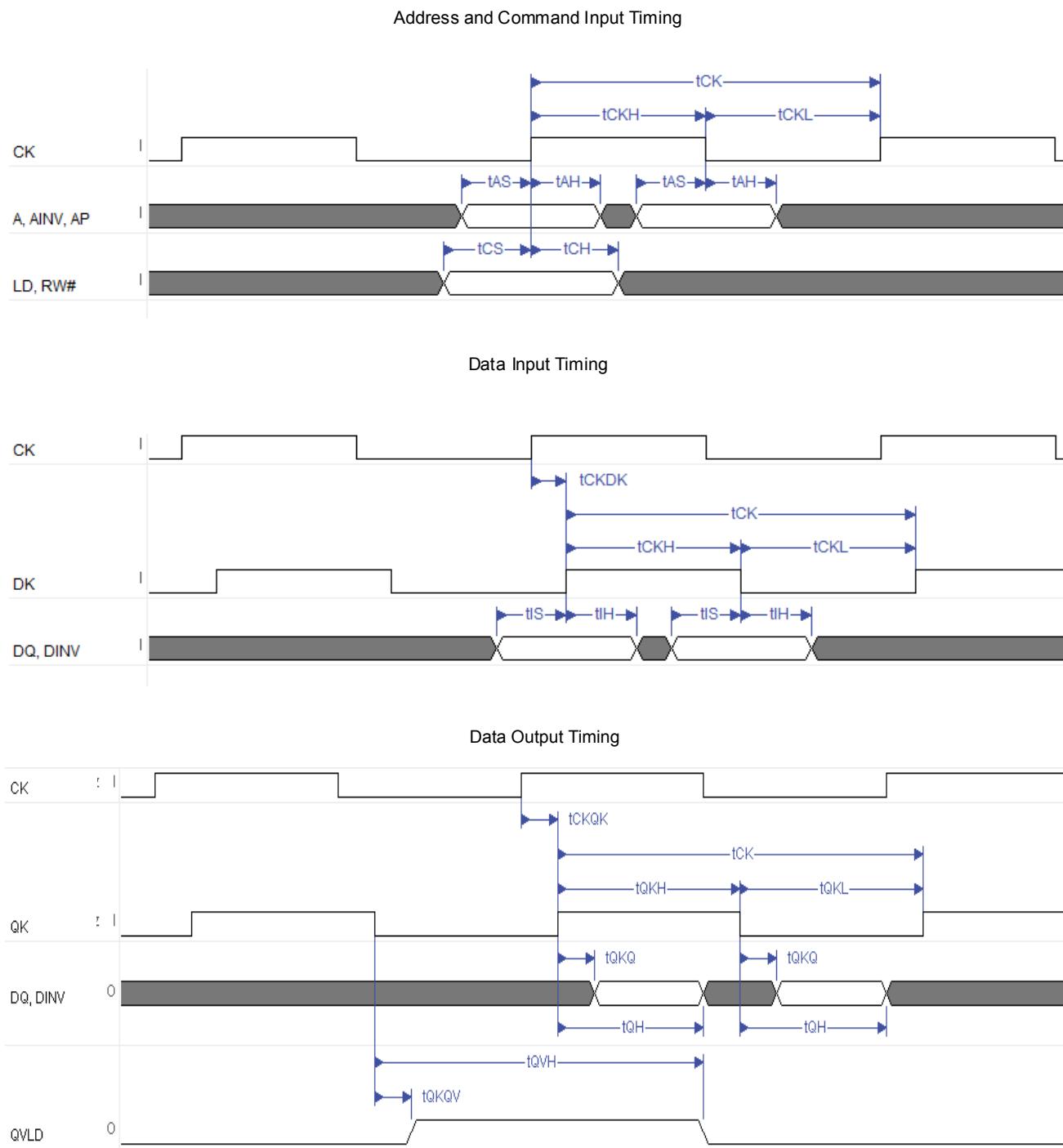

### クロック

クロック信号はCK/CK#、DKx/DKx#、QKx/QKx#の3グループに分けられています。ここで、xはAかBであり、対応するポートを示します。

CK/CK#クロックは、アドレスと制御ピン(A[24:0]、LDA#、LDB#、RWA#、RWB#)に対応します。アドレスと制御信号の遷移と遷移の中央でCK/CK#が遷移します。

DKx/DKx#クロックは書き込みデータに対応します。DDR動作するDQxとDINVxがデータ書き込みの入力として動作する時、DKx/DKx#クロックはDQxとDINVx信号の遷移と遷移の中央で遷移します。

QKx/QKx#クロックは読み出しデータに対応します。DDR動作するDQxとDINVxがデータ読み出しの出力として動作する時、QKx/QKx#クロックはDQxとDINVx信号と同期して遷移します。

### コマンドサイクル

QDR-IV HP SRAM読み出しと書き込みコマンドは、制御入力(LDA#、LDB#、RWA#、およびRWB#)とアドレスバスによって駆動されます。

ポートAの制御入力(LDA#およびRWA#)は、入力クロックの立ち上がりエッジでサンプリングされます。ポートBの制御入力(LDB#およびRWB#)は、入力クロックの立ち下がりエッジでサンプリングされます。

ポートAでは、

LDA#=0およびRWA#=1の時、読み出し動作が開始されます。

LDA#=0およびRWA#=0の時、書き込み動作が開始されます。

アドレスは入力クロックの立ち上がりエッジでサンプリングされます。

ポートBでは、

LDB#=0およびRWB#=1の時、読み出し動作が開始されます。

LDB#=0およびRWB#=0の時、書き込み動作が開始されます。

アドレスは入力クロックの立ち下がりエッジでサンプリングされます。

### 読み出しと書き込みデータサイクル

読み出しデータは、読み出しコマンド開始に対応するCK信号の立ち上がりエッジの5クロックサイクル後にDQAピンに供給されます。QLDAは、最初のデータワードがバスで駆動される半クロックサイクル前にアサートされます。最後のデータワードがバスで駆動される半クロックサイクル前にデアサートされます。データ出力は、最後のデータワードの後のクロックでトライステートになります。

読み出しデータは、読み出しコマンドの発行完了時点に対応するCK信号の立ち下がりエッジから5クロックサイクル後にDQBピンに出力されます。QLDBは、最初のデータワードがバスで駆動される半クロックサイクル前にアサートされます。最後のデータワードがバスで駆動される半クロックサイクル

前にデアサートされます。データ出力は、最後のデータワードの後のクロックでトライステートになります。

書き込みデータは、書き込みコマンドの発行完了時点に対応するCK信号の立ち上がりエッジから3クロックサイクル後にDQAピンに供給されます。

書き込みデータは、書き込みコマンドの発行完了時点に対応するCK信号の立ち下がりエッジから3クロックサイクル後にDQBピンに供給されます。

### アドレスおよびデータバス反転

QDR-IV HP SRAMは、同期スイッチングノイズとI/O電流を減少させるために全てのアドレスまたはデータピンを反転することができます。

AINVピンは、アドレスバスA[24:0]およびアドレスパリティビットAPが反転されるかを示します。アドレスバスとアドレスパリティビットは1つのグループと見なされます。AINVの機能はメモリコントローラによって制御されます。但し、システム設計では以下のルールに従ってください。

■ ×36構成の製品では、20アドレスピンと1パリティビットの21信号が1つのアドレスグループとして使用されます。アドレスグループ内の論理0の数が≥11の場合、AINVはコントローラによって1にセットされます。結果として、各ビット時間中に同じ方向に切り替わるピン数は11以下です。

■ ×18データ幅の製品では、21アドレスピンと1パリティビットの22信号が1つのアドレスグループに対応します。アドレスグループ内の論理0の数が≥12の場合、AINVはコントローラによって1にセットされます。結果として、各ビット時間中に同じ方向に切り替わるピン数は12以下です。

DINVAとDINVBピンは、それぞれDQAとDQBピンが反転されるかを示します。

■ ×36データ幅の製品では、各ポート用のデータバスは18ピンのグループに分けられています。各18ピンデータグループに対して、特定のサイクルで10ピン以下がローレベルに駆動されることを保証します。データグループ内の論理0の数が≥10の場合、DINVは1にセットされます。その結果として、各ビット時間中に同じ方向に切り替わるピン数は10以下です。

■ ×18データ幅の製品では、各ポート用のデータバスは9ピンのグループに分けられています。各9ピンデータグループに対して、特定のサイクルで5ピン以下がローレベルに駆動されることを保証します。データグループ内の論理0の数が≥5の場合、DINVは1にセットされます。その結果として、各ビット時間中に同じ方向に切り替わるピン数は5以下です。

AINV、DINVA[1:0]、DINVB[1:0]は全てハイアクティブです。1にセットされると、対応するバスは反転されます。データ反転機能がオフにプログラムされた場合、DINVA/DINVB出力ビットは常に0に駆動されます。

これらの機能はコンフィギュレーションレジスタを使用してプログラムすることができます。アドレスバスとデータバス用に独立に有効か無効にすることができます。

コンフィギュレーションレジスタの読み出しおよび書き込みサイクル中、アドレス反転入力は無視されます。さらにレジスタ読み出しデータがデータバスに出力されている時、データ反転出力は常に0に駆動されます。つまりレジスタ読み出しデータはDQA[7:0]で駆動され、DINVA[0]ビットは0に駆動されます。他の全てのDQA/DQBデータビットとDINVA/DINVBビッ

トはトライステートになります。さらにアドレス パリティ入力 (AP) は無視されます。

### アドレス パリティ

QDR-IV HP SRAM は、アドレス バスでの整合性を保証するためにアドレス パリティ機能を備えています。この機能をサポートするピンは、AP と PE# の 2 本あります。

AP ピンはアドレス ピンに偶数パリティを提供するのに使用されます。AP 値は、ビット 1 の総数 (AP を含む) が偶数であるようにセットされます。AP ピンは DDR 入力です。

内部では、アドレス パリティ エラーが検出され、メモリ アレイへのアクセスが書き込みサイクルである場合は無視されます。読み出しアクセスは、アドレス パリティ エラーが検出されても正常に継続します。

外部には、PE# ピンがアドレス パリティ エラーの発生を示します。このピンはローアクティブであり、パリティ エラーが検出されてから RL サイクル以内に 0 にクリアされます。エラーがコンフィギュレーション レジスタでクリアされるまで、アサートされたままになります。

アドレス パリティ 機能は任意であり、コンフィギュレーション レジスタで有効か無効にすることができます。

コンフィギュレーション レジスタの読み出しおよび書き込みサイクル中に、アドレス パリティ 入力は無視されます。パリティはこれらのサイクル中に確認されません。

**注：**メモリ コントローラはまず、アドレス バスに基づいてアドレス パリティを生成する必要があります。アドレス反転はその後で、アドレス バスとアドレス パリティ ビットで行われます。

### ポート イネーブル

QDR-IV HP SRAM は、2 個の独立した双方向データ ポートを備えています。設計者によって、1 個だけを使用する場合、読み出し専用と書き込み専用をそれぞれ 1 個使用する場合があります。

ポートを単向モードで使用する場合、システム内の EMI の影響を減少させるためにデータ クロック (DKx/DKx# または QKx/QKx#) を無効にします。さらに対応する制御入力 (RWx#) を無効にします。

ポート B は完全に無効であるようプログラムできます。ポート B を使用しない場合、以下のことを行わなければなりません。

- データ クロック (DKB/DKB# と QKB/QKB#) と制御入力 (LDB# と RWB#) を無効にします。

- 全てのデータバス信号をトライステートにします。データバス信号は DQB、DINVB および QVLDB を含みます。

- ポート B に対応する全ての入力信号をフローティング状態とするか、ポート A の動作に悪影響を与えないよう 1 か 0 に接続します。

- ポート B が使用されない場合、ポート B に対応する全ての出力信号は非アクティブになります。

コンフィギュレーション レジスタに、1 つのポートを使用しないか、単向モードで動作させるかを指定する項目があります。

### オンダイ終端 (ODT) 動作

有効な場合、チップの ODT 回路は全ての NOP および書き込みサイクル中に有効になります。読み出しサイクル中にのみ、読み出しデータが駆動されるため、ODT は一時的に無効になります。

つまり ODT はデータ読み出しの最初の段階がデータ バスで駆動される半クロック サイクル前に無効になり、読み出し動作が終るまで無効のままであります。データ読み出しの最後の段階がデータ バスで駆動されてから半クロック サイクル後、ODT は再度有効になります。

### JTAG 動作

JTAG インターフェースは 5 つの信号を使用します：TRST#、TCK、TMS、TDI、TDO。通常の JTAG 動作の場合、このデバイスでは、TRST# の使用は任意ではありません。

JTAG モードの時、以下の条件が真です。

- 全てのピンの ODT 機能が無効にされます。

JTAG 機能がシステム内で使用されない場合、TRST# ピンを VDD に接続し、TCK 入力をローレベルに駆動するか VSS に接続する必要があります。TMS、TDI、TDO はどこにも接続しないことがあります。

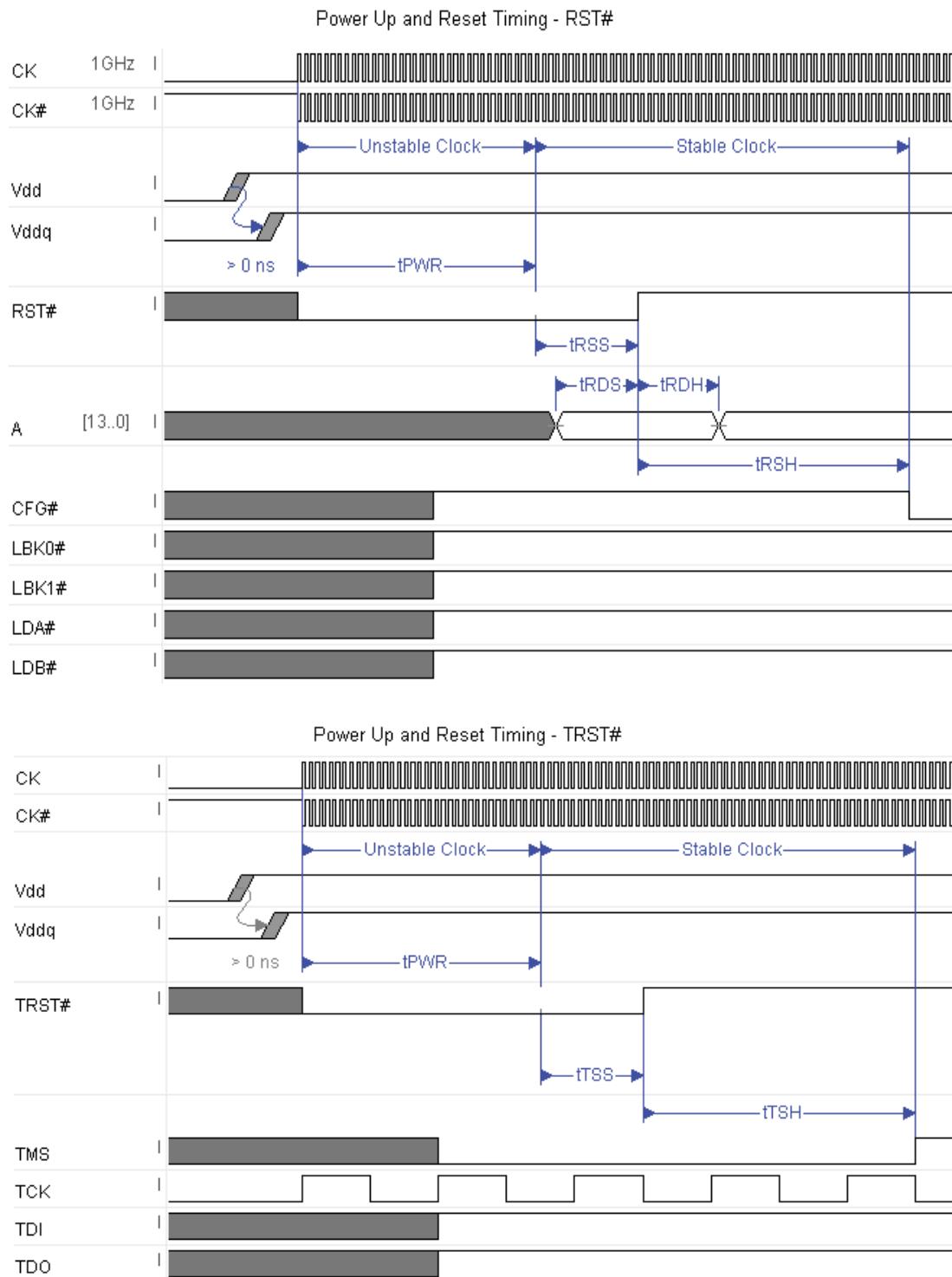

### 電源投入およびリセット

QDR-IV HP SRAM には、信頼性がある動作を保証するため、電源投入およびリセット要件があります。

#### 電源投入シーケンス

- V<sub>DD</sub> を V<sub>DDQ</sub> の前に印加します。

- V<sub>DDQ</sub> を V<sub>REF</sub> の前に、または V<sub>REF</sub> と同時に印加します。

#### リセット シーケンス

リセット タイミング図(41ページの図16)を参照してください。

1. 電源投入時、t<sub>PWR</sub> の間ローレベルである必要がある RST# と TRST# を除き、全ての入力は不定状態であることがあります。

2. デバイスに加える最初の信号は、t<sub>PWR</sub> の間に安定していないかも知れませんが入力クロック (CK/CK#) です。

3. 入力クロックが安定した後、全ての制御入力を以下の値に駆動する必要があります。

- a. RST#=0

- b. CFG#=1

- c. LBK0#=1

- d. LBK1#=1

- e. LDA#=1

- f. LDB#=1

4. 他の全ての制御入力がデアサートされている間、少なくとも 200μs (t<sub>RSS</sub>) の間、リセットをアサートしたままにします。

5. リセットの立ち上がりエッジで、アドレスビット A[13:0] が、ODT 値とポート イネーブル値にロードするためにサンプリングされます。リセット後、デバイスの内部動作が開始できます。これらの動作は、PLL の初期化と内部レジスタのリセットを含むことがあります。

6. 但し、全ての外部制御信号は少なくとも 400000 クロック (t<sub>RSH</sub>) の間、デアサートされたままでなければなりません。この間、他の全ての信号 (データおよびアドレス バス) は有効なレベルに駆動する必要があります。デバイスの入力は有効なレベルに駆動する必要があります。

7. その後、デバイスは通常動作モードに入り、制御入力に応答できるようになります。

通常、リセット シーケンスの後、システムは、次の節で記述される手順に従ってトレーニング シーケンスを実行し始めます。

しかし、RST# はいつでもシステムによってアサートされ、システムはリセット シーケンス後、再びトレーニング シーケンスを経ずに通常の読み出し／書き込み動作を開始したい場合があります。チップは RST# のデアサート後、 $t_{RSH}$  の直後に通常の読み出し／書き込みを受け取れるようになります。

#### PLL リセット動作

コンフィギュレーション レジスタには、PLL をリセットするビットがあります。PLL が有効でない QDR-IV HP SRAM デバイスの動作はサポートされません。タイミング特性は、PLL が無効の時に保証されません。しかしこのビットは、システムが PLL ループ回路をリセットできるように意図されています。

PLL をリセットするには、まず PLL リセットビットを 1 にセットし PLL を無効にし、その後このビットを 0 にクリアして PLL を有効にします。この手順の後に、PLL は入力クロックに再度ロックします。 $t_{PLL}$  の待機時間が必要です。

#### 動作モード

QDR-IV HP SRAM には 3 つの動作モードがあります。

1. コンフィギュレーション

2. ループバック

3. メモリ アクセス

このモードは、CFG#、LBK0#、LBK1#、LDA#、LDB# の制御信号レベルにより定義されます。

この動作が相互排他的な関係になるようにしています。それは、ある動作モードが他の動作モードと同時に実行されないということです。

誤ったタイミングで制御信号を不注意にアサートしても、何の影響もありません。内部チップの動作は、誤った制御信号のアサートには定義されません。デバイスの正常な動作のために、システムは以下の節で定義されるように、正常なモード遷移手順を厳守する必要があります。

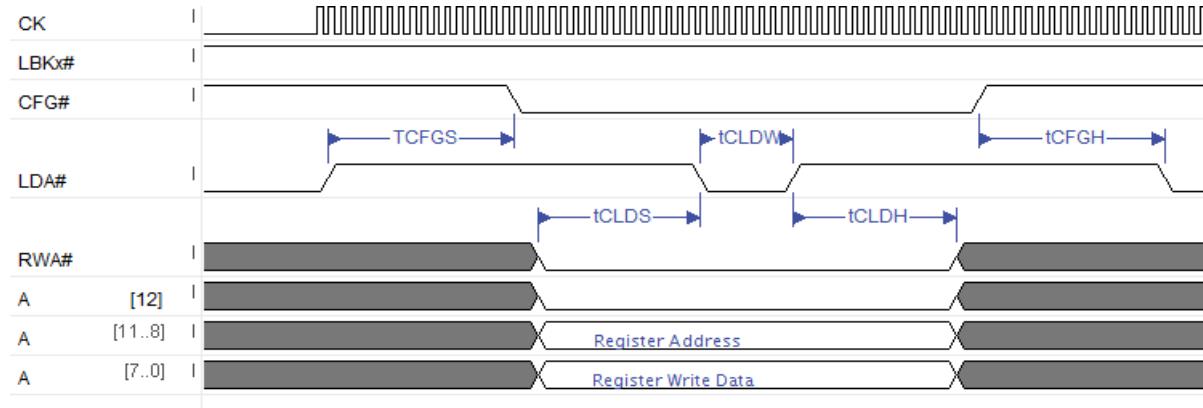

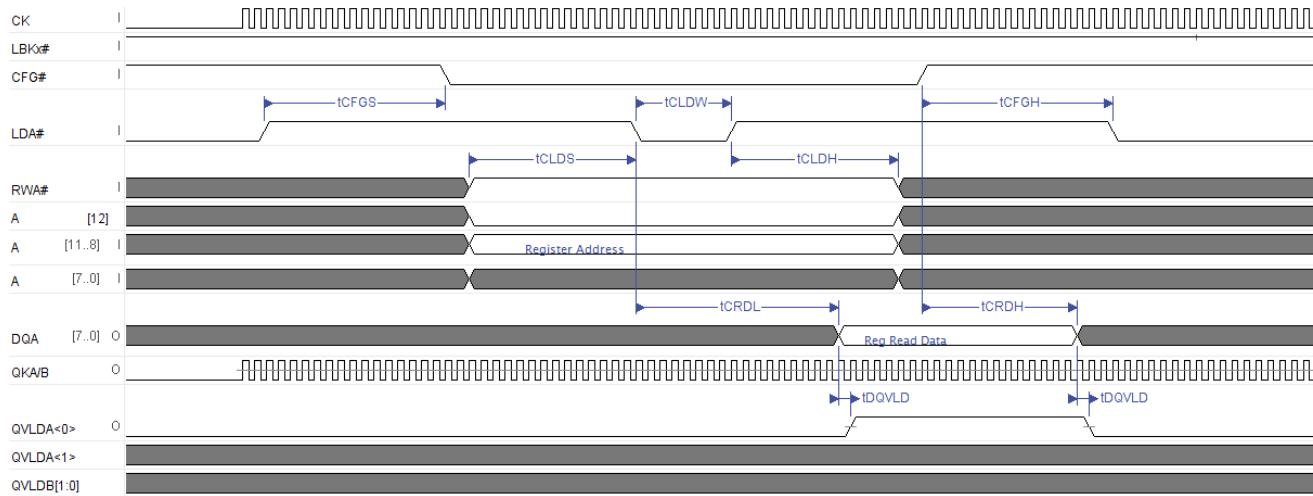

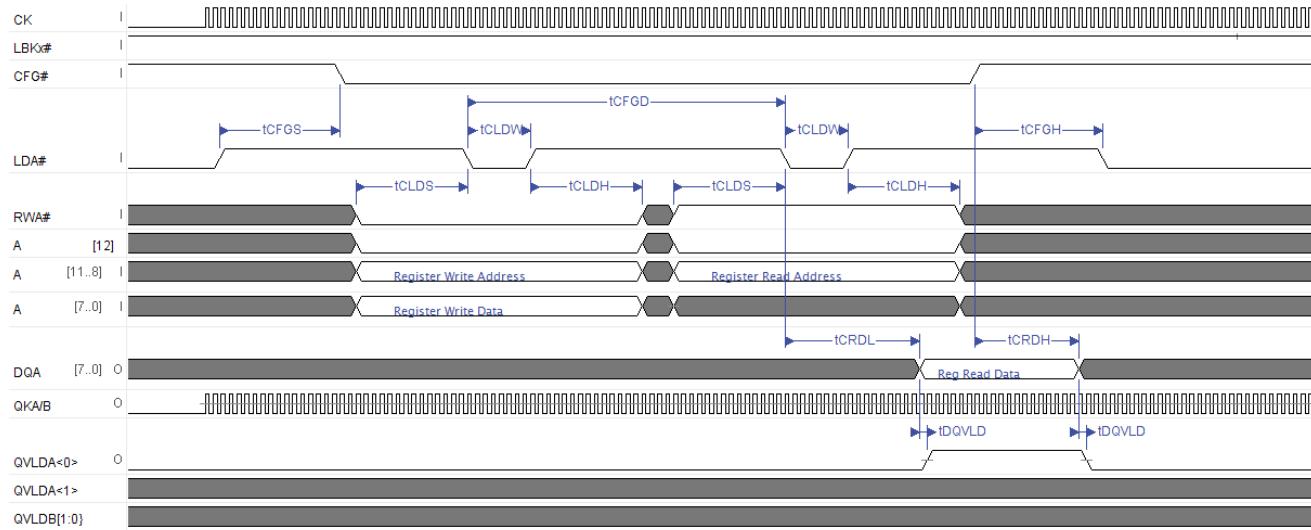

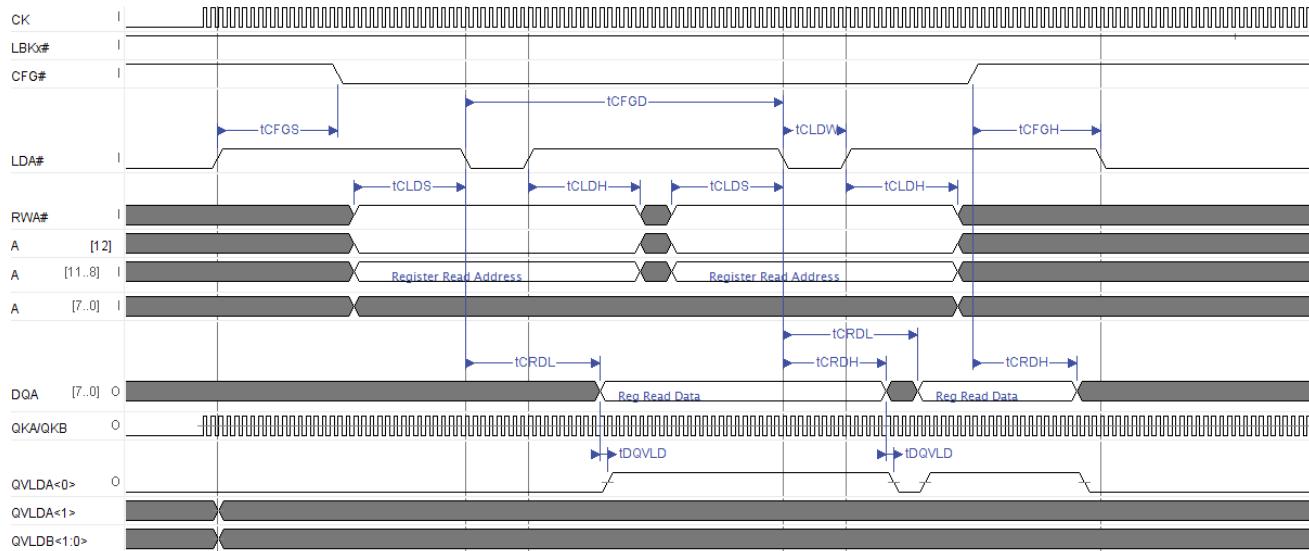

#### コンフィギュレーション

CFG# 信号がアサートされると、デバイスは設定動作モードに移行します。メモリ アクセスまたはループバック動作は、このモードに移行する少なくとも 32 クロック前に実行してはいけません。

このモード中に、LDB#、LBK0#、LBK1# 制御信号をアサートしてはいけません。但し、LDA# はレジスタの実際の読み出しと書き込み動作を実行するのに使用されます。

メモリ アクセスまたはループバック動作は、このモードを終了してから少なくとも 32 クロック以内に実行してはいけません。

#### ループバック

LBK0#、LBK1# の内 1 つでもアサートされると、デバイスはループバック動作モードに移行します。メモリ アクセスまたは設定動作は、このモードに移行する少なくとも 32 クロック前に実行してはいけません。

このモードに入った直後に、製品がトレーニング用の有効な入力をトグルする準備ができるまで、32 クロックが必要です。

このモード中に、LDA# と LDB# はトレーニング用に切り替わることがあります。

メモリ アクセスまたは設定動作は、このモードを終了してから少なくとも 32 クロック以内に実行してはいけません。

ループバック モード中に、データ反転機能は使用されません。この機能はコンフィギュレーション レジスタで有効になっても、ループバック モード中に一時的に無視されます。

#### メモリ アクセス

CFG#、LBK0#、LBK1# 制御信号がアサートされない場合、デバイスはメモリ アクセス モードになります。このモードはデバイスの通常の動作モードです。

このモード中に、LDA#、LDB# の内 1 つでもアサートされると、メモリ アクセス サイクルが実行されます。CFG#、LBK0#、LBK1# 制御信号は、メモリ アクセス サイクルを実行する時にアサートしてはいけません。

このモードを終了する少なくとも 32 クロック以内に、メモリ アクセスを実行してはいけません。

#### デスキュート レーニング シーケンス

QDR-IV HP SRAM は、メモリ コントローラが高速動作のため信号をデスキュートすることに対応しています。デスキュートが必要な時、メモリ コントローラはデスキュート機能を提供します。デスキュート動作中、QDR-IV HP SRAM はループバック モードで動作します。

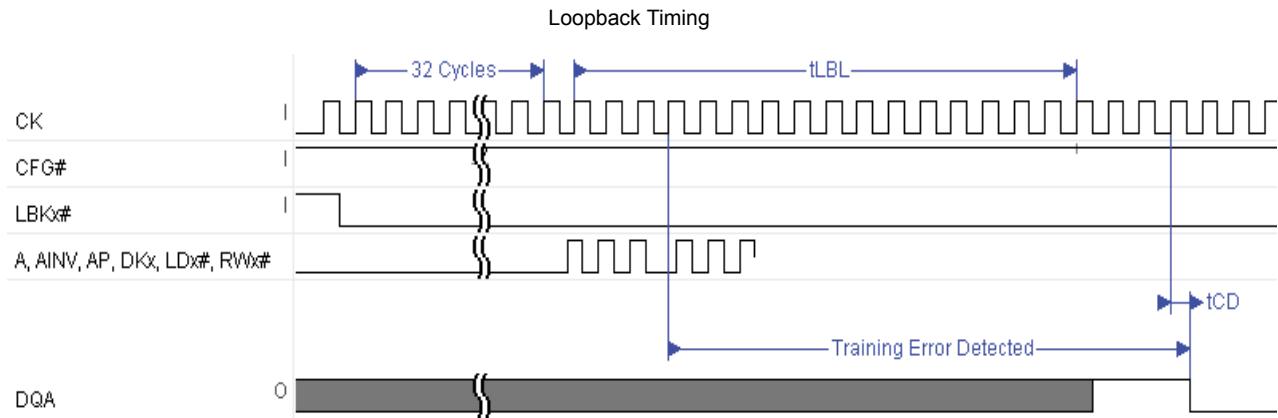

ループバック タイミング図 (40 ページの図 15) を参照してください。

デスキュートは、3 つのステップで実行されます。

1. 制御／アドレスのデスキュート

2. 読み出しデータのデスキュート

3. 書き込みデータのデスキュート

#### 制御／アドレスのデスキュート

LBK0、LBK1# の内少なくとも 1 つを 0 にアサート

以下の 39 信号がループバックされます。

- DKA0、DKA0#、DKA1、DKA1#

- DKB0、DKB0#、DKB1、DKB1#

- LDA#、RWA#、LDB#、RWB#

- A[24:0]、AINV、AP

クロック入力 DKA0、DKA0#、DKA1#、DKB0、DKB0#、DKB1、DKB1# はフリーランのクロック入力であり、トレーニング シーケンスの間に継続して動作します。また  $t_{PLL}$  の待機時間が必要です。

ループバック信号マッピングについては、14 ページの表 1 を参照してください。

ループバックされた各ピンに対しては、入力ピンは入力クロック (CK/CK#) の立ち上がりエッジと立ち下がりエッジの両方でサンプリングされます。

出力クロック (QKA / QKA#) の立ち上がりエッジで出力される値は、入力クロックの立ち上がりエッジでサンプリングされた値となります。

出力クロック (QKA / QKA#) の立ち下がりエッジで出力される値は、入力クロックの立ち下がりエッジでサンプリングされた値を反転したものになります。

入力ピンから DQA 出力までの遅延は  $t_{LBL}$  で、16 クロックです。

### 読み出しデータのデスキュー

この時点で、アドレス、制御およびデータ入力クロックは既にデスキューされています。

読み出しデータ デスキューは、一定の値に保持されたデータを使用してメモリに書き込まれるトレーニング パターンを必要とします。

複雑なデータ パターンが、デスキューされない DQA、DQB 信号の少なくとも 1 本と書き込みトレーニング イネーブル ビットを使用してメモリに書き込まれることがあります。

書き込みトレーニング イネーブルを 1 にセットし：

書き込みデータ サイクル中に：

最初のデータ段階（最初のデータ バースト）がデータ バス上でサンプリングされます。

2 番目のデータ段階（2 番目のデータ バースト）はデータ バスを反転したサンプルです。

書き込みトレーニング イネーブルを 0 にクリアし：

書き込みデータ サイクル中に：

通常の動作として、1 番目と 2 番目両方のデータ 段階がデータ バスからサンプリングされます。

書き込みトレーニング イネーブル ビットは読み出しデータ サイクルに影響を与えません。

データ パターンがメモリに書き込まれた後、標準読み出しコマンドは、QK / QK# データ出力クロックに対してシステムが以下の信号をデスキューすることを許可します。

DQA、DINVA、QVLDA、DQB、DINVB、QVLDB

### 書き込みデータのデスキュー

書き込みデータ デスキューは、読み出しコマンドに続いてメモリへの書き込みコマンドを使用して実行されます。

デスキュー読み出しデータ パスは、書き込みデータがデバイスによって正常に受信されたかを判定するために使用されます。

これによってシステムがDK/DK#入力データ クロックに対して以下の信号をデスキューすることを許可します。

DQA、DINVA、DQB、DINVB

### 入出力の信号規格

QDR-IV HP SRAM は、プログラムできる幾つかの入出力信号規格をサポートします。それらは以下のとおりです。

■ 1.2V と 1.25V HSTL/SSTL

■ 1.1V と 1.2V POD

入出力信号規格は、アドレス バス入力をサンプリングすることでリセットの立ち上がりリエッジでプログラムされます。プログラムされた値は変更することができません。リセットの立ち上がりリエッジでのみ値を変更できます。

（「LVC MOS 信号方式」節で示された LVC MOS としてリストされている）6 本のピンを除き、全てのアドレス、制御、データ入出力信号は、HSTL/SSTL または POD と互換性があるようにプログラムされます。

### HSTL/SSTL 信号方式

HSTL/SSTL は公称電圧 1.2V および 1.25 V の  $V_{DDQ}$  電圧に対応します。

ODT 終端値は以下のように設定されます。

■ 220Ω のリファレンス抵抗の場合は、40、60、120Ω

■ 180Ω のリファレンス抵抗の場合は、50 または 100Ω

駆動能力は以下のようにプログラムされます。

■ 220Ω の基準抵抗の場合は、40Ω または 60Ω

■ 180Ω の基準抵抗の場合は 50Ω

180Ω または 220Ω のリファレンス抵抗は HSTL/SSTL 信号でサポートされます。

### POD 信号方式

POD は公称電圧 1.1V および 1.2V の  $V_{DDQ}$  電圧に対応します。

ODT 終端値は次のように設定されます。

■ 180Ω のリファレンス抵抗の場合は、50 または 100Ω

■ 220Ω のリファレンス抵抗の場合は、60 または 120Ω

駆動能力は以下のようにプログラムされます。

■ 180Ω のリファレンス抵抗の場合は 50Ω

■ 220Ω のリファレンス抵抗の場合は、40 または 60Ω

180Ω または 220Ω のリファレンス抵抗は POD 信号でサポートされます。

### LVC MOS 信号方式

6 つの入出力信号は、公称電圧 1.25V の LVC MOS 信号方式に固定的に設定されます。これらの信号はコア電圧源 ( $V_{DD}$ ) を基準とします。以下の信号です。

RST#、TRST#、TCK、TMS、TDI、TDO

5 つの JTAG 信号とメイン リセット入力は 1.25 V LVC MOS です。

また ODT は LVC MOS 信号上で常に無効状態です。

### 初期化

QDR-IV HP SRAM は、通常機能モードで動作する前に初期化しなければなりません。初期化には、4 本の特別なピンを使用します：

■ デバイスをリセットするための RST# ピン

■ コンフィギュレーション レジスタをプログラムするための CFG# ピン

■ ループバック機能のための LBK0# と LBK1# ピン

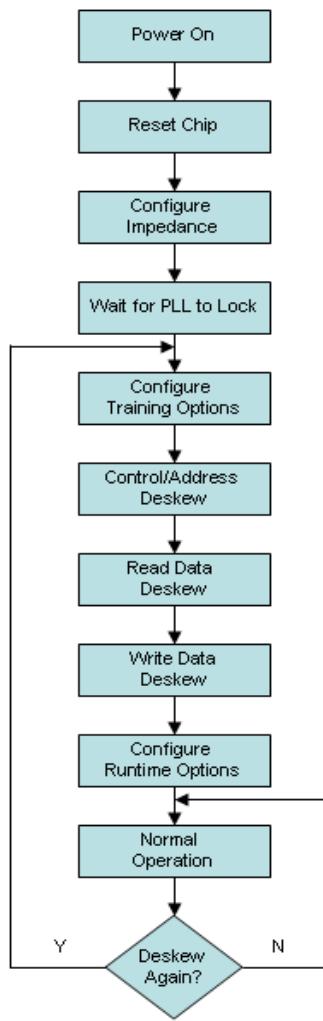

以下のフローチャートに初期化手順を示します。

**図3. 初期化手順のフローチャート**

**チップをリセット**

リセット シーケンスで説明したように、QDR-IV HP SRAM をリセットします。

**インピーダンスを設定**

Config をアサートして (CFG#=0)、インピーダンス制御レジスタをプログラムします。

**PLL がロックするまで待機**

入力インピーダンスが変更されたため、入力クロックに PLL がロックするまで PLL 時間 ( $t_{PLL}$ ) 待ちます。

**トレーニングオプションの設定**

この時点で、アドレスおよびデータ反転オプションをプログラムする必要があります。さらに書き込みトレーニング機能を有効にする必要があります。

Config をアサートして (CFG#=0)、以下をプログラムします。

- 書き込みトレーニング (オンにする)

- アドレス反転イネーブル

- データ反転イネーブル

**制御／アドレスのデスキュー**

この時点で、制御とアドレスのデスキューはメモリ コントローラで実行できるようになります。

**読み出しデータのデスキュー**

制御およびアドレスのデスキュー後、読み出しデータ パスは、デスキュー トレーニング シーケンスで説明されたようにデスキューされます。

**書き込みデータのデスキュー**

書き込みデータ パスは、読み出しデータ パス の後にデスキューされます。

**実行時のオプションの設定**

トレーニングが完了した後、書き込みトレーニング機能を無効にします。最後に、アドレス パリティ オプションを有効にします。

Config をアサートして (CFG#=0)、以下をプログラムします。

- 書き込みトレーニング (オンにする)

- パリティ イネーブル

**通常動作**

システムが再びデスキューする必要性を検出した場合、プロセスは設定トレーニング オプションのステップから再度開始する必要があります。次にループバックマッピングの表を示します。

**電源投入**

電源投入シーケンスで説明したように、チップに電源を供給します。

**表1. ループバック信号マッピング**

| 入力ピン               | 入力ピン               | 入力ピン               | 出力ピン  |

|--------------------|--------------------|--------------------|-------|

| LBK0#=0<br>LBK1#=0 | LBK0#=0<br>LBK1#=1 | LBK0#=1<br>LBK1#=0 |       |

| A0                 | A13                | DKA0               | DQA0  |

| A1                 | A14                | DKA0#              | DQA1  |

| A2                 | A15                | DKA1               | DQA2  |

| A3                 | A16                | DKA1#              | DQA3  |

| A4                 | A17                | LDA#               | DQA4  |

| A5                 | A18                | RWA#               | DQA5  |

| A6                 | A19                | DKB0               | DQA6  |

| A7                 | A20                | DKB0#              | DQA7  |

| A8                 | A21                | DKB1               | DQA8  |

| A9                 | A22                | DKB1#              | DQA9  |

| A10                | A23                | LDB#               | DQA10 |

| A11                | A24                | RWB#               | DQA11 |

| A12                | AINV               | AP                 | DQA12 |

### コンフィギュレーション レジスタ

QDR-IV HP SRAM には、特別な設定サイクルを使用してシステムによってプログラムされる内部レジスタが含まれています。

### コンフィギュレーション レジスタの説明

**表2. コンフィギュレーション レジスタの表**

| レジスタ アドレス | 説明                    |

|-----------|-----------------------|

| 0         | 終端制御レジスタ              |

| 1         | インピーダンス制御レジスタ         |

| 2         | オプション制御レジスタ           |

| 3         | 機能制御レジスタ              |

| 4         | アドレス パリティ ステータスレジスタ 0 |

| 5         | アドレス パリティ ステータスレジスタ 1 |

| 6         | アドレス パリティ ステータスレジスタ 2 |

| 7         | アドレス パリティ ステータスレジスタ 3 |

### コンフィギュレーション レジスタの定義

**表3. アドレス 0 : 終端制御レジスタ (読み出し/書き込み)**

| 機能                                                            | ODT グローバル イネーブル | ODT / ZQ 自動更新 | アドレス / コマンド入カグループ IU[2] | アドレス / コマンド入カグループ IU[1] | アドレス / コマンド入カグループ IU[0] | クロック入カグループ KU[2] | クロック入カグループ KU[1] | クロック入カグループ KU[0] |

|---------------------------------------------------------------|-----------------|---------------|-------------------------|-------------------------|-------------------------|------------------|------------------|------------------|

| ビット位置                                                         | 7               | 6             | 5                       | 4                       | 3                       | 2                | 1                | 0                |

| リセット値                                                         | A7              | A6            | A5                      | A4                      | A3                      | A2               | A1               | A0               |

| 注 : ODT / ZQ コンフィギュレーションを変更する場合、ODT / ZQ 自動更新機能をオンにする必要があります。 |                 |               |                         |                         |                         |                  |                  |                  |

す。これらのレジスタは本節で説明するように、幾つかのオプションを有効にし、制御するのに使用されます。全てのレジスタは8ビット幅です。書き込み動作は、レジスタアドレスとレジスタ書き込みデータを定義するために、アドレスピンのみを使用して実行されます。読み出し動作に対しては、レジスタ読み出しデータがデータポートA出力ピンに提供されます。プログラミングの詳細については、39ページの図14を参照してください。

RST# の立ち上りエッジでアドレスピン A[9:0] がサンプリングされます。サンプリングされた値は以下に定義するレジスタの特定のビットのリセット値になります。これはリセットした直後に終端、インピーダンス、ポート構成の値を設定するのに使用されます。これらの値は、レジスタ書き込み動作により後で上書きすることができます。

パリティエラーが発生した場合、最初のエラーの完全なアドレスが、ポートA/Bエラービットと共にレジスタ4、5、6、7に記録されます。ポートA/Bエラービットは、アドレスパリティエラーが発生するポートを示します（0がポートA、1がポートBを示します）。この情報は、レジスタ3内のアドレスパリティエラークリアビットに1を書き込むことでクリアされるまで、ラッチされたままです。

2つのカウンタは、複数のアドレスパリティエラーが発生したかを示します。ポートAエラー カウントは、ポートAアドレスのパリティエラー数のランニング カウントです。同様にポートBエラー カウントは、ポートBアドレスのパリティエラー数のランニング カウントです。それぞれ最大値3までカウントして、停止します。両方のカウンタはフリー ランであり、レジスタ3のアドレスパリティエラークリアビットに1を書き込むことでリセットされます。

**表 4. アドレス 1: インピーダンス制御レジスタ (読み出し/書き込み)**

| 機能    | プルダウン<br>グループ<br>PD[1] | プルダウン<br>グループ<br>PD[0] | プルアップ<br>グループ<br>PU[1] | プルアップ<br>グループ<br>PU[0] | 未使用 | データ入力<br>グループ<br>QU[2] | データ入力<br>グループ<br>QU[1] | データ入力<br>グループ<br>QU[0] |

|-------|------------------------|------------------------|------------------------|------------------------|-----|------------------------|------------------------|------------------------|

| ビット位置 | 7                      | 6                      | 5                      | 4                      | 3   | 2                      | 1                      | 0                      |

| リセット値 | 1                      | 0                      | 1                      | 0                      | 0   | A10                    | A9                     | A8                     |

**表 5. 2I アドレス 2: オプション制御レジスタ (読み出し/書き込みビット 7-3) (読み出し専用ビット 2-0) [2]**

| 機能    | 書き込みト<br>レーニング<br>イネーブル | データ反転<br>イネーブル | アドレス反<br>転イネーブ<br>ル | アドレスパ<br>リティイ<br>ネーブル | PLL リセッ<br>ト | I/O 形式 | ポートイ<br>ネーブル[1] | ポートイ<br>ネーブル[0] |

|-------|-------------------------|----------------|---------------------|-----------------------|--------------|--------|-----------------|-----------------|

| ビット位置 | 7                       | 6              | 5                   | 4                     | 3            | 2      | 1               | 0               |

| リセット値 | 0                       | 0              | 0                   | 0                     | 0            | A13    | A12             | A11             |

**表 6. アドレス 3: 機能制御レジスタ (書き込み専用)**

| 機能    | 未使用 | アドレスパ<br>リティエ<br>ラークリア |

|-------|-----|-----|-----|-----|-----|-----|-----|------------------------|

| ビット位置 | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0                      |

| リセット値 | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0                      |

**注**

2. ビット 2-0 は読み出し専用で、リセットの立ち上がりエッジでのみ変更できます。

**表7. アドレス4: アドレスパリティステータスレジスタ0 (読み出し専用)**

| 機能    | ポートBエラー カウント (1:0) | ポートAエラー カウント (1:0) | ポートA/Bエラー | AINVビット | 未使用 | 未使用 |

|-------|--------------------|--------------------|-----------|---------|-----|-----|

| ビット位置 | 7:6                | 5:4                | 3         | 2       | 1   | 0   |

| リセット値 | 00                 | 00                 | 0         | 0       | 0   | 0   |

**表8. アドレス5: アドレスパリティステータスレジスタ1 (読み出し専用)**

|                            |              |

|----------------------------|--------------|

| 機能                         | アドレス (23:16) |

| ビット位置                      | 7:0          |

| リセット値                      | 00000000     |

| 注: 未使用的アドレス位置は0として読み込まれます。 |              |

**表9. アドレス6: アドレスパリティステータスレジスタ2 (読み出し専用)**

|       |             |

|-------|-------------|

| 機能    | アドレス (15:8) |

| ビット位置 | 7:0         |

| リセット値 | 00000000    |

**表10. アドレス7: アドレスパリティステータスレジスタ3 (読み出し専用)**

|       |            |

|-------|------------|

| 機能    | アドレス (7:0) |

| ビット位置 | 7:0        |

| リセット値 | 00000000   |

**I/O 形式およびポート イネーブル ビットの定義**

**表 11. 「アドレス 2 : オプション制御レジスタ」の I/O 形式 ビット定義**

| I/O 形式 | 機能          |

|--------|-------------|

| 0      | HSTL / SSTL |

| 1      | POD         |

**表 12. 「アドレス 2 : オプション制御レジスタ」のポート イネーブル ビット定義**

| ポート イネーブル [1:0] |   | 機能          | ポート B モード | ポート A モード | ポート B クロック および制御                               | ポート A クロック および制御                               |

|-----------------|---|-------------|-----------|-----------|------------------------------------------------|------------------------------------------------|

| 0               | 0 | 固定ポート モード   | 書き込み専用    | 読み出し専用    | DKB - オン<br>QKB - オフ<br>LDB# - オン<br>RWB# - オフ | DKA - オフ<br>QKA - オン<br>LDA# - オン<br>RWA# - オフ |

| 0               | 1 | ポート A のみ 有効 | 無効        | 有効        | DKB - オフ<br>QKB - オフ<br>LDB# - オフ<br>RWB# - オフ | DKA - オン<br>QKA - オン<br>LDA# - オン<br>RWA# - オン |

| 1               | 0 | 非対応         | 無効        | 無効        | DKB - オフ<br>QKB - オフ<br>LDB# - オフ<br>RWB# - オフ | DKA - オフ<br>QKA - オフ<br>LDA# - オフ<br>RWA# - オフ |

| 1               | 1 | 両方のポート が有効  | 有効        | 有効        | DKB - オン<br>QKB - オン<br>LDB# - オン<br>RWB# - オン | DKA - オン<br>QKA - オン<br>LDA# - オン<br>RWA# - オン |

**ODT 終端ビットの定義**

**表 13. 「アドレス 0 : 終端制御レジスタ」のクロック入力グループ ビット定義**

| ODT グローバルイネーブル | KU[2:0] |   |   | 除数値    | HSTL/SSTL モードの終端値 |        | POD モードの終端値 |        |

|----------------|---------|---|---|--------|-------------------|--------|-------------|--------|

|                |         |   |   |        | ZT180Ω            | ZT220Ω | ZT180Ω      | ZT220Ω |

| 0              | X       | X | X | -      | オフ                | オフ     | オフ          | オフ     |

| 1              | 0       | 0 | 0 | -      | オフ                | オフ     | オフ          | オフ     |

| 1              | 0       | 0 | 1 | 8.33%  | 非対応               | 非対応    | 非対応         | 非対応    |

| 1              | 0       | 1 | 0 | 12.50% | 非対応               | 非対応    | 非対応         | 非対応    |

| 1              | 0       | 1 | 1 | 16.67% | 非対応               | 40Ω    | 非対応         | 非対応    |

| 1              | 1       | 0 | 0 | 25%    | 50Ω               | 60Ω    | 50Ω         | 60Ω    |

| 1              | 1       | 0 | 1 | 50%    | 100Ω              | 120Ω   | 100Ω        | 120Ω   |

| 1              | 1       | 1 | 0 | -      | 非対応               | 非対応    | 非対応         | 非対応    |

| 1              | 1       | 1 | 1 | -      | 非対応               | 非対応    | 非対応         | 非対応    |

注 : 終端値の誤差は +/- 15% ; ZQ の誤差は 1%

**表 14. 「アドレス 0 : 終端制御レジスタ」のアドレス/コマンド入力グループ ビット定義**

| ODT グローバルイネーブル | IU[2:0] |   |   | 除数値    | HSTL/SSTL モードの終端値 |        | POD モードの終端値 |        |

|----------------|---------|---|---|--------|-------------------|--------|-------------|--------|

|                |         |   |   |        | ZT180Ω            | ZT220Ω | ZT180Ω      | ZT220Ω |

| 0              | X       | X | X | -      | オフ                | オフ     | オフ          | オフ     |

| 1              | 0       | 0 | 0 | -      | オフ                | オフ     | オフ          | オフ     |

| 1              | 0       | 0 | 1 | 8.33%  | 非対応               | 非対応    | 非対応         | 非対応    |

| 1              | 0       | 1 | 0 | 12.50% | 非対応               | 非対応    | 非対応         | 非対応    |

| 1              | 0       | 1 | 1 | 16.67% | 非対応               | 40Ω    | 非対応         | 非対応    |

| 1              | 1       | 0 | 0 | 25%    | 50Ω               | 60Ω    | 50Ω         | 60Ω    |

| 1              | 1       | 0 | 1 | 50%    | 100Ω              | 120Ω   | 100Ω        | 120Ω   |

| 1              | 1       | 1 | 0 | -      | 非対応               | 非対応    | 非対応         | 非対応    |

| 1              | 1       | 1 | 1 | -      | 非対応               | 非対応    | 非対応         | 非対応    |

注 : 終端値の誤差は +/- 15% ; ZQ の誤差は 1%

**表 15. 「アドレス 1 : インピーダンス制御レジスタ」のデータ入力グループ ビット定義**

| ODT グローバルイネーブル | QU[2:0] |   |   | 除数値    | HSTL/SSTL モードの終端値 |        | POD モードの終端値 |        |

|----------------|---------|---|---|--------|-------------------|--------|-------------|--------|

|                |         |   |   |        | ZT180Ω            | ZT220Ω | ZT180Ω      | ZT220Ω |

| 0              | X       | X | X | -      | オフ                | オフ     | オフ          | オフ     |

| 1              | 0       | 0 | 0 | -      | オフ                | オフ     | オフ          | オフ     |

| 1              | 0       | 0 | 1 | 8.33%  | 非対応               | 非対応    | 非対応         | 非対応    |

| 1              | 0       | 1 | 0 | 12.50% | 非対応               | 非対応    | 非対応         | 非対応    |

| 1              | 0       | 1 | 1 | 16.67% | 非対応               | 40Ω    | 非対応         | 非対応    |

| 1              | 1       | 0 | 0 | 25%    | 50Ω               | 60Ω    | 50Ω         | 60Ω    |

| 1              | 1       | 0 | 1 | 50%    | 100Ω              | 120Ω   | 100Ω        | 120Ω   |

| 1              | 1       | 1 | 0 | -      | 非対応               | 非対応    | 非対応         | 非対応    |

| 1              | 1       | 1 | 1 | -      | 非対応               | 非対応    | 非対応         | 非対応    |

注 : 終端値の誤差は +/- 15% ; ZQ の誤差は 1%

**駆動能力ビットの定義**

**表 16. 「アドレス 1: インピーダンス制御レジスタ」のプルアップ ドライバビット定義**

| PU[1:0] |   | 除数値    | HSTL/ SSTL モードのインピーダンス値 |        | POD モードのインピーダンス値 |        |

|---------|---|--------|-------------------------|--------|------------------|--------|

|         |   |        | ZT180Ω                  | ZT220Ω | ZT180Ω           | ZT220Ω |

| 0       | 0 | 14.17% | 非対応                     | 非対応    | 非対応              | 非対応    |

| 0       | 1 | 16.67% | 非対応                     | 40Ω    | 非対応              | 40Ω    |

| 1       | 0 | 25%    | 50Ω                     | 60Ω    | 50Ω              | 60Ω    |

| 1       | 1 | –      | 非対応                     | 非対応    | 非対応              | 非対応    |

注：終端値の誤差は +/- 15%

ZQ の誤差は 1%

**表 17. プルダウン ドライバビット定義**

| PD[1:0] |   | 除数値    | HSTL/ SSTL モードのインピーダンス値 |        | POD モードのインピーダンス値 |        |

|---------|---|--------|-------------------------|--------|------------------|--------|

|         |   |        | ZT180Ω                  | ZT220Ω | ZT180Ω           | ZT220Ω |

| 0       | 0 | 14.17% | 非対応                     | 非対応    | 非対応              | 非対応    |

| 0       | 1 | 16.67% | 非対応                     | 40Ω    | 非対応              | 40Ω    |

| 1       | 0 | 25%    | 50Ω                     | 60Ω    | 50Ω              | 60Ω    |

| 1       | 1 | –      | 非対応                     | 非対応    | 非対応              | 非対応    |

注：終端値の誤差は +/- 15%

ZQ の誤差は 1%

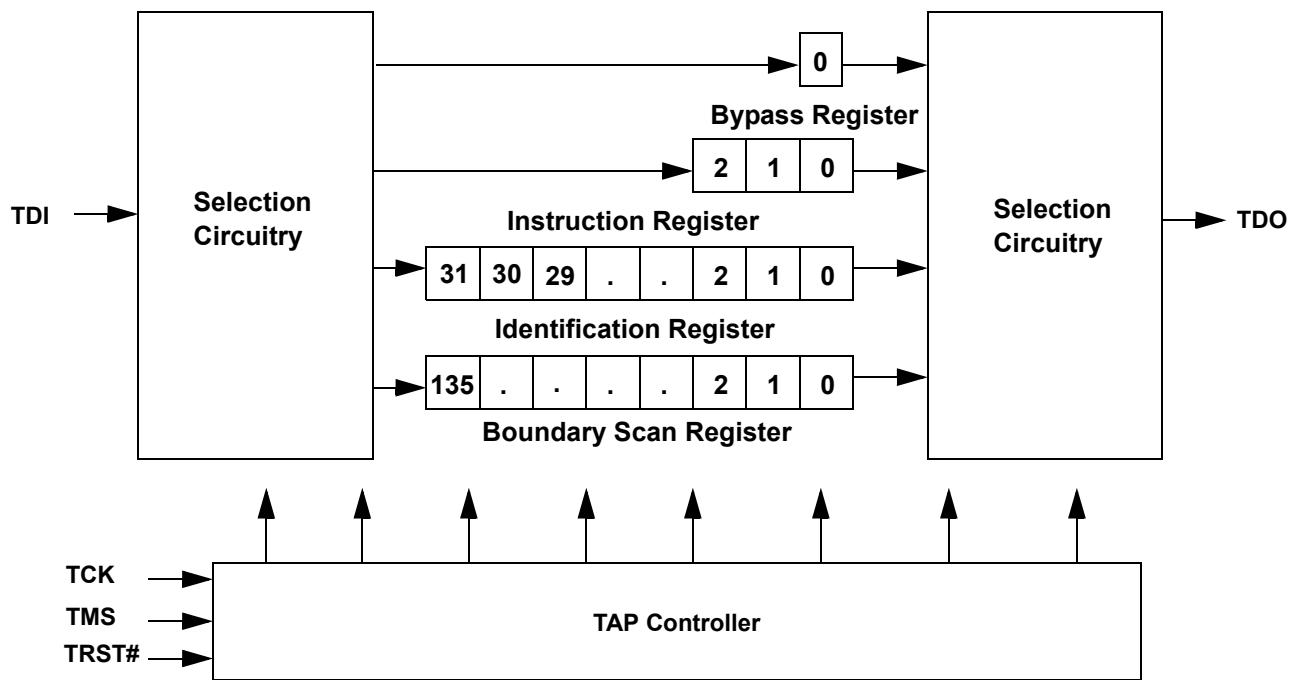

## IEEE 1149.1 シリアル バウンダリ スキャン (JTAG)

QDR-IV HP SRAM は、FCBGA パッケージにシリアル バウンダリ スキャン テスト アクセス ポート (TAP) を内蔵します。この部分は、IEEE 標準 #1149.1-2001 に完全に準拠しています。JTAG モードでは ODT 機能は全てのピンについて無効にされます。

JTAG 機能を回路で使用しない場合は、TCK 入力をローレベルに駆動するか、VSS に接続しなければいけません。TRST#、TMS、TDI、TDO はどこにも接続しないことがあります。 $t_{PWR}$  の間に TRST#、TMS、TDI 入力がハイレベルであることを確保するために、内部プルアップ抵抗がこれらの入力に実装されています。

### Test Access Port (テスト アクセス ポート)

#### TCK (テスト クロック)

テスト クロックは TAP コントローラと共にのみ使用されます。全ての入力を TCK の立ち上がりエッジで取り込みます。全ての出力は TCK の立ち下がりエッジで駆動されます。

#### テスト モード選択 (TMS)

TMS 入力は、TAP コントローラにコマンドを送信するのに使用され、TCK の立ち上がりエッジでサンプリングされます。TAP を使用しない場合、このピンはどこにも接続しないことがあります。ピンは内部でプルアップされ、その結果ハイレベルになります。

#### TDI (テスト データ入力)

TDI ピンは、レジスタに情報をシリアル入力するのに使用され、どのレジスタの入力にも接続することができます。TDI と TDO の間につながるレジスタは、TAP 命令レジスタにロードされる命令によって選択されます。命令レジスタにロードする方法については、[22 ページの図 4](#) を参照してください。TAP がアプリケーションで使用されていない場合 TDI は内部でプルアップされ、開放することができます。TDI はレジスタの最上位ビット (MSB) に接続されます。

#### TDO (テスト データアウト)

TDO 出力ピンは、レジスタからデータをシリアル出力するのに使用されます。TAP ステート マシンの状態に応じて、出力はアクティブです ([命令コード ページの 26](#) を参照)。出力は TCK の立ち下がりエッジで変化します。TDO は、レジスタの最下位ビット (LSB) に接続されます。

#### TRST# (テスト リセット)

TRST# 入力ピンは TAP コントローラをリセットするのに使用されます。

リセットは、TCK の立ち上がりエッジ 5 つ分の時間、TMS をハイレベル ( $V_{DD}$ ) にすることでも実行されます。

このリセットは、SRAM の動作に影響を与えることなく、SRAM の動作中に実行できます。電源投入時に、TDO を High Z 状態にすることで、TAP は内部でリセットされます。

#### TAP レジスタ

SRAM テスト回路の入力と出力データをスキャンするために、TDI と TDO の間にレジスタが接続されます。命令レジスタを通

して、一度に 1 つのレジスタのみが選択されます。データは TCK の立ち上がりエッジで TDI ピンにロードされます。データは TCK の立ち下がりエッジで TDO ピンに出力されます。

#### 命令レジスタ

3 ビットの命令を命令レジスタにロードすることができます。このレジスタは [23 ページの図 5](#) に示すように、TDI と TDO ピン間に配置された時にロードされます。電源投入時に、IDCODE 命令が命令レジスタにロードされます。前述したように、コントローラが RST 状態になる場合にも、IDCODE 命令が命令レジスタにロードされます。

TAP コントローラが Capture-IR 状態になる時、基板レベルのシリアル テスト パスの障害分離を可能にするために、2 進数「01」パターンが最下位 2 ビットにロードされます。

#### バイパス レジスタ

レジスタを通してデータをシフトする際の時間を節約するため、特定のチップをスキップすることが有利な場合もあります。バイパス レジスタは、TDI と TDO ピンの間に配置される 1 ビットのレジスタです。これにより、最小限の遅延で SRAM を介してデータをシフトすることができます。BYPASS 命令が実行される時、バイパス レジスタはローレベル (VSS) に設定されます。

#### バウンダリ スキャン レジスタ

バウンダリ スキャン レジスタは、SRAM 上の全ての入力と出力ピンに接続されます。また幾つかの接続なし (NC) のピンは、容量の大きいデバイスにピンを予約するために、スキャン レジスタに含まれています。

バウンダリ スキャン レジスタは、TAP コントローラが Capture-DR 状態になる時に RAM 入力と出力リーディングの内容がロードされ、そしてコントローラが Shift-DR 状態に遷移する時に TDI と TDO ピン間に配置されます。EXTEST、SAMPLE/PRELOAD、SAMPLE Z 命令は、入力と出力リーディングの内容を取り込むのに使用されます。

バウンダリ スキャン 順序 ページの [27](#) はビットが接続されている順序を示します。各ビットは、SRAM パッケージ上の 1 つの端子に対応します。レジスタの MSB は TDI に、LSB は TDO に接続されます。

#### 識別 (ID) レジスタ

IDCODE コマンドが命令レジスタにロードされる時、Capture-DR 状態の間に、ID レジスタにベンダ固有の 32 ビット コードがロードされます。IDCODE は、TAP コントローラが Shift-DR 状態の間に SRAM に接続され、シフトアウトされます。ID レジスタのベンダ コードおよび他の情報は [ID レジスタの定義 ページの 26](#) の通りです。

#### TAP 命令セット

3 ビットの命令レジスタにより、8 つの異なる命令があります。全ての組み合わせを [命令コード ページの 26](#) に示します。これらの命令の内 3 つが RESERVED であり、使用してはいけません。他の 5 つの命令を本節で詳しく説明します。

命令レジスタが TDI と TDO の間に配置される時、命令は Shift-IR 状態の間に TAP コントローラにロードされます。この状態の間に、命令レジスタを通して命令は TDI から TDO までシフトされます。シフトインされた命令を実行するために、TAP コントローラを Update-IR 状態に遷移させる必要があります。

#### IDCODE

IDCODE 命令はベンダ固有の 32 ビット コードを命令レジスタにロードします。また、命令レジスタを TDI と TDO ピンの間に配置して、TAP コントローラが Shift-DR 状態に入る時に IDCODE をデバイスからシフトアウトします。IDCODE 命令は、電源投入時または TAP コントローラが Test-Logic-RST 状態に入るたびに、命令レジスタにロードされます。

#### SAMPLE Z

TAP コントローラが Shift-DR 状態の時に、SAMPLE Z 命令はバウンダリスキャンレジスタを TDI と TDO ピンの間に接続します。SAMPLE Z コマンドは Update-IR 状態中に次のコマンドが供給されるまで、出力バスを High Z 状態に移行させます。このコマンドが実行されると、ポート A とポート B の両方が有効になります。

#### SAMPLE/PRELOAD

SAMPLE/PRELOAD は 1149.1 標準の必須命令です。SAMPLE/PRELOAD 命令が命令レジスタにロードされ、TAP コントローラが Capture-DR 状態になっている場合、入力と出力ピン上のデータのスナップショットは、バウンダリスキャンレジスタに取り込まれます。

TAP コントローラ クロックは最大 20MHz の周波数で動作するのに対して、SRAM クロックは桁違いに速い周波数で動作することに注意してください。クロック周波数に大きな差があるため、入出力は Capture-DR 状態中に遷移する可能性があります。その後、TAP は遷移中（メタステーブル状態）の信号を取り込もうとするかもしれません。これはデバイスに悪影響を及ぼしませんが、取り込まれた値に対する保証がありません。結果を再現できない場合があります。

バウンダリスキャンレジスタが信号の正しい値を取り込むために、SRAM 信号は、TAP コントローラのキャプチャセットアップ + ホールド時間 ( $t_{CS}+t_{CH}$ ) を満たすのに十分な安定時間をとらなければいけません。SAMPLE/PRELOAD 命令の間にクロックを停止する（または遅くする）方法が設計にない場合、SRAM クロック入力は正常に取り込まれない可能性があります。これが問題になっても、他の全ての信号を取り込むことはまだ可能で、単にバウンダリスキャンレジスタに取り込まれた CK および CK の値を無視してもかまいません。

データが取り込まれた後 TAP を Shift-DR 状態に移行させることで、データをシフトアウトすることができます。これはバウンダリスキャンレジスタを TDI と TDO ピンの間に配置します。

PRELOAD は、他のバウンダリスキャン テスト動作の選択の前に、初期データパターンをバウンダリスキャンレジスタセルのラッチされたパラレル出力に配置します。

SAMPLE および PRELOAD フェーズ用のデータのシフトは、必要に応じて同時に発生することができます。つまり取り込まれたデータがシフトアウトされている間にプリロードされたデータがシフトインされます。

#### BYPASS

BYPASS 命令が命令レジスタにロードされ、TAP が Shift-DR 状態になる時、バイパスレジスタは TDI と TDO ピンの間に配置されます。BYPASS 命令の利点は、複数のデバイスが基板上で互いに接続されている時に、バウンダリスキャンバスを短縮することです。

#### EXTEST

EXTEST 命令は、システム出力ピンを通してプリロードされたデータを駆動します。またコントローラが Shift-DR 状態の間に、この命令はシリアルアクセスのためにバウンダリスキャンレジスタを TDI と TDO の間に接続します。このコマンドが実行された後、ポート A とポート B の両方が有効になります。

#### EXTEST OUTPUT BUS TRISTATE

IEEE 標準 1149.1 によると、TAP コントローラが出力バスをトライステートにできることが必須です。

バウンダリスキャンレジスタで、ビット #49 およびビット #50 は出力イネーブル制御ビットです。ビット #49 は DQB の出力ピンを有効にし、ビット #50 は DQA および PE# ピンを有効にします。

「extest 出力バス トライステート」と呼ばれるこれらのスキャンセルは、TAP コントローラで Update-DR 状態中にプリロードレジスタにラッチされた時、EXTEST が現時点の命令として入力されると、出力 (Q バス) ピンの状態を直接制御します。ハイレベルの時、出力バッファが出力バスを駆動します。ローレベルの時、出力バスを High Z 状態に移行させます。

Shift-DR 状態中に、SAMPLE/PRELOAD または EXTEST コマンドを入力して、所望のビットをそのセルにシフトすることで、これらのビットをセットします。Update-DR の間に、そのシフトレジスタセルにロードされた値はプリロードレジスタにラッチします。EXTEST 命令に入った時、これらのビットは出力 Q バス ピンを直接制御します。デバイスの電源投入時および TAP コントローラが Test-Logic-RST 状態になる時に出力を無効にするために、これらのビットはローレベルにあらかじめセットされることに注意してください。

#### Reserved

命令は実装されていませんが、将来のために予約されました。この命令を使用しないでください。

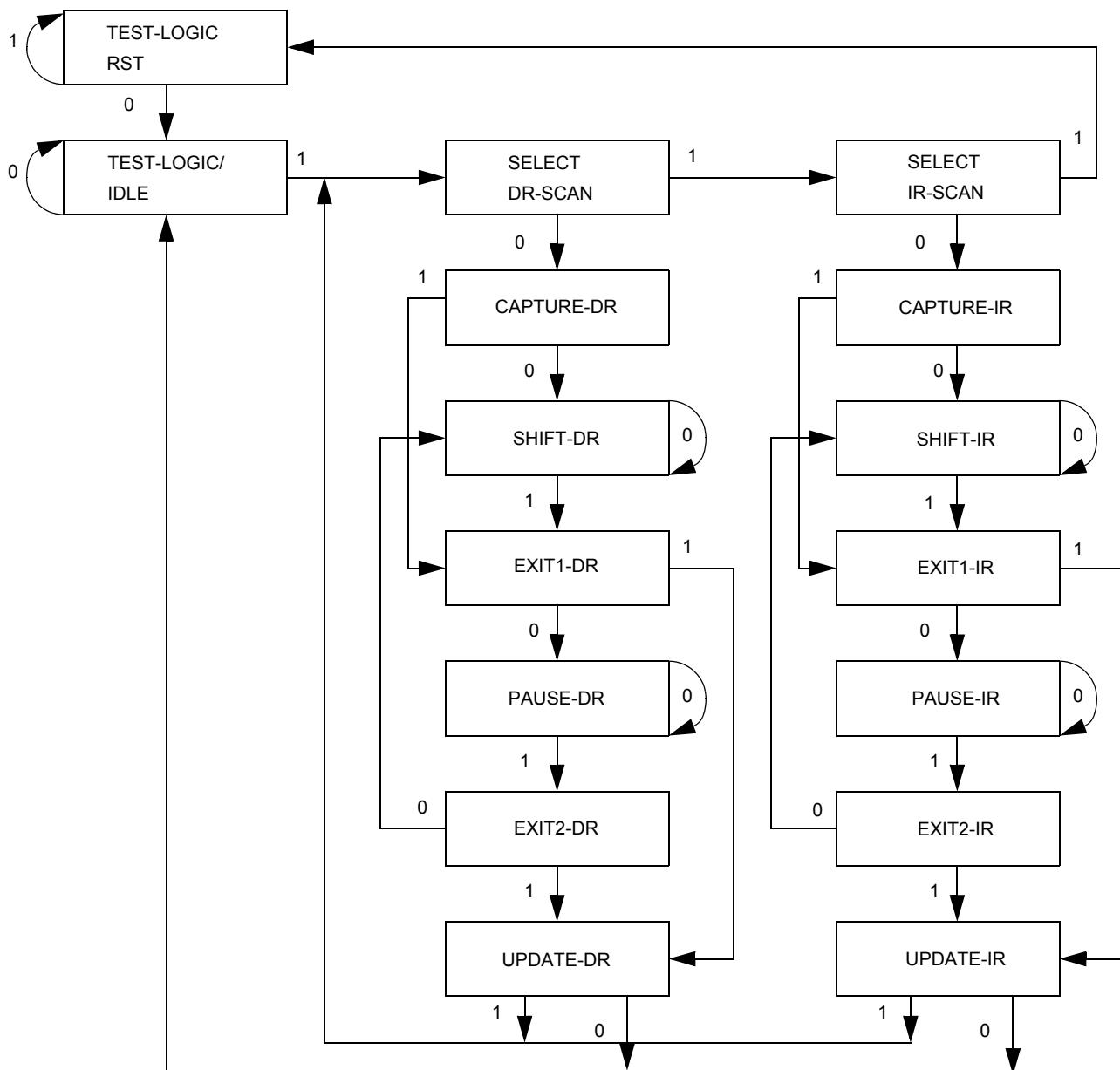

## TAP コントローラ状態遷移図

図 4. TAP コントローラ状態遷移図 [3]

注

3. 状態遷移の 0 / 1 は、TCK の立ち上がりエッジでの TMS の値を表します。

## TAP コントローラのブロック図

図 5. TAP コントローラのブロック図

## TAP 電気的特性

動作範囲において

| 記号       | 項目                     | テスト条件             | Min                 | Max                 | 単位      |

|----------|------------------------|-------------------|---------------------|---------------------|---------|

| $V_{OH}$ | LVCMOS ハイ レベル出力電圧      | $I_{OH}=100\mu A$ | $V_{DD} \times 0.8$ | –                   | V       |

| $V_{OL}$ | LVCMOS ロー レベル出力電圧      | $I_{OL}=100\mu A$ | –                   | $V_{DD} \times 0.2$ | V       |

| $V_{IH}$ | LVCMOS ハイ レベル入力電圧 (DC) |                   | $V_{DD} \times 0.7$ | $V_{DD} + 0.2$      | V       |

| $V_{IL}$ | LVCMOS ロー レベル入力電圧 (DC) |                   | -0.2                | $V_{DD} \times 0.3$ | V       |

| $I_x$    | LVCMOS 入力漏れ電流          |                   | –                   | 10                  | $\mu A$ |

| $I_{oz}$ | LVCMOS 出力漏れ電流          |                   | –                   | 10                  | $\mu A$ |

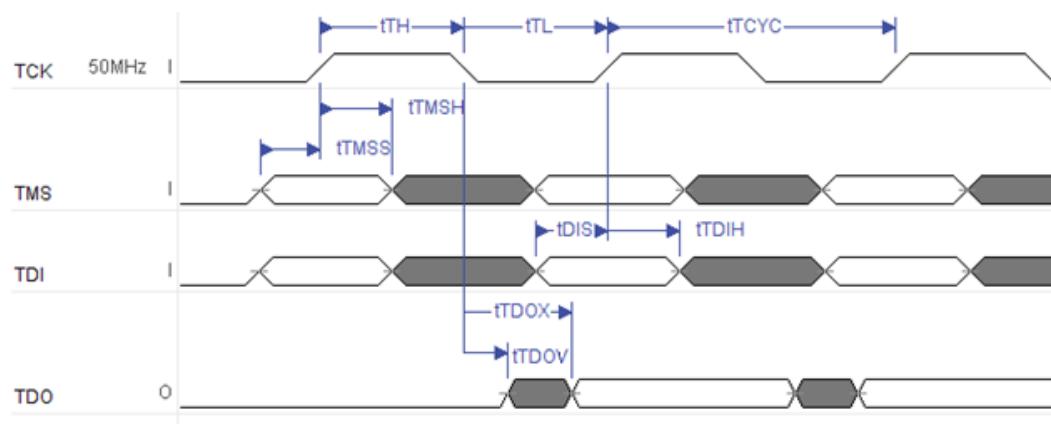

## TAP AC スイッチング特性

動作範囲において

| 記号                                                                         | 項目                                    | Min | Max | 単位  |

|----------------------------------------------------------------------------|---------------------------------------|-----|-----|-----|

| $t_{TCYC}$                                                                 | TCK クロック サイクル時間                       | 50  | –   | ns  |

| $t_{TF}$                                                                   | TCK クロック周波数                           | –   | 20  | MHz |

| $t_{TH}$                                                                   | TCK クロックハイレベル                         | 20  | –   | ns  |

| $t_{TL}$                                                                   | TCK クロックローレベル                         | 20  | –   | ns  |

| セットアップ時間                                                                   |                                       |     |     |     |

| $t_{TMSS}$                                                                 | TMS セットアップから TCK クロックの立ち上がりまでの時間      | 5   | –   | ns  |

| $t_{TDIS}$                                                                 | TDI セットアップから TCK クロックの立ち上がりまでの時間      | 5   | –   | ns  |

| $t_{CS}$                                                                   | キャプチャ セットアップから TCK の立ち上がりまでの時間        | 5   | –   | ns  |

| ホールド時間                                                                     |                                       |     |     |     |

| $t_{TMSH}$                                                                 | TCK クロック立ち上がり後の TMS ホールド時間            | 5   | –   | ns  |

| $t_{TDIH}$                                                                 | クロック立ち上がり後の TDI ホールド時間                | 5   | –   | ns  |

| $t_{CH}$                                                                   | クロック立ち上がり後のキャプチャ ホールド時間               | 5   | –   | ns  |

| 出力時間                                                                       |                                       |     |     |     |

| $t_{TDOV}$                                                                 | TCK クロックがロー レベルになってから TDO が有効になるまでの時間 | –   | 10  | ns  |

| $t_{TDOX}$                                                                 | TCK クロックがロー レベルになってから TDO 無効までの時間     | 0   | –   | ns  |

| 注 : $t_{CS}$ と $t_{CH}$ は、バウンダリ スキャン レジスタからデータをラッチするためのセットアップとホールド時間を示します。 |                                       |     |     |     |

## TAP タイミング図

図 6. TAP タイミング図

## ID レジスタの定義

| 命令フィールド                | 値                 |                   | 項目               |

|------------------------|-------------------|-------------------|------------------|

|                        | CY7C4021KV13      | CY7C4041KV13      |                  |

| 改訂番号 (31:29)           | 000               | 000               | バージョン番号。         |

| サイプレスのデバイス ID (28:12)  | 11011010001010100 | 11011010001100100 | SRAM の種類を定義します。  |

| サイプレスの JEDEC ID (11:1) | 00000110100       | 00000110100       | SRAM ベンダーを識別します。 |

| ID レジスタの有無 (0)         | 1                 | 1                 | ID レジスタの有無を示します。 |

## スキャン レジスタ サイズ

| レジスタ名     | ビット サイズ |

|-----------|---------|

| 命令        | 3       |

| バイパス      | 1       |

| ID        | 32      |

| バウンダリスキャン | 136     |

## 命令コード

| 命令             | コード | 項目                                                                                    |

|----------------|-----|---------------------------------------------------------------------------------------|

| EXTEST         | 000 | 入力および出カーリングの内容をキャプチャします。                                                              |

| IDCODE         | 001 | ベンダ ID コードを ID レジスタにロードし、レジスタを TDI と TDO の間に配置します。この動作は SRAM 動作に影響を与えません。             |

| SAMPLE Z       | 010 | 入力と出力の内容を取り込みます。バウンダリスキャン レジスタを TDI と TDO の間に配置します。全ての SRAM 出力ドライバを High Z 状態に移行させます。 |

| RESERVED       | 011 | 未使用：この命令は将来のために予約されます。                                                                |

| SAMPLE/PRELOAD | 100 | 入力と出力の内容を取り込みます。バウンダリスキャン レジスタを TDI と TDO の間に配置します。SRAM 動作に影響を与えません。                  |

| RESERVED       | 101 | 未使用：この命令は将来のために予約されます。                                                                |

| RESERVED       | 110 | 未使用：この命令は将来のために予約されます。                                                                |

| BYPASS         | 111 | バイパス レジスタを TDI と TDO の間に配置します。この動作は SRAM 動作に影響を与えません。                                 |

**バウンダリスキャン順序**

| ビット | 端子  | CY7C4041KV13 | CY7C4021KV13 |

|-----|-----|--------------|--------------|

|     |     | ×36 デバイス     | ×18 デバイス     |

| 0   | 12A | DQA<26>      | DQA<17>      |

| 1   | 13B | DQA<19>      | DQA<10>      |

| 2   | 14A | DQA<25>      | DQA<16>      |

| 3   | 15B | DQA<35>      | NC           |

| 4   | 16A | DQA<23>      | DQA<14>      |

| 5   | 18B | DQA<31>      | NC           |

| 6   | 17C | QVLDA<1>     | QVLDA<1>     |

| 7   | 16C | QKA<1>       | QKA<1>       |

| 8   | 14C | DQA<20>      | DQA<11>      |

| 9   | 12C | DQA<18>      | DQA<9>       |

| 10  | 12D | DINVA<1>     | DINVA<1>     |

| 11  | 13D | DQA<22>      | DQA<13>      |

| 12  | 15D | DQA<21>      | DQA<12>      |

| 13  | 17D | QKA#<1>      | QKA#<1>      |

| 14  | 18E | DQA<32>      | NC           |

| 15  | 15F | DQA<24>      | DQA<15>      |

| 16  | 16F | DKA<1>       | DKA<1>       |

| 17  | 17F | DKA#<1>      | DKA#<1>      |

| 18  | 18G | DQA<33>      | NC           |

| 19  | 16G | DQA<34>      | NC           |

| 20  | 17H | DQA<27>      | NC           |

| 21  | 15H | DQA<28>      | NC           |

| 22  | 16J | DQA<30>      | NC           |

| 23  | 18J | DQA<29>      | NC           |

| 24  | 18K | RST#         | RST#         |

| 25  | 18L | DQB<29>      | NC           |

| 26  | 16L | DQB<30>      | NC           |

| 27  | 15M | DQB<28>      | NC           |

| 28  | 17M | DQB<27>      | NC           |

| 29  | 18N | DQB<33>      | NC           |

| 30  | 16N | DQB<34>      | NC           |

| 31  | 15P | DQB<24>      | DQB<15>      |

| 32  | 16P | DKB<1>       | DKB<1>       |

| 33  | 17P | DKB#<1>      | DKB#<1>      |

| 34  | 18R | DQB<32>      | NC           |

| 35  | 17T | QKB#<1>      | QKB#<1>      |

| 36  | 15T | DQB<21>      | DQB<12>      |

| 37  | 13T | DQB<22>      | DQB<13>      |

| 38  | 12T | DINVB<1>     | DINVB<1>     |

| 39  | 12U | DQB<18>      | DQB<9>       |

| 40  | 14U | DQB<20>      | DQB<11>      |

| 41  | 16U | QKB<1>       | QKB<1>       |

| 42  | 17U | QVLDB<1>     | QVLDB<1>     |

| 43  | 18V | DQB<31>      | NC           |

| 44  | 15V | DQB<35>      | NC           |

| 45  | 13V | DQB<19>      | DQB<10>      |

| 46  | 12W | DQB<26>      | DQB<17>      |

**パウンダリスキャン順序**

| ビット | 端子  | CY7C4041KV13 | CY7C4021KV13 |

|-----|-----|--------------|--------------|

|     |     | ×36 デバイス     | ×18 デバイス     |

| 47  | 14W | DQB<25>      | DQB<16>      |

| 48  | 16W | DQB<23>      | DQB<14>      |

| 49  |     | Internal_DQB | Internal_DQB |

| 50  |     | Internal_DQA | Internal_DQA |

| 51  | 10V | PE#          | PE#          |

| 52  | 8P  | A<15>        | A<15>        |

| 53  | 7N  | A<9>         | A<9>         |

| 54  | 9N  | NC/1152M     | NC/576M      |

| 55  | 10P | AP           | AP           |

| 56  | 10N | A<2>         | A<2>         |

| 57  | 11N | NC/2304M     | NC/1152M     |

| 58  | 12P | A<16>        | A<16>        |

| 59  | 13N | A<10>        | A<10>        |

| 60  | 13L | A<8>         | A<8>         |

| 61  | 12M | A<12>        | A<12>        |

| 62  | 11L | A<18>        | A<18>        |

| 63  | 10L | RWB#         | RWB#         |

| 64  | 10M | AINV         | AINV         |

| 65  | 9L  | A<17>        | A<17>        |

| 66  | 8M  | A<11>        | A<11>        |

| 67  | 7L  | A<7>         | A<7>         |

| 68  | 7J  | A<5>         | A<5>         |

| 69  | 9J  | A<19>        | A<19>        |

| 70  | 10K | CK#          | CK#          |

| 71  | 10J | CK           | CK           |

| 72  | 11J | NC/144M      | A<20>        |

| 73  | 13J | A<6>         | A<6>         |

| 74  | 12H | LDB#         | LDB#         |

| 75  | 10H | RWA#         | RWA#         |

| 76  | 8H  | LDA#         | LDA#         |

| 77  | 7G  | A<3>         | A<3>         |

| 78  | 9G  | NC/288M      | NC/144M      |

| 79  | 10G | A<1>         | A<1>         |

| 80  | 11G | NC/576M      | NC/288M      |

| 81  | 13G | A<4>         | A<4>         |

| 82  | 12F | A<14>        | A<14>        |

| 83  | 10F | A<0>         | A<0>         |

| 84  | 8F  | A<13>        | A<13>        |

| 85  | 10D | CFG#         | CFG#         |

| 86  | 10B | LBK#<1>      | LBK#<1>      |

| 87  | 10A | LBK#<0>      | LBK#<0>      |

| 88  | 8A  | DQA<8>       | DQA<8>       |

| 89  | 7B  | DQA<1>       | DQA<1>       |

| 90  | 6A  | DQA<7>       | DQA<7>       |

| 91  | 5B  | DQA<17>      | NC           |

| 92  | 4A  | DQA<5>       | DQA<5>       |

| 93  | 2B  | DQA<13>      | NC           |

| 94  | 3C  | QVLDA<0>     | QVLDA<0>     |

| 95  | 4C  | QKA<0>       | QKA<0>       |

**パウンダリスキャン順序**

| ビット | 端子 | CY7C4041KV13 | CY7C4021KV13 |

|-----|----|--------------|--------------|

|     |    | ×36 デバイス     | ×18 デバイス     |

| 96  | 6C | DQA<2>       | DQA<2>       |

| 97  | 8C | DQA<0>       | DQA<0>       |

| 98  | 8D | DINVA<0>     | DINVA<0>     |

| 99  | 7D | DQA<4>       | DQA<4>       |

| 100 | 5D | DQA<3>       | DQA<3>       |

| 101 | 3D | QKA#<0>      | QKA#<0>      |

| 102 | 2E | DQA<14>      | NC           |

| 103 | 3F | DKA#<0>      | DKA#<0>      |

| 104 | 4F | DKA<0>       | DKA<0>       |

| 105 | 5F | DQA<6>       | DQA<6>       |

| 106 | 4G | DQA<16>      | NC           |

| 107 | 2G | DQA<15>      | NC           |

| 108 | 3H | DQA<9>       | NC           |

| 109 | 5H | DQA<10>      | NC           |

| 110 | 4J | DQA<12>      | NC           |

| 111 | 2J | DQA<11>      | NC           |

| 112 | 2L | DQB<11>      | NC           |

| 113 | 4L | DQB<12>      | NC           |

| 114 | 5M | DQB<10>      | NC           |

| 115 | 3M | DQB<9>       | NC           |

| 116 | 2N | DQB<15>      | NC           |

| 117 | 4N | DQB<16>      | NC           |

| 118 | 5P | DQB<6>       | DQB<6>       |

| 119 | 4P | DKB<0>       | DKB<0>       |

| 120 | 3P | DKB#<0>      | DKB#<0>      |

| 121 | 2R | DQB<14>      | NC           |

| 122 | 3T | QKB#<0>      | QKB#<0>      |

| 123 | 5T | DQB<3>       | DQB<3>       |

| 124 | 7T | DQB<4>       | DQB<4>       |

| 125 | 8T | DINVB<0>     | DINVB<0>     |

| 126 | 8U | DQB<0>       | DQB<0>       |

| 127 | 6U | DQB<2>       | DQB<2>       |

| 128 | 4U | QKB<0>       | QKB<0>       |

| 129 | 3U | QLVDB<0>     | QLVDB<0>     |

| 130 | 2V | DQB<13>      | NC           |

| 131 | 5V | DQB<17>      | NC           |

| 132 | 7V | DQB<1>       | DQB<1>       |

| 133 | 8W | DQB<8>       | DQB<8>       |

| 134 | 6W | DQB<7>       | DQB<7>       |

| 135 | 4W | DQB<5>       | DQB<5>       |

## 最大定格

最大定格を超えると、デバイスの寿命が短くなる可能性があります。これらのユーザガイドラインはテストされていません。

保存温度 .....  $0^{\circ}\text{C}$  to  $+150^{\circ}\text{C}$

通電時

の周囲温度 .....  $55^{\circ}\text{C}$  to  $+125^{\circ}\text{C}$

最大接合部温度 .....  $125^{\circ}\text{C}$

GND を基準とした

$V_{DD}$  電源電圧 .....  $0.3\text{V}$  to  $+1.35\text{V}$

GND を基準とした

$V_{DDQ}$  電源電圧 .....  $0.3\text{V}$  to  $+1.35\text{V}$

DC 入力電圧 .....  $0.3\text{V}$  to  $+1.35\text{V}$

出力への電流 (ローレベル) ..... 20 mA

静電気放電電圧

(MIL-STD-883、M. 3015) ..... >2001V

ラッピング電流 ..... >200mA

## 動作範囲

| 範囲 | ケース温度 ( $T_C$ )                              | $V_{DD}$                      | $V_{DDQ}$                     |

|----|----------------------------------------------|-------------------------------|-------------------------------|

| 商用 | $0^{\circ}\text{C}$ to $+70^{\circ}\text{C}$ | $1.3\text{V} \pm 40\text{mV}$ | $1.1\text{V} \pm 50\text{mV}$ |

|    |                                              |                               | $1.2\text{V} \pm 50\text{mV}$ |

## 中性子ソフトエラー耐性

| 記号   | 項目             | テスト条件                | Typ | Max* | 単位        |

|------|----------------|----------------------|-----|------|-----------|

| LSBU | 単一論理ビット反転      | $25^{\circ}\text{C}$ | 0   | 0.01 | FIT / Mb  |

| LMBU | 複数論理ビット反転      | $25^{\circ}\text{C}$ | 0   | 0.01 | FIT / Mb  |

| SEL  | シングルイベントラップチップ | $85^{\circ}\text{C}$ | 0   | 0.1  | FIT / Dev |

\* テスト中に LMBU または SEL イベントは発生しない; 本項は  $\chi^2$  分布の 95% 信頼上限を示します。詳細は、「Accelerated Neutron SER Testing and Calculation of Terrestrial Failure Rates – AN54908」のアプリケーションノートを参照してください。

## 電気的特性

動作範囲において

| 記号                  | 項目                               | Min                   | Typ                  | Max                   | 単位     |

|---------------------|----------------------------------|-----------------------|----------------------|-----------------------|--------|

| <b>POD 信号モード</b>    |                                  |                       |                      |                       |        |

| $V_{DD}$ [4]        | コア電源電圧 (1.3V $\pm$ 40mV)         | 1.26                  | 1.3                  | 1.34                  | V      |

| $V_{DDQ}$ [4]       | POD I/O 電源電圧 (1.1V $\pm$ 50mV)   | 1.05                  | 1.1                  | 1.15                  | V      |

|                     | POD I/O 電源電圧 (1.2V $\pm$ 50mV)   | 1.15                  | 1.2                  | 1.25                  | V      |

| $V_{REF}$ [4, 5]    | POD 基準電圧                         | $V_{DDQ} \times 0.69$ | $V_{DDQ} \times 0.7$ | $V_{DDQ} \times 0.71$ | V      |

| $V_{OL(DC)}$ [4]    | POD ローレベル出力電圧 (DC)               | –                     | –                    | 0.5                   | V      |

| $V_{IH(DC)}$ [4, 6] | POD ハイレベル入力電圧 (DC)               | $V_{REF} + 0.08$      | –                    | $V_{DDQ} + 0.15$      | V      |

| $V_{IL(DC)}$ [4, 6] | POD ローレベル入力電圧                    | –0.15                 | –                    | $V_{REF} - 0.08$      | V      |

| $V_{IH(AC)}$ [4, 7] | POD ハイレベル入力電圧 (AC)               | $V_{REF} + 0.15$      | –                    | –                     | V      |

| $V_{IL(AC)}$ [4, 7] | POD ローレベル入力電圧                    | –                     | –                    | $V_{REF} - 0.15$      | V      |

| $V_{MP(DC)}$        | POD 差動入力中点電圧 ; ピンとピン #           | $V_{REF} - 0.08$      | –                    | $V_{REF} + 0.08$      | V      |

| $V_{ID(DC)}$        | POD 差動入力差動電圧 (DC) ; ピンとピン #      | 0.16                  | –                    | –                     | V      |

| $V_{ID(AC)}$        | POD 差動入力差動電圧 (AC) ; ピンとピン #      | 0.30                  | –                    | –                     | V      |

| $V_{IN}$            | POD シングルエンド入力電圧 ; ピンとピン #        | 0.27                  | –                    | $V_{DDQ} + 0.15$      | V      |

| $V_{INS}$           | POD シングルエンド入力電圧のスルーレート ; ピンとピン # | 3                     | –                    | –                     | V / ns |

| $V_{IX(AC)}$        | POD 差動入力交差点電圧 (AC) ; ピンとピン #     | $V_{REF} - 0.08$      | –                    | $V_{REF} + 0.08$      | V      |

### 注

- 全ての電圧は VSS (GND) を基準にしています。

- $V_{REF}$  の AC ノイズは、ピークツーピークで  $V_{DDQ}$  (DC) の +/-2% を超えてはいけません。

- $V_{IH}/V_{IL}$  (DC) は、ODT が無効になっている状態で規定されます。

- $V_{IH}/V_{IL}$  (AC) は、ODT が有効になっている状態でレシーバがそのタイミング仕様を満たすように規定されたテスト条件です。

## 電気的特性

動作範囲において

| 記号                 | 項目                          | Min | Typ  | Max  | 単位 |

|--------------------|-----------------------------|-----|------|------|----|

| $I_X^{[8]}$        | POD 入力漏れ電流                  | —   | —    | 200  | μA |

| $I_{OZ}^{[8]}$     | POD 出力漏れ電流                  | —   | —    | 200  | μA |

| $I_{DD}^{[9, 10]}$ | $V_{DD}$ 動作電源 (667MHz, ×18) | —   | 1710 | 2500 | mA |

|                    | $V_{DD}$ 動作電源 (667MHz, ×36) | —   | 2150 | 3200 | mA |

|                    | $V_{DD}$ 動作電源 (600MHz, ×18) | —   | 1600 | 2300 | mA |

|                    | $V_{DD}$ 動作電源 (600MHz, ×36) | —   | 2010 | 2700 | mA |

### HSTL / SSTL 信号モード

|                          |                                                                        |                        |                       |                        |    |

|--------------------------|------------------------------------------------------------------------|------------------------|-----------------------|------------------------|----|

| $V_{DD}^{[11]}$          | コア電源電圧 (1.3V±40mV)                                                     | 1.26                   | 1.3                   | 1.34                   | V  |

| $V_{DDQ}^{[11]}$         | I/O 電源電圧 (1.2V±50mV)                                                   | 1.15                   | 1.2                   | 1.25                   | V  |

|                          | I/O 電源電圧 (1.25V±50mV)                                                  | 1.2                    | 1.25                  | 1.3                    | V  |

| $V_{REF(DC)}^{[11, 12]}$ | HSTL / SSTL 基準電圧 (DC)                                                  | $V_{DDQ} \times 0.48$  | $V_{DDQ} \times 0.5$  | $V_{DDQ} \times 0.52$  | V  |

| $V_{REF(AC)}^{[11, 12]}$ | HSTL / SSTL 基準電圧 (AC)                                                  | $V_{DDQ} \times 0.47$  | $V_{DDQ} \times 0.5$  | $V_{DDQ} \times 0.53$  | V  |

| $V_{IH(DC)}^{[11, 14]}$  | HSTL / SSTL ハイ レベル入力電圧 (DC)                                            | $V_{REF} + 0.08$       | —                     | $V_{DDQ} + 0.15$       | V  |

| $V_{IL(DC)}^{[11, 14]}$  | HSTL / SSTL ロー レベル入力電圧 (DC)                                            | —0.15                  | —                     | $V_{REF} - 0.08$       | V  |

| $V_{IH(AC)}^{[11, 14]}$  | HSTL / SSTL ハイ レベル入力電圧 (AC)                                            | $V_{REF} + 0.15$       | —                     | $V_{DDQ} + 0.24$       | V  |

| $V_{IL(AC)}^{[11, 14]}$  | HSTL / SSTL ロー レベル入力電圧 (AC)                                            | —0.24                  | —                     | $V_{REF} - 0.15$       | V  |

| $V_{OH(DC)}^{[11]}$      | HSTL / SSTL ハイ レベル出力電圧 (DC) – $I_{OH} = -0.25 \times V_{DDQ} / R_{OH}$ | $V_{DDQ} \times 0.712$ | $V_{DDQ} \times 0.75$ | —                      | V  |

| $V_{OL(DC)}^{[11]}$      | HSTL / SSTL ロー レベル出力電圧 (DC) – $I_{OL} = 0.25 \times V_{DDQ} / R_{OL}$  | —                      | $V_{DDQ} \times 0.25$ | $V_{DDQ} \times 0.288$ | V  |

| $V_{IX}$                 | HSTL / SSTL 入力交差点電圧                                                    | —                      | $V_{DDQ} \times 0.5$  | —                      | V  |

| $V_{DIF(AC)}$            | HSTL / SSTL AC 入力差動電圧                                                  | 0.30                   | —                     | $V_{DDQ} + 0.48$       | V  |

| $V_{DIF(DC)}$            | HSTL / SSTL DC 入力差動電圧                                                  | 0.16                   | —                     | $V_{DDQ} + 0.30$       | V  |

| $V_{DIF(CM)}$            | HSTL / SSTL DC コモン モード入力                                               | $V_{DDQ} \times 0.4$   | $V_{DDQ} \times 0.5$  | $V_{DDQ} \times 0.6$   | V  |

| $V_{OX}$                 | HSTL / SSTL 出力交差点電圧                                                    | —                      | $V_{DDQ} \times 0.5$  | —                      | V  |

| $V_{OUT(AC)}$            | HSTL / SSTL AC 出力電圧                                                    | —0.24                  | —                     | $V_{DDQ} + 0.24$       | V  |

| $V_{OUT(DC)}$            | HSTL / SSTL DC 出力電圧                                                    | —0.15                  | —                     | $V_{DDQ} + 0.15$       | V  |

| $I_X^{[8]}$              | HSTL / SSTL 入力漏れ電流                                                     | —                      | —                     | 200                    | μA |

| $I_{OZ}^{[8]}$           | HSTL / SSTL 出力漏れ電流                                                     | —                      | —                     | 200                    | μA |

| $I_{DD}^{[9, 10]}$       | $V_{DD}$ 動作電源 (667MHz, ×18)                                            | —                      | 1710                  | 2500                   | mA |

|                          | $V_{DD}$ 動作電源 (667MHz, ×36)                                            | —                      | 2150                  | 3200                   | mA |

|                          | $V_{DD}$ 動作電源 (600MHz, ×18)                                            | —                      | 1600                  | 2300                   | mA |

|                          | $V_{DD}$ 動作電源 (600MHz, ×36)                                            | —                      | 2010                  | 2700                   | mA |

注

8. ODT が無効になっている状態で出力ドライバを High Z にする

9. 動作電流は、読み出しサイクル 50%、書き込みサイクル 50% で計算されます。

10. 標準動作電流の仕様は 1.3V の VDD でテストされます。

11. 全ての電圧は VSS (GND) を基準にしています。

12.  $V_{REF}$  でのピーク ツー ピーク AC ノイズは、 $V_{DDQ} (DC)$  の  $+/-2\%$  を超えてはいけません。

13.  $V_{IH}/V_{IL} (DC)$  は、ODT が無効になっている状態で規定されます。

14.  $V_{IH}/V_{IL} (AC)$  は、ODT が有効になっている状態でレシーバがそのタイミング仕様を満たすように規定されたテスト条件です。

## 静電容量

表 18. 静電容量

| 記号 [15]  | 項目   | テスト条件                                                                                            | Max | 単位 |

|----------|------|--------------------------------------------------------------------------------------------------|-----|----|

| $C_{IN}$ | 入力容量 | $T_A=25\text{ }^\circ\text{C}$ 、 $f=1\text{MHz}$ 、 $V_{DD}=1.3\text{V}$ 、 $V_{DDQ}=1.25\text{V}$ | 4   | pF |

| $C_O$    | 出力容量 |                                                                                                  | 4   | pF |

## 熱抵抗

表 19. 热抵抗

| 記号 [15]       | 項目                | テスト条件                                                    | 361 ポール FCBGA パッケージ | 単位                        |

|---------------|-------------------|----------------------------------------------------------|---------------------|---------------------------|

| $\Theta_{JA}$ | 熱抵抗<br>(接合部から周囲)  | テスト条件は、EIA/JESD51 による、熱インピーダンスを測定するための標準的なテスト方法と手順に従います。 | 11.4                | $^\circ\text{C}/\text{W}$ |

| $\Theta_{JC}$ | 熱抵抗<br>(接合部からケース) |                                                          | 0.04                | $^\circ\text{C}/\text{W}$ |

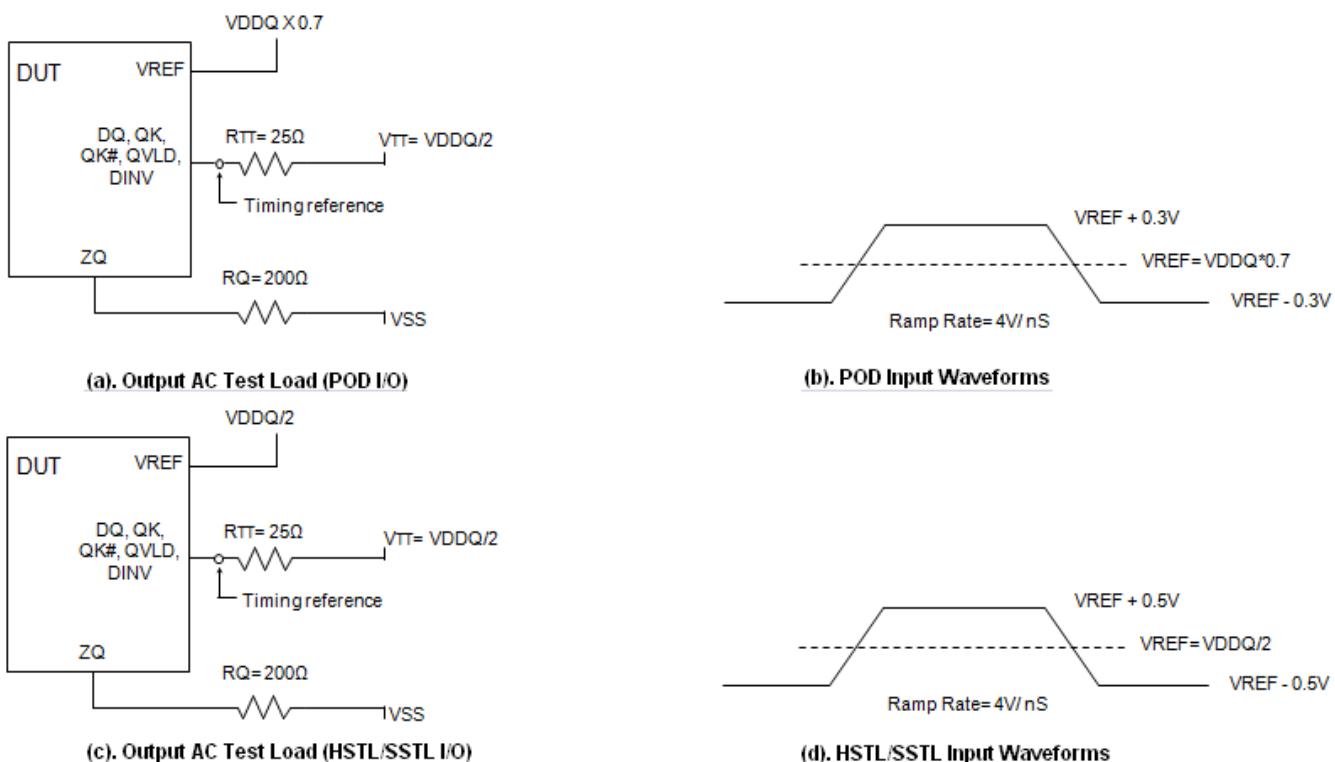

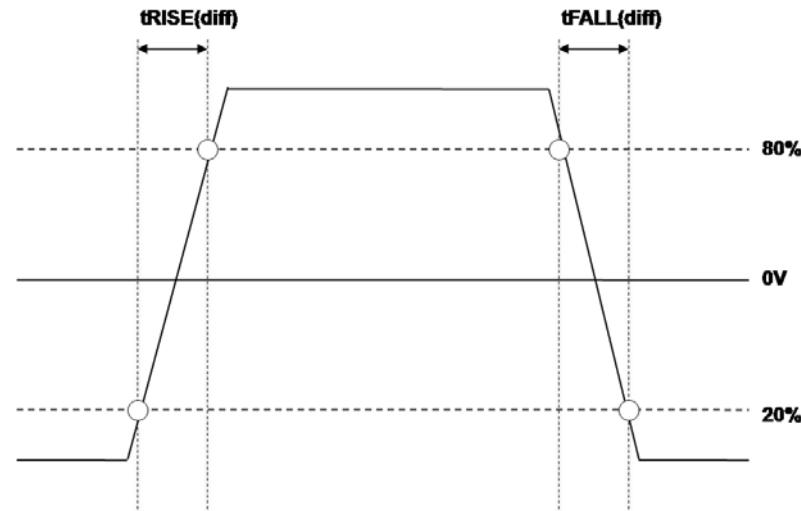

## AC テストの負荷と波形

図 7. AC テストの負荷と波形

### 注

15. 開発時とこれらのパラメータが影響を受ける設計またはプロセス変更があった後テストされます。

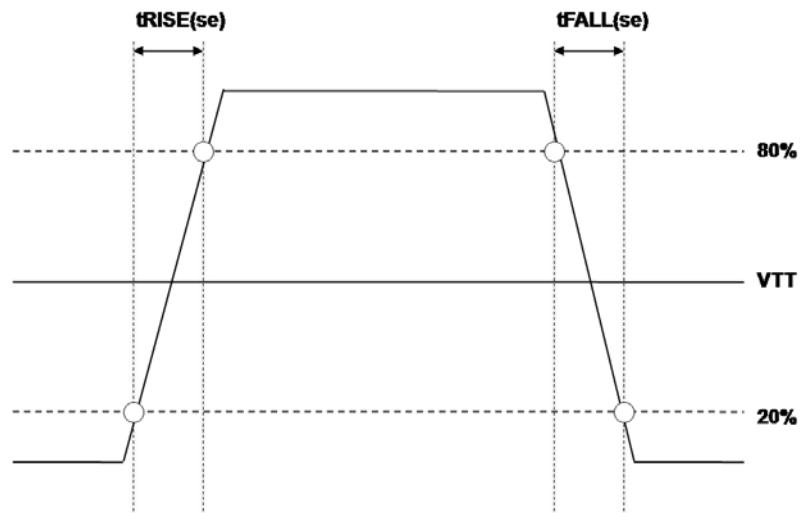

## スイッチング特性

動作範囲において [16、17、18、19、20、21、22、23]

| サイプレス<br>の記号      | 項目                                                                                  | 667MHz  |       | 600MHz  |       | 単位       |

|-------------------|-------------------------------------------------------------------------------------|---------|-------|---------|-------|----------|

|                   |                                                                                     | Min     | Max   | Min     | Max   |          |

| $t_{CK}$          | CK、DKx、QKx クロック周期                                                                   | 1.5     | 3.0   | 1.667   | 3.333 | ns       |

| $t_{CKL}$         | CK、DKx ローレベル時間                                                                      | 0.45*   | —     | 0.45*   | —     | $t_{CK}$ |

| $t_{CKH}$         | CK、DKx ハイレベル時間                                                                      | 0.45*   | —     | 0.45*   | —     | $t_{CK}$ |

| $t_{JIT}$ (per)   | クロック周期ジッタ                                                                           | -0.070  | 0.070 | -0.080  | 0.080 | ns       |

| $t_{JIT}$ (cc)    | サイクルツーサイクルジッタ                                                                       | —       | 0.140 | —       | 0.160 | ns       |

| $t_{AS}$          | A から CK までのセットアップ時間                                                                 | 0.160   | —     | 0.180   | —     | ns       |