**CY7C1516KV18/CY7C1527KV18

CY7C1518KV18/CY7C1520KV18**

72 Mb DDR II SRAM 2

字突发架构

## 特性

- 72-Mbit 容量 ( $8 \text{ M} \times 8$ 、 $8 \text{ M} \times 9$ 、 $4 \text{ M} \times 18$ 、 $2 \text{ M} \times 36$ )

- 333 MHz 时钟实现高带宽

- 2 字突发降低地址总线频率

- 双数据速率 (DDR) 接口 (数据传输速率 666 MHz)，工作频率 333 MHz

- 两个输入时钟 ( $K$  和  $\bar{K}$ )，能够实现精确的 DDR 时序

- SRAM 仅使用上升沿

- 两个用于输出数据的输入时钟 ( $C$  和  $\bar{C}$ )，能够最大限度地减少时钟时滞 (Clock Skew) 和传输时间 (Flight Time) 不匹配

- 随路时钟 ( $CQ$  和  $\bar{CQ}$ )，能够简化高速系统中的数据捕获

- 同步内部自定时写入

- 当  $\overline{\text{DOFF}}$  置为高电平时，DDR II 会有 1.5 个周期的读延迟

- 当  $\overline{\text{DOFF}}$  置为低电平时，其工作方式与 QDR I 器件类似，会有 1 个周期的读延迟

- 1.8 V 内核电源，提供 HSTL 输入和输出

- 驱动能力可调的 HSTL 输出缓冲器

- 扩展 HSTL 输出电压 ( $1.4 \text{ V} - V_{DD}$ )

- 支持 1.5 V 和 1.8 V I/O 电源

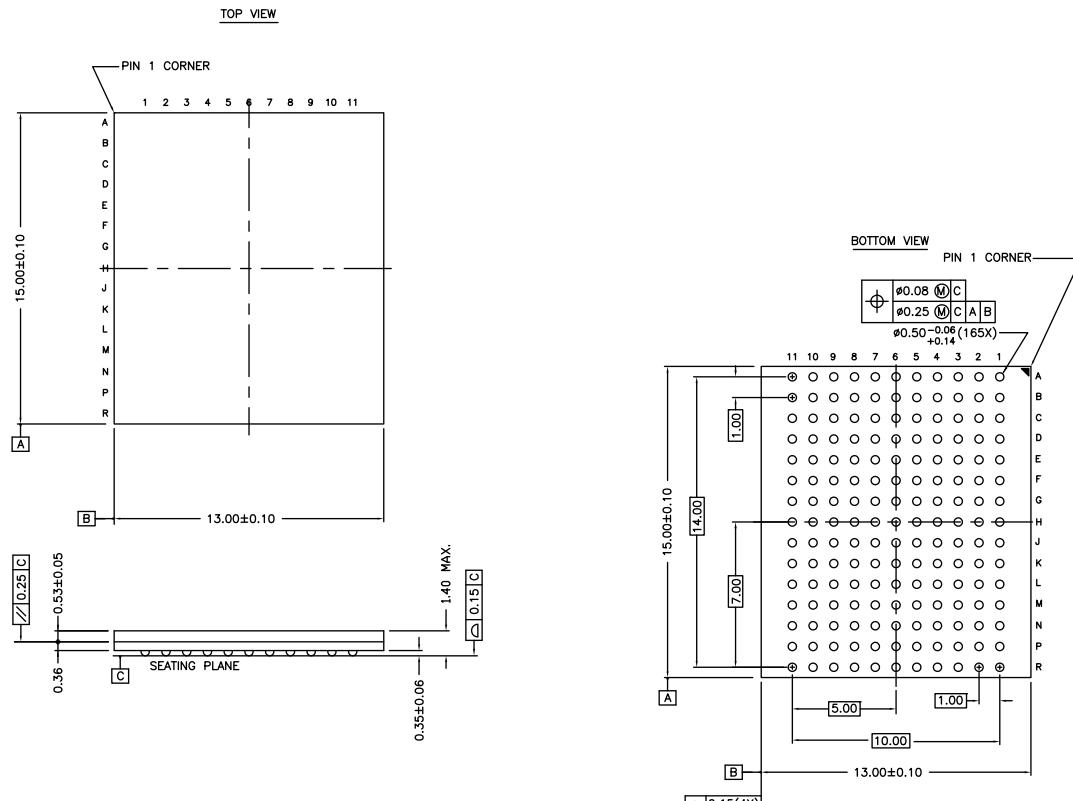

- 可提供 165 脚小间距 BGA (FBGA) 封装 ( $13 \times 15 \times 1.4 \text{ mm}$ )

- 有含铅和不含铅封装可供选择

- JTAG 1149.1 兼容测试端口

- 锁相环 (PLL)，能够实现精确的数据放置

## 配置

CY7C1516KV18 -  $8 \text{ M} \times 8$

CY7C1527KV18 -  $8 \text{ M} \times 9$

CY7C1518KV18 -  $4 \text{ M} \times 18$

CY7C1520KV18 -  $2 \text{ M} \times 36$

## 功能描述

CY7C1516KV18、CY7C1527KV18、CY7C1518KV18 和 CY7C1520KV18 都是包含 DDR II 架构的 1.8 V 同步流水线 SRAM。DDR II 包含一个带有先进同步外围电路的 SRAM 内核和一个 1 位突发计数器。用于读和写的地址被锁止在输入 ( $K$ ) 时钟的备选上升沿。写数据同时在  $K$  和  $\bar{K}$  的上升沿被寄存。读数据在  $C$  和  $\bar{C}$  (如有) 或在  $K$  和  $\bar{K}$  (如果没有  $C/\bar{C}$ ) 的上升沿被驱动。每个地址都与两个 8 位字 (在 CY7C1516KV18 情况下)、两个 9 位字 (在 CY7C1527KV18 情况下) 相关联，这些字以突发模式顺序传入或传出器件。在 CY7C1516KV18 和 CY7C1527KV18 情况下，突发计数器通常在内部以“0”开始。在 CY7C1518KV18 和 CY7C1520KV18 上，突发计数器接收外部地址的最低有效位，并将两个 18 位字 (在 CY7C1518KV18 情况下) 和两个 36 位字 (在 CY7C1520KV18 情况下) 以突发模式顺序传入或传出器件。

异步输入包含输出阻抗匹配输入 ( $ZQ$ )。同步数据输出 ( $Q$ ，与数据输入  $D$  共享相同的物理引脚) 与两个输出随路时钟  $CQ/CQ$  紧密匹配，消除了系统设计中从单个 DDR SRAM 单独捕获数据的需要。输出数据时钟 ( $C/\bar{C}$ ) 启用最大系统时钟和数据同步灵活性。

所有同步输入都会通过由  $K$  或  $\bar{K}$  控制的输入寄存器。所有数据输出都会通过由  $C$  或  $\bar{C}$  (在单时钟域中为  $K$  或  $\bar{K}$ ) 控制的输出寄存器。写操作通过片上同步自定时写电路进行。

## 产品选择指南

| 说明     | 333 MHz     | 300 MHz | 250 MHz | 200 MHz | 167 MHz | 单位  |

|--------|-------------|---------|---------|---------|---------|-----|

| 最大工作频率 | 333         | 300     | 250     | 200     | 167     | MHz |

| 最大工作电流 | $\times 8$  | 510     | 480     | 420     | 370     | mA  |

|        | $\times 9$  | 510     | 480     | 420     | 370     |     |

|        | $\times 18$ | 520     | 490     | 430     | 380     |     |

|        | $\times 36$ | 640     | 600     | 530     | 450     |     |

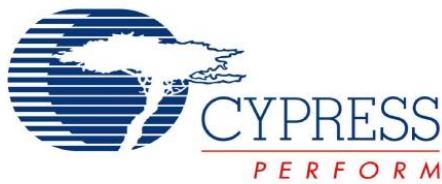

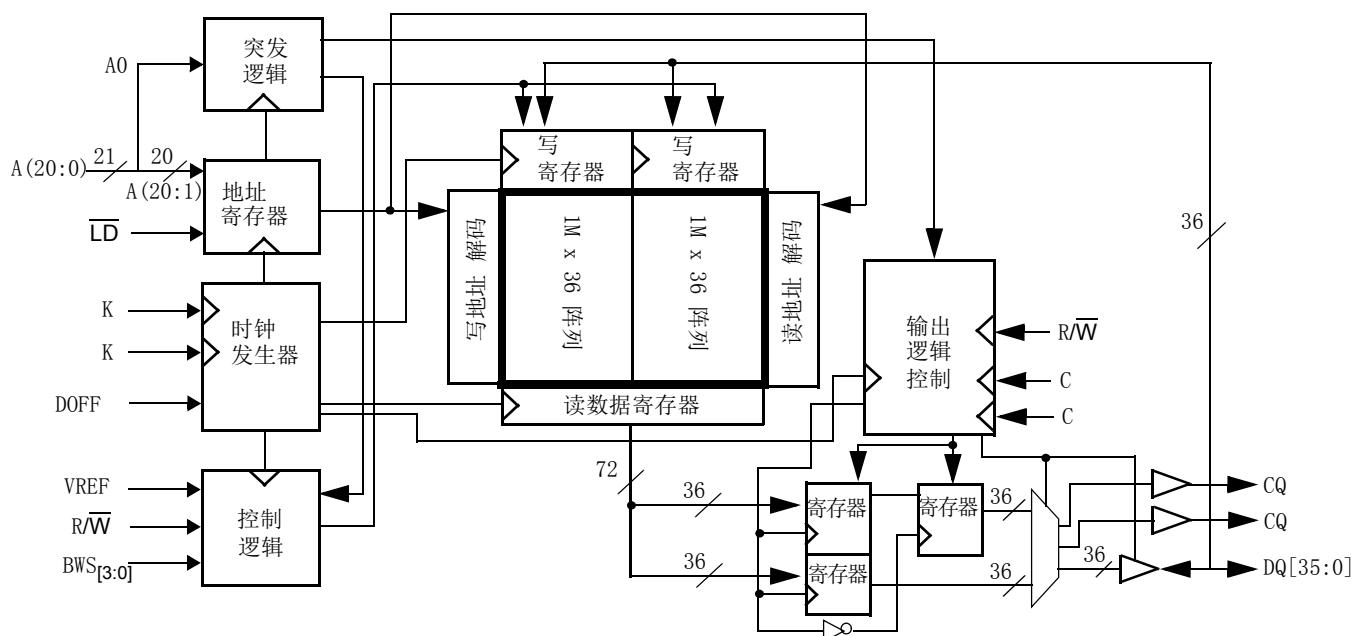

逻辑框图 (CY7C1516KV18)

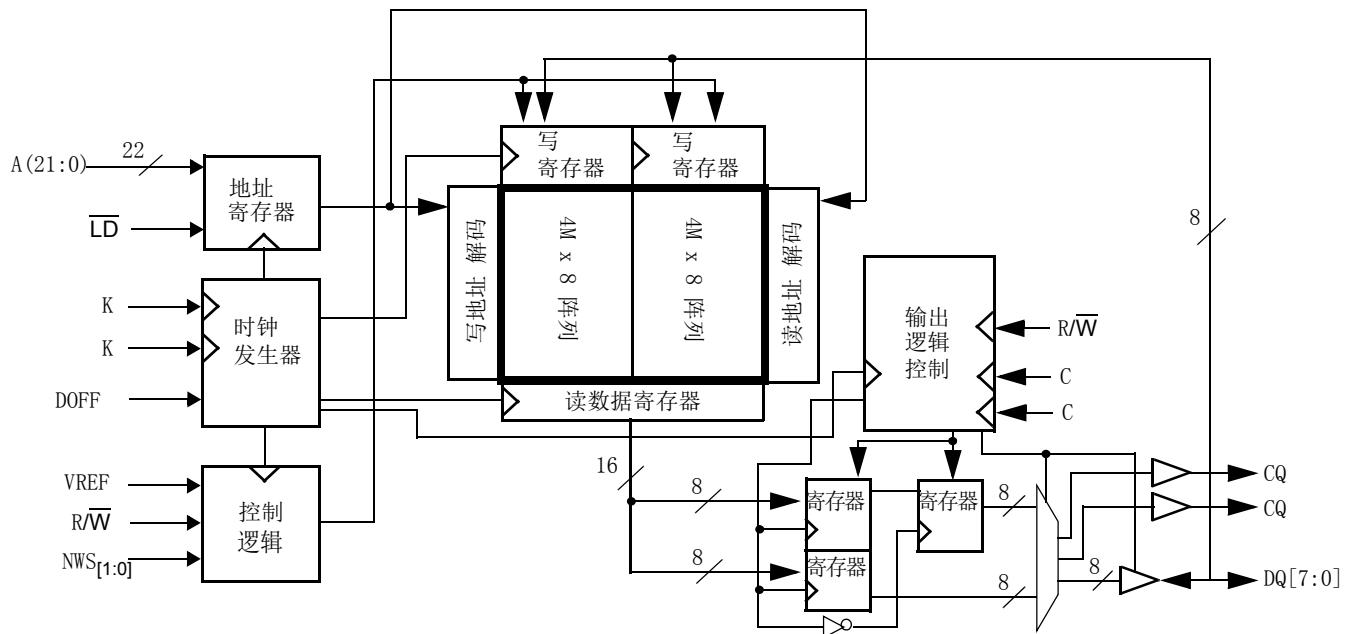

逻辑框图 (CY7C1527KV18)

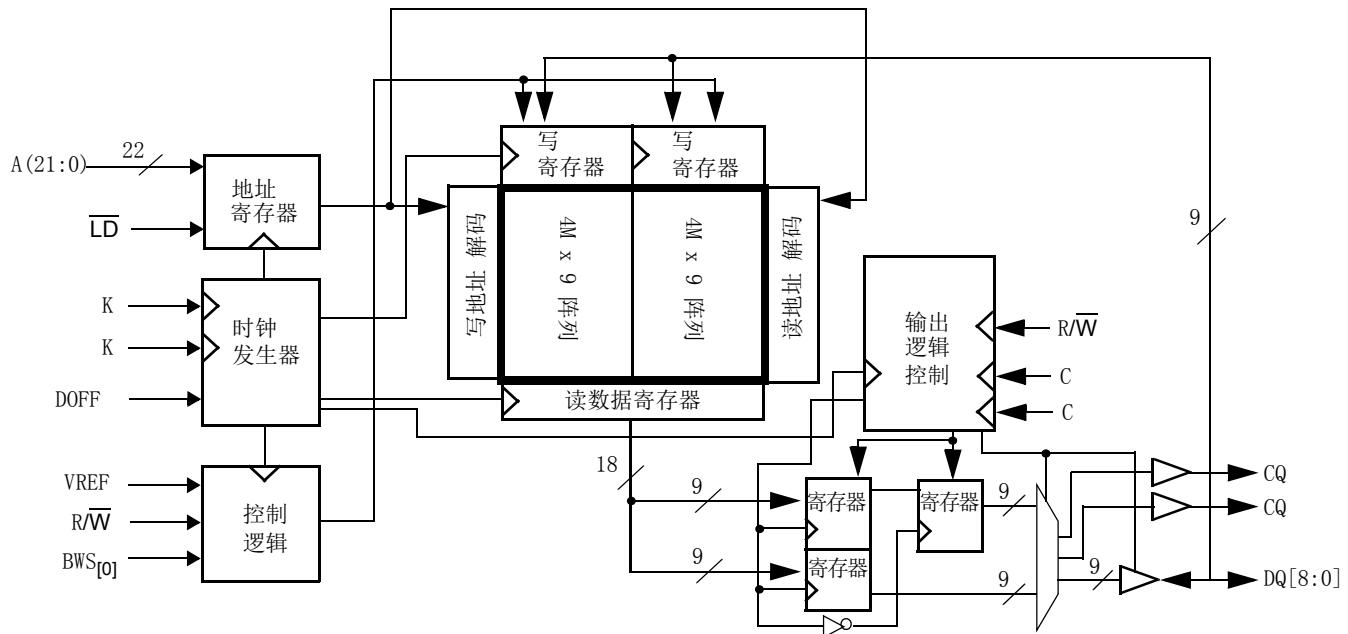

逻辑框图 (CY7C1518KV18)

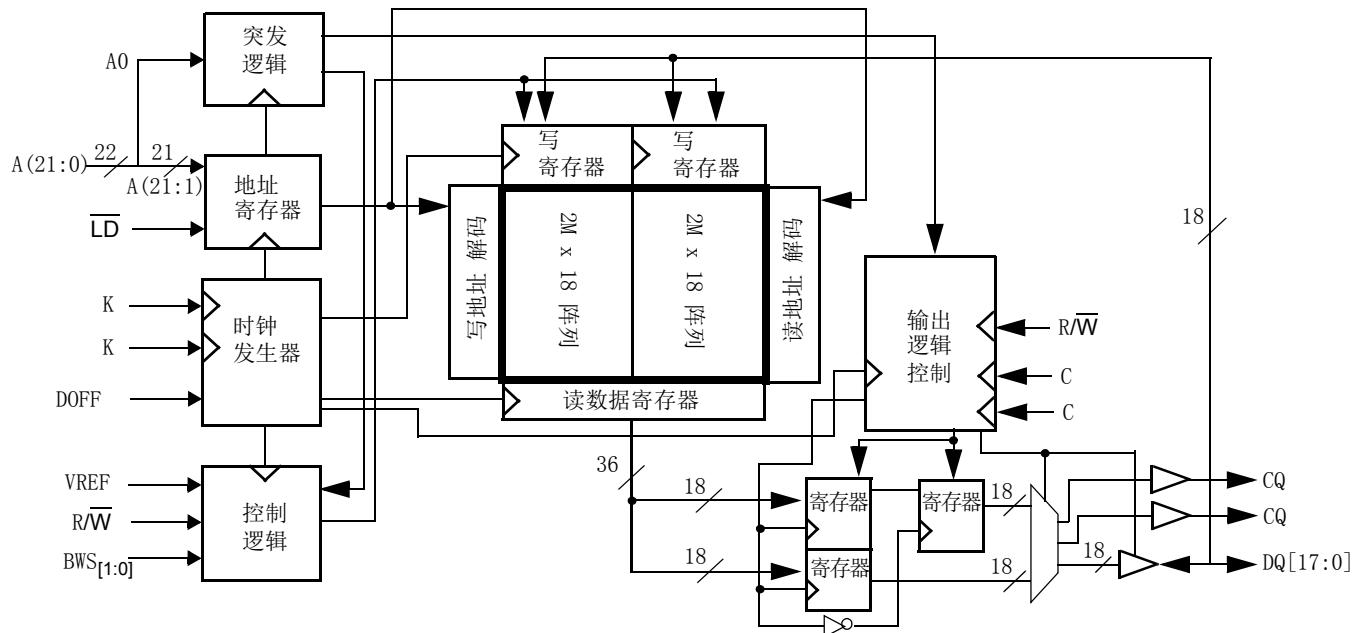

逻辑框图 (CY7C1520KV18)

## 目录

|                                           |    |                         |    |

|-------------------------------------------|----|-------------------------|----|

| 目录 .....                                  | 4  | 标识寄存器定义.....            | 20 |

| 引脚配置 .....                                | 5  | 扫描寄存器大小.....            | 20 |

| 165 脚 Ball FBGA (13 × 15 × 1.4 mm) 引脚分布 . | 5  | 指令代码.....               | 20 |

| 引脚定义.....                                 | 7  | 边界扫描顺序.....             | 21 |

| 功能概述.....                                 | 9  | DDR II SRAM 中的加电顺序..... | 22 |

| 读操作.....                                  | 9  | 加电顺序 .....              | 22 |

| 写操作.....                                  | 9  | PLL 限制 .....            | 22 |

| 字节写操作.....                                | 9  | 最大额定值.....              | 23 |

| 单时钟模式 .....                               | 9  | 工作范围.....               | 24 |

| DDR 操作.....                               | 9  | 抗中子软失效.....             | 23 |

| 深度扩展.....                                 | 9  | 电气特性.....               | 23 |

| 可编程阻抗.....                                | 9  | 直流电气特性 .....            | 23 |

| 随路时钟.....                                 | 10 | 交流电气特性 .....            | 25 |

| PLL.....                                  | 10 | 电容.....                 | 26 |

| 应用示例.....                                 | 10 | 热阻.....                 | 26 |

| 真值表.....                                  | 11 | 交流测试负载和波形 .....         | 26 |

| 突发地址表 .....                               | 11 | 开关特性.....               | 27 |

| 写周期说明.....                                | 12 | 开关波形.....               | 29 |

| 写周期说明.....                                | 12 | 读 / 写 / 取消选中操作过程 .....  | 29 |

| 写周期说明 .....                               | 13 | 订购信息.....               | 30 |

| IEEE 1149.1 串行边界扫描 (JTAG) .....           | 14 | 订购代码定义 .....            | 31 |

| 禁用 JTAG 特性 .....                          | 14 | 封装图.....                | 32 |

| 测试端口 .....                                | 14 | 缩略语.....                | 33 |

| 执行 TAP 复位 .....                           | 14 | 文档规范.....               | 33 |

| TAP 寄存器 .....                             | 14 | 测量单位 .....              | 33 |

| TAP 指令集 .....                             | 14 | 文档修订记录页.....            | 34 |

| TAP 控制器状态图 .....                          | 16 | 销售、解决方案和法律信息.....       | 35 |

| TAP 控制器框图 .....                           | 17 | 全球销售和设计支持 .....         | 35 |

| TAP 电气特性 .....                            | 17 | 产品 .....                | 35 |

| TAP 交流开关特性 .....                          | 18 | PSoC 解决方案 .....         | 35 |

| TAP 时序和测试条件.....                          | 19 |                         |    |

## 引脚配置

CY7C1516KV18、CY7C1527KV18、CY7C1518KV18 和 CY7C1520KV18 的引脚配置如下所示。<sup>[1]</sup>

**165 脚 Ball FBGA (13 × 15 × 1.4 mm) 引脚分布**

**CY7C1516KV18 (8 M × 8)**

|   | 1                 | 2         | 3         | 4                 | 5                  | 6              | 7                  | 8               | 9         | 10        | 11  |

|---|-------------------|-----------|-----------|-------------------|--------------------|----------------|--------------------|-----------------|-----------|-----------|-----|

| A | $\overline{CQ}$   | A         | A         | R/ $\overline{W}$ | $\overline{NWS}_1$ | $\overline{K}$ | NC/144M            | $\overline{LD}$ | A         | A         | CQ  |

| B | NC                | NC        | NC        | A                 | NC/288M            | K              | $\overline{NWS}_0$ | A               | NC        | NC        | DQ3 |

| C | NC                | NC        | NC        | $V_{SS}$          | A                  | A              | $V_{SS}$           | NC              | NC        | NC        | NC  |

| D | NC                | NC        | NC        | $V_{SS}$          | $V_{SS}$           | $V_{SS}$       | $V_{SS}$           | NC              | NC        | NC        | NC  |

| E | NC                | NC        | DQ4       | $V_{DDQ}$         | $V_{SS}$           | $V_{SS}$       | $V_{DDQ}$          | NC              | NC        | DQ2       |     |

| F | NC                | NC        | NC        | $V_{DDQ}$         | $V_{DD}$           | $V_{SS}$       | $V_{DD}$           | $V_{DDQ}$       | NC        | NC        | NC  |

| G | NC                | NC        | DQ5       | $V_{DDQ}$         | $V_{DD}$           | $V_{SS}$       | $V_{DD}$           | $V_{DDQ}$       | NC        | NC        | NC  |

| H | $\overline{DOFF}$ | $V_{REF}$ | $V_{DDQ}$ | $V_{DDQ}$         | $V_{DD}$           | $V_{SS}$       | $V_{DD}$           | $V_{DDQ}$       | $V_{DDQ}$ | $V_{REF}$ | ZQ  |

| J | NC                | NC        | NC        | $V_{DDQ}$         | $V_{DD}$           | $V_{SS}$       | $V_{DD}$           | $V_{DDQ}$       | NC        | DQ1       | NC  |

| K | NC                | NC        | NC        | $V_{DDQ}$         | $V_{DD}$           | $V_{SS}$       | $V_{DD}$           | $V_{DDQ}$       | NC        | NC        | NC  |

| L | NC                | DQ6       | NC        | $V_{DDQ}$         | $V_{SS}$           | $V_{SS}$       | $V_{SS}$           | $V_{DDQ}$       | NC        | NC        | DQ0 |

| M | NC                | NC        | NC        | $V_{SS}$          | $V_{SS}$           | $V_{SS}$       | $V_{SS}$           | $V_{SS}$        | NC        | NC        | NC  |

| N | NC                | NC        | NC        | $V_{SS}$          | A                  | A              | A                  | $V_{SS}$        | NC        | NC        | NC  |

| P | NC                | NC        | DQ7       | A                 | A                  | C              | A                  | A               | NC        | NC        | NC  |

| R | TDO               | TCK       | A         | A                 | A                  | $\overline{C}$ | A                  | A               | A         | TMS       | TDI |

**CY7C1527KV18 (8 M × 9)**

|   | 1                 | 2         | 3         | 4                 | 5        | 6              | 7                  | 8               | 9         | 10        | 11  |

|---|-------------------|-----------|-----------|-------------------|----------|----------------|--------------------|-----------------|-----------|-----------|-----|

| A | $\overline{CQ}$   | A         | A         | R/ $\overline{W}$ | NC       | $\overline{K}$ | NC/144M            | $\overline{LD}$ | A         | A         | CQ  |

| B | NC                | NC        | NC        | A                 | NC/288M  | K              | $\overline{BWS}_0$ | A               | NC        | NC        | DQ3 |

| C | NC                | NC        | NC        | $V_{SS}$          | A        | A              | $V_{SS}$           | NC              | NC        | NC        | NC  |

| D | NC                | NC        | NC        | $V_{SS}$          | $V_{SS}$ | $V_{SS}$       | $V_{SS}$           | NC              | NC        | NC        | NC  |

| E | NC                | NC        | DQ4       | $V_{DDQ}$         | $V_{SS}$ | $V_{SS}$       | $V_{DDQ}$          | NC              | NC        | DQ2       |     |

| F | NC                | NC        | NC        | $V_{DDQ}$         | $V_{DD}$ | $V_{SS}$       | $V_{DD}$           | $V_{DDQ}$       | NC        | NC        | NC  |

| G | NC                | NC        | DQ5       | $V_{DDQ}$         | $V_{DD}$ | $V_{SS}$       | $V_{DD}$           | $V_{DDQ}$       | NC        | NC        | NC  |

| H | $\overline{DOFF}$ | $V_{REF}$ | $V_{DDQ}$ | $V_{DDQ}$         | $V_{DD}$ | $V_{SS}$       | $V_{DD}$           | $V_{DDQ}$       | $V_{DDQ}$ | $V_{REF}$ | ZQ  |

| J | NC                | NC        | NC        | $V_{DDQ}$         | $V_{DD}$ | $V_{SS}$       | $V_{DD}$           | $V_{DDQ}$       | NC        | DQ1       | NC  |

| K | NC                | NC        | NC        | $V_{DDQ}$         | $V_{DD}$ | $V_{SS}$       | $V_{DD}$           | $V_{DDQ}$       | NC        | NC        | NC  |

| L | NC                | DQ6       | NC        | $V_{DDQ}$         | $V_{SS}$ | $V_{SS}$       | $V_{SS}$           | $V_{DDQ}$       | NC        | NC        | DQ0 |

| M | NC                | NC        | NC        | $V_{SS}$          | $V_{SS}$ | $V_{SS}$       | $V_{SS}$           | $V_{SS}$        | NC        | NC        | NC  |

| N | NC                | NC        | NC        | $V_{SS}$          | A        | A              | A                  | $V_{SS}$        | NC        | NC        | NC  |

| P | NC                | NC        | DQ7       | A                 | A        | C              | A                  | A               | NC        | NC        | DQ8 |

| R | TDO               | TCK       | A         | A                 | A        | C              | A                  | A               | A         | TMS       | TDI |

### 注

1. NC/144M 和 NC/288M 未连接到 Die，可连接到任何电压水平。

**引脚配置 (续)**

CY7C1516KV18、CY7C1527KV18、CY7C1518KV18 和 CY7C1520KV18 的引脚配置如下所示。<sup>[1]</sup>

**165 脚 Ball FBGA (13 × 15 × 1.4 mm) 引脚分布**

**CY7C1518KV18 (4 M × 18)**

|          | 1           | 2                | 3                | 4                | 5                       | 6               | 7                       | 8                | 9                | 10               | 11  |

|----------|-------------|------------------|------------------|------------------|-------------------------|-----------------|-------------------------|------------------|------------------|------------------|-----|

| <b>A</b> | <u>CQ</u>   | A                | A                | R/ <u>W</u>      | <u>BWS</u> <sub>1</sub> | K               | NC/144M                 | <u>LD</u>        | A                | A                | CQ  |

| <b>B</b> | NC          | DQ9              | NC               | A                | NC/288M                 | K               | <u>BWS</u> <sub>0</sub> | A                | NC               | NC               | DQ8 |

| <b>C</b> | NC          | NC               | NC               | V <sub>SS</sub>  | A                       | A0              | A                       | V <sub>SS</sub>  | NC               | DQ7              | NC  |

| <b>D</b> | NC          | NC               | DQ10             | V <sub>SS</sub>  | V <sub>SS</sub>         | V <sub>SS</sub> | V <sub>SS</sub>         | V <sub>SS</sub>  | NC               | NC               | NC  |

| <b>E</b> | NC          | NC               | DQ11             | V <sub>DDQ</sub> | V <sub>SS</sub>         | V <sub>SS</sub> | V <sub>SS</sub>         | V <sub>DDQ</sub> | NC               | NC               | DQ6 |

| <b>F</b> | NC          | DQ12             | NC               | V <sub>DDQ</sub> | V <sub>DD</sub>         | V <sub>SS</sub> | V <sub>DD</sub>         | V <sub>DDQ</sub> | NC               | NC               | DQ5 |

| <b>G</b> | NC          | NC               | DQ13             | V <sub>DDQ</sub> | V <sub>DD</sub>         | V <sub>SS</sub> | V <sub>DD</sub>         | V <sub>DDQ</sub> | NC               | NC               | NC  |

| <b>H</b> | <u>DOFF</u> | V <sub>REF</sub> | V <sub>DDQ</sub> | V <sub>DDQ</sub> | V <sub>DD</sub>         | V <sub>SS</sub> | V <sub>DD</sub>         | V <sub>DDQ</sub> | V <sub>DDQ</sub> | V <sub>REF</sub> | ZQ  |

| <b>J</b> | NC          | NC               | NC               | V <sub>DDQ</sub> | V <sub>DD</sub>         | V <sub>SS</sub> | V <sub>DD</sub>         | V <sub>DDQ</sub> | NC               | DQ4              | NC  |

| <b>K</b> | NC          | NC               | DQ14             | V <sub>DDQ</sub> | V <sub>DD</sub>         | V <sub>SS</sub> | V <sub>DD</sub>         | V <sub>DDQ</sub> | NC               | NC               | DQ3 |

| <b>L</b> | NC          | DQ15             | NC               | V <sub>DDQ</sub> | V <sub>SS</sub>         | V <sub>SS</sub> | V <sub>SS</sub>         | V <sub>DDQ</sub> | NC               | NC               | DQ2 |

| <b>M</b> | NC          | NC               | NC               | V <sub>SS</sub>  | V <sub>SS</sub>         | V <sub>SS</sub> | V <sub>SS</sub>         | V <sub>SS</sub>  | NC               | DQ1              | NC  |

| <b>N</b> | NC          | NC               | DQ16             | V <sub>SS</sub>  | A                       | A               | A                       | V <sub>SS</sub>  | NC               | NC               | NC  |

| <b>P</b> | NC          | NC               | DQ17             | A                | A                       | C               | A                       | A                | NC               | NC               | DQ0 |

| <b>R</b> | TDO         | TCK              | A                | A                | A                       | <u>C</u>        | A                       | A                | A                | TMS              | TDI |

**CY7C1520KV18 (2 M × 36)**

|          | 1           | 2                | 3                | 4                | 5                       | 6               | 7                       | 8                | 9                | 10               | 11   |

|----------|-------------|------------------|------------------|------------------|-------------------------|-----------------|-------------------------|------------------|------------------|------------------|------|

| <b>A</b> | <u>CQ</u>   | NC/144M          | A                | R/ <u>W</u>      | <u>BWS</u> <sub>2</sub> | K               | <u>BWS</u> <sub>1</sub> | <u>LD</u>        | A                | A                | CQ   |

| <b>B</b> | NC          | DQ27             | DQ18             | A                | <u>BWS</u> <sub>3</sub> | K               | <u>BWS</u> <sub>0</sub> | A                | NC               | NC               | DQ8  |

| <b>C</b> | NC          | NC               | DQ28             | V <sub>SS</sub>  | A                       | A0              | A                       | V <sub>SS</sub>  | NC               | DQ17             | DQ7  |

| <b>D</b> | NC          | DQ29             | DQ19             | V <sub>SS</sub>  | V <sub>SS</sub>         | V <sub>SS</sub> | V <sub>SS</sub>         | V <sub>SS</sub>  | NC               | NC               | DQ16 |

| <b>E</b> | NC          | NC               | DQ20             | V <sub>DDQ</sub> | V <sub>SS</sub>         | V <sub>SS</sub> | V <sub>SS</sub>         | V <sub>DDQ</sub> | NC               | DQ15             | DQ6  |

| <b>F</b> | NC          | DQ30             | DQ21             | V <sub>DDQ</sub> | V <sub>DD</sub>         | V <sub>SS</sub> | V <sub>DD</sub>         | V <sub>DDQ</sub> | NC               | NC               | DQ5  |

| <b>G</b> | NC          | DQ31             | DQ22             | V <sub>DDQ</sub> | V <sub>DD</sub>         | V <sub>SS</sub> | V <sub>DD</sub>         | V <sub>DDQ</sub> | NC               | NC               | DQ14 |

| <b>H</b> | <u>DOFF</u> | V <sub>REF</sub> | V <sub>DDQ</sub> | V <sub>DDQ</sub> | V <sub>DD</sub>         | V <sub>SS</sub> | V <sub>DD</sub>         | V <sub>DDQ</sub> | V <sub>DDQ</sub> | V <sub>REF</sub> | ZQ   |

| <b>J</b> | NC          | NC               | DQ32             | V <sub>DDQ</sub> | V <sub>DD</sub>         | V <sub>SS</sub> | V <sub>DD</sub>         | V <sub>DDQ</sub> | NC               | DQ13             | DQ4  |

| <b>K</b> | NC          | NC               | DQ23             | V <sub>DDQ</sub> | V <sub>DD</sub>         | V <sub>SS</sub> | V <sub>DD</sub>         | V <sub>DDQ</sub> | NC               | DQ12             | DQ3  |

| <b>L</b> | NC          | DQ33             | DQ24             | V <sub>DDQ</sub> | V <sub>SS</sub>         | V <sub>SS</sub> | V <sub>SS</sub>         | V <sub>DDQ</sub> | NC               | NC               | DQ2  |

| <b>M</b> | NC          | NC               | DQ34             | V <sub>SS</sub>  | V <sub>SS</sub>         | V <sub>SS</sub> | V <sub>SS</sub>         | V <sub>SS</sub>  | NC               | DQ11             | DQ1  |

| <b>N</b> | NC          | DQ35             | DQ25             | V <sub>SS</sub>  | A                       | A               | A                       | V <sub>SS</sub>  | NC               | NC               | DQ10 |

| <b>P</b> | NC          | NC               | DQ26             | A                | A                       | C               | A                       | A                | NC               | DQ9              | DQ0  |

| <b>R</b> | TDO         | TCK              | A                | A                | A                       | C               | A                       | A                | A                | TMS              | TDI  |

## 引脚定义

| 引脚名称                                                                      | I/O    | 引脚说明                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|---------------------------------------------------------------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DQ <sub>[x:0]</sub>                                                       | 输入输出同步 | <b>数据输入输出信号。</b> 在有效的写操作期间，在 K 和 $\bar{K}$ 时钟的上升沿被采样。在有效的读操作期间，这些引脚会输出所请求的数据。在读操作期间，有效数据在 C 和 $\bar{C}$ 时钟（在单时钟模式下为 K 和 $\bar{K}$ ）的上升沿输出。未选中读端口时，Q <sub>[x:0]</sub> 会自动进入三态。<br>CY7C1516KV18 – DQ <sub>[7:0]</sub><br>CY7C1527KV18 – DQ <sub>[8:0]</sub><br>CY7C1518KV18 – DQ <sub>[17:0]</sub><br>CY7C1520KV18 – DQ <sub>[35:0]</sub>                                                                                                                                                                                                                                |

| LD                                                                        | 输入同步   | <b>同步负载。</b> 定义总线周期序列时，该输入为低电平。该定义包括地址和读 / 写方向。所有数据操作在 2 数据突发上运行。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| NWS <sub>0</sub> , $\bar{NWS}_1$                                          | 输入同步   | <b>半字节写选择 0、1 – 低电平有效（仅限 CY7C1516KV18）。</b> 在写操作期间，在 K 和 $\bar{K}$ 时钟的上升沿被采样。用于选择在写操作的当前部分，将哪个半字节写入到器件中。不写入的半字节将保持不变。<br>$\bar{NWS}_0$ 控制 D <sub>[3:0]</sub> , $\bar{NWS}_1$ 控制 D <sub>[7:4]</sub> 。<br>所有“半字节写选择 (Nibble Write Select)”均在数据采样的相同沿被采样。取消选中“半字节写选择 (Nibble Write Select)”会忽略相应的数据半字节，并且不会将其写入到器件中。                                                                                                                                                                                                                                                      |

| BWS <sub>0</sub> ,<br>$\bar{BWS}_1$ ,<br>$\bar{BWS}_2$ ,<br>$\bar{BWS}_3$ | 输入同步   | <b>字节写选择 0、1、2 和 3 – 低电平有效。</b> 在写操作期间，在 K 和 $\bar{K}$ 时钟的上升沿被采样。用于选择在写操作的当前部分，将哪个字节写入到器件中。不写入的字节将保持不变。<br>CY7C1527KV18 – $\bar{BWS}_0$ 控制 D <sub>[8:0]</sub><br>CY7C1518KV18 – $\bar{BWS}_0$ 控制 D <sub>[8:0]</sub> , $\bar{BWS}_1$ 控制 D <sub>[17:9]</sub> 。<br>CY7C1520KV18 – $\bar{BWS}_0$ 控制 D <sub>[8:0]</sub> , $\bar{BWS}_1$ 控制 D <sub>[17:9]</sub> , $\bar{BWS}_2$ 控制 D <sub>[26:18]</sub> , $\bar{BWS}_3$ 控制 D <sub>[35:27]</sub> 。<br>所有“字节写选择 (Byte Write Select)”均在数据采样的相同沿被采样。取消选中“字节写选择 (Byte Write Select)”会忽略相应的数据字节，并且不会将其写入到器件中。                      |

| A, A <sub>0</sub>                                                         | 输入同步   | <b>地址输入。</b> 这些地址输入复用于读操作和写操作。在器件内部，CY7C1516KV18 采取的是 8M × 8 (2 个阵列，每个阵列均为 4M × 8) 的组织方式，CY7C1527KV18 采取的是 8M × 9 (2 个阵列，每个阵列均为 4M × 9) 的组织方式，CY7C1518KV18 采取 4M × 18 (2 个阵列，每个阵列均为 2M × 18) 的组织方式，CY7C1520KV18 采取 2M × 36 (2 个阵列，每个阵列均为 1M × 36) 的组织方式。<br>CY7C1516KV18 – 由于地址在内部的最低有效位为“0”，仅需 22 个外部地址输入就可访问整个存储器阵列。<br>CY7C1527KV18 – 由于地址在内部的最低有效位为“0”，仅需 22 个外部地址输入就可访问整个存储器阵列。<br>CY7C1518KV18 – A <sub>0</sub> 是突发计数器的输入。这些在内部以线性方式递增。需要 22 个地址输入以访问整个存储器阵列。<br>CY7C1520KV18 – A <sub>0</sub> 是突发计数器的输入。这些在内部以线性方式递增。需要 21 个地址输入以访问整个存储器阵列。未选中相应端口时，所有地址输入会被忽略。 |

| R/W                                                                       | 输入同步   | <b>同步读或写输入。</b> 当 LD 为低电平时，该输入指定加载的地址的访问类型（当 R/W 为高电平时读取，当 R/W 为低电平时写入）。R/W 必须满足 K 边沿周围的建立和保持时间。                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| C                                                                         | 输入时钟   | <b>用于输出数据的正向输入时钟。</b> C 与 $\bar{C}$ 一起用来输出器件中的读数据。C 和 $\bar{C}$ 一起使用，能够消除模块上各种器件到控制器的传输时间。有关更多详细信息，请参见应用程序示例。                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| C                                                                         | 输入时钟   | <b>用于输出数据的负向输入时钟。</b> $\bar{C}$ 与 C 一起用来输出器件中的读数据。C 和 $\bar{C}$ 一起使用，能够消除模块上各种器件到控制器的传输时间。有关更多详细信息，请参见应用程序示例。                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| K                                                                         | 输入时钟   | <b>正向输入时钟输入。</b> 在单时钟模式下，K 的上升沿用于捕获器件的同步输入，并通过 Q <sub>[x:0]</sub> 输出数据。所有访问都在 K 的上升沿启动。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| $\bar{K}$                                                                 | 输入时钟   | <b>负向输入时钟输入。</b> 在单时钟模式下，K 用于捕获器件的同步数据，并通过 Q <sub>[x:0]</sub> 输出数据。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

## 引脚定义 (续)

| 引脚名称      | I/O     | 引脚说明                                                                                                                                                                                              |

|-----------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CQ        | 输出时钟    | <b>CQ 参照 C。</b> 这是一个自由运行的时钟，与 DDR II 中“用于输出数据的输入时钟 (C)”保持同步。在单时钟模式下，会参照 K 来生成 CQ。随路时钟的时序如交流时序表所示。                                                                                                 |

| CQ        | 输出时钟    | <b>CQ 参照 <math>\bar{C}</math>。</b> 这是一个自由运行的时钟，与 DDR II 中“用于输出数据的输入时钟 ( $\bar{C}$ )”保持同步。在单时钟模式下，会参照 $\bar{K}$ 来生成 $\bar{CQ}$ 。随路时钟的时序如 AC 时序表所示。                                                 |

| ZQ        | 输入      | <b>输出阻抗匹配输入。</b> 此输入用于调整器件输出相对于系统数据总线的阻抗。CQ、 $\bar{CQ}$ 和 $Q_{[x:0]}$ 输出阻抗为 $0.2 \times R_Q$ 。其中， $R_Q$ 是位于 ZQ 与接地之间的电阻。也可以将此引脚直接连接到 $V_{DDQ}$ ，这样会启用最小阻抗模式。此引脚不能直接连接到 GND，也不能保持未连接状态。            |

| DOFF      | 输入      | <b>PLL 关闭 – 低电平有效。</b> 将此引脚接地会关闭器件内部的 PLL。PLL 处于关闭状态时，工作时序会与本数据表中列出的时序有所不同。在正常工作时，请将此引脚通过一个 $10\text{ k}\Omega$ 或更小的电阻上拉。PLL 处于关闭状态时，器件会以 DDR I 模式工作。在此模式下，器件能够以高达 167 MHz 的频率工作，同时满足 DDR I 时序要求。 |

| TDO       | 输出      | JTAG 的测试数据输出 (TDO)                                                                                                                                                                                |

| TCK       | 输入      | JTAG 的测试时钟 (TCK) 引脚                                                                                                                                                                               |

| TDI       | 输入      | JTAG 的测试数据输入 (TDI) 引脚                                                                                                                                                                             |

| TMS       | 输入      | JTAG 的测试模式选择 (TMS) 引脚                                                                                                                                                                             |

| NC        | 不可用     | 未连接到 die。可连接到任何电压电平。                                                                                                                                                                              |

| NC/144M   | 输入      | 未连接到 die。可连接到任何电压电平。                                                                                                                                                                              |

| NC/288M   | 输入      | 未连接到 die。可连接到任何电压电平。                                                                                                                                                                              |

| $V_{REF}$ | 输入 - 参考 | 参考电压输入。静态输入，用于设置 HSTL 输入、输出和 AC 测量点的参考电平。                                                                                                                                                         |

| $V_{DD}$  | 电源      | 器件内核的电源输入。                                                                                                                                                                                        |

| $V_{SS}$  | 接地      | 器件的接地。                                                                                                                                                                                            |

| $V_{DDQ}$ | 电源      | 器件输出的电源输入。                                                                                                                                                                                        |

## 功能概述

CY7C1516KV18、CY7C1527KV18、CY7C1518KV18 和 CY7C1520KV18 同步的流水线突发 SRAM，包含一个 DDR 接口，当 D<sub>OFF</sub> 引脚连接到高电平时，会有 1.5 个周期的读延迟。当 D<sub>OFF</sub> 引脚置为低电平或连接到 V<sub>SS</sub> 时，器件会以 DDR I 模式工作，并有 1 个时钟周期的读延迟。

访问都在正向输入时钟 (K) 的上升沿启动。所有同步输入时序均参照输入时钟 (K 和 K) 的上升沿，所有输出时序均参照输出时钟 (C/C，在单时钟模式下为 K/K)。

所有同步数据输入 (D<sub>[x:0]</sub>) 都会通过由输入时钟 (K 和 K) 控制的输入寄存器。所有同步数据输出 (Q<sub>[x:0]</sub>) 都会通过由输出时钟 (C/C，在单时钟模式下为 K/K) 的上升沿控制的输出寄存器。

所有同步控制 (R/W、LD、BWS<sub>[0:X]</sub>) 输入都会通过由输入时钟 (K) 的上升沿控制的输入寄存器。

CY7C1518KV18 在以下章节中进行了说明。这些基本说明同样适用于 CY7C1516KV18、CY7C1527KV18 和 CY7C1520KV18。

### 读操作

CY7C1518KV18 在器件内部采取的是 2 M × 18 的两个阵列的组织方式。访问在 2 个连续的 18 位数据字的突发中完成。通过在正向输入时钟 (K) 的上升沿将 R/W 置为高电平并将 LD 置为低电平，即可启动读操作。呈现给地址输入的地址会存储在读地址寄存器中，且地址的最低有效位呈现给突发计数器。突发计数器以线性方式对地址进行递增。在 K 时钟的下一个上升沿，会使用 C 作为输出时序参考，将相应的 18 位数据字写入到 Q<sub>[17:0]</sub>。在接下来的 C 上升沿，下一个 18 位数据字会从突发计数器生成的地址位置写入到 Q<sub>[17:0]</sub>。所请求的数据在输出时钟 (C 或 C，在单时钟模式的 200 MHz、250 MHz 和 300 MHz 器件下为 K 和 K) 上升沿后的 0.45 ns 内有效。若要保持内部逻辑，必须完成每次读访问。读访问都在正向输入时钟 (K) 的上升沿启动。

未选中读端口时，CY7C1518KV18 首先完成待处理的读数据操作。内部同步电路会在输出时钟 (C) 的下一个上升沿自动使输出进入三态。这样一来，在深度扩展的情况下，无需插入等待状态，即可在器件之间实现切换。

### 写操作

通过在正向输入时钟 (K) 的上升沿将 R/W 置为低电平并将 LD 置为低电平，即可启动写操作。呈现给地址输入的地址会存储在写地址寄存器中，且地址的最低有效位呈现给突发计数器。突发计数器以线性方式对地址进行递增。如果 BWS<sub>[1:0]</sub> 均置为有效，则在以下 K 时钟上升沿，呈现给 D<sub>[17:0]</sub> 的数据会被锁存，并会存储到 18 位写数据寄存器中。如果 BWS<sub>[1:0]</sub> 均置为有效，则在接下来的负向输入时钟 (K) 上升沿，呈现给 D<sub>[17:0]</sub> 的信息将被存储到写数据寄存器中。36 位数据随后会写入到内存阵列的指定位置。写访问在每一个正向输入时钟 (K) 的上升沿启动。这样

做即可传输数据流，从而在每个输入时钟 (K 和 K) 的上升沿将 18 位数据传入器件。

未选中写端口时，器件会在待定写操作完成之后忽略所有输入。

### 字节写操作

CY7C1518KV18 支持字节写操作。关于写操作的启动，请参见写操作一节。写入哪些字节由 BWS<sub>0</sub> 和 BWS<sub>1</sub> 决定，并且字节会以每组 18 位数据字的方式被采样。在写操作的数据部分，如果将相应的“字节写选择 (Byte Write Select)”置为输入，则会锁存当前呈现的数据并将其写入到器件中。否则，器件中存储的该字节的数据将保持不变。此特性用于将读操作、修改操作或写操作简化为字节写操作。

### 单时钟模式

CY7C1518KV18 采用单一时钟，该时钟同时控制输入和输出寄存器。在这种模式下，器件仅识别一对输入时钟 (K 和 K)，这对时钟同时控制输入和输出寄存器。这相当于器件 K/K 和 C/C 时钟之间的时滞 (Skew) 为零。在这种模式下，所有时序参数都将保持不变。要使用这种工作模式，用户必须在加电时将 C 和 C 连接到高电平。此功能是一个固定选项，在器件工作期间不能更改。

### DDR 操作

CY7C1518KV18 可通过高时钟频率实现高性能操作（通过流水线实现）和 DDR 模式操作。CY7C1518KV18 在从读周期到写周期跃变期间需要一个无操作 (NOP) 周期。在较高的频率，某些应用需要第二个 NOP 周期才能避免争用。

如果读取发生在写周期之后，则写入的地址和数据存储在寄存器中。由于 SRAM 不能在不与读操作冲突的情况下将最后一个字写入阵列，所以必须存储写信息。数据停留在该寄存器中，直到下一个写周期发生为止。在读操作之后的第一个写周期，由之前的写操作存储的数据将被写入到 SRAM 阵列。这称为已发布的写入。

如果读操作在上一个周期执行写操作的地址上执行，则 SRAM 读出最新数据。SRAM 通过绕过存储器阵列并读取寄存器的数据实现这一操作。

### 深度扩展 (Depth Expansion)

深度扩展需要复制每一组的 LD 控制信号。根据情况，组之间的所有其他控制信号可以共用。

### 可编程阻抗

SRAM 上的 ZQ 引脚与 V<sub>SS</sub> 之间必须连接一个外部电阻 RQ，以便 SRAM 能够调整其输出驱动器阻抗。RQ 的值必须相当于由 SRAM 控制的目标线路阻抗的 5 倍。当 V<sub>DDQ</sub> = 1.5 V 时，保证阻抗容错性不超过 ±15% 的 RQ 允许范围为 175 Ω 和 350 Ω。输出阻抗在加电后每 1024 个周期调整一次，以补偿电源电压漂移和温度漂移。

## 随路时钟

DDR II 上提供了随路时钟，能够简化高速系统中的数据捕获。两个随路时钟由 DDR II 生成。CQ 参照 C,  $\overline{\text{CQ}}$  参照  $\overline{\text{C}}$ 。它们是自由运行时钟，与 DDR II 的输出时钟保持同步。在单时钟模式下，会参照 K 来生成 CQ，并参照  $\overline{\text{K}}$  来生成  $\overline{\text{CQ}}$ 。随路时钟的时序如第 27 页的开关特性所示。

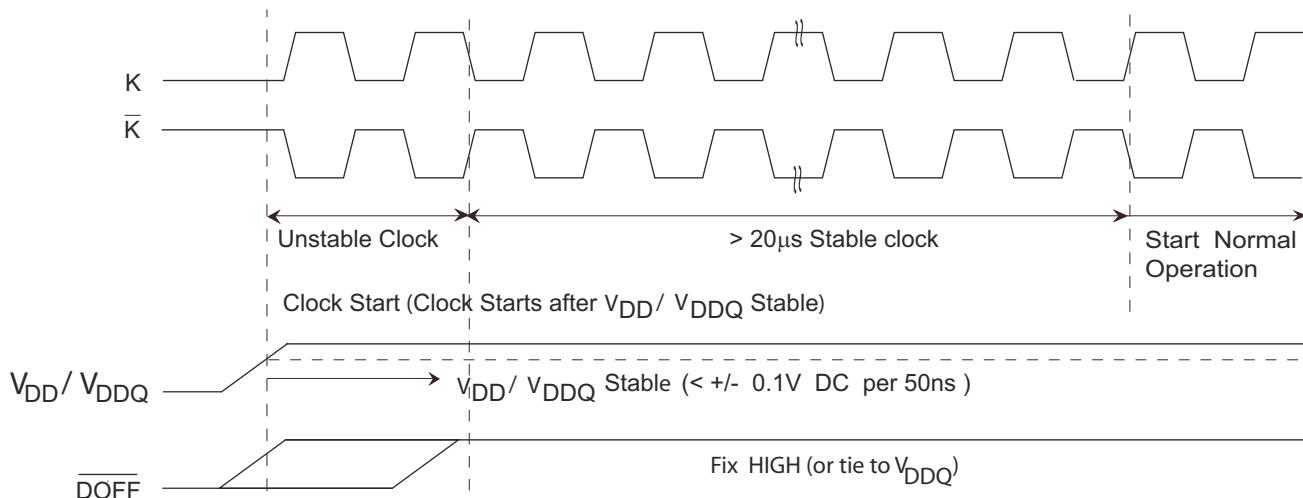

## PLL

这些芯片使用了一个 PLL，其工作频率介于 120 MHz 与指定的最大时钟频率之间。在加电期间，当  $\overline{\text{DOFF}}$  连接到高电平时，PLL 在有  $20\mu\text{s}$  的稳定时钟输入后锁定。通过使输入时钟 K 和  $\overline{\text{K}}$  减慢或停止至少 30 ns，可以将 PLL 复位。不过，无需复位 PLL，即可将其锁定至所需的频率。在时钟稳定  $20\ \mu\text{s}$  后，PLL 会自动锁定。通过将  $\overline{\text{DOFF}}$  引脚接地，可禁用 PLL。当 PLL 处于关闭状态时，器件会以 DDR I 模式工作（具有 1 个周期的延迟，并且访问时间更长）。

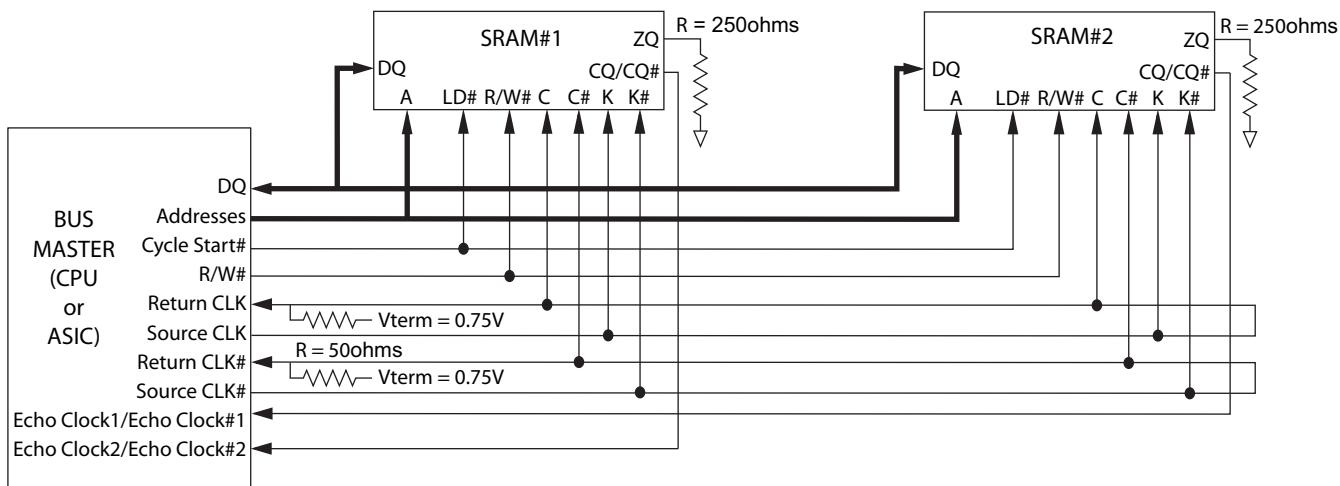

## 应用示例

图 1 所示为某应用中采用的两个 QDR II。

图 1. 应用示例

## 真值表

CY7C1516KV18、CY7C1527KV18、CY7C1518KV18 和 CY7C1520KV18 的真值表如下所示。[2, 3, 4, 5, 6, 7]

| 操作                                                  | K     | LD | R/ $\bar{W}$ | DQ                                   | DQ                                   |

|-----------------------------------------------------|-------|----|--------------|--------------------------------------|--------------------------------------|

| 写周期:<br>加载地址；等待一个周期；<br>在连续 K 和 $\bar{K}$ 上升沿输入写数据。 | L - H | L  | L            | 在 $K(t + 1) \uparrow$<br>D(A1)       | 在 $\bar{K}(t + 1) \uparrow$<br>D(A2) |

| 读周期：<br>加载地址；等待一个半周期；<br>在连续 $\bar{C}$ 和 C 上升沿读取数据。 | L - H | L  | H            | 在 $\bar{C}(t + 1) \uparrow$<br>Q(A1) | 在 $C(t + 2) \uparrow$<br>Q(A2)       |

| NOP：无操作                                             | L - H | H  | X            | High-Z                               | High-Z                               |

| 待机：时钟停止                                             | 停止    | X  | X            | 前一个状态                                | 前一个状态                                |

## 突发地址表

(CY7C1518KV18, CY7C1520KV18)

| 第一个地址（外部） | 第二个地址（内部） |

|-----------|-----------|

| X..X0     | X..X1     |

| X..X1     | X..X0     |

### 注

2. X = “无需关注”，H = 逻辑高电平，L = 逻辑低电平、↑代表上升沿。

3. 器件加电时将处于非选中状态，并且输出处于三态。

4. 在 CY7C1518KV18 和 CY7C1520KV18 上，“A1”代表在启动数据操作时，由器件锁存的地址，“A2”代表突发中的地址顺序。在 CY7C1516KV18 和 CY7C1527KV18 上，“A1”代表 A + ‘0’，“A2”代表 A + ‘1’。

5. “t”代表开始读 / 写操作的周期。 $t + 1$  和  $t + 2$  分别代表“t”时钟周期之后的第一个和第二个时钟周期。

6. 数据输入会在 K 和  $\bar{K}$  上升沿被寄存。数据输出在 C 和  $\bar{C}$  上升沿提供，在单时钟模式下除外。

7. 确保当时钟停止时，K =  $\bar{K}$  且 C =  $\bar{C}$  = 高电平。虽然这并不是必须的，但可以通过对称地克服传输线路充电，帮助实现最快的重启。

## 写周期说明

CY7C1516KV18 和 CY7C1518KV18 的写周期说明表如下所示。[8, 9]

| $\overline{BWS_0}/\overline{NWS_0}$ | $\overline{BWS_1}/\overline{NWS_1}$ | K     | $\bar{K}$ | 注释                                                                                                                                                 |

|-------------------------------------|-------------------------------------|-------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| L                                   | L                                   | L - H | -         | 在写过程的数据部分：<br>CY7C1516KV18 – 两个半字节 ( $D_{[7:0]}$ ) 均写入到器件中。<br>CY7C1518KV18 – 两个字节 ( $D_{[17:0]}$ ) 均写入到器件中。                                       |

| L                                   | L                                   | -     | L - H     | 在写过程的数据部分：<br>CY7C1516KV18 – 两个半字节 ( $D_{[7:0]}$ ) 均写入到器件中。<br>CY7C1518KV18 – 两个字节 ( $D_{[17:0]}$ ) 均写入到器件中。                                       |

| L                                   | H                                   | L - H | -         | 在写过程的数据部分：<br>CY7C1516KV18 – 仅低位半字节 ( $D_{[3:0]}$ ) 写入到器件中, $D_{[7:4]}$ 将保持不变。<br>CY7C1518KV18 – 仅低位字节 ( $D_{[8:0]}$ ) 写入到器件中, $D_{[17:9]}$ 将保持不变。 |

| L                                   | H                                   | -     | L - H     | 在写过程的数据部分：<br>CY7C1516KV18 – 仅低位半字节 ( $D_{[3:0]}$ ) 写入到器件中, $D_{[7:4]}$ 将保持不变。<br>CY7C1518KV18 – 仅低位字节 ( $D_{[8:0]}$ ) 写入到器件中, $D_{[17:9]}$ 将保持不变。 |

| H                                   | L                                   | L - H | -         | 在写过程的数据部分：<br>CY7C1516KV18 – 仅高位半字节 ( $D_{[7:4]}$ ) 写入到器件中, $D_{[3:0]}$ 将保持不变。<br>CY7C1518KV18 – 仅高位字节 ( $D_{[17:9]}$ ) 写入到器件中, $D_{[8:0]}$ 将保持不变。 |

| H                                   | L                                   | -     | L - H     | 在写过程的数据部分：<br>CY7C1516KV18 – 仅高位半字节 ( $D_{[7:4]}$ ) 写入到器件中, $D_{[3:0]}$ 将保持不变。<br>CY7C1518KV18 – 仅高位字节 ( $D_{[17:9]}$ ) 写入到器件中, $D_{[8:0]}$ 将保持不变。 |

| H                                   | H                                   | L - H | -         | 在写操作的这一部分，不会有数据写入到器件中。                                                                                                                             |

| H                                   | H                                   | -     | L - H     | 在写操作的这一部分，不会有数据写入到器件中。                                                                                                                             |

## 写周期说明

CY7C1527KV18 的写周期说明表如下所示。[8, 10]

| $\overline{BWS_0}$ | K     | $\bar{K}$ | 注释                                     |

|--------------------|-------|-----------|----------------------------------------|

| L                  | L - H | -         | 在写过程的数据部分，单个字节 ( $D_{[8:0]}$ ) 写入到器件中。 |

| L                  | -     | L - H     | 在写过程的数据部分，单个字节 ( $D_{[8:0]}$ ) 写入到器件中。 |

| H                  | L - H | -         | 在写操作的这一部分，不会有数据写入到器件中。                 |

| H                  | -     | L - H     | 在写操作的这一部分，不会有数据写入到器件中。                 |

### 注

8. X = “无需关注”，H = 逻辑高电平，L = 逻辑低电平、↑代表上升沿。

9. 基于根据写周期说明表启动的写周期。可以在写周期的不同部分更改  $\overline{NWS_0}$ 、 $\overline{NWS_1}$ 、 $\overline{BWS_0}$ 、 $\overline{BWS_1}$ 、 $\overline{BWS_2}$ 、和  $\overline{BWS_3}$ ，只要达到建立和保留要求即可。

10. 基于根据写周期说明表启动的写周期。可以在写周期的不同部分更改  $\overline{NWS_0}$ 、 $\overline{NWS_1}$ 、 $\overline{BWS_0}$ 、 $\overline{BWS_1}$ 、 $\overline{BWS_2}$ 、和  $\overline{BWS_3}$ ，只要达到建立和保留要求即可。

## 写周期说明

CY7C1520KV18 的写周期说明表如下所示。[11, 12]

| $\overline{BWS_0}$ | $\overline{BWS_1}$ | $\overline{BWS_2}$ | $\overline{BWS_3}$ | K     | $\bar{K}$ | 注释                                                                          |

|--------------------|--------------------|--------------------|--------------------|-------|-----------|-----------------------------------------------------------------------------|

| L                  | L                  | L                  | L                  | L - H | -         | 在写过程的数据部分，全部四个字节 ( $D_{[35:0]}$ ) 都写入到器件中。                                  |

| L                  | L                  | L                  | L                  | -     | L - H     | 在写过程的数据部分，全部四个字节 ( $D_{[35:0]}$ ) 都写入到器件中。                                  |

| L                  | H                  | H                  | H                  | L - H | -         | 在写过程的数据部分，仅低位字节 ( $D_{[8:0]}$ ) 写入到器件中。 $D_{[35:9]}$ 将保持不变。                 |

| L                  | H                  | H                  | H                  | -     | L - H     | 在写过程的数据部分，仅低位字节 ( $D_{[8:0]}$ ) 写入到器件中。 $D_{[35:9]}$ 将保持不变。                 |

| H                  | L                  | H                  | H                  | L - H | -         | 在写过程的数据部分，仅字节 ( $D_{[17:9]}$ ) 写入到器件中。 $D_{[8:0]}$ 和 $D_{[35:18]}$ 将保持不变。   |

| H                  | L                  | H                  | H                  | -     | L - H     | 在写过程的数据部分，仅字节 ( $D_{[17:9]}$ ) 写入到器件中。 $D_{[8:0]}$ 和 $D_{[35:18]}$ 将保持不变。   |

| H                  | H                  | L                  | H                  | L - H | -         | 在写过程的数据部分，仅字节 ( $D_{[26:18]}$ ) 写入到器件中。 $D_{[17:0]}$ 和 $D_{[35:27]}$ 将保持不变。 |

| H                  | H                  | L                  | H                  | -     | L - H     | 在写过程的数据部分，仅字节 ( $D_{[26:18]}$ ) 写入到器件中。 $D_{[17:0]}$ 和 $D_{[35:27]}$ 将保持不变。 |

| H                  | H                  | H                  | L                  | L - H | -         | 在写过程的数据部分，仅字节 ( $D_{[35:27]}$ ) 写入到器件中。 $D_{[26:0]}$ 将保持不变。                 |

| H                  | H                  | H                  | L                  | -     | L - H     | 在写过程的数据部分，仅字节 ( $D_{[35:27]}$ ) 写入到器件中。 $D_{[26:0]}$ 将保持不变。                 |

| H                  | H                  | H                  | H                  | L - H | -         | 在写操作的这一部分，不会有数据写入到器件中。                                                      |

| H                  | H                  | H                  | H                  | -     | L - H     | 在写操作的这一部分，不会有数据写入到器件中。                                                      |

### 注

11. X = “无需关注”，H = 逻辑高电平，L = 逻辑低电平、↑代表上升沿。

12. 基于根据写周期说明表启动的写周期。可以在写周期的不同部分更改  $\overline{NWS_0}$ 、 $\overline{NWS_1}$ 、 $\overline{BWS_0}$ 、 $\overline{BWS_1}$ 、 $\overline{BWS_2}$ 、和  $\overline{BWS_3}$ ，只要满足建立和保留要求即可。

## IEEE 1149.1 串行边界扫描 (JTAG)

这些 SRAM 在 FBGA 封装中加入了串行边界扫描测试端口 (TAP)。此部件完全符合 IEEE 标准 #1149.1-2001。TAP 在工作时采用 JEDEC 标准 1.8 V IO 逻辑电平。

### 禁用 JTAG 特性

可以在不使用 JTAG 特性的情况下运行 SRAM。要禁用 TAP 控制器，必须将 TCK 连接到低电平 ( $V_{SS}$ )，以防止额外的时钟输入到器件中。TDI 和 TMS 在内部上拉，并可处于未连接状态。它们也可以通过电阻上拉到  $V_{DD}$ 。TDO 必须保持未连接状态。在加电时，器件会复位，这不会干扰器件的工作。

### 测试端口

#### 测试时钟

测试时钟仅能与 TAP 控制器配合使用。所有输入都在 TCK 的上升沿被捕获。所有输出都从 TCK 的下降沿被输出。

#### 测试模式选择 (TMS)

TMS 输入用于向 TAP 控制器提供指令，并在 TCK 的上升沿被采样。如果未使用 TAP，此引脚可以保持未连接状态。此引脚在内部上拉，从而产生逻辑高电平。

#### 测试数据输入 (TDI)

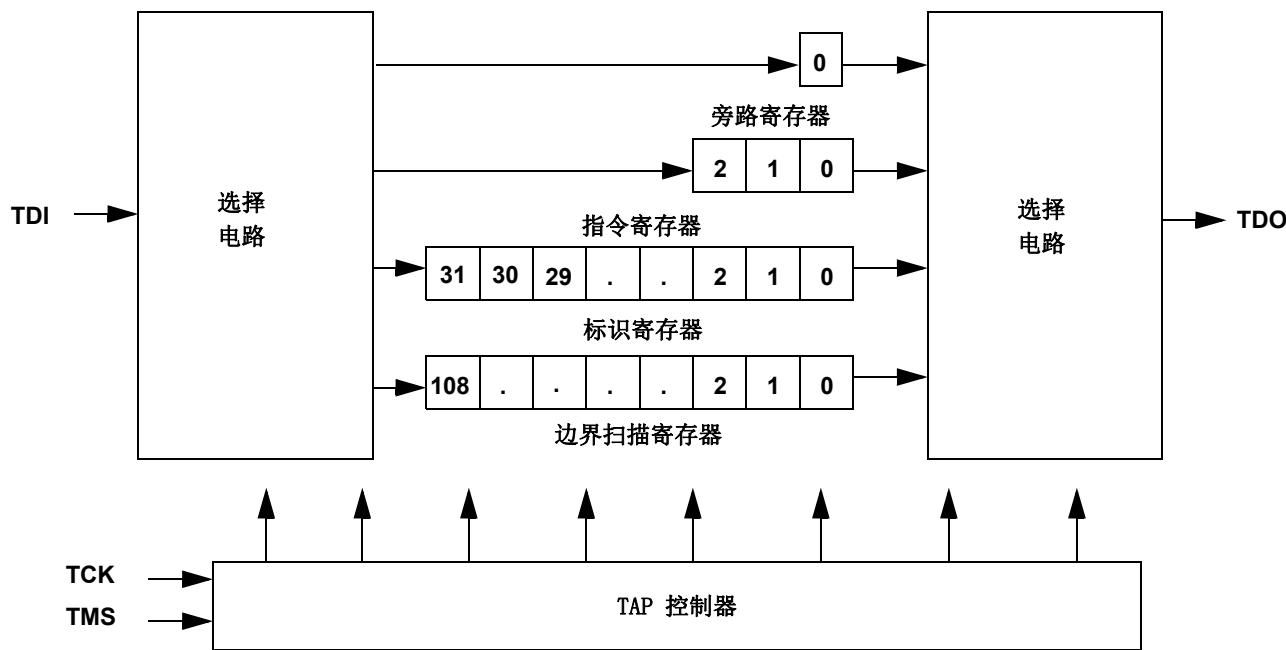

TDI 引脚用于以串行方式将信息输入到寄存器中，并可以连接到任何寄存器的输入。TDI 和 TDO 之间的寄存器由加载到 TAP 指令寄存器中的指令进行选择。有关加载指令寄存器的信息，请参见[第 16 页的 TAP 控制器状态图](#)。TDI 在内部上拉。如果未使用 TAP，此引脚可以保持未连接状态。TDI 连接到任何寄存器的最高有效位 (MSB)。

#### 测试数据输出 (TDO)

TDO 输出引脚用于以串行方式从寄存器输出时钟数据。输出有效，取决于 TAP 状态机的当前状态（请参见[第 20 页的指令代码](#)）。输出会在 TCK 的下降沿改变。TDO 连接到任何寄存器的最低有效位 (LSB)。

### 执行 TAP 复位

通过将 TMS 强制置为高电平 ( $V_{DD}$ ) 达 5 个 TCK 上升沿，即可进行复位。此复位不会影响 SRAM 的工作，并且在 SRAM 工作期间执行。在加电时，TAP 会在内部复位，以确保 TDO 处于 High Z 状态。

### TAP 寄存器

此类寄存器位于 TDI 和 TDO 引脚之间，用于扫描 SRAM 测试电路的数据输入和输出。一次只能通过指令寄存器选择一个寄存

器。在 TCK 的上升沿，数据会以串行方式加载到 TDI 引脚。在 TCK 的下降沿，数据会从 TDO 引脚输出。

#### 指令寄存器

三位指令会以串行方式加载到指令寄存器中。此寄存器在置于 TDI 和 TDO 引脚之间时被加载，如[第 17 页的 TAP 控制器框图](#)所示。在加电时，指令寄存器会加载 IDCODE 指令。即使控制器处于复位状态，也会加载 IDCODE 指令，如上一节所述。

当 TAP 控制器处于 Capture-IR 状态时，两个最低有效位会加载二进制“01”样本，以便实现模块级别串行测试路径的故障隔离。

#### 旁路寄存器

当数据以串行方式写入寄存器时，跳过某些芯片可能会有助于节省时间。旁路寄存器为单比特寄存器，可置于 TDI 和 TDO 引脚之间，从而使数据在写入 SRAM 时具有较小的延迟。执行 BYPASS 指令时，旁路寄存器会置为低电平 ( $V_{SS}$ )。

#### 边界扫描寄存器

边界扫描寄存器连接到 SRAM 上的所有输入和输出引脚。扫描寄存器中还包含一些无连接 (NC) 引脚，以便供更高密度的器件使用。

当 TAP 控制器处于 Capture-DR 状态时，边界扫描寄存器会加载 RAM 输入和输出环的内容。当控制器转入 Shift-DR 状态后，该寄存器会被置于 TDI 和 TDO 引脚之间。EXTEST、SAMPLE/PRELOAD 和 SAMPLE Z 指令用于捕获输入和输出环的内容。

[第 21 页的边界扫描顺序](#)显示了各个位的连接顺序。每个位都对应于 SRAM 封装上的一个管脚。寄存器的 MSB 连接到 TDI，LSB 连接到 TDO。

#### 标识 (ID) 寄存器

当指令寄存器中加载了 IDCODE 指令时，ID 寄存器会在 Capture-DR 状态期间加载供货商特定的 32 位代码。IDCODE 已硬连线到 SRAM 中，当 TAP 控制器处于 Shift-DR 状态时，可以将其读出。ID 寄存器具有供货商代码和[第 20 页的标识寄存器定义](#)中所述的其他信息。

### TAP 指令集

三位指令寄存器可实现八个不同的指令。[第 20 页的指令代码](#)中列出了所有组合。其中三个指令列为了 RESERVED，请勿使用这些指令。本节将详细说明其他五个指令。

当指令寄存器置于 TDI 和 TDO 之间时，这些指令会在 Shift-IR 状态期间加载到 TAP 控制器中。在此状态期间，指令会通过 TDI 和 TDO 引脚被写入指令寄存器。要在写入指令后执行指令，必须使 TAP 控制器转入 Update-IR 状态。

#### *IDCODE*

*IDCODE* 指令用于将供货商特定的 32 位代码加载到指令寄存器中。它还会将指令寄存器置于 TDI 和 TDO 引脚之间，并会在 TAP 控制器进入 Shift-DR 状态后，将 *IDCODE* 移出器件。在加电时，或每当 TAP 控制器处于 Test-Logic-Reset 状态时，*IDCODE* 指令都会加载到指令寄存器中。

#### *SAMPLE Z*

当 TAP 控制器处于 Shift-DR 状态时，*SAMPLE Z* 指令会将边界扫描寄存器置于 TDI 和 TDO 引脚之间。*SAMPLE Z* 指令会将输出总线置于 High-Z 状态，直到在 Update-IR 状态期间提供了下一条指令为止。

#### *SAMPLE/PRELOAD*

*SAMPLE/PRELOAD* 是 1149.1 强制指令。当 *SAMPLE/PRELOAD* 指令加载到指令寄存器中并且 TAP 控制器处于 Capture-DR 状态时，边界扫描寄存器中会捕获输入和输出引脚上数据的快照。

TAP 控制器时钟的最高工作频率仅为 20 MHz，而 SRAM 时钟的工作频率要比它高一个数量级。由于在时钟频率方面存在较大差距，因此在 Capture-DR 状态期间，输入或输出可能会出现跃变。TAP 则可能会在跃变（半稳态）期间尝试捕获信号。虽然这并不会损坏器件，但无法保证捕获到的值是正确的，并且结果可能无法重复。

为了确保边界扫描寄存器捕获到正确的信号值，SRAM 信号必须在足够长的时间内保持稳定，以达到 TAP 控制器的捕获建立加保持时间 ( $t_{CS}$  和  $t_{CH}$ ) 要求。如果在设计上无法在 *SAMPLE/PRELOAD* 指令期间停止（或减慢）时钟，则可能无法正确捕获 SRAM 时钟输入。即使存在这一问题，仍可以捕获所有其他信号，只要忽略边界扫描寄存器中捕获的 CK 和  $\bar{CK}$  的值即可。

捕获数据后，通过将 TAP 置于 Shift-DR 状态，可以读出数据。这会将边界扫描寄存器置于 TDI 和 TDO 引脚之间。

在选择另一个边界扫描测试操作之前，*PRELOAD* 用于在边界扫描寄存器单元的已锁存并行输出处放置一个初始数据样本。

必要时，*SAMPLE* 和 *PRELOAD* 阶段的数据读写可以并发执行，即可以在读出所捕获数据的同时，读入预加载的数据。

#### *BYPASS*

当 *BYPASS* 指令加载到指令寄存器中并且 TAP 处于 Shift-DR 状态时，旁路寄存器会被置于 TDI 和 TDO 引脚之间。*BYPASS* 指令的优势是当模块上有多个器件连接在一起时，可以缩短边界扫描路径。

#### *EXTEST*

*EXTEST* 指令用于通过系统输出引脚输出预加载的数据。在 Shift-DR 控制器状态下，此指令还会将用于串行访问的边界扫描寄存器置于 TDI 和 TDO 之间。

#### *EXTEST OUTPUT BUS TRISTATE*

IEEE 标准 1149.1 强制规定，TAP 控制器需要能够将输出总线置于三态模式。

边界扫描寄存器在 108 位有一个特殊位。当此扫描单元（称为“外测试输出总线三态”）在 TAP 控制器处于 Update-DR 状态期间被锁存到预加载寄存器中时，如果输入 *EXTEST* 作为当前指令，则该单元会直接控制输出（Q 总线）引脚的状态。在置于高电平时，它将允许输出缓冲器控制输出总线。在置于低电平时，此位会将输出总线置于 High Z 状态。

通过输入 *SAMPLE/PRELOAD* 或 *EXTEST* 指令，然后在 Shift-DR 状态期间将所需的位读入到该单元中，即可设置该位。在 Update-DR 期间，加载到该移位寄存器单元中的值会被锁存到预加载寄存器中。输入 *EXTEST* 指令后，此位会直接控制输出 Q 总线引脚。请注意，此位会预置为高电平，以便在器件加电时，以及当 TAP 控制器处于 Test-Logic-Reset 状态时，启动输出。

#### *Reserved*

这些指令尚未实现，但可以留作日后使用。请勿使用这些指令。

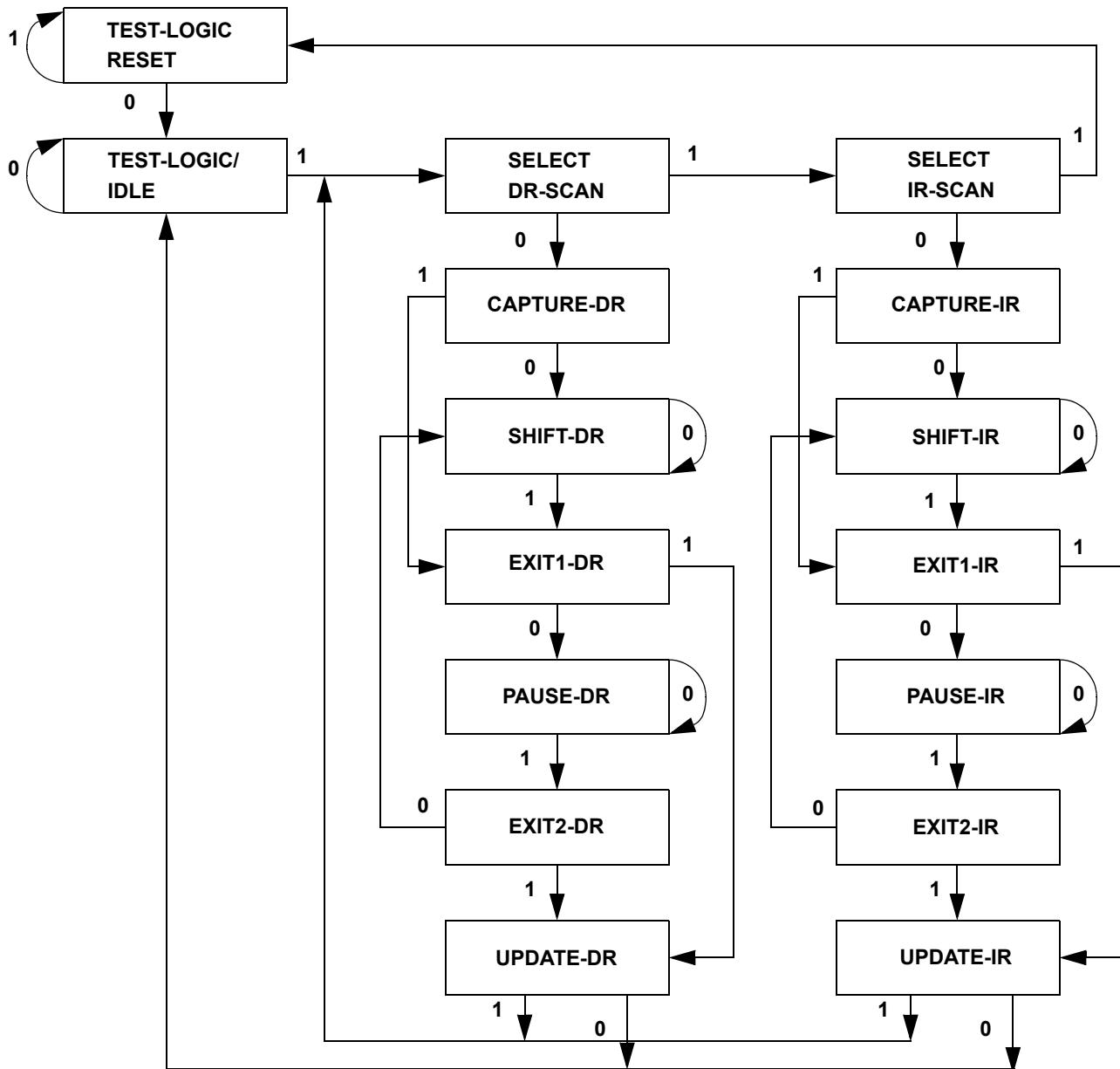

## TAP 控制器状态图

TAP 控制器的状态图如下所示。[13]

注

13. 每个状态旁边的 0/1 代表 TCK 上升沿上对应的 TMS 的值。

## TAP 控制器框图

## TAP 电气特性

### 超出工作范围

| 参数 [14, 15, 16] | 说明        | 测试条件                        | 最小值                  | 最大值                  | 单位 |

|-----------------|-----------|-----------------------------|----------------------|----------------------|----|

| $V_{OH1}$       | 输出高电平电压   | $I_{OH} = -2.0 \text{ mA}$  | 1.4                  | -                    | V  |

| $V_{OH2}$       | 输出高电平电压   | $I_{OH} = -100 \mu\text{A}$ | 1.6                  | -                    | V  |

| $V_{OL1}$       | 输出低电平电压   | $I_{OL} = 2.0 \text{ mA}$   | -                    | 0.4                  | V  |

| $V_{OL2}$       | 输出低电平电压   | $I_{OL} = 100 \mu\text{A}$  | -                    | 0.2                  | V  |

| $V_{IH}$        | 输入高电平电压   |                             | $0.65 \times V_{DD}$ | $V_{DD} + 0.3$       | V  |

| $V_{IL}$        | 输入低电平电压   |                             | -0.3                 | $0.35 \times V_{DD}$ | V  |

| $I_X$           | 输入和输出负载电流 | $GND \leq V_I \leq V_{DD}$  | -5                   | 5                    | ?A |

### 注

14. 这些特性为 TAP 输入 (TMS、TCK、TDI 和 TDO) 的特性。并行负载电平在第 23 页的电气特性中指定。

15. 过冲:  $V_{IH}$  (交流)  $< V_{DDQ} + 0.85 \text{ V}$  (脉冲宽度小于  $t_{Cyc}/2$ )，下冲:  $V_{IL}$  (交流)  $> -1.5 \text{ V}$  (脉冲宽度小于  $t_{Cyc}/2$ )。

16. 所有电压都是相对于接地的电压。

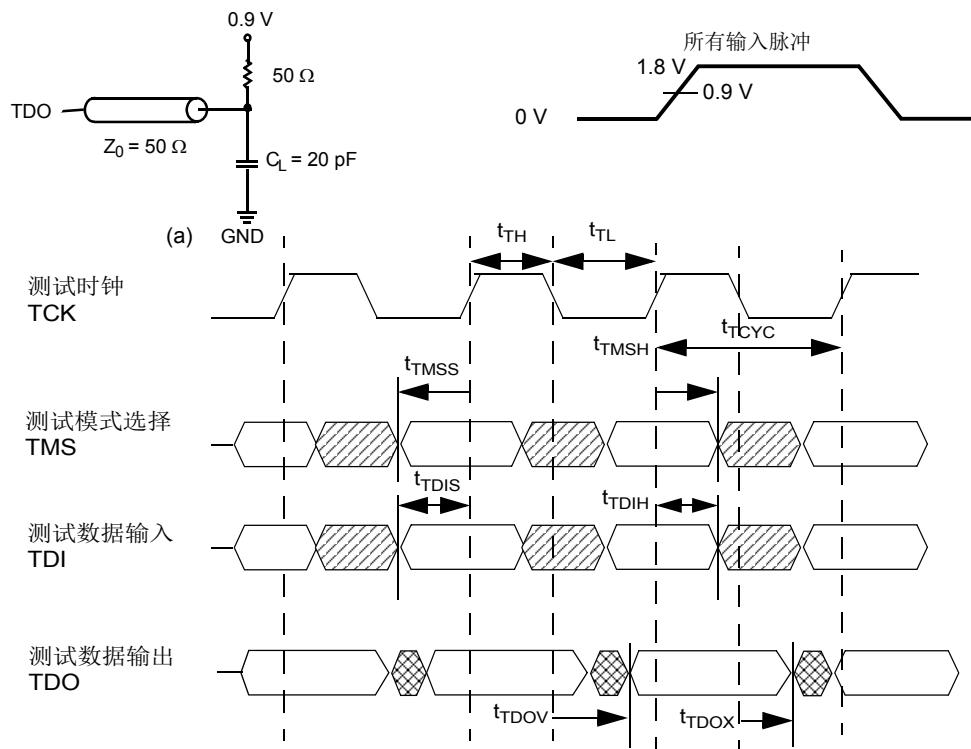

## TAP 交流开关特性

超出工作范围

| 参数 [17, 18] | 说明                     | 最小值 | 最大值 | 单位  |

|-------------|------------------------|-----|-----|-----|

| $t_{TCYC}$  | TCK 时钟周期时间             | 50  | -   | ns  |

| $t_{TF}$    | TCK 时钟频率               | -   | 20  | MHz |

| $t_{TH}$    | TCK 时钟高电平              | 20  | -   | ns  |

| $t_{TL}$    | TCK 时钟低电平              | 20  | -   | ns  |

| 建立时间        |                        |     |     |     |

| $t_{TMSS}$  | 从 TMS 建立到 TCK 时钟上升沿的时间 | 5   | -   | ns  |

| $t_{TDIS}$  | 从 TDI 建立到 TCK 时钟上升沿的时间 | 5   | -   | ns  |

| $t_{CS}$    | 从捕获建立到 TCK 上升沿的时间      | 5   | -   | ns  |

| 保持时间        |                        |     |     |     |

| $t_{TMSH}$  | TCK 时钟上升沿之后的 TMS 保持时间  | 5   | -   | ns  |

| $t_{TDIH}$  | 时钟上升沿之后的 TDI 保持时间      | 5   | -   | ns  |

| $t_{CH}$    | 时钟上升沿之后的捕获保持时间         | 5   | -   | ns  |

| 输出时间        |                        |     |     |     |

| $t_{TDOV}$  | 从 TCK 时钟为低到 TDO 有效的时间  | -   | 10  | ns  |

| $t_{TDOX}$  | 从 TCK 时钟为低到 TDO 无效的时间  | 0   | -   | ns  |

### 注

17.  $t_{CS}$  和  $t_{CH}$  指从边界扫描寄存器锁存数据的建立和保持时间要求。

18. 测试条件是使用 TAP 交流测试条件中的负载确定的。 $t_R/t_F = 1$  ns。

## TAP 时序和测试条件

图 2 所示为 TAP 时序和测试条件。[19]

图 2. TAP 时序和测试条件

注

19. 测试条件是使用 TAP 交流测试条件中的负载确定的。 $t_R/t_F = 1 \text{ ns}$ 。

## 标识寄存器定义

| 指令字段                   | Value (值)         |                   |                   |                   | 说明                  |

|------------------------|-------------------|-------------------|-------------------|-------------------|---------------------|

|                        | CY7C1516KV18      | CY7C1527KV18      | CY7C1518KV18      | CY7C1520KV18      |                     |

| 版本号 (31:29)            | 000               | 000               | 000               | 000               | 版本号。                |

| 赛普拉斯公司器件 ID (28:12)    | 11010100010000100 | 11010100010001100 | 11010100010010100 | 11010100010100100 | 定义 SRAM 的类型。        |

| 赛普拉斯公司 JEDEC ID (11:1) | 00000110100       | 00000110100       | 00000110100       | 00000110100       | 允许对 SRAM 供货商使用唯一标识。 |

| ID 寄存器存在情况 (0)         | 1                 | 1                 | 1                 | 1                 | 指示是否存在 ID 寄存器。      |

## 扫描寄存器大小

| 寄存器名称 | 位大小 |

|-------|-----|

| 指令    | 3   |

| 绕过    | 1   |

| ID    | 32  |

| 边界扫描  | 109 |

## 指令代码

| 指令             | 代码  | 说明                                                               |

|----------------|-----|------------------------------------------------------------------|

| EXTEST         | 000 | 捕获输入和输出环的内容。                                                     |

| IDCODE         | 001 | 在 ID 寄存器中加载供货商 ID 代码，并将该寄存器置于 TDI 和 TDO 之间。此操作不会影响 SRAM 的工作。     |

| SAMPLE Z       | 010 | 捕获输入和输出内容。将边界扫描寄存器置于 TDI 和 TDO 之间。强制使所有 SRAM 输出驱动器均进入 High Z 状态。 |

| RESERVED       | 011 | 请勿使用：此指令留作日后使用。                                                  |

| SAMPLE/PRELOAD | 100 | 捕获输入和输出环的内容。将边界扫描寄存器置于 TDI 和 TDO 之间。不会影响 SRAM 的工作。               |

| RESERVED       | 101 | 请勿使用：此指令留作日后使用。                                                  |

| RESERVED       | 110 | 请勿使用：此指令留作日后使用。                                                  |

| BYPASS         | 111 | 将旁路寄存器置于 TDI 和 TDO 之间。此操作不会影响 SRAM 的工作。                          |

**边界扫描顺序**

| 位编号 | 管脚 ID |

|-----|-------|

| 0   | 6R    |

| 1   | 6P    |

| 2   | 6N    |

| 3   | 7P    |

| 4   | 7N    |

| 5   | 7R    |

| 6   | 8R    |

| 7   | 8P    |

| 8   | 9R    |

| 9   | 11P   |

| 10  | 10P   |

| 11  | 10N   |

| 12  | 9P    |

| 13  | 10M   |

| 14  | 11N   |

| 15  | 9M    |

| 16  | 9N    |

| 17  | 11L   |

| 18  | 11M   |

| 19  | 9L    |

| 20  | 10L   |

| 21  | 11K   |

| 22  | 10K   |

| 23  | 9J    |

| 24  | 9K    |

| 25  | 10J   |

| 26  | 11J   |

| 27  | 11H   |

| 位编号 | 管脚 ID |

|-----|-------|

| 28  | 10G   |

| 29  | 9G    |

| 30  | 11F   |

| 31  | 11G   |

| 32  | 9F    |

| 33  | 10F   |

| 34  | 11E   |

| 35  | 10E   |

| 36  | 10D   |

| 37  | 9E    |

| 38  | 10C   |

| 39  | 11D   |

| 40  | 9C    |

| 41  | 9D    |

| 42  | 11B   |

| 43  | 11C   |

| 44  | 9B    |

| 45  | 10B   |

| 46  | 11A   |

| 47  | 10A   |

| 48  | 9A    |

| 49  | 8B    |

| 50  | 7C    |

| 51  | 6C    |

| 52  | 8A    |

| 53  | 7A    |

| 54  | 7B    |

| 55  | 6B    |

| 位编号 | 管脚 ID |

|-----|-------|

| 56  | 6A    |

| 57  | 5B    |

| 58  | 5A    |

| 59  | 4A    |

| 60  | 5C    |

| 61  | 4B    |

| 62  | 3A    |

| 63  | 2A    |

| 64  | 1A    |

| 65  | 2B    |

| 66  | 3B    |

| 67  | 1C    |

| 68  | 1B    |

| 69  | 3D    |

| 70  | 3C    |

| 71  | 1D    |

| 72  | 2C    |

| 73  | 3E    |

| 74  | 2D    |

| 75  | 2E    |

| 76  | 1E    |

| 77  | 2F    |

| 78  | 3F    |

| 79  | 1G    |

| 80  | 1F    |

| 81  | 3G    |

| 82  | 2G    |

| 83  | 1H    |

| 位编号 | 管脚 ID |

|-----|-------|

| 84  | 1J    |

| 85  | 2J    |

| 86  | 3K    |

| 87  | 3J    |

| 88  | 2K    |

| 89  | 1K    |

| 90  | 2L    |

| 91  | 3L    |

| 92  | 1M    |

| 93  | 1L    |

| 94  | 3N    |

| 95  | 3M    |

| 96  | 1N    |

| 97  | 2M    |

| 98  | 3P    |

| 99  | 2N    |

| 100 | 2P    |

| 101 | 1P    |

| 102 | 3R    |

| 103 | 4R    |

| 104 | 4P    |

| 105 | 5P    |

| 106 | 5N    |

| 107 | 5R    |

| 108 | 内部    |

## DDR II SRAM 中的加电顺序

DDR II SRAM 必须按预定义的方式加电并初始化，以免执行未定义的操作。

### 加电顺序

- 通电并将  $\overline{DOFF}$  置为高电平或低电平（所有其他输入都可以是高电平或低电平）。

- 在施加  $V_{DDQ}$  之前施加  $V_{DD}$ 。

- 在施加  $V_{REF}$  之前或与  $V_{REF}$  同时施加  $V_{DDQ}$ 。

- 将  $DOFF$  置为高电平。

- 提供连续 20  $\mu s$  的稳定  $\overline{DOFF}$ （高电平）、电源和时钟（K、 $\bar{K}$ ），以便锁定 PLL。

### PLL 限制

- PLL 使用 K 时钟作为其同步输入。输入必须具有较低的相位抖动（以  $t_{KC\ Var}$  表示）。

- PLL 能够正常工作的最低频率为 120 MHz。

- 如果输入时钟不稳定并且启用了 PLL，则 PLL 可能会锁定到不正确的频率，从而导致 SRAM 工作不稳定。为了避免这种情况，请提供 20  $\mu s$  的稳定时钟，以便重新锁定到所需的时钟频率。

图 3. 加电波形

## 最大额定值

超过最大额定值可能会影响器件的使用寿命。这些用户指导未经测试。

存放温度 ..... -65 °C 到 +150 °C

通电状态下的环境温度 ..... -55 °C 到 +125 °C

$V_{DD}$  上相对于 GND 的供电电压 ..... -0.5 V 到 +2.9 V

$V_{DDQ}$  上相对于 GND 的供电电压 ..... -0.5 V 到  $+V_{DD}$

High Z 状态下为

输出施加的直流电压 ..... -0.5 V 到  $V_{DDQ} + 0.3$  V

直流输入电压 [20] ..... -0.5 V 到  $V_{DD} + 0.3$  V

输出电流 (低电平) ..... 20 mA

静电放电电压 (MIL-STD-883、M 3015) ..... >2001 V

栓锁电流 ..... > 200 mA

## 工作范围

| 范围 | 环境温度 ( $T_A$ )  | $V_{DD}^{[21]}$ | $V_{DDQ}^{[21]}$ |

|----|-----------------|-----------------|------------------|

| 商用 | 0 °C 至 +70 °C   | 1.8 ± 0.1 V     |                  |

| 工业 | -40 °C 至 +85 °C |                 | VDD              |

## 抗中子软失效

| 参数   | 说明      | 测试条件  | 典型值 | 最大值 * | 单位      |

|------|---------|-------|-----|-------|---------|

| LSBU | 逻辑单比特错误 | 25 °C | 197 | 216   | FIT/Mb  |

| LMBU | 逻辑多比特错误 | 25 °C | 0   | 0.01  | FIT/Mb  |

| SEL  | 软栓锁     | 85 °C | 0   | 0.1   | FIT/Dev |

\* 测试期间未出现 LMBU 或 SEL 事件；此列为统计得出的  $\chi^2$ ，按 95% 置信区间计算。如需详细信息，请参考应用笔记 AN 54908 “Accelerated Neutron SER Testing and Calculation of Terrestrial Failure Rates”。

## 电气特性

超出工作范围

### 直流电气特性

超出工作范围

| 参数 [22]       | 说明                  | 测试条件                                | 最小值                | 典型值  | 最大值                | 单位 |

|---------------|---------------------|-------------------------------------|--------------------|------|--------------------|----|

| $V_{DD}$      | 电源电压                |                                     | 1.7                | 1.8  | 1.9                | V  |

| $V_{DDQ}$     | I <sub>O</sub> 供电电压 |                                     | 1.4                | 1.5  | $V_{DD}$           | V  |

| $V_{OH}$      | 输出高电平电压             | 注 23                                | $V_{DDQ}/2 - 0.12$ | -    | $V_{DDQ}/2 + 0.12$ | V  |

| $V_{OL}$      | 输出低电平电压             | 注 24                                | $V_{DDQ}/2 - 0.12$ | -    | $V_{DDQ}/2 + 0.12$ | V  |

| $V_{OH(LOW)}$ | 输出高电平电压             | $I_{OH} = -0.1$ mA, 额定阻抗            | $V_{DDQ} - 0.2$    | -    | $V_{DDQ}$          | V  |

| $V_{OL(LOW)}$ | 输出低电平电压             | $I_{OL} = 0.1$ mA, 额定阻抗             | $V_{SS}$           | -    | 0.2                | V  |

| $V_{IH}$      | 输入高电平电压             |                                     | $V_{REF} + 0.1$    | -    | $V_{DDQ} + 0.3$    | V  |

| $V_{IL}$      | 输入低电平电压             |                                     | -0.3               | -    | $V_{REF} - 0.1$    | V  |

| $I_X$         | 输入漏电流               | $GND \leq V_I \leq V_{DDQ}$         | -5                 | -    | 5                  | ?A |

| $I_{OZ}$      | 输出漏电流               | $GND \leq V_I \leq V_{DDQ}$ , 输出被禁用 | -5                 | -    | 5                  | ?A |

| $V_{REF}$     | 输入参考电压 [25]         | 典型值 = 0.75V                         | 0.68               | 0.75 | 0.95               | V  |

### 注

20. 过冲:  $V_{IH}$  (交流) <  $V_{DDQ} + 0.85$  V (脉冲宽度小于  $t_{CYC}/2$ )，下冲:  $V_{IL}$  (交流) > -1.5 V (脉冲宽度小于  $t_{CYC}/2$ )。

21. 加电: 假设在 200 ms 内从 0 V 线性上升到  $V_{DD(\min)}$ 。在此期间,  $V_{IH} < V_{DD}$  且  $V_{DDQ} \leq V_{DD}$ 。

22. 所有电压都是相对于接地的电压。

23. 输出受阻抗控制。对于  $175 \Omega \leq RQ \leq 350 \Omega$  的值,  $I_{OH} = -(V_{DDQ}/2)/(RQ/5)$

24. 输出受阻抗控制。对于  $175 \Omega \leq RQ \leq 350 \Omega$  的值,  $I_{OL} = (V_{DDQ}/2)/(RQ/5)$ 。

25.  $V_{REF(\min)} = 0.68$  V 或  $0.46V_{DDQ}$  中的较大者;  $V_{REF(\max)} = 0.95$  V 或  $0.54V_{DDQ}$  中的较小者。

## 电气特性 (续)

超出工作范围

### 直流电气特性 (续)

超出工作范围

| 参数 [22]         | 说明                                                                                            | 测试条件    |                |   |   | 最小值 | 典型值 | 最大值 | 单位 |

|-----------------|-----------------------------------------------------------------------------------------------|---------|----------------|---|---|-----|-----|-----|----|

| $I_{DD}^{[26]}$ | $V_{DD}$ 的工作电流<br>$V_{DD} = \text{最大值}, I_{OUT} = 0 \text{ mA},$<br>$f = f_{MAX} = 1/t_{CYC}$ | 333 MHz | ( $\times$ 8)  | - | - | 510 | mA  |     |    |

|                 |                                                                                               |         | ( $\times$ 9)  | - | - | 510 |     |     |    |

|                 |                                                                                               |         | ( $\times$ 18) | - | - | 520 |     |     |    |

|                 |                                                                                               |         | ( $\times$ 36) | - | - | 640 |     |     |    |

|                 |                                                                                               | 300 MHz | ( $\times$ 8)  | - | - | 480 | mA  |     |    |

|                 |                                                                                               |         | ( $\times$ 9)  | - | - | 480 |     |     |    |

|                 |                                                                                               |         | ( $\times$ 18) | - | - | 490 |     |     |    |

|                 |                                                                                               |         | ( $\times$ 36) | - | - | 600 |     |     |    |

|                 |                                                                                               | 250 MHz | ( $\times$ 8)  | - | - | 420 | mA  |     |    |

|                 |                                                                                               |         | ( $\times$ 9)  | - | - | 420 |     |     |    |

|                 |                                                                                               |         | ( $\times$ 18) | - | - | 430 |     |     |    |

|                 |                                                                                               |         | ( $\times$ 36) | - | - | 530 |     |     |    |

|                 |                                                                                               | 200 MHz | ( $\times$ 8)  | - | - | 370 | mA  |     |    |

|                 |                                                                                               |         | ( $\times$ 9)  | - | - | 370 |     |     |    |

|                 |                                                                                               |         | ( $\times$ 18) | - | - | 380 |     |     |    |

|                 |                                                                                               |         | ( $\times$ 36) | - | - | 450 |     |     |    |

|                 |                                                                                               | 167 MHz | ( $\times$ 8)  | - | - | 340 | mA  |     |    |

|                 |                                                                                               |         | ( $\times$ 9)  | - | - | 340 |     |     |    |

|                 |                                                                                               |         | ( $\times$ 18) | - | - | 340 |     |     |    |

|                 |                                                                                               |         | ( $\times$ 36) | - | - | 400 |     |     |    |

#### 注

26. 工作电流根据 50% 读周期和 50% 写周期计算得出。

## 电气特性 (续)

超出工作范围

### 直流电气特性 (续)

超出工作范围

| 参数 [22]   | 说明                                                                                                                          | 测试条件    |                |   | 最小值 | 典型值 | 最大值 | 单位 |

|-----------|-----------------------------------------------------------------------------------------------------------------------------|---------|----------------|---|-----|-----|-----|----|

| $I_{SB1}$ | 自动断电电流<br>最大 $V_{DD}$ ,<br>两个端口均未选中,<br>$V_{IN} \geq V_{IH}$ or $V_{IN} \leq V_{IL}$<br>$f = f_{MAX} = 1/t_{CYC}$ ,<br>输入静态 | 333 MHz | ( $\times$ 8)  | - | -   | 290 | mA  |    |

|           |                                                                                                                             |         | ( $\times$ 9)  | - | -   | 290 |     |    |

|           |                                                                                                                             |         | ( $\times$ 18) | - | -   | 290 | mA  |    |

|           |                                                                                                                             |         | ( $\times$ 36) | - | -   | 290 |     |    |

|           |                                                                                                                             | 300 MHz | ( $\times$ 8)  | - | -   | 280 | mA  |    |

|           |                                                                                                                             |         | ( $\times$ 9)  | - | -   | 280 |     |    |

|           |                                                                                                                             |         | ( $\times$ 18) | - | -   | 280 |     |    |

|           |                                                                                                                             |         | ( $\times$ 36) | - | -   | 280 |     |    |

|           |                                                                                                                             | 250 MHz | ( $\times$ 8)  | - | -   | 270 | mA  |    |

|           |                                                                                                                             |         | ( $\times$ 9)  | - | -   | 270 |     |    |

|           |                                                                                                                             |         | ( $\times$ 18) | - | -   | 270 |     |    |

|           |                                                                                                                             |         | ( $\times$ 36) | - | -   | 270 |     |    |

|           |                                                                                                                             | 200 MHz | ( $\times$ 8)  | - | -   | 250 | mA  |    |

|           |                                                                                                                             |         | ( $\times$ 9)  | - | -   | 250 |     |    |

|           |                                                                                                                             |         | ( $\times$ 18) | - | -   | 250 |     |    |

|           |                                                                                                                             |         | ( $\times$ 36) | - | -   | 250 |     |    |

|           |                                                                                                                             | 167 MHz | ( $\times$ 8)  | - | -   | 250 | mA  |    |

|           |                                                                                                                             |         | ( $\times$ 9)  | - | -   | 250 |     |    |

|           |                                                                                                                             |         | ( $\times$ 18) | - | -   | 250 |     |    |

|           |                                                                                                                             |         | ( $\times$ 36) | - | -   | 250 |     |    |

## 交流电气特性

超出工作范围

| 参数 [27]  | 说明      | 测试条件 | 最小值             | 典型值 | 最大值             | 单位 |

|----------|---------|------|-----------------|-----|-----------------|----|

| $V_{IH}$ | 输入高电平电压 |      | $V_{REF} + 0.2$ | -   | -               | V  |

| $V_{IL}$ | 输入低电平电压 |      | -               | -   | $V_{REF} - 0.2$ | V  |

### 注

27. 过冲:  $V_{IH}$  (交流) <  $V_{DDQ} + 0.85$  V (脉冲宽度小于  $t_{CYC}/2$ ), 下冲:  $V_{IL}$  (交流) > -1.5 V (脉冲宽度小于  $t_{CYC}/2$ )。

## 电容

| 参数 [28]  | 说明   | 测试条件                                                                                   | 最大值 | 单位 |

|----------|------|----------------------------------------------------------------------------------------|-----|----|

| $C_{IN}$ | 输入电容 | $T_A = 25^\circ C, f = 1 \text{ MHz}, V_{DD} = 1.8 \text{ V}, V_{DDQ} = 1.5 \text{ V}$ | 4   | pF |

| $C_0$    | 输出电容 |                                                                                        | 4   | pF |

## 热阻

| 参数 [28]       | 说明       | 测试条件                                     | 165 脚 FBGA 封装 | 单位   |

|---------------|----------|------------------------------------------|---------------|------|

| $\Theta_{JA}$ | 热电阻 (结温) | 根据 EIA/JESD51 的要求, 测试条件遵循测试热阻的标准测试方法和过程。 | 13.7          | °C/W |

| $\Theta_{JC}$ | 热电阻 (壳温) |                                          | 3.73          | °C/W |

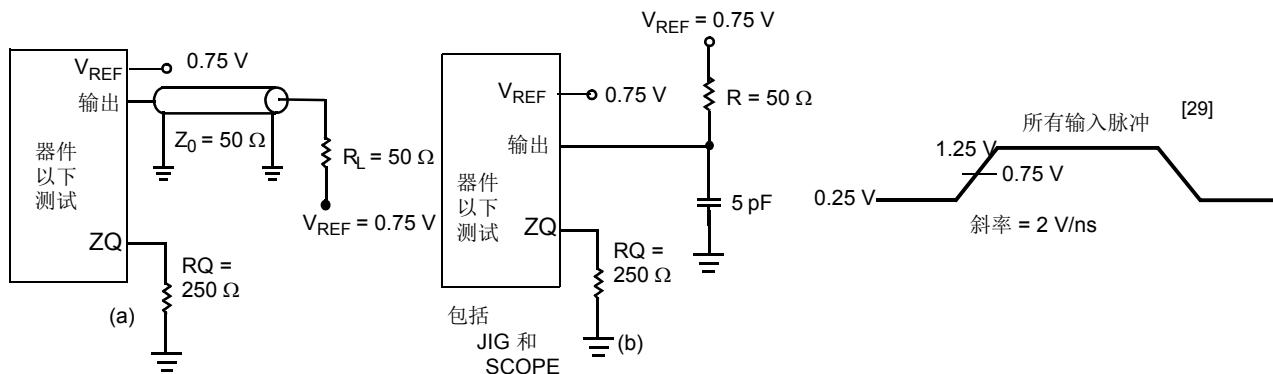

## 交流测试负载和波形

图 4. 交流测试负载和波形

### 注

28. 在进行可能会影响这些参数的任何设计或工艺更改之前和之后测试。

29. 除非另行指定, 否则测试条件基于 2V/ns 的信号跃变时间、0.75V 的时序参考电平、 $V_{REF} = 0.75 \text{ V}$ 、 $RQ = 250 \Omega$ 、 $V_{DDQ} = 1.5 \text{ V}$ 、0.25V 至 1.25V 的输入脉冲电平以及具有指定  $I_{OL}/I_{OH}$  和负载电容的输出负载, 如图 4 的 (a) 所示。

## 开关特性

超出工作范围

| 参数 [30, 31] |            | 说明                                                                               | 333 MHz |      | 300 MHz |      | 250 MHz |     | 200 MHz |     | 167 MHz |     | 单位 |

|-------------|------------|----------------------------------------------------------------------------------|---------|------|---------|------|---------|-----|---------|-----|---------|-----|----|

| 赛普拉斯参数      | 联盟参数       |                                                                                  | 最小值     | 最大值  | 最小值     | 最大值  | 最小值     | 最大值 | 最小值     | 最大值 | 最小值     | 最大值 |    |

| $t_{POWER}$ |            | 从 $V_{DD}$ (典型值) 到第一次访问的时间 [32]                                                  | 1       | -    | 1       | -    | 1       | -   | 1       | -   | 1       | -   | ms |

| $t_{CYC}$   | $t_{KHKH}$ | K 时钟和 C 时钟周期时间                                                                   | 3.0     | 8.4  | 3.3     | 8.4  | 4.0     | 8.4 | 5.0     | 8.4 | 6.0     | 8.4 | ns |

| $t_{KH}$    | $t_{KHKL}$ | 输入时钟 ( $K/\bar{K}$ 和 $C/\bar{C}$ ) 高电平                                           | 1.20    | -    | 1.32    | -    | 1.6     | -   | 2.0     | -   | 2.4     | -   | ns |

| $t_{KL}$    | $t_{KLKH}$ | 输入时钟 ( $K/\bar{K}$ 和 $C/\bar{C}$ ) 低电平                                           | 1.20    | -    | 1.32    | -    | 1.6     | -   | 2.0     | -   | 2.4     | -   | ns |

| $t_{KHKH}$  | $t_{KHKH}$ | 从 K 时钟上升沿到 $\bar{K}$ 时钟上升沿和从 C 到 $\bar{C}$ 上升沿的时间 (从上升沿到上升沿)                     | 1.35    | -    | 1.49    | -    | 1.8     | -   | 2.2     | -   | 2.7     | -   | ns |

| $t_{KHCH}$  | $t_{KHCH}$ | 从 $K/\bar{K}$ 时钟上升沿到 $C/\bar{C}$ 时钟上升沿的时间 (从上升沿到上升沿)                             | 0.0     | 1.30 | 0.0     | 1.45 | 0.0     | 1.8 | 0.0     | 2.2 | 0.0     | 2.7 | ns |

| <b>建立时间</b> |            |                                                                                  |         |      |         |      |         |     |         |     |         |     |    |

| $t_{SA}$    | $t_{AVKH}$ | 从地址建立到 K 时钟上升沿的时间                                                                | 0.4     | -    | 0.4     | -    | 0.5     | -   | 0.6     | -   | 0.7     | -   | ns |

| $t_{SC}$    | $t_{IVKH}$ | 从控制建立到 K 时钟上升沿的时间 ( $LD$ 、 $R/W$ )                                               | 0.4     | -    | 0.4     | -    | 0.5     | -   | 0.6     | -   | 0.7     | -   | ns |

| $t_{SCDDR}$ | $t_{IVKH}$ | 双倍数据速率控制建立到时钟 ( $K/\bar{K}$ ) 上升沿 ( $BWS_0$ 、 $BWS_1$ 、 $BWS_2$ 、 $BWS_3$ ) 的时间  | 0.3     | -    | 0.3     | -    | 0.35    | -   | 0.4     | -   | 0.5     | -   | ns |

| $t_{SD}$    | $t_{DVKH}$ | 从 $D_{[X:0]}$ 建立到时钟 ( $K/\bar{K}$ ) 上升沿的时间                                       | 0.3     | -    | 0.3     | -    | 0.35    | -   | 0.4     | -   | 0.5     | -   | ns |

| <b>保持时间</b> |            |                                                                                  |         |      |         |      |         |     |         |     |         |     |    |

| $t_{HA}$    | $t_{KHAX}$ | K 时钟上升沿之后的地址保持时间                                                                 | 0.4     | -    | 0.4     | -    | 0.5     | -   | 0.6     | -   | 0.7     | -   | ns |

| $t_{HC}$    | $t_{KHIX}$ | K 时钟上升沿之后的控制保持时间 ( $LD$ 、 $R/W$ )                                                | 0.4     | -    | 0.4     | -    | 0.5     | -   | 0.6     | -   | 0.7     | -   | ns |

| $t_{HCDDR}$ | $t_{KHIX}$ | 时钟 ( $K/\bar{K}$ ) 上升沿 ( $BWS_0$ 、 $BWS_1$ 、 $BWS_2$ 、 $BWS_3$ ) 之后的双倍数据速率控制保持时间 | 0.3     | -    | 0.3     | -    | 0.35    | -   | 0.4     | -   | 0.5     | -   | ns |

| $t_{HD}$    | $t_{KHDX}$ | 时钟 ( $K/\bar{K}$ ) 上升沿之后的 $D_{[X:0]}$ 保持时间                                       | 0.3     | -    | 0.3     | -    | 0.35    | -   | 0.4     | -   | 0.5     | -   | ns |

**注**

30. 除非另行指定，否则测试条件基于 2V/ns 的信号跃变时间、0.75V 的时序参考电平、 $V_{REF} = 0.75$  V、 $R_Q = 250 \Omega$ 、 $V_{DDQ} = 1.5$  V、0.25V 至 1.25V 的输入脉冲电平以及具有指定  $I_{OL}/I_{OH}$  和负载电容的输出负载，如第 26 页的图 4 的 (a) 所示。

31. 当最大频率高于 167 MHz 的部件在较低时钟频率下工作时，它需要工作频率范围的输入时序，并会以该频率范围的输出时序来输出数据。

32. 此部件拥有内部电压调节器； $t_{POWER}$  为要启动读操作或写操作，开始提供的电源必须高于  $V_{DD}$  最小值的时间。

## 开关特性 (续)

超出工作范围

| 参数 [30, 31]<br>赛普拉斯<br>参数 | 说明<br>联盟<br>参数     | 333 MHz                                                   |       | 300 MHz |       | 250 MHz |       | 200 MHz |       | 167 MHz |       | 单位      |

|---------------------------|--------------------|-----------------------------------------------------------|-------|---------|-------|---------|-------|---------|-------|---------|-------|---------|

|                           |                    | 最小值                                                       | 最大值   | 最小值     | 最大值   | 最小值     | 最大值   | 最小值     | 最大值   | 最小值     | 最大值   |         |

| <b>输出时间</b>               |                    |                                                           |       |         |       |         |       |         |       |         |       |         |

| $t_{CO}$                  | $t_{CHQV}$         | 从 $C/\bar{C}$ 时钟上升沿 (在单时钟模式下为 $K/\bar{K}$ ) 到数据有效的时间      | -     | 0.45    | -     | 0.45    | -     | 0.45    | -     | 0.45    | -     | 0.50 ns |

| $t_{DOH}$                 | $t_{CHQX}$         | 输出 $C/\bar{C}$ 时钟上升沿之后的数据输出保持时间 (从有效到有效)                  | -0.45 | -       | -0.45 | -       | -0.45 | -       | -0.45 | -       | -0.50 | - ns    |

| $t_{CCQO}$                | $t_{CHCQV}$        | 从 $C/\bar{C}$ 时钟上升沿到随路时钟有效的时间                             | -     | 0.45    | -     | 0.45    | -     | 0.45    | -     | 0.45    | -     | 0.50 ns |

| $t_{CQOH}$                | $t_{CHCQX}$        | $C/\bar{C}$ 时钟上升沿之后的随路时钟保持时间                              | -0.45 | -       | -0.45 | -       | -0.45 | -       | -0.45 | -       | -0.50 | - ns    |

| $t_{CQD}$                 | $t_{CQHQV}$        | 从随路时钟为高到数据有效的时间                                           | -     | 0.25    | -     | 0.27    | -     | 0.30    | -     | 0.35    | -     | 0.40 ns |

| $t_{CQDOH}$               | $t_{CQHQX}$        | 从随路时钟为高到数据无效的时间                                           | -0.25 | -       | -0.27 | -       | -0.30 | -       | -0.35 | -       | -0.40 | - ns    |

| $t_{CQH}$                 | $t_{CQHCQL}$       | 输出时钟 ( $CQ/\bar{CQ}$ ) 高电平 [33]                           | 1.25  | -       | 1.40  | -       | 1.75  | -       | 2.25  | -       | 2.75  | - ns    |

| $t_{CQH\bar{CQH}}$        | $t_{CQH\bar{CQH}}$ | 从 $CQ$ 时钟上升沿到 $\bar{CQ}$ 时钟上升沿的时间 (上升沿到上升沿) [33]          | 1.25  | -       | 1.40  | -       | 1.75  | -       | 2.25  | -       | 2.75  | - ns    |

| $t_{CHZ}$                 | $t_{CHQZ}$         | 时钟 ( $C/\bar{C}$ ) 上升沿到 High Z 的时间 (从有效到 High Z) [34, 35] | -     | 0.45    | -     | 0.45    | -     | 0.45    | -     | 0.45    | -     | 0.50 ns |

| $t_{CLZ}$                 | $t_{CHQX1}$        | 从时钟 ( $C/\bar{C}$ ) 上升沿到 Low-Z 的时间 [34, 35]               | -0.45 | -       | -0.45 | -       | -0.45 | -       | -0.45 | -       | -0.50 | - ns    |

| <b>PLL 时序</b>             |                    |                                                           |       |         |       |         |       |         |       |         |       |         |

| $t_{KC Var}$              | $t_{KC Var}$       | 时钟相位抖动                                                    | -     | 0.20    | -     | 0.20    | -     | 0.20    | -     | 0.20    | -     | 0.20 ns |

| $t_{KC}$ 时钟               | $t_{KC}$ 时钟        | PLL 锁定时间 (K、C) [36]                                       | 20    | -       | 20    | -       | 20    | -       | 20    | -       | 20    | - ?s    |

| $t_{KC}$ 复位               | $t_{KC}$ 复位        | 从 K 为静态到 PLL 复位的时间                                        | 30    | -       | 30    | -       | 30    | -       | 30    | -       | 30    | - ns    |

### 注

- 33. 这些参数是根据输入时序参数 ( $t_{Cyc}/2 - 250$  ps, 其中 250 ps 是内部抖动) 推导出来的。这些参数仅由设计保证, 未在生产中进行过测试。

- 34. 如第 26 页的图 4 的 (b) 部分所示,  $t_{CHZ}$ 、 $t_{CLZ}$  是用一个 5 pF 的负载电容确定的。跃变在稳定状态电压  $\pm 100$  mV 的条件下测量。

- 35. 在任何电压和温度下,  $t_{CHZ}$  均小于  $t_{CLZ}$ , 且  $t_{CHZ}$  均小于  $t_{CO}$ 。

- 36. 对于 300 MHz 或以下的频率, 按照上一个 90 nm 版本, 赛普拉斯 QDR II 器件的 PLL 锁定时间 ( $t_{KC lock}$ ) 超过了 QDR 联盟规范 20  $\mu$ s (最小规范) 并将在时钟稳定后的 1024 个时钟循环 (最小规范) 后锁定。

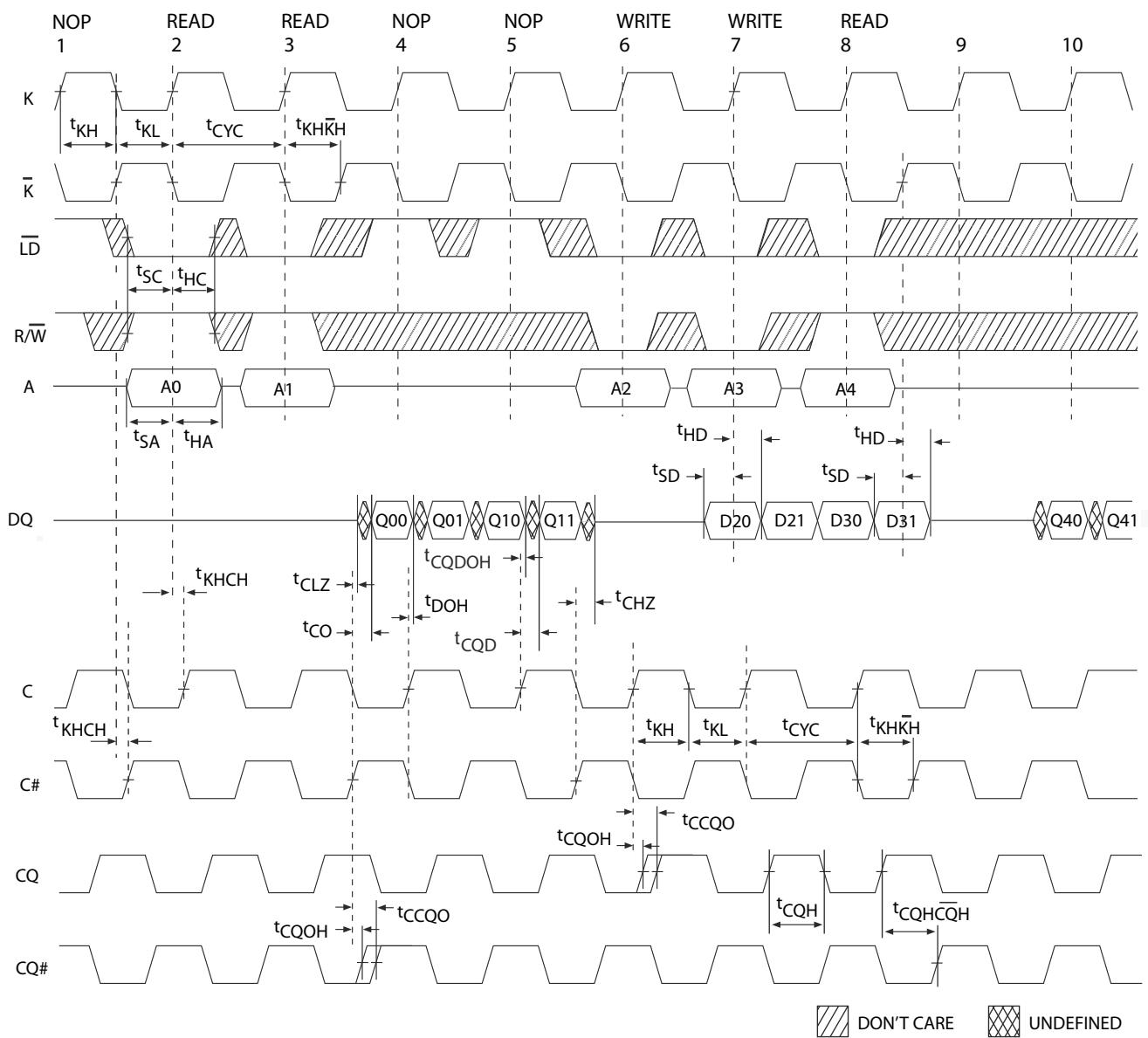

## 开关波形

### 读 / 写 / 取消选中操作过程

图 5. 2.0 个周期读取延迟的波形 [37, 38, 39]

#### 注

37. Q00 指地址 A0 的输出。Q01 指 A0 后的下一个内部突发 (Burst) 地址 (即 A0+1) 的输出。

38. 在 NOP 后的一个时钟周期内会禁用输出 (High Z)。

39. 在此示例中, 如果地址 A4 = A3, 则数据 Q40 = D30 且 Q41 = D31。写数据会立即作为读结果往前传。此注解适用于整个示意图。

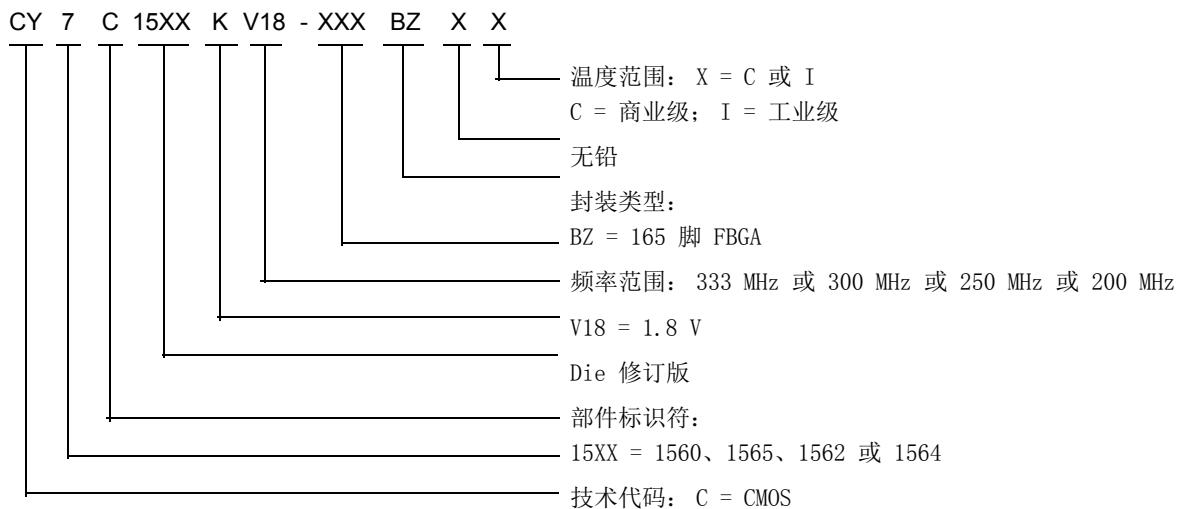

## 订购信息

下表仅包含目前可以供应的部件。如果您没有看到自己需要的部件，请与当地销售代表联系。如需更多信息，请访问赛普拉斯公司网站 [www.cypress.com](http://www.cypress.com)，并参考 <http://www.cypress.com/products> 上的产品汇总页。

赛普拉斯公司拥有一个由办事处、解决方案中心、工厂和经销商组成的全球性网络。要查找距您最近的办事处，请访问 <http://www.cypress.com/go/datasheet/offices>。

| 速度<br>(MHz) | 订购代码                 | 封装图      | 封装类型                                   | 工作范围 |

|-------------|----------------------|----------|----------------------------------------|------|

| 333         | CY7C1518KV18-333BZC  | 51-85180 | 165 脚 Ball FBGA (13 × 15 × 1.4 mm)     | 商用   |

|             | CY7C1520KV18-333BZC  |          |                                        |      |

|             | CY7C1518KV18-333BZXC | 51-85180 | 165 脚 Ball FBGA (13 × 15 × 1.4 mm) 不含铅 |      |

|             | CY7C1520KV18-333BZXC |          |                                        |      |

|             | CY7C1518KV18-333BZI  | 51-85180 | 165 脚 Ball FBGA (13 × 15 × 1.4 mm)     | 工业   |

|             | CY7C1520KV18-333BZI  |          |                                        |      |

|             | CY7C1518KV18-333BZXI | 51-85180 | 165 脚 Ball FBGA (13 × 15 × 1.4 mm) 不含铅 |      |

|             | CY7C1520KV18-333BZXI |          |                                        |      |

| 300         | CY7C1518KV18-300BZC  | 51-85180 | 165 脚 Ball FBGA (13 × 15 × 1.4 mm)     | 商用   |

|             | CY7C1520KV18-300BZC  |          |                                        |      |

|             | CY7C1518KV18-300BZXC | 51-85180 | 165 脚 Ball FBGA (13 × 15 × 1.4 mm) 不含铅 |      |

|             | CY7C1520KV18-300BZXC |          |                                        |      |