## サイプレスはインフィニオンテクノロジーズになりました

この表紙に続く文書には「サイプレス」と表記されていますが、これは同社が最初にこの製品を開発したからです。新規および既存のお客様いずれに対しても、引き続きインフィニオンがラインアップの一部として当該製品をご提供いたします。

### 文書の内容の継続性

下記製品がインフィニオンの製品ラインアップの一部として提供されたとしても、それを理由としてこの文書に変更が加わることはありません。今後も適宜改訂は行いますが、変更があった場合は文書の履歴ページでお知らせします。

### 注文時の部品番号の継続性

インフィニオンは既存の部品番号を引き続きサポートします。ご注文の際は、データシート記載の注文部品番号をこれまで通りご利用下さい。

CY7C1441KV33

CY7C1443KV33

CY7C1441KVE33

## 36M ビット (1M×36/2M×18) フロースルー SRAM (ECC 付き )

### 機能

- 133MHz バス動作に対応

- 1M×36/2M×18 共通 I/O

- 3.3V コア電源

- 2.5V、3.3V I/O 電源

- クロック～出力の時間が速い

- 6.5ns (133MHz バージョン )

- 2-1-1-1 アクセス速度を提供

- Intel® Pentium® インターリープまたはリニア バースト シーケンスに対応するユーザー選択可能なバースト カウンター

- 独立したプロセッサとコントローラー アドレスストローブ

- セルフタイム同期書き込み

- 非同期出力イネーブル

- CY7C1441KV33、CY7C1443KV33、および CY7C1441KVE33 は、JEDEC 標準の 100 ピン TQFP、165 ポール FBGA 鉛フレーパッケージで出荷

- IEEE 1149.1 JTAG 準拠のパウンダリ スキャン

- “ZZ” スリープ モード オプション

- ソフトエラーレート (SER) を低減するためのエラー訂正コード (ECC) を内蔵

### 機能の詳細

CY7C1441KV33/CY7C1443KV33/CY7C1441KVE33 は、3.3 V、1M×36/2M×18/1M×36 同期フロースルーハードウェア SRAM であり、高速マイクロプロセッサと最小限のグルーロジックでインターフェースできるように設計されています。クロックの立ち上がりからのアクセス遅延は最大で 6.5ns (133MHz のデバイス バージョン) です。2 ビットの内蔵カウンターは、バーストシーケンスで最初のアドレスを取り込んで、バーストアクセスの残りでは自動的にアドレスをインクリメントします。すべての同期入力は、ポジティブ エッジでトリガされるクロック (CLK) 入力で制御したレジスタにより取り込まれます。同期入力は、すべてのアドレス、すべてのデータ入力、アドレス パイプラインチップ イネーブル ( $CE_1$ )、深度拡張チップ イネーブル ( $CE_2$ 、 $CE_3$ )、バースト制御入力 (ADSC、ADSP、ADV)、書き込みイネーブル ( $BW_x$ 、BWE)、およびグローバル書き込み (GW) を含みます。非同期入力は出力イネーブル (OE) と ZZ ピンです。

CY7C1441KV33/CY7C1443KV33/CY7C1441KVE33 は、MODE 入力ピンで選択するインターリープとリニア バースト シーケンスの両方に対応します。このピンを HIGH にすると、インターリープ シーケンスが選択され、LOW にすると、リニア バースト シーケンスが選択されます。バーストアクセスは、プロセッサアドレスストローブ (ADSP) またはキャッシュコントローラー アドレスストローブ (ADSC) 入力で開始できます。アドレスの増加は、アドレス増加 (ADV) 入力で制御されます。

アドレスストローブ プロセッサ (ADSP) またはアドレスストローブ コントローラー (ADSC) がアクティブになると、アドレスとチップ イネーブルはクロックの立ち上りエッジで読み込まれます。後続バースト アドレスは、アドバンス ピン (ADV) の制御によって内部的に生成できます。

CY7C1441KV33/CY7C1443KV33/CY7C1441KVE33 は、+3.3 V のコア電源で動作しますが、すべての出力は +2.5V または +3.3 V 電源のいずれかでも動作できます。すべての入力と出力は JEDEC 基準の JESD8-5 に準拠します。

### セレクション ガイド

| 説明       | 133MHz | 単位  |

|----------|--------|-----|

| 最大アクセス時間 | 6.5    | ns  |

| 最大動作電流   | ×18    | 150 |

|          | ×36    | 170 |

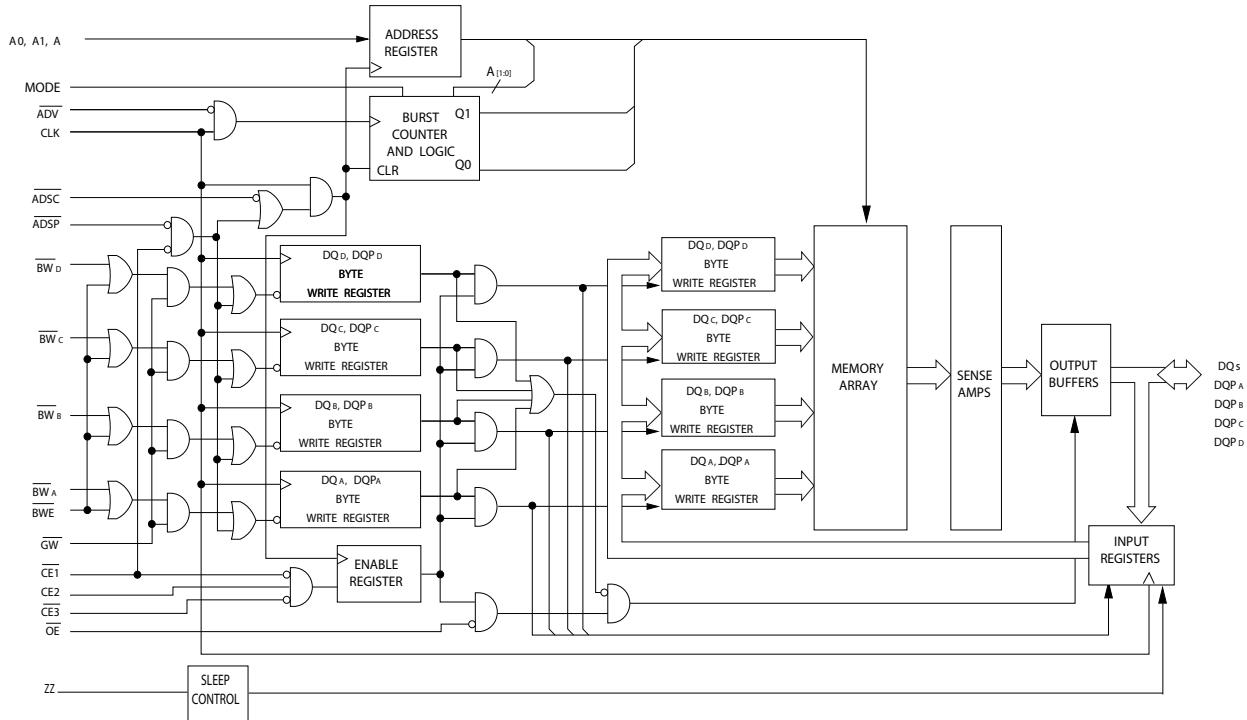

### 論理ブロックダイヤグラム – CY7C1441KV33

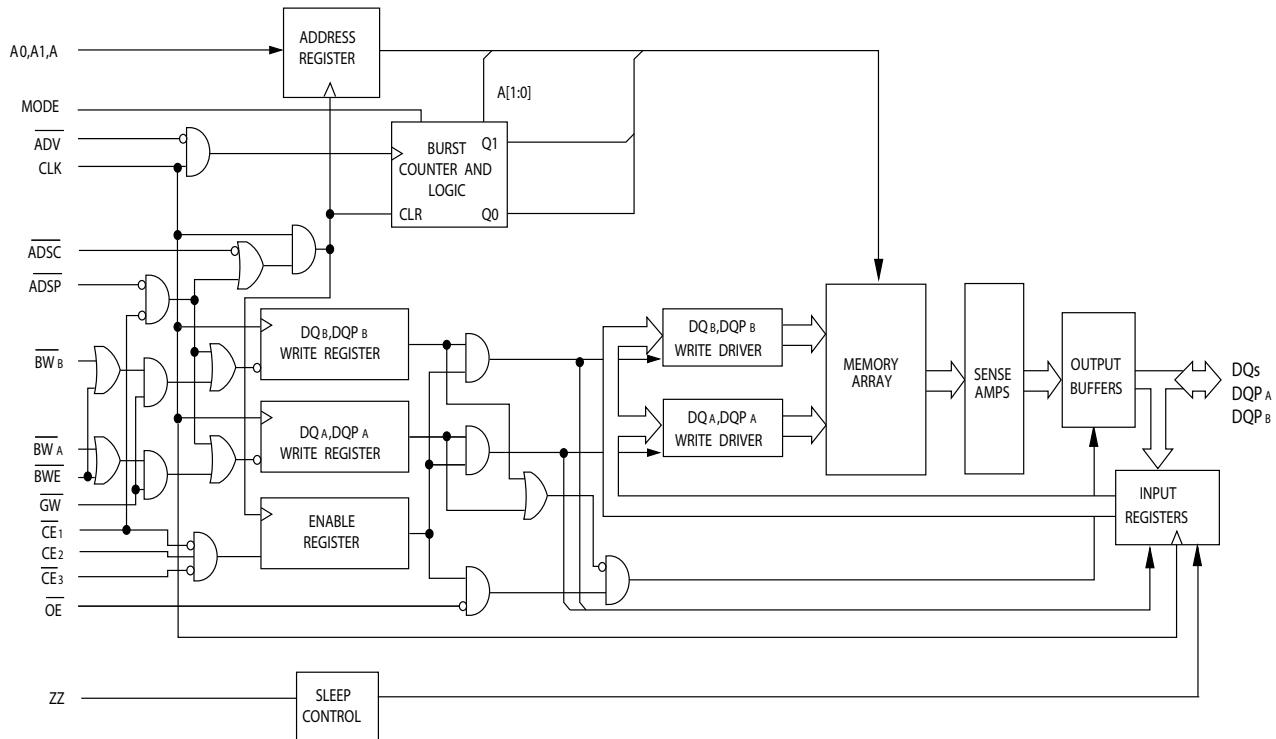

### 論理ブロックダイヤグラム – CY7C1443KV33

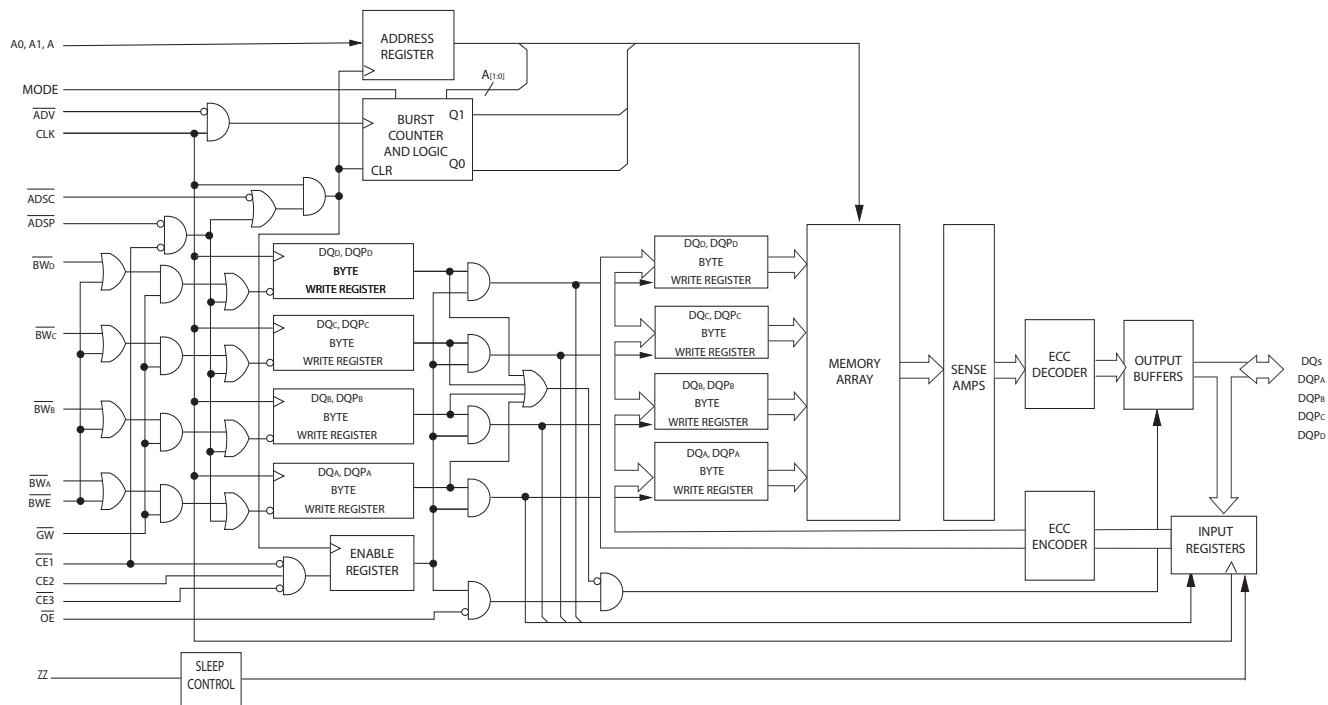

## 論理ブロックダイヤグラム – CY7C1441KVE33

## 目次

|                                         |    |                           |    |

|-----------------------------------------|----|---------------------------|----|

| ピンのコンフィギュレーション .....                    | 5  | TAP DC電気的特性および動作条件 .....  | 16 |

| ピン機能 .....                              | 7  | IDレジスタの定義 .....           | 17 |

| 機能概要 .....                              | 8  | スキャン レジスタ サイズ .....       | 17 |

| シングル読み出しアクセス .....                      | 8  | IDコード .....               | 17 |

| ADSPで開始されるシングル書き込みアクセス .....            | 8  | バウンダリ スキャン順序 .....        | 18 |

| ADSCで開始されるシングル書き込みアクセス .....            | 9  | 最大定格 .....                | 19 |

| バーストシーケンス .....                         | 9  | 動作範囲 .....                | 19 |

| スリープ モード .....                          | 9  | 中性子ソフト エラー耐性 .....        | 19 |

| 内蔵ECC .....                             | 9  | 電気的特性 .....               | 19 |

| インターリーブ バーストアドレス表 .....                 | 9  | DC特性 .....                | 19 |

| リニア バーストアドレス表 .....                     | 9  | 静電容量 .....                | 21 |

| ZZモード電気的特性 .....                        | 9  | 熱抵抗 .....                 | 21 |

| 真理値表 .....                              | 10 | ACテストの負荷と波形 .....         | 21 |

| 書き込み／読み出しの部分真理値表 .....                  | 11 | スイッチング特性 .....            | 22 |

| 書き込み／読み出しの部分真理値表 .....                  | 11 | タイミング図 .....              | 23 |

| IEEE 1149.1シリアル バウンダリ スキャン (JTAG) ..... | 12 | 注文情報 .....                | 27 |

| JTAG機能の無効化 .....                        | 12 | 注文コードの定義 .....            | 27 |

| テスト アクセス ポート (TAP) .....                | 12 | パッケージ図 .....              | 28 |

| TAPIリセットの実行 .....                       | 12 | 略語 .....                  | 30 |

| TAPレジスタ .....                           | 12 | 本書の表記法 .....              | 30 |

| TAP命令セット .....                          | 13 | 測定単位 .....                | 30 |

| TAPコントローラーのブロックダイヤグラム .....             | 14 | 改訂履歴 .....                | 31 |

| TAPタイミング .....                          | 14 | セールス、ソリューションおよび法律情報 ..... | 32 |

| TAP ACスイッチング特性 .....                    | 15 | ワールドワイドな販売と設計サポート .....   | 32 |

| 3.3V TAP ACテスト条件 .....                  | 15 | 製品 .....                  | 32 |

| 2.5V TAP ACテスト条件 .....                  | 15 | PSoC®ソリューション .....        | 32 |

| 3.3V TAP AC出力負荷の等価回路 .....              | 15 | サイプレス開発者コミュニティ .....      | 32 |

| 2.5V TAP AC出力負荷の等価回路 .....              | 15 | テクニカル サポート .....          | 32 |

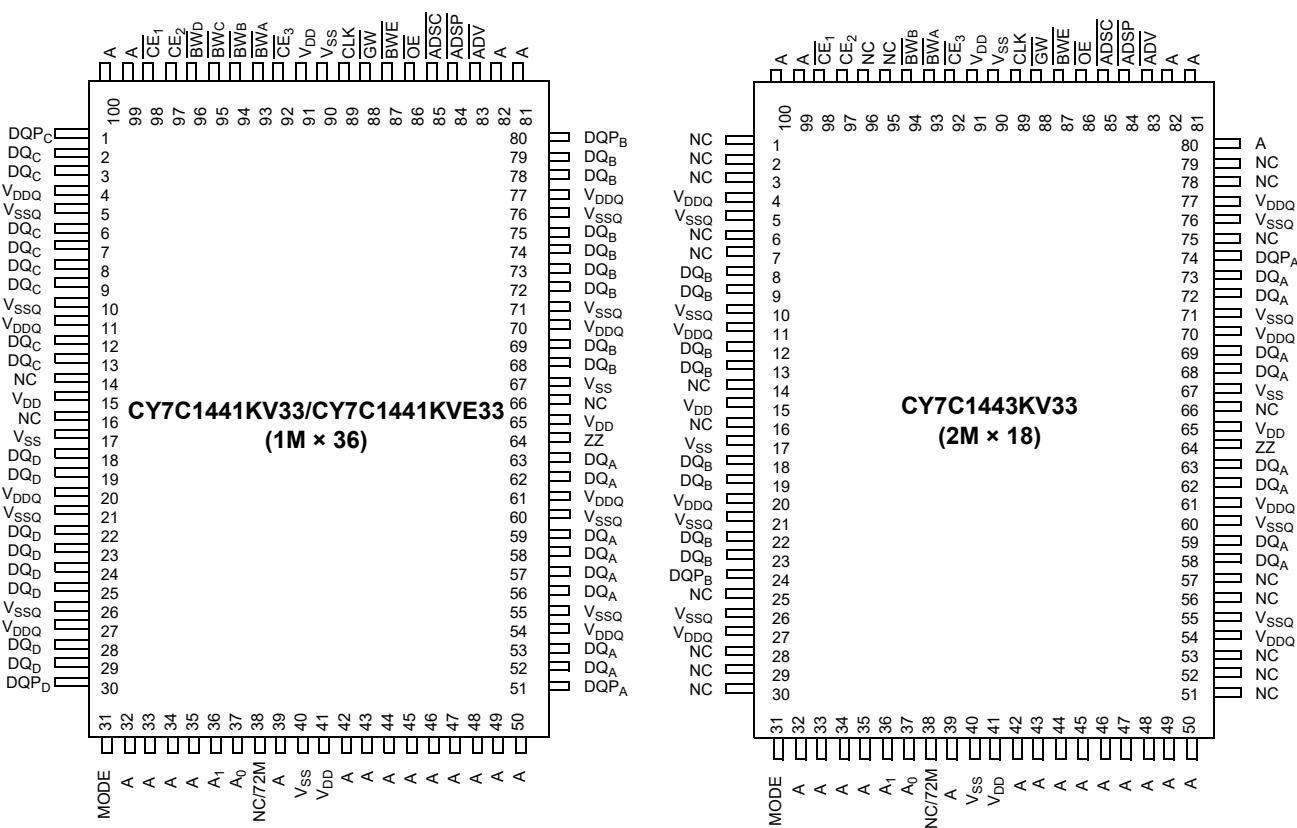

## ピンのコンフィギュレーション

図 1. 100 ピン TQFP ピン配置

## ピンのコンフィギュレーション(続き)

図2. 165 ポール FBGA ピン配置

**CY7C1441KV33 (1M × 36)**

|          | <b>1</b> | <b>2</b> | <b>3</b>          | <b>4</b>          | <b>5</b>          | <b>6</b>          | <b>7</b>          | <b>8</b>          | <b>9</b>          | <b>10</b> | <b>11</b> |

|----------|----------|----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-----------|-----------|

| <b>A</b> | NC/288M  | A        | $\overline{CE}_1$ | $\overline{BW}_C$ | $\overline{BW}_B$ | $\overline{CE}_3$ | $\overline{BW}_E$ | $\overline{ADSC}$ | $\overline{ADV}$  | A         | NC        |

| <b>B</b> | NC/144M  | A        | $CE_2$            | $\overline{BW}_D$ | $\overline{BW}_A$ | CLK               | $\overline{GW}$   | $\overline{OE}$   | $\overline{ADSP}$ | A         | NC/576M   |

| <b>C</b> | $DQP_C$  | NC       | $V_{DDQ}$         | $V_{SS}$          | $V_{SS}$          | $V_{SS}$          | $V_{SS}$          | $V_{SS}$          | $V_{DDQ}$         | NC/1G     | $DQP_B$   |

| <b>D</b> | $DQ_C$   | $DQ_C$   | $V_{DDQ}$         | $V_{DD}$          | $V_{SS}$          | $V_{SS}$          | $V_{SS}$          | $V_{DD}$          | $V_{DDQ}$         | $DQ_B$    | $DQ_B$    |

| <b>E</b> | $DQ_C$   | $DQ_C$   | $V_{DDQ}$         | $V_{DD}$          | $V_{SS}$          | $V_{SS}$          | $V_{DD}$          | $V_{DDQ}$         | $DQ_B$            | $DQ_B$    |           |

| <b>F</b> | $DQ_C$   | $DQ_C$   | $V_{DDQ}$         | $V_{DD}$          | $V_{SS}$          | $V_{SS}$          | $V_{DD}$          | $V_{DDQ}$         | $DQ_B$            | $DQ_B$    |           |

| <b>G</b> | $DQ_C$   | $DQ_C$   | $V_{DDQ}$         | $V_{DD}$          | $V_{SS}$          | $V_{SS}$          | $V_{DD}$          | $V_{DDQ}$         | $DQ_B$            | $DQ_B$    |           |

| <b>H</b> | NC       | NC       | NC                | $V_{DD}$          | $V_{SS}$          | $V_{SS}$          | $V_{DD}$          |                   | NC                | NC        | ZZ        |

| <b>J</b> | $DQ_D$   | $DQ_D$   | $V_{DDQ}$         | $V_{DD}$          | $V_{SS}$          | $V_{SS}$          | $V_{DD}$          | $V_{DDQ}$         | $DQ_A$            | $DQ_A$    |           |

| <b>K</b> | $DQ_D$   | $DQ_D$   | $V_{DDQ}$         | $V_{DD}$          | $V_{SS}$          | $V_{SS}$          | $V_{DD}$          | $V_{DDQ}$         | $DQ_A$            | $DQ_A$    |           |

| <b>L</b> | $DQ_D$   | $DQ_D$   | $V_{DDQ}$         | $V_{DD}$          | $V_{SS}$          | $V_{SS}$          | $V_{DD}$          | $V_{DDQ}$         | $DQ_A$            | $DQ_A$    |           |

| <b>M</b> | $DQ_D$   | $DQ_D$   | $V_{DDQ}$         | $V_{DD}$          | $V_{SS}$          | $V_{SS}$          | $V_{DD}$          | $V_{DDQ}$         | $DQ_A$            | $DQ_A$    |           |

| <b>N</b> | $DQP_D$  | NC       | $V_{DDQ}$         | $V_{SS}$          | NC                | A                 | NC                | $V_{SS}$          | $V_{DDQ}$         | NC        | $DQP_A$   |

| <b>P</b> | NC       | NC/72M   | A                 | A                 | TDI               | A1                | TDO               | A                 | A                 | A         | A         |

| <b>R</b> | MODE     | A        | A                 | A                 | TMS               | A0                | TCK               | A                 | A                 | A         | A         |

## ピン機能

| 名称                                                                 | I/O       | 説明                                                                                                                                                                                                                                                                                                                                                            |

|--------------------------------------------------------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A <sub>0</sub> 、A <sub>1</sub> 、A                                  | 入力 - 同期   | アドレス位置の1つを選択するために使用されるアドレス入力。 <u>ADSP</u> 、 <u>ADSC</u> がアクティブLOW、CE <sub>1</sub> 、CE <sub>2</sub> 、CE <sub>3</sub> がアクティブにサンプリングされる場合、CLKの立ち上りエッジでサンプリングされる。A <sub>[1:0]</sub> は2ビットのカウンター供給される                                                                                                                                                              |

| BW <sub>A</sub> 、BW <sub>B</sub> 、BW <sub>C</sub> 、BW <sub>D</sub> | 入力 - 同期   | バイト書き込み選択入力、アクティブLOW。SRAMへバイト書き込みをBWEと共に有効する。CLKの立ち上りエッジでサンプリング                                                                                                                                                                                                                                                                                               |

| GW                                                                 | 入力 - 同期   | グローバル書き込みイネーブル入力、アクティブLOW。CLKの立ち上りエッジでLOWにアサートされた時、グローバル書き込みが実行される(BW <sub>X</sub> とBWE上の値に関わらず、すべてのバイトは書き込まれる)                                                                                                                                                                                                                                               |

| CLK                                                                | 入力 - クロック | クロック入力。デバイスへのすべての同期入を取り込むために使用。ADVがLOWにアサートされる時、バースト処理中にバーストカウンターをインクリメントするためにも使用                                                                                                                                                                                                                                                                             |

| CE <sub>1</sub>                                                    | 入力 - 同期   | チップイネーブル1入力、アクティブLOW。CLKの立ち上りエッジでサンプリング。デバイスを選択／選択解除するためにCE <sub>2</sub> とCE <sub>3</sub> と併用。CE <sub>1</sub> がHIGHの場合、ADSPは無視される。CE <sub>1</sub> は、新規外部アドレスがロードされる時にのみサンプリングされる                                                                                                                                                                              |

| CE <sub>2</sub>                                                    | 入力 - 同期   | チップイネーブル2入力、アクティブHIGH。CLKの立ち上りエッジでサンプリング。デバイスを選択／選択解除するためにCE <sub>1</sub> とCE <sub>3</sub> と併用。CE <sub>2</sub> は、新規外部アドレスがロードされる時にのみサンプリングされる                                                                                                                                                                                                                 |

| CE <sub>3</sub>                                                    | 入力 - 同期   | チップイネーブル3入力、アクティブLOW。CLKの立ち上りエッジでサンプリング。デバイスを選択／選択解除するためにCE <sub>1</sub> 、CE <sub>2</sub> と併用。BGAの場合、CE <sub>3</sub> は、この資料の全体ではアクティブと見なされる。CE <sub>3</sub> は、新規外部アドレスがロードされる時にのみサンプリングされる                                                                                                                                                                    |

| OE                                                                 | 入力 - 非同期  | 出力イネーブル、非同期入力、アクティブLOW。I/Oピンの方向を制御。LOWの場合、I/Oピンは出力として機能。HIGHにアサートされた時、I/Oピンはトライステートに入り、入力データピンとして機能。OEは、読み出しサイクルの最初のクロック中に選択解除の状態から移行する時にマスクされる                                                                                                                                                                                                               |

| ADV                                                                | 入力 - 同期   | CLKの立ち上りエッジでサンプリングされるアドバンス入力信号。このピンがアサートされる時、バーストサイクルで自動的にアドレスをインクリメント                                                                                                                                                                                                                                                                                        |

| ADSP                                                               | 入力 - 同期   | CLKの立ち上りエッジでサンプリングされるプロセッサからのアドレスストローブ、アクティブLOW。LOWにアサートされた時、デバイスに入力されたアドレスはアドレスレジスタに取り込まれる。A <sub>[1:0]</sub> はバーストカウンターにもロードされる。ADSPとADSCの両方がアサートされた時、ADSPのみ認識される。CE <sub>1</sub> がHIGHにアサートされた時、ADSPは無視される                                                                                                                                                 |

| ADSC                                                               | 入力 - 同期   | CLKの立ち上りエッジでサンプリングされる、コントローラからのアドレスストローブ、アクティブLOW。LOWにアサートされた時、デバイスに入力されたアドレスはアドレスレジスタに取り込まれる。A <sub>[1:0]</sub> はバーストカウンターにもロードされる。ADSPとADSCの両方がアサートされた時、ADSCのみ認識される                                                                                                                                                                                         |

| BWE                                                                | 入力 - 同期   | バイト書き込みイネーブル入力、アクティブLOW。CLKの立ち上りエッジでサンプリング。バイト書き込みシーケンスを開始するためにこの信号をLOWにアサートすることが必要                                                                                                                                                                                                                                                                           |

| ZZ                                                                 | 入力 - 非同期  | ZZ「スリープ」入力、アクティブHIGH。HIGHにアサートされた時、デバイスはデータの統合性が保持されたまま非タイムクリティカルな「スリープ」状態に入る。通常動作では、このピンをLOWにする、またはフローティング状態のままにする必要。ZZピンは内部プルダウン抵抗に接続                                                                                                                                                                                                                       |

| DQ <sub>s</sub>                                                    | I/O- 同期   | 双方向データI/Oライン。入力として機能している場合、これらのI/Oラインはデータをオンチップデータレジスタに供給。このデータ供給はCLKの立ち上りエッジでトリガされる。出力として機能している場合、読み出しサイクル中に供給されたアドレスにより指定されるメモリ位置に含まれるデータを送信。このピンの方向はOEによって制御される。OEがLOWにアサートされる時、このピンは出力として機能。HIGHの場合、DQ <sub>s</sub> とDQP <sub>x</sub> は、トライステート状態にされる。OEの状態に関わらず、出力は、書き込みシーケンスのデータ転送の間、または選択解除された状態からの出現、またはデバイスが選択解除された時から最初のクロックサイクルの間に自動的にトライステート状態に移行 |

| DQP <sub>x</sub>                                                   | I/O- 同期   | 双方向データパリティI/Oライン。機能的に、これら信号はDQ <sub>s</sub> と同一。書き込みシーケンスの間、DQP <sub>x</sub> は、BW <sub>[A:H]</sub> により制御される                                                                                                                                                                                                                                                   |

## ピン機能 ( 続き )

| 名称                                                   | I/O                  | 説明                                                                                                                                                                            |

|------------------------------------------------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MODE                                                 | 入力 -<br>スタティック       | <b>バースト順序を選択。</b> GND に接続された場合、リニア バースト シーケンスが選択される。V <sub>DD</sub> に接続するまたはフローティングのままにする時、インターリーブ バースト シーケンスが選択される。これはストラップ ピンであり、デバイス動作中に静的のままにすることが必要。MODE ピンは内部プルアップ抵抗に接続 |

| V <sub>DD</sub>                                      | 電源供給                 | <b>デバイスコアへの電源入力</b>                                                                                                                                                           |

| V <sub>DDQ</sub>                                     | I/O 電源供給             | <b>I/O 回路へ電源供給</b>                                                                                                                                                            |

| V <sub>SS</sub>                                      | グランド                 | <b>デバイスのコアのグランド</b>                                                                                                                                                           |

| V <sub>SSQ</sub>                                     | I/O グランド             | <b>I/O 回路のグランド</b>                                                                                                                                                            |

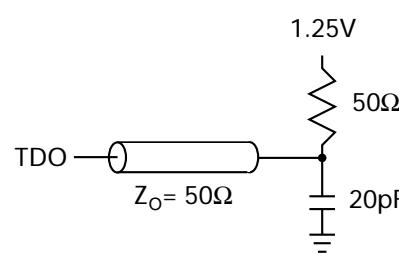

| TDO                                                  | JTAG シリアル<br>データ同期出力 | <b>JTAG 回路へのシリアル データ出力。</b> TCK のネガティブ エッジでデータを送信 JTAG 機能を使用しない場合は、このピンを未接続にする必要があります。このピンは TQFP パッケージには存在しない                                                                 |

| TDI                                                  | JTAG シリアル<br>データ同期入力 | <b>JTAG 回路へのシリアル データ入力。</b> TCK の立ち上りエッジでサンプリング。JTAG 機能を使用しない場合、このピンを未接続にするか、またはプルアップ抵抗を介して V <sub>DD</sub> に接続することが可能。このピンは TQFP パッケージには存在しない                                |

| TMS                                                  | JTAG シリアル<br>データ同期入力 | <b>JTAG 回路へのシリアル データ入力。</b> TCK の立ち上りエッジでサンプリング。JTAG 機能を使用しない場合、このピンを未接続にするか、または V <sub>DD</sub> に接続することが可能。このピンは TQFP パッケージには存在しない                                           |

| TCK                                                  | JTAG クロック            | <b>JTAG 回路へのクロック入力。</b> JTAG 機能を使用しない場合、このピンを V <sub>SS</sub> に接続することが必要。このピンは TQFP パッケージには存在しない                                                                              |

| NC                                                   | -                    | <b>未接続。</b> ダイに内部で接続されていない。72M、144M および 288M は、ダイに内部的に接続されていないアドレス拡張ピン                                                                                                        |

| NC/72M、<br>NC/144M、<br>NC/288M、<br>NC/576M、<br>NC/1G | -                    | <b>未接続。</b> ダイに内部的に接続されていない NC/72M、NC/144M、NC/288M、NC/576M、および NC/1G は、ダイに内部的に接続されていないアドレス拡張ピン                                                                                |

## 機能概要

すべての同期入力は、クロックの立ち上りエッジにより制御される入力レジスタを通過します。クロック立ち上りからの最大アクセス遅延 ( $t_{CDV}$ ) は 6.5ns ( デバイス速度が 133MHz の場合 ) です。

CY7C1441KV33/CY7C1443KV33/CY7C1441KVE33 は、リニアまたはインターリーブ バースト シーケンスのいずれかを使用しているシステムでは二次キャッシュをサポートします。インターリーブ バースト順序は Pentium プロセッサをサポートします。バースト順序はユーザーにより選択可能であり、MODE 入力をサンプリングすることで判定されます。アクセスはプロセッサ アドレス ストローブ (ADSP) またはコントローラー アドレス ストローブ (ADSC) いずれか一方で開始できます。バースト シーケンスを介したアドレスの増加は、ADV 入力で制御されます。2 ビットの内蔵ラップアラウンド バースト カウンターは、バースト シーケンスの最初のアドレスを取り込んで、バースト アクセスの残りにおいて自動的にアドレスをインクリメントします。

バイト書き込み処理は、バイト書き込みイネーブル (BWE) とバイト書き込みセレクト (BW<sub>x</sub>) 入力により可能になります。グローバル書き込みイネーブル (GW) はすべてのバイト書き込み入力を無効にし、すべての 4 バイトにデータを書き込みます。すべての書き込みは、内蔵のセルフタイム同期書き込み回路で簡素化されます。

3 つの同期チップ セレクト ( $\overline{CE}_1$ 、 $CE_2$ 、 $\overline{CE}_3$ ) と非同期出力イネーブル (OE) 信号は、バンクを容易に選択し、出力トライステートを制御するためにを提供されます。 $CE_1$  が HIGH の場合、ADSP は無視されます。

## シングル読み出しアクセス

クロックの立ち上りで次の要件が満たされると、シングル読み出しアクセスは開始されます。(1)  $CE_1$ 、 $CE_2$ 、および  $CE_3$  はすべてアクティブにアサートされ、(2) ADSP と ADSC のいずれかが LOW にアサートされ (ADSC でアクセスを開始する場合、この最初のサイクルの間書き込み入力をデアサートする必要があります)。アドレス入力に供給されたアドレスはアドレス レジスタおよびバースト カウンター／制御論理回路にラッチされ、メモリ コアに送信されます。OE 入力が LOW にアサートされると、要求されたデータは、クロックの立ち上りの後に最大  $t_{CDV}$  の間、データ出力で使用可能になります。 $CE_1$  が HIGH の場合、ADSP は無視されます。

## ADSP で開始されるシングル書き込みアクセス

クロックの立ち上りで次の条件の両方とも満たされると、このアクセスは開始されます。(1)  $CE_1$ 、 $CE_2$ 、 $\overline{CE}_3$  はすべてアクティブにアサートされ、(2) ADSP は LOW にアサートされます。送信されたアドレスは、アドレス レジスタにロードされ、バースト入力 (GW、BWE、BW<sub>x</sub>) はこの最初のクロック サイクルの間無視されます。次のクロックの立ち上りで書き込み入力がアクティブにアサートされると (書き込みを示す対応状態については書き込みサイクル説明表を参照してください)、対応デー

タはデバイスにラッチされ、書き込まれます。バイト書き込みは許可されます。すべての I/O は、バイト書き込みの間トライステートになります。これは共通 I/O デバイスのため、データを DQ に送信する前に非同期 OE 入力信号をデアサートし、I/O をトライステートにする必要があります。安全対策としては、OE の状態に関わらず、書き込みサイクルが検出されると、データラインをトライステートにします。

### ADSC で開始されるシングル書き込みアクセス

クロックの立ち上がりで次の要件が満たされると、この書き込みアクセスは開始されます。(1)  $\overline{CE}_1$ 、 $\overline{CE}_2$ 、 $\overline{CE}_3$  はすべてアクティブにアサートされ、(2) ADSC は LOW にアサートされ、(3) ADSP は HIGH にデアサートされ、(4) 書き込み入力信号 ( $\overline{GW}$ 、 $BWE$ 、 $\overline{BW}_X$ ) は書き込みアクセスを示します。ADSP がアクティブ LOW になると ADSC は無視されます。

供給されたアドレスはアドレス レジスタとバースト カウンター／制御論理回路にロードされ、メモリ コアに送信されます。DQ<sub>S</sub> に供給される情報は、特定のアドレス位置に書き込まれます。バイト書き込みは許可されます。書き込みサイクルが検出されると、バイト書き込みサイクル中でもすべての I/O は、トライステートに入ります。これは共通の I/O デバイスのため、データを DQ に送信する前に、非同期 OE 入力信号をデアサートし、I/O をトライステートにする必要があります。安全対策としては、OE の状態に関わらず、書き込みサイクルが検出されると、データラインをトライステートにします。

### バースト シーケンス

CY7C1441KV33/CY7C1443KV33/CY7C1441KVE33 は、SRAM に 2 ビット ラップアラウンド バースト カウンターを内蔵します。バースト カウンターは、A<sub>[11:0]</sub> でロードされ、リニアとインターリーブ バースト順序のどちらかに対応できます。バースト順序は、MODE 入力の状態で決まります。MODE ピンが LOW になると、リニア バースト シーケンスが選択されます。MODE ピンが HIGH になれば、インターリーブ バースト順序が選択されます。MODE ピンを開放にすると、デバイスはインターリーブ バースト シーケンスをデフォルトにします。

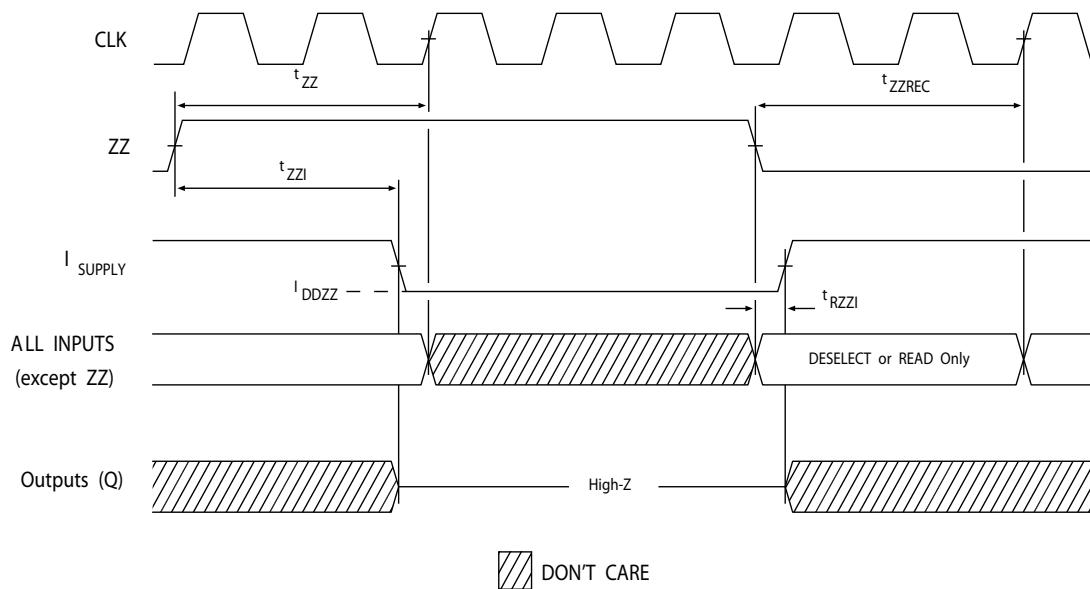

### スリープ モード

ZZ 入力ピンは非同期入力です。ZZ をアサートすると、SRAM は省電力「スリープ」モードに入れます。このスリープ モードへの移行および復帰には 2 クロック サイクルかかります。このモードでは、データの統合性が保証されます。スリープ モードに入った時に保留中のアクセスは有効として見なされず、動作完了も保証されません。デバイスはスリープ モードに入る前に、選択解除する必要があります。ZZ 入力が LOW に復帰した

後、 $\overline{CE}_1$ 、 $\overline{CE}_2$ 、 $\overline{CE}_3$ 、 $\overline{ADSP}$ 、 $\overline{ADSC}$  は  $t_{ZZREC}$  の間非アクティブのままにする必要があります。

### 内蔵 ECC

CY7C1441KVE33 SRAM は、宇宙線やアルファ粒子などに起因するソフト エラー アップセット (SEU) イベントを含む単一ビット メモリ エラーをすべて検出し、訂正する ECC アルゴリズムを内蔵します。これらデバイスのソフト エラー率 (SER) は、一般的に SER が 200FIT/Mb 以上である ECC なしの SRAM より 4 枠改善され、0.01FIT/Mb 未満です。内部データを保護するために、ECC パリティ ビット (ユーザーには不可視) を使用します。

ECC アルゴリズムは、マルチビット エラーを訂正しません。しかし、サイプレスの SRAM は、シングル SER イベントで任意のデータ ワードにマルチビット エラーが起こる可能性は非常に低くなるように設計されています。マルチビット エラーは非常に少なく、SER はわずか 0.01FIT/Mb 未満です。

### インターリーブ バースト アドレス表

(MODE = 開放または V<sub>DD</sub>)

| 1番目のアドレス<br>A1: A0 | 2番目のアドレス<br>A1: A0 | 3番目のアドレス<br>A1: A0 | 4番目のアドレス<br>A1: A0 |

|--------------------|--------------------|--------------------|--------------------|

| 00                 | 01                 | 10                 | 11                 |

| 01                 | 00                 | 11                 | 10                 |

| 10                 | 11                 | 00                 | 01                 |

| 11                 | 10                 | 01                 | 00                 |

### リニア バースト アドレス表

(MODE = GND)

| 1番目のアドレス<br>A1: A0 | 2番目のアドレス<br>A1: A0 | 3番目のアドレス<br>A1: A0 | 4番目のアドレス<br>A1: A0 |

|--------------------|--------------------|--------------------|--------------------|

| 00                 | 01                 | 10                 | 11                 |

| 01                 | 10                 | 11                 | 00                 |

| 10                 | 11                 | 00                 | 01                 |

| 11                 | 00                 | 01                 | 10                 |

### ZZ モード電気的特性

| パラメーター             | 説明                     | テスト条件                       | Min               | Max               | 単位 |

|--------------------|------------------------|-----------------------------|-------------------|-------------------|----|

| I <sub>DDZZ</sub>  | スリープ モード スタンバイ電流       | ZZ ≥ V <sub>DD</sub> - 0.2V | -                 | 75                | mA |

| t <sub>ZZS</sub>   | デバイスの動作から ZZ までの時間     | ZZ ≥ V <sub>DD</sub> - 0.2V | -                 | 2t <sub>CYC</sub> | ns |

| t <sub>ZZREC</sub> | ZZ 復帰時間                | ZZ ≤ 0.2V                   | 2t <sub>CYC</sub> | -                 | ns |

| t <sub>ZZI</sub>   | ZZ がスリープ電流にアクティブ       | このパラメーターはサンプリングされた値です       | -                 | 2t <sub>CYC</sub> | ns |

| t <sub>RZZI</sub>  | スリープ電流までの ZZ 非アクティブ 時間 | このパラメーターはサンプリングされた値です       | 0                 | -                 | ns |

## 真理値表

以下は CY7C1441KV33/CY7C1443KV33/CY7C1441KVE33 の真理値表です。[1、2、3、4、5]

| サイクルの説明         | 使用されるアドレス | <u>CE<sub>1</sub></u> | <u>CE<sub>2</sub></u> | <u>CE<sub>3</sub></u> | <u>ZZ</u> | <u>ADSP</u> | <u>ADSC</u> | <u>ADV</u> | <u>WRITE</u> | <u>OE</u> | <u>CLK</u> | DQ      |

|-----------------|-----------|-----------------------|-----------------------|-----------------------|-----------|-------------|-------------|------------|--------------|-----------|------------|---------|

| 選択解除サイクル、電源切断   | 無         | H                     | X                     | X                     | L         | X           | L           | X          | X            | X         | L-H        | トライステート |

| 選択解除サイクル、電源切断   | 無         | L                     | L                     | X                     | L         | L           | X           | X          | X            | X         | L-H        | トライステート |

| 選択解除サイクル、電源切断   | 無         | L                     | X                     | H                     | L         | L           | X           | X          | X            | X         | L-H        | トライステート |

| 選択解除サイクル、電源切断   | 無         | L                     | L                     | X                     | L         | H           | L           | X          | X            | X         | L-H        | トライステート |

| 選択解除サイクル、電源切断   | 無         | X                     | X                     | H                     | L         | H           | L           | X          | X            | X         | L-H        | トライステート |

| スリープ モード、電源切断   | 無         | X                     | X                     | X                     | H         | X           | X           | X          | X            | X         | X          | トライステート |

| 読み出しサイクル、バースト開始 | 外部        | L                     | H                     | L                     | L         | L           | X           | X          | X            | L         | L-H        | Q       |

| 読み出しサイクル、バースト開始 | 外部        | L                     | H                     | L                     | L         | L           | X           | X          | X            | H         | L-H        | トライステート |

| 書き込みサイクル、バースト開始 | 外部        | L                     | H                     | L                     | L         | H           | L           | X          | L            | X         | L-H        | D       |

| 読み出しサイクル、バースト開始 | 外部        | L                     | H                     | L                     | L         | H           | L           | X          | H            | L         | L-H        | Q       |

| 読み出しサイクル、バースト開始 | 外部        | L                     | H                     | L                     | L         | H           | L           | X          | H            | H         | L-H        | トライステート |

| 読み出しサイクル、バースト継続 | 後続        | X                     | X                     | X                     | L         | H           | H           | L          | H            | L         | L-H        | Q       |

| 読み出しサイクル、バースト継続 | 後続        | X                     | X                     | X                     | L         | H           | H           | L          | H            | H         | L-H        | トライステート |

| 読み出しサイクル、バースト継続 | 後続        | H                     | X                     | X                     | L         | X           | H           | L          | H            | L         | L-H        | Q       |

| 読み出しサイクル、バースト継続 | 後続        | H                     | X                     | X                     | L         | X           | H           | L          | H            | H         | L-H        | トライステート |

| 書き込みサイクル、バースト継続 | 後続        | X                     | X                     | X                     | L         | H           | H           | L          | X            | L-H       | D          |         |

| 書き込みサイクル、バースト継続 | 後続        | H                     | X                     | X                     | L         | X           | H           | L          | L            | X         | L-H        | D       |

| 読み出しサイクル、バースト停止 | 現行        | X                     | X                     | X                     | L         | H           | H           | H          | H            | L         | L-H        | Q       |

| 読み出しサイクル、バースト停止 | 現行        | X                     | X                     | X                     | L         | H           | H           | H          | H            | H         | L-H        | トライステート |

| 読み出しサイクル、バースト停止 | 現行        | H                     | X                     | X                     | L         | X           | H           | H          | H            | L         | L-H        | Q       |

| 読み出しサイクル、バースト停止 | 現行        | H                     | X                     | X                     | L         | X           | H           | H          | H            | H         | L-H        | トライステート |

| 書き込みサイクル、バースト停止 | 現行        | X                     | X                     | X                     | L         | H           | H           | H          | L            | X         | L-H        | D       |

| 書き込みサイクル、バースト停止 | 現行        | H                     | X                     | X                     | L         | X           | H           | H          | L            | X         | L-H        | D       |

### 注

- X = 「ドント ケア」。H = 論理 HIGH、L = 論理 LOW。

- 1つ以上のバイト書き込みイネーブル信号と BWE = L または GW = L の時、WRITE = L です。すべてのバイト書き込みイネーブル信号、BWE、GW = H の時、WRITE = H です。

- DQ ピンは現行のサイクルと OE 信号によって制御されます。OE は非同期で、クロックと同期してサンプリングされません。

- GW、BWE、または BW<sub>X</sub> の状態に関わらず、ADSP がアサートされると、SRAM は読み出しサイクルを開始します。書き込みは、ADSP の後に、または ADSC のアサート後の後続のクロックサイクルでのみ行われます。従って、出力がトライステートになるために、OE を書き込みサイクルを開始する前に HIGH レベルに駆動する必要があります。OE はその後の書き込みサイクルでは「ドント ケア」です。

- OE は非同期で、クロック立ち上りと同期してサンプリングされません。これは、書き込みサイクル中に内部でマスキングされます。読み出しサイクルでは、OE が非アクティブ、またはデバイスが選択解除された場合、すべてのデータビットは、トライステートになります。OE がアクティブ (LOW) の場合、すべてのデータビットは出力として機能します。

## 書き込み／読み出しの部分真理値表

以下は CY7C1441KV33/CY7C1441KVE33 の書き込み／読み出しの部分真理値表です。[6、7、8]

| 機能 (CY7C1441KV33/CY7C1441KVE33)                                                                                           | $\overline{GW}$ | $\overline{BWE}$ | $\overline{BW_D}$ | $\overline{BW_C}$ | $\overline{BW_B}$ | $\overline{BW_A}$ |

|---------------------------------------------------------------------------------------------------------------------------|-----------------|------------------|-------------------|-------------------|-------------------|-------------------|

| 読み出し                                                                                                                      | H               | H                | X                 | X                 | X                 | X                 |

| 読み出し                                                                                                                      | H               | L                | H                 | H                 | H                 | H                 |

| バイト A 書き込み (DQ <sub>A</sub> 、DQP <sub>A</sub> )                                                                           | H               | L                | H                 | H                 | H                 | L                 |

| バイト B 書き込み (DQ <sub>B</sub> 、DQP <sub>B</sub> )                                                                           | H               | L                | H                 | H                 | L                 | H                 |

| バイト A、B 書き込み (DQ <sub>A</sub> 、DQ <sub>B</sub> 、DQP <sub>A</sub> 、DQP <sub>B</sub> )                                      | H               | L                | H                 | H                 | L                 | L                 |

| バイト C 書き込み (DQ <sub>C</sub> 、DQP <sub>C</sub> )                                                                           | H               | L                | H                 | L                 | H                 | H                 |

| バイト C、A 書き込み (DQ <sub>C</sub> 、DQ <sub>A</sub> 、DQP <sub>C</sub> 、DQP <sub>A</sub> )                                      | H               | L                | H                 | L                 | H                 | L                 |

| バイト C、B 書き込み (DQ <sub>C</sub> 、DQ <sub>B</sub> 、DQP <sub>C</sub> 、DQP <sub>B</sub> )                                      | H               | L                | H                 | L                 | L                 | H                 |

| バイト C、B、A 書き込み (DQ <sub>C</sub> 、DQ <sub>B</sub> 、DQ <sub>A</sub> 、DQP <sub>C</sub> 、DQP <sub>B</sub> 、DQP <sub>A</sub> ) | H               | L                | H                 | L                 | L                 | L                 |

| バイト D 書き込み (DQ <sub>D</sub> 、DQP <sub>D</sub> )                                                                           | H               | L                | L                 | H                 | H                 | H                 |

| バイト D、A 書き込み (DQ <sub>D</sub> 、DQ <sub>A</sub> 、DQP <sub>D</sub> 、DQP <sub>A</sub> )                                      | H               | L                | L                 | H                 | H                 | L                 |

| バイト D、B 書き込み (DQ <sub>D</sub> 、DQ <sub>B</sub> 、DQP <sub>D</sub> 、DQP <sub>B</sub> )                                      | H               | L                | L                 | H                 | L                 | H                 |

| バイト D、B、A 書き込み (DQ <sub>D</sub> 、DQ <sub>B</sub> 、DQ <sub>A</sub> 、DQP <sub>D</sub> 、DQP <sub>B</sub> 、DQP <sub>A</sub> ) | H               | L                | L                 | H                 | L                 | L                 |

| バイト D、B、C 書き込み (DQ <sub>D</sub> 、DQ <sub>B</sub> 、DQ <sub>C</sub> 、DQP <sub>D</sub> 、DQP <sub>B</sub> 、DQP <sub>C</sub> ) | H               | L                | L                 | L                 | H                 | L                 |

| すべてのバイト書き込み                                                                                                               | H               | L                | L                 | L                 | L                 | L                 |

| すべてのバイト書き込み                                                                                                               | L               | X                | X                 | X                 | X                 | X                 |

## 書き込み／読み出しの部分真理値表

以下は CY7C1443KV33 の書き込み／読み出しの部分真理値表です。[6、7、8]

| 機能 (CY7C1443KV33)                                 | $\overline{GW}$ | $\overline{BWE}$ | $\overline{BW_B}$ | $\overline{BW_A}$ |

|---------------------------------------------------|-----------------|------------------|-------------------|-------------------|

| 読み出し                                              | H               | H                | X                 | X                 |

| 読み出し                                              | H               | L                | H                 | H                 |

| バイト A 書き込み - (DQ <sub>A</sub> 、DQP <sub>A</sub> ) | H               | L                | H                 | L                 |

| バイト B 書き込み - (DQ <sub>B</sub> 、DQP <sub>B</sub> ) | H               | L                | L                 | H                 |

| すべてのバイト書き込み                                       | H               | L                | L                 | L                 |

| すべてのバイト書き込み                                       | L               | X                | X                 | X                 |

### 注

6. X = 「ドント ケア」。H = 論理 HIGH、L = 論理 LOW。

7. この表では、バイト書き込みの組み合わせの一部を示します。どの  $\overline{BW}_X$  の組合せも可能です。書き込みは、アクティブになるバイト書き込み信号に応じて適切に行われます。

8.  $\overline{BW}_X$  は、任意の書き込み信号  $\overline{BW}_{[A..H]}$  を示します。任意のバイト書き込み  $\overline{BW}_X$  を有効にするために、論理 LOW 信号をクロックの立ち上がりで適用する必要があります。任意の書き込みに対してバイト書き込みを何件でも同時に有効にできます。

## IEEE 1149.1 シリアル バウンダリ スキャン (JTAG)

CY7C1441KV33 は、シリアル バウンダリ スキャン テスト アクセス ポート (TAP) を内蔵します。このデバイスは、1149.1 に完全に準拠します。TAP は、JEDEC 標準の 3.3 V または 2.5 V I/O 論理レベルで動作します。

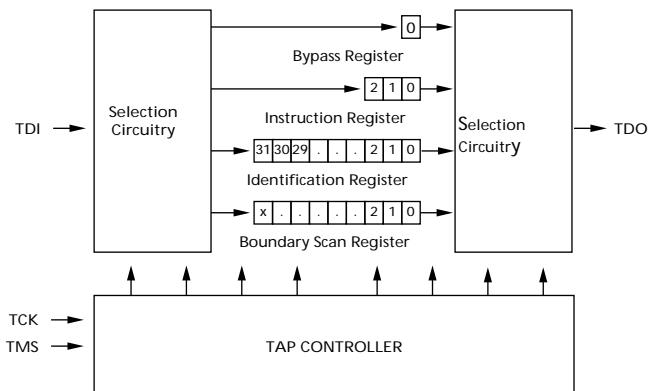

CY7C1441KV33 は、TAP コントローラー、命令レジスタ、バウンダリ スキャン レジスタ、バイパス レジスタ、および ID レジスタを含みます。

### JTAG 機能の無効化

JTAG 機能を使用せず、SRAM を動作させることができます。TAP コントローラーを無効にするためには、TCK を LOW ( $V_{SS}$ ) に接続してデバイスへのクロック供給を防ぐ必要があります。TDI と TMS は内部でプルアップされ、未接続にできます。かわりに、プルアップ抵抗を介して  $V_{DD}$  にも接続できます。TDO は未接続にする必要があります。電源投入時にデバイスは、デバイス動作を妨げないリセット状態に入ります。

### テスト アクセス ポート (TAP)

#### テスト クロック (TCK)

テスト クロックは TAP コントローラーとのみ併用できます。すべての入力を TCK の立ち上りエッジで取り込みます。すべての出力は TCK の立ち下りエッジで駆動されます。

#### テスト モード選択 (TMS)

TMS 入力は、TAP コントローラーにコマンドを送信するために使用され、TCK の立ち上りエッジでサンプリングされます。TAP を使用しない場合、このポートを未接続にできます。ポートは内部で引き上げられるため、論理 HIGH レベルです。

#### テスト データ入力 (TDI)

TDI ポートは、レジスタに情報をシリアル入力するために使用され、どのレジスタの入力にも接続できます。TDI と TDO 間のレジスタは、TAP 命令レジスタにロードされた命令によって選択されます。TAP がアプリケーションで使用されていない場合 TDI は内部でプルアップされ、開放できます。TDI はあらゆるレジスタの最上位ビット (MSB) に接続されます。[\(14 ページの TAP コントローラーのブロックダイヤグラムを参照してください\)](#)

#### テスト データ出力 (TDO)

TDO 出力ポートは、レジスタからデータをクロックに同期してシリアル出力するために使用されます。出力は、TAP ステートマシンの状態に応じてアクティブになります。出力は TCK の立ち下りエッジで変化します。TDO は、レジスタの最下位ビット (LSB) に接続されます。[\(14 ページの TAP コントローラー状態遷移図を参照してください\)](#)

### TAP リセットの実行

リセットは、TCK の 5 つの立ち上りエッジの間 TMS を HIGH ( $V_{DD}$ ) にすることによって実行されます。このリセットは、SRAM の動作に影響を与えず、SRAM の動作中に実行できます。

電源投入時に、TDO が HIGH Z 状態に初期化されるために、TAP を内部でリセットします。

### TAPレジスタ

TDI と TDO の間にレジスタを接続し SRAM テスト回路の入力と出力データをスキャンできます。命令レジスタを介して、一度に選択されるレジスタは 1 つのみです。データは TCK の立ち上りエッジで TDI ポールに順次ロードされます。データは TCK の立ち下りエッジで TDO ポールに出力されます。

#### 命令レジスタ

3 ビットの命令を命令レジスタに順次ロードできます。このレジスタは、[14 ページの TAP コントローラーのブロックダイヤグラム](#)に示すように、TDI と TDO ポール間に配置された時にロードされます。電源投入時に、IDCODE 命令が命令レジスタにロードされます。前述したように、コントローラーがリセット状態になった場合にも、IDCODE 命令が命令レジスタにロードされます。

TAP コントローラーが Capture-IR 状態になった時、基板レベルのシリアル テスト データ パスの障害防止を可能にするために、2 進数「01」パターンが最下位 2 ビットにロードされます。

#### バイパスレジスタ

レジスタをとおしてデータを順次シフトする際の時間を節約するために、特定のチップをスキップすることが有効な場合もあります。バイパス レジスタは、TDI と TDO ポール間に配置できる 1 ビットのレジスタです。これにより、最小限の遅延で SRAM を介してデータをシフトできます。BYPASS 命令が実行されると、バイパス レジスタは LOW ( $V_{SS}$ ) に設定されます。

#### バウンダリ スキャン レジスタ

バウンダリ スキャン レジスタは、SRAM 上のすべての入力および双方向ポートに接続されます。

バウンダリ スキャン レジスタは、TAP コントローラーが Capture-DR 状態になった時に RAM I/O リングの内容でロードされ、そしてコントローラーが Shift-DR 状態になると TDI と TDO ポール間に配置されます。EXTEST、SAMPLE/PRELOAD、SAMPLE Z 命令は、I/O リングの内容を取り込むために使用できます。

[18 ページのバウンダリ スキャン順序](#)に、ビットが接続されている順序を示します。各ビットは、SRAM パッケージ上の 1 つの端子に対応します。レジスタの MSB は TDI に、 LSB は TDO に接続されます。

#### 識別 (ID) レジスタ

IDCODE コマンドが命令レジスタにロードされた時、Capture-DR 状態の間に、ID レジスタにベンダー固有の 32 ビット コードがロードされます。IDCODE は SRAM 内に格納され、TAP コントローラーが Shift-DR 状態になるとシフトアウトされます。ID レジスタのベンダー コードおよびその他の情報は [17 ページの ID レジスタの定義](#) を参照してください。

## TAP 命令セット

### 概要

3 ビットの命令レジスタにより、8 つの異なる命令があります。すべての組合せは、命令コード表に一覧表示します。これらの命令の内 3 つは RESERVED で、使用できません。残りの 5 つの命令を本節で詳しく説明します。

命令レジスタが TDI と TDO の間に配置されると、命令は Shift-IR 状態の間に TAP コントローラーにロードされます。この状態の間に、命令は命令レジスタを通して TDI ポールから TDO ポールまでシフトされます。シフトインされた命令を実行するために、TAP コントローラーを Update-IR 状態にする必要があります。

### IDCODE

IDCODE 命令はベンダー固有の 32 ビットコードを命令レジスタにロードします。また、命令レジスタを TDI と TDO ポールの間に配置して、TAP コントローラが Shift-DR 状態に入る時に IDCODE をデバイスからシフトアウトします。

IDCODE 命令は、電源投入時または TAP コントローラが「Test-Logic-Reset」状態に入る度に、命令レジスタにロードされます。

### SAMPLE Z

TAP コントローラが Shift-DR 状態の時に、SAMPLE Z 命令はバウンダリスキャンレジスタを TDI と TDO ピンの間に接続します。SAMPLE Z コマンドにより、「Update IR」状態中に次のコマンドが発行されるまで出力バスが High Z 状態です。

### SAMPLE/PRELOAD

SAMPLE/PRELOAD は 1149.1 標準の必須命令です。

SAMPLE/PRELOAD 命令が命令レジスタにロードされ、TAP コントローラが Capture-DR 状態になると、入力と出力ピン上のデータのスナップショットがバウンダリスキャンレジスタに取り込まれます。

TAP コントローラ クロックは最大 20MHz の周波数で動作するのに対して、SRAM クロックは桁違いに速い周波数で動作することに注意してください。クロック周波数に大きな差があるため、入出力は Capture-DR 状態中に変化する可能性があります。そのため、TAP は遷移中（メタステーブル状態）の信号を取り込もうとするかもしれません。これはデバイスに悪影響を与えるが、取り込まれた値に対する保証はありません。結果を再現できない場合があります。

バウンダリスキャンレジスタが信号の正しい値を取り込むために、SRAM 信号は、TAP コントローラのキャプチャ セットアップ + ホールド時間 ( $t_{CS} + t_{CH}$ ) を満たす十分な安定時間を取る必要があります。SAMPLE/PRELOAD 命令の間にクロックを停止する（または遅くする）方法がデザインにない場合、SRAM クロック入力は正常に取り込まれない場合があります。その場合でも、他のすべての信号を取り込み、単にクロックでバウンダリスキャンレジスタに取り込まれた値を無視することも可能です。

データが取り込まれた後、TAP を Shift-DR 状態に移行させることでデータをシフトアウトできます。これにより、バウンダリスキャンレジスタが TDI と TDO ピンの間に配置されます。

PRELOAD では、他のバウンダリスキャンテスト動作の選択の前に、初期データパターンをバウンダリスキャンレジスタセルのラッチされたパラレル出力に配置します。

SAMPLE および PRELOAD のデータのシフトは、必要に応じて同時に実行できます。つまり取り込まれたデータがシフトアウトされている間にプリロードされたデータがシフトインされます。

### BYPASS

BYPASS 命令が命令レジスタにロードされ、TAP が Shift-DR 状態になる時、バイパスレジスタは TDI と TDO ピンの間に配置されます。BYPASS 命令の利点は、複数のデバイスが基板上で互いに接続されている時に、バウンダリスキャンバスを短縮することです。

### EXTEST

EXTEST 命令は、プリロードされたデータをシステム出力ピンをとおして駆動します。また、コントローラーが Shift-DR 状態の間に、この命令はシリアルアクセスのためにバウンダリスキャンレジスタを TDI と TDO の間に接続します。

### EXTEST OUTPUT BUS TRI-STATE

IEEE 標準 1149.1 では、TAP コントローラーは出力バスをトライステートモードにできることを義務づけています。

バウンダリスキャンレジスタには、ビット 89 に位置付けられた特別なビットがあります（165 ポール FBGA パッケージの場合）。「extest output bus tristate」と呼ばれるこのスキャンセルは、TAP コントローラーで「Update-DR」状態中にプリロードレジスタにラッチされた時、EXTEST が現時点の命令として入力されると、出力（Q バス）ピンの状態を直接制御します。このビットは HIGH の時、出力バッファに出力バスを駆動させます。LOW の時、出力バスを High Z 状態に移行させます。

Shift-DR 状態中に、SAMPLE/PRELOAD または EXTEST コマンドを入力して、所望のビットをそのセルにシフトすることでこのビットをセットできます。「Update-DR」の間に、そのシフトレジスタセルにロードされた値はプリロードレジスタにラッチされます。EXTEST 命令を入力すると、このビットは出力 Q バスピンを直接制御します。デバイスが電源投入された時や TAP コントローラーが「Test-Logic-Reset」状態になった時に出力を有効にするために、このビットは HIGH にあらかじめセットされることに注意してください。

### Reserved

これら命令は実装されていませんが、将来のために予約されます。これらの命令を使用しないでください。

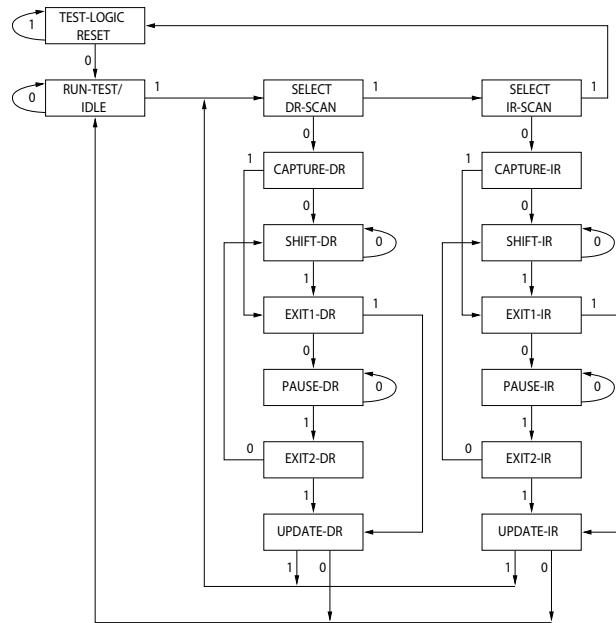

## TAP コントローラー状態遷移図

遷移状態の隣の 0, 1 の数字は、TCK の立ち上りエッジでの TMS の値を示します。

## TAP コントローラーのブロックダイヤグラム

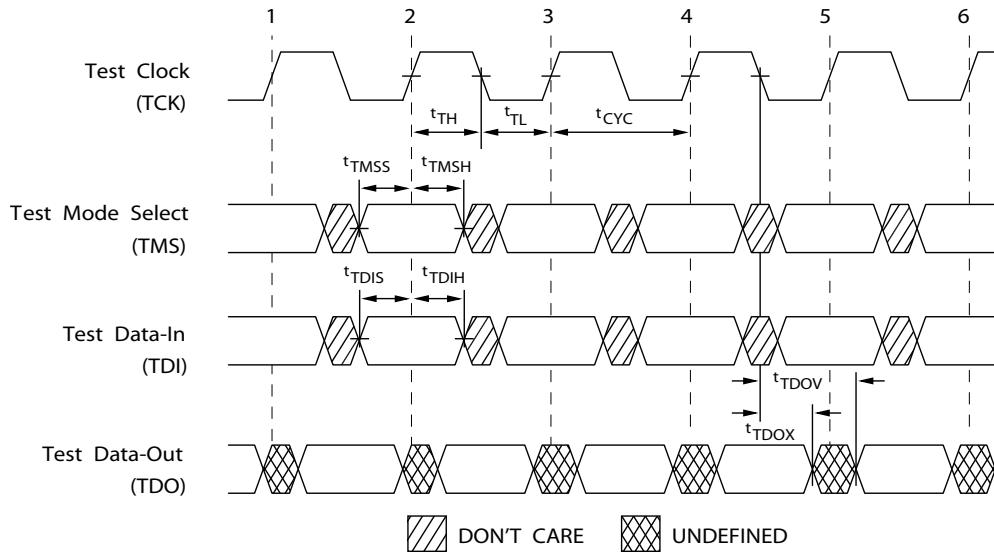

## TAP タイミング

## TAP AC スイッチング特性

動作範囲において

| パラメーター [9, 10]  | 説明                            | Min | Max | 単位  |

|-----------------|-------------------------------|-----|-----|-----|

| <b>クロック</b>     |                               |     |     |     |

| $t_{TCYC}$      | TCK クロック サイクル時間               | 50  | –   | ns  |

| $t_{TF}$        | TCK クロック周波数                   | –   | 20  | MHz |

| $t_{TH}$        | TCK クロック HIGH 時間              | 20  | –   | ns  |

| $t_{TL}$        | TCK クロック LOW 時間               | 20  | –   | ns  |

| <b>出力時間</b>     |                               |     |     |     |

| $t_{TDOV}$      | TCK クロック LOW から TDO 有効までの時間   | –   | 10  | ns  |

| $t_{TDOX}$      | TCK クロック LOW から TDO 無効までの時間   | 0   | –   | ns  |

| <b>セットアップ時間</b> |                               |     |     |     |

| $t_{TMSS}$      | TCK クロックの立ち上りまでの TMS セットアップ時間 | 5   | –   | ns  |

| $t_{TDIS}$      | TCK クロックの立ち上りまでの TDI セットアップ時間 | 5   | –   | ns  |

| $t_{CS}$        | TCK の立ち上りまでのキャプチャ セットアップ時間    | 5   | –   | ns  |

| <b>ホールド時間</b>   |                               |     |     |     |

| $t_{TMSH}$      | TCK クロック立ち上り後の TMS ホールド時間     | 5   | –   | ns  |

| $t_{TDIH}$      | TCK クロック立ち上り後の TDI ホールド時間     | 5   | –   | ns  |

| $t_{CH}$        | TCK クロック立ち上り後のキャプチャ ホールド時間    | 5   | –   | ns  |

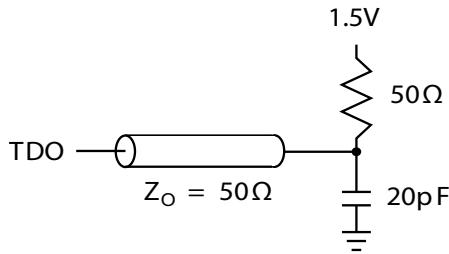

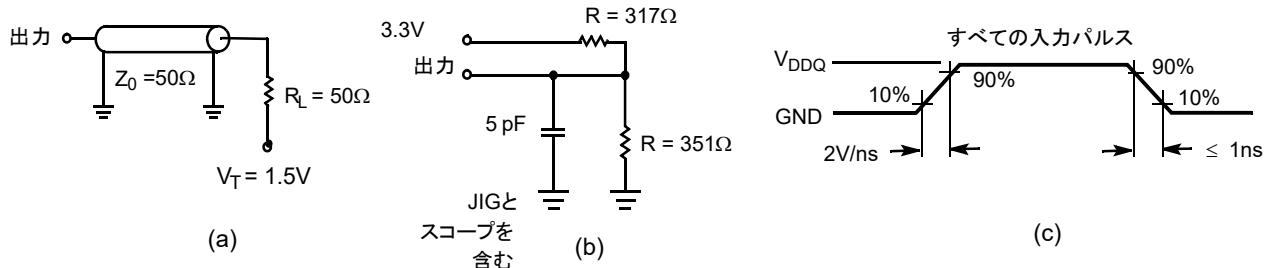

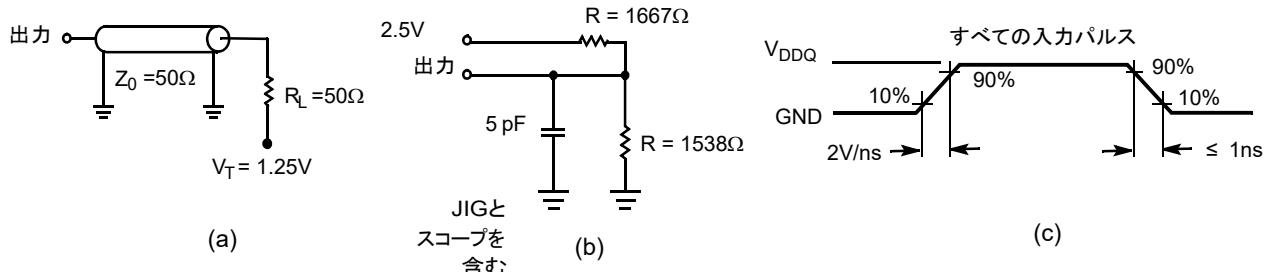

### 3.3V TAP AC テスト条件

入力パルス レベル .....  $V_{SS} \sim 3.3V$

入力の立ち上りと立ち下り時間 (スルーレート) ..... 2V/ns

入力タイミングのリファレンス電圧レベル ..... 1.5V

出力のリファレンス電圧レベル ..... 1.5V

テスト負荷終端電源電圧 ..... 1.5V

### 2.5V TAP AC テスト条件

入力パルス レベル .....  $V_{SS} \sim 2.5V$

入力の立ち上りと立ち下り時間 (スルーレート) ..... 2V/ns

入力のタイミングのリファレンス電圧レベル ..... 1.25V

出力のリファレンス電圧レベル ..... 1.25V

テスト負荷終端電源電圧 ..... 1.25V

### 3.3V TAP AC 出力負荷の等価回路

### 2.5V TAP AC 出力負荷の等価回路

#### 注

9.  $t_{CS}$  と  $t_{CH}$  は、バウンダリスキャン レジスタからデータをラッチするためのセットアップとホールド時間を示します。

10. テスト条件は、TAP AC テスト条件での負荷を使用して指定されます。 $t_R/t_F = 2V/ns$  (スルーレート)。

## TAP DC 電気的特性および動作条件

(特記されていない限り、 $0^{\circ}\text{C} < T_A < +70^{\circ}\text{C}$  ;  $V_{\text{DD}} = 3.135\text{V} \sim 3.6\text{V}$ )

| パラメーター [11]      | 説明         | 説明                                                  | 条件                           | Min  | Max                 | 単位            |

|------------------|------------|-----------------------------------------------------|------------------------------|------|---------------------|---------------|

| $V_{\text{OH1}}$ | 出力 HIGH 電圧 | $I_{\text{OH}} = -4.0\text{mA}$                     | $V_{\text{DDQ}}=3.3\text{V}$ | 2.4  | -                   | V             |

|                  |            | $I_{\text{OH}} = -1.0\text{mA}$                     | $V_{\text{DDQ}}=2.5\text{V}$ | 2.0  | -                   | V             |

| $V_{\text{OH2}}$ | 出力 HIGH 電圧 | $I_{\text{OH}}=-100\mu\text{A}$                     | $V_{\text{DDQ}}=3.3\text{V}$ | 2.9  | -                   | V             |

|                  |            |                                                     | $V_{\text{DDQ}}=2.5\text{V}$ | 2.1  | -                   | V             |

| $V_{\text{OL1}}$ | 出力 LOW 電圧  | $I_{\text{OL}}=8.0\text{mA}$                        | $V_{\text{DDQ}}=3.3\text{V}$ | -    | 0.4                 | V             |

|                  |            | $I_{\text{OL}}=1.0\text{mA}$                        | $V_{\text{DDQ}}=2.5\text{V}$ | -    | 0.4                 | V             |

| $V_{\text{OL2}}$ | 出力 LOW 電圧  | $I_{\text{OL}}=100\mu\text{A}$                      | $V_{\text{DDQ}}=3.3\text{V}$ | -    | 0.2                 | V             |

|                  |            |                                                     | $V_{\text{DDQ}}=2.5\text{V}$ | -    | 0.2                 | V             |

| $V_{\text{IH}}$  | 入力 HIGH 電圧 |                                                     | $V_{\text{DDQ}}=3.3\text{V}$ | 2.0  | $V_{\text{DD}}+0.3$ | V             |

|                  |            |                                                     | $V_{\text{DDQ}}=2.5\text{V}$ | 1.7  | $V_{\text{DD}}+0.3$ | V             |

| $V_{\text{IL}}$  | 入力 LOW 電圧  |                                                     | $V_{\text{DDQ}}=3.3\text{V}$ | -0.3 | 0.8                 | V             |

|                  |            |                                                     | $V_{\text{DDQ}}=2.5\text{V}$ | -0.3 | 0.7                 | V             |

| $I_x$            | 入力負荷電流     | $\text{GND} \leq V_{\text{IN}} \leq V_{\text{DDQ}}$ |                              |      | -5                  | 5             |

|                  |            |                                                     |                              |      |                     | $\mu\text{A}$ |

### 注

11. すべての電圧は  $V_{\text{SS}}$  (GND) を基準にします。

## ID レジスタの定義

| 命令フィールド                                 | CY7C1441KV33<br>(1M×36) | 説明                 |

|-----------------------------------------|-------------------------|--------------------|

| リビジョン番号 (31:29)                         | 000                     | リビジョン番号を示します。      |

| デバイス深部 (28:24)                          | 01011                   | 内部使用のために予約済み       |

| アーキテクチャ/メモリ タイプ (23:18) <sup>[12]</sup> | 000001                  | メモリ タイプとアーキテクチャを定義 |

| バス幅/容量 (17:12)                          | 100111                  | 幅と容量を定義            |

| サイプレスの JEDEC ID コード (11:1)              | 00000110100             | SRAM ベンダーを識別       |

| ID レジスタの有無インジケータ (0)                    | 1                       | ID レジスタの有無を示します。   |

## スキャン レジスタ サイズ

| レジスタ名                              | ビット サイズ (×36) |

|------------------------------------|---------------|

| 命令バイパス                             | 3             |

| バイパス                               | 1             |

| ID                                 | 32            |

| バウンダリ スキャン順序 (165 ポール FBGA パッケージ ) | 89            |

## ID コード

| 命令             | コード | 説明                                                                                      |

|----------------|-----|-----------------------------------------------------------------------------------------|

| EXTTEST        | 000 | I/O リングの内容を取り込みます。                                                                      |

| IDCODE         | 001 | ベンダー ID コードを ID レジスタにロードし、レジスタを TDI と TDO の間に配置。この処理は SRAM 動作に影響を与えません。                 |

| SAMPLE Z       | 010 | I/O リングの内容を取り込みます。バウンダリ スキャン レジスタを TDI と TDO の間に配置。すべての SRAM 出力ドライバーを HIGH Z 状態に移行させます。 |

| RESERVED       | 011 | 未使用。将来のために予約されます。                                                                       |

| SAMPLE/PRELOAD | 100 | 入力および出力リングの内容を取り込みます。バウンダリ スキャン レジスタを TDI と TDO の間に配置。SRAM 動作に影響を与えません。                 |

| RESERVED       | 101 | 未使用。将来のために予約されます。                                                                       |

| RESERVED       | 110 | 未使用。将来のために予約されます。                                                                       |

| BYPASS         | 111 | バイパス レジスタを TDI と TDO の間に配置。この動作は SRAM 動作に影響を与えません。                                      |

### 注

12. 本デバイスの 2.5V と 3.3V バージョンの両方の ID レジスタ定義ではビット 24 が「1」です。

## パウンダリスキャン順序

165 ボール FBGA [13、14]

**CY7C1441KV33 (1M×36)**

| ビット番号 | ボール ID | ビット番号 | ボール ID | ビット番号 | ボール ID |

|-------|--------|-------|--------|-------|--------|

| 1     | N6     | 26    | E11    | 51    | A3     |

| 2     | N7     | 27    | D11    | 52    | A2     |

| 3     | N10    | 28    | G10    | 53    | B2     |

| 4     | P11    | 29    | F10    | 54    | C2     |

| 5     | P8     | 30    | E10    | 55    | B1     |

| 6     | R8     | 31    | D10    | 56    | A1     |

| 7     | R9     | 32    | C11    | 57    | C1     |

| 8     | P9     | 33    | A11    | 58    | D1     |

| 9     | P10    | 34    | B11    | 59    | E1     |

| 10    | R10    | 35    | A10    | 60    | F1     |

| 11    | R11    | 36    | B10    | 61    | G1     |

| 12    | H11    | 37    | A9     | 62    | D2     |

| 13    | N11    | 38    | B9     | 63    | E2     |

| 14    | M11    | 39    | C10    | 64    | F2     |

| 15    | L11    | 40    | A8     | 65    | G2     |

| 16    | K11    | 41    | B8     | 66    | H1     |

| 17    | J11    | 42    | A7     | 67    | H3     |

| 18    | M10    | 43    | B7     | 68    | J1     |

| 19    | L10    | 44    | B6     | 69    | K1     |

| 20    | K10    | 45    | A6     | 70    | L1     |

| 21    | J10    | 46    | B5     | 71    | M1     |

| 22    | H9     | 47    | A5     | 72    | J2     |

| 23    | H10    | 48    | A4     | 73    | K2     |

| 24    | G11    | 49    | B4     | 74    | L2     |

| 25    | F11    | 50    | B3     | 75    | M2     |

### 注

13. NC (未接続) のボールは LOW にプリセットされます。

14. ビット 89 は HIGH にプリセットされます。

## 最大定格

|                                                                                  |

|----------------------------------------------------------------------------------|

| 最大定格を超えるとデバイスの寿命が短くなる可能性があります。ユーザー ガイドラインはテストされません。                              |

| 保存温度 ..... $-65^{\circ}\text{C} \sim +150^{\circ}\text{C}$                       |

| 通電時の周囲温度 ..... $-55^{\circ}\text{C} \sim +125^{\circ}\text{C}$                   |

| GND を基準とした $V_{\text{DD}}$ 電源電圧 ..... $-0.3\text{V} \sim +4.6\text{V}$           |

| GND を基準とした $V_{\text{DDQ}}$ 電源電圧 ..... $-0.3\text{V} \text{ to } +V_{\text{DD}}$ |

| トライステート状態の出力に印加できる DC 電圧 ..... $-0.5\text{V} \sim V_{\text{DDQ}}+0.5\text{V}$    |

| DC 入力電圧 ..... $-0.5\text{V} \sim V_{\text{DD}}+0.5\text{V}$                      |

| 出力 (LOW) への電流 ..... 20mA                                                         |

| 静電放電時の電圧<br>(MIL-STD-883、メソッド 3015) ..... >2001V                                 |

| ラッピングアップ電流 ..... >200mA                                                          |

| DC 入力電圧 ..... $-0.5\text{V} \sim V_{\text{DD}}+0.5\text{V}$                      |

| 出力 (LOW) への電流 ..... 20mA                                                         |

| 静電放電時の電圧<br>(MIL-STD-883 準拠、メソッド 3015) ..... >2001V                              |

| ラッピングアップ電流 ..... >200mA                                                          |

## 電気的特性

動作範囲において

### DC 特性

動作範囲において

| パラメーター <sup>[15、16]</sup> | 説明                         | テスト条件                                         | Min   | Max                           | 単位            |

|---------------------------|----------------------------|-----------------------------------------------|-------|-------------------------------|---------------|

| $V_{\text{DD}}$           | 電源電圧                       |                                               | 3.135 | 3.6                           | V             |

| $V_{\text{DDQ}}$          | I/O 電源電圧                   | 3.3V I/O の場合                                  | 3.135 | $V_{\text{DD}}$               | V             |

|                           |                            | 2.5V I/O の場合                                  | 2.375 | 2.625                         | V             |

| $V_{\text{OH}}$           | 出力 HIGH 電圧                 | 3.3V I/O、 $I_{\text{OH}} = -4.0\text{mA}$ の場合 | 2.4   | -                             | V             |

|                           |                            | 2.5V I/O、 $I_{\text{OH}} = -1.0\text{mA}$ の場合 | 2.0   | -                             | V             |

| $V_{\text{OL}}$           | 出力 LOW 電圧                  | 3.3V I/O、 $I_{\text{OL}} = 8.0\text{mA}$ の場合  | -     | 0.4                           | V             |

|                           |                            | 2.5V I/O、 $I_{\text{OL}} = 1.0\text{mA}$ の場合  | -     | 0.4                           | V             |

| $V_{\text{IH}}$           | 入力 HIGH 電圧 <sup>[15]</sup> | 3.3V I/O の場合                                  | 2.0   | $V_{\text{DD}} + 0.3\text{V}$ | V             |

|                           |                            | 2.5V I/O の場合                                  | 1.7   | $V_{\text{DD}} + 0.3\text{V}$ | V             |

| $V_{\text{IL}}$           | 入力 LOW 電圧 <sup>[15]</sup>  | 3.3V I/O の場合                                  | -0.3  | 0.8                           | V             |

|                           |                            | 2.5V I/O の場合                                  | -0.3  | 0.7                           | V             |

| $I_x$                     | 入力リード電流 (ZZ と MODE を除く)    | $\text{GND} \leq V_I \leq V_{\text{DDQ}}$     | -5    | 5                             | $\mu\text{A}$ |

|                           | MODE の入力電流                 | 入力 = $V_{\text{SS}}$                          | -30   | -                             | $\mu\text{A}$ |

|                           |                            | 入力 = $V_{\text{DD}}$                          | -     | 5                             | $\mu\text{A}$ |

|                           | ZZ の入力電流                   | 入力 = $V_{\text{SS}}$                          | -5    | -                             | $\mu\text{A}$ |

|                           |                            | 入力 = $V_{\text{DD}}$                          | -     | 30                            | $\mu\text{A}$ |

注

15. オーバーシュート :  $V_{\text{IH}}(\text{AC}) < V_{\text{DD}} + 1.5\text{V}$  ( パルス幅が  $t_{\text{CYC}}/2$  未満 )、アンダーシュート :  $V_{\text{IL}}(\text{AC}) > -2\text{V}$  ( パルス幅が  $t_{\text{CYC}}/2$  未満 )。

16.  $T_{\text{Power-up}}$ : 200ms 以内に 0V から  $V_{\text{DD(min)}}$  までの直線傾斜を前提とします。この間では、 $V_{\text{IH}} < V_{\text{DD}}$ 、 $V_{\text{DDQ}} \leq V_{\text{DD}}$ 。

## 動作範囲

| 範囲  | 周囲温度          | $V_{\text{DD}}$   | $V_{\text{DDQ}}$            |

|-----|---------------|-------------------|-----------------------------|

| 商業用 | 0°C ~ +70°C   | 3.3V - 5% / + 10% | 2.5V - 5% ~ $V_{\text{DD}}$ |

|     | -40°C ~ +85°C |                   |                             |

## 中性子ソフト エラー耐性

| パラメーター             | 説明                | テスト条件 | Typ | Max* | 単位      |

|--------------------|-------------------|-------|-----|------|---------|

| LSBU (ECC なしのデバイス) | 単一論理ビット反転         | 25 °C | <5  | 5    | FIT/Mb  |

|                    |                   |       | 0   | 0.01 | FIT/Mb  |

| LMBU (すべてのデバイス)    | 複数論理ビット反転         | 25 °C | 0   | 0.01 | FIT/Mb  |

| SEL (すべてのデバイス)     | シングルイベント ラッピングアップ | 85 °C | 0   | 0.1  | FIT/Dev |

\* テスト中に LMBU または SEL イベントは発生しません。本項は  $\chi^2$  分布の 95% 信頼上限を示します。詳細は、[AN54908 「中性子の SER 加速試験と地上における故障率の計算」](#) のアプリケーション ノートを参照してください。

## 電気的特性(続き)

動作範囲において

### DC 特性(続き)

動作範囲において

| パラメーター <sup>[15, 16]</sup> | 説明                           | テスト条件                                                                                                                                             |                        |     | Min | Max | 単位 |

|----------------------------|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-----|-----|-----|----|

| I <sub>OZ</sub>            | 出力リーコンデンサー電流                 | GND ≤ V <sub>I</sub> ≤ V <sub>DDQ</sub> 、出力が無効                                                                                                    |                        |     | -5  | 5   | μA |

| I <sub>DD</sub>            | V <sub>DD</sub> の動作時供給電流     | V <sub>DD</sub> = Max.、I <sub>OUT</sub> = 0mA、f = f <sub>MAX</sub> = 1/t <sub>CYC</sub>                                                           | 7.5ns のサイクル、133MHz     | ×18 | -   | 150 | mA |

|                            |                              |                                                                                                                                                   |                        | ×36 | -   | 170 |    |

| I <sub>SB1</sub>           | 自動 CE のパワーダウン電流<br>- TTL 入力  | 最大 V <sub>DD</sub> 、<br>デバイス選択解除、<br>V <sub>IN</sub> ≥ V <sub>IH</sub> または<br>V <sub>IN</sub> ≤ V <sub>IL</sub> 、f = f <sub>MAX</sub> 、<br>入力切り替え | 7.5ns のサイクル、<br>133MHz | ×18 | -   | 85  | mA |

|                            |                              |                                                                                                                                                   |                        | ×36 | -   | 90  |    |

| I <sub>SB2</sub>           | 自動 CE のパワーダウン電流<br>- CMOS 入力 | 最大 V <sub>DD</sub> 、<br>デバイス選択解除、<br>V <sub>IN</sub> ≥ V <sub>DD</sub> - 0.3V<br>または V <sub>IN</sub> ≤ 0.3V、<br>f = 0、入力が静止状態<br>にある              | 7.5ns のサイクル、<br>133MHz | ×18 | -   | 75  | mA |

|                            |                              |                                                                                                                                                   |                        | ×36 | -   | 80  |    |

| I <sub>SB3</sub>           | 自動 CE のパワーダウン電流<br>- CMOS 入力 | 最大 V <sub>DD</sub> 、<br>デバイス選択解除、<br>V <sub>IN</sub> ≥ V <sub>DD</sub> - 0.3V<br>または V <sub>IN</sub> ≤ 0.3V、<br>f = f <sub>MAX</sub> 、入力切り替え      | 7.5ns のサイクル、<br>133MHz | ×18 | -   | 85  | mA |

|                            |                              |                                                                                                                                                   |                        | ×36 | -   | 90  |    |

| I <sub>SB4</sub>           | 自動 CE のパワーダウン電流<br>- TTL 入力  | 最大 V <sub>DD</sub> 、<br>デバイス選択解除、<br>V <sub>IN</sub> ≥ V <sub>DD</sub> - 0.3V<br>または V <sub>IN</sub> ≤ 0.3V、<br>f = 0、入力が静止状態<br>にある              | 7.5ns のサイクル、<br>133MHz | ×18 | -   | 75  | mA |

|                            |                              |                                                                                                                                                   |                        | ×36 | -   | 80  |    |

## 静電容量

| パラメーター <sup>[17]</sup> | 説明         | テスト条件                                                                                  | 100 ピン<br>TQFP 最大値 | 165 ボール<br>FBGA 最大値 | 単位 |

|------------------------|------------|----------------------------------------------------------------------------------------|--------------------|---------------------|----|

| $C_{IN}$               | 入力静電容量     | $T_A = 25^\circ\text{C}, f = 1\text{MHz}, V_{DD} = 3.3\text{V}, V_{DDQ} = 2.5\text{V}$ | 5                  | 5                   | pF |

| $C_{CLK}$              | クロック入力静電容量 |                                                                                        | 5                  | 5                   | pF |

| $C_{IO}$               | 入力／出力の静電容量 |                                                                                        | 5                  | 5                   | pF |

## 熱抵抗

| パラメーター <sup>[17]</sup> | 説明                | テスト条件                                                | 100 ピン<br>TQFP<br>パッケージ | 165 ボール<br>FBGA<br>パッケージ | 単位    |

|------------------------|-------------------|------------------------------------------------------|-------------------------|--------------------------|-------|

| $\Theta_{JA}$          | 熱抵抗<br>(接合部から周囲)  | テスト条件は、EIA/JESD51による、熱インピーダンスを測定するための標準的なテスト方法と手順に従う | エア静止 (0 m/s)            | 35.36                    | 14.24 |

|                        |                   |                                                      | エアーフロー (1 m/s)          | 31.30                    | 12.47 |

|                        |                   |                                                      | エアーフロー (3 m/s)          | 28.86                    | 11.40 |

| $\Theta_{JC}$          | 熱抵抗<br>(接合部からケース) |                                                      | -                       | 7.52                     | 3.92  |

| $\Theta_{JB}$          | 熱抵抗<br>(接合部から基板へ) |                                                      |                         | 28.89                    | 7.19  |

## AC テストの負荷と波形

図 3. AC テストの負荷と波形

### 3.3V I/O テスト負荷

### 2.5V I/O テスト負荷

### 注

17. 開発時とこれらのパラメーターに影響を与える可能性のある設計／プロセス変更があった後にテストされます。

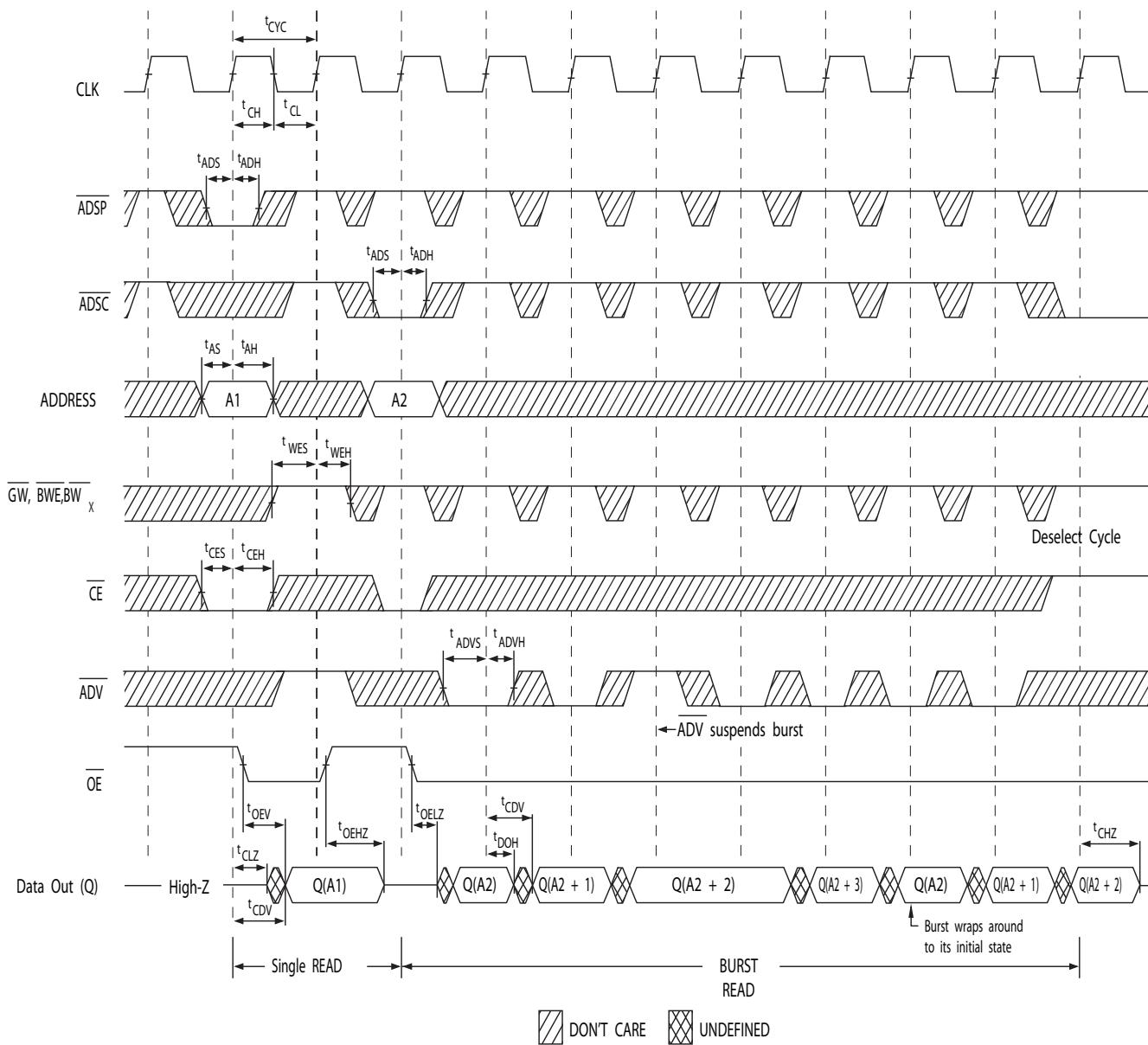

## スイッチング特性

動作範囲において

| パラメーター <sup>[18、19]</sup> | 説明                                                                         | -133 |     | 単位 |

|---------------------------|----------------------------------------------------------------------------|------|-----|----|

|                           |                                                                            | Min  | Max |    |

| $t_{POWER}$               | $V_{DD}$ (Min) から最初のアクセスまでの時間 <sup>[20]</sup>                              | 1    | -   | ms |

| <b>クロック</b>               |                                                                            |      |     |    |

| $t_{CYC}$                 | クロック サイクル期間                                                                | 7.5  | -   | ns |

| $t_{CH}$                  | クロック HIGH                                                                  | 2.5  | -   | ns |

| $t_{CL}$                  | クロック LOW                                                                   | 2.5  | -   | ns |

| <b>出力時間</b>               |                                                                            |      |     |    |

| $t_{CDV}$                 | CLK 立ち上り後のデータ出力有効時間                                                        | -    | 6.5 | ns |

| $t_{DOH}$                 | CLK 立ち上り後のデータ出力ホールド時間                                                      | 2.5  | -   | ns |

| $t_{CLZ}$                 | クロックから LOW Z までの時間 <sup>[21、22、23]</sup>                                   | 2.5  | -   | ns |

| $t_{CHZ}$                 | クロックから HIGH Z までの時間 <sup>[21、22、23]</sup>                                  | -    | 3.8 | ns |

| $t_{OEV}$                 | OELOW から出力有効までの時間                                                          | -    | 3.0 | ns |

| $t_{OELZ}$                | OE LOW から出力 LOW Z までの時間 <sup>[21、22、23]</sup>                              | 0    | -   | ns |

| $t_{OEHZ}$                | OE HIGH から出力 HIGH Z までの時間 <sup>[21、22、23]</sup>                            | -    | 3.0 | ns |

| <b>セットアップ時間</b>           |                                                                            |      |     |    |

| $t_{AS}$                  | CLK 立ち上り前のアドレス セットアップ時間                                                    | 1.5  | -   | ns |

| $t_{ADS}$                 | CLK 立ち上り前の ADSP、ADSC                                                       | 1.5  | -   | ns |

| $t_{ADVS}$                | CLK 立ち上り前の ADV セットアップ時間                                                    | 1.5  | -   | ns |

| $t_{WES}$                 | CLK 立ち上り前の $\overline{GW}$ 、 $\overline{BWE}$ 、 $\overline{BW}_X$ セットアップ時間 | 1.5  | -   | ns |

| $t_{DS}$                  | CLK 立ち上り前のデータ入力セットアップ時間                                                    | 1.5  | -   | ns |

| $t_{CES}$                 | チップ イネーブル セットアップ時間                                                         | 1.5  | -   | ns |

| <b>ホールド時間</b>             |                                                                            |      |     |    |

| $t_{AH}$                  | CLK 立ち上り後のアドレス ホールド時間                                                      | 0.5  | -   | ns |

| $t_{ADH}$                 | CLK 立ち上り後の ADSP、ADSC ホールド時間                                                | 0.5  | -   | ns |

| $t_{WEH}$                 | CLK 立ち上り後の $\overline{GW}$ 、 $\overline{BWE}$ 、 $\overline{BW}_X$ ホールド時間   | 0.5  | -   | ns |

| $t_{ADVH}$                | CLK 立ち上り後の ADV ホールド時間                                                      | 0.5  | -   | ns |

| $t_{DH}$                  | CLK 立ち上り後のデータ入力ホールド時間                                                      | 0.5  | -   | ns |

| $t_{CEH}$                 | CLK 立ち上り後のチップ イネーブル ホールド時間                                                 | 0.5  | -   | ns |

### 注

18. タイミングのリファレンス電圧レベルは、 $V_{DDQ} = 3.3V$  の場合は 1.5V であり、 $V_{DDQ} = 2.5V$  の場合は 1.25V です。

19. 特に明記しない限り、テスト条件は、AC テスト負荷の (a) に示します。

20. このデバイスは電圧レギュレータを内蔵します。 $t_{POWER}$  は、読み出しちゃまたは書き込み処理が開始される前に、 $V_{DD}$  (最小値) を超えた電源を供給する必要がある時間です。

21.  $t_{CHZ}$ 、 $t_{CLZ}$ 、 $t_{OELZ}$ 、 $t_{OEHZ}$  は、[21 ページの図 3](#) の (b) に示した AC テスト条件で指定されます。遷移は定常状態での電圧  $\pm 200mV$  の電圧レベルで測定されます。

22. 任意の時刻の電圧と温度において、同じデータバスを共用する時、SRAM 間にバス競合を回避するために、 $t_{OEHZ}$  は  $t_{OELZ}$  より少なく、 $t_{CHZ}$  は  $t_{CLZ}$  より少ないです。これらの仕様では、バス競合条件を説明しませんが、最悪の場合のユーザー条件において保証されるパラメーターを示します。デバイスは、同じシステム条件下 LOW Z の前に HIGH Z を達成するように設計されています。

23. このパラメーターはサンプリングされた値であり、すべてのデバイスでは試験されません。

## タイミング図

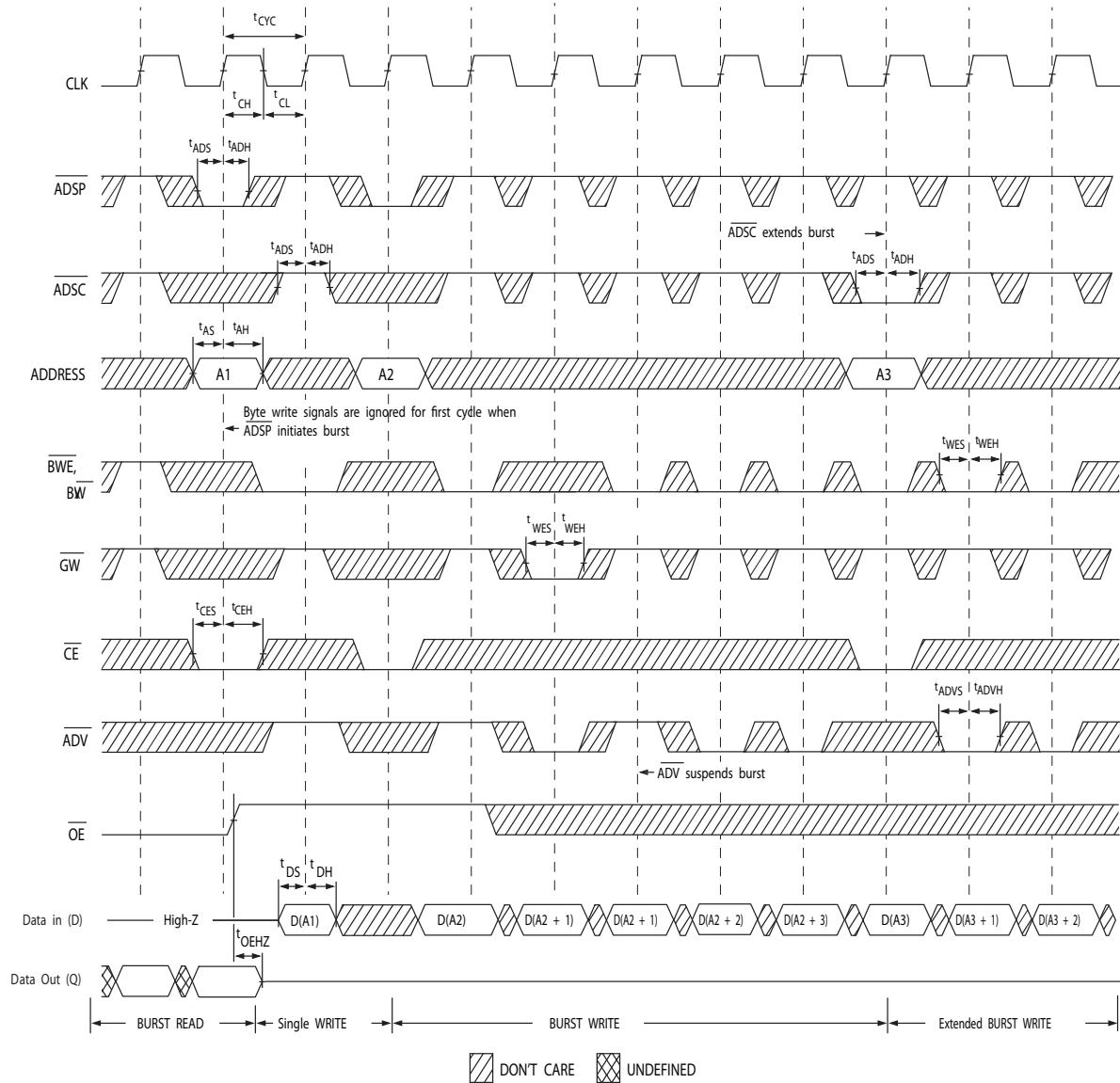

図4. 読み出しサイクルタイミング<sup>[24]</sup>

注

24. この図では、 $\overline{CE}$  が LOW の場合、 $\overline{CE}_1$  は LOW、 $CE_2$  は HIGH、 $\overline{CE}_3$  は LOW です。 $\overline{CE}$  が HIGH の場合、 $\overline{CE}_1$  は HIGH、または  $CE_2$  は LOW、または  $\overline{CE}_3$  は HIGH です。

## タイミング図(続き)

図5. 書き込みサイクルタイミング [25, 26]

### 注

25. この図では、 $\overline{CE}$  が LOW の場合、 $\overline{CE}_1$  は LOW、 $CE_2$  は HIGH、 $\overline{CE}_3$  は LOW です。 $\overline{CE}$  が HIGH の場合、 $\overline{CE}_1$  は HIGH、または  $CE_2$  は LOW、または  $\overline{CE}_3$  は HIGH です。

26. 全幅の書き込みは、 $\overline{GW}$  が LOW、または  $\overline{GW}$  が HIGH、 $\overline{BWE}$  が LOW、 $\overline{BW}_X$  が LOW になると開始できます。

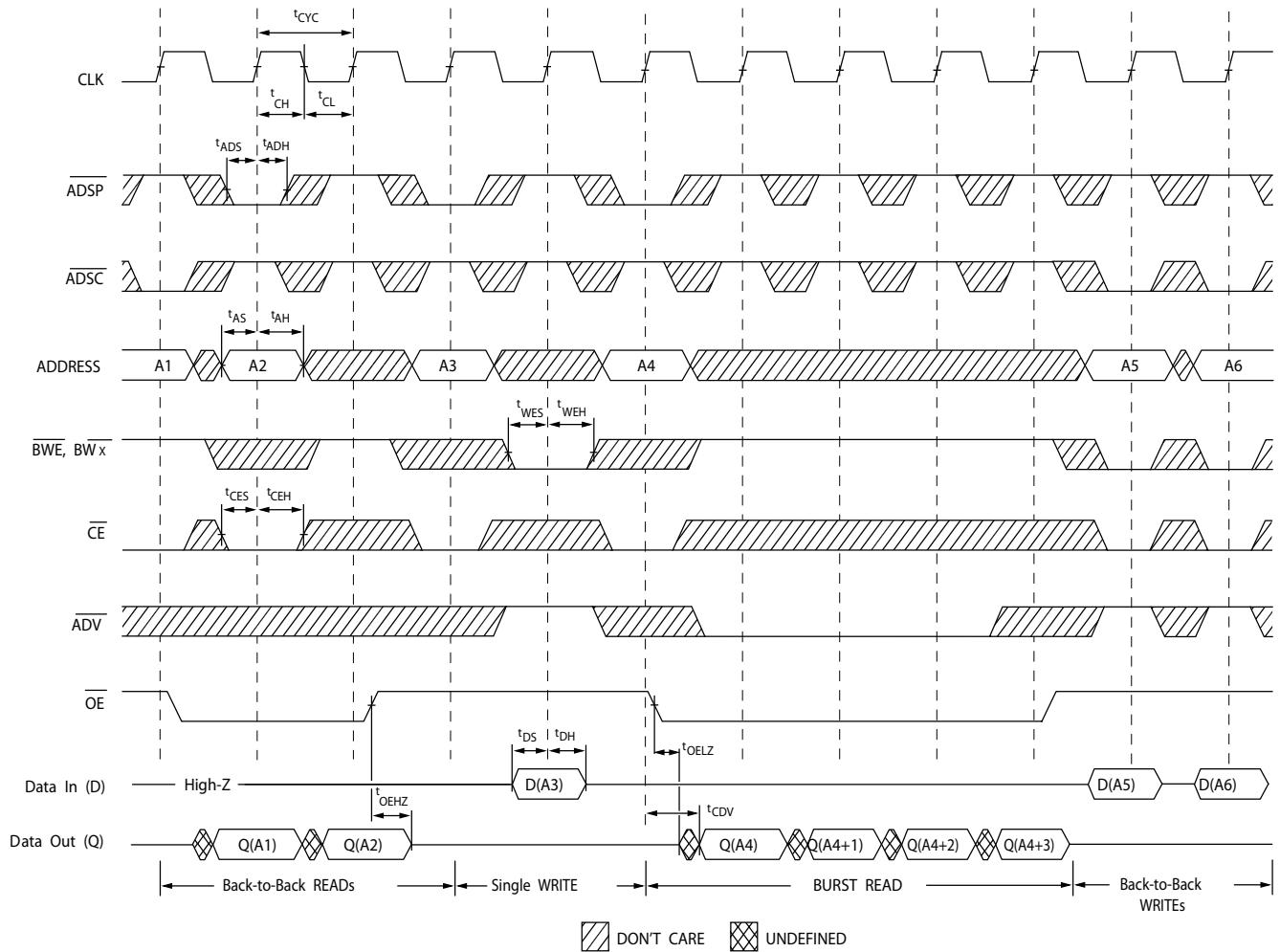

## タイミング図(続き)

図6. 読み出し／書き込みサイクル タイミング [27、28、29]

### 注

27. この図では、 $\overline{CE}$  が LOW の場合、 $\overline{CE}_1$  は LOW、 $\overline{CE}_2$  は HIGH、 $\overline{CE}_3$  は LOW です。 $\overline{CE}$  が HIGH の場合、 $\overline{CE}_1$  は HIGH、または  $CE_2$  は LOW、または  $\overline{CE}_3$  は HIGH です。

28. 新しい読み出しアクセスが  $\overline{ADSP}$  または  $\overline{ADSC}$  により開始されない限り、データバス (Q) は書き込みサイクルの後 HIGH Z のままでです。

29. GW は HIGH です。

## タイミング図(続き)

図7. ZZ モード タイミング [30、31]

- 注**

- 30.ZZ モードに入る時、デバイスを選択解除する必要があります。デバイスを選択解除するためのすべての可能な信号条件については、サイクル説明表を参照してください。

- 31.ZZ スリープ モードを終了する時、DQ 信号は HIGH Z 状態です。

## 注文情報

表 1 に注文コードを示します。この表には、現在入手可能な部品のみが含まれます。あなたが探しているものが見つからない場合は、最寄りの販売代理店にお問い合わせください。詳細については、サイプレスのウェブサイト [www.cypress.com](http://www.cypress.com) にアクセスし、製品概要のページ <http://www.cypress.com/products> を参照してください。

表 1. 注文情報

| 速度<br>(MHz) | 注文コード                | パッケージ図   | 部品とパッケージ タイプ                    | 動作範囲 |

|-------------|----------------------|----------|---------------------------------|------|

| 133         | CY7C1441KV33-133AXC  | 51-85050 | 100 ピン TQFP (14×20×1.4mm) 鉛フリー  | 商業用  |

|             | CY7C1441KVE33-133AXC |          |                                 | 産業用  |

|             | CY7C1441KV33-133AXI  |          |                                 |      |

|             | CY7C1443KV33-133AXI  |          |                                 |      |

|             | CY7C1441KV33-133BZI  | 51-85195 | 165 ポール FBGA (15×17×1.4mm) 鉛フリー |      |

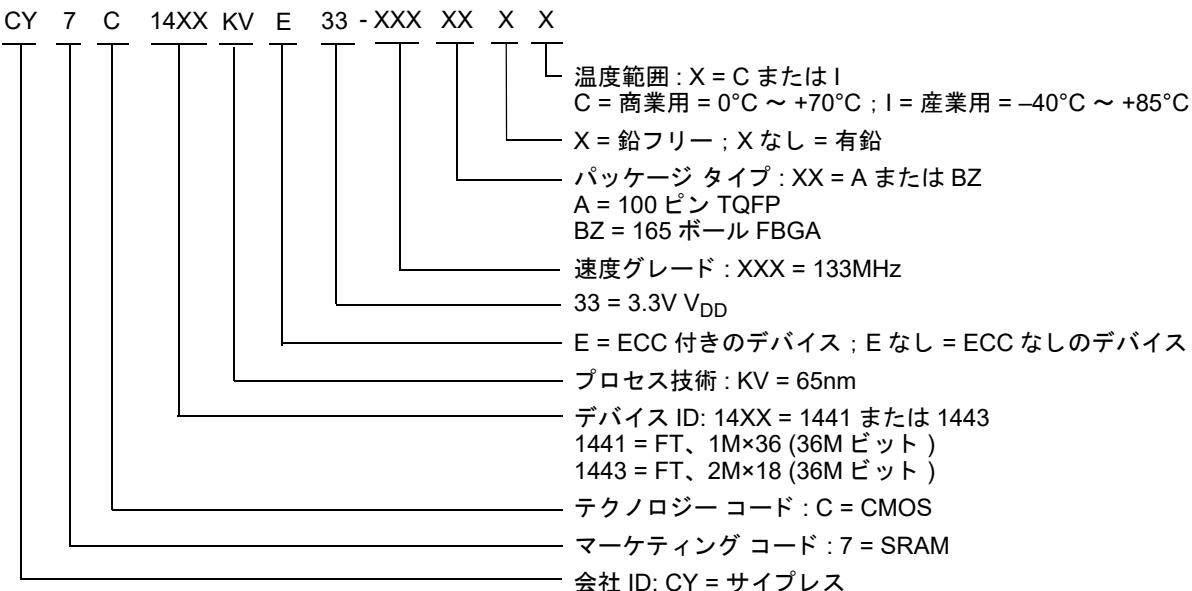

## 注文コードの定義

## パッケージ図

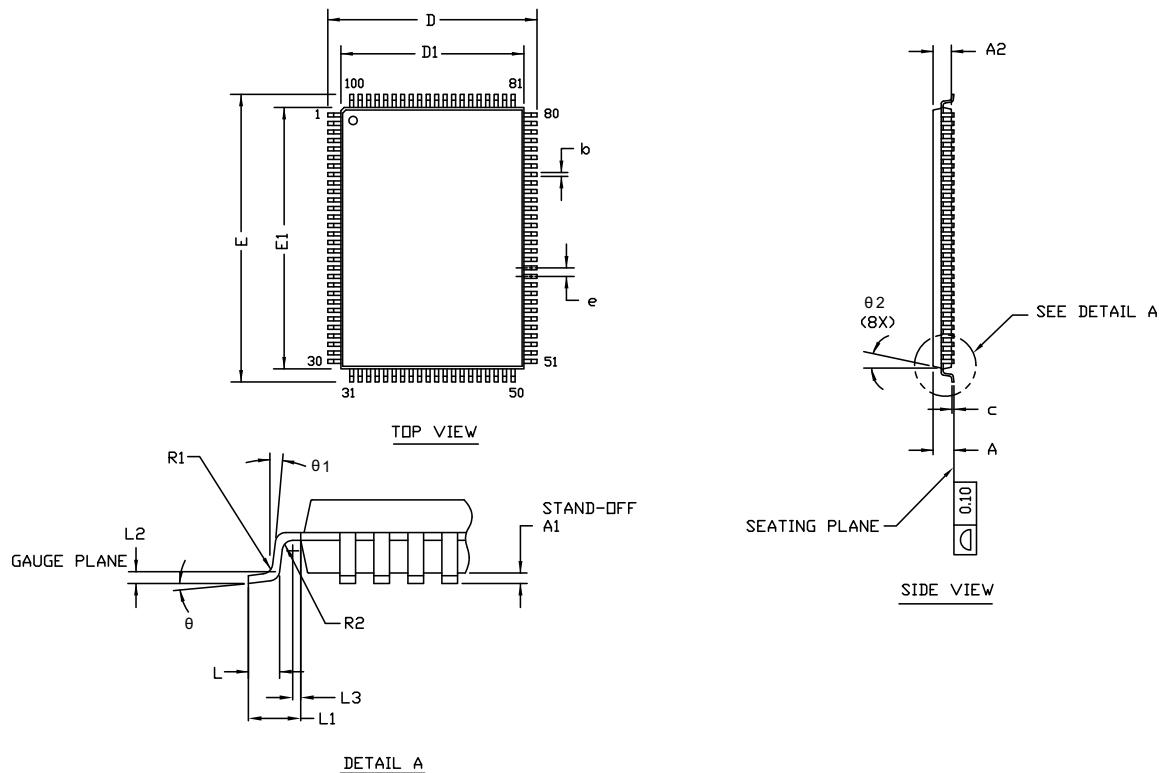

図 8. 100 ピン TQFP (14×20×1.4mm) A100RA パッケージの図、51-85050

| SYMBOL | DIMENSIONS |       |       |

|--------|------------|-------|-------|

|        | MIN.       | NOM.  | MAX.  |

| A      | —          | —     | 1.60  |

| A1     | 0.05       | —     | 0.15  |

| A2     | 1.35       | 1.40  | 1.45  |

| D      | 15.80      | 16.00 | 16.20 |

| D1     | 13.90      | 14.00 | 14.10 |

| E      | 21.80      | 22.00 | 22.20 |

| E1     | 19.90      | 20.00 | 20.10 |

| R1     | 0.08       | —     | 0.20  |

| R2     | 0.08       | —     | 0.20  |

| θ      | 0°         | —     | 7°    |

| θ1     | 0°         | —     | —     |

| θ2     | 11°        | 12°   | 13°   |

| c      | —          | —     | 0.20  |

| b      | 0.22       | 0.30  | 0.38  |

| L      | 0.45       | 0.60  | 0.75  |

| L1     | 1.00 REF   |       |       |

| L2     | 0.25 BSC   |       |       |

| L3     | 0.20       | —     | —     |

| e      | 0.65 TYP   |       |       |

### NOTE:

- ALL DIMENSIONS ARE IN MILLIMETERS.

- BODY LENGTH DIMENSION DOES NOT INCLUDE MOLD PROTRUSION/END FLASH. MOLD PROTRUSION/END FLASH SHALL NOT EXCEED 0.0098 in (0.25 mm) PER SIDE.

- BODY LENGTH DIMENSIONS ARE MAX PLASTIC BODY SIZE INCLUDING MOLD MISMATCH.

- JEDEC SPECIFICATION NO. REF: MS-026.

51-85050 \*G

## パッケージ図(続き)

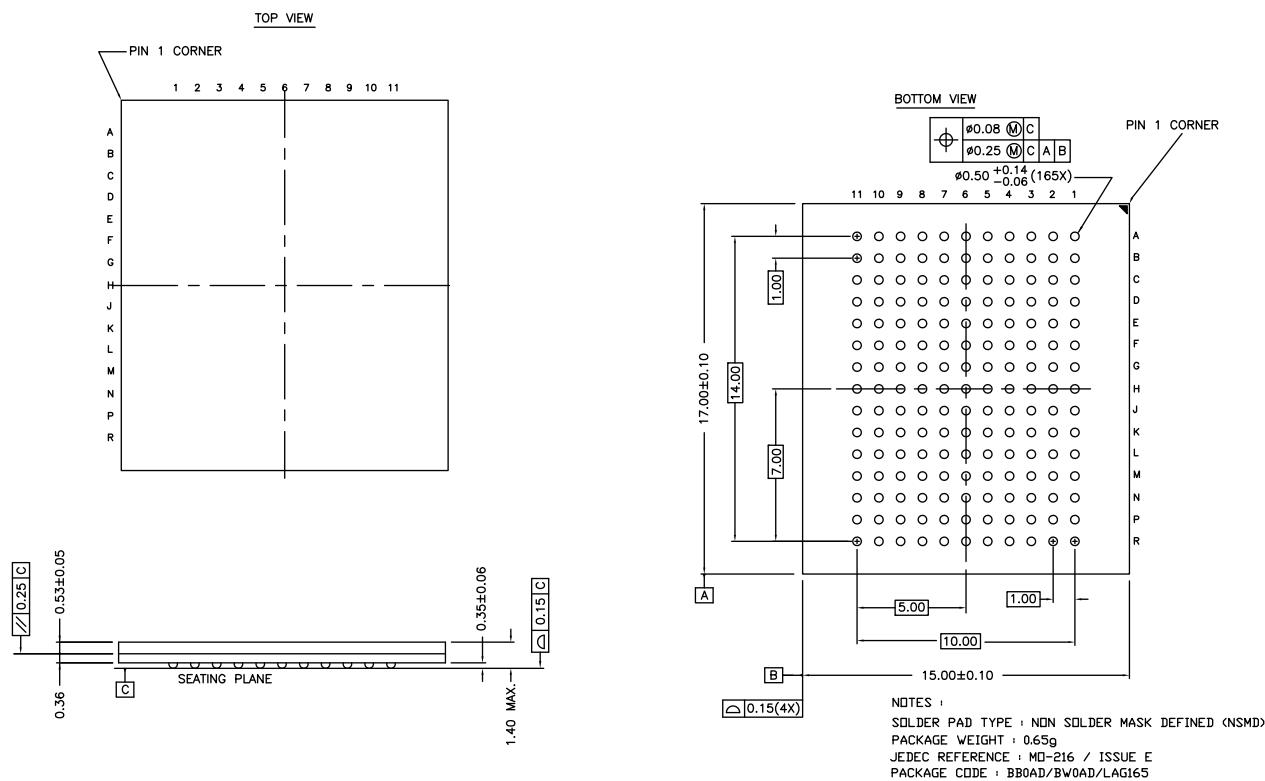

図9. 165 ボール FBGA (15×17×1.4mm (0.5 ボール直径)) パッケージの図、51-85195

51-85195 \*E

## 略語

表 2. 本書で使用される略語

| 略語   | 説明                                                         |

|------|------------------------------------------------------------|

| CE   | Chip Enable ( チップ イネーブル )                                  |

| CMOS | Complementary Metal Oxide Semiconductor<br>( 相補型金属酸化膜半導体 ) |

| FBGA | Fine-Pitch Ball Grid Array<br>( フайн ピッチ ボール グリッド アレイ )    |

| I/O  | Input/Output ( 入力／出力 )                                     |

| JTAG | Joint Test Action Group<br>( ジョイント テスト アクション グループ )        |

| NoBL | No Bus Latency ( バス レイテンシーなし )                             |

| OE   | Output Enable ( 出力イネーブル )                                  |

| SRAM | Static Random Access Memory<br>( スタティック ランダム アクセス メモリ )    |

| TCK  | Test Clock ( テスト クロック )                                    |

| TDI  | Test Data-In ( テスト データ入力 )                                 |

| TDO  | Test Data-Out ( テスト データ出力 )                                |

| TMS  | Test Mode Select ( テスト モード選択 )                             |

| TQFP | Thin Quad Flat Pack<br>( 薄型クアッド フラット パック )                 |

| WE   | Write Enable ( 書き込みイネーブル )                                 |

| ECC  | Error Correcting Code ( エラー訂正コード )                         |

## 本書の表記法

### 測定単位

表 3. 測定単位

| 記号  | 測定単位     |

|-----|----------|

| °C  | 摂氏温度     |

| MHz | メガヘルツ    |

| µA  | マイクロアンペア |

| mA  | ミリアンペア   |

| ms  | ミリ秒      |

| mm  | ミリメートル   |

| ns  | ナノ秒      |

| pF  | ピコファラド   |

| V   | ボルト      |

| W   | ワット      |

## 改訂履歴

文書名 : CY7C1441KV33/CY7C1443KV33/CY7C1441KVE33、36M ピット (1M×36/2M×18) フロースルー SRAM (ECC 付き )

文書番号 : 001-96008

| 版  | ECN 番号  | 発行日        | 変更内容                                                     |

|----|---------|------------|----------------------------------------------------------|

| ** | 4636622 | 01/23/2015 | これは英語版 001-66677 Rev. *D を翻訳した日本語版 001-96008 Rev. ** です。 |

| *A | 4718923 | 04/09/2015 | 決勝への変換                                                   |

| *B | 4780390 | 05/28/2015 | 更新 $I_{DDZz}$ 値                                          |

| *C | 6915521 | 07/17/2020 | これは英語版 001-66677 Rev. *J を翻訳した日本語版 001-96008 Rev. *C です。 |

## セールス、ソリューションおよび法律情報

### ワールドワイドな販売と設計サポート

サイプレスは、事業所、ソリューションセンター、メーカー代理店、および販売代理店の世界的なネットワークを保持しています。お客様の最寄りのオフィスについては、[サイプレスのロケーションのウェブページ](#)をご覧ください。

#### 製品

Arm® Cortex® Microcontrollers

[cypress.com/arm](http://cypress.com/arm)

車載用

[cypress.com/automotive](http://cypress.com/automotive)

クロック & バッファ

[cypress.com/clocks](http://cypress.com/clocks)

インターフェース

[cypress.com/interface](http://cypress.com/interface)

IoT (モノのインターネット)

[cypress.com/iot](http://cypress.com/iot)

メモリ

[cypress.com/memory](http://cypress.com/memory)

マイクロコントローラ

[cypress.com/mcu](http://cypress.com/mcu)

PSoC

[cypress.com/psoc](http://cypress.com/psoc)

電源用 IC

[cypress.com/pmic](http://cypress.com/pmic)

タッチ センシング

[cypress.com/touch](http://cypress.com/touch)

USB コントローラー

[cypress.com/usb](http://cypress.com/usb)

ワイヤレス

[cypress.com/wireless](http://cypress.com/wireless)

#### PSoC® ソリューション

[PSoC 1](#) | [PSoC 3](#) | [PSoC 4](#) | [PSoC 5LP](#) | [PSoC 6 MCU](#)

#### サイプレス開発者コミュニティ

[コミュニティ](#) | [サンプルコード](#) | [Projects](#) | [ビデオ](#) | [ブログ](#) | [トレーニング](#) | [Components](#)

#### テクニカル サポート

[cypress.com/support](http://cypress.com/support)

© Cypress Semiconductor Corporation, 2011-2020. 本書面は、Cypress Semiconductor Corporation 及び Spansion LLC を含むその子会社（以下「Cypress」という。）に帰属する財産である。本書面（本書面に含まれ又は言及されているあらゆるソフトウェア若しくはファームウェア（以下「本ソフトウェア」という。）を含む）は、アメリカ合衆国及び世界のその他の国における知的財産法令及び条約に基づき Cypress が所有する。Cypress はこれらの法令及び条約に基づく全ての権利を留保し、本段落で特に記載されているものを除き、その特許権、著作権、商標権又はその他の知的財産権のライセンスを一切許諾しない。本ソフトウェアにライセンス契約書が伴っておらず、かつ Cypress との間で別途本ソフトウェアの使用方法を定める書面による合意がない場合、Cypress は、(1) 本ソフトウェアの著作権に基づき、(a) ソースコード形式で提供されている本ソフトウェアについて、Cypress ハードウェア製品と共に用いるためにのみ、かつ組織内部でのみ、本ソフトウェアの修正及び複製を行うこと、並びに(b) Cypress のハードウェア製品ユニットに用いるためにのみ、（直接又は再販売者及び販売代理店を介して間接のいずれかで）本ソフトウェアをバイナリコード形式で外部エンドユーザーに配布すること、並びに(2) 本ソフトウェア（Cypress により提供され、修正がなされていないもの）が抵触する Cypress の特許権のクレームに基づき、Cypress ハードウェア製品と共に用いるためにのみ、本ソフトウェアの作成、利用、配布及び輸入を行うことについての非独占的で譲渡不能な一身専属的ライセンス（サプライセンスの権利を除く）を付与する。本ソフトウェアのその他の使用、複製、修正、変換又はコンパイルを禁止する。

**適用される法律により許される範囲内で、Cypress は、本書面又はいかなる本ソフトウェア若しくはこれに伴うハードウェアに関する限りでも、明示又は默示をとわず、いかなる保証（商品性及び特定の目的への適合性の默示の保証を含むがこれらに限られない）も行わない。**いかなるコンピューティングデバイスも絶対に安全ということはない。従って、Cypress のハードウェアまたはソフトウェア製品に講じられたセキュリティ対策にもかかわらず、Cypress は、Cypress 製品への権限のないアクセスまたは使用といったセキュリティ違反から生じる一切の責任を負わない。加えて、本書面に記載された製品には、エラッタと呼ばれる設計上の欠陥またはエラーが含まれている可能性があり、公表された仕様とは異なる動作をする場合がある。適用される法律により許される範囲内で、Cypress は、別途通知することなく、本書面を変更する権利を留保する。Cypress は、本書面に記載のある、いかなる製品若しくは回路の適用又は使用から生じる一切の責任を負わない。本書面で提供されたあらゆる情報（あらゆるサンプルデザイン情報又はプログラムコードを含む）は、参照目的のためにのみに提供されたものである。この情報で構成するあらゆるアプリケーション及びその結果としてのあらゆる製品の機能性及び安全性を適切に設計、プログラム、かつテストすることは、本書面のユーザーの責任において行われるものとする。Cypress 製品は、兵器、兵器システム、原子力施設、生命維持装置若しくは生命維持システム、蘇生用の設備及び外科的移植を含むその他の医療機器若しくは医療システム、汚染管理若しくは有害物質管理の運用のために設計され若しくは意図されたシステムの重要な構成部分としての使用、又は装置若しくはシステムの不具合が人身傷害、死亡若しくは物的損害を生じさせるようなその他の使用（以下「本目的外使用」という。）のためには設計、意図又は承認されていない。重要な構成部分とは、それの不具合が装置若しくはシステムの不具合を生じさせるか又はその安全性若しくは実効性に影響すると合理的に予想できるような装置若しくはシステムのあらゆる構成部分をいう。Cypress 製品のあらゆる本目的外使用から生じ、若しくは本目的外使用に関連するいかなる請求、損害又はその他の責任についても、Cypress はその全部又は一部をとわず一切の責任を負わず、かつ Cypress はそれら一切から本書により免除される。Cypress は Cypress 製品の本目的外使用から生じ又は本目的外使用に関連するあらゆる請求、費用、損害及びその他の責任（人身傷害又は死亡に基づく請求を含む）から免責補償される。

Cypress、Cypress のロゴ、Spansion、Spansion のロゴ及びこれらの組み合わせ、WICED、PSoC、CapSense、EZ-USB、F-RAM、及び Traveo は、米国及びその他の国における Cypress の商標又は登録商標である。Cypress のより完全な商標のリストは、[cypress.com](http://cypress.com) を参照すること。その他の名称及びブランドは、それぞれの権利者の財産として権利主張がなされている可能性がある。