CY7C1386KV33

CY7C1387KV33

## 18M ビット (512K × 36/1M × 18) 同期式パイプライン DCD SRAM

### 特徴

- 最大 200MHzまでのバス動作をサポート

- 提供速度グレード : 200MHz、167MHz

- パイプライン動作用レジスタ付入出力

- 性能に最適化 (ダブルサイクル選択解除)

- ウェイトステートなしの深度拡張

- 3.3V コア電源 ( $V_{DD}$ )

- 2.5V または 3.3V I/O 電源 ( $V_{DDQ}$ )

- 高速なクロッカー出力時間

- 3ns (デバイス速度が 200MHzの場合)

- 高性能 3-1-1-1 アクセス速度を提供

- インターリーブまたはリニア バースト シーケンスに対応するユーザー選択可能バーストカウンター

- 独立したプロセッサとコントローラー アドレスストローブ

- セルフトライム同期書き込み

- 非同期出力イネーブル

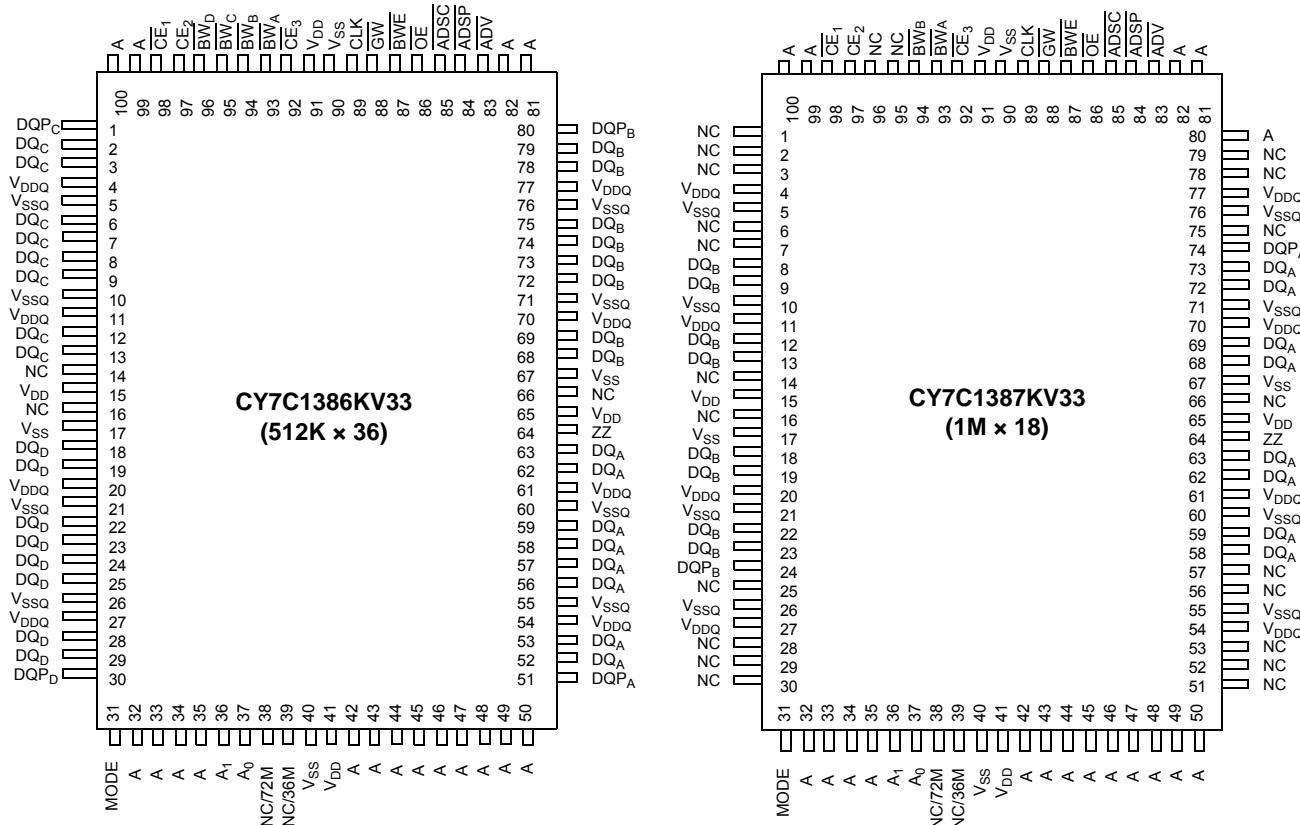

- CY7C1386KV33、CY7C1387KV33 は JEDEC 準拠の鉛フリー 100 ピン TQFP で提供

- ZZ スリープモードオプション

### 機能の詳細説明

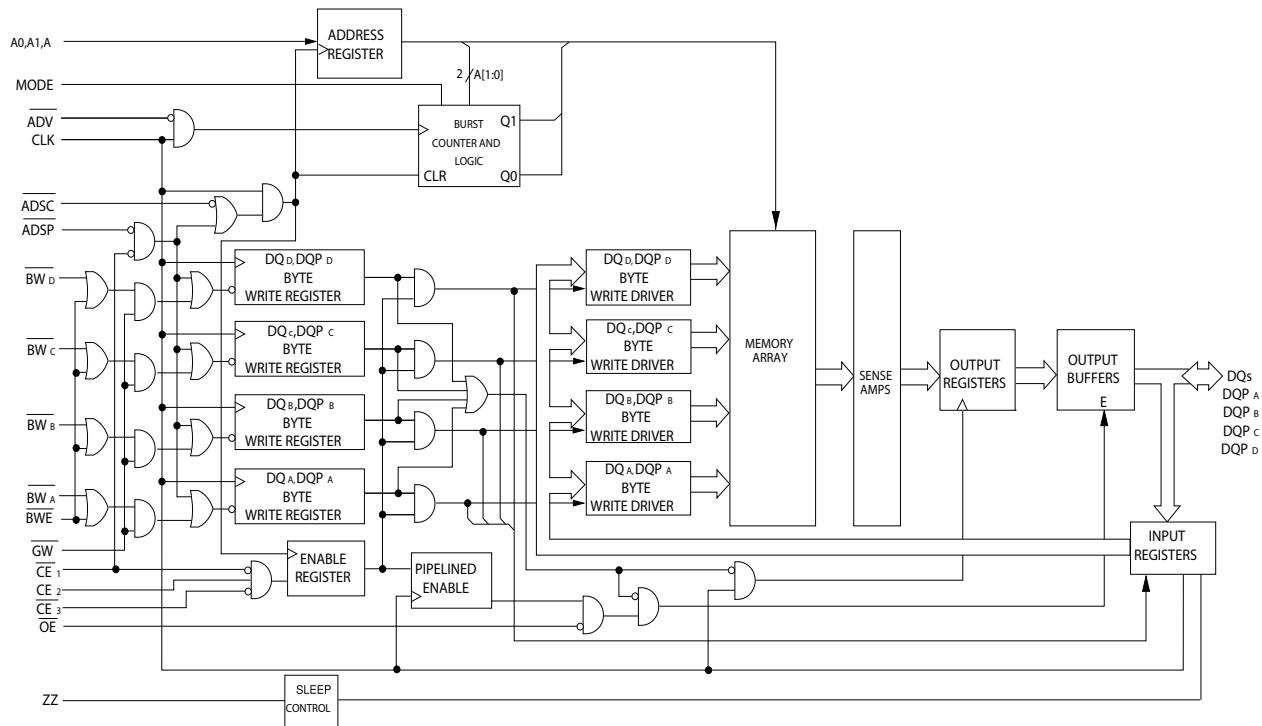

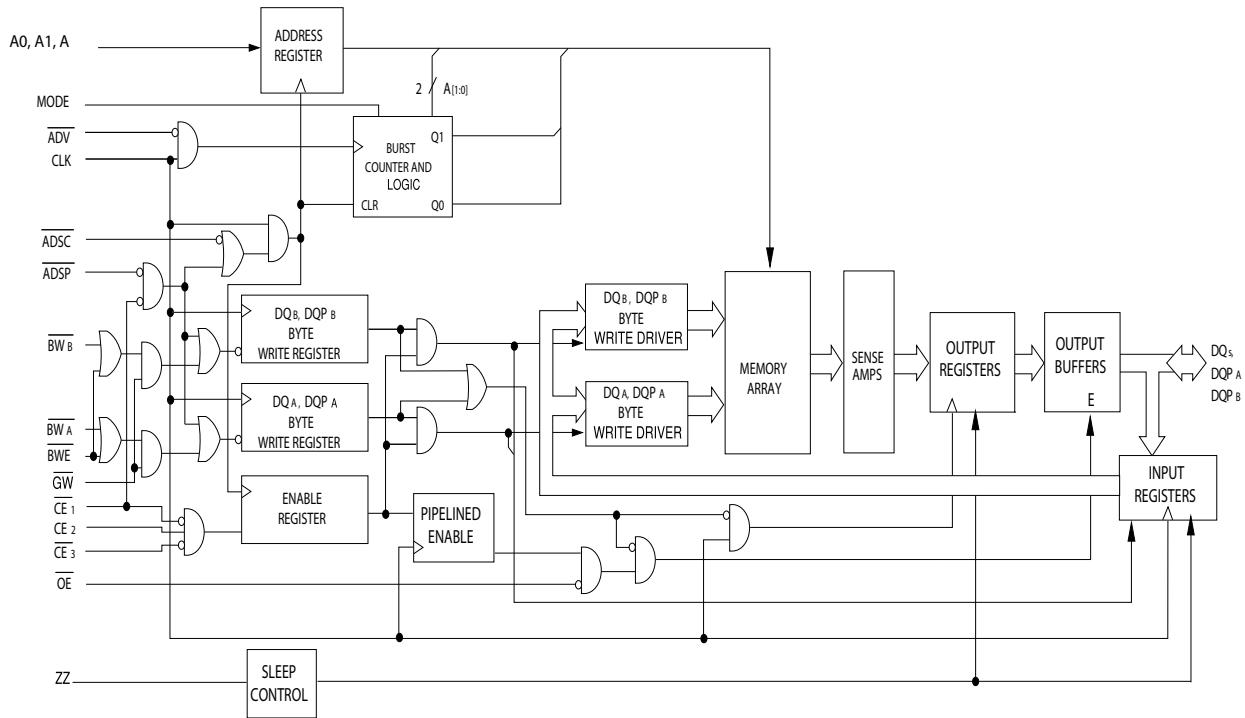

CY7C1386KV33 / CY7C1387KV33 SRAM は、内部バースト動作のために、高度な同期ペリフェラル回路および 2 ビットカウンターを 512K ビット × 36 と 1M ビット × 18 SRAM セルに組み込んでいます。すべての同期入力は、ポジティブエッジでトリガされるクロック入力 (CLK) で制御するレジスタにより取り込まれます。同期入力は、すべてのアドレス、すべてのデータ入力、アドレス パイプライン チップ イネーブル ( $\overline{CE}_1$ )、深度拡張チップ イネーブル ( $CE_2$ 、 $CE_3$ )、バースト制御入力 ( $ADSC$ 、 $ADSP$ 、と  $ADV$ )、書き込みイネーブル ( $BW_XBW_E$ )、およびグローバル書き込み ( $GW$ ) を含みます。非同期入力は出力イネーブル ( $OE$ ) 信号と ZZ ピンです。

アドレスストローブ プロセッサ ( $ADSP$ ) またはアドレスストローブ コントローラー ( $ADSC$ ) がアクティブの時、アドレスとチップ イネーブルはクロックの立ち上がりエッジで読み出されます。後続バーストアドレスは、アドバンス ピン ( $ADV$ ) の制御によって内部的に生成できます。

アドレス、データ入力、および書き込み制御信号は、セルフライム書き込みサイクルを開始するために、内部でレジスタに読み込まれます。デバイスはバイト書き込み動作をサポートします(詳細については、5 ページの「ピン配置」と 9 ページの「真理値表」を参照してください)。書き込みサイクルは、バイト書き込み制御入力の制御によって 1 ~ 4 バイト幅になります。 $GW$  がアクティブ LOWになると、すべてのバイトが書き込まれます。このデバイスは、追加のパイプライン イネーブル レジスタを内蔵しており、これにより選択解除が実行された時に出力バッファをオフにすることをもう 1 サイクル遅延させます。この機能はシステム性能へ影響を与えることなく深度拡張を可能にします。

CY7C1386KV33 / CY7C1387KV33 は +3.3V のコア電源で動作しますが、すべての出力は +3.3V または +2.5V 電源で動作します。すべての入力と出力は JEDEC 標準規格と JESD8-5 に準拠しています。

### セレクションガイド

| 説明       | 200MHz | 167MHz | 単位  |

|----------|--------|--------|-----|

| 最大アクセス時間 | 3.0    | 3.4    | ns  |

| 最大動作電流   | × 18   | 158    | 143 |

|          |        | 178    | 163 |

## 論理ブロック図 – CY7C1386KV33

## 論理ブロック図 – CY7C1387KV33

## 目次

|                         |    |

|-------------------------|----|

| ピン配置                    | 5  |

| ピン定義                    | 6  |

| 機能の概要                   | 7  |

| シングル読み出しアクセス            | 7  |

| ADSP で開始されるシングル書き込みアクセス | 7  |

| ADSC で開始されるシングル書き込みアクセス | 8  |

| バースト シーケンス              | 8  |

| スリープ モード                | 8  |

| インターリーブ バースト アドレス表      | 8  |

| リニア バースト アドレス表          | 8  |

| ZZ モード 電気的特性            | 8  |

| 真理値表                    | 9  |

| 書き込み／読み出しの真理値表          | 10 |

| 書き込み／読み出しの真理値表          | 10 |

| 最大定格                    | 11 |

| 動作範囲                    | 11 |

| 中性子ソフト エラー耐性            | 11 |

| 電気的特性                   | 11 |

| 静電容量                    | 13 |

|                     |    |

|---------------------|----|

| 熱抵抗                 | 13 |

| AC テストの負荷および波形      | 13 |

| スイッチング特性            | 14 |

| スイッチング波形            | 15 |

| 注文情報                | 19 |

| 注文コードの定義            | 19 |

| パッケージ図              | 20 |

| 略語                  | 21 |

| 本書の表記法              | 21 |

| 測定単位                | 21 |

| 改訂履歴                | 22 |

| セールス、ソリューションおよび法律情報 | 23 |

| ワールドワイド販売と設計サポート    | 23 |

| 製品                  | 23 |

| PSoC® ソリューション       | 23 |

| サイプレス開発者コミュニティ      | 23 |

| テクニカル サポート          | 23 |

## ピン配置

図 1. 100 ピン TQFP (14 × 20 × 1.4mm) ピン配置 (3 チップ イネーブル)

## ピン定義

| ピン名                                                                                           | I/O       | 説明                                                                                                                                                                                                                                                          |

|-----------------------------------------------------------------------------------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A <sub>0</sub> 、A <sub>1</sub> 、A                                                             | 入力 - 同期   | アドレス位置の1つを選択するために使用されるアドレス入力。 <u>ADSP</u> または <u>ADSC</u> がアクティブ LOW であり、CE <sub>1</sub> 、CE <sub>2</sub> 、CE <sub>3</sub> がアクティブとしてサンプリングされた場合、CLK の立ち上がりエッジでサンプリング。A1:A0 は 2 ビット カウンターに供給される                                                              |

| <u>BW<sub>A</sub></u> 、 <u>BW<sub>B</sub></u> 、 <u>BW<sub>C</sub></u> 、 <u>BW<sub>D</sub></u> | 入力 - 同期   | バイト書き込み選択入力、アクティブ LOW。SRAM へのバイト書き込みを実行するために <u>BWE</u> で有効にする。CLK の立ち上がりエッジでサンプリング                                                                                                                                                                         |

| <u>GW</u>                                                                                     | 入力 - 同期   | グローバル書き込みイネーブル 入力、アクティブ LOW。CLK の立ち上がりエッジで LOW にアサートされた時、グローバル書き込みが実行される ( <u>BW<sub>X</sub></u> と <u>BWE</u> 上の値に関わらず、すべてのバイトが書き込まれる)                                                                                                                      |

| <u>BWE</u>                                                                                    | 入力 - 同期   | バイト書き込みイネーブル入力、アクティブ LOW。CLK の立ち上がりエッジでサンプリング。バイト書き込みシーケンスを開始するためにこの信号を LOW にアサートすることが必要                                                                                                                                                                    |

| <u>CLK</u>                                                                                    | 入力 - クロック | クロック入力。デバイスへの全ての同期入力を取り込むために使用。バースト処理中に、 <u>ADV</u> が LOW にアサートされた際のバースト カウンターのインクリメントのためにも使用                                                                                                                                                               |

| <u>CE<sub>1</sub></u>                                                                         | 入力 - 同期   | チップ イネーブル 1 入力、アクティブ LOW。CLK の立ち上がりエッジでサンプリング。デバイスを選択／選択解除するために CE <sub>2</sub> と CE <sub>3</sub> と併用。CE <sub>1</sub> が HIGH の場合、ADSP は無視される。CE <sub>1</sub> は、新しい外部アドレスがロードされた時にのみサンプリングされる                                                                |

| CE <sub>2</sub>                                                                               | 入力 - 同期   | チップ イネーブル 2 入力、アクティブ HIGH。CLK の立ち上がりエッジでサンプリング。デバイスを選択／選択解除するために <u>CE<sub>1</sub></u> と <u>CE<sub>3</sub></u> と併用。CE <sub>2</sub> は、新しい外部アドレスがロードされた時にのみサンプリングされる                                                                                          |

| <u>CE<sub>3</sub></u>                                                                         | 入力 - 同期   | チップ イネーブル 3 入力、アクティブ LOW。CLK の立ち上がりエッジでサンプリング。デバイスを選択／選択解除するために <u>CE<sub>1</sub></u> と CE <sub>2</sub> と併用。CE <sub>3</sub> は、新しい外部アドレスがロードされた時にのみサンプリングされる                                                                                                 |

| <u>OE</u>                                                                                     | 入力 - 非同期  | 出力イネーブル、非同期入力、アクティブ LOW。I/O ピンの方向を制御。LOW の場合、I/O ピンは出力として機能。HIGH にデアサートされた時、DQ ピンはトライステートになり、入力データ ピンとして機能。 <u>OE</u> は、選択解除の状態から移行後の読み出しサイクルの最初のクロックの間マスクされる                                                                                               |

| <u>ADV</u>                                                                                    | 入力 - 同期   | CLK の立ち上がりエッジでサンプリングされるアクティブ LOW アドバス入力信号。このピンがアサートされる時、バースト サイクルで自動的にアドレスをインクリメント                                                                                                                                                                          |

| <u>ADSP</u>                                                                                   | 入力 - 同期   | CLK の立ち上がりエッジでサンプリングされるプロセッサからのアドレス ストローブ、アクティブ LOW。LOW にアサートされた時、デバイスに入力されたアドレスはアドレス レジスタに取り込まれる。A1:A0 はバースト カウンターにもロードされる。ADSP と ADSC の両方がアサートされた時、ADSP のみが認識される。CE <sub>1</sub> が HIGH にデアサートされた時、ADSP は無視される                                            |

| <u>ADSC</u>                                                                                   | 入力 - 同期   | CLK の立ち上がりエッジでサンプリングされる、コントローラからのアドレス ストローブ、アクティブ LOW。LOW にアサートされた時、デバイスに入力されたアドレスはアドレス レジスタに取り込まれる。A1:A0 はバースト カウンターにもロードされる。ADSP と ADSC の両方がアサートされた時、ADSP のみが認識される                                                                                        |

| <u>ZZ</u>                                                                                     | 入力 - 非同期  | ZZ スリープ入力、アクティブ HIGH。HIGH にアサートされた時、デバイスはデータの統合性が保持されたまま非タイム クリティカルなスリープの状態に入る。通常動作では、このピンを LOW にする。ZZ ピンは内部プルダウン抵抗に接続                                                                                                                                      |

| DQs、DQP <sub>X</sub>                                                                          | I/O - 同期  | 双方向データ I/O ライン。入力として機能している場合、CLK の立ち上がりエッジでトリガーされる内蔵データ レジスタに供給される。出力として機能している場合、読み出しサイクルの以前のクロック中に供給されたアドレスにより指定されるメモリ位置に含まれるデータを送信。このピンの入出力の方向は <u>OE</u> で制御。 <u>OE</u> が LOW にアサートされた時、このピンは出力として機能。この信号が HIGH の場合、DQs と DQP <sub>X</sub> はトライステート状態になる |

| V <sub>DD</sub>                                                                               | 電源        | デバイス コアの電源入力                                                                                                                                                                                                                                                |

| V <sub>SS</sub>                                                                               | グランド      | デバイス コアのグランド                                                                                                                                                                                                                                                |

| V <sub>SSQ</sub>                                                                              | I/O グランド  | I/O 回路のグランド                                                                                                                                                                                                                                                 |

| V <sub>DDQ</sub>                                                                              | I/O 電源    | I/O 回路の電源                                                                                                                                                                                                                                                   |

## ピン定義 (続き)

| ピン名                                                | I/O            | 説明                                                                                                                                                                                |

|----------------------------------------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MODE                                               | 入力 -<br>スタティック | <b>バースト順序を選択。</b> GND に接続された場合、リニア バースト シーケンスが選択される。V <sub>DD</sub> に接続するまたはフローティングのままにする時、インターリーブ バースト シーケンスが選択される。これはストラップ ピンであり、デバイス動作中にスタティックのままにすることが必要。MODE ピンは内部プルアップ抵抗に接続 |

| NC                                                 | -              | <b>未接続。</b> ダイに内部的に接続されていない                                                                                                                                                       |

| NC/(36M、<br>72M、<br>144M、<br>288M、<br>576M、<br>1G) | -              | これらのピンは接続されていない。36M、72M、144M、288M、576M および 1G の容量に拡張するため<br>に使用される                                                                                                                |

## 機能の概要

すべての同期入力は、クロックの立ち上がりエッジで制御される入力レジスタを通過します。全てのデータ出力は、クロックの立ち上がりエッジで制御される出力レジスタを通過します。

CY7C1386KV33 / CY7C1387KV33 は、リニアまたはインターリーブ バースト シーケンスを使用するシステムでは二次キャッシュをサポートしています。リニア バースト シーケンスは、リニア バースト シーケンスを使うプロセッサに対応できるように設計されています。バースト順序はユーザーにより選択可能であり、MODE 入力をサンプリングすることで決定されます。アクセスはプロセッサ アドレス ストローブ (ADSP) またはコントローラー アドレス ストローブ (ADSC) いずれか一方で開始できます。バースト シーケンスを介したアドレスの増加は、ADV 入力で制御されます。2 ビットの内蔵ラップアラウンド バースト カウンターは、バースト シーケンスの最初のアドレスを取り込んで、以降のバースト アクセスでは自動的にアドレスをインクリメントします。

バイト書き込み処理は、バイト書き込みイネーブル (BWE) とバイト書き込み選択 (BW<sub>X</sub>) 入力で制御されます。グローバル書き込みイネーブル (GW) は全てのバイト書き込み入力を無効にし、すべての 4 バイトにデータを書き込みます。全ての書き込み動作は、内蔵のセルフトライム同期書き込み回路で単純化されます。

同期チップ セレクト信号  $\overline{CE}_1$ 、 $CE_2$ 、 $\overline{CE}_3$  と非同期出力イネーブル 信号 ( $\overline{OE}$ ) は、容易なバンク選択および出力トライステート制御を提供します。 $\overline{CE}_1$  が HIGH の場合、ADSP は無視されます。

## シングル読み出しアクセス

クロックの立ち上がりで次の条件が満たされると、このアクセスが開始されます：(1) ADSP または ADSC が LOW にアサートされ、(2) チップ選択信号が全てアクティブにアサートされ、(3) 書き込み信号 (GW, BWE) が全て HIGH にデアサートされます。 $CE_1$  が HIGH の場合、ADSP は無視されます。アドレス入力に供給されたアドレスは、メモリ コアに提供されながら、アドレス増加論理ブロックとアドレス レジスタに保存されます。対応するデータを出力レジスタの入力へ伝播することができます。 $OE$  がアクティブ LOW であれば、次のクロックの立ち上がりエッジで、データは  $t_{CO}$  以内に出力レジスタを介してデータ バスに

伝播されます。唯一の例外は、SRAM が選択解除状態から選択状態に復帰する時にのみ発生します。SRAM の出力は最初のアクセス サイクルの間常にトライステートになります。最初のアクセス サイクルの後、出力は  $\overline{OE}$  信号で制御されます。連続的シングル読み出しサイクルがサポートされています。

CY7C1386KV33 / CY7C1387KV33 は、ダブル サイクル選択解除のデバイスです、チップ セレクト信号及び ADSP か ADSC 信号のクロック立ち上がりで SRAM が選択解除された後、出力は次のクロック立ち上がりの直後にトライステートになります。

## ADSP で開始されるシングル書き込みアクセス

クロックの立ち上がりで次の条件の両方とも満たされると、このアクセスは開始されます：(1) ADSP が LOW にアサートされ、(2) チップ選択信号がアクティブにアサートされる。供給されたアドレスはメモリ コアに提供されながら、アドレス レジスタとアドレスを進める論理ブロックにロードされます。書き込み信号 (GW, BWE, BW<sub>X</sub>) および ADV 入力は最初のサイクル中は無視されます。

ADSP でトリガーされる書き込みアクセスは完了するのに 2 クロック サイクルを要します。 $GW$  が 2 番目のクロックの立ち上がりエッジで LOW にアサートされた場合、DQ<sub>x</sub> 入力に供給されたデータは、メモリ コア上の対応するアドレス位置に書き込まれます。 $GW$  が HIGH の場合、書き込み動作は BWE と BW<sub>X</sub> 信号で制御されます。

CY7C1386KV33/CY7C1387KV33 は、書き込みサイクル説明表で説明されたバイト書き込み機能を備えています。選択したバイト書き込み入力を使ってバイト書き込みイネーブル入力 (BWE) をアサートすると、所望のバイトのみが選択的に書き込まれます。バイト書き込み動作中に選択されないバイトは、不变のままであります。書き込み動作を単純化するためにセルフトライム同期書き込みメカニズムが提供されています。

CY7C1386KV33/CY7C1387KV33 が共通 I/O デバイスであるため、データを DQ 入力に供給する前に、出力イネーブル ( $\overline{OE}$ ) を HIGH にデアサートする必要があります。このようにすると、出力ドライバーがトライステートになります。安全策として、 $\overline{OE}$  の状態にかかわらず、書き込みサイクルが検出される度に DQ は自動的にトライステートになります。

### ADSC で開始されるシングル書き込みアクセス

次の条件が満たされると、ADSC 書き込みアクセスは開始されます：(1) ADSC が LOW にアサートされ、(2) ADSP が HIGH にデアサートされ、(3) チップ選択信号がアクティブにアサートされ、(4) 書き込み入力 (GW、BWE、BW<sub>X</sub>) の適切な組み合わせが、所望のバイトへの書き込みを実行するためにアクティブにアサートします。ADSC でトリガーされる書き込みアクセスが完了するのに 1 クロックサイクルを要します。供給されたアドレスはメモリコアに提供されながら、アドレスレジスタとアドレス増加論理ブロックにロードされます。ADV 入力はこのサイクル中に無視されます。グローバル書き込みを行う場合、DQ<sub>X</sub> に供給されたデータはメモリコア上の対応するアドレス位置に書き込まれます。バイト書き込みを行う場合、選択されたバイトのみが書き込まれます。バイト書き込み動作中に選択されないバイトは、不变のままであります。書き込み動作を単純化するためにセルフタイム同期書き込みメカニズムが提供されています。

CY7C1386KV33 / CY7C1387KV33 が共通 I/O デバイスであるため、データを DQ<sub>X</sub> 入力に供給する前に、出力イネーブル (OE) を HIGH にデアサートする必要があります。このようにすると、出力ドライバーがトライステートになります。安全策として、OE の状態にかかわらず、書き込みサイクルが検出される度に DQ<sub>X</sub> は自動的にトライステートになります。

### バーストシーケンス

CY7C1386KV33 / CY7C1387KV33 は A<sub>[1:0]</sub> によって供給される 2 ビットのラップアラウンドカウンターを内蔵しています。このカウンターはインターリーブまたはリニアバーストシーケンスを実装しています。バーストシーケンスは MODE 入力によりユーザー選択可能です。

クロックの立ち上がりで ADV を LOW にアサートすると、バーストカウンターはバーストシーケンスで次のアドレスに自動的にインクリメントされます。読み出しと書き込みバースト動作の両方がサポートされています。

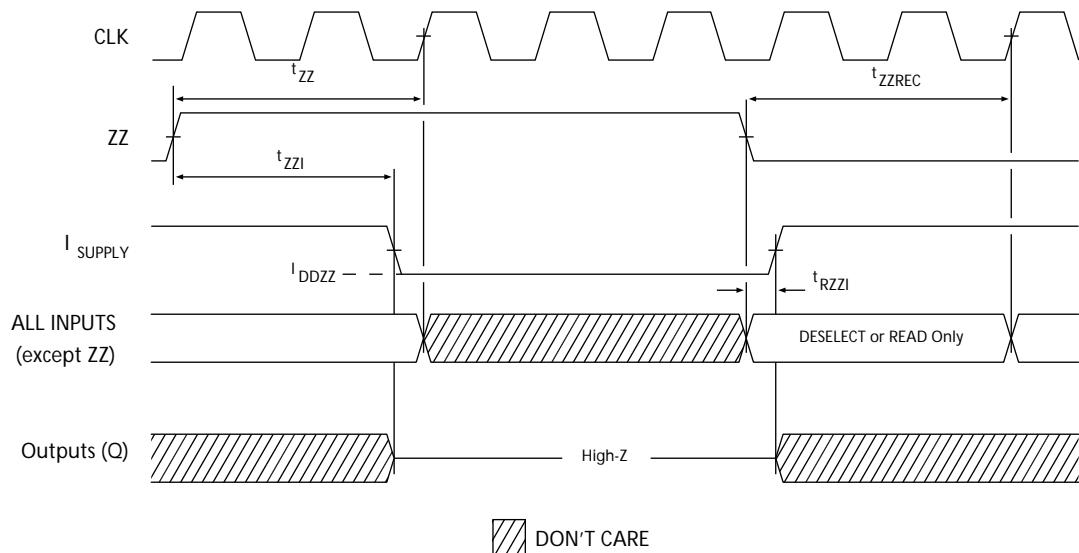

### ZZ モード電気的特性

| パラメーター             | 説明                    | テスト条件                       | Min               | Max               | 単位 |

|--------------------|-----------------------|-----------------------------|-------------------|-------------------|----|

| I <sub>DDZZ</sub>  | スリープモードスタンバイ電流        | ZZ ≥ V <sub>DD</sub> - 0.2V | -                 | 65                | mA |

| t <sub>ZZS</sub>   | デバイス動作から ZZ までの時間     | ZZ ≥ V <sub>DD</sub> - 0.2V | -                 | 2t <sub>CYC</sub> | ns |

| t <sub>ZZREC</sub> | ZZ 復帰時間               | ZZ ≤ 0.2V                   | 2t <sub>CYC</sub> | -                 | ns |

| t <sub>ZZI</sub>   | ZZ アクティブからスリープ電流開始まで  | このパラメーターはサンプリング             | -                 | 2t <sub>CYC</sub> | ns |

| t <sub>RZZI</sub>  | ZZ 非アクティブからスリープ電流終了まで | このパラメーターはサンプリング             | 0                 | -                 | ns |

### スリープモード

ZZ 入力ピンは非同期入力です。ZZ をアサートすると、SRAM は省電力スリープモードに入ります。このスリープモードへの移行および復帰には 2 クロックサイクルかかります。このモードでは、データの整合性が保証されます。スリープモードに入った時に保留中のアクセスは有効として見なされず、動作完了も保証されません。デバイスはスリープモードに入る前に、選択解除する必要があります。ZZ 入力が LOW に戻った後、CEs、ADSP、および ADSC は t<sub>ZZREC</sub> の間、非アクティブのままにする必要があります。

### インターリーブバーストアドレス表

(MODE = 開放または V<sub>DD</sub>)

| 1番目のアドレス A1:A0 | 2番目のアドレス A1:A0 | 3番目のアドレス A1:A0 | 4番目のアドレス A1:A0 |

|----------------|----------------|----------------|----------------|

| 00             | 01             | 10             | 11             |

| 01             | 00             | 11             | 10             |

| 10             | 11             | 00             | 01             |

| 11             | 10             | 01             | 00             |

### リニアバーストアドレス表

(MODE = GND)

| 1番目のアドレス A1:A0 | 2番目のアドレス A1:A0 | 3番目のアドレス A1:A0 | 4番目のアドレス A1:A0 |

|----------------|----------------|----------------|----------------|

| 00             | 01             | 10             | 11             |

| 01             | 10             | 11             | 00             |

| 10             | 11             | 00             | 01             |

| 11             | 00             | 01             | 10             |

## 真理値表

以下は CY7C1386KV33 及び CY7C1387KV33 の真理値表 [1, 2, 3, 4, 5]

| 動作              | 使用されているアドレス | <u>CE<sub>1</sub></u> | CE <sub>2</sub> | <u>CE<sub>3</sub></u> | ZZ | <u>ADSP</u> | <u>ADSC</u> | <u>ADV</u> | <u>WRITE</u> | <u>OE</u> | CLK | DQ      |

|-----------------|-------------|-----------------------|-----------------|-----------------------|----|-------------|-------------|------------|--------------|-----------|-----|---------|

| 選択解除サイクル、パワーダウン | 無           | H                     | X               | X                     | L  | X           | L           | X          | X            | X         | L-H | トライステート |

| 選択解除サイクル、パワーダウン | 無           | L                     | L               | X                     | L  | L           | X           | X          | X            | X         | L-H | トライステート |

| 選択解除サイクル、パワーダウン | 無           | L                     | X               | H                     | L  | L           | X           | X          | X            | X         | L-H | トライステート |

| 選択解除サイクル、パワーダウン | 無           | L                     | L               | X                     | L  | H           | L           | X          | X            | X         | L-H | トライステート |

| 選択解除サイクル、パワーダウン | 無           | L                     | X               | H                     | L  | H           | L           | X          | X            | X         | L-H | トライステート |

| スリープ モード、パワーダウン | 無           | X                     | X               | X                     | H  | X           | X           | X          | X            | X         | X   | トライステート |

| 読み出しサイクル、バースト開始 | 外部          | L                     | H               | L                     | L  | L           | X           | X          | X            | L         | L-H | Q       |

| 読み出しサイクル、バースト開始 | 外部          | L                     | H               | L                     | L  | L           | X           | X          | X            | H         | L-H | トライステート |

| 書き込みサイクル、バースト開始 | 外部          | L                     | H               | L                     | L  | H           | L           | X          | L            | X         | L-H | D       |

| 読み出しサイクル、バースト開始 | 外部          | L                     | H               | L                     | L  | H           | L           | X          | H            | L         | L-H | Q       |

| 読み出しサイクル、バースト開始 | 外部          | L                     | H               | L                     | L  | H           | L           | X          | H            | H         | L-H | トライステート |

| 読み出しサイクル、バースト継続 | 後続          | X                     | X               | X                     | L  | H           | H           | L          | H            | L         | L-H | Q       |

| 読み出しサイクル、バースト継続 | 後続          | X                     | X               | X                     | L  | H           | H           | L          | H            | H         | L-H | トライステート |

| 読み出しサイクル、バースト継続 | 後続          | H                     | X               | X                     | L  | X           | H           | L          | H            | L         | L-H | Q       |

| 読み出しサイクル、バースト継続 | 後続          | H                     | X               | X                     | L  | X           | H           | L          | H            | H         | L-H | トライステート |

| 書き込みサイクル、バースト継続 | 後続          | X                     | X               | X                     | L  | H           | H           | L          | L            | X         | L-H | D       |

| 書き込みサイクル、バースト継続 | 後続          | H                     | X               | X                     | L  | X           | H           | L          | L            | X         | L-H | D       |

| 読み出しサイクル、バースト停止 | 現行          | X                     | X               | X                     | L  | H           | H           | H          | H            | L         | L-H | Q       |

| 読み出しサイクル、バースト停止 | 現行          | X                     | X               | X                     | L  | H           | H           | H          | H            | H         | L-H | トライステート |

| 読み出しサイクル、バースト停止 | 現行          | H                     | X               | X                     | L  | X           | H           | H          | H            | L         | L-H | Q       |

| 読み出しサイクル、バースト停止 | 現行          | H                     | X               | X                     | L  | X           | H           | H          | H            | H         | L-H | トライステート |

| 書き込みサイクル、バースト停止 | 現行          | X                     | X               | X                     | L  | H           | H           | H          | L            | X         | L-H | D       |

| 書き込みサイクル、バースト停止 | 現行          | H                     | X               | X                     | L  | X           | H           | H          | L            | X         | L-H | D       |

注:

1. X = ドントケア, H = 論理 HIGH, L = 論理 LOW。

2. 1つ以上のバイト書き込みイネーブル信号と BWE = L または GW = L の時、WRITE = L です。全てのバイト書き込みイネーブル信号、BWE、GW = H の時、WRITE = H です。

3. DQ ピンは現行のサイクルと OE 信号によって制御されます。OE は非同期で、クロックと同期してサンプリングされません。

4. GW、BWE、または BW<sub>x</sub> の状態に関わらず、ADSP がアサートされると、SRAM は読み出しサイクルを開始します。書き込みは、ADSP に続くクロックサイクルで、または ADSC のアサートにより行われます。従って、出力をトライステートにするために、OE を書き込みサイクルの開始前に HIGH に駆動する必要があります。OE はその後の書き込みサイクルからは「ドントケア」です。

5. OE は非同期で、クロック立ち上がりと同期してサンプリングされません。これは、書き込みサイクル中に内部的にマスキングされます。読み出しサイクルでは、OE が非アクティブになる、またはデバイスが選択解除された場合、全てのデータビットはトライステートになります。OE がアクティブ (LOW) になった場合、全てのデータビットは出力として機能します。

## 書き込み／読み出しの真理値表

以下は CY7C1386KV33 の真理値表です。[6, 7]

| CY7C1386KV33                                      | $\overline{GW}$ | $\overline{BWE}$ | $\overline{BW}_D$ | $\overline{BW}_C$ | $\overline{BW}_B$ | $\overline{BW}_A$ |

|---------------------------------------------------|-----------------|------------------|-------------------|-------------------|-------------------|-------------------|

| 読み出し                                              | H               | H                | X                 | X                 | X                 | X                 |

| 読み出し                                              | H               | L                | H                 | H                 | H                 | H                 |

| バイト A 書き込み – (DQ <sub>A</sub> 、DQP <sub>A</sub> ) | H               | L                | H                 | H                 | H                 | L                 |

| バイト B 書き込み – (DQ <sub>B</sub> 、DQP <sub>B</sub> ) | H               | L                | H                 | H                 | L                 | H                 |

| バイト B、A 書き込み                                      | H               | L                | H                 | H                 | L                 | L                 |

| バイト C 書き込み – (DQ <sub>C</sub> 、DQP <sub>C</sub> ) | H               | L                | H                 | L                 | H                 | H                 |

| バイト C、A 書き込み                                      | H               | L                | H                 | L                 | H                 | L                 |

| バイト C、B 書き込み                                      | H               | L                | H                 | L                 | L                 | H                 |

| バイト C、B、A 書き込み                                    | H               | L                | H                 | L                 | L                 | L                 |

| バイト D 書き込み – (DQ <sub>D</sub> 、DQP <sub>D</sub> ) | H               | L                | L                 | H                 | H                 | H                 |

| バイト D、A 書き込み                                      | H               | L                | L                 | H                 | H                 | L                 |

| バイト D、B 書き込み                                      | H               | L                | L                 | H                 | L                 | H                 |

| バイト D、B、A 書き込み                                    | H               | L                | L                 | H                 | L                 | L                 |

| バイト D、C 書き込み                                      | H               | L                | L                 | L                 | H                 | H                 |

| バイト D、C、A 書き込み                                    | H               | L                | L                 | L                 | H                 | L                 |

| バイト D、C、B 書き込み                                    | H               | L                | L                 | L                 | L                 | H                 |

| すべてのバイト書き込み                                       | H               | L                | L                 | L                 | L                 | L                 |

| すべてのバイト書き込み                                       | L               | X                | X                 | X                 | X                 | X                 |

## 書き込み／読み出しの真理値表

以下は CY7C1387KV33 の書き込み／読み出しの真理値表です。[6, 7]

| CY7C1387KV33                                      | $\overline{GW}$ | $\overline{BWE}$ | $\overline{BW}_B$ | $\overline{BW}_A$ |

|---------------------------------------------------|-----------------|------------------|-------------------|-------------------|

| 読み出し                                              | H               | H                | X                 | X                 |

| 読み出し                                              | H               | L                | H                 | H                 |

| バイト A 書き込み – (DQ <sub>A</sub> 、DQP <sub>A</sub> ) | H               | L                | H                 | L                 |

| バイト B 書き込み – (DQ <sub>B</sub> 、DQP <sub>B</sub> ) | H               | L                | L                 | H                 |

| すべてのバイト書き込み                                       | H               | L                | L                 | L                 |

| すべてのバイト書き込み                                       | L               | X                | X                 | X                 |

### 注：

6. DQ ピンは現行のサイクルと  $\overline{OE}$  信号によって制御されます。 $\overline{OE}$  は非同期で、クロックと同期してサンプリングされません。

7. この表では、バイト書き込みの組み合わせの一部のみを示します。どの  $\overline{BW}_X$  の組み合わせも可能です。書き込みは、アクティブになるバイト書き込み信号に応じて適切に行われます。

## 最大定格

最大定格を超えるとデバイスの寿命が短くなる可能性があります。ユーザー ガイドラインはテストされていません。

|                                        |       |                                |

|----------------------------------------|-------|--------------------------------|

| 保存温度                                   | ..... | -65°C ~ +150°C                 |

| 通電時の周囲温度                               | ..... | -55°C ~ +125°C                 |

| GND を基準とした V <sub>DD</sub> 上の電源電圧      | ..... | -0.5V ~ +4.6V                  |

| GND を基準とした V <sub>DDQ</sub> 上の電源電圧     | ..... | -0.5V ~ +V <sub>DD</sub>       |

| トライステート状態の出力に印加される DC 電圧               | ..... | -0.5V ~ V <sub>DDQ</sub> +0.5V |

| DC 入力電圧                                | ..... | -0.5V ~ V <sub>DD</sub> + 0.5V |

| 出力への電流 (LOW)                           | ..... | 20mA                           |

| 静電気放電電圧<br>(MIL-STD-883、メソッド 3015 による) | ..... | > 2001V                        |

| ラッピングアップ電流                             | ..... | > 200mA                        |

## 動作範囲

| 範囲  | 周囲温度        | V <sub>DD</sub>  | V <sub>DDQ</sub>            |

|-----|-------------|------------------|-----------------------------|

| 民生用 | 0°C ~ +70°C | 3.3V - 5% / +10% | 2.5V - 5% ~ V <sub>DD</sub> |

## 中性子ソフト エラー耐性

| パラメーター                    | 説明                       | テスト条件 | Typ | Max* | 単位          |

|---------------------------|--------------------------|-------|-----|------|-------------|

| LSBU<br>(ECC なし<br>のデバイス) | 単一論理<br>ビット反転            | 25°C  | 197 | 216  | FIT/<br>Mb  |

| LMBU                      | 論理<br>マルチビット<br>アップセット   | 25°C  | 0   | 0.01 | FIT/<br>Mb  |

| SEL                       | シングル<br>イベント<br>ラッピングアップ | 85°C  | 0   | 0.1  | FIT/<br>Dev |

\* テスト中に LMBU または SEL イベントの発生無し；本項は  $\chi^2$  分布の 95% 信頼上限を示す。詳細は、アプリケーション ノート AN54908 「Accelerated Neutron SER Testing and Calculation of Terrestrial Failure Rates」を参照

## 電気的特性

### 動作範囲において

| パラメーター <sup>[8, 9]</sup> | 説明                         | テスト条件                                          | Min   | Max                    | 単位 |

|--------------------------|----------------------------|------------------------------------------------|-------|------------------------|----|

| V <sub>DD</sub>          | 電源電圧                       |                                                | 3.135 | 3.6                    | V  |

| V <sub>DDQ</sub>         | I/O 電源電圧                   | 3.3V I/O の場合                                   | 3.135 | V <sub>DD</sub>        | V  |

|                          |                            | 2.5V I/O の場合                                   | 2.375 | 2.625                  | V  |

| V <sub>OH</sub>          | 出力 HIGH 電圧                 | 3.3V I/O、I <sub>OH</sub> = -4.0mA の場合          | 2.4   | -                      | V  |

|                          |                            | 2.5V I/O、I <sub>OH</sub> = -1.0mA の場合          | 2.0   | -                      | V  |

| V <sub>OL</sub>          | 出力 LOW 電圧                  | 3.3V I/O、I <sub>OL</sub> = 8.0mA の場合           | -     | 0.4                    | V  |

|                          |                            | 2.5V I/O、I <sub>OL</sub> = 1.0mA の場合           | -     | 0.4                    | V  |

| V <sub>IH</sub>          | 入力 HIGH 電圧 <sup>[8]</sup>  | 3.3V I/O の場合                                   | 2.0   | V <sub>DD</sub> + 0.3V | V  |

|                          |                            | 2.5V I/O の場合                                   | 1.7   | V <sub>DD</sub> + 0.3V | V  |

| V <sub>IL</sub>          | 入力 LOW 電圧 <sup>[8]</sup>   | 3.3V I/O の場合                                   | -0.3  | 0.8                    | V  |

|                          |                            | 2.5V I/O の場合                                   | -0.3  | 0.7                    | V  |

| I <sub>x</sub>           | 入力リード電流<br>(ZZ と MODE を除く) | GND ≤ V <sub>I</sub> ≤ V <sub>DDQ</sub>        | -5    | 5                      | μA |

|                          | MODE の入力電流                 | 入力 = V <sub>SS</sub>                           | -30   | -                      | μA |

|                          |                            | 入力 = V <sub>DD</sub>                           | -     | 5                      | μA |

|                          | ZZ の入力電流                   | 入力 = V <sub>SS</sub>                           | -5    | -                      | μA |

|                          |                            | 入力 = V <sub>DD</sub>                           | -     | 30                     | μA |

| I <sub>OZ</sub>          | 出力リード電流                    | GND ≤ V <sub>I</sub> ≤ V <sub>DDQ</sub> 、出力が無効 | -5    | 5                      | μA |

注：

8. オーバーシュート : V<sub>IH(AC)</sub> < V<sub>DD</sub> + 1.5V (パルス幅は t<sub>CYC</sub>/2 未満)、アンダーシュート : V<sub>IL(AC)</sub> > -2V (パルス幅は t<sub>CYC</sub>/2 未満)。

9. T<sub>Power-up</sub>: 少なくとも 200ms 以上での 0V から V<sub>DD(min)</sub> までの直線昇圧を前提としています。この期間中は、V<sub>IH</sub> < V<sub>DD</sub>、V<sub>DDQ</sub> ≤ V<sub>DD</sub> です。

## 電気的特性（続き）

動作範囲において

| パラメーター <sup>[8, 9]</sup> | 説明                           | テスト条件                                                                                                                      |                     |      | Min | Max | 単位 |

|--------------------------|------------------------------|----------------------------------------------------------------------------------------------------------------------------|---------------------|------|-----|-----|----|

| $I_{DD}$                 | $V_{DD}$ 動作時電源               | $V_{DD} = \text{Max}$ 、 $I_{OUT} = 0\text{mA}$ 、<br>$f = f_{MAX} = 1/t_{CYC}$                                              | 5ns サイクル、<br>200MHz | × 18 | —   | 180 | mA |

|                          |                              |                                                                                                                            |                     | × 36 | —   | 200 |    |

|                          |                              | $V_{IN} \geq V_{IH}$ または<br>$V_{IN} \leq V_{IL}$ 、 $f = f_{MAX} = 1/t_{CYC}$                                               | 6ns サイクル、<br>167MHz | × 18 | —   | 158 |    |

|                          |                              |                                                                                                                            |                     | × 36 | —   | 178 |    |

| $I_{SB1}$                | 自動 CE パワーダウン<br>電流 – TTL 入力  | 最大 $V_{DD}$ 、デバイス選択解除、 $V_{IN} \geq V_{IH}$ または<br>$V_{IN} \leq V_{IL}$ 、 $f = f_{MAX} = 1/t_{CYC}$                        | 5ns サイクル、<br>200MHz | × 18 | —   | 75  | mA |

|                          |                              |                                                                                                                            |                     | × 36 | —   | 80  |    |

|                          |                              | $V_{IN} \leq 0.3\text{V}$ または<br>$V_{IN} \geq V_{DDQ} - 0.3\text{V}$ 、 $f = 0$                                             | 6ns サイクル、<br>167MHz | × 18 | —   | 75  |    |

|                          |                              |                                                                                                                            |                     | × 36 | —   | 80  |    |

| $I_{SB2}$                | 自動 CE パワーダウン<br>電流 – CMOS 入力 | 最大 $V_{DD}$ 、デバイス選択解除、 $V_{IN} \leq 0.3\text{V}$ または<br>$V_{IN} \geq V_{DDQ} - 0.3\text{V}$ 、 $f = 0$                      | すべての速度<br>グレード      | × 18 | —   | 65  | mA |

|                          |                              |                                                                                                                            |                     | × 36 | —   | 70  |    |

| $I_{SB3}$                | 自動 CE パワーダウン<br>電流 – CMOS 入力 | 最大 $V_{DD}$ 、デバイス選択解除、 $V_{IN} \leq 0.3\text{V}$ または<br>$V_{IN} \geq V_{DDQ} - 0.3\text{V}$ 、<br>$f = f_{MAX} = 1/t_{CYC}$ | 5ns サイクル、<br>200MHz | × 18 | —   | 75  | mA |

|                          |                              |                                                                                                                            |                     | × 36 | —   | 80  |    |

|                          |                              | $V_{IN} \leq 0.3\text{V}$ または<br>$V_{IN} \geq V_{DDQ} - 0.3\text{V}$ 、<br>$f = f_{MAX} = 1/t_{CYC}$                        | 6ns サイクル、<br>167MHz | × 18 | —   | 75  |    |

|                          |                              |                                                                                                                            |                     | × 36 | —   | 80  |    |

| $I_{SB4}$                | 自動 CE パワーダウン<br>電流 – TTL 入力  | 最大 $V_{DD}$ 、デバイス選択解除、 $V_{IN} \geq V_{IH}$ または<br>$V_{IN} \leq V_{IL}$ 、 $f = 0$                                          | すべての速度<br>グレード      | × 18 | —   | 65  | mA |

|                          |                              |                                                                                                                            |                     | × 36 | —   | 70  |    |

## 静電容量

| パラメーター    | 説明         | テスト条件                                                                                  | 100ピンTQFP<br>パッケージ | 単位 |

|-----------|------------|----------------------------------------------------------------------------------------|--------------------|----|

| $C_{IN}$  | 入力静電容量     | $T_A = 25^\circ\text{C}, f = 1\text{MHz}, V_{DD} = 3.3\text{V}, V_{DDQ} = 2.5\text{V}$ | 5                  | pF |

| $C_{CLK}$ | クロック入力静電容量 |                                                                                        | 5                  | pF |

| $C_{IO}$  | 入力／出力静電容量  |                                                                                        | 5                  | pF |

## 熱抵抗

| パラメーター        | 説明                    | テスト条件                                                | 100ピンTQFP<br>パッケージ | 単位         |

|---------------|-----------------------|------------------------------------------------------|--------------------|------------|

| $\Theta_{JA}$ | 熱抵抗<br>(ジャンクションから周囲)  | テスト条件は、EIA/JESD51による、熱インピーダンスを測定するための標準的なテスト方法と手順に従う | 無風時<br>(0m/s)      | 37.95 °C/W |

|               |                       |                                                      | 空冷 (1m/s)          | 33.19 °C/W |

|               |                       |                                                      | 空冷 (3m/s)          | 30.44 °C/W |

| $\Theta_{JB}$ | 熱抵抗<br>(ジャンクションからボード) |                                                      | --                 | 24.07 °C/W |

| $\Theta_{JC}$ | 熱抵抗<br>(ジャンクションからケース) |                                                      |                    | 8.36 °C/W  |

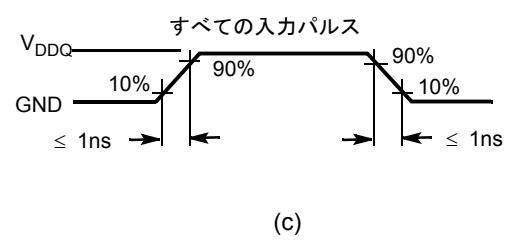

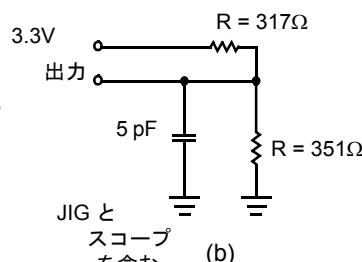

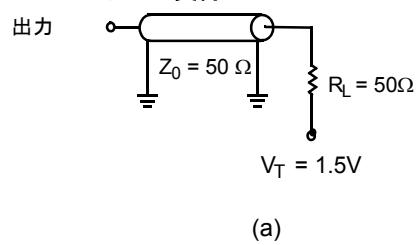

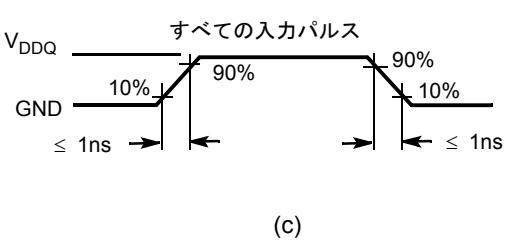

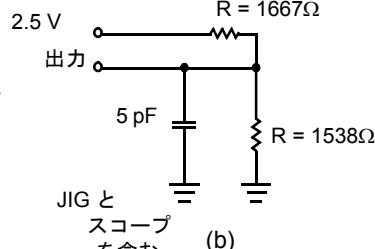

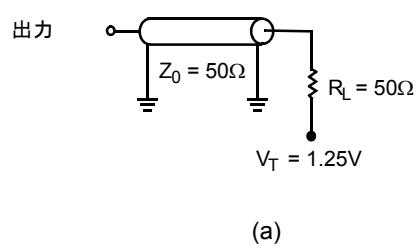

## AC テストの負荷および波形

図 2. AC テストの負荷と波形

### 3.3V I/O テスト負荷

### 2.5V I/O テスト負荷

## スイッチング特性

動作範囲において

| パラメーター [10, 11] | 説明                                                                          | -200 |     | -167 |     | 単位 |

|-----------------|-----------------------------------------------------------------------------|------|-----|------|-----|----|

|                 |                                                                             | Min  | Max | Min  | Max |    |

| $t_{POWER}$     | $V_{DD}$ (Typ) から最初のアクセスまで [12]                                             | 1    | -   | 1    | -   | ms |

| <b>クロック</b>     |                                                                             |      |     |      |     |    |

| $t_{CYC}$       | クロック サイクル時間                                                                 | 5.0  | -   | 6.0  | -   | ns |

| $t_{CH}$        | クロック HIGH                                                                   | 2.0  | -   | 2.2  | -   | ns |

| $t_{CL}$        | クロック LOW 時間                                                                 | 2.0  | -   | 2.2  | -   | ns |

| <b>出力時間</b>     |                                                                             |      |     |      |     |    |

| $t_{CO}$        | CLK 立ち上がり後のデータ出力有効時間                                                        | -    | 3.0 | -    | 3.4 | ns |

| $t_{DOH}$       | CLK 立ち上がり後のデータ出力ホールド時間                                                      | 1.3  | -   | 1.3  | -   | ns |

| $t_{CLZ}$       | クロックから Low Z まで [13, 14, 15]                                                | 1.3  | -   | 1.3  | -   | ns |

| $t_{CHZ}$       | クロックから High Z まで [13, 14, 15]                                               | -    | 3.0 | -    | 3.4 | ns |

| $t_{OEV}$       | $\overline{OE}$ LOW から出力有効まで                                                | -    | 3.0 | -    | 3.4 | ns |

| $t_{OELZ}$      | $\overline{OE}$ LOW から出力 Low Z まで [13, 14, 15]                              | 0    | -   | 0    | -   | ns |

| $t_{OEHZ}$      | $\overline{OE}$ HIGH から出力 High Z まで [13, 14, 15]                            | -    | 3.0 | -    | 3.4 | ns |

| <b>セットアップ時間</b> |                                                                             |      |     |      |     |    |

| $t_{AS}$        | CLK 立ち上がり前のアドレス セットアップ時間                                                    | 1.4  | -   | 1.5  | -   | ns |

| $t_{ADS}$       | CLK 立ち上がり前の $\overline{ADSC}$ 、 $\overline{ADSP}$ セットアップ時間                  | 1.4  | -   | 1.5  | -   | ns |

| $t_{ADVS}$      | CLK 立ち上がり前の $\overline{ADV}$ セットアップ時間                                       | 1.4  | -   | 1.5  | -   | ns |

| $t_{WES}$       | CLK 立ち上がり前の $\overline{GW}$ 、 $\overline{BWE}$ 、 $\overline{BW_X}$ セットアップ時間 | 1.4  | -   | 1.5  | -   | ns |

| $t_{DS}$        | CLK 立ち上がり前のデータ入力セットアップ時間                                                    | 1.4  | -   | 1.5  | -   | ns |

| $t_{CES}$       | CLK 立ち上がり前のチップ イネーブル セットアップ時間                                               | 1.4  | -   | 1.5  | -   | ns |

| <b>ホールド時間</b>   |                                                                             |      |     |      |     |    |

| $t_{AH}$        | CLK 立ち上がり後のアドレス ホールド時間                                                      | 0.4  | -   | 0.5  | -   | ns |

| $t_{ADH}$       | CLK 立ち上がり後の $\overline{ADSP}$ 、 $\overline{ADSC}$ ホールド時間                    | 0.4  | -   | 0.5  | -   | ns |

| $t_{ADVH}$      | CLK 立ち上がり後の $\overline{ADV}$ ホールド時間                                         | 0.4  | -   | 0.5  | -   | ns |

| $t_{WEH}$       | CLK 立ち上がり後の $\overline{GW}$ 、 $\overline{BWE}$ 、 $\overline{BW_X}$ ホールド時間   | 0.4  | -   | 0.5  | -   | ns |

| $t_{DH}$        | CLK 立ち上がり後のデータ入力ホールド時間                                                      | 0.4  | -   | 0.5  | -   | ns |

| $t_{CEH}$       | CLK 立ち上がり後のチップ イネーブル ホールド時間                                                 | 0.4  | -   | 0.5  | -   | ns |

注:

10. タイミングのリファレンス電圧レベルは、 $V_{DDQ} = 3.3V$  の場合は 1.5V であり、 $V_{DDQ} = 2.5V$  の場合は 1.25V です。

11. 特記されていない限り、テスト条件は [13 ページの図 2](#) の (a) に示す通りです。

12. このデバイスは電圧レギュレータを内蔵しています； $t_{POWER}$  は、読み出しましたは書き込み処理が開始される前に、 $V_{DD(minimum)}$  を超えた電源を供給する必要がある時間です。

13.  $t_{CHZ}$ 、 $t_{CLZ}$ 、 $t_{OELZ}$ 、および  $t_{OEHZ}$  は [13 ページの図 2](#) の (b) に示した AC テスト条件で指定されます。遷移は定常状態での電圧  $\pm 200mV$  の電圧レベルで測定されます。

14. 全ての電圧と温度において、同じデータバスを共用する際の、SRAM 間のバス競合を回避するために、 $t_{OEHZ}$  は  $t_{OELZ}$  より小さく、 $t_{CHZ}$  は  $t_{CLZ}$  より小さいことが必要です。これらの仕様は、バス競合条件を意味せず、最悪の場合のユーザー条件において保証されるパラメーターを反映しています。デバイスは、同じシステム条件の下で Low Z の前に High Z を達成するように設計されています。

15. このパラメーターはサンプリングされ、すべてのデバイスで試験されるわけではありません。

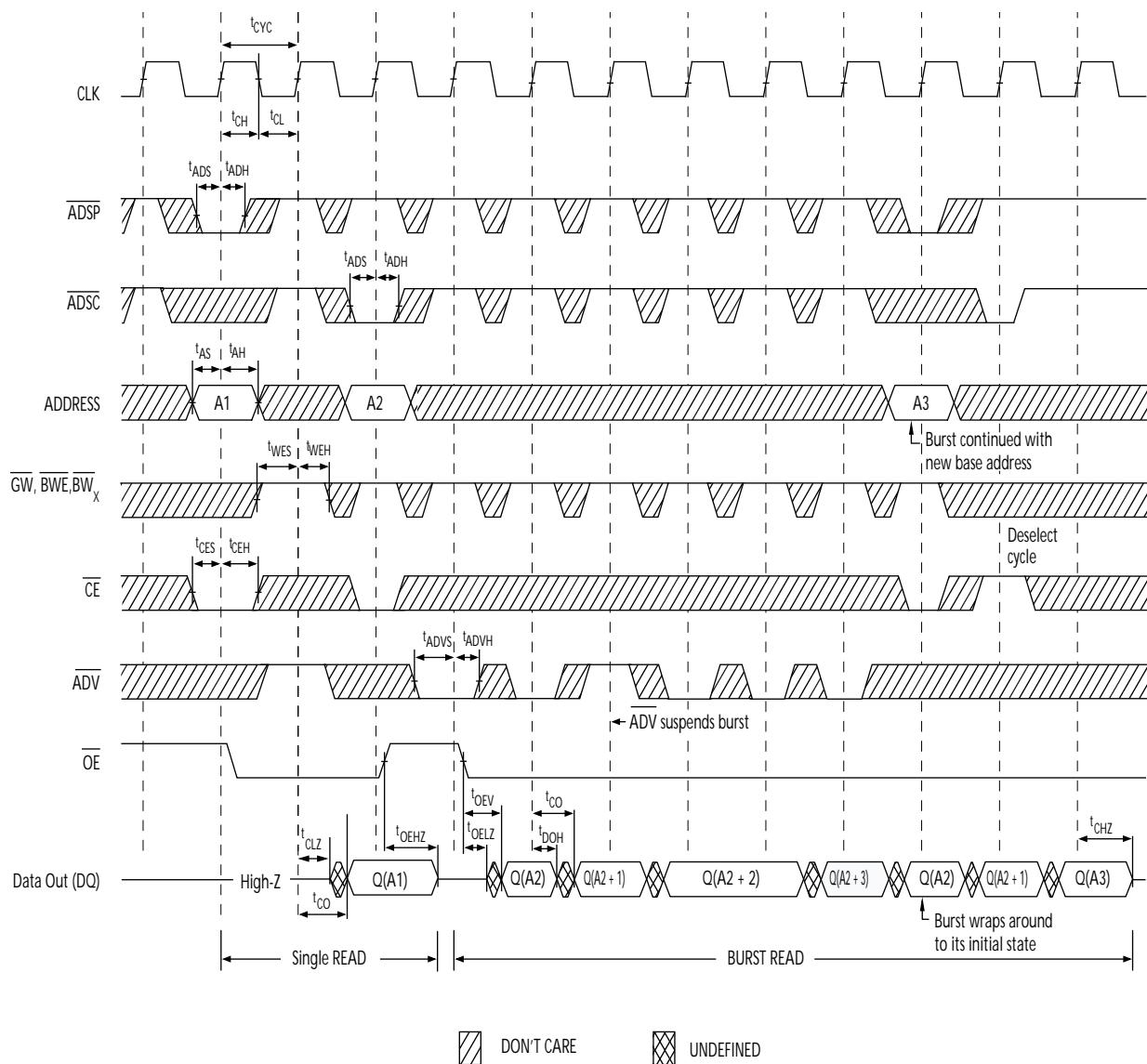

## スイッチング波形

図 3. 読み出しサイクル タイミング [16]

注:

16. この図では、 $\overline{CE}$  が LOW の場合、 $\overline{CE}_1$  は LOW、 $CE_2$  は HIGH、 $\overline{CE}_3$  は LOW です。 $\overline{CE}$  が HIGH の場合、 $\overline{CE}_1$  は HIGH、または  $CE_2$  は LOW、または  $\overline{CE}_3$  は HIGH です。

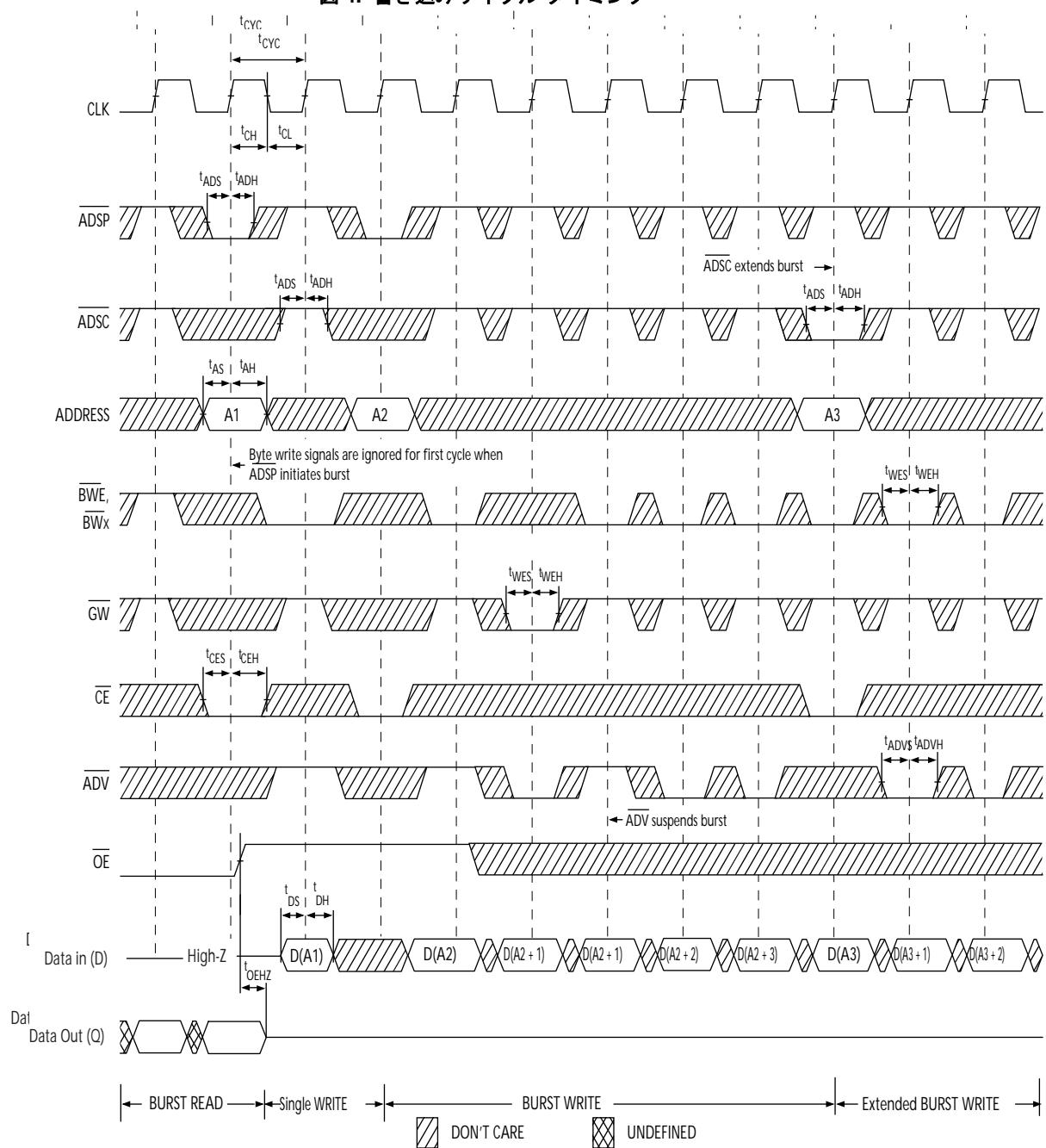

## スイッチング波形 ( 続き )

図 4. 書き込みサイクル タイミング [17、18]

注:

17. このブロック図では、 $\overline{CE}$  が LOW の場合、 $\overline{CE}_1$  は LOW、 $CE_2$  は HIGH、 $\overline{CE}_3$  は LOW です。 $\overline{CE}$  が HIGH の場合、 $\overline{CE}_1$  は HIGH、または  $CE_2$  は LOW、または  $\overline{CE}_3$  は HIGH です。

18. フル幅の書き込みは、 $\overline{GW}$  が LOW になると開始できます。

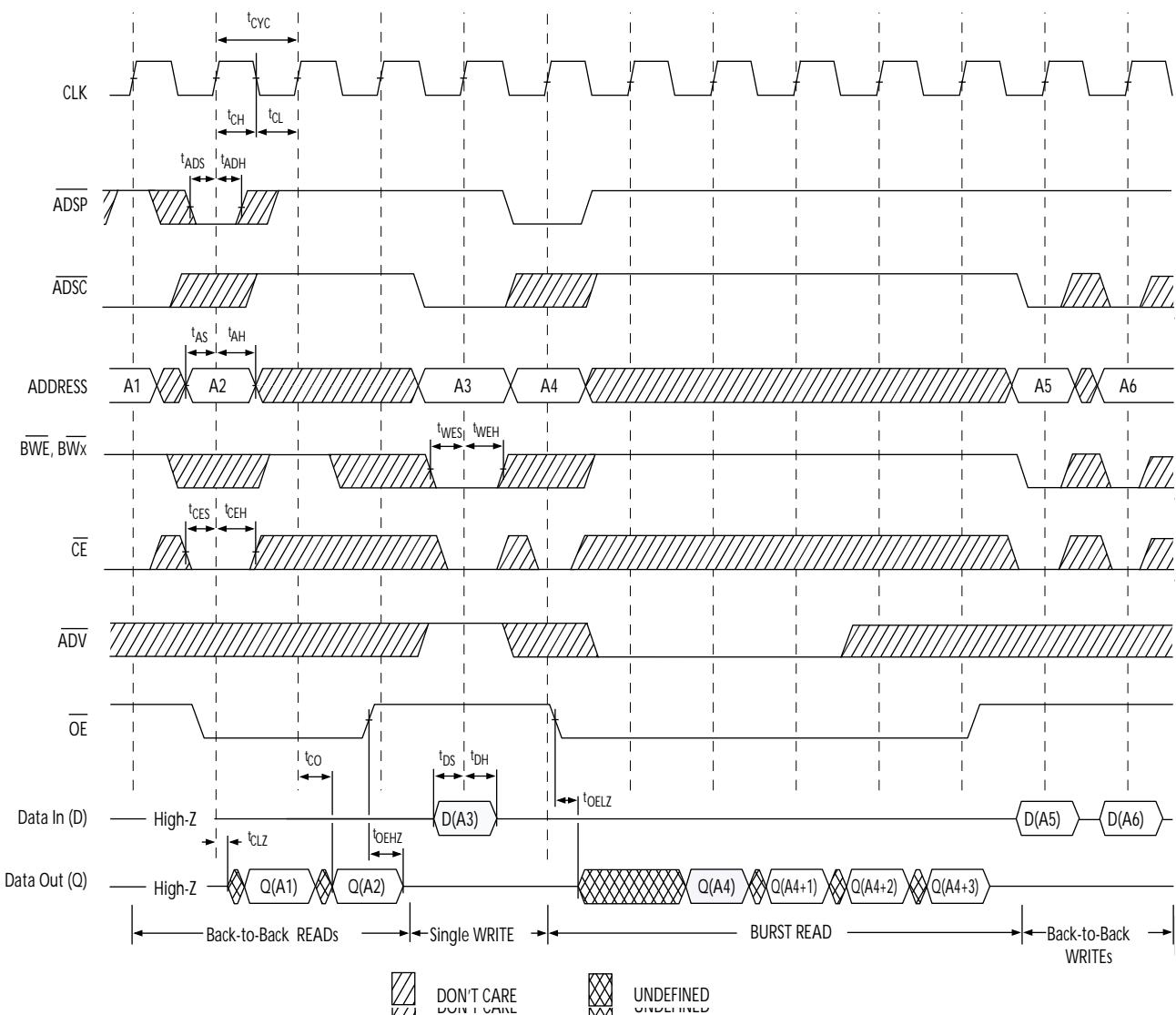

## スイッチング波形(続き)

図5. 読み出し/書き込みサイクルタイミング [19、20、21]

注:

19. このブロック図では、 $\overline{CE}$ がLOWの場合、 $\overline{CE}_1$ はLOW、 $CE_2$ はHIGH、 $\overline{CE}_3$ はLOWです。 $\overline{CE}$ がHIGHの場合、 $\overline{CE}_1$ はHIGH、または $CE_2$ はLOW、または $\overline{CE}_3$ はHIGHです。

20. 新しい読み出しアクセスが $\overline{ADSP}$ または $\overline{ADSC}$ により開始されない限り、データバス(Q)は書き込みサイクルの後HIGH Zになったままです。

21.  $\overline{GW}$ はHIGHです。

## スイッチング波形(続き)

図 6. ZZ モード タイミング [22、23]

注:

22. ZZ モードに入る時、デバイスを選択解除する必要があります。デバイスを選択解除するための全ての可能な信号条件については、サイクル説明表をご参照ください。

23. ZZ スリープ モードを終了する時、DQ 信号は High Z 状態になります。

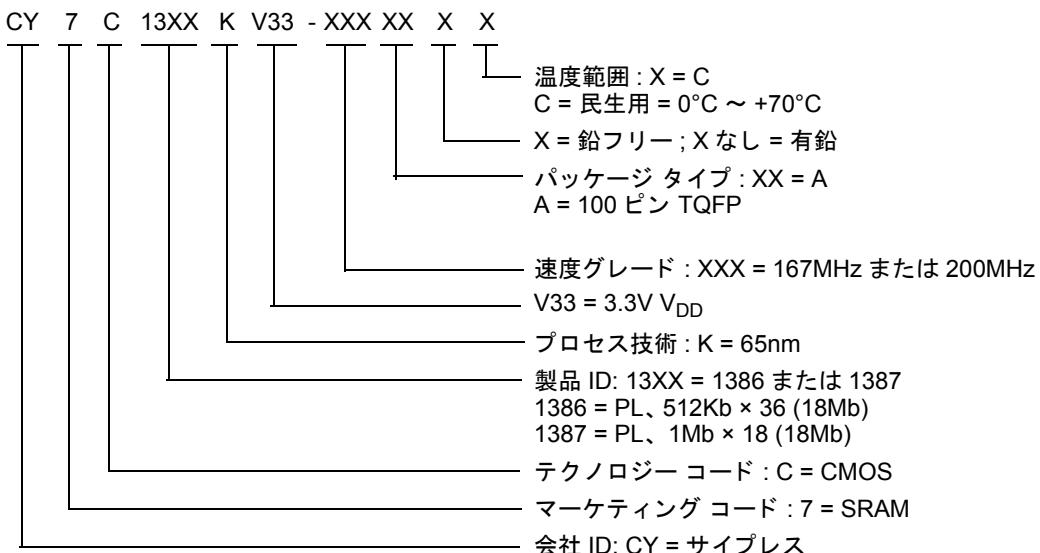

## 注文情報

この表には、現在供給可能な部品のみを示します。お探しのものが見つからない場合は、最寄りの販売代理店にお問い合わせください。詳細は、サイプレスのウェブサイト [www.cypress.com](http://www.cypress.com) にアクセスし、製品概要のページ <http://www.cypress.com/products> を参照して下さい。

サイプレスは、事業所、ソリューション センター、メーカー代理店および販売代理店の世界的なネットワークを保持しています。お客様の最寄りのオフィスについては、サイプレスの <http://www.cypress.com/go/datasheet/offices> をご覧ください。

| 速度<br>(MHz) | 注文コード               | パッケージ図   | 製品とパッケージ タイプ                       | 動作範囲 |

|-------------|---------------------|----------|------------------------------------|------|

| 167         | CY7C1386KV33-167AXC | 51-85050 | 100 ピン TQFP (14 × 20 × 1.4mm) 鉛フリー | 民生用  |

|             | CY7C1387KV33-167AXC |          |                                    |      |

| 200         | CY7C1386KV33-200AXC | 51-85050 | 100 ピン TQFP (14 × 20 × 1.4mm) 鉛フリー | 民生用  |

## 注文コードの定義

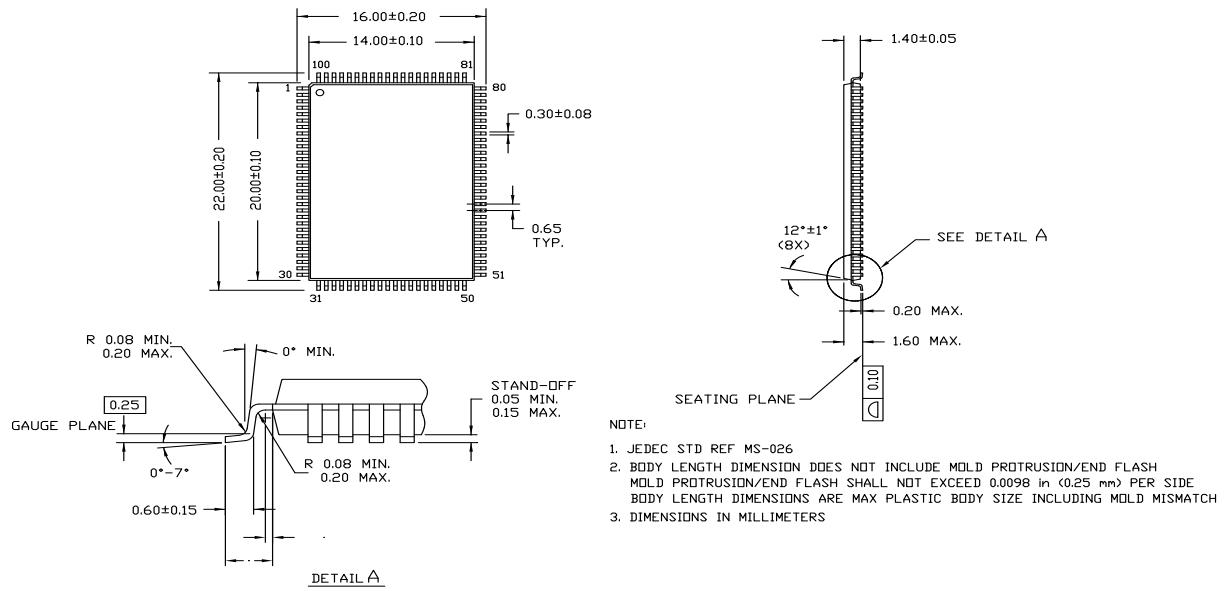

## パッケージ図

図 10. 100 ピン TQFP (14 × 20 × 1.4mm) A100RA パッケージ図、51-85050

## 略語

| 略語              | 説明                                                         |

|-----------------|------------------------------------------------------------|

| CE              | Chip Enable ( チップ イネーブル )                                  |

| CMOS            | Complementary Metal Oxide Semiconductor<br>( 相補型金属酸化膜半導体 ) |

| FBGA            | Fine-Pitch Ball Grid Array<br>( フайн ピッチ ボール グリッド アレイ )    |

| I/O             | Input/Output ( 入力／出力 )                                     |

| LMBU            | Logical Multiple-Bit Upsets<br>( 論理マルチ ビット アップセット )        |

| LSB             | Least Significant Bit ( 最下位ビット )                           |

| LSBU            | Logical Single-Bit Upsets<br>( 論理シングル ビット アップセット )         |

| MSB             | Most Significant Bit ( 最上位ビット )                            |

| $\overline{OE}$ | Output Enable ( 出力イネーブル )                                  |

| SEL             | Single Event Latch-Up<br>( シングル イベント ラッチアップ )              |

| SRAM            | Static Random Access Memory<br>( スタティック ランダム アクセス メモリ )    |

| TQFP            | Thin Quad Flat Pack<br>( 薄型クアッド フラット パッケージ )               |

| TTL             | Transistor-Transistor Logic<br>( トランジスタ - トランジスタ ロジック )    |

## 本書の表記法

### 測定単位

| 記号  | 測定単位     |

|-----|----------|

| °C  | 摂氏温度     |

| kΩ  | キロオーム    |

| MHz | メガヘルツ    |

| μA  | マイクロアンペア |

| μs  | マイクロ秒    |

| mA  | ミリアンペア   |

| mV  | ミリボルト    |

| mm  | ミリメートル   |

| ms  | ミリ秒      |

| ns  | ナノ秒      |

| Ω   | オーム      |

| %   | パーセント    |

| pF  | ピコファラッド  |

| ps  | ピコ秒      |

| V   | ボルト      |

| W   | ワット      |

## 改訂履歴

文書名 : CY7C1386KV33 / CY7C1387KV33、18M ビット (512K × 36/1M × 18) 同期式パイプライン DCD SRAM

文書番号 : 001-98231

| 版  | ECN     | 変更者  | 提出日        | 変更内容                                                     |

|----|---------|------|------------|----------------------------------------------------------|

| ** | 4837735 | HZEN | 07/23/2015 | これは英語版 001-97893 Rev. ** を翻訳した日本語版 001-98231 Rev. ** です。 |

| *A | 5013026 | HZEN | 11/19/2015 | これは英語版 001-97893 Rev. *B を翻訳した日本語版 001-98231 Rev. *A です。 |

## セールス、ソリューションおよび法律情報

### ワールドワイド販売と設計サポート

サイプレスは、事業所、ソリューションセンター、メーカー代理店および販売代理店の世界的なネットワークを保持しています。お客様の最寄りのオフィスについては、[サイプレスのロケーション](#)ページをご覧ください。

#### 製品

|             |                                                                          |

|-------------|--------------------------------------------------------------------------|

| 車載用         | <a href="http://cypress.com/go/automotive">cypress.com/go/automotive</a> |

| クロック & バッファ | <a href="http://cypress.com/go/clocks">cypress.com/go/clocks</a>         |

| インターフェース    | <a href="http://cypress.com/go/interface">cypress.com/go/interface</a>   |

| 照明 & 電力制御   | <a href="http://cypress.com/go/powerpsoc">cypress.com/go/powerpsoc</a>   |

| メモリ         | <a href="http://cypress.com/go/memory">cypress.com/go/memory</a>         |

| PSoC        | <a href="http://cypress.com/go/psoc">cypress.com/go/psoc</a>             |

| タッチ センシング   | <a href="http://cypress.com/go/touch">cypress.com/go/touch</a>           |

| USB コントローラー | <a href="http://cypress.com/go/USB">cypress.com/go/USB</a>               |

| ワイヤレス／RF    | <a href="http://cypress.com/go/wireless">cypress.com/go/wireless</a>     |

#### PSoC® ソリューション

[psoc.cypress.com/solutions](http://psoc.cypress.com/solutions)

[PSoC 1 | PSoC 3 | PSoC 4 | PSoC 5LP](#)

#### サイプレス開発者コミュニティ

[コミュニティ](#) | [フォーラム](#) | [ブログ](#) | [ビデオ](#) | [トレーニング](#)

#### テクニカル サポート

[cypress.com/go/support](http://cypress.com/go/support)

© Cypress Semiconductor Corporation, 2015. 本文書に記載される情報は、予告なく変更される場合があります。Cypress Semiconductor Corporation (サイプレス セミコンダクタ社) は、サイプレス製品に組み込まれた回路以外のいかなる回路を使用することに対して一切の責任を負いません。サイプレス セミコンダクタ社は、特許またはその他の権利に基づくライセンスを譲渡することも、または含意することもありません。サイプレス製品は、サイプレスとの書面による合意に基づくものでない限り、医療、生命維持、救命、重要な管理、または安全の用途のために使用することを保証するものではなく、また使用することを意図したものでもありません。さらにサイプレスは、誤作動や故障によって使用者に重大な傷害をもたらすことが合理的に予想される生命維持システムの重要なコンポーネントとしてサイプレス製品を使用することを許可していません。生命維持システムの用途にサイプレス製品を供することは、製造者がそのような使用におけるあらゆるリスクを負うことを意味し、その結果サイプレスはあらゆる責任を免除されることを意味します。

すべてのソース コード (ソフトウェアおよび／またはファームウェア) はサイプレス セミコンダクタ社 (以下「サイプレス」) が所有し、全世界の特許権保護 (米国および他の国)、米国の著作権法ならびに国際協定の条項により保護され、かつそれらに従います。サイプレスが本書面によりライセンサーに付与するライセンスは、個人的、非独占的かつ譲渡不能のライセンスであり、適用される契約で指定されたサイプレスの集積回路と併用されるライセンシーの製品のみをサポートするカスタムソフトウェアおよび／またはカスタム ファームウェアを作成する目的に限って、サイプレスのソース コードの派生著作物をコピー、使用、変更そして作成するためのライセンス、ならびにサイプレスのソース コードおよび派生著作物をコンパイルするためのライセンスです。上記で指定された場合を除き、サイプレスの書面による明示的な許可なくして本ソース コードを複製、変更、変換、コンパイル、または表示することはすべて禁止します。

免責条項：サイプレスは、明示的または默示的問わず、本資料に関するいかなる種類の保証も行いません。これには、商品性または特定目的への適合性の默示的な保証が含まれますが、これに限定されません。サイプレスは、本文書に記載される資料に対して今後予告なく変更を加える権利を留保します。サイプレスは、本文書に記載されるいかなる製品または回路を適用または使用したことによって生ずるいかなる責任も負いません。サイプレスは、誤作動や故障によって使用者に重大な傷害をもたらすことが合理的に予想される生命維持システムの重要なコンポーネントとしてサイプレス製品を使用することを許可していません。生命維持システムの用途にサイプレス製品を供することは、製造者がそのような使用におけるあらゆるリスクを負うことを意味し、その結果サイプレスはあらゆる責任を免除されることを意味します。

ソフトウェアの使用は、適用されるサイプレス ソフトウェア ライセンス契約によって制限され、かつ制約される場合があります。