**NoBL™ アーキテクチャの 18M ビット

(512K × 36/1M × 18) パイプライン SRAM**

## 特長

- ZBT™ とピン互換で、機能的に ZBT™ と同等

- 待ち状態なしの 200MHz バス動作

- 速度グレード 200MHz、167MHz

- 内部セルフタイム出力バッファ制御(非同期 $\overline{OE}$ 信号の使用が不要)

- パイプライン動作用の入出力レジスタが完全に装備される

- バイト書き込み機能

- 単一の 2.5V コア電源 ( $V_{DD}$ )

- 2.5V I/O 電源 ( $V_{DDQ}$ )

- 高速なクロック→出力時間

- 3.2ns (デバイス速度が 200MHz の場合)

- 動作停止用クロック イネーブル ( $\overline{CEN}$ ) ピン

- セルフタイム同期書き込み

- JEDEC 標準の鉛フリー 100 ピン TQFP、鉛フリーでない 165 ボール FBGA パッケージで出荷

- IEEE 1149.1 JTAG 準拠のバウンダリ スキャン

- バースト機能 — リニア／インターリーブ バースト シーケンス

- 「ZZ」スリープ モード オプションとストップ クロック オプション

## 機能の詳細

CY7C1370KV25 と CY7C1372KV25 は、2.5V 動作の 512K ビット ×36 と 1M ビット ×18 の No Bus Latency™ (NoBL™) 論理付き同期パイプライン バースト SRAM です。これらのデバイスは、待ち状態なしの真の無制限連続読み書き動作に対応するよう設計されています。

CY7C1370KV25 と CY7C1372KV25 は、データがクロック サイクル毎に転送される連続的読み書き処理を実現する高度な NoBL 論理を備えています。この機能は、頻繁な読み書き遷移が必要なシステム内でのデータ スループットを大幅に向上させます。CY7C1370KV25 と CY7C1372KV25 は、ZBT デバイスとピン互換で、機能も同じです。

全ての同期入力は、クロックの立ち上がりエッジで制御される入力レジスタを通過します。全てのデータ出力は、クロックの立ち上がりエッジにより制御される出力レジスタを通過します。クロック入力がクロック イネーブル ( $\overline{CEN}$ ) 信号により有効にされます。この信号は、デアサートされると、動作を停止し、前のクロック サイクルを延長します。

書き込み動作は、バイト書き込み選択信号 (CY7C1370KV25 の場合は  $\overline{BW_a}$ – $\overline{BW_d}$ 、CY7C1372KV25 の場合は  $\overline{BW_a}$ – $\overline{BW_b}$ ) と書き込みイネーブル ( $WE$ ) 入力により制御されます。全ての書き込みは、内蔵のセルフタイム同期書き込み回路で制御されます。

3 つの同期チップ セレクト ( $\overline{CE}_1$ 、 $CE_2$ 、 $\overline{CE}_3$ ) と非同期出力イネーブル ( $\overline{OE}$ ) は、バンクを容易に選択し、出力ピンのトライステートを制御するために提供されます。バス競合を回避するために、出力ドライバーは、書き込みシーケンスのデータ転送の間同時にトライステートになります。

## 選択ガイド

| 説明       | 200MHz | 167MHz | 単位  |

|----------|--------|--------|-----|

| 最大アクセス時間 | 3.2    | 3.4    | ns  |

| 最大動作電流   | ×18    | 158    | mA  |

|          | ×36    | 178    | 163 |

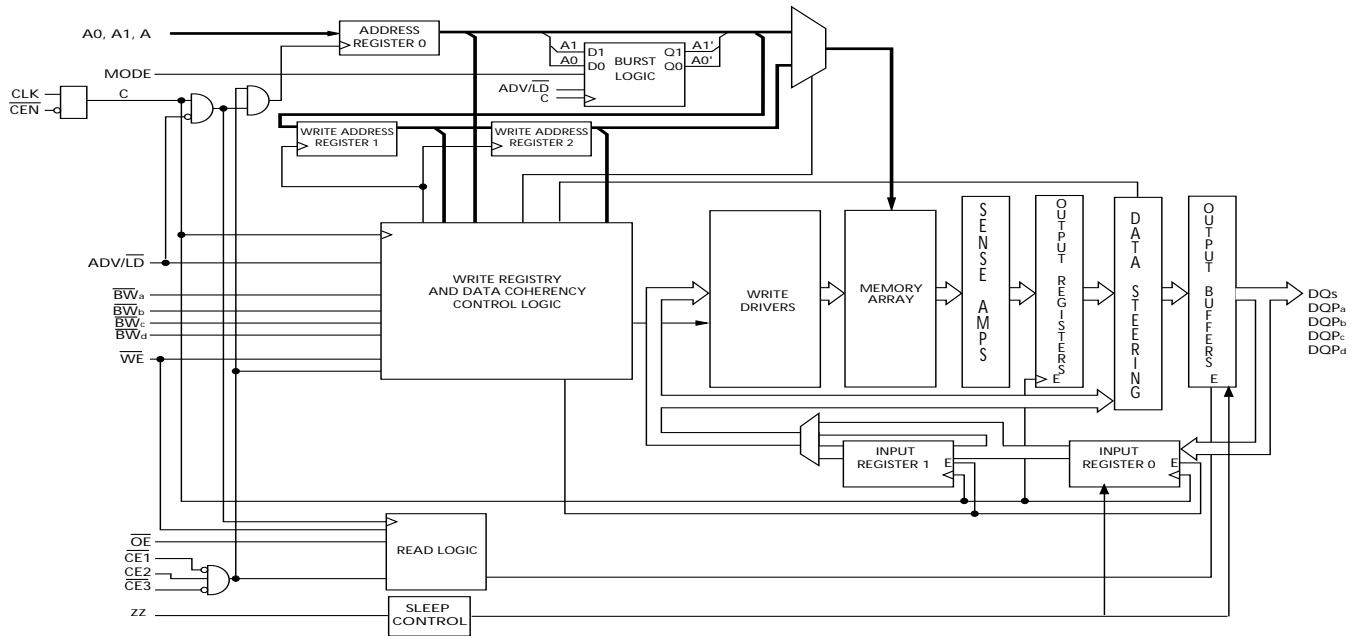

### 論理ブロック図 – CY7C1370KV25

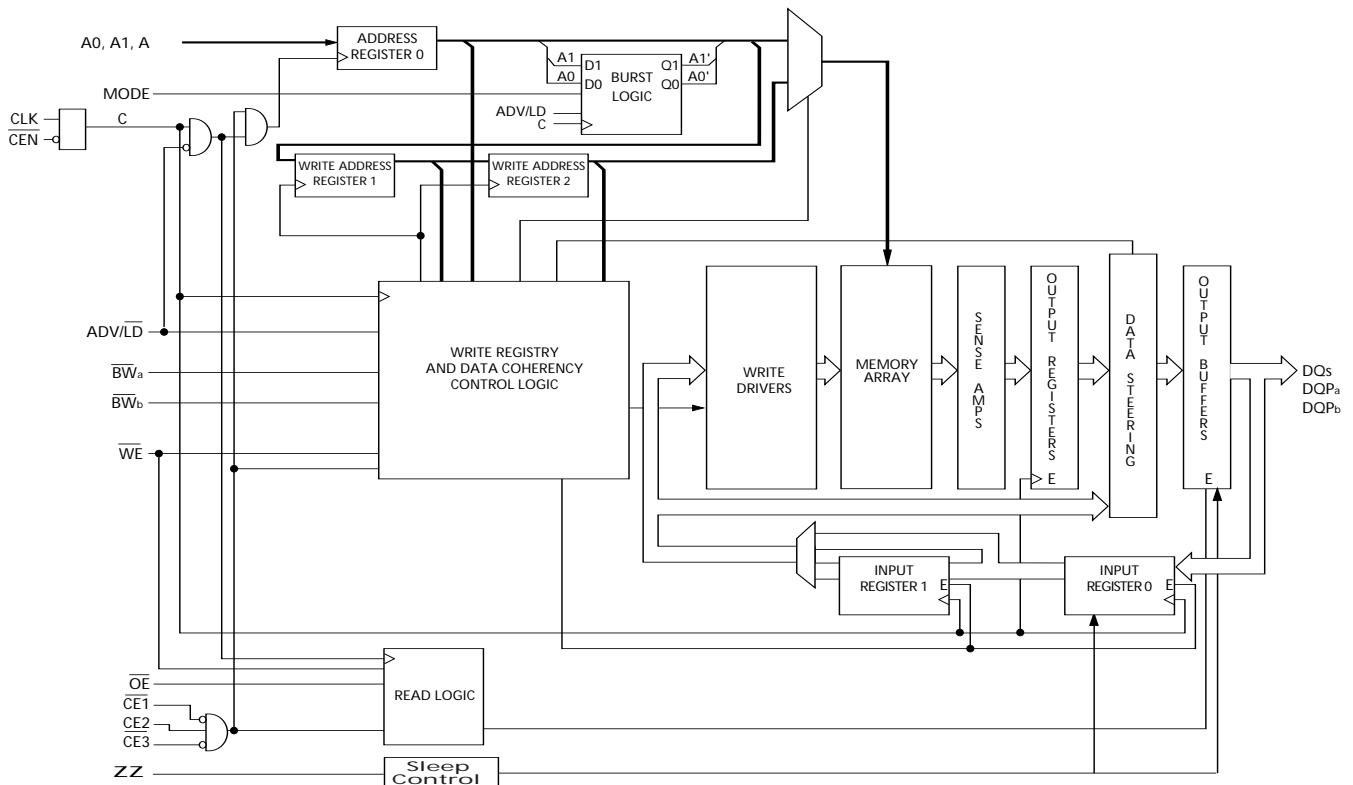

### 論理ブロック図 – CY7C1372KV25

## 目次

|                                   |    |                     |    |

|-----------------------------------|----|---------------------|----|

| ピン配置                              | 4  | スキャン レジスタ サイズ       | 18 |

| ピン機能                              | 6  | ID レジスタの定義          | 18 |

| 機能概要                              | 8  | 命令コード               | 18 |

| シングル読み出しアクセス                      | 8  | バウンダリ スキャン順序        | 19 |

| バースト読み出しアクセス                      | 8  | 最大定格                | 20 |

| シングル書き込みアクセス                      | 8  | 動作範囲                | 20 |

| バースト書き込みアクセス                      | 9  | 中性子ソフト エラー耐性        | 20 |

| スリープ モード                          | 9  | 電気的特性               | 20 |

| インターリーブ バースト アドレス表                | 9  | 容量                  | 22 |

| リニア バースト アドレス表                    | 9  | 熱抵抗                 | 22 |

| ZZ モード 電気的特性                      | 9  | AC テストの負荷と波形        | 22 |

| 真理値表                              | 10 | スイッチング特性            | 23 |

| 書き込み／読み出しの部分真理値表                  | 11 | スイッチング波形            | 24 |

| 書き込み／読み出しの部分真理値表                  | 11 | 注文情報                | 26 |

| IEEE 1149.1シリアル バウンダリ スキャン (JTAG) | 12 | 注文コードの定義            | 26 |

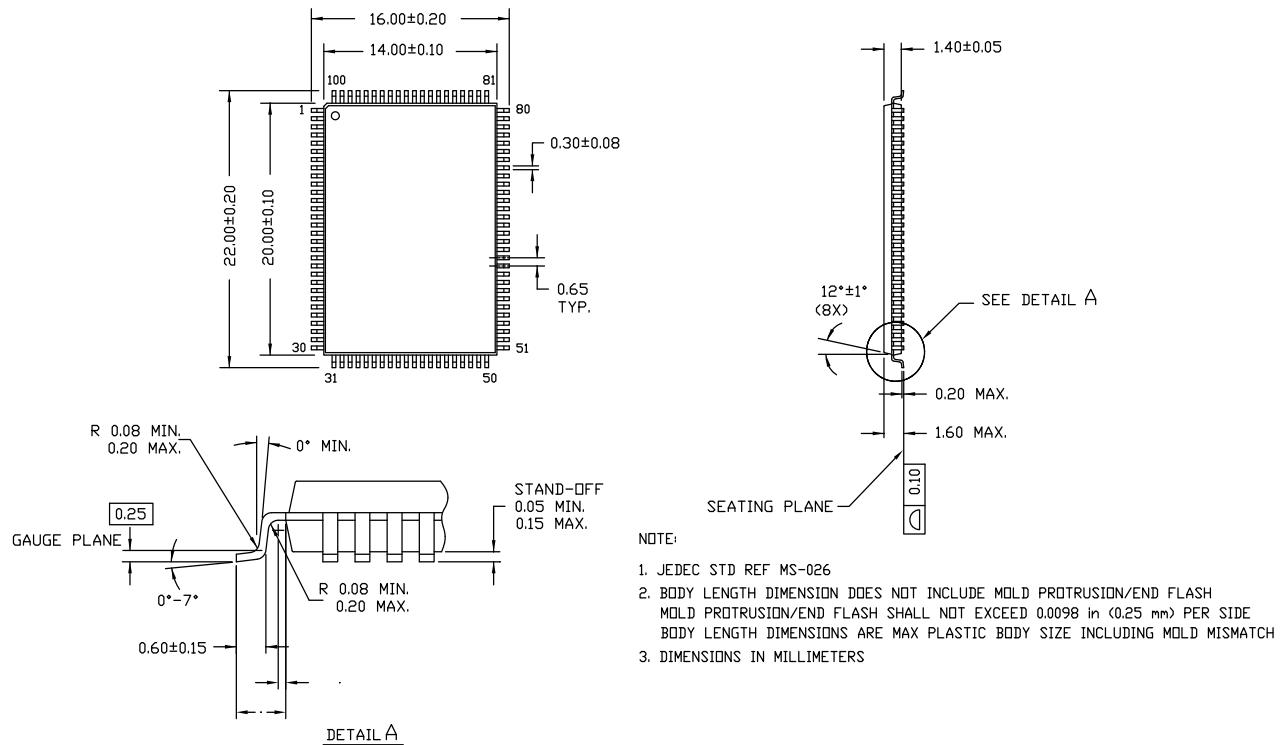

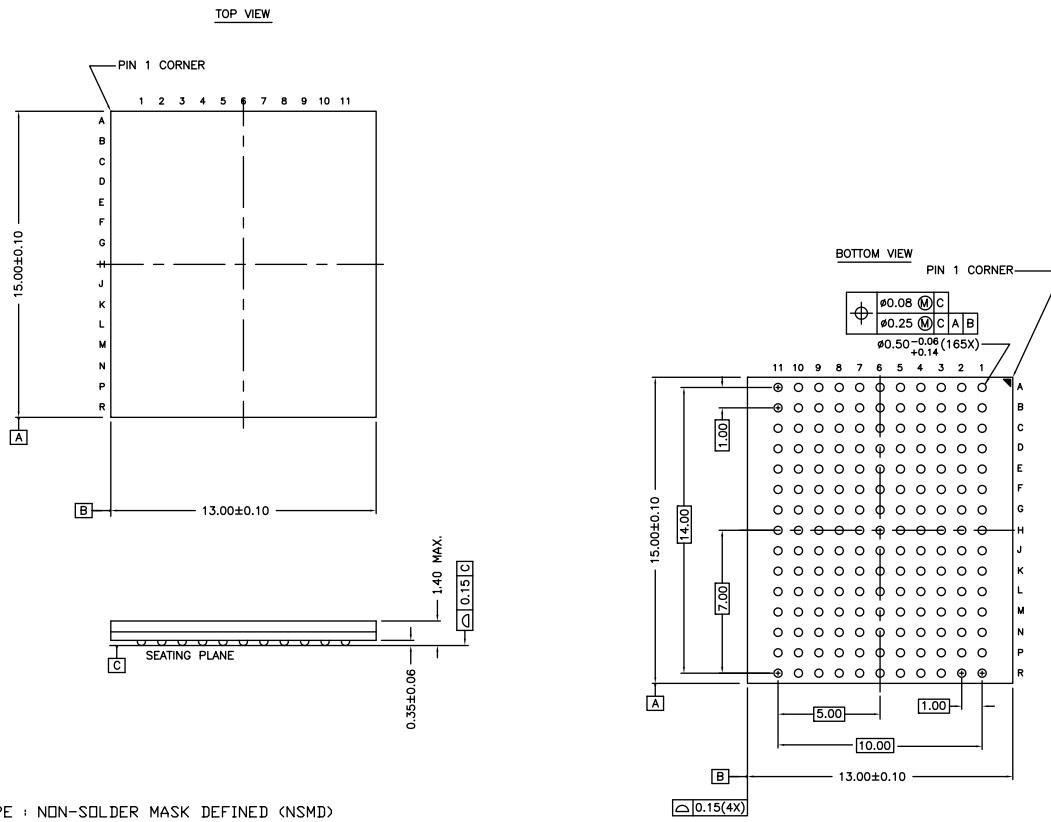

| JTAG 機能の無効化                       | 12 | パッケージ図              | 27 |

| テスト アクセス ポート (TAP)                | 12 | 略語                  | 29 |

| TAP リセットの実行                       | 12 | 本書の表記法              | 29 |

| TAP レジスタ                          | 12 | 測定単位                | 29 |

| TAP 命令セット                         | 13 | 改訂履歴                | 30 |

| TAP コントローラー状態遷移図                  | 14 | セールス、ソリューションおよび法律情報 | 31 |

| TAP コントローラーのブロック図                 | 15 | ワールドワイド販売と設計サポート    | 31 |

| TAP タイミング                         | 15 | 製品                  | 31 |

| TAP AC スイッチング特性                   | 16 | PSoC® ソリューション       | 31 |

| 2.5V TAP AC テスト条件                 | 17 | サイプレス開発者コミュニティ      | 31 |

| 2.5V TAP AC 出力負荷の等価回路             | 17 | テクニカル サポート          | 31 |

| TAP DC 電気的特性と動作条件                 | 17 |                     |    |

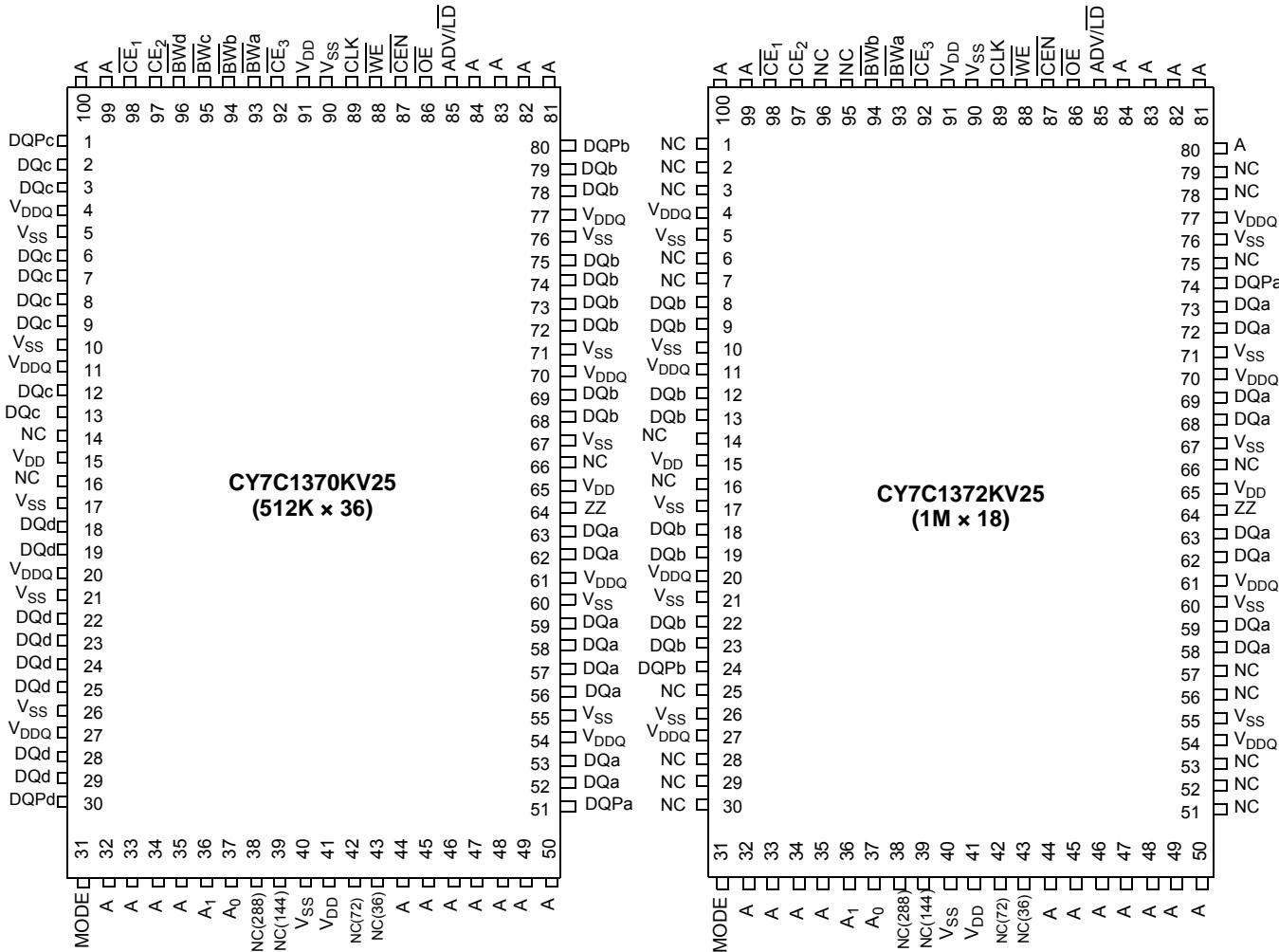

## ピン配置

図 1. 100 ピン TQFP (14 × 20 × 1.4 mm) ピン配置

**ピン配置 (続き)**

**図 2. CY7C1370KV25 (512K x 36)- 165 ポール FBGA (13 x 15 x 1.4mm) ピン配置**

|          | <b>1</b> | <b>2</b> | <b>3</b>          | <b>4</b>          | <b>5</b>          | <b>6</b>          | <b>7</b>         | <b>8</b>          | <b>9</b>          | <b>10</b> | <b>11</b> |

|----------|----------|----------|-------------------|-------------------|-------------------|-------------------|------------------|-------------------|-------------------|-----------|-----------|

| <b>A</b> | NC/288M  | A        | $\overline{CE}_1$ | $\overline{BW}_C$ | $\overline{BW}_B$ | $\overline{CE}_3$ | $\overline{BWE}$ | $\overline{ADSC}$ | $\overline{ADV}$  | A         | NC        |

| <b>B</b> | NC/144M  | A        | CE2               | $\overline{BW}_D$ | $\overline{BW}_A$ | CLK               | $\overline{GW}$  | $\overline{OE}$   | $\overline{ADSP}$ | A         | NC/576M   |

| <b>C</b> | $DQP_C$  | NC       | $V_{DDQ}$         | $V_{SS}$          | $V_{SS}$          | $V_{SS}$          | $V_{SS}$         | $V_{DDQ}$         | NC/1G             | $DQP_B$   |           |

| <b>D</b> | $DQ_C$   | $DQ_C$   | $V_{DDQ}$         | $V_{DD}$          | $V_{SS}$          | $V_{SS}$          | $V_{SS}$         | $V_{DD}$          | $V_{DDQ}$         | $DQ_B$    | $DQ_B$    |

| <b>E</b> | $DQ_C$   | $DQ_C$   | $V_{DDQ}$         | $V_{DD}$          | $V_{SS}$          | $V_{SS}$          | $V_{SS}$         | $V_{DD}$          | $V_{DDQ}$         | $DQ_B$    | $DQ_B$    |

| <b>F</b> | $DQ_C$   | $DQ_C$   | $V_{DDQ}$         | $V_{DD}$          | $V_{SS}$          | $V_{SS}$          | $V_{SS}$         | $V_{DD}$          | $V_{DDQ}$         | $DQ_B$    | $DQ_B$    |

| <b>G</b> | $DQ_C$   | $DQ_C$   | $V_{DDQ}$         | $V_{DD}$          | $V_{SS}$          | $V_{SS}$          | $V_{DD}$         | $V_{DDQ}$         | $DQ_B$            | $DQ_B$    |           |

| <b>H</b> | NC       | NC       | NC                | $V_{DD}$          | $V_{SS}$          | $V_{SS}$          | $V_{SS}$         | $V_{DD}$          | NC                | NC        | ZZ        |

| <b>J</b> | $DQ_D$   | $DQ_D$   | $V_{DDQ}$         | $V_{DD}$          | $V_{SS}$          | $V_{SS}$          | $V_{SS}$         | $V_{DD}$          | $V_{DDQ}$         | $DQ_A$    | $DQ_A$    |

| <b>K</b> | $DQ_D$   | $DQ_D$   | $V_{DDQ}$         | $V_{DD}$          | $V_{SS}$          | $V_{SS}$          | $V_{DD}$         | $V_{DDQ}$         | $DQ_A$            | $DQ_A$    |           |

| <b>L</b> | $DQ_D$   | $DQ_D$   | $V_{DDQ}$         | $V_{DD}$          | $V_{SS}$          | $V_{SS}$          | $V_{DD}$         | $V_{DDQ}$         | $DQ_A$            | $DQ_A$    |           |

| <b>M</b> | $DQ_D$   | $DQ_D$   | $V_{DDQ}$         | $V_{DD}$          | $V_{SS}$          | $V_{SS}$          | $V_{DD}$         | $V_{DDQ}$         | $DQ_A$            | $DQ_A$    |           |

| <b>N</b> | $DQP_D$  | NC       | $V_{DDQ}$         | $V_{SS}$          | NC                | A                 | NC               | $V_{SS}$          | $V_{DDQ}$         | NC        | $DQP_A$   |

| <b>P</b> | NC       | NC/72M   | A                 | A                 | TDI               | A1                | TDO              | A                 | A                 | A         | A         |

| <b>R</b> | MODE     | NC/36M   | A                 | A                 | TMS               | A0                | TCK              | A                 | A                 | A         | A         |

## ピン機能

| ピン名                                                                           | I/O 形式            | ピンの説明                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------------------------------------------------------------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A <sub>0</sub> 、A <sub>1</sub> 、A                                             | 入力 - 同期           | アドレス位置の 1 つを選択するために使用されるアドレス入力。CLK の立ち上がりエッジでサンプリング                                                                                                                                                                                                                                                                                                                                                                                                     |

| $\overline{BW}_a$ 、 $\overline{BW}_b$ 、 $\overline{BW}_c$ 、 $\overline{BW}_d$ | 入力 - 同期           | バイト書き込み選択入力、アクティブ LOW。SRAM へバイト書き込みを駆動するために $\overline{WE}$ で有効にされる。CLK の立ち上がりエッジでサンプリングされる。 $\overline{BW}_a$ は DQ <sub>a</sub> と DQP <sub>a</sub> 、 $\overline{BW}_b$ は DQ <sub>b</sub> と DQP <sub>b</sub> 、 $\overline{BW}_c$ は DQ <sub>c</sub> と DQP <sub>c</sub> 、 $\overline{BW}_d$ は DQ <sub>d</sub> と DQP <sub>d</sub> を制御                                                                                                                      |

| WE                                                                            | 入力 - 同期           | 書き込みイネーブル入力、アクティブ LOW。 $\overline{CEN}$ がアクティブ LOW の場合、CLK の立ち上がりエッジでサンプリングされる。書き込みシーケンスを開始するためにこの信号を LOW にアサートすることが必要                                                                                                                                                                                                                                                                                                                                  |

| ADV/LD                                                                        | 入力 - 同期           | オンチップのアドレス カウンターを進める、または新しいアドレスをロードするために使用されるアドバンス／ロード入力。この入力が HIGH になり、CEN が LOW にアサートされると、内部バースト カウンターが進む。LOW の場合、アクセスの度に新しいアドレスをデバイスにロードすることが可能。選択解除した後、新しいアドレスをロードするために、ADV/LD を LOW に駆動する必要がある                                                                                                                                                                                                                                                     |

| CLK                                                                           | 入力 - クロック         | クロック入力。デバイスへの全ての同期入力を取り込むために使用。CLK は $\overline{CEN}$ により有効にされる。CLK は、CEN がアクティブ LOW の場合のみに有効になる                                                                                                                                                                                                                                                                                                                                                        |

| $\overline{CE}_1$                                                             | 入力 - 同期           | チップイネーブル 1 入力、アクティブ LOW。CLK の立ち上がりエッジでサンプリングされる。デバイスを選択／選択解除するために $\overline{CE}_2$ と $\overline{CE}_3$ と併用                                                                                                                                                                                                                                                                                                                                             |

| $\overline{CE}_2$                                                             | 入力 - 同期           | チップイネーブル 2 入力、アクティブ HIGH。CLK の立ち上がりエッジでサンプリングされる。デバイスを選択／選択解除するために $\overline{CE}_1$ と $\overline{CE}_3$ と併用                                                                                                                                                                                                                                                                                                                                            |

| $\overline{CE}_3$                                                             | 入力 - 同期           | チップイネーブル 3 入力、アクティブ LOW。CLK の立ち上がりエッジでサンプリングされる。デバイスを選択／選択解除するために $\overline{CE}_1$ と $\overline{CE}_2$ と併用                                                                                                                                                                                                                                                                                                                                             |

| $\overline{OE}$                                                               | 入力 - 非同期          | 出力イネーブル、アクティブ LOW。I/O ピンの方向を制御するために、デバイスに内蔵された同期論理ブロックと組み合わせられる。この入力が LOW の場合、I/O ピンは出力として動作可能。HIGH にデアサートされた時、I/O ピンはトライステートになり、入力データ ピンとして機能。 $\overline{OE}$ は、書き込みシーケンスのデータ転送の間、選択解除の状態から復帰してから最初のクロック サイクルの間、およびデバイスが選択解除された時にマスクされる                                                                                                                                                                                                               |

| CEN                                                                           | 入力 - 同期           | クロックイネーブル入力、アクティブ LOW。LOW にアサートされると、クロック信号が SRAM により認識される。HIGH にデアサートされた場合、クロック信号がマスクされる。 $\overline{CEN}$ をデアサートするとデバイスが選択解除されないため、 $\overline{CEN}$ は、必要に応じて以前のサイクルを延長するために使用可能                                                                                                                                                                                                                                                                       |

| DQ <sub>S</sub>                                                               | I/O- 同期           | 双方向データ I/O ライン。入力として機能している場合、これらの I/O ラインはデータをオンチップデータレジスタに供給。このデータ供給は CLK の立ち上がりエッジでトリガされる。出力として機能している場合、読み出しサイクルの前回のクロック立ち上がり中に $A_{[17:0]}$ により指定されたメモリ位置に保存されたデータを転送。これらのピンの方向は、 $\overline{OE}$ と内部制御論理により制御される。 $\overline{OE}$ が LOW にアサートされた時、これらピンは出力として動作可能。この信号が HIGH の場合、DQ <sub>a</sub> -DQ <sub>d</sub> は、トライステート状態に移行。出力は、 $\overline{OE}$ の状態に関わらず、書き込みシーケンスのデータ転送の間、または選択解除状態から復帰した時から最初のクロック サイクルの間、またはデバイスが選択解除された時に自動的にトライステート状態に移行 |

| DQP <sub>X</sub>                                                              | I/O- 同期           | 双方向データ パリティ I/O ライン。機能的には、これら信号は DQ <sub>S</sub> と同一。書き込みシーケンスの間、DQP <sub>a</sub> は $\overline{BW}_a$ 、DQP <sub>b</sub> は $\overline{BW}_b$ 、DQP <sub>c</sub> は $\overline{BW}_c$ 、および DQP <sub>d</sub> は $\overline{BW}_d$ により制御される                                                                                                                                                                                                                    |

| MODE                                                                          | 入力<br>ストラップ<br>ピン | モード入力。デバイスのバースト順序を選択。HIGH の場合は、インターリーブ バースト順序。LOW の場合は、リニア バースト順序。MODE ピンの状態は動作中に変更不可。開放される場合、MODE ピンはデフォルトで HIGH になり、よってバースト順序はインターリーブ バースト順序                                                                                                                                                                                                                                                                                                          |

**ピン機能 ( 続き )**

| ピン名                                                             | I/O 形式             | ピンの説明                                                                                                                                      |

|-----------------------------------------------------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| TDO                                                             | JTAG シリアル データ 同期出力 | JTAG 回路へのシリアル データ出力。TCK のネガティブ エッジでデータを送信                                                                                                  |

| TDI                                                             | JTAG シリアル データ 同期入力 | JTAG 回路へのシリアル データ入力。TCK の立ち上がりエッジでサンプリングされる                                                                                                |

| TMS                                                             | テスト モード 同期選択       | このピンは、テスト アクセス ポート ステート マシンを制御。TCK の立ち上がりエッジでサンプリングされる                                                                                     |

| TCK                                                             | JTAG クロック          | JTAG 回路へクロック入力                                                                                                                             |

| V <sub>DD</sub>                                                 | 電源                 | デバイスのコアへ電源供給                                                                                                                               |

| V <sub>DDQ</sub>                                                | I/O 電源             | I/O 回路へ電源供給                                                                                                                                |

| V <sub>SS</sub>                                                 | グランド               | デバイスのグランド。システムのグランドに接続する必要がある                                                                                                              |

| NC                                                              | –                  | 未接続。このピンはダイに接続されていない                                                                                                                       |

| NC/36M、<br>NC/72M、<br>NC/144M、<br>NC/288M、<br>NC/576M、<br>NC/1G | –                  | これらのピンは接続されない。36M、72M、144M、288M、576M および 1G の容量に拡張するため に使用される                                                                              |

| ZZ                                                              | 入力 - 非同期           | ZZ 「スリープ」入力。アクティブ HIGH 入力により、デバイスはデータの統合性が保持されている 非タイム クリティカルな「スリープ」状態に入る。通常動作では、このピンを LOW にする、または フローティング状態のままにすることが必要。ZZ ピンは内部プルダウン抵抗に接続 |

## 機能概要

CY7C1370KV25 と CY7C1372KV25 は、読み書き処理中に待ち状態を除去するために設計されている同期パイプライン バースト NoBL SRAM です。全ての同期入力は、クロックの立ち上がりエッジで制御される入力レジスタを通過します。クロック信号は、クロック イネーブル入力信号 (CEN) により有効にされます。CEN が HIGH の場合、クロック信号は有効にされず、すべての内部状態は保持されます。すべての同期動作は、CEN により可能になります。全てのデータ出力は、クロックの立ち上がりエッジで制御される出力レジスタを通過します。クロック立ち上がりからの最大アクセス遅延 ( $t_{CO}$ ) は 3.2ns (デバイス速度が 200MHz の場合) です。

クロックの立ち上がりエッジで全ての3つのチップ イネーブル (CE<sub>1</sub>、CE<sub>2</sub>、CE<sub>3</sub>) をアクティブにアサートすることでアクセスを開始することができます。クロック イネーブル (CEN) がアクティブ LOW であり、ADV/LD が LOW にアサートされた時、デバイスに送信されたアドレスはラッチされます。アクセスは、書き込みイネーブル (WE) の状態に応じて、読み出しありは書き込み動作が行われます。BW<sub>X</sub> はバイト書き込み動作を行うために使用できます。

書き込み動作は書き込みイネーブル (WE) により有効にされます。すべての書き込みは、内蔵のセルフタイム同期書き込み回路で単純化されています。

3つの同期チップ イネーブル (CE<sub>1</sub>、CE<sub>2</sub>、CE<sub>3</sub>) および非同期出力イネーブル (OE) は動作深度の拡大を簡単にします。全ての動作 (読み出し、書き込み、選択解除) はパイプライン化されています。次の動作用に新しいアドレスをロードするために、デバイスが選択解除されると、ADV/LD を LOW に駆動する必要があります。

### シングル読み出しアクセス

クロックの立ち上がりで次の要件が満たされると、読み出しアクセスが開始されます : (1) CEN が LOW にアサート、(2) CE<sub>1</sub>、CE<sub>2</sub>、CE<sub>3</sub> はすべてアクティブにアサート、(3) 書き込みイネーブル入力信号 WE が HIGH にデアサート、(4) ADV/LD が LOW にアサートされる。アドレス入力に供給されたアドレスはアドレス レジスタにラッチされ、メモリ コアおよび制御論理回路に送信されます。制御論理回路は読み出しアクセスが実行中であると判定し、要求されたデータが出力レジスタの入力に伝播することを可能にします。次のクロックの立ち上がりエッジでは、OE がアクティブ LOW であれば、要求されたデータは 3.2ns (デバイス速度が 200MHz の場合) 以内に出力レジスタを介してデータ バスに伝播することができます。読み出しアクセスの最初のクロックの後、出力バッファは OE および内部制御論理回路によって制御されます。デバイスが要求されたデータを出力するためには、OE を LOW に駆動する必要があります。2番目のクロックの間、後続の動作 (読み出し/書き込み/選択解除) を開始できます。デバイスの選択解除動作もパイプライン化されています。そのため、クロック立ち上がり時に SRAM がチップ イネーブル信号のいずれかにより選択解除されると、そ

の出力は次のクロック立ち上がりにトライステートになります。

### バースト読み出しアクセス

CY7C1370KV25 と CY7C1372KV25 は、バースト カウンターを内蔵しており、単一のアドレスを送信しアドレス入力を再アサートせずに最大 4 回の読み出しを行うことを可能にします。シングル読み出しアクセスで説明したように、新しいアドレスを SRAM にロードするために ADV/LD を LOW に駆動する必要があります。バースト カウンターのシーケンスは MODE 入力信号で決まります。MODE 入力信号は、LOW にするとリニアバースト モードを選択し、HIGH にするとインターリーブバースト シーケンスを選択します。両方のバースト カウンターはバースト シーケンスに A0 と A1 ビットを使用し、上限までインクリメントされたらラップ アラウンドします。ADV/LD 入力信号を HIGH にすると、チップ イネーブルまたは WE の状態にかかわらず内部バースト カウンターはインクリメントします。WE はバースト サイクルの始まりにラッチされます。そのため、アクセスタイプ (読み出しか書き込み) はバースト シーケンスの間変わりません。

### シングル書き込みアクセス

クロックの立ち上がりで次の要件が満たされると、書き込みアクセスは開始されます : (1) CEN が LOW にアサート、(2) CE<sub>1</sub>、CE<sub>2</sub>、CE<sub>3</sub> がすべてアクティブにアサート、(3) 書き込み信号 WE が LOW にアサートされる。送信されたアドレスはアドレス レジスタにロードされます。書き込み信号は制御論理回路にラッチされます。

次のクロック立ち上がり時に、OE 入力信号の状態にかかわらずデータ ラインは自動的にトライステートになります。これにより、外部論理回路はデータを DQ と DQP (CY7C1370KV25 では DQ<sub>a,b,c,d</sub> / DQP<sub>a,b,c,d</sub> CY7C1372KV25 では DQ<sub>a,b</sub> / DQP<sub>a,b</sub>) に出すことができます。さらに、適切な制御信号がアサートされていれば、後続のアクセス (読み出し/書き込み/選択解除) 用のアドレスはアドレス レジスタにラッチされます。

次のクロック立ち上がりでは、DQ と DQP (CY7C1370KV25 では DQ<sub>a,b,c,d</sub> / DQP<sub>a,b,c,d</sub> CY7C1372KV25 では DQ<sub>a,b</sub> / DQP<sub>a,b</sub>) (または書き込み動作用のサブセット (詳細は真理値表を参照)) 入力に送信されたデータはデバイスにラッチされ、書き込みが完了します。

書き込み動作中に書き込まれたデータは、BW (CY7C1370KV25 では BW<sub>a,b,c,d</sub> CY7C1372KV25 では BW<sub>a,b</sub>) 信号により制御されます。CY7C1370KV25 / CY7C1372KV25 は、書き込みサイクル説明表で説明されたバイト書き込み機能を備えています。選択したバイト書き込みセレクト (BW) 入力と書き込みイネーブル入力 (WE) をアサートすると、所望のバイトのみが選択的に書き込まれます。バイト書き込み動作中に選択されないバイトは、不变のままでです。書き込み動作を簡素化するためにセルフタイム同期書き込みメカニズムが提供されています。読み出し/変更/書き込み (read-modify-write) シーケンスを大幅に単純化するようバイト書き込み機能が含まれており、これを単なるバイト書き込み操作に単純化しています。

CY7C1370KV25 と CY7C1372KV25 は共通 I/O デバイスであるため、出力がアクティブな時にデータをデバイスに駆動してはなりません。

データを DQ 、 DQP (CY7C1370KV25 では  $DQ_{a,b,c,d} / DQP_{a,b,c,d}$  、 CY7C1372KV25 では  $DQ_{a,b} / DQP_{a,b}$  ) 入力に送信する前に、出力イネーブル ( $\overline{OE}$ ) を HIGH にアサートすることができます。この場合、出力ドライバーがトライステートになります。安全対策としては、 DQ 、 DQP (CY7C1370KV25 では  $DQ_{a,b,c,d} / DQP_{a,b,c,d}$  、 CY7C1372KV25 では  $DQ_{a,b} / DQP_{a,b}$  ) は、  $\overline{OE}$  の状態に関係なく、書き込みサイクルのデータ転送中に自動的にトライステートになります。

### バースト書き込みアクセス

CY7C1370KV25 / CY7C1372KV25 は、バースト カウンターを内蔵しており、単一のアドレスを送信しアドレス入力を再アサートせずに最大 4 回の書き込みを行うことを可能にします。

8 ページの「シングル書き込みアクセス」で説明したように、初期アドレスをロードするために ADV/LD を LOW に駆動する必要があります。次のクロック立ち上がりで ADV/LD が HIGH に駆動されると、チップ イネーブル ( $\overline{CE}_1$ 、  $CE_2$ 、  $\overline{CE}_3$  ) および WE 入力は無視され、バースト カウンターはインクリメントされます。正しいデータ バイトを書き込むために、バースト書き込みの各サイクルで正しい BW (CY7C1370KV25 では  $BW_{a,b,c,d}$  、 CY7C1372KV25 では  $BW_{a,b}$  ) 入力を駆動する必要があります。

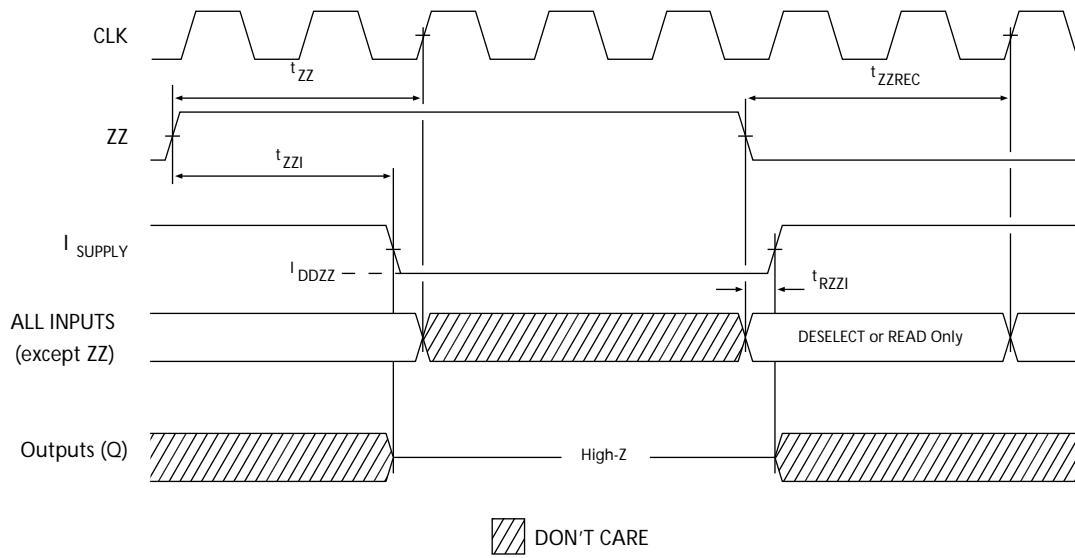

### スリープ モード

ZZ 入力ピンは非同期入力です。ZZ をアサートすると、SRAM は省電力「スリープ」モードに入ります。このスリープ モードへの移行およびそこからの復帰には 2 クロック サイクルかかります。このモードでは、データの統合性が保証されます。スリープ モードに入った時に保留中のアクセスは有効として見なされず、動作完了も保証されません。デバイスはスリープ モードに入る前に、選択解除する必要があります。ZZ 入力が LOW に戻った後、  $\overline{CE}_1$  、  $CE_2$  および  $\overline{CE}_3$  は  $t_{ZZREC}$  の間非アクティブのままにする必要があります。

### インターリーブ バースト アドレス表

(MODE = 開放または  $V_{DD}$  )

| 1番目のアドレス A1:A0 | 2番目のアドレス A1:A0 | 3番目のアドレス A1:A0 | 4番目のアドレス A1:A0 |

|----------------|----------------|----------------|----------------|

| 00             | 01             | 10             | 11             |

| 01             | 00             | 11             | 10             |

| 10             | 11             | 00             | 01             |

| 11             | 10             | 01             | 00             |

### リニア バースト アドレス表

( モード = GND )

| 1番目のアドレス A1:A0 | 2番目のアドレス A1:A0 | 3番目のアドレス A1:A0 | 4番目のアドレス A1:A0 |

|----------------|----------------|----------------|----------------|

| 00             | 01             | 10             | 11             |

| 01             | 10             | 11             | 00             |

| 10             | 11             | 00             | 01             |

| 11             | 00             | 01             | 10             |

### ZZ モード電気的特性

| パラメーター      | 説明                     | テスト条件                   | Min        | Max        | 単位 |

|-------------|------------------------|-------------------------|------------|------------|----|

| $I_{DDZZ}$  | スリープ モード スタンバイ電流       | $ZZ \geq V_{DD} - 0.2V$ | —          | 65         | mA |

| $t_{ZZS}$   | デバイスの動作から ZZ までの時間     | $ZZ \geq V_{DD} - 0.2V$ | —          | $2t_{CYC}$ | ns |

| $t_{ZZREC}$ | ZZ 復帰時間                | $ZZ \leq 0.2V$          | $2t_{CYC}$ | —          | ns |

| $t_{RZI}$   | ZZ アクティブからスリープ 電流までの時間 | このパラメーターはサンプリングされた値     | —          | $2t_{CYC}$ | ns |

| $t_{RZZI}$  | スリープ電流までの ZZ 非 アクティブ時間 | このパラメーターはサンプリングされた値     | 0          | —          | ns |

## 真理値表

以下は CY7C1370KV25 / CY7C1372KV25 の真理値表です。[1、2、3、4、5、6、7、8]

| 動作                     | 使用されるアドレス | $\overline{CE}$ | ZZ | ADV/LD | $\overline{WE}$ | $\overline{BW}_x$ | $\overline{OE}$ | $\overline{CEN}$ | CLK | DQ        |

|------------------------|-----------|-----------------|----|--------|-----------------|-------------------|-----------------|------------------|-----|-----------|

| ディセレクト サイクル            | 無し        | H               | L  | L      | X               | X                 | X               | L                | L-H | トライステート   |

| ディセレクト サイクル継続          | 無し        | X               | L  | H      | X               | X                 | X               | L                | L-H | トライステート   |

| 読み出しサイクル (バースト開始)      | 外部        | L               | L  | L      | H               | X                 | L               | L                | L-H | データ出力 (Q) |

| 読み出しサイクル (バースト継続)      | 後続        | X               | L  | H      | X               | X                 | L               | L                | L-H | データ出力 (Q) |

| NOP / ダミー読み出し (バースト開始) | 外部        | L               | L  | L      | H               | X                 | H               | L                | L-H | トライステート   |

| ダミー読み出し (バースト継続)       | 後続        | X               | L  | H      | X               | X                 | H               | L                | L-H | トライステート   |

| 書き込みサイクル (バースト開始)      | 外部        | L               | L  | L      | L               | L                 | X               | L                | L-H | データ入力 (D) |

| 書き込みサイクル (バースト継続)      | 後続        | X               | L  | H      | X               | L                 | X               | L                | L-H | データ入力 (D) |

| NOP / 書き込み中止 (バースト開始)  | 無し        | L               | L  | L      | L               | H                 | X               | L                | L-H | トライステート   |

| 書き込み中止 (バースト継続)        | 後続        | X               | L  | H      | X               | H                 | X               | L                | L-H | トライステート   |

| クロック エッジの無視 (ストール)     | 電流        | X               | L  | X      | X               | X                 | X               | H                | L-H | -         |

| スリープ モード               | 無し        | X               | H  | X      | X               | X                 | X               | X                | X   | トライステート   |

### 注:

1. X = 「ドントケア」、H = 論理 HIGH、L = 論理 LOW、 $\overline{CE}$  はすべてのチップ イネーブルがアクティブになっていることを示します。「 $\overline{BW}_x = L$ 」は、少なくとも 1 つのバイト書き込み選択信号がアクティブになっていることを示し、「 $\overline{BW}_x = \text{valid}$ 」は、対象のバイト書き込み選択信号がアサートされたことを示します。詳細については、書き込みサイクル説明表を参照してください。

2. 書き込みは、 $\overline{WE}$  と  $\overline{BW}_x$  を使って定義されます。詳細については、書き込みサイクル説明表を参照してください。

3. 書き込みサイクルが検出された場合、バイト書き込み中でも、すべての I/O はトライステートになります。

4. DQ ピンと DQP ピンは現行のサイクルと  $\overline{OE}$  信号によって制御されます。

5.  $\overline{CEN} = H$  の場合は、待ち状態が挿入されます。

6. デバイスの電源投入時は、 $\overline{OE}$  に関わらず、各ピンは選択解除の状態で、I/O はトライステートの状態です。

7.  $\overline{OE}$  は非同期で、クロック立ち上がりと同期してサンプリングされません。書き込みサイクル中にマスキングされます。読み出しサイクルでは、 $\overline{OE}$  が非アクティブ、またはデバイスが選択解除された場合、DQ<sub>s</sub> と DQP<sub>x</sub> はトライステートになり、 $\overline{OE}$  がアクティブの場合は、DQ<sub>s</sub> はデータを格納します。

8. この表では、バイト書き込みの組み合わせの一部を示します。どの  $\overline{BW}_x$  の組み合わせも有効です。アクティブになるバイト書き込み信号に応じて、適切な書き込みが行われます。

## 書き込み／読み出しの部分真理値表

以下は CY7C1370KV25 の書き込み／読み出しの部分真理値表です。[9、10、11、12]

| CY7C1370KV25                                      | $\overline{WE}$ | $\overline{BW}_d$ | $\overline{BW}_c$ | $\overline{BW}_b$ | $\overline{BW}_a$ |

|---------------------------------------------------|-----------------|-------------------|-------------------|-------------------|-------------------|

| 読み出し                                              | H               | X                 | X                 | X                 | X                 |

| 書き込み - バイト書き込みなし                                  | L               | H                 | H                 | H                 | H                 |

| バイト a 書き込み - (DQ <sub>a</sub> 、DQP <sub>a</sub> ) | L               | H                 | H                 | H                 | L                 |

| バイト b 書き込み - (DQ <sub>b</sub> 、DQP <sub>b</sub> ) | L               | H                 | H                 | L                 | H                 |

| バイト b、a 書き込み                                      | L               | H                 | H                 | L                 | L                 |

| バイト c 書き込み - (DQ <sub>c</sub> 、DQP <sub>c</sub> ) | L               | H                 | L                 | H                 | H                 |

| バイト c、a 書き込み                                      | L               | H                 | L                 | H                 | L                 |

| バイト c、b 書き込み                                      | L               | H                 | L                 | L                 | H                 |

| バイト c、b、a 書き込み                                    | L               | H                 | L                 | L                 | L                 |

| バイト d 書き込み - (DQ <sub>d</sub> 、DQP <sub>d</sub> ) | L               | L                 | H                 | H                 | H                 |

| バイト d、a 書き込み                                      | L               | L                 | H                 | H                 | L                 |

| バイト d、b 書き込み                                      | L               | L                 | H                 | L                 | H                 |

| バイト d、b、a 書き込み                                    | L               | L                 | H                 | L                 | L                 |

| バイト d、c 書き込み                                      | L               | L                 | L                 | H                 | H                 |

| バイト d、c、a 書き込み                                    | L               | L                 | L                 | H                 | L                 |

| バイト d、c、b 書き込み                                    | L               | L                 | L                 | L                 | H                 |

| すべてのバイト書き込み                                       | L               | L                 | L                 | L                 | L                 |

## 書き込み／読み出しの部分真理値表

以下は CY7C1372KV25 の書き込み／読み出しの部分真理値表です。[9、10、11、12]

| CY7C1372KV25                                      | $\overline{WE}$ | $\overline{BW}_b$ | $\overline{BW}_a$ |

|---------------------------------------------------|-----------------|-------------------|-------------------|

| 読み出し                                              | H               | X                 | X                 |

| 書き込み - バイト書き込みなし                                  | L               | H                 | H                 |

| バイト a 書き込み - (DQ <sub>a</sub> 、DQP <sub>a</sub> ) | L               | H                 | L                 |

| バイト b 書き込み - (DQ <sub>b</sub> 、DQP <sub>b</sub> ) | L               | L                 | H                 |

| 両バイト書き込み                                          | L               | L                 | L                 |

### 注:

9. X = 「ドントケア」、H = 論理 HIGH、L = 論理 LOW、 $\overline{CE}$  はすべてのチップ イネーブルがアクティブになっていることを示します。「 $\overline{BW}_x = L$ 」は、少なくとも 1 つのバイト書き込み選択信号がアクティブになっていることを示し、「 $BW_x = valid$ 」は、対象のバイト書き込み選択信号がアサートされたことを示します。詳細については、書き込みサイクル説明表を参照してください。

10. 書き込みは、 $WE$  と  $BW_x$  を使って定義されます。詳細は、[10 ページの「真理値表」](#) を参照してください。

11. 書き込みサイクルが検出された場合、バイト書き込み中でも、すべての I/O はトライステートになります。

12. この表では、バイト書き込みの組み合わせの一部を示します。どの  $\overline{BW}_x$  の組み合わせも有効です。アクティブになるバイト書き込み信号に応じて、適切な書き込みが行われます。

## IEEE 1149.1 シリアル バウンダリ スキャン (JTAG)

CY7C1370KV25 は、シリアル バウンダリ スキャン テスト アクセス ポート (TAP) を組み込んでいます。この製品は 1149.1 に完全に準拠しています。TAP は、JEDEC 標準の 2.5V または 2.5V I/O 論理レベルを使用して動作します。

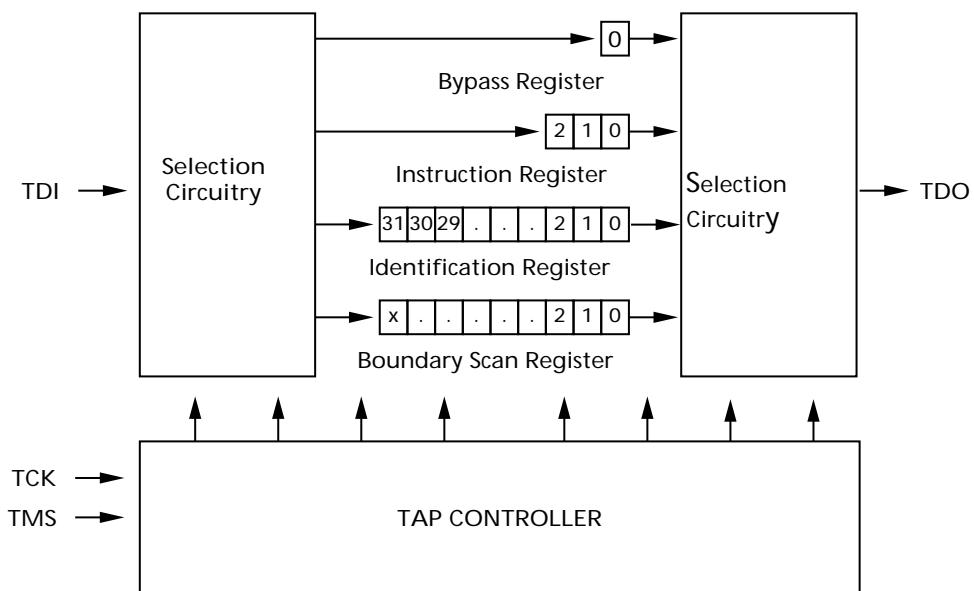

CY7C1370KV25 は、TAP コントローラー、命令レジスタ、バウンダリ スキャン レジスタ、バイパス レジスタ、および ID レジスタを含んでいます。

### JTAG 機能の無効化

JTAG 機能を使用せず、SRAM を動作させることができます。TAP コントローラーを無効にするためには、TCK を LOW ( $V_{SS}$ ) に接続してデバイスへのクロック供給を防ぐ必要があります。TDI と TMS は内部でプルアップされており、未接続にすることができます。かわりに、プルアップ抵抗を介して  $V_{DD}$  に接続することもできます。TDO は未接続にする必要があります。電源投入時にデバイスは、デバイス動作を妨げないリセット状態に入ります。

### テスト アクセス ポート (TAP)

#### テスト クロック (TCK)

テスト クロックは TAP コントローラーとのみ併用できます。全ての入力を TCK の立ち上がりエッジで取り込みます。すべての出力は TCK の立ち下がりエッジで駆動されます。

#### テスト モード選択 (TMS)

TMS 入力は、TAP コントローラーにコマンドを送信するために使用され、TCK の立ち上がりエッジでサンプリングされます。TAP を使用しない場合、このポートを未接続とすることができます。ポートは内部でプルアップされているため、論理 HIGH レベルになります。

#### テスト データ入力 (TDI)

TDI ポートは、レジスタに情報をシリアル入力するのに使用され、どのレジスタの入力にも接続することができます。TDI と TDO 間の接続レジスタは、TAP 命令レジスタにロードされた命令によって選択されます。命令レジスタにロードする方法については、[14 ページの「TAP コントローラー状態遷移図」](#) を参照してください。アプリケーションで TAP を使用しない場合、TDI は内部でプルアップされており、未接続とすることができます。TDI はあらゆるレジスタの最上位ビット (MSB) に接続されます。

#### テスト データ出力 (TDO)

TDO 出力ポートは、レジスタからデータをシリアル出力するために使用されます。TAP ステート マシンの状態に応じて、出力はアクティブになります ([18 ページの「命令コード」](#) を参照してください)。出力は TCK の立ち下がりエッジで変化します。TDO は、レジスタの最下位ビット (LSB) に接続されます。

### TAP リセットの実行

リセットは、TCK の 5 つの立ち上がりエッジの間 TMS を HIGH ( $V_{DD}$ ) に固定することで実行されます。このリセットは SRAM の動作に影響を与えず、SRAM の動作中に実行できます。

電源投入時に、TDO が必ず HIGH Z 状態となるよう、TAP を内部でリセットします。

### TAP レジスタ

SRAM テスト回路の入力と出力データをスキャンすることを可能にするために、TDI と TDO の間にレジスタが接続されます。命令レジスタを介して、一度に選択されるレジスタは 1 つのみです。データは TCK の立ち上がりエッジで TDI ポートに順次にロードされます。データは TCK の立ち下がりエッジで TDO ポートに出力されます。

#### 命令レジスタ

3 ビットの命令を命令レジスタに順次にロードすることができます。[15 ページの「TAP コントローラーのブロック図」](#) に示すように、このレジスタは TDI と TDO ポート間に配置された時にロードされます。電源投入時に、IDCODE 命令が命令レジスタにロードされます。前述したように、コントローラーがリセット状態になった場合にも、IDCODE 命令が命令レジスタにロードされます。

TAP コントローラーが Capture-IR 状態になった時、基板レベルのシリアル テスト データ パスの障害分離を可能にするために、2 進数「01」パターンが最下位 2 ビットにロードされます。

#### バイパス レジスタ

レジスタを通してデータを順次シフトする際の時間を節約するために、特定のチップをスキップすることが有効な場合もあります。バイパス レジスタは、TDI と TDO ポート間に配置できる 1 ビットのレジスタです。これにより、最小限の遅延で SRAM を介してデータをシフトすることができます。BYPASS 命令が実行されると、バイパス レジスタは LOW ( $V_{SS}$ ) に設定されます。

#### バウンダリ スキャン レジスタ

バウンダリ スキャン レジスタは、SRAM 上の全ての入力および双向ポートに接続されます。

バウンダリ スキャン レジスタは、TAP コントローラーが Capture-DR 状態になった時に RAM I/O リングの内容でロードされ、そしてコントローラーが Shift-DR 状態に入ると TDI と TDO ポート間に配置されます。EXTEST、SAMPLE/PRELOAD、SAMPLE Z 命令は、I/O リングの内容を取り込むために使用されます。

[19 ページの「バウンダリ スキャン順序」](#) に、ビットが接続されている順序を示します。各ビットは、SRAM パッケージ上の 1 つの端子に対応します。レジスタの MSB は TDI に、LSB は TDO に接続されます。

#### 識別 (ID) レジスタ

IDCODE コマンドが命令レジスタにロードされた時、Capture-DR 状態の間に、ID レジスタにベンダー固有の 32 ビット コードがロードされます。IDCODE は、TAP コントローラーが Shift-DR 状態の間に SRAM に接続され、シフトアウトされます。ID レジスタのベンダー コードおよび他の情報は [18 ページの「ID レジスタの定義」](#) の通りです。

## TAP 命令セット

### 概要

3 ビットの命令レジスタにより、8 つの異なる命令があります。すべての組み合わせは、命令コード表に一覧表示します。これらの命令の内 3 つは RESERVED で、使用できません。残りの 5 つの命令を以下で詳しく説明します。

命令レジスタが TDI と TDO の間に配置されると、命令は Shift-IR 状態の間に TAP コントローラーにロードされます。この状態の間に、命令は命令レジスタを通して TDI ボールから TDO ボールまでシフトされます。シフトインされた命令を実行するために、TAP コントローラーを Update-IR 状態にする必要があります。

### EXTEST

EXTEST 命令は、プリロードされたデータをシステム出力ピンを通して駆動します。この命令では、Shift-DR 状態の間にシリアルアクセス用にバウンダリスキャンレジスタを TDI と TDO の間に接続します。

### IDCODE

IDCODE 命令では、ベンダー固有の 32 ビット コードを命令レジスタにロードします。また、命令レジスタを TDI ボールと TDO ボールの間に配置して、TAP コントローラーが Shift-DR 状態に入った時に IDCODE をデバイスからシフトアウトします。

IDCODE 命令は、電源投入時または TAP コントローラーが「Test-Logic-Reset」状態に入る度に、命令レジスタにロードされます。

### SAMPLE Z

SAMPLE Z 命令により、TAP コントローラーが Shift-DR 状態に入った時にバウンダリスキャンレジスタが TDI と TDO ボールの間に接続されます。また、この命令は、全ての SRAM 出力を High Z 状態にします。

### SAMPLE/PRELOAD

SAMPLE/PRELOAD は 1149.1 標準の必須命令です。SAMPLE/PRELOAD 命令が命令レジスタにロードされ、TAP コントローラーが Capture-DR 状態になると、入力と出力ピン上のデータのスナップショットがバウンダリスキャンレジスタに取り込まれます。

TAP コントローラークロックは最大 20MHz の周波数で動作するのに対して、SRAM クロックは桁違いに速い周波数で動作することに注意してください。クロック周波数に大きな差があるため、入力または出力は Capture-DR 状態中に変化する可能性があります。その後、TAP は変化中（メタステーブル状態）の信号を取り込もうとするかもしれません。これはデバイスに悪影響を与えませんが、取り込まれた値に対する保証はありません。再現性のない結果となる場合があります。

バウンダリスキャンレジスタが信号の正しい値を取り込むために、SRAM 信号は、TAP コントローラーのキャプチャ セッ

トアップ + ホールド時間 ( $t_{CS} + t_{CH}$ ) を満たす十分な安定時間を取る必要があります。SAMPLE/PRELOAD 命令の間にクロックを停止する（または遅くする）方法がデザインにない場合、SRAM クロック入力は正常に取り込まれない場合があります。これが問題になっても、他の全ての信号を取り込むことはまだ可能で、単にバウンダリスキャンレジスタに取り込まれた CK および CK の値を無視してもかまいません。

データが取り込まれると、TAP を Shift-DR 状態に移行することでデータをシフトアウトすることができます。これにより、バウンダリスキャンレジスタが TDI と TDO ピンの間に配置されます。

PRELOAD では、他のバウンダリスキャンテスト動作の選択の前に、初期データパターンをバウンダリスキャンレジスタセルのラッチされたパラレル出力に配置します。

SAMPLE および PRELOAD のデータのシフトは、必要に応じて同時に実行することができます。つまり取り込まれたデータがシフトアウトされている間にプリロードされたデータがシフトインされます。

### BYPASS

BYPASS 命令が命令レジスタにロードされ、TAP が Shift-DR 状態になると、バイパスレジスタは TDI と TDO ピンの間に配置されます。BYPASS 命令の利点は、複数のデバイスが基板上で互いに接続されている時にバウンダリスキャンパスを短縮することです。

### EXTEST OUTPUT BUS TRISTATE

IEEE 標準 1149.1 では、TAP コントローラーは出力バスをトライステートにできる必要があります。

バウンダリスキャンレジスタには、ビット 89 に位置付けられた特別なビットがあります（165 ボール FBGA パッケージの場合）。「extest output bus tristate」と呼ばれるこのスキャンセルは、TAP コントローラーで「Update-DR」状態中にプリロードレジスタにラッチされた時、EXTEST が現時点の命令として入力されると、出力（Q バス）ピンの状態を直接制御します。このビットは HIGH の時、出力バッファに出力バスを駆動させます。LOW の時、出力バスを High Z 状態に移行させます。

Shift-DR 状態中に、SAMPLE/PRELOAD または EXTEST コマンドを入力して、所望のビットをそのセルにシフトすることでこのビットをセットできます。「Update-DR」状態の間に、そのシフトレジスタセルにロードされた値はプリロードレジスタにラッチされます。EXTEST 命令を入力すると、このビットは出力 Q バスピンを直接制御します。デバイスが電源投入された時や TAP コントローラーが「Test-Logic-Reset」状態になつた時に出力を有効にするために、このビットは HIGH にあらかじめセットされることに注意してください。

### Reserved

これら命令は実装されていませんが、将来使用のために予約されています。これらの命令を使用しないでください。

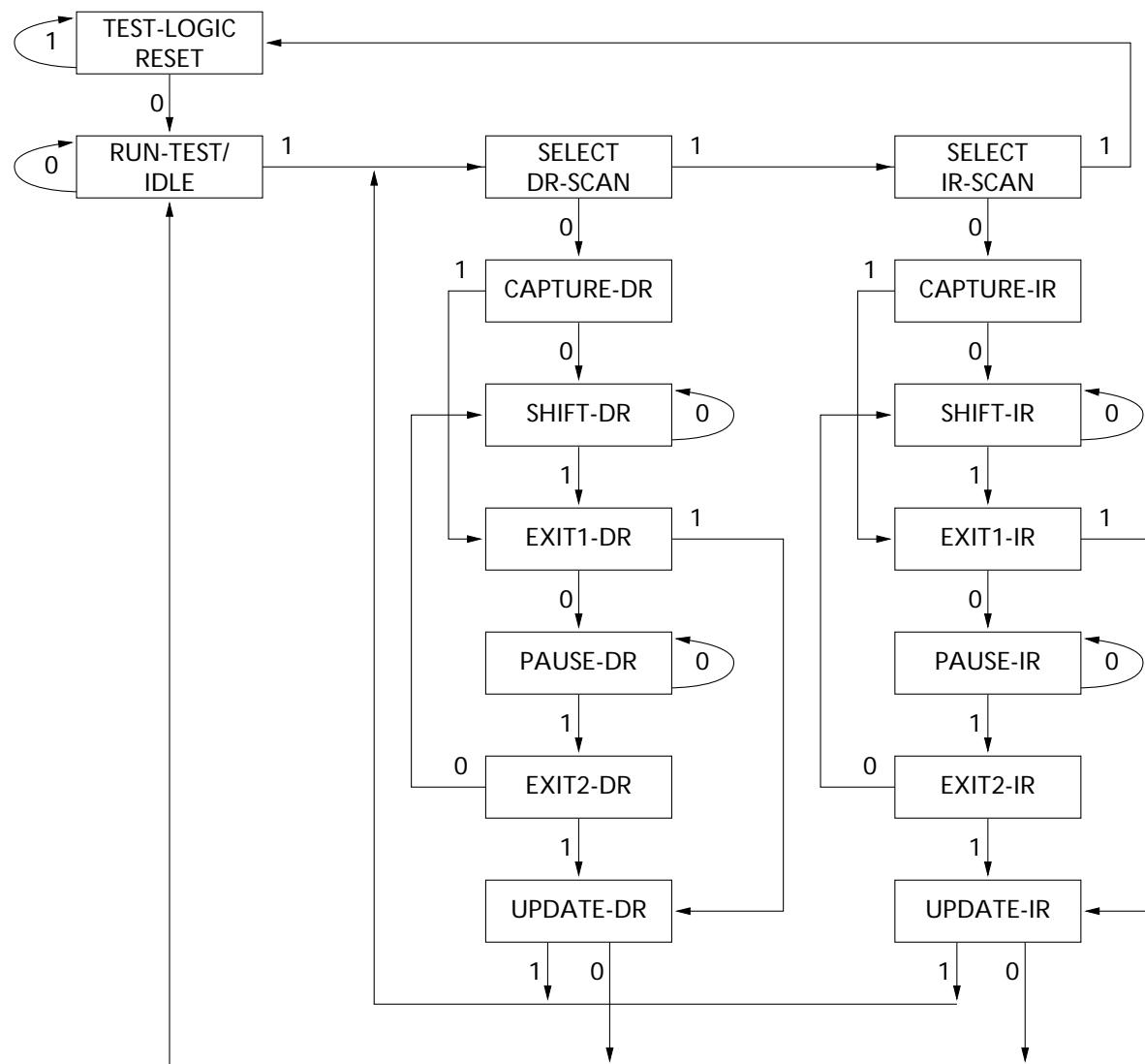

**TAP コントローラー状態遷移図**

## TAP コントローラーのブロック図

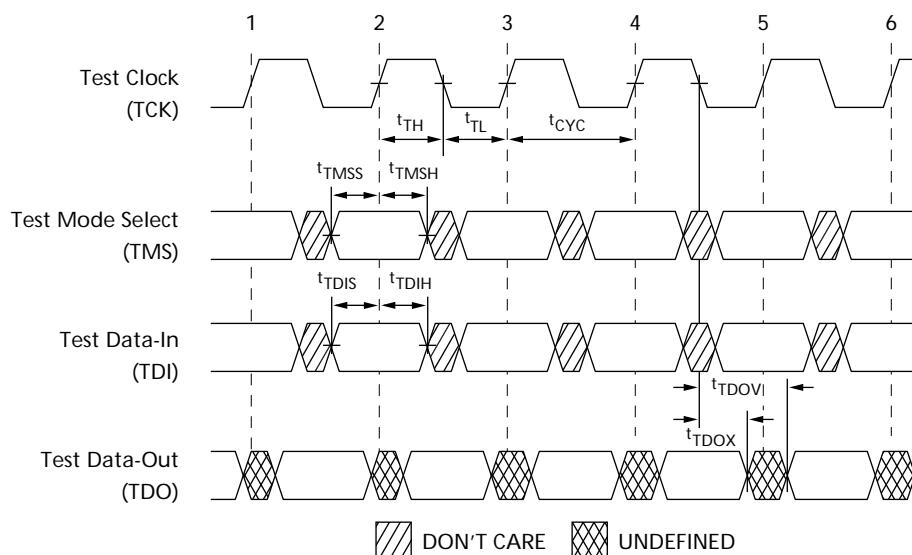

## TAP タイミング

図 3. TAP タイミング

## TAP AC スイッチング特性

動作範囲において

| パラメーター [13, 14] | 説明                             | Min | Max | 単位  |

|-----------------|--------------------------------|-----|-----|-----|

| <b>クロック</b>     |                                |     |     |     |

| $t_{TCYC}$      | TCK クロック サイクル時間                | 50  | –   | ns  |

| $t_{TF}$        | TCK クロック周波数                    | –   | 20  | MHz |

| $t_{TH}$        | TCK クロック HIGH 時間               | 20  | –   | ns  |

| $t_{TL}$        | TCK クロック LOW 時間                | 20  | –   | ns  |

| <b>出力時間</b>     |                                |     |     |     |

| $t_{TDOV}$      | TCK クロック LOW から TDO 有効まで       | –   | 10  | ns  |

| $t_{TDOX}$      | TCK クロック LOW から TDO 無効まで       | 0   | –   | ns  |

| <b>セットアップ時間</b> |                                |     |     |     |

| $t_{TMSS}$      | TCK クロックの立ち上がりまでの TMS セットアップ時間 | 5   | –   | ns  |

| $t_{TDIS}$      | TCK クロックの立ち上がりまでの TDI セットアップ時間 | 5   | –   | ns  |

| $t_{CS}$        | TCK の立ち上がりまでのキャプチャ セットアップ時間    | 5   | –   | ns  |

| <b>ホールド時間</b>   |                                |     |     |     |

| $t_{TMSH}$      | TCK クロック立ち上がり後の TMS ホールド時間     | 5   | –   | ns  |

| $t_{TDIH}$      | TCK クロック立ち上がり後の TDI ホールド時間     | 5   | –   | ns  |

| $t_{CH}$        | TCK クロック立ち上がり後のキャプチャ ホールド時間    | 5   | –   | ns  |

**注:**

13.  $t_{CS}$  と  $t_{CH}$  は、バウンダリ スキャン レジスタからデータをラッチするためのセットアップとホールド時間を示します。

14. テスト条件は、TAP AC テスト条件での負荷を使用して指定されます。 $t_R/t_F = 1\text{ns}$ 。

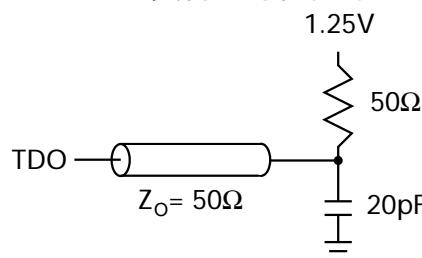

## 2.5V TAP AC テスト条件

|                              |                    |

|------------------------------|--------------------|

| 入力パルス レベル                    | $V_{SS} \sim 2.5V$ |

| 入力の立ち上がりと立ち下がり時間<br>(スルーレート) | 2V/ns              |

| 入力タイミングのリファレンス電圧レベル          | 1.25V              |

| 出力のリファレンス電圧レベル               | 1.25V              |

| テスト負荷終端電源電圧                  | 1.25V              |

## 2.5V TAP AC 出力負荷の等価回路

## TAP DC 電気的特性と動作条件

(特記されていない限り、 $0^{\circ}\text{C} < T_A < +70^{\circ}\text{C}$  ;  $V_{DD} = 2.5V \pm 0.125V$ )

| パラメーター <sup>[15]</sup> | 説明         | テスト条件                                         | Min              | Max  | 単位             |   |

|------------------------|------------|-----------------------------------------------|------------------|------|----------------|---|

| $V_{OH1}$              | 出力 HIGH 電圧 | $I_{OH} = -1.0\text{mA}$ 、 $V_{DDQ} = 2.5V$   | 2.0              | —    | V              |   |

| $V_{OH2}$              | 出力 HIGH 電圧 | $I_{OH} = -100\mu\text{A}$ 、 $V_{DDQ} = 2.5V$ | 2.1              | —    | V              |   |

| $V_{OL1}$              | 出力 LOW 電圧  | $I_{OL} = 8.0\text{mA}$ 、 $V_{DDQ} = 2.5V$    | —                | 0.4  | V              |   |

| $V_{OL2}$              | 出力 LOW 電圧  | $I_{OL} = 100\mu\text{A}$                     | $V_{DDQ} = 2.5V$ | —    | 0.2            | V |

| $V_{IH}$               | 入力 HIGH 電圧 |                                               | $V_{DDQ} = 2.5V$ | 1.7  | $V_{DD} + 0.3$ | V |

| $V_{IL}$               | 入力 LOW 電圧  |                                               | $V_{DDQ} = 2.5V$ | -0.3 | 0.7            | V |

| $I_X$                  | 入力負荷電流     | $GND \leq V_{IN} \leq V_{DDQ}$                | -5               | 5    | $\mu\text{A}$  |   |

注:

15. 全ての電圧は  $V_{SS}$  (GND) を基準にしています。

## スキャン レジスタ サイズ

| レジスタ名                              | ビット サイズ (×18) |

|------------------------------------|---------------|

| 命令                                 | 3             |

| バイパス                               | 1             |

| ID                                 | 32            |

| バウンダリ スキャン順序 (165 ボール FBGA パッケージ ) | 89            |

## ID レジスタの定義

| 命令フィールド                | CY7C1370KV25      | 説明            |

|------------------------|-------------------|---------------|

| バージョン番号 (31:29)        | 000               | バージョン番号用に予約済み |

| サイプレスのデバイス ID (28:12)  | 01011001000010101 | 将来使用のために予約済み  |

| サイプレスの JEDEC ID (11:1) | 00000110100       | SRAM ベンダーを識別  |

| ID レジスタの有無 (0)         | 1                 | ID レジスタの有無を示す |

## 命令コード

| 命令             | コード | 説明                                                                                 |

|----------------|-----|------------------------------------------------------------------------------------|

| EXTEST         | 000 | 入力および出力リングの内容を取り込む。バウンダリ スキャン レジスタを TDI と TDO の間に配置。全ての SRAM 出力ドライバーを High Z 状態に移行 |

| IDCODE         | 001 | ベンダー ID コードを ID レジスタにロードし、レジスタを TDI と TDO の間に配置。この処理は SRAM 動作に影響を与えない              |

| SAMPLE Z       | 010 | I/O リングの内容を取り込む。バウンダリ スキャン レジスタを TDI と TDO の間に配置。全ての SRAM 出力ドライバーを HIGH Z 状態に移行    |

| RESERVED       | 011 | 未使用：将来使用のために予約済み                                                                   |

| SAMPLE/PRELOAD | 100 | I/O リングの内容を取り込む。バウンダリ スキャン レジスタを TDI と TDO の間に配置。SRAM 動作に影響を与えない                   |

| RESERVED       | 101 | 未使用：将来使用のために予約済み                                                                   |

| RESERVED       | 110 | 未使用：将来使用のために予約済み                                                                   |

| BYPASS         | 111 | バイパス レジスタを TDI と TDO の間に配置。この動作は SRAM 動作に影響を与えない                                   |

## バウンダリスキャン順序

165 ポール FBGA [16、17]

| ビット番号 | ポール ID |

|-------|--------|

| 1     | N6     |

| 2     | N7     |

| 3     | N10    |

| 4     | P11    |

| 5     | P8     |

| 6     | R8     |

| 7     | R9     |

| 8     | P9     |

| 9     | P10    |

| 10    | R10    |

| 11    | R11    |

| 12    | H11    |

| 13    | N11    |

| 14    | M11    |

| 15    | L11    |

| 16    | K11    |

| 17    | J11    |

| 18    | M10    |

| 19    | L10    |

| 20    | K10    |

| 21    | J10    |

| 22    | H9     |

| 23    | H10    |

| 24    | G11    |

| 25    | F11    |

| 26    | E11    |

| 27    | D11    |

| 28    | G10    |

| 29    | F10    |

| 30    | E10    |

| ビット番号 | ポール ID |

|-------|--------|

| 31    | D10    |

| 32    | C11    |

| 33    | A11    |

| 34    | B11    |

| 35    | A10    |

| 36    | B10    |

| 37    | A9     |

| 38    | B9     |

| 39    | C10    |

| 40    | A8     |

| 41    | B8     |

| 42    | A7     |

| 43    | B7     |

| 44    | B6     |

| 45    | A6     |

| 46    | B5     |

| 47    | A5     |

| 48    | A4     |

| 49    | B4     |

| 50    | B3     |

| 51    | A3     |

| 52    | A2     |

| 53    | B2     |

| 54    | C2     |

| 55    | B1     |

| 56    | A1     |

| 57    | C1     |

| 58    | D1     |

| 59    | E1     |

| 60    | F1     |

| ビット番号 | ポール ID |

|-------|--------|

| 61    | G1     |

| 62    | D2     |

| 63    | E2     |

| 64    | F2     |

| 65    | G2     |

| 66    | H1     |

| 67    | H3     |

| 68    | J1     |

| 69    | K1     |

| 70    | L1     |

| 71    | M1     |

| 72    | J2     |

| 73    | K2     |

| 74    | L2     |

| 75    | M2     |

| 76    | N1     |

| 77    | N2     |

| 78    | P1     |

| 79    | R1     |

| 80    | R2     |

| 81    | P3     |

| 82    | R3     |

| 83    | P2     |

| 84    | R4     |

| 85    | P4     |

| 86    | N5     |

| 87    | P6     |

| 88    | R6     |

| 89    | 内部     |

注:

16. NC (未接続) のポールは LOW にプリセットされます。

17. ビット 89 は HIGH にプリセットされます。

## 最大定格

|                                                                             |

|-----------------------------------------------------------------------------|

| 最大定格を超えるとデバイスの寿命が短くなる可能性があります。ユーザー ガイドラインはテストされていません。                       |

| 保存温度 ..... $-65^{\circ}\text{C} \sim +150^{\circ}\text{C}$                  |

| 通電時の周囲温度 ..... $-55^{\circ}\text{C} \sim +125^{\circ}\text{C}$              |

| GND を基準とした $V_{\text{DD}}$ 上の電源電圧 ..... $-0.5\text{V} \sim +3.6\text{V}$    |

| GND を基準とした $V_{\text{DDQ}}$ 上の電源電圧 ..... $-0.5\text{V} \sim +V_{\text{DD}}$ |

| トライステート状態の出力に与える                                                            |

| DC 電圧 ..... $-0.5\text{V} \sim V_{\text{DDQ}}+0.5\text{V}$                  |

| DC 入力電圧 ..... $-0.5\text{V} \sim V_{\text{DD}}+0.5\text{V}$                 |

| 出力 (LOW) への電流 ..... 20mA                                                    |

| 静電放電時の電圧<br>(MIL-STD-883、メソッド 3015) ..... $> 2001\text{V}$                  |

| ラッチアップ電流 ..... $> 200\text{mA}$                                             |

## 動作範囲

| 範囲  | 周囲温度                                         | $V_{\text{DD}}/V_{\text{DDQ}}$ |

|-----|----------------------------------------------|--------------------------------|

| 民生用 | $0^{\circ}\text{C} \sim +70^{\circ}\text{C}$ | $2.5\text{V} \pm 5\%$          |

## 中性子ソフト エラー耐性

| パラメーター             | 説明                | テスト条件                | Typ | Max* | 単位      |

|--------------------|-------------------|----------------------|-----|------|---------|

| LSBU (ECC なしのデバイス) | 単一論理ビット反転         | $25^{\circ}\text{C}$ | 197 | 216  | FIT/Mb  |

| LMBU               | 論理マルチビットアップセット    | $25^{\circ}\text{C}$ | 0   | 0.01 | FIT/Mb  |

| SEL                | シングルイベント ラッピングアップ | $85^{\circ}\text{C}$ | 0   | 0.1  | FIT/Dev |

\* テスト中に LMBU または SEL イベントは発生しない; この欄は  $\chi^2$  分布の 95% 信頼上限を示す。詳細は、「AN54908 - Accelerated Neutron SER Testing and Calculation of Terrestrial Failure Rates」のアプリケーション ノートを参照

## 電気的特性

### 動作範囲において

| パラメーター <sup>[18, 19]</sup> | 説明                         | テスト条件                                                    | Min   | Max                           | 単位            |

|----------------------------|----------------------------|----------------------------------------------------------|-------|-------------------------------|---------------|

| $V_{\text{DD}}$            | 電源電圧                       |                                                          | 2.375 | 2.625                         | V             |

| $V_{\text{DDQ}}$           | I/O 電源電圧                   | 2.5V I/O の場合                                             | 2.375 | $V_{\text{DD}}$               | V             |

| $V_{\text{OH}}$            | 出力 HIGH 電圧                 | 2.5V I/O, $I_{\text{OH}} = -1.0\text{mA}$ の場合            | 2.0   | –                             | V             |

| $V_{\text{OL}}$            | 出力 LOW 電圧                  | 2.5V I/O, $I_{\text{OL}} = 1.0\text{mA}$ の場合             | –     | 0.4                           | V             |

| $V_{\text{IH}}$            | 入力 HIGH 電圧 <sup>[18]</sup> | 2.5V I/O の場合                                             | 1.7   | $V_{\text{DD}} + 0.3\text{V}$ | V             |

| $V_{\text{IL}}$            | 入力 LOW 電圧 <sup>[18]</sup>  | 2.5V I/O の場合                                             | -0.3  | 0.7                           | V             |

| $I_{\text{X}}$             | 入力リード電流<br>(ZZ と MODE を除く) | $\text{GND} \leq V_{\text{I}} \leq V_{\text{DDQ}}$       | -5    | 5                             | $\mu\text{A}$ |

|                            | MODE の入力電流                 | 入力 = $V_{\text{SS}}$                                     | -30   | –                             |               |

|                            |                            | 入力 = $V_{\text{DD}}$                                     | –     | 5                             |               |

|                            | ZZ の入力電流                   | 入力 = $V_{\text{SS}}$                                     | -5    | –                             |               |

|                            |                            | 入力 = $V_{\text{DD}}$                                     | –     | 30                            |               |

| $I_{\text{OZ}}$            | 出力リード電流                    | $\text{GND} \leq V_{\text{I}} \leq V_{\text{DD}}$ 、出力が無効 | -5    | 5                             | $\mu\text{A}$ |

### 注:

18. オーバーシュート :  $V_{\text{IH}(\text{AC})} < V_{\text{DD}} + 1.5\text{V}$  (パルス幅は  $t_{\text{CYC}}/2$  未満)、アンダーシュート :  $V_{\text{IL}(\text{AC})} > -2\text{V}$  (パルス幅は  $t_{\text{CYC}}/2$  未満)。

19.  $T_{\text{Power-up}}$ : 少なくとも 200ms 以上での 0V から  $V_{\text{DD}(\text{min})}$  までの直線昇圧を前提としています。この期間中は、 $V_{\text{IH}} < V_{\text{DD}}$ 、 $V_{\text{DDQ}} \leq V_{\text{DD}}$  です。

## 電気的特性 ( 続き )

動作範囲において

| パラメーター <sup>[18, 19]</sup> | 説明                       | テスト条件                                                                                                                                               |                      |      |   | Min | Max | 単位 |

|----------------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|------|---|-----|-----|----|

| I <sub>DD</sub>            | V <sub>DD</sub> 動作時電源    | V <sub>DD</sub> = Max.、I <sub>OUT</sub> = 0mA、<br>f = f <sub>MAX</sub> = 1/t <sub>CYC</sub>                                                         | 5ns のサイクル、<br>200MHz | ×18  | — | 158 |     |    |

|                            |                          |                                                                                                                                                     |                      | ×36  | — | 178 |     |    |

|                            |                          |                                                                                                                                                     | 6ns のサイクル、<br>167MHz | ×18  | — | 143 |     |    |

|                            |                          |                                                                                                                                                     |                      | ×36  | — | 163 |     |    |

| I <sub>SB1</sub>           | 自動 CE パワーダウン電流 – TTL 入力  | 最大 V <sub>DD</sub> 、デバイス選択解除、V <sub>IN</sub> ≥ V <sub>IH</sub> または V <sub>IN</sub> ≤ V <sub>IL</sub> 、<br>f = f <sub>MAX</sub> = 1/t <sub>CYC</sub> | 5ns のサイクル、<br>200MHz | × 18 | — | 75  |     | mA |

|                            |                          |                                                                                                                                                     |                      | × 36 | — | 80  |     |    |

|                            |                          |                                                                                                                                                     | 6ns のサイクル、<br>167MHz | × 18 | — | 75  |     |    |

|                            |                          |                                                                                                                                                     |                      | × 36 | — | 80  |     |    |

| I <sub>SB2</sub>           | 自動 CE パワーダウン電流 – CMOS 入力 | 最大 V <sub>DD</sub> 、デバイス選択解除、V <sub>IN</sub> ≤ 0.3V または V <sub>IN</sub> ≥ V <sub>DDQ</sub> - 0.3V、f = 0                                             | すべてのスピード<br>グレード     | × 18 | — | 65  |     | mA |

|                            |                          |                                                                                                                                                     |                      | × 36 | — | 70  |     |    |

| I <sub>SB3</sub>           | 自動 CE パワーダウン電流 – CMOS 入力 | 最大 V <sub>DD</sub> 、デバイス選択解除、V <sub>IN</sub> ≤ 0.3V または V <sub>IN</sub> ≥ V <sub>DDQ</sub> - 0.3V、<br>f = f <sub>MAX</sub> = 1/t <sub>CYC</sub>     | 5ns のサイクル、<br>200MHz | × 18 | — | 75  |     | mA |

|                            |                          |                                                                                                                                                     |                      | × 36 | — | 80  |     |    |

|                            |                          |                                                                                                                                                     | 6ns のサイクル、<br>167MHz | × 18 | — | 75  |     |    |

|                            |                          |                                                                                                                                                     |                      | × 36 | — | 80  |     |    |

| I <sub>SB4</sub>           | 自動 CE パワーダウン電流 – TTL 入力  | 最大 V <sub>DD</sub> 、デバイス選択解除、V <sub>IN</sub> ≥ V <sub>IH</sub> または V <sub>IN</sub> ≤ V <sub>IL</sub> 、f = 0                                         | すべてのスピード<br>グレード     | ×18  | — | 65  |     | mA |

|                            |                          |                                                                                                                                                     |                      | ×36  | — | 70  |     |    |

## 容量

| パラメーター    | 説明         | テスト条件                                                                                              | 100 ピン TQFP パッケージ | 165 ポール FBGA パッケージ | 単位 |

|-----------|------------|----------------------------------------------------------------------------------------------------|-------------------|--------------------|----|

| $C_{IN}$  | 入力静電容量     | $T_A = 25^\circ\text{C}$ 、 $f = 1\text{MHz}$ 、<br>$V_{DD} = 2.5\text{V}$ 、 $V_{DDQ} = 2.5\text{V}$ | 5                 | 5                  | pF |

| $C_{CLK}$ | クロック入力静電容量 |                                                                                                    | 5                 | 5                  | pF |

| $C_{I/O}$ | 入力／出力の静電容量 |                                                                                                    | 5                 | 5                  | pF |

## 熱抵抗

| パラメーター        | 説明                      | テスト条件                                                                     | 100 ピン TQFP パッケージ | 165 ポール FBGA パッケージ | 単位    |

|---------------|-------------------------|---------------------------------------------------------------------------|-------------------|--------------------|-------|

| $\Theta_{JA}$ | 熱抵抗<br>( ジャンクションから周囲 )  | テスト条件は、<br>EIA/JESD51 による、<br>熱インピーダンスを<br>測定するための標準<br>的なテスト方法と手<br>順に従う | 無風時 (0 m/s)       | 37.95              | 17.34 |

|               |                         |                                                                           | 空冷 (1 m/s)        | 33.19              | 14.33 |

|               |                         |                                                                           | 空冷 (3 m/s)        | 30.44              | 12.63 |

|               |                         |                                                                           | --                | 24.07              | 8.95  |

| $\Theta_{JB}$ | 熱抵抗<br>( ジャンクションからボード ) |                                                                           |                   | 8.36               | 3.50  |

| $\Theta_{JC}$ | 熱抵抗<br>( ジャンクションからケース ) |                                                                           |                   |                    | °C/W  |

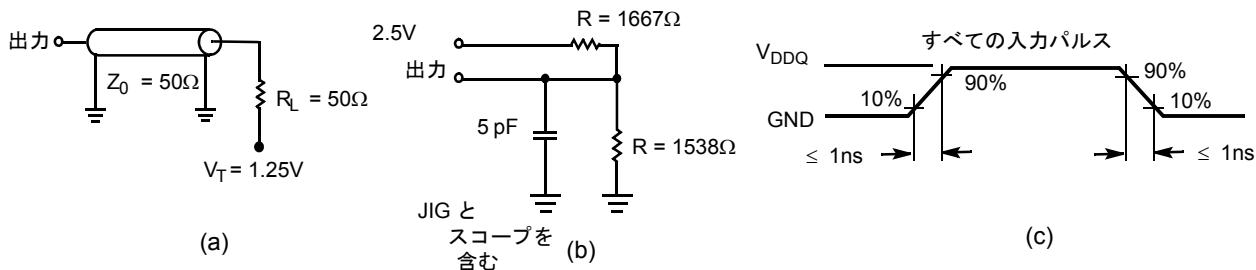

## AC テストの負荷と波形

図 4. AC テストの負荷と波形

### 2.5V I/O テスト負荷

## スイッチング特性

動作範囲において

| パラメーター <sup>[20, 21]</sup> | 説明                                                          | -200 |     | -167 |     | 単位  |

|----------------------------|-------------------------------------------------------------|------|-----|------|-----|-----|

|                            |                                                             | Min  | Max | Min  | Max |     |

| $t_{Power}^{[22]}$         | $V_{CC}(\text{typ})$ から最初の読み出し／書き込みアクセス                     | 1    | —   | 1    | —   | ms  |

| <b>クロック</b>                |                                                             |      |     |      |     |     |

| $t_{CYC}$                  | クロック サイクル時間                                                 | 5    | —   | 6    | —   | ns  |

| $F_{MAX}$                  | 最大動作周波数                                                     | —    | 200 | —    | 167 | MHz |

| $t_{CH}$                   | クロック HIGH                                                   | 2.0  | —   | 2.2  | —   | ns  |

| $t_{CL}$                   | クロック LOW 時間                                                 | 2.0  | —   | 2.2  | —   | ns  |

| <b>出力時間</b>                |                                                             |      |     |      |     |     |

| $t_{CO}$                   | CLK 立ち上がり後のデータ出力有効時間                                        | —    | 3.2 | —    | 3.4 | ns  |

| $t_{EOV}$                  | $\overline{OE}$ LOW から出力有効まで                                | —    | 3.0 | —    | 3.4 | ns  |

| $t_{DOH}$                  | CLK 立ち上がり後のデータ出力ホールド時間                                      | 1.5  | —   | 1.5  | —   | ns  |

| $t_{CHZ}$                  | クロックから High Z まで <sup>[23, 24, 25]</sup>                    | —    | 3.0 | —    | 3.4 | ns  |

| $t_{CLZ}$                  | クロックから Low Z まで <sup>[23, 24, 25]</sup>                     | 1.3  | —   | 1.5  | —   | ns  |

| $t_{EOHZ}$                 | $\overline{OE}$ HIGH から出力 High Z まで <sup>[23, 24, 25]</sup> | —    | 3.0 | —    | 3.4 | ns  |

| $t_{EOLZ}$                 | $\overline{OE}$ LOW から出力 Low Z まで <sup>[23, 24, 25]</sup>   | 0    | —   | 0    | —   | ns  |

| <b>セットアップ時間</b>            |                                                             |      |     |      |     |     |

| $t_{AS}$                   | CLK 立ち上がり前のアドレス セットアップ時間                                    | 1.4  | —   | 1.5  | —   | ns  |

| $t_{DS}$                   | CLK 立ち上がり前のデータ入力 セットアップ時間                                   | 1.4  | —   | 1.5  | —   | ns  |

| $t_{CENS}$                 | CLK 立ち上がり前の $\overline{CEN}$ セットアップ時間                       | 1.4  | —   | 1.5  | —   | ns  |

| $t_{WES}$                  | CLK 立ち上がり前の $\overline{WE}$ 、 $\overline{BW}_x$ セットアップ      | 1.4  | —   | 1.5  | —   | ns  |

| $t_{ALS}$                  | CLK 立ち上がり前の $ADV/\overline{LD}$ セットアップ時間                    | 1.4  | —   | 1.5  | —   | ns  |

| $t_{CES}$                  | チップ セレクトのセットアップ時間                                           | 1.4  | —   | 1.5  | —   | ns  |

| <b>ホールド時間</b>              |                                                             |      |     |      |     |     |

| $t_{AH}$                   | CLK 立ち上がり後のアドレス ホールド時間                                      | 0.4  | —   | 0.5  | —   | ns  |

| $t_{DH}$                   | CLK 立ち上がり後のデータ入力 ホールド時間                                     | 0.4  | —   | 0.5  | —   | ns  |

| $t_{CENH}$                 | CLK 立ち上がり後の $\overline{CEN}$ ホールド時間                         | 0.4  | —   | 0.5  | —   | ns  |

| $t_{WEH}$                  | CLK 立ち上がり後の $\overline{WE}$ 、 $\overline{BW}_x$ ホールド時間      | 0.4  | —   | 0.5  | —   | ns  |

| $t_{ALH}$                  | CLK 立ち上がり後の $ADV/\overline{LD}$ ホールド時間                      | 0.4  | —   | 0.5  | —   | ns  |

| $t_{CEH}$                  | CLK 立ち上がり後のチップ セレクト ホールド時間                                  | 0.4  | —   | 0.5  | —   | ns  |

注：

20.  $V_{DDQ} = 2.5V$  時、タイミングのリファレンス電圧は 1.25V です。

21. 特記されていない限り、テスト条件は [22 ページの図 4](#) の (a) に示します。

22. このデバイスは電圧レギュレータを内蔵しています； $t_{power}$  は、読み出しあり書き込み処理が開始できる前に、最初に  $V_{DD}$  (最小値) を超えた電源を供給することが必要な時間です。

23.  $t_{CHZ}$ 、 $t_{CLZ}$ 、 $t_{EOLZ}$ 、 $t_{EOHZ}$  は [22 ページの図 4](#) の (b) に示した AC テスト条件で指定されます。変化は定常状態での電圧  $\pm 200mV$  の電圧レベルで測定されます。

24. 任意の所与の電圧と温度において、同じデータバスを共用する時、SRAM 間にバス競合を回避するために、 $t_{EOHZ}$  は  $t_{EOLZ}$  より小さく、 $t_{CHZ}$  は  $t_{CLZ}$  より小さいことが必要です。これらの仕様は、バス競合条件を意味しませんが、最悪の場合のユーザー条件において保証されるパラメーターを示します。デバイスは、同じシステム条件の下で Low Z の前に High Z を達成するように設計されています。

25. このパラメーターはサンプリングされた値であり、すべてのデバイスで試験されるわけではありません。

## スイッチング波形

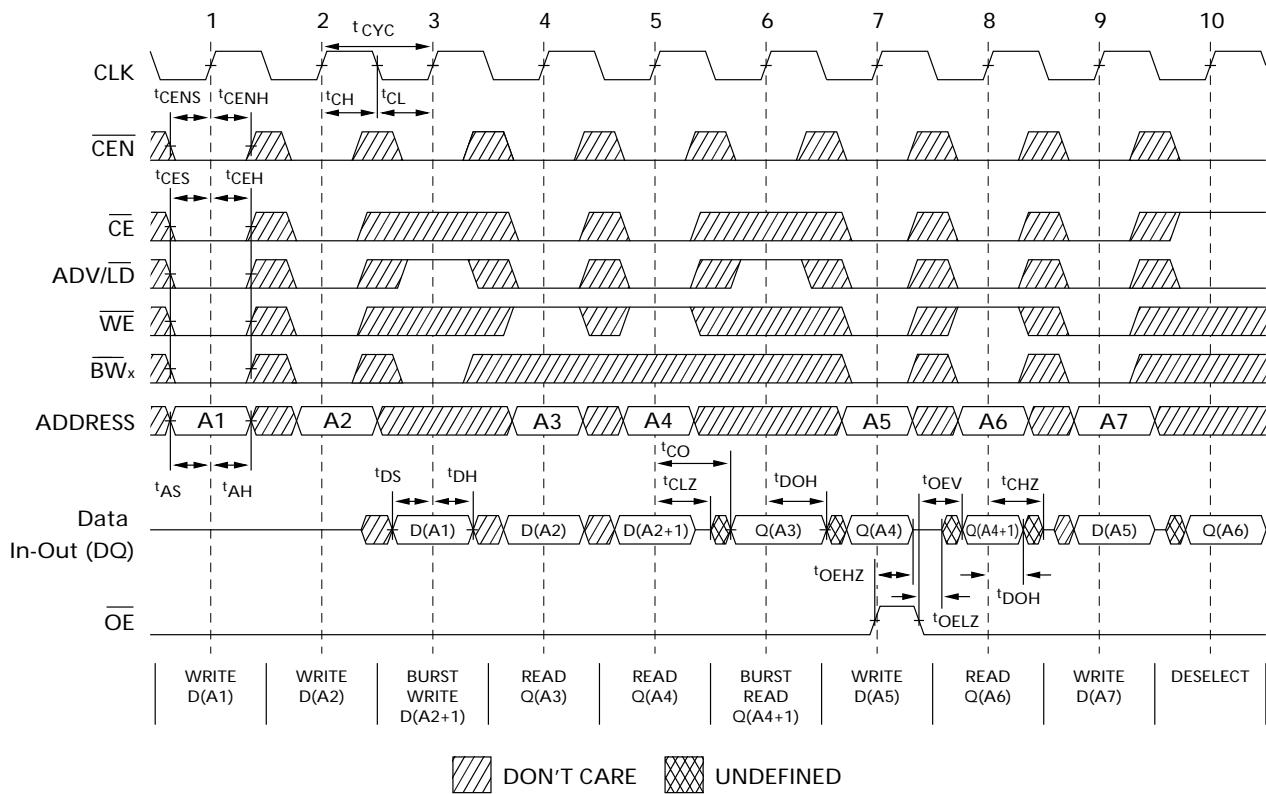

図 5. 読み出し／書き込みサイクル タイミング [26, 27, 28]

注：

26. この波形の場合は ZZ は LOW に保持されます。

27.  $\overline{CE}$  が LOW の場合、 $\overline{CE}_1$  は LOW、 $\overline{CE}_2$  は HIGH、 $\overline{CE}_3$  は LOW です。 $\overline{CE}$  が HIGH の場合、 $\overline{CE}_1$  は HIGH、または  $CE_2$  は LOW、または  $\overline{CE}_3$  は HIGH です。

28. バースト シーケンスの順序は、MODE ピンのステータスにより判定されます (0 = リニア、1 = インターリープ)。バースト動作は任意です。

## スイッチング波形 ( 続き )

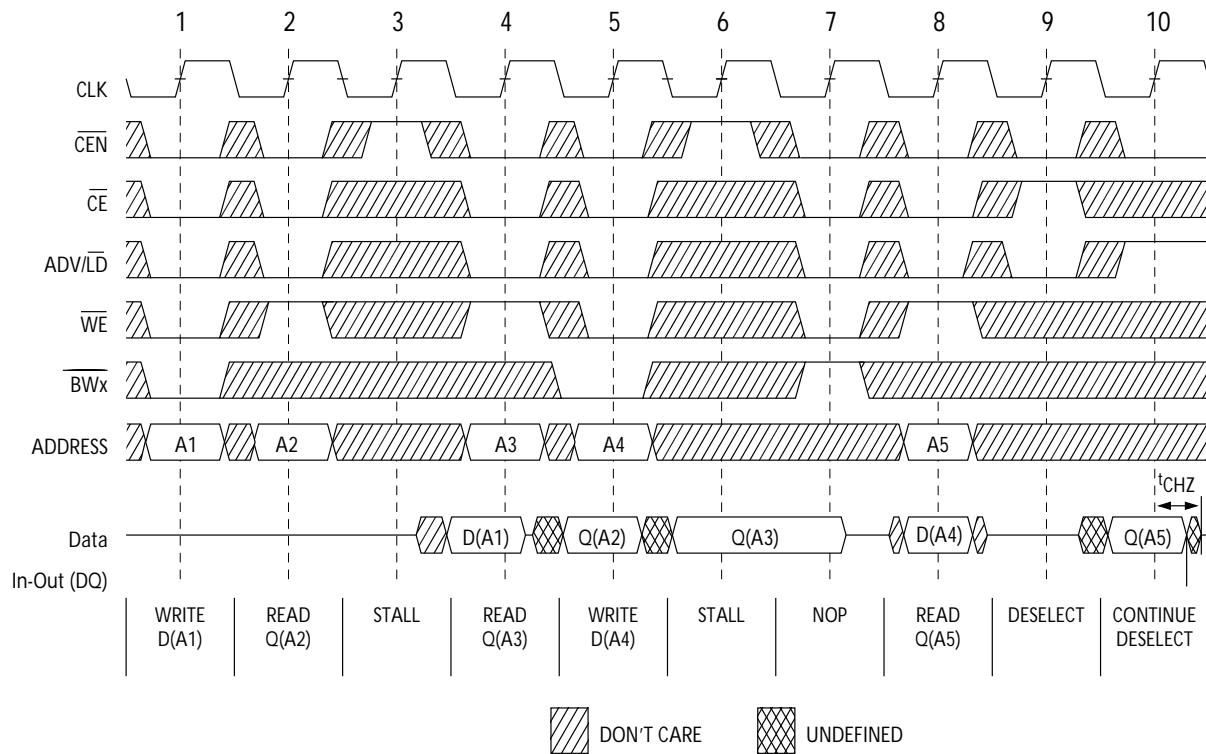

図 6. NOP、STALL、DESELECT サイクル [29、30、31]

図 7. ZZ モード タイミング [32、33]

注:

29. この波形の場合は ZZ は LOW に保持されます。

30.  $\overline{CE}$  が LOW の場合、 $\overline{CE}_1$  は LOW、 $CE_2$  は HIGH、 $\overline{CE}_3$  は LOW です。 $\overline{CE}$  が HIGH の場合、 $\overline{CE}_1$  は HIGH、または  $CE_2$  は LOW、または  $\overline{CE}_3$  は HIGH です。

31. クロック エッジ無視サイクルやストール サイクル ( クロック 3 ) は、 $\overline{CEN}$  が一時停止をもたらすために使用されていることを示します。このサイクルでは、書き込みは行われません。

32. ZZ モードに入る際、デバイスを選択解除する必要があります。デバイスを選択解除するための全ての可能な信号条件については、サイクル説明表を参照してください。

33. ZZ スリープ モードを終了した時、I/O は high Z 状態になります。

## スイッチング波形 ( 続き )

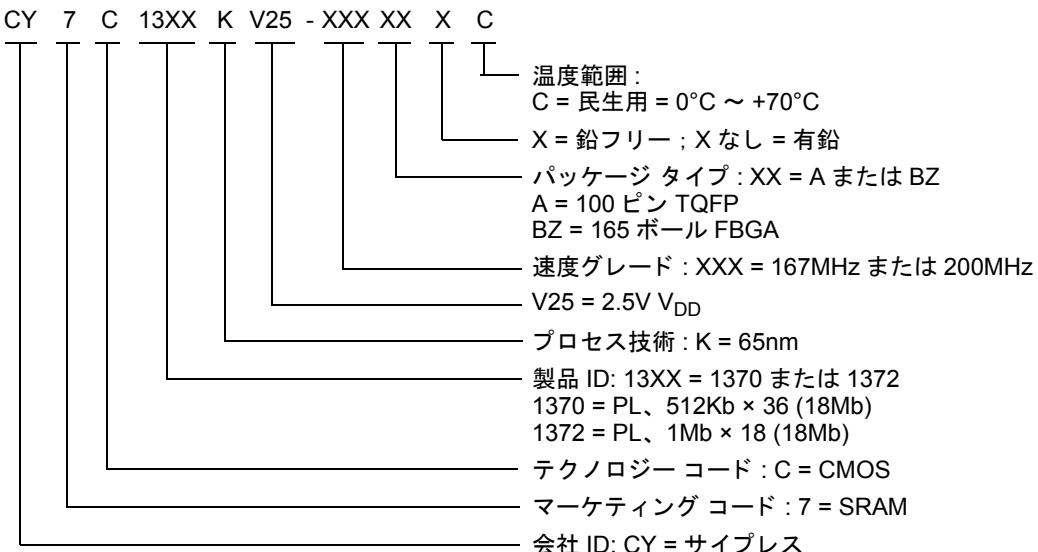

### 注文情報

このタイプの製品で、サイプレスは、様々なコンフィギュレーションおよび特長を有する他の多くのバージョンを提供しています。以下の表には、現在入手可能な製品のみを示します。

すべてのオプションの完全なリストについては、サイプレスのウェブサイト [www.cypress.com](http://www.cypress.com) にアクセスし、製品概要のページ <http://www.cypress.com/products> を参照し、または最寄りのサイプレスの販売代理店にお問い合わせください。

サイプレスは、事業所、ソリューションセンター、メーカー代理店および販売代理店の世界的なネットワークを保持しています。お客様の最寄りのオフィスについては、サイプレスの <http://www.cypress.com/go/datasheet/offices> をご覧ください。

| 速度<br>(MHz) | 注文コード               | パッケージ図   | 製品とパッケージ タイプ                       | 動作範囲 |

|-------------|---------------------|----------|------------------------------------|------|

| 167         | CY7C1370KV25-167AXC | 51-85050 | 100 ピン TQFP (14 × 20 × 1.4mm) 鉛フリー | 民生用  |

|             | CY7C1372KV25-167AXC |          |                                    |      |

|             | CY7C1370KV25-167BZC | 51-85180 | 165 ボール FBGA (13 × 15 × 1.4mm)     |      |

| 200         | CY7C1370KV25-200AXC | 51-85050 | 100 ピン TQFP (14 × 20 × 1.4mm) 鉛フリー | 民生用  |

|             | CY7C1370KV25-200BZC | 51-85180 | 165 ボール FBGA (13 × 15 × 1.4mm)     |      |

### 注文コードの定義

## パッケージ図

図 8. 100 ピン TQFP (14 × 20 × 1.4mm) A100RA パッケージ図、51-85050

51-85050 \*E

**パッケージ図 ( 続き )**

**図 9. 165 ポール FBGA (13 × 15 × 1.4mm) BB165D/BW165D (0.5 ポール直径) パッケージ図、51-85180**

NOTES :

SOLDER PAD TYPE : NON-SOLDER MASK DEFINED (NSMD)

JEDEC REFERENCE : MO-216 / ISSUE E

PACKAGE CODE : BB0AC/BW0AC

PACKAGE WEIGHT : SEE CYPRESS PACKAGE MATERIAL DECLARATION

DATASHEET (PMDD) POSTED ON THE CYPRESS WEB.

51-85180 \*G

**略語**

| 略語    | 説明                                                         |

|-------|------------------------------------------------------------|

| CE    | Chip Enable ( チップ イネーブル )                                  |

| CEN   | Clock Enable ( クロック イネーブル )                                |

| CMOS  | Complementary Metal Oxide Semiconductor<br>( 相補型金属酸化膜半導体 ) |

| EIA   | Electronic Industries Alliance ( 米国電子工業会 )                 |

| FBGA  | Fine-Pitch Ball Grid Array<br>( フайн ピッチ ボール グリッド アレイ )    |

| I/O   | Input/Output ( 入力／出力 )                                     |

| JEDEC | Joint Electron Devices Engineering Council<br>( 半導体技術協会 )  |

| JTAG  | Joint Test Action Group<br>( ジョイント テスト アクション グループ )        |

| LSB   | Least Significant Bit ( 最下位ビット )                           |

| MSB   | Most significant bit ( 最上位ビット )                            |

| NoBL  | No Bus Latency ( バス レイテンシーなし )                             |

| OE    | Output Enable ( 出力イネーブル )                                  |

| SRAM  | Static Random Access Memory<br>( スタティック ランダム アクセス メモリ )    |

| TAP   | Test Access Port ( テスト アクセス ポート )                          |

| TCK   | Test Clock ( テスト クロック )                                    |

| TDI   | Test Data-In ( テスト データ入力 )                                 |

| TDO   | Test Data-Out ( テスト データ出力 )                                |

| TMS   | Test Mode Select ( テスト モード選択 )                             |

| TQFP  | Thin Quad Flat Pack<br>( 薄型クアッド フラット パッケージ )               |

| TTL   | Transistor-Transistor Logic<br>( トランジスタ - トランジスタ ロジック )    |

| WE    | 書き込みイネーブル                                                  |

**本書の表記法**

**測定単位**

| 記号  | 測定単位     |

|-----|----------|

| °C  | 摂氏温度     |

| MHz | メガヘルツ    |

| µA  | マイクロアンペア |

| mA  | ミリアンペア   |

| mm  | ミリメートル   |

| ms  | ミリ秒      |

| mV  | ミリボルト    |

| ns  | ナノ秒      |

| Ω   | オーム      |

| %   | パーセント    |

| pF  | ピコファラッド  |

| V   | ボルト      |

| W   | ワット      |

## 改訂履歴

文書名 : CY7C1370KV25 / CY7C1372KV25、NoBL™ アーキテクチャの 18M ピット (512K × 36/1M × 18) パイプライン SRAM

文書番号 : 001-98233

| 版  | ECN 番号  | 変更者  | 提出日        | 変更内容                                                     |

|----|---------|------|------------|----------------------------------------------------------|

| ** | 4860232 | HZEN | 07/27/2015 | これは英語版 001-97851 Rev. *B を翻訳した日本語版 001-98233 Rev. ** です。 |

| *A | 5013022 | HZEN | 11/19/2015 | これは英語版 001-97851 Rev. ** を翻訳した日本語版 001-98233 Rev. *A です。 |

## セールス、ソリューションおよび法律情報

### ワールドワイド販売と設計サポート

サイプレスは、事業所、ソリューションセンター、メーカー代理店および販売代理店の世界的なネットワークを保持しています。お客様の最寄りのオフィスについては、[サイプレスのロケーションページ](#)をご覧ください。

#### 製品

車載用

[cypress.com/go/automotive](http://cypress.com/go/automotive)

クロック & バッファ

[cypress.com/go/clocks](http://cypress.com/go/clocks)

インターフェース

[cypress.com/go/interface](http://cypress.com/go/interface)

照明 & 電力制御

[cypress.com/go/powerpsoc](http://cypress.com/go/powerpsoc)

メモリ

[cypress.com/go/memory](http://cypress.com/go/memory)

PSoC

[cypress.com/go/psoc](http://cypress.com/go/psoc)

タッチ センシング

[cypress.com/go/touch](http://cypress.com/go/touch)

USB コントローラー

[cypress.com/go/USB](http://cypress.com/go/USB)

ワイヤレス／RF

[cypress.com/go/wireless](http://cypress.com/go/wireless)

#### PSoC® ソリューション

[psoc.cypress.com/solutions](http://psoc.cypress.com/solutions)

PSoC 1 | PSoC 3 | PSoC 4 | PSoC 5LP

#### サイプレス開発者コミュニティ

[コミュニティ](#) | [フォーラム](#) | [ブログ](#) | [ビデオ](#) | [トレーニング](#)

#### テクニカル サポート

[cypress.com/go/support](http://cypress.com/go/support)

© Cypress Semiconductor Corporation, 2015. 本文書に記載される情報は、予告なく変更される場合があります。Cypress Semiconductor Corporation (サイプレス セミコンダクタ社) は、サイプレス製品に組み込まれた回路以外のいかなる回路を使用することに対して一切の責任を負いません。サイプレス セミコンダクタ社は、特許またはその他の権利に基づくライセンスを譲渡することも、または含意することもありません。サイプレス製品は、サイプレスとの書面による合意に基づくものでない限り、医療、生命維持、救命、重要な管理、または安全の用途のために使用することを保証するものではなく、また使用することを意図したものでもありません。さらにサイプレスは、誤作動や故障によって使用者に重大な傷害をもたらすことが合理的に予想される生命維持システムの重要なコンポーネントとしてサイプレス製品を使用することを許可していません。生命維持システムの用途にサイプレス製品を供することは、製造者がそのような使用におけるあらゆるリスクを負うことを意味し、その結果サイプレスはあらゆる責任を免除されることを意味します。

すべてのソース コード (ソフトウェアおよび／またはファームウェア) はサイプレス セミコンダクタ社 (以下「サイプレス」) が所有し、全世界の特許権保護 (米国および他の国)、米国の著作権法ならびに国際協定の条項により保護され、かつそれらに従います。サイプレスが本書面によりライセンサーに付与するライセンスは、個人的、非独占的かつ譲渡不能のライセンスであり、適用される契約で指定されたサイプレスの集積回路と併用されるライセンサーの製品のみをサポートするカスタムソフトウェアおよび／またはカスタム ファームウェアを作成する目的に限って、サイプレスのソース コードの派生著作物をコピー、使用、変更そして作成するためのライセンス、ならびにサイプレスのソース コードおよび派生著作物をコンパイルするためのライセンスです。上記で指定された場合を除き、サイプレスの書面による明示的な許可なくして本ソース コードを複製、変更、変換、コンパイル、または表示することはすべて禁止します。

免責条項：サイプレスは、明示的または默示的を問わず、本資料に関するいかなる種類の保証も行いません。これには、商品性または特定目的への適合性の默示的な保証が含まれますが、これに限定されません。サイプレスは、本文書に記載される資料に対して今後予告なく変更を加える権利を留保します。サイプレスは、本文書に記載されるいかなる製品または回路を適用または使用したことによって生ずるいかなる責任も負いません。サイプレスは、誤作動や故障によって使用者に重大な傷害をもたらすことが合理的に予想される生命維持システムの重要なコンポーネントとしてサイプレス製品を使用することを許可していません。生命維持システムの用途にサイプレス製品を供することは、製造者がそのような使用におけるあらゆるリスクを負うことを意味し、その結果サイプレスはあらゆる責任を免除されることを意味します。

ソフトウェアの使用は、適用されるサイプレス ソフトウェア ライセンス契約によって制限され、かつ制約される場合があります。