## 特長

- 高速

- $t_{AA}$ =10ns/15ns

- シングル ビット エラー訂正用の組み込みエラー訂正コード (ECC)

- Low アクティブおよびスタンバイ電流

- $I_{CC}$ = 最大 110mA

- $I_{SB2}$ = 最大 30mA

- 動作電圧範囲 : 1.65V ~ 2.2V、2.2V ~ 3.6V

- 1.0V データ保持

- 選択解除の時、自動的にパワーダウン

- トランジスタ - トランジスタ ロジック (TTL) と互換性のある入出力

- 1 ビット エラー検出と訂正を示す ERR ピン

- 無鉛 119 ボール プラスチック ボール グリッド アレイ (PBGA) パッケージで実装

## 機能の詳細

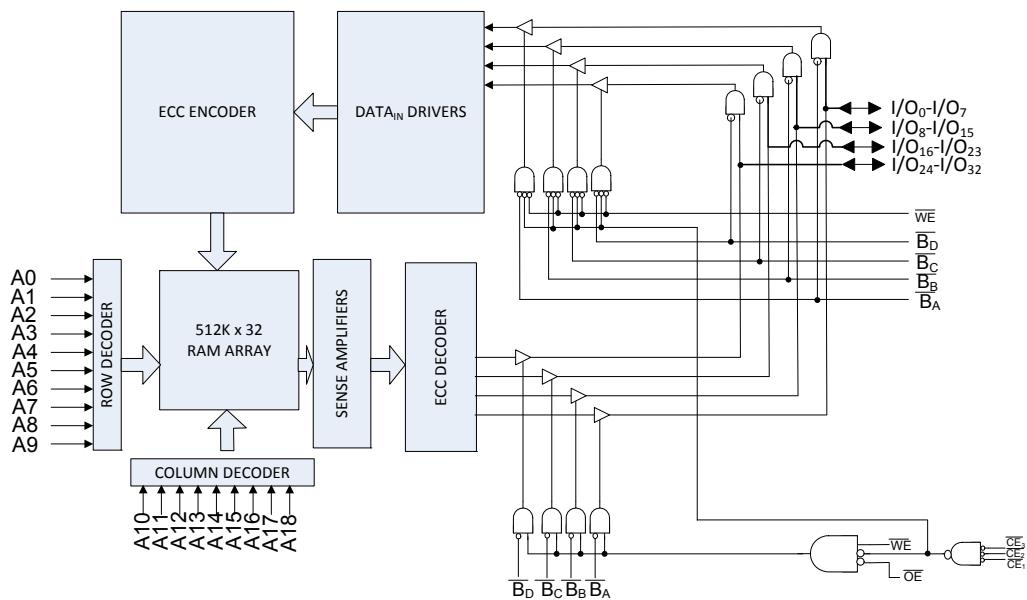

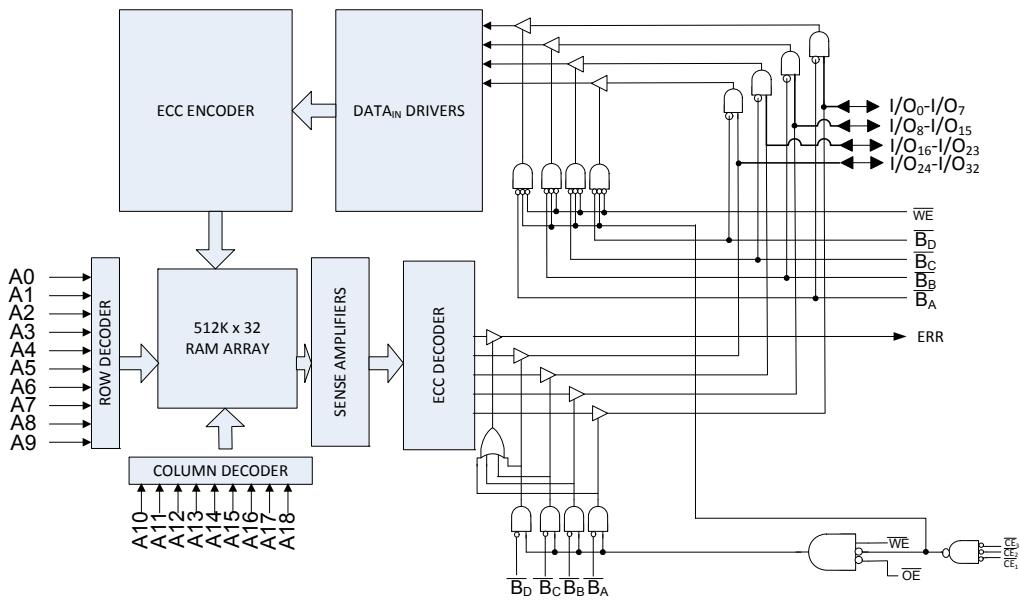

CY7C1062G 及び CY7C1062GE は組み込み ECC と共に、CMOS 高速スタティック RAM デバイスの高性能版です。両方は、三つのチップ イネーブルがあるので、メモリ拡張機能が簡単に付け加えられます。CY7C1062GE デバイスは、シングル ビット エラー検出及び訂正イベントが発生した時、ホスト プロセッサに通知するエラー表示ピンを備えています。

デバイスに書き込むために、チップ イネーブル ( $\overline{CE}_1$ 、 $\overline{CE}_2$  と  $\overline{CE}_3$  LOW) 及び書き込みイネーブル ( $\overline{WE}$ ) 入力を LOW にします。バイト イネーブル A ( $\overline{BA}$ ) が LOW になった場合、I/O ピン ( $I/O_0$  ~  $I/O_7$ ) からのデータはアドレス ピン ( $A_0$  ~  $A_{18}$ ) で示された位置に書き込まれます。バイト イネーブル B ( $\overline{BA}$ ) が LOW になった場合、I/O ピン ( $I/O_8$  ~  $I/O_{15}$ ) からのデータはアドレス ピン ( $A_0$  ~  $A_{18}$ ) で示された位置に書き込まれます。同様に、 $\overline{BC}$  及び  $\overline{BD}$  は I/O ピンのそれぞれの  $I/O_{16}$  から  $I/O_{23}$  まで及び  $I/O_{24}$  から  $I/O_{31}$  まで対応します。

デバイスから読み出すために、書き込みイネーブル ( $\overline{WE}$ ) を強制的に HIGH にしている間、チップ イネーブル ( $CE_1$ 、 $CE_2$ 、および  $CE_3$  LOW) 及び出力カイネーブル ( $OE$ ) を LOW にします。もし  $\overline{BA}$  が LOW の時に、アドレス ピンで示されるメモリ位置からのデータは、 $I/O_0$  から  $I/O_7$  に現れます。もし  $\overline{BB}$  が LOW の時に、メモリからのデータは、 $I/O_8$  から  $I/O_{15}$  に現われます。同様に、 $\overline{BC}$  及び  $\overline{BD}$  は 3 番目のバイト及び 4 番目のバイトに対応します。読み出しと書き込みモードの詳細については、[16 ページの真理値表 – CY7C1062G/CY7C1062GE](#) を参照してください。

デバイスの選択が解除される ( $\overline{CE}_1$ 、 $\overline{CE}_2$  又は  $\overline{CE}_3$  HIGH)、出力が無効になる ( $OE$  HIGH)、選択されたバイトが無効になる ( $\overline{BA-D}$  HIGH) のような場合、又は書き込み動作の間 ( $CE_1$ 、 $CE_2$ 、 $CE_3$  LOW 及び  $\overline{WE}$  LOW)、入力ピンと出力ピン ( $I/O_0$  ~  $I/O_{31}$ ) は高インピーダンス状態になります。

CY7C1062GE デバイスで、アクセスされた位置のシングルビット エラー検出および訂正を表示することは ERR 出力 (ERR = High)<sup>[1]</sup> のアサートによって示されます。

CY7C1062G 及び CY7C1062GE は鉛フリー 119 ボール プラスチック ボール グリッド アレイ (PBGA) パッケージで供給されます。

## 注

1. このデバイスは、エラー検出時に自動再書き込みをサポートしません。

**論理ブロック図 – CY7C1062GE**

**ロジックブロック図 – CY7C1062GE**

## 目次

|                             |    |

|-----------------------------|----|

| ピン配置                        | 4  |

| 製品ポートフォリオ                   | 6  |

| 最大定格                        | 7  |

| 動作範囲                        | 7  |

| DC 電気的特性                    | 7  |

| 容量                          | 8  |

| 熱抵抗                         | 8  |

| AC テストの負荷と波形                | 8  |

| データ保持特性                     | 9  |

| データ保持波形                     | 9  |

| AC スイッチング特性                 | 10 |

| スイッチング 波形                   | 11 |

| 真理値表 – CY7C1062G/CY7C1062GE | 16 |

| ERR 出力 –CY7C1062GE          | 16 |

|                     |    |

|---------------------|----|

| 注文情報                | 17 |

| 注文コードの定義            | 17 |

| 外形図                 | 18 |

| 略語                  | 19 |

| 本書の表記法              | 19 |

| 測定単位                | 19 |

| 変更履歴                | 20 |

| セールス、ソリューションおよび法律情報 | 21 |

| ワールドワイドな販売と設計サポート   | 21 |

| 製品                  | 21 |

| PSoC® ソリューション       | 21 |

| サイプレス開発者コミュニティ      | 21 |

| テクニカル サポート          | 21 |

## ピン配置

図 1. 119 ポール PBGA ピン配置 (上面図) - CY7C1062G [2]

|   | 1                 | 2               | 3               | 4               | 5               | 6               | 7                 |

|---|-------------------|-----------------|-----------------|-----------------|-----------------|-----------------|-------------------|

| A | I/O <sub>16</sub> | A <sub>4</sub>  | A <sub>3</sub>  | A <sub>2</sub>  | A <sub>1</sub>  | A <sub>0</sub>  | I/O <sub>0</sub>  |

| B | I/O <sub>17</sub> | A <sub>18</sub> | A <sub>17</sub> | CE <sub>1</sub> | A <sub>16</sub> | A <sub>15</sub> | I/O <sub>1</sub>  |

| C | I/O <sub>18</sub> | B <sub>c</sub>  | CE <sub>2</sub> | NC              | CE <sub>3</sub> | B <sub>a</sub>  | I/O <sub>2</sub>  |

| D | I/O <sub>19</sub> | V <sub>DD</sub> | V <sub>SS</sub> | V <sub>SS</sub> | V <sub>SS</sub> | V <sub>DD</sub> | I/O <sub>3</sub>  |

| E | I/O <sub>20</sub> | V <sub>SS</sub> | V <sub>DD</sub> | V <sub>SS</sub> | V <sub>DD</sub> | V <sub>SS</sub> | I/O <sub>4</sub>  |

| F | I/O <sub>21</sub> | V <sub>DD</sub> | V <sub>SS</sub> | V <sub>SS</sub> | V <sub>SS</sub> | V <sub>DD</sub> | I/O <sub>5</sub>  |

| G | I/O <sub>22</sub> | V <sub>SS</sub> | V <sub>DD</sub> | V <sub>SS</sub> | V <sub>DD</sub> | V <sub>SS</sub> | I/O <sub>6</sub>  |

| H | I/O <sub>23</sub> | V <sub>DD</sub> | V <sub>SS</sub> | V <sub>SS</sub> | V <sub>SS</sub> | V <sub>DD</sub> | I/O <sub>7</sub>  |

| J | NC                | V <sub>SS</sub> | V <sub>DD</sub> | V <sub>SS</sub> | V <sub>DD</sub> | V <sub>SS</sub> | NC                |

| K | I/O <sub>24</sub> | V <sub>DD</sub> | V <sub>SS</sub> | V <sub>SS</sub> | V <sub>SS</sub> | V <sub>DD</sub> | I/O <sub>8</sub>  |

| L | I/O <sub>25</sub> | V <sub>SS</sub> | V <sub>DD</sub> | V <sub>SS</sub> | V <sub>DD</sub> | V <sub>SS</sub> | I/O <sub>9</sub>  |

| M | I/O <sub>26</sub> | V <sub>DD</sub> | V <sub>SS</sub> | V <sub>SS</sub> | V <sub>SS</sub> | V <sub>DD</sub> | I/O <sub>10</sub> |

| N | I/O <sub>27</sub> | V <sub>SS</sub> | V <sub>DD</sub> | V <sub>SS</sub> | V <sub>DD</sub> | V <sub>SS</sub> | I/O <sub>11</sub> |

| P | I/O <sub>28</sub> | V <sub>DD</sub> | V <sub>SS</sub> | V <sub>SS</sub> | V <sub>SS</sub> | V <sub>DD</sub> | I/O <sub>12</sub> |

| R | I/O <sub>29</sub> | A <sub>14</sub> | B <sub>d</sub>  | NC              | B <sub>b</sub>  | A <sub>13</sub> | I/O <sub>13</sub> |

| T | I/O <sub>30</sub> | A <sub>12</sub> | A <sub>11</sub> | WE              | A <sub>10</sub> | A <sub>9</sub>  | I/O <sub>14</sub> |

| U | I/O <sub>31</sub> | A <sub>8</sub>  | A <sub>7</sub>  | OE              | A <sub>6</sub>  | A <sub>5</sub>  | I/O <sub>15</sub> |

## 注

2. NC ピンはパッケージ内部でダイに接続されていません。

## ピン配置(続き)

図2. 119 ポール PBGA ピン配置(上面図) - CY7C1062GE<sup>[3]</sup>

|   | 1                 | 2               | 3               | 4               | 5               | 6               | 7                 |

|---|-------------------|-----------------|-----------------|-----------------|-----------------|-----------------|-------------------|

| A | I/O <sub>16</sub> | A <sub>4</sub>  | A <sub>3</sub>  | A <sub>2</sub>  | A <sub>1</sub>  | A <sub>0</sub>  | I/O <sub>0</sub>  |

| B | I/O <sub>17</sub> | A <sub>18</sub> | A <sub>17</sub> | CE <sub>1</sub> | A <sub>16</sub> | A <sub>15</sub> | I/O <sub>1</sub>  |

| C | I/O <sub>18</sub> | B <sub>c</sub>  | CE <sub>2</sub> | NC              | CE <sub>3</sub> | B <sub>a</sub>  | I/O <sub>2</sub>  |

| D | I/O <sub>19</sub> | V <sub>DD</sub> | V <sub>SS</sub> | V <sub>SS</sub> | V <sub>SS</sub> | V <sub>DD</sub> | I/O <sub>3</sub>  |

| E | I/O <sub>20</sub> | V <sub>SS</sub> | V <sub>DD</sub> | V <sub>SS</sub> | V <sub>DD</sub> | V <sub>SS</sub> | I/O <sub>4</sub>  |

| F | I/O <sub>21</sub> | V <sub>DD</sub> | V <sub>SS</sub> | V <sub>SS</sub> | V <sub>SS</sub> | V <sub>DD</sub> | I/O <sub>5</sub>  |

| G | I/O <sub>22</sub> | V <sub>SS</sub> | V <sub>DD</sub> | V <sub>SS</sub> | V <sub>DD</sub> | V <sub>SS</sub> | I/O <sub>6</sub>  |

| H | I/O <sub>23</sub> | V <sub>DD</sub> | V <sub>SS</sub> | V <sub>SS</sub> | V <sub>SS</sub> | V <sub>DD</sub> | I/O <sub>7</sub>  |

| J | ERR               | V <sub>SS</sub> | V <sub>DD</sub> | V <sub>SS</sub> | V <sub>DD</sub> | V <sub>SS</sub> | NC                |

| K | I/O <sub>24</sub> | V <sub>DD</sub> | V <sub>SS</sub> | V <sub>SS</sub> | V <sub>SS</sub> | V <sub>DD</sub> | I/O <sub>8</sub>  |

| L | I/O <sub>25</sub> | V <sub>SS</sub> | V <sub>DD</sub> | V <sub>SS</sub> | V <sub>DD</sub> | V <sub>SS</sub> | I/O <sub>9</sub>  |

| M | I/O <sub>26</sub> | V <sub>DD</sub> | V <sub>SS</sub> | V <sub>SS</sub> | V <sub>SS</sub> | V <sub>DD</sub> | I/O <sub>10</sub> |

| N | I/O <sub>27</sub> | V <sub>SS</sub> | V <sub>DD</sub> | V <sub>SS</sub> | V <sub>DD</sub> | V <sub>SS</sub> | I/O <sub>11</sub> |

| P | I/O <sub>28</sub> | V <sub>DD</sub> | V <sub>SS</sub> | V <sub>SS</sub> | V <sub>SS</sub> | V <sub>DD</sub> | I/O <sub>12</sub> |

| R | I/O <sub>29</sub> | A <sub>14</sub> | B <sub>d</sub>  | NC              | B <sub>b</sub>  | A <sub>13</sub> | I/O <sub>13</sub> |

| T | I/O <sub>30</sub> | A <sub>12</sub> | A <sub>11</sub> | WE              | A <sub>10</sub> | A <sub>9</sub>  | I/O <sub>14</sub> |

| U | I/O <sub>31</sub> | A <sub>8</sub>  | A <sub>7</sub>  | OE              | A <sub>6</sub>  | A <sub>5</sub>  | I/O <sub>15</sub> |

## 注

3. ERR は出力ピンです。

**製品ポートフォリオ**

| 製品           | 特長およびオプション<br>(4 ページのピン配置を<br>参照) | 範囲  | V <sub>CC</sub> の範囲 (V) | 速度<br>(ns) | 消費電力                                            |     |                                |     |

|--------------|-----------------------------------|-----|-------------------------|------------|-------------------------------------------------|-----|--------------------------------|-----|

|              |                                   |     |                         |            | I <sub>CC</sub> 動作、(mA)<br>f = f <sub>max</sub> |     | スタンバイ、I <sub>SB2</sub><br>(mA) |     |

|              |                                   |     |                         |            | Typ <sup>[4]</sup>                              | Max | Typ <sup>[4]</sup>             | Max |

| CY7C1062G18  | 組み込み ECC。ERR 出力<br>なし             | 産業用 | 1.65V ~ 2.2V            | 15         | 70                                              | 80  | 20                             | 30  |

| CY7C1062G30  |                                   |     | 2.2 V ~ 3.6 V           | 10         | 90                                              | 110 |                                |     |

| CY7C1062GE18 |                                   |     | 1.65V ~ 2.2V            | 15         | 70                                              | 80  |                                |     |

| CY7C1062GE30 |                                   |     | 2.2V ~ 3.6V             | 10         | 90                                              | 110 |                                |     |

**注記**

4. 標準値は単なる基準値であり、保証又は検査されていません。標準値は、V<sub>CC</sub>=1.8V (1.65V ~ 2.2V の V<sub>CC</sub> の範囲)、V<sub>CC</sub> = 3 V (2.2V ~ 3.6V の V<sub>CC</sub> の範囲)、T<sub>A</sub>=25°C で測定しています。

## 最大定格

最大定格を超えると、デバイスの寿命が短くなる可能性があります。これらのユーザー ガイドラインは試験されていません。

保存温度 .....  $-65^{\circ}\text{C} \sim +150^{\circ}\text{C}$

通電時の周囲温度 .....  $-55^{\circ}\text{C} \sim +125^{\circ}\text{C}$

GND を基準とした  $V_{\text{CC}}$

の電源電圧 .....  $-0.5\text{V} \sim +6.0\text{V}$

High Z 状態の出力

に印加される電圧<sup>[5]</sup> .....  $-0.5\text{V} \sim V_{\text{CC}}+0.5\text{V}$

DC 入力電圧<sup>[5]</sup> .....  $-0.5\text{V} \sim V_{\text{CC}}+0.5\text{V}$

出力への電流 (LOW) .....  $20\text{mA}$

静電気放電電圧

(MIL-STD-883、Method 3015) .....  $> 2001\text{V}$

ラッチアップ電流 .....  $> 140\text{mA}$

## 動作範囲

| グレード | 周囲温度                                           | $V_{\text{CC}}$                                                     |

|------|------------------------------------------------|---------------------------------------------------------------------|

| 産業用  | $-40^{\circ}\text{C} \sim +85^{\circ}\text{C}$ | $1.65\text{V} \sim 2.2\text{V}$ 、<br>$2.2\text{V} \sim 3.6\text{V}$ |

## DC 電気的特性

動作範囲は  $-40^{\circ}\text{C} \sim 85^{\circ}\text{C}$ 。

| 記号               | 項目                           | テスト条件                                                                                                                                                                                         | 10ns/15ns |                    |       | 単位            |

|------------------|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--------------------|-------|---------------|

|                  |                              |                                                                                                                                                                                               | Min       | Typ <sup>[6]</sup> | Max   |               |

| $V_{\text{OH}}$  | 出力 HIGH<br>電圧                | 1.65V ~ 2.2V<br>$V_{\text{CC}}=\text{Min}$ 、 $I_{\text{OH}}=-0.1\text{mA}$                                                                                                                    | 1.4       | -                  | -     | V             |

|                  |                              | 2.2V ~ 2.7V<br>$V_{\text{CC}}=\text{Min}$ 、 $I_{\text{OH}}=-1.0\text{mA}$                                                                                                                     | 2.0       | -                  | -     |               |

|                  |                              | 2.7V ~ 3.6V<br>$V_{\text{CC}}=\text{Min}$ 、 $I_{\text{OH}}=-4.0\text{mA}$                                                                                                                     | 2.2       | -                  | -     |               |

| $V_{\text{OL}}$  | 出力 LOW<br>電圧                 | 1.65V ~ 2.2V<br>$V_{\text{CC}}=\text{Min}$ 、 $I_{\text{OL}}=0.1\text{mA}$                                                                                                                     | -         | -                  | 0.2   | V             |

|                  |                              | 2.2V ~ 2.7V<br>$V_{\text{CC}}=\text{Min}$ 、 $I_{\text{OL}}=2\text{mA}$                                                                                                                        | -         | -                  | 0.4   |               |

|                  |                              | 2.7V ~ 3.6V<br>$V_{\text{CC}}=\text{Min}$ 、 $I_{\text{OL}}=8\text{mA}$                                                                                                                        | -         | -                  | 0.4   |               |

| $V_{\text{IH}}$  | 入力 HIGH<br>電圧                | 1.65V ~ 2.2V                                                                                                                                                                                  | -         | 1.4                | -     | V             |

|                  |                              | 2.2V ~ 2.7V                                                                                                                                                                                   | -         | 2.0                | -     |               |

|                  |                              | 2.7V ~ 3.6V                                                                                                                                                                                   | -         | 2.0                | -     |               |

| $V_{\text{IL}}$  | 入力 LOW<br>電圧 <sup>[5]</sup>  | 1.65V ~ 2.2V                                                                                                                                                                                  | -         | -0.2               | -     | V             |

|                  |                              | 2.2V ~ 2.7V                                                                                                                                                                                   | -         | -0.3               | -     |               |

|                  |                              | 2.7V ~ 3.6V                                                                                                                                                                                   | -         | -0.3               | -     |               |

| $I_{\text{IX}}$  | 入力リーク電流                      | $\text{GND} \leq V_{\text{IN}} \leq V_{\text{CC}}$                                                                                                                                            | -1.0      | -                  | +1.0  | $\mu\text{A}$ |

| $I_{\text{OZ}}$  | 出力リーク電流                      | $\text{GND} \leq V_{\text{OUT}} \leq V_{\text{CC}}$ 、出力が無効                                                                                                                                    | -1.0      | -                  | +1.0  | $\mu\text{A}$ |

| $I_{\text{CC}}$  | 動作電源電流                       | $V_{\text{CC}}=\text{Max}$ 、 $I_{\text{OUT}}=0\text{mA}$ 、<br>$f = 100\text{MHz}$                                                                                                             | -         | 90.0               | 110.0 | $\text{mA}$   |

|                  |                              | $f = 66.7\text{MHz}$                                                                                                                                                                          | -         | 90.0               | 80.0  |               |

| $I_{\text{SB1}}$ | 自動 CE のパワーダウン電流<br>- TTL 入力  | $\text{Max } V_{\text{CC}} \text{, } \overline{\text{CE}} \geq V_{\text{IH}}^{[7]}$<br>$V_{\text{IN}} \geq V_{\text{IH}}$ 又は $V_{\text{IN}} \leq V_{\text{IL}}$ , $f = f_{\text{MAX}}$        | -         | -                  | 40.0  | $\text{mA}$   |

| $I_{\text{SB2}}$ | 自動 CE のパワーダウン電流<br>- CMOS 入力 | $\text{Max } V_{\text{CC}} \text{, } \overline{\text{CE}} \geq V_{\text{CC}}-0.2\text{V}^{[7]}$<br>$V_{\text{IN}} \geq V_{\text{CC}}-0.2\text{V}$ 又は $V_{\text{IN}} \leq 0.2\text{V}$ , $f=0$ | -         | 20.0               | 30.0  | $\text{mA}$   |

### 注記

5. 2ns 以下のパルス幅の場合、 $V_{\text{IL}(\text{min})} = -2.0\text{V}$  および  $V_{\text{IH}(\text{max})} = V_{\text{CC}} + 2\text{V}$ 。

6. 標準値は単なる参照値であり、保証又は検査されていません。標準値は、 $V_{\text{CC}}=1.8\text{V}$  (1.65V ~ 2.2V の  $V_{\text{CC}}$  の範囲)、 $V_{\text{CC}}=3\text{V}$  (2.2V ~ 3.6V の  $V_{\text{CC}}$  の範囲)、 $T_A=25^{\circ}\text{C}$  で測定しています。

7.  $\overline{\text{CE}}$  は三つのチップ イネーブルの組み合わせを示します。LOW アクティブの時、 $\overline{\text{CE}} = \overline{\text{CE}}_1$ 、 $\overline{\text{CE}}_2$ 、及び  $\overline{\text{CE}}_3$  LOW を示します。HIGH の時、 $\overline{\text{CE}} = \overline{\text{CE}}_1$ 、 $\overline{\text{CE}}_2$ 、又は  $\overline{\text{CE}}_3$  HIGH を示します。

## 容量

| 記号 <sup>[8]</sup> | 説明     | テスト条件                                                                        | 119 ポール PBGA | 単位 |

|-------------------|--------|------------------------------------------------------------------------------|--------------|----|

| $C_{IN}$          | 入力容量   | $T_A = 25^\circ\text{C}$ 、 $f = 1\text{MHz}$ 、 $V_{CC} = V_{CC(\text{typ})}$ | 10           | pF |

| $C_{OUT}$         | I/O 容量 |                                                                              | 10           | pF |

## 熱抵抗

| 記号 <sup>[8]</sup> | 説明                | テスト条件                            | 119 ポール PBGA | 単位    |

|-------------------|-------------------|----------------------------------|--------------|-------|

| $\Theta_{JA}$     | 熱抵抗<br>(接合部から周囲)  | 無風状態、3×4.5 インチ、4 層プリント回路基板にばんだ付け | 20.92        | °C /W |

| $\Theta_{JC}$     | 熱抵抗<br>(接合部からケース) |                                  | 15.84        | °C /W |

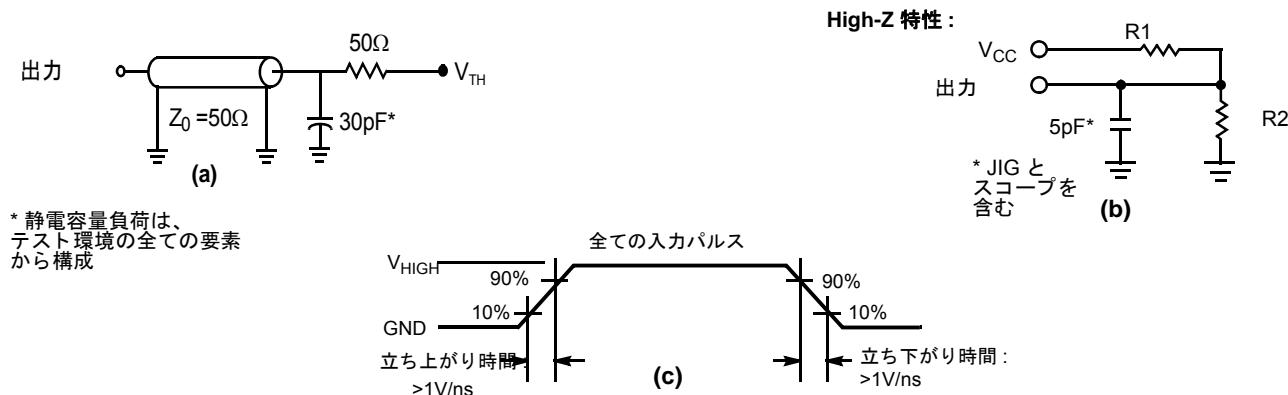

## AC テストの負荷と波形

図 3. AC テストの負荷と波形<sup>[9]</sup>

| 記号         | 1.8V | 3.0V | 単位 |

|------------|------|------|----|

| R1         | 1667 | 317  | Ω  |

| R2         | 1538 | 351  | Ω  |

| $V_{TH}$   | 0.9  | 1.5  | V  |

| $V_{HIGH}$ | 1.8  | 3    | V  |

### 注記

- 最初にテストされますが、設計またはプロセスで変更があった後に、これらのパラメータが影響を受ける場合があります。

- 完全なデバイスの AC 動作には、0 から  $V_{CC}(\text{min})$  への  $100\mu\text{s}$  のランプ時間、及び  $V_{CC}$  が安定した後、 $100\mu\text{s}$  の待機時間を想定しています。

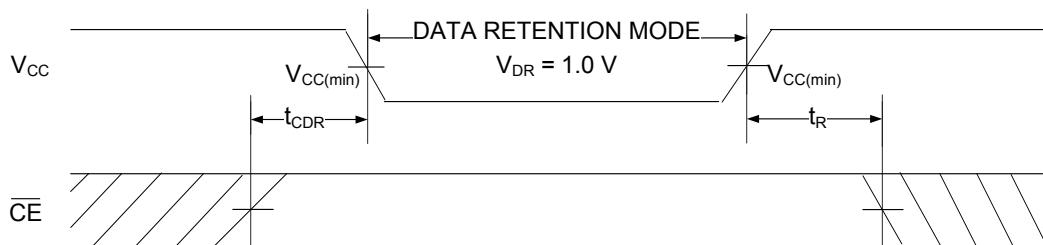

## データ保持特性

動作範囲は  $-40^{\circ}\text{C} \sim 85^{\circ}\text{C}$ 。

| 記号                      | 項目                      | 条件                                                                                                                                                                                                  | Min  | Max  | 単位 |

|-------------------------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|----|

| $V_{\text{DR}}$         | データ保持用の $V_{\text{CC}}$ | —                                                                                                                                                                                                   | 1.0  | —    | V  |

| $I_{\text{CCDR}}$       | データ保持電流                 | $V_{\text{CC}} = V_{\text{DR}}$ 、 $\overline{\text{CE}} \geq V_{\text{CC}} - 0.2\text{V}$ <sup>[10]</sup> 、<br>$V_{\text{IN}} \geq V_{\text{CC}} - 0.2\text{V}$ 又は $V_{\text{IN}} \leq 0.2\text{V}$ | —    | 30.0 | mA |

| $t_{\text{CDR}}^{[11]}$ | チップの選択解除からデータ保持までの時間    | —                                                                                                                                                                                                   | 0    | —    | ns |

| $t_{\text{R}}^{[12]}$   | 動作回復時間                  | $V_{\text{CC}} \geq 2.2\text{V}$                                                                                                                                                                    | 10.0 | —    | ns |

|                         |                         | $V_{\text{CC}} < 2.2\text{V}$                                                                                                                                                                       | 15.0 | —    | ns |

## データ保持波形

図 4. データ保持波形<sup>[10]</sup>

### 注記

10.  $\overline{\text{CE}}$  は三つのチップ イネーブルの組み合わせを示します。LOW アクティブの時、 $\overline{\text{CE}}$  は  $\overline{\text{CE}}_1$ 、 $\overline{\text{CE}}_2$ 、及び  $\overline{\text{CE}}_3$  LOW を示します。HIGH の時、 $\overline{\text{CE}}$  は  $\overline{\text{CE}}_1$ 、 $\overline{\text{CE}}_2$ 、又は  $\overline{\text{CE}}_3$  HIGH を示します。

11. 最初にテストされますが、設計またはプロセスで変更があった後に、これらのパラメータが影響を受ける場合があります。

12. 完全なデバイス動作は、 $V_{\text{DR}}$  から  $V_{\text{CC}(\text{min.})} \geq 100\text{ ms}$  までリニア  $V_{\text{CC}}$  ランプ又は  $V_{\text{CC}(\text{min.})} \geq 100\text{ ms}$  で安定である必要があります。

## AC スイッチング特性

動作範囲が  $-40^{\circ}\text{C} \sim 85^{\circ}\text{C}$ 。

| 記号 <sup>[13]</sup>                  | 説明                                                              | 10ns  |      | 15ns  |      | 単位 |

|-------------------------------------|-----------------------------------------------------------------|-------|------|-------|------|----|

|                                     |                                                                 | Min   | Max  | Min   | Max  |    |

| <b>読み出しサイクル</b>                     |                                                                 |       |      |       |      |    |

| $t_{\text{POWER}}$                  | $V_{\text{CC}}$ ( 安定 ) から初アクセスまでの時間 <sup>[14]</sup>             | 100.0 | —    | 100.0 | —    | μs |

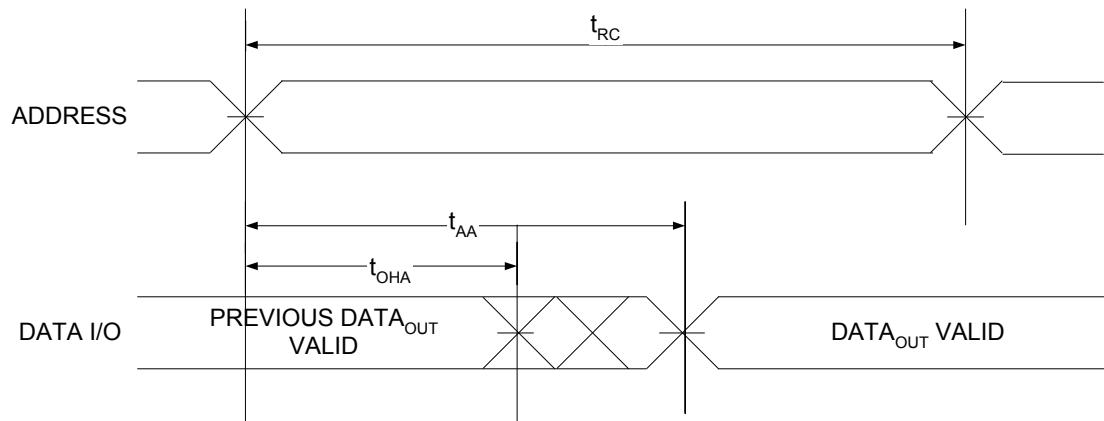

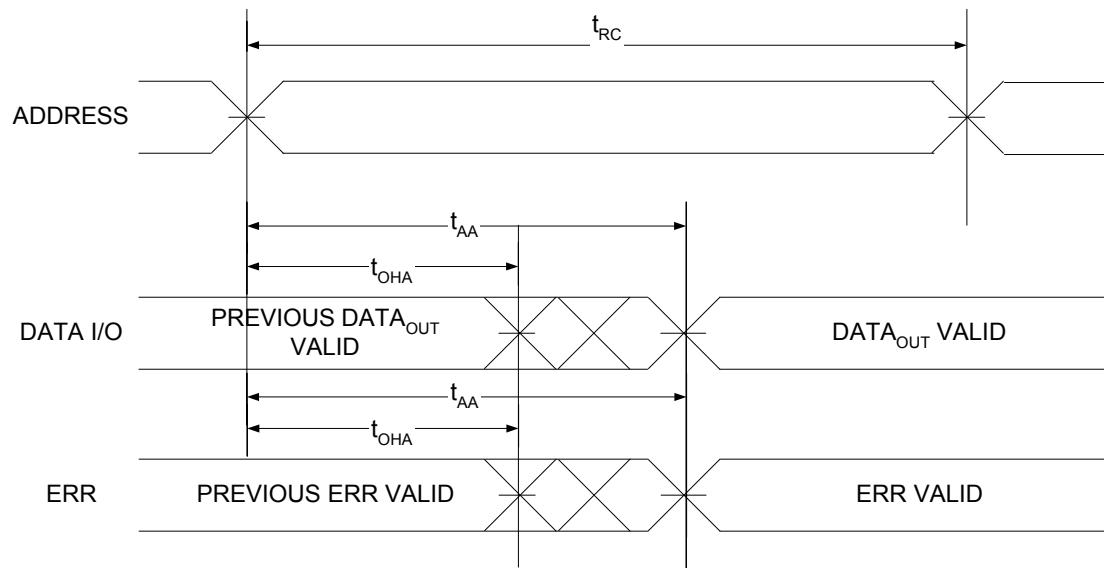

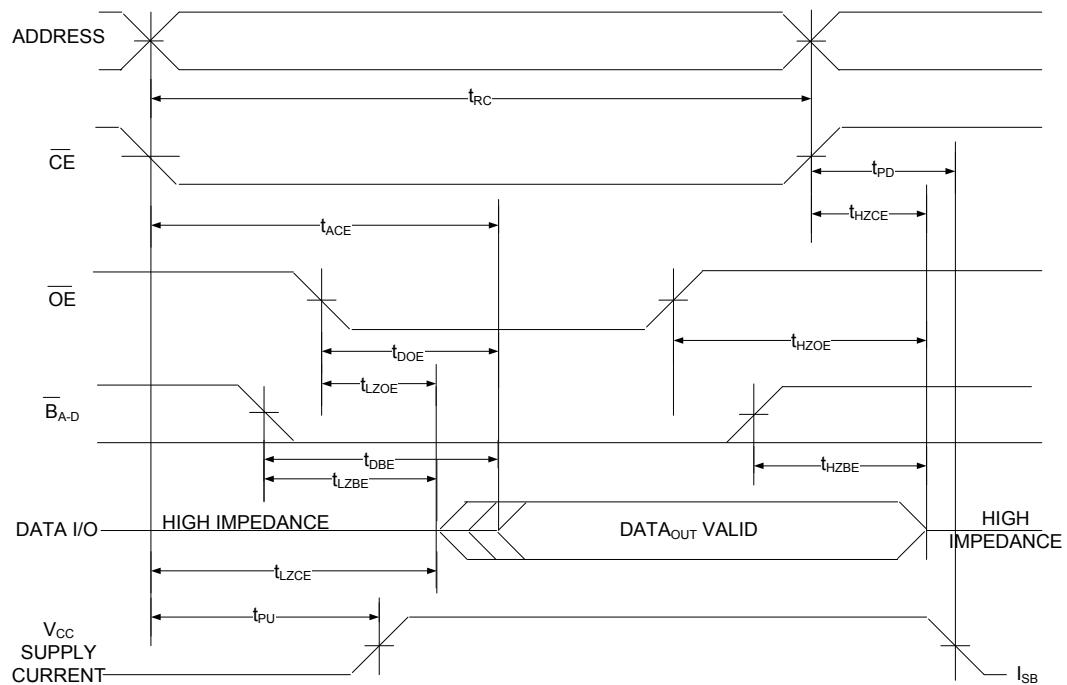

| $t_{\text{RC}}$                     | 読み出しサイクル時間                                                      | 10.0  | —    | 15.0  | —    | ns |

| $t_{\text{AA}}$                     | アドレスからデータ／ERR 有効までの時間                                           | —     | 10.0 | —     | 15.0 | ns |

| $t_{\text{OHA}}$                    | アドレス変更からのデータ／ERR ホールド時間                                         | 3.0   | —    | 3.0   | —    | ns |

| $t_{\text{ACE}}$                    | $\overline{\text{CE}}$ LOW からデータ／ERR 有効までの時間 <sup>[15]</sup>    | —     | 10.0 | —     | 15.0 | ns |

| $t_{\text{DOE}}$                    | $\overline{\text{OE}}$ LOW からデータ／ERR 有効までの時間                    | —     | 5.0  | —     | 8.0  | ns |

| $t_{\text{LZOE}}$                   | $\overline{\text{OE}}$ LOW から low Z までの時間 <sup>[16]</sup>       | 0     | —    | 1.0   | —    | ns |

| $t_{\text{HZOE}}$                   | $\overline{\text{OE}}$ HIGH から high Z までの時間 <sup>[16]</sup>     | —     | 5.0  | —     | 8.0  | ns |

| $t_{\text{LZCE}}$                   | $\overline{\text{CE}}$ LOW から low Z までの時間 <sup>[15, 16]</sup>   | 3.0   | —    | 3.0   | —    | ns |

| $t_{\text{HZCE}}$                   | $\overline{\text{CE}}$ HIGH から high Z までの時間 <sup>[15, 16]</sup> | —     | 5.0  | —     | 8.0  | ns |

| $t_{\text{PU}}$                     | $\overline{\text{CE}}$ LOW からパワーアップまでの時間 <sup>[15, 17]</sup>    | 0     | —    | 0     | —    | ns |

| $t_{\text{PD}}$                     | $\overline{\text{CE}}$ HIGH からパワーダウンまでの時間 <sup>[15, 17]</sup>   | —     | 10.0 | —     | 15.0 | ns |

| $t_{\text{DBE}}$                    | バイト イネーブルからデータ有効までの時間                                           | —     | 5.0  | —     | 8.0  | ns |

| $t_{\text{LZBE}}$                   | バイト イネーブルから low Z までの時間                                         | 0     | —    | 1.0   | —    | ns |

| $t_{\text{HZBE}}$                   | バイト ディセーブルから high Z までの時間                                       | —     | 6.0  | —     | 8.0  | ns |

| <b>書き込みサイクル</b> <sup>[18, 19]</sup> |                                                                 |       |      |       |      |    |

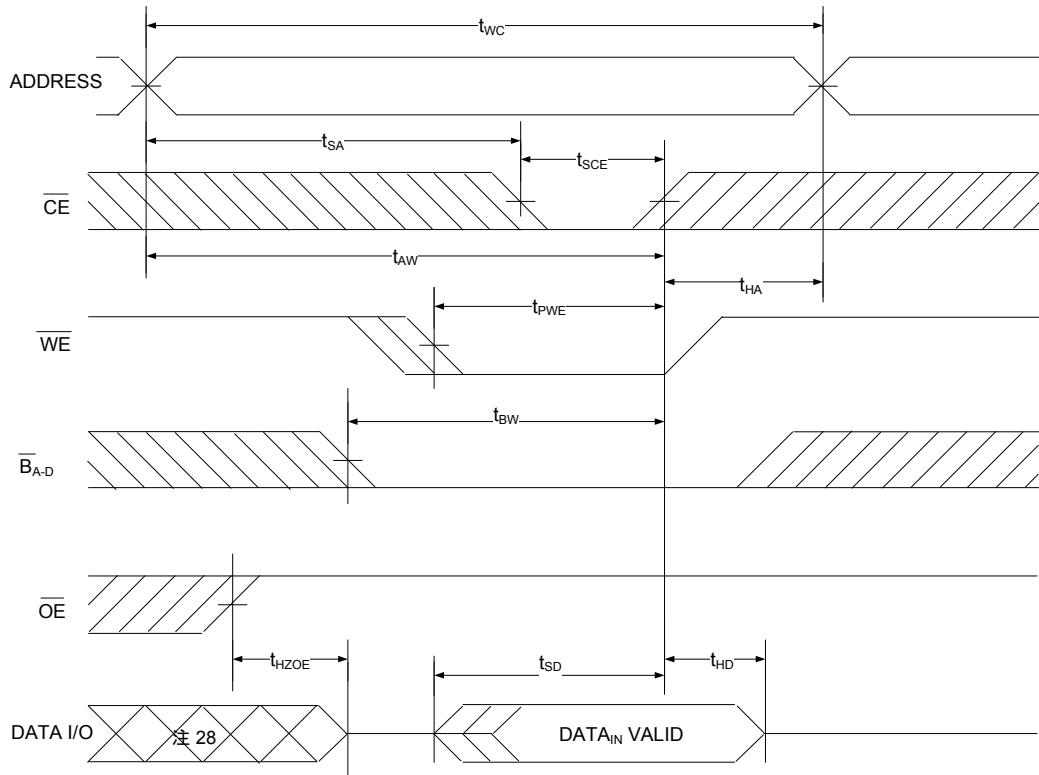

| $t_{\text{WC}}$                     | 書き込みサイクル時間                                                      | 10.0  | —    | 15.0  | —    | ns |

| $t_{\text{SCE}}$                    | $\overline{\text{CE}}$ LOW から書き込み終了までの時間 <sup>[15]</sup>        | 7.0   | —    | 12.0  | —    | ns |

| $t_{\text{AW}}$                     | アドレス セットアップから書き込み終了までの時間                                        | 7.0   | —    | 12.0  | —    | ns |

| $t_{\text{HA}}$                     | 書き込み終了からのアドレス ホールド時間                                            | 0     | —    | 0     | —    | ns |

| $t_{\text{SA}}$                     | アドレス セットアップから書き込み開始までの時間                                        | 0     | —    | 0     | —    | ns |

| $t_{\text{PWE}}$                    | $\overline{\text{WE}}$ パルス幅                                     | 7.0   | —    | 12.0  | —    | ns |

| $t_{\text{SD}}$                     | データ セットアップから書き込み終了までの時間                                         | 5.0   | —    | 8.0   | —    | ns |

| $t_{\text{HD}}$                     | 書き込み終了からのデータ ホールド時間                                             | 0     | —    | 0     | —    | ns |

| $t_{\text{LZWE}}$                   | $\overline{\text{WE}}$ HIGH から low Z までの時間 <sup>[16]</sup>      | 3.0   | —    | 3.0   | —    | ns |

| $t_{\text{HZWE}}$                   | $\overline{\text{WE}}$ LOW から high Z までの時間 <sup>[16]</sup>      | —     | 5.0  | —     | 8.0  | ns |

| $t_{\text{BW}}$                     | バイト イネーブルから書き込み終了までの時間                                          | 7.0   | —    | 12.0  | —    | ns |

### 注記

13. テスト条件では、信号遷移時間（立ち上がり／立ち下がり）が 3ns 以下、タイミング参照レベルが  $1.5V$  ( $V_{\text{CC}} \geq 3V$  の場合) と  $V_{\text{CC}}/2$  ( $V_{\text{CC}} < 3V$  の場合)、入力パルス レベルが  $0V \sim 3V$  ( $V_{\text{CC}} \geq 3V$  の場合) と  $0 \sim V_{\text{CC}}$  ( $V_{\text{CC}} < 3V$  の場合) と想定しています。出力負荷を使用する読み出しサイクル用のテスト条件は、特に記載のない限り、[ページ 8](#) の図 3 の (a) で示されます。

14.  $t_{\text{POWER}}$  は、電源供給が  $V_{\text{CC}}$  で安定した時から最初のメモリ アクセスが実行されるまでの最短時間を示します。

15.  $\overline{\text{CE}}$  は三つのチップ イネーブルの組み合わせを示します。LOW アクティブの時、 $\overline{\text{CE}}$  は  $\overline{\text{CE}}_1$ 、 $\overline{\text{CE}}_2$ 、及び  $\overline{\text{CE}}_3$  LOW を示します。HIGH の時、 $\overline{\text{CE}}$  は  $\overline{\text{CE}}_1$ 、 $\overline{\text{CE}}_2$ 、又は  $\overline{\text{CE}}_3$  HIGH を示します。

16.  $t_{\text{LZOE}}$ 、 $t_{\text{HZCE}}$ 、 $t_{\text{HZWE}}$ 、 $t_{\text{LZBE}}$ 、 $t_{\text{LZCE}}$ 、 $t_{\text{LZWE}}$  及び  $t_{\text{HZBE}}$  は、[ページ 8](#) の図 3 の (b) のように 5pF の負荷容量が付いた状態で測定されています。遷移は定常状態の電圧から  $\pm 200mV$  で測定されます。

17. これらのパラメータは設計上では保証されますが、テストされていません。

18. メモリの内部書き込み期間は  $\text{WE} = V_{\text{IL}}$ 、 $\text{CE} = V_{\text{IL}}$  のオーバラップで定義されます。これらの信号は、書き込みを開始するために LOW である必要があります、これらいずれかの信号が HIGH への遷移することで操作を終了することができます。入力データのセットアップとホールドのタイミングは、書き込みを終了する信号のエッジを基準にすること必要があります。

## スイッチング 波形

図 5. CY7C1062G の読み出しサイクル 1 (アドレス遷移制御) [20、21]

図 6. CY7C1062GE の読み出しサイクル 1 (アドレス遷移制御) [20、21]

## 注記

20. デバイスが連続的に選択されます、 $\overline{OE}$ 、 $\overline{CE}$ 、 $\overline{B}_A$ 、 $\overline{B}_B$ 、 $\overline{B}_C$ 、 $\overline{B}_D = V_{IL}$ 。

21. 読み込みサイクルの間は WE が HIGH です。

## スイッチング 波形 ( 続き )

図 7. 読み出しサイクル 2 ( $\overline{OE}$  制御) [22, 23, 24]

### 注記

22.  $\overline{CE}$  は三つのチップ イネーブルの組み合わせを示します。LOW アクティブの時、 $\overline{CE}$  は  $\overline{CE}_1$ 、 $\overline{CE}_2$ 、及び  $\overline{CE}_3$  LOW を示します。HIGH の時、 $\overline{CE}$  は  $\overline{CE}_1$ 、 $\overline{CE}_2$ 、又は  $\overline{CE}_3$  HIGH を示します。

23. 読み出しサイクルの間は WE が HIGH です。

24. アドレスは  $\overline{CE}$  遷移 LOW の前に有効になるか、又は遷移 LOW と同じです。

## スイッチング 波形 ( 続き )

図 8. 書き出しサイクル 1 (CE 制御) [25, 26, 27]

### 注記

25.  $\overline{CE}$  は三つのチップ イネーブルの組み合わせを示します。LOW アクティブの時、 $\overline{CE}$  は  $\overline{CE}_1$ 、 $\overline{CE}_2$ 、及び  $\overline{CE}_3$  LOW を示します。HIGH の時、 $\overline{CE}$  は  $\overline{CE}_1$ 、 $\overline{CE}_2$ 、又は  $\overline{CE}_3$  HIGH を示します。

26. メモリの内部書き込み期間は  $\overline{WE} = V_{IL}$ 、 $\overline{CE} = V_{IL}$  のオーバラップで定義されます。これらの信号は、書き込みを開始するために LOW である必要があります。これらいずれかの信号が HIGH への遷移することで操作を終了することができます。入力データのセットアップとホールドのタイミングは、書き込みを終了する信号のエッジを基準にする必要があります。

27.  $\overline{OE}$  又は  $\overline{B}_A$ 、 $\overline{B}_B$ 、 $\overline{B}_C$ 、 $\overline{B}_D = V_{IH}$  の場合、データ I/O がハイインピーダンス状態にあります。

28. この期間中、I/O は出力状態にあります。入力信号を適用しないでください。

## スイッチング 波形 ( 続き )

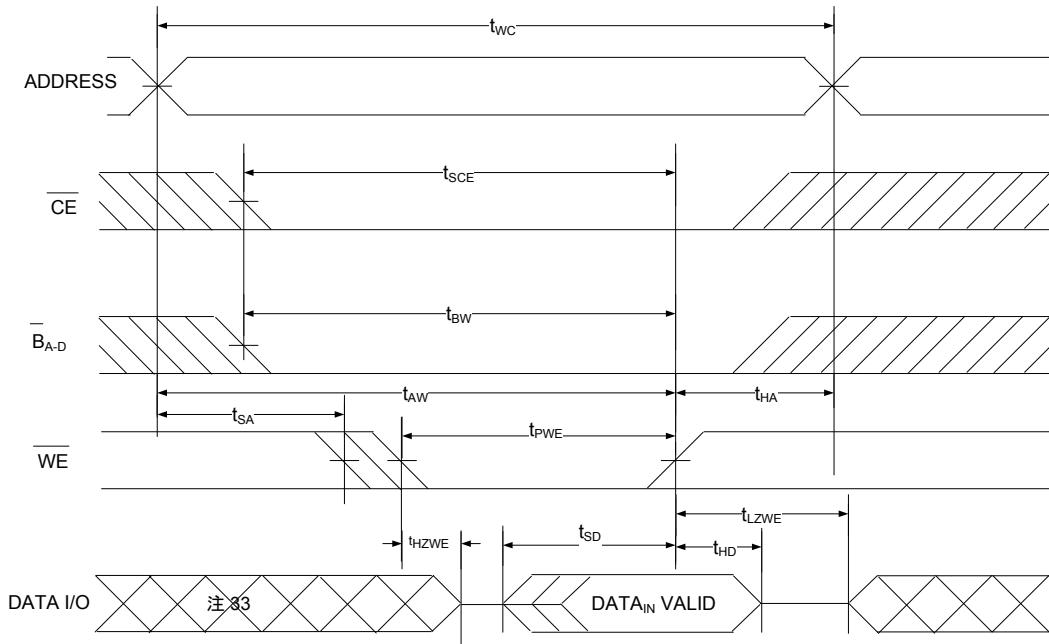

図 9. 書き出しサイクル 2 ( $\overline{WE}$  制御、 $\overline{OE}$  LOW) [29、30、31、32]

### 注記

29.  $\overline{CE}$  は三つのチップ イネーブルの組み合わせを示します。LOW アクティブの時、 $\overline{CE}$  は  $\overline{CE}_1$ 、 $\overline{CE}_2$ 、及び  $\overline{CE}_3$  LOW を示します。HIGH の時、 $\overline{CE}$  は  $\overline{CE}_1$ 、 $\overline{CE}_2$ 、又は  $CE_3$  HIGH を示します。

30. メモリの内部書き込み期間は  $\overline{WE} = V_{IL}$ 、 $\overline{CE} = V_{IL}$  のオーバラップで定義されます。これらの信号は、書き込みを開始するために LOW である必要があります、これらいずれかの信号が HIGH への遷移することで操作を終了することができます。入力データのセットアップとホールドのタイミングは、書き込みを終了する信号のエッジを基準にする必要があります。

31.  $OE$  又は  $B_A$ 、 $B_B$ 、 $B_C$ 、 $B_D = V_{IH}$  の場合、データ I/O がハイインピーダンス状態にあります。

32. 最少の書き込みサイクルのパルス幅は、 $t_{HZWE}$  と  $t_{SD}$  の合計に等しいです。

33. この期間中、I/O は出力状態にあります。入力信号を適用しないでください。

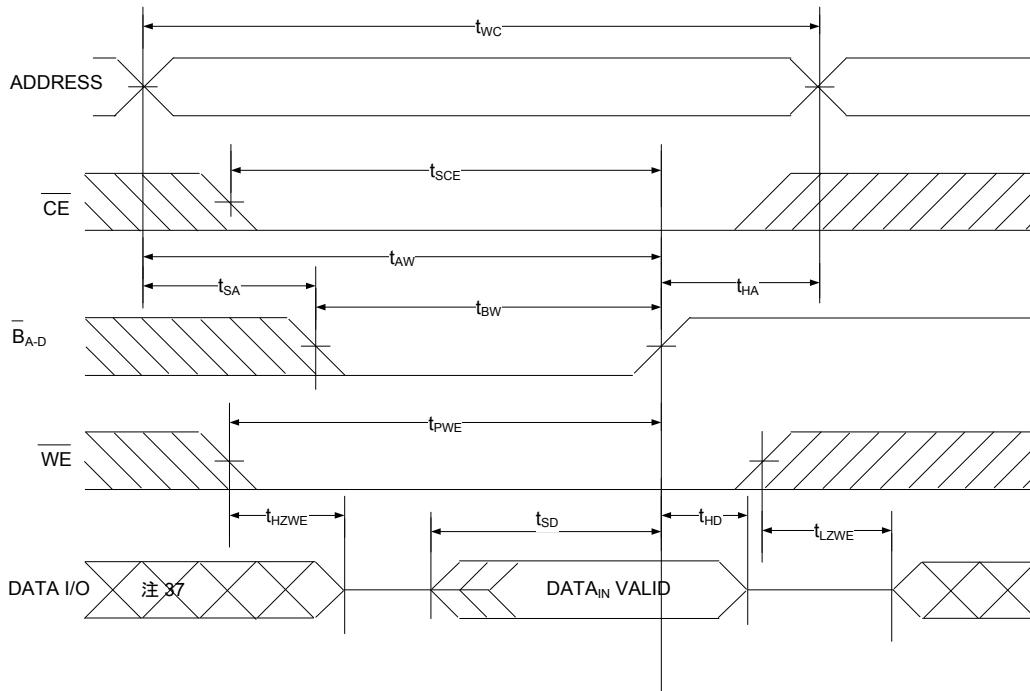

## スイッチング 波形( 続き )

図 10. 書き出しサイクル 3 ( $\overline{B}_A$ 、 $\overline{B}_B$ 、 $\overline{B}_C$ 、 $\overline{B}_D$  制御) [34、35、36]

### 注記

34.  $\overline{CE}$  は三つのチップ イネーブルの組み合わせを示します。LOW アクティブの時、 $\overline{CE}$  は  $\overline{CE}_1$ 、 $\overline{CE}_2$ 、及び  $\overline{CE}_3$  LOW を示します。HIGH の時、 $\overline{CE}$  は  $\overline{CE}_1$ 、 $\overline{CE}_2$ 、又は  $\overline{CE}_3$  HIGH を示します。

35. メモリの内部書き込み期間は  $\overline{WE} = V_{IL}$ 、 $\overline{CE} = V_{IL}$  のオーバラップで定義されます。これらの信号は、書き込みを開始するために LOW である必要があります。これらいずれかの信号が HIGH への遷移することで操作を終了することができます。入力データのセットアップとホールドのタイミングは、書き込みを終了する信号のエッジを基準にする必要があります。

36.  $\overline{OE}$  又は  $B_A$ 、 $\overline{B}_B$ 、 $B_C$ 、 $\overline{B}_D = V_{IH}$  の場合、データ I/O がハイインピーダンス状態にあります。

37. この期間中、I/O は出力状態にあります。入力信号を適用しないでください。

**真理値表 – CY7C1062G/CY7C1062GE**

| CE <sub>1</sub>   | CE <sub>2</sub>   | CE <sub>3</sub>   | OE                | WE                | B <sub>A</sub>    | B <sub>B</sub>    | B <sub>C</sub>    | B <sub>D</sub>    | I/O <sub>0</sub> –I/O <sub>7</sub> | I/O <sub>8</sub> –I/O <sub>15</sub> | I/O <sub>16</sub> –I/O <sub>23</sub> | I/O <sub>24</sub> –I/O <sub>31</sub> | モード                | 電源                 |

|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------------------------|-------------------------------------|--------------------------------------|--------------------------------------|--------------------|--------------------|

| H                 | X <sup>[39]</sup> | High Z                             | High Z                              | High Z                               | High Z                               | パワーダウン             | (I <sub>SB</sub> ) |

| X <sup>[39]</sup> | H                 | X <sup>[39]</sup> | High Z                             | High Z                              | High Z                               | High Z                               | パワーダウン             | (I <sub>SB</sub> ) |

| X <sup>[39]</sup> | X <sup>[39]</sup> | H                 | X <sup>[39]</sup> | High Z                             | High Z                              | High Z                               | High Z                               | パワーダウン             | (I <sub>SB</sub> ) |

| L                 | L                 | L                 | L                 | H                 | L                 | L                 | L                 | L                 | データ出力                              | データ出力                               | データ出力                                | データ出力                                | 全ビット読み出し           | (I <sub>CC</sub> ) |

| L                 | L                 | L                 | L                 | H                 | L                 | H                 | H                 | H                 | データ出力                              | High Z                              | High Z                               | High Z                               | バイト A<br>ビットのみ読み出し | (I <sub>CC</sub> ) |

| L                 | L                 | L                 | L                 | H                 | H                 | L                 | H                 | H                 | High Z                             | データ出力                               | High Z                               | High Z                               | バイト B<br>ビットのみ読み出し | (I <sub>CC</sub> ) |

| L                 | L                 | L                 | L                 | H                 | H                 | H                 | L                 | H                 | High Z                             | High Z                              | データ出力                                | High Z                               | バイト C<br>ビットのみ読み出し | (I <sub>CC</sub> ) |

| L                 | L                 | L                 | L                 | H                 | H                 | H                 | H                 | L                 | High Z                             | High Z                              | High Z                               | データ出力                                | バイト D<br>ビットのみ読み出し | (I <sub>CC</sub> ) |

| L                 | L                 | L                 | X <sup>[39]</sup> | L                 | L                 | L                 | L                 | L                 | データ入力                              | データ入力                               | データ入力                                | データ入力                                | 全ビット書き込み           | (I <sub>CC</sub> ) |

| L                 | L                 | L                 | X <sup>[39]</sup> | L                 | L                 | H                 | H                 | H                 | データ入力                              | High Z                              | High Z                               | High Z                               | バイト A<br>ビットのみ書き込み | (I <sub>CC</sub> ) |

| L                 | L                 | L                 | X <sup>[39]</sup> | L                 | H                 | L                 | H                 | H                 | High Z                             | データ入力                               | High Z                               | High Z                               | バイト B<br>ビットのみ書き込み | (I <sub>CC</sub> ) |

| L                 | L                 | L                 | X <sup>[39]</sup> | L                 | H                 | H                 | L                 | H                 | High Z                             | High Z                              | データ入力                                | High Z                               | バイト C<br>ビットのみ書き込み | (I <sub>CC</sub> ) |

| L                 | L                 | L                 | X <sup>[39]</sup> | L                 | H                 | H                 | H                 | L                 | High Z                             | High Z                              | High Z                               | データ入力                                | バイト D<br>ビットのみ書き込み | (I <sub>CC</sub> ) |

| L                 | L                 | L                 | H                 | H                 | X <sup>[39]</sup> | X <sup>[39]</sup> | X <sup>[39]</sup> | X <sup>[39]</sup> | High Z                             | High Z                              | High Z                               | High Z                               | 選択され、出力が無効         | (I <sub>CC</sub> ) |

| L                 | L                 | L                 | X <sup>[39]</sup> | X <sup>[39]</sup> | H                 | H                 | H                 | H                 | High Z                             | High Z                              | High Z                               | High Z                               | 選択された場合、出力はディスエーブル | (I <sub>CC</sub> ) |

**ERR 出力 –CY7C1062GE**

| 出力     | モード                           |

|--------|-------------------------------|

| 0      | 読み出し動作、保存データにはシングルビット エラーなし   |

| 1      | 読み出し動作、シングルビット エラーが検出され、訂正された |

| High Z | デバイスが選択解除／出力が無効／書き込み動作        |

**注記**

38. 全てのデュアル イネーブル デバイスに対応して  $\overline{CE}$  は  $\overline{CE}_1$  と  $CE_2$  の論理結合です。 $\overline{CE}_1$  が LOW で、 $CE_2$  が HIGH の場合、 $\overline{CE}$  は LOW ;  $\overline{CE}_1$  が HIGH または  $CE_2$  が LOW の場合は  $\overline{CE}$  は HIGH です。

39. これらのピンの入力電圧レベルは  $V_{IH}$  又は  $V_{IL}$  です。

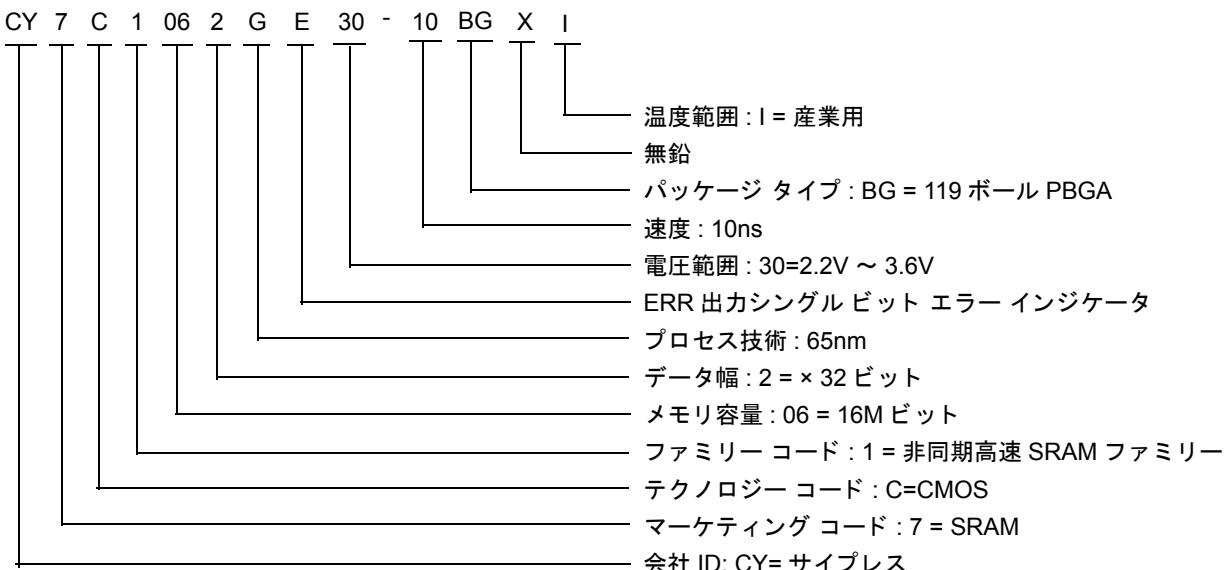

**注文情報**

| 速度<br>(ns) | 注文コード               | 外形図      | パッケージ タイプ             | 動作範囲 |

|------------|---------------------|----------|-----------------------|------|

| 10         | CY7C1062G30-10BGXI  | 51-85115 | 119 ボール PBGA ( 鉛フリー ) | 産業用  |

|            | CY7C1062GE30-10BGXI | 51-85115 | 119 ボール PBGA ( 鉛フリー ) |      |

**注文コードの定義**

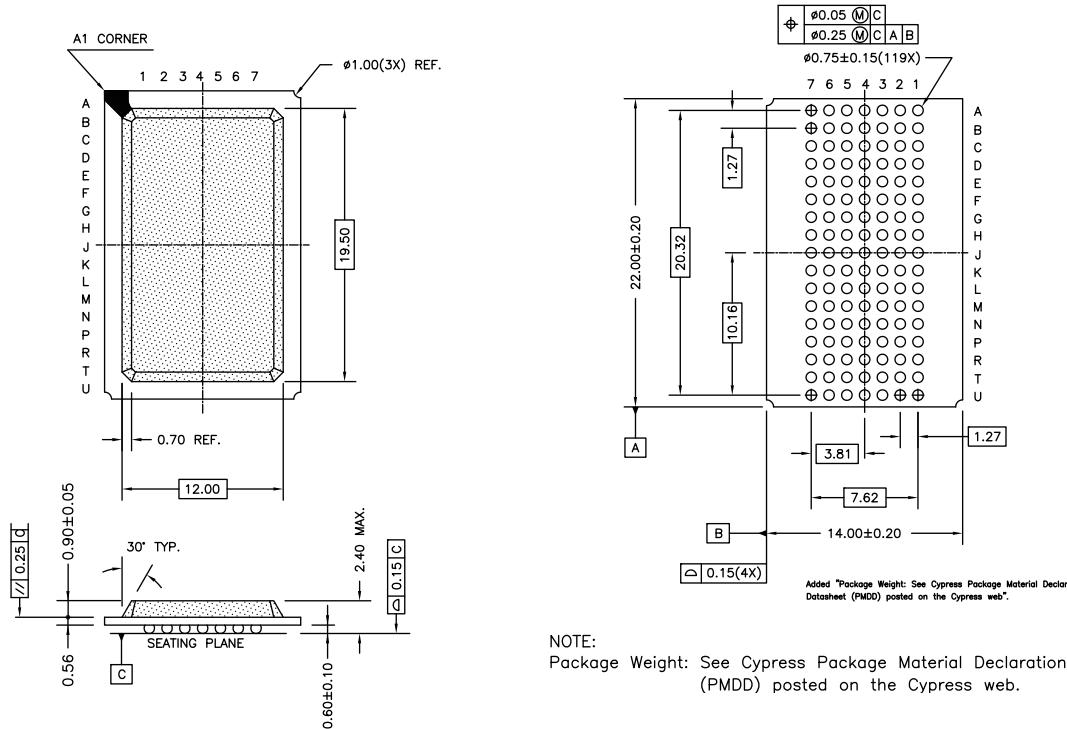

## 外形図

図 11. 119 ピン PBGA (14×22×2.4mm) BG119 パッケージの外形、51-85115

**略語**

| 略語   | 説明                                                      |

|------|---------------------------------------------------------|

| CE   | Chip Enable ( チップ イネーブル )                               |

| CMOS | Complementary Metal Oxide Semiconductor ( 相補型金属酸化膜半導体 ) |

| I/O  | Input/Output ( 入力／出力 )                                  |

| OE   | Output Enable ( 出力イネーブル )                               |

| PBGA | Plastic ball grid array ( プラスチック ボール グリッド アレイ )         |

| SRAM | Static Random Access Memory ( スタティック ランダム アクセス メモリ )    |

| TTL  | Transistor-Transistor Logic ( トランジスタ - トランジスタ ロジック )    |

| WE   | Write Enable ( 書き込みイネーブル )                              |

**本書の表記法**

**測定単位**

| 記号  | 測定単位     |

|-----|----------|

| °C  | 摂氏温度     |

| MHz | メガヘルツ    |

| µA  | マイクロアンペア |

| µs  | マイクロ秒    |

| mA  | ミリアンペア   |

| mm  | ミリメートル   |

| ns  | ナノ秒      |

| Ω   | オーム      |

| %   | パーセント    |

| pF  | ピコファラッド  |

| V   | ボルト      |

| W   | ワット      |

## 変更履歴

文書名 : CY7C1062G / CY7C1062GE、16M ビット (512K ワード x32 ビット) スタティック RAM とエラー訂正コード (ECC)

文書番号 : 001-92162

| 版  | ECN 番号  | 変更者  | 発行日        | 変更内容                                           |

|----|---------|------|------------|------------------------------------------------|

| ** | 4347364 | HZEN | 04/15/2014 | これは英語版 001-81609 Rev. *B を翻訳した日本語版 Rev. ** です。 |

| *A | 4471872 | HZEN | 08/11/2014 | これは英語版 001-81609 Rev. *C を翻訳した日本語版 Rev. *A です。 |

## セールス、ソリューションおよび法律情報

### ワールドワイドな販売と設計サポート

サイプレスは、事業所、ソリューションセンター、メーカー代理店および販売代理店の世界的なネットワークを保持しています。お客様の最寄りのオフィスについては、[サイプレスのロケーションページ](#)をご覧ください。

#### 製品

|             |                                                                                                                                      |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------|

| 車載用         | <a href="http://cypress.com/go/automotive">cypress.com/go/automotive</a>                                                             |

| クロック & バッファ | <a href="http://cypress.com/go/clocks">cypress.com/go/clocks</a>                                                                     |

| インターフェース    | <a href="http://cypress.com/go/interface">cypress.com/go/interface</a>                                                               |

| 照明 & 電力制御   | <a href="http://cypress.com/go/powerpsoc">cypress.com/go/powerpsoc</a><br><a href="http://cypress.com/go/plc">cypress.com/go/plc</a> |

| メモリ         | <a href="http://cypress.com/go/memory">cypress.com/go/memory</a>                                                                     |

| PSoC        | <a href="http://cypress.com/go/psoc">cypress.com/go/psoc</a>                                                                         |

| タッチ センシング   | <a href="http://cypress.com/go/touch">cypress.com/go/touch</a>                                                                       |

| USB コントローラ  | <a href="http://cypress.com/go/USB">cypress.com/go/USB</a>                                                                           |

| ワイヤレス / RF  | <a href="http://cypress.com/go/wireless">cypress.com/go/wireless</a>                                                                 |

#### PSoC® ソリューション

|                                                                            |

|----------------------------------------------------------------------------|

| <a href="http://psoc.cypress.com/solutions">psoc.cypress.com/solutions</a> |

| <a href="#">PSoC 1   PSoC 3   PSoC 4   PSoC 5LP</a>                        |

#### サイプレス開発者コミュニティ

|                        |                       |                     |                     |                        |

|------------------------|-----------------------|---------------------|---------------------|------------------------|

| <a href="#">コミュニティ</a> | <a href="#">フォーラム</a> | <a href="#">ブログ</a> | <a href="#">ビデオ</a> | <a href="#">トレーニング</a> |

|------------------------|-----------------------|---------------------|---------------------|------------------------|

#### テクニカル サポート

|                                                                    |

|--------------------------------------------------------------------|

| <a href="http://cypress.com/go/support">cypress.com/go/support</a> |

|--------------------------------------------------------------------|

© Cypress Semiconductor Corporation, 2012-2014. 本文書に記載される情報は、予告なく変更される場合があります。Cypress Semiconductor Corporation (サイプレス セミコンダクタ社) は、サイプレス製品に組み込まれた回路以外のいかなる回路を使用することに対して一切の責任を負いません。サイプレス セミコンダクタ社は、特許またはその他の権利に基づくライセンスを譲渡することも、または含意することもありません。サイプレス製品は、サイプレスとの書面による合意に基づくものでない限り、医療、生命維持、救命、重要な管理、または安全の用途のために使用することを保証するものではなく、また使用することを意図したものでもありません。さらにサイプレスは、誤動作や故障によって使用者に重大な傷害をもたらすことが合理的に予想される生命維持システムの重要なコンポーネントとしてサイプレス製品を使用することを許可していません。生命維持システムの用途にサイプレス製品を供することは、製造者がそのような使用におけるあらゆるリスクを負うことを意味し、その結果サイプレスはあらゆる責任を免除されることを意味します。

全てのソースコード（ソフトウェアおよび／またはファームウェア）はサイプレス セミコンダクタ社（以下「サイプレス」）が所有し、全世界の特許権保護（米国およびその他の国）、米国の著作権法ならびに国際協定の条項により保護され、かつそれらに従います。サイプレスが本書面によりライセンサーに付与するライセンスは、個人的、非独占かつ譲渡不能のライセンスであり、適用される契約で指定されたサイプレスの集積回路と併用されるライセンサーの製品のみをサポートするカスタムソフトウェアおよび／またはカスタム ファームウェアを作成する目的に限って、サイプレスのソースコードの派生著作物をコピー、使用、変更そして作成するためのライセンス、ならびにサイプレスのソースコードおよび派生著作物をコンパイルするためのライセンスです。上記で指定された場合を除き、サイプレスの書面による明示的な許可なくして本ソースコードを複製、変更、変換、コンパイル、または表示することは全て禁止します。

免責条項：サイプレスは、明示的または默示的を問わず、本資料に関するいかなる種類の保証も行いません。これには、商品性または特定目的への適合性の默示的な保証が含まれますが、これに限定されません。サイプレスは、本文書に記載される資料に対して今後予告なく変更を加える権利を留保します。サイプレスは、本文書に記載されるいかなる製品または回路を適用または使用したことによって生ずるいかなる責任も負いません。サイプレスは、誤動作や故障によって使用者に重大な傷害をもたらすことが合理的に予想される生命維持システムの重要なコンポーネントとしてサイプレス製品を使用することを許可していません。生命維持システムの用途にサイプレス製品を供することは、製造者がそのような使用におけるあらゆるリスクを負うことを意味し、その結果サイプレスはあらゆる責任を免除されることを意味します。

ソフトウェアの使用は、適用されるサイプレス ソフトウェア ライセンス契約によって制限され、かつ制約される場合があります。