请注意赛普拉斯已正式并入英飞凌科技公司。

此封面页之后的文件标注有“赛普拉斯”的文件即该产品为此公司最初开发的。请注意作为英飞凌产品组合的部分，英飞凌将继续为新的及现有客户提供该产品。

#### 文件内容的连续性

事实是英飞凌提供如下产品作为英飞凌产品组合的部分不会带来对于此文件的任何变更。未来的变更将在恰当的时候发生，且任何变更将在历史页面记录。

#### 订购零件编号的连续性

英飞凌继续支持现有零件编号的使用。下单时请继续使用数据表中的订购零件编号。

## 特性

- 使用于高性能时钟应用的低噪声 PLL

- 差分时钟输出：4 种频率可供选择，可通过 I<sup>2</sup>C 重新配置

- 支持 15 MHz 到 2.1 GHz 的输出频率范围

- 具有高度集成 VCO 的分数倍分频锁相环

- 支持固定频率的三次泛音（OT3），低基频（LFF），高基频（HFF）模式的晶振，也支持低频率输入。

- 支持 LVPECL、CML、HCSL、LVDS 或 LVC MOS 等输出标准格式

- 适用于 3.3、2.5 和 1.8 V 的供电电压

- 输出频率 > 150 MHz（频率偏移 = 12 kHz ~ 20 MHz）时，集成抖动的典型值为 150 fs

- 提供 VCXO 功能，拉电压总范围 TPR (+/- 50 ppm 到 +/- 275 ppm) 可调校

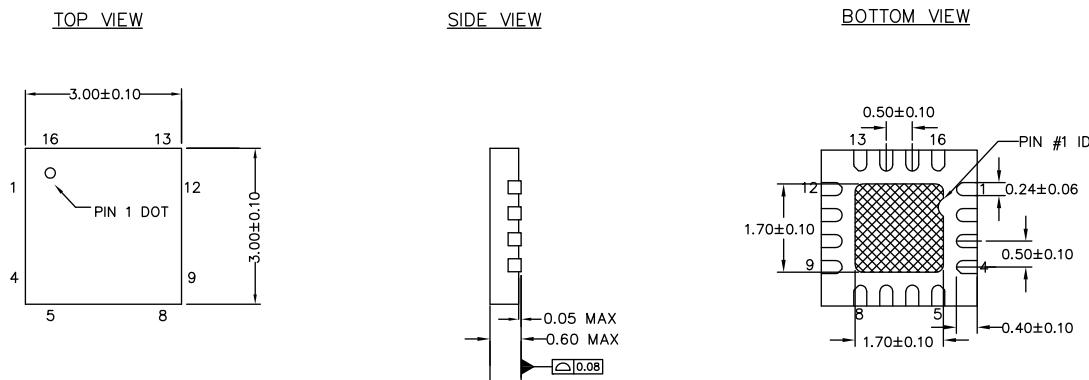

- 16-QFN 封装尺寸：3 × 3 × 0.6 mm

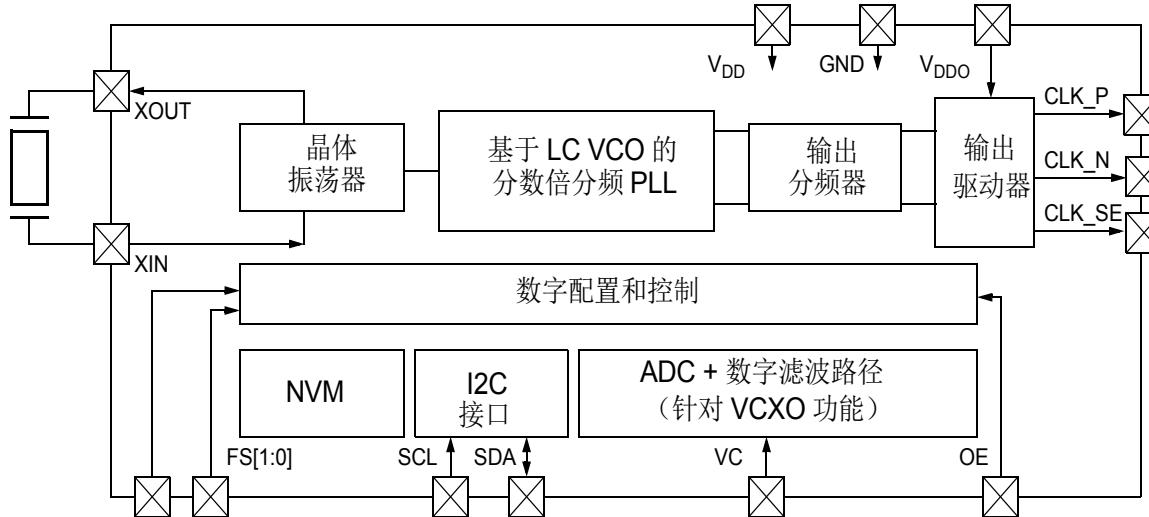

## 功能说明

CY29430 是基于 PLL 的可编程晶体振荡器解决方案，它支持多种输出频率选项。输出频率可在现场编程或由厂家编程，所支持的频率范围从 15 MHz 到 2.1 GHz。支持 4 种频率，通过频率选择（FS）引脚，可对差分输出频率进行独立的配置。此外，还可以通过 I<sup>2</sup>C 接口配置其他频率。该时钟合成器采用了先进的设计技术，在电压为 1.8 V ~ 3.3 V、环境温度为 -40°C ~ +105°C 的条件下，可在整个输出频率范围内提供优越可靠的防抖动特性。因此，本产品系列非常适用于通信应用（如 OTN、SONET/SDH、xDSL、GbE、网络、无线基础设施）、测试和仪器仪表应用，以及高速数据转换器。此外，由于具有 VCXO 功能，CY29430 能够使用于要求压控时钟源的应用和同步定时应用的数字时钟解决方案。

## 逻辑框图

## 目录

|                                 |    |                        |    |

|---------------------------------|----|------------------------|----|

| 引脚图 .....                       | 3  | LVCMOS 输出的交流电气规范 ..... | 11 |

| 引脚说明 .....                      | 3  | HFF 晶振规范 .....         | 12 |

| 功能概述 .....                      | 4  | OT3 晶振规范 .....         | 12 |

| 可编程特性 .....                     | 4  | LFF 晶振规范 .....         | 12 |

| 架构概述 .....                      | 4  | LF 低频率参考 .....         | 13 |

| 内部状态框图 .....                    | 5  | 时序参数 .....             | 13 |

| 少量 / 大量更改 .....                 | 5  | 输入时钟的测量点 .....         | 13 |

| 编程支持 .....                      | 5  | 相位抖动特性 .....           | 14 |

| 频率配置 .....                      | 5  | I2C 总线时序规范 .....       | 14 |

| 可编程 OE 极性 .....                 | 5  | 电压和时序定义 .....          | 15 |

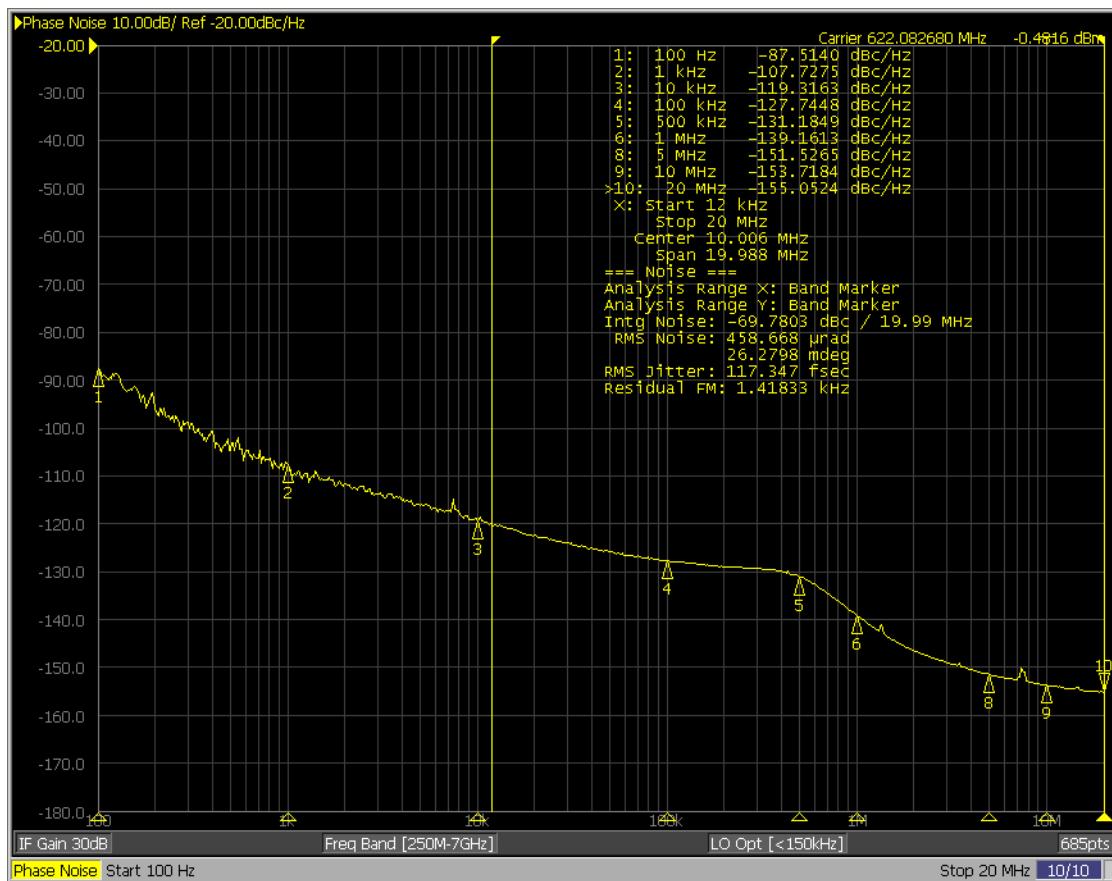

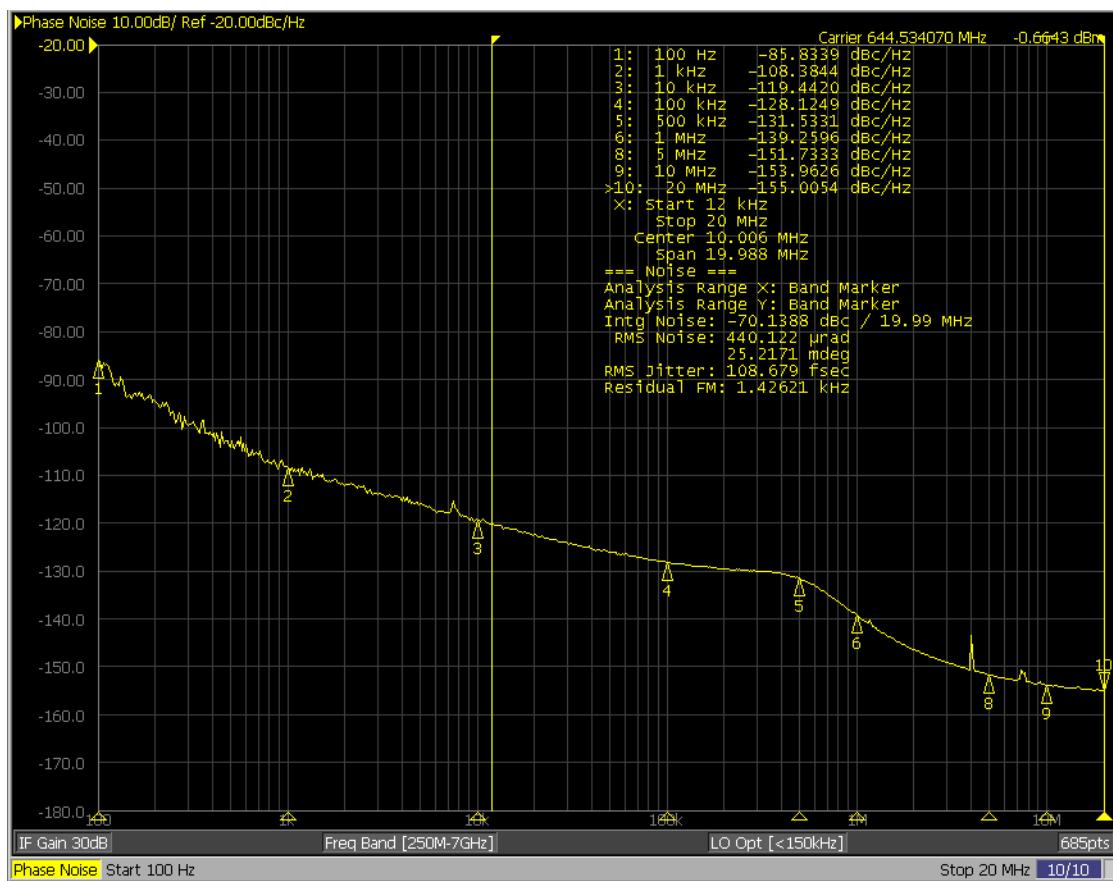

| 可编程 VCXO .....                  | 5  | 相位噪声图 .....            | 17 |

| 供电电压序列 .....                    | 5  | 订购信息 .....             | 20 |

| I2C 接口 .....                    | 5  | 订购代码定义 .....           | 20 |

| 存储器映射 .....                     | 6  | 封装图 .....              | 21 |

| 最大绝对额定值 .....                   | 7  | 缩略语 .....              | 22 |

| 建议的工作条件 .....                   | 7  | 文档规范 .....             | 22 |

| 直流电气规范 .....                    | 7  | 测量单位 .....             | 22 |

| LVDS 输出的直流规范 .....              | 8  | 文档修订记录页 .....          | 23 |

| LVPECL 输出的直流规范 .....            | 8  | 销售、解决方案和法律信息 .....     | 24 |

| 直流规范 .....                      | 8  | 全球销售和设计支持 .....        | 24 |

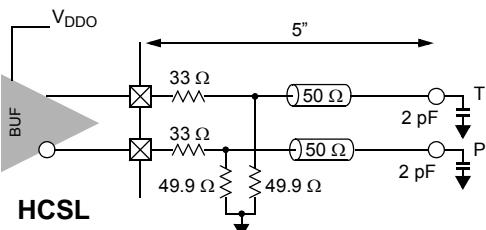

| HCSL 输出的直流规范 .....              | 8  | 产品 .....               | 24 |

| LVCMOS 输出的直流规范 .....            | 9  | PSoC® 解决方案 .....       | 24 |

| VCXO 特定参数 .....                 | 9  | 赛普拉斯开发者社区 .....        | 24 |

| LVPECL、LVDS、CML 输出的交流电气规范 ..... | 10 | 技术支持 .....             | 24 |

| HSCL 输出的交流电气规范 .....            | 11 |                        |    |

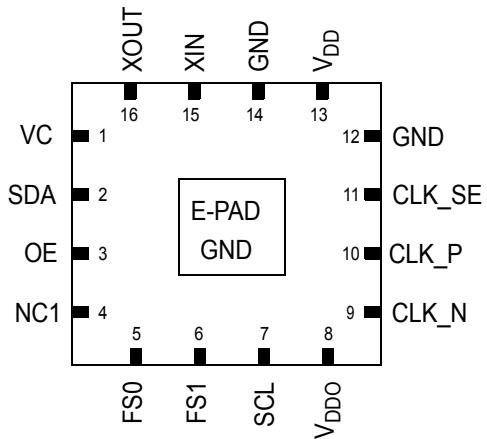

## 引脚图

CY29430 引脚分布

## 引脚说明

| 名称                    | 引脚编号 | 说明                                   |

|-----------------------|------|--------------------------------------|

| VC <sup>[1]</sup>     | 1    | VCXO 的输入电压                           |

| SDA                   | 2    | I <sup>2</sup> C 的串行数据输入 / 输出        |

| OE                    | 3    | 输出启用输入                               |

| NC1                   | 4    | 无连接                                  |

| FS0                   | 5    | 频率选择 0 (使用 100 kΩ 的下拉电阻)             |

| FS1                   | 6    | 频率选择 1 (使用 100 kΩ 的下拉电阻)             |

| SCL                   | 7    | I <sup>2</sup> C 的串行时钟输入             |

| V <sub>DDO</sub>      | 8    | 输出驱动器的电源电压                           |

| CLK_N <sup>[2]</sup>  | 9    | 时钟互补输出                               |

| CLK_P <sup>[2]</sup>  | 10   | 时钟主输出                                |

| CLK_SE <sup>[2]</sup> | 11   | (可选的) LVC MOS 时钟输出                   |

| GND                   | 12   | 输出驱动器的电源地                            |

| V <sub>DD</sub>       | 13   | 内核的电源                                |

| GND                   | 14   | 接地电源                                 |

| XIN                   | 15   | 晶振或时钟参考输入                            |

| XOUT                  | 16   | 晶振参考输出。时钟输入连接至 XIN 时, XOUT 引脚处于悬空状态。 |

| E-PAD                 |      | 裸露焊盘必须将其接地。                          |

### 注释:

1. 如果未使用 VC, 请勿将其进入悬空状态, 将其连接至 VDD 或 GND。

2. CLK\_SE 和 (CLK\_P, CLK\_N) 不能同时使用。VDD 应等于 VDDO。

## 功能概述

### 可编程特性

表 1. 可编程特性

| 特性   | 描述                                    |

|------|---------------------------------------|

| 频率调校 | PLL 的频率                               |

|      | 振荡器调校（使用负载电容值）                        |

| 功能   | OE 极性                                 |

| 电源   | $V_{DD}$ (1.8 V、2.5 V 或 3.3 V)        |

| VCXO | 使能 / 禁用 VCXO                          |

|      | Kv 极性                                 |

|      | 拉电压总范围                                |

|      | 调制带宽                                  |

| 输出   | 输出标准 (LVPECL、LVDS、HCSL、CML 或 LVC MOS) |

| 功能   | I <sup>2</sup> C 地址                   |

|      | 4-/2-/1- 默认频率                         |

| 参考   | 晶振 (HFF、OT3、LFF) 或时钟输入                |

### 架构概述

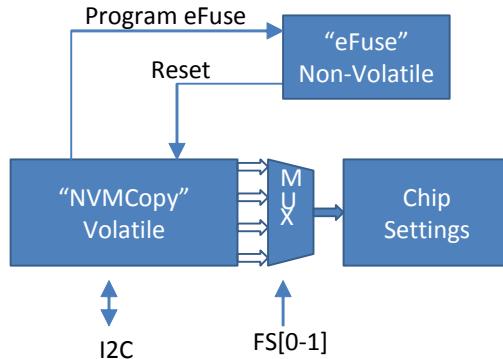

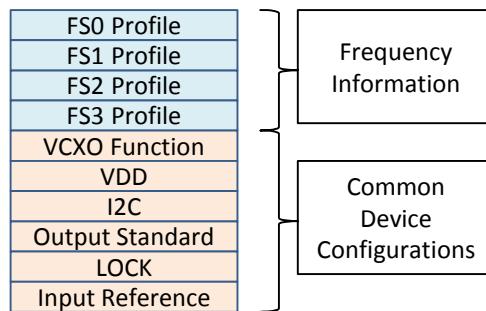

CY29430 是高性能、可编程 PLL 的晶体振荡器芯片，它支持多种功能和多种输出规范。该器件具有一个一次性可编程 (OTP) 非易失性存储器 (NVM)，可用于存储通用器件配置以及与输出频率有关的设置（请参考图 2）。通用器件配置不受输出频率的影响，这些配置包括：芯片电源、OE 极性、I<sup>2</sup>C 器件地址、输入参考、输出规范和 VCXO。器件还包含易失性存储器，器件退出上电复位模式时，该存储器将存储 NVM 的准确副本。芯片设置取决于易失性存储器中的内容，输出频率则取决于这些配置，如图 1 所示。可以通过 I<sup>2</sup>C 总线访问和更改易失性存储器。

图 1. 存储器的理论结构

图 2. 用于配置的存储器结构

### 存储器结构设置的说明

- 配置文件 [FS0-3]: 包含频率信息

- VCXO 功能: 包含 VCXO 使能/禁用、TPR、调制带宽和 Kv (VC 与频率的斜率) 等信息

- $V_{DD}$ : 1.8/2.5/3.3 V 电压范围的信息

- I<sup>2</sup>C: 使能 / 禁用、I<sup>2</sup>C 地址信息

- 输出标准: LVPECL、LVDS、CML、HCSL 或 LVC MOS

- 锁定格式: 使用 2 位格式表示 eFuse 的锁定状态

- 输入参考: 晶振 (OT3、HFF、LFF) 或时钟

## 内部状态框图

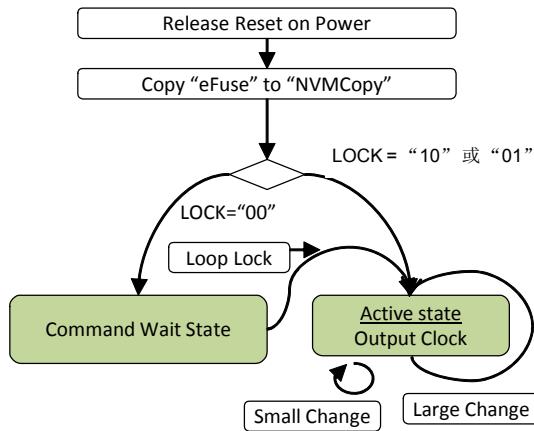

CY29430 有一个用于控制器件操作的状态机。复位后，该状态机将“eFuse”内容加载到“NVMCopy”内，如图3所示。根据“LOCK”的值，该状态机会进入“命令等待状态”或“活动状态”。在“命令等待状态”中，用户可以访问所有寄存器，并能读取/写入“NVMCopy”的数据。在这种状态下会使用以下命令：

- 编程 eFuse

- 选择性编程 eFuse

- 将 eFuse 的内容复制到 NVMCopy 内

- 将 NVMCopy 的内容复制到 NVM 寄存器内

### ■ 环路锁存

通过发送“环路锁存”命令使状态机进入“活动状态”（不需编程“LOCK”），用户可以测试器件的功能。器件会根据这些设置进行工作。

图3. 状态框图

将 LOCK 编程为“10”或“01”，器件将进入“活动状态”，并且在完成上电周期后，输出时钟可用。

在“活动状态”中，用户可以通过使用“Small Change”（少量更改）或“Large Change”（大量更改）命令来更改输出频率。如果 TCXO 或外部时钟信号被路由到 XIN，那么 V<sub>DD</sub> 上升到指定电平前需要有一个稳定的输入。这是因为上电时进行了片上频率校准，该过程开始时需要有一个稳定的参考输入。

### 少量 / 大量更改

少量更改指的是频率的更改范围在  $\pm 500 \text{ ppm}$  内。频率信息通过 I<sup>2</sup>C 加载，并且输出频率从原始值改变为新值时不会产生任何窄脉冲。注意：整数倍分频 PLL 不支持少量更改功能。更多有关信息，请参见 [LVPECL、LVDS、CML 输出的交流电气规范](#)。

大量更改指的是频率的改变范围超过  $\pm 500 \text{ ppm}$ ，并且通过 I<sup>2</sup>C 或 FS 状态改变。器件需要重新校准并重新配置 PLL，该过程完成前输出不稳定。

## 编程支持

CY29430 是一种软件可配置的解决方案，在该解决方案中，赛普拉斯提供的编程规范用于定义全部所需配置位。从而，用户可以通过自己的编程硬件开发编程软件。

## 频率配置

根据 FS0 和 FS1 引脚上的逻辑电平可配置 FS[0-3]，如第 6 页上的表 5 中所示。频率配置包括与 FS[0-3] 设置项相对应的所需输出频率。将所需要的值加载到分数倍分频 PLL 内（根据输入晶振频率，可以使用该值为各种设置生成频率）。表 3 提供了 FS[0-3] 的频率配置。

## 可编程 OE 极性

CY29430 有一个用于设置 OE 极性的位（默认为低电平有效）。用户可以将 OE 极性设为高电平有效或低电平有效。OE 被取消确认时，输出被禁用。

## 可编程 VCXO

器件采用了专有技术，根据 VC 控制电压对 VCO 频率进行调制，从而调制频率。与 OT3/HFF 输入相比，使用 FS 引脚上的时钟输入可提供线性度和准确度更高的输出。此外，VCXO 的特性也非常稳定，并不受温度、供电电压或处理过程变化的影响。

可以对 Kv（频率与 VC 的斜率）、TPR、VC 带宽和 VCXO 使能/禁用状态进行编程。注意，整数倍分频 PLL 不支持 VCXO 功能。

## 供电电压序列

CY29430 对启动序列没有任何特殊要求。启动过程要求 V<sub>DD</sub> 是单调上升的，如本数据手册所述。上升后，V<sub>DD</sub> 必须保持在“推荐的工作条件”所指定的范围内。另外，系统还要实现欠压检测和保护功能。

其它输入信号（如 VC、FS0 或 FS1）的上电时间可以比 V<sub>DD</sub> 更早或更晚，这些输入信号与 V<sub>DD</sub> 之间没有任何时序要求。所有输入信号被配置后，器件可正常运行。

如果 TCXO 或外部时钟信号被路由到 XIN，那么 V<sub>DD</sub> 上升到指定电平前需要有一个稳定的输入。这是因为上电时进行了片上频率校准，该过程开始时需要有一个稳定的参考输入。

## I<sup>2</sup>C 接口

CY29430 支持两线式串行接口 I<sup>2</sup>C，该接口支持快速模式（400 kbps）和 7 位地址。器件地址是可编程的，默认情况下它为 55h。只能对它进行单字节访问。VDD 达到指定的最小电压后，至少要等待 5 ms I<sup>2</sup>C 才能对器件进行第一次访问。

## 存储器映射

表 2. 通用配置

| 存储器地址   | 说明   |

|---------|------|

| 50h–57h | 器件配置 |

用户必须编写配置工具所创建的全部内容，并不能将部分内容写入到器件内。

对其他位置进行访问会导致器件发生严重错误。

表 3. FS[0-3]: 频率配置

| 存储器地址                                         | 说明                    |

|-----------------------------------------------|-----------------------|

| 10h、20h、30h、40h                               | DIVO                  |

| 11h、21h、31h、41h                               | DIVO、DIVN_INT         |

| 12h、22h、32h、42h                               | ICP、DIVN_INT、PLL_MODE |

| 13h、23h、33h、43h                               | DIVN_FRAC_L           |

| 14h、24h、34h、44h                               | DIVN_FRAC_M           |

| 15h、25h、35h、45h                               | DIVN_FRAC_H           |

| 1xh = FS0, 2xh = FS1,<br>3xh = FS2, 4xh = FS3 | —                     |

表 5. FS 设置

| FS1 | FS0 | FS 设置 |

|-----|-----|-------|

| 0   | 0   | FS0   |

| 0   | 1   | FS1   |

| 1   | 0   | FS2   |

| 1   | 1   | FS3   |

表 4. 其他信息

| 存储器地址    | 描述            |

|----------|---------------|

| 00h (只读) | 器件 ID (= 51h) |

| D4h–D6h  | 用户可配置信息       |

## 最大绝对额定值

超过最大额定值<sup>[3]</sup>可能会缩短器件的使用寿命。用户指南未经测试。

|            |                  |

|------------|------------------|

| 接地电压电位范围   | -0.5 V 到 +3.8 V  |

| 输入电压       | -0.5 V 到 3.8 V   |

| 存放温度 (非冷凝) | -55 °C 到 +150 °C |

| 结温         | -40 °C 到 +125 °C |

| 编程温度       | +25 °C 到 +125 °C |

|                                      |               |

|--------------------------------------|---------------|

| 编程电压                                 | 2.5 V ± 0.1 V |

| 用于编程 eFuse 的电源                       | 50 mA         |

| 数据保留时间 ( $T_J = 125^\circ\text{C}$ ) | > 10 年        |

| 最多的编程周期                              | 1             |

| ESD HBM (JEDEC JS-001-2012)          | 2000 V        |

| ESD MM (JEDEC JESD22-A115B)          | 200 V         |

| ESD CDM (JEDEC JESD22-C101E)         | 500 V         |

| 栓锁电流                                 | > ±140 mA     |

## 建议的工作条件

| 参数                   | 说明                      | 最小值  | 最大值  | 单位  |

|----------------------|-------------------------|------|------|-----|

| $V_{DD}$ 、 $V_{DDO}$ | 供电电压、工作电压范围为 1.8 V ±5%  | 1.71 | 1.89 | V   |

|                      | 供电电压、工作电压范围为 2.5 V ±10% | 2.25 | 2.75 |     |

|                      | 供电电压、工作电压范围为 3.3 V ±10% | 2.97 | 3.63 |     |

| TA                   | 环境温度                    | -40  | +105 | °C  |

| $f_{RES}$            | 频率分辨率                   | -    | 2    | ppb |

| $T_{PLLHOLD}$        | PLL 的工作温度范围             | -    | 125  | °C  |

## 直流电气规范

| 参数             | 说明            | 测试条件                                                                                                                                    | 最小值                 | 典型值 | 最大值                 | 单位 |

|----------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----|---------------------|----|

| $I_{DD}$       | 供电电流, LVPECL  | $V_{DD} = 3.3 \text{ V}、2.5 \text{ V} \text{ 或 } 1.8 \text{ V}$ , 将一个 $50 \Omega$ 的电阻连接到 $V_{TT}$ ( $V_{DD} - 2.0 \text{ V}$ ) 上, 有共模电流 | -                   | 93  | 106                 | mA |

|                | 供电电流, LVPECL  | $V_{DD} = 3.3 \text{ V}、2.5 \text{ V} \text{ 或 } 1.8 \text{ V}$ , 将一个 $50 \Omega$ 的电阻连接到 $V_{TT}$ ( $V_{DD} - 2.0 \text{ V}$ ) 上, 无共模电流 | -                   | 81  | 94                  |    |

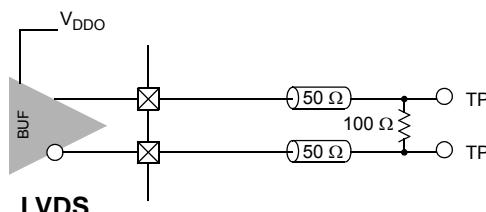

|                | 供电电流, LVDS    | $V_{DD} = 3.3 \text{ V}、2.5 \text{ V} \text{ 或 } 1.8 \text{ V}$ , 在 CLKP 和 CLKN 之间连接一个 $100 \Omega$ 的电阻                                 | -                   | 69  | 81                  |    |

|                | 供电电流, HCSL    | $V_{DD} = 3.3 \text{ V}、2.5 \text{ V} \text{ 或 } 1.8 \text{ V}$ , 将 $33 \Omega$ 和 $49.9 \Omega$ 的电阻接地                                   | -                   | 80  | 93                  |    |

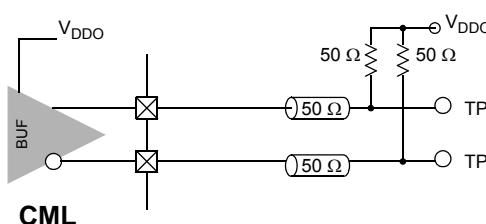

|                | 供电电流, CML     | $V_{DD} = 3.3 \text{ V}、2.5 \text{ V} \text{ 或 } 1.8 \text{ V}$ , 将 $50 \Omega$ 的电阻连接到 $V_{DD}$ 上                                       | -                   | 73  | 86                  |    |

|                | 供电电流, CMOS    | $V_{DD} = 3.3 \text{ V}、2.5 \text{ V} \text{ 或 } 1.8 \text{ V}$ , 负载 = 0 pF, 频率 = 33.33 MHz                                             | -                   | 58  | 70                  |    |

|                | 供电电流, CMOS    | $V_{DD} = 3.3 \text{ V}、2.5 \text{ V} \text{ 或 } 1.8 \text{ V}$ , 负载 = 10 pF, 频率 = 33.33 MHz                                            | -                   | 66  | 78                  |    |

|                | 供电电流, 仅针对 PLL | $V_{DD} = 3.3 \text{ V}/2.5 \text{ V}/1.8 \text{ V}$                                                                                    | -                   | 59  | 70                  |    |

| $I_{IH}$       | 输入高电流         | 逻辑输入, 输入电压 = $V_{DD}$                                                                                                                   | -                   | 30  | 50                  | μA |

| $I_{IL}$       | 输入低电流         | 逻辑输入, 将输入连接至 GND                                                                                                                        | -                   | 30  | 50                  | μA |

| $V_{IH}^{[4]}$ | 输入高电平电压       | OE、FS、SCL、SDA 的逻辑电平 = 1                                                                                                                 | $0.7 \times V_{DD}$ | -   | -                   | V  |

| $V_{IL}^{[4]}$ | 输入低电平电压       | OE、FS、SCL、SDA 的逻辑电平 = 0                                                                                                                 | -                   | -   | $0.3 \times V_{DD}$ | V  |

| $V_{IN}$       | 输入的电压电平       | 所有输入, 相对于 GND                                                                                                                           | -0.5                | -   | 3.8                 | V  |

| $R_P$          | 内部上拉电阻        | OE, 被配置为高电平有效                                                                                                                           | -                   | 200 | -                   | kΩ |

| $R_D$          | 内部下拉电阻        | OE, 被配置为低电平有效                                                                                                                           | -                   | 200 | -                   | kΩ |

|                |               | FS0、FS1 引脚                                                                                                                              | -                   | 100 | -                   | kΩ |

### 注释:

3. 如果使用大于最大绝对额定值中所列出的数值, 可能造成永久性损害。这只是强制的额定值, 并不表示设备使用这些值或超过建议的工作条件表中所列出的任何其他条件下都能正常运行。如果器件长期工作在最大绝对额定值的条件下, 会影响器件的可靠性或会导致永久性损坏。

4. I<sup>2</sup>C 操作仅适用于  $V_{DD} = 1.8 \text{ V}$  和  $2.5 \text{ V}$ 。

## LVDS 输出的直流规范

( $V_{DDO} = 1.8 \text{ V}, 2.5 \text{ V} \text{ 或 } 3.3 \text{ V}$ )

| 参数               | 说明                        | 条件                                                   | 最小值   | 典型值   | 最大值   | 单位 |

|------------------|---------------------------|------------------------------------------------------|-------|-------|-------|----|

| $V_{OCM}^{[5]}$  | 输出共模电压                    | $V_{DDO} = 2.5 \text{ V} \text{ 或 } 3.3 \text{ V}$   | 1.125 | 1.200 | 1.375 | V  |

| $\Delta V_{OCM}$ | 各个互补输出状态改变时 $V_{OCM}$ 的改变 | -                                                    | -     | -     | 50    | mV |

| $I_{OZ}$         | 输出漏电流                     | 输出关闭, $V_{OUT} = 0.75 \text{ V} \sim 1.75 \text{ V}$ | -20   | -     | 20    | mA |

## LVPECL 输出的直流规范

( $V_{DDO} = 2.5 \text{ V} \text{ 或 } 3.3 \text{ V}$ )

| 参数       | 说明      | 条件                                                            | 最小值               | 典型值 | 最大值               | 单位 |

|----------|---------|---------------------------------------------------------------|-------------------|-----|-------------------|----|

| $V_{OH}$ | 输出高电平电压 | 终端电阻 R-term = 50 Ω 连接到 $V_{TT}$ ( $V_{DDO} - 2.0 \text{ V}$ ) | $V_{DDO} - 1.165$ | -   | $V_{DDO} - 0.800$ | V  |

| $V_{OL}$ | 输出低电平电压 | 终端电阻 R-term = 50 Ω 连接到 $V_{TT}$ ( $V_{DDO} - 2.0 \text{ V}$ ) | $V_{DDO} - 2.0$   | -   | $V_{DDO} - 1.55$  | V  |

## 直流规范

针对 CML 输出 ( $V_{DDO} = 1.8 \text{ V}, 5 \text{ V} \text{ 或 } 3.3 \text{ V}$ )

| 参数       | 说明      | 条件                               | 最小值               | 典型值              | 最大值              | 单位 |

|----------|---------|----------------------------------|-------------------|------------------|------------------|----|

| $V_{OH}$ | 输出高电平电压 | 终端电阻 R-term = 50 Ω 连接到 $V_{DDO}$ | $V_{DDO} - 0.085$ | $V_{DDO} - 0.01$ | $V_{DDO}$        | V  |

| $V_{OL}$ | 输出低电平电压 | 终端电阻 R-term = 50 Ω 连接到 $V_{DDO}$ | $V_{DDO} - 0.6$   | $V_{DDO} - 0.4$  | $V_{DDO} - 0.32$ | V  |

## HCSL 输出的直流规范

( $V_{DDO} = 1.8 \text{ V}, 2.5 \text{ V} \text{ 或 } 3.3 \text{ V}$ )

| 参数                     | 说明                         | 条件         | 最小值  | 典型值 | 最大值  | 单位 |

|------------------------|----------------------------|------------|------|-----|------|----|

| $V_{MAX}^{[6]}$        | 输出高电平的最大电压                 | 在单端波形上进行测量 | -    | -   | 1150 | mV |

| $V_{MIN}^{[6]}$        | 输出低电平的最小电压                 | 在单端波形上进行测量 | -300 | -   | -    | mV |

| $V_{OHDIFF}$           | 差分输出高电平电压                  | 在差分波形上进行测量 | 150  | -   | -    | mV |

| $V_{OLDIFF}$           | 差分输出低电平电压                  | 在差分波形上进行测量 | -    | -   | -150 | mV |

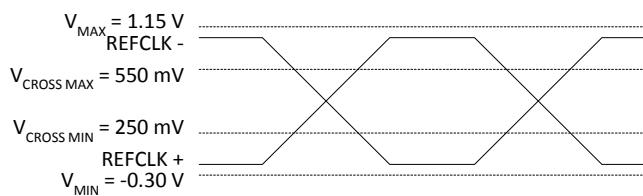

| $V_{CROSS}^{[6]}$      | 交叉点的绝对电压                   | 在单端波形上进行测量 | 250  | -   | 600  | mV |

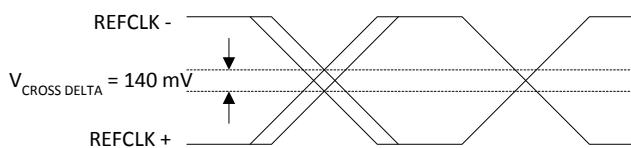

| $V_{CROSSDELTA}^{[6]}$ | $V_{CROSS}$ 在所有时钟上升沿上发生的变化 | 在单端波形上进行测量 | -    | -   | 140  | mV |

### 注释:

5. 对于  $V_{DDO} = 1.8 \text{ V}$ , 需要使用外部交流耦合, 如图 9 所述。需要生成 1.2 V 的共模电压并在外部使用。

6. 这些参数均由设计和出厂校准保证。并非 100% 经过生产测试。

## LVCMOS 输出的直流规范

| 参数       | 说明      | 条件                                  | 最小值             | 典型值 | 最大值 | 单位 |

|----------|---------|-------------------------------------|-----------------|-----|-----|----|

| $V_{OH}$ | 输出高电平电压 | 负载 = 100 mA                         | $V_{DDO} - 0.2$ | -   | -   | V  |

|          |         | 负载 = 4 mA, $V_{DD} = 3.3$ V         | $V_{DDO} - 0.3$ | -   | -   |    |

|          |         | 负载 = 4 mA, $V_{DD} = 1.8$ V 和 2.5 V | $V_{DDO} - 0.4$ | -   | -   |    |

| $V_{OL}$ | 输出低电平电压 | 负载 = 100 mA                         | -               | -   | 0.2 | V  |

|          |         | 负载 = 4 mA                           | -               | -   | 0.3 |    |

## VCXO 特定参数

| 参数 <sup>[7]</sup> | 说明              | 条件                                               | 最小值                 | 典型值                 | 最大值                 | 单位  |

|-------------------|-----------------|--------------------------------------------------|---------------------|---------------------|---------------------|-----|

| TPR               | 拉电压总范围          | VC 范围为 $0.1 \times V_{DD}$ 到 $0.9 \times V_{DD}$ | $\pm 50$            | -                   | $\pm 275$           | ppm |

| $K_{BSL}$         | 最佳拟合直线 (BSL) 线性 | 同 BSL 线的偏差                                       | -5                  | -                   | 5                   | %   |

| $K_{INC}$         | 递增线性            | $K_V$ 斜率偏差                                       | -10                 | -                   | 10                  | %   |

| $K_{BW}$          | $K_V$ 调制的带宽     | 可编程                                              | 5                   | 10                  | 20                  | kHz |

| $K_{RANGE}$       | 控制端口上所允许的电压范围   | -                                                | 0                   | -                   | $V_{DD}$            | V   |

| $V_{CTYP}$        | 额定中心电压          | VC 控制电压                                          | -                   | $0.5 \times V_{DD}$ | -                   | V   |

| $R_{VCIN}^{[8]}$  | $V_C$ 的输入电阻     | -                                                | 5                   | -                   | -                   | MΩ  |

| $V_{RANGE}$       | 输入电压范围          | 控制端口上允许的输入电压范围                                   | $0.1 \times V_{DD}$ | -                   | $0.9 \times V_{DD}$ | V   |

### 注释:

7. 这些参数均由设计和出厂校准保证。并非 100% 经过生产测试。

8.  $R_{VCIN}$  已经过 100% 测试。

## LVPECL、LVDS、CML 输出的交流电气规范

| 参数 [8]           | 说明                  | 详情 / 条件                                                           | 最小值 | 典型值 | 最大值  | 单位     |

|------------------|---------------------|-------------------------------------------------------------------|-----|-----|------|--------|

| $f_{OUT}$        | 时钟输出频率              | 符合 LVPECL、CML、LVDS 输出规范                                           | 15  | -   | 2100 | MHz    |

| $t_{TRF}$        | LVPECL 输出的上升 / 下降时间 | 交流电平为 20% 到 80%。LVPECL 输出的频率为 156.25 MHz 时进行测量。                   | -   | -   | 350  | ps     |

|                  | CML 输出的上升 / 下降时间    | 交流电平为 20% 到 80%。CML 输出在频率为 156.25 MHz 时进行测量。                      | -   | -   | 350  | ps     |

|                  | LVDS 输出的上升 / 下降时间   | 交流电平为 20% 到 80%。LVDS 输出的频率为 156.25 MHz 时进行测量。                     | -   | -   | 350  | ps     |

| $t_{ODC}$        | 输出占空比               | 差分电平为 50%，输出频率为 156.25 MHz。                                       | 45  | 50  | 55   | %      |

| $V_P$            | LVDS 输出差分峰值         | 输出频率为 15 MHz ~ 700 MHz                                            | 247 | -   | 454  | mV     |

| $V_P$            | LVDS 输出差分峰值         | 输出频率为 700 MHz ~ 2100 MHz                                          | 150 | -   | 454  | mV     |

| $\Delta V_P$     | 各互补输出状态间的 VP 值变化    | -                                                                 | -   | -   | 50   | mV     |

| $V_P$            | LVPECL 输出差分峰值       | $f_{OUT} = 15 \text{ MHz} \sim 325 \text{ MHz}$                   | 450 | -   | -    | mV     |

| $V_P$            |                     | $f_{OUT} = 325 \text{ MHz} \sim 700 \text{ MHz}$                  | 350 | -   | -    | mV     |

| $V_P$            |                     | $f_{OUT} = 700 \text{ MHz} \sim 2100 \text{ MHz}$                 | 250 | -   | -    | mV     |

| $V_P$            | CML 输出差分峰值          | $f_{OUT} = 15 \text{ MHz} \sim 700 \text{ MHz}$                   | 250 | -   | 600  | mV     |

| $V_P$            | CML 输出差分峰值          | $f_{OUT} = 700 \sim 2100 \text{ MHz}$                             | 200 | -   | 600  | mV     |

| $t_{CCJ}$        | 周期间抖动               | 峰值，在差分信号上进行测量，输出频率 = 156.25 MHz，一万个周期，晶振频率 = 100 ~ 130 MHz        | -   | -   | 50   | ps     |

| $t_{PJ}$         | 周期抖动时间              | 峰值，在差分信号上进行测量，输出频率 = 156.25 MHz，一万个周期，晶振频率 = 100 ~ 130 MHz        | -   | -   | 50   | ps     |

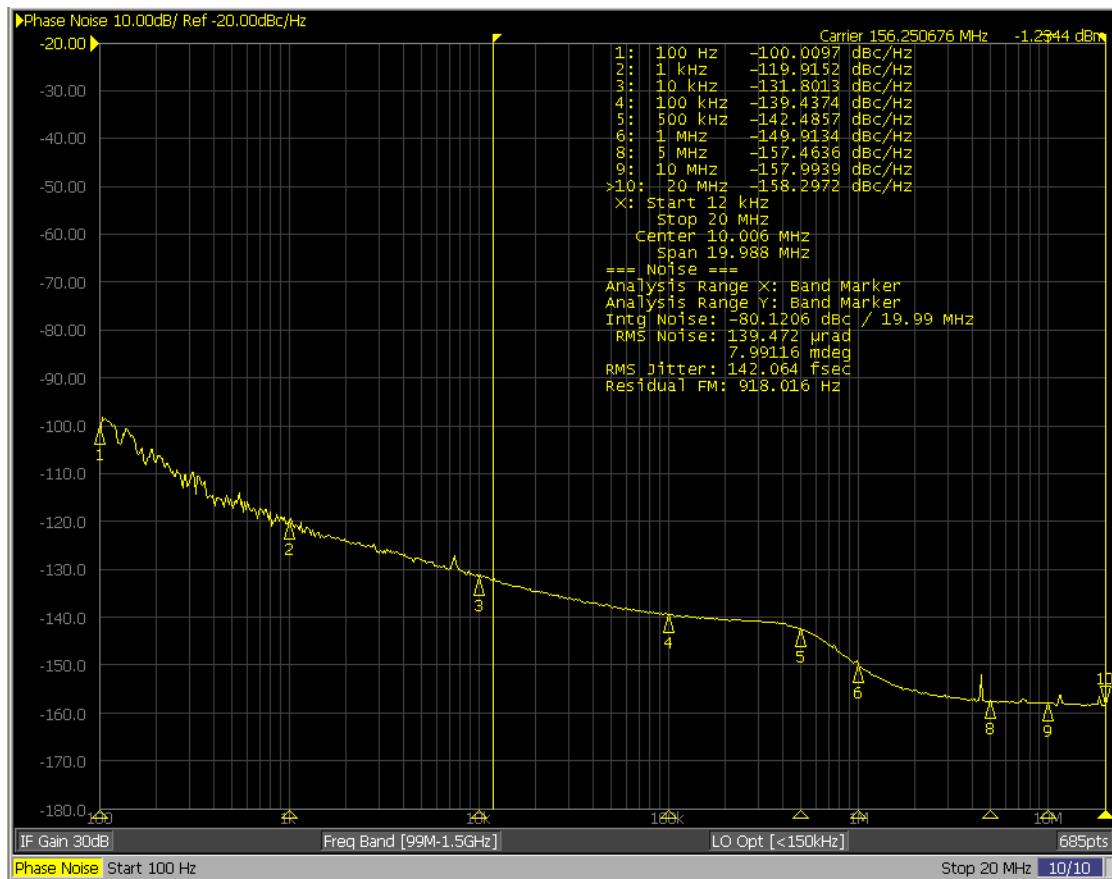

| $J_{RMS}$        | RMS 相位抖动            | $f_{OUT} = 156.25 \text{ MHz}$ ,<br>频率偏移 = 12 ~ 20 MHz, 非 VCXO 模式 | -   | 150 | 250  | fs     |

| <b>非 VCXO 模式</b> |                     |                                                                   |     |     |      |        |

| PN1k             | 相位噪声, 偏移 = 1 kHz    | 晶振的参考频率 = 100 ~ 130 MHz,<br>$f_{OUT} = 156.25 \text{ MHz}$        | -   | -   | -113 | dBc/Hz |

| PN10k            | 相位噪声, 偏移 = 10 kHz   | 晶振的参考频率 = 100 ~ 130 MHz,<br>$f_{OUT} = 156.25 \text{ MHz}$        | -   | -   | -127 | dBc/Hz |

| PN100k           | 相位噪声, 偏移 = 100 kHz  | 晶振的参考频率 = 100 ~ 130 MHz,<br>$f_{OUT} = 156.25 \text{ MHz}$        | -   | -   | -135 | dBc/Hz |

| PN1M             | 相位噪声, 偏移 = 1 MHz    | 晶振的参考频率 = 100 ~ 130 MHz,<br>$f_{OUT} = 156.25 \text{ MHz}$        | -   | -   | -144 | dBc/Hz |

| PN10M            | 相位噪声, 偏移 = 10 MHz   | 晶振的参考频率 = 100 ~ 130 MHz,<br>$f_{OUT} = 156.25 \text{ MHz}$        | -   | -   | -152 | dBc/Hz |

| PN-SPUR          | Spur                | 频率偏移 $\geq$ PLL 的更新速率                                             | -   | -   | -65  | dBc/Hz |

### 注释:

9. 这些参数均由设计和出厂校准保证，并非 100% 经过生产测试。

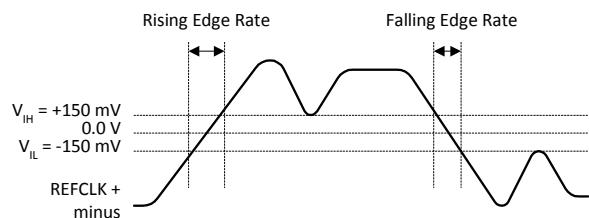

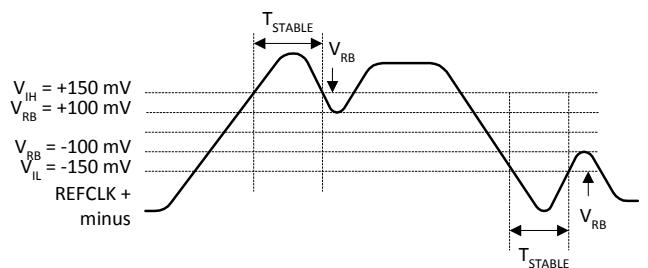

## HSCL 输出的交流电气规范

| 参数 <sup>[10]</sup>  | 说明                  | 测试条件                                     | 最小值  | 典型值 | 最大值                 | 单位       |

|---------------------|---------------------|------------------------------------------|------|-----|---------------------|----------|

| f <sub>OUT</sub>    | 输出频率                | HCSL                                     | 15   | —   | 700                 | MHz      |

| E <sub>R</sub>      | 上升沿速率               | 在差分波形上进行测量, 电压范围: -150 mV ~ +150 mV      | 0.6  | —   | 5.7 <sup>[11]</sup> | V/ns     |

| E <sub>F</sub>      | 下降沿速率               | 在差分波形上进行测量, 电压范围: -150 mV ~ +150 mV      | 0.6  | —   | 5.7 <sup>[11]</sup> | V/ns     |

| t <sub>STABLE</sub> | 电压环路 (VRB) 稳定所需要的时间 | 在差分波形上进行测量, 电压范围: -150 mV ~ +150 mV      | 500  | —   | —                   | ps       |

| R-F_MATCHING        | 上升 / 下降时间匹配         | 在单端波形上进行测量, 上升沿速率和下降沿速率相互匹配, 频率为 100 MHz | -100 | —   | 100                 | ps       |

| t <sub>DC</sub>     | 输出占空比               | 在差分波形上进行测量, f <sub>OUT</sub> = 100 MHz   | 45   | —   | 55                  | %        |

| t <sub>CCJ</sub>    | 周期间抖动               | 在差分波形上进行测量, 频率为 100 MHz                  | —    | —   | 50                  | ps       |

| J <sub>RMSPCI</sub> | 随机抖动, 符合PCIE规范版本3.0 | 频率为 100 ~ 130 MHz 的晶振                    | —    | —   | 1                   | ps (RMS) |

## LVCMOS 输出的交流电气规范

(Cload = 10 pF (Fout < 100 MHz 时), 7.5 pF (Fout < 150 MHz 时), 5 pF (Fout > 150 MHz 时))

| 参数 <sup>[10]</sup>  | 说明        | 测试条件                                                                            | 最小值 | 典型值 | 最大值 | 单位  |

|---------------------|-----------|---------------------------------------------------------------------------------|-----|-----|-----|-----|

| f <sub>OUT</sub>    | 输出频率      |                                                                                 | 15  | —   | 250 | MHz |

| t <sub>DC</sub>     | 输出占空比     | 测量电压 = V <sub>DDO</sub> /2, 输出与负载连接, f <sub>OUT</sub> < 100 MHz                 | 45  | —   | 55  | %   |

|                     |           | 测量电压 = V <sub>DDO</sub> /2, 输出与负载连接, f <sub>OUT</sub> > 100 MHz                 | 40  | —   | 60  | %   |

| t <sub>RFCMOS</sub> | 上升 / 下降时间 | V <sub>DDO</sub> = 1.8 V, 从输出电平的20%到80%                                         | —   | —   | 2   | ns  |

|                     |           | V <sub>DDO</sub> = 2.5 V, 从输出电平的20%到80%                                         | —   | —   | 1.5 | ns  |

|                     |           | V <sub>DDO</sub> = 3.3 V, 从输出电平的20%到80%                                         | —   | —   | 1.2 | ns  |

| t <sub>CCJ</sub>    | 周期间抖动     | 峰值, 在一万个周期内, 且电压 = V <sub>DDO</sub> /2 和 f <sub>OUT</sub> = 156.25 MHz 的条件下进行测量 | —   | —   | 50  | ps  |

| t <sub>PJ</sub>     | 周期抖动时间    | 峰值, 在一万个周期内, 且电压 = V <sub>DDO</sub> /2 和 f <sub>OUT</sub> = 156.25 MHz 的条件下进行测量 | —   | —   | 100 | ps  |

### 注释:

10. 这些参数均由设计和出厂校准保证。并非 100% 经过生产测试。

11. 边沿速率大于 4 V/ns, 以符合抖动性能的要求。

## HFF 晶振规范

| 参数 <sup>[12]</sup> | 说明                                    | 测试条件                                                                                       | 最小值 | 典型值 | 最大值 | 单位  |

|--------------------|---------------------------------------|--------------------------------------------------------------------------------------------|-----|-----|-----|-----|

| f <sub>XTAL</sub>  | 晶振的频率范围                               | —                                                                                          | 100 | —   | 130 | MHz |

| C <sub>0</sub>     | 晶振的并联电容                               | —                                                                                          | —   | —   | 2   | pF  |

| C <sub>L</sub>     | 晶振的负载电容                               | —                                                                                          | —   | 5   | —   | pF  |

| ESR                | 晶振的等效串联电阻<br>R <sub>m</sub> = 晶振的动态电阻 | ESR = R <sub>m</sub> (1 + C <sub>0</sub> /C <sub>L</sub> ) ^ 2<br>R <sub>m</sub> = 晶振的动态电阻 | —   | 20  | —   | Ω   |

| DL                 | 驱动电平                                  | —                                                                                          | —   | —   | 200 | mW  |

## OT3 晶振规范

| 参数 <sup>[12]</sup> | 说明                                    | 测试条件                                                                                       | 最小值 | 典型值 | 最大值 | 单位  |

|--------------------|---------------------------------------|--------------------------------------------------------------------------------------------|-----|-----|-----|-----|

| f <sub>XTAL</sub>  | 晶振的频率范围                               | —                                                                                          | 100 | —   | 130 | MHz |

| C <sub>0</sub>     | 晶振的并联电容                               | —                                                                                          | —   | —   | 2   | pF  |

| C <sub>L</sub>     | 晶振的负载电容                               | —                                                                                          | —   | 5   | —   | pF  |

| ESR                | 晶振的等效串联电阻<br>R <sub>m</sub> = 晶振的动态电阻 | ESR = R <sub>m</sub> (1 + C <sub>0</sub> /C <sub>L</sub> ) ^ 2<br>R <sub>m</sub> = 晶振的动态电阻 | —   | 60  | 90  | Ω   |

| DL                 | 驱动电平                                  | —                                                                                          | —   | —   | 200 | mW  |

## LFF 晶振规范

| 参数 <sup>[12]</sup> | 说明                                    | 测试条件                                                                                       | 最小值 | 典型值 | 最大值 | 单位  |

|--------------------|---------------------------------------|--------------------------------------------------------------------------------------------|-----|-----|-----|-----|

| f <sub>XTAL</sub>  | 晶振的频率范围                               | —                                                                                          | 50  | —   | 60  | MHz |

| C <sub>0</sub>     | 晶振的并联电容                               | —                                                                                          | —   | —   | 2   | pF  |

| C <sub>L</sub>     | 晶振的负载电容                               | —                                                                                          | —   | —   | 8   | pF  |

| ESR                | 晶振的等效串联电阻<br>R <sub>m</sub> = 晶振的动态电阻 | ESR = R <sub>m</sub> (1 + C <sub>0</sub> /C <sub>L</sub> ) ^ 2<br>R <sub>m</sub> = 晶振的动态电阻 | —   | —   | 90  | Ω   |

| DL                 | 驱动电平                                  | —                                                                                          | —   | —   | 200 | mW  |

### 注释:

12. 这些参数均由设计和出厂校准保证，并非 100% 经过生产测试。

## LF 低频率参考

(TCXO 参考输入)

| 参数 <sup>[13]</sup> | 说明           | 测试条件           | 最小值 | 典型值 | 最大值  | 单位     |

|--------------------|--------------|----------------|-----|-----|------|--------|

| $f_{IN}$           | 输入频率         | -              | 50  | -   | 60   | MHz    |

| $t_{DC}$           | 输入占空比        | 在输入的 1/2 周期下测量 | 40  | -   | 60   | %      |

| $V_{PP}$           | 输入摆幅电压峰 - 峰值 | 交流耦合输入         | 0.8 | -   | 1.2  | V      |

| $V_{IL}$           | 输入低电平电压      | 直流耦合输入         | -   | -   | 0.2  | V      |

| $V_{IH}^{[14]}$    | 输入高电平电压      | 直流耦合输入         | 0.8 | -   | 1.2  | V      |

| $t_R$              | 输入上升时间       | 输入电平的 20-80%   | -   | -   | 1.5  | ns     |

| $t_F$              | 输入下降时间       | 输入电压的 20-80%   | -   | -   | 1.5  | ns     |

| $PN_{10K}$         | 输入相位噪声       | 10 kHz 偏移      | -   | -   | -151 | dBc/Hz |

| $PN_{100K}$        | 输入相位噪声       | 100 kHz 偏移     | -   | -   | -155 | dBc/Hz |

| $PN_{1M}$          | 输入相位噪声       | 1 MHz 偏移       | -   | -   | -156 | dBc/Hz |

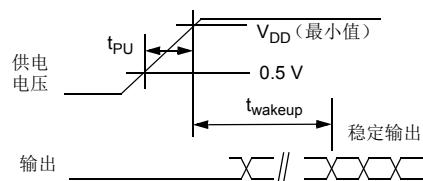

## 时序参数

| 参数 <sup>[13]</sup>  | 说明                                                                                                                                   | 最小值  | 最大值  | 单位 |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------|------|------|----|

| $t_{PU}$            | 电源电压的上升 (从 0.5 V 到 $V_{DD(min)}$ ) 时间。                                                                                               | 0.01 | 3000 | ms |

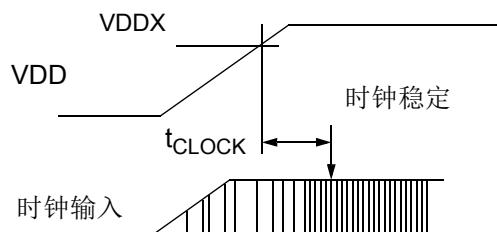

| $t_{WAKEUP}^{[14]}$ | 从供电电压为最低指定值到时钟输出频率的精度小于 $\pm 0.1 \text{ ppm}$ 的可编程时间 (达到 $V_{DDX}$ 电压电平后, 时钟脉冲会在 2.2 ms (最长时间) 内得到稳定, 请参考 <a href="#">输入时钟的测量点</a> ) | -    | 10   | ms |

|                     | 从供电电压为最低指定值到时钟输出频率的精度小于 $\pm 0.1 \text{ ppm}$ 的可编程时间 (达到 $V_{DDX}$ 电压电平后, 时钟脉冲会在 5.8 ms (最长时间) 内得到稳定, 请参考 <a href="#">输入时钟的测量点</a> ) | -    | 15   |    |

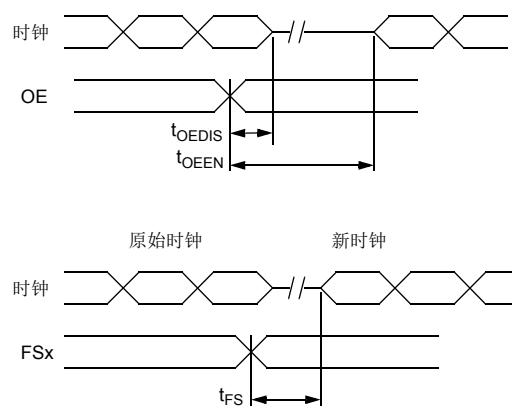

| $t_{OEEN}$          | 从 OE 信号边沿发生变化到输出被使能的时间                                                                                                               | -    | 2.5  | ms |

| $t_{OEDIS}$         | 从 OE 信号边沿发生变化到输出禁用的时间                                                                                                                | -    | 10   | ms |

| $t_{FS}$            | 从 FS 发生变化到生成新频率的时间                                                                                                                   | -    | 2.5  | ms |

| $t_{FSMALL}$        | 频率发生变化的时间 (针对小触发, 即 $\leq \pm 500 \text{ ppm}$ )                                                                                     | -    | 400  | ms |

| $t_{FLARGE}$        | 频率发生变化的时间 (针对大触发, 即 $> \pm 500 \text{ ppm}$ )                                                                                        | -    | 2.5  | ms |

| $t_{CLOCK}$         | 从 $V_{DD}$ 上升到时钟稳定的延迟 (请参考 <a href="#">图 5</a> ), 普通配置                                                                               | -    | 2.2  | ms |

|                     | 从 $V_{DD}$ 上升到时钟稳定的延迟 (请参考 <a href="#">图 5</a> ), 编程后的延迟                                                                             | -    | 5.8  |    |

## 输入时钟的测量点

| 参数                  | 说明               | 测试条件        | 最小值 | 典型值 | 最大值 | 单位 |

|---------------------|------------------|-------------|-----|-----|-----|----|

| $V_{DDX}^{[13、15]}$ | $t_{CLOCK}$ 的测量点 | 供电电压为 1.8 V | 1.4 | -   | -   | V  |

|                     |                  | 供电电压为 2.5 V | 1.8 | -   | -   |    |

|                     |                  | 供电电压为 3.3 V | 2.3 | -   | -   |    |

### 注释:

13. 这些参数均由设计和出厂校准保证。并非 100% 经过生产测试。

14.  $V_{DD} = 0 \text{ V}$  时,  $V_{IH}$  应小于 0.5 V。

15. 适用于 TCXO/ 外部时钟输入。

## 相位抖动特性

(集成带宽为 12 kHz ~ 20 MHz)

| 参数 [16]                                                   | 说明     | 条件                              | 最小值 | 典型值 | 最大值 | 单位 |

|-----------------------------------------------------------|--------|---------------------------------|-----|-----|-----|----|

| 不支持 VCXO 功能                                               |        |                                 |     |     |     |    |

| J <sub>RMS</sub>                                          | RMS 抖动 | f <sub>OUT</sub> = 644.53 MHz   | -   | 110 | -   | fs |

| J <sub>RMS</sub>                                          | RMS 抖动 | f <sub>OUT</sub> = 622.08 MHz   | -   | 120 | -   | fs |

| J <sub>RMS</sub>                                          | RMS 抖动 | f <sub>OUT</sub> = 156.25 MHz   | -   | 145 | -   | fs |

| J <sub>RMS</sub>                                          | RMS 抖动 | f <sub>OUT</sub> = 2.105 GHz    | -   | 145 | -   | fs |

| 调制带宽 = 10 kHz, VDD = 3.3 V, f <sub>OUT</sub> = 622.08 MHz |        |                                 |     |     |     |    |

| J <sub>RMS</sub>                                          | RMS 抖动 | TPR = 50 ppm, Kv = 37.9 ppm/V   | -   | 151 | -   | fs |

| J <sub>RMS</sub>                                          | RMS 抖动 | TPR = 155 ppm, Kv = 117.4 ppm/V | -   | 158 | -   | fs |

| J <sub>RMS</sub>                                          | RMS 抖动 | TPR = 275 ppm, Kv = 208.3 ppm/V | -   | 170 | -   | fs |

| 调制带宽 = 10 kHz, VDD = 2.5 V, f <sub>OUT</sub> = 622.08 MHz |        |                                 |     |     |     |    |

| J <sub>RMS</sub>                                          | RMS 抖动 | TPR = 50 ppm, Kv = 50 ppm/V     | -   | 152 | -   | fs |

| J <sub>RMS</sub>                                          | RMS 抖动 | TPR = 155 ppm, Kv = 155 ppm/V   | -   | 160 | -   | fs |

| J <sub>RMS</sub>                                          | RMS 抖动 | TPR = 275 ppm, Kv = 275 ppm/V   | -   | 175 | -   | fs |

| 调制带宽 = 10 kHz, VDD = 1.8 V, f <sub>OUT</sub> = 622.08 MHz |        |                                 |     |     |     |    |

| J <sub>RMS</sub>                                          | RMS 抖动 | TPR = 50 ppm, Kv = 69.4 ppm/V   | -   | 153 | -   | fs |

| J <sub>RMS</sub>                                          | RMS 抖动 | TPR = 155 ppm, Kv = 215.3 ppm/V | -   | 166 | -   | fs |

| J <sub>RMS</sub>                                          | RMS 抖动 | TPR = 275 ppm, Kv = 381.9 ppm/V | -   | 190 | -   | fs |

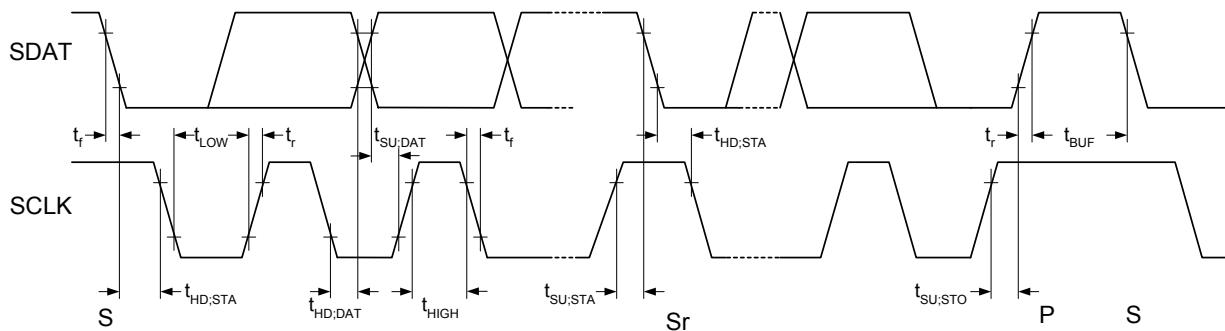

## I<sup>2</sup>C 总线时序规范

| 参数 [16、17]          | 说明                | 最小值 | 典型值 | 最大值 | 单位  |

|---------------------|-------------------|-----|-----|-----|-----|

| f <sub>SCL</sub>    | SCL 时钟频率          | -   | -   | 400 | kHz |

| t <sub>HD:STA</sub> | 启动条件的保持时间         | 0.6 | -   | -   | μs  |

| t <sub>LOW</sub>    | SCL 为低电平的时间       | 1.3 | -   | -   | μs  |

| t <sub>HIGH</sub>   | SCL 为高电平的时间       | 0.6 | -   | -   | μs  |

| t <sub>SU:STA</sub> | 重复启动条件的建立时间       | 0.6 | -   | -   | μs  |

| t <sub>HD:DAT</sub> | 数据保留时间            | 0   | -   | -   | μs  |

| t <sub>SU:DAT</sub> | 数据建立时间            | 100 | -   | -   | ns  |

| t <sub>R</sub>      | 上升时间              | -   | -   | 300 | ns  |

| t <sub>F</sub>      | 下降时间              | -   | -   | 300 | ns  |

| t <sub>SU:STO</sub> | STOP (停止) 条件的建立时间 | 0.6 | -   | -   | μs  |

| t <sub>BUF</sub>    | 停止和启动条件之间的总线空闲时间  | 1.3 | -   | -   | μs  |

### 注释:

16. 这些参数均由设计和出厂校准保证。并非 100% 经过生产测试。

17. I<sup>2</sup>C 操作仅适用于 V<sub>DD</sub> = 1.8 V 和 2.5 V。

## 电压和时序定义

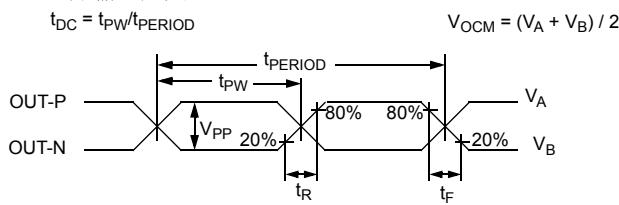

图 4. 差分输出定义

图 5. 输入时钟的稳定时间

图 6. 输出使能 / 禁用 / 频率选择时序

图 7. 电压上升和 PLL 锁定时间

### 注释:

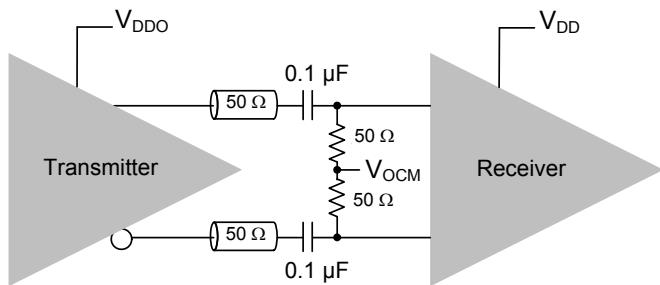

18. 该图中所示的终端电路是针对于 LVDS 输出标准 ( $V_{DD} = 1.8 \text{ V}$ )。需要使用交流耦合 (100 nF 的串联电容)。在目标电路上需要安装 50 Ω 的终端电阻以及偏置电压 ( $V_{OCM}$ )，如该图中所示。

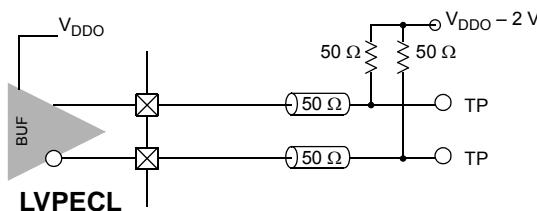

图 8. 输出终端电路

图 9. 1.8 V LVDS 终端 [18]

图 10. HCSL: 绝对交叉点的单端测量点

图 11. HCSL: Delta 交叉点的单端测量点

图 12. HCSL: 上升和下降时间的差分测量点

图 13. HCSL: 环路的差分测量点

图 14. I<sup>2</sup>C 总线时序规范

## 相位噪声图

图 15. 频率为 156.25 MHz (偏移 = 12 kHz ~ 20 MHz) 时的典型相位噪声

图 16. 频率为 622.08 MHz (12 kHz ~ 20 MHz) 时的典型相位噪声

图 17. 频率为 644.53 MHz (12 kHz ~ 20 MHz) 时的典型相位噪声

## 订购信息

| 订购代码            | 配置    | 封装说明        | 产品流程                   |

|-----------------|-------|-------------|------------------------|

| CY29430FLQXIT   | 现场可编程 | 16-QFN 盘带封装 | 工业温度范围: -40°C 到 +105°C |

| CY29430LQXIxxxT | 工厂配置  | 16-QFN 盘带封装 | 工业温度范围: -40°C 到 +105°C |

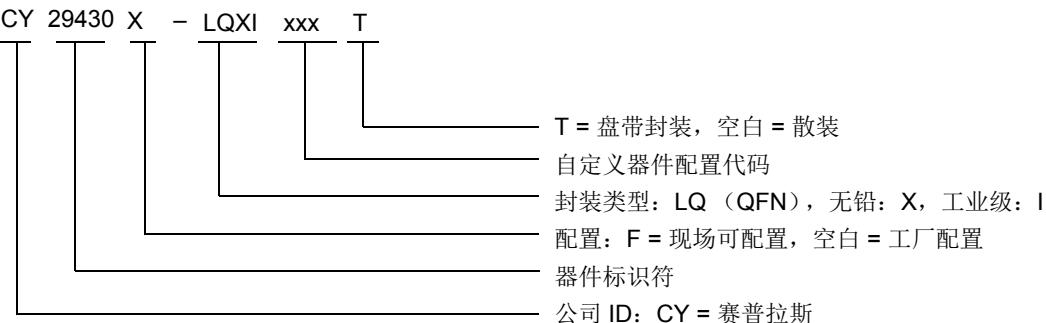

## 订购代码定义

## 封装图

图 18. 16-QFN ( $3 \times 3 \times 0.6$  mm) LQ16A 1.7 × 1.7 E-Pad (Sawn) 封装外形, 001-87187

### NOTES

1.  HATCH AREA IS SOLDERABLE EXPOSED PAD

2. REFERENCE JEDEC # MO-248

3. ALL DIMENSIONS ARE IN MILLIMETERS

4. PACKAGE WEIGHT: See Cypress Package Material Declaration Datasheet (PMDD) posted on the Cypress web

001-87187 \*A

## 缩略语

| 缩略语              | 说明                     |

|------------------|------------------------|

| AC               | 交流                     |

| ADC              | 模数转换器                  |

| BSL              | 最佳拟合直线                 |

| CML              | 电流模式逻辑                 |

| DC               | 直流                     |

| ESD              | 静电放电                   |

| FS               | 频率选择                   |

| HCSL             | 高速电流驱动逻辑               |

| I <sup>2</sup> C | 内部集成电路                 |

| JEDEC            | 电子器件工程联合委员会            |

| LDO              | 低压差（电压调节器）             |

| LVCMOS           | 低压互补金属氧化物半导体           |

| LVDS             | 低压差分信号                 |

| LVPECL           | 低电压正射极耦合逻辑             |

| NV               | 非易失性                   |

| OE               | 输出使能                   |

| PLL              | 锁相环                    |

| POR              | 上电复位                   |

| PSoC®            | 可编程片上系统                |

| QFN              | 四方扁平无引脚                |

| RMS              | 均方根                    |

| SCL              | 串行 I <sup>2</sup> C 时钟 |

| SDA              | 串行 I <sup>2</sup> C 数据 |

| VRB              | 电压环路                   |

| VCXO             | 压控振荡器                  |

| XTAL             | 晶振                     |

## 文档规范

### 测量单位

| 符号  | 测量单位 |

|-----|------|

| °C  | 摄氏度  |

| fs  | 飞秒   |

| GHz | 千兆赫  |

| kΩ  | 千欧   |

| kHz | 千赫兹  |

| MHz | 兆赫   |

| MΩ  | 兆欧   |

| μA  | 微安   |

| μm  | 微米   |

| μs  | 微秒   |

| μW  | 微瓦   |

| mA  | 毫安   |

| mm  | 毫米   |

| mΩ  | 毫欧   |

| ms  | 毫秒   |

| mV  | 毫伏   |

| nH  | 纳亨   |

| ns  | 纳秒   |

| Ω   | 欧姆   |

| ppm | 百万分率 |

| ppb | 十亿分率 |

| %   | 百分比  |

| pF  | 皮法   |

| ps  | 皮秒   |

| V   | 伏特   |

## 文档修订记录页

文档标题: CY29430 — 高性能时钟合成器

文档编号: 002-11681

| 版本 | ECN 编号  | 提交日期       | 变更者  | 变更说明                                                 |

|----|---------|------------|------|------------------------------------------------------|

| ** | 5205127 | 04/05/2016 | YLIU | 本文档版本号为 Rev**, 译自英文版 002-11000 Rev**。                |

| *A | 5223871 | 04/15/2016 | GPL  | 本文档版本号为 Rev*A, 译自英文版 002-11000 Rev*A。                |

| *B | 5285920 | 05/26/2016 | PSR  | 更新了 <a href="#">第 8 页上的直流规范</a> ：<br>删除了 1.8 V 相关信息。 |

| *C | 5615564 | 02/07/2017 | YLIU | 本文档版本号为 Rev*C, 译自英文版 002-11000 Rev*D。                |

## 销售、解决方案和法律信息

### 全球销售和设计支持

赛普拉斯公司拥有一个由办事处、解决方案中心、厂商代表和经销商组成的全球性网络。要想找到离您最近的办事处，请访问[赛普拉斯所在地](#)。

### 产品

ARM® Cortex® 微控制器

汽车级产品

时钟与缓冲区

接口

物联网

照明与电源控制

存储器

PSoC

触摸感应

USB 控制器

无线 / 射频

[cypress.com/arm](http://cypress.com/arm)

[cypress.com/automotive](http://cypress.com/automotive)

[cypress.com/clocks](http://cypress.com/clocks)

[cypress.com/interface](http://cypress.com/interface)

[cypress.com/iot](http://cypress.com/iot)

[cypress.com/powerpsoc](http://cypress.com/powerpsoc)

[cypress.com/memory](http://cypress.com/memory)

[cypress.com/psoc](http://cypress.com/psoc)

[cypress.com/touch](http://cypress.com/touch)

[cypress.com/usb](http://cypress.com/usb)

[cypress.com/wireless](http://cypress.com/wireless)

### PSoC® 解决方案

[PSoC 1](#) | [PSoC 3](#) | [PSoC 4](#) | [PSoC 5LP](#)

### 赛普拉斯开发者社区

[论坛](#) | [项目](#) | [视频](#) | [博客](#) | [培训](#) | [组件](#)

### 技术支持

[cypress.com/support](http://cypress.com/support)

© 赛普拉斯半导体公司，2016-2017 年。本文件是赛普拉斯半导体公司及其子公司，包括 Spansion LLC（“赛普拉斯”）的财产。本文件，包括其包含或引用的任何软件或固件（“软件”），根据全球范围内的知识产权法律以及美国与其他国家签署条约由赛普拉斯所有。除非在本款中另有明确规定，赛普拉斯保留在该等法律和条约下的所有权利，且未就其专利、版权、商标或其他知识产权授予任何许可。如果软件并不附随有一份许可协议且贵方未以其他方式与赛普拉斯签署关于使用软件的书面协议，赛普拉斯特此授予贵方属人性质的、非独家且不可转让的如下许可（无再许可权）（1）在赛普拉斯特软件著作权项下的下列许可权（一）对以源代码形式提供的软件，仅出于在赛普拉斯硬件产品上使用之目的且仅在贵方集团内部修改和复制软件；和（二）仅限于在有关赛普拉斯硬件产品上使用之目的将软件以二进制代码形式的向外部最终用户提供（无论直接提供或通过经销商和分销商间接提供），和（2）在被软件（由赛普拉斯公司提供，且未经修改）侵犯的赛普拉斯专利的权利主张项下，仅出于在赛普拉斯硬件产品上使用之目的制造、使用、提供和进口软件的许可。禁止对软件的任何其他使用、复制、修改、翻译或汇编。

在适用法律允许的限度内，赛普拉斯未对本文件或任何软件作出任何明示或暗示的担保，包括但不限于关于适销性和特定用途的默示保证。赛普拉斯保留更改本文件的权利，届时将不另行通知。在适用法律允许的限度内，赛普拉斯不对因应用或使用本文件所述任何产品或电路引起的任何后果负责。本文件，包括任何样本设计信息或程序代码信息，仅为供参考之目的提供。文件使用人应负责正确设计、计划和测试信息应用和由此生产的任何产品的功能和安全性。赛普拉斯产品不应被设计为、设定为或授权用作武器操作、武器系统、核设施、生命支持设备或系统、其他医疗设备或系统（包括急救设备和手术植入物）、污染控制或有害物质管理系统中的关键部件，或产品植入之设备或系统故障可能导致人身伤害、死亡或财产损失其他用途（“非预期用途”）。关键部件指，若该部件发生故障，经合理预期会导致设备或系统故障或会影响设备或系统安全性和有效性的部件。针对由赛普拉斯产品非预期用途产生或相关的任何主张、费用、损失和其他责任，赛普拉斯不承担全部或部分责任且贵方不应追究赛普拉斯之责任。贵方应赔偿赛普拉斯因赛普拉斯产品任何非预期用途产生或相关的所有索赔、费用、损失和其他责任，包括因人身伤害或死亡引起的主张，并使其免受损失。

赛普拉斯、赛普拉斯徽标、Spansion、Spansion 徽标，及上述项目的组合，WICED，及 PSoC、CapSense、EZ-USB、F-RAM 和 Traveo 应视为赛普拉斯在美国和其他国家的商标或注册商标。请访问 [cypress.com](http://cypress.com) 获取赛普拉斯商标的完整列表。其他名称和品牌可能由其各自所有者主张为该方财产。