## サイプレスはインフィニオンテクノロジーズになりました

この表紙に続く文書には「サイプレス」と表記されていますが、これは同社が最初にこの製品を開発したからです。新規および既存のお客様いずれに対しても、引き続きインフィニオンがラインアップの一部として当該製品をご提供いたします。

### 文書の内容の継続性

下記製品がインフィニオンの製品ラインアップの一部として提供されたとしても、それを理由としてこの文書に変更が加わることはありません。今後も適宜改訂は行いますが、変更があった場合は文書の履歴ページでお知らせします。

### 注文時の部品番号の継続性

インフィニオンは既存の部品番号を引き続きサポートします。ご注文の際は、データシート記載の注文部品番号をこれまで通りご利用下さい。

## 高性能プログラマブル発振器

### 特長

- 内蔵水晶発振器用の低ノイズ PLL

- 差動クロック出力 : I<sup>2</sup>C を介して再設定可能

- 15MHz ~ 2.1GHz 出力周波数をサポート

- 完全に集積された VCO のフラクショナル N PLL

- 統合された周波数固定水晶で動作可能

- LVPECL、LVDS、HCSL および CML の出力規格が利用可能

- 3.3V、2.5V および 1.8V 電源に対応

- 150MHz より大きい出力用の 150fs の標準的内蔵ジッタ性能 (周波数オフセット 12kHz ~ 20MHz)

- VCXO 機能、調整可能な総周波数可変範囲が ±50ppm ~ ±275ppm

- 8 ピン LCC パッケージ 7.0 × 5.0 (CY2941x) または 5.0 × 3.2 (CY2942x) mm

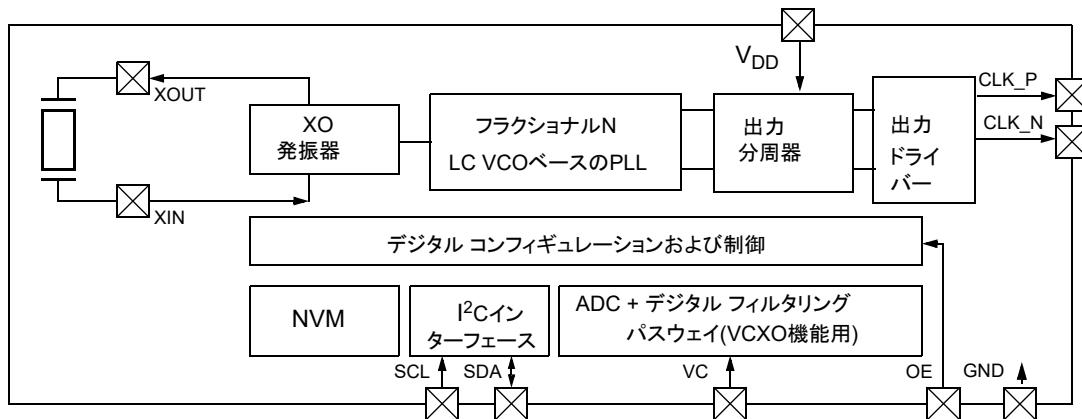

### 機能説明

CY2941x / CY2942x は様々な出力周波数オプションを持つプログラマブル PLL ベースの水晶発振器ソリューションです。現場でまたは工場出荷時に、15MHz ~ 2.1GHz の範囲内のどの出力周波数にもプログラム可能です。I<sup>2</sup>C インターフェースを使用して他の周波数のオプションを設定することができます。高度な設計技術を使用して、出力周波数の全体範囲にわたって優れたジッタ性能を提供し、周囲温度が -40°C ~ 105°C で 1.8V ~ 3.3V の電源電圧で確実に動作します。このことにより、このデバイスシリーズは、通信アプリケーション（例えば、OTN、SONET / SDH、xDSL、GbE、ネットワーキング、無線インフラストラクチャ）、テストと計測アプリケーション、および高速データコンバータに最適です。その上、VCXO 機能により、電圧で制御されるクロックソースを必要とするアプリケーション、および同期タイミングアプリケーション向けの個別のクロッキングソリューションに、CY2941x / CY2942x シリーズを使用することが可能になります。

CY2941x/CY2942x デバイス構成は、ClockWizard 2.1 を使用して作成できます。プログラミングサポートについては、[Cypress Technical Support](#) にお問い合わせくださいか、[clocks@cypress.com](mailto:clocks@cypress.com) にご連絡ください。

関連するすべての文書については、[ここ](#)をクリックしてください。

### 論理ブロック図

## 目次

|                           |    |

|---------------------------|----|

| ピン配置図                     | 3  |

| ピンの説明                     | 3  |

| 機能概要                      | 4  |

| プログラム可能な機能                | 4  |

| アーキテクチャ概要                 | 4  |

| 内部の状態遷移図                  | 4  |

| 小さな／大きな変更                 | 5  |

| プログラミング サポート              | 5  |

| プログラム可能なOE極性              | 5  |

| プログラム可能なVCXO              | 5  |

| 電源供給シーケンス                 | 5  |

| I <sup>2</sup> Cインターフェース  | 5  |

| メモリ マップ                   | 5  |

| 絶対最大定格                    | 6  |

| 推奨動作範囲                    | 6  |

| DC電気的仕様                   | 6  |

| LVDS出力のDC仕様               | 7  |

| LVPECL出力のDC仕様             | 7  |

| CML出力のDC仕様                | 7  |

| HCSL出力のDC仕様               | 7  |

| VCXO固有パラメーター              | 8  |

| LVPECL、LVDS、CML出力のAC電気的仕様 | 9  |

| HCSL出力のAC電気的仕様            | 10 |

| タイミング パラメーター              | 10 |

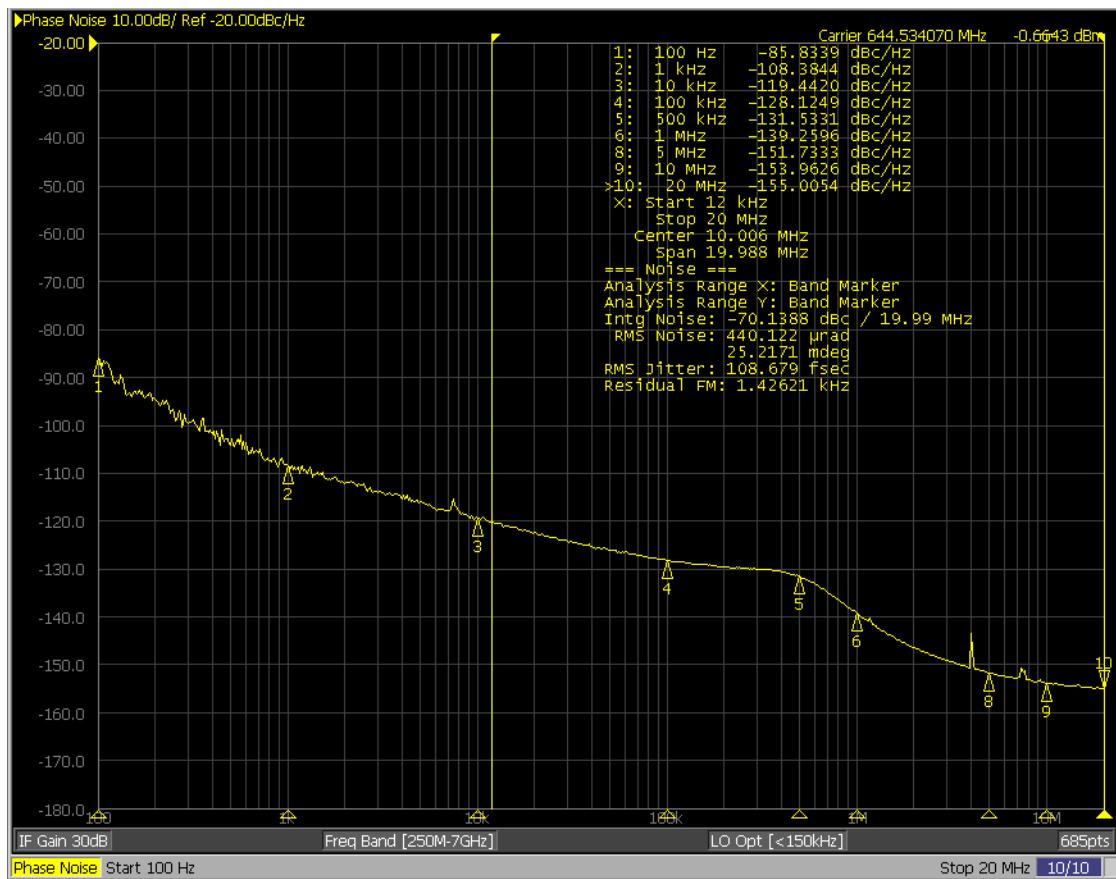

| 位相ジッタの特性                  | 11 |

| I <sup>2</sup> Cバスタイミング仕様 | 11 |

| 周波数の安定度                   | 12 |

| 電圧とタイミングの定義               | 13 |

| 位相ノイズのプロット                | 15 |

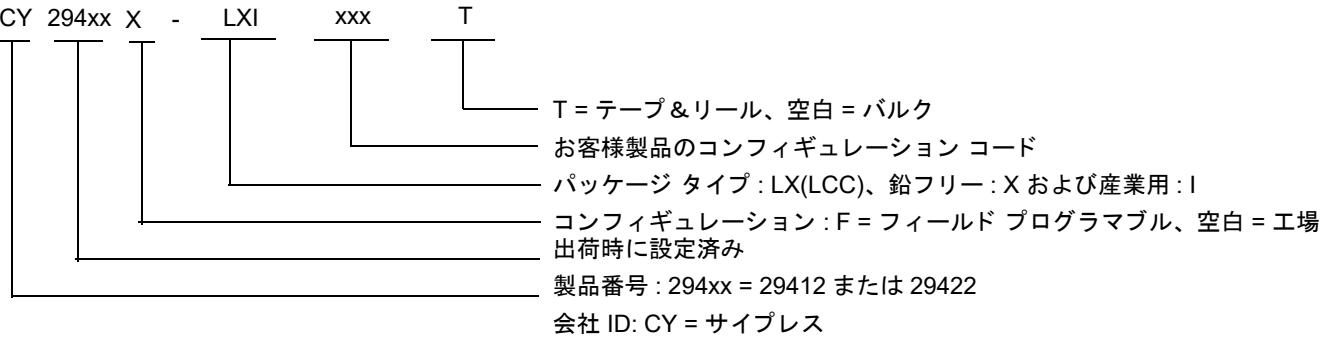

| 注文情報                      | 18 |

| 注文コードの定義                  | 18 |

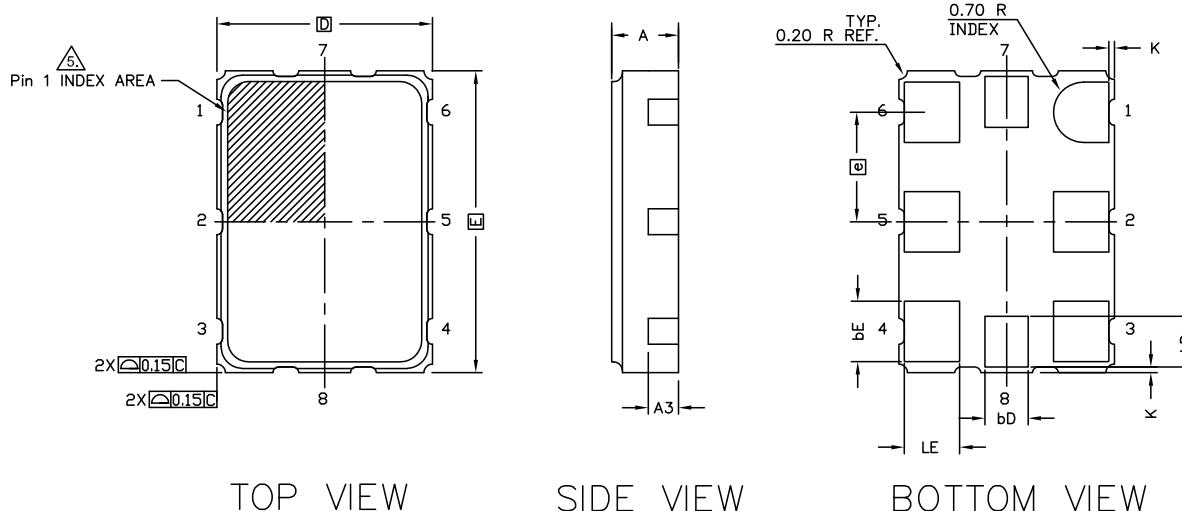

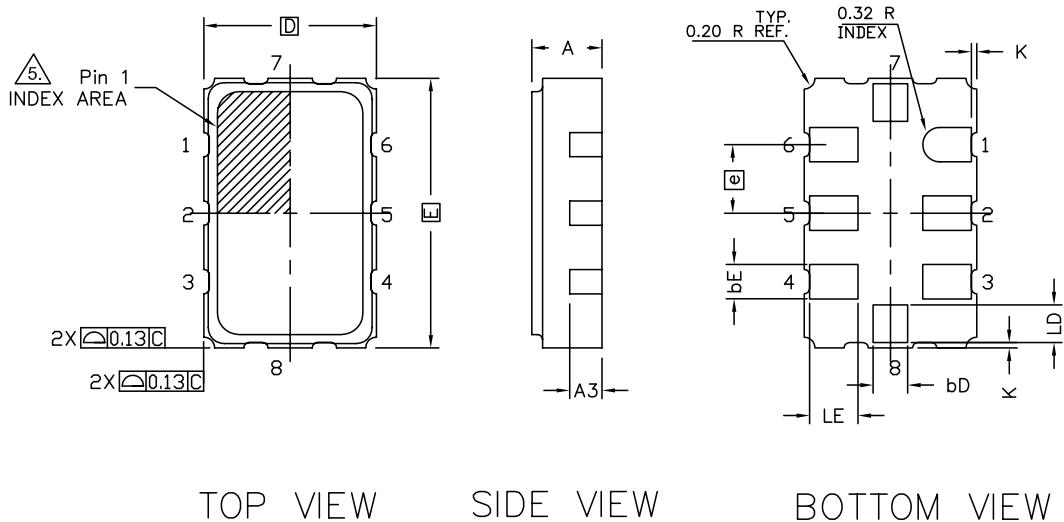

| パッケージ図                    | 19 |

| 略語                        | 21 |

| 本書の表記法                    | 21 |

| 測定単位                      | 21 |

| 改訂履歴                      | 22 |

| セールス、ソリューションおよび法律情報       | 23 |

| ワールドワイド販売と設計サポート          | 23 |

| 製品                        | 23 |

| PSoC®ソリューション              | 23 |

| サイプレス開発者コミュニティ            | 23 |

| テクニカルサポート                 | 23 |

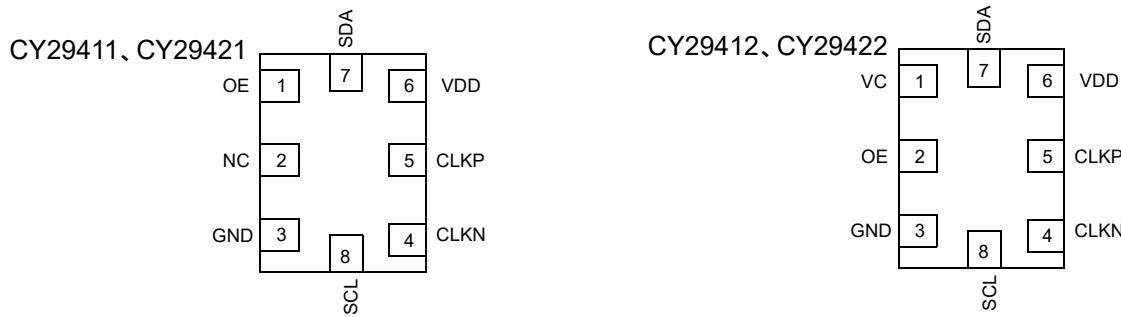

## ピン配置図

## ピンの説明

| ピン名                                 | ピン番号 | 説明                          |

|-------------------------------------|------|-----------------------------|

| <b>CY29411 / CY29421 (8 ピン LCC)</b> |      |                             |

| OE                                  | 1    | 出力イネーブル入力                   |

| NC                                  | 2    | 未接続                         |

| GND                                 | 3    | 電源グランド                      |

| CLKN                                | 4    | 相補クロック出力                    |

| CLKP                                | 5    | 真クロック出力                     |

| V <sub>DD</sub>                     | 6    | 電源                          |

| SDA                                 | 7    | シリアルデータ入力／出力                |

| SCL                                 | 8    | I <sup>2</sup> C用シリアルクロック入力 |

| <b>CY29411 / CY29421 (8 ピン LCC)</b> |      |                             |

| VC <sup>[1]</sup>                   | 1    | VCXO用入力電圧                   |

| OE                                  | 2    | 出力イネーブル入力                   |

| GND                                 | 3    | 電源グランド                      |

| CLKN                                | 4    | 相補クロック出力                    |

| CLKP                                | 5    | 真クロック出力                     |

| V <sub>DD</sub>                     | 6    | 電源                          |

| SDA                                 | 7    | シリアルデータ入力／出力                |

| SCL                                 | 8    | I <sup>2</sup> C用シリアルクロック入力 |

### 注：

1. VCが未使用の場合、フローティングにせず、VDDまたはGNDに接続してください。

## 機能概要

### プログラム可能な機能

表 1. プログラム可能な機能

| 機能        | 詳細                                   |

|-----------|--------------------------------------|

| 周波数チューニング | PLL 用の周波数                            |

|           | 発振器チューニング (負荷容量値)                    |

| 機能        | OE 極性、I <sup>2</sup> C アドレス          |

| 電源        | V <sub>DD</sub> (1.8V、2.5V または 3.3V) |

| VCXO      | VCXO イネーブル／ディセーブル                    |

|           | Kv 極性                                |

|           | TPR                                  |

|           | 変調帯域幅                                |

| 出力規格      | LVPECL、LVDS、HCSL、CML                 |

### アーキテクチャ概要

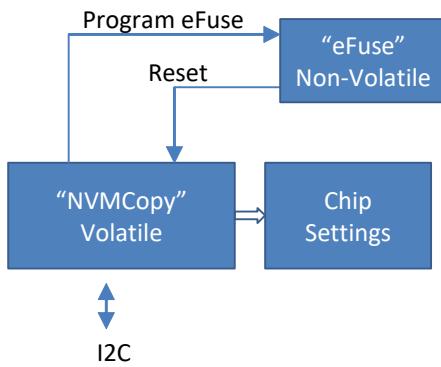

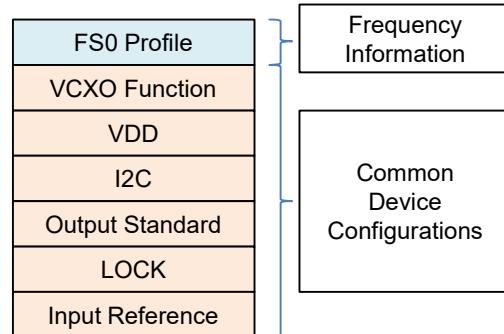

CY2941x / CY2942x デバイスは、複数の機能と複数の出力規格をサポートする高性能プログラマブル PLL 型水晶発振器です。このデバイスは、共通デバイスコンフィギュレーションと出力周波数関連情報に区分することができる内部ワンタイムプログラマブル (OTP) 不揮発性メモリ (NVM) を内蔵しています (図 2 をご参照ください)。共通デバイスコンフィギュレーションは、出力周波数で変化せず、チップ電源、OE 極性、I<sup>2</sup>C デバイスアドレス、入力リファレンス、出力規格と VCXO から成ります。CY2941x / CY2942x デバイスは電源オンのリセット解除時に NVM の正確なコピーを格納する揮発性メモリ ('NVMCopy' として図 1 に示す) を有します。図 1 で説明したように、チップの設定は揮発性メモリの内容に依存し、そして出力周波数はその揮発性メモリに保存されているコンフィギュレーションに依存します。揮発性メモリは I<sup>2</sup>C バスを介してアクセスされ、変更することができます。

図 1. NVM および揮発性メモリの構造

図 2 は周波数プロファイルと共に共通デバイスコンフィギュレーション設定からなる内部メモリの概念的構造を示します。

図 2. メモリの構造

### メモリ構造の設定の説明

- FS0: 周波数情報を含む

- VCXO 機能 : VCXO 機能、有効化／無効化、TPR、変調帯域幅および Kv (周波数対 VC のスロープ) 情報に関するパラメーターを含みます。

- V<sub>DD</sub>: 1.8 / 2.5 / 3.3V の範囲の情報

- I<sup>2</sup>C アドレス : I<sup>2</sup>C アドレス (プログラム可能な) 情報

- 出力規格 : LVPECL、LVDS、HCSL または CML

- LOCK: NVM ロックを示すための 2 ビットのパターン

- 入力リファレンス : 情報は固定され、ユーザーによる変更不可

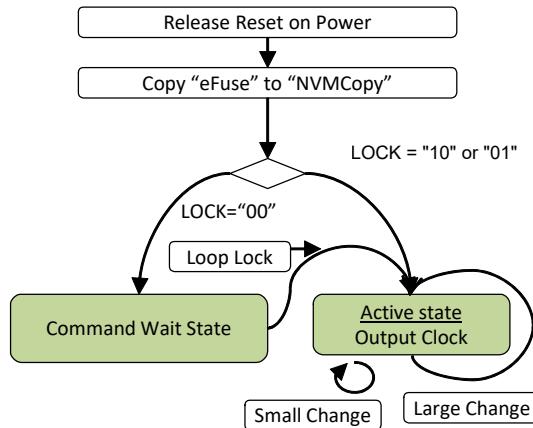

### 内部の状態遷移図

CY2941x / CY2942x はデバイスの動作を制御するステートマシンを含んでいます。5 ページの図 3 に示すように、ステートマシンはリセットの後、「eFuse」の内容を「NVMCopy」にロードします。ステートマシンは LOCK の値に応じて「Command Wait state」または「Active state」のいずれかの状態に入ります。「Command Wait state」の状態では、ユーザーはすべてのレジスタにアクセスし、「NVMCopy」の内容を読み出す／書き込むことができます。以下のコマンドは「Command Wait state」の状態において使用されます：

LOCK 状態は、00、01、10 あるいは 11 の 2 ビット パターンによって決定されます。電源レールが指定された範囲の値に達すると、デバイスはリセット状態から出ます。

5 ページの図 3 では、ブランク デバイスは、LOCK='00' (NVM はロックされない) なので、リセット後「Command Wait state」の状態に移行します。ステートマシンは、以下のコマンドを待ちます：

- 挥発性メモリへの書き込み

- 不揮発性メモリ (NVM) のプログラム

- ループ ロック

**図 3. 状態遷移図**

LOCK が「10」または「01」にプログラムされると、デバイスは「Active state」になり、プログラムされた周波数で動作します。

「Command Wait state」では、ユーザーは NVM への書き込み有りまたは書き込み無しでデバイスを設定することができます。ユース ケースのシナリオは以下の通りです：

#### ■ 出力周波数の確認

- 振発性メモリへの書き込み、必要に応じて NVM への選択的な書き込み

- テスト目的でループ ロックを任意に行うことができる

- NVM ロック状態では、NVM は再プログラマムすることはできません。必要に応じて、出力周波数は、大きな／小さな変更のコマンドを使用して変更することができます。

#### 小さな／大きな変更

小さな変更は、周波数が  $\pm 500\text{ppm}$  の範囲で変化していることを示します。周波数情報が I<sup>2</sup>C を介してロードされ、出力周波数が、グリッチせずに、元の周波数から新しい周波数に変わります。詳細については、LVPECL、LVDS、CML 出力の AC 電気的仕様をご参照ください。

大きな変更は周波数が  $\pm 500\text{ppm}$  を超えて変化していることを示し、I<sup>2</sup>C インターフェースを通して行われます。デバイスは PLL を再較正および再設定します。処理中の出力は同期して差動 LOW になります。

#### プログラミング サポート

CY2941x / CY2942x はソフトウェア設定可能なソリューションで、サイプレスはユーザーが自身の要件に応じてデバイスのプログラム可能な機能を設定するためのプログラミング ソフトウェアを提供します。

#### プログラム可能な OE 極性

CY2941x / CY2942x は OE 極性設定用のビット（デフォルトはアクティブ LOW）を含みます。ユーザーは、OE 機能にアクティブ HIGH 極性またはアクティブ LOW 極性を選択することができます。OE がデアサートされると、出力は同期して差動 LOW になります。

#### プログラム可能な VCXO

本デバイスは、VC 制御電圧に応じて VCO の周波数を変更することによる周波数変調のための独自の技術を組み込んでいます。プルプロファイルは直線的で、水晶リファレンスのプルに比べて正確です。また、VCXO 特性は非常に安定しており、温度、電源電圧またはプロセス変動に対して変化しません。

Kv (周波数対 VC のスロープ)、TPR VC 帯域幅と VCXO オン／オフはプログラム可能です。

#### 電源供給シーケンス

CY2941x / CY2942x は、起動のための特有シーケンスを必要としません。起動するためには、データシートで指定された単調な V<sub>DD</sub> の立ち上がりが必要です。ランプアップの後、V<sub>DD</sub> は推奨動作条件で指定された範囲で維持される必要があります。電圧低下の検出および保護はシステム内の他の場所で実装される必要があります。

他の入力信号は V<sub>DD</sub> より早くも遅くも利用可能になることができ、V<sub>DD</sub> に関する入力信号のタイミング要求は特にありません。すべての入力信号が設定した状態で安定すると、デバイスは正常に動作します。

#### I<sup>2</sup>C インターフェース

CY2941x / CY2942x は 2 線式シリアルインターフェースおよび高速モード (400kbps) および 7 ビット アドレッシング モードでの I<sup>2</sup>C に対応します。デバイスアドレスはプログラム可能であり、デフォルトで 55h になります。シングル バイト アクセスのみ対応します。デバイスへの最初の I<sup>2</sup>C アクセスは、VDD が最小規定電圧に達してから少なくとも 5ms 後に行う必要があります。

#### メモリ マップ

**表 2. 共通コンフィギュレーション**

| メモリアドレス   | 説明               |

|-----------|------------------|

| 50h ~ 57h | デバイス コンフィギュレーション |

**表 3. FS0: 周波数コンフィギュレーション**

| メモリアドレス | 説明                    |

|---------|-----------------------|

| 10h     | DIV0                  |

| 11h     | DIV0、DIVN_INT         |

| 12h     | ICP、DIVN_INT、PLL_MODE |

| 13h     | DIVN_FRAC_L           |

| 14h     | DIVN_FRAC_M           |

| 15h     | DIVN_FRAC_H           |

**表 4. その他の情報**

| メモリアドレス      | 説明              |

|--------------|-----------------|

| 00h (読み出し専用) | デバイス ID (= 51h) |

| D4h ~ D6h    | ユーザー設定可能な情報     |

ユーザーはコンフィギュレーション ツールによって作成されたすべての内容を書き込む必要があります。デバイスの部分的な更新は許可されません。ここで説明された以外の場所へのアクセスは、デバイスの動作で致命的なエラーが発生する可能性があります。

## 絶対最大定格

|                                                                       |                |

|-----------------------------------------------------------------------|----------------|

| 最大定格 <sup>[2]</sup> を超えると、デバイスの寿命が短くなる可能性があります。ユーザー ガイドラインは試験されていません。 |                |

| グランド電位に対する電源電圧                                                        | -0.5V ~ +3.8V  |

| 入力電圧                                                                  | -0.5V ~ +3.8V  |

| 保存温度（非結露）                                                             | -55°C ~ +150°C |

| 接合部温度                                                                 | -40°C ~ +125°C |

| プログラミング温度                                                             | 0°C ~ +125°C   |

|                                  |            |

|----------------------------------|------------|

| プログラミング電圧                        | 2.5V ±0.1V |

| eFuse プログラミング用電源電流               | 50mA       |

| T <sub>J</sub> = 100°C でのデータ保持期間 | >10 年      |

| 最大プログラミング サイクル                   | 1          |

| ESD HBM (JEDEC JS-001-2012)      | 2000V      |

| ESD MM (JEDEC JESD22-A115B)      | 200V       |

| ESD CDM (JEDEC JESD22-C101E)     | 400 V      |

| ラッチアップ電流                         | ±140mA     |

## 推奨動作範囲

| パラメーター               | 説明                           | Min  | Max  | 単位  |

|----------------------|------------------------------|------|------|-----|

| V <sub>DD</sub>      | コアの電源電圧、1.8V の動作範囲、1.8V ±5%  | 1.71 | 1.89 | V   |

|                      | コアの電源電圧、2.5V の動作範囲、2.5V ±10% | 2.25 | 2.75 |     |

|                      | コアの電源電圧、3.3V の動作範囲、3.3V ±10% | 2.97 | 3.63 |     |

| T <sub>A</sub>       | 周囲温度                         | -40  | +105 | °C  |

| UL-94                | 燃焼性規格。1/8 インチで V-0           | -    | 10   | ppm |

| f <sub>RES</sub>     | 周波数の分解能                      | -    | 2    | ppb |

| T <sub>PLLHOLD</sub> | PLL 保持温度範囲                   | -    | 125  | °C  |

## DC 電気的仕様

| パラメーター                         | 説明          | テスト条件                                                                                                               | Min                   | Typ | Max                   | 単位 |

|--------------------------------|-------------|---------------------------------------------------------------------------------------------------------------------|-----------------------|-----|-----------------------|----|

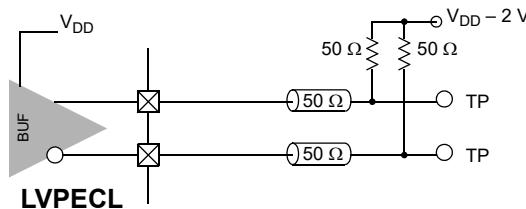

| I <sub>DD</sub>                | 電源電流、LVPECL | V <sub>DD</sub> = 3.3V / 2.5V、<br>V <sub>TT</sub> (V <sub>DD</sub> - 2.0V) に接続した 50Ω、<br>コモン モード電流あり                | -                     | 93  | 106                   | mA |

|                                | 電源電流、LVPECL | V <sub>DD</sub> = 3.3V / 2.5V、<br>V <sub>TT</sub> (V <sub>DD</sub> - 2.0V) に接続した 50Ω、<br>コモン モード電流なし <sup>[3]</sup> | -                     | 81  | 94                    |    |

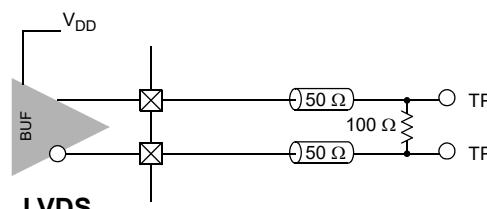

|                                | 電源電流、LVDS   | V <sub>DD</sub> = 3.3V / 2.5V / 1.8V、<br>CLKP と CLKN 間に 100Ω                                                        | -                     | 69  | 81                    |    |

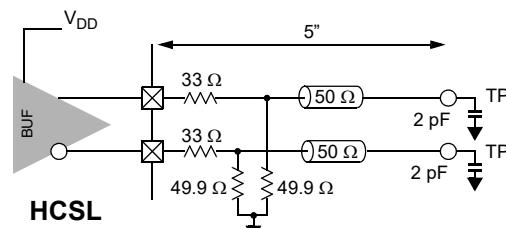

|                                | 電源電流、HCSL   | V <sub>DD</sub> = 3.3V / 2.5V / 1.8V、<br>GND に接続した 33Ω および 49.9Ω                                                    | -                     | 80  | 93                    |    |

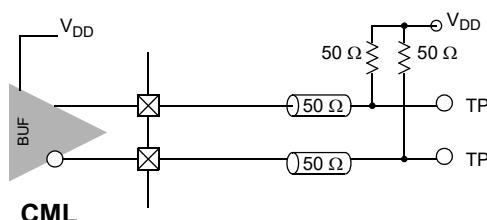

|                                | 電源電流、CML    | V <sub>DD</sub> = 3.3V / 2.5V / 1.8V、<br>V <sub>DD</sub> に接続した 50Ω                                                  | -                     | 73  | 86                    |    |

|                                | 電源電流、PLL のみ | V <sub>DD</sub> = 3.3V / 2.5V / 1.8V                                                                                | -                     | 59  | 70                    |    |

| I <sub>IH</sub>                | 入力 HIGH 電流  | 論理入力、入力 = V <sub>DD</sub>                                                                                           | -                     | 30  | 50                    | μA |

| I <sub>IL</sub>                | 入力 LOW 電流   | 論理入力、入力 = GND                                                                                                       | -                     | 30  | 50                    | μA |

| V <sub>IH</sub> <sup>[4]</sup> | 入力 HIGH 電圧  | OE、SCL、SDA 論理レベル = 1                                                                                                | 0.7 × V <sub>DD</sub> | -   | -                     | V  |

| V <sub>IL</sub> <sup>[4]</sup> | 入力 LOW 電圧   | OE、SCL、SDA 論理レベル = 0                                                                                                | -                     | -   | 0.3 × V <sub>DD</sub> | V  |

| V <sub>IN</sub>                | 入力電圧レベル     | GND を基準としたすべての入力                                                                                                    | -0.5                  | -   | 3.8                   | V  |

| R <sub>P</sub>                 | 内部プルアップ抵抗   | OE、アクティブ HIGH に設定                                                                                                   | -                     | 200 | -                     | kΩ |

| R <sub>D</sub>                 | 内部プルダウン抵抗   | OE、アクティブ LOW に設定                                                                                                    | -                     | 200 | -                     | kΩ |

注：

2. 絶対最大定格に記載されている動作範囲を超えて動作すると、デバイスに永久的な損傷を与える場合があります。ただし、これはストレスのみに対する定格です。上記の条件あるいは推奨動作範囲に記載されている条件を超える条件におけるデバイスの機能動作は保証されません。長時間にわたってデバイスを絶対最大定格条件に放置すると、デバイスの信頼性に影響を与えるか、またはデバイスに永久的な損傷を負わせます。

3. ClockWizad 2.1 では、出力規格を LVPECL2 に設定すると、出力は「Common Mode 電流なしの LVPECL」に設定されます。さまざまな使用ケースに応じた LVPECL 終端については、[AN210253](#) を参照してください。

4. 1.8V と 2.5V の V<sub>DD</sub> のみに適用可能な I<sup>2</sup>C 動作

## LVDS 出力の DC 仕様

( $V_{DD} = 1.8V, 2.5V$  または  $3.3V$  の範囲)

| パラメーター           | 説明                      | 条件                                  | Min   | Typ   | Max   | 単位      |

|------------------|-------------------------|-------------------------------------|-------|-------|-------|---------|

| $V_{OCM}^{[5]}$  | コモン モード出力電圧             | $V_{DD} = 2.5V$ または $3.3V$ の範囲      | 1.125 | 1.200 | 1.375 | V       |

| $\Delta V_{OCM}$ | 相補出力状態間での $V_{OCM}$ の変化 | -                                   | -     | -     | 50    | mV      |

| $I_{OZ}$         | 出カリーク電流                 | 出力がオフ、 $V_{OUT} = 0.75V \sim 1.75V$ | -20   | -     | 20    | $\mu A$ |

## LVPECL 出力の DC 仕様

( $V_{DD} = 2.5V$  または  $3.3V$  の範囲, Common Mode 電流あり)

| パラメーター   | 説明         | 条件                                                 | Min              | Typ | Max              | 単位 |

|----------|------------|----------------------------------------------------|------------------|-----|------------------|----|

| $V_{OH}$ | 出力 HIGH 電圧 | $V_{TT} (V_{DD} - 2.0V)$ に接続した R-term = $50\Omega$ | $V_{DD} - 1.165$ | -   | $V_{DD} - 0.800$ | V  |

| $V_{OL}$ | 出力 LOW 電圧  | $V_{TT} (V_{DD} - 2.0V)$ に接続した R-term = $50\Omega$ | $V_{DD} - 2.0$   | -   | $V_{DD} - 1.55$  | V  |

## CML 出力の DC 仕様

( $V_{DD} = 1.8V, 2.5V$  または  $3.3V$  の範囲)

| パラメーター   | 説明         | 条件                                 | Min              | Typ             | Max             | 単位 |

|----------|------------|------------------------------------|------------------|-----------------|-----------------|----|

| $V_{OH}$ | 出力 HIGH 電圧 | $V_{DD}$ に接続する R-term = $50\Omega$ | $V_{DD} - 0.085$ | $V_{DD} - 0.01$ | $V_{DD}$        | V  |

| $V_{OL}$ | 出力 LOW 電圧  | $V_{DD}$ に接続する R-term = $50\Omega$ | $V_{DD} - 0.6$   | $V_{DD} - 0.4$  | $V_{DD} - 0.32$ | V  |

## HCSL 出力の DC 仕様

( $V_{DD} = 1.8V, 2.5V$  または  $3.3V$  の範囲)

| パラメーター                 | 説明                                    | 条件           | Min  | Typ | Max  | 単位 |

|------------------------|---------------------------------------|--------------|------|-----|------|----|

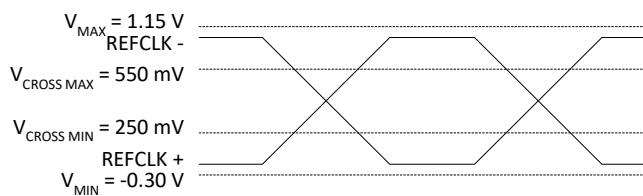

| $V_{MAX}^{[6]}$        | 最大の出力 HIGH 電圧                         | シングルエンド波形で測定 | -    | -   | 1150 | mV |

| $V_{MIN}^{[6]}$        | 最小の出力 LOW 電圧                          | シングルエンド波形で測定 | -300 | -   | -    | mV |

| $V_{OHDIFF}$           | 差動出力 HIGH 電圧                          | 差動波形で測定      | 150  | -   | -    | mV |

| $V_{OLDIFF}$           | 差動出力 LOW 電圧                           | 差動波形で測定      | -    | -   | -150 | mV |

| $V_{CROSS}^{[6]}$      | 交差点絶対電圧                               | シングルエンド波形で測定 | 250  | -   | 600  | mV |

| $V_{CROSSDELTA}^{[6]}$ | すべての立ち上がりクロック エッジにわたる $V_{CROSS}$ の変動 | シングルエンド波形で測定 | -    | -   | 140  | mV |

注:

5. 図 9 に示すように、 $V_{DD} = 1.8V$  の範囲に外部の AC カップリングが必要です。

6. パラメーターは、設計および特性評価で保証されます。すべてのデバイスでテストはされていません。

## V<sub>CXO</sub> 固有パラメーター

| パラメーター <sup>[7]</sup>                       | 説明                        | 条件                                                 | Min                 | Typ  | Max                 | 単位  |

|---------------------------------------------|---------------------------|----------------------------------------------------|---------------------|------|---------------------|-----|

| TPR                                         | 総周波数可変範囲                  | $0.1 \times V_{DD} \sim 0.9 \times V_{DD}$ の VC 範囲 | $\pm 50$            | —    | $\pm 275$           | ppm |

| K <sub>BSL</sub>                            | ベストフィット直線 (BSL)<br>リニアリティ | BSL ラインからの偏差                                       | -5                  | —    | 5                   | %   |

| K <sub>INC</sub>                            | インクリメンタル リニアリティ           | K <sub>v</sub> スロープ偏差                              | -10                 | —    | 10                  | %   |

| K <sub>BW</sub>                             | K <sub>v</sub> 変調の帯域幅     | プログラム可能                                            | 5                   | 10   | 20                  | kHz |

| K <sub>RANGE</sub>                          | 電圧範囲                      | 許容電圧範囲                                             | 0                   | —    | $V_{DD}$            | V   |

| V <sub>CTYP</sub>                           | 定格の中心電圧                   | $V_{DD}$ configuration = 1.8 V                     | —                   | 0.9  | —                   | V   |

|                                             |                           | $V_{DD}$ configuration = 2.5 V                     | —                   | 1.25 | —                   | V   |

|                                             |                           | $V_{DD}$ configuration = 3.3 V                     | —                   | 1.65 | —                   | V   |

| R <sub>V<sub>CIN</sub></sub> <sup>[8]</sup> | VC 用の入力抵抗                 | —                                                  | 5                   | —    | —                   | MΩ  |

| V <sub>RANGE</sub>                          | 入力電圧範囲                    | リニアリティ保証範囲                                         | $0.1 \times V_{DD}$ | —    | $0.9 \times V_{DD}$ | V   |

**注:**

7. パラメーターは、設計および特性評価で保証されます。すべてのデバイスでテストはされていません。

8. RVCIN は 100% テストされます。

## LVPECL、LVDS、CML 出力の AC 電気的仕様

( $V_{DD} = 3.3\text{ V}$  および  $2.5\text{ V}$  (LVPECL), Common Mode 電流あり,  $V_{DD} = 3.3\text{ V}, 2.5\text{ V}, 1.8\text{ V}$  (LVDS, CML 出力))

| パラメーター <sup>[9]</sup> | 説明                      | 詳細／条件                                                                         | Min | Typ | Max  | 単位     |

|-----------------------|-------------------------|-------------------------------------------------------------------------------|-----|-----|------|--------|

| $f_{OUT}$             | クロック出力周波数               | LVPECL、CML、LVDS 出力規格                                                          | 15  | —   | 2100 | MHz    |

| $t_{RF}$              | LVPECL 出力の立ち上がり／立ち下がり時間 | AC レベルの 20% ~ 80%。PECL 出力用に 156.25MHz で測定                                     | —   | —   | 350  | ps     |

|                       | CML 出力の立ち上がり／立ち下がり時間    | AC レベルの 20% ~ 80%。CML 出力用に 156.25MHz で測定                                      | —   | —   | 350  | ps     |

|                       | LVDS 出力の立ち上がり／立ち下がり時間   | AC レベルの 20% ~ 80%。LVDS 出力用に 156.25MHz で測定                                     | —   | —   | 350  | ps     |

| $t_{ODC}$             | 出力デューティ比                | 差動 50% レベル、156.25MHz で測定                                                      | 45  | 50  | 55   | %      |

| $V_P$                 | LVDS 出力差動ピーク            | 15MHz ~ 700MHz                                                                | 247 | —   | 454  | mV     |

| $V_P$                 | LVDS 出力差動ピーク            | 700MHz ~ 2100MHz                                                              | 150 | —   | 454  | mV     |

| $\Delta V_P$          | 相補出力状態間での VP の変化        | —                                                                             | —   | —   | 50   | mV     |

| $V_P$                 | LVPECL 出力差動ピーク          | $f_{OUT} = 15\text{MHz} \sim 325\text{MHz}$                                   | 450 | —   | —    | mV     |

| $V_P$                 |                         | $f_{OUT} = 325\text{MHz} \sim 700\text{MHz}$                                  | 350 | —   | —    | mV     |

| $V_P$                 |                         | $f_{OUT} = 700\text{MHz} \sim 2100\text{MHz}$                                 | 250 | —   | —    | mV     |

| $V_P$                 | CML 出力差動ピーク             | $f_{OUT} = 15\text{MHz} \sim 700\text{MHz}$                                   | 250 | —   | 600  | mV     |

| $V_P$                 | CML 出力差動ピーク             | $f_{OUT} = 700\text{MHz} \sim 2100\text{MHz}$                                 | 200 | —   | 600  | mV     |

| $t_{CCJ}$             | サイクル ツー サイクル ジッタ        | ピーク、1 万サイクルにわたり 156.25MHz 差動信号で測定、100MHz ~ 130MHz 水晶                          | —   | —   | 50   | ps     |

| $t_{PJ}$              | 周期ジッタ                   | ピーク ツー ピーク、1 万サイクルにわたり 156.25MHz 差動信号で測定、100MHz ~ 130MHz 水晶                   | —   | —   | 50   | ps     |

| $J_{RMS}$             | RMS 位相ジッタ               | $f_{OUT} = 156.25\text{MHz}, 12\text{kHz} \sim 20\text{MHz}$ オフセット、非 VCXO モード | —   | 150 | 250  | fs     |

| <b>非 VCXO モード</b>     |                         |                                                                               |     |     |      |        |

| PN1k                  | 位相ノイズ、1kHz のオフセット       | 100 ~ 130MHz 水晶リファレンス、<br>$f_{OUT} = 156.25\text{MHz}$                        | —   | —   | -113 | dBc/Hz |

| PN10k                 | 位相ノイズ、10kHz のオフセット      | 100 ~ 130MHz 水晶リファレンス、<br>$f_{OUT} = 156.25\text{MHz}$                        | —   | —   | -127 | dBc/Hz |

| PN100k                | 位相ノイズ、100kHz のオフセット     | 100 ~ 130MHz 水晶リファレンス、<br>$f_{OUT} = 156.25\text{MHz}$                        | —   | —   | -135 | dBc/Hz |

| PN1M                  | 位相ノイズ、1MHz のオフセット       | 100 ~ 130MHz 水晶リファレンス、<br>$f_{OUT} = 156.25\text{MHz}$                        | —   | —   | -144 | dBc/Hz |

| PN10M                 | 位相ノイズ、10MHz のオフセット      | 100 ~ 130MHz 水晶リファレンス、<br>$f_{OUT} = 156.25\text{MHz}$                        | —   | —   | -152 | dBc/Hz |

| PN-SPUR               | Spur                    | PLL の更新速度以上の周波数オフセットで測定                                                       | —   | —   | -65  | dBc/Hz |

注：

9. パラメーターは、設計および特性評価で保証されます。すべてのデバイスでテストはされていません。

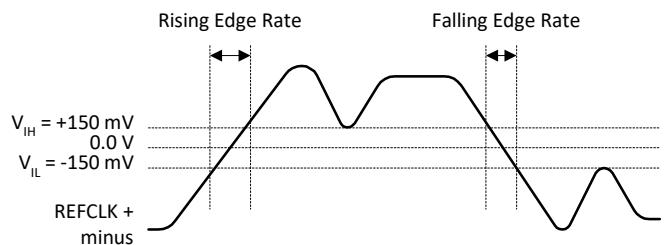

## HCSL 出力の AC 電気的仕様

| パラメーター <sup>[10]</sup> | 説明                       | テスト条件                                           | Min  | Typ | Max                 | 単位       |

|------------------------|--------------------------|-------------------------------------------------|------|-----|---------------------|----------|

| $f_{OUT}$              | 出力周波数                    | HCSL                                            | 15   | —   | 700                 | MHz      |

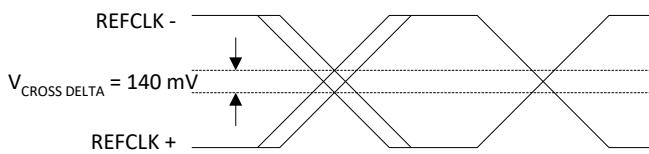

| $E_R$                  | 立ち上がりエッジ速度               | -150mV ~ +150mV の差動波形で測定                        | 0.6  | —   | 5.7 <sup>[11]</sup> | V/ns     |

| $E_F$                  | 立ち下がりエッジ速度               | -150mV ~ +150mV の差動波形で測定                        | 0.6  | —   | 5.7 <sup>[11]</sup> | V/ns     |

| $t_{STABLE}$           | 電圧リング バック (VRB) が許容される時間 | -150mV ~ +150mV の差動波形で測定                        | 500  | —   | —                   | ps       |

| R-F_MATCHING           | 立ち上がり／立ち下がりのマッチング        | シングルエンド波形で測定、立ち上がりエッジ速度と立ち下がりエッジ速度がマッチング、100MHz | -100 | —   | 100                 | ps       |

| $t_{DC}$               | 出力デューティ比                 | 差動波形で測定、 $f_{OUT} = 100\text{MHz}$              | 45   | —   | 55                  | %        |

| $t_{CCJ}$              | サイクル ツー サイクル ジッタ         | 差動波形で測定、100MHz                                  | —    | —   | 50                  | ps       |

| $J_{RMSPCIE}$          | ランダム ジッタ、PCIE 仕様 3.0     | 100MHz ~ 130MHz 水晶                              | —    | —   | 1                   | ps (RMS) |

## タイミング パラメーター

| パラメーター <sup>[10]</sup> | 説明                                                               | Min  | Max  | 単位 |

|------------------------|------------------------------------------------------------------|------|------|----|

| $t_{PU}$               | 電源ランプ時間 ( $0.5V \sim V_{DD(\min)}$ )。電源ランプは単調増加でなければならぬ          | 0.01 | 3000 | ms |

| $t_{WAKEUP}$           | 仕様の最小電源の時から出力周波数のクロックが安定する (精度 $<\pm 0.1\text{ppm}$ ) までの時間      | —    | 10   | ms |

| $t_{OEEN}$             | OE エッジから出力有効までの時間                                                | —    | 2.5  | ms |

| $t_{OEDIS}$            | OE エッジから出力無効までの時間                                                | —    | 10   | μs |

| $t_{FSMALL}$           | 小さなトリガー ( $\leq \pm 500\text{ppm}$ ) の周波数変化時間、ターゲット周波数 $\pm 1\%$ | —    | 20   | μs |

| $t_{FLARGE}$           | 大きなトリガー ( $> \pm 500\text{ppm}$ ) の周波数変化時間                       | —    | 2.5  | ms |

### 注：

10. パラメーターは、設計および特性評価で保証されます。すべてのデバイスでテストはされていません。

11. ジッタ性能の要件により、エッジ速度が 4V/ns を超えます。

## 位相ジッタの特性

12kHz ~ 20MHz の統合帯域幅

| パラメーター <sup>[12]</sup>                                            | 説明      | 条件                           | Min | Typ | Max | 単位 |

|-------------------------------------------------------------------|---------|------------------------------|-----|-----|-----|----|

| VCXO 機能以外                                                         |         |                              |     |     |     |    |

| J <sub>RMS</sub>                                                  | RMS ジッタ | F <sub>OUT</sub> = 644.53MHz | -   | 110 | -   | fs |

| J <sub>RMS</sub>                                                  | RMS ジッタ | F <sub>OUT</sub> = 622.08MHz | -   | 120 | -   | fs |

| J <sub>RMS</sub>                                                  | RMS ジッタ | F <sub>OUT</sub> = 156.25MHz | -   | 145 | -   | fs |

| J <sub>RMS</sub>                                                  | RMS ジッタ | F <sub>OUT</sub> = 2.105GHz  | -   | 145 | -   | fs |

| 変調帯域幅 = 10kHz、V <sub>DD</sub> = 3.3V、F <sub>OUT</sub> = 622.08MHz |         |                              |     |     |     |    |

| J <sub>RMS</sub>                                                  | RMS ジッタ | TPR = 50ppm、Kv = 37.9ppm/V   | -   | 151 | -   | fs |

| J <sub>RMS</sub>                                                  | RMS ジッタ | TPR = 155ppm、Kv = 117.4ppm/V | -   | 158 | -   | fs |

| J <sub>RMS</sub>                                                  | RMS ジッタ | TPR = 275ppm、Kv = 208.3ppm/V | -   | 170 | -   | fs |

| 変調帯域幅 = 10kHz、V <sub>DD</sub> = 2.5V、F <sub>OUT</sub> = 622.08MHz |         |                              |     |     |     |    |

| J <sub>RMS</sub>                                                  | RMS ジッタ | TPR = 50ppm、Kv = 50ppm/V     | -   | 152 | -   | fs |

| J <sub>RMS</sub>                                                  | RMS ジッタ | TPR = 155ppm、Kv = 155ppm/V   | -   | 160 | -   | fs |

| J <sub>RMS</sub>                                                  | RMS ジッタ | TPR = 275ppm、Kv = 275ppm/V   | -   | 175 | -   | fs |

| 変調帯域幅 = 10kHz、V <sub>DD</sub> = 1.8V、F <sub>OUT</sub> = 622.08MHz |         |                              |     |     |     |    |

| J <sub>RMS</sub>                                                  | RMS ジッタ | TPR = 50ppm、Kv = 69.4ppm/V   | -   | 153 | -   | fs |

| J <sub>RMS</sub>                                                  | RMS ジッタ | TPR = 155ppm、Kv = 215.3ppm/V | -   | 166 | -   | fs |

| J <sub>RMS</sub>                                                  | RMS ジッタ | TPR = 275ppm、Kv = 381.9ppm/V | -   | 190 | -   | fs |

## I<sup>2</sup>C バス タイミング仕様

| パラメーター <sup>[12, 13]</sup> | 説明                        | Min | Typ | Max | 単位  |

|----------------------------|---------------------------|-----|-----|-----|-----|

| f <sub>SCL</sub>           | SCL クロック周波数               | -   | -   | 400 | kHz |

| t <sub>HD:STA</sub>        | START 条件のホールド時間           | 0.6 | -   | -   | μs  |

| t <sub>LOW</sub>           | SCL の LOW 期間              | 1.3 | -   | -   | μs  |

| t <sub>HIGH</sub>          | SCL の HIGH 期間             | 0.6 | -   | -   | μs  |

| t <sub>SU:STA</sub>        | 反復 START 条件のセットアップ時間      | 0.6 | -   | -   | μs  |

| t <sub>HD:DAT</sub>        | データ ホールド時間                | 0   | -   | -   | μs  |

| t <sub>SU:DAT</sub>        | データ セットアップ時間              | 100 | -   | -   | ns  |

| t <sub>R</sub>             | 立ち上がり時間                   | -   | -   | 300 | ns  |

| t <sub>F</sub>             | 立ち下がり時間                   | -   | -   | 300 | ns  |

| t <sub>SU:STO</sub>        | STOP 条件のセットアップ時間          | 0.6 | -   | -   | μs  |

| t <sub>BUF</sub>           | STOP 条件と START 条件間のバス空き時間 | 1.3 | -   | -   | μs  |

注:

- 12. パラメーターは、設計および特性評価で保証されます。すべてのデバイスでテストはされていません。

- 13. 1.8V と 2.5V の V<sub>DD</sub> のみに適用可能な I<sup>2</sup>C 動作

## 周波数の安定度

| パラメーター          | 説明      | テスト条件                                                                                        | Min | Typ | Max | 単位     |

|-----------------|---------|----------------------------------------------------------------------------------------------|-----|-----|-----|--------|

| $f_{TOLERANCE}$ | 周波数許容誤差 | $V_{DD} = \text{Min} \sim \text{Max}$ ,<br>$T_A = +25^\circ\text{C}$                         | -20 | -   | +20 | ppm    |

| $f_{TC}$        | 温度特性    | $V_{DD} = \text{Min} \sim \text{Max}$ ,<br>$T_A = -40^\circ\text{C} \sim +85^\circ\text{C}$  | -20 | -   | +20 | ppm    |

| $f_{TC}$        | 温度特性    | $V_{DD} = \text{Min} \sim \text{Max}$ ,<br>$T_A = -40^\circ\text{C} \sim +105^\circ\text{C}$ | -30 | -   | +30 | ppm    |

| $f_{AGE}$       | 周波数経時変化 |                                                                                              | -5  | -   | +5  | ppm/ 年 |

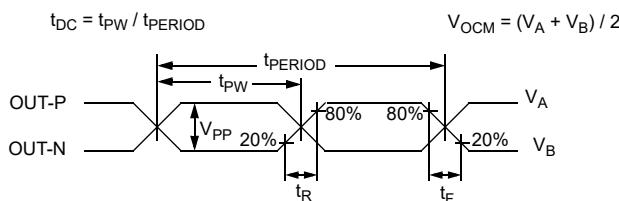

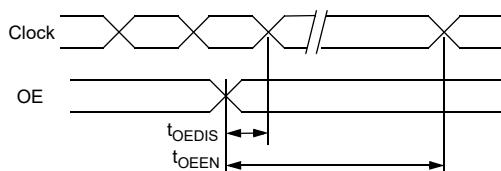

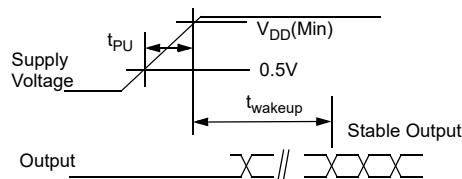

## 電圧とタイミングの定義

図 4. 差動出力の定義

図 5. 出力イネーブル／ディセーブル タイミング

図 6. 電源立ち上げと PLL ロック時間

図 7. 出力終端回路

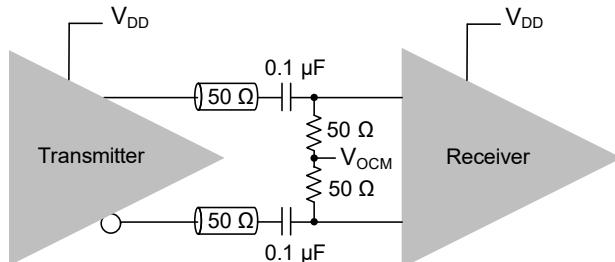

図 8. 1.8V 用の LVDS 終端 [14]

注：

14. この図に示す終端回路は  $V_{DD} = 1.8V$  動作時の LVDS 出力規格に特化したものです。これは AC 結合が必要です (100nF 直列コンデンサ)。図に示すように、バイアス電圧 ( $V_{OCM}$ ) と  $50\Omega$  の終端抵抗は、受信回路で設定する必要があります。

図 9. HCSL: 絶対交差点のシングル エンドの測定ポイント

図 10. HCSL: デルタ交差点のシングル エンドの測定ポイント

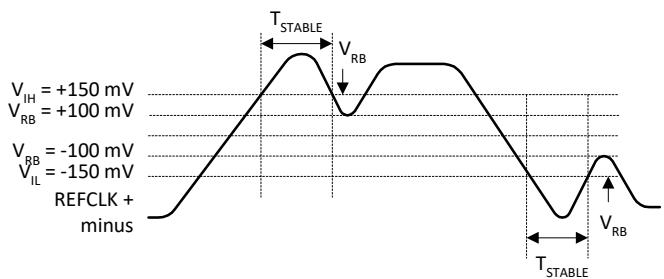

図 11. HCSL: 立ち上がりと立ち下がり時間の差動測定ポイント

図 12. HCSL: リング バック用の差動測定ポイント

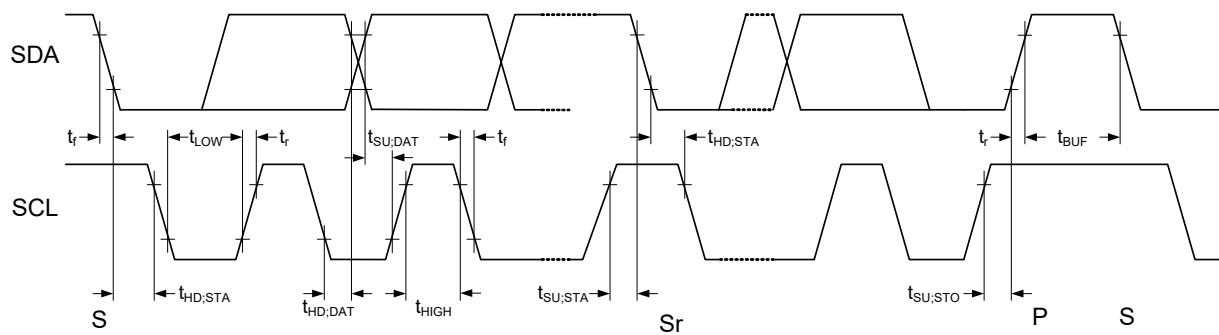

図 13. I<sup>2</sup>C バス タイミング仕様

## 位相ノイズのプロット

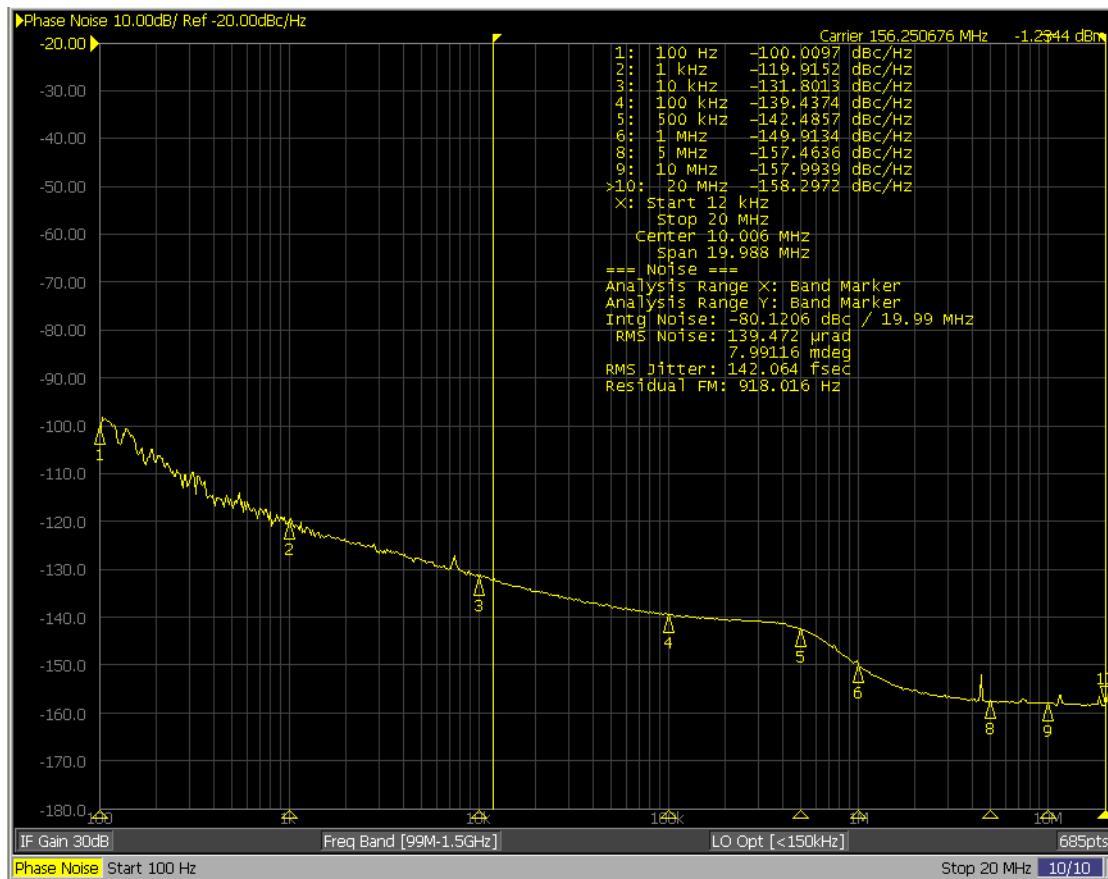

図 14. 標準位相ノイズ、156.25MHz (12kHz ~ 20MHz)

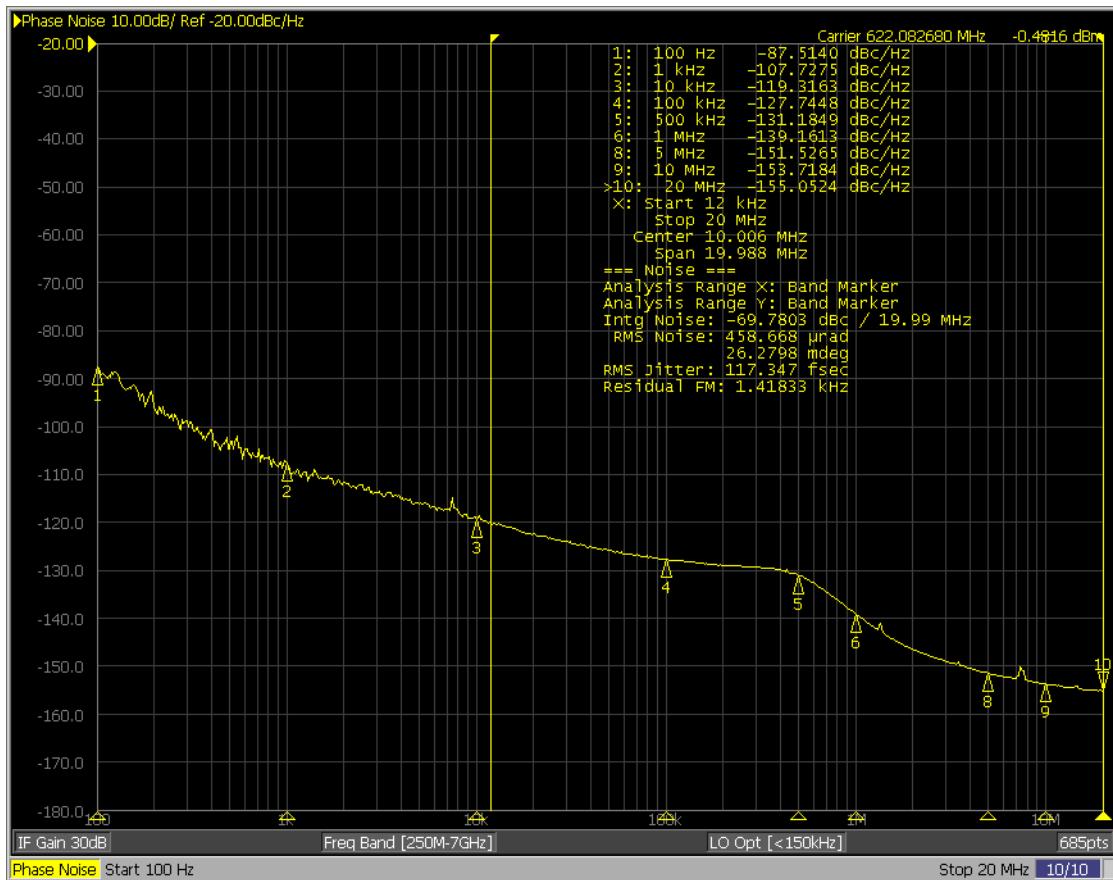

図 15. 標準位相ノイズ、622.08MHz (12kHz ~ 20MHz)

**図 16. 標準位相ノイズ、644.53MHz (12kHz ~ 20MHz)**

## 注文情報

| 注文コード          | コンフィギュレーション  | パッケージ説明                          | 動作範囲               |

|----------------|--------------|----------------------------------|--------------------|

| CY29411FLXIT   | フィールドプログラマブル | 8 ピン LCC 7.0 × 5.0mm - テープ & リール | 産業用、-40°C ~ +105°C |

| CY29411LXIxxxT | 工場設定 [15]    | 8 ピン LCC 7.0 × 5.0mm - テープ & リール | 産業用、-40°C ~ +105°C |

| CY29412FLXIT   | フィールドプログラマブル | 8 ピン LCC 7.0 × 5.0mm - テープ & リール | 産業用、-40°C ~ +105°C |

| CY29412LXIxxxT | 工場設定 [15]    | 8 ピン LCC 7.0 × 5.0mm - テープ & リール | 産業用、-40°C ~ +105°C |

| CY29421FLXIT   | フィールドプログラマブル | 8 ピン LCC 5.0 × 3.2mm - テープ & リール | 産業用、-40°C ~ +105°C |

| CY29421LXIxxxT | 工場設定 [15]    | 8 ピン LCC 5.0 × 3.2mm - テープ & リール | 産業用、-40°C ~ +105°C |

| CY29422FLXIT   | フィールドプログラマブル | 8 ピン LCC 5.0 × 3.2mm - テープ & リール | 産業用、-40°C ~ +105°C |

| CY29422LXIxxxT | 工場設定 [15]    | 8 ピン LCC 5.0 × 3.2mm - テープ & リール | 産業用、-40°C ~ +105°C |

## 注文コードの定義

### 注 :

15. これらは工場出荷時にプログラムされたお客様固有の型番です。詳細情報は、最寄りのサイプレスの FAE または販売代理店にお問い合わせください。

## パッケージ図

図 17. 8 ピン セラミック LCC (5.0 × 7.0 × 1.90mm) パッケージ図、002-10174

| SYMBOL | DIMENSIONS |      |      |

|--------|------------|------|------|

|        | MIN.       | NOM. | MAX. |

| A      | 1.65       | -    | 1.75 |

| A3     | 0.70 REF   |      |      |

| D      | 5.00 BSC   |      |      |

| E      | 7.00 BSC   |      |      |

| bD     | 1.00       |      |      |

| bE     | 1.40       |      |      |

| LD     | 1.18       |      |      |

| LE     | 1.28       |      |      |

| K      | 0.13       |      |      |

| e      | 2.54 BSC   |      |      |

| N      | 8          |      |      |

| ND     | 1          |      |      |

| NE     | 3          |      |      |

### NOTES:

1. ALL DIMENSIONS ARE IN MILLIMETERS.

2. N IS THE TOTAL NUMBER OF TERMINALS.

3. ND IS THE NUMBER OF TERMINALS ON "D" DIMENSION.

4. NE IS THE NUMBER OF TERMINALS ON "E" DIMENSION.

5. PIN #1 ID ON TOP WILL BE LOCATED WITHIN THE INDICATED ZONE.

002-10174 \*A

図 18. 8 ピン セラミック LCC (3.2 × 5.0 × 1.55mm) パッケージ図、002-10273

TOP VIEW

SIDE VIEW

BOTTOM VIEW

| SYMBOL | DIMENSIONS |      |      |

|--------|------------|------|------|

|        | MIN.       | NOM. | MAX. |

| A      | 1.35       | -    | 1.45 |

| A3     | 0.60 REF   |      |      |

| D      | 3.20 BSC   |      |      |

| E      | 5.00 BSC   |      |      |

| bD     | 0.64       |      |      |

| bE     | 0.64       |      |      |

| LD     | 0.70       |      |      |

| LE     | 0.90       |      |      |

| K      | 0.10       |      |      |

| e      | 1.27 BSC   |      |      |

| N      | 8          |      |      |

| ND     | 1          |      |      |

| NE     | 3          |      |      |

NOTES:

1. ALL DIMENSIONS ARE IN MILLIMETERS.

2. N IS THE TOTAL NUMBER OF TERMINALS.

3. ND IS THE NUMBER OF TERMINALS ON "D" DIMENSION.

4. NE IS THE NUMBER OF TERMINALS ON "E" DIMENSION.

5. PIN #1 ID ON TOP WILL BE LOCATED WITHIN THE INDICATED ZONE.

002-10273 \*A

## 略語

表 5. 本書で使用する略語

| 略語               | 説明                                                               |

|------------------|------------------------------------------------------------------|

| AC               | alternating current ( 交流電流 )                                     |

| ADC              | analog-to-digital converter<br>( アナログ - デジタル変換器 )                |

| BCL              | best-fit straight line ( ベストフィット直線 )                             |

| CML              | current mode logic ( 電流モード論理 )                                   |

| DC               | direct current ( 直流 )                                            |

| ESD              | electrostatic discharge ( 静電気放電 )                                |

| FS               | frequency select ( 周波数選択 )                                       |

| HCSL             | high-speed current steering logic<br>( 高速電流ステアリング ロジック )         |

| I <sup>2</sup> C | inter-integrated circuit<br>( インター インテグレーテッド サーキット )             |

| JEDEC            | Joint Electron Device Engineering Council ( 半導体 技術協会 )           |

| LDO              | low dropout (regulator)<br>( 低ドロップアウト ( レギュレーター ) )              |

| LVCMOS           | low voltage complementary metal oxide semiconductor ( 低電圧 CMOS ) |

| LVDS             | low-voltage differential signals ( 低電圧差動信号 )                     |

| LVPECL           | low-voltage positive emitter-coupled logic<br>( 低電圧正エミッタ結合論理 )   |

| NVM              | non-volatile memory ( 不揮発性メモリ )                                  |

| OE               | output enable ( 出力イネーブル )                                        |

| PLL              | phase-locked loop ( 位相同期回路 )                                     |

| POR              | power on reset ( パワーオン リセット )                                    |

| PSoC®            | Programmable System-on-Chip<br>( プログラマブル システムオンチップ )             |

| QFN              | quad flat no-lead<br>( クアッド フラット リードなしパッケージ )                    |

| RMS              | root mean square ( 二乗平均平方根 )                                     |

| SCL              | serial I <sup>2</sup> C clock ( シリアル I <sup>2</sup> C クロック )     |

| SDA              | serial I <sup>2</sup> C data ( シリアル I <sup>2</sup> C データ )       |

| VCXO             | voltage controlled crystal oscillator<br>( 電圧制御発振器 )             |

| VRB              | voltage ring back ( 電圧リング バック )                                  |

| XTAL             | crystal ( 水晶 )                                                   |

| OTP              | one time programmable<br>( ワンタイム プログラマブル )                       |

## 本書の表記法

### 測定単位

表 6. 測定単位

| 記号  | 単位        |

|-----|-----------|

| °C  | 摂氏温度      |

| fs  | フェムト秒     |

| GHz | ギガヘルツ     |

| kΩ  | キロオーム     |

| kHz | キロヘルツ     |

| MHz | メガヘルツ     |

| MΩ  | メガオーム     |

| μA  | マイクロアンペア  |

| μm  | マイクロメートル  |

| μs  | マイクロ秒     |

| μW  | マイクロワット   |

| mA  | ミリアンペア    |

| mm  | ミリメートル    |

| mΩ  | ミリオーム     |

| ms  | ミリ秒       |

| mV  | ミリボルト     |

| nH  | ナノヘンリー    |

| ns  | ナノ秒       |

| Ω   | オーム       |

| %   | パーセント     |

| pF  | ピコファラッド   |

| ps  | ピコ秒       |

| ppm | 100 万分の 1 |

| ppb | 10 億分の 1  |

| V   | ボルト       |

## 改訂履歴

文書名 : CY2941x／CY2942x、高性能プログラマブル発振器

文書番号 : 002-03966

| 版  | ECN 番号  | 発行日        | 変更者  | 変更内容                                                     |

|----|---------|------------|------|----------------------------------------------------------|

| ** | 5013010 | 11/19/2015 | HZEN | これは英語版 001-97768 Rev. ** を翻訳した日本語版 002-03966 Rev. ** です。 |

| *A | 5250076 | 05/06/2016 | HZEN | これは英語版 001-97768 Rev. *B を翻訳した日本語版 002-03966 Rev. *A です。 |

| *B | 5621510 | 02/10/2017 | HZEN | これは英語版 001-97768 Rev. *E を翻訳した日本語版 002-03966 Rev. *B です。 |

| *C | 6375503 | 11/05/2018 | SSAS | これは英語版 001-97768 Rev. *J を翻訳した日本語版 002-03966 Rev. *C です。 |

## セールス、ソリューションおよび法律情報

### ワールドワイド販売と設計サポート

サイプレスは、事業所、ソリューションセンター、メーカー代理店、および販売代理店の世界的なネットワークを保持しています。お客様の最寄りのオフィスについては、[サイプレスのロケーションページ](#)をご覧ください。

#### 製品

Arm® Cortex® Microcontrollers

[cypress.com/arm](http://cypress.com/arm)

車載用

[cypress.com/automotive](http://cypress.com/automotive)

クロック & バッファ

[cypress.com/clocks](http://cypress.com/clocks)

インターフェース

[cypress.com/interface](http://cypress.com/interface)

IoT (モノのインターネット)

[cypress.com/iot](http://cypress.com/iot)

メモリ

[cypress.com/memory](http://cypress.com/memory)

マイクロコントローラ

[cypress.com/mcu](http://cypress.com/mcu)

PSoC

[cypress.com/psoc](http://cypress.com/psoc)

電源用 IC

[cypress.com/pmic](http://cypress.com/pmic)

タッチ センシング

[cypress.com/touch](http://cypress.com/touch)

USB コントローラー

[cypress.com/usb](http://cypress.com/usb)

ワイヤレス

[cypress.com/wireless](http://cypress.com/wireless)

#### PSoC® ソリューション

[PSoC 1](#) | [PSoC 3](#) | [PSoC 4](#) | [PSoC 5LP](#) | [PSoC 6 MCU](#)

#### サイプレス開発者コミュニティ

[コミュニティ](#) | [Projects](#) | [ビデオ](#) | [ブログ](#) | [トレーニング](#) | [Components](#)

#### テクニカルサポート

[cypress.com/support](http://cypress.com/support)

© Cypress Semiconductor Corporation, 2015-2018. 本書面は、Cypress Semiconductor Corporation 及び Spansion LLC を含むその子会社（以下「Cypress」という。）に帰属する財産である。本書面（本書面に含まれ又は言及されているあらゆるソフトウェア若しくはファームウェア（以下「本ソフトウェア」という。）を含む）は、アメリカ合衆国及び世界のその他の国における知的財産法令及び条約に基づき Cypress が所有する。Cypress はこれらの法令及び条約に基づく全ての権利を留保し、本段落で特に記載されているものを除き、その特許権、著作権、商標権又はその他の知的財産権のライセンスを一切許諾しない。本ソフトウェアにライセンス契約書が伴つておらず、かつ Cypress との間で別途本ソフトウェアの使用方法を定める書面による合意がない場合、Cypress は、(1) 本ソフトウェアの著作権に基づき、(a) ソースコード形式で提供されている本ソフトウェアについて、Cypress ハードウェア製品と共に用いるためにのみ、かつ組織内部でのみ、本ソフトウェアの修正及び複製を行うこと、並びに (b) Cypress のハードウェア製品ユニットに用いるためにのみ、（直接又は再販売者及び販売代理店を介して間接のいずれかで）本ソフトウェアをバイナリーコード形式で外部エンドユーザーに配布すること、並びに (2) 本ソフトウェア（Cypress により提供され、修正がなされていないもの）が抵触する Cypress の特許権のクレームに基づき、Cypress ハードウェア製品と共に用いるためにのみ、本ソフトウェアの作成、利用、配布及び輸入を行うことについての非独占的で譲渡不能な一身専属的ライセンス（サブライセンスの権利を除く）を付与する。本ソフトウェアのその他の使用、複製、修正、変換又はコンパイルを禁止する。

**適用される法律により課される範囲内で、Cypress は、本書面又はいかなる本ソフトウェア若しくはこれに伴うハードウェアに関するも、明示又は默示をとわず、いかなる保証（商品性及び特定の目的への適合性の默示の保証を含むがこれらに限られない）も行わない。**いかなるコンピューティングデバイスも絶対に安全ということはない。従って、Cypress のハードウェアまたはソフトウェア製品に講じられたセキュリティ対策にもかかわらず、Cypress は、Cypress 製品への権限のないアクセスまたは使用といったセキュリティ違反から生じる一切の責任を負わない。加えて、本書面に記載された製品には、エラッタと呼ばれる設計上の欠陥またはエラーが含まれている可能性があり、公表された仕様とは異なる動作をする場合がある。適用される法律により許される範囲内で、Cypress は、別途通知することなく、本書面を変更する権利を留保する。Cypress は、本書面に記載のある、いかなる製品若しくは回路の適用又は使用から生じる一切の責任を負わない。本書面で提供されたあらゆる情報（あらゆるサンプルデザイン情報又はプログラムコードを含む）は、参照目的のためのみに提供されたものである。この情報で構成するあらゆるアプリケーション及びその結果としてのあらゆる製品の機能性及び安全性を適切に設計、プログラム、かつテストすることは、本書面のユーザーの責任において行われるものとする。Cypress 製品は、兵器、兵器システム、原子力施設、生命維持システム、蘇生用の設備及び外科的移植を含むその他の医療機器若しくは医療システム、汚染管理若しくは有害物質管理の運用のために設計され若しくは意図されたシステムの重要な構成部品としての使用、又は装置若しくはシステムの不具合が人身傷害、死亡若しくは物的損害を生じさせるようなその他の使用（以下「本目的外使用」という。）のためには設計、意図又は承認されていない。重要な構成部品とは、それの不具合が装置若しくはシステムの不具合を生じさせるか又はその安全性若しくは実効性に影響すると合理的に予想できるような装置若しくはシステムのあらゆる構成部品をいう。Cypress 製品のあらゆる本目的外使用から生じ、若しくは本目的外使用に関連するいかなる請求、損害又はその他の責任についても、Cypress はその全部又は一部をとわず一切の責任を負わず、かつ Cypress はそれら一切から本書により免除される。Cypress は Cypress 製品の本目的外使用から生じ又は本目的外使用に関連するあらゆる請求、費用、損害及びその他の責任（人身傷害又は死亡に基づく請求を含む）から免責補償される。

Cypress, Cypress のロゴ、Spansion, Spansion のロゴ及びこれらの組み合わせ、WICED, PSoC, CapsSense, EZ-USB, F-RAM, 及び Traveo は、米国及びその他の国における Cypress の商標又は登録商標である。Cypress のより完全な商標のリストは、[cypress.com](http://cypress.com) を参照すること。その他の名称及びブランドは、それぞれの権利者の財産として権利主張がなされている可能性がある。