## サイプレスはインフィニオンテクノロジーズになりました

この表紙に続く文書には「サイプレス」と表記されていますが、これは同社が最初にこの製品を開発したからです。新規および既存のお客様いずれに対しても、引き続きインフィニオンがラインアップの一部として当該製品をご提供いたします。

### 文書の内容の継続性

下記製品がインフィニオンの製品ラインアップの一部として提供されたとしても、それを理由としてこの文書に変更が加わることはありません。今後も適宜改訂は行いますが、変更があった場合は文書の履歴ページでお知らせします。

### 注文時の部品番号の継続性

インフィニオンは既存の部品番号を引き続きサポートします。ご注文の際は、データシート記載の注文部品番号をこれまで通りご利用下さい。

# 4-PLL スペクトラム拡散 クロックジェネレータ

## 特長

- 入力周波数

- 水晶発振子入力 : 8MHz ~ 48MHz

- リファレンス クロック : 8MHz ~ 250MHz LVCMOS

- リファレンス クロック : 8MHz ~ 700MHz 差動

- 出力周波数

- 25MHz ~ 700MHz LVDS, LVPECL, HCSL, CML

- 3MHz ~ 250MHz LVCMOS

- 1kHz ~ 8MHz の 1 出力 LVCMOS

- RMS 位相ジッタ : 1ps 最大、12kHz ~ 20MHz オフセット

- PCIe 1.0/2.0/3.0 対応

- SATA 2.0, USB 2.0/3.0, 1/10GbE 対応

- 最大 12 出力をサポート、6 出力ずつ 2 バンク

- 最大 8 差動出力ペア (HCSL, LVPECL, CML または LVDS)

- 最大 12 LVCMOS 出力

- バンク内の差動出力スキューは最大 100ps

- 以下のものを備えた 4 個のフラクショナル N 型位同期回路 (PLL)

- VCXO ( $\pm 120\text{ppm}$ 、 $0.23\text{ppm}$  のステップ)

- スペクトラム拡散機能 (論理 SS と Lexmark プロファイル, 0.1% ~ 5%, 0.1% のステップ, 下方または中央 拡散)

- 電源電圧 : 1.8V, 2.5V, 3.3V

- ゼロ遅延バッファ (ZDB) と非ゼロ遅延バッファ (NZDB) コンフィギュレーション

- I<sup>2</sup>C 経由で再コンフィギュレーション(基板上のプログラム)が可能

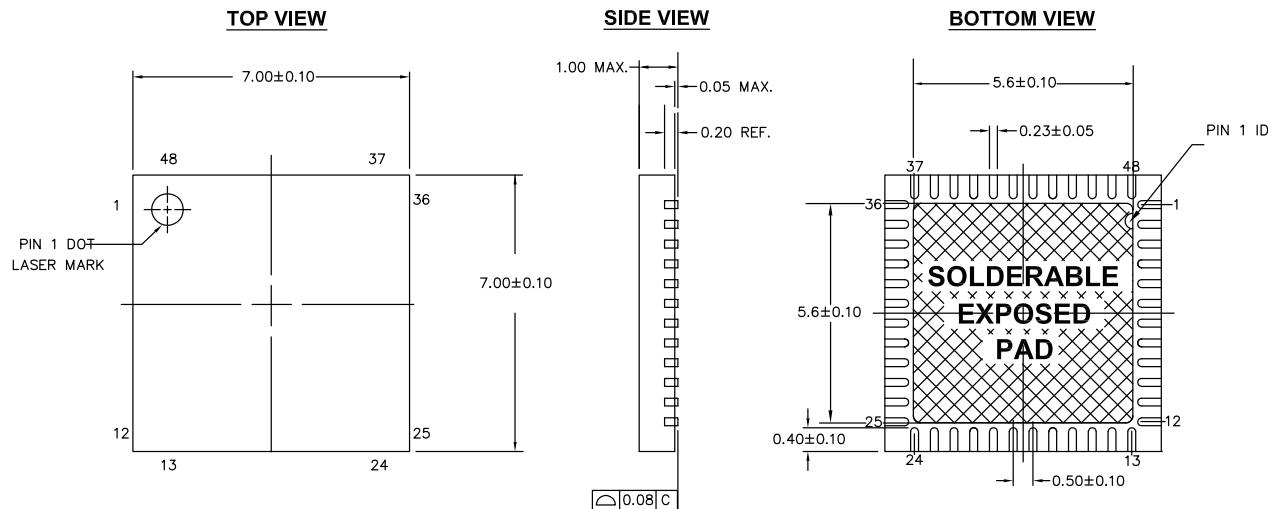

- 産業グレードのデバイス、48 ピン QFN (7×7×1.0mm) パッケージで提供

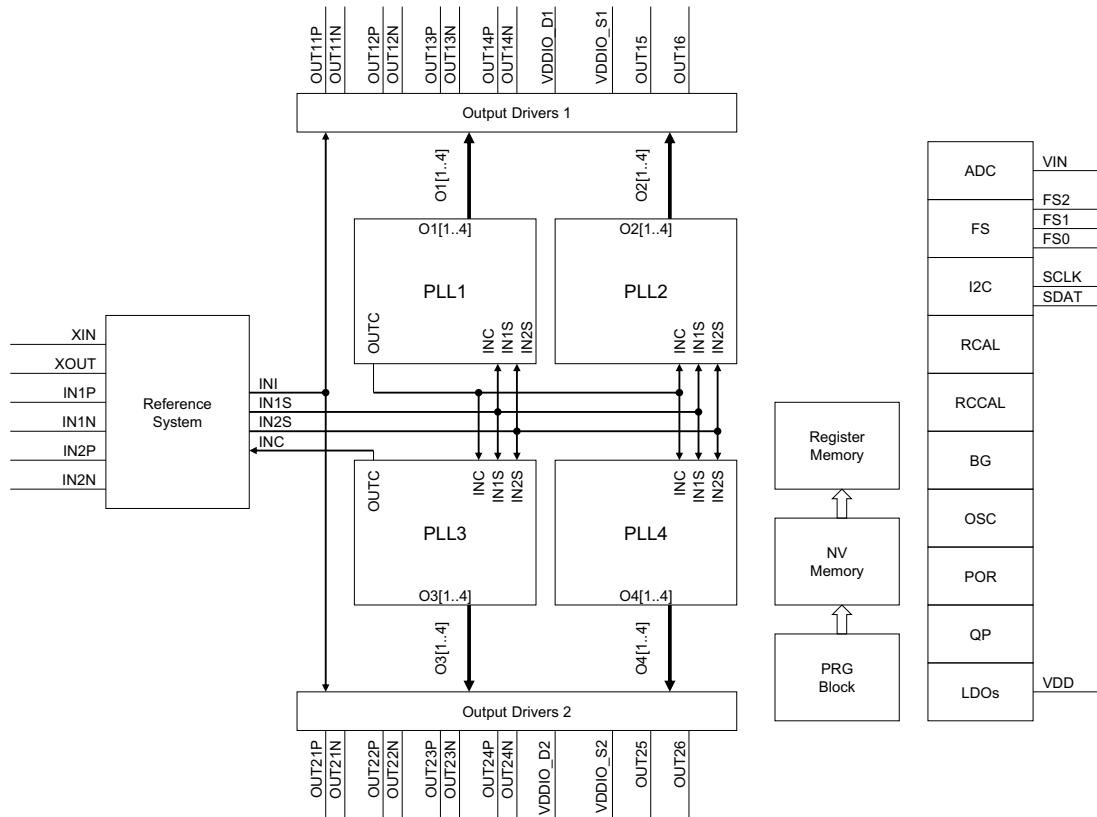

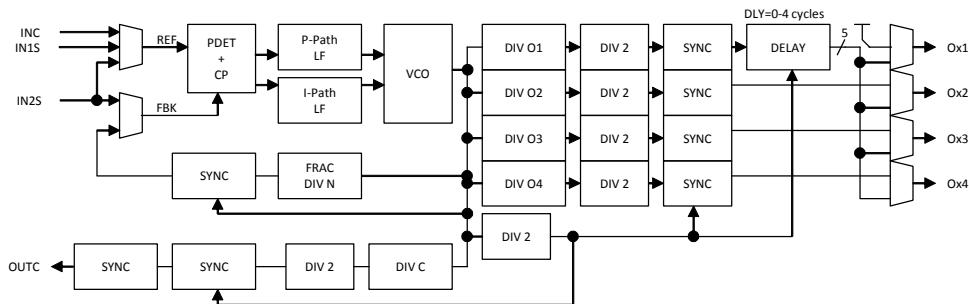

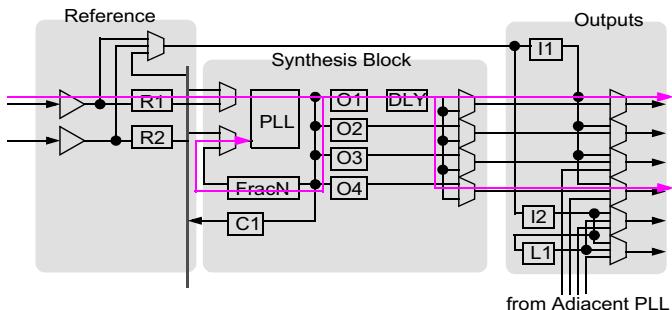

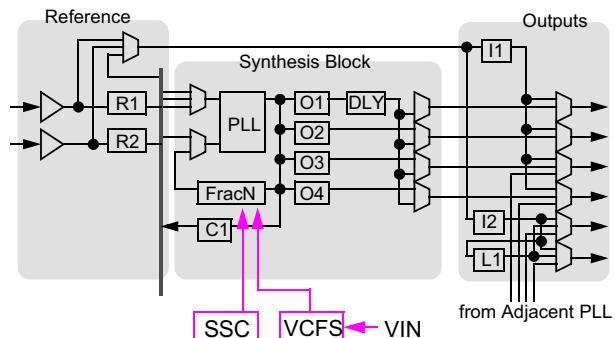

## 論理ブロック図

## 目次

|                            |           |

|----------------------------|-----------|

| <b>機能の詳細</b>               | <b>3</b>  |

| 入力システム                     | 3         |

| VCXO 入力ブロック                | 3         |

| 周波数選択入力                    | 3         |

| I2C ブロック (SCLK、SDAT)       | 4         |

| クロック生成セクション                | 4         |

| 出力セクション                    | 4         |

| 基板上のプログラミング                | 5         |

| 機能的な特長とアプリケーションの考慮事項       | 5         |

| <b>ピン配置</b>                | <b>10</b> |

| <b>電気的仕様</b>               | <b>13</b> |

| 絶対最大定格                     | 13        |

| 動作温度                       | 13        |

| 動作電源                       | 13        |

| チップ レベルの DC 仕様             | 14        |

| 出力の DC 仕様                  | 15        |

| 入力クロックの AC 仕様              | 16        |

| 出力の AC 仕様                  | 17        |

| <b>テストと測定回路</b>            | <b>23</b> |

| 電圧とタイミングの定義                | 24        |

| <b>パッケージ情報</b>             | <b>26</b> |

| はんだリフローの仕様                 | 26        |

| <b>注文情報</b>                | <b>27</b> |

| 注文コードの定義                   | 27        |

| <b>略語</b>                  | <b>28</b> |

| <b>本書の表記法</b>              | <b>28</b> |

| 測定単位                       | 28        |

| <b>改訂履歴</b>                | <b>29</b> |

| <b>セールス、ソリューションおよび法律情報</b> | <b>30</b> |

| ワールドワイド販売と設計サポート           | 30        |

| 製品                         | 30        |

| PSoC® ソリューション              | 30        |

| サイプレス開発者コミュニティ             | 30        |

| テクニカル サポート                 | 30        |

## 機能の詳細

CY27410 は、4 個の独立したフラクショナル PLL を備えた標準性能のプログラマブルなクロック ジェネレータであり、0ppm の合成誤差でいかなる周波数も生成できます。それぞれの PLL の後に、1 つの PLL から 4 つの異なる周波数を生成する独立した 4 個の分周器の一式が続きます。4 個の分周器は、最小限のスキーで位相の揃ったクロック出力を生成するために同期されます。PLL は、EMI を減少させるためのスペクトラム拡散機能にも対応しています。PLL1 は、VCXO 機能を備えており、出力周波数を ppm 単位で変更できます。

CY27410 の入力には、水晶振動子またはシングルエンド／差動リファレンス クロックを使用できます。デバイスは最大 12 出力をサポートし、それぞれ 6 出力ずつの 2 バンクに分けられています。PLL1 と PLL2 の 4 出力はバンク 1 の出力に多重化され、PLL3 と PLL4 の 4 クロック出力はバンク 2 の出力に多重化されています。これら 2 バンクの 12 出力は、8 差動出力、12 シングルエンド出力、または差動出力とシングルエンド出力の組合せに設定できます。

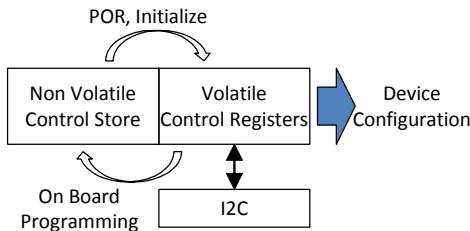

CY27410 は、デバイスのコンフィギュレーション設定を格納する揮発性メモリと 8 レジスタからなる不揮発性メモリを内蔵しています。これらのレジスタは基板上で I<sup>2</sup>C インタフェース経由でアクセスし、プログラムすることができます。また、アプリケーション基板上でデバイスを完全に再プログラムすることもできます。I<sup>2</sup>C インタフェース以外の外部信号は以下のようないくつかの機能を持った多機能ピンに設定できます。

- 出力周波数を動的に変更

- 出力イネーブル／ディセーブル

- 電源切断

- 拡散の有効化／無効化

また 32.768kHz など、幅広く使用されているリファレンス周波数を得るための低周波数クロック出力(kHz のレンジ)を 1 つ備えています。CY27410 のジッタ仕様は、PCIe 1.0/2.0/3.0、USB 2.0/3.0、SATA 1.0/2.0、および 1/10GbE 通信プロトコルに適合しています。

## 入力システム

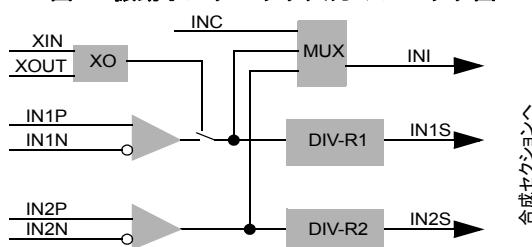

入力システムは以下のものに対応しています(図 1 を参照)

- XIN/XOUT は水晶振動子入力に対応します。

- IN1 は差動とシングルエンド クロック入力に対応します。

- IN2 は差動とシングルエンド クロック入力に対応します。

図 1. 振動子／クロック入力のブロック図

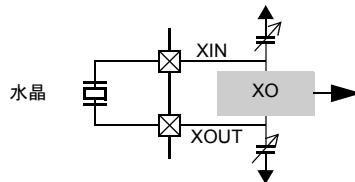

水晶振動子を使用する場合、図 2 に示すように XIN と XOUT を水晶振動子に接続することで必要な内部周波数を生成します。サポートされる差動チューニング コンデンサの範囲は 8pF ~ 12pF です。

図 2. 水晶の接続

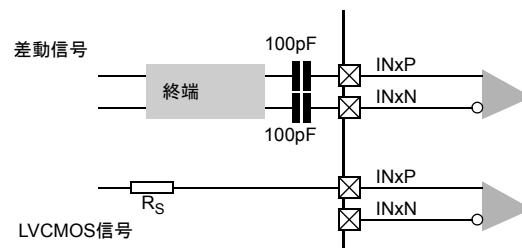

IN1 と IN2 は、シングルエンドまたは差動リファレンス入力を受け入れるように設計されています。IN2 は、デバイスに ZDB 機能を実装する時にフィードバック信号を受信するために使用します。

差動入力では、LVPECL、LVDS、CML、HCSL など複数の信号規格で入力できます。図 3 に示すように、差動信号は AC カップリングしなければなりません。

図 3. 差動信号とシングルエンド信号の入力

## VCXO 入力ブロック

VIN 入力は、デバイスの VCXO 機能用に使用します。AV(オーディオビジュアル)向けアプリケーション等で必要とされるこの機能では、入力電圧に応じて出力周波数を変更できます。出力周波数は、最大 ±120ppm まで可変できます。この入力電圧は、VCXO 機能を提供するために PLL1 分数分周器を直接制御します。

## 周波数選択入力

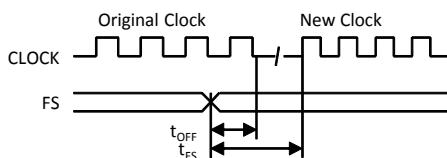

CY27410 は周波数選択機能に対応しており、動作中に出力周波数を変更できます。デバイスには 8 つのコンフィギュレーションレジスタがあり、事前にプログラムするか、または I<sup>2</sup>C を介して書き込みます。FS ピンの信号レベル (HIGH か LOW) を変更することで、適切なコンフィギュレーション レジスタを選択し、それに応じて出力周波数を変更します。

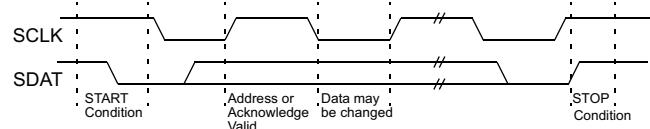

## I<sup>2</sup>C ブロック (SCLK、SDAT)

CY27410 は、I<sup>2</sup>C 経由で内部レジスタのプログラミングに対応しており、デバイスを設定することができます。CY27410 はまた、フラッシュメモリ（不揮発メモリ）へのユーザープログラムプロファイルプログラミングおよび部分的な更新をサポートしています。メモリ内容のプロテクションは、読み出し、書き込み、読み出し／書き込みおよびプロテクションなしを設定できます。デバイスは、I<sup>2</sup>C バス仕様 Ver. 2.1 以降に準拠しています。主な仕様は以下のとおりです。

- 400kb/s ( ファスト モード )

- 7 ビット アドレッシングに対応

■ 選択可能なデバイスアドレス（プログラム可能）、デフォルト = 69 (16進数) (7ビット)

## クロック生成セクション

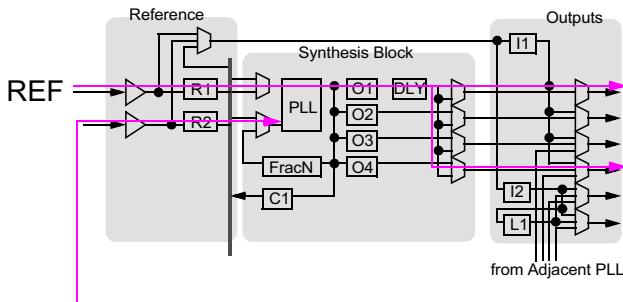

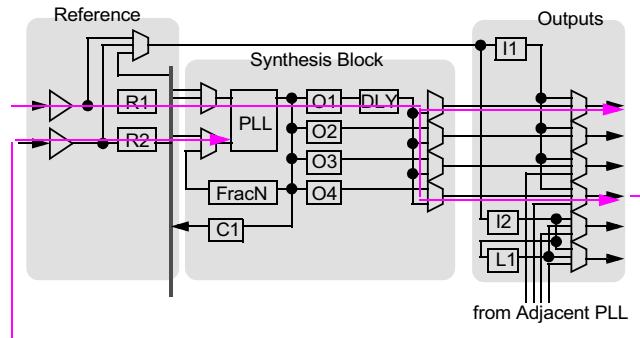

CY27410 は、コアブロックである 4 個の PLL から構成されます。それぞれの PLL はフランクショナル N 機能を備えており、入力リファレンス周波数から 100ppb までの精度で出力周波数を生成できます。PLL の出力は 4 個の分周器に供給された後、シンクロナイザで同期されます。グリッチなしのクロック遷移機能を実現する、または可変遅延生成回路を使ってプログラマブル遅延機能も実現できます。出力分周器とマルチプレクサも、このサブシステムの一部として含まれています。図 4 に示す構成は、全 4 個の PLL で同じ構造を持っています。

図 4. PLL の構造

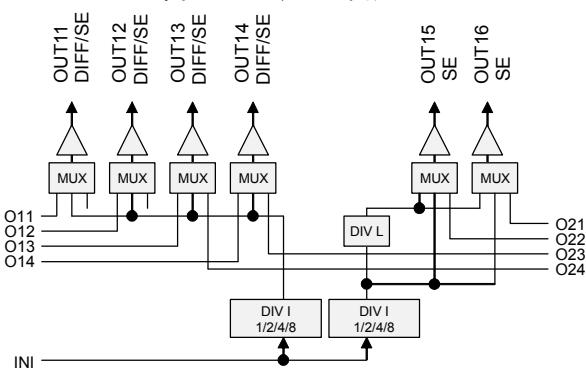

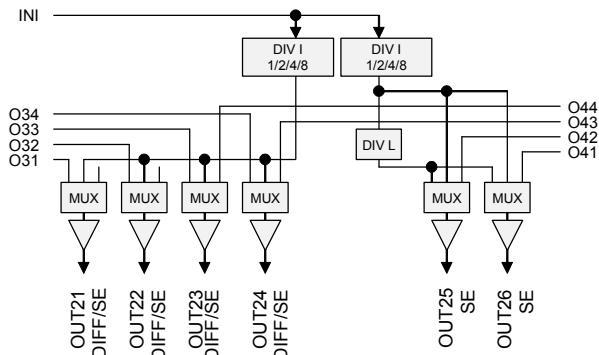

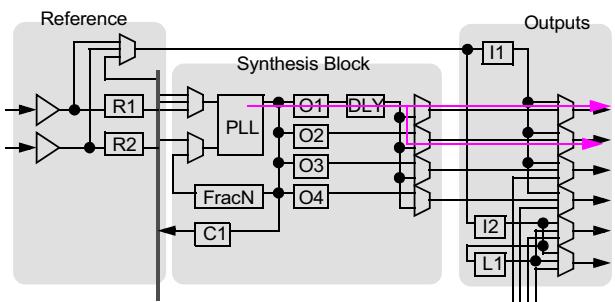

## 出力セクション

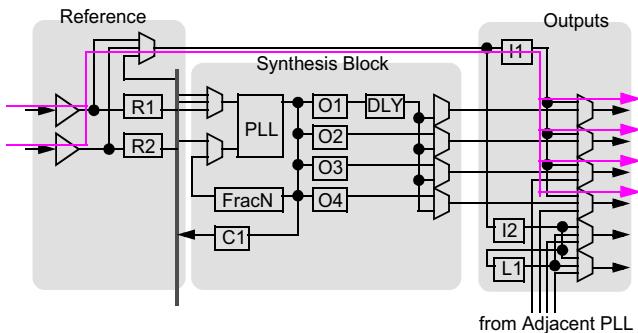

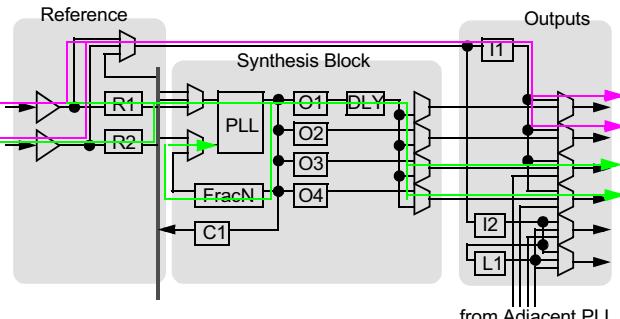

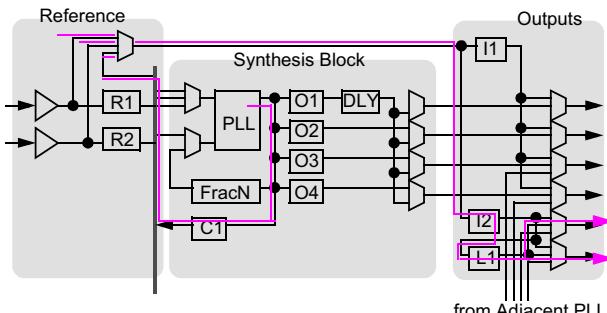

CY27410 には、デバイスの上部と下部 2 つの出力バンクがあります。それぞれのバンクは 6 出力からなります。そのうち、OUT11 ~ OUT14 および OUT21 ~ OUT24 は差動とシングルエンド出力に対応しており、OUT15 ~ OUT16 および OUT25 ~ OUT26 はシングルエンド出力のみに対応します。

PLL から分周器を経由して供給されたクロックソースは図 5 と図 6 に示すように、マルチプレクサでどのソースを出力するかを決定します。

図 5. バンク 1 の出力

図 6. バンク 2 の出力

## 基板上のプログラミング

ユーザー基板上でフラッシュメモリ（不揮発メモリ）に書き込むことが可能なため、あらかじめプログラムされていない空のデバイスを使用できます。これにより、同じデバイスを複数のプロジェクトに使用でき、各々のプロジェクトに基づいてデバイスをプログラムできます。基板上のプログラミングの概念図を図 7 に示します。

図 7. 基板上のプログラミング

## 機能的な特長とアプリケーションの考慮事項

CY27410 は商用、産業用およびローエンド ネットワーキング アプリケーション向けの 4 PLL スペクトラム拡散クロックジェネレータです。このデバイスの主な仕様は、最大 700MHz までの周波数に対応する差動入力 (2) と出力 (12) です。デバイスは最大 1ps の低い RMS 位相ジャッタ、および VCXO、周波数選択、PLL バイパス モードなどの各種機能を備えています。デバイスは PCIe 1.0/2.0/3.0、USB 2.0/3.0、10GbE などの主な規格に準拠するよう設計されています。

本製品は LVDS、LVPECL、CML、HCSL、および LVCMS の論理レベルに対応しています。

### クロック ジェネレータ

CY27410 の主な機能は、外部クロック (IN1) または水晶リファレンスからの周波数生成です。出力周波数を決定するためには、4 つの変数があります。これらは REF 入力、DIV-R (R1)、FracN (DIV-N) 分周器、ポスト分周器 (DIV-O) です。出力周波数を決定する基本式は下記のとおりです。

- クロック ジェネレータ モード

- $f_{OUT} = ((REF \times DIV-N) / DIV-R) / DIV-O$

- PLL バイパス モード

- $f_{OUT} = REF / DIV-I$  または  $REF / DIV-I / DIV-L$

基本的な PLL のブロック図を図 8 に示します。PLL の各出力は遅延回路を介して出力マルチプレクサに供給されます。この遅延回路は必要に応じて各々のクロックを一定時間遅延させます。

図 8. PLL ブロック図、クロック生成

### PCIE (HCSL) のクロック生成

PCIe アプリケーション用に、CY27410 は差動出力を 8 ペア 提供します。これらの差動出力は、常に同じ拡散を持っています。

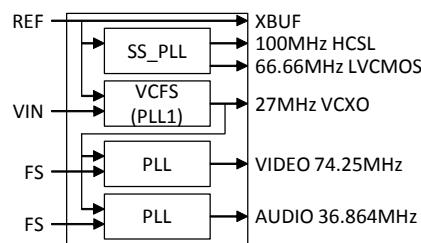

### VCXO およびそれに対応する周波数

CY27410 は VCXO 機能および PLL カスケード接続オプションを備えており、固定リファレンスから可変周波数および高精度の周波数を生成します。デジタル テレビでは、オーディオとビデオ クロックは 27MHz VCXO 信号に同期して生成されなければなりません。図 9 のように、チップのアーキテクチャはカスケード接続によりこれを保証しています。

図 9. PLL のカスケード接続

オーディオとビデオ クロックは、27MHz VCXO 入力と同時に生成される要件以外に、出力周波数を生成するために複雑な分周比も必要とします。オーディオとビデオ信号用の一般に使用されている分周比は、表 1 に示されます。

表 1. オーディオとビデオ周波数

| 出力周波数       | 比率        |

|-------------|-----------|

| 74.17582418 | 91:250    |

| 33.8688     | 625:784   |

| 22.5792     | 1875:1568 |

| 16.9344     | 1250:784  |

| 11.2896     | 1875:784  |

| 5.6448      | 1875:392  |

| 36.864      | 375:512   |

### ゼロ遅延バッファ機能

CY27410 は、ゼロ遅延バッファ (ZDB) として機能します。この機能を実装するためには、同一 PLL 出力のいずれかをフィードバック リファレンスとして使います。フィードバック ループ内に分周器を使用することで、周波数遅倍 ZDB としても機能できます (図 10 を参照)。この機能は、PLL が整数 N モードにある時にのみサポートされます。

**図 10. ZDB コンフィギュレーション**

CY27410 は、R1 と R2 を整数比で変更することで、周波数遅倍 ZDB を実装します。二つの値が一致している場合は、CY27410 は単純な ZDB として動作します。

### 進み位相／遅延位相

CY27410 は、0 ~ 4×VCO/2 サイクルを提供するために、分周器で遅延回路をサポートします。したがって、この機能を使用すると、ある出力は他の出力に比べて一定の遅延位相または進み位相を持たせることができます。この機能は、ZDB モードにも使用でき、リファレンス入力に対して「進み」位相や「遅延」位相を 提供します。図 11 と図 12 を参考ください。

**図 11. 進み位相／遅延位相の出力**

**図 12. ZDB コンフィギュレーションでの進み位相／遅延位相**

### 非ゼロ遅延バッファ

CY27410 は、PLL バイパス モードに対応しています。これは、図 13 に示されるように、PLL ブロック全体をバイパスして、設定可能な非ゼロ遅延バッファ (NZDB) として動作します。入出力のレベル 変換と選択入力にも対応しています。

**図 13. NZDB コンフィギュレーション**

### クロック ジェネレータとバッファの組合せ

CY27410 は、単一のデバイス内でクロック ジェネレータとバッファの組合せを提供しています。これは入出力のコンフィギュレーションを組み合わせることで実現します。このアプリケーションの例を図 14 に示します。

**図 14. クロック ジェネレータと NZDB**

## 低周波数出力

CY27410 は図 15 に示されるように、LVC MOS 出力のできる低周波数ジェネレータ カウンタを内蔵しています。これは、ウォッチドッグタイマや kHz レンジのクロック生成に使用できます。

図 15. 低周波数出力オプション

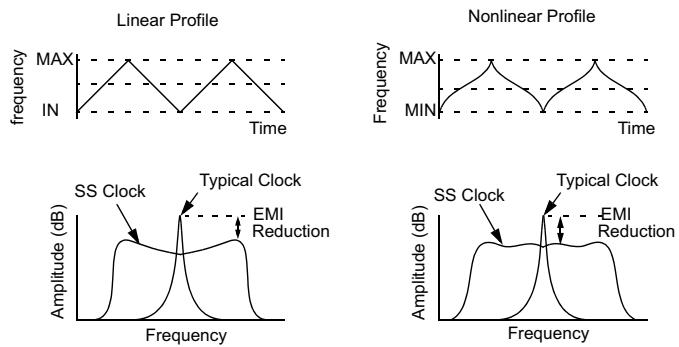

## スペクトラム拡散

電磁妨害 (EMI) を減少させるために、CY27410 はスペクトラム拡散変調を提供しています。出力クロックは、より幅広い周波数範囲にわたってエネルギーを拡散し、システム EMI を低減するよう変調できます。CY27410 は、変調用に線形と非線形の 2 種類の拡散プロファイルを実装しています。

スペクトラム拡散は、いかなる出力クロック、いかなる周波数、0.1% ~ 5% (0.1% のステップ) のいかなる拡散量にも適用できます。中央または下方拡散もプログラムできます。

拡散変調レートは、30kHz ~ 60kHz に制限されます。

スペクトラム拡散は、FracN の変調でデジタル処理で生成されます。つまり、すべてのパラメータはプロセスや電圧、温度変化とは無関係で安定しています。同一 PLL から生成されるすべてのクロックは、同じ変調量を持っています。

図 16 に示すように、変調されたクロックの高調波は、変調されない信号の高調波に比べてピークが低くなります。この減少量は、周波数 (F) および拡散量 (P) に依存します。非線形プロファイルの場合、減少量は次の式で計算します。

$$dB = 6.5 + 9 * \log_{10}(P) + 9 * \log_{10}(F)$$

P は拡散量 (%), F は MHz での周波数です。

図 16. スペクトラム拡散のプロファイル

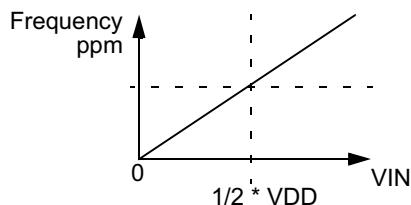

## VCXO (VCFS) 機能

CY27410 は、水晶振動子周波数を変更せずに VCXO 機能を実現します。この機能は、図 17 のように、FracN カウンタを VIN レベルに応じて変調することで実装しています。したがって、これは電圧制御周波数シフト (VCFS, voltage-controlled frequency shift) と呼ばれています。

VCFS 機能は、FracN 分割器を変調することで実装されます。つまり、すべてのパラメータはプロセスや電圧、温度変化に影響されることなく安定した特性を示します。

VCFS 動作はスペクトラム拡散と組み合わせられません (図 18 を参照)。

図 17. VCFS プロファイル

図 18. VCFS とスペクトラム拡散

### 水晶発振回路

CY27410 の IN1 (XIN/XOUT) にあるリファレンス発振回路は様々な低コスト水晶振動子に対応しています。CY27410 は、8pF ~ 12pF の定格負荷容量の水晶振動子に対応しています。<sup>3</sup> ページの図 2 に示すように、CY27410 はフィードバック抵抗やチューニング コンデンサなどすべてのコンポーネントを内蔵しており、発振回路は以下の仕様で水晶振動子によるクロック発振を行います。

適切な動作を可能にするために、水晶の仕様は 3 つのレンジに分けられています。

■ 低レンジ ( $F_{NOM}$ ) = 8 ~ 12MHz

■ 中レンジ = 12 ~ 20MHz

■ 高レンジ = 20 ~ 48MHz

対応する水晶発振子および回路のパラメータを表 2 に示します。

**表 2. 水晶の仕様**

| レンジ                      | 最小周波数 (MHz) | 最大周波数 (MHz)       | 最大 R1 ( $\Omega$ ) | 最大 DL (uW) |

|--------------------------|-------------|-------------------|--------------------|------------|

| 低                        | 8           | 12                | 150                | 100        |

| 中                        | 12          | 20                | 70                 | 100        |

| 高                        | 20          | 48                | 50                 | 100        |

| すべてのレンジに適用される $C_L$ (pF) |             | 対応する最大 $C_0$ (pF) |                    |            |

| 8                        |             | 2                 |                    |            |

| 9                        |             | 2                 |                    |            |

| 10                       |             | 2                 |                    |            |

| 12                       |             | 3                 |                    |            |

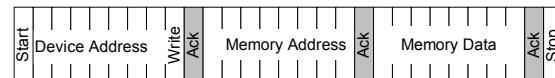

### シリアルプログラミング インタフェース プロトコル

CY27410 は、読み出しと書き込みモードで最大 400Kb/s で動作する 2 線式シリアル インタフェース用に SDAT と SCLK ピンを使用します。これは、I<sup>2</sup>C バスの規格に準拠しています。基本的な書き込みプロトコルは以下のとおりです。

スタート ビット ; 7 ビット デバイス アドレス ; R/W ビット ; スレーブ アクノリッジ (ACK); 8 ビット メモリ アドレス (MA); ACK ; 8 ビット データ ; ACK ; ( 必要な場合 ) MA+1 アドレス

の 8 ビット データ ; ACK ; MA+2 アドレスの 8 ビット データ ; ACK 等 ;... ; ストップ ビット ( 終端 )。

基本的なシリアル フォーマットを図 19 に示します。

**図 19. シリアル バス上のデータ転送シーケンス**

書き込み動作は、マスタからのデバイス アドレス ワードの後に完全な 8 ビット メモリ アドレスが続き、次にスレーブからのアクノリッジ ビット (SDAT=0/LOW) が続いたら、有効となります。次の 8 ビットは、書き込み用のデータ ワードを含めてください。データ ワードが受信された後、スレーブはもう 1 つのアクノリッジ ビット (SDAT=0/LOW) で応答し、マスタは書き込みシーケンスを STOP 条件で終了します ( 図 20 を参照 )。網掛け部分は CY27410 がドライブする信号です。

**図 20. データ フレーム アーキテクチャ ( 書込み )**

#### ランダム書き込み

#### 連続書き込み

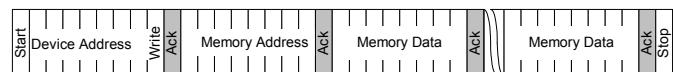

読み出し動作は、スレーブ アドレスの R/W ビットが「1」(HIGH) にセットされることを除き、書き込み動作と同じ方法で開始されます。ランダム読み出しとシーケンシャル読み出しという 2 つの基本的な読み出し動作があります。図 21 に、これらの動作を示します。

図 21. データフレームアーキテクチャ(読み出し)

マスタは、ランダム読み出し動作を通してメモリのいかなる位置にもアクセスできます。この読み出し動作タイプを実行するためには、まず読み出したいメモリアドレスをセットします。このアドレスを書き込み動作と同様に CY27410 に送信します。メモリアドレスが送信された後、マスタはアクノリッジの後に続いて START 条件を生成します。これにより内部アドレスポインターがセットされ、データがそのアドレスに格納されることなしに、書き込み動作を終了します。次に、マスタは R/W ビットを「1」にセットしてデバイスアドレスを再発行します。

すると、CY27410 はアクノリッジを発行して 8 ビットデータを送信します。マスタデバイスは転送をアクノリッジせず

(NACK)、STOP 条件を生成することで、CY27410 に送信を停止させます。

シーケンシャル読み出し動作は、最初の 8 ビットメモリデータを受信した後にマスタが STOP 条件ではなくアクノリッジを発行することを除き、ランダム読み出しと同じプロセスになります。アクノリッジを発行することにより、内部アドレスポインターがインクリメントされて、その後、次の 8 ビットメモリデータが output されます。マスタは STOP 条件ではなくアクノリッジを引き続き発行することで、スレーブデバイスメモリの内容全体を順次読み出せます。

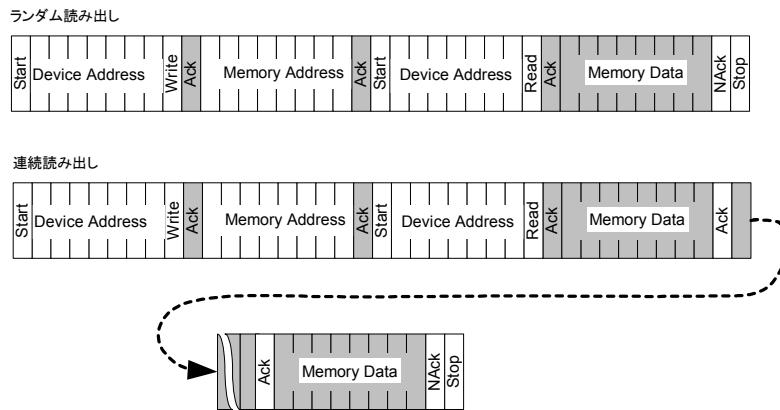

## ピン配置

CY27410 は 48 ピン QFN パッケージで提供されています。

表 3. CY27410 のピン機能

| ピン名    | I/O | タイプ        | ピン数 | ピン番号 | 機能                                                                   |

|--------|-----|------------|-----|------|----------------------------------------------------------------------|

| XIN    | I   | 水晶         | 1   | 8    | 水晶振動子接続 入力 XIN                                                       |

| XOUT   | O   | 水晶         | 1   | 9    | 水晶振動子接続 出力 XOUT                                                      |

| IN1P   | I   | LVC MOS／差動 | 1   | 6    | IN1 差動ペアの正相入力。LVC MOS 入力用の IN1 差動入力では外付け直列コンデンサが必要                   |

| IN1N   | I   | 差動         | 1   | 5    | IN1 差動ペアの逆相入力。LVC MOS 時は不使用 差動入力では外付け直列コンデンサが必要                      |

| IN2P   | I   | LVC MOS／差動 | 1   | 4    | ZDB モードのフィードバック入力。IN2 差動ペアの正相入力。LVC MOS 入力用の IN2 差動入力では外付け直列コンデンサが必要 |

| IN2N   | I   | 差動         | 1   | 3    | ZDB モードのフィードバック入力<br>IN2 差動ペアの逆相入力。LVC MOS 時は不使用 差動入力では外付け直列コンデンサが必要 |

| OUT15  | O   | LVC MOS    | 1   | 39   | LVC MOS クロック出力 15                                                    |

| OUT16  | O   | LVC MOS    | 1   | 37   | LVC MOS クロック出力 16                                                    |

| OUT11P | O   | LVC MOS／差動 | 1   | 48   | 正相出力 11 ( 差動 ) または LVC MOS 出力 11                                     |

| OUT11N | O   | 差動         | 1   | 47   | 逆相出力 11 ( 差動 )、LVC MOS の場合は OUT11P に接続                               |

| OUT12P | O   | LVC MOS／差動 | 1   | 46   | 正相出力 12 ( 差動 ) または LVC MOS クロック出力 12                                 |

| OUT12N | O   | 差動         | 1   | 45   | 逆相出力 12 ( 差動 )、LVC MOS の場合は OUT12P に接続                               |

| OUT13P | O   | LVC MOS／差動 | 1   | 43   | 正相出力 13 ( 差動 ) または LVC MOS 出力 13                                     |

| OUT13N | O   | 差動         | 1   | 42   | 逆相出力 13 ( 差動 )、LVC MOS の場合は OUT13P に接続                               |

| OUT14P | O   | LVC MOS／差動 | 1   | 41   | 正相出力 14 ( 差動 ) または LVC MOS 出力 14                                     |

| OUT14N | O   | 差動         | 1   | 40   | 逆相出力 14 ( 差動 )、LVC MOS の場合は OUT14P に接続                               |

| OUT21P | O   | LVC MOS／差動 | 1   | 13   | 正相出力 21 ( 差動 ) または LVC MOS 出力 21                                     |

| OUT21N | O   | 差動         | 1   | 14   | 逆相出力 21 ( 差動 )、LVC MOS の場合は OUT21P に接続                               |

| OUT22P | O   | LVC MOS／差動 | 1   | 15   | 正相出力 22 ( 差動 ) または LVC MOS 出力 22                                     |

| OUT22N | O   | 差動         | 1   | 16   | 逆相出力 22 ( 差動 )、LVC MOS の場合は OUT22P に接続                               |

| OUT23P | O   | LVC MOS／差動 | 1   | 18   | 正相出力 23 ( 差動 ) または LVC MOS 出力 23                                     |

| OUT23N | O   | 差動         | 1   | 19   | 逆相出力 23 ( 差動 )、LVC MOS の場合は OUT23P に接続                               |

| OUT24P | O   | LVC MOS／差動 | 1   | 20   | 正相出力 24 ( 差動 ) または LVC MOS 出力 24                                     |

| OUT24N | O   | 差動         | 1   | 21   | 逆相出力 24 ( 差動 )、LVC MOS の場合は OUT24P に接続                               |

| OUT25  | O   | LVC MOS    | 1   | 22   | LVC MOS クロック出力 25                                                    |

| OUT26  | O   | LVC MOS    | 1   | 24   | LVC MOS クロック出力 26                                                    |

| DNU    |     |            | 1   | 10   | Do Not Use                                                           |

**表 3. CY27410 のピン機能 ( 続き )**

| ピン名      | I/O  | タイプ              | ピン数   | ピン番号                            | 機能                                                                               |

|----------|------|------------------|-------|---------------------------------|----------------------------------------------------------------------------------|

| SDAT     | I/O  | LVC MOS／オープンドレイン | 1     | 33                              | I <sup>2</sup> C シリアルデータピン                                                       |

| SCLK     | I    | LVC MOS          | 1     | 34                              | I <sup>2</sup> C クロックピン                                                          |

| FS0      | I    | LVC MOS          | 1     | 30                              | 周波数選択入力端子                                                                        |

| FS1      | I    | LVC MOS          | 1     | 31                              | 周波数選択入力端子                                                                        |

| FS2      | I    | LVC MOS          | 1     | 32                              | 周波数選択入力端子                                                                        |

| VIN      | I    | アナログ             | 1     | 26                              | ADC の電圧入力                                                                        |

| VDDIO_D1 | PWR  | PWR              | 1     | 44                              | バンク 1 の差動出力 (OUT11~14) の出力電源                                                     |

| VDDIO_S1 | PWR  | PWR              | 1     | 38                              | バンク 1 の LVC MOS 出力 (OUT15~16) の出力電源                                              |

| VDDIO_D2 | PWR  | PWR              | 1     | 17                              | バンク 2 の差動出力 (OUT21~24) の出力電源                                                     |

| VDDIO_S2 | PWR  | PWR              | 1     | 23                              | バンク 2 の LVC MOS 出力 (OUT25~26) の出力電源                                              |

| VDD      | PWR  | PWR              | 9     | 1, 2, 7, 11, 12, 25, 29, 35, 36 | コア電源                                                                             |

| XRES     | I    | LVC MOS          | 1     | 27                              | リセット信号 (アクティブ LOW)                                                               |

| GND      | GND  | GND              | E-PAD |                                 | 電源グランド                                                                           |

| VCCD     | アナログ | アナログ             | 1     | 28                              | 1.8V 動作の場合、VDD に接続。<br>2.5V と 3.3V 動作の場合、VDD に接続しない。このピンと GND 間を 100nF のコンデンサで接続 |

図 22. 48 ピン QFN のピン配置

## 電気的仕様

最大定格を超えると、デバイスの寿命が短くなる可能性があります。

### 絶対最大定格

表 4. 絶対最大定格

| 記号                 | 説明                      | 条件                     | Min  | Typ | Max                  | 単位  |

|--------------------|-------------------------|------------------------|------|-----|----------------------|-----|

| V <sub>DD</sub>    | コア電源電圧                  |                        | -0.5 | -   | 4.6                  | V   |

| V <sub>DDIOX</sub> | 出力バンク電源電圧               |                        | -0.5 | -   | 4.6                  | V   |

| V <sub>IN</sub>    | 入力電圧                    | V <sub>SS</sub> を基準とする | -0.5 | -   | V <sub>DD</sub> +0.4 | V   |

| V <sub>INI2C</sub> | I <sup>2</sup> C バス入力電圧 | SCLK、SDAT ピン           | -0.5 | -   | 6                    | V   |

| T <sub>S</sub>     | 保管温度                    | 非動作中                   | -55  | -   | +150                 | °C  |

| ESD <sub>HBM</sub> | ESD ( 人体モデル )           | JEDEC JS-001-2012      | 2000 | -   | -                    | V   |

| ESD <sub>CDM</sub> | ESD ( デバイス帯電モデル )       | JEDEC JESD22-C101E     | 500  | -   | -                    | V   |

| ESD <sub>MM</sub>  | ESD ( マシン モデル )         | JEDEC JESD22-A115B     | 200  | -   | -                    | V   |

| LU                 | ラッピング                   | JEDEC JESD78D          | -    | -   | 140                  | mA  |

| UL-94              | 可燃性定格                   | V-0、1/8 インチ            | -    | -   | 10                   | ppm |

| MSL                | 耐湿性レベル                  |                        | -    | 3   | -                    |     |

### 動作温度

表 5. 動作温度

| 記号             | 説明    | 条件 | Min | Typ | Max  | 単位 |

|----------------|-------|----|-----|-----|------|----|

| T <sub>A</sub> | 周囲温度  |    | -40 | -   | +85  | °C |

| T <sub>J</sub> | 接合部温度 |    | -40 | -   | +100 | °C |

### 動作電源

表 6. 動作電源

| 記号                  | 説明               | 条件                                                              | Min  | Typ  | Max   | 単位 |

|---------------------|------------------|-----------------------------------------------------------------|------|------|-------|----|

| V <sub>DD</sub>     | コア電源電圧           | 1.8V レンジ : ±5%                                                  | 1.71 | 1.80 | 1.89  | V  |

|                     |                  | 2.5V レンジ : ±10%                                                 | 2.25 | 2.50 | 2.75  | V  |

|                     |                  | 3.3V レンジ : 5%                                                   | 3.13 | 3.3  | 3.46  | V  |

| V <sub>DDIO</sub>   | 出力電源電圧           | 1.8V レンジ : ±5%                                                  | 1.71 | 1.80 | 1.89  | V  |

|                     |                  | 2.5V レンジ : ±10%                                                 | 2.25 | 2.50 | 2.75  | V  |

|                     |                  | 3.3V レンジ : 5%                                                   | 3.13 | 3.30 | 3.46  | V  |

| I <sub>DDO</sub>    | ペア毎の供給電流         | LVPECL、出力ペアは 50Ω で V <sub>TT</sub> (V <sub>DD</sub> - 2V) に終端   | -    | -    | 38.0  | mA |

|                     |                  | LVPECL、出力ペアは 50Ω で V <sub>TT</sub> (V <sub>DD</sub> - 1.7V) に終端 | -    | -    | 27.0  | mA |

| I <sub>DDO</sub>    | ペア毎の供給電流         | LVDS、出力ペアは 100Ω で終端                                             | -    | -    | 13.25 | mA |

| I <sub>DDO</sub>    | ペア毎の供給電流         | HCSL、出力ペアは 33Ω + 49.9Ω でグランドに終端                                 | -    | -    | 26.5  | mA |

| I <sub>DDO</sub>    | ペア毎の供給電流         | CML、出力ペアは 50Ω で V <sub>DD</sub> に終端                             | -    | -    | 18.0  | mA |

| I <sub>DDO</sub>    | ペア毎の供給電流         | CMOS、10pF 負荷、33MHz                                              | -    | -    | 6.0   | mA |

| I <sub>DDPLL1</sub> | PLL 毎の消費電流       | DIVC を含む                                                        | -    | -    | 26.5  | mA |

| I <sub>DDXO</sub>   | XO / 入力ブロックの消費電流 | XO または IN1 入力バッファが有効、IN2 入力バッファが無効                              | -    | -    | 3.5   | mA |

**表 6. 動作電源 (続き)**

| 記号                    | 説明             | 条件                                                                                                                                                                                                                                                 | Min | Typ | Max  | 単位            |

|-----------------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|---------------|

| I <sub>DDPM</sub>     | 電源管理ブロックの消費電流  |                                                                                                                                                                                                                                                    | —   | —   | 2.5  | mA            |

| t <sub>PLLLOCK</sub>  | PLL ロック時間      | PLL 有効から PLL 安定 (PLL の精度が $\pm 1\text{ppm}$ ) までの時間                                                                                                                                                                                                | —   | —   | 250  | $\mu\text{s}$ |

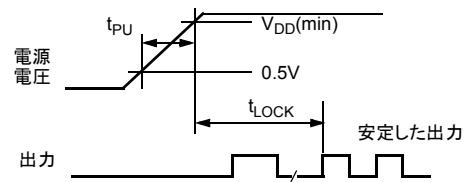

| t <sub>LOCK</sub>     | デバイス電源投入時間     | XO ベース クロック生成モードで指定の最小 $V_{DD}$ から出力安定までの時間。外部クロック入力の場合、t <sub>LOCK</sub> は水晶発振器の起動時間 (t <sub>OSCSTART</sub> ) の分減少。本仕様はリファレンスが起動時に使用可能で安定した場合に有効。<br>電源投入時にユーザーが XRES を使用し、電源立ち上がりが t <sub>PU_SR</sub> 仕様より遅い場合、本仕様は、XRES が開放されてから出力が安定するまで計算される。 | —   | —   | 10.0 | ms            |

| t <sub>OSCSTART</sub> | 水晶発振器起動時間      | 水晶発振器が電源投入されてから安定するまでの時間。水晶 FNOM = 25MHz、C1>1F                                                                                                                                                                                                     | —   | —   | 4    | ms            |

| t <sub>PU_SR</sub>    | 電源投入時の電源スルーレート | $V_{DD}$ が指定の最小電圧に到達するための電源立ち上がりレート ( 電源立ち上がりは単調でなければならない )。1V/ms より遅い電源の場合は、電源投入時に XRES を使って外部からデバイスをリセットのままにし、 $V_{DD}$ が仕様の最小値に達した後 XRES を解放すること                                                                                                | 1   | —   | 67   | V/ms          |

### チップレベルの DC 仕様

**表 7. 入力の DC 電気的仕様**

| 記号                    | 説明                | 条件                                       | Min  | Typ | Max  | 単位            |

|-----------------------|-------------------|------------------------------------------|------|-----|------|---------------|

| V <sub>IH33</sub>     | 入力 HIGH 電圧        | LVC MOS および論理入力、 $V_{DD} = 3.3\text{V}$  | 2.0  | —   | —    | V             |

| V <sub>IH25</sub>     | 入力 HIGH 電圧        | LVC MOS および論理入力、 $V_{DD} = 2.5\text{V}$  | 1.7  | —   | —    | V             |

| V <sub>IH18</sub>     | 入力 HIGH 電圧        | LVC MOS および論理入力、 $V_{DD} = 1.8\text{V}$  | 1.1  | —   | —    | V             |

| V <sub>IL33</sub>     | 入力 LOW 電圧         | LVC MOS および論理入力、 $V_{DD} = 3.3\text{V}$  | —    | —   | 0.8  | V             |

| V <sub>IL25</sub>     | 入力 LOW 電圧         | LVC MOS および論理入力、 $V_{DD} = 2.5\text{V}$  | —    | —   | 0.7  | V             |

| V <sub>IL18</sub>     | 入力 LOW 電圧         | LVC MOS および論理入力、 $V_{DD} = 1.8\text{V}$  | —    | —   | 0.5  | V             |

| V <sub>DIFF</sub>     | 差動入力              | LVDS、CML、PECL、HCSL。差動振幅、ピーク。             | 0.30 | —   | 1.45 | V             |

| DC <sub>DIFF</sub>    | デューティ比、差動入力       | 交差する点で測定                                 | 40   | 50  | 60   | %             |

| DC <sub>LVC MOS</sub> | デューティ比、LVC MOS 入力 | 1/2 $V_{DD}$ で測定                         | 40   | 50  | 60   | %             |

| I <sub>IH</sub>       | 入力 HIGH 電流        | 入力 = $V_{DD}$                            | —    | —   | 150  | $\mu\text{A}$ |

| I <sub>IL</sub>       | 入力 LOW 電流         | 入力 = GND                                 | -150 | —   | —    | $\mu\text{A}$ |

| C <sub>IN</sub>       | 入力静電容量、IN1、IN2    | 10MHz で測定、差動                             | —    | —   | 3.0  | pF            |

| V <sub>PPSINE</sub>   | AC 入力スイング ピーク     | Clipped Sine 波、通常 1000pF コンデンサを介して AC 結合 | 0.8  | 1.0 | 1.2  | V             |

| R <sub>P</sub>        | 入力プルダウン抵抗         | LVC MOS 入力                               | 75   | 115 | 170  | k $\Omega$    |

## 出力の DC 仕様

表 8. LVCMOS 出力の DC 仕様

| 記号       | 説明         | 条件     | Min            | Typ | Max | 単位 |

|----------|------------|--------|----------------|-----|-----|----|

| $V_{OH}$ | 出力 HIGH 電圧 | 4mA 負荷 | $V_{DDIO}-0.3$ | -   | -   | V  |

| $V_{OL}$ | 出力 LOW 電圧  | 4mA 負荷 | -              | -   | 0.3 | V  |

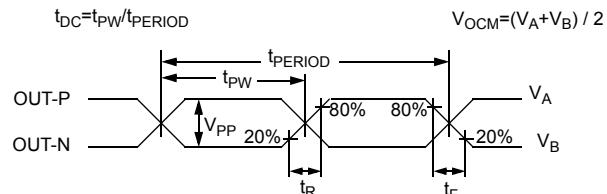

表 9. LVDS 出力の DC 仕様 ( $V_{DDIO} = 2.5V$  または  $3.3V$ )

| 記号               | 説明                              | 条件                                  | Min   | Typ   | Max   | 単位      |

|------------------|---------------------------------|-------------------------------------|-------|-------|-------|---------|

| $V_{PP}$         | LVDS 出力、AC シングルエンンド、ピーク ツー ピーク、 | 8MHz ~ 325MHz                       | 250   | -     | 510   | mV      |

| $V_{PP}$         | LVDS 出力、AC シングルエンンド、ピーク ツー ピーク、 | 325MHz ~ 700MHz                     | 200   | -     | 510   | mV      |

| $\Delta V_{PP}$  | 逆相出力状態間での $V_{PP}$ の変化          |                                     | -     | -     | 50    | mV      |

| $V_{OCM}$        | コモンモード出力電圧                      | 2.5V と 3.3V。1.8V 動作では AC 結合が必要      | 1.125 | 1.200 | 1.375 | V       |

| $\Delta V_{OCM}$ | 逆相出力状態間での VOCM の変化              |                                     | -     | -     | 50    | mV      |

| $I_{OZ}$         | 出カリーク電流                         | 出力が無効、 $V_{OUT} = 0.75V \sim 1.75V$ | -20   | -     | 20    | $\mu A$ |

表 10. LVPECL 出力の DC 仕様 ( $V_{DDIO} = 2.5V$  または  $3.3V$ )

| 記号       | 説明                               | 条件                                                             | Min                | Typ    | Max                | 単位 |

|----------|----------------------------------|----------------------------------------------------------------|--------------------|--------|--------------------|----|

| $V_{OH}$ | 出力 HIGH 電圧                       | R-term = $50\Omega$ で $V_{TT}$ ( $V_{DDIO}-2.0V$ ) に接続         | $V_{DDIO} - 1.165$ | -      | $V_{DDIO} - 0.800$ | V  |

| $V_{OL}$ | 出力 LOW 電圧                        | R-term = $50\Omega$ で $V_{TT}$ ( $V_{DDIO}-2.0V$ ) に接続         | $V_{DDIO} - 2.0$   | -      | $V_{DDIO} - 1.620$ | V  |

| $V_{PP}$ | LVPECL 出力、AC シングルエンンド、ピーク ツー ピーク | $f_{OUT} = 8MHz \sim 150MHz$<br>$f_{OUT} = 150MHz \sim 700MHz$ | 450<br>320         | -<br>- | -<br>-             | mV |

表 11. CML 出力の DC 仕様 ( $V_{DDIO} = 2.5V$  または  $3.3V$ )

| 記号       | 説明                                | 条件                                   | Min              | Typ | Max              | 単位 |

|----------|-----------------------------------|--------------------------------------|------------------|-----|------------------|----|

| $V_{OH}$ | 出力 HIGH 電圧                        | R-term = $50\Omega$ で $V_{DDIO}$ に接続 | $V_{DDIO} - 0.1$ | -   | -                | V  |

| $V_{OL}$ | 出力 LOW 電圧                         | R-term = $50\Omega$ で $V_{DDIO}$ に接続 | $V_{DDIO} - 0.7$ | -   | $V_{DDIO} - 0.3$ | V  |

| $V_{PP}$ | CML 出力時の AC ピーク ツー ピーク電圧、シングルエンンド | $f_{OUT} = 8MHz \sim 150MHz$         | 250              | -   | 700              | mV |

| $V_{PP}$ | CML 出力時の AC ピーク ツー ピーク電圧、シングルエンンド | $150 < f_{OUT} < 700MHz$             | 200              | -   | 600              | mV |

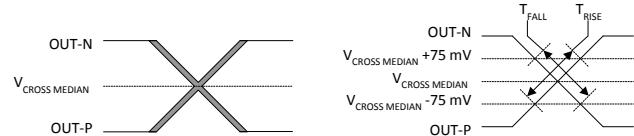

**表 12. HCSL 出力の DC 仕様 ( $V_{DDIO} = 2.5V$  または  $3.3V$ )**

| 記号               | 説明                                  | 条件           | Min | Typ | Max  | 単位 |

|------------------|-------------------------------------|--------------|-----|-----|------|----|

| $V_{OCM}$        | コモンモード出力電圧                          | コモンモード       | 350 | —   | 400  | mV |

| $V_{OHDIFF}$     | 差動出力 HIGH 電圧                        | 差動波形で測定      | 150 | —   | —    | mV |

| $V_{OLDIFF}$     | 差動出力 LOW 電圧                         | 差動波形で測定      | —   | —   | -150 | mV |

| $V_{CROSS}$      | 交差点絶対電圧                             | シングルエンド波形で測定 | 250 | —   | 550  | mV |

| $V_{CROSSDELTA}$ | クロックのすべての立上りエッジにわたる $V_{CROSS}$ の変化 | シングルエンド波形で測定 | —   | —   | 140  | mV |

**表 13. 入力周波数範囲**

| 記号              | 説明             | 条件                             | Min | Typ | Max | 単位  |

|-----------------|----------------|--------------------------------|-----|-----|-----|-----|

| $F_{CRYSTAL}$   | 水晶発振器周波数       | 基本 AT カット水晶                    | 8   | —   | 48  | MHz |

| $F_{REFERENCE}$ | リファレンス周波数      | PLL の内部リファレンス周波数               | 8   | —   | 40  | MHz |

| $F_{INCMOS}$    | LVC MOS 入力周波数  | バッファ モード、すべての PLL が無効          | 8   | —   | 250 | MHz |

| $F_{INCMOS}$    | LVC MOS 入力周波数  | バッファ モード、1 個以上の PLL が有効        | 8   | —   | 125 | MHz |

| $F_{INCMOS}$    | LVC MOS 入力周波数  | CLKGEN モード                     | 8   | —   | 250 | MHz |

| $F_{INCMOS}$    | LVC MOS 入力周波数  | ZDB モード、PLL は整数 N 型コンフィギュレーション | 8   | —   | 250 | MHz |

| $F_{INDIFF}$    | 差動クロック入力周波数    | バッファ モード、すべての PLL が無効          | 8   | —   | 700 | MHz |

| $F_{INDIFF}$    | 差動クロック入力周波数    | バッファ モード、1 個以上の PLL が有効        | 8   | —   | 125 | MHz |

| $F_{INDIFF}$    | 差動クロック入力周波数    | CLKGEN モード                     | 8   | —   | 300 | MHz |

| $F_{INDIFF}$    | 差動クロック入力周波数    | ZDB モード、PLL は整数 N 型コンフィギュレーション | 8   | —   | 300 | MHz |

| $F_{INCAS}$     | カスケード接続クロック周波数 | バッファ モードの内部カスケード周波数            | 8   | —   | 125 | MHz |

### 入力クロックの AC 仕様

**表 14. 入力クロックの AC 電気的仕様**

| 記号           | 説明                   | 条件                                 | Min | Typ | Max | 単位 |

|--------------|----------------------|------------------------------------|-----|-----|-----|----|

| $t_{CMOSDC}$ | LVC MOS 入力のデューティ比    | $1/2 V_{DD}$ の 20 ~ 80% で測定、動作保証範囲 | 40  | 50  | 60  | %  |

| $t_{DIFFDC}$ | 差動入力のデューティ比          | $V_{OCM}$ の 20 ~ 80% で測定、動作保証範囲    | 40  | 50  | 60  | %  |

| $t_{RFCMOS}$ | LVC MOS 入力の立上り／立下り時間 | $V_{DD}$ の 20 ~ 80% で測定            | —   | —   | 4   | ns |

## 出力の AC 仕様

表 15. LVC MOS 出力の AC 電気的仕様。負荷 : 15pF < 100MHz、7.5pF < 200MHz、5pF > 200MHz

| 記号                                                         | 説明               | 条件                                                                                                                                                                     | Min   | Typ | Max | 単位  |

|------------------------------------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----|-----|-----|

| <b>コモン AC 電気的仕様</b>                                        |                  |                                                                                                                                                                        |       |     |     |     |

| $t_{RFCMOS}$                                               | 立上り／立下り時間        | $f_{OUT} < 100MHz$ 、20% ~ 80%                                                                                                                                          | -     | -   | 2.0 | ns  |

| $t_{RFCMOS}$                                               | 立上り／立下り時間        | $f_{OUT} < 200MHz$ 、20% ~ 80%                                                                                                                                          | -     | -   | 1.5 | ns  |

| $t_{RFCMOS}$                                               | 立上り／立下り時間        | $f_{OUT} < 250MHz$ 、20% ~ 80%                                                                                                                                          | -     | -   | 1.3 | ns  |

| $t_{SKew}$                                                 | 出力間スキー           | 等価負荷 , $1/2 V_{IOX}$ で測定 , 同一バンク内 , 同一 PLL から出力                                                                                                                        | -     | -   | 150 | ps  |

| <b>バッファ モード</b>                                            |                  |                                                                                                                                                                        |       |     |     |     |

| $f_{OUT}$                                                  | 出力周波数            | 全ての PLL が無効                                                                                                                                                            | 8     |     | 250 | MHz |

| $f_{OUT}$                                                  | 出力周波数            | 1 個以上の PLL が動作中                                                                                                                                                        | 8     |     | 125 | MHz |

| $t_{DC}$                                                   | 出力デューティ比         | $V_{IOX}$ の 1/2 で測定<br>入力 DC=50%                                                                                                                                       | 40    | 50  | 60  | %   |

| $t_{JIT\_ADD}$                                             | 追加の RMS 位相ジッタ    | $f_{OUT} = 156.25MHz$ , 12k ~ 20MHz オフセット ,<br>$DIVL=1$ 。 $V_{DD}$ の 20% ~ 80% で入力スルーレートが 1.8V/ns                                                                      | -     | 0.7 | 1.0 | ps  |

| $t_{DELAY}$                                                | 伝播遅延             | 入力と出力間の遅延                                                                                                                                                              | -     | -   | 7.0 | ns  |

| <b>ZDB モード (IN1 = REF、IN2 に差動または LVC MOS フィードバック入力を接続)</b> |                  |                                                                                                                                                                        |       |     |     |     |

| $f_{OUT}$                                                  | 出力周波数            |                                                                                                                                                                        | 8     | -   | 250 | MHz |

| $t_{DC}$                                                   | 出力デューティ比         | 1/2 $V_{IOX}$ で測定<br>$f_{OUT} > 200MHz$ 、 $V_{DDIO} = 2.5V$ または 3.3V。<br>$f_{OUT} > 100MHz$ 、 $V_{DDIO} = 1.8V$                                                        | 40    | 50  | 60  | %   |

| $t_{DC}$                                                   | 出力デューティ比         | 1/2 $V_{IOX}$ で測定、<br>$f_{OUT} \leq 200MHz$ 、 $V_{DDIO} = 2.5V$ または 3.3V。<br>$f_{OUT} \leq 100MHz$ 、 $V_{DDIO} = 1.8V$                                                 | 45    | 50  | 55  | %   |

| $t_{OCCJ}$                                                 | サイクル ツー サイクル ジッタ | ピーク , 1 万サイクル , 1/2 $V_{IOX}$ ,<br>$f_{OUT} = 100MHz$ で測定。 $V_{DD}$ の 20% ~ 80% で入力スルーレートが 1.8V/ns。コンフィギュレーション依存                                                       | -     | -   | 50  | ps  |

| $t_{PJ}$                                                   | 周期ジッタ            | ピーク ツー ピーク , 1 万サイクル , 1/2 $V_{IOX}$ , $f_{OUT} = 100MHz$ で測定。 $V_{DD}$ の 20% ~ 80% で入力スルーレートが 1.8V/ns。コンフィギュレーション依存                                                   | -     | -   | 100 | ps  |

| $t_{PDELAY}$                                               | 伝播遅延             | $V_{IOX}$ の 1/2 で測定<br>$\pm 250ps$ ( 基板上の遅延 ( 出力から入力まで ) を含まない )。<br>最大の基板遅延 ( $t_{DELAY\_BOARD}$ ) は 2ns を超えてはならない。<br>ZDB モード中の合計遅延は $t_{DELAY\_BOARD} + t_{PDELAY}$ | -350  | -   | 350 | ps  |

| <b>CLKGEN モード</b>                                          |                  |                                                                                                                                                                        |       |     |     |     |

| $f_{OUT}$                                                  | 出力周波数            |                                                                                                                                                                        | 3     | -   | 250 | MHz |

| $f_{OUTL}$                                                 | 低周波数出力           | 1kHz まで対応 (DIVL への最大入力周波数は 48MHz)                                                                                                                                      | 0.001 | -   | 50  | MHz |

| $t_{DC}$                                                   | 出力デューティ比         | 1/2 $V_{IOX}$ で測定、<br>$f_{OUT} > 200MHz$ 、 $V_{DDIO} = 2.5V$ または 3.3V。<br>$f_{OUT} > 100MHz$ 、 $V_{DDIO} = 1.8V$                                                       | 40    | 50  | 60  | %   |

| $t_{DC}$                                                   | 出力デューティ比         | 1/2 $V_{IOX}$ で測定、<br>$f_{OUT} \leq 200MHz$ 、 $V_{DDIO} = 2.5V$ または 3.3V。<br>$f_{OUT} \leq 100MHz$ 、 $V_{DDIO} = 1.8V$                                                 | 45    | -   | 55  | %   |

表 15. LVC MOS 出力の AC 電気的仕様。負荷 : 15pF < 100MHz、7.5pF < 200MHz、5pF > 200MHz( 続き )

| 記号             | 説明             | 条件                                                                                                                                                         | Min | Typ | Max | 単位  |

|----------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-----|

| $t_{CCJ}$      | サイクルツー サイクルジッタ | ピーク , 1万サイクル , 1/2 $V_{IOX}$ , $f_{OUT} = 100\text{MHz}$ で測定。コンフィギュレーション依存                                                                                 | —   | —   | 50  | ps  |

| $t_{PJ}$       | 周期ジッタ          | ピーク ツー ピーク , 1万サイクル , 1/2 $V_{IOX}$ , $f_{OUT} = 100\text{MHz}$ で測定。25MHz 水晶の入力リファレンス。コンフィギュレーション依存                                                        | —   | —   | 100 | ps  |

| <b>SSC モード</b> |                |                                                                                                                                                            |     |     |     |     |

| $f_{OUT}$      | 出力周波数          |                                                                                                                                                            | 3   | —   | 250 | MHz |

| $t_{DC}$       | 出力デューティ比       | 1/2 $V_{IOX}$ で測定、<br>$f_{OUT} > 200\text{MHz}$ 、 $V_{DDIO} = 2.5\text{V}$ または $3.3\text{V}$<br>$f_{OUT} > 100\text{MHz}$ 、 $V_{DDIO} = 1.8\text{V}$       | 40  | 50  | 60  | %   |

| $t_{DC}$       | 出力デューティ比       | 1/2 $V_{IOX}$ で測定、<br>$f_{OUT} \leq 200\text{MHz}$ 、 $V_{DDIO} = 2.5\text{V}$ または $3.3\text{V}$<br>$f_{OUT} \leq 100\text{MHz}$ 、 $V_{DDIO} = 1.8\text{V}$ | 45  | 50  | 55  | %   |

| $t_{CCJ}$      | サイクルツー サイクルジッタ | ピーク , 1万サイクル , 1/2 $V_{IOX}$ ,<br>$f_{OUT} = 100\text{MHz}$ , スペクトラム拡散 0.5% で測定<br>25MHz 水晶の入力リファレンス。コンフィギュレーション依存                                         | —   | —   | 100 | ps  |

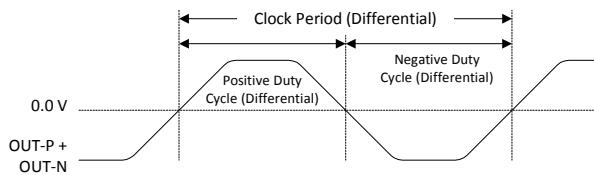

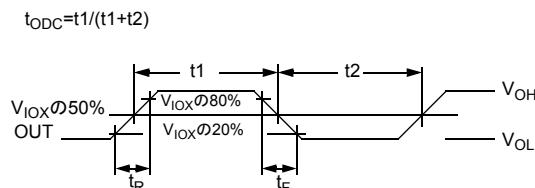

**表 16. 差動出力の AC 電気的仕様 (LVPECL、CML、LVDS) [1]**

| 記号                                              | 説明                   | 条件                                                                                                                                                                                  | Min  | Typ | Max  | 単位     |

|-------------------------------------------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|------|--------|

| <b>コモン AC 電気的仕様</b>                             |                      |                                                                                                                                                                                     |      |     |      |        |

| $t_{RF}$                                        | PECL 出力立上り／立下り時間     | AC レベルの 20% ~ 80%、622.08MHz で測定                                                                                                                                                     | -    | -   | 450  | ps     |

| $t_{RF}$                                        | CML 出力立上り／立下り時間      | AC レベルの 20% ~ 80%、622.08MHz で測定                                                                                                                                                     | -    | -   | 450  | ps     |

| $t_{RF}$                                        | LVDS 出力立上り／立下り時間     | AC レベルの 20% ~ 80%、622.08MHz で測定                                                                                                                                                     | -    | -   | 450  | ps     |

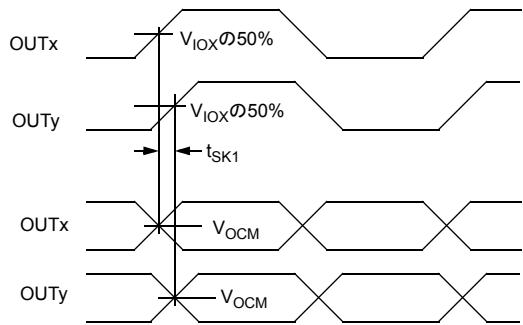

| $t_{SK1}$                                       | 出力スキュー               | 同一バンク内、同一 PLL から出力した 4 つの差動出力ペア ( 同一出力スタンダードおよび負荷条件 )                                                                                                                               | -    | -   | 100  | ps     |

| <b>パッファ モード</b>                                 |                      |                                                                                                                                                                                     |      |     |      |        |

| $t_{ODC}$                                       | 出力デューティ比             | 50% デューティ比の差動入力信号、差動信号、622.08MHz                                                                                                                                                    | 45   | 50  | 55   | %      |

| $t_{ODC}$                                       | 出力デューティ比             | 50% デューティ比の LVCMOS 入力信号、差動信号、250MHz                                                                                                                                                 | 40   | 50  | 60   | %      |

| $t_{PD}$                                        | 伝播遅延                 | 差動信号、156.25MHz で測定                                                                                                                                                                  | -    | -   | 4    | ns     |

| $t_{JIT\_ADD}$                                  | 追加の RMS 位相ジッタ        | $f_{OUT} = 156.25MHz$ , 12k ~ 20MHz オフセット , DIV1 = 1。入力差動電圧振幅 400mV でスルーレートが 4V/ns                                                                                                  | -    | -   | 400  | fs     |

| <b>ZDB モード (REF = IN1、1 出力ペアを IN2 にフィードバック)</b> |                      |                                                                                                                                                                                     |      |     |      |        |

| $t_{ODC}$                                       | 出力デューティ比             | 差動信号、100MHz で測定                                                                                                                                                                     | 45   | 50  | 55   | %      |

| $t_{CCJ}$                                       | サイクル ツー サイクル ジッタ     | ピーク、差動信号、1 万サイクル、 $f_{OUT} = 156.25MHz$ で測定。入力差動電圧振幅 400mV でスルーレートが 4V/ns ( 全ての差動出力を出力 )                                                                                            | -    | -   | 50   | ps     |

| $t_{PJ}$                                        | 周期ジッタ                | ピーク ツー ピーク、差動信号、1 万サイクル、 $f_{OUT} = 156.25MHz$ で測定。入力差動電圧振幅 400mV でスルーレートが 4V/ns ( 全ての差動出力を出力 )                                                                                     | -    | -   | 50   | ps     |

| $t_{PD}$                                        | 伝播遅延                 | 差動信号、 $f_{OUT} = 156.25MHz$ で測定。<br>$\pm 250ps$ ( 基板上の遅延 ( 出力から入力まで ) を含まない )。<br>最大の基板遅延 ( $t_{DELAY\_BOARD}$ ) は 2ns を超えてはならない。<br>ZDB モード中の合計遅延は $t_{DELAY\_BOARD} + t_{PDELAY}$ | -300 | -   | 300  | ps     |

| $t_{JRMS}$                                      | RMS 位相ジッタ            | $f_{IN} = f_{OUT} = 156.25MHz$ , 12k ~ 20MHz オフセット。入力差動電圧振幅 400mV でスルーレートが 4V/ns                                                                                                    | -    | 0.7 | 1.0  | ps     |

| PNg10k                                          | 位相ノイズ、オフセット = 10kHz  | $f_{IN} = f_{OUT} = 156.25MHz$ 。入力差動電圧振幅 400mV でスルーレートが 4V/ns                                                                                                                       | -    | -   | -110 | dBc/Hz |

| PNg100k                                         | 位相ノイズ、オフセット = 100kHz | $f_{IN} = f_{OUT} = 156.25MHz$ 。入力差動電圧振幅 400mV でスルーレートが 4V/ns                                                                                                                       | -    | -   | -119 | dBc/Hz |

| PNg1M                                           | 位相ノイズ、オフセット = 1MHz   | $f_{IN} = f_{OUT} = 156.25MHz$ 。入力差動電圧振幅 400mV でスルーレートが 4V/ns                                                                                                                       | -    | -   | -131 | dBc/Hz |

| PNg10M                                          | 位相ノイズ、オフセット = 10MHz  | $f_{IN} = f_{OUT} = 156.25MHz$ 。入力差動電圧振幅 400mV でスルーレートが 4V/ns                                                                                                                       | -    | -   | -147 | dBc/Hz |

注 :

- 差動出力用の AC パラメータは差動出力のみに対して保証されます。LVCMOS 無しの設定。

**表 16. 差動出力の AC 電気的仕様 (LVPECL、CML、LVDS)<sup>[1]</sup>( 続き )**

| 記号                | 説明                   | 条件                                                                                 | Min | Typ | Max  | 単位     |

|-------------------|----------------------|------------------------------------------------------------------------------------|-----|-----|------|--------|

| PN-SPUR           | Spur                 | PLL の更新速度以上の周波数オフセットで測定。入力差動電圧振幅 400mV でスルーレートが 4V/ns                              | -   | -   | -65  | dBc/Hz |

| <b>CLKGEN モード</b> |                      |                                                                                    |     |     |      |        |

| $t_{ODC}$         | 出力デューティ比             | 差動信号、622.08MHz で測定                                                                 | 45  | 50  | 55   | %      |

| $t_{CCJ}$         | サイクルツー サイクルジッタ       | ピーク、差動信号、1万サイクル、156.25MHz で測定。入力周波数 (24MHz ~ 40MHz) 水晶 (すべての差動出力を出力)               | -   | -   | 50   | ps     |

| $t_{PJ}$          | 周期ジッタ                | ピーク ツーピーク、差動信号、1万サイクル、156.25MHz で測定。入力周波数 (24MHz ~ 40MHz) 水晶 (すべての差動出力を出力)         | -   | -   | 50   | ps     |

| $t_{JRMS}$        | RMS 位相ジッタ            | $f_{OUT} = 156.25\text{MHz}$ 、12k ~ 20MHz オフセット                                    | -   | 0.7 | 1.0  | ps     |

| PNg10k            | 位相ノイズ、オフセット = 10kHz  | $f_{OUT} = 156.25\text{MHz}$ 。25MHz 水晶の入カリファレンス                                    | -   | -   | -110 | dBc/Hz |

| PNg100k           | 位相ノイズ、オフセット = 100kHz | $f_{OUT} = 156.25\text{MHz}$ 。25MHz 水晶の入カリファレンス                                    | -   | -   | -119 | dBc/Hz |

| PNg1M             | 位相ノイズ、オフセット = 1MHz   | $f_{OUT} = 156.25\text{MHz}$ 。25MHz 水晶の入カリファレンス                                    | -   | -   | -131 | dBc/Hz |

| PNg10M            | 位相ノイズ、オフセット = 10MHz  | $f_{OUT} = 156.25\text{MHz}$ 。25MHz 水晶の入カリファレンス                                    | -   | -   | -147 | dBc/Hz |

| PN-SPUR           | Spur                 | PLL の更新速度以上の周波数オフセットにて                                                             | -   | -   | -65  | dBc/Hz |

| <b>SSC モード</b>    |                      |                                                                                    |     |     |      |        |

| $t_{CCJ}$         | サイクルツー サイクルジッタ       | ピーク、差動信号、1万サイクル、156.25MHz で測定。入力周波数 (24MHz ~ 40MHz) 水晶、スペクトラム拡散 0.5% (すべての差動出力を出力) | -   | -   | 70   | ps     |

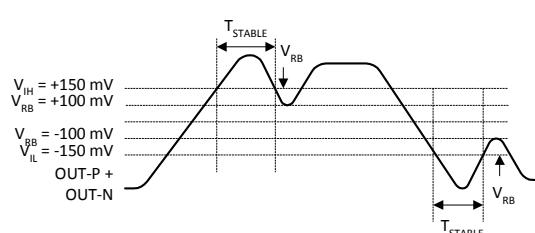

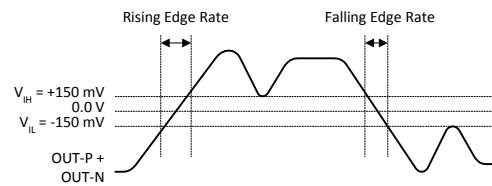

**表 17. HSCL 出力の AC 電気的仕様<sup>[2, 3]</sup>**

| 記号                  | 説明                  | 条件                             | Min   | Typ | Max    | 単位   |

|---------------------|---------------------|--------------------------------|-------|-----|--------|------|

| <b>コモン AC 電気的仕様</b> |                     |                                |       |     |        |      |

| $f_{OC}$            | 出力周波数               | HCSL                           | 96    | -   | 400    | MHz  |

| $E_R$               | 立上りエッジ速度            | -150mV ~ +150mV の差動波形で測定       | 0.6   | -   | 4      | V/ns |

| $E_F$               | 立下りエッジ速度            | -150mV ~ +150mV の差動波形で測定       | 0.6   | -   | 4      | V/ns |

| $T_{STABLE}$        | $V_{RB}$ が安定するまでの時間 | -150mV ~ +150mV の差動波形で測定       | 500   | -   | -      | ps   |

| $T_{PERIOD_AVG}$    | 平均クロック周期の精度、100MHz  | 差動波形、スペクトラム拡散が有効、下方拡散 0.5% で測定 | -300  | -   | 2800   | ppm  |

| $T_{PERIOD_ABS}$    | 絶対周期、100MHz         | 差動波形、スペクトラム拡散が有効、下方拡散 0.5% で測定 | 9.874 | -   | 10.203 | ns   |

注:

2. 差動出力用の AC パラメータは差動出力のみに対して保証されます。LVC MOS 出力無しの設定。

3. すべての出力は 100MHz のクロック (HCSL フォーマット)。ジッタは PCIE ジッタ フィルタの中で最も大きいジッタによるもの。

**表 17. HSCL 出力の AC 電気的仕様<sup>[2, 3]</sup>( 続き )**

| 記号                                              | 説明                           | 条件                                                                        | Min  | Typ | Max | 単位       |

|-------------------------------------------------|------------------------------|---------------------------------------------------------------------------|------|-----|-----|----------|

| R-FMATCHING                                     | 立上りエッジと立下りエッジの一致             | シングルエンドの波形で測定。100MHz で立上りエッジと立下りエッジの一致レート                                 | -20  | -   | +20 | %        |

| <b>パッファ モード</b>                                 |                              |                                                                           |      |     |     |          |

| T <sub>DC</sub>                                 | デューティ比                       | 差動波形で測定                                                                   | 45   | 50  | 55  | %        |

| t <sub>RMS_ADD</sub>                            | 追加される位相ノイズ                   | 入力差動電圧振幅 400mV でスルーレートが 4V/ns                                             | -    | -   | 0.4 | ps (RMS) |

| <b>ZDB モード (REF = IN1、1 出力ペアを IN2 にフィードバック)</b> |                              |                                                                           |      |     |     |          |

| T <sub>DC</sub>                                 | デューティ比                       | 差動波形で測定                                                                   | 45   | 50  | 55  | %        |

| T <sub>CCJITTER</sub>                           | サイクルツーサイクルジッタ                | ピーク, 差動信号, 1万サイクル, 100MHz で測定。差動電圧振幅 400mV で入力スルーレートが 4V/ns (すべての差動出力を出力) | -    | -   | 50  | ps       |

| J <sub>RMS</sub>                                | PCIe 3.0 コモンクロックモード。ランダム ジッタ | PCIe Gen3 フィルタ。差動電圧振幅 400mV で入力スルーレートが 4V/ns                              | -    | 0.7 | 1.0 | ps (RMS) |

| t <sub>PD</sub>                                 | 伝播遅延                         | 早い／遅いオプションが無効                                                             | -300 | -   | 300 | ps       |

| <b>CLKGEN モード</b>                               |                              |                                                                           |      |     |     |          |

| T <sub>DC</sub>                                 | デューティ比                       | 差動波形で測定                                                                   | 45   | 50  | 55  | %        |

| T <sub>CCJITTER</sub>                           | サイクルツーサイクルジッタ                | ピーク, 差動信号, 1万サイクル, 100MHz で測定。入力周波数 (24MHz ~ 40MHz) 水晶 (すべての差動出力を出力)      | -    | -   | 50  | ps       |

| J <sub>RMS</sub>                                | PCIe 3.0 コモンクロックモード。ランダム ジッタ | REF = 25MHz 水晶、f <sub>OUT</sub> = 100MHz、PCIe Gen3 フィルタ                   | -    | 0.7 | 1.0 | ps       |

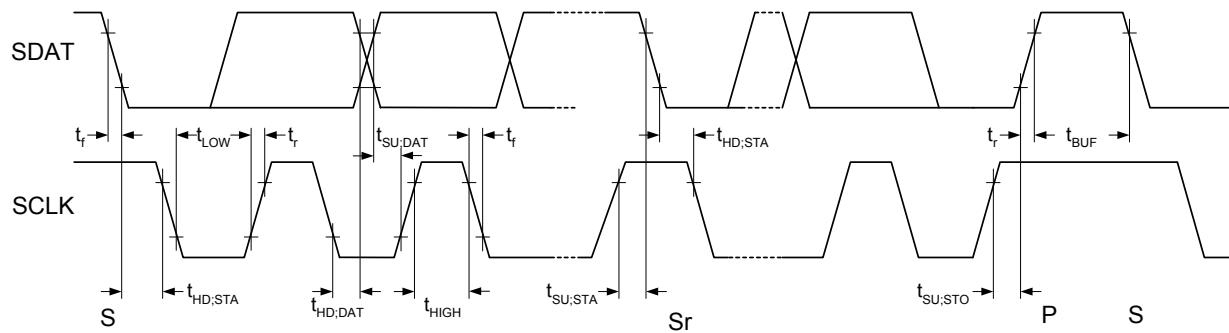

**表 18. AC I<sup>2</sup>C 仕様**

| 記号                  | 説明                        | 条件 | Min | Typ | Max | 単位  |

|---------------------|---------------------------|----|-----|-----|-----|-----|

| f <sub>SCK</sub>    | SCK クロック周波数               |    | 0   | -   | 400 | kHz |

| t <sub>HD:STA</sub> | START 条件のホールド時間           |    | 0.6 | -   | -   | μs  |

| t <sub>LOW</sub>    | SCK クロック LOW 期間           |    | 1.3 | -   | -   | μs  |

| t <sub>HIGH</sub>   | SCK クロック HIGH 期間          |    | 0.6 | -   | -   | μs  |

| t <sub>SU:STA</sub> | 反復 START 条件のセットアップ時間      |    | 0.6 | -   | -   | μs  |

| t <sub>HD:DAT</sub> | データ ホールド時間                |    | 0   | -   | -   | μs  |

| t <sub>SU:DAT</sub> | データ セットアップ時間              |    | 100 | -   | -   | ns  |

| t <sub>R</sub>      | 立上り時間                     |    | -   | -   | 300 | ns  |

| t <sub>F</sub>      | 立下り時間                     |    | -   | -   | 300 | ns  |

| t <sub>SU:STO</sub> | STOP 条件のセットアップ時間          |    | 0.6 | -   | -   | μs  |

| t <sub>BUF</sub>    | STOP 条件と START 条件間のバス空き時間 |    | 1.3 | -   | -   | μs  |

**表 19. スペクトラム拡散仕様**

| 記号               | 説明                 | 条件      | Min | Typ | Max | 単位  |

|------------------|--------------------|---------|-----|-----|-----|-----|

| F <sub>MOD</sub> | 変調速度               |         | 30  | —   | 60  | kHz |

| SSper            | スペクトラム拡散量          | 合計パーセント | 0.1 | —   | 5.0 | %   |

| SSStep           | スペクトラム拡散ステップ パーセント |         | —   | 0.1 | —   | %   |

**表 20. 出力選択仕様**

| 記号               | 説明       | 条件                                                      | Min | Typ | Max  | 単位 |

|------------------|----------|---------------------------------------------------------|-----|-----|------|----|

| t <sub>FS</sub>  | 周波数切換え時間 | OUT13, 14, 23, 24 の周波数切換え時間。両方の PLL 変更なし (MUX 選択ビットを変更) | —   | —   | 500  | μs |

| t <sub>FS</sub>  | 周波数切換え時間 | 出力周波数切換え時間 (DIVO 値を変更)                                  | —   | —   | 500  | μs |

| t <sub>FS</sub>  | 周波数切換え時間 | 全ての出力用の周波数切換え時間 PLL 値の変更                                | —   | —   | 1000 | μs |

| t <sub>FS</sub>  | 出力オン時間   | FS から出力が有効になる時間。PLL 変更なし (OE か MUX を変更)                 | —   | —   | 500  | μs |

| t <sub>FS</sub>  | 出力オン時間   | FS から出力が有効になる時間。電源遮断から PLL を再開                          | —   | —   | 1000 | μs |

| t <sub>OFF</sub> | 出力オフ時間   | FS から出力が無効になる時間。PLL 変更なし (OE か MUX を変更)                 | —   | —   | 500  | μs |

**表 21. 不揮発性メモリの仕様**

| 記号                    | 説明              | 条件                 | Min  | Typ | Max | 単位   |

|-----------------------|-----------------|--------------------|------|-----|-----|------|

| DRET                  | 不揮発性メモリのデータ保持期間 |                    | 10   | —   | —   | 年    |

| PROG <sub>CYCLE</sub> | プログラム サイクル      | 不揮発性メモリのプログラム サイクル | 100K | —   | —   | サイクル |

**表 22. その他の仕様**

| 記号                 | 説明              | 条件 | Min | Typ | Max | 単位 |

|--------------------|-----------------|----|-----|-----|-----|----|

| t <sub>XRES</sub>  | XRES LOW 時間     |    | 10  | —   | —   | μs |

| T <sub>PROG</sub>  | フラッシュ プログラミング温度 |    | 5   | —   | 55  | °C |

| C <sub>INADC</sub> | VIN ピンの入力静電容量   |    | —   | —   | 10  | pF |

**表 23. 熱抵抗**

| 記号              | 説明               | 条件                                                   | 48-pin QFN | 単位   |

|-----------------|------------------|------------------------------------------------------|------------|------|

| θ <sub>JA</sub> | 熱抵抗<br>(接合部～周囲)  | 試験条件は、EIA / JESD51 にしたがった標準試験法および熱インピーダンス測定の手順に従います。 | 15.64      | °C/w |

| θ <sub>JC</sub> | 熱抵抗<br>(接合部～ケース) |                                                      | 2.21       | °C/w |

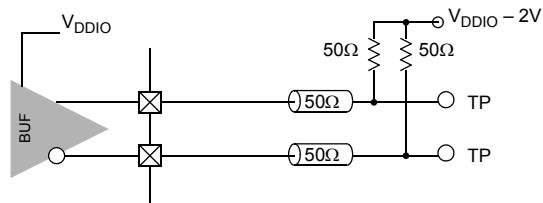

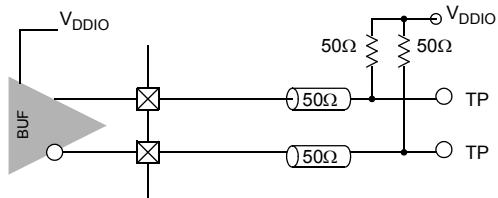

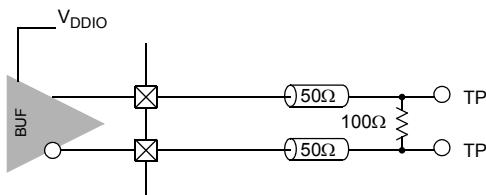

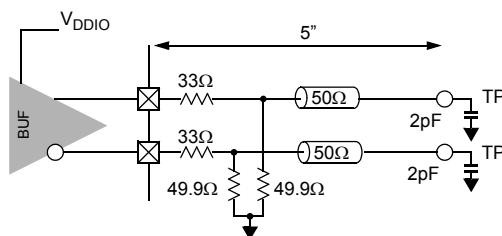

## テストと測定回路

図 23. LVPECL 出力の負荷とテスト回路

図 25. CML 出力の負荷とテスト回路

図 24. LVDS 出力の負荷とテスト回路

図 26. HCSL 出力負荷とテスト回路

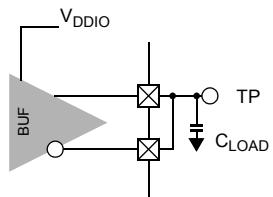

図 27. LVCMOS 出力負荷とテスト回路

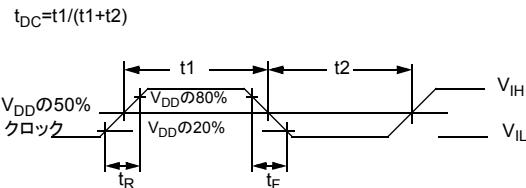

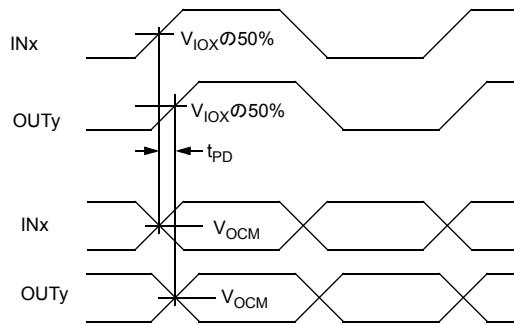

## 電圧とタイミングの定義

図 28. LVC MOS 入力の定義

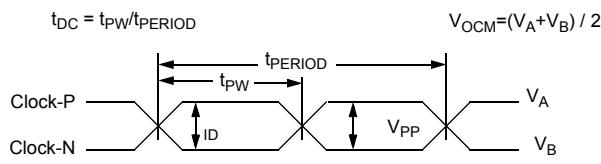

図 30. 差動入力の定義

図 32. スキューの定義

図 34. 出力イネーブル／ディセーブル／周波数選択のタイミング

図 36. HCSL 差動の測定点

デューティ比および周期

図 29. LVC MOS 出力の定義

図 31. 差動出力の定義

図 33. 伝播遅延の定義

図 35. HCSL シングルエンドの測定点 - 2

立上り時間と立下り時間が一致

図 37. リングバック用の HCSL 差動測定

図 38. HCSL の立上りと立下り時間

立上りと立下り時間

図 39. 電源立上げと PLL ロック時間

図 40. ファスト／標準モードの I<sup>2</sup>C バス タイミングの定義

## パッケージ情報

本節では、CY27410 デバイスのパッケージ仕様を示します。

注：EPAD は、熱抵抗の低減および電源グランドのためにグランドに接続する必要があります。

図 41. 48 ピン QFN (7 × 7 × 1.00mm) LT48D 5.5 × 5.5 EPAD (Sawn) パッケージ図

### NOTES:

1. HATCH AREA IS SOLDERABLE EXPOSED METAL.

2. REFERENCE JEDEC#: MO-220

3. PACKAGE WEIGHT: REFER TO PMDD SPEC.

4. ALL DIMENSIONS ARE IN MM [MIN/MAX]

5. PACKAGE CODE

| PART # | DESCRIPTION |

|--------|-------------|

| LT48D  | LEAD FREE   |

001-45616 \*F

QFN パッケージを取り付ける際の推奨寸法については、サイプレスの [アプリケーション ノート「AN72845 - Design Guidelines for Cypress Quad Flat No Extended Lead \(QFN\) Packaged Devices」](#) を参照してください。

## はんだリフローの仕様

表 24 に、超えてはならないはんだリフロー温度限界値を示します。

表 24. はんだリフローの仕様

| パッケージ     | 最高ピーク温度 ( $T_C$ ) | $T_C-5^\circ\text{C}$ 以上の最大時間 |

|-----------|-------------------|-------------------------------|

| 48 ピン QFN | 260°C             | 30 秒                          |

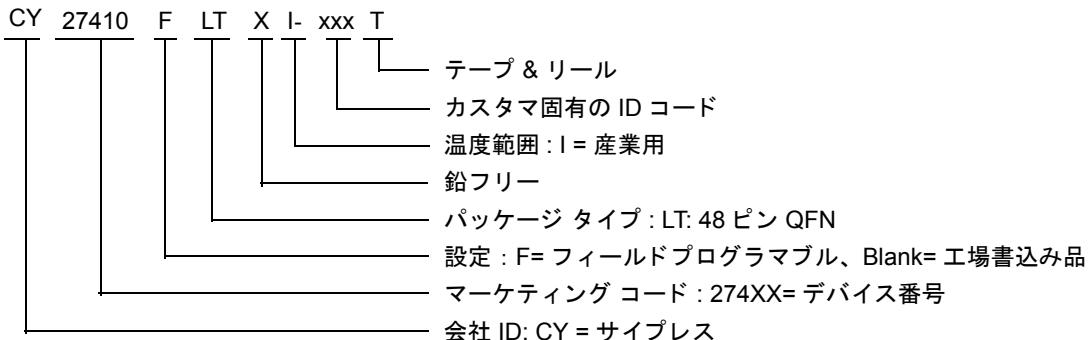

## 注文情報

以下の表に、CY27410 デバイスの主なパッケージの機能と注文コードを示します。

表 25. 注文情報

| 製品番号             | 設定           | パッケージ               | タイプ                |

|------------------|--------------|---------------------|--------------------|

| CY27410FLTXI     | フィールドプログラマブル | 48 ピン QFN           | 産業用, -40°C ~ +85°C |

| CY27410FLTXIT    | フィールドプログラマブル | 48 ピン QFN テープ & リール | 産業用, -40°C ~ +85°C |

| CY27410LTXI-xxx  | 工場書込み        | 48 ピン QFN           | 産業用, -40°C ~ +85°C |

| CY27410LTXI-xxxT | 工場書込み        | 48 ピン QFN テープ & リール | 産業用, -40°C ~ +85°C |

## 注文コードの定義

## 略語

表 26. 本書で使用する略語

| 略語               | 説明                                                               |

|------------------|------------------------------------------------------------------|

| AC               | alternating current ( 交流電流 )                                     |

| ADC              | analog-to-digital converter<br>( アナログ～デジタル変換器 )                  |

| API              | application programming interface ( アプリケーション プログラミング インタフェース )   |

| CML              | current-mode logic ( 電流モード ロジック )                                |

| CMOS             | complementary metal oxide semiconductor<br>( 相補型金属酸化膜半導体 )       |

| DC               | direct current ( 直流 )                                            |

| ESD              | electrostatic discharge ( 静電気放電 )                                |

| FS               | frequency select ( 周波数選択 )                                       |

| GUI              | graphical user interface<br>( グラフィカル ユーザー インタフェース )              |

| HCSL             | high-speed current steering logic<br>( 高速電流ステアリング ロジック )         |

| I <sup>2</sup> C | inter-integrated circuit<br>( インター インテグレーテッド サーキット )             |

| I/O              | input/output ( 入力／出力 )                                           |

| ISSP             | in-system serial programming<br>( インシステム シリアル プログラミング )          |

| JEDEC            | Joint Electron Devices Engineering Council<br>( 半導体技術協会 )        |

| LDO              | low dropout (regulator)<br>( 低ドロップアウト ( レギュレータ ) )               |

| LSB              | least-significant bit ( 最下位ビット )                                 |

| LVCMOS           | low voltage complementary metal oxide semiconductor ( 低電圧 CMOS ) |

| LVDS             | low-voltage differential signals ( 低電圧差動信号 )                     |

| LVPECL           | low-voltage positive emitter-coupled logic<br>( 低電圧正エミッタ結合論理 )   |

| MSB              | most-significant bit ( 最上位ビット )                                  |

| NV               | non-volatile ( 不揮発性 )                                            |

| NZDB             | non-zero delay buffer ( 非ゼロ遅延バッファ )                              |

| OE               | output enable ( 出力イネーブル )                                        |

| PCIe             | PCI express ( ピーシーアイ エクスプレス )                                    |

| POR              | power on reset ( パワーオン リセット )                                    |

| PSoC®            | Programmable System-on-Chip<br>( プログラマブル システムオンチップ )             |

| QFN              | quad flat no-lead<br>( クアッド フラット リードなしパッケージ )                    |

| RMS              | root mean square ( 二乗平均平方根 )                                     |

| SCLK             | serial I <sup>2</sup> C clock ( シリアル I <sup>2</sup> C クロック )     |

| SDAT             | serial I <sup>2</sup> C data ( シリアル I <sup>2</sup> C データ )       |

| TSSOP            | thin shrunk small outline package<br>( 薄型シュリンク 小型パッケージ )         |

| USB              | universal serial bus<br>( ユニバーサル シリアル バス )                       |

| XTAL             | crystal ( 水晶 )                                                   |

| ZDB              | zero delay buffer ( ゼロ遅延バッファ )                                   |

## 本書の表記法

### 測定単位

表 27. 測定単位

| 記号   | 測定単位                   |

|------|------------------------|

| °C   | 摂氏温度                   |

| dBc  | キャリア レベルを基準としたデシベル     |

| fF   | フェムト フラッド              |

| fs   | フェムト 秒                 |

| g    | グラム                    |

| GHz  | ギガヘルツ                  |

| Hz   | ヘルツ                    |

| KHz  | キロヘルツ                  |

| Ksps | キロサンプル毎秒               |

| kΩ   | キロオーム                  |

| MHz  | メガヘルツ                  |

| MΩ   | メガオーム                  |

| μA   | マイクロアンペア               |

| μF   | マイクロ フラッド              |

| μH   | マイクロヘンリー               |

| μs   | マイクロ秒                  |

| μW   | マイクロワット                |

| mA   | ミリアンペア                 |

| ms   | ミリ秒                    |

| mV   | ミリボルト                  |

| nA   | ナノアンペア                 |

| nF   | ナノ フラッド                |

| ns   | ナノ秒                    |

| nV   | ナノボルト                  |

| Ω    | オーム                    |

| pA   | ピコアンペア                 |

| pF   | ピコ フラッド                |

| pp   | ピーク ツー ピーク             |

| ppm  | 100 万分の 1              |

| ppb  | 10 億分の 1               |

| ps   | ピコ秒                    |

| sps  | 1 秒あたりのサンプル数           |

| σ    | シグマ : 標準偏差値を 1 単位とした表記 |

| V    | ボルト                    |

| W    | ワット                    |

## 改訂履歴

文書名 : CY27410、4-PLL スペクトラム拡散クロックジェネレータ

文書番号 : 001-96106

| 版  | ECN     | 変更者  | 発行日        | 変更内容                                                     |

|----|---------|------|------------|----------------------------------------------------------|

| ** | 4669732 | HZEN | 03/05/2015 | これは英語版 001-89074 Rev. *C を翻訳した日本語版 001-96106 Rev. ** です。 |

| *A | 4928474 | HZEN | 09/28/2015 | これは英語版 001-89074 Rev. *G を翻訳した日本語版 001-96106 Rev. *A です。 |

| *B | 5141074 | XHT  | 02/17/2016 | これは英語版 001-89074 Rev. *J を翻訳した日本語版 001-96106 Rev. *B です。 |

| *C | 5658410 | XHT  | 03/14/2017 | これは英語版 001-89074 Rev. *K を翻訳した日本語版 001-96106 Rev. *C です。 |

| *D | 6100831 | SSAS | 03/20/2018 | これは英語版 001-89074 Rev. *L を翻訳した日本語版 001-96106 Rev. *D です。 |

## セールス、ソリューションおよび法律情報

### ワールドワイドな販売と設計サポート

サイプレスは、事業所、ソリューションセンター、メーカー代理店および販売代理店の世界的なネットワークを保持しています。お客様の最寄りのオフィスについては、[サイプレスのロケーションページ](#)をご覧ください。

#### 製品

Arm® Cortex® Microcontrollers

[cypress.com/arm](http://cypress.com/arm)

車載用

[cypress.com/automotive](http://cypress.com/automotive)

クロック & バッファ

[cypress.com/clocks](http://cypress.com/clocks)

インターフェース

[cypress.com/interface](http://cypress.com/interface)

IoT (モノのインターネット)

[cypress.com/iot](http://cypress.com/iot)

メモリ

[cypress.com/memory](http://cypress.com/memory)

マイクロコントローラ

[cypress.com/mcu](http://cypress.com/mcu)

PSoC

[cypress.com/psoc](http://cypress.com/psoc)

電源用 IC

[cypress.com/pmic](http://cypress.com/pmic)

タッチ センシング

[cypress.com/touch](http://cypress.com/touch)

USB コントローラー

[cypress.com/usb](http://cypress.com/usb)

ワイヤレス

[cypress.com/wireless](http://cypress.com/wireless)

#### PSoC® ソリューション

[PSoC 1](#) | [PSoC 3](#) | [PSoC 4](#) | [PSoC 5LP](#) | [PSoC 6 MCU](#)

#### サイプレス開発者コミュニティ

[コミュニティ](#) | [Projects](#) | [ビデオ](#) | [ブログ](#) | [トレーニング](#) | [Components](#)

#### テクニカル サポート

[cypress.com/support](http://cypress.com/support)

© Cypress Semiconductor Corporation, 2013-2018. 本書面は、Cypress Semiconductor Corporation 及び Spansion LLC を含むその子会社（以下「Cypress」という。）に帰属する財産である。本書面（本書面に含まれ又は言及されているあらゆるソフトウェア若しくはファームウェア（以下「本ソフトウェア」という。）を含む）は、アメリカ合衆国及び世界のその他の国における知的財産法令及び条約に基づき Cypress が所有する。Cypress はこれらの法令及び条約に基づく全ての権利を留保し、本段落で特に記載されているものを除き、その特許権、著作権、商標権又はその他の知的財産権のライセンスを一切許諾しない。本ソフトウェアにライセンス契約書が伴っておらず、かつ Cypress との間で別途本ソフトウェアの使用方法を定める書面による合意がない場合、Cypress は、(1) 本ソフトウェアの著作権に基づき、(a) ソースコード形式で提供されている本ソフトウェアについて、Cypress ハードウェア製品と共に用いるためにのみ、かつ組織内部でのみ、本ソフトウェアの修正及び複製を行うこと、並びに(b) Cypress のハードウェア製品ユニットに用いるためにのみ、（直接又は再販売者及び販売代理店を介して間接のいずれかで）本ソフトウェアをバイナリコード形式で外部エンドユーザーに配布すること、並びに(2) 本ソフトウェア（Cypressにより提供され、修正がなされていないもの）が抵触するCypressの特許権のクレームに基づき、Cypress ハードウェア製品と共に用いるためにのみ、本ソフトウェアの作成、利用、配布及び輸入を行うことについての非独占的で譲渡不能な一身専属的ライセンス（サブライセンスの権利を除く）を付与する。本ソフトウェアのその他の使用、複製、修正、変換又はコンパイルを禁止する。

適用される法律により許される範囲内で、Cypress は、本書面又はいかなる本ソフトウェア若しくはこれに伴うハードウェアに関してても、明示又は默示をとわず、いかなる保証（商品性及び特定の目的への適合性の默示の保証を含むがこれらに限られない）も行わない。いかなるコンピューティングデバイスも絶対に安全ということはない。従って、Cypress のハードウェアまたはソフトウェア製品に講じられたセキュリティ対策にもかかわらず、Cypress は、Cypress 製品への権限のないアクセスまたは使用といったセキュリティ違反から生じる一切の責任を負わない。加えて、本書面に記載された製品には、エラッタと呼ばれる設計上の欠陥またはエラーが含まれている可能性があり、公表された仕様とは異なる動作をする場合がある。適用される法律により許される範囲内で、Cypress は、別途通知することなく、本書面を変更する権利を留保する。Cypress は、本書面に記載のある、いかなる製品若しくは回路の適用又は使用から生じる一切の責任を負わない。本書面で提供されたあらゆる情報（あらゆるサンプルデザイン情報又はプログラムコードを含む）は、参照目的のためにのみに提供されたものである。この情報で構成するあらゆるアプリケーション及びその結果としてのあらゆる製品の機能性及び安全性を適切に設計、プログラム、かつテストすることは、本書面のユーザーの責任において行われるものとする。Cypress 製品は、兵器、兵器システム、原子力施設、生命維持装置若しくは生命維持システム、蘇生用の設備及び外科的移植を含むその他の医療機器若しくは医療システム、汚染管理若しくは有害物質管理の運用のために設計され若しくは意図されたシステムの重要な構成部分としての使用、又は装置若しくはシステムの不具合が人身傷害、死亡若しくは物的損害を生じさせるようなその他の使用（以下「本目的外使用」という。）のためには設計、意図又は承認されていない。重要な構成部分とは、それの不具合が装置若しくはシステムの不具合を生じさせるか又はその安全性若しくは実効性に影響すると合理的に予想できるような装置若しくはシステムのあらゆる構成部分をいう。Cypress 製品のあらゆる本目的外使用から生じ、若しくは本目的外使用に関連するいかなる請求、損害又はその他の責任についても、Cypress はその全部又は一部をとわず一切の責任を負わず、かつ Cypress はそれら一切から本書により免除される。Cypress は Cypress 製品の本目的外使用から生じ又は本目的外使用に関連するあらゆる請求、費用、損害及びその他の責任（人身傷害又は死亡に基づく請求を含む）から免責補償される。

Cypress、Cypress のロゴ、Spansion、Spansion のロゴ及びこれらの組み合わせ、WICED、PSoC、CapSense、EZ-USB、F-RAM、及び Traveo は、米国及びその他の国における Cypress の商標又は登録商標である。Cypress のより完全な商標のリストは、[cypress.com](http://cypress.com) を参照すること。その他の名称及びブランドは、それぞれの権利者の財産として権利主張がなされている可能性がある。