## 汎用フラッシュ プログラマブル 1PLL クロック ジェネレータ

### 特長

- 集積された位相同期回路 (PLL)

- 民生用および産業用動作温度範囲

- フラッシュプログラマブル

- フィールドプログラマブル

- 低スキュー、低ジッタ、高精度出力

- 2.5V 出力のオプションで、3.3V 電圧で動作

- 16 ピン TSSOP パッケージ (CY22050)

- 16 ピン TSSOP パッケージ (NiPdAu リード 仕上げ処理済み)

(CY220501)

- 入力周波数範囲 :

- 8MHz ~ 30MHz (外部水晶)

- 1MHz ~ 133MHz (直接駆動クロック)

- 出力周波数範囲 :

- 民生用温度範囲

- 8kHz ~ 200MHz (3.3V)

- 8kHz ~ 166.6MHz (2.5V)

- 産業用温度範囲

- 8kHz ~ 166.6MHz (3.3V)

- 8kHz ~ 150MHz (2.5V)

### 機能の詳細

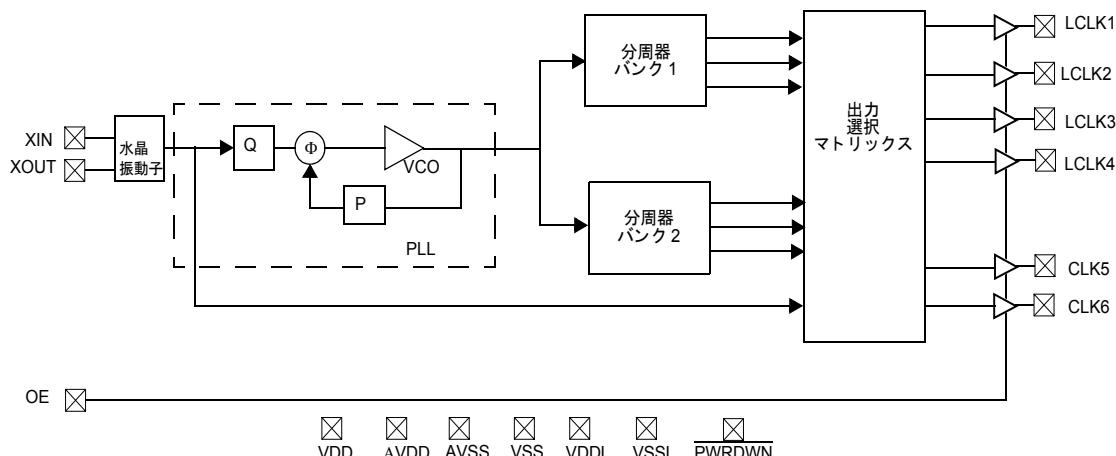

CY22050 は、ネットワーキング、テレコミュニケーション、データコム、および他の汎用アプリケーションで使用するため設計されているプログラマブルクロックジェネレータです。CY22050 は、3.3V 電源を消費する 16 ピン TSSOP に最大 6 個までのコンフィギュレーション可能な出力を提供します。内蔵のリファレンス振動子は、8MHz ~ 30MHz の水晶、または 1MHz ~ 133MHz の外部クロック信号を使用するために設計されています。

CY22050 は、6 つのプログラム可能な出力クロックを駆動している 1 つの PLL を持っています。出力クロックは、PLL またはリファレンス周波数 (REF) から派生します。出力ポスト分周器は、両方に適用可能です。低消費電力のポータブルアプリケーションの多くで使用するために出力の内の 4 つを 3.3V か 2.5V に接続することができます。

CY220501 は、NiPdAu リードの仕上げで処理された CY22050 です。

### 論理ブロック図

## 目次

|                               |    |

|-------------------------------|----|

| ピン配置 .....                    | 3  |

| ピン機能 .....                    | 3  |

| プログラミングの説明 .....              | 4  |

| CY22050F のフィールド プログラミング ..... | 4  |

| CyberClocks™ ソフトウェア .....     | 4  |

| CY3672 開発キット .....            | 4  |

| アプリケーション .....                | 4  |

| 制御ジッタ .....                   | 4  |

| CY22050 周波数の計算 .....          | 5  |

| クロック出力の設定：                    |    |

| クロスポイントスイッチマトリクス .....        | 5  |

| リファレンス水晶入力 .....              | 6  |

| 水晶駆動レベルと電源 .....              | 6  |

| 絶対最大条件 .....                  | 6  |

| 推奨動作範囲 .....                  | 7  |

| 推奨の水晶仕様 .....                 | 7  |

| DC 電気的特性 .....                | 8  |

| AC 電気的特性 .....                | 8  |

| テスト回路 .....                   | 9  |

| スイッチング波形 .....                | 9  |

| 注文情報 .....                    | 10 |

| 可能なコンフィギュレーション .....          | 10 |

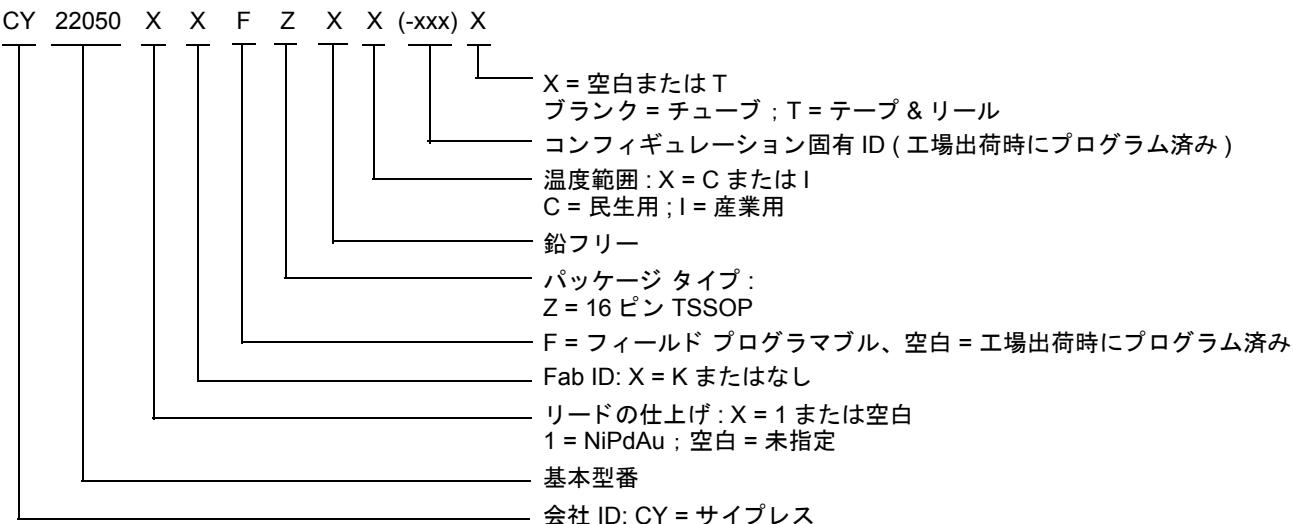

| 注文コードの定義 .....                | 10 |

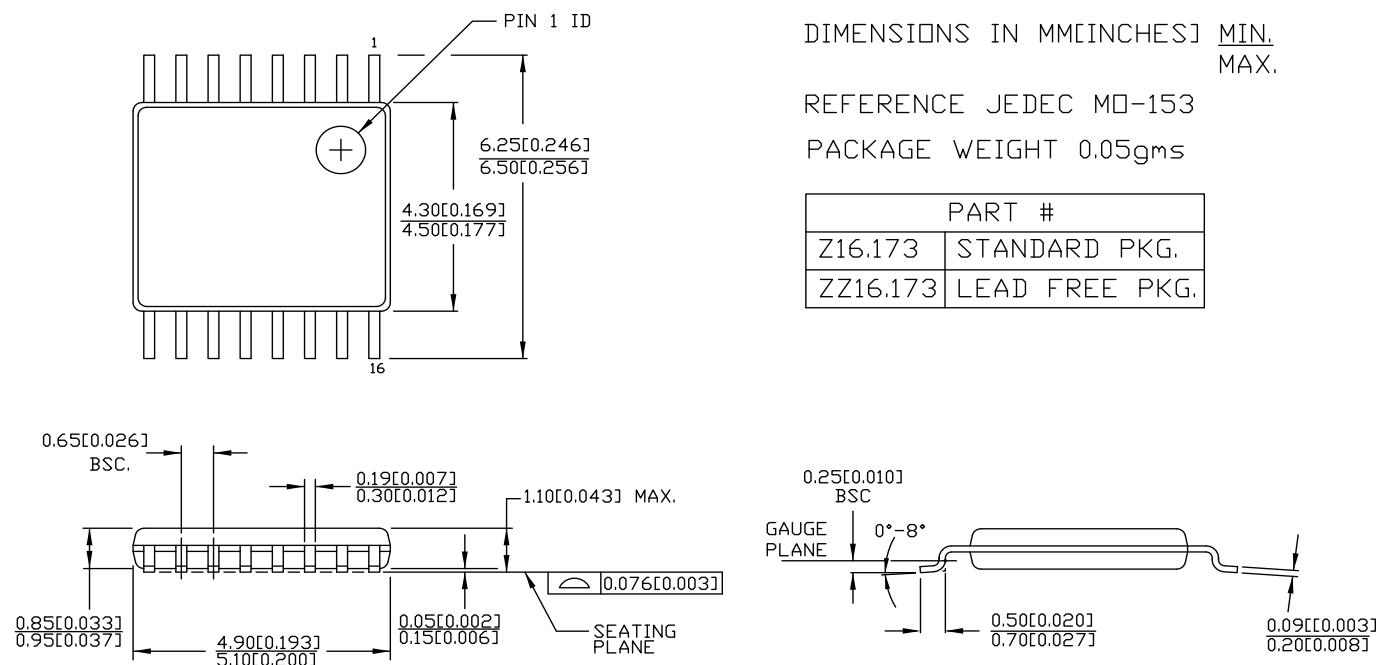

| 16 ピン TSSOP パッケージの特性 .....    | 11 |

| パッケージ図および寸法 .....             | 11 |

| 略語 .....                      | 12 |

| 本書の表記法 .....                  | 12 |

| 測定単位 .....                    | 12 |

| 改訂履歴 .....                    | 13 |

| セールス、ソリューションおよび法律情報 .....     | 14 |

| ワールドワイドな販売と設計サポート .....       | 14 |

| 製品 .....                      | 14 |

| PSoC® ソリューション .....           | 14 |

| サイプレス開発者コミュニティ .....          | 14 |

| テクニカル サポート .....              | 14 |

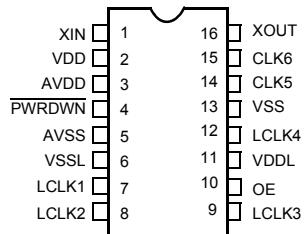

## ピン配置

図 1. 16 ピン TSSOP のピン配置

## ピン機能

| 名称         | ピン番号 | 説明                                                                                                                               |

|------------|------|----------------------------------------------------------------------------------------------------------------------------------|

| XIN        | 1    | リファレンス電圧入力。水晶振動子 (8MHz ~ 30MHz) か、または外部クロック (1MHz ~ 133MHz) により駆動される。メーカー、プロセス、性能や品質に応じて水晶振動子を最大限柔軟に選択することを可能にするプログラマブル入力負荷コンデンサ |

| VDD        | 2    | 3.3V 電源電圧                                                                                                                        |

| AVDD       | 3    | 3.3V アナログ電源電圧                                                                                                                    |

| PWRDWN [1] | 4    | 電源切断。ピン 4 は LOW に駆動されると、CY22050 はシャットダウン モードに入る                                                                                  |

| AVSS       | 5    | アナログ ブロックのグランド                                                                                                                   |

| VSSL       | 6    | LCLK グランド                                                                                                                        |

| LCLK1      | 7    | $V_{DDL}$ 電圧レベル (3.3V あるいは 2.5V) でのコンフィギュレーション可能なクロック出力 1                                                                        |

| LCLK2      | 8    | $V_{DDL}$ 電圧レベル (3.3V あるいは 2.5V) でのコンフィギュレーション可能なクロック出力 2                                                                        |

| LCLK3      | 9    | $V_{DDL}$ 電圧レベル (3.3V あるいは 2.5V) でのコンフィギュレーション可能なクロック出力 3                                                                        |

| OE [1]     | 10   | 出カイネーブル ピン 10 を LOW に駆動すると、すべての出力はトライステート状態になる                                                                                   |

| VDDL       | 11   | LCLK 電源電圧 (2.5V あるいは 3.3V)                                                                                                       |

| LCLK4      | 12   | $V_{DDL}$ 電圧レベル (3.3V あるいは 2.5V) でのコンフィギュレーション可能なクロック出力 4                                                                        |

| VSS        | 13   | グランド                                                                                                                             |

| CLK5       | 14   | コンフィギュレーション可能なクロック出力 5 (3.3V)                                                                                                    |

| CLK6       | 15   | コンフィギュレーション可能なクロック出力 6 (3.3V)                                                                                                    |

| XOUT [2]   | 16   | リファレンス出力                                                                                                                         |

### 注

1. CY22050 は、内部プルアップとプルダウン抵抗を持っていません。PWRDWN と OE ピンは、必要に応じて駆動されるか、または電源やグランドに接続される必要があります。

2. XIN が外部のクロック ソースにより駆動される場合、XOUT をフローティング状態にします。

## プログラミングの説明

### CY22050F のフィールド プログラミング

CY22050 は、パッケージ レベル、すなわち、PCB に搭載される前のプログラマ ソケットでプログラムされます。CY22050 は、フラッシュ メモリ技術ベースのものであるため、最大 100 回再プログラムすることができます。これにより、デザインを速く容易に変更したり、製品をアップデートしたり、旧式かつ時代遅れの在庫製品による問題を回避することができます。

サンプルと少量のプロトタイプを CY3672 プログラムでプログラムすることができます。サイプレスの付加価値流通業者と BP Microsystems、HiLo Systems、および他のメーカーからの第 3 者のプログラミング システムは、量産対応が可能です。

### CyberClocks™ ソフトウェア

CyberClocks は、使いやすいソフトウェア アプリケーションです。これにより、ユーザーは CY22050 に対してカスタム設定を行なうことができます。CyberClocks ソフトウェアでは、CyClocksRT™ ツールを選択します。ユーザーは、REF、PLL 周波数、出力周波数および／またはポスト分周器、と異なった機能オプションを指定することができます。CyClocksRT は、CY22050 のプログラミングに使用される産業標準の JEDEC ファイルを出力します。

サイプレス ウェブサイト <http://www.cypress.com> から無料の CyClocksRT ソフトウェアをダウンロードすることができます。ダウンロード後、Windows オペレーティング システムを実行している任意の PC にそれをインストールし実行します。

### CY3672 開発キット

サイプレスの CY3672 開発キットは、CY22050 を設計するために必要な要素、プログラム サンプルと一部のプロトコルを備えていますこのキットは、CyClocksRT の最新バージョン、およびデバイス動作中にカスタム周波数をプログラミングするために PC に接続可能な小型のポータブル プログラマを持っています。

CyClocksRT が出力する JEDEC ファイルは、小量のプログラムの開発のために、ポータブル プログラマにダウンロードする、または大量のプログラムの開発用に、量産プログラム システムと併用するためにダウンロードすることができます。

## アプリケーション

### 制御ジッタ

ジッタは、位相ノイズ、ロングターム ジッタ、サイクル間のジッタ、周期ジッタ、絶対的ジッタおよび決定的ジッタなどのいろいろな種類に定義されています。これらのジッタ定義技術用語は常に、二乗平均平方根、ピークツーピーク、または基本周波数に関連する位相ノイズ  $\text{dBC/Hz}$  に関して作り出されます。実際のジッタは、XIN ジッタ、エッジ レート、アクティブ出力の数、出力周波数、 $V_{\text{DD}} (2.5V, 3.3V)$ 、温度、および出力負荷によります。

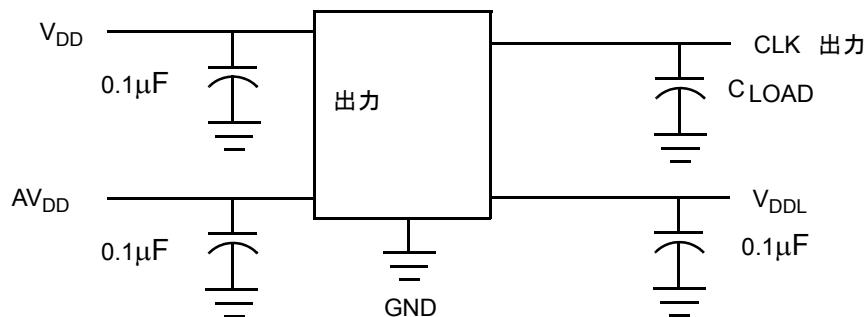

電源ノイズとクロック 出力のロードは、クロック ジッタの 2つの主なシステム ソースです。電源ノイズは、( $0.1\mu\text{F}$  セラミック コンデンサを使用して) クロックの電源を適切にデカップリングして、グランドからチップへの低インピーダンス回路を設計することにより減少することができます。静電容量のクロックのロードを最小限に減少すると、クロック エッジ上の電流スパイクが低減し、よってジッタも減少されます。

アクティブな出力の総数を削減すると、ジッタは線形的に低減されます。しかし、1つの出力ではなく 2つの出力を使って、2つの負荷を駆動したほうが良いでしょう。

VCO 周波数を訂正するために PLL が使用するレートと大きさは、ジッタ性能に直接関係します。レートが遅すぎると、ロングターム ジッタと位相ノイズが不良になります。そのため、ロングターム ジッタと位相ノイズを改善するために、Q の値を最小限にすることをお勧めします。この技術は VCO の入力電圧を順に駆動する位相周波数検出器の速度を増加させます。同様に、VCO が最大の定格速度の近くに到達するまで P を増加すると、長期のジッタと位相ノイズが低減します。例えば、入力リファレンス周波数が 12MHz では、期待出力周波数は 33.3MHz です。1つの設定方法は、Q = 3、P = 25、ポスト分周器 = 3 ですが、最良なジッタ結果を与えるのは、Q = 2、P = 50、ポスト分周器 = 9 のソリューションです。

詳細については、<http://www.cypress.com> に掲載している「PLL ベースのシステムにおけるジッタ：原因、影響およびソリューション」アプリケーション ノートを参照する（「アプリケーション ノート」をクリック）か、または最寄りのサイプレスのフィールド アプリケーション エンジニアにお問い合わせください。

## CY22050 周波数の計算

CY22050 は、集積 PLL から生成される 6 個までの独立な出力を備えているため、非常にフレキシブルなクロックジェネレータです。

最終の出力周波数を判定するために 4 つの変数が使用されます。それは、入力 REF、P と Q 分周器、およびポスト分周器です。CY22150 ベースのデザインの最終の出力周波数を判定する 3 つの基本式は以下の通りです。

- CLK = ((REF \* P)/Q)/Post Divider

- CLK = REF/Post Divider

- CLK = REF

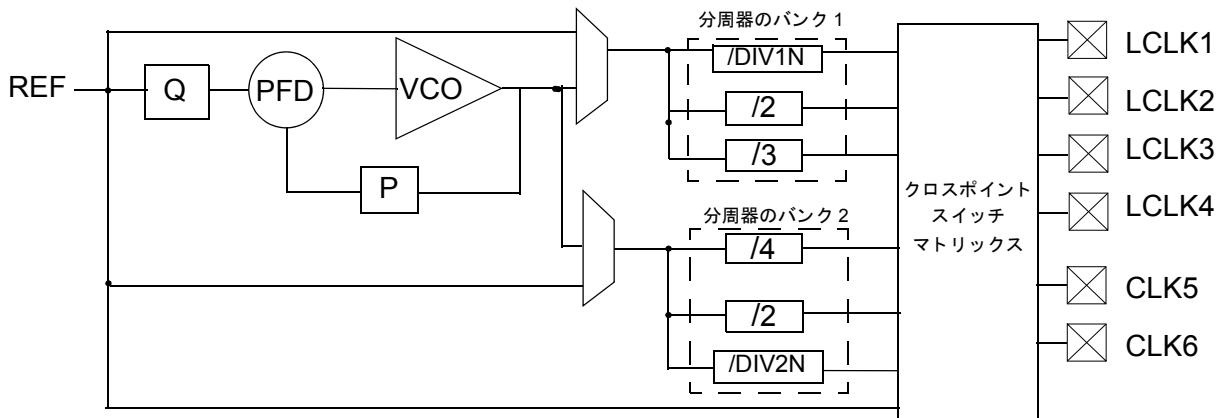

基本的な PLL のブロック図は、図 2 に示されます。6 つのクロック出力のそれぞれの使用可能な出力オプションは全部で 7 つです。6 つのポスト分周器のオプションがあります：/2 (2 個)、/3、/4、/DIV1N、DIV2N。DIV1N と DIV2N は、独立して動作可能で、別々に計算することができます。計算された PLL 周波数や REF にポスト分周器のオプションを直接適用することができます。

6 つのポスト分周器のオプションに加え、第 7 のオプションは PLL をバイパスして、REF をクロスポイントのスイッチマトリクスに直接に伝えます。

図 2. 基本 PLL ブロック図

## クロック出力の設定： クロスポイントスイッチマトリクス

6 つのクロック出力のそれぞれは、7 つの固有の周波数発生源のいずれかに由来することが可能です。クロスポイントスイッ

チマトリクスは、どの発生源が各個別クロック出力に接続されるか定義します。分周器オプションが無限のようですが、分周器オプションを選択する時にいくつかのルールに注意する必要があります。

表 1. クロック出力定義

| クロック出力分周器 | 定義および注意事項                                                                                           |

|-----------|-----------------------------------------------------------------------------------------------------|

| なし        | クロック出力ソースは、リファレンス入力周波数                                                                              |

| /DIV1N    | クロック出力は分周器のバンク 1 から生成された /DIV1N オプションを使用。DIV1N の使用可能な値は 4 ~ 130。分周器バンク 1 を使用していない場合、DIV1N の値を 8 に設定 |

| /2        | クロック出力は、分周器のバンク 1 からの固定 /2 のオプションを使用。このオプションを選択すると、DIV1N の値は 4 で分周可能でなければならない                       |

| /3        | クロック出力は、分周器のバンク 1 からの固定 /3 のオプションを使用。このオプションを選択すると、DIV1N の値を 6 に設定                                  |

| /DIV2N    | クロック出力は分周器のバンク 2 から生成された /DIV2N オプションを使用。DIV2N の使用可能な値は 4 ~ 130。分周器バンク 2 を使用していない場合、DIV2N の値を 8 に設定 |

| /2        | クロック出力は、分周器のバンク 2 からの固定 /2 のオプションを使用。このオプションを選択すると、DIV2N の値は 4 で分周可能でなければならない                       |

| /4        | クロック出力 2 は、分周器のバンク 2 からの固定 /4 のオプションを使用。このオプションを選択すると、DIV2N の値は 8 で分周可能でなければならない                    |

## リファレンス水晶入力

CY22050 の入力水晶振動子は、柔軟性が高くて水晶をリファレンス クロック ソースとして使用することを可能にするため、重要な機能となります。振動子のインバータは、プログラム可能なゲインがあるため、メーカー、プロセス、性能、および品質に応じてあるリファレンス水晶振動子との互換性を最大限にすることができます。

入力負荷容量の値は、プログラム可能なレジスタ内の 8 ビットにより決まります。合計の負荷容量は、以下の式で計算されます：

$$\text{CapLoad} = (C_L - C_{BRD} - C_{CHIP})/0.09375 \text{ pF}$$

CyClocksRT では、水晶容量 ( $C_L$ ) を入力します。CapLoad の値は自動的に判定され、CY22050 へプログラムされます。

CapLoad の値を制御する必要があれば、CY22150 を入力負荷コンデンサのシリアル コンフィギュレーションと制御に使用することを検討してください。外部クロック ソースの場合は、デフォルト値が 0 です。

外部コンポーネントのコストを削減するために入力負荷容量を CY22050 ダイの上に搭載します。これらのコンデンサは、非線形負荷容量が負荷、バイアス、電源と温度変化から影響を受ける時に発生する周波数シフトを減らすために設計される真の平行平板コンデンサです。

## 水晶駆動レベルと電源

水晶振動子は、最大の駆動レベルを受け入れるために規定されます。一般的に、より大型の水晶振動子は、より多くの電源による駆動が可能です。下表に示している駆動能力の仕様は、CY22050 内の発振回路により駆動される電源の一般的な上限です。

所与の電圧スイングに対して、水晶振動子の消費電力は ESR に比例し、水晶周波数の二乗に比例します。( 実際の ESR が時々水晶振動子のメーカーが規定した値よりも大幅に低いことに注意してください )。電力は、 $C_L$  の二乗にもほぼ比例します。

周波数が低減された低  $C_L$  と低  $R_1$ (ESR) の水晶を選択することで、下表に示している DL 仕様よりも電力を低減することができます。

## 絶対最大条件

| パラメーター    | 項目                                   | Min             | Max             | 単位 |

|-----------|--------------------------------------|-----------------|-----------------|----|

| $V_{DD}$  | 電源電圧                                 | -0.5            | 7.0             | V  |

| $V_{DDL}$ | I/O 電源電圧                             | -0.5            | 7.0             | V  |

| $T_S$     | 保存温度 [3]                             | -65             | 125             | °C |

| $T_J$     | 接合部温度                                | -               | 125             | °C |

|           | パッケージの消費電力 — 民生用温度範囲                 | -               | 450             | mW |

|           | パッケージの消費電力 — 産業用温度範囲                 | -               | 380             | mW |

|           | デジタル入力                               | $AV_{SS} - 0.3$ | $AV_{DD} + 0.3$ | V  |

|           | $V_{DD}$ を基準とするデジタル出力                | $V_{SS} - 0.3$  | $V_{DD} + 0.3$  | V  |

|           | $V_{DDL}$ を基準とするデジタル出力               | $V_{SS} - 0.3$  | $V_{DDL} + 0.3$ | V  |

| ESD       | 静電放電時の電圧 (MIL-STD-833、メソッド 3015 による) | -               | 2000            | V  |

### 注

- 3. 10 年間で評価されました。

## 推奨動作範囲

| パラメーター        | 項目                                                                | Min   | Typ | Max   | 単位  |

|---------------|-------------------------------------------------------------------|-------|-----|-------|-----|

| $V_{DD}$      | 動作電圧                                                              | 3.135 | 3.3 | 3.465 | V   |

| $V_{DDL\_HI}$ | 動作電圧                                                              | 3.135 | 3.3 | 3.465 | V   |

| $V_{DDL\_LO}$ | 動作電圧                                                              | 2.375 | 2.5 | 2.625 | V   |

| $T_{AC}$      | 民生用周囲温度                                                           | 0     | –   | 70    | °C  |

| $T_{AI}$      | 産業用周囲温度                                                           | -40   | –   | 85    | °C  |

| $C_{LOAD}$    | 最大負荷容量 $V_{DD}/V_{DDL} = 3.3V$                                    | –     | –   | 15    | pF  |

| $C_{LOAD}$    | 最大負荷容量 $V_{DDL} = 2.5V$                                           | –     | –   | 15    | pF  |

| $f_{REFD}$    | 駆動 REF                                                            | 1     | –   | 133   | MHz |

| $f_{REFC}$    | 水晶 REF                                                            | 8     | –   | 30    | MHz |

| $t_{PU}$      | すべての $V_{DD}$ が指定の最小電圧に到達するまでの電源投入時間<br>( 電源立ち上がり傾斜は単調でなければならない ) | 0.05  | –   | 500   | ms  |

## 推奨の水晶仕様

| パラメーター     | 説明           | コメント          | Min | Typ | Max | 単位  |

|------------|--------------|---------------|-----|-----|-----|-----|

| $f_{NOM}$  | 公称水晶周波数      | 並列共振、基本モード    | 8   | –   | 30  | MHz |

| $C_{LNOM}$ | 公称負荷容量       |               | 10  | –   | 20  | pF  |

| $R_1$      | 等価直列抵抗 (ESR) | 基本モード         | –   | –   | 50  | Ω   |

| DL         | 水晶駆動レベル      | 外部シリアル抵抗無しとする | –   | 0.5 | 2   | mW  |

## DC 電気的特性

| パラメーター <sup>[4]</sup>                  | 説明         | 条件                                                                                 | Min | Typ | Max | 単位              |

|----------------------------------------|------------|------------------------------------------------------------------------------------|-----|-----|-----|-----------------|

| I <sub>OH3.3</sub>                     | 出力 HIGH 電流 | V <sub>OH</sub> = V <sub>DD</sub> - 0.5V、V <sub>DD</sub> /V <sub>DDL</sub> = 3.3V  | 12  | 24  | —   | mA              |

| I <sub>OL3.3</sub>                     | 出力 LOW 電流  | V <sub>OL</sub> = 0.5V、V <sub>DD</sub> /V <sub>DDL</sub> = 3.3V                    | 12  | 24  | —   | mA              |

| I <sub>OH2.5</sub>                     | 出力 HIGH 電流 | V <sub>OH</sub> = V <sub>DDL</sub> - 0.5V、V <sub>DD</sub> /V <sub>DDL</sub> = 2.5V | 8   | 16  | —   | mA              |

| I <sub>OL2.5</sub>                     | 出力 LOW 電流  | V <sub>OL</sub> = 0.5V、V <sub>DD</sub> /V <sub>DDL</sub> = 2.5V                    | 8   | 16  | —   | mA              |

| V <sub>IH</sub>                        | 入力 HIGH 電圧 | CMOS レベル、V <sub>DD</sub> の 70%                                                     | 0.7 | —   | 1.0 | V <sub>DD</sub> |

| V <sub>IL</sub>                        | 入力 LOW 電圧  | CMOS レベル、V <sub>DD</sub> の 30%                                                     | 0   | —   | 0.3 | V <sub>DD</sub> |

| I <sub>VDD</sub> <sup>[5, 6]</sup>     | 供給電流       | A <sub>VDD</sub> /V <sub>DD</sub> 電流                                               | —   | 45  | —   | mA              |

| I <sub>VDDL3.3</sub> <sup>[5, 6]</sup> | 供給電流       | V <sub>DDL</sub> 電流 (V <sub>DDL</sub> = 3.465V)                                    | —   | 25  | —   | mA              |

| I <sub>VDDL2.5</sub> <sup>[5, 6]</sup> | 供給電流       | V <sub>DDL</sub> 電流 (V <sub>DDL</sub> = 2.625V)                                    | —   | 17  | —   | mA              |

| I <sub>DDS</sub>                       | 電源切断時の電流   | V <sub>DD</sub> = V <sub>DDL</sub> = A <sub>VDD</sub> = 3.465V                     | —   | —   | 50  | μA              |

| I <sub>OHZ</sub><br>I <sub>OLZ</sub>   | 出力時のリーク電流  | V <sub>DD</sub> = V <sub>DDL</sub> = A <sub>VDD</sub> = 3.465V                     | —   | —   | 10  | μA              |

## AC 電気的特性

| パラメーター <sup>[4]</sup>         | 説明                                        | 条件                                                                                                        | Min          | Typ  | Max   | 単位   |

|-------------------------------|-------------------------------------------|-----------------------------------------------------------------------------------------------------------|--------------|------|-------|------|

| t <sub>1</sub>                | 出力周波数、民生用温度範囲                             | クロック出力制限、3.3V                                                                                             | 0.008 (8kHz) | —    | 200   | MHz  |

|                               |                                           | クロック出力制限、2.5V                                                                                             | 0.008 (8kHz) | —    | 166.6 | MHz  |

|                               | 出力周波数、産業用温度範囲                             | クロック出力制限、3.3V                                                                                             | 0.008 (8kHz) | —    | 166.6 | MHz  |

|                               |                                           | クロック出力制限、2.5V                                                                                             | 0.008 (8kHz) | —    | 150   | MHz  |

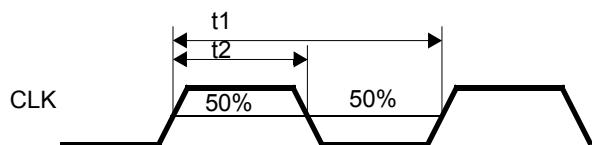

| t <sub>2</sub>                | 出力デューティ比                                  | デューティ比は、図 4 に示すように、t <sub>1</sub> /t <sub>2</sub> 、f <sub>OUT</sub> > 166MHz、V <sub>DD</sub> の 50% で定義される | 40           | 50   | 60    | %    |

|                               |                                           | デューティ比は、図 4 に示すように、t <sub>1</sub> /t <sub>2</sub> 、f <sub>OUT</sub> < 166MHz、V <sub>DD</sub> の 50% で定義される | 45           | 50   | 55    | %    |

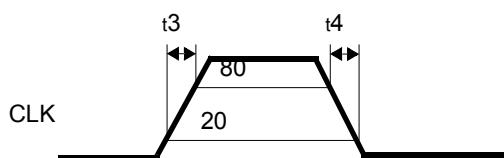

| t <sub>3LO</sub>              | 立ち上がりエッジのスルーレート (V <sub>DDL</sub> = 2.5V) | 図 5 に示すように、V <sub>DDL</sub> の 20% ~ 80% で定義される出力クロックの立ち上がり時間                                              | 0.6          | 1.2  | —     | V/ns |

| t <sub>4LO</sub>              | 立ち下がりエッジのスルーレート (V <sub>DDL</sub> = 2.5V) | 図 5 に示すように、V <sub>DDL</sub> の 80% ~ 20% で定義される出力クロックの立ち下がり時間                                              | 0.6          | 1.2  | —     | V/ns |

| t <sub>3HI</sub>              | 立ち上がりエッジのスルーレート (V <sub>DDL</sub> = 3.3V) | 図 5 に示すように、V <sub>DD</sub> /V <sub>DDL</sub> の 20% ~ 80% で定義される出力クロックの立ち上がり時間                             | 0.8          | 1.4  | —     | V/ns |

| t <sub>4HI</sub>              | 立ち下がりエッジのスルーレート (V <sub>DDL</sub> = 3.3V) | 図 5 に示すように、V <sub>DD</sub> /V <sub>DDL</sub> の 80% ~ 20% で定義される出力クロックの立ち下がり時間                             | 0.8          | 1.4  | —     | V/ns |

| t <sub>5</sub> <sup>[7]</sup> | スキュー                                      | 関連出力同士間の出力間スキュー                                                                                           | —            | —    | 250   | ps   |

| t <sub>6</sub> <sup>[8]</sup> | クロック ジッタ                                  | ピークツーピーク周期ジッタ (図 6 を参照)                                                                                   | —            | 250  | —     | ps   |

| t <sub>10</sub>               | PLL ロック時間                                 |                                                                                                           | —            | 0.30 | 3     | ms   |

### 注

4. 設計保証であり、すべてのデバイスではテストされていません。

5. 125MHz で動作している 2 つの CLK 出力、80MHz で動作している 2 つの LCLK、66.6MHz で動作している 2 つの LCLK 用に指定された I<sub>VDD</sub> すべての出力は、15pF でロードされます。

6. CyClocksRT を使って特定の出力周波数コンフィギュレーション用の実際の I<sub>VDD</sub> と I<sub>VDDL</sub> を計算します。

7. 出力が同じ分周器バンクから生成された場合はスキュー値は保証されます。詳細については、ロジック ブロック図を参照してください。

8. ジッタの測定値は変わり得ます。実際のジッタは、X<sub>N</sub> ジッタ、エッジ レート、アクティブ出力の数、出力周波数、V<sub>DD</sub> (2.5V、3.3V)、温度、および出力負荷によります。詳細については、<http://www.cypress.com> に掲載している「PLL ベースのシステムにおけるジッタ：原因、影響およびソリューション」アプリケーション ノートを参照するか、または最寄りのサイプレスのフィールド アプリケーション エンジニアにお問い合わせください。

## テスト回路

図 3. テスト回路

## スイッチング波形

図 4. デューティ比の定義 :  $DC = t_2/t_1$

図 5. 立ち上がり、立ち下がり時間の定義

図 6. ピークツーピーク ジッタ

## 注文情報

| 注文コード         | パッケージ タイプ                                          | 動作温度範囲             | 動作電圧 |

|---------------|----------------------------------------------------|--------------------|------|

| CY22050KFC    | 16 ピン TSSOP                                        | 民生用 (0°C ~ 70°C)   | 3.3V |

| CY22050KF1    | 16 ピン TSSOP                                        | 産業用 (-40°C ~ 85°C) | 3.3V |

| <b>鉛フリー</b>   |                                                    |                    |      |

| CY22050KFZXC  | 16 ピン TSSOP                                        | 民生用 (0°C ~ 70°C)   | 3.3V |

| CY22050KFZXCT | 16 ピン TSSOP – テープおよびリール                            |                    |      |

| CY22050KFZXI  | 16 ピン TSSOP                                        | 産業用 (-40°C ~ 85°C) | 3.3V |

| <b>プログラマ</b>  |                                                    |                    |      |

| CY3672-USB    | 開発キット                                              |                    |      |

| CY3695        | CY3672 プログラマ向けの CY22050F、CY22050KF、CY220501KF アダプタ |                    |      |

いくつかの提供される製品は、工場でプログラムされ、カスタマイズされた型番を持つ特定ユーザー向けデバイスです。可能なコンフィギュレーション表は、使用可能なデバイス タイプを示しますが、完全な型番を示していません。詳細情報は、最寄りのサイプレスのFAE または販売代理店にお問い合わせください。

## 可能なコンフィギュレーション

| 注文コード               | パッケージ タイプ               | 動作温度範囲             | 動作電圧 |

|---------------------|-------------------------|--------------------|------|

| CY22050KZXI-xxx [9] | 16 ピン TSSOP             | 産業用 (-40°C ~ 85°C) | 3.3V |

| CY22050KZXI-xxxT    | 16 ピン TSSOP – テープ & リール | 産業用 (-40°C ~ 85°C) | 3.3V |

## 注文コードの定義

### 注

9. これらは工場出荷時にプログラムされたコンフィギュレーションです。これらのコンフィギュレーションは年当たり 10 万個あるいはそれ以上の量産に対応する大規模な設計に適用可能です。詳細情報については、最寄りのサイプレスのフィールド アプリケーション エンジニアまたは販売代理店にお問い合わせください。

## 16 ピン TSSOP パッケージの特性

| パラメーター        | 名称       | 値      | 単位   |

|---------------|----------|--------|------|

| $\theta_{JA}$ | theta JA | 115    | °C/W |

| コンプレクシティ      | トランジスタの数 | 74,600 | 個    |

## パッケージ図および寸法

図 7. 16 ピン TSSOP 4.40mm 本体 Z16.173/ZZ16.173 パッケージ図、51-85091

51-85091 \*E

## 略語

| 略語    | 説明                                                                       |

|-------|--------------------------------------------------------------------------|

| ESR   | Equivalent Series Resistance ( 等価直列抵抗 )                                  |

| FAE   | Field Application Engineer<br>( フィールド アプリケーション エンジニア )                   |

| I/O   | Input/Output ( 入力／出力 )                                                   |

| JEDEC | Joint Electron Devices Engineering Council<br>( 半導体技術協会 ( 旧電子機器技術評議会 ) ) |

| OE    | Output Enable ( 出力イネーブル )                                                |

| PC    | Personal Computer ( パーソナル コンピュータ )                                       |

| PCB   | Printed Circuit Board ( プリント回路基板 )                                       |

| PLL   | Phase-Locked Loop ( 位相同期回路 )                                             |

| TSSOP | Thin Shrunk Small Outline Package<br>( 薄型シュリンク小型パッケージ )                  |

| VCO   | Voltage Controlled Oscillator ( 電圧制御振動子 )                                |

## 本書の表記法

### 測定単位

| 記号  | 測定単位           |

|-----|----------------|

| °C  | 摂氏温度           |

| dBC | キャリアを基準としたデシベル |

| Hz  | ヘルツ            |

| kHz | キロヘルツ          |

| MHz | メガヘルツ          |

| µA  | マイクロアンペア       |

| µF  | マイクロファラッド      |

| mA  | ミリアンペア         |

| mm  | ミリメートル         |

| ms  | ミリ秒            |

| mW  | ミリワット          |

| ns  | ナノ秒            |

| Ω   | オーム            |

| %   | パーセント          |

| pF  | ピコファラッド        |

| ps  | ピコ秒            |

| V   | ボルト            |

| W   | ワット            |

## 改訂履歴

文書名 : CY22050 ／ CY220501、汎用フラッシュ プログラマブル 1PLL クロック ジェネレータ

文書番号 : 001-95873

| 版  | ECN     | 変更者  | 発行日        | 変更内容                                                    |

|----|---------|------|------------|---------------------------------------------------------|

| ** | 4700349 | HZEN | 04/16/2015 | これは英語版 38-07006 Rev. *M を翻訳した日本語版 001-95873 Rev. ** です。 |

## セールス、ソリューションおよび法律情報

### ワールドワイドな販売と設計サポート

サイプレスは、事業所、ソリューションセンター、メーカー代理店および販売代理店の世界的なネットワークを保持しています。お客様の最寄りのオフィスについては、[サイプレスのロケーションページ](#)をご覧ください。

#### 製品

|             |                                                                                                                                      |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------|

| 車載用         | <a href="http://cypress.com/go/automotive">cypress.com/go/automotive</a>                                                             |

| クロック & バッファ | <a href="http://cypress.com/go/clocks">cypress.com/go/clocks</a>                                                                     |

| インターフェース    | <a href="http://cypress.com/go/interface">cypress.com/go/interface</a>                                                               |

| 照明 & 電力制御   | <a href="http://cypress.com/go/powerpsoc">cypress.com/go/powerpsoc</a><br><a href="http://cypress.com/go/plc">cypress.com/go/plc</a> |

| メモリ         | <a href="http://cypress.com/go/memory">cypress.com/go/memory</a>                                                                     |

| PSoC        | <a href="http://cypress.com/go/psoc">cypress.com/go/psoc</a>                                                                         |

| タッチ センシング   | <a href="http://cypress.com/go/touch">cypress.com/go/touch</a>                                                                       |

| USB コントローラー | <a href="http://cypress.com/go/USB">cypress.com/go/USB</a>                                                                           |

| ワイヤレス / RF  | <a href="http://cypress.com/go/wireless">cypress.com/go/wireless</a>                                                                 |

#### PSoC® ソリューション

[psoc.cypress.com/solutions](http://psoc.cypress.com/solutions)

[PSoC 1](http://PSoC_1) | [PSoC 3](http://PSoC_3) | [PSoC 4](http://PSoC_4) | [PSoC 5LP](http://PSoC_5LP)

#### サイプレス開発者コミュニティ

[コミュニティ](#) | [フォーラム](#) | [ブログ](#) | [ビデオ](#) | [トレーニング](#)

#### テクニカル サポート

[cypress.com/go/support](http://cypress.com/go/support)

© Cypress Semiconductor Corporation, 2001-2015. 本文書に記載される情報は、予告なく変更される場合があります。Cypress Semiconductor Corporation (サイプレス セミコンダクタ社)は、サイプレス製品に組み込まれた回路以外のいかなる回路を使用することに対して一切の責任を負いません。サイプレス セミコンダクタ社は、特許またはその他の権利に基づくライセンスを譲渡することも、または含意することもありません。サイプレス製品は、サイプレスとの書面による合意に基づくものでない限り、医療、生命維持、救命、重要な管理、または安全の用途のために使用することを保証するものではなく、また使用することを意図したものでもありません。さらにサイプレスは、誤動作や故障によって使用者に重大な傷害をもたらすことが合理的に予想される生命維持システムの重要なコンポーネントとしてサイプレス製品を使用することを許可していません。生命維持システムの用途にサイプレス製品を供することは、製造者がそのような使用におけるあらゆるリスクを負うことを意味し、その結果サイプレスはあらゆる責任を免除されることを意味します。

全てのソース コード（ソフトウェアおよび／またはファームウェア）はサイプレス セミコンダクタ社（以下「サイプレス」）が所有し、全世界の特許権保護（米国およびその他の国）、米国の著作権法ならびに国際協定の条項により保護され、かつそれらに従います。サイプレスが本書面によりライセンサーに付与するライセンスは、個人的、非独占かつ譲渡不能のライセンスであり、適用される契約で指定されたサイプレスの集積回路と併用されるライセンサーの製品のみをサポートするカスタムソフトウェアおよび／またはカスタム ファームウェアを作成する目的に限って、サイプレスのソース コードの派生著作物をコピー、使用、変更そして作成するためのライセンス、ならびにサイプレスのソース コードおよび派生著作物をコンパイルするためのライセンスです。上記で指定された場合を除き、サイプレスの書面による明示的な許可なくして本ソース コードを複製、変更、変換、コンパイル、または表示することはすべて禁止します。

免責条項：サイプレスは、明示的または默示的を問わず、本資料に関するいかなる種類の保証も行いません。これには、商品性または特定目的への適合性の默示的な保証が含まれますが、これに限定されません。サイプレスは、本文書に記載される資料に対して今後予告なく変更を加える権利を留保します。サイプレスは、本文書に記載されるいかなる製品または回路を適用または使用したことによって生ずるいかなる責任も負いません。サイプレスは、誤動作や故障によって使用者に重大な傷害をもたらすことが合理的に予想される生命維持システムの重要なコンポーネントとしてサイプレス製品を使用することを許可していません。生命維持システムの用途にサイプレス製品を供することは、製造者がそのような使用におけるあらゆるリスクを負うことを意味し、その結果サイプレスはあらゆる責任を免除されることを意味します。

ソフトウェアの使用は、適用されるサイプレス ソフトウェア ライセンス契約によって制限され、かつ制約される場合があります。