# 8M ビット EXCELON™ LP 強誘電体 RAM (F-RAM)

シリアル (SPI), 1024K × 8, 40 MHz, 産業用

## 特長

- 1024K × 8 論理構成として設計された 8M ビット強誘電体 RAM (F-RAM)

- 1000 兆回 ( $10^{15}$ ) の読み出し / 書き込みの無限の耐久性

- 151 年間のデータ保持 (データ保持期間およびアクセス可能回数を参照してください)

- Infineon 遅延なし不揮発性書き込み技術

- 高信頼性強誘電体プロセス

- 高速シリアルペリフェラルインターフェース (SPI)

- 最大周波数 40 MHz

- SPI モード 0 (0, 0) およびモード 3 (1, 1) をサポート

- 洗練された書き込み保護スキーム

- 書き込み保護 (WP) ピンを使用したハードウェアによる保護

- 書き込みディセーブル (WRDI) 命令を使用したソフトウェアによる保護

- アレイの 1/4, 1/2, または全体を対象としたソフトウェアブロック保護

- デバイス ID およびシリアル番号

- メーカー ID および製品 ID

- 固有デバイス ID

- シリアル番号

- 専用 256 バイト特殊セクタ F-RAM

- 専用特殊セクタの書き込みと読み出し

- 保存コンテンツは最大 3 回の標準はんだリフロー サイクルに耐え得る

- 低消費電力

- 40MHz で 2.6 mA (Typ) のアクティブ電流

- 3.5 μA (Typ) のスタンバイ電流

- 0.90 μA (Typ) のディープパワーダウン モード電流

- 0.1 μA (Typ) のハイバネート モード電流

- 低電圧動作

- CY15V108QN:  $V_{DD} = 1.71 \text{ V} \sim 1.89 \text{ V}$

- CY15B108QN:  $V_{DD} = 1.8 \text{ V} \sim 3.6 \text{ V}$

- 民家用および産業用動作温度

- 民家用動作温度:  $0^\circ\text{C} \sim +70^\circ\text{C}$

- 産業用動作温度:  $-40^\circ\text{C} \sim +85^\circ\text{C}$

- パッケージ

- 8 ピンスモールアウトライン IC (SOIC) パッケージ

- 8 ピンリードレス クアッド フラット グリッド アレイ (QFN) パッケージ (NRND)<sup>[1]</sup>

- 8 ピン超薄型ファインピッチ ランド グリッド アレイ (UFLGA) パッケージ

- RoHS 準拠

## 注:

1. NRND - 新規設計には推奨しません。

## 機能説明

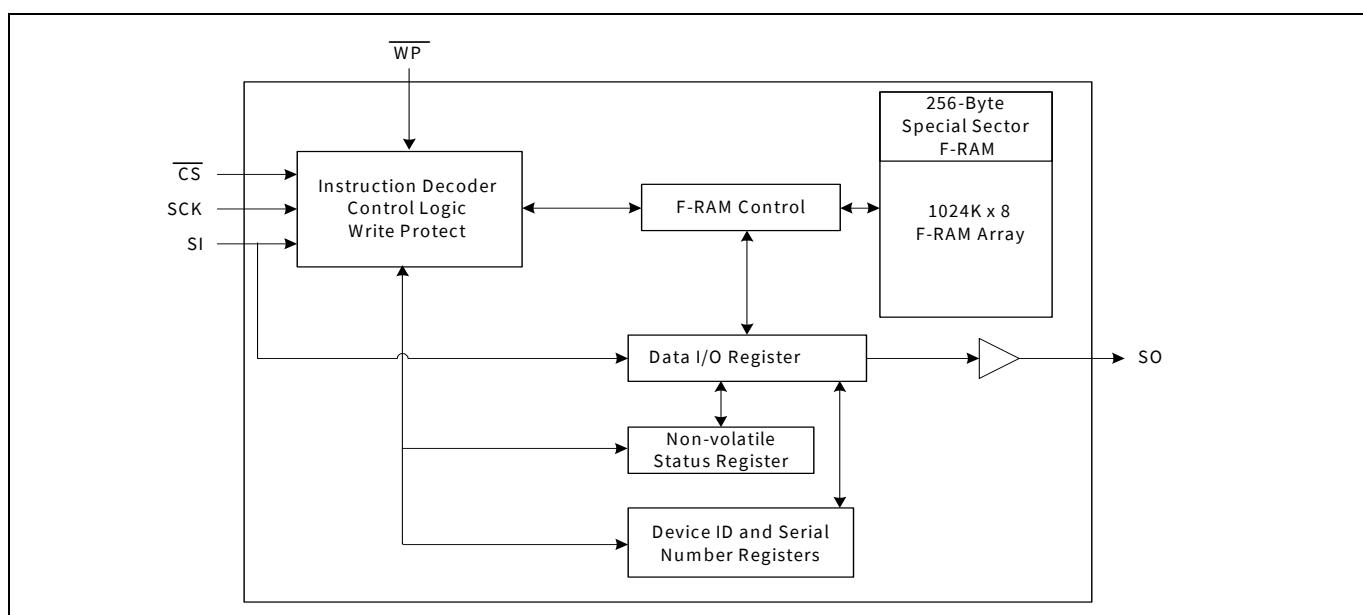

EXCELON™ LP CY15X108QN は高度な強誘電体プロセスを適用した低消費電力な 8M ビットの不揮発性メモリです。強誘電体ランダム アクセス メモリ (F-RAM) は不揮発性であり、RAM 同様に読み書きを実行します。シリアル フラッシュや EEPROM、その他の不揮発性メモリによる複雑さ、オーバーヘッド、システム レベルの信頼性関連問題を回避し、151 年間にわたって信頼できるデータ保持が可能です。

シリアル フラッシュや EEPROM と異なり、CY15X108QN はバス速度で書き込み動作を実行します。書き込み遅延は発生しません。データは各バイトがデバイスに正常に転送された直後にメモリアレイに書き込まれます。次のバスサイクルはデータ ポーリングなしに開始できます。また、本製品は他の不揮発性メモリと比べ多くの書き換え回数を提供しています。CY15X108QN は  $10^{15}$  回の読み出し / 書き込みサイクル、即ち EEPROM に比べ 10 億倍の書き込みサイクルに対応できます。

これらの能力により、CY15X108QN は頻繁な高速書き込みを必要とする不揮発性メモリの用途に理想的なものになります。これらの用途例は、書き込み回数を重視するデータ収集から、シリアル フラッシュや EEPROM を使った長い書き込みデータ保持期間に起因してデータを損失する可能性がある厳しい工業用制御まで及びます。

CY15X108QN はハードウェア置き換えができるため、シリアル EEPROM やフラッシュを使用するユーザーに大幅な利点を提供します。CY15X108QN は F-RAM 技術の高速書き込み機能を強化する高速 SPI バスを使用します。このデバイスは読み出し専用のデバイス ID と固有 ID 機能が組み込まれており、ホストが各製品のメーカー、メモリ容量、製品の Revision および固有 ID を判断できます。本製品はまた、基板またはシステムを特定するために使用できる書き込み可能な 8 バイトシリアル番号レジスタを備えています。デバイス仕様は  $0^{\circ}\text{C} \sim +70^{\circ}\text{C}$  の民生用温度範囲において保証されます。

すべての関連資料の一覧については、[ここ](#)をクリックしてください。

## 論理ブロックダイヤグラム

## 目次

|                                   |    |

|-----------------------------------|----|

| <b>特長</b> .....                   | 1  |

| <b>機能説明</b> .....                 | 2  |

| <b>論理ブロックダイヤグラム</b> .....         | 2  |

| <b>目次</b> .....                   | 3  |

| <b>1 ピン配置</b> .....               | 4  |

| <b>2 ピン機能</b> .....               | 5  |

| <b>3 機能概要</b> .....               | 6  |

| 3.1 メモリ アーキテクチャ .....             | 6  |

| 3.2 SPI バス .....                  | 6  |

| 3.3 SPI 概要 .....                  | 6  |

| 3.4 SPI プロトコルで使用される用語 .....       | 7  |

| 3.4.1 SPI マスター .....              | 7  |

| 3.4.2 SPI スレーブ .....              | 7  |

| 3.4.3 チップセレクト (CS) .....          | 7  |

| 3.4.4 シリアル クロック (SCK) .....       | 7  |

| 3.4.5 データ転送 (SI/SO) .....         | 8  |

| 3.4.6 最上位ビット (MSb) .....          | 9  |

| 3.4.7 シリアル オペコード .....            | 9  |

| 3.4.8 無効なオペコード .....              | 9  |

| 3.4.9 ステータスレジスタ .....             | 9  |

| 3.5 SPI モード .....                 | 10 |

| 3.6 電源投入時から最初のアクセスまで .....        | 10 |

| <b>4 機能説明</b> .....               | 11 |

| 4.1 コマンドの構成 .....                 | 11 |

| 4.1.1 書き込みイネーブル制御コマンド .....       | 12 |

| 4.1.2 レジスタアクセスコマンド .....          | 13 |

| 4.1.3 メモリの動作 .....                | 14 |

| 4.1.4 メモリ書き込み動作コマンド .....         | 15 |

| 4.1.5 メモリ読み出しコマンド .....           | 16 |

| 4.1.6 特殊セクタメモリアクセスコマンド .....      | 17 |

| 4.1.7 ID およびシリアル番号コマンド .....      | 18 |

| 4.1.8 低消費電力モード コマンド .....         | 20 |

| <b>5 最大定格</b> .....               | 22 |

| <b>6 動作範囲</b> .....               | 23 |

| <b>7 DC 電気的特性</b> .....           | 24 |

| <b>8 データ保持期間およびアクセス可能回数</b> ..... | 26 |

| <b>9 静電容量</b> .....               | 27 |

| <b>10 熱抵抗</b> .....               | 28 |

| <b>11 AC テスト条件</b> .....          | 29 |

| <b>12 AC スイッチング特性</b> .....       | 30 |

| <b>13 パワー サイクルタイミング</b> .....     | 32 |

| <b>14 注文情報</b> .....              | 33 |

| 14.1 注文コードの定義 .....               | 34 |

| <b>15 パッケージ図</b> .....            | 35 |

| <b>16 略語</b> .....                | 38 |

| <b>17 本書の表記法</b> .....            | 39 |

| 17.1 測定単位 .....                   | 39 |

| <b>改訂履歴</b> .....                 | 40 |

| <b>免責事項</b> .....                 | 41 |

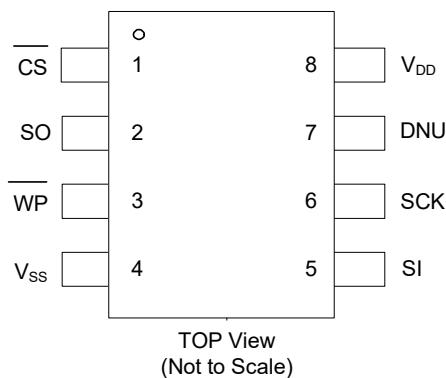

ピン配置

## 1 ピン配置

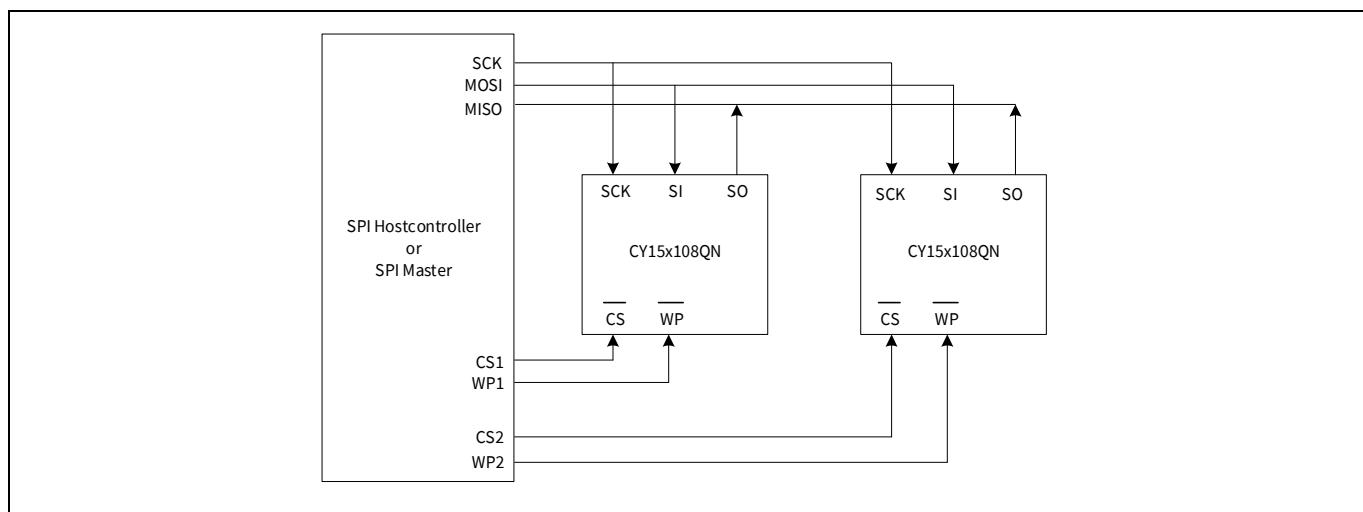

Figure 1 8 ピン SOIC ピン配置

Figure 2 8 ピン GQFN/UFLGA ピン配置

ピン機能

## 2 ピン機能

Table 1 ピン機能

| ピン名               | 入出力  | 説明                                                                                                                                                                                                                                              |

|-------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CS                | 入力   | <b>チップセレクト</b> : このアクティブLOW入力はデバイスをアクティブにします。HIGH の場合、デバイスは低消費電力スタンバイモードに移行し、他の入力を無視し、出力はトライステートになります。LOW の場合、デバイスはSCK信号を内部でアクティブにします。CSの立ち下りエッジは、すべてのオペコードの発行前に発生しなければならない。                                                                    |

| SCK               | 入力   | <b>シリアルクロック</b> : すべての入出力はシリアルクロックに同期します。入力はシリアルクロックの立ち上りエッジでラッチされ、出力は立ち下りエッジで発生します。クロック周波数は0～40MHzの範囲内であり、同期特性のためいつでも割り込まれる可能性がある。                                                                                                             |

| SI <sup>[2]</sup> | 入力   | <b>シリアル入力</b> : このピンからデバイスにすべてのデータを入力します。入力はSCKの立ち上りエッジでサンプリングされ、そのとき以外では無効です。電源(V <sub>DD</sub> )仕様を満たすために、常に有効な論理レベルに駆動する必要があります。                                                                                                             |

| SO <sup>[2]</sup> | 出力   | <b>シリアル出力</b> : これはデータ出力ピンです。このピンは読み出し中に駆動され、そのとき以外はトライステートを保持します。データ遷移はシリアルクロックSCKの立ち下りエッジで駆動されます。                                                                                                                                             |

| WP                | 入力   | <b>書き込み保護</b> : このアクティブLOWピンは、ステータスレジスタのWPENビットが「1」にセットされる時、ステータスレジスタへの書き込みを防ぎます。その他の書き込み保護機能は <b>ステータスレジスタ</b> および <b>書き込み保護</b> を参照。このピンは内部で弱プルアップ抵抗に接続され、フローティング(基板上で接続しない)状態の場合この抵抗によってHIGHに維持されます。このピンを使用しない場合、V <sub>DD</sub> に接続することも可能。 |

| DNU               | 使用禁止 | <b>使用禁止</b> : このピンは、フローティングのままにする。(ボード上で接続しないか)か、V <sub>DD</sub> に接続します。                                                                                                                                                                        |

| V <sub>SS</sub>   | 電源   | デバイスグランド : システムのグランドに接続する必要がある。                                                                                                                                                                                                                 |

| V <sub>DD</sub>   | 電源   | デバイスの電源入力                                                                                                                                                                                                                                       |

注:

2. SIをSOと接続し1本のデータインターフェースとして利用することができます

機能概要

### 3 機能概要

CY15X108QN はシリアル F-RAM メモリです。メモリ アレイは  $1,048,576 \times 8$  ビットに論理構成され、業界標準のシリアルペリフェラルインターフェース (SPI) バスを使用してアクセスされます。F-RAM の機能動作はシリアルフラッシュやシリアル EEPROM と類似しています。同じピン配置の CY15X108QN とシリアルフラッシュや EEPROM との相違点は、F-RAM の優れた書き込み性能、高耐久性および低消費電力です。

#### 3.1 メモリアーキテクチャ

CY15X108QN のアクセスには、8 データビットごとに 1,024K 箇所の位置をアドレス指定します。これら 8 個のデータビットは順次シフトイン / シフトアウトされます。アドレスは、チップセレクト (バス上で複数デバイスを可能にする) とオペコード、3 バイトのアドレスを含む SPI プロトコルを使ってアクセスされます。アドレス範囲の上位 4 ビットは「ドントケア」値です。20 ビットのアドレスで、一義的に各バイトアドレスを指定します。

CY15X108QN の殆どの機能は、SPI インターフェースにより制御されるか、または基板に搭載された回路によって処理されます。メモリ動作に要するアクセス時間は、シリアルプロトコルに必要な時間以外は基本的に 0 です。すなわち、メモリは SPI バスの速度で読み書きされます。シリアルフラッシュや EEPROM と異なり、書き込み処理がバス速度で行われるので、デバイスの書き込み準備を知るためにポーリングする必要はありません。新しいバストランザクションがデバイスに送り込まれるまでに書き込み動作は完了します。これはインターフェースの節で詳しく説明されています。

#### 3.2 SPI バス

CY15X108QN は SPI スレーブデバイスであり、40MHz までの速度で動作します。この高速シリアルバスにより、SPI マスターとの間で高性能なシリアル通信が可能です。多くの一般的なマイクロコントローラーは、ハードウェア SPI ポートを持っているため、直接インターフェースを可能にします。この機能を持たないマイクロコントローラーで、通常のポートピンを使用して SPI ポートをエミュレートすることは容易です。CY15X108QN は SPI モード 0 および 3 で動作します。

#### 3.3 SPI 概要

SPI は、チップセレクト ( $\overline{CS}$ ) とシリアル入力 (SI)、シリアル出力 (SO)、シリアルクロック (SCK) ピンから成る 4 ピンインターフェースです。

SPI は、メモリアクセスにクロックとデータピンを使用し、データバス上の複数デバイスをサポートする同期シリアルインターフェースです。SPI バス上のデバイスは、 $\overline{CS}$  ピンを使用してアクティブにされます。

チップセレクト、クロック、データの相互関係は SPI モードによります。このデバイスは、SPI モード 0 および 3 をサポートします。これらの両モードで、 $\overline{CS}$  がアクティブになった後の最初の立ち上りエッジから始まる SCK の立ち上りエッジで、データが F-RAM にクロック入力されます。

SPI プロトコルはオペコードによって制御されます。これらのオペコードは、バスマスターからスレーブデバイスへのコマンドを指定します。 $\overline{CS}$  がアクティブにされた後、バスマスターから最初に転送されるバイトがオペコードです。オペコードに続いて、アドレスとデータが転送されます。処理が完了した後、新しいオペコードが発行される前に、 $\overline{CS}$  を非アクティブにする必要があります。

### 3.4 SPI プロトコルで使用される用語

SPI プロトコルで一般的に使用される用語は以下のとおりです。

#### 3.4.1 SPI マスター

SPI マスター デバイスは SPI バス上の動作を制御します。SPI バスは、複数のスレーブ デバイスを制御する 1 個のマスターのみを持っている場合があります。すべてのスレーブが同じ SPI バス ラインを共有し、マスターは  $\overline{CS}$  ピンを使用してスレーブ デバイスのいずれかを選択できます。すべての処理は、マスターがスレーブの  $\overline{CS}$  ピンを LOW にすることによってスレーブ デバイスをアクティブにして開始する必要があります。マスターは SCK も生成し、SI と SO ライン上のすべてのデータ転送はこのクロックに同期されます。

#### 3.4.2 SPI スレーブ

SPI スレーブ デバイスは、チップセレクト ラインを介してマスターによってアクティブにされます。スレーブ デバイスは、SPI マスターからの入力として SCK を取得し、すべての通信はこのクロックに同期されます。SPI スレーブはそれ自体として SPI バス上で通信を開始することはなく、マスターからの命令に従ってのみ動作します。

CY15X108QN は SPI スレーブとして動作し、他の SPI スレーブ デバイスと SPI バスを共有する場合があります。

#### 3.4.3 チップセレクト ( $\overline{CS}$ )

特定のスレーブ デバイスを選択するためには、マスターは対応する  $\overline{CS}$  ピンをプルダウンする必要があります。 $\overline{CS}$  ピンが LOW になっている時のみ、命令をスレーブ デバイスに発行できます。デバイスが選択されていない場合、SI ピン経由のデータは無視され、シリアル出力ピン (SO) は高インピーダンス状態が保持されます。

注: 新しい命令は  $\overline{CS}$  の立ち下りエッジで開始する必要があります。したがって、アクティブなチップセレクト サイクルごとに 1 個のオペコードのみが発行されます。

#### 3.4.4 シリアルクロック (SCK)

シリアル クロックは SPI マスターによって生成され、 $\overline{CS}$  が LOW になった後、通信はこのクロックと同期されます。

CY15X108QN はデータ通信のために SPI モード 0 と 3 をサポートします。これらの両モードにおいて、入力は SCK の立ち上りエッジでスレーブ デバイスによってラッチされ、出力は立ち下りエッジで発行されます。従って、SCK の最初の立ち上りエッジは、SI ピンに SPI 命令の最上位ビット (MSB) が到着したことを意味します。さらに、すべてのデータの入力と出力は SCK と同期されます。

### 3.4.5 データ転送 (SI/SO)

SPI データバスは、シリアルデータ通信用に SI と SO の 2 ラインで構成されます。SI はマスター アウトスレーブイン (MOSI)、SO はマスターインスレーブアウト (MISO) とも呼ばれています。マスターは SI ピンを介してスレーブに命令を発行し、スレーブは SO ピンを介して応答します。複数のスレーブ デバイスは、前述のように SI と SO ラインを共有する場合があります。

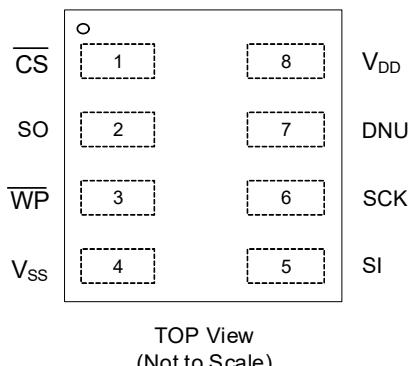

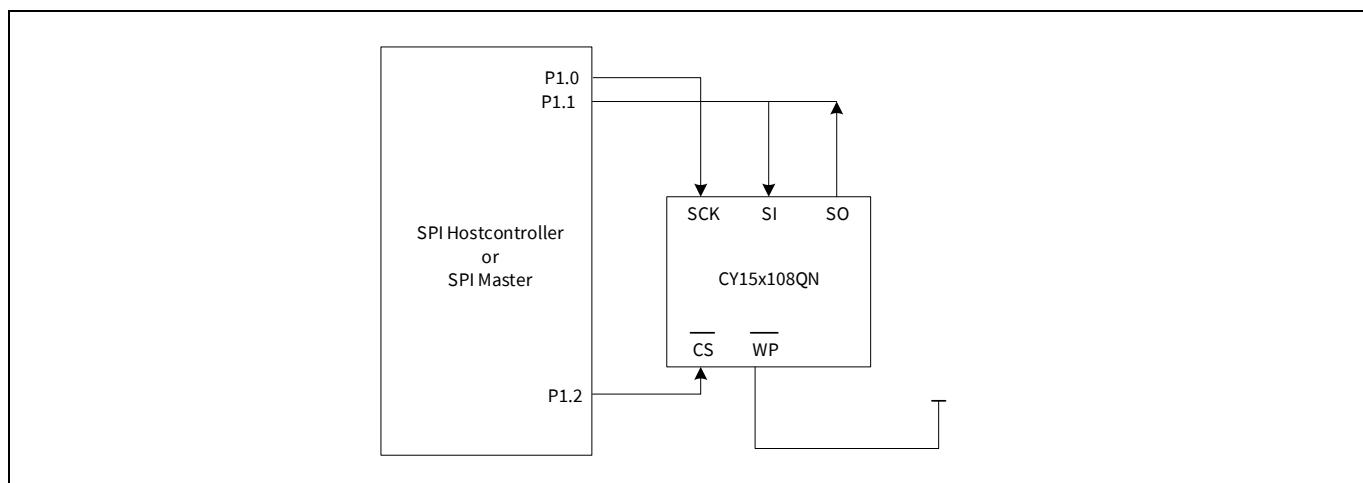

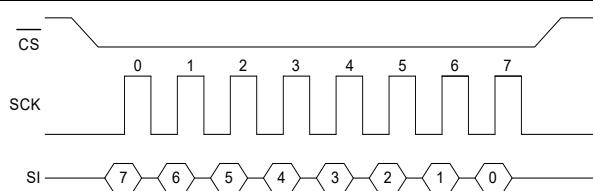

CY15X108QN は、Figure 3 に示すようにマスターと接続できる SI と SO 用の 2 本の独立したピンを備えています。専用 SPI バスを持たないマイクロコントローラーでは、汎用ポートが使用されることもあります。マイクロコントローラーのハードウェアリソースを減らすために、2 つのデータピン (SI、SO) を 1 つにまとめて接続し、WP ピンを HIGH に固定接続できます。Figure 4 はピンを 3 本のみ使用したこのコンフィギュレーションを示します。

Figure 3 SPI ポートを使用するシステム コンフィギュレーション

Figure 4 SPI ポートを使用しないシステム コンフィギュレーション

### 3.4.6 最上位ビット (MSb)

SPI プロトコルでは、送信される最初のビットが MSb である必要があります。この方式はアドレスとデータ転送共に適用されます。

8M ビットシリアル F-RAM は、あらゆる読み書き動作のために 3 バイトのアドレスを必要とします。アドレスが 20 ビットであるため、入力された最初の 4 ビットはデバイスによって無視されます。これらの 4 ビットは「ドントケア」ですが、より高容量メモリへの円滑な移行を可能にするために、これらを「0」に設定することをインフィニオンは推奨します。

### 3.4.7 シリアルオペコード

$\overline{CS}$  が LOW になる状態でスレーブ デバイスが選択された後、最初に受信されたバイトは、意図されている動作のオペコードとして扱われます。CY15X108QN は標準オペコードをメモリアクセスに使用します。

### 3.4.8 無効なオペコード

無効なオペコードが受信されるとそのオペコードは無視され、デバイスは次の  $\overline{CS}$  の立ち下りエッジまで SI ピン上にある追加のシリアルデータを無視し、SO ピンはトライステートのままとなります。

### 3.4.9 ステータスレジスタ

CY15X108QN には、8 ビットのステータスレジスタが 1 個あります。ステータスレジスタ内のビットはデバイス動作を設定するために使用されます。これらのビットは [Table 4](#) で説明されています。

機能概要

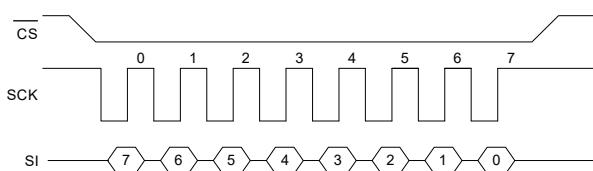

### 3.5 SPI モード

CY15X108QN は、SPI ペリフェラルが次の 2 つのモードのいずれかで動作しているマイクロコントローラによって駆動できます。

- SPI モード 0 (CPOL = 0、CPHA = 0)

- SPI モード 3 (CPOL = 1、CPHA = 1)

この両モードでは、入力データは  $\overline{CS}$  がアクティブにされた後の最初の立ち上りエッジから始まる SCK の立ち上りエッジでラッチされます。クロックが HIGH 状態から起動される場合 (モード 3) では、入力データはクロックトグル後の最初の立ち上りエッジでラッチされます。出力データは SCK の立ち下りエッジで利用可能となります。2 つの SPI モードは Figure 5 と Figure 6 に示されています。バスマスターがデータを転送していない時のクロックの状態は以下のとおりです。

- モード 0 では SCK が 0 のまま

- モード 3 では SCK が 1 のまま

$\overline{CS}$  ピンを LOW にすることによりデバイスが選択された時、デバイスは SCK ピンの状態から SPI モードを検出します。デバイスが選択された時、SCK ピンが LOW ならデバイスは SPI モード 0 で動作し、SCK ピンが HIGH ならデバイスは SPI モード 3 で動作します。

Figure 5 SPI モード 0

Figure 6 SPI モード 3

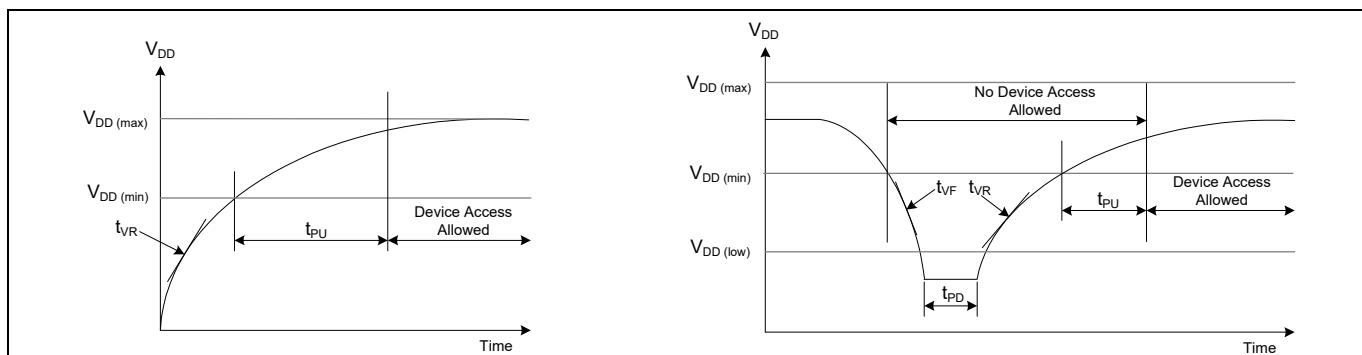

### 3.6 電源投入時から最初のアクセスまで

電源投入後の  $t_{PU}$  の間、CY15X108QN へはアクセスできません。ユーザーは、 $t_{PU}$  (VDD (min) から  $\overline{CS}$  が初めて LOW になる時までの最短期間) のタイミングパラメーターに従わなければいけません。詳細は [パワーサイクルタイミング](#) を参照してください。

## 4 機能説明

### 4.1 コマンドの構成

バスマスターが CY15X108QN に発行するコマンド（オペコードと呼ばれる）は 15 個あります（Table 2 を参照してください）。これらのオペコードはメモリが実行する機能を制御します。

Table 2 オペコード コマンド

| 名称                  | 説明                | オペコード                      |            |

|---------------------|-------------------|----------------------------|------------|

|                     |                   | 16進数                       | 2進数        |

| <b>書き込みイネーブル制御</b>  |                   |                            |            |

| WREN                | 書き込みイネーブル ラッチセット  | 06h                        | 0000 0110b |

| WRDI                | 書き込みイネーブル ラッチリセット | 04h                        | 0000 0100b |

| <b>レジスタアクセス</b>     |                   |                            |            |

| RDSR                | ステータス レジスタ読み出し    | 05h                        | 0000 0101b |

| WRSR                | ステータス レジスタ書き込み    | 01h                        | 0000 0001b |

| <b>メモリ書き込み</b>      |                   |                            |            |

| WRITE               | メモリデータ書き込み        | 02h                        | 0000 0010b |

| <b>メモリ読み出し</b>      |                   |                            |            |

| READ                | メモリデータ読み出し        | 03h                        | 0000 0011b |

| FSTRD               | メモリデータ高速読み出し      | 0Bh                        | 0000 1011b |

| <b>特殊セクタメモリアクセス</b> |                   |                            |            |

| SSWR                | 特殊セクタ書き込み         | 42h                        | 0100 0010b |

| SSRD                | 特殊セクタ読み出し         | 4Bh                        | 0100 1011b |

| <b>ID およびシリアル番号</b> |                   |                            |            |

| RDID                | デバイス ID 書き込み      | 9Fh                        | 1001 1111b |

| RUID                | 固有 ID 読み出し        | 4Ch                        | 0100 1100b |

| WRSN                | シリアル番号書き込み        | C2h                        | 1100 0010b |

| RDSN                | シリアル番号読み出し        | C3h                        | 11000 011b |

| <b>低消費電力モード</b>     |                   |                            |            |

| DPD                 | ディープパワーダウン モード開始  | BAh                        | 1011 1010b |

| HBN                 | ハイバネート モード開始      | B9h                        | 1011 1001b |

| 予約済み                | 予約済み              | 未使用のオペコードは<br>将来使用のために予約済み |            |

#### 4.1.1 書き込みイネーブル制御コマンド

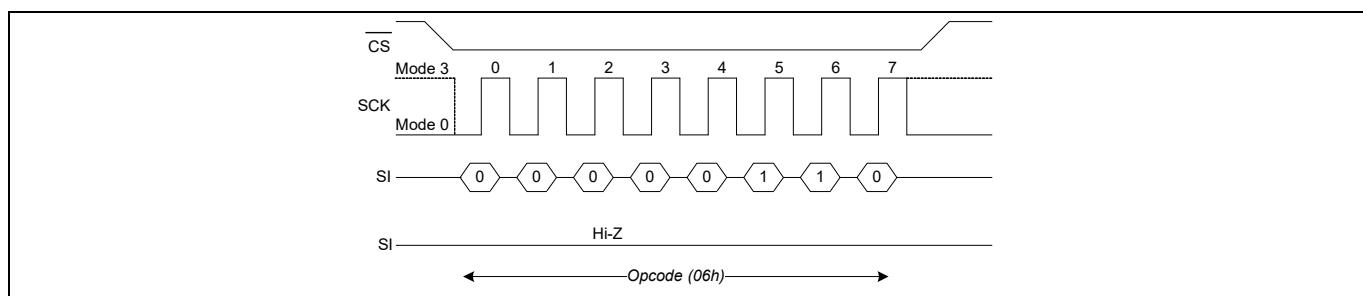

##### 4.1.1.1 書き込みイネーブル ラッチ セット (WREN, 06h)

CY15X108QN は書き込みが無効の状態で電源投入されます。WREN コマンドを書き込み動作の前に発行する必要があります。WREN オペコードを送信することにより、ユーザーは書き込み動作作用に次のオペコードを発行できます。書き込み動作には、ステータスレジスタ (WRSR)、メモリ (WRITE)、特殊セクタ (SSWR)、書き込みシリアル番号 (WRSN) への書き込みが含まれています。

WREN オペコードを発行すると、内部書き込みイネーブル ラッチがセットされます。WEL と呼ばれるステータスレジスタ内のフラグビットはラッチの状態を示します。WEL = 「1」は、書き込みが許可されることを示します。ステータスレジスタの WEL ビットに書き込んでもこのビットの状態に影響を与えません。WREN オペコードだけがこのビットをセットできます。WEL ビットは、WRDI や WRSR、WRITE、SSWR、WRSN 動作の後に続く CS の立ち上りエッジで自動的にクリアされます。これにより、別の WREN コマンドを発行せず、ステータスレジスタまたは F-RAM アレイへの二重の書き込みを防げます。[Figure 7](#) は、WREN コマンドのバスコンフィギュレーションを示します。

**Figure 7** WREN バス コンフィギュレーション

##### 4.1.1.2 書き込みイネーブル ラッチ リセット (WRDI, 04h)

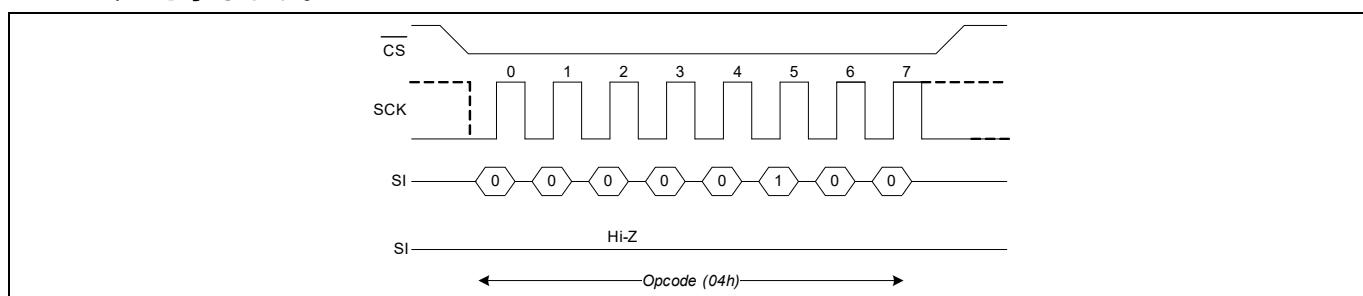

WRDI コマンドは、書き込みイネーブル ラッチをクリアすることによりすべての書き込み動作を無効にします。ステータスレジスタ内の WEL ビットを読み出し、WEL ビットが「0」であることを確認することにより、書き込みが無効であることを確認できます。[Figure 8](#) は、WRDI コマンドのバスコンフィギュレーションを示します。

**Figure 8** WRDI バス コンフィギュレーション

#### 4.1.2 レジスタアクセスコマンド

##### 4.1.2.1 ステータスレジスタおよび書き込み保護

CY15X108QN の書き込み保護機能は多層的であり、ステータスレジスタによって有効にされます。ステータスレジスタは以下のように構成されています (WEL, BP0, BP1, ビット 4 ~ 5 および WPEN の工場出荷時の初期値は「0」であり、ビット 6 の初期値は「1」です)。

**Table 3** ステータスレジスタ

| ビット 7    | ビット 6 | ビット 5 | ビット 4 | ビット 3   | ビット 2   | ビット 1   | ビット 0 |

|----------|-------|-------|-------|---------|---------|---------|-------|

| WPEN (0) | X (1) | X (0) | X (0) | BP1 (0) | BP0 (0) | WEL (0) | X (0) |

**Table 4** ステータスレジスタのビット定義

| ビット          | 定義             | 説明                                                                                                  |

|--------------|----------------|-----------------------------------------------------------------------------------------------------|

| ビット 0        | ドントケア          | このビットは書き込み不可ですが、読み出し時に「0」を返します。                                                                     |

| ビット 1 (WEL)  | 書き込みイネーブル      | WEL はデバイスの書き込みが有効かどうかを示します。電源投入時、このビットの初期値は「0」(無効)です。<br>WEL = 「1」--> 書き込み有効<br>WEL = 「0」--> 書き込み無効 |

| ビット 2 (BP0)  | ブロック保護ビット「0」   | ブロック保護に使用。詳細は <a href="#">Table 5</a> を参照してください。                                                    |

| ビット 3 (BP1)  | ブロック保護ビット「1」   | ブロック保護に使用。詳細は <a href="#">Table 5</a> を参照してください。                                                    |

| ビット 4 ~ 5    | ドントケア          | これらのビットは書き込み不可であり、読み出し時に常に「0」を返します。                                                                 |

| ビット 6        | ドントケア          | このビットは書き込み不可であり、読み出し時に常に「1」を返します。                                                                   |

| ビット 7 (WPEN) | 書き込み保護イネーブルビット | 書き込み保護ピン (WP) の機能を有効にするために使用。詳細は <a href="#">Table 6</a> を参照してください。                                 |

ビット 0 と 4 ~ 5 は「0」に、ビット 6 は「1」に固定され、これらのビットは修正できません。F-RAM はリアルタイムで書き込まれ、ビジー状態がないため、ビット 0 (シリアルフラッシュや EEPROM では「Ready or Write in progress」(待機または書き込み中) の状態を示すビット) は不要であり、「0」として読み出されます。例外は、[ディープパワーダウンモード \(DPD, BAh\)](#) または [ハイバネートモード \(HBN, B9h\)](#) からデバイスがウェイクアップしているときです。BP1 および BP0 は、ソフトウェア書き込み保護機能を制御する不揮発性ビットです。WEL フラグは、書き込みイネーブルラッチの状態を示しています。ステータスレジスタの WEL ビットに直接書き込んでも、その状態は変化しません。このビットは、内部で WREN および WRDI コマンドでそれぞれセットおよびクリアされます。

BP1 および BP0 はメモリブロックの書き込み保護ビットです。[Table 5](#) に示すように、書き込み保護されるメモリ領域を指定します。

**Table 5** ブロックメモリの書き込み保護

| BP1 | BP0 | 保護されるアドレス範囲                |

|-----|-----|----------------------------|

| 0   | 0   | 無し                         |

| 0   | 1   | C0000h ~ FFFFFFFh (上位 1/4) |

| 1   | 0   | 80000h ~ FFFFFFFh (上位 1/2) |

| 1   | 1   | 00000h ~ FFFFFFFh (全体)     |

機能説明

BP1とBP0ビットおよび書き込みイネーブルラッチは、メモリへの書き込みを防止する唯一のメカニズムです。残りの書き込み保護機能は、ブロック保護ビットへの不用意な変更を防止します。

ステータスレジスタの書き込み保護イネーブルビット(WPEN)は、ハードウェア書き込み保護( $\overline{WP}$ )ピンの効果を制御します。WPピンのタイミング図は、Figure 24を参照してください。WPENビットが「0」にクリアされると、WPピンの状態は無視されます。WPENビットが「1」にセットされる時、WPピンがLOWになるとステータスレジスタへの書き込みは防止されます。そのため、ステータスレジスタはWPEN =「1」および $\overline{WP}$  =「0」の場合のみ書き込みから保護されます。Table 6に書き込み保護条件をまとめます。

Table 6 書き込み保護

| <b>WEL</b> | <b>WPEN</b> | <b>WP</b> | <b>保護ブロック</b> | <b>非保護ブロック</b> | <b>ステータスレジスタ</b> |

|------------|-------------|-----------|---------------|----------------|------------------|

| 0          | X           | X         | 保護            | 保護             | 保護               |

| 1          | 0           | X         | 保護            | 非保護            | 非保護              |

| 1          | 1           | 0         | 保護            | 非保護            | 保護               |

| 1          | 1           | 1         | 保護            | 非保護            | 非保護              |

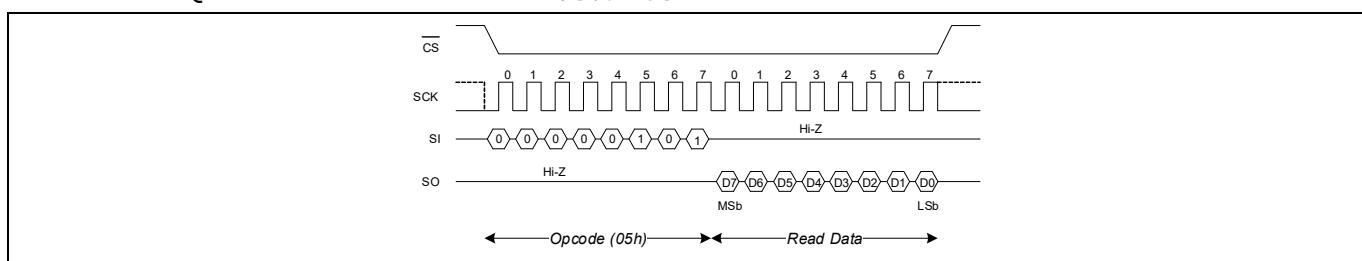

#### 4.1.2.2 ステータス レジスタ読み出し (RDSR, 05h)

RDSR コマンドでは、バスマスターはステータスレジスタの内容を検証できます。ステータスレジスタを読み出すことで、書き込み保護機能の現時点の状態に関する情報を得ます。RDSR オペコードに続いて、CY15X1080N はステータスレジスタの内容を持つ 1 バイトを返します。

Figure 9 RDSR バスコンフィギュレーション

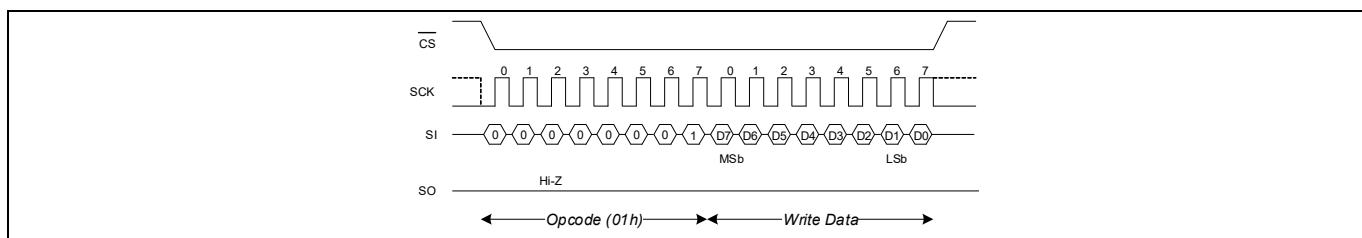

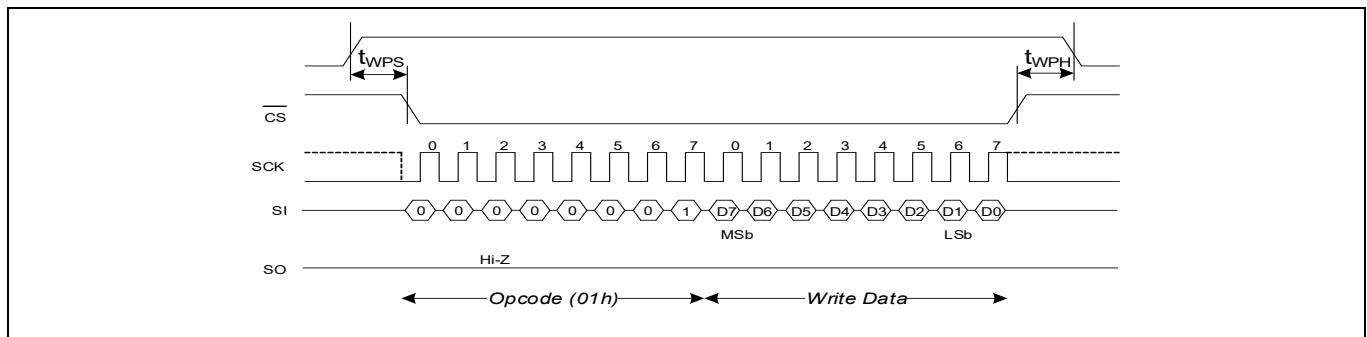

#### 4.1.2.3 ステータスレジスタ書き込み (WRSR, 01h)

WRSR コマンドを使って、SPI バス マスターがステータス レジスタへ書き込み、WPEN, BP0, BP1, およびビットを必要に応じて設定することで書き込み保護のコンフィギュレーションを変更できます。WRSR コマンドを発行する前に、WP ピンが HIGH または非アクティブである必要があります。CY15X108QN では、WP がメモリアレイではなくステータスレジスタのみへの書き込みを防止することに注意してください。WRSR コマンドを送信する前に、書き込みを有効にするために WREN コマンドを送信する必要があります。WRSR コマンドの実行は書き込み動作であるため、書き込みイネーブル ラッチがクリアされます。

Figure 10 WRSR バス コンフィギュレーション (WREN が非表示 )

### 4.1.3 メモリの動作

高いクロック周波数での動作が可能な SPI インターフェースは、F-RAM 技術の高速書き込み機能を際立たせます。シリアル フラッシュや EEPROM と異なり、CY15X108QN はバス速度で順次に書き込みを実行できます。ページレジスタは不要であり、シーケンシャルな書き込みは何回でも実行できます。

#### 4.1.4 メモリ書き込み動作コマンド

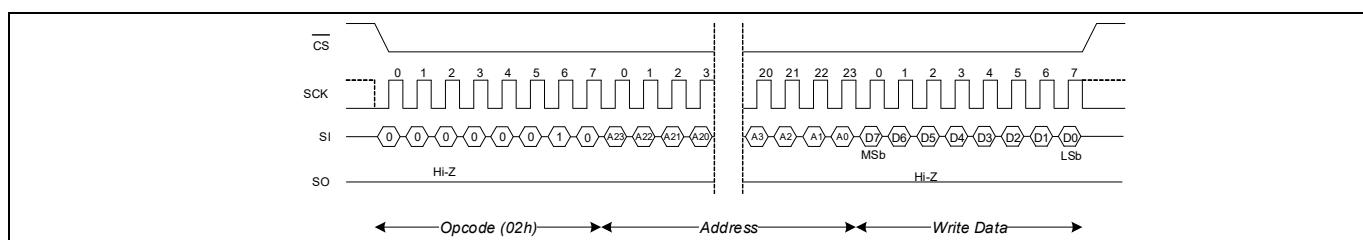

##### 4.1.4.1 書き込み (WRITE, 02h)

メモリへのすべての書き込みは、アサートおよびデアサートされている  $\overline{CS}$  を伴い WREN オペコードで始まります。次のオペコードは WRITE です。WRITE オペコードの後には、メモリへ書き込む最初のデータ バイトを指定する 20 ビット アドレス (A19 ~ A0) を含む 3 バイト アドレスが続きます。3 バイト アドレスの上位 4 ビットは無視されます。後続のバイトは順次に書き込まれるデータ バイトです。バス マスターがクロックを送り、 $\overline{CS}$  を LOW に維持している限り、アドレスは内部でインクリメントされます。FFFFFh の最終アドレスに達すると、内部アドレス カウンターは 00000h に戻ります。書き込まれるすべてのデータ バイトは、最初に MSb、最後に LSb が 8 クロックサイクルで SI に送信されます。 $\overline{CS}$  の立ち上がりエッジで書き込み操作が終了します。CY15X108QN 書き込み動作を Figure 11 に示します。

注：

- バースト書き込みが保護されたブロックに達すると、アドレスの自動インクリメントは停止し、書き込み用に受信された後続のデータ バイトのすべてがデバイスに無視されます。EEPROM はページ バッファを使用して書き込みスループットを上げます。ページ バッファは、書き込み動作が遅いという本来の特性を補完するものです。F-RAM メモリは、各データ バイトが(8 番目のクロックの後)クロック入力された直後に F-RAM アレイに書き込まれるため、ページ バッファを持っていません。そのため、ページ バッファの遅延なしにバイトをいくつも書き込めます。

- 書き込み中に電源を喪失すると、最後に完了したバイトのみが書き込まれます。

Figure 11 メモリ書き込み動作 (WREN が非表示 )

## 4.1.5 メモリ読み出しコマンド

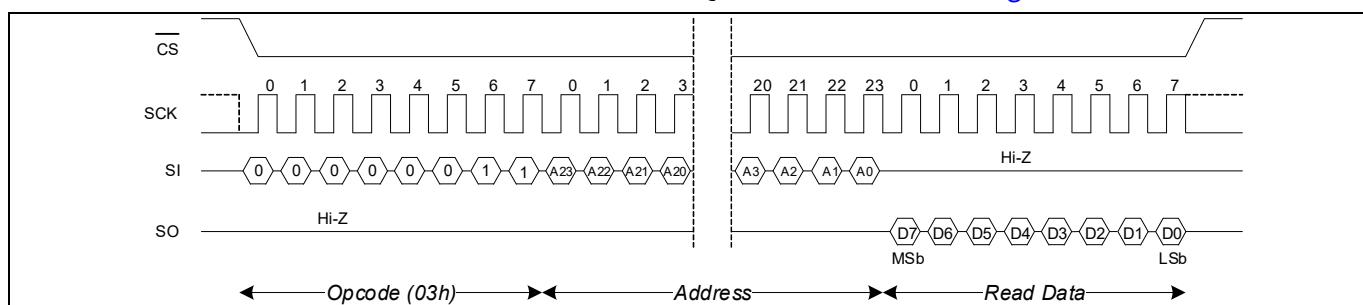

### 4.1.5.1 読み出し (READ, 03h)

$\overline{CS}$  の立ち下りエッジの後に、バス マスターは READ オペコードを発行できます。READ コマンドの後には、読み出し動作の最初のバイトを指定する 20 ビット アドレス (A19 ~ A0) を含む 3 バイト アドレスが続きます。アドレスの上位 4 ビットは無視されます。オペコードとアドレスが発行された後、デバイスは次の 8 クロックサイクルの間読み出しデータを出力します。SI 入力は読み出しデータ バイトの出力中は無視されます。後続のバイトは順次に読み出されるデータ バイトです。バス マスターがクロックを送り、 $\overline{CS}$  が LOW である限り、アドレスは内部でインクリメントされます。FFFFFh の最終アドレスに達すると、内部アドレスカウンターは 00000h に戻ります。SO 上のすべての読み出しデータ バイトは、最初に MSb、最後に LSb が 8 クロックサイクルで駆動されます。 $\overline{CS}$  の立ち上りエッジで読み出し動作が終了し、SO ピンがトライステートになります。CY15X108QN の読み出し動作を Figure 12 に示します。

Figure 12 メモリ読み出し動作

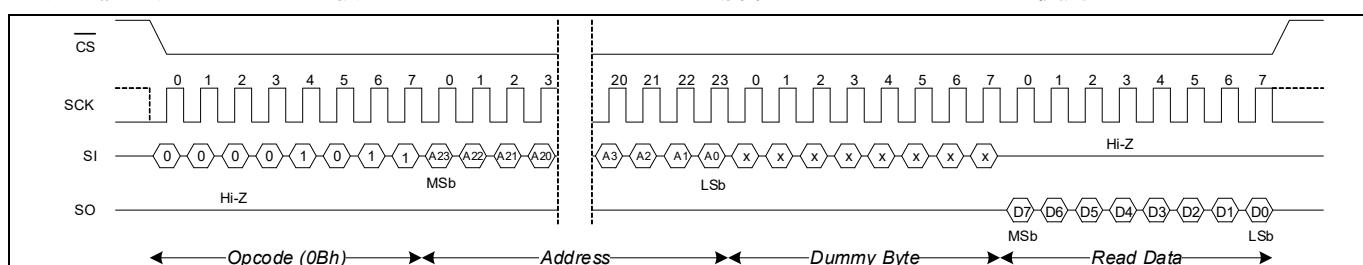

### 4.1.5.2 高速読み出し (FAST\_READ, 0Bh)

CY15X108QN は、シリアルフラッシュ デバイスとのコード互換性のために提供される FAST READ オペコード (0Bh) をサポートします。FAST READ オペコードの後には、読み出し動作の最初のバイトを指定する 20 ビット アドレス (A19 ~ A0) を含む 3 バイト アドレス、およびダミー バイトが続きます。ダミー バイトでは、8 クロックサイクルの読み出し遅延を入れます。ダミー バイトを追加することを除き、高速読み出し動作は通常の読み出し動作と同じです。オペコード、アドレス、ダミー バイトを受信した後、CY15X108QN は SO ラインで MSb ファースト形式でデータ バイトを出力し始めます。またデバイスが選択されクロックが有効である限り出力を継続します。バルク読み出しの場合、内部アドレスカウンターは自動的にインクリメントされ、最終アドレス FFFFh に達するとカウンターは 00000h に戻ります。デバイスが SO ラインでデータを出力している間、SI ライン上の遷移は無視されます。 $\overline{CS}$  の立ち上りエッジで高速読み出し動作が終了し、SO ピンはトライステートになります。CY15X108QN の高速読み出し動作を Figure 13 に示します。

**注:** ダミー バイトは Axh (8'b1010xxxx) 以外のいかなる 8 ビット値も可能です。Axh の下位 4 ビットはドントケア ビットです。そのため、Axh は本質的にダミー バイトとして送信してはならない 16 の異なる 8 ビット値を表します。一般的には、00h はほとんどの場合ダミー バイトとして使用されています。

Figure 13 高速読み出し動作

#### 4.1.6 特殊セクタメモリアクセスコマンド

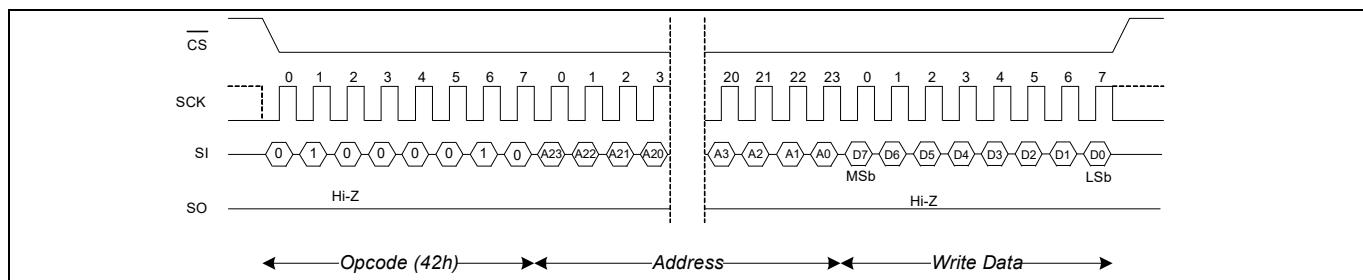

##### 4.1.6.1 特殊セクタ書き込み (SSWR, 42h)

256 バイトの特殊セクタへのすべての書き込みは、アサートおよびデアサートされている  $\overline{CS}$  を伴い WREN オペコードで始まります。次のオペコードは SSWR です。SSWR オペコードの後には、特殊セクタメモリへ書き込む最初のデータバイトを指定する 8 ビットセクタアドレス (A7 ~ A0) を含む 3 バイトアドレスが続きます。3 バイトアドレスの上位 16 ビットは無視されます。後続のバイトは順次に書き込まれるデータバイトです。バスマスターがクロックを送り、 $\overline{CS}$  を LOW に維持している限り、アドレスは内部でインクリメントされます。内部アドレスカウンターが XXXFFh に自動インクリメントすると、 $\overline{CS}$  は進行中の SSWR 動作を終了するために HIGH にトグルする必要があります。書き込まれるすべてのデータバイトは、最初に MSb、最後に LSb が 8 クロックサイクルで SI に送信されます。 $\overline{CS}$  の立ち上りエッジで書き込み操作が終了します。CY15X108QN 特殊セクタ書き込み操作を Figure 14 に示します。

注:

- 書き込み中に電源を喪失すると、最後に完了したバイトのみが書き込まれます。

- 特殊セクタ F-RAM メモリは、標準的なはんだリフローの最大 3 サイクルにわたってデータの完全性を維持することを保証しています。

Figure 14 特殊セクタ書き込み動作 (WREN が非表示)

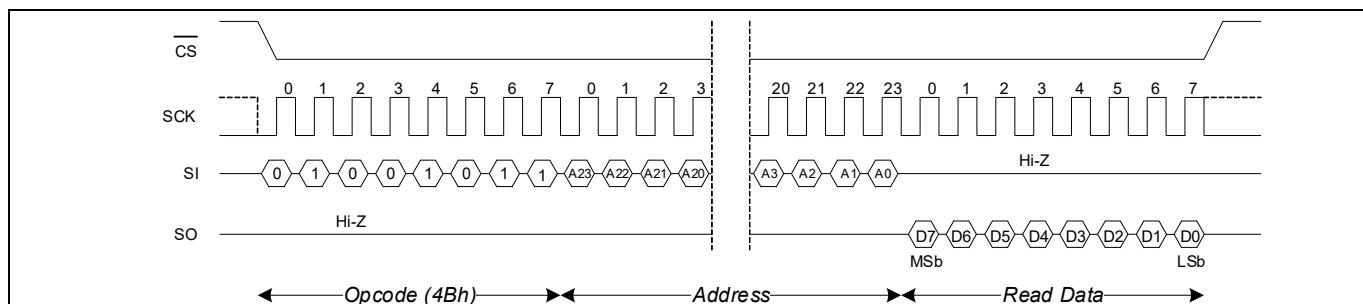

##### 4.1.6.2 特殊セクタ読み出し (SSRD, 4Bh)

$\overline{CS}$  の立ち下りエッジの後に、バスマスターは SSRD オペコードを発行できます。SSRD コマンドの後には、特殊セクタ読み出し動作の最初のバイトを指定する 8 ビットアドレス (A7 ~ A0) を含む 3 バイトアドレスが続きます。アドレスの上位 16 ビットは無視されます。オペコードとアドレスが発行された後、デバイスは次の 8 クロックサイクルの間読み出しデータを出力します。SI 入力は読み出しデータバイトの出力中は無視されます。後続のバイトは順次に読み出されるデータバイトです。バスマスターがクロックを送り、 $\overline{CS}$  が LOW である限り、アドレスは内部でインクリメントされます。SSRD では、アドレスラップはサポートされません。内部アドレスカウンターが XXXFFh に自動インクリメントすると、 $\overline{CS}$  は進行中の SSRD 動作を終了するために HIGH にトグルする必要があります。SO 上のすべての読み出しデータバイトは、最初に MSb が、最後に LSb が 8 クロックサイクルで駆動されます。 $\overline{CS}$  の立ち上りエッジにより、特別なセクタの読み出し操作が終了し、SO ピンがトライステートになります。CY15X108QN の特殊セクタの読み出し操作を Figure 15 に示します。

注: 特殊セクタ F-RAM メモリは、標準的なはんだリフローの最大 3 サイクルにわたってデータの完全性を維持することを保証しています。

Figure 15 特殊セクタ読み出し動作

#### 4.1.7 ID およびシリアル番号コマンド

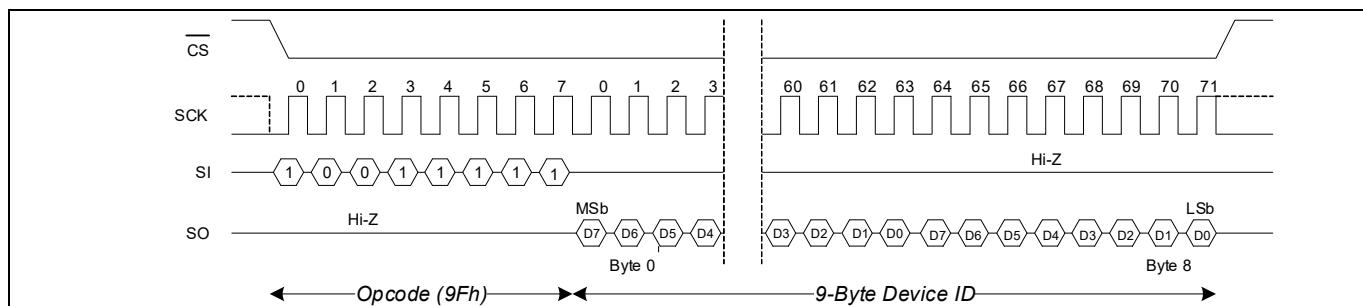

##### 4.1.7.1 デバイス ID 読み出し (RDID, 9Fh)

CY15X108QN デバイスは、メーカー、製品 ID、ダイ レビジョンについて問い合わせを行えます。RDID オペコード 9Fh では、両方とも読み出し専用バイトであるメーカー ID と製品 ID を読みます。JEDEC から割り当てられたメーカー ID は、バンク 7 の中に Ramtron の識別子を配置しています。そのため、1 バイトの C2h の後に 6 バイトの連続コード 7Fh が続きます。2 バイトの製品 ID はファミリコードとメモリ容量コード、サブコード、製品 Revision コードを含みます。Table 7 に 9 バイトデバイス ID のフィールド説明を示します。各製品の 9 バイトデバイス ID については、[注文情報](#)を参照してください。CY15X108QN のデバイス ID 読み出し動作を Figure 16 に示します。

**注:** 最下位のデータ バイト (バイト 0) は最初に、最上位のデータ バイト (バイト 8) は最後にシフトアウトされます。

Table 7 9 バイトのデバイス ID

| デバイス ID のフィールド説明   |                 |                 |             |                |                |           |              |

|--------------------|-----------------|-----------------|-------------|----------------|----------------|-----------|--------------|

| メーカー ID<br>[71:16] | ファミリ<br>[15:13] | メモリ容量<br>[12:9] | 突入電流<br>[8] | サブタイプ<br>[7:5] | レビジョン<br>[4:3] | 電圧<br>[2] | 周波数<br>[1:0] |

| 56 ビット             | 3 ビット           | 4 ビット           | 1 ビット       | 3 ビット          | 2 ビット          | 1 ビット     | 2 ビット        |

各製品の 9 バイト デバイス ID については、[注文情報](#)を参照してください。

Figure 16 デバイス ID 読み出し

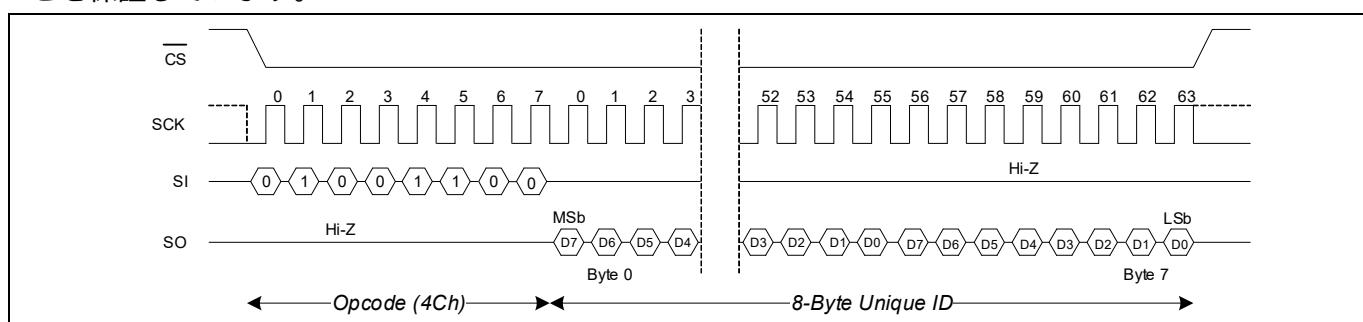

##### 4.1.7.2 固有 ID 読み出し (RUID, 4Ch)

CY15X102QN デバイスは、出荷時にプログラムされた、各デバイスに固有の 64 ビット番号である固有 ID について問い合わせできます。RUID オペコード 4Ch は、8 バイトを読み出せて、固有 ID のみを読み出せます。CY15X102QN の固有 ID 読み出し動作を Figure 17 に示します。

**注:**

- 最下位のデータ バイト (バイト 0) は最初に、最上位のデータ バイト (バイト 7) は最後にシフトアウトされます。

- 固有 ID レジスタは、標準的なハンドリフローの最大 3 サイクルにわたってデータの完全性を維持することを保証しています。

Figure 17 固有 ID 読み出し

機能説明

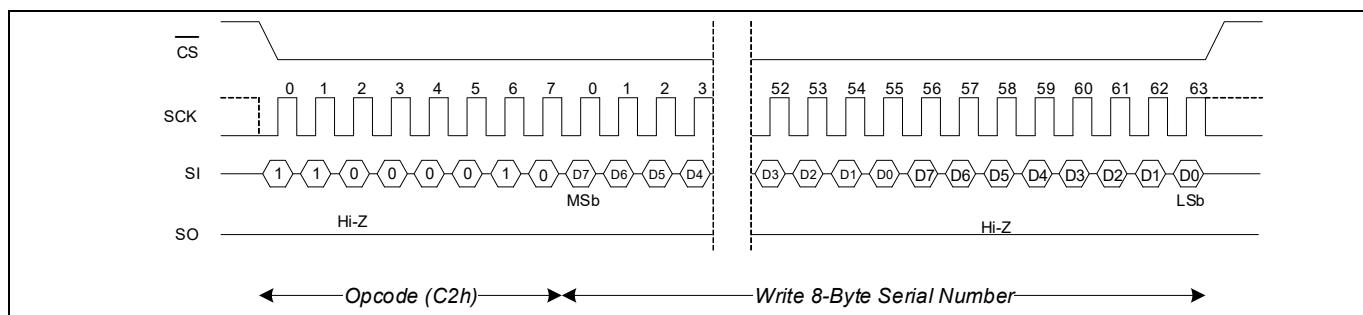

#### 4.1.7.3 シリアル番号書き込み (WRSN, C2h)

シリアル番号は、PC 基板またはシステムを一義的に識別するためにユーザーに提供される 8 バイトのワントライムプログラマブルメモリ空間です。通常、シリアル番号は 2 バイトのカスタマ ID、その後に続く 5 バイトの固有のシリアル番号と 1 バイトの CRC チェックで構成されています。しかし、エンドアプリケーションは 8 バイトシリアル番号の独自のフォーマットを定義できます。シリアル番号レジスタへのすべての書き込みは、アサートおよびデアサートされている CS を伴い WREN オペコードで始まります。次のオペコードは WRSN です。WRSN 命令は、シリアル番号のすべての 8 バイトを書き込むためにバーストモードで使用できます。シリアル番号の最後のバイトがシフトインされた後、WRSN 動作を完了するため CS を High に駆動する必要があります。CY15X108QN のシリアル番号書き込み動作を Figure 18 に示します。

**注:**CRC チェックサムはデバイスによって計算されません。システムファームウェアは 7 バイトの内容に対して CRC チェックサムを計算し、チェックサムを 7 バイトのユーザー定義のシリアル番号に付け加えてから、この 8 バイトシリアル番号をシリアル番号レジスタにプログラムする必要があります。8 バイトシリアル番号の工場出荷時の初期値は「0000000000000000h」です。

Table 8 8 バイトのシリアル番号

| 16 ビットのカスタマ識別子 |           | 40 ビットの固有番号 |           |           |           |          |         | 8 ビットの CRC |

|----------------|-----------|-------------|-----------|-----------|-----------|----------|---------|------------|

| SN[63:56]      | SN[55:48] | SN[47:40]   | SN[39:32] | SN[31:24] | SN[23:16] | SN[15:8] | SN[7:0] |            |

Figure 18 シリアル番号書き込み動作 (WREN が非表示 )

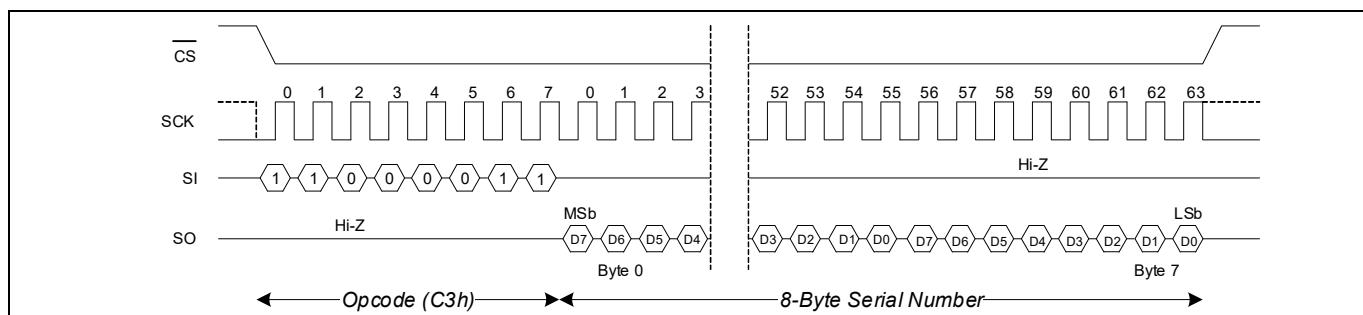

#### 4.1.7.4 シリアル番号読み出し (RDSN, C3h)

CY15X108QN デバイスはデバイスを一義的に識別するためにユーザーに提供される 8 バイトのシリアル番号のスペースを組み込んでいます。シリアル番号は RDSN 命令で読み出されます。シリアル番号読み出しは、バーストモードで実行して一度にすべての 8 バイトを読み出せます。シリアル番号の最後のバイトが読み出された後、デバイスはシリアル番号の最初のバイトにループバックします。CS が Low になった後、RDSN のオペコードをシフトすることで RDSN 命令を発行できます。CY15X108QN のシリアル番号読み出し動作を Figure 19 に示します。

**注:** 最下位のデータバイト (バイト 0) は最初に、最上位のデータバイト (バイト 7) は最後にシフトアウトされます。

Figure 19 シリアル番号読み出し動作

#### 4.1.8 低消費電力モード コマンド

##### 4.1.8.1 ディープパワーダウンモード (DPD, BAh)

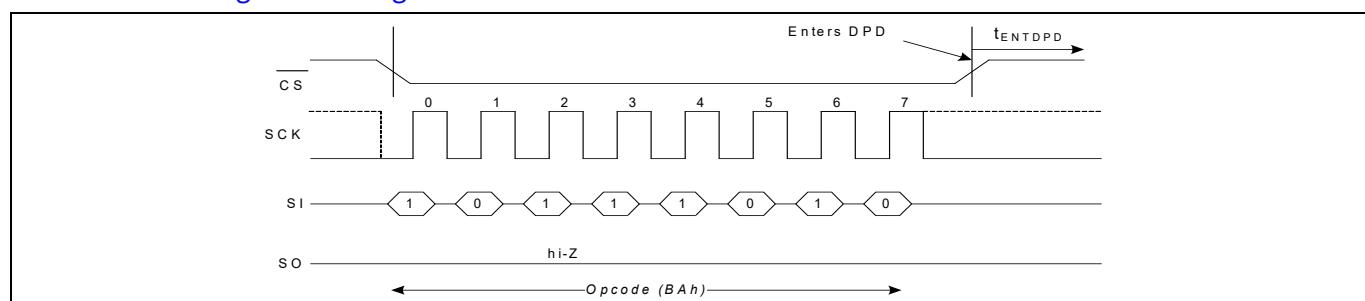

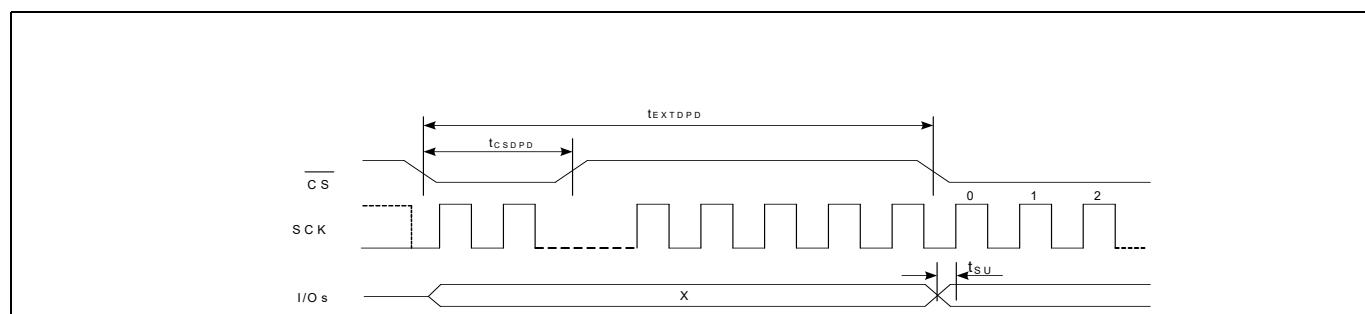

CY15X108QN デバイスには省電力のディープパワーダウンモードが実装されています。デバイスは、DPD オペコード BAh がクロック入力され、CS の立ち上がりエッジが適用されてから  $t_{ENTDPD}$  の時間後にディープパワーダウンモードに入ります。ディープパワーダウンモードでは、SCK と SI ピンが無視され、SO が Hi-Z となります。また、CS ピンの監視を継続します。

$t_{CSDPD}$  の CS パルス幅は  $t_{EXTDPD}$  時間後に DPD モードを終了します。CS パルス幅は、ダミー命令を送信することで、または SCK と I/O がドントケアである間に CSだけをトグルすることで生成します。ディープパワーダウンモードからの復帰中に、I/O は Hi-Z 状態のままであります。DPD の開始と終了タイミングについては、それぞれ Figure 20 と Figure 21 を参照してください。

Figure 20 DPD 開始タイミング

Figure 21 DPD 終了タイミング

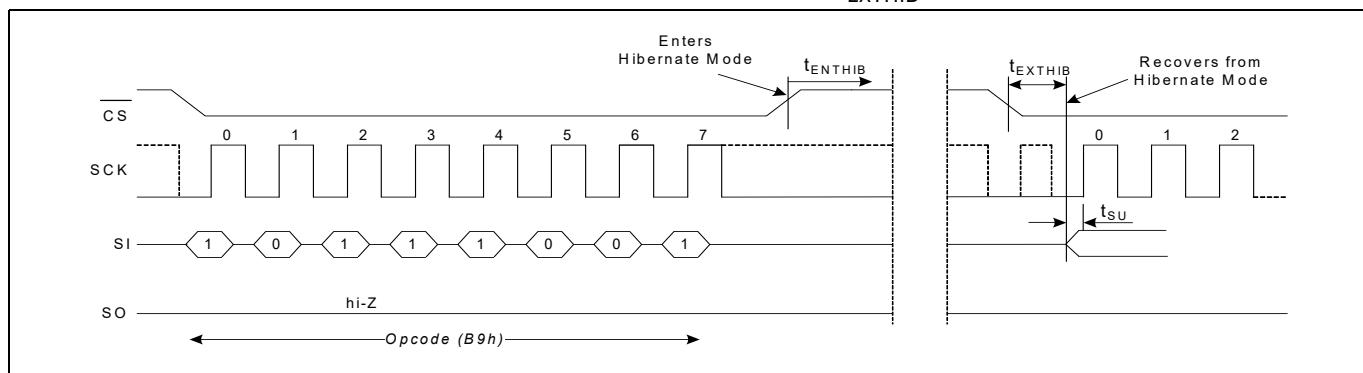

#### 4.1.8.2 ハイバネート モード (HBN, B9h)

CY15X108QN デバイスには最低消費電力のハイバネート モードが実装されています。デバイスは、HBN オペコード B9h がクロック入力され、CS の立ち上りエッジが適用されてから  $t_{ENTHIB}$  の時間後にハイバネート モードに入ります。ハイバネート モードでは、SCK と SI ピンが無視され、SO が Hi-Z となります。また、デバイスは CS ピンの監視を継続します。CS の次の立ち下りエッジで、デバイスは  $t_{EXTHIB}$  以内に通常の動作に復帰します。ハイバネート モードからの復帰中は、SO ピンは Hi-Z 状態のままであります。デバイスは、復帰期間内では必ずしもオペコードに応答しません。ハイバネート モードを終了するために、コントローラーは、例えば「ダミー」読み出しを送信し、残りの  $t_{EXTHIB}$  時間待機することができます。

Figure 22 ハイバネート モード動作

#### 4.1.8.3 アクセス可能回数

CY15X108QN デバイスには  $10^{15}$  回以上、読み書きを問わずアクセスできます。

F-RAM メモリは読み出しと格納メカニズムを併用して動作します。そのため、メモリアレイへのアクセス（読み出し / 書き込み）に対して、アクセスサイクルが行単位で適用されます。F-RAM のアーキテクチャは、64 ビットの列と 128K の行から成るアレイを基にしています。読み出しありまたは書き込みは行単位に行われます。1 行内のデータのアクセスバイト数に関わらず内部的に行に対するアクセスは 1 回です。行内の各バイトは、アクセス可能回数の計算では 1 回だけカウントされます。Table 9 は、オペコード、開始アドレス、順次 64 バイトデータの流れを含む、64 バイトの繰り返しループに対応したアクセス可能回数を示します。これはループによって各バイトがアクセス 1 回を費やしたことになります。

F-RAM の読み出しと書き込み可能回数は、40 MHz のクロック速度で事実上無制限です。

Table 9 64 バイト ループの繰り返しでアクセス可能回数に達する期間

| SCK 周波数 (MHz) | アクセス回数<br>(サイクル / 秒) | アクセス回数<br>(サイクル / 年)  | $10^{15}$ 限界到達年数 |

|---------------|----------------------|-----------------------|------------------|

| 40            | 73,040               | $2.30 \times 10^{12}$ | 432              |

| 20            | 36,520               | $1.16 \times 10^{12}$ | 864              |

| 10            | 18,380               | $5.79 \times 10^{11}$ | 1727             |

| 5             | 9,190                | $2.90 \times 10^{11}$ | 3454             |

最大定格

## 5 最大定格

最大定格を超えると、デバイスの寿命が短くなる可能性があります。ユーザー ガイドラインはテストされていません。

**Table 10 絶対最大定格**

| パラメーター                                                                          | 最大定格                                 |

|---------------------------------------------------------------------------------|--------------------------------------|

| 保存温度                                                                            | -65°C ~ +125°C                       |

| 最大累積保存時間<br>周囲温度 125 °C の場合<br>周囲温度 85 °C の場合                                   | 1000 時間<br>10 年                      |

| 最大接合部温度                                                                         | 125°C                                |

| $V_{SS}$ を基準とした $V_{DD}$ の電源電圧<br>CY15V108QN:<br>CY15B108QN:                    | -0.5 V ~ +2.4 V<br>-0.5 V ~ +4.1 V   |

| 入力電圧                                                                            | $V_{IN} \leq V_{DD} + 0.5 \text{ V}$ |

| High-Z 状態の出力に印加されるDC電圧                                                          | -0.5 V ~ $V_{DD} + 0.5 \text{ V}$    |

| グランド電位を基準にした任意のピンの過渡電圧 (< 20 ns)                                                | -2.0 V ~ $V_{DD} + 2.0 \text{ V}$    |

| パッケージ許容電力損失 ( $T_A = 25^\circ\text{C}$ )                                        | 1.0 W                                |

| 表面実装はんだ付け温度 (3 秒)                                                               | +260°C                               |

| DC 出力電流 (一度に1 出力、1秒間)                                                           | 15 mA                                |

| 静電気の放電電圧<br>人体モデル (JEDEC規格 JESD22-A114-B)<br>荷電デバイス モデル (JEDEC規格 JESD22-C101-A) | 2 kV<br>500 V                        |

| ラッチアップ電流                                                                        | >140 mA                              |

動作範囲

## 6 動作範囲

Table 11 動作範囲

| デバイス       | 範囲  | 周囲温度          | $V_{DD}$        |

|------------|-----|---------------|-----------------|

| CY15V108QN | 民生用 | 0°C ~ +70°C   | 1.71 V ~ 1.89 V |

| CY15B108QN |     |               | 1.8 V ~ 3.6 V   |

| CY15V108QN | 産業用 | -40°C ~ +85°C | 1.71 V ~ 1.89 V |

| CY15B108QN |     |               | 1.8 V ~ 3.6 V   |

DC 電気的特性

## 7 DC 電気的特性

Table 12 DC 電気的特性

動作範囲において

| パラメーター   | 説明               | テスト条件                                                                                                                                    | 温度                         | Min  | Typ [3, 4] | Max  | 単位            |  |

|----------|------------------|------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|------|------------|------|---------------|--|

| $V_{DD}$ | 電源               | CY15V108QN                                                                                                                               | -                          | 1.71 | 1.80       | 1.89 | V             |  |

|          |                  | CY15B108QN                                                                                                                               |                            | 1.80 | 3.30       | 3.60 |               |  |

|          | $V_{DD}$ 電源電流    | $V_{DD} = 1.71V \sim 1.89V$ ; SCK は $V_{DD} - 0.2V$ と $V_{SS}$ 間でトグル。<br>他の入力は $V_{SS}$ または $V_{DD} - 0.2V$ 。SO = 開放;<br>CY15V108QN-20LP | 民生用                        | -    | 0.3        | 0.38 |               |  |

|          |                  | $f_{SCK} = 1 \text{ MHz}$                                                                                                                |                            | -    | 1.3        | 1.5  |               |  |

|          |                  | $f_{SCK} = 20 \text{ MHz}$                                                                                                               | 産業用                        | -    | 0.3        | 0.58 |               |  |

|          |                  | $f_{SCK} = 1 \text{ MHz}$                                                                                                                |                            | -    | 1.3        | 1.6  |               |  |

|          | $V_{DD}$ 電源電流    | $V_{DD} = 1.8V \sim 3.6V$ ; SCK は $V_{DD} - 0.2V$ と $V_{SS}$ 間でトグル。<br>他の入力は $V_{SS}$ または $V_{DD} - 0.2V$ 。SO = 開放;<br>CY15B108N-20LP    | 民生用                        | -    | 0.35       | 0.52 | mA            |  |

|          |                  | $f_{SCK} = 20 \text{ MHz}$                                                                                                               |                            | -    | 1.4        | 1.6  |               |  |

|          |                  | $f_{SCK} = 1 \text{ MHz}$                                                                                                                | 産業用                        | -    | 0.35       | 0.7  |               |  |

|          |                  | $f_{SCK} = 20 \text{ MHz}$                                                                                                               |                            | -    | 1.4        | 1.75 |               |  |

|          | $I_{DD}$         | $V_{DD} = 1.71V \sim 1.89V$ ; SCK は $V_{DD} - 0.2V$ と $V_{SS}$ 間でトグル。他の入力は $V_{SS}$ または $V_{DD} - 0.2V$ 。SO = 開放;<br>CY15V108QN-40LP     | $f_{SCK} = 40 \text{ MHz}$ | 産業用  | -          | 2.6  | 3.2           |  |

|          |                  | $V_{DD} = 1.8V \sim 3.6V$ ; SCK は $V_{DD} - 0.2V$ と $V_{SS}$ 間でトグル。他の入力は $V_{SS}$ または $V_{DD} - 0.2V$ 。SO = 開放;<br>CY15B108QN-40LP       |                            |      |            |      |               |  |

| $I_{SB}$ | $V_{DD}$ スタンバイ電流 | $V_{DD} = 1.71V \sim 1.89V$ ; $CS = V_{DD}$ 。<br>他の入力は $V_{SS}$ または $V_{DD}$ 。                                                           | $T_A = 25^\circ\text{C}$   | -    | 3.5        | -    | $\mu\text{A}$ |  |

|          |                  | $T_A = 70^\circ\text{C}$                                                                                                                 | -                          |      | 52         |      |               |  |

|          |                  | $T_A = 85^\circ\text{C}$                                                                                                                 | -                          |      | 110        |      |               |  |

|          |                  | $V_{DD} = 1.8V \sim 3.6V$ ; $CS = V_{DD}$ 。<br>他の入力は $V_{SS}$ または $V_{DD}$ 。                                                             | $T_A = 25^\circ\text{C}$   |      | 3.8        | -    |               |  |

|          |                  | $T_A = 70^\circ\text{C}$                                                                                                                 | -                          |      | -          | 55   |               |  |

|          |                  | $T_A = 85^\circ\text{C}$                                                                                                                 |                            |      | -          | 120  |               |  |

注:

3. Typ 値は  $25^\circ\text{C}$ 、 $V_{DD} = V_{DD}(\text{Typ})$  で測定されます。

4. このパラメーターは特性によって保証され、量産中にテストされません。

DC 電気的特性

**Table 12 DC 電気的特性 (continued)**

動作範囲において

| パラメーター           | 説明                     | テスト条件                                                                                                     | 温度                                                                      | Min                   | Typ <sup>[3, 4]</sup> | Max                   | 単位 |

|------------------|------------------------|-----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|-----------------------|-----------------------|-----------------------|----|

| I <sub>DPD</sub> | ディープ<br>パワーダウン<br>電流   | V <sub>DD</sub> = 1.71V ~ 1.89V;<br>CS = V <sub>DD</sub> °<br>他の入力は V <sub>SS</sub> または V <sub>DD</sub> ° | T <sub>A</sub> = 25°C<br>T <sub>A</sub> = 70°C<br>T <sub>A</sub> = 85°C | -                     | 0.9                   | -                     | μA |

|                  |                        |                                                                                                           |                                                                         | -                     | -                     | 11                    |    |

|                  |                        |                                                                                                           |                                                                         | -                     | -                     | 24                    |    |

|                  |                        | V <sub>DD</sub> = 1.8V ~ 3.6V;<br>CS = V <sub>DD</sub> °<br>他の入力は V <sub>SS</sub> または V <sub>DD</sub> °   | T <sub>A</sub> = 25°C<br>T <sub>A</sub> = 70°C<br>T <sub>A</sub> = 85°C | -                     | 1                     | -                     |    |

|                  |                        |                                                                                                           |                                                                         | -                     | -                     | 12                    |    |

|                  |                        |                                                                                                           |                                                                         | -                     | -                     | 26                    |    |

|                  |                        |                                                                                                           |                                                                         | -                     | 0.1                   | -                     |    |

|                  |                        | V <sub>DD</sub> = 1.71V ~ 1.89V;<br>CS = V <sub>DD</sub> °<br>他の入力は V <sub>SS</sub> または V <sub>DD</sub> ° | T <sub>A</sub> = 25°C<br>T <sub>A</sub> = 70°C<br>T <sub>A</sub> = 85°C | -                     | -                     | 0.4                   |    |

| I <sub>HBN</sub> | ハイバネート<br>モード電流        |                                                                                                           |                                                                         | -                     | -                     | 0.9                   |    |

|                  |                        | V <sub>DD</sub> = 1.8V ~ 3.6V;<br>CS = V <sub>DD</sub> °<br>他の入力は V <sub>SS</sub> または V <sub>DD</sub> °   |                                                                         | -                     | 0.1                   | -                     |    |

|                  |                        |                                                                                                           |                                                                         | -                     | -                     | 0.75                  |    |

|                  |                        |                                                                                                           |                                                                         | -                     | -                     | 1.6                   |    |

|                  |                        |                                                                                                           |                                                                         | -                     | -1                    | -                     | μA |

|                  |                        | WP ピンを除く<br>I/O ピンの入力<br>リーコンデンサー電流                                                                       |                                                                         | -                     | -100                  | -                     |    |

| I <sub>LI</sub>  | WP ピンの入力<br>リーコンデンサー電流 | V <sub>SS</sub> < V <sub>IN</sub> < V <sub>DD</sub>                                                       | -                                                                       | -                     | -                     | 1                     |    |

| I <sub>LO</sub>  | 出力リーコンデンサー電流           | V <sub>SS</sub> < V <sub>OUT</sub> < V <sub>DD</sub>                                                      | -                                                                       | -1                    | -                     | 1                     |    |

| V <sub>IH</sub>  | 入力 HIGH 電圧             | -                                                                                                         | -                                                                       | 0.7 × V <sub>DD</sub> | -                     | V <sub>DD</sub> + 0.3 | V  |

| V <sub>IL</sub>  | 入力 LOW 電圧              | -                                                                                                         | -                                                                       | -0.3                  | -                     | 0.3 × V <sub>DD</sub> |    |

| V <sub>OH1</sub> | 出力 HIGH 電圧             | I <sub>OH</sub> = -1 mA, V <sub>DD</sub> = 2.7 V.                                                         | -                                                                       | 2.4                   | -                     | -                     |    |

| V <sub>OH2</sub> | 出力 HIGH 電圧             | I <sub>OH</sub> = -100 μA                                                                                 | -                                                                       | V <sub>DD</sub> - 0.2 | -                     | -                     |    |

| V <sub>OL1</sub> | 出力 LOW 電圧              | I <sub>OL</sub> = 2 mA, V <sub>DD</sub> = 2.7 V                                                           | -                                                                       | -                     | -                     | 0.4                   |    |

| V <sub>OL2</sub> | 出力 LOW 電圧              | I <sub>OL</sub> = 150 μA                                                                                  | -                                                                       | -                     | -                     | 0.2                   |    |

注:

3. Typ 値は 25°C、V<sub>DD</sub> = V<sub>PP</sub>(Typ) で測定されます。

4. このパラメーターは特性によって保証され、量産中にテストされません。

データ保持期間およびアクセス可能回数

## 8 データ保持期間およびアクセス可能回数

Table 13 データ保持期間およびアクセス可能回数

| パラメーター          | 説明       | テスト条件                 | Min              | Max | 単位   |

|-----------------|----------|-----------------------|------------------|-----|------|

| T <sub>DR</sub> | データ保持期間  | T <sub>A</sub> = 85°C | 10               | -   | 年    |

|                 |          | T <sub>A</sub> = 70°C | 141              | -   |      |

|                 |          | T <sub>A</sub> = 60°C | 151              | -   |      |

|                 |          | T <sub>A</sub> = 50°C | 160              | -   |      |

| NV <sub>C</sub> | アクセス可能回数 | 動作温度範囲内               | 10 <sup>15</sup> | -   | サイクル |

静電容量

## 9 静電容量

**Table 14 静電容量**

すべてのパッケージに該当

| パラメーター [5] | 説明            | テスト条件                                                                    | Max | 単位 |

|------------|---------------|--------------------------------------------------------------------------|-----|----|

| $C_O$      | 出力ピン静電容量 (SO) | $T_A = 25^\circ\text{C}, f = 1 \text{ MHz}, V_{DD} = V_{DD(\text{typ})}$ | 8   | pF |

| $C_I$      | 入力ピン静電容量      |                                                                          | 6   |    |

注:

- このパラメーターは特性によって保証され、量産中にテストされません。

熱抵抗

## 10 热抵抗

Table 15 热抵抗

| パラメーター <sup>[6]</sup> | 説明                  | テスト条件                                                                         | 8 ピン SOIC<br>パッケージ | 8 ピン GQFN<br>パッケージ | 8 ピン UFLGA<br>パッケージ | 単位   |

|-----------------------|---------------------|-------------------------------------------------------------------------------|--------------------|--------------------|---------------------|------|

| $\theta_{JA}$         | 熱抵抗<br>( 接合部から周囲 )  | テス ト 条 件 は、<br>EIA/JESD51 による、<br>熱インピーダンス<br>を測定するための<br>標準的なテスト方<br>法と手順に従う | 81.5               | 113.5              | 103.5               | °C/W |

| $\theta_{JC}$         | 熱抵抗<br>( 接合部からケース ) |                                                                               | 96.5               | 99                 | 35.3                |      |

注:

- このパラメーターは特性によって保証され、量産中にテストされません。

AC テスト条件

## 11 AC テスト条件

Table 16 AC テスト条件

| パラメーター           | 値                    |

|------------------|----------------------|

| 入力パルス レベル        | $V_{DD}$ の 10% と 90% |

| 入力の立ち上りと立ち下り時間   | 3 ns                 |

| 入力と出力のタイミング参照レベル | $0.5 \times V_{DD}$  |

| 出力不可容量           | 30 pF                |

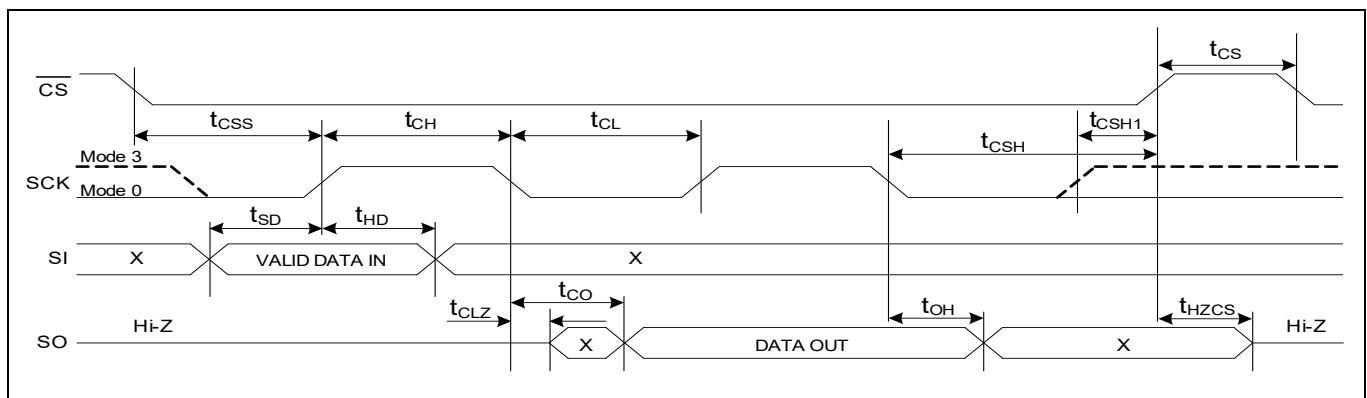

AC スイッチング特性

## 12 AC スイッチング特性

Table 17 AC スイッチング特性

動作範囲において

| パラメーター <sup>[7]</sup>         | 代替パラメーター   | 説明                                               | 20 MHz |     | 40 MHz |     | 単位  |

|-------------------------------|------------|--------------------------------------------------|--------|-----|--------|-----|-----|

|                               |            |                                                  | Min    | Max | Min    | Max |     |

| $t_{SCK}$                     | -          | SCK クロック周波数                                      | 0      | 20  | 0      | 40  | MHz |

| $t_{CH}$                      | -          | クロック HIGH 時間                                     | 22     | -   | 11     | -   |     |

| $t_{CL}$                      | -          | クロック LOW 時間                                      | 22     | -   | 11     | -   |     |

| $t_{CLZ}$ <sup>[8]</sup>      | -          | クロック LOW から出力 low-Z までの時間                        | 0      | -   | 0      | -   |     |

| $t_{CSS}$                     | $t_{CSU}$  | チップセレクトセットアップ時間                                  | 10     | -   | 5      | -   |     |

| $t_{CSH}$                     | $t_{CSH}$  | チップセレクトホールド時間 - SPI モード 0                        | 10     | -   | 5      | -   |     |

| $t_{CSH1}$                    | -          | チップセレクトホールド時間 - SPI モード 3                        | 10     | -   | 10     | -   |     |

| $t_{HZCS}$ <sup>[9, 10]</sup> | $t_{OD}$   | 出力ディセーブル時間                                       | -      | 20  | -      | 12  |     |

| $t_{CO}$                      | $t_{ODV}$  | 出力データ有効時間                                        | -      | 20  | -      | 9   |     |

| $t_{OH}$                      | -          | 出力ホールド時間                                         | 1      | -   | 1      | -   |     |

| $t_{CS}$                      | $t_D$      | 選択解除時間                                           | 60     | -   | 40     | -   |     |

| $t_{SD}$                      | $t_{SU}$   | データセットアップ時間                                      | 5      | -   | 5      | -   |     |

| $t_{HD}$                      | $t_H$      | データホールド時間                                        | 5      | -   | 5      | -   |     |

| $t_{WPS}$                     | $t_{WHSL}$ | $\overline{WP}$ セットアップ時間 ( $\overline{CS}$ に対する) | 20     | -   | 20     | -   |     |

| $t_{WPH}$                     | $t_{SHWL}$ | $\overline{WP}$ ホールド時間 ( $\overline{CS}$ に対する)   | 20     | -   | 20     | -   |     |

ns

注:

7. テスト条件は [AC テスト条件](#) に示す 3 ns 以下の信号遷移時間、 $0.5 \times V_{DD}$  のタイミング参照レベル、 $V_{DD}$  の 10% ~ 90% の入力パルスレベル、指定の  $I_{OL}/I_{OH}$  の出力負荷および 30pF の負荷容量を前提にしています。

8. 設計上では保証されます。

9.  $t_{HZCS}$  は 5 pF の負荷容量が付いている状態で測定されます。遷移は出力が高インピーダンス状態に入るときに測定されます。

10. このパラメーターは特性によって保証され、量産中にテストされません。

AC スイッチング特性

Figure 23 同期データタイミング(モード0およびモード3)

Figure 24 ステータス レジスタ書き込み動作(WRSR)中の書き込み保護タイミング

パワー サイクル タイミング

## 13 パワー サイクル タイミング

Table 18 パワー サイクル タイミング

動作範囲において

| パラメーター [11]                 |           | 説明                                                                                     | Min   | Max                  | 単位   |

|-----------------------------|-----------|----------------------------------------------------------------------------------------|-------|----------------------|------|

| パラメーター                      | 代替パラメーター  |                                                                                        |       |                      |      |

| $t_{PU}$                    | -         | 電源投入時 $V_{DD(min)}$ から最初のアクセス ( $\overline{CS}$ LOW) までの時間                             | 450   | -                    | μs   |

| $t_{VR}^{[12]}$             | -         | $V_{DD}$ 電源投入時変化速度                                                                     | 30    | -                    | μs/V |

| $t_{VF}^{[12, 13]}$         | -         | $V_{DD}$ 電源切断時変化速度                                                                     | 20    | -                    | μs/V |

| $t_{ENTDPD}^{[14]}$         | $t_{DP}$  | $\overline{CS}$ HIGH からディープパワーダウンモード開始までの時間 ( $\overline{CS}$ HIGH からハイバネートモード開始までの時間) | -     | 3                    | μs   |

| $t_{CSDPD}$                 | -         | ディープパワーダウンモードから復帰するための $\overline{CS}$ パルス幅                                            | 0.015 | $4 \times 1/f_{SCK}$ |      |

| $t_{EXTDPD}$                | $t_{RDP}$ | ディープパワーダウンモードからの復帰時間 ( $\overline{CS}$ LOW からアクセスできるまでの時間)                             | -     | 10                   |      |

| $t_{ENTHIB}^{[15]}$         | -         | ハイバネートモードへの移行時間 ( $\overline{CS}$ HIGH からハイバネートモード開始までの時間)                             | -     | 3                    |      |

| $t_{EXTHIB}^{[15]}$         | $t_{REC}$ | ハイバネートモードからの復帰時間 ( $\overline{CS}$ LOW からアクセスできるまでの時間)                                 | -     | 450                  |      |

| $V_{DD}(\text{low})^{[13]}$ | -         | 初期化が発生する低 $V_{DD}$                                                                     | 0.6   | -                    | V    |

| $t_{PD}^{[13]}$             | -         | $V_{DD}(\text{low})$ が 0.6V である $V_{DD}(\text{low})$ 時間                                | 130   | -                    | μs   |

|                             | -         | $V_{DD}(\text{low})$ が $V_{SS}$ である $V_{DD}(\text{low})$ 時間                            | 70    | -                    | μs   |

Figure 25 パワー サイクル タイミング

注:

11. テスト条件は [AC テスト条件](#) に示す 3ns 以下の信号遷移時間,  $0.5 \times V_{DD}$  のタイミング参照レベル,  $V_{DD}$  の 10% ~ 90% の入力レベル, 指定の  $I_{OL}/I_{OH}$  の出力負荷および 30pF の負荷容量を前提にしています。

12.  $V_{DD}$  波形上の任意の点で測定した傾きです。

13. このパラメーターは特性によって保証され、量産中にテストされません。

14. 設計上では保証されます。ディープスリープモードからの復帰タイミングについては [Figure 20](#) を参照してください。

15. 設計上では保証されます。ハイバネートモードからの復帰タイミングについては [Figure 22](#) を参照してください。

注文情報

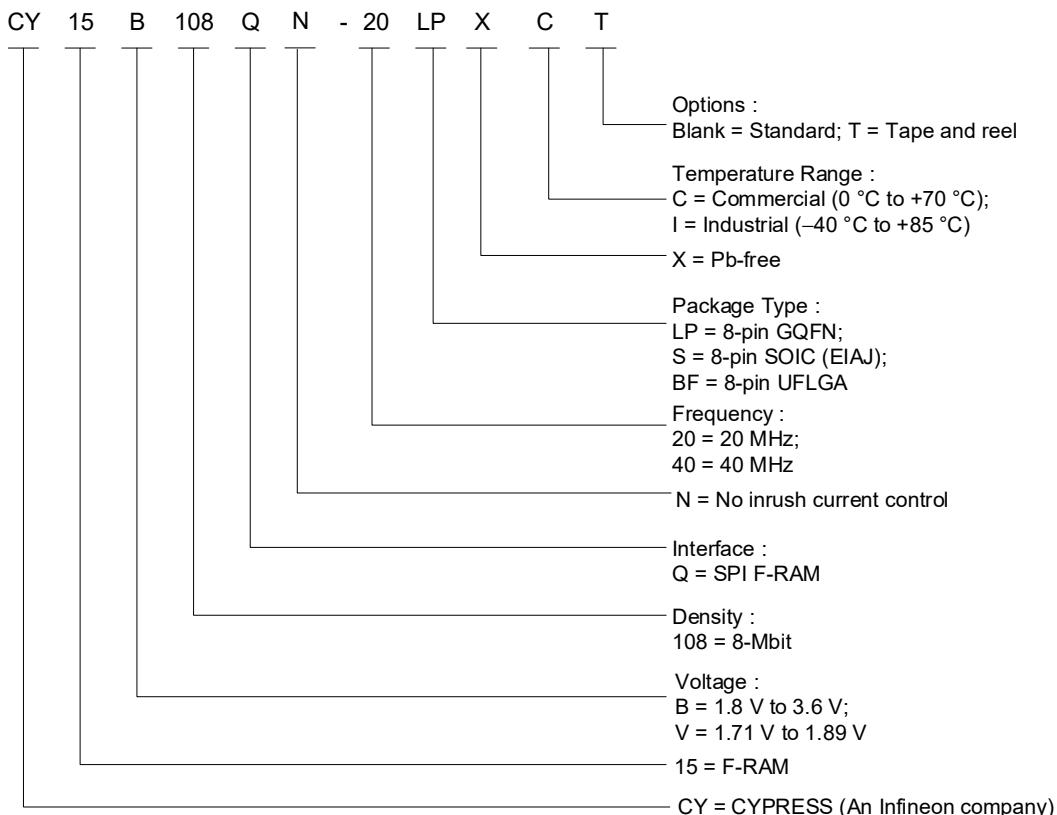

## 14 注文情報

Table 19 注文情報

| 注文コード              | デバイス ID          | パッケージ図    | パッケージタイプ                         | 動作範囲 |

|--------------------|------------------|-----------|----------------------------------|------|

| CY15B108QN-40SXI   | 7F7F7F7F7FC22E03 | 001-85261 | 8 ピン SOIC (EIAJ)                 | 産業用  |

| CY15B108QN-40SXIT  |                  |           |                                  |      |

| CY15B108QN-20LPXC  | 7F7F7F7F7FC22EA1 |           |                                  |      |

| CY15B108QN-20LPXCT |                  |           |                                  |      |

| CY15V108QN-20LPXC  | 7F7F7F7F7FC22EA5 |           |                                  | 民生用  |

| CY15V108QN-20LPXCT |                  |           |                                  |      |

| CY15B108QN-20LPXI  | 7F7F7F7F7FC22E01 | 002-18131 | 8 ピン GQFN (NRND) <sup>[16]</sup> |      |

| CY15B108QN-20LPXIT |                  |           |                                  |      |

| CY15V108QN-20LPXI  | 7F7F7F7F7FC22E05 |           |                                  |      |

| CY15V108QN-20LPXIT |                  |           |                                  |      |

| CY15B108QN-40LPXI  | 7F7F7F7F7FC22E03 |           |                                  |      |

| CY15B108QN-40LPXIT |                  |           |                                  |      |

| CY15V108QN-40LPXI  | 7F7F7F7F7FC22E07 |           |                                  |      |

| CY15V108QN-40LPXIT |                  |           |                                  |      |

| CY15B108QN-20BFXI  | 7F7F7F7F7FC22E01 |           |                                  |      |

| CY15B108QN-20BFXIT |                  |           |                                  |      |

| CY15B108QN-40BFXI  | 7F7F7F7F7FC22E03 | 002-34146 | 8 ピン UFLGA                       |      |

| CY15B108QN-40BFXIT |                  |           |                                  |      |

| CY15V108QN-20BFXI  | 7F7F7F7F7FC22E05 |           |                                  |      |

| CY15V108QN-20BFXIT |                  |           |                                  |      |

| CY15V108QN-40BFXI  | 7F7F7F7F7FC22E07 |           |                                  |      |

| CY15V108QN-40BFXIT |                  |           |                                  |      |

これらすべての製品は鉛フリーです。在庫状況については、最寄りの当社の販売代理店にお問い合わせください。

### 注:

16.NRND - 新規設計には推奨しません。

## 14.1 注文コードの定義

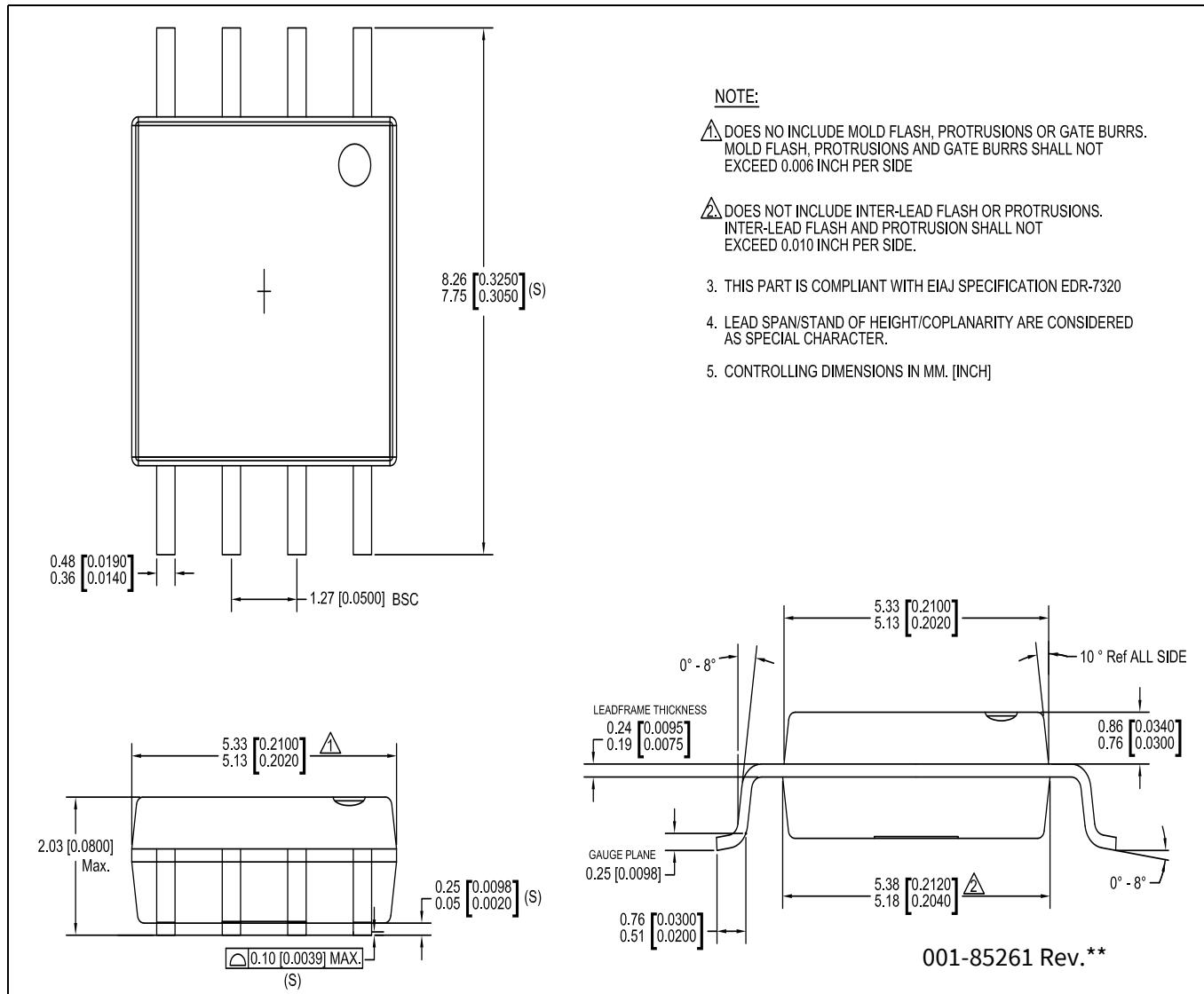

## 15 パッケージ図

Figure 26 8 ピン SOIC (208 mil) SZ820 パッケージ外形図 , 001-85261 (PG-DSO-8)

# 8M ビット EXCELON™ LP 強誘電体 RAM (F-RAM) シリアル (SPI), 1024K × 8, 40 MHz, 産業用

パッケージ図

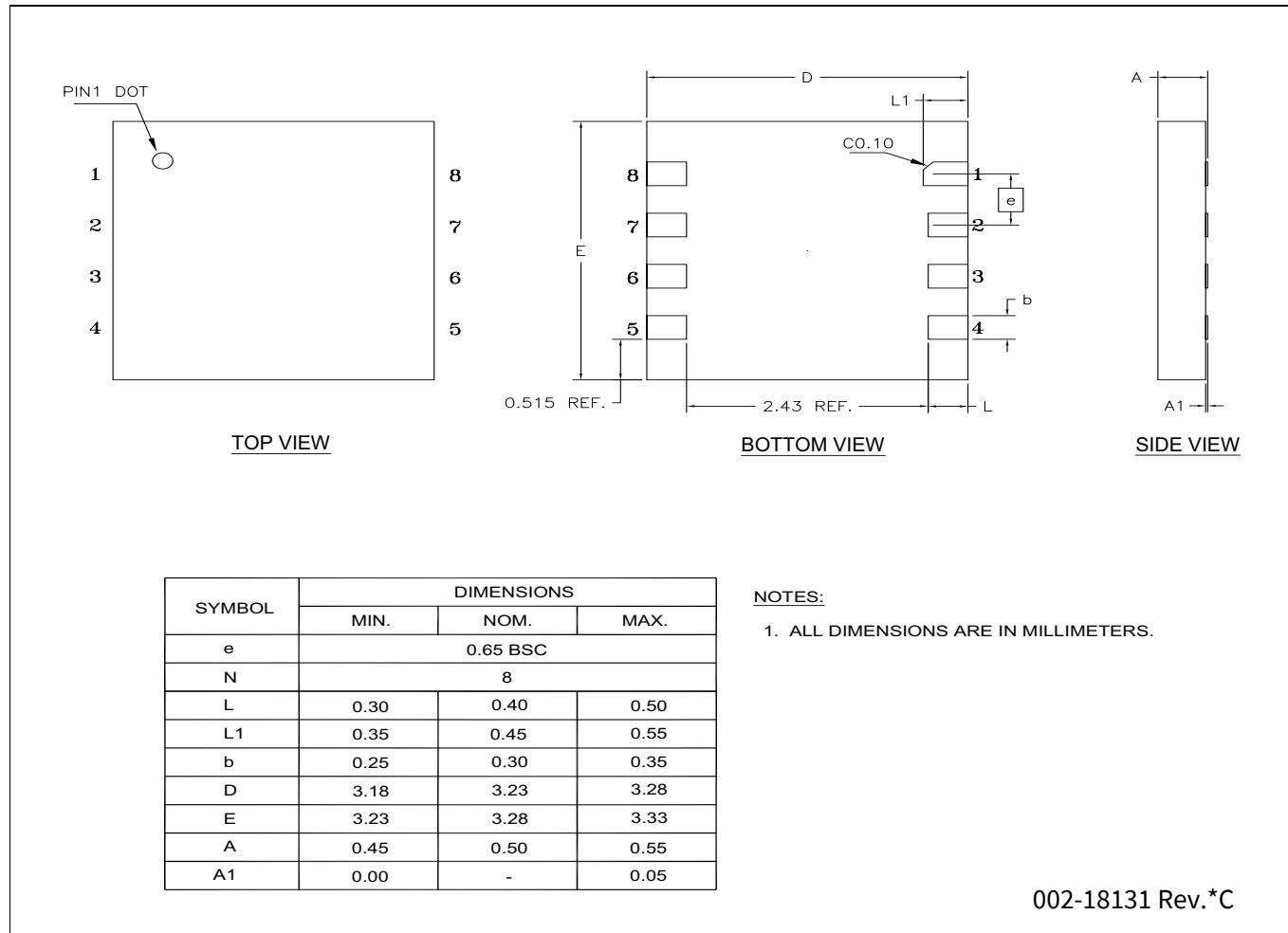

Figure 27 8 ピン GQFN (3.23 × 3.28 × 0.55 mm) LP08A パッケージ外形図 , 002-18131 (PG-VQFN-8)

# 8M ビット EXCELON™ LP 強誘電体 RAM (F-RAM) シリアル (SPI), 1024K × 8, 40 MHz, 産業用

目次

| SYMBOL | DIMENSIONS |          |      |

|--------|------------|----------|------|

|        | MIN.       | NOM.     | MAX. |

| e      |            | 0.65 BSC |      |

| N      |            | 8        |      |

| ND     |            | 4        |      |

| L      | 0.30       | 0.40     | 0.50 |

| b      | 0.25       | 0.30     | 0.35 |

| D      | 3.28 BSC   |          |      |

| E      | 3.23 BSC   |          |      |

| A      | -          | -        | 0.55 |

| L1     | 0.10 REF   |          |      |

| L2     | 0.35       | 0.45     | 0.55 |

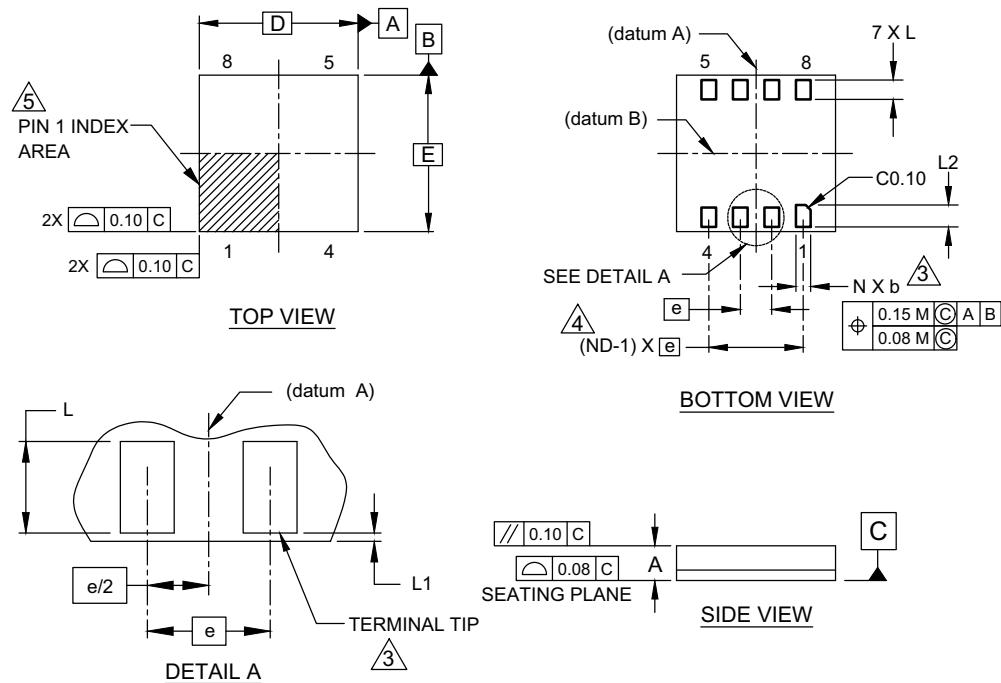

#### NOTES:

1. ALL DIMENSIONS ARE IN MILLIMETERS.

2. N IS THE TOTAL NUMBER OF LANDS.

- (3) DIMENSION "b" IS MEASURED AT THE MAXIMUM LAND WIDTH IN A PLANE PARALLEL TO DATUM C.

- (4) ND REFERS TO THE NUMBER OF LANDS ON D SIDE.

- (5) PIN #1 ID ON TOP WILL BE LOCATED WITHIN THE INDICATED ZONE.

002-34146 Rev. \*\*

8 ピン UFLGA (3.28 × 3.23 × 0.55 mm) BF08A パッケージ外形図 , 002-34146 (PG-UFLGA-8)

略語

## 16 略語

Table 20 本書で使用される略語

| 略語     | 説明                                                                            |

|--------|-------------------------------------------------------------------------------|

| CPHA   | clock phase ( クロック位相 )                                                        |

| CPOL   | clock polarity ( クロック極性 )                                                     |

| EEPROM | electrically erasable programmable read-only memory ( 電気的消去書き込み可能な読み出し専用メモリ ) |

| EIA    | electronic industries alliance ( 米国電子工業会 )                                    |

| F-RAM  | ferroelectric random access memory ( 強誘電体ランダム アクセス メモリ )                      |

| GQFN   | grid array flat no-lead ( リードレス フラット グリッド アレイ )                               |

| I/O    | input/output ( 入力 / 出力 )                                                      |

| JEDEC  | Joint Electron Devices Engineering Council ( 半導体技術協会 )                        |

| JESD   | JEDEC standards ( JEDEC 規格 )                                                  |

| LSb    | least significant bit ( 最下位ビット )                                              |

| MSb    | most significant bit ( 最上位ビット )                                               |

| RoHS   | Restriction of Hazardous Substances ( 特定有害物質使用制限指令 )                          |

| SOIC   | small outline integrated circuit ( 小型外形集積回路 )                                 |

| SPI    | serial peripheral interface ( シリアルペリフェラルインターフェース )                            |

| UFLGA  | ultra thin fine-pitch land grid array ( 超薄型ファインピッチ ランド グリッド アレイ )             |

## 17 本書の表記法

### 17.1 測定単位

Table 21 測定単位

| 記号  | 測定単位     |

|-----|----------|

| °C  | 摂氏温度     |

| Hz  | ヘルツ      |

| kHz | キロヘルツ    |

| kΩ  | キロオーム    |

| Mb  | メガビット    |

| MHz | メガヘルツ    |

| μA  | マイクロアンペア |

| μF  | マイクロファラド |

| μs  | マイクロ秒    |

| mA  | ミリアンペア   |

| ms  | ミリ秒      |

| ns  | ナノ秒      |

| Ω   | オーム      |

| %   | パーセント    |

| pF  | ピコファラド   |

| V   | ボルト      |

| W   | ワット      |

## 改訂履歴

| 版数 | 発行日        | 変更内容                                                     |

|----|------------|----------------------------------------------------------|

| ** | 2017-12-07 | これは英語版 002-21761 Rev. ** を翻訳した日本語版 002-22052 Rev. ** です。 |

| *A | 2020-04-16 | これは英語版 002-21761 Rev. *I を翻訳した日本語版 002-22052 Rev. *A です。 |

| *B | 2022-06-20 | これは英語版 002-21761 Rev. *J を翻訳した日本語版 002-22052 Rev. *B です。 |

| *C | 2023-10-31 | これは英語版 002-21761 Rev. *L を翻訳した日本語版 002-22052 Rev. *C です。 |

## Trademarks

All referenced product or service names and trademarks are the property of their respective owners.

**Edition 2023-10-31**

**Published by**

**Infineon Technologies AG

81726 Munich, Germany**

**© 2023 Infineon Technologies AG.

All Rights Reserved.**

**Do you have a question about this

document?**

**Email:**

[erratum@infineon.com](mailto:erratum@infineon.com)

**Document reference

002-22052 Rev. \*C**

## 重要事項

本文書に記載された情報は、いかなる場合も、条件または特性の保証とみなされるものではありません（「品質の保証」）。

本文に記された一切の事例、手引き、もしくは一般的な価値、および／または本製品の用途に関する一切の情報に關し、インフィニオンテクノロジーズ（以下、「インフィニオン」）はここに、第三者の知的所有権の不侵害の保証を含むがこれに限らず、あらゆる種類の一切の保証および責任を否定いたします。

さらに、本文書に記載された一切の情報は、お客様の用途におけるお客様の製品およびインフィニオン製品の一切の使用に關し、本文書に記載された義務ならびに一切の関連する法的要件、規範、および基準をお客様が遵守することを条件としています。

本文書に含まれるデータは、技術的訓練を受けた従業員のみを対象としています。本製品の対象用途への適合性、およびこれら用途に関連して本文書に記載された製品情報の完全性についての評価は、お客様の技術部門の責任にて実施してください。

## 警告事項

技術的要件に伴い、製品には危険物質が含まれる可能性があります。当該種別の詳細については、インフィニオンの最寄りの営業所までお問い合わせください。

インフィニオンの正式代表者が署名した書面を通じ、インフィニオンによる明示の承認が存在する場合を除き、インフィニオンの製品は、当該製品の障害またはその使用に関する一切の結果が、合理的に人的傷害を招く恐れのある一切の用途に使用することはできないこと予めご了承ください。