请注意赛普拉斯已正式并入英飞凌科技公司。

此封面页之后的文件标注有“赛普拉斯”的文件即该产品为此公司最初开发的。请注意作为英飞凌产品组合的部分，英飞凌将继续为新的及现有客户提供该产品。

#### 文件内容的连续性

事实是英飞凌提供如下产品作为英飞凌产品组合的部分不会带来对于此文件的任何变更。未来的变更将在恰当的时候发生，且任何变更将在历史页面记录。

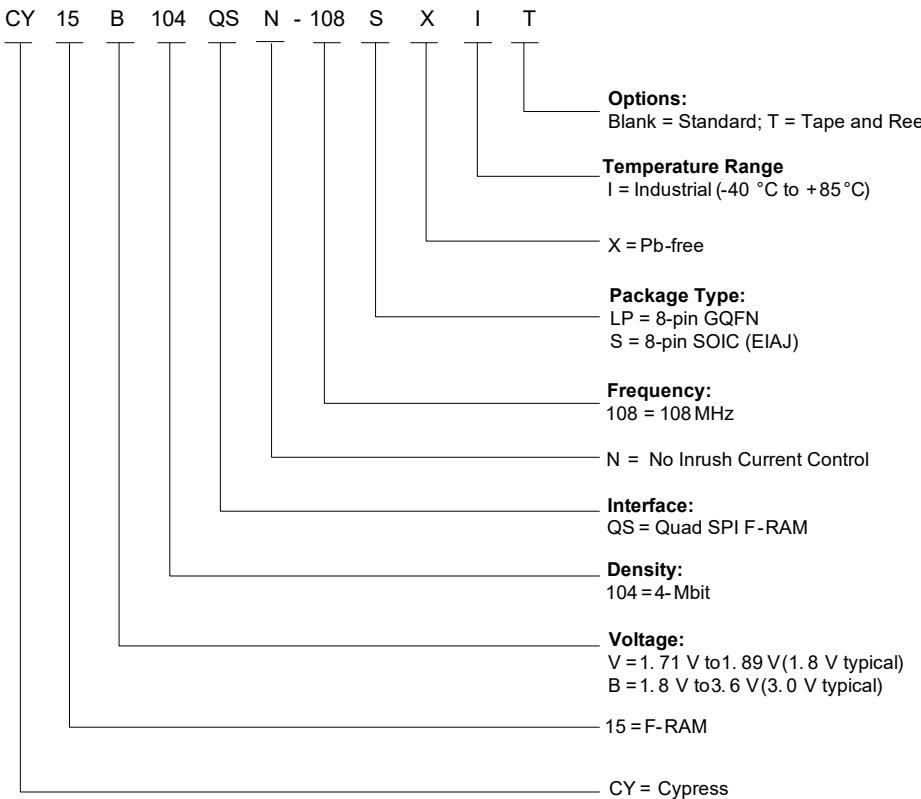

#### 订购零件编号的连续性

英飞凌继续支持现有零件编号的使用。下单时请继续使用数据表中的订购零件编号。

CY15B104QSN

CY15V104QSN

## Excelon™-Ultra 4 Mbit (512K × 8) 四线 SPI F-RAM

### 性能

- 4 Mbit 铁电性随机存取存储器 (F-RAM) 的逻辑组织方式为 512K × 8

- 提供了一百万亿次 ( $10^{14}$ ) 的读 / 写周期，几乎为无限次数的耐久性。

- 151 年数据保留时间 (见第 79 页上的数据保留时间与耐久性)

- NoDelay™ 写操作

- 高级高可靠性的铁电工艺

- 单线和多线 I/O 串行外设接口 (SPI)

- 串行总线接口 SPI 协议

- 支持 SPI 模式 0 (0, 0) 和模式 3 (1, 1)，适用于所有 SDR 模式转换

- 支持 SPI 模式 0 (0, 0)，适用于所有 DDR 模式转换

- 扩展型 I/O SPI 协议

- 双线 SPI (DPI) 协议

- 四线 SPI (QPI) 协议

- SPI 时钟频率

- 最高 108 MHz 频率 SPI 的单倍数据速率 (SDR)

- 最高 54 MHz 频率 SPI 的双倍数据速率 (DDR)

- 芯片内执行 (XIP) 模式下的存储器读 / 写操作

- 写入保护，数据安全性，数据完整性

- 使用写保护 (WP) 引脚提供硬件保护

- 软件模块保护

- 提高数据完整性的纠错码 (ECC) 和循环冗余校验 (CRC)

- 检测并纠正但比特错误的 ECC。在发生双比特错误时，它将不纠正错误，但将通过 ECC 状态寄存器进行错误报告

- CRC 将检测原始数据的任意意外更改

- 扩展的电子签名

- 器件 ID 包含制造商 ID 和产品 ID

- 唯一 ID

- 用户可编程序列号。

- 专用 256 字节特殊扇区 F-RAM

- 专用特殊扇区写和读操作

- 内容可以在最多 3 个标准回流焊周期内保持不变

- 高速度，低功耗

- SPI SDR 频率为 108 MHz 时，有效电流为 10 mA (典型值)

- QSPI SDR 频率为 108 MHz 并且 QSPI DDR 频率为 54 MHz 时，有效电流为 16 mA (典型值)

- 待机电流为 110  $\mu$ A (典型值)

- 深度掉电模式电流为 0.80  $\mu$ A (典型值)

- 休眠模式电流为 0.1  $\mu$ A (典型值)

### ■ 低电压操作：

- CY15V104QSN:  $V_{DD} = 1.71$  V 到 1.89 V

- CY15B104QSN:  $V_{DD} = 1.8$  V 到 3.6 V

### ■ 工作温度范围: -40 °C 到 +85 °C

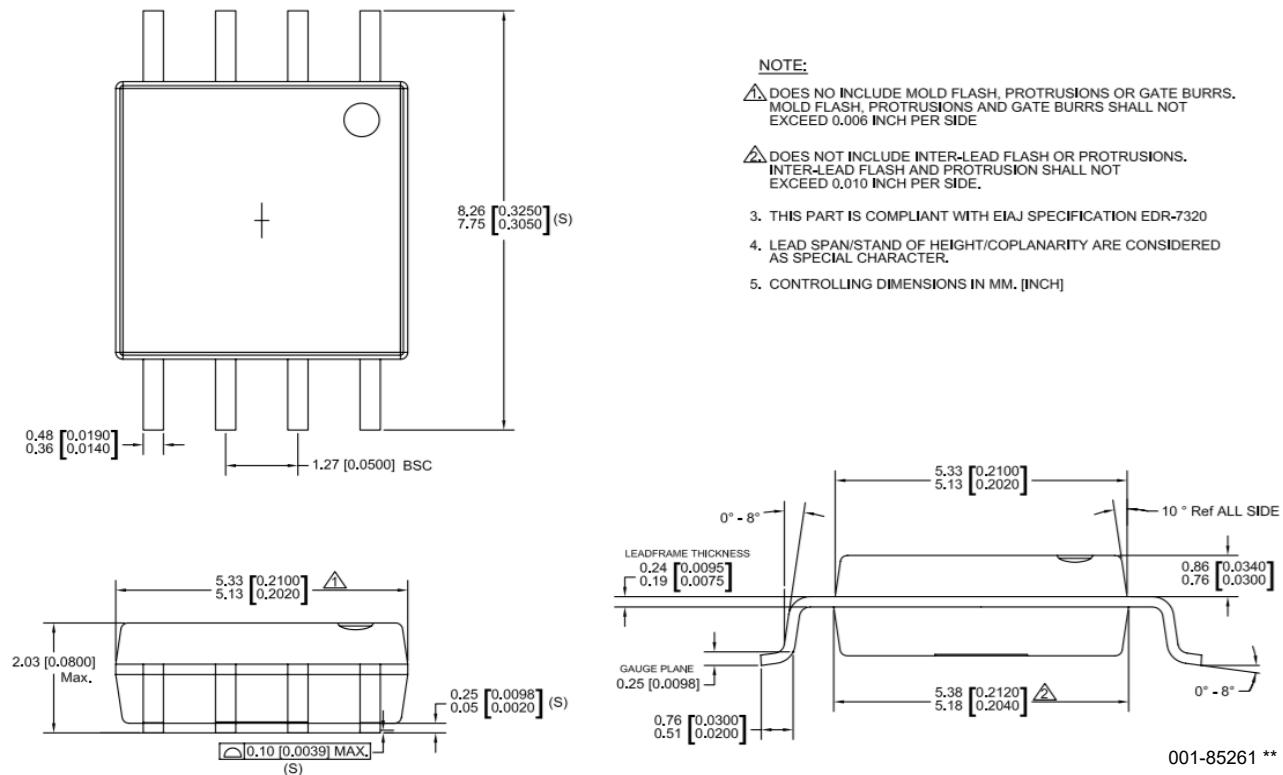

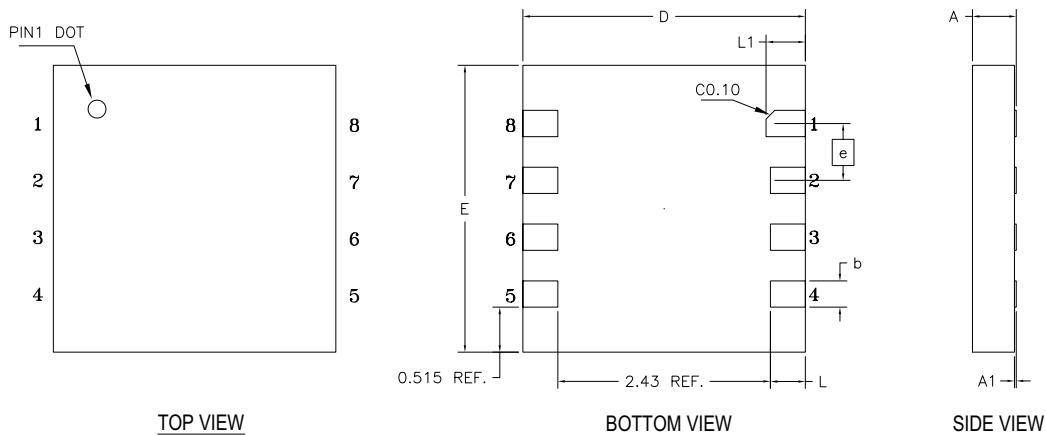

### ■ 封装

- 8 pin 小型塑封集成电路 (SOIC) 封装

- 8 pin 网格阵列四方扁平无引线 (QFN) 封装

### ■ 符合有害物质限制标准 (RoHS)

### 功能说明

Excelon-Ultra CY15x104QSN 采用了高级铁电工艺的高性能 4 Mbit 非易失性存储器。铁电随机存取存储器 (即 F-RAM) 与 RAM 相同，是执行读和写操作的易失性存储器。它提供 151 年的可靠数据保留时间，并解决了由串行闪存和其他非易失性存储器造成的复杂性、开销和系统级可靠性的问题。

与串行闪存不同的是，CY15x104QSN 以总线速度执行写操作。并且不引起写操作的延迟。在每个字节成功传输到器件后，数据立即被写入到存储器阵列内。这时，可以开始执行下一个总线周期而不需要轮询数据。此外，与其他非易失性存储器相比，该产品提供了更多的擦写次数。CY15x104QSN 能够提供  $10^{14}$  次的读 / 写周期，或支持比 EEPROM 多 1 亿次的写周期。由于具有这些特性，因此 CY15x104QSN 非常适用于需要频繁或快速写操作的非易失性存储器应用。示例的范围包括从数据收集（其中写周期数量是非常重要的）到满足工业级控制（其中串行 Flash 的较长写时间会使数据丢失）。

CY15x104QSN 将 4 Mbit F-RAM 与高速度四线 SPI (QPI) SDR 和 DDR 接口相结合，从而增强 F-RAM 技术的非易失性写入功能。该器件包含一个只读的器件 ID 和唯一 ID 特性，通过它们，SPI 总线主设备可以确定器件的制造商、产品容量、产品版本和唯一 ID。该器件包含一个唯一只读序列号，可用来识别某个电路板或系统。

该器件支持片上 ECC 逻辑，可以在每个 8 字节数据单元内检测和纠正单比特错误。该器件还包含在 8 字节数据单元中提供双比特错误报告的扩展功能。CY15x104QSN 还支持循环冗余校验 (CRC)，可用来校验存储器阵列中所存储数据的完整性。

要获取相关资源的完整列表，请单击 [此处](#)。

## 逻辑框图

## 目录

|                              |           |                           |           |

|------------------------------|-----------|---------------------------|-----------|

| 引脚布局 .....                   | 4         | 交流测试条件 .....              | 80        |

| 引脚定义 .....                   | 5         | SDR 交流切换特性 .....          | 81        |

| 功能概述 .....                   | 6         | DDR 交流切换特性 .....          | 83        |

| 存储器架构 .....                  | 6         | 写保护（WP）时序参数 .....         | 85        |

| 串行外设接口（SPI）总线 .....          | 6         | 复位（RESET）时序参数 .....       | 85        |

| SPI 协议中使用的术语 .....           | 7         | 电源周期时序 .....              | 86        |

| SPI 模式 .....                 | 9         | 订购信息 .....                | 87        |

| 从上电到第一次访问的时间 .....           | 10        | 订购代码定义 .....              | 87        |

| <b>CY15x104QSN 寄存器 .....</b> | <b>11</b> | <b>封装图 .....</b>          | <b>88</b> |

| 状态寄存器 .....                  | 11        | 缩略语 .....                 | 90        |

| 配置寄存器 .....                  | 15        | 文档规范 .....                | 90        |

| <b>功能说明 .....</b>            | <b>23</b> | 测量单位 .....                | 90        |

| 命令结构 .....                   | 23        | <b>文档修订记录 .....</b>       | <b>91</b> |

| <b>最大额定值 .....</b>           | <b>77</b> | <b>销售、解决方案和法律信息 .....</b> | <b>92</b> |

| 工作范围 .....                   | 77        | 全球销售和设计支持 .....           | 92        |

| 直流电气特性 .....                 | 77        | 产品 .....                  | 92        |

| 数据保留时间与耐久性 .....             | 79        | PSoC® 解决方案 .....          | 92        |

| 电容 .....                     | 79        | 赛普拉斯开发者社区 .....           | 92        |

| 热阻 .....                     | 79        | 技术支持 .....                | 92        |

## 引脚布局

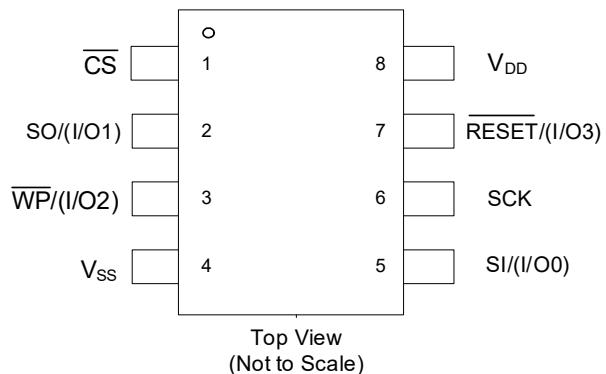

图 1. 8 pin SOIC 的引脚分布

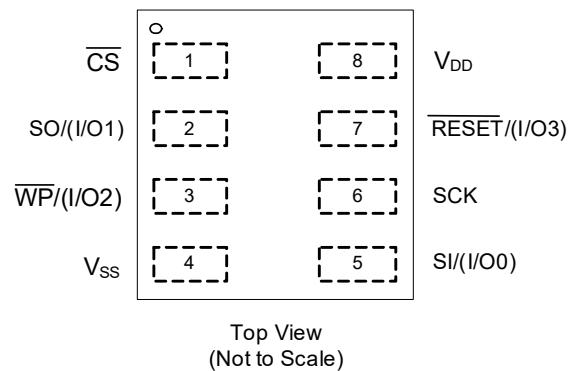

图 2. 8 pin GQFN 的引脚分步

## 引脚定义

| 引脚名称            | I/O 类型  | 说明                                                                                                                                                                                                                            |

|-----------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CS              | 输入      | <b>芯片选择。</b> 通过输入有效低电平可以使能器件。当该输入为高电平时，则器件会进入低功耗待机模式，忽略其他输入，并且输出是三态的。该输入为低电平时，器件将内部激活 SCK 信号。发送每一个新操作码前，CS 上必须产生下降沿。                                                                                                          |

| SCK             | 输入      | <b>串行时钟。</b> 所有输入 / 输出操作均与串行时钟同步。各输入被锁存在上升沿上，并且各输出在下降沿上发生。由于该器件是同步的，因此时钟频率的值范围为 0 到 108 MHz，可以随时中断该时钟频率。                                                                                                                      |

| SI/(I/O0)       | 输入      | <b>串行输入。</b> 所有数据均通过该引脚转送到器件内。该引脚在 SCK 的上升沿上进行采样，并且在其他时间内被忽略。                                                                                                                                                                 |

|                 | 输入 / 输出 | <b>I/O0：</b> 当该器件处于双路模式或者四路模式时，SI 引脚将成为输入 / 输出 (I/O0) 引脚，在命令和地址周期内作为输入使用，并且在数据输出周期内作为输出使用。                                                                                                                                    |

| SO/(I/O1)       | 输出      | <b>串行输出。</b> 这是数据输出引脚。该引脚在进行读操作时被驱动，并在其他时间内（包括 RESET 为低电平的情况）保持三态。数据传输在串行时钟的下降沿上被驱动。                                                                                                                                          |

|                 | 输入 / 输出 | <b>I/O1：</b> 当该器件处于双路模式或者四路模式时，SO 引脚将成为输入 / 输出 (I/O1) 引脚，在命令和地址周期内作为输入使用，并且在数据输出周期内作为输出使用。                                                                                                                                    |

| WP/(I/O2)       | 输入      | <b>写保护。</b> 当 SRWD 位 (SR1[7]) 为 “1” 时，该低电平有效引脚防止对状态寄存器和配置寄存器进行写操作。有关写保护的完整说明，请参考第 11 页上的状态寄存器 1 (SR1)。该引脚具有一个内部弱上拉电阻，该电阻会使该引脚在悬空（未在电路板上连接）时处于高电平状态。如果不使用该引脚，也可以将它连接到 V <sub>DD</sub> 。                                        |

|                 | 输入 / 输出 | <b>I/O2：</b> 当该器件处于四路模式时，WP 引脚将成为输入 / 输出 (I/O2) 引脚，在命令和地址周期内作为输入使用，并且在数据输出周期内作为输出使用。                                                                                                                                          |

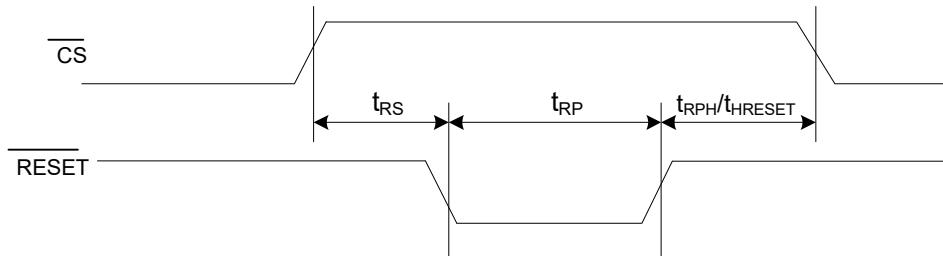

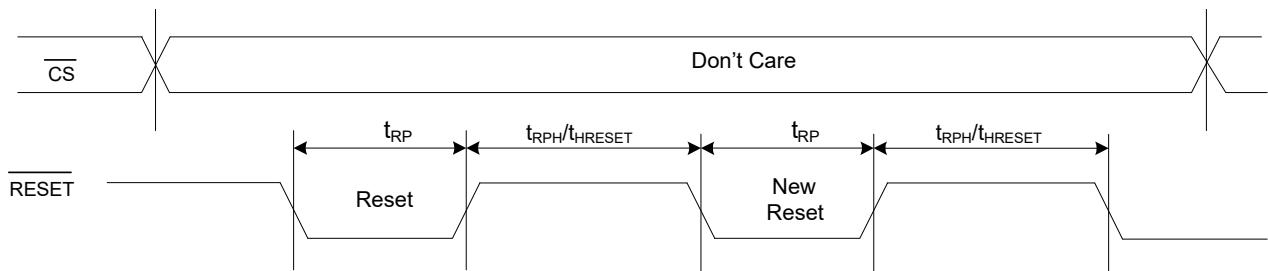

| RESET/(I/O3)    | 输入      | <b>硬件复位引脚。</b> 通过该低电平有效引脚可以进行器件复位。当 RESET 为低电平时，器件将自初始化。并在 RESET 输入被释放为高电平时，根据 CS 的高电平或低电平状态，器件将返回到待机状态或有效状态。该引脚具有一个内部弱上拉电阻，该电阻会使该引脚在悬空（未在电路板上连接）时处于高电平状态。如果不使用该引脚，也可以将它连接到 V <sub>DD</sub> 。RESET/(I/O3) 操作如第 19 页上的表 20 说明。 |

|                 | 输入 / 输出 | <b>I/O3：</b> 当该器件处于四路模式时，RESET 引脚将成为输入 / 输出 (I/O3) 引脚，在命令和地址周期内作为输入使用，并且在数据输出周期内作为输出使用。当该引脚被配置为 I/O3 时，内部上拉电阻被禁用。                                                                                                             |

| V <sub>SS</sub> | 电源      | 器件的接地。必须连接至系统的接地端。                                                                                                                                                                                                            |

| V <sub>DD</sub> | 电源      | 器件的电源输入。                                                                                                                                                                                                                      |

## 功能概述

CY15x104QSN 是一个串行 F-RAM 存储器。该存储器阵列被逻辑组织为  $524,288 \times 8$  位。通过使用工业标准的串行外设接口 (SPI) 总线可以访问该存储器阵列。F-RAM 的功能操作与单线 SPI EEPROM 或单线 / 双线 / 四线 SPI 闪存的功能操作相同。CY15x104QSN 与具有相同引脚分布的串行闪存之间的主要区别在于 F-RAM 具有更好的写性能、高的耐久性和较低的功耗。

## 存储器架构

访问 CY15x104QSN 时，用户可以寻址 512 K 地址的每 8 个数据位。通过单线、双线或四线 I/O，这 8 个数据位被连续移入或移出。通过使用 SPI 协议可以访问这些地址，该协议包含一个芯片选择（用于支持总线上的多个器件）、一个操作码和一个三字节（24 位）地址。然而，因为只需要 19 位来寻址 CY15x104QSN 的所有 512K 字节地址，所以“无需关注”最高有效地址字节的高 5 位。19 位地址指定了 512K 存储器阵列中每个数据字节的唯一位置。

存储器的访问时间几乎为零，但要考虑串行协议所需要的时间。因此，该存储器以 SPI 总线的速度进行读 / 写操作。与串行 Flash 或 EEPROM 不同的是，在初始化新的命令前，不需要轮询器件的就绪条件。[第 23 页上的功能说明](#) 中详细介绍了该功能。

**表 1. SPI 模式与信号的详细信息**

| 接口  | 单通道 SPI                           | 扩展型 SPI <sup>[1]</sup>                |                                                 |                                       |                                                 | 多通道 SPI                               |                                                 |

|-----|-----------------------------------|---------------------------------------|-------------------------------------------------|---------------------------------------|-------------------------------------------------|---------------------------------------|-------------------------------------------------|

|     |                                   | 双线数据                                  | 四线数据                                            | 双线 I/O                                | 四线 I/O                                          | DPI                                   | QPI                                             |

| 信号  | $\overline{\text{CS}}$ 、SCK、SI、SO | $\overline{\text{CS}}$ 、SCK、I/O0、I/O1 | $\overline{\text{CS}}$ 、SCK、I/O0、I/O1、I/O2、I/O3 | $\overline{\text{CS}}$ 、SCK、I/O0、I/O1 | $\overline{\text{CS}}$ 、SCK、I/O0、I/O1、I/O2、I/O3 | $\overline{\text{CS}}$ 、SCK、I/O0、I/O1 | $\overline{\text{CS}}$ 、SCK、I/O0、I/O1、I/O2、I/O3 |

| 操作码 | SI                                | I/O0                                  | I/O0                                            | I/O0                                  | I/O0                                            | I/O0、I/O1                             | I/O0、I/O1、I/O2、I/O3                             |

| 地址  | SI                                | I/O0                                  | I/O0                                            | I/O0、I/O1                             | I/O0、I/O1、I/O2、I/O3                             | I/O0、I/O1                             | I/O0、I/O1、I/O2、I/O3                             |

| 数据  | SI/SO                             | I/O0、I/O1                             | I/O0、I/O1、I/O2、I/O3                             | I/O0、I/O1                             | I/O0、I/O1、I/O2、I/O3                             | I/O0、I/O1                             | I/O0、I/O1、I/O2、I/O3                             |

## 串行外设接口 (SPI) 总线

SPI 是同步的串行接口，它使用时钟和数据引脚进行存储器访问并支持数据总线上的多个器件。使用 CS 引脚可激活 SPI 总线上的器件。芯片选择、时钟和数据之间的关系是由 SPI 模式决定的。该器件支持 SPI 模式 0 和模式 3。在两种模式下，数据都在 SCK 上升沿（从  $\overline{\text{CS}}$  变为有效之后的第一个上升沿）上记录到 F-RAM 内。SPI 协议由操作码控制。在完成某个操作并发出新的操作码前， $\overline{\text{CS}}$  必须进入无效状态。

CY15x104QSN 是一个 SPI 从设备，其运行速度在单倍数据速率 (SDR) 模式下可达 108 MHz，在双数据速率 (DDR) 模式下为 54 MHz。该高速串行总线允许与 SPI 主设备进行高性能的串行通信。CY15x104QSN 支持四个不同的 SPI 接口 / 协议选项：单通道 SPI、扩展型 SPI、双线 SPI、四线 SPI。

更多有关上述各种 SPI 模式下操作码、地址和数据阶段中 I/O 信号的详细信息，请查阅[表 1](#)。

### 注释：

- 扩展的 SPI 模式没有用户设置。器件始终在 SPI 模式下开始运行，然后根据所收到的操作码转换到相应的扩展型 SPI 模式。

### 单通道 SPI

单通道 SPI 是一个四引脚接口，包括芯片选择 ( $\overline{CS}$ )、串行输入 (SI)、串行输出 (SO) 和串行时钟 (SCK) 等引脚。激活  $\overline{CS}$  后，总线主设备传输的第一个字节便是操作码。随后，可以传输任何地址和数据。在完成某个操作并发出新的操作码前， $CS$  必须进入无效状态。在该模式下分别使用了 SI 和 SO 作为输入和输出引脚。主设备通过 SI 线传输操作码和地址，并通过 SO 线读取数据。

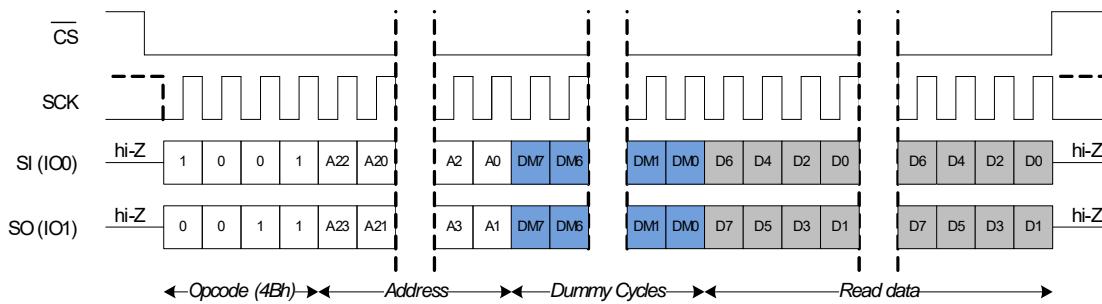

### 扩展型 SPI

CY15x104QSN 还能重新配置标准的 SPI 引脚，以便可以在双线或四线 I/O 模式下工作，即为扩展型 SPI 模式。扩展型的 SPI 模式提供：双线数据、双线输入 / 输出 (I/O)、四线数据和四线输入 / 输出 (I/O) 等模式。发生扩展型的 SPI 命令或器件复位（上电复位或硬件 / 软件复位）后， $CS$  变为高电平，使器件返回到单道 SPI 模式。扩展型 SPI 模式包括以下 I/O 配置：

- 当器件在双线输出或双线 I/O 模式时，SI 引脚和 SO 引脚分别为 I/O0 引脚和 I/O1 引脚。

- 当器件在四线输出或四线 I/O 模式时，SI 引脚、SO 引脚、 $\overline{WP}$  引脚和 RESET 引脚分别成为 I/O0 引脚、I/O1 引脚、I/O2 引脚和 I/O3 引脚。

- 只通过 SI 信号将双线和四线数据命令传送给存储器。数据可以按双比特一组的方式通过 I/O0 和 I/O1 从存储器回送到主机，也可以按四比特（半字节）一组的方式通过 I/O0、I/O1、I/O2 和 I/O3 回送。

- 只通过 SI 信号将双线或四线输入 / 输出 (I/O) 命令发送到存储器，但可以按照双比特一组通过 I/O0 和 I/O1 将主机的地址传输，也可以按照四比特（半字节）一组通过 I/O0、I/O1、I/O2 和 I/O3 从主机发送。数据同样可以按照双比特一组的方式通过 I/O0 和 I/O1 从存储器回送给主机，也可以按照四比特（半字节）一组的方式通过 I/O0、I/O1、I/O2 和 I/O3 被回送。

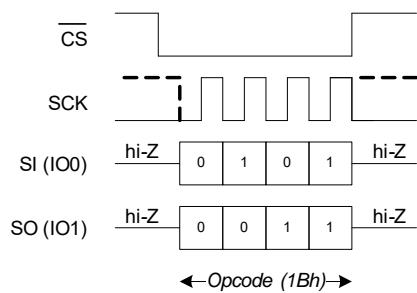

### 双线 SPI (DPI)

通过将 ‘1’ 写入到配置寄存器 2 (CR2) 的位 4，即 CR2[4] = ‘1’，可以使能 CY15x104QSN 的多通道 DPI 模式。由于配置寄存器 2 (CR2) 都有易失性和非易失性的空间，所以非易失性寄存器中的用户设置在电源和硬复位周期内保持不变。因此，当在非易失性 CR2 中设置了双线 SPI (DPI) 模式时，它将始终返回 DPI 模式，直到主机在非易失性 CR2 [4] 中将 DPI 位清除位 “0” 为止。通过将 ‘1’ 写入易失性寄存器 CR2 [4]，主机可以将器件接口更改为 DPI 模式；但是这个易失性设置将无法保持电源和硬件复位周期。在上电或硬复位周期发生后，易失性 CR2 [4] 设置将被覆盖为相关非易失性位置所存储的默认设置。

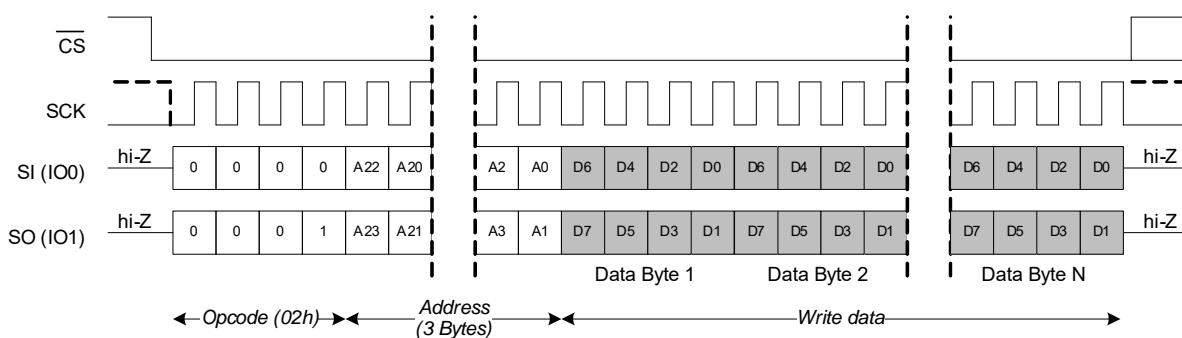

当器件在双线 SPI 模式时，SI 引脚和 SO 引脚分别为 I/O0 引脚和 I/O1 引脚。命令、地址和数据按照双比特一组的方式通过 I/O0 和 I/O1 引脚从主机被发送到存储器。数据同样可以按照双比特一组的方式通过 I/O0 和 I/O1 从存储器回送给主机。

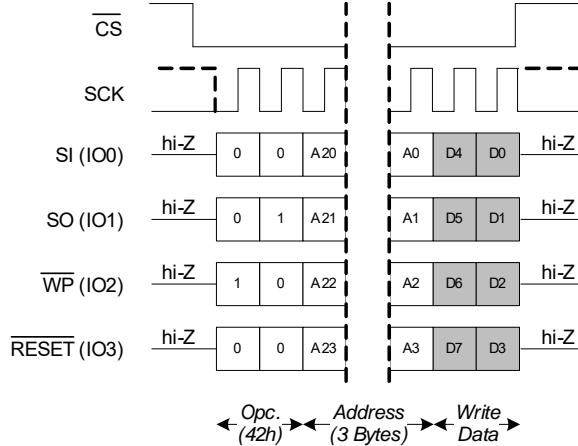

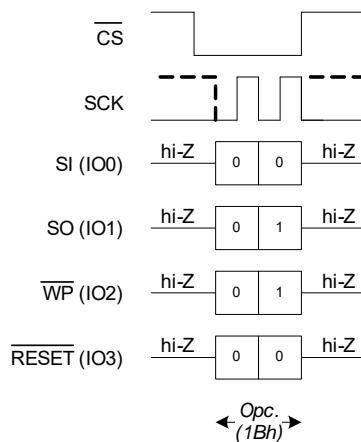

### 四线 SPI (QPI)

通过将 ‘1’ 写入到配置寄存器 2 (CR2) 的位 6，即 CR2[6] = ‘1’，可以使能 CY15x104QSN 的多通道 QPI 模式。由于配置寄存器 2 (CR2) 是易失性寄存器，也是非易失性寄存器，所以非易失性寄存器中的用户设置在电源和硬复位周期内保持不变。因此，当在非易失性 CR2 中设置了四线 QPI (QPI) 模式时，它将始终返回 QPI 模式，直到主机在非易失性 CR2 [6] 中将 QPI 位清除位 “0” 为止。通过将 ‘1’ 写入易失性寄存器 CR2 [6]，主机可以将器件接口更改为 QPI 模式；但是这个易失性设置将无法保持电源和硬件复位周期。在上电或硬复位周期发生后，易失性 CR2 [6] 设置将被覆盖为相关非易失性位置所存储的默认设置。

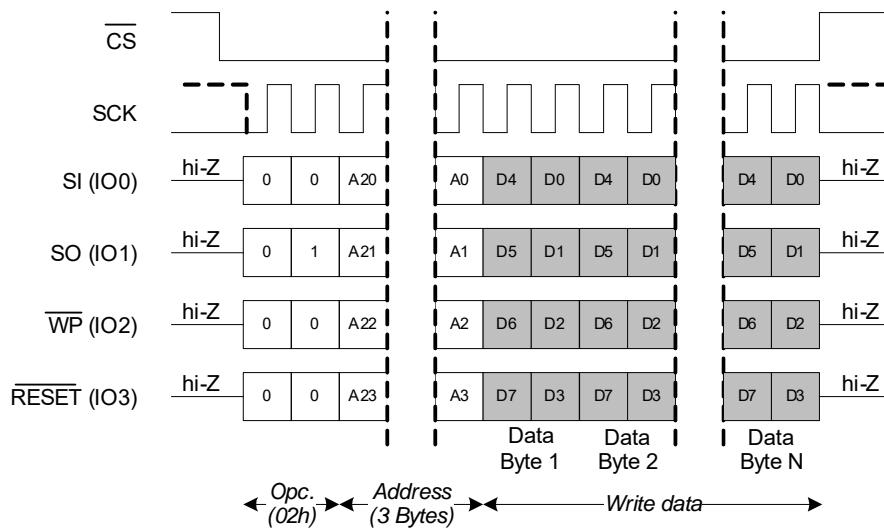

当器件处于四线 SPI 模式时，SI 引脚、SO 引脚、 $\overline{WP}$  引脚和 RESET 引脚分别作为 I/O0 引脚、I/O1 引脚、I/O2 引脚和 I/O3 引脚。命令、地址和数据按照四比特（半字节）一组的方式通过 I/O0、I/O1、I/O2 和 I/O3 引脚从主机被发送到存储器。数据同样可以按四比特（半字节）一组的方式通过 I/O0、I/O1、I/O2 和 I/O3 回送到主机内。

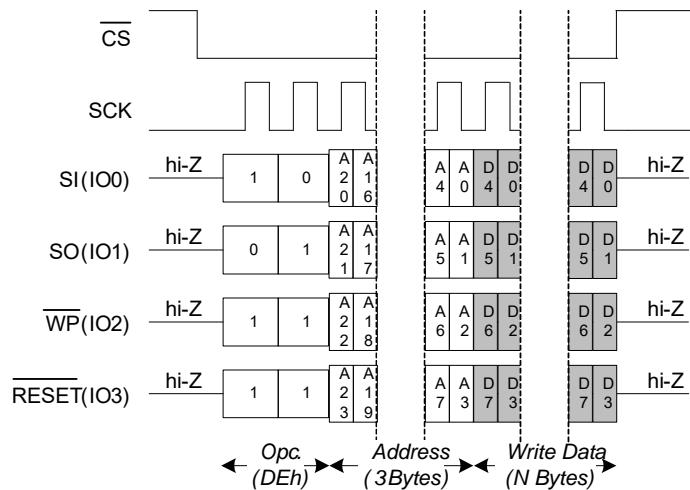

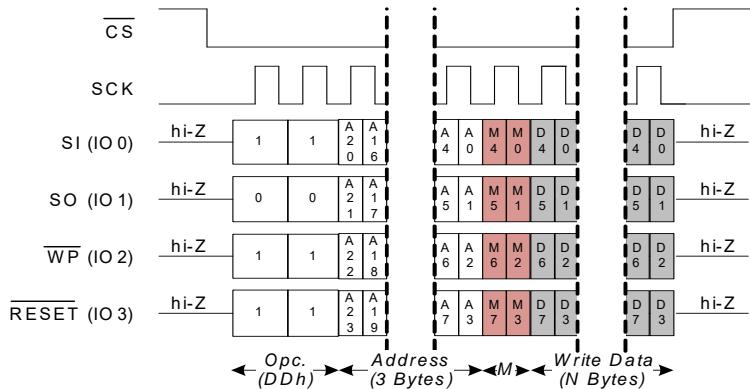

QPI 模式还通过特殊的操作码支持双倍数据速率 (DDR)，这样，可以在时钟的上升沿和下降沿时传输地址、模式和数据字节。在操作码阶段中没有 DDR 模式，即为始终在 SDR 模式下传输操作码。主机在 SDR 模式下发送一个特定的命令，用于确定处于 DDR 模式的地址，模式和数据。然后，器件才进入 DDR 模式。没有使能 DDR 模式的设置。只有在进行存储器读和写操作时，才通过特殊操作码支持四线 SPI DDR 模式。

### SPI 协议中使用的术语

SPI 协议中的常用术语如下：

#### SPI 主设备

SPI 总线上的操作由 SPI 主设备控制。SPI 总线可能只有一个主设备，但可以有一个或多个从设备。所有从设备共享同一 SPI 总线。主设备可通过 CS 引脚选择任意从设备。所有操作必须由主设备启动，主设备通过将从设备的 CS 引脚置于低电平状态来激活从设备。主设备也生成 SCK (串行时钟)，SI 和 SO 线上的所有数据传输均与该时钟同步。

#### SPI 从设备

SPI 从设备由主设备通过芯片选择线激活。来自 SPI 主设备的串行时钟 SCK 作为从设备的输入，所有通信均与该时钟同步。SPI 从设备不会在 SPI 总线上发起通信，而仅执行主设备所发出的指令。

CY15x104QSN 可用作 SPI 从设备，并可以与其他 SPI 从设备共享 SPI 总线。

#### 芯片选择 ( $\overline{CS}$ )

要选择任一从设备，主设备必须下拉相应  $\overline{CS}$  引脚。仅当  $\overline{CS}$  引脚为低电平状态时，才能将指令发送到从设备。未选择器件时，通过 SI 引脚传输的数据将被忽略，同时，串行输出引脚 (SO) 保持高阻抗状态。

**注意：**必须从  $\overline{CS}$  的下降沿上开始执行新指令。因此，每次有效 CS 从高电平转为低电平时，只能发出一个操作码。

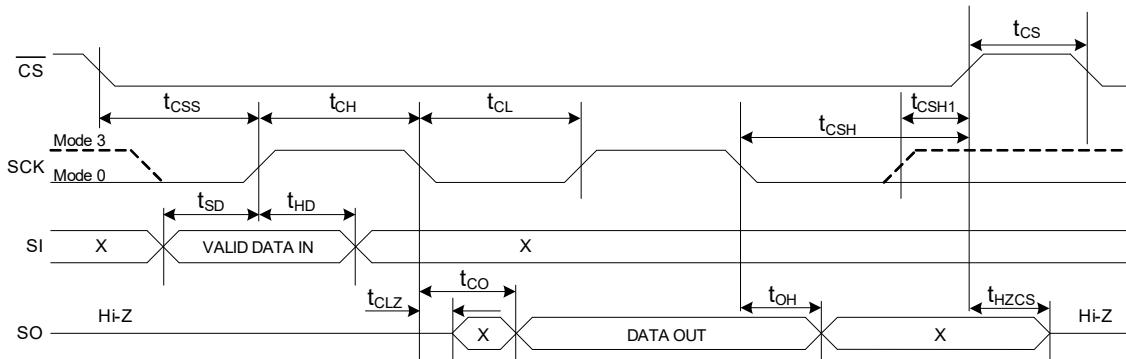

### 串行时钟 (SCK)

串行时钟由 SPI 主设备生成，在  $\overline{CS}$  变为低电平后，通信将与该时钟同步。

CY15x104QSN 在 SPI 模式 0 和模式 3 下进行数据通信。在两种模式下，从设备在 SCK 的上升沿上锁存输入，而输出在下降沿上被发出。因此，SCK 的第一个上升沿表示已经在 SI 引脚上接收到 SPI 指令的第一个最高有效位 (MSB)。此外，所有数据输入和输出均与 SCK 同步。

### 数据传输 (SI/SO)

SPI 数据总线包括 SI 和 SO 两条线，用于串行数据通信。SI 又称为主出从入 (MOSI)，SO 又称为主入从出 (MISO)。主设备通过 SI 引脚将指令发送给从设备，从设备通过 SO 引脚发出响应。如上所述，多个从设备可共享 SI 和 SO 线。

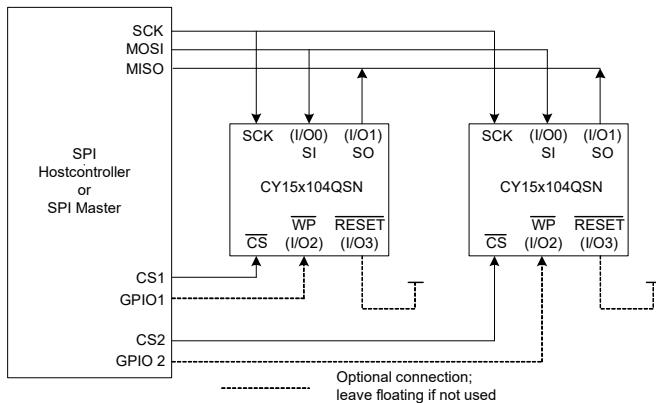

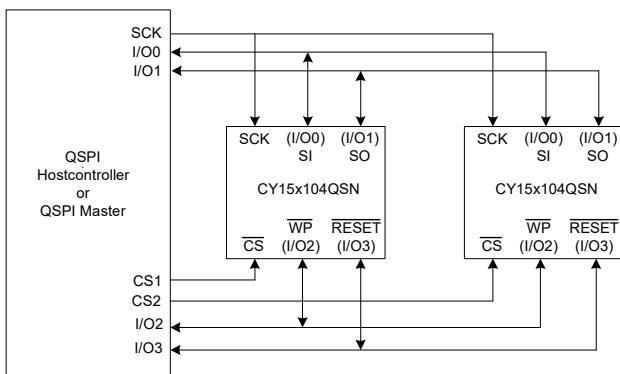

CY15x104QSN 具有 SI 和 SO 两个独立引脚，用于连接至主设备，如图 3 所示。在双线或四线 I/O 模式下，这些引脚被配置为 I/O 引脚。图 4 显示了使用 QSPI 端口的系统接口。

图 3. 使用 SPI 端口进行系统配置

图 4. 使用 QSPI 端口的系统配置

### 最高有效位 (MSb)

SPI 协议要求发送的第一位为最高有效位 (MSb)。该条件也适用于地址和数据传输。

4 Mbit 串行 F-RAM 需要一个 3 字节地址才能进行读取或写入操作。因为地址只有 19 位，所以器件会忽略所载入的 5 位。虽然无需关注这 5 位，但赛普拉斯建议将这些位设置为 ‘0’，以通过无缝切换实现更高存储容量。

### 串行操作码

通过将  $\overline{CS}$  置于低电平来选择从设备后，可将收到的第一个字节作为预期操作的操作码。CY15x104QSN 使用标准操作码（参阅第 23 页上的表 31）进行存储器访问。

### 无效操作码

如果接收到保留的操作码，则操作码可能会内部触发意外操作，并以非确定性数据输出开始驱动 I/O 引脚。因此，当 CY15x104QSN 的芯片选择 CS 为低电平时，应避免通过 SI 引脚传输保留类别的所有操作码。

### 指令

指令是用于访问存储器和寄存器的操作码、地址、模式和 / 或虚拟字节 / 周期的组合。

### 模式字节

模式字节适用于支持现场执行 (XIP) 的所有写入和读取命令。XIP 是直接从外部存储器执行程序（代码）的方法，而不用将代码复制或映射到 RAM 中。当将某个写或读命令设置为 XIP 时，器件在命令周期终止 ( $\overline{CS}$  切换为高电平) 后一直处于 XIP 模式，以便后续命令周期 ( $\overline{CS}$  为低电平) 直接从地址阶段开始（跳过操作码阶段）。在 XIP 中，器件执行与上一个周期相同的操作。为了在 XIP 中启动新的诸如从存储器写入切换到存储器读取，或反过来切换等操作，器件应首先退出当前命令周期所在的 XIP，并使用操作码阶段启动下一个命令周期。模式阶段的操作码仅支持 XIP。欲了解需要模式阶段的操作码列表，请参阅第 23 页上的表 31。

在操作码和 3 字节地址周期之后，在模式阶段期间传输的模式字节 0xA<sub>X</sub> (<sub>X</sub> 为无需关注的位) 或 0xA5 (取决于操作码) 将使器件在下一个命令周期中进入 XIP 模式。必须在每个命令周期期间设置 XIP，以保持下一个命令周期仍然处于 XIP 状态。在模式阶段期间发送的任何非 0xA<sub>X</sub> 或 0xA5 值 (!0xA<sub>X</sub> 或 !0xA5) 将使当前操作退出 XIP。在这种情况下，下一个命令周期必须始终从操作码阶段开始，从而开始相同的操作或新的操作。根据 SPI 模式和接口类型，传输模式字节所需要的时钟数量将为一个时钟（四线，DDR）到八个时钟（SPI，SDR）。

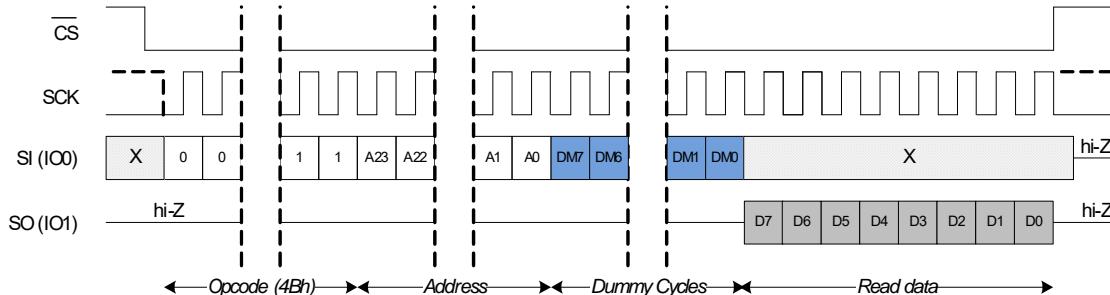

### 等待状态或虚拟周期

等待状态（也称为虚拟周期）附加在地址位和模式位之后（如果适用）。等待状态周期的数量可分别通过配置寄存器 1 (CR1) 和配置寄存器 2 (CR2) 进行编程。只有经过特定数量的虚拟周期后才能在输出总线上驱动有效数据。支持等待状态的存储器和寄存器读取指令发生之后，紧接着是这些虚拟周期。无论 SPI 模式和数据速率 (SDR 或 DDR) 如何，虚拟周期都是一个完整的时钟周期。在虚拟周期中，无需关注 I/O 的状态。

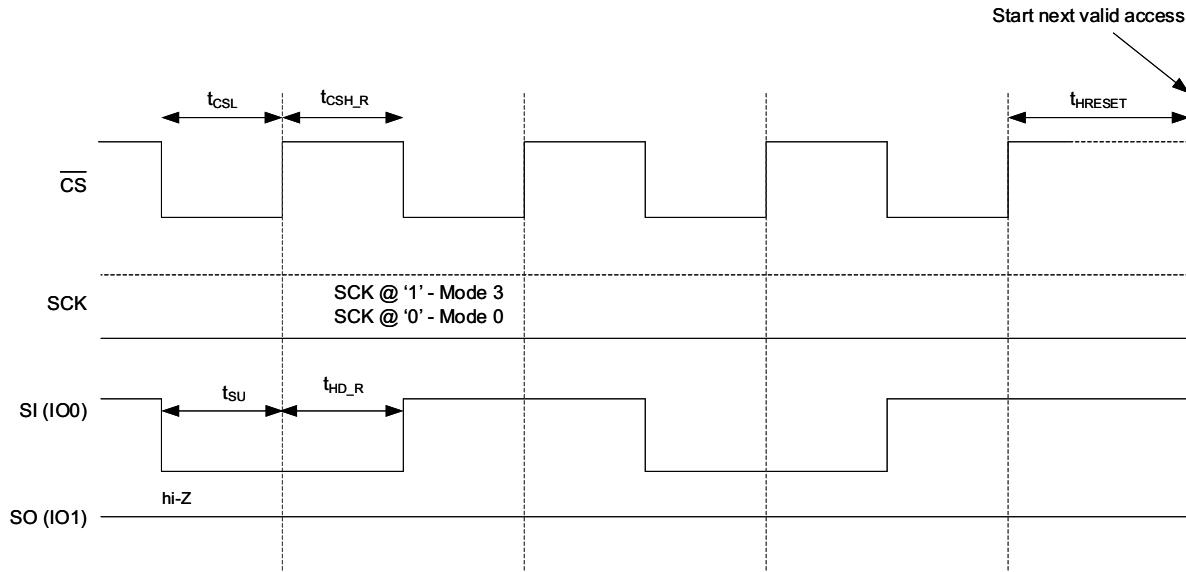

## SPI 模式

CY15x104QSN 可由微控制器驱动，该控制器的 SPI 外设可运行于下列任一模式：

- SPI 模式 0 (CPOL = 0, CPHA = 0)

- SPI 模式 3 (CPOL = 1, CPHA = 1)

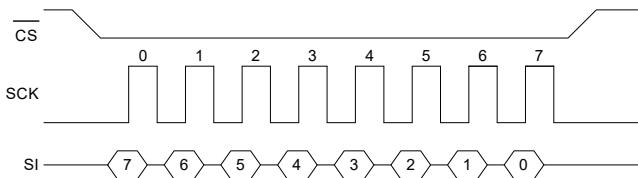

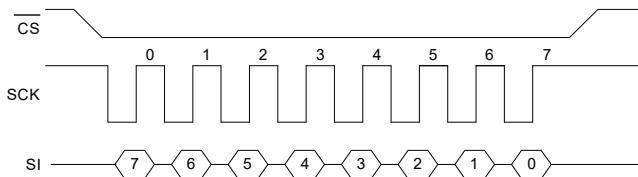

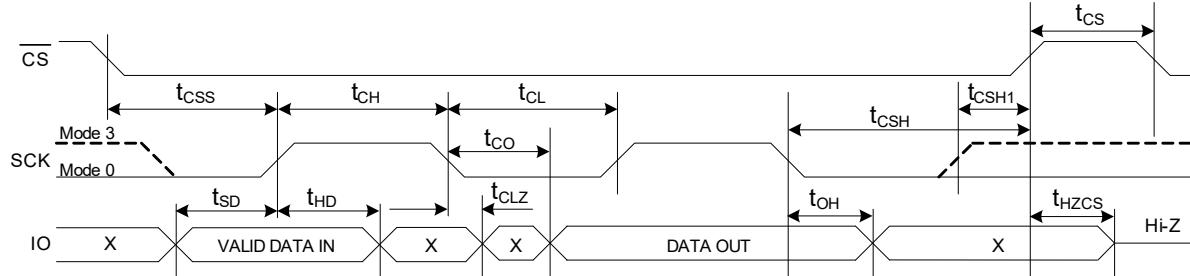

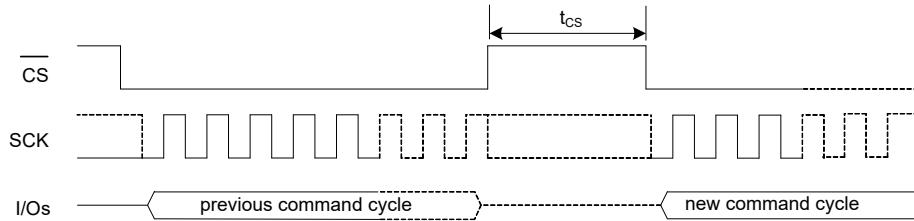

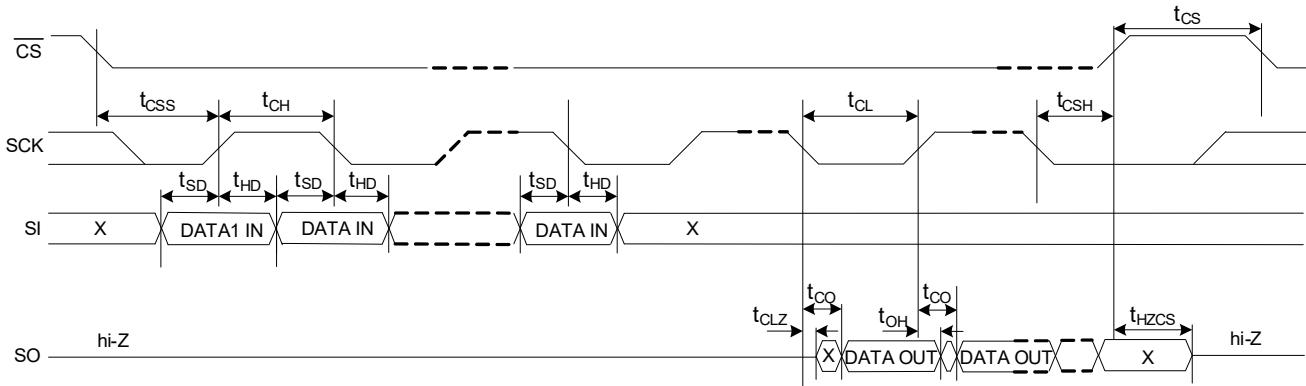

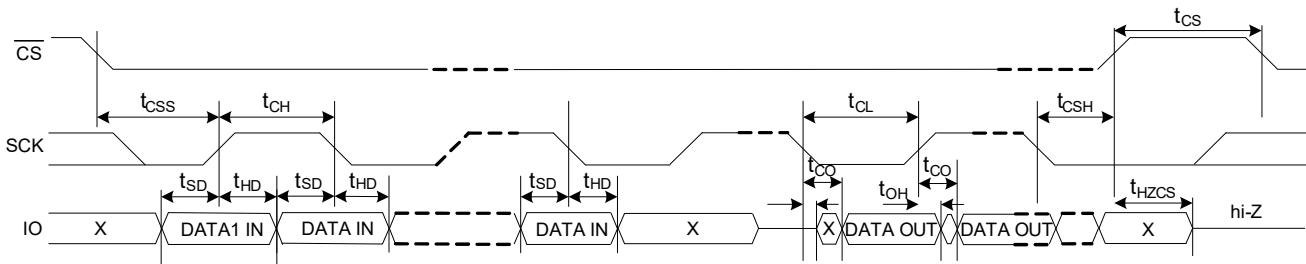

通过将 **CS** 引脚置为低电平而选中该器件时，该器件会通过 SCK 引脚状态来检测出 SPI 模式。器件被选中时，如果 SCK 引脚处于低电平状态，它将工作于 SPI 模式 0；如果 SCK 引脚处于高电平状态，它将工作于 SPI 模式 3。[图 5](#) 和 [图 6](#) 中显示了这两个 SPI 模式。当总线主设备不传输数据时，SCK 时钟的状态为：

- 在模式 0 下，串行时钟保持为 0

- 在模式 3 下，串行时钟保持为 1

所有 SDR 模式命令都支持 SPI 模式 0 和模式 3。但是，所有 DDR 模式命令仅支持 SPI 模式 0。

**图 5. SPI 模式 0**

**图 6. SPI 模式 3**

## SDR

始终在 SCK 的上升沿 (**CS** 有效后的第一个上升沿开始) 上锁存输入数据位（包括指令、地址、数据）。如果时钟从高电平状态启动（在模式 3 中），则采用时钟触发后的第一个上升沿。输出数据在 SCK 的下降沿上可用。

## DDR

始终在 SCK 的上升沿 (**CS** 有效后的第一个上升沿开始) 上锁存指令位。如果时钟从高电平状态启动（在模式 3 中），则采用时钟触发后的第一个上升沿。但是指令后的地址和输入数据则在 SCK 的双边沿上被锁存。最后指令位在 SCK 的下降沿上被锁存之后，第一个地址位会在随后的第一个 SCK 上升沿上被锁存。第一个输出数据位则在最后访问延迟（虚拟）周期结束后的 SCK 下降沿上被发送。

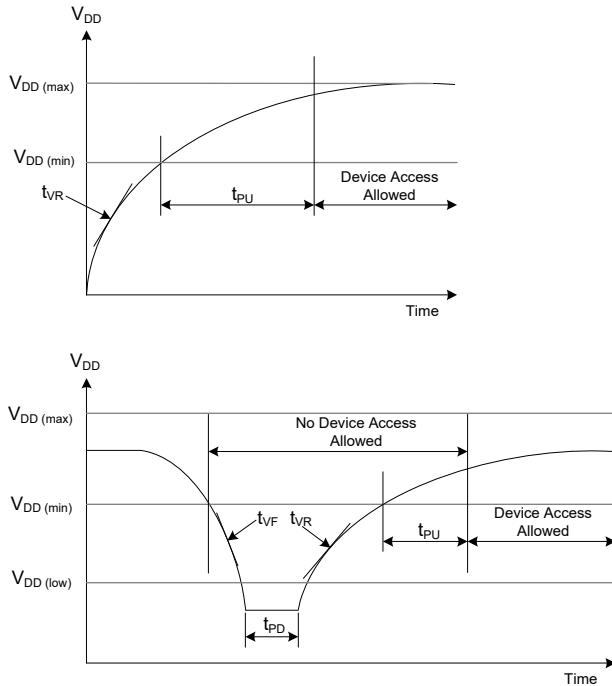

## 从上电到第一次访问的时间

当 CY15x104QSN 电源 ( $V_{DD}$ ) 低于  $V_{DD}(\text{low})$  时，上电周期开始。CY15x104QSN 等待 VDD 电源上升到最小  $V_{DD}(\text{min})$ ，然后器件开始其内部启动序列。CY15x104QSN 的启动序列包括内部上电复位 (POR)，然后加载内部器件配置和调整寄存器以及设置用户可访问的寄存器。启动周期完成后，所有用户可访问的寄存器（状态和配置，模式，ID，ECC 和 CRC）均被设置为默认值。表 2 显示了上电（或 POR）序列成功后 CY15x104QSN 中每个寄存器的状态。

器件会忽略所有指令，直到  $V_{DD}$  上升到超过  $V_{DD}(\text{min})$  后再经过  $t_{PU}$  延迟时间为止。在  $t_{PU}$  结束前，不应该发出任何指令。在  $t_{PU}$  之后，如果 CS 为高电平，则器件将进入待机模式并消耗待机电流 ( $I_{SB}$ )。如果配置寄存器 4 (CR4) 中 POR 的深度掉电模式 (DPDPOR) 被设置为 ‘1’ (CR4 [2] = ‘1’ )，器件将在  $t_{PU}$  后进入深度掉电模式。

POR 事件发生后，不能使用状态寄存器 1 的 WIP 位 (SR1[0]) 轮询器件的就绪状态，因为在  $t_{PU}$  时间结束前，仍无法访问器件，

并且不能对它执行任何指令，包括 RDSR1。但是，如果  $t_{PU}$  时间结束或者不能访问器件后，WIP 状态仍保持高电平，则表示器件没有正确启动（启动错误）。一旦发生启动错误，器件进入以下默认状态：

- 接口模式设置为单线 SPI (SDR)

- 必须将 CR2 的 IO3R 位（即 CR2[5]）内部位置为“1”，从而使能 IO3 引脚上的硬件复位 (RESET) 功能。

- 寄存器延迟设置为三个时钟周期（最大值）

- 输出阻抗设置为 45 欧姆

- 只能通过 RDSR1 和 RDAR 命令（仅限 SPI SDR 模式）读取 SR1。所有其他命令将保持禁用状态，如被执行，将返回未定义的数据。

- 读取 SR1 将返回启动错误标识 0x61

CY15x104QSN 将需要电源或硬件复位周期来重新启动启动序列。启动周期完成后，上述所有默认设置将被替换为实际的用户配置。

**表 2. 上电复位 (POR) 后 CY15x104QSN 寄存器的状态**

| 功能       | 寄存器类型         | 上电复位 (POR) 后 CY15x104QSN 寄存器的状态       |

|----------|---------------|---------------------------------------|

| 器件状态     | 状态寄存器 1 (SR1) | 默认为相应的非易失性位                           |

|          | 状态寄存器 2 (SR2) | 0x00                                  |

| 器件配置 [2] | 配置寄存器 1 (CR1) | 默认为相应的非易失性位                           |

|          | 配置寄存器 2 (CR2) | 默认为相应的非易失性位                           |

|          | 配置寄存器 4 (CR4) | 默认为相应的非易失性位                           |

|          | 配置寄存器 5 (CR5) | 默认为相应的非易失性位                           |

| 标识       | 标识寄存器         | 默认为相应的非易失性位（出厂设置）                     |

|          | 唯一标识寄存器       | 默认为相应的非易失性位（出厂设置）                     |

|          | 序列号寄存器        | 默认为相应的非易失性位（出厂设置为 0x0000000000000000） |

| 修改错误     | ECC 状态寄存器     | 0x00                                  |

|          | ECC 计数寄存器     | 0x0000                                |

|          | ECC 地址陷阱寄存器   | 0x00000000                            |

| 循环冗余校验   | CRC 寄存器       | 0x00000000                            |

**注释：**

2. 配置寄存器 3 (CR3) 被预留供将来使用。

## CY15x104QSN 寄存器

CY15x104QSN 支持各种状态和配置寄存器，用于进行器件状态更新和配置设置。以下各章节介绍了 CY15x104QSN 寄存器及其访问的详细信息。

### 状态寄存器

CY15x104QSN 支持两个状态寄存器：状态寄存器 1（SR1）和状态寄存器 2（SR2），为器件提供写保护设置以及就绪 /CRC 状态。SR1 寄存器在 F-RAM 中具有易失性和相关非易失性寄存器空间。非易失性寄存器在掉电期间保留器件配置。然后，在上电期间或硬件复位（JEDEC 复位或 RESET 引脚）后，器件配置将被复制到相应的易失性寄存器中。在正常访问期间，CY15x104QSN 状态机仅使用易失性寄存器设置更改设备配置。由于 CY15x104QSN 为易失性和非易失性配置寄存器提供独立空间，因此主机只能对易失性寄存器进行编程，以使当前电源周期的配置有效。非易失性的写入操作将改变易失性和非易失性寄存器的内容。因此，新配置将立即对当前电源周期以及后续电源周期或硬件复位周期有效。SR2 是一个只读字段。

**表 3. 状态寄存器 1（SR1）**

| SR1[7]   | SR16    | SR1[5]     | SR1[4]  | SR1[3]  | SR1[2]  | SR1[1]  | SR1[0]  |

|----------|---------|------------|---------|---------|---------|---------|---------|

| SRWD (0) | RFU (0) | TBPROT (0) | BP2 (0) | BP1 (0) | BP0 (0) | WEL (0) | WIP (0) |

**表 4. 状态寄存器 1（SR1）— 非易失性**

| 位      | 位名     | 位功能         | 类型 | 读 / 写 | 说明                                                                                 |

|--------|--------|-------------|----|-------|------------------------------------------------------------------------------------|

| SR1[7] | SRWD   | 状态寄存器写入被禁用  | NV | R/W   | 1 = $\overline{WP}$ 为低电平时状态寄存器和配置寄存器的锁定状态<br>0 = 无论 WP 引脚状态如何，寄存器写保护不被禁用           |

| SR16   | RFU    | 预留 (0)      |    |       | 保留供将来使用                                                                            |

| SR1[5] | TBPROT | 高地址或低地址相对保护 | NV | R/W   | 1 = 保护开始于存储器阵列底部<br>0 = 保护开始于存储器阵列顶部                                               |

| SR1[4] | BP2    | 模块保护位       | NV | R/W   | 保护存储器阵列的选择地址范围                                                                     |

| SR1[3] | BP1    |             | NV |       |                                                                                    |

| SR1[2] | BP0    |             | NV |       |                                                                                    |

| SR1[1] | WEL    | 写使能锁存       | V  | R     | WEL 表示器件是否使能写入功能。上电时，该位默认为 '0' (禁用)。<br>WEL = '1' --> 使能写操作<br>WEL = '0' --> 禁用写操作 |

| SR1[0] | WIP    | 正在进行        | V  | R     | 1 = 器件处于忙碌状态<br>0 = 器件处于就绪状态                                                       |

NV - 非易失性； V - 易失性

通过使用专用状态寄存器读取操作码（RDSR1、RDSR2）或使用跟随状态寄存器地址的 RDAR 可以对状态寄存器进行读取操作。状态寄存器读取始终返回易失性寄存器内容。有关状态寄存器的详细信息，请参见以下章节。

### 状态寄存器 1（SR1）

表 3 中所示的状态寄存器 1（CR1）包含状态和写保护控制位。可通过 WRSR 或 WRAR 命令访问 SR1。同时，可通过 RDSR1 或 RDAR 命令对 SR1 进行读操作。第 27 页上的寄存器访问命令中介绍了 SR1 访问的详细信息。

WRAR 非易失性写地址 — 0x000000

WRAR 易失性写地址 — 0x070000

RDAR 读取地址 — 0x000000 或 0x070000

表 3 中每个位后面的默认状态是出厂编程值。

**表 5. 状态寄存器 1 (SR1) — 易失性**

| 位      | 位名     | 位功能         | 类型 | 读 / 写 | 说明                                                                                    |

|--------|--------|-------------|----|-------|---------------------------------------------------------------------------------------|

| SR1[7] | SRWD   | 状态寄存器写入被禁用  | V  | R/W   | 1 = $\overline{WP}$ 为低电平时状态寄存器和配置寄存器的锁定状态<br>0 = 无论 $\overline{WP}$ 引脚状态如何，寄存器写保护不被禁用 |

| SR16   | RFU    | 预留 (0)      |    |       | 保留供将来使用                                                                               |

| SR1[5] | TBPROT | 高地址或低地址相对保护 | V  | R/W   | 1 = 保护开始于存储器阵列底部<br>0 = 保护开始于存储器阵列顶部                                                  |

| SR1[4] | BP2    | 模块保护位       |    |       | 保护存储器阵列的选择地址范围                                                                        |

| SR1[3] | BP1    | V           |    |       |                                                                                       |

| SR1[2] | BP0    | V           |    |       |                                                                                       |

| SR1[1] | WEL    | 写使能锁存       | V  | R     | WEL 表示器件是否使能写入功能。上电时，该位默认为‘0’（禁用）。<br>WEL = ‘1’ --> 使能写操作<br>WEL = ‘0’ --> 禁用写操作      |

| SR1[0] | WIP    | 正在进行        | V  | R     | 1 = 器件处于忙碌状态<br>0 = 器件处于就绪状态                                                          |

V - 易失性

**状态寄存器保护 (SRWD) SR1 [7]**

当该位被设置为“1”并且写保护 ( $\overline{WP}$ ) 引脚被驱动为低电平时，该位使能状态和配置寄存器的写保护。在该模式下，会忽略更改状态寄存器或配置寄存器内容的任何指令，从而有效锁定器件的状态。如果 SRWD 设置为‘0’，无论 WP 状态如何（低电平还是高电平），状态和配置寄存器写保护仍然被禁用。请参阅第 13 页上的表 8，了解存储器和状态寄存器保护的各个选项。

**顶部和底部保护 (TBPROT) SR1 [5]**

该位对块保护位 BP2, BP1 和 BP0 的操作进行定义。该位控制由块保护位保护的存储器阵列（从顶部或底部）存储器的起始点。

**表 6. 保护开始于顶部 (TBPROT = ‘0’)**

| 状态寄存器内容 |     |     | 受保护的存储器阵列部分               | 受保护的地址范围          |

|---------|-----|-----|---------------------------|-------------------|

| BP2     | BP1 | BP0 |                           |                   |

| 0       | 0   | 0   | 不支持                       | 不支持               |

| 0       | 0   | 1   | 存储器阵列高 1/64 <sup>th</sup> | 0x07E000–0X07FFFF |

| 0       | 1   | 0   | 存储器阵列高 1/32 <sup>nd</sup> | 0x07C000–0X07FFFF |

| 0       | 1   | 1   | 存储器阵列高 1/16 <sup>th</sup> | 0x078000–0X07FFFF |

| 1       | 0   | 0   | 存储器阵列高 1/8 <sup>th</sup>  | 0x070000–0X07FFFF |

| 1       | 0   | 1   | 存储器阵列高 1/4 <sup>th</sup>  | 0x060000–0X07FFFF |

| 1       | 1   | 0   | 存储器阵列高 1/2                | 0x040000–0X07FFFF |

| 1       | 1   | 1   | 整个存储器                     | 0x000000–0X07FFFF |

**表 7. 保护开始于底部 (TBPROT = ‘1’)**

| 状态寄存器内容 |     |     | 受保护的存储器阵列部分               | 受保护的地址范围          |

|---------|-----|-----|---------------------------|-------------------|

| BP2     | BP1 | BP0 |                           |                   |

| 0       | 0   | 0   | 不支持                       | 不支持               |

| 0       | 0   | 1   | 存储器阵列低 1/64 <sup>th</sup> | 0x000000–0x001FFF |

| 0       | 1   | 0   | 存储器阵列低 1/32 <sup>nd</sup> | 0x000000–0x003FFF |

| 0       | 1   | 1   | 存储器阵列低 1/16 <sup>th</sup> | 0x000000–0x007FFF |

| 1       | 0   | 0   | 存储器阵列低 1/8 <sup>th</sup>  | 0x000000–0x00FFFF |

| 1       | 0   | 1   | 存储器阵列低 1/4 <sup>th</sup>  | 0x000000–0x01FFFF |

| 1       | 1   | 0   | 存储器阵列低 1/2                | 0x000000–0x03FFFF |

| 1       | 1   | 1   | 整个存储器                     | 0x000000–0x07FFFF |

**块保护 (BP2、BP1 和 BP0) SR1 [4:2]**

这些位定义由写保护的存储器阵列，以便防止对该阵列执行写入命令。当一个或多个 BP 位被设置为 ‘1’ 时，相应的存储器地址被保护，这样便不能对其进行写操作。可通过块保护位 (BP2、BP1 和 BP0) 与 TBPROT 位的组合来保护存储器阵列的地址范围。地址范围的大小由 BP 位的值和由 TBPROT 选择的该范围的上限或下限起始点决定。[表 6](#) 和 [表 7](#) 显示了 CY15x104QSN 器件 BP[2:0] 位设置的受保护的地址范围。

**写入使能锁存 (WEL) SR1 [1]**

必须将 WEL 位设置为 ‘1’ 才能对存储器阵列或寄存器进行写操作，如[表 8](#) 所示。只有通过执行写入使能 (WREN) 命令，该位才被置 “1” 。WRDI (04h), WRSR (01h), SSWR (42h), WRAR (71h) 以及 WRSN (C2h) 等操作码后的 CS 的上升沿到来时，WEL 位 (SR1[1]) 自动被清零。在跟随存储器写入操作码的 CS 的上升沿到来时，WEL 位 (SR1[1]) 不会被清零。WEL 位是易失性的，并且在 POR 和所有复位事件之后返回到默认的 “0” 状态。

**表 8. 写保护**

| SRWD | WP | WEL | 受保护的模块 | 无保护的模块 | 状态和配置寄存器 <sup>[3]</sup> |

|------|----|-----|--------|--------|-------------------------|

| X    | X  | 0   | 受保护    | 受保护    | 受保护                     |

| 0    | X  | 1   | 受保护    | 可写     | 可写                      |

| 1    | 0  | 1   | 受保护    | 可写     | 受保护                     |

| 1    | 1  | 1   | 受保护    | 可写     | 可写                      |

### 正在进行的操作 (WIP) SR[0]

这是一个只读位，并在正常操作期间指示器件就绪或忙碌状态。执行 CRC 计算时，CY15x104QSN 将该位设置为“1”。在 CY15x104QSN 中，没有其他命令和事件会将 WIP 设置为“1”。当 WIP 为“1”时，CY15x104QSN 只能执行读取状态寄存器（使用 RDSR1/RDSR2），或读取任何寄存器（状态寄存器地址随后的 RDAR）、CRC 挂起（EPCS）和软件复位（RST 随后的 RSTEN）等命令。WIP 为“1”时，其他命令将被忽略。在上电或复位周期中，WIP 位不能用于轮询器件就绪状态。该位是易失性的，并且在 POR 和所有复位事件之后返回到默认的“0”状态。

表 9. 状态寄存器 2 (SR2)

| SR2[7]  | SR2[6]  | SR2[5]  | SR2[4]   | SR2[3]   | SR2[2]  | SR2[1]  | SR2[0]  |

|---------|---------|---------|----------|----------|---------|---------|---------|

| RFU (0) | RFU (0) | RFU (0) | CRCS (0) | CRCA (0) | RFU (0) | RFU (0) | RFU (0) |

表 10. 状态寄存器 2 (SR2) — 仅适用于易失性寄存器

| 位      | 位名   | 位功能    | 类型 | 读 / 写 | 说明                                  |

|--------|------|--------|----|-------|-------------------------------------|

| SR2[7] | RFU  | 预留 (0) |    |       | 保留供将来使用                             |

| SR2[6] | RFU  | 预留 (0) |    |       | 保留供将来使用                             |

| SR2[5] | RFU  | 预留 (0) |    |       | 保留供将来使用                             |

| SR2[4] | CRCS | CRC 挂起 | V  | R     | 1 = 处于 CRC 挂起模式<br>0 = 无处于 CRC 挂起模式 |

| SR2[3] | CRCA | CRC 中止 | V  | R     | 1 = CRC 命令被中止<br>0 = CRC 命令不被中止     |

| SR2[2] | RFU  | 预留 (0) |    |       | 保留供将来使用                             |

| SR2[1] | RFU  | 预留 (0) |    |       | 保留供将来使用                             |

| SR2[0] | RFU  | 预留 (0) |    |       | 保留供将来使用                             |

V - 易失性

### CRC 挂起 (CRCS) SR2 [4]

该 CRC 挂起 (CRCS) 位用于确定器件处于 CRC 挂起模式的时间。在器件 CRC 计算期间进行 CRC 挂起命令 (EPCS) 将该位置为“1”，表示 CRC 挂起状态。CRC 恢复 (EPCR) 命令将 CRCS 位清零，表示器件退出 CRC 挂起模式。这是一个只读位。复位 (POR，硬件和软件) 后，该位也被清除。

### 状态寄存器 2 (SR2)

表 9 中的状态寄存器 2 (SR2) 展示了 CRC 操作时的器件状态。SR2 是只读易失性寄存器，可由 RDSR2 或 RDAR 命令访问，用于读取操作。[第 27 页上的寄存器访问命令](#) 中介绍了 SR1 访问的详细信息。

RDAR 读取地址 — 0x000001 或 0x070001

表 8 中每个位后面的默认状态是出厂编程值。

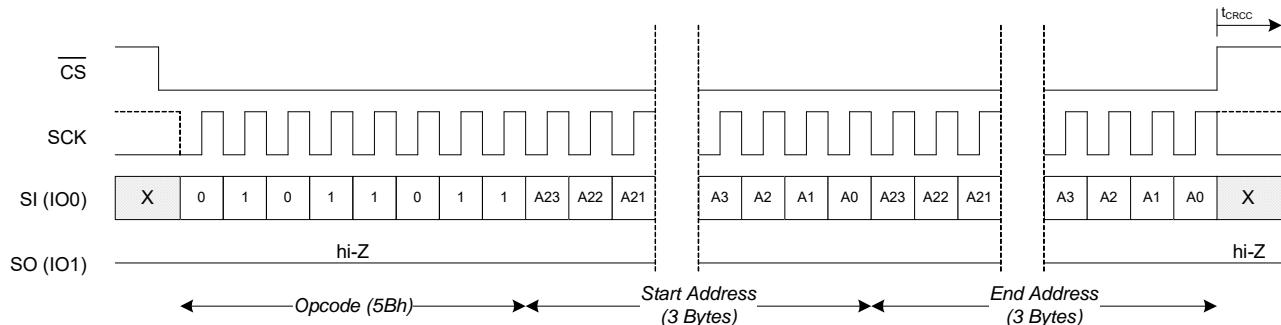

### CRC 中止 (CRCA) SR2 [3]

该位表示 CRC 计算 (CRCC) 操作是否中止。当结束地址和起始地址标准 (EA < SA + 3，即为结束地址应至少高于起始地址 32 位对齐字) 不能满足时，CRC 计算将被中止。当后续 CRC 计算成功启动时，该位被清零。复位 (POR，硬件和软件) 后，该位也被清除。

#### 注释：

3. 所有位（只读位和保留位除外）

## 配置寄存器

CY15x104QSN 支持四个用户配置寄存器: CR1、CR2、CR4 和 CR5，用于编程器件中的各种控制。每个配置寄存器在 F-RAM 中具有易失性和相关非易失性寄存器空间。非易失性寄存器在掉电期间保留器件配置。然后，在上电期间或硬件复位 (JEDEC 复位或 RESET 引脚) 后，器件配置将被复制到相应的易失性寄存器中。在正常访问期间，CY15x104QSN 状态机仅使用易失性寄存器设置更改设备配置。由于 CY15x104QSN 为易失性和非易失性配置寄存器提供独立空间，因此主机只能对易失性寄存器进行编程，以使当前电源周期的配置有效。非易失性的写入操作将改变易失性和非易失性寄存器的内容。因此，新配置将立即对当前电源周期以及后续电源周期或硬件复位周期有效。

使用专用配置寄存器读取操作码 (RDCR1、RDCR2、RDCR3、RDCR4) 或 RDAR 命令对配置寄存器进行读取操作将始终返回易失性寄存器内容。有关配置寄存器的详细信息，请参见以下章节。

### 配置寄存器 1 (CR1)

配置寄存器 1 (CR1)，如表 11 中所示，配置存储器的延迟 (虚拟) 周期以及特殊扇区读取，并在扩展 SPI 访问期间启用四线 I/O。可通过 WRAR 命令访问 CR1。同时，可通过 RDCR1 或 RDAR 命令对 SR1 进行读操作。[第 27 页上的寄存器访问命令](#) 中介绍了 CR1 访问的详细信息。

WRAR 非易失性写地址 — 0x000002

WRAR 易失性写地址 — 0x070002

RDAR 读取地址 — 0x000002 或 0x070002

表 11 中每个位后面的默认状态是出厂编程值。

表 11. 配置寄存器 1 (CR1)

| CR1[7]   | CR1[6]   | CR1[5]   | CR1[4]   | CR1[3]  | CR1[2]  | CR1[1]   | CR1[0]  |

|----------|----------|----------|----------|---------|---------|----------|---------|

| MLC3 (0) | MLC2 (0) | MLC1 (0) | MLC0 (0) | RFU (0) | RFU (0) | QUAD (0) | RFU (0) |

表 12. 配置寄存器 1 (CR1) — 非易失性

| 位      | 位名   | 位功能     | 类型 | 读 / 写 | 说明                                                                                    |  |

|--------|------|---------|----|-------|---------------------------------------------------------------------------------------|--|

| CR1[7] | MLC3 | 存储器延迟代码 | NV | R/W   | 为存储器以及特殊扇区读取操作码配置延迟 (虚拟) 周期数。<br>示例：<br>0000 - 0 个周期<br>0110 - 6 个周期<br>1111 - 15 个周期 |  |

| CR1[6] | MLC2 |         | NV |       |                                                                                       |  |

| CR1[5] | MLC1 |         | NV |       |                                                                                       |  |

| CR1[4] | MLC0 |         | NV |       |                                                                                       |  |

| CR1[3] | RFU  | 预留 (0)  |    |       | 保留供将来使用                                                                               |  |

| CR1[2] | RFU  | 预留 (0)  |    |       | 保留供将来使用                                                                               |  |

| CR1[1] | QUAD | 四线      | NV | R/W   | 1 = 四线<br>0 = 双线或串行                                                                   |  |

| CR1[0] | RFU  | 预留 (0)  |    |       | 保留供将来使用                                                                               |  |

NV - 非易失性

**表 13. 配置寄存器 1 (CR1) — 易失性**

| 位      | 位名   | 位功能     | 类型 | 读 / 写 | 说明                                                                                    |  |

|--------|------|---------|----|-------|---------------------------------------------------------------------------------------|--|

| CR1[7] | MLC3 | 存储器延迟代码 | V  | R/W   | 为存储器以及特殊扇区读取操作码配置延迟 (虚拟) 周期数。<br>示例：<br>0000 - 0 个周期<br>0110 - 6 个周期<br>1111 - 15 个周期 |  |

| CR1[6] | MLC2 |         | V  |       |                                                                                       |  |

| CR1[5] | MLC1 |         | V  |       |                                                                                       |  |

| CR1[4] | MLC0 |         | V  |       |                                                                                       |  |

| CR1[3] | RFU  | 预留 (0)  |    |       | 保留供将来使用                                                                               |  |

| CR1[2] | RFU  | 预留 (0)  |    |       | 保留供将来使用                                                                               |  |

| CR1[1] | QUAD | 四线      | V  | R/W   | 1 = 四线<br>0 = 双线或串行                                                                   |  |

| CR1[0] | RFU  | 预留 (0)  |    |       | 保留供将来使用                                                                               |  |

V - 易失性

**存储器延迟代码 (MLC) CR1 [7:4]**

这四个位配置所有可变延迟存储器读取指令中的延迟 (虚拟) 周期。通过这些位，用户可以在正常操作期间调整存储器读取延迟，从而优化不同工作频率下各种指令的延迟。无论 SPI 模式和数据速率 (SDR 或 DDR) 如何，虚拟周期都是一个完整的时钟周期。

一些读取操作码支持地址周期后面附加虚拟周期。在数据可以返回到主机系统前，这些虚拟周期提供完成存储器阵列的初始读取访问所需的额外延迟。SPI 时钟 (SCK) 频率增大，虚拟周期数也要增加，以满足相应的延迟。

表 14 和第 17 页上的表 16 中显示了支持虚拟周期的每个操作码的最大 SPI 时钟频率和相应的时钟延迟。主机控制器可以通过为每个操作码设置独立的延迟周期来确定优化时序，或者通过设置满足所有操作码的延迟要求的最差情况延迟，以便得到所需要的

工作频率。为较高频率设置的存储器读取延迟也适用于所有较低频率。因此，当主机将 SPI 时钟 (SCK) 从较高频率降低到较低频率时，调整时钟延迟变为可选的。

头文件表 14 中的各个格式 (CMD, ADD, DATA) 表示这些字节在不同 SPI 模式下的 I/O 数量的传输。例如：(2,2,2) 代表所有命令 (CMD)、地址 (ADDR) 和数据 (DATA) 字节在 DPI 模式下通过两个 I/O (I/O0 和 I/O1) 得到发送。与此类似，(1,2,2) 表示 CMD 字节通过单个 I/O (I/O0) 被发送，而 ADDR 和 DATA 字节在双线 I/O 模式下通过两个 I/O (I/O0, I/O1) 被发送。(1, 1, 4) 表示 CMD、ADDR 字节通过单个 I/O (I/O0) 被发送，而 DATA 字节在四线数据模式下通过四个 I/O (I/O0, I/O1, I/O2, I/O3) 得到发送。

模式 (Mode) 表示在各种 SPI 接口模式下所需的时钟周期数量，用于在地址位之后传输模式字节。由于在地址周期之后传输模式位，所以传输模式位所需的时钟周期内部被添加到延迟计算中。

**表 14. XIP 模式 (SDR) 下存储器读命令的延迟 (虚拟) 周期**

| 延迟 (虚拟)<br>周期 — 十进制 | SPI (SDR) | DPI (SDR)             | QPI (SDR)             | 双线数据<br>(SDR) | 双线 I/O<br>(SDR)       | 四线数据<br>(SDR) | 四线 I/O<br>(SDR)       |

|---------------------|-----------|-----------------------|-----------------------|---------------|-----------------------|---------------|-----------------------|

|                     | FAST_READ | FAST_READ             | FAST_READ、<br>QIOR    | DOR           | DIOR                  | QOR           | QIOR                  |

|                     | (1, 1, 1) | (2, 2, 2)             | (4, 4, 4)             | (1, 1, 2)     | (1, 2, 2)             | (1, 1, 4)     | (1, 4, 4)             |

|                     | 模式 = 8    | 模式 = 4                | 模式 = 2                | 模式 = 8        | 模式 = 4                | 模式 = 8        | 模式 = 2                |

| 0                   | 108 MHz   | 55 MHz <sup>[4]</sup> | 10 MHz <sup>[4]</sup> | 108 MHz       | 55 MHz <sup>[4]</sup> | 108 MHz       | 10 MHz <sup>[4]</sup> |

| 1                   | 108 MHz   | 70 MHz <sup>[4]</sup> | 25 MHz <sup>[4]</sup> | 108 MHz       | 70 MHz <sup>[4]</sup> | 108 MHz       | 25 MHz <sup>[4]</sup> |

| 2                   | 108 MHz   | 80 MHz <sup>[4]</sup> | 40 MHz <sup>[4]</sup> | 108 MHz       | 80 MHz <sup>[4]</sup> | 108 MHz       | 40 MHz <sup>[4]</sup> |

| 3                   | 108 MHz   | 95 MHz <sup>[4]</sup> | 55 MHz <sup>[4]</sup> | 108 MHz       | 95 MHz <sup>[4]</sup> | 108 MHz       | 55 MHz <sup>[4]</sup> |

| 4                   | 108 MHz   | 108 MHz               | 70 MHz <sup>[4]</sup> | 108 MHz       | 108 MHz               | 108 MHz       | 70 MHz <sup>[4]</sup> |

| 5                   | 108 MHz   | 108 MHz               | 80 MHz <sup>[4]</sup> | 108 MHz       | 108 MHz               | 108 MHz       | 80 MHz <sup>[4]</sup> |

| 6                   | 108 MHz   | 108 MHz               | 95 MHz <sup>[4]</sup> | 108 MHz       | 108 MHz               | 108 MHz       | 95 MHz <sup>[4]</sup> |

| 7-15                | 108 MHz   | 108 MHz               | 108 MHz               | 108 MHz       | 108 MHz               | 108 MHz       | 108 MHz               |

**注释：**

- 该参数由出厂校准保证，并非经过生产测试。

**表 15. XIP 模式（DDR）下存储器读命令的延迟（虚拟）周期**

| 延迟（虚拟）<br>周期—十进制 | QPI (DDR)             |  | 四线 I/O (DDR)          |

|------------------|-----------------------|--|-----------------------|

|                  | DDRFR、DDRQIOR         |  | DDRQIOR               |

|                  | (4, 4, 4)             |  | (1, 4, 4)             |

|                  | 模式 = 1                |  | 模式 = 1                |

| 0                | 不适用                   |  | 不适用                   |

| 1                | 不适用                   |  | NA                    |

| 2                | 10 MHz <sup>[5]</sup> |  | 10 MHz <sup>[5]</sup> |

| 3                | 25 MHz <sup>[5]</sup> |  | 25 MHz <sup>[5]</sup> |

| 4                | 33 MHz <sup>[5]</sup> |  | 33 MHz <sup>[5]</sup> |

| 5                | 40 MHz <sup>[5]</sup> |  | 40 MHz <sup>[5]</sup> |

| 6                | 50 MHz <sup>[5]</sup> |  | 50 MHz <sup>[5]</sup> |

| 7–15             | 54 MHz                |  | 54 MHz                |

**表 16. 无 XIP 模式下存储器读命令的延迟（虚拟）周期**

| 延迟（虚拟）<br>周期—十进制 | SPI (SDR)             | DPI (SDR)             | QPI (SDR)             |

|------------------|-----------------------|-----------------------|-----------------------|

|                  | READ、ECCRD、SSRD       |                       |                       |

|                  | (1, 1, 1)             | (2, 2, 2)             | (4, 4, 4)             |

|                  | 模式 = 不适用              | 模式 = 不适用              | 模式 = 不适用              |

| 0                | 40 MHz <sup>[5]</sup> | 不适用                   | 不适用                   |

| 1                | 55 MHz <sup>[5]</sup> | 不适用                   | NA                    |

| 2                | 70 MHz <sup>[5]</sup> | 25 MHz <sup>[5]</sup> | 10 MHz <sup>[5]</sup> |

| 3                | 80 MHz <sup>[5]</sup> | 40 MHz <sup>[5]</sup> | 25 MHz <sup>[5]</sup> |

| 4                | 95 MHz <sup>[5]</sup> | 55 MHz <sup>[5]</sup> | 40 MHz <sup>[5]</sup> |

| 5                | 108 MHz               | 70 MHz <sup>[5]</sup> | 55 MHz <sup>[5]</sup> |

| 6                | 108 MHz               | 80 MHz <sup>[5]</sup> | 70 MHz <sup>[5]</sup> |

| 7                | 108 MHz               | 95 MHz <sup>[5]</sup> | 80 MHz <sup>[5]</sup> |

| 8                | 108 MHz               | 108 MHz               | 95 MHz <sup>[5]</sup> |

| 9–15             | 108 MHz               | 108 MHz               | 108 MHz               |

**注释：**

5. 该参数由出厂校准保证，并非经过生产测试。

#### 四线数据宽度 (QUAD) CR1 [1]

当该位设置为‘1’时，它将器件的数据宽度切换为 4 个 I/O — 四线模式，即  $\overline{WP}$  变为 I/O2,  $\overline{RESET} / (I/O3)$  变为 I/O3。如果通过设置配置寄存器 2(CR2[5]) 中的 IO3R 位来使能 I/O3 上的备用功能，那么当 CS 为低电平时， $\overline{RESET} / (I/O3)$  作为 I/O3 工作，CS 为高电平时，该引脚为  $\overline{RESET}$  输入。WP 输入被禁用，并内部设置为“1”。当执行四线输出读取、四线 I/O 读取和 DDR 四线 I/O 读取等扩展型 SPI 读取命令时，必须将 QUAD 位设置为“1”。第 19 页上的表 20. 中显示了“QUAD”位设置对各种 SPI 接口的影响。

#### 配置寄存器 2 (CR2)

表 17 中所示的配置寄存器 2 (CR2) 用于控制串行接口设置。可通过 WRAR 命令访问 CR2。同时，可通过 RDCR2 或 RDAR 命令对 SR1 进行读操作。第 27 页上的寄存器访问命令中介绍了 CR2 访问的详细信息。

WRAR 非易失性写地址 — 0x000003

WRAR 易失性写地址 — 0x070003

RDAR 读取地址 — 0x000003 或 0x070003

表 17 中每个位后面的默认状态是出厂编程值。

表 17. 配置寄存器 2 (CR2)

| CR2[7]  | CR2[6]  | CR2[5]   | CR2[4]  | CR2[3]  | CR2[2]  | CR2[1]  | CR2[0]  |

|---------|---------|----------|---------|---------|---------|---------|---------|

| RFU (0) | QPI (0) | IO3R (0) | DPI (0) | RFU (0) | RFU (0) | RFU (0) | RFU (0) |

表 18. 配置寄存器 2 (CR2) — 非易失性

| 位      | 位名   | 位功能       | 类型 | 读 / 写 | 说明                                                                  |

|--------|------|-----------|----|-------|---------------------------------------------------------------------|

| CR2[7] | RFU  | 预留 (0)    |    |       | 保留供将来使用                                                             |

| CR2[6] | QPI  | 四线 SPI 使能 | NV | R/W   | 1 = 使能 QPI 协议<br>0 = 使能 SPI 协议 (如果 DPI 位被置为‘0’)                     |

| CR2[5] | IO3R | IO3 复位    | NV | R/W   | 1 = 当 CS 为高电平时， I/O3 被作为 $\overline{RESET}$ 输入使用<br>0 = I/O3 没有复用功能 |

| CR2[4] | DPI  | 双线 SPI 使能 | NV | R/W   | 1 = 使能 DPI 协议<br>0 = 使能 SPI 协议 (如果 QPI 位被置为‘0’)                     |

| CR2[3] | RFU  | 预留 (0)    |    |       | 保留供将来使用                                                             |

| CR2[2] | RFU  | 预留 (0)    |    |       | 保留供将来使用                                                             |

| CR2[1] | RFU  | 预留 (0)    |    |       | 保留供将来使用                                                             |

| CR2[0] | RFU  | 预留 (0)    |    |       | 保留供将来使用                                                             |

NV - 非易失性

表 19. 配置寄存器 2 (CR2) — 易失性

| 位      | 位名   | 位功能       | 类型 | 读 / 写 | 说明                                                                  |

|--------|------|-----------|----|-------|---------------------------------------------------------------------|

| CR2[7] | RFU  | 预留 (0)    |    |       | 保留供将来使用                                                             |

| CR2[6] | QPI  | 四线 SPI 使能 | V  | R/W   | 1 = 使能 QPI 协议<br>0 = 使能 SPI 协议 (如果 DPI 位被置为‘0’)                     |

| CR2[5] | IO3R | IO3 复位    | V  | R/W   | 1 = 当 CS 为高电平时， I/O3 被作为 $\overline{RESET}$ 输入使用<br>0 = I/O3 没有复用功能 |

| CR2[4] | DPI  | 双线 SPI 使能 | V  | R/W   | 1 = 使能 DPI 协议<br>0 = 使能 SPI 协议 (如果 QPI 位被置为‘0’)                     |

| CR2[3] | RFU  | 预留 (0)    |    |       | 保留供将来使用                                                             |

| CR2[2] | RFU  | 预留 (0)    |    |       | 保留供将来使用                                                             |

| CR2[1] | RFU  | 预留 (0)    |    |       | 保留供将来使用                                                             |

| CR2[0] | RFU  | 预留 (0)    |    |       | 保留供将来使用                                                             |

NV - 非易失性

#### 四线 SPI (QPI) CR2 [6]

该位控制四线 SPI 模式下的指令和数据宽度。在该模式下，主机系统和存储器之间的所有传输在 I/O0 到 I/O3 上实现，传输宽度为 4 比特，包括所有指令。对于 QPI 模式，不需要将 CR1 [1] 中的 QUAD 位置 1。更多信息，请查阅表 21。

#### IO3 复位 (IO3R) CR2 [5]

该位控制着 RESET / (I/O3) 引脚的行为。该位被置“1”时，在正常操作期间使能 RESET 输入。表 20 显示了基于接口模式的 RESET / (I/O3) 功能。

**表 20. RESET/ (I/O3) 引脚功能**

| 接口模式 | 四线位<br>(CR1 <sup>[6]</sup> ) | RESET/ (I/O3) 引脚功能              |               |                                 |               |

|------|------------------------------|---------------------------------|---------------|---------------------------------|---------------|

|      |                              | IO3R (CR2[5]) = 0<br>(IO3 复位禁用) |               | IO3R (CR2[5]) = 1<br>(IO3 复位使能) |               |

|      |                              | <u>CS</u> = 0                   | <u>CS</u> = 1 | <u>CS</u> = 0                   | <u>CS</u> = 1 |

| SPI  | QUAD = 0                     | 无功能                             | 无功能           | RESET                           | 复位            |

| SPI  | QUAD = 1                     | I/O3 <sup>[7]</sup>             | 无功能           | I/O3 <sup>[7]</sup>             | 复位            |

| DPI  | QUAD = 0                     | 无功能                             | 无功能           | RESET                           | 复位            |

| DPI  | QUAD = 1                     | 无功能                             | 无功能           | 无功能                             | 复位            |

| QPI  | QUAD = x (无需关注)              | I/O3                            | 无功能           | I/O3                            | 复位            |

**表 21. SPI 工作模式设置**

| QUAD <sup>[8]</sup><br>CR1 <sup>[6]</sup> | DPI<br>CR2 <sup>[4]</sup> | QPI<br>CR2 <sup>[6]</sup> | 工作模式                                              |

|-------------------------------------------|---------------------------|---------------------------|---------------------------------------------------|

| 0                                         | 0                         | 0                         | SPI、扩展型 SPI (双线)                                  |

| 1                                         | 0                         | 0                         | SPI、扩展型 SPI (双线 / 四线)                             |

| X                                         | 1                         | 0                         | DPI                                               |

| X                                         | 0                         | 1                         | QPI                                               |

| 0                                         | 1                         | 1                         | SPI <sup>[9]</sup> , 扩展型 SPI (双线) — 不建议使用该配置      |

| 1                                         | 1                         | 1                         | SPI <sup>[9]</sup> , 扩展型 SPI (双线 / 四线) — 不建议使用该配置 |

**注释:**

6. 所有扩展型 SPI 开始于 SPI 模式。

7. SPI 和 DPI 模式没有该功能。四线数据或四线 I/O 模式将使用 I/O3。

8. QUAD = ‘1’ 将重新配置 I/O 为四线模式，并且会影响到 WP 和 RESET 的工作。请参考表 20，了解更详细内容。

9. 寄存器读取将始终返回对其写入的内容，即使这是不建议的配置。

#### 配置寄存器 4 (CR4)

表 22 中所示的配置寄存器 4 (CR4) 控制着输出驱动阻抗和深度掉电 (DPD) 模式设置。可通过 WRAR 命令访问 CR4。同时，可通过 RDCR4 或 RDAR 命令对 SR1 进行读操作。[第 27 页上的寄存器访问命令](#)中介绍了 CR4 访问的详细信息。

表 22. 配置寄存器 4 (CR4)

| CR4[7] | CR4[6] | CR4[5] | CR4[4]  | CR4[3]  | CR4[2]     | CR4[1]  | CR4[0]  |

|--------|--------|--------|---------|---------|------------|---------|---------|

| OI (0) | OI (0) | OI (0) | RFU (0) | RFU (1) | DPDPOR (0) | RFU (0) | RFU (0) |

表 23. 配置寄存器 4 (CR4) — 非易失性

| 位      | 位名     | 位功能          | 类型 | 读 / 写 | 说明                                                                                                              |

|--------|--------|--------------|----|-------|-----------------------------------------------------------------------------------------------------------------|

| CR4[7] | OI     | 输出阻抗         | NV | R/W   | 输出阻抗选择                                                                                                          |

| CR4[6] |        |              | NV | R/W   |                                                                                                                 |

| CR4[5] |        |              | NV | R/W   |                                                                                                                 |

| CR4[4] | RFU    | 预留 (0)       |    |       | 保留供将来使用                                                                                                         |

| CR4[3] | RFU    | 预留 (1)       |    |       | 保留供将来使用 <sup>[10]</sup>                                                                                         |

| CR4[2] | DPDPOR | 上电复位时的深度掉电模式 | NV | R/W   | 1 = 当 CS 为高电平时，在完成上电复位或硬件复位（包括 JEDEC 复位）后，器件将进入深度掉电模式<br>0 = 当 CS 为高电平时，在完成上电或上电复位或硬件复位（包括 JEDEC 复位）后，器件将进入休眠模式 |

| CR4[1] | RFU    | 预留 (0)       |    |       | 保留供将来使用                                                                                                         |

| CR4[0] | RFU    | 预留 (0)       |    |       | 保留供将来使用                                                                                                         |

NV - 非易失性

表 24. 配置寄存器 4 (CR4) — 易失性

| 位      | 位名     | 位功能          | 类型 | 读 / 写 | 说明                                                                                                              |

|--------|--------|--------------|----|-------|-----------------------------------------------------------------------------------------------------------------|

| CR4[7] | OI     | 输出阻抗         | V  | R/W   | 输出阻抗选择                                                                                                          |

| CR4[6] |        |              | V  | R/W   |                                                                                                                 |

| CR4[5] |        |              | V  | R/W   |                                                                                                                 |

| CR4[4] | RFU    | 预留 (0)       |    |       | 保留供将来使用                                                                                                         |

| CR4[3] | RFU    | 预留 (1)       |    |       | 保留供将来使用 <sup>[10]</sup>                                                                                         |

| CR4[2] | DPDPOR | 上电复位时的深度掉电模式 | V  | R/W   | 1 = 当 CS 为高电平时，在完成上电复位或硬件复位（包括 JEDEC 复位）后，器件将进入深度掉电模式<br>0 = 当 CS 为高电平时，在完成上电或上电复位或硬件复位（包括 JEDEC 复位）后，器件将进入休眠模式 |

| CR4[1] | RFU    | 预留 (0)       |    |       | 保留供将来使用                                                                                                         |

| CR4[0] | RFU    | 预留 (0)       |    |       | 保留供将来使用                                                                                                         |

V - 易失性

### 输出阻抗 (OI) CR4 [7:5]

这三位控制 I/O 引脚的输出阻抗（驱动强度）。用户可通过输出阻抗配置位调整驱动强度，以便在印刷电路板上获得更好的信号完整性。

**表 25. 阻抗选择**

| 阻抗选择 | 典型阻抗 ( $\Omega$ ) [11] | 说明                                                  |

|------|------------------------|-----------------------------------------------------|

| 000  | 45                     | 45 $\Omega$ 是出厂默认配置值。通过写入阻抗选择位 CR4[7:5] 可以编程其他驱动强度。 |

| 001  | 120                    |                                                     |

| 010  | 90                     |                                                     |

| 011  | 60                     |                                                     |

| 100  | 45                     |                                                     |

| 101  | 30                     |                                                     |

| 110  | 20                     |                                                     |

| 111  |                        |                                                     |

### POR 时的深度掉电模式 (DPDPOR) CR4 [2]

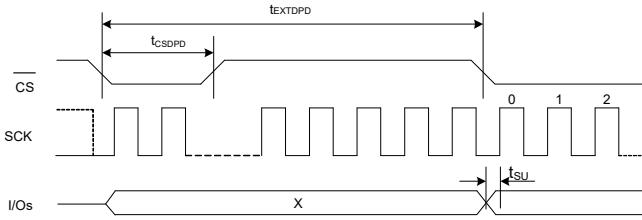

该位控制着在上电复位 (POR)、硬件复位 (RESET 引脚或 JEDEC 复位) 完成后器件进入深度掉电 (DPD) 模式还是待机模式、或退出休眠模式。当 CS 为高电平时，DPDPOR 配置位允许器件在 DPD 模式下启动，而不是在待机模式下。经过  $t_{EXTDPD}$  的时间后，通过 CS 脉宽  $t_{CSDPD}$  或硬件复位可以退出深度掉电模式。可以通过单独切换 CS (SCK 和 I/O 是无需关注) 来生成 CS 脉冲宽度。在软件复位期间，DPDPOR 位状态被忽略，软件复位后器件始终进入待机状态。

### 配置寄存器 5 (CR5)

表 26 中所示的配置寄存器 5 (CR5) 将配置寄存器读取延迟 (虚拟) 周期。可通过 WRAR 命令访问 CR5。同时，可通过 RDCR5 或 RDAR 命令对 SR1 进行读操作。第 27 页上的寄存器访问命令中介绍了 CR5 访问的详细信息。

WRAR 非易失性写地址 — 0x000006

WRAR 易失性写地址 — 0x070006

RDAR 读取地址 — 0x000006 或 0x070006

表 26 中每个位后面的默认状态是出厂编程值。

**表 26. 配置寄存器 5 (CR5)**

| CR5[7]   | CR5[6]   | CR5[5]  | CR5[4]  | CR5[3]  | CR5[2]  | CR5[1]  | CR5[0]  |

|----------|----------|---------|---------|---------|---------|---------|---------|

| RLC1 (0) | RLC0 (0) | RFU (0) |

**表 27. 配置寄存器 5 (CR5) — 非易失性**

| 位      | 位名   | 位功能     | 类型 | 读 / 写   | 说明                                      |  |  |

|--------|------|---------|----|---------|-----------------------------------------|--|--|

| CR5[7] | RLC1 | 寄存器延迟代码 | NV | R/W     | 通过选择存储器延迟周期数 (从 0 到 3 的时钟周期) 可以对寄存器进行访问 |  |  |

| CR5[6] | RLC0 |         |    | R/W     |                                         |  |  |

| CR5[5] | RFU  | 预留 (0)  |    | 保留供将来使用 |                                         |  |  |

| CR5[4] | RFU  | 预留 (0)  |    | 保留供将来使用 |                                         |  |  |

| CR5[3] | RFU  | 预留 (0)  |    | 保留供将来使用 |                                         |  |  |

| CR5[2] | RFU  | 预留 (0)  |    | 保留供将来使用 |                                         |  |  |

| CR5[1] | RFU  | 预留 (0)  |    | 保留供将来使用 |                                         |  |  |

| CR5[0] | RFU  | 预留 (0)  |    | 保留供将来使用 |                                         |  |  |

NV - 非易失性

**注释：**

10. 当对该配置寄存器进行写入时，SPI 总线主设备必须保证位 CR4 [3] 保持为 ‘1’。将该位置为 ‘0’ 可能会影响到器件的功能。

11.  $V_{DD}/2$  条件下所测量的典型电容。

**表 28. 配置寄存器 5 (CR5) — 易失性**

| 位      | 位名   | 位功能         | 类型 | 读 / 写   | 说明                                    |  |  |

|--------|------|-------------|----|---------|---------------------------------------|--|--|

| CR5[7] | RLC1 | 寄存器延迟<br>代码 | V  | R/W     | 通过选择存储器延迟周期数（从 0 到 3 的时钟周期）可以对寄存器进行访问 |  |  |

| CR5[6] | RLC0 |             |    | R/W     |                                       |  |  |

| CR5[5] | RFU  | 预留 (0)      |    | 保留供将来使用 |                                       |  |  |

| CR5[4] | RFU  | 预留 (0)      |    | 保留供将来使用 |                                       |  |  |

| CR5[3] | RFU  | 预留 (0)      |    | 保留供将来使用 |                                       |  |  |

| CR5[2] | RFU  | 预留 (0)      |    | 保留供将来使用 |                                       |  |  |

| CR5[1] | RFU  | 预留 (0)      |    | 保留供将来使用 |                                       |  |  |

| CR5[0] | RFU  | 预留 (0)      |    | 保留供将来使用 |                                       |  |  |

V — 易失性

**寄存器延迟代码 (RLC [1:0]) CR5 [7:6]**

这两个位控制所有可变延迟寄存器读取指令中的读取延迟（虚拟周期）。通过这些位，用户可以在正常操作期间调整读取延迟，从而优化不同工作频率下各种寄存器读取指令的延迟。表 29 中显示了寄存器读取命令的延迟周期。

**表 29. 寄存器读命令的虚拟周期**

| 延迟 (虚拟) 周期 | SPI (SDR)                                                | DPI (SDR)              | QPI (SDR)              |

|------------|----------------------------------------------------------|------------------------|------------------------|

|            | RDSR1、RDSR2、RDCR1、RDCR2、RDCR4、RDCR5、RDAR、RUID、RDID2、RDSN | 50 MHz <sup>[12]</sup> | 50 MHz <sup>[12]</sup> |

| 0          | 50 MHz <sup>[12]</sup>                                   | 50 MHz <sup>[12]</sup> | 50 MHz <sup>[12]</sup> |

| 1–3        | 108 MHz                                                  | 108 MHz                | 108 MHz                |

**注释：**

12. 该参数由出厂校准保证，并非经过生产测试。

## 功能说明

CY15x104QSN 采用了一个 8 位指令寄存器。下面列出了所有指令及其操作码。所有指令、地址和数据都在 CS 从高电平转为低电平时开始传输。此外，WP 和 RESET 引脚提供了额外的硬件控制功能。

表 30. 通过不同 SPI 模式下的 I/O 传输命令

| 命令阶段   | 在各 I/O 上传输命令                                                                                                |           |                     |           |                     |           |                     |  |

|--------|-------------------------------------------------------------------------------------------------------------|-----------|---------------------|-----------|---------------------|-----------|---------------------|--|

|        | 单通道 SPI                                                                                                     | 扩展型 SPI   |                     |           |                     | 多通道 SPI   |                     |  |

|        |                                                                                                             | 双线数据      | 四线数据                | 双线 I/O    | 四线 I/O              | DPI       | QPI                 |  |

| 操作码    | SI                                                                                                          | I/O0      | I/O0                | I/O0      | I/O0                | I/O0、I/O1 | I/O0、I/O1、I/O2、I/O3 |  |

| 地址     | SI                                                                                                          | I/O0      | I/O0                | I/O0、I/O1 | I/O0、I/O1、I/O2、I/O3 | I/O0、I/O1 | I/O0、I/O1、I/O2、I/O3 |  |

| 模式     | SI                                                                                                          | I/O0      | I/O0                | I/O0、I/O1 | I/O0、I/O1、I/O2、I/O3 | I/O0、I/O1 | I/O0、I/O1、I/O2、I/O3 |  |

| 虚拟（延迟） | 虚拟 SPI 时钟周期数不依赖于 SPI 接口。<br>0 至 15 个时钟周期用于访问存储器（可通过 CR1[7:4] 进行配置）<br>0 至 3 个时钟周期用于寄存器访问（可通过 CR5[7:6] 进行配置） |           |                     |           |                     |           |                     |  |

| 数据     | SI/SO                                                                                                       | I/O0、I/O1 | I/O0、I/O1、I/O2、I/O3 | I/O0、I/O1 | I/O0、I/O1、I/O2、I/O3 | I/O0、I/O1 | I/O0、I/O1、I/O2、I/O3 |  |

有 44 个称为操作码的命令，可由总线主设备发送到 CY15x104QSN，如表 31 中所示。这些操作码控制由存储器执行的功能。

表 31. 操作码指令

| 命令           |               | SPI 总线接口 |          |          |           |           |     | 数据传输 |     | 延迟  |           | XIP       |           |

|--------------|---------------|----------|----------|----------|-----------|-----------|-----|------|-----|-----|-----------|-----------|-----------|

| 命令           | 操作码<br>(十六进制) | SPI      | 双线<br>数据 | 四线<br>数据 | 双线<br>I/O | 四线<br>I/O | DPI | QPI  | SDR | DDR | 寄存器<br>延迟 | 存储器<br>延迟 | 芯片内<br>执行 |

| <b>写使能控制</b> |               |          |          |          |           |           |     |      |     |     |           |           |           |

| WREN         | 06            | 支持       | 不适用      |          |           | 支持        | 支持  | 支持   | 不适用 | 不适用 | 不适用       | 不适用       | 不适用       |

| WRDI         | 04            | 支持       | 不适用      |          |           | 支持        | 支持  | 支持   | 不适用 | 不适用 | 不适用       | 不适用       | 不适用       |

| <b>寄存器访问</b> |               |          |          |          |           |           |     |      |     |     |           |           |           |

| WRSR         | 01            | 支持       | 不适用      |          |           | 支持        | 支持  | 支持   | 不适用 | 不适用 | 不适用       | 不适用       | 不适用       |

| RDSR1        | 05            | 支持       | 不适用      |          |           | 支持        | 支持  | 支持   | 不适用 | 支持  | 不适用       | 不适用       | 不适用       |

| RDSR2        | 07            | 支持       | 不适用      |          |           | 支持        | 支持  | 支持   | 不适用 | 支持  | 不适用       | 不适用       | 不适用       |

| RDCR1        | 35            | 支持       | 不适用      |          |           | 支持        | 支持  | 支持   | 不适用 | 支持  | 不适用       | 不适用       | 不适用       |

| RDCR2        | 3F            | 支持       | 不适用      |          |           | 支持        | 支持  | 支持   | 不适用 | 支持  | 不适用       | 不适用       | 不适用       |

| RDCR4        | 45            | 支持       | 不适用      |          |           | 支持        | 支持  | 支持   | 不适用 | 支持  | 不适用       | 不适用       | 不适用       |

| RDCR5        | 5E            | 支持       | 不适用      |          |           | 支持        | 支持  | 支持   | 不适用 | 支持  | 不适用       | 不适用       | 不适用       |

| WRAR         | 71            | 支持       | 不适用      |          |           | 支持        | 支持  | 支持   | 不适用 | 不适用 | 不适用       | 不适用       | 不适用       |

| RDAR         | 65            | 支持       | 不适用      |          |           | 支持        | 支持  | 支持   | 不适用 | 支持  | 不适用       | 不适用       | 不适用       |

**表 31. 操作码指令 (续)**

| 命令               |               | SPI 总线接口 |          |          |           |           |     | 数据传输 |     | 延迟  |           | XIP       |           |

|------------------|---------------|----------|----------|----------|-----------|-----------|-----|------|-----|-----|-----------|-----------|-----------|

| 命令               | 操作码<br>(十六进制) | SPI      | 双线<br>数据 | 四线<br>数据 | 双线<br>I/O | 四线<br>I/O | DPI | QPI  | SDR | DDR | 寄存器<br>延迟 | 存储器<br>延迟 | 芯片内<br>执行 |

| <b>存储器读取</b>     |               |          |          |          |           |           |     |      |     |     |           |           |           |

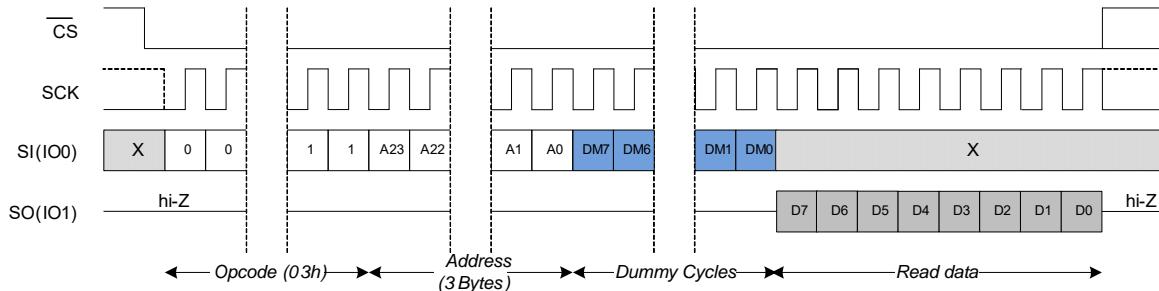

| READ             | 03            | 支持       | 不适用      |          |           | 支持        | 支持  | 支持   | 不适用 | 不适用 | 支持        | 不适用       |           |

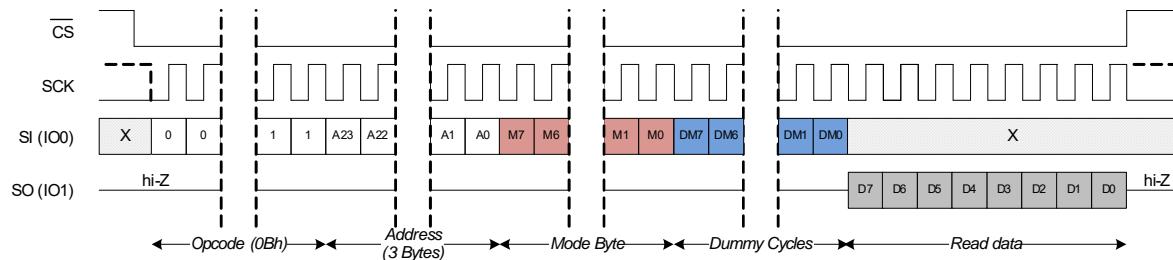

| FAST_READ        | 0B            | 支持       | 不适用      |          |           | 支持        | 支持  | 支持   | 不适用 | 不适用 | 支持        | 支持        |           |

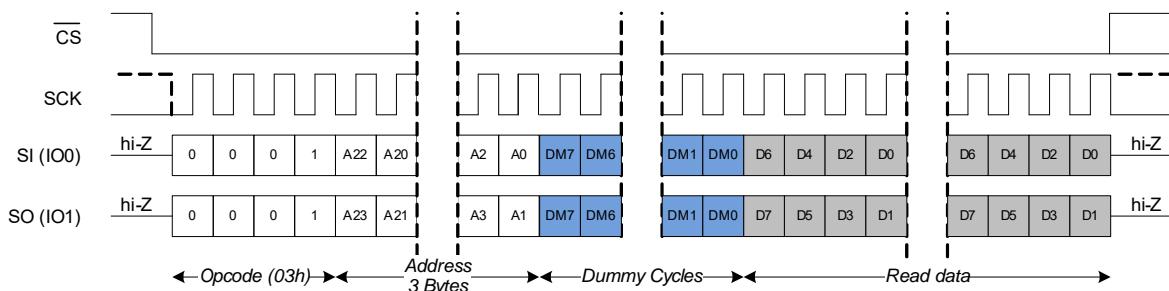

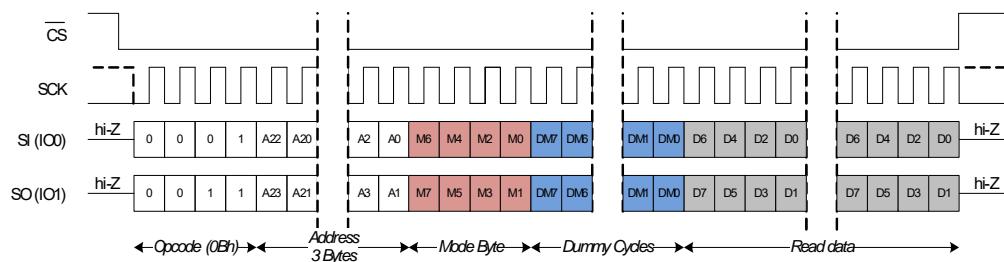

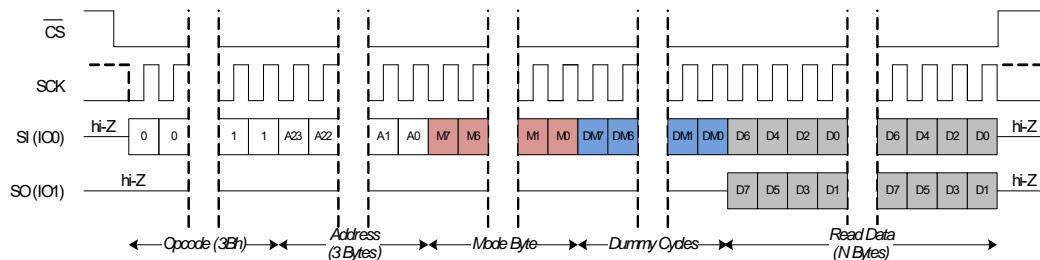

| DOR              | 3B            | 不适用      | 支持       | 不适用      |           |           |     | 支持   | 不适用 | 不适用 | 支持        | 支持        |           |

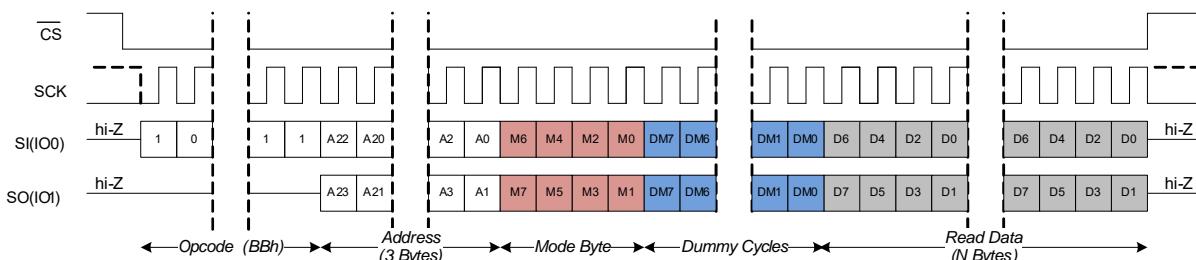

| DIOR             | BB            | 不适用      |          | 支持       | 不适用       |           |     | 支持   | 不适用 | 不适用 | 支持        | 支持        |           |

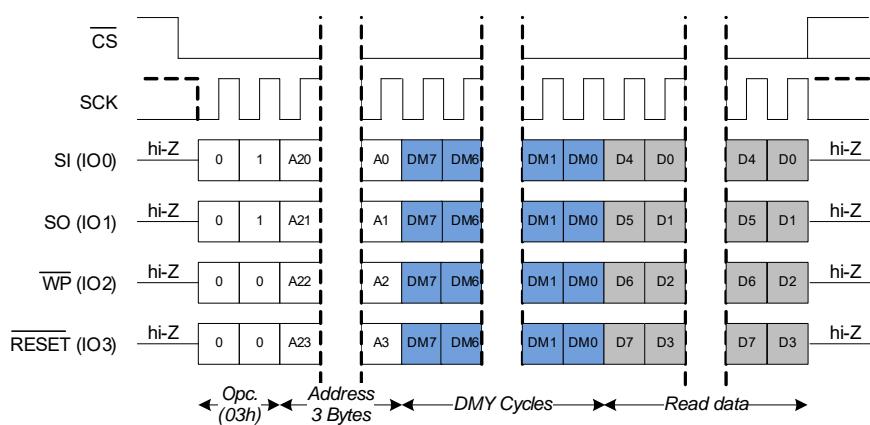

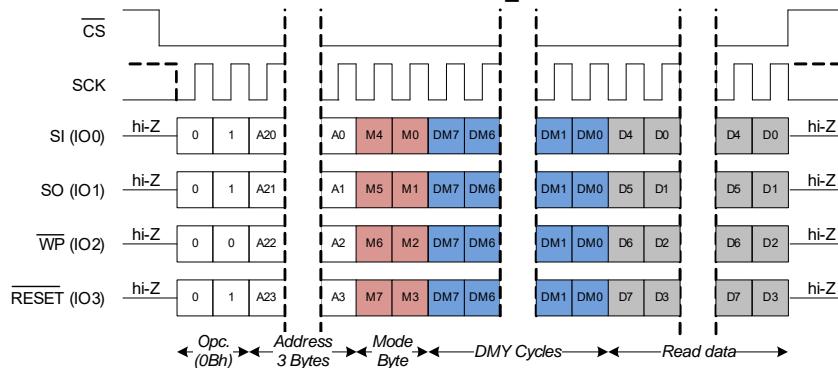

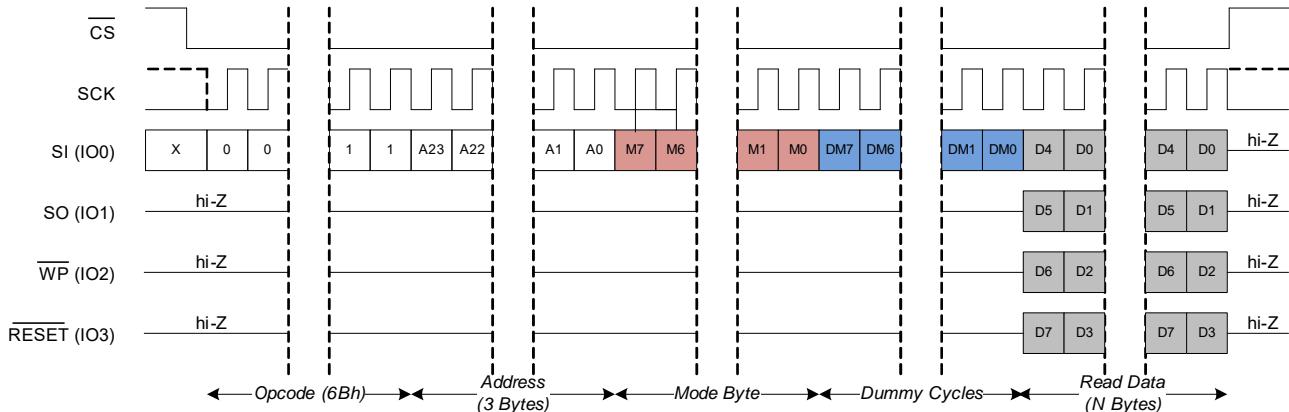

| QOR              | 6B            | 不适用      |          | 支持       | 不适用       |           |     | 支持   | 不适用 | 不适用 | 支持        | 支持        |           |

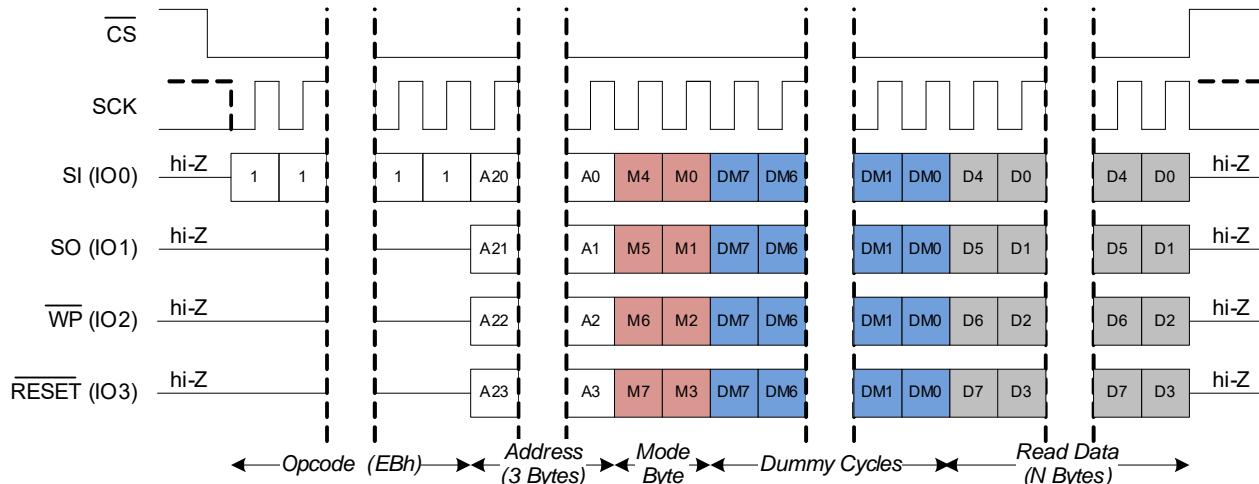

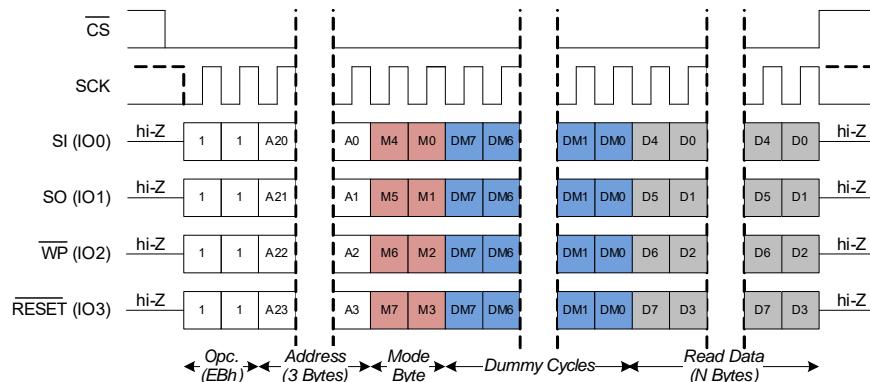

| QIOR             | EB            | 不适用      |          |          | 支持        | 不适用       | 支持  | 支持   | 不适用 | 不适用 | 支持        | 支持        |           |

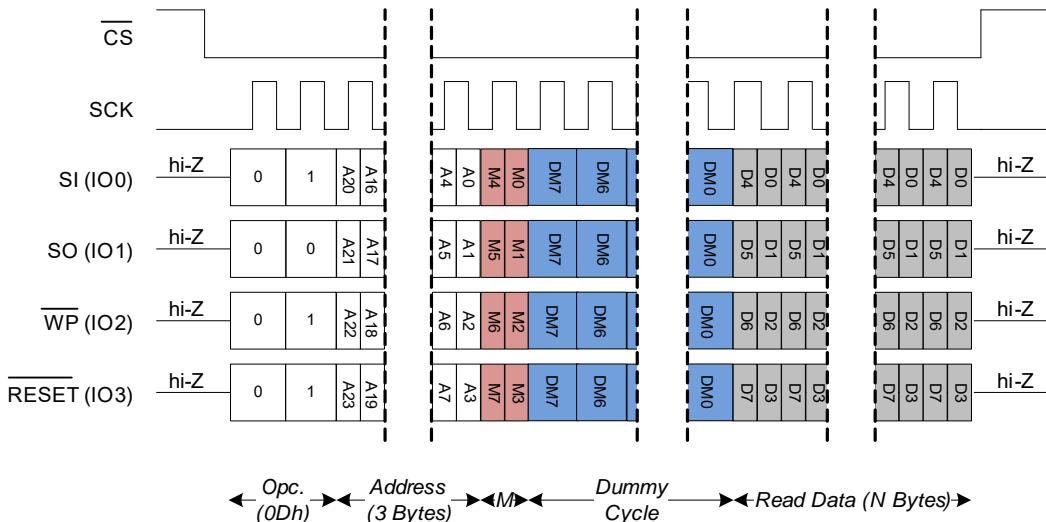

| DDRRFR           | 0D            | 不适用      |          |          |           | 支持        | 不适用 | 支持   | 不适用 | 支持  | 支持        | 支持        |           |

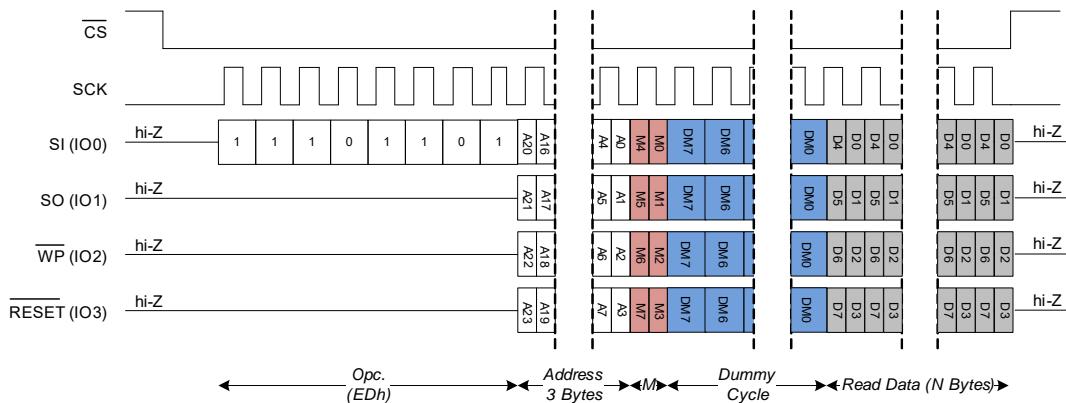

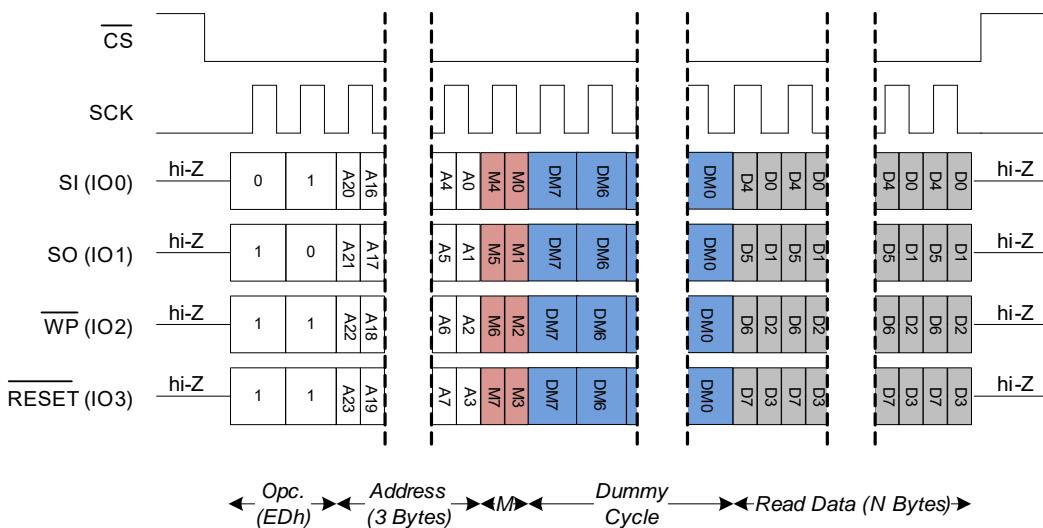

| DDRQIOR          | ED            | 不适用      |          |          | 支持        | 不适用       | 支持  | 不适用  | 支持  | 不适用 | 支持        | 支持        |           |

| <b>存储器写入操作</b>   |               |          |          |          |           |           |     |      |     |     |           |           |           |

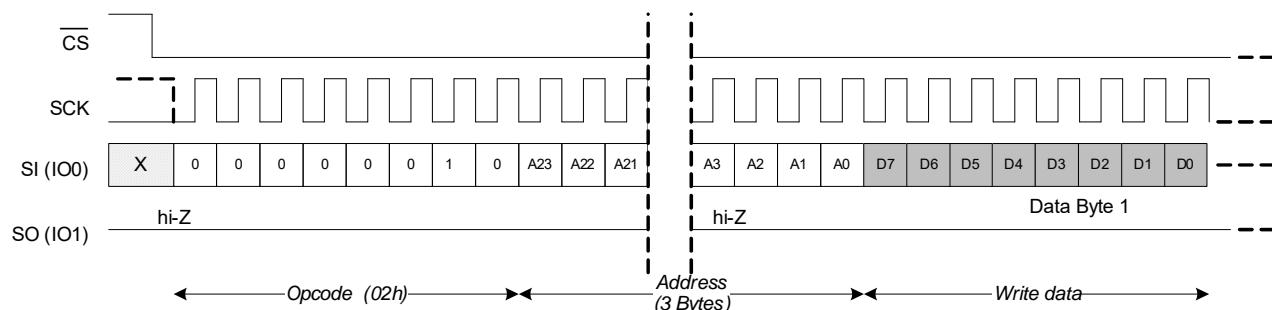

| WRITE            | 02            | 支持       | 不适用      |          |           | 支持        | 支持  | 支持   | 不适用 | 不适用 | 不适用       | 不适用       |           |

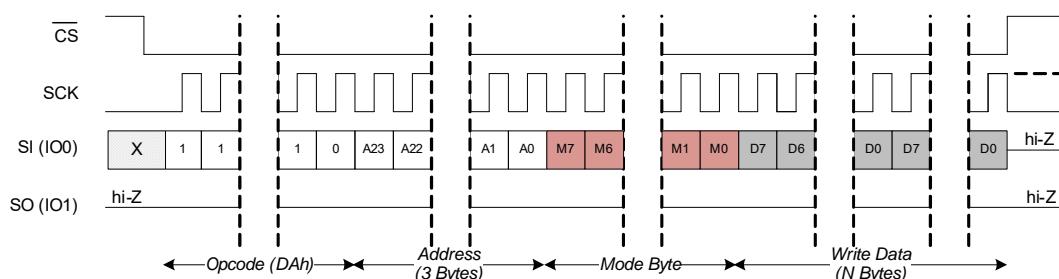

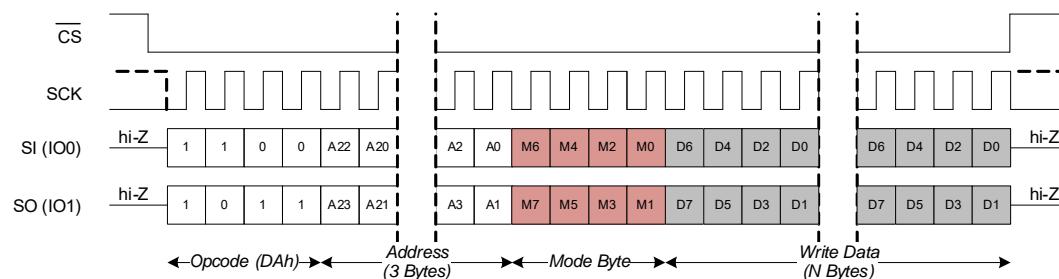

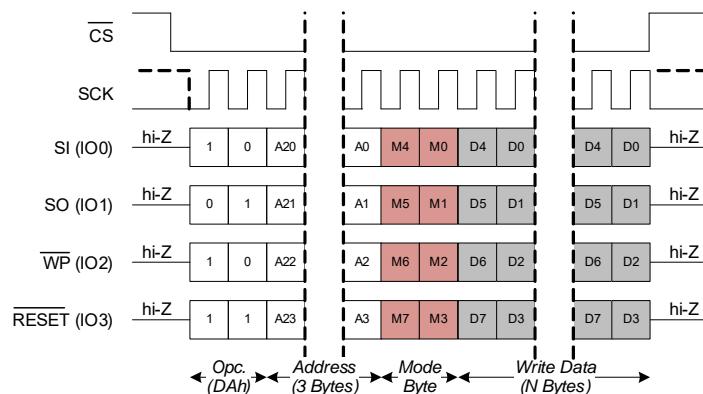

| FAST_WRITE       | DA            | 支持       | 不适用      |          |           | 支持        | 支持  | 支持   | 不适用 | 不适用 | 不适用       | 支持        |           |

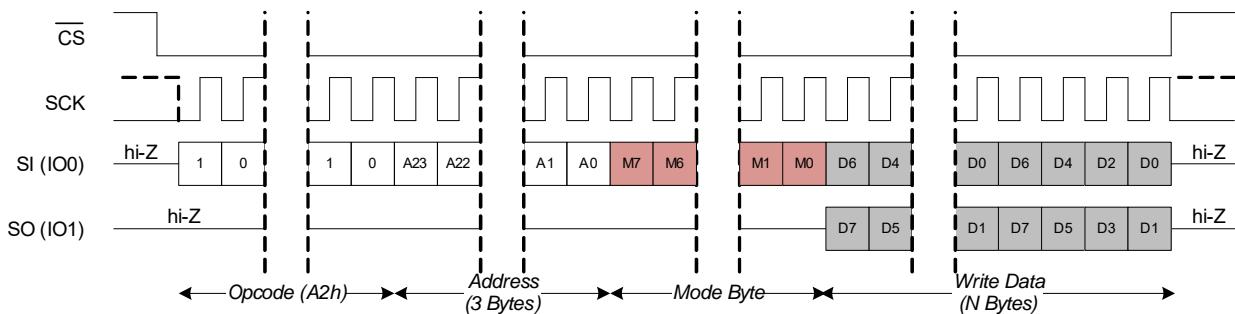

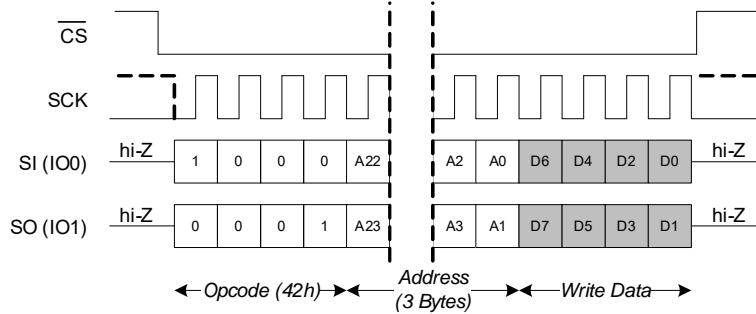

| DIW              | A2            | 不适用      | 支持       | 不适用      |           |           | 支持  | 不适用  | 不适用 | 不适用 | 不适用       | 支持        |           |

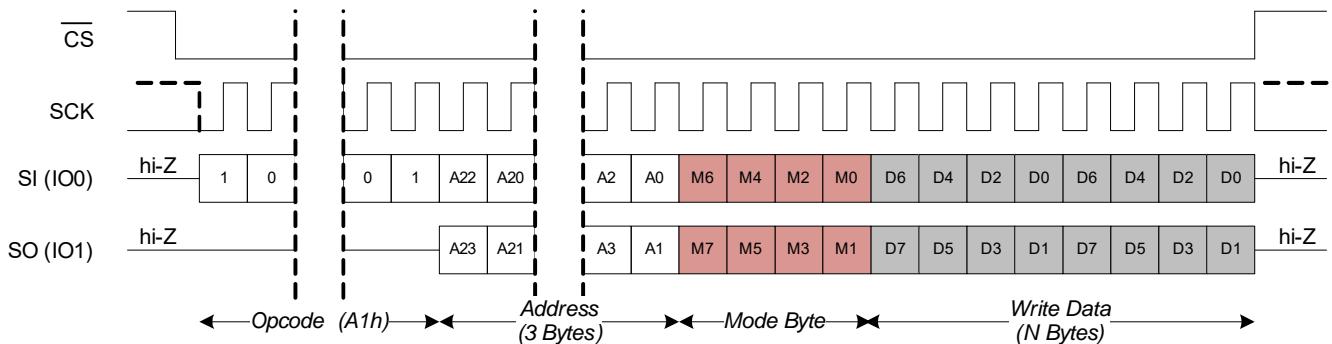

| DIOW             | A1            | 不适用      |          | 支持       | 不适用       |           |     | 支持   | 不适用 | 不适用 | 不适用       | 支持        |           |

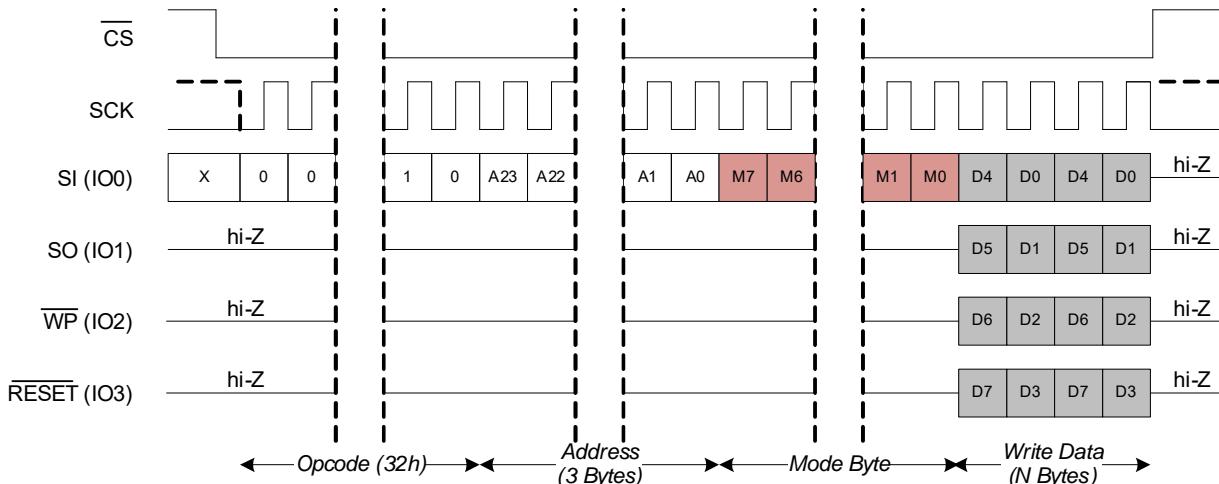

| QIW              | 32            | 不适用      |          | 支持       | 不适用       |           |     | 支持   | 不适用 | 不适用 | 不适用       | 支持        |           |

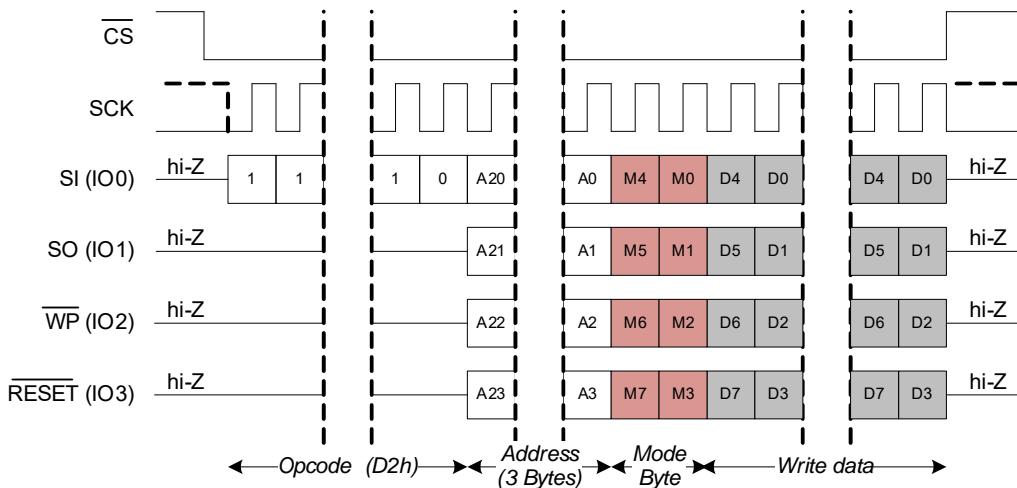

| QIOW             | D2            | 不适用      |          |          | 支持        | 不适用       |     | 支持   | 不适用 | 不适用 | 不适用       | 支持        |           |

| DDR_FAST_WRITE   | DD            | 不适用      |          |          |           | 支持        | 不适用 | 支持   | 不适用 | 不适用 | 不适用       | 支持        |           |

| DDRWWRITE        | DE            | 不适用      |          |          |           | 支持        | 不适用 | 支持   | 不适用 | 不适用 | 不适用       | NA        |           |

| DDRQIOW          | D1            | 不适用      |          |          | 支持        | 不适用       |     | 不适用  | 支持  | 不适用 | 不适用       | 支持        |           |

| <b>特殊扇区存储器访问</b> |               |          |          |          |           |           |     |      |     |     |           |           |           |

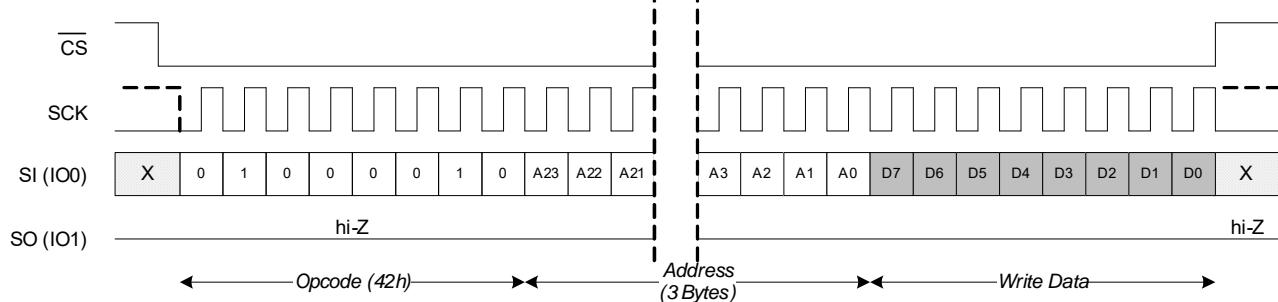

| SSWR             | 42            | 支持       | 不适用      |          |           | 支持        | 支持  | 支持   | 不适用 | 不适用 | 不适用       | 不适用       |           |

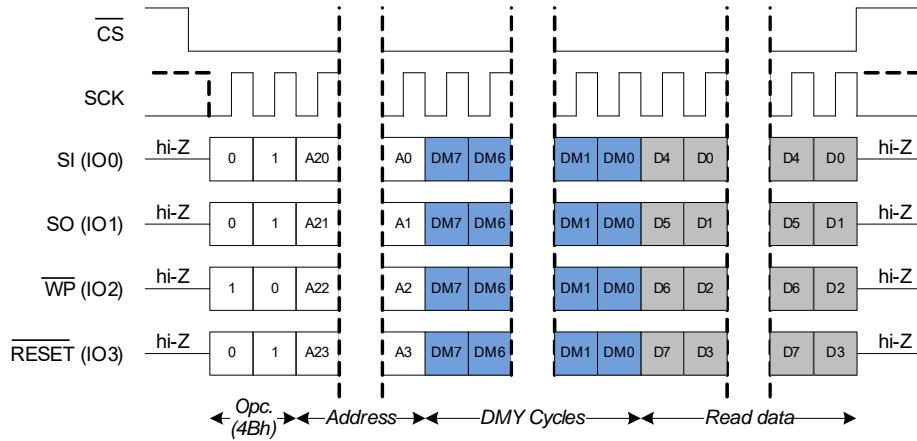

| SSRD             | 4B            | 支持       | 不适用      |          |           | 支持        | 支持  | 支持   | 不适用 | 不适用 | 支持        | 不适用       |           |

| <b>ECC 和 CRC</b> |               |          |          |          |           |           |     |      |     |     |           |           |           |

| CLECC            | 1B            | 支持       | 不适用      |          |           | 支持        | 支持  | 支持   | 不适用 | 不适用 | 不适用       | 不适用       |           |

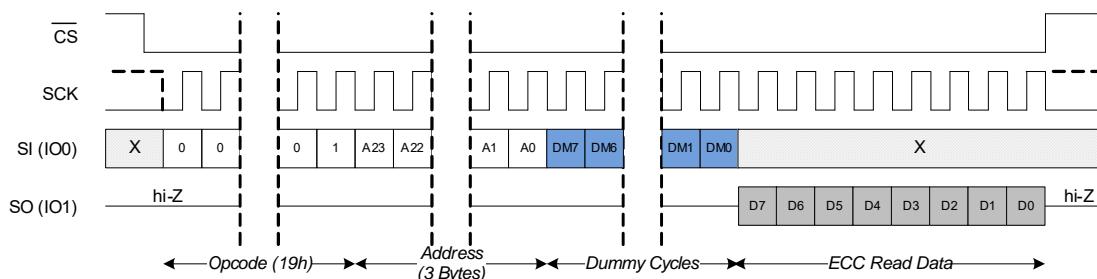

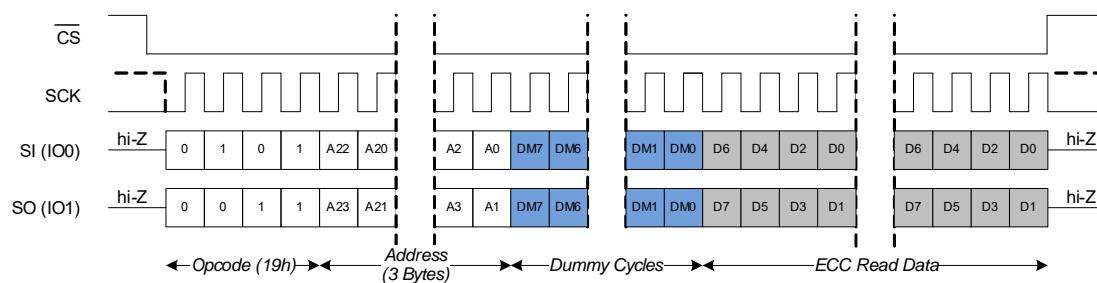

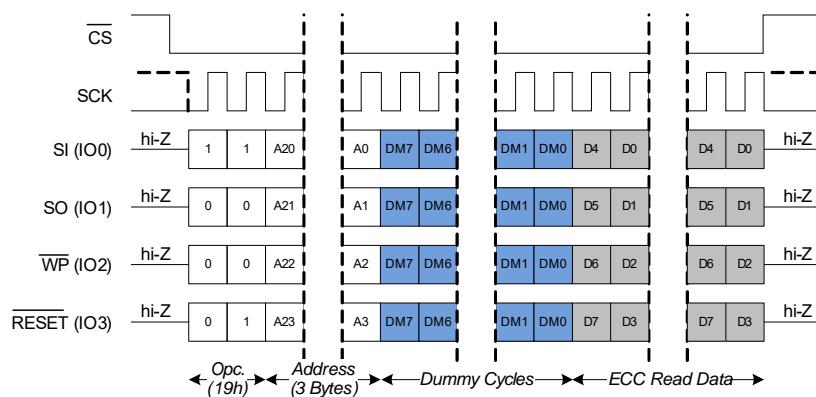

| ECCRD            | 19            | 支持       | 不适用      |          |           | 支持        | 支持  | 支持   | 不适用 | 不适用 | 支持        | 不适用       |           |

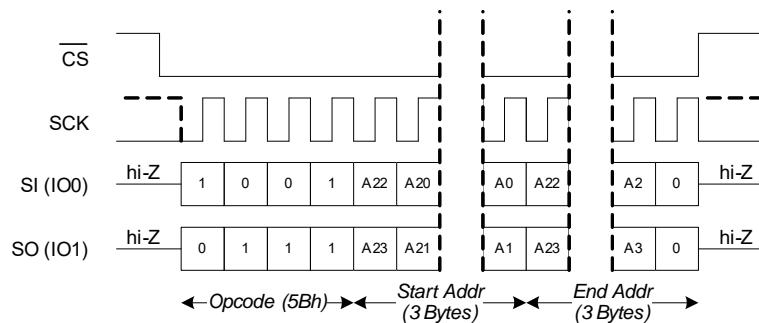

| CRCC             | 5B            | 支持       | 不适用      |          |           | 支持        | 支持  | 支持   | 不适用 | 不适用 | 不适用       | 不适用       |           |

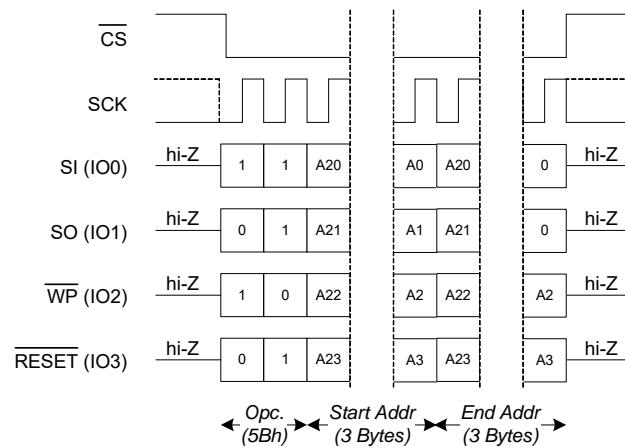

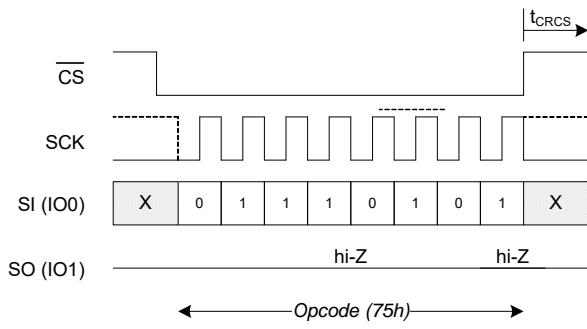

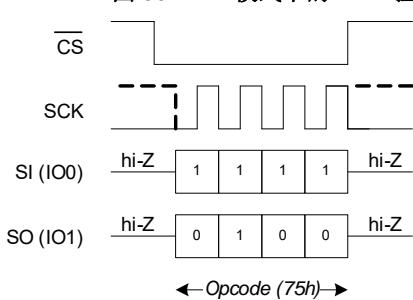

| EPCS             | 75            | 支持       | 不适用      |          |           | 支持        | 支持  | 支持   | 不适用 | 不适用 | 不适用       | 不适用       |           |

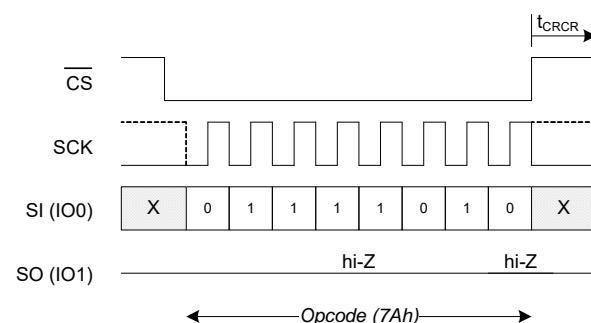

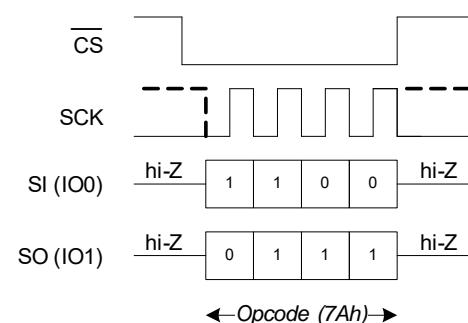

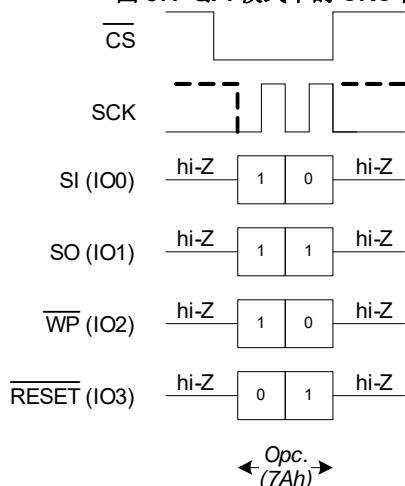

| EPCR             | 7A            | 支持       | 不适用      |          |           | 支持        | 支持  | 支持   | 不适用 | 不适用 | 不适用       | 不适用       |           |

| <b>标识和序列号</b>    |               |          |          |          |           |           |     |      |     |     |           |           |           |

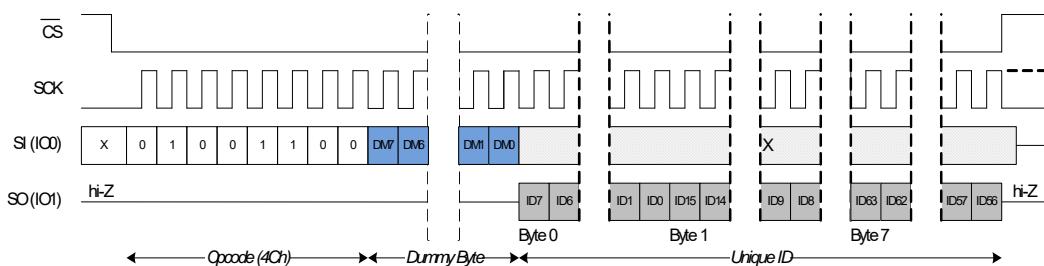

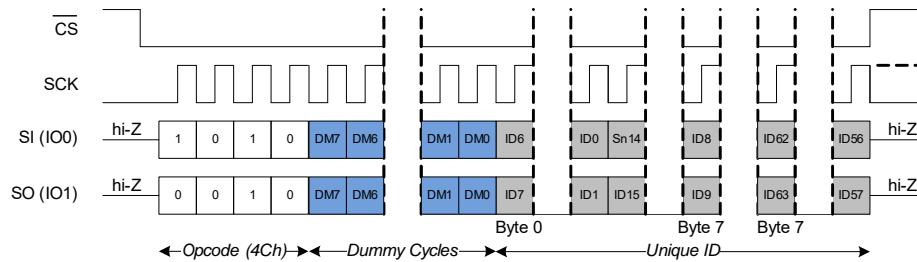

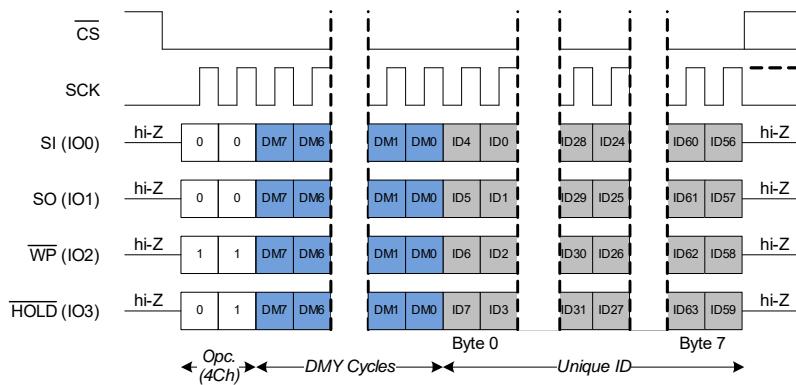

| RUID             | 4C            | 支持       | 不适用      |          |           | 支持        | 支持  | 支持   | 不适用 | 支持  | 不适用       | 不适用       |           |

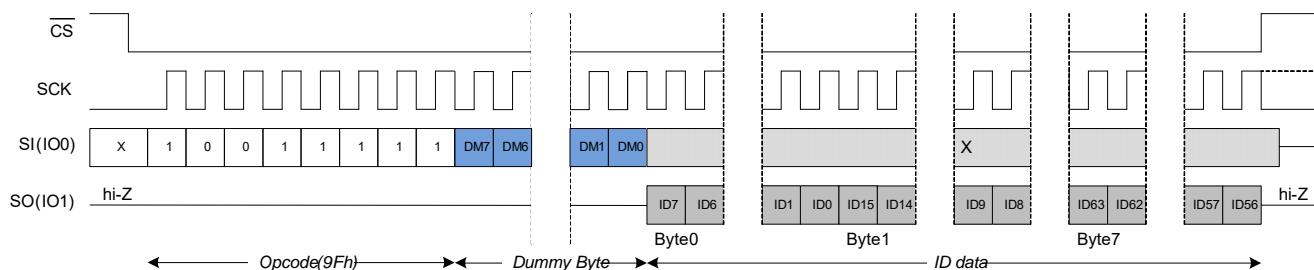

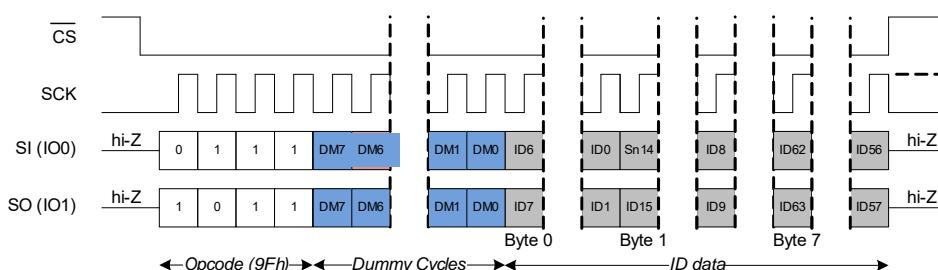

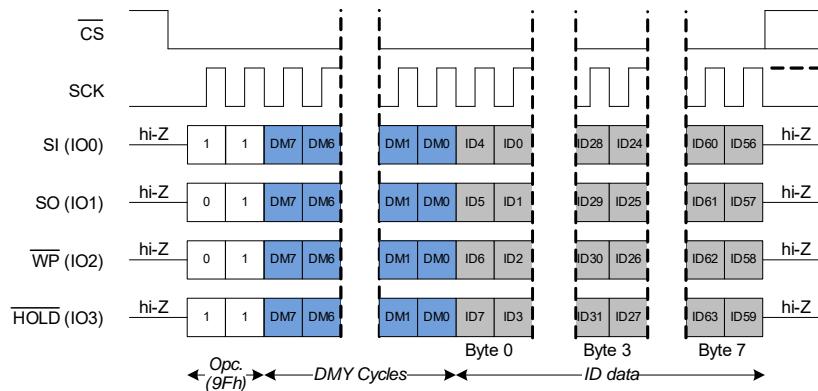

| RDID             | 9F            | 支持       | 不适用      |          |           | 支持        | 支持  | 支持   | 不适用 | 支持  | 不适用       | 不适用       |           |

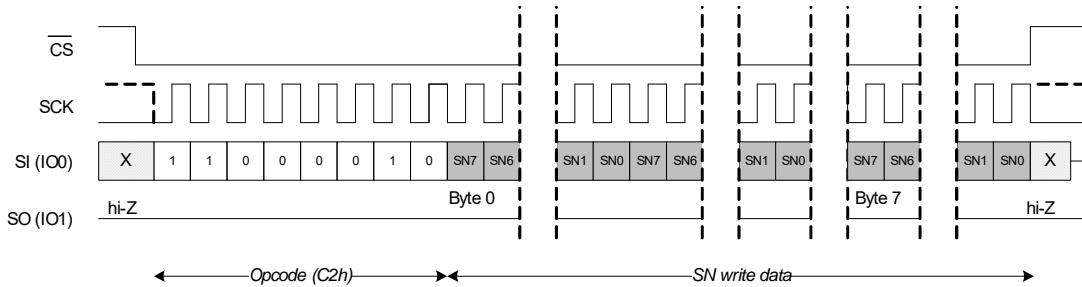

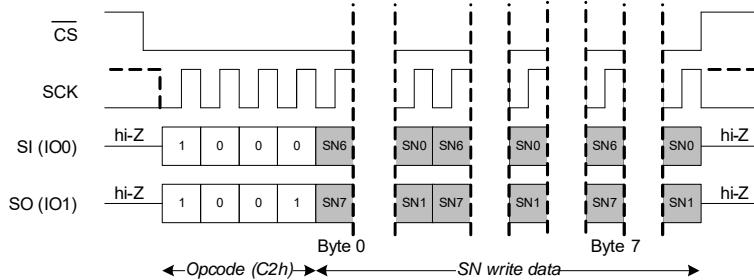

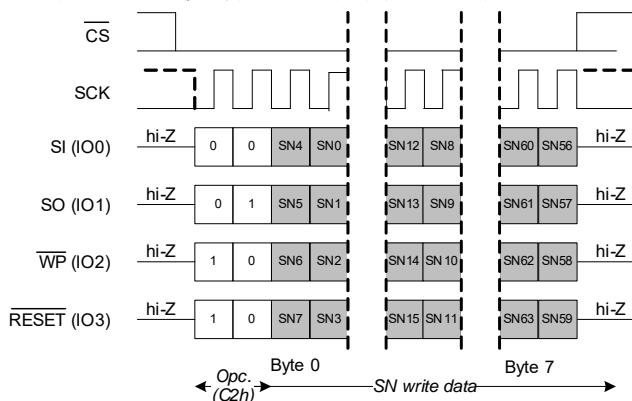

| WRSN             | C2            | 支持       | 不适用      |          |           | 支持        | 支持  | 支持   | 不适用 | 支持  | 不适用       | 不适用       |           |

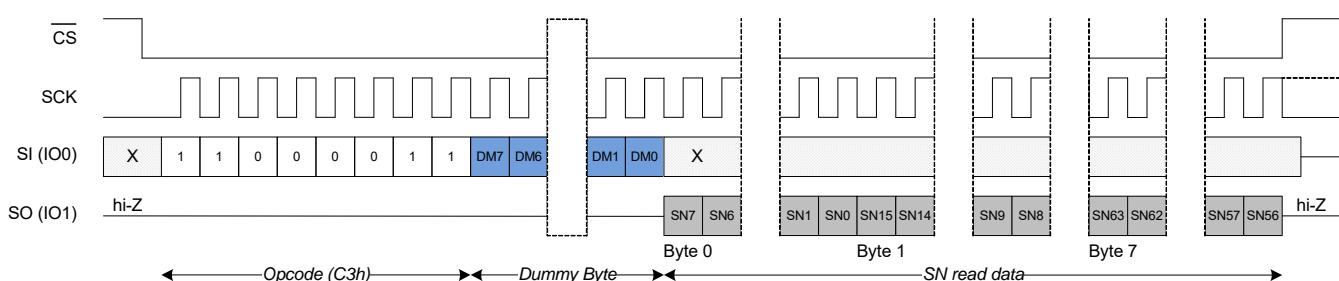

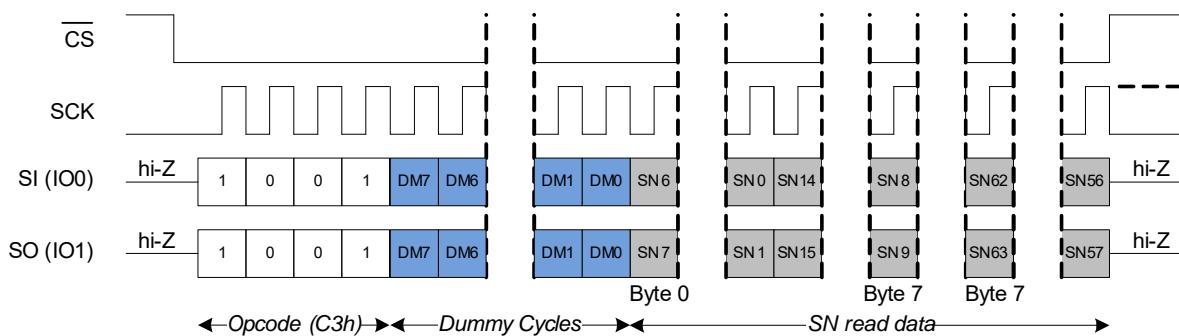

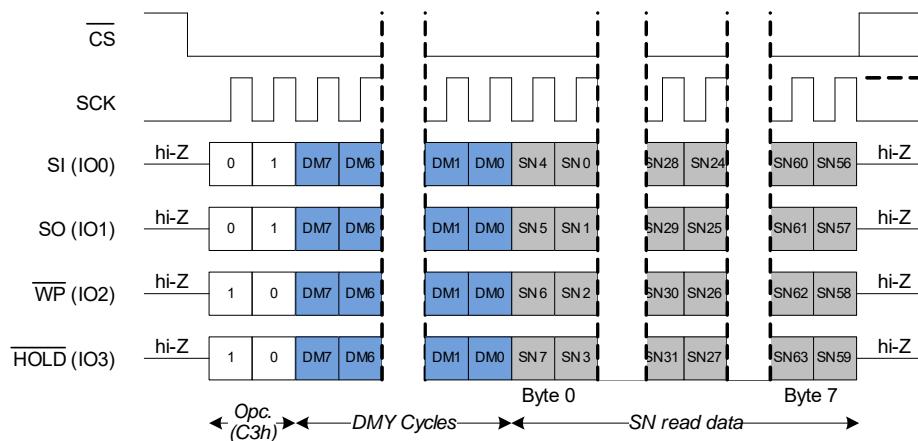

| RDSN             | C3            | 支持       | 不适用      |          |           | 支持        | 支持  | 支持   | 不适用 | 支持  | 不适用       | 不适用       |           |

| <b>功耗模式和复位</b>   |               |          |          |          |           |           |     |      |     |     |           |           |           |

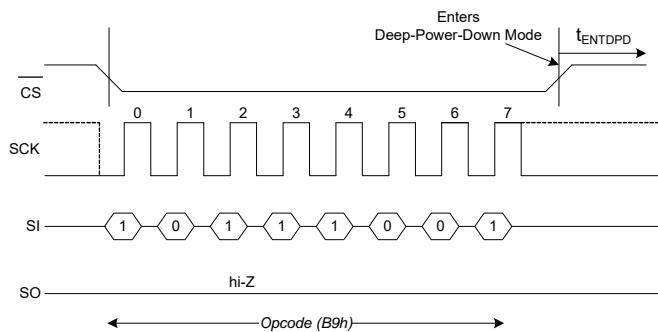

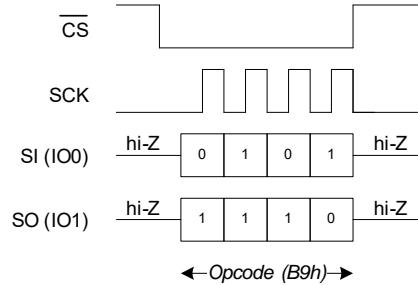

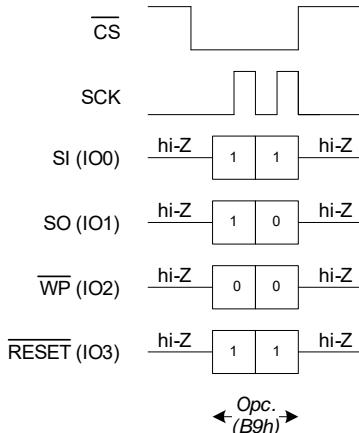

| DPD              | B9            | 支持       | 不适用      |          |           | 支持        | 支持  | 支持   | 不适用 | 不适用 | 不适用       | 不适用       |           |

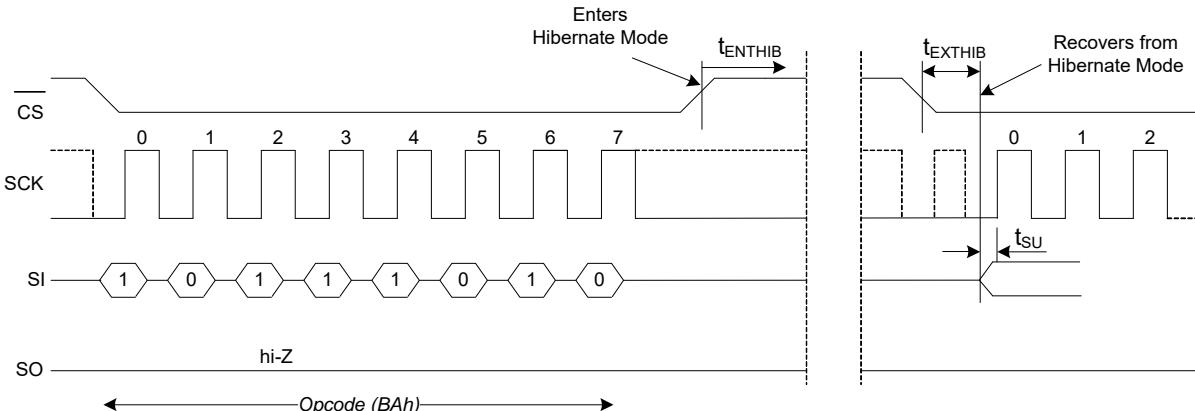

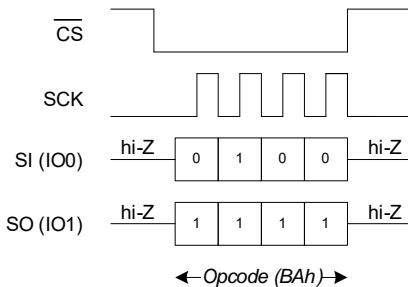

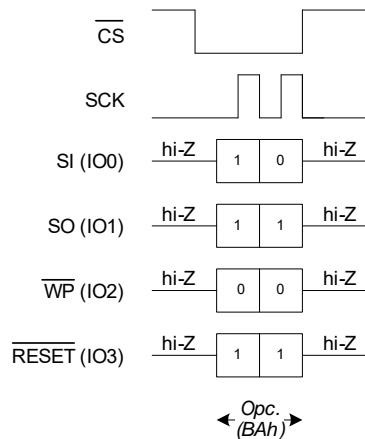

| HBN              | BA            | 支持       | 不适用      |          |           | 支持        | 支持  | 支持   | 不适用 | 不适用 | 不适用       | 不适用       |           |

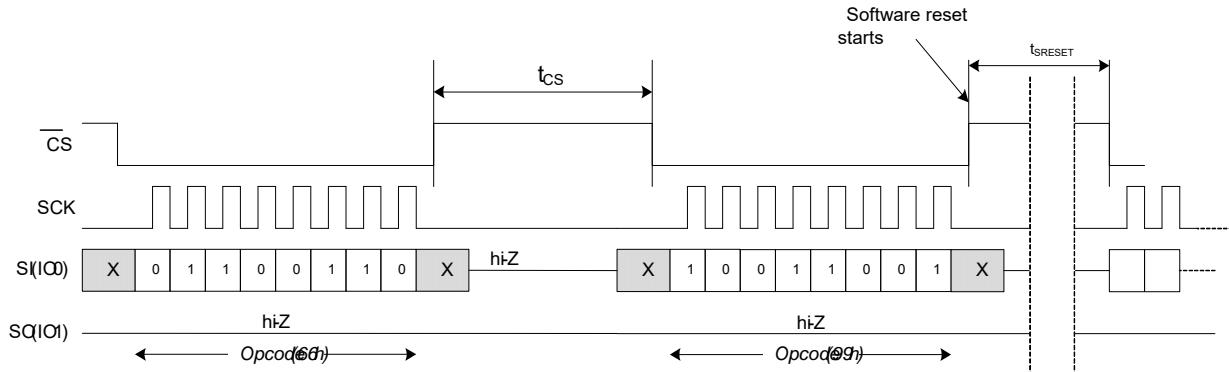

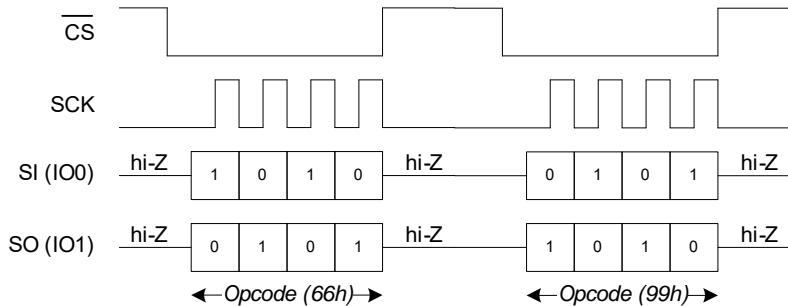

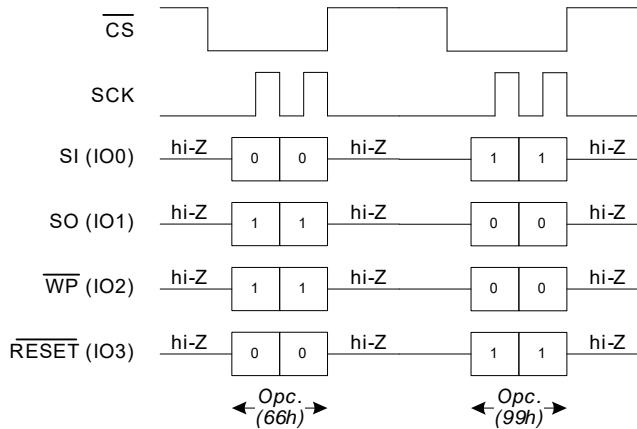

| RSTEN            | 66            | 支持       | 不适用      |          |           | 支持        | 支持  | 支持   | 不适用 | 不适用 | 不适用       | 不适用       |           |

| RST              | 99            | 支持       | 不适用      |          |           | 支持        | 支持  | 支持   | 不适用 | 不适用 | 不适用       | 不适用       |           |

### 写入使能控制命令

这些命令设置或清除状态寄存器 1 中的写入使能锁存位 (SR1[1])。

**表 32. 写入使能控制命令**

| 命令   | 操作码<br>(十六进制) | 命令说明                          |

|------|---------------|-------------------------------|

| WREN | 06            | 写入使能 — 设置状态寄存器 1 的 WEL 位为 ‘1’ |

| WRDI | 04            | 写入禁用 — 设置状态寄存器 1 的 WEL 位为 ‘0’ |

**表 33. 写入使能控制命令的详情**

| 操作码<br>(十六进制) | 地址长度 | SPI 总线接口 |          |          |           |           |     | 数据传输 |     | XIP | 延迟    | 最大时钟<br>频率 |         |

|---------------|------|----------|----------|----------|-----------|-----------|-----|------|-----|-----|-------|------------|---------|

|               |      | SPI      | 双线<br>数据 | 四线<br>数据 | 双线<br>I/O | 四线<br>I/O | DPI | QPI  | SDR | DDR | 芯片内执行 | 虚拟周期       |         |

| 06            | 0    | 支持       | 不适用      |          |           | 支持        | 支持  | 支持   | 不适用 | 不适用 | 不适用   | 不适用        | 108 MHz |

| 04            | 0    | 支持       | 不适用      |          |           | 支持        | 支持  | 支持   | 不适用 | 不适用 | 不适用   | 不适用        | 108 MHz |

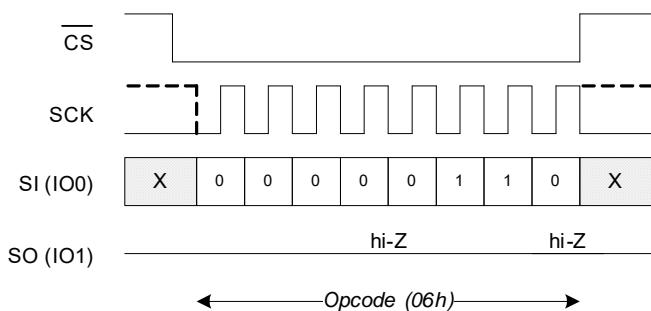

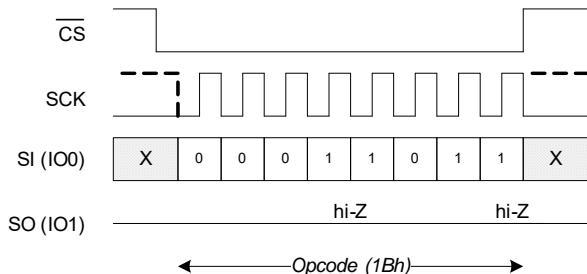

### 设置写入使能锁存 (WREN, 06h)

WREN 命令将状态寄存器 1 中的 WEL 位 (SR1[1]) 置 ‘1’。在发出任何写入命令之前, CY15x104QSN 要求 WEL 位被置 ‘1’。在执行之前, 要求将 WEL 设置为 ‘1’ 的 CY15x104QSN 命令包括: WRSR、WRAR、WRITE、FAST\_WRITE、DIW、DIOW、QIW、QIOW、DDR\_FAST\_WRITE、DDRWWRITE、DDRQIOW、SSWR 和 WRSN。

指令字节的第 8 位通过 SI 锁存在芯片内之后, 必须将  $\overline{CS}$  信号驱动为逻辑高电平状态。在 8 位 WREN 操作码成功锁存后, 接着  $\overline{CS}$  被驱动为高电平后, CY15x104QSN 将执行 WREN 命令并将 WEL 位 (SR1 [1]) 置 1。

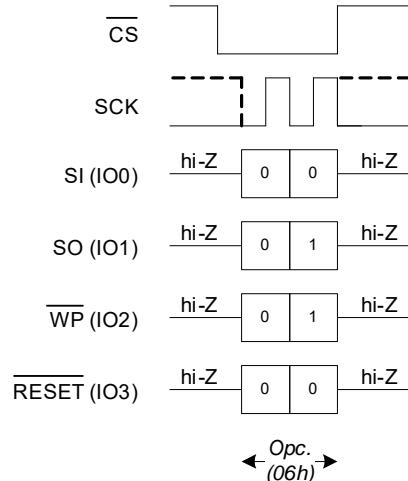

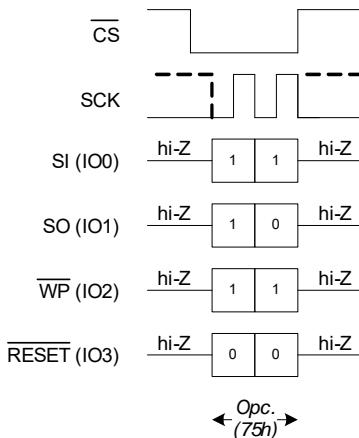

**图 7. SPI 模式下的 WREN 总线配置**

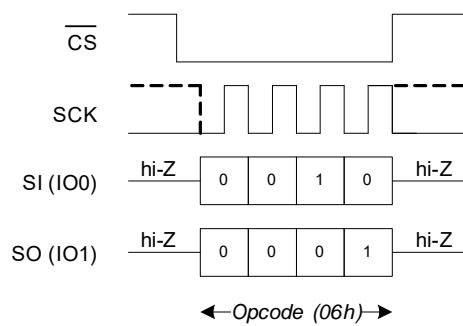

**图 8. DPI 模式下的 WREN 总线配置**

**图 9. QPI 模式下的 WREN 总线配置**

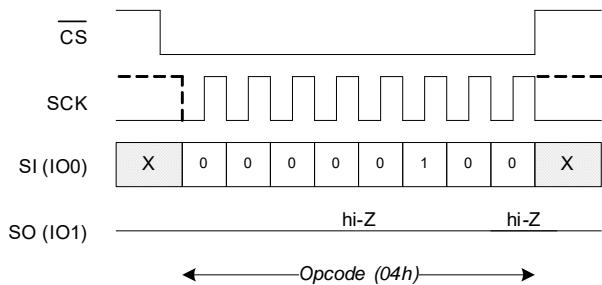

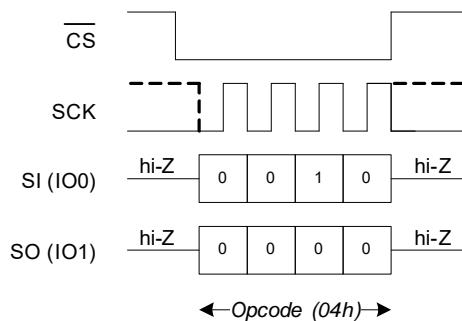

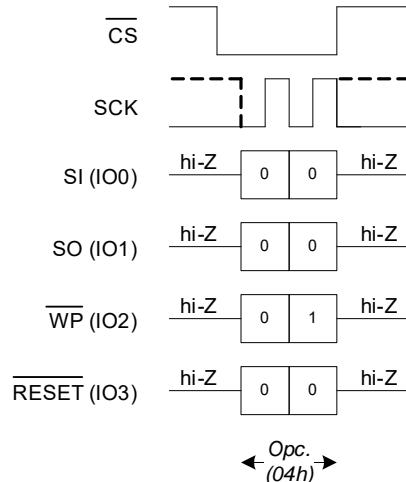

### 复位写入使能锁存 (WRDI, 04h)

WRDI 指令将状态寄存器 1(SR1[1]) 中的写入使能锁存 (WEL) 位清零。这样，在执行之前要求 WEL 被设置为“1”的写入状态寄存器 (WRSR)，写入任何寄存器 (WRAR)，特殊扇区写入 (SSWR) 以及其他指令都被禁用。WRDI 指令可用于保护存储器和 SPI 寄存器，避免对它们进行意外写入。WIP 位 = 1 时，WRDI 命令在执行嵌入式操作期间被忽略。

指令字节的第 8 位通过 SI 锁存在芯片内之后，必须将  $\overline{CS}$  信号驱动为逻辑高电平状态。在 8 位 WRDI 操作码成功锁存后，接着  $CS$  被驱动为高电平后，CY15x104QSN 将执行 WRDI 命令并将 WEL 位 (SR1 [1]) 清零。

图 10. SPI 模式下的 WRDI 总线配置

图 11. DPI 模式下的 WRDI 总线配置

图 12. QPI 模式下的 WRDI 总线配置

### 寄存器访问命令

CY15x104QSN 提供了各种配置和状态寄存器。它们都是用户可写寄存器，通过编程它们可以使能或禁用器件中的某些配置 / 功能，也可以通过轮询它们来了解器件的状态。这些寄存器由称为操作码的特定命令访问。

单个寄存器位可以是多种类型之一：写 / 读、只读或保留供将来使用（RFU）。在其各自的寄存器部分中指定每个位的具体类型。寄存器位可以是易失性的或非易失性的。所有易失性（V）位在上电复位（POR）或任何复位事件（通过硬件或软件复位）后都被设置为默认值；而所有非易失性（NV）位在上电复位（POR）或任何复位事件（通过硬件或软件复位）后都恢复到用户配置值。

**表 34. 寄存器访问命令**

| 命令    | 操作码<br>(十六进制) | 命令说明                                                  |

|-------|---------------|-------------------------------------------------------|

| WRSR  | 01            | 写状态寄存器 1                                              |

| RDSR1 | 05            | 读取状态寄存器 2                                             |

| RDSR2 | 07            | 读取状态寄存器 2                                             |

| RDCR1 | 35            | 读取配置寄存器 1                                             |

| RDCR2 | 3F            | 读取配置寄存器 2                                             |

| RDCR4 | 45            | 读取配置寄存器 4                                             |

| RDCR5 | 5E            | 读取配置寄存器 5                                             |

| WRAR  | 71            | 写入到任何寄存器 — 包括状态寄存器、配置寄存器和序列寄存器                        |

| RDAR  | 65            | 读取任何寄存器 — 包括状态寄存器、配置寄存器、CRC 寄存器、ECC 寄存器、序列存储器和 ID 寄存器 |

**表 35. 寄存器访问命令详情**

| 操作码<br>(十六进制) | 地址长度 | SPI 总线接口 |          |          |           |           |     | 数据传输 |     | 寄存器<br>延迟 | 最大时钟<br>频率 | 寄存器<br>延迟 |  |

|---------------|------|----------|----------|----------|-----------|-----------|-----|------|-----|-----------|------------|-----------|--|

|               |      | SPI      | 双线<br>数据 | 四线<br>数据 | 双线<br>I/O | 四线<br>I/O | DPI | QPI  | SDR | DDR       |            |           |  |

| 01            | 0    | 支持       | 不适用      |          |           | 支持        | 支持  | 支持   | 不适用 | 不适用       | 108 MHz    | NA        |  |

| 05            | 0    | 支持       | 不适用      |          |           | 支持        | 支持  | 支持   | 不适用 | 支持        | 108 MHz    | 支持        |  |

| 07            | 0    | 支持       | 不适用      |          |           | 支持        | 支持  | 支持   | 不适用 | 支持        | 108 MHz    | 支持        |  |

| 35            | 0    | 支持       | 不适用      |          |           | 支持        | 支持  | 支持   | 不适用 | 支持        | 108 MHz    | 支持        |  |

| 3F            | 0    | 支持       | 不适用      |          |           | 支持        | 支持  | 支持   | 不适用 | 支持        | 108 MHz    | 支持        |  |

| 45            | 0    | 支持       | 不适用      |          |           | 支持        | 支持  | 支持   | 不适用 | 支持        | 108 MHz    | 支持        |  |

| 5E            | 0    | 支持       | 不适用      |          |           | 支持        | 支持  | 支持   | 不适用 | 支持        | 108 MHz    | 支持        |  |

| 71            | 三个字节 | 支持       | 不适用      |          |           | 支持        | 支持  | 支持   | 不适用 | 不适用       | 108 MHz    | 不适用       |  |

| 65            | 三个字节 | 支持       | 不适用      |          |           | 支持        | 支持  | 支持   | 不适用 | 支持        | 108 MHz    | 支持        |  |

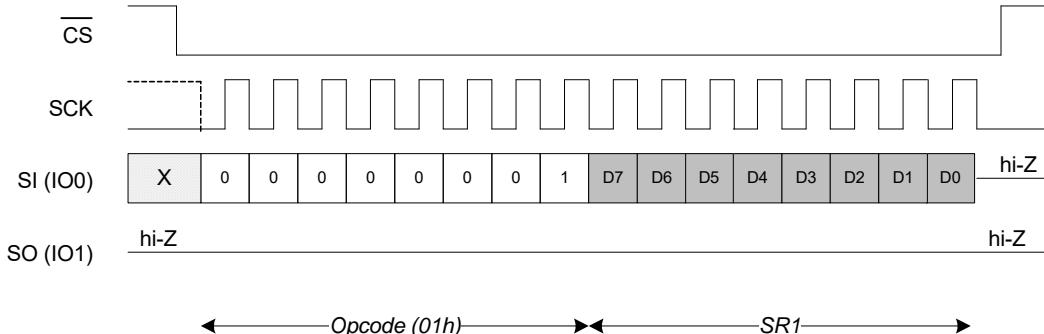

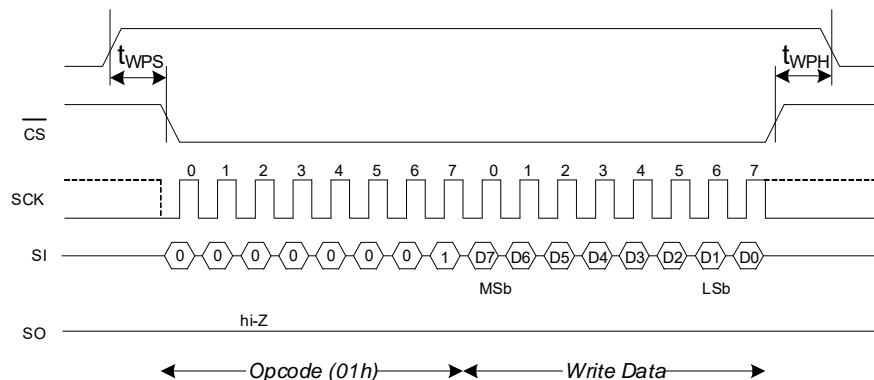

### 写状态寄存器 (WRSR, 01h)

写状态寄存器 (WRSR) 指令允许在状态寄存器 1 (SR1) 中编程新值。该指令写入非易失性 SR1，因此保持电源周期。当 SR1 寄存器中的 SRWD 位 (SR1[7]) 被设置为 “1”，并且 WP 引脚被确认为低电平时，WRSR 命令将被忽略。

### 注意:

- 仅当 SR1 中的 WEL 位被置为 “1” 时才能执行 WRSR 指令。否则，WRSR 指令将被忽略。

- 终止 WRSR 命令后（在  $\overline{\text{CS}}$  的上升沿上），状态寄存器 1 中的 WEL 位 (SR1[1]) 自动被清零。

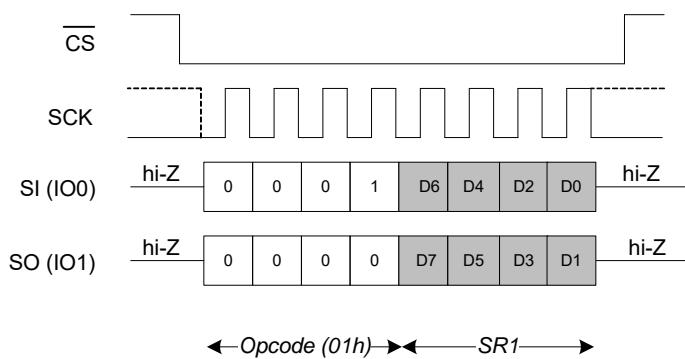

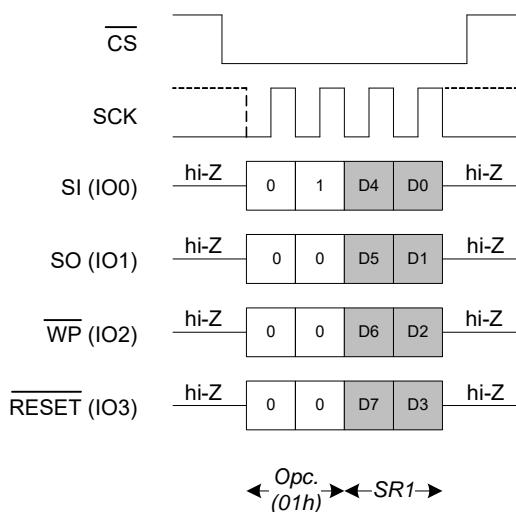

图 13. SPI 模式下的 WRSR (不显示 WREN)

图 14. DPI 模式下的 WRSR (不显示 WREN)

图 15. QPI 模式下的 WRSR (不显示 WREN)

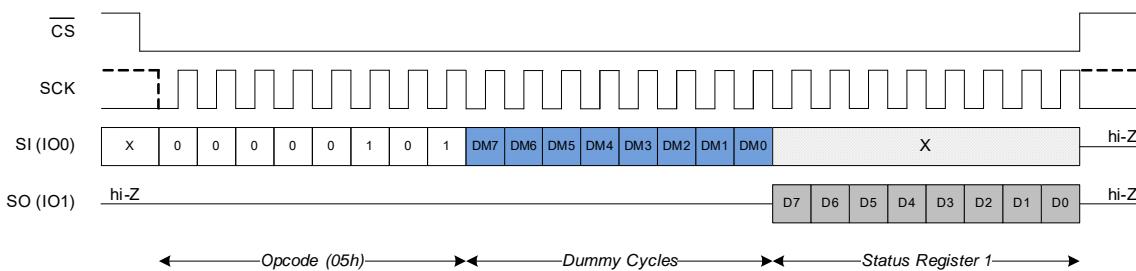

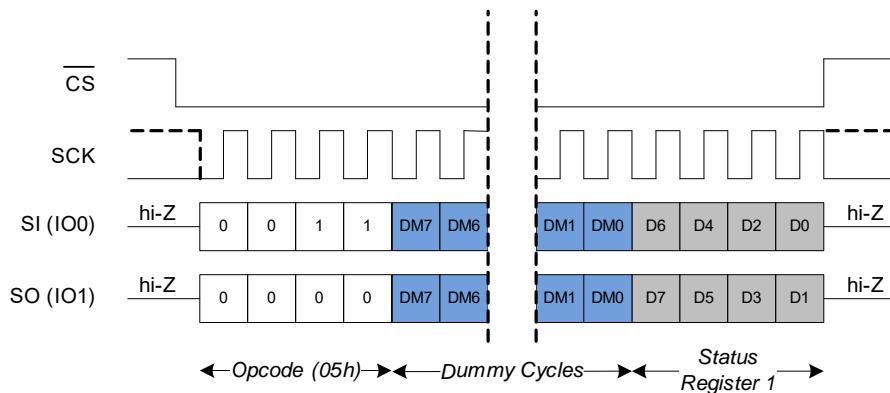

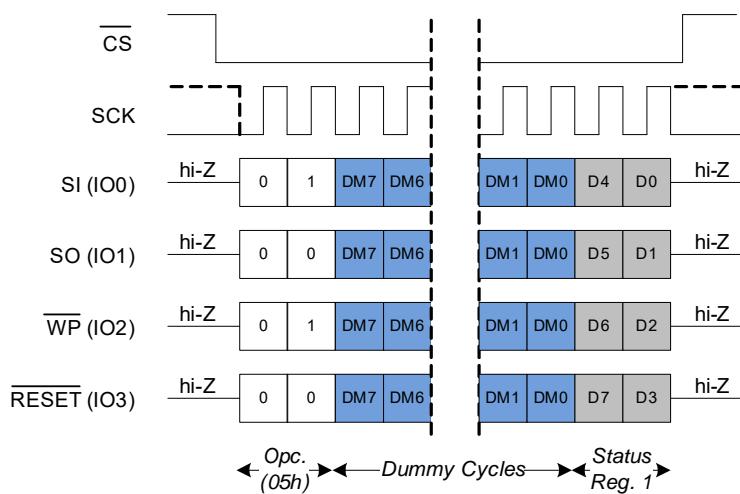

### 读取状态寄存器 1 (RDSR1, 05h)

通过使用 RDSR1 命令，总线主设备可以验证状态寄存器 1 (SR1) 中的内容。读取 SR1 后可以了解写保护特性的当前状态，WEL 和 WIP 的状态。执行 RDSR1 操作码后，CY15x104QSN 将返回一个字节的 SR1 内容。

**注意：**RDSR1 将返回 SR1 的易失性内容。

**注意：**所示的虚拟周期数可通过 CR5 中的寄存器延迟代码位 (RLC0、RLC1) 进行配置。

图 16. SPI 模式下的读取 SR1 (RDSR1)

图 17. DPI 模式下的读取 SR1 (RDSR1)

图 18. QPI 模式下的读取 SR1 (RDSR1)

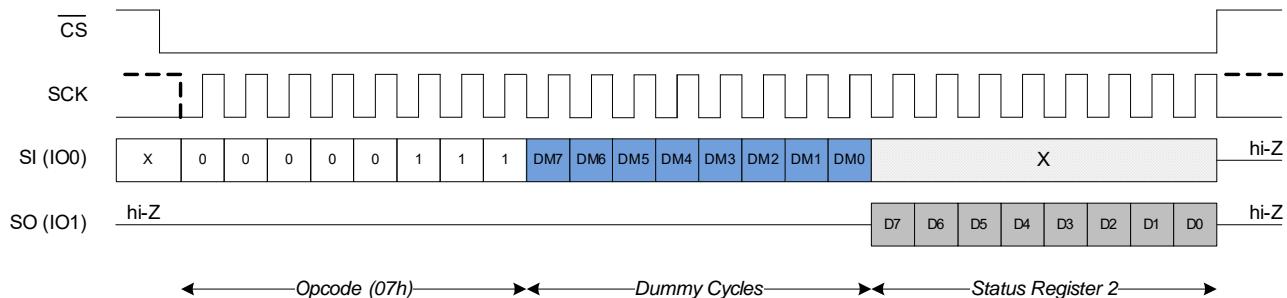

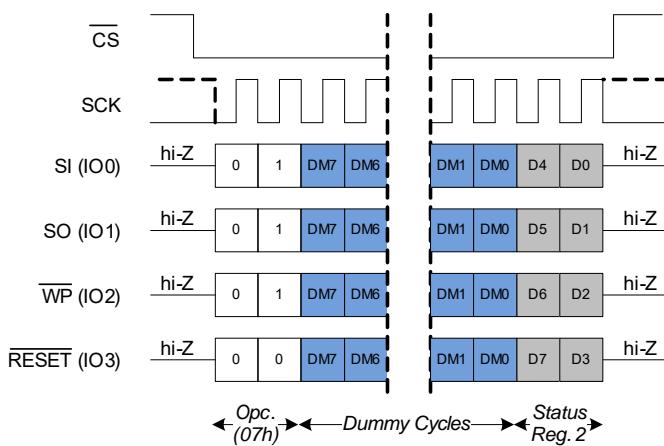

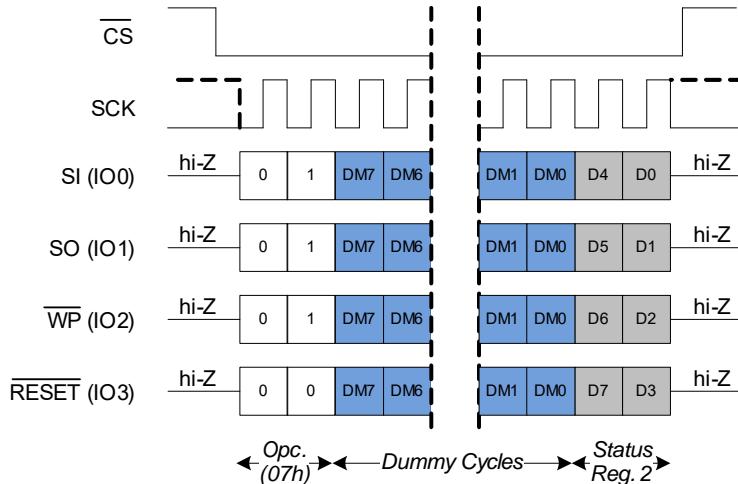

### 读取状态寄存器 2 (RDSR2, 07h)

通过使用 RDSR2 命令，总线主设备可以验证状态寄存器 2(SR2) 中的内容。这是一个只读寄存器，它提供了有关 CRC 挂起和 CRC 中止状态的信息。只有 SR1 的 WIP 位为“0”时，SR2 位才指示正确的状态 (CRCS 和 CRCA)。WIP 为“1”时读取 SR2 将返回未确定的状态。

**注意：**RDSR2 将返回 SR1 的易失性内容。

**注意：**所示的虚拟周期数可通过 CR5 中的寄存器延迟代码位 (RLC0、RLC1) 进行配置。

图 19. SPI 模式下的读取 SR2 (RDSR2)

图 20. DPI 模式下的读取 SR2 (RDSR2)

图 21. QPI 模式下的读取 SR2 (RDSR2)

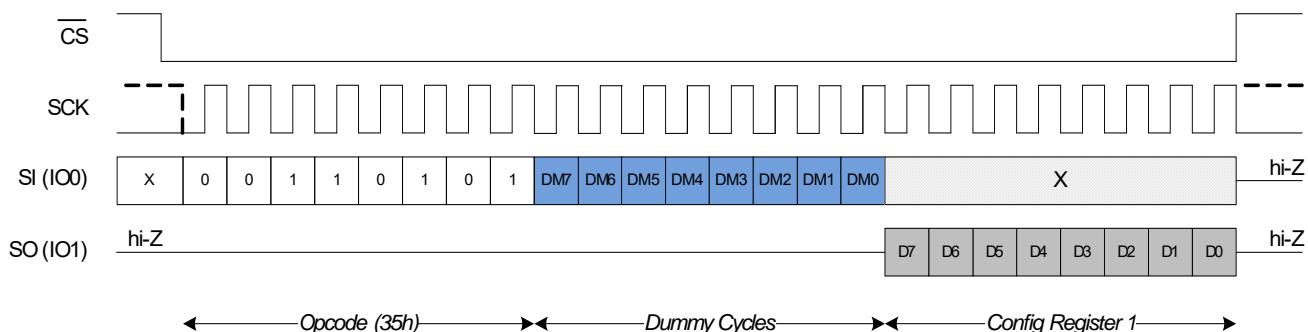

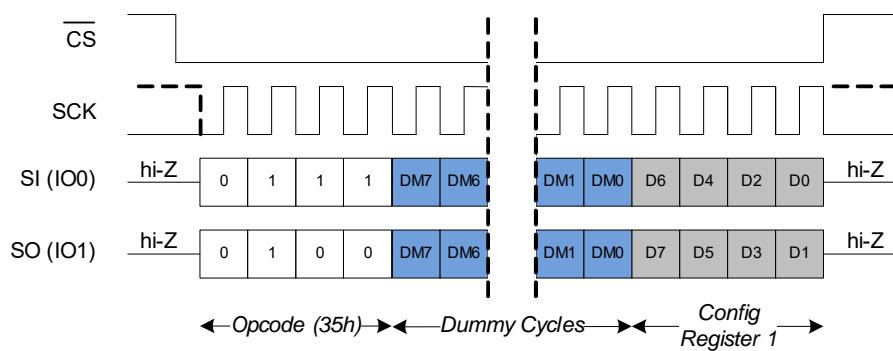

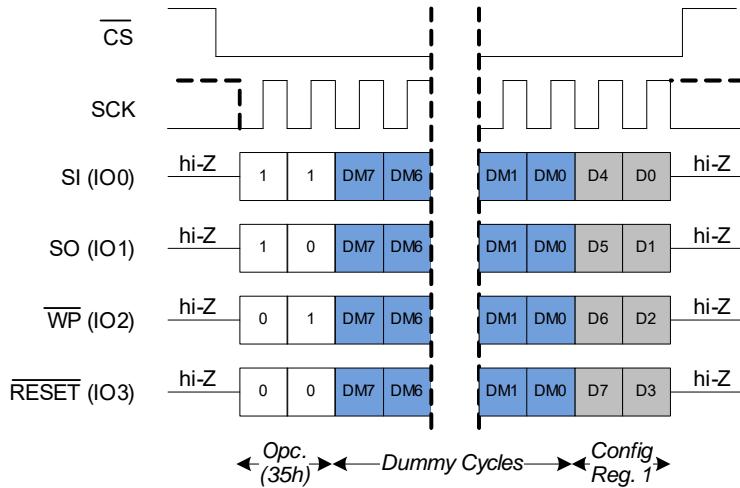

### 读取配置寄存器 1 (RDCR1, 35h)

通过使用 RDCR1 命令，总线主设备可以验证配置寄存器 1(CR1)中的内容。通过读取 CR1，可以了解有关存储器延迟代码的当前状态和 QUAD 位的状态等信息。执行 RDCR1 操作码后，CY15x104QSN 将返回一个字节的 CR1 内容。

### 注意：

- RDCR1 将返回 CR1 的易失性内容。

- 所示的虚拟周期是通过 CR5 中寄存器等待时间码位 (RLC0、RLC1) 配置的选项。

图 22. SPI 模式下的读取 CR1 (RDCR1)

图 23. DPI 模式下的读取 CR1 (RDCR1)

图 24. QPI 模式下的读取 CR1 (RDCR1)

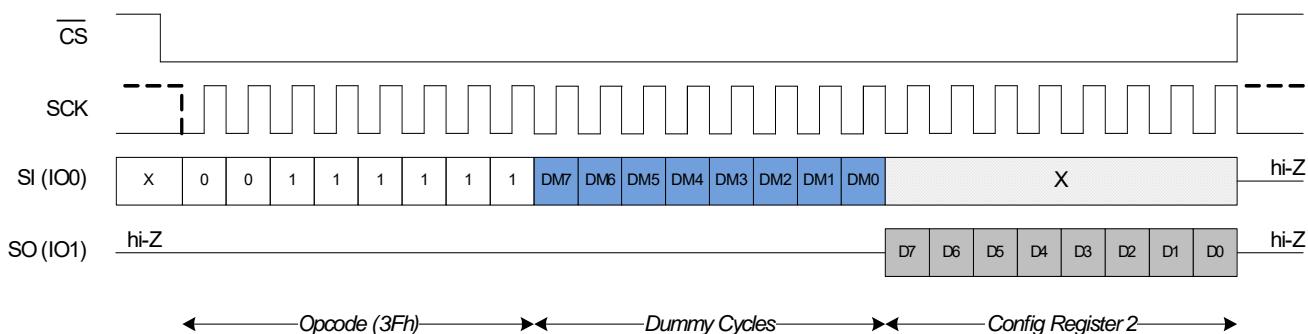

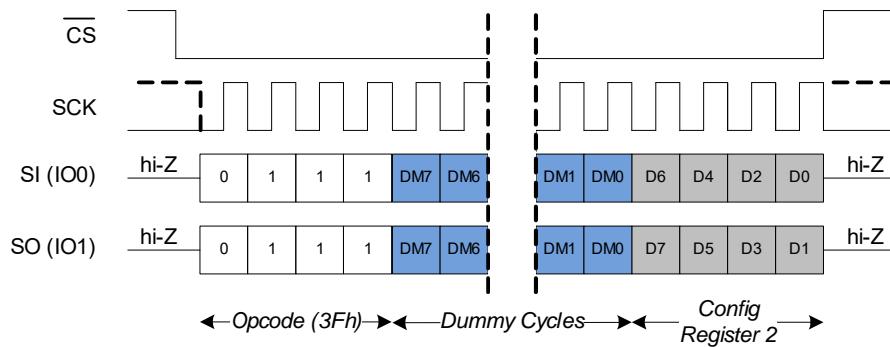

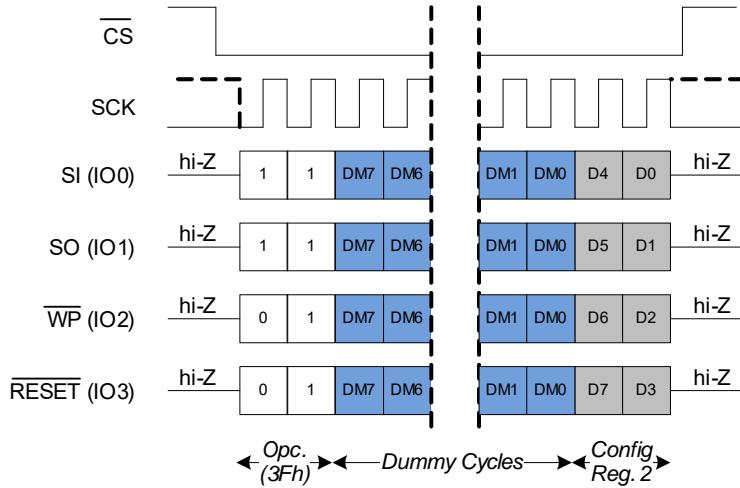

### 读取配置寄存器 2 (RDCR2, 3Fh)

通过使用 RDCR2 命令，总线主设备可以验证配置寄存器 2(CR2)中的内容。通过读取 CR2，可以了解当前 SPI 接口的选项 (SPI、DPI、QPI) 和 RESET/(I/O3) 的状态。执行 RDCR2 操作码后，CY15x104QSN 将返回一个字节的 CR2 内容。

### 注意：

- RDCR2 将返回 CR2 的易失性内容。

- 所示的虚拟周期是通过 CR5 中寄存器等待时间码位 (RLC0、RLC1) 配置的选项。

图 25. SPI 模式下的读取 CR2 (RDCR2)

图 26. DPI 模式下的读取 CR2 (RDCR2)

图 27. QPI 模式下的读取 CR2 (RDCR2)

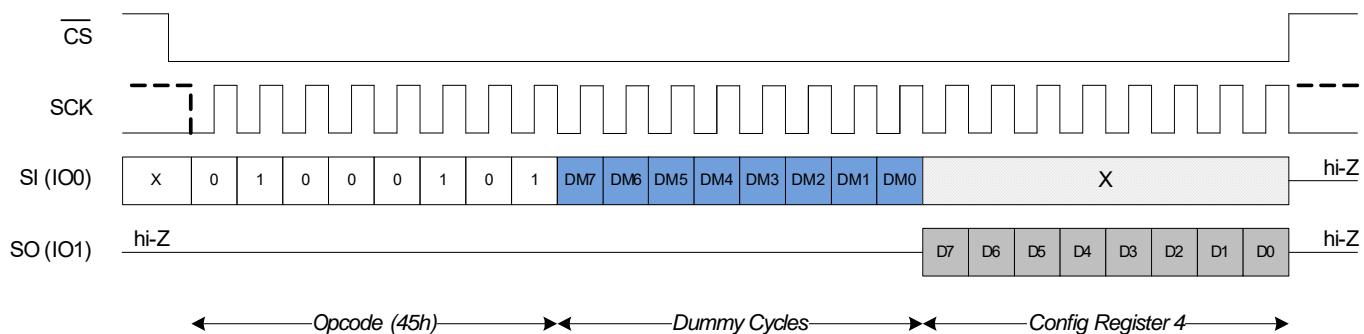

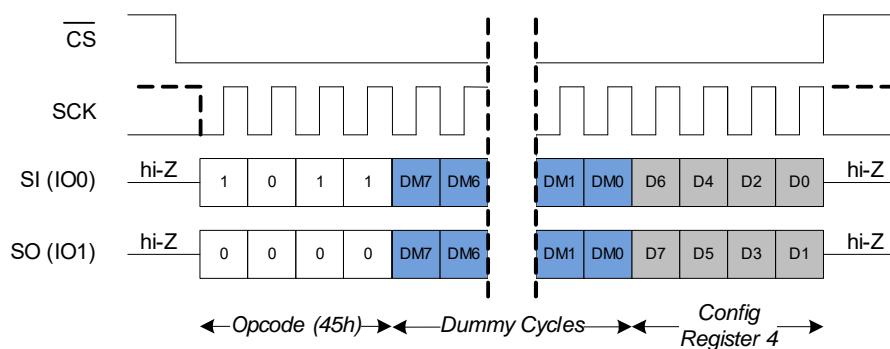

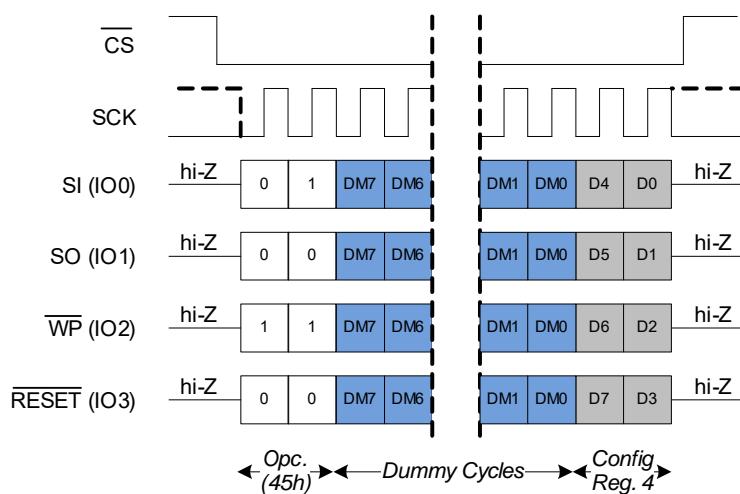

### 读取配置寄存器 4 (RDCR4, 45h)

通过使用 RDCR4 命令，总线主设备可以验证配置寄存器 4(CR4)中的内容。通过读取 CR4，可以了解输出阻抗的设置和 POR 后的器件电源模式（深度掉电或待机）。执行 RDCR4 操作码后，CY15x104QSN 将返回一个字节的 CR4 内容。

### 注意：

- RDCR4 将返回 CR4 的易失性内容。

- 所示的虚拟周期是通过 CR5 中寄存器等待时间码位 (RLC0、RLC1) 配置的选项。

图 28. SPI 模式下的读取 CR4 (RDCR4)

图 29. DPI 模式下的读取 CR4 (RDCR4)

图 30. QPI 模式下的读取 CR4 (RDCR4)

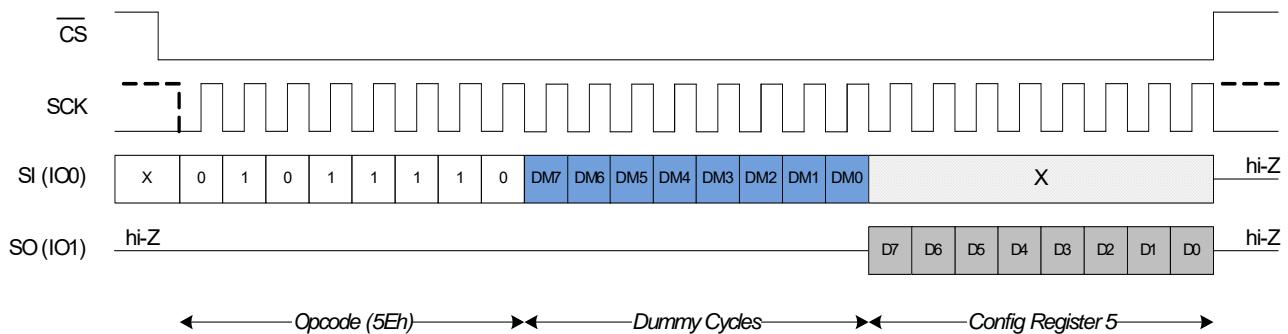

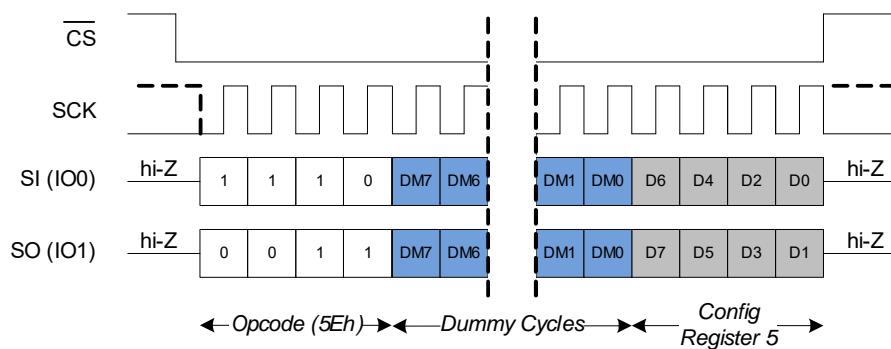

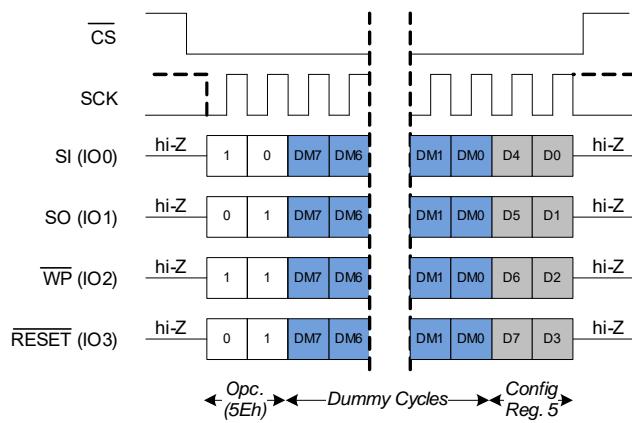

### 读取配置寄存器 5 (RDCR5, 5Eh)

通过使用 RDCR5 命令，总线主设备可以验证配置寄存器 5(CR5)中的内容。通过读取CR5，可以了解寄存器读取延迟周期 (RLC0、RLC1) 的设置。执行 RDCR5 操作码后，CY15x104QSN 将返回一个字节的 CR5 内容。

### 注意：

- RDCR5 将返回 CR5 的易失性内容。

- 所示的虚拟周期是通过 CR5 中寄存器等待时间码位 (RLC0、RLC1) 配置的选项。

图 31. SPI 模式下的读取 CR5 (RDCR5)

图 32. DPI 模式下的读取 CR5 (RDCR5)

图 33. QPI 模式下的读取 CR5(RDCR5)

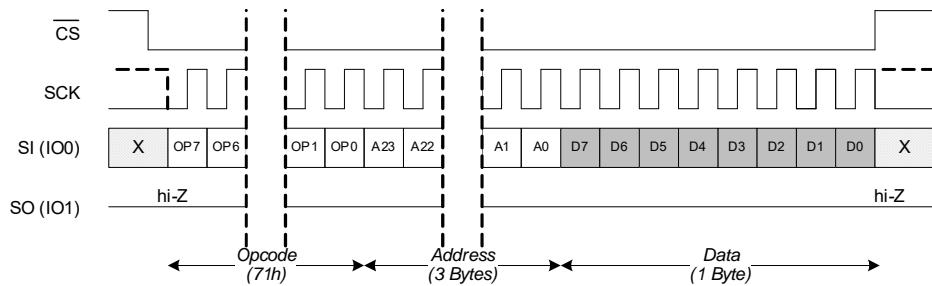

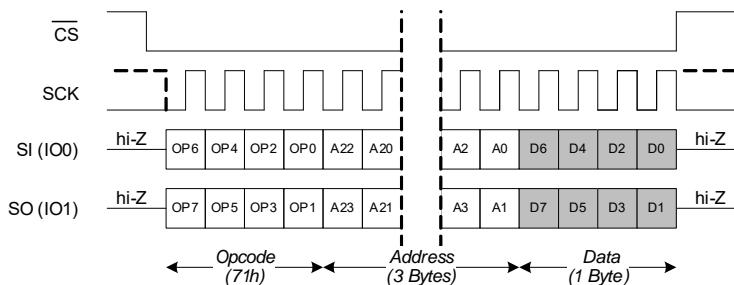

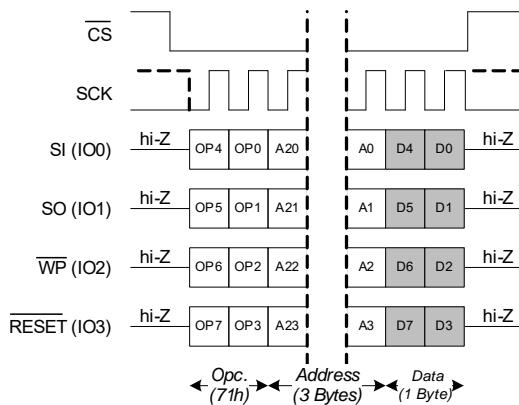

### 写入任何寄存器 (WRAR, 71h)

通过 WRAR 命令，可以对各个 CY15x104QSN 寄存器进行写操作，每次只能写入一个寄存器，并通过其各自 3 字节地址进行寻址。WRAR 操作码后面是该寄存器的 3 字节地址，如第 36 页上的表 37 中所示，然后是写入的 1 字节寄存器数据。执行 WRAR 之前，WREN 命令会先将 WEL 位置 ‘1’。WRAR 命令终止后（即在 CS 的上升沿上），WEL 位将被自动清除为 ‘1’。当 SR1 寄存器中的 SRWD 位 (SR1[7]) 被设置为 ‘1’，并且 WP 引脚被驱动为低电平时，WRAR 命令将被忽略。

表 36. 存储器的通用写指令

| 指令名称 | 指令说明    | 操作码 | 地址字节 | 数据字节 |

|------|---------|-----|------|------|

| WRAR | 写入任何寄存器 | 71h | 3    | 1    |

### 注意：

- 每次发送 WRAR 命令，仅支持将其 1 字节对已给的寄存器地址进行写操作。WRAR 命令的格式如表 36 所示。

- 进行 WRAR 操作码后在 3 字节地址字段中发送的寄存器地址确定了新配置是否仅被编程到易失性状态 / 配置寄存器中，还是都被编程到易失性和非易失性状态 / 配置寄存器中。第 36 页上的表 37 显示了易失性和非易失性寄存器的寄存器地址。

图 34. SPI 模式下的写入任何寄存器 (WRAR)

图 35. DPI 模式下的写入任何寄存器 (WRAR)

图 36. QPI 模式下的写入任何寄存器 (WRAR)

表 37. 通用存储器访问的存储器地址

| 功能     | 寄存器类型               | 状态寄存器内容 <sup>[14]</sup> | WRAR | RDAR <sup>[14]</sup> | 寄存器地址 <sup>[13]</sup> |          |

|--------|---------------------|-------------------------|------|----------------------|-----------------------|----------|

|        |                     |                         |      |                      | 易失性                   | 非易失性     |

| 器件状态   | 状态寄存器 1             | 易失性和非易失性                | 支持   | 支持                   | 0x070000              | 0x000000 |

|        | 状态寄存器 2             | 仅适用于易失性寄存器              | 不适用  |                      | 0x070001 或 0x000001   |          |

| 器件配置   | 配置寄存器 1             | 易失性和非易失性                | 支持   | 支持                   | 0x070002              | 0x000002 |

|        | 配置寄存器 2             |                         |      |                      | 0x070003              | 0x000003 |

|        | 配置寄存器 4             |                         |      |                      | 0x070005              | 0x000005 |

|        | 配置寄存器 5             |                         |      |                      | 0x070006              | 0x000006 |

| 错误修正   | ECC 状态寄存器           | 仅适用于易失性寄存器              | 不适用  | 支持                   | 0x070089 或 0x000089   |          |

|        | ECC 计数寄存器 [7:0]     |                         |      |                      | 0x07008A 或 0x00008A   |          |

|        | ECC 计数寄存器 [15:8]    |                         |      |                      | 0x07008B 或 0x00008B   |          |

|        | ECC 地址陷阱寄存器 [7:0]   |                         |      |                      | 0x07008E 或 0x00008E   |          |

|        | ECC 地址陷阱寄存器 [15:8]  |                         |      |                      | 0x07008F 或 0x00008F   |          |

|        | ECC 地址陷阱寄存器 [23:16] |                         |      |                      | 0x070040 或 0x000040   |          |

|        | ECC 地址陷阱寄存器 [31:24] |                         |      |                      | 0x070041 或 0x000041   |          |

| 循环冗余校验 | CRC 寄存器 [7:0]       |                         |      |                      | 0x070095 或 0x000095   |          |

|        | CRC 寄存器 [15:8]      |                         |      |                      | 0x070096 或 0x000096   |          |

|        | CRC 寄存器 [23:16]     |                         |      |                      | 0x070097 或 0x000097   |          |

|        | CRC 寄存器 [31:24]     |                         |      |                      | 0x070098 或 0x000098   |          |

**注释：**

13. 发生 POR 或硬件复位后，易失性寄存器将返回其默认状态。有关 POR 或任何复位事件后的易失性寄存器状态，请查阅第 76 页上的表 58。

14. RDAR 命令将始终返回易失性寄存器内容。因此，随后易失性寄存器地址或非易失性寄存器地址的 RDAR 命令将返回相同的值（仅从相应的易失性寄存器）。仅易失性寄存器没有相关的非易失性寄存器。

### 读取任何寄存器 (RDAR, 65h)

通过 RDAR 命令，可以对各个 CY15x104QSN 寄存器进行读取操作，每次只能写入一个寄存器，并通过其各自 3 字节地址进行寻址。RDAR 操作码后面是 3 字节地址和虚拟周期（该周期数量取决于 CR5 中所设置的延迟值），然后 CY15x104QSN 将在其输出总线上返回寄存器的一字节。当接收到一个寄存器字节后，主机会通过将 CS 上拉为高电平来终止 RDAR 命令。接收到第一个数据字节后保持 CS 为低电平会返回未定义的数据。RDAR 命令的时序图如图 37 至图 39 所示。

### 注意

- 由于状态寄存器和配置寄存器始终返回其易失性空间的寄存器内容，因此 WRAR 操作吗随后的 3 字节地址可以是易失性寄存器或其相关的非易失性寄存器的寄存器地址。

第 36 页上的表 37 显示了易失性和非易失性寄存器的寄存器地址。

- 所示的虚拟周期是通过 CR5 中寄存器等待时间码位 (RLC0、RLC1) 配置的选项。

图 37. SPI 模式下的读取任何寄存器 (RDAR)

图 38. DPI 模式下的读取任何寄存器 (RDAR)

图 39. QPI 模式下的读取任何寄存器 (RDAR)

### 存储器操作

可接受高时钟频率的 SPI 接口突出显示了 F-RAM 技术的快速写入功能。与串行 Flash 不同的是，CY15x104QSN 能以总线速度执行连续写操作。无需任何页寄存器，仍能够执行多个连续写操作。

### 存储器写操作指令

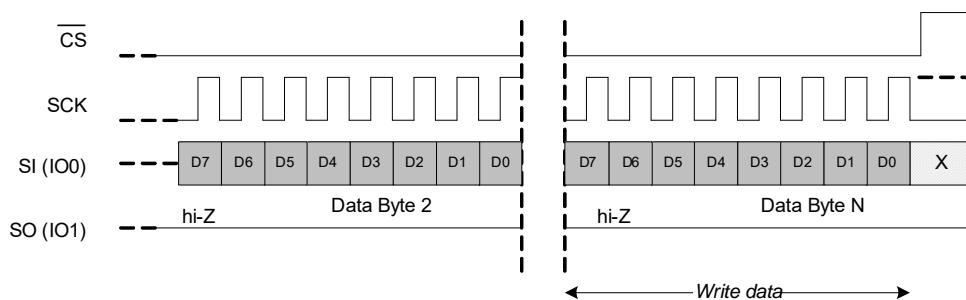

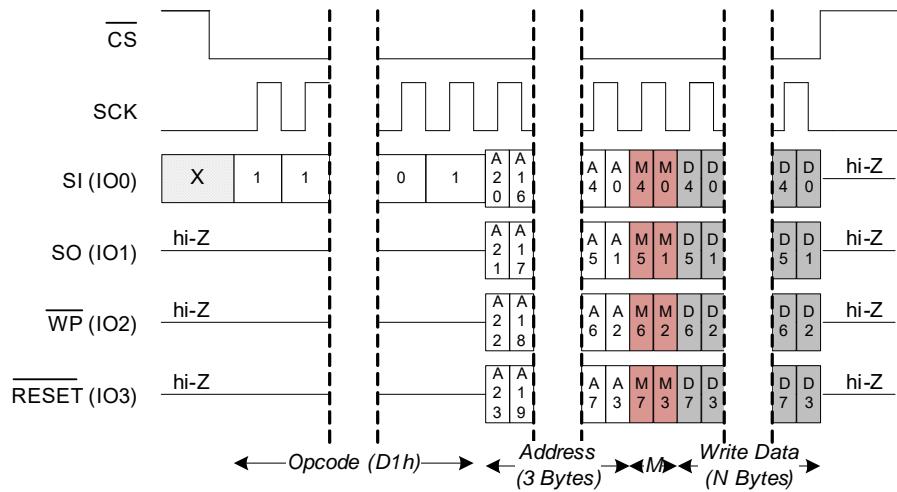

CS 引脚被下拉为低电平后会发送存储器写操作命令。写入操作码后面是一个 3 字节地址和 XIP 的模式字节（若有）。针对每 4 Mbit（512K × 8）的密度，CY15x104QSN 都会有一个 19 位地址空间。最高有效地址字节包括 3 个有效 A16、A17 和 A18，其余的位 A[23:19] 可被忽略。传送（XIP）模式字节（若器件支持 XIP 模式）后，各个地址位 A18 ~ A0 会以 3 字节为一组在 SPI 总线上进行传输。最后地址位或最后模式位（若支持 XIP）被传送后，将

立即通过输入线传送数据字节（[D7:0]）。在 SDR 和 DDR 总线接口的 SPI、扩展式 SPI、DPI 或 QPI 模式下支持存储器写操作。其中，一些模式支持芯片内执行（XIP）。表 38 显示了在各种不同的 SPI 总线接口和数据传输的模式下 CY15x104QSN 所支持的存储器写命令列表。

#### 注意：

- 当突发写入达到受保护的块地址时，它仍会在受保护空间内保持地址递增，但是不将任何数据写入到受保护的存储器内。如果地址翻转并进行突发写入到不受保护的空间，则可恢复写入操作。如果在写入保护的块中启动了突发写入，将执行同一操作。

- 在写操作过程中，如果传输数据字节时被断电，则只有最后完成的字节被写入。

表 38. 存储器写命令

| 命令             | 操作码<br>(十六进制) | 命令说明                                                                                          |

|----------------|---------------|-----------------------------------------------------------------------------------------------|

| WRITE          | 02            | 存储器写入 — 写入到 F-RAM 阵列                                                                          |

| DDRWRITE       | DE            | DDR 写入 — QPI DDR 模式下的写操作                                                                      |

| FAST_WRITE     | DA            | 存储器快速写入 — “芯片内执行” 模式下的存储器写操作                                                                  |

| DDR_FAST_WRITE | DD            | DDR 快速写入 — DDR 模式下的快速写操作                                                                      |

| DIW            | A2            | 双线输入写入 — 命令、地址和模式字节在单个 SI 线上被传输，而数据字节在双线输入 I/O1 (SO)、I/O0 (SI) 上被传输                           |

| DIOW           | A1            | DDR 双线 I/O 写入 — 命令在单个 SI 线上被传输，而地址、模式和数据字节在双线输入 I/O1 (SO)、I/O0 (SI) 上被传输                      |