# 2M ビット EXCELON™ Ultra 強誘電体 RAM (F-RAM)

シリアル( クアッド SPI), 256K × 8, 108 MHz, 産業用

## 特長

- 256K × 8 に論理構成された 2M ビット強誘電体 RAM (F-RAM)

- 100 兆回 ( $10^{14}$ ) の読み出し / 書き込みサイクルの無限の耐久性

- 151 年のデータ保持 ( [データ保持期間とアクセス可能回数を参照](#) )

- Infineon インスタンスト不揮発性書き込み技術

- 先端の高信頼性強誘電体プロセス

- シングルおよびマルチ I/O SPI

- シリアルバスインターフェース SPI プロトコル

- すべての SDR モード転送で SPI モード 0 (0, 0) およびモード 3 (1, 1) をサポート

- すべての DDR モード転送で SPI モード 0 (0, 0) をサポート

- 拡張 I/O SPI プロトコル

- デュアル SPI (DPI) プロトコル

- クアッド SPI (QPI) プロトコル

- SPI クロック周波数

- 最大 108 MHz の周波数 SPI SDR

- 最大 54 MHz の周波数 SPI DDR

- メモリの読み出し / 書き込み用のインプレース実行 (XIP)

- 書き込み保護、データセキュリティ、およびデータ整合性

- 書き込み保護 ( $\overline{WP}$ ) ピンを使用したハードウェアによる保護

- ソフトウェアブロック保護

- データの整合性を強化するための組込み ECC および CRC

- ECC は、1 ビットエラーを検出して修正します。2 ビットエラーが発生した場合、修正されませんが、ECC ステータス レジスタを介して報告されます

- CRC は、生データへの偶発的な変更を検出します

- 拡張電子署名

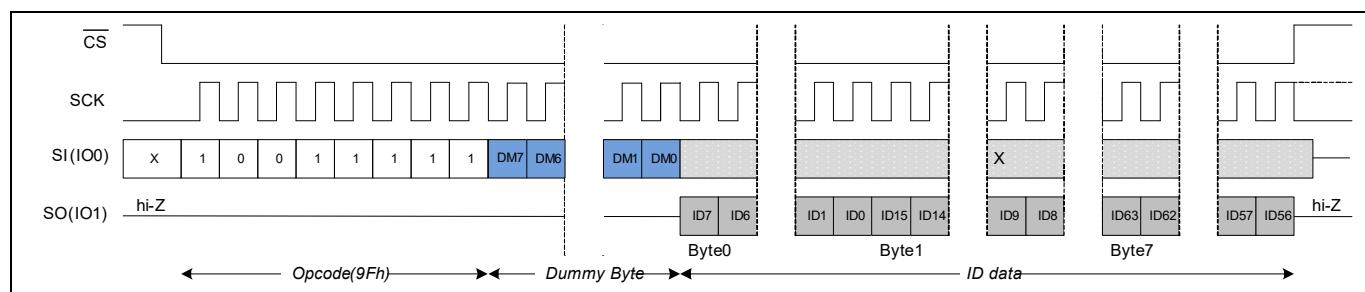

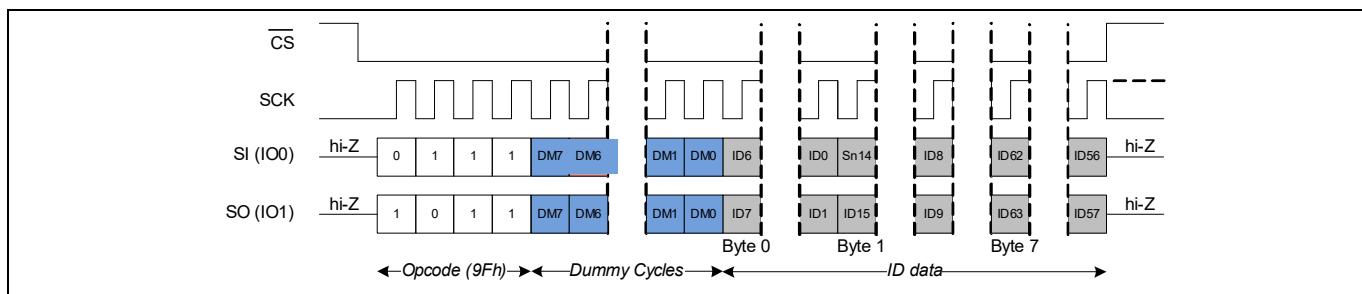

- メーカー ID および製品 ID を含むデバイス ID

- 固有 ID

- ユーザーがプログラム可能なシリアル番号

- 専用 256 バイト特殊セクタ F-RAM

- 専用特殊セクタの書き込みと読み出し

- コンテンツは最大 3 回の標準リフローサイクルに耐え得る

- 高速での低消費電力

- 108 MHz SPI SDR の 10 mA (Typ) アクティブ電流

- 108 MHz QSPI SDR および 54 MHz QSPI DDR の 16 mA (Typ) アクティブ電流

- 110  $\mu$ A (Typ) のスタンバイ電流

- 0.80  $\mu$ A (Typ) のディープパワーダウンモード電流

- 0.1  $\mu$ A (Typ) のハイバネートモード電流

- 低電圧動作 :

- CY15V102QSN:  $V_{DD} = 1.71 \text{ V} \sim 1.89 \text{ V}$

- CY15B102QSN:  $V_{DD} = 1.8 \text{ V} \sim 3.6 \text{ V}$

- 動作温度 : -40°C ~ +85°C

- 8 ピン小型集積回路 (SOIC) パッケージ

- RoHS 準拠

## 機能説明

EXCELON™ Ultra CY15X102QSN は高度な強誘電体プロセスを適用した低消費電力の 2M ビット不揮発性メモリです。強誘電体ランダムアクセスメモリまたは F-RAM は不揮発性であり、RAM と同様に読み出しと書き込みを実行します。シリアルフラッシュやその他の不揮発性メモリによって引き起こされる複雑さ、オーバーヘッド、およびシステムレベルの信頼性の問題を排除しながら、151 年間の信頼性の高いデータ保持を提供します。

シリアルフラッシュと違って、CY15X102QSN はバス速度で書き込み動作を実行します。書き込み遅延は発生しません。データは各バイトがデバイスに正常に転送された直後にメモリアレイに書き込まれます。次のバスサイクルはデータポーリングを必要とせず開始できます。また、本製品は他の不揮発性メモリと比べ多くの書き換え回数を提供しています。CY15X102QSN は、 $10^{14}$  回の読み出し / 書き込みサイクル、つまり EEPROM の 1 億倍の書き込みサイクルをサポートできます。これらの能力により、CY15X102QSN は頻繁で高速書き込みを必要とする不揮発性メモリの用途に理想的です。用途例は、書き込み回数を重視するデータ収集から、シリアルフラッシュを使った長い書き込み時間に起因してデータを損失する可能性がある厳しい工業用制御まで及びます。

CY15X102QSN は、2M ビットの F-RAM と、F-RAM テクノロジの不揮発性書き込み機能を強化する高速クアッド SPI (QPI) SDR および DDR インターフェースを組み合わせたものです。このデバイスには、読み出し専用のデバイス ID と一意の ID 機能が組み込まれているため、SPI バスマスターは、各部品のメーカー、メモリ容量、リビジョン、および固有 ID を判別できます。CY15X102QSN は読み出し専用の固有のシリアル番号を含みます。このシリアル番号を使用して、基板またはシステムを識別できます。

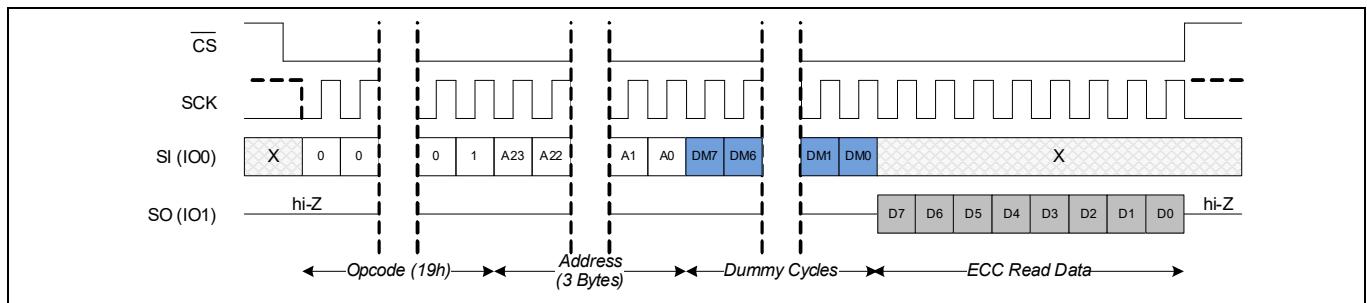

このデバイスは、8 バイト単位のデータごとに 1 ビットエラーを検出して修正できるオンダイ ECC ロジックをサポートしています。このデバイスは、8 バイト単位のデータで 2 ビットエラーを報告する機能も拡張しています。また、メモリアレイに格納されているデータのデータ整合性をチェックするために使用できる巡回冗長検査 (CRC) 機能もサポートしています。

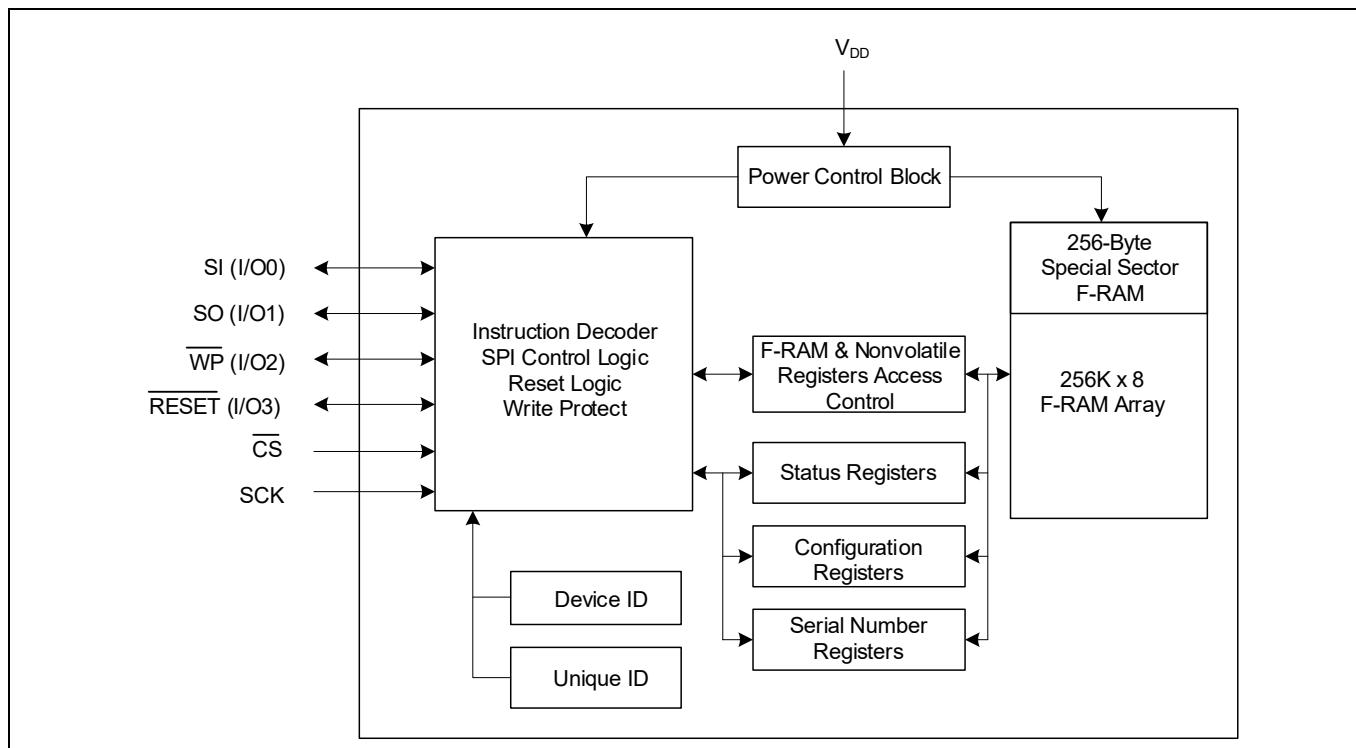

## 論理ブロック図

## 目次

|                                          |           |

|------------------------------------------|-----------|

| <b>特長</b> .....                          | <b>1</b>  |

| <b>機能説明</b> .....                        | <b>2</b>  |

| <b>論理ブロック図</b> .....                     | <b>2</b>  |

| <b>目次</b> .....                          | <b>3</b>  |

| <b>1 端子配置</b> .....                      | <b>5</b>  |

| <b>2 端子機能</b> .....                      | <b>6</b>  |

| <b>3 機能概要</b> .....                      | <b>7</b>  |

| 3.1 メモリ アーキテクチャ .....                    | 7         |

| 3.2 SPI バス .....                         | 7         |

| 3.2.1 シングル チャネル SPI .....                | 8         |

| 3.2.2 拡張 SPI .....                       | 8         |

| 3.2.3 デュアル SPI (DPI) .....               | 8         |

| 3.2.4 クアッド SPI (QPI) .....               | 9         |

| 3.3 SPI プロトコルで使用される用語 .....              | 9         |

| 3.3.1 SPI マスター .....                     | 9         |

| 3.3.2 SPI スレーブ .....                     | 9         |

| 3.3.3 チップセレクト ( $\overline{CS}$ ) .....  | 9         |

| 3.3.4 シリアルクロック (SCK) .....               | 10        |

| 3.3.5 データ転送 (SI/SO) .....                | 10        |

| 3.3.6 最上位ビット (MSb) .....                 | 10        |

| 3.3.7 シリアルオペコード .....                    | 11        |

| 3.3.8 無効なオペコード .....                     | 11        |

| 3.3.9 命令 .....                           | 11        |

| 3.3.10 モード バイト .....                     | 11        |

| 3.3.11 待機状態またはダミー サイクル .....             | 11        |

| 3.4 SPI モード .....                        | 12        |

| 3.4.1 SDR .....                          | 12        |

| 3.4.2 DDR .....                          | 12        |

| 3.5 電源投入時から最初のアクセスまで .....               | 13        |

| <b>4 CY15x102QSN レジスタ</b> .....          | <b>15</b> |

| 4.1 ステータス レジスタ .....                     | 15        |

| 4.1.1 ステータス レジスタ 1 (SR1) .....           | 15        |

| 4.1.2 ステータス レジスタ 2 (SR2) .....           | 18        |

| 4.2 コンフィギュレーション レジスタ .....               | 19        |

| 4.2.1 コンフィギュレーション レジスタ 1 (CR1) .....     | 19        |

| 4.2.2 コンフィギュレーション レジスタ 2 (CR2) .....     | 22        |

| 4.2.3 コンフィギュレーション レジスタ 4 (CR4) .....     | 25        |

| 4.2.4 コンフィギュレーション レジスタ 5 (CR5) .....     | 27        |

| <b>5 機能説明</b> .....                      | <b>29</b> |

| 5.1 コマンドの構成 .....                        | 29        |

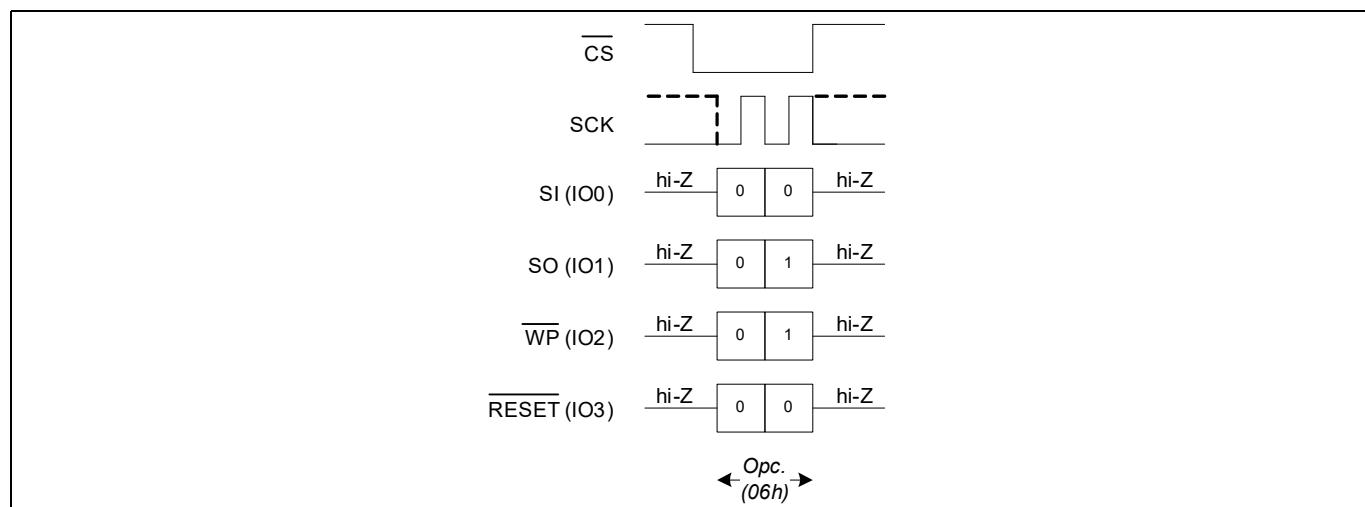

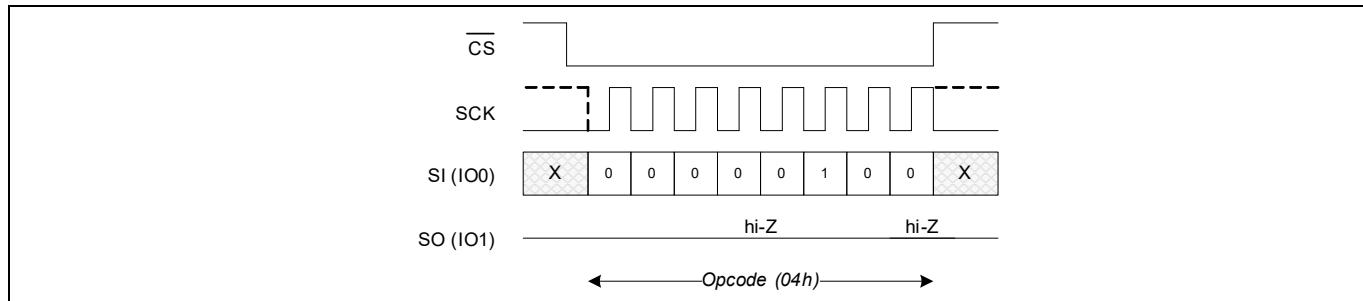

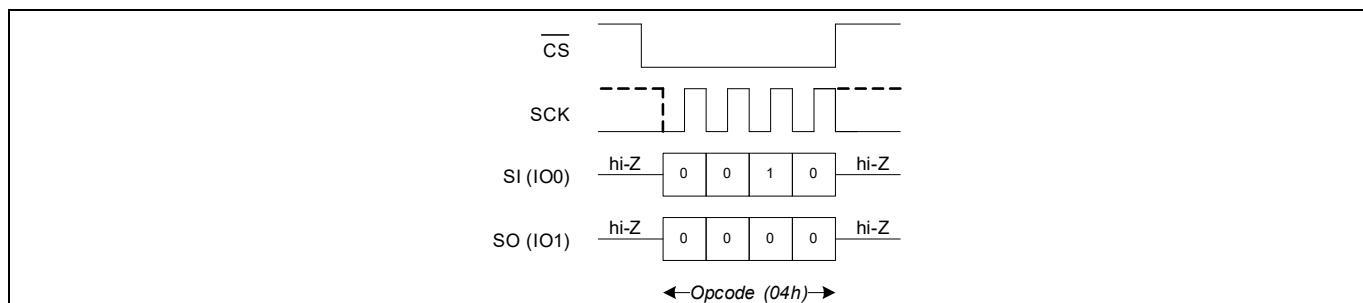

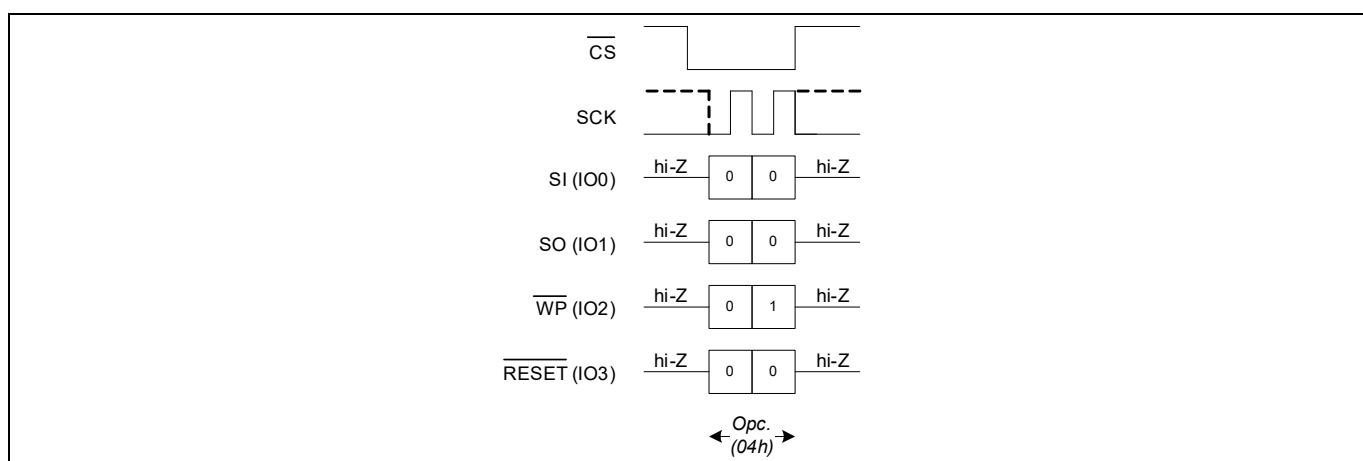

| 5.1.1 書き込みイネーブル制御コマンド .....              | 31        |

| 5.1.2 レジスタアクセスのコマンド .....                | 34        |

| 5.1.3 メモリの動作 .....                       | 46        |

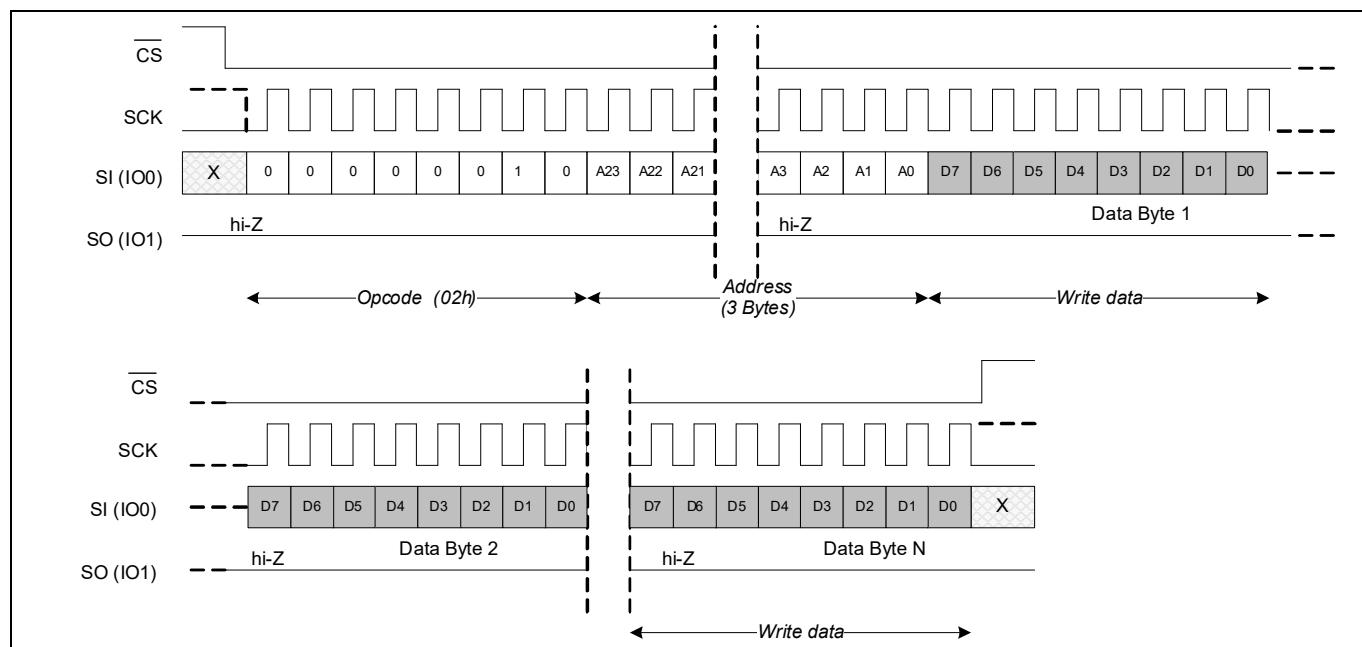

| 5.1.4 メモリ書き込み動作コマンド .....                | 46        |

| 5.1.5 メモリ読み出し動作コマンド .....                | 57        |

| 5.1.6 特殊セクタメモリアクセスコマンド .....             | 68        |

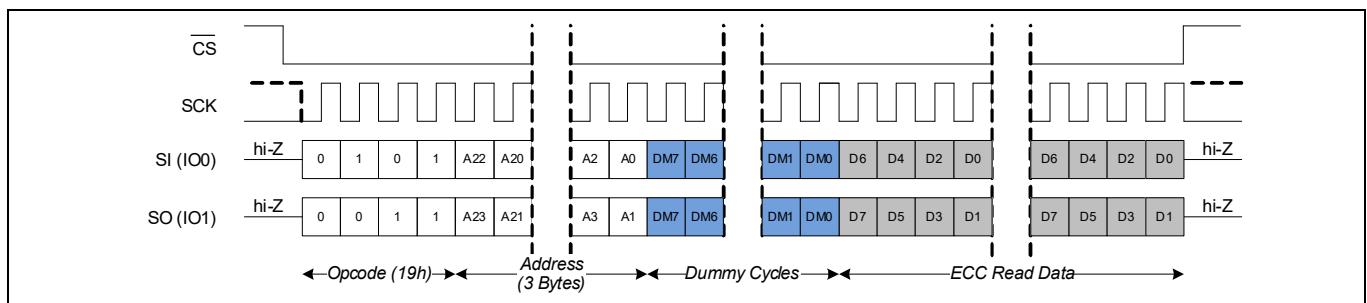

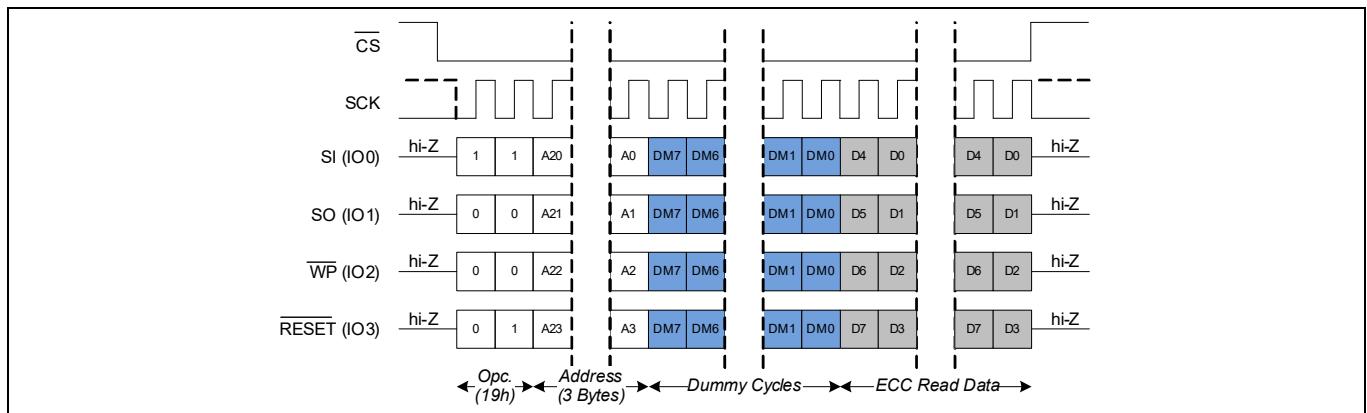

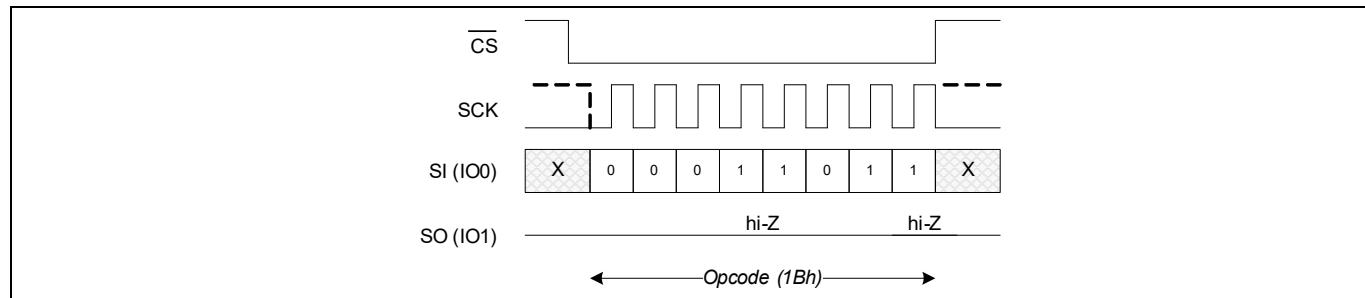

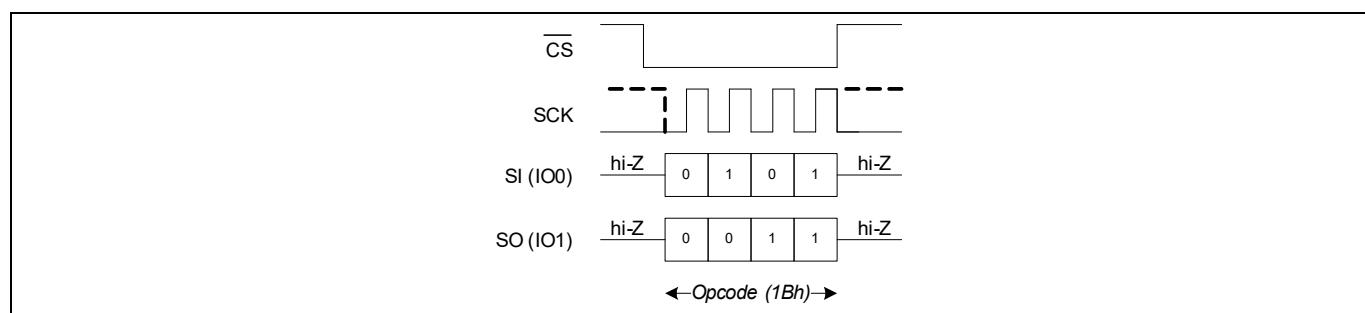

| 5.1.7 エラー訂正コード (ECC) および巡回冗長検査コマンド ..... | 71        |

| 5.1.8 ID およびシリアル番号コマンド .....             | 80        |

| 5.1.9 低消費電力モードとリセット .....                | 85        |

| <b>6 電気的特性</b> .....                     | <b>92</b> |

| 6.1 最大定格 .....                           | 92        |

目次

|                                   |     |

|-----------------------------------|-----|

| 7 動作範囲 .....                      | 93  |

| 8 DC 電気的特性 .....                  | 94  |

| 9 データ保持期間とアクセス可能回数 .....          | 97  |

| 10 静電容量 .....                     | 98  |

| 11 熱抵抗 .....                      | 99  |

| 12 AC テスト条件 .....                 | 100 |

| 13 SDR AC スイッチング特性 .....          | 101 |

| 14 DDR AC スイッチング特性 .....          | 104 |

| 15 書き込み保護 (WP) タイミング パラメータ .....  | 106 |

| 16 リセット (RESET) タイミング パラメータ ..... | 107 |

| 17 パワーサイクルタイミング .....             | 108 |

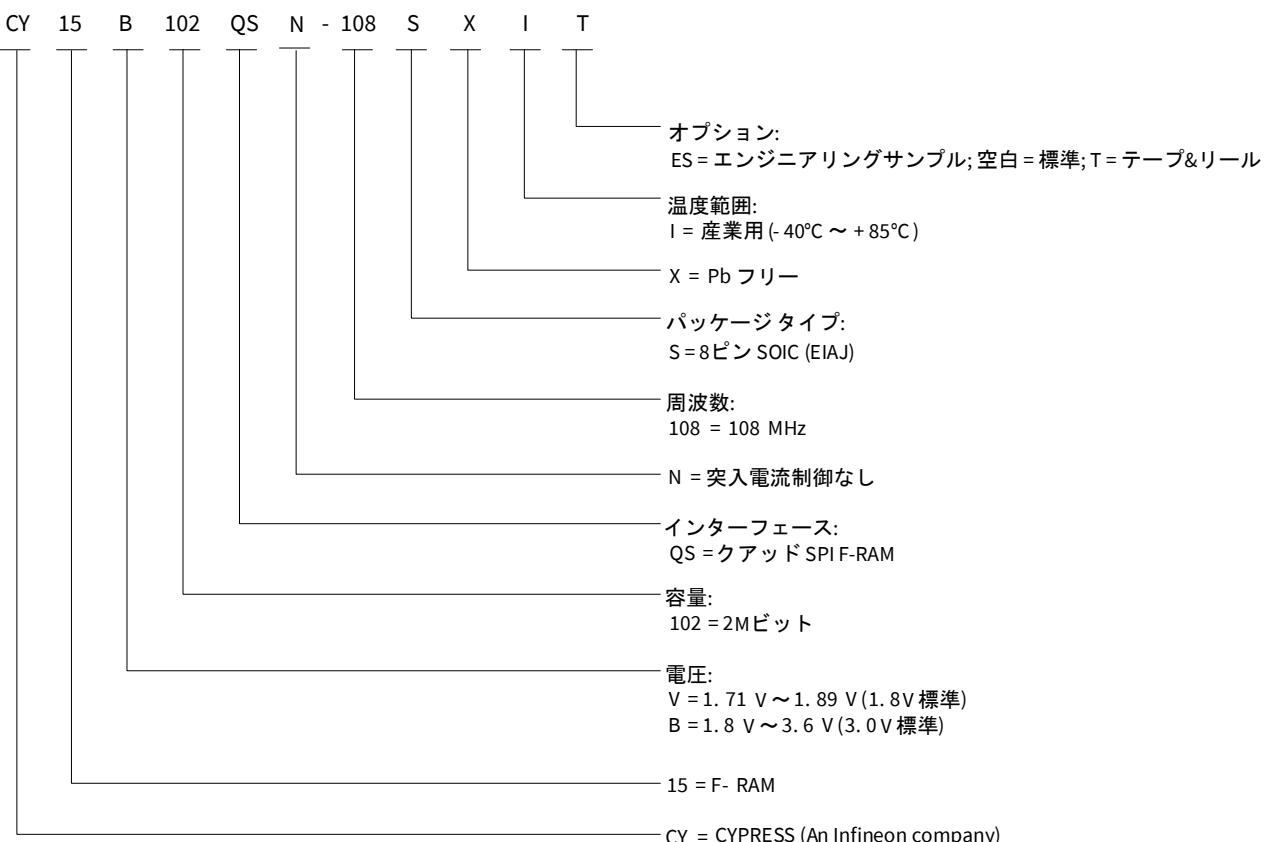

| 18 注文情報 .....                     | 110 |

| 18.1 注文コードの定義 .....               | 110 |

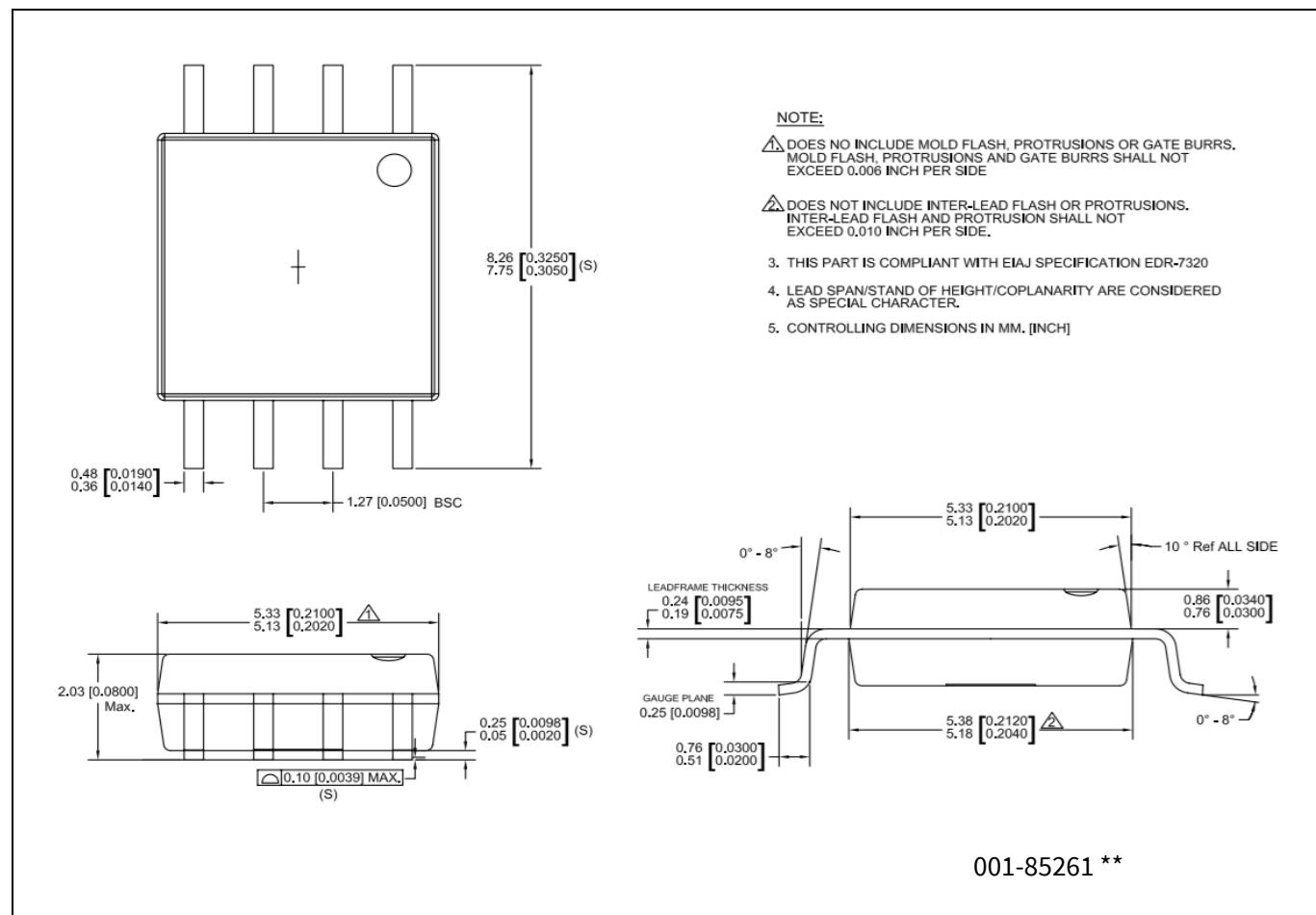

| 19 パッケージ外形図 .....                 | 111 |

| 20 略語 .....                       | 112 |

| 21 本書の表記法 .....                   | 113 |

| 21.1 測定単位 .....                   | 113 |

| 改訂履歴 .....                        | 114 |

| 免責事項 .....                        | 115 |

端子配置

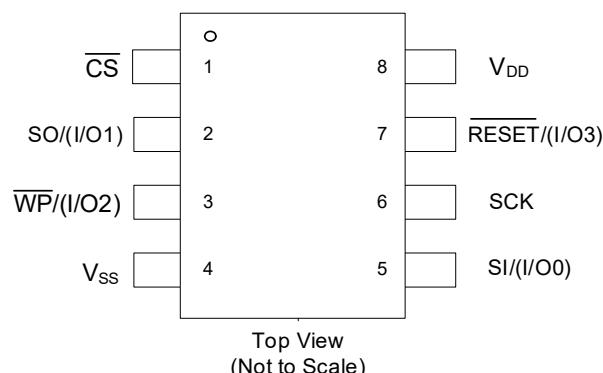

## 1 端子配置

Figure 1 8 ピン SOIC 端子配置

端子機能

## 2 端子機能

Table 1 端子機能

| 端子名             | 入出力     | 説明                                                                                                                                                                                                                                                     |

|-----------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CS              | 入力      | <b>チップセレクト。</b> このアクティブ LOW 入力でデバイスを起動させます。HIGH になった場合、デバイスは低消費電力のスタンバイ モードに移行し、他の入力を無視し、出力をトライステートにします。LOW になった場合、デバイスが SCK 信号を内部でアクティブにします。CS の立ち下りエッジは、新しいオペコードが発行される前に発生させる必要があります。                                                                |

| SCK             | 入力      | <b>シリアルクロック。</b> 入出力はシリアルクロックに同期されます。入力は立ち上りエッジにラッピングされ、出力は立ち下りエッジで駆動されます。デバイスは同期しているため、クロック周波数は 0 ~ 108 MHz の範囲内であり、同期特性のためいつでも割り込まれる可能性があります。                                                                                                        |

| SI / (I/O0)     | 入力      | <b>シリアル入力。</b> このピンからデバイスにデータを入力します。入力は SCK の立ち上りエッジでサンプリングされ、それ以外では無視されます。                                                                                                                                                                            |

|                 | 入力 / 出力 | <b>I/O0。</b> 製品がデュアルモードまたはクアッドモードの場合、SI ピンは入力 / 出力 (I/O0) ピンになり、コマンドおよびアドレスサイクル中に入力として機能し、データ出力サイクル中に出力されます。                                                                                                                                           |

| SO / (I/O1)     | 出力      | <b>シリアル出力。</b> データ出力ピンです。このピンは読み出し中に駆動され、そのとき以外( RESET が LOW のときも含む)トライステートを保持します。データ遷移はシリアルクロックの立ち下りエッジで実現します。                                                                                                                                        |

|                 | 入力 / 出力 | <b>I/O1。</b> 製品がデュアルモードまたはクアッドモードの場合、SO ピンは入力 / 出力 (I/O1) ピンになり、コマンドおよびアドレスサイクル中に入力として機能し、データ出力サイクル中に出力します。                                                                                                                                            |

| WP / (I/O2)     | 入力      | <b>書き込み保護。</b> このアクティブ LOW ピンは、SRWD ビット (SR1[7]) が「1」に設定されている場合にステータスレジスタとコンフィギュレーションレジスタへの書き込み動作を防ぎます。書き込み保護の完全な説明は、 <a href="#">ステータスレジスタ 1 (SR1)</a> に記載されています。このピンを使用しない場合、V <sub>DD</sub> に接続する必要があります。                                           |

|                 | 入力 / 出力 | <b>I/O2。</b> 製品がクワッドモードの場合、WP ピンは入出力 (I/O2) ピンになり、コマンドおよびアドレスサイクル中は入力として機能し、データ出力サイクル中は出力として機能します。                                                                                                                                                     |

| RESET / (I/O3)  | 入力      | <b>ハードウェアリセット端子。</b> このアクティブ LOW ピンはデバイスをリセットします。RESET が LOW の場合、デバイスは自己初期化され、RESET 入力が HIGH に解放された後、CS HIGH または LOW ステータスに応じてスタンバイ状態またはアクティブ状態に戻ります。このピンを使用しない場合、V <sub>DD</sub> に接続する必要があります。RESET/(I/O3) の動作については、 <a href="#">Table 21</a> で説明します。 |

|                 | 入力 / 出力 | <b>I/O3。</b> 製品がクワッドモードの場合、RESET ピンは入力 / 出力 (I/O3) ピンになり、コマンドおよびアドレスサイクル中は入力として機能し、データ出力サイクル中は出力として機能します。                                                                                                                                              |

| V <sub>SS</sub> | 電源      | <b>デバイス用のグランド。</b> システムアースに接続する必要があります。                                                                                                                                                                                                                |

| V <sub>DD</sub> | 電源      | <b>デバイス電源入力</b>                                                                                                                                                                                                                                        |

機能概要

### 3 機能概要

CY15X102QSN はシリアル F-RAM メモリです。メモリアレイは  $262,144 \times 8$  ビットに論理構成され、業界標準のシリアルペリフェラルインターフェース (SPI) バスを使用してアクセスされます。F-RAM の機能動作は、シングル SPI EEPROM またはシングル / デュアル / クアッド SPI フラッシュに似ています。

CY15X102QSN と同じピン配置のシリアルフラッシュとの違いは、F-RAM の優れた書き込み性能、高アクセス可能回数、低消費電力です。

#### 3.1 メモリアーキテクチャ

CY15X102QSN のアクセスには、8 データビットごとの 256K 箇所の位置をアドレス指定します。これらの 8 つのデータビットは、シングル、デュアル、またはクアッド I/O のいずれかでシリアルにシフトインまたはシフトアウトされます。アドレスは、チップセレクト (バス上で複数のデバイスを許可するため), オペコード、および 3 バイト (24 ビット) アドレスを含む SPI プロトコルを使用してアクセスされます。ただし、256K バイトの位置全体をアドレス指定するために必要なのは 18 ビットのみであるため、最上位アドレスバイトの上位 6 ビットは「ドントケア」値です。18 ビットアドレスは 256K メモリアレイ内の各データバイト位置を一意的に識別します。

メモリ動作のためのアクセス時間は基本的にシリアルプロトコルに必要な時間以外は 0 です。すなわちメモリは SPI バスの速度で読み書きされます。シリアルフラッシュや EEPROM とは異なり、新しいコマンドを開始する前に、デバイスをポーリングして準備完了状態を確認する必要はありません。これについては、[機能説明](#)で詳しく説明します。

#### 3.2 SPI バス

SPI は、メモリアクセスにクロックとデータピンを使用し、データバス上の複数デバイスをサポートする同期シリアルインターフェースです。SPI バス上のデバイスは、 $\overline{CS}$  ピンを使用してアクティブにされます。チップセレクト、クロック、およびデータの相互関係は SPI モードによります。このデバイスは、SPI モード 0 および 3 をサポートしています。これらの両モードで、 $\overline{CS}$  がアクティブになった後の最初の立ち上がりエッジから始まる SCK の立ち上がりエッジで、データが FRAM にクロック入力されます。SPI プロトコルはオペコードによって制御されます。動作完了後、新しいオペコードが発行される前に、 $\overline{CS}$  が非アクティブ化される必要があります。

CY15X102QSN は SPI スレーブデバイスであり、シングルデータレート (SDR) モードで最大 108 MHz の速度で動作し、DDR モードで最大 54MHz の速度で動作します。この高速シリアルバスにより、SPI マスターとの間で高性能のシリアル通信が可能です。CY15X102QSN は、シングルチャネル SPI、拡張 SPI、デュアル SPI、クアッド SPI の 4 つの異なる SPI インターフェース / プロトコルオプションをサポートします。

**Table 2** に、上記のさまざまな SPI モードでのオペコード、アドレス、およびデータフェーズ中の I/O シグナリングの詳細を示します。

Table 2 SPI モードと信号の詳細

| インターフェース | シグナルチャネル SPI                  | 拡張 SPI <sup>[1]</sup>             |                                               |                                   |                                               | マルチチャネル SPI                       |                                               |

|----------|-------------------------------|-----------------------------------|-----------------------------------------------|-----------------------------------|-----------------------------------------------|-----------------------------------|-----------------------------------------------|

|          |                               | デュアルデータ                           | クアッドデータ                                       | デュアル入出力                           | クアッド入出力                                       | DPI                               | QPI                                           |

| 信号       | $\overline{CS}$ , SCK, SI, SO | $\overline{CS}$ , SCK, I/O0, I/O1 | $\overline{CS}$ , SCK, I/O0, I/O1, I/O2, I/O3 | $\overline{CS}$ , SCK, I/O0, I/O1 | $\overline{CS}$ , SCK, I/O0, I/O1, I/O2, I/O3 | $\overline{CS}$ , SCK, I/O0, I/O1 | $\overline{CS}$ , SCK, I/O0, I/O1, I/O2, I/O3 |

| オペコード    | SI                            | I/O0                              | I/O0                                          | I/O0                              | I/O0                                          | I/O0, I/O1                        | I/O0, I/O1, I/O2, I/O3                        |

| アドレス     | SI                            | I/O0                              | I/O0                                          | I/O0, I/O1                        | I/O0, I/O1, I/O2, I/O3                        | I/O0, I/O1                        | I/O0, I/O1, I/O2, I/O3                        |

| データ      | SI/SO                         | I/O0, I/O1                        | I/O0, I/O1, I/O2, I/O3                        | I/O0, I/O1                        | I/O0, I/O1, I/O2, I/O3                        | I/O0, I/O1                        | I/O0, I/O1, I/O2, I/O3                        |

注:

- 拡張 SPI モードのユーザー設定はありません。デバイスは常に SPI モードで開始し、受信したオペコードに基づいてそれぞれの拡張 SPI モードに変更します。

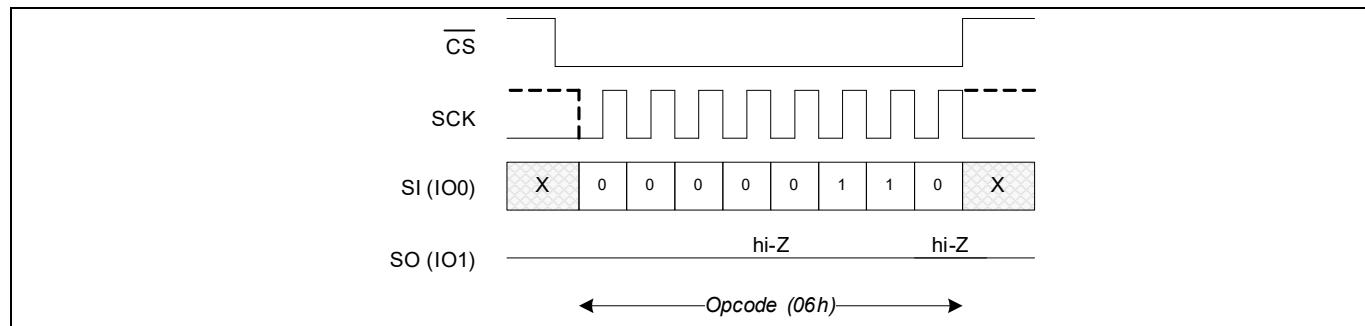

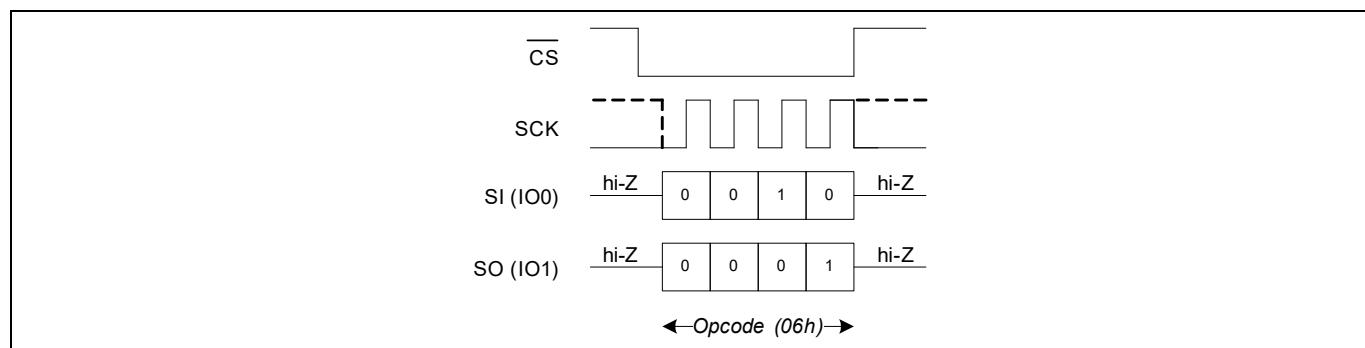

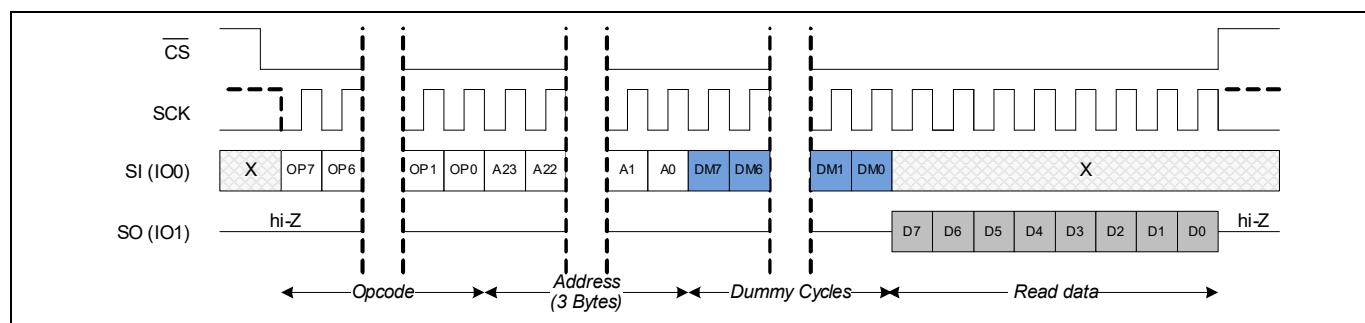

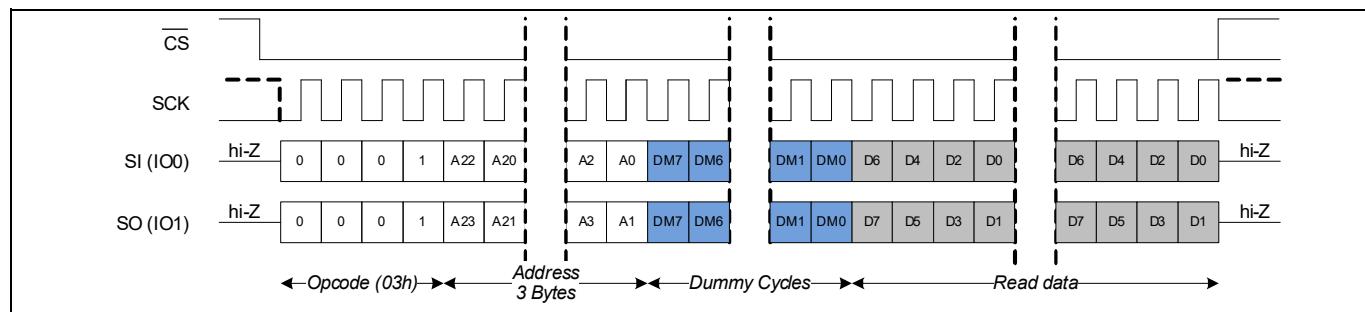

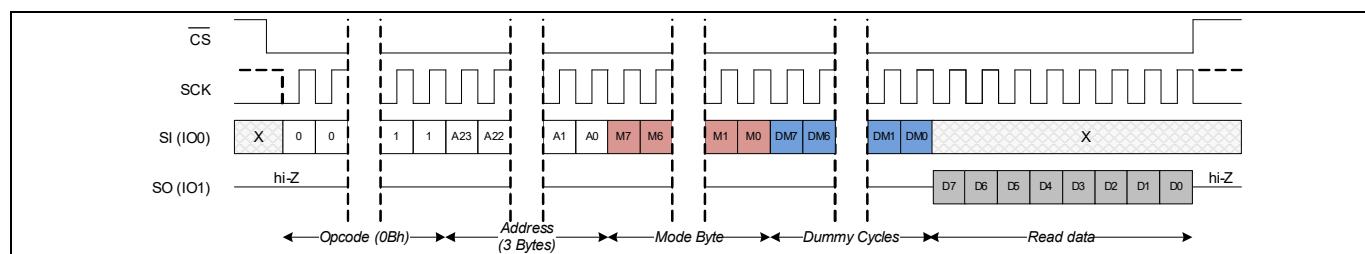

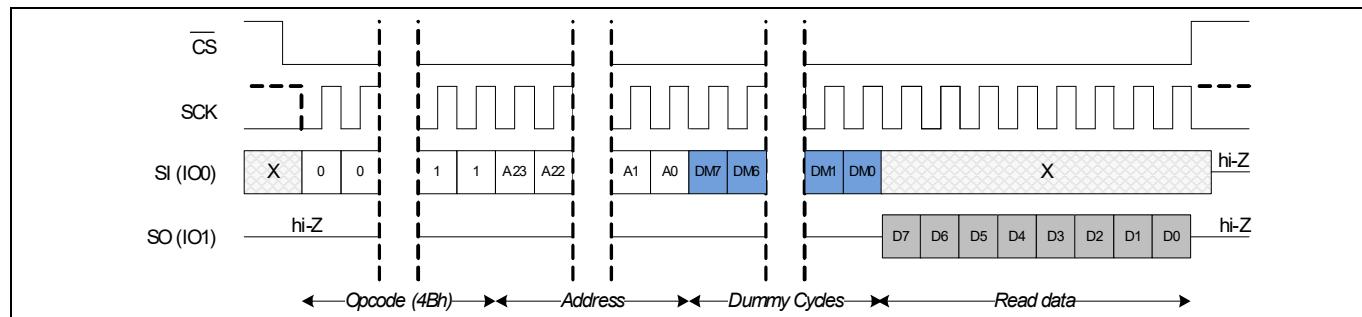

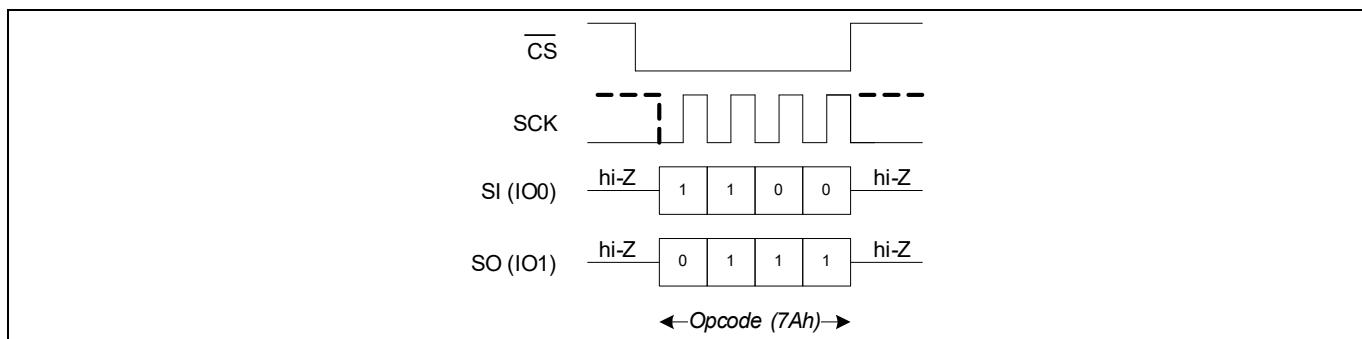

### 3.2.1 シングルチャネル SPI

シングルチャネル SPI は、チップセレクト ( $\overline{CS}$ ), シリアル入力 (SI), シリアル出力 (SO), およびシリアルクロック (SCK) ピンを備えた 4 ピンインターフェースです。 $\overline{CS}$  がアクティブ化された後、バスマスターから転送される最初のバイトがオペコードです。オペコードに続いて、任意のアドレスとデータが転送されます。 $\overline{CS}$  は、操作が完了した後、新しいオペコードを発行する前に、HIGH (非アクティブ) になると必要があります。このモードでは、入力と出力にそれぞれ SI ピンと SO ピンを使用します。オペコードとアドレスは SI ラインのマスターによって転送され、データは SO のマスターによって読み出されます。

### 3.2.2 拡張 SPI

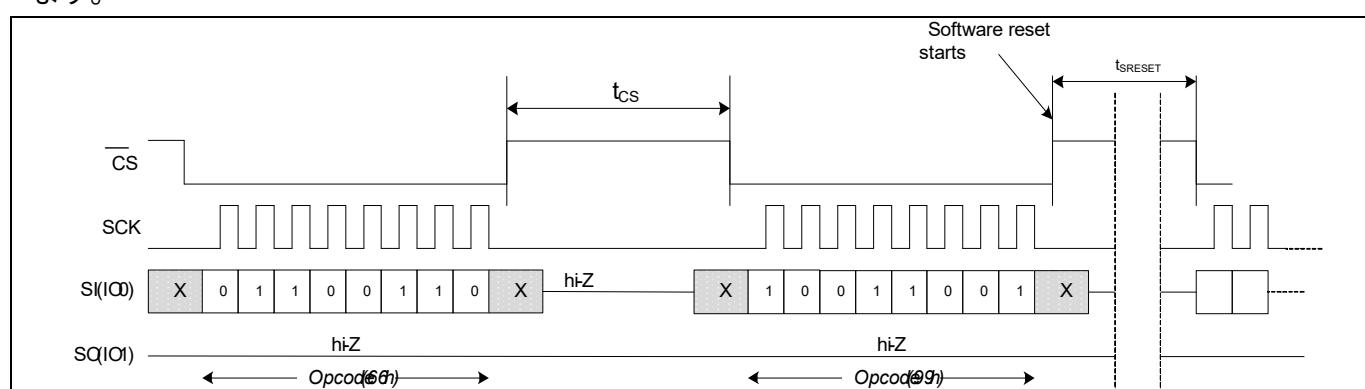

CY15X102QSN には、拡張 SPI モードと呼ばれるデュアルまたはクアッド I/O モードで動作するように標準 SPI ピンを再設定する機能があります。拡張 SPI モードは、デュアルデータ, デュアル入力 / 出力 (I/O), クアッドデータ, およびクアッド入力 / 出力 (I/O) モードを提供します。拡張 SPI コマンドまたはデバイスリセット (POR またはハードウェア / ソフトウェアリセット) 後に  $\overline{CS}$  が HIGH になると、デバイスはシングルチャネル SPI モードに戻ります。拡張 SPI モードは、以下の I/O 設定を備えます。

- 製品がデュアル出力またはデュアルI/Oモードの場合、SIピンとSOピンはそれぞれI/00ピンとI/01ピンになります。

- クアッド出力またはクアッドI/Oモードの場合、SIピン, SOピン,  $\overline{WP}$ ピン,  $\overline{RESET}$ ピンはそれぞれI/00ピン, I/01ピン, I/02ピン, I/03ピンになります。

- デュアルまたはクアッドデータコマンドとアドレスは、SI 信号でのみメモリに送信されます。データは、I/00 と I/01 のビットペアのシーケンス、または I/00, I/01, I/02, I/03 の 4 ビット (ニブル) グループとしてホストに返されます。

- デュアルまたはクアッド入力 / 出力 (I/O) コマンドは、SI 信号でのみメモリに送信され、アドレスは I/00 と I/01 のビットペア、または I/00, I/01, I/02, および I/03 の 4 ビット (ニブル) グループとしてそれぞれホストから送信されます。データは、I/00 と I/01 のビットペア、または I/00, I/01, I/02, I/03 の 4 ビット (ニブル) グループと同様にホストに返されます。

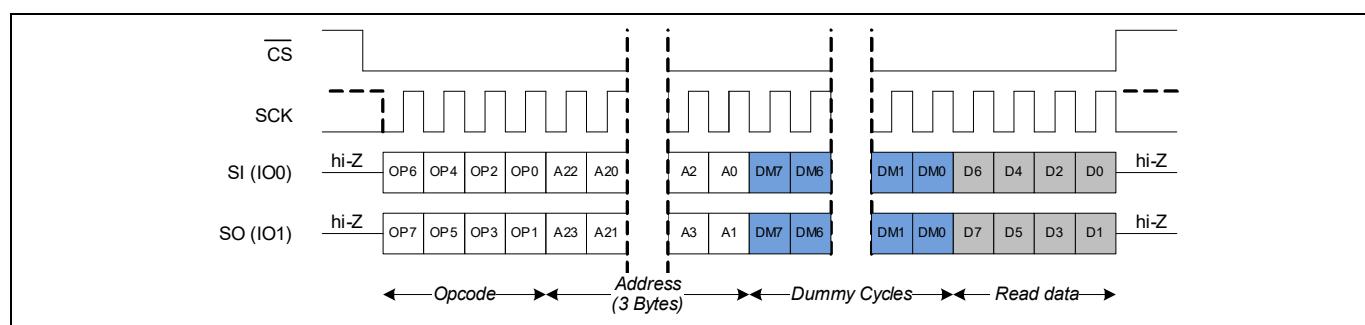

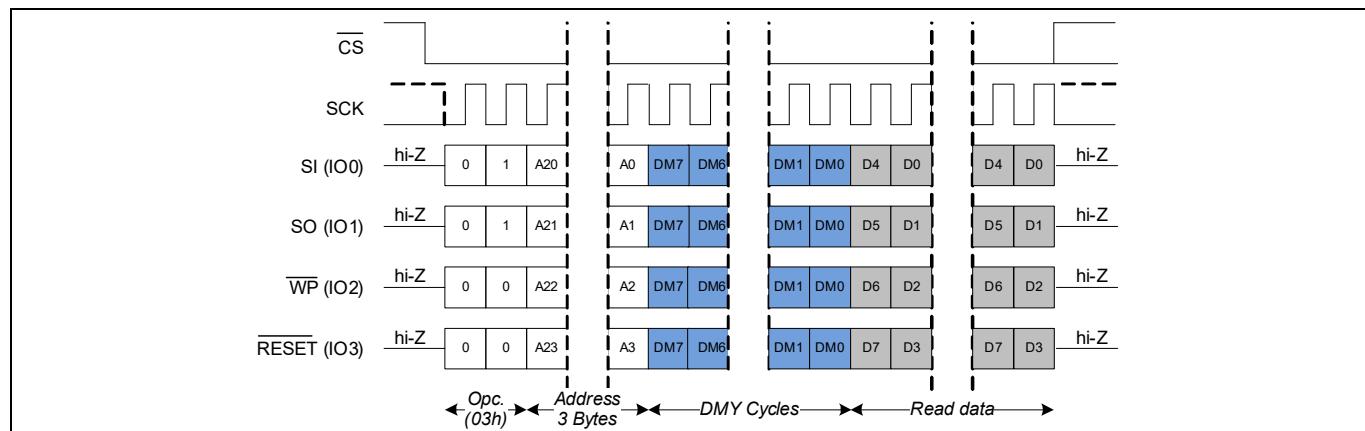

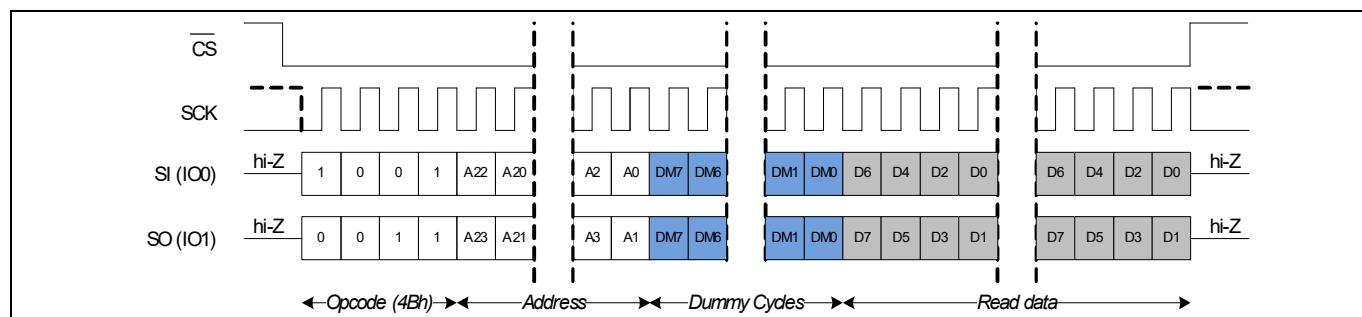

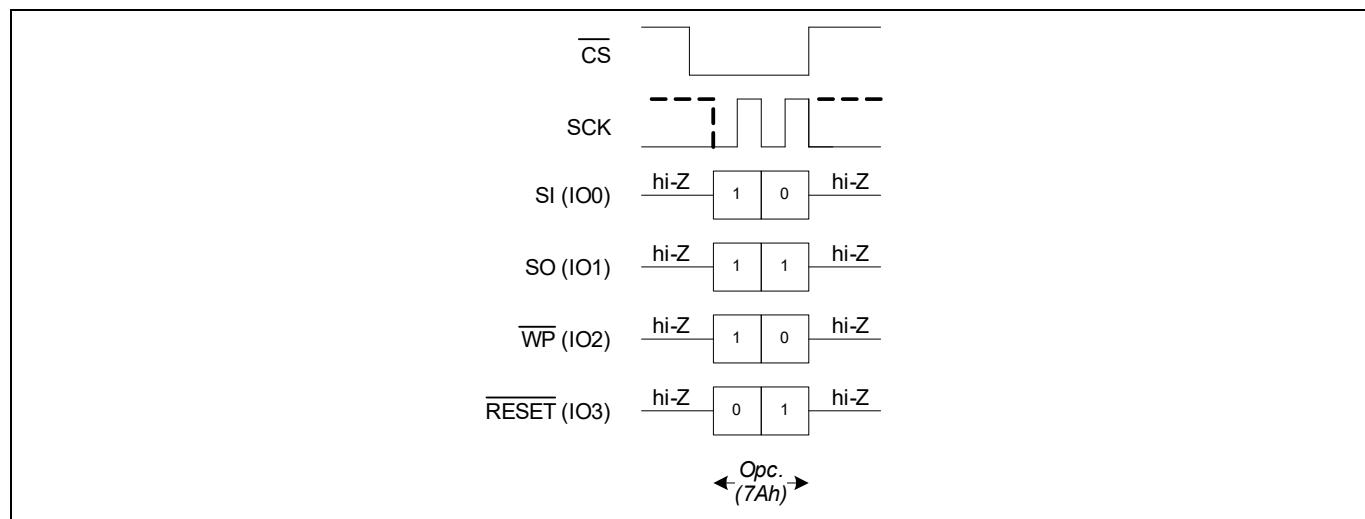

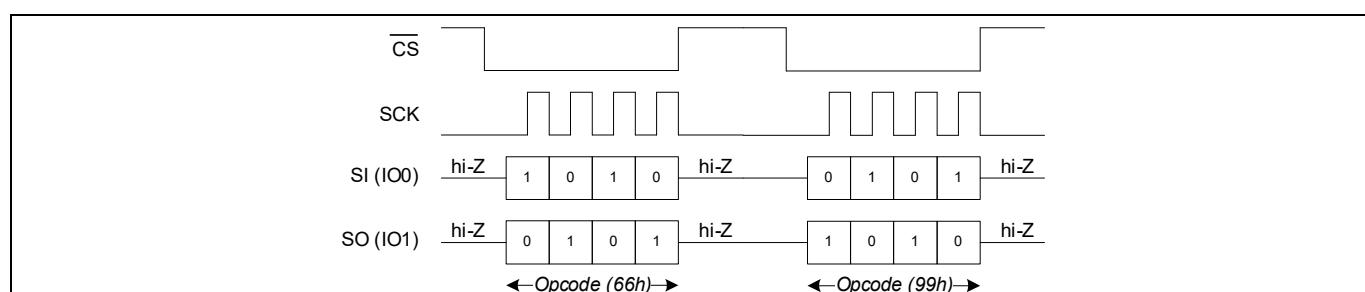

### 3.2.3 デュアル SPI (DPI)

DPI モードは、コンフィギュレーションレジスタ 2 (CR2) のビット 4 に「1」を書き込むことによって有効になります。CR2[4] = 「1」。コンフィギュレーションレジスタ 2 (CR2) には揮発性スペースと不揮発性スペースの両方があるため、不揮発性レジスタでのユーザー設定は、電源とハードウェアのリセットサイクル後も存続します。したがって、デュアル SPI (DPI) モードが不揮発性 CR2 に設定されると、ホストが不揮発性 CR2[4] に「0」を書き込んで DPI ビットをクリアするまで、常に DPI モードに戻ります。ホストは、揮発性レジスタ CR2[4] に「1」を書き込むことにより、デバイスインターフェースを DPI モードに変更できます。ただし、この揮発性設定は電源とハードウェアのリセットサイクルに耐えられず、揮発性 CR2[4] 設定は、電源投入時またはハードウェアリセットサイクル後に関連する不揮発性の場所に保存されているデフォルト設定で上書きされます。

製品がデュアル SPI モードの場合、SI ピンと SO ピンはそれぞれ I/00 ピンと I/01 ピンになります。コマンド, アドレス, およびデータビットは、I/00 および I/01 のビットペアとしてホストからメモリに送信されます。データビットは、I/00 と I/01 のビットペアと同様にホストに返されます。

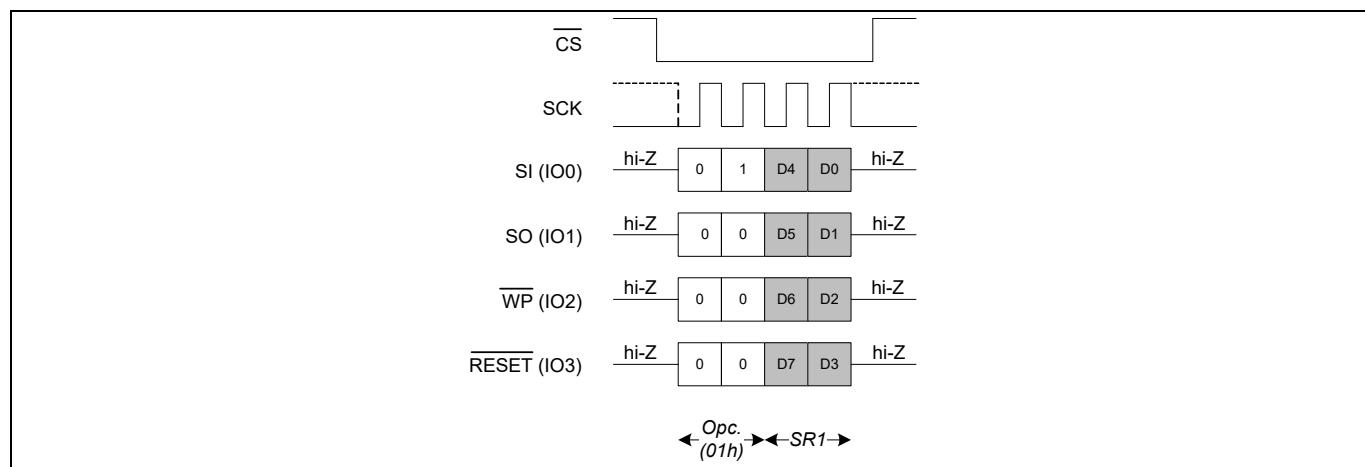

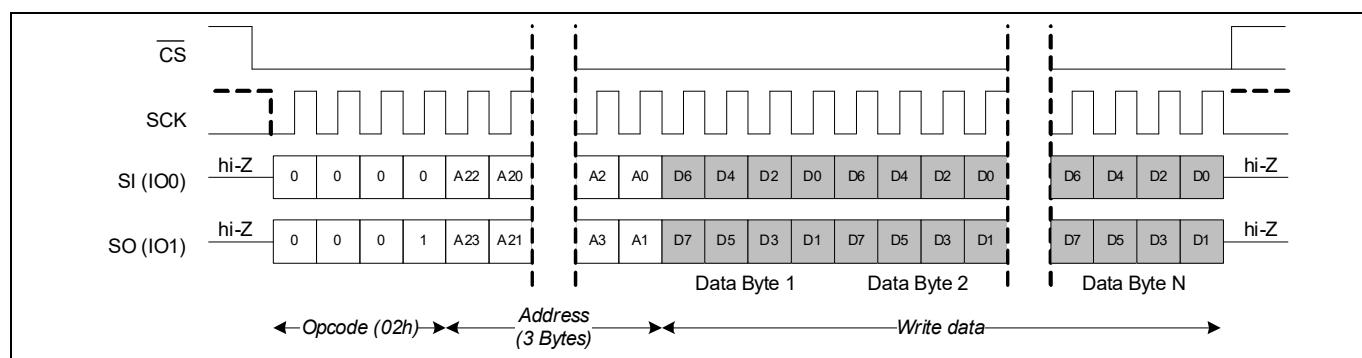

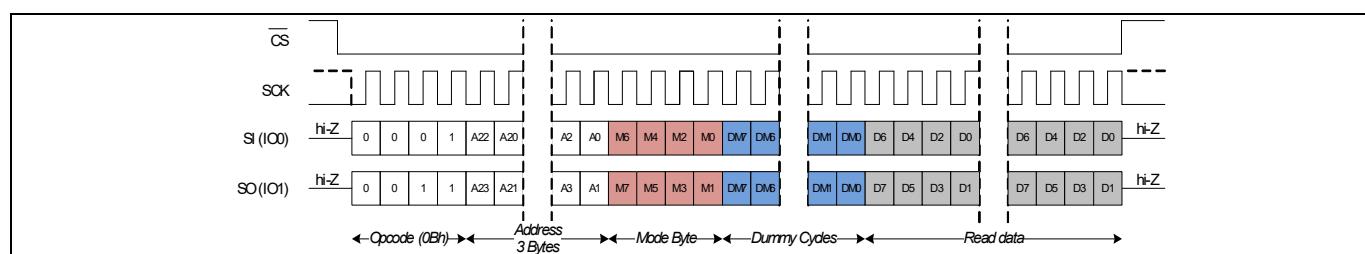

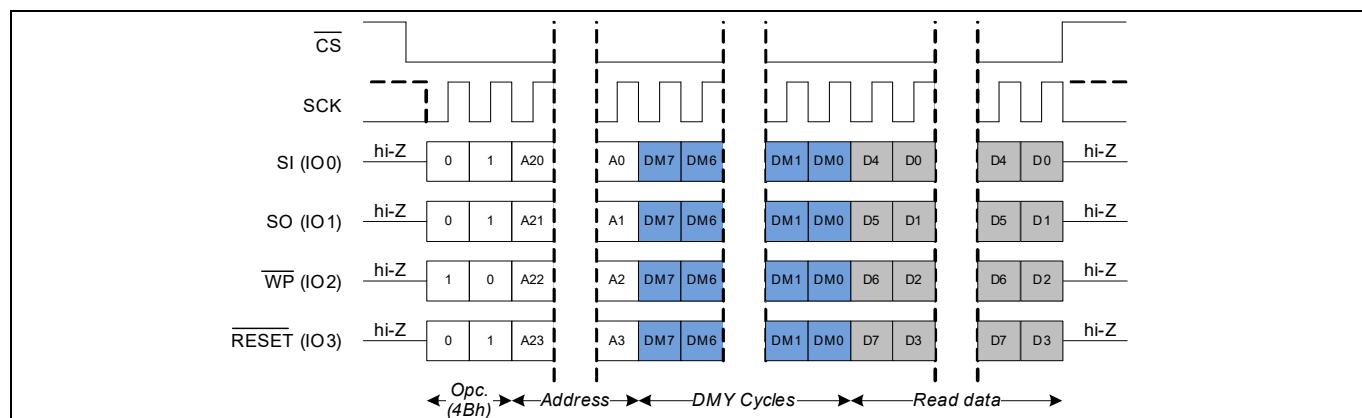

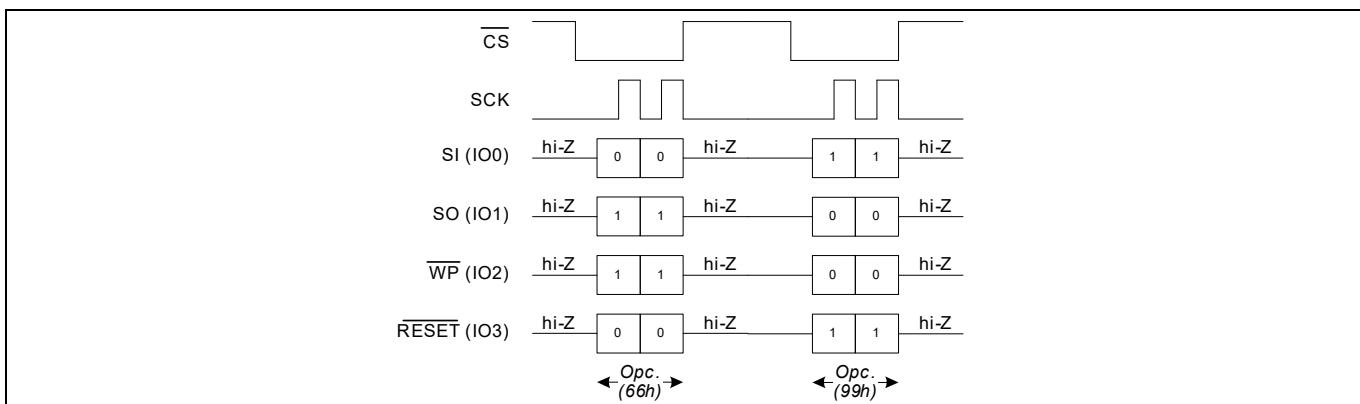

### 3.2.4 クアッド SPI (QPI)

マルチチャネル QPI モードは、コンフィギュレーションレジスタ 2 (CR2) のビット 6 に「1」を書き込むことで有効になります。CR2[6] = 「1」です。コンフィギュレーションレジスタ 2 (CR2) には揮発性スペースと不揮発性スペースの両方があるため、不揮発性レジスタでのユーザー設定は、電源とハードウェアのリセットサイクル後も存続します。したがって、クアッド SPI (QPI) モードが不揮発性 CR2 に設定されると、ホストが不揮発性 CR2[6] に「0」を書き込んで QPI ビットをクリアするまで、常に QPI モードに戻ります。ホストは、揮発性レジスタ CR2[6] に「1」を書き込むことにより、デバイスインターフェースを QPI モードに変更できます。ただし、この揮発性設定は電源とハードウェアのリセットサイクルに耐えられず、揮発性 CR2[6] 設定は、電源投入時またはハードウェアリセットサイクル後に関連する不揮発性の場所に保存されているデフォルト設定で上書きされます。

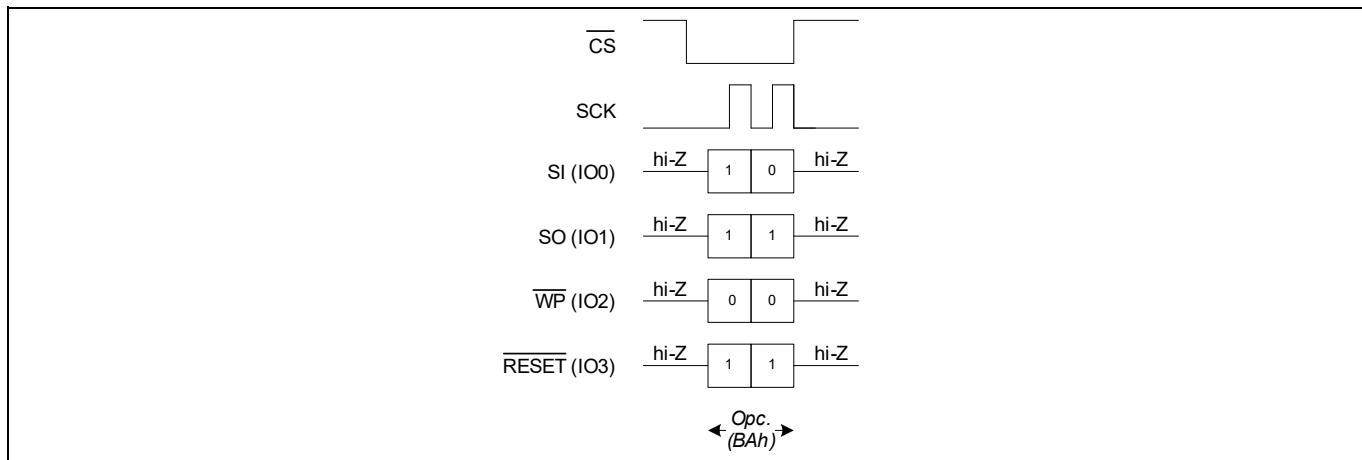

クアッド SPI モードの場合、SI ピン, SO ピン,  $\overline{WP}$  ピン,  $\overline{RESET}$  ピンはそれぞれ I/O0 ピン, I/O1 ピン, I/O2 ピン, I/O3 ピンになります。コマンド, アドレス, およびデータビットは、I/O0, I/O1, I/O2, および I/O3 の 4 ビット (ニブル) グループとしてホストからメモリに送信されます。データは同様に I/O0, I/O1, I/O2, I/O3 の 4 ビットグループ (ニブル) でホストへ戻されます。

QPI モードは、アドレス, モード, およびデータバイトのバイト転送がクロックの両端で発生する特別なオペコードを介した DDR もサポートします。オペコードフェーズ中は DDR モードはありません。すなわち、オペコードは常に SDR モードで伝送されます。特定のコマンドが SDR モードで送信された後、デバイスは DDR モードに入ります。これにより、DDR のアドレス, モード, およびデータサイクルが決定されます。DDR モードを有効にする設定はありません。クアッド SPI DDR モードは、特別なオペコードを含むメモリの書き込みと読み出しの動作に対してのみ対応します。

## 3.3 SPI プロトコルで使用される用語

SPI プロトコルで一般的に使用される用語は以下のとおりです。

### 3.3.1 SPI マスター

SPI マスター デバイスは SPI バス上の動作を制御します。SPI バスは、複数のスレーブ デバイスを制御する 1 つのマスターを持っている場合があります。すべてのスレーブが同じ SPI バス ラインを共有し、マスターは CS ピンを使用してスレーブ デバイスのいずれかを選択できます。すべてのオペレーションは、マスターがスレーブの CS ピンを LOW にプルダウンすることによってスレーブ デバイスをアクティブにして開始する必要があります。また、マスターは SCK を生成し、SI と SO ライン上のすべてのデータ送信はこのクロックと同期されます。

### 3.3.2 SPI スレーブ

SPI スレーブ デバイスは、チップセレクト ラインを介してマスターによってアクティブ化されます。スレーブ デバイスは、SPI マスターからの入力として SCK を取得し、すべての通信はこのクロックに同期されます。SPI スレーブはそれ自体として SPI バス上で通信を開始することはなく、マスターからの命令に従ってのみ動作します。

CY15X102QSN は SPI スレーブとして動作し、他の SPI スレーブ デバイスと SPI バスを共有する場合があります。

### 3.3.3 チップセレクト (CS)

すべてのスレーブ デバイスを選択するためには、マスターは対応する CS ピンをプルダウンする必要があります。CS ピンが LOW の間だけ、命令をスレーブ デバイスに発行できます。デバイスが選択されていない場合、SI ピン経由のデータは無視され、シリアル出力ピン (SO) は高インピーダンス状態が保持されます。

**注:** 新しい命令は CS の立ち下りエッジで開始する必要があります。したがって、アクティブな CS の HIGH から LOW への遷移ごとに発行できるオペコードは 1 つだけです。

機能概要

### 3.3.4 シリアルクロック (SCK)

シリアルクロックは SPI マスターによって生成され、 $\overline{CS}$  が LOW になった後、通信はこのクロックと同期されます。

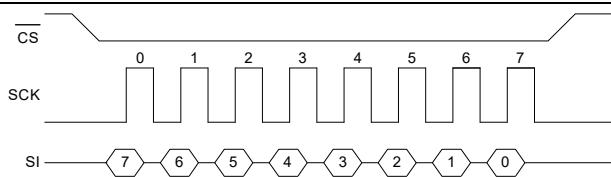

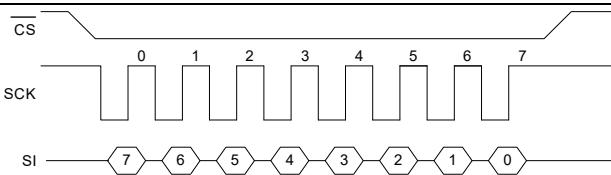

CY15X102QSN は、データ通信のために SPI モード 0 と 3 を有効にします。これらの両モードにおいて、入力は SCK の立ち上りエッジでスレーブデバイスによってラッチされ、出力は立ち下りエッジで発行されます。そのため、SCK の最初の立ち上りエッジが、SPI 命令の最上位ビット (MSb) が SI ピンに到着したことを意味します。さらにすべてのデータの入力と出力は SCK と同期されます。

### 3.3.5 データ転送 (SI/SO)

SPI データバスは、シリアルデータ通信用に SI と SO の 2 線で構成されます。SI は Master-Out-Slave-In (MOSI) とも呼ばれ、SO は Master-In-Slave-Out (MISO) とも呼ばれます。マスターは SI ピンを介してスレーブに命令を発行し、スレーブは SO ピンを介して応答します。複数のスレーブデバイスは、前述のように SI と SO ラインを共有する場合があります。

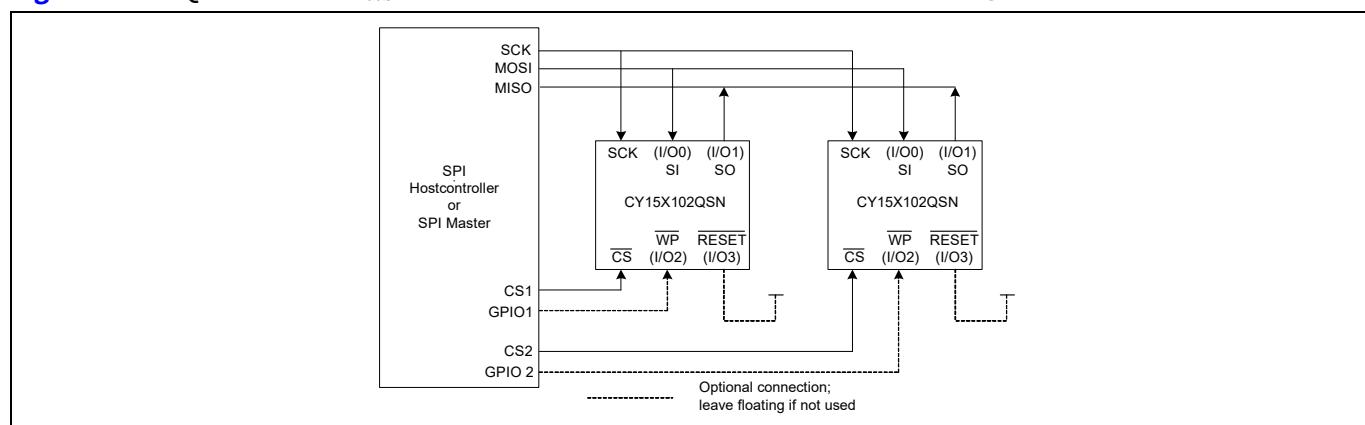

CY15X102QSN には Figure 2 に示すようにマスターと接続できる SI と SO 用の 2 つの独立したピンがあります。デュアルまたはクアッド I/O モードの場合、これらのピンは I/O ピンとして設定されます。

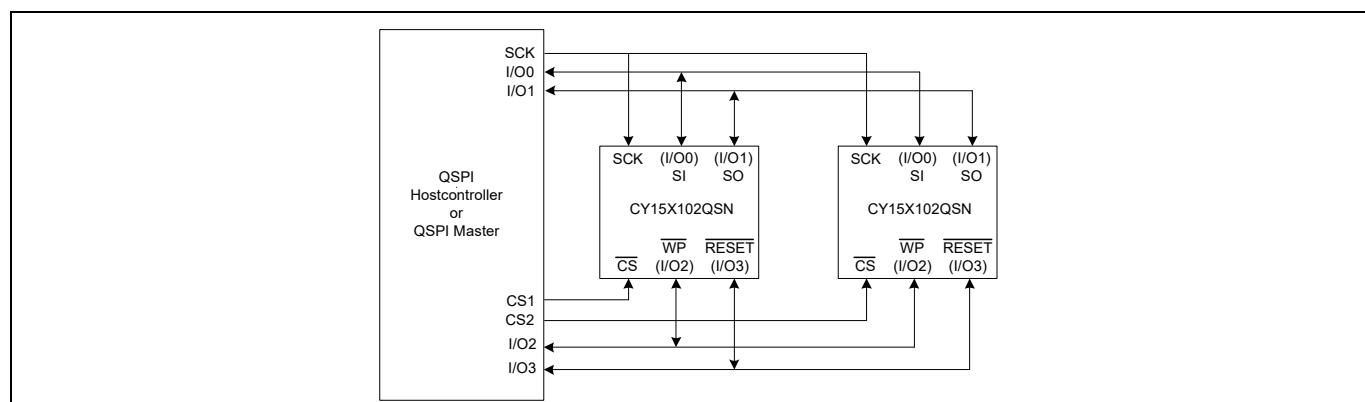

Figure 3 に、QSPI ポートを備えたこのようなシステムインターフェースを示します。

Figure 2 SPI ポートを使用するシステム コンフィギュレーション

Figure 3 QSPI ポートを使用するシステム コンフィギュレーション

### 3.3.6 最上位ビット (MSb)

SPI プロトコルでは、最初に送信されるビットが最上位ビット (MSb) でなければいけません。これはアドレスとデータ転送共に該当します。

2M ビットシリアル F-RAM は、すべての読み出しあり書き込み動作に対応して 3 バイトのアドレスを必要とします。アドレスは 18 ビットであるため、入力された 6 ビットはデバイスによって無視されます。これらの 5 ビットは「ドントケア」ですが、より高容量メモリへの円滑な移行を可能にするために、これらを「0」に設定することをインフィニオンは推奨します。

機能概要

### 3.3.7 シリアル オペコード

$\overline{CS}$  が LOW になる状態でスレーブデバイスが選択された後、最初に受信されたバイトは、意図されているオペレーションのオペコードとして扱われます。メモリアクセスには、標準のオペコード ([Table 32](#) を参照) を使用します。

### 3.3.8 無効なオペコード

予約されたオペコードが受信された場合、オペコードは内部的に意図しない動作をトリガーし、不定なデータ出力で I/O ピンを駆動する場合があります。したがって、チップセレクト  $\overline{CS}$  が LOW の場合、予約済みカテゴリのすべてのオペコードは SI ピンを介して送信しないようにする必要があります。

### 3.3.9 命令

命令は、メモリとレジスタにアクセスするために使用されるオペコード、アドレス、モード、またはダミーバイト / サイクルの組合せです。

### 3.3.10 モード バイト

モード バイトは直接実行 (XIP) をサポートするすべての書き込みおよび読み出しコマンドに適用されます。XIP は、コードを RAM にコピーまたはシャドウイングするのではなく、外部メモリから直接プログラム (コード) を実行する方法です。XIP が書き込みまたは読み出しコマンドに設定されている場合、コマンドサイクルが終了した後 ( $\overline{CS}$  が HIGH に切り替わる)、デバイスは XIP モードのままであるため、 $\overline{CS}$  LOW の後続のコマンドサイクルはアドレスフェーズから直接開始されます (オペコードフェーズはスキップされます)。XIP では、デバイスは前のサイクルと同じ動作を実行します。XIP の間に新しい動作を開始するためには (例えば、メモリ書き込みからメモリ読み出しに変わり、またはその逆)、デバイスはまず現行のコマンド サイクルを XIP モードから終了し、次のコマンド サイクルをオペコード フェーズから開始する必要があります。モード フェーズを必要とするオペコードは XIP のみをサポートします。モード フェーズを必要とするオペコードの一覧は [Table 32](#) を参照してください。

オペコードおよび 3 バイト アドレス サイクルに続き、モード フェーズ中に送信されたモード バイト 0xA(X はドントケアビット) または 0xA5 (オペコードに依存) は、次のコマンド サイクルのためにデバイスを XIP のままにします。次のコマンド サイクルで XIP のままにするためには、XIP が各コマンド サイクルでセットされる必要があります。0xA(X または 0xA5 以外 (!0xA(X) または !0xA5)) の値をモード フェーズ中に送信すると、現行の動作に対して XIP は終了されます。この場合、次のコマンド サイクルは同じ動作または新しい動作を行うために常にオペコード フェーズから開始する必要があります。SPI モードとインターフェースタイプに応じて、モード バイトを送信するクロック数は 1 クロック (Quad、DDR) から 8 クロック (SPI、SDR) まで異なります。

### 3.3.11 待機状態またはダミー サイクル

待機状態は、ダミーサイクルとも呼ばれ、アドレスビットとモードビット (該当する場合) の後に追加されます。待機状態サイクルの数は、メモリとレジスタの両方の読み出しに対して、それぞれコンフィギュレーションレジスタ 1(CR1) とコンフィギュレーションレジスタ 2(CR2) を介してプログラム可能です。有効なデータは、待機状態をサポートするメモリおよびレジスタ読み出しコマンドに続いて特定の数のダミーサイクルが経過した後にのみ、出力バス上で駆動されます。ダミーサイクルは SPI モードおよびデータレート (SDR または DDR) に関係なく、フルクロック サイクルです。I/O ステータスは、ダミーサイクル中ドントケアです。

機能概要

### 3.4 SPI モード

CY15X102QSN は、SPI ペリフェラルが次の 2 つのモードのいずれかで動作するマイクロコントローラによって駆動できます。

- SPI モード 0 (CPOL = 0, CPHA = 0)

- SPI モード 3 (CPOL = 1, CPHA = 1)

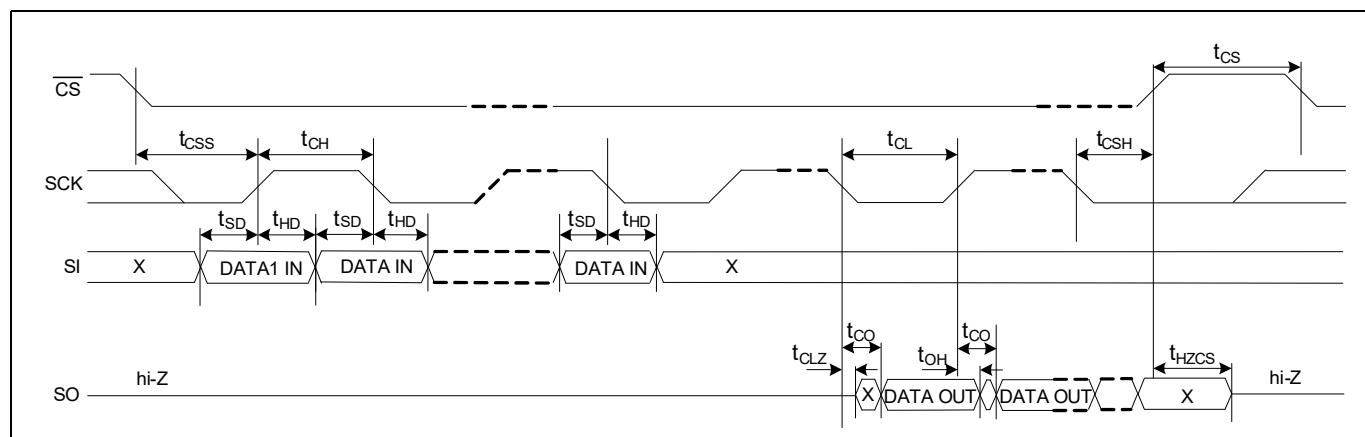

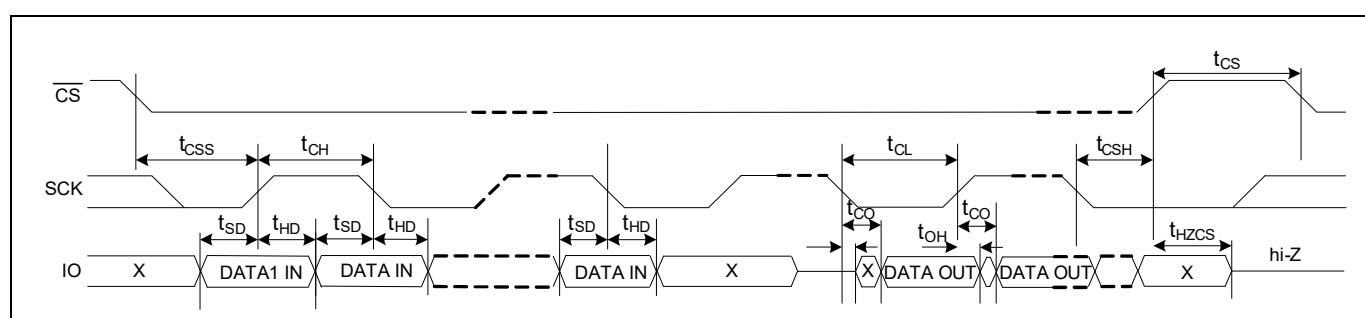

$\overline{CS}$  ピンを LOW にすることによりデバイスが選択された時、デバイスは SCK ピンの状態から SPI モードを検出します。デバイス選択時に、SCK ピンが LOW ならデバイスは SPI モード 0 で動作し、SCK ピンが HIGH ならデバイスは SPI モード 3 で動作します。2 つの SPI モードを [Figure 4](#) と [Figure 5](#) に示します。バスマスターがデータを転送していないときのクロック SCK のステータスは次のとおりです。

- モード 0 では SCK は 0 のまま

- モード 3 では SCK は 1 のまま

SPI モード 0 および SPI モード 3 は、すべての SDR モードコマンドでサポートされます。一方、すべての DDR モードコマンドは SPI モード 0 のみをサポートします。

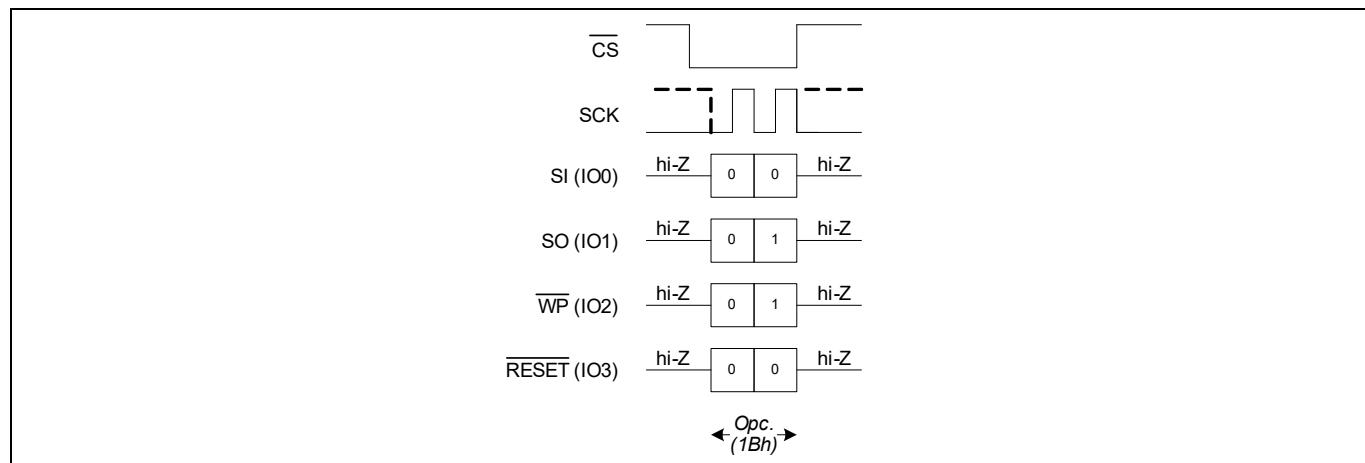

Figure 4 SPI モード 0

Figure 5 SPI モード 3

#### 3.4.1 SDR

入力データビット(命令, アドレス, およびデータを含む)は、 $\overline{CS}$  がアクティブになった後、最初の立ち上りエッジから始まる SCK の立ち上りエッジで常にラッチされます。クロックが HIGH 状態から起動される場合(モード 3)では、入力データはクロックトグル後の最初の立ち上りエッジでラッチされます。出力データは SCK の立ち下りエッジで利用可能となります。

#### 3.4.2 DDR

命令ビットは、 $\overline{CS}$  がアクティブになった後、最初の立ち上りエッジから始まる SCK の立ち上りエッジで常にラッチされます。クロックが HIGH 状態から起動される場合(モード 3)では、入力データはクロックトグル後の最初の立ち上りエッジでラッチされます。ただし、命令の後に続くアドレスおよび入力データは SCK の立ち上りエッジと立ち下りエッジの両方でラッチされます。最初のアドレスビットは、直前の命令ビットの終わりの立ち下りエッジの後に続く SCK の最初の立ち上りエッジでラッチされます。出力データの最初のビットは、最後のアクセス遅延(ダミー)サイクルの終わりに SCK の立ち下りエッジで駆動されます。

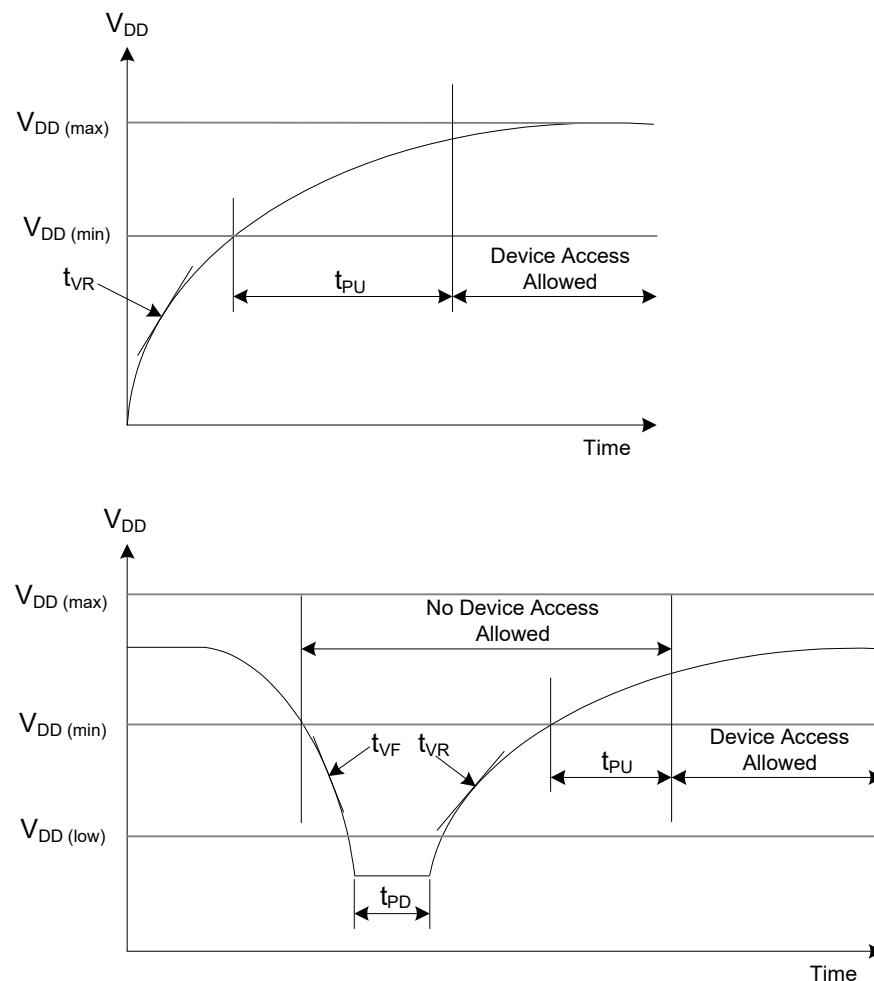

### 3.5 電源投入時から最初のアクセスまで

CY15X102QSN は電源 ( $V_{DD}$ ) が  $V_{DD}(\text{low})$  を下回ると、電源投入サイクルが開始されます。 $V_{DD}$  電源が最小  $V_{DD}(\text{min})$  を超えて上昇するのを待ちます。その後、デバイスは内部起動シーケンスを開始します。この起動シーケンスには、内部パワーオンリセット (POR) が含まれ、その後、内部デバイス設定とトリムレジスタがロードされ、ユーザーがアクセス可能なレジスタが設定されます。ユーザーがアクセスできるすべてのレジスタ (ステータスとコンフィギュレーション、モード、ID、ECC、および CRC) は、起動サイクルが成功した後、デフォルト値に設定されます。Table 3 に、電源投入 (または POR) シーケンスが成功した後の各レジスタのステータスを示します。

$V_{DD}$  が  $V_{DD}(\text{min})$  を超えた瞬間から  $t_{PU}$  の時間遅延が経過するまで、CY15X102QSN はすべての命令を無視します。 $t_{PU}$  が終了するまで、デバイスに命令を送信しないでください。 $t_{PU}$  が経過した後、が HIGH になる場合、デバイスはスタンバイ モードになり、スタンバイ電流 (ISB) を消費します。コンフィギュレーションレジスタ 4 (CR4) の POR 時のディープパワーダウンモード (DPDPOR) が「1」(CR4[2] = 1') に設定されている場合、デバイスは  $t_{PU}$  後にディープパワーダウンモードに入ります。'

ステータスレジスタ 1 の WIP ビット (SR1[0]) は、 $t_{PU}$  時間が経過するまで、RDSR1 を含むコマンドを実行するためにデバイスにアクセスできないため、POR イベント後のデバイスの準備状況をポーリングするために使用できません。ただし、 $t_{PU}$  時間後も WIP ステータスが HIGH のままであるか、デバイスにアクセスできない場合は、デバイスが正しく起動しなかったことを示します (起動エラー)。ブート エラーが発生すると、デバイスは次のデフォルト状態になります。

- ・インターフェースモードはシングル SPI (SDR) に設定されます

- ・CR2 の IO3R ビット (CR2[5]) は、内部で「1」に設定され、IO3 のハードウェアリセット ( $\overline{\text{RESET}}$ ) を有効にします

- ・レジスタ レイテンシは 3 クロック サイクル (最大値) に設定されます

- ・出力インピーダンスは 45 オームに設定されます

- ・SR1 の読み出しは、RDSR1 および RDAR コマンドのみが許可されます (SPI SDR モードのみ)。他のすべてのコマンドは無効になり、実行された場合、未定義データが返されます。

- ・SR1 を読み出すと、ブートエラーシグネチャとして 0x61 が返されます

CY15X102QSN の起動を再開するためには、電源を入れ直すかハードウェアをリセットする必要があります。上記のデフォルト設定は、起動が成功すると実際のユーザー設定に置き換えられます。

## 機能概要

Table 3 POR 後の CY15X102QSN レジスタ ステータス

| 機能                              | レジスタ タイプ                 | POR 後の CY15X102QSN レジスタ ステータス                           |

|---------------------------------|--------------------------|---------------------------------------------------------|

| デバイス ステータス                      | ステータス レジスタ 1 (SR1)       | デフォルトは対応する不揮発性ビット                                       |

|                                 | ステータス レジスタ 2 (SR2)       | 0x00                                                    |

| デバイス コンフィギュレーション <sup>[2]</sup> | コンフィギュレーション レジスタ 1 (CR1) | デフォルトは対応する不揮発性ビット                                       |

|                                 | コンフィギュレーション レジスタ 2 (CR2) | デフォルトは対応する不揮発性ビット                                       |

|                                 | コンフィギュレーション レジスタ 4 (CR4) | デフォルトは対応する不揮発性ビット                                       |

|                                 | コンフィギュレーション レジスタ 5 (CR5) | デフォルトは対応する不揮発性ビット                                       |

| 識別                              | 識別 レジスタ                  | デフォルトは対応する不揮発性ビット (工場出荷時設定)                             |

|                                 | 固有の識別 レジスタ               | デフォルトは対応する不揮発性ビット (工場出荷時設定)                             |

|                                 | シリアル番号 レジスタ              | デフォルトは対応する不揮発性ビット (工場出荷時は 0x0000000000000000 に設定されています) |

| エラー訂正                           | ECC ステータス レジスタ           | 0x00                                                    |

|                                 | ECC カウント レジスタ            | 0x0000                                                  |

|                                 | ECC アドレス トラップ レジスタ       | 0x00000000                                              |

| 巡回冗長検査                          | CRC レジスタ                 | 0x00000000                                              |

注:

2. コンフィギュレーション レジスタ 3 (CR3) は、将来の使用のために予約済みです。

## 4 CY15x102QSN レジスタ

CY15X102QSN はデバイスの状態更新やコンフィギュレーション設定のために各種のステータスおよびコンフィギュレーションレジスタをサポートします。CY15X102QSN のレジスタとアクセス方法の詳細について、以下で説明します。

### 4.1 ステータス レジスタ

CY15X102QSN は、2 つのステータスレジスタ (ステータスレジスタ 1 (SR1) とステータスレジスタ 2 (SR2)) をサポートして、デバイスの書き込み保護設定と準備完了 / CRC ステータスを提供します。SR1 レジスタには、F-RAM に揮発性および関連する不揮発性レジスタスペースがあります。不揮発性レジスタは、電源切断時もデバイス設定を保持し、電源投入時またはハードウェアリセット (JEDEC リセットまたは RESET ピン) 後にそれぞれの揮発性レジスタにコピーされます。CY15X102QSN ステートマシンは、揮発性レジスタ設定のみを使用して、通常のアクセス中にデバイス設定を変更します。CY15X102QSN は、揮発性と不揮発性の両方の設定レジスタに独立したスペースを提供するため、ホストは、現在のパワーサイクルで設定を有効にするためにのみ揮発性レジスタをプログラムできます。不揮発性書き込みは、揮発性レジスタと不揮発性レジスタの両方の内容を変更します。したがって、新しい設定は、現在の電源サイクルだけでなく、後続の電源サイクルまたはハードウェアリセットサイクルでもすぐに有効になります。SR2 は読み出し専用レジスタです。

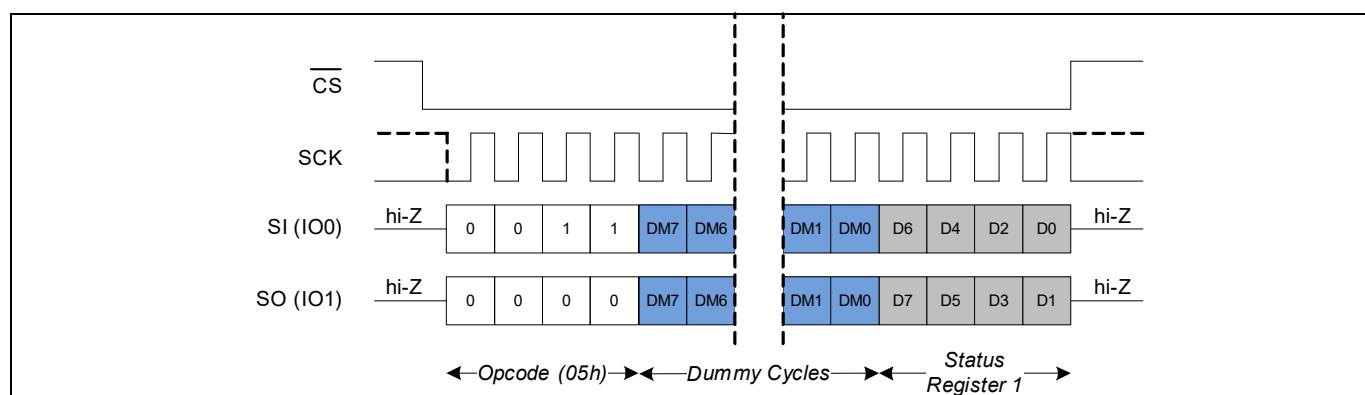

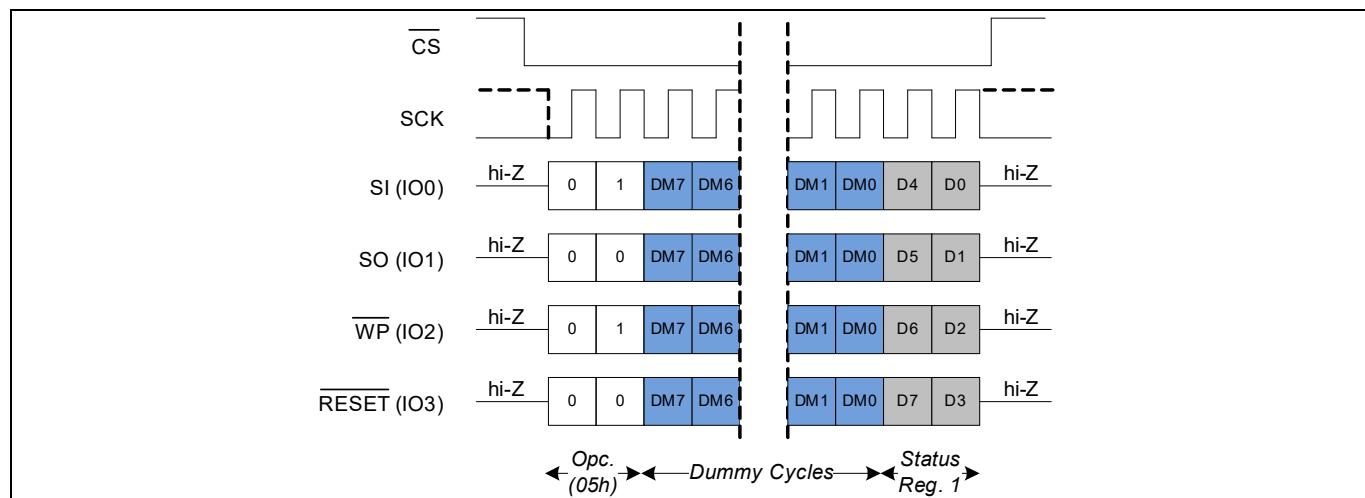

ステータスレジスタからの読み出しへは、専用のステータスレジスタ読み出しオペコード (RDSR1、RDSR2) を使用するか、RDAR に続くステータスレジスタアドレスを使用します。ステータスレジスタの読み出しへは、常に揮発性レジスタの内容を返します。個々のステータスレジスタの詳細は、以下で説明します。

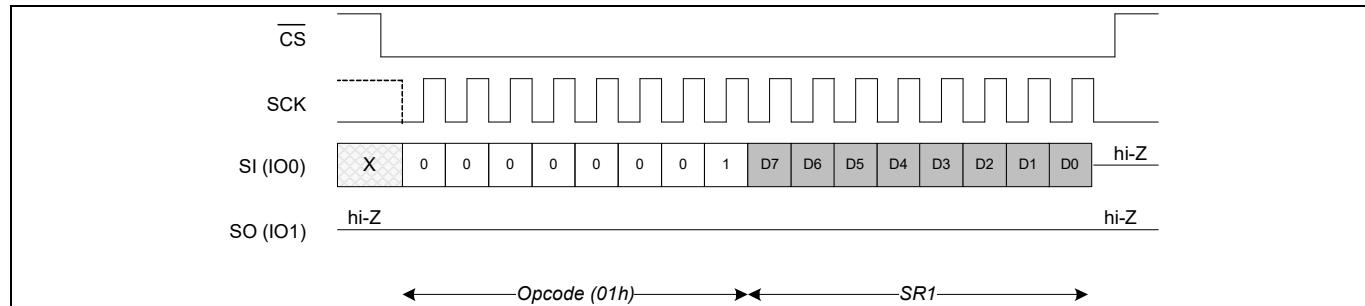

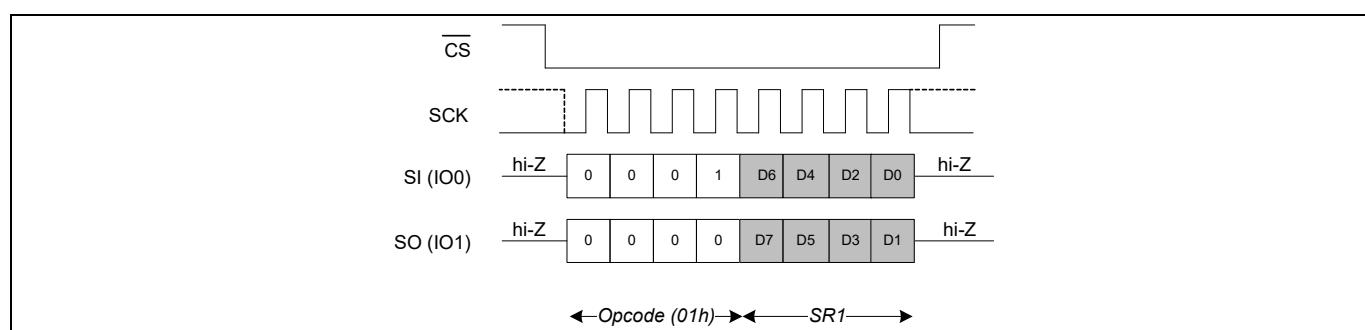

#### 4.1.1 ステータス レジスタ 1 (SR1)

**Table 4** に示すように、ステータスレジスタ 1 (SR1) には、ステータスと書き込み保護の両方の制御ビットが含まれます。SR1 には、書き込みの場合は WRSR および WRAR コマンド、読み出し操作の場合は RDSR1 または RDAR コマンドからアクセスできます。SR1 アクセスの詳細は、[レジスタアクセスのコマンド](#)で説明します。

WRAR 不揮発性書き込みアドレス - 0x000000

WRAR 挥発性書き込みアドレス - 0x070000

RDAR 読み出しアドレス - 0x000000 or 0x070000

**Table 4** の各ビットの後に示されるデフォルトの状態は、工場でプログラムされた値です。

Table 4 ステータス レジスタ 1 (SR1)

| SR1[7]   | SR1[6]  | SR1[5]     | SR1[4]  | SR1[3]  | SR1[2]  | SR1[1]  | SR1[0]  |

|----------|---------|------------|---------|---------|---------|---------|---------|

| SRWD (0) | RFU (0) | TBPROT (0) | BP2 (0) | BP1 (0) | BP0 (0) | WEL (0) | WIP (0) |

Table 5 ステータス レジスタ 1 (SR1) - 不揮発性

| ビット    | ビット名   | ビット機能                | 分類 | 読み出し / 書き込み (R/W) | 説明                                                                                                      |

|--------|--------|----------------------|----|-------------------|---------------------------------------------------------------------------------------------------------|

| SR1[7] | SRWD   | ステータス レジスタ書き込みディセーブル | NV | R/W               | 1 = $\overline{WP}$ が LOW の時、ステータス レジスタとコンフィギュレーション レジスタの状態をロック<br>0 = WP ピンのステータスに関係なく、レジスタ保護なし        |

| SR1[6] | RFU    | 予約済み (0)             |    |                   | 将来の使用のため予約済み                                                                                            |

| SR1[5] | TBPROT | 上位 / 下位関連保護          | NV | R/W               | 1 = 保護はメモリアレイの下位から開始<br>0 = 保護はメモリアレイの上位から開始                                                            |

| SR1[4] | BP2    | ブロック保護ビット            | NV | R/W               | メモリアレイの選択されたアドレス範囲を保護                                                                                   |

| SR1[3] | BP1    |                      | NV |                   |                                                                                                         |

| SR1[2] | BP0    |                      | NV |                   |                                                                                                         |

| SR1[1] | WEL    | 書き込みインエーブル ラッチのセット   | V  | R                 | WEL はデバイスの書き込みが有効かどうかを示します。電源投入時、このビットの初期値は「0」(無効)です。<br>WEL = '1' --> 書き込みが有効<br>WEL = '0' --> 書き込みが無効 |

| SR1[0] | WIP    | 動作中                  | V  | R                 | 1 = デバイス ビジー<br>0 = デバイス レディ                                                                            |

NV - 不揮発性 ; V - 挥発性

Table 6 ステータス レジスタ 1 (SR1) - 挥発性

| ビット    | ビット名   | ビット機能                | 分類 | 読み出し / 書き込み (R/W) | 説明                                                                                                      |

|--------|--------|----------------------|----|-------------------|---------------------------------------------------------------------------------------------------------|

| SR1[7] | SRWD   | ステータス レジスタ書き込みディセーブル | V  | R/W               | 1 = $\overline{WP}$ が LOW の時、ステータス レジスタとコンフィギュレーション レジスタの状態をロック<br>0 = WP ピンのステータスに関係なく、レジスタ保護なし        |

| SR1[6] | RFU    | 予約済み (0)             |    |                   | 将来の使用のため予約済み                                                                                            |

| SR1[5] | TBPROT | 上位 / 下位関連保護          | V  | R/W               | 1 = 保護はメモリアレイの下位から開始<br>0 = 保護はメモリアレイの上位から開始                                                            |

| SR1[4] | BP2    | ブロック保護ビット            | V  | R/W               | メモリアレイの選択されたアドレス範囲を保護                                                                                   |

| SR1[3] | BP1    |                      | V  |                   |                                                                                                         |

| SR1[2] | BP0    |                      | V  |                   |                                                                                                         |

| SR1[1] | WEL    | 書き込みインエーブル ラッチのセット   | V  | R                 | WEL はデバイスの書き込みが有効かどうかを示します。電源投入時、このビットの初期値は「0」(無効)です。<br>WEL = '1' --> 書き込みが有効<br>WEL = '0' --> 書き込みが無効 |

| SR1[0] | WIP    | 動作中                  | V  | R                 | 1 = デバイス ビジー<br>0 = デバイス レディ                                                                            |

V - 挥発性

#### 4.1.1.1 ステータス レジスタ保護 (SRWD) SR1 [7]

このビットは、「1」に設定され、書き込み保護 ( $\overline{WP}$ ) ピンが LOW に駆動されると、ステータス レジスタとコンフィギュレーション レジスタの書き込み保護を有効にします。このモードでは、ステータス レジスタまたはコンフィギュレーション レジスタの内容を変更する命令はすべて無視され、デバイスの状

態を効果的にロックします。SRWD が「0」に設定されている場合、WP ステータス (LOW または HIGH) に関係なく、ステータスおよびコンフィギュレーションレジスタの書き込み保護は無効のままになります。メモリおよびステータスレジスタの保護オプションについては、Table 9 を参照してください。

#### 4.1.1.2 上位と下位アレイの保護 (TBPROT) SR1 [5]

このビットは、ブロック保護ビット BP2, BP1, および BP0 の動作を定義します。このビットは、ブロック保護ビットによって保護されるメモリ配列 (上または下から) メモリの開始点を制御します。

Table 7 上位からの保護の開始 (TBPROT = '0')

| ステータス レジスタの内容 |     |     | メモリアレイの保護部分    | 保護されるアドレス範囲         |

|---------------|-----|-----|----------------|---------------------|

| BP2           | BP1 | BP0 |                |                     |

| 0             | 0   | 0   | 無し             | 無し                  |

| 0             | 0   | 1   | メモリアレイの上位 1/64 | 0x03F000 ~ 0X03FFFF |

| 0             | 1   | 0   | メモリアレイの上位 1/32 | 0x03E000 ~ 0X03FFFF |

| 0             | 1   | 1   | メモリアレイの上位 1/16 | 0x03C000 ~ 0X03FFFF |

| 1             | 0   | 0   | メモリアレイの上位 1/8  | 0x038000 ~ 0X03FFFF |

| 1             | 0   | 1   | メモリアレイの上位 1/4  | 0x030000 ~ 0x03FFFF |

| 1             | 1   | 0   | メモリアレイの上半分     | 0x020000 ~ 0x03FFFF |

| 1             | 1   | 1   | フルメモリ          | 0x000000 ~ 0x03FFFF |

Table 8 下位からの保護の開始 (TBPROT = '1')

| ステータス レジスタの内容 |     |     | メモリアレイの保護部分    | 保護されるアドレス範囲         |

|---------------|-----|-----|----------------|---------------------|

| BP2           | BP1 | BP0 |                |                     |

| 0             | 0   | 0   | 無し             | 無し                  |

| 0             | 0   | 1   | メモリアレイの下位 1/64 | 0x000000 ~ 0x000FFF |

| 0             | 1   | 0   | メモリアレイの下位 1/32 | 0x000000 ~ 0x001FFF |

| 0             | 1   | 1   | メモリアレイの下位 1/16 | 0x000000 ~ 0x003FFF |

| 1             | 0   | 0   | メモリアレイの下位 1/8  | 0x000000 ~ 0x007FFF |

| 1             | 0   | 1   | メモリアレイの下位 1/4  | 0x000000 ~ 0x00FFFF |

| 1             | 1   | 0   | メモリアレイの下半分     | 0x000000 ~ 0x01FFFF |

| 1             | 1   | 1   | フルメモリ          | 0x000000 ~ 0x03FFFF |

#### 4.1.1.3 ブロック保護 (BP2, BP1, および BP0) SR1 [4:2]

これらのビットは、メモリ書き込みコマンドに対して書き込み保護されるメモリアレイを定義します。1つまたは複数の BP ビットが「1」に設定されている場合、それぞれのメモリアドレスは書き込みから保護されます。ブロック保護ビット (BP2, BP1, および BP0) を TBPROT ビットと組み合わせて使用すると、メモリアレイのアドレス範囲を保護できます。範囲のサイズは、BP ビットの値と、TBPROT によって選択された範囲の上限または下限の開始点によって決定されます。Table 7 および Table 8 に、BP[2:0] ビット設定の保護アドレス範囲を示します。

#### 4.1.1.4 書き込みイネーブル ラッチ (WEL) SR1 [1]

Table 9 に示すように、メモリアレイまたはレジスタへの書き込み操作を有効にするためには、WEL ビットを 1 に設定する必要があります。このビットは、書き込みイネーブル (WREN) コマンドを実行することによってのみ「1」に設定されます。WEL ビット (SR1[1]) は、WRDI (04h), WRSR (01h), SSWR (42h), WRAR (71h), および WRSN (C2h) を含むオペコードに従って CS の立ち上りエッジで自動的に「0」にクリアされます。WEL ビット (SR1 [1]) は、メモリ書き込みオペコードに続く CS の立ち上りエッジで「0」にクリアされません。WEL ビットは揮発性であり、POR およびすべてのリセットイベントの後にデフォルトの「0」状態に戻ります。

**Table 9 書き込み保護**

| SRWD | WP | WEL | 保護ブロック | 非保護ブロック | ステータスおよびコンフィギュレーションレジスタ <sup>[3]</sup> |

|------|----|-----|--------|---------|----------------------------------------|

| X    | X  | 0   | 保護     | 保護      | 保護                                     |

| 0    | X  | 1   | 保護     | 書き込み可能  | 書き込み可能                                 |

| 1    | 0  | 1   | 保護     | 書き込み可能  | 保護                                     |

| 1    | 1  | 1   | 保護     | 書き込み可能  | 書き込み可能                                 |

注:

- 読み出し専用ビットと予約済みビットを除くすべてのビット。

#### 4.1.1.5 動作中 (WIP) SR1 [0]

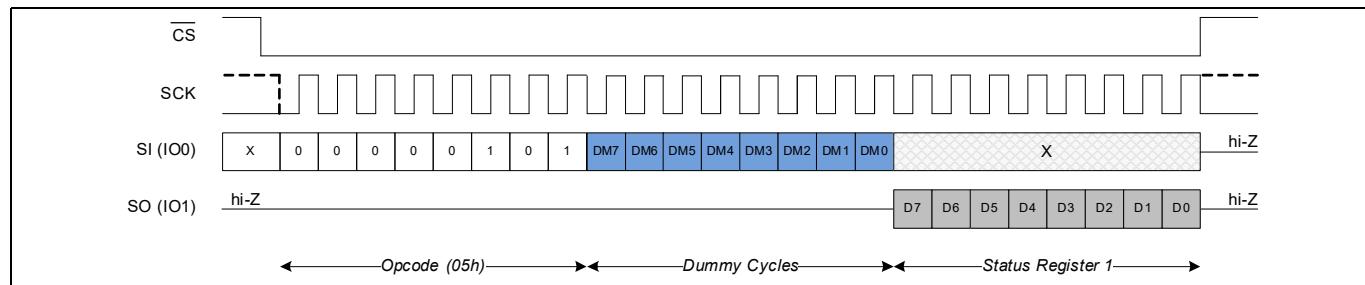

これは読み出し専用ビットであり、通常の動作中のデバイスの準備完了またはビジー状態を示します。CRC 計算の実行中に、このビットを「1」に設定します。他のコマンドおよびイベントは、で WIP を「1」に設定しません。WIP が「1」の場合、は RDSR1/RDSR2 または Read Any Register (RDAR の後にステータスレジスタアドレス ), CRC Suspend (EPCS), および Software Reset (RSTEN の後に RST) コマンドを使用してステータスレジスタの読み出しのみを実行できます。WIP が「1」の場合、他のコマンドは無視されます。WIP ビットを使用して、電源投入またはリセットサイクル中にデバイスの準備完了ステータスをポーリングできません。このビットは揮発性であり、POR およびすべてのリセットイベントの後にデフォルト状態に戻ります。

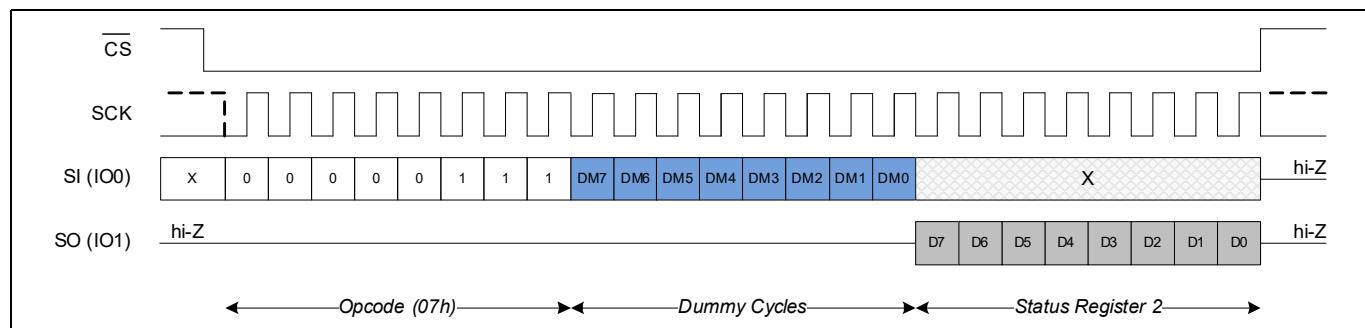

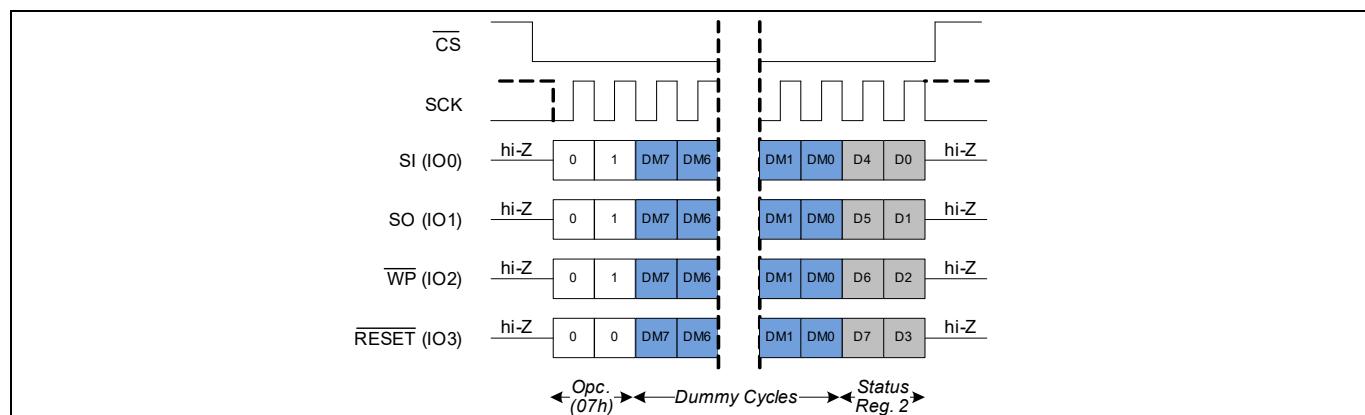

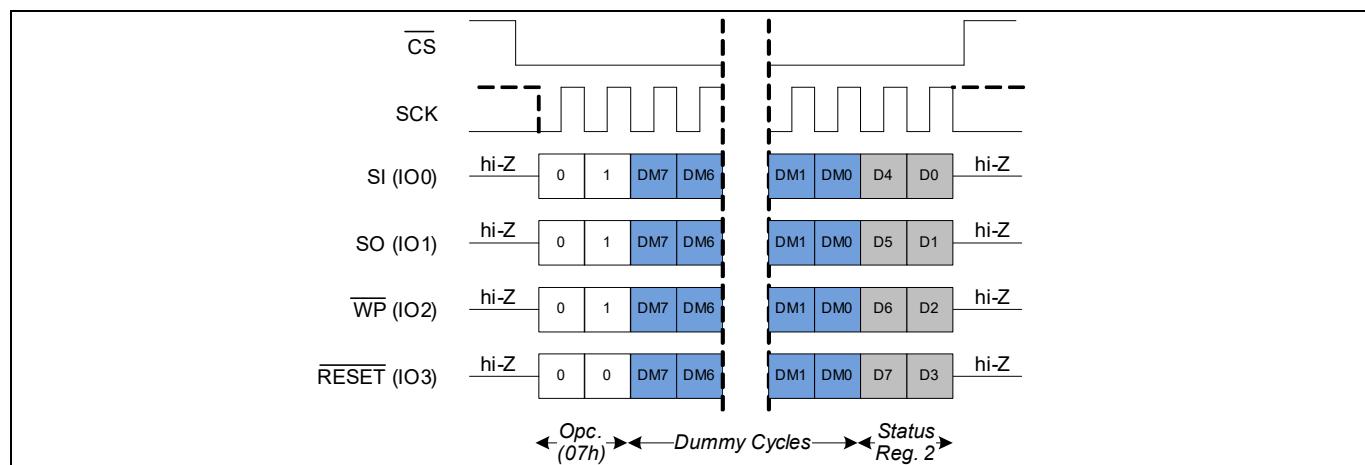

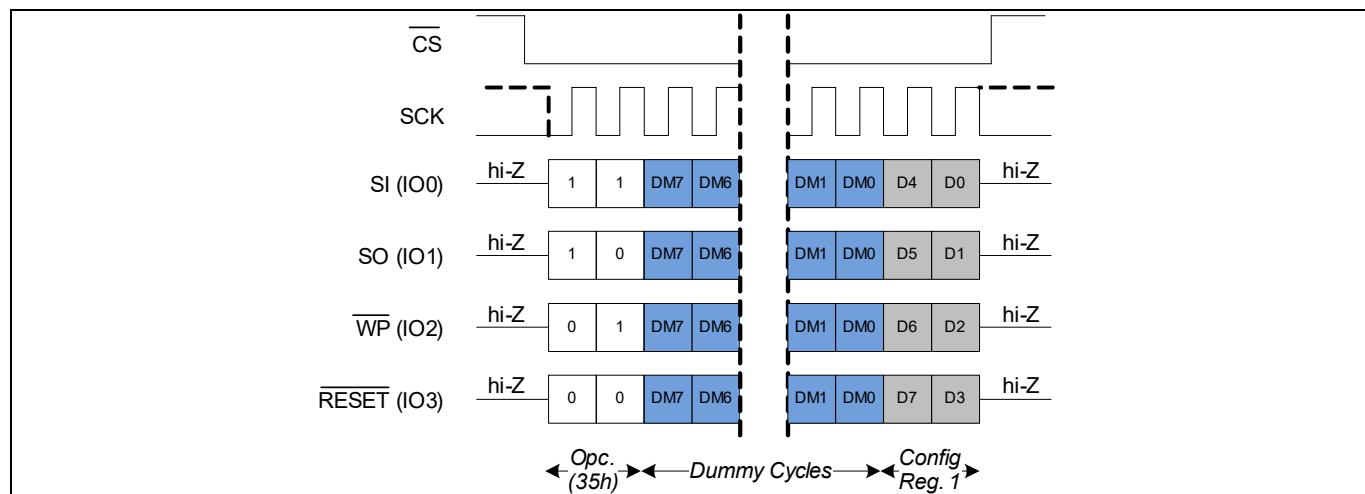

#### 4.1.2 ステータス レジスタ 2 (SR2)

**Table 10** に示すように、ステータスレジスタ 2 (SR2) は、CRC 操作のデバイスステータスを提供します。SR2 は読み出し専用の揮発性レジスタであり、RDSR2 または読み出し操作用の RDAR コマンドからアクセスできます。SR1 アクセスの詳細は、[レジスタアクセスのコマンド](#)に記載されています。

RDAR 読み出しアドレス -0x000001 または 0x070001

**Table 11** の各ビットの後に示されるデフォルトの状態は、工場でプログラムされた値です。

**Table 10 ステータス レジスタ 2 (SR2)**

| SR2[7]  | SR2[6]  | SR2[5]  | SR2[4]   | SR2[3]   | SR2[2]  | SR2[1]  | SR2[0]  |

|---------|---------|---------|----------|----------|---------|---------|---------|

| RFU (0) | RFU (0) | RFU (0) | CRCS (0) | CRCA (0) | RFU (0) | RFU (0) | RFU (0) |

**Table 11 ステータス レジスタ 2 (SR2) - 挥発性のみ**

| ビット    | ビット名 | ビット機能      | 分類 | 読み出し / 書き込み (R/W) | 説明                                               |

|--------|------|------------|----|-------------------|--------------------------------------------------|

| SR2[7] | RFU  | 予約済み (0)   |    |                   | 将来の使用のため予約済み                                     |

| SR2[6] | RFU  | 予約済み (0)   |    |                   | 将来の使用のため予約済み                                     |

| SR2[5] | RFU  | 予約済み (0)   |    |                   | 将来の使用のため予約済み                                     |

| SR2[4] | CRCS | CRC サスPEND | V  | R                 | 1 = CRC サスPEND モードの場合<br>0 = CRC サスPEND モードでない場合 |

| SR2[3] | CRCA | CRC 中止     | V  | R                 | 1 = CRC コマンドは中止<br>0 = CRC コマンドは中止されません          |

| SR2[2] | RFU  | 予約済み (0)   |    |                   | 将来の使用のため予約済み                                     |

| SR2[1] | RFU  | 予約済み (0)   |    |                   | 将来の使用のため予約済み                                     |

| SR2[0] | RFU  | 予約済み (0)   |    |                   | 将来の使用のため予約済み                                     |

V - 挥発性

#### 4.1.2.1 CRC サスペンド (CRCS) SR2 [4]

CRC サスペンド (CRCS) ビットは、デバイスが CRC サスペンドモードであるかどうかを判別するために使用されます。デバイスの CRC 計算が進行中の場合、CRC サスペンドコマンド (EPCS) を実行すると、このビットが「1」に設定され、CRC サスペンドステータスが示されます。CRC 再開 (EPCR) コマンドは、CRCS ビットを「0」にクリアし、デバイスが CRC サスペンドモードを終了したことを示します。これは読み出し専用ビットです。このビットは、リセット (POR, ハードウェア, およびソフトウェア) 後にもクリアされます。

#### 4.1.2.2 CRC 中止 (CRCA) SR2 [3]

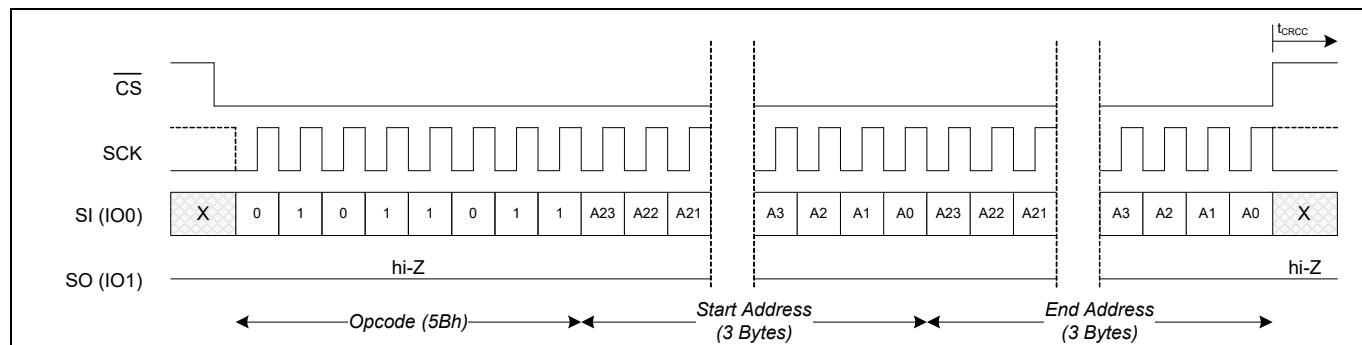

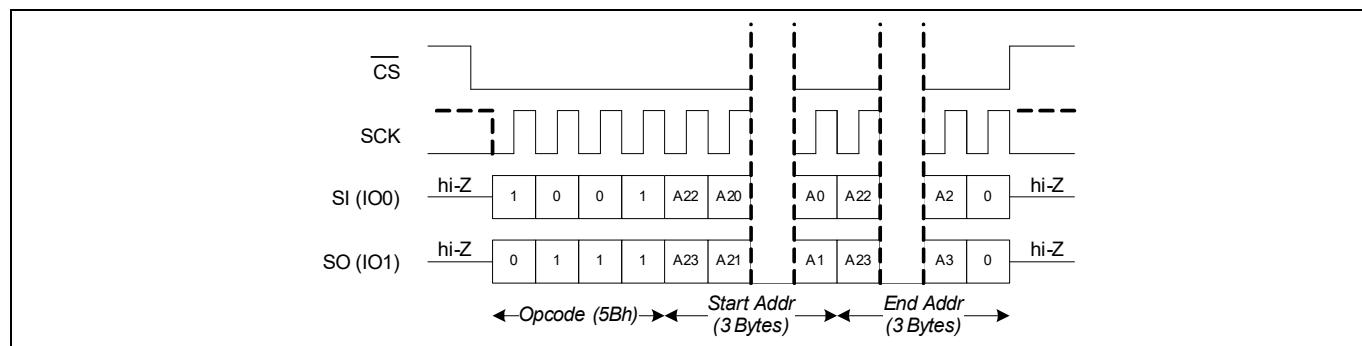

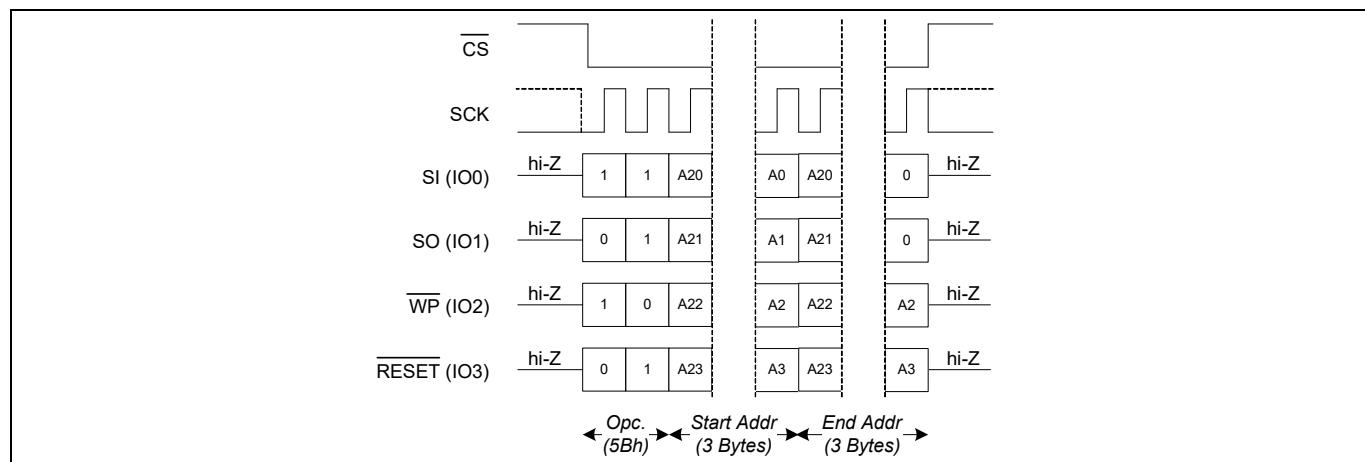

このビットは、CRC 計算 (CRCC) 操作が中止されるかどうかを示します。CRC 計算は、終了アドレスと開始アドレスの基準 ( $EA < SA + 3$ ) が満たされない場合に中止されます。これは、終了アドレスが開始アドレスより少なくとも 32 ビット整列されたワード高い必要があります。このビットは、後続の CRC 計算が正常に開始されるとクリアされます。このビットは、リセット後にもクリアされます (POR, ハードウェア, およびソフトウェア)。

### 4.2 コンフィギュレーションレジスタ

CY15X102QSN は、デバイスのさまざまな制御をプログラムするために、4 つのユーザー コンフィギュレーションレジスタ (CR1, CR2, CR4, および CR5) をサポートします。各コンフィギュレーションレジスタには、F-RAM に揮発性および関連する不揮発性レジスタスペースがあります。不揮発性レジスタは、電源切断時にデバイス設定を保持し、電源投入時またはハードウェアリセット (JEDEC リセットまたは RESET ピン) 後にそれぞれの揮発性レジスタにコピーされます。ステートマシンは、揮発性レジスタ設定のみを使用して、通常のアクセス中にデバイス設定を変更します。CY15X102QSN は、揮発性と不揮発性の両方のコンフィギュレーションレジスタに独立したスペースを提供するため、ホストは、現在のパワーサイクルで設定を有効にするためにのみ揮発性レジスタをプログラムできます。不揮発性書き込みは、揮発性レジスタと不揮発性レジスタの両方の内容を変更します。したがって、新しいコンフィギュレーションは、現在の電源サイクルだけでなく、後続の電源サイクルまたはハードウェアリセットサイクルでもすぐに有効になります。

専用のコンフィギュレーションレジスタ読み出しオペコード (RDCR1, RDCR2, RDCR3, RDCR4) を使用してコンフィギュレーションレジスタから読み出すか、RDAR は常に揮発性レジスタの内容を返します。個々のコンフィギュレーションレジスタの詳細は、以下で説明します。

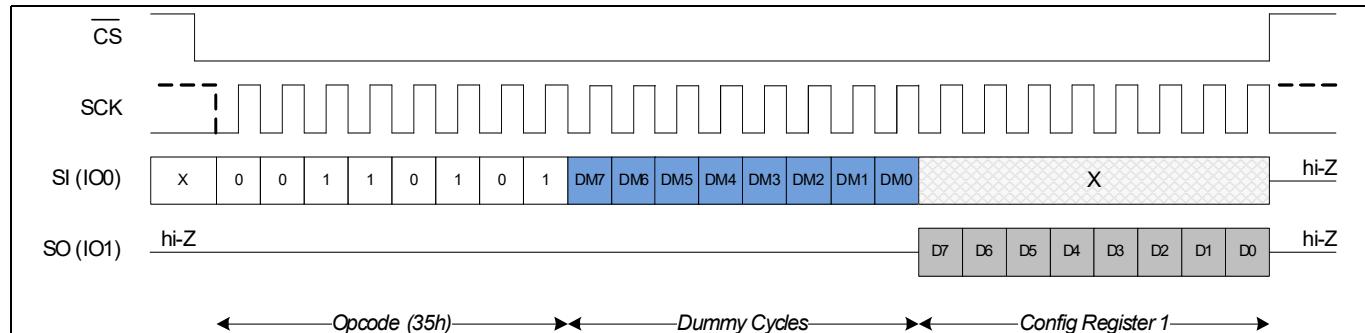

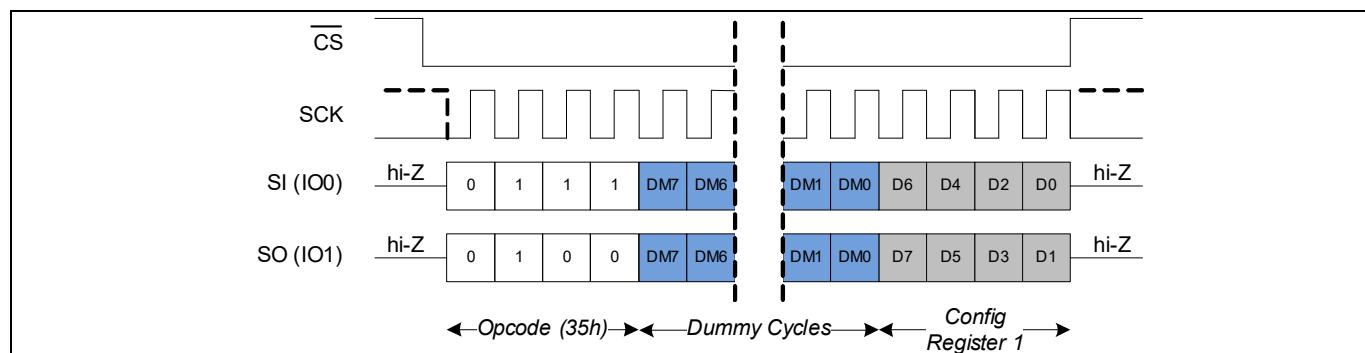

#### 4.2.1 コンフィギュレーションレジスタ 1 (CR1)

**Table 12** に示すように、コンフィギュレーションレジスタ 1 (CR1) は、メモリおよび特殊セクタの読み出しの遅延 (ダミー) サイクルを設定し、拡張 SPI アクセス中にクアッド I/O を有効にします。CR1 には、書き込みの場合は WRAR コマンド、読み出し操作の場合は RDAR コマンドからアクセスできます。CR1 アクセスの詳細は、[レジスタアクセスのコマンド](#)で説明します。

WRAR 不揮発性書き込みアドレス - 0x000002

WRAR 挥発性書き込みアドレス - 0x070002

RDAR 読み出しあドレス - 0x000002 または 0x070002

**Table 12** の各ビットの後に示されているデフォルトの状態は、工場でプログラムされた値です。

**Table 12 コンフィギュレーションレジスタ 1 (CR1)**

| CR1[7]   | CR1[6]   | CR1[5]   | CR1[4]   | CR1[3]  | CR1[2]  | CR1[1]   | CR1[0]  |

|----------|----------|----------|----------|---------|---------|----------|---------|

| MLC3 (0) | MLC2 (0) | MLC1 (0) | MLC0 (0) | RFU (0) | RFU (0) | QUAD (0) | RFU (0) |

**Table 13 コンフィギュレーションレジスタ 1(CR1) - 不揮発性**

| ビット    | ビット名 | ビット機能               | 分類 | 読み出し / 書き込み (R/W) | 説明                                                                                                        |  |

|--------|------|---------------------|----|-------------------|-----------------------------------------------------------------------------------------------------------|--|

| CR1[7] | MLC3 | メモリ<br>レイテンシ<br>コード | NV | R/W               | メモリおよび特殊セクタ読み出しオペコードの<br>レイテンシ(ダミー)サイクル数を設定します。<br>例:<br>0000 - 0 サイクル<br>0110 - 6 サイクル<br>1111 - 15 サイクル |  |

| CR1[6] | MLC2 |                     | NV |                   |                                                                                                           |  |

| CR1[5] | MLC1 |                     | NV |                   |                                                                                                           |  |

| CR1[4] | MLC0 |                     | NV |                   |                                                                                                           |  |

| CR1[3] | RFU  | 予約済み (0)            |    |                   | 将来の使用のため予約済み                                                                                              |  |

| CR1[2] | RFU  | 予約済み (0)            |    |                   | 将来の使用のため予約済み                                                                                              |  |

| CR1[1] | QUAD | クアッド                | NV | R/W               | 1 = クアッド<br>0 = デュアルまたはシリアル                                                                               |  |

| CR1[0] | RFU  | 予約済み (0)            |    |                   | 将来の使用のため予約済み                                                                                              |  |

NV - 不揮発性

**Table 14 コンフィギュレーションレジスタ 1(CR1) - 挥発性**

| ビット    | ビット名 | ビット機能               | 分類 | 読み出し / 書き込み (R/W) | 説明                                                                                                        |  |

|--------|------|---------------------|----|-------------------|-----------------------------------------------------------------------------------------------------------|--|

| CR1[7] | MLC3 | メモリ<br>レイテンシ<br>コード | V  | R/W               | メモリおよび特殊セクタ読み出しオペコードの<br>レイテンシ(ダミー)サイクル数を設定します。<br>例:<br>0000 - 0 サイクル<br>0110 - 6 サイクル<br>1111 - 15 サイクル |  |

| CR1[6] | MLC2 |                     | V  |                   |                                                                                                           |  |

| CR1[5] | MLC1 |                     | V  |                   |                                                                                                           |  |

| CR1[4] | MLC0 |                     | V  |                   |                                                                                                           |  |

| CR1[3] | RFU  | 予約済み (0)            |    |                   | 将来の使用のため予約済み                                                                                              |  |

| CR1[2] | RFU  | 予約済み (0)            |    |                   | 将来の使用のため予約済み                                                                                              |  |

| CR1[1] | QUAD | クアッド                | V  | R/W               | 1 = クアッド<br>0 = デュアルまたはシリアル                                                                               |  |

| CR1[0] | RFU  | 予約済み (0)            |    |                   | 将来の使用のため予約済み                                                                                              |  |

V - 挥発性

#### 4.2.1.1 メモリ レイテンシ コード (MLC) CR1 [7:4]

これらの 4 ビットは、すべての可変レイテンシメモリ読み出し命令のレイテンシ(ダミー)サイクルを設定します。これにより、ユーザーは通常の操作中にメモリ読み出しレイテンシを調整して、さまざまな動作周波数でのさまざまな命令のレイテンシを最適化できます。ダミーサイクルは、SPI モードとデータレート (SDR と DDR) に関係なく、SCK のフルクロックサイクルです。

一部の読み出しオペコードは、アドレスサイクルに続くダミーサイクルをサポートします。これらのダミーサイクルは、データがホストシステムに返される前に、メモリアレイの初期読み出しみを完了するために必要な追加の遅延を提供します。SPI クロック (SCK) の周波数が高くなると、レイテンシを満たすためにダミーサイクルの数を増やす必要があります。

**Table 15 ~ Table 17** に、ダミーサイクルをサポートする各オペコードの最大 SPI クロック周波数とクロックレイテンシを示します。ホストコントローラーは、各オペコードに個別の遅延サイクルを設定することでタイミングを最適化するか、目的の動作周波数ですべてのオペコードの遅延要件を満たす最悪の場合の遅延を設定できます。より高い周波数に設定されたメモリ読み出しレイテンシは、すべてのより低い周波数にも適用されます。したがって、ホストが SPI クロック (SCK) を高い周波数から低い周波数に下げる場合、クロック遅延の調整はオプションになります。

**Table 15** ヘッダーの形式 (CMD, ADD, DATA) は、さまざまな SPI モードでの I/O の数に対するこれらのバイトの送信を表します。次に例を示します。(2, 2, 2) は、すべてのコマンド (CMD), アドレス (ADDR), および

# 2M ビット EXCELON™ Ultra 強誘電体 RAM (F-RAM) シリアル ( クアッド SPI ), 256K × 8, 108 MHz, 産業用

CY15x102QSN レジスタ

データ (DATA) バイトが DPI モードの 2 つの I/O (I/O0 および I/O1) を介して送信されることを表します。同様に、(1, 2, 2) は、CMD バイトがシングル I/O (I/O0) を介して送信されるのに対し、ADDR および DATA バイトはデュアル I/O モードの 2 つの I/O (I/O0, I/O1) を介して送信されることを表します。(1, 1, 4) は CMD を表し、ADDR バイトは単一の I/O (I/O0) で送信され、DATA バイトはクアッドデータモードの 4 つの I/O (I/O0, I/O1, I/O2, I/O3) で送信されます。

モードは、アドレスビットの後にモードバイトを送信するためにさまざまな SPI インターフェースモードで必要なクロックサイクル数を表します。モードビットはアドレスサイクルの後に送信されるため、モードビットの送信に必要なクロックサイクルは内部でレイテンシ計算に追加されます。

**Table 15 メモリ読み出しコマンドのレイテンシ (ダミー) サイクル - XIP モード (SDR) を使用**

| レイテンシ<br>(ダミー)<br>サイクル -<br>10 進数 | SPI (SDR) | DPI (SDR)             | QPI (SDR)             | デュアル<br>データ<br>(SDR) | デュアル<br>I/O (SDR)     | クアッド<br>データ<br>(SDR) | クアッド<br>I/O (SDR)     |

|-----------------------------------|-----------|-----------------------|-----------------------|----------------------|-----------------------|----------------------|-----------------------|

|                                   | FAST_READ | FAST_READ             | FAST_READ,<br>QIOR    | DOR                  | DIOR                  | QOR                  | QIOR                  |

|                                   | (1, 1, 1) | (2, 2, 2)             | (4, 4, 4)             | (1, 1, 2)            | (1, 2, 2)             | (1, 1, 4)            | (1, 4, 4)             |

|                                   | Mode = 8  | Mode = 4              | Mode = 2              | Mode = 8             | Mode = 4              | Mode = 8             | Mode = 2              |

| 0                                 | 108 MHz   | 55 MHz <sup>[4]</sup> | 10 MHz <sup>[4]</sup> | 108 MHz              | 55 MHz <sup>[4]</sup> | 108 MHz              | 10 MHz <sup>[4]</sup> |

| 1                                 | 108 MHz   | 70 MHz <sup>[4]</sup> | 25 MHz <sup>[4]</sup> | 108 MHz              | 70 MHz <sup>[4]</sup> | 108 MHz              | 25 MHz <sup>[4]</sup> |

| 2                                 | 108 MHz   | 80 MHz <sup>[4]</sup> | 40 MHz <sup>[4]</sup> | 108 MHz              | 80 MHz <sup>[4]</sup> | 108 MHz              | 40 MHz <sup>[4]</sup> |

| 3                                 | 108 MHz   | 95 MHz <sup>[4]</sup> | 55 MHz <sup>[4]</sup> | 108 MHz              | 95 MHz <sup>[4]</sup> | 108 MHz              | 55 MHz <sup>[4]</sup> |

| 4                                 | 108 MHz   | 108 MHz               | 70 MHz <sup>[4]</sup> | 108 MHz              | 108 MHz               | 108 MHz              | 70 MHz <sup>[4]</sup> |

| 5                                 | 108 MHz   | 108 MHz               | 80 MHz <sup>[4]</sup> | 108 MHz              | 108 MHz               | 108 MHz              | 80 MHz <sup>[4]</sup> |

| 6                                 | 108 MHz   | 108 MHz               | 95 MHz <sup>[4]</sup> | 108 MHz              | 108 MHz               | 108 MHz              | 95 MHz <sup>[4]</sup> |

| 7-15                              | 108 MHz   | 108 MHz               | 108 MHz               | 108 MHz              | 108 MHz               | 108 MHz              | 108 MHz               |

注:

- このパラメータは特性によって保証され、量産中にテストされません。

**Table 16 メモリ読み出しコマンドのレイテンシ (ダミー) サイクル - XIP モード (DDR) を使用**

| レイテンシ<br>(ダミー)<br>サイクル -<br>10 進数 | QPI (DDR)             |  | クアッド I/O (DDR)        |

|-----------------------------------|-----------------------|--|-----------------------|

|                                   | DDRFR, DDRQIOR        |  | DDRQIOR               |

|                                   | (4, 4, 4)             |  | (1, 4, 4)             |

|                                   | モード = 1               |  | モード = 1               |

| 0                                 | 該当なし                  |  | 該当なし                  |

| 1                                 | 該当なし                  |  | 該当なし                  |

| 2                                 | 10 MHz <sup>[5]</sup> |  | 10 MHz <sup>[5]</sup> |

| 3                                 | 25 MHz <sup>[5]</sup> |  | 25 MHz <sup>[5]</sup> |

| 4                                 | 33 MHz <sup>[5]</sup> |  | 33 MHz <sup>[5]</sup> |

| 5                                 | 40 MHz <sup>[5]</sup> |  | 40 MHz <sup>[5]</sup> |

| 6                                 | 50 MHz <sup>[5]</sup> |  | 50 MHz <sup>[5]</sup> |

| 7-15                              | 54 MHz                |  | 54 MHz                |

注:

- このパラメータは特性によって保証され、量産中にテストされません。

**Table 17 メモリ読み出しコマンドのレイテンシ(ダミー)サイクル - XIP モードなし**

| レイテンシ(ダミー)サイクル-10進数 | SPI (SDR)             | DPI (SDR)             | QPI (SDR)             |

|---------------------|-----------------------|-----------------------|-----------------------|

|                     | READ, ECCRD, SSRD     |                       |                       |

|                     | (1, 1, 1)             | (2, 2, 2)             | (4, 4, 4)             |

| モード = 該当なし          | モード = 該当なし            | モード = 該当なし            | モード = 該当なし            |

| 0                   | 40 MHz <sup>[6]</sup> | 該当なし                  | 該当なし                  |

| 1                   | 55 MHz <sup>[6]</sup> | 該当なし                  | 該当なし                  |

| 2                   | 70 MHz <sup>[6]</sup> | 25 MHz <sup>[6]</sup> | 10 MHz <sup>[6]</sup> |

| 3                   | 80 MHz <sup>[6]</sup> | 40 MHz <sup>[6]</sup> | 25 MHz <sup>[6]</sup> |

| 4                   | 95 MHz <sup>[6]</sup> | 55 MHz <sup>[6]</sup> | 40 MHz <sup>[6]</sup> |

| 5                   | 108 MHz               | 70 MHz <sup>[6]</sup> | 55 MHz <sup>[6]</sup> |

| 6                   | 108 MHz               | 80 MHz <sup>[6]</sup> | 70 MHz <sup>[6]</sup> |

| 7                   | 108 MHz               | 95 MHz <sup>[6]</sup> | 80 MHz <sup>[6]</sup> |

| 8                   | 108 MHz               | 108 MHz               | 95 MHz <sup>[6]</sup> |

| 9-15                | 108 MHz               | 108 MHz               | 108 MHz               |

注:

6. このパラメータは特性によって保証され、量産中にテストされません。

#### 4.2.1.2 クアッドデータ幅(QUAD) CR1 [1]

「1」に設定すると、このビットはデバイスのデータ幅を 4 I/O に切り替えます。クアッドモード、つまり WP は I/O2 になり、RESET/(I/O3) は I/O3 になります。コンフィギュレーションレジスタ 2 (CR2[5]) の IO3R ビットをセットして I/O3 で代替機能を有効にすると、CS が Low のときは RESET/(I/O3) が I/O3 として機能し、CS が High のときは RESET 入力として機能します。WP 入力は無効になっており、内部的に「1」に設定されます。拡張 SPI 読み出しコマンド (クアッド出力読み出し、クアッド I/O 読み出し、および DDR クアッド I/O 読み出し) を実行するときは、QUAD ビットを「1」に設定する必要があります。さまざまな SPI インターフェースに対する「QUAD」ビット設定の影響を [Table 21](#) に示します。

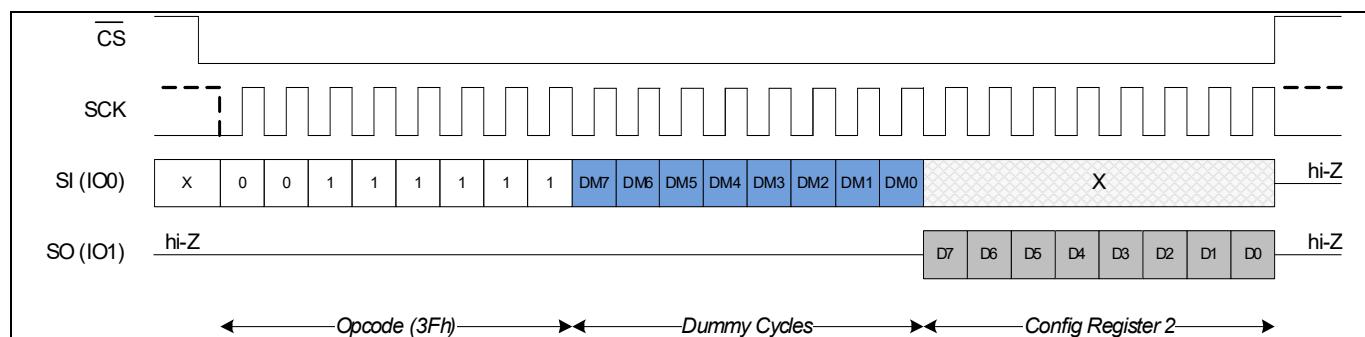

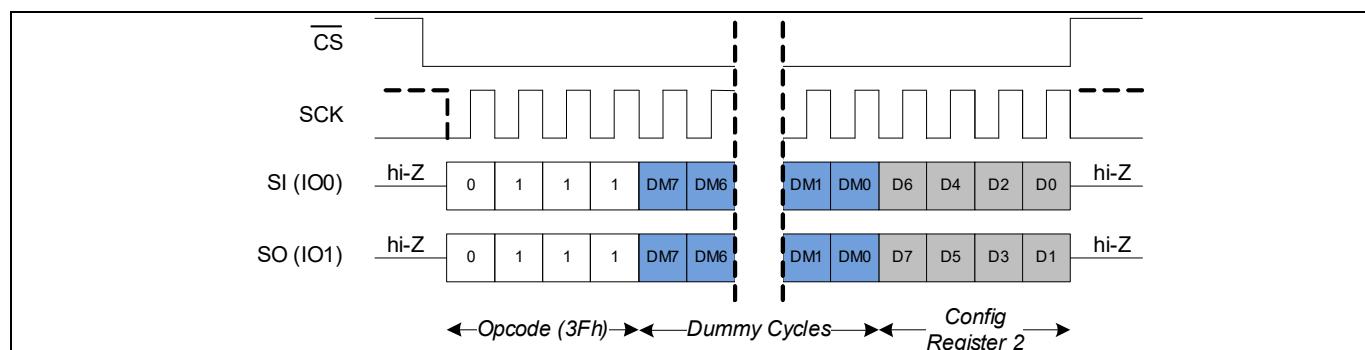

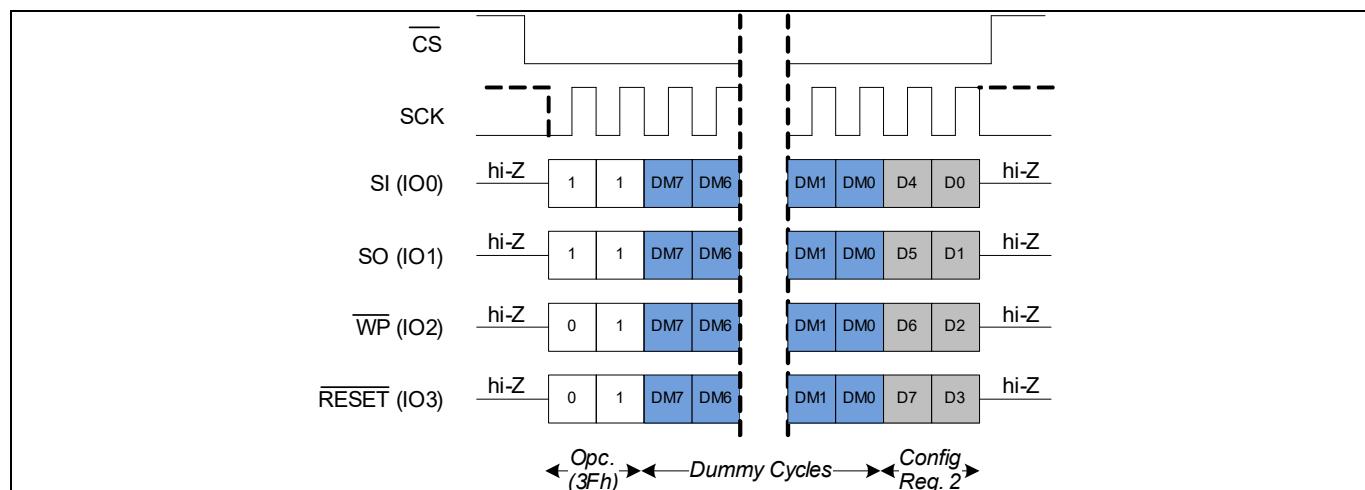

#### 4.2.2 コンフィギュレーションレジスタ 2 (CR2)

[Table 18](#) に示すように、コンフィギュレーションレジスタ 2 (CR2) は、シリアルインターフェース設定を制御します。CR2 には、書き込みの場合は WRAR コマンド、読み出し操作の場合は RDRC2 または RDAR コマンドからアクセスできます。CR2 アクセスの詳細は、[レジスタアクセスのコマンド](#)で説明します。

WRAR 不揮発性書き込みアドレス - 0x000003

WRAR 挥発性書き込みアドレス - 0x070003

RDAR 読み出しアドレス - 0x000003 または 0x070003

[Table 18](#) の各ビットの後に示されるデフォルトの状態は、工場でプログラムされた値です。

**Table 18 コンフィギュレーションレジスタ 2 (CR2)**

| CR2[7]  | CR2[6]  | CR2[5]   | CR2[4]  | CR2[3]  | CR2[2]  | CR2[1]  | CR2[0]  |

|---------|---------|----------|---------|---------|---------|---------|---------|

| RFU (0) | QPI (0) | IO3R (0) | DPI (0) | RFU (0) | RFU (0) | RFU (0) | RFU (0) |

**Table 19 コンフィギュレーションレジスタ 2 (CR2) - 不揮発性**

| ビット    | ビット名 | ビット機能          | 分類 | 読み出し / 書き込み (R/W) | 説明                                                                                         |

|--------|------|----------------|----|-------------------|--------------------------------------------------------------------------------------------|

| CR2[7] | RFU  | 予約済み (0)       |    |                   | 将来の使用のため予約済み                                                                               |

| CR2[6] | QPI  | クアッド SPI イネーブル | NV | R/W               | 1=QPI プロトコルを有効にします<br>0=DPI ビットが「0」に設定されている場合、SPI プロトコルを有効にします                             |

| CR2[5] | IO3R | IO3 リセット       | NV | R/W               | 1= $\overline{CS}$ が HIGH の場合、I/O3 が $\overline{RESET}$ 入力として使用されます<br>0=I/O3 には代替機能がありません |

| CR2[4] | DPI  | デュアル SPI イネーブル | NV | R/W               | 1=DPI プロトコルを有効にします<br>0=QPI ビットが「0」に設定されている場合、SPI プロトコルを有効にします                             |

| CR2[3] | RFU  | 予約済み (0)       |    |                   | 将来の使用のため予約済み                                                                               |

| CR2[2] | RFU  | 予約済み (0)       |    |                   | 将来の使用のため予約済み                                                                               |

| CR2[1] | RFU  | 予約済み (0)       |    |                   | 将来の使用のため予約済み                                                                               |

| CR2[0] | RFU  | 予約済み (0)       |    |                   | 将来の使用のため予約済み                                                                               |

NV - 不揮発性

**Table 20 コンフィギュレーションレジスタ 2 (CR2) - 挥発性**

| ビット    | ビット名 | ビット機能          | 分類 | 読み出し / 書き込み (R/W) | 説明                                                                                         |

|--------|------|----------------|----|-------------------|--------------------------------------------------------------------------------------------|

| CR2[7] | RFU  | 予約済み (0)       |    |                   | 将来の使用のため予約済み                                                                               |

| CR2[6] | QPI  | クアッド SPI イネーブル | V  | R/W               | 1=QPI プロトコルを有効にします<br>0=DPI ビットが「0」に設定されている場合、SPI プロトコルを有効にします                             |

| CR2[5] | IO3R | IO3 リセット       | V  | R/W               | 1= $\overline{CS}$ が HIGH の場合、I/O3 が $\overline{RESET}$ 入力として使用されます<br>0=I/O3 には代替機能がありません |

| CR2[4] | DPI  | デュアル SPI イネーブル | V  | R/W               | 1=DPI プロトコルを有効にします<br>0=QPI ビットが「0」に設定されている場合、SPI プロトコルを有効にします                             |

| CR2[3] | RFU  | 予約済み (0)       |    |                   | 将来の使用のため予約済み                                                                               |

| CR2[2] | RFU  | 予約済み (0)       |    |                   | 将来の使用のため予約済み                                                                               |

| CR2[1] | RFU  | 予約済み (0)       |    |                   | 将来の使用のため予約済み                                                                               |

| CR2[0] | RFU  | 予約済み (0)       |    |                   | 将来の使用のため予約済み                                                                               |

NV - 不揮発性

#### 4.2.2.1 クアッド SPI (QPI) CR2 [6]

このビットは、クアッド SPI モードの命令幅とデータ幅を制御します。このモードでは、ホストシステムとメモリ間のすべての転送は、すべての命令を含め、I/O0 ~ I/O3 で 4 ビット幅です。CR1[1] の QUAD ビットセット「1」は不要であるため、QPI モードでは無視されます。詳細については、Table 22 を参照してください。

#### 4.2.2.2 IO3 リセット (IO3R) CR2 [5]

このビットは、RESET/(I/O3) ピンの動作を制御します。このビットが「1」に設定されている場合、通常動作中に RESET 入力を有効にします。[Table 21](#) に、インターフェースモードに基づく RESET/(I/O3) 機能を示します。

#### 4.2.2.3 デュアル (DPI) CR2 [4]

このビットは、デュアル SPI モードの命令幅とデータ幅を制御します。このモードでは、ホストシステムとメモリ間のすべての転送は、すべての命令を含め、I/00 ~ I/01 で 2 ビット幅です。詳細については、[Table 22](#) を参照してください。

**Table 21** RESET / (I/O3) ピン機能

| インターフェースモード | クアッドビット (CR1 <sup>[7]</sup> ) | RESET / (I/O3) ピン機能                   |        |                                      |              |

|-------------|-------------------------------|---------------------------------------|--------|--------------------------------------|--------------|

|             |                               | IO3R (CR2[5]) = 0<br>(IO3 リセットディセーブル) |        | IO3R (CR2[5]) = 1<br>(IO3 リセットイネーブル) |              |

|             |                               | CS = 0                                | CS = 1 | CS = 0                               | CS = 1       |

| SPI         | QUAD = '0'                    | 機能なし                                  | 機能なし   | <u>RESET</u>                         | <u>RESET</u> |

| SPI         | QUAD = '1'                    | I/O3 <sup>[8]</sup>                   | 機能なし   | I/O3 <sup>[8]</sup>                  | <u>RESET</u> |

| DPI         | QUAD = '0'                    | 機能なし                                  | 機能なし   | <u>RESET</u>                         | <u>RESET</u> |

| DPI         | QUAD = '1'                    | 機能なし                                  | 機能なし   | 機能なし                                 | <u>RESET</u> |

| QPI         | QUAD = x (ドントケア)              | I/O3                                  | 機能なし   | I/O3                                 | <u>RESET</u> |

注:

7. すべての拡張 SPI は SPI モードで起動します。

8. SPI および DPI モードでは機能しません。クアッドデータまたはクアッド I/O モードの I/O3。

**Table 22** SPI 動作モード設定

| QUAD <sup>[10]</sup><br>CR1 <sup>[9]</sup> | DPI<br>CR2 <sup>[9]</sup> | QPI<br>CR2 <sup>[9]</sup> | 動作モード                                                       |

|--------------------------------------------|---------------------------|---------------------------|-------------------------------------------------------------|

| 0                                          | 0                         | 0                         | SPI, 拡張 SPI (デュアル)                                          |

| 1                                          | 0                         | 0                         | SPI, 拡張 SPI (デュアル / クアッド)                                   |

| X                                          | 1                         | 0                         | DPI                                                         |

| X                                          | 0                         | 1                         | QPI                                                         |

| 0                                          | 1                         | 1                         | SPI <sup>[11]</sup> , 拡張 SPI (デュアル) - 推奨される設定ではありません        |

| 1                                          | 1                         | 1                         | SPI <sup>[11]</sup> , 拡張 SPI (デュアル / クアッド) - 推奨される設定ではありません |

注:

9. すべての拡張 SPI は SPI モードで起動します。

10. QUAD = '1' は、I/O を QUAD モードに再設定し、WP および RESET 操作に影響を与えます ([Table 21](#) を参照)。

11. レジスタの読み出しが、推奨される設定ではありませんが、常に書き込まれたものを返します。

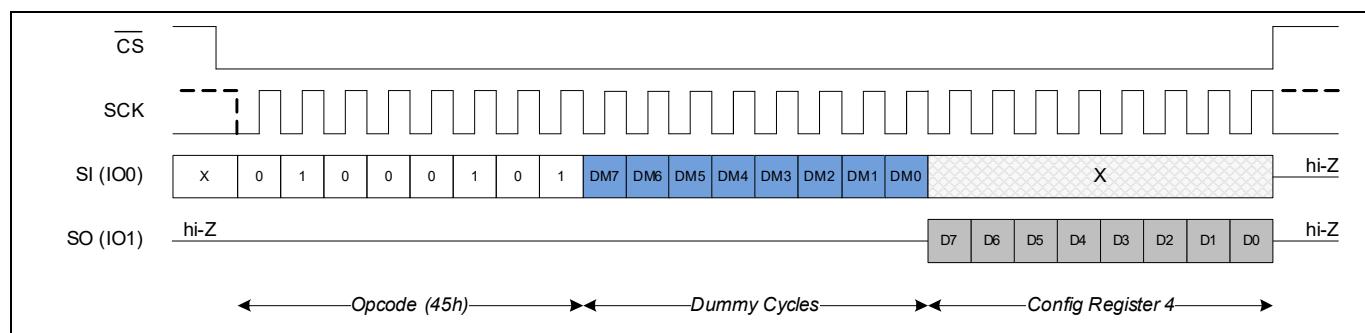

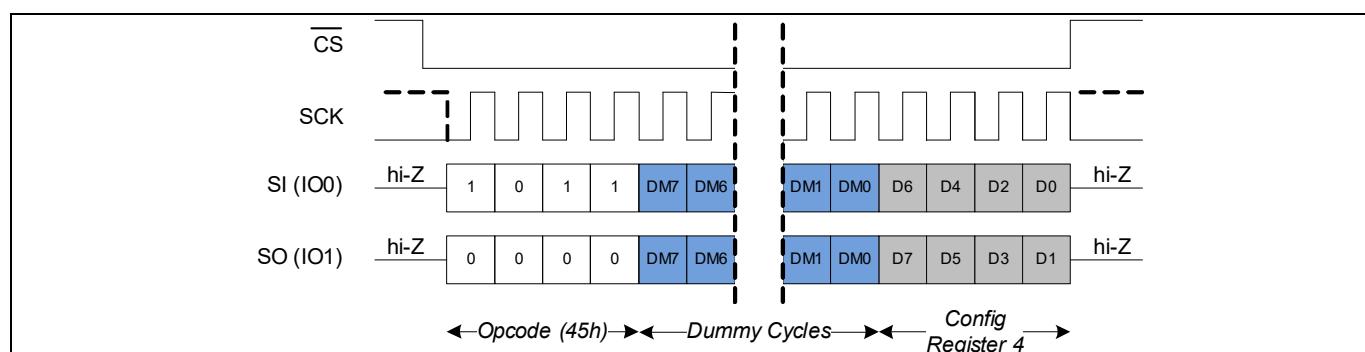

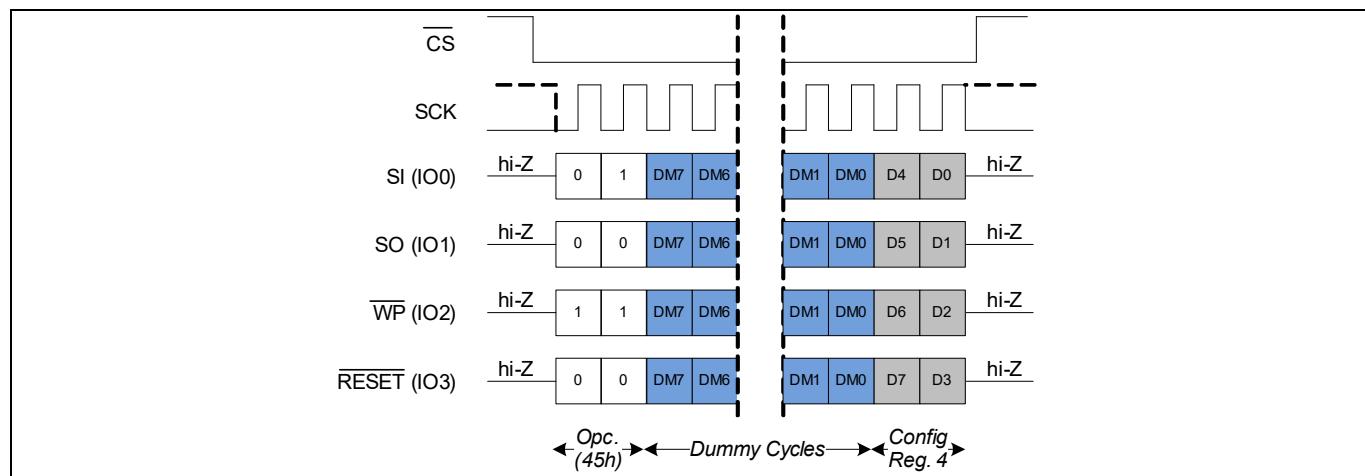

#### 4.2.3 コンフィギュレーションレジスタ 4 (CR4)

**Table 23** に示すように、コンフィギュレーションレジスタ 4 (CR4) は、出力ドライブインピーダンスとディープパワーダウン (DPD) モードの設定を制御します。CR4 には、書き込みの場合は WRAR コマンド、読み出し操作の場合は RDCR4 または RDAR コマンドからアクセスできます。CR4 アクセスの詳細は、[レジスタアクセスのコマンド](#)で説明します。

WRAR 不揮発性書き込みアドレス - 0x000005

WRAR 挥発性書き込みアドレス - 0x070005

RDAR 読み出しアドレス - 0x000005 or 0x070005

**Table 23** の各ビットの後に示されるデフォルトの状態は、工場でプログラムされた値です。

**Table 23 コンフィギュレーションレジスタ 4 (CR4)**

| CR4[7] | CR4[6] | CR4[5] | CR4[4]  | CR4[3]  | CR4[2]     | CR4[1]  | CR4[0]  |

|--------|--------|--------|---------|---------|------------|---------|---------|

| OI (0) | OI (0) | OI (0) | RFU (0) | RFU (1) | DPDPOR (0) | RFU (0) | RFU (0) |

**Table 24 コンフィギュレーションレジスタ 4 (CR4) - 不揮発性**

| ビット    | ビット名   | ビット機能              | 分類 | 読み出し / 書き込み (R/W)            | 説明                                                                                                                                                                                    |  |

|--------|--------|--------------------|----|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| CR4[7] | OI     | 出力インピーダンス          | NV | R/W                          | 出力インピーダンスの選択                                                                                                                                                                          |  |

| CR4[6] |        |                    | NV | R/W                          |                                                                                                                                                                                       |  |

| CR4[5] |        |                    | NV | R/W                          |                                                                                                                                                                                       |  |

| CR4[4] | RFU    | 予約済み (0)           |    | 将来の使用のため予約済み                 |                                                                                                                                                                                       |  |

| CR4[3] | RFU    | 予約済み (1)           |    | 将来の使用のため予約済み <sup>[12]</sup> |                                                                                                                                                                                       |  |

| CR4[2] | DPDPOR | POR のディープパワーダウンモード | NV | R/W                          | 1 = $\overline{CS}$ が HIGH の場合、POR またはハードウェアリセット (JEDEC リセットを含む) の完了時にディープパワーダウンになります。<br>0 = $\overline{CS}$ が HIGH の場合、電源投入またはPOR またはハードウェアリセット (JEDEC リセットを含む) の完了時にスタンバイモードになります。 |  |

| CR4[1] | RFU    | 予約済み (0)           |    | 将来の使用のため予約済み                 |                                                                                                                                                                                       |  |

| CR4[0] | RFU    | 予約済み (0)           |    | 将来の使用のため予約済み                 |                                                                                                                                                                                       |  |

NV - 不揮発性

注:

12.SPI バスマスターは、このコンフィギュレーションレジスタに書き込むときに、ビット CR4[3] が「1」のままであることを確認する必要があります。このビットに「0」を書き込むと、デバイスの機能に影響を与える可能性があります。

Table 25 コンフィギュレーションレジスタ 4 (CR4) - 指定

| ビット    | ビット名   | ビット機能              | 分類 | 読み出し / 書き込み (R/W)            | 説明                                                                                                                                                           |  |

|--------|--------|--------------------|----|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| CR4[7] | OI     | 出力インピーダンス          | V  | R/W                          | 出力インピーダンスの選択                                                                                                                                                 |  |

| CR4[6] |        |                    | V  | R/W                          |                                                                                                                                                              |  |

| CR4[5] |        |                    | V  | R/W                          |                                                                                                                                                              |  |

| CR4[4] | RFU    | 予約済み (0)           |    | 将来の使用のため予約済み                 |                                                                                                                                                              |  |

| CR4[3] | RFU    | 予約済み (1)           |    | 将来の使用のため予約済み <sup>[13]</sup> |                                                                                                                                                              |  |

| CR4[2] | DPDPOR | POR のディープパワーダウンモード | V  | R/W                          | 1 = CS が HIGH の場合、POR またはハードウェアリセット (JEDEC リセットを含む) の完了時にディープパワーダウンになります。<br>0 = CS が HIGH の場合、電源投入または POR またはハードウェアリセット (JEDEC リセットを含む) の完了時にスタンバイモードになります。 |  |

| CR4[1] | RFU    | 予約済み (0)           |    | 将来の使用のため予約済み                 |                                                                                                                                                              |  |

| CR4[0] | RFU    | 予約済み (0)           |    | 将来の使用のため予約済み                 |                                                                                                                                                              |  |

注:

13.SPI バスマスターは、このコンフィギュレーションレジスタに書き込むときに、ビット CR4[3] が「1」のままであることを確認する必要があります。このビットに「0」を書き込むと、デバイスの機能に影響を与える可能性があります。

#### 4.2.3.1 出力インピーダンス (OI) CR4 [7:5]

これらの 3 ビットは、I/O ピンの出力インピーダンス (ドライブ強度) を制御します。出力インピーダンス設定ビットにより、ユーザーはドライブ強度を調整して、プリント回路基板のシグナルインテグリティを向上できます。

Table 26 インピーダンスの選択

| インピーダンスの選択 | 標準的なインピーダンス ( $\Omega$ ) <sup>[14]</sup> | 備考                                                                              |

|------------|------------------------------------------|---------------------------------------------------------------------------------|

| 000        | 45                                       | 45 $\Omega$ が工場出荷時のデフォルト設定です。その他の駆動強度は、CR4[7:5] のインピーダンス選択ビットに書き込むことでプログラマできます。 |

| 001        | 120                                      |                                                                                 |

| 010        | 90                                       |                                                                                 |

| 011        | 60                                       |                                                                                 |

| 100        | 45                                       |                                                                                 |

| 101        | 30                                       |                                                                                 |

| 110        | 20                                       |                                                                                 |

| 111        |                                          |                                                                                 |

注:

14. $V_{DD}/2$  で測定された標準的なインピーダンス。

#### 4.2.3.2 POR 後のディープパワーダウンモード (DPDPOR) CR4 [2]

このビットはデバイスがパワーオンリセット (POR), ハードウェアリセット (RESET) ピンまたは JEDEC リセット), またはハイバネートモードの後にディープパワーダウン (DPD) またはスタンバイモードに入るかどうかを制御します。DPDPOR コンフィギュレーションビットは、CS が HIGH のときにデバイスがスタンバイモードではなく DPD モードで起動するようにします。 $t_{EXTDPD}$  時間の後に、 $t_{CSDPD}$  の CS パルス幅、またはハードウェアリセットによって DPD モードを終了します。CS パルス幅は、SCK と I/O が関係なく、CS のみを切り替えることで生成できます。DPDPOR ビット状態はソフトウェアリセットでは無視され、ソフトウェアリセットの後、デバイスは常にスタンバイになります。

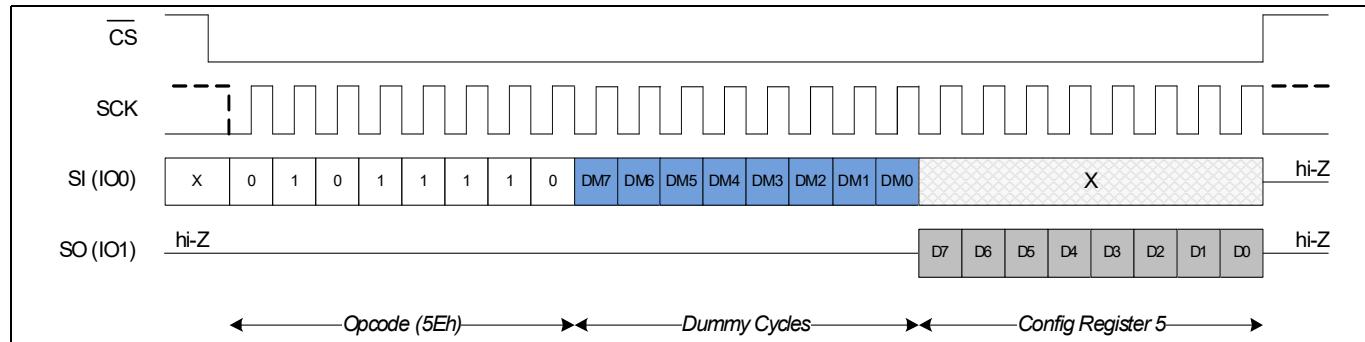

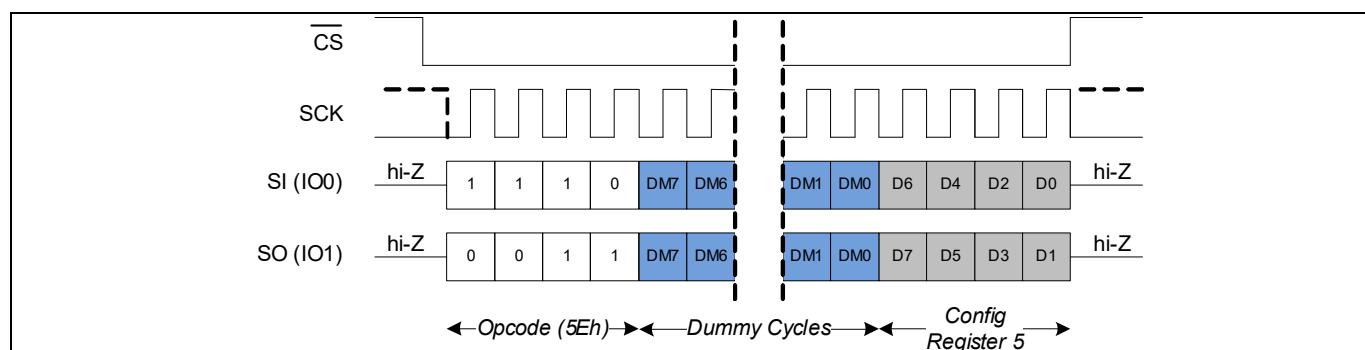

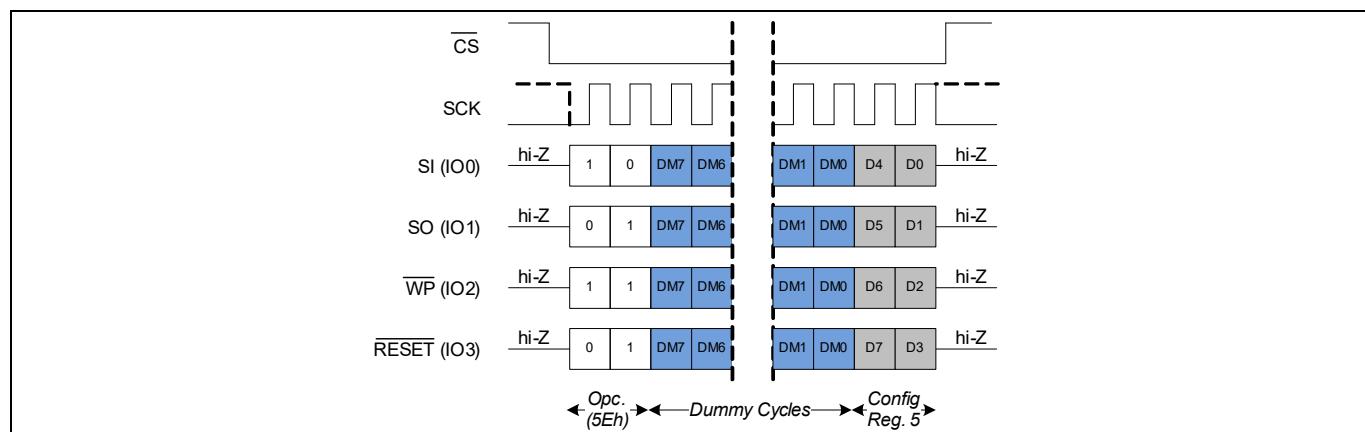

#### 4.2.4 コンフィギュレーションレジスタ 5 (CR5)

**Table 27** に示すように、コンフィギュレーションレジスタ 5 (CR5) は、レジスタ読み出しの読み出し待ち時間 (ダミー) サイクルを設定します。CR5 には、書き込みの場合は WRAR コマンド、読み出し操作の場合は RDCR5 または RDAR コマンドからアクセスできます。CR5 アクセスの詳細は、[レジスタアクセスのコマンド](#)で説明します。

WRAR 不揮発性書き込みアドレス - 0x000006

WRAR 挥発性書き込みアドレス - 0x070006

RDAR 読み出しアドレス - 0x000006 または 0x070006

**Table 27** の各ビットの後に示されるデフォルトの状態は、工場でプログラムされた値です。

**Table 27 コンフィギュレーションレジスタ 5 (CR5)**

| CR5[7]   | CR5[6]   | CR5[5]  | CR5[4]  | CR5[3]  | CR5[2]  | CR5[1]  | CR5[0]  |

|----------|----------|---------|---------|---------|---------|---------|---------|

| RLC1 (0) | RLC0 (0) | RFU (0) |

**Table 28 コンフィギュレーションレジスタ 5 (CR5) - 不揮発性**

| ビット    | ビット名 | ビット機能         | 分類 | 読み出し / 書き込み (R/W) | 説明                                                |  |  |

|--------|------|---------------|----|-------------------|---------------------------------------------------|--|--|

| CR5[7] | RLC1 | レイテンシコードを登録する | NV | R/W               | レジスタアクセスの 0 ~ 3 クロックサイクルのレジスタ読み出しレイテンシサイクル数を選択します |  |  |

| CR5[6] | RLC0 |               |    | R/W               |                                                   |  |  |

| CR5[5] | RFU  | 予約済み (0)      |    | 将来の使用のために予約済み     |                                                   |  |  |

| CR5[4] | RFU  | 予約済み (0)      |    | 将来の使用のために予約済み     |                                                   |  |  |

| CR5[3] | RFU  | 予約済み (0)      |    | 将来の使用のために予約済み     |                                                   |  |  |

| CR5[2] | RFU  | 予約済み (0)      |    | 将来の使用のために予約済み     |                                                   |  |  |

| CR5[1] | RFU  | 予約済み (0)      |    | 将来の使用のために予約済み     |                                                   |  |  |

| CR5[0] | RFU  | 予約済み (0)      |    | 将来の使用のために予約済み     |                                                   |  |  |

NV - 不揮発性

**Table 29 コンフィギュレーションレジスタ 5 (CR5) - 挥発性**

| ビット    | ビット名 | ビット機能         | 分類 | 読み出し / 書き込み (R/W) | 説明                                                |  |  |

|--------|------|---------------|----|-------------------|---------------------------------------------------|--|--|

| CR5[7] | RLC1 | レイテンシコードを登録する | V  | R/W               | レジスタアクセスの 0 ~ 3 クロックサイクルのレジスタ読み出しレイテンシサイクル数を選択します |  |  |

| CR5[6] | RLC0 |               |    | R/W               |                                                   |  |  |

| CR5[5] | RFU  | 予約済み (0)      |    | 将来の使用のために予約済み     |                                                   |  |  |

| CR5[4] | RFU  | 予約済み (0)      |    | 将来の使用のために予約済み     |                                                   |  |  |

| CR5[3] | RFU  | 予約済み (0)      |    | 将来の使用のために予約済み     |                                                   |  |  |

| CR5[2] | RFU  | 予約済み (0)      |    | 将来の使用のために予約済み     |                                                   |  |  |

| CR5[1] | RFU  | 予約済み (0)      |    | 将来の使用のために予約済み     |                                                   |  |  |

| CR5[0] | RFU  | 予約済み (0)      |    | 将来の使用のために予約済み     |                                                   |  |  |

V - 挥発性

#### 4.2.4.1 レイテンシ コードの登録 (RLC [1:0]) CR5 [7:6]

これらの 2 ビットは、すべての可変レイテンシレジスタ読み出し命令の読み出しレイテンシ (ダミーサイクル) 遅延を制御します。これにより、ユーザーは通常の操作中に読み出しレイテンシを調整して、さまざまな動作周波数でのさまざまなレジスタ読み出し命令のレイテンシを最適化できます。[Table 30](#) に、レジスタ読み出しコマンドのレイテンシサイクルを示します。

**Table 30** レジスタ読み出しコマンドのダミーサイクル

| レイテンシ<br>(ダミーサイクル) | SPI (SDR)                                                         | DPI (SDR)              | QPI (SDR)              |

|--------------------|-------------------------------------------------------------------|------------------------|------------------------|

|                    | RDSR1, RDSR2, RDCR1, RDGR2, RDGR4, RDGR5, RDAR, RUID, RDID2, RDSN |                        |                        |

| 0                  | 50 MHz <sup>[15]</sup>                                            | 50 MHz <sup>[15]</sup> | 50 MHz <sup>[15]</sup> |

| 1 ~ 3              | 108 MHz                                                           | 108 MHz                | 108 MHz                |

注:

15.このパラメータは特性によって保証され、量産中にテストされません。

機能説明

## 5 機能説明

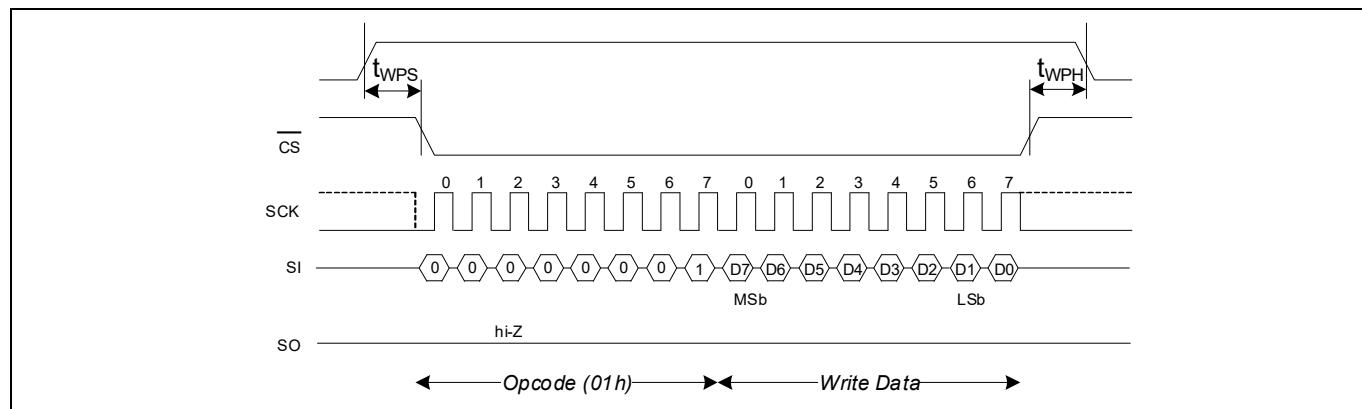

CY15X102QSN は 8 ビットの命令レジスタを備えています。すべての命令とそのオペコードの一覧を以下に示します。すべての命令, アドレス, およびデータは CS が HIGH から LOW へ遷移することにより転送されます。さらに、WP ピンと RESET ピンは、追加のハードウェア制御機能を提供します。

### 5.1 コマンドの構成

CY15X102QSN コマンド サイクルは最大で 5 つの異なるコマンドフェーズからなっています (オペコード, アドレス, モード, ダミー(レイテンシ)およびデータ)。コマンドサイクルごとのコマンドフェーズの数は、オペコードフェーズで送信されたオペコードに応じて 1 から 5 まで変化します。オペコード, アドレス, モード, およびデータフェーズの伝送ラインの数は、SPI, DPI, または QPI インターフェースでそれぞれ 1, 2, または 4 に設定できます。**Table 31** に、さまざまな SPI インターフェースでの各コマンドサイクルのコマンドフェーズを示します。

**Table 31** 異なる SPI モードでの I/O 上のコマンド送信

| コマンド<br>フェーズ | I/O 上のコマンド送信                                                                                                            |             |                           |             |                           |                           |                           |

|--------------|-------------------------------------------------------------------------------------------------------------------------|-------------|---------------------------|-------------|---------------------------|---------------------------|---------------------------|

|              | シングル<br>チャネル SPI                                                                                                        | 拡張 SPI      |                           |             |                           | マルチチャネル SPI               |                           |

|              |                                                                                                                         | デュアル<br>データ | クアッド<br>データ               | デュアル<br>I/O | クアッド<br>I/O               | DPI                       | QPI                       |

| オペコード        | SI                                                                                                                      | I/00        | I/00                      | I/00        | I/00                      | I/00, I/01,<br>I/02, I/03 |                           |

| アドレス         | SI                                                                                                                      | I/00        | I/00                      | I/00, I/01  | I/00, I/01,<br>I/02, I/03 | I/00, I/01                | I/00, I/01,<br>I/02, I/03 |

| モード          | SI                                                                                                                      | I/00        | I/00                      | I/00, I/01  | I/00, I/01,<br>I/02, I/03 | I/00, I/01                | I/00, I/01,<br>I/02, I/03 |

| ダミー(レイテンシ)   | 固定ダミー SPI クロック数は SPI インターフェースに独立。<br>メモリアクセスごとに 0 ~ 15 クロック (CR1[7:4] で設定可能)<br>レジスタアクセスごとに 0 ~ 3 クロック (CR5[7:6] で設定可能) |             |                           |             |                           |                           |                           |

| データ          | SI/SO                                                                                                                   | I/00, I/01  | I/00, I/01,<br>I/02, I/03 | I/00, I/01  | I/00, I/01,<br>I/02, I/03 | I/00, I/01                | I/00, I/01,<br>I/02, I/03 |

**Table 32** に示すように、バスマスターが CY15X102QSN に発行できるオペコードと呼ばれる 44 個のコマンドがあります。これらのオペコードはメモリが実行する機能を制御します。

**Table 32** オペコード コマンド

| コマンド |                    | SPI バスインターフェース |             |             |                 |             |     | データ<br>転送 |     | レイテンシ |                  | XIP              |                  |

|------|--------------------|----------------|-------------|-------------|-----------------|-------------|-----|-----------|-----|-------|------------------|------------------|------------------|

| コマンド | オペ<br>コード<br>(HEX) | SPI            | デュアル<br>データ | クアッド<br>データ | デュ<br>アル<br>I/O | クアッド<br>I/O | DPI | QPI       | SDR | DDR   | レイテ<br>ンシの<br>登録 | メモリ<br>レイテ<br>ンシ | Execute-In-Place |

#### 書き込みイネーブル制御

|      |    |    |    |  |    |    |    |    |    |    |    |    |

|------|----|----|----|--|----|----|----|----|----|----|----|----|

| WREN | 06 | あり | なし |  | あり | あり | あり | なし | なし | なし | なし | なし |

| WRDI | 04 | あり | なし |  | あり | あり | あり | なし | なし | なし | なし | なし |

#### レジスタのアクセス

|       |    |    |    |  |    |    |    |    |    |    |    |    |

|-------|----|----|----|--|----|----|----|----|----|----|----|----|

| WRSR  | 01 | あり | なし |  | あり | あり | あり | なし | なし | なし | なし | なし |

| RDSR1 | 05 | あり | なし |  | あり | あり | あり | なし | あり | なし | なし | なし |

| RDSR2 | 07 | あり | なし |  | あり | あり | あり | なし | あり | なし | なし | なし |

| RDCR1 | 35 | あり | なし |  | あり | あり | あり | なし | あり | なし | なし | なし |

| RDCR2 | 3F | あり | なし |  | あり | あり | あり | なし | あり | なし | なし | なし |

| RDCR4 | 45 | あり | なし |  | あり | あり | あり | なし | あり | なし | なし | なし |

機能説明

Table 32 オペコード コマンド (続き)

| コマンド                |             | SPI バスインターフェース |         |         |         |         |     |     | データ転送 |     | レイテンシ    |          | XIP              |

|---------------------|-------------|----------------|---------|---------|---------|---------|-----|-----|-------|-----|----------|----------|------------------|

| コマンド                | オペコード (HEX) | SPI            | デュアルデータ | クアッドデータ | デュアルI/O | クアッドI/O | DPI | QPI | SDR   | DDR | レイテンシの登録 | メモリレイテンシ | Execute-In-Place |

| RDCR5               | 5E          | あり             |         | なし      |         |         | あり  | あり  | あり    | なし  | あり       | なし       | なし               |

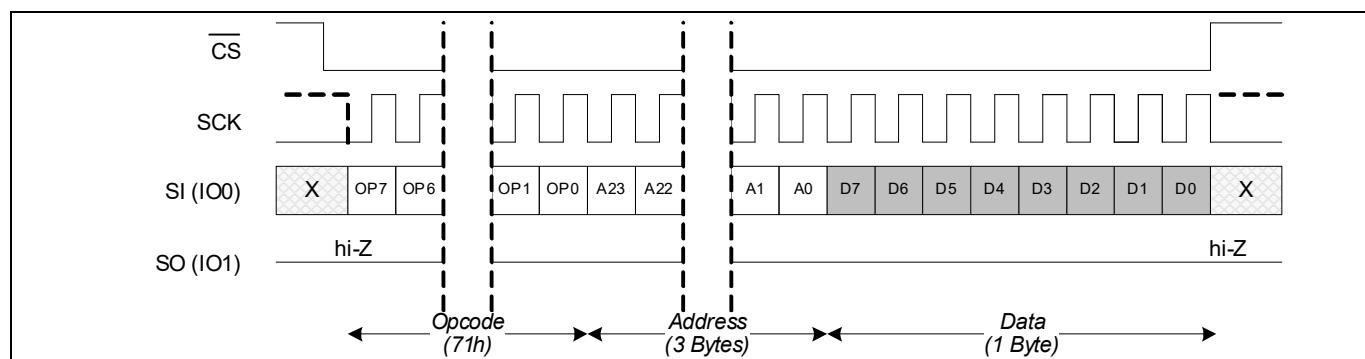

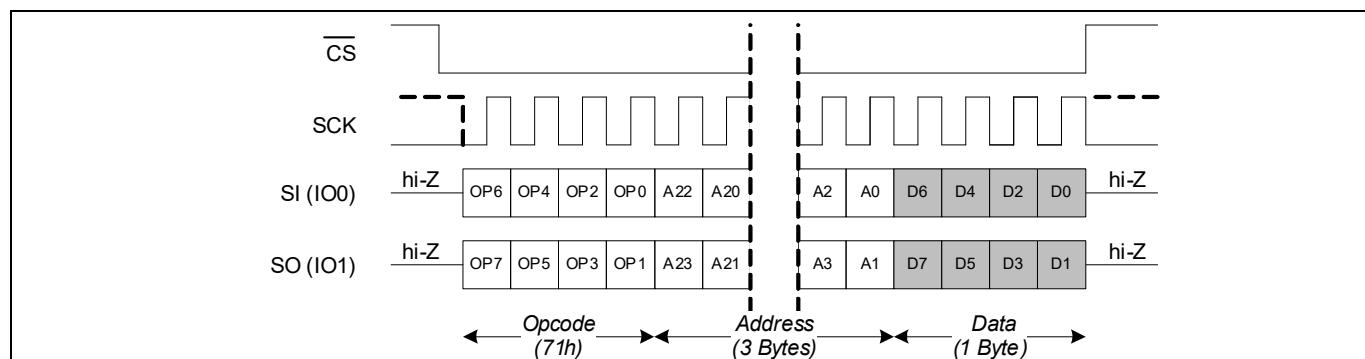

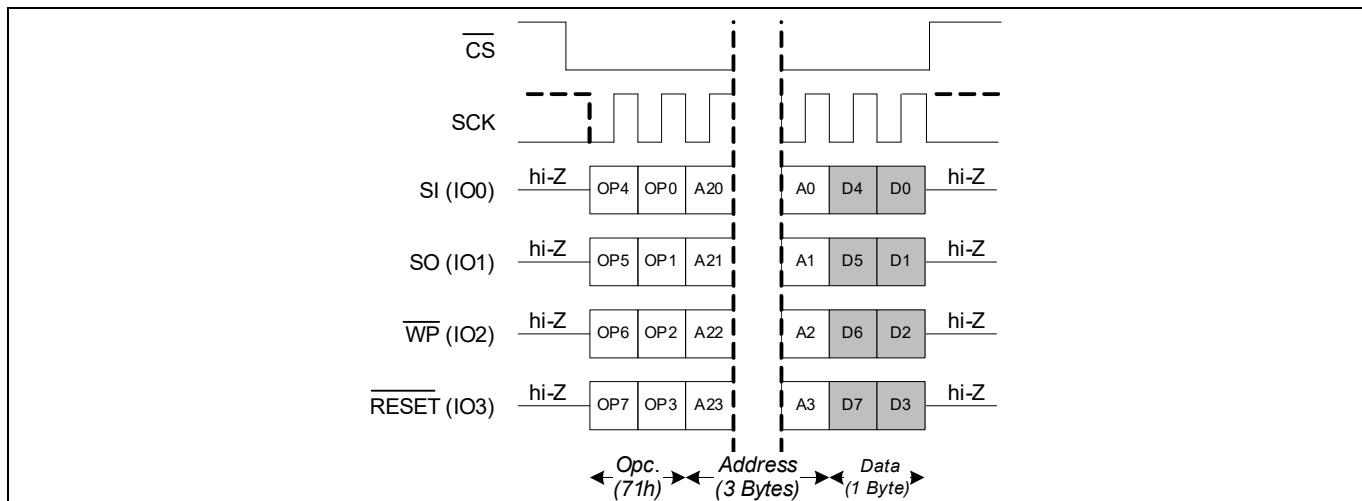

| WRAR                | 71          | あり             |         | なし      |         |         | あり  | あり  | あり    | なし  | なし       | なし       | なし               |

| RDAR                | 65          | あり             |         | なし      |         |         | あり  | あり  | あり    | なし  | あり       | なし       | なし               |

| <b>メモリ読み出し</b>      |             |                |         |         |         |         |     |     |       |     |          |          |                  |

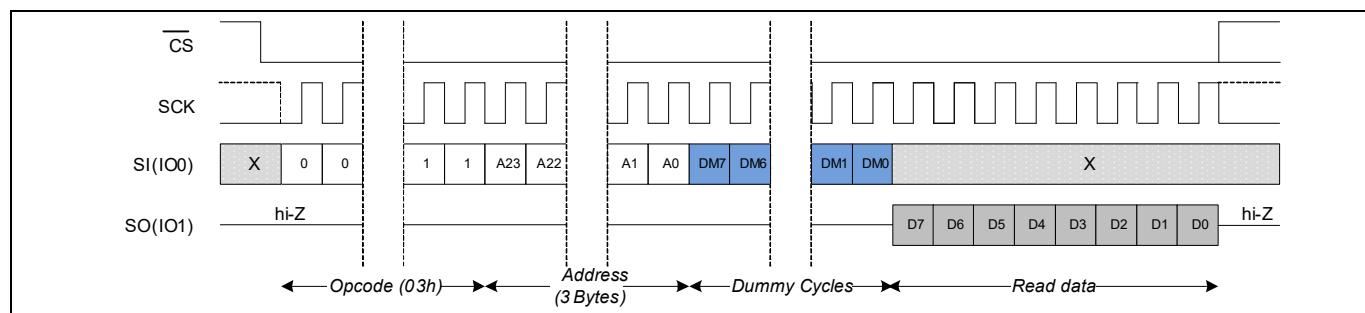

| READ                | 03          | あり             |         | なし      |         |         | あり  | あり  | あり    | なし  | なし       | あり       | なし               |

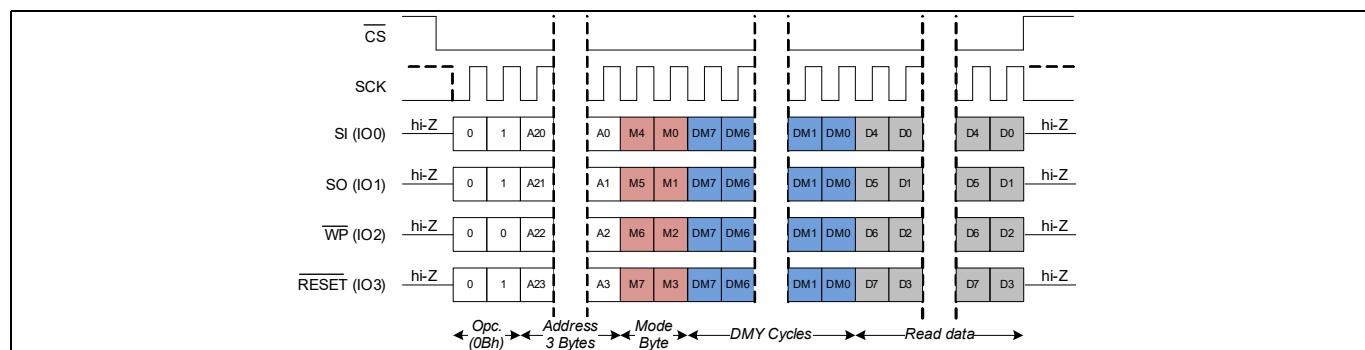

| FAST_READ           | 0B          | あり             |         | なし      |         |         | あり  | あり  | あり    | なし  | なし       | あり       | あり               |

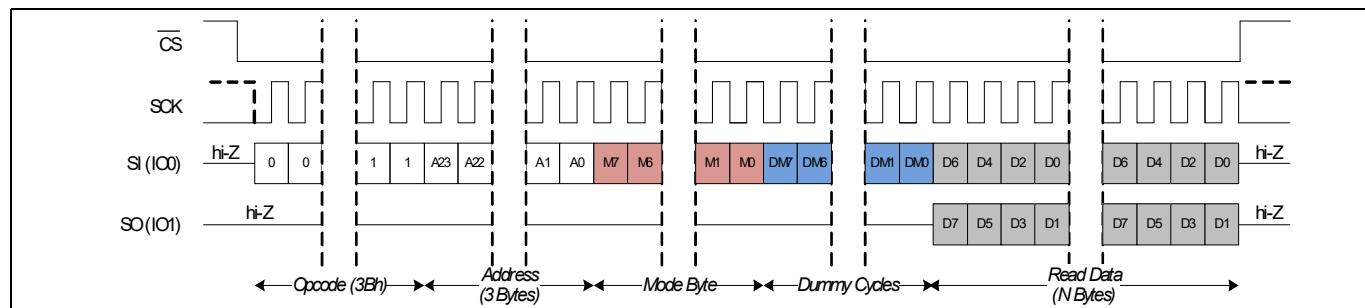

| DOOR                | 3B          | なし             | あり      |         | なし      |         | あり  |     | なし    | なし  | あり       | あり       |                  |

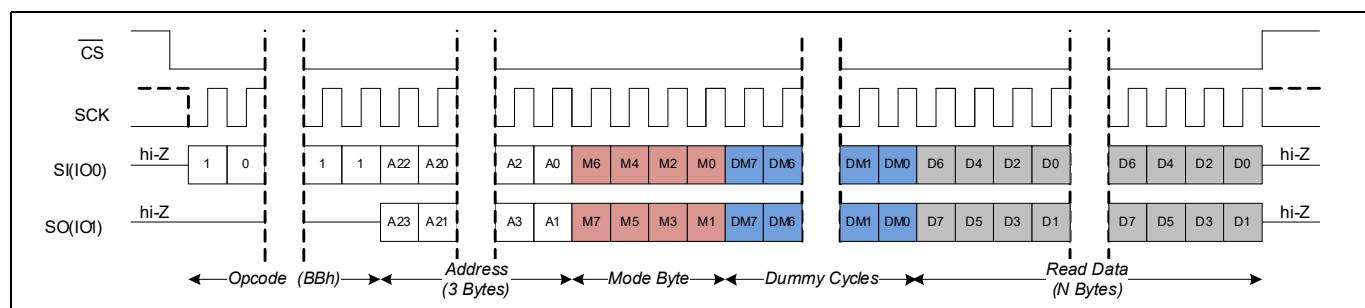

| DIOR                | BB          |                | なし      |         | あり      |         | なし  |     | あり    | なし  | なし       | あり       | あり               |

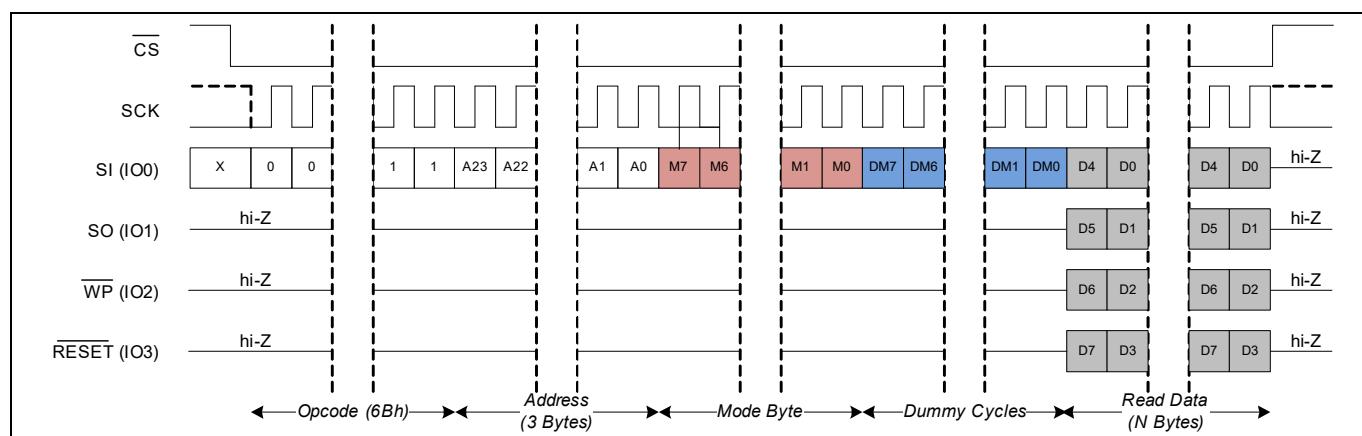

| QOR                 | 6B          |                | なし      | あり      |         | なし      |     |     | あり    | なし  | なし       | あり       | あり               |

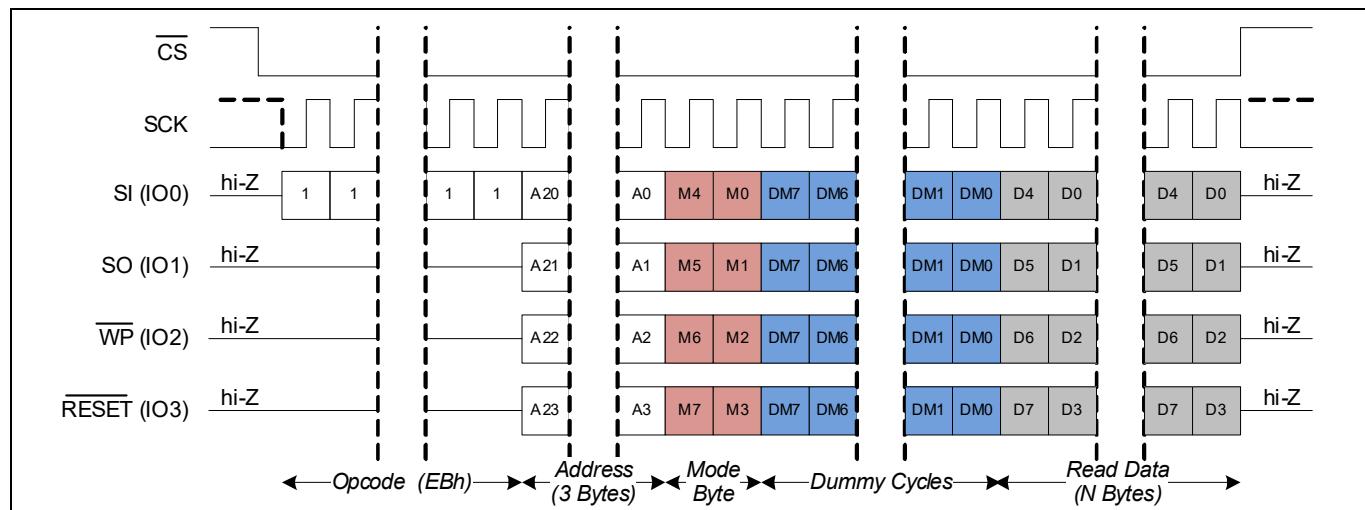

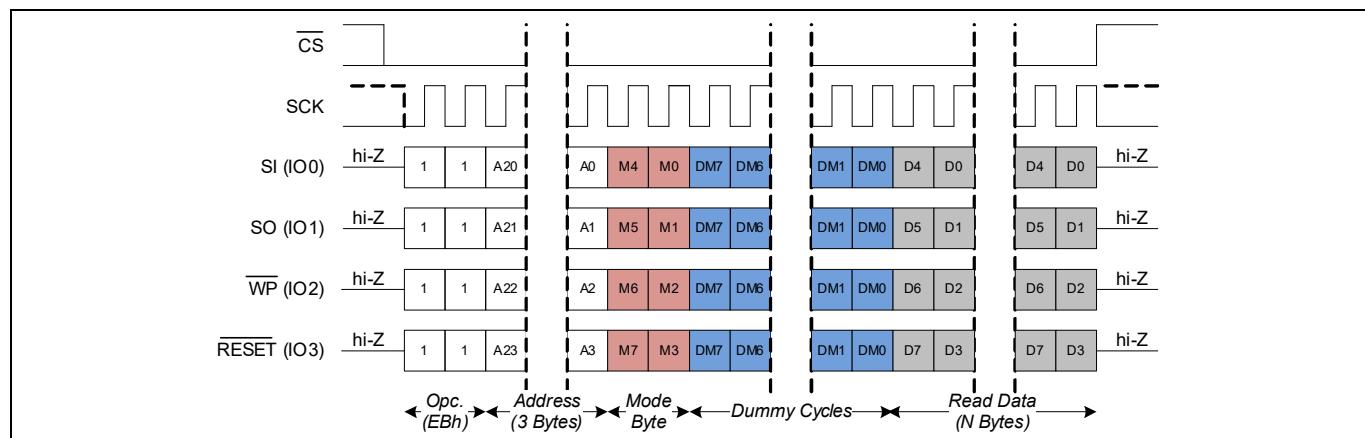

| QIOR                | EB          |                | なし      |         | あり      | なし      | あり  | あり  | なし    | なし  | なし       | あり       | あり               |

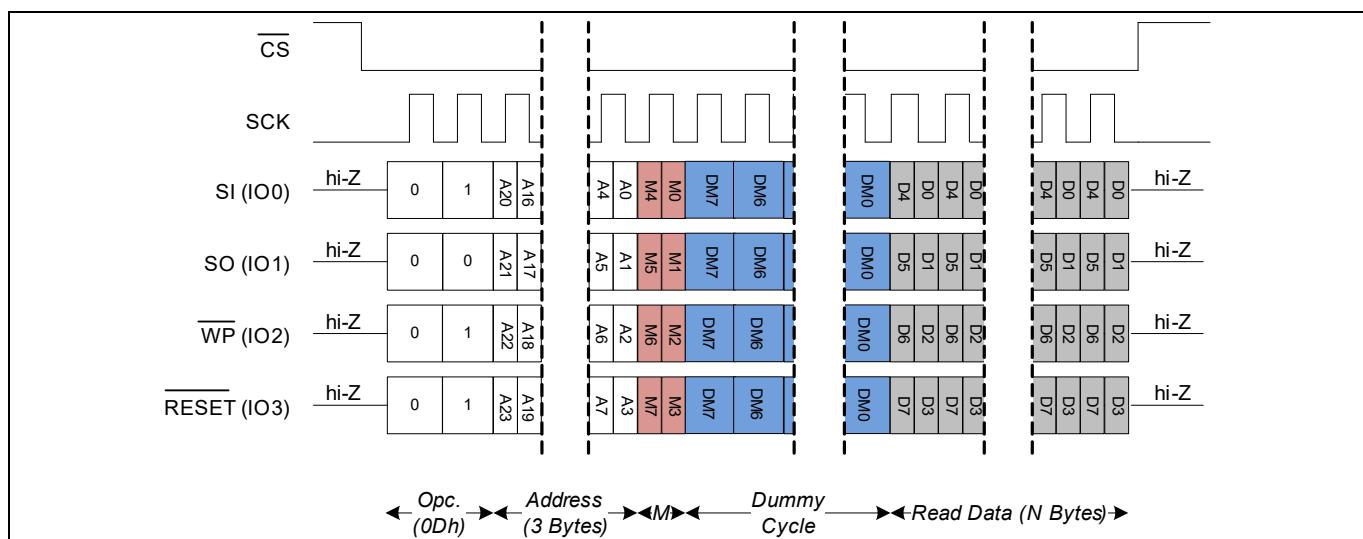

| DDRFR               | 0D          |                |         | なし      |         |         | あり  | なし  | あり    | なし  | なし       | あり       | あり               |

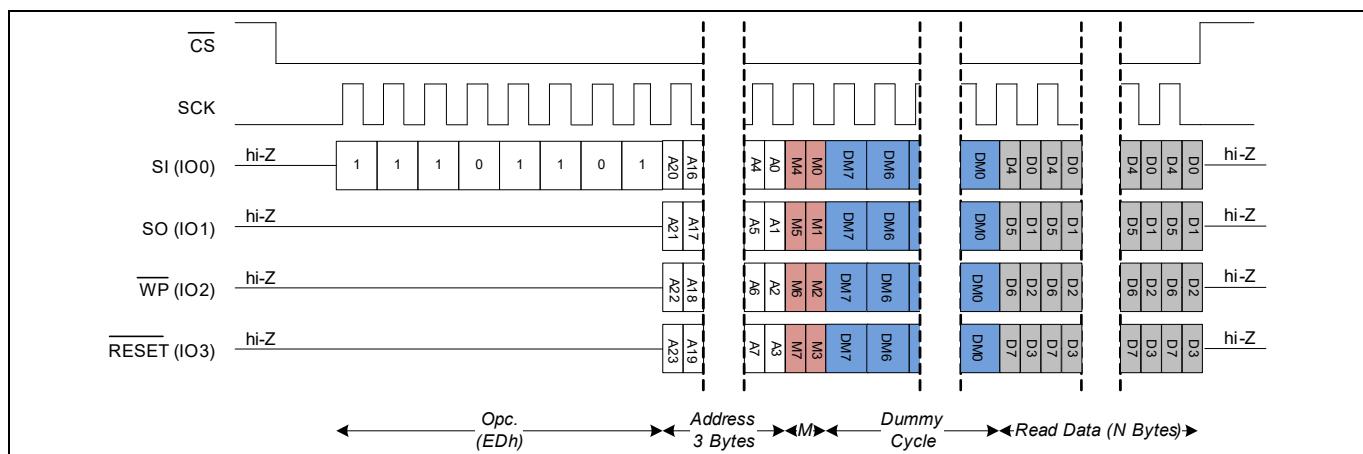

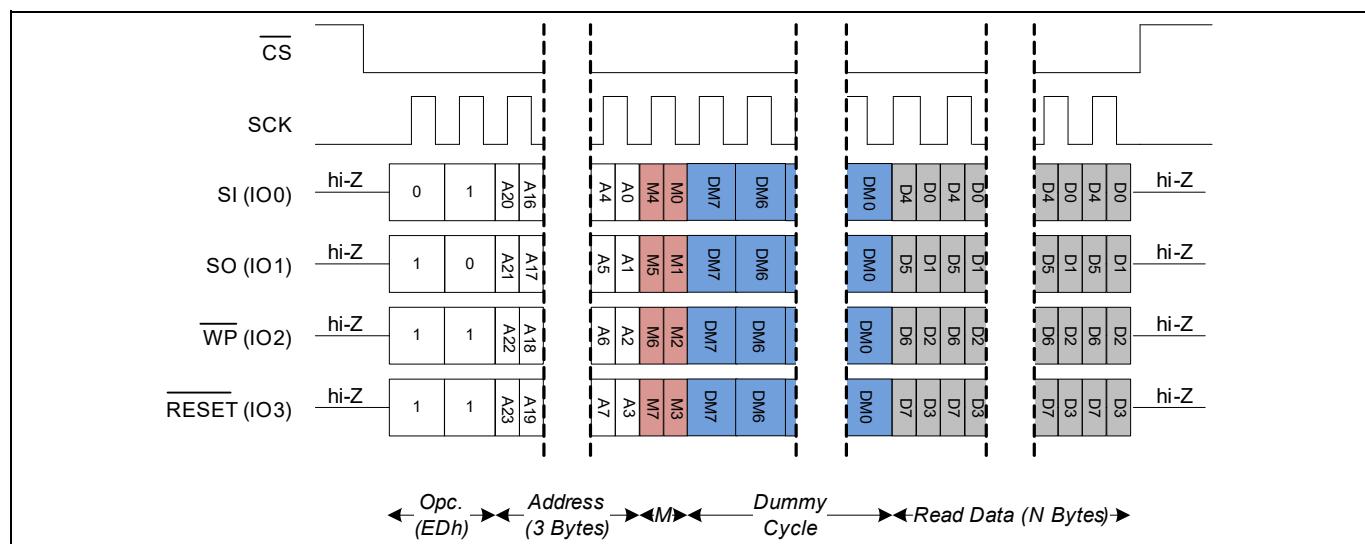

| DDRQIOR             | ED          |                |         | なし      |         | あり      | なし  | あり  | なし    | あり  | なし       | あり       | あり               |

| <b>メモリ書き込み</b>      |             |                |         |         |         |         |     |     |       |     |          |          |                  |

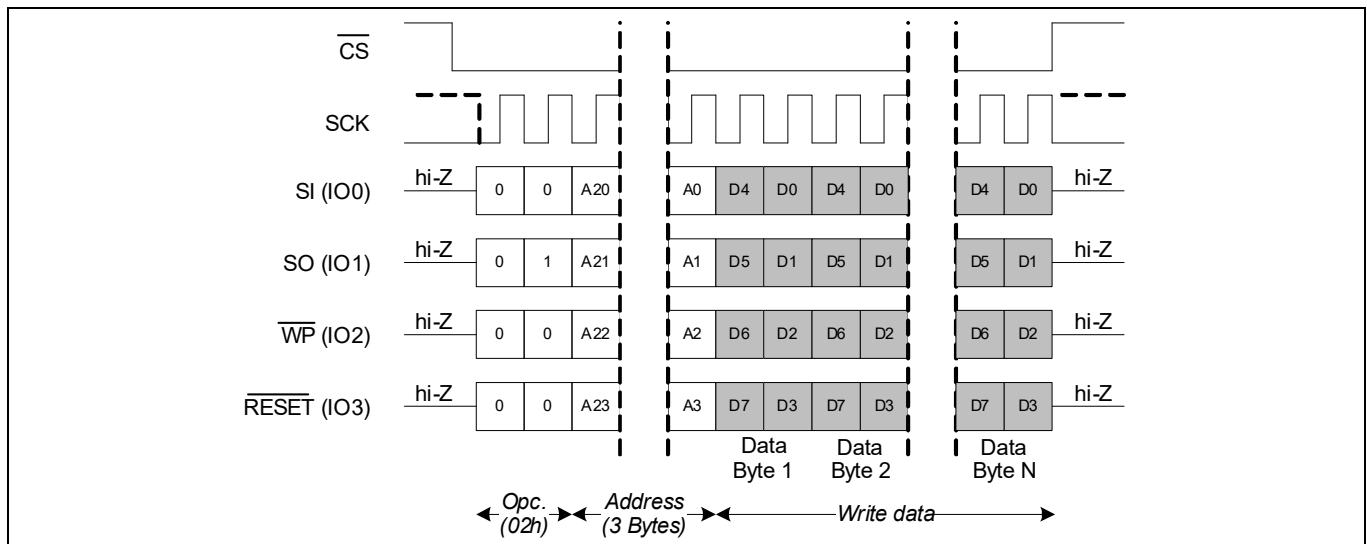

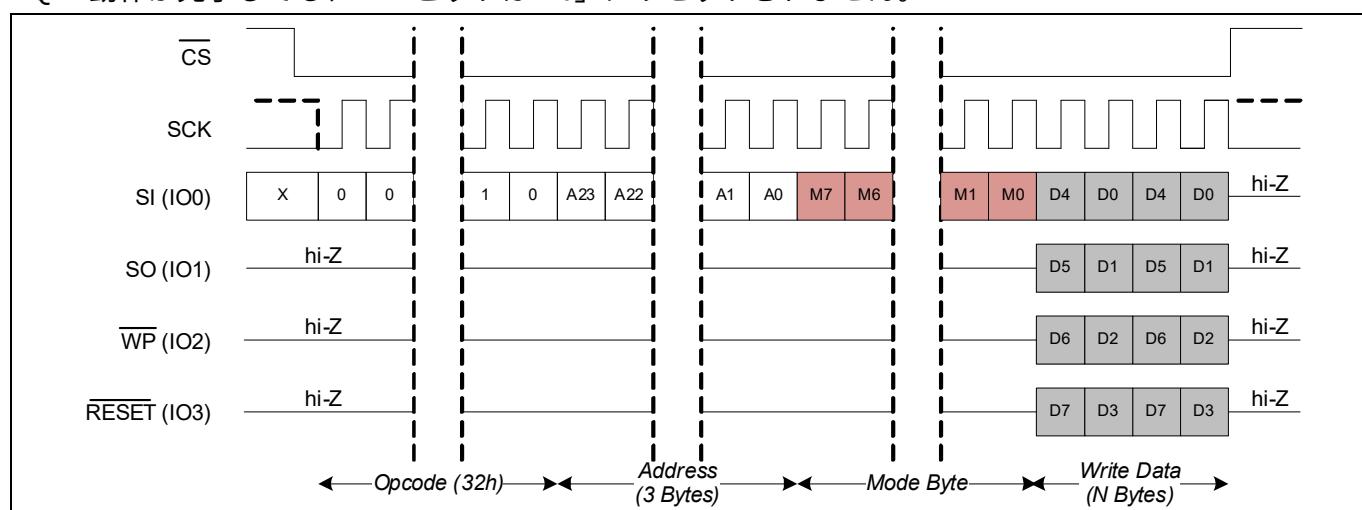

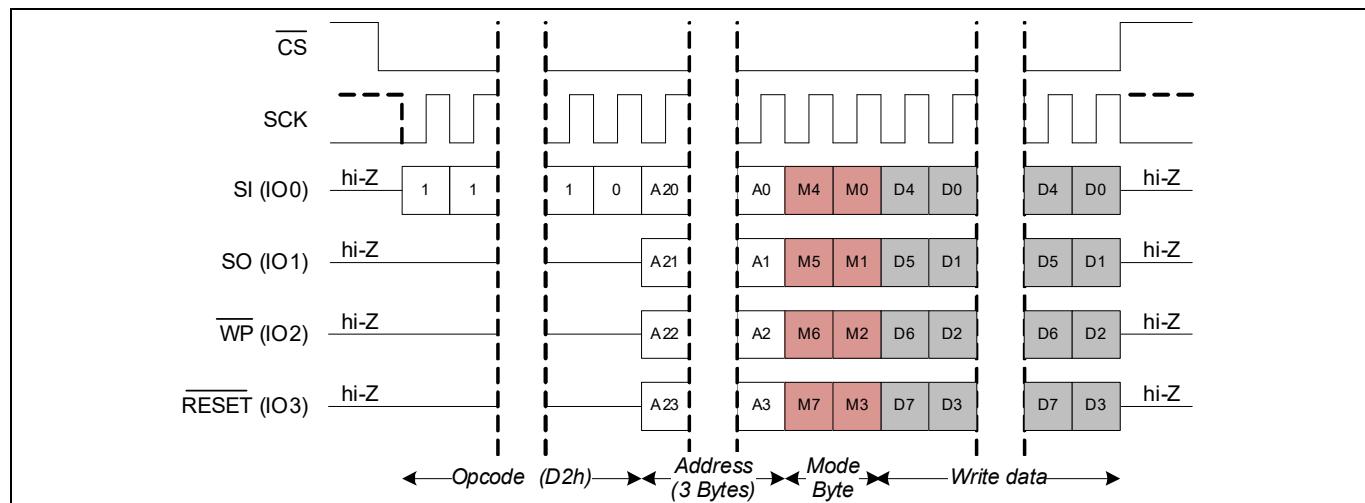

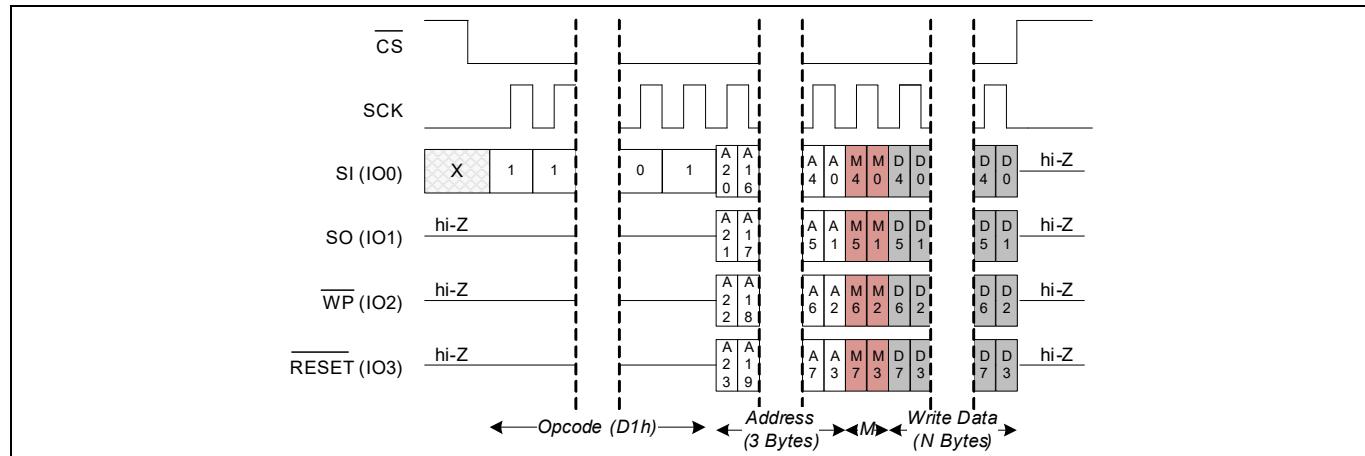

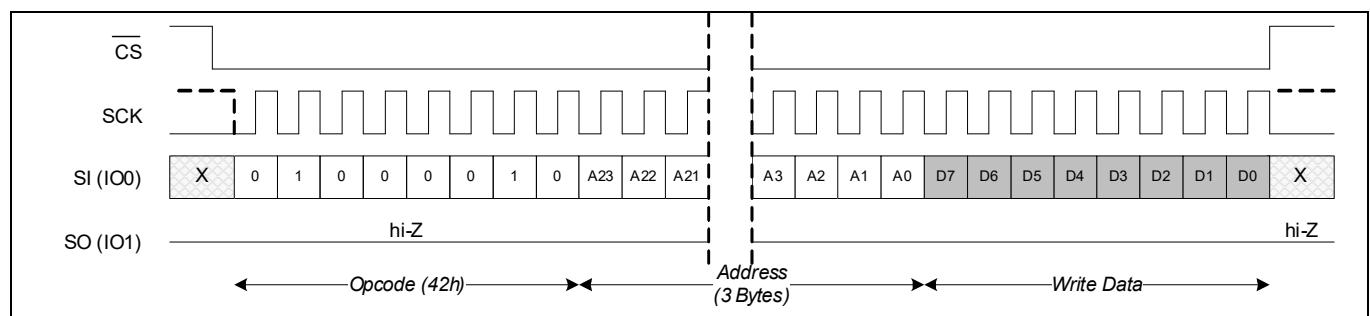

| WRITE               | 02          | あり             |         | なし      |         |         | あり  | あり  | あり    | なし  | なし       | なし       | なし               |

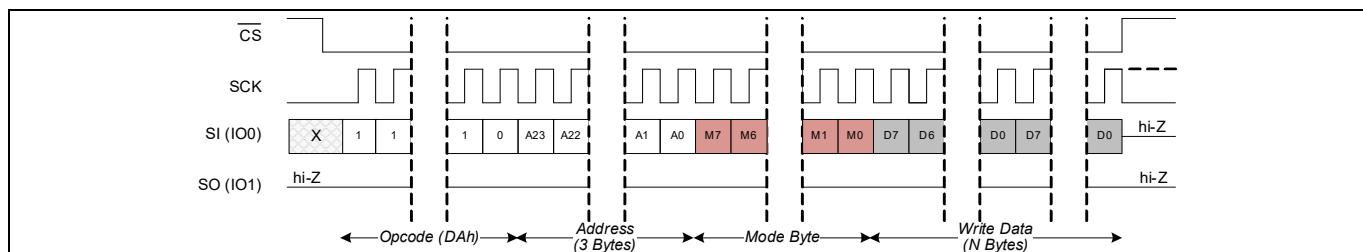

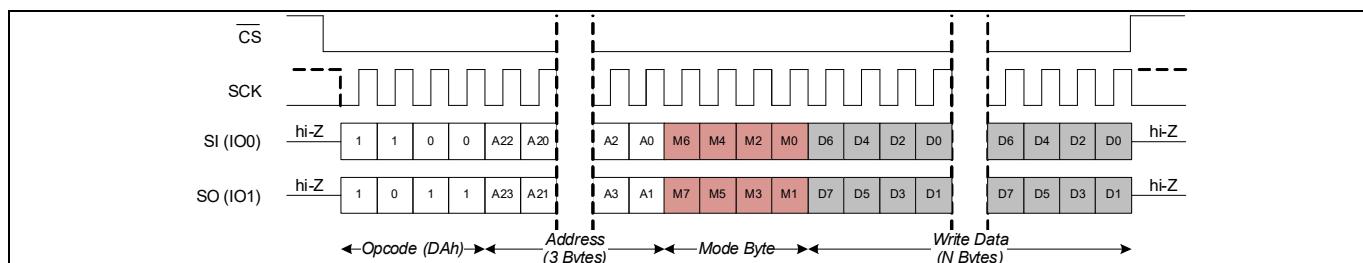

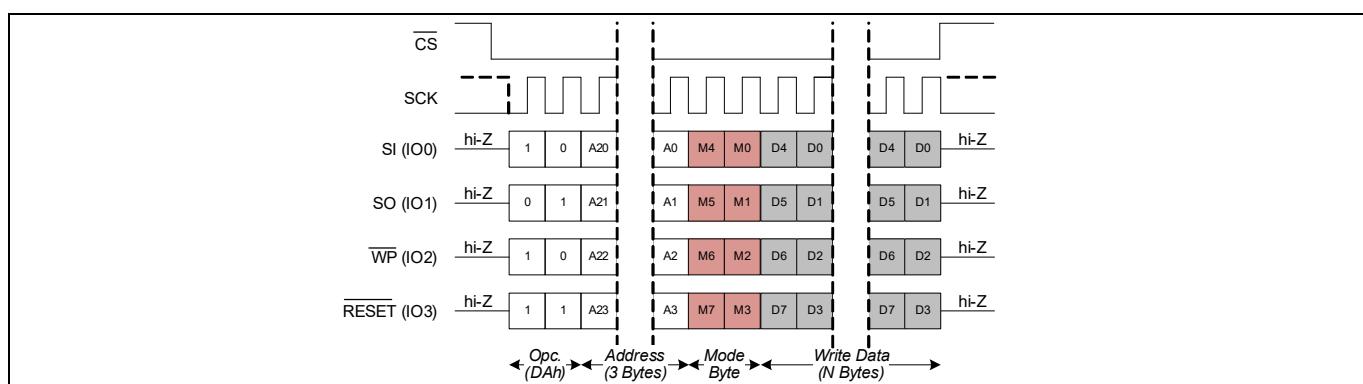

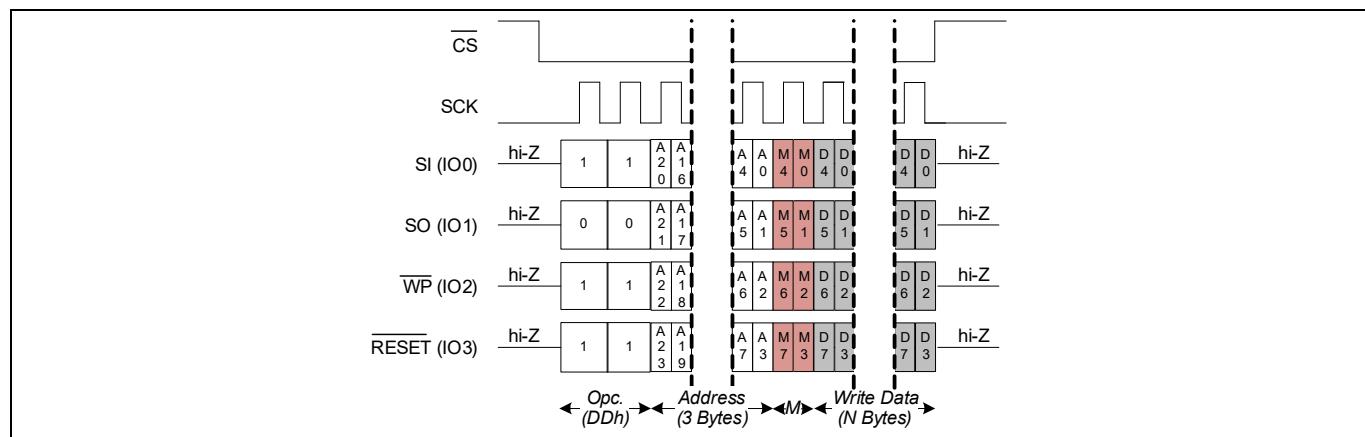

| FAST_WRITE          | DA          | あり             |         | なし      |         |         | あり  | あり  | あり    | なし  | なし       | なし       | あり               |

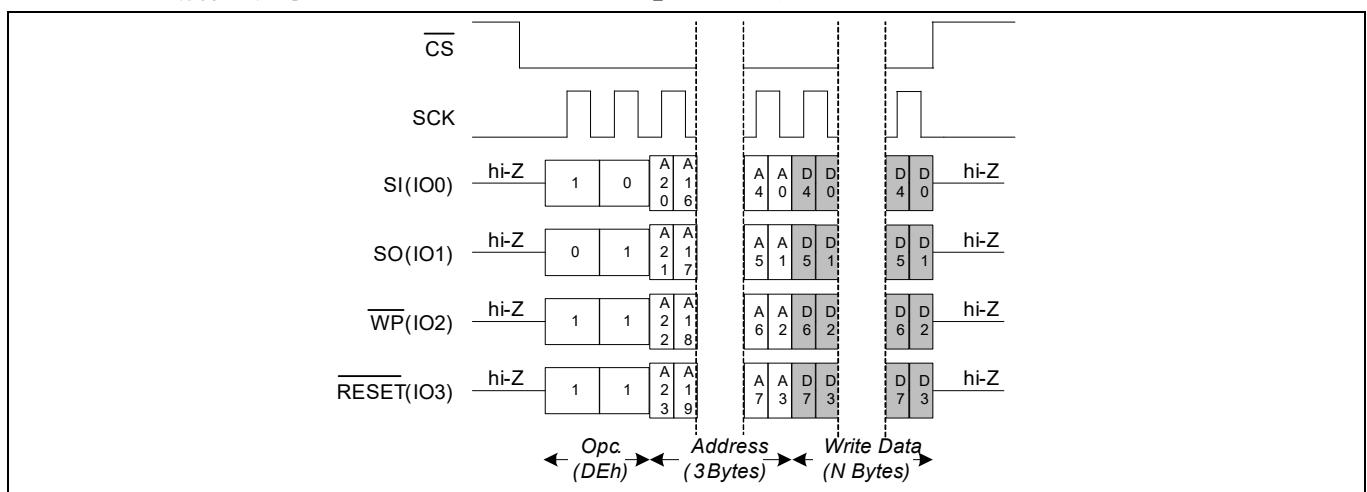

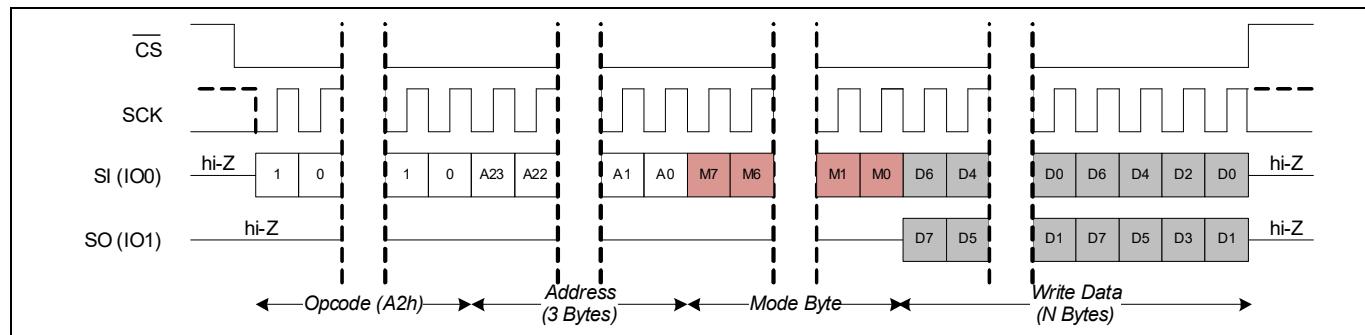

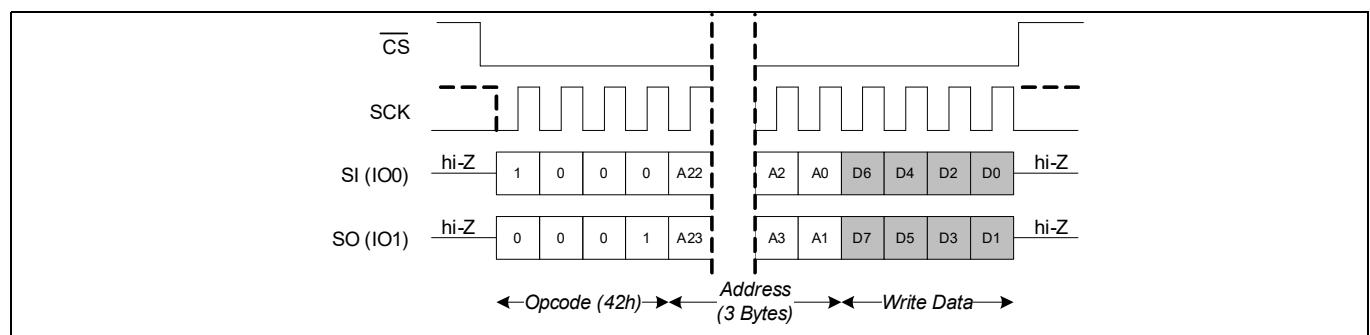

| DIW                 | A2          | なし             | あり      |         | なし      |         | あり  |     | なし    | なし  | なし       | なし       | あり               |

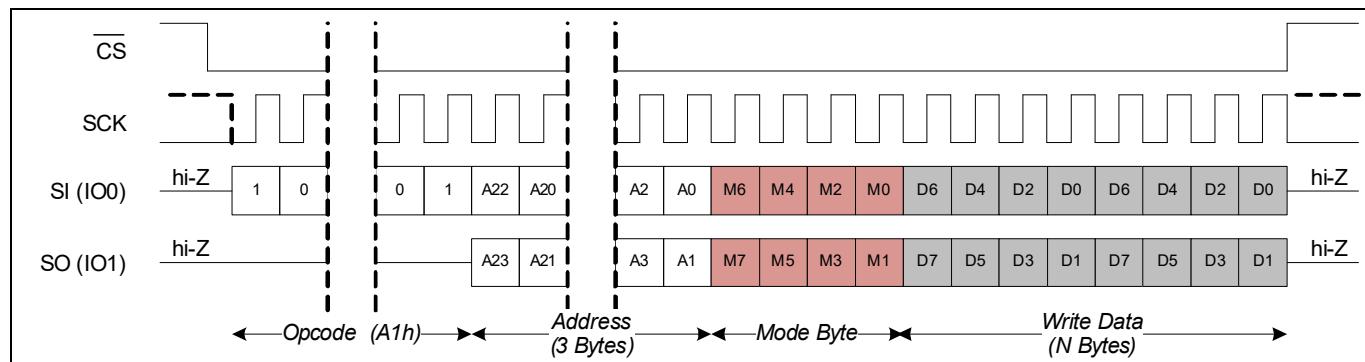

| DIOW                | A1          |                | なし      |         | あり      |         | なし  |     | あり    | なし  | なし       | なし       | あり               |

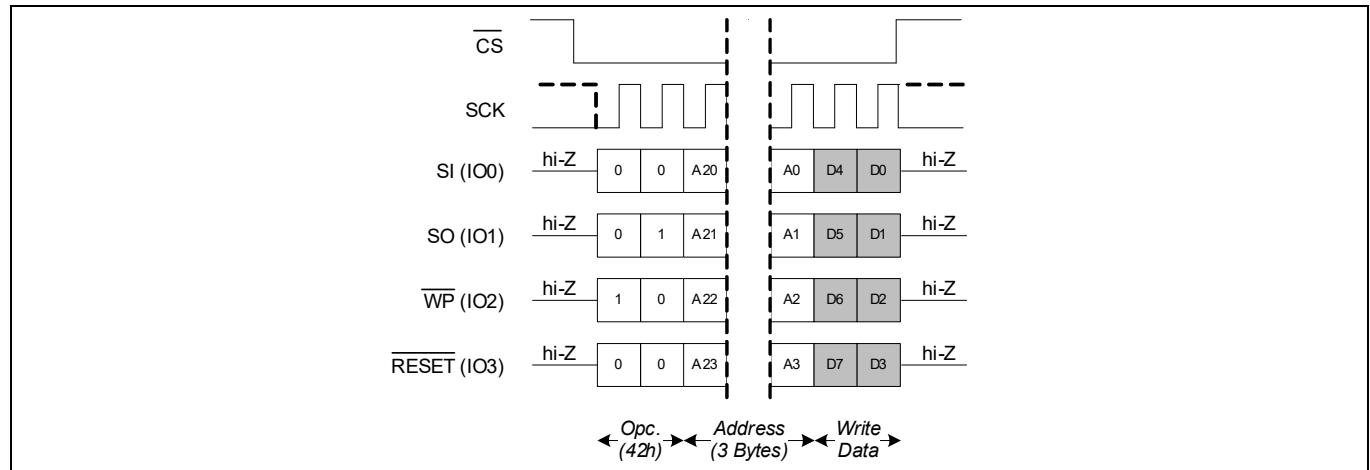

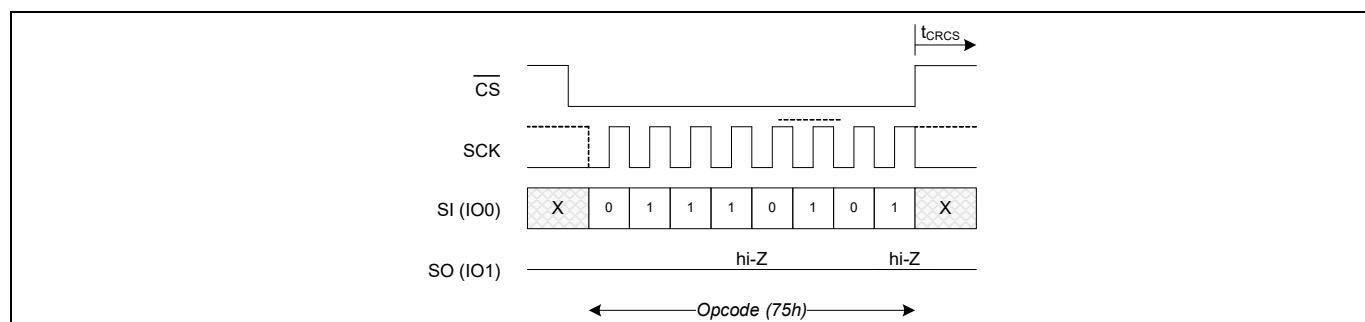

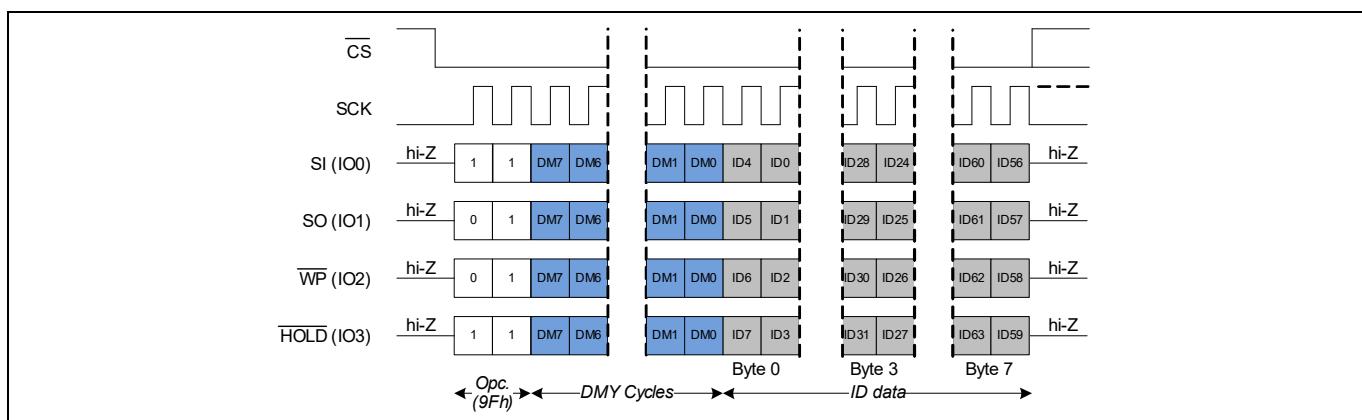

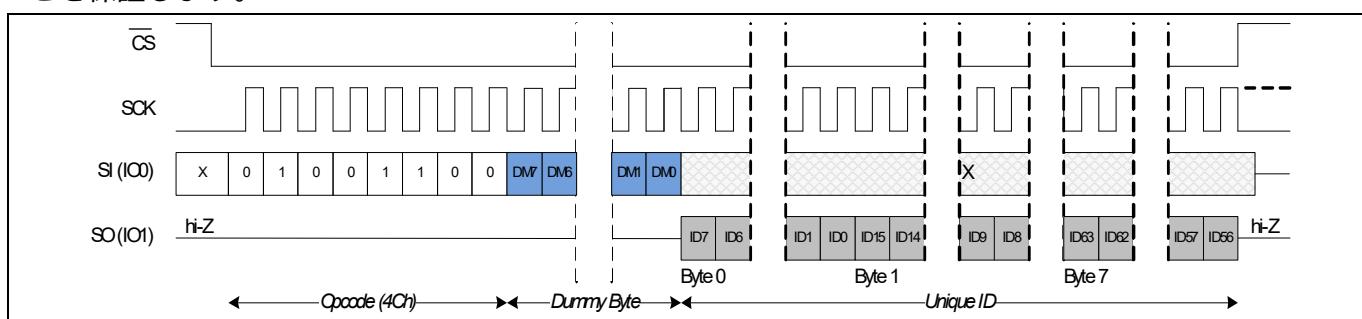

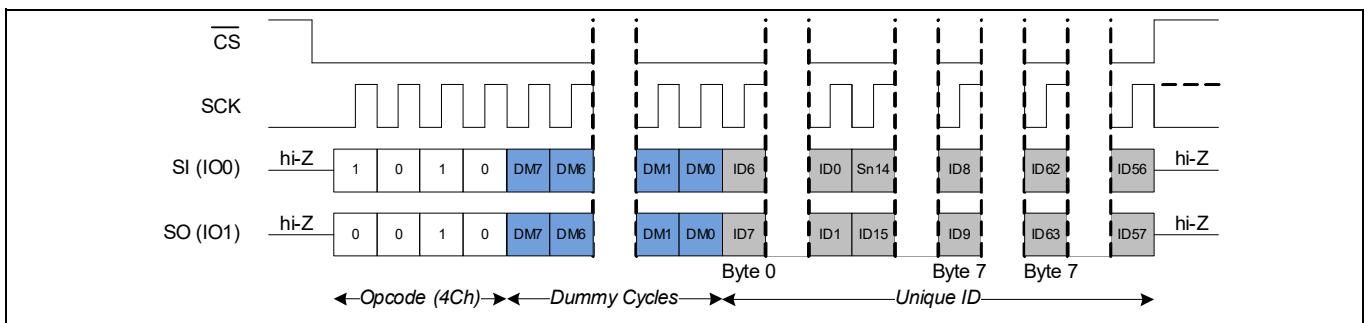

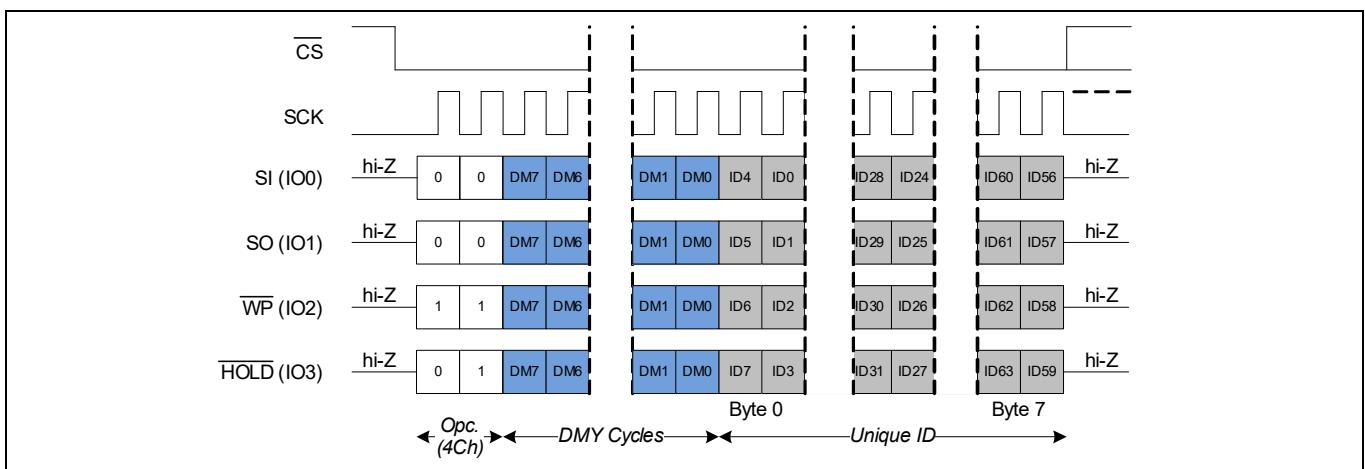

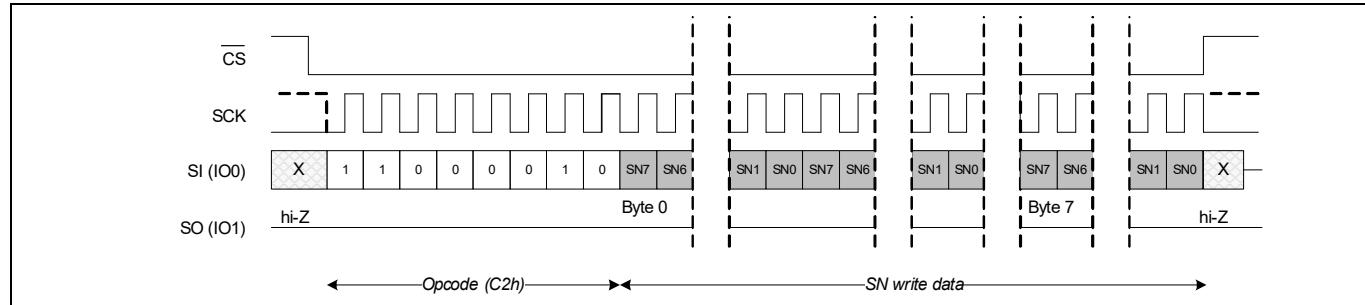

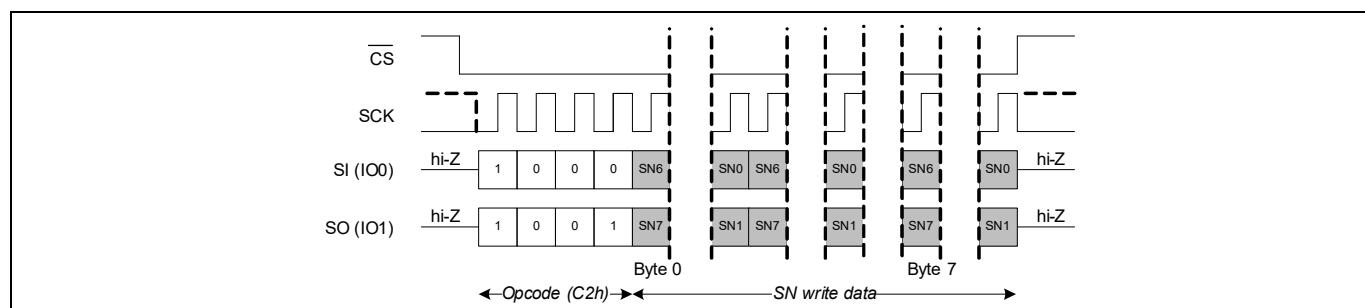

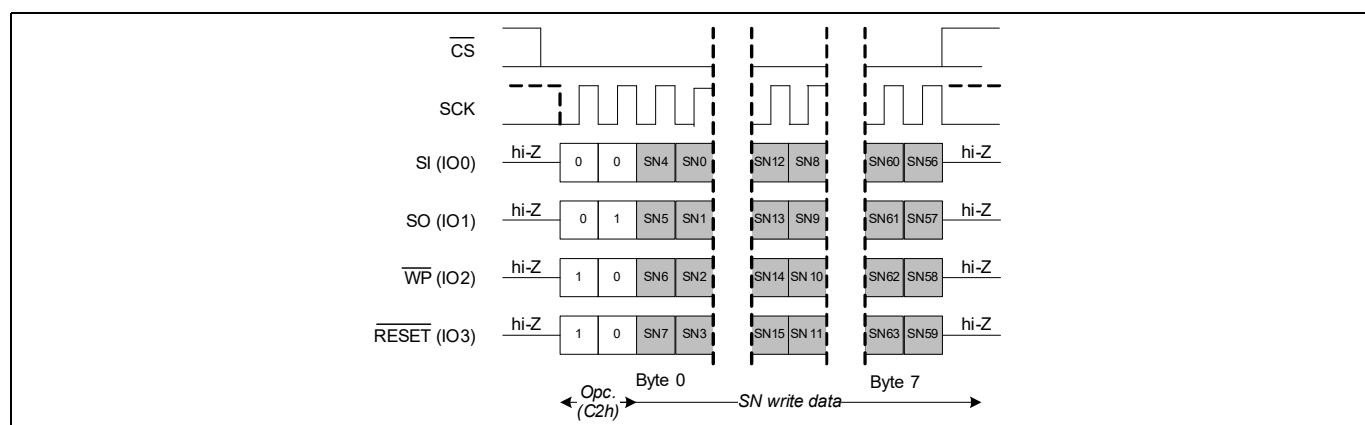

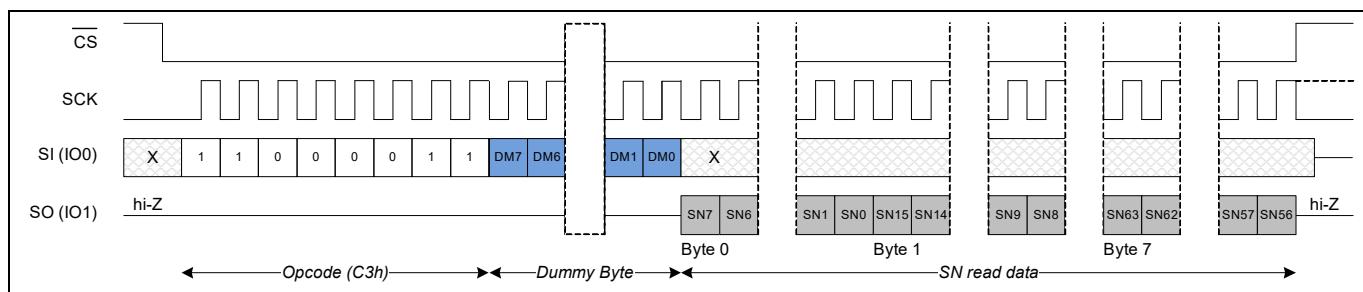

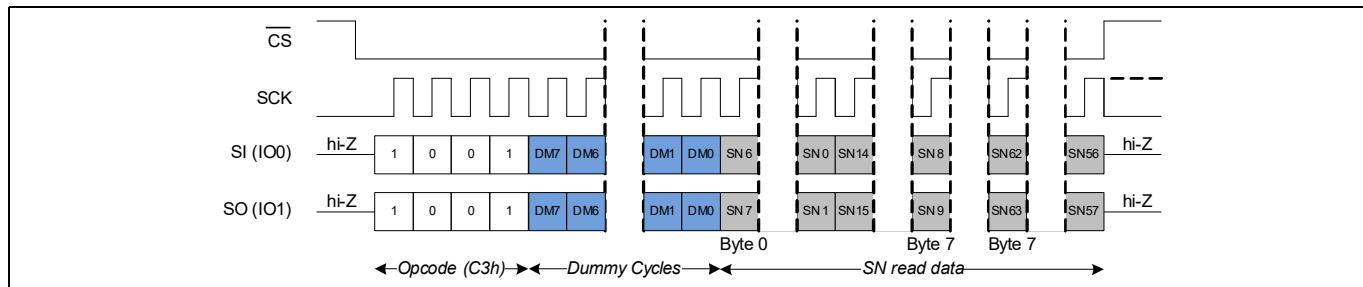

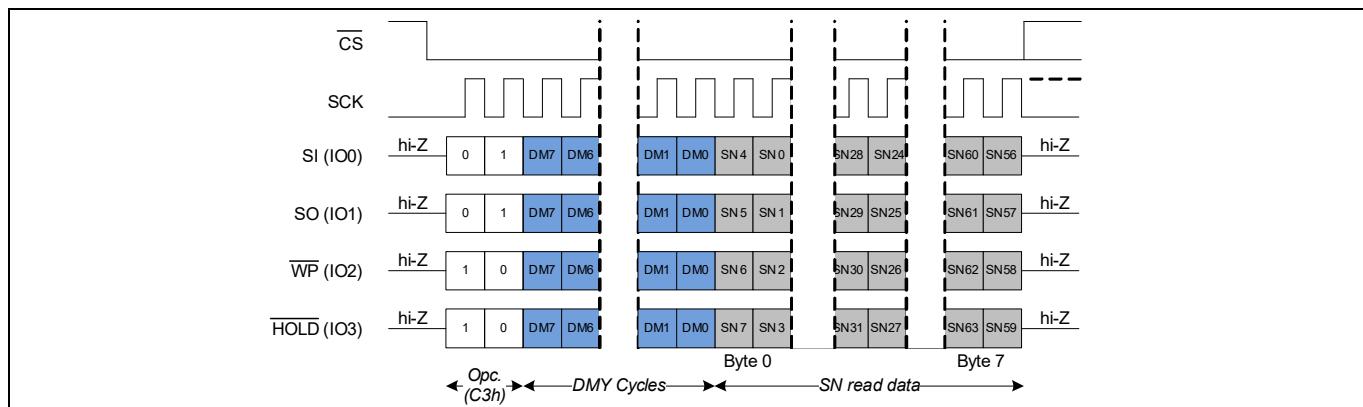

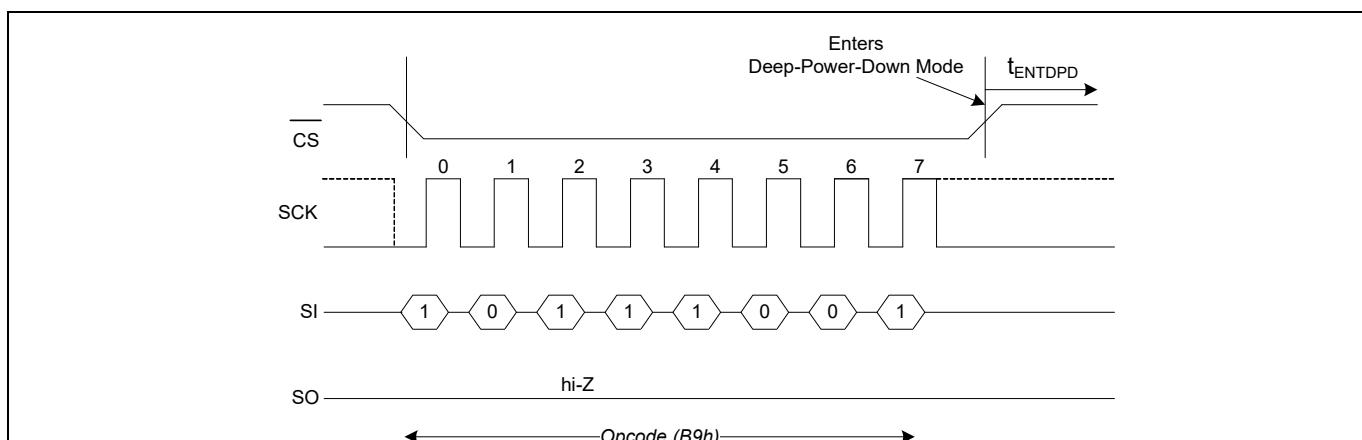

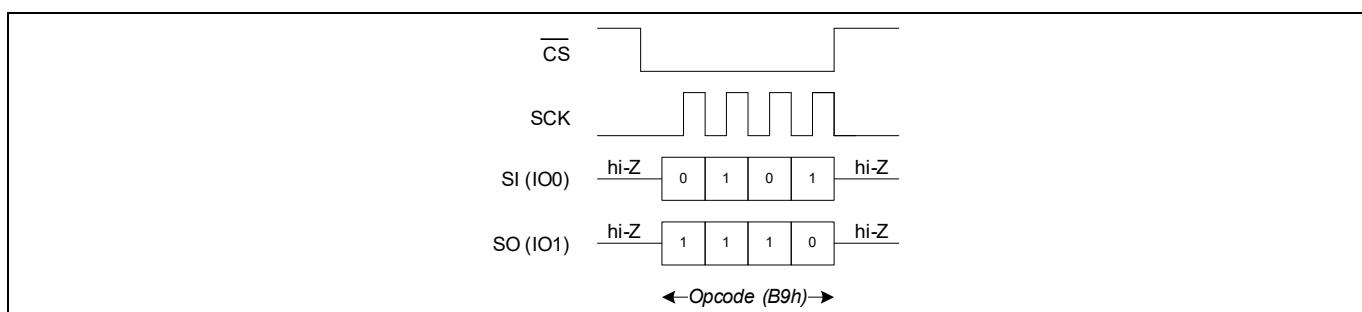

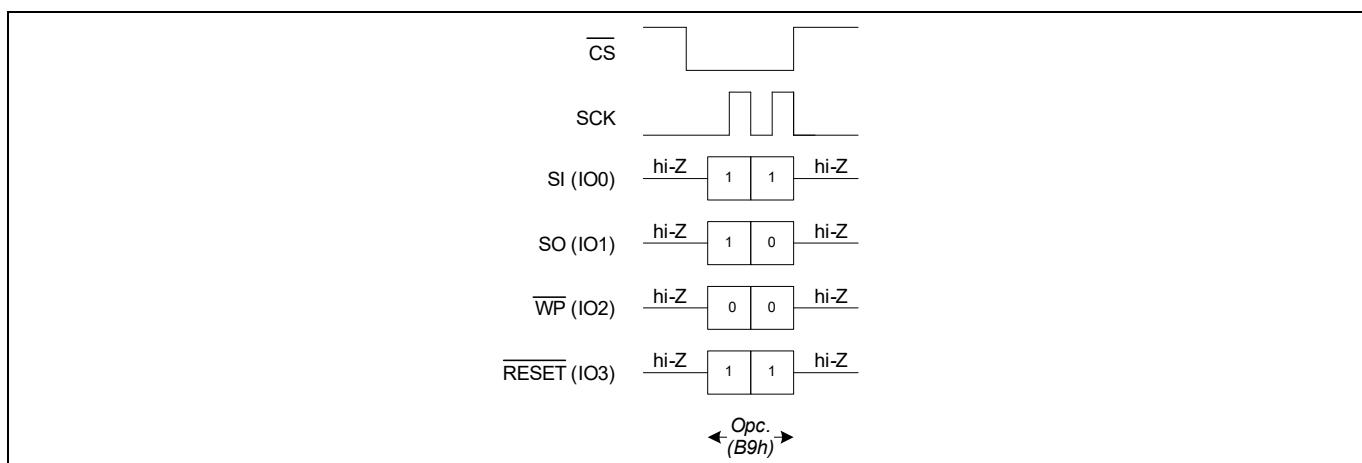

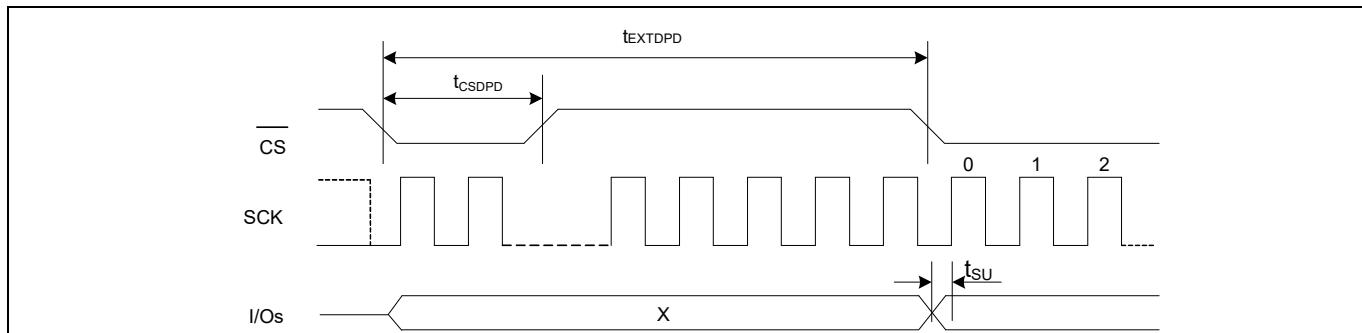

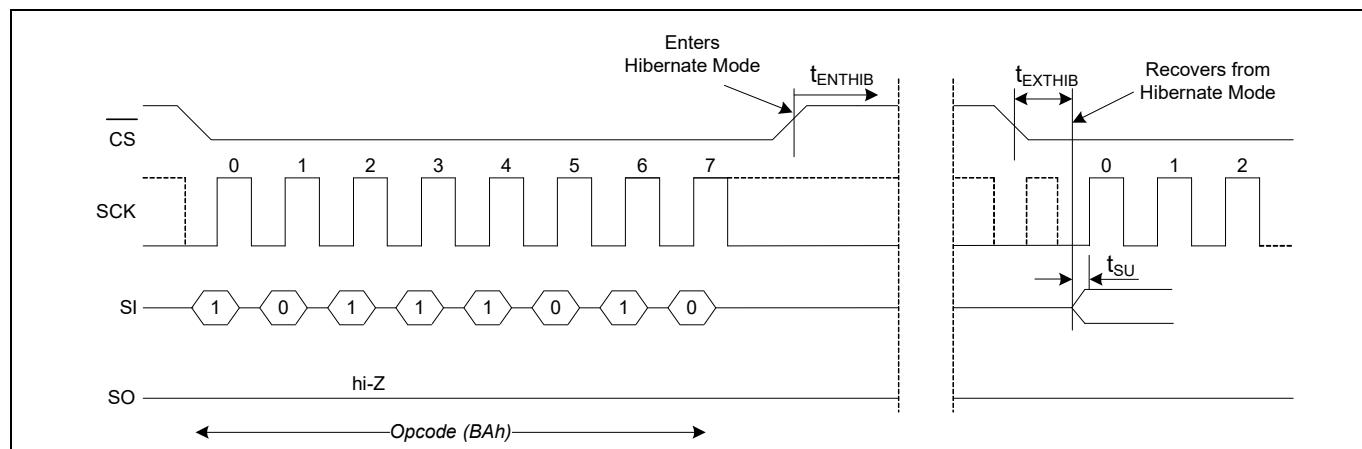

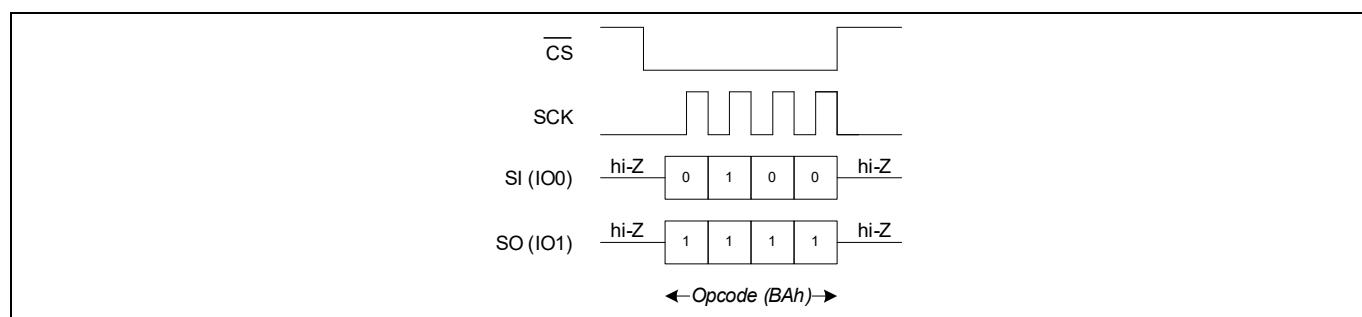

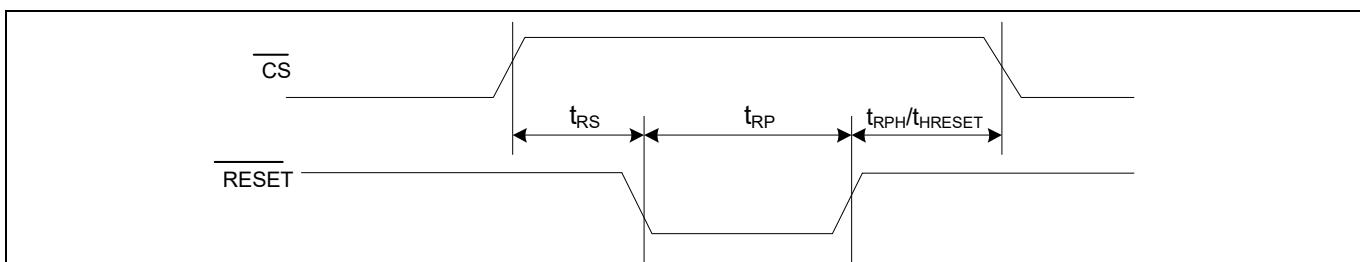

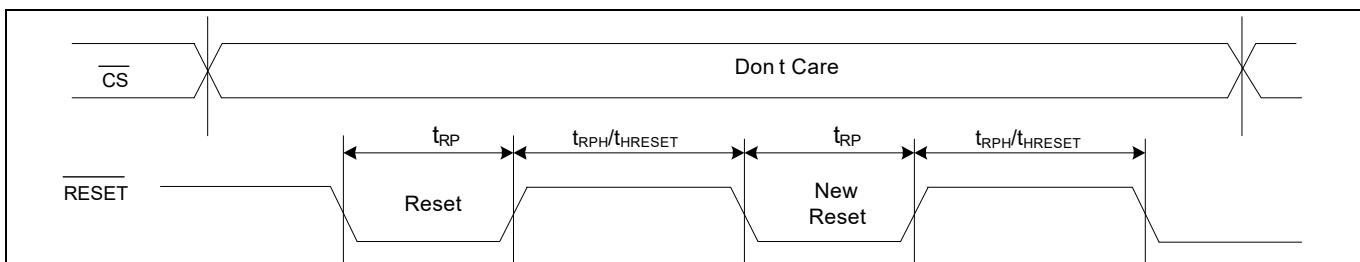

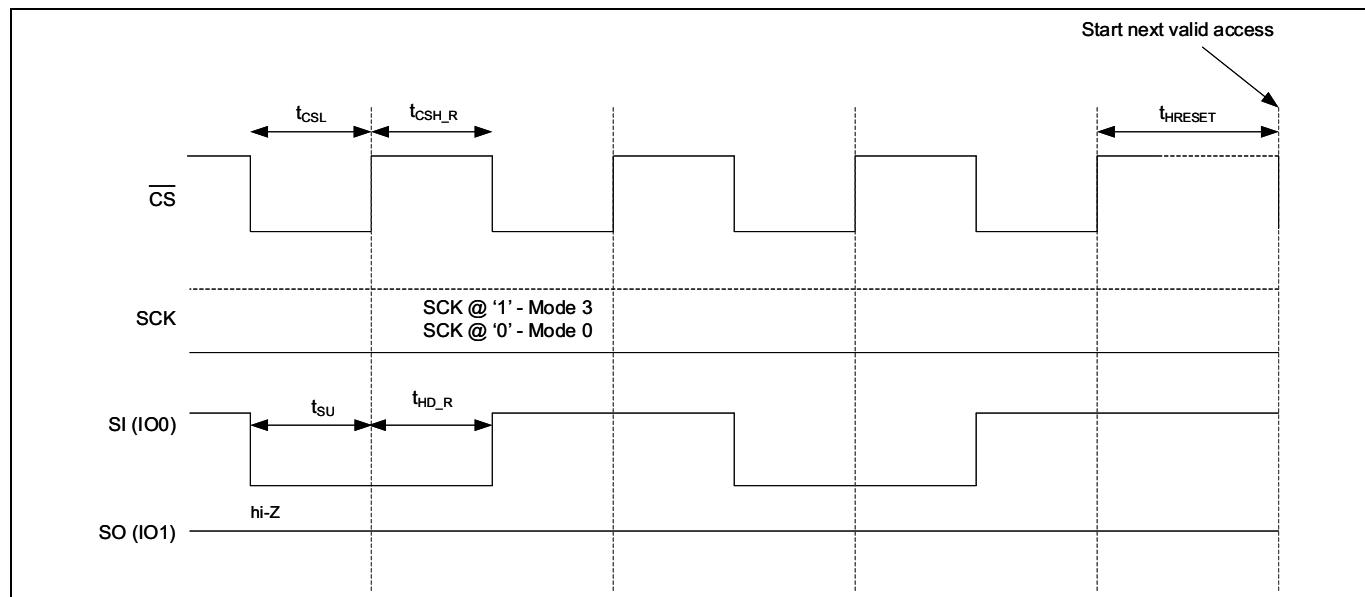

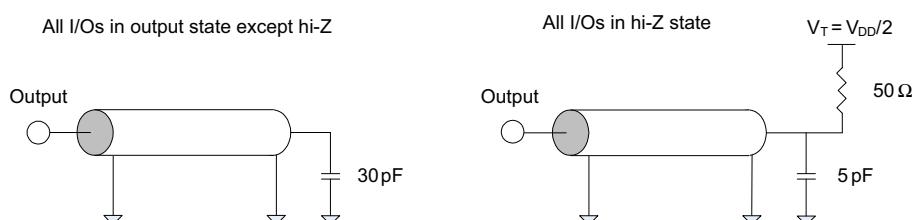

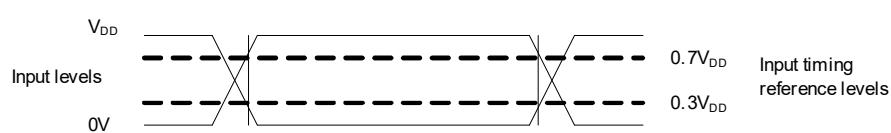

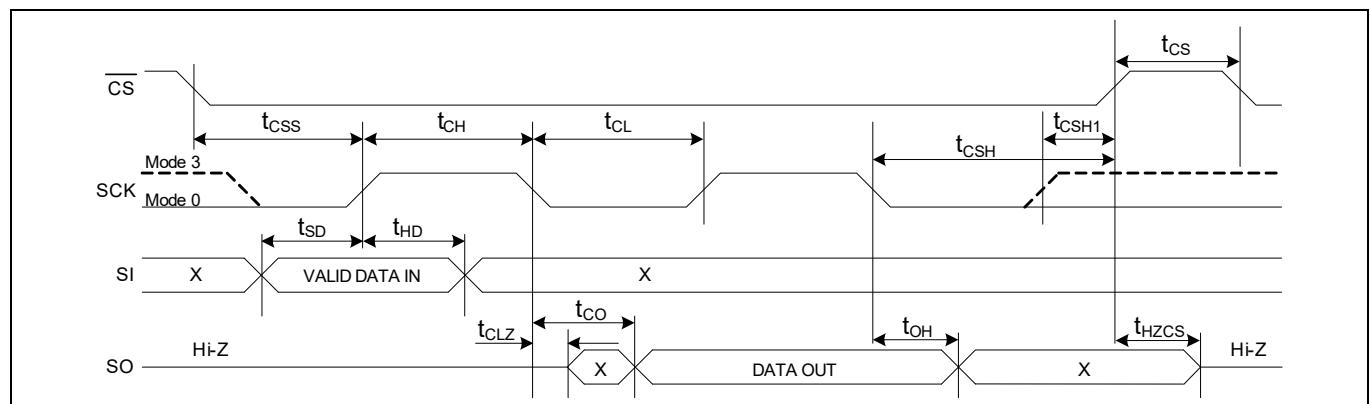

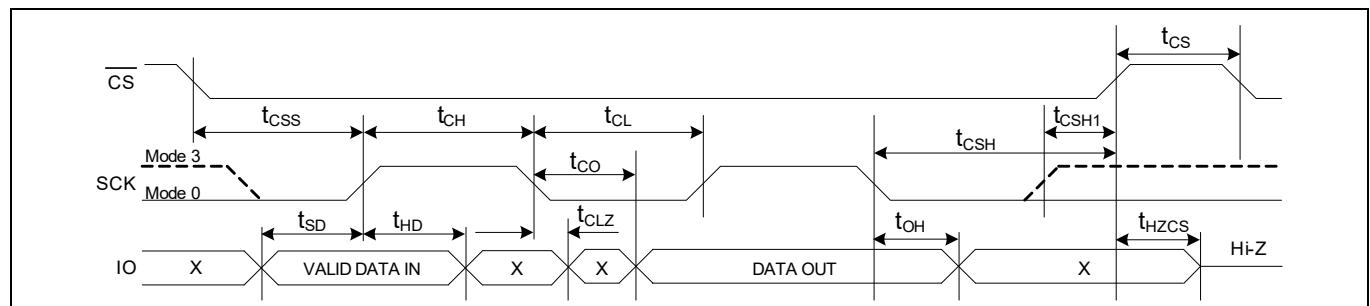

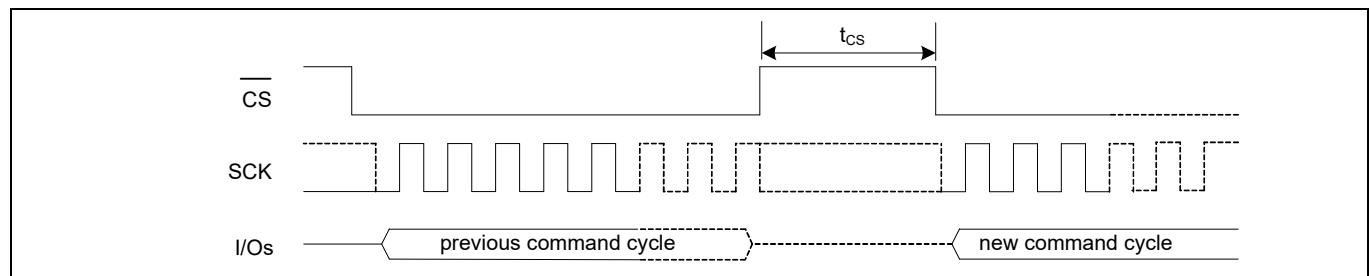

| QIW                 | 32          |                | なし      | あり      |         | なし      |     |     | あり    | なし  | なし       | なし       | あり               |