请注意赛普拉斯已正式并入英飞凌科技公司。

此封面页之后的文件标注有“赛普拉斯”的文件即该产品为此公司最初开发的。请注意作为英飞凌产品组合的部分，英飞凌将继续为新的及现有客户提供该产品。

#### 文件内容的连续性

事实是英飞凌提供如下产品作为英飞凌产品组合的部分不会带来对于此文件的任何变更。未来的变更将在恰当的时候发生，且任何变更将在历史页面记录。

#### 订购零件编号的连续性

英飞凌继续支持现有零件编号的使用。下单时请继续使用数据表中的订购零件编号。

## 性能

- 2 Mbit 铁电随机存取存储器 (F-RAM) 被逻辑组织为 256K × 8

- 提供了十万亿次 ( $10^{13}$ ) 的读 / 写周期, 几乎为无限次数的耐久性。

- 数据保留时间为 121 年 (见第 19 页上的数据保留时间与耐久性)

- NoDelay™ 写操作

- 高级高可靠性的铁电工艺

- 快速串行外设接口 (SPI)

- 高达 50 MHz 的频率

- 支持 SPI 模式 0 (0, 0) 和模式 3 (1, 1)

- 精密的写入保护方案

- 使用写保护 ( $\overline{WP}$ ) 引脚提供硬件保护

- 使用写禁用 ( $WRDI$ ) 指令提供软件保护

- 可对 1/4、1/2 或整个阵列进行软件模块保护

- 器件 ID 和序列号

- 器件 ID 包含制造商 ID 和产品 ID

- 唯一 ID

- 序列号

- 专用 256 字节特殊扇区 F-RAM

- 专用特殊扇区写和读操作

- 存储的内容可以在最多 3 个标准回流焊周期内保持不变

- 低功耗

- 频率为 40 MHz 时, 有效电流为 3.7 mA (典型值)

- 待机电流为 2.7  $\mu$ A (典型值)

- 深度掉电模式电流为 1.1  $\mu$ A (典型值)

- 休眠模式电流为 0.1  $\mu$ A (典型值)

- 低电压操作:

- CY15V102QN:  $V_{DD} = 1.71$  V 到  $1.89$  V

- CY15B102QN:  $V_{DD} = 1.8$  V 到  $3.6$  V

- 汽车级工作温度:  $-40$  °C 到  $+125$  °C

- 符合 AEC-Q100 一级标准

- 8 pin 小型塑封集成电路 (SOIC) 封装

- 符合有害物质限制标准 (RoHS)

## 功能说明

Excelon-Auto CY15X102QN 是采用了高级铁电工艺的汽车级 2 Mbit 非易失性存储器。铁电性随机存取存储器 (即 F-RAM) 是一种非易失性存储器, 它跟 RAM 一样, 能够执行读和写操作。它提供了 121 年的可靠数据保留时间, 并解决了串行闪存、EEPROM 和其他非易失性存储器所造成的复杂性、开销和系统级可靠性等问题。

与串行闪存和 EEPROM 不同的是, CY15X102QN 以总线速度执行写操作。并不会产生写延迟。在每个字节成功传输到器件后, 数据立即被写入到存储器阵列内。这时, 可以开始执行下一个总线周期而不需要轮询数据。此外, 与其他非易失性存储器相比, 该产品提供了更多的擦写次数。CY15X102QN 能够提供  $10^{13}$  次的读 / 写周期, 或支持比 EEPROM 多 1 千万次的写周期。

由于具有这些特性, 因此 CY15X102QN 非常适用于需要频繁或快速写操作的非易失性存储器应用。示例的范围包括从数据收集 (其中写周期数量是非常重要的) 到满足工业级控制 (其中串行闪存或 EEPROM 的较长写时间会使数据丢失)。

作为硬件替代时, CY15X102QN 为串行 EEPROM 或闪存的用户提供极大好处。CY15X102QN 使用高速的 SPI 总线, 从而可以改进 F-RAM 技术的高速写入能力。该器件包含一个只读的器件 ID 和唯一 ID 特性, 通过它们, 主机可以确定各器件的制造商、产品容量、产品版本和唯一 ID。该器件还提供可写的 8 字节序列号的寄存器, 这些寄存器可用于识别特定电路板或系统。

要获取相关资源的完整列表, 请单击 [此处](#)。

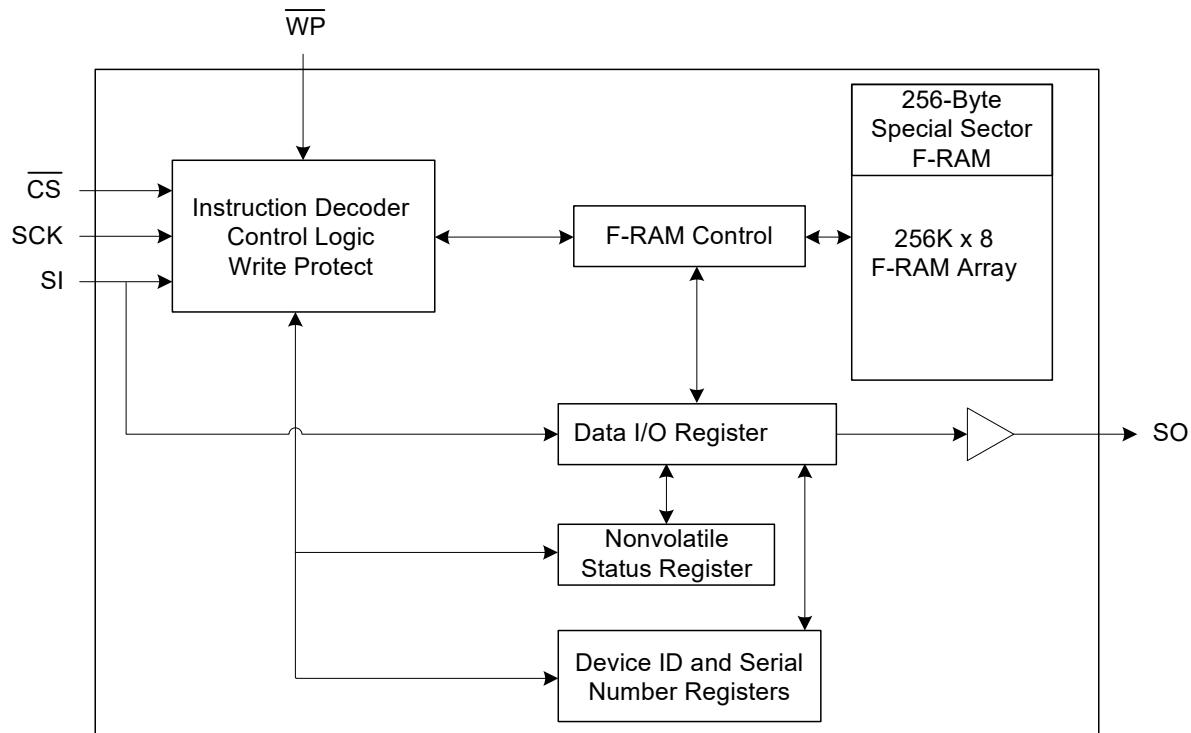

## 逻辑框图

## 目录

|                                      |    |                    |    |

|--------------------------------------|----|--------------------|----|

| 引脚分配 .....                           | 4  | 交流测试条件 .....       | 20 |

| 引脚定义 .....                           | 4  | 交流切换特性 .....       | 21 |

| 功能概述 .....                           | 5  | 电源周期时序 .....       | 23 |

| 存储器架构 .....                          | 5  | 订购信息 .....         | 24 |

| 串行外设接口 (SPI) 总线 .....                | 5  | 订购代码定义 .....       | 24 |

| SPI 协议中使用的术语 .....                   | 5  | 封装图 .....          | 25 |

| SPI 模式 .....                         | 6  | 缩略语 .....          | 26 |

| 从加电到第一次访问的时间 .....                   | 6  | 文档规范 .....         | 26 |

| 功能描述 .....                           | 7  | 测量单位 .....         | 26 |

| 指令结构 .....                           | 7  | 文档修订记录 .....       | 27 |

| 最大额定值 .....                          | 18 | 销售、解决方案和法律信息 ..... | 28 |

| 工作范围 .....                           | 18 | 全球销售和设计支持 .....    | 28 |

| 直流电气特性 .....                         | 18 | 产品 .....           | 28 |

| 数据保留时间与耐久性 .....                     | 19 | PSoC® 解决方案 .....   | 28 |

| 在 AEC-Q100 汽车应用中有关 F-RAM 寿命的示例 ..... | 20 | 赛普拉斯开发者社区 .....    | 28 |

| 电容 .....                             | 20 | 技术支持 .....         | 28 |

| 热阻 .....                             | 20 |                    |    |

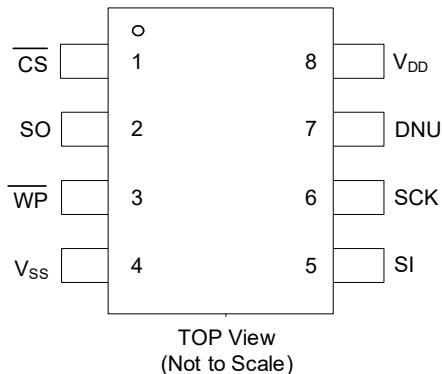

## 引脚分配

图 1. 8 pin SOIC 的引脚分布

## 引脚定义

| 引脚名称              | I/O 类型 | 说明                                                                                                                                                                                                           |

|-------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CS                | 输入     | <b>芯片选择。</b> 通过输入有效低电平可以使能器件。当该输入为高电平时，则器件会进入低功耗待机模式，忽略其他输入，并且输出是三态的。该输入为低电平时，器件将内部激活 SCK 信号。进行每一个操作码前，CS 上必须产生一个下降沿。                                                                                        |

| SCK               | 输入     | <b>串行时钟。</b> 所有输入 / 输出操作都与串行时钟同步。各输入都在上升沿上进行，而各输出则发生在串行时钟的下降沿上。由于该器件是同步的，因此时钟频率的范围为 0 到 50 MHz，可以随时中断该时钟频率。                                                                                                  |

| SI <sup>[1]</sup> | 输入     | <b>串行输入。</b> 所有数据均通过该引脚转送到器件内。该引脚在 SCK 的上升沿上进行采样，并且在其他时间内被忽略。应该始终将该引脚驱动到有效的逻辑电平，以满足电源 (I <sub>DD</sub> ) 规范。                                                                                                 |

| SO <sup>[1]</sup> | 输出     | <b>串行输出。</b> 这是数据输出引脚。该引脚在进行读操作中被驱动，在其他时间内保持三态。数据传输在串行时钟 SCK 的下降沿上被驱动。                                                                                                                                       |

| WP                | 输入     | <b>写保护。</b> 当状态寄存器中的 WPEN 位被设置为 ‘1’ 时，该低电平有效引脚防止对状态寄存器进行写操作。因为其他写保护特性都是通过状态寄存器控制的，所以该引脚是很重要的。有关写保护的完整说明，请参考表 2 和 第 9 页上的表 5。该引脚具有一个内部弱上拉电阻，该电阻会使该引脚在悬空（未在电路板上连接）时处于高电平状态。如果不使用该引脚，也可以将它连接到 V <sub>DD</sub> 。 |

| DNU               | 请勿使用   | <b>请勿使用。</b> 将该引脚保持悬空（没有板上连接）或连接至 V <sub>DD</sub> 。                                                                                                                                                          |

| V <sub>SS</sub>   | 电源     | 器件的接地引脚。必须连接至系统接地端。                                                                                                                                                                                          |

| V <sub>DD</sub>   | 电源     | 器件的电源输入。                                                                                                                                                                                                     |

### 注释：

- 对于单引脚数据接口，可将 SI 连接到 SO。

## 功能概述

CY15X102QN 是一个串行 **F-RAM** 存储器。该存储器阵列被逻辑组织为  $262,144 \times 8$  位，通过使用行业标准的串行外设接口 (**SPI**) 总线可以访问该存储器阵列。**F-RAM** 同串行闪存和串行 **EEPROM** 的功能操作是相同的。CY15X102QN 与相同引脚分布的串行闪存或 **EEPROM** 的主要区别在于 **F-RAM** 具有更好的写性能、高耐久性和低功耗。

## 存储器架构

访问 CY15X102QN 时，用户可寻址 256K 地址，每个地址包括 8 个数据位。这些 8 位数据被连续移入或移出。通过使用 **SPI** 协议可以访问这些地址，该协议包含一个芯片选择（用于支持总线上的多个器件）、一个操作码和一个 3 字节地址。该地址范围的高 6 位的值是“无需关注”的。18 位的完整地址独立指定每个字节的地址。

CY15X102QN 的大多数功能可以由 **SPI** 接口控制，或通过板上电路处理。在没有考虑到串行协议所需要的时间的情况下，存储器的访问时间几乎为零。因此，该存储器以 **SPI** 总线的速度进行读 / 写操作。与串行闪存或 **EEPROM** 不同的是，不需要轮询器件的就绪条件，这是因为写操作是以总线速度进行的。这样，在将新的总线数据传输移入器件时，已经在存储器中完成了写操作。更多详细信息，请参阅‘接口’部分所介绍的内容。

## 串行外设接口 (**SPI**) 总线

CY15X102QN 是一个 **SPI** 从设备，它的运行速度可达 50 MHz。该高速串行总线为 **SPI** 主设备提供了高性能的串行通信。许多通用微控制器具有硬件 **SPI** 端口，用于执行直接连接。对于没有硬件 **SPI** 端口的微控制器，通过使用普通端口引脚可以简单地模拟该端口。CY15X102QN 在 **SPI** 模式 0 和模式 3 下运行。

### SPI 概述

**SPI** 是带有芯片选择 (**CS**)、串行输入 (**SI**)、串行输出 (**SO**) 和串行时钟 (**SCK**) 引脚的四引脚接口。

**SPI** 是同步的串行接口，它使用时钟和数据引脚进行存储器访问并支持数据总线上的多个器件。使用 **CS** 引脚可激活 **SPI** 总线上的器件。

芯片选择、时钟和数据之间的关系是由 **SPI** 模式决定的。该器件支持 **SPI** 模式 0 和模式 3。在两种模式下，数据都在 **SCK** 上升沿（从 **CS** 变为有效之后的第一个上升沿）上记录到 **F-RAM** 内。

**SPI** 协议由操作码控制。这些操作码规定了从总线主设备到从设备的所有指令。激活 **CS** 后，总线主设备传输的第一个字节便是操作码。随后，可以传输任何地址和数据。在完成某个操作并发出新的操作码前，**CS** 必须进入无效状态。

### SPI 协议中使用的术语

**SPI** 协议中的常用术语如下：

#### SPI 主设备

**SPI** 总线上的操作由 **SPI** 主设备控制。**SPI** 总线可能只有一个主设备，但可以有一个或多个从设备。所有从设备共享同一 **SPI** 总线。主设备可通过 **CS** 引脚选择任意从设备。所有操作必须由主设备启动，主设备通过将从设备的 **CS** 引脚置于低电平状态来激活从设备。主设备也生成 **SCK**（串行时钟），**SI** 和 **SO** 线上的所有数据传输均与该时钟同步。

#### SPI 从设备

**SPI** 从设备由主设备通过芯片选择线激活。来自 **SPI** 主设备的串行时钟 **SCK** 作为从设备的输入，所有通信均与该时钟同步。**SPI** 从设备不会在 **SPI** 总线上发起通信，而仅执行主设备所发出的指令。

CY15X102QN 可用作 **SPI** 从设备，并与其他 **SPI** 从设备共享 **SPI** 总线。

#### 芯片选择 (**CS**)

要选择任一从设备，主设备必须下拉相应 **CS** 引脚。仅当 **CS** 引脚为低电平状态时，才能将指令发送到从设备。未选择器件时，通过 **SI** 引脚传输的数据将被忽略，同时，串行输出引脚 (**SO**) 保持高阻抗状态。

**注意：**必须从 **CS** 的下降沿上开始执行新指令。因此，每个有效芯片选择周期只能生成一个操作码。

#### 串行时钟 (**SCK**)

串行时钟由 **SPI** 主设备生成，在 **CS** 变为低电平后，通信将与该时钟同步。

CY15X102QN 在 **SPI** 模式 0 和模式 3 下进行数据通信。在两种模式下，从设备在 **SCK** 的上升沿上锁存输入，且输出在下降沿发出。因此，**SCK** 的第一个上升沿表示已经在 **SI** 引脚上接收到 **SPI** 指令的第一个最高有效位（**MSB**）。此外，所有数据输入和输出均与 **SCK** 同步。

### 数据传输 (SI/SO)

SPI 数据总线由 SI 和 SO 两条线组成, 可用于串行数据通信。SI 也称为主出从入 (MOSI), SO 则称为主入从出 (MISO)。主设备通过 SI 引脚将指令发送到从设备, 从设备通过 SO 引脚进行响应。如上所述, 多个从设备可共享 SI 和 SO 线。

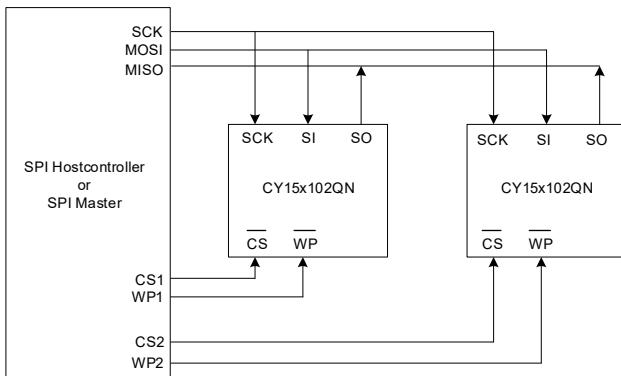

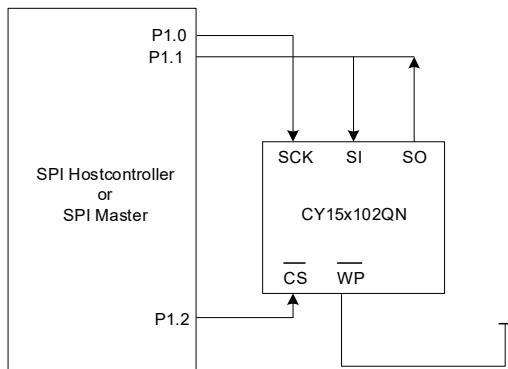

CY15X102QN 为 SI 和 SO 提供可连接至主设备的两个独立引脚, 如图 2 中所示。对于没有专用 SPI 总线的微控制器, 可以使用通用地址端口。为了减少微控制器的硬件资源, 可以将两个数据引脚 (SI, SO) 连接在一起, 并将 WP 引脚置于高电平。图 3 显示了仅使用三个引脚的配置。

图 2. 使用 SPI 端口进行系统配置

图 3. 不使用 SPI 端口的系统配置

### 最高有效位 (MSB)

SPI 协议要求发送的第一位是最高有效位 (MSB)。该条件也适用于地址和数据传输。

2 Mbit 串行 F-RAM 需要一个 3 字节地址才能进行读取和写入操作。由于地址只有 18 位, 所以器件会忽略所载入的前六位。虽然无需关注前六位, 但赛普拉斯建议将这些位设置为 ‘0’ , 以通过无缝切换实现更高存储容量。

### 串行操作码

通过将  $\overline{CS}$  置于低电平来选择从设备后, 可将收到的第一个字节作为操作码进行期望的操作。CY15X102QN 使用标准操作码进行存储器访问。

### 无效的操作码

如果收到无效的操作码, 该操作码将被忽略。器件将忽略在 SI 引脚上的所有额外串行数据, 直到  $\overline{CS}$  的下一个下降沿为止, 与此同时, SO 引脚保持三态。

### 状态寄存器

CY15X102QN 具有一个 8 位的状态寄存器。状态寄存器中的各位用于配置器件。第 9 页上的表 3 对这些位进行了说明。

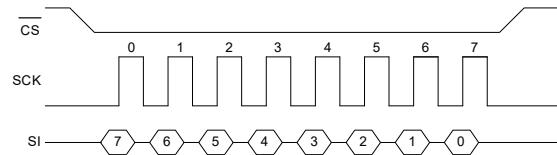

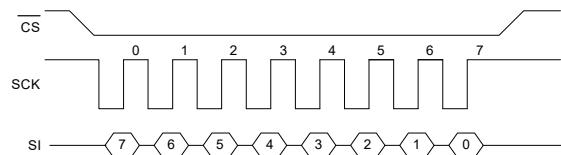

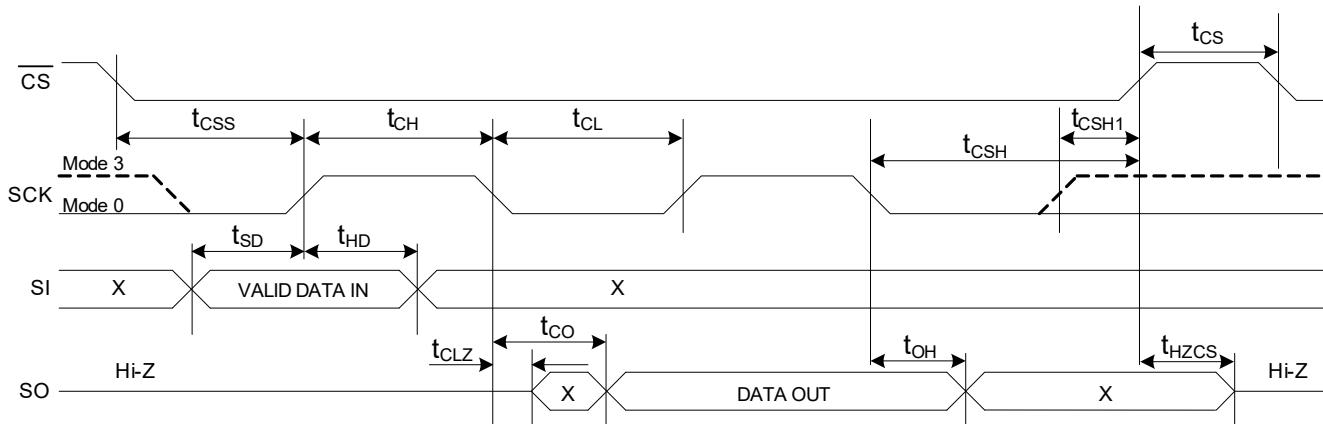

### SPI 模式

CY15X102QN 可由微控制器进行驱动, 该控制器的 SPI 外设可运行于下列任一模式:

- SPI 模式 0 ( $CPOL = 0$ ,  $CPHA = 0$ )

- SPI 模式 3 ( $CPOL = 1$ ,  $CPHA = 1$ )

在两种模式下,  $\overline{CS}$  有效后, 输入数据将在 SCK 的第一次上升沿上被锁存。如果时钟从高电平状态启动 (在模式 3 中), 则采用时钟触发后的第一个上升沿。输出数据在 SCK 的下降沿上可用。图 4 和图 5 分别显示了两种 SPI 模式。当总线主设备不传输数据时, 时钟的状态为:

- 在模式 0 下, 串行时钟保持为 0

- 在模式 3 下, 串行时钟保持为 1

通过将  $\overline{CS}$  引脚置为低电平而选中该器件时, 该器件会通过 SCK 引脚状态来检测出 SPI 模式。器件被选中时, 如果 SCK 引脚处于低电平状态, 它将工作于 SPI 模式 0 ; 如果 SCK 引脚处于高电平状态, 它将工作于 SPI 模式 3。

图 4. SPI 模式 0

图 5. SPI 模式 3

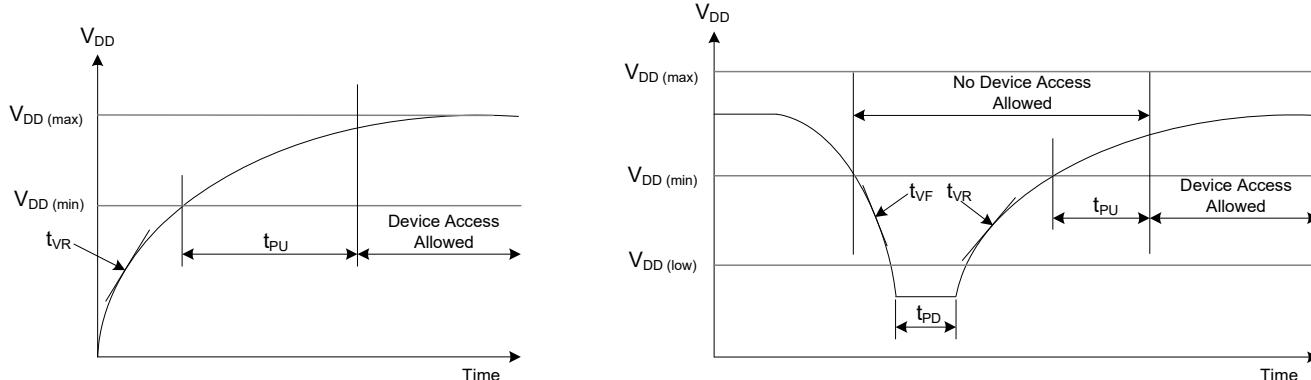

### 从加电到第一次访问的时间

上电后, 在  $t_{PU}$  时间内不能访问 CY15X102QN。用户必须遵守时序参数  $t_{PU}$ , 该参数是从  $V_{DD}$  (最小值) 到第一次  $\overline{CS}$  为低电平的最短时间。更多信息, 请查阅第 23 页上的电源周期时序。

## 功能描述

### 指令结构

有 15 个称为操作码的指令，总线主设备可以将这些指令发送到 CY15X102QN（见表 1）。它们控制存储器执行的各项功能。

表 1. 操作码指令

| 名称               | 说明        | 操作码               |            | 最大频率 (MHz) |

|------------------|-----------|-------------------|------------|------------|

|                  |           | 十六进制              | 二进制        |            |

| <b>写使能控制</b>     |           |                   |            |            |

| WREN             | 置位写使能锁存   | 06h               | 0000 0110b | 50         |

| WRDI             | 复位写入使能锁存  | 04h               | 0000 0100b | 50         |

| <b>寄存器访问</b>     |           |                   |            |            |

| RDSR             | 读取状态寄存器   | 05h               | 0000 0101b | 50         |

| WRSR             | 写状态寄存器    | 01h               | 0000 0001b | 50         |

| <b>存储器写入操作</b>   |           |                   |            |            |

| WRITE            | 写入存储器数据   | 02h               | 0000 0010b | 50         |

| <b>存储器读取</b>     |           |                   |            |            |

| READ             | 读取存储器数据   | 03h               | 0000 0011b | 40         |

| FSTRD            | 快速读取存储器数据 | 0Bh               | 0000 1011b | 50         |

| <b>特殊扇区存储器访问</b> |           |                   |            |            |

| SSWR             | 特殊扇区写入操作  | 42h               | 0100 0010b | 50         |

| SSRD             | 特殊扇区读取操作  | 4Bh               | 0100 1011b | 40         |

| <b>标识和序列号</b>    |           |                   |            |            |

| RDID             | 读取器件 ID   | 9Fh               | 1001 1111b | 50         |

| RUID             | 读取唯一 ID   | 4Ch               | 0100 1100b | 50         |

| WRSN             | 写入序列号     | C2h               | 1100 0010b | 50         |

| RDSN             | 读取序列号     | C3h               | 11000 011b | 50         |

| <b>低功耗模式</b>     |           |                   |            |            |

| DPD              | 进入深度下电模式  | BAh               | 1011 1010b | 50         |

| HBN              | 进入休眠模式    | B9h               | 1011 1001b | 50         |

| <b>预留</b>        |           |                   |            |            |

| 预留               | 预留        | 未使用的操作码被保留以供将来使用。 |            | -          |

### 写使能控制指令

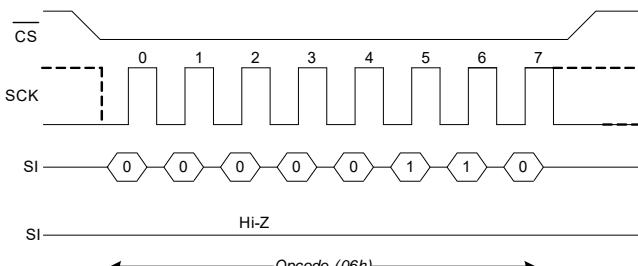

#### 设置写使能锁存 (WREN, 06h)

为 CY15X102QN 上电后将禁止写操作。在进行任何写操作前，都必须发送 WREN 指令。发送 WREN 操作码后，用户可以发送后续操作码，以用于写操作。这些写操作包括写入状态寄存器 (WRSR)、写入存储器 (WRITE)、写入特殊扇区 (SSWR)、写入序列号 (WRSN) 的操作。

发送 WREN 操作码后，将设置内部写使能锁存。状态寄存器中的标志位（名称为 WEL）表示锁存的状态。WEL = ‘1’ 表示可以进行写操作。尝试写状态寄存器中的 WEL 位不会影响到该位的状态 — 这是因为只有 WREN 操作码才能设置该位。进行 WRDI、WRSR、WRITE、SSWR 或 WRSN 写操作后，WEL 位将在 CS 的上升沿上自动清除。这样可阻止对状态寄存器或 F-RAM 阵列进行其他写操作而不需要使用另一个 WREN 指令。图 6 显示的是 WREN 指令总线配置。

图 6. WREN 总线配置

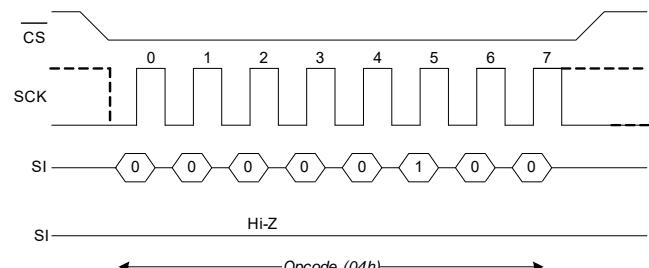

#### 复位写入使能锁存 (WRDI, 04h)

WRDI 指令通过清除写使能锁存来禁用所有写操作。通过读取状态寄存器中的 WEL 位和验证 WEL 为 ‘0’，可以验证各写操作已被禁用。图 7 显示的是 WRDI 指令的总线配置。

图 7. WRDI 总线配置

### 状态寄存器和写保护

CY15X102QN 的写保护特性是多层次的，并由状态寄存器使能。状态寄存器的组织方式如下所示。（WEL、BP0、BP1、位 4–5、WPEN 的默认出厂设置值为 ‘0’，位 6 的默认出厂设置值为 ‘1’）。

**表 2. 状态寄存器**

| 位 7      | 位 6   | 位 5   | 位 4   | 位 3     | 位 2     | 位 1     | 位 0   |

|----------|-------|-------|-------|---------|---------|---------|-------|

| WPEN (0) | X (1) | X (0) | X (0) | BP1 (0) | BP0 (0) | WEL (0) | X (0) |

**表 3. 状态寄存器位定义**

| 位          | 定义        | 说明                                                                                |

|------------|-----------|-----------------------------------------------------------------------------------|

| 位 0        | 无需关注      | 该位是不可写的，并且读取时始终返回 ‘0’。                                                            |

| 位 1 (WEL)  | 写使能       | WEL 表示器件是否使能写入功能。上电时，该位默认为 ‘0’（禁用）。<br>WEL = ‘1’ --> 使能写操作<br>WEL = ‘0’ --> 禁用写操作 |

| 位 2 (BP0)  | 模块保护位 ‘0’ | 用于保护模块有关详细信息，请参见表 4。                                                              |

| 位 3 (BP1)  | 模块保护位 ‘1’ |                                                                                   |

| 位 4–5      | 无需关注      | 这些位都是不可写的，并且读取时始终返回 ‘0’。                                                          |

| 位 6        | 无需关注      | 该位是不可写的，并且读取时始终返回 ‘1’。                                                            |

| 位 7 (WPEN) | 写保护使能位    | 用于使能写保护引脚 (WP) 的功能。有关详细信息，请参见表 5。                                                 |

位 0 和位 4–5 的固定值为 ‘0’，位 6 的固定值为 ‘1’；不能修改这些位的值。请注意，不需要位 0（串行 Flash 和 EEPROM 中的“就绪或正在进行写过程”位），由于 F-RAM 在实时进行写操作时并非处于繁忙状态，因此读取它时始终会返回 ‘0’。器件从第 16 页上的深度掉电模式 (DPD, BAh) 或第 17 页上的休眠模式 (HBN, B9h) 唤醒的情况属于例外。BP1 和 BP0 控制软件保护特性，这两位是非易失性位。WEL 标志表示写使能锁存的状态。尝试将 WEL 位直接写入到状态寄存器中不会对其状态产生影响。该位分别由 WREN 指令内部设置以及由 WRDI 指令清除。

BP1 和 BP0 是存储器模块写保护位。它们指定受写保护的存储器部分，如表 4 中所示。

**表 4. 模块存储器写保护**

| BP1 | BP0 | 受保护的地址范围                |

|-----|-----|-------------------------|

| 0   | 0   | 否                       |

| 0   | 1   | 30000h 到 3FFFFh (高 1/4) |

| 1   | 0   | 20000h 到 3FFFFh (高 1/2) |

| 1   | 1   | 00000h 到 3FFFFh (所有地址)  |

BP1 和 BP0 位，以及写使能锁存是保护写入存储器的唯一机制。其他写保护特性会防止对模块保护位进行意外更改。

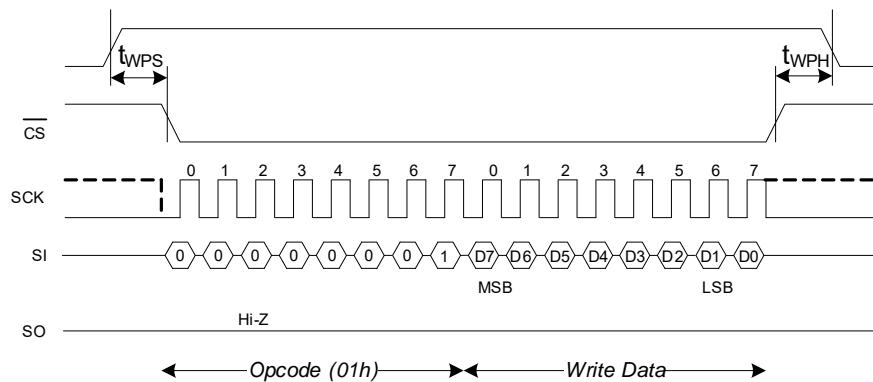

状态寄存器中的写保护使能位 (WPEN) 控制硬件写保护 (WP) 引脚的效果。有关 WP 引脚时序框图的信息，请参考第 22 页上的图 23 部分。WPEN 位为 ‘0’ 时，WP 引脚的状态将被忽略。WPEN 位为 ‘1’ 时，低电平的 WP 引脚将禁止写入到状态寄存器。因此，只有 WPEN = ‘1’ 和 WP = ‘0’ 时，状态寄存器才受写保护。表 5 汇总了写保护条件。

**表 5. 写保护**

| WEL | WPEN | WP | 受保护的模块 | 无保护的模块 | 状态寄存器 |

|-----|------|----|--------|--------|-------|

| 0   | X    | X  | 受保护    | 受保护    | 受保护   |

| 1   | 0    | X  | 受保护    | 无保护    | 无保护   |

| 1   | 1    | 0  | 受保护    | 无保护    | 受保护   |

| 1   | 1    | 1  | 受保护    | 无保护    | 无保护   |

### 寄存器访问命令

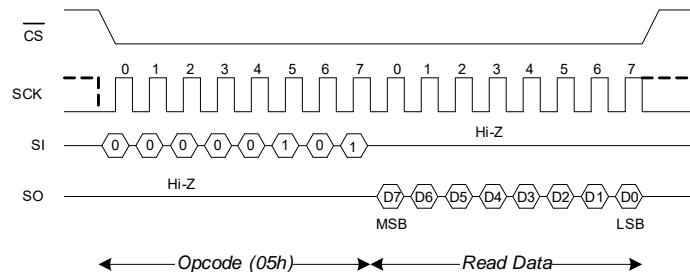

#### 读状态寄存器 (RDSR, 05h)

通过使用 RDSR 指令, 总线主设备可以验证状态寄存器中的内容。读取状态寄存器后可以了解写保护特性的当前状态。执行 RDSR 操作码后, CY15X102QN 将返回一个字节, 该字节包含状态寄存器的内容。

图 8. RDSR 总线配置

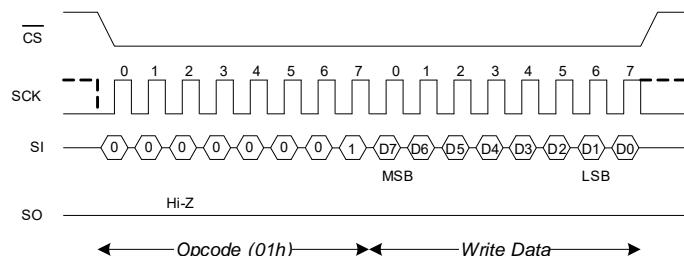

#### 写状态寄存器 (WRSR, 01h)

WRSR 指令允许 SPI 总线主设备写入状态寄存器并通过根据要求设置 WPEN、BP0 和 BP1 位修改写保护配置。在发送 WRSR 指令前, WP 引脚必须为高电平或处于无效状态。请注意, 在 CY15X102QN 上, WP 仅防止写入状态寄存器而不能防止写入存储器阵列。发送 WRSR 指令前, 用户必须发送 WREN 指令来使能写操作。执行 WRSR 指令就是执行一个写操作, 因此可以清除写使能锁存。

图 9. WRSR 总线配置 (不显示 WREN)

### 存储器操作

可接受高时钟频率的 SPI 接口突出显示了 F-RAM 技术的快速写入能力。与串行闪存和 EEPROM 不同的是，CY15X102QN 能以总线速度执行连续写操作。无需任何页寄存器，仍能够执行所有连续写操作数。

### 存储器写操作指令

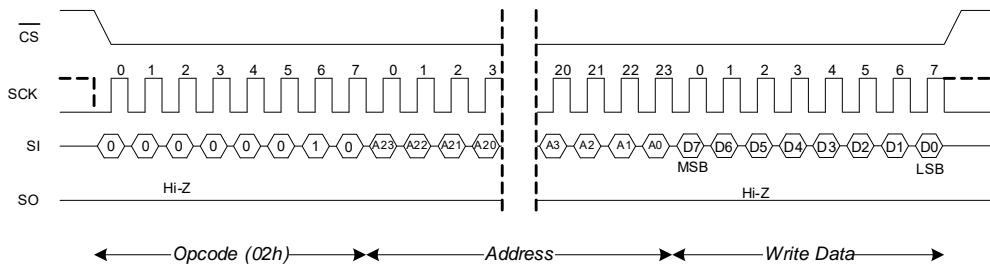

#### 写操作 (WRITE, 02h)

对存储器进行的所有写操作都以 WREN 操作码开始，这时将依次确认和取消确认 CS。下一个操作码是 WRITE。WRITE 操作码后面是一个三字节的地址，该地址包含了将写入到存储器的第一个数据字节的 18 位地址 (A17-A0)。三字节地址的高六位被忽略。后续字节是连续写入的数据字节。如果总线主设备继续发送时钟并保持 CS 为低电平，则各地址将内部递增。如果达到最后地址 3FFFFh，内部地址计数器将翻转到 00000h。先写入数据的最高有效位。CS 的上升沿终止写操作。CY15X102QN 写操作如图 10 中显示。

### 注意：

- 突发写操作达到保护模块地址时，便停止自动递增地址，而且器件将忽略写操作所接收的所有后续数据字节。EEPROM 使用页面缓冲器来增加它们的写吞吐量。这样可以补偿技术的慢速写操作。F-RAM 存储器没有页面缓冲器，因为在每个字节定时后（在第八个时钟周期后），它将立即被写入到 F-RAM 阵列内。这样可以写入任何字节数量而不需要页面缓冲器延迟。

- 如果写操作过程中断电，那么只有最后完成的字节被写入。

图 10. 存储器写 (WREN 不显示) 操作

### 存储器读操作指令

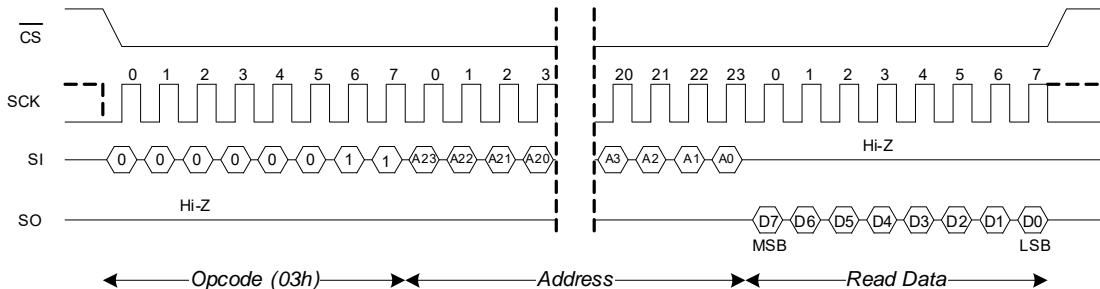

#### 读操作 (READ, 03h)

**CS** 的下降沿后, 总线主设备将发送一个 READ 操作码。READ 指令后面是一个三字节地址, 该地址包含读操作第一个字节的 18 位地址 (A17-A0)。该地址的高六位被忽略。发送操作码和地址

后, 在随后的八个时钟内器件将输出读数据。在驱动读取数据字节期间, **SI** 输入被忽略。后续字节是连续读取的数据字节。只要总线主设备继续发送时钟并保持 **CS** 为低电平, 地址将内部递增。如果达到最后地址 3FFFFh, 内部地址计数器将翻转到 00000h。先读取数据的最高有效位。**CS** 的上升沿终止读操作并使 **SO** 引脚处于三态。CY15X102QN 读操作如图 11 中显示。

图 11. 存储器读操作

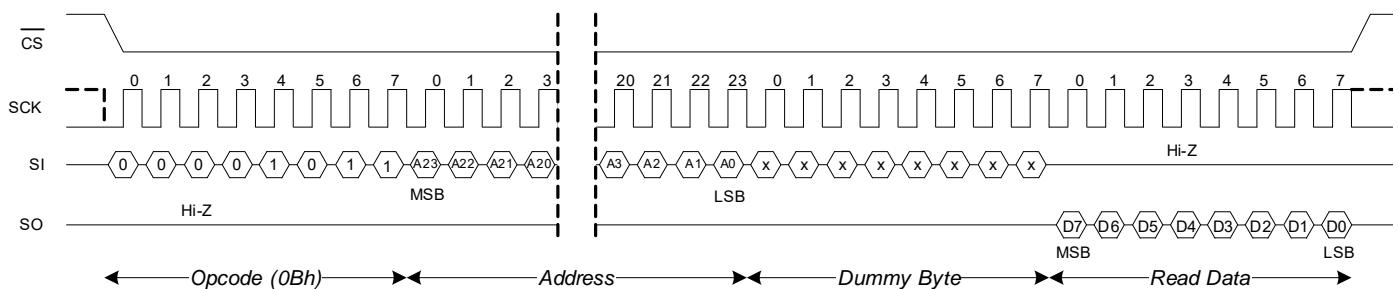

#### 快速读操作 (FAST\_READ, 0Bh)

CY15X102QN 支持 FAST READ 操作码 (0Bh), 用于与串行闪存器件相兼容的操作码。FAST READ 操作码后面是一个三字节地址 (该地址包含读操作第一个字节的 18 位地址 (A17 到 A0) 和一个虚拟字节。虚拟字节插入一个 8 时钟周期的读延迟。快速读操作与普通的读操作相同, 但它需要另一个虚拟字节。收到操作码、地址和虚拟字节后, CY15X102QN 开始在 **SO** 线上驱动数据字节, 优先驱动最高有效位。如果器件被选择并且时钟有效, 则将继续进行发送。进行批量读取时, 内部地址计数器将自

动递增。另外, 在达到最后地址 3FFFFh 后, 计数器将翻转到 00000h。当器件在 **SO** 线上驱动数据时, **SI** 线上的转换将被忽略。**CS** 的上升沿终止快速读操作并使 **SO** 引脚处于三态。CY15X102QN 快速读操作如图 12 中显示。

**注意:** 虚拟字节可以是任意 8 位值 (Axh (8'b1010xxxx) 除外)。Axh 的低 4 位均是无需关注的位。因此, Axh 基本上表示 16 个不同的 8 位值, 不应该作为虚拟字节传输。在大多数情况下, 通常将 00h 用作虚拟字节。

图 12. 快读操作

### 特殊扇区存储器访问命令

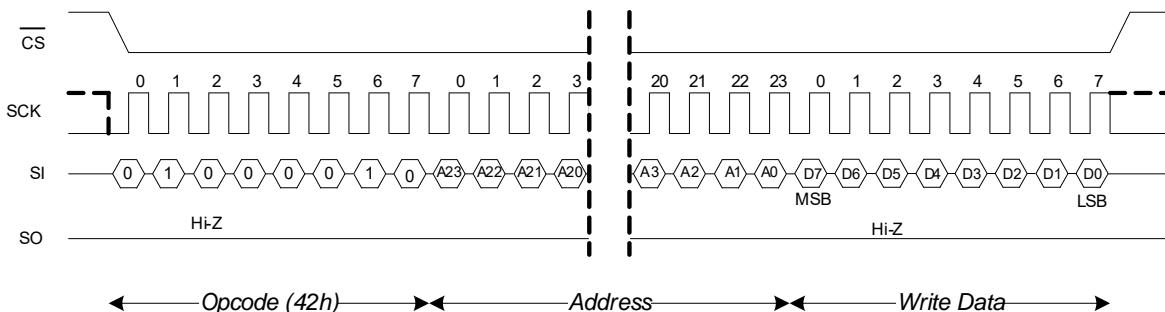

#### 特殊扇区写操作 (SSWR, 42h)

对 256 字节特殊扇区进行的所有写操作都开始于 WREN 操作码，这时将依次确认和取消确认 CS。下一个操作码是 SSWR。跟着 SSWR 操作码是一个三字节的地址，该地址包含了将写入到特殊扇区存储器的第一个数据字节的 8 位扇区地址 (A7-A0)。三字节地址的高 16 位被忽略。后续字节是连续写入的数据字节。如果总线主设备继续发送时钟并保持 CS 为低电平，则各地址将内部递增。一旦内部地址计数器自动递增到 XXXFFh，那么 CS 将变为高电平，以便终止进行中的 SSWR 操作。先写入数据的最高有效位。CS 的上升沿终止写操作。CY15X102QN 特殊扇区写操作如图 13 中显示。

#### 注意：

- 如果写操作过程中断电，那么只有最后完成的字节被写入。

- 特殊扇区 F-RAM 存储器保证其数据可以在多达三个标准回流焊的周期内保持不变。

图 13. 特殊扇区写 (不显示 WREN) 操作

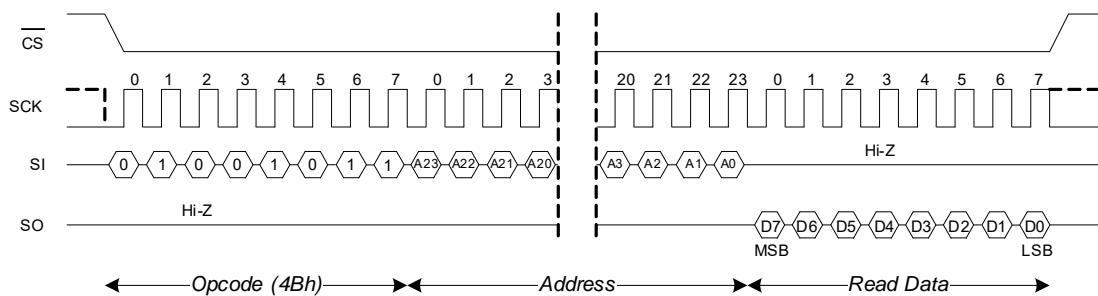

#### 特殊扇区读操作 (SSRD, 4Bh)

CS 的下降沿后，总线主设备将发送一个 SSRD 操作码。SSRD 指令后面是一个三字节地址，该地址包含特殊扇区读操作第一个字节的 8 位地址 (A7-A0)。地址的高 16 位被忽略。发送操作码和地址后，在随后的八个时钟内器件将输出读数据。在驱动读取数据字节期间，SI 输入被忽略。后续字节是连续读取的数据字节。只要总线主设备继续发送时钟并 CS 保持为低电平，地址将

内部递增。一旦内部地址计数器自动递增到 XXXFFh，那么 CS 将变为高电平，以便终止进行中的 SSRD 操作。先读取数据的最高有效位。CS 的上升沿终止特殊扇区读操作并使 SO 引脚处于三态。CY15X104QN 特殊扇区读操作如图 14 中显示。

注意：特殊扇区 F-RAM 存储器保证其数据可以在多达三个标准回流焊的周期内保持不变。

图 14. 特殊扇区读操作

### 标识和序列号指令

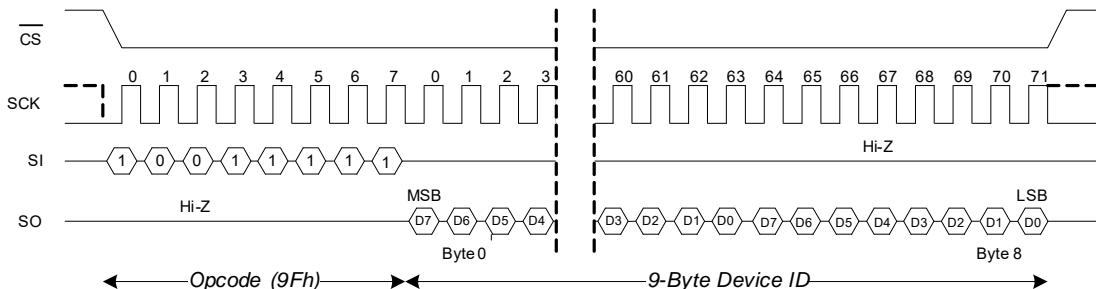

#### 读取器件 ID (RDID, 9Fh)

可以询问 CY15X102QN 器件的制造商、产品标识和晶圆版本。通过使用 RDID 操作码 9Fh，用户可以读取制造商 ID 和产品 ID，这两个 ID 都是只读字节。JEDEC 分配制造商 ID 将赛普拉斯 (Ramtron) 标识符放置于数据库 7 内，包括连续六个字节的 7Fh

和单字节 C2h。产品 ID 的长度为两个字节，包括系列代码、密度代码、子代码和产品版本代码。表 6 显示了 9 字节器件 ID 字段说明。有关单独器件的 9 字节器件 ID，请参考第 24 页上的订购信息。CY15X102QN 读取器件 ID 操作如第 14 页上的图 15 中显示。

**注意：**最低有效数据字节 (Byte 0) 首先移出，最高有效数据字节 (Byte 8) 最后移出。

**表 6. 9 字节器件 ID**

| 器件 ID 字段说明        |                 |              |           |              |             |           |             |

|-------------------|-----------------|--------------|-----------|--------------|-------------|-----------|-------------|

| 制造商 ID<br>[71:16] | 产品系列<br>[15:13] | 容量<br>[12:9] | 电涌<br>[8] | 子类型<br>[7:5] | 版本<br>[4:3] | 电压<br>[2] | 频率<br>[1:0] |

| 56 位              | 3 位             | 4 位          | 1 位       | 3 位          | 2 位         | 1 位       | 2 位         |

**图 15. 读取器件 ID**

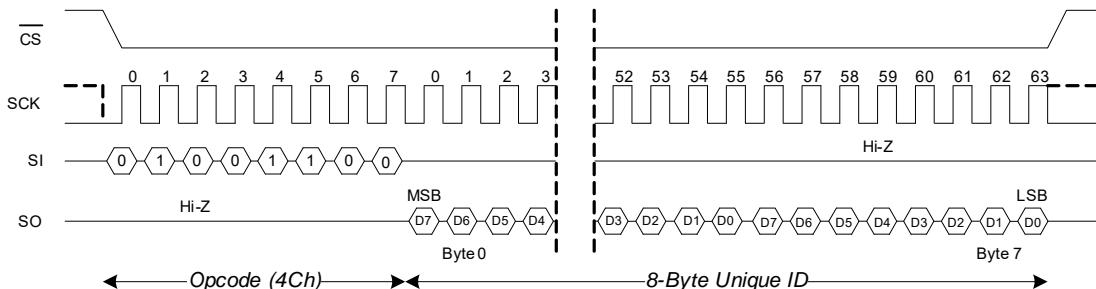

#### 读取唯一 ID (RUID, 4Ch)

可以询问 CY15X102QN 器件的唯一 ID，该 ID 是每个器件唯一的出厂设置 64 位编号。通过使用 RUID 操作码 4Ch，用户可以读取 8 字节唯一 ID，该 ID 是只读字节。CY15X102QN 读唯一 ID 操作如图 16 中显示。

**注意：**

- 最低有效数据字节 (Byte 0) 最先移出，最高有效数据字节 (Byte 7) 最后移出。

- 唯一 ID 寄存确保完整的数据可以在多达三个标准回流焊的周期内保持不变。

**图 16. 读取唯一 ID**

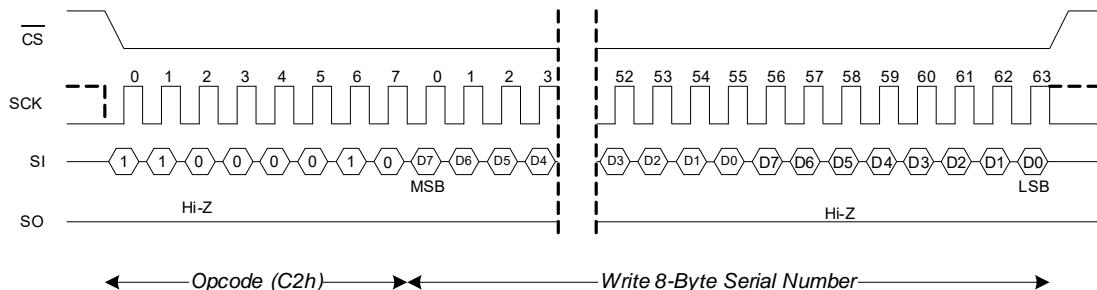

### 写入序列号 (WRSN, C2h)

序列号是一个 8 字节一次性可编程的存储空间，允许用户唯一标识 PC 电路板或系统。序列号通常由一个 2 字节的客户 ID、五个字节的唯一序列号以及一个字节的 CRC 校验组成。然而，对于 8 字节序列号，最终应用可以定义自己的格式。对序列号寄存器进行的所有写操作都始于 WREN 操作码，这时将依次确认和取消确认 CS。下一个操作码是 WRSN。可在突发模式下采用

表 7. 8 字节序列号

| 16 位客户标识符 |           | 40 位唯一编号  |           |           |           |          |         | 8 位 CRC |

|-----------|-----------|-----------|-----------|-----------|-----------|----------|---------|---------|

| SN[63:56] | SN[55:48] | SN[47:40] | SN[39:32] | SN[31:24] | SN[23:16] | SN[15:8] | SN[7:0] |         |

WRSN 指令写入 8 字节的序列号。移入序列号的最后字节后，必须将 CS 置为高电平以完成 WRSN 操作。CY15X102QN 写入序列号操作如图 17 中显示。

**注意：**器件将不计算 CRC 校验和。系统固件必须计算 7 字节内容中的 CRC 校验和并将其附加到 7 字节用户定义序列号，然后将 8 字节序列号编程到序列号寄存器内。8 字节序列号的出厂默认值为 ‘0000000000000000h’。

图 17. 写入序列号 (WREN 不显示) 操作

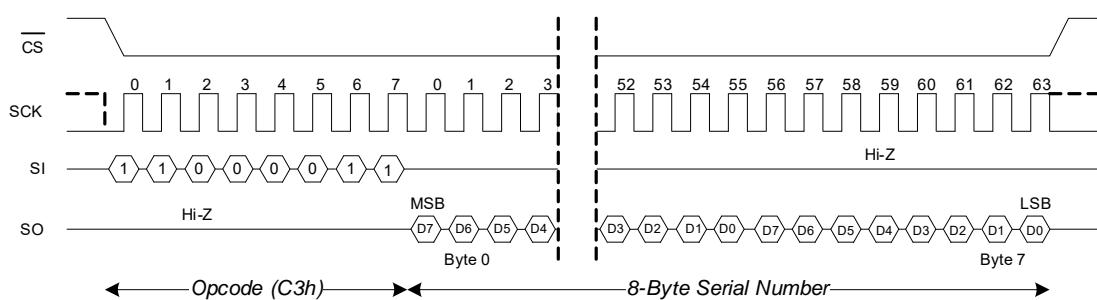

### 读取序列号 (RDSN, C3h)

CY15X102QN 包含一个用于唯一识别器件的 8 字节串行空间。序列号通过 RDSN 指令进行读取。可以在突发模式下读取序列号，实现一次性读取所有八个字节。读取序列号的最后字节后，器件将返回到序列号的第一个 (MSB) 字节。CS 变为低电平后，通过移入 RDSN 的操作码可以发送 RDSN 指令。CY15X102QN 序列号操作如图 18 中显示。

**注意：**最低有效数据字节 (Byte 0) 首先移出，最高有效数据字节 (Byte 7) 最后移出。

图 18. 读取序列号操作

### 低功耗模式命令

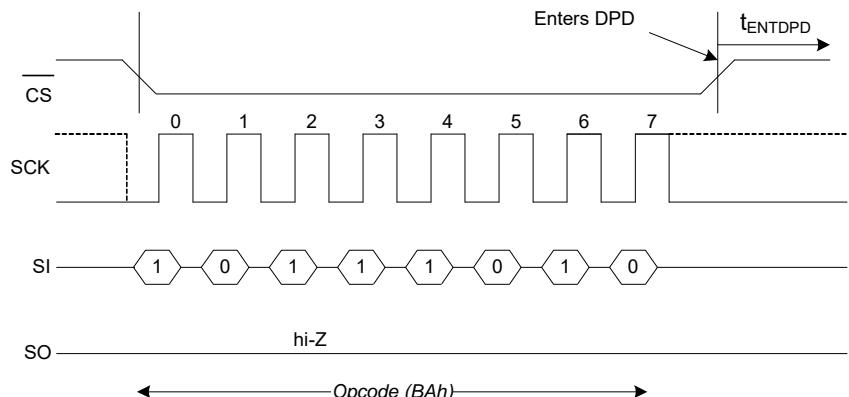

#### 深度掉电模式 (DPD, BAh)

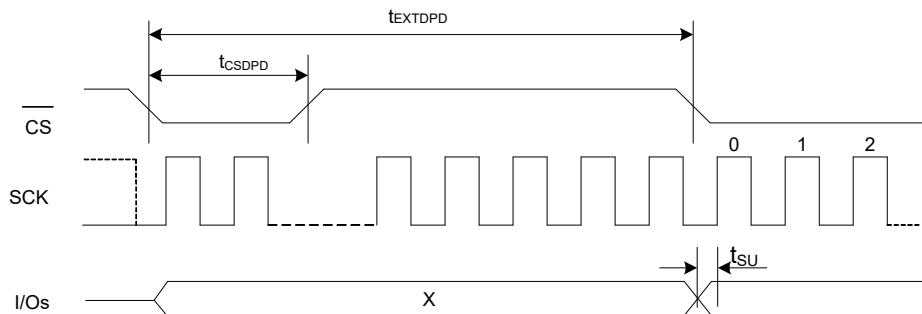

CY15X102QN 器件会实现节能的深度掉电模式。在 DPD 操作码 BAh 被输入并处于  $\overline{\text{CS}}$  上升沿后, 经过  $t_{\text{ENTDPD}}$  的时间, 器件将进入深度掉电模式。一旦处于深度掉电模式, 将忽略 SCK 和 SI 引脚, 并且将 SO 引脚置于高阻态 (Hi-Z), 但是器件仍继续监控  $\overline{\text{CS}}$  引脚。

经过  $t_{\text{EXTDPD}}$  的时间后, 通过  $\overline{\text{CS}}$  脉宽  $t_{\text{CSDPD}}$  可以退出深度掉电模式。可以通过发送虚拟指令周期或单独切换  $\overline{\text{CS}}$  (而 SCK 和 I/O 是无需关注的) 来生成  $\overline{\text{CS}}$  脉冲宽度。在从深度掉电模式唤醒的期间, I/O 保持高阻态 (hi-Z)。请分别参考图 19 和图 20, 了解有关深度掉电进入和深度掉电退出的时序信息。

图 19. 深度下电进入时序

图 20. 深度下电退出时序

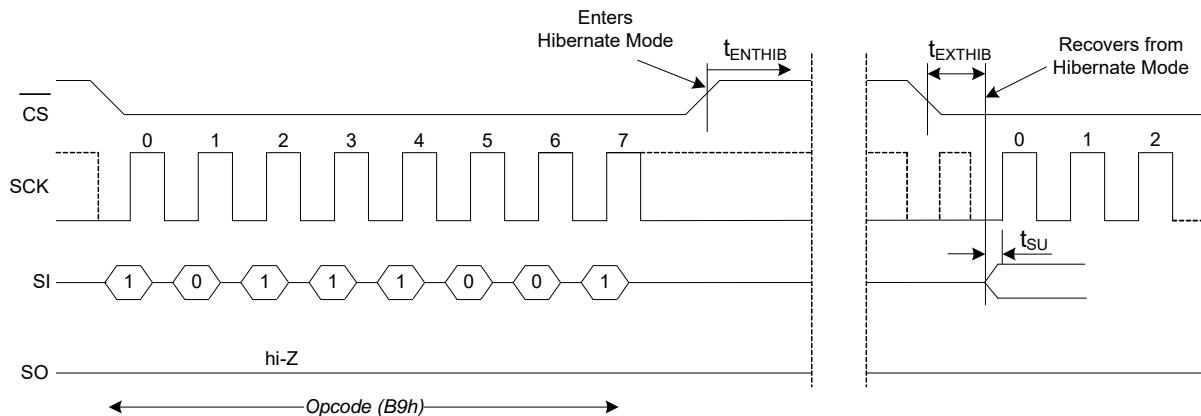

### 休眠模式 (HBN, B9h)

CY15X102QN 器件会实现功耗最低的休眠模式。HBN 操作码 B9h 被输入并处于 CS 上升沿后，经过  $t_{ENTDPD}$  的时间，器件将进入休眠模式。一旦处于休眠模式，将忽略 SCK 和 SI 引脚，并且将 SO 引脚置于高阻态 (HI-Z)，但是器件仍继续监控 CS 引脚。在

CS 的下一个下降沿上，器件需要  $t_{REC}$  时间来返回正常操作。在从休眠模式唤醒的时间内，SO 引脚保持高阻态 (HI-Z)。这时，器件不需要响应操作码。要退出休眠模式，控制器将发送一个“虚拟”读取操作 (作为一个示例)，并等待余下的  $t_{EXTHIB}$  时间。

图 21. 休眠模式操作

### 耐久性

可以对 CY15X102QN 器件进行至少  $10^{13}$  次读或写访问。

F-RAM 存储器以读取和恢复机制运行。因此，对存储器阵列进行访问（读或写）时，擦写周期将以行的基础被采用。F-RAM 架构是基于一个包括行和列阵列的，每列有 32K 行，每行有 64 位。

对单字节或所有八个字节进行读或写访问时，只一次性地内部访问整个行。在计算耐久性时，行中的每个字节只得算一次。表 8 显示的是 64 字节重复循环的耐久性计算，包括操作码、起始地址和连续 64 字节数据流。这样，通过该循环每个字节需要经过一个擦写周期。

表 8. 重复 64 字节循环达到耐久极限所需要的时间

| SCK 频率 (MHz) | 耐久性 (周期 / 秒) | 耐久性周期 / 年             | 达到 $10^{13}$ 极限需要的年数 |

|--------------|--------------|-----------------------|----------------------|

| 50           | 91,900       | $2.9 \times 10^{12}$  | 3.45                 |

| 40           | 73,520       | $2.32 \times 10^{12}$ | 4.31                 |

| 10           | 18,380       | $5.79 \times 10^{11}$ | 17.27                |

| 5            | 9,190        | $2.90 \times 10^{11}$ | 34.54                |

## 最大额定值

超过最大额定值可能会影响器件的使用寿命。用户指南未经测试。

存放温度 .....  $-65^{\circ}\text{C}$  至  $+150^{\circ}\text{C}$

最长的累积存储时间:

环境温度为  $150^{\circ}\text{C}$  ..... 1000 个小时

环境温度为  $125^{\circ}\text{C}$  ..... 11000 个小时

环境温度为  $85^{\circ}\text{C}$  ..... 121 年

最高结温为 .....  $135^{\circ}\text{C}$

相对于  $V_{\text{SS}}$  的  $V_{\text{DD}}$  供电电压:

$\text{CY15V102QN}$ : .....  $-0.5\text{ V}$  到  $+2.4\text{ V}$

$\text{CY15B102QN}$ : .....  $-0.5\text{ V}$  到  $+4.1\text{ V}$

输入电压 .....  $V_{\text{IN}} \leq V_{\text{DD}} + 0.5\text{ V}$

直流电压应用于

高阻 (High Z) 状态的输出 .....  $-0.5\text{ V}$  到  $V_{\text{DD}} + 0.5\text{ V}$

处于接地电位的任何引脚的跳变电压

( $< 20\text{ ns}$ ) .....  $-2.0\text{ V}$  到  $V_{\text{DD}} + 2.0\text{ V}$

## 直流电气特性

适用条件为 [工作范围](#)

| 参数              | 说明                   | 测试条件                                                                                                                                                                                      | 最小值                              | Typ <sup>[2, 3]</sup> | 最大值  | 单位  |

|-----------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|-----------------------|------|-----|

| $V_{\text{DD}}$ | 电源                   | $\text{CY15V102QN}$                                                                                                                                                                       | 1.71                             | 1.8                   | 1.89 | V   |

|                 |                      | $\text{CY15B102QN}$                                                                                                                                                                       | 1.8                              | 3.3                   | 3.6  |     |

| $I_{\text{DD}}$ | $V_{\text{DD}}$ 供电电流 | $V_{\text{DD}} = 1.71\text{ V}$ 到 $1.89\text{ V}$ ; SCK 的电压值在 $V_{\text{DD}} - 0.2\text{ V}$ 和 $V_{\text{SS}}$ 之间进行切换, 其他输入的电压为 $V_{\text{SS}}$ 或 $V_{\text{DD}} - 0.2\text{ V}$ 。SO = 打开 | $f_{\text{SCK}} = 1\text{ MHz}$  | —                     | 0.4  | 1.1 |

|                 |                      | $f_{\text{SCK}} = 40\text{ MHz}$                                                                                                                                                          | —                                | 3.7                   | 6.0  |     |

|                 |                      | $f_{\text{SCK}} = 50\text{ MHz}$                                                                                                                                                          | —                                | 5.0                   | 7.0  |     |

|                 |                      | $V_{\text{DD}} = 1.8\text{ V}$ 到 $3.6\text{ V}$ ; SCK 的电压值在 $V_{\text{DD}} - 0.2\text{ V}$ 和 $V_{\text{SS}}$ 之间进行切换, 其他输入的电压为 $V_{\text{SS}}$ 或 $V_{\text{DD}} - 0.2\text{ V}$ 。SO = 打开   | $f_{\text{SCK}} = 1\text{ MHz}$  | —                     | 0.5  | 1.4 |

|                 |                      |                                                                                                                                                                                           | $f_{\text{SCK}} = 40\text{ MHz}$ | —                     | 4.3  | 8.0 |

|                 |                      |                                                                                                                                                                                           | $f_{\text{SCK}} = 50\text{ MHz}$ | —                     | 6.0  | 8.0 |

| $I_{\text{SB}}$ | $V_{\text{CC}}$ 待机电流 | $V_{\text{DD}} = 1.71\text{ V}$ 到 $1.89\text{ V}$ ; CS = $V_{\text{DD}}$ 。所有其他输入的电压为 $V_{\text{SS}}$ 或 $V_{\text{DD}}$ 。                                                                  | $T_A = 25^{\circ}\text{C}$       | —                     | 2.7  | —   |

|                 |                      | $T_A = 85^{\circ}\text{C}$                                                                                                                                                                | —                                | —                     | 75   |     |

|                 |                      | $T_A = 125^{\circ}\text{C}$                                                                                                                                                               | —                                | —                     | 340  |     |

|                 |                      | $V_{\text{DD}} = 1.8\text{ V}$ 到 $3.6\text{ V}$ ; CS = $V_{\text{DD}}$ 。所有其他输入的电压为 $V_{\text{SS}}$ 或 $V_{\text{DD}}$ 。                                                                    | $T_A = 25^{\circ}\text{C}$       | —                     | 3.2  | —   |

|                 |                      |                                                                                                                                                                                           | $T_A = 85^{\circ}\text{C}$       | —                     | —    | 75  |

|                 |                      |                                                                                                                                                                                           | $T_A = 125^{\circ}\text{C}$      | —                     | —    | 350 |

### 注释:

2. 典型值的适用条件为  $25^{\circ}\text{C}$ 、 $V_{\text{DD}} = V_{\text{DD}}$  (typ)。

3. 该参数由出厂校准保证, 并非经过生产测试。

|                                       |                        |

|---------------------------------------|------------------------|

| 封装功耗能力 ( $T_A = 25^{\circ}\text{C}$ ) | 1.0 W                  |

| 表面组装铅焊温度 (3 秒)                        | $+260^{\circ}\text{C}$ |

| 直流输出电流 (每次只输出 1 路电流, 输出时间为 1 秒)       | 15 mA                  |

| 静电放电电压                                |                        |

| 人体模型 (JEDEC Std JESD22-A114-B)        | 2 kV                   |

| 充电器器件模型 (JEDEC Std JESD22-C101-A)     | 500 V                  |

| 栓锁电流                                  | $> 100\text{ mA}$      |

## 工作范围

| 器件                  | 范围    | 环境温度                                           | $V_{\text{DD}}$ |

|---------------------|-------|------------------------------------------------|-----------------|

| $\text{CY15V102QN}$ | 汽车级 E | $-40^{\circ}\text{C}$ 到 $+125^{\circ}\text{C}$ | 1.71 V 到 1.89 V |

| $\text{CY15B102QN}$ |       |                                                | 1.8 V 到 3.6 V   |

## 直流电气特性 (续)

适用条件为 [工作范围](#)

| 参数               | 说明                                                                                                                                                                                                                                     | 测试条件                                                                                                   |                         | 最小值                   | Typ <sup>[2, 3]</sup> | 最大值                   | 单位 |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|-------------------------|-----------------------|-----------------------|-----------------------|----|

| I <sub>DPD</sub> | 深度掉电电流<br><br>V <sub>DD</sub> = 1.71 V 到 1.89 V ; CS = V <sub>DD</sub> 。所有其他输入的电压为 V <sub>SS</sub> 或 V <sub>DD</sub> 。<br><br>V <sub>DD</sub> = 1.8 V 到 3.6 V ; CS = V <sub>DD</sub> 。所有其他输入的电压为 V <sub>SS</sub> 或 V <sub>DD</sub> 。   | V <sub>DD</sub> = 1.71 V 到 1.89 V ; CS = V <sub>DD</sub> 。所有其他输入的电压为 V <sub>SS</sub> 或 V <sub>DD</sub> | T <sub>A</sub> = 25 °C  | —                     | 1.1                   | —                     | μA |

|                  |                                                                                                                                                                                                                                        |                                                                                                        | T <sub>A</sub> = 85 °C  | —                     | —                     | 15                    |    |

|                  |                                                                                                                                                                                                                                        |                                                                                                        | T <sub>A</sub> = 125 °C | —                     | —                     | 70                    |    |

|                  |                                                                                                                                                                                                                                        | V <sub>DD</sub> = 1.8 V 到 3.6 V ; CS = V <sub>DD</sub> 。所有其他输入的电压为 V <sub>SS</sub> 或 V <sub>DD</sub>   | T <sub>A</sub> = 25 °C  | —                     | 1.3                   | —                     |    |

|                  |                                                                                                                                                                                                                                        |                                                                                                        | T <sub>A</sub> = 85 °C  | —                     | —                     | 17                    |    |

|                  |                                                                                                                                                                                                                                        |                                                                                                        | T <sub>A</sub> = 125 °C | —                     | —                     | 80                    |    |

|                  |                                                                                                                                                                                                                                        | V <sub>DD</sub> = 1.71 V 到 1.89 V ; CS = V <sub>DD</sub> 。所有其他输入的电压为 V <sub>SS</sub> 或 V <sub>DD</sub> | T <sub>A</sub> = 25 °C  | —                     | 0.1                   | —                     |    |

|                  |                                                                                                                                                                                                                                        |                                                                                                        | T <sub>A</sub> = 85 °C  | —                     | —                     | 0.9                   |    |

| I <sub>HBN</sub> | 休眠模式下的电流<br><br>V <sub>DD</sub> = 1.71 V 到 1.89 V ; CS = V <sub>DD</sub> 。所有其他输入的电压为 V <sub>SS</sub> 或 V <sub>DD</sub> 。<br><br>V <sub>DD</sub> = 1.8 V 到 3.6 V ; CS = V <sub>DD</sub> 。所有其他输入的电压为 V <sub>SS</sub> 或 V <sub>DD</sub> 。 | V <sub>DD</sub> = 1.71 V 到 1.89 V ; CS = V <sub>DD</sub> 。所有其他输入的电压为 V <sub>SS</sub> 或 V <sub>DD</sub> | T <sub>A</sub> = 25 °C  | —                     | —                     | 8.0                   |    |

|                  |                                                                                                                                                                                                                                        |                                                                                                        | T <sub>A</sub> = 85 °C  | —                     | —                     | 1.6                   |    |

|                  |                                                                                                                                                                                                                                        |                                                                                                        | T <sub>A</sub> = 125 °C | —                     | —                     | 14                    |    |

|                  |                                                                                                                                                                                                                                        | V <sub>SS</sub> < V <sub>IN</sub> < V <sub>DD</sub>                                                    |                         | -5                    | —                     | 5                     |    |

|                  |                                                                                                                                                                                                                                        |                                                                                                        |                         | -100                  | —                     | 5                     |    |

|                  |                                                                                                                                                                                                                                        | V <sub>SS</sub> < V <sub>OUT</sub> < V <sub>DD</sub>                                                   |                         | -5                    | —                     | 5                     |    |

| I <sub>LI</sub>  | I/O 引脚的输入漏电流 (WP 引脚除外)                                                                                                                                                                                                                 | V <sub>SS</sub> < V <sub>IN</sub> < V <sub>DD</sub>                                                    |                         | 0.7 × V <sub>DD</sub> | —                     | V <sub>DD</sub> + 0.3 | V  |

|                  | WP 引脚的输入漏电流                                                                                                                                                                                                                            |                                                                                                        |                         | -0.3                  | —                     | 0.3 × V <sub>DD</sub> |    |

| I <sub>LO</sub>  | 输出漏电流                                                                                                                                                                                                                                  | V <sub>SS</sub> < V <sub>OUT</sub> < V <sub>DD</sub>                                                   |                         | -5                    | —                     | 5                     |    |

| V <sub>IH</sub>  | 输入高电平电压                                                                                                                                                                                                                                |                                                                                                        |                         | 2.4                   | —                     | —                     |    |

| V <sub>IL</sub>  | 输入低电平电压                                                                                                                                                                                                                                |                                                                                                        |                         | V <sub>DD</sub> - 0.2 | —                     | —                     |    |

| V <sub>OH1</sub> | 输出高电平电压                                                                                                                                                                                                                                | I <sub>OH</sub> = -1 mA, V <sub>DD</sub> = 2.7 V                                                       |                         |                       | —                     | —                     |    |

| V <sub>OH2</sub> |                                                                                                                                                                                                                                        | I <sub>OH</sub> = -100 μA                                                                              |                         |                       | —                     | —                     |    |

| V <sub>OL1</sub> | 输出低电平电压                                                                                                                                                                                                                                | I <sub>OL</sub> = 2 mA, V <sub>DD</sub> = 2.7 V                                                        |                         |                       | —                     | —                     |    |

| V <sub>OL2</sub> |                                                                                                                                                                                                                                        | I <sub>OL</sub> = 150 μA                                                                               |                         |                       | —                     | —                     |    |

## 数据保留时间与耐久性

| 参数              | 说明     | 测试条件                    |  | 最小值   | 最大值 | 单位 |

|-----------------|--------|-------------------------|--|-------|-----|----|

| T <sub>DR</sub> | 数据保留时间 | T <sub>A</sub> = 125 °C |  | 11000 | —   | 小时 |

|                 |        | T <sub>A</sub> = 105 °C |  | 11    | —   | 年  |

|                 |        | T <sub>A</sub> = 85 °C  |  | 121   | —   |    |

| NV <sub>C</sub> | 耐久性    | 在工作温度范围内                |  | 1013  | —   | 周期 |

## 在 AEC-Q100 汽车应用中有关 F-RAM 寿命的示例

一个应用在整个使用过程中不可能总是在一个稳定的温度条件下运行。但用户却希望它在整个使用过程中能够适宜多种温度的条件。因此，应用中的 F-RAM 保留规范应经常需要进行计算和更新。下表提供的是多个温度条件下的热阻配置的示例计算表。

| 温度<br>T     | 时间因素<br>t | 在 <b>Tmax A</b> 条件下的加速系数 <sup>[4]</sup>                                                         | 热阻配置系数<br>P                                                                                          | 热阻配置的使用寿命<br>L (P)           |

|-------------|-----------|-------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|------------------------------|

|             |           | $A = \frac{L(T)}{L(T_{max})} = e^{\frac{Ea}{k} \left( \frac{1}{T} - \frac{1}{T_{max}} \right)}$ | $P = \frac{1}{\left( \frac{t_1}{A_1} + \frac{t_2}{A_2} + \frac{t_3}{A_3} + \frac{t_4}{A_4} \right)}$ | $L(P) = P \times L(T_{max})$ |

| T1 = 125 °C | t1 = 0.1  | A1 = 1                                                                                          | 8.33                                                                                                 | > 10.46 年                    |

| T2 = 105 °C | t2 = 0.15 | A2 = 8.67                                                                                       |                                                                                                      |                              |

| T3 = 85 °C  | t3 = 0.25 | A3 = 95.68                                                                                      |                                                                                                      |                              |

| T4 = 55 °C  | t4 = 0.50 | A4 = 6074.80                                                                                    |                                                                                                      |                              |

## 电容

适用于所有封装。

| 参数 <sup>[5]</sup> | 说明          | 测试条件                                                                     | 最大值 | 单位 |

|-------------------|-------------|--------------------------------------------------------------------------|-----|----|

| C <sub>O</sub>    | 输出引脚电容 (SO) | $T_A = 25^\circ\text{C}, f = 1 \text{ MHz}, V_{DD} = V_{DD(\text{typ})}$ | 8   | pF |

| C <sub>I</sub>    | 输入引脚电容      |                                                                          | 6   |    |

## 热阻

| 参数 <sup>[5]</sup> | 说明           | 测试条件                                    | 8 pin SOIC 封装 | 单位   |

|-------------------|--------------|-----------------------------------------|---------------|------|

| $\Theta_{JA}$     | 热阻<br>(结至环境) | 根据 EIA/JESD51 的要求，测试条件遵循测试热阻的标准测试方法和过程。 | 88.6          | °C/W |

| $\Theta_{JC}$     | 热阻<br>(结至外壳) |                                         | 56            |      |

## 交流测试条件

- 输入脉冲电平 .....  $V_{DD}$  的 10% 和 90%

- 输入上升和下降时间 ..... 3 ns

- 输入和输出时序参考电平 .....  $0.5 \times V_{DD}$

- 输出负载电容 ..... 30 pF

### 注释：

4. “k”为 Boltzmann 常量  $8.617 \times 10^{-5} \text{ eV/K}$  时， $T_{max}$  为器件特定的最高温度，并且 “T” 为 F-RAM 产品规范中任意一个温度。公式中的所有温度均以 Kelvin 为单位。

5. 该参数由出厂校准保证，并非经过生产测试。

## 交流切换特性

适用条件为 [工作范围](#)

| 参数 <sup>[6]</sup>            |            | 说明                                 | 40 MHz |     | 50 MHz |     | 单位  |

|------------------------------|------------|------------------------------------|--------|-----|--------|-----|-----|

| 赛普拉斯参数                       | 备用参数       |                                    | 最小值    | 最大值 | 最小值    | 最大值 |     |

| $t_{SCK}$                    | —          | SCK 时钟频率                           | 0      | 40  | 0      | 50  | MHz |

| $t_{CH}$                     | —          | 时钟为高电平的时间                          | 11     | —   | 9      | —   |     |

| $t_{CL}$                     | —          | 时钟为低电平的时间                          | 11     | —   | 9      | —   |     |

| $t_{CLZ}$ <sup>[9]</sup>     | —          | 从时钟为低电平到输出为低阻态的时间                  | 0      | —   | 0      | —   |     |

| $t_{CSS}$                    | $t_{CSU}$  | 芯片选择建立时间                           | 5      | —   | 5      | —   |     |

| $t_{CSH}$                    | $t_{CSH}$  | 芯片选择的保留时间 — SPI 模式 0               | 5      | —   | 5      | —   |     |

| $t_{CSH1}$                   | —          | 芯片选择的保留时间 — SPI 模式 3               | 10     | —   | 10     | —   |     |

| $t_{HZCS}$ <sup>[7, 8]</sup> | $t_{OD}$   | 输出禁用时间                             | —      | 12  | —      | 10  |     |

| $t_{CO}$                     | $t_{ODV}$  | 输出数据有效的时间                          | —      | 9   | —      | 8   |     |

| $t_{OH}$                     | —          | 输出保留时间                             | 1      | —   | 1      | —   |     |

| $t_{CS}$                     | $t_D$      | 取消选择时间                             | 40     | —   | 40     | —   |     |

| $t_{SD}$                     | $t_{SU}$   | 数据设置时间                             | 5      | —   | 5      | —   |     |

| $t_{HD}$                     | $t_H$      | 数据保留时间                             | 5      | —   | 5      | —   |     |

| $t_{WPS}$                    | $t_{WHSL}$ | WP 数据设置时间 (w.r.t $\overline{CS}$ ) | 20     | —   | 20     | —   |     |

| $t_{WPH}$                    | $t_{SHWL}$ | WP 保持时间 (w.r.t $\overline{CS}$ )   | 20     | —   | 20     | —   |     |

### 注释:

6. 假设测试条件为: 信号跳变时间不超过 3 ns, 时序参考电平为  $0.5 \times V_{DD}$ , 输入脉冲电平为  $V_{DD}$  的 10% 至 90%, 以及指定  $I_{OL}/I_{OH}$  的输出负载和 30 pF 大小的负载电容, 如第 20 页上的交流测试条件下所示。

7.  $t_{HZCS}$  的负载电容为 5 pF。切换是在输出进入高阻态时测试的。

8. 该参数由出厂校准保证, 并非经过生产测试。

9. 由设计保证

图 22. 同步数据时序（模式0 和模式3）

图 23. 写入状态寄存器（WRSR）操作中的写入保护时序

## 电源周期时序

适用条件为工作范围

| 参数 <sup>[10]</sup>          |           | 说明                                                                       | 最小值   | 最大值                  | 单位        |

|-----------------------------|-----------|--------------------------------------------------------------------------|-------|----------------------|-----------|

| 赛普拉斯参数                      | 备用参数      |                                                                          |       |                      |           |

| $t_{PU}$                    |           | 从上电 $V_{DD}$ (最小值) 到第一次访问 ( $\overline{CS}$ 为低电平) 的时间                    | 450   | —                    | $\mu s$   |

| $t_{VR}^{[11]}$             |           | $V_{DD}$ 上电斜率                                                            | 30    | —                    | $\mu s/V$ |

| $t_{VF}^{[11, 12]}$         |           | $V_{DD}$ 掉电斜率                                                            | 20    | —                    |           |

| $t_{ENTDPD}^{[13]}$         | $t_{DP}$  | 从 $\overline{CS}$ 为高电平到器件进入深度掉电模式的时间 ( $\overline{CS}$ 为高电平到进入深度下电模式的时间) | —     | 3                    | $\mu s$   |

| $t_{CSDPD}$                 |           | $\overline{CS}$ 脉冲宽度到从深度下电模式唤醒的时间                                        | 0.015 | $4 \times 1/f_{SCK}$ |           |

| $t_{EXTDPD}$                | $t_{RDP}$ | 从深度掉电模式恢复的时间 ( $\overline{CS}$ 为低电平到就绪访问的时间)                             | —     | 10                   |           |

| $t_{ENTHIB}^{[14]}$         |           | $\overline{CS}$ 为高电平到进入休眠模式 ( $\overline{CS}$ 为高电平到进入休眠模式的时间)            | —     | 3                    |           |

| $t_{EXTHIB}$                | $t_{REC}$ | 从休眠模式恢复的时间 ( $\overline{CS}$ 为低电平到就绪访问的时间)                               | —     | 450                  |           |

| $V_{DD}(\text{low})^{[12]}$ |           | 保证发生初始化操作的 $V_{DD}$ (低电平)                                                | 0.6   | —                    | V         |

| $t_{PD}^{[12]}$             |           | $V_{DD}$ (低) 为 0.6 V 时的 $V_{DD}$ (低) 时间                                  | 130   | —                    | $\mu s$   |

|                             |           | $V_{DD}$ (低) 为 $V_{SS}$ 时的 $V_{DD}$ (低) 时间                               | 70    | —                    |           |

图 24. 电源周期时序

**注释:**

10. 测试条件假设为: 信号切换时间不超过 3 ns, 时序参考电平为  $0.5 \times V_{DD}$ , 输入脉冲电平为  $V_{DD}$  的 10% 至 90% 以及输出负载为指定  $I_{OL}/I_{OH}$  和负载电容为 30 pF, 如 [第 20 页上的交流测试条件](#) 中所示。

11. 在  $V_{DD}$  波形的任何位置测量的斜率。

12. 该参数由出厂校准保证, 并非经过生产测试。

13. 由设计保证有关深度睡眠模式时序的详细信息, 请参见 [第 16 页上的图 19](#)。

14. 由设计保证有关休眠模式时序的详细信息, 请参见 [第 17 页上的图 21](#)。

## 订购信息

| 订购代码              | 器件 ID            | 封装图       | 封装类型              | 工作范围  |

|-------------------|------------------|-----------|-------------------|-------|

| CY15V102QN-50SXE  | 7F7F7F7F7FC22A64 | 001-85261 | 8 pin SOIC (EIAJ) | 汽车级 E |

| CY15V102QN-50SXET | 7F7F7F7F7FC22A64 |           |                   |       |

| CY15B102QN-50SXE  | 7F7F7F7F7FC22A60 |           |                   |       |

| CY15B102QN-50SXET | 7F7F7F7F7FC22A60 |           |                   |       |

这些芯片都不含铅。想要了解这些芯片的供应情况, 请联系赛普拉斯本地销售代表。

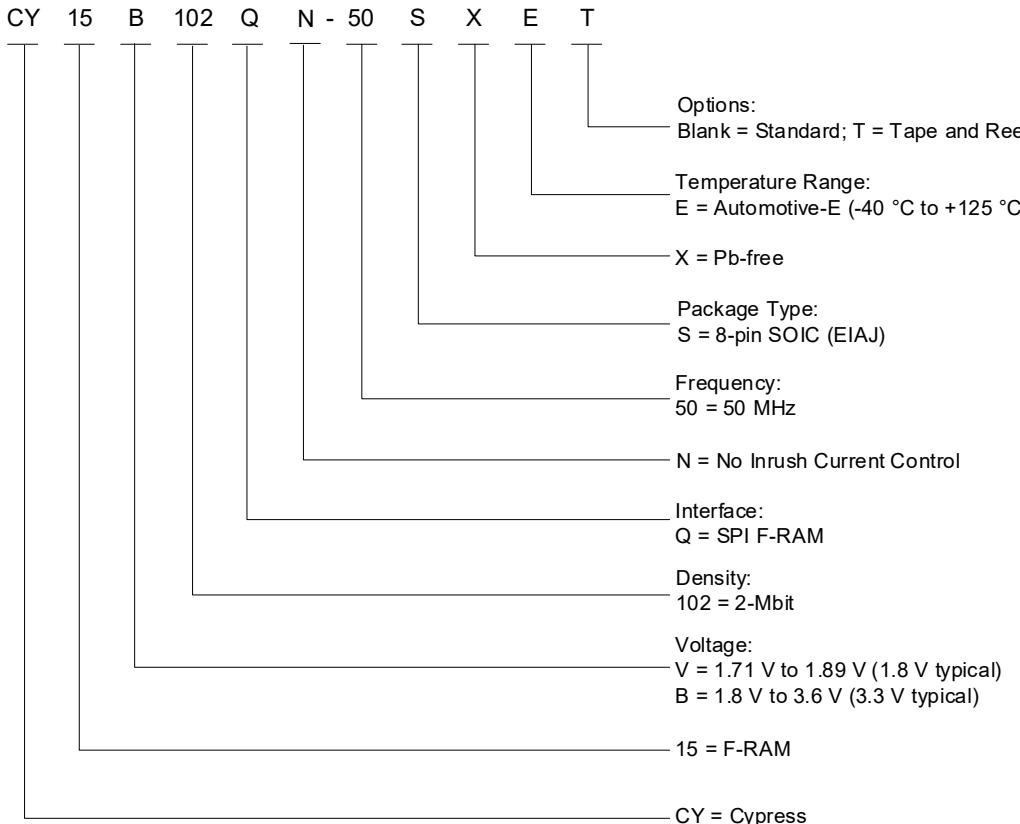

## 订购代码定义

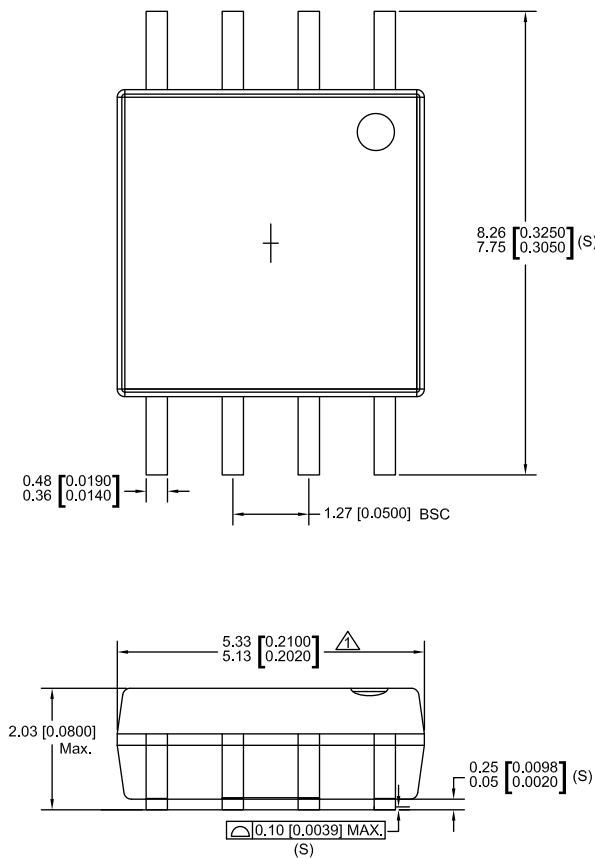

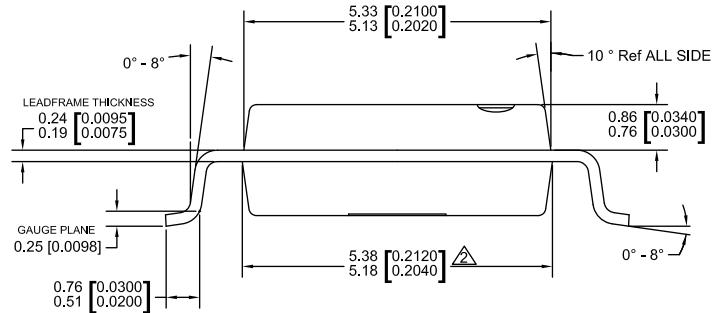

## 封装图

图 25. 8 pin SOIC (208 Mil) 封装外形, 001-85261

NOTE:

△ DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS.

MOLD FLASH, PROTRUSIONS AND GATE BURRS SHALL NOT

EXCEED 0.006 INCH PER SIDE

△ DOES NOT INCLUDE INTER-LEAD FLASH OR PROTRUSIONS.

INTER-LEAD FLASH AND PROTRUSION SHALL NOT

EXCEED 0.010 INCH PER SIDE.

3. THIS PART IS COMPLIANT WITH EIAJ SPECIFICATION EDR-7320

4. LEAD SPAN/STAND OF HEIGHT/COPLANARITY ARE CONSIDERED

AS SPECIAL CHARACTER.

5. CONTROLLING DIMENSIONS IN MM. [INCH]

001-85261 \*\*

## 缩略语

表 9. 本文档中使用的缩略语

| 缩略语    | 说明            |

|--------|---------------|

| CPHA   | 时钟相位          |

| CPOL   | 时钟极性          |

| EEPROM | 带电可擦除可编程只读存储器 |

| EIA    | 电子工业联盟        |

| F-RAM  | 铁电随机存取存储器     |

| I/O    | 输入 / 输出       |

| JEDEC  | 联合电子设备工程委员会   |

| JESD   | JEDEC 标准      |

| LSB    | 最低有效位         |

| MSB    | 最高有效位         |

| RoHS   | 有害物质限制        |

| SPI    | 串行外设接口        |

| SOIC   | 小外形集成电路       |

| GQFN   | 网格阵列无引线       |

## 文档规范

### 测量单位

表 10. 测量单位

| 符号   | 测量单位 |

|------|------|

| °C   | 摄氏度  |

| Hz   | 赫兹   |

| kHz  | 千赫兹  |

| kΩ   | 千欧   |

| Mbit | 兆位   |

| MHz  | 兆赫兹  |

| μA   | 微安   |

| μF   | 微法   |

| μs   | 微秒   |

| mA   | 毫安   |

| ms   | 毫秒   |

| ns   | 纳秒   |

| W    | 欧姆   |

| %    | 百分比  |

| pF   | 皮法   |

| V    | 伏特   |

| W    | 瓦特   |

## 文档修订记录

文档标题: **CY15B102QN/CY15V102QN、Excelon™-Auto 2 Mbit (256K × 8) 汽车级 E 串行 (SPI) F-RAM**

文档版本: **002-20519**

| 版本 | ECN 编号  | 变更者  | 提交日期       | 变更说明                                  |

|----|---------|------|------------|---------------------------------------|

| ** | 5972064 | WAHY | 11/22/2017 | 本文档版本号为 Rev**, 译自英文版 002-19073 Rev*C。 |

| *A | 6369024 | WAHY | 10/29/2018 | 本文档版本号为 Rev*A, 译自英文版 002-19073 Rev*I。 |

| *B | 6590017 | WAHY | 06/12/2019 | 本文档版本号为 Rev*B, 译自英文版 002-19073 Rev*M。 |

## 销售、解决方案和法律信息

### 全球销售和设计支持

赛普拉斯公司拥有一个由办事处、解决方案中心、厂商代表和经销商组成的全球性网络。要想找到最靠近您的办事处，请访问[赛普拉斯所在地](#)。

### 产品

Arm® Cortex® 微控制器

汽车级

时钟与缓冲器

接口

物联网

存储器

微控制器

PSoC

电源管理 IC

触摸感应

USB 控制器

无线连接

[cypress.com/arm](http://cypress.com/arm)

[cypress.com/automotive](http://cypress.com/automotive)

[cypress.com/clocks](http://cypress.com/clocks)

[cypress.com/interface](http://cypress.com/interface)

[cypress.com/iot](http://cypress.com/iot)

[cypress.com/memory](http://cypress.com/memory)

[cypress.com/mcu](http://cypress.com/mcu)

[cypress.com/psoc](http://cypress.com/psoc)

[cypress.com/pmic](http://cypress.com/pmic)

[cypress.com/touch](http://cypress.com/touch)

[cypress.com/usb](http://cypress.com/usb)

[cypress.com/wireless](http://cypress.com/wireless)

### PSoC® 解决方案

[PSoC 1](#) | [PSoC 3](#) | [PSoC 4](#) | [PSoC 5LP](#) | [PSoC 6 MCU](#)

### 赛普拉斯开发者社区

[社区](#) | [项目](#) | [视频](#) | [博客](#) | [培训](#) | [组件](#)

### 技术支持

[cypress.com/support](http://cypress.com/support)

© 赛普拉斯半导体公司, 2017-2019 年。本文件是赛普拉斯半导体公司及其子公司, 包括 Spansion LLC ("赛普拉斯") 的财产。本文件, 包括其包含或引用的任何软件或固件 ("软件"), 根据全球范围内的知识产权法律以及美国与其他国家签署条约由赛普拉斯所有。除非在本款中另有明确规定, 赛普拉斯保留在该等法律和条约下的所有权利, 且未就其专利、版权、商标或其他知识产权授予任何许可。如果软件并不附随有一份许可协议且贵方未以其他方式与赛普拉斯签署关于使用软件的书面协议, 赛普拉斯特此授予贵方属人性质的、非独家且不可转让的如下许可 (无再许可权) (1) 在赛普拉斯软件著作权项下的下列许可权 (一) 对以源代码形式提供的软件, 仅出于在赛普拉斯硬件产品上使用之目的且仅在贵方集团内部修改和复制软件, 和 (2) 仅限于在有关赛普拉斯硬件产品上使用之目的将软件以二进制代码形式的向外部最终用户提供 (无论直接提供或通过经销商和分销商间接提供), 和 (2) 在被软件 (由赛普拉斯公司提供, 且未经修改) 侵犯的赛普拉斯专利的权利主张项下, 仅出于在赛普拉斯硬件产品上使用之目的制造、使用、提供和进口软件的许可。禁止对软件的任何其他使用、复制、修改、翻译或汇编。

在适用法律允许的限度内, 赛普拉斯未对本文件或任何软件作出任何明示或暗示的担保, 包括但不限于关于适销性和特定用途的默示保证。没有任何电子设备是绝对安全的。因此, 尽管赛普拉斯在其硬件和软件产品中采取了必要的安全措施, 但是赛普拉斯并不承担任何由于使用赛普拉斯产品而引起的安全问题及安全漏洞的责任, 例如未经授权的访问或使用赛普拉斯产品。此外, 本材料中所介绍的赛普拉斯产品有可能存在设计缺陷或设计错误, 从而导致产品的性能与公布的规格不一致。(如果发现此类问题, 赛普拉斯会提供勘误表) 赛普拉斯保留更改本文件的权利, 届时将不另行通知。在适用法律允许的限度内, 赛普拉斯不对因应用或使用本文件所述任何产品或电路引起的任何后果负责。本文件, 包括任何样本设计信息或程序代码信息, 仅为供参考之目的提供。文件使用人应负责正确设计、计划和测试信息应用和由此生产的任何产品的功能和安全性。赛普拉斯产品不应被设计为、设定为或授权用作武器操作、武器系统、核设施、生命支持设备或系统、其他医疗设备或系统 (包括急救设备和手术植入物)、污染控制或有害物质管理系统中的关键部件, 或产品植入之设备或系统故障可能导致人身伤害、死亡或财产损失其他用途 ("非预期用途")。关键部件指, 若该部件发生故障, 经合理预期会导致设备或系统故障或会影响设备或系统安全性和有效性的部件。针对由赛普拉斯产品非预期用途产生或相关的任何主张、费用、损失和其他责任, 赛普拉斯不承担全部或部分责任且贵方不应追究赛普拉斯之责任。贵方应赔偿赛普拉斯因赛普拉斯产品任何非预期用途产生或相关的所有索赔、费用、损失和其他责任, 包括因人身伤害或死亡引起的主张, 并使之免受损失。

赛普拉斯、赛普拉斯徽标、Spansion、Spansion 徽标, 及上述项目的组合, WICED, 及 PSoC、CapSense、EZ-USB、F-RAM 和 Traveo 应视为赛普拉斯在美国和其他国家的商标或注册商标。请访问 [cypress.com](http://cypress.com) 获取赛普拉斯商标的完整列表。其他名称和品牌可能由其各自所有者主张为该方财产。