## 特長

- 16M ビットの不揮発性ステティック RAM (nvSRAM)

- 性能は I/O 毎に最大 33MT/s

- ×16 バスを利用するデータ スループットは最大 528Mbps

- 縮小された命令セット付き業界標準の非同期 NAND フラッシュ インターフェース

- 共有アドレス、データおよびコマンド バス

- ・ アドレスおよびコマンド バスは 8 ビット

- ・ コマンドは 1 か 2 コマンド サイクルで送信

- ・ アドレスは 5 アドレス サイクルで送信

- ・ データ バス幅は ×8 または ×16 ビット

- 動作モード :

- アクセス時間が 30ns の非同期 NAND インターフェース I/O

- ソフトウェアで次のものを検出するステータスレジスタ :

- ・ 不揮発性 STORE 完了

- ・ 前のコマンドの成功／失敗状態

- ・ 書き込み保護の状態

- 小さいコンデンサのみによる電源切断時の自動 STORE ハンドオフ

- QuantumTrap 不揮発性素子への STORE をソフトウェアコマンド、専用ハードウェアピン、または電源切断時の AutoStore により起動

- SRAMへのRECALL処理はソフトウェアまたは電源投入で起動

- 高い信頼性

- 回数に制限のない読み出し、書き込み、および RECALL サイクル

- QuantumTrap に対する 100 万回の STORE サイクル

- データ保持期間 : 20 年間 (85°C)

- 動作電圧

- コア  $V_{CC} = 2.7V \sim 3.6V$  ; I/O  $V_{CCQ} = 1.70V \sim 1.95V$

- 165 ボール微細ピッチ ボール グリッド アレイ (FBGA) パッケージ

- 産業用温度範囲 :  $-40^{\circ}C \sim +85^{\circ}C$

- RoHS 準拠

## 概要

サイプレスの nvSRAM は、モノリシック集積回路で高性能 SRAM セルを不揮発性素子と組み合わせています。組込み型不揮発性素子には、世界最高レベルの信頼性を備えた不揮発性メモリを実現する SONOS 技術を採用しています。SRAM の読み出し／書き込みの回数は無制限です。不揮発性データは不揮発性素子に保持され、SRAM に書き込まれると変化しません。

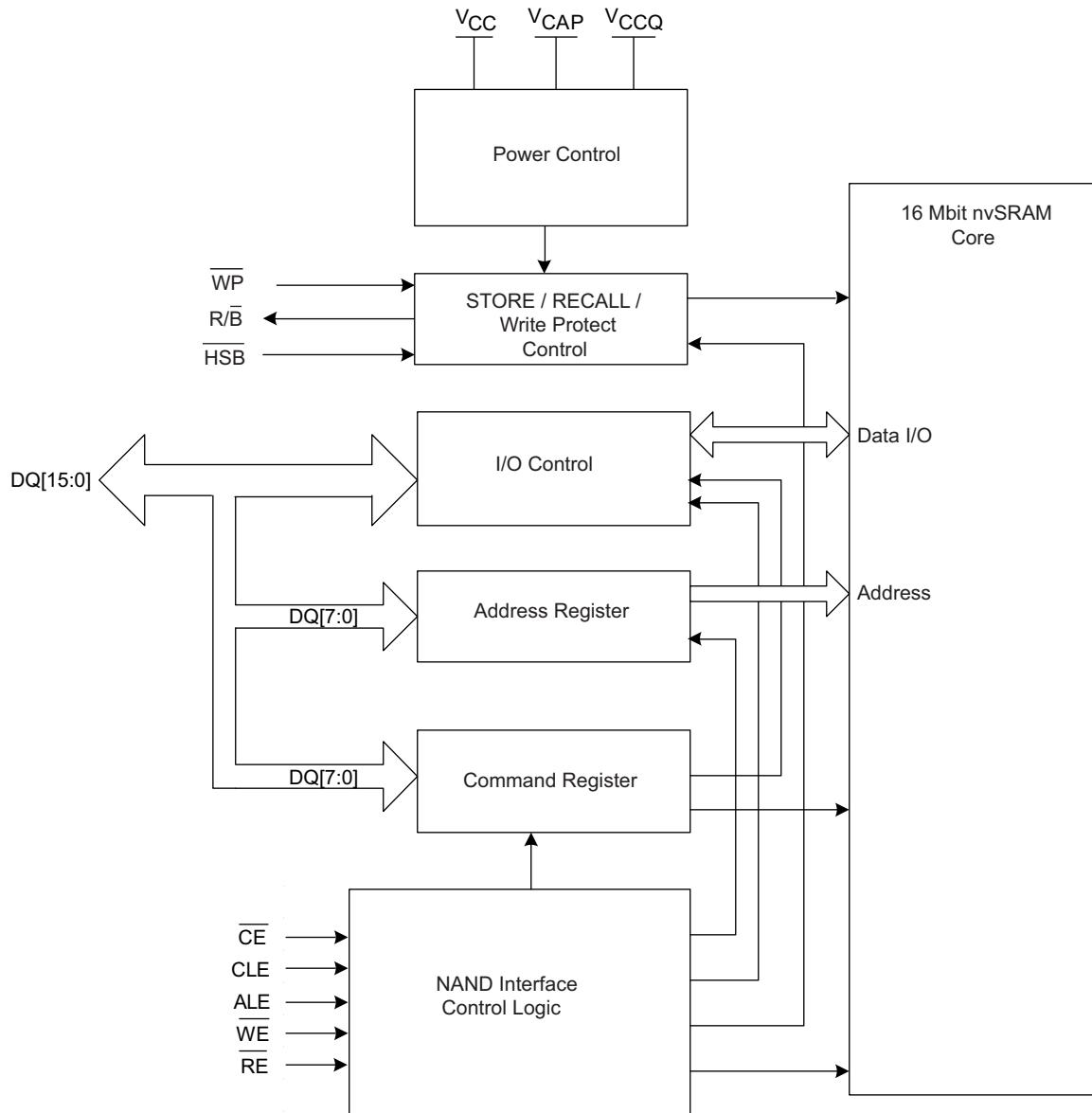

CY14V116F7 / CY14V116G7 nvSRAM は、標準の非同期 NAND インターフェースによるアクセスをサポートし、×8 と ×16 インターフェースのオプションを提供しています。×16 インターフェースの場合、データ バイトは DQ[15:0] ラインを介して転送され、DQ[7:0] バスに比べて 2 倍のスループットを持っています。CY14V116F7 / CY14V116G7 は高度に多重化された DQ バスを使用してデータ、アドレスおよび命令を転送します。すべてのアドレスとコマンドは常にデータバス DQ[7:0] を経由して転送されます。したがって、×16 バス インターフェースの場合には、上位の 8 データ ビット DQ[15:8] はアドレスとコマンド サイクルの間に「ドント ケア」になります。CY14V116F7 / CY14V116G7 は、5 つの制御ピン (CLE, ALE, CE, RE と WE) を用いて読み出しと書き込み処理の時にコマンド、アドレスおよびデータを転送します。書き込み保護 (WP)、レディーノビギー (R/B) や HSB STORE などの追加 I/O ピンはデバイスの機能をサポートするために使用されます。

非同期 NAND インターフェース nvSRAM は、ONFI 1.0 仕様のほとんどに適合し、速度が 33MHz までのデータ アクセスをサポートします。

すべての関連資料の一覧については、[ここ](#)をクリックしてください。

## ブロック図

### シングル チャネル アーキテクチャ

## 目次

|                               |    |                                   |    |

|-------------------------------|----|-----------------------------------|----|

| ピン配置                          | 4  | nvSRAM RECALL 処理                  | 19 |

| ピン機能                          | 5  | ハードウェア RECALL (電源投入)              | 19 |

| 発見と初期化                        | 5  | ソフトウェア Recall                     | 19 |

| nvSRAM バス処理                   | 5  | 最大定格                              | 20 |

| 制御信号                          | 5  | 動作範囲                              | 20 |

| nvSRAM バス モード                 | 6  | DC 特性                             | 20 |

| nvSRAM イネーブル／スタンバイ            | 6  | データ保持期間および書き換え可能回数                | 21 |

| nvSRAM バス アイドル                | 6  | 静電容量                              | 21 |

| nvSRAM コマンド                   | 6  | 熱抵抗                               | 21 |

| nvSRAM アドレス入力                 | 7  | AC テスト条件                          | 22 |

| nvSRAM データ入力                  | 8  | AC スイッチング特性                       | 23 |

| nvSRAM データ出力                  | 8  | タイミング モード                         | 23 |

| コマンドの定義                       | 9  | nvSRAM AutoStore／パワーアップ RECALL 特性 | 24 |

| 基本動作                          | 10 | ハードウェア STORE 特性                   | 25 |

| ID 読み出し (90h) の定義             | 10 | 注文情報                              | 26 |

| パラメータ ページ読み出し (ECh)           | 12 | 注文コードの定義                          | 26 |

| ステータス読み出し (70h) の定義           | 14 | パッケージ図                            | 27 |

| ステータス フィールドの定義                | 15 | 略語                                | 28 |

| nvSRAM バースト モード読み出し (00h、30h) | 15 | 本書の表記法                            | 28 |

| nvSRAM バースト書き込み (80h、10h)     | 16 | 測定単位                              | 28 |

| リセット (FFh) の定義                | 16 | 改訂履歴                              | 29 |

| nvSRAM ソフトウェア RECALL (FCh)    | 17 | セールス、ソリューションおよび法律情報               | 30 |

| nvSRAM ソフトウェア STORE (84h、A5h) | 17 | ワールドワイドな販売と設計サポート                 | 30 |

| nvSRAM AutoStore ディセーブル (A3h) | 17 | 製品                                | 30 |

| nvSRAM AutoStore イネーブル (ACh)  | 17 | PSoC® ソリューション                     | 30 |

| 書き込み保護                        | 18 | サイプレス開発者コミュニティ                    | 30 |

| nvSRAM Store 処理               | 18 | テクニカル サポート                        | 30 |

| AutoStore 処理                  | 18 |                                   |    |

| ハードウェア STORE (HSB) 処理         | 19 |                                   |    |

| ソフトウェア Store 処理               | 19 |                                   |    |

## ピン配置

図 1. シングル チャネル (x8) ピン配置図 : 165 ボール FBGA

|          | 1  | 2         | 3         | 4                | 5               | 6  | 7        | 8               | 9         | 10               | 11 |

|----------|----|-----------|-----------|------------------|-----------------|----|----------|-----------------|-----------|------------------|----|

| <b>A</b> | R  | R         | R         | NC               | NC              | NC | NC       | R               | R         | R                | R  |

| <b>B</b> | R  | R         | R         | NC               | NC              | NC | NC       | R               | R         | R                | R  |

| <b>C</b> | R  | $V_{CCQ}$ | $V_{CCQ}$ | NC               | $V_{SS}$        | NC | $V_{CC}$ | NC              | $V_{CCQ}$ | $V_{CCQ}$        | R  |

| <b>D</b> | R  | $V_{SS}$  | NC        | $V_{SS}$         | NC              | NC | NC       | $V_{SS}$        | NC        | $V_{SS}$         | R  |

| <b>E</b> | NC | NC        | NC        | NC               | NC              | NC | NC       | NC              | NC        | NC               | NC |

| <b>F</b> | NC | $V_{SS}$  | $V_{CCQ}$ | NC               | NC              | NC | NC       | $V_{CCQ}$       | $V_{SS}$  | $V_{SS}$         | NC |

| <b>G</b> | NC | NC        | NC        | NC               | R               | NC | NC       | NC              | NC        | $\overline{HSB}$ | NC |

| <b>H</b> | NC | $V_{SS}$  | $V_{CC}$  | $R/\overline{B}$ | NC              | NC | NC       | $V_{CC}$        | $V_{SS}$  | $V_{SS}$         | NC |

| <b>J</b> | NC | $V_{CAP}$ | NC        | $\overline{CE}$  | NC              | NC | NC       | $\overline{WP}$ | R         | NC               | NC |

| <b>K</b> | NC | $V_{SS}$  | $V_{CCQ}$ | NC               | NC              | NC | CLE      | ALE             | $V_{CCQ}$ | $V_{SS}$         | NC |

| <b>L</b> | NC | DQ7       | DQ6       | NC               | $\overline{WE}$ | NC | NC       | NC              | DQ1       | DQ0              | NC |

| <b>M</b> | R  | $V_{SS}$  | DQ5       | $V_{SS}$         | $\overline{RE}$ | NC | NC       | $V_{SS}$        | DQ2       | $V_{SS}$         | R  |

| <b>N</b> | R  | $V_{CCQ}$ | $V_{CCQ}$ | DQ4              | $V_{CC}$        | NC | $V_{SS}$ | DQ3             | $V_{CCQ}$ | $V_{CCQ}$        | R  |

| <b>P</b> | R  | R         | R         | NC               | NC              | NC | NC       | NC              | R         | R                | R  |

| <b>R</b> | R  | R         | R         | NC               | NC              | NC | NC       | NC              | R         | R                | R  |

図 2. シングル チャネル (x16) ピン配置図 : 165 ボール FBGA

|          | 1  | 2         | 3         | 4                | 5               | 6  | 7        | 8               | 9         | 10               | 11 |

|----------|----|-----------|-----------|------------------|-----------------|----|----------|-----------------|-----------|------------------|----|

| <b>A</b> | R  | R         | R         | NC               | NC              | NC | NC       | R               | R         | R                | R  |

| <b>B</b> | R  | R         | R         | NC               | NC              | NC | NC       | R               | R         | R                | R  |

| <b>C</b> | R  | $V_{CCQ}$ | $V_{CCQ}$ | DQ11             | $V_{SS}$        | NC | $V_{CC}$ | DQ12            | $V_{CCQ}$ | $V_{CCQ}$        | R  |

| <b>D</b> | R  | $V_{SS}$  | DQ10      | $V_{SS}$         | NC              | NC | NC       | $V_{SS}$        | DQ13      | $V_{SS}$         | R  |

| <b>E</b> | NC | DQ8       | DQ9       | NC               | NC              | NC | NC       | DQ14            | DQ15      | DQ15             | NC |

| <b>F</b> | NC | $V_{SS}$  | $V_{CCQ}$ | NC               | NC              | NC | NC       | $V_{CCQ}$       | $V_{SS}$  | $V_{SS}$         | NC |

| <b>G</b> | NC | NC        | NC        | NC               | R               | NC | NC       | NC              | NC        | $\overline{HSB}$ | NC |

| <b>H</b> | NC | $V_{SS}$  | $V_{CC}$  | $R/\overline{B}$ | NC              | NC | NC       | $V_{CC}$        | $V_{SS}$  | $V_{SS}$         | NC |

| <b>J</b> | NC | $V_{CAP}$ | NC        | $\overline{CE}$  | NC              | NC | NC       | $\overline{WP}$ | R         | NC               | NC |

| <b>K</b> | NC | $V_{SS}$  | $V_{CCQ}$ | NC               | NC              | NC | CLE      | ALE             | $V_{CCQ}$ | $V_{SS}$         | NC |

| <b>L</b> | NC | DQ7       | DQ6       | NC               | $\overline{WE}$ | NC | NC       | NC              | DQ1       | DQ0              | NC |

| <b>M</b> | R  | $V_{SS}$  | DQ5       | $V_{SS}$         | $\overline{RE}$ | NC | NC       | $V_{SS}$        | DQ2       | $V_{SS}$         | R  |

| <b>N</b> | R  | $V_{CCQ}$ | $V_{CCQ}$ | DQ4              | $V_{CC}$        | NC | $V_{SS}$ | DQ3             | $V_{CCQ}$ | $V_{CCQ}$        | R  |

| <b>P</b> | R  | R         | R         | NC               | NC              | NC | NC       | NC              | R         | R                | R  |

| <b>R</b> | R  | R         | R         | NC               | NC              | NC | NC       | NC              | R         | R                | R  |

## ピン機能

| ピン名                     | 入出力   | 説明                                                                                                                                                                                      |

|-------------------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R/B                     | 出力    | レディー／ビジー：デバイスの状態を示す。LOW にされた時、この信号は nvSRAM が STORE 处理、パワーアップ RECALL 处理、またはソフトウェア RECALL／ソフトウェア STORE／AutoStore 無効化／AutoStore 有効化処理のいずれかを実行していることを示す。この信号はオープン ドレイン出力であり、外部プルアップ抵抗を必要とする |

| RE                      | 入力    | 読み出しイネーブル：読み出し処理中にデータ出力を有効にする                                                                                                                                                           |

| CE                      | 入力    | チップ イネーブル：LOW にされる時、デバイスを選択。HIGH にされ、デバイスが STORE 处理を行っていない時、デバイスは低消費電力スタンバイ状態に入る                                                                                                        |

| CLE                     | 入力    | コマンド ラッチ イネーブル：コマンド バイトをラッチするために使用。これは、バス サイクルの種類（コマンド、アドレス、データ）を示すためにホストによって使用される信号の 1 つ                                                                                               |

| ALE                     | 入力    | アドレス ラッチ イネーブル：アドレス バイトをラッチするために使用。これは、バス サイクルの種類（コマンド、アドレス、データ）を示すためにホストによって使用される信号の 1 つ                                                                                               |

| WE                      | 入力    | 書き込みイネーブル：立ち上がりエッジ毎に入力データのラッチを制御                                                                                                                                                        |

| WP                      | 入力    | 書き込み保護：LOW にされる時、nvSRAM 内の SRAM 書き込み動作を無効にする                                                                                                                                            |

| DQ[7:0] <sup>[1]</sup>  | 入力／出力 | I/O ポート、×8 構成では 8 ビット：I/O ポートは、デバイスからまたはデバイスへ、アドレス、コマンド、データを転送するための 8 ビット幅の双方向ポート                                                                                                       |

| DQ[15:0] <sup>[1]</sup> | 入力／出力 | I/O ポート、×16 構成では 16 ビット：I/O ポートは、書き込みと読み出し処理中にデバイスからまたはデバイスへデータ ワードを転送するための 16 ビット幅の双方向バス。アドレスとコマンドは常に下位 8 ビット DQ[7:0] を経由して転送                                                          |

| HSB                     | 入力    | ハードウェア STORE：外部で LOW にされる時、不揮発性 STORE 处理を開始                                                                                                                                             |

| V <sub>CAP</sub>        | 電源    | AutoStore コンデンサ：SRAM から不揮発性素子にデータを格納するため、電力喪失時に nvSRAM に電源を供給                                                                                                                           |

| V <sub>CC</sub>         | 電源    | 電源：デバイスのコアの電源入力                                                                                                                                                                         |

| V <sub>CCQ</sub>        | 電源    | I/O 電源：デバイスの入力と出力の電源入力                                                                                                                                                                  |

| V <sub>SS</sub>         | 電源    | デバイスのグランド：システムのグランドに接続する                                                                                                                                                                |

| R                       | R     | 予約済み：これらのピンは予約済みであり、ホストによって未接続状態にされる必要がある                                                                                                                                               |

| NC                      | NC    | 未接続：ダイ パッドはパッケージ ピンに接続されていない                                                                                                                                                            |

## 発見と初期化

電源投入サイクルが開始し、V<sub>CC</sub> が V<sub>SWITCH</sub> 閾値を超えると、デバイスは内部パワーアップ RECALL 处理を初期化し、R/B ピンを t<sub>RECALL</sub> の間 LOW にプルダウンします。電源投入サイクルが完了すると、デバイスは R/B ピンを解放します。このピンはその後、それに接続している外部プルアップ抵抗によって HIGH にプルアップされます。R/B HIGH はデバイスのレディ状態を示し、オペコードを実行することでホスト コントローラがデバイスと通信することを許可します。サポートされているすべてのオペコードは [9 ページの表 3](#) で説明します。

## nvSRAM バス処理

nvSRAM デバイスの I/O は多重化されます。データ I/O、アドレスおよびコマンドは同じ I/O ピンを共有します。DQ[15:8] は ×16 構成でのデータにのみ使用されます。×16 構成では、アド

レスとコマンドは常に DQ[7:0] を、データは DQ[15:0] を経由して転送されます。

コマンド シーケンスは通常、コマンド ラッチ サイクル、アドレス入力サイクルおよび 1 つ以上のデータ サイクル（読み出しまたは書き込み）で構成されています。

## 制御信号

CE、WE、RE、CLE、ALE、WP 等の nvSRAM 制御信号は、nvSRAM デバイスの読み出しと書き込み処理を制御します。CE が LOW にプルダウンされ、デバイスがビジー状態でない場合、この信号はデバイスを有効にします。選択されると、nvSRAM はコマンド、アドレスおよびデータ バイトを受け付けます。データが転送されており、デバイスがビジーでない時、CE が HIGH になると nvSRAM はスタンバイ モードに移行します。HIGH の CLE 信号は CE と WE LOW と共に、コマンド入力サイクルを示します。同様に、HIGH の ALE 信号は CE と WE LOW と共に、アドレス入力サイクルを示します。

### 注：

1. ×8 構成のデータは DQ[7:0]、×16 構成のデータは DQ[15:0] です。

## nvSRAM バス モード

入力制御信号の状態に応じて、nvSRAM は表 1 で定義されたように以下のバス状態のいずれかです。

表 1. 非同期 NAND インターフェース バス モード

| CE | ALE | CLE | WE | RE | WP | バス状態           |

|----|-----|-----|----|----|----|----------------|

| 1  | X   | X   | X  | X  | X  | スタンバイ          |

| 0  | 0   | 0   | 1  | 1  | X  | バス アイドル        |

| 0  | 0   | 1   | 0  | 1  | X  | コマンド サイクル      |

| 0  | 1   | 0   | 0  | 1  | X  | アドレス サイクル      |

| 0  | 0   | 0   | 0  | 1  | H  | 書き込み サイクル      |

| 0  | 0   | 0   | 1  | 0  | X  | 読み込み サイクル      |

| 0  | 1   | 1   | X  | X  | X  | 未定義            |

| 0  | 0   | 0   | 0  | 1  | L  | SRAM への書き込み 保護 |

注：状態「X」の信号は  $\geq V_{IH}$  または  $\leq V_{IL}$  です。

## nvSRAM イネーブル/スタンバイ

チップ イネーブル ( $\overline{CE}$ ) 信号はデバイスを有効または無効にするために使用されます。CE が LOW に駆動されると、すべての

nvSRAM 入力信号は有効になります。 $\overline{CE}$  が LOW の時、nvSRAM は DQ ライン上でコマンド、アドレスおよびデータを受け付けることができます。CE が HIGH に駆動されると、デバイスがビジー状態であっても nvSRAM は無効になります。デバイスがレディー状態で R/B が外部のプルアップ抵抗によって HIGH にプルアップされた場合、nvSRAM は低消費電力のスタンバイモードに移行します。CE が無効の時、WP、R/B および HSB を除き、nvSRAM のすべての I/O は無効にされます。

## nvSRAM バス アイドル

CE、ALE、CLE が LOW で、WE、RE が HIGH の時、nvSRAM はバス アイドル状態になります。バス アイドル中に、すべての入力信号は有効になりますが、コマンド、アドレスおよびデータはデバイスでラッチされておらず、デバイスからのデータ出力もありません。

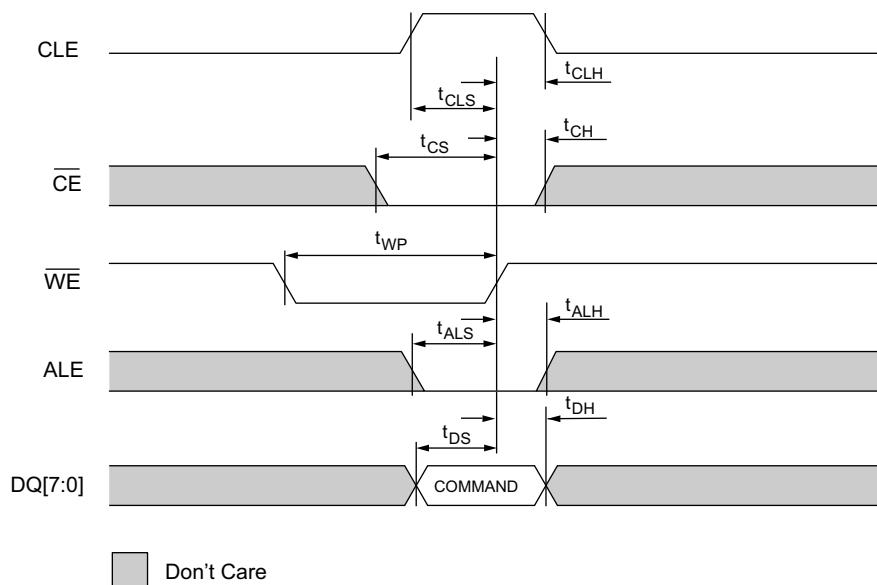

## nvSRAM コマンド

CE が LOW、ALE が LOW、CLE が HIGH および  $\overline{RE}$  が HIGH の時に、コマンドは WE の立ち上がりエッジで DQ[7:0] からコマンド レジスタに書き込まれます。nvSRAM がビジー状態 (RDY ビットがステータス レジスタで「0」にセットされた) の場合、ステータス レジスタ読み出し (70h) およびリセット (FFh) を除き、すべてのコマンドは無視されます。

図 3. コマンド ラッチ サイクル

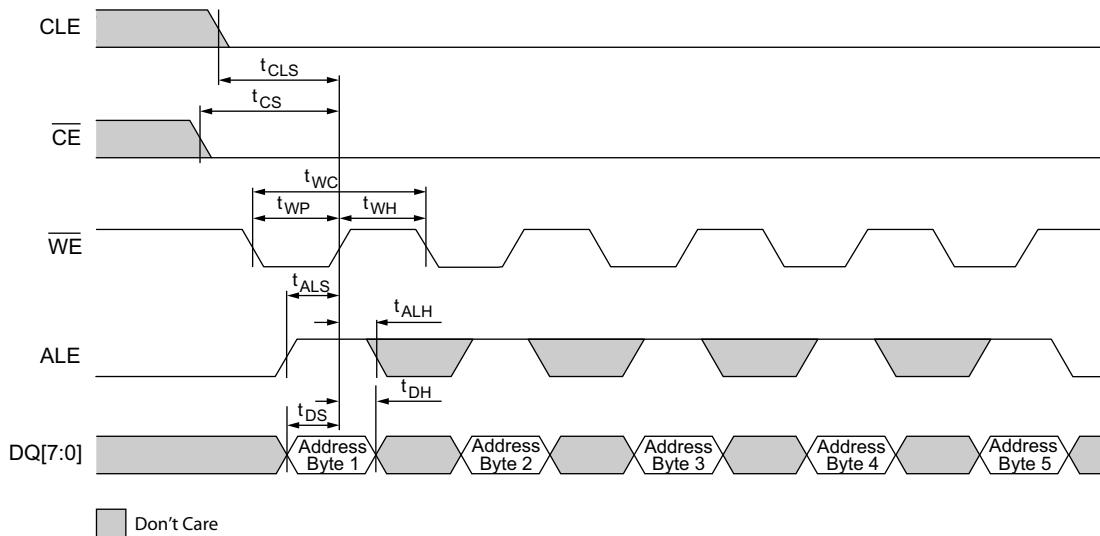

### nvSRAM アドレス入力

nvSRAM アドレス サイクル中、 $\overline{CE}$  が LOW、 $ALE$  が HIGH、 $CLE$  が LOW および  $RE$  が HIGH の時、ホストは WE トグルの立ち上がりエッジ毎に  $DQ[7:0]$  を通して 5 つの連続したアドレス バイトをアドレス レジスタに送信します。5 バイトのアドレス サイクルで、最下位のアドレス バイトは最初のアドレス サイクルで、最上位のアドレス バイトは 5 番目のアドレス サイクルで送信されます。nvSRAM は、その 16M ビット メモリ全體をアドレス指定するために最初の 3 つのアドレス バイトのみ

を必要とします。したがって、5 バイトのアドレスでの 2 つの追加アドレス バイトはドント ケアのバイトです。ドント ケア ビットを含むすべての未使用アドレス ビットはホスト コントローラによって「0」にセットする必要があります。ビジー (RDY がステータス レジスタで「0」にセットされた) 時間に、アドレス サイクルは nvSRAM に無視されます。nvSRAM のアドレス サイクルの詳細については、9 ページの表 2 を参照してください。

図 4. アドレス ラッチ サイクル

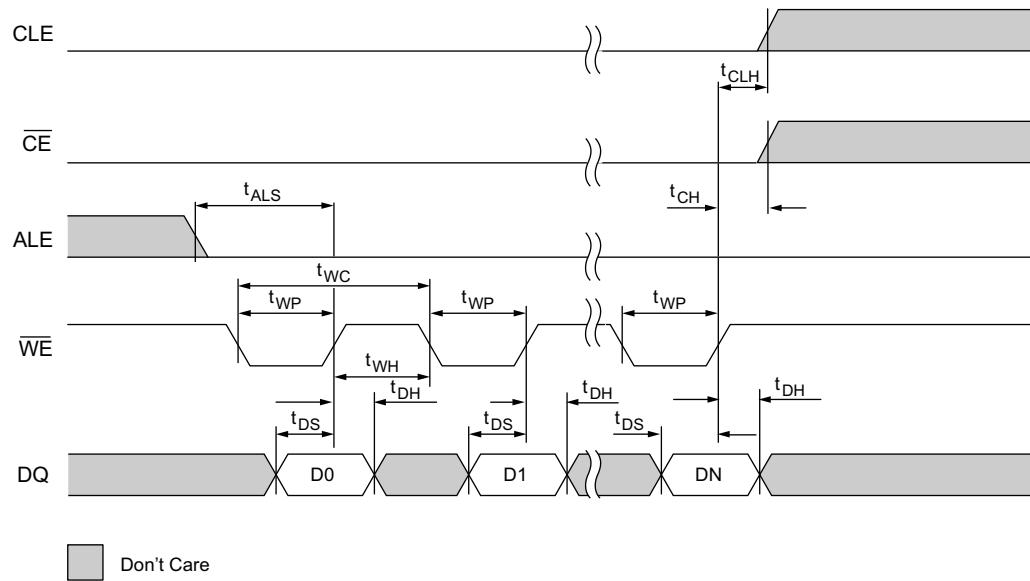

### nvSRAM データ入力

CE が LOW、ALE が LOW、CLE が LOW および RE が HIGH の場合、データは WE の立ち上がりエッジで DQ (DQ[7:0] または DQ[15:0]) から nvSRAM のデータレジスタに書き込まれます。デバイスビジー状態 (RDY がステータスレジスタで「0」にセットされた) では、nvSRAM はデータ入力を無視します。

図 5. データ入力サイクル

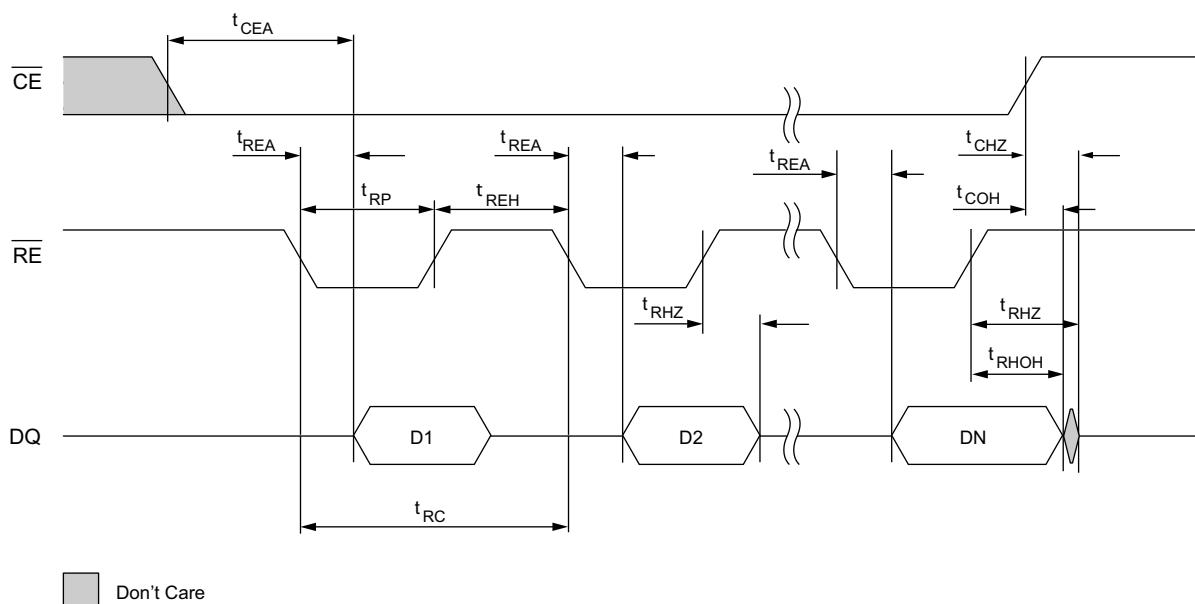

### nvSRAM データ出力

nvSRAM がレディー状態の場合、データは読み出し中に DQ バス (DQ[7:0] または DQ[15:0]) 上で nvSRAM によって送信されます。CE が LOW、ALE が LOW、CLE が LOW および WE が HIGH の場合、データは RE の立ち下がりエッジ毎にデータレジスタから出力されます。STORE サイクル中に nvSRAM がビジー状態 (RDY がステータスレジスタで「0」にセットされた) の場合は読み出し要求を無視します。

図 6. データ出力サイクル

**表 2. nvSRAM アドレス入力**

| アドレス サイクル | DQ7                   | DQ6 | DQ5 | DQ4                      | DQ3 | DQ2 | DQ1 | DQ0 |

|-----------|-----------------------|-----|-----|--------------------------|-----|-----|-----|-----|

| 1 番目      | A7                    | A6  | A5  | A4                       | A3  | A2  | A1  | A0  |

| 2 番目      | A15                   | A14 | A13 | A12                      | A11 | A10 | A9  | A8  |

| 3 番目      | ドント ケア <sup>[3]</sup> |     |     | A20 / LOW <sup>[2]</sup> | A19 | A18 | A17 | A16 |

| 4 番目      | ドント ケア <sup>[3]</sup> |     |     |                          |     |     |     |     |

| 5 番目      | ドント ケア <sup>[3]</sup> |     |     |                          |     |     |     |     |

### コマンドの定義

アドレス、コマンドおよびデータは nvSRAM の I/O で多重化されます。CE と CLE が LOW、ALE が HIGH (アドレス サイクルの場合)、または CE と ALE が LOW、CLE が HIGH (コマンド サイクルの場合) の時に WE を LOW にトグルすることで、すべてのコマンドとアドレスは DQ バスの DQ[7:0] 経由で書き

込まれます。すべての入力ピンの状態は WE の立ち上がりエッジでラッチされます。その後、デバイスはバス サイクルがコマンド サイクル、アドレス サイクル、データ入力サイクル、またはデータ出力サイクルであるかを判定します。すべての非同期 NAND インターフェースの nvSRAM コマンドは表 3 に一覧表示されています。

**表 3. nvSRAM コマンド表**

| nvSRAM 機能        | 最初のサイクル | 第 2 サイクル           | 項目                                                                                                    |

|------------------|---------|--------------------|-------------------------------------------------------------------------------------------------------|

| ID 読み出し          | 90h     |                    | ターゲット デバイスが ONFI 仕様をサポートするかを同定する。ターゲット デバイスが ONFI 仕様をサポートする場合、ONFI シグネチャが返される                         |

| パラメータ ページ読み出し    | ECh     |                    | パラメータ ページ読み出し機能は、ターゲットの構成、機能、タイミングおよび他の動作パラメータを記述するデータ構造を検索                                           |

| ステータス読み出し        | 70h     |                    | 最後に発行された処理の状態の値を読み出す                                                                                  |

| 読み出し             | 00h     | 30h                | 読み出し機能は、アドレス バイトによって指定された nvSRAM アレイ位置から読み出す                                                          |

| 書き込み             | 80h     | 10h <sup>[4]</sup> | データは nvSRAM の SRAM アレイに書き込まれる。10h は nvSRAM 書き込み処理用のオプションのコマンド サイクルであり、ホストがこのコマンドを発行しなくても書き込みは正常に実行される |

| リセット             | FFh     |                    | 現行の処理 (すべての読み出し/書き込み) を中止し、nvSRAM を電源投入状態に移行させる。NV 処理が実行中の場合、それが完了してからリセット要求は処理される                    |

| ソフトウェア RECALL    | FCh     |                    | ソフトウェア RECALL                                                                                         |

| ソフトウェア STORE     | 84h     | A5h                | ソフトウェア STORE                                                                                          |

| AutoStore ディセーブル | A3h     |                    | AutoStore 機能を無効にする                                                                                    |

| AutoStore イネーブル  | ACh     |                    | AutoStore 機能を有効にする                                                                                    |

| 予約済み             | EEh     |                    | 予約済み                                                                                                  |

| 予約済み             | EFh     |                    | 予約済み                                                                                                  |

**注:**

2. ×16 構成では、A20 アドレス ビットは LOW に設定されます。

3. これらのアドレス ビットは「ドント ケア」ですが、サイプレスはこれらを「0」として扱うことを推奨します。

4. 書き込みサイクルの終わりの 10h コマンドは任意であり、フラッシュ互換性にのみ使用されます。

## 基本動作

次の節で nvSRAM コマンドを説明します。

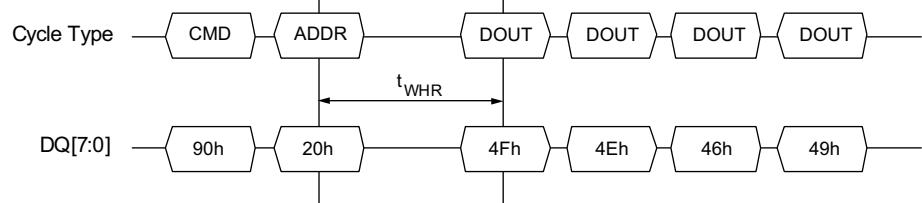

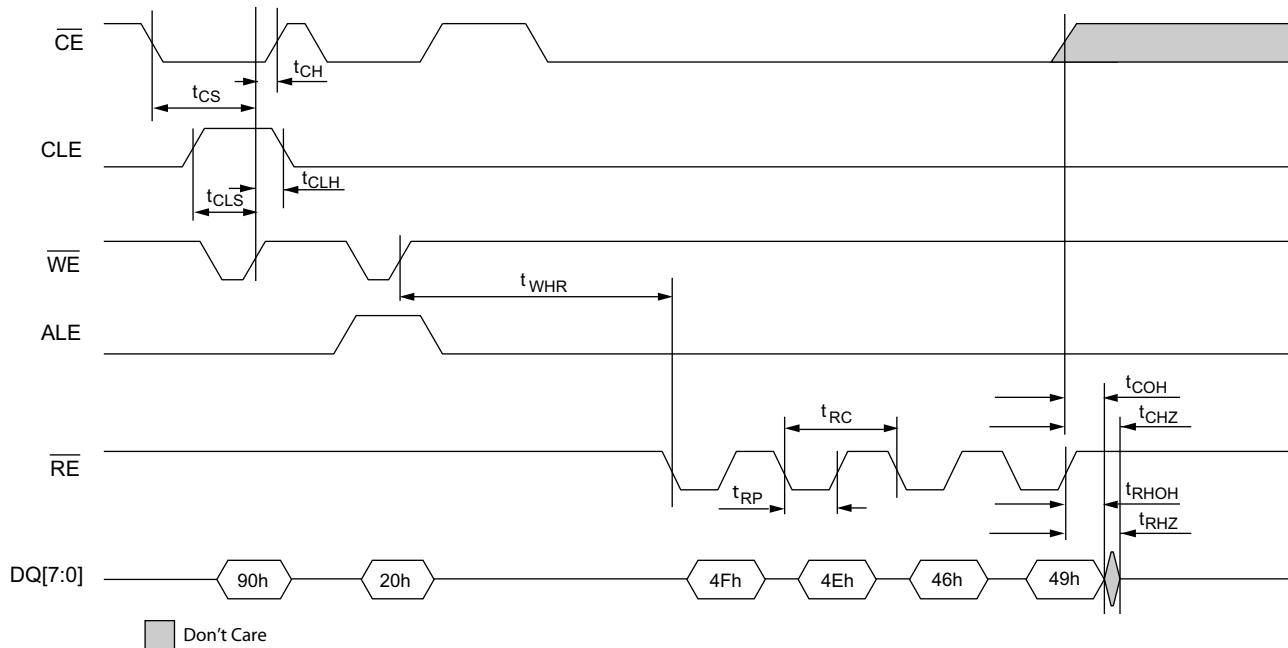

### ID 読み出し (90h) の定義

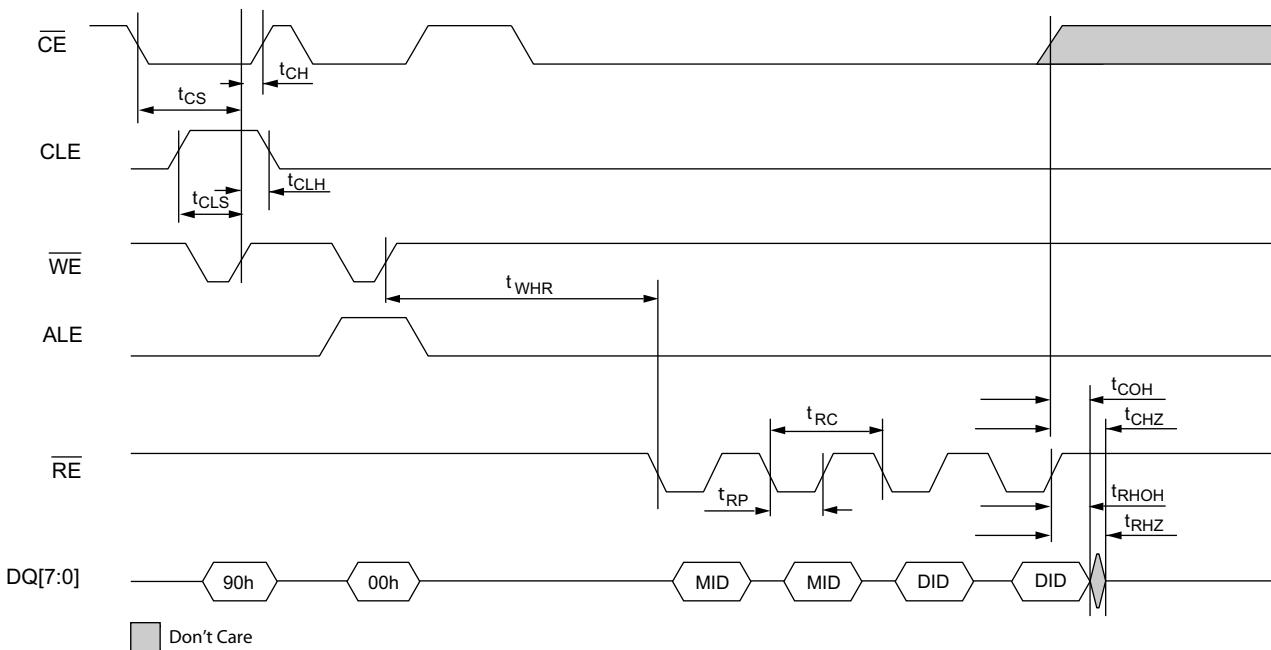

ID 読み出し機能はターゲットのデバイスが ONFI 仕様をサポートするかを同定します。nvSRAM が ONFI 仕様をサポートする場合、ONFI シグネチャが返されます。ONFI シグネチャは「ONFI」の ASCII 符号化です。そこで、「O」 = 4Fh、「N」 = 4Eh、「F」 = 46h、および「I」 = 49h。4 バイトを超えて読み出すと不定値が得られます。図 7 と図 8 は ID 読み出しの動作とタイミングを定義します。

ID 読み出しコマンドでは、00h と 20h のアドレスのみが有効です。ID 読み出しコマンド (90h) に続く他のアドレス (00h と 20h を除き) はホストに無効なデータを返します。ONFI シグネチャを検索するために、20h のアドレスを入力します。

16 ビットのデータ アクセスをサポートするデバイスでは、上位 8 ビット DQ[15:8] は「ドント ケア」ビットであり、使用されません。

図 7. ONFI シグネチャの ID 読み出し処理図

図 8. ONFI シグネチャの ID 読み出しタイミング図

ID 読み出し機能は、00h のアドレスを指定することで特定 NAND 製品の JEDEC メーカー ID およびデバイス ID を判定するためにも使用できます。図 9 はデバイス ID を読み出すための ID 読み出しの動作とタイミングを定義します。最初の 2 バイトを超えて読み出すと不定値が得られます。

図 9. メーカー ID の ID 読み出し処理図

図 10. メーカー ID の ID 読み出しタイミング図

MID は割り当てられたメーカー ID で構成される 2 バイトのコードです。MID レジスタは工場出荷時に設定され、ユーザーにとっては読み出し専用のレジスタです。これはサイプレス用に JEDEC が割り当てたメーカーの ID です。JEDEC は異なるバンクでメーカー ID を割り当てます。最初の 8 ビットは ID が割り当てられているバンクを表しています。次の 8 ビットはメーカー ID を表しています。サイプレスのメーカー ID はバンク 0 で 34h です。したがって、サイプレス NAND インターフェース nvSRAM 製品のメーカー ID は以下の通りです。

MID: 0000\_0000\_0011\_0100

DID は、サイプレスによって割り当てられた製品のデバイス ID からなる 2 バイトのコードです。デバイスの ID は、 $\times 8$  製品では 22h、00h であり、 $\times 16$  製品では 22h、40h です。

DID ( $\times 8$ ): 0010\_0010\_0000\_0000

DID ( $\times 16$ ): 0010\_0010\_0100\_0000

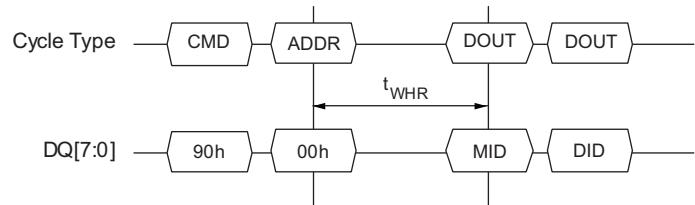

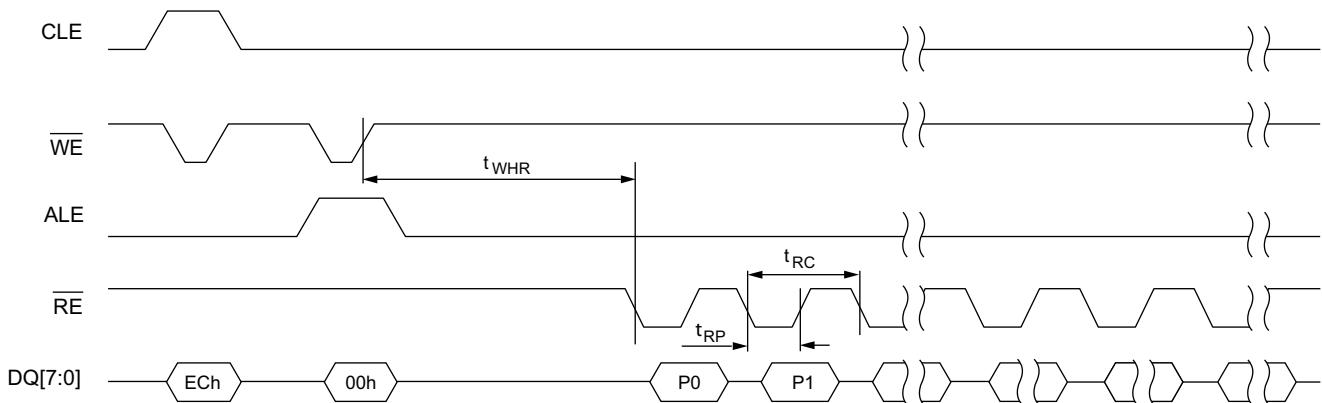

### パラメータ ページ読み出し (ECh)

パラメータ ページ読み出しコマンド (ECh) はターゲットの構成、機能、タイミングおよび他の動作パラメータを記述するデータ構造を読み出します。図 11 はパラメータ ページ読み出しコマンドを定義します。このコマンドは、nvSRAM がアイドルの時にターゲットによって受け付けられます。ECh をコマンド レジスタに書き込むと、ターゲット デバイスはパラメータ ページ読み出しモードになります。デバイスは、他の有効なコマンドが発行されるまでこのモードのままで。

ECh コマンドの後に続いて 00h アドレス サイクルが送信されると、ホストはパラメータ ページ バイトを読み出す前に少な

くとも  $t_{WHR}$  時間待機する必要があります。 $\overline{RE}$  トグルのたびに nvSRAM はパラメータ バイトの送信を開始します。

パラメータ ページ読み出し (ECh) の出力データは、nvSRAM デバイスの適切な使用のための内部の設定のためにホストによって使用されます。パラメータ ページのデータはいかなる製品でもスタティックです。しかし、値はデバイスの製品サイクルを通じて変更されることがあります。ホストはデータを解釈し、それに応じて自分自身を設定します。

図 11. パラメータ ページ コマンド読み出しタイミング

### パラメータ ページのデータ構造の定義

表 4 は nvSRAM のパラメータ ページのデータ構造を定義します。パラメータ ページは複数のバイトにわたり、パラメータの最下位バイトはパラメータ ページのデータ構造の最初のバイトに対応します。値はパラメータ ページでバイトの単位で報告

します。16 ビットのデータ アクセスをサポートするデバイスでは、上位 8 ビット DQ[15:8] は「ドント ケア」ビットであり、使用されません。

表 4. パラメータ ページのデータ構造の定義

| バイト   | パラメータの説明 <sup>[5]</sup>     | 値 (SDR タイミング モード 3) |          | 値 (SDR タイミング モード 2) |          |

|-------|-----------------------------|---------------------|----------|---------------------|----------|

|       |                             | ×8                  | ×16      | ×8                  | ×16      |

| 0 ~ 3 | パラメータ ページのシグネチャ             |                     |          |                     |          |

|       | バイト 0: 4Fh、「O」              | 4Fh                 | 4Fh      | 4Fh                 | 4Fh      |

|       | バイト 1: 4Eh、「N」              | 4Eh                 | 4Eh      | 4Eh                 | 4Eh      |

|       | バイト 2: 46h、「F」              | 46h                 | 46h      | 46h                 | 46h      |

|       | バイト 3: 49h、「I」              | 49h                 | 49h      | 49h                 | 49h      |

| 4 ~ 5 | リビジョン番号                     | 00h, 02h            | 00h, 02h | 00h, 02h            | 00h, 02h |

|       | ビット 15 ~ 2: 予約済み (0)        |                     |          |                     |          |

|       | ビット 1: ONFI バージョン 1.0 をサポート |                     |          |                     |          |

|       | ビット 0: 予約済み (0)             |                     |          |                     |          |

注:

5. () は、工場出荷時の値を示します。

**表 4. パラメータ ページのデータ構造の定義 (続き)**

| バイト       | パラメータの説明 <sup>[5]</sup>                                      | 値 (SDR タイミング モード 3) |          | 値 (SDR タイミング モード 2) |          |  |  |  |

|-----------|--------------------------------------------------------------|---------------------|----------|---------------------|----------|--|--|--|

|           |                                                              | ×8                  | ×16      | ×8                  | ×16      |  |  |  |

| 6 ~ 7     | サポートされている機能                                                  | 00h, 00h            | 00h, 01h | 00h, 00h            | 00h, 01h |  |  |  |

|           | ビット 15 ~ 1: 予約済み (0)                                         |                     |          |                     |          |  |  |  |

|           | ビット 0: 「1」にセットされると、16 ビットデータ バス幅をサポート                        |                     |          |                     |          |  |  |  |

| 8 ~ 9     | サポートされているオプションのコマンド                                          | 00h, 00h            | 00h, 00h | 00h, 00h            | 00h, 00h |  |  |  |

|           | ビット 15 ~ 3: 予約済み (0)                                         |                     |          |                     |          |  |  |  |

|           | ビット 2: 機能取得と機能設定コマンドをサポート                                    |                     |          |                     |          |  |  |  |

|           | ビット 1 ~ 0: 予約済み (0)                                          |                     |          |                     |          |  |  |  |

| 10 ~ 31   | 予約済み (0)                                                     | 全バイト 00h            |          |                     |          |  |  |  |

| 32 ~ 43   | デバイス メーカー (12 ASCII 文字)                                      | 全バイト 00h            |          |                     |          |  |  |  |

| 44 ~ 63   | デバイス モデル (20 ASCII 文字)                                       | 全バイト 00h            |          |                     |          |  |  |  |

| 64        | JEDEC メーカー ID                                                | 34h                 | 34h      | 34h                 | 34h      |  |  |  |

| 65 ~ 66   | 日付コード (オプション)                                                | 全バイト 00h            |          |                     |          |  |  |  |

| 67 ~ 79   | 予約済み (0)                                                     | 全バイト 00h            |          |                     |          |  |  |  |

| 80 ~ 100  | 未使用 (0)                                                      | 全バイト 00h            |          |                     |          |  |  |  |

| 101       | アドレス サイクル数<br>ビット 7 ~ 4: 列アドレス サイクル<br>ビット 3 ~ 0: 行アドレス サイクル | 32h                 | 32h      | 32h                 | 32h      |  |  |  |

| 102 ~ 127 | 未使用 (0)                                                      | 全バイト 00h            |          |                     |          |  |  |  |

| 128       | I/O ピン容量                                                     | 08h                 | 08h      | 08h                 | 08h      |  |  |  |

| 129 ~ 130 | タイミング モード サポート                                               | 00h, 08h            | 00h, 08h | 00h, 04h            | 00h, 04h |  |  |  |

|           | ビット 15 ~ 4: 予約済み (0)                                         |                     |          |                     |          |  |  |  |

|           | ビット 3: 「1」にセットすると、タイミング モード 3 をサポート                          |                     |          |                     |          |  |  |  |

|           | ビット 2: 「1」にセットすると、タイミング モード 2 をサポート                          |                     |          |                     |          |  |  |  |

|           | ビット 1 ~ 0: 予約済み (0)                                          |                     |          |                     |          |  |  |  |

| 131 ~ 140 | 未使用 (0)                                                      | 全バイト 00h            |          |                     |          |  |  |  |

| 141 ~ 163 | 予約済み (0)                                                     | 全バイト 00h            |          |                     |          |  |  |  |

| 164 ~ 253 | 未使用 (0)                                                      | 全バイト 00h            |          |                     |          |  |  |  |

| 254 ~ 255 | インテグリティ CRC                                                  | 全バイト 00h            |          |                     |          |  |  |  |

| 256 ~ 768 | 予約済み (0)                                                     | 全バイト 00h            |          |                     |          |  |  |  |

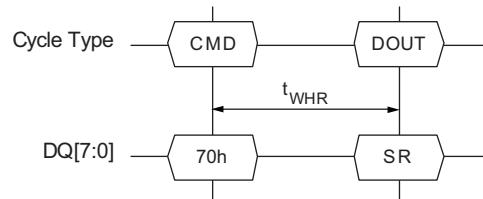

### ステータス読み出し (70h) の定義

ステータス読み出しこマンドは、最後に発行された処理の状態の値を読み出します。ステータス レジスタ ビットの定義は [15 ページの表 5「ステータス フィールドの定義」](#) を参照してください。図 12 と図 13 はステータス読み出しの動作とタイミングを定義します。

SR: ステータス レジスタ ビットは [15 ページの表 6](#) で定義されます。

図 12. ステータス読み出し処理

図 13. ステータス読み出しタイミング

## ステータス フィールドの定義

ステータス読み出しレジスタコマンドはステータス レジスタ バイトの値 (SR) を返します。RDY ビットが 0 にクリアされると、ステータス バイトでの (WP を除く) 他の全てのビットは無効で、ホストに無視されます。nvSRAM STORE またはソフトウェア RECALL サイクルが進行中、レディー/ビジー状態を確認するために、RDY ビットをポーリングすることができます。

表 5. ステータス フィールドの定義

| SR ビット     | 7  | 6   | 5     | 4     | 3     | 2     | 1     | 0    |

|------------|----|-----|-------|-------|-------|-------|-------|------|

| ステータス レジスタ | WP | RDY | X (0) | X (0) | X (0) | R (0) | X (0) | FAIL |

表 6. ステータス レジスタのビット定義

| SR ビット | SR ビットの定義 | SR ビットの説明                                                                                                                                                                                                 |

|--------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ビット 0  | FAIL      | これは nvSRAM によって最後に実行されたコマンドの状態を示す。最後のコマンドが正常に実行されなかった場合、FAIL ビットは「1」にセットされる。ホストによって最後に発行されたコマンドが適切に登録されなかった場合、コマンドが対応するアドレス バイトを受信しなかった場合、またはホストによって送信されたコマンドが無効な場合は、nvSRAM は FAIL ビットをセット                |

| ビット 1  | ドント ケア    | このビットを読み出すと常に「0」が返される                                                                                                                                                                                     |

| ビット 2  | 予約済み      | このビットを読み出すと常に「0」が返される                                                                                                                                                                                     |

| ビット 3  | ドント ケア    | このビットを読み出すと常に「0」が返される                                                                                                                                                                                     |

| ビット 4  | ドント ケア    | このビットを読み出すと常に「0」が返される                                                                                                                                                                                     |

| ビット 5  | ドント ケア    | このビットを読み出すと常に「0」が返される                                                                                                                                                                                     |

| ビット 6  | RDY       | 「1」にセットすると、nvSRAM は他のコマンドの受け入れが可能になっており、状態値の他のすべてのビットは有効となる。「0」にクリアすると、最後に発行されたコマンドはまだ完了しておらず、SR ビット 5:0 は無効になり、ホストによって無視される。従ってこのビットは R/B の値に影響を与える。STORE またはソフトウェア RECALL の実行中、このビットはデバイスによって「0」にセットされる |

| ビット 7  | WP        | 「1」にセットすると、デバイスは書き込みから保護されない。「0」にクリアすると、デバイスは書き込みから保護される。RDY ビットの状態に関わらず、このビットは常に有効                                                                                                                       |

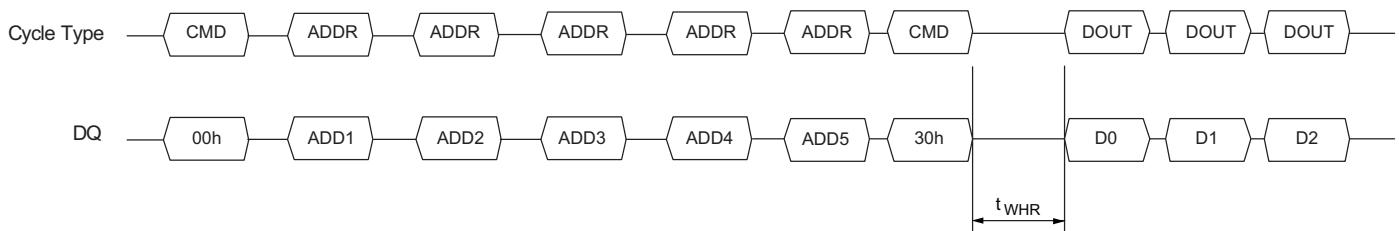

## nvSRAM パースト モード読み出し (00h, 30h)

ホスト コントローラ 00h コマンドの後に続いて 5 アドレス バイトおよび 30h の 2 番目のコマンド サイクルを送信すると、nvSRAM は読み出しモードになります。読み出しコマンドが登録された後、nvSRAM は RE 制御信号のトグルのたびに RE の立ち下がりエッジから  $t_{REA}$  時間後 DQ バス上でデータを送信します。nvSRAM はパースト モードで読み出すことが可能です。この処理では、ホストは最大の  $t_{RC}$  率で RE を繰り返してパルスすることでデバイスからデータを読み出し続けることができます。ホスト コントローラは単一読み出し要求を開始することができます。

でメモリ全体を読み出すことができます。パースト モード読み出しでは、nvSRAM の内部アドレス カウンタは自動的に次のアドレス指定可能な位置までインクリメントし、デバイスは DQ バス上でデータを送信し続けます。内部のアドレス カウンタが最後のアドレス指定可能なメモリ位置に到達した後、カウンタは開始アドレスにロールオーバーし、データ バイトを送信し続けます。読み出しが他の有効なコマンドによって割り込まれるまでデバイスは読み出しモードを維持します。データ出力サイクル タイミングについては、図 14 を参照してください。

図 14. 読み出しタイミング

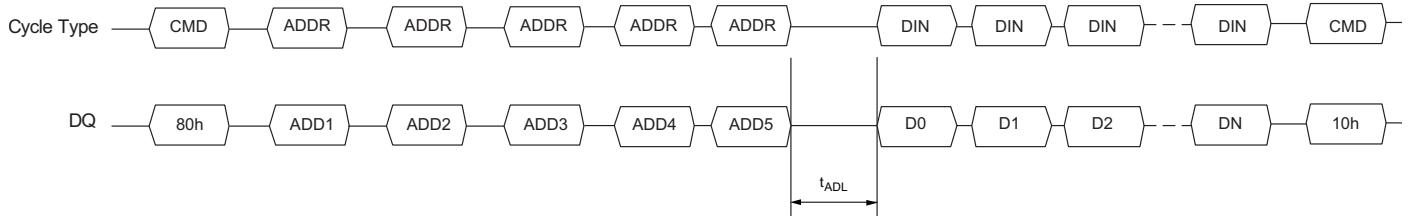

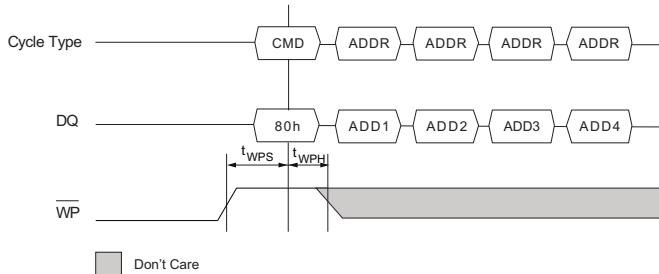

### nvSRAM バースト書き込み (80h、10h)

ホスト コントローラが 80h コマンドの後に続いて 5 アドレス バイトおよび書き込まれるデータ バイトを送信すると、nvSRAM は書き込みモードになります。書き込みコマンドが開始された後、後続のデータ バイトは WE トグルのたびに nvSRAM に書き込まれます。ホストが書き込みデータ サイクルの最後に 10h コマンドを送信すると、書き込みモードは終了します。nvSRAM はバースト モード書き込み処理をサポートしています。この処理では、ホストは最初の書き込みサイクルの時に一度だけ書き込みコマンドを開始し、WE をパルスすることで書き込みデータ バイトを送信し続けます。ホストは、WE の最小書き込みパルス幅 ( $t_{WP}$ ) および CE 信号のセットアップ時間 ( $t_{CS}$ ) とホールド時間 ( $t_{CH}$ ) を維持する必要があります。バースト モード書き込みが進行中、nvSRAM の内部アドレス カウンタは各データ ワード書き込みの後に自動的に進みます。内部のアドレス カウンタが最後のアドレス指定可能なメモリ位置に到達した後、アドレス カウンタは開始アドレスにロールオーバーし、以前に書き込まれたデータを上書きすることで開始アドレスの位置からデータを書き続けます。

注：コマンド 10h は、nvSRAM 書き込み処理のオプション コマンドであり、ホストがこのコマンドを発行せずに書き込みは正常に実行されます。ホストが書き込みの実行中に 10h コマンドを実行すると、書き込みモードは終了します。

データ入力サイクル タイミングについては、図 15 を参照してください。

図 15. 書き込みタイミング

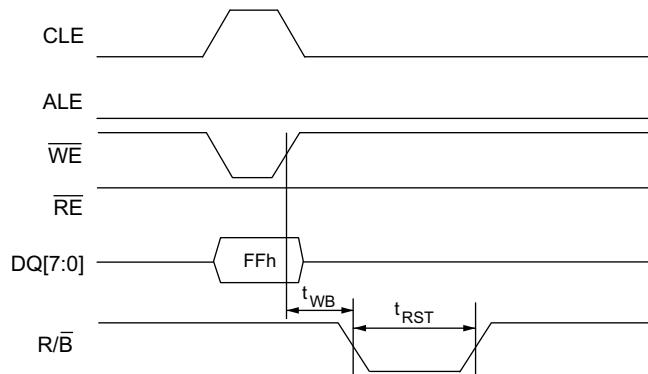

### リセット (FFh) の定義

リセット機能は nvSRAM を電源投入状態にします。パワーアップ RECALL 処理が実行中の場合を除き、リセット コマンドはデバイスの状態に関係なく実行されます。パワーアップ RECALL 処理の実行中、リセット コマンドは発行されず、ホストはデバイスがレディ状態になった後に R/B が HIGH になるまで待機しなければなりません。図 16 はリセットの動作とタイミングを定義します。

16 ビットのデータ アクセスをサポートするデバイスでは、上位 8 ビット DQ[15:8] は「ドント ケア」ビットであり、使用されません。

注：NV 処理の実行中にリセット (FFh) コマンドを発行すると、リセット要求は進行中の NV 処理が完了した後にのみ実行されます。デバイスの現時点の状態に応じて、 $t_{RST}$  タイミングは以下の条件によって異なります。

- デバイスがレディーの時にリセット コマンドを実行すると、リセット要求を処理するのに  $t_{SS}$  時間を要します。

- ソフトウェア RECALL サイクルの進行中にリセット コマンドを発行すると、リセット要求を処理するのに  $t_{RECALL}$  時間を要します。

- ソフトウェアまたは HSB STORE サイクルの進行中にリセット コマンドを発行すると、リセット要求を処理するのに  $t_{STORE}$  時間を要します。

図 16. リセットタイミング図

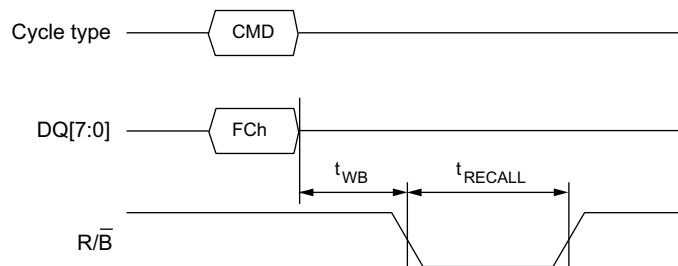

### nvSRAM ソフトウェア RECALL (FCh)

ソフトウェア RECALL は nvSRAM でソフトウェア RECALL 处理を開始します。デバイスがレディー状態の場合、コマンドはいつでも実行されます。[図 17](#) は nvSRAM ソフトウェア RECALL の動作とタイミングを定義します。ソフトウェア RECALL コマンドが nvSRAM によって登録された後、ソフトウェア RECALL 处理を内部的に開始する前にソフトウェア コマンドを処理するのに  $t_{SS}$  時間を要します。リセット (FFh) とステータス読み出し (70h) を除き、nvSRAM へのすべてのアクセスは  $t_{RECALL}$

時間の間禁止されます。RECALL 处理の進行中、nvSRAM はステータスレジスタの RDY ビットを「0」にセットし、R/B ピンを  $t_{RECALL}$  の間 LOW にプルダウンします。RECALL が完了した後、RDY ビットは「1」にセットされ、R/B は外部プルアップ抵抗によって HIGH にプルアップされ、レディー状態を示します。

16 ビットのデータ アクセスをサポートするデバイスでは、上位 8 ビット DQ[15:8] は「ドント ケア」ビットであり、使用されません。

**図 17. nvSRAM ソフトウェア RECALL**

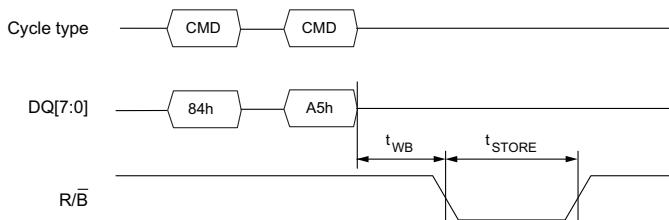

### nvSRAM ソフトウェア STORE (84h, A5h)

SRAM 書き込みの有無に関わらず、ソフトウェア STORE コマンドを送信することで nvSRAM 内でソフトウェア STORE 处理を開始します。ソフトウェア STORE コマンドが登録された後、デバイスは STORE 处理を完了するのに  $t_{STORE}$  時間を要します。リセット (FFh) とステータス読み出し (70h) を除き、nvSRAM へのすべてのアクセスは STORE 处理の進行中禁止されます。STORE サイクルを開始した後、nvSRAM は  $t_{STORE}$  の間 R/B ピンを LOW にプルします。ステータスレジスタ SR[6] の RDY ビットは「1」から「0」に遷移し、STORE サイクルが完了するまで「0」のままです。[図 18](#) はソフトウェア STORE の動作とタイミングを定義します。ソフトウェア STORE コマンドが開始された後、 $t_{STORE}$  の間 R/B 信号が LOW にプルダウンされ、FFh リセットを含む nvSRAM へのすべてのアクセスは無効になります。

16 ビットのデータ アクセスをサポートするデバイスでは、上位 8 ビット DQ[15:8] は「ドント ケア」ビットであり、使用されません。

**図 18. ソフトウェア STORE タイミング**

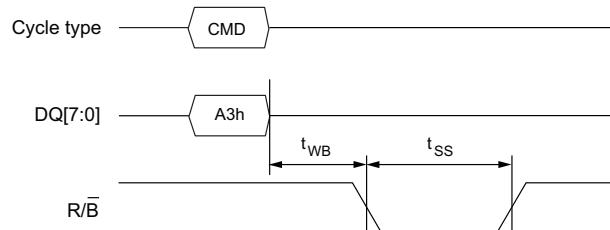

### nvSRAM AutoStore ディセーブル (A3h)

AutoStore ディセーブル コマンド (A3h) は nvSRAM AutoStore を無効にします。リセット (FFh) とステータス読み出し (70h) を除き、nvSRAM へのすべてのアクセスは  $t_{SS}$  時間禁止されます。AutoStore イネーブル コマンドが実行中の場合、デバイスは R/B

を  $t_{SS}$  の間 LOW にプルダウンします。この設定は揮発性であるため、後続のパワーサイクルにわたり維持されるようにするには、手動ソフトウェア STORE 处理を実行する必要があります。デバイスがレディー状態の場合、コマンドはどの時でも実行可能です。[図 19](#) は nvSRAM AutoStore ディセーブル タイミングを定義します。

16 ビットのデータ アクセスをサポートするデバイスでは、上位 8 ビット DQ[15:8] は「ドント ケア」ビットであり、使用されません。

**図 19. nvSRAM の AutoStore ディセーブル**

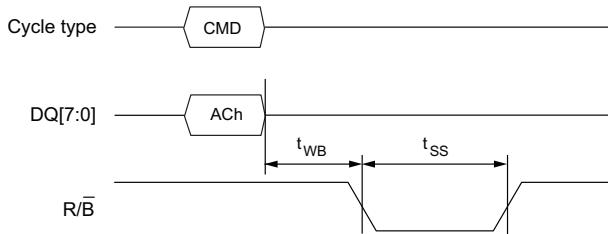

### nvSRAM AutoStore イネーブル (ACh)

AutoStore イネーブル コマンド (ACh) は nvSRAM AutoStore を有効にします。リセット (FFh) とリード ステータス (70h) を除き、nvSRAM へのアクセスは  $t_{SS}$  時間の間禁止されます。AutoStore イネーブル コマンドが実行している場合、デバイスは R/B を  $t_{SS}$  の間にローにプルダウンします。この設定は揮発性を有するため、後続のパワーサイクルの後も維持されるようにするには手動ソフトウェア STORE 处理を実行する必要があります。デバイスがレディー状態の場合、コマンドはどの時でも実行可能です。[図 20](#) は nvSRAM AutoStore イネーブル タイミングを定義します。

16 ビットのデータ アクセスをサポートするデバイスでは、上位 8 ビット DQ[15:8] は「ドント ケア」ビットであり、使用されません。

**図 20. nvSRAM の AutoStore イネーブル**

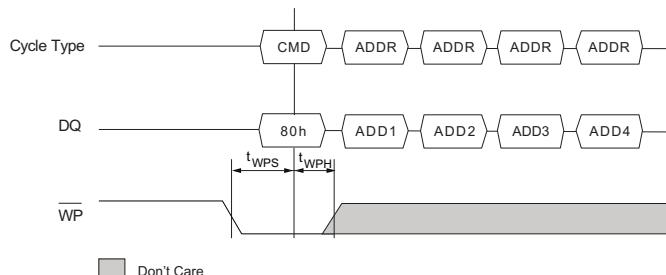

### 書き込み保護

書き込み保護機能は nvSRAM で書き込み処理を無効にします。書き込みコマンド (80h) を開始する前に、ホストが WP ピンを外部から LOW にプルすると、nvSRAM はステータスレジスタで WP の状態 (SR[7]) をクリアし、SRAM メモリへの書き込みを無効にします。しかし、ステータスレジスタへの書き込みは保護されません。書き込み保護ピンの状態は、WE 信号の立ち上がりエッジで書き込みコマンド (80h) が行われるとデバイスによってラッチされます。書き込み保護の状態がラッチされた後、現時点の書き込みサイクルの間ロックされます。WP の値を変更した後、ホストは少なくとも  $t_{WW}$  時間デバイスに新しいコマンドを発行しません。ホストはコマンドサイクル中に WP ピンをトグルしてはいけません。図 21 は、WP をトグルした後の nvSRAM 書き込みコマンドの開始を示す  $t_{WW}$  タイミング要件について説明します。WP 信号の遷移は非同期です。LOW から HIGH へ、または HIGH から LOW への WP 遷移の後、新しいコマンドがホストによって発行される前に、バスは  $t_{WW}$  時間アイドル状態です。

**図 21. 書き込み保護ディセーブルタイミング**

**図 22. 書き込み保護イネーブルタイミング**

### nvSRAM Store 処理

nvSRAM は、3 つの Store 処理のいずれかを使用してデータを不揮発性メモリセルに格納します。これらの 3 つの処理は、デバイス電源切断時に自動的にトリガされる AutoStore、HSB によって有効化されるハードウェア STORE、およびソフトウェアコマンドを発行することで有効化されるソフトウェア STORE です。

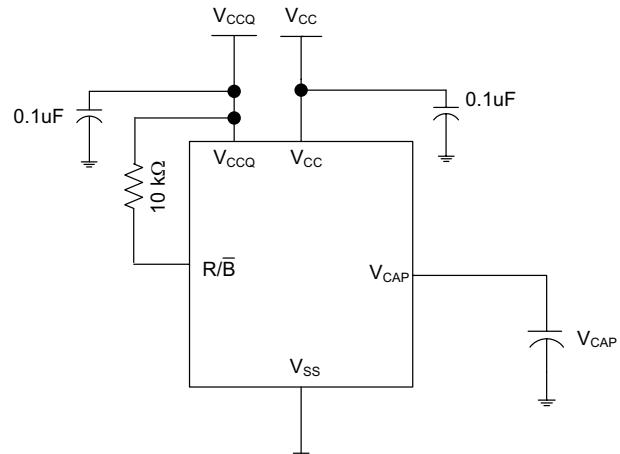

#### AutoStore 処理

AutoStore 処理は、SONOS テクノロジ独自の機能であり、デバイスではデフォルトで有効になっています。通常処理中、デバイスは  $V_{CAP}$  ピンに接続されたコンデンサを充電するのに  $V_{CC}$  から電流を引き込みます。この充電は、チップが電源切断時に STORE 処理を実行するためのものです。 $V_{CC}$  ピンの電圧が  $V_{SWITCH}$  を下回った場合、デバイスは自動的に  $V_{CAP}$  ピンを  $V_{CC}$  から切断し、STORE 処理は  $V_{CAP}$  コンデンサによって提供された電力で起動されます。

注: コンデンサが  $V_{CAP}$  ピンに接続されていない場合、AutoStore ディセーブルコマンド (A3h) を使用して AutoStore を無効にしてください。AutoStore が  $V_{CAP}$  ピンに接続されているコンデンサなしで有効にされた場合、デバイスは STORE 処理を完了するために十分な電荷がないまま AutoStore 処理を実行しようとします。このため、nvSRAM 内に格納されたデータが破壊されます。

**図 23. AutoStore モード**

図 23 に、自動的な STORE 処理用のストレージコンデンサ ( $V_{CAP}$ ) の適切な接続方法を示します。 $V_{CAP}$  の容量については、20 ページの DC 特性を参照してください。 $V_{CAP}$  ピンの電圧は、チップ上のレギュレータによって  $V_{VCAP}$  に駆動されます。電源投入時に R/B をアクティブでない状態に保つために、このピン上にプルアップ抵抗を配置する必要があります。このプルアップ抵抗は、電源投入時に R/B 信号がトライステート状態にある場合のみ有効です。nvSRAM がパワーアップ RECALL を終了する時、ホストマイクロコントローラは有効であるか、またはホストマイクロコントローラのリセットが終了するまで R/B を無効状態に保つ必要があります。不要な不揮発性 STORE 処理を低減するために、最後の STORE か RECALL サイクルの実行後、少なくとも 1 回の書き込み処理が行われない限り、AutoStore およびハードウェア STORE 処理は無視されます。

## ハードウェア STORE (HSB) 処理

デバイスには、ハードウェア STORE 処理を制御するための HSB ピンがあります。HSB ピンは、ハードウェア STORE サイクルの要求に使用されます。HSB ピンが LOW にされると、デバイスは  $t_{DELAY}$  の後、条件に従って STORE 処理を開始します。実際の STORE サイクルは、最後の STORE または RECALL サイクル以降、SRAM への書き込みが実行された場合にのみ開始します。HSB が（任意の手段で）LOW に駆動されている間に実行中の SRAM 書き込み処理は、STORE 処理が開始される前に完了するのに  $t_{DELAY}$  の時間を要します。しかし HSB が LOW になった後、すべての要求された SRAM 書き込みサイクルは、R/B が HIGH に戻るまで禁止されます。HSB が LOW である限り、R/B はデバイスによって LOW に維持されます。SRAM のすべての読み出しと書き込みサイクルは、ホストマイクロコントローラまたは他の外部ソースによって HSB が HIGH に戻るまで禁止されます。デバイスの通常処理中、HSB ピンを HIGH にセットする必要があります。HSB がアプリケーションで使用されない場合、このピンは 4.7kW ~ 10kW の外部プルアップ抵抗を用いて HIGH にプルアップする必要があります。

## ソフトウェア Store 処理

ソフトウェア Store 処理は、ソフトウェア STORE コマンド (84h, A5h) を送信することで開始されます。書き込みラッチがセットされたかどうかに関係なく、nvSRAM は STORE サイクルを開始します。詳細は [17 ページの nvSRAM ソフトウェア STORE \(84h, A5h\)](#) を参照してください。

## nvSRAM RECALL 処理

nvSRAM は、2 つの Recall 処理のいずれかを使用してデータを不揮発性メモリセルから復元します。これらの 2 つの Recall 処理は、パワーサイクルまたは電圧低下時にデバイスによって自動的に有効化されるハードウェア Recall、およびソフトウェアによって開始される RECALL サイクルです。

### ハードウェア RECALL (電源投入)

電源投入時または低電圧状態 ( $V_{CC} < V_{SWITCH}$ ) の後は、内部の RECALL 要求がラッチされます。 $V_{CC}$  が電源投入時に再度  $V_{SWITCH}$  を超えた場合、RECALL サイクルが自動的に開始し、完了するのに  $t_{HRECALL}$  を要します。この間、R/B ピンは nvSRAM によって LOW に駆動され、nvSRAM へのすべての読み書きは禁止されます。

### ソフトウェア Recall

ソフトウェア Recall 処理は、ソフトウェア RECALL コマンド (FCh) を送信することで開始されます。nvSRAM は RECALL サイクルを開始し、不揮発性セルから復元したデータで SRAM データを上書きします。詳細は [17 ページの nvSRAM ソフトウェア RECALL \(FCh\)](#) を参照してください。

## 最大定格

最大定格を超えると、デバイスの寿命が短くなる可能性があります。これらのユーザー ガイドラインはテストされていません。

保存温度 .....  $-65^{\circ}\text{C} \sim +150^{\circ}\text{C}$

最大累積保存時間

周囲温度  $150^{\circ}\text{C}$  で ..... 1000 時間

周囲温度  $85^{\circ}\text{C}$  で ..... 20 年

最大接合部温度 .....  $150^{\circ}\text{C}$

$V_{\text{SS}}$  を基準とした  $V_{\text{CC}}$  の電源電圧 .....  $-0.5\text{V} \sim +4.1\text{V}$

$V_{\text{SS}}$  を基準とした  $V_{\text{CCQ}}$  の電源電圧 .....  $-0.5\text{V} \sim +2.4\text{V}$

High Z 状態の出力に印加される

DC 電圧 .....  $-0.5\text{V} \sim V_{\text{CCQ}} + 0.5\text{V}$

入力電圧 .....  $-0.5\text{V} \sim V_{\text{CCQ}} + 0.5\text{V}$

グランド電位を基準とした任意のピンの過渡電圧 ( $<20\text{ns}$ ) .....  $-2.0\text{V} \sim V_{\text{CCQ}} + 2.0\text{V}$

パッケージ許容電力損失 ( $T_A = 25^{\circ}\text{C}$ ) ..... 1.0W

パッケージ ハンダ付け温度 (3 秒) .....  $+260^{\circ}\text{C}$

DC 出力電流 (一度に 1 出力、1 秒間) ..... 20mA

静電気放電電圧

(MIL-STD-883、Method 3015 による) .....  $> 2001\text{V}$

ラッチアップ電流 .....  $> 140\text{mA}$

## 動作範囲

| 範囲  | 周囲温度 ( $T_A$ )                                 | $V_{\text{CC}}$                | $V_{\text{CCQ}}$                 |

|-----|------------------------------------------------|--------------------------------|----------------------------------|

| 産業用 | $-40^{\circ}\text{C} \sim +85^{\circ}\text{C}$ | $2.7\text{V} \sim 3.6\text{V}$ | $1.70\text{V} \sim 1.95\text{V}$ |

## DC 特性

### 動作範囲において

| パラメータ                  | 説明                                                                                                                                     | テスト条件                                                                                                                    | Min                         | Typ <sup>[6]</sup> | Max                         | 単位 |

|------------------------|----------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|-----------------------------|--------------------|-----------------------------|----|

| $V_{\text{CC}}$        | コア電源                                                                                                                                   |                                                                                                                          | 2.7                         | 3.0                | 3.6                         | V  |

| $V_{\text{CCQ}}$       | I/O 電源                                                                                                                                 |                                                                                                                          | 1.70                        | 1.80               | 1.95                        | V  |

| $I_{\text{CC1}}$       | 平均 $V_{\text{CC}}$ 電流                                                                                                                  | $t_{\text{RC}} \geq 30\text{ns}$                                                                                         | —                           | —                  | 100                         | mA |

| $I_{\text{CCQ1}}$      | 平均 $V_{\text{CCQ}}$ 電流                                                                                                                 | $t_{\text{RC}} \geq 30\text{ ns}$<br>出力負荷なしで得られた<br>値 ( $I_{\text{OUT}} = 0\text{mA}$ )                                  | CY14V116F7                  | —                  | 30                          | mA |

| $I_{\text{CC2}}$       | STORE 中の平均 $V_{\text{CC}}$ 電流                                                                                                          | 全入力はドント ケア。 $V_{\text{CC}} = V_{\text{CC}} (\text{Max})$<br>$t_{\text{STORE}}$ 期間の平均電流                                   | —                           | —                  | 10                          | mA |

| $I_{\text{CC3}}$       | 平均 $V_{\text{CC}}$ 電流<br>$t_{\text{RC}} \geq 200\text{ns}$ ;<br>$V_{\text{CC}} = V_{\text{CC}} (\text{Typ})$ 、 $25^{\circ}\text{C}$    | 全入力は CMOS レベルで切り替わる                                                                                                      | —                           | —                  | 50                          | mA |

| $I_{\text{CCQ3}}$      | 平均 $V_{\text{CCQ}}$ 電流<br>$t_{\text{RC}} \geq 200\text{ns}$ ;<br>$V_{\text{CCQ}} = V_{\text{CCQ}} (\text{Typ})$ 、 $25^{\circ}\text{C}$ | 全入力は CMOS レベルで<br>切り替わる。出力負荷な<br>しで得られた値<br>( $I_{\text{OUT}} = 0\text{mA}$ )                                            | CY14V116F7                  | —                  | 15                          | mA |

| $I_{\text{CC4}}^{[7]}$ | AutoStore サイクル中の平均<br>$V_{\text{CAP}}$ 電流                                                                                              | 全入力はドント ケア。 $t_{\text{STORE}}$ 期間の平均<br>電流                                                                               | —                           | —                  | 6                           | mA |

| $I_{\text{SB}}$        | $V_{\text{CC}}$ スタンバイ電流                                                                                                                | $CE \geq (V_{\text{CCQ}} - 0.2\text{V})$ 。<br>$V_{\text{IN}} \leq 0.2\text{V}$ または $\geq (V_{\text{CCQ}} - 0.2\text{V})$ | —                           | —                  | 5                           | mA |

| $I_{\text{SB1}}$       | $V_{\text{CCQ}}$ スタンバイ電流                                                                                                               |                                                                                                                          | —                           | —                  | 2                           | mA |

| $I_{\text{IX}}$        | 入力リード電流                                                                                                                                | $V_{\text{CCQ}} = V_{\text{CCQ}} (\text{Max})$ 、 $V_{\text{SS}} \leq V_{\text{IN}} \leq V_{\text{CCQ}}$                  | -1                          | —                  | +1                          | mA |

| $I_{\text{OZ}}$        | 出力リード電流                                                                                                                                | $V_{\text{CCQ}} = V_{\text{CCQ}} (\text{Max})$ 、 $V_{\text{SS}} \leq V_{\text{IN}} \leq V_{\text{CCQ}}$ ;<br>出力は無効       | -1                          | —                  | +1                          | mA |

| $V_{\text{IH}}$        | 入力 HIGH 電圧                                                                                                                             |                                                                                                                          | $0.8 \times V_{\text{CCQ}}$ | —                  | $V_{\text{CCQ}} + 0.3$      | V  |

| $V_{\text{IL}}$        | 入力 LOW 電圧                                                                                                                              |                                                                                                                          | $V_{\text{SS}} - 0.3$       | —                  | $0.2 \times V_{\text{CCQ}}$ | V  |

注:

6. Typ 値は  $25^{\circ}\text{C}$ 、 $V_{\text{CC}} = V_{\text{CC}} (\text{Typ})$  および  $V_{\text{CCQ}} = V_{\text{CCQ}} (\text{Typ})$  でのものです。100% のテストは行われていません。

7. このパラメータは設計保証であり、テストされていません。

## DC 特性 ( 続き )

### 動作範囲において

| パラメータ                | 説明                               | テスト条件                       | Min             | Typ <sup>[6]</sup> | Max       | 単位 |

|----------------------|----------------------------------|-----------------------------|-----------------|--------------------|-----------|----|

| $V_{OH}$             | 出力 HIGH 電圧                       | $I_{OH} = -100\text{mA}$    | $V_{CCQ} - 0.1$ | -                  | $V_{CCQ}$ | V  |

| $V_{OL}$             | 出力 LOW 電圧 (R/B を除き )             | $I_{OL} = 100\text{mA}$     | -               | -                  | 0.1       | V  |

|                      | 出力 LOW 電圧 (R/B に対して )            | $I_{OL} = 3\text{mA}$       | -               | -                  | 0.2       | V  |

| $V_{CAP}^{[8]}$      | ストレージ コンデンサ                      | $V_{CAP}$ ピンと $V_{SS}$ ピンの間 | 19.8            | 22.0               | 82.0      | mF |

| $V_{VCAP}^{[9, 10]}$ | デバイスによって $V_{CAP}$ ピン上で駆動された最大電圧 | $V_{CC} = V_{CC}$ (Max)     | -               | -                  | 5.0       | V  |

## データ保持期間および書き換え可能回数

### 動作範囲において

| パラメータ    | 説明              | Min       | 単位   |

|----------|-----------------|-----------|------|

| $DATA_R$ | データ保持期間         | 20        | 年    |

| $NV_C$   | 不揮発性 STORE 処理回数 | 1,000,000 | サイクル |

## 静電容量

| パラメータ <sup>[10]</sup> | 説明                    | テスト条件                                                                                             | Max | 単位 |

|-----------------------|-----------------------|---------------------------------------------------------------------------------------------------|-----|----|

| $C_{IN}$              | クロックおよび入力ピンでの入力静電容量   | $T_A = 25^\circ\text{C}$ 、 $f = 1\text{MHz}$ 、 $V_{CC} = V_{CC}$ (Typ)、 $V_{CCQ} = V_{CCQ}$ (Typ) | 10  | pF |

| $C_{IO}$              | データおよび I/O ピンでの入力静電容量 |                                                                                                   | 10  | pF |

| $C_{OTHER}$           | 他のすべての制御ピンでの静電容量      |                                                                                                   | 10  | pF |

## 熱抵抗

| パラメータ <sup>[10]</sup> | 説明                | テスト条件                                                 | 165 ボール FBGA | 単位   |

|-----------------------|-------------------|-------------------------------------------------------|--------------|------|

| $\Theta_{JA}$         | 熱抵抗<br>(接合部から周囲)  | テスト条件は、EIA/JESD51 による、熱インピーダンスを測定するための標準的なテスト方法と手順に従う | 15.6         | °C/W |

| $\Theta_{JC}$         | 熱抵抗<br>(接合部からケース) |                                                       | 2.9          | °C/W |

### 注 :

- $V_{CAP}$  の Min 値は、AutoStore 処理を完了するのに十分な電荷があることを保証するものです。 $V_{CAP}$  の Max 値は、即時の電源切断サイクルが発生しても AutoStore 処理が正常に完了するようにパワーアップ RECALL サイクルの間に  $V_{CAP}$  のコンデンサが必要な最小電圧まで充電されることを保証するものです。したがって、指定した Min と Max の範囲内でコンデンサを使用することを常に推奨します。

- $V_{CAP}$  ピンの最大電圧 ( $V_{VCAP}$ ) は、 $V_{CAP}$  コンデンサを選択する際に指針として提供されています。動作温度範囲における  $V_{CAP}$  コンデンサの定格電圧は、 $V_{VCAP}$  電圧より高くなればなりません。

- これらのパラメータは設計保証であり、テストされていません。

## AC テスト条件

入力パルス レベル ..... 0V ~  $V_{CCQ}$

入力立ち上がり／立ち下がり時間 (10% ~ 90%) ..... 5ns

入力と出力のタイミング参照レベル .....  $V_{CCQ}/2$

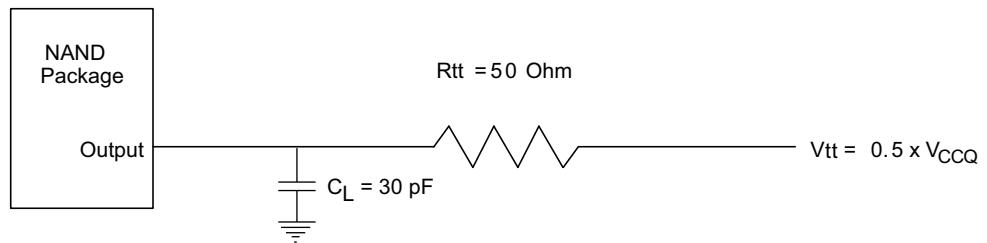

図 24. ドライバ出カリファレンス

## AC スイッチング特性

### タイミング モード

動作範囲 において

| パラメータ <sup>[1]</sup> | 説明                                                     | モード 2 |                  | モード 3 |                  | 単位 |  |

|----------------------|--------------------------------------------------------|-------|------------------|-------|------------------|----|--|

|                      |                                                        | 35ns  |                  | 30ns  |                  |    |  |

|                      |                                                        | Min   | Max              | Min   | Max              |    |  |

| $t_{ADL}$            | アドレス サイクルからデータ ロードまでの時間                                | 100   | —                | 100   | —                | ns |  |

| $t_{ALH}$            | ALE ホールド時間                                             | 10    | —                | 5     | —                | ns |  |

| $t_{ALS}$            | ALE セットアップ時間                                           | 15    | —                | 10    | —                | ns |  |

| $t_{AR}$             | ALE から RE までの遅延時間                                      | 10    | —                | 10    | —                | ns |  |

| $t_{CEA}$            | $\overline{CE}$ アクセス時間                                 | —     | 30               | —     | 25               | ns |  |

| $t_{CH}$             | $\overline{CE}$ ホールド時間                                 | 10    | —                | 5     | —                | ns |  |

| $t_{CHZ}^{[12]}$     | $\overline{CEHIGH}$ から出力 HIGH Z までの時間                  | —     | 50               | —     | 50               | ns |  |

| $t_{CLH}$            | CLE ホールド時間                                             | 10    | —                | 5     | —                | ns |  |

| $t_{CLR}$            | CLE から RE までの遅延時間                                      | 10    | —                | 10    | —                | ns |  |

| $t_{CLS}$            | CLE セットアップ時間                                           | 15    | —                | 10    | —                | ns |  |

| $t_{COH}$            | CE HIGH から出力ホールドまでの時間                                  | 15    | —                | 15    | —                | ns |  |

| $t_{IR}$             | 出力 HIGH Z から $\overline{RE LOW}$ までの時間                 | 0     | —                | 0     | —                | ns |  |

| $t_{CS}$             | $\overline{CE}$ セットアップ時間                               | 25    | —                | 25    | —                | ns |  |

| $t_{DH}$             | データ ホールド時間                                             | 5     | —                | 5     | —                | ns |  |

| $t_{DS}$             | データ セットアップ時間                                           | 15    | —                | 10    | —                | ns |  |

| $t_{RC}$             | $\overline{RE}$ サイクル時間                                 | 35    | —                | 30    | —                | ns |  |

| $t_{REA}$            | $\overline{RE}$ アクセス時間                                 | —     | 25               | —     | 20               | ns |  |

| $t_{REH}$            | $\overline{RE HIGH}$ ホールド時間                            | 15    | —                | 10    | —                | ns |  |

| $t_{RHOH}$           | $\overline{RE HIGH}$ から出力ホールドまでの時間                     | 15    | —                | 15    | —                | ns |  |

| $t_{RHW}$            | $\overline{RE HIGH}$ から $\overline{WE LOW}$ までの時間      | 100   | —                | 100   | —                | ns |  |

| $t_{RHZ}^{[12]}$     | $\overline{RE HIGH}$ から出力 HIGH Z までの時間                 | —     | 100              | —     | 100              | ns |  |

| $t_{RP}$             | $\overline{RE}$ パルス幅                                   | 17    | —                | 15    | —                | ns |  |

| $t_{RST}^{[13]}$     | デバイスのリセット時間                                            | —     | 500 / 600 / 8000 | —     | 500 / 600 / 8000 | μs |  |

| $t_{WC}$             | $\overline{WE}$ サイクル時間                                 | 35    | —                | 30    | —                | ns |  |

| $t_{WB}$             | $\overline{WE HIGH}$ またはクロック立ち上がりエッジから SR[6] LOW までの時間 | —     | 100              | —     | 100              | ns |  |

| $t_{WH}$             | $\overline{WE HIGH}$ ホールド時間                            | 15    | —                | 10    | —                | ns |  |

| $t_{WHR}$            | $\overline{WE}$ コマンド、アドレスまたはデータ入力サイクルからデータ出力サイクルまでの時間  | 80    | —                | 80    | —                | ns |  |

| $t_{WP}$             | $\overline{WE}$ パルス幅                                   | 17    | —                | 15    | —                | ns |  |

| $t_{WW}$             | $\overline{WP}$ 遷移からコマンド サイクルまでの時間                     | 100   | —                | 100   | —                | ns |  |

| $t_{WPS}$            | $\overline{WP}$ セットアップ時間                               | 25    | —                | 25    | —                | ns |  |

| $t_{WPH}$            | $\overline{WP}$ ホールド時間                                 | 10    | —                | 10    | —                | ns |  |

注:

1. テスト条件は、以下を想定しています: 5ns 以下の信号遷移時間、 $V_{CCQ}/2$  のタイミング参照レベル、0V から  $V_{CCQ}$  (Typ) までの入力パルス レベル、および図 24 に示した指定の  $I_{OL} / I_{OH}$  の出力負荷と 30pF の負荷容量。

2. これらのパラメータは設計保証であり、テストされていません。

3.  $t_{RST}$  には 3 つの最大値が示されます。それぞれは、デバイスが STORE または RECALL 処理を実行していない場合／デバイスが RECALL 処理を実行している場合／およびデバイスが STORE 処理を実行している場合に対応しています。

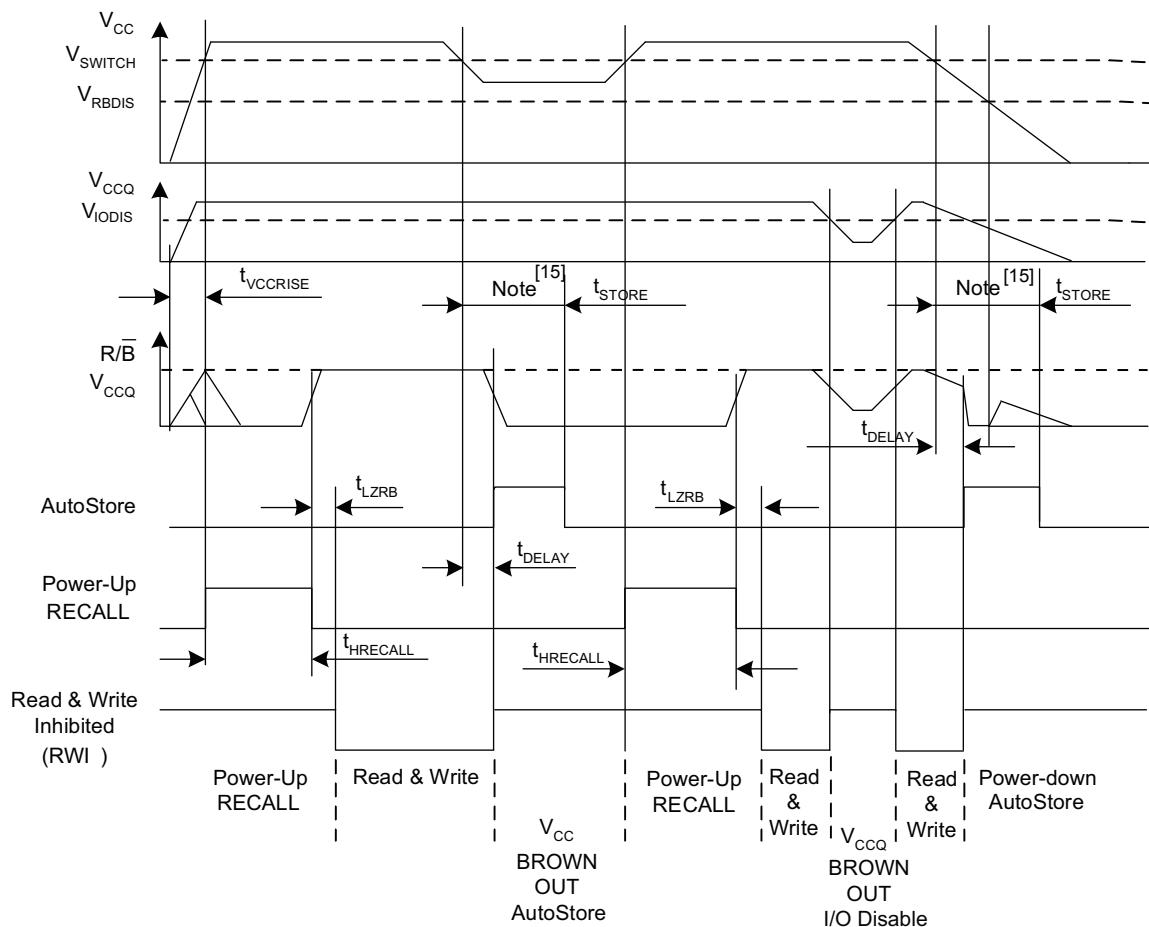

## nvSRAM AutoStore／パワーアップ RECALL 特性

| パラメータ                         | 説明                        | Min | Max  | 単位      |

|-------------------------------|---------------------------|-----|------|---------|

| $t_{HRECALL}$ <sup>[14]</sup> | パワーアップ RECALL 期間          | —   | 30   | ms      |

| $t_{STORE}$ <sup>[15]</sup>   | STORE サイクル期間              | —   | 8    | ms      |

| $t_{DELAY}$ <sup>[16]</sup>   | SRAM 書き込みサイクルを完了する時間      | —   | 45   | ns      |

| $t_{VCCRISE}$ <sup>[17]</sup> | $V_{CC}$ 立ち上がり時間          | 150 | —    | $\mu$ s |

| $V_{SWITCH}$                  | $V_{CC}$ の低電圧トリガ レベル      | —   | 2.65 | V       |

| $V_{IODIS}$                   | $V_{CCQ}$ での I/O ディセーブル電圧 | —   | 1.6  | V       |

| $t_{LZRB}$ <sup>[17]</sup>    | R/B から出力アクティブまでの時間        | —   | 5    | $\mu$ s |

| $V_{RBDIS}$ <sup>[17]</sup>   | R/B $V_{CC}$ での出カディセーブル電圧 | —   | 1.9  | V       |

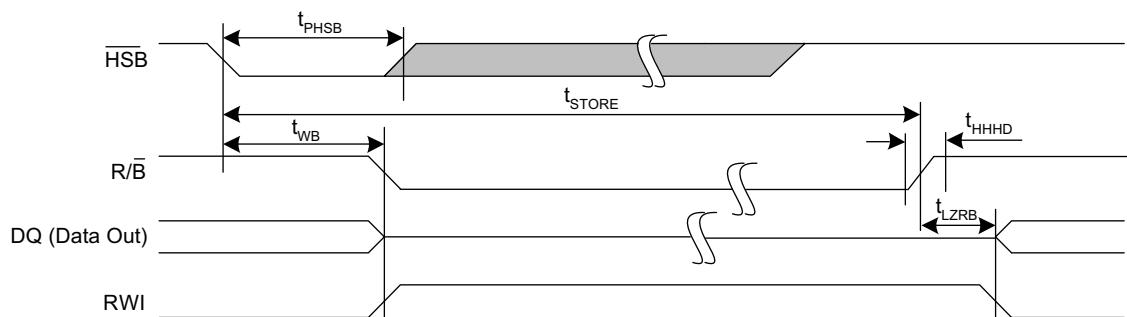

図 25. AutoStore またはパワーアップ RECALL<sup>[18, 19]</sup>

注:

14.  $t_{HRECALL}$  は、 $V_{CC}$  が  $V_{SWITCH}$  を超える時から始まります。

15. SRAM の書き込みが最後の不揮発性サイクル以降に実施されていない場合、AutoStore またはハードウェア STORE は実行されません。

16. ハードウェア STORE と AutoStore の開始時に、SRAM の書き込み処理は  $t_{DELAY}$  の間有効のままです。

17. これらのパラメータは設計保証であり、テストされていません。

18. 読み出しおよび書き込みサイクルは、STORE、RECALL の実行中、および  $V_{CC}$  が  $V_{SWITCH}$  未満の時は無視されます。

19. 外部ブループラットが R/B ピンに接続されている時にのみ、ピンは  $V_{CCQ}$  に HIGH に駆動されます。R/B ドライバは無効にされます。

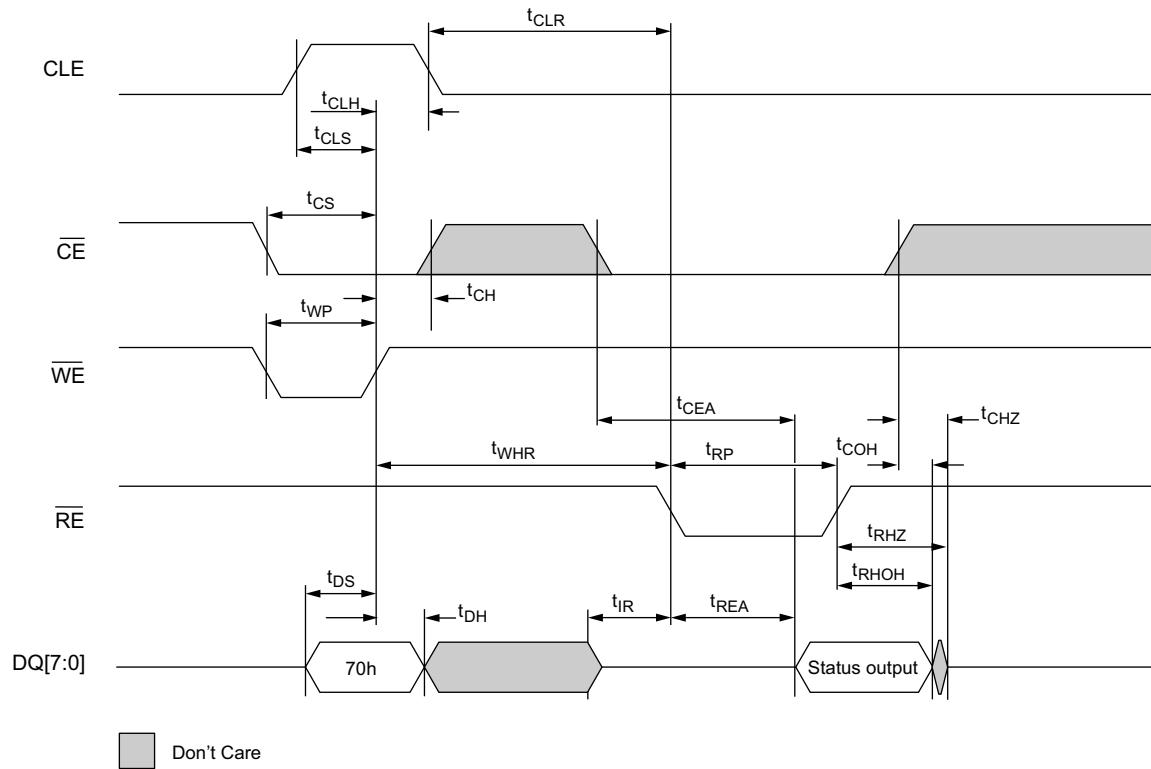

## ハードウェア STORE 特性

動作範囲において

| パラメータ           | 説明                                             | Min | Max | 単位 |

|-----------------|------------------------------------------------|-----|-----|----|

| $t_{PHSB}$      | ハードウェア STORE パルス幅                              | 15  | –   | ns |

| $t_{DRB}$       | 書き込みラッチがセットされていない時の $R/\bar{B}$ から出力アクティブまでの時間 | –   | 100 | ns |

| $t_{RECALL}$    | RECALL 期間                                      | –   | 600 | μs |

| $t_{SS}^{[20]}$ | ソフト シーケンス処理時間                                  | –   | 500 | μs |

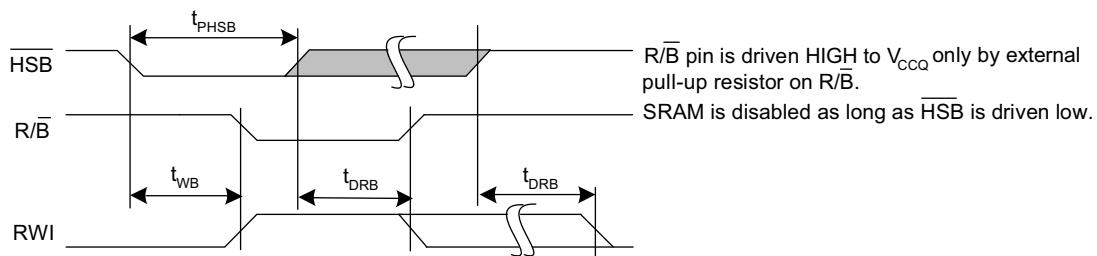

図 26. ハードウェア STORE サイクル<sup>[21]</sup>

### Write latch set

### Write latch not set

#### 注:

20. これは、ソフト シーケンス コマンドの処理に要する時間です。効果的にコマンドを登録するには、Vcc 電圧は HIGH のままでなければなりません。

21. SRAM の書き込みが最後の不揮発性サイクル以降に行われていない場合、AutoStore またはハードウェア STORE は実行されません。

## 注文情報

| 注文コード              | パッケージ図   | パッケージ タイプ    | 動作範囲 |

|--------------------|----------|--------------|------|

| CY14V116G7-BZ30XI  | 51-85195 | 165 ポール FBGA |      |

| CY14V116G7-BZ30XIT |          |              | 産業用  |

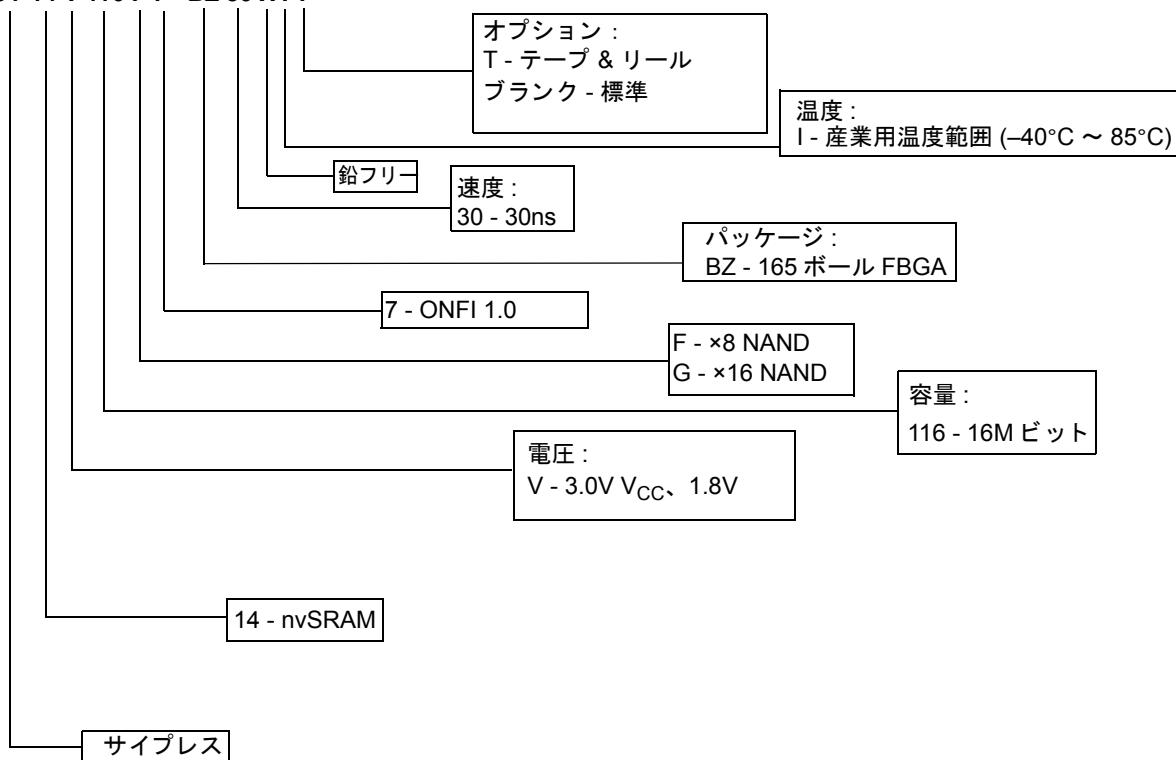

## 注文コードの定義

**CY 14 V 116 F 7 - BZ 30 X I T**

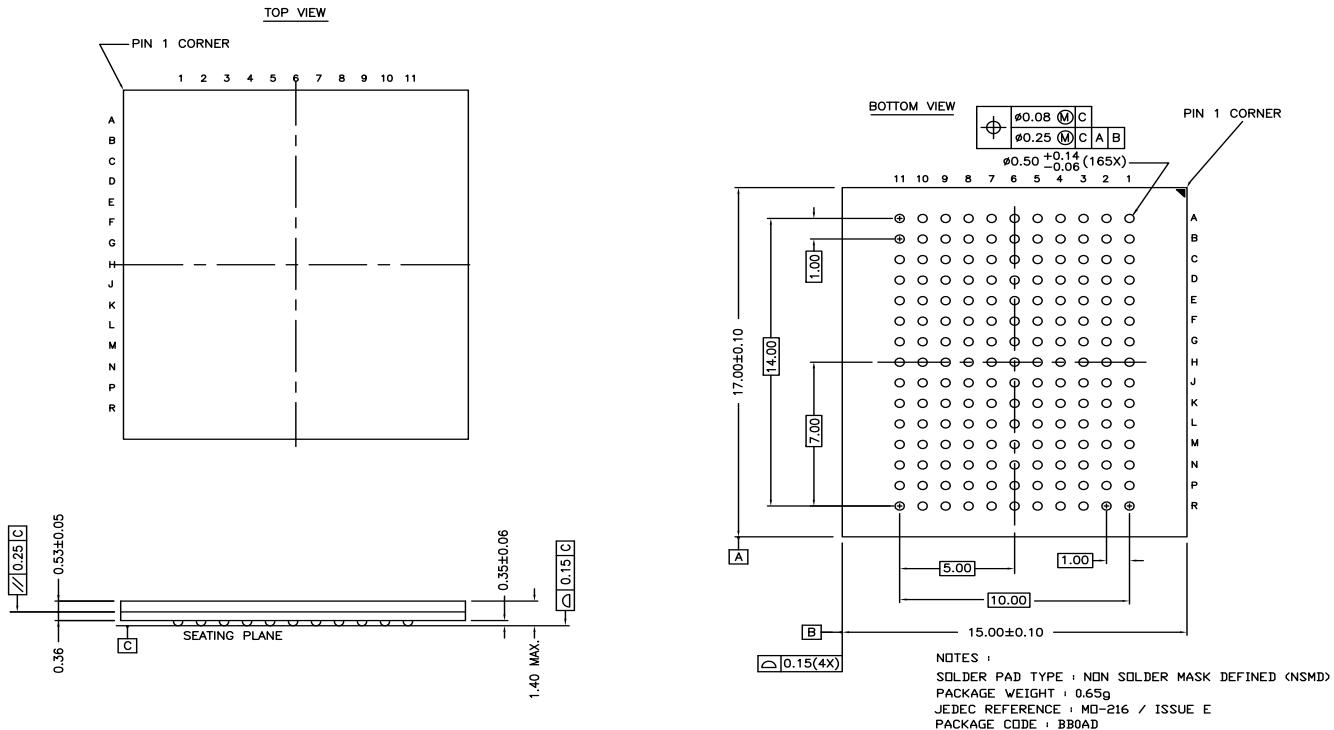

## パッケージ図

図 27. 165 ポール FBGA (15mm × 17mm × 1.40mm) パッケージ外形図 (51-85195)

51-85195 \*D

**略語**

| 略語     | 説明                                                                       |

|--------|--------------------------------------------------------------------------|

| ALE    | アドレス ラッチ イネーブル                                                           |

| CE     | チップ イネーブル                                                                |

| CLE    | コマンド ラッチ イネーブル                                                           |

| CMOS   | CMOS ( 相補型金属酸化膜半導体 )                                                     |

| CRC    | Cyclic Redundancy Check ( 巡回冗長検査 )                                       |

| EIA    | Electronic Industries Alliance ( 米国電子工業会 )                               |

| I/O    | input/output ( 入力／出力 )                                                   |

| JEDEC  | Joint Electron Devices Engineering Council<br>( 半導体技術協会 ( 旧電子機器技術評議会 ) ) |

| JESD   | JEDEC Standards ( JEDEC 規格 )                                             |

| nvSRAM | 不揮発性スタティック ランダム アクセス メモリ                                                 |

| ONFI   | オープン NAND フラッシュ インターフェース                                                 |

| NV     | 不揮発性                                                                     |

| RE     | 読み出し イネーブル                                                               |

| RoHS   | 特定有害物質使用制限                                                               |

| R/W    | 読み出し／書き込み                                                                |

| RWI    | 読み出しおよび書き込み禁止                                                            |

| SR     | ステータス レジスタ                                                               |

| WE     | 書き込み イネーブル                                                               |

**本書の表記法**

**測定単位**

| 記号   | 測定単位       |

|------|------------|

| °C   | 摂氏温度       |

| Hz   | ヘルツ        |

| kHz  | キロヘルツ      |

| kΩ   | キロオーム      |

| MHz  | メガヘルツ      |

| MT/s | 100 万回転送／秒 |

| μA   | マイクロアンペア   |

| μF   | マイクロファラッド  |

| μs   | マイクロ秒      |

| mA   | ミリアンペア     |

| ms   | ミリ秒        |

| ns   | ナノ秒        |

| Ω    | オーム        |

| pF   | ピコファラッド    |

| V    | ボルト        |

| W    | ワット        |

## 改訂履歴

文書名 : CY14V116F7 / CY14V116G7、非同期 NAND インターフェース付 16M ピット nvSRAM

文書番号 : 001-92097

| 版  | ECN 番号  | 発行日        | 変更者  | 変更内容                                                    |

|----|---------|------------|------|---------------------------------------------------------|

| ** | 4341315 | 4/11/2014  | HZEN | これは英語版 001-75528 Rev *C を翻訳した日本語版 Rev. ** です。           |

| *A | 4661082 | 2/13/2015  | HZEN | Template Updates                                        |

| *B | 5702665 | 04/25/2017 | HZEN | これは英語版 001-75528 Rev *J を翻訳した日本語版 001-92097 Rev. *B です。 |

## セールス、ソリューションおよび法律情報

### ワールドワイドな販売と設計サポート

サイプレスは、事業所、ソリューションセンター、メーカー代理店および販売代理店の世界的なネットワークを保持しています。お客様の最寄りのオフィスについては、[サイプレスのロケーションページ](#)をご覧ください。

#### 製品

|                  |                                                                          |

|------------------|--------------------------------------------------------------------------|

| 車載用              | <a href="http://cypress.com/go/automotive">cypress.com/go/automotive</a> |

| クロック & バッファ      | <a href="http://cypress.com/go/clocks">cypress.com/go/clocks</a>         |

| インターフェース         | <a href="http://cypress.com/go/interface">cypress.com/go/interface</a>   |

| IoT (モノのインターネット) | <a href="http://cypress.com/interface">cypress.com/interface</a>         |

| メモリ              | <a href="http://cypress.com/memory">cypress.com/memory</a>               |

| マイクロコントローラ       | <a href="http://cypress.com/mcu">cypress.com/mcu</a>                     |

| PSoC             | <a href="http://cypress.com/go/psoc">cypress.com/go/psoc</a>             |

| 電源用 IC           | <a href="http://cypress.com/pmic">cypress.com/pmic</a>                   |

| タッチ センシング        | <a href="http://cypress.com/go/touch">cypress.com/go/touch</a>           |

| USB コントローラ       | <a href="http://cypress.com/go/USB">cypress.com/go/USB</a>               |

| ワイヤレス／RF         | <a href="http://cypress.com/go/wireless">cypress.com/go/wireless</a>     |

#### PSoC® ソリューション

[psoc.cypress.com/solutions](http://psoc.cypress.com/solutions)

[PSoC 1 | PSoC 3 | PSoC 4 | PSOc 5LP](http://PSoC 1 | PSoC 3 | PSoC 4 | PSOc 5LP)

#### サイプレス開発者コミュニティ

[コミュニティ](#) | [WICED IOT Forums](#) | [Projects](#) | [ビデオ](#) | [ブログ](#) | [トレーニング](#) | [Components](#)

#### テクニカル サポート

[cypress.com/support](http://cypress.com/support)

© Cypress Semiconductor Corporation, 2012-2017. 本書面は、Cypress Semiconductor Corporation 及び Spansion LLC を含むその子会社（以下「Cypress」という。）に帰属する財産である。本書面（本書面に含まれ又は言及されているあらゆるソフトウェア若しくはファームウェア（以下「本ソフトウェア」という。）を含む）は、アメリカ合衆国及び世界のその他の国における知的財産法令及び条約に基づき Cypress が所有する。Cypress はこれらの法令及び条約に基づく全ての権利を留保し、本段落で特に記載されているものを除き、その特許権、著作権、商標権又はその他の知的財産権のライセンスを一切許諾しない。本ソフトウェアにライセンス契約書が付属しておらず、かつ Cypress との間で別途本ソフトウェアの使用方法を定める書面による合意がない場合、Cypress は、(1) 本ソフトウェアの著作権に基づき、(a) ソースコード形式で提供されている本ソフトウェアについて、Cypress ハードウェア製品と共に用いるためにのみ、かつ組織内部でのみ、本ソフトウェアの修正及び複製を行うこと、並びに (b) Cypress のハードウェア製品ユニットに用いるためにのみ、（直接又は再販売者及び販売代理店を介して間接のいずれかで）本ソフトウェアをバイナリコード形式で外部エンデューザーに配布すること、並びに (2) 本ソフトウェア（Cypressにより提供され、修正がなされていないもの）が抵触するCypressの特許権のクレームに基づき、Cypress ハードウェア製品と共に用いるためにのみ、本ソフトウェアの作成、利用、配布及び輸入を行うことについての非独占的で譲渡不能な一身専属的ライセンス（サプライセンスの権利を除く）を付与する。本ソフトウェアのその他の使用、複製、修正、変換又はコンパイルを禁止する。

**適用される法律により許される範囲内で、Cypress は、本書面又はいかなる本ソフトウェア若しくはこれに伴うハードウェアに関するても、明示又は默示をとわず、いかなる保証（商品性及び特定の目的への適合性の默示を含むがこれらに限られない）も行わない。**適用される法律により許される範囲内で、Cypress は、別途通知することなく、本書面を変更する権利を留保する。Cypress は、本書面に記載のある、いかなる製品若しくは回路の適用又は使用から生じる一切の責任を負わない。本書面で提供されたあらゆる情報（あらゆるサンプルデザイン情報又はプログラムコードを含む）は、参照目的のためのみに提供されたものである。この情報で構成するあらゆるアプリケーション及びその結果としてのあらゆる製品の機能性及び安全性を適切に設計、プログラム、かつテストすることは、本書面のユーザーの責任において行われるものとする。Cypress 製品は、兵器、兵器システム、原子力施設、生命維持装置若しくは生命維持システム、蘇生用の設備及び外科的移植を含むその他の医療機器若しくは医療システム、汚染管理若しくは有害物質管理の運用のために設計され若しくは意図されたシステムの重要な構成部分としての使用、又は装置若しくはシステムの不具合が人身傷害、死亡若しくは物的損害を生じさせるようなその他の使用（以下「本目的外使用」という。）のためには設計、意図又は承認されていない。重要な構成部分とは、それの不具合が装置若しくはシステムの不具合を生じさせるか又はその安全性若しくは実効性に影響すると合理的に予想できるような装置若しくはシステムのあらゆる構成部分をいう。Cypress 製品のあらゆる本目的外使用から生じ、若しくは本目的外使用に関連するいかなる請求、損害又はその他の責任についても、Cypress はその全部又は一部をとわざ一切の責任を負わず、かつ Cypress はそれら一切から本書面により免除される。Cypress は Cypress 製品の本目的外使用から生じ又は本目的外使用に関連するあらゆる請求、費用、損害及びその他の責任（人身傷害又は死亡に基づく請求を含む）から免責補償される。

Cypress, Cypress のロゴ、Spansion, Spansion のロゴ及びこれらの組み合わせ、WICED, PSoC, CapsSense, EZ-USB, F-RAM, 及び Traveo は、米国及びその他の国における Cypress の商標又は登録商標である。Cypress のより完全な商標のリストは、[cypress.com](http://cypress.com) を参照すること。その他の名称及びブランドは、それぞれの権利者の財産として権利主張がなされている可能性がある。