## 1M ビット (128K × 8) クアッド SPI nvSRAM

### 特長

- メモリ容量

- 1M ビット (128K × 8)

- 帯域幅

- 108MHz 高速インターフェース

- 54Mbps での読み書き

- シリアルペリフェラル インターフェース

- クロック極性と位相モード 0 と 3

- 複数 I/O オプション – シングル SPI (SPI)、デュアル SPI (DPI)、クアッド SPI (QPI)

- 高い信頼性

- 回数に制限のない読み出し、書き込み、RECALL サイクル

- 不揮発性要素 (SONOS FLASH 量子トラップ) への 100 万 STORE サイクル

- データ保持期間 : 85°C で 20 年

- 読み出し

- コマンド : 標準、ファースト、デュアル I/O、クアッド I/O

- モード : バースト ラップ、連続 (XIP)

- 書き込み

- コマンド : 標準、ファースト、デュアル I/O、クアッド I/O

- モード : バースト ラップ

- データ保護

- ハードウェア : 書き込み保護ピン (WP) を使用

- ソフトウェア : 書き込みディスエーブル命令を使用

- ブロック保護 : 保護を制御するためにステータス レジスタ ビットを使用

- 特殊命令

- STORE/RECALL: SRAM と量子トラップ間のデータアクセス

- シリアル番号 : 8 バイト ユーザー選択可能 (OTP)

- ID 番号 : 4 バイトのメーカー ID および製品 ID

- SRAM から不揮発性 SONOS FLASH 量子トラップに格納

- AutoStore: 小容量コンデンサ ( $V_{CAP}$ ) で電源切断時に自動的に開始

- ソフトウェア : SPI 命令 (STORE) を使用

- ハードウェア : HSB ピンを使用

- 非揮発性 SONOS FLASH 量子トラップから SRAM にリコール

- AutoRECALL: 電源投入時に自動的に開始

- ソフトウェア : SPI 命令 (RECALL) を使用

- 低消費電力モード

- スリープ : 平均電流 = 280μA (85°C の時)

- ハイバネート : 平均電流 = 8μA (85°C の時)

- 動作電源電圧

- コア  $V_{CC}$ : 2.7V ~ 3.6V

- I/O  $V_{CCQ}$ : 1.71V ~ 2.0V

### ■ 温度範囲

- 拡張された産業用温度範囲 : -40°C ~ 105°C

- 産業用温度範囲 : -40°C ~ 85°C

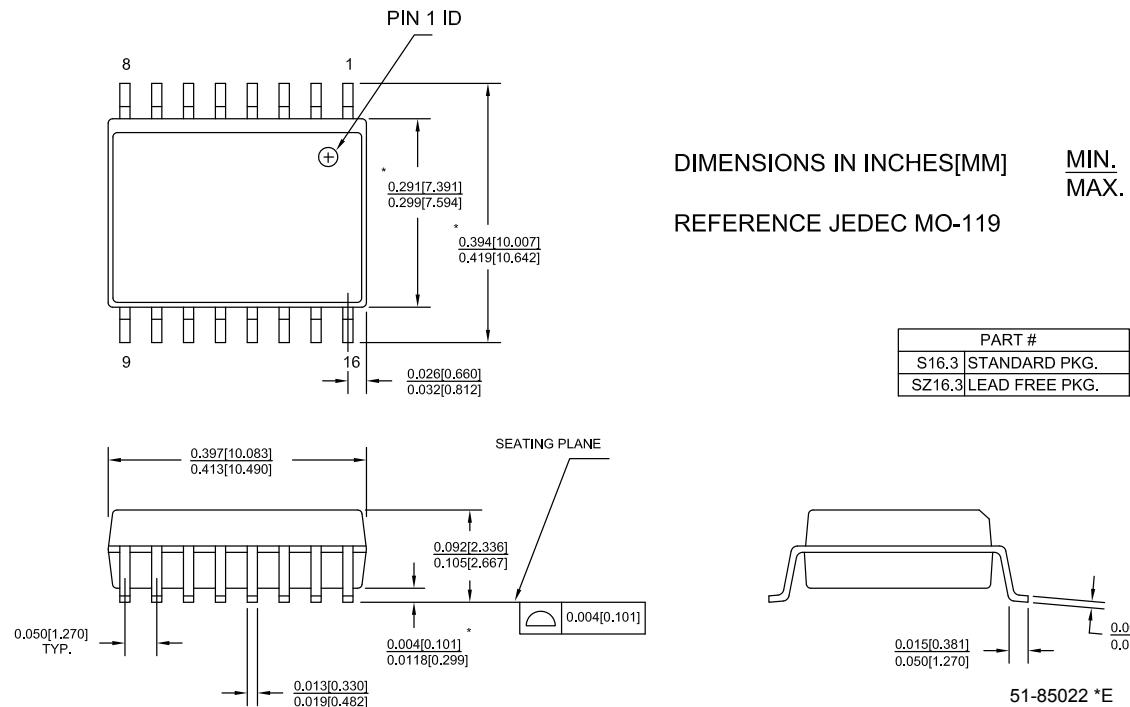

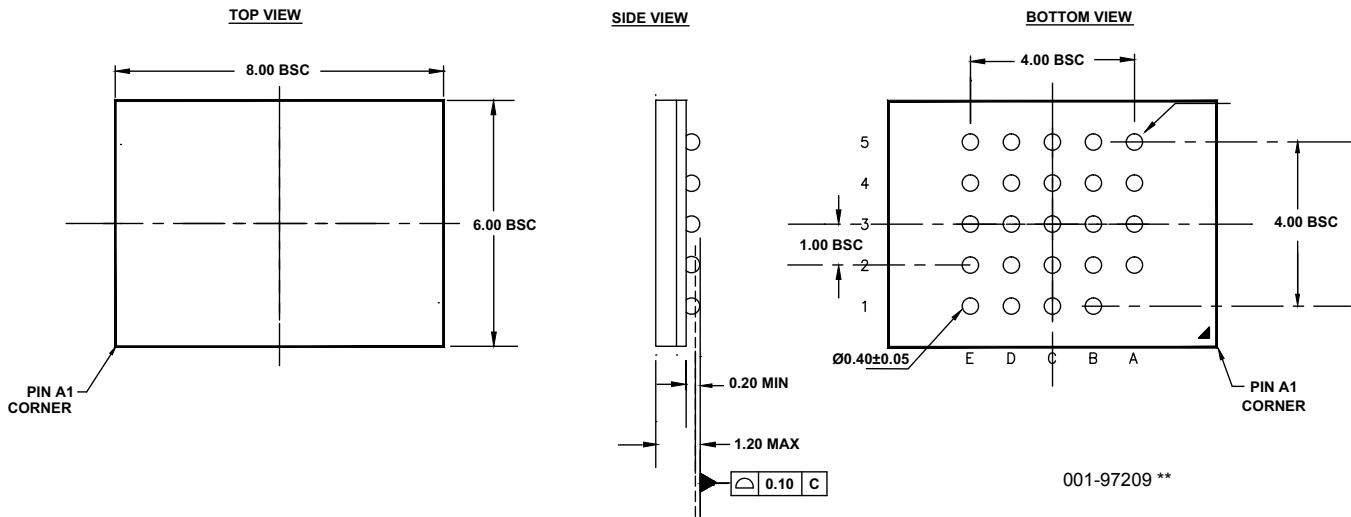

### ■ パッケージ

- 16 ピン SOIC

- 24 ボール FBGA

### 機能の概要

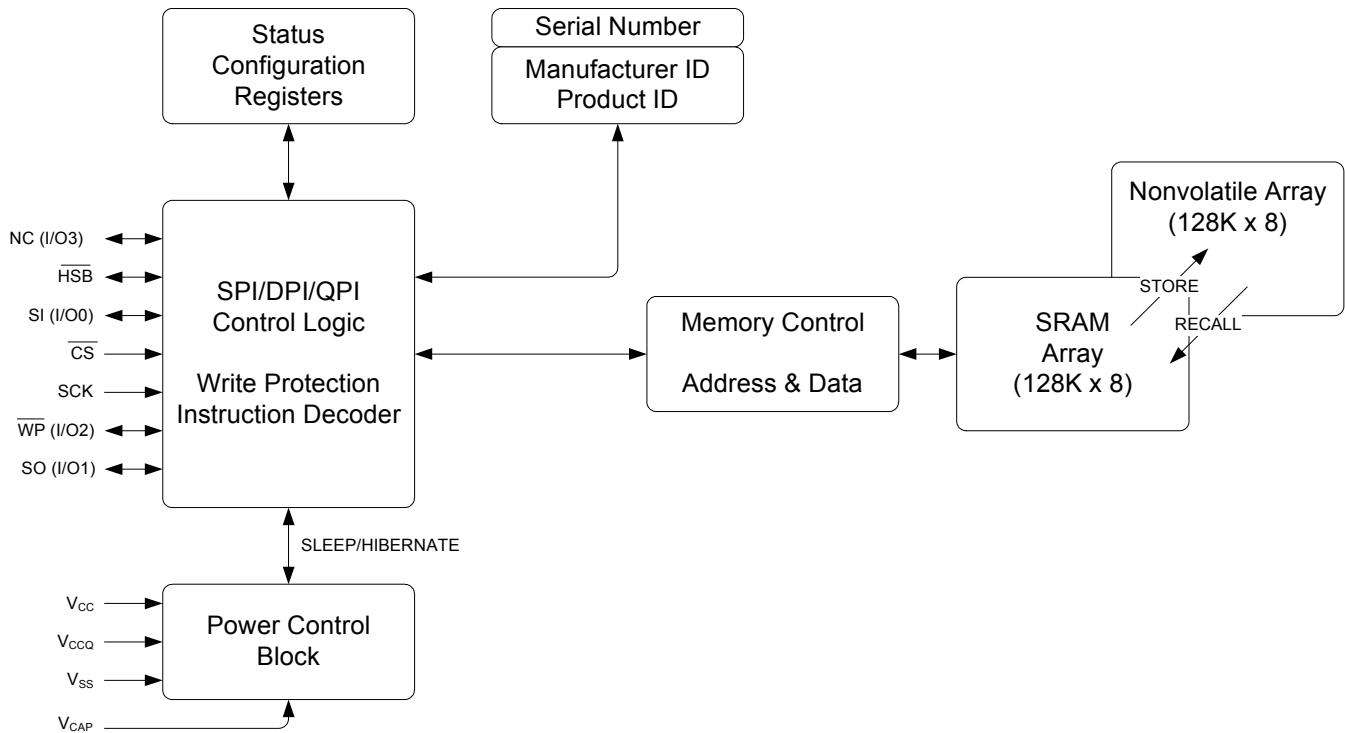

サイプレスの CY14V101QS は、QPI インターフェースに対応している、1M ビット nvSRAM です。QPI では、選択したオペコードを使用してシングル (1 ビット / クロック サイクルで 1 I/O チャネル)、デュアル (2 ビット / クロック サイクルで 2 I/O チャネル)、またはクアッド (4 ビット / クロック サイクルで 4 I/O チャネル) でメモリの読み書きが可能です。

メモリは SRAM と不揮発性 SONOS FLASH 量子トラップ セルから成り、128K バイトとして構成されています。回数に制限のない読み出しと書き込みを SRAM で可能にする一方、信頼性の高いデータ記憶を不揮発性セルで実現しています。SRAM から不揮発性セルへのデータ転送 (STORE 処理) は、電源切断時に自動的に行われます。電源投入時には、データが不揮発性セルから SRAM に復元されます (RECALL 処理)。SPI 命令を使用して STORE、RECALL 処理を開始することもできます。

## 論理ブロック図

## 目次

|                                         |    |

|-----------------------------------------|----|

| ピン配置 .....                              | 4  |

| ピン機能 .....                              | 5  |

| デバイスの動作 .....                           | 6  |

| SRAM 書き込み .....                         | 6  |

| SRAM 読み出し .....                         | 6  |

| STORE 処理 .....                          | 6  |

| AutoStore 処理 .....                      | 6  |

| ソフトウェア STORE 処理 .....                   | 7  |

| ハードウェア STORE 処理と HSB ピンの動作 .....        | 7  |

| RECALL 処理 .....                         | 7  |

| ハードウェア RECALL ( 電源投入 ) .....            | 7  |

| ソフトウェア RECALL .....                     | 7  |

| AutoStore のディスエーブルとイネーブル .....          | 7  |

| クアッドシリアル ペリフェラル インターフェース .....          | 8  |

| SPI 概要 .....                            | 8  |

| デュアルおよびクアッド I/O モード .....               | 10 |

| SPI モード .....                           | 10 |

| SPI 動作の特長 .....                         | 11 |

| 電源投入 .....                              | 11 |

| 電源切断 .....                              | 11 |

| アクティブ電力モードおよびスタンバイ状態 .....              | 11 |

| SPI 機能の説明 .....                         | 12 |

| ステータスレジスタ .....                         | 14 |

| 書き込みディスエーブル (WRDI) 命令 .....             | 18 |

| 書き込みイネーブル (WREN) 命令 .....               | 18 |

| DPI イネーブル (DPIEN) 命令 .....              | 19 |

| QPI イネーブル (QPIEN) 命令 .....              | 19 |

| SPI イネーブル (SPIEN) 命令 .....              | 19 |

| SPI メモリ読み出し命令 .....                     | 20 |

| 読み出し命令 .....                            | 20 |

| 高速読み出し命令 .....                          | 21 |

| 書き込み命令 .....                            | 24 |

| システムリソース命令 .....                        | 28 |

| ソフトウェアリセット (RESET) 命令 .....             | 28 |

| デフォルトの復帰命令 .....                        | 29 |

| ハイバネート (HIBEN) 命令 .....                 | 30 |

| スリープ (SLEEP) 命令 .....                   | 31 |

| レジスタ命令 .....                            | 33 |

| ステータスレジスタ読み出し (RDSR) 命令 .....           | 33 |

| ステータスレジスタ書き込み (WRSR) 命令 .....           | 33 |

| コンフィギュレーション レジスタ読み出し<br>(RDCR) 命令 ..... | 34 |

|                                         |    |

|-----------------------------------------|----|

| コンフィギュレーション レジスタ書き込み<br>(WRCR) 命令 ..... | 35 |

| レジスタ識別 (RDID) 命令 .....                  | 36 |

| レジスタ識別 (FAST_RID) 命令 .....              | 37 |

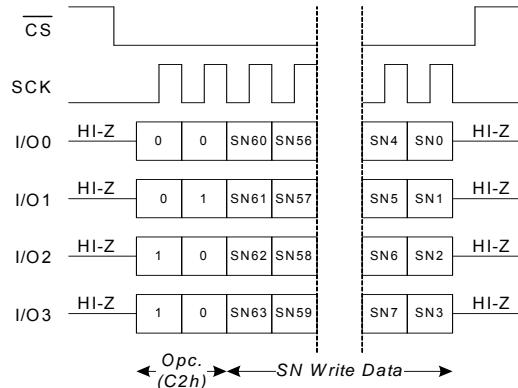

| シリアル番号レジスタ書き込み (WRSN) 命令 .....          | 38 |

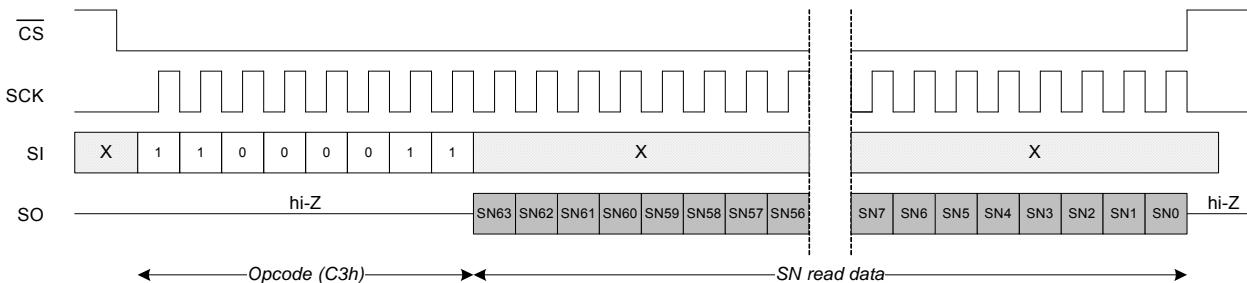

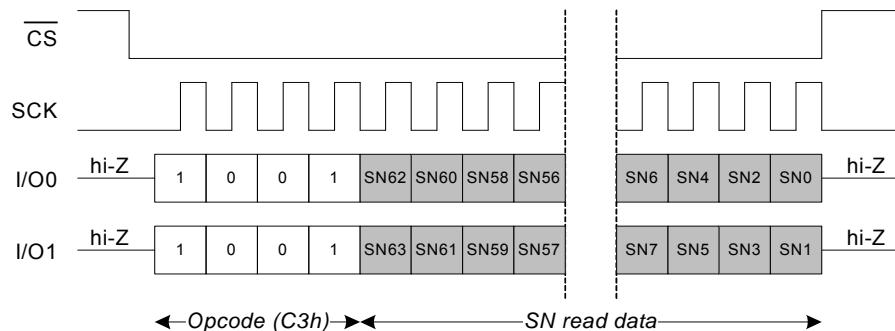

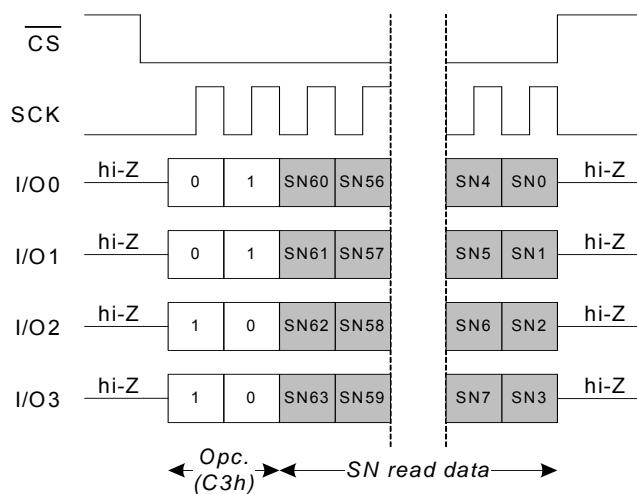

| シリアル番号レジスタ読み出し (RDSN) 命令 .....          | 39 |

| 高速シリアル番号読み出し (FAST_RDSN) 命令 .....       | 40 |

| 不揮発性メモリ固有の命令 .....                      | 41 |

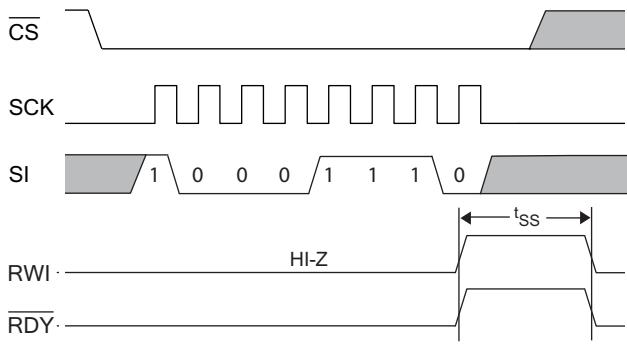

| ソフトウェアストア (STORE) 命令 .....              | 41 |

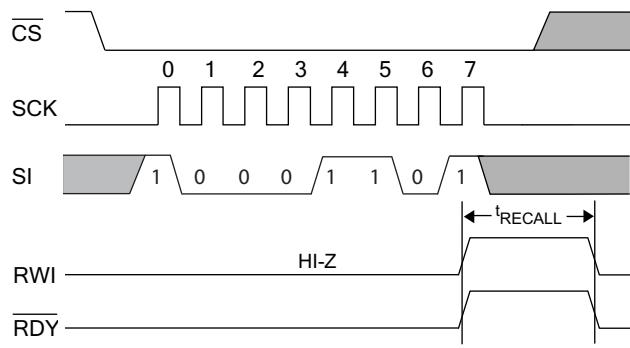

| ソフトウェアリコール (RECALL) 命令 .....            | 41 |

| Autostore イネーブル (ASEN) 命令 .....         | 42 |

| Autostore ディスエーブル (ASDI) 命令 .....       | 42 |

| 最大定格 .....                              | 43 |

| 動作範囲 .....                              | 43 |

| DC 仕様 .....                             | 43 |

| データ保持期間およびアクセス可能回数 .....                | 44 |

| 静電容量 .....                              | 44 |

| 熱抵抗 .....                               | 44 |

| AC テストの負荷および波形 .....                    | 45 |

| AC テスト条件 .....                          | 45 |

| RTC 特性 .....                            | 45 |

| AC スイッチング特性 .....                       | 46 |

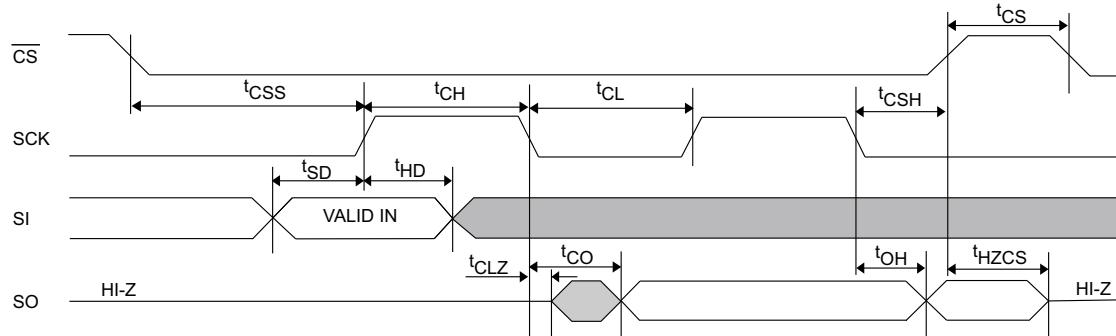

| スイッチング波形 .....                          | 46 |

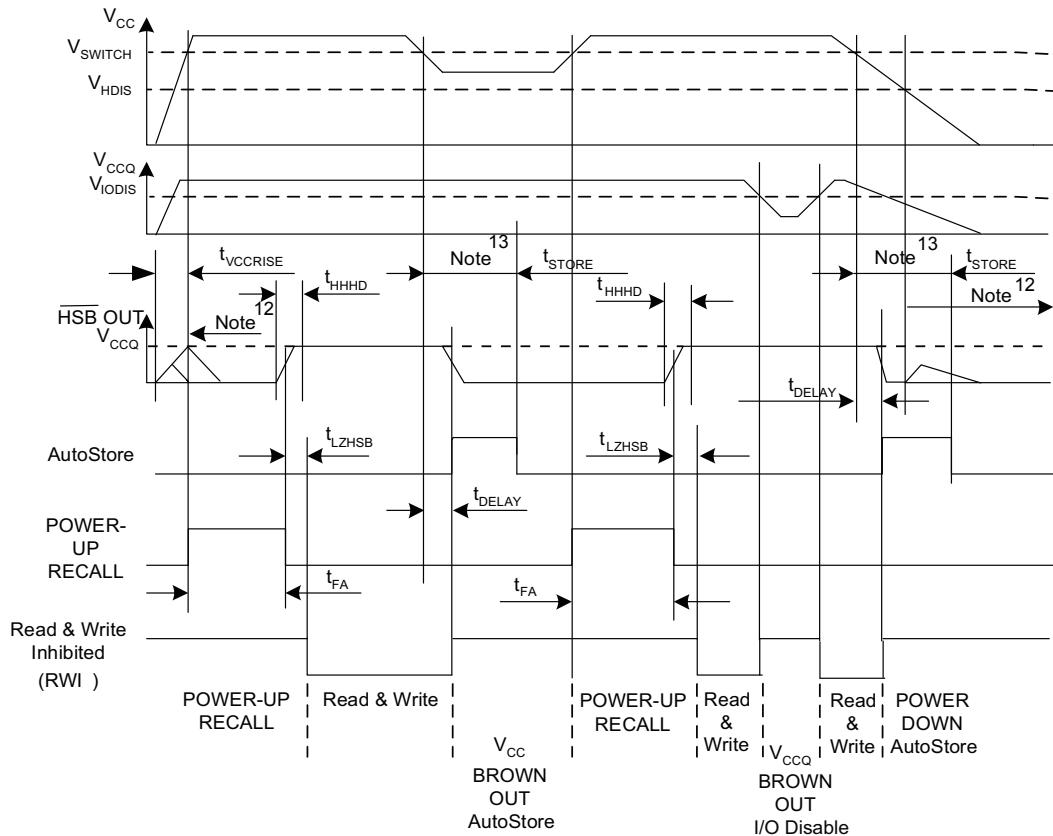

| AutoStore またはパワーアップ RECALL .....        | 47 |

| スイッチング波形 .....                          | 48 |

| ソフトウェア制御 STORE および RECALL サイクル .....    | 49 |

| スイッチング波形 .....                          | 49 |

| ハードウェア STORE サイクル .....                 | 50 |

| スイッチング波形 .....                          | 50 |

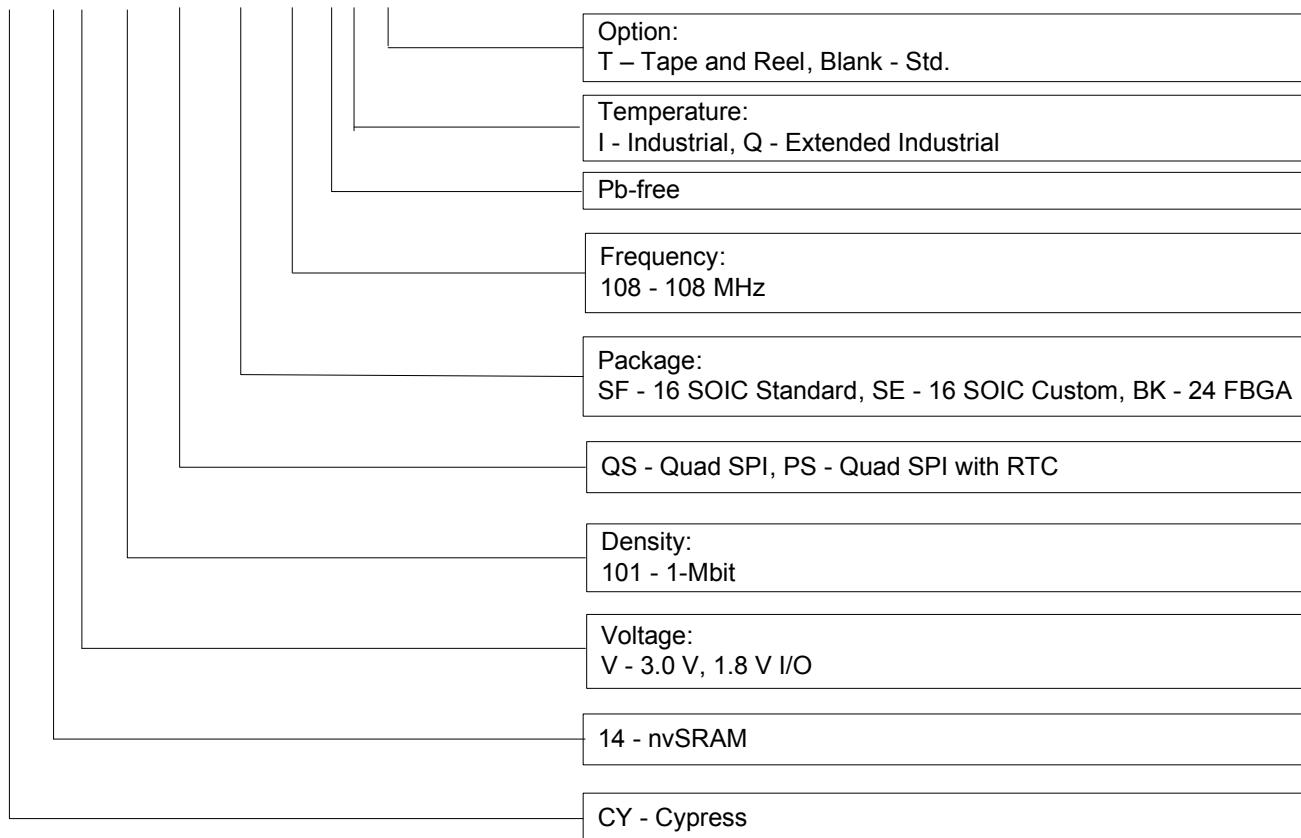

| 注文情報 .....                              | 51 |

| 注文コードの定義 .....                          | 51 |

| パッケージ図 .....                            | 52 |

| 略語 .....                                | 53 |

| 本書の表記法 .....                            | 53 |

| 測定単位 .....                              | 53 |

| 改訂履歴 .....                              | 54 |

| セールス、ソリューションおよび法律情報 .....               | 55 |

| ワールドワイド販売と設計サポート .....                  | 55 |

| 製品 .....                                | 55 |

| PSoC® ソリューション .....                     | 55 |

| サイプレス開発者コミュニティ .....                    | 55 |

| テクニカルサポート .....                         | 55 |

## ピン配置

図 1. 16 ピン SOIC 標準ピン配置

|                 |   |                |    |           |

|-----------------|---|----------------|----|-----------|

| NC (I/O3)       | 1 | ○              | 16 | SCK       |

| VCC             | 2 |                | 15 | SI (I/O0) |

| RFU             | 3 |                | 14 | VCCQ      |

| NC              | 4 | 16-pin<br>SOIC | 13 | VCAP      |

| NC              | 5 | Top View       | 12 | HSB       |

| RFU             | 6 |                | 11 | NC        |

| $\overline{CS}$ | 7 |                | 10 | VSS       |

| SO (I/O1)       | 8 |                | 9  | WP (I/O2) |

図 2. 16 ピン SOIC カスタム ピン配置

|                 |   |                |    |           |

|-----------------|---|----------------|----|-----------|

| NC (I/O3)       | 1 | ○              | 16 | SCK       |

| VCCQ            | 2 |                | 15 | SI (I/O0) |

| VCC             | 3 | 16-pin<br>SOIC | 14 | NC        |

| NC              | 4 |                | 13 | VCAP      |

| NC              | 5 | Top View       | 12 | HSB       |

| NC              | 6 |                | 11 | NC        |

| $\overline{CS}$ | 7 |                | 10 | VSS       |

| SO (I/O1)       | 8 |                | 9  | WP (I/O2) |

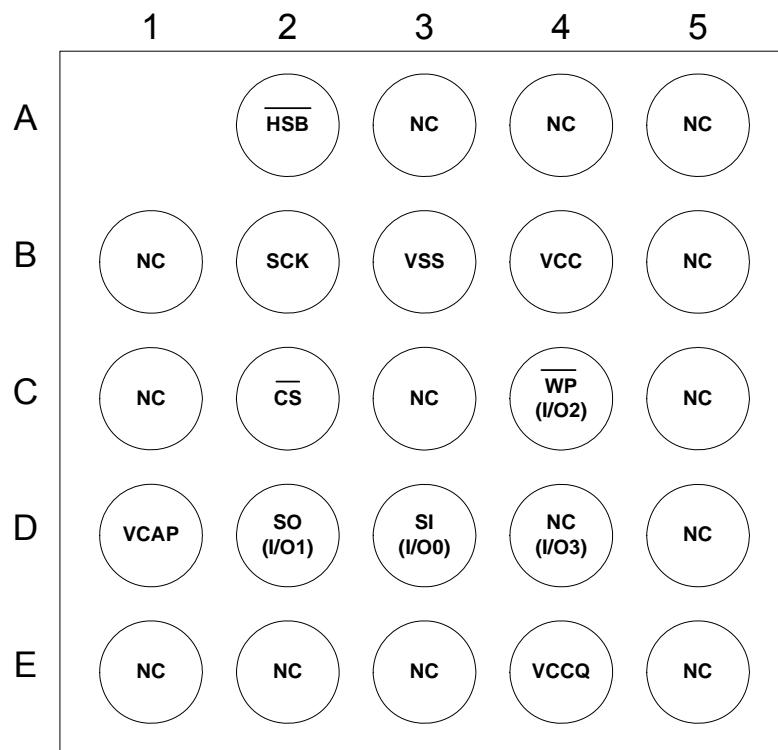

図 3. 24 ポール FPGA 標準ピン配置 - 上面 ( ポール側下 )

## ピン機能

| ピン名              | I/O タイプ | 説明                                                                                                                                                                                                                                          |

|------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NC (I/O3)        | 入力      | 未接続 : シングルまたはデュアル モードでは、このピンは接続されないで、開放される。このモードでは QSPI 命令をサポートしない                                                                                                                                                                          |

|                  | 入力／出力   | I/O3: デバイスがクアッド モードに入っている時、NC (I/O3) ピンは I/O3 ピンになり、入力／出力として機能する<br>SPI／DPI 命令対応のクアッド モードでは、このピンは $\overline{CS}$ が有効になっている間はトライステートにする必要がある                                                                                                |

| V <sub>CCQ</sub> | 電源      | デバイスの I/O の電源入力                                                                                                                                                                                                                             |

| V <sub>CC</sub>  | 電源      | デバイスのコアへの電源供給                                                                                                                                                                                                                               |

| $\overline{CS}$  | 入力      | チップ セレクト : LOW にプルダウンされた時、デバイスをアクティブにする。このピンを HIGH に駆動すると、デバイスがスタンバイ モードに入る                                                                                                                                                                 |

| SO (I/O1)        | 出力      | シリアル出力 : SPI を介してデータを出力するためのピン                                                                                                                                                                                                              |

|                  | 入力／出力   | I/O1: デバイスがデュアルまたはクアッド モードに入っている時、SO (I/O1) ピンは I/O1 ピンになり、入力／出力として機能                                                                                                                                                                       |

| WP (I/O2)        | 入力      | 書き込み保護 : SPI/DPI モードにハードウェア書き込み保護を実装                                                                                                                                                                                                        |

|                  | 入力／出力   | I/O2: デバイスがクアッド モードに入っている時、WP (I/O2) ピンは I/O2 ピンになり、入力／出力として機能                                                                                                                                                                              |

| V <sub>SS</sub>  | グランド    | デバイスのコアと I/O へのグランド電源供給                                                                                                                                                                                                                     |

| $\overline{HSB}$ | 入力／出力   | ハードウェア STORE ビジー：<br>出力 : LOW の時、nvSRAM のビジー状態を示す。各ハードウェアとソフトウェア STORE 処理の後、 $\overline{HSB}$ は標準の出力 HIGH 電流で短期間 ( $t_{HHD}$ ) HIGH に駆動されてから、内部の弱プルアップ抵抗により HIGH 状態を維持（外部プルアップ抵抗接続は任意）<br>入力 : このピンを外部で LOW にプルダウンすることによって実施されるハードウェア STORE |

| V <sub>CAP</sub> | 電源      | AutoStore コンデンサ : SRAM から不揮発性要素にデータを STORE (格納) するため、電力喪失時に nvSRAM に電源を供給。AutoStore が必要でない場合は、このピンを未接続の状態にしなければならない。これは絶対にグランドに接続しないでください。                                                                                                  |

| SI (I/O0)        | 入力      | シリアル入力 : すべての SPI 命令とデータの入力ピン                                                                                                                                                                                                               |

|                  | 入力／出力   | I/O0: デバイスがデュアルまたはクアッド モードに入っている時、SI (I/O0) ピンは I/O0 ピンになり、入力／出力として機能                                                                                                                                                                       |

| SCK              | 入力      | シリアル クロック : $f_{SCK}$ までの速度で動作。シリアル入力はこのクロックの立ち上がりエッジでラッチされる。シリアル出力はクロックの立ち下がりエッジで駆動される                                                                                                                                                     |

| NC               | —       | 未接続                                                                                                                                                                                                                                         |

| RFU              | —       | 将来使用のために予約済み                                                                                                                                                                                                                                |

## デバイスの動作

CY14V101QS は、各メモリ セル内の SRAM 要素とインターリープする SONOS FLASH 不揮発性要素を持つ 1M ビットのクアッドシリアルインターフェース nvSRAM メモリです。nvSRAM へのすべての読み出しと書き込みは SRAM に対し行われます。これにより、nvSRAM は、メモリへの無限な書き込みを処理できる独自の能力を持っています。SRAM 内のデータの安全性は、不揮発性セルにデータを転送する STORE シーケンスによって確保されます。小容量コンデンサ ( $V_{CAP}$ ) は、電源切断時に不揮発性セルに SRAM データを AutoStore (自動格納) するために使用され、データ整合性を提供します。高信頼性の SONOS 技術で設計された不揮発性セルにより、nvSRAM はデータ記憶に理想的なオプションとなります。

1M ビットのメモリアレイは 128K バイトで構成されます。メモリは、読み書き処理時にゼロ サイクルの遅延を持つ最大 40MHz のクロック速度で標準 SPI インターフェース (シングルモード、デュアルモード、クアッドモード) を介してアクセスすることができます。この SPI インターフェースはまた、読み出し処理のみがサイクルレイトレインシがある 108MHz での動作 (シングルモード、デュアルモード、クアッドモード) をサポートします。デバイスは SPI スレーブとして動作し、SPI モード 0 と SPI モード 3 (CPOL, CPHA = [0, 0] と [1, 1]) をサポートします。シングルモードとデュアルモードでは、すべての命令はチップセレクト (CS)、シリアル入力 (SI) (I/O0)、シリアル出力 (SO) (I/O1)、シリアルクロック (SCK) のピンを使用して実行されます。クアッドモードでは、WP (I/O2 と I/O3) ピンをコマンド、アドレスとデータ入力にも使用します。

デバイスは SPI オペコードを使用してメモリへアクセスします。オペコードは読み書き処理用に、SPI、デュアルデータ、デュアルアドレス/データ、デュアル I/O、クアッドデータ、クアッドアドレス/データ、およびクアッド I/O モードをサポートします。また、nvSRAM 固有の機能の使用を可能にする 4 つの専用命令も含まれています：STORE、RECALL、AutoStore ディスエーブル (ASDI)、AutoStore イネーブル (ASEN)。

デバイスには、データセキュリティ機能を組み込んでいます。これにより、WP ピンと WRDI 命令それぞれを介したハードウェアとソフトウェアの書き込み保護が可能になります。さらに、メモリアレイブロックはステータスレジスタブロック保護ビットにより書き込みから保護されます。

## SRAM 書き込み

nvSRAM へのすべての書き込みは SRAM セル上で行われており、SONOS FLASH 不揮発性メモリのアクセス可能サイクルを 1 つも使用することはありません。これにより、無限の書き込み動作を実行することができます。書き込みサイクルは、書き込み命令の 1 つを介して開始されます：WRITE、DIW、QIW、DIOW、QIOW。書き込み命令は書き込みオペコード、アドレス 3 バイト、およびデータ 1 バイトで構成されています。nvSRAM への書き込みは、ゼロ サイクル遅延の SPI バス速度で行われます。

デバイスはバーストモード書き込みに対応しています。これにより、新しい書き込み命令を発行せずに連続したアドレスで書き込み処理を実行できます。バーストモードでメモリの最後のアドレスに到達した時、アドレスは 0x00000 に戻り、デバイスは書き込みを継続します。

SPI 書き込みサイクル シーケンスは、12 ページの「SPI 機能の説明」の読み書き命令のセクションで詳しく定義されます。

## SRAM 読み出し

nvSRAM へのすべての読み出しは SRAM セルで SPI バス速度で行われます。読み出し命令 (READ) は 40MHz でゼロ サイクル遅延で実行します。この命令は、読み出しオペコード バイトとそれに後続する 3 つのアドレス バイトからなります。データはデータ出力ピンで読み出されます。

40MHz より高い速度 (108MHz 以下) は高速読み出し命令を必要とします：FAST\_READ、DOR、QOR、DIOR、QIOR。高速読み出し命令は高速読み出しオペコード 1 バイト、アドレス 3 バイト、1 ダミー/モード バイトで構成されています。データはデータ出力ピンで読み出されます。

デバイスはバーストモード読み出しに対応しています。これにより、新しい読み出し命令を発行せずに連続したアドレス上で読み出し処理を実行できます。バーストモードでメモリの最後のアドレスに到達した時、アドレスは 0x00000 に戻り、デバイスは読み出しを継続します。

SPI 読み出しサイクル シーケンスは、12 ページの「SPI 機能の説明」の読み書き命令のセクションで詳しく定義されます。

## STORE 処理

STORE 処理は、データを SRAM から不揮発性セルへ転送します。デバイスは、次の 3 つの STORE 処理のいずれかを使用してデータを格納します：AutoStore (デバイスの電源切断時にアクティブになり、 $V_{CAP}$  が必要)、ソフトウェア STORE (STORE 命令でアクティブになる)、ハードウェア STORE (HSB ピンでアクティブになる)。STORE サイクル中に、最初は不揮発性セルが消去されてからプログラムされます。STORE サイクルが開始されると、デバイスへの読み書きはそのサイクルが完了するまで禁止されます。

HSB 信号またはステータスレジスタ内の WIP ビットは、STORE サイクルが実行中かを検出するためにシステムで監視することができます。nvSRAM のビジー状態は、HSB が LOW にプルされるか、または WIP ビットが「1」にセットされることで示されます。不要な不揮発性の STORE を避けるために、一番最近の STORE サイクルが実行されてから少なくとも 1 回の SRAM 書き込み処理が実行されない限り、AutoStore およびハードウェア STORE 処理が無視されます。ただし、ソフトウェアで起動された STORE サイクルは、SRAM 書き込み処理が行われたかどうかに関係なく実行されます。

## AutoStore 処理

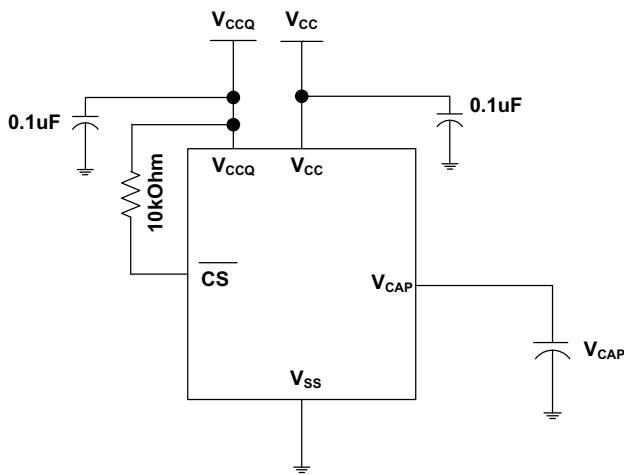

AutoStore 処理は nvSRAM 独自の機能であり、電源切断時に SRAM データを SONOS FLASH 不揮発性セルに自動的に格納します。この STORE 処理は外付けコンデンサ ( $V_{CAP}$ ) を活用して、デバイスが電源切断時に不揮発性メモリへ安全にデータを保存できるようにします。

通常処理中に、デバイスは  $V_{CC}$  から電流を引き出して、 $V_{CAP}$  ピンに接続されたコンデンサを充電します。電源切断時に  $V_{CC}$  ピンの電圧が  $V_{SWITCH}$  を下回った場合、デバイスは nvSRAM へのメモリアクセスをすべて禁止し、 $V_{CAP}$  コンデンサからの電荷を使って自動的に STORE 処理を実行します。AutoStore 処理は、一番最近の RECALL の実行以降に書き込みサイクルが一度も実行されていない場合は起動されません。

**注:** コンデンサが  $V_{CAP}$  ピンに接続されていない場合、AutoStore ディスエーブル命令を発行して AutoStore を無効にする必要があります(42 ページの **Autostore ディスエーブル (ASDI) 命令**)。AutoStore が  $V_{CAP}$  ピンに接続されているコンデンサなしで有効にされた場合、デバイスは処理を完了するために充分な電荷がないまま AutoStore 処理を実行しようとします。これにより、メモリ アレイ、シリアル番号とステータスレジスタに格納されたデータが壊れてしまいます。通常の機能を再開するためにデータを更新する必要があります。

図 4 に、AutoStore 処理向けのストレージコンデンサ ( $V_{CAP}$ ) の適切な接続方法を示しています。 $V_{CAP}$  の容量については、43 ページを参照してください。

**図 4. AutoStore モード**

### ソフトウェア STORE 处理

ソフトウェア STORE では命令ベースの STORE 处理が可能です。STORE 处理はその前に書き込み命令が実行されたかどうかに関係なく、STORE 命令の実行によって開始します。

STORE サイクルが完了するためには  $t_{STORE}$  の期間を要しますが、その間、nvSRAMへのすべてのメモリアクセスは禁止されます。nvSRAMのレディーまたはビジー状態を検出するため、ステータスレジスタの WIP ビット、または HSB ピンをポーリングすることができます。 $t_{STORE}$  サイクル時間が終了した後、nvSRAMが読み出し／書き込み処理のためにレディーになります。

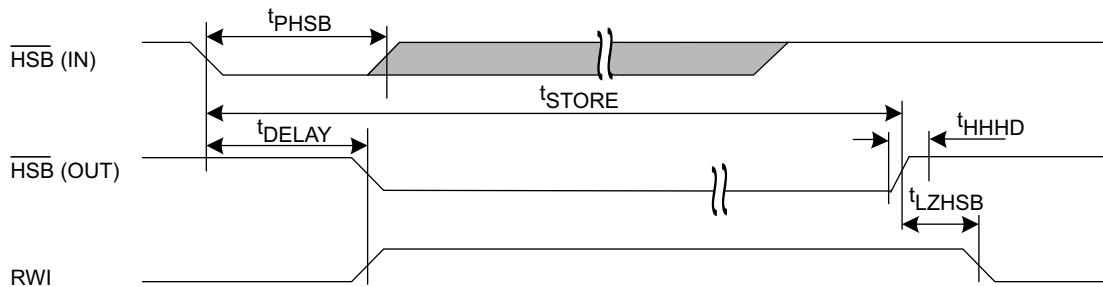

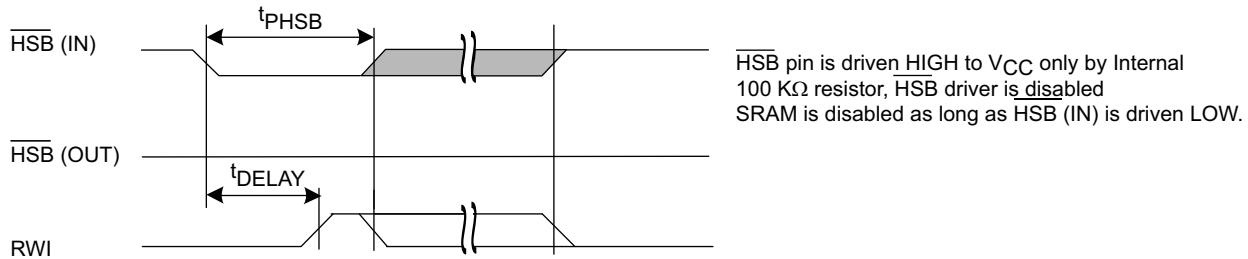

### ハードウェア STORE 处理と HSB ピンの動作

デバイス内の HSB ピンは STORE 处理を開始するか、または STORE / RECALL の完了ステータスをポーリングするのに使用される兼用ピンです。STORE または RECALL が進行中でない場合、HSB ピンはハードウェア STORE サイクルを開始するために LOW に駆動することができます。

HSB が LOW になると、nvSRAM は  $t_{DELAY}$  期間後に STORE 处理を開始します。ハードウェア STORE サイクルは、最後の STORE / RECALL サイクル以降に SRAM 書き込み処理が実行された場合にのみ可能になります。これにより、SONOS FLASH アクセス可能サイクル数を最適化することができます。メモリへのすべての読み書きは  $t_{STORE}$  の間禁止されます。HSB ピンは、STORE / RECALL 处理中にビジー状態を示すために

内部で LOW に駆動されるオープンドレインドライバー(内部  $100\text{k}\Omega$  の弱いプルアップ抵抗)としても動作します。

**注:** 各ハードウェアとソフトウェア STORE 处理後、HSB は、標準出力 HIGH 電流で短時間( $t_{HIGH}$ ) HIGH に駆動されてから、 $100\text{k}\Omega$ の内部プルアップ抵抗により HIGH の状態を維持します。

**注:** 最後のデータバイトに対して STORE を正常に実行するために、ハードウェア STORE は、最後のデータビット D0 が受信されてから少なくとも 1 クロックサイクル後に開始する必要があります。

**注:** デバイスのスタンバイ状態でのみハードウェア STORE を実行することをお勧めします。また、Execute-in-place (XIP) を終了する必要があります。

STORE 处理が完了すると、HSB ピンが HIGH 状態に戻った後に nvSRAM メモリアクセスは  $t_{LZHHSB}$  の間禁止されます。HSB ピンを使用しない場合は、未接続状態にしてください。

### RECALL 处理

RECALL 处理は、不揮発性セルに格納されているデータを SRAM セルへ転送します。RECALL 处理は次の 2 つの方法で開始されます：ハードウェア RECALL (電源投入時に開始) およびソフトウェア RECALL (SPI RECALL 命令により開始)。

内部的に、RECALL は 2 段階の手順を踏みます。まず、SRAM データがクリアされます(「0」にセットします)。次に、不揮発性情報が SRAM セルに転送されます。RECALL サイクルの実行中、メモリアクセスはすべて禁止されます。RECALL 处理では、不揮発性要素内のデータが変更されません。

### ハードウェア RECALL (電源投入)

電源投入時に  $V_{CC}$  が  $V_{SWITCH}$  を超えると、SRAM セルに不揮発性セルの内容を転送する RECALL シーケンスが自動的に開始されます。

パワーアップ RECALL サイクルが完了するまでには  $t_{FA}$  の時間がかかり、この間にメモリアクセスは無効となります。HSB ピンはデバイスのレディー状態を検出するために使用されます。

### ソフトウェア RECALL

ソフトウェア RECALL では、RECALL 处理を開始して不揮発性メモリの内容を SRAM に復元できます。ソフトウェア RECALL は、RECALL 命令を使用して実行されます。

ソフトウェア RECALL が完了するには  $t_{RECALL}$  の期間を要しますが、その間は nvSRAM へのメモリアクセスは禁止されます。

### AutoStore のディスエーブルとイネーブル

アプリケーションに AutoStore 機能が不要な場合、ASDI 命令により無効にすることができます。そうすると、nvSRAM は電源切断時に STORE 处理を実行しません。

AutoStore は ASEN 命令を使って再度有効にすることができます。しかし、ASEN と ASDI 处理は、不揮発性になるために STORE 处理が必要です。

**注:** 工場出荷時 AutoStore は有効になっており、すべてのセルに 0x00 と書き込まれています。

**注:** AutoStore が無効、かつ  $V_{CAP}$  が不要の場合、 $V_{CAP}$  ピンは未接続のままにしておく必要があります。 $V_{CAP}$  ピンは絶対にグランドに接続しないでください。パワーアップ RECALL 处理は無効にすることはできません。

## クアッドシリアルペリフェラルインターフェース

### SPI概要

SPIは、チップセレクト( $\overline{CS}$ )とシリアル入力(SI)、シリアル出力(SO)、シリアルクロック(SCK)ピンの4ピンインターフェースです。デバイスはSPIインターフェースを介してnvSRAMへのシリアルアクセスを提供しています。デバイスのSPIバスは、最大108MHzの速度で動作することができます。

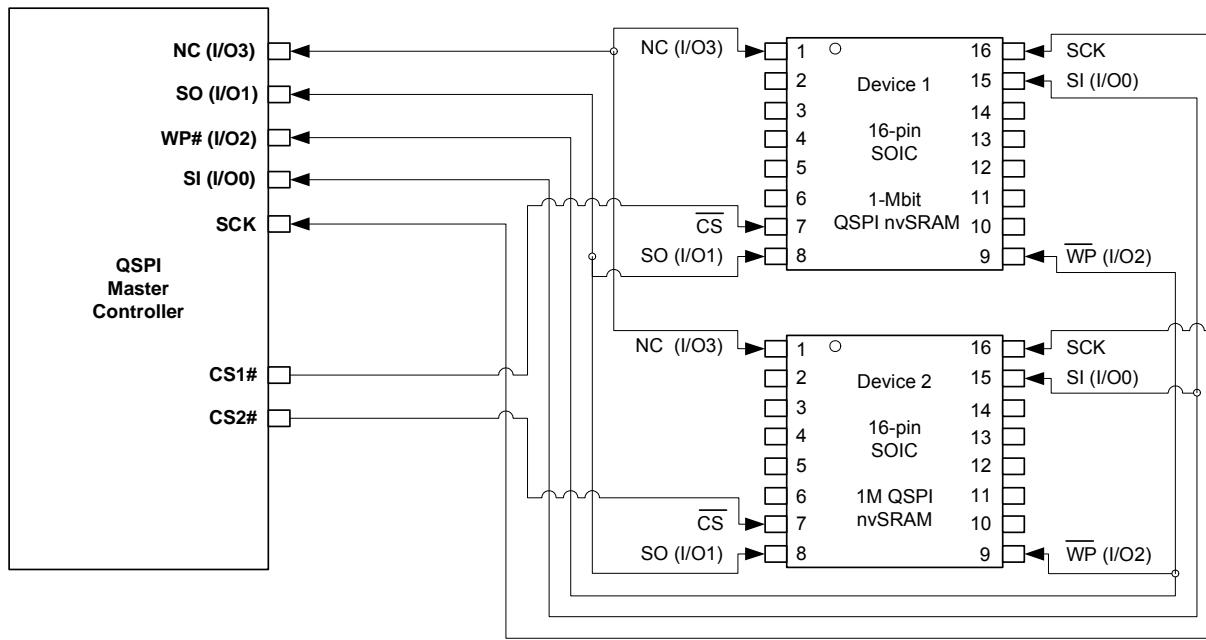

SPIは、メモリアクセスにクロックとデータピンを使用し、データバス上の複数デバイスをサポートする同期シリアルインターフェースです。SPIバス上のデバイスは、CSピンを使用してアクティブにされます。

チップセレクト、クロック、データの間の関係は、SPIモードによります。このデバイスはSPIモード0と3をサポートしています。この両方のモードで、 $\overline{CS}$ がアクティブになった後の最初のSCK立ち上がりエッジからSCKの立ち上がりエッジ毎にデータがnvSRAMにクロック入力されます。

SPIプロトコルはオペコードで制御されます。これらのオペコードは、バスマスターからスレーブデバイスへのコマンドを指定します。CSがアクティブにされた後、バスマスターから最初に転送されるバイトがオペコードです。オペコードに続いて、アドレスとデータが転送されます。処理が完了した後、新しいオペコードが発行される前に、CSを非アクティブにする必要があります。SPIプロトコルでよく使用される用語は以下の通りです。

### SPIマスター

SPIマスターデバイスは、SPIバス上の処理を制御します。SPIバスは、1つまたは複数のスレーブデバイスを制御するマスターを1つだけ持つことがあります。すべてのスレーブが同じSPIバスラインを共有し、マスターは自持のCSピンを使用してスレーブデバイスのいずれかを選択できます。すべての処理は、マスターがスレーブのCSピンをLOWにプルダウンすることによってスレーブデバイスをアクティブにすることで開始する必要があります。マスターはまた、SCKを生成し、SIとSOライン上のすべてのデータ転送はこのクロックに同期化されます。

### SPIスレーブ

SPIスレーブデバイスは、チップセレクトラインを介してマスターによってアクティブにされます。スレーブデバイスはSPIマスターからの入力としてSCKを取得し、すべての通信はこのクロックと同期化されます。SPIスレーブはSPIバスでの通信を開始することはなく、これはマスターからの命令に従って機能します。

デバイスはSPIスレーブとして動作し、他のSPIスレーブデバイスとSPIバスを共有する場合があります。

### チップセレクト( $\overline{CS}$ )

すべてのスレーブデバイスを選択するためには、マスターは対応するCSピンをプルダウンする必要があります。CSピンがLOWの間だけ、命令をスレーブデバイスに発行することができます。デバイスが選択されていない場合、SIピン経由のデータは無視され、シリアル出力ピン(SO)は高インピーダンス状態のままとなります。

注：新しい命令は $\overline{CS}$ の立ち下がりエッジで開始する必要があります。したがって、アクティブなチップセレクトサイクル毎に1つのオペコードのみが発行されます。

注： $V_{CCQ}$ に接続した外部10kΩプルアップ抵抗を、 $\overline{CS}$ ピンに接続することをお勧めします。

### シリアルクロック(SCK)

シリアルクロックはSPIマスターによって生成され、 $\overline{CS}$ がLOWになった後、通信がこのクロックと同期されます。

デバイスはデータ通信のためにSPIモード0と3を有効にします。両方のモードでは、入力はSCKの立ち上がりエッジでスレーブデバイスによってラッチされ、出力は立ち下がりエッジで発行されます。そのため、SCKの最初の立ち上がりエッジが、SPI命令の最初のビット(MSB)がSIピンに到着したこと意味します。さらにすべてのデータの入力と出力はSCKと同期されます。

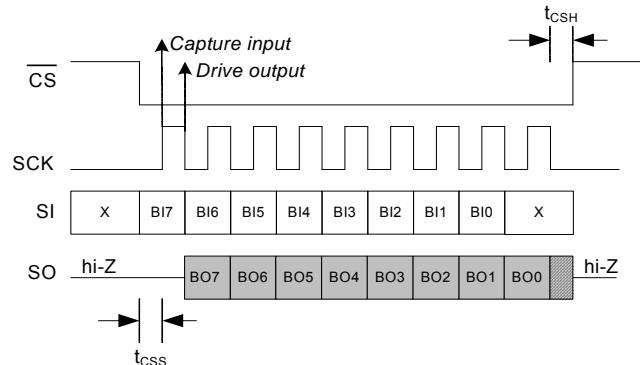

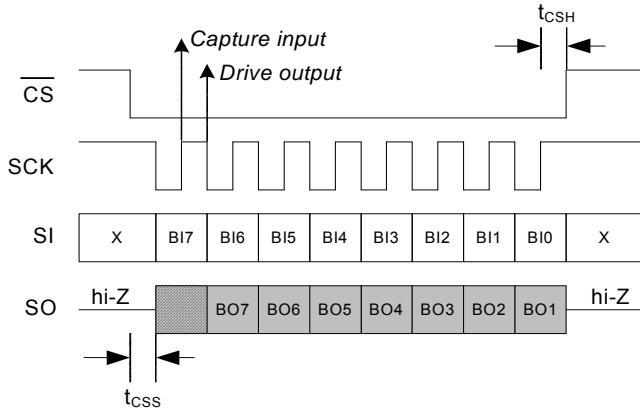

### データ転送-SI/SO

SPIデータバスは、シリアルデータ通信用にSIとSOの2線で構成されます。SIはマスターアウトスレーブイン(MOSI)、SOはマスターインスレーブアウト(MISO)とも呼ばれています。マスターはSIピンを介してスレーブに命令を発行し、スレーブはSOピンを介して応答します。複数のスレーブデバイスは、前述のようにSIとSOラインを共有する場合があります。

9ページの図5に示すように、デバイスにはマスターと接続することができるSIとSO用の2本の独立したピンがあります。

SI入力信号はデータをデバイスに順次転送することに使用されます。これは、プログラムされるオペコード、アドレスおよびデータを受信します。値はシリアルSCKクロック信号の立ち上がりエッジでラッチされます。拡張SPIとDPI/QPIコマンドの実行中にSIは、書き込まれるオペコード、アドレス、データ(シリアルSCKクロック信号の立ち上がりエッジでラッチされる値)の受信、およびデータのシフトアウト(SCKの立ち下がりエッジ)のために入出力I/Oとなります。SOではリピーター/バスホールド回路を実装しています。

SO入力信号はデータをデバイスから順次転送することに使用されます。データはシリアルSCKクロック信号の立ち下がりエッジでシフトアウトされます。拡張SPIとDPI/QPIコマンドの実行中にSOは、プログラムされるオペコード、アドレス、データ(シリアルSCKクロック信号の立ち上がりエッジでラッチされる値)の受信、およびデータのシフトアウト(SCKの立ち下がりエッジ)のために入出力I/O1となります。SOではリピーター/バスホールド回路を実装しています。

### 書き込み保護(WP)

SPIモードでは、WPピンはLOWに駆動されると、ステータスレジスタおよびそれら内のブロック保護ビットによって保護されたメモリバイトへの書き込みを防止します。

WPがLOWに駆動された時、WRSRコマンドの実行中、およびステータスレジスタのステータスレジスタ書き込みディスエーブル(SRWD)ビットが1にセットされた時、ステータスおよびコンフィギュレーションレジスタに書き込むことができません。これにより、ブロック保護(BP2、BP1、BP0)およびTBPROTビットの変更が防止されます。結果として、WRSRコマンドの実行中にWPがLOWであれば、ブロック保護およびTBPROTビットによって保護されたメモリ領域のすべてのデータバイトは、データ変更から保護されます。

WP機能はクアッド転送モードでは使用不可能です。それらのモードでは、WP機能は、書き込まれる/プログラムされるオペコード、アドレス、データの受信およびデータのシフトアウトのために入出力I/O2と置き換えられます。WPは内部プルアップ抵抗に接続しており、クアッド転送モードに使用されない場合は開放のままにすることができます。SPIモードでは、WPは内部100kΩの弱プルアップ抵抗に接続します。

### NC (I/O3)

クアッド転送モードでは、NC (I/O3) ピンは書き込まれる／プログラムされるオペコード、アドレス、データの受信およびデータのシフトアウトのために入出力 I/O3 として動作します。NC (I/O3) は内部プルアップ抵抗に接続しており、クアッド転送モードに使用されない場合は開放のままにすることがあります。SPI モードでは、NC (I/O3) は内部  $100\text{k}\Omega$  の弱プルアップ抵抗に接続します。

### 最上位ビット (MSB)

SPI プロトコルでは、送信される最初のビットが MSB である必要があります。この方式はアドレス転送にもデータ転送にも適用されます。

1M ビット シリアル nvSRAM は、すべての読み出しままたは書き込み処理に 3 バイトのアドレスを必要とします。しかし、アドレスは 17 ビットであるため、入力された最初の 7 ビットはデバイスによって無視されることとなります。これらの 7 ビットは「ドントケア」ですが、より高いメモリ密度へのシームレスな移行を可能するために、これらを 0 として扱うことをサイプレスはお勧めします。

### シリアル オペコード

CS が LOW になる状態でスレーブ デバイスが選択された後、最初に受信されたバイトは、意図されている処理のオペコードとして扱われます。デバイスはメモリアクセスに標準オペコードを使用します。メモリアクセス以外、nvSRAM 固有の機能 (STORE、RECALL、AutoStore イネーブル、および AutoStore ディスエーブル ) に追加のオペコードを提供します。詳細は、[12 ページの表 2](#) を参照してください。

### 無効なオペコード

無効なオペコードが受信されるとそのオペコードは無視され、デバイスは SI ピン上にある追加のシリアルデータを次の CS の立ち下がりエッジまで無視し、SO ピンはトライステートのままとなります。

### 命令

コマンドを発行するためのオペコード、アドレス、モード／ダミー サイクルの組み合わせです。

### モード ビット

アドレス ビットの後に続く制御ビットです。デバイスは制御ビットを使用して execute-in-place (XIP) を有効にします。これらのビットは、指定された場合、システム コントローラーによって駆動されます。

### ウェイト ステート

アドレス ビットまたはオプションのモード ビットに後続する必要なダミー クロック サイクルです。

### ステータス レジスタ

デバイスには、1 個の 8 ビット ステータス レジスタがあります。ステータス レジスタ内のビットは、SPI バスをコンフィギュレーションするために使用されます。これらのビットは [14 ページの表 3 と表 4](#) で説明されています。

図 5. 複数の 1M ビット クワッド SPI nvSRAM のデバイスを使用したシステム コンフィギュレーション

## デュアルおよびクアッド I/O モード

また、デバイスはデュアルまたはクアッド I/O モードで動作するように標準 SPI ピンを再コンフィギュレーションする機能があります。

デバイスがデュアル I/O モードに入ると、SI ピンと SO ピンはオペコード、アドレス、およびデータ（デュアル I/O モード）、またはアドレスとデータの両方（デュアル アドレス/データモード）、またはデータのみ（デュアル データ モード）のいずれかのために I/O0 ピンと I/O1 ピンになります。

デバイスがクアッド I/O モードに入ると、SI ピン、SO ピン、WP ピン、および NC (I/O3) ピンはオペコード、アドレス、およびデータ（クアッド I/O モード）、またはアドレスとデータの両方（クアッド アドレス/データ モード）、またはデータのみ（クアッド データ モード）のいずれかのためにそれぞれ I/O0 ピン、I/O1 ピン、I/O2 ピン、I/O3 ピンになります。

表 1. I/O モード

| プロトコル                        | コマンド入力   | アドレス入力   | データ入出力   |

|------------------------------|----------|----------|----------|

| SPI                          | SI       | SI       | SI/SO    |

| DPI                          | I/O[1:0] | I/O[1:0] | I/O[1:0] |

| QPI                          | I/O[3:0] | I/O[3:0] | I/O[3:0] |

| デュアル データ モード（デュアル 出力）        | I/O[0]   | I/O[0]   | I/O[1:0] |

| デュアル アドレス / データ モード（デュアル入出力） | I/O[0]   | I/O[1:0] | I/O[1:0] |

| クアッド データ モード（クアッド出力）         | I/O[0]   | I/O[0]   | I/O[3:0] |

| クアッド アドレス / データ モード（クアッド入出力） | I/O[0]   | I/O[3:0] | I/O[3:0] |

詳細については、本データシートの後半に記載する読み書きタイミング図を参照してください。

## SPI モード

デバイスは再コンフィギュレーションが可能です。デバイスは、SPI ベリフェラルが次の 2 つのモードのいずれかで動作しているマイクロコントローラによって駆動することができます。

### ■ SPI モード 0 (CPOL = 0, CPHA = 0)

### ■ SPI モード 3 (CPOL = 1, CPHA = 1)

この両モードでは、入力データは、 $\overline{CS}$  がアクティブになった後最初の SCK 立ち上がりエッジから SCK 立ち上がりエッジ毎にラッチされます。クロックが HIGH 状態（モード 3）から始まる場合は、クロックのトグル後の最初の立ち上がりエッジが選択されます。データは SCK の立ち下がりエッジで出力されます。

2 つの SPI モードは図 6 と図 7 に示されています。バス マスターがスタンバイ状態で、データを転送していないクロックの状態は以下の通りです。

### ■ モード 0 では、SCK が「0」のままで。

### ■ モード 3 では、SCK が「1」のままで。

CS ピンを LOW にすることによってデバイスが選択された時、デバイスは SCK ピンの状態から SPI モードを検出します。デバイスが選択された時に、SCK ピンが LOW ならデバイスは SPI モード 0 で動作し、SCK ピンが HIGH なら SPI モード 3 で動作します。

図 6. SPI モード 0

図 7. SPI モード 3

## SPI 動作の特長

### 電源投入

電源投入は、電源がオンになっていて、 $V_{CC}$  が  $V_{SWITCH}$  電圧を上回る条件として定義されます。

前述のように電源投入時、nvSRAM はすべてのメモリアクセスが無効になった  $t_{FA}$  の間でパワーアップ RECALL 処理を実行します。電源投入後、nvSRAM のレディー／ビジー状態を確認するために HSB ピンをプローブすることができます。

電源投入後のデバイス状態は以下のとおりです。

- SPI I/O モード

- HSB のプルアップ抵抗がアクティブ

- SO がトライステート

- CS ピンが HIGH の場合はスタンバイ電力モード。CS ピンが LOW の場合はアクティブ電力モード

- ステータスレジスタの状態：

- 書き込みイネーブル ビットが「0」にリセットされる

- SRWD が前回の STORE 処理後の状態のまま

- SNL が前回の STORE 処理後の状態のまま

- ブロック保護ビットが前回の STORE 後の状態のまま

- WP と NC(I/O3) 機能がクアッドデータ幅(QUAD)CR[1]で定義された通り。クアッドデータ幅 CR[1] が論理「0」の場合、WP と NC(I/O3) のプルアップ抵抗がアクティブ

### 電源切断

電源切断 ( $V_{CC}$  の連続減衰) 時に、 $V_{CC}$  は通常動作電圧から低下し、 $V_{SWITCH}$  閾値電圧を下回ると、デバイスはそれに送られたすべての命令への応答を停止します。

電源が切断された時に、書き込みサイクルがまだ進行中で、最後のデータビット D0 が受信された場合は、その書き込みが完了するまで  $t_{DELAY}$  時間は許可されています。この後は、すべてのメモリアクセスが禁止され、AutoStore 処理が実行されます（一番最近の RECALL サイクル以降に書き込みが行われていない場合は、AutoStore は実行されません）。この機能により、電源切断時にnvSRAMへの不注意な書き込みを防ぐことができます。

しかし、電源切断時の不注意な書き込みを完全に防止するためには、デバイスが選択解除され、スタンバイ状態に入ったことと、CS が  $V_{CC}$  に印加される電圧レベルに引き上げられたことを保証する必要があります。

### アクティブ電力モードおよびスタンバイ状態

CS が LOW の時、デバイスは選択され、アクティブの電力モードになります。ページ 43 で指定されたように、デバイスは  $I_{CC}$  ( $I_{CC1} + I_{CCQ1}$ ) 電流を消費します。CS が HIGH の時、デバイスは選択解除され、STORE または RECALL サイクルが進行中でなければ、スタンバイ状態に移行します。STORE/RECALL サイクルが進行中の場合、STORE または RECALL サイクルが完了した後に、デバイスはスタンバイ状態になります。

## SPI 機能の説明

デバイスは8ビット命令レジスタを使用します。命令とそのオペコードの一覧は表2に示されています。すべての命令、アドレスおよびデータはCSがHIGHからLOWへ遷移することにより転送されます。SPI命令は、WP、NC(I/O3)およびHSBピンと共にnvSRAM内のすべての機能の使用を可能にします。

表2. 命令セット

| 命令カテゴリ              | 命令名       | オペコード | SPI | デュアル出力 | クアッド出力 | デュアル入出力 | クアッド入出力 | DPI | QPI | 最大周波数(MHz) |

|---------------------|-----------|-------|-----|--------|--------|---------|---------|-----|-----|------------|

| <b>制御</b>           |           |       |     |        |        |         |         |     |     |            |

| 書き込みディスエーブル         | WRDI      | 04h   | 有   | -      | -      | -       | -       | 有   | 有   | 108        |

| 書き込みイネーブル           | WREN      | 06h   | 有   | -      | -      | -       | -       | 有   | 有   | 108        |

| DPIイネーブル            | DPIEN     | 37h   | 有   | -      | -      | -       | -       | -   | 有   | 108        |

| QPIイネーブル            | QPIEN     | 38h   | 有   | -      | -      | -       | -       | 有   | -   | 108        |

| SPIイネーブル            | SPIEN     | FFh   | -   | -      | -      | -       | -       | 有   | 有   | 108        |

| <b>メモリ読み出し</b>      |           |       |     |        |        |         |         |     |     |            |

| 読み出し                | READ      | 03h   | 有   | -      | -      | -       | -       | 有   | 有   | 40         |

| 高速読み出し              | FAST_READ | 0Bh   | 有   | -      | -      | -       | -       | 有   | 有   | 108        |

| デュアル出力(高速)読み出し      | DOR       | 3Bh   | -   | 有      | -      | -       | -       | -   | -   | 108        |

| クアッド出力(高速)読み出し      | QOR       | 6Bh   | -   | -      | 有      | -       | -       | -   | -   | 108        |

| デュアル入出力(高速)読み出し     | DIOR      | BBh   | -   | -      | -      | 有       | -       | -   | -   | 108        |

| クアッド入出力(高速)読み出し     | QIOR      | EBh   | -   | -      | -      | -       | 有       | -   | -   | 108        |

| <b>メモリ書き込み</b>      |           |       |     |        |        |         |         |     |     |            |

| 書き込み                | WRITE     | 02h   | 有   | -      | -      | -       | -       | 有   | 有   | 108        |

| デュアル入力書き込み          | DIW       | A2h   | -   | 有      | -      | -       | -       | -   | -   | 108        |

| クアッド入力書き込み          | QIW       | 32h   | -   | -      | 有      | -       | -       | -   | -   | 108        |

| デュアル入出力書き込み         | DIOW      | A1h   | -   | -      | -      | 有       | -       | -   | -   | 108        |

| クアッド入出力書き込み         | QIOW      | D2h   | -   | -      | -      | -       | 有       | -   | -   | 108        |

| <b>SRのコマンド</b>      |           |       |     |        |        |         |         |     |     |            |

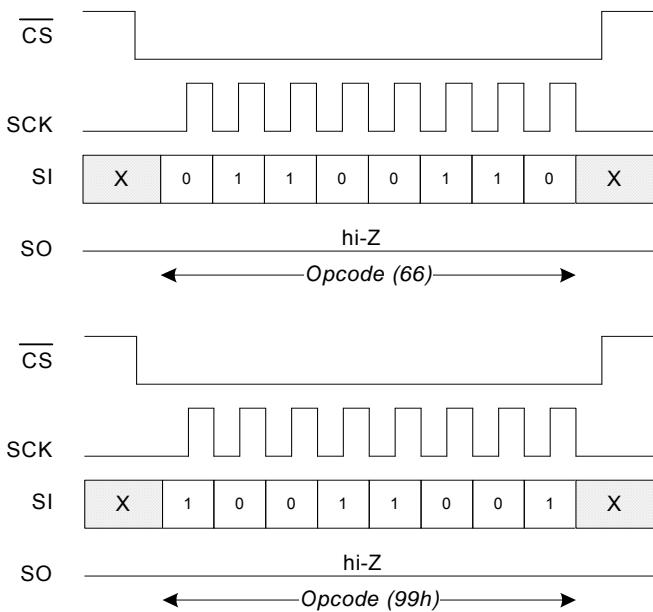

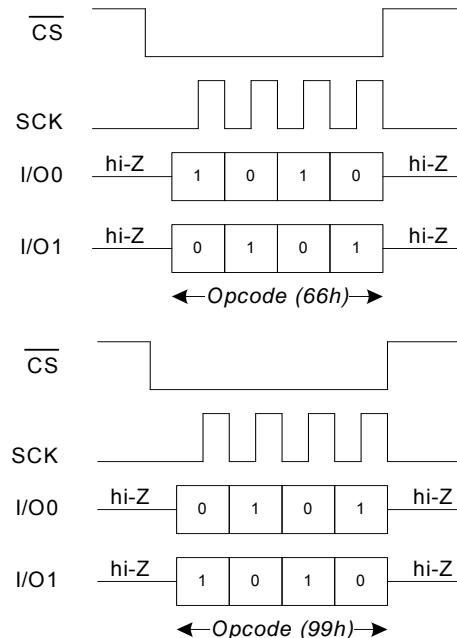

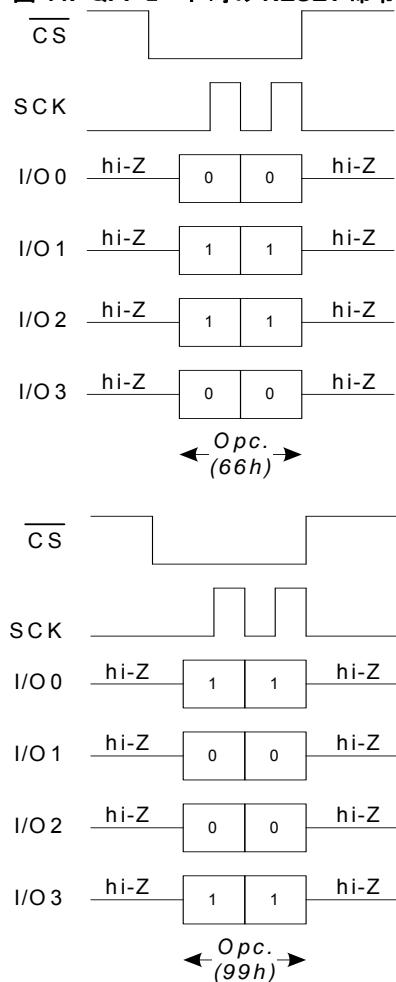

| ソフトウェアリセットイネーブル     | RSTEN     | 66h   | 有   | -      | -      | -       | -       | 有   | 有   | 108        |

| ソフトウェアリセット          | RESET     | 99H   | 有   | -      | -      | -       | -       | 有   | 有   | 108        |

| ハイバネートモード移行         | HIBEN     | BAh   | 有   | -      | -      | -       | -       | 有   | 有   | 108        |

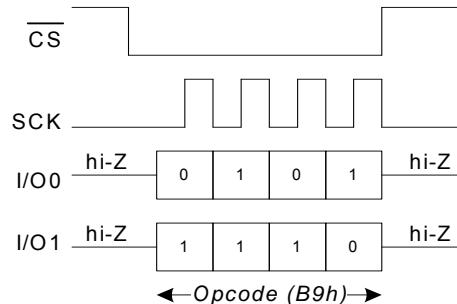

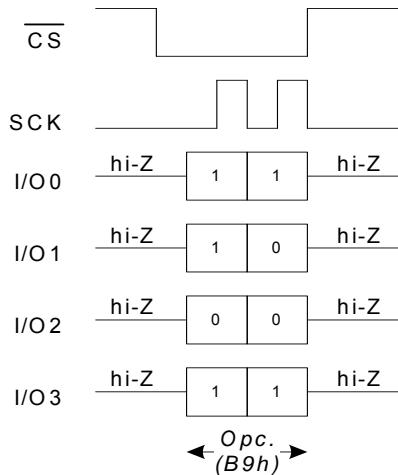

| スリープモード移行           | SLEEP     | B9h   | 有   | -      | -      | -       | -       | 有   | 有   | 108        |

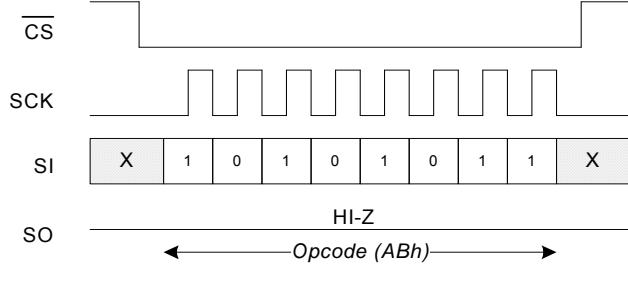

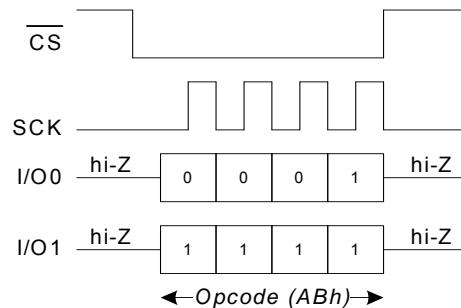

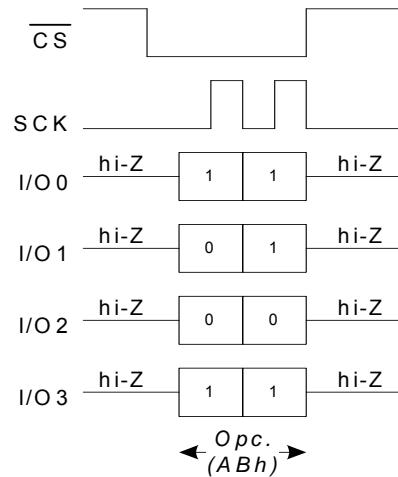

| スリープモード終了           | EXSLP     | ABh   | 有   | -      | -      | -       | -       | 有   | 有   | 108        |

| <b>レジスタのコマンド</b>    |           |       |     |        |        |         |         |     |     |            |

| ステータスレジスタ読み出し       | RDSR      | 05h   | 有   | -      | -      | -       | -       | 有   | 有   | 108        |

| ステータスレジスタ書き込み       | WRSR      | 01h   | 有   | -      | -      | -       | -       | 有   | 有   | 108        |

| コンフィギュレーションレジスタ読み出し | RDCR      | 35h   | 有   | -      | -      | -       | -       | 有   | 有   | 108        |

| コンフィギュレーションレジスタ書き込み | WRCR      | 87h   | 有   | -      | -      | -       | -       | 有   | -   | 108        |

**表 2. 命令セット ( 続き )**

| 命令カテゴリ               | 命令名       | オペコード     | SPI | デュアル出力 | クアッド出力 | デュアル入出力 | クアッド入出力 | DPI | QPI | 最大周波数 (MHz) |

|----------------------|-----------|-----------|-----|--------|--------|---------|---------|-----|-----|-------------|

| ID レジスタ読み出し          | RDID      | 9Fh       | 有   | -      | -      | -       | -       | 有   | 有   | 40          |

| ID レジスタ高速読み出し        | FAST_RID  | 9Eh       | 有   | -      | -      | -       | -       | 有   | 有   | 108         |

| シリアル番号レジスタ書き込み       | WRSN      | C2h       | 有   | -      | -      | -       | -       | 有   | 有   | 108         |

| シリアル番号レジスタ読み出し       | RDSN      | C3h       | 有   | -      | -      | -       | -       | 有   | 有   | 40          |

| シリアル番号レジスタ高速読み出し     | FAST_RDSN | C9h       | 有   | -      | -      | -       | -       | 有   | 有   | 108         |

| <b>NV 固有のコマンド</b>    |           |           |     |        |        |         |         |     |     |             |

| ストア                  | STORE     | 8Ch       | 有   | -      | -      | -       | -       | 有   | 有   | 108         |

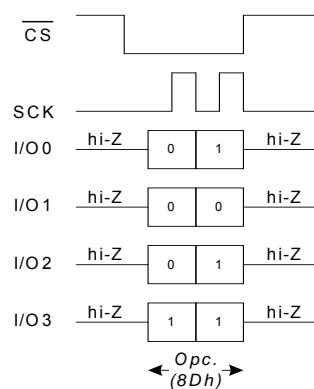

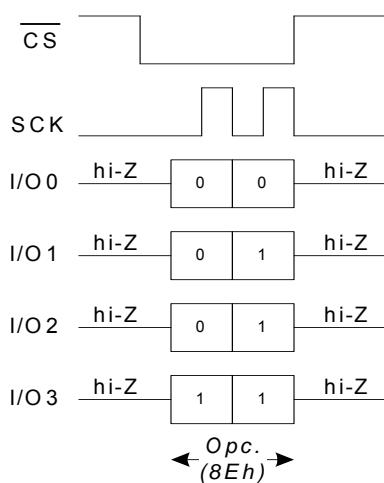

| リコール                 | RECALL    | 8Dh       | 有   | -      | -      | -       | -       | 有   | 有   | 108         |

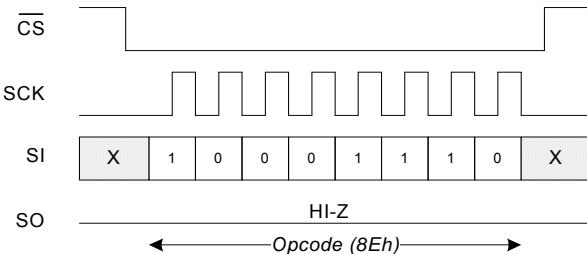

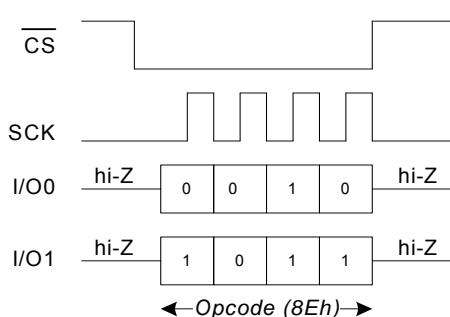

| AutoStore イネーブル      | ASEN      | 8Eh       | 有   | -      | -      | -       | -       | 有   | 有   | 108         |

| AutoStore ディスエーブル    | ASDI      | 8Fh       | 有   | -      | -      | -       | -       | 有   | 有   | 108         |

| <b>モード ビット</b>       |           |           |     |        |        |         |         |     |     |             |

| モード ビット ( セット、リセット ) | -         | Axh、非 Axh | 有   | -      | -      | -       | -       | 有   | 有   | -           |

SPI 命令は、機能に基づいて以下のタイプに分類されます。

■ 制御命令：

- 書込み保護 : WREN、WRDI 命令

- I/O モード : DPIEN、QPIEN、SPIEN

■ メモリ読み出し命令：

- メモリ アクセス : READ、FAST\_READ、DOR、QOR、DIOR、QIOR

■ メモリ書き込み命令：

- メモリ アクセス : WRITE、DIW、QIW、DIOW、QIOW

■ システム リソース命令：

- ソフトウェア リセット : RSTEN、RESET

- 電力モード : HIBEN、SLEEP、EXSLP

■ レジスタ命令：

- コンフィギュレーション レジスタ : RDCR、WRCR

- ステータス レジスタ : RDSR、WRSR

- 識別 : RDID、FAST\_RID

- シリアル番号 : RDSN、WRSN、FAST\_RDSN

■ nvSRAM 固有の命令：

- ストア : STORE

- リコール : RECALL

- イネーブル／ディスエーブル : ASEN、ASDI

注：以下の節に示す命令波形は、 $\overline{WP}$  (I/O2)、NC (I/O3) および SO に接続されたリピーター／バス ホールド回路に対する、プルアップ抵抗の影響を含んでいません。

注：命令オペコード C5h、1Eh、C8h、CEh、CBh、CCh、CDh はサイプレスの予約済みのオペコードで、デバイスのコンフィギュレーションを変更します。これらのオペコードのいずれかが誤って入力されると、デバイスを正しいコンフィギュレーションに戻させるためにソフトウェア リセット (66h、99h) が必要になります。そうしないと、デバイスは正常に動作しません。

## ステータス レジスタ

デバイスには 1 個のステータス レジスタがあります。これはビットの説明と共に表 3 に示されます。ステータス レジスタ内のビットのフォーマットは、ビットが読み出し専用 (R) か読み書きが可能である (W/R) かを示します。唯一の例外は、シリアル番号ロック ビット (SNL) です。SNL ビットが「0」である時は、シリアル番号は WRSN 命令を使用して複数回書き込むこ

とができます。「1」にセットされた場合、このビットはシリアル番号への変更を防止します。このビットは工場出荷時に「0」にプログラムされており、一度だけ書き込むことができます。このビットは「1」にセットされた後は、「0」にクリアすることはできません。

表 3. ステータス レジスタ形式およびビットの定義

| ビット | フィールド名 | 機能                            | タイプ | R/W | デフォルト状態 | 説明                                                                                                                                                                 |

|-----|--------|-------------------------------|-----|-----|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | SRWD   | ステータス レジ<br>スタ書き込み<br>ディスエーブル | NV  | R/W | 0       | 1 = <u>WP</u> が LOW 時に WRSR コマンドを無視することで<br>SR の状態をロック<br>0 = 保護無し (WP が LOW になった場合を含む)                                                                            |

| 6   | SNL    | シリアル番号<br>ロック                 | OTP | R/W | 0       | シリアル番号をロック                                                                                                                                                         |

| 5   | TBPROT | ブロックの開始<br>を設定                | NV  | R/W | 0       | 1 = BP が下位 (低いアドレス) から開始<br>0 = BP が上位 (高いアドレス) から開始                                                                                                               |

| 4   | BP2    | ブロック保護                        | NV  | R/W | 0       | ブロックの選択した範囲を書き込み、プログラムまたは<br>消去から保護                                                                                                                                |

| 3   | BP1    |                               | NV  | R/W | 0       |                                                                                                                                                                    |

| 2   | BP0    |                               | NV  | R/W | 0       |                                                                                                                                                                    |

| 1   | WEL    | 書き込みイネー<br>ブルラッチ              | V   | R   | 0       | 1 = デバイスがレジスタ書き込み (WRSR)、書き込み、<br>プログラムまたは消去コマンドを受け入れる<br>0 = デバイスがレジスタ書き込み (WRSR)、書き込み、<br>プログラムまたは消去コマンドを無視<br>このビットは WRSR から影響されず、WREN と WRDI<br>コマンドのみから影響を受ける |

| 0   | WIP    | 動作中                           | V   | R   | 0       | 1 = デバイス ビジー (レジスタ書き込み (WRSR)、プロ<br>グラム、消去または他の処理が進行中)<br>0 = レディ デバイスはスタンバイ状態にあり、コマンド<br>を受け入れることが可能                                                              |

ステータス レジスタ書き込みディスエーブル (SRWD) SR[7]

このビットが「1」にセットされ、WP 入力が LOW に駆動されると、デバイスはハードウェア保護モードに入ります。このモードでは、WEL 以外のすべての SRWD ビットは読み出し専用ビットになり、レジスタ書き込み (WRSR) コマンドは実行できなくなります。WP が HIGH の場合、SRWD ビットは WRSR コマンドで変更されることがあります。SRWD が「0」の場合 WP は何の影響も与えず、SRWD ビットは WRSR コマンドで変更されることがあります。

注：コンフィギュレーション レジスタのクアッド ビット CR[1] がセットされた場合、WP は内部的にデフォルトで論理「0」となります。SRWD が論理「1」にセットされると、クアッド ビット CR[1] が論理「0」にリセットされるまで保護は変更できません。

表 4. SRWD、WP、WEL および保護

| SRWD | <u>WP</u> | WEL | 保護ブロック | 非保護ブロック | ステータス レジスタ<br>(WEL を除く) |

|------|-----------|-----|--------|---------|-------------------------|

| X    | X         | 0   | 保護     | 保護      | 保護                      |

| 0    | X         | 1   | 保護     | 書き込み可能  | 書き込み可能                  |

| 1    | LOW       | 1   | 保護     | 書き込み可能  | 保護                      |

| 1    | HIGH      | 1   | 保護     | 書き込み可能  | 書き込み可能                  |

注：WP は書き込みレジスタ命令中にハードウェア保護が有効になったかを確定するために CS に応じてサンプリングされます。タイミング波形を図 8 に示します。

**図 8.  $\overline{CS}$  に応じた  $\overline{WP}$**

#### シリアル番号ロック (SNL) SR[6]

「1」にセットされた場合、このビットはシリアル番号への変更を防止します。このビットは工場出荷時に「0」にプログラムされており、一度だけ書き込むことができます。このビットは「1」にセットされた後は、「0」にクリアすることはできません。

#### 上位と下位アレイの保護 (TBPROT) CR[5]

このビットはブロック保護ビット BP2、BP1、BP0 の動作を定義します。TBPROT の所望の状態は、システム製造時のデバイスの初期設定時に選択する必要があります。

#### ブロック保護 (BP2、BP1、BP0) SR[4:2]

これらのビットは書き込みコマンドに対してソフトウェア保護されるメモリアレイ領域を定義します。BP ビットは不揮発性です。1つ以上の BP ビットが「1」にセットされると、該当するメモリ領域は書き込み、プログラム、消去から保護されます。

ブロック保護ビット (ステータスレジスタのビット BP2、BP1、BP0) は、TBPROT と組み合わせて、メモリアレイの1つのアドレス範囲を保護するために使用できます。範囲のサイズは BP ビットの値で決定され、範囲の上位と下位のスタートポイントはステータスレジスタの TBPROT ビットで選択されます。

**表 5. 上位保護アレイのスタート ポイント (TBPROT = 0)**

| ステータスレジスタの内容 |     |     | メモリアレイの保護部分 | アドレス範囲            |

|--------------|-----|-----|-------------|-------------------|

| BP2          | BP1 | BP0 |             |                   |

| 0            | 0   | 0   | 無し          | 無し                |

| 0            | 0   | 1   | 上位 64 番目の部分 | 0x1F800 ~ 0x1FFFF |

| 0            | 1   | 0   | 上位 32 番目の部分 | 0x1F000 ~ 0x1FFFF |

| 0            | 1   | 1   | 上位 16 番目の部分 | 0x1E000 ~ 0x1FFFF |

| 1            | 0   | 0   | 上位 8 番目の部分  | 0x1C000 ~ 0x1FFFF |

| 1            | 0   | 1   | 上位 4 番目の部分  | 0x18000 ~ 0x1FFFF |

| 1            | 1   | 0   | 上位半分        | 0x10000 ~ 0x1FFFF |

| 1            | 1   | 1   | すべてのセクター    | 0x00000 ~ 0x1FFFF |

**表 6. 下位保護アレイのスタート ポイント (TBPROT = 1)**

| ステータスレジスタの内容 |     |     | メモリアレイの保護部分 | アドレス範囲            |

|--------------|-----|-----|-------------|-------------------|

| BP2          | BP1 | BP0 |             |                   |

| 0            | 0   | 0   | 無し          | 無し                |

| 0            | 0   | 1   | 下位 64 番目の部分 | 0x00000 ~ 0x007FF |

| 0            | 1   | 0   | 下位 32 番目の部分 | 0x00000 ~ 0x00FFF |

| 0            | 1   | 1   | 下位 16 番目の部分 | 0x00000 ~ 0x01FFF |

| 1            | 0   | 0   | 下位 8 番目の部分  | 0x00000 ~ 0x03FFF |

| 1            | 0   | 1   | 下位 4 番目の部分  | 0x00000 ~ 0x07FFF |

| 1            | 1   | 0   | 下位半分        | 0x00000 ~ 0x0FFFF |

| 1            | 1   | 1   | すべてのセクター    | 0x00000 ~ 0x1FFFF |

### 書き込みイネーブル (WEL) SR[1]

メモリまたはレジスタ値への不注意な変更に対する保護手段としてプログラム、書き込みまたは消去処理を可能にするために、WEL ビットを「1」にセットする必要があります。書き込みイネーブル (WREN) コマンドを実行すると、書き込みイネーブルラッチを「1」に設定し、その後のすべての書き込みコマンドの実行を許可します。すべての書き込みコマンドを実行しないようにするために書き込みディスエーブル (WRDI) コマンドで書き込みイネーブルラッチを「0」にセットします。WEL ビットは、レジスタへの書き込み、STORE、RECALL、プログラムまたは消去処理が正常に終了する時に「0」にクリアされます。メモリマクロへの書き込み処理後にはクリアされないことに注意してください。電源切断／電源投入シーケンス、ハードウェアリセットまたはソフトウェアリセットの後、書き込みイネーブルラッチは「0」にセットされます。WRSR コマンドはこのビットには影響しません。

注：AutoStore、パワーアップ RECALL およびハードウェア STORE (HSB ベース) は WEL ビットから影響を受けません。

表 7. WEL ビットをセットすることを必要とする命令

| 命令の説明                | 命令名    | オペコード |

|----------------------|--------|-------|

| <b>メモリの書き込み</b>      |        |       |

| 書き込み                 | WRITE  | 02h   |

| デュアル入力書き込み           | DIW    | A2h   |

| クアッド入力書き込み           | QIW    | 32h   |

| デュアル入出力書き込み          | DIOW   | A1h   |

| クアッド入出力書き込み          | QIOW   | D2h   |

| <b>レジスタのコマンド</b>     |        |       |

| ステータス レジスタ書き込み       | WRSR   | 01h   |

| コンフィギュレーション レジスタ書き込み | WRCR   | 87h   |

| シリアル番号レジスタ書き込み       | WRSN   | C2h   |

| <b>NV 固有のコマンド</b>    |        |       |

| ストア                  | STORE  | 8Ch   |

| リコール                 | RECALL | 8Dh   |

| AutoStore イネーブル      | ASEN   | 8Eh   |

| AutoStore ディスエーブル    | ASDI   | 8Fh   |

表 8. コンフィギュレーション レジスタ

| ビット | フィールド名 | 機能                  | タイプ | R/W | デフォルト状態 | 説明                         |

|-----|--------|---------------------|-----|-----|---------|----------------------------|

| 7   | RFU    | 予約済み                | –   | R/W | 0       | 将来に使用するために予約済み             |

| 6   | RFU    | 予約済み                | –   | R/W | 1       | 将来に使用するために予約済み             |

| 5   | RFU    | 予約済み                | –   | –   | 0       | 将来に使用するために予約済み             |

| 4   | RFU    | 予約済み                | –   | –   | 0       | 将来に使用するために予約済み             |

| 3   | RFU    | 予約済み                | –   | –   | 0       | 将来に使用するために予約済み             |

| 2   | RFU    | 予約済み                | –   | –   | 0       | 将来に使用するために予約済み             |

| 1   | QUAD   | デバイスをクアッド モードに移行させる | NV  | R/W | 0       | 1 = クアッド ; 0 = デュアルまたはシリアル |

| 0   | RFU    | 予約済み                | –   | –   | 0       | 将来に使用するために予約済み             |

#### クアッド データ幅 (QUAD) CR[1]

「1」にセットされると、このビットはデバイスのデータ幅を4ビットに切り替え、すなわち、WPはI/O2に、NC(I/O3)はI/O3になります。WP入力の通常機能は監視されずに、この信号は内部でアクティブにセットされます。シリアル、デュアル出力およびデュアル I/O 読み出しのコマンドは正常に動作しますが、異なるデータ パス幅を使ってコマンドを切り替える際はコマンドのために WP入力を駆動する必要がありません。クアッド出力読み出し、クアッド I/O 読み出し、クアッド入力書き込み、クアッド I/O 書き込みおよびすべてのクアッド SPI コマンドを使用する際、クアッド ビットを「1」にセットする必要があります。クアッド ビットは不揮発性です。

**注：**クアッド ビットをセットするために、コンフィギュレーション レジスタに 0x42 を書き込みます。同様に、クアッド ビットをリセットするために、コンフィギュレーション レジスタに 0x40 を書き込みます。他のすべてのデータ組み合わせはデバイスのコンフィギュレーションを変更し、デバイスを使用不可能にします。

**注：**コンフィギュレーション レジスタのクアッド ビット CR[1] がセットされた場合、WPは内部的にデフォルトで論理「0」となります。

**注：**コンフィギュレーション レジスタに書き込まれた値は、STORE 処理が完了した後にのみ不揮発性メモリに保存されます。AutoStore が無効になると、コンフィギュレーション レジスタへの変更はソフトウェア STORE 処理を実行して確保する必要があります。ハードウェア Store は SRAM への書き込みがある場合にのみ非揮発性メモリにコンフィギュレーション レジスタの値をコミットします。

## SPI 制御命令

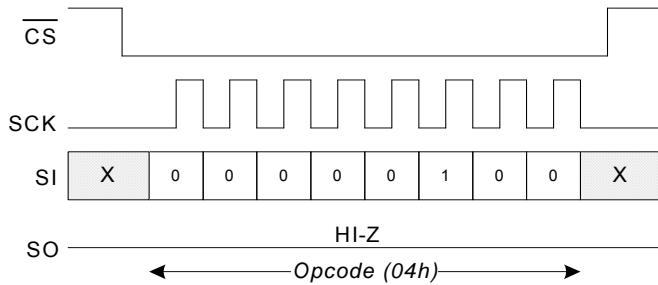

### 書き込みディスエーブル (WRDI) 命令

不注意による書き込みからデバイスを保護するために、書き込みディスエーブル命令で WEL ビットを「0」にクリアして、すべての書き込みを無効にします。この命令は CS の立ち下がりエッジ後に発行され、その後に WRDI 命令のオペコードが続けます。WEL ビットは CS の立ち上がりエッジでクリアされます。

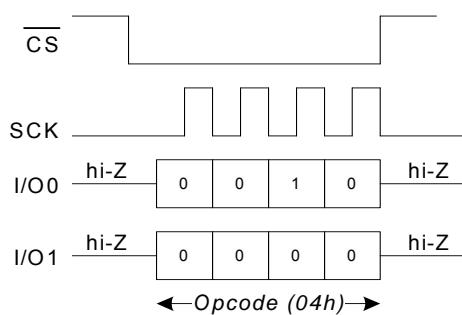

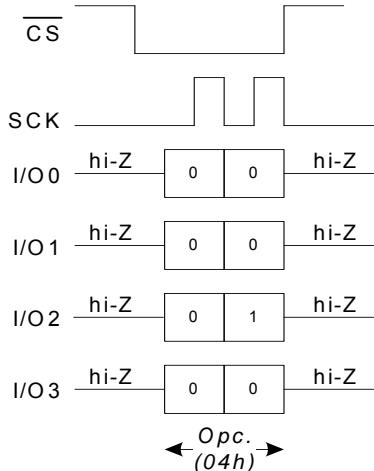

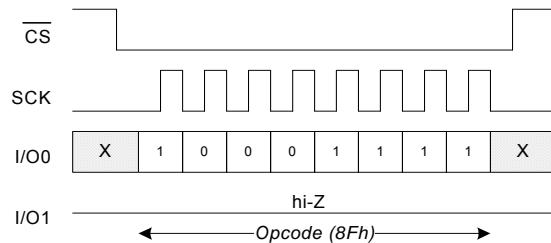

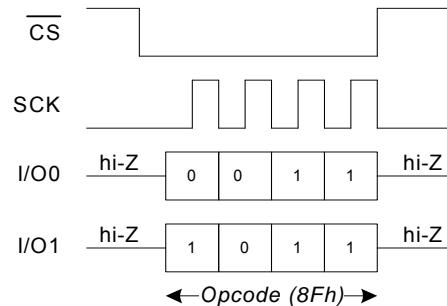

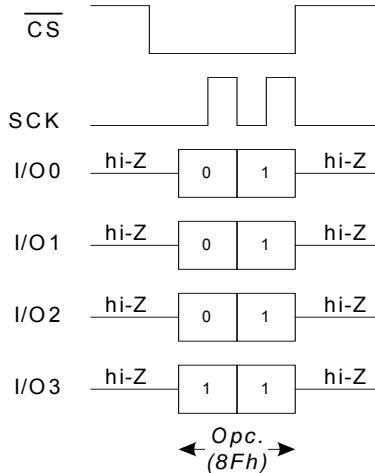

図 9. SPI モード時の WRDI 命令

図 10. DPI モード時の WRDI 命令

図 11. QPI モード時の WRDI 命令

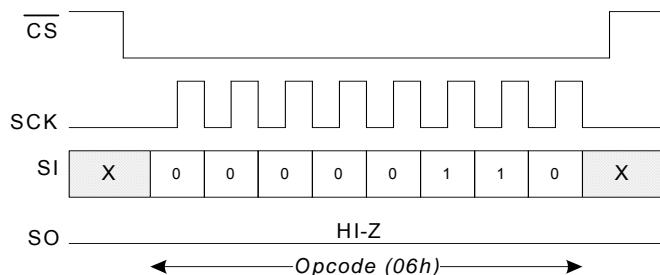

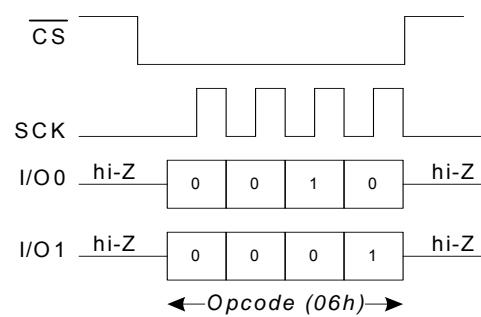

### 書き込みイネーブル (WREN) 命令

電源投入時、デバイスは常に書き込みディスエーブル状態にあります。したがって、書き込み命令と nvSRAM 固有の命令を実行したい場合、書き込みイネーブル命令を先立って発行する必要があります。デバイスは書き込み可能になっていない (WEL=「0」) 場合は、書き込み命令を無視し、CS が HIGH になるとスタンバイ状態に戻ります。この命令は、CS の立ち下がりエッジの後に発行され、WEL ビットを「1」にセットします。電源投入時、このビットはデフォルトで「0」にセットされています。

注：WEL ビットはレジスタへの正常の書き込み、STORE、RECALL、ASEN および ASDI の終了時に、「0」にクリアされます。メモリマクロへの書き込み後にはクリアされません。

図 12. SPI モード時の WREN 命令

図 13. DPI モード時の WREN 命令

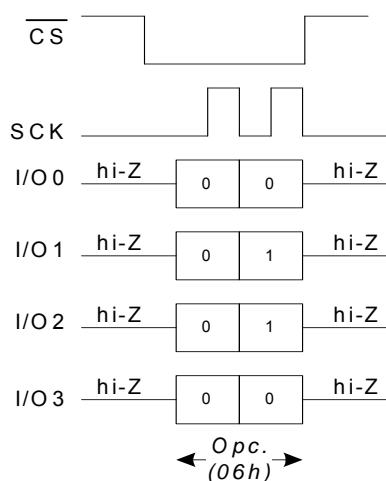

図 14. QPI モード時の WREN 命令

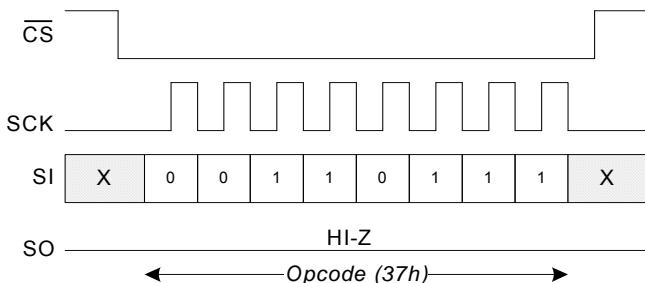

### DPI イネーブル (DPIEN) 命令

DPIEN でオペコード、アドレス、モード ビットおよびデータが I/O0 と I/O1 経由で送信されるデュアル I/O モードを有効にします。

図 15. SPI モード時のデュアル I/O イネーブル命令

図 16. QPI モード時のデュアル I/O イネーブル命令

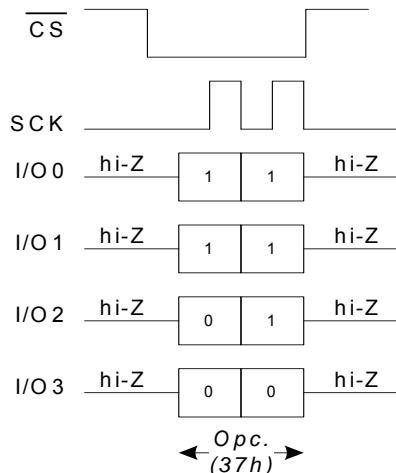

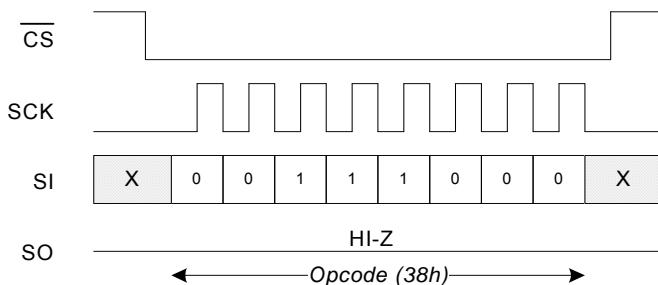

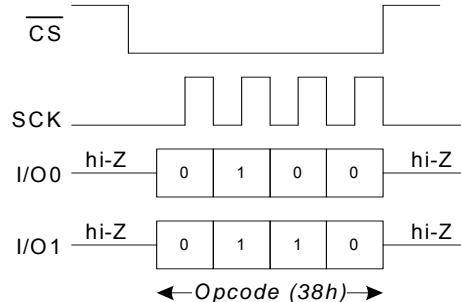

### QPI イネーブル (QPIEN) 命令

QPIEN でオペコード、アドレス、ダミー／モード ビットおよびデータが I/O0、I/O1、I/O2、I/O3 経由で送信される QPI モードを有効にします。QPIEN 命令はコンフィギュレーション レジスタのクアッド ビット CR[1] をセットしません。WRCR 命令はクアッド ビット CR[1] をセットするために、QPIEN 命令を開始する必要があります。

注：QPI モードを無効にしてもクアッド ビット CR[1] がリセットされません。

図 17. SPI モード時のクアッド I/O イネーブル命令

図 18. DPI モード時のクアッド I/O イネーブル命令

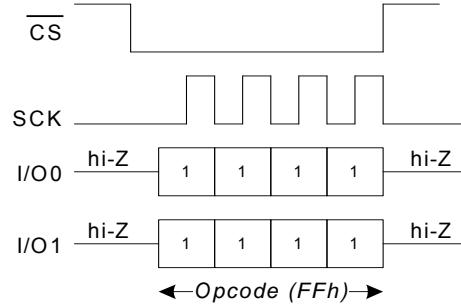

### SPI イネーブル (SPIEN) 命令

SPIEN はデュアル I/O またはクアッド I/O モードを無効にし、デバイスを SPI モードに戻させます。SPIEN 命令はコンフィギュレーション レジスタのクアッド ビット CR[1] をリセットしません。

図 19. DPI モード時の SPI イネーブル命令

図 20. QPI モード時の SPI イネーブル命令

## SPI メモリ読み出し命令

読み出し命令でメモリアレイにアクセスします。STORE または RECALL サイクルが進行中の場合、これらの命令を使用することはできません。STORE サイクルの進行中状態は、ステータスレジスタの WIP ビットおよび HSB ピンによって示されます。

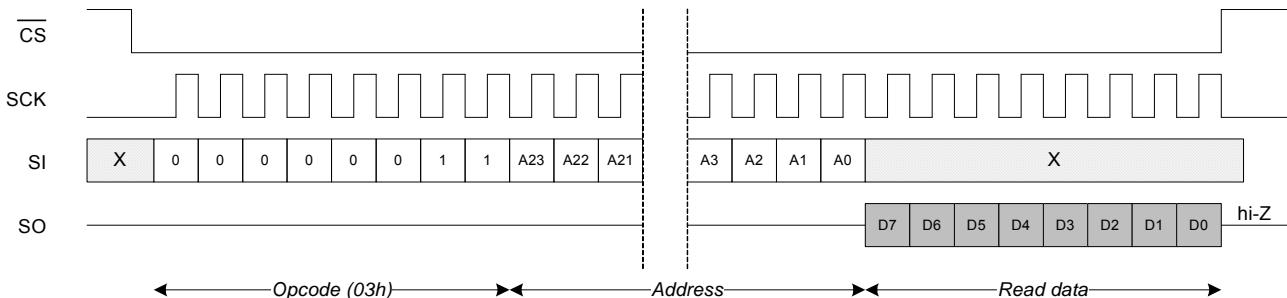

### 読み出し命令

デバイスは読み出し命令オペコードが SI ピンに提供されると読み出し処理を実行し、読み出しデータを SO ピン (SPI モード時)、または I/O1、I/O0 ピン (デュアル I/O モード時)、または I/O3、I/O2、I/O1、I/O0 ピン (クアッド I/O モード時) を介して供給します。デバイスを選択するために CS ピンが LOW にプルダウンされると、読み出しオペコードが入力され、その後に 3 アドレス バイトが続きます。デバイスは 1M ビット コンフィギュレーションのために 17 ビットのアドレス空間が用意されています。

最上位アドレス バイトはビット 0 に A16 が含まれており、他のビットは「ドントケア」です。アドレス ビット A15 ~ A0 が次の 2 つのアドレス バイトで送信されます。最後のアドレス ビットが送信された後、特定のアドレス位置のデータ (D7 ~ D0) は D7 から SCK の立ち下がりエッジでシフトアウトされます。CS が LOW に保持されている場合、読み出しがバーストモードで実行することができます。

各データ バイトが出力された後、デバイスが次の上位アドレスに自動的にインクリメントします。最後のデータ メモリアドレス (0xFFFF) に到達すると、アドレスは 0x00000 に戻り、デバイスは読み出し命令を継続します。読み出し処理は、データ出力中の任意の時点で CS を HIGH に駆動することで終了します。

**注：**読み出し命令は最大 40MHz までの周波数で実行します。デュアルおよびクアッドの I/O モードでは、アドレス バイト出力の後にダミー サイクルが必要です。これにより、デバイスは

最初のバイトをプリフェッチし、パイプライン流れを開始することができます。

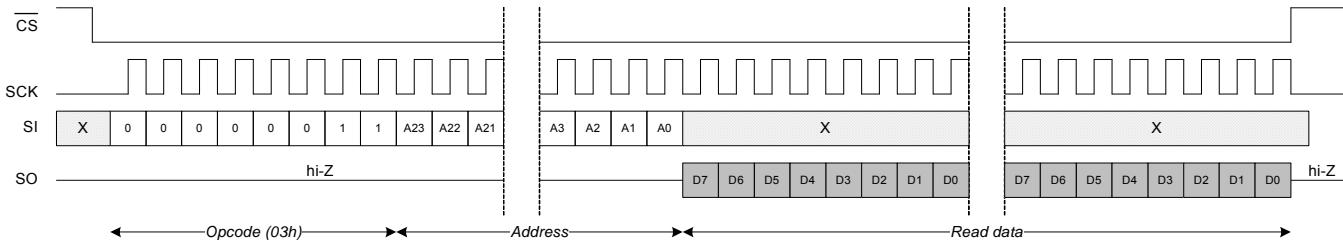

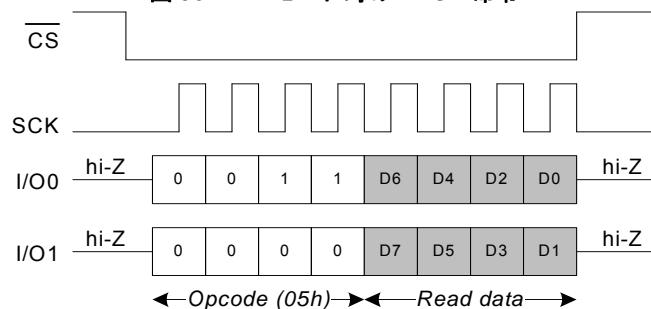

### 読み出し (READ) 命令

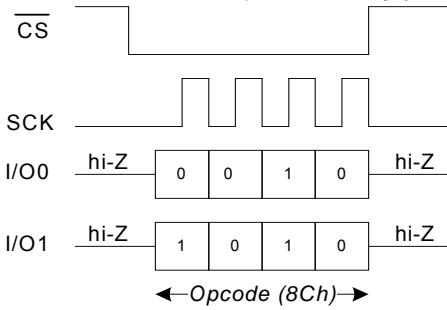

READ 命令は SPI、デュアル I/O (DPI)、または クアッド I/O (QPI) モードで使用できます。SPI モードでは、オペコードとアドレス バイトは SI ピンを介してクロック サイクル毎に 1 ビット送信されます。最後のアドレス サイクルの SCK の立ち下がりエッジで、特定のアドレス位置のデータ (D7 ~ D0) は SO ピンを介して D7 からクロック サイクル毎に 1 ビット シフトアウトされます。

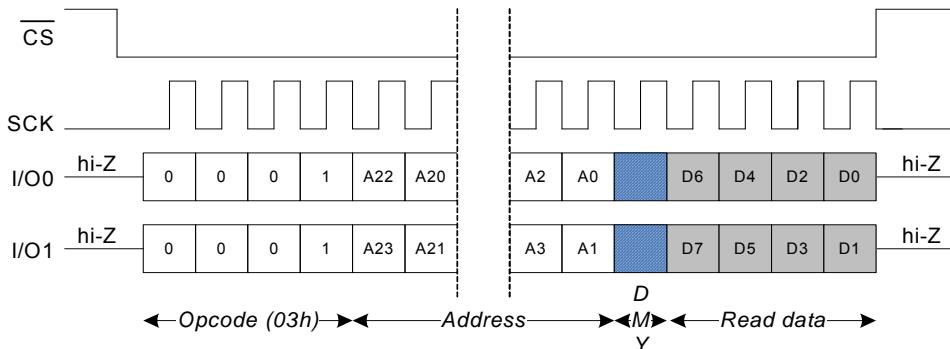

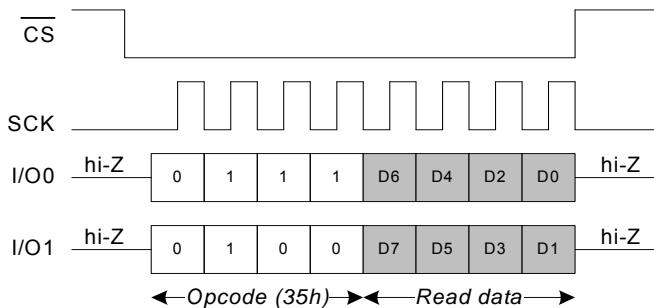

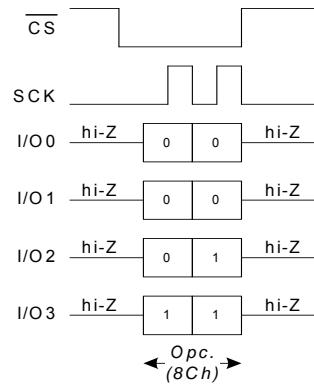

DPI モードでは、オペコードとアドレス バイトは I/O1 と I/O0 ピンを介してクロック サイクル毎に 2 ビット送信されます。最後のアドレス サイクルの SCK の立ち下がりエッジで、特定のアドレス位置のデータ (D7 ~ D0) は I/O1 ピンを介して D7、I/O0 を介して D6 からクロック サイクル毎に 2 ビット シフトアウトされます。QPI モードでは、オペコードとアドレス バイトは I/O3、I/O2、I/O1、I/O0 ピンを介してクロック サイクル毎に 4 ビット送信されます。最後のアドレス サイクルの SCK の立ち下がりエッジで、特定のアドレス位置のデータ (D7 ~ D0) は I/O3 ピンを介して D7、I/O2 を介して D6、I/O1 を介して D5、I/O0 を介して D4 からクロック サイクル毎に 4 ビット シフトアウトされます。

図 21. SPI モード時の READ 命令

図 22. SPI モード時のバースト モード READ 命令

**図 23. DPI モード時の READ 命令**

**図 24. QPI モード時の READ 命令**

注: QPI モードでは、READ 命令を実行する前にクアッド ビット CR[1] を論理「1」にする必要があります。

### 高速読み出し命令

高速読み出し命令により、最大 108MHz (Max) までの SPI 速度でメモリを読み出すことができます。この命令は、すべての I/O コンフィギュレーションにはウェイト ステートが加えられた通常の読み出し命令と同様で、モード バイトがアドレスの後、最初のデータが送信される前に送信されなければなりません。これにより、デバイスは最初のバイトをプリフェッチし、パイプライン流れを開始することができます。ホストシステムは、最初に CS を LOW に駆動することでデバイスを選択する必要があり、それから 3 アドレス バイトと、最後はモード バイトを送信します。SCK の次の立ち下がりエッジで、特定のアドレス位置からのデータは、SPI モードでは SO ピンを介して、デュアル I/O モードでは I/O1, I/O0 ピンを介して、クアッド I/O モードでは I/O3, I/O2, I/O1, I/O0 ピンを介してシフトアウトされ

ます。指定される最初のバイトは、どの位置でもかまいません。各データ バイトが出力された後、デバイスが次の上位アドレスに自動的にインクリメントします。したがって、メモリアレイ全体を 1 つの FAST\_READ 命令で読み出すことができます。メモリアレイの最上位アドレスに到達すると、アドレス カウンターは開始アドレス 0x00000 に戻り、読み出しシーケンスが永久に続行することを可能にします。高速読み出し命令は、データ出力中の任意の時点で CS を HIGH に駆動して終了します。

注: これらの命令は最大 108MHz までの SPI 周波数で動作します。

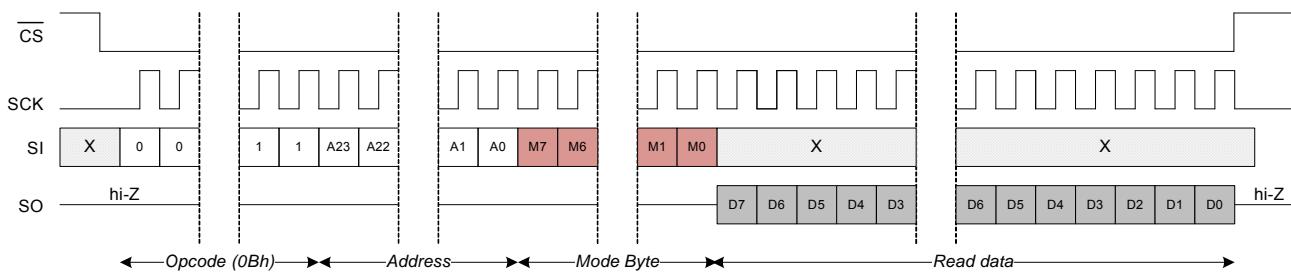

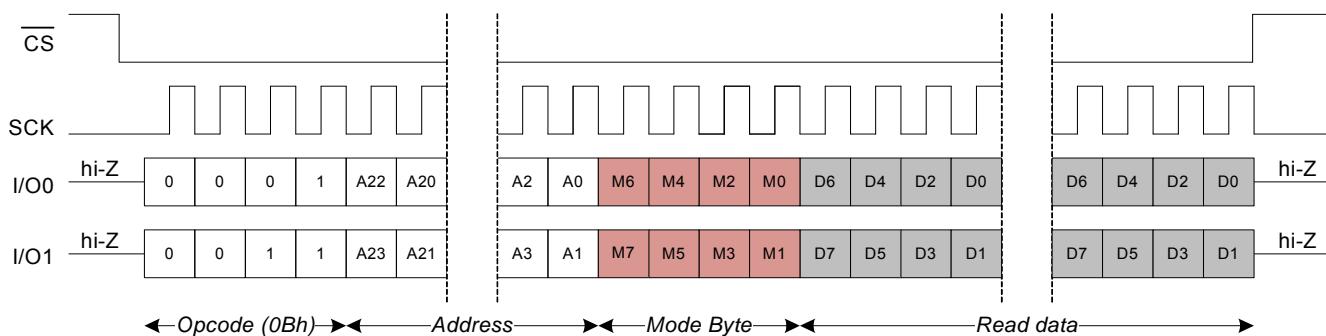

### 高速読み出し (FAST\_READ) 命令

FAST\_READ 命令は、SPI、デュアル I/O (DPI)、またはクアッド I/O (QPI) モードで使用できます。SPI モードでは、オペコード、アドレスおよびモード バイトは SI ピンを介してクロックサイクル毎に 1 ビット送信されます。最後のモード バイト サイクルの SCK の立ち下がりエッジで、特定のアドレス位置のデータ (D7 ~ D0) は SO ピンを介して D7 からクロックサイクル毎に 1 ビットシフトアウトされます。DPI モードでは、オペコードとモード バイトは I/O1 と I/O0 ピンを介してクロックサイクル毎に 2 ビット送信されます。最後のモード サイクルの立ち下がりエッジで、特定のアドレス位置のデータ (D7 ~ D0) は、I/O1 ピンを介して D7, I/O0 を介して D6 からクロック サイクル毎に 2 ビットシフトアウトされます。QPI モードでは、オペコードとアドレス バイトは I/O3, I/O2, I/O1, I/O0 ピンを介してクロック サイクル毎に 4 ビット送信されます。最後のモード サイクルの SCK の立ち下がりエッジで、特定のアドレス位置のデータ (D7 ~ D0) は、I/O3 を介して D7, I/O2 を介して D6, I/O1 を介して D5, I/O0 を介して D4 からクロック サイクル毎に 4 ビットシフトアウトされます。

**図 25. SPI モード時の FAST\_READ 命令**

**図 26. DPI モード時の FAST\_READ 命令**

**図 27. QPI モード時の FAST\_READ 命令**

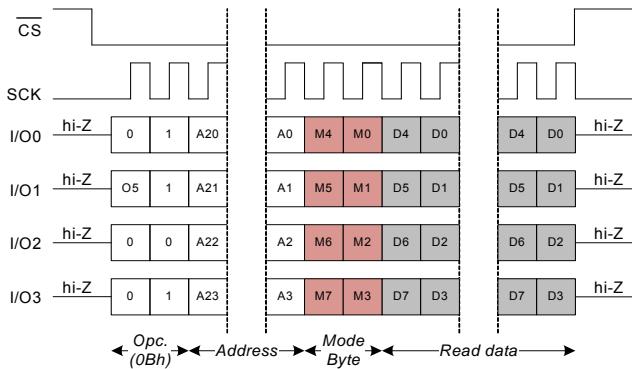

#### DOR 命令

DOR命令は拡張SPI読み出しコマンドの一部で、デュアルデータモードで使用されます。デュアルデータモードでは、オペコード、アドレスおよびモードバイトはSIピンを介してクロックサイクル毎に1ビット送信されます。最後のモードサイクルのSCKの立ち下がりエッジでは、SOがI/O1、SIがI/O0に再コンフィギュレーションされます。特定のアドレス位置のデータ(D7～D0)は、I/O1を介してD7、I/O0を介してD6からクロックサイクル毎に2ビットシフトアウトされます。

#### QOR 命令

QOR命令は拡張SPI読み出しコマンドの一部で、クアッドデータモードで使用されます。クアッドデータモードでは、オペコード、アドレスおよびモードバイトはSIピンを介してクロックサイクル毎に1ビット送信されます。最後のモードサイクルのSCKの立ち下がりエッジでは、NCがI/O3、WPがI/O2、SOがI/O1、SIがI/O0に再コンフィギュレーションされます。特定のアドレス位置のデータ(D7～D0)はI/O3を介してD7、I/O2を介してD6、I/O1を介してD5、I/O0を介してD4からクロックサイクル毎に4ビットシフトアウトされます。

注: QOR命令を実行する前にクアッドビットCR[1]を論理「1」にする必要があります。

**図 28. DOR 命令**

**図 29. QOR 命令**

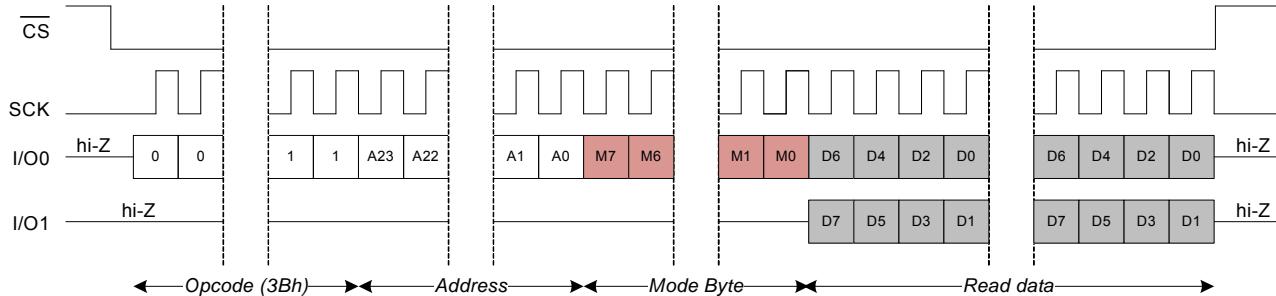

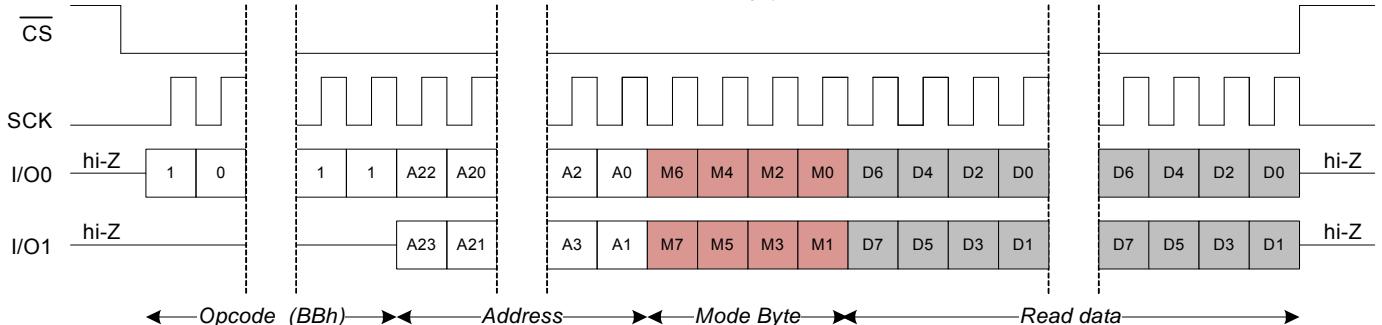

#### DIOR 命令

DIOR 命令は拡張 SPI 読み出しコマンドの一部で、デュアル アドレス／データ モードで使用されます。デュアル アドレス／データ モードでは、オペコードは SI ピンを介してクロック サイクル毎に 1 ビット送信されます。オペコードの最後のビットが送信された後、SO ピンが I/O1、SI が I/O0 に再コンフィギュレーションされます。その後、3 アドレス バイトが入力される

までアドレスはデバイスに I/O1、I/O0 ピン経由で、I/O1 を介して A23、I/O0 を介して A22 からクロック サイクル毎に 2 ビット送信されます。特定のアドレス位置のデータ (D7 ~ D0) は I/O1 を介して D7 から、I/O0 を介して D6 からクロック サイクル毎に 2 ビットシフトアウトされます。

**図 30. DIOR 命令**

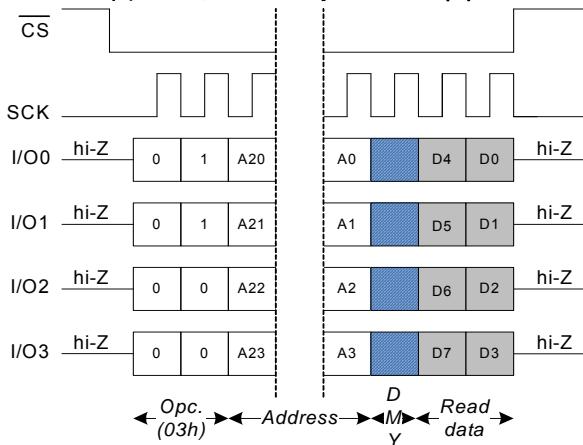

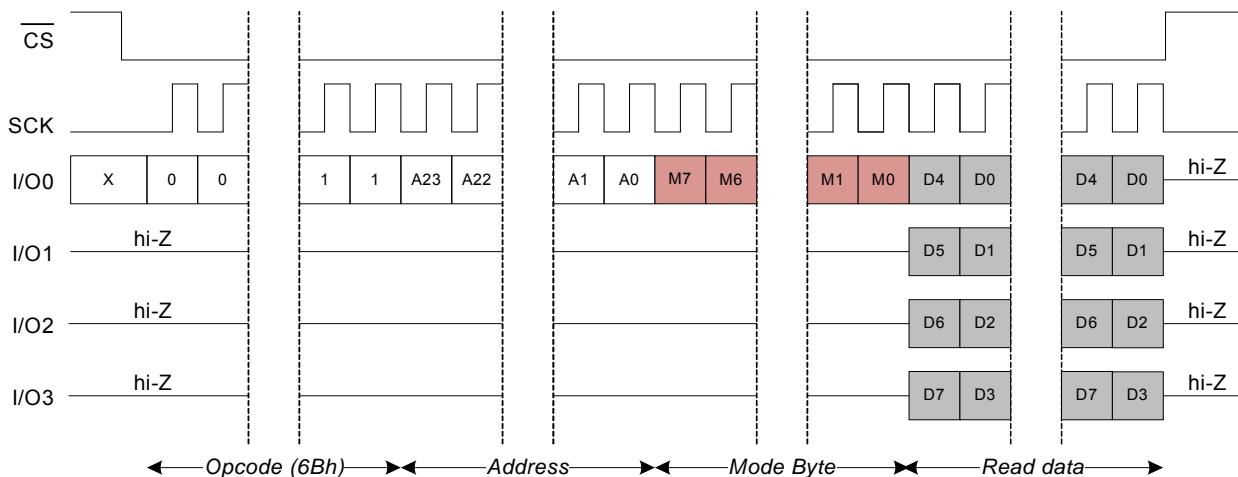

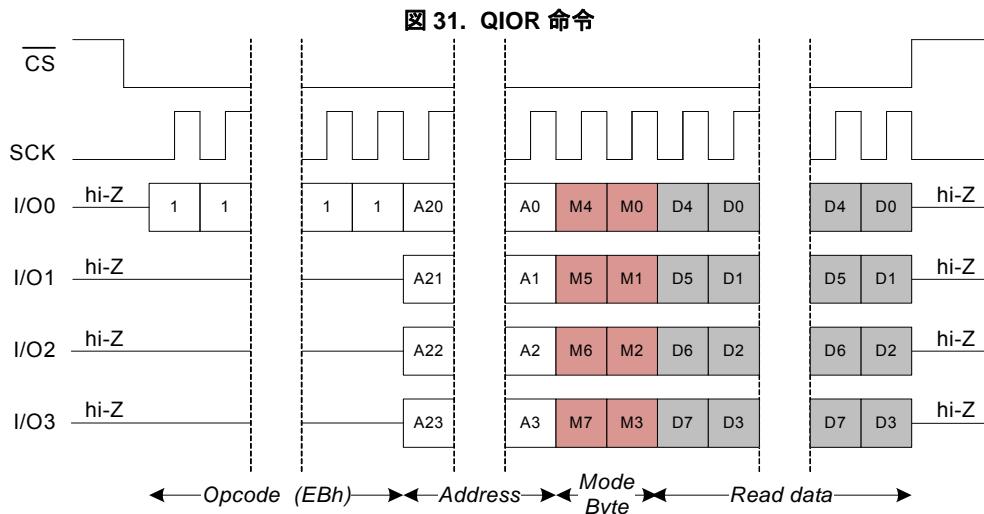

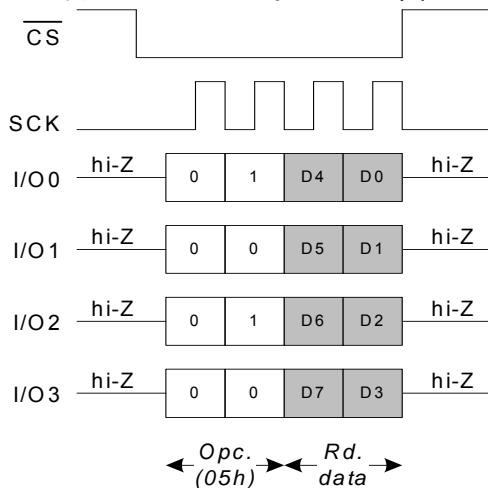

#### QIOR 命令

QIOR 命令は拡張 SPI 読み出しコマンドの一部で、クアッド アドレス／データ モードで使用されます。クアッド アドレス／データ モードでは、オペコードは SI ピンを介してクロック サイクル毎に 1 ビット送信されます。オペコードの最後のビットが送信された後、NC が I/O3 に、WP が I/O2、SO が I/O1、SI が I/O0 に再コンフィギュレーションされます。その後、3 アドレス バイトが入力されるまでアドレスはデバイスに I/O3、I/O2、I/O1、I/O0 ピン経由で、I/O3 を介して A23、I/O2 を介して A22、I/O1 を介して A21、I/O0 を介して A20 からクロック サイクル毎に 4 ビット送信されます。特定のアドレス位置のデータ (D7 ~ D0) は I/O3 を介して D7、I/O2 を介して D6、I/O1 を介して D5、I/O0 を介して D4 からクロック サイクル毎に 4 ビットシフトアウトされます。

注：QIOR 命令を実行する前にクアッド ビット CR[1] を論理「1」にする必要があります。

### 書き込み命令

デバイスは、読み出し命令オペコードと書き込みデータが SI ピン (SPI モード時)、または I/O1、I/O0 ピン (デュアル I/O モード時)、I/O3、I/O2、I/O1、I/O0 ピン (クアッド I/O モード時) を介して供給される時に書き込み処理を実行します。デバイスは書き込みが無効である場合、書き込み処理を実行するには、まず WREN 命令を使用して書き込みを有効にする必要があります。書き込みが有効である場合 (WEL=「1」)、WRITE 命令は CS の立ち下がリエッジの後に発行されます。nvSRAM は書き込みがバーストで実行することを可能にします。この時、さらなる書き込み命令を発行せず、アドレスを連続して書き込むことができます。1 バイトだけが書き込まれる場合、D0 (データの LSB) が送信された後、CS ピンを HIGH に駆動する必要があります。しかし、より多くのバイトが書き込まれる場合は、CS ピンを LOW に維持しなければなりません。この時、アドレスは自動的にインクリメントされます。入力ピン上のデータバイトが連続するアドレスに書き込まれます。最後のデータメモリアドレス (0xFFFF) に到達すると、アドレスは 0x000000 に戻り、デバイスは書き込みを継続します。

注：ステータスレジスタの WEL ビットは、メモリアレイへの書き込みシーケンスの終了時に「0」にリセットされません。

注：バースト書き込みが保護されたブロックアドレスに到達すると、保護された空間へのアドレスのインクリメントを継続しますが、保護されたメモリにデータを書き込みません。アドレスがロールオーバーし、保護されていない空間に対しバースト書き込みを実行する場合、書き込みが再開されます。バースト

書き込みが書き込み保護されたブロック内で開始された場合、同じ処理は行われます。

注：これらの命令は最大 108MHzまでの周波数で動作します。デバイスを選択するため CS ピンを LOW にプルダウンすると、書き込みオペコードとそれに後続する 3 アドレス バイトが入力されます。デバイスは 1M ビット コンフィギュレーションのために 17 ビットのアドレス空間が用意されています。最上位アドレス バイトはビット 0 に A16 が含まれており、残りのビットは「ドントケア」です。アドレス ビット A15 ~ A0 は次の 2 つのアドレス バイトで送信されます。最後のアドレス ビットが送信された直後、データ (D7 ~ D0) は入力ラインを介して送信されます。このコマンドは SPI、DPI、QPI モードで使用できます。

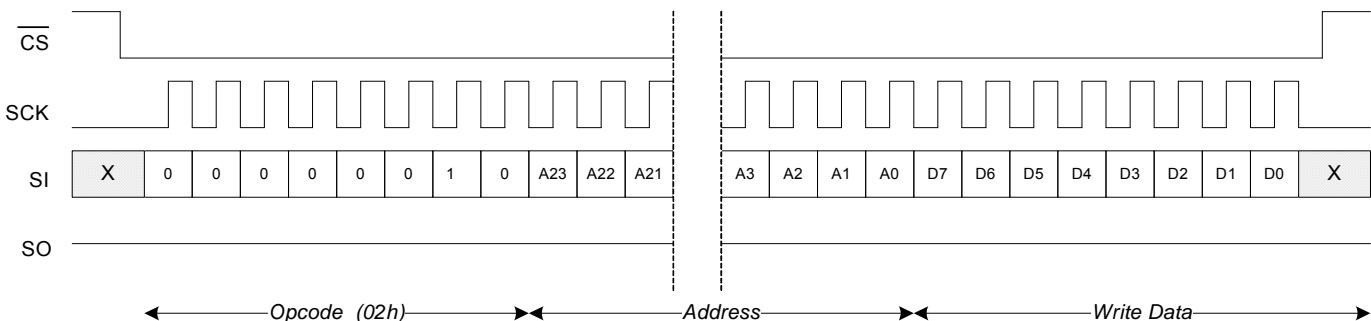

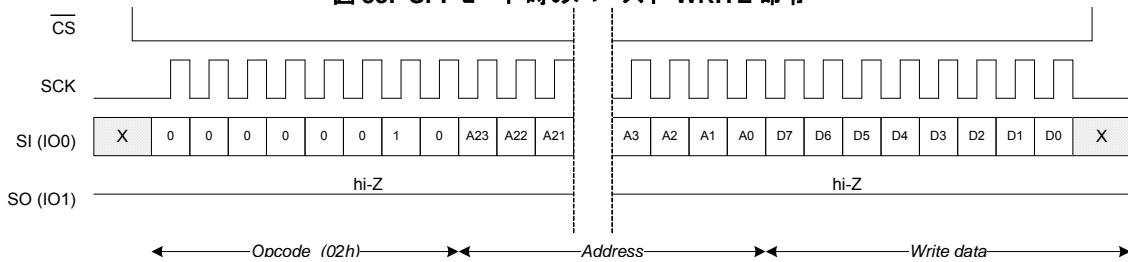

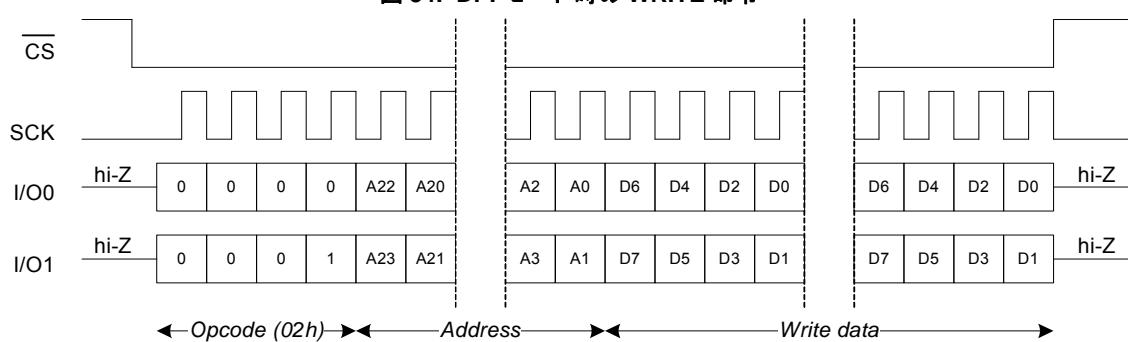

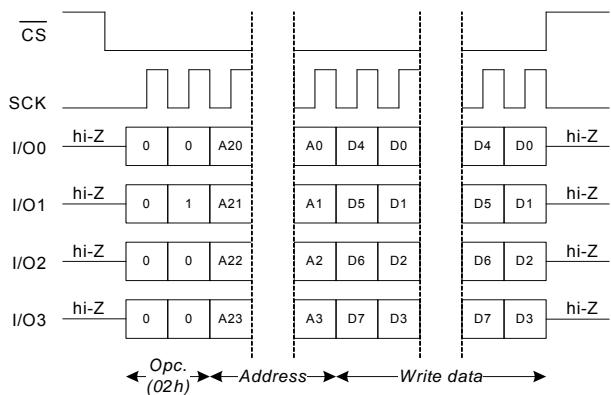

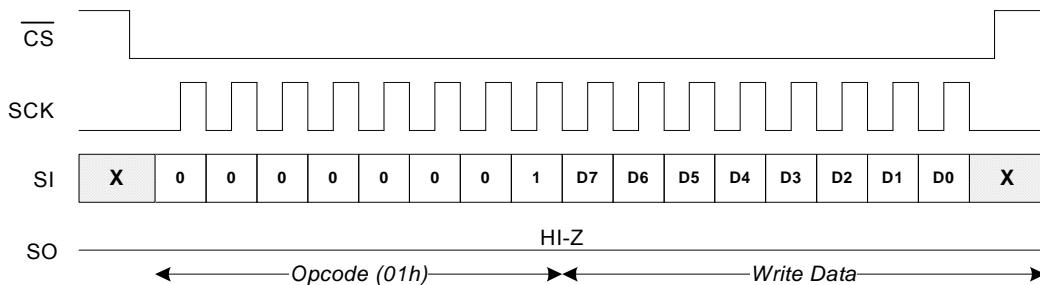

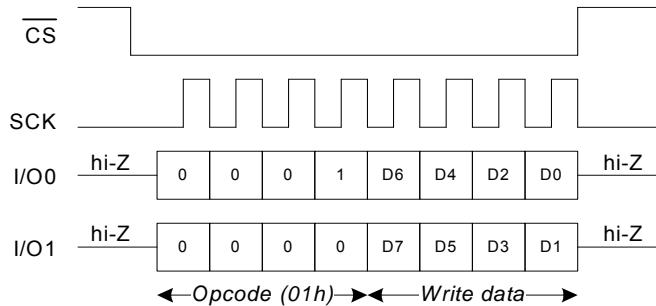

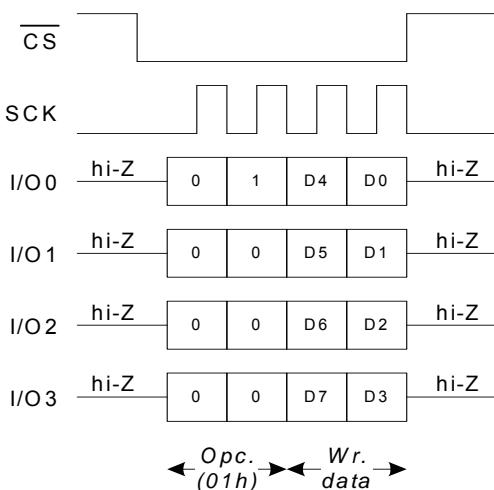

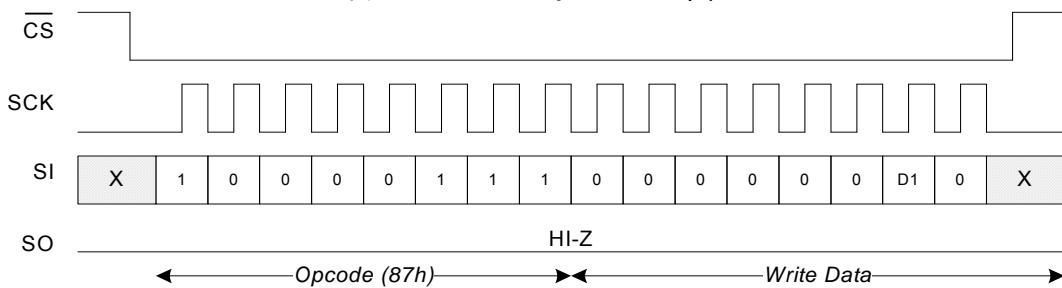

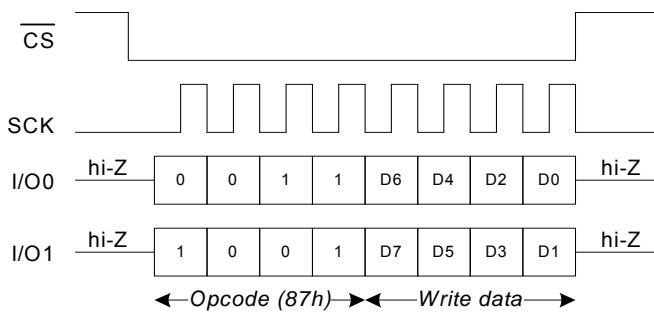

### WRITE 命令

WRITE 命令は SPI、DPI、QPI モードで使用できます。SPI モードでは、オペコード、アドレス バイトおよびデータ バイトは SI ピンを介して D7 からクロックサイクル毎に 1 ビット送信されます。DPI モードでは、オペコード、アドレス バイトおよびデータ バイトは I/O1 と I/O0 ピン経由で、I/O1 を介して D7、I/O0 を介して D6 からクロックサイクル毎に 2 ビット送信されます。QPI モードでは、オペコード、アドレス バイトおよびデータ バイトは I/O3、I/O2、I/O1、I/O0 ピン経由で、I/O3 を介して D7、I/O2 を介して D6、I/O1 を介して D5、I/O0 を介して D4 からクロックサイクル毎に 4 ビット送信されます。

**図 32. SPI モード時の WRITE 命令**

**図 33. SPI モード時のバースト WRITE 命令**

**図 34. DPI モード時の WRITE 命令**

**図 35. QPI モード時の WRITE 命令**

**DIW 命令**

DIW 命令は拡張 SPI 書き込みコマンドの一部で、デュアルデータ モードで使用できます。デュアルデータ モードでは、オペコードとアドレス バイトは SI ピンを介してクロック サイクル毎に 1 ビット送信されます。最後のアドレス ビットが送信された直後、SO が I/O1、SI が I/O0 に再コンフィギュレーションされます。この時、データ (D7 ~ D0) は I/O1 を介して D7、I/O0 を介して D6 からクロック サイクル毎に 2 ビット送信されます。

注: QPI モードでは、WRITE 命令を実行する前にクアッド ビット CR[1] を論理「1」にする必要があります。

**図 36. DIW 命令**

### QIW 命令

QIW 命令は拡張 SPI 書き込みコマンドの一部で、クアッド データ モードで使用できます。クアッド データ モードでは、オペコードとアドレス バイトは SI ピンを介してクロック サイクル毎に 1 ビット送信されます。最後のアドレス ビットが送信された直後、NC が I/O3、WP が I/O2、SO が I/O1、SI が I/O0 に再

コンフィギュレーションされます。この時、データ (D7 ~ D0) は I/O3、I/O2、I/O1、I/O0 経由で、I/O3 を介して D7、I/O2 を介して D6、I/O1 を介して D5、I/O0 を介して D4 からクロック サイクル毎に 4 ビット送信されます。

注：QIW 命令を実行する前にクアッド ビット CR[1] を論理「1」にする必要があります。

図 37. QIW 命令

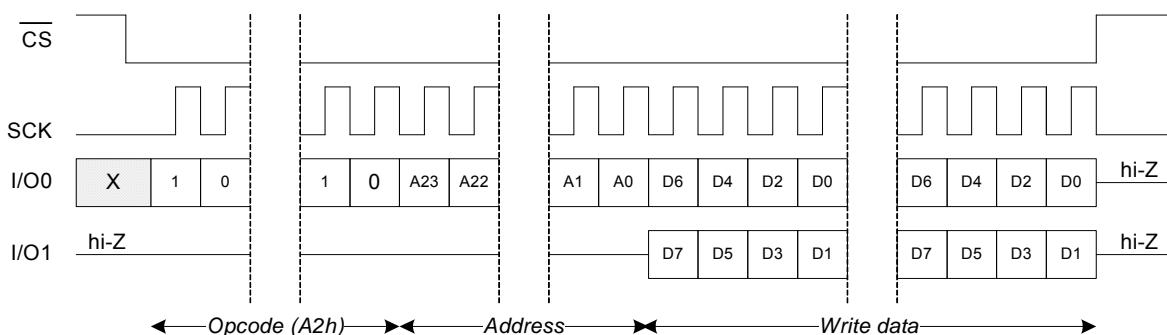

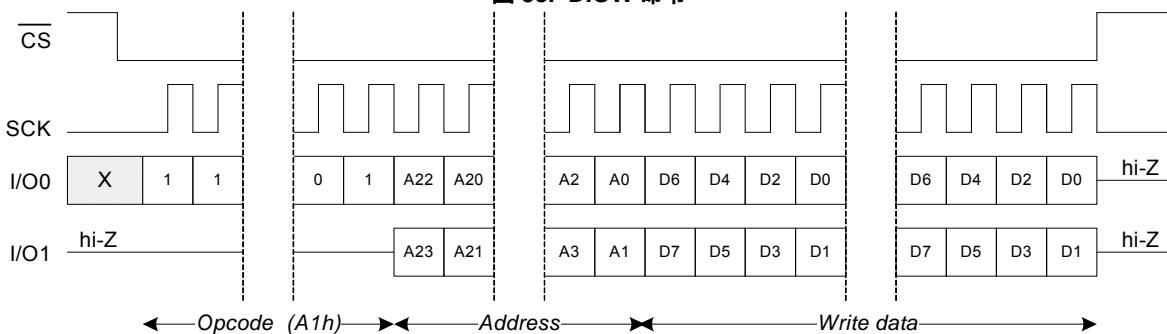

### DIOW 命令

DIOW 命令は拡張 SPI 書き込みコマンドの一部で、デュアル アドレス/データ モードで使用できます。デュアル アドレス/データ モードでは、オペコードは SI ピンを介してクロック サイクル毎に 1 ビット送信されます。最後のオペコード ビットが送信された直後、SO が I/O1、SI が I/O0 に再コンフィギュレーションされます。この時、3 アドレス バイトが入力されるまで

データ (D7 ~ D0) は I/O1 と I/O0 ピン経由で、I/O1 を介して A23、I/O0 を介して A22 からクロック サイクル毎に 2 ビット送信されます。最後のアドレス ビットが送信された後、データ (D7 ~ D0) はデバイスに I/O1 と I/O0 経由で、I/O1 を介して D7、I/O0 を介して D6 からクロック サイクル毎に 2 ビット送信されます。

図 38. DIOW 命令

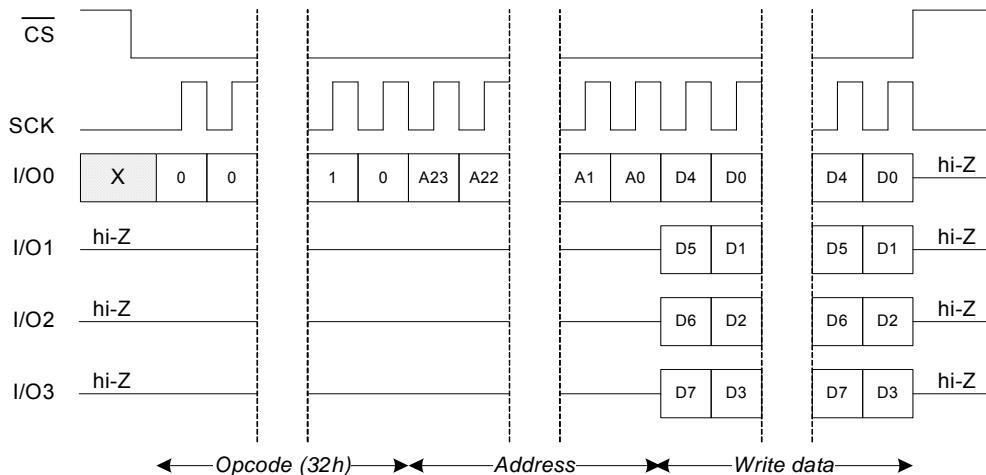

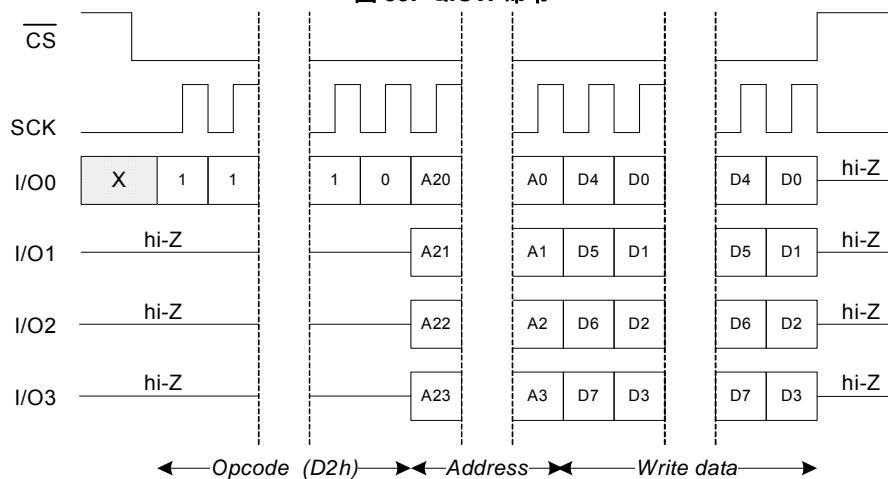

### QIOW 命令

QIOW 命令は拡張 SPI 書き込みコマンドの一部で、クアッド アドレス/データ モードで使用できます。クアッド アドレス/データ モードでは、オペコードは SI ピンを介してクロック サイクル毎に 1 ビット送信されます。最後のオペコード ビットが送信された直後、NC が I/O3、WP が I/O2、SO が I/O1、SI が I/O0 に再コンフィギュレーションされます。この時、3 アドレス バイトが入力されるまでデータ (D7 ~ D0) は I/O3、I/O2、I/O1、I/O0 経由で、I/O3 を介して A23、I/O2 を介して A22、I/O1 を介して A21、I/O0 を介して A20 からクロック サイクル毎に 4 ビット送信されます。最後のアドレス ビットが送信した後、データ (D7 ~ D0) は I/O3、I/O2、I/O1、I/O0 経由で、I/O3

を介して D7、I/O2 を介して D6、I/O1 を介して D5、I/O0 を介して D4 からクロック サイクル毎に 4 ビット送信されます。

注：QIOW 命令を実行する前にクアッド ビット CR[1] を論理「1」にする必要があります。

**図 39. QIOW 命令**

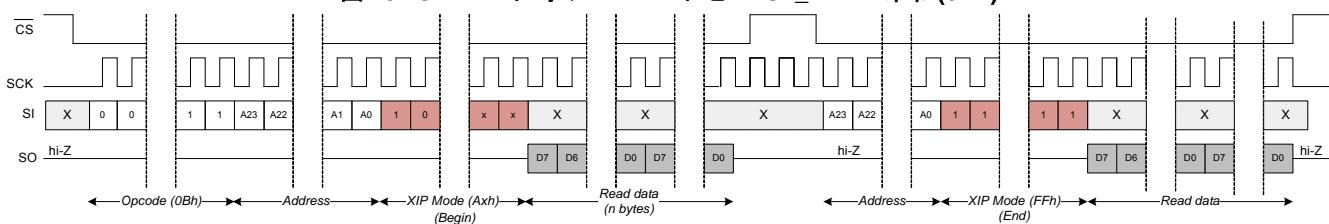

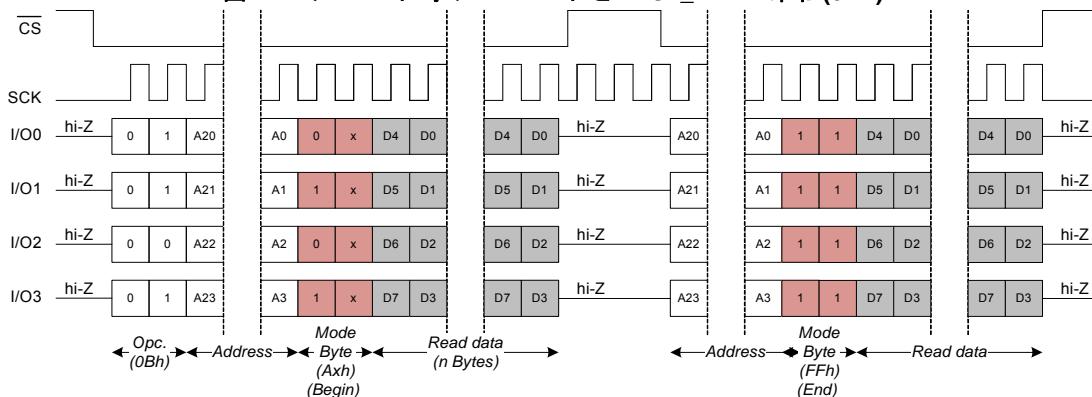

#### Execute In Place (XIP) ( 直接実行 )

Execute-in-place (XIP) モードでは、メモリはすべての読み出し処理のコマンドコードをロードせずに異なったアドレスで始まる一連の読み出し処理を実行できます。これにより、ランダムアクセス時間が短縮され、高速実行のための RAM のコードシャドーが不要になります。XIP モードでサポートされる読み出しコマンドは FAST\_READ (SPI、DPI、QPI モード時)、DOR、DIOR、QOR および QIOR です。

これらのコマンドの XIP モードはモード ビットを入力することでセットまたはリセットされます。モード ビットの上位ニブル (ビット 7 ~ 4) は、最初のバイトの命令コードの包含または除外により前述の次の読み出しコマンドの長さを制御します。モード ビットの下位ニブル (ビット 3 ~ 0) は「ドントケア」(「x」) で、高インピーダンスであることがあります。多くの場

合、マイクロコントローラによってデータ読み出しのためにバスの回転に使用されます。モード ビットが「Exh」の場合、下図に示すように、デバイスは読み出しモードに設定され／保持され、次のアドレスはオペコードなしで入力することができます。これにより、オペコード シーケンスのサイクルをいくつか減少できます。モード ビットが「Fxh」の場合、XIP モードはリセットされ、デバイスは現時点のトランザクションの終了後にはオペコードを期待します。

これらのコマンドの間、すべてのシーケンスで、いつでも XIP モードへ／から移行／復帰することができます。書き込みなど、XIP モードがサポートされない別の処理を実行する必要がある場合、新しいコマンドコードを所望の処理のために入力する前に、XIP モードを終了しなければなりません。

**図 40. SPI モード時の XIP モードと FAST\_READ 命令 (0Bh)**

**図 41. QPI モード時の XIP モードと FAST\_READ 命令 (0Bh)**

## システム リソース命令

### ソフトウェアリセット (RESET) 命令

RESET 命令ではデバイス全体がリセットされ、コマンド受信の準備ができます。I/O モードが SPI にコンフィギュレーションされます。すべての不揮発性レジスタや不揮発性レジスタビットはそのままの値となります。すべての揮発性レジスタや揮発性レジスタビットはデフォルトで論理「0」になります。この命令は完了するのに  $t_{RESET}$  の時間を要します。STORE / RECALL 処理は実行されません。ソフトウェアリセットプロセスを開始するには、リセットイネーブル (RSTEN) 命令が必要です。これにより、不注意によるリセットが防止されます。したがって、ソフトウェアリセットは 2 つのコマンドのシーケンスです。

表9. ソフトウェアリセットステート

| ステート 1 | ステート 2     | ステート 3 | I/O モードおよびレジスタビット                                                                                                                                                                                                                 |

|--------|------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| スタンバイ  | ソフトウェアリセット | スタンバイ  | I/O モード : SPI<br>SRWD SR[7]: ステート 1 と同じ<br>SNL SR[6]: ステート 1 と同じ<br>TBPROT SR[5]: ステート 1 と同じ<br>BP2 SR[4]: ステート 1 と同じ<br>BP1 SR[3]: ステート 1 と同じ<br>BP0 SR[2]: ステート 1 と同じ<br>WEL SR[1]: 0<br>WIP SR[0]: 0<br>QUAD CR[1]: ステート 1 と同じ |

図 42. SPI モード時の RESET 命令

図 43. DPI モード時の RESET 命令

**図 44. QPI モード時の RESET 命令**

**注 :** QPI モードでは、RSTEN/RESET 命令を実行する前にクアッド ビット CR[1] を論理「1」にする必要があります。

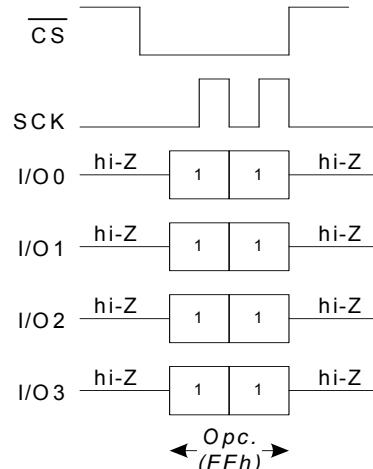

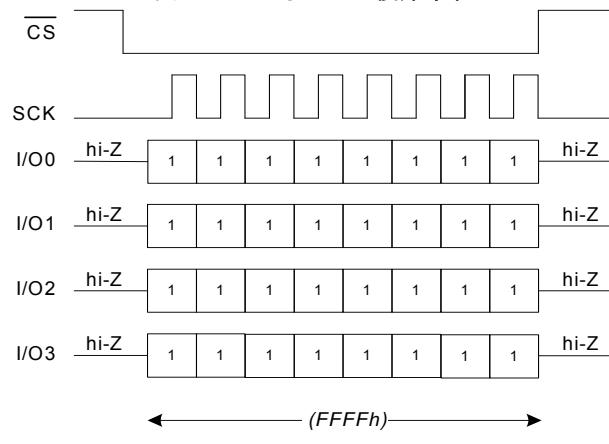

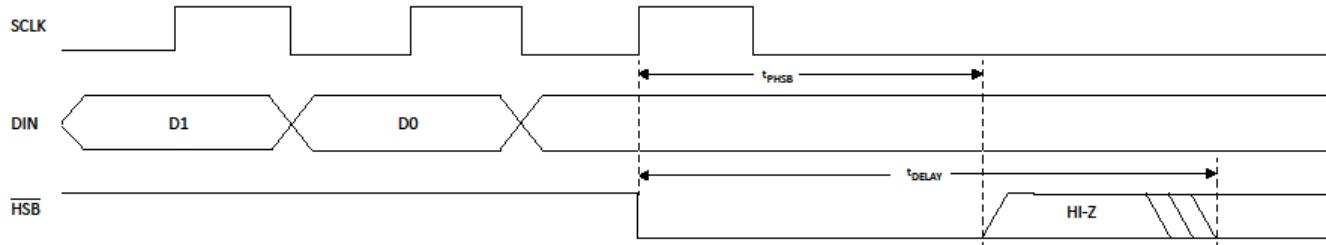

#### デフォルトの復帰命令

デバイスは、デバイスが SPI モードに復帰するデフォルトの復帰モードがあります。すべての I/O (I/O3, I/O2, I/O1, I/O0) での論理 HIGH と 8 つの SCLK により、スタート モードが未知の場合、ホストがデバイスに通信できるようにデバイスは既知のモード (SPI) に移行します。

**注 :**  $\overline{WP}$  と NC (I/O3) の機能はコンフィギュレーション レジスタのクアッド ビット CR[1] によって制御されます。クアッド ビットが論理「1」にセットされた場合、 $\overline{WP}$  と NC (I/O3) はそれぞれ I/O2 と I/O3 にコンフィギュレーションされます。そうしないと、 $\overline{WP}$  と NC (I/O3) の機能がコンフィギュレーションされます。

**図 45. デフォルトの復帰命令**

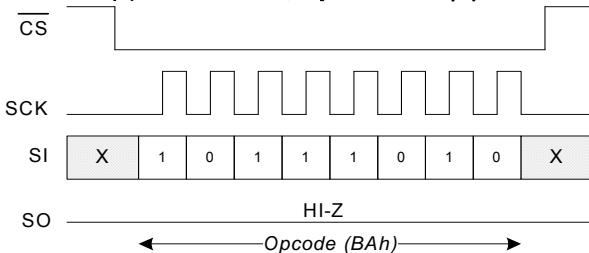

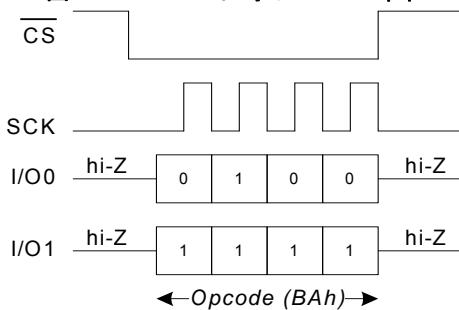

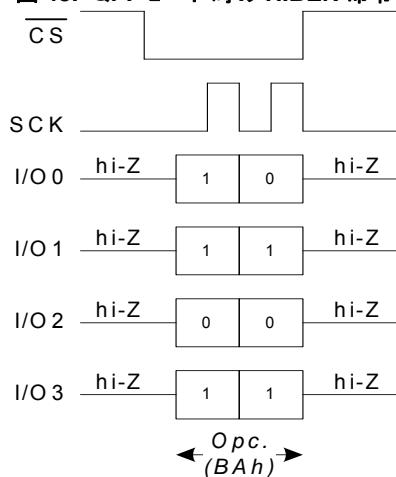

### ハイバネート (HIBEN) 命令

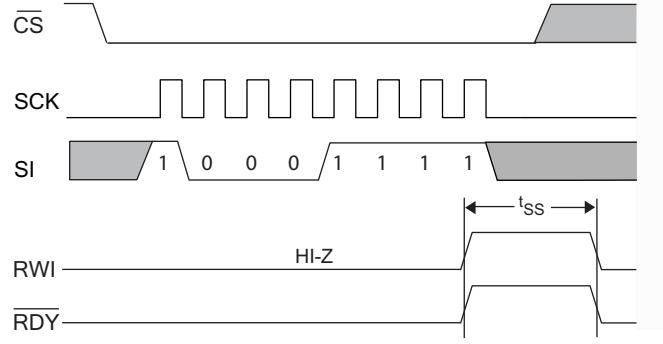

HIBEN 命令は nvSRAM をハイバネート モードに移行させます。HIBEN 命令が発行されると、nvSRAM は HIBEN 要求を処理するのに tSS 時間を要します。HIBEN コマンドが正常に取り込まれて処理されると、nvSRAM は HSB を LOW にトグルし、不揮発性セルにデータを保存するために STORE 処理を実行してから、ハイバネート モードに入ります。デバイスは、HIBEN 命令が取り込まれてから  $t_{HIBEN}$  時間後に  $I_{ZZ}$  電流を消費し始めます。HIBEN 命令が発行された後は、デバイスは通常の動作を実行することはできません。ハイバネート モードでは、SCK と SI ピンは無視され、SO は Hi-Z になりますが、デバイスは CS ピンの監視を継続します。

表 10. ウェイク (ハイバネートの終了) ステート

| ステート 1 | ステート 2 | ステート 3 | I/O モードおよびレジスタ ビット                                                                                                                                                                                                                                        |

|--------|--------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| スタンバイ  | ハイバネート | スタンバイ  | I/O モード : ステート 1 と同じモード (SPI/DPI/QPI)<br>SRWD SR[7]: ステート 1 と同じ<br>SNL SR[6]: ステート 1 と同じ<br>TBPROT SR[5]: ステート 1 と同じ<br>BP2 SR[4]: ステート 1 と同じ<br>BP1 SR[3]: ステート 1 と同じ<br>BP0 SR[2]: ステート 1 と同じ<br>WEL SR[1]: 0<br>WIP SR[0]: 0<br>QUAD CR[1]: ステート 1 と同じ |

図 46. SPI モード時の HIBEN 命令

図 47. DPI モード時の HIBEN 命令

nvSRAM をハイバネート モードから復帰させるには、 $\overline{CS}$  ピンを HIGH から LOW にトグルしてデバイスを選択する必要があります。CS ピンの立ち下がりエッジが検出された後、tWAKE 期間が経過すると、デバイスはウェイクアップし、通常の動作を実行することができます。デバイスは HIBEN 命令が実行された前のモードに復帰します。

注: nvSRAM はハイバネート モードに入ると、不揮発性 STORE サイクルを開始します。その結果として、ハイバネート コマンド実行の度に 1 回のアクセス サイクルとなります。前回の STORE または RECALL サイクル以降に SRAM への書き込みが実行された場合にのみ、STORE サイクルが開始されます。

表 10 は、デバイスのハイバネート状態からの復帰をまとめます。

**図 48. QPI モード時の HIBEN 命令**

**注 :** QPI モードでは、HIBEN 命令を実行する前にクアッド ビット CR[1] を論理「1」にする必要があります。

**表 11. スリープ モード終了 (EXSLP) ステート**

| ステート 1 | ステート 2 | ステート 3 | I/O モードおよびレジスタ ビット                                                                                                                                                                                                                                                 |

|--------|--------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| スタンバイ  | スリープ   | スタンバイ  | I/O モード : ステート 1 と同じモード (SPI/DPI/QPI)<br>SRWD SR[7]: ステート 1 と同じ<br>SNL SR[6]: ステート 1 と同じ<br>TBPROT SR[5]: ステート 1 と同じ<br>BP2 SR[4]: ステート 1 と同じ<br>BP1 SR[3]: ステート 1 と同じ<br>BP0 SR[2]: ステート 1 と同じ<br>WEL SR[1]: ステート 1 と同じ<br>WIP SR[0]: 0<br>QUAD CR[1]: ステート 1 と同じ |

**図 49. SPI モード時の SLEEP 命令**

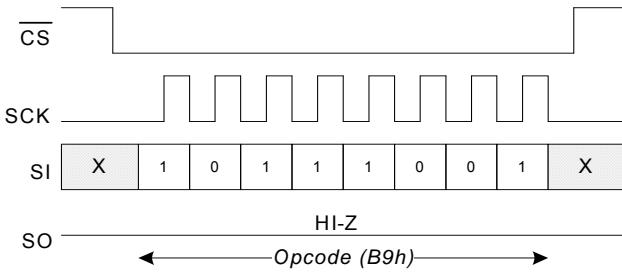

### スリープ (SLEEP) 命令

SLEEP 命令は nvSRAM をスリープ モードに移行させます。SLEEP 命令が発行されると、nvSRAM は SLEEP 要求を処理するのに  $t_{SLEEP}$  時間を要し、 $I_{SLEEP}$  電流を消費し始めます。SLEEP 命令が発行された後は、デバイスで通常の動作を実行することはできません。スリープ モードでは、すべてのピンはアクティブです。

nvSRAM をスリープ モードから復帰させるには、EXSLP 命令を入力する必要があります。 $t_{EXSLP}$  期間が経過した後、nvSRAM で通常の動作を実行することができます。デバイスは SLEEP 命令が実行される前のモードに復帰します。EXSLP と RDSR 命令を除き、デバイスがスリープ モード中に入力された命令はすべて無視されます。

表 11 は、デバイスのスリープ状態からの復帰をまとめます。

**図 50. DPI モード時の SLEEP 命令**

**図 51. QPI モード時の SLEEP 命令**

**図 52. SPI モード時の EXSLP 命令**

**図 53. DPI モード時の EXSLP 命令**

**図 54. QPI モード時の EXSLP 命令**

## レジスタ命令

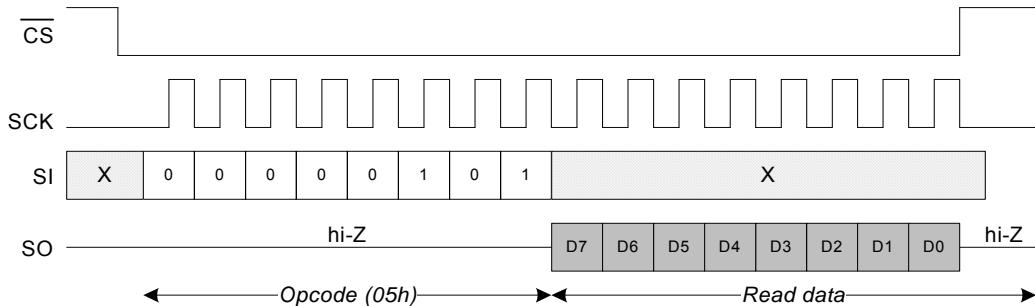

#### ステータス レジスタ読み出し (RDSR) 命令

RDSR 命令は、最大 108MHzまでの SPI 周波数でステータスレジスタへのアクセスを提供します。この命令は、デバイスのステータスをプローブするために使用されます。

**注:**ステータスレジスタの最後のビットが読み出された後、デバイスはステータスレジスタの最初のビットに戻ります。

図 55. SPI モード時の RDSR 命令

図 56. DPI モード時の RDSR 命令

図 57. QPI モード時の RDSR 命令

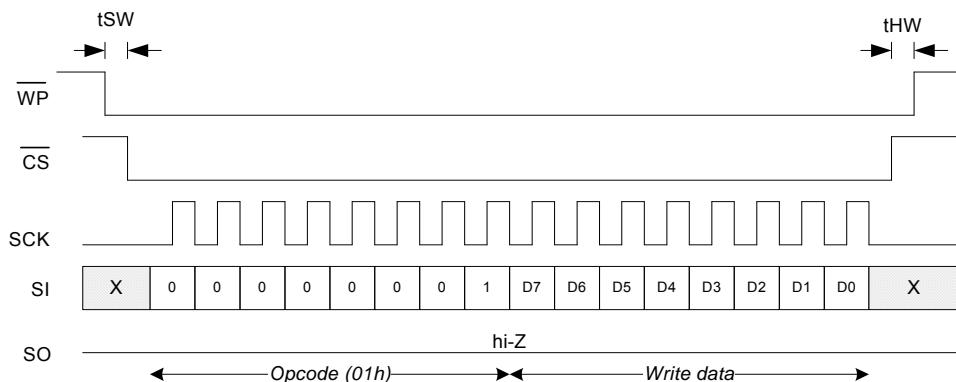

#### ステータス レジスタ書き込み (WRSR) 命令

WRSR 命令により、ユーザーはステータス レジスタへ書き込むことができます。ただし、この命令は書き込み可能なビットのみ（ビット 2 (BP0)、ビット 3 (BP1)、ビット 4 (BP2)、ビット 5 (TBPROT)、ビット 6 (SNL)、およびビット 7 (SRWD)）を変更できます。WRSR 命令は書き込み命令であり、(WREN 命令を使用して) WEL ビットを「1」にセットする必要があります。WRSR 命令は、CS の立ち下がりエッジの後にオペコードを送信してから、データレジスタに格納される 8 ビットのデータを送信することで発行されます。前述のように、WRSR 命令でステータスレジスタのビット 2、3、4、5、6、および 7 のみを変更することができます。

注：ステータス レジスタに書き込まれた値は、STORE 処理が完了した後にのみ不揮発性メモリに保存されます。AutoStore が無効になると、ステータス レジスタへの変更はソフトウェア STORE 処理を実行して確保する必要があります。

注：ステータスレジスタ書き込みシーケンスの終了時にステータスレジスタのWE1ビットが「0」にリセットします。

**図 58. SPI モード時の WRSR 命令**

**図 59. DPI モード時の WRSR 命令**

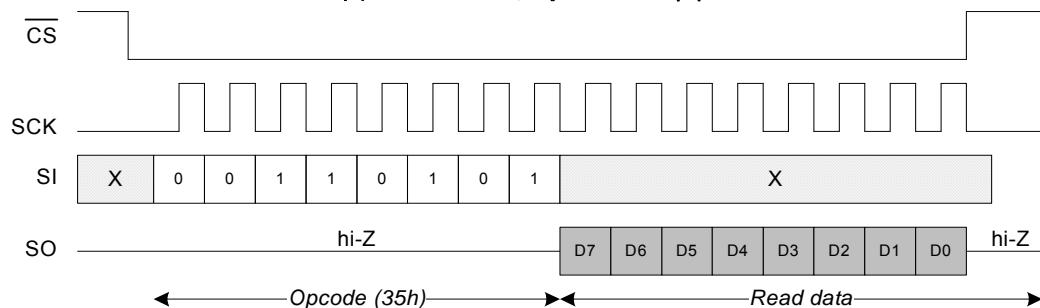

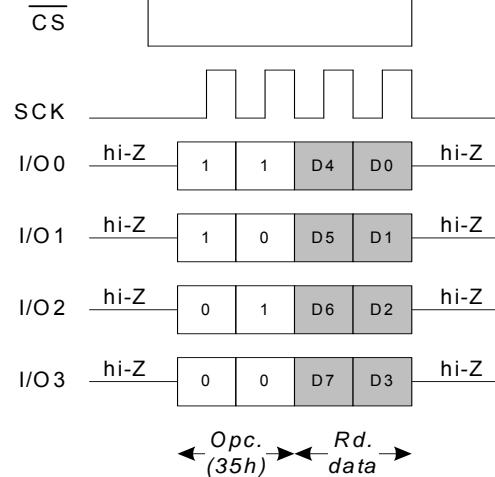

**コンフィギュレーションレジスタ読み出し (RDCR) 命令**

RDCR 命令は、最大 108MHz までの SPI 周波数でステータスレジスタへのアクセスを提供します。以下の図は、SPI、DPI、QPI モード時のコンフィギュレーションレジスタ命令の転送波形を示します。

注：コンフィギュレーションレジスタの最後のビットが読み出された後、デバイスはコンフィギュレーションレジスタの最初のビットに戻ります。

**図 60. QPI モード時の WRSR 命令**

**図 61. SPI モード時の RDCR 命令**

**図 62. DPI モード時の RDCR 命令**

**図 63. QPI モード時の RDCR 命令**

注: QPI モードでは、RDCR 命令を実行する前にクアッド ビット CR[1] を論理「1」にする必要があります。

### コンフィギュレーション レジスタ書き込み (WRCR) 命令

WRCR 命令により、ユーザーはクアッド ビットをセットすることでデバイスのデータ幅を変更することができます。クアッド出力読み出し、クアッド I/O 読み出しおよびクアッド入力書き込みコマンドを使用する際、クアッド ビットを「1」にセットする必要があります。クアッド ビットは不揮発性です。

注: (QPIEN 命令で) QPI モードを有効にしても、コンフィギュレーション レジスタのクアッド ビットがセットされません。

注: RFU ビットは常に表 8 に示すように書き込むことが推奨されています。

**図 64. SPI モード時の WRCR 命令**

**図 65. DPI モード時の WRCR 命令**

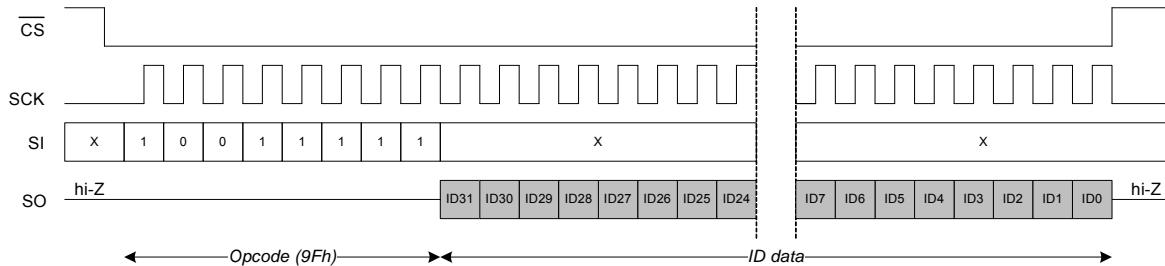

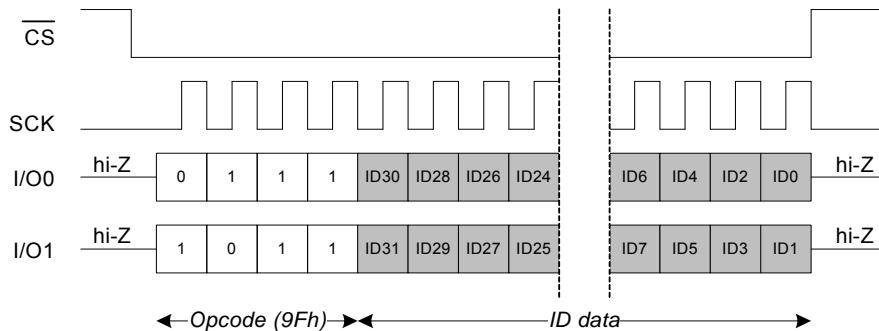

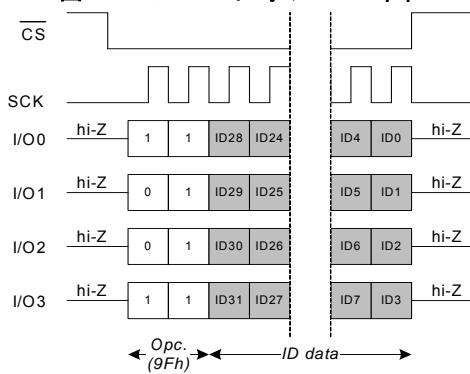

### レジスタ識別 (RDID) 命令

RDID 命令は、JEDEC 割り当てのメーカー ID とデバイスの製品 ID を最大 40MHz までの SPI 周波数で読み出すために使用されます。この命令は、バス上のデバイスを識別するために使用することができます。CS# が LOW になった後、RDID のオペコードをシフトすることにより、RDID 命令を発行することができます。デバイス ID は一意に 1M ビット QPI nvSRAM 製品を識別するための 4 バイトの読み出し専用コードです。これには、製品の製品ファミリコード、コンフィギュレーションおよび容量が含まれています。

RDID コマンドで、4 バイトのデバイス ID 構造を読み出します（この構造には書き込むことができません）。この構造は一度に 1

表 12. デバイス ID

| デバイス       | メーカー ID     |  | 製品 ID          |  | メモリ容量 | ダイリビジョン |  |  |

|------------|-------------|--|----------------|--|-------|---------|--|--|

|            | 31 ~ 21     |  | 20 ~ 7         |  |       |         |  |  |

|            | 11 ビット      |  | 14 ビット         |  |       |         |  |  |

| CY14V101QS | 00000110100 |  | 00001100010001 |  | 0100  | 001     |  |  |

図 66. SPI モード時の RDID 命令

図 67. DPI モード時の RDID 命令

図 68. QPI モード時の RDID 命令

バイト アクセスされます。最初にアクセスされるバイトは構造の最上位バイト ID[31:24]、2 番目にアクセスされるバイトは ID[23:16]、…、最後にアクセスされるバイトは ID[7:0] です。

注：構造はいつでも同じ順番でアクセスされるため、アドレス転送は不要です。その代わりに、オペコードがデコードされると「0」に初期化される内部 2 ビット アドレスポインターが使用されます。各バイトアクセスの後、内部アドレスポインターはインクリメントされます。アドレスポインターは「3」から「0」までラップアラウンドし、4 番目のバイト ID[7:0] がアクセスされると、1 番目のバイト ID[31:24] がアクセスされます。このコマンドは SPI、DPI、QPI モードで発行できます。

注：QPI モードでは、RDID 命令を実行する前にクアッド ビット CR[1] を論理「1」にする必要があります。

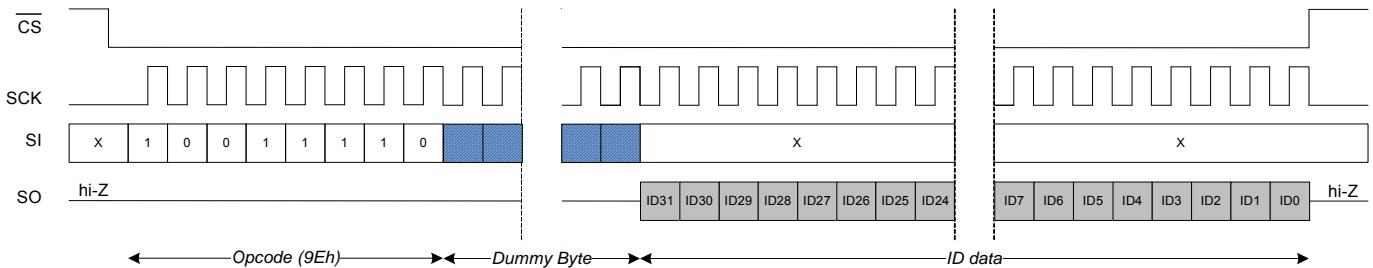

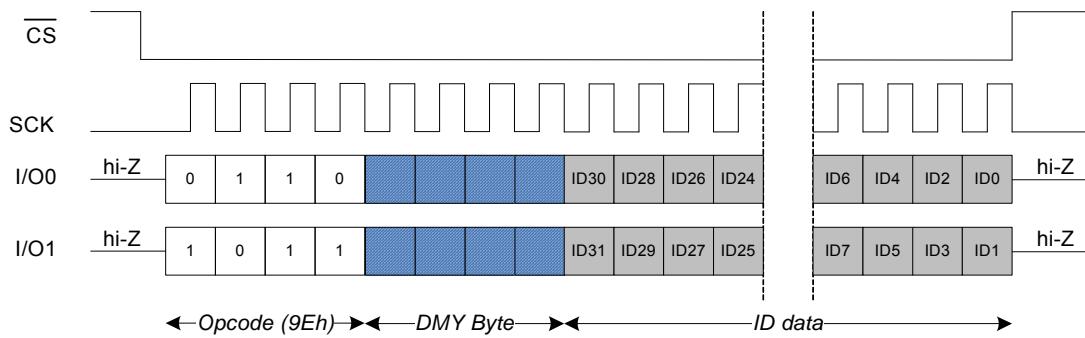

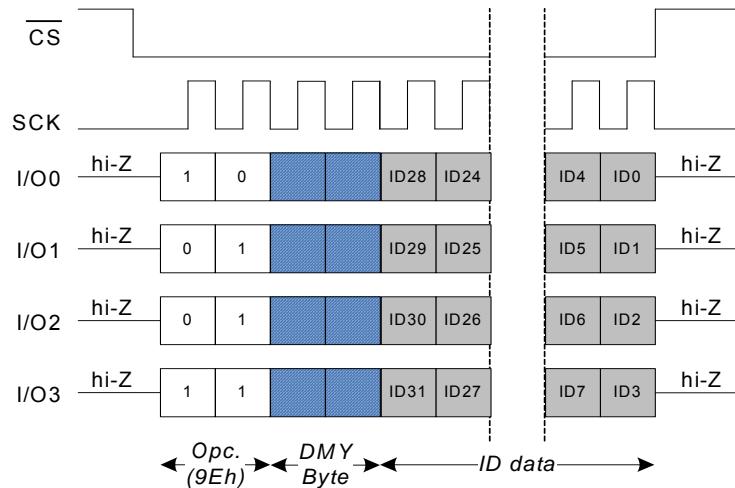

### レジスタ識別 (FAST\_RDID) 命令

オペコードの後にダミーバイトが後続することを除いて、FAST\_RDID 命令は RDID と同じです。FAST\_RDID 命令は、JEDEC 割り当てのメーカー ID とデバイスの製品 ID を最大 108MHz までの SPI 周波数で読み出すために使用されます。

図 69. SPI モード時の FAST\_RDID 命令

図 70. DPI モード時の FAST\_RDID 命令

図 71. QPI モード時の FAST\_RDID 命令

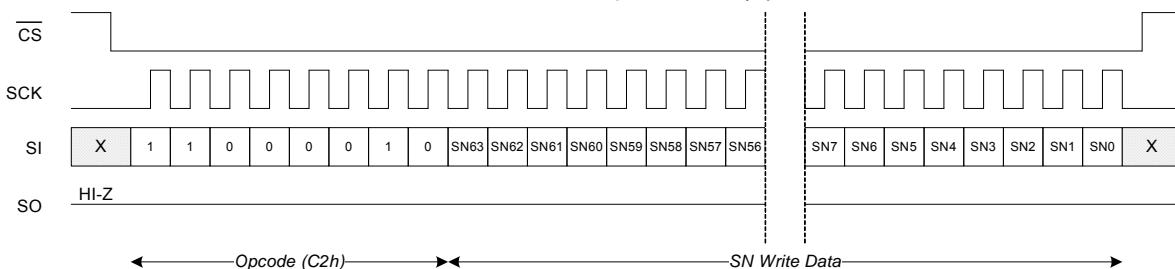

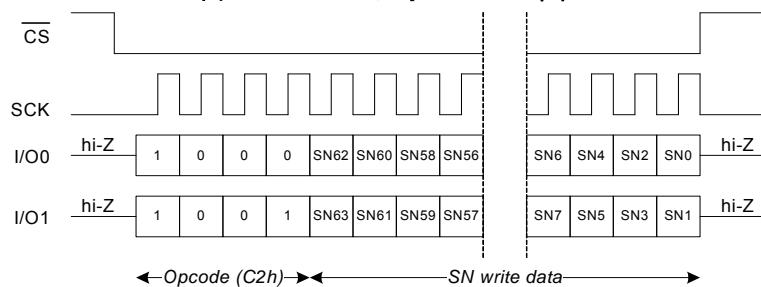

### シリアル番号レジスタ書き込み (WRSN) 命令

シリアル番号はデバイスを一意に識別するためにユーザーに提供される8バイトのプログラム可能なメモリ空間です。一般的には、シリアル番号はカスタマ ID の2バイト、その後に続く固有のシリアル番号の5バイトとCRCチェックの1バイトで構成されています。しかし、デバイスはCRCを計算しないため、所望の形式で8バイトのメモリ空間を利用するかどうかはシステム設計者次第となります。8バイトの位置のデフォルト値は「0x00」に設定されています。

シリアル番号は WRSN コマンドで書き込まれます。シリアル番号を書き込むには、WREN コマンドを使用して書き込みを有効にする必要があります。WRSN コマンドは、バーストモードで実行してシリアル番号の8バイトをすべて書き込むことができます。シリアル番号の最後のバイトが書き込まれると、デバイスはシリアル番号の最初のバイト (MSB) に戻ります。シリアル番号は、ステータスレジスタの SNL ビットを使用してロックされます。このビットが一旦「1」にセットされると、シリアル番号への変更はできなくなります。SNL ビットが「1」にセットされた後は、WRSN コマンドの実行はシリアル番号に影響を与えません。このコマンドは実行する前に WEL ビットを

セットする必要があります。ステータスレジスタの SRWD ビットが「1」にセットされていない場合、WEL ビットはこのコマンドの完了後に「0」にリセットします。このコマンドは SPI、DPI、QPI モードで発行できます。

シリアル番号は、WRSN 命令を 108MHz までの SPI 周波数で実行して書き込まれます。

**注:** シリアル番号を不揮発性メモリに格納するには、STORE 動作 (AutoStore またはソフトウェア STORE) が必要です。AutoStore が無効になっている場合、ソフトウェア STORE 处理を実行して、シリアル番号を保存してロックする必要があります。SNL ビットが「1」にセットされ、格納されていない (AutoStore が無効) 場合は、次のパワーサイクル (電源を切断して再度投入する) 時に SNL ビットとシリアル番号はデフォルトで「0」となります。SNL ビットを一旦「1」にセットして格納すると、「0」にクリアすることはできません。この命令は実行する前に WEL ビットをセットする必要があります。この命令は SPI、DPI、QPI モードで発行可能です。

**注:** この命令の完了後、WEL ビットは「0」にリセットされます。

図 72. SPI モード時の WRSN 命令

図 73. DPI モード時の WRSN 命令

図 74. QPI モード時の WRSN 命令

### シリアル番号レジスタ読み出し (RDSN) 命令

シリアル番号は 40MHzまでの SPI 周波数で RDSN 命令を使用して読み出されます。シリアル番号読み出しは、バーストモードで実行して一度にすべての 8 バイトを読み出すことができます。シリアル番号の最後のバイトが読み出されると、デバイスはシリアル番号の最初のバイト (MSB) に戻ります。CS が LOW

になった後、RDSN のオペコードをシフトすることで RDSN 命令を発行することができます。その後、nvSRAM はシリアル番号の 8 バイトをシフトアウトします。この命令は SPI、DPI、QPI モードで発行可能です。

図 75. SPI モード時の RDSN 命令

図 76. DPI モード時の RDSN 命令

図 77. QPI モード時の RDSN 命令

注: QPI モードでは、RDSN 命令を実行する前にクアッド ビット CR[1] を論理「1」にする必要があります。

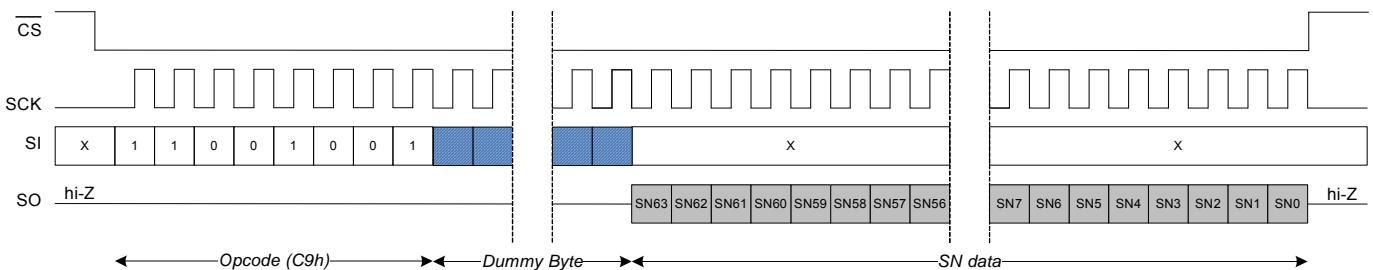

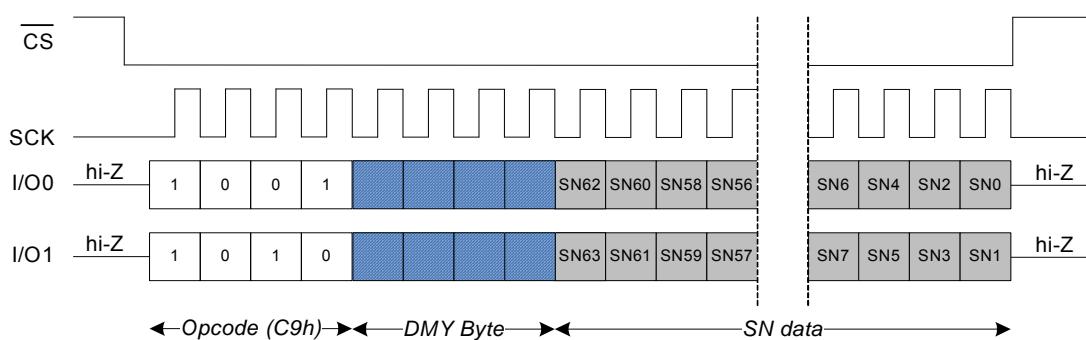

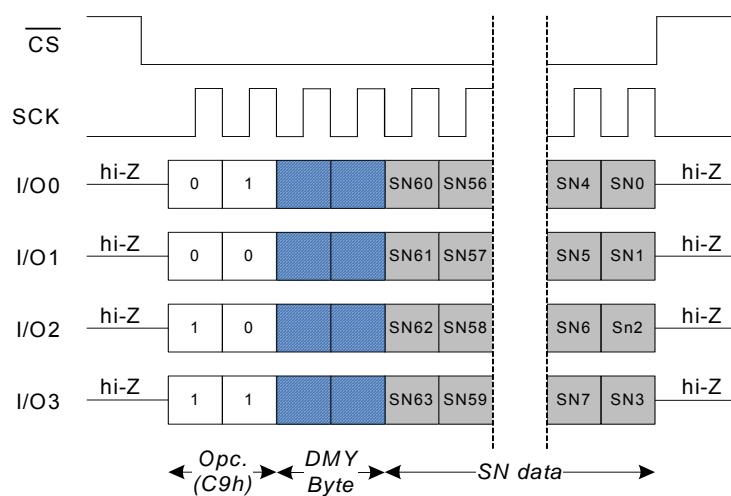

### 高速シリアル番号読み出し (FAST\_RDSN) 命令

オペコードの後にダミーバイトが後続することを除いて、FAST\_RDSN命令はRDSNと同じです。FAST\_RDSN命令は最大108MHzで実行可能です。

図 78. SPI モード時の FAST\_RDSN 命令

図 79. DPI モード時の FAST\_RDSN 命令

図 80. QPI モード時の FAST\_RDSN 命令

## 不揮発性メモリ固有の命令

nvSRAM デバイスは、nvSRAM 固有の機能の使用を可能にする次の 4 つの専用命令を提供します：STORE、RECALL、ASEN、ASDI。

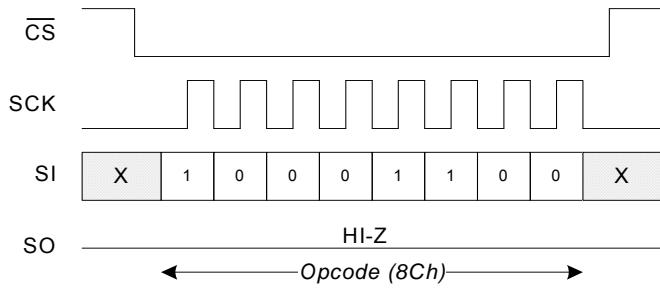

### ソフトウェアストア (STORE) 命令

STORE 命令を実行すると、nvSRAM はソフトウェア STORE 处理を実行します。STORE 处理は、前回の STORE または RECALL 動作以降に書き込みが行われたかどうかに関係なく実行されます。この命令を発行するには、デバイスは書き込み可能になる (WEL ビット =「1」) 必要があります。この命令は SPI、DPI、QPI モードで発行可能です。

注：STORE 命令後の  $\overline{CS}$  の立ち上がりエッジで、WEL ビットがクリアされます。

図 81. SPI モード時の STORE 命令

図 82. DPI モード時の STORE 命令

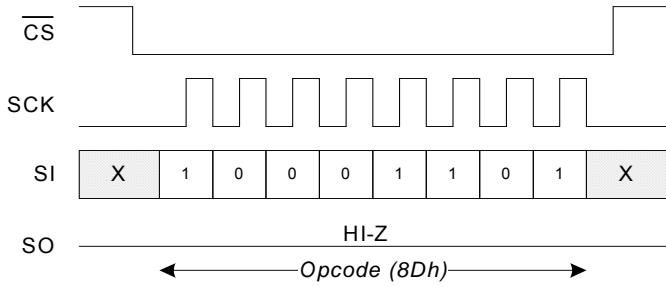

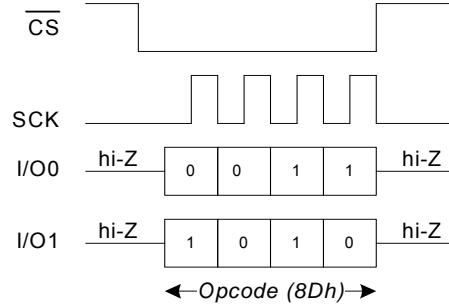

### ソフトウェアリコール (RECALL) 命令

RECALL 命令を実行すると、nvSRAM はソフトウェア RECALL 处理を実行します。この命令を発行するには、デバイスは書き込み可能になる (WEL=「1」) 必要があります。この命令は SPI、DPI、QPI モードで発行可能です。

注 RECALL 命令実行後の  $\overline{CS}$  の立ち上がりエッジで、WEL ビットがクリアされます。

図 83. QPI モード時の STORE 命令

図 84. SPI モード時の RECALL 命令

図 85. DPI モード時の RECALL 命令

図 86. QPI モード時の RECALL 命令

### Autostore イネーブル (ASEN) 命令

AutoStore イネーブル命令により、nvSRAM での AutoStore 处理が可能になります。この設定は不揮発性ではなく、電源を切断して再度投入しても保存されるには、この命令の後に STORE シーケンスを行う必要があります。この命令を発行するには、デバイスは書き込み可能になる (WEL=「1」) 必要があります。この命令は SPI、DPIO、QPI モードで発行可能です。

注：ASDI と ASEN 命令を実行すると、デバイスはソフトウェアシーケンス処理時間 ( $t_{SS}$ ) の間ビジー状態になります。

注：ASEN 命令実行後の  $\overline{CS}$  の立ち上がりリエッジで WEL ビットをクリアします。

図 87. SPI モード時の ASEN 命令

図 88. DPI モード時の ASEN 命令

図 89. QPI モード時の ASEN 命令

### Autostore ディスエーブル (ASDI) 命令

デフォルトでは、AutoStore はこのデバイスで有効です。ASDI 命令は AutoStore 処理を無効にします。この設定は不揮発性ではなく、電源を切断して再度投入しても保存されるには、この命令の後に STORE シーケンスを行う必要があります。この命令を発行するには、デバイスは書き込み可能になる (WEL=「1」) 必要があります。この命令は SPI、DPI、QPI モードで発行可能です。

注：ASDI 命令実行後の  $\overline{CS}$  の立ち上がりリエッジで、WEN ビットがクリアされます。

図 90. SPI モード時の ASDI 命令

図 91. DPI モード時の ASDI 命令

図 92. QPI モード時の ASDI 命令

注：QPI モードでは、ASDI 命令を実行する前にクアッド ビット CR[1] を論理「1」にする必要があります。

## 最大定格

最大定格を超えると、デバイスの寿命が短くなる可能性があります。これらのユーザー ガイドラインはテストされていません。

保存温度 .....  $-65^{\circ}\text{C} \sim +150^{\circ}\text{C}$

最大累積保存時間

周囲の温度 ( $150^{\circ}\text{C}$  時) ..... 1000 時間

周囲の温度 ( $85^{\circ}\text{C}$  時) ..... 20 年

最大接合部温度 .....  $150^{\circ}\text{C}$

$V_{\text{SS}}$  を基準とした  $V_{\text{CC}}$  の電源電圧 .....  $-0.5\text{V} \sim +4.1\text{V}$

$V_{\text{SS}}$  を基準とした  $V_{\text{CCQ}}$  の電源電圧 .....  $-0.5\text{V} \sim +2.45\text{V}$

High Z 状態の出力に

印加される DC 電圧 .....  $-0.5\text{V} \sim V_{\text{CCQ}}+0.5\text{V}$

入力電圧 .....  $-0.5\text{V} \sim V_{\text{CCQ}}+0.5\text{V}$

任意のピンからグランド電位への

過渡電圧 (20ns 以下) .....  $-2.0\text{V} \sim V_{\text{CCQ}}+2.0\text{V}$

パッケージ許容電力損失 ( $T_A = 25^{\circ}\text{C}$ )

16 ピン SOIC ..... 1.0W

24 ボール FPGA ..... 1.0W

パッケージ許容電力損失 ( $T_A = 25^{\circ}\text{C}$ ) ..... 1.0W

表面実装ハンダ付け時

温度 (3 秒) .....  $+260^{\circ}\text{C}$

DC 出力電流 (一度に 1 出力、1 秒間) ..... 15mA

静電放電時の電圧

(MIL-STD-883、メソッド 3015) .....  $> 2001\text{V}$

ラッチアップ電流 .....  $> 140\text{mA}$

## 動作範囲

| 範囲            | 周囲温度                                            | $V_{\text{CC}}$                | $V_{\text{CCQ}}$                |

|---------------|-------------------------------------------------|--------------------------------|---------------------------------|

| 産業用           | $-40^{\circ}\text{C} \sim +85^{\circ}\text{C}$  | $2.7\text{V} \sim 3.6\text{V}$ | $1.71\text{V} \sim 2.0\text{V}$ |

| 産業用拡張<br>温度範囲 | $-40^{\circ}\text{C} \sim +105^{\circ}\text{C}$ | $2.7\text{V} \sim 3.6\text{V}$ | $1.71\text{V} \sim 2.0\text{V}$ |

## DC 仕様

| パラメーター            | 説明                                                      | テスト条件                                                                                                                                 | Min  | Typ [1] | Max    | 単位            |

|-------------------|---------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|------|---------|--------|---------------|

| $V_{\text{CC}}$   | 電源供給 - コア電圧                                             | —                                                                                                                                     | 2.70 | 3.00    | 3.60   | V             |

| $V_{\text{CCQ}}$  | 電源供給 - I/O 電圧                                           | —                                                                                                                                     | 1.71 | 1.80    | 2.00   | V             |

| $I_{\text{CC1}}$  | 平均読み出し／書き込み $V_{\text{CC}}$ 電流 (すべての入力が切り替わっている；出力負荷無し) | SPI = 1MHz                                                                                                                            | —    | —       | 1.00   | mA            |

|                   |                                                         | SPI = 40MHz                                                                                                                           | —    | —       | 3.00   | mA            |

|                   |                                                         | QPI = 108MHz                                                                                                                          | —    | —       | 33.00  | mA            |

| $I_{\text{CCQ1}}$ | 平均 $V_{\text{CCQ}}$ 電流 (すべての入力が切り替わっている；出力負荷無し)         | SPI = 1MHz                                                                                                                            | —    | —       | 150.00 | $\mu\text{A}$ |

|                   |                                                         | SPI = 40MHz                                                                                                                           | —    | —       | 1.00   | mA            |

|                   |                                                         | QPI = 108MHz                                                                                                                          | —    | —       | 5.00   | mA            |

| $I_{\text{SB1}}$  | 85°C でのスタンバイ電流 ( $V_{\text{CC}} + V_{\text{CCQ}}$ )     | CS > ( $V_{\text{CCQ}} - 0.2\text{V}$ )。<br>不揮発性サイクルが完了した後のスタンバイ電流レベル。(CS が HIGH；他の I/O は制限が無い； $f_{\text{SCK}} \leq 108\text{MHz}$ ) | —    | —       | 1.70   | mA            |

|                   | 105°C でのスタンバイ電流 ( $V_{\text{CC}} + V_{\text{CCQ}}$ )    | —                                                                                                                                     | —    | —       | 2.00   | mA            |

| $I_{\text{SB2}}$  | 85°C でのスタンバイ電流 ( $V_{\text{CC}} + V_{\text{CCQ}}$ )     | CS > ( $V_{\text{CCQ}} - 0.2\text{V}$ )。<br>不揮発性のサイクルが完了した後のスタンバイ電流レベル。すべての I/O はスタティック； $f_{\text{SCK}} = 0\text{MHz}$               | —    | —       | 280.00 | $\mu\text{A}$ |

|                   | 105°C でのスタンバイ電流 ( $V_{\text{CC}} + V_{\text{CCQ}}$ )    | —                                                                                                                                     | —    | —       | 540.00 | $\mu\text{A}$ |

| $I_{\text{CC2}}$  | STORE 中の平均 $V_{\text{CC}}$ 電流                           | —                                                                                                                                     | —    | —       | 6.00   | mA            |

| $I_{\text{CC4}}$  | AUTOSTORE サイクル中の平均 $V_{\text{CAP}}$ 電流                  | —                                                                                                                                     | —    | —       | 6.00   | mA            |

注：

- 標準値は  $25^{\circ}\text{C}$ 、 $V_{\text{CC}} = V_{\text{CC(Typ)}}$ 、および  $V_{\text{CCQ}} = V_{\text{CCQ(Typ)}}$  でのものです。100% のテストは行われていません。

| パラメーター                           | 説明                                                           | テスト条件                                                                                                      | Min                     | Typ <sup>[1]</sup> | Max                     | 単位 |

|----------------------------------|--------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|-------------------------|--------------------|-------------------------|----|

| I <sub>SLEEP</sub>               | 85°C でのスリープ モード電流<br>(V <sub>CC</sub> + V <sub>CCQ</sub> )   | $\overline{CS} > (V_{CCQ} - 0.2V)$ 。<br>不揮発性のサイクルが完了した後のスリープ電流レベル。すべてのI/Oはスタティック ; f <sub>SCK</sub> = 0MHz | -                       | -                  | 280.00                  | μA |

| I <sub>ZZ</sub>                  | 85°C でのハイバネート モード電流<br>(V <sub>CC</sub> + V <sub>CCQ</sub> ) | $\overline{CS} > (V_{CCQ} - 0.2V)$ 。HIBEN 命令が登録された後の t <sub>HIBEN</sub> 時間。すべての入力はスタティックで、CMOS 論理レベルで設定    | -                       | -                  | 8.00                    | μA |

| I <sub>IX</sub>                  | 入力リーク電流 (HSB を除く )                                           | $V_{CCQ} = \text{Max}$ 、V <sub>SS</sub> < V <sub>IN</sub> < V <sub>CCQ</sub>                               | -1.00                   | -                  | 1.00                    | μA |

|                                  | 入力リーク電流 (HSB)                                                |                                                                                                            | -100.00                 | -                  | 1.00                    | μA |

|                                  | 入力リーク電流 (SPI / DPI モードでの WP 向け )                             |                                                                                                            | -2                      | -                  | 1                       | μA |

| I <sub>OZ</sub>                  | オフ状態の出力リーク電流                                                 | $V_{CCQ} = \text{Max}$ 、V <sub>SS</sub> < V <sub>IN</sub> < V <sub>CCQ</sub>                               | -1.00                   | -                  | 1.00                    | μA |

| V <sub>IH</sub>                  | 入力 HIGH 電圧                                                   | -                                                                                                          | 0.70 * V <sub>CCQ</sub> | -                  | V <sub>CCQ</sub> + 0.30 | V  |

| V <sub>IL</sub>                  | 入力 LOW 電圧                                                    | -                                                                                                          | -0.30                   | -                  | 0.30 * V <sub>CCQ</sub> | V  |

| V <sub>OH</sub>                  | -2mA 時の出力 HIGH 電圧                                            | I <sub>OH</sub> = -2mA                                                                                     | V <sub>CCQ</sub> - 0.45 | -                  | -                       | V  |

| V <sub>OL</sub>                  | 2mA 時の出力 LOW 電圧                                              | I <sub>OL</sub> = 2mA                                                                                      | -                       | -                  | 0.45                    | V  |

| V <sub>CAP</sub> <sup>[2]</sup>  | ストレージ コンデンサ                                                  | V <sub>CAP</sub> ピンと V <sub>SS</sub> 間                                                                     | 61.00                   | 68.00              | 120.00                  | μF |

| V <sub>VCAP</sub> <sup>[3]</sup> | V <sub>CAP</sub> ピン上で駆動された最大電圧                               | -                                                                                                          | -                       | -                  | V <sub>CC</sub>         | V  |

### データ保持期間およびアクセス可能回数

| パラメーター            | 説明              | Min   | 単位 |

|-------------------|-----------------|-------|----|

| DATA <sub>R</sub> | 85°C 時のデータ保持期間  | 20    | 年  |

| NV <sub>C</sub>   | 不揮発性 STORE 処理回数 | 1,000 | K  |

### 静電容量

| パラメーター <sup>[3]</sup> | 説明         | テスト条件                                                                                                            | Max  | 単位 |

|-----------------------|------------|------------------------------------------------------------------------------------------------------------------|------|----|

| C <sub>IN</sub>       | 入力静電容量     |                                                                                                                  |      |    |

| C <sub>SCK</sub>      | クロック入力静電容量 | T <sub>A</sub> = 25 °C、f = 1MHz、V <sub>CC</sub> = V <sub>CC(typ)</sub> 、V <sub>CCQ</sub> = V <sub>CCQ(typ)</sub> | 6.00 | pF |

| C <sub>OUT</sub>      | 出力ピン静電容量   |                                                                                                                  |      |    |

### 熱抵抗

| パラメーター <sup>[3]</sup> | 説明               | テスト条件                                            | 16 ピン SOIC | 24 ポール FBGA | 単位   |

|-----------------------|------------------|--------------------------------------------------|------------|-------------|------|

| Θ <sub>JA</sub>       | 熱抵抗<br>(接合部から周囲) | テスト条件は EIA/JESD51 で定めた熱インピーダンス測定の標準テスト方法および手順に従う | 61.21      | 32.08       | °C/W |

| Θ <sub>JC</sub>       | 熱抵抗<br>(接合部から周囲) |                                                  | 26.20      | 14.29       |      |

#### 注:

2. V<sub>CAP</sub> 最小値は、AutoStore 处理を正常に完了するのに十分な電荷があることを保証するものです。V<sub>CAP</sub> 最大値は、即時の電源切断サイクルで AutoStore 处理を正常に完了できるようにパワーアップ RECALL サイクルの間に V<sub>CAP</sub> のコンデンサが必要な最小電圧まで充電されることを保証するものです。したがって、指定した最小値と最大値の範囲内でコンデンサを使用することをお勧めします。V<sub>CAP</sub> のオプションの詳細については、アプリケーション ノート AN43593 を参照してください。

3. これらのパラメーターは設計保証であり、テストは行われていません。

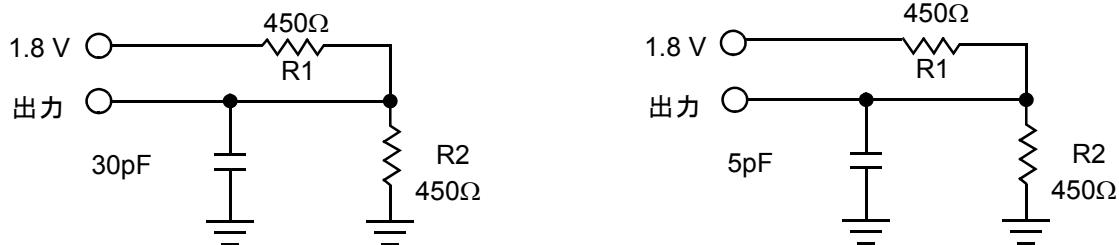

## AC テストの負荷および波形

図 93. AC テストの負荷および波形

## AC テスト条件

| 説明                          | CY14V101QS |

|-----------------------------|------------|

| 入力パルス レベル                   | 0V ~ 1.8V  |

| 入力立ち上がり／立ち下がり時間 (10% ~ 90%) | ≤ 1.8ns    |

| 入力と出力のタイミング リファレンス レベル      | 0.9V       |

## AC スイッチング特性

| パラメーター <sup>[4]</sup>    | 説明                                               | Min                         | Max         | 単位             |

|--------------------------|--------------------------------------------------|-----------------------------|-------------|----------------|

| $f_{SCK}$                | クロック周波数 (QPI)                                    | —                           | 108.00      | MHz            |

| $t_{CL}$                 | クロック LOW パルス幅                                    | $0.45 * 1/f_{SCK}$          | —           | ns             |