## 特長

- 25ns および 45ns のアクセス時間

- 32K × 8 の内部構成 (CY14E256LA)

- 小容量コンデンサのみで電源切断時の自動 STORE を実行

- QuantumTrap不揮発性要素へのSTORE処理はソフトウェア、デバイス ピン、または電源切断時の AutoStore により開始

- SRAMへのRECALL処理はソフトウェアまたは電源投入により開始

- 回数制限のない読み出し、書き込み、およびRECALLサイクル

- QuantumTrap に対する 100 万回の STORE サイクル

- 20 年のデータ保持期間

- 5V ± 10% の単一電源で動作

- 産業用温度範囲

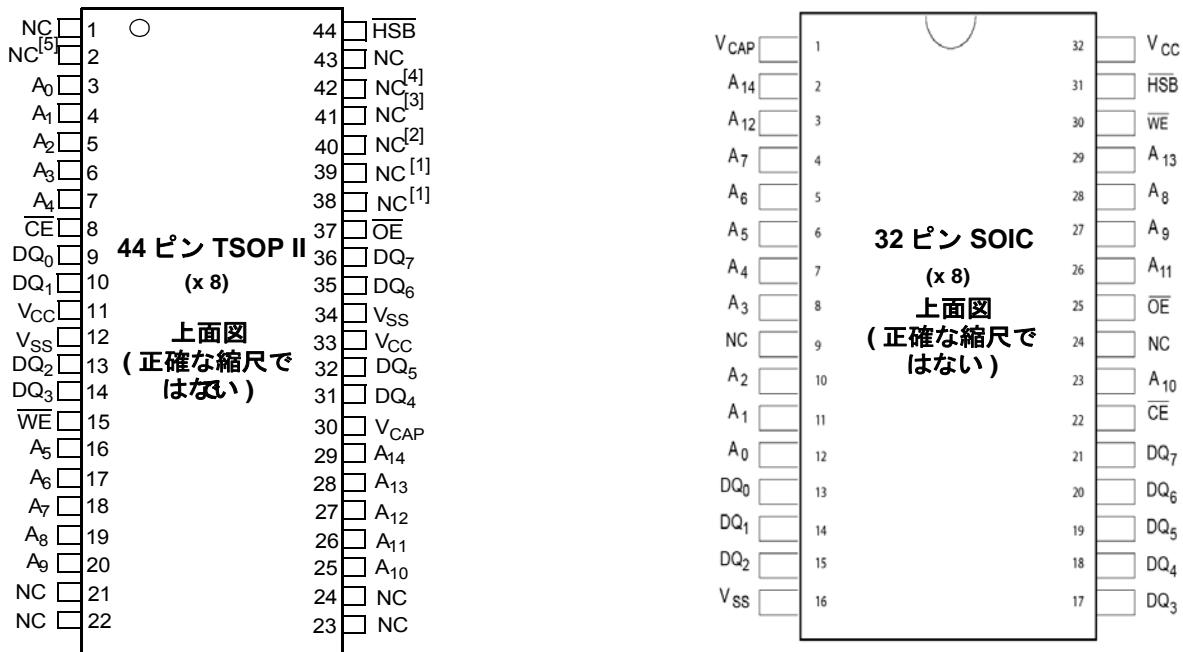

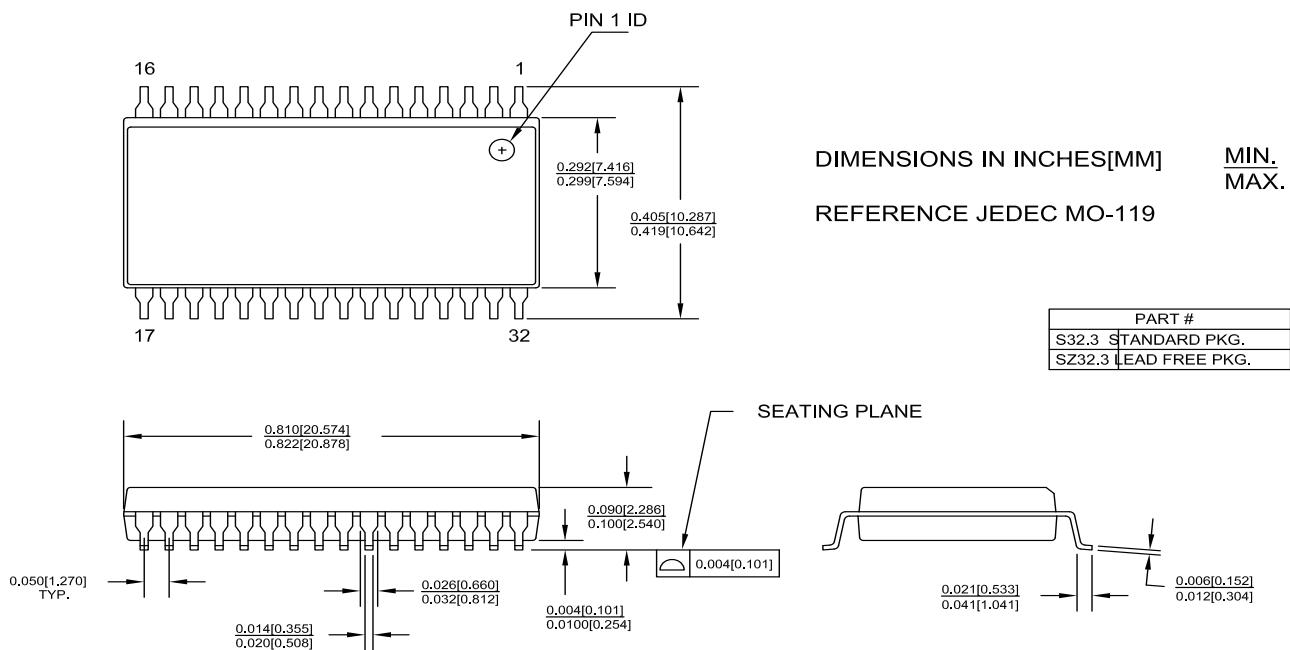

- 44 ピン薄型小型パッケージ (TSOP) タイプII および 32 ピン小型集積回路 (SOIC) パッケージ

- 鉛フリーおよび特定有害物質使用制限 (RoHS) に準拠

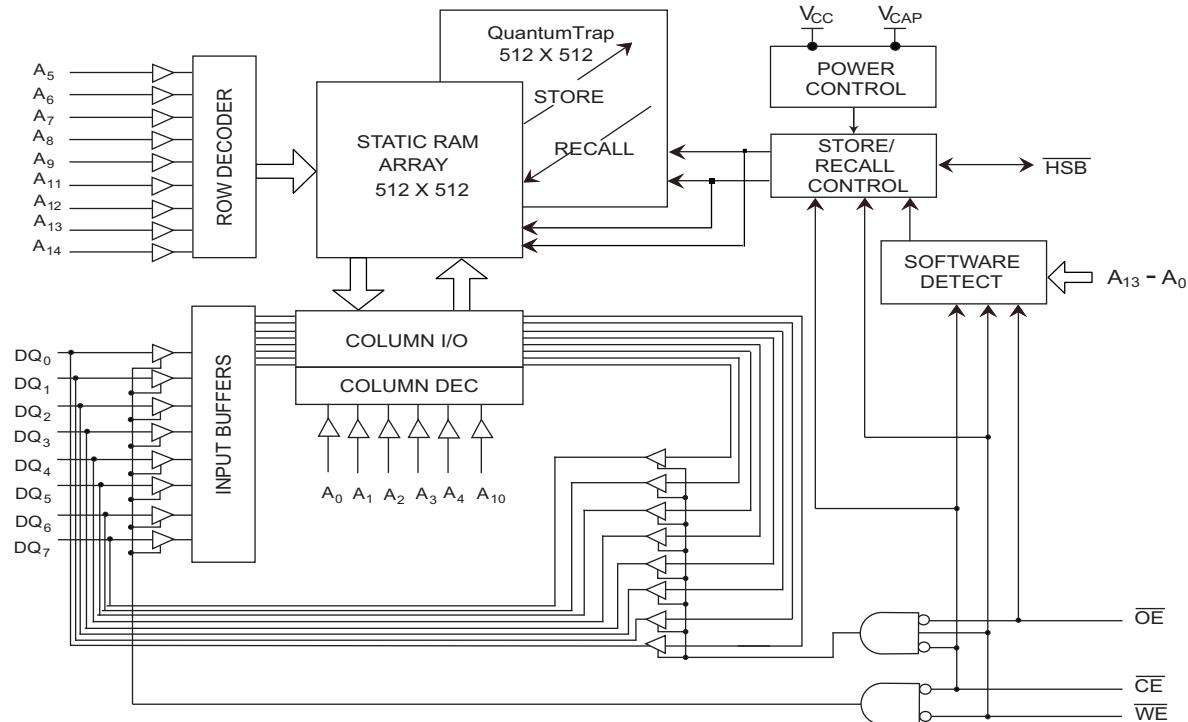

## 論理ブロック図

## 機能の詳細

サイプレスの CY14E256LA は、メモリ セルごとに不揮発性要素を組み込んだ高速 static RAM です。このメモリは 32KB で構成されています。組み込み型不揮発性素子には、世界最高級の信頼性を備えた不揮発性メモリを実現する QuantumTrap 技術を採用しています。回数に制限のない読み出しと書き込みを SRAM で可能にする一方、不揮発性データを不揮発性素子に独立して保持できるようにしています。SRAM から不揮発性要素へのデータ転送 (STORE 処理) は、電源切断時に自動的に実行されます。電源投入時には、不揮発性メモリから SRAM にデータが復元されます (RECALL 処理)。STORE と RECALL 両方の処理はソフトウェア制御でも実行することができます。

すべての関連資料の一覧は、[ここ](#)をクリックしてください。

## 目次

|                      |    |                            |    |

|----------------------|----|----------------------------|----|

| ピン配置                 | 3  | SRAM 書き込みサイクル              | 10 |

| ピン機能                 | 3  | スイッチング波形                   | 10 |

| デバイスの動作              | 4  | AutoStore／電源投入 RECALL      | 12 |

| SRAM 読み出し            | 4  | スイッチング波形                   | 12 |

| SRAM 書き込み            | 4  | ソフトウェア制御 STORE/RECALL サイクル | 13 |

| AutoStore 処理         | 4  | スイッチング波形                   | 13 |

| ハードウェア STORE 処理      | 4  | ハードウェア STORE サイクル          | 14 |

| ハードウェア RECALL (電源投入) | 5  | スイッチング波形                   | 14 |

| ソフトウェア STORE         | 5  | SRAM の動作真理値表               | 15 |

| ソフトウェア RECALL        | 5  | 注文情報                       | 15 |

| AutoStore の防止        | 6  | 注文コードの定義                   | 15 |

| データ保護                | 6  | パッケージ図                     | 16 |

| 最大定格                 | 7  | 略語                         | 17 |

| 動作範囲                 | 7  | 本書の表記法                     | 17 |

| DC 電気的特性             | 7  | 測定単位                       | 17 |

| データ保持期間およびアクセス可能回数   | 8  | 改訂履歴                       | 18 |

| 静電容量                 | 8  | セールス、ソリューション、および法律情報       | 19 |

| 熱抵抗                  | 8  | ワールドワイドな販売と設計サポート          | 19 |

| AC テスト負荷             | 9  | 製品                         | 19 |

| AC テスト条件             | 9  | PSoC ソリューション               | 19 |

| AC スイッチング特性          | 10 |                            |    |

| SRAM 読み出しサイクル        | 10 |                            |    |

## ピン配置

図 1. 44 ピン TSOP II / 32 ピン SOIC ピン配置

## ピン機能

| ピン名                               | 入出力   | 説明                                                                                                                                                                                                                       |

|-----------------------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A <sub>0</sub> ~A <sub>14</sub>   | 入力    | アドレス入力: nvSRAM の 32,768 バイトから 1 つを選択するのに使用                                                                                                                                                                               |

| DQ <sub>0</sub> ~ DQ <sub>7</sub> | 入力／出力 | 双方向データ I/O ライン。動作に応じて入力または出力ラインとして使用                                                                                                                                                                                     |

| WE                                | 入力    | 書き込みイネーブル入力、アクティブ LOW。チップが有効で、WE が LOW になると、I/O ピンのデータは特定のアドレス位置に書き込まれる                                                                                                                                                  |

| CE                                | 入力    | チップイネーブル入力、アクティブ LOW。LOW の場合は、チップを選択する。HIGH の場合は、チップの選択を解除                                                                                                                                                               |

| OE                                | 入力    | 出力イネーブル、アクティブ LOW。アクティブ LOW OE 入力は、読み出しサイクル中にデータ出力バッファを有効にする。OE が HIGH にデアサートすると、I/O ピンはトライステートになる                                                                                                                       |

| V <sub>SS</sub>                   | グランド  | デバイス用のグランド。システムのグランドに接続する必要がある                                                                                                                                                                                           |

| V <sub>CC</sub>                   | 電源    | デバイスへの電源入力。                                                                                                                                                                                                              |

| HSB                               | 入力／出力 | ハードウェア STORE ビジー (HSB)。この出力は LOW である時にハードウェア STORE が進行中であることを示す。外部で LOW にする場合、不揮発性 STORE 処理を開始する。各ハードウェアとソフトウェア STORE 処理の後、HSB は標準の出力 HIGH 電流で短期間 ( $t_{HHD}$ ) HIGH に駆動されてから、内部の弱プルアップ抵抗により HIGH 状態を維持 (外部プルアップ抵抗接続は任意) |

| V <sub>CAP</sub>                  | 電源    | AutoStore コンデンサ。電力不足の際、SRAM から不揮発性素子にデータを格納するため、nvSRAM へ電源を供給                                                                                                                                                            |

| NC                                | 接続なし  | 接続なし このピンはダイに接続されていません                                                                                                                                                                                                   |

### 注

- 1M ピットのアドレス拡張に対応しています。NC ピンはダイに接続されていません。

- 2M ピットのアドレス拡張に対応しています。NC ピンはダイに接続されていません。

- 4M ピットのアドレス拡張に対応しています。NC ピンはダイに接続されていません。

- 8M ピットのアドレス拡張に対応しています。NC ピンはダイに接続されていません。

- 16M ピットのアドレス拡張に対応しています。NC ピンはダイに接続されていません。

## デバイスの動作

CY14E256LAは、同じ物理セル内で対になった2個の機能コンポーネントで構成されています。それらはSRAMメモリセルおよび不揮発性QuantumTrapセルです。SRAMメモリセルは標準の高速スタティックRAMとして動作します。SRAM内のデータは不揮発性セルに転送される(STORE処理)、または不揮発性セルからSRAMに転送されます(RECALL処理)。この独特的なアーキテクチャを使って、全てのセルは並行してストアされリコールされます。STORE処理とRECALL処理中、SRAMの読み出しと書き込み処理は禁止されています。CY14E256LAは一般的なSRAMと同様に、回数無制限の読み出しと書き込みに対応しています。さらに、不揮発性セルから回数無制限のRECALL処理および最大100万回までのSTORE処理が可能です。読み出しモードと書き込みモードの詳細については、[15ページの「SRAMの動作真理値表」](#)を参照してください。

### SRAM読み出し

CY14E256LAは、 $\overline{CE}$ と $\overline{OE}$ がLOW、 $\overline{WE}$ と $\overline{HSB}$ がHIGHの場合、読み出しサイクルを実行します。ピン $A_0 \sim 14$ で指定されたアドレスは、32,768データバイトのどれがアクセスされるかを決定します。アドレス遷移によって読み出しが開始された場合、出力は $t_{AA}$ (読み出しサイクル1)の遅延後に有効になります。CEまたはOEによって読み出しが開始された場合、出力は $t_{ACE}$ と $t_{DOE}$ のどちらか遅い方(読み出しサイクル2)の終了時点で有効になります。データ出力は、制御入力ピンでの変化を必要としないで $t_{AA}$ アクセス時間内に繰り返してアドレス変更に応答します。これは、別のアドレス変更が発生するか、または $CE$ か $OE$ がHIGHになるか、あるいは $WE$ か $HSB$ がLOWになるまで有効な状態が続きます。

### SRAM書き込み

書き込みサイクルは、 $\overline{CE}$ と $\overline{WE}$ がLOW、および $\overline{HSB}$ がHIGHの場合に実行されます。アドレス入力が安定な状態になってから書き込みサイクルに入らなければいけません。また、サイクルの終わりに $CE$ か $WE$ がHIGHになるまで安定な状態を保つ必要があります。WEで制御する書き込み終了前に、または $CE$ で制御する書き込み終了前にデータが $t_{SD}$ の間に有効であれば、共通I/Oピンである $DQ_0 \sim 7$ のデータはメモリに書き込まれます。共通I/Oラインでのデータバスの競合を避けるために、書き込みサイクル中は終始 $OE$ をHIGHに維持してください。 $OE$ がLOWのままであると、 $WE$ がLOWになった後に内部回路は $t_{HZWE}$ の間出力バッファを停止します。

### AutoStore処理

CY14E256LAは、次の3つのストレージ動作のいずれかを使ってnvSRAMにデータを格納します：HSBによって有効にされたハードウェアSTORE；アドレスのシーケンスによって有効にされたソフトウェアSTORE；デバイスの電源切断時のAutoStore。AutoStore処理はQuantumTrap技術固有の機能であり、CY14E256LAの初期設定では有効になっています。

通常動作中にデバイスは、 $V_{CAP}$ ピンに接続されたコンデンサを充電するのに $V_{CC}$ から電流を引き込みます。充電された電荷はチップが一回STORE処理を実行するのに使用されます。 $V_{CC}$ ピンの電圧が $V_{SWITCH}$ を下回ると、デバイスは $V_{CC}$ と $V_{CAP}$ ピンの接続を自動的に切ります。STORE処理は、 $V_{CAP}$ コンデンサから供給される電力で起動されます。

注：コンデンサが $V_{CAP}$ ピンに接続されていない場合、[6ページの「AutoStoreの防止」](#)に指定したソフトシーケンスを使ってAutoStoreを無効にする必要があります。 $V_{CAP}$ ピンに接続して

いるコンデンサがない状態でAutoStoreが有効になった場合、STORE処理を完了するために、デバイスは十分な充電量がないままAutoStore処理を実行しようとします。これにより、nvSRAM内にストアされたデータが破壊されます。

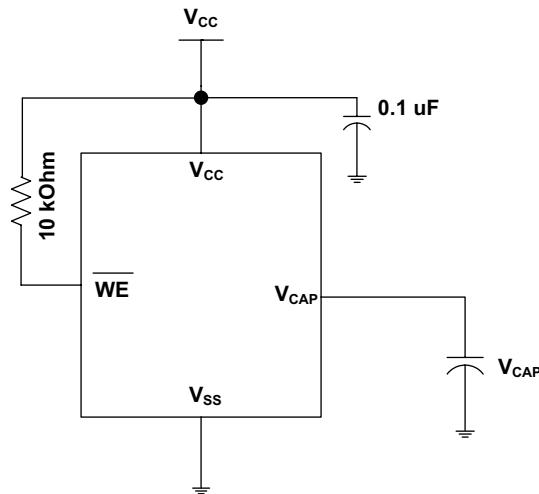

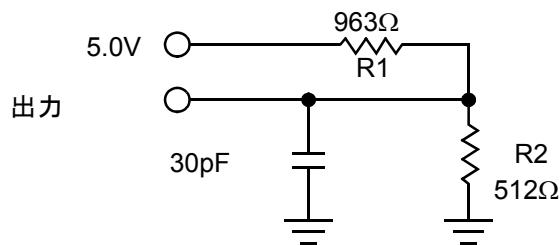

図2に、自動的なSTORE処理用のストレージコンデンサ( $V_{CAP}$ )の適切な接続方法を示します。 $V_{CAP}$ の容量については、[7ページの「DC電気的特性」](#)を参照してください。 $V_{CAP}$ ピンの電圧は、チップ上のレギュレータによって $V_{CC}$ に駆動されます。電源投入時にアクティブにならないようにするために、 $WE$ をプルアップ抵抗に接続します。このプルアップ抵抗は、電源投入時に $WE$ 信号がトライステート状態にある場合のみ有効です。多くのMPUが電源投入時にそれらの制御をトライステートします。プルアップ抵抗を使用する場合には確認してください。nvSRAMが電源投入時のRECALLから復帰する時、MPUがアクティブであるか、MPUのリセットが終了するまで $WE$ をアクティブでない状態に保つ必要があります。

不要な不揮発性のSTOREを避けるため、AutoStoreおよびハードウェアSTORE処理は、一番最後にSTOREまたはRECALLサイクルが実行されてから少なくとも1回の書き込み処理が行われるまでは無視されます。ソフトウェアにより起動されたSTOREサイクルは、書き込み処理が行われたかどうかに関係なく実行されます。HSB信号は、AutoStoreサイクルが処理中かどうかを検出するためにシステムによって監視されています。

図2. AutoStoreモード

### ハードウェアSTORE処理

CY14E256LAには、STORE処理を制御し応答するためのHSBピンがあります。HSBピンは、ハードウェアSTOREサイクルの要求に使用してください。HSBピンがLOWに駆動されると、CY14E256LAは $t_{DELAY}$ 後に条件に従ってSTORE処理を開始します。実際のSTOREサイクルは、最後のSTOREまたはRECALLサイクル以降、SRAMへの書き込みが実行された場合にのみ開始します。HSBピンは、STORE処理(任意の手段で開始)中にはビギー状態を示すために内部でLOWに駆動されるオープンドレインドライバ(チップ内部に100kΩの弱いプルアップ抵抗)としても動作します。

注：ハードウェアおよびソフトウェアSTORE処理の後、HSBは標準出力HIGH電流で短時間( $t_{HHHD}$ )HIGHに駆動され、その後100kΩの内部プルアップ抵抗によりHIGH状態を継続します。

SRAM書き込み処理は HSB が LOW にされた時に実行中であれば、STORE 処理が開始される前に  $t_{DELAY}$  以内に終了します。しかし HSB が LOW になった後に要求された SRAM 書き込みサイクルは、HSB が HIGH に戻るまで禁止されます。書き込みラッチがセットされていない場合、HSB は CY14E256LA によって LOW に駆動されることはありません。しかし全ての SRAM 読み出しと書き込みサイクルは、MPU または他の外部ソースにより HSB が HIGH に戻るまで禁止されます。

STORE 処理がどのように起動されたかに関わらず、その処理中には、CY14E256LA は HSB ピンを LOW に駆動し続け、STORE 処理が完了した時にのみ解除します。STORE 処理が完了すると、HSB ピンが HIGH 状態に戻った後に nvSRAM メモリ アクセスは  $t_{LZHSB}$  間禁止されます。HSB ピンは使用しない場合、開放してください。

### ハードウェア RECALL (電源投入)

電源投入時または低電圧状態 ( $V_{CC} < V_{SWITCH}$ ) の後は、内部的に RECALL 要求がラッチされます。 $V_{CC}$  が再度  $V_{SWITCH}$  の検知電圧を超えた場合、RECALL サイクルが自動的に開始され、完了するのに  $t_{HRECALL}$  かかります。この間、HSB は HSB ドライバーによって LOW に駆動されます。

### ソフトウェア STORE

データは、ソフトウェアアドレスシーケンスによって SRAM から不揮発性メモリに転送されます。CY14E256LA のソフトウェア STORE サイクルは、CE または OE に制御された読み出し処理を、6 つの特定のアドレスから正しい順番で実行することにより開始されます。STORE サイクルの間、まず前の不揮発性データが消去されてから、不揮発性素子がプログラムされます。STORE サイクルが開始されると、それ以降の入出力は STORE サイクルが完了するまで無効になります。

特定のアドレスからの READ のシーケンスが STORE の開始に使われるため、シーケンス中に他の読み書きアクセスが干渉しないことが重要です。そうしないと、シーケンスがアボートされ、STORE や RECALL が実行されません。

ソフトウェア STORE サイクルを開始するために、次の読み出しシーケンスを実行してください。

表 1. モード選択

| CE | WE | OE | $A_{14} \sim A_0^{[6]}$                                  | モード                                                                                | I/O                                                | 電源                   |

|----|----|----|----------------------------------------------------------|------------------------------------------------------------------------------------|----------------------------------------------------|----------------------|

| H  | X  | X  | X                                                        | 未選択                                                                                | 出力 High Z                                          | スタンバイ                |

| L  | H  | L  | X                                                        | SRAM 読み出し                                                                          | 出力データ                                              | アクティブ                |

| L  | L  | X  | X                                                        | SRAM 書き込み                                                                          | 入力データ                                              | アクティブ                |

| L  | H  | L  | 0x0E38<br>0x31C7<br>0x03E0<br>0x3C1F<br>0x303F<br>0x0B45 | SRAM 読み出し<br>SRAM 読み出し<br>SRAM 読み出し<br>SRAM 読み出し<br>SRAM 読み出し<br>AutoStore ディスエーブル | 出力データ<br>出力データ<br>出力データ<br>出力データ<br>出力データ<br>出力データ | アクティブ <sup>[7]</sup> |

注

- CY14E256LA にアドレスラインが 15 本ありますが、その下の 14 本のみがソフトウェアモードの制御に使われます。

- 6 つの連続アドレス位置は指定された順番でなければなりません。WE は不揮発性サイクルを可能にするため、全ての 6 つのサイクル中は HIGH でなければなりません。

**表 1. モード選択 ( 続き )**

| <b>CE</b> | <b>WE</b> | <b>OE</b> | <b>A<sub>14</sub> ~ A<sub>0</sub><sup>[6]</sup></b>      | <b>モード</b>                                                                       | <b>I/O</b>                                             | <b>電源</b>                                |

|-----------|-----------|-----------|----------------------------------------------------------|----------------------------------------------------------------------------------|--------------------------------------------------------|------------------------------------------|

| L         | H         | L         | 0x0E38<br>0x31C7<br>0x03E0<br>0x3C1F<br>0x303F<br>0x0B46 | SRAM 読み出し<br>SRAM 読み出し<br>SRAM 読み出し<br>SRAM 読み出し<br>SRAM 読み出し<br>AutoStore イネーブル | 出力データ<br>出力データ<br>出力データ<br>出力データ<br>出力データ<br>出力データ     | アクティブ <sup>[8]</sup>                     |

| L         | H         | L         | 0x0E38<br>0x31C7<br>0x03E0<br>0x3C1F<br>0x303F<br>0x0FC0 | SRAM 読み出し<br>SRAM 読み出し<br>SRAM 読み出し<br>SRAM 読み出し<br>SRAM 読み出し<br>不揮発性 STORE      | 出力データ<br>出力データ<br>出力データ<br>出力データ<br>出力データ<br>出力 High-Z | アクティブ<br>I <sub>CC2</sub> <sup>[8]</sup> |

| L         | H         | L         | 0x0E38<br>0x31C7<br>0x03E0<br>0x3C1F<br>0x303F<br>0x0C63 | SRAM 読み出し<br>SRAM 読み出し<br>SRAM 読み出し<br>SRAM 読み出し<br>SRAM 読み出し<br>不揮発性 RECALL     | 出力データ<br>出力データ<br>出力データ<br>出力データ<br>出力データ<br>出力 High-Z | アクティブ <sup>[8]</sup>                     |

### AutoStore の防止

AutoStore 機能は AutoStore ディスエーブル シーケンスを開始することで無効にされます。読み出し処理のシーケンスは、ソフトウェア STORE の開始と同様の方法で実行されます。AutoStore ディスエーブル シーケンスを開始するために、CE または OE に制御された読み出し処理を以下の順番で実行してください。

1. アドレス 0x0E38 の読み出し – 有効な READ

2. アドレス 0x31C7 の読み出し – 有効な READ

3. アドレス 0x03E0 の読み出し – 有効な READ

4. アドレス 0x3C1F の読み出し – 有効な READ

5. アドレス 0x303F の読み出し – 有効な READ

6. アドレス 0x0B45 の読み出し – AutoStore の無効化

AutoStore 機能は AutoStore 有効シーケンスの起動によって再度有効化されます。読み出し処理のシーケンスは、ソフトウェア RECALL の開始と同様の方法で実行されます。AutoStore イ

ネーブル シーケンスを開始するために、CE または OE に制御された読み出し処理を以下の順番で実行してください。

1. アドレス 0x0E38 の読み出し – 有効な READ

2. アドレス 0x31C7 の読み出し – 有効な READ

3. アドレス 0x03E0 の読み出し – 有効な READ

4. アドレス 0x3C1F の読み出し – 有効な READ

5. アドレス 0x303F の読み出し – 有効な READ

6. アドレス 0x0B46 の読み出し – AutoStore の有効化

AutoStore 機能が無効にされた、または再度有効にされた場合、その後に電源切断サイクルを経過しても AutoStore 状態を保持するために STORE 処理（ハードウェアまたはソフトウェア）を手動で実行する必要があります。工場出荷時 AutoStore は有効になっており、全てのセルに 0x00 と書き込まれています。

### データ保護

CY14E256LA は、外部から実行される STORE および書き込み処理をすべて禁止することで、低電圧状態の間に破損からデータを保護します。低電圧状態は V<sub>CC</sub> が V<sub>SWITCH</sub> を下回ると検出されます。電源投入時に CY14E256LA が書き込みモードにある (CE と WE の両方が LOW) 場合、RECALL または STORE 後、t<sub>LZHSB</sub> (HSB から出力有効までの時間) が経過して SRAM が有効になるまでは、書き込みは禁止されます。これは電源投入時や電圧低下状態の間に不注意による書き込みを保護します。

### 注

8. 6つの連続アドレス位置は指定された順番でなければなりません。WE は不揮発性サイクルを可能にするため、すべての 6 つのサイクル中は HIGH でなければなりません。

## 最大定格

最大定格を超えるとデバイスの寿命が短くなる可能性があります。これらのユーザー ガイドラインはテストされていません。

保存温度 .....  $-65^{\circ}\text{C} \sim +150^{\circ}\text{C}$

最大累積保存時間 :

周囲温度  $150^{\circ}\text{C}$  時 ..... 1000 時間

周囲温度  $85^{\circ}\text{C}$  時 ..... 20 年

最大接合部温度 1 .....  $150^{\circ}\text{C}$

$V_{\text{SS}}$  を基準とした  $V_{\text{CC}}$  の電源電圧 .....  $-0.5\text{V} \sim 7.0\text{V}$

High-Z 状態の出力に印加される電圧 .....  $-0.5\text{V} \sim V_{\text{CC}} + 0.5\text{V}$

入力電圧 .....  $-0.5\text{V} \sim V_{\text{CC}} + 0.5\text{V}$

任意のピンの過渡電圧、グランド基準

(20ns 以下) .....  $-2.0\text{V} \sim V_{\text{CC}} + 2.0\text{V}$

パッケージ許容電力損失 ( $T_A=25^{\circ}\text{C}$ ) ..... 1.0W

表面実装のハンダ付け温度 (3 秒) .....  $+260^{\circ}\text{C}$

DC 出力電流 (一度に 1 出力、1 秒間) ..... 15mA

静電放電時の電圧

(MIL-STD-883、メソッド 3015 による) .....  $>2001\text{V}$

ラッチアップ電流 .....  $>200\text{mA}$

## 動作範囲

| 範囲  | 周囲温度                                           | $V_{\text{CC}}$                |

|-----|------------------------------------------------|--------------------------------|

| 産業用 | $-40^{\circ}\text{C} \sim +85^{\circ}\text{C}$ | $4.5\text{V} \sim 5.5\text{V}$ |

## DC 電気的特性

### 動作範囲において

| パラメーター                 | 説明                                                                                                            | テスト条件                                                                                                                                                                                        | Min  | Typ <sup>[9]</sup>    | Max                   | 単位            |   |

|------------------------|---------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----------------------|-----------------------|---------------|---|

| $V_{\text{CC}}$        | 電源                                                                                                            |                                                                                                                                                                                              | 4.5  | 5.0                   | 5.5                   | V             |   |

| $I_{\text{CC}1}$       | 平均 $V_{\text{CC}}$ 電流                                                                                         | $t_{\text{RC}} = 25\text{ns}$<br>$t_{\text{RC}} = 45\text{ns}$<br>出力負荷なしで得られた値 ( $I_{\text{OUT}} = 0\text{mA}$ )                                                                             | -    | -                     | 70<br>52              | mA<br>mA      |   |

| $I_{\text{CC}2}$       | STORE 中の平均 $V_{\text{CC}}$ 電流                                                                                 | 全ての入力は「ドント ケア」、<br>$V_{\text{CC}} = \text{Max}$<br>$t_{\text{STORE}}$ 期間の平均電流                                                                                                                | -    | -                     | 10                    | mA            |   |

| $I_{\text{CC}3}$       | $t_{\text{RC}} = 200\text{ns}$ 時の平均 $V_{\text{CC}}$ 電流、<br>$V_{\text{CC}(\text{Typ})}$ 、 $25^{\circ}\text{C}$ | すべての入力は CMOS レベルで動作。<br>出力負荷なしで得られた値 ( $I_{\text{OUT}} = 0\text{mA}$ )                                                                                                                       | -    | 35                    | -                     | mA            |   |

| $I_{\text{CC}4}$       | AutoStore サイクル中の平均 $V_{\text{CAP}}$ 電流                                                                        | 全ての入力は「ドント ケア」である。<br>$t_{\text{STORE}}$ 期間の平均電流                                                                                                                                             | -    | -                     | 8                     | mA            |   |

| $I_{\text{SB}}$        | $V_{\text{CC}}$ スタンバイ電流                                                                                       | $\text{CE} \geq (V_{\text{CC}} - 0.2\text{V})$<br>$V_{\text{IN}} \leq 0.2\text{V}$ または $\geq (V_{\text{CC}} - 0.2\text{V})$ 。<br>不揮発性のサイクルが完了した後のスタンバイ電流レベル。<br>入力はステティック。 $f = 0\text{MHz}$ | -    | -                     | 8                     | mA            |   |

| $I_{\text{IX}}^{[10]}$ | 入力リード電流 ( $\text{HSB}$ を除く)                                                                                   | $V_{\text{CC}} = \text{Max}$ 、 $V_{\text{SS}} \leq V_{\text{IN}} \leq V_{\text{CC}}$                                                                                                         | -1   | -                     | +1                    | $\mu\text{A}$ |   |

|                        | 入力リード電流 ( $\text{HSB}$ 用)                                                                                     | $V_{\text{CC}} = \text{Max}$ 、 $V_{\text{SS}} \leq V_{\text{IN}} \leq V_{\text{CC}}$                                                                                                         | -100 | -                     | +1                    | $\mu\text{A}$ |   |

| $I_{\text{OZ}}$        | オフ状態の出力リード電流                                                                                                  | $V_{\text{CC}} = \text{Max}$ 、<br>$V_{\text{SS}} \leq V_{\text{OUT}} \leq V_{\text{CC}}$ 、<br>$\text{CE}$ または $\text{OE} \geq V_{\text{IH}}$ または $\text{WE} \leq V_{\text{IL}}$              | -1   | -                     | +1                    | $\mu\text{A}$ |   |

| $V_{\text{IH}}$        | 入力 HIGH 電圧                                                                                                    |                                                                                                                                                                                              | 2.0  | -                     | $V_{\text{CC}} + 0.5$ | V             |   |

| $V_{\text{IL}}$        | 入力 LOW 電圧                                                                                                     |                                                                                                                                                                                              |      | $V_{\text{SS}} - 0.5$ | -                     | 0.8           | V |

| $V_{\text{OH}}$        | 出力 HIGH 電圧                                                                                                    | $I_{\text{OUT}} = -2\text{mA}$                                                                                                                                                               | 2.4  | -                     | -                     | V             |   |

| $V_{\text{OL}}$        | 出力 LOW 電圧                                                                                                     | $I_{\text{OUT}} = 4\text{mA}$                                                                                                                                                                | -    | -                     | 0.4                   | V             |   |

### 注

9. 標準値は  $25^{\circ}\text{C}$ 、 $V_{\text{CC}} = V_{\text{CC}(\text{Typ})}$  のものです。100% のテストは行われていません。

10. HSB ピンは、アクティブ HIGH と LOW ドライバーの両方が無効になっている場合に、 $V_{\text{OH}} = 2.4\text{V}$  に対して、 $I_{\text{OUT}}$  が  $-2\mu\text{A}$  です。それらのドライバーがイネーブルの場合、標準の  $V_{\text{OH}}$  と  $V_{\text{OL}}$  が有効になります。このパラメーターは特性付けされていますが、テストされていません。

## DC 電気的特性 ( 続き )

### 動作範囲において

| パラメーター                   | 説明                            | テスト条件                     | Min | Typ <sup>[9]</sup> | Max            | 単位      |

|--------------------------|-------------------------------|---------------------------|-----|--------------------|----------------|---------|

| $V_{CAP}^{[11]}$         | ストレージ コンデンサ                   | $V_{CAP}$ ピンと $V_{SS}$ の間 | 61  | 68                 | 180            | $\mu F$ |

| $V_{V_{CAP}}^{[12, 13]}$ | デバイスで $V_{CAP}$ ピン上に駆動された最大電圧 | $V_{CC} = \text{Max}$     | —   | —                  | $V_{CC} - 0.5$ | V       |

## データ保持期間およびアクセス可能回数

### 動作範囲において

| パラメーター   | 説明                   | Min   | 単位 |

|----------|----------------------|-------|----|

| $DATA_R$ | データ保持期間              | 20    | 年  |

| $NV_C$   | 不揮発性 STORE オペレーション回数 | 1,000 | K  |

## 静電容量

| パラメーター <sup>[13]</sup> | 説明             | テスト条件                                                           | Max | 単位 |

|------------------------|----------------|-----------------------------------------------------------------|-----|----|

| $C_{IN}$               | 入力容量 (HSB を除く) | $T_A = 25^\circ C$ 、 $f = 1MHz$ 、 $V_{CC} = V_{CC(\text{Typ})}$ | 7   | pF |

|                        | 入力容量 (HSB)     |                                                                 | 8   | pF |

| $C_{OUT}$              | 出力容量 (HSB を除く) |                                                                 | 7   | pF |

|                        | 出力容量 (HSB)     |                                                                 | 8   | pF |

## 熱抵抗

| パラメーター <sup>[13]</sup> | 説明                  | テスト条件                                                     | 44 ピン TSOP II | 32 ピン SOIC | 単位           |

|------------------------|---------------------|-----------------------------------------------------------|---------------|------------|--------------|

| $\Theta_{JA}$          | 熱抵抗<br>( 接合部から周囲 )  | テスト条件は、EIA/JESD51 に記載されている熱インピーダンスを測定するための標準的なテスト方法と手順に従う | 41.74         | 41.55      | $^\circ C/W$ |

| $\Theta_{JC}$          | 熱抵抗<br>( 接合部からケース ) |                                                           | 11.90         | 24.43      | $^\circ C/W$ |

### 注

- $V_{CAP}$  最小値は、AutoStore 処理を完了するのに十分な電荷があることを保証するものです。 $V_{CAP}$  最大値は、即時の電源切断が発生しても AutoStore 処理が正常に完了するように電源投入 RECALL サイクルの間に  $V_{CAP}$  のコンデンサが必要な最小電圧まで充電されることを保証するものです。したがって、指定した最小値と最大値の範囲内のコンデンサを使用することをお勧めします。 $V_{CAP}$  オプションの詳細については、アプリケーションノート [AN43593](#) を参照してください。

- $V_{CAP}$  ピン ( $V_{V_{CAP}}$ ) の最大電圧は、 $V_{CAP}$  コンデンサを選択する際に指針として提供されています。動作温度範囲内においての  $V_{CAP}$  コンデンサの定格電圧は、 $V_{V_{CAP}}$  電圧より高くななければなりません。

- これらのパラメーターは設計保証されますが、テストされていません。

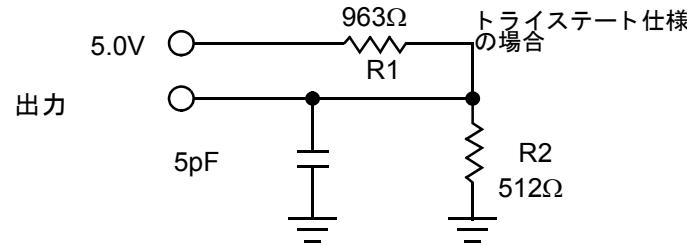

## AC テスト負荷

図 3. AC テスト負荷

## AC テスト条件

入力パルス レベル ..... 0V ~ 3V

入力の立ち上がり／立ち下がり時間 (10% ~ 90%) ....  $\leq 3\text{ns}$

入力と出力タイミングの基準レベル ..... 1.5V

## AC スイッチング特性

### 動作範囲において

| パラメーター <sup>[14]</sup>                  |                  | 説明                         | 25ns |     | 45ns |     | 単位 |

|-----------------------------------------|------------------|----------------------------|------|-----|------|-----|----|

| サイプレス<br>パラメーター                         | 代替のパラ<br>メーター    |                            | Min  | Max | Min  | Max |    |

| <b>SRAM 読み出しサイクル</b>                    |                  |                            |      |     |      |     |    |

| t <sub>ACE</sub>                        | t <sub>ACS</sub> | チップ イネーブル アクセス時間           | —    | 25  | —    | 45  | ns |

| t <sub>RC</sub> <sup>[15]</sup>         | t <sub>RC</sub>  | 読み出しサイクル時間                 | 25   | —   | 45   | —   | ns |

| t <sub>AA</sub> <sup>[16]</sup>         | t <sub>AA</sub>  | アドレス アクセス時間                | —    | 25  | —    | 45  | ns |

| t <sub>DOE</sub>                        | t <sub>OE</sub>  | 出力イネーブルからデータ有効までの時間        | —    | 12  | —    | 20  | ns |

| t <sub>OH</sub> <sup>[16]</sup>         | t <sub>OH</sub>  | アドレス変更後の出力ホールド時間           | 3    | —   | 3    | —   | ns |

| t <sub>LZCE</sub> <sup>[17、18]</sup>    | t <sub>LZ</sub>  | チップ イネーブルから出力アクティブまでの時間    | 3    | —   | 3    | —   | ns |

| t <sub>HZCE</sub> <sup>[17、18]</sup>    | t <sub>HZ</sub>  | チップ ディスエーブルから出力非アクティブまでの時間 | —    | 10  | —    | 15  | ns |

| t <sub>LZOE</sub> <sup>[17、18]</sup>    | t <sub>OLZ</sub> | 出力イネーブルから出力アクティブまでの時間      | 0    | —   | 0    | —   | ns |

| t <sub>HZOE</sub> <sup>[17、18]</sup>    | t <sub>OHZ</sub> | 出力ディスエーブルから出力非アクティブまでの時間   | —    | 10  | —    | 15  | ns |

| t <sub>PU</sub> <sup>[17]</sup>         | t <sub>PA</sub>  | チップ イネーブルから電源アクティブまでの時間    | 0    | —   | 0    | —   | ns |

| t <sub>PD</sub> <sup>[17]</sup>         | t <sub>PS</sub>  | チップ ディスエーブルから電源スタンバイまでの時間  | —    | 25  | —    | 45  | ns |

| <b>SRAM 書き込みサイクル</b>                    |                  |                            |      |     |      |     |    |

| t <sub>WC</sub>                         | t <sub>WC</sub>  | 書き込みサイクル時間                 | 25   | —   | 45   | —   | ns |

| t <sub>PWE</sub>                        | t <sub>WP</sub>  | 書き込みパルス幅                   | 20   | —   | 30   | —   | ns |

| t <sub>SCE</sub>                        | t <sub>CW</sub>  | チップ イネーブルから書き込み終了までの時間     | 20   | —   | 30   | —   | ns |

| t <sub>SD</sub>                         | t <sub>DW</sub>  | データ セットアップから書き込み終了までの時間    | 10   | —   | 15   | —   | ns |

| t <sub>HD</sub>                         | t <sub>DH</sub>  | 書き込み終了後のデータ ホールド時間         | 0    | —   | 0    | —   | ns |

| t <sub>AW</sub>                         | t <sub>AW</sub>  | アドレス セットアップから書き込み終了までの時間   | 20   | —   | 30   | —   | ns |

| t <sub>SA</sub>                         | t <sub>AS</sub>  | アドレス セットアップから書き込み開始までの時間   | 0    | —   | 0    | —   | ns |

| t <sub>HA</sub>                         | t <sub>WR</sub>  | 書き込み終了後のアドレス ホールド時間        | 0    | —   | 0    | —   | ns |

| t <sub>HZWE</sub> <sup>[17、18、19]</sup> | t <sub>WZ</sub>  | 書き込みイネーブルから出力ディスエーブルまでの時間  | —    | 10  | —    | 15  | ns |

| t <sub>LZWE</sub> <sup>[17、18]</sup>    | t <sub>OW</sub>  | 書き込み終了後の出力アクティブ時間          | 3    | —   | 3    | —   | ns |

## スイッチング波形

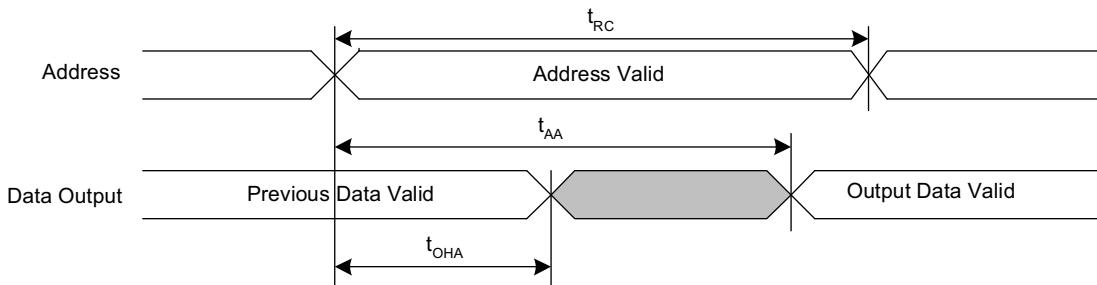

図 4. SRAM 読み出しサイクル 1 (アドレス制御)<sup>[15、16、20]</sup>

### 注

14. テスト条件は、信号遷移時間が 3ns 以下で、タイミング参照レベルが  $V_{CC}/2$  で、入力パルス レベル 0 が  $V_{CC}$  (typ) で、 $I_{OL}/I_{OH}$  の出力負荷と負荷容量が図 3 に示される通りであることを前提にしています。

15.  $\overline{WE}$  は SRAM 読み出しサイクル中は HIGH でなければなりません。

16.  $CE$  と  $OE$  が LOW であれば、デバイスは連続的に選択されます。

17. これらのパラメーターは設計保証されますが、テストされていません。

18. 定常状態の出力電圧から  $\pm 200mV$  で測定されました。

19.  $CE$  が LOW の時に  $WE$  が LOW であれば、出力は高インピーダンスのままで。

20. HSB は読み出しと書き込みサイクル中は HIGH でなければなりません。

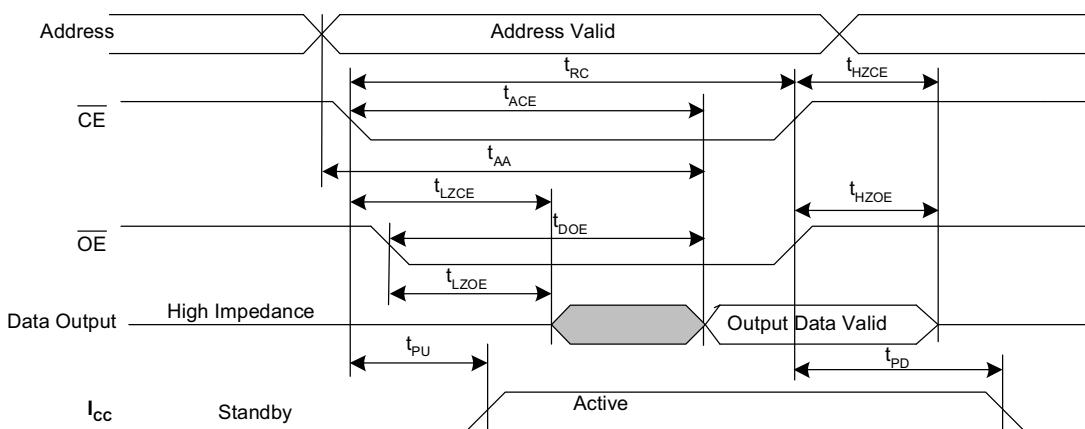

## スイッチング波形(続き)

図5. SRAM 読み出しサイクル2 ( $\overline{CE}$  および  $\overline{OE}$  制御) [21, 22]

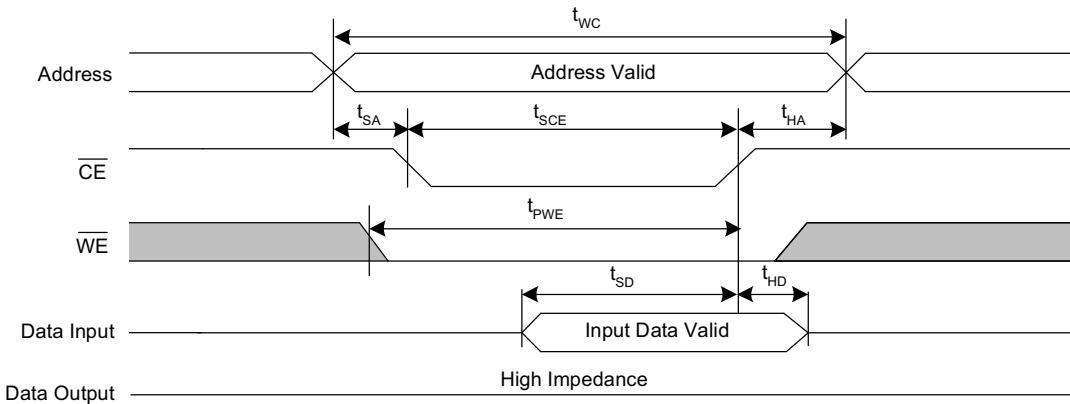

図6. SRAM 書き込みサイクル1 ( $\overline{WE}$  制御) [22, 23, 24]

図7. SRAM 書き込みサイクル2 ( $\overline{CE}$  制御) [22, 23, 24]

### 注

21.  $\overline{WE}$  は SRAM 読み出しサイクル中は HIGH でなければなりません。

22. HSB は読み出しと書き込みサイクル中は HIGH でなければなりません。

23.  $\overline{CE}$  が LOW の時に  $WE$  が LOW であれば、出力は高インピーダンスのままです。

24.  $\overline{CE}$  または  $\overline{WE}$  はアドレスの遷移中は  $V_{IH}$  より高くななければなりません。

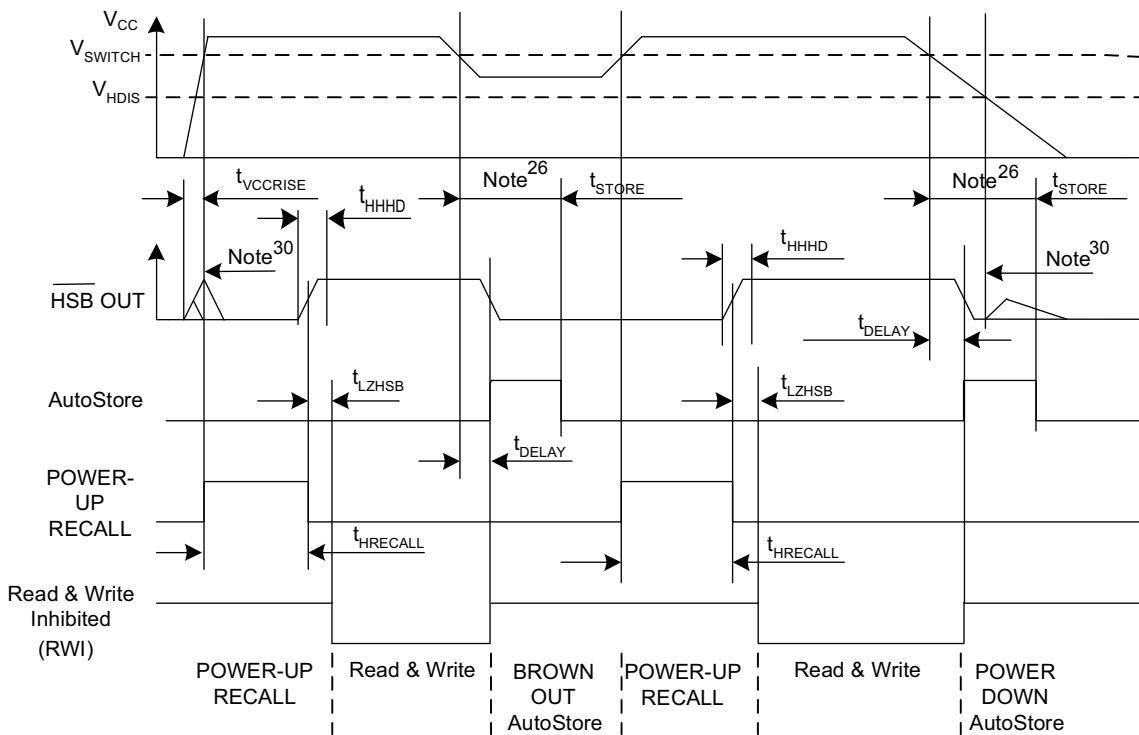

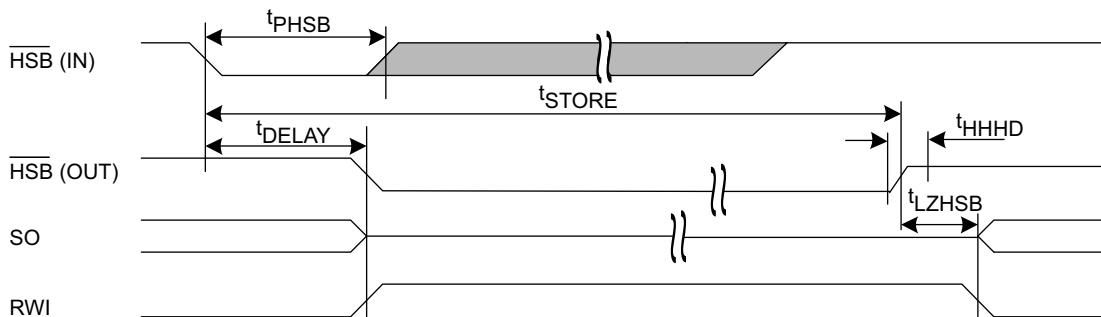

## AutoStore ／電源投入 RECALL

### 動作範囲において

| パラメーター                        | 説明                   | CY14E256LA |     | 単位 |

|-------------------------------|----------------------|------------|-----|----|

|                               |                      | Min        | Max |    |

| $t_{HRECALL}$ <sup>[25]</sup> | 電源投入 RECALL 期間       | —          | 20  | ms |

| $t_{STORE}$ <sup>[26]</sup>   | STORE サイクル期間         | —          | 8   | ms |

| $t_{DELAY}$ <sup>[27]</sup>   | SRAM 書き込みサイクルを完了する時間 | —          | 25  | ns |

| $V_{SWITCH}$                  | 低電圧トリガー レベル          | —          | 4.4 | V  |

| $t_{VCCRISE}$ <sup>[28]</sup> | $V_{CC}$ 立ち上がり時間     | 150        | —   | μs |

| $V_{HDIS}$ <sup>[28]</sup>    | HSB 出力ディスエーブル電圧      | —          | 1.9 | V  |

| $t_{LZHSB}$ <sup>[28]</sup>   | HSB から出力アクティブまでの時間   | —          | 5   | μs |

| $t_{HHHD}$ <sup>[28]</sup>    | HSB HIGH アクティブ時間     | —          | 500 | ns |

### スイッチング波形

図 8. AutoStore または電源投入 RECALL<sup>[29]</sup>

### 注

25.  $t_{HRECALL}$  は、 $V_{CC}$ が $V_{SWITCH}$ を超えた時から始まります。

26. SRAM の書き込みが最後の不揮発性サイクル以降に実施されていない場合、AutoStore またはハードウェア STORE は実行されません。

27. ハードウェア STORE と AutoStore の開始時に、SRAM の書き込み処理は  $t_{DELAY}$  の間有効になったままです。

28. これらのパラメーターは設計保証されますが、テストされていません。

29. STORE、RECALL サイクルの間、および  $V_{CC}$ が $V_{SWITCH}$ を下回っている時に、読み出しと書き込みサイクルは無視されます。

30. 電源投入および電源切断中に、HSB ピンが外部抵抗を介してプルアップされている場合、HSB ピンにグリッチが発生します。

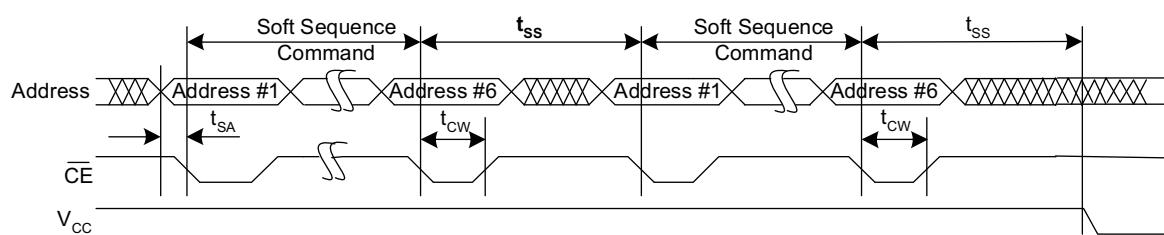

## ソフトウェア制御 STORE/RECALL サイクル

動作範囲において

| パラメーター <sup>[31, 32]</sup> | 説明                       | 25ns |     | 45ns |     | 単位 |

|----------------------------|--------------------------|------|-----|------|-----|----|

|                            |                          | Min  | Max | Min  | 最大値 |    |

| $t_{RC}$                   | STORE ／ RECALL 開始のサイクル期間 | 25   | —   | 45   | —   | ns |

| $t_{SA}$                   | アドレスセットアップ時間             | 0    | —   | 0    | —   | ns |

| $t_{CW}$                   | クロックパルス幅                 | 20   | —   | 30   | —   | ns |

| $t_{HA}$                   | アドレスホールド時間               | 0    | —   | 0    | —   | ns |

| $t_{RECALL}$               | RECALL期間                 | —    | 200 | —    | 200 | μs |

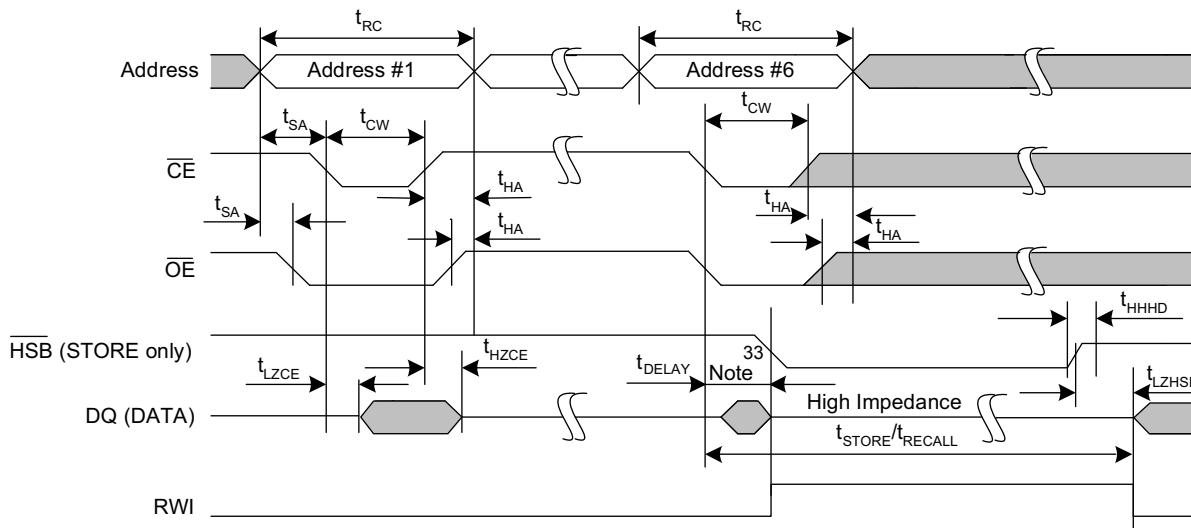

## スイッチング波形

図 9.  $\overline{CE}$  と  $\overline{OE}$  制御によるソフトウェア STORE/RECALL サイクル<sup>[32]</sup>

図 10. AutoStore イネーブル／ディスエーブルサイクル<sup>[32]</sup>

### 注

31. ソフトウェアのシーケンスは、 $\overline{CE}$  または  $\overline{OE}$  を制御する読み込み処理を伴いクロック供給されます。

32. 6つの連続アドレスは 5 ページの表 1 に指定された順番で読み出す必要があります。WE は、全 6 連続サイクル中は HIGH でなければなりません。

33. 出力が  $t_{DELAY}$  期間中に無効にされるため、6 番目に読み出された DQ 出力データは無効となることがあります。

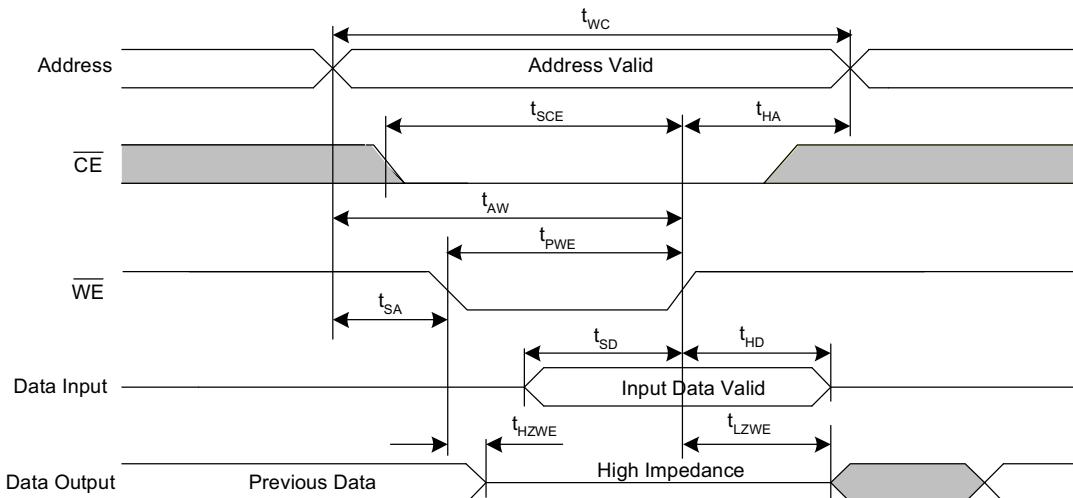

## ハードウェア STORE サイクル

動作範囲において

| 記号                           | 説明                                                               | CY14E256LA |     | 単位            |

|------------------------------|------------------------------------------------------------------|------------|-----|---------------|

|                              |                                                                  | Min        | Max |               |

| $t_{DHSB}$                   | 書き込みラッチがセットされていない場合に、 $\overline{\text{HSB}}$ から出力がアクティブになるまでの時間 | —          | 25  | ns            |

| $t_{PHSB}$                   | ハードウェア STORE パルス幅                                                | 15         | —   | ns            |

| $t_{SS}$ <sup>[34, 35]</sup> | ソフト シーケンス処理時間                                                    | —          | 100 | $\mu\text{s}$ |

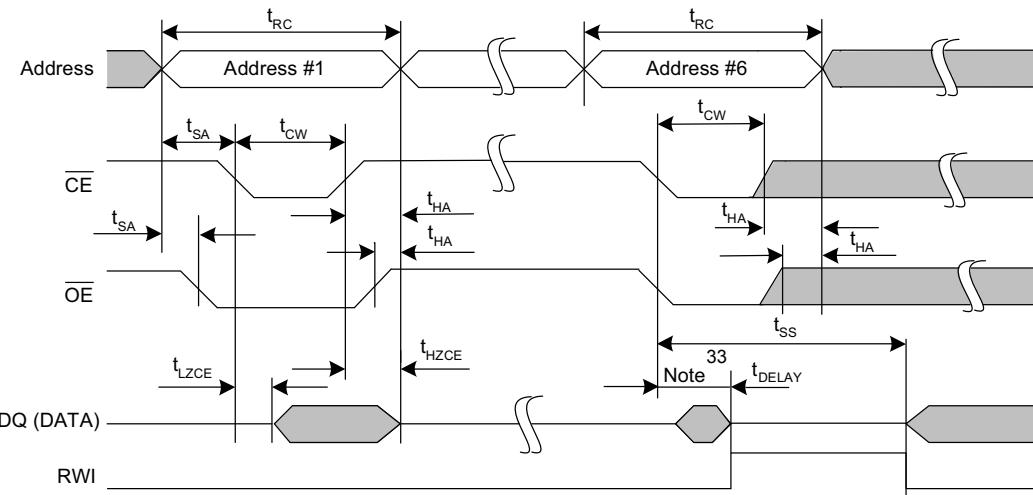

## スイッチング波形

図 11. ハードウェア STORE サイクル<sup>[36]</sup>

### Write Latch set

### Write Latch not set

図 12. ソフト シーケンス処理時間<sup>[34, 35]</sup>

### 注

34. これはソフト シーケンス コマンドを処理するのに必要な時間です。効果的にコマンドを登録するには、Vcc 電圧は HIGH でなければなりません。

35. STORE や RECALL などのコマンドは、その処理が完了するまで I/O をロックし、この時間を更に増加させます。詳しくは個々のコマンドを参照してください。

36. SRAM の書き込みが最後の不揮発性サイクル以降に実施されていない場合、AutoStore またはハードウェア STORE は実行されません。

## SRAM の動作真理値表

HSB は SRAM 動作では HIGH 状態を維持する必要があります。

表 2. 真理値表

| CE | WE | OE | 入力／出力                                      | モード       | 電源    |

|----|----|----|--------------------------------------------|-----------|-------|

| H  | X  | X  | High Z                                     | 選択解除／電源切斷 | スタンバイ |

| L  | H  | L  | データ出力 (DQ <sub>0</sub> ~ DQ <sub>7</sub> ) | 読み出し      | アクティブ |

| L  | H  | H  | High Z                                     | 出力が無効     | アクティブ |

| L  | -  | X  | データ入力 (DQ <sub>0</sub> ~ DQ <sub>7</sub> ) | 書き込み      | アクティブ |

## 注文情報

| 速度<br>(ns) | 注文コード              | パッケージ図   | パッケージ タイプ  | 動作範囲 |

|------------|--------------------|----------|------------|------|

| 25         | CY14E256LA-SZ25XIT | 51-85127 | 32 ピン SOIC | 産業用  |

|            | CY14E256LA-SZ25XI  |          |            |      |

| 45         | CY14E256LA-SZ45XIT | 51-85127 | 32 ピン SOIC |      |

|            | CY14E256LA-SZ45XI  |          |            |      |

上記のすべての製品は鉛フリーです。

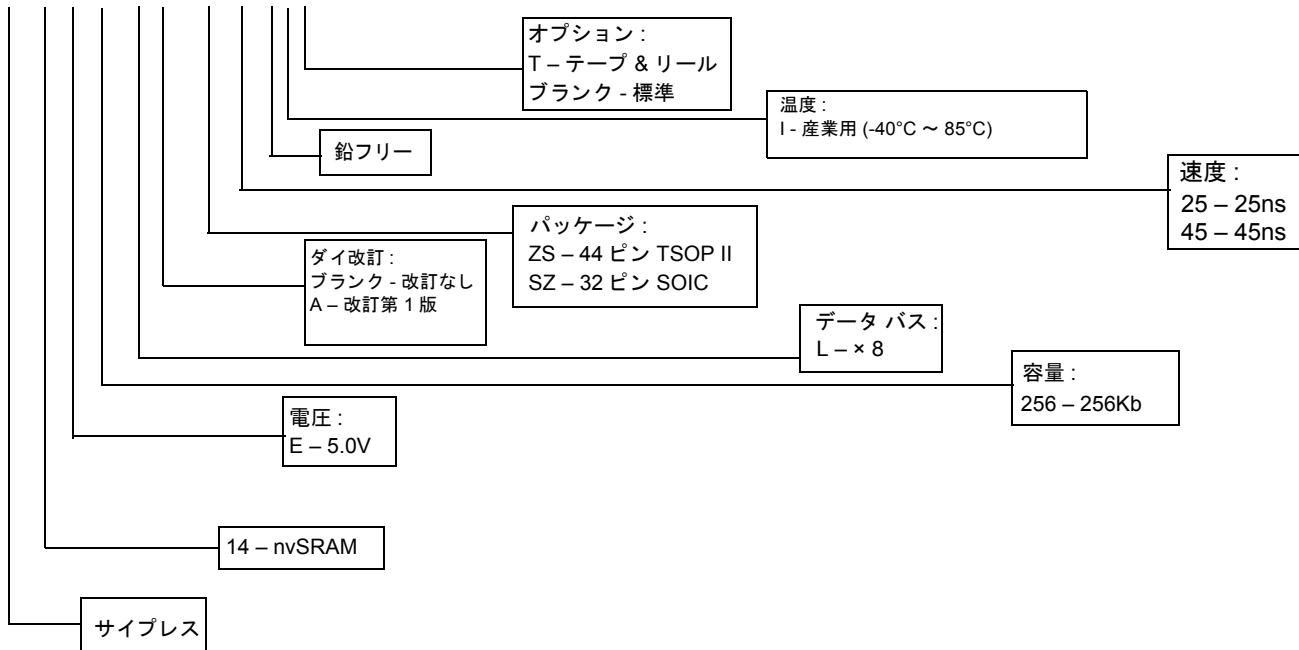

## 注文コードの定義

CY 14 E 256 L A - ZS 25 X IT

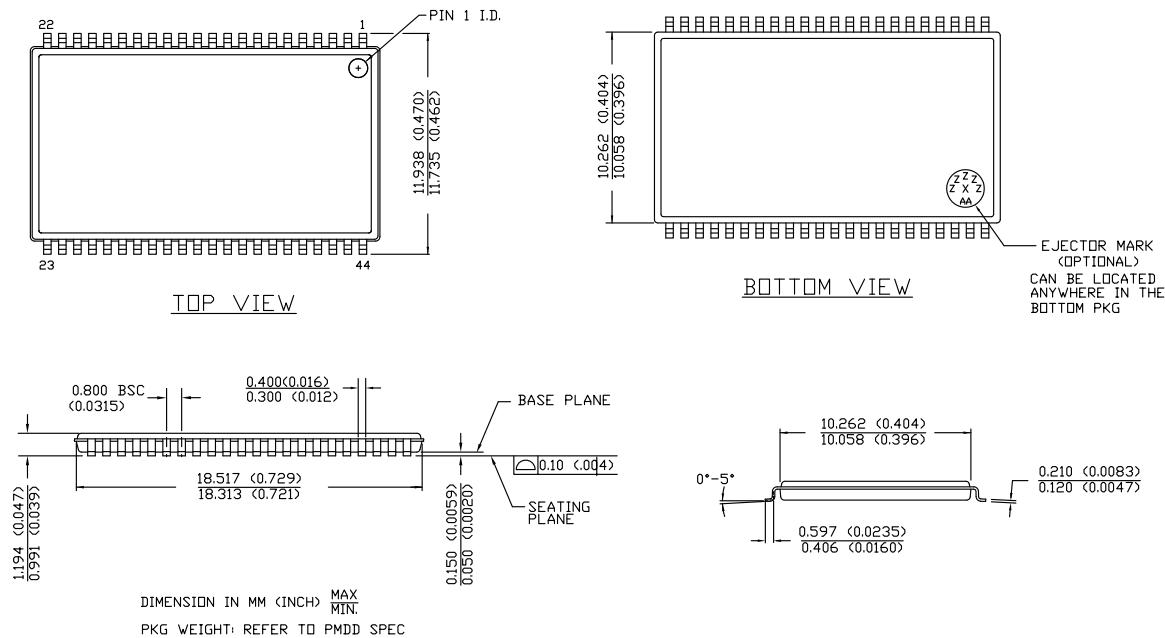

## パッケージ図

図 13. 44 ピン TSOP II パッケージ図、51-85087

図 14. 32 ピン SOIC (300Mil) パッケージ図、51-85127

**略語**

| 略語     | 説明                                                                    |

|--------|-----------------------------------------------------------------------|

| CE     | chip enable ( チップ イネーブル )                                             |

| CMOS   | complementary metal oxide semiconductor<br>( 相補型金属酸化膜半導体 )            |

| EIA    | electronic industries alliance ( 米国電子工業会 )                            |

| HSB    | hardware store busy<br>( ハードウェア ストア ビジー )                             |

| I/O    | input/output ( 入力／出力 )                                                |

| JEDEC  | joint electron devices engineering council<br>( 半導体技術協会 )             |

| nvSRAM | non-volatile static random access memory ( 不揮発性スタティック ランダム アクセス メモリ ) |

| OE     | output enable ( 出力イネーブル )                                             |

| RoHS   | restriction of hazardous substances<br>( 特定有害物質使用制限指令 )               |

| RWI    | read and write inhibited<br>( 読み出しおよび書き込み禁止 )                         |

| SOIC   | small outline integrated circuit<br>( 小型外形集積回路 )                      |

| SRAM   | static random access memory<br>( スタティック ランダム アクセス メモリ )               |

| TSOP   | thin small outline package ( 薄型小型パッケージ )                              |

| WE     | write enable ( 書き込みイネーブル )                                            |

**本書の表記法**

**測定単位**

| 記号  | 測定単位      |

|-----|-----------|

| °C  | 摂氏温度      |

| kΩ  | キロオーム     |

| MHz | メガヘルツ     |

| μA  | マイクロアンペア  |

| μF  | マイクロファラッド |

| μs  | マイクロ秒     |

| mA  | ミリアンペア    |

| ms  | ミリ秒       |

| mV  | ミリボルト     |

| ns  | ナノ秒       |

| Ω   | オーム       |

| %   | パーセント     |

| pF  | ピコファラッド   |

| ps  | ピコ秒       |

| V   | ボルト       |

| W   | ワット       |

## 改訂履歴

文書名 : CY14E256LA、256K ピット (32K × 8) nvSRAM

文書番号 : 001-95858

| 版  | ECN 番号  | 変更者  | 発行日        | 変更内容                                                     |

|----|---------|------|------------|----------------------------------------------------------|

| ** | 4722790 | HZEN | 05/14/2015 | これは英語版 001-54952 Rev. *K を翻訳した日本語版 001-95858 Rev. ** です。 |

## セールス、ソリューション、および法律情報

### ワールドワイドな販売と設計サポート

サイプレスは、事業所、ソリューションセンター、メーカー代理店および販売代理店の世界的なネットワークを保持しています。お客様の最寄りのオフィスについては、[サイプレスのロケーションページ](#)をご覧ください。

#### 製品

|               |                                                                                                                                      |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------|

| 車載用           | <a href="http://cypress.com/go/automotive">cypress.com/go/automotive</a>                                                             |

| クロック & バッファ   | <a href="http://cypress.com/go/clocks">cypress.com/go/clocks</a>                                                                     |

| インターフェース      | <a href="http://cypress.com/go/interface">cypress.com/go/interface</a>                                                               |

| 照明 & 電力制御     | <a href="http://cypress.com/go/powerpsoc">cypress.com/go/powerpsoc</a><br><a href="http://cypress.com/go/plc">cypress.com/go/plc</a> |

| メモリ           | <a href="http://cypress.com/go/memory">cypress.com/go/memory</a>                                                                     |

| 光学 & イメージ センサ | <a href="http://cypress.com/go/image">cypress.com/go/image</a>                                                                       |

| PSoC          | <a href="http://cypress.com/go/psoc">cypress.com/go/psoc</a>                                                                         |

| タッチ センシング     | <a href="http://cypress.com/go/touch">cypress.com/go/touch</a>                                                                       |

| USB コントローラー   | <a href="http://cypress.com/go/USB">cypress.com/go/USB</a>                                                                           |

| ワイヤレス／RF      | <a href="http://cypress.com/go/wireless">cypress.com/go/wireless</a>                                                                 |

#### PSoC ソリューション

|                                                                            |

|----------------------------------------------------------------------------|

| <a href="http://psoc.cypress.com/solutions">psoc.cypress.com/solutions</a> |

| PSoC 1   PSoC 3   PSoC 5                                                   |

© Cypress Semiconductor Corporation, 2009-2015. 本文書に記載される情報は、予告なく変更される場合があります。Cypress Semiconductor Corporation (サイプレス セミコンダクタ社)は、サイプレス製品に組み込まれた回路以外のいかなる回路を使用することに対して一切の責任を負いません。サイプレス セミコンダクタ社は、特許またはその他の権利に基づくライセンスを譲渡することも、または含意することもありません。サイプレス製品は、サイプレスとの書面による合意に基づくものでない限り、医療、生命維持、救命、重要な管理、または安全の用途のために使用することを保証するものではなく、また使用することを意図したものでもありません。さらにサイプレスは、誤動作や故障によって使用者に重大な傷害をもたらすことが合理的に予想される生命維持システムの重要なコンポーネントとしてサイプレス製品を使用することを許可していません。生命維持システムの用途にサイプレス製品を供することは、製造者がそのような使用におけるあらゆるリスクを負うことを意味し、その結果サイプレスはあらゆる責任を免除されることを意味します。

全てのソース コード (ソフトウェアおよび／またはファームウェア) はサイプレス セミコンダクタ社 (以下「サイプレス」) が所有し、全世界の特許権保護 (米国およびその他の国)、米国の著作権法ならびに国際協定の条項により保護され、かつそれらに従います。サイプレスが本書面によりライセンサーに付与するライセンスは、個人的、非独占的かつ譲渡不能のライセンスであり、適用される契約で指定されたサイプレスの集積回路と併用されるライセンサーの製品のみをサポートするカスタムソフトウェアおよび／またはカスタム ファームウェアを作成する目的に限って、サイプレスのソース コードの派生著作物をコピー、使用、変更そして作成するためのライセンス、ならびにサイプレスのソース コードおよび派生著作物をコンパイルするためのライセンスです。上記で指定された場合を除き、サイプレスの書面による明示的な許可なくして本ソース コードを複製、変更、変換、コンパイル、または表示することはすべて禁止します。

免責条項：サイプレスは、明示的または默示的を問わず、本資料に関するいかなる種類の保証も行いません。これには、商品性または特定目的への適合性の默示的な保証が含まれますが、これに限定されません。サイプレスは、本文書に記載される資料に対して今後予告なく変更を加える権利を留保します。サイプレスは、本文書に記載されるいかなる製品または回路を適用または使用したことによって生ずるいかなる責任も負いません。サイプレスは、誤動作や故障によって使用者に重大な傷害をもたらすことが合理的に予想される生命維持システムの重要なコンポーネントとしてサイプレス製品を使用することを許可していません。生命維持システムの用途にサイプレス製品を供することは、製造者がそのような使用におけるあらゆるリスクを負うことを意味し、その結果サイプレスはあらゆる責任を免除されることを意味します。

ソフトウェアの使用は、適用されるサイプレス ソフトウェア ライセンス契約によって制限され、かつ制約される場合があります。