## リアルタイムクロック付き 1-Mbit (128 K × 8) シリアル(I<sup>2</sup>C) nvSRAM

### 特長

- 1 M ビットの不揮発性スタティック RAM (nvSRAM)

- 128K x 8 としてメモリを内部的に編成

- QuantumTrap 不揮発性要素へ STORE は、パワーダウン時に自動的に (AutoStore)、または I<sup>2</sup>C コマンド (ソフトウェア STORE) あるいは HSB ピン (ハードウェア STORE) でインシートされます。

- SRAM への RECALL 处理は、パワーアップ (パワーアップ RECALL) または I<sup>2</sup>C コマンド (ソフトウェア RECALL) によって実行

- 電源オフ時に小容量コンデンサにより、自動的に STORE 处理

- 高い信頼性

- 回数に制限のないリード、ライト、RECALL サイクル

- QuantumTrap に対する 100 万回の STORE サイクル

- データ保存期間 : 85°C で 20 年

- リアルタイムクロック (RTC)

- フル機能 RTC

- ウオッチドッグタイマ

- プログラマブル割り込みクロックアラーム

- バックアップ電源異常表示

- プログラマブル周波数の方形波出力 (1 Hz, 512 Hz, 4096Hz, 32.768kHz)

- RTC コンデンサまたはバックアップバッテリ

- 0.45μA( 代表値 ) のバックアップ電流

- 高速 I<sup>2</sup>C インターフェイス [1]

- 業界標準 100kHz および 400kHz の速度

- 高速モードプラス : 1MHz の速度

- 高速 : 3.4MHz

- 読み書きサイクルの遅延サイクルゼロ

- 書き込み保護

- 書き込み保護ピン (WP) を使ったハードウェアによる保護

- アレイの 1/4、1/2、または全体を対象としたソフトウェアブロック保護

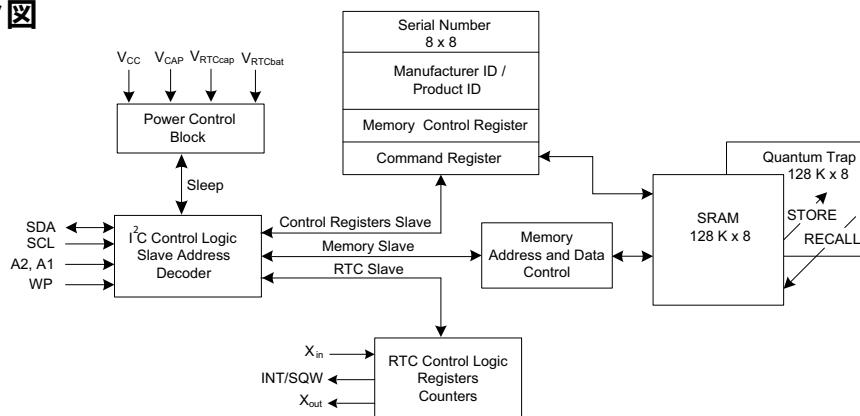

### ロジックブロック図

#### 注

1. I<sup>2</sup>C nvSRAM は、以下の分野における NXP I<sup>2</sup>C の仕様には準拠していません。V<sub>OL</sub>/I<sub>OL</sub>、I/O ヒステリシス、および t<sub>H</sub>/t<sub>OF</sub> 仕様です。詳細は DC 特性 および AC スイッチング特性 の表をご覧ください。

2. シリアル(I<sup>2</sup>C)nvSRAM は、データシート全ページで nvSRAM と示されています。

## 目次

|                                   |    |

|-----------------------------------|----|

| ピン配列 .....                        | 3  |

| ピン機能 .....                        | 3  |

| I2C インターフェイス .....                | 4  |

| プロトコル概要 .....                     | 4  |

| I2C プロトコル – データ転送 .....           | 4  |

| データ有効性 .....                      | 5  |

| START コンディション (S) .....           | 5  |

| STOP コンディション (P) .....            | 5  |

| 反復 START(Sr) .....                | 5  |

| バイト形式 .....                       | 5  |

| アクノレッジ / ノーアクノレッジ .....           | 5  |

| 高速モード (Hs モード) .....              | 6  |

| スレーブデバイスアドレス .....                | 7  |

| 書き込み保護 (WP) .....                 | 9  |

| AutoStore 動作 .....                | 9  |

| ハードウェア STORE 動作および HSB ピン動作 ..... | 9  |

| ハードウェア RECALL(パワーアップ) .....       | 10 |

| 書き込み動作 .....                      | 10 |

| 読み取り動作 .....                      | 10 |

| メモリスレーブアクセス .....                 | 10 |

| RTC レジスタスレーブアクセス .....            | 14 |

| 制御レジスタスレーブ .....                  | 16 |

| シリアル番号 .....                      | 18 |

| シリアル番号書き込み .....                  | 18 |

| シリアル番号ロック .....                   | 18 |

| シリアル番号読み取り .....                  | 18 |

| デバイス ID .....                     | 19 |

| コマンドレジスタを使用したコマンドの実行 .....        | 19 |

| リアルタイムクロック動作 .....                | 20 |

| nvTIME の動作 .....                  | 20 |

| クロックの動作 .....                     | 20 |

| クロックの読み取り .....                   | 20 |

| クロックの時間設定 .....                   | 20 |

| バックアップ電源 .....                    | 20 |

| 発振器の停止と開始 .....                   | 20 |

| クロックの校正 .....                     | 21 |

|                                  |    |

|----------------------------------|----|

| アラーム .....                       | 21 |

| ウォッチドッグタイマ .....                 | 21 |

| プログラマブル方形波発生器 .....              | 22 |

| 電源モニタ .....                      | 22 |

| バックアップ電源モニタ .....                | 22 |

| 割り込み .....                       | 22 |

| 割り込みレジスタ .....                   | 22 |

| フラグレジスタ .....                    | 23 |

| 最大定格 .....                       | 29 |

| 動作範囲 .....                       | 29 |

| DC 電気特性 .....                    | 29 |

| データ保持期間および書き換え回数 .....           | 30 |

| 熱抵抗 .....                        | 30 |

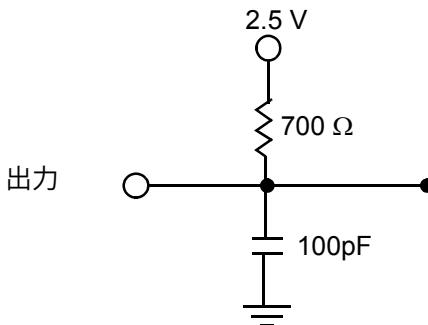

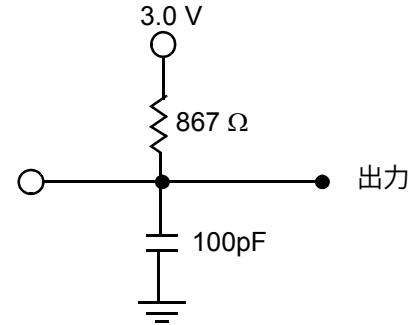

| AC テストの負荷および波形 .....             | 31 |

| AC テスト条件 .....                   | 31 |

| RTC 特性 .....                     | 31 |

| AC スイッチング特性 .....                | 32 |

| スイッチング波形 .....                   | 32 |

| nvSRAM 仕様 .....                  | 33 |

| スイッチング波形 .....                   | 33 |

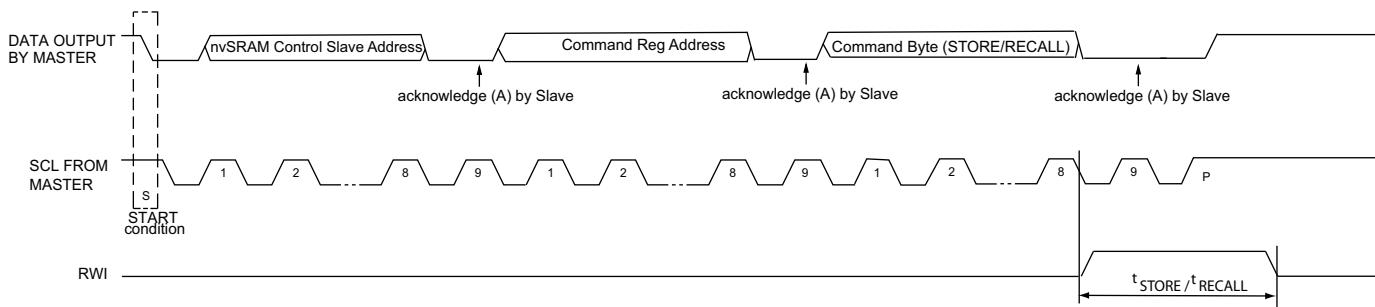

| ソフトウェア制御 STORE/RECALL サイクル ..... | 34 |

| スイッチング波形 .....                   | 34 |

| ハードウェア STORE サイクル .....          | 35 |

| スイッチング波形 .....                   | 35 |

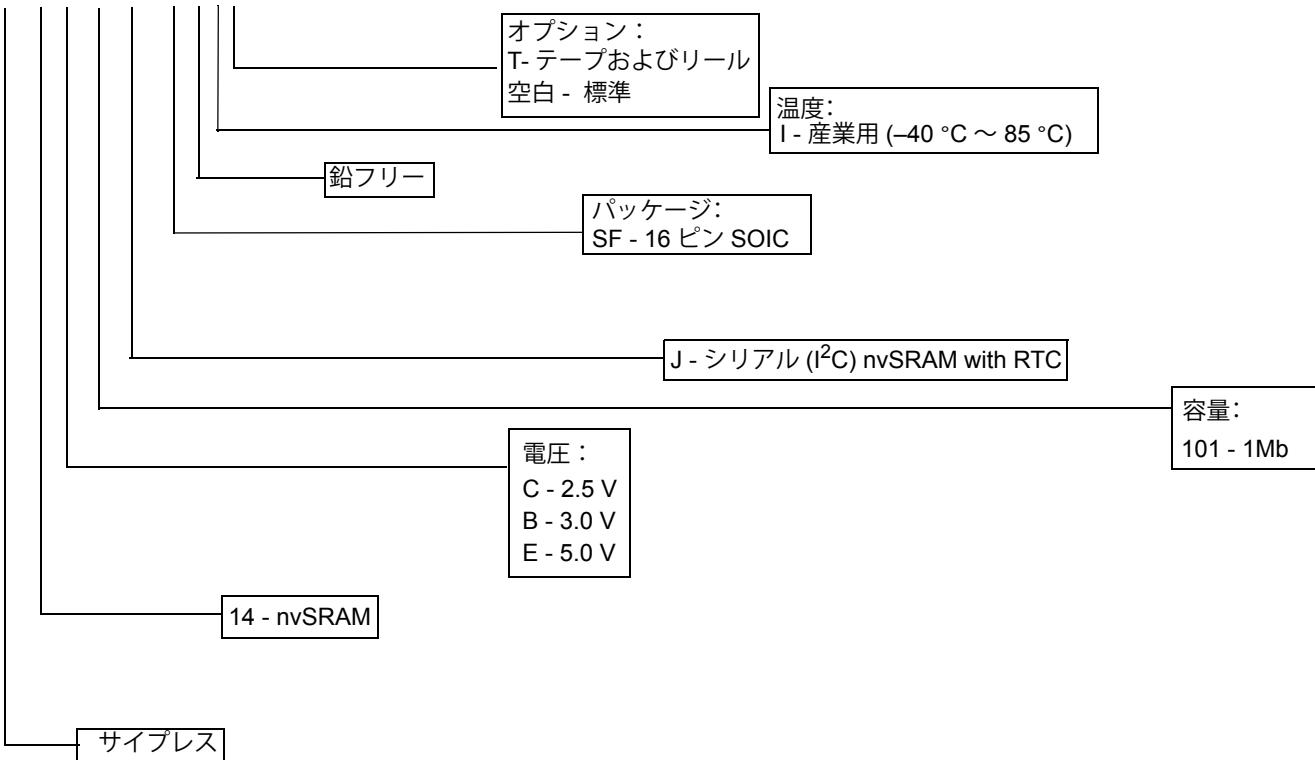

| 製品名(発注)情報 .....                  | 36 |

| 注文コードの定義 .....                   | 36 |

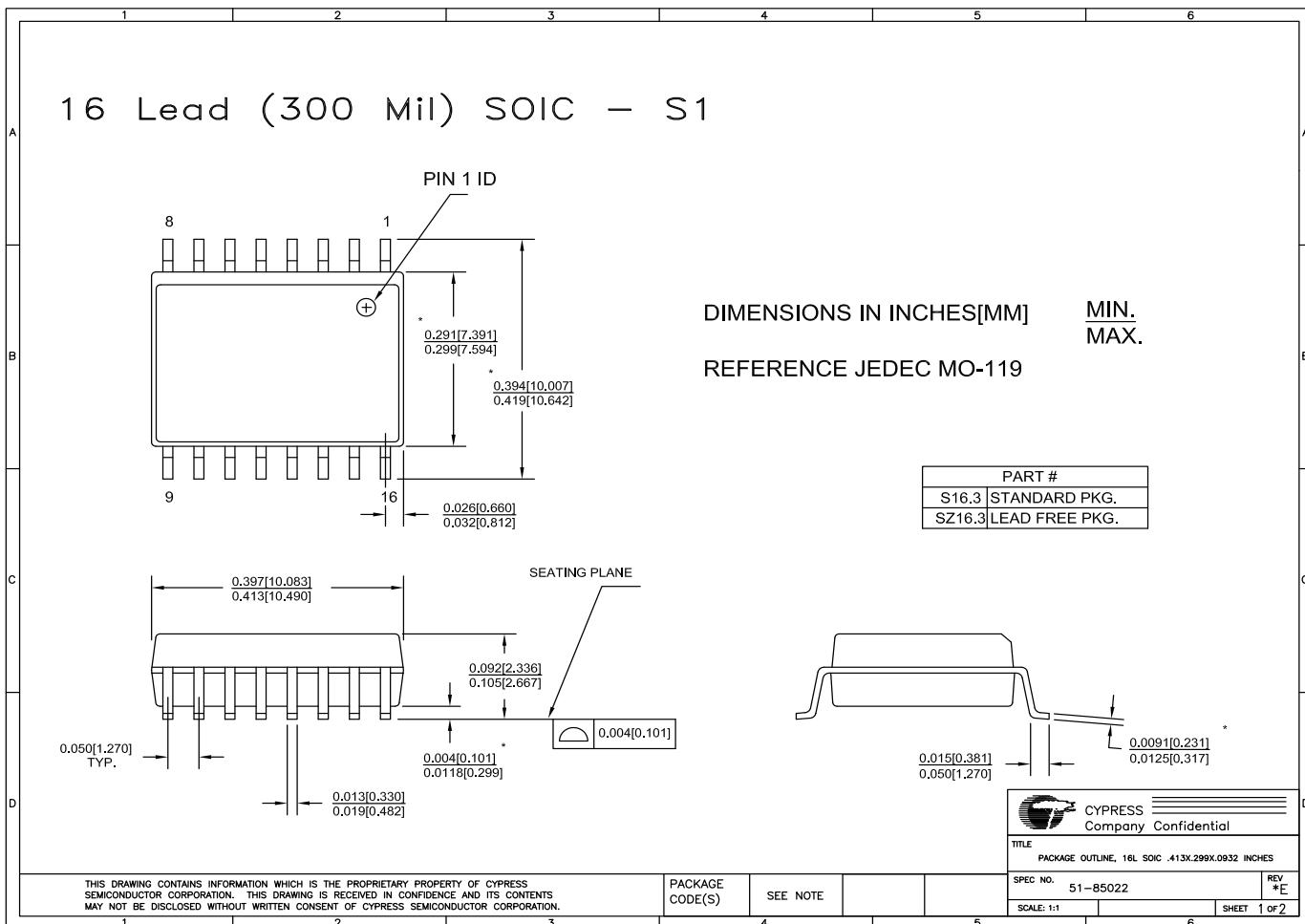

| パッケージ図 .....                     | 37 |

| 略号 .....                         | 38 |

| 本書の表記法 .....                     | 38 |

| 測定単位 .....                       | 38 |

| 改訂履歴 .....                       | 39 |

| 販売、ソリューション、および法律情報 .....         | 40 |

| ワールドワイドな販売および設計サポート .....        | 40 |

| 製品 .....                         | 40 |

| PSoC ソリューション .....               | 40 |

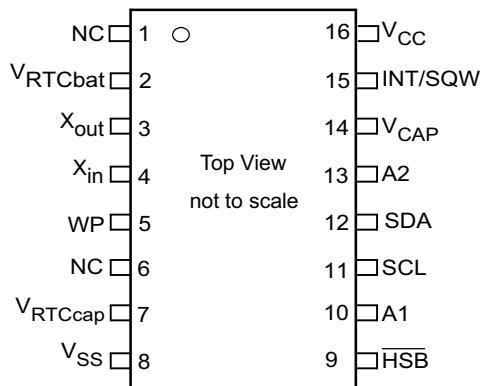

## ピン配列

図 1. 16 ピン SOIC ピン配列

## ピン機能

| ピン名                                | 入出力  | 内容                                                                                                                                                                                                                    |

|------------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SCL                                | 入力   | クロック：最大 $f_{SCL}$ までの速度で動作します。                                                                                                                                                                                        |

| SDA                                | 入出力  | I/O : I <sup>2</sup> Cインターフェイスを介してデータを入出力します。<br>出力：オープンドレインで、外部プルアップ抵抗を必要とします。                                                                                                                                       |

| WP                                 | 入力   | 書き込み保護：すべての書き込みからメモリを保護します。このピンは内部的にLOWにプルダウンされ、そのため接続されていない場合はオープンのままにすることができます。                                                                                                                                     |

| A2-A1                              | 入力   | Slave Address(スレーブアドレス)：I <sup>2</sup> Cのスレーブアドレスを定義します。これらのピンは内部的にLOWにプルダウンされ、そのため接続されていない場合はオープンのままにすることができます。                                                                                                      |

| HSB                                | 入出力  | ハードウェアSTOREビジー状態：<br>出力：LOWの時、nvSRAMのビジー状態を示します。ハードウェアおよびソフトウェアSTORE動作の後、HSBはHIGH出力標準電流で短時間( $t_{HHD}$ )HIGH駆動され、その後内部プルアップ抵抗でHIGH状態を継続します(外部プルアップ抵抗接続はオプションです)。<br>入力：ハードウェアSTOREは、外部的にこのピンをLOWにプルダウンすることによって実装されます。 |

| V <sub>CAP</sub>                   | 電源   | AutoStoreコンデンサ：SRAMから不揮発性要素にデータを格納するため、電力損失時にnvSRAMへ電源を供給します。不要な場合は、AutoStoreをディスエーブルにする必要があり、このピンは未接続のままになります。これは絶対にグランドに接続しないでください。                                                                                 |

| V <sub>RTCcap</sub> <sup>[3]</sup> | 電源   | RTCのコンデンサバックアップ：V <sub>RTCbat</sub> が使用される場合は、未接続のままになります。                                                                                                                                                            |

| V <sub>RTCbat</sub> <sup>[3]</sup> | 電源   | RTCのバッテリバックアップ：V <sub>RTCCap</sub> が使用される場合は、未接続のままになります。                                                                                                                                                             |

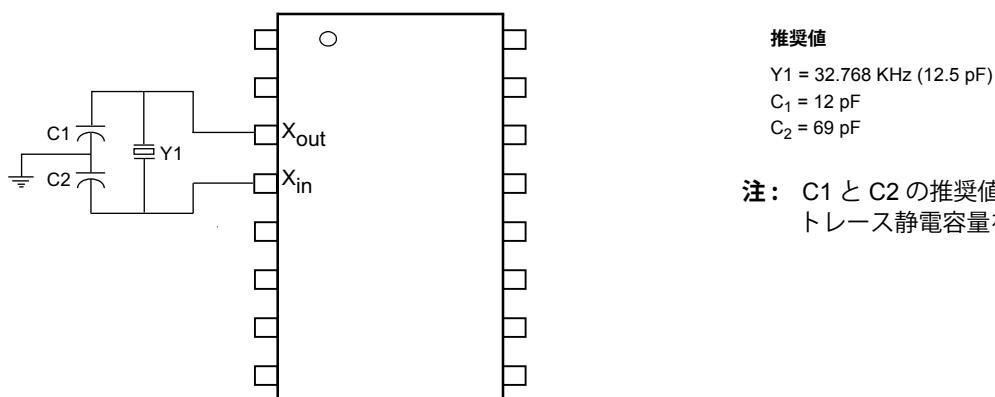

| X <sub>out</sub> <sup>[3]</sup>    | 出力   | 水晶出力接続                                                                                                                                                                                                                |

| X <sub>in</sub> <sup>[3]</sup>     | 入力   | 水晶入力接続                                                                                                                                                                                                                |

| INT/SQW <sup>[3]</sup>             | 出力   | 出力/校正/方形波の割り込みが発生します。クロックアラーム、ウォッチドッグタイマ、および電力モニタに対応するようにプログラム可能です。アクティブHIGH(プッシュまたはプル)またはLOW(オープンドレイン)のいずれにもプログラム可能です。校正モードでは、512Hz方形波が送出されます。方形波モードでは、ユーザーは連続出力として使用される1Hz、512Hz、4096Hz、または32768Hzの周波数を選択することができます。 |

| NC                                 | 接続なし | 未接続。このピンはダイに接続されません。                                                                                                                                                                                                  |

| V <sub>SS</sub>                    | 電源   | グランド                                                                                                                                                                                                                  |

| V <sub>CC</sub>                    | 電源   | 電源                                                                                                                                                                                                                    |

注

3. RTC 機能を使用しない場合は未接続のままになります。

## I<sup>2</sup>C インターフェイス

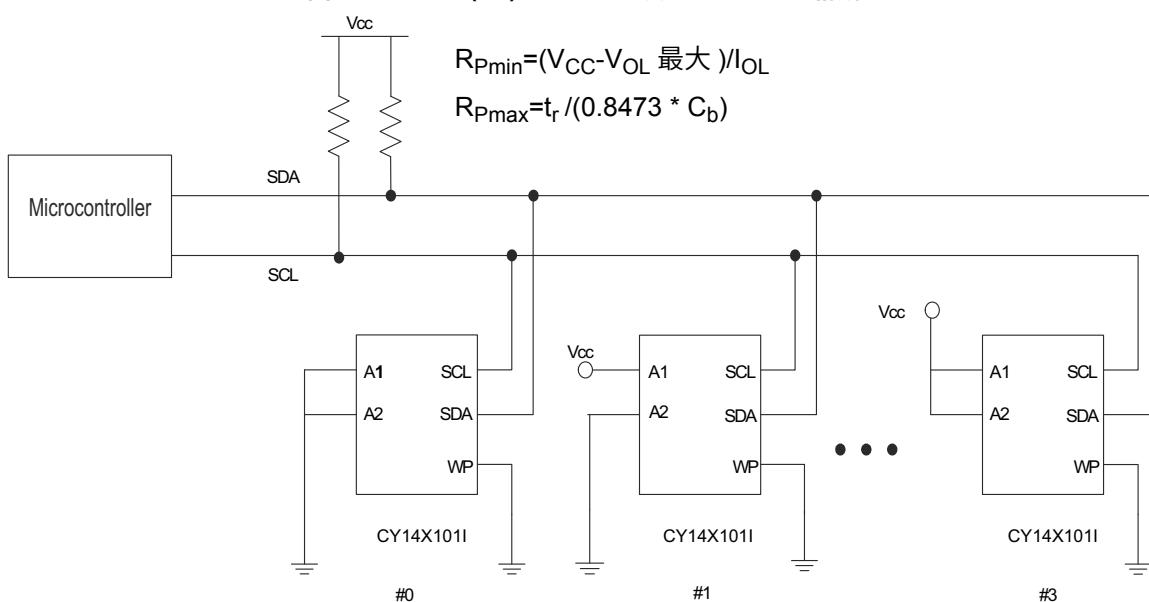

I<sup>2</sup>C バスは、バス上の複数デバイス間で情報を運ぶシリアルクロックライン(SCL)とシリアルデータライン(SDA)の2つのラインで構成されています。I<sup>2</sup>C はマルチマスタおよびマルチスレーブ構成をサポートしています。データは SDA ラインでトランスマッタからレシーバに送信され、マスタによって生成されたクロック SCL と同期されます。

SCL と SDA ラインはオープンドレインラインで、抵抗を用いて V<sub>CC</sub> にプルアップされます。システムのプルアップ抵抗の選択は、バス容量と動作の目的の速度に依存します。マスタがクロックを生成し、すべてのデータ I/O はこのクロックに同期して送信されます。CY14X101I は、SCL ライン上の最大 3.4MHz までのクロック速度をサポートします。

## プロトコル概要

このデバイスは、7 ビットのアドレス指定可能なスキームをサポートしています。マスタが START コンディションを生成し、通信を開始してスレーブ選択バイトを発行します。スレーブ選択バイトはスレーブの 7 ビットアドレスで構成されており、これはマスタが通信するもので、読み取りまたは書き込み動作を示す R/W ビットです。選択されたスレーブがこれにアクノレッジ(ACK)で応じます。スレーブが選択された後は、その後の通信はマスタと選択されたスレーブ間で行われます。バスの他のデバイスは、STOP または反復 START コンディションが検出されるまで SDA ラインの信号を無視します。データ転送は、マスタによって生成された SCL クロックに同期して SDA ピンを通して、マスタと選択されたスレーブデバイス間で行われます。

## I<sup>2</sup>C プロトコル - データ転送

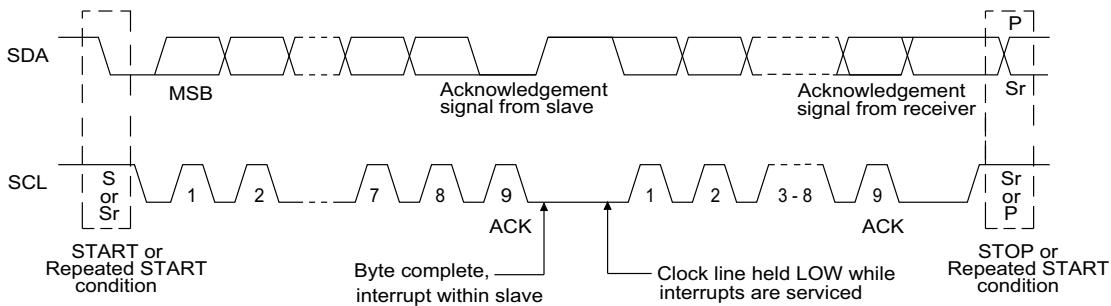

I<sup>2</sup>C プロトコルの各トランザクションは、マスタによるバスの START コンディション生成から始まり、7 ビットスレーブアドレス、そしてその後に読み取り(1)と書き込み(0)動作を示す 8

番目のビット(R/W)が続きます。すべての信号は、オープンドレイン SDA ラインで送信され、SCL ラインのクロックと同期されます。I<sup>2</sup>C バスで送信されるデータの各バイトは、9 番目のクロックパルスで SDA 信号ラインを LOW に保持することでレシーバによってアクノレッジされます。マスタによる書き込み要求の後に、SDA ラインのメモリアドレスとデータバイトが続きます。書き込みはデータの複数バイトを送信することにより、バーストモードで行うことができます。9 番目のクロックサイクルの立ち下がりエッジで各バイトを送受信した後、メモリアドレスが自動的にインクリメントされます。新しいアドレスは、確認応答ビットを送受信する直前にラッチされます。これにより、追加のアドレス指定なしで次の連続バイトにアクセスすることができます。最後のメモリ位置に到達すると、アドレスは 0x0000 にロールバックされ、書き込みが続行します。書き込み動作中、スレーブがマスタによって送信された各バイトに ACK で応答します。書き込みシーケンスは、マスタが STOP または反復 START コンディションを生成することによって終了することができます。

読み取り要求は、現在のアドレス位置(読み取りまたは書き込みのために最後にアクセスした位置の次のアドレス)で行われます。メモリスレーブデバイスは、現在のアドレス位置のデータをマスタに送信して、読み取り要求に応答します。最初に読み取りの目的のアドレスで書き込み要求を送信することによって、ランダムアドレス読み取りも行うことができます。最後のアドレスバイトの直後にマスタは書き込みを中止し、書き込み動作を防止するために反復 START または STOP 信号を発行する必要があります。次の読み取り動作はこのアドレスから開始されます。マスタは9番目のクロックパルスのSDAピンをLOWに保持することで、データの1バイトの受信にアクノレッジします。最後のデータバイトの後に、マスタが SDA ラインでノーアクノレッジ(NACK)信号を送信することで、読み取りを終了することができます。NACK 信号により CY14X101I が SDA ラインを解放するため、マスタは STOP または反復 START コンディションを生成して新しい動作を開始することができます。

図 2. シリアル(I<sup>2</sup>C) nvSRAM を用いたシステム構成

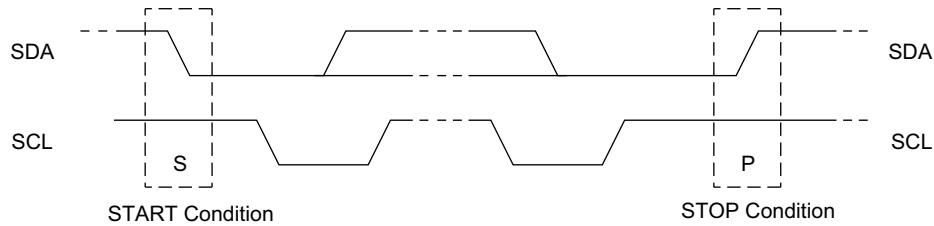

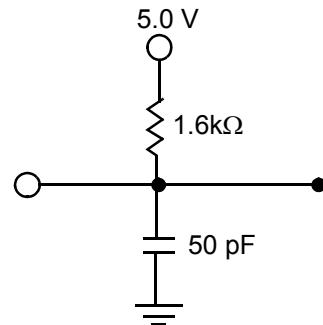

## データ有効性

SDA ラインのデータは、クロックの HIGH 期間中は安定している必要があります。データを有効にするために、データラインの状態は SCL ラインのクロックが LOW の場合のみ変更することができます。SDA が HIGH の状態で SCL ラインの状態を変更することができるコンディションは、START および STOP コンディションの 2 つだけです。START および STOP コンディションはマスタにより生成され、I<sup>2</sup>C バスの通信シーケンスの開始と終了を通知します。

## START コンディション (S)

SCL が HIGH になっている際の SDA ラインの HIGH から LOW への遷移は、START コンディションを示すものです。I<sup>2</sup>C の各トランザクションは、マスタが START コンディションを生成することから始まります。

## STOP コンディション (P)

SCL が HIGH になっている際の SDA ラインの LOW から HIGH への遷移は、STOP コンディションを示します。このコンディションは、進行中のトランザクションの終了を示すものです。START および STOP コンディションは、常にマスタによって生成されます。バスは START コンディションの後はビジー状態にあると見なされます。バスは STOP コンディションの後は解放された状態にあると見なされます。

## 反復 START (Sr)

STOP コンディションの代わりに反復 START コンディションが生成された場合は、バスのビジー状態が継続されます。I<sup>2</sup>C ラインの進行中のトランザクションが停止され、バスは通信を再開するためにマスタがスレーブ ID を送信するのを待ちます。

図 3. START および STOP コンディション

図 4. I<sup>2</sup>C バスのデータ転送

## バイト形式

I<sup>2</sup>C の各動作は、8 ビットワードを使用して行われます。ビットは SDA ラインで MSB の最初の形式で送信され、各バイトの後にレシーバによる ACK 信号が続きます。

レシーバから NACK が送信されるまで、またはマスタによって STOP か反復 START コンディションが生成されるまで、動作は継続します。START または STOP コンディションを除き、クロック (SCL) が HIGH である時には SDA ラインは安定状態にある必要があります。

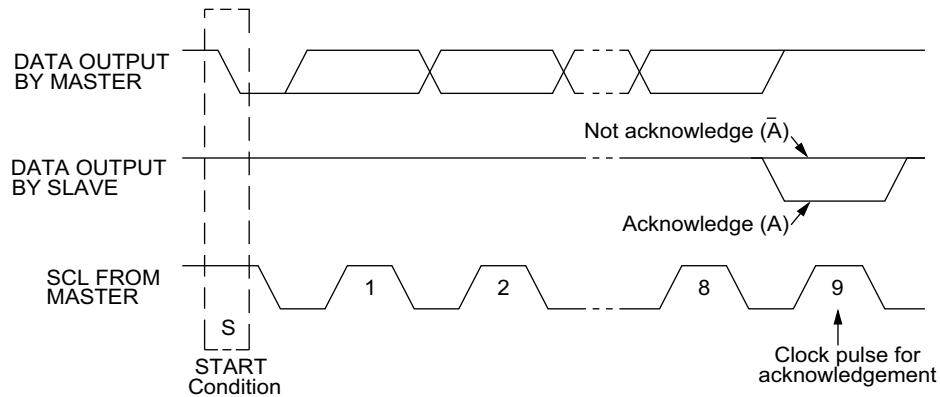

## アクノレッジ / ノーアクノレッジ

データまたはアドレスの 1 バイトを送信した後、トランスマスターは SDA ラインを解放します。レシーバは SDA ラインを LOW にプルダウンして、バイトの受信をアクノレッジします。動作を継続するには、I<sup>2</sup>C バスで転送されるデータの各バイトがレシーバによって ACK 信号で応答される必要があります。そうでない場合は、NACK 状態と見なされます。NACK はレシーバが

データ受信をアクノレッジしていない状態であり、動作が中止されます。

次の場合に、読み取り動作中に NACK がマスタによって生成される可能性があります。

- ノイズが原因で、マスタが有効なデータを受信しなかった場合です。

- マスタは NACK を生成して、読み取りシーケンスを中止します。NACK がマスタによって発行された後、nvSRAM スレーブが SDA ピンの制御を解放するので、マスタは反復 START または STOP コンディションを生成できるようになります。

次の場合に、書き込み動作中に NACK が nvSRAM スレーブによって生成される可能性があります。

- ノイズが原因で、nvSRAM が有効なデータを受信しなかった場合です。

- マスターはnvSRAMの書き込み保護された位置にアクセスしようとします。マスターはSTOPまたは反復STARTコンディションを生成することで通信を再開する必要があります。

図 5. I<sup>2</sup>C バスの確認応答

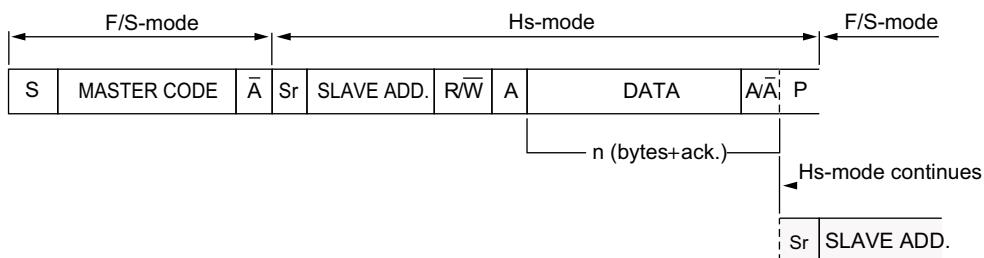

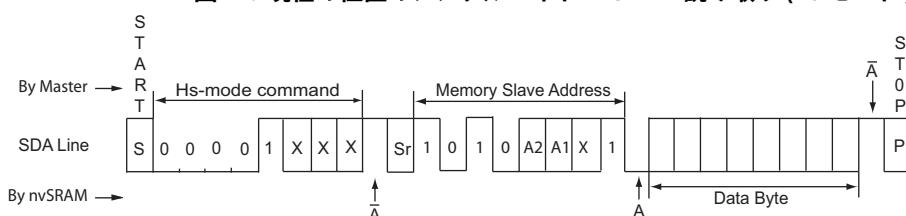

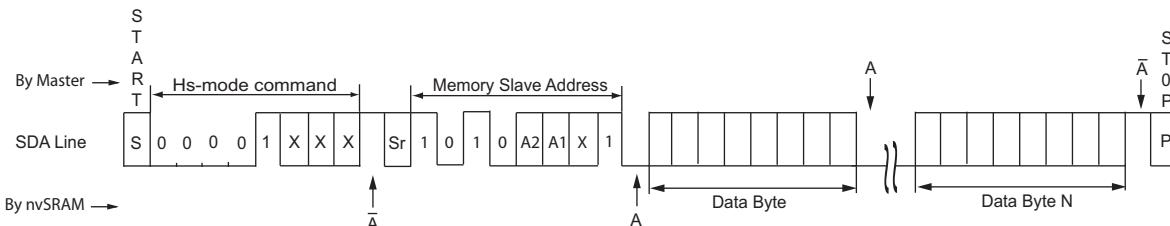

### 高速モード (Hs モード)

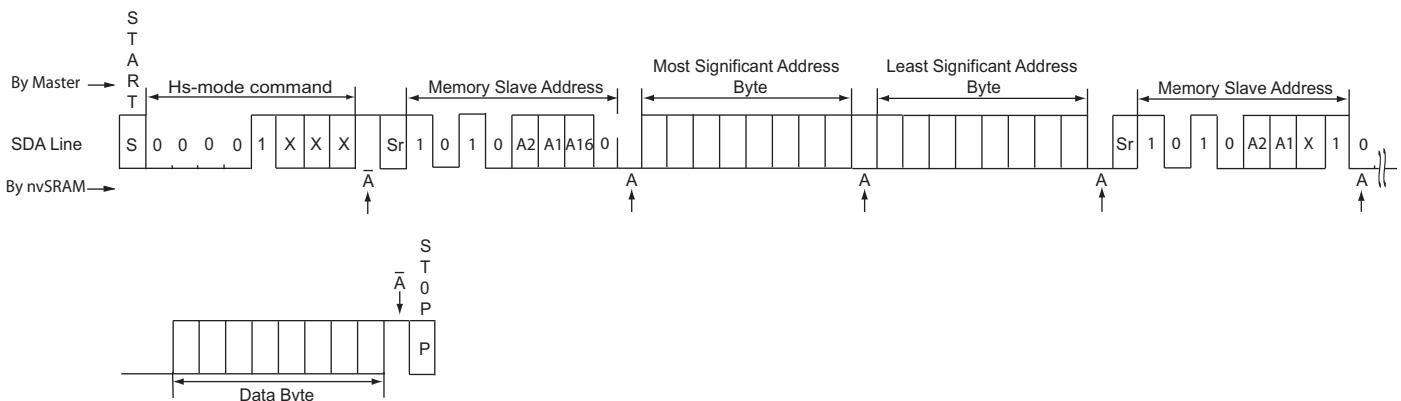

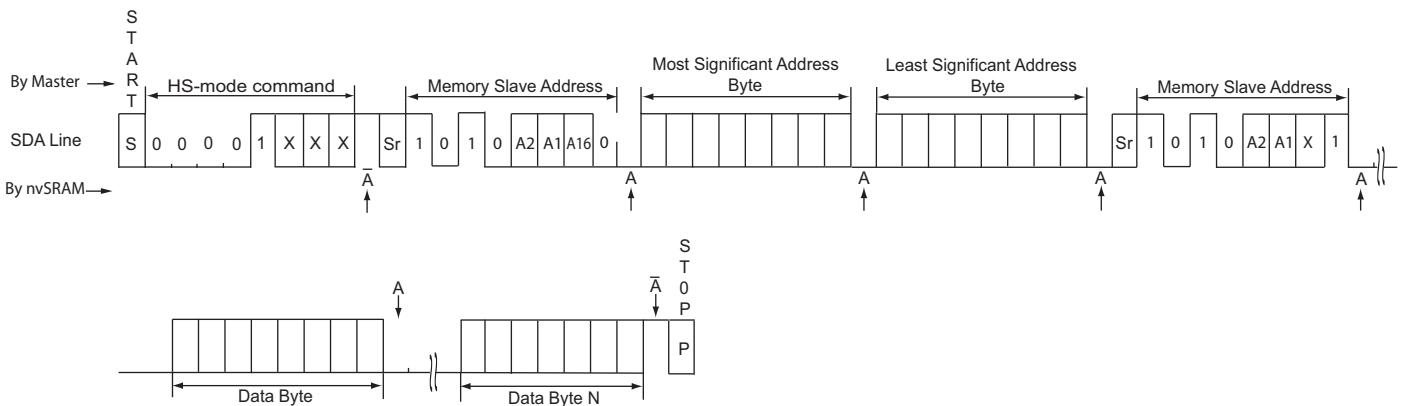

Hs モードでは、nvSRAM は最高 3.4 Mbit/sまでのビットレートでデータを転送することができます。デバイスを高速モードにするには、マスターコード (0000 1XXXb) が発行される必要があります。これにより、最高 3.4MHz の速度のマスター / スレーブ通信が可能となります。STOP コンディションにより Hs モードが終了します。

Hs モードにおけるシリアルデータフォーマット

Hs モードでのシリアルデータ転送フォーマットは、I<sup>2</sup>C バス仕様の標準モードを満たしています。Hs モードは、以下の条件下でのみ開始することができます (F/S モードにあるものすべて)。

1. START コンディション (S)

2. 8 ビットマスターコード (0000 1XXXb)

3. ノーアクノリッジビット ( $\bar{A}$ )

シングルおよびマルチバイトの読み取りと書き込みがサポートされています。デバイスが Hs モードに入った後に、マスタデバイスによって STOP コンディションが送信されるまでデータ転送は Hs モードで続行されます。STOP コンディション (P) 後、スレーブは F/S モードに切り替わります。Hs モードでデータ転送を続行するために、マスターが反復 START(Sr) を送信する必要があります。

読み取りおよび書き込み動作の Hs モードのタイミングの詳細については、[11 ページの図 13](#) および [12 ページの図 16](#) をご覧ください。

図 6. Hs モードにおけるデータ転送フォーマット

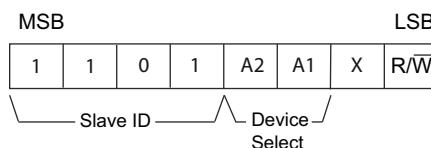

## スレーブデバイスアドレス

I<sup>2</sup>C バスの各スレーブデバイスには、デバイス選択アドレスがあります。START コンディションの後の最初のハイトには、マスタが通信をしようとするスレーブデバイスアドレスが含まれています。7つのMSB はデバイスアドレスであり、LSB (R/W ビット) は読み取りまたは書き込み動作を示すために使用されます。CY14X101I は、メモリ、RTC レジスタ、および制御レジスタのアクセスのために、スレーブデバイスアドレスフィール

表1. スレーブデバイスアドレス指定

| ビット7 | ビット6 | ビット5 | ビット4 | ビット3      | ビット2 | ビット1 | ビット0      | nvSRAM 機能選択                                                                          |  |

|------|------|------|------|-----------|------|------|-----------|--------------------------------------------------------------------------------------|--|

| 1    | 0    | 1    | 0    | デバイス選択 ID | A16  | R/W  | メモリ選択     | <b>CY14X101I スレーブデバイス</b><br>メモリ、128K × 8                                            |  |

| 1    | 1    | 0    | 1    | デバイス選択 ID | X    | R/W  | RTCレジスタ選択 | RTC レジスタ、16 × 8                                                                      |  |

| 0    | 0    | 1    | 1    | デバイス選択 ID | X    | R/W  | 制御レジスタ選択  | 制御レジスタ<br>- メモリ制御レジスタ、1 × 8<br>- シリアル番号、8 × 8<br>- デバイス ID、4 × 8<br>- コマンドレジスタ、1 × 8 |  |

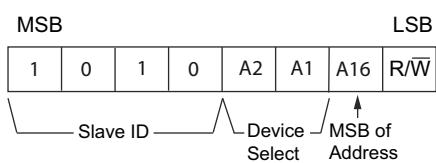

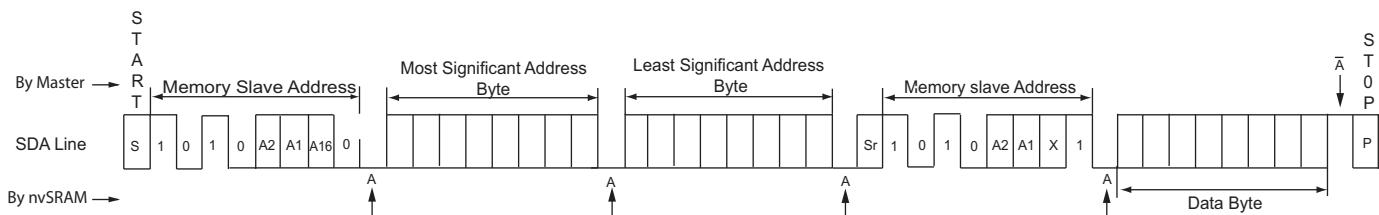

### メモリスレーブデバイス

マスタが 1010b としてスレーブアドレスを発行し、その後に選択されたデバイスの 2 ビットが続く場合、nvSRAM デバイスが読み取り / 書き込み用に選択されます。マスタから送信されたスレーブアドレスがメモリスレーブデバイスアドレスに一致した場合、スレーブアドレスの R/W ビットに応じて、データは nvSRAM から読み取られる (R/W=「1」) または nvSRAM に書き込まれる (R/W=「0」) かのどちらかです。

CY14X101I のアドレス長は 17 ビットで、したがって全体のメモリアドレス位置をマッピングするためにそれには 3 つのアドレスビットが必要です。メモリアドレス指定のために余分なバイトを保存するには、17 番目のビット (A16) はスレーブアドレス選択ビット (A0) にマッピングされます。専用の 2 つのアドレスビットは、A0 ~ A15 を表しています。

図7. メモリスレーブデバイスアドレス

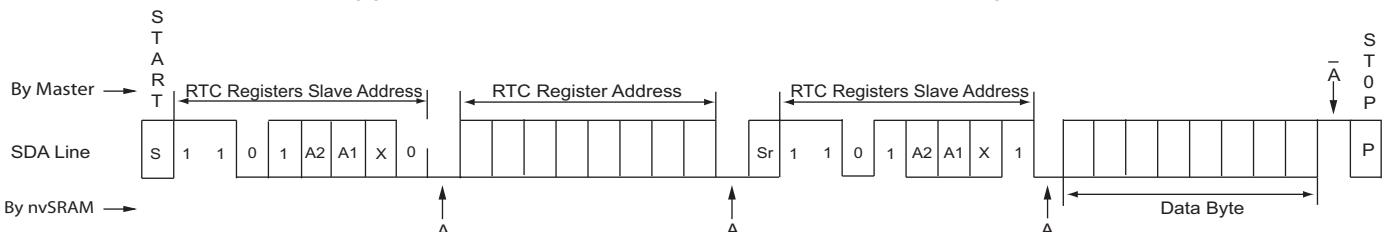

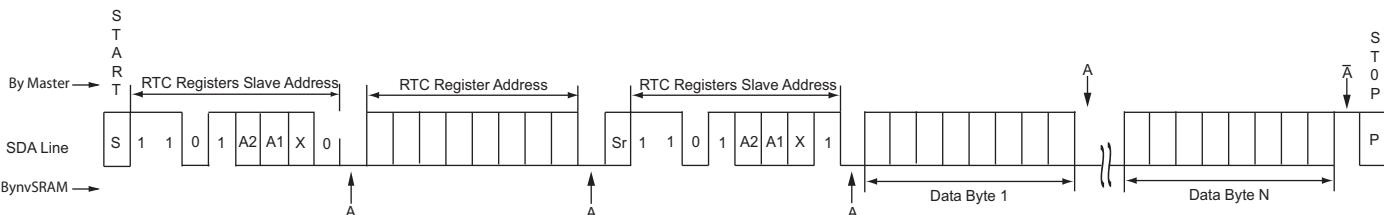

### RTC レジスタスレーブデバイス

マスタが 1101b としてスレーブアドレスを発行し、その後に選択されたデバイスの 2 ビットが続く場合、RTC レジスタが読み取り/書き込み用に選択されます。スレーブアドレスの R/W ビット

ドに上位 4 つの MSB [7:4] を 3 セット有します。アクセスメカニズムについては、次のセクションで説明されています。

nvSRAM 製品は、3 つの異なる機能を提供します。メモリ、RTC レジスタ、および制御レジスタ機能 (シリアル番号や製品 ID など) です。デバイスの 3 つの機能は、異なるスレーブデバイスアドレスを介してアクセスされます。

デバイスアドレスレジスタの最初の 4 つの最上位ビット [7:4] は、nvSRAM 機能を選択するために使用されます。

トに応じて、データは RTC レジスタから読み取られる (R/W=「1」) または RTC レジスタに書き込まれる (R/W=「0」) かのどちらかです。RTC レジスタスレーブアドレスの後に、読み取り / 書き込み動作用に RTC レジスタの 1 バイトアドレスが続きます。RTC レジスタマップは [表 10](#) で説明されています。

図8. RTC レジスタスレーブデバイスアドレス

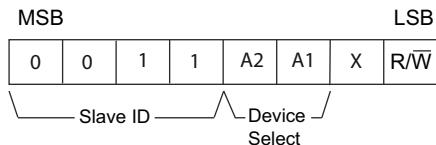

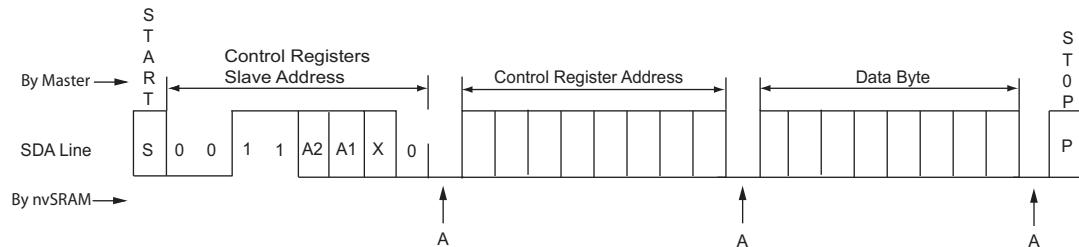

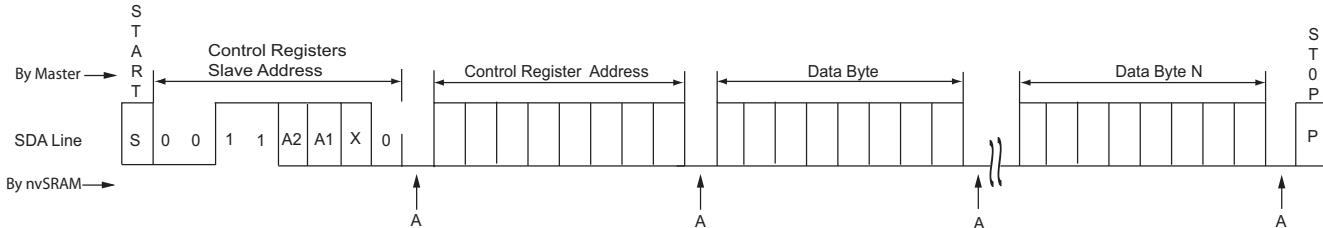

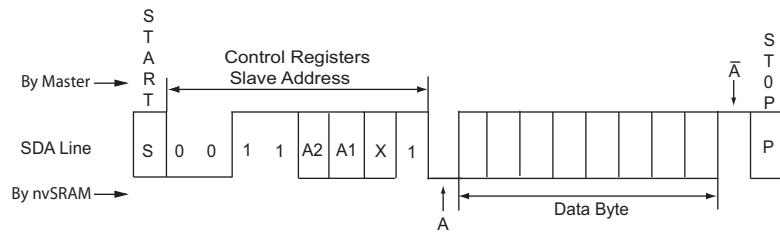

### 制御レジスタスレーブデバイス

制御レジスタスレーブデバイスには、シリアル番号、製品 ID、メモリ制御、およびコマンドレジスタが含まれています。

マスタが 0011b としてスレーブアドレスを発行し、その後に選択されたデバイスの 2 ビットが続く場合、nvSRAM 制御レジスタスレーブデバイスが読み取り/書き込み用に選択されます。スレーブアドレスの R/W ビットに応じて、データはデバイスから読み取られる (R/W=「1」) またはデバイスに書き込まれる (R/W=「0」) かのどちらかです。

**図 9. 制御レジスタスレーブデバイスアドレス**

**表 2. 制御レジスタマップ**

| アドレス | 内容           | 読み取り / 書き込み                         | 詳細                                                        |

|------|--------------|-------------------------------------|-----------------------------------------------------------|

| 0x00 | メモリ制御レジスタ    | 読み取り / 書き込み                         | ロック保護ビットおよびシリアル番号ロックビットを含む                                |

| 0x01 | シリアル番号 8 バイト | 読み取り / 書き込み (SNL が設定されている場合、読み取り専用) | プログラマブルシリアル番号メモリ制御レジスタのシリアル番号ロックビットを「1」に設定することによってロックされる。 |

| 0x02 |              |                                     |                                                           |

| 0x03 |              |                                     |                                                           |

| 0x04 |              |                                     |                                                           |

| 0x05 |              |                                     |                                                           |

| 0x06 |              |                                     |                                                           |

| 0x07 |              |                                     |                                                           |

| 0x08 |              |                                     |                                                           |

| 0x09 | デバイス ID      | 読み取り専用                              | デバイスIDは工場出荷時にプログラムされている。                                  |

| 0x0A |              |                                     |                                                           |

| 0x0B |              |                                     |                                                           |

| 0x0C |              |                                     |                                                           |

| 0x0D | 予約済み         | 予約済み                                | 予約済み                                                      |

| 0xAA | コマンドレジスタ     | 書き込み専用                              | TORE、RECALL、AutoStoreイネーブル、ディスエーブル、SLEEPモードのコマンドを許可       |

#### メモリ制御レジスタ

メモリ制御レジスタには以下のビットが含まれています。

**表 3. メモリ制御レジスタビット**

| ビット 7 | ビット 6   | ビット 5 | ビット 4 | ビット 3   | ビット 2   | ビット 1 | ビット 0 |

|-------|---------|-------|-------|---------|---------|-------|-------|

| 0     | SNL (0) | 0     | 0     | BP1 (0) | BP0 (0) | 0     | 0     |

■ **BP1:BP0 :** ブロック保護ビットは、1/4、1/2、またはフルメモリアレイを保護するために使用されます。これらのビットは、制御レジスタスレーブデバイスの0x00の位置への書き込み命令を介して書き込むことができます。しかし、ブロックが保護されているかどうかにかかわらず、任意の STORE サイクルにより SRAM データが不揮発性セルへ転送されます。工場出荷時の BP0 と BP1 のデフォルト値は「0」です。

**表 4. ブロック保護**

| Level (レベル) | BP1:BP0 | ブロック保護          |

|-------------|---------|-----------------|

| 0           | 00      | なし              |

| 1/4         | 01      | 0x18000–0x1FFFF |

| 1/2         | 10      | 0x10000–0x1FFFF |

| 1           | 11      | 0x00000–0x1FFFF |

■ **SNL(S/Nロック)ビット:** シリアル番号ロックビット(SNL)は、シリアル番号をロックするために使用されます。ビットが一旦「1」に設定されると、シリアル番号レジスタがロックされ、変更できなくなります。このビットは「0」にクリアすることはできません。シリアル番号は次の STORE 動作に固定されます(ソフトウェア STORE または AutoStore)。AutoStore がイネーブルでない場合、ユーザーはロックビット状態を確保するために、ソフトウェア STORE 動作を実行する必要があります。STORE が実行されない場合、シリアル番号ロックビットはパワーサイクルに耐えられません。工場出荷時の SNL のデフォルト値は「0」です。

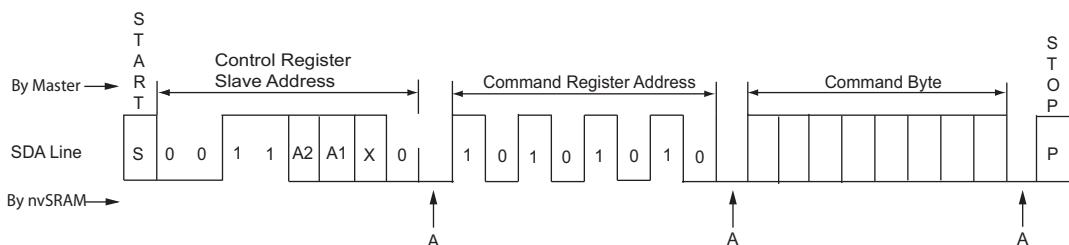

#### コマンドレジスタ

コマンドレジスタは、制御レジスタスレーブデバイスのアドレス「AA」に入っています。これは書き込み専用レジスタです。このレジスタに書き込まれたバイトにより、表 5 に記載されているように、STORE、RECALL、AutoStore イネーブル化、AutoStore ディスエーブル化、スリープモード動作が開始されます。コマンドレジスタバイトを実行する方法については、19ページのコマンドレジスタを使用したコマンドの実行セクションで説明されています。

**表 5. コマンドレジスタバイト**

| データ バイト [7:0] | コマンド   | 内容                           |

|---------------|--------|------------------------------|

| 0011 1100     | STORE  | 不揮発性メモリへの STORE SRAM データ     |

| 0110 0000     | RECALL | 不揮発性メモリから SRAM への RECALL データ |

| 0101 1001     | ASENB  | AutoStore をイネーブル化            |

| 0001 1001     | ASDISB | AutoStore をディスエーブル化          |

| 1011 1001     | SLEEP  | 低消費電力のためにスリープモードに入る          |

■ **STORE:** nvSRAM ソフトウェア STORE を開始します。この命令が実行された後は、nvSRAM は  $t_{STORE}$  時間にアクセスすることはできません。開始されると、最後の NV 動作以降に書き込みが行われたかどうかにかかわりなく、デバイスは STORE 動作を実行します。 $t_{STORE}$  サイクル時間が終了した後、SRAM が読み取り / 書き込み動作のために再びアクティベートされます。

■ **RECALL:** nvSRAM ソフトウェア RECALL を開始します。この命令が実行された後は、nvSRAM は  $t_{RECALL}$  時間にアクセスすることはできません。RECALL 処理では不揮発性素子内のデータは変更されません。RECALL はハードウェアによる RECALL (パワーアップで開始) およびソフトウェアによる RECALL ( $I^2C$  命令によって開始) の 2 つの方法で実行することができます。

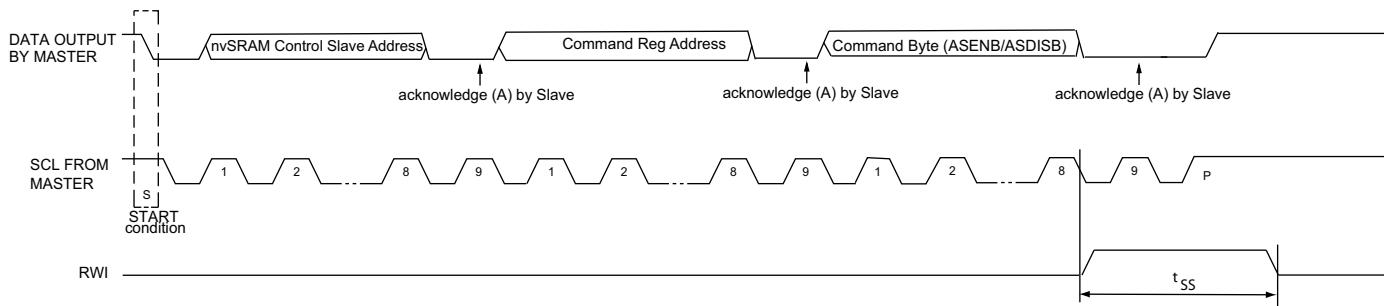

■ **ASENB:** nvSRAM AutoStore をイネーブルにします。この命令が実行された後は、nvSRAM は  $t_{SS}$  時間にアクセスすることはできません。この設定は不揮発性ではなく、これがパワーサイクルで耐えられるようにするには、その後に手動で STORE シーケンスを行なう必要があります。工場出荷時 AutoStore はイネーブルになっており、すべてのセルに 0x00 と書き込まれています。

■ **ASDISB:** nvSRAM AutoStore をディスエーブルにします。この命令が実行された後は、nvSRAM は  $t_{SS}$  時間にアクセスすることはできません。この設定は不揮発性ではなく、これがパワーサイクルで耐えられるようにするには、その後に手動で STORE シーケンスを行なう必要があります。

**注** AutoStore がディスエーブルかつ  $V_{CAP}$  が不要の場合、 $V_{CAP}$  ピンはオープンのままにしておく必要があります。 $V_{CAP}$  ピンは絶対にグランドに接続しないでください。電源オン RECALL 処理は、どのような場合でもディスエーブル化できません。

■ **SLEEP** : SLEEP 命令により、nvSRAM はスリープモードとなります。SLEEP 命令が取り込まれると、nvSRAM は  $t_{SLEEP}$  時間を取り SLEEP 要求を処理します。一旦 SLEEP コマンドが正常に取り込まれて処理されると、nvSRAM は HSB を LOW にトグルし、不揮発性メモリにデータを安置するために STORE 動作を実行してから、スリープモードに入ります。nvSRAM がスリープモードに入る際は常に不揮発性 STORE サイクルを開始し、その結果として SLEEP コマンド実行のたびに耐久サイクルを失います。STORE サイクルは、最後の STORE または RECALL サイクル以降、SRAM への書き込みが実行された場合にのみ開始されます。

nvSRAM は以下のようにしてスリープモードに入ります。

1. マスタが START コマンドを送信します。

2. マスタが I<sup>2</sup>C 書き込みビットセット (R/W=「0」) で制御レジスタスレーブデバイス ID を送信します。

3. スレーブ (nvSRAM) がマスタに ACK を返信します。

4. マスタはコマンドレジスタアドレス (0xAA) を送信します。

5. スレーブ (nvSRAM) がマスタに ACK を返信します。

6. スリープモードに入るために、マスタがコマンドレジスタバイトを送信します。

7. スレーブ (nvSRAM) がマスタに ACK を返信します。

8. マスタが STOP コンディションを生成します。

一旦スリープモードになると、SLEEP 命令が取り込まれた後、デバイスは  $I_{ZT}$  現在の  $t_{SLEEP}$  時間を消費し始めます。スリープモードでなくなるまで、デバイスは通常の動作ではアクセスできなくなります。デバイススレーブアドレスがマスタによって送信されると、nvSRAM は  $t_{WAKE}$  期間の後ウェーカアップします。

3 つのスレーブアドレスのいずれかを送信すると、nvSRAM がスリープモードからウェーカアップします。nvSRAM デバイスは  $t_{SLEEP}$  および  $t_{WAKE}$  の間はアクセスできず、マスタが nvSRAM デバイスにアクセスしようとしてもそれは無視され、nvSRAM がマスタに NACK を送信します。デバイスの準備ができているかどうかを判断する別の方法として、マスタは読み取りまたは書き込みコマンドを送ることができます。そして ACK を探します。

### 書き込み保護 (WP)

書き込み保護 (WP) ピンはアクティブ HIGH ピンであり、書き込み動作からメモリ全体およびすべてのレジスタを保護します。すべての書き込み動作を禁止するには、このピンを HIGH に保持する必要があります。このピンが HIGH になっていると、すべてのメモリとレジスタ書き込みが禁止され、アドレスカウンタはインクリメントされません。このピンは内部的に LOW にプルダウンされ、そのため使用されていない場合はオープンのままにすることができます。

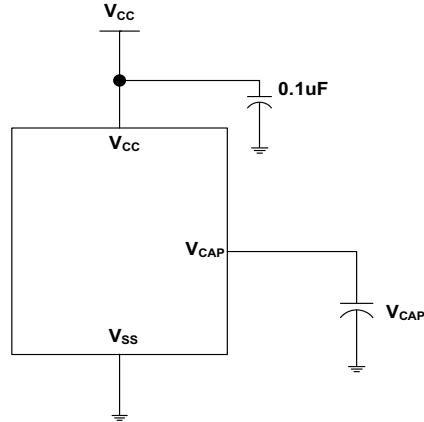

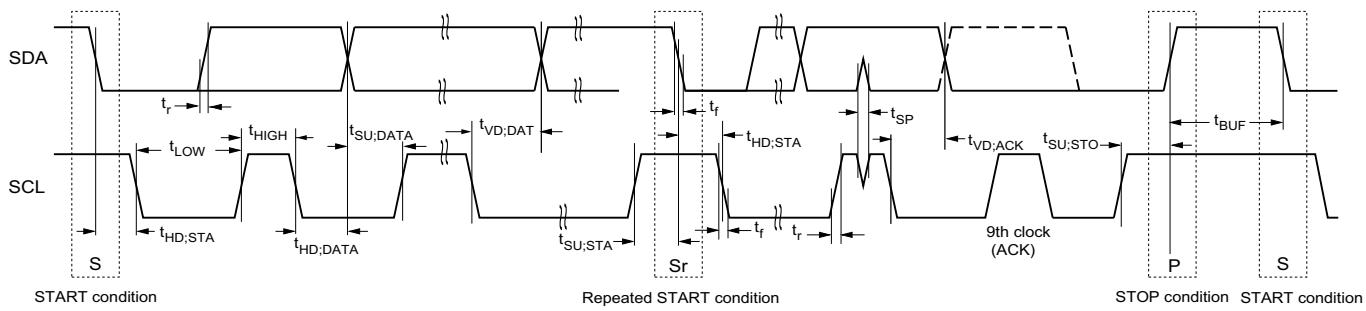

### AutoStore 動作

AutoStore 動作は、パワーダウン時に SRAM データを QuantumTrap セルに自動的に格納する nvSRAM 独自の機能です。この STORE 处理では外付けコンデンサ ( $V_{CAP}$ ) を活用し、デバイスは電源遮断時に不揮発性メモリへ安全にデータを保存することができます。

通常動作時、デバイスは  $V_{CC}$  から電流を得て、 $V_{CAP}$  ピンに接続されたコンデンサにチャージします。パワーダウン時に  $V_{CC}$

ピンの電圧が  $V_{SWITCH}$  未満に下がった場合、デバイスは nvSRAM へのメモリアクセスをすべて禁止し、 $V_{CAP}$  コンデンサからのチャージを使って自動的に条件付き STORE 動作を実行します。AutoStore 動作は、最後の STORE または RECALL の実行以降に書き込みサイクルが一度も実行されていない場合は起動されません。

**注** コンデンサが  $V_{CAP}$  ピンに接続されていない場合、8ページの **コマンドレジスタ** に規定されているように、AutoStore ディスエーブル化命令を発行して AutoStore をディスエーブルにする必要があります。 $V_{CAP}$  ピンに接続されたコンデンサなしで AutoStore がイネーブルにされる場合、デバイスは STORE 動作を完了するため、十分なチャージがないまま AutoStore 動作を実行しようとします。これにより、nvSRAM に格納されているデータおよびシリアル番号が破壊され、SNL ビットのロックが解除されます。

図 10 に、AutoStore 处理向けのストレージコンデンサ ( $V_{CAP}$ ) の適切な接続方法を示します。 $V_{CAP}$  のサイズについては、29 ページの DC 特性を参照してください。

図 10. AutoStore モード

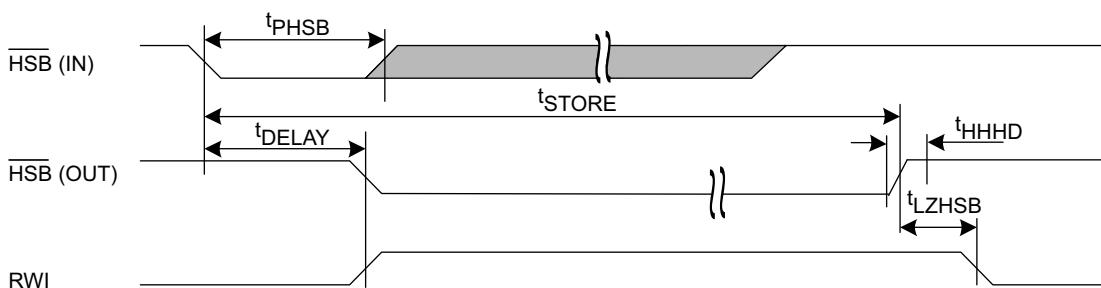

### H ハードウェア STORE 動作および $\overline{HSB}$ ピン動作

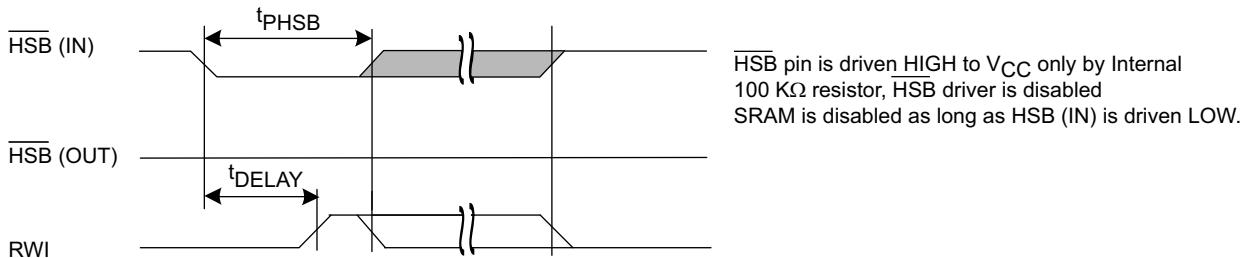

CY14X101I 内の  $\overline{HSB}$  ピンは、STORE 動作を制御しアクノレッジするために使用されます。実行中の STORE または RECALL 处理が存在しなければ、この端子はハードウェアによる STORE サイクルをリクエストするために使用できます。HSB ピンが LOW に駆動された場合、デバイスは  $t_{DELAY}$  の継続後、条件付きで STORE 動作を開始します。実際の STORE サイクルは、最後の STORE または RECALL サイクル以降、SRAM への書き込みが実行された場合にのみ開始します。 $t_{STORE}$  が継続中か HSB ピンが LOW である限り、メモリへの読み書きは禁止されます。

$\overline{HSB}$  ピンは、チップ内部で 100 kΩ のプルアップ抵抗を持つオープンドレイン出力もあります。開始イベントを問わず、STORE が進行中にはビジー状態を意味する LOW レベルを出力します。

**注** ハードウェアおよびソフトウェア STORE 動作の後、 $\overline{HSB}$  は HIGH 出力標準電流で短時間 ( $t_{HHHD}$ ) HIGH 駆動され、その後 100 kΩ の内部プルアップ抵抗により HIGH 状態を継続します。

**注** 最後のデータバイトのストアを正常に実行するため、最後のデータビット D0 が受信された後、ハードウェアストアを最低 1 クロックサイクルインシエートするべきです。

STORE動作が完了すると、HSBピンが HIGH を返した後、nvSRAMメモリアクセスは  $t_{LZHSB}$  時間の間禁止されます。HSBピンは、未使用の場合は未接続の状態である必要があります。

### ハードウェア RECALL ( パワーアップ )

パワーアップの間に  $V_{CC}$  が  $V_{SWITCH}$  を超えると、SRAMに不揮発性メモリの内容を転送するRECALLシーケンスが自動的に開始されます。データはそれ以前に STORE シーケンスを通じて不揮発性メモリにストアされている場合があります。

パワーアップ RECALLサイクルが完了するまでには  $t_{FA}$  時間がかかり、その間のメモリアクセスは禁止されます。HSBピンはデバイスのレディ状態を検出するために使われる場合があります。

### 書き込み動作

スレーブデバイスアドレスの最後のビットは、読み取りまたは書き込み動作を示しています。書き込み動作の場合には、スレーブデバイスアドレスの後にメモリまたはレジスタアドレスおよびデータが続きます。STOP または反復 START コンディションがマスタによって生成された場合、または nvSRAM によって NACK が発行された場合に、書き込み動作が継続されます。

NACKは以下の条件下で nvSRAM から発行されます。

1. 有効なデバイス ID は受信されていません。

2. 保護されたメモリブロックアドレスへの書き込み(バースト書き込み)アクセスにより、データバイト受信後、nvSRAM から NACK が返されます。しかし、アドレスカウンタはこのアドレスに設定されており、現在の次の読み取り動作はこのアドレスから開始されます。

3. 無効または範囲外のメモリアドレスへの書き込み/ランダム読み取りアクセスにより、アドレス受信後、nvSRAM から NACK が返されます。アドレスカウンタはこのような場合には変更されません。

NACKが nvSRAM から送信された後、書き込み動作が終了し、STOP または反復 START コンディションがマスタによって生成されるまで、SDA ラインのすべてのデータは無視されます。

例えば、バースト書き込みアクセスがシリアル番号を書き込むために制御レジスタスレーブアドレス 0x01 で実行され、読み取り専用レジスタであるアドレス 0x09 に継続された場合を考えてみてください。デバイスは NACK を返し、アドレスカウンタはインクリメントされません。次の読み取り動作は、アドレス 0x09 から開始されます。さらに、書き込み保護されたアドレス(例えば、0x09)から始まる任意の書き込み動作は、データバイトが送信され、このアドレスにアドレスカウンタが設定された後、nvSRAM によって NACK で応答されます。この場合も、次の読み取り動作は、アドレス 0x09 から開始されます。

**注** ユーザーが存在しないアドレス( 例えば、制御レジスタスレーブの 0x0 または RTC レジスタの 0x3F) に読み取り / 書き込みアクセスを試みた場合は、範囲外のアドレスが送信された直後に、nvSRAM が NACK で応答します。アドレスカウンタはそのまままで、前に成功した読み取りまたは書き込み動作のアドレスが保持されます。

データの 8 番目のビットが送信された後、書き込み動作が遅延なしで内部的に実行されます。書き込み動作が意図されていない場合は、8 番目のクロックサイクルの前に、マスタが STOP または反復 START コンディションを生成して書き込み動作を終了する必要があります。

書き込み命令の詳細については、[メモリスレーブアクセスセクション](#)をご覧ください。

### 読み取り動作

スレーブデバイスアドレスの最後のビットが「1」の場合、読み取り動作が想定され、マスタによってスレーブデバイスアドレスバイトが送信された直後に、nvSRAM が SDA ラインを制御します。読み取り動作は現在のアドレス位置(前回成功した書き込みまたは読み取り動作の後の位置)から開始します。最後のアドレスに到達すると、アドレスカウンタは最初のアドレスにループバックします。

制御レジスタスレーブの場合には、バースト読み取りが存在しないアドレスへフローするよう実行されるたびに、この読み取り動作は 0x00 にループバックします。これは特にコマンドレジスタに適用されます。

読み取り動作を終了するには、以下の方法があります。

1. 9 番目のクロックサイクルでマスタが NACK を発行し、その後 10 番目のクロックサイクルでの STOP または反復 START コンディションが続きます。

2. マスタが 9 番目のクロックサイクルで STOP または反復 START コンディションを生成します。

書き込み命令の詳細については、[メモリスレーブアクセスセクション](#)をご覧ください。

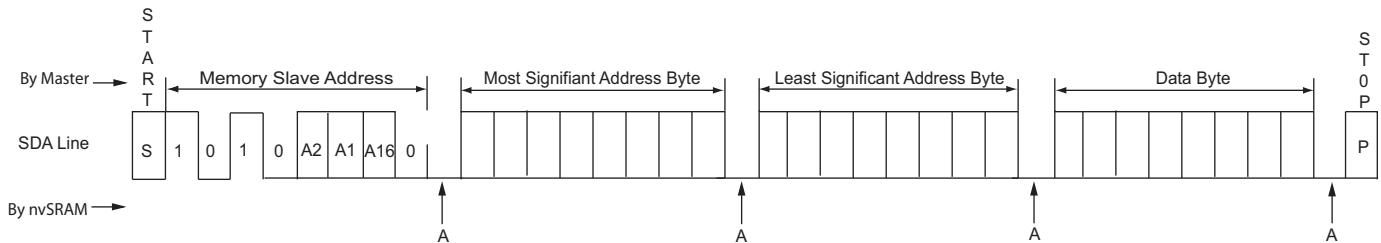

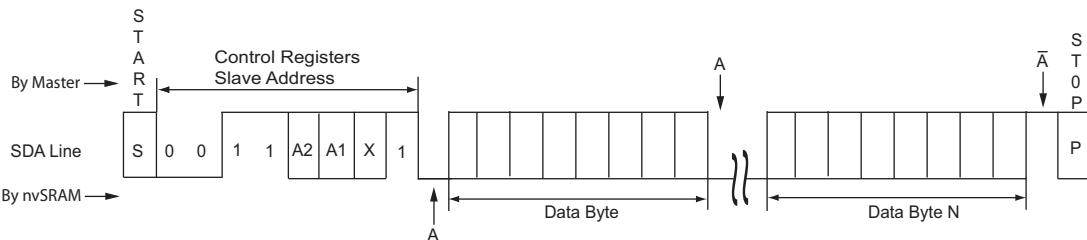

### メモリスレーブアクセス

次のセクションでは、nvSRAM からの読み取りまたは書き込み動作を実行するために必要なデータ転送シーケンスを説明します。

#### nvSRAM 書き込み

各書き込み動作は、START コンディション後に送信されるスレーブアドレスで構成されています。スレーブアドレスの最後のビットは、書き込み動作を示すために「0」に設定されている必要があります。内部アドレスカウンタが自動的にインクリメントし続ける間、マスタは 1 バイトのデータを書き込む場合と、複数の連続したアドレス位置を書き続ける場合があります。メモリの最後のアドレスがアクセスされた後、アドレスレジスタは 0x00000 にリセットされます。STOP または反復 START コンディションがマスタによって生成された場合、または nvSRAM によって NACK が発行された場合に、書き込み動作が継続されます。

8つすべてのデータビットが nvSRAM により受信された後でのみ、書き込み動作が実行されます。書き込み動作が正常に行われた後、nvSRAM は ACK 信号を送信します。マスタが STOP コンディションまたは反復 START 動作を生成することにより、書き込み動作を終了させることができます。メモリ内容を変更せずにマスタが現在の書き込み動作を中止する場合は、8 番目のデータビットの前に START/STOP コンディションを使用して実行されるべきです。

マスタが nvSRAM の書き込み保護されたメモリアドレスへのアクセスを試みると、保護されたアドレスに書き込みしようとするデータバイトが送信された後に NACK が返され、アドレスカウンタはインクリメントされません。同様に、バーストモードの書き込み動作でも、データバイトが保護されたメモリ位置への書き込みを試みると NACK が返され、アドレスカウンタはインクリメントされません。

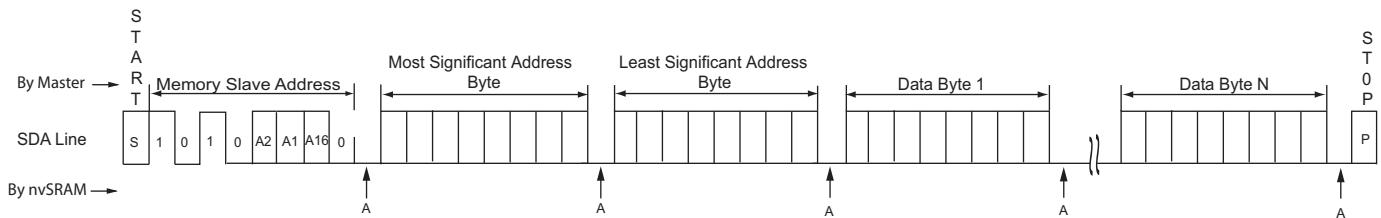

**図 11. シングルバイトの nvSRAM への書き込み (Hs モードを除く )**

**図 12. マルチバイトの nvSRAM への書き込み (Hs モードを除く )**

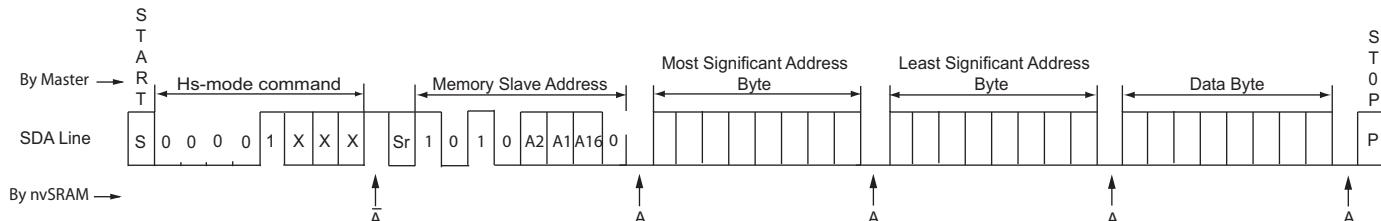

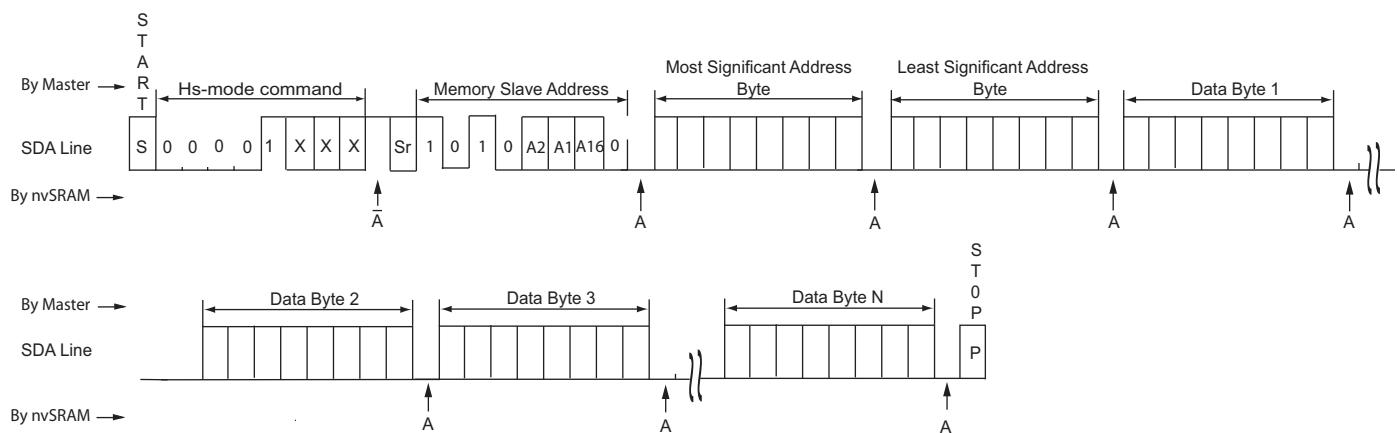

**図 13. シングルバイトの nvSRAM への書き込み (Hs モード )**

**図 14. マルチバイトの nvSRAM への書き込み (Hs モード )**

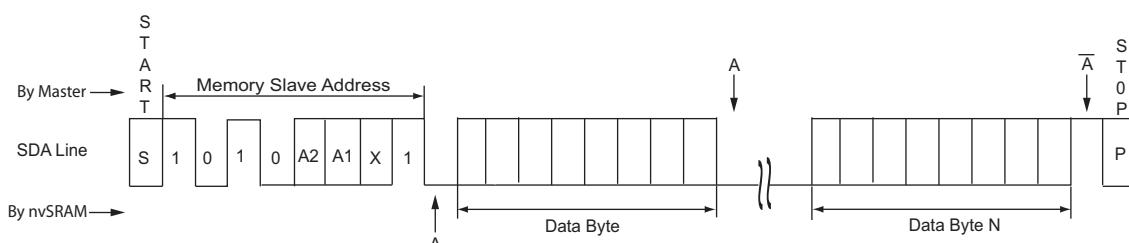

### 現在のnvSRAM 読み取り

各読み取り動作は、「読み取り」を示す「1」に設定された LSB でマスタから nvSRAM スレーブアドレスが送信されることで開始されます。アドレスカウンタのアドレスから読み取りが始まります。アドレスカウンタは、「書き込み」または「読み取り」動作によって最後にアクセスされた位置の次のアドレス位置に設定されています。マスターは 1 バイトを読み取った後に読み取り動作を終了する場合もあれば、アドレスカウンタがアドレス 0x00000 にロールバックした後のメモリの最後のアドレスまで連続的にアドレスを読み続ける場合もあります。読み取リーアクセスを終了させる有効な方法については、[10 ページの読み取り動作セクション](#)をご覧ください。

**注** 現在の nvSRAM の読み取りを使用している間は、A16 ビットは無視されます。

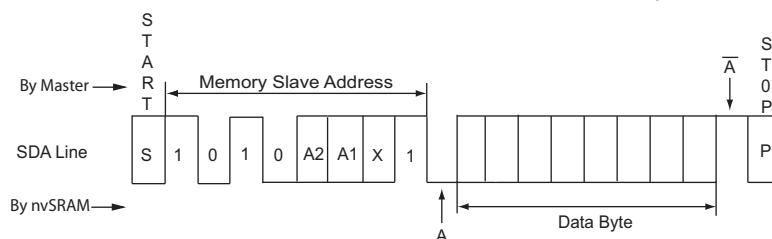

図 15. 現在の位置のシングルバイト nvSRAM 読み取り (Hs モードを除く )

図 16. 現在の位置のマルチバイト nvSRAM 読み取り (Hs モードを除く )

図 17. 現在の位置のシングルバイト nvSRAM 読み取り (Hs モード)

図 18. 現在の位置のマルチバイト nvSRAM 読み取り (Hs モード)

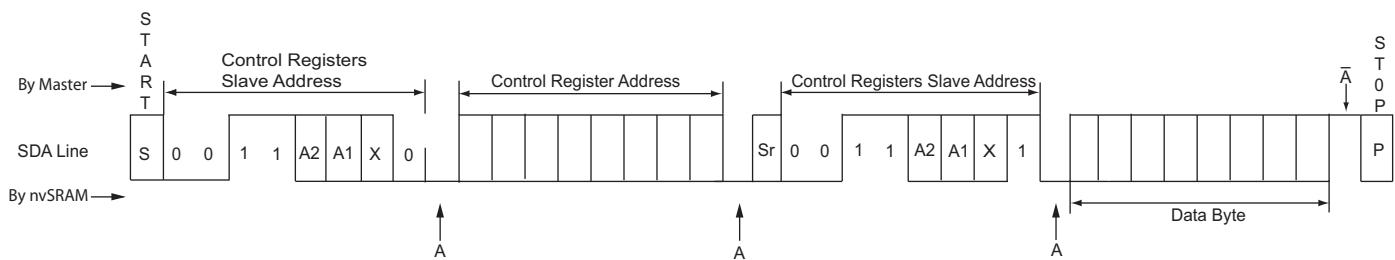

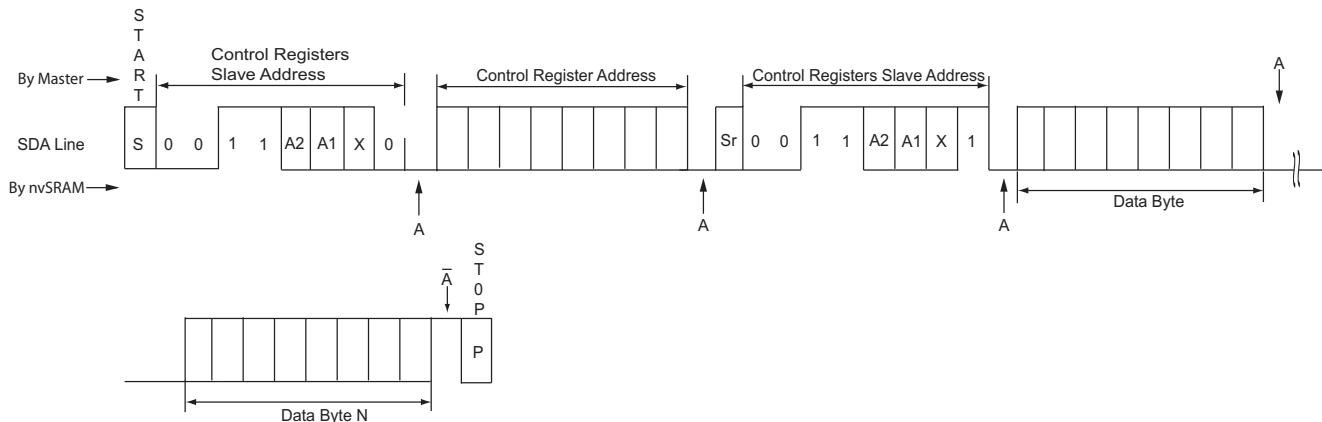

### ランダムアドレス読み取り

ランダムアドレス読み取りは、まず書き込み動作を開始し、最後のアドレスバイトがアクノレッジされた直後に反復 START を生成することによって実行されます。アドレスカウンタはこのアドレスに設定され、このスレーブへの次の読み取りアクセスがここから読み取り動作を開始します。マスターは 1 バイトを読み取った後に読み取り動作を終了する場合もあれば、アドレスカウンタが開始アドレス 0x00000 にロールバックした後のメモリの最後のアドレスまで連続的にアドレスを読み続ける場合もあります。

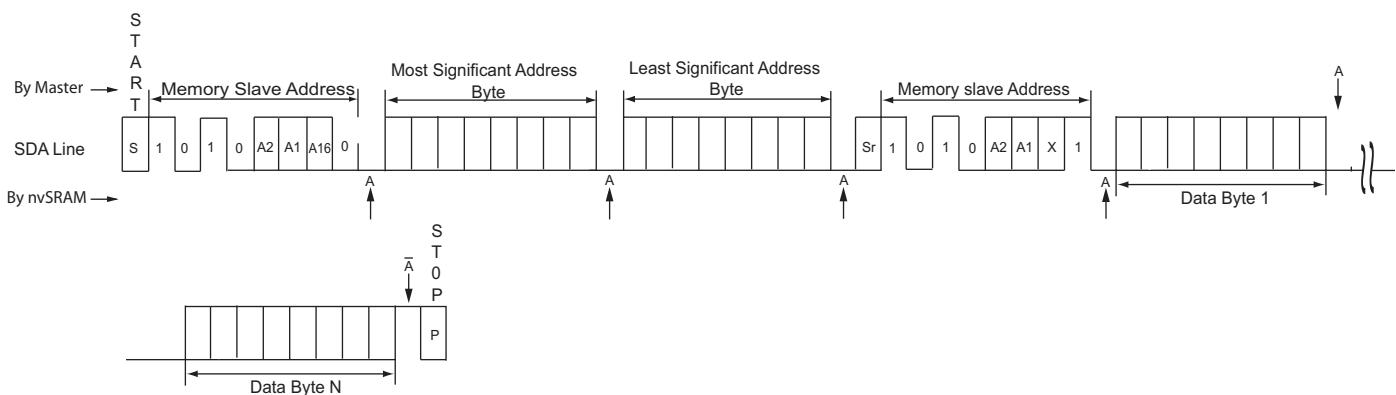

図 19. ランダムアドレスシングルバイト読み取り (Hs モードを除く )

図 20. ランダムアドレスマルチバイト読み取り (Hs モードを除く )

図 21. ランダムアドレスシングルバイト読み取り (Hs モード )

図 22. ランダムアドレスマルチバイト読み取り (Hs モード)

### RTC レジスタスレーブアクセス

次のセクションでは、RTC レジスタからの読み取りまたは書き込み動作を実行するために必要なデータ転送シーケンスを説明します。

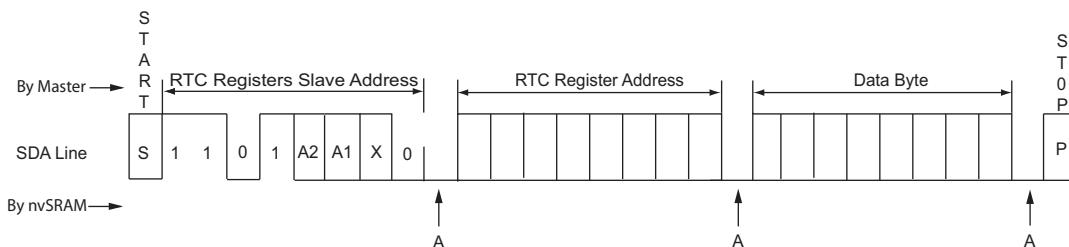

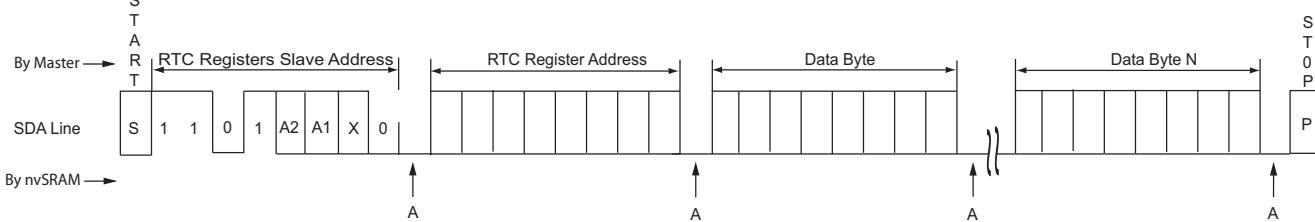

#### 書き込み RTC レジスタ

RTC レジスタへの書き込みは、RTC レジスタスレーブアドレスとその後に続くアドレスとデータの 1 バイトで開始されます。内部アドレスカウンタが自動的にインクリメントし続ける間、マスターは 1 バイトのデータを書き込む場合と、複数の連続したアドレス位置を書き続ける場合があります。最後の RTC レジスタにアクセスした後、アドレスレジスタは 0x00 にリセットされます。STOP または反復 START コンディションがマスターによって生成された場合、または nvSRAM RTC レジスタスレー

プによって NACK が発行された場合に、書き込み動作が継続されます。

8つすべてのデータビットが nvSRAM により受信された後でのみ、書き込み動作が実行されます。書き込み命令が正常に動作した後、nvSRAM は ACK 信号を送信します。最後のデータビットが送信される前に、マスターが STOP コンディションまたは反復 START 動作を生成することにより、書き込み動作を終了させることができます。

マスターが RTC レジスタスレーブの範囲外のメモリアドレスにアクセスしようとすると、アドレスバイトが送信された後、NACK が返されます。アドレスカウンタは影響を受けないまま、現在の次の読み出し動作はアドレスカウンタに保持されているアドレス値から始まります。

図 23. RTC レジスタへのシングルバイト書き込み

図 24. RTC レジスタへのマルチバイト書き込み

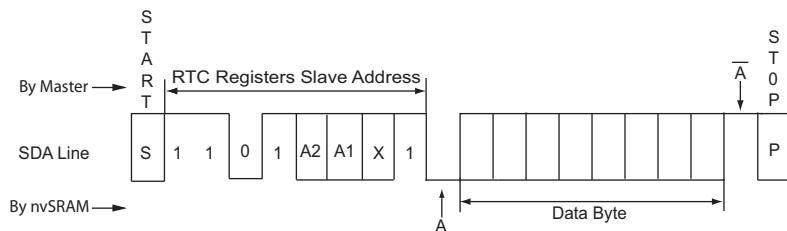

### 現在のアドレス RTC レジスタ読み取り

RTC レジスタの現在の読み取りは、START コンディションの後、マスタが RTC レジスタスレーブアドレスを送信することで始まります。すべての読み取り動作は、現在のアドレス（前にアクセスされたアドレス位置の次のアドレス）から始まります。最後のアドレスが連続的に読み取られた後、アドレスラッチは最初の位置（0x00）にループバックし、読み取り動作が継続されます。マスターは 1 バイトを読み取った後に読み取り動作を終了する場合もあれば、アドレスカウンタがアドレス 0x00 にロールバックした後のメモリの最後のアドレスまで連続的にアドレスを読み続ける場合もあります。マスターが STOP コンディション、反復 START 動作、または NACK を生成することにより、読み取り動作を終了させることができます。

図 25. 現在のアドレス RTC レジスタシングルバイト読み取り

図 26. 現在のアドレス RTC レジスタマルチバイト読み取り

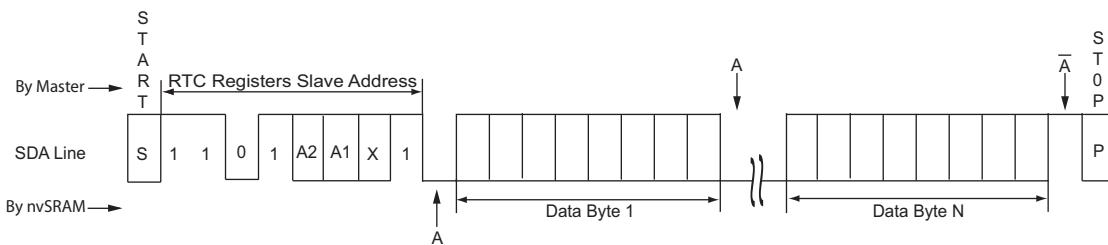

### 現在のアドレス RTC レジスタ読み取り

ランダムアドレス読み取りは、まず書き込み動作を開始し、最後のアドレスバイトがアクノレッジされた直後に反復 START を生成することによって実行されます。アドレスカウンタはこのアドレスに設定され、このスレーブへの次の読み取りアクセスがここから読み取り動作を開始します。マスターは 1 バイトを読み取った後に読み取り動作を終了する場合もあれば、アドレスカウンタが RTC の開始アドレス位置（0x00）にロールバック

した後のメモリの最後のアドレスまで連続的にアドレスを読み続ける場合もあります。

RTC レジスタスレーブの範囲外のメモリアドレスへのランダムアドレス読み取りが試みられると、アドレスバイトが送信された後、nvSRAM から NACK が返されます。アドレスカウンタは影響を受けないままで、現在の次の読み出し動作はアドレスカウンタに保持されているアドレス値から始まります。

図 27. ランダムアドレス RTC レジスタシングルバイト読み取り

図 28. ランダムアドレス RTC レジスタマルチバイト読み取り

## 制御レジスタスレーブ

次のセクションでは、制御レジスタスレーブからの読み取りまたは書き込み動作を実行するために必要なデータ転送シーケンスを説明します。

### 制御レジスタ書き込み

制御レジスタスレーブに書き込むには、マスターは START コンディションを生成した後に制御レジスタスレーブアドレスを送信する必要があります。マスターが STOP コンディションまたは最後の書き込み可能なアドレス位置を生成するまで、マスターによって指定されたアドレス位置から書き込みシーケンスが続行されます。

通常の書き込みまたはバースト中に、書き込み動作で書き込み不可能なアドレス位置へのアクセスが発生した場合は、データバイトが送信された後にスレーブが NACK を生成し、書き込みシーケンスは終了します。次のデータバイトはすべて無視され、アドレスカウンタはインクリメントされません。

書き込み動作がコマンドレジスタ (0xAA) 上で実行されると、このケースでは現在のアドレスが範囲外のアドレスであるため、次の読み取り動作も最初のアドレス (0x00) から開始されます。アドレスはインクリメントされず、現在の次の読み取り動作はこのアドレス位置から開始されます。書き込み動作が範囲外のアドレス位置に試行された場合、アドレスバイトが送られた直後に nvSRAM が NACK を送信します。

さらに、シリアル番号がロックされていると、制御レジスタスレーブに書き込めるのは 2つのアドレス (0xAA またはコマンドレジスタ、および 0x00 またはメモリ制御レジスタ) のみとなります。他のアドレス位置への書き込み動作では、デバイスはコマンドバイトおよびアドレスバイトをアクノレッジしますが、データバイトの制御レジスタスレーブから NACK が返されます。この場合、アドレスはインクリメントされず、現在の読み取りは最後にアクノレッジされたアドレスから発生します。

マスターが書き込み動作で範囲外のメモリアドレスにアクセスすると、nvSRAM 制御レジスタスレーブは NACK を送信します。この場合、現在の次の読み取り動作は最後にアクノレッジされたアドレスから始まります。

図 29. 制御レジスタへのシングルバイト書き込み

図 30. 制御レジスタへのマルチバイト書き込み

### 現在の制御レジスタ読み取り

制御レジスタスレーブの読み取りは、LSBが「1」に設定されている START コンディションの後、マスターが制御レジスタスレーブアドレスを送信することで開始されます。読み取りは、最後にアクセスされた位置の次のアドレスである現在のアドレスから開始されます。制御レジスタスレーブの読み取りは最後の読み取り可能なアドレス位置まで続き、最初の位置(0x00)にループバックします。コマンドレジスタは書き込み専用レジスタであり、連続的な読み取り動作経由ではアクセスできないことに注意してください。バースト読み取り動作がコマンドレジスタ(0xAA)から始まつた場合は、アドレスカウンタはレジスタマップ(0x00)の最初のアドレスにラップアラウンドします。

図 31. 制御レジスタシングルバイト読み取り

図 32. 制御レジスタマルチバイト読み取り

### ランダム制御レジスタ読み取り

ランダムアドレスの読み取りは、読み取りが目的の位置への書き込み動作を開始した直後に反復 START 動作を続けることで実行することができます。制御レジスタスレーブの読み取りは最後の読み取り可能なアドレス位置まで続き、最初の位置(0x00)にループバックします。コマンドレジスタは書き込み専

用レジスタであり、連続的な読み取り動作経由ではアクセスできないことに注意してください。コマンドレジスタ(0xAA)から始まるランダム読み取りは、制御レジスタマップ(0x00)の最初のアドレスにループバックします。ランダム読み取り動作が範囲外のメモリアドレスから開始される場合、アドレスバイトが送信された後に nvSRAM が NACK を送信します。

図 33. ランダム制御レジスタシングルバイト読み取り

**図 34. ランダム制御レジスタマルチバイト読み取り**

## シリアル番号

シリアル番号は、このデバイスを一意に識別するためにユーザーに提供される 8 バイトのメモリ空間です。通常 2 バイトのカスタマ ID、その後に続く固有の 5 バイトのシリアル番号と 1 バイトの CRC チェックで構成されています。ただし、nvSRAM は CRC を計算しないため、所望の形式で 8 バイトのメモリ空間を利用するかどうかはユーザ一次第となります。8 バイトの位置のデフォルト値は「0 X00」に設定されています。

### シリアル番号書き込み

シリアル番号には、制御レジスタスレーブデバイスを介してアクセスすることができます。シリアル番号を書き込むには、START コンディションの後にマスタが制御レジスタスレーブアドレスを送信し、0x01 から 0x08 のアドレス位置に書き込みます。シリアル番号レジスタのコンテンツは、次の STORE 動作の不揮発性メモリに確保されています。AutoStore がイネーブルになっている場合は、パワーダウン時に nvSRAM が自動的に不揮発性メモリにシリアル番号を格納します。しかし、AutoStore がディスエーブルになっている場合は、ユーザーが STORE 動作を実行して、シリアル番号レジスタのコンテンツを確保する必要があります。

注 シリアル番号ロック (SNL) ビットが設定されていない場合、シリアル番号レジスタは STORE が実行されたか否かにかかわらず書き換えることができます。一旦シリアル番号ロックビットが設定されると、シリアル番号レジスタへは書き込めません。シリアル番号ロックビットを設定中に、マスタがレジスタへの書き込み動作を実行しようとすると、NACK が返され、書き込みは行われません。

## シリアル番号ロック

シリアル番号レジスタへの書き込み完了後、メモリ制御レジスタ (0x00) でシリアル番号ロックビットを「1」に設定してシリアル番号をロックする責任はマスタにあります。メモリ制御レジスタおよびシリアル番号のコンテンツは、次の STORE 動作 (STORE または AutoStore) に確保されます。AutoStore がイネーブルでない場合は、ユーザーが STORE 動作を実行して、ロックビット状態を確保する必要があります。

STORE が実行されない場合、シリアル番号ロックビットはパワーサイクルに耐えられません。シリアル番号ロックビットおよび 8 バイトのシリアル番号は、パワーアップ時「0」がデフォルトです。

### シリアル番号読み取り

シリアル番号は、制御レジスタスレーブの目的のアドレスの読み取り動作によって読み取ることができます。制御レジスタデバイスは、バースト読み取り動作実行中に、最後のアドレス (コマンドレジスタを除く) から 0x00 アドレス位置ヘループッシュします。シリアル番号は 0x01 から 0x08 の位置に存在します。シリアル番号がロックされていない場合でも、シリアル番号読み取り動作により、シリアル番号レジスタに書き込まれている現在の値を戻すことができます。ロックビットが設定される前に、正しいシリアル番号がレジスタに書き込まれているかどうかを確認するために、マスタがシリアル番号読み取り動作を実行する可能性があります。

## デバイス ID

デバイス ID は、JEDEC 割り当てのメーカー ID、製品 ID、容量 ID、およびダイ改訂で構成される 4 バイトコードです。これらのレジスタは工場出荷時に設定され、ユーザーには読み取り専用のレジスタです。

表6. デバイス ID

| デバイス      | デバイス ID<br>(4 バイト) | デバイス ID の説明       |                  |                |                |

|-----------|--------------------|-------------------|------------------|----------------|----------------|

|           |                    | 31-21<br>(11 ビット) | 20-7<br>(14 ビット) | 6-3<br>(4 ビット) | 2-0<br>(3 ビット) |

|           |                    | メーカー ID           | 製品 ID            | 容量 ID          | ダイ改訂           |

| CY14C101I | 0x0681E2A0         | 00000110100       | 00001111000101   | 0100           | 000            |

| CY14B101I | 0x0681EAA0         | 00000110100       | 00001111010101   | 0100           | 000            |

| CY14E101I | 0x0681F2A0         | 00000110100       | 00001111100101   | 0100           | 000            |

表6 に示されているように、デバイス ID は 4 つの部分に分かれています。

### 1. メーカー ID (11 ビット)

これはサイプレス用に JEDEC が割り当てたメーカーの ID です。JEDEC は異なるバンクでメーカー ID を割り当てます。メーカー ID の最初の 3 ビットは、ID が割り当てられているバンクを表しています。次の 8 ビットはメーカー ID を表しています。

サイプレスのメーカー ID はバンク 0 の 0x34 です。したがって、すべてのサイプレスの nvSRAM 製品のメーカー ID は以下のようになっています。

サイプレス ID - 000\_0011\_0100

### 2. 製品 ID (14 ビット)

デバイスの製品 ID は表6 に示されています。

### 3. 容量 ID (4 ビット)

表6 に示されているように、4 ビットの容量 ID は製品の 1Mb 容量を示すためのものです。

### 4. ダイ改訂 (3 ビット)

これは製品の設計への大幅な変更を表すために使用されます。初期設定は常に 0x0 です。

## コマンドレジスタを使用したコマンドの実行

制御レジスタスレーブにより、コマンドレジスタ (0xAA) に特定のコマンドバイトを書き込むことで異なるコマンドの実行が可能となります。各コマンドのバイトコードは表5 に指定されています。これらのコマンドの実行中は、デバイスにアクセスすることができず、3 つのスレーブデバイスのいずれかが選択されている場合は NACK が返されます。無効なコマンドがマスターによって送信された場合、コマンドが NOP (演算なし) とアクリティブ化されたことを示す ACK で nvSRAM が応答します。アドレスは 0x00 の位置にロールオーバーします。

図35. コマンドレジスタを使用したコマンドの実行

## リアルタイムクロック動作

### nvTIME の動作

CY14X101I には、クロック、アラーム、ウォッチドッグ、割り込み、および制御機能を含む内部レジスタがあります。RTC レジスタは nvSRAM からの独立したアドレス空間を占有し、レジスタアドレス 0x00～0x0F の読み取り RTC レジスタおよび書き込み RTC レジスタのシーケンスを介してアクセスできます。クロックとタイマ情報レジスタの内部ダブルバッファは、読み込みまたは書き込み動作中の過渡的な内部クロックデータへのアクセスを防ぎます。またダブルバッファリングは、外部からクロックデータにアクセスする際、通常のタイミングカウントを中断させず、内部クロック精度の劣化を回避します。クロックおよびアラーム レジスタは BCD 形式でデータをストアします。

### クロックの動作

クロックレジスタは、1 秒単位で 9,999 年までの時間を維持します。時刻は任意のカレンダー時間に設定することができ、クロックは曜日と月の日、うるう年、世紀の遷移を自動的に刻みます。クロック機能には 8 つの専用レジスタがあります。これは書き込みサイクルで時間を設定し、読み取りサイクルで時間を読み取ります。これらのレジスタには BCD 形式で時間が含まれます。「0」として定義されたビットは、現在使用されておらず、将来使用するために予約されています。

### クロックの読み込み

ダブルバッファ RTC レジスタの構造は、クロックから不正なデータを読み取る可能性を減らします。遷移におけるデータの読み取りを防止するために、CY14X101I 時間保持レジスタの内部更新は、読み取りクロックデータの前に、読み取りビット「R」(フラグレジスター - 0x00) が「1」に設定されると停止されます。レジスタの更新停止は、クロックの精度に影響を与えません。

RTC デバイスの読み取りシーケンスが開始されると、ユーザーの時間保持レジスタの更新が停止され、STOP または反復 START コンディションが生成されるまで再開されません。内部クロックが動作している状態で、RTC レジスタが読み込まれます。読み取りシーケンスの終了後、すべての RTC レジスタが、20ms 以内に同時に更新されます。

### クロックの時刻設定

書き込みビット「W」(フラグレジスター 0x00) が「1」に設定されると、RTC デバイスへの書き込みアクセスが時間保持レジスタの更新を停止し、時間の設定が可能になります。次に、正しい曜日、日付、および時間がレジスタに書き込まれます。正しい形式は、24 時間 BCD 形式です。書き込まれた時間は、「基準時刻」と呼ばれます。この値は、不揮発性レジスタに格納され、現在の時刻の計算に使用されます。「0」が書き込まれて書き込みビット「W」がクリアされ、STOP または反復 START コンディションが検出されると、クロックが通常の動作を再開した後、時間保持レジスタの値は実際のクロックカウンタに転送されます。有効な STOP または反復 START コンディションがマスクによって生成されない場合は、RTC レジスタに書き込まれた時間は実際のクロックカウンタに転送されません。

時間保持レジスタに書き込まれた時間が正しい BCD 形式でない場合は、RTC レジスタの各無効二ブルは、RTC が通常の処理を再開した後で、0x0 にロールオーバーする前に、0xF までカウントを継続します。

注 「W」ビットが「0」に設定される後、時間保持、アラーム、校正、および割り込みレジスタに書き込まれる値は、 $t_{RTCP}$  時間に RTC 時間保持カウンタに転送されます。これらのカウンタの

値は、ソフトウェア / ハードウェア STORE または AutoStore 動作を開始することにより、不揮発性メモリに保存する必要があります。AutoStore をディスエーブルにしたモードでは、変更が正しく記録されるよう、RTC レジスタへの書き込みを行なながら、 $t_{RTCP}$  時間の後に STORE 処理を実行してください。

### バックアップ電源

CY14X101I の RTC は、長期間電源を確保するよう設計されています。用途に応じバックアップ電源にコンデンサかバッテリを選択します。これにより  $V_{RTCCap}$  または  $V_{RTCBat}$  ピンを使用します。主電源が供給されている時、 $V_{CC}$  が異常になり、 $V_{SWITCH}$  を下回ると、デバイスは電源をバックアップ電源に切り替えます。

クロック発振器の消費電流は非常に小さいため、バックアップ電源によるバックアップ時間が長くなります。主電源を喪失した状態のクロック動作にかかるらず、nvSRAM に格納されたデータは電源が失われたときに不揮発性素子に格納されるため、データが失われることはありません。

バックアップ動作中に、CY14X101I は室温で  $0.45 \mu\text{A}$ ( 代表値 ) を消費します。ユーザは、用途に応じてコンデンサやバッテリの値を選択する必要があります。

最大電流仕様に基づくバックアップ時間の値を、以下の表に示します。公称バックアップ時間は約 2 倍長くなります。

表 7. RTC のバックアップ時間

| コンデンサの値 | バックアップ時間<br>(CY14B101I) |

|---------|-------------------------|

| 0.1F    | 60 時間                   |

| 0.47F   | 12 日                    |

| 1.0F    | 25 日                    |

コンデンサを使用すると、システムの電源が投入されるたびにバックアップ電源が充電されるという明白な利点があります。バッテリバックアップを使用する場合は、3V リチウムバッテリをお勧めします。CY14X101I は、主電源を喪失した場合に、バッテリからのみ電流を受けます。ただし、バッテリは、CY14X101I によって常に充電されるわけではありません。バッテリ容量は、システムのライフサイクルを通して、必要なダウントIME の合計予想時間を考慮して選択する必要があります。

### 発振器の起動と停止

0x08 制御にある校正レジスタの OSCEN ビットが、発振器のイネーブルまたはディスエーブルを制御します。このビットは不揮発性であり、「イネーブル状態」(「0」に設定されている) でお客様に出荷されます。システムが保存状態にある場合にバッテリを保たせるには、OSCEN を「1」に設定する必要があります。これにより発振回路が停止し、バッテリ寿命が延長されます。OSCEN ビットがディスエーブルからイネーブルになる場合は、発振器が開始されるのに約 1 秒 (最大 2 秒) かかります。

システムの電源がオフである時にバックアップ電源の電圧 ( $V_{RTCCap}$  または  $V_{RTCBat}$ ) がそれぞれの最小レベルを下回ると、発振器が動作しなくなることがあります。CY14X101I には、システム電源が回復された時に、発振器の異常を検出する能力があります。これは、アドレス 0x00 にあるフラグレジスタの発振器異常フラグ (OSCF) に記録されます。デバイスに電流が供給されている ( $V_{CC}$  が  $V_{SWITCH}$  を上回る) 場合、OSCEN ビットがチェックされ、「イネーブル」状態であることを確認されます。OSCEN ビットがイネーブルになっていて、発振器が最初の 5ms 以内にアクティブにならない場合は、OSCF ビットが

「1」に設定されます。システムはこの条件を点検し、フラグをクリアするために「0」を書き込む必要があります。

OSCF フラグビットを設定することに加え、時間レジスタが「基準時刻」にリセットされることに注意してください。この時間は、時間保持レジスタに書き込まれる最後の値です。制御または校正レジスタと OSCEN ビットは、「発振器異常」コンディションによる影響は受けません。

OSCF の値は、時間レジスタが最初に書き込まれた際に、「0」にリセットする必要があります。これは、システムが最初に電源を投入された時に設定されている可能性があり、このビットの状態を初期化します。

OSCF をリセットするには、書き込みビット「W」(フラグレジスタ - 0x00)を「1」に設定し、フラグレジスタへの書き込みをイネーブルにします。書き込みをディスエーブルにするには、OSCF に「0」を書き込み、書き込みビットを「0」にリセットします。

## クロックの校正

RTC は 32.768kHz の公称周波数を持つクオーツ水晶によって駆動されます。クロックの精度は、水晶と校正の品質に依存します。市場で入手可能な水晶には、通常、±20ppm ~ ±35ppm の誤差があります。しかし、CY14X101I は、25 °C で +1.2 ppm まで精度向上させる校正回路を採用しています。これは、月当たり +2.5 ~ -5 秒の誤差を意味します。

校正回路は、この精度を達成するため、発振器分周回路からカウントを加算または減算します。サブレス(減算、マイナス校正)またはスプリット(加算、プラス校正)されるパルス数は、0x08 にある校正レジスタの 5 つの校正ビットに格納された値により異なります。校正ビットは、校正レジスタの 5 つの下位ビットを占有します。これらのビットは、バイナリ形式で「0」と 31 間の任意の値を表すために設定されます。ビット D5 は符号ビットで、「1」がプラス校正、「0」がマイナス校正を示します。カウントを加算するとクロックが速くなり、減算するとクロックが遅くなります。二進数の「1」がレジスタにロードされると、符号に応じて、発振器の誤差に 4.068 または -2.034 ppm のオフセット調整を行います。

校正は、64 分サイクル内で発生します。サイクルの最初の 62 分は、毎分 1 回、128 の発振器サイクルで 1 秒短縮されるか、256 の発振器サイクルで 1 秒長くなります。二進数の「1」がレジスタにロードされると、64 分サイクルの最初の 2 分のみが変更されます。二進数の 6 がロードされると、最初の 12 が影響を受け、同じパターンが続きます。したがって、各校正の手順は、実際の 125,829,120 回発振器サイクルごとに、512 を加算または 256 を減算する効果があります。これは、校正レジスタの校正ステップごとに、4.068 または -2.034 ppm の調整を行うことを意味します。

必要な校正を決定するには、フラグレジスタ(0x00)の CAL ビットを「1」に設定する必要があります。これは、512 Hz の公称周波数で INT ピンをトグルします。512 Hz から測定される任意の偏差は、必要な補正の程度と方向を示します。たとえば、512.01024 Hz の読み込みは +20 ppm の誤差を示します。したがって、-10 (001010b) の 10 進値を校正レジスタにロードし、この誤差を相殺する必要があります。

**注：**校正レジスタを設定または変更しても、テスト出力周波数には影響しません。

CAL をリセットするには、書き込みビット「W」(フラグレジスタ - 0x00)を「1」に設定し、フラグレジスタへの書き込みをイネーブルにします。CAL に値を書き込み、次に書き込みビットを「0」にリセットし、書き込みをディスエーブルにします。

## アラーム

アラーム機能は、ユーザーがプログラムしたアラームの時間と日付(レジスタ 0x01-5 に格納されている)の値を、該当する曜日と日付の値と比較します。一致すると、アラーム内部フラグ(AF)が設定され、アラーム割込みイネーブル(AIE)ビットが設定されている場合は、割り込みが INT ピンで生成されます。

日付、時間、分、秒という、4 つのアラーム一致フィールドがあります。これらの各フィールドは、フィールドがアラーム一致ロジックで使用されているかどうかを判断するために使用される一致ビットを持ちます。一致ビットが「0」に設定されている場合は、対応するフィールドが一致プロセスで使用されることを示します。一致ビットに応じて、アラームは、月に一度など特定の頻度で発生します。最小頻度は、毎分 1 回です。一致ビットを選択しない(すべて 1)場合は、一致が必要とされないため、アラームがディスエーブルになることを示します。すべての一致ビット(すべて 0)を選択すると、正確な時間と日付の一致が発生します。

アラームイベントを検出するには、AF フラグを読み込むまたは INT ピンを監視するという 2 つの方法を使用します。0x00 にあるフラグレジスタの AF フラグは、日付や時間の一一致が発生したことを示します。一致が発生すると、AF ビットが「1」に設定されます。フラグレジスタを読み込むと、アラーム フラグビット(および他のすべて)がクリアされます。ハードウェア割り込みピンも、アラーム イベントを検出するために使用することができます。

これを設定するには、書き込みビット「W」(フラグレジスタ - 0x00)を「1」に設定し、アラームレジスタへの書き込みをイネーブルにします。アラームの値を書き込んだ後、「W」ビットを「0」にクリアし、変更を有効にします。

**注** CY14X101I は、アラームフラグと割り込みを適切に処理するため、アラーム一致ビット(アラーム秒レジスタ 0x02 のビット「D7」)を数秒間「0」に設定する必要があります。

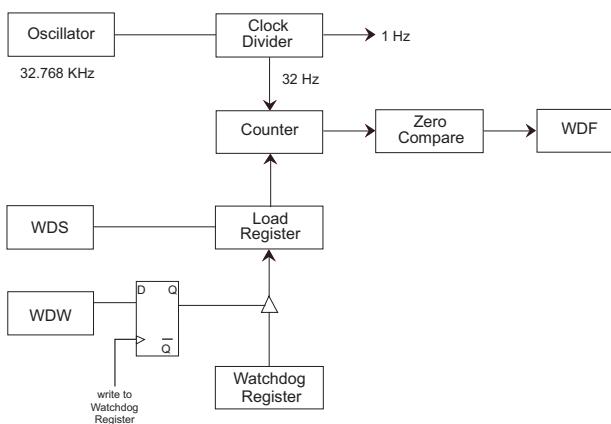

## ウォッチドッグタイマ

ウォッチドッグタイマは、水晶発振器から派生した 32 Hz のクロック(31.25ms)を使用する、フリーランダウンカウンタです。発振器は、関数へのウォッチドッグとして実行する必要があります。ウォッチドッグ タイマ レジスタにロードされた値からカウントダウンを開始します。

タイマは、ロード可能なレジスタとフリーラン カウンタで構成されています。パワーアップ時に、レジスタ 0x07 のウォッチドッグタイムアウト値が、カウンタのロードレジスタにロードされます。カウントは、ウォッチドッグストロープ(WDS)ビットが「1」に設定されるたびに、ロード可能な値からの電源投入と再起動を開始します。カウンタは、「0」のピン値と比較されます。カウンタがこの値に達すると、内部フラグとオプションの割り込み出力が発生します。カウンタが「0」に到達する前に WDS ビットを「1」に設定することにより、割り込みタイムアウトを防ぐことができます。これにより、カウンタにウォッチドッグタイムアウト値がリロードされ、再起動されます。カウンタがピンの値に達する前に WDS ビットを設定する限り、割り込みとウォッチドッグ タイマ フラグは発生しません。

ウォッチドッグ書き込みビットを「0」に設定することで、新しいタイムアウト値が書き込まれます。WDW が「0」である場合、ウォッチドッグタイムアウト値ビット D5-D0 への新しい値の書き込みがイネーブルになり、タイムアウト値が変更されます。WDW が「1」である場合、D5-D0 ビットへの書き込みは無視されます。WDW 機能は、ウォッチドッグ タイマの値が変更されることを考慮せずに、WDS ビットを設定できるようにします。ウォッチドッグ タイマの論理図を、[22 ページの図 36](#) に

示します。ウォッチドッグタイムアウト値を「0」に設定すると、ウォッチドッグ機能がディスエーブルになることに注意してください。

ウォッチドッグ タイマの出力は、ウォッチドッグがタイムアウトまで許可されている場合に設定されるフラグビット WDF です。割り込みレジスタのウォッチドッグ割り込みイネーブル (WIE) ビットが設定されている場合は、INT ピンのハードウェア割り込みも、ウォッチドッグタイムアウトで生成されます。フラグおよびハードウェア割り込みは、ユーザーがフラグレジスタを読み込んだ時に両方クリアされます。

**図 36. ウォッチドッグタイマブロック図**

### プログラマブル方形波ジェネレータ

方形波ジェネレータブロックは、デバイスの INT ピンに所望の周波数を生成するために水晶出力を使用します。出力周波数は、以下のいずれかになるようにプログラムすることができます。

- 1. 1Hz

- 2. 512 Hz

- 3. 4096Hz

- 4. 32768Hz

デバイスがバックアップ電源で実行されている時は、方形波出力は生成されません。

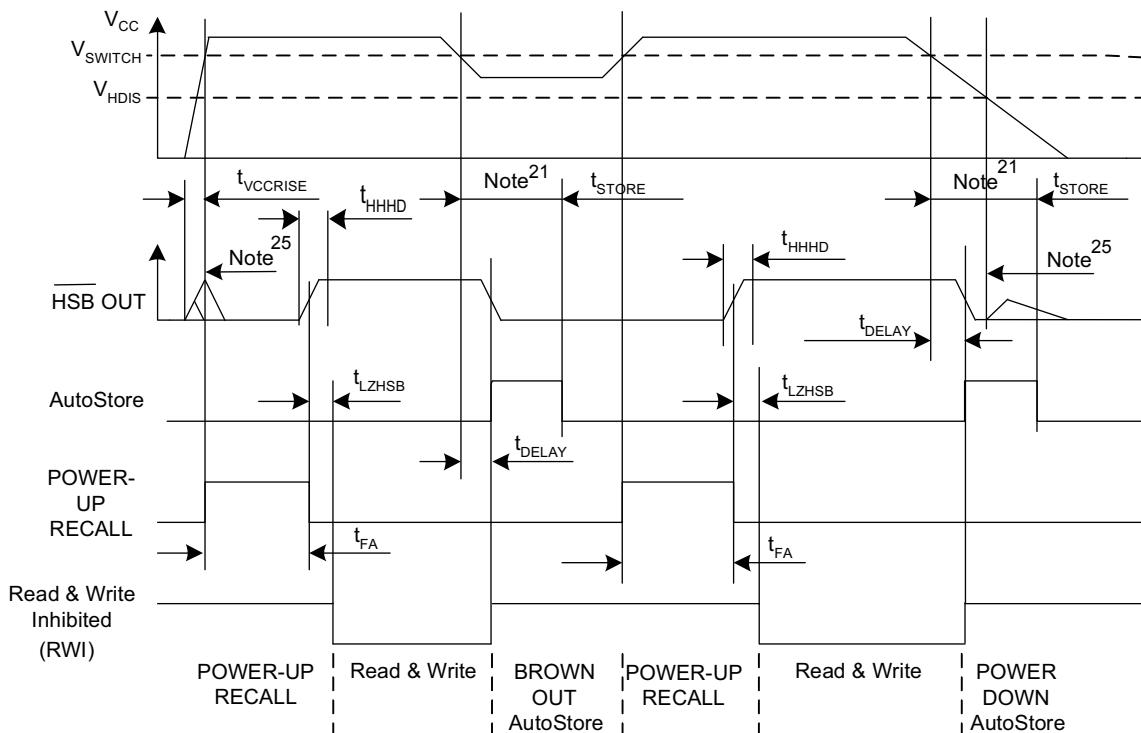

### Power Monitor

CY14X101I は、電源異常割り込み機能による電力管理機能を提供します。また、クロック用のバックアップ電源への内部スイッチを制御し、低  $V_{CC}$  アクセスからメモリを保護します。電源モニタは、 $V_{CC}$  電圧を  $V_{SWITCH}$  閾値と比較する、内部バンドギャップ参照回路に基づきます。

$V_{CC}$  が電源を喪失した際に  $V_{SWITCH}$  がに達すると、データ STORE 動作が SRAM から不揮発性要素に対して開始され、最後の SRAM データ状態を確保します。また、電源が  $V_{CC}$  からバックアップ電源 (バッテリまたはコンデンサ) に切り替えられ、RTC 発振器を処理します。

バックアップ電源から動作している場合、nvSRAM との読み込みおよび書き込み処理が抑制され、RTC 機能が利用できなくなります。RTC クロックは、バックグラウンドで処理を継続しま

す。更新された RTC 時間保持レジスタは、 $V_{CC}$  が回復された後で利用できるようになります(33ページのnvSRAM仕様を参照)。

### バックアップ電源モニタ

CY14X101I は、バックアップ電源 (バッテリまたはコンデンサバックアップ) 故障を検出するバックアップ電源監視システムを提供します。バックアップ電源に障害が発生した場合、次のパワーアップでバックアップ電源障害フラグ (BPF) が発行されます。バックアップ電圧が  $V_{BAKFAIL}$  よりも下がった場合に、BPF フラグが設定されます。RTC がバックアップモードで実行中である際もバックアップ電源が監視されます。バックアップモード中に検出された低電圧は、BPF フラグを通してフラグが立てられます。BPF がデータを保持することができるるのは、バックアップ電圧の定義された低レベルまでです ( $V_{DR}$ )。

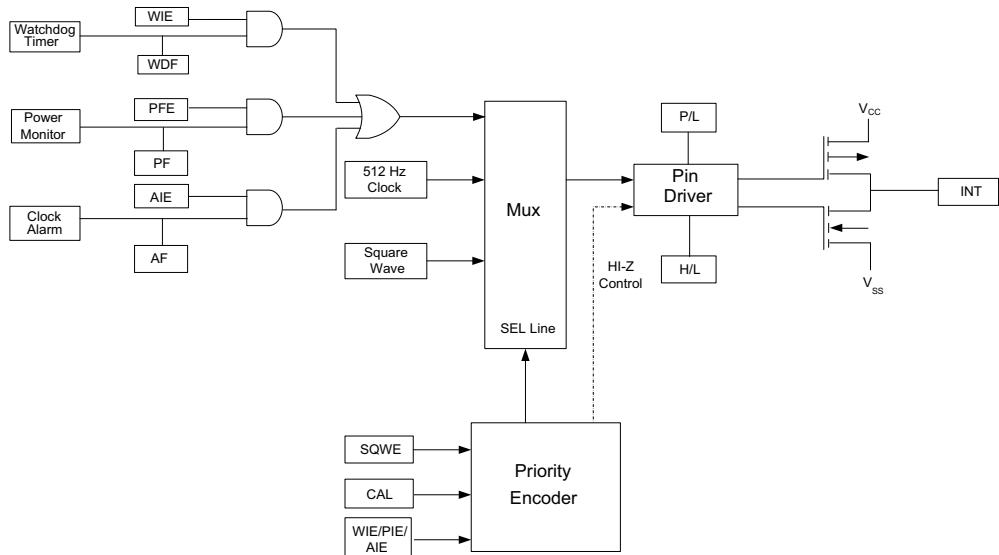

### 割り込み

CY14X101I は、フラグレジスタ、割り込みレジスタ、およびマイクロコントローラへの割り込み信号を送ることができるロジックを持っています。割り込みには、ウォッチドッグタイマ、電源モニタ、アラームタイマという 3 つの潜在的ソースがあります。それぞれ、個別に割り込みレジスタ (0x06) の適切な設定によって、INT ピンを駆動するためインエーブルにできます。さらに、ホストプロセッサが割り込みの原因を判別するために使用するフラグレジスタ (0x00) に、関連するフラグビットを持っています。INT ピンのドライバは、割り込みが発生したときにその動作を指定する 2 つのビットを持っています。

割り込みは、両方のフラグが、3 つのソースのいずれかによってオンになった場合、および割り込みレジスタで該当する割り込みイネーブルビット ('1' に設定) がイネーブルになった場合にのみ発生します。割り込みソースがアクティブになった後、2 つのプログラマブルビット、H/L と P/L は、INT ピンで出力ピンドライバの動作を決定します。これらの 2 ビットは割り込みレジスタにあり、INT ピンからレベルまたはパルスモードの出力を駆動するために使用できます。パルスモードでは、パルス幅が内部で約 200ms に固定されます。このモードは、ホストマイクロコントローラをリセットするためのモードです。レベルモードでは、フラグレジスタがユーザによって読み込まれるまで、ピンはアクティブ極性になります。このモードは、ホストマイクロコントローラへの割り込みとして使用されます。制御ビットについては、次のセクションで説明します。

割り込みは、通常の電源による動作中にのみ生成され、システムがバックアップ電源モードで実行されているときにはトリガされません。

**注** CY14X101I は、パワーアップ RECALL シーケンスが完了した後でのみ有効な割り込みを生成します。INT ピンの全イベントは、パワーアップ後、 $t_{FA}$  中は無視される必要があります。

### 割り込みレジスタ

**ウォッチドッグ割り込み有効 (WIE)**：「1」に設定すると、ウォッチドッグタイマは、ウォッチドッグタイムアウトが発生した際に INT ピンと内部フラグを駆動します。WIE を「0」に設定すると、ウォッチドッグタイマは、フラグレジスタの WDF フラグにのみ影響します。

**アラーム割り込み有効 (AIE)**：「1」に設定すると、アラームの一一致により、INT ピンと内部フラグが駆動されます。AIE を「0」に設定すると、アラームの一一致はフラグレジスタの AF フラグにのみ影響します。

**電源異常割り込み有効 (PFE)**：「1」に設定すると、電源異常モニタにより、ピンと内部フラグが駆動されます。PFE を「0」に

**方形波有効 (SQWE)**：「1」に設定されると、プログラマブル周波数の方形波が INT ピンに生成されます。周波数は割り込みレジスタの SQ1 と SQ0 ビットによって決定されます。このビットは不揮発性であり、パワーサイクルに耐えます。SQWE ビットは他すべての割り込みよりも優先されます。しかし、CAL ビットは方形波ジェネレータよりも優先されます。このビットのデフォルトは工場出荷時に「0」に設定されています。

**HIGH/LOW (H/L)**：「1」に設定すると、INT ピンがアクティブ HIGH になり、ドライバ モードがプッシュ ブルになります。INT ピンは、 $V_{CC}$  が  $V_{SWITCH}$  を上回る場合にのみ HIGH を駆動します。「0」に設定すると、INT ピンがアクティブ LOW になり、ドライバ モードがオープン ドレインになります。アクティブ LOW モードで割り込みを使用している間、INT ピンは 10k 抵抗で  $V_{CC}$  にプルアップする必要があります。

**パルス / レベル (P/L)**：「1」に設定し、割り込みが発生すると、INT ピンが約 200ms 秒間駆動されます。P/L が「0」に設定されると、INT ピンは、フラグ レジスタが読み込まれるまで、HIGH または LOW (H/L により決定される) に駆動されます。

**SQ1 および SQ0**：SQWE ビットが「1」に設定されている時、これらのビットは INT ピン出力で方形波の周波数を固定するために一緒に使用されます。これらのビットは非揮発性であり、パワーサイクルに耐えます。この表に示されているように、出力周波数が決定されます。

**表 8. SQW 出力選択**

| SQ1 | SQ0 | 周波数     | 備考           |

|-----|-----|---------|--------------|

| 0   | 0   | 1Hz     | 1Hz 信号       |

| 0   | 1   | 512 Hz  | 512Hz クロック出力 |

| 1   | 0   | 4096Hz  | 4kHz クロック出力  |

| 1   | 1   | 32768Hz | 発振器出力周波数     |

イネーブルな割り込みソースが INT ピンをアクティブ化すると、外部ホストはレジスタのフラグを読み込んで、原因を特定します。レジスタが読み込まれる際には、すべてのフラグがクリアされることに注意してください。INT ピンがレベルモードにプログラムされている場合、条件はクリアされ、INT ピンは非アクティブ状態に戻ります。ピンがパルスモードにプログラムされている場合、フラグの読み込みによってもフラグとピンがクリアされます。フラグ レジスタが読み込まれると、パルスは、その指定された期間を完了しません。INT ピンがホストのリセットとして使用されている場合は、フラグ レジスタはリセット時に読み込まれません。

以下は INT ピンの状態をまとめた表です。

**表 9. INT ピンの状態**

| CAL | SQWE | WIE/AIE/PFE | INT ピン出力 |

|-----|------|-------------|----------|

| 1   | X    | X           | 512 Hz   |

| 0   | 1    | X           | 方形波出力    |

| 0   | 0    | 1           | アラーム     |

| 0   | 0    | 0           | HI-Z     |

### フラグレジスタ

フラグ レジスタには、3 つのフラグ ビットがあります。これらは、割り込みを生成するために使用することができる WDF、AF、および PF です。これらのフラグは、ウォッチドッグタイマー アウト、アラーム一致、または電源異常モニタによってそれぞれ設定されます。フラグが設定される際、プロセッサは、このレジスタをポーリングすること、または割り込みをイネーブルにすることができます。これらのフラグは、レジスタが読み込まれると自動的にリセットされます。フラグ レジスタは、電源投入時に値 0x00 を使って自動的にロードされます (OSCF ビットを除く。[20 ページの発振器の起動と停止を参照](#) )。

図 37. RTC の推奨コンポーネント構成<sup>[4]</sup>

図 38. 割り込みブロック図

WDF - ウオッチ ドッグタイマフラグ

WIE - ウオッチ ドッグ割り込み

イネーブル

PF - 電源異常フラグ

PFE - 電源異常有効

AF - アラームフラグ

AIE - アラーム割り込みイネーブル

P/L - パルスレベル

H/L - HIGH/LOW

SQWE - 方形波イネーブル

**注**

4. nvSRAMRTC の設計ガイドラインおよびベストプラクティスについては、アプリケーションノート AN61546 を参照してください。

**表 10. RTC レジスタマップ<sup>[5, 6]</sup>**

| レジスタ | BCD 形式のデータ   |                |                  |                     |                    |         |         |         | 機能 / 範囲                |  |  |  |  |  |  |  |

|------|--------------|----------------|------------------|---------------------|--------------------|---------|---------|---------|------------------------|--|--|--|--|--|--|--|

|      | D7           | D6             | D5               | D4                  | D3                 | D2      | D1      | D0      |                        |  |  |  |  |  |  |  |

| 0x0F | 年 (10 年の位)   |                |                  |                     | 年                  |         |         |         | 年 : 00~99              |  |  |  |  |  |  |  |

| 0x0E | 0            | 0              | 0                | 月 (10ヶ月の位)          | 月                  |         |         |         | 月 : 01~12              |  |  |  |  |  |  |  |

| 0x0D | 0            | 0              | 日 (10 日の位)       |                     | 日 (1 日の位)          |         |         |         | 今月の日 : 01~31           |  |  |  |  |  |  |  |

| 0x0C | 0            | 0              | 0                | 0                   | 0                  | 曜日      |         |         | 曜日 : 01~07             |  |  |  |  |  |  |  |

| 0x0B | 0            | 0              | 時間 (10 時間の位)     |                     | 時間                 |         |         |         | 時間 : 00~23             |  |  |  |  |  |  |  |

| 0x0A | 0            | 分 (10 分の位)     |                  |                     | 分 (1 分の位)          |         |         |         | 分 : 00~59              |  |  |  |  |  |  |  |

| 0x09 | 0            | 秒 (10 秒の位)     |                  |                     | 秒 (1 秒の位)          |         |         |         | 秒 : 00~59              |  |  |  |  |  |  |  |

| 0x08 | OSCEN (0)    | 0              | Cal Sign (0)     | 校正 (00000)          |                    |         |         |         | 校正值 <sup>[7]</sup>     |  |  |  |  |  |  |  |

| 0x07 | WDS (0)      | WDW (0)        | WDT (000000)     |                     |                    |         |         |         | ウォッチドッグ <sup>[7]</sup> |  |  |  |  |  |  |  |

| 0x06 | WIE (0)      | AIE (0)        | PFE (0)          | SQWE (0)            | H/L (1)            | P/L (0) | SQ1 (0) | SQ0 (0) | 割り込み <sup>[7]</sup>    |  |  |  |  |  |  |  |

| 0x05 | M (1)        | 0              | アラーム日 (10 日の位)   |                     | アラーム日 (1 日の位)      |         |         |         | アラーム、今月の日 : 01~31      |  |  |  |  |  |  |  |

| 0x04 | M (1)        | 0              | アラーム時間 (10 時間の位) |                     | アラーム時間 (1 時間の位)    |         |         |         | アラーム時間 : 00~23         |  |  |  |  |  |  |  |

| 0x03 | M (1)        | アラーム分 (10 分の位) |                  |                     | アラーム分 (1 分の位)      |         |         |         | アラーム分 : 00~59          |  |  |  |  |  |  |  |

| 0x02 | M (1)        | アラーム秒 (10 秒の位) |                  |                     | アラーム秒 (1 秒の位)      |         |         |         | アラーム秒 : 00~59          |  |  |  |  |  |  |  |

| 0x01 | 世紀 (10 世紀の位) |                |                  |                     | 世紀 (1 世紀の位)        |         |         |         | 世紀 : 00~99             |  |  |  |  |  |  |  |

| 0x00 | WDF          | AF             | PF               | OSCF <sup>[8]</sup> | BPF <sup>[8]</sup> | CAL (0) | W (0)   | R (0)   | フラグ <sup>[7]</sup>     |  |  |  |  |  |  |  |

**注**

5. ()は、工場出荷時の値を示しています。

6. RTC レジスタの未使用ビットは後の使用のために予約されており、「0」に設定されている必要があります。

7. これは、バイナリ値ではなく、BCD 値です。

8. ユーザーが OSCF と BPF フラグビットをリセットする場合は、フラグレジスタは、t<sub>RTCp</sub> 時間の後に更新されます。

表 11. レジスタ マップ詳細

| レジスタ                                                                                                                          | 内容                                                                                       |            |              |            |           |    |    |    |  |  |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|------------|--------------|------------|-----------|----|----|----|--|--|--|--|--|--|--|

| 0x0F                                                                                                                          | 時間管理 - 年                                                                                 |            |              |            |           |    |    |    |  |  |  |  |  |  |  |

|                                                                                                                               | D7                                                                                       | D6         | D5           | D4         | D3        | D2 | D1 | D0 |  |  |  |  |  |  |  |

|                                                                                                                               | 年 (10 年の位)                                                                               |            |              |            | 年         |    |    |    |  |  |  |  |  |  |  |

| 年の下位2桁のBCD桁が含まれています。下位ニブル (4ビット) には、年の値が含まれています。上位ニブル (4ビット) には、10単位の年の値が含まれます。各ニブルは0から9までになります。レジスタの範囲は0から99です。              |                                                                                          |            |              |            |           |    |    |    |  |  |  |  |  |  |  |

| 0x0E                                                                                                                          | 時間管理 - 月                                                                                 |            |              |            |           |    |    |    |  |  |  |  |  |  |  |

|                                                                                                                               | D7                                                                                       | D6         | D5           | D4         | D3        | D2 | D1 | D0 |  |  |  |  |  |  |  |

|                                                                                                                               | 0                                                                                        | 0          | 0            | 月 (10ヶ月の位) | 月         |    |    |    |  |  |  |  |  |  |  |

| 月のBCD桁が含まれています。下位ニブル (4ビット) は、下位桁が含まれており、0から9まで動作します。上位ニブル (1ビット) は、上位桁が含まれており、0から1で動作します。レジスタの範囲は1から12です。                    |                                                                                          |            |              |            |           |    |    |    |  |  |  |  |  |  |  |

| 0x0D                                                                                                                          | 時間管理 - 日                                                                                 |            |              |            |           |    |    |    |  |  |  |  |  |  |  |

|                                                                                                                               | D7                                                                                       | D6         | D5           | D4         | D3        | D2 | D1 | D0 |  |  |  |  |  |  |  |

|                                                                                                                               | 0                                                                                        | 0          | 日 (10 日の位)   |            | 日 (1 日の位) |    |    |    |  |  |  |  |  |  |  |

| 今月の日のBCD桁が含まれています。下位ニブル (4ビット) は、下位桁が含まれており、0から9まで動作します。上位ニブル (2ビット) は、上位桁が含まれており、0から3で動作します。レジスタの範囲は1から31です。うるう年は自動的に調整されます。 |                                                                                          |            |              |            |           |    |    |    |  |  |  |  |  |  |  |

| 0x0C                                                                                                                          | 時間管理 - 曜日                                                                                |            |              |            |           |    |    |    |  |  |  |  |  |  |  |

|                                                                                                                               | D7                                                                                       | D6         | D5           | D4         | D3        | D2 | D1 | D0 |  |  |  |  |  |  |  |

|                                                                                                                               | 0                                                                                        | 0          | 0            | 0          | 0         | 曜日 |    |    |  |  |  |  |  |  |  |

| 下位ニブル (3ビット) は、曜日に関する値が含まれます。曜日は、1から7までカウントしてから1に戻るリングカウンタです。曜日は日付と統合されていないため、ユーザが、曜日の値に意味を割り当てる必要があります。                      |                                                                                          |            |              |            |           |    |    |    |  |  |  |  |  |  |  |

| 0x0B                                                                                                                          | 時間管理 - 時間                                                                                |            |              |            |           |    |    |    |  |  |  |  |  |  |  |

|                                                                                                                               | D7                                                                                       | D6         | D5           | D4         | D3        | D2 | D1 | D0 |  |  |  |  |  |  |  |

|                                                                                                                               | 0                                                                                        | 0          | 時間 (10 時間の位) |            | 時間        |    |    |    |  |  |  |  |  |  |  |

| 24時間形式で時間のBCD値が含まれます。下位ニブル (4ビット) は、下位桁が含まれており、0から9まで動作します。上位ニブル (2ビット) は、上位桁が含まれており、0から2で動作します。レジスタの範囲は0から23です。              |                                                                                          |            |              |            |           |    |    |    |  |  |  |  |  |  |  |

| 0x0A                                                                                                                          | 時間管理 - 分                                                                                 |            |              |            |           |    |    |    |  |  |  |  |  |  |  |

|                                                                                                                               | D7                                                                                       | D6         | D5           | D4         | D3        | D2 | D1 | D0 |  |  |  |  |  |  |  |

|                                                                                                                               | 0                                                                                        | 分 (10 分の位) |              |            | 分 (1 分の位) |    |    |    |  |  |  |  |  |  |  |

| 分のBCD値が含まれます。下位ニブル (4ビット) は、下位桁が含まれており、0から9まで動作します。上位ニブル (3ビット) は、分の上位の桁が含まれており、0から5で動作します。レジスタの範囲は0から59です。                   |                                                                                          |            |              |            |           |    |    |    |  |  |  |  |  |  |  |

| 0x09                                                                                                                          | 時間管理 - 秒                                                                                 |            |              |            |           |    |    |    |  |  |  |  |  |  |  |

|                                                                                                                               | D7                                                                                       | D6         | D5           | D4         | D3        | D2 | D1 | D0 |  |  |  |  |  |  |  |

|                                                                                                                               | 0                                                                                        | 秒 (10 秒の位) |              |            | 秒 (1 秒の位) |    |    |    |  |  |  |  |  |  |  |

| 秒のBCD値が含まれます。下位ニブル (4ビット) は、下位桁が含まれており、0から9まで動作します。上位ニブル (3ビット) は、上位桁が含まれており、0から5で動作します。レジスタの範囲は0から59です。                      |                                                                                          |            |              |            |           |    |    |    |  |  |  |  |  |  |  |

| 0x08                                                                                                                          | 校正 / 制御                                                                                  |            |              |            |           |    |    |    |  |  |  |  |  |  |  |

|                                                                                                                               | D7                                                                                       | D6         | D5           | D4         | D3        | D2 | D1 | D0 |  |  |  |  |  |  |  |

|                                                                                                                               | OSCEN                                                                                    | 0          | 校正<br>符号     | 校正         |           |    |    |    |  |  |  |  |  |  |  |

| OSCEN                                                                                                                         | 発振器イネーブル 「1」にセットすると、発振器を停止させます。「0」にクリアすると、発振器を起動します。発振器を停止させると、保存中にバッテリやコンデンサの電力を節約できます。 |            |              |            |           |    |    |    |  |  |  |  |  |  |  |

| 校正サイン                                                                                                                         | タイムベースへの加算 (1) またはタイムベースからの減算 (0) として校正を適用するかどうかを決定します。                                  |            |              |            |           |    |    |    |  |  |  |  |  |  |  |

| 校正                                                                                                                            | これらの5ビットは、クロックの校正を制御します。                                                                 |            |              |            |           |    |    |    |  |  |  |  |  |  |  |

| 0x07                                                                                                                          | ウォッチ ドッグ タイマ                                                                             |            |              |            |           |    |    |    |  |  |  |  |  |  |  |

|                                                                                                                               | D7                                                                                       | D6         | D5           | D4         | D3        | D2 | D1 | D0 |  |  |  |  |  |  |  |

|                                                                                                                               | WDS                                                                                      | WDW        | WDT          |            |           |    |    |    |  |  |  |  |  |  |  |

**表 11. レジスタ マップ詳細 (つづき)**

| レジスタ                                     | 内容                                                                                                                                                                                                                                                  |                                                                                                                                                                               |                  |      |     |                 |     |     |  |  |  |

|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------|-----|-----------------|-----|-----|--|--|--|

| WDS                                      | ウォッチドッグストローブ。このビットを「1」にセットすると、ウォッチドッグ タイマが再起動されます。このビットを「0」にクリアしても何の影響もありません。ウォッチドッグ タイマをリセットした後、ビットは自動的にクリアされます。WDSビットは書き込み専用です。これを読み込むと常に「0」が返されます。                                                                                               |                                                                                                                                                                               |                  |      |     |                 |     |     |  |  |  |

| WDW                                      | ウォッチドッグ書き込み有効。このビットを「1」にセットすると、ウォッチドッグタイムアウト値(D5-D0)への全書き込みがディスエーブルになります。これにより、ユーザーはタイムアウト値を変更することなく、ウォッチドッグストローブのビットを設定することができます。このビットを「0」にクリアすると、次の書き込みサイクルが完了した際に、ビットD5-D0がウォッチドッグに書き込まれます。この関数の詳細は、 <a href="#">21ページのウォッチドッグタイマ</a> に説明されています。 |                                                                                                                                                                               |                  |      |     |                 |     |     |  |  |  |

| WDT                                      | ウォッチドッグ タイムアウトの選択。ウォッチドッグ タイマの間隔は、このレジスタの6ビットの値によって選択されます。それは、32 Hzカウント (31.25 ms) の乗数を表します。タイムアウト値の範囲は、31.25ms(「1」の設定)から2秒(3FHの設定)です。ウォッチドッグ タイマレジスタを「0」にクリアすると、タイマがディスエーブルになります。WDWビットが前のサイクルで0に設定されている場合にのみ、これらのビットを書き込むことができます。                 |                                                                                                                                                                               |                  |      |     |                 |     |     |  |  |  |

| 0x06                                     | 割り込みステータス / 制御                                                                                                                                                                                                                                      |                                                                                                                                                                               |                  |      |     |                 |     |     |  |  |  |

|                                          | D7                                                                                                                                                                                                                                                  | D6                                                                                                                                                                            | D5               | D4   | D3  | D2              | D1  | D0  |  |  |  |

|                                          | WIE                                                                                                                                                                                                                                                 | AIE                                                                                                                                                                           | PFE              | SQWE | H/L | P/L             | SQ1 | SQ0 |  |  |  |

|                                          | WIE                                                                                                                                                                                                                                                 | ウォッチドッグ割り込みイネーブル。「1」にセットし、ウォッチドッグ タイムアウトが発生すると、ウォッチドッグ タイマがINTピンとWDFフラグを駆動します。「0」にクリアすると、ウォッチドッグ タイムアウトは、WDFフラグにのみ影響を与えます。                                                    |                  |      |     |                 |     |     |  |  |  |

|                                          | AIE                                                                                                                                                                                                                                                 | アラーム割り込み有効。「1」にセットすると、アラームの一一致により、INTピンとAFフラグが駆動されます。「0」にクリアすると、アラームの一一致は、AFフラグにのみ影響します。                                                                                      |                  |      |     |                 |     |     |  |  |  |

|                                          | PFE                                                                                                                                                                                                                                                 | 電源異常有効。「1」にセットすると、アラームの一一致により、INTピンとPFフラグが駆動されます。「0」にクリアすると、電源異常 モニタは、PFフラグにのみ影響します。                                                                                          |                  |      |     |                 |     |     |  |  |  |

|                                          | SQWE                                                                                                                                                                                                                                                | 方形波イネーブル。「1」に設定すると、方形波は、SQ1とSQ0ビットを使用してプログラムされた周波数でINTピンに駆動されます。方形波出力は割り込みロジックよりも優先されます。SQWEビットが「1」に設定されている場合、イネーブル化された割り込みソースがアクティブになった時に、該当するフラグのみが立てられ、INTピンは方形波の駆動を継続します。 |                  |      |     |                 |     |     |  |  |  |

|                                          | H/L                                                                                                                                                                                                                                                 | HIGH/LOW。「1」にセットすると、INTピンはアクティブHIGHに駆動されます。「0」に設定すると、INTピンはオーブンドレインで、アクティブLOWとなります。                                                                                           |                  |      |     |                 |     |     |  |  |  |

|                                          | P/L                                                                                                                                                                                                                                                 | パルス/レベル。「1」に設定すると、INTピンは約200ms間、割り込みソースによってアクティブに駆動されます(H/Lにより決定される)。「0」にクリアすると、INTピンはフラグレジスタが読み込まれるまで、アクティブレベル(H/Lにより決定される)に駆動されます。                                          |                  |      |     |                 |     |     |  |  |  |

| 0x05                                     | SQ1、SQ0 SQ1、SQ0。SQWEビットが「1」に設定されている時、これらのビットはINTピン出力で方形波の周波数を決定するために使用されます。以下は、それぞれの組み合わせ(SQ1、SQ0)の周波数出力です。<br>(0、0) - 1Hz<br>(0、1) - 512Hz<br>(1、0) - 4096Hz<br>(1、1) - 32768Hz                                                                    |                                                                                                                                                                               |                  |      |     |                 |     |     |  |  |  |

|                                          | アラーム - 日                                                                                                                                                                                                                                            |                                                                                                                                                                               |                  |      |     |                 |     |     |  |  |  |

|                                          | D7                                                                                                                                                                                                                                                  | D6                                                                                                                                                                            | D5               | D4   | D3  | D2              | D1  | D0  |  |  |  |

|                                          | M                                                                                                                                                                                                                                                   | 0                                                                                                                                                                             | アラーム日 (10日の位)    |      |     | アラーム日 (1日の位)    |     |     |  |  |  |

| 月の日の値とマスク ビットのアラーム値を含め、日の値を選択または選択解除します。 |                                                                                                                                                                                                                                                     |                                                                                                                                                                               |                  |      |     |                 |     |     |  |  |  |

| M                                        | 一致。このビットを「0」にクリアすると、日の値がアラーム一致で使用されます。このビットを「1」にセットすると、一致回路が日の値を無視します。                                                                                                                                                                              |                                                                                                                                                                               |                  |      |     |                 |     |     |  |  |  |

| 0x04                                     | アラーム - 時間                                                                                                                                                                                                                                           |                                                                                                                                                                               |                  |      |     |                 |     |     |  |  |  |

|                                          | D7                                                                                                                                                                                                                                                  | D6                                                                                                                                                                            | D5               | D4   | D3  | D2              | D1  | D0  |  |  |  |

|                                          | M                                                                                                                                                                                                                                                   | 0                                                                                                                                                                             | アラーム時間 (10 時間の位) |      |     | アラーム時間 (1 時間の位) |     |     |  |  |  |

|                                          | 時間の値とマスクビットのアラーム値が含まれ、時間の値を選択または選択解除します。                                                                                                                                                                                                            |                                                                                                                                                                               |                  |      |     |                 |     |     |  |  |  |

| M                                        | 一致。このビットを「0」にクリアすると、時間の値がアラーム一致で使用されます。このビットを「1」にセットすると、一致回路が時間の値を無視します。                                                                                                                                                                            |                                                                                                                                                                               |                  |      |     |                 |     |     |  |  |  |

**表 11. レジスタ マップ詳細 (つづき)**

| レジスタ | 内容                                                                                                                                                                                                                                                                      |                |    |      |             |               |    |    |  |  |  |  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|----|------|-------------|---------------|----|----|--|--|--|--|

| 0x03 | アラーム - 分                                                                                                                                                                                                                                                                |                |    |      |             |               |    |    |  |  |  |  |

|      | D7                                                                                                                                                                                                                                                                      | D6             | D5 | D4   | D3          | D2            | D1 | D0 |  |  |  |  |

|      | M                                                                                                                                                                                                                                                                       | アラーム分 (10 分の位) |    |      |             | アラーム分 (1 分の位) |    |    |  |  |  |  |

|      | 分の値とマスクビットのアラーム値が含まれ、分の値を選択または選択解除します。                                                                                                                                                                                                                                  |                |    |      |             |               |    |    |  |  |  |  |