リアル タイム クロック付き

8M ビット (1024K × 8/512K × 16) nvSRAM

## 特長

- 25ns と 45ns のアクセス時間

- 1024K × 8 (CY14B108K) または 512K × 16 (CY14B108M) としてメモリを内部的に編成

- 小容量のコンデンサだけで電源切断時の自動 STORE 処理を実行

- QuantumTrap 不揮発性素子への STORE をソフトウェア、デバイス ピン、または電源喪失時の AutoStore により起動

- SRAMへのRECALL 処理はソフトウェアまたは電源投入で実行

- 高い信頼性

- 回数に制限のない読み出し、書き込み、RECALL サイクル

- QuantumTrap に対する 100 万回の STORE サイクル

- 20 年のデータ保持期間

- 3V (+20%、-10%) の単一電源で動作

- フル機能のリアル タイム クロック (RTC) と組み合わせたサイプレスの不揮発性スタティック RAM (nvSRAM) のデータ統合性

- ウオッチドッグ タイマー

- プログラム可能な割り込み付きのクロック アラーム

- RTC 用のコンデンサまたはバックアップ バッテリー

- 工業用温度範囲

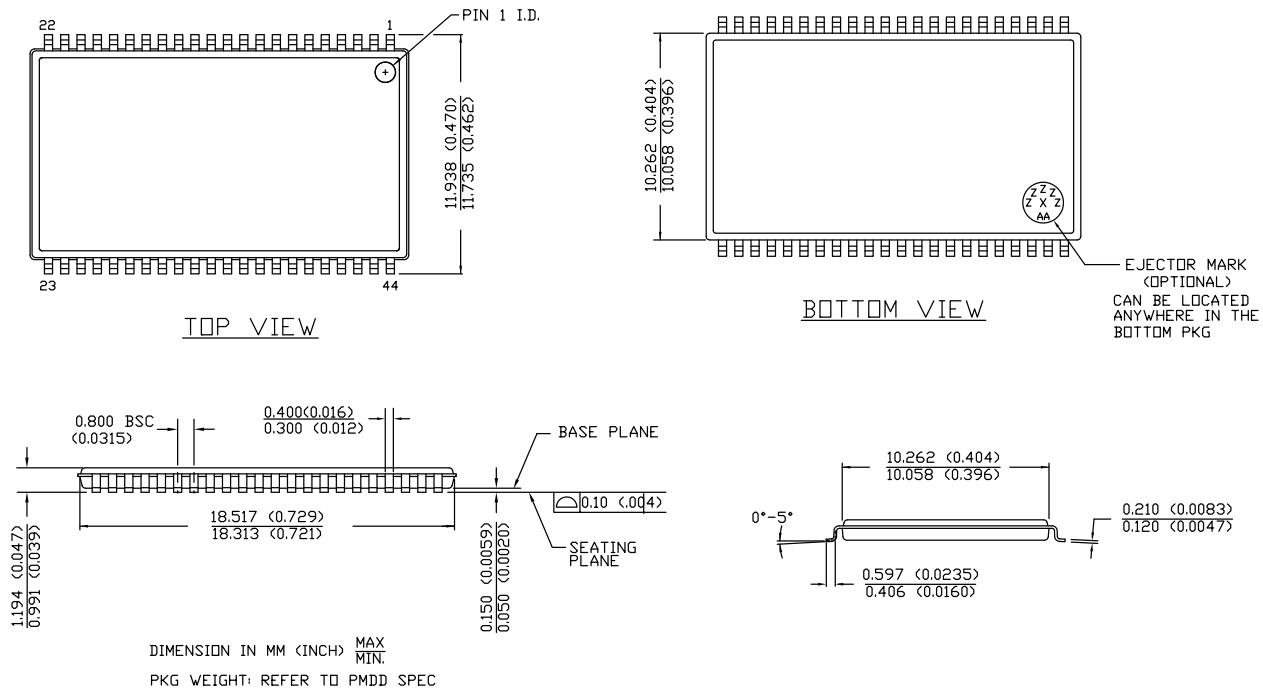

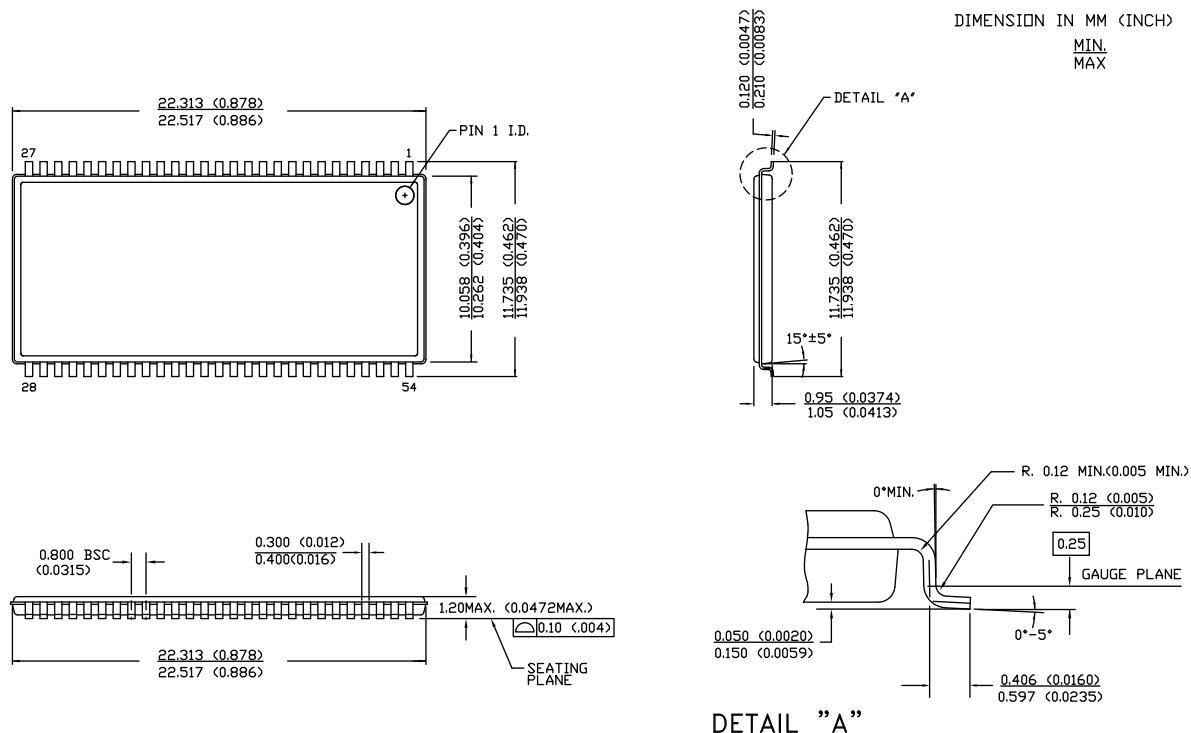

- 44 ピンと 54 ピン TSOP Type II パッケージ

- 鉛フリーおよび有害物質の制限 (RoHS) に準拠

## 機能の説明

サイプレスの CY14B108K / CY14B108M は、8M ビットの不揮発性スタティック RAM (nvSRAM) にフル機能の RTC を組み合わせたモノリシック集積回路です。埋め込み型不揮発性素子には、世界最高級の信頼性を備えた不揮発性メモリを実現する QuantumTrap 技術を採用しています。独立した不揮発性データを不揮発性素子に保持しながら、SRAM は読み書き回数に制限がありません。

RTC 機能は、うるう年対応の正確なクロックとプログラマブルな高精度発振器を備えています。アラーム機能は、定期的な分、時、日、または月のアラームに応じてプログラムできます。また、プロセス制御を目的としたプログラマブル ウオッチドッグタイマーも備えています。

全ての関連資料の一覧を表示するには、[ここ](#)をクリックしてください。

**エラッタ** : AutoStore ディスエーブル機能はこのデバイスで正常に動作しません。詳細については、[33 ページの「エラッタ」](#) を参照してください。詳細情報は、エラッタのトリガー条件、影響の範囲、可能な回避方法、シリコン チップ バージョンの適用可能性などを含んでいます。

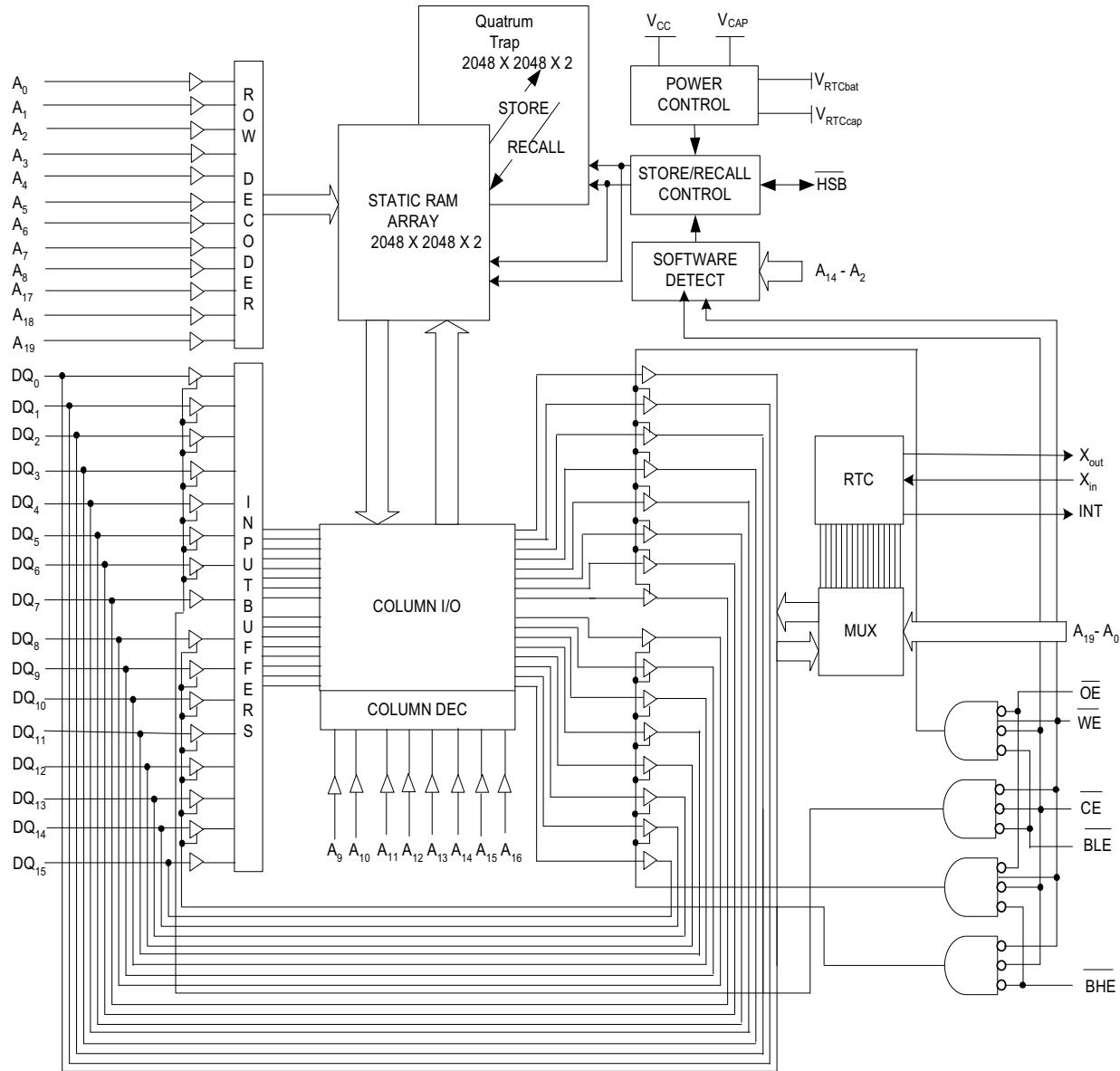

**論理ブロック図 [1, 2, 3]**

**注**

1.  $\times 8$  コンフィギュレーションのアドレスは A<sub>0</sub> ~ A<sub>19</sub>、 $\times 16$  コンフィギュレーションのアドレスは A<sub>0</sub> ~ A<sub>18</sub> です。

2.  $\times 8$  コンフィギュレーションではデータ DQ<sub>0</sub> ~ DQ<sub>7</sub>、 $\times 16$  コンフィギュレーションではデータ DQ<sub>0</sub> ~ DQ<sub>15</sub> です。

3. BHE と BLE は、 $\times 16$  コンフィギュレーションでのみ使用できます。

## 目次

|                       |    |                                        |    |

|-----------------------|----|----------------------------------------|----|

| ピン配置                  | 4  | 熱抵抗                                    | 20 |

| ピンの定義                 | 5  | AC テスト負荷                               | 21 |

| デバイスの動作               | 6  | AC テスト条件                               | 21 |

| SRAM 読み出し             | 6  | RTC 特性                                 | 21 |

| SRAM 書き込み             | 6  | AC スイッチング特性                            | 22 |

| AutoStore 処理          | 6  | スイッチング波形                               | 22 |

| ハードウェア STORE (HSB) 処理 | 6  | AutoStore ／電源投入時の RECALL               | 25 |

| ハードウェア RECALL (電源投入)  | 7  | スイッチング波形                               | 25 |

| ソフトウェア STORE          | 7  | ソフトウェア制御の STORE と RECALL サイクル          | 26 |

| ソフトウェア RECALL         | 7  | スイッチング波形                               | 26 |

| AutoStore の防止         | 9  | ハードウェア STORE サイクル                      | 27 |

| データ保護                 | 9  | スイッチング波形                               | 27 |

| リアル タイム クロックの動作       | 10 | SRAM 真理値表                              | 28 |

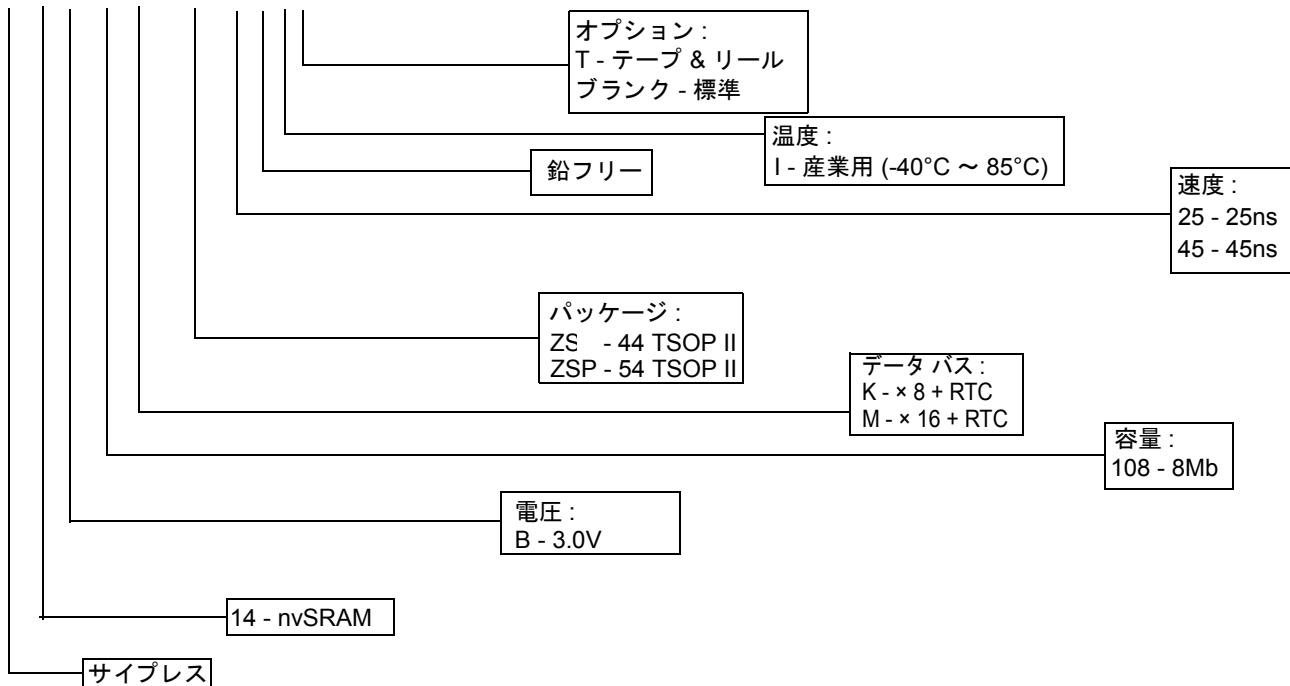

| nvTime の動作            | 10 | 注文情報                                   | 29 |

| クロックの動作               | 10 | 注文コードの定義                               | 29 |

| クロックの読み出し             | 10 | パッケージ図                                 | 30 |

| クロックの時刻設定             | 10 | 略語                                     | 32 |

| バックアップ電源              | 10 | 本書の表記法                                 | 32 |

| 発振器の起動と停止             | 10 | 測定単位                                   | 32 |

| クロックの校正               | 11 | エラッタ                                   | 33 |

| アラーム                  | 11 | 影響を受ける製品                               | 33 |

| ウォッチドッグ タイマー          | 11 | 8M ビット (1024K × 8, 512K × 16) nvSRAM の |    |

| 電源モニター                | 12 | 認定状況                                   | 33 |

| 割り込み                  | 12 | 8M ビット (1024K × 8, 512K × 16) nvSRAM の |    |

| フラグレジスタ               | 12 | エラッタのまとめ                               | 33 |

| RTC 外部コンポーネント         | 13 | 改訂履歴                                   | 34 |

| RTC に関する PCB 設計上の注意事項 | 14 | セールス、ソリューションおよび法律情報                    | 35 |

| レイアウトに関する要件           | 14 | ワールドワイドな販売と設計サポート                      | 35 |

| 最大定格                  | 19 | 製品                                     | 35 |

| 動作範囲                  | 19 | PSoC® ソリューション                          | 35 |

| DC 電気的特性              | 19 | サイプレス開発者コミュニティ                         | 35 |

| データ保持期間および書き換え可能回数    | 20 | テクニカル サポート                             | 35 |

| 静電容量                  | 20 |                                        |    |

## ピン配置

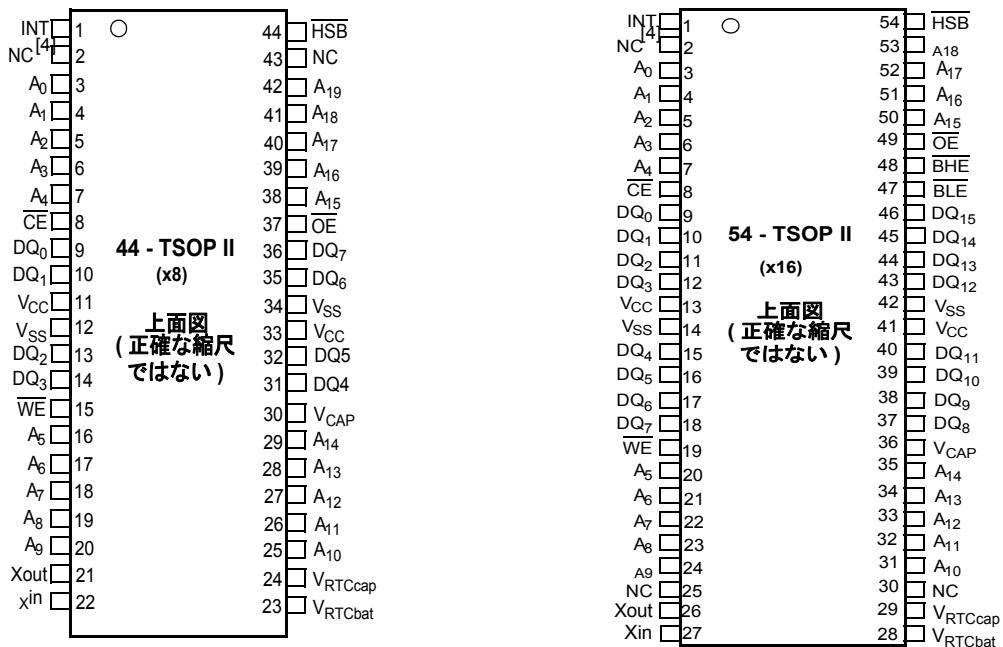

図 1. ピン配置図 – 44 ピンと 54 ピンの TSOP II

### 注

4. 16M ビットのアドレス拡張に対応しています。NC ピンはダイに接続されていません。

## ピンの定義

| ピン名                                | I/O タイプ | 説明                                                                                                                                                                                                                                                  |

|------------------------------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A <sub>0</sub> ~ A <sub>19</sub>   | 入力      | アドレス入力。×8 コンフィギュレーションで nvSRAM の 1,048,576 バイトのいずれかを選択するために使用される                                                                                                                                                                                     |

| A <sub>0</sub> ~ A <sub>18</sub>   |         | アドレス入力。×16 コンフィギュレーションで nvSRAM の 524,288 ワードのいずれかを選択するために使用される                                                                                                                                                                                      |

| DQ <sub>0</sub> ~ DQ <sub>7</sub>  | 入力／出力   | ×8 コンフィギュレーションの双方向データ I/O ライン。動作に応じて入力または出力ラインとして使用                                                                                                                                                                                                 |

| DQ <sub>0</sub> ~ DQ <sub>15</sub> |         | ×16 コンフィギュレーションの双方向データ I/O ライン。処理に応じて入力／出力ラインとして使用                                                                                                                                                                                                  |

| NC                                 | 未接続     | 未接続。このピンはダイに接続されていない                                                                                                                                                                                                                                |

| WE                                 | 入力      | 書き込みイネーブル入力、アクティブ LOW。LOW を選択すると、I/O ピンのデータが、特定のアドレス位置に書き込まれる                                                                                                                                                                                       |

| CE                                 | 入力      | チップイネーブル入力、アクティブ LOW: LOW の場合は、チップを選択。HIGH の場合は、チップの選択を解除                                                                                                                                                                                           |

| OE                                 | 入力      | 出力イネーブル、アクティブ LOW: アクティブ LOW の OE 入力は、読み出しサイクル中にデータ出力バッファを有効にする。OEHIGH をデアサートすると、I/O ピンがトライステートになる                                                                                                                                                  |

| BHE                                | 入力      | バイト HIGH イネーブル、アクティブ LOW。DQ <sub>15</sub> ~ DQ <sub>8</sub> を制御                                                                                                                                                                                     |

| BLE                                | 入力      | バイト LOW イネーブル、アクティブ LOW。DQ <sub>7</sub> ~ DQ <sub>0</sub> を制御                                                                                                                                                                                       |

| X 出力 <sup>[5]</sup>                | 出力      | 水晶振動子接続：起動時に水晶発振子を駆動                                                                                                                                                                                                                                |

| X 入力 <sup>[5]</sup>                | 入力      | 水晶発振子接続：32.768kHz 水晶発振子用                                                                                                                                                                                                                            |

| V <sub>RTCcap</sub> <sup>[5]</sup> | 電源供給    | コンデンサから供給された RTC のバックアップ電源電圧：V <sub>RTCbat</sub> が使用されている場合は、未接続のままになる                                                                                                                                                                              |

| V <sub>RTCbat</sub> <sup>[5]</sup> | 電源供給    | バッテリにより供給されるバックアップ RTC 電源電圧。V <sub>RTCcap</sub> が使用される場合は、未接続のままにされる                                                                                                                                                                                |

| INT <sup>[5]</sup>                 | 出力      | 割り込み出力：クロックアラーム、ウォッチドッグタイマーおよび電力モニターに対応するようにプログラム可能。アクティブ HIGH (プッシュまたはプル) または LOW (オープンドレイン) にもプログラム可能                                                                                                                                             |

| V <sub>SS</sub>                    | グランド    | デバイス用のグランド。システムのグランドに接続する必要がある                                                                                                                                                                                                                      |

| V <sub>CC</sub>                    | 電源供給    | デバイスへの電源供給入力。3.0V +20%、-10%。                                                                                                                                                                                                                        |

| HSB                                | 入力／出力   | ハードウェア STORE ビジー (HSB)<br>出力：LOW の時、nvSRAM のビジー状態を示す。ハードウェアとソフトウェア STORE 動作の後、HSB が標準の出力 HIGH 電流で短期間 (t <sub>HHHD</sub> ) に HIGH に駆動される。<br>その後、内部の低プルアップ抵抗でこのピンが HIGH のままに維持する（外部プルアップ抵抗にも接続可能）<br>入力：このピンを外部で LOW にプルダウンすることによって実施されるハードウェア STORE |

| V <sub>CAP</sub>                   | 電源      | AutoStore コンデンサ：SRAM から不揮発性素子にデータを格納するため、電力喪失時に nvSRAM へ電源を供給                                                                                                                                                                                       |

### 注

5. RTC 機能を使用しない場合は未接続のままにします。

## デバイスの動作

CY14B108K/CY14B108M nvSRAM は、同じ物理セル内で、対になった 2 個の機能コンポーネントで構成されています。これらは SRAM メモリ セルと不揮発性 QuantumTrap セルです。SRAM メモリ セルは標準の高速スタティック RAM として動作します。SRAM 内のデータは不揮発性セルに転送される (STORE 处理) か、または不揮発性セルから SRAM に転送されます (RECALL 处理)。この独特的なアーキテクチャを使って、全てのセルは並行して格納され復元されます。STORE 处理と RECALL 处理中、SRAM の読み書き処理は禁止されています。CY14B108K/CY14B108M は、一般的な SRAM と同様に、回数無制限の読み書きに対応しています。さらに、不揮発性セルから回数無制限のRECALL処理および最大100万回までのSTORE処理が可能です。読み出しと書き込みモードの詳細については、28 ページの「SRAM 真理値表」を参照してください。

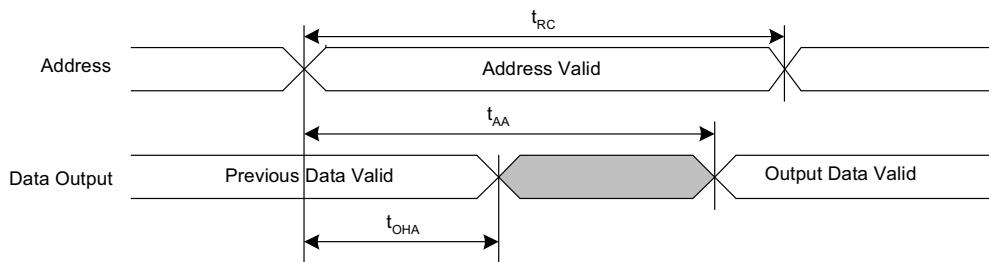

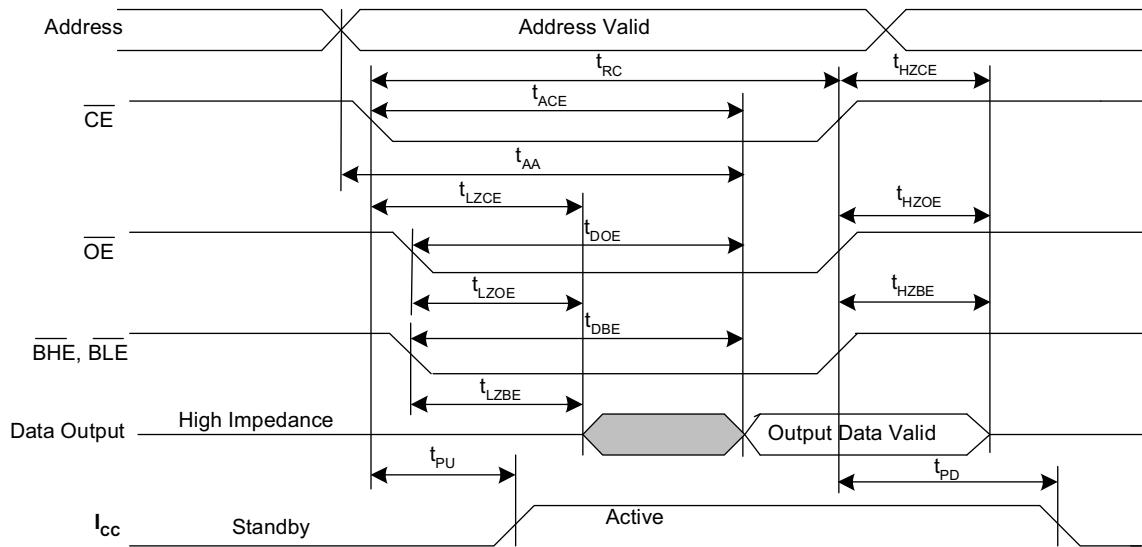

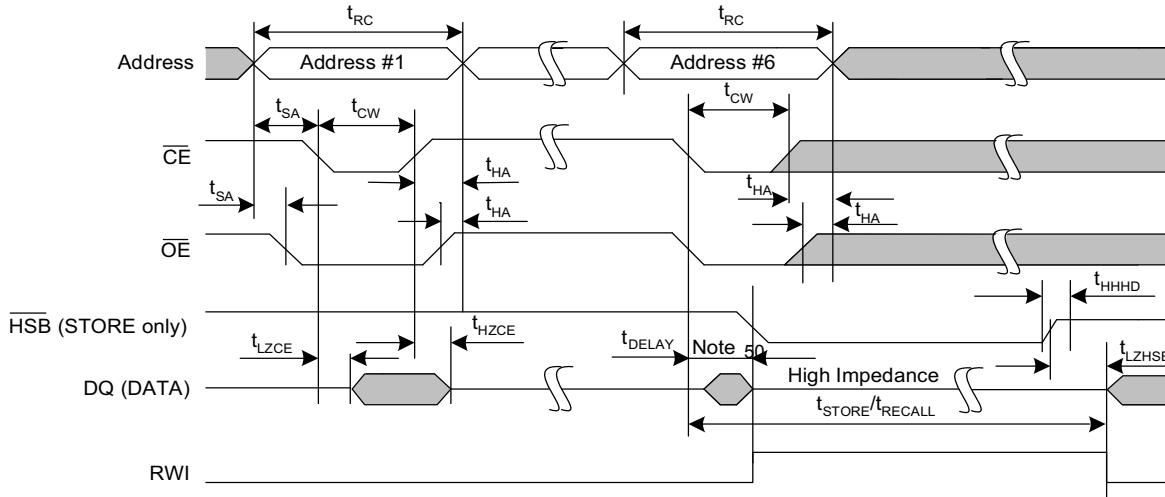

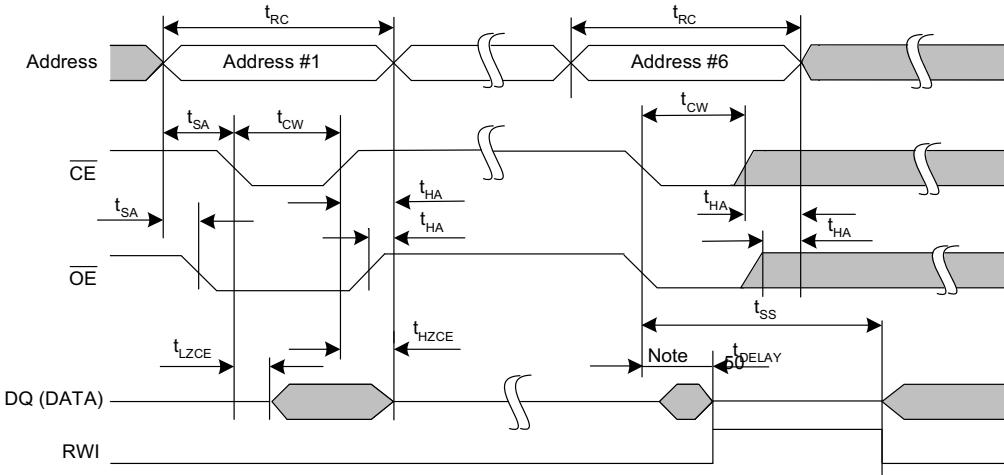

### SRAM 読み出し

CY14B108K/CY14B108M は、 $\overline{CE}$  と  $\overline{OE}$  が LOW、および  $\overline{WE}$  と HSB が HIGH の場合、読み出しサイクルを実行します。ピン  $A_0 \sim 19$  または  $A_0 \sim 18$  で指定されたアドレスは、1,048,576 データ バイトのどれが、または 524,288 ワード (16 ビット) のどれがアクセスされるかを決定します。バイト イネーブル (BHE, BLE) は、1 ワードが 16 ビットの場合にどのバイトを出力するかを決定します。アドレス遷移によって読み出しが開始された場合、出力は  $t_{AA}$  (読み出しサイクル 1) の遅延後に有効になります。CE または OE によって読み出しが開始された場合、出力は  $t_{ACE}$  と  $t_{DOE}$  のどちらか遅い方 (読み出しサイクル 2) の終了時に有効になります。データ出力は、任意の制御入力ピンでの変化を必要としないで  $t_{AA}$  アクセス時間内に、繰り返しアドレス変更に応答します。これは、別のアドレスの変化が発生するか、または CE か OE が HIGH になるか、あるいは WE か HSB が LOW になるまで有効な状態が続きます。

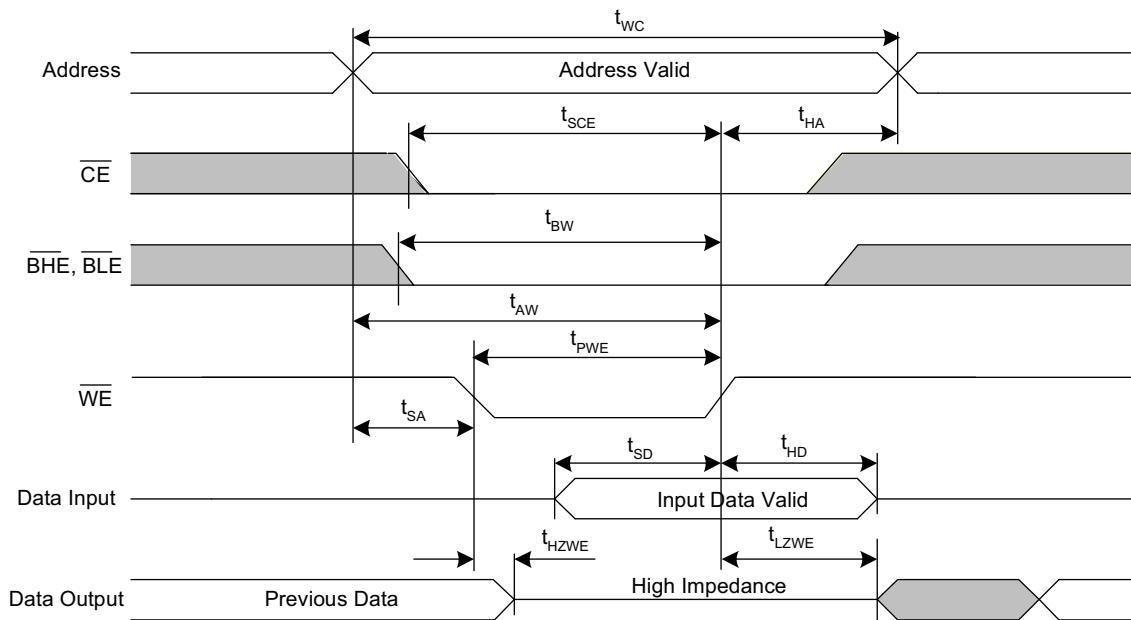

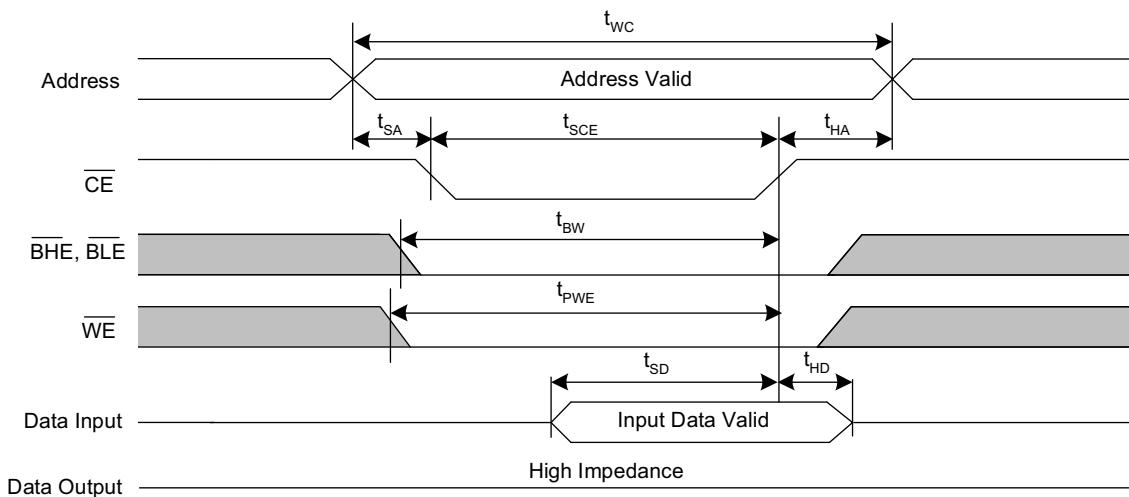

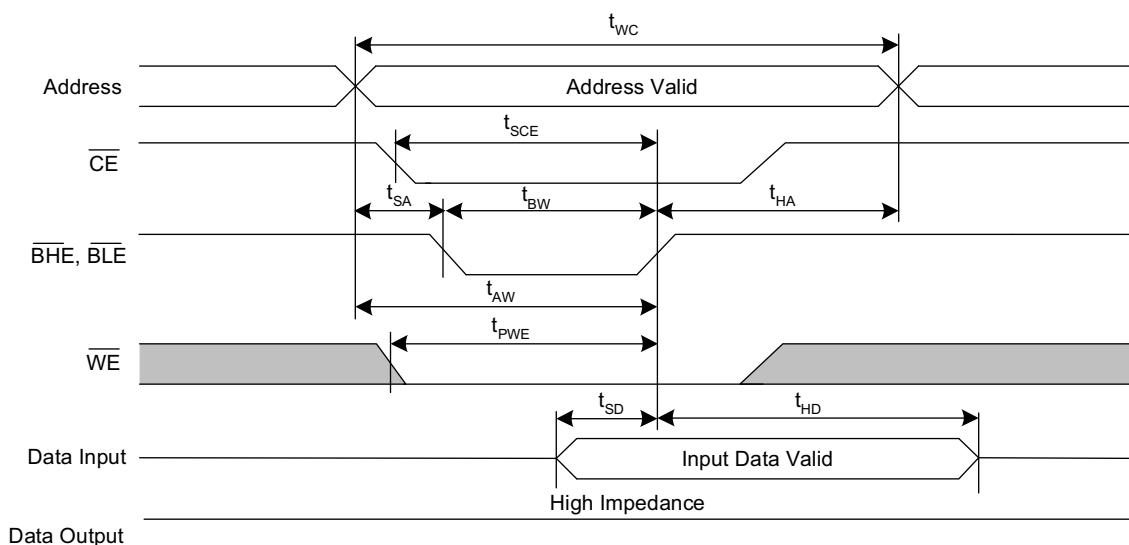

### SRAM 書き込み

書き込みサイクルは、 $\overline{CE}$  と  $\overline{WE}$  が LOW、 $\overline{HSB}$  が HIGH の時に実行されます。アドレス入力が安定な状態になってから書き込みサイクルに入らなければいけません。また、サイクルの終わりに  $CE$  か  $WE$  が HIGH になるまで安定な状態を保つ必要があります。共通 I/O ピンである  $DO_{0 \sim 15}$  のデータは、WE が制御する書き込み終了前に、または CE が制御する書き込み終了前に、データが有効 ( $t_{SD}$  時間) であれば、メモリに書き込まれます。バイト イネーブル入力 (BHE, BLE) は、1 ワードが 16 ビットの場合に、どのバイトを書き込むかを決定します。共通 I/O ラインでのデータバスの競合を避けるために、書き込みサイクル中は終始  $OE$  を HIGH に維持してください。OE が LOW のままであると、 $WE$  が LOW になった後に内部回路は  $t_{HZWE}$  の間出力バッファを停止します。

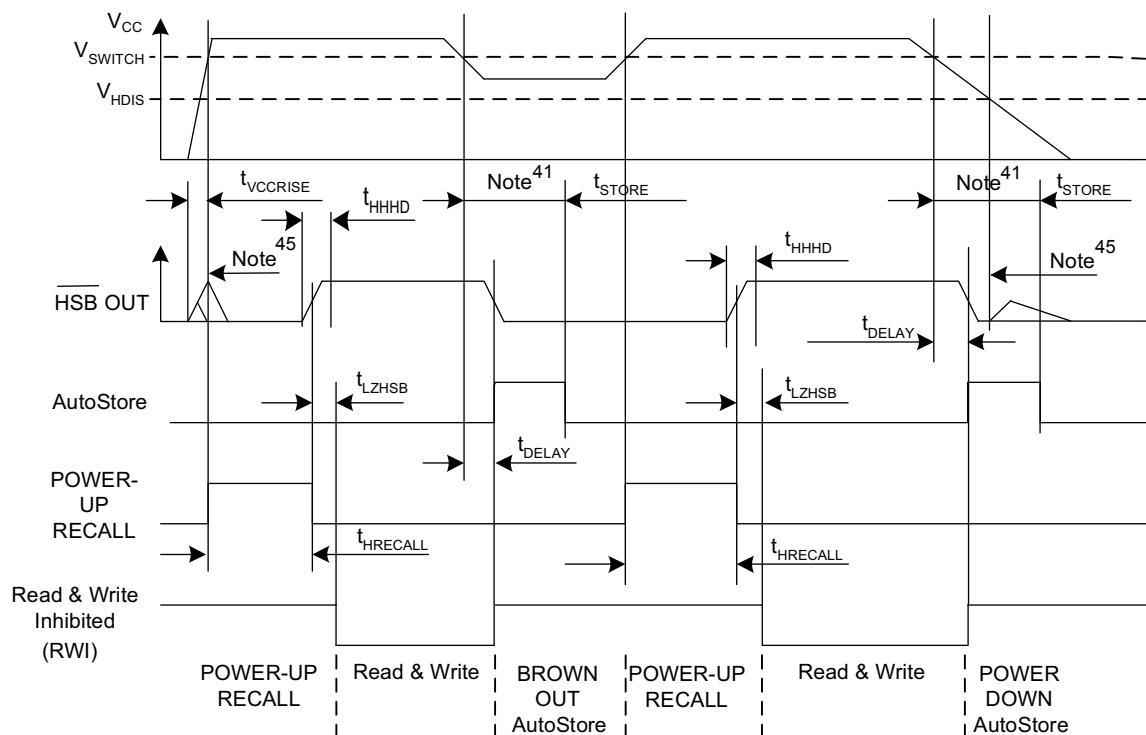

### AutoStore 处理

CY14B108K/CY14B108M は、3 つのストレージ処理のいずれかを処理してデータを nvSRAM へ格納します。これら 3 つの処理は、次の通りです。ハードウェア STORE: HSB によって有効化されます。ソフトウェア STORE: アドレス命令によって有効化されます。AutoStore: デバイスの電源オフ時に有効になります。AutoStore 处理は、QuantumTrap テクノロジー独自の機能であり、CY14B108K/CY14B108M ではデフォルトで有効になっています。

通常動作中にデバイスは、 $V_{CAP}$  ピンに接続されたコンデンサを充電するのに  $V_{CC}$  から電流を引き込みます。充電された電荷はチップが一回 STORE 处理を実行するのに使用されます。 $V_{CC}$

ピンの電圧が  $V_{SWITCH}$  を下回ると、デバイスは  $V_{CC}$  と  $V_{CAP}$  ピンの接続を自動的に切ります。STORE 处理は、 $V_{CAP}$  コンデンサから供給される電力で起動されます。

注: コンデンサが  $V_{CAP}$  ピンに接続されていない場合、9 ページの「AutoStore の防止」に指定されているソフトシーケンスを使って AutoStore を無効にする必要があります。 $V_{CAP}$  ピンに接続しているコンデンサがない状態で AutoStore が有効になつた場合、デバイスは STORE 处理を完了するために十分な充電量がないまま AutoStore 处理を実行しようとします。これにより、nvSRAM 内に格納されたデータが破壊されます。

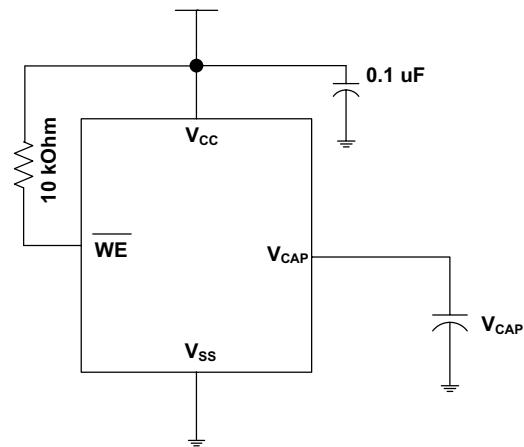

図 2. AutoStore モード

図 2 に、自動的な STORE 处理用のストレージ コンデンサ ( $V_{CAP}$ ) の適切な接続方法を示します。 $V_{CAP}$  の容量については、19 ページの「DC 電気的特性」を参照してください。 $V_{CAP}$  ピンの電圧は、内蔵レギュレータによって  $V_{CC}$  に送られます。電源投入時にアクティブにならないようにするために、WE をプルアップ抵抗に接続する必要があります。このプルアップ抵抗は、電源投入時に WE 信号がトライステート状態にある場合のみ有効です。多くの MPU が電源投入時にそれらの制御信号をトライステートにします。プルアップ抵抗を使用する場合には確認してください。nvSRAM が電源投入時の RECALL から復帰する時、MPU がアクティブであるか、MPU のリセットが終了するまで WE をアクティブでない状態に保つ必要があります。

不要な不揮発性 STORE 处理を低減するために、最後の STORE か RECALL サイクルの実行後、少なくとも 1 回の書き込み処理が行われない限り、AutoStore およびハードウェア STORE 处理は無視されます。ソフトウェアにより起動された STORE サイクルは、書き込み処理が行われたかどうかに関係なく実行されます。

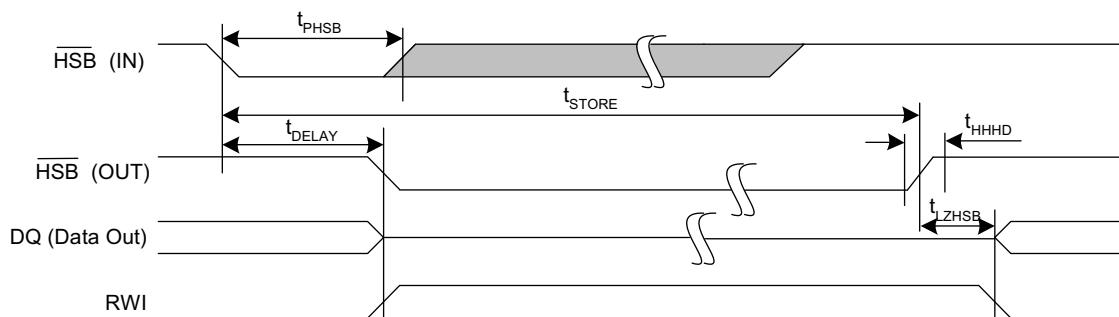

### ハードウェア STORE (HSB) 处理

CY14B108K/CY14B108M には、STORE 处理を制御し応答するための HSB ピンがあります。HSB ピンは、ハードウェア STORE サイクルの要求に使用されます。HSB ピンが LOW にされると、CY14B108K/CY14B108M は  $t_{DELAY}$  の後、条件に従って STORE 处理を開始します。実際の STORE サイクルは、最後の STORE または RECALL サイクル以降、SRAM への書き込みが実行された場合にのみ開始します。HSB ピンは、STORE 处理 (任意の手段で開始) 中にはビジー状態を示すために内部で LOW に駆動されるオープンドレインドライバー (チップ内部の 100kΩ の弱いプルアップ抵抗) としても動作します。

**注:**各ハードウェアおよびソフトウェア STORE 处理の後、HSB は標準出力 HIGH 電流で短時間 ( $t_{HHHD}$ ) HIGH に駆動され、その後  $100\text{k}\Omega$  の内部プルアップ抵抗により HIGH 状態を継続します。

SRAM 書き込み処理は HSB が (任意の手段で) LOW にされた時に実行中であれば、STORE 处理が開始される前に  $t_{DELAY}$  以内に終了します。しかし、HSB が LOW になった後に要求された SRAM 書き込みサイクルは、HSB が HIGH に戻るまで禁止されます。書き込みラッチがセットされていない場合、HSB は CY14B108K/CY14B108M によって LOW に駆動されることはありません。しかし、SRAM のすべての読み出しと書き込みサイクルは、MPU または他の外部ソースにより HSB が HIGH 状態に戻るまで禁止されます。

STORE 处理中には、開始方法に関係なく、CY14B108K / CY14B108M は HSB ピンを LOW に駆動し続け、STORE 处理が完了した時にのみ解除します。STORE 处理が完了すると、nvSRAM メモリアクセスは HSB ピン が HIGH 状態に戻ってから  $t_{LZHSB}$  の間は禁止されます。HSB ピンは使用しない場合、開放にしてください。

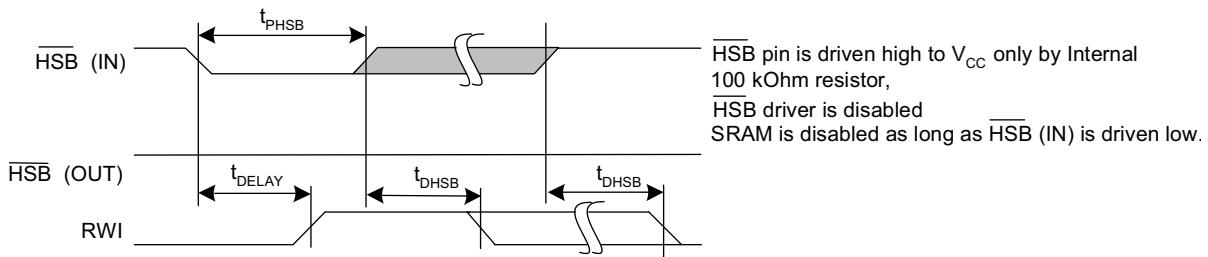

### ハードウェア RECALL (電源投入)

電源投入時または低電圧状態 ( $V_{CC} < V_{SWITCH}$ ) の後は、内部的に RECALL 要求がラッチされます。 $V_{CC}$  が電源投入時に再度  $V_{SWITCH}$  を超えた場合、RECALL サイクルが自動的に開始され、完了するのに  $t_{HRECALL}$  を要します。この間、HSB ピンは HSB ドライバーによって LOW に駆動され、nvSRAM へのすべての読み書きは禁止されます。

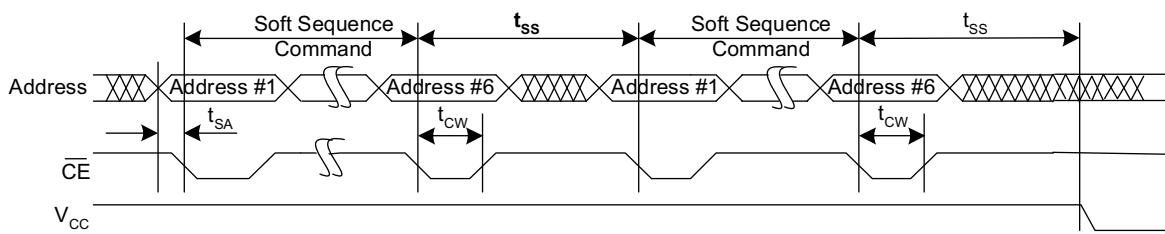

### ソフトウェア STORE

データは、ソフトウェア アドレス シーケンスによって SRAM から不揮発性メモリに転送されます。CY14B108K/CY14B108M のソフトウェア STORE サイクルは、CE または OE に制御された読み出し処理を、6 つの特定のアドレスから正しい順番で実行することにより開始されます。STORE サイクルの間、先ず前の不揮発性データの消去が実行され、次に不揮発性素子のプログラムが実行されます。STORE サイクルが開始されると、それ以降の入出力は STORE サイクルが完了するまで無効になります。

特定のアドレスからの読み出しシーケンスが STORE 開始用に使われるため、他の読み書きアクセスがシーケンスに干渉しないこと、あるいはシーケンスが中止され STORE や RECALL が実行されないことが重要です。

ソフトウェア STORE サイクルを開始するために、次の読み出しシーケンスを実行してください。

- アドレス 0x4E38 の読み出し - 有効 READ

- アドレス 0xB1C7 の読み出し - 有効 READ

- アドレス 0x83E0 の読み出し - 有効 READ

- アドレス 0x7C1F の読み出し - 有効 READ

- アドレス 0x703F の読み出し - 有効 READ

- アドレス 0x8FC0 の読み出し - STORE サイクルの開始

ソフトウェア シーケンスは CE に制御された読み出しあり OE に制御された読み出しを伴いクロック供給され、全ての 6 つの READ シーケンスの間 WE を HIGH 状態に維持することが必要です。シーケンスの6番目のアドレスが入力された後、STORE サイクルは開始され、チップが無効になります。HSB は LOW に駆動されます。 $t_{STORE}$  サイクル時間が経過した後、SRAM は読み書き処理を再び実行します。

### ソフトウェア RECALL

データは、ソフトウェア アドレス シーケンスによって不揮発性メモリから SRAM に転送されます。ソフトウェア RECALL サイクルは、ソフトウェア STORE の開始と同様の方法で、読み出し処理のシーケンスによって開始されます。ソフトウェア RECALL サイクルを開始するには、CE または OE に制御された読み出し処理を下記の順序で実行します。

- 読み出しアドレス 0x4E38 の有効な READ

- アドレス 0xB1C7 の読み出し - 有効 READ

- アドレス 0x83E0 の読み出し - 有効 READ

- アドレス 0x7C1F の読み出し - 有効 READ

- アドレス 0x703F の読み出し - 有効 READ

- アドレス 0x4C63 の読み出し、RECALL サイクルの開始

内部的に、RECALL は 2 段階の手順を踏みます。まず、SRAM データがクリアされます。次に、不揮発性情報が SRAM セルに転送されます。 $t_{RECALL}$  サイクル時間が完了した後、SRAM は再度読み書き処理が有効になります。RECALL 処理では、不揮発性要素内のデータが変更されません。

**表 1. モード選択**

| <b><u>CE</u></b> | <b><u>WE</u></b> | <b><u>OE</u></b> | <b><u>BHE</u>、<u>BLE</u><sup>[6]</sup></b> | <b><u>A<sub>15</sub> ~ A<sub>0</sub></u><sup>[7]</sup></b> | <b>モード</b>                                                                                      | <b>I/O</b>                                                      | <b>電源</b>                                               |

|------------------|------------------|------------------|--------------------------------------------|------------------------------------------------------------|-------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|---------------------------------------------------------|

| H                | X                | X                | X                                          | X                                                          | 未選択                                                                                             | 出力 High Z                                                       | スタンバイ                                                   |

| L                | H                | L                | —                                          | X                                                          | SRAM 読み出し                                                                                       | 出力データ                                                           | アクティブ                                                   |

| L                | —                | X                | L                                          | X                                                          | SRAM 書き込み                                                                                       | 入力データ                                                           | アクティブ                                                   |

| L                | H                | L                | X                                          | 0x4E38<br>0xB1C7<br>0x83E0<br>0x7C1F<br>0x703F<br>0x8B45   | SRAM 読み出し<br>SRAM 読み出し<br>SRAM 読み出し<br>SRAM 読み出し<br>SRAM 読み出し<br>SRAM 読み出し<br>AutoStore ディスエーブル | 出力データ<br>データ出力<br>データ出力<br>データ出力<br>データ出力<br>データ出力<br>出力データ     | アクティブ <sup>[8]</sup>                                    |

| L                | H                | L                | X                                          | 0x4E38<br>0xB1C7<br>0x83E0<br>0x7C1F<br>0x703F<br>0x4B46   | SRAM 読み出し<br>SRAM 読み出し<br>SRAM 読み出し<br>SRAM 読み出し<br>SRAM 読み出し<br>SRAM 読み出し<br>AutoStore イネーブル   | 出力データ<br>データ出力<br>データ出力<br>データ出力<br>データ出力<br>データ出力<br>出力データ     | アクティブ <sup>[8]</sup>                                    |

| L                | H                | L                | X                                          | 0x4E38<br>0xB1C7<br>0x83E0<br>0x7C1F<br>0x703F<br>0x8FC0   | SRAM 読み出し<br>SRAM 読み出し<br>SRAM 読み出し<br>SRAM 読み出し<br>SRAM 読み出し<br>SRAM 読み出し<br>不揮発性 STORE        | 出力データ<br>データ出力<br>データ出力<br>データ出力<br>データ出力<br>出力データ<br>出力 High Z | アクティブ <sup>[8]</sup><br>I <sub>CC2</sub> <sup>[8]</sup> |

| L                | H                | L                | X                                          | 0x4E38<br>0xB1C7<br>0x83E0<br>0x7C1F<br>0x703F<br>0x4C63   | SRAM 読み出し<br>SRAM 読み出し<br>SRAM 読み出し<br>SRAM 読み出し<br>SRAM 読み出し<br>SRAM 読み出し<br>不揮発性 RECALL       | データ出力<br>データ出力<br>データ出力<br>データ出力<br>データ出力<br>出力データ<br>出力 High Z | アクティブ <sup>[8]</sup>                                    |

**エラッタ :** AutoStore ディスエーブル機能はこのデバイスで正常に動作しません。詳細については、33 ページの「エラッタ」を参照してください。

**注**

6. BHE と BLE は、×16 コンフィギュレーションでのみ使用できます。

7. CY14B108K に 20 本のアドレス線がありますが (CY14B108M は 19 本のアドレス線)、その内 13 本のアドレス線 (A<sub>14</sub> ~ A<sub>2</sub>) のみがソフトウェア モードの制御に使われます。残りのアドレス線は「ドントケア」です。

8. 6 つの連続アドレス位置は指定された順番でなければなりません。WE は不揮発性サイクルを可能にするため、全ての 6 つのサイクル中は HIGH でなければなりません。

## AutoStore の防止

AutoStore 機能は AutoStore ディスエーブル シーケンスを開始することで無効にされます。読み出し処理のシーケンスは、ソフトウェア STORE の開始と同様の方法で実行されます。AutoStore ディスエーブル シーケンスを開始するために、CE または OE に制御された読み出し処理を以下の順番で実行してください。

1. アドレス 0x4E38 の読み出し - 有効 READ

2. アドレス 0xB1C7 の読み出し - 有効 READ

3. アドレス 0x83E0 の読み出し - 有効 READ

4. アドレス 0x7C1F の読み出し - 有効 READ

5. アドレス 0x703F の読み出し - 有効 READ

6. アドレス 0x8B45 の読み出し - AutoStore を無効

**注: エラッタ:** AutoStore ディスエーブル機能はデバイスで正常に動きません。詳細については、[33 ページの「エラッタ」](#)を参照してください。

AutoStore は、AutoStore イネーブル シーケンスを開始することによって再度有効にされます。読み出し処理のシーケンスは、ソフトウェア RECALL の開始と同様の方法で実行されます。AutoStore 有効シーケンスを開始するには、CE または OE に制御された読み出し処理を下記の順序で実行しなければなりません。

1. アドレス 0x4E38 の読み出し - 有効 READ

2. アドレス 0xB1C7 の読み出し - 有効 READ

3. アドレス 0x83E0 の読み出し - 有効 READ

4. アドレス 0x7C1F の読み出し - 有効 READ

5. アドレス 0x703F の読み出し - 有効 READ

6. アドレス 0x4B46 の読み出し - AutoStore を有効

AutoStore 機能が無効にされるか、または再度有効にされた場合、手動 STORE 処理（ハードウェアまたはソフトウェア）を行い、その後の電源オフ サイクルの間、AutoStore 状態を持続する必要があります。工場出荷時 AutoStore は有効になっており、すべてのセルに 0x00 と書き込まれています。

## データ保護

CY14B108K/CY14B108M は、外部から実行された STORE および書き込み処理をすべて禁止することにより、低電圧状態の間での破損からデータを保護します。低電圧状態は  $V_{CC}$  が  $V_{SWITCH}$  を下回ると検出されます。CY14B108K/CY14B108M が電源投入時に書き込みモードの場合 ( $\overline{CE}$  と  $\overline{WE}$  の両方が LOW)、RECALL または STORE 後、書き込みは  $t_{LZHSB}$  (HSB から出力有効まで) の後、SRAM が有効になるまで禁止されます。これは電源投入時や電圧低下状態の間に不注意による書き込みを保護します。

## リアル タイム クロックの動作

### nvTime の動作

CY14B108K/CY14B108M には、クロック、アラーム、ウォッチドッグ、割り込み、および制御機能を備えている内部レジスタがあります。RTC レジスタは SRAM 末尾の 16 アドレス位置を占めます。クロックとタイマー情報レジスタの内部ダブルバッファリングは、読み出しままたは書き込み処理時の過渡的な内部クロックデータへのアクセスを防ぎます。ダブルバッファリングはまた、クロックデータにアクセスする際に通常のタイミングカウントの中斷を、または内部クロックのクロック精度の劣化を回避します。クロックおよびアラームレジスタは BCD 形式でデータを格納します。

RTC 機能は、次の節で、CY14B108K に関連して説明されています。同じ説明が、RTC レジスタのアドレスを除いて CY14B108M にも適用されます。RTC レジスタアドレスの範囲は、CY14B108K では 0xFFFF0 から 0xFFFF まで、CY14B108M では 0x7FFF0 から 0x7FFF までです。レジスタマップの詳細については、[15 ページの表 3](#) と [16 ページの表 4](#) を参照してください。

### クロックの動作

クロックレジスタは、1 秒単位で 9,999 年までの時間を維持します。時間は任意のカレンダー時間に設定することができます。クロックは曜日と月の日、うるう年、世紀の変遷を自動的に刻みます。クロック機能には 8 つの専用レジスタがあります。これらは書き込みサイクルで時間を設定し、読み出しそうに時間で時間を読み出すのに使われます。これらのレジスタには BCD 形式で時間を表す値が含まれています。「0」として定義されたビットは、現在使用されておらず、将来使用するために予約されています。

### クロックの読み出し

ダブルバッファ RTC レジスタの構造は、クロックから不正なデータを読み出す可能性を減らします。CY14B108K 時間保持レジスタへの内部更新は、遷移中のデータ読み出しを防止するためにクロックデータを読み出す前に、読み出しひつ「R」(0xFFFF0 にあるフラグレジスタ内) が「1」にセットされると、停止されます。レジスタの更新停止は、クロックの精度に影響を与えません。

RTC デバイスの読み出しシーケンスが開始されると、ユーザーの時間保持レジスタの更新が停止し、「0」が読み出しひつ「R」(0xFFFF0 にあるフラグレジスタ内) に書き込まれるまで再起動しません。読み出しシーケンスの終了後、すべての RTC レジスタが、20ms 以内に同時に更新されます。

### クロックの時刻設定

書き込みビット「W」(0xFFFF0 にあるフラグレジスタ内) が 1 にセットされると、RTC デバイスへの書き込みアクセスは、時間保持レジスタの更新を停止し、時間の設定を可能にします。次に、正しい曜日、日付、および時間がレジスタに書き込まれます。正しい形式は、24 時間 BCD 形式です。書き込まれた時間は、「基準時刻」と呼ばれます。この値は不揮発性レジスタに格納され、現時点の時間の計算に使用されます。「0」を書き込むことで書き込みビット「W」がクリアされると、時間管理レジスタの値は実際のクロックカウンターに転送されます。その後、クロックは通常の動作を再開します。

時間管理レジスタに書き込まれた時間が正しい BCD 形式でない場合は、RTC レジスタの各無効ビットが 0xF までカウントを継続してから 0x0 にロールオーバーし、その後、RTC は通常の動作を再開します。

注：「W」ビットが「0」にセットされた後、時間管理、アラーム、校正および割り込みレジスタに書き込まれる値は  $t_{RTC}$  時間に RTC 時間管理カウンターに転送されます。これらのカウン

ターの値は、ソフトウェア／ハードウェア STORE または AutoStore 処理を起動させることにより、不揮発性メモリに保存する必要があります。AutoStore ディスエーブルモードでは、変更が正しく記録されるように、RTC レジスタへの書き込みを行なながら、 $t_{RTC}$  時間の後に、STORE 処理を実行してください。

### バックアップ電源

CY14B108K の RTC は、永続的電源供給動作に設計されています。 $V_{RTCCap}$  または  $V_{RTCbat}$  ピンは、バックアップ電源用にコンデンサかバッテリーが選択されるかに応じて接続されます。主電源 ( $V_{CC}$ ) が異常になり、 $V_{SWITCH}$  を下回ると、デバイスは電源をバックアップ電源に切り替えます。

クロック発振子の消費電流は非常に小さいため、バックアップ電源によるバックアップ時間が長くなります。主電源を喪失した状態のクロック動作にかかるわらず、nvSRAM に格納されたデータは電源が失われた時に不揮発性素子に格納されているため、失われることはありません。

バックアップ処理中に、CY14B108K は室温で  $0.35\mu A$  (Typ) を消費します。ユーザーは、用途に応じてコンデンサかバッテリーの値を選択する必要があります。

注：バッテリーが  $V_{CC}$  に接続する前に  $V_{RTCCbat}$  ピンに接続すると、チップは高い  $I_{BAK}$  電流が流れます。発振子が無効の場合でも、この事象は発生します。バッテリーの持続時間を長くするため、バッテリーを  $V_{RTCCbat}$  ピンに接続する前に  $V_{CC}$  に接続する必要があります。

最大電流仕様に基づくバックアップ時間の値を、次の表 2 に示します。公称バックアップ時間は約 2 倍長くなります。

表 2. RTC のバックアップ時間

| コンデンサの値 | バックアップ時間 |

|---------|----------|

| 0.1F    | 72 時間    |

| 0.47F   | 14 日     |

| 1.0F    | 30 日     |

コンデンサを使用すると、システムに電源を投入する度にバックアップ電源が充電されるという明白な利点があります。バッテリーを使用する場合は、3V のリチウムバッテリーをお奨めします。CY14B108K は、主電源を喪失した場合に、バッテリーからのみ電流を供給されます。ただしバッテリーは、CY14B108K によって常に充電されるわけではありません。バッテリー容量は、システムのライフサイクルを通して、必要なダウンタイムの合計予想時間を考慮して選択する必要があります。

### 発振器の起動と停止

0xFFFF8 番地にある校正レジスタの OSCEN ビットは、発振器の起動または停止を制御します。このビットは不揮発性であり、イネーブル状態 (0 に設定されている状態) でお客様に出荷されます。システムが保存状態にある場合にバッテリーを長持ちさせるには、OSCEN を「1」に設定する必要があります。これにより発振回路が停止し、バッテリー寿命が伸びます。OSCEN ビットが無効から有効に切り替わる場合は、発振子が開始されるのに約 1 秒 (最大 2 秒) かかります。

システム電源がオフの間に、バックアップ電源の電圧 ( $V_{RTCCap}$  または  $V_{RTCbat}$ ) が、それぞれの最小レベルを下回ると、発振器が動作しなくなることがあります。CY14B108K には、システム電源が回復した時に、発振器の異常を検出する能力があります。これは、アドレス 0xFFFF0 にあるフラグレジスタの発振器異常フラグ (OSCF) に記録されます。デバイスに電流が供給されている ( $V_{CC}$  が  $V_{SWITCH}$  を上回る) 場合、「イネーブル」状態を確認するために、OSCEN ビットをチェックします。OSCEN ビットが有効になり、発振子が最初の 5ms 以内に起動

しない場合は、OSCF ビットを「1」にセットします。システムはこの条件を確認して、フラグをクリアするために「0」を書き込む必要があります。

OSCF フラグ ビットを設定することに加え、時間レジスタは時間保持レジスタに書き込まれる最後の値である「基準時刻」にリセットされることにも注意してください。制御または校正レジスタと OSCEN ビットは、「発振子異常」の状態による影響を受けません。

OSCF の値は、時間レジスタが最初に書き込まれた際に、「0」にリセットする必要があります。これは、システムが最初の電源投入時に設定している可能性があり、このビットの状態を初期化します。

OSCF をリセットするには、書き込みビット「W」(0xFFFFF0 にあるフラグレジスタ内)を「1」に設定し、フラグレジスタへの書き込みを有効にします。書き込みを無効にするには、OSCF に「0」を書き込んでから書き込みビットを「0」にリセットします。

## クロックの校正

RTC は、32.768kHz の公称周波数を持つクオーツ水晶発振子によって駆動されます。クロック精度は、水晶と校正の品質に依存します。市販されている水晶発振子は通常、+20ppm ~ ±35ppm の誤差を持ちます。しかし、CY14B108K は 25°C で +1/-2ppm まで精度を向上させる校正回路を採用しています。これは、月当たりの誤差が +2.5 ~ -5 秒であることを意味します。

校正回路は、この精度を達成するため、発振器分周回路からカウントを加算または減算します。抑制 (減算、マイナス校正) または分割 (加算、プラス校正) されるパルスの数は、0xFFFFF8 アドレスにある校正レジスタ内の 5 つの校正ビットにロードされた値に依存します。校正ビットは、校正レジスタの 5 つの下位ビットを占めます。これらのビットは、2 進数形式で「0」と 31 間の任意の値を表すために設定されます。ビット D5 は符号ビットで、「1」がプラス校正、「0」がマイナス校正を示します。カウントを加算するとクロックが速くなり、減算するとクロックが遅くなります。2 進数の「1」がレジスタにロードされると、符号に応じて発振子の誤差に 4.068 または -2.034ppm のオフセット調整を行います。

校正は、64 分サイクル内で発生します。サイクルの最初の 62 分は、毎分には、128 の発振子サイクルにより 1 秒短縮される、あるいは 256 の発振子サイクルにより 1 秒延長される可能性があります。二進数の「1」がレジスタにロードされると、64 分サイクルの最初の 2 分のみが変更されます。2 進数の 6 がロードされると、最初の 12 分が変更され、同じパターンが続きます。したがって、各校正ステップは、実際の 125,829,120 回の発振器サイクルごとに、512 を加算または 256 を減算する効果があります。これは、校正レジスタの校正ステップごとに、4.068 または -2.034ppm の調整を行うことを意味します。

必要な校正を決定するには、フラグレジスタ (0xFFFFF0) の CAL ビットを「1」にセットする必要があります。これは、INT ピンを 512Hz の公称周波数でトグルさせます。512Hz から測定されるすべての偏差は、必要な補正の程度と方向を示します。たとえば、512.01024Hz の測定結果は、+20ppm の誤差を示します。したがって、-10 (001010b) の 10 進値を校正レジスタにロードし、この誤差を補正する必要があります。

**注：**校正レジスタを設定や変更しても、テスト出力周波数には影響しません。

CAL をセットまたはクリアするには、書き込みビット「W」(0xFFFFF0 にあるフラグレジスタ内)を「1」にセットし、フラグレジスタへの書き込みを有効にします。CAL に値を書き込み、次に書き込みビットを「0」にリセットし、書き込みを無効にします。

## アラーム

アラーム機能は、ユーザーがプログラムしたアラームの時間と日付 (レジスタ 0xFFFF1-5 に格納されている) の値を、該当する曜日と日付の値と比較します。一致すると、アラーム内部フ

ラグ (AF) が設定され、アラーム割り込みイネーブル (AIE) ビットが設定されている場合は、割り込みが INT ピンで生成されます。

日付、時間、分、秒という、4 つのアラームのマッチ フィールドがあります。これらの各フィールドは、フィールドがアラームのマッチ論理で使用されているかどうかを決定するために使用されるマッチ ビットを持っています。マッチ ビットが「0」にセットされている場合は、対応するフィールドがマッチ プロセスで使用されていることを示します。マッチ ビットに応じて、アラームは、月に一度など特定の頻度で発生します。最小頻度は毎分 1 回です。マッチ ビットのいずれもを選択しない (すべて 1) 場合は、マッチが必要とされないため、アラームが無効になることを示します。すべてのマッチ ビット (すべて 0) を選択すると、正確な時間と日付のマッチが発生します。

アラーム イベントを検出するには、AF フラグを読み出すか、または INT ピンを監視するという 2 つの方法を使用します。0xFFFFF0 アドレスにあるフラグレジスタの AF フラグは、日付や時間のマッチが発生したことを示します。マッチが発生すると、AF ビットが「1」にセットされます。フラグレジスタを読み出すと、アラーム フラグ ビット (および他のすべて) がクリアされます。ハードウェア割り込みピンも、アラーム イベントを検出するために使用されることがあります。

アラームをセット、クリア、またはイネーブルするには、書き込みビット「W」(0xFFFFF0 にあるフラグレジスタ内)を「1」にセットし、アラーム レジスタへの書き込みを有効にします。アラームの値を書き込んだ後、「W」ビットを「0」にクリアし、変更を有効にします。

**注：**CY14B108K アラーム フラグと割り込みを適切に動作するため、秒のアラーム マッチビット (アラーム秒レジスタ 0xFFFFF2 内の「D7」ビット) を「0」にセットする必要があります。

## ウォッチドッグ タイマー

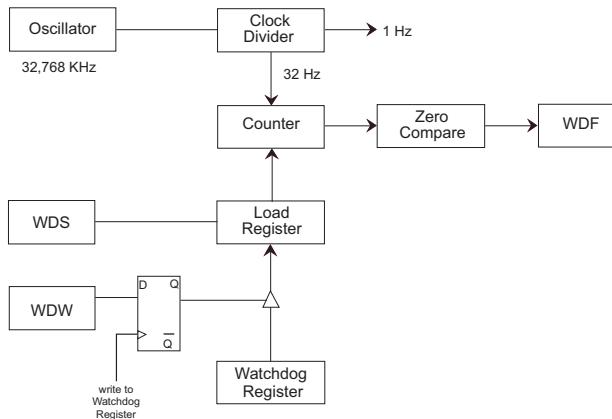

ウォッチドッグ タイマーは、水晶発振子から派生した 32Hz のクロック (31.25ms) を使用するフリーランニングのダウン カウンターです。発振子は、ウォッチドッグ タイマーに連続してクロックを供給する必要があります。ウォッチドッグ タイマー レジスタにロードされた値からカウントダウンを開始します。

タイマは、ロード可能なレジスタとフリーランニング カウンターで構成されています。電源投入時に、レジスタ 0xFFFFF7 のウォッチドッグ タイムアウト値が、カウンターのロード レジスタにロードされます。カウントは、電源投入時に開始し、ウォッチドッグストローブ (WDS) ビットが「1」にセットされるたびに、ロード可能な値から再起動します。カウンターは、「0」の終端値と比較されます。カウンターがこの値に達すると、内部フラグと任意の割り込み出力が発生します。カウンターが「0」に到達する前に WDS ビットを「1」にセットすることで、タイムアウト割り込みを防ぐことができます。これにより、カウンターにウォッチドッグ タイムアウト値がリロードされ、再起動されます。カウンターが終点の値に達する前に WDS ビットをセットする限り、割り込みと WDT フラグは発生しません。

ウォッチドッグ書き込みビットを「0」にセットすることで、新しいタイムアウト値が書き込まれます。WDW が「0」の場合、ウォッチドッグ タイムアウト値ビット D5 ~ D0 への新しい値の書き込みが有効になり、タイムアウト値が変更されます。WDW が「1」の場合、D5 ~ D0 ビットへの書き込みは無視されます。WDW 機能は、ウォッチドッグ タイマー値が変更されるかをかかわらず、WDS ビットをセットできるようにします。ウォッチドッグ タイマーの論理図を **図 3** に示します。ウォッチドッグ タイムアウト値を「0」に設定すると、ウォッチドッグ機能が無効になることに注意してください。

ウォッチドッグ タイマーの出力は、ウォッチドッグのタイムアウトが許可されている場合にセットされるフラグ ビット WDF です。割り込みレジスタのウォッチドッグ割り込みイネーブル

(WIE) ビットがセットされている場合は、INT ピンのハードウェア割り込みも、ウォッチドッグ タイムアウトで生成されます。ユーザーがフラグ レジスタを読み出す時に、フラグとハードウェア割り込みの両方がクリアされます。

図 3. ウォッチドッグ タイマーのブロック図

## 電源モニター

CY14B108Kは、電源異常割り込み機能を備えた電力管理スキームを提供しています。また、クロック用のバックアップ電源への内部切り替えを制御し、低  $V_{CC}$  アクセスからメモリを保護します。電源モニターは、 $V_{CC}$  電圧を  $V_{SWITCH}$  閾値と比較する内部バンドギャップ参照回路に基づきます。

6 ページの「AutoStore 処理」で説明したように、 $V_{CC}$  が電源切断時に  $V_{SWITCH}$  に達すると、データ STORE 処理が SRAM から不揮発性素子に向けて開始され、最後の SRAM データ状態を確保します。また、電源は  $V_{CC}$  からバックアップ電源（バッテリーまたはコンデンサ）に切り替えられて、RTC 発振器を稼動します。

バックアップ電源から動作している場合、nvSRAM への読み書き処理が抑制され、RTC 機能が利用できなくなります。RTC クロックは、バックグラウンドで処理を継続します。更新された RTC 時間管理レジスタのデータは、 $V_{CC}$  がデバイスに復旧された後に利用できるようになります（25 ページの「AutoStore / 電源投入時の RECALL」を参照してください）。

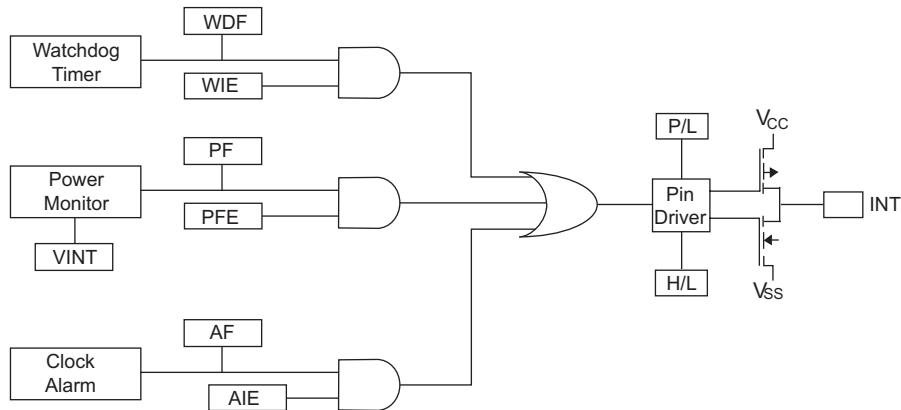

## 割り込み

CY14B108Kは、フラグ レジスタ、割り込みレジスタ、およびマイクロ コントローラへの割り込み信号を送ることができる割り込みロジックを持っています。割り込みには、ウォッチドッグ タイマー、電源モニター、アラーム タイマーという 3 種類の可能なソースがあります。それぞれは、割り込みレジスタ（0x1FFFF6）において適切な設定を実施することによって、INT ピンを駆動するために独立して有効にできます。さらに、ホスト プロセッサが割り込みの原因を判別するために使用するフラグ レジスタ（0xFFFF0）内のフラグ ビットを持っています。INT ピンのドライバは、割り込みが発生した時にその動作を指示する 2 つのビットを持っています。

割り込みは、両方のフラグが 3 種類のソースのいずれかによって立てられた場合、および割り込みレジスタ内の該当する割り込みイネーブル ビットが有効になった（「1」にセットされた）場合にのみ発生します。割り込みソースがアクティブになった後、H/L と P/L の 2 つのプログラマブル ビットは INT ピン上の出力ピン ドライバーの動作を決定します。これらの 2 ビットは割り込みレジスタにあり、INT ピンからレベル モードまたはパルス モードの出力を駆動するために使用できます。パルス モードでは、パルス幅が内部で約 200ms に固定されます。このモー

ドは、ホストマイクロコントローラをリセットするために用意されています。レベル モードでは、フラグ レジスタがユーザーによって読み出されるまで、ピンはアクティブ 極性になります。このモードは、ホストマイクロコントローラへの割り込みとして使用されます。制御ビットについては、次の節で説明します。

割り込みは、システムが通常の電源モードで動作する時にのみ生成され、バックアップ電源モードで実行されている時にはトリガされません。

注：CY14B108K は、パワーアップ RECALL シーケンスが完了した後でのみ有効な割り込みを生成します。INT ピンの全イベントは、電源投入後、 $t_{HRECALL}$  中に無視される必要があります。

## 割り込みレジスタ

**ウォッチドッグ割り込みイネーブル (WIE):** WIE を「1」にセットした場合、ウォッチドッグ タイムアウトが発生すると、ウォッチドッグ タイマーは INT ピンと内部フラグを駆動します。WIE を「0」にセットした場合、ウォッチドッグ タイマーはフラグ レジスタの WDF フラグにのみ影響します。

**アラーム割り込みイネーブル (AIE):** 「1」に設定すると、アラームの一一致により、INT ピンと内部フラグが駆動されます。AIE を「0」にクリアすると、アラームの一一致は、AF フラグ レジスタにのみ影響します。

**電源異常割り込みイネーブル (PFE):** PFE を「1」にセットした場合、電源異常モニターはピンと内部フラグを駆動します。PFE を「0」にセットした場合、電源異常モニターはフラグ レジスタの PF フラグにのみ影響します。

**HIGH/LOW (H/L):** 「1」に設定すると、INT ピンがアクティブ HIGH になり、ドライバ モードがプッシュ プルになります。INT ピンは、 $V_{CC}$  が  $V_{SWITCH}$  を上回る場合にのみ HIGH に駆動されます。「0」に設定すると、INT ピンがアクティブ LOW になり、ドライバ モードがオープン ドレインになります。アクティブ LOW モードで割り込みを使用している間、INT ピンは  $10k\Omega$  の抵抗を介して  $V_{cc}$  にプルアップする必要があります。

**パルス / ベル (P/L):** 「1」に設定し、割り込みが発生すると、INT ピンが約 200ms 間駆動されます。P/L が「0」に設定されると、INT ピンは、フラグ レジスタが読み出されるまで、HIGH または LOW (H/L) により決定される）に駆動されます。

有効な割り込みソースが INT ピンをアクティブにすると、外部ホストは、レジスタのフラグを読み込んで、原因を特定します。レジスタが読み出される際には、すべてのフラグがクリアされることに注意してください。INT ピンがレベル モードにプログラマされている場合、条件はクリアされ、INT ピンは非アクティブ状態に戻ります。ピンがパルス モードにプログラマされている場合、フラグを読み出すと、フラグとピンはクリアされます。フラグ レジスタが読み出されると、パルスは、その指定された期間を完了しません。INT ピンがホストのリセットとして使用されている場合は、フラグ レジスタはリセット時に読み込まれません。

## フラグ レジスタ

フラグ レジスタには、割り込みを生成するために使用される WDF、AF および PF の 3 つのフラグ ビットがあります。これらのフラグは、ウォッチドッグ タイムアウト、アラームマッチ、または電源異常モニターによってそれぞれ設定されます。フラグが設定されると、プロセッサはこのレジスタをポーリングするか、または割り込みを有効にすることができます。これらのフラグは、レジスタが読み出されると自動的にリセットされます。フラグ レジスタは、電源投入時に値 0x00 を使って自動的にロードされます (OSCF ビットを除く)。10 ページの「発振器の起動と停止」を参照）。

**図 4. 割り込みブロック図**

WDF - ウオッチドッグ タイマー

WIE - ウオッチドッグ割り込みイネーブル

PF - 電源異常フラグ

PFE - 電源異常イネーブル

AF - アラーム フラグ

AIE - アラーム割り込みイネーブル

P/L - パルス レベル

H/L - HIGH / LOW

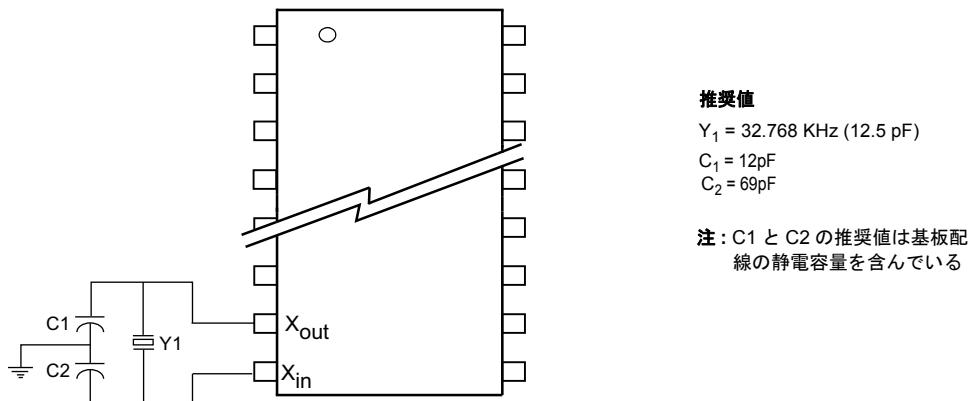

### RTC 外部コンポーネント

RTC は図 5 に示すように、外部の 32.768kHz 水晶発振子と  $C_1$ 、 $C_2$  の負荷容量を接続する必要があります。この図では推奨する RTC 外付け部品の値を示しています。負荷容量  $C_1$  と  $C_2$  は、プリント基板 (PCB) の寄生容量を含んでいます。PCB の寄生容量は、水晶発振子のパッド／ピンのランド パターン、 $X_{in}$ ／ $X_{out}$  のパッドおよび水晶発振子とデバイスピンを接続する銅配線に生じる静電容量を含んでいます。

**図 5. RTC の推奨コンポーネント コンフィギュレーション [9]**

**注**

9. 不揮発性スタティック ランダム アクセス メモリ (nvSRAM)、リアル タイム クロック (RTC) 設計ガイドラインおよびベスト プラクティスについては、アプリケーション ノート [AN61546](#) を参照してください。

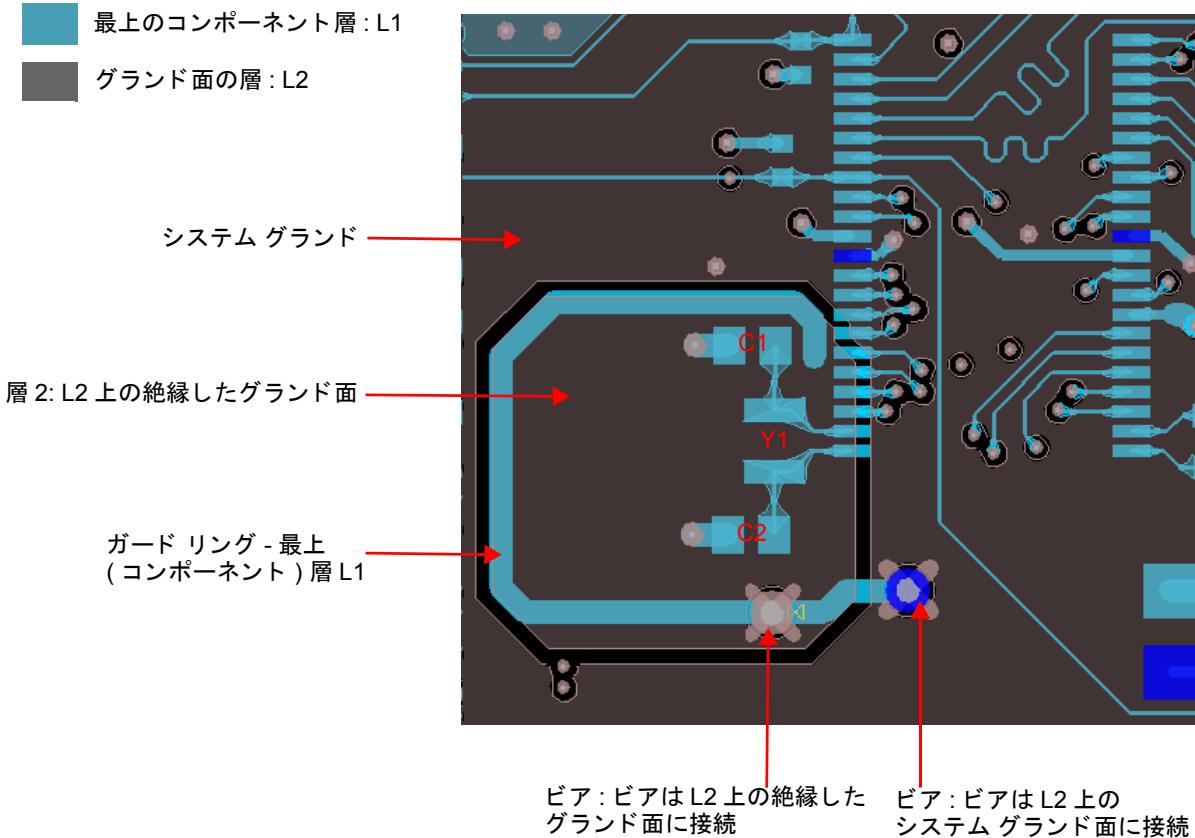

## RTC に関する PCB 設計上の注意事項

RTC 水晶発振子は、その水晶発振子ピンに高インピーダンスノードが付いた低電流の回路です。RTC の時間管理をする信号の電流が小さいので、基板上の水晶発振子の接続はノイズに非常に敏感です。そのため、RTC 回路を基板上の他の信号から分離する必要があります。

PCB 上の浮遊容量を最小限に抑えることも重要です。浮遊容量は水晶発振子の負荷容量に追加されるので、発振周波数エラーを引き起します。最適な RTC 性能を得るためにには、適切にバイパス処理を施した慎重なレイアウトをする必要があります。

### レイアウトに関する要件

基板レイアウトは、RTC 回路を配線する際に、次のガイドラインを順守しなければなりません（しかし、限定はされません）。次のガイドラインは、RTC 設計の最適な性能を得る手助けになります。

■ 水晶発振子をできる限り  $X_{in}$  と  $X_{out}$  ピンの近くに配置するのが重要です。水晶発振子と RTC 間の配線長を同じにし、配線長を可能な限り短くしてアンテナの長さを短くすることでノイズ カップリングを起こさないようにします。

- $X_{in}$  と  $X_{out}$  配線幅を 8mil 以下にします。配線幅が太いほど、配線容量が高くなります。これらの接着パッドと配線が大きいほど、隣接する信号からノイズが乗る可能性が高くなります。

- 水晶発振回路をガード リングで囲んで  $X_{in}$  と  $X_{out}$  信号を保護します。このガード リングは、近接している信号からのノイズ カップリングを防止します。

- RTC 配線の近くで何か他の高速信号を配線する時にも注意してください。水晶発振子が基板上で他の信号から分離されるほど、ノイズが水晶発振子に乗る可能性が低くなります。基板上で、 $X_{in}$ 、 $X_{out}$  配線と他の高速信号線の距離を 200mil 以上離してください。

- 同一PCB層で水晶コンポーネントの直下に信号を配線しないでください。

- PCB の別の信号層上を走っている配線からカップリングされる不要なノイズを防止するために、隣接した PCB 層および水晶発振回路の真下に、絶縁した銅のベタ面を造ってください。ローカル面は、同じ PCB 層上の隣接した面から少なくとも 40mil 分離する必要があります。ベタ面は RTC コンポーネントの近くに置いて、その周辺部はガード リング周辺に等しく保つ必要があります。図 6 は RTC 回路の推奨レイアウトを示しています。

図 6. RTC 用の推奨レイアウト

**表 3. RTC レジスタ マップ<sup>[10]</sup>**

| レジスタ      |           | BCD フォーマットのデータ <sup>[11]</sup> |              |              |                      |               |         |       |       | 機能／範囲                   |  |  |  |  |  |  |  |

|-----------|-----------|--------------------------------|--------------|--------------|----------------------|---------------|---------|-------|-------|-------------------------|--|--|--|--|--|--|--|

| CY14B108K | CY14B108M | D7                             | D6           | D5           | D4                   | D3            | D2      | D1    | D0    |                         |  |  |  |  |  |  |  |

| 0xFFFFF   | 0x3FFF0   | 年 (10 年の位)                     |              |              |                      | 年の 1 の位       |         |       |       | 年 : 00 ~ 99             |  |  |  |  |  |  |  |

| 0xFFFFE   | 0x7FFF    | 0                              | 0            | 0            | 月の 10 の位             | 月の 1 の位       |         |       |       | 月 : 01 ~ 12             |  |  |  |  |  |  |  |

| 0xFFFFD   | 0x7FFF    | 0                              | 0            | 日 (10 日の位)   |                      | 日の 1 の位       |         |       |       | 月の日 : 01 ~ 31           |  |  |  |  |  |  |  |

| 0xFFFFC   | 0x7FFF    | 0                              | 0            | 0            | 0                    | 0             | 曜日      |       |       | 週の日 : 01 ~ 07           |  |  |  |  |  |  |  |

| 0xFFFFB   | 0x7FFF    | 0                              | 0            | 時間 (10 時間の位) |                      | 時の 1 の位       |         |       |       | 時間 : 00 ~ 23            |  |  |  |  |  |  |  |

| 0xFFFFA   | 0x7FFF    | 0                              | 分 (10 分の位)   |              |                      | 分の 1 の位       |         |       |       | 分 : 00 ~ 59             |  |  |  |  |  |  |  |

| 0xFFFF9   | 0x7FFF    | 0                              | 秒 (10 秒の位)   |              |                      | 秒の 1 の位       |         |       |       | 秒 : 00 ~ 59             |  |  |  |  |  |  |  |

| 0xFFFF8   | 0x7FFF8   | OSCEN (0)                      | 0            | 校正の符号 (0)    | 校正 (00000)           |               |         |       |       |                         |  |  |  |  |  |  |  |

| 0xFFFF7   | 0x7FFF7   | WDS (0)                        | WDW (0)      | WDT (000000) |                      |               |         |       |       | ウォッチドッグ <sup>[12]</sup> |  |  |  |  |  |  |  |

| 0xFFFF6   | 0x7FFF6   | WIE (0)                        | AIE (0)      | PFE (0)      | 0                    | H/L (1)       | P/L (0) | 0     | 0     | 割り込み <sup>[12]</sup>    |  |  |  |  |  |  |  |

| 0xFFFF5   | 0x7FFF5   | M (1)                          | 0            | アラーム日の 10 の位 |                      | アラーム日 (1 日の位) |         |       |       | アラーム、月の日 : 01 ~ 31      |  |  |  |  |  |  |  |

| 0xFFFF4   | 0x7FFF4   | M (1)                          | 0            | アラーム時の 10 の位 |                      | アラーム時の 1 の位   |         |       |       | アラーム、時間 : 00 ~ 23       |  |  |  |  |  |  |  |

| 0xFFFF3   | 0x7FFF3   | M (1)                          | アラーム分の 10 の位 |              |                      | アラーム分の 1 の位   |         |       |       | アラーム、分 : 00 ~ 59        |  |  |  |  |  |  |  |

| 0xFFFF2   | 0x7FFF2   | M (1)                          | アラーム秒の 10 の位 |              |                      | アラーム秒の 1 の位   |         |       |       | アラーム、秒 : 00 ~ 59        |  |  |  |  |  |  |  |

| 0xFFFF1   | 0x7FFF1   | 世紀 (10 世紀の位)                   |              |              |                      | 世紀の 1 の位      |         |       |       | 世紀 : 00 ~ 99            |  |  |  |  |  |  |  |

| 0xFFFF0   | 0x7FFF0   | WDF                            | AF           | PF           | OSCF <sup>[13]</sup> | 0             | CAL (0) | W (0) | R (0) | フラグ <sup>[12]</sup>     |  |  |  |  |  |  |  |

**注**

10. RTC レジスタの上位バイト D<sub>15</sub> ~ D<sub>8</sub> (CY14B108M) は将来の使用のために予約されています。

11. () は、工場出荷時の値を示します。

12. これは、BCD 値ではなく、2 進値です。

13. ユーザーが OSCF フラグ ビットをリセットする場合は、フラグ レジスタは、t<sub>RTCp</sub> 時間の後に更新されます。

**表 4. レジスタ マップの詳細**

| レジスタ      |           | 説明                                                                                                                      |            |              |           |             |    |    |    |  |  |  |  |  |  |  |

|-----------|-----------|-------------------------------------------------------------------------------------------------------------------------|------------|--------------|-----------|-------------|----|----|----|--|--|--|--|--|--|--|

| CY14B108K | CY14B108M |                                                                                                                         |            |              |           |             |    |    |    |  |  |  |  |  |  |  |

| 0xFFFFF   | 0x3FFF0   | <b>時間管理 - 年</b>                                                                                                         |            |              |           |             |    |    |    |  |  |  |  |  |  |  |

|           |           | D7                                                                                                                      | D6         | D5           | D4        | D3          | D2 | D1 | D0 |  |  |  |  |  |  |  |

|           |           | 年 (10 年の位)                                                                                                              |            |              |           | 年 (1 年の位)   |    |    |    |  |  |  |  |  |  |  |

|           |           | 年の下位 2 枠の BCD 表記を格納。下位ニブル (4 ビット) は年の 1 の位の値を格納し、上位ニブル (4 ビット) は年の 10 の位の値を格納。それぞれのニブルは 0 ~ 9 の値を持っている。レジスタの範囲は 0 ~ 99  |            |              |           |             |    |    |    |  |  |  |  |  |  |  |

| 0xFFFFE   | 0x7FFFFE  | <b>時間管理 - 月</b>                                                                                                         |            |              |           |             |    |    |    |  |  |  |  |  |  |  |

|           |           | D7                                                                                                                      | D6         | D5           | D4        | D3          | D2 | D1 | D0 |  |  |  |  |  |  |  |

|           |           | 0                                                                                                                       | 0          | 0            | 月 (1ヶ月の位) | 月 (1ヶ月の位)   |    |    |    |  |  |  |  |  |  |  |

|           |           | 月の桁の BCD 表記を格納。下位ニブル (4 ビット) は、下位桁が含まれており、0 から 9 で動作する。上位ニブル (1 ビット) は、上位桁が含まれており、0 から 1 で動作する。レジスタの範囲は 1 ~ 12          |            |              |           |             |    |    |    |  |  |  |  |  |  |  |

| 0xFFFFD   | 0x7FFFFD  | <b>時間管理 - 日</b>                                                                                                         |            |              |           |             |    |    |    |  |  |  |  |  |  |  |

|           |           | D7                                                                                                                      | D6         | D5           | D4        | D3          | D2 | D1 | D0 |  |  |  |  |  |  |  |

|           |           | 0                                                                                                                       | 0          | 日 (10 日の位)   | 日 (1 日の位) |             |    |    |    |  |  |  |  |  |  |  |

|           |           | 日の桁の BCD 表記を格納。下位ニブル (4 ビット) は下位桁を格納し、0 ~ 9 の値を持つ。上位ニブル (2 ビット) は上位桁を格納し、0 ~ 3 の値を持つ。レジスタの範囲は 1 ~ 31。うるう年は自動的に調整される。    |            |              |           |             |    |    |    |  |  |  |  |  |  |  |

| 0xFFFFC   | 0x7FFFC   | <b>時間管理 - 曜日</b>                                                                                                        |            |              |           |             |    |    |    |  |  |  |  |  |  |  |

|           |           | D7                                                                                                                      | D6         | D5           | D4        | D3          | D2 | D1 | D0 |  |  |  |  |  |  |  |

|           |           | 0                                                                                                                       | 0          | 0            | 0         | 0           | 曜日 |    |    |  |  |  |  |  |  |  |

|           |           | 下位ニブル (3 ビット) は曜日に対応する値を格納。曜日は、1 から 7 までカウントした後、また 1 に戻るリング カウンターである。曜日は日付で統合されていないので、この値にユーザーの責任で曜日の意味を割り当てる           |            |              |           |             |    |    |    |  |  |  |  |  |  |  |

| 0xFFFFB   | 0x7FFFFB  | <b>時間管理 - 時間</b>                                                                                                        |            |              |           |             |    |    |    |  |  |  |  |  |  |  |

|           |           | D7                                                                                                                      | D6         | D5           | D4        | D3          | D2 | D1 | D0 |  |  |  |  |  |  |  |

|           |           | 0                                                                                                                       | 0          | 時間 (10 時間の位) |           | 時間 (1 時間の位) |    |    |    |  |  |  |  |  |  |  |

|           |           | 24 時間形式での時の値の BCD 表記を格納。下位ニブル (4 ビット) は、下位桁が含まれており、0 から 9 で動作する。上位ニブル (2 ビット) は、上位桁が含まれており、0 から 2 で動作する。レジスタの範囲は 1 ~ 23 |            |              |           |             |    |    |    |  |  |  |  |  |  |  |

| 0xFFFFA   | 0x7FFFFA  | <b>時間管理 - 分</b>                                                                                                         |            |              |           |             |    |    |    |  |  |  |  |  |  |  |

|           |           | D7                                                                                                                      | D6         | D5           | D4        | D3          | D2 | D1 | D0 |  |  |  |  |  |  |  |

|           |           | 0                                                                                                                       | 分 (10 分の位) |              |           | 分 (1 分の位)   |    |    |    |  |  |  |  |  |  |  |

|           |           | 分の値の BCD 表記を格納。下位ニブル (4 ビット) は、下位桁が含まれており、0 から 9 で動作する。上位ニブル (3 ビット) は、分の上位の桁が含まれており、0 から 5 で動作する。レジスタの範囲は 0 ~ 59       |            |              |           |             |    |    |    |  |  |  |  |  |  |  |

| 0xFFFF9   | 0x7FFF9   | <b>時間管理 - 秒</b>                                                                                                         |            |              |           |             |    |    |    |  |  |  |  |  |  |  |

|           |           | D7                                                                                                                      | D6         | D5           | D4        | D3          | D2 | D1 | D0 |  |  |  |  |  |  |  |

|           |           | 0                                                                                                                       | 秒 (10 秒の位) |              |           | 秒 (1 秒の位)   |    |    |    |  |  |  |  |  |  |  |

|           |           | 秒の BCD 値が含まれる。下位ニブル (4 ビット) は、下位桁が含まれており、0 から 9 で動作する。上位ニブル (3 ビット) は、上位桁が含まれており、0 から 5 で動作する。レジスタの範囲は 0 ~ 59           |            |              |           |             |    |    |    |  |  |  |  |  |  |  |

**表 4. レジスタ マップの詳細 ( 続き )**

| レジスタ                                   |                                                                                                                                                                                                                                               | 説明           |    |     |     |            |    |    |    |  |  |  |  |

|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|----|-----|-----|------------|----|----|----|--|--|--|--|

| CY14B108K                              | CY14B108M                                                                                                                                                                                                                                     |              |    |     |     |            |    |    |    |  |  |  |  |

| 0xFFFF8                                | 0x7FFF8                                                                                                                                                                                                                                       | 校正／制御        |    |     |     |            |    |    |    |  |  |  |  |

|                                        |                                                                                                                                                                                                                                               | D7           | D6 | D5  | D4  | D3         | D2 | D1 | D0 |  |  |  |  |

| OSCEN                                  | 0                                                                                                                                                                                                                                             | 校正符号         | 校正 |     |     |            |    |    |    |  |  |  |  |

| OSCEN                                  | 発振器イネーブル。「1」にセットすると、発振器が停止する。「0」にクリアすると、発振器が動作する。発振器を無効にすると、保持中のバッテリやコンデンサの電力を節約できる。                                                                                                                                                          |              |    |     |     |            |    |    |    |  |  |  |  |

| 校正符号                                   | タイムベースへの加算(1)かタイムベースからの減算(0)として校正調整を適用するかを判定                                                                                                                                                                                                  |              |    |     |     |            |    |    |    |  |  |  |  |

| 校正                                     | これらの5ビットは、クロックの校正を制御する。                                                                                                                                                                                                                       |              |    |     |     |            |    |    |    |  |  |  |  |

| 0xFFFF7                                | 0x7FFF7                                                                                                                                                                                                                                       | ウォッチドッグ タイマー |    |     |     |            |    |    |    |  |  |  |  |

|                                        |                                                                                                                                                                                                                                               | D7           | D6 | D5  | D4  | D3         | D2 | D1 | D0 |  |  |  |  |

| WDS                                    | WDW                                                                                                                                                                                                                                           | WDT          |    |     |     |            |    |    |    |  |  |  |  |

| WDS                                    | ウォッチドッグ ストローブ：このビットを「1」にセットすると、ウォッチドッグ タイマーが再起動。このビットを「0」にクリアしても何の影響もない。ウォッチドッグ タイマーをリセットした後、ビットは自動的にクリアされる。WDS ビットは書き込み専用。これを読み出すと常に「0」が返される                                                                                                 |              |    |     |     |            |    |    |    |  |  |  |  |

| WDW                                    | ウォッチドッグ書き込みイネーブル。このビットを「1」にセットすると、ウォッチドッグ タイムアウト値(D5 ~ D0)への全書き込みが無効になる。これにより、ユーザはタイムアウト値を変更することなく、ウォッチドッグ ストローブのビットを設定できる。このビットを0にクリアすると、次の書き込みサイクルが完了した際に、ビット D5 ~ D0 がウォッチドッグに書き込まれる。この機能の詳細は、 <a href="#">11 ページの「ウォッチドッグ タイマー」</a> で説明する |              |    |     |     |            |    |    |    |  |  |  |  |

| WDT                                    | ウォッチドッグ タイムアウト選択：ウォッチドッグ タイマーの間隔はこのレジスタの6ビットの値によって選択。それは32Hzのカウント(31.25ms)の乗数を表す。タイムアウト値の範囲は、31.25ms(「1」の設定)から2秒(3FHの設定)である。ウォッチドッグ タイマー レジスタを「0」にセットすると、タイマがディセーブルになる。WDW ビットが前のサイクルで0に設定されている場合にのみ、これらのビットを書き込むことができる                       |              |    |     |     |            |    |    |    |  |  |  |  |

| 0xFFFF6                                | 0x7FFF6                                                                                                                                                                                                                                       | 割り込みステータス／制御 |    |     |     |            |    |    |    |  |  |  |  |

|                                        |                                                                                                                                                                                                                                               | D7           | D6 | D5  | D4  | D3         | D2 | D1 | D0 |  |  |  |  |

| WIE                                    | AIE                                                                                                                                                                                                                                           | PFE          | 0  | H/L | P/L | 0          | 0  |    |    |  |  |  |  |

| WIE                                    | ウォッチドッグ割り込みイネーブル。「1」セットした場合、ウォッチドッグ タイムアウトが発生すると、ウォッチドッグ タイマーがINTピンとWDF フラグを駆動。「0」にクリアした場合、ウォッチドッグ タイムアウトはWDF フラグにのみ影響を与える                                                                                                                    |              |    |     |     |            |    |    |    |  |  |  |  |

| AIE                                    | アラーム割り込みイネーブル。「1」にセットすると、アラームの一一致はINTピンとAF フラグを駆動。「0」にクリアすると、アラームの一一致はAF フラグにのみ影響を与える                                                                                                                                                         |              |    |     |     |            |    |    |    |  |  |  |  |

| PFE                                    | 電源異常イネーブル。「1」にセットすると、電源異常モニターはINTピンとPF フラグを駆動。「0」にクリアすると、電源異常モニターは、PF フラグにのみ影響を与える                                                                                                                                                            |              |    |     |     |            |    |    |    |  |  |  |  |

| 0                                      | 将来に使用するために予約済み                                                                                                                                                                                                                                |              |    |     |     |            |    |    |    |  |  |  |  |

| H/L                                    | HIGH/LOW: 「1」にセットすると、INTピンはアクティブ HIGH に駆動される。「0」にクリアすると、INTピンはオープンドレインで、アクティブ LOW となる                                                                                                                                                         |              |    |     |     |            |    |    |    |  |  |  |  |

| P/L                                    | パルス／レベル：「1」にセットすると、INTピンは約200msの間割り込みソースによってアクティブ(H/L で決まる)に駆動される。「0」にクリアすると、INTピンはフラグレジスタが読み込まれるまで、アクティブレベル(H/L により決定される)に駆動される                                                                                                              |              |    |     |     |            |    |    |    |  |  |  |  |

| 0xFFFF5                                | 0x7FFF5                                                                                                                                                                                                                                       | アラーム - 日     |    |     |     |            |    |    |    |  |  |  |  |

|                                        |                                                                                                                                                                                                                                               | D7           | D6 | D5  | D4  | D3         | D2 | D1 | D0 |  |  |  |  |

| M                                      | 0                                                                                                                                                                                                                                             | アラーム日の10の位   |    |     |     | アラーム日の1日の位 |    |    |    |  |  |  |  |

| 月の日のアラーム値とおよび日の値を選択または選択解除するマスク ビットを含む |                                                                                                                                                                                                                                               |              |    |     |     |            |    |    |    |  |  |  |  |

| M                                      | 一致：このビットを「0」にクリアすると、日の値はアラーム一致に使用。このビットを「1」にセットすると、一致回路は日の値を無視                                                                                                                                                                                |              |    |     |     |            |    |    |    |  |  |  |  |

**表 4. レジスタ マップの詳細 ( 続き )**

| レジスタ      |           | 説明                                                                                                                                                                                                                                       |              |              |      |          |              |             |    |  |  |  |  |  |  |  |

|-----------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------|------|----------|--------------|-------------|----|--|--|--|--|--|--|--|

| CY14B108K | CY14B108M |                                                                                                                                                                                                                                          |              |              |      |          |              |             |    |  |  |  |  |  |  |  |

| 0xFFFF4   | 0x7FFF4   | アラーム - 時間                                                                                                                                                                                                                                |              |              |      |          |              |             |    |  |  |  |  |  |  |  |

|           |           | D7                                                                                                                                                                                                                                       | D6           | D5           | D4   | D3       | D2           | D1          | D0 |  |  |  |  |  |  |  |

|           |           | M                                                                                                                                                                                                                                        | 0            | アラーム時の 10 の位 |      |          |              | アラーム時の 1 の位 |    |  |  |  |  |  |  |  |

|           |           | 時のアラーム値および時の値を選択または選択解除するマスク ビットを含む                                                                                                                                                                                                      |              |              |      |          |              |             |    |  |  |  |  |  |  |  |

| M         |           | 一致 : このビットを「0」にクリアすると、時間の値はアラーム一致に使用。このビットを「1」にセットすると、一致回路が時間の値を無視                                                                                                                                                                       |              |              |      |          |              |             |    |  |  |  |  |  |  |  |

| 0xFFFF3   | 0x7FFF3   | アラーム - 分                                                                                                                                                                                                                                 |              |              |      |          |              |             |    |  |  |  |  |  |  |  |

|           |           | D7                                                                                                                                                                                                                                       | D6           | D5           | D4   | D3       | D2           | D1          | D0 |  |  |  |  |  |  |  |

|           |           | M                                                                                                                                                                                                                                        | アラーム分の 10 の位 |              |      |          | アラーム分の 1 分の位 |             |    |  |  |  |  |  |  |  |

|           |           | 分のアラーム値および分の値を選択または選択解除するマスク ビットを含む                                                                                                                                                                                                      |              |              |      |          |              |             |    |  |  |  |  |  |  |  |

| M         |           | 一致 : このビットを「0」にクリアすると、分の値はアラーム一致に使用。このビットを「1」にセットすると、一致回路が分の値を無視                                                                                                                                                                         |              |              |      |          |              |             |    |  |  |  |  |  |  |  |

| 0xFFFF2   | 0x7FFF2   | アラーム - 秒                                                                                                                                                                                                                                 |              |              |      |          |              |             |    |  |  |  |  |  |  |  |

|           |           | D7                                                                                                                                                                                                                                       | D6           | D5           | D4   | D3       | D2           | D1          | D0 |  |  |  |  |  |  |  |

|           |           | M                                                                                                                                                                                                                                        | アラーム秒の 10 の位 |              |      |          | アラーム秒の 1 の位  |             |    |  |  |  |  |  |  |  |

|           |           | 秒のアラーム値および秒の値を選択または選択解除するマスク ビットを含む                                                                                                                                                                                                      |              |              |      |          |              |             |    |  |  |  |  |  |  |  |

| M         |           | 一致 : このビットを「0」にクリアすると、秒の値はアラーム一致に使用。このビットを「1」にセットすると、一致回路が秒の値を無視                                                                                                                                                                         |              |              |      |          |              |             |    |  |  |  |  |  |  |  |

| 0xFFFF1   | 0x7FFF1   | 時間管理 - 世紀                                                                                                                                                                                                                                |              |              |      |          |              |             |    |  |  |  |  |  |  |  |

|           |           | D7                                                                                                                                                                                                                                       | D6           | D5           | D4   | D3       | D2           | D1          | D0 |  |  |  |  |  |  |  |

|           |           | 世紀の 10 の位                                                                                                                                                                                                                                |              |              |      | 世紀の 1 の位 |              |             |    |  |  |  |  |  |  |  |

|           |           | 世紀の BCD 値が含まれる。下位ニブルは、下位桁が含まれており、0 から 9 で動作する。上位ニブルは、上位桁が含まれており、0 から 9 で動作する。レジスタの範囲は 1 ~ 99                                                                                                                                             |              |              |      |          |              |             |    |  |  |  |  |  |  |  |

| 0xFFFF0   | 0x7FFF0   | フラグ                                                                                                                                                                                                                                      |              |              |      |          |              |             |    |  |  |  |  |  |  |  |

|           |           | D7                                                                                                                                                                                                                                       | D6           | D5           | D4   | D3       | D2           | D1          | D0 |  |  |  |  |  |  |  |

|           |           | WDF                                                                                                                                                                                                                                      | AF           | PF           | OSCF | 0        | CAL          | W           | R  |  |  |  |  |  |  |  |

| WDF       |           | ウォッチドッグ タイマー フラグ。この読み出し専用ビットは、ウォッチドッグ タイマーが、ユーザーによってリセットされずに 0 に到達できるよう、「1」にセットされる。フラグ レジスタが読み出される際、または電源投入時に「0」にクリアされる                                                                                                                  |              |              |      |          |              |             |    |  |  |  |  |  |  |  |

| AF        |           | アラーム フラグ : この読み出し専用ビットは、一致ビット = 0 の時、時間と月の日がアラーム レジスタに保存された値と一致する場合、「1」にセットされる。フラグ レジスタが読み出される時、または電源投入時にクリアされる                                                                                                                          |              |              |      |          |              |             |    |  |  |  |  |  |  |  |

| PF        |           | 電源異常 フラグ。この読み出し専用ビットは、電源が電源異常の閾値 $V_{SWITCH}$ を下回ると、「1」にセットされる。フラグ レジスタが読み出される際、または電源投入時に「0」にクリアされる。                                                                                                                                     |              |              |      |          |              |             |    |  |  |  |  |  |  |  |

| OSCF      |           | 発振子異常 フラグ。電源投入時、発振子が有効になったのに最初の 5ms 間に起動しない場合、「1」にセットされる。これは、RTC バックアップ電源に異常が発生し、クロックの値が有効でなくなったことを示す。このビットは、電源切断後に再投入しても保持され、内部的にチップによってクリアされない。この条件を確認し、フラグをクリアするために「0」を書き込む必要がある。ユーザーが OSCF フラグ ビットをリセットすると、ビットは $t_{RTCp}$ 時間後に更新される |              |              |      |          |              |             |    |  |  |  |  |  |  |  |

| CAL       |           | 校正モード。「1」にセットすると、512Hz の方形波は INT ピンに出力される。「0」にクリアすると、INT ピンは通常動作を再開。電源投入時、このビットの初期設定値は 0 (無効)                                                                                                                                            |              |              |      |          |              |             |    |  |  |  |  |  |  |  |

| W         |           | 書き込みイネーブル。「W」ビットを「1」にセットした場合、RTC レジスタの更新が停止される。これで、RTC レジスタ、アラーム レジスタ、校正 レジスタ、割り込み レジスタ、フラグ レジスタへの書き込みが可能になる。「W」ビットを「0」にセットした場合、時間が変更されると、RTC レジスタの内容が時間管理 カウンターに転送される。この転送プロセスは完了するのに $t_{RTCp}$ の時間を要する。電源投入時、このビットの初期設定値は 0           |              |              |      |          |              |             |    |  |  |  |  |  |  |  |

| R         |           | 読み出しイネーブル。「R」ビットを「1」にセットすると、読み出し処理中にはクロックの更新を見ていないので、ユーザー RTC レジスタへのクロック更新を停止する。「R」ビットを「0」にクリアすると、保持 レジスタへのクロックの更新が再開される。このビットの設定には、「W」ビットを「1」にセットする必要はない。電源投入時、このビットの初期設定値は 0                                                           |              |              |      |          |              |             |    |  |  |  |  |  |  |  |

## 最大定格

|                                                           |                         |

|-----------------------------------------------------------|-------------------------|

| 最大定格を超えると、デバイスの寿命が短くなる可能性があります。これらのユーザー ガイドラインは試験されていません。 |                         |

| 保存温度                                                      | -65°C ~ +150°C          |

| 最大累積保存時間                                                  |                         |

| 周囲の温度 (150°C 時)                                           | 1000 時間                 |

| 周囲温度 85°C                                                 | 20 年                    |

| 最大接合部温度                                                   | 150°C                   |

| $V_{SS}$ を基準とした $V_{CC}$ の電源電圧                            | -0.5V ~ 4.1V            |

| High Z 状態の出力に印加する電圧                                       | -0.5V ~ $V_{CC} + 0.5V$ |

| 入力電圧                                                      | -0.5V ~ $V_{CC} + 0.5V$ |

|                                      |                         |

|--------------------------------------|-------------------------|

| 任意のピンからグランド電位への過渡電圧 (20ns 以下)        | -2.0V ~ $V_{CC} + 2.0V$ |

| パッケージの許容電力損失 ( $T_A = 25^\circ C$ )  | 1.0W                    |

| 表面実装の鉛はんだ付け温度 (3 秒)                  | +260 °C                 |

| DC 出力電流 (一度に 1 出力、1 秒間)              | 15mA                    |

| 静電放電時の電圧 (MIL-STD-883、メソッド 3015 による) | > 2001V                 |

| ラッチアップ電流                             | > 200mA                 |

## 動作範囲

| 範囲  | 周囲温度          | $V_{CC}$    |

|-----|---------------|-------------|

| 産業用 | -40°C ~ +85°C | 2.7V ~ 3.6V |

## DC 電気的特性

### 動作範囲において

| パラメーター          | 説明                                                                            | テスト条件                                                                                                                                                  | Min            | Typ <sup>[14]</sup> | Max            | 単位            |

|-----------------|-------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|---------------------|----------------|---------------|

| $V_{CC}$        | 電源供給                                                                          |                                                                                                                                                        | 2.7            | 3.0                 | 3.6            | V             |

| $I_{CC1}$       | 平均 $V_{CC}$ 電流                                                                | $t_{RC} = 25\text{ns}$<br>$t_{RC} = 45\text{ns}$<br>出力負荷なしで得られた値 ( $I_{OUT} = 0\text{mA}$ )                                                            | -              | -                   | 75<br>57       | mA<br>mA      |

| $I_{CC2}$       | STORE 中の平均 $V_{CC}$ 電流                                                        | すべての入力は「ドント ケア」、 $V_{CC} = \text{Max. } t_{STORE}$ 時間の平均電流                                                                                             | -              | -                   | 20             | mA            |

| $I_{CC3}$       | $t_{RC} = 200\text{ns}$ 時の平均 $V_{CC}$ 電流、 $V_{CC(\text{Typ})}$ 、 $25^\circ C$ | すべての入力は CMOS レベルで動作。<br>出力負荷なしで得られた値 ( $I_{OUT} = 0\text{mA}$ )                                                                                        | -              | 40                  | -              | mA            |

| $I_{CC4}$       | AutoStore サイクル中の平均 $V_{CAP}$ 電流                                               | すべての入力は「ドント ケア」。<br>$t_{STORE}$ 時間の平均電流                                                                                                                | -              | -                   | 10             | mA            |

| $I_{SB}$        | $V_{CC}$ スタンバイ電流                                                              | $CE \geq (V_{CC} - 0.2V)$ 。<br>$V_{IN} \leq 0.2V$ または $\geq (V_{CC} - 0.2V)$ 。<br>W ビットを「0」に設定。不揮発性のサイクルが完了した後のスタンバイ電流レベル。入力はスタティック。 $f = 0\text{MHz}$ | -              | -                   | 10             | mA            |

| $I_{IX}^{[15]}$ | 入力リード電流 ( $\overline{HSB}$ を除く)                                               | $V_{CC} = \text{最大. } V_{SS} \leq V_{IN} \leq V_{CC}$                                                                                                  | -2             | -                   | +2             | $\mu\text{A}$ |

|                 | 入力リード電流 ( $HSB$ 用)                                                            | $V_{CC} = \text{最大. } V_{SS} \leq V_{IN} \leq V_{CC}$                                                                                                  | -200           | -                   | +2             | $\mu\text{A}$ |

| $I_{OZ}$        | オフ状態の出力リード電流                                                                  | $V_{CC} = \text{最大. } V_{SS} \leq V_{OUT} \leq V_{CC}$ 、<br>$CE$ または $OE \geq V_{IH}$ または $BHE/BLE \geq V_{IH}$ または $WE \leq V_{IL}$                   | -2             | -                   | +2             | $\mu\text{A}$ |

| $V_{IH}$        | 入力 HIGH 電圧                                                                    |                                                                                                                                                        | 2.0            | -                   | $V_{CC} + 0.5$ | V             |

| $V_{IL}$        | 入力 LOW 電圧                                                                     |                                                                                                                                                        | $V_{SS} - 0.5$ | -                   | 0.8            | V             |

| $V_{OH}$        | 出力 HIGH 電圧                                                                    | $I_{OUT} = -2\text{mA}$                                                                                                                                | 2.4            | -                   | -              | V             |

| $V_{OL}$        | 出力 LOW 電圧                                                                     | $I_{OUT} = 4\text{mA}$                                                                                                                                 | -              | -                   | 0.4            | V             |

### 注

14. 標準値は  $25^\circ C$ 、 $V_{CC} = V_{CC(\text{Typ})}$  です。100% テストされているわけではありません。

15.  $HSB$  ピンは、アケティブ HIGH と LOW 駆動の両方が無効になっている場合に、 $V_{OH} 2.4V$  に対して、 $I_{OUT} = -2\mu\text{A}$  となります。それらのドライバが有効の場合、標準の  $V_{OH}$  と  $V_{OL}$  が有効になります。この項目は特性として記載されていますが、試験されていません。

## DC 電気的特性 ( 続き )

### 動作範囲において

| パラメーター                | 説明                            | テスト条件                            | Min | Typ <sup>[14]</sup> | Max      | 単位 |

|-----------------------|-------------------------------|----------------------------------|-----|---------------------|----------|----|

| $V_{CAP}^{[16]}$      | ストレージ コンデンサ                   | $V_{CAP}$ ピンと $V_{SS}$ ピン間、5V 定格 | 122 | 150                 | 360      | μF |

| $V_{VCAP}^{[17, 18]}$ | デバイスで $V_{CAP}$ ピン上に駆動された最大電圧 | $V_{CC} = \text{Max}$            | —   | —                   | $V_{CC}$ | V  |

## データ保持期間および書き換え可能回数

### 動作範囲において

| パラメーター   | 説明              | Min   | 単位 |

|----------|-----------------|-------|----|

| $DATA_R$ | データ保持期間         | 20    | 年  |

| $NV_C$   | 不揮発性 STORE 処理回数 | 1,000 | K  |

## 静電容量

| パラメーター <sup>[18]</sup> | 説明     | テスト条件                                                                  | 最大値 | 単位 |

|------------------------|--------|------------------------------------------------------------------------|-----|----|

| $C_{IN}$               | 入力静電容量 | $T_A = 25^\circ\text{C}, f = 1\text{MHz}, V_{CC} = V_{CC}(\text{Typ})$ | 14  | pF |

| $C_{OUT}$              | 出力静電容量 |                                                                        | 14  | pF |

## 熱抵抗

| パラメーター <sup>[18]</sup> | 説明                  | テスト条件                                                 | 44 ピン TSOP II | 54 ピン TSOP II | 単位   |

|------------------------|---------------------|-------------------------------------------------------|---------------|---------------|------|

| $\Theta_{JA}$          | 熱抵抗<br>( 接合部から周囲 )  | テスト条件は、EIA/JESD51 による、熱インピーダンスを測定するための標準的なテスト方法と手順に従う | 45.3          | 44.22         | °C/W |

| $\Theta_{JC}$          | 熱抵抗<br>( 接合部からケース ) |                                                       | 5.2           | 8.26          | °C/W |

### 注

16.  $V_{CAP}$  最小値は、AutoStore 処理を完了するのに十分な電荷があることを保証するものです。 $V_{CAP}$  最大値は、即時の電源切断サイクルが発生しても AutoStore 処理が正常に完了するようにパワーアップ RECALL サイクルの間に  $V_{CAP}$  のコンデンサが必要な最小電圧まで充電されることを保証するものです。したがって、指定した最小値と最大値の範囲内のコンデンサを使用することをお勧めします。 $V_{CAP}$  オプションの詳細については、アプリケーションノート [AN43593](#) を参照してください。

17.  $V_{CAP}$  ピン ( $V_{VCAP}$ ) の最大電圧は、 $V_{CAP}$  コンデンサを選択する際に指針として提供されています。動作温度範囲における  $V_{CAP}$  コンデンサの定格電圧は、 $V_{VCAP}$  電圧より高い必要があります。

18. これらのパラメーターは設計保証であり、試験されていません。

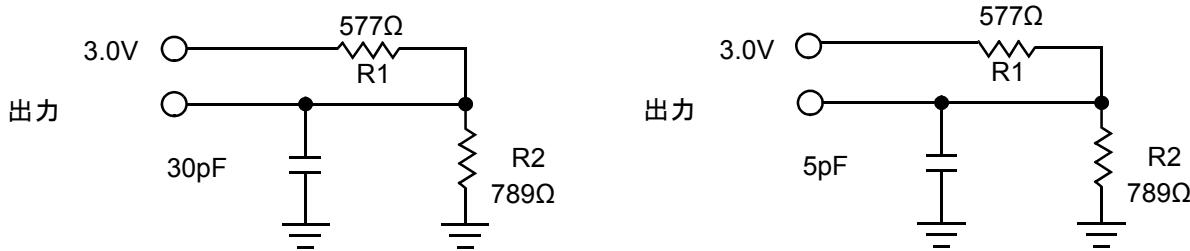

## AC テスト負荷

図 7. AC テスト負荷

## AC テスト条件

入力パルス レベル ..... 0V ~ 3V

入力の立ち上がり／立ち下がり時間 (10% ~ 90%) ....  $\leq 3\text{ns}$

入力と出力タイミングの基準レベル ..... 1.5V

## RTC 特性

### 動作範囲において

| パラメーター                       | 説明                                           | Min         | Typ <sup>[19]</sup> | Max  | 単位            |

|------------------------------|----------------------------------------------|-------------|---------------------|------|---------------|

| $V_{RTCbat}$                 | RTC バッテリー ピン電圧                               | 1.8         | 3.0                 | 3.6  | V             |

| $I_{BAK}$ <sup>[20]</sup>    | RTC バックアップ電流<br>(RTC の推奨外部コンポーネントは、図 5 を参照 ) | $T_A$ (Min) | —                   | 0.35 | $\mu\text{A}$ |

|                              |                                              | 25°C        | 0.35                | —    | $\mu\text{A}$ |

|                              |                                              | $T_A$ (Max) | —                   | 0.5  | $\mu\text{A}$ |

| $V_{RTCCap}$ <sup>[21]</sup> | RTC コンデンサ ピン電圧                               | $T_A$ (Min) | 1.6                 | 3.6  | V             |

|                              |                                              | 25°C        | 1.5                 | 3.6  | V             |

|                              |                                              | $T_A$ (Max) | 1.4                 | 3.6  | V             |

| $t_{OCS}$                    | RTC 発振子の発振開始時間                               | —           | 1                   | 2    | 秒             |