## サイプレスはインフィニオンテクノロジーズになりました

この表紙に続く文書には「サイプレス」と表記されていますが、これは同社が最初にこの製品を開発したからです。新規および既存のお客様いずれに対しても、引き続きインフィニオンがラインアップの一部として当該製品をご提供いたします。

### 文書の内容の継続性

下記製品がインフィニオンの製品ラインアップの一部として提供されたとしても、それを理由としてこの文書に変更が加わることはありません。今後も適宜改訂は行いますが、変更があった場合は文書の履歴ページでお知らせします。

### 注文時の部品番号の継続性

インフィニオンは既存の部品番号を引き続きサポートします。ご注文の際は、データシート記載の注文部品番号をこれまで通りご利用下さい。

## 1 M ビット ( 128K x 8 ) シリアル SPI nvSRAM

### 特長

- 1 M ビットの不揮発性スタティック RAM ( nvSRAM )

- 128K x 8 としてメモリを内部的に編成

- QuantumTrap の不揮発性要素への STORE 处理は、電源オフ時に自動的に実行できるほか ( AutoStore ) 、 HSB ピン ( ハードウェアによる保存 ) または SPI 命令 ( ソフトウェアによる保存 ) を使用してユーザが明示的に実行することも可能

- SRAM への RECALL 处理は、電源オン ( Power-Up Recall ) または SPI 命令 ( Software Recall ) によって実行

- 電源オフ時に小容量コンデンサにより、自動的に STORE 处理 ( CY14B101Q1 を除く )

- 高信頼性

- 回数無制限の読み取り、書き込み、および RECALL サイクル

- QuantumTrap に対する 100 万回の STORE サイクル

- データ保存期間 : 20 年

- 高速のシリアル ベリフェラル インタフェース ( SPI )

- 40 MHz のクロック速度

- SPI モード 0 ( 0,0 ) および SPI モード 3 ( 1,1 ) をサポート

- 書き込み保護

- 書き込み保護ピン (  $\overline{WP}$  ) を使ったハードウェアによる保護

- 書き込みディスエーブル命令を使用したソフトウェアによる保護

- アレイの 1/4, 1/2, または全体を対象としたソフトウェア ブロック保護

- 低消費電力

- 3V ( +20%, -10% ) の単一電源で動作

- 40 MHz 動作で平均 10 mA のアクティブ電流

- 業界標準の構成

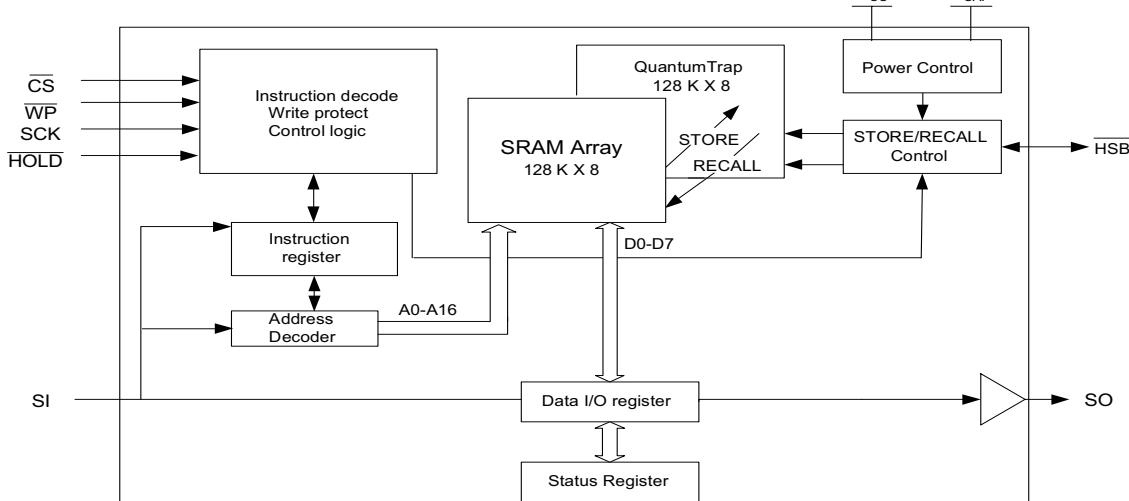

### ロジック ブロック図

## デバイスの動作

CY14B101Q1/CY14B101Q2/CY14B101Q3 は、メモリ セルごとに不揮発性要素を組み込んだ 1M ビット nvSRAM メモリです。nvSRAM へのすべての読み取りと書き込みは、メモリへの書き込みを無制限に処理可能にする独自の SRAM に対して行われます。SRAM 内のデータは、不揮発性 QuantumTrap セルへパラレルでデータを転送する STORE 命令によって保護されます。小容量コンデンサ ( $V_{CAP}$ ) は、電源が切れたり時に不揮発性セルに SRAM データを AutoStore するために使われ、電源遮断時のデータセキュリティを提供します。信頼性の高い SONOS 技術を用いた QuantumTrap 不揮発性要素により、nvSRAM は安全なデータストレージのための理想的な選択肢を提供します。

1M ビットのメモリアレイが 128 K ワード x 8 ビットとして組織されます。メモリは、読み書きサイクルの遅延サイクル値ゼロで最大 40 MHz の非常に高いクロック速度が可能な標準 SPI インタフェースを通じてアクセスされます。デバイスは SPI モード 0 および SPI モード 3 (CPOL, CPHA = 0, 0 および 1, 1) をサポートし、SPI スレーブとして動作します。デバイスはチップセレクト ( $\overline{CS}$ ) 端子が使用でき、シリアル入力端子 (SI)、シリアル出力端子 (SO)、シリアルクロック端子 (SCK) を通じてアクセスします。

このデバイスは、 $\overline{WP}$  端子と WRDI 命令によるハードウェアおよびソフトウェアの書き込み保護機能に加え、状態レジスタ内に BP0 端子と BP1 端子を使用して、ブロック書き込み保護 (アレイの 1/4, 1/2、またはすべてを保護) のメカニズムを提供します。さらに HOLD 端子は、シリアルシーケンスをリセットせずにすべてのシリアル通信を一時停止するために使われます。

CY14B101Q1/CY14B101Q2/CY14B101Q3 は、メモリへのアクセスに標準 SPI オペレーションコードを使用します。読み書き用の一般的な SPI 命令に加え、4 つの nvSRAM の特定機能にアクセス可能な、独自の 4 つの命令、STORE、RECALL、AutoStore Disable (ASDISB)、AutoStore Enable (ASENB) を提供します。

シリアル EEPROM に対するシリアル (SPI) nvSRAM の主な利点は、nvSRAM のすべての読み書きは遅延サイクルゼロの SPI バス速度で実行されることです。そのため、どのメモリアクセスの後でも待ち時間は不要です。STORE 处理と RECALL 处理は制限された時間で完了し、その間すべてのメモリアクセスは禁止されます。STORE または RECALL 处理の実行中は、ハードウェアの STORE Busy ( $\overline{HSB}$ ) 端子にデバイスの BUSY 状態が表示され、状態レジスタの RDY ビットにも反映されます。

デバイスは、ユーザがアプリケーションに最適なパートを選択できるよう、3 つの異なるピン構成で提供されています。機能の概要について

表 1. 機能概要

| 機能               | CY14B101Q1 | CY14B101Q2 | CY14B101Q3 |

|------------------|------------|------------|------------|

| WP               | あり         | なし         | あり         |

| $V_{CAP}$        | なし         | あり         | あり         |

| $\overline{HSB}$ | なし         | なし         | あり         |

| AutoStore        | なし         | あり         | あり         |

| 電源オン RECALL      | あり         | あり         | あり         |

| ハードウェア STORE     | なし         | なし         | あり         |

| ソフトウェア STORE     | あり         | あり         | あり         |

ては、表 1 をご覧ください。

## SRAM 書き込み

nvSRAM へのすべての書き込みは SRAM 上で実施され、不揮発性メモリのどのような持続サイクルも使い切ることはできません。これにより、ユーザは 無制限の書き込み処理を実行することができます。書き込みサイクルは WRITE 命令を通じて実行されます。WRITE 命令は nvSRAM の SI 端子より発行され、WRITE オペレーションコードと、3 バイトのアドレス、1 バイトのデータで構成されます。nvSRAM への書き込みは遅延サイクルゼロの SPI バス速度で行われます。

デバイスは、SPI 経由で実行されるバーストモードの書き込みが使用可能です。これにより、新しい WRITE 命令を発行せずに、連続したアドレス上で書き込み処理を実行できます。バーストモードでメモリの最後のアドレスに到達したとき、アドレスは 0x0000 にロールオーバーし、デバイスは書き込みを継続します。

SPI 書き込みサイクル命令は、SPI プロトコル記述のメモリアクセスセクションに定義されています。

## SRAM 読み込み

読み込みサイクルは SPI バス速度で実行され、データは READ 命令が実行された後、遅延ゼロサイクルで読み出されます。READ 命令は nvSRAM の SI 端子経由で発行され、READ オペレーションコードと 3 バイトのアドレスで構成されます。データは SO 端子で読み出されます。

このデバイスは、SPI 経由で実行されるバーストモードの読み込みが使用可能です。これにより、新しい READ 命令を発行せずに、連続したアドレス上で読み込み処理を実行できます。バーストモード読み込みでメモリの最後のアドレスに到達したとき、アドレスは 0x0000 にロールオーバーし、デバイスは読み込みを継続します。

SPI 読み込みサイクル命令は、SPI プロトコル記述のメモリアクセスセクションに定義されています。

## STORE 处理

STORE 处理は、SRAM から不揮発性 QuantumTrap セルへデータを転送します。デバイスは、次の 3 つの STORE 处理のいずれかを使用してデータを不揮発性セルへストアします。デバイスの電源オフにより有効化される AutoStore、STORE 命令によって有効化されるソフトウェア STORE、 $\overline{HSB}$  によって有効化されるハードウェア STORE です。STORE サイクルの実行中、まず以前の不揮発性データの消去が実行され、次に不揮発性要素のプログラムが実行されます。STORE サイクルが開始されると、CY14B101Q1/CY14B101Q2/CY14B101Q3 への読み書きはそのサイクルが完了するまで禁止されます。

状態レジスタ内の  $\overline{HSB}$  シグナルまたは  $\overline{RDY}$  ビットは、STORE またはソフトウェアによる RECALL サイクルが実行中かどうかを検出するため、システムによる監視が可能です。nvSRAM の BUSY ステータスは、 $\overline{HSB}$  が LOW の状態になっているか、 $\overline{RDY}$  ビットが「1」に設定されていることによって示されます。不要な不揮発性の STORE を避けるため、AutoStore およびハードウェアによる STORE 命令は、一番最後に STORE または RECALL サイクルが実行されてから少なくとも 1 回の書き込み処理が行われるまでは無視されます。ただし、STORE サイクルが起動されたソフトウェアは、書き込み処理が行われたかどうかに関係なく実行されます。

## AutoStore 处理

AutoStore 处理は、電源遮断時に SRAM データを QuantumTrap に自動的に保存する、nvSRAM 独自の機能です。この STORE 处理では外付けコンデンサ ( $V_{CAP}$ ) を活用し、デバイスは電源遮断時に不揮発性メモリへ安全にデータを保存することができます。

通常動作時、デバイスは  $V_{CC}$  から電流を得て、 $V_{CAP}$  端子に接続されたコンデンサにチャージします。電源遮断時に  $V_{CC}$  端子の電圧が  $V_{SWITCH}$  未満に下がった場合、デバイスは nvSRAM へのメモリアクセスをすべて禁止し、 $V_{CAP}$  コンデンサからのチャージを使って自動的に条件付き STORE 处理を実行します。AutoStore 处理は、最後の RECALL の実行以降に書き込みサイクルが一度も実行されていない場合は起動されません。

注 コンデンサが  $V_{CAP}$  端子に接続されていない場合、に規定されている AutoStore Disable 命令を発行し、AutoStore を無効にする必要があります [AutoStore Disable \(ASDISB\) instruction on page 13](#)。 $V_{CAP}$  端子に接続されたコンデンサなしで AutoStore が有効にされた場合、デバイスは STORE 处理を完了するため、十分なチャージがないまま AutoStore 处理を実行しようとします。これにより、nvSRAM と状態レジスタ内のデータが破壊されます。通常の機能を再開するには WRSR 命令を発行し、状態レジスタ内の不揮発性ビット BP0、BP1、WPEN を更新する必要があります。

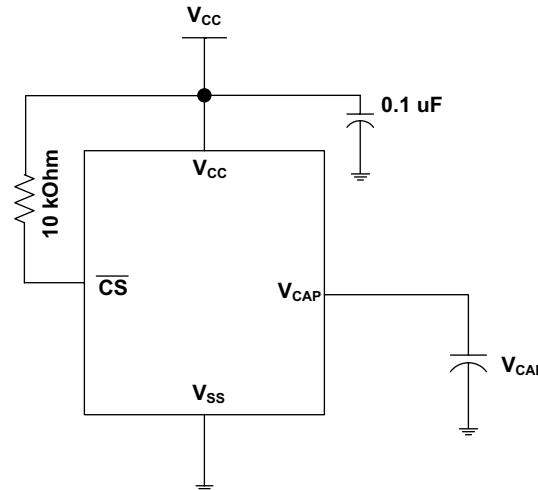

図 1 に、AutoStore 处理向けのストレージコンデンサ ( $V_{CAP}$ ) の適切な接続方法を示します。 $V_{CAP}$  のサイズについては、[DC Electrical Characteristics on page 15](#) を参照してください。

注 CY14B101Q1 は AutoStore 处理をサポートしていません。ユーザはデータ保護のために SPI STORE 命令を使用して、ソフトウェアによる STORE 处理を実行する必要があります。

## ソフトウェア STORE 处理

ソフトウェア STORE 处理では、ユーザは特定の SPI 命令を通じて STORE 处理をトリガーすることができます。STORE 处理は最後の NV 处理以降に書き込みが実行されたかどうかに関係なく、STORE 命令の実行によって開始します。

STORE サイクルが完了するまでに  $t_{STORE}$  の時間がかかりますが、その間 nvSRAM へのすべてのメモリアクセスは禁止されます。状態レジスタの RDY ビットまたは HSB 端子は、nvSRAM の Ready または Busy ステータスを検出するためにポーリングされる可能性があります。 $t_{STORE}$  サイクル時間が完了した後、SRAM は再度読み書き処理が有効になります。

## ハードウェア STORE 处理 および HSB 端子処理

CY14B101Q3 内の HSB 端子は、STORE 处理を制御し応答するために使用されます。実行中の STORE または RECALL 处理が存在しなければ、この端子はハードウェアによる STORE サイクルをリクエストするため使用できます。HSB 端子が LOW で駆動された場合、nvSRAM は  $t_{DELAY}$  の継続後、条件付きで STORE 处理を開始します。実際の STORE サイクルは、最後の STORE または RECALL サイクル以降、SRAM への書き込みが実行された場合にのみ開始します。 $t_{STORE}$  が継続中か HSB 端子が LOW である限り、メモリへの読み書きは禁止されます。

HSB 端子はまた、内部的に LOW で駆動され、STORE ( 必ず開始される ) が処理中の場合に busy 状態を表示する、オープンドレインドライバ ( 内部 100 kW の弱いプルアップ抵抗 ) としても動作します。

注 各ハードウェアおよびソフトウェアによる STORE 处理後、HSB は標準出力高電流で短時間 ( $t_{HHD}$ ) HIGH で駆動し、内部 100 kW のプルアップ抵抗により、HIGH の状態を継続します。

注 最後のデータバイトのストアを正常に実行するため、ハードウェアストアでは最後のデータビット D0 が受信された後、最低 1 クロックサイクルを開始するべきです。

STORE 操作が完了すると、HSB 端子が HIGH を返した後、nvSRAM メモリアクセスは  $t_{LZHSB}$  時間の間禁止されます。HSB 端子は、未使用の場合は接続していない状態である必要があります。

注 CY14B101Q1/CY14B101Q2 には HSB 端子がありません。SPI 状態レジスタの RDY ビットは、nvSRAM の Ready または Busy ステータスを判断するためにプローブされる可能性があります。

図 1. AutoStore モード

## RECALL 处理

RECALL 处理は、QuantumTrap 不揮発性要素内にストアされたデータを SRAM へ転送します。RECALL はハードウェアによる RECALL ( 電源オンで開始 ) およびソフトウェアによる RECALL ( SPI RECALL 命令によって開始 ) の 2 つの方法で実行することができます。

内部的に、RECALL は 2 段階の手順を踏みます。まず SRAM データがクリアされ、次に不揮発性情報が SRAM セルに転送されます。RECALL サイクルの実行中、メモリアクセスはすべて禁止されます。RECALL 处理では不揮発性要素内のデータは変更されません。

## ハードウェア RECALL ( 電源オン )

電源オンの間に  $V_{CC}$  が  $V_{SWITCH}$  を超えると、SRAM 上に不揮発性メモリの内容を転送する RECALL シーケンスが自動的に開始されます。データはそれ以前に STORE シーケンスを通じて不揮発性メモリにストアされることになっています。

電源オン RECALL サイクルが完了するまでには  $t_{FA}$  の時間がかかり、その間のメモリアクセスは禁止されます。HSB 端子はデバイスの Ready ステータスを検出するために使われます。

## ソフトウェア RECALL

ソフトウェア RECALL 处理により、ユーザは RECALL 处理を実行し、SRAM で不揮発性メモリの内容をリストアできます。ソフトウェアによる RECALL は、SPI で RECALL 命令を発行することにより実行されます。

ソフトウェア RECALL が完了するまでには  $t_{RECALL}$  の時間がかかり、その間 nvSRAM へのすべてのメモリアクセスは禁止されます。コントローラは、すべてのメモリアクセス命令の発行前に RECALL 处理を完了するよう、十分な遅延を提供する必要があります。

## AutoStore の無効化と有効化

アプリケーションに AutoStore 機能が不要な場合、ASDISB 命令により無効化できます。これを実行すると、nvSRAM は電源オフ時に STORE 处理を実行しません。

AutoStore は ASENB 命令を使って再度有効できます。しかし、これらの命令は不揮発性ではないため、ユーザがパワーサイクルを存続する

ためにこの設定を必要とする場合、AutoStore の無効化と有効化処理の後に必ず STORE 処理を実行しなければなりません。

注 CY14B101Q2/CY14B101Q3 の AutoStore は工場出荷時有効になっています。CY14B101Q1 では V<sub>CAP</sub> 端子は存在しないため、AutoStore 処理はご利用いただけません。そのため、CY14B101Q1 への AutoStore 処理の有効化および無効化命令は無視されます。

注 AutoStore が無効かつ V<sub>CAP</sub> が不要の場合、V<sub>CAP</sub> 端子は開回路のままにしておく必要があります。V<sub>CAP</sub> 端子は絶対にグランドに接続しないでください。電源オン RECALL 処理は、どのような場合でも無効化できません。

## Document History Page

**Document Title: CY14B101Q1/CY14B101Q2/CY14B101Q3 1 MBit (128K X 8) Serial SPI nvSRAM (JA)**

**Document Number: 001-62735**

| Revision | ECN     | Orig. of Change | Submission Date | Description of Change             |

|----------|---------|-----------------|-----------------|-----------------------------------|

| **       | 2967390 | FSU             | 7/2/2010        | New Spec                          |

| *A       | 3297672 | MOTMP           | 6/30/2011       | Updated to 001-50091 *H revision. |

| *B       | 4149555 | HZEN            | 10/7/2013       | No changes required               |

## 販売、ソリューション、および法律情報

### ワールドワイドな販売と設計サポート

サイプレスは、事業所、ソリューションセンター、メーカー代理店、および販売代理店の世界的なネットワークを保持しています。お客様の最寄りの事業所については、サイプレスの Web サイト [サイプレスのロケーション](#)をご覧ください。

#### 製品

|               |                                                                          |

|---------------|--------------------------------------------------------------------------|

| 自動車           | <a href="http://cypress.com/go/automotive">cypress.com/go/automotive</a> |

| クロック & バッファ   | <a href="http://cypress.com/go/clocks">cypress.com/go/clocks</a>         |

| インターフェース      | <a href="http://cypress.com/go/interface">cypress.com/go/interface</a>   |

| 照明 & 電源管理     | <a href="http://cypress.com/go/powerpsoc">cypress.com/go/powerpsoc</a>   |

| メモリ           | <a href="http://cypress.com/go/memory">cypress.com/go/memory</a>         |

| 光学 & イメージ センサ | <a href="http://cypress.com/go/image">cypress.com/go/image</a>           |

| PSoC          | <a href="http://cypress.com/go/psoc">cypress.com/go/psoc</a>             |

| タッチセンサ        | <a href="http://cypress.com/go/touch">cypress.com/go/touch</a>           |

| USB コントローラ    | <a href="http://cypress.com/go/USB">cypress.com/go/USB</a>               |

| ワイヤレス /RF     | <a href="http://cypress.com/go/wireless">cypress.com/go/wireless</a>     |

#### PSoC Solutions

[psoc.cypress.com/solutions](http://psoc.cypress.com/solutions)

PSoC 1 | PSoC 3 | PSoC 5

© Cypress Semiconductor Corporation (サイプレス セミコンダクタ コーポレーション)、2010-2013。本文書に記載される情報は、事前の予告なく変更されることがあります。サイプレス セミコンダクタ コーポレーションは、サイプレス製品に組み込まれた回路以外のいかなる回路を使用することに対しても一切の責任を負いません。かつ、サイプレス セミコンダクタ コーポレーションは、特許またはその他の権利に基づくライセンスを譲渡することも、又は含意することもありません。サイプレス製品は、サイプレスとの書面による明示的な合意に基づくものではない限り、医療、生命維持、救命、重要な管理、または安全の用途のために使用することを保証するものではなく、また使用することを意図したものでもありません。さらにサイプレスは、誤動作や故障によって使用者に重大な傷害をもたらすことが合理的に予想される、生命維持システムの重要なコンポーネントとしてサイプレス製品を使用することを許可していません。生命維持システムの用途にサイプレス 製品を供することは、製造者がそのような使用におけるあらゆるリスクを負うことを意味し、その結果サイプレスはあらゆる責任を免除されることを意味します。

全てのソースコード(ソフトウェアおよび/またはファームウェア)はサイプレス セミコンダクタ コーポレーション(以下サイプレス)が所有し、全世界の特許権保護(米国およびその他の国)、米国の著作権ならびに国際協定の条項により保護され、かつそれらに従います。サイプレスが本書面によりライセンサーに付与するライセンスは、個人的、非独占的かつ譲渡不能のライセンスであって、適用される契約で指定されたサイプレスの集積回路と併用されるライセンサーの製品のみをサポートするカスタムソフトウェアおよび/またはカスタムファームウェアを作成する目的に限って、サイプレスのソースコードの派生著作物をコピー、使用、変更そして作成するためのライセンス、ならびにサイプレスのソースコードおよび派生著作物をコンパイルするためのライセンスです。上記で指定された場合を除き、サイプレスの書面による明示的な許可なくして本ソースコードを複製、変更、変換、コンパイル、または表示することは全て禁止されます。

免責条項：サイプレスは、明示的または黙示的を問わず、本資料に関するいかなる種類の保証も行いません。これには、商品性または特定目的への適合性の默示的な保証が含まれますが、これに限定されません。サイプレスは、本文書に記載される資料に対して今後予告なく変更を加える権利を留保します。サイプレスは、本文書に記載されるいかなる製品または回路を適用または使用したことによって生ずるいかなる責任も負いません。サイプレスは、誤動作や故障によって使用者に重大な傷害をもたらすことが合理的に予想される生命維持システムの重要なコンポーネントとしてサイプレス 製品を使用することを許可していません。生命維持システムの用途にサイプレス 製品を供することは、製造者がそのような使用におけるあらゆるリスクを負うことを意味し、その結果サイプレスはあらゆる責任を免除されることを意味します。

ソフトウェアの使用は、適用されるサイプレス ソフトウェア ライセンス契約によって制限され、かつ制約される場合があります。