# **512M ビット (64MB)/256M ビット (32MB)/128M ビット (16MB) HYPERFLASH™ ファミリ**

**HYPERRBUS™, 3.0 V/1.8 V**

## **特長**

- 3.0 V I/O, 11 本のバス信号

- シングルエンド クロック

- 1.8 V I/O, 12 本のバス信号

- 差動クロック (CK, CK#)

- チップセレクト (CS#)

- 8 ビットデータバス (DQ[7:0])

- 読み書きデータストローブ (RWDS)

- HYPERFLASH™ メモリは RWDS を読み出しデータストローブのみとして使用する。

- 最大 333 MBps の持続される読み出しが可能

- DDR - クロックサイクルごとに 2 回のデータ転送

- $V_{CC}$  が 1.8 V の時、166 MHz クロックレート (333 MBps)

- $V_{CC}$  が 3.0 V の時、100 MHz クロックレート (200 MBps)

- 96 ns の初期ランダム読み出しが可能

- 初期ランダムアクセスレイテンシ : 5 ~ 16 クロックサイクル

- シーケンシャルバーストトランザクション

- 設定可能なバースト特性

- ラップされるバースト長:

- 16 バイト (8 クロック)

- 32 バイト (16 クロック)

- 64 バイト (32 クロック)

- リニアバースト

- ハイブリッドオプション: 1 つのラップバーストの後にリニアバーストが続く

- 各トランザクションでラップバーストまたはリニアバーストのデータ転送方式を選択可能

- 設定可能な出力駆動強度

- 低消費電力モード

- 読み出し時のアクティブクロック停止: 12 mA、ウェイクアップが不要

- スタンバイ: 25  $\mu$ A (typ)、ウェイクアップが不要

- ディープパワーダウン: 8  $\mu$ A (typ)

- 300  $\mu$ s のウェイクアップが必要

- 外部割込みを生成するための INT# 出力

- ビジーからレディへの遷移

- ECC 検出

- システムレベルのパワーオンリセットを生成するための RSTO# 出力

- ユーザー設定可能な RSTO# LOW 周期

- 512 バイトのプログラムバッファ

特長

- セクタ消去

- ユニフォーム 256 KB セクタ

- オプションの 8 つの 4 KB パラメーターセクタ (合計 32 KB)

- 先進的セクタ保護

- セクタごとの揮発性および不揮発性の保護方式

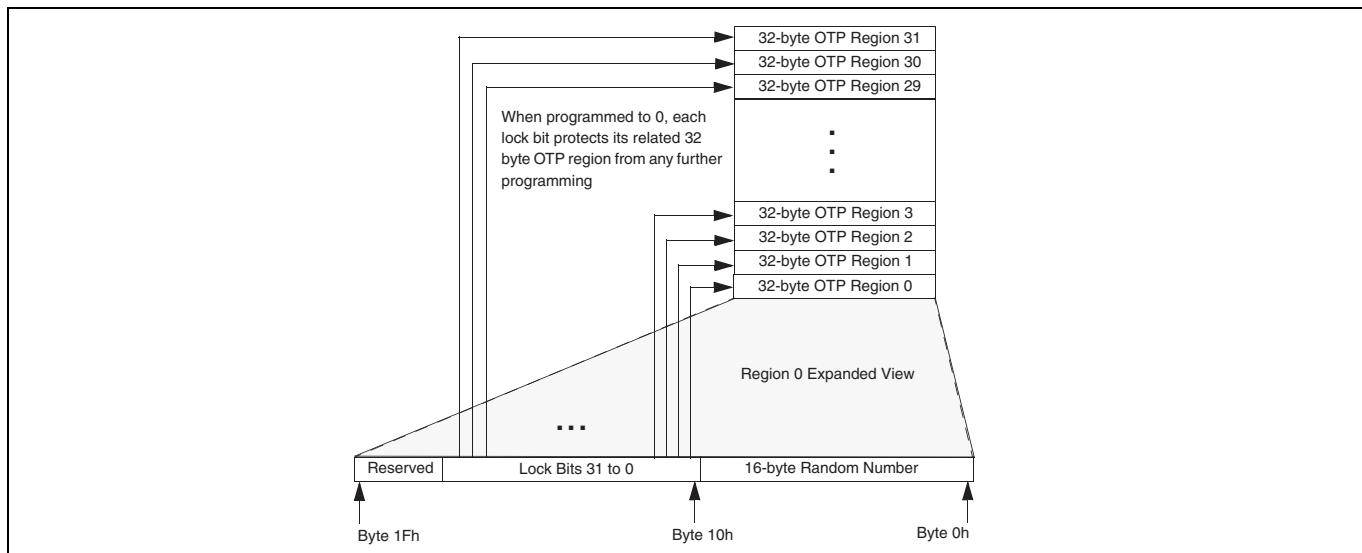

- 個別の 1024 バイトでワンタイム プログラム アレイ

- 動作温度

- 産業機器用温度範囲 (-40°C ~ +85°C)

- 産業機器用温度範囲プラス (-40°C ~ +105°C)

- 拡張温度範囲 (-40°C ~ +125°C)

- 車載用温度範囲 , AEC-Q100 グレード 3 (-40°C ~ +85°C)

- 車載用温度範囲 , AEC-Q100 グレード 2 (-40°C ~ +105°C)

- 車載用温度範囲 , AEC-Q100 グレード 1 (-40°C ~ +125°C)

- ISO/TS16949 および AEC Q100 準拠

- アクセス可能回数

- 10 万プログラム / 消去サイクル

- 保持

- 20 年のデータ保持期間

- 消去およびプログラム時の電流

- 最高ピーク  $\leq$  100 mA

- パッケージ オプション

- 24 ボール FBGA

- 追加機能

- ECC 1 ビット訂正、2 ビット検出

- CRC

性能概要

## 性能概要

**Table 1 読み出しアクセスのタイミング**

|                                     |         |

|-------------------------------------|---------|

| 1.8 V $V_{CC}/V_{CCQ}$ での最大クロック レート | 166 MHz |

| 3.0 V $V_{CC}/V_{CCQ}$ の最大クロック レート  | 100 MHz |

| 最大アクセス時間 ( $t_{ACC}$ )              | 96 ns   |

| 166 MHz での最初のワードまでの最大 CS# アクセス時間    | 118 ns  |

**Table 2 標準的なプログラム / 消去時間**

|                               |                        |

|-------------------------------|------------------------|

| シングルワード プログラム (2B = 16b)      | 500 $\mu$ s (~ 4 KBps) |

| 書き込みバッファ プログラム (512B = 4096b) | 475 $\mu$ s (~ 1 MBps) |

| セクタ消去時間 (256 KB = 2 Mb)       | 930 ms (~ 282 KBps)    |

**Table 3 標準的な消費電流**

|                                |                         |

|--------------------------------|-------------------------|

| バースト読み出し (166 MHz での連続読み出し )   | 80 mA                   |

| パワーオンリセット                      | 80 mA                   |

| セクタ消去電流                        | 60 mA                   |

| 書き込みバッファ プログラム電流               | 60 mA                   |

| スタンバイ (CS# = HIGH)             | 25 $\mu$ A              |

| ディープ パワーダウン (CS# = HIGH, 85°C) | 30 $\mu$ A (512 Mb)     |

|                                | 4 $\mu$ A (他のすべてのメモリ容量) |

目次

## 目次

|                                                                             |            |

|-----------------------------------------------------------------------------|------------|

| 特長 .....                                                                    | 1          |

| 性能概要 .....                                                                  | 3          |

| 目次 .....                                                                    | 4          |

| <b>1 概要 .....</b>                                                           | <b>5</b>   |

| 1.1 DDR center aligned read strobe (DCARS) 機能 .....                         | 7          |

| 1.2 エラー検出および訂正機能 .....                                                      | 7          |

| <b>2 接続図 .....</b>                                                          | <b>10</b>  |

| 2.1 FBGA 24 ボール 5×5 アレイのフットプリント .....                                       | 10         |

| <b>3 信号の説明 .....</b>                                                        | <b>11</b>  |

| <b>4 HYPERBUS™ プロトコル .....</b>                                              | <b>12</b>  |

| 4.1 コマンド / アドレスビットの割り当て .....                                               | 13         |

| 4.2 読み出し動作 .....                                                            | 14         |

| 4.3 DCARS タイミングでの HYPERFLASH™ 読み出し .....                                    | 17         |

| 4.4 書き込み動作 .....                                                            | 18         |

| <b>5 アドレス空間マップ .....</b>                                                    | <b>20</b>  |

| 5.1 フラッシュメモリアレイ .....                                                       | 21         |

| 5.2 デバイス ID および CFI (ID-CFI) ASO .....                                      | 23         |

| <b>6 組込み動作 .....</b>                                                        | <b>25</b>  |

| 6.1 組込みアルゴリズム コントローラー (EAC) .....                                           | 25         |

| 6.2 プログラムおよび消去のまとめ .....                                                    | 26         |

| 6.3 データ保護 .....                                                             | 59         |

| <b>7 デバイス ID および共通フラッシュインターフェース (ID-CFI) の ASO マップ .....</b>                | <b>70</b>  |

| 7.1 デバイス ID および共通フラッシュインターフェース (ID-CFI) の ASO マップ – 標準 .....                | 70         |

| 7.2 デバイス ID および共通フラッシュインターフェース (ID-CFI) の ASO マップ – 車載グレード / AEC-Q100 ..... | 75         |

| <b>8 ソフトウェアインターフェース参考資料 .....</b>                                           | <b>76</b>  |

| 8.1 コマンドのまとめ .....                                                          | 76         |

| <b>9 データ整合性 .....</b>                                                       | <b>81</b>  |

| 9.1 アクセス可能回数 .....                                                          | 81         |

| 9.2 データ保持 .....                                                             | 81         |

| <b>10 ハードウェアインターフェース .....</b>                                              | <b>82</b>  |

| <b>11 電気的仕様 .....</b>                                                       | <b>83</b>  |

| 11.1 絶対最大定格 .....                                                           | 83         |

| 11.2 熱抵抗 .....                                                              | 84         |

| 11.3 ラッチアップ特性 .....                                                         | 84         |

| 11.4 動作範囲 .....                                                             | 85         |

| 11.5 DC 特性 (CMOS 互換性) .....                                                 | 86         |

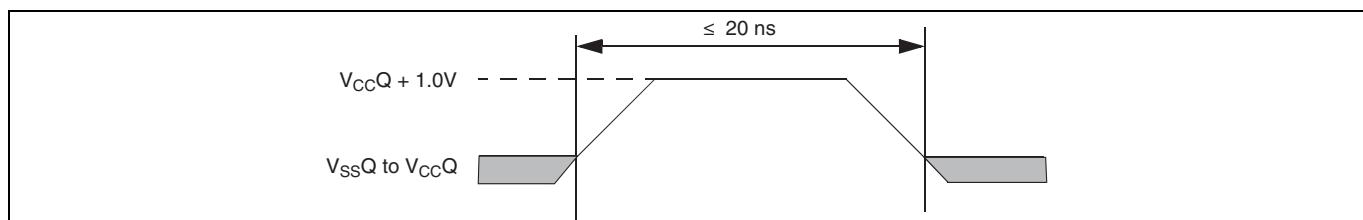

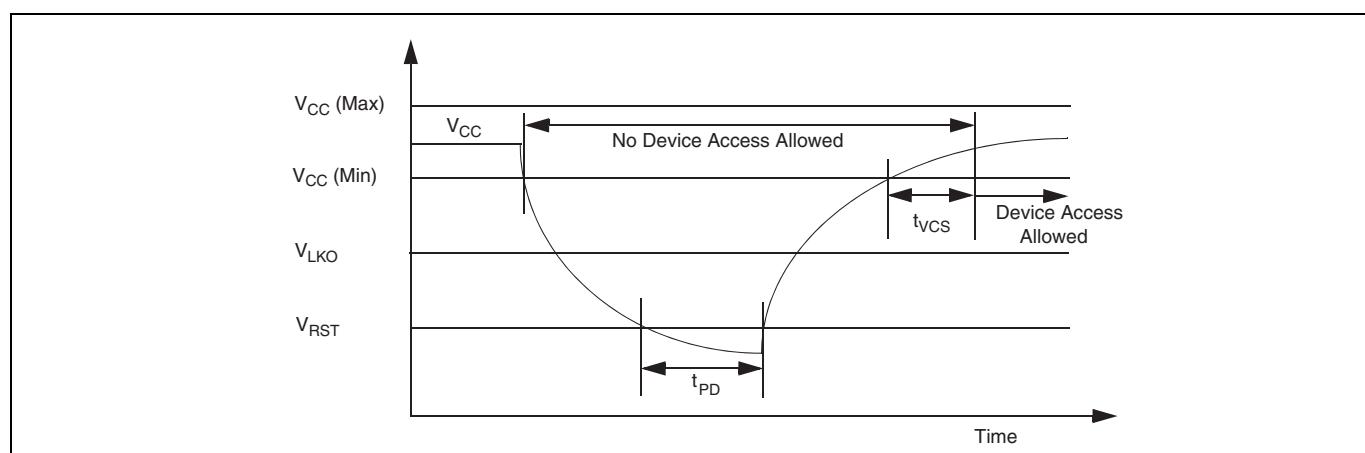

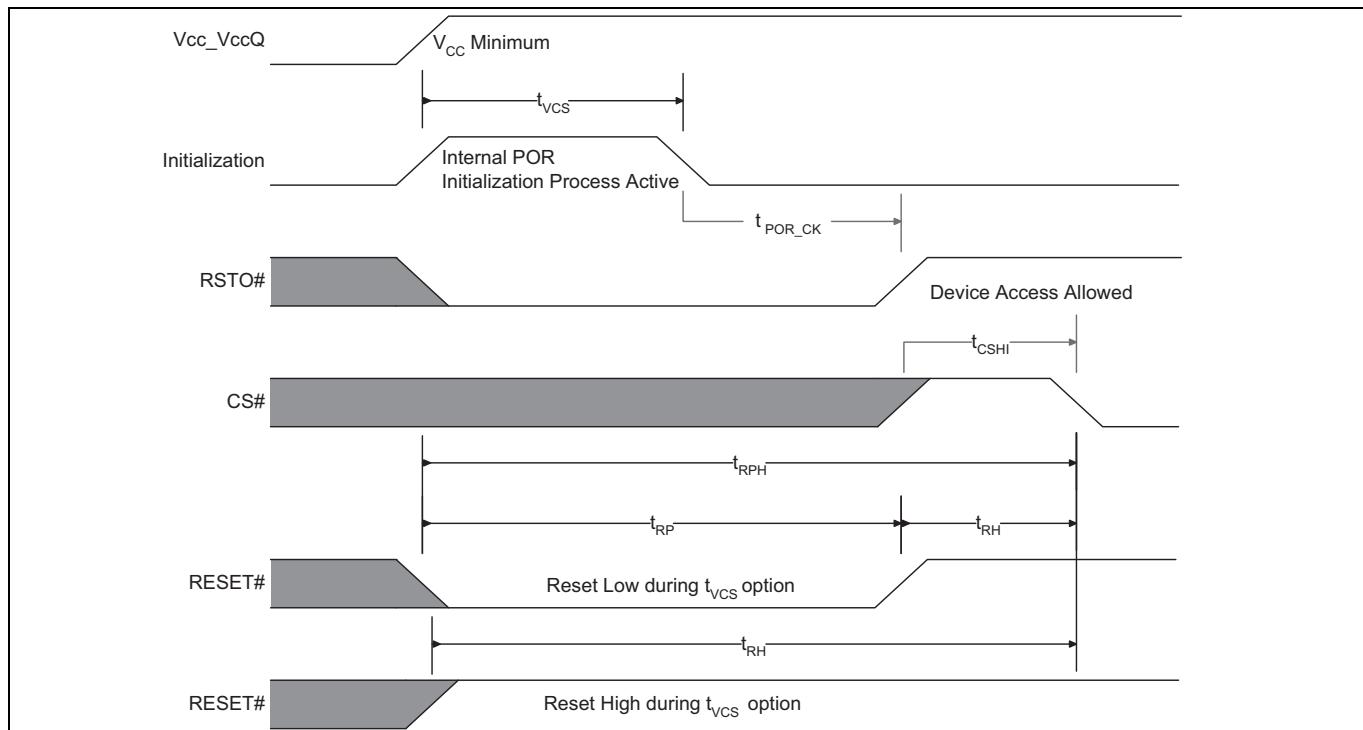

| 11.6 電源投入時および電源切断時 .....                                                    | 89         |

| 11.7 ハードウェアデータ保護による電源オフ .....                                               | 94         |

| 11.8 省電力モード .....                                                           | 94         |

| <b>12 タイミング仕様 .....</b>                                                     | <b>96</b>  |

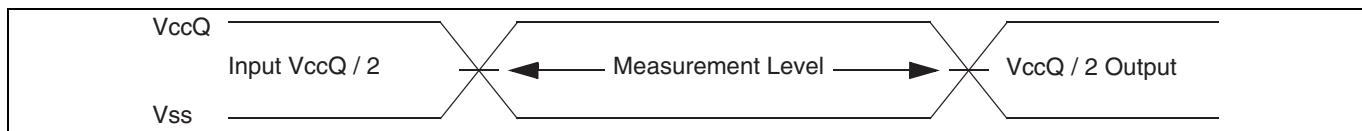

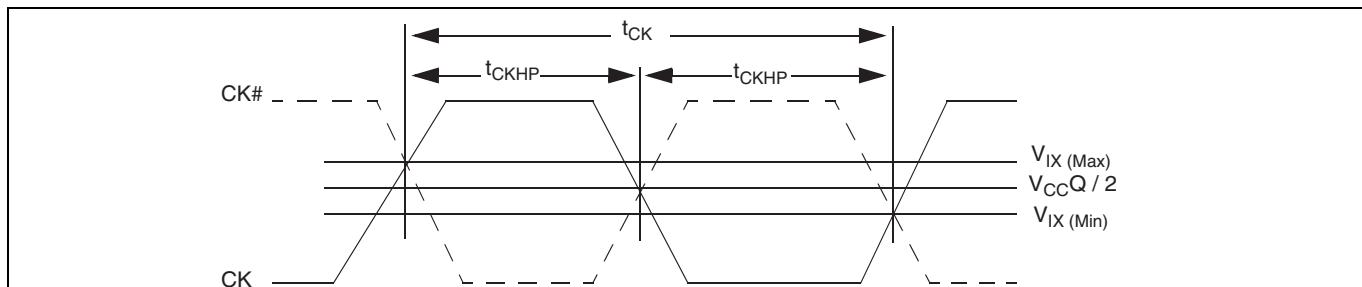

| 12.1 AC テスト条件 .....                                                         | 96         |

| 12.2 AC 特性 .....                                                            | 97         |

| <b>13 組込みアルゴリズムのパフォーマンス .....</b>                                           | <b>103</b> |

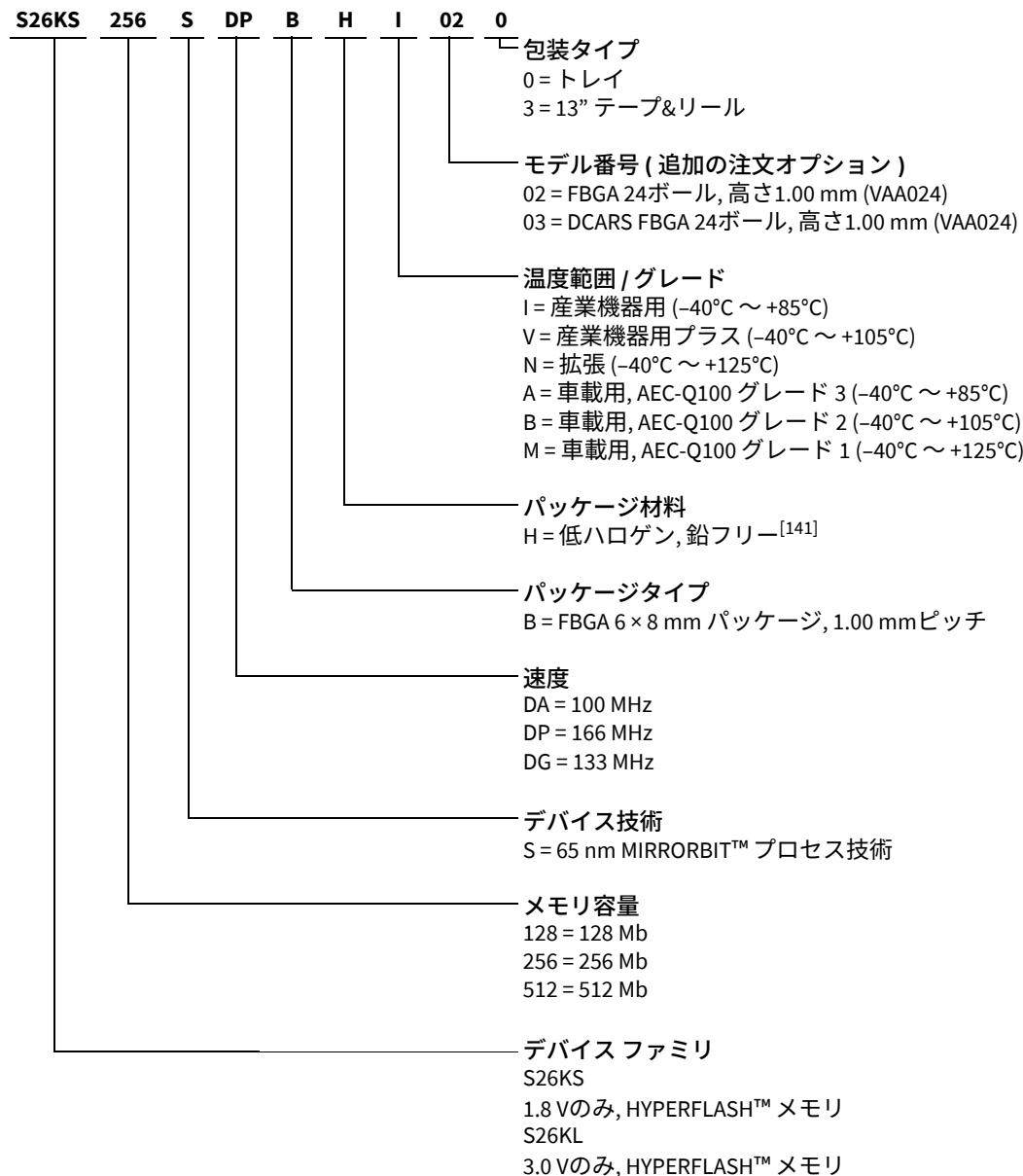

| <b>14 注文情報 .....</b>                                                        | <b>104</b> |

| 14.1 注文製品番号 .....                                                           | 104        |

| 14.2 有効な組合せ – 標準 .....                                                      | 105        |

| 14.3 有効な組合せ – 車載用グレード / AEC-Q100 .....                                      | 107        |

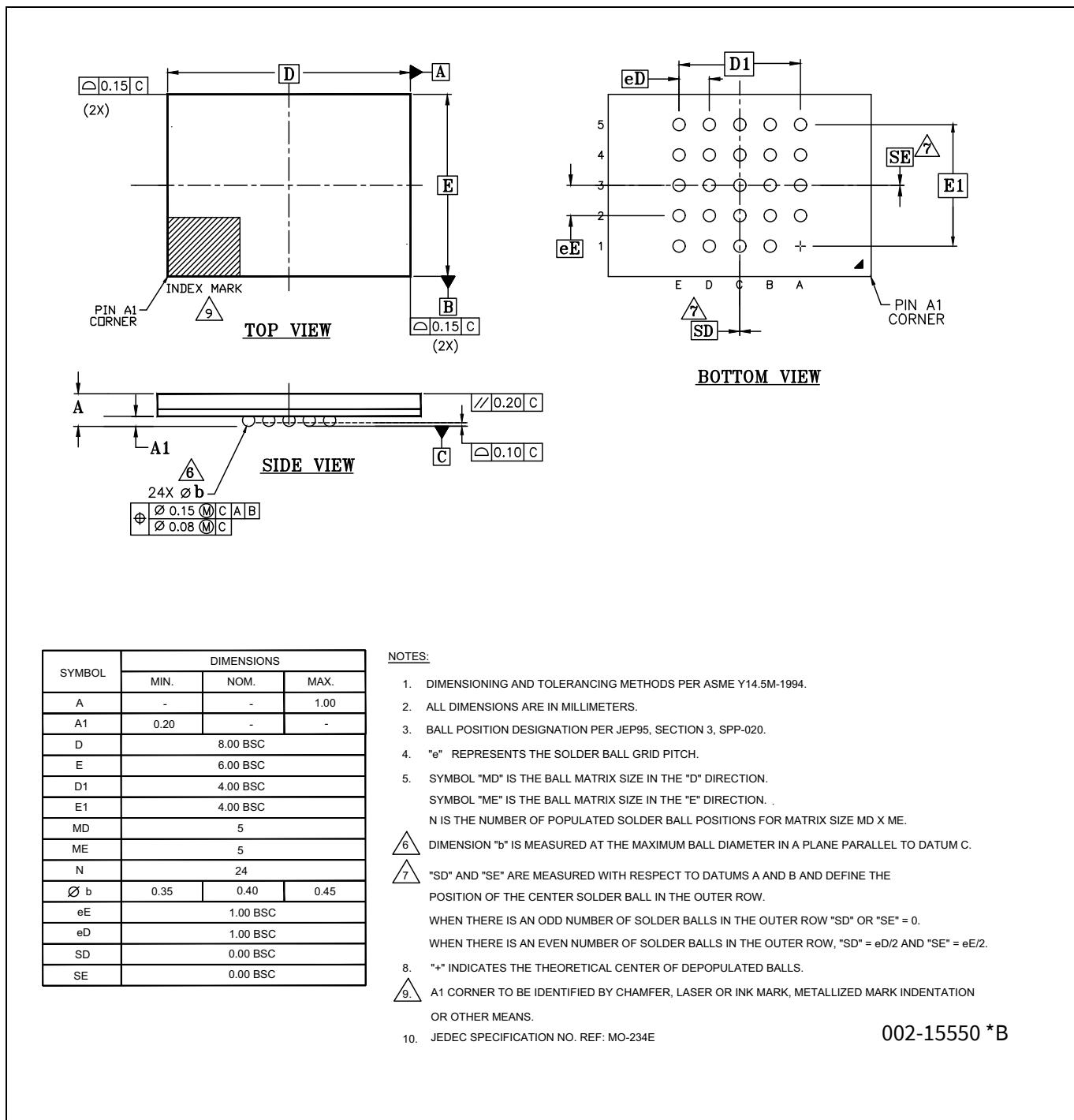

| <b>15 パッケージ図 .....</b>                                                      | <b>109</b> |

| 15.1 強化ボールグリッドアレイ 24 ボール 6×8×1.0 mm (VAA024) .....                          | 109        |

| 改訂履歴 .....                                                                  | 110        |

| 免責事項 .....                                                                  | 111        |

概要

## 1 概要

HYPERFLASH™ 製品ファミリは、HYPERBUS™ 少信号数 DDR (ダブルデータレート) インターフェースを利用して高速読み出しスループットを取得する高速 CMOS、MIRRORBIT™ NOR フラッシュデバイスです。DDR 方式により、クロックサイクルごとに 2 個のデータバイトがデータ信号 (DQ) 上に転送されます。HYPERFLASH™ の読み書きトランザクションは、内部 HYPERFLASH™ コア内の一連の 16 ビット幅で 1 クロックサイクルのデータ転送です。それぞれの転送は DQ 信号上の 2 つの対応する 8 ビット幅で 0.5 クロックサイクルのデータ転送からなります。

データとコマンド / アドレス情報の両方は 8 ビットのデータバスを介して DDR 方式で転送されます。クロック入力信号は、DQ 信号からコマンド / アドレス / データ情報を受信する際に、信号取り込みのために HYPERFLASH™ デバイスにより使用されます。読み書きデータストローブ (RWDS) は HYPERFLASH™ デバイスからの出力信号で、データがメモリからホストに転送される時点を示します。RWDS は、読み出し動作のデータ転送中に CK の立ち上りと立ち下りエッジを基準にしています。

コマンド / アドレス / 書き込みデータの値はクロックエッジの中央に揃えますが、読み出しデータの値は RWDS 遷移のエッジに揃えます。

HYPERFLASH™ デバイスに対する読み出し / 書き込み動作はバースト指向です。読み出しトランザクションはラップバーストカリニアバースト方式で行えるように設定できます。ラップ動作中に、アクセスは選択したアドレスから開始して、設定した値までグループラップシーケンス内の位置にアクセスし続けます。リニア動作中に、アクセスは選択した位置から開始して、読み出し動作が終了する (CS# が HIGH に戻る) まで逐次的に継続します。書き込みトランザクションは 1 つかそれ以上の 16 ビット値を転送します。

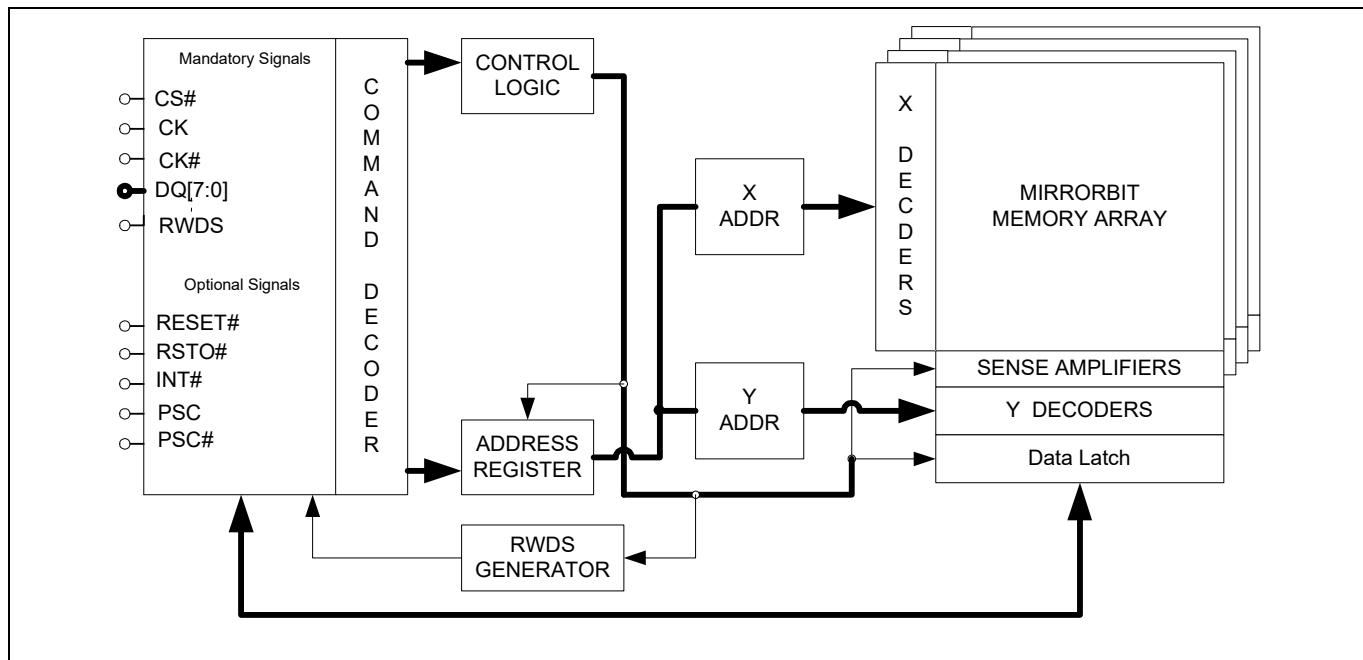

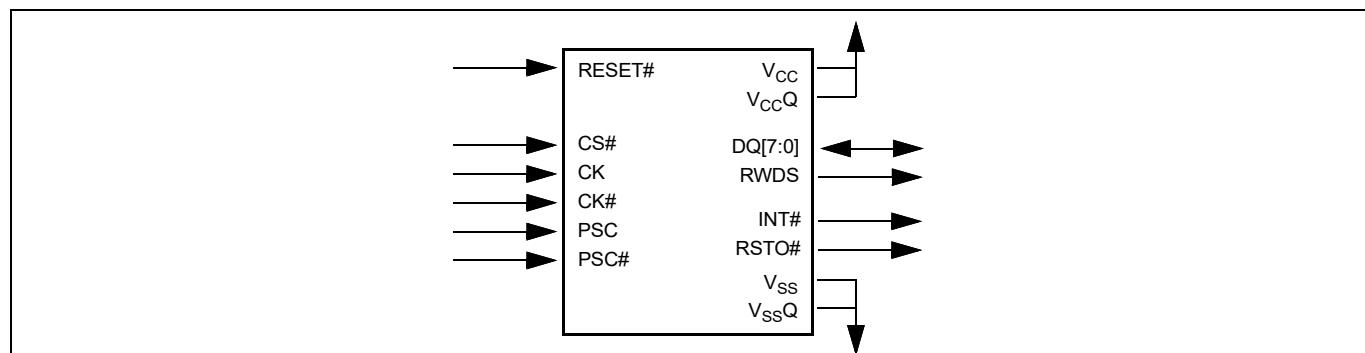

Figure 1 ロジックブロックダイヤグラム

HYPERFLASH™ ファミリは多種のメモリ容量を持っており 1.8V か 3.0V のコアと I/O を備えた不揮発性同期フラッシュメモリデバイスを含んでいます。これらのデバイスは 1 個の 8 ビット (1 バイト) 幅 DDR データバスを持ち、ワード幅 (16 ビットデータ) のアドレス境界のみを使用します。読み出し動作はクロックサイクルごとに 16 ビット (クロックエッジごとに 8 ビット) のデータを提供します。書き込み動作はクロックサイクルごとに 16 ビット (クロックエッジごとに 8 ビット) のデータを使用します。

各ランダム読み出しはページ (長さ 32 バイトにアラインされるデータセット) にアクセスします。各ページは 1 対のハーフページ (長さ 16 バイトにアラインされるデータアレイのグループ) から構成されます。半ページは 16 バイトアドレス境界にアラインされます。読み出しアクセスは、対象のハーフページアドレスとバースト種類を定義するために 2 クロックサイクルを要し、かつ追加初期レイテンシ

## 概要

を要します。初期レイテンシ期間中の 3 番目のクロックサイクルでは対象のハーフページの開始アドレスが指定されます。初期データ値が出力された後、後続のクロックサイクルで追加のデータはラップバーストかリニアバースト方式に従ってページから読み出されます。リニアバーストモードに設定した場合、ページがバースト出力されている間にデバイスは自動的に MIRRORBIT™ フラッシュメモリアレイから次の連続ページをフェッチします。アレイからのフェッチが進行中に同時にバースト出力すると、連続リニアバースト動作が実行可能になり、333 MBps の持続データ出力を実現できます [1 バイト (8 ビットデータバス) \* 2 (両クロックエッジのデータ) \* 166 MHz = 333 MBps]。

**Table 1 S26KS および S26KL アドレスマップ**

| 種類                                     | カウント                                        | アドレス     | 注記      |

|----------------------------------------|---------------------------------------------|----------|---------|

| ハーフページのワードアドレス (16 バイト)                | 8 (ワードアドレス)                                 | A2-A0    | 16 バイト  |

| 書き込みバッファライン内のワードアドレス (512 バイト)         | 256 (ワードアドレス)                               | A7-A0    | 512 バイト |

| 消去セクタ (256 KB) 内のハーフページ (16 バイト)       | 8192 (ハーフページ)                               | A16-A3   | -       |

| 消去セクタ (256 KB) 内の書き込みバッファライン (512 バイト) | 512 (ライン)                                   | A16-A8   | -       |

| 消去セクタ (256 KB) の合計                     | 256 (512 Mb)<br>128 (256 Mb)<br>64 (128 Mb) | Amax-A17 | -       |

デバイス制御回路は、ホストインターフェースコントローラー (HIC) と組込みアルゴリズム コントローラー (EAC) の 2 つの並行する動作に分かれています。HIC は必要に応じてデバイス入力とデバイス出力の信号レベルを監視し、ホストシステム (HYPERFLASH™ マスター) とのデータ読み出しと書き込み転送を完了します。HIC は読み出し転送で、現在入力されたアドレスマップからデータを出力します。書き込み転送アドレスとデータ情報を EAC コマンドメモリに配置します。電源遷移と書き込み転送を EAC に通知します。EAC は、コマンドメモリを参照して、適切なコマンドシーケンスが発行されたかチェックした後、組込みアルゴリズム (EA) を実行します。

メモリアレイ内の不揮発性データの書換えには、EA と呼ばれる複雑な動作シーケンスを必要とします。アルゴリズムは内部の EAC によって完全に管理されています。主要なアルゴリズムは、メインアレイデータのプログラミングと消去を実行します。ホストシステムはフラッシュデバイスのアドレス空間にコマンドコードを書き込みます。EAC はコマンドを受け取り、コマンドを完了するために必要なすべてのステップを実行し、EA の進行中にステータス情報を提供します。

各メモリビットの消去済み状態はロジック「1」です。プログラムによりロジック "1" (HIGH) からロジック「0」(LOW) に変更します。「0」から「1」への変更を実行できるのは消去動作のみです。消去動作は、セクタと呼ばれる 256 KB (パラメーターセクタなら 4 KB) にアラインされたデータグループ全体に対して実行します。インフィニオンから出荷時は、すべてのセクタは消去されています。

プログラミングは 512 バイトの書き込みバッファを介して行われます。プログラミング動作を開始する前に、書き込みバッファに 1 ~ 256 ワードを書き込みます。フラッシュメモリアレイ内では、512 バイト整列のデータグループはラインと呼ばれます。プログラム動作は揮発性書き込みバッファから不揮発性メモリアレイのラインにデータを転送します。この動作は書き込みバッファプログラミングと呼ばれます。

書き込みバッファは、リセット後または書き込みバッファを使用した任意の動作完了後、「1」にセットされます。バッファ書き込みコマンドによって「0」が書き込まれていない位置は、デフォルトの「1」

## 概要

の値のままで埋められています。書き込みバッファ内の「1」は、プログラミング動作中にメモリアレイのデータには影響しません。

HYPERBUS™ 専用の必須信号 (CS#, CK, CK#, DQ[7:0], RWDS) に加え、このデバイスには追加信号 (RESET#, INT#, RSTO#, および Phase Shifted クロック PSC/PSC#) も含まれています。

RESET# 信号は LOW から HIGH に遷移すると、デバイスは内部のパワーオンリセット (POR) 後のデフォルト状態に戻ります。

INT# 出力信号は、プログラム動作が消去動作の終了時に HYPERFLASH™ がビジーからレディの状態に遷移した時点を示すために HYPERFLASH™ マスターに割込みを提供できます。

RSTO# はデバイス内で POR が発生している時点を示すオープンドレイン出力であり、システムレベルのリセット信号として使用できます。内部 POR の完了後、ユーザにより定義されたタイムアウト期間が経過した後 RSTO# 信号は LOW インピーダンスから HIGH インピーダンスに遷移します。HIGH インピーダンス状態に遷移した後、外部プルアップ抵抗により RSTO# 信号は HIGH レベルに引っ張られて、デバイスは瞬時に Standby 状態になります。

PSC/PSC# は、CK/CK# の替わりに RWDS エッジの基準として使用される Phase Shifted Clock 入力です。詳細については、[DDR center aligned read strobe \(DCARS\) 機能](#) を参照してください。

## 1.1 DDR center aligned read strobe (DCARS) 機能

HYPERFLASH™ メモリは、読み出しデータ出力に対する RWDS 信号の独立したスキー (位相シフト) を可能にする設定可能な機能を提供します。

DCARS 機能が有効な場合、CK/CK# の代わりに 2 番目の差動位相シフトクロック入力 PSC/PSC# が RWDS エッジの基準として使用されます。通常、2 番目のクロックは 90° 位相シフトされた CK/CK# のコピーであり、RWDS エッジを DQ 信号の有効なデータウィンドウ内の中央に配置します。ただし、CK/CK# と PSC/PSC# の間の他の位相シフトを使用して、DQ 信号の有効なデータウィンドウ内の RWDS エッジの位置を最適化し、RWDS が必要な量のデータセットアップと RWDS エッジに関する保持時間を提供できるようにします。

PSC/PSC# は、書き込みトランザクション中には使用されません。PSC と PSC# は、それぞれ LOW と HIGH で駆動されるか、書き込みトランザクション中に両方とも LOW で駆動されます。

## 1.2 エラー検出および訂正機能

### 1.2.1 エラー訂正コード (ECC)

HYPERFLASH™ メモリは、フラッシュメモリアレイプログラミング中に組込みハミング ECC を生成し、読み出し中にエラーを検出および修正します。

書き込みバッファにロードされた 16 バイトに揃えられたデータの各ハーフページが 512 バイトのフラッシュメモリアレイラインに転送されると、各ハーフページ ECC ユニットの ECC もホストシステムソフトウェアからは見えないメモリアレイの部分にプログラムされます。

ECC 情報は、各ハーフページフラッシュアレイの読み出し操作中にチェックされます。ハーフページ内の 1 ビットエラーは、各ハーフページのアクセス中に ECC ロジックによって修正されます。

各ハーフページの ECC 情報は、各ハーフページを含むセクタの各消去後に 1 回書き込みます。同じハーフページ内で複数回プログラミングすると、そのハーフページ内でエラーの検出と修正が無効になります。

ハーフページで 2 回以上のワードプログラムと書き込みバッファ プログラムはレガシーソフトウェア互換性に対応しています。ただし、最高のデータ整合性を得るために、ワードプログラミングまたは書き込みバッファプログラミングを使用して、ハーフページ内で複数回プログラミングしないことを推奨します。消去せずに同じハーフページに複数の書き込みを行うと、ECC シンドロームが無効になるため、ECC 機能が無効になります。同じハーフページ内で複数のプログラミング操作を必要とするアプリケーションの場合、システムソフトウェアのエラー検出と修正を追加して、複数回プログラミングされるハーフページのデータ整合性をより確実にすることを推奨します。

2 ビットのエラー検出を有効にできるモードがあります。このモードを有効にすると、ハーフページの 1 ビットエラーが修正され、2 ビットエラーが検出されて報告されます。このモードでは、消去後に同

## 概要

じハーフページに複数回書き込む機能は無効になります。このモードでは、同じハーフページで複数回プログラムしようとすると、プログラミング操作の失敗ステータスになります。

ECC エラーは、ECC ステータスレジスタの読み出し、割込みの有効化、または修正不可能なエラーが発生した場合の RWDS の停止を有効にして、データを HYPERBUS™ マスターに転送する前にバスエラーを作成することで検出できます。

ECC エラーのアドレス位置をキャプチャするためのレジスタが提供されています。

ECC 修正または修正不可能なエラーをカウントするためのカウンターが提供されています。

### 1.2.2 巡回冗長検査

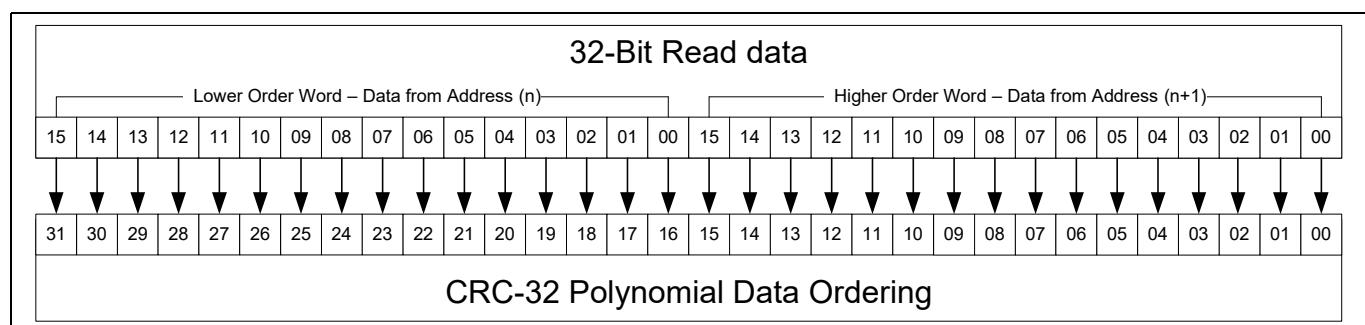

ユーザー定義のアドレス範囲でハードウェアアクセラレーション CRC 計算を実行するためのコマンドグループが用意されています。計算はプログラムや消去と同じような組込み動作のもう一つのタイプであり、計算実行中はデバイスがビジーになります。CRC 操作は、最大 32 ビットのエラービットグループを検出できる 32 ビット多項式を使用します。

コマンドを使用して、CRC Address Space Overlay (ASO) を入力し、CRC 計算を開始するために必要なアドレス範囲をロードします。CRC ASO に入力されている間、CRC 操作のステータスがチェックされ、メモリアレイからの読み出しが一時停止され、再開され、結果のチェック値が読み取られます。詳細については、[アドレス空間マップ](#)を参照してください。

#### 1.2.2.1 CRC check-value の計算

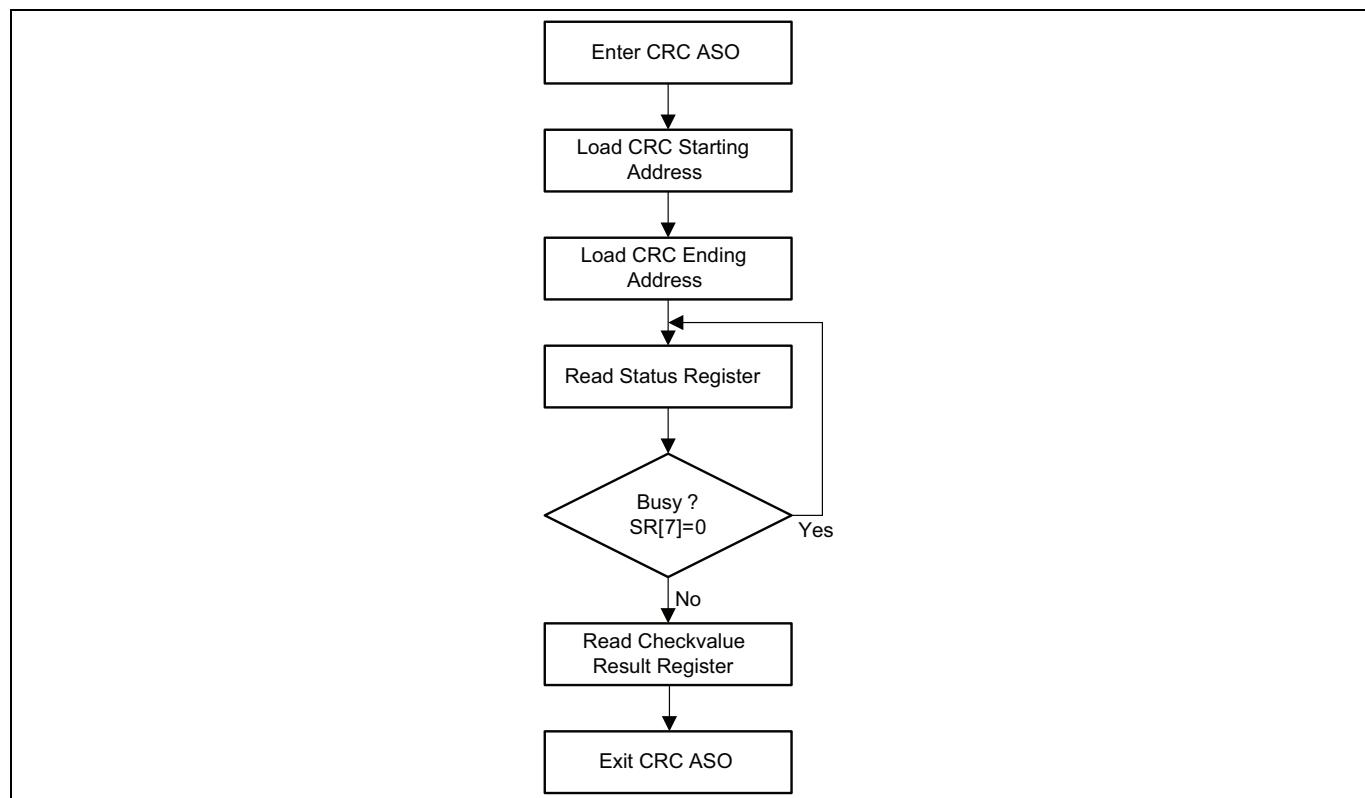

Check-value 計算コマンドシーケンスにより、デバイスはユーザー定義のアドレス範囲で CRC 計算を実行します。CRC の計算は、Figure 2 で説明されている多項式で実現されます。

CRC ASO を入力すると、Check-value 生成シーケンスが開始されます。次のステップは、CRC 計算でカバーされるアドレス範囲の開始を識別する開始アドレスを CRC Start Address レジスタにロードすることです。次に、終了アドレスが CRC End Address レジスタにロードされ、このステップで CRC 計算が開始されます。CRC プロセスは、開始アドレスから終了アドレスまでに含まれるデータの Check-value を計算します。

計算期間中、デバイスは Busy 状態 (SR[7] = 0) になります。Check-value の計算が完了すると、デバイスは Ready 状態 (SR[7] = 1) に戻り、計算された Check-value は Check-value Low Result レジスタと Check-value High Result レジスタで利用可能になります。Check-value Low Result レジスタには Check-value ビット 0 ~ 15 が含まれ、デバイスが CRC ASO にある間にアドレス 0 から読み出せます。Check-value High Result レジスタにはビット 16 ~ 31 が含まれ、デバイスが CRC ASO にある間、アドレス 1 から読み出せます。CRC 計算プロセスが開始されると、Check-value Low Result レジスタと Check-value High Result レジスタに 0 がロードされます。

チェック値の計算は、デバイスが Standby 状態にある場合にのみ開始でき、いったん開始すると、CRC Suspend シーケンスで中断してアレイからデータを読み出せます。Suspend 状態の間、ステータスレジスタの CRC Suspend Status Bit (CRCSSB) がセットされます (SR[8] = 1)。一時停止すると、ホストは Status レジスタを読み出し、アレイからデータを読み出し、CRC Resume コマンドシーケンスを使用して CRC 計算を再開できます。CRC ASO は、開始されると、ASO Exit コマンドまたはハードウェアリセットで終了して、デバイスをアレイ読み出しモードに戻せます。別の ASO がアクティブな間は、Check-value の計算を実行できません。ハードウェアリセットは、CRC Start Address レジスタ、CRC End Address レジスタ、Check-value High Result レジスタ、および Check-value Low Result レジスタの値をクリアします。

Ending Address (EA) は、Starting Address (SA) より少なくとも 2 つ高いアドレスでなければいけません。EA < SA+2 の場合、Check-value 計算は中止され、デバイスは準備完了状態 (SR[7] = 1) に戻ります。SR[3] は (1) に設定され、中断状態を示します。EA < SA+2 の場合、Check-value High Result レジスタと Check-value Low Result レジスタは不定データを保持します。

$$\text{CRC-32C Polynomial} = X^{32} + X^{28} + X^{27} + X^{26} + X^{25} + X^{23} + X^{22} + X^{20} + X^{19} + X^{18} + X^{14} + X^{13} + X^{11} + X^{10} + X^9 + X^8 + X^6 + 1$$

Figure 2 CRC-32 多項式

## 概要

**Figure 3** Check-value 計算シーケンス

CRC-32 多項式から Check-value を計算する際に使用される読み出しデータの順序を [Figure 4](#) に示します。

**Figure 4** 読み出しデータの順序

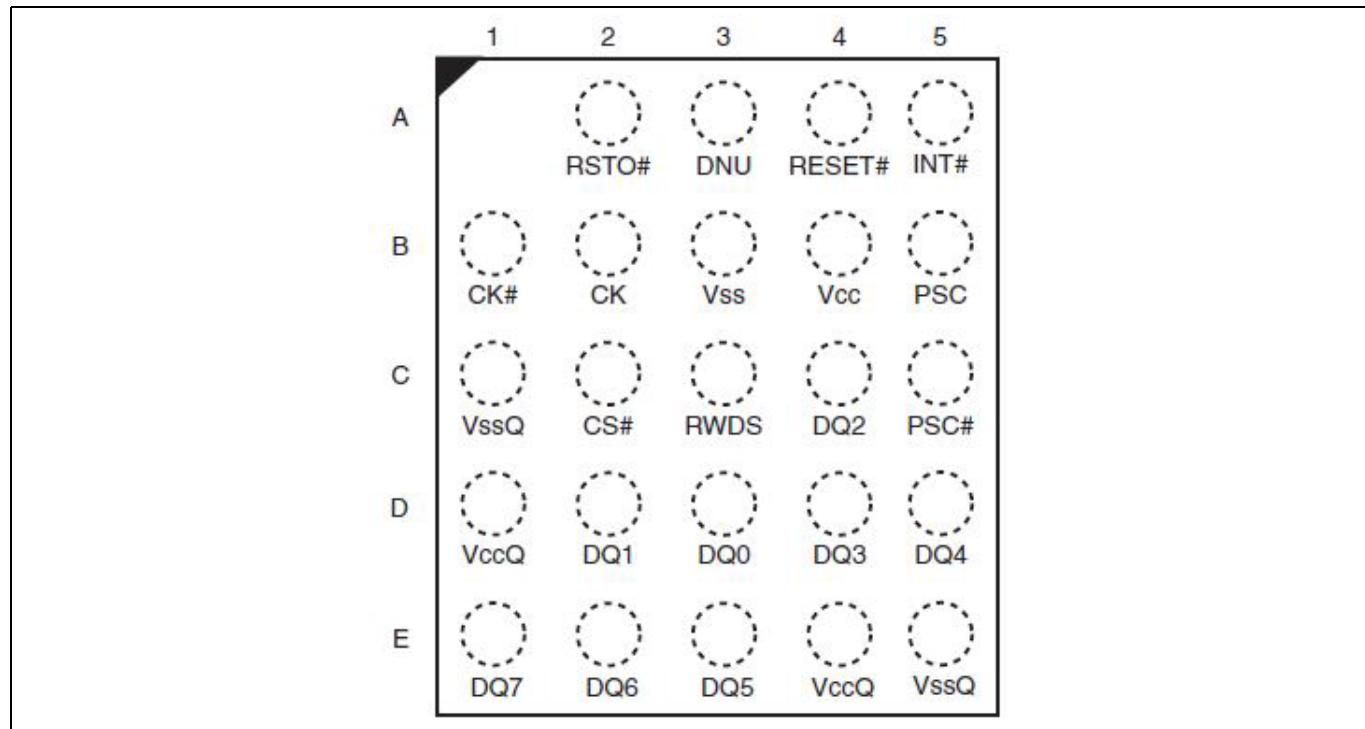

## 2 接続図

### 2.1 FBGA 24 ボール 5×5 アレイのフットプリント

HYPERFLASH™ デバイスは、6mm x 8mm の本体を持つ Fortified Ball Grid Array (FBGA), 1mm ピッチ , 24 ボール , 5×5 ボールアレイのフットプリントで提供されます。パッケージの高さはデバイスによって異なり、1 mm または 1.2 mm です。詳細については、[注文情報](#)を参照してください。使用中のパッケージについては、デバイスのデータシートの注文部品番号の有効な組合せを参照してください。

Figure 5 24 ボール FBGA, 6 × 8 mm, 5 × 5 ボール フットプリント , 上面図 [1, 2, 3]

注:

1. B1 (CK#) は、3.0 V デバイス ( モデル 02 ) 上の RFU です。

2. B5 (PSC) および C5 (PSC#) は、標準の 3.0 V および 1.8 V デバイス ( モデル 02 ) の RFU です。C5 (PSC#) は、3 V DCARS デバイス ( モデル 03 ) 上の RFU です。

3. DNU — Do not Use。このピン / ボールは内部で接続されており、未接続のままにしておく必要があります。

信号の説明

### 3 信号の説明

Figure 6 HYPERFLASH™ のインターフェース

Table 2 信号の説明

| 記号               | 種類               | M/O | 説明                                                                                                                                                                                                                                               |

|------------------|------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CS#              | 入力               | M   | チップセレクト：HYPERFLASH™ バストランザクションは HIGH から LOW への移行で開始。HYPERFLASH™ バストランザクションは LOW から HIGH への移行で終了。                                                                                                                                                 |

| CK, CK#          | 入力               | M   | 差動クロック：コマンド / アドレス / データ情報は、CK と CK# 信号の交差に対する入力または出力。CK# は、1.8V デバイスでのみ使用し、開放にする、または 3V デバイス上の CK に接続できます。                                                                                                                                      |

| RWDS             | 出力               | M   | 読み書きデータストローブ：読み出しトランザクション中の出力データは RWDS とエッジを揃えます。                                                                                                                                                                                                |

| DQ[7..0]         | 入力 / 出力          | M   | データ入力 / 出力：コマンド / アドレス / データ情報は読み出しと書き込みトランザクション中に、これらの DQ 信号上に転送されます。                                                                                                                                                                           |

| PSC, PSC#        | 入力               | O   | 位相シフトクロック：PSC/PSC# を使用すると、CK/CK# 入力に対して RWDS 信号を個別にスキーできます。PSC# は 1.8V デバイスでのみ使用。PSC と PSC# は、それぞれ書き込みトランザクション中に HIGH と LOW に駆動されるか、両方が LOW に駆動されます。                                                                                             |

| INT#             | 出力<br>(オープンドレイン) | O   | INT 出力：LOW の時、デバイスは内部イベントが発生したことを示します。この信号は、オンチップイベントが発生したことを示すために、デバイスに対するシステムレベルの割込みとして使用されることを意図しています。INT# はオープンドレイン出力。                                                                                                                       |

| RESET#           | 入力               | O   | ハードウェアリセット：LOW の時、デバイスは自己初期化してアレイ読み出し状態に戻ります。RESET# が LOW の時、RWDS と DQ[7:0] が High-Z 状態に移行されます。RESET# は弱プルアップを含み、RESET# が未接続にされると HIGH 状態にプルアップされます。                                                                                             |

| RSTO#            | 出力<br>(オープンドレイン) | O   | RSTO# 出力：RSTO# はデバイス内で POR が発生している時点を示すために使用されるオープンドレイン出力であり、システムレベルのリセット信号として使用できます。内部 POR の完了後ただちに、ユーザーにより定義されたタイムアウト期間が経過した後、RSTO# 信号は低インピーダンスから高インピーダンスに遷移します。高インピーダンス状態に遷移した後ただちに、外部プルアップ抵抗は RSTO# 信号を HIGH に引き上げ、デバイスは瞬時に Standby 状態になります。 |

| V <sub>CC</sub>  | 電源               | P/G | 電源                                                                                                                                                                                                                                               |

| V <sub>CCQ</sub> | 電源               | P/G | 入力 / 出力電源                                                                                                                                                                                                                                        |

| V <sub>SS</sub>  | 電源               | P/G | グランド                                                                                                                                                                                                                                             |

| V <sub>SSQ</sub> | 電源               | P/G | 入力 / 出力グランド                                                                                                                                                                                                                                      |

注：

4. M = Mandatory; O = Optional; P/G = Power / Ground

## 4 HYPERRBUS™ プロトコル

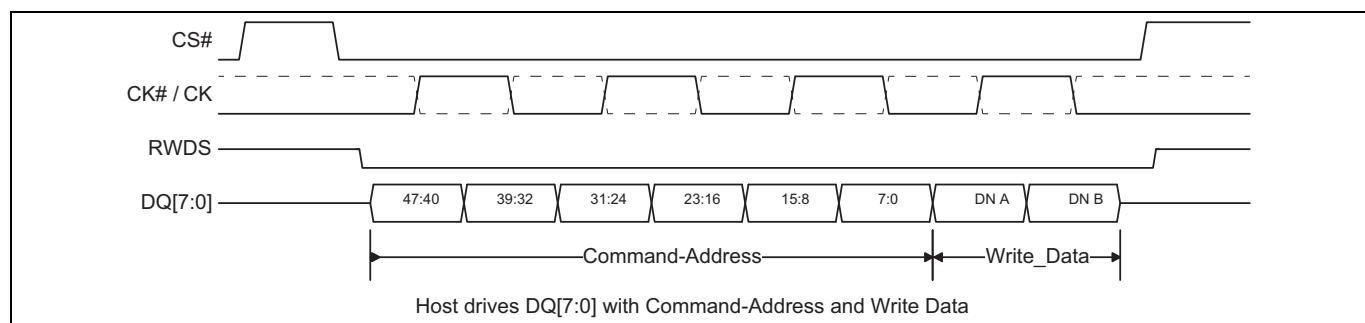

すべてのバストランザクションは読み出しと書き込みの2種類に分けられます。CK=LOW, CK#=HIGH の時、CS# が LOW になると、バストランザクションは開始します。実行されるトランザクションは最初の3クロックサイクル中に DDR 方式(合計 6 クロックエッジを使用すること)で HYPERFLASH™ デバイスに提供されます。これらの最初の3クロックでは、3ワードのコマンド / アドレス情報 (CA0, CA1, CA2) が転送され、トランザクションの次の特性を定義します。

- 読み出しトランザクションか書き込みトランザクション

- トランザクションの宛先はメモリアレイかレジスタ空間か

- HYPERRBUS™ プロトコルはメモリとレジスタアドレス空間の両方とも備えるスレーブデバイスに対応しますが、本仕様書で説明する HYPERFLASH™ メモリでは、メモリとレジスタが個別のアドレス空間として区別されません。トランザクションの宛先位置がメモリ空間かレジスタ空間にかかわらず、トランザクションが選択できるアドレス空間は1つのみあります。書き込みトランザクションでは、トランザクションアドレスとデータを1つのコマンドレジスタセット(バッファ)に格納します。読み出しトランザクションは、コマンドを実行することで単一アドレス空間内に一時的にオーバレイされるメモリアレイかレジスタアドレス空間のウィンドウからデータを返します。レジスタ空間オーバレイ方法を持つ、この単一アドレス空間はレガシーのパラレル NOR フラッシュメモリプログラムと消去ソフトウェアドライバーと下位互換性があります。

- トランザクションはリニアバーストかラップバーストシーケンスを使用するか

- HYPERFLASH™ 書き込みトランザクションはバーストシーケンスをサポートせず、バーストタイプの表示を無視します。書き込みコマンドトランザクションは、書き込みごとに1ワードを転送します。ワードプログラムコマンドの書き込みデータ転送のみ、最大 50 MHz の線形バーストで実行できます。

- ターゲットのハーフページアドレス(列と上位行アドレス)

- (ハーフページ内の)ターゲットのワードアドレス(下位行アドレス)

- トランザクション定義後かつデータ転送前の間で、読み出しレイテンシの要件を満たすためにいくつかのアイドルクロックサイクルが必要になります。ターゲットとなるデータが転送された後、HYPERRBUS™ マスタホストは CK=LOW と CK#=HIGH の状態で CS# を HIGH に駆動することでトランザクションを終了します。データは 16 ビット値として転送されます。この 16 ビットの最初の 8 ビット(ビット 15 ~ ビット 8)は CK の立ち上りエッジ(書き込みデータか CA ビットの場合)または RWDS のエッジ(読み出しどうデータの場合)にて転送され、2 番目の 8 ビット(ビット 7 ~ ビット 0)は CK の立ち下りエッジまたは RWDS のエッジで転送されます。CK=LOW、CK#=HIGH の時、CS# を HIGH にすることで、読み書き動作中のデータ転送を終了できます。読み出しどうデータは RWDS の遷移と同時に変化し、書き込みデータはクロックエッジと中央が揃います。

## 4.1 コマンド / アドレス ビットの割り当て

**Table 3** コマンド / アドレス ビットの割り当て

| CA ビット番号                                                                   | ビット名          | ビット機能                                                                                                                                                                            |

|----------------------------------------------------------------------------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 47                                                                         | R/W#          | トランザクションを読み出しか書き込みとして識別<br>1 = 読み出し動作<br>0 = 書き込み動作<br>ターゲット空間は CA46 で定義                                                                                                         |

| 46                                                                         | ターゲット         | 読み書き動作がメモリかレジスタ空間にアクセスするかを示します。<br>0 = メモリ空間<br>1 = レジスタ空間<br>レジスタ空間は不揮発性メモリとペリフェラルデバイスが使用するよう用意されます。 HYPERFLASH™ デバイスは、この機能を備えていないため、読み出しや書き込みトランザクションの間このビットを 0 にセットする必要があります。 |

| 45                                                                         | バースト タイプ      | バーストがリニアかラップであるのかを示します。<br>0 = ラップ バースト<br>1 = リニア バースト                                                                                                                          |

| 44 ~ 39 (1 Gb)<br>44 ~ 38 (512 Mb)<br>44 ~ 37 (256 Mb)<br>44 ~ 36 (128 Mb) | 予約済み          | 将来のアドレス拡張用に予約済み。<br>ホストコントローラーは予約済みビットを 0 にセットする必要があります。                                                                                                                         |

| 38 ~ 16 (1 Gb)<br>37 ~ 16 (512 Mb)<br>36 ~ 16 (256 Mb)<br>35 ~ 16 (128 Mb) | 列と上位行<br>アドレス | ターゲットアドレスのハーフページコンポーネント                                                                                                                                                          |

| 15 ~ 3                                                                     | 予約済み          | 将来の列アドレス拡張用に予約済み。<br>ホストコントローラーは予約済みビットを 0 にセットする必要があります。                                                                                                                        |

| 2 ~ 0                                                                      | 下位行アドレス       | ターゲットアドレスの下位列コンポーネント : システムワードアドレスビット A2 ~ 0 で、ハーフページ内の開始ワードを選択                                                                                                                  |

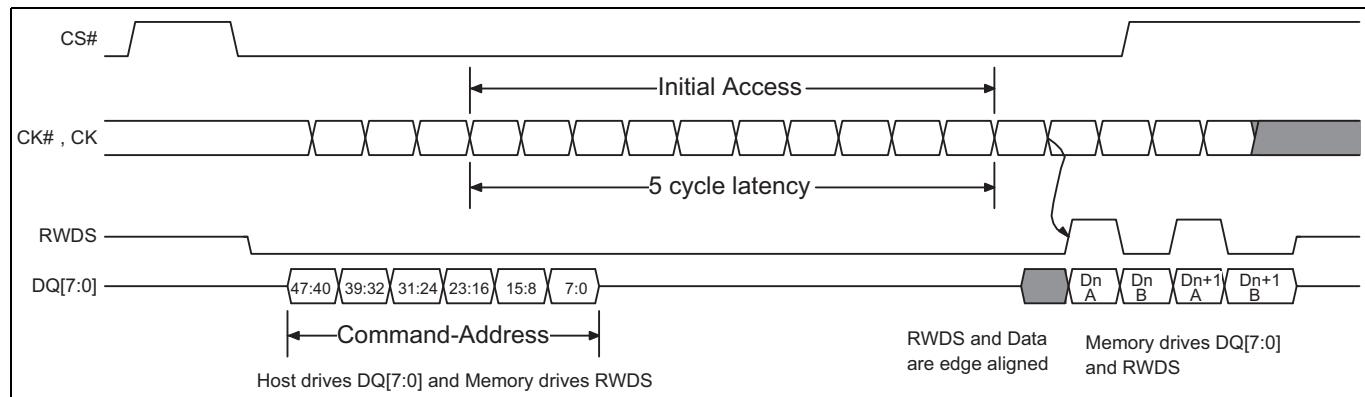

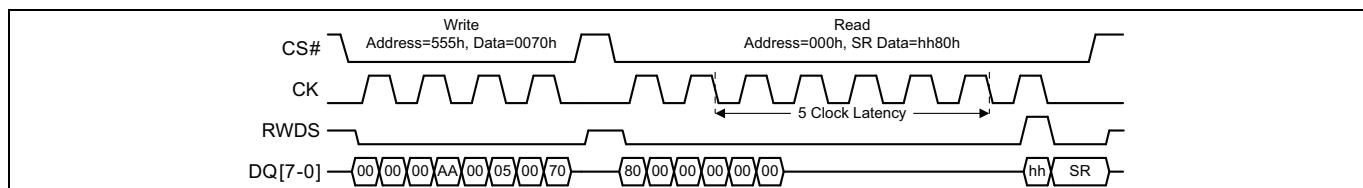

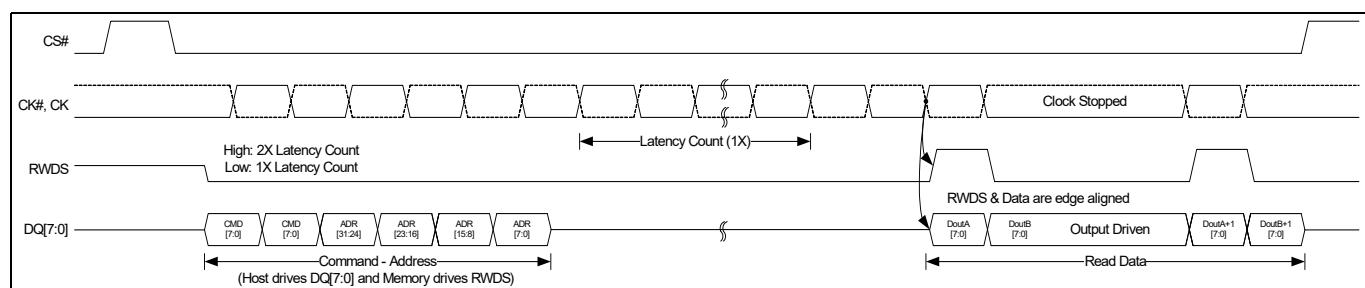

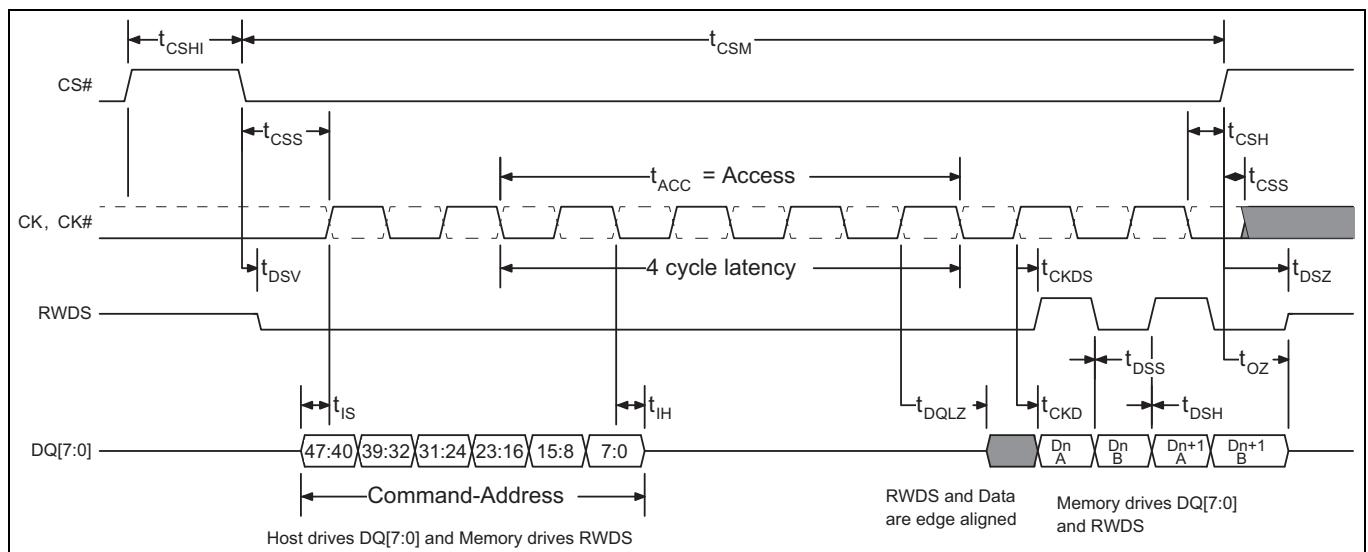

## 4.2 読み出し動作

CA0 は読み出し動作が次に実行されることを示す一方、バースト種類 (ラップかリニア) も表示します。ハーフページアドレスが CA0 と CA1 にて提供され次第、読み出し動作は内部のアレイアクセスを開始します。CA2 は選択したハーフページ内の対象のワードアドレスを指定します。ホストはコンフィギュレーションレジスタに設定したレイテンシカウントの値により定義されたサイクル数の期間でクロックを供給し続けます。これらのレイテンシクロックサイクルの設定値に達すると、読み出し / 書き込みデータストローブ (RWDS) の遷移と同時にターゲットデータの出力が開始されます。新しいデータがエッジ揃えの方法にて、毎回の RWDS の遷移によって出力されます。ホストから供給されるクロック (CK と CK#) の遷移が続いている限り、データは引き続き出力されます。ラップバーストはバースト長の範囲内で引き続きラップし、リニアバーストはページ境界を越えて順次データを出力します。[ハイブリッドバースト](#)に示すようにハイブリッドバーストは 1 個の初期ラップバーストの後にリニアバーストが後続することを提供します。ラップの読み出しは主要なアレイ ([デバイス ID および共通フラッシュインターフェース \(ID-CFI\) の ASO マップ](#) の CFI 表とセキュアシリコン領域 ([ハイブリッドバーストを参照](#)) ) から実行されます。CK = LOW, CK# = HIGH の時、CS# を HIGH にすることで、読み出し転送を終了できます。

リニアバーストがアレイの最後のアドレスに到達すると、バーストが続く場合、アドレスカウンターがラップアラウンドしてアドレス 000000h にロールバックし、読み出しシーケンスを無期限に継続できるようにします。したがって、メモリ全体を 1 つの読み出し命令で読み出せます。

16 バイトと 32 バイトのラップバーストはページ境界を越えず、ページ境界越えのレイテンシも発生させません。64 バイトのラップバースト読み出しでは、開始アドレスに応じて対象のアドレスと次のページの境界を超える時にレイテンシが発生する可能性があります ([Table 22](#) を参照してください)。

Figure 7 読み出し動作 [5, 6, 7, 8]

### 注:

5. トランザクションは CK = LOW および CK# = HIGH 状態で開始する必要があります。CS# は新しいトランザクションが開始する前に HIGH に復帰しなければいけません。

6. CA[23:16] が取り込まれるとフラッシュアレイからの読み出しアクセスは開始します。

7. 読み出しレイテンシは揮発性コンフィギュレーションレジスタ (または不揮発性コンフィギュレーションレジスタ) 内の読み出しレイテンシ値により定義されます。

8. この読み出し動作の例ではレイテンシカウントは 5 クロックに設定されています。

Table 4 レイテンシ コード オプションの最大動作周波数

| レイテンシ コード | レイテンシ クロック | 最大動作周波数 (MHz) |

|-----------|------------|---------------|

| 0000      | 5          | 52            |

| 0001      | 6          | 62            |

| 0010      | 7          | 72            |

| 0011      | 8          | 83            |

| 0100      | 9          | 93            |

| 0101      | 10         | 104           |

| 0110      | 11         | 114           |

| 0111      | 12         | 125           |

| 1000      | 13         | 135           |

| 1001      | 14         | 145           |

| 1010      | 15         | 156           |

| 1011      | 16         | 166           |

| 1100      | 予約済み       | 該当なし          |

| 1101      | 予約済み       | 該当なし          |

| 1110      | 予約済み       | 該当なし          |

| 1111      | 予約済み       | 該当なし          |

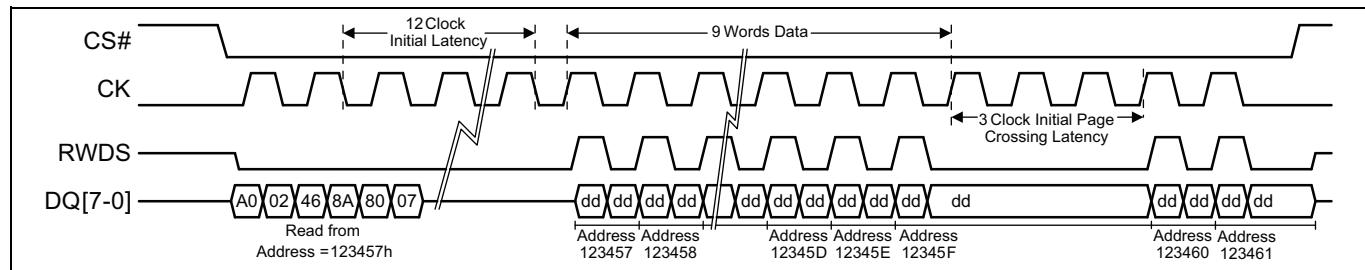

Figure 8 ページ境界を超える読み出しトランザクション [12, 13, 14, 15, 16]

#### 注:

9. 工場出荷時のデバイスでは NVCR レイテンシ 設定がデフォルトで 16 クロックです。

10. レイテンシ コードは(不)揮発性コンフィギュレーションレジスタ ビット xVCR[7:4] にロードされる値です。

11.  $t_{ACC} = 96 \text{ ns}$  のデバイスを使用する場合の最大動作周波数です。

12. 読み出しトランザクションは 123457h のデバイス アドレスから開始します。

13. コンフィギュレーションレジスタにロードされるレイテンシ コードは 0111b で、12 のレイテンシ クロック サイクルに該当します。

14. この場合ではページ境界を越えるために 3 クロック要します(12 クロックの初期レイテンシから 9 クロック(ワード)の初期データを引いた結果です)。

15. CK# は表示されていませんが、CK 信号の反転信号です。

16. CA45=1 はリニア読み出しバーストを意味します。

**Table 5** リニア読み出し中の最初のページ境界越え (レイテンシカウント = 11 クロック)

| ターゲットアドレス | クロックサイクル          |                    |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |

|-----------|-------------------|--------------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

|           | 0                 | 1                  | 2   | 3   | ... | 12  | 13  | 14  | 15  | 16  | 17  | 18  | 19  | 20  | 21  | 22  | 23  | 24  | 25  | 26  | 27  | 28  | 29  | 30  |     |     |     |     |     |

| 0         | CA0<br>CA1<br>CA2 | バスターンアラウンド+初期レイテンシ | D0  | D1  | D2  | D3  | D4  | D5  | D6  | D7  | D8  | D9  | D10 | D11 | D12 | D13 | D14 | D15 | D16 | D17 |     |     |     |     |     |     |     |     |     |

| 1         |                   |                    | D1  | D2  | D3  | D4  | D5  | D6  | D7  | D8  | D9  | D10 | D11 | D12 | D13 | D14 | D15 | D16 | D17 | D18 |     |     |     |     |     |     |     |     |     |

| 2         |                   |                    | D2  | D3  | D4  | D5  | D6  | D7  | D8  | D9  | D10 | D11 | D12 | D13 | D14 | D15 | D16 | D17 | D18 | D19 |     |     |     |     |     |     |     |     |     |

| 3         |                   |                    | D3  | D4  | D5  | D6  | D7  | D8  | D9  | D10 | D11 | D12 | D13 | D14 | D15 | D16 | D17 | D18 | D19 | D20 |     |     |     |     |     |     |     |     |     |

| 4         |                   |                    | D4  | D6  | D6  | D7  | D8  | D9  | D10 | D11 | D12 | D13 | D14 | D15 | D16 | D17 | D18 | D19 | D20 | D21 |     |     |     |     |     |     |     |     |     |

| 5         |                   |                    | D5  | D6  | D7  | D8  | D9  | D10 | D11 | D12 | D13 | D14 | D15 | D16 | D17 | D18 | D19 | D20 | D21 | D22 |     |     |     |     |     |     |     |     |     |

| 6         |                   |                    | D6  | D7  | D8  | D9  | D10 | D11 | D12 | D13 | D14 | D15 | X   | D16 | D17 | D18 | D19 | D20 | D21 | D22 |     |     |     |     |     |     |     |     |     |

| 7         |                   |                    | D7  | D8  | D9  | D10 | D11 | D12 | D13 | D14 | D15 | X   | X   | D16 | D17 | D18 | D19 | D20 | D21 | D22 |     |     |     |     |     |     |     |     |     |

| 8         |                   |                    | D8  | D9  | D10 | D11 | D12 | D13 | D14 | D15 | D16 | D17 | D18 | D19 | D20 | D21 | D22 | D23 | D24 | D25 | D26 | D27 | D28 | D29 | D30 | D31 | D32 | D33 |     |

| 9         |                   |                    | D9  | D10 | D11 | D12 | D13 | D14 | D15 | D16 | D17 | D18 | D19 | D20 | D21 | D22 | D23 | D24 | D25 | D26 | D27 | D28 | D29 | D30 | D31 | D32 | D33 | D34 |     |

| 10        |                   |                    | D10 | D11 | D12 | D13 | D14 | D15 | D16 | D17 | D18 | D19 | D20 | D21 | D22 | D23 | D24 | D25 | D26 | D27 | D28 | D29 | D30 | D31 | D32 | D33 | D34 | D35 |     |

| 11        |                   |                    | D11 | D12 | D13 | D14 | D15 | D16 | D17 | D18 | D19 | D20 | D21 | D22 | D23 | D24 | D25 | D26 | D27 | D28 | D29 | D30 | D31 | D32 | D33 | D34 | D35 | D36 |     |

| 12        |                   |                    | D12 | D13 | D14 | D15 | D16 | D17 | D18 | D19 | D20 | D21 | D22 | D23 | X   | D24 | D25 | D26 | D27 | D28 | D29 | D30 | D31 | D32 | D33 | D34 | D35 | D36 | D37 |

| 13        |                   |                    | D13 | D14 | D15 | D16 | D17 | D18 | D19 | D20 | D21 | D22 | D23 | X   | D24 | D25 | D26 | D27 | D28 | D29 | D30 | D31 | D32 | D33 | D34 | D35 | D36 | D37 | D38 |

| 14        |                   |                    | D14 | D15 | D16 | D17 | D18 | D19 | D20 | D21 | D22 | D23 | X   | X   | D24 | D25 | D26 | D27 | D28 | D29 | D30 | D31 | D32 | D33 | D34 | D35 | D36 | D37 | D38 |

| 15        |                   |                    | D15 | D16 | D17 | D18 | D19 | D20 | D21 | D22 | D23 | X   | X   | D24 | D25 | D26 | D27 | D28 | D29 | D30 | D31 | D32 | D33 | D34 | D35 | D36 | D37 | D38 | D39 |

| 16        |                   |                    | D16 | D17 | D18 | D19 | D20 | D21 | D22 | D23 | D24 | D25 | D26 | D27 | D28 | D29 | D30 | D31 | D32 | D33 | D34 | D35 | D36 | D37 | D38 | D39 | D40 | D41 |     |

|           | -                 | -                  | 1   | 2   | ... | 11  | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   |

|           | レイテンシ数            |                    |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |

**Table 6** リニア読み出し中の最初のページ境界越え (レイテンシカウント = 16 クロック)

| ターゲットアドレス | CS#がLOWになった後のクロックサイクル |                    |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |

|-----------|-----------------------|--------------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

|           | 0                     | 1                  | 2   | 3   | ... | 17  | 18  | 19  | 20  | 21  | 22  | 23  | 24  | 25  | 26  | 27  | 28  | 29  | 30  | 31  | 32  | 33  | 34  | 35  |     |     |     |     |     |     |     |

| 0         | CA0<br>CA1<br>CA2     | バスターンアラウンド+初期レイテンシ | D0  | D1  | D2  | D3  | D4  | D5  | D6  | D7  | D8  | D9  | D10 | D11 | D12 | D13 | D14 | D15 | D16 | D17 |     |     |     |     |     |     |     |     |     |     |     |

| 1         |                       |                    | D1  | D2  | D3  | D4  | D5  | D6  | D7  | D8  | D9  | D10 | D11 | D12 | D13 | D14 | D15 | X   | D16 | D17 |     |     |     |     |     |     |     |     |     |     |     |

| 2         |                       |                    | D2  | D3  | D4  | D5  | D6  | D7  | D8  | D9  | D10 | D11 | D12 | D13 | D14 | D15 | X   | X   | D16 | D17 |     |     |     |     |     |     |     |     |     |     |     |

| 3         |                       |                    | D3  | D4  | D5  | D6  | D7  | D8  | D9  | D10 | D11 | D12 | D13 | D14 | D15 | X   | X   | X   | D16 | D17 |     |     |     |     |     |     |     |     |     |     |     |

| 4         |                       |                    | D4  | D6  | D6  | D7  | D8  | D9  | D10 | D11 | D12 | D13 | D14 | D15 | X   | X   | X   | X   | D16 | D17 |     |     |     |     |     |     |     |     |     |     |     |

| 5         |                       |                    | D5  | D6  | D7  | D8  | D9  | D10 | D11 | D12 | D13 | D14 | D15 | X   | X   | X   | X   | X   | D16 | D17 |     |     |     |     |     |     |     |     |     |     |     |

| 6         |                       |                    | D6  | D7  | D8  | D9  | D10 | D11 | D12 | D13 | D14 | D15 | X   | X   | X   | X   | X   | X   | D16 | D17 |     |     |     |     |     |     |     |     |     |     |     |

| 7         |                       |                    | D7  | D8  | D9  | D10 | D11 | D12 | D13 | D14 | D15 | X   | X   | X   | X   | X   | X   | X   | D16 | D17 |     |     |     |     |     |     |     |     |     |     |     |

| 8         |                       |                    | D8  | D9  | D10 | D11 | D12 | D13 | D14 | D15 | D16 | D17 | D18 | D19 | D20 | D21 | D22 | D23 | D24 | D25 | D26 | D27 | D28 | D29 | D30 | D31 | D32 | D33 |     |     |     |

| 9         |                       |                    | D9  | D10 | D11 | D12 | D13 | D14 | D15 | D16 | D17 | D18 | D19 | D20 | D21 | D22 | D23 | D24 | D25 | D26 | D27 | D28 | D29 | D30 | D31 | D32 | D33 | D34 |     |     |     |

| 10        |                       |                    | D10 | D11 | D12 | D13 | D14 | D15 | D16 | D17 | D18 | D19 | D20 | D21 | D22 | D23 | X   | X   | D24 | D25 | D26 | D27 | D28 | D29 | D30 | D31 | D32 | D33 | D34 |     |     |

| 11        |                       |                    | D11 | D12 | D13 | D14 | D15 | D16 | D17 | D18 | D19 | D20 | D21 | D22 | D23 | X   | X   | X   | X   | X   | X   | X   | X   | D24 | D25 | D26 | D27 | D28 | D29 | D30 |     |

| 12        |                       |                    | D12 | D13 | D14 | D15 | D16 | D17 | D18 | D19 | D20 | D21 | D22 | D23 | X   | X   | X   | X   | X   | X   | X   | X   | X   | X   | D24 | D25 | D26 | D27 | D28 | D29 | D30 |

| 13        |                       |                    | D13 | D14 | D15 | D16 | D17 | D18 | D19 | D20 | D21 | D22 | D23 | X   | X   | X   | X   | X   | X   | X   | X   | X   | X   | X   | D24 | D25 | D26 | D27 | D28 | D29 | D30 |

| 14        |                       |                    | D14 | D15 | D16 | D17 | D18 | D19 | D20 | D21 | D22 | D23 | X   | X   | X   | X   | X   | X   | X   | X   | X   | X   | X   | X   | D24 | D25 | D26 | D27 | D28 | D29 | D30 |

| 15        |                       |                    | D15 | D16 | D17 | D18 | D19 | D20 | D21 | D22 | D23 | X   | X   | X   | X   | X   | X   | X   | X   | X   | X   | X   | X   | X   | D24 | D25 | D26 | D27 | D28 | D29 | D30 |

| 16        |                       |                    | D16 | D17 | D18 | D19 | D20 | D21 | D22 | D23 | D24 | D25 | D26 | D27 | D28 | D29 | D30 | D31 | D32 | D33 | D34 | D35 | D36 | D37 | D38 | D39 | D40 | D41 |     |     |     |

|           | -                     | -                  | 1   | 2   | ... | 16  | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   |     |

|           | レイテンシ数                |                    |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |

ページの境界を越えるときの待ち時間を計算するには、次の式を使用します。

```

if ((PS - LTCY) < ADDR & (SP - 1))

{

((ADDR & (SP - 1)) - PS + LTCY)

}

else

{ 0 }

```

ここで

PS = ページサイズ = 16 ワード

SP = サブページサイズ = 8 ワード

LTCY = レイテンシ

ADDR = ターゲットアドレス

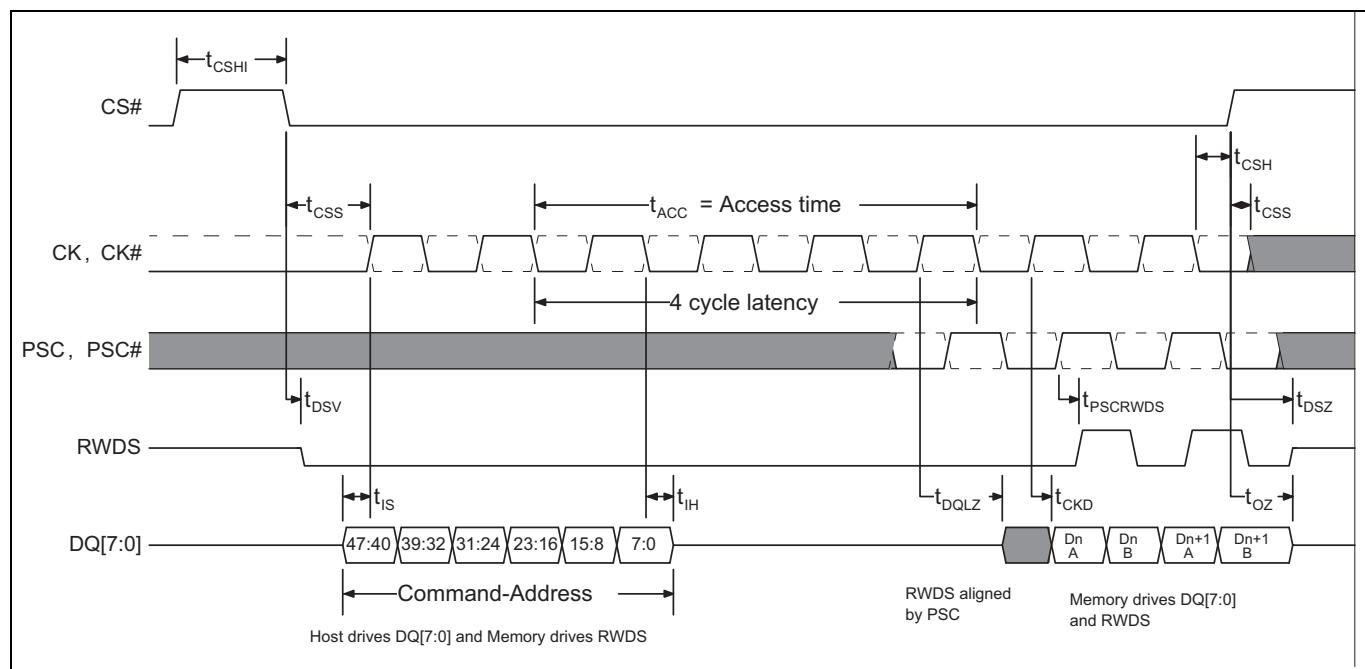

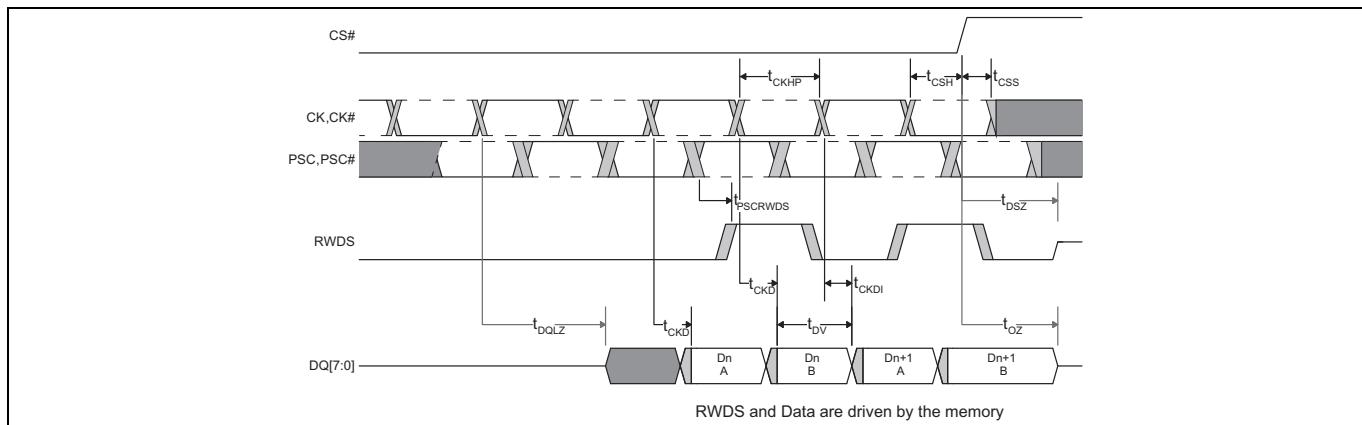

#### 4.3 DCARS タイミングでの HYPERFLASH™ 読み出し

ここでの図とパラメーターは、DCARS 機能を定義し、位相シフトクロック、RWDS、およびデータ間の関係を示すために必要なもののみです。

Figure 9 HYPERFLASH™ 読み出し DCARS タイミング ダイヤグラム [17, 18, 19, 20]

注:

17. トランザクションは CK=LOW および CK#=HIGH 状態で開始する必要があります。CS# は新しいトランザクションが開始する前に HIGH に復帰しなければいけません。

18. CK# と PSC# はオプションであり、破線の波形として表示されます。

19. メモリは、読み出しトランザクション中に RWDS を駆動します。

20. この例は、4 クロックのレイテンシコード設定をしており、追加の初期レイテンシは不要です。

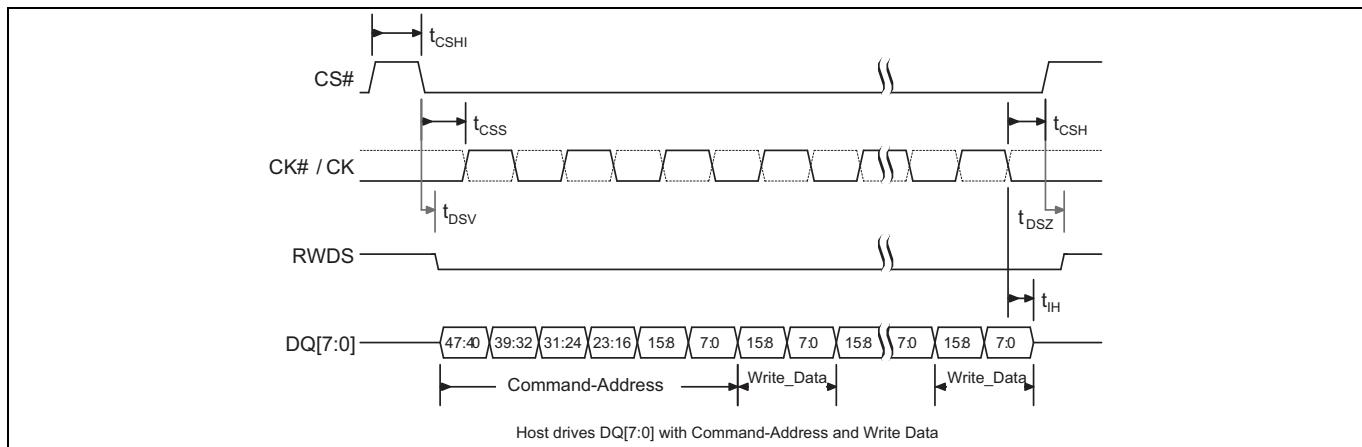

#### 4.4 書き込み動作

書き込み動作は、トランザクション属性を指示する CAx(コマンド / アドレス)情報を提供する最初の3クロックサイクルから開始します。HYPERFLASH™デバイスは16ビットのシングル書き込みトランザクションのみに対応するか、またはワードプログラムコマンドでデータをロードする時のみ連続リニアバーストに対応するため、バーストタイプビット CA[45]は「ドントケア」です。CA情報に従って、ホストは瞬時に書き込みデータを DQ バスに転送できます。最初のデータバイト (A) は CK の立ち上りエッジにあり、2番目のデータバイト (B) は CK の立ち下りエッジにあります。書き込みデータは CK と CK# 入力信号と中央が揃います。CK = LOW、CK# = HIGH の時、CS# を HIGH にすることで、書き込み転送を終了できます。

Figure 10 書き込み動作 [21, 22, 23]

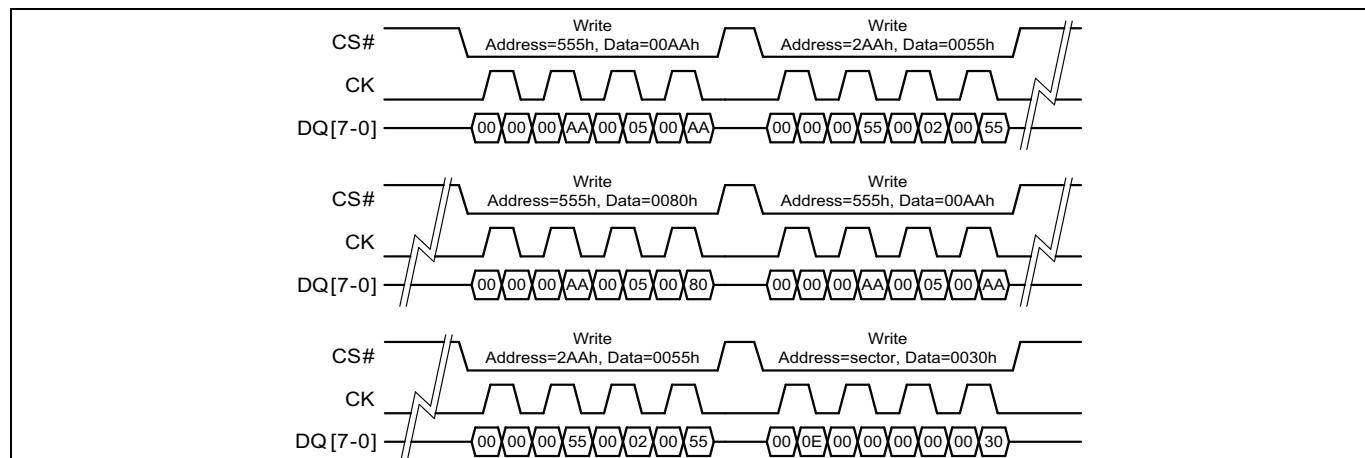

Figure 11 書き込みトランザクションの使用例：動作消去コマンド シーケンス [24, 25, 26, 27]

#### 注：

- 21.トランザクションは CK = LOW および CK# = HIGH 状態で開始する必要があります。CS# は新しいトランザクションが開始する前に HIGH に復帰しなければいけません。

- 22.CS# が LOW である限り、RWDS は LOW に駆動されます。

- 23.書き込み動作はシングルワード(16ビット)のトランザクションか、またはワードプログラムコマンドでデータをロードする時のみ対応するリニア書き込みバーストのトランザクションに制限されます。この例は、4クロックのレイテンシコード設定を示しており、追加の初期レイテンシは不要です。

- 24.動作消去コマンドシーケンスのフローチャートについては [Figure 17](#) を参照してください。

- 25.セクタ消去動作は 0700000h から開始します。

- 26.CK# は表示されていませんが、CK 信号の反転信号です。

- 27.書き込みトランザクションでは RWDS が表示されず使用されません。

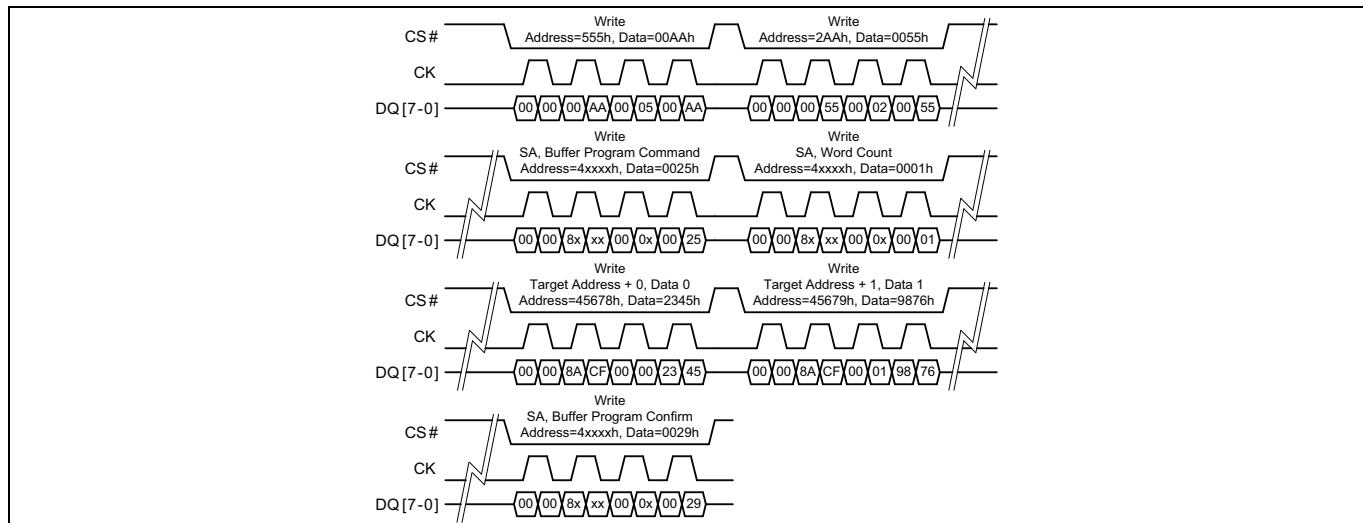

**Figure 12 書き込みトランザクションの使用例：バッファプログラム書き込みコマンド シーケンス**

[28, 29, 30, 31]

**Figure 13 ステータス読み出しトランザクションの例** [30]

#### 注：

28. バッファプログラム動作の書き込みコマンドシーケンスのフローチャートについては [Figure 15](#) を参照してください。

29. 2345h を 45678h アドレスに、9876h を 45679h アドレスにプログラムします。

30. CK# は表示されていませんが、CK 信号の反転信号です。

31. 書き込みトランザクションでは RWDS が表示されず使用されません。

## アドレス空間マップ

### 5 アドレス空間マップ

HYPERSBUS™ プロトコルはメモリとレジスタアドレス空間の両方とも備えるスレーブデバイスに対応しますが、本仕様書で説明する HYPERFLASH™ メモリでは、メモリとレジスタが個別のアドレス空間として区別されません。HYPERSBUS™ トランザクションの宛先位置が選択したデバイスのメモリ空間かレジスタ空間にかかわらず、トランザクションが選択できるアドレス空間は 1 つのみあります。

書き込みトランザクションでは、トランザクションアドレスとデータを 1 つのコマンドレジスタセット(バッファ)に格納します。

読み出しトランザクションは、コマンドを実行することで単一のアドレス空間内に一時的にオーバレイされるメモリアレイかレジスタアドレス空間のウィンドウからデータを返します。レジスタ空間オーバレイ方法を持つ、この單一アドレス空間はレガシーのパラレル NOR フラッシュメモリプログラムと消去ソフトウェアドライバーと下位互換性があります。

フラッシュメモリデバイスのアドレス範囲内には複数の個別のアドレス空間が表示されることがあります。1 つのアドレス空間がいつでも表示(入力済み)されます。

- フラッシュメモリアレイ: データ格納用の主要な不揮発性メモリアレイであり、読み出し動作によってランダムにアクセスすることができます。

- ID/CFI: インフィニオンの工場でプログラムされたデバイス特性情報格納用のメモリアレイです。この領域には、デバイス識別(ID)と共通フラッシュインターフェース(CFI)の情報テーブルが含まれます。

- セキュアシリコン領域(SSR): インフィニオンの工場でプログラムされた恒久データおよびカスタマープログラム可能恒久データ格納用の 1024 バイト 1 回書き込み可能な OTP 不揮発性メモリアレイです。

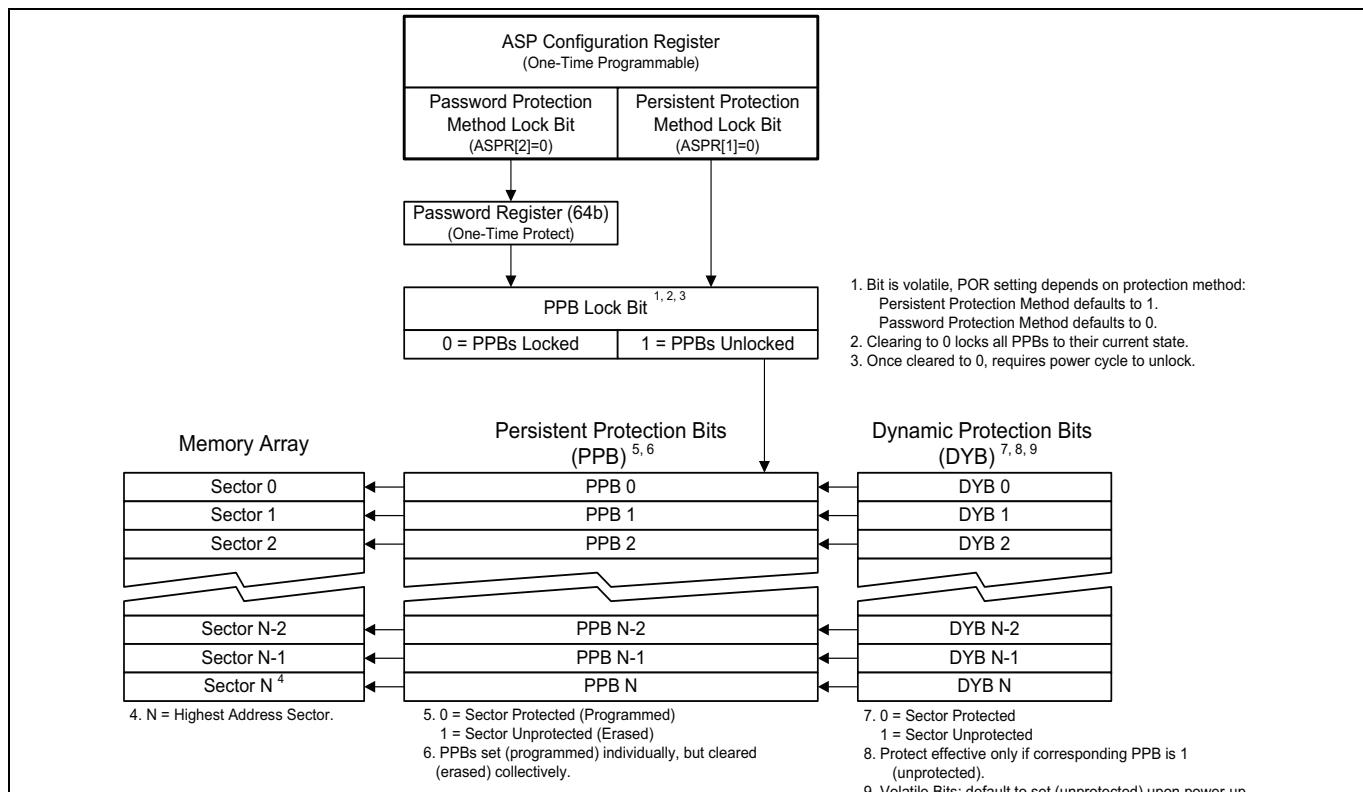

- 恒久的保護ビット(PPB): 不揮発性メモリアレイであり、セクタごとに 1 ビット幅を有します。プログラムされると、該当するセクタを消去とプログラミングから保護します。

- PPB ロックビット: PPB ビットの消去とプログラミングを有効/無効化する揮発性レジスタビットです。

- パスワード: パスワードモードのセクタ保護を使用する際に PPB ロックビットの状態を変更可能にするために使用される 64 ビットパスワード格納用の OTP 型不揮発性アレイです。

- ダイナミック保護ビット(DYB): 揥発性アレイであり、セクタごとに 1 ビット幅を有します。セットされると、該当するセクタを消去とプログラミングから保護します。

- ECC ステータス: ECC 修正データのアドレスと合計 ECC エラーカウントを読み出します。

- CRC: CRC Check-value を読み出します。

- ステータスレジスタ/ペリフェラルレジスタ: 組込みアルゴリズムの状態を表示するか他のレジスタに読み書きするためのレジスタアクセス空間です。

フラッシュメモリアレイはプライマリおよびデフォルトのアドレス空間ですが、いつでも別のアドレス空間によってオーバーレイされる可能性があります。各代替アドレス空間は ASO と呼ばれます。

各 ASO は、ASO エントリコマンドに応じて、選択したセクタかフラッシュデバイスのすべてのアドレス空間を置換(オーバーレイ)します。ASO に置き換えられたセクタが 1 個のみの場合、メモリアレイの残りのセクタの読み出しはそのまま実現できます。特定の ASO アドレスマップで定義されていないアドレス範囲は将来に使用するために予約されます。特に指定のない限り、ASO アドレスマップ外のすべての読み出しアクセスは無効な(未定義)データを返します。その位置にはアクティブに駆動されたデータが表示されますが、それらの意味は定義されていません。

任意の時点においてフラッシュデバイスのアドレス空間に表示される内容を決定するアドレスマップモードが多くあります。

- 読み出しモード

- ステータスレジスタ(SR)モード

- ASO モード

- ペリフェラルレジスタモード

## アドレス空間マップ

読み出しモードでは、フラッシュメモリアレイ全体が、ホストのシステムメモリコントローラによって直接読み出せます。メモリデバイスのEACは、電源投入時、ハードウェアリセット後、コマンドリセット後、またはEAが一時停止された後にデバイスを読み出すモードに入ります。読み出しモードでは読み出しアクセスと読み出しコマンドを実現できます。EAが一時停止されている時に読み出しモードでコマンドのサブセットを実現できます。

どのモードでも、ステータスレジスタ読み出しコマンドを発行することで、デバイスのアドレス空間内のあらゆるワードアドレスでステータスレジスタASOを表示させられます。このステータスレジスタASOモードでは、デバイスインターフェースは読み出しアクセスだけに対応し、書き込みアクセスはすべて無視されます。デバイスへの次の読み出しアクセスはステータスレジスタの内容にアクセスします。その後、ステータスレジスタASOを終了し、デバイスはステータスレジスタ読み出しコマンドを受け取る前の(呼び出し)モードに戻ります。

同様に、他のレジスタを読み書きするコマンドはペリフェラルレジスタモードを利用します。このモードでは、レジスタは臨時のASOとして表示し、コマンドによって選択されたレジスタの読み書き動作が完了すると自動的にモードを終了します。読み出しと書き込み動作はレジスタアクセスコマンドシーケンスの最後のサイクルで実現されます。

EAモードでEACは不揮発性メモリアレイのプログラミングや消去のようなEAを実現します。このEAモードではフラッシュメモリアレイはすべて読み出し不可です。プログラム/消去一時停止コマンド、またはステータスレジスタ読み出しコマンドのみがこのモードで実行可能です。他のすべてのコマンドは無視されます。したがって、EAモードで他のASOへの移動は許可されません。

ASOモードでは、残っているオーバーレイアドレス空間の1つが入ります(フラッシュメモリアレイのアドレスマップにオーバーレイされます)。一度に移行できるASOは1つだけです。デバイスへのコマンドは、現在移行されたASOに影響を与えます。ASOに応じて特定のコマンドが有効です。有効なコマンドはTable 41のASO関連セクションに示されます。

下記のASOは、1を0に変更するようにプログラムできる不揮発性データを持っています。

- セキュアシリコン領域

- ASPコンフィギュレーションレジスタ(ASPR)

- 恒久的保護ビット(PPB)

- パスワード

- PPB ASOだけが、0を1に変更するように消去できる不揮発性データを持っています。

任意の不揮発性ASOが入っている間にプログラムコマンドか消去コマンドが発行されると、EAはそのASO上で動作します。EAが有効の間はそのASOの読み出しは不可です。EAが完了すると、ASOが入っている状態のままで再度読み出し可能になります。EAがこれらの任意のASOで動作している間は、一時停止コマンドと再開コマンドが無視されます。

ペリフェラルレジスタモードは、PORタイマー、割込みコンフィギュレーションレジスタ、割込みステータスレジスタ、揮発性コンフィギュレーションレジスタ、および不揮発性コンフィギュレーションレジスタを管理するために使用されます。

## 5.1 フラッシュメモリアレイ

S26KL/S26KSファミリは、セクタサイズが256Kバイトのユニフォームセクタアーキテクチャを搭載しています。下記の表はデバイスのセクタアーキテクチャを示します。

最初のセクタ(SA00)から最後のセクタ(SAmax)を8個の4Kバイトパラメーターセクタにオーバーレイするために1つのユーザー設定のオプションが用意されます。最下位セクタや最上位セクタの分割方法を示すパラメーターセクタのアドレスマップは、下記のメモリアドレスマップの表に示されています。パラメーターセクタは、該当するパラメーターセクタアドレスを対象に標準の消去とプログラムコマンドシーケンスを利用して通常の方法で消去/プログラムできます。比較的小さいパラメーターセクタは、消去およびプログラムコマンドシーケンスでは、対象となるパラメーターセクタを識別するアドレスの一部としてA[16:11]を追加する必要があるため、ご注意ください。最初や最後のユニフォームセクタにパラメーターセクタを追加するように設定することは不揮発性コンフィギュレーションレジスタで実現されます。

注:次の表は、1ページでデバイス全体のセクタ関連情報を示すようにまとめました。(SA001～SA510のように明示的に記載されていないセクタやそのアドレス範囲に対して、そのセクタの開始と終了アド

## アドレス空間マップ

レスは、同じサイズを持つ他のすべてのセクタと同じパターンを持っています。例えば、すべての 256K バイトセクタは XX00000h ~ XX1FFFFh のアドレス範囲パターンを持っています。

**Table 7 S26KL512S および S26KS512S のセクタとメモリアドレスマップ**

| セクタ サイズ (KB) | セクタ数 | セクタ範囲 | アドレス範囲 (16 ビット)     | 注記        |

|--------------|------|-------|---------------------|-----------|

| 256          | 256  | SA00  | 0000000h ~ 001FFFFh | セクタ開始アドレス |

|              |      | :     | :                   | -         |

|              |      | SA255 | 1FE0000h ~ 1FFFFFFh | セクタ終了アドレス |

**Table 8 S26KL256S および S26KS256S のセクタとメモリアドレスマップ**

| セクタ サイズ (KB) | セクタ数 | セクタ範囲 | アドレス範囲 (16 ビット)     | 注記        |

|--------------|------|-------|---------------------|-----------|

| 256          | 128  | SA00  | 0000000h ~ 001FFFFh | セクタ開始アドレス |

|              |      | :     | :                   | -         |

|              |      | SA127 | 0FE0000h ~ 0FFFFFFh | セクタ終了アドレス |

**Table 9 S26KL128S および S26KS128S のセクタとメモリアドレスマップ**

| セクタ サイズ (KB) | セクタ数 | セクタ範囲 | アドレス範囲 (16 ビット)      | 注記        |

|--------------|------|-------|----------------------|-----------|

| 256          | 64   | SA00  | 0000000h ~ 001FFFFh  | セクタ開始アドレス |

|              |      | :     | :                    | -         |

|              |      | SA63  | 07E0000h ~ 07FFFFFFh | セクタ終了アドレス |

**Table 10 8 つの 4 KB パラメーター セクタで重複される主アレイセクタ 0**

| 主アレイ<br>セクタ サイズ | パラメーター<br>セクタ番号    | アドレス<br>サイズ | アドレス範囲 (16 ビット)     | 注記                           |

|-----------------|--------------------|-------------|---------------------|------------------------------|

| 256 KB          | 0                  | 4 KB        | 0000000h ~ 00007FFh | パラメーター セクタ 0 の開始             |

|                 | 1                  | 4 KB        | 0000800h ~ 0000FFFh | パラメーター セクタ 1                 |

|                 | 2                  | 4 KB        | 0001000h ~ 00017FFh | パラメーター セクタ 2                 |

|                 | 3                  | 4 KB        | 0001800h ~ 0001FFFh | パラメーター セクタ 3                 |

|                 | 4                  | 4 KB        | 0002000h ~ 00027FFh | パラメーター セクタ 4                 |

|                 | 5                  | 4 KB        | 0002800h ~ 0002FFFh | パラメーター セクタ 5                 |

|                 | 6                  | 4 KB        | 0003000h ~ 00037FFh | パラメーター セクタ 6                 |

|                 | 7                  | 4 KB        | 0003800h ~ 0003FFFh | パラメーター セクタ 7 の終了             |

|                 | 主アレイセクタ 0<br>の露出部分 | 224 KB      | 0004000h ~ 001FFFFh | 主アレイセクタ 0 の露出部分<br>にマッピングされる |

**Table 11 8つの4 KB パラメーター セクタで重複される最終セクタ**

| 主アレイ セクタサイズ | パラメーター セクタ番号    | アドレス サイズ | アドレス範囲(16ビット)       | 注記                       |

|-------------|-----------------|----------|---------------------|--------------------------|

| 256 KB      | 主アレイの最終セクタの露出部分 | 224 KB   | xx00000h ~ xx1BFFFh | 主アレイの最終セクタの露出部分にマッピングされる |

|             | 0               | 4 KB     | xx1C000h ~ xx1C7FFh | パラメーター セクタ 0 の開始         |

|             | 1               | 4 KB     | xx1C800h ~ xx1CFFFh | パラメーター セクタ 1             |

|             | 2               | 4 KB     | xx1D000h ~ xx1D7FFh | パラメーター セクタ 2             |

|             | 3               | 4 KB     | xx1D800h ~ xx1DFFFh | パラメーター セクタ 3             |

|             | 4               | 4 KB     | xx1E000h ~ xx1E7FFh | パラメーター セクタ 4             |

|             | 5               | 4 KB     | xx1E800h ~ xx1EFFFh | パラメーター セクタ 5             |

|             | 6               | 4 KB     | xx1F000h ~ xx1F7FFh | パラメーター セクタ 6             |

|             | 7               | 4 KB     | xx1F800h ~ xx1FFFFh | パラメーター セクタ 7 の終了         |

## 5.2 デバイス ID および CFI (ID-CFI) ASO

システムに搭載されたフラッシュメモリの種類を識別するには、次の2つの従来方式があります。1つはデバイス識別(ID)です。もう一つの方法は、共通フラッシュインターフェース(CFI)と呼ばれています。

IDについて、1つのコマンドを使用してASOを有効にし、その最大16ワードの位置を読み出すことでJEDEC製造者識別(ID), デバイスID, およびいくつかの構成情報と保護ステータス情報をフラッシュメモリから取得します。システムはこの製造者IDとデバイスIDを用いて、フラッシュデバイスと動作する適切なドライバーソフトウェアを選択できます。

CFIも1つのコマンドを使用してASOを有効にし、フラッシュメモリの構成や動作方法についての基本情報を提供する拡張可能なテーブルの読み出しを実現できます。この方法を用いると、使用するそれぞれのメモリデバイス仕様をドライバソフトウェアに書き込む必要はありません。代わりに、ドライバソフトウェアは多くの異なるデバイスを扱うためにより一般的な方法で書き込まれ、ドライバの動作はCFIテーブルの情報に基づいて調整されます。

これまででは、これら2つのアドレス空間は個別のコマンドを使用し個別のオーバーレイ領域でした。しかし、これら2つのアドレス空間のマッピングは重複しないため、単一のアドレス空間に組み合わせ、単一のオーバーレイで共に表示できます。自動選択(ID)またはCFIオーバーレイにアクセス(入る)するために使用される従来のコマンドのどちらも、組み合わせID-CFIアドレスマップを表示させます。

ID-CFIアドレスマップは、ID-CFI入力コマンド内で使用するアドレスによって選択されたセクタ内に表示され、フラッシュアレイデータをオーバーレイします。ID-CFI ASOが入っている間は、他のすべてのセクタの内容は未定義です。

ID-CFIアドレスマップは、選択されたセクタの0の位置から開始します。ID-CFI ASOの最大定義アドレス以上から、選択したセクタの最大アドレスまでの位置のデータは未定義です。ID-CFI入力コマンドは前世代のメモリと同じアドレスとデータ値を使用してそれぞれJEDEC製造者ID(自動選択)とCFI情報をアクセスします。

**Table 12 ID-CFIのアドレスマップの概要**

| ワードアドレス            | 説明               | 読み出し / 書き込み |

|--------------------|------------------|-------------|

| (SA)+0000h ~ 000Fh | デバイスID(従来の自動選択値) | 読み出し専用      |

| (SA)+0010h ~ 0079h | CFIデータ構造         | 読み出し専用      |

| (SA)+007Ah ~ 00FFh | 未定義              | 読み出し専用      |

完全なアドレスマップについてはTable 35を参照してください。

### 5.2.1 デバイス ID

JEDEC の標準 JEP106T は、準拠メモリ用の製造者 ID を定義します。一般的な業界使用として、メモリデバイスから製造者 ID とデバイス固有 ID を読み出す方法とフォーマットを定義しました。製造者 ID とデバイス ID 情報は、デバイスを対応するプログラミングアルゴリズムと自動的に一致させるように主にプログラミング機器に使用されます。インフィニオンはこの 32 バイトのアドレス空間内に追加フィールドを追加しました。

オリジナルの業界フォーマットは、あらゆるメモリデータバス幅 (例えば x8, x16, x32) で動作できるように構成されました。ID コード値は従来はバイト幅ですが、バス幅アドレス境界に位置されます。よって、デバイスアドレス入力のインクリメントは、常にデータバスの最下位バイトに位置する ID コード付きの連続バイト、ワード、またはダブルワード位置を読み出します。デバイスのデータバスはワード幅で、各コードバイトはワード位置の下半部 (下位バイト) に位置します。オリジナルの業界フォーマットでは上位バイトが常に 0 です。インフィニオンはアドレス空間のいくつかのワードで両方のバイトを使用するようにフォーマットを変更しました。デバイス ID のアドレスマップの詳細については Table 35 を参照してください。

### 5.2.2 共通フラッシュメモリインターフェース

JEDEC CFI 仕様 (JESD68.01) は、フラッシュメモリデバイスから読み出し可能な標準化されたデータ構造を定義し、全デバイスファミリで使用されるベンダー固有ソフトウェアアルゴリズムを可能にします。データ構造には、さまざまな電気的パラメーターとタイミングパラメーター、およびデバイスがサポートする特別な機能などのシステム構成情報が含まれます。ソフトウェアサポートはデバイスに依存せず、デバイス ID に依存せず、全フラッシュデバイスファミリで上位下位互換性があります。

システムは、[デバイス ID および共通フラッシュインターフェース \(ID-CFI\)](#) の ASO マップに示すように、選択されたセクタ内のアドレスにある CFI 情報を読み出せます。

デバイス ID 情報と同様に、CFI 情報はメモリデータバス幅 (例えば x8, x16, x32) で動作できるように構成されます。コード値は常にバイト幅ですが、データバス幅アドレス境界に位置されます。よって、デバイスアドレスのインクリメントは、常にデータバスの最下位バイトに位置するコード付きの連続バイト、ワード、またはダブルワード位置を読み出します。デバイスのデータバスはワード幅で、各コードバイトはワード位置の下半部 (下位バイト) に位置し、上位バイトは常に 0 です。

詳細は、CFI Specification, Version 1.5 (またはそれ以降のバージョン)、および JEDEC publications JEP137-A and JESD68.01 を参照してください。

組込み動作

## 6 組込み動作

### 6.1 組込みアルゴリズム コントローラー (EAC)

EAC は、不揮発メモリ状態を変更するために、フラッシュメモリアレイのプログラミングと消去を行うコマンドを受け取り、必要なすべての複雑な操作を実行します。これにより、ホストシステムはプログラムおよび消去のプロセスを管理する必要がなくなります。

EAC 動作は 5 つのカテゴリに分けられます。

- ・ディープパワーダウン (DPD)

- ・スタンバイ (リードモード)

- ・アドレス空間の切換え

- ・組込みアルゴリズム (EA)

- ・アドバンスドセクタ保護 (ASP) 管理

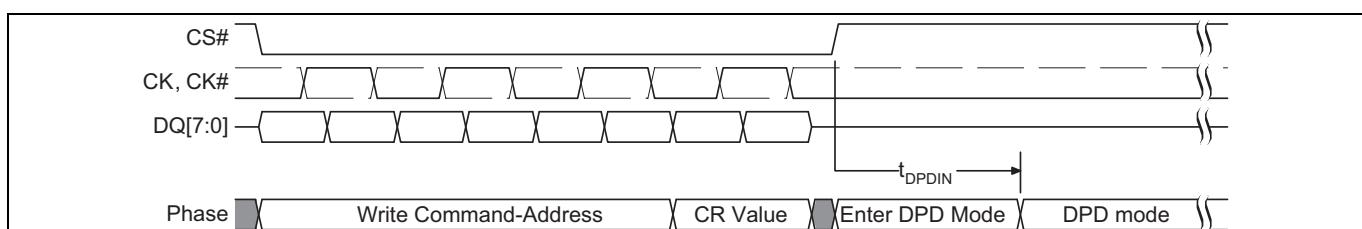

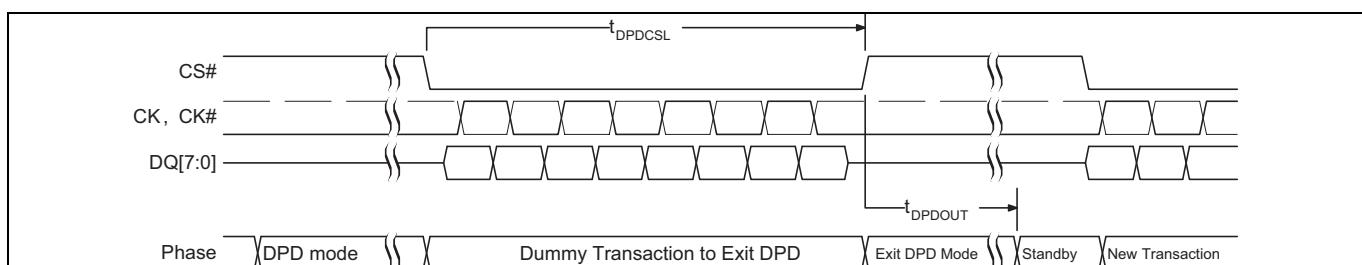

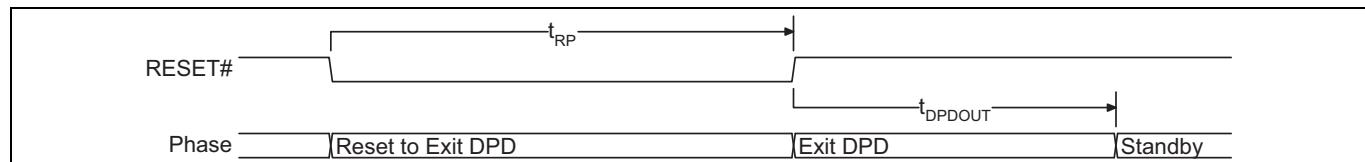

#### 6.1.1 ディープパワーダウン

DPD モードでは、消費電流は低レベルに駆動されます。ASO ではない場合、デバイスはスタンバイ状態の時に DPD モードに入る必要があります。

#### 6.1.2 EAC スタンバイ

スタンバイ状態では消費電流を大幅に低減できます。処理中のコマンドがなく、実行中の組込みアルゴリズムもないとき、EAC はスタンバイ状態に入ります。その EA の進行中にデバイスの選択を外すと (CS# が HIGH)、その動作が完了するまでデバイスは依然としてアクティブ電流を消費します ( $I_{CC3}$ )。[DC 特性 \(CMOS 互換性\)](#) の  $I_{CC4}$  はホストインターフェースと EAC の両方がスタンバイ状態にあるときのスタンバイ電流の仕様を示しています。

#### 6.1.3 アドレス空間の切替え

特定のアドレスとデータ配列 (コマンドシーケンス) を書き込むと、メモリデバイスのアドレス空間をフラッシュメモリアレイから ASO の 1 つに切り替えます。

EA は、現在アクティブな (入っている) ASO で表示されている情報を対象にして動作します。システムが ASO 終了コマンドを発行し、ハードウェアリセットを実行するか、またはデバイスの電源が切られるまで、システムは ASO へのアクセスを継続します。ASO 終了コマンドは、ASO をフラッシュメモリアレイのアドレス空間に戻すように切り替えます。特定の ASO に入る時に許可されるコマンドは、コマンド定義テーブルの ASO エントリコマンドと ASO 終了コマンドの間にリストアップされています。すべてのコマンドシーケンスのアドレスとデータの要件については、[コマンドのまとめ](#) を参照してください。

#### 6.1.4 組込みアルゴリズム (EA)

メモリアレイ内の不揮発性データの書換えには、EA と呼ばれる複雑な動作シーケンスを必要とします。アルゴリズムはデバイスの内部 EAC によって完全に管理されています。主要なアルゴリズムは、メインアレイデータと ASO のプログラミングと消去を実行します。ホストシステムはフラッシュデバイスのアドレス空間にコマンドコードを書き込みます。EAC はコマンドを受け取り、コマンドを完了するため必要なすべてのステップを実行し、EA の進行中にステータス情報を提供します。

組込み動作

## 6.2 プログラムおよび消去のまとめ

フラッシュのデータビットは、セクタと呼ばれる大きなグループの中で、並列して消去されます。消去動作によりセクタ内の各データビットが論理 1 状態 (HIGH) になります。フラッシュデータビットは、消去済み状態 (論理 1) からプログラム状態 (論理 0, LOW) に個別にプログラムできます。'0' のデータビットをプログラムで '1' に戻すことはできません。読み出しを連続に実行すると、データが '0' のままであることを示します。'0' から '1' に変換できるのは、消去動作のみです。同じワード位置を別の 0 ビットで複数回プログラムすると、直前のデータと新しくプログラムされたデータが論理和 (AND) されます。

プログラム動作と消去動作の時間を [組込みアルゴリズムのパフォーマンス](#) に示します。

プログラムと消去動作を一時停止できます。

- 消去動作を中断 (一時停止) することで、消去動作中に (消去セクタ以外の) 別のセクタのプログラムや読み出しを行えます。消去一時停止中は他の消去動作を開始できません。

- プログラム動作を中断することで、別の位置 (プログラム中のライン以外の位置) の読み出しを行えます。

- プログラム動作の中断中は、他のプログラム動作または消去動作を開始できません。つまり、プログラム動作の中断中はプログラムコマンドと消去コマンドが無視されます。

- 間に挟んだプログラム動作または読み出しアクセスが完了すると、中断していた消去動作やプログラム動作が再開されます。

- プログラム動作と消去動作は、必要に応じて何度でも中断できますが、プログラム動作または消去動作を進捗させ完了させるためには、再開コマンドと次の一時停止コマンドの間は [組込みアルゴリズムのパフォーマンス](#) に示すように  $t_{PRS}$  または  $t_{ERS}$  以上の時間を置く必要があります。

- EA が完了すると、EAC は、EA 開始 (消去一時停止または EAC スタンバイ) 前の動作状態とアドレス空間に戻ります。

システムは、ステータスレジスタを読み出してプログラム動作または消去動作のステータスを調べられます ([エラー タイプおよび消去手順](#) を参照してください)。

組込みプログラムアルゴリズムの実行中にデバイスに書き込まれるコマンドは、プログラム一時停止とステータス読み出しコマンド以外は無視されます。

組込み消去アルゴリズムの実行中にデバイスに書き込まれるコマンドは、消去一時停止とステータス読み出しコマンド以外は無視されます。

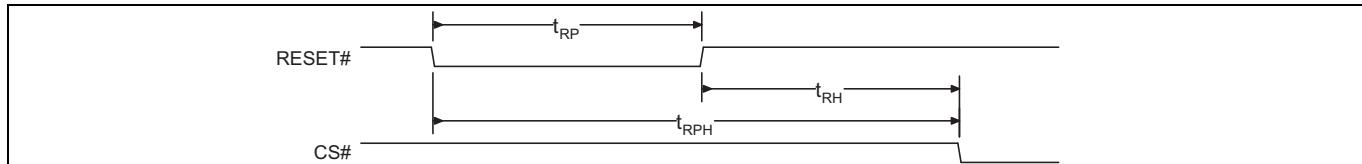

ハードウェアリセットが発生すると、進行中のプログラム / 消去動作が直ちに終了し、 $t_{RPH}$  時間後に読み出しモードに戻ります。データの整合性を確保するために、終了した動作は、デバイスがスタンバイ状態に戻ったら再開する必要があります。

パフォーマンスと信頼性を考慮したうえ、プログラミングは 16 バイトにアラインされたアドレス範囲を利用して 16 バイト ハーフページ上で内部的に行われます。

[DC 特性 \(CMOS 互換性\)](#) の  $I_{CC3}$  は書き込み (組込みアルゴリズム) 動作時のアクティブ電流仕様を示しています。

組込み動作

### 6.2.1 プログラム粒度

S26KL/S26KS は、ワードのプログラムと、書き込みバッファを使用したプログラムの 2 つ的方式によるプログラムをサポートしています。

ワード プログラムは、コマンドによって提供されたデータ ワードを検査し、コマンドのデータ ワードの 0 と一致させるようにアドレス指定したメモリアレイのワードに 0 をプログラムします。

書き込みバッファ プログラムは、書き込みバッファを検査し、書き込みバッファの 0 と一致させるようアドレス指定したメモリアレイのラインに 0 をプログラムします。書き込みバッファのすべてをデータで満たす必要はありません。单一ビット、複数ビット、單一ワード、複数ワード、1 ハーフページ、複数ハーフページ、またはバッファすべてを 1 つのプログラム動作で実現できます。書き込みバッファ方式を使用すると、プログラム コマンドを書き込む時のホストシステムのオーバーヘッドが削減され、プログラム動作時のメモリ デバイスの内部オーバーヘッドが削減されるため、書き込みバッファによるプログラムはより効率的になり、ワード プログラム コマンドによって個別ワードをプログラムする方式よりプログラム時間がさらに短縮されます。

各ハーフページはそれらの方式のどちらかでプログラムできます。異なる方式でプログラムされたハーフページが 1 つのラインに混在する場合もあります。

半ページで 2 回以上のワード プログラミングと書き込みバッファ プログラミングは、レガシーソフトウェア互換性用にサポートされます。ただし、消去せずにハーフページ内でワード プログラミングまたは書き込みバッファ プログラミングを複数回使用すると、そのハーフページに対するデバイスの ECC 機能が無効になります。同じ半ページで複数のプログラミング動作を要求するアプリケーションの場合、半ページのデータ整合性を強化するためにシステム ソフトウェアのエラー検出および訂正機能を追加することを推奨します。

注: 2 ビット ECC が有効な場合、同じページ内で複数のワード プログラミングまたは書き込みバッファ プログラミングを行うと、プログラム エラーが発生します。

シリコンでの次世代の HYPERFLASH™ では、ハーフページを含むセクタに消去動作がない同じハーフページでの複数プログラムの動作を対応しなくなる可能性があります。次世代向けソフトウェア置き換え計画として、ハーフページごとおよび 1 つの消去動作ごとの単一プログラム動作のみ対応するデータ構造とデータ管理方式を受け取るようにする必要があります。

### 6.2.2 インクリメンタル プログラム

同じワード位置では、ワードまたはライトバッファ プログラミング方式のいずれによっても、1 から 0 へのインクリメントな変更を 1 回以上プログラム可能です。ただし、[プログラム粒度](#)で記述されているように、追加プログラムは ECC シンドローム ビットに影響し、デバイスがその半ページの ECC を無効にします。

注: 2 ビット ECC が有効な場合、同じページ内で複数のワード プログラミングまたは書き込みバッファ プログラミングを行うと、プログラム エラーが発生します。

組込み動作

## 6.2.3 プログラム方式

### 6.2.3.1 ワードのプログラム

ワード プログラミングは、フラッシュ メモリ アレイの任意の場所に単一ワードやワード グループをプログラムするために使用されます。

ワード プログラムのコマンド シーケンスは最小で 4 つのコマンド 書き込みトランザクションを要します。プログラム コマンド シーケンスは、ロックされない 2 つのコマンド 書き込みトランザクション (トランザクション 1 と 2) の後にプログラム 設定コマンド (トランザクション 3) を発行することで開始されます。プログラム アドレスとデータが次に書き込まれ (トランザクション 4)、順番に組込みプログラム アルゴリズムが開始されます。システムは、さらに制御やタイミングを提供する必要はありません。デバイスは自動的にプログラム パルスを生成し、内部でプログラムされたセル マージンを検証します。組込みプログラム アルゴリズムが完了すると、EAC はスタンバイ 状態に戻ります。

ワード プログラム コマンド シーケンスのこの 4 つのトランザクションは単一 (16 ビット) ワード (2 バイト) のプログラムに使用されます。バースト書き込み機能を使用することで、複数の順次ワードをワード プログラム シーケンスでプログラムできます。Unlock および Program のコマンド シーケンスは単一ワード プログラム シーケンスと同一ですが、データ / アドレストランザクション中に、1 回の CS# アサートで多くの順次データ値がロードされます。現存のデータは、バースト書き込みトランザクションのコマンド / アドレス フェーズで識別された対象のアドレスから開始する順次アドレスにプログラムされます。整列される 256 ワード (512 バイト) アドレス境界を越えないかぎり、最大 256 ワード (512 バイト) をプログラムできます。

システムは、ステータス レジスタを読み出してプログラム動作のステータスを調べられます。[エラータイプおよび消去手順](#)を参照してください。

組込みプログラム アルゴリズムの実行中にデバイスに書き込まれるプログラム一時停止とステータス レジスタ読み出し以外のコマンドはすべて無視されます。

ハードウェアリセット (RESET# = V<sub>IL</sub>) や電源切断により、プログラム動作が瞬時に終了し、t<sub>RPH</sub> 時間後にデバイスが読み出しモードに戻ることに、注意してください。しかし、この動作終了では、プログラム進行中の領域は、データ値が無効か不安定である中間的な状態になる場合があります。データが完全にプログラムされるために、デバイスのハードウェアリセット動作が完了すると、プログラム コマンド シーケンスは同様のデータで再度開始しプログラム動作を完成できます。ただし、最高のデータ整合性を保証するためには、プログラム動作が終了されたセクタを消去し再プログラムする必要があります。

ワード プログラム コマンドは、SSR ASO に入ったときに使用することもできます。

ロックされない書き込みサイクルなしの修正済みワード プログラム コマンドは、ASP コンフィギュレーション レジスタ (ASPR), パスワード, および PPB ASO に入るときのプログラミングとして使用されます。PPB ロックと DYB ASO に入るときに、揮発性ビットを変更するために、同様のコマンドが使用されます。プログラム コマンド シーケンスについては、[Table 41](#) を参照してください。

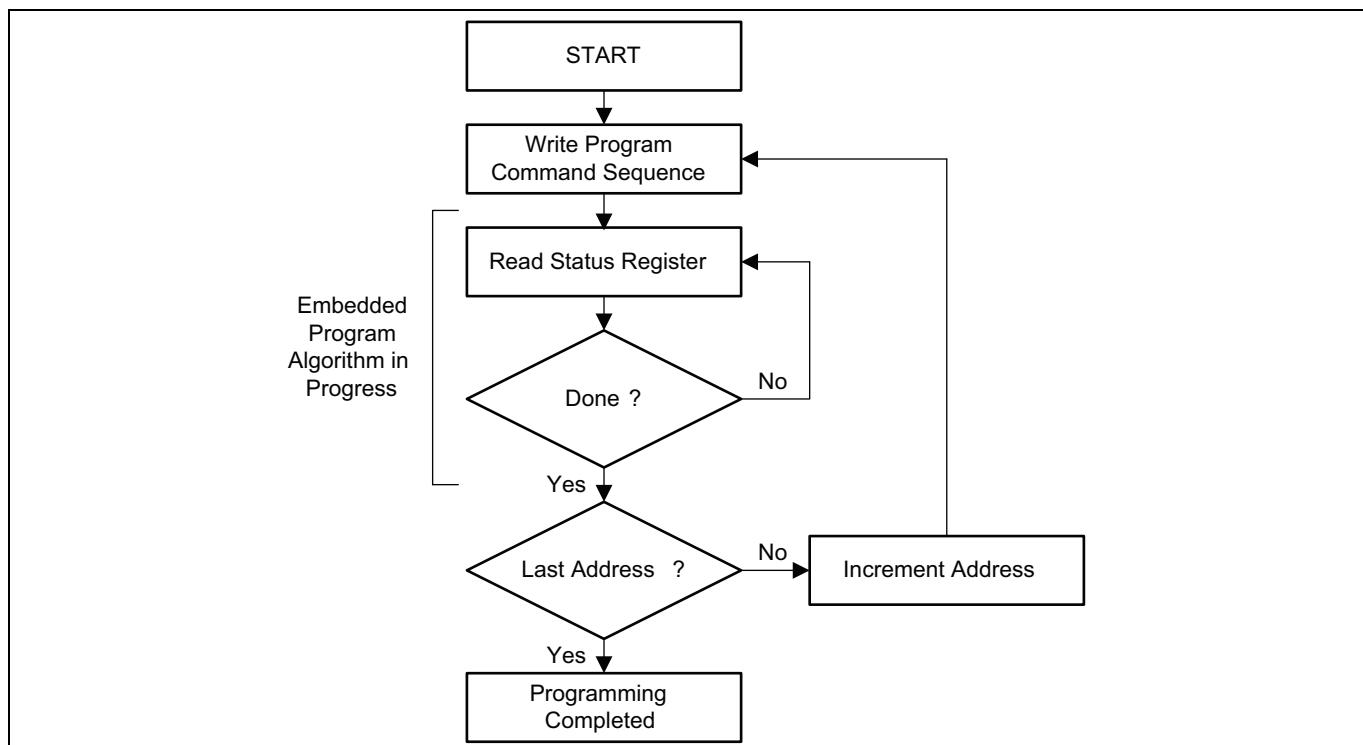

Figure 14 ワード プログラム動作

### 6.2.3.2 書き込みバッファ プログラム

書き込みバッファは、512 バイトの境界（ライン）にアラインされた 512 バイトのアドレス範囲内のデータをプログラムする際に使用されます。このように、フルサイズの書き込みバッファ プログラム動作はライン境界に整列される必要があります。512 バイト以下のプログラム動作は、任意のワード境界で開始できますが、ライン境界を越えることはできません。書き込みバッファ プログラム動作の開始時に、バッファ内のすべてのビット位置は 1 (FFFFh ワード) であるため、ロードされない位置には既存のデータが保持されます。アドレスマップについては、Table 1 を参照してください。

書き込みバッファ プログラムでは、1 回の動作で最大 512 バイトプログラミングできます。各書き込みバッファ プログラム動作では、1 ビットから 512 バイトまでのプログラムが可能です。複数の 16 バイト（半ページ）に書き込み、各半ページは 1 回だけ書き込むことを強く推奨します。最高のパフォーマンスを得るには、512 バイト境界上の 512 バイト整列ライン全体でプログラムする必要があります。

書き込みバッファ プログラムはフラッシュメモリアレイまたは SSR ASO でのみサポートされます。

最初にロックされないサイクルを 2 回書き込みして、書き込みバッファ プログラム動作を開始します。この後、プログラミング中のセクタアドレス (SA) で、バッファ書き込みコマンドの 3 回目の書き込みサイクルが続けます。次に、システムはワード位置 -1 の値を書き込みます。これにより、デバイスはデータをロードする書き込みバッファアドレス数を認識し、したがって、プログラムバッファの確認コマンドの実行タイミングを認識します。バッファーへの書き込みコマンドと、ワード数書き込みコマンド内のセクタアドレスは一致しなければいけません。プログラム対象のセクタはアンロック（非保護）になる必要があります。プログラミング動作をロックされたセクタで行おうとする場合、その動作は中止され、失敗がステータスレジスタに表示されます（Table 17 を参照してください）。

この後、システムは開始アドレスとデータワードを書き込みます。この開始アドレスはプログラムされる最初のアドレスとデータのペアで、書き込みバッファ ライン内の開始アドレスを選択します。セクタアドレスは、バッファコマンドセクタアドレスへの書き込みと一致する必要があります。そうでない場合は、動作が中断され、開始状態に戻ります。それ以降のすべてのアドレスとデータのペアは順次に書き込まれる必要があります。すべての書き込みバッファアドレスは同じライン内にある必要があります。

## 組込み動作

す。システムがこの範囲外のデータをロードしようとすると、動作は中止され、開始状態に戻ります。データワードのロード中は、線形バーストシーケンスはサポートされないことに注意してください。

ワードカウントは、データのロード動作ごとにデクリメントします。データ書き込みをカウントダウンしながら、毎回の書き込みは、書き込みバッファヘロードされているデータと見なされることに注意してください。書き込みバッファロード中は、すべてのコマンドが不可能です。書き込みバッファのロードを停止する唯一の方法は、プログラミング動作のライン外にあるアドレスを使って書き込むことです。無効なアドレスを受け取ると、バッファへの書き込みコマンドは直ちに停止し、バッファ書き込み停止ステータスビット (SR[3]) を設定します。

書き込みバッファ位置の指定した数をロードしたら、システムは SA に対してプログラムバッファを書き込み、フラッシュコマンドを実行しなければなりません。デバイスはビジー状態になります。組込みプログラムアルゴリズムはデータを自動的にプログラムし、データパターンが正しいかを検証します。システムは、これらの動作中に制御やタイミングを提供する必要はありません。書き込みバッファ位置の不正な数がロードされた場合、動作は中止され、開始状態に戻ります。データワードのワードカウント数の最後にプログラムバッファフラッシュコマンドが書き込まれずに、別のコマンドやデータが書き込まれると、動作は中止されます。

書き込みバッファの組込みプログラム動作は、プログラム中止コマンドにより中止できます。組込みプログラムアルゴリズムが完了すると、EAC は、プログラム動作が開始された時の EAC スタンバイまたは消去中止スタンバイの状態に戻ります。

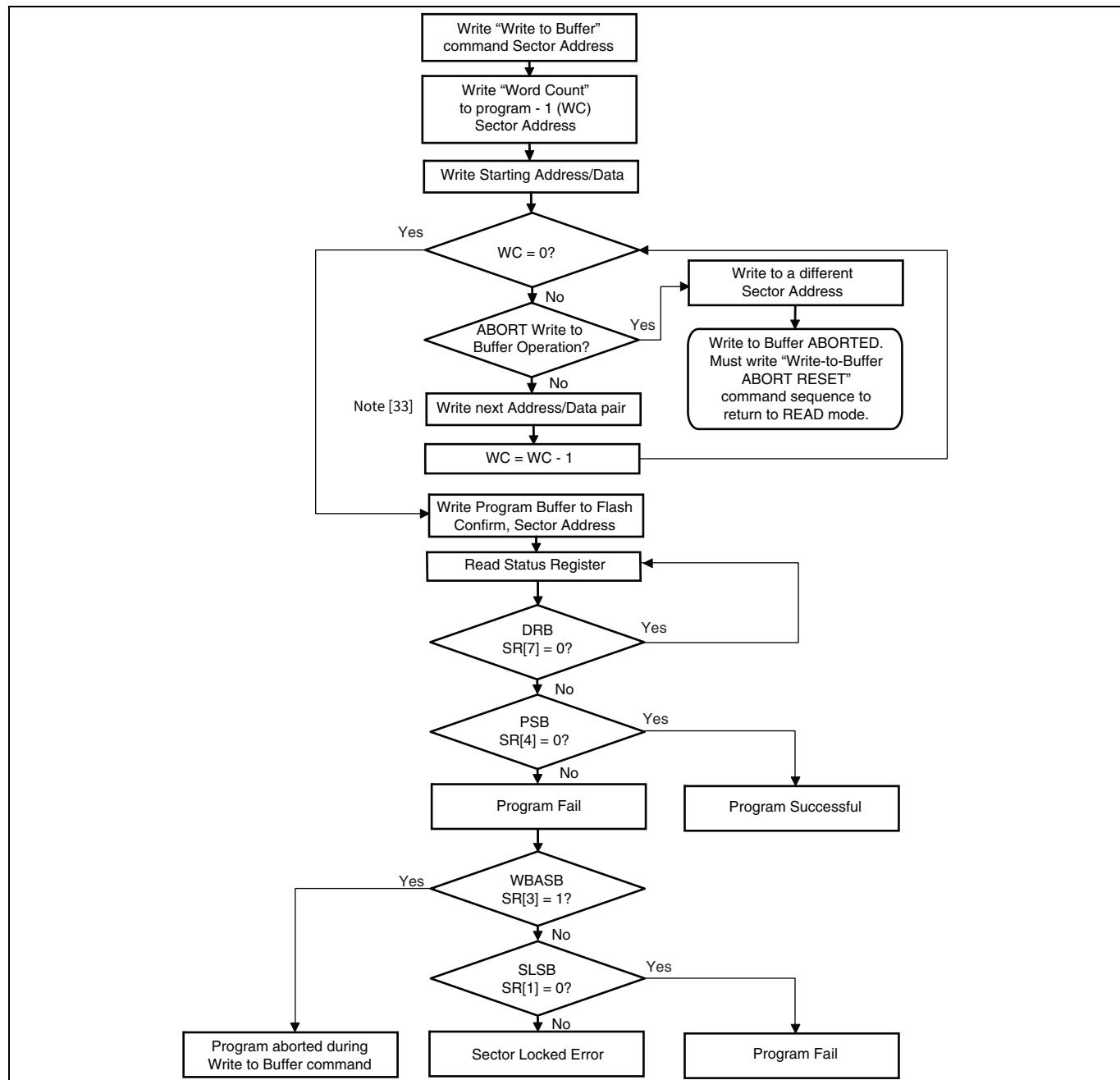

システムは、ステータスレジスタを使用してプログラム動作のステータスを調べられます (Table 17 を参照してください)。プログラム動作図については、Figure 15 を参照してください。

バッファ書き込みプログラミングシーケンスは、以下の条件で中止されます。

- ・バッファサイズ (255) を越えるワードカウント値をロードしました。

- ・バッファへの書き込みコマンドで指定されたラインに属さないアドレスを書き込みました。

- ・書き込みワードカウント数で指定したデータワードがロードされた後に、フラッシュへのバッファプログラムコマンドが実行されませんでした。

バッファ書き込みコマンドの強制終了の原因となる何らかの状態が発生すると、動作は直ちに終了し、ステータスレジスタのビット位置 4 (PSB=1) に、バッファ書き込み中止のビット位置 3 (WBASB=1) によるプログラム失敗が報告されます。その後、プログラム動作が成功すると、この失敗の状態はクリアされます。またはクリアステータスレジスタが実行されて、PSBステータスピットがクリアされます。

バッファ書き込みプログラミングシーケンスは、ハードウェアリセットまたはパワーサイクルにより終了させられます。しかし、これらの方のいずれかの使用は、中間的な不安定な状態のデータになってしまふ場合があります。この場合は、同じデータで同じ領域を再プログラムするか、または消去してデータ値を正しくプログラムまたは消去する必要があります。最高のデータ整合性を確実にするために、プログラム動作が終了しセクタを消去し再プログラムする必要があります。

組込み動作

Figure 15 ステータス レジスタを使用した書き込みバッファ プログラム動作<sup>[32, 33]</sup>

注:

- 32. 書き込みバッファプログラムに必要なコマンドシーケンスについては [Table 41](#) を参照してください。

- 33. SA が定義された時、選択されたセクタのいずれのアドレスも有効になります。ただし、書き込みバッファアドレス位置をデータとともにロードする場合は、すべてのアドレスは選択されたライン内に収める必要があります。

組込み動作

**Table 13 書き込みバッファプログラムでのコマンド シーケンス**

| シーケンス                                            | アドレス   | データ   | コメント                                                       |

|--------------------------------------------------|--------|-------|------------------------------------------------------------|

| Unlock コマンド 1 を発行                                | 555h   | AAh   | -                                                          |

| Unlock コマンド 2 を発行                                | 2AAh   | 55h   | -                                                          |

| セクタアドレスで書き込みバッファ コマンドを発行                         | SA     | 0025h | -                                                          |

| セクタアドレスで位置数を発行                                   | SA     | WC    | WC = プログラムするワード数 - 1                                       |

| 例:<br>WC = 0: 1 ワードをプログラム<br>WC = 1: 2 ワードをプログラム | -      | -     | -                                                          |

| 開始アドレス / データのペアをロード                              | 開始アドレス | PD    | 1 行を選択し、最初のアドレス / データのペアをロード。                              |

| 次のアドレス / データのペアをロード                              | WBL    | PD    | アドレスはすべて、選択した行の境界内に収まり、逐次的な順序でロードされる必要がある。                 |

| 最後のアドレス / データのペアをロード                             | WBL    | PD    | アドレスはすべて、選択した行の境界内に収まり、逐次的な順序でロードされる必要がある。                 |

| セクタアドレスで書き込みバッファ プログラム確認コマンドを発行                  | SA     | 0029h | このコマンドは、ロードされた最後の書き込みバッファ位置の直後に実行される必要があります。それ以外の場合は動作が終了。 |

| デバイスがビジーになる                                      | -      | -     | -                                                          |

凡例:

SA = セクタアドレス (非セクタアドレス ビットは「ドントケア」です。セクタ内の任意のアドレスで十分です。)

WBL = 書き込みバッファ位置 (開始アドレスで指定されたラインの境界内にある必要があります。)

WC = ワードカウント

PD = プログラムデータ

組込み動作

#### 6.2.4 プログラム中止 / プログラム再開コマンド

プログラム中止コマンドにより、システムは組込みプログラム動作に割り込み、中止されていない他のラインからデータを書き込みます。プログラミング実行中にプログラム中止コマンドを書き込むと、デバイスは  $t_{PSL}$  (プログラム中止レイテンシー) の間、そのプログラム動作を停止して、ステータスビットを更新します。プログラム中止コマンドを書き込む際、アドレスは「ドントケア」です。

プログラム動作が中止すると、システムは中止されていない任意のラインからデータアレイを読み出せるようになります。消去中止時に他のセクタにプログラムしている場合でも、プログラム中止が可能です。この場合、消去中止またはプログラム中止状態になっていないアドレスのいずれからでもデータを読み出せます。

プログラム再開コマンドを書き込むと、デバイスはプログラム動作に戻り、ステータスビットが更新されます。システムは、ステータスレジスタを読み出してプログラム動作のステータスを調べられます。これらのステータスビットについては、[エラータイプおよび消去手順](#)を参照してください。

プログラム中止中に有効なアクセスとコマンドは次のとおりです。

- 非消去中止セクタに対する読み出し

- 非プログラム中止ラインに対する読み出し

- ステータス読み出しコマンド

- ASO 終了またはコマンドセット終了

- プログラム再開コマンド

- ロード割込みコンフィギュレーションレジスタ

- ロード割込みステータスレジスタ

プログラム中止モードを終了して、プログラム動作を続けるには、プログラム再開コマンドを書き込む必要があります。さらにプログラム再開コマンドを書き込んでも無視されます。デバイスがプログラム動作を再開した後は、プログラム中止コマンドを再度書き込みます。

プログラム動作は、何度でも必要なだけ中止できますが、プログラム動作を進捗させ完了させるためには、再開コマンドと次の中止コマンドの間を、 $t_{PRS}$  以上にする必要があります。[組込みアルゴリズムコントローラ \(EAC\)](#) を参照してください。

プログラムの中止と再開は、ASOに入っている間はサポートされません。プログラムの中止の間は、ASOに入ることはサポートされません。

#### 6.2.5 ブランクチェック

ブランクチェックコマンドにより、選択したフラッシュメモリアレイセクタが完全に消去されているかどうかを確認できます。ブランクチェックコマンドの実行中は、対象アレイの読み出しへはできなくなります。このコマンドの実行中に対象アレイを読み出すと、不明なデータが返されます。

任意のセクタでブランクチェックを開始するには、EACがスタンバイ状態になっている時に、そのセクタのアドレス 555h に 33h を書き込みます。

デバイスがプログラムまたは消去を実行中、または中止中であると、ブランクチェックコマンドが書き込まれない場合があります。

ステータスレジスタの書き込みコマンドを使用して、デバイスがビジーであるかどうか、また、完了後にセクタがブランクになっているかどうかを確認してください。ステータスレジスタのビット 7 に、デバイスがブランクチェックを実行中であるかどうかが示されます(消去動作と同様)。ステータスレジスタのビット 5 は、セクタが消去された場合は '0' にクリアされ、消去されなかった場合は '1' にセットされます。

消去されなかったビットを発見するとすぐに、デバイスは動作を停止して、結果を報告します。

ブランクチェックが完了すると、EAC はスタンバイ状態に戻ります。

組込み動作

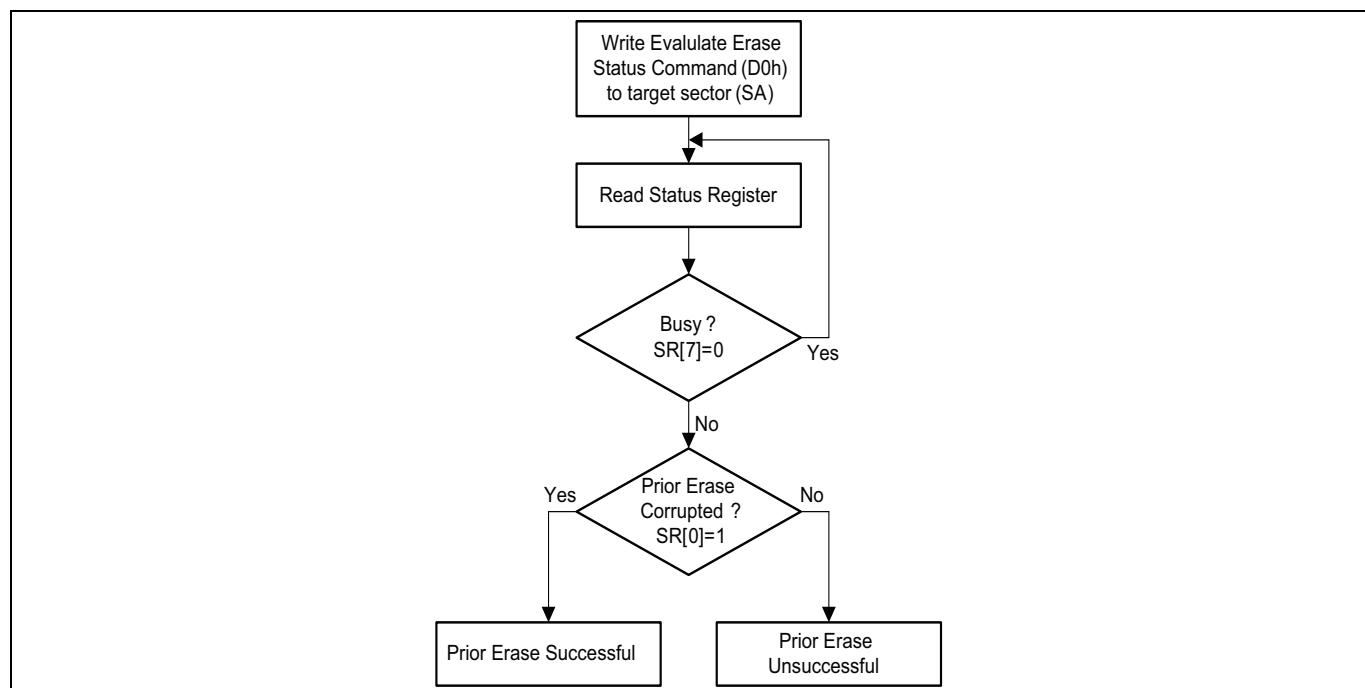

### 6.2.6 消去ステータス評価

消去ステータス評価(EES)コマンドは、アドレス指定されたセクタの最後の消去動作が正常に完了したかを確認します。選択されたセクタが正常に消去された場合は、ステータスレジスタ内のセクタ消去ステータスビット(SR[0])が‘1’にセットされます。選択したセクタが完全に消去されていない場合はSR[0]が‘0’にクリアされます。詳細は、Figure 16を参照してください。

EESコマンドは、消去動作中の電力喪失、リセット、または失敗による消去動作を検出できます。

EESコマンドは、ステータスレジスタ内のセクタ消去ステータスビット(SR[0])を完了し、更新するため $t_{EES}$ を要します。ステータスレジスタ内のデバイスレディビット(SR[7])は書き込みステータスレジスタ(70h)コマンドを使用してEESコマンドの完了タイミングを確定します。ステータスレジスタ内のデバイスレディビットは、デバイスがレディ(1)状態に戻ったことを示したら、セクタ消去ステータスビット(SR[0])は対象セクタが正常に消去されたかどうかを示します。任意のセクタが消去されない(SR[0]=0)ことが検出された場合、そのセクタ内のデータ格納を確保するために、セクタを再び消去しなければいけません。

Figure 16 消去ステータス評価ソフトウェアシーケンス

組込み動作

## 6.2.7 消去方式

### 6.2.7.1 チップ消去

チップ消去機能は、フラッシュメモリアレイ全体を消去します。消去の前にデバイスをプリプログラムする必要はありません。組込み消去アルゴリズムは自動的にプログラムし、電気的な消去実行の前に、メモリ全体がすべて 0 になっているかを検証します。チップ消去が正常に完了すると、デバイス内のすべての領域が FFFFh になります。システムは、これらの動作中に、制御やタイミングを提供する必要はありません。アンロックサイクル(2回)の後に、セットアップコマンドを書き込んで、チップ消去コマンドシーケンスを開始します。さらに、アンロック書き込みサイクル2回の後にチップ消去コマンドを書き込むと、組込み消去アルゴリズムが開始します。

組込み消去アルゴリズムが完了すると、EAC はスタンバイ状態に戻ります。組込み消去動作の実行中は、デバイスから有効なデータを書き込めません。システムは、ステータスレジスタを読み出して消去動作のステータスを調べられます。これらのステータスピットについては、[エラータイプおよび消去手順](#)を参照してください。チップ消去動作が一旦開始すると、ステータス書き込み、ハードウェアリセット、パワーサイクルのみが有効です。その他のすべてのコマンドは無視されます。ただし、ハードウェアリセットまたはパワーサイクルを実行すると、消去動作が直ちに終了し、 $t_{RPH}$  時間後に読み出しモードに戻ります。チップ消去動作が終了した場合は、データの完全性を確保するために、デバイスがスタンバイ状態に戻ったらチップ消去コマンドシーケンスを再度実行してください。

ASP DYB および PPB ビットによって保護されたセクタは消去されません。[ソフトウェアインターフェース参考資料](#)を参照してください。チップ消去は、保護されたセクタを飛ばして、次のセクタの消去を続行します。保護されたセクタで失敗した消去動作があっても、ステータスレジスタの消去ステータスピットとセクタロックビットは '1' にセットされません。

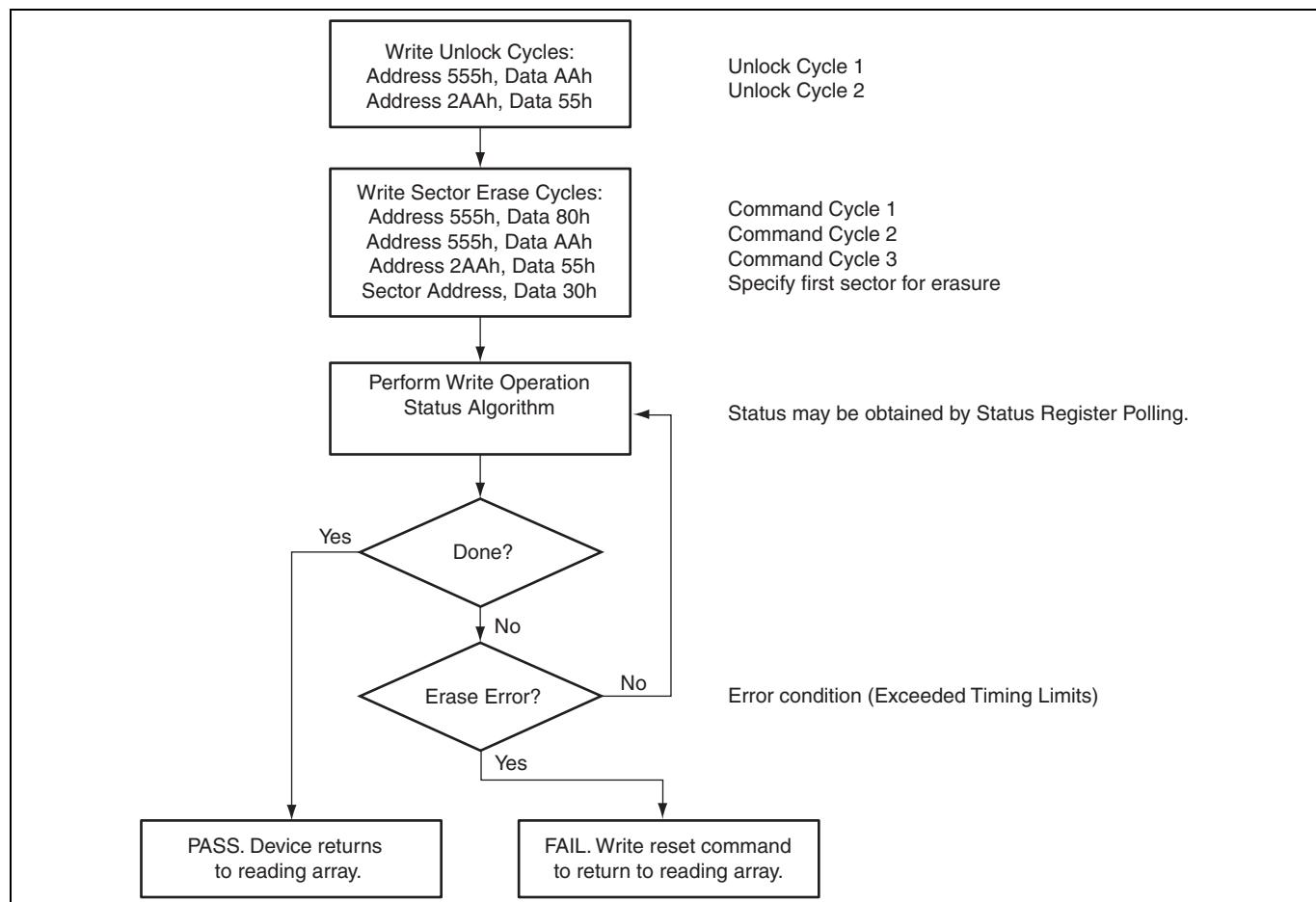

### 6.2.7.2 セクタ消去

セクタ消去機能は、メモリアレイ内の 1 つのセクタを消去します。消去の前にデバイスをプリプログラムする必要はありません。組込み消去アルゴリズムは自動的にプログラムし、電気的な消去の前に、セクタ全体がすべて 0 になっているかを検証します。セクタ消去が正常に完了すると、消去されたセクタ内のすべての領域が FFFFh になります。システムは、これらの動作中に、制御やタイミングを提供する必要はありません。アンロックサイクル(2回)の後に、プログラムセットアップコマンドを書き込んで、セクタ消去コマンドシーケンスを開始します。次に、追加の 2 つのアンロック書き込みサイクルの後に、消去対象セクタのアドレスと、セクタ消去コマンドが続きます。

システムは、ステータスレジスタを読み出して消去動作のステータスを調べられます。これらのステータスピットについては、[エラータイプおよび消去手順](#)を参照してください。

一旦セクタ消去動作が始まると、ステータスレジスタ書き込みコマンドと消去中止コマンドが有効となります。他のコマンドはすべて組込みアルゴリズムコントローラにより無視されます。ただし、ハードウェアリセットを実行すると、直ちに消去動作が終了し、 $t_{RPH}$  時間後に読み出しモードに戻ります。セクタ消去動作が終了した場合は、デバイスの動作がリセットされたらセクタ消去コマンドシーケンスを再度実行して、データの完全性を確保してください。

パラメーターとタイミング図については、[組込みアルゴリズムコントローラ\(EAC\)](#) を参照してください。

ASP DYB および PPB ビットによって保護されたセクタは消去されません。[ソフトウェアインターフェース参考資料](#)を参照してください。プログラミング動作をロックされたセクタで行おうとする場合、その動作は中止され、失敗がステータスレジスタに表示されます([Table 17](#) を参照してください)。

組込み動作

Figure 17 セクタ消去動作

組込み動作

## 6.2.8 消去中止 / 消去再開

消去中止コマンドを実行すると、システムはセクタ消去動作を中止して、フラッシュメモリアレイのデータ読み出し / 書き込みができるようになります。このコマンドはセクタ消去またはセクタプログラムの動作中にのみ有効です。チップ消去動作中に消去中止コマンドを書き込んでも無視されます。

セクタ消去動作中に消去中止コマンドが書き込まれると、デバイスは消去動作を中止するまでに最大  $t_{ESL}$  (消去中止レイテンシ) を必要とします。

消去動作が中止された後、デバイスは消去中止モードに入ります。この時、システムは、フラッシュメモリアレイのデータ読み出し / 書き込みができるようになります。消去中止の対象セクタ内のいずれかのアドレスから読み出すと、不確定なデータが返されます。システムは、ステータスレジスタを読み出すごとで、セクタが消去中、あるいは消去中止中かどうかを調べられます。これらのステータスビットについては、[エラータイプおよび消去手順](#)を参照してください。

消去中止中のプログラム動作が完了すると、EAC は消去中止状態に戻ります。通常のプログラム動作と同じように、システムはステータスレジスタを読み出すことで、プログラム動作の状態を確認できます。

消去中止中にプログラムが失敗した場合は、ステータスレジスタクリアまたはソフトウェアリセットコマンドにより、デバイスを消去中止状態に復帰させられます。そのメモリアレイに再度プログラムする場合は、その前に消去を再開し完了させる必要があります。

以下は消去中止中に有効なアクセスとコマンドです。

- 中止状態でないセクタからの読み出し

- 中止状態でないセクタへのプログラム

- ステータス読み出しコマンド

- ASO 終了またはコマンドセット終了

- 消去再開コマンド

- SSR エントリ

- SSR 読み出し

- SSR プログラム

セクタ消去動作を再開させるには、消去再開コマンドを書き込む必要があります。デバイスは消去動作に戻り、ステータスビットが更新されます。また、この後に再開コマンドを書き込んでも無視されます。チップが消去動作を再開すると、消去中止コマンドを再度書き込みます。

デバイスが消去中止状態である間はコマンドが DYB ASO に入力できないことに注意してください。

組込み動作

## 6.2.9 振発性および不揮発性レジスタのまとめ

### 6.2.9.1 不揮発性コンフィギュレーションレジスタ

**Table 14** 不揮発性コンフィギュレーションレジスタ

| 記号      | 名前                  | 幅(ビット)       | NV<br>タイプ | デフォルト<br>値              | 参照                                       |

|---------|---------------------|--------------|-----------|-------------------------|------------------------------------------|

| NVCR    | 不揮発性コンフィギュレーションレジスタ | 16           | P/E       | 8EBBh                   | 不揮発性コンフィギュレーションレジスタおよび揮発性コンフィギュレーションレジスタ |

| PASS    | パスワード保護レジスタ         | 64k          | OTP       | FFFF FFFF<br>FFFF FFFFh | パスワード保護モード                               |

| PPB     | 恒久的保護ビット            | セクタあたり 1 ビット | P/E       | 1                       | 恒久的保護ビット (PPB)                           |

| ASPR    | ASP コンフィギュレーションレジスタ | 16           | OTP       | FEEEh                   | ASP コンフィギュレーションレジスタ                      |

| PORTime | パワーオンリセット時間         | 16           | OTP       | FFFFh                   | パワーオンリセット (POR)( コールド )                  |

### 6.2.9.2 挥発性コンフィギュレーションレジスタ

**Table 15** 挥発性コンフィギュレーションレジスタ

| 記号   | 名前                   | 幅(ビット)       | デフォルト<br>値 | 参照                                       |

|------|----------------------|--------------|------------|------------------------------------------|

| VCR  | 揮発性コンフィギュレーションレジスタ 0 | 16           | NVCR       | 不揮発性コンフィギュレーションレジスタおよび揮発性コンフィギュレーションレジスタ |

| DYB  | 動的保護ビット              | セクタあたり 1 ビット | 1          | 動的保護ビット (DYB)                            |

| PPBL | PPB ロック ビット          | 1            | ASPR[2]    | PPB ロック                                  |

| ICR  | 割込みコンフィギュレーションレジスタ   | 16           | FFFFh      | INT# 出力                                  |

| CRCs | CRC 開始アドレス レジスタ      | 26 (1 Gb)    | 3FFFFFFh   | CRC check-value の計算                      |

| CRCE | CRC 終了アドレス レジスタ      | 26 (1 Gb)    | 3FFFFFFh   | CRC check-value の計算                      |

組込み動作

## 6.2.10 振発性結果およびステータスレジスタ

**Table 16** 振発性結果およびステータスレジスタ

| 名前                                | 幅(ビット)       | デフォルト値 | 参照                                 |

|-----------------------------------|--------------|--------|------------------------------------|

| セクタロックステータス                       | セクタあたり 3 ビット | 該当なし   | <a href="#">Table 41</a> の注 79 を参照 |

| ステータスレジスタ                         | 16           | xx80h  | <a href="#">Table 17</a>           |

| 割込みステータスレジスタ                      | 16           | FFFFBh | <a href="#">Table 34</a>           |

| ECC ステータスレジスタ                     | 16           | 該当なし   | -                                  |

| エラー下位アドレストラップレジスタ                 | 16           | 該当なし   | <a href="#">Table 41</a>           |

| エラー上位アドレストラップレジスタ                 | 16           | 該当なし   | <a href="#">Table 41</a>           |

| 読み出し Check-Value Low Result レジスタ  | 16           | 該当なし   | CRC 値レジスタ                          |

| 読み出し Check-Value High Result レジスタ | 16           | 該当なし   | CRC 値レジスタ                          |

## 6.2.11 ステータスおよびコンフィギュレーションレジスタの定義

### 6.2.11.1 ステータスレジスタモード

EA のステータスは、単一の 16 ビットステータスレジスタによって提供されます。ステータスレジスタ読み出しコマンドが発行され、続いてステータスレジスタ情報の読み出しアクセスが 1 回実行されます。ステータスレジスタの内容は、デバイスアドレス空間のすべての場所でエイリアス(オーバレイ)されます。オーバレイは、1 回の読み出しアクセス、特にステータスレジスタ読み出しコマンドに続く次の読み出しアクセスに対して有効です。ステータスレジスタに 1 回アクセスすると、ステータスレジスタ ASO が終了します。

ステータスレジスタには、最後に開始された EA の結果(成功または失敗)に関連するビットが含まれています。

- 消去ステータス(ビット 5)

- プログラムステータス(ビット 4)

- 書き込みバッファ中止(ビット 3)

- セクタロックステータス(ビット 1)

- セクタ消去ステータスピット(ビット 0)

そして、プロセス中 EA の現在の状態に関連するビットも含まれています。

- デバイスビジー(ビット 7)

- 消去中止(ビット 6)

- プログラム中止(ビット 2)

- CRC 計算中止(ビット 8)

現在のステータスピットは、EA が処理中、中止、または完了したかどうかを示します。

上位 7 ビット(ビット 15:9)は予約されています。これらには未定義の HIGH または LOW の値があり、ある状態から別の状態に変わる可能性があります。これらのビットは「ドントケア」として扱われ、ソフトウェア読み出しステータスでは無視されます。

クリアステータスレジスタコマンドおよびソフトウェアリセットコマンドは、ステータスレジスタの結果関連ビット(ビット 5, 4, 3, 2, 1、および 0)を '0' にクリアしますが、現在の状態ビットには影響しません。

組込み動作

Table 17 ステータス レジスタ

| ビット番号  | ビット説明                         | ビット名   | リセットステータス | ビギンステータス | レディステータス                                                                                |

|--------|-------------------------------|--------|-----------|----------|-----------------------------------------------------------------------------------------|

| [15:9] | 予約済み                          | -      | X         | 無効       | X                                                                                       |

| [8]    | CRC 中止<br>ステータス ビット           | CRCSSB | 0         | 無効       | 0=CRC 中止なし<br>1=CRC 中止                                                                  |

| [7]    | デバイス レディ ビット                  | DRB    | 1         | 0        | 1                                                                                       |

| [6]    | 消去中止<br>ステータス ビット             | ESSB   | 0         | 無効       | 0=消去中止なし<br>1=消去中止                                                                      |

| [5]    | 消去ステータス ビット                   | ESB    | 0         | 無効       | 0=消去成功<br>1=消去失敗                                                                        |

| [4]    | プログラム<br>ステータス ビット            | PSB    | 0         | 無効       | 0=プログラム成功<br>1=プログラム失敗                                                                  |

| [3]    | 書き込みバッファ<br>アボート<br>ステータス ビット | WBASB  | 0         | 無効       | 0=プログラム中止なし<br>1=バッファ コマンドへの書き込み<br>中プログラムが中止                                           |

| [2]    | プログラム中止<br>ステータス ビット          | PSSB   | 0         | 無効       | 0=プログラム中止なし<br>1=プログラム中止                                                                |

| [1]    | セクタロック<br>ステータス ビット           | SLSB   | 0         | 無効       | 0=動作中のセクタロックなし<br>1=セクタロック エラー                                                          |

| [0]    | セクタ消去<br>ステータス ビット            | ESTAT  | 0         | 無効       | 0=セクタ消去ステータス コマンド<br>結果 = 前の消去が正常に完了しな<br>かった<br>1=セクタ消去ステータス コマンド<br>結果 = 前の消去が正常に完了した |

注:

- 34.ビット 15 ~ 9 は、将来の使用のために予約されており、'0' または '1' として表示される場合があります。これらのビットは、ステータスをチェックするときに無視(マスク)する必要があります。

- 35.デバイスで進行中の EA がない場合、ビット 7 は '1' です。

- 36.ビット 8 およびビット 6 ~ 0 は、ビット 7 が '1' の場合にのみ有効です。

- 37.すべてのビットは、コールドリセットまたはウォームリセットによってリセット状態になります。

- 38.ビット 5, 4, 3, 1, および 0 は、ステータスレジスタのクリアコマンドまたはソフトウェアリセットコマンドによって '0' にクリアされます。

- 39.消去中止コマンドを発行すると、ユーザーは DRB が '1' になるまでステータスの読み出しを続ける必要があります。

- 40.ESSB は、消去再開コマンドによって '0' にクリアされます。

- 41.ESB は、最新の消去操作の成功または失敗を反映しています。

- 42.PSB は、最新のプログラム操作の成功または失敗を反映しています。

- 43.消去中止中に、中止されたセクタにプログラミングすると、プログラムエラーが発生し、プログラムステータスピットが '1' に設定されます。

- 44.消去中止中、消去操作により消去エラーが発生し、消去ステータスピットが '1' に設定されます。

- 45.プログラム中止中、プログラミング操作によりプログラムが失敗し、プログラムステータスピットが '1' に設定されます。

- 46.プログラム中止中に、消去操作により消去エラーが発生し、消去ステータスピットが '1' に設定されます。

- 47.プログラム中止コマンドを発行すると、ユーザーは DRB が '1' になるまでステータスの読み出しを続ける必要があります。

- 48.PSSB は、プログラム再開コマンドによって '0' にクリアされます。

- 49.SLSB は、ターゲットメモリ領域がロックされているため、プログラムまたは消去操作が失敗したこと示します。

- 50.SLSB は、最新のプログラムまたは消去操作のステータスを反映します。

- 51.CRCSSB — CRC 計算の中止中は、アレイからの読み出し操作のみが許可されます。

### 6.2.12 不揮発性コンフィギュレーションレジスタおよび揮発性コンフィギュレーションレジスタ

不揮発性構成レジスタ (NVCR) および揮発性構成レジスタ (VCR) は HYPERFLASH™ バスの動作条件を定義するためには使用されます。以下は設定可能な特性です。

1. ラップ式バースト長 (16 バイト, 32 バイト, または 64 バイトのラップ式バースト)

- a. 16 バイトおよび 32 バイトのラップ式バーストは、従来の方法で動作し、64 バイトのラップ式バーストは [Table 22](#) のように動作します。

2. 読み出しレイテンシ (最初の読み出しレイテンシを可能にするために 5 ~ 16 のクロックを供給)

3. 出力ドライバー駆動強度

4. 4 KB のパラメーター セクタが使用されるかどうか、そしてそれらがどのようにアドレス マップにマップされるか

5. セキュアシリコン領域をロックするための SSR フリーズ ビット

6. 挥発性コンフィギュレーションレジスタと不揮発性コンフィギュレーションレジスタをロックするための xVCR フリーズ ビット

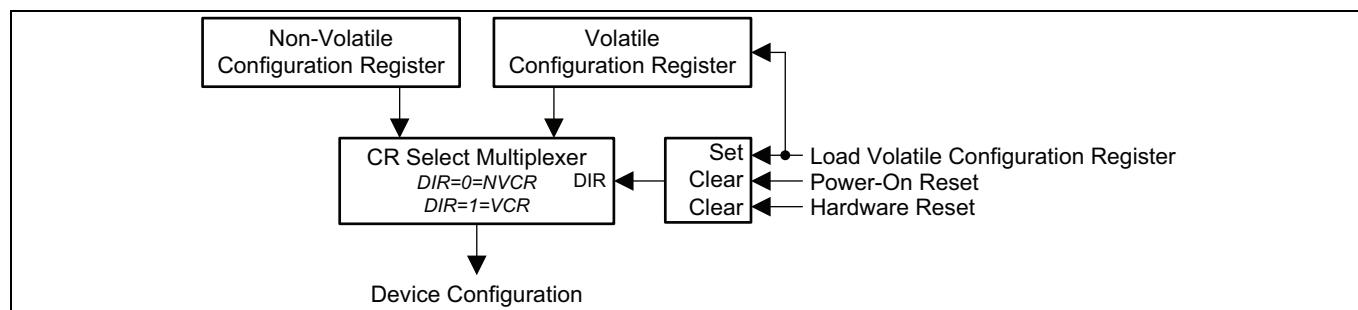

[Table 41](#) で説明するように VCR と NVCR の内容をロードし、読み戻せます。HYPERFLASH™ デバイスは、NVCR の内容を電源投入時、またはハードウェアリセット後にバス特性を定義するために使用します。ホストシステムが VCR をロードする場合、バス特性は VCR 内容によって定義されます ([Figure 18](#) を参照してください)。NVCR は、初期設定を保持して起動中にホスト コントローラー設定との整合を取りために意図されます。VCR は、起動中にしばしば最適設定に更新されます。VCR がロードされると、バス特性のソースが NVCR から VCR に (電源投入またはハードウェアリセット後) 切り替わります。一旦 VCR をロードした場合、バス特性は電源投入またはハードウェアリセットのみにより NVCR 設定に戻されます。VCR は、ロック解除されている限り、デバイスがアイドルの時にいつでも変更できます。

NVCR の消去および再プログラム可能な回数は n\_NVCR 仕様で定義されています。NVCR のプログラミング中およびその後にバスコンフィギュレーションの一貫性を確保できるよう、NVCR プログラミング時に VCR をバス動作特性の定義に使用してください。

組込み動作

**Table 18 VCR および NVCR コンフィギュレーションレジスタ ビットの割り当て**

| xVCR ビット    | 機能               | 設定 (2 進数)                                                                                                                                                                                                                |

|-------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| xVCR[15]    | 予約済み             | 1 = 予約済み (デフォルト)                                                                                                                                                                                                         |

| xVCR[14:12] | 駆動強度             | <a href="#">Table 19</a> を参照してください。                                                                                                                                                                                      |

| xVCR[11]    | xVCR フリーズ        | 0 = VCR または NVCR がロックされる (NVCR のプログラムや消去も VCR の変更もない)<br>1 = VCR および NVCR がロック解除される (工場出荷時のデフォルト状態)                                                                                                                      |

| xVCR[10]    | SSR フリーズ         | 0 = セキュアシリコン領域がロックされる (プログラムは不可)<br>1 = セキュアシリコン領域がロック解除される (工場出荷時のデフォルト状態)                                                                                                                                              |

| xVCR[9:8]   | パラメーター セクタ マッピング | 00 = パラメーター セクタと読み出しパスワード セクタは最下位のアドレスにマッピングされる<br>01 = パラメーター セクタと読み出しパスワード セクタは最上位のアドレスにマッピングされる<br>10 = ユニフォーム セクタと読み出しパスワード セクタが最下位のアドレスにマッピングされる (工場出荷時のデフォルト状態)<br>11 = ユニフォーム セクタと読み出しパスワード セクタが最上位のアドレスにマッピングされる |

| xVCR[7:4]   | 読み出し レイテンシ       | 0000 = 5 クロック レイテンシ<br>0001 = 6 クロック レイテンシ<br>0010 = 7 クロック レイテンシ<br>0011 = 8 クロック レイテンシ<br>0100 = 9 クロック レイテンシ<br>...<br>1011 = 16 クロック レイテンシ (工場出荷時のデフォルト状態)<br><a href="#">Table 4</a> を参照してください。                     |

| xVCR[3]     | 予約済み             | 1 = 予約済み (デフォルト)                                                                                                                                                                                                         |

| xVCR[2]     | RWDS ストール 制御     | 0 = デュアルエラー検出時に RWDS はストール (LOW のまま) します (デフォルト)<br>1 = デュアルエラー検出時に RWDS ガストールしない                                                                                                                                        |

| xVCR[1:0]   | バースト長            | 00 = 予約済み<br>01 = 64 バイト<br>10 = 16 バイト<br>11 = 32 バイト (工場出荷時のデフォルト状態)                                                                                                                                                   |

注:

52. コンフィギュレーションレジスタ ビットの配置は、不揮発性と揮発性コンフィギュレーションレジスタでは同じです。

組込み動作

Table 19 駆動強度コード

| xVCR[14:12] | 標準インピーダンス $1.8\text{ V }V_{CCQ}$ | 標準インピーダンス $3\text{ V }V_{CCQ}$ | 単位       |

|-------------|----------------------------------|--------------------------------|----------|