サイプレス

# 大容量 FIFO

## 製品概要

### プログラマブルな機能を備えた大容量 FIFO

サイプレスのプログラマブル FIFO(first in first out) ファミリは、業界最大容量のプログラマブル FIFO メモリ デバイスを提供します。最大 144Mb の容量に加え、150MHz というクラス最高の速度、さらにはマルチキューイングおよび選択可能なメモリ構成といった、セグメント固有の付加価値機能を備えています。これはすべて、お客様が設計をより早く効率的に行うのに役立ち、広い範囲のアプリケーションに最適のものとなっています。

SRAM 技術に基づき、大容量(HD) FIFO はデータ信頼性が高く、レイテンシが低くなっています。使いやすいバス インタフェースにより、実装とデバッグの手間が軽減されます。商品化までの時間を短縮するすぐに使えるソリューションであり、関連するエンジニアリング工数を減らします。このデバイスには、幅拡張のオプションもあります。

ビデオ ブロードキャスティング、軍事、医療イメージング、および基地局(ネットワーク)セグメントに適しており、以下のような多数のアプリケーションに対応しています。

- 一般的な HD フォーマット(720p、1080i、1080p)用のフレーム バッファ : 1080p の解像度のフレームを 4 枚まで格納

- HDTV/SDTV のフレーム同期

- 切り替え装置またはフォーマット変換ボックス

- ハイエンドのデジタルビデオ カメラ

- 軍事レーダの大容量バッファ

- 医療イメージング

- 基地局 - 3G、4G、およびネットワーク

### 主な仕様

容量 : 18 Mb、36 Mb、72 Mb、144 Mb

速度 : 150 MHz

スループット : 最高 5.4 Gbps

バス幅 : ユーザが選択可能な x9、x12、x16、x18、x20、x24、x32、x36

コア電圧 : 1.5 V、1.8 V

パッケージ : 209-BALL BGA (14 mm X 22 mm)

工業用温度範囲 : -40 °C ~ +85 °C

### 主な特長

マルチキューイング用に提供されているさまざまなデバイス

- シングル キュー(最大 150 MHz)

- 2 キュー(最大 100 MHz)

- 8 キュー(最大 100 MHz)

- 128 キュー(最大 100 MHz)

### I/O 電圧オプション

- 1.5 V、1.8 V、2.5 V、3.3 V をサポート

- LVTTL、LVCMS、および HSTL で使用可能

## 主な特長

- 独立した読み取り／書き込みポートによる単方向動作 - 同時読み取り／書き込み動作をサポート

- 書き込みマスクと読み取リスキップ動作用の入出力イネーブルコントロール

- マークおよび再送信機能で読み取りリポインタをユーザがマークした位置にリセット

- FIFO シーケンスをバイパスして入力ポートから出力ポートへデータを送るメール ボックス レジスタ

- コンフィギュレーション レジスタのシリアルプログラミング用の独立した SCLK 入力

- エンプティ、フル、ハーフフルに加え、プログラマブルで設定できるほとんどエンプティおよびほとんどフルのステータス フラグ

- プログラマブル フラグはシリアルな手段でもパラレルな手段でもプログラム可能

- データは消去してもプログラマブルな設定は保持する、部分的なりセット

- バウンダリスキャン機能用の JTAG ポート

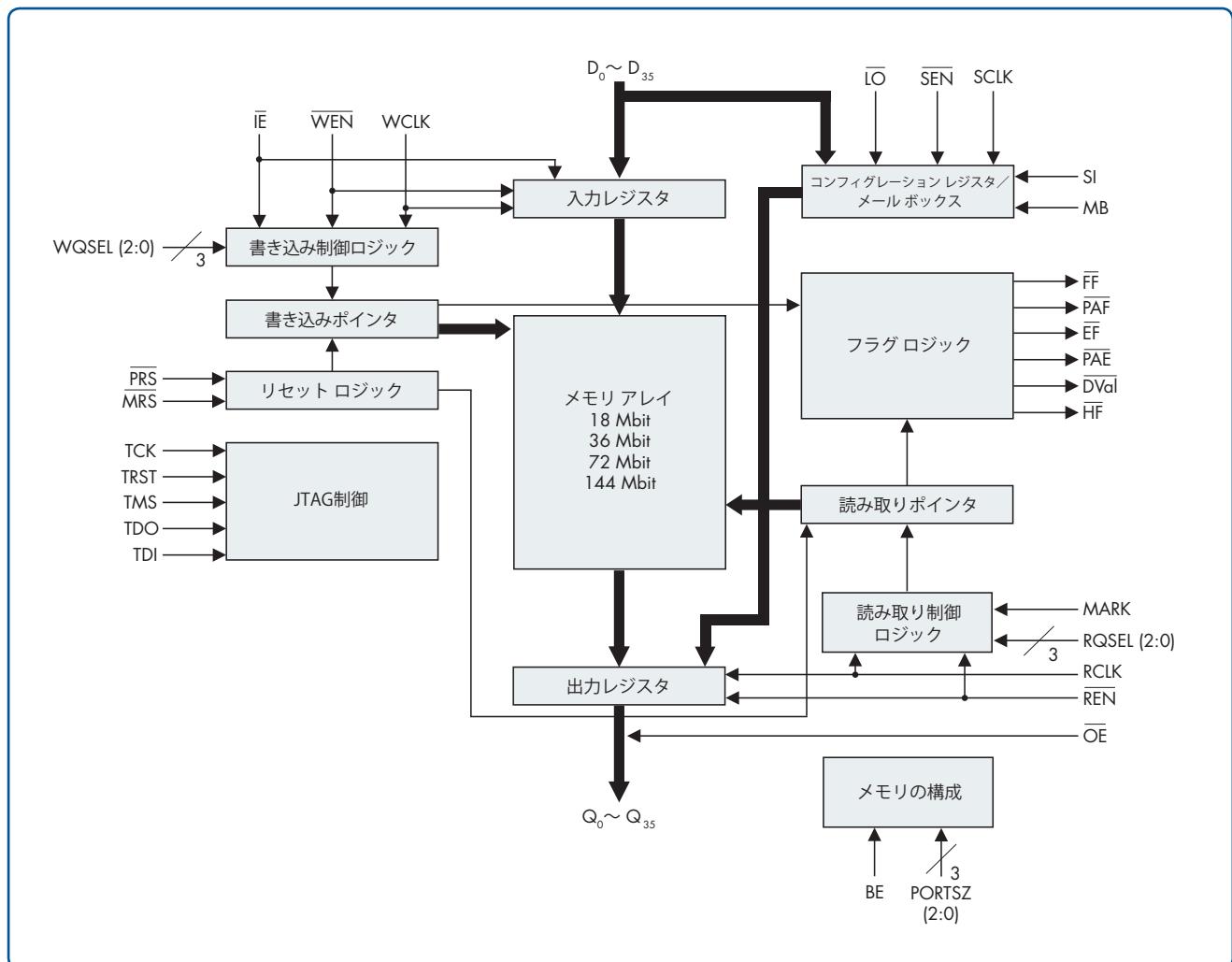

HD FIFO の機能ブロック図

## 主な利点

### 簡略化されたシステムアーキテクチャ - HD FIFO 対他のディスクリート FIFO

今日の市場のディスクリート FIFO には、提供する容量およびメガビットあたりの高いコストの制約があります。サイプレスの HD FIFO のマルチキューイング機能は、高性能イメージング、ビデオ処理、およびネットワークシステムのシステムアーキテクチャを簡素化する、切望されていたツールを提供します。これにより、お客様は他のディスクリートソリューションに比べて、ソリューションを素早くコスト効率よく設計できます。

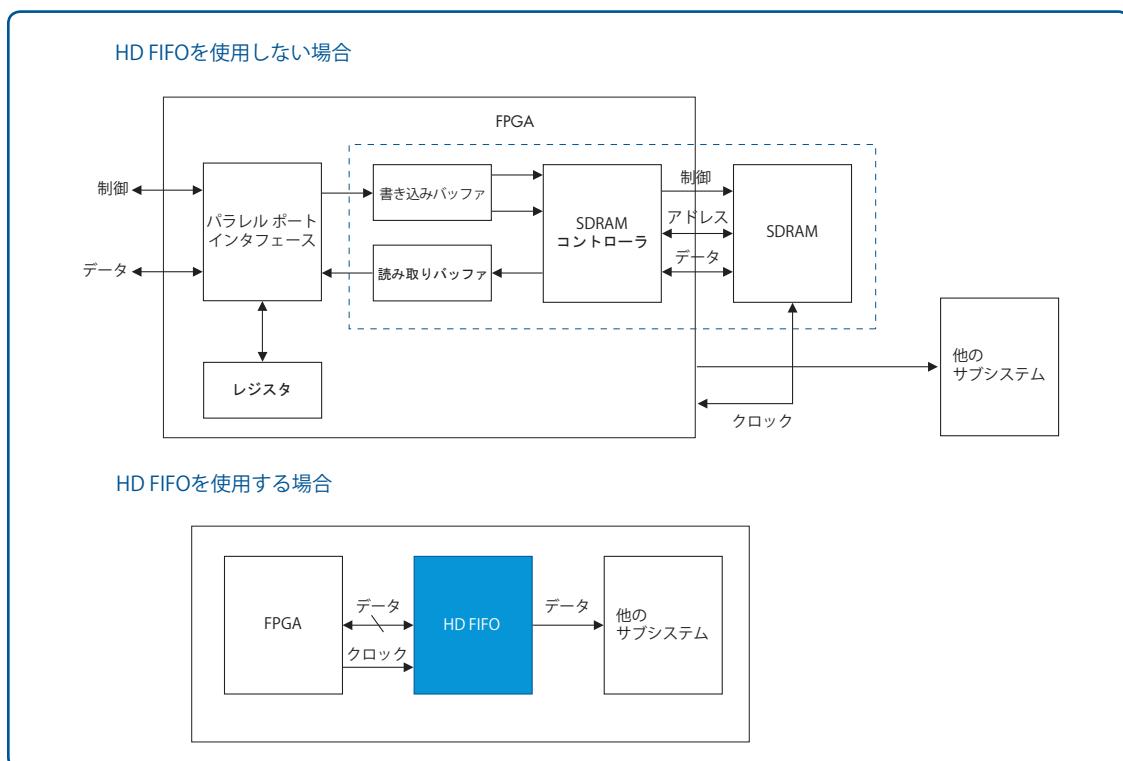

### FPGA/DSP 統合メモリ - HD FIFO および FPGA 対 SDRAM および FPGA ソリューション

イメージ処理システムは、FPGA によって処理される非常に大容量のデータバッファリングが必要です。この大容量メモリバッファリングを達成するために、FPGA はしばしば外部 SDRAM と組み合わせられます。FIFO コントローラロジックを FPGA 内で実装することにより、外部 SDRAM は FIFO のように機能します。外部 DRAM のレイテンシを補償するためには、FPGA 内に小さいメモリバッファが作成されます。しかし、これには多少欠点があり、そのためお客様はより高性能の FPGA を使用せざるを得ません。

- FPGA 内の貴重なロジックリソースが使用されるので、設計が複雑になり、効率が低下します。

- FPGA 内に実装されるコントローラとして使用される貴重な FPGA I/O は、アドレス信号を外部 SDRAM メモリに送信する必要があります。

- FPGA の内部メモリ空間(スクラッチパッドメモリ)が必要なので、他の目的に使用できません。

- システムの複雑さが増し、性能が低下します。

サイプレスのプログラマブル HD FIFO を使用すれば、お客様はより低容量の FPGA を選べるので、システムコストが低減します。以下の図に、これら 2 つのシステムの比較を示します。HD FIFO は、お客様の要件および機能の優先順位に合わせて、さまざまな部品の組み合わせも可能にします。

HD FIFO を使用する場合と使用しない場合を比較するブロック図

## オーダ情報

| 容量 (Mb) | 構成                                  | V <sub>DD</sub> (V) | 温度 (°C)     | 周波数 (MHz) | キュー数           | I/O電圧標準 (V)        | パッケージ     | 出荷状況                                 |

|---------|-------------------------------------|---------------------|-------------|-----------|----------------|--------------------|-----------|--------------------------------------|

| 144     | ユーザが選択可能なx9、x16、x18、x20、x24、x32、x36 |                     |             |           |                |                    |           |                                      |

| 72      |                                     | 1.5, 1.8            | -40°C～+85°C | 150       | シングル、ダブル、8、128 | 1.5, 1.8, 2.5, 3.3 | 209ボールBGA |                                      |

| 36      |                                     |                     |             |           |                |                    |           |                                      |

| 18      |                                     |                     |             |           |                |                    |           | 現在はエンジニアリングサンプルが入手可能。量産開始は2010年第4四半期 |

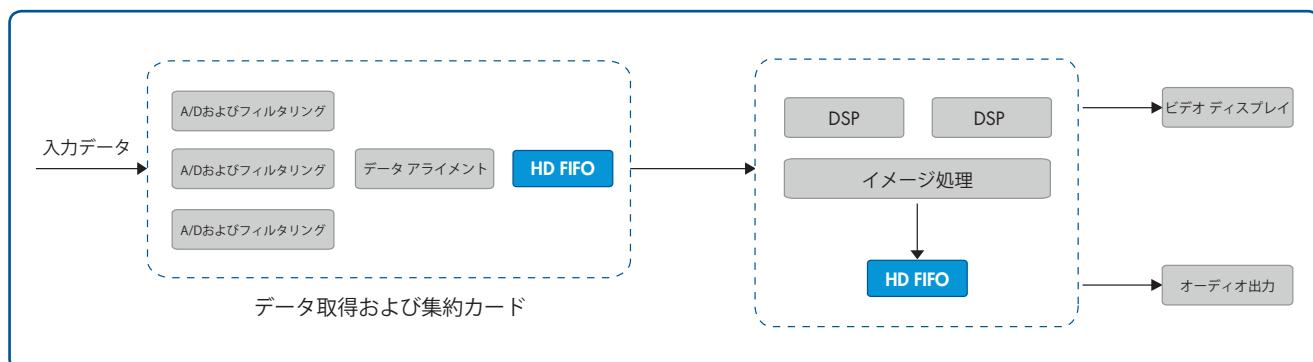

## イメージングシステムにおける HD FIFO - 使用例

下図に、HD FIFO を使用したイメージングシステムの仕組みを示します。標準的なイメージングシステムは、2 セットのカードで構成されます。

**データ取得および集約カード** - データ取得カードは、入ってくるデータをフィルタ処理します。診断イメージングシステムは、複数のデータ取得カードで構成されることもあります。データ集約カードは、取得したデータのバッファ処理とアライメントを行います。CT および PET スキャナの場合、検出器が人体の周囲を回り、データは直列化され、スリップリング電気機械サブアセンブリを通じて送信されます。

**イメージ／データ処理カード** - これらのカードは、極めて重要なフィルタリングと最もアルゴリズム集約的なイメージ再構築を行います。

カードを使用したアプリケーション例のブロック図

## 今すぐ始めよう

HD FIFO のより詳細な情報は [www.cypress.com/go/HDFIFO](http://www.cypress.com/go/HDFIFO) にアクセスするか、または [spcm\\_mktg@cypress.com](mailto:spcm_mktg@cypress.com) までご連絡ください。

## 日本サイプレス株式会社

〒164-0012 東京都中野区本町1-32-2 ハーモニータワービル17階

電話：03-5371-1921 FAX：03-5371-1955 <http://www.cypress.com>

© 2010 Cypress Semiconductor Corporation. All rights reserved. All other trademarks are the property of their respective owners.

Doc# 001-65453 Rev\*\* 1110/HKV/NITA