# **Programming specification**

#### **About this document**

#### **Scope and purpose**

This document provides the information necessary to program the nonvolatile memory of the PSOC<sup>™</sup> 6 MCU family. It describes the communication protocol required for access by an external programmer, explains the programming algorithm, and gives a basic description of the physical connection. The pin locations, electrical, and timing specifications of the physical connection are not part of this document. They can be found in the device datasheet. The programming algorithms described in the following sections are compatible with all PSOC<sup>™</sup> 6 MCUs except PSOC<sup>™</sup> 64 devices, which are described in [1].

#### **Intended audience**

This programming specification is intended for those developing programming solutions for the target devices. This includes third-party production programmers, as well as customers wanting to develop their programming systems. For more information, see Programming Solutions for Industrial and IoT Microcontrollers.

# **Programming specification**

# **Table of contents**

# **Table of contents**

| Abou   | t this document                                        | 1  |

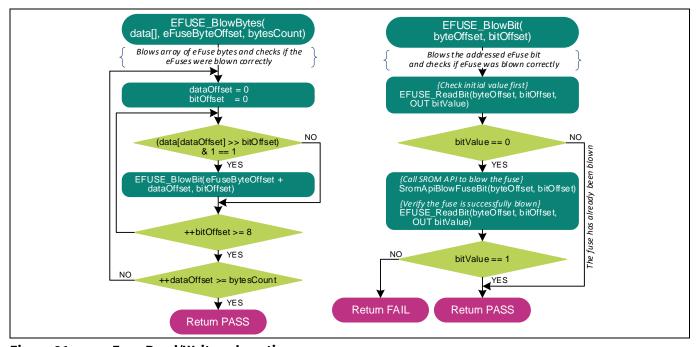

|--------|--------------------------------------------------------|----|

| Table  | e of contents                                          | 2  |

| 1      | Introduction                                           | 4  |

| 1.1    | Programmer                                             | 4  |

| 1.2    | PSOC™ 6 MCU family overview                            | 5  |

| 2      | Nonvolatile memory subsystem                           | 6  |

| 2.1    | Application flash                                      |    |

| 2.2    | Auxiliary flash (AUXflash)                             |    |

| 2.3    | Supervisory flash (Sflash)                             |    |

| 2.4    | Electronic fuses (eFuse)                               |    |

| 2.5    | Execute-in-place (XIP)                                 |    |

| 3      | Hex file                                               | 10 |

| 3.1    | Organization of the hex file                           |    |

| 4      | Protocol stack                                         | 13 |

| 4.1    | Communication interface                                | 14 |

| 4.2    | Program and debug interface                            |    |

| 4.2.1  | DAP security                                           |    |

| 4.2.2  | DAP power domain                                       |    |

| 4.2.3  | SWD/JTAG selection                                     |    |

| 4.2.4  | Hardware access commands                               |    |

| 4.2.5  | Pseudocode                                             |    |

| 4.3    | Physical layer                                         |    |

| 5      | Programming algorithm                                  |    |

| 5.1    | High-level programming flow                            |    |

| 5.2    | Constants and subroutines used in the programming flow |    |

| 5.2.1  | Constants                                              |    |

| 5.2.2  | Subroutines                                            | 27 |

| 5.3    | Step 1.A – Acquire PSOC™ 6 MCU                         | 32 |

| 5.4    | Step 1.B – Acquire PSOC™ 6 MCU (alternate method)      | 35 |

| 5.5    | Step 2 – Identify silicon                              | 37 |

| 5.6    | Step 3 – Erase application flash                       | 38 |

| 5.7    | Step 4 – Verify blank checksum (optional)              | 39 |

| 5.7.1  | Pseudocode – Step 4. Verify checksum                   | 39 |

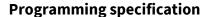

| 5.8    | Step 5 – program application flash                     | 40 |

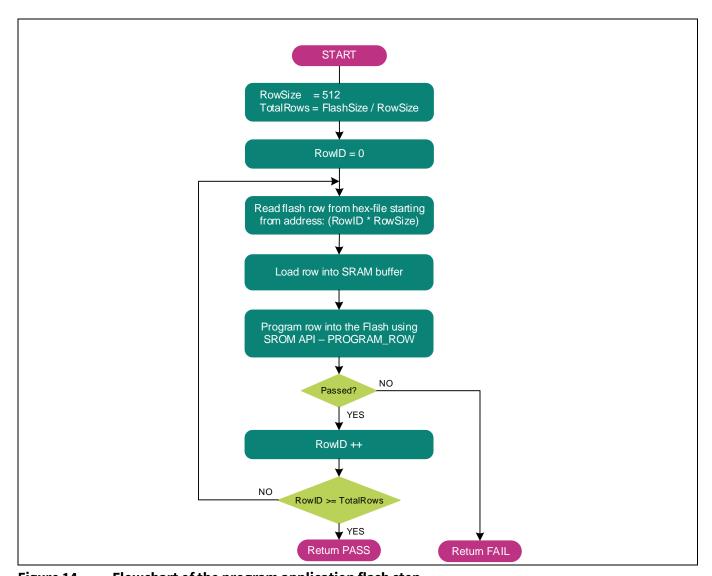

| 5.9    | Step 6 – Verify application flash                      | 41 |

| 5.10   | Step 7 – Verify checksum (optional)                    | 43 |

| 5.10.1 | 1 Pseudocode – Step 7. Verify checksum                 | 43 |

| 5.11   | Step 8 – Program and verify AUXflash                   | 43 |

| 5.12   | Step 9 – Program and verify Sflash                     | 46 |

| 5.13   | Step 10 – Program eFuse                                | 46 |

| 5.14   | Step 11 – Verify eFuse (optional)                      | 54 |

| 6      | Appendix A: Intel hex file format                      | 56 |

| 7      | Appendix B: eFuse data mapping in file                 | 58 |

| 8      | Appendix C: Serial wire debug (SWD) Protocol           | 62 |

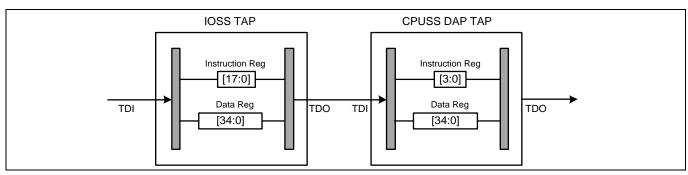

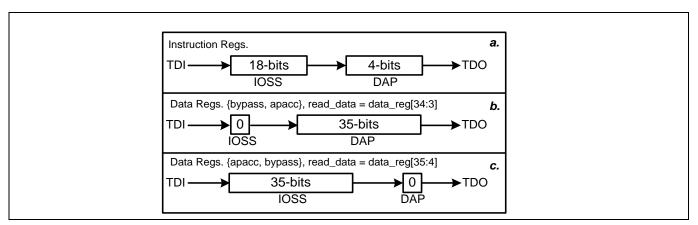

| 9      | Appendix D: Joint test action group (JTAG) protocol    | 65 |

| Refer  | rences                                                 | 67 |

# **Programming specification**

# **Table of contents**

| Revision history | 68 |

|------------------|----|

| Disclaimer       | 74 |

#### **Programming specification**

# infineon

#### Introduction

### 1 Introduction

This document provides the information necessary to program the nonvolatile memory of the PSOC™ 6 MCU family. It describes the communication protocol required for access by an external programmer, explains the programming algorithm, and gives a basic description of the physical connection. The pin locations and the electrical and timing specifications of the physical connection are not a part of this document. They can be found in the device datasheet. The programming algorithms described in the following sections are compatible with all PSOC™ 6 MCUs.

### 1.1 Programmer

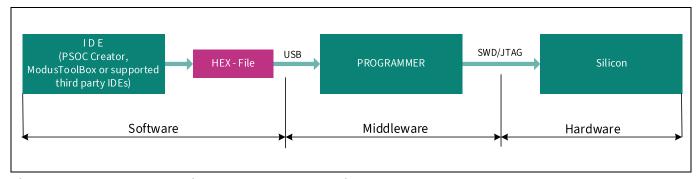

Figure 1 illustrates a high-level view of the programmer environment.

Figure 1 Programmer in the development environment

In the manufacturing environment, the integrated development environment (IDE) block is absent because its main purpose is to produce the binary file (hex, elf, and so on). Figure 1 shows, that the programmer performs the functions:

- Parses the binary file and extracts the necessary information

- Interfaces with the silicon as a serial wire debug (SWD) or JTAG master

- Implements the programming algorithm by translating the data from the binary file into SWD or JTAG signals

The structure of the programmer depends on its requirements. It can be software- or firmware-centric.

In a software-centric structure, the programmer's hardware is between the protocol (USB) and SWD. An external device (software) passes all the SWD commands to the hardware through the protocol. The bridge is not involved in parsing the binary file and programming algorithm; this is the task of the upper layer (software)—for example, MiniProg3 and Segger J-Link.

A firmware-centric structure is an independent hardware design in which all the functions of the programmer are implemented in one device, including storage for the binary file. Its main purpose is to act as a mass programmer in manufacturing.

This document does not discuss the specific implementation of the programmer. It focuses on data flow, algorithms, and physical interfacing.

#### **Programming specification**

# infineon

#### Introduction

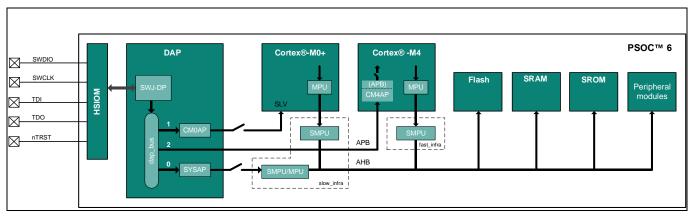

### 1.2 PSOC™ 6 MCU family overview

The PSOC™ 6 MCU family is a dual-CPU solution, with both the Arm® Cortex®-M4 and Cortex®-M0+ processor cores. This MCU family supports the Arm® SWJ-DP Interface for programming and debugging operations, using SWD or JTAG protocols.

The nonvolatile subsystem of the silicon consists of a flash memory system. The flash memory system stores the user's program or data, as well as eFuses.

The part can be programmed after it is installed in the system by way of the SWD or JTAG interface (in-system programming).

See the device datasheet for the specifications on memory size and programming frequency range.

This document focuses on the specific programming operations without referencing the silicon architecture. Many important topics are detailed in the appendices. Other device-specific information can be found in the device's datasheet or technical reference manual.

This document includes the following appendices:

- Appendix A: Intel hex file format

- Appendix B: eFuse data mapping in file

- Appendix C: Serial wire debug (SWD) Protocol

- Appendix D: Joint test action group (JTAG) protocol

# infineon

Nonvolatile memory subsystem

# 2 Nonvolatile memory subsystem

This chapter describes the nonvolatile memory subsystem of the PSOC™ 6 MCU silicon.

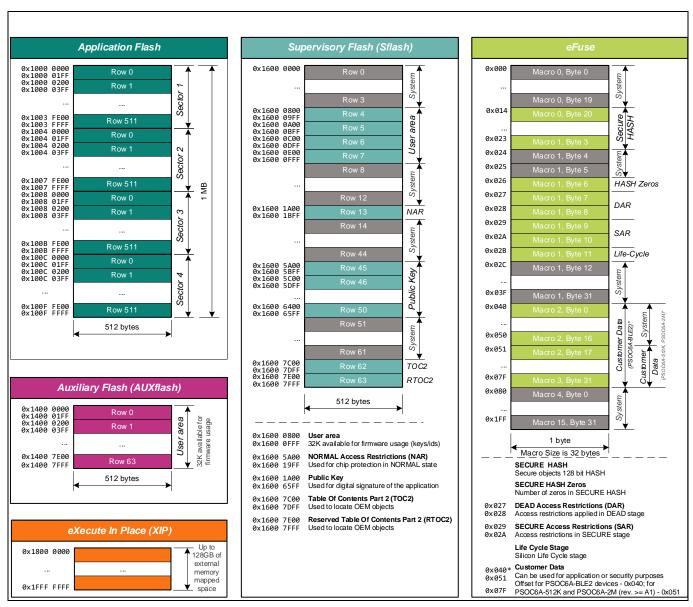

Figure 2 Nonvolatile subsystem

#### **Programming specification**

# infineon

#### Nonvolatile memory subsystem

## 2.1 Application flash

The application flash is organized into sectors. Sector size can be either 128 KB for parts with 256 KB flash or 256 KB for all the rest. There are eight such sectors for parts with 2 MB flash on board, four and two sectors for parts with 1 MB and 256/512 KB flash, respectively. There are 256 or 512 rows in the sector, depending on the sector size (128 KB or 256 KB), each consisting of 512 bytes.

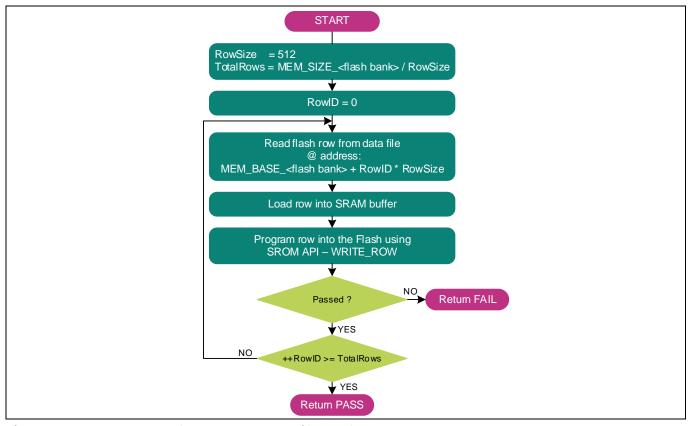

The programming granularity is one row at a time. The maximum number of rows during programming depends only on the part's flash size. The formulae are as follows:

L = 512 (L is the row size in bytes)

$$N = \frac{FlashSize}{L}$$

(N is the total number of rows)

The flash memory is mapped directly to the CPU's address space starting from 0x10000000. Therefore, the firmware or external programmer can read its content directly from the given address.

## 2.2 Auxiliary flash (AUXflash)

In addition to the application flash, the flash macros may contain auxiliary flash. The AUXflash is typically used to store frequently updated data; for example, AUXflash can be used to emulate EEPROM memory.

The AUXflash is mapped directly to the CPU's address space starting from 0x14000000. Therefore, the firmware or external programmer can read its content directly from the given address.

Some devices may not have AUXflash, check its availability in the device datasheet.

# 2.3 Supervisory flash (Sflash)

In addition to the application flash and AUXflash regions, the flash macros contain supervisory flash (Sflash), which can store various application-specific data.

The Sflash memory is mapped directly to the CPU's address space; therefore, the firmware or external programmer can read its content directly from the given address.

These sub-regions are accessible in Sflash memory:

- 0x1600 0800 0x1600 0FFF User area. Up to 32 KB can be used by the application to store arbitrary data

- **0x1600 1A00 0x1600 1BFF** NORMAL access restrictions (NAR)

Used for chip protection in the NORMAL lifecycle stage. Ensure that the NAR sub-region cannot be overwritten or erased if the new data is less restrictive than the existing data.

- 0x1600 5A00 0x1600 65FF Public Key. Used for digital signature of the application.

- 0x1600 7C00 0x1600 7DFF Table of contents part 2 (TOC2).

Used to locate various OEM objects such as application(s) start address(es) and format, address of SMIF configuration structure. Also used during the boot process to apply device's initial settings such as clock

#### **Programming specification**

#### Nonvolatile memory subsystem

frequency configuration, duration of the Listen window, SWJ pins availability, and digital signature verification (authentication).

• 0x1600 7E00 - 0x1600 7FFF - Reserved table of contents part 2 (RTOC2)

Writing to listed sub-regions is not possible when the chip is in the SECURE lifecycle stage. Writing to any Sflash address outside the specified sub-regions is not possible in any Life Cycle stage except VIRGIN, which is a factory-only stage.

### 2.4 Electronic fuses (eFuse)

PSOC<sup>™</sup> 6 MCUs contain Electronic Fuses (eFuses), which include up to 16 nonvolatile memory macros of 256 bits each (4096 bits in total), with each bit being one-time programmable (OTP). These are implemented as a regular advanced high-performance Bus (AHB) peripheral with the following characteristics and assumptions:

- eFuses store the device lifecycle stage (NORMAL, SECURE, and SECURE\_WITH\_DEBUG), the protection settings, and up to 512 bits (64 bytes) of customer data

- eFuse memory can be programmed (eFuse bit value changed from '0' to '1') only once. If an eFuse bit is blown, it cannot be cleared

- Programming fuses require the associated I/O supply to be at a specific level: the device VDDIO0 (or VDDIO if

only one VDDIO is present in the package) supply should be set to 2.5 V (±5%)

- The eFuse array can be read eight bits at a time using normal memory-mapped AHB register reads or corresponding system calls

- eFuses are programmed one bit at a time using a Command register

These eFuse bytes are accessible for production programming:

- **0x014 0x023** SECURE HASH. 128-bit (16 bytes) HASH is used by boot code to authenticate objects in the table of contents part 2 (TOC2).

- **0x26** SECURE HASH Zeros. The number of bits that are '0' (fuses that are not blown) in the SECURE HASH above. This guarantees that once a HASH is programmed, it cannot be changed into another valid HASH value

- **0x027 0x028** DEAD access restrictions (DAR). Chip access restrictions applied in the DEAD lifecycle stage:

- **0x029 0x02A** SECURE access restrictions (SAR). Chip access restrictions applied in the SECURE lifecycle stage

- **0x02B** Silicon lifecycle stage (NORMAL, SECURE\_WITH\_DEBUG, or SECURE)

- **0x040 (0x051) 0x07F** Customer data. It can be used by customers for application or security purposes. Offset for PSOC6A-BLE2 devices 0x040; for PSOC6A-256K, PSOC6A-512K, and PSOC6A-2M (rev. >= A1) 0x051

Because blowing an eFuse is an irreversible process, programming is recommended only in mass production programming under controlled factory conditions and not prototyping stages. See Appendix B for eFuse data mapping in the data file. For more details, see the "eFuse Memory" section of the reference manual.

#### **Programming specification**

# infineon

#### Nonvolatile memory subsystem

## 2.5 Execute-in-place (XIP)

Unlike other memory regions, the XIP region is not associated with any physical memory in PSOC<sup>™</sup> 6 MCUs. The purpose of the XIP region is to map the address space of the external memory devices, which are connected to PSOC<sup>™</sup> 6 MCU silicon using the SMIF IP block. When the SMIF block is configured in XIP/Memory mode, it maps the AHB bus accesses to the external memory device addresses to make it behave like internal memory. This allows the CPU to execute code directly from external memory or use it as additional data storage.

Programming of the external flash memory devices via the SMIF IP block can be supported using a flash loader. A flash loader is an application compiled for a target CPU that implements programming algorithms and follows specific rules (framework) defined by a third-party IDE like Keil  $\mu$ Vision, where CMSIS-based flash loaders are used. Such algorithms are loaded into target SRAM by programming software and executed from there for memory bank programming. Infineon supports such algorithms for third-party development tools like Keil  $\mu$ Vision (MDK-ARM), IAR Embedded Workbench, and SEGGER J-Link Software and Documentation Pack. Flash loaders developed by Infineon include the system and SMIF driver middleware and have the following requirements:

- Configuration structures for the SMIF driver must be in the application flash. The Loader uses these structures to determine the design-specific settings of the external memory devices. It also uses these structures for the SMIF driver initialization for further read/write operations.

- The TOC2 must contain the pointer to the location in flash where the configuration structures for the SMIF driver are located. TOC2 is the predefined 512-byte-wide data structure, located at address 0x1600 6C00 in the Sflash region.

- An external flash memory device must be write-enabled and mapped to the XIP address space in PSOC™ MCUs (within the address range 0x1800 0000 - 0x1FFF FFFF).

- Data for the external memory device in the input binary file (hex, elf, and so on) must be allocated in the exact range of XIP address space, where the memory device is mapped.

These requirements necessitate a specific order of memory bank operations:

- For program operation, the application and supervisory flash banks must be programmed first, before the SMIF bank is programmed

- For the erase operation, the SMIF bank must be erased first, before the application and supervisory flash banks are erased

#### **Programming specification**

Hex file

### 3 Hex file

This chapter describes the information that the programmer must extract from the hex file to program the PSOC™ 6 MCU.

## 3.1 Organization of the hex file

The hexadecimal (hex) file describes the nonvolatile configuration of the project. It is the data source for the programmer.

The hex file for the PSOC<sup>™</sup> 6 MCUs follows the Intel Hex File format. Intel's specification is very generic and defines only some types of records that can make up the hex file. The specification allows customizing the format for any possible silicon architecture. The silicon vendor defines the functional meaning of the records, which typically varies for different chip families. See Appendix A for details of the Intel hex file format.

The PSOC<sup>™</sup> 6 MCU defines these data sections in the hex file:

- User program (code) for the application flash region

- User data for the AUXflash region

- User / OEM data for the Sflash region

- User data or code for the external flash memory

- Checksum

- Metadata

- Chip-level protection data (eFuses)

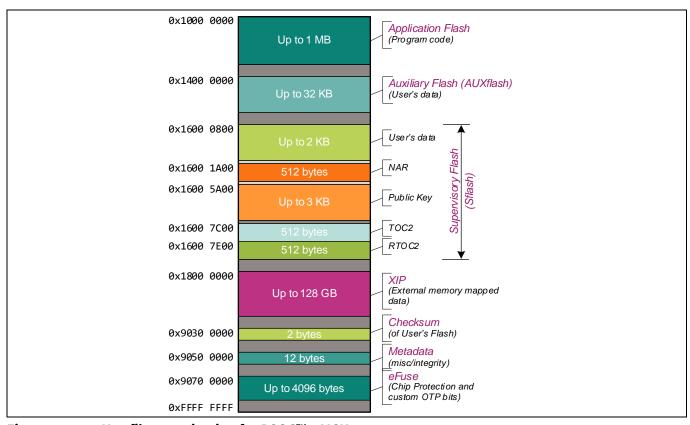

See Figure 3 to determine the allocation of these sections in the address space of the Intel hex file.

The address space of the hex file does not map to the physical addresses of the CPU (other than the user flash). The programmer uses hex addresses (see Figure 3) to read sections from the hex file into its local buffer. Later, this data is programmed (translated) into the corresponding addresses of the silicon.

# infineon

Hex file

Figure 3 Hex file organization for PSOC™ 6 MCUs

- **0x1000 0000 application flash**: This is the user code that must be programmed. The maximum size of this section must not exceed the flash size of the PSOC<sup>™</sup> 6 MCU (up to 2 MB). The address space of this section in the hex file is directly mapped to the physical addresses of the CPU. See the section Application flash for the region description.

- **0x1400 0000 AUXflash**: Can store up to 32 KB of application-specific information. The address space of the AUXflash section in the hex file is directly mapped to the physical addresses of the CPU. Availability of this section in hex file is optional and depends on linker scripts usage in user's project. See the section Auxiliary flash (AUXflash) for the region description.

- 0x1600 0000 -Sflash: Can store application-specific information in five fragmented sub-sections. The

address space of the Sflash section in the hex file is directly mapped to the physical addresses of the CPU.

Availability of this section in hex file is optional and depends on linker scripts usage in user's project. See

Supervisory flash (Sflash) for the region description.

- **0x1800 0000 -XIP**: Can be used to store up to 128 MB of the external memory-mapped data. The address space of the XIP section in the hex file is mapped to the physical addresses of the CPU only in case the user's program configures SMIF block in XIP/Memory mode. Availability of this section in hex file is optional and depends on linker scripts usage in user's project. Seethe section Execute-in-place (XIP) for the region description.

- **0x9030 0000 Checksum** (two bytes): This is the checksum of the entire application flash section—the arithmetical sum of every byte in the user's flash. Only the two least significant bytes (LSB) of the result are saved in this section, in big-endian format (most significant byte, or MSB, first). This must be used by the programmer to check the integrity of the hex file and to verify the quality of the programming. In this context, "integrity" means that the checksum and user's flash sections must correspond in this file. At the end of programming, the checksum of flash (two LSBs) is compared to the checksum from the hex file.

#### **Programming specification**

#### Hex file

• 0x9050 0000 - Metadata (12 bytes): This section contains data that is not programmed into the PSOC<sup>™</sup> 6 MCU. Instead, it is used to check the data integrity of the hex file and the silicon ID of the PSOC<sup>™</sup> 6 MCU. Table 1 lists the fields in this section.

Table 1 Metadata in hex file

| Offset | Data type        | Length in bytes |

|--------|------------------|-----------------|

| 0x00   | Hex file version | 2 (big-endian)  |

| 0x02   | Silicon ID       | 4 (big-endian)  |

| 0x06   | Reserved         | 1               |

| 0x07   | Reserved         | 1               |

| 0x08   | Internal use     | 4               |

- Hex file version: This 2-byte field in the Infineon hex file defines its version (or type). The version for the PSOC™ 6 MCU is '5'. The programmer should use this field to ensure the file corresponds to the PSOC™ 6 MCU, or to select the appropriate parsing algorithm if the file supports several families.

- **Silicon ID**: This 4-byte field (big-endian) represents the ID of the PSOC<sup>™</sup> 6 MCU silicon:

- byte[0] Silicon ID Hi

- byte[1] Silicon ID Lo

- byte[2] Revision ID

- byte[3] Family ID

During programming, the ID of the acquired device is compared to the content of this field. To start programming, three of these fields must match. The Revision ID must be skipped because it is not essential for programming—there are many silicon revisions possible that do not change functionality. Infineon does not guarantee reliable programming (or data retention) if third-party programmers ignore this condition.

- **Reserved**: Not used by the PSOC<sup>™</sup> 6 MCU

- Internal Use: This 4-byte field is used internally by the PSOC™ Programmer software. Because it is not related to actual programming, this field should be ignored by third-party vendors' tools.

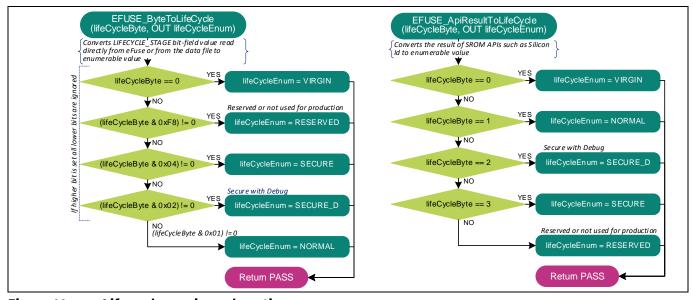

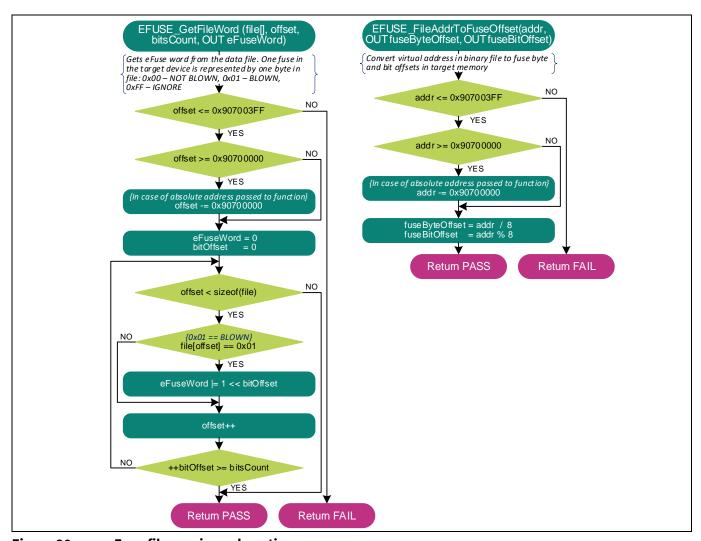

- **0x9070 0000 eFuse** (up to 4096 bytes): eFuse memory provides security functions with far more flexibility than exist in the Flash Protection, Write Once NVL, and Chip Protection options in prior devices. Each eFuse bit setting is stored in the hex file as a full byte. This is done for two reasons. First, it allows the programmer to distinguish bytes that are being set from bytes that we don't care about, or where we don't know the value. The second reason is that it more accurately reflects how these bits are programmed: the SROM functions sets one bit per call. The values are: 0x00 Not blown; 0x01 Blown; 0xFF Ignore. Note: The programmer can only perform a "not blown" to "blown" operation. The programmer should read the corresponding eFuse bit from the device first and blow it only if the device value is '0' (not blown) and the hex value is 0x01 (blown). See the device datasheet for the number of eFuse bits available on the device. See Appendix B for eFuse data mapping in the hex file.

# infineon

**Protocol stack**

#### 4 Protocol stack

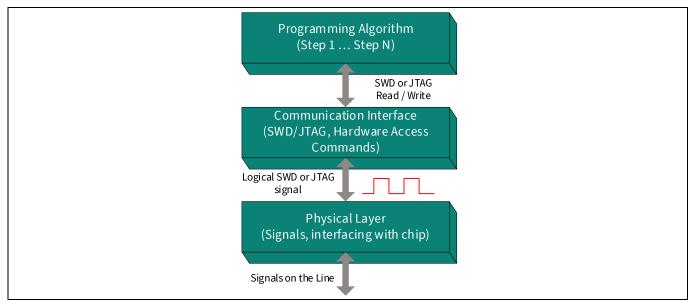

This chapter explains the low-level details of the communication interface. Figure 4 illustrates the stack of protocols involved in the programming process. The programmer must implement both hardware and software components.

Figure 4 Programmer protocol stack

- **Programming algorithm** protocol, the topmost protocol, implements the whole programming flow in terms of logical and algorithmic steps. This protocol is implemented completely in software. Its smallest building block is the SWD or JTAG command. The whole programming algorithm is the meaningful flow of these blocks.

- All programming algorithms are based on system API, stored in SROM (SROM API). During the programming of the flash row, the system code is executed from the SROM. It communicates with the Inter Processor Communication (IPC) module, which "knows" how to program flash. In contrast to a write operation, reading from flash is an immediate operation that is carried out directly from the necessary address (see Figure 2 for address space). Reading works on a word basis (4-byte); writing works on a row basis (512-byte).

- The Programming algorithm protocol is the fundamental part of this specification. For more information on this algorithm, see Chapter 5: Programming Algorithm.

- **Communication interface** layer acts as a bridge between pure software and hardware implementations. SWJ interface implements a set of lower-level (protocol-dependent) commands. It also transforms the software representation of these commands into line signals (digital form). The SWJ interface helps to isolate the programming algorithm from hardware specifics, which makes the algorithm reusable.

- **Physical layer** is the complete hardware specification of the signals and interfacing pins and includes drive modes, voltage levels, resistance, and other components.

# infineon

#### **Protocol stack**

#### 4.1 Communication interface

The external device (whether it is an Infineon-supplied programmer and debugger or a third-party device that supports programming and debugging) can access most internal resources through the Program and Debug Interface provided in PSOC™ 6 MCU silicon. The Serial Wire Debug (SWD) or the JTAG interface can be the communication protocol between the external device and the PSOC™ 6 MCU.

## 4.2 Program and debug interface

The main purpose of PSOC<sup>™</sup> 6 MCU program and debug interface is to support programming and debugging through the JTAG or SWD interface and to provide read and write access to all memory and registers in the system while debugging, including the Cortex®-M4 and Cortex®-M0+ register banks when the core is running or halted.

The PSOC<sup>™</sup> 6 MCU silicon implements a debug access port (DAP), which integrates Serial Wire/JTAG Debug Port (SWJ-DP) and complies with the Arm® specification. For more information, see [1].

Figure 5 Top-level silicon architecture

The debug physical port pins communicate with the DAP through the high-speed I/O matrix (HSIOM). The DAP communicates with the Cortex®-M0+ CPU using the Arm® specified advanced high-performance bus (AHB) interface. AHB is the systems interconnect protocol used inside the device, which facilitates memory and peripheral register access by the AHB master. The PSOC™ 6 MCU has several AHB masters, including the Arm® CM4 CPU core, Arm® CM0+ CPU core, and DAP. The external host can effectively take control of the entire device through the DAP to perform programming and debugging operations.

The debug port (DP) connects to the DAP bus, which in turn connects to one of three access ports (AP), namely:

- CMO-AP connects directly to the AHB debug slave port (SLV) of the CM0+ and gives access to the CM0+ internal debug components. This also allows access to the rest of the system through the CM0+ AHB master interface. This provides the debug host the same view as an application running on the CM0+. This includes access to the MMIO registers of other debug components of the Cortex® M0+ subsystem. These debug components can also be accessed by the CM0+ CPU but cannot be reached through the other APs or by the CM4 core.

- **CM4-AP** is located inside the CM4 gives access to the CM4 internal debug components. The CM4-AP also allows access to the rest of the system through the CM4 AHB master interfaces. This provides the debug host the same view as an application running on the CM4 core. Additionally, the CM4-AP provides access to the debug components in the CM4 core through the external peripheral bus (EPB). These debug components can also be accessed by the CM4 CPU but cannot be reached through the other APs or by the CM0+ core.

#### **Programming specification**

#### **Protocol stack**

• **System-AP** gives access to the rest of the system. This allows access to the System ROM table, which cannot be reached any other way. The System ROM table provides the MCU ID.

## 4.2.1 DAP security

For security reasons, all three APs can be independently disabled. Each AP disable is controlled by two MMIO bits. One bit, CPUSS\_DP\_CTL.xxx\_ENABLE (where xxx can be CMO or CM4, or SYS), is a regular read/write bit. This bit also resets to '0' and is set to '1' by either the ROM boot code or the flash boot code, depending on the lifecycle stage. This feature can be used to block debug access during normal operation but re-enable some debug access after successful authentication.

The second bit, CPUSS\_DP\_CTL.xxx\_DISABLE, can be set during boot, before the debugger can connect, based on eFuse settings for SECURE or DEAD lifecycle stage or based on NAR settings in Supervisory flash for NORMAL lifecycle. After this bit is set, it cannot be cleared. This bit takes priority over the CPUSS\_DP\_CTL.xxx\_ENABLE.

In addition, debug privileges are regulated by the platform protection mechanism using the memory protection units (MPUs), shared memory protection units (SMPUs), and peripheral protection units (PPUs).

Refer to the "Device Security" and "Protection Units" sections of the reference manual for more details on the security settings for the PSOC™ 6 MCU.

### 4.2.2 DAP power domain

Almost all the debug components are part of the Active power domain. The only exception is the SWD/JTAG-DP, which is part of the Deep Sleep power domain. This allows the debug host to connect during Deep Sleep mode, while the application is 'running' or powered down. This enables in field debugging for low-power applications in which the chip is mostly in Deep Sleep mode.

After the debugger is connected to the chip, it must bring the chip to the Active state before any operation. For this, the SWD/JTAG-DP has a register (DP\_CTL\_STAT) with two power request bits. The two bits are CDBGPWRUPREQ and CSYSPWRUPREQ, which request debug power and system power, respectively. These bits must remain set for the duration of the debug session.

Note that only the two SWD pins (SWCLKTCK and SWDIOTMS) are operational during the Deep Sleep mode – the JTAG pins are operational only in Active mode. The JTAG debug and JTAG boundary scan is not available when the system is in Deep Sleep mode.

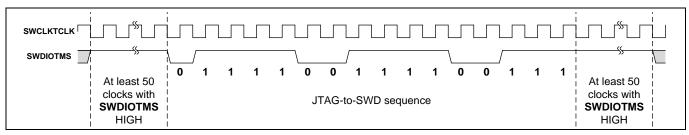

#### 4.2.3 SWD/JTAG selection

The JTAG and SWD are mutually exclusive because of Arm® SWJ-DP implementation and because they share pins. Therefore, an external programmer/debugger must be able to switch to the required protocol. The watcher circuit, implemented in SWJ-DP, detects a specific 16-bit select sequence on SWDIOTMS and decides if the JTAG or SWD interface is active. By default, JTAG operations are selected on powerup reset and therefore the JTAG protocol can be used from reset without sending a select sequence. The protocol switching can only occur when the selected interface is in its reset state (test-logic-reset for JTAG and line-reset for SWD).

To switch SWJ-DP from JTAG to SWD operation:

Send at least 50 SWCLKTCK cycles with SWDIOTMS HIGH. This ensures that the current interface is in its

reset state. The JTAG interface detects only the 16-bit JTAG-to-SWD sequence starting from the test-logicreset state.

#### **Programming specification**

#### **Protocol stack**

- Send the 16-bit JTAG-to-SWD select sequence on SWDIOTMS: 0b0111 1001 1110 0111, most significant bit (MSb) first. This can be represented as 0x79E7, transmitted MSB first or 0xE79E, transmitted least significant bit (LSb) first.

- Send at least 50 SWCLKTCK cycles with SWDIOTMS HIGH. This ensures that if SWJ-DP was already in SWD operation before sending the select sequence, the SWD interface enters line reset state.

Figure 6 JTAG-to-SWD sequence timing

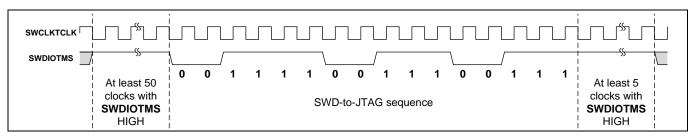

To switch SWJ-DP from SWD to JTAG operation:

- Send at least 50 SWCLKTCK cycles with SWDIOTMS HIGH. This ensures that the current interface is in its reset state. The SWD interface detects the 16-bit SWD-to-JTAG sequence only when it is in the reset state.

- Send the 16-bit SWD-to-JTAG select sequence on SWDIOTMS: 0b0011 1100 1110 0111, MSb first. This can be represented as 0x3CE7, transmitted MSb first, or 0xE73C, transmitted LSb first.

- Send at least five SWCLKTCK cycles with SWDIOTMS HIGH. This ensures that if SWJ-DP was already in JTAG operation before sending the select sequence, the JTAG TAP enters the test-logic-reset state.

Figure 7 SWD-to-JTAG sequence timing

For a more detailed description, see the "SWD and JTAG select mechanism" section of [1].

#### **Programming specification**

# infineon

#### **Protocol stack**

#### 4.2.4 Hardware access commands

The SWJ-DP supports several types of transactions: Interface selection, Target Selection, Read, Write, and Port Reset. All are defined in the Arm® specification. The APIs must be implemented by the Communication Interface layer shown in Figure 4. In addition, the upper protocol, Programming Algorithm, requires two extra commands to manipulate the hardware: Power(state) and ToggleReset(). Table 2 lists the hardware access commands used by the software layer.

Table 2 Hardware access commands

| Command       | Parameters                                               | Description                                                                                                                                                                                                                                                  |

|---------------|----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DAP_JTAGtoSWD | -                                                        | Standard Arm® command to switch SWJ-DP from JTAG to SWD operations. This sequence synchronizes the programmer and chip; it is the first transaction in programming flow if SWD protocol is used. See SWD/JTAG selection for implementation details.          |

| DAP_SWDtoJTAG | _                                                        | Standard Arm® command to switch SWJ-DP from SWD to JTAG operations. This sequence synchronizes the programmer and chip; it is the first transaction in the programming flow if the JTAG protocol is used. See SWD/JTAG selection for implementation details. |

| SWD_Write     | IN APnDP, IN addr, IN data32, OUT ack                    | Sends 32-bit data to the specified register of the DAP using the SWD interface. The register is defined by the "APnDP" (1-bit) and "addr" (2-bit) parameters. The DAP returns a 3-bit status in "ack".                                                       |

| SWD_Read      | IN APnDP, IN addr,<br>OUT data32, OUT ack,<br>OUT parity | Reads 32-bit data from the specified register of the DAP using the SWD interface. The register is defined by the "APnDP" (1-bit) and "addr" (2-bit) parameters. DAP returns a 32-bit data, status, and parity (control) bit of the read 32-bit word.         |

| JTAG_Write    | IN APnDP, IN addr, IN<br>data32,<br>OUT ack              | Sends 32-bit data to the specified register of the DAP using the JTAG interface. The register is defined by the "APnDP" (1-bit) and "addr" (2-bit) parameters. The DAP returns a 3-bit status in "ack".                                                      |

| JTAG_Read     | IN APnDP, IN addr,<br>OUT data32, OUT ack                | Reads 32-bit data from the specified register of the DAP using JTAG interface. The register is defined by the "APnDP" (1-bit) and "addr" (2-bit) parameters. DAP returns a 32-bit data and status.                                                           |

| ToggleReset   | -                                                        | Generates the reset signal for PSOC™ 6 MCU. The programmer must have a dedicated pin connected to the XRES pin of the PSOC™ 6 MCU.                                                                                                                           |

| Power         | IN state                                                 | If the programmer powers the PSOC™ 6 MCU, it must have this function to supply power to the device.                                                                                                                                                          |

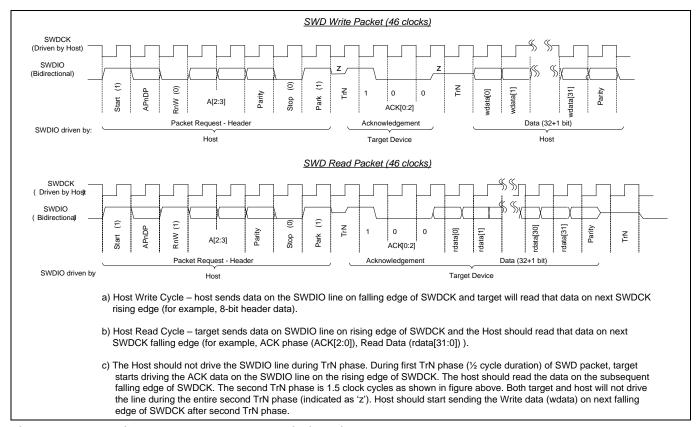

For information on the structure of the SWD read and write packets and their waveform on the bus, see Appendix C: Serial wire debug (SWD) Protocol. For information on the structure of the JTAG, see Appendix D: Joint test action group (JTAG) protocol.

#### **Programming specification**

#### **Protocol stack**

The SWJ Read/Write commands allow accessing registers of the SWJ-DP module from Figure 6. The DAP functionally is split into two control units:

- Debug port (DP) Is responsible for the physical connection to the programmer or debugger.

- Access port (AP) Provides the interface between the DAP module and one or more debug components (such as the Cortex®-M0+ CPU).

The external programmer can access the registers of these access ports using the following bits in the SWJ packet:

- APnDP: Select access port (0 DP, 1 AP)

- ADDR: 2-bit field addressing a register in the selected access port

The SWJ Read/Write commands are used to access these registers. They are the smallest transactions that can appear on the SWJ bus. Table 3 shows the DAP registers that are used during programming.

Table 3 DAP registers (in Arm® notation)

| Register  | APnDP (1-bit) | Address (2-bit) | Access (R/W) | Full name                          |

|-----------|---------------|-----------------|--------------|------------------------------------|

| IDCODE    | 0             | 2'b00           | R            | Identification Code Register       |

| ABORT     | 0             | 2'b00           | W            | AP ABORT Register                  |

| CTRL/STAT | 0             | 2'b01           | R/W          | Control/Status Register            |

| SELECT    | 0             | 2'b10           | W            | AP Select Register                 |

| RDBUFF    | 0             | 2'b11           | R            | Data buffer register               |

| CSW       | 1             | 2'b00           | R/W          | Control Status/Word Register (CSW) |

| TAR       | 1             | 2'b01           | R/W          | Transfer Address Register          |

| DRW       | 1             | 2'b11           | R/W          | Data Read/Write Register           |

For more information about these registers, see [1].

#### 4.2.5 Pseudocode

This document uses an easy-to-read C-style pseudocode to show the programming algorithm. Pseudocode does not include low-level algorithmic details such as variable definitions or error handling. Ensure to implement error handling in the final code, which is typically to stop programming and return failure status if any programming step fails.

The following two commands are used for the programming script:

```

Write_DAP (Register, data32)

Read_DAP (Register, OUT data32)

```

Where the Register parameter is an AP/DP register defined by APnDP and address bits (see Table 3). The pseudo commands correspond to read or write SWJ transactions. Following are some examples:

```

Write_DAP (TAR, 0x08000000)

Write_DAP (DRW, 0x12345678)

Read_DAP (IDCODE, OUT swd_id)

```

The Register parameter technically can be represented as a structure in C:

#### **Protocol stack**

```

struct DAP_Register {

BYTE APnDP; // 1-bit field

BYTE Addr; // 2-bit field

};

```

Then, DAP registers will be defined as:

```

DAP_Register TAR = {1, 1},

DRW = {1, 3},

IDCODE = {0, 0};

```

The defined Write and Read pseudo commands are successful if both return the ACK status of the SWJ transaction. For the Read transaction, the parity bit must be considered (corresponds to the read data32 value). If the status of the transaction or the parity bit is (or both are) incorrect, the transaction has failed. In this case, depending on the programming context, programming must terminate, or the transaction must be tried again.

The implementation of Write and Read pseudo commands based on the hardware access commands SWJ Read and Write (Table 2) is as follows.

```

//- DAP Read/Write subroutines -----

SWJ Status Write DAP (Register, data32) {

if (Interface == SWD)

SWD Write (Register.APnDP, Register.Addr, data32, OUT ack);

else // Interface == JTAG

JTAG Write (Register.APnDP, Register.Addr, data32, OUT ack);

return ack;

}

SWJ Status Read DAP (Register, OUT data32) {

ack = ACK FAIL;

if (Interface == SWD) {

SWD Read (Register.APnDP, Register.Addr, OUT data32, OUT ack, OUT parity);

if (ack == 3'b001) { //ACK, then check the parity bit as well

parityData32 = 0 \times 00;

for (i = 0; i < 32; i++)</pre>

parityData32 ^= ((data32 >> i) & 0x01);

if (parityData32 != parity)

ack = 3'b111; //NACK

}

}

else if (Interface == JTAG)

JTAG Read(Register.APnDP, Register.Addr, OUT data32, OUT ack);

return ack;

}

```

The programming code in Programming algorithm is based mostly on the Write and Read pseudo commands and some commands in Table 2.

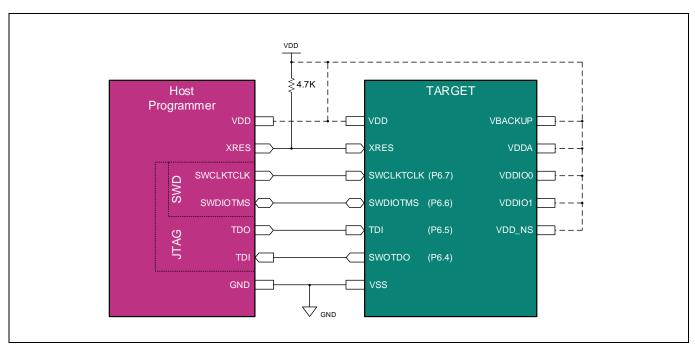

# 4.3 Physical layer

This section summarizes the hardware connection between the programmer and the PSOC™ 6 MCU for programming. Figure 8 shows the generic connection between the PSOC™ 6 MCU and the programmer. See Table 4 for pins/signals description.

# **Programming specification**

### **Protocol stack**

See the device datasheet for the part's package pins location, electrical, and timing specifications.

Figure 8 Connection schematic of programmer

# **Programming specification**

# **Protocol stack**

Table 4 Pins/signals description

| Pin       | SWD                                             |     | JTAG                      |     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|-----------|-------------------------------------------------|-----|---------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|           | Signal name   Mandatory                         |     |                           |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| SWCLKTCLK | Serial wire clock (SWCLK)                       | Yes | Test clock<br>(TCLK)      | Yes | Data synchronization clock, driven by the host programmer/debugger.  Although the Arm® specification does not define the minimum frequency of the SWD bus, the minimum for the PSOC™ 6 MCU family is 1.5 MHz. It is needed only on the first step to acquire the silicon during the boot window. After that, programming frequency can be as low as needed.  For SWD, the host should perform all read or write operations on the SWDIO line on the falling edge of SWDCK. The PSOC™ 6 MCU performs read or write operations on SWDIO on the rising edge of SWDCK.  For JTAG, the host writes to the TMS and TDI pins of the PSOC™ 6 MCU on the falling edge of TCK |  |  |

|           |                                                 |     |                           |     | and the PSOC <sup>™</sup> 6 MCU reads data<br>on its TMS and TDI lines on the<br>rising edge of TCK. PSOC <sup>™</sup> 6 MCU<br>writes to its TDO line on the falling<br>edge of TCK and the host reads<br>from the TDO line of the PSOC <sup>™</sup> 6<br>MCU on the rising edge of TCK.                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| SWDIOTMS  | Serial wire<br>data input/<br>output<br>(SWDIO) | Yes | Test mode<br>select (TMS) | Yes | SWDIO is a bidirectional data input/output signal.  TMS is the JTAG Test Mode Select signal, which is sampled at the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

|           |                                                 |     |                           |     | rising edge of TCK to determine the next state.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| SWOTDO    | Serial wire<br>output<br>(SWO)                  | No  | Test data<br>out (TDO)    | Yes | SWO signal (also known as TRACESWO) is required for Serial Wire Viewer (SWV) and not required for SWD programming. It provides real-time data trace information from the PSOC™ 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

# **Programming specification**

#### **Protocol stack**

| Pin  | SWD                             |                   | JTAG                            |                   | Description                                                                                                                                                                           |  |

|------|---------------------------------|-------------------|---------------------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|      | Signal name                     | Mandatory         | Signal name                     | Mandatory         |                                                                                                                                                                                       |  |

|      |                                 |                   |                                 |                   | MCU, via the SWO pin, while the CPU continues to run at full speed. Data trace via SWV is not available using the JTAG interface.  TDO signal represents the data                     |  |

|      |                                 |                   |                                 |                   | shifted out of the device's test or programming logic and is valid on the falling edge of TCK when the internal state machine is in the correct state.                                |  |

| TDI  | -                               | _                 | Test data<br>in (TDI)           | Yes               | TDI signal represents the data shifted into the device's test or programming logic. It is sampled at the rising edge of TCK.                                                          |  |

| XRES | External<br>reset (XRES)        | NO <sup>[1]</sup> | Reset<br>(XRES)                 | No <sup>[1]</sup> | External reset active LOW signal. The XRES is not related to the ARM standard. It is used to reset the part as a first step in a programming flow.  Note: XRES pin/signal is not TRST |  |

|      |                                 |                   |                                 |                   | Note: XRES pin/signal is not TRST (Test Reset) signal for JTAG Interface, which is the optional pin that asynchronously resets only the JTAG test logic.                              |  |

| GND  | Ground<br>(GND)                 | Yes               | Ground<br>(GND)                 | Yes               | Negative supply voltage (ground)                                                                                                                                                      |  |

| VDD  | Voltage<br>drain drain<br>(VDD) | No <sup>[2]</sup> | Voltage<br>drain drain<br>(VDD) | No <sup>[2]</sup> | Positive supply voltage. The PSOC™ 6 MCU can be powered by external power supply or by programmer.                                                                                    |  |

$<sup>^{1} \</sup>quad \text{XRES pin is mandatory for "Reset" PSOC$^{\text{\tiny{TM}}}$ 6 MCU Acquisition mode, but not used for "Power Cycle" mode.}$

<sup>&</sup>lt;sup>2</sup> VDD pin is mandatory for "Power Cycle" PSOC™ 6 MCU Acquisition mode, where programmer powers the PSOC™ 6 MCU and external power is not applied. For "Reset" Acquisition mode, the source of power supplier does not matter, so the pin is optional.

#### **Programming specification**

#### **Protocol stack**

You can program a chip in either Reset (recommended) or Power Cycle mode. The mode affects only the first step - how to reset the part at the start of the programming flow. All other steps are the same.

- **Reset mode**: To start programming, the host toggles the XRES line and then sends SWD/JTAG commands (see Table 2). The power on the PSOC<sup>™</sup> 6 MCU board can be supplied by the host or by an external power adapter (the VDD line can be optional).

- **Power Cycle mode**: To start programming, the host powers on the PSOC<sup>™</sup> 6 MCU and then starts sending the SW/JTAG commands. The XRES line is not used.

The programmer should implement PSOC<sup>™</sup> 6 MCU acquisition in the Reset mode. It is also the only way to acquire the PSOC<sup>™</sup> 6 MCU if the board consumes too much current, which the programmer cannot supply. Power Cycle mode support is optional and should be used only the following:

- XRES pin is not available on the part's package, or

- The third-party programmer does not implement the XRES line but can supply power to the PSOC™ 6 MCU.

# infineon

**Programming algorithm**

# 5 Programming algorithm

This chapter describes in detail the programming flow of the PSOC<sup>™</sup> 6 MCU. It starts with a high-level description of the algorithm and then describes every step using pseudocode. All code is based on upper-level subroutines composed of atomic SWJ instructions (see Pseudocode). These subroutines are defined in the section Constants and subroutines used in the programming flow. The ToggleReset() and Power() commands are also used (see Table 2).

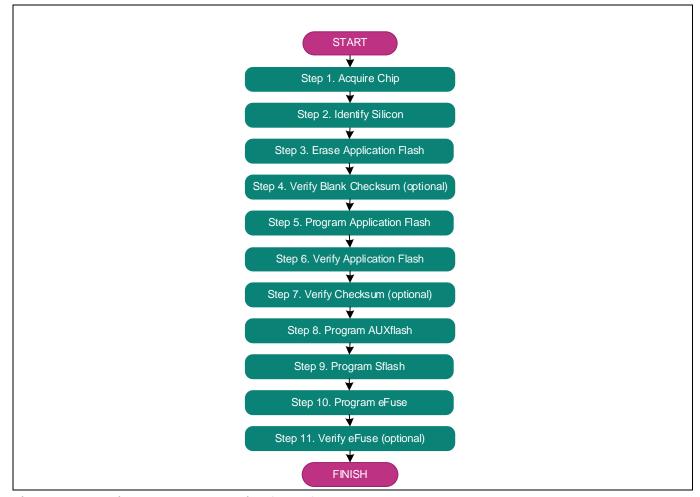

# 5.1 High-level programming flow

Figure 9 shows the sequence of steps that must be executed to program the PSOC™6 MCU. These steps are described in detail in the following sections. All the steps in this programming flow must be completed successfully for a successful programming operation. The programmer should stop the programming flow if any step fails. In addition, in pseudocode, it is assumed that the programmer checks the status of each SWJ transaction (Write\_DAP, Read\_DAP, WriteIO, ReadIO). This extra code is not shown in the programming script. If any of these transactions fail, then programming must be aborted.

The flash programming in the PSOC<sup>™</sup> 6 MCU family is implemented using the SROM API. The external programmer puts the parameters into the SRAM (or registers) and requests system calls, which in turn perform flash updates.

Figure 9 High-level programming flow of PSOC™ 6 MCU

#### **Programming algorithm**

## 5.2 Constants and subroutines used in the programming flow

To make the pseudocode easier to understand, many registers and frequently used constants are named. The defined symbols are used in the pseudocode. Following is the complete list of constants used in the programming steps:

#### 5.2.1 Constants

```

#if defined(PSOC™6ABLE2)

/* Specific for CY8C6xx6 and CY8C6xx7 devices -----*/

#define MEM SIZE ROM

0x00020000 // Size of System ROM

0x40230000 // Base addr. of IPC structures

#define MEM BASE IPC

0x402102B0 // CM0_VECTOR_TABLE_BASE

0x40014100 // PPU[4] base address

0x40231000 // IPC_INTR structure address

OFFSET 0x10 // IPC lock status

#define MEM_VTBASE

#define MEM BASE PPU4

#define IPC_INTR_STRUCT 0x402

#define IPC_STRUCT_LOCK_STATUS_OFFSET 0x10

#elif defined(PSOC6A2M) || defined(PSOC6A512K) || defined(PSOC6A256K)

/* Specific for CY8C6xx4, CY8C6xx5, CY8C6xx8, CY8C6xxA devices ------/*/

0x00010000 // Size of System ROM

#define MEM SIZE ROM

#define MEM_BASE_IPC

0x40220000 // Base addr. Of IPC structures

#define MEM_VTBASE

0x40201120 // CM0_VECTOR_TABLE_BASE

#endif /* End of target-specific constants definition ------/

#define MEM_BASE_ROM

#define MEM_BASE_SRAM

#define MEM_BASE_FLASH

#define MEM_BASE_FLASH

#define MEM_BASE_AUXFLASH

#define MEM_SIZE_AUXFLASH

#define MEM_SIZE_AUXFLASH

#define MEM_SIZE_AUXFLASH

#define MEM_SIZE_AUXFLASH

#define MEM_SIZE_OF SIZE OF SUPERVISORY Flash

#define MEM_SIZE_OF SUPERVISORY F

#define IPC_STRUCT_SIZE

0x20

#define IPC_STRUCTO MEM_BASE_IPC // CM0+ IPC_STRUCT

#define IPC_STRUCT_ACQUIRE_OFFSET 0x00 // Used to acquire a lock

#define IPC_STRUCT_NOTIFY_OFFSET 0x08 // Used for Notification events

#define IPC_STRUCT_DATA_OFFSET 0x0C // 32-bit data element

#define IPC STRUCT LOCK STATUS ACQUIRED MSK 0x80000000 // Is lock acquired

#define IPC STRUCT ACQUIRE SUCCESS MSK 0x80000000 // Is acquired

#define IPC INTR STRUCT INTR MASK OFFSET 0x08 // Interrupt mask

#define SROMAPI DATA LOCATION MSK 0x00000001 // [0]: 1 - arguments in IPC.DATA;

// 0 - arguments in SRAM

#define SROMAPI STATUS MSK 0xF0000000

0x00000001 // SiliconId API code

#define SROMAPI PROGRAMROW CODE 0x06000100 // ProgramRow API code

#define SROMAPI ERASEALL CODE

0x0A000001 // EraseAll API code

#define SROMAPI ERASESECTOR CODE 0x14000100 // EraseSector API code

#define SROMAPI CHECKSUM CODE 0x0B000001 // Checksum API code

#define SROMAPI CHECKSUM DATA MSK 0x0FFFFFFF // Checksum mask

#define SROMAPI BLOW FUSE CODE 0x01000001 // BlowFuse API code

#define SROMAPI_READ_FUSE_CODE

0 \times 03000001 // ReadFuse API code

```

### **Programming specification**

# **Programming specification**

# infineon

# **Programming algorithm**

## **5.2.2** Subroutines

The programming flow includes some operations that are used in all steps. These are implemented as subroutines in the pseudocode.

Table 5 Subroutines used in programming flow

| Subroutine                                        | Description                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bool WriteIO(addr32, data32)                      | Writes 32-bit data into the specified address of the CPU address space.<br>Returns "true" if all SWJ transactions succeeded (ACKed).                                                                                                                                                                                                                                                                                 |

| bool ReadIO(addr32, OUT data 32)                  | Reads 32-bit data from the specified address of the CPU address space. Note that the actual size of the read data (8, 16, or 32 bits) depends on the setting in the CSW register of DAP (see Table 3). By default, all accesses are 32 bits long.  Returns "true" if all SWDJ transactions succeeded (ACKed).                                                                                                        |

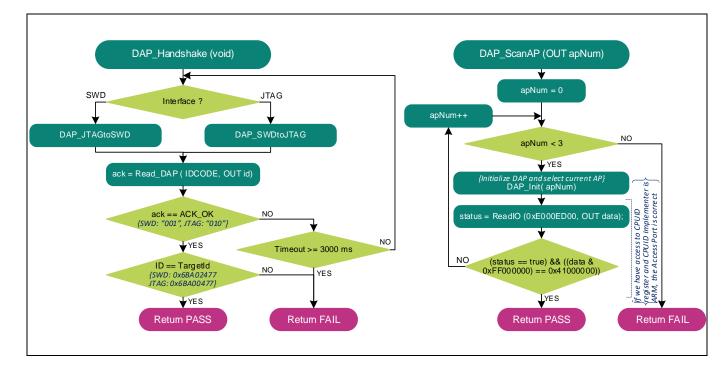

| bool DAP_Handshake()                              | Performs device handshake after the reset. Uses DAP_JTAGtoSWD or DAP_SWDtoJTAG hardware access command to set the SWJ-DP in known state and reads the DP.IDCODE register. This sequence is repeated until read IDCODE register request is acknowledged or until timeout.                                                                                                                                             |

| bool DAP_Init (apNum)                             | Initialize the Debug Port for programming operations. Accepts Access Port number as input parameter: 0 – System AP; 1 – CM0+ AP; 2 – CM4 AP.                                                                                                                                                                                                                                                                         |

| bool DAP_ScanAP (OUT apNum)                       | Scans the Access Ports for the first available with CPU register access                                                                                                                                                                                                                                                                                                                                              |

| bool Ipc_PollLockStatus (ipcId, isLockExpected)   | Depending on isLockExpected parameter, waits until LOCK status bit of the IPC structure is released or acquired. ipcld input parameter determines the number of IPC structure (ipcld = 0 : CM0+ IPC_STRUCT; ipcld = 1 : CM4 IPC_STRUCT; ipcld = 2 : DAP IPC_STRUCT). Timeout is 1s. Returns "true" (success) if LOCK status bit corresponds to desired status; otherwise, returns "false".                           |

| bool Ipc_Acquire (ipcId)                          | Acquires IPC structure. The timeout is 1s. Returns "true" (success) if IPC structure is acquired; otherwise, returns "false".                                                                                                                                                                                                                                                                                        |

| bool PollSromApiStatus<br>(addr32, OUT data32)    | Waits until the SROM function is completed and then checks its status. addr32 is the address, where the SROM function status word is expected (IPC_STRUCT.DATA field or address in RAM if parameters for SROM function are passed in RAM). Timeout is 1s.  Output parameter data32 is the status/result word, provided by the SROM function.  Returns "true" (success) if the command is completed and its status is |

|                                                   | successful; otherwise, returns "false".                                                                                                                                                                                                                                                                                                                                                                              |

| bool CallSromApi<br>(callIdAndParams, OUT data32) | Executes SROM function. The input parameter is the API OpCode and parameters word. Output parameter data32 is the status/result word, provided by the SROM function.  Returns "true" (success) if SROM function executed and returned success status; otherwise, returns "false".                                                                                                                                    |

The implementation of these subroutines follows. It is based on the pseudocode and registers defined in the sections: Hardware access commands and Pseudocode. It uses the constants defined in this chapter.

002-15554 Rev.\*Q

```

//--- CPU/MMIO registers Read/Write subroutines

bool WriteIO (addr32, data32) {

ackOK = (Interface == SWD)? 3b'001 /*SWD*/: 3b'010 /*JTAG*/;

ack1 = Write DAP (TAR, addr32);

ack2 = Write DAP (DRW, data32);

return (ack1 == ackOK) && (ack2 == ackOK);

bool ReadIO (addr32, OUT data32) {

ackOK = (Interface == SWD)? 3b'001 /*SWD*/: 3b'010 /*JTAG*/;

ack1 = Write DAP (TAR, addr32);

ack2 = Read DAP (DRW, OUT data32);

ack3 = Read DAP (RDBUFF, OUT data32);

return (ack1 == ack0K) && (ack2 == ack0K) && (ack3 == ack0K);

//--- DAP initialization subroutines

bool DAP Handshake () {

// Timeout waiting for debug interface becomes enabled after device reset (t_{boot}).

// In worst case, when the boot code performs application HASH verification,

// t<sub>boot</sub> is around 600ms and depends on CPU clock used by boot code.

\ensuremath{//} For PowerCycle, timeout depends on the design schematic and must be longer.

timeout = 3000 \text{ ms};

/*SWD*/: 3b'010

= (Interface == SWD)? 3b'001

targetID = (Interface == SWD)? 0x6BA02477 /*SWD*/: 0x6BA00477 /*JTAG*/;

// Execute connection sequence - acquire port.

// This is used as handshake between the debugger and target device.

// Once the target device replied on request to read the IDCODE,

// it means that the device is already booted after reset and ready to

communicate.

do {

if (Interface == SWD) DAP_JTAGtoSWD(); // SWD

else DAP SWDtoJTAG(); // JTAG

ack = Read_DAP (IDCODE, OUT id);

} while ((ack != ackOK) && (TimeElapsed < timeout));</pre>

return (TimeElapsed <= timeout) && (id == targetID);</pre>

bool DAP_Init (apNum) {

if (DAP_Handshake() == false) return false; // Handshake (e.g. after reset)

if (Interface == JTAG) {

// Power up debug port using the next bits in CTRL/STAT register:

// [30]:CSYSPWRUPREQ and [28]:CDBGPWRUPREQ - power-up requests.

// [5]:STICKYERR, [4]:STICKYCMP and [1]:STICKYORUN - sticky errors bits

// Note: for JTAG, sticky error bits are read-write enabled and writing '1'

// to these bits clears associated sticky errors.

// For SWD, these bits are read-only and to clean the sticky errors,

// you should write to appropriate bits of DP.ABORT register

Write DAP (CTRL/STAT, 0x50000032);

else { // SWD

// Clear any Sticky Errors which could be left from previous sessions

// Otherwise only power-down-up cycle helps to restore DAP.

Write DAP (ABORT, 0x0000001E);

// Power up DAP

Write DAP (CTRL/STAT, 0x50000000);

// Select desired Access Port and set bank 0 in APACC space

apSelect = apNum << 24;</pre>

Write DAP (SELECT, apSelect);

// Set CSW (DbgSwEnable=0, Prot=0x23, SPIDEN=0, Mode=0x0, TrInProg=0,

```

#### **Programming specification**

```

// DeviceEn=0, AddrInc=Auto-increment off, Size=Word (32 bits))

// Note: Set Prot bits in DAP CSW register, because of no access to CPU

// registers via M4 AP without these bits

Write DAP (CSW, 0x23000002);

return true;

}

bool DAP ScanAP (OUT apNum) {

// Try all possible Access Ports

// Scan only three APs [0]-[3], what is sufficient for MXS40 architecture.

for (apNum = 0; apNum < 3; apNum++) {

// Initializes DAP and selects Access Port with provided number

if (DAP_Init (apNum) == false) continue;

// Try to read the CPUID register. If the Implementer is ARM, the Access Port

\ensuremath{//} is correct (we have access to the ARM registers)

status = ReadIO (0xE000ED00, OUT data);

if ((status == true) && ((data & 0 \times FF0000000) == 0 \times 410000000))

return true;

return false;

```

#### **Programming specification**

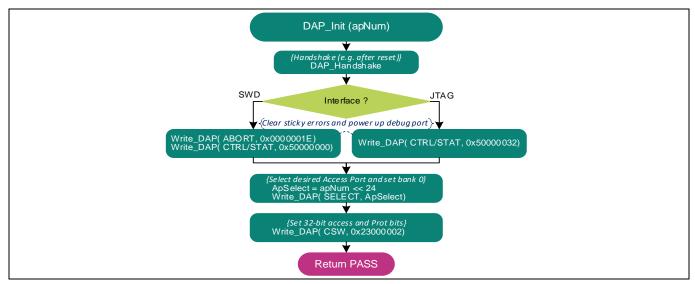

Figure 10 DAP initialization subroutines

```

//--- SROM API usage subroutines

bool Ipc PollLockStatus (ipcId, isLockExpected) {

ipcAddr = IPC STRUCTO + IPC STRUCT_SIZE * ipcId;

do{

ReadIO (ipcAddr + IPC STRUCT LOCK STATUS OFFSET, OUT status);

isLocked = (status & IPC STRUCT LOCK STATUS ACQUIRED MSK) != 0;

isExpectedStatus = (isLockExpected && isLocked) || (!isLockExpected &&

!isLocked)

while ((!isExpectedStatus) && (TimeElapsed < 1 sec))</pre>

return (TimeElapsed <= 1 sec)? true /* OK */: false /* timeout */;</pre>

}

bool Ipc Acquire (ipcId) {

ipcAddr = IPC STRUCTO + IPC STRUCT SIZE * ipcId;

do {

// Workaround for the SROM code issue. Write to IPC ACQUIRE register may

// fail because IPC structure is left protected by the PPU after previous

// SROM API call.

status = ReadIO (MEM BASE PPU4, OUT NULL); // Ignore output value

if(status == false) DAP Init(apNum);

// To acquire the IPC[2] (IPC structure for DAP),

// debugger must write any value to IPC[2].ACQUIRE register.

// The write operation acquires the lock. The write value is irrelevant.

// Note: This write is NOT required for flash loaders (running on CM0+ or CM4)

status = WriteIO (ipcAddr + IPC STRUCT ACQUIRE OFFSET,

IPC STRUCT ACQUIRE SUCCESS MSK);

// To acquire the IPC[0] (CM\overline{0}) or IPC[1] (CM\overline{4}) (e.g. in flash loaders)

// Master must read IPC[x].ACQUIRE register

// If the SUCCESS field returns a '1', the read acquired the lock.

// If the SUCCESS field returns a '0', the read did not acquire the lock.

\ensuremath{//} Note that a single read access performs two functions:

// - The attempt to acquire a lock.

// - Return the result of the acquisition attempt (SUCCESS field).

ReadIO (ipcAddr + IPC STRUCT ACQUIRE OFFSET, OUT status);

status &= IPC STRUCT ACQUIRE SUCCESS MSK;

```

#### **Programming specification**

```

} while ((status == 0) && (TimeElapsed < 1 sec))</pre>

return (TimeElapsed <= 1 sec)? true /* OK */: false /* timeout */;</pre>

bool PollSromApiStatus (addr32, OUT data32) {

ReadIO (addr32, OUT data32);

status = data32 & SROMAPI STATUS MSK;

} while (status != SROMAPI STAT SUCCESS) && (TimeElapsed < 1 sec))</pre>

return (TimeElapsed <= 1 sec)? true /* OK */: false /* timeout */;</pre>

bool CallSromApi (callIdAndParams, OUT data32) {

// Use IPC for CMO+ (IpcId = 0) if using flash loader running on CMO+ core

// Use IPC for CM4

(IpcId = 1) if using flash loader running on CM4 core

// Use IPC for DAP (IpcId = 2) if using external debugger

ipcId = 2;

ipcAddr = IPC STRUCTO + IPC STRUCT SIZE * ipcId;

// Check where the arguments for SROM function are located

// [0]: 1 - arguments are passed in IPC.DATA. 0 - arguments are passed in SRAM

isDataInRam = (callIdAndParams & SROMAPI DATA LOCATION MSK) == 0;

// Acquire IPC STRUCT[ipcId]

if(Ipc Acquire (ipcId) == false) return false;

// Write one of these to IPC STRUCT[ipcId].DATA:

// a) SROM OpCode with Parameters (if all API parameters fit in one word)

// b) Address in SRAM, where they are located

if (isDataInRam) WriteIO (ipcAddr + IPC STRUCT DATA OFFSET, SRAM SCRATCH ADDR);

else

WriteIO (ipcAddr + IPC STRUCT DATA OFFSET, callIdAndParams);

// Set IPC INTR STRUCT[0(CM0+)].INTR MASK to enable notification interrupt for

// IPC STRUCT[ipcId]. Read initial value first to restore other bits of

// INTR MASK field after system call

intrMskDapEnabled = 1 << (16 + ipcId);</pre>

ReadIO (IPC INTR STRUCT + IPC INTR STRUCT INTR MASK OFFSET , &intrMskInitial);

doWriteRestoreIntrMsk = intrMskInitial != intrMskDapEnabled;

// Set just DAP enabled bit - do not OR it with initial mask, because of other

// enabled interrupts notifications may hurt programming if the user application

// running by 2nd core invokes system calls.

if (doWriteRestoreIntrMsk) WriteIO (IPC INTR STRUCT +

IPC INTR STRUCT INTR MASK OFFSET, intrMskDapEnabled);

// Notify to IPC INTR STRUCT[0]. IPC STRUCT[IpcId].MASK <- Notify

// This starts SROM function execution

WriteIO (ipcAddr + IPC STRUCT NOTIFY OFFSET, 1 << 0 /*IPC INTR STRUCTO*/);

// Poll lock status for released state and poll Data word

if (Ipc PollLockStatus(ipcId, false) == false) return false;

if (isDataInRam) status = PollSromApiStatus (SRAM SCRATCH ADDR, data32);

else status = PollSromApiStatus (ipcAddr + IPC STRUCT DATA OFFSET, data32);

// Restore IPC INTR STRUCT[0(CMO+)].INTR MASK if was modified

if (doWriteRestoreIntrMsk)

WriteIO (IPC INTR STRUCT + IPC INTR STRUCT INTR MASK OFFSET, intrMskInitial);

return status;

```

# infineon

#### **Programming algorithm**

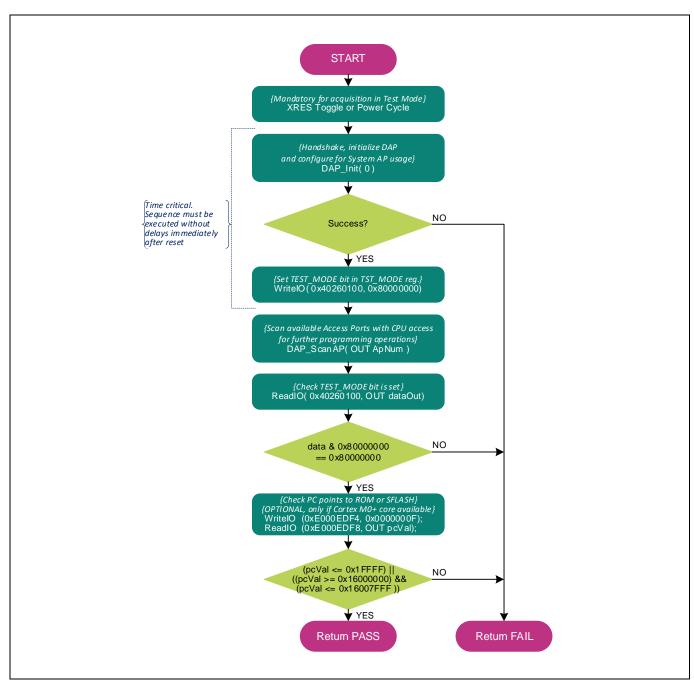

## 5.3 Step 1.A - Acquire PSOC<sup>™</sup> 6 MCU

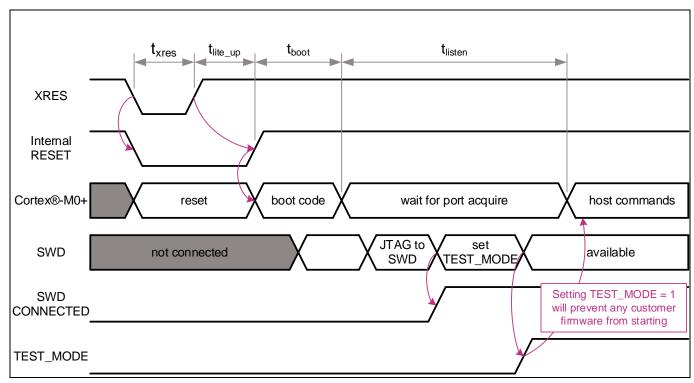

The first step in programming the PSOC<sup>™</sup> 6 MCU is to put it into Test mode (or Programming mode). This is a special mode in which the CPU is controlled by the external programmer, which can also access other system resources such as SRAM and registers. The main purpose of this step is to prevent the execution of the user code from the application flash region. After the user's code starts, it can repurpose the SWJ pins <sup>[3]</sup> (use them as GPIO), so the external debugger will not be able to communicate with the device. Additionally, if there is corrupted user code in the application flash region, the Cortex®-M0+ core may enter a lockup state. This step has strict timing requirements that the host must meet to enter Test mode successfully. Figure 11 shows the timing diagram for entering Test mode.

Figure 11 Timing diagram for entering test mode

<sup>&</sup>lt;sup>3</sup> Application firmware is expected to follow this procedure for SWJ pin configuration:

a) Do not touch the configuration of the SWJ pins for parts that have a permanent SWD interface. They will be properly configured and may have already connected to the SWD probe when the firmware starts.

b) For parts that repurpose their SWD pins:

<sup>•</sup> If the SWD interface is presently active (CPUSS\_DP\_STATUS.SWJ\_CONNECTED bit is '1'), leave the pins in their current state; a probe has connected during the acquire window and the pins should not be repurposed.

<sup>•</sup> If the SWD interface is not active, you may configure the pins and enable the alternate purpose.

#### **Programming specification**

#### **Programming algorithm**

This diagram details the chip's internal signals while entering Test mode. Everything starts from toggling the XRES line (or applying power), so the chip enters Internal Reset mode for t<sub>lite\_up</sub>period. After that, the system boot code starts execution. When completed, the CPU waits during a t<sub>listen</sub> period for a special connection sequence on the SWJ port. If, during this time, the host sends the correct sequence of SWJ commands, the CPU enters Test mode. Otherwise, it starts the execution of the user's code from the application flash region. Timing parameters may vary depending on the boot code execution flow (see Table 6). Therefore, the best way to enter Test mode is to start sending an acquire sequence immediately after XRES is toggled (or power is supplied in Power Cycle mode). This sequence is sent iteratively until it succeeds (all SWJ transactions are ACKed and all conditions are met).

Table 6 Boot timing parameters

| Parameter            | Description                                                                                                                                                                                                                                                                                                                                   | Min | Max | Unit |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|

| t <sub>lite_up</sub> | Time from Reset release until CPU begins executing boot code                                                                                                                                                                                                                                                                                  | -   | 250 | μs   |

| t <sub>boot</sub>    | Time from when boot code started execution until it opens SWJ lines and starts waiting for TEST_MODE sequence. This time varies depending on CPU clock, device lifecycle stage, and amount of data for HASH verification by boot code for SECURE application.                                                                                 | 0.7 | 600 | ms   |

| t <sub>listen</sub>  | Amount of time boot code waits and listens for the SWJ port initialization sequence before starting the application firmware execution. Note that the default duration of listen window (t <sub>listen</sub> ) is 20 ms, but it may vary from 0 ms to 100 ms. This can be configured by specific bits in the table of contents part 2 (TOC2). | 0   | 100 | ms   |

Figure 12 shows the Acquire Chip procedure. It is detailed in terms of the SWD transaction. Note that the recommended minimum frequency of the programmer is 1.5 MHz, which meets the timing requirement of this step.

# infineon

#### **Programming algorithm**

Figure 12 Flowchart of the acquire chip step

#### Code Listing 1 Pseudocode - Step 1.A. Acquire chip

```

// Reset Target depending on acquire mode - Reset or Power Cycle

if (AcquireMode == RESET) ToggleXRES(); // Toggle XRES pin, target must be powered

else if (AcquireMode == POWER_CYCLE) PowerOn();// Supply power to target

// Do handshake between the debugger and target device after reset,

// Initialize the Debug Port and select System Access Port (AP[0])

DAP_Init (0);

// Enter CPU into Test Mode

// Set TEST_MODE bit in TST_MODE SRSS register

WriteIO (SRSS TST MODE, SRSS TST MODE TEST MODE MSK);

```

#### **Programming specification**

#### **Programming algorithm**

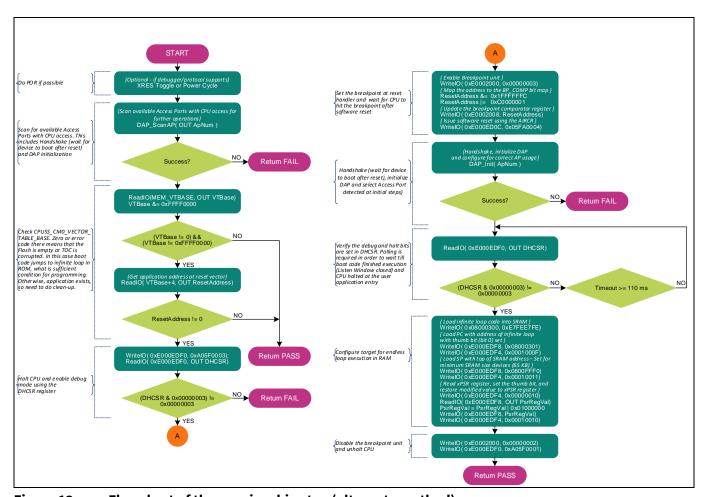

## 5.4 Step 1.B – Acquire PSOC™ 6 MCU (alternate method)