# **TLE9879QXA20**

Microcontroller with LIN and BLDC MOSFET Driver for Automotive Applications

BF-Step

# **Data Sheet**

Rev. 1.0, 2017-03-03

# **Automotive Power**

### **Table of Contents**

# **Table of Contents**

| <b>1</b><br>1.1                                                     | Overview     Abbreviations                                                                                                                                                                                                   |                                        |

|---------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 2                                                                   | Block Diagram                                                                                                                                                                                                                | 10                                     |

| <b>3</b><br>3.1<br>3.2                                              | Device Pinout and Pin Configuration  Device Pinout  Pin Configuration                                                                                                                                                        | 11                                     |

| 4                                                                   | Modes of Operation                                                                                                                                                                                                           | 15                                     |

| 5<br>5.1<br>5.2<br>5.2.1<br>5.2.2<br>5.3<br>5.3.1<br>5.3.2<br>5.3.3 | Power Management Unit (PMU)  Features Introduction Block Diagram PMU Modes Overview  Power Supply Generation Unit (PGU) Voltage Regulator 5.0V (VDDP) Voltage Regulator 1.5V (VDDC) External Voltage Regulator 5.0V (VDDEXT) | 18<br>19<br>21<br>22<br>22<br>23       |

| 6.1<br>6.2<br>6.2.1<br>6.3<br>6.3.1<br>6.3.2<br>6.3.2.1<br>6.3.2.2  | System Control Unit - Digital Modules (SCU-DM)  Features Introduction Block Diagram Clock Generation Unit Low Precision Clock High Precision Oscillator Circuit (OSC_HP) External Input Clock Mode External Crystal Mode     | 25<br>25<br>26<br>27<br>28<br>28<br>28 |

| <b>7</b><br>7.1<br>7.2<br>7.2.1                                     | System Control Unit - Power Modules (SCU-PM)  Features Introduction Block Diagram                                                                                                                                            | 30<br>30                               |

| <b>8</b><br>8.1<br>8.2<br>8.2.1                                     | ARM Cortex-M3 Core  Features Introduction Block Diagram                                                                                                                                                                      | 32<br>33                               |

| 9<br>9.1<br>9.2<br>9.2.1<br>9.3<br>9.3.1                            | DMA Controller  Features Introduction Block Diagram  Functional Description DMA Mode Overview                                                                                                                                | 34<br>35<br>35<br>36                   |

| 10                                                                  | Address Space Organization                                                                                                                                                                                                   | 37                                     |

| 11<br>11.1<br>11.2<br>11.2.1<br>11.3                                | Memory Control Unit  Features Introduction Block Diagram NVM Module (Flash Memory)                                                                                                                                           | 38<br>38<br>38                         |

| 11.0                                                                | 14 v IVI IVIOQUIO (1 10311 IVIGITIOI y )                                                                                                                                                                                     | ΨU                                     |

### **Table of Contents**

| 1 <b>2</b><br>12.1<br>12.2<br>12.2.1                                                         | Interrupt System Features Introduction Overview                                                                                                                                 | 41<br>41                                     |

|----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| 1 <b>3</b><br>13.1<br>13.2                                                                   | Watchdog Timer (WDT1) Features Introduction                                                                                                                                     | 43                                           |

| 14.1<br>14.2<br>14.2.1<br>14.2.2<br>14.3<br>14.3.1<br>14.3.2<br>14.3.2<br>14.3.2.1<br>14.3.3 | GPIO Ports and Peripheral I/O  Features Introduction Port 0 and Port 1 Port 2  TLE9879QXA20 Port Module Port 0 Port 0 Functions Port 1 Port 1 Functions Port 2 Port 2 Functions | 45<br>45<br>47<br>48<br>48<br>48<br>50<br>50 |

| 15.1<br>15.1.1<br>15.1.2<br>15.2<br>15.2.1<br>15.2.2                                         | General Purpose Timer Units (GPT12)  Features  Features Block GPT1  Features Block GPT2  Introduction  Block Diagram GPT1  Block Diagram GPT2                                   | 53<br>53<br>53<br>53<br>54                   |

| 16<br>16.1<br>16.2<br>16.2.1                                                                 | Timer2 and Timer21  Features Introduction Timer2 and Timer21 Modes Overview                                                                                                     | 56<br>56                                     |

| 1 <b>7</b><br>17.1<br>17.2<br>17.3<br>17.3.1                                                 | Timer3 Features Introduction Functional Description Timer3 Modes Overview                                                                                                       | 57<br>57<br>57                               |

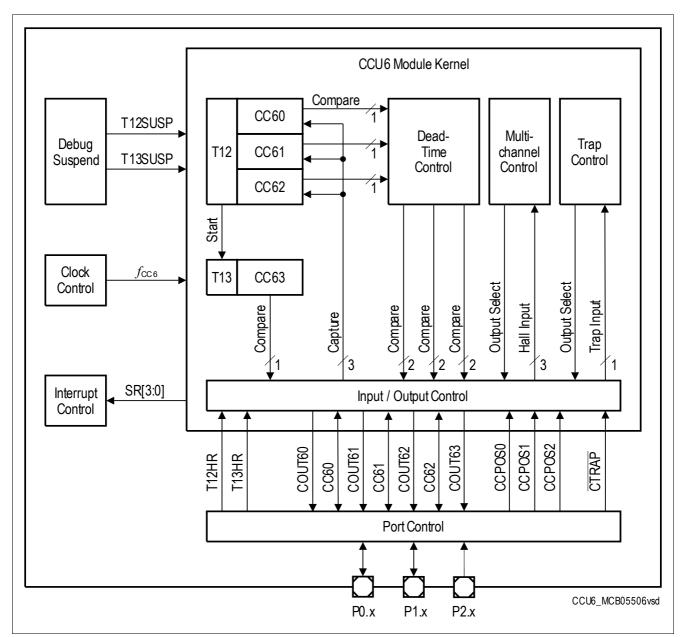

| 1 <b>8</b><br>18.1<br>18.2<br>18.2.1                                                         | Capture/Compare Unit 6 (CCU6)  Feature Set Overview  Introduction  Block Diagram                                                                                                | 59<br>59                                     |

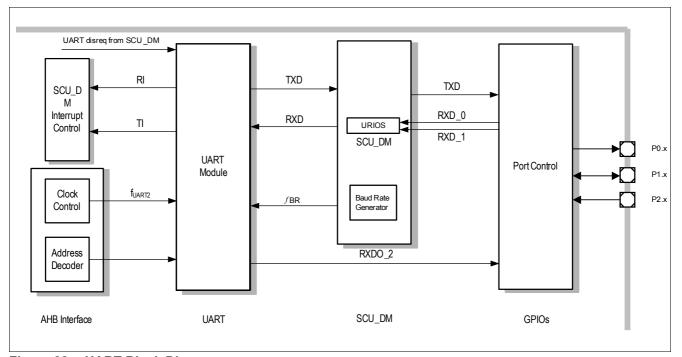

| 19<br>19.1<br>19.2<br>19.2.1<br>19.3                                                         | UART1/UART2  Features  Introduction  Block Diagram  UART Modes                                                                                                                  | 61<br>61<br>61                               |

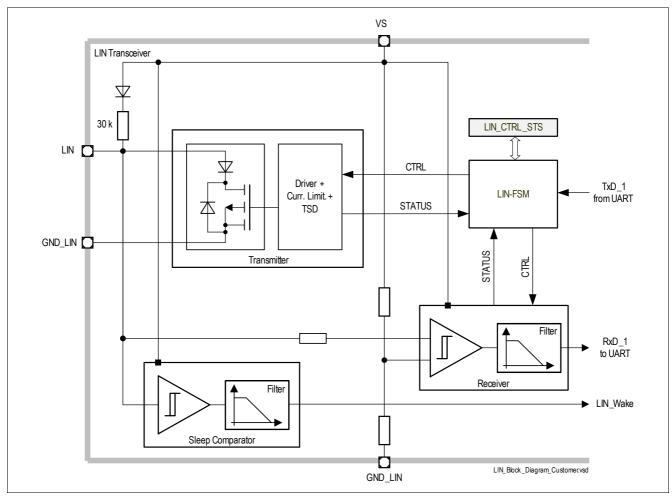

| <b>20</b><br>20.1<br>20.2                                                                    | LIN Transceiver  Features Introduction Block Diagram                                                                                                                            | 63<br>63                                     |

3

## **Table of Contents**

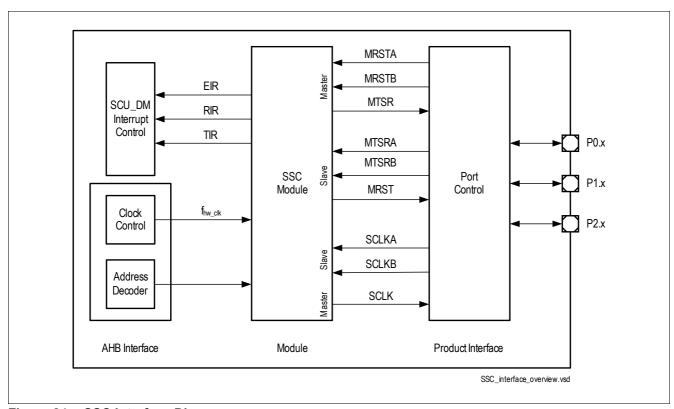

| <b>21</b><br>21.1<br>21.2<br>21.2.1                    | High-Speed Synchronous Serial Interface (SSC1/SSC2)  Features Introduction Block Diagram                                                                                                                               | 65<br>66             |

|--------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

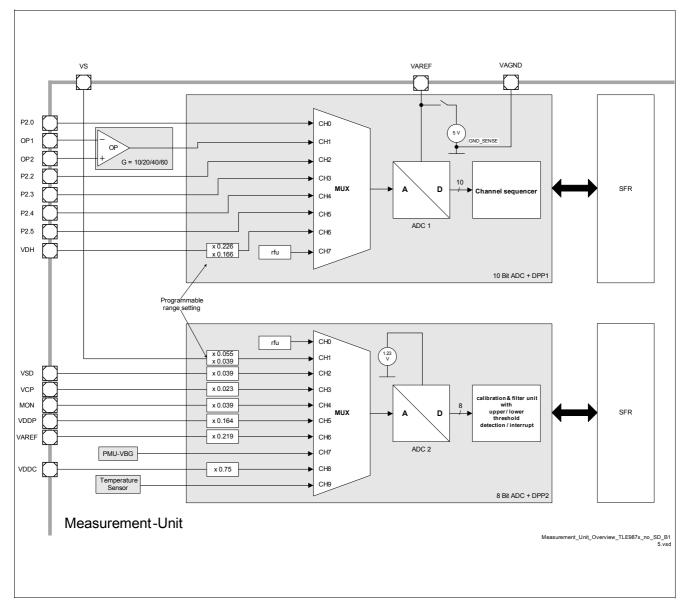

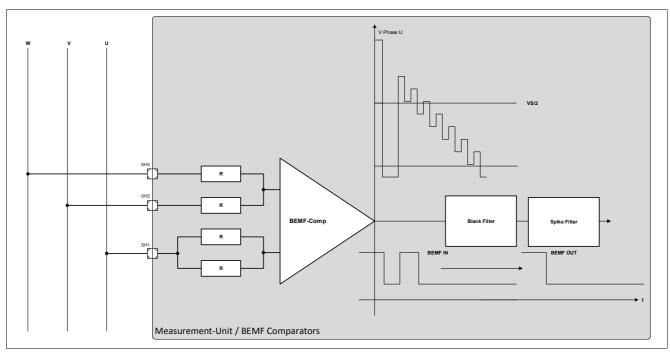

| 22<br>22.1<br>22.2<br>22.2.1<br>22.2.1.1               | Measurement Unit Features Introduction Block Diagram Block Diagram BEMF Comparator                                                                                                                                     | 67<br>67<br>68       |

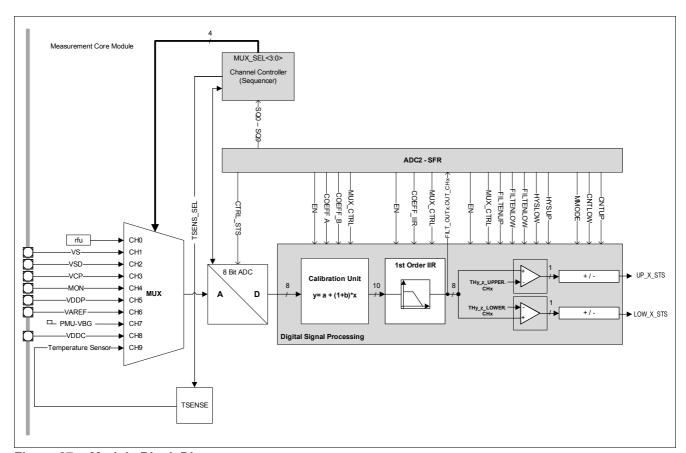

| 23<br>23.1<br>23.2<br>23.2.1<br>23.2.2                 | Measurement Core Module (incl. ADC2) Features Introduction Block Diagram Measurement Core Module Modes Overview                                                                                                        | 70<br>70<br>70       |

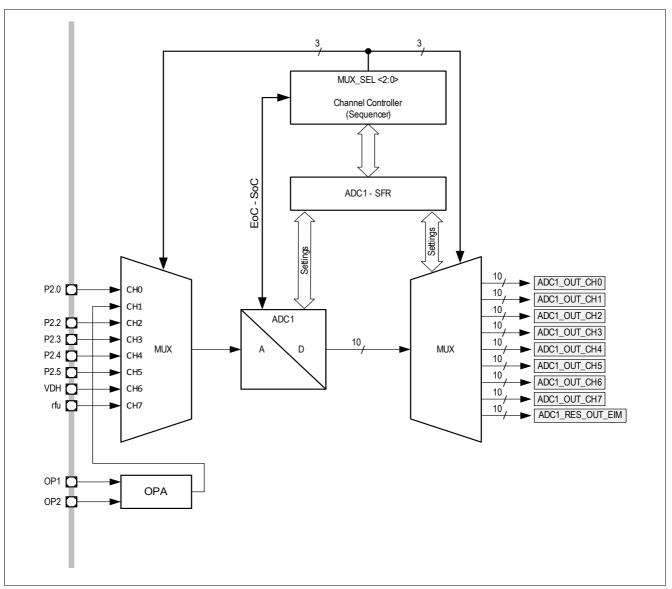

| <b>24</b><br>24.1<br>24.2<br>24.2.1                    | 10-Bit Analog Digital Converter (ADC1)  Features  Introduction  Block Diagram                                                                                                                                          | 72<br>72             |

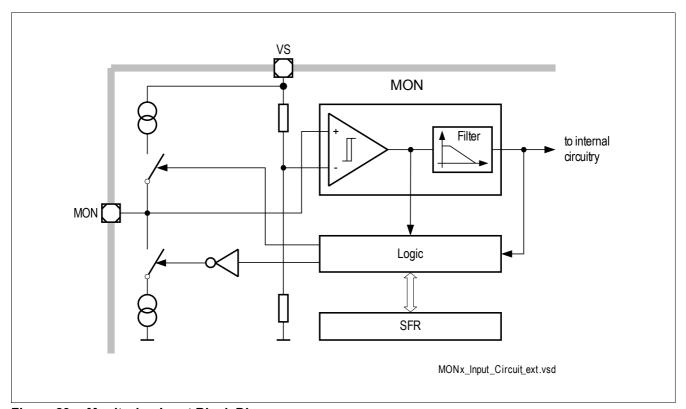

| <b>25</b><br>25.1<br>25.2<br>25.2.1                    | High-Voltage Monitor Input Features Introduction Block Diagram                                                                                                                                                         | 74<br>74             |

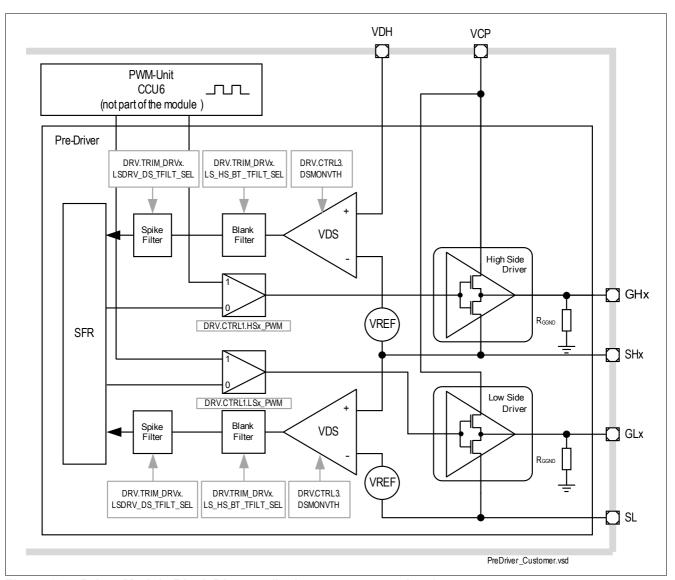

| 26<br>26.1<br>26.2<br>26.2.1<br>26.2.2                 | Bridge Driver (incl. Charge Pump)  Features Introduction Block Diagram General                                                                                                                                         | 75<br>75<br>76       |

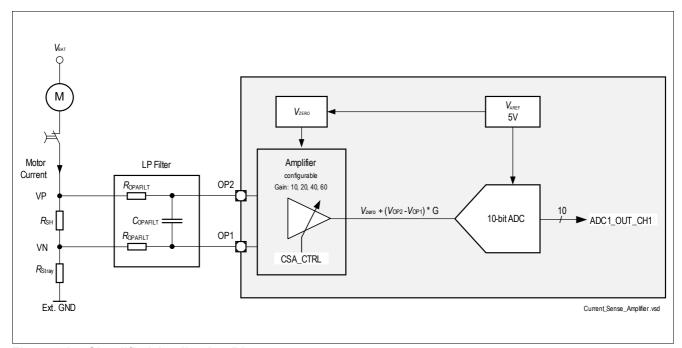

| <b>27</b><br>27.1<br>27.2<br>27.2.1                    | Current Sense Amplifier Features Introduction Block Diagram                                                                                                                                                            | 77<br>77             |

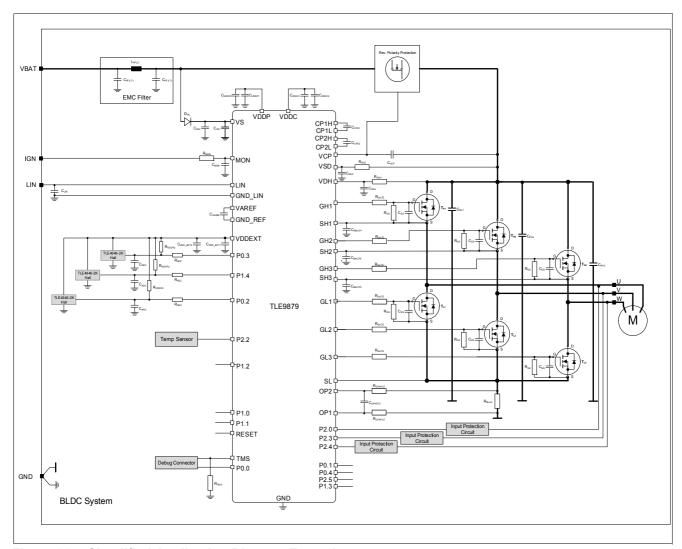

| <b>28</b><br>28.1<br>28.2                              | Application Information  BLDC Driver  ESD Immunity According to IEC61000-4-2                                                                                                                                           | 78                   |

| 29<br>29.1<br>29.1.1<br>29.1.2<br>29.1.3<br>29.1.4     | Electrical Characteristics General Characteristics Absolute Maximum Ratings Functional Range Current Consumption Thermal Resistance                                                                                    | 81<br>84<br>85<br>87 |

| 29.1.5<br>29.2<br>29.2.1<br>29.2.2<br>29.2.3<br>29.2.4 | Timing Characteristics  Power Management Unit (PMU)  PMU I/O Supply (VDDP) Parameters  PMU Core Supply (VDDC) Parameters  VDDEXT Voltage Regulator (5.0V) Parameters  VPRE Voltage Regulator (PMU Subblock) Parameters | 88<br>88<br>90<br>91 |

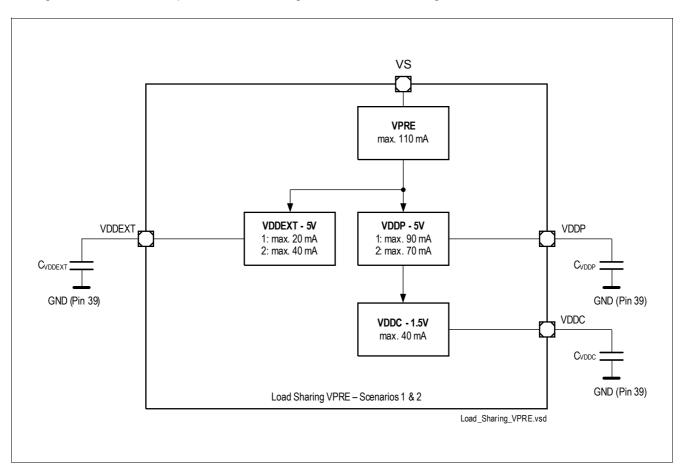

| 29.2.4.1<br>29.2.5                                     | Load Sharing Scenarios of VPRE Regulator                                                                                                                                                                               | 93                   |

# **TLE9879QXA20**

## **Table of Contents**

| 31       | Revision History                               | 125 |

|----------|------------------------------------------------|-----|

| 30       | Package Outlines                               | 124 |

| 29.13.1  | Electrical Characteristics                     | 122 |

|          | Operational Amplifier                          |     |

| 29.12.1  | Electrical Characteristics                     |     |

|          | MOSFET Driver                                  |     |

| 29.11.1  | Electrical Characteristics                     |     |

|          | High-Voltage Monitoring Input                  |     |

|          | Reserved                                       |     |

| 29.9.2   | Electrical Characteristics ADC1 (10-Bit)       |     |

| 29.9.1   | Electrical Characteristics VAREF               |     |

|          | ADC1 Reference Voltage - VAREF                 |     |

| 29.8.3.2 | ADC2 Specifications                            |     |

| 29.8.3.1 | ADC2 Reference Voltage VBG                     |     |

| 29.8.3   | ADC2-VBG                                       |     |

| 29.8.2   | Central Temperature Sensor Parameters          |     |

| 29.8.1   | System Voltage Measurement Parameters          |     |

|          | Measurement Unit                               |     |

| 29.7.1   | SSC Timing Parameters                          |     |

|          | High-Speed Synchronous Serial Interface        |     |

| 29.6.1   | Electrical Characteristics                     |     |

|          | LIN Transceiver                                |     |

| 29.5.3   | DC Parameters of Port 2                        |     |

| 29.5.2   | DC Parameters of Port 0, Port 1, TMS and Reset |     |

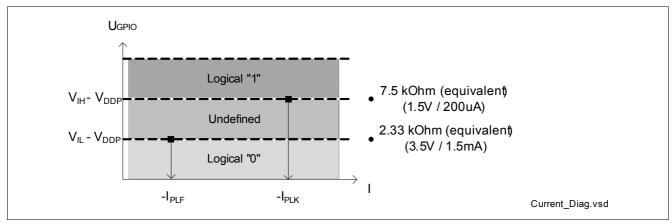

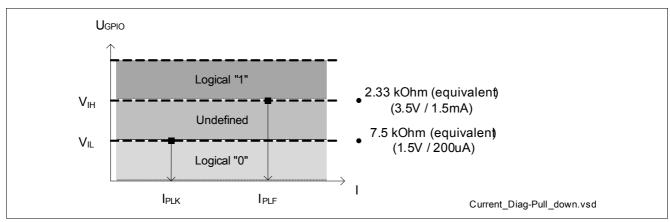

| 29.5.1   | Description of Keep and Force Current          |     |

| 29.5     | Parallel Ports (GPIO)                          | 98  |

| 29.4.1   | Flash Parameters                               | 97  |

| 29.4     | Flash Memory                                   | 97  |

| 29.3.2   | External Clock Parameters XTAL1, XTAL2         | 96  |

| 29.3.1   | Oscillators and PLL Parameters                 | 95  |

| 29.3     | System Clocks                                  | 95  |

|          |                                                |     |

# Microcontroller with LIN and BLDC MOSFET Driver for Automotive Applications

### **TLE9879QXA20**

### 1 Overview

### **Summary of Features**

- 32 bit ARM Cortex M3 Core

- up to 24 MHz clock frequency

- one clock per machine cycle architecture

- · On-chip memory

- 128 kByte Flash including

- 4 kByte EEPROM (emulated in Flash)

- 512 Byte 100 Time Programmable Memory (100TP)

- 6 kByte RAM

- Boot ROM for startup firmware and Flash routines

- On-chip OSC and PLL for clock generation

- PLL loss-of-lock detection

- MOSFET driver including charge pump

- 10 general-purpose I/O Ports (GPIO)

- 5 analog inputs, 10-bit A/D Converter (ADC1)

- 16-bit timers GPT12, Timer 2, Timer 21 and Timer 3

- Capture/compare unit for PWM signal generation (CCU6)

- 2 full duplex serial interfaces (UART) with LIN support (for UART1 only)

- 2 synchronous serial channels (SSC)

- · On-chip debug support via 2-wire SWD

- 1 LIN 2.2 transceiver

- · 1 high voltage monitoring input

- Single power supply from 5.5 V to 27 V

- Extended power supply voltage range from 3 V to 28 V

- Low-dropout voltage regulators (LDO)

- · High speed operational amplifier for motor current sensing via shunt

- 5 V voltage supply for external loads (e.g. Hall sensor)

- Core logic supply at 1.5 V

- Programmable window watchdog (WDT1) with independent on-chip clock source

- Power saving modes

- MCU slow-down Mode

- Sleep Mode

- Stop Mode

- Cyclic wake-up Sleep Mode

- Power-on and undervoltage/brownout reset generator

| VQFN-48-31 |

|------------|

| Туре         | Package    | Marking |

|--------------|------------|---------|

| TLE9879QXA20 | VQFN-48-31 |         |

Overview

- Overtemperature protection

- Short circuit protection

- Loss of clock detection with fail safe mode entry for low system power consumption

- Temperature Range  $T_i$  = -40 °C to +150 °C

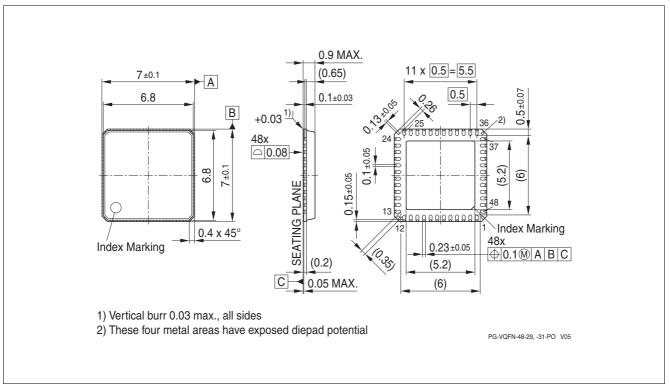

- Package VQFN-48 with LTI feature

- Green package (RoHS compliant)

- · AEC qualified

Overview

# 1.1 Abbreviations

The following acronyms and terms are used within this document. List see in Table 1.

Table 1 Acronyms

| Acronyms | Name                                                |  |  |  |  |  |  |

|----------|-----------------------------------------------------|--|--|--|--|--|--|

| AHB      | Advanced High-Performance Bus                       |  |  |  |  |  |  |

| APB      | Advanced Peripheral Bus                             |  |  |  |  |  |  |

| CCU6     | Capture Compare Unit 6                              |  |  |  |  |  |  |

| CGU      | Clock Generation Unit                               |  |  |  |  |  |  |

| CMU      | Cyclic Management Unit                              |  |  |  |  |  |  |

| CP       | Charge Pump for MOSFET driver                       |  |  |  |  |  |  |

| CSA      |                                                     |  |  |  |  |  |  |

|          | Current Sense Amplifier                             |  |  |  |  |  |  |

| DPP      | Data Post Processing                                |  |  |  |  |  |  |

| ECC      | Error Correction Code                               |  |  |  |  |  |  |

| EEPROM   | Electrically Erasable Programmable Read Only Memory |  |  |  |  |  |  |

| EIM      | Exceptional Interrupt Measurement                   |  |  |  |  |  |  |

| FSM      | Finite State Machine                                |  |  |  |  |  |  |

| GPIO     | General Purpose Input Output                        |  |  |  |  |  |  |

| H-Bridge | Half Bridge                                         |  |  |  |  |  |  |

| ICU      | Interrupt Control Unit                              |  |  |  |  |  |  |

| IEN      | Interrupt Enable                                    |  |  |  |  |  |  |

| IIR      | Infinite Impulse Response                           |  |  |  |  |  |  |

| LDM      | Load Instruction                                    |  |  |  |  |  |  |

| LDO      | Low DropOut voltage regulator                       |  |  |  |  |  |  |

| LIN      | Local Interconnect Network                          |  |  |  |  |  |  |

| LSB      | Least Significant Bit                               |  |  |  |  |  |  |

| LTI      | Lead Tip Inspection                                 |  |  |  |  |  |  |

| MCU      | Memory Control Unit                                 |  |  |  |  |  |  |

| MF       | Measurement Functions                               |  |  |  |  |  |  |

| MSB      | Most Significant Bit                                |  |  |  |  |  |  |

| MPU      | Memory Protection Unit                              |  |  |  |  |  |  |

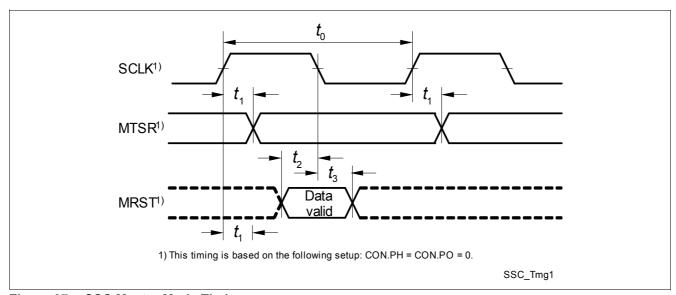

| MRST     | Master Receive Slave Transmit                       |  |  |  |  |  |  |

| MTSR     | Master Transmit Slave Receive                       |  |  |  |  |  |  |

| MU       | Measurement Unit                                    |  |  |  |  |  |  |

| NMI      | Non Maskable Interrupt                              |  |  |  |  |  |  |

| NVIC     | Nested Vector Interrupt Controller                  |  |  |  |  |  |  |

| NVM      | Non-Volatile Memory                                 |  |  |  |  |  |  |

| ОТР      | One Time Programmable                               |  |  |  |  |  |  |

| OSC      | Oscillator                                          |  |  |  |  |  |  |

| PBA      | Peripheral Bridge                                   |  |  |  |  |  |  |

|          |                                                     |  |  |  |  |  |  |

Overview

# Table 1 Acronyms

| Acronyms | Name                                        |  |  |  |  |  |

|----------|---------------------------------------------|--|--|--|--|--|

| PCU      | Power Control Unit                          |  |  |  |  |  |

| PD       | Pull Down                                   |  |  |  |  |  |

| PGU      | Power supply Generation Unit                |  |  |  |  |  |

| PLL      | Phase Locked Loop                           |  |  |  |  |  |

| PPB      | Private Peripheral Bus                      |  |  |  |  |  |

| PU       | Pull Up                                     |  |  |  |  |  |

| PWM      | Pulse Width Modulation                      |  |  |  |  |  |

| RAM      | Random Access Memory                        |  |  |  |  |  |

| RCU      | Reset Control Unit                          |  |  |  |  |  |

| RMU      | Reset Management Unit                       |  |  |  |  |  |

| ROM      | Read Only Memory                            |  |  |  |  |  |

| SCU-DM   | System Control Unit - Digital Modules       |  |  |  |  |  |

| SCU-PM   | System Control Unit - Power Modules         |  |  |  |  |  |

| SFR      | Special Function Register                   |  |  |  |  |  |

| SOW      | Short Open Window (for WDT)                 |  |  |  |  |  |

| SPI      | Serial Peripheral Interface                 |  |  |  |  |  |

| SSC      | Synchronous Serial Channel                  |  |  |  |  |  |

| STM      | Store Instruction                           |  |  |  |  |  |

| SWD      | ARM Serial Wire Debug                       |  |  |  |  |  |

| TCCR     | Temperature Compensation Control Register   |  |  |  |  |  |

| TMS      | Test Mode Select                            |  |  |  |  |  |

| TSD      | Thermal Shut Down                           |  |  |  |  |  |

| UART     | Universal Asynchronous Receiver Transmitter |  |  |  |  |  |

| VBG      | Voltage reference Band Gap                  |  |  |  |  |  |

| VCO      | Voltage Controlled Oscillator               |  |  |  |  |  |

| VPRE     | Pre Regulator                               |  |  |  |  |  |

| WDT      | Watchdog Timer in SCU-DM                    |  |  |  |  |  |

| WDT1     | Watchdog Timer in SCU-PM                    |  |  |  |  |  |

| WMU      | Wake-up Management Unit                     |  |  |  |  |  |

| 100TP    | 100 Time Programmable                       |  |  |  |  |  |

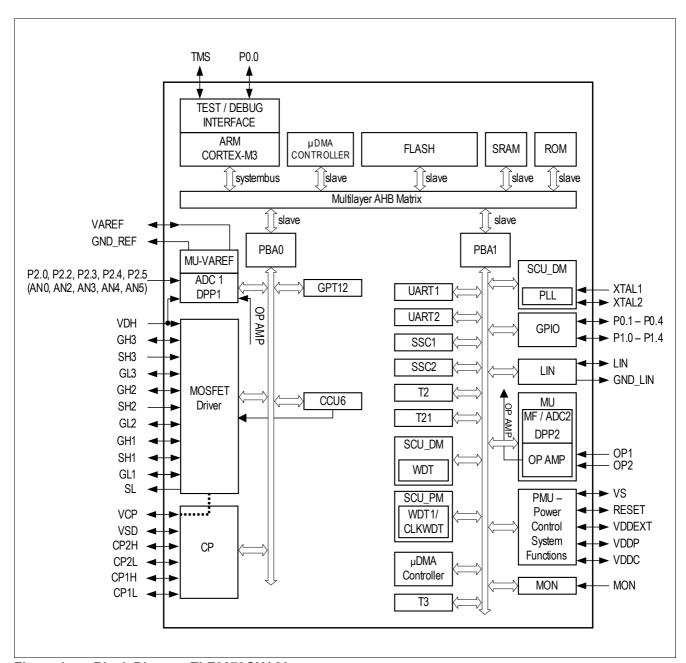

**Block Diagram**

# 2 Block Diagram

Figure 1 Block Diagram TLE9879QXA20

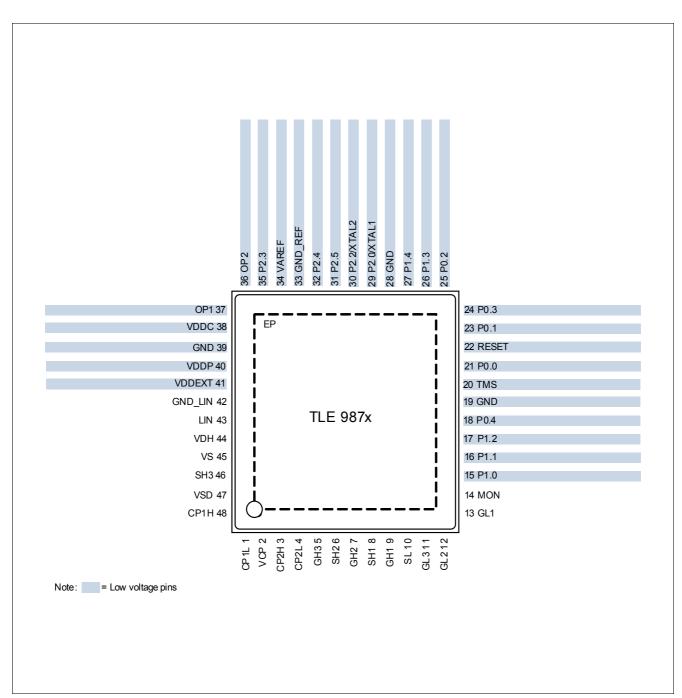

# 3 Device Pinout and Pin Configuration

## 3.1 Device Pinout

Figure 2 Device Pinout, TLE9879QXA20

# 3.2 Pin Configuration

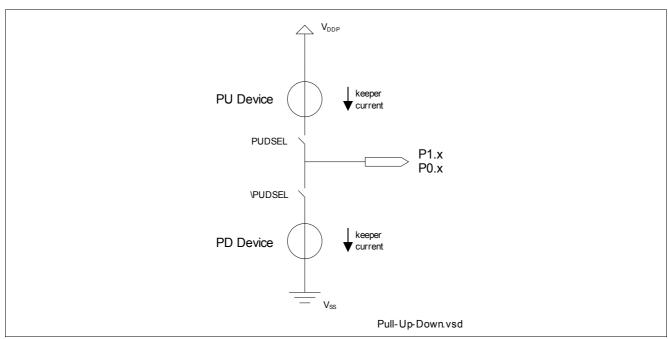

After reset, all pins are configured as input (except supply and LIN pins) with one of the following settings:

- Pull-up device enabled only (PU)

- Pull-down device enabled only (PD)

- Input with both pull-up and pull-down devices disabled (I)

- Output with output stage deactivated = high impedance state (Hi-Z)

The functions and default states of the TLE9879QXA20 external pins are provided in the following table.

Type: indicates the pin type.

- I/O: Input or output

- I: Input only

- O: Output only

- P: Power supply

Not all alternate functions listed.

Table 2 Pin Definitions and Functions

| Symbol | Pin Number | Туре | Reset<br>State <sup>1)</sup> | Function                                                                                                                                                                               |                                                                                                                                        |  |

|--------|------------|------|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|--|

| P0     |            |      |                              | Port 0 Port 0 is a 5-bit bidirectional general purpose I/O port. Alternate functions can be assigned and are listed in the port description. Main function is listed below.            |                                                                                                                                        |  |

| P0.0   | 21         | I/O  | I/PU                         | SWD                                                                                                                                                                                    | Serial Wire Debug Clock                                                                                                                |  |

| P0.1   | 23         | I/O  | I/PU                         | GPIO                                                                                                                                                                                   | General Purpose IO Alternate function mapping see Table 8                                                                              |  |

| P0.2   | 25         | I/O  | I/PD                         | GPIO                                                                                                                                                                                   | General Purpose IO Alternate function mapping see <b>Table 8</b> Note: For a functional SWD connection this GPIO must be tied to zero! |  |

| P0.3   | 24         | I/O  | I/PU                         | GPIO                                                                                                                                                                                   | General Purpose IO Alternate function mapping see Table 8                                                                              |  |

| P0.4   | 18         | I/O  | I/PD                         | GPIO                                                                                                                                                                                   | General Purpose IO Alternate function mapping see Table 8                                                                              |  |

| P1     |            |      |                              | Port 1 Port 1 is a 5-bit bidirectional general purpose I/O port. Alternate functions can be assigned and are listed in the Port description. The principal functions are listed below. |                                                                                                                                        |  |

| P1.0   | 15         | I/O  | I                            | GPIO                                                                                                                                                                                   | General Purpose IO Alternate function mapping see Table 9                                                                              |  |

| P1.1   | 16         | I/O  | I                            | GPIO                                                                                                                                                                                   | General Purpose IO Alternate function mapping see Table 9                                                                              |  |

| P1.2   | 17         | I/O  | 1                            | GPIO                                                                                                                                                                                   | General Purpose IO Alternate function mapping see Table 9                                                                              |  |

| P1.3   | 26         | I/O  | I                            | GPIO                                                                                                                                                                                   | General Purpose IO, used for Inrush Transistor Alternate function mapping see <b>Table 9</b>                                           |  |

| P1.4   | 27         | I/O  | 1                            | GPIO                                                                                                                                                                                   | General Purpose IO Alternate function mapping see Table 9                                                                              |  |

Data Sheet 12 Rev. 1.0, 2017-03-03

Table 2

Pin Definitions and Functions (cont'd)

| Symbol               | Pin Number | Туре                                                                                                                                                                 | Reset<br>State <sup>1)</sup> | Function                                                                                                                 |                                                                   |  |

|----------------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|--------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|--|

| P2                   |            | Port 2 Port 2 is a 5-bit general purpose input-only port. Alternate functions can be assigned and are listed in the Port description. Main function is listed below. |                              |                                                                                                                          |                                                                   |  |

| P2.0/XTAL1           | 29         | 1/1                                                                                                                                                                  | I                            | AN0                                                                                                                      | ADC analog input 0 Alternate function mapping see <b>Table 10</b> |  |

| P2.2/XTAL2           | 30         | I/O                                                                                                                                                                  | I                            | AN2                                                                                                                      | ADC analog input 2 Alternate function mapping see <b>Table 10</b> |  |

| P2.3                 | 35         | I                                                                                                                                                                    | 1                            | AN3                                                                                                                      | ADC analog input 3 Alternate function mapping see <b>Table 10</b> |  |

| P2.4                 | 32         | I                                                                                                                                                                    | I                            | AN4                                                                                                                      | ADC analog input 4 Alternate function mapping see Table 10        |  |

| P2.5                 | 31         | I                                                                                                                                                                    | I                            | AN5                                                                                                                      | ADC analog input 5 Alternate function mapping see <b>Table 10</b> |  |

| Power Supply         | /          | 1                                                                                                                                                                    |                              |                                                                                                                          |                                                                   |  |

| VS                   | 45         | Р                                                                                                                                                                    | _                            | Battery sup                                                                                                              | ply input                                                         |  |

| VDDP                 | 40         | Р                                                                                                                                                                    | _                            | 2)I/O port su                                                                                                            | ipply (5.0 V). Connect external buffer capacitor.                 |  |

| VDDC                 | 38         | Р                                                                                                                                                                    | _                            | <sup>3)</sup> Core supply (1.5 V during Active Mode).  Do not connect external loads, connect external buffer capacitor. |                                                                   |  |

| VDDEXT               | 41         | Р                                                                                                                                                                    | _                            | External voltage supply output (5.0 V, 20 mA)                                                                            |                                                                   |  |

| GND                  | 19         | Р                                                                                                                                                                    | _                            | GND digital                                                                                                              |                                                                   |  |

| GND                  | 28         | Р                                                                                                                                                                    | _                            | GND digital                                                                                                              |                                                                   |  |

| GND                  | 39         | Р                                                                                                                                                                    | _                            | GND analog                                                                                                               |                                                                   |  |

| <b>Monitor Input</b> | :          | •                                                                                                                                                                    | <del></del>                  | •                                                                                                                        |                                                                   |  |

| MON                  | 14         | I                                                                                                                                                                    | _                            | High Voltag                                                                                                              | e Monitor Input                                                   |  |

| LIN Interface        |            |                                                                                                                                                                      |                              | 1                                                                                                                        |                                                                   |  |

| LIN                  | 43         | I/O                                                                                                                                                                  | _                            | LIN bus inte                                                                                                             | erface input/output                                               |  |

| GND_LIN              | 42         | Р                                                                                                                                                                    | _                            | LIN ground                                                                                                               |                                                                   |  |

| Charge Pump          | )          |                                                                                                                                                                      |                              | 1                                                                                                                        |                                                                   |  |

| CP1H                 | 48         | Р                                                                                                                                                                    | _                            | Charge Pur                                                                                                               | np Capacity 1 High, connect external C                            |  |

| CP1L                 | 1          | Р                                                                                                                                                                    | _                            | Charge Pur                                                                                                               | np Capacity 1 Low, connect external C                             |  |

| CP2H                 | 3          | Р                                                                                                                                                                    | _                            | Charge Pur                                                                                                               | np Capacity 2 High, connect external C                            |  |

| CP2L                 | 4          | Р                                                                                                                                                                    | _                            | Charge Pump Capacity 2 Low, connect external C                                                                           |                                                                   |  |

| VCP                  | 2          | Р                                                                                                                                                                    | _                            | Charge Pump Capacity                                                                                                     |                                                                   |  |

| VSD                  | 47         | Р                                                                                                                                                                    | _                            | Battery supply input for Charge Pump                                                                                     |                                                                   |  |

| MOSFET Driv          | er         | •                                                                                                                                                                    | •                            | •                                                                                                                        |                                                                   |  |

| VDH                  | 44         | Р                                                                                                                                                                    | _                            | Voltage Drain High Side MOSFET Driver                                                                                    |                                                                   |  |

| SH3                  | 46         | Р                                                                                                                                                                    | _                            | Source High                                                                                                              | h Side FET 3                                                      |  |

| SH2                  | 6          | Р                                                                                                                                                                    | _                            | Source High Side FET 2                                                                                                   |                                                                   |  |

Table 2

Pin Definitions and Functions (cont'd)

| Symbol  | Pin Number | Туре     | Reset<br>State <sup>1)</sup> | Function                                                      |  |  |

|---------|------------|----------|------------------------------|---------------------------------------------------------------|--|--|

| GH2     | 7          | Р        | _                            | Gate High Side FET 2                                          |  |  |

| SH1     | 8          | Р        | _                            | Source High Side FET 1                                        |  |  |

| GH1     | 9          | Р        | _                            | Gate High Side FET 1                                          |  |  |

| SL      | 10         | Р        | _                            | Source Low Side FET                                           |  |  |

| GL2     | 12         | Р        | _                            | Gate Low Side FET 2                                           |  |  |

| GL1     | 13         | Р        | _                            | Gate Low Side FET 1                                           |  |  |

| GH3     | 5          | Р        | _                            | Gate High Side FET 3                                          |  |  |

| GL3     | 11         | Р        | _                            | Gate Low Side FET 3                                           |  |  |

| Others  |            |          |                              |                                                               |  |  |

| GND_REF | 33         | Р        | _                            | GND for VAREF                                                 |  |  |

| VAREF   | 34         | I/O      | _                            | 5V ADC1 reference voltage, optional buffer or input           |  |  |

| OP1     | 37         | I        | _                            | Negative operational amplifier input                          |  |  |

| OP2     | 36         | I        | _                            | Positive operational amplifier input                          |  |  |

| TMS     | 20         | I<br>I/O | I/PD                         | TMS Test Mode Select input SWD Serial Wire Debug input/output |  |  |

| RESET   | 22         | I/O      | _                            | Reset input, not available during Sleep Mode                  |  |  |

| EP      | _          | _        | _                            | Exposed Pad, connect to GND                                   |  |  |

<sup>1)</sup> Only valid for digital IOs

<sup>2)</sup> Also named VDD5V.

<sup>3)</sup> Also named VDD1V5.

**Modes of Operation**

# 4 Modes of Operation

This highly integrated circuit contains analog and digital functional blocks. An embedded 32-bit microcontroller is available for system and interface control. On-chip, low-dropout regulators are provided for internal and external power supply. An internal oscillator provides a cost effective clock that is particularly well suited for LIN communications. A LIN transceiver is available as a communication interface. Driver stages for a Motor Bridge or BLDC Motor Bridge with external MOSFET are integrated, featuring PWM capability, protection features and a charge pump for operation at low supply voltage. A 10-bit SAR ADC is implemented for high precision sensor measurement. An 8-bit ADC is used for diagnostic measurements.

The Micro Controller Unit supervision and system protection (including a reset feature) is complemented by a programmable window watchdog. A cyclic wake-up circuit, supply voltage supervision and integrated temperature sensors are available on-chip.

All relevant modules offer power saving modes in order to support automotive applications connected to terminal 30. A wake-up from power-save mode is possible via a LIN bus message, via the monitoring input or using a programmable time period (cyclic wake-up).

Featuring LTI, the integrated circuit is available in a VQFN-48-31 package with 0.5 mm pitch, and is designed to withstand the severe conditions of automotive applications.

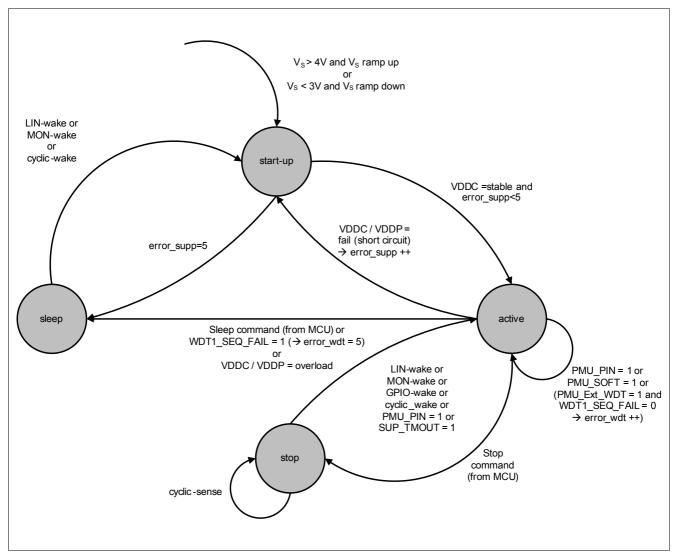

The TLE9879QXA20 has several operation modes mainly to support low power consumption requirements.

#### **Reset Mode**

The Reset Mode is a transition mode used e.g. during power-up of the device after a power-on reset, or after wake-up from Sleep Mode. In this mode, the on-chip power supplies are enabled and all other modules are initialized. Once the core supply VDDC is stable, the device enters Active Mode. If the watchdog timer WDT1 fails more than four times, the device performs a fail-safe transition to Sleep Mode.

#### **Active Mode**

In Active Mode, all modules are activated and the TLE9879QXA20 is fully operational.

#### Stop Mode

Stop Mode is one of two major low power modes. The transition to the low power modes is performed by setting the corresponding bits in the mode control register. In Stop Mode the embedded microcontroller is still powered, allowing faster wake-up response times. Wake-up from this mode is possible through LIN bus activity, by using the high-voltage monitoring pin or the corresponding 5V GPIOs.

### Stop Mode with Cyclic Wake-Up

The Cyclic Wake-Up Mode is a special operating mode of the Stop Mode. The transition to the Cyclic Wake-Up Mode is done by first setting the corresponding bits in the mode control register followed by the Stop Mode command. In addition to the cyclic wake-up behavior (wake-up after a programmable time period), asynchronous wake events via the activated sources (LIN and/or MON) are available, as in normal Stop Mode.

### Sleep Mode

The Sleep Mode is a low-power mode. The transition to the low-power mode is done by setting the corresponding bits in the MCU mode control register or in case of failure, see below. In Sleep Mode the embedded microcontroller power supply is deactivated allowing the lowest system power consumption. A wake-up from this mode is possible by LIN bus activity, the High Voltage Monitor Input pin or Cyclic Wake-up.

#### Sleep Mode in Case of Failure

**Modes of Operation**

Sleep Mode is activated after 5 consecutive watchdog failures or in case of supply failure (5 times). In this case, MON is enabled as the wake source and Cyclic Wake-Up is activated with 1s of wake time.

### Sleep Mode with Cyclic Wake-Up

The Cyclic Wake-Up Mode is a special operating mode of the Sleep Mode. The transition to Cyclic Wake-Up Mode is performed by first setting the corresponding bits in the mode control register followed by the Sleep and Stop Mode command. In addition to the cyclic wake-up behavior (wake-up after a programmable time period), asynchronous wake events via the activated sources (LIN and/or MON) are available, as in normal Sleep Mode.

When using Sleep Mode with cyclic wake-up the voltage regulator is switched off and started again with the wake. A limited number of registers is buffered during sleep, and can be used by SW e.g. for counting sleep/wake cycles.

#### **MCU Slow Down Mode**

In MCU Slow Down Mode the MCU frequency is reduced for saving power during operation. LIN communication is still possible. LS MOSFET can be activated.

### **Wake-Up Source Prioritization**

All wake-up sources have the same priority. In order to handle the asynchronous nature of the wake-up sources, the first wake-up signal will initiate the wake-up sequence. Nevertheless all wake-up sources are latched in order to provide all wake-up events to the application software. The software can clear the wake-up source flags. This is to ensure that no wake-up event is lost.

As default wake-up source, the MON input is activated after power-on reset only. Additionally, the device is in Cyclic Wake-Up Mode with the max. configurable dead time setting.

The following table shows the possible power mode configurations including the Stop Mode.

**Table 3** Power Mode Configurations

| Module/Function   | <b>Active Mode</b>              | Stop Mode                           | Sleep Mode             | Comment                      |

|-------------------|---------------------------------|-------------------------------------|------------------------|------------------------------|

| VDDEXT            | ON/OFF                          | ON (no dynamic load)/OFF            | OFF                    | -                            |

| Bridge Driver     | ON/OFF                          | OFF                                 | OFF                    |                              |

| LIN TRx           | ON/OFF                          | wake-up only/<br>OFF                | wake-up only/<br>OFF   | _                            |

| VS sense          | ON/OFF<br>brownout<br>detection | brownout detection                  | POR on VS              | brownout det. done in<br>PCU |

| GPIO 5V (wake-up) | n.a.                            | disabled/static                     | OFF                    | _                            |

| GPIO 5V (active)  | ON                              | ON                                  | OFF                    | _                            |

| WDT1              | ON                              | OFF                                 | OFF                    | _                            |

| CYCLIC WAKE       | n.a.                            | cyclic wake-up/<br>cyclic sense/OFF | cyclic wake-up/<br>OFF | _                            |

| Measurement       | ON <sup>1)</sup>                | OFF                                 | OFF                    | _                            |

| MCU               | ON/slow-<br>down/STOP           | STOP <sup>2)</sup>                  | OFF                    | -                            |

| CLOCK GEN (MC)    | ON                              | OFF                                 | OFF                    | _                            |

| LP_CLK (18 MHz)   | ON                              | OFF                                 | OFF                    | WDT1                         |

| LP_CLK2 (100 kHz) | ON/OFF                          | ON/OFF                              | ON/OFF                 | for cyclic wake-up           |

Data Sheet 16 Rev. 1.0, 2017-03-03

**Modes of Operation**

- 1) May not be switched off due to safety reasons

- 2) MC PLL clock disabled, MC supply reduced to 1.1  $\rm V$

## **Wake-Up Levels and Transitions**

The wake-up can be triggered by rising, falling or both signal edges for the monitor input, by LIN or by cyclic wake-up.

Data Sheet 17 Rev. 1.0, 2017-03-03

# 5 Power Management Unit (PMU)

### 5.1 Features

- System modes control (startup, sleep, stop and active)

- Power management (cyclic wake-up)

- Control of system voltage regulators with diagnosis (overload, short, overvoltage)

- · Fail safe mode detection and operation in case of system errors (watchdog fail)

- Wake-up sources configuration and management (LIN, MON, GPIOs)

- System error logging

### 5.2 Introduction

The power management unit is responsible for generating all required voltage supplies for the embedded MCU (VDDC, VDDP) and the external supply (VDDEXT). The power management unit is designed to ensure fail-safe behavior of the system IC by controlling all system modes including the corresponding transitions. Additionally, the PMU provides well defined sequences for the system mode transitions and generates hierarchical reset priorities. The reset priorities control the reset behavior of all system functionalities especially the reset behavior of the embedded MCU. All these functions are controlled by a state machine. The system master functionality of the PMU make use of an independent logic supply and system clock. For this reason, the PMU has an "Internal logic supply and system clock" module which works independently of the MCU clock.

Data Sheet 18 Rev. 1.0, 2017-03-03

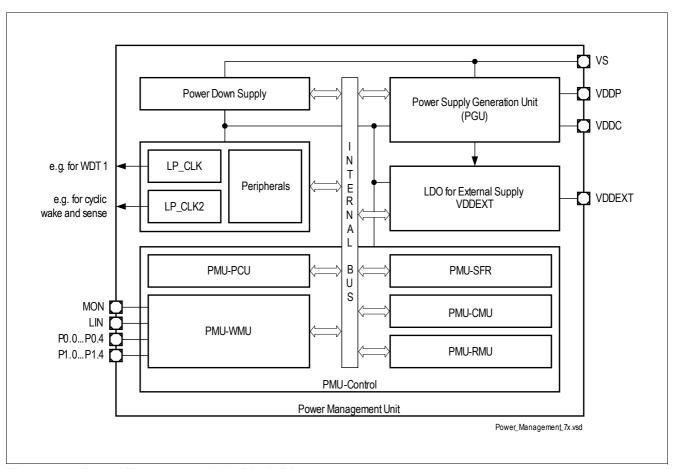

# 5.2.1 Block Diagram

The following figure shows the structure of the Power Management Unit. **Table 4** describes the submodules in more detail.

Figure 3 Power Management Unit Block Diagram

Table 4 Description of PMU Submodules

| Mod.<br>Name           | Modules                                                                                                 | Functions                                                                                                                                                                                          |

|------------------------|---------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power Down<br>Supply   | Independent supply voltage generation for PMU                                                           | This supply is dedicated to the PMU to ensure an independent operation from generated power supplies (VDDP, VDDC).                                                                                 |

| LP_CLK<br>(= 18 MHz)   | - Clock source for all PMU<br>submodules<br>- Backup clock source for System<br>- Clock source for WDT1 | This ultra low power oscillator generates the clock for the PMU.  This clock is also used as backup clock for the system in case of PLL Clock failure and as an independent clock source for WDT1. |

| LP_CLK2<br>(= 100 kHz) | Clock source for PMU                                                                                    | This ultra low power oscillator generates the clock for the PMU in Stop Mode and in the cyclic modes.                                                                                              |

| Peripherals            | Peripheral blocks of PMU                                                                                | These blocks include the analog peripherals to ensure a stable and fail-safe PMU startup and operation (bandgap, bias).                                                                            |

Table 4 Description of PMU Submodules (cont'd)

| Mod.<br>Name                             | Modules                                                                | Functions                                                                                                                                                                                                                                          |

|------------------------------------------|------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power Supply<br>Generation<br>Unit (PGU) | Voltage regulators for VDDP and VDDC                                   | This block includes the voltage regulators for the pad supply (VDDP) and the core supply (VDDC).                                                                                                                                                   |

| VDDEXT                                   | Voltage regulator for VDDEXT to supply external modules (e.g. sensors) | This voltage regulator is a dedicated supply for external modules and can also be used for cyclic sense operations (e.g. with hall sensor).                                                                                                        |

| PMU-SFR                                  | All Extended Special Function registers that are relevant to the PMU.  | This module contains all registers needed to control and monitor the PMU.                                                                                                                                                                          |

| PMU-PCU                                  | Power Control Unit of the PMU                                          | This block is responsible for controlling all power related actions within the PGU Module. It also contains all regulator related diagnostics such as undervoltage and overvoltage detection as well as overcurrent and short circuit diagnostics. |

| PMU-WMU                                  | Wake-Up Management Unit of the PMU                                     | This block is responsible for controlling all wake-up related actions within the PMU Module.                                                                                                                                                       |

| PMU-CMU                                  | Cyclic Management Unit of the PMU                                      | This block is responsible for controlling all actions in cyclic mode.                                                                                                                                                                              |

| PMU-RMU                                  | Reset Management Unit of the PMU                                       | This block generates resets triggered by the PMU such as undervoltage or short circuit reset, and passes all resets to the relevant modules and their register.                                                                                    |

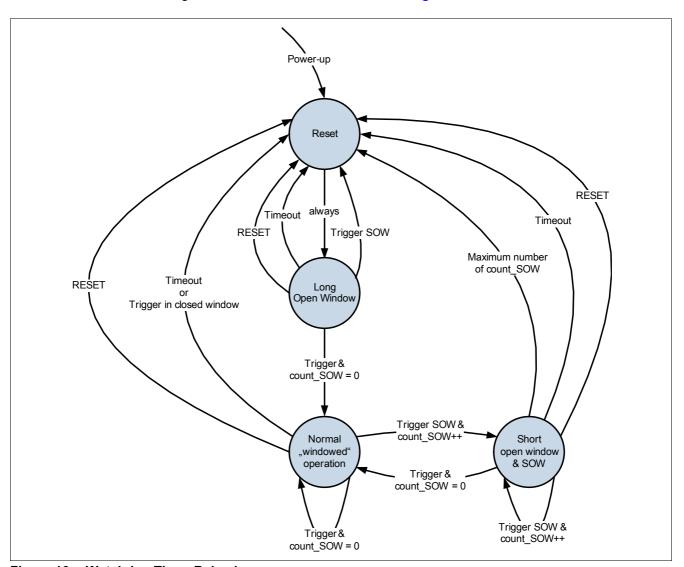

## 5.2.2 PMU Modes Overview

The following state diagram shows the available modes of the device.

Figure 4 Power Management Unit System Modes

# 5.3 Power Supply Generation Unit (PGU)

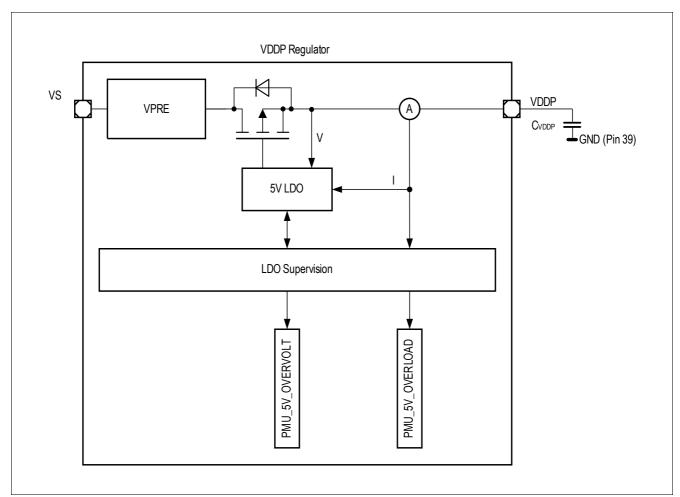

# 5.3.1 Voltage Regulator 5.0V (VDDP)

This module represents the 5 V voltage regulator, which provides the pad supply for the parallel port pins and other 5 V analog functions (e.g. LIN Transceiver).

### **Features**

- · 5 V low-drop voltage regulator

- Overcurrent monitoring and shutdown with MCU signaling (interrupt)

- Overvoltage monitoring with MCU signaling (interrupt)

- Undervoltage monitoring with MCU signaling (interrupt)

- Undervoltage monitoring with reset (Undervoltage Reset,  $V_{\rm DDPUV}$ )

- Pre-Regulator for VDDC Regulator

- GPIO Supply

- Pull Down Current Source at the output for Sleep Mode only (typ. 5 mA)

The output capacitor  $C_{\text{VDDP}}$  is mandatory to ensure proper regulator functionality.

Figure 5 Module Block Diagram of VDDP Voltage Regulator

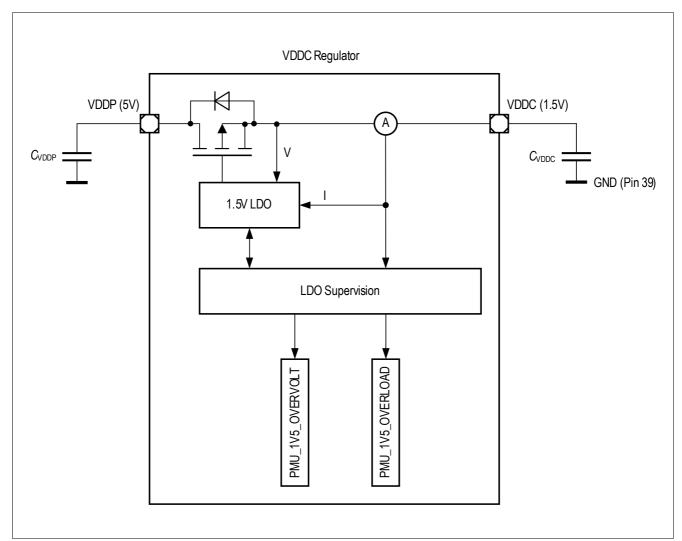

# 5.3.2 Voltage Regulator 1.5V (VDDC)

This module represents the 1.5 V voltage regulator, which provides the supply for the microcontroller core, the digital peripherals and other internal analog 1.5 V functions (e.g. ADC2) of the chip. To further reduce the current consumption of the MCU during Stop Mode the output voltage can be lowered to 1.1 V.

### **Features**

- 1.5 V low-drop voltage regulator

- · Overcurrent monitoring and shutdown with MCU signaling (interrupt)

- Overvoltage monitoring with MCU signaling (interrupt)

- Undervoltage monitoring with MCU signaling (interrupt)

- · Undervoltage monitoring with reset

- Pull Down Current Source at the output for Sleep Mode only (typ. 100 μA)

The output capacitor  $C_{\mathrm{VDDC}}$  is mandatory to ensure a proper regulator functionality.

Figure 6 Module Block Diagram of VDDC Voltage Regulator

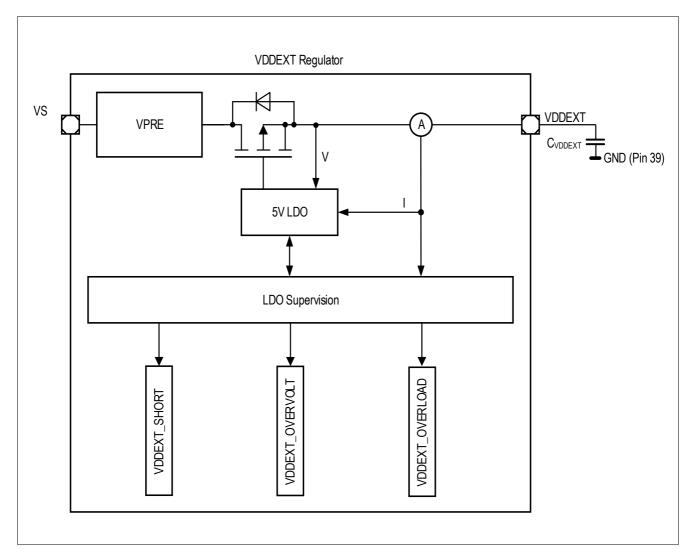

# 5.3.3 External Voltage Regulator 5.0V (VDDEXT)

This module represents the 5 V voltage regulator, which serves as a supply for external circuits. It can be used e.g. to supply an external sensor, LEDs or potentiometers.

### **Features**

- Switchable +5 V, low-drop voltage regulator

- · Switch-on overcurrent blanking time in order to drive small capacitive loads

- Overcurrent monitoring and shutdown with MCU signaling (interrupt)

- Overvoltage monitoring with MCU signaling (interrupt)

- Undervoltage monitoring with MCU signaling (interrupt)

- Pull Down current source at the output for Sleep Mode only (typ. 100 μA)

- · Cyclic sense option together with GPIOs

The output capacitor  $C_{\text{VDDEXT}}$  is mandatory to ensure a proper regulator functionality.

Figure 7 Module Block Diagram of External Voltage Regulator

# 6 System Control Unit - Digital Modules (SCU-DM)

### 6.1 Features

- · Flexible clock configuration features

- · Reset management of all system resets

- System modes control for all power modes (active, power down, sleep)

- Interrupt enabling for many system peripherals

- General purpose input output control

- Debug mode control of system peripherals

### 6.2 Introduction

The System Control Unit (SCU) supports all central control tasks in the TLE9879QXA20. The SCU is made up of the following sub-modules:

- Clock System and Control

- Reset Control

- Power Management

- Interrupt Management

- General Port Control

- Flexible Peripheral Management

- Module Suspend Control

- · Watchdog Timer

- · Error Detection and Correction in Data Memory

- Miscellaneous Control

Data Sheet 25 Rev. 1.0, 2017-03-03

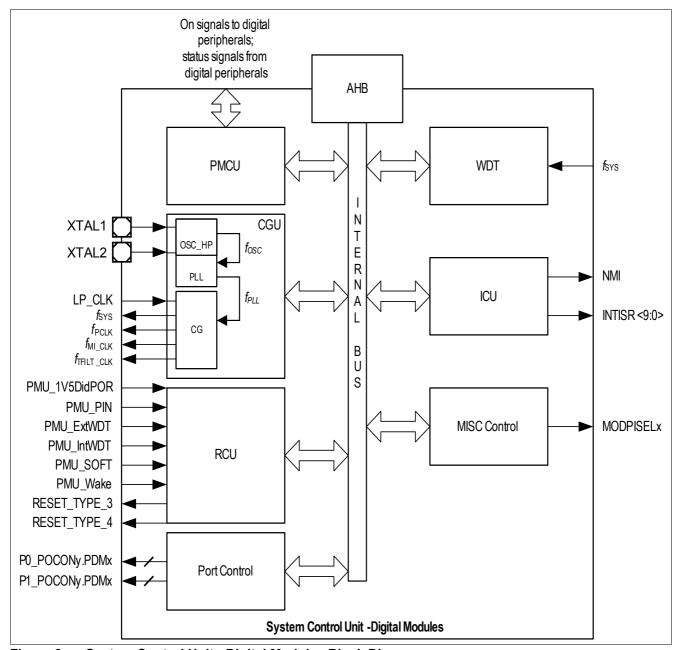

# 6.2.1 Block Diagram

Figure 8 System Control Unit - Digital Modules Block Diagram

**AHB (Advanced High-Performance Bus)**

**PMCU (Power Module Control Unit)**

### WDT (Watchdog Timer in SCU-DM)

f<sub>SYS</sub> System clock

### **CGU (Clock Generation Unit)**

- f<sub>SYS</sub> System clock

- $f_{PCLK}$  Peripheral clock

- f<sub>MI CLK</sub> Measurement interface clock

- $f_{\text{TFILT CLK}}$  Analog module filter clock

- LP CLK Clock source for all PMU submodules and WDT1

### **ICU (Interrupt Control Unit)**

- NMI (Non-Maskable Interrupt)

- INTISR<15,13:4,1,0> External interrupt signals

### **RCU (Reset Control Unit)**

- PMU\_1V5DidPOR Undervoltage reset of power down supply

- PMU\_PIN Reset generated by reset pin

- PMU ExtWDT WDT1 reset

- PMU IntWDT WDT (SCU) reset

- PMU\_SOFT Software reset

- PMU\_Wake Sleep Mode/Stop Mode exit with reset

- RESET TYPE 3 Peripheral reset (contains all resets)

- RESET\_TYPE\_4 Peripheral reset (without SOFT and WDT reset)

#### **Port Control**

- P0 POCONy.PDMx driver strength control

- P1\_POCONy.PDMx driver strength control

### **MISC Control**

MODPISELx Mode selection registers for UART (source section) and Timer (trigger or count selection)

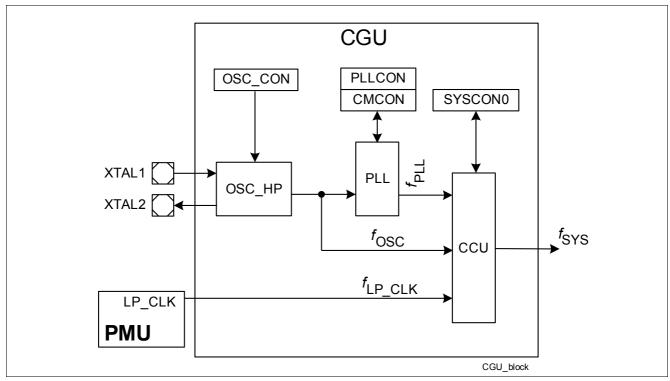

### 6.3 Clock Generation Unit

The Clock Generation Unit (CGU) enables a flexible clock generation for TLE9879QXA20. During user program execution, the frequency can be modified to optimize the performance/power consumption ratio, allowing power consumption to be adapted to the actual application state.

The CGU in the TLE9879QXA20 consists of one oscillator circuit (OSC\_HP), a Phase-Locked Loop (PLL) module with an internal oscillator (OSC\_PLL), and a Clock Control Unit (CCU). The CGU can convert a low-frequency input/external clock signal to a high-frequency internal clock.

The system clock  $f_{SYS}$  is generated from of the following selectable clocks:

- PLL clock output  $f_{PLL}$

- Direct clock from oscillator OSC\_HP  $f_{OSC}$

- Low precision clock  $f_{LP}$  CLK (HW-enabled for startup after reset and during power-down wake-up sequence)

Data Sheet 27 Rev. 1.0, 2017-03-03

Figure 9 Clock Generation Unit Block Diagram

The following sections describe the different parts of the CGU.

### 6.3.1 Low Precision Clock

The clock source LP\_CLK is a low-precision RC oscillator (LP-OSC) with a nominal frequency of 18 MHz that is enabled by hardware as an independent clock source for the TLE9879QXA20 startup after reset and during the power-down wake-up sequence.  $f_{\text{LP CLK}}$  is not user configurable.

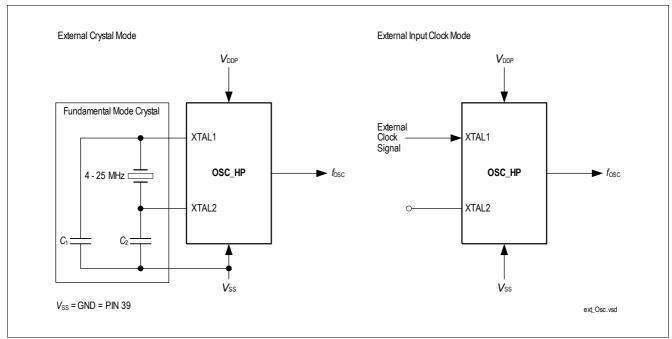

### 6.3.2 High Precision Oscillator Circuit (OSC\_HP)

The high precision oscillator circuit, designed to work with both an external crystal oscillator or an external stable clock source, consists of an inverting amplifier with XTAL1 as the input, and XTAL2 as the output.

Figure 10 shows the recommended external circuitry for both operating modes, External Crystal Mode and External Input Clock Mode.

## 6.3.2.1 External Input Clock Mode

When supplying the clock signal directly, not using an external crystal and bypassing the oscillator, the input frequency needs to be equal or greater than 4 MHz if the PLL VCO part is used.

When using an external clock signal it must be connected to XTAL1. XTAL2 is left open (unconnected).

### 6.3.2.2 External Crystal Mode

When using an external crystal, its frequency can be within the range of 4 MHz to 25 MHz. An external oscillator load circuitry must be used, connected to both pins, XTAL1 and XTAL2. It normally consists of the two load capacitances C1 and C2. A series damping resistor could be required for some crystals. The exact values and the corresponding operating ranges depend on the crystal and have to be determined and optimized in cooperation with the crystal vendor using the negative resistance method. The following load cap values can be used as starting point for the evaluation:

Table 5 External CAP Capacitors

| Fundamental Mode Crystal Frequency (approx., MHz) | Load Caps $C_1$ , $C_2$ (pF) |

|---------------------------------------------------|------------------------------|

| 4                                                 | 33                           |

| 8                                                 | 18                           |

| 12                                                | 12                           |

| 16                                                | 10                           |

| 20                                                | 10                           |

| 25                                                | 8                            |

Figure 10 TLE9879QXA20 External Circuitry for the OSC\_HP

System Control Unit - Power Modules (SCU-PM)

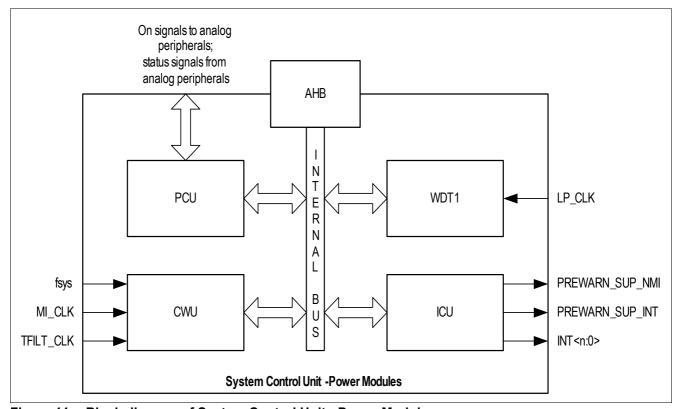

# 7 System Control Unit - Power Modules (SCU-PM)

### 7.1 Features

- Clock Watchdog Unit (CWU): supervision of all clocks with NMI signaling relevant to power modules

- · Interrupt Control Unit (ICU): all interrupt flags and status flags with system relevance

- · Power Control Unit (PCU): takes over control when device enters and exits Sleep and Stop Mode

- External Watchdog (WDT1): independent system watchdog for monitoring system activity

### 7.2 Introduction

# 7.2.1 Block Diagram

The System Control Unit of the power modules consists of the sub-modules in the figure shown below:

Figure 11 Block diagram of System Control Unit - Power Modules

### AHB (Advanced High-Performance Bus)

# **CWU (Clock Watchdog Unit)**

- $f_{\text{sys}}$  system frequency: PLL output

- MI\_CLK measurement interface clock (analog clock): derived from fsys using division factors 1/2/3/4

- · TFILT CLK clock used for digital filters: derived from fsys using configurable division factors

System Control Unit - Power Modules (SCU-PM)

### **WDT1 (System Watchdog)**

LP\_CLK clock source for all PMU submodules and WDT1

### **ICU (Interrupt Control Unit)**

- PREWARN\_SUP\_NMI supply prewarning NMI request

- PREWARN SUP INT supply prewarning interrupt

- grouping of peripheral interrupts for external interupt nodes:

- grouping single peripheral interrupts for interrupt node INT<2> (Measurement Unit (MU))

- grouping single peripheral interrupts for interrupt node INT<3> (ADC1-VAREF)

- grouping single peripheral interrupts for interrupt node INT<10> (UART1-LIN Transceiver)

- grouping single peripheral interrupts for interrupt node INT<14> (Bridge Driver)

Data Sheet 31 Rev. 1.0, 2017-03-03

**ARM Cortex-M3 Core**

### 8 ARM Cortex-M3 Core

### 8.1 Features

The key features of the Cortex-M3 implemented are listed below.

### Processor Core; a low gate count core, with low latency interrupt processing:

- A subset of the Thumb<sup>®</sup>-2 Instruction Set

- Banked stack pointer (SP) only

- 32-bit hardware divide instructions, SDIV and UDIV (Thumb-2 instructions)

- · Handler and Thread Modes

- Thumb and debug states

- Interruptible-continued instructions LDM/STM, Push/Pop for low interrupt latency

- Automatic processor state saving and restoration for low latency Interrupt Service Routine (ISR) entry and exit

- ARM architecture v7-M Style BE8/LE support

- · ARMv6 unaligned accesses

# Nested Vectored Interrupt Controller (NVIC) closely integrated with the processor core to achieve low latency interrupt processing:

- Interrupts, configurable from 1 to 16

- Bits of priority (4)

- Dynamic reprioritization of interrupts

- · Priority grouping. This enables selection of preemptive interrupt levels and non-preemptive interrupt levels

- Support for tail-chaining and late arrival of interrupts. This enables back-to-back interrupt processing without the overhead of state saving and restoration between interrupts.

- Processor state automatically saved on interrupt entry, and restored on interrupt exit, with no instruction overhead

### **Bus interfaces**

- Advanced High-performance Bus-Lite (AHB-Lite) interfaces: ICode, DCode, and System bus interface

- Memory access alignment

- · Write buffer for buffering of write data

Data Sheet 32 Rev. 1.0, 2017-03-03

**ARM Cortex-M3 Core**

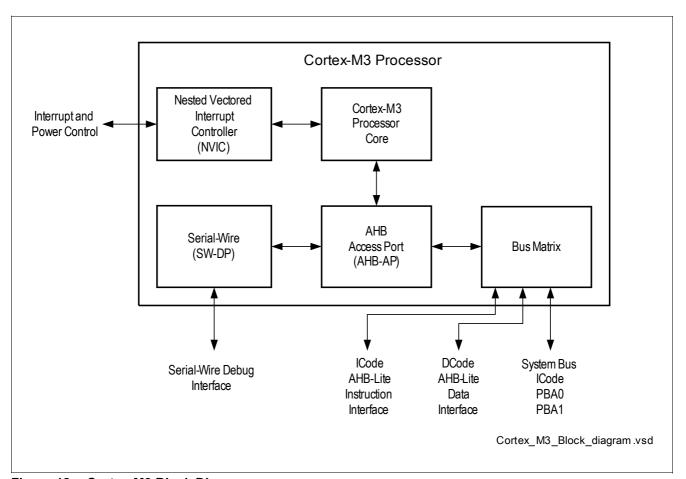

### 8.2 Introduction

The ARM Cortex-M3 processor is a leading 32-bit processor and provides a high-performance and cost-optimized platform for a broad range of applications including microcontrollers, automotive body systems and industrial control systems. Like the other Cortex family processors, the Cortex-M3 processor implements the Thumb<sup>®</sup>-2 instruction set architecture. With the optimized feature set the Cortex-M3 delivers 32-bit performance in an application space that is usually associated with 8- and 16-bit microcontrollers.

## 8.2.1 Block Diagram

Figure 12 shows the functional blocks of the Cortex-M3.

Figure 12 Cortex-M3 Block Diagram

**DMA Controller**

## 9 DMA Controller

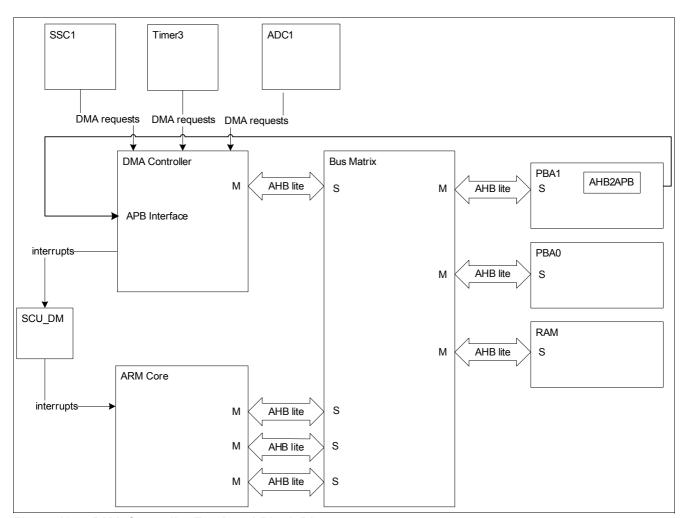

Figure 13 shows the Top Level Block Diagram of the TLE9879QXA20.

The bus matrix allows the µDMA to access the PBA0, PBA1 and RAM.

### 9.1 Features

The principal features of the DMA Controller are that:

- · it is compatible with AHB-Lite for the DMA transfers

- it is compatible with APB for programming the registers

- it has a single AHB-Lite master for transferring data using a 32-bit address bus and 32-bit data bus

- it supports 13 DMA channels

- each DMA channel has dedicated handshake signals

- · each DMA channel has a programmable priority level

- each priority level arbitrates using a fixed priority that is determined by the DMA channel number. The DMA also supports multiple transfer types:

- memory-to-memory

- memory-to-peripheral

- peripheral-to-memory

- it supports multiple DMA cycle types

- it supports multiple DMA transfer data widths

- each DMA channel can access a primary, and alternate, channel control data structure

- all the channel control data is stored in system memory (RAM) in little-endian format

- it performs all DMA transfers using the single AHB-Lite burst type. The destination data width is equal to the source data width.

- the number of transfers in a single DMA cycle can be programmed from 1 to 1024

- the transfer address increment can be greater than the data width

Data Sheet 34 Rev. 1.0, 2017-03-03

**DMA Controller**

## 9.2 Introduction

Please also refer to Chapter 9.3, Functional Description.

# 9.2.1 Block Diagram

Figure 13 DMA Controller Top Level Block Diagram

**DMA Controller**

# 9.3 Functional Description

### 9.3.1 DMA Mode Overview

The DMA controller implements the following 13 hardware DMA requests:

- ADC1 complete sequence 1 done: DMA transfer is requested on completion of the ADC1 channel conversion sequence.

- ADC1 exceptional sequence 2 (ESM) done: DMA transfer is requested on completion of the ADC1 conversion sequence triggered by an exceptional measurement request.

- SSC1/2 transmit byte: DMA transfer is requested upon the completion of data transmission via SSC1/2

- SSC1/2: receive byte: DMA transfer is requested upon the completion of data reception via SSC1/2.

- ADC1 channel 0 conversion done: DMA transfer is requested on completion of the ADC1 channel 0 conversion.

- ADC1 channel 1 conversion done: DMA transfer is requested on completion of the ADC1 channel 1 conversion.

- ADC1 channel 2 conversion done: DMA transfer is requested on completion of the ADC1 channel 2 conversion.

- ADC1 channel 3 conversion done: DMA transfer is requested on completion of the ADC1 channel 3 conversion.

- ADC1 channel 4 conversion done: DMA transfer is requested on completion of the ADC1 channel 4 conversion.

- ADC1 channel 5 conversion done: DMA transfer is requested on completion of the ADC1 channel 5 conversion.

- ADC1 channel 6 conversion done: DMA transfer is requested on completion of the ADC1 channel 6 conversion.

- ADC1 channel 7 conversion done: DMA transfer is requested on completion of the ADC1 channel 7 conversion

- Timer3 ccu6\_int: DMA transfer is requested following a timer trigger.

Data Sheet 36 Rev. 1.0, 2017-03-03

**Address Space Organization**

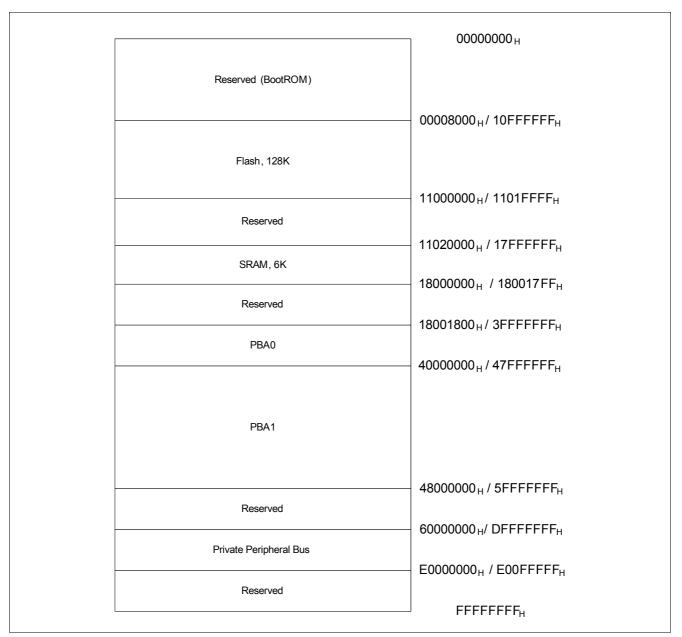

# 10 Address Space Organization

The TLE9879QXA20 manipulates operands in the following memory spaces:

- · 128 KByte of Flash memory in code space

- 32 KByte Boot ROM memory in code space (used for boot code and IP storage)

- 6 KByte RAM memory in code space and data space (RAM can be read/written as program memory or external data memory)

- · Special function registers (SFRs) in peripheral space

The figure below shows the detailed address alignment of TLE9879QXA20:

Figure 14 TLE9879QXA20 Memory Map

**Memory Control Unit**

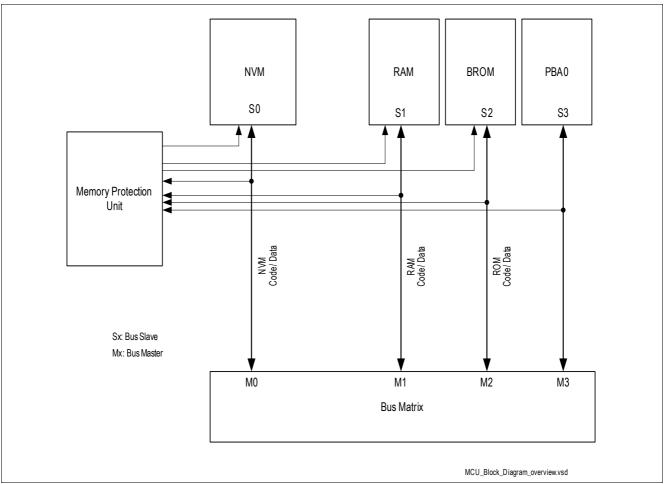

# 11 Memory Control Unit

## 11.1 Features

- · Handles all system memories and their interaction with the CPU

- Memory protection functions for all system memories (D-Flash, P-Flash, RAM)

- Address management with access violation detection including reporting

- Linear address range for all memories (no paging)

## 11.2 Introduction

## 11.2.1 Block Diagram

The Memory Control Unit (MCU) is divided in the following sub-modules:

- NVM memory module (embedded Flash Memory)

- · RAM memory module

- BootROM memory module

- · Memory Protection Unit (MPU) module

- Peripheral Bridge PBA0

Data Sheet 38 Rev. 1.0, 2017-03-03

## **Memory Control Unit**

Figure 15 MCU Block View

**Memory Control Unit**

# 11.3 NVM Module (Flash Memory)

The Flash Memory provides an embedded user-programmable non-volatile memory, allowing fast and reliable storage of user code and data.

#### **Features**

- In-system programming via LIN (Flash Mode) and SWD

- Error Correction Code (ECC) for detection of single-bit and double-bit errors and dynamic correction of single Bit errors.

- Interrupts and signals double-bit error by NMI

- Program width of 128 byte (page)

- Minimum erase width of 128 bytes (page)

- Integrated hardware support for EEPROM emulation

- 8 byte read access

- Physical read access time: 75 ns

- Code read access acceleration integrated; read buffer and automatic pre-fetch

- Page program time: 3 ms

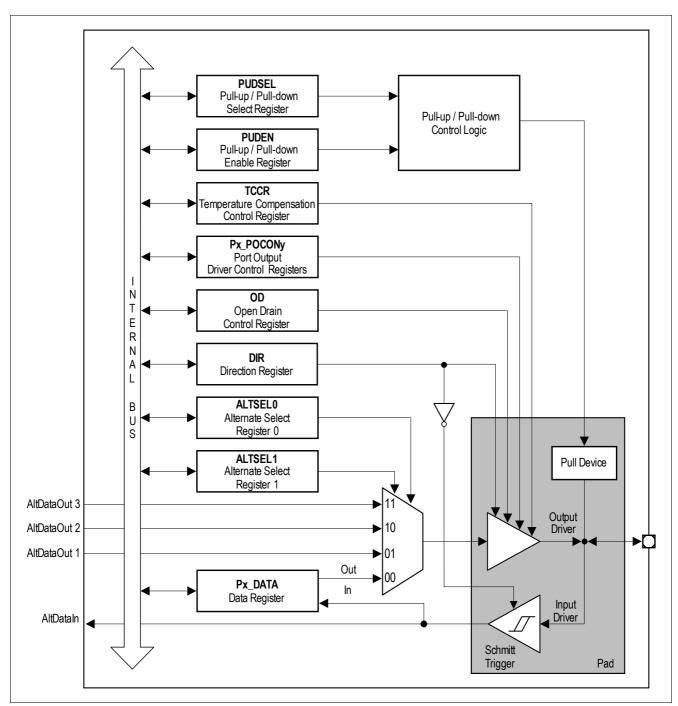

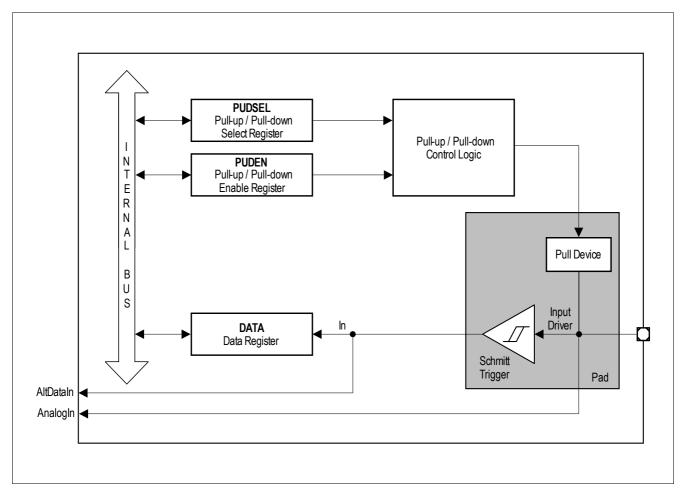

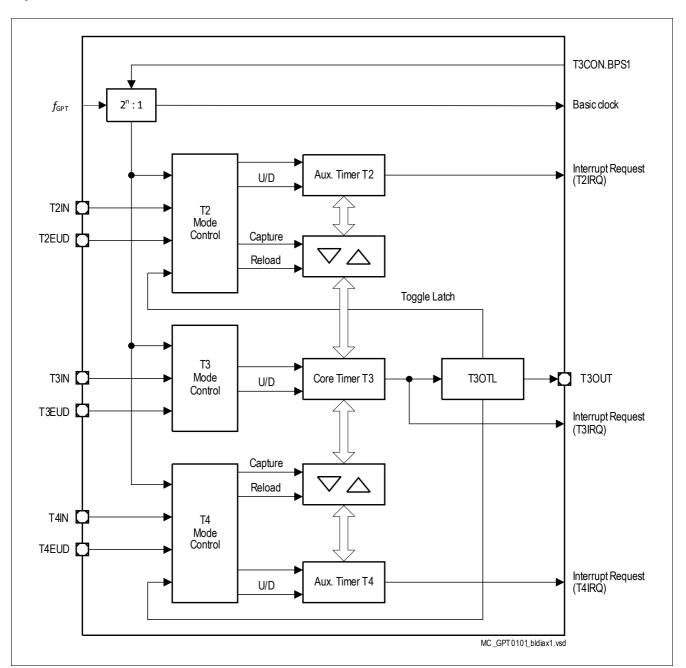

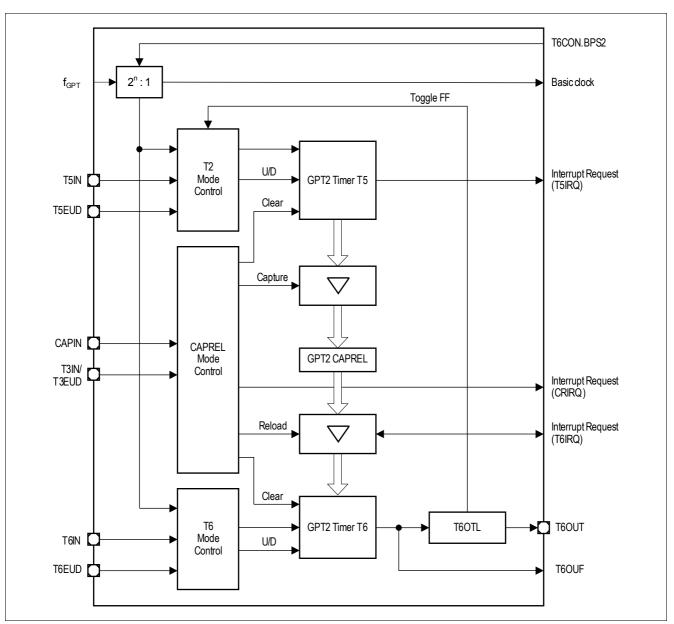

- · Page erase (128 bytes) and sector erase (4K bytes) time: 4ms