Direct Memory Access (DMA_PDL)

综述

General Description

The DMA Component transfers data to and from memory, Components, and registers. These transfers occur independent of the CPU. The DMA transfers can be set up in a byte, halfword (2 bytes), or word (4 bytes) wide. The DMA starts each transaction through an external trigger that can come from a DMA channel (including itself), another DMA channel, a peripheral, or the CPU. The DMA is best used to offload data transfer tasks from the CPU.

- Devices support up to two DMA hardware blocks

- Each DMA block supports up to 16 DMA channels

- Supports channel descriptors in SRAM

- 4 Priority Levels for each channel

- Byte, Halfword (2 bytes), and Word (4 bytes) transfers

- Configurable source and destination addresses

- Four Transfer Modes

- Single Data Element per Trigger

- One X (inner) loop transfer per trigger

- Entire descriptor per trigger

- Entire descriptor chain per trigger

- Configurable output trigger

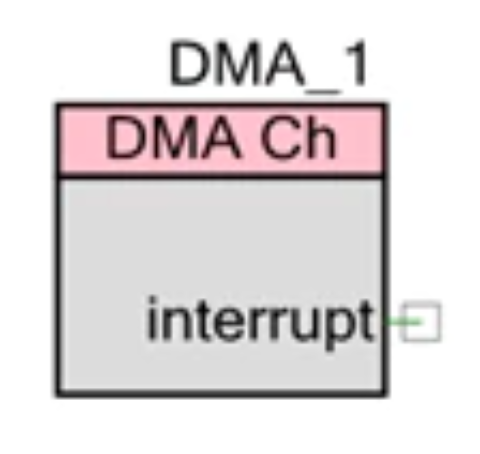

- Configurable interrupt generation

支持